# Low-loss slot waveguides with silicon (111) surfaces realized using anisotropic wet etching

- 1 Kapil Debnath<sup>1\*</sup>, Ali Z. Khokhar<sup>2</sup>, Stuart A. Boden<sup>1</sup>, Hideo Arimoto<sup>1</sup>, Swe Zin Oo<sup>1</sup>, Harold M.

- 2 H. Chong<sup>1</sup>, Graham T. Reed<sup>2</sup>, Shinichi Saito<sup>1</sup>

- <sup>1</sup>Faculty of Physical Sciences and Engineering, University of Southampton, Southampton SO17 1BJ,

- 4 UK

- <sup>2</sup>Optoelectronics Research Centre, University of Southampton, Southampton SO17 1BJ, UK

- \* Correspondence: Kapil Debnath, Faculty of Physical Sciences and Engineering, University of

- 7 Southampton, Southampton SO17 1BJ, UK

- 8 K.Debnath@soton.ac.uk

- 9 Keywords: silicon photonics, waveguide, anisotropic wet etching, slot waveguide, integrated

- 10 **photonics.**

- 11 **Abstract**

- We demonstrate low-loss slot waveguides on silicon-on-insulator (SOI) platform. Waveguides

- oriented along the (11-2) direction on the Si (110) plane were first fabricated by a standard e-beam

- 14 lithography and dry etching process. A TMAH based anisotropic wet etching technique was then

- used to remove any residual side wall roughness. Using this fabrication technique propagation loss as

- low as 3.7dB/cm was realized in silicon slot waveguide for wavelengths near 1550nm. We also

- 17 realized low propagation loss of 1dB/cm for silicon strip waveguides.

### 18 1 Introduction

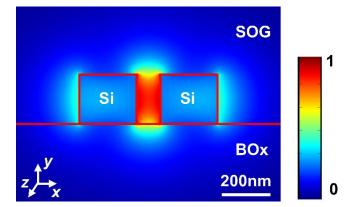

- 19 The slot waveguide structure was first proposed by Almeida et al. (Almeida et al., 2004) as a simple

- 20 way to achieve extremely strong optical confinement in a low refractive index medium. Typically, an

- 21 all-dielectric slot waveguide is formed by two high index waveguiding regions (e.g. silicon)

- separated by a narrow region of low index material (e.g. air, silica or polymer). Due to the

- 23 discontinuity in the electric field at the high index contrast interfaces, such a structure supports an

- 24 optical mode which can confine and guide light along the nanometer-size region of low index

- 25 material, as shown in Fig. 1. This unique property of slot waveguides has been exploited in many

- areas such as sensing (Barrios et al., 2007; Carlborg et al., 2010), nonlinear optics (Martínez et al.,

- 27 2010; Muellner et al., 2009), electro-optic modulation (Koos et al., 2009; Baehr-Jones et al., 2008;

- 28 Chen et al., 2009), light sources (Guo et al., 2012; Tengattini et al., 2013) etc. However, a major

- 29 limitation of slot waveguides is their high propagation loss. Since the light is more confined in the

- 30 slot region, any surface roughness, introduced during the fabrication process, causes significant

- 31 scattering loss. Therefore, fabrication of low loss slot waveguides is challenging and the lowest

- reported propagation loss was 10dB/cm (Baehr-Jones et al., 2005) from a standard vertical slot

- waveguide. There are different approaches proposed in the literature to reduce this propagation loss.

- For example, strip-loaded slot waveguides have been proposed with improved propagation loss of

6.5dB/cm (Ding et al., 2010); albeit for a reduced mode confinement in the slot region. Spott et al. reported a record low propagation loss of 1.7dB/cm (Spott et al., 2011) from a slot waveguide by introducing different silicon arm widths. This geometry also compromises the mode confinement in the slot region due the asymmetry in the waveguide geometry. Alasaarela et al. adopted a different approach to reduce the propagation loss by coating the waveguide surface by a thin layer of titanium dioxide (Alasaarela et al., 2011). This layer with intermediate refractive index effectively reduces the optical field intensity at the high index contrast interface and they reported a propagation loss of 7dB/cm for a slot waveguide.

Fig. 1. Dominant Electric field (|Ex|) of the fundamental TE mode guided by the silicon slot waveguide on a buried oxide (BOx) substrate with a spin-on glass (SOG) surrounding medium. The waveguide is 220nm high and the slot width is 100nm with 225nm wide silicon arms on both sides.

In this letter we present a new and simple method of reducing waveguide loss by surface smoothening using a combination of dry and anisotropic wet etching processes. The wet etching process was used to smoothen the residual side wall roughness after dry etching. Here we used an aqueous solution of Tetramethylammonium hydroxide (TMAH), which is widely used for anisotropic wet etching of silicon. Due to its strong alkalinity, TMAH reacts very differently with silicon depending on the crystallographic orientation of the exposed region. For example, while (100) and (110) planes are etched by a TMAH solution, (111) planes remains almost unaffected. Since this is a completely chemical process and strongly depends on the crystallographic orientation of the etched surface, ideally we should expect an ultra-smooth surface with atomic level irregularity. Previously sub-dB propagation loss in silicon strip waveguides have been demonstrated using TMAH based wet etching process (Debnath et al., 2016; Lee et al., 2001). In this work, by combining dry and wet etching processes we managed to reduce the propagation loss of a slot waveguide with 200nm slot width from 10.5dB/cm to 3.7dB/cm and for a strip waveguide from 2.7dB/cm to 1dB/cm.

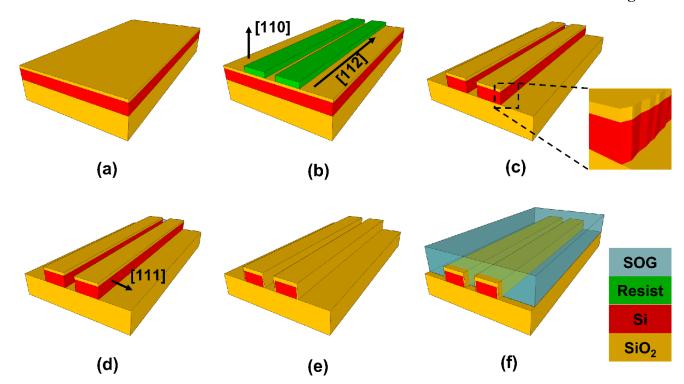

#### Fabrication Process

The fabrication process flow is shown in Fig. 2. The slot waveguides were fabricated on two Silicon-on-Insulator (SOI) substrates, namely sample A and sample B. Both the SOI substrates had 220nm thick layers of Si with (110) surface orientation on 2µm thick Buried Oxide (BOx). The advantage of choosing the (110) oriented substrate lies in the fact that (111) planes are normal to the (110) surface along (112) direction. As a result, when the waveguides are designed along the (112) directions, the (111) planes will act as an etch stop during the smoothening process. During the fabrication process, first a 20nm thick layer of SiO<sub>2</sub> was thermally grown by annealing the SOI substrates at 1000°C in O<sub>2</sub> (dry anneal) for 6 minutes in a quartz furnace tube. The substrates were then spin-coated with a

#### **Running Title**

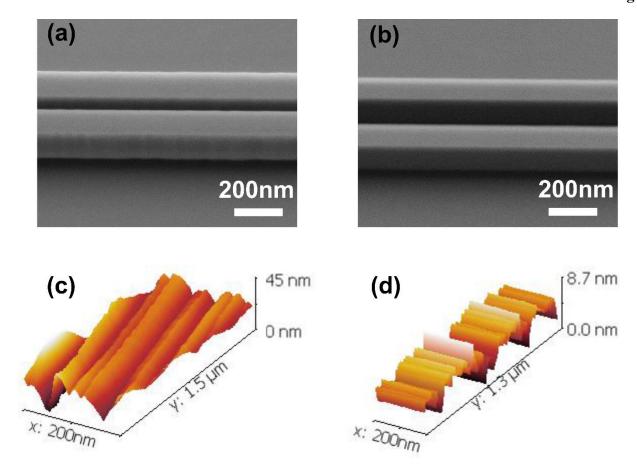

69 250nm thick ZEP-520A positive e-beam resist layer. Using e-beam lithography, the desired 70 waveguide patterns were exposed onto the ZEP layer via a 5nm spot size. The waveguides were 71 designed to align along the (11-2) direction on the SOI substrates. After developing the exposed 72 resist layer, the waveguide patterns were transferred to the SiO<sub>2</sub> hard mask and subsequently to the 73 SOI layer in an inductively coupled plasma (ICP) etcher using a SF<sub>6</sub>/C<sub>4</sub>F<sub>8</sub> chemistry. After the dry 74 etching process, the remaining resist was removed in an O<sub>2</sub> plasma asher. Final cleaning was carried 75 out in fuming nitric acid and then diluted hydrofluoric acid. Surface roughness smoothening using 76 anisotropic wet etching was carried out only on sample B. To avoid the formation of any native oxide 77 layer, immediately after the HF cleaning process, the substrate was immersed in a 25% aqueous 78 solution of TMAH at room temperature for 10 minutes. This duration was sufficient to significantly 79 reduce the roughness from the waveguide surfaces. During this wet etching process, the top surfaces 80 of the waveguides were protected by the SiO<sub>2</sub> hard mask while any roughness on the waveguide side 81 walls was reduced. Since the etch rate is very slow along the (111) direction we expect an atomically 82 flat and vertical side walls after the wet etching process. For comparison the wet etching step was 83 omitted for sample A. Figure 3a and 3b show the SEM images of the slot waveguides without 84 (sample A) and with (sample B) roughness smoothening using TMAH wet etching respectively. 85 From the images, it is obvious that the surface roughness has been significantly reduced after the wet etching process. We have further carried out a detailed sidewall roughness analysis using Atomic 86 87 Force Microscopy (AFM). We have used a special tapered AFM tip from Bruker (CDF100) to easily 88 access the vertical side walls of the waveguides. The AFM image was then processed using 89 Gwyddion AFM analysis software to extract the surface roughness information of the sidewalls. In 90 the images Fig. 3c and Fig. 3d, the y-axis is along the length and the x-axis is along the height of the 91 waveguide, whereas the surface roughness is represented along z-axis. The AFM images clearly 92 reveals that the roughness reduces from an rms value of 6.7nm (Fig. 3c) for the dry etched waveguide 93 to 1.4nm (Fig. 3d) for the wet etched waveguide. It is also important to note here that the slot 94 waveguides which had undergone the wet etching step had 20nm larger slot width than designed, due 95 to the slow etching of (111) plane. This slow etching of the (111) plane can also be used to precisely 96 control the slot width by simply optimizing the wet etching time. Although in this work we have used 97 e-beam lithography due to its quick turned around time, the same wet etching process can be used to smoothen the waveguide surfaces realized using standard photolithography processes. Finally, 98 99 another thermal oxidation was carried on both the substrates to grow a 5nm thick layer of SiO<sub>2</sub>, 100 which acts as a surface passivation layer. In most applications the slot waveguides are cladded with 101 low index materials such as polymers (Koos et al., 2009) or silica (Martínez et al., 2010). Here we 102 spin coated the substrate with 500nm thick spin-on glass (SOG, Fox-16, Dow Corning) and annealed 103 at 400°C in N<sub>2</sub> environment for 4 hours to cure the SOG. This acts as a low-loss cladding for the slot 104 waveguides which has the refractive index of around 1.45, similar to silica.

## **Running Title**

Fig. 2. Fabrication process flow: (a) a 20nm thick layer of  $SiO_2$  was thermally grown on SOI substrate; (b) slot and strip waveguide patterns were written on the resist layer using e-beam lithography; (c) waveguide patterns were transferred to the silicon layer using ICP dry etching process; (d) SOI substrate was dipped into TMAH solution to remove any surface roughness (only for sample B); (e) a thin  $SiO_2$  layer was thermally grown to serve as surface passivation; (f) finally 500nm thick layer of SOG was spin coated and cured.

Fig. 3. SEM images of a waveguide (a) on the dry etched only sample (sample A) and (b) on the TMAH treated sample (sample B), imaged at an angle of 45°; (c) AFM image of the side wall of dry etched waveguide with rms roughness of 6.7nm; (d) AFM image of the side wall of wet etched waveguide with rms roughness of 1.4nm.

#### 2.1 Measurement and results

112

113

114115

116

117

118

119

120

121

122

123124

125

126 127

128129

130

131

132

133

134

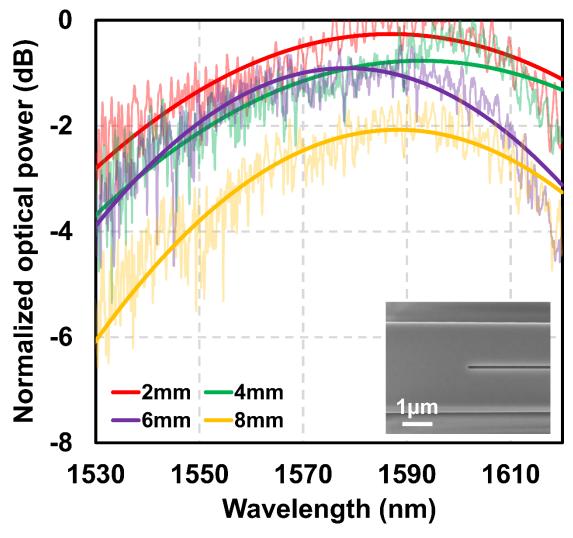

The transmission through the fabricated slot waveguides was measured using a fibre-coupled tunable laser source with a tuning range from 1530nm to 1630nm. For all the measurements 10dBm laser power was used. Since the slot mode is a TE mode, the input of only TE polarized light was ensured with a fibre polarization controller. Coupling light onto the chip was achieved by fibre-grating couplers (Covey et al., 2013). The wavelength was scanned using the built-in sweeping ability of the laser, and the detector automatically recorded the output spectra. For both samples, the total fibre to fibre insertion loss was around 20dB, which includes the system loss and the grating coupler losses. For estimating the propagation loss in the strip waveguide and slot waveguides a cut-back method was used. Waveguides with four different lengths ranging from 2mm to 8mm were designed. For strip waveguides the waveguide width was 450nm. For slot waveguides, we designed 3 different slot widths of 100nm, 150nm and 200nm with 225nm wide silicon arms on both sides. Figure 4 shows the normalized transmission spectra, represented in light colors, of a set of slot waveguides with fixed slot width of 100nm and varied lengths. The peak transmission values for each length were estimated from the fitted curve using a quadratic function to match the grating coupler spectrum. The fitted curves are represented in dark colors in Fig. 4. We also observed ~1dB ripple in the measured transmission spectra. We attribute such fluctuations to the imperfect coupling region between the strip and slot section of the waveguide (shown in the inset of Fig. 4). This is caused due to sudden

change in effective index of the optical mode at the coupling region. The coupling efficiency between the strip and slot waveguide region can be improved by carefully designing the coupling region as proposed previously in Han et al., 2016; Säynätjoki et al., 2011 and Passaro, 2012.

Fig. 4. Spectrum and quadratic function fitting for different waveguide lengths with slot width of 100nm. The inset shows the coupling region between the strip region and the slot region of the waveguide.

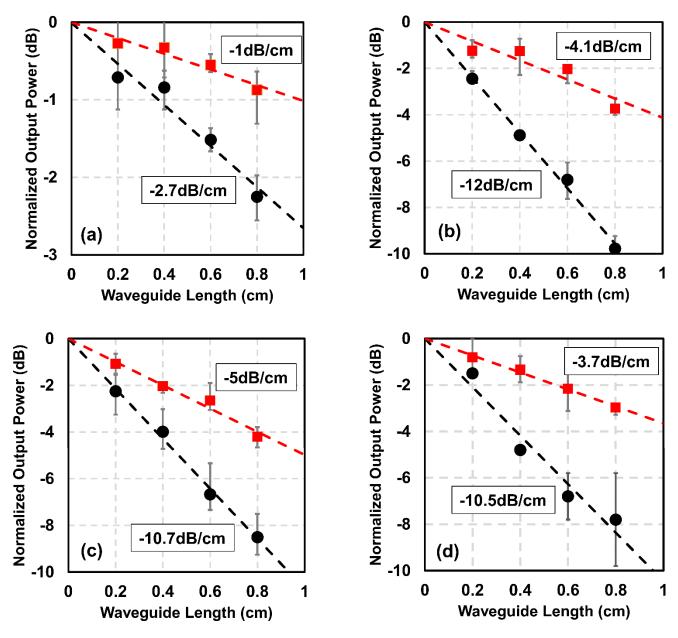

Figure 5 shows the cutback measurement results for different waveguide geometries under different etching conditions. In order to avoid any unwanted variation in the coupling condition, for each propagation length, we have measured a set of four waveguides and considered the average value for estimating the propagation loss. To emphasize the effect of our surface smoothening process on the waveguide loss, we have also normalized the waveguide transmission by setting the background loss (i.e. setup and coupling loss) to 0dB. In Fig. 5a-5d, the black circles represent the normalized transmission for dry etched waveguides on sample A and the red squares represent the normalized transmission of the waveguides after the surface smoothening step on sample B. The dashed lines represent the linear fits for the transmission data. For every waveguide geometry, we observed a significant reduction in the propagation loss. For strip waveguides the propagation loss reduced from 2.7dB/cm to 1dB/cm and for slot waveguides with 100nm, 150nm and 220nm the propagation loss

153 dropped from 12dB/cm to 4.1dB/cm, 10.7dB/cm to 5dB/cm and 10. 5dB/cm to 3.7dB/cm 154 respectively. We expected that the slot waveguide loss to monotonically reduce with increasing slot 155 width, since the optical confinement also reduces with increasing slot width. However, we found that, although waveguide with 200nm slot has lower loss in comparison to waveguide with 100nm slot, 156 the loss of 150nm slot is relatively higher. We believe this is due to experimental error and within our 157 158 error limit. Also, we would like to mention that 20nm increase in slot width after wet etching should 159 not have a significant effect on the propagation loss and according to our experimental results for 160 such variation in the slot width we expect to see the loss value to change by less than 0.3dB/cm.

Fig. 5. Normalized optical output power vs. waveguide length after dry etching (black circle) and wet etching (red square) for (a) strip waveguide with no slot and slot waveguides with slot widths of (b) 100nm, (c) 150nm and (d) 200nm.

#### 3 Conclusion

161

162

163

164

165

- To summarize, in this letter, we have proposed and demonstrated a simple fabrication technique to

- realize low-loss strip and slot waveguides on SOI platform. Here we combined both dry and

- anisotropic wet etching processes to reduce propagation loss. The waveguides were first defined

- during the dry etching process and then the anisotropic wet etching process was used to remove any

- sidewall roughness. Using this fabrication technique we realized a slot waveguide with a minimum

- propagation loss of 3.7dB/cm for a slot width of 200nm. There are several advantages of our

- proposed fabrication technique. First, without using any asymmetry or multilayer structures, the

- propagation loss can be reduced in a symmetric slot waveguide. Secondly, our surface smoothening

- technique can be applicable to patterns realized using standard photolithography. Finally the slow

- etching rate of the (111) plane can be used to precisely control the slot width.

- Anisotropic wet etching is very selective to crystallographic orientation of silicon. Although on one

- hand this allowed us to realize atomically flat surfaces and reduce propagation loss through silicon

- waveguides; due to its dependence on the crystallographic planes, out fabrication process restricts

- designing of nanophotonic components only along certain directions. This limitation can be avoided

- by adopting a hybrid fabrication process, where only certain components of the photonic integrated

- circuit, e.g. slot waveguide, undergoes the roughness smoothening process using anisotropic wet

- 182 etching.

## 183 4 Acknowledgements

- 184 This work is supported by EPSRC Standard Grant (EP/M009416/1), EPSRC Manufacturing

- Fellowship (EP/M008975/1), EPSRC Platform Grant (EP/N013247/1), EU FP7 Marie-Curie Carrier-

- 186 Integration-Grant (PCIG13-GA-2013-618116), University of Southampton Zepler Institute Research

- 187 Collaboration Stimulus Fund, and Hitachi.

### 188 **5 Data Availability**

- All data supporting this study are available upon request from the University of Southampton

- repository at http://dx.doi.org/10.5258/SOTON/397774.

## 191 **6 References**

- 192 Almeida, V. R., Xu, Q., Barrios, C. A., and Lipson, M. (2004). Guiding and confining light in void

- nanostructure. *Optics Letters* 29, 1209-1211. doi: 10.1364/OL.29.001209

- Barrios, C. A., Gylfason, K. B., Sánchez, B., Griol, A., Sohlström, H., Holgado, M., and Casquel, R.

- 195 (2007). Slot-waveguide biochemical sensor. *Optics Letters* 32, 3080-3082. doi:

- 196 10.1364/OL.32.003080

- 197 Carlborg, C. F., Gylfason, K. B., Kaźmierczak, A., Dortu, F., Polo, M. B., Catala, A. M., Kresbach,

- 198 G. M., Sohlström, H., Moh, T., Vivien, L., and Popplewell, J. (2010). A packaged optical slot-

- 199 waveguide ring resonator sensor array for multiplex label-free assays in labs-on-chips. Lab on a Chip

- 200 10, 281-290. doi: 10.1039/B914183A

- Martínez, A., Blasco, J., Sanchis, P., Galán, J. V., García-Rupérez, J., Jordana, E., Gautier, P.,

- Lebour, Y., Hernández, S., Spano, R., Guider, R. (2010). Ultrafast all-optical switching in a silicon-

- 203 nanocrystal-based silicon slot waveguide at telecom wavelengths. Nano letters 31, 1506-1511. doi:

- 204 10.1021/nl9041017

- Muellner, P., Wellenzohn, M., and Hainberger R. (2009). Nonlinearity of optimized silicon photonic

- 206 slot waveguides. Optics Express 17, 9282-9287. doi: 10.1364/OE.17.009282.

- Koos, C., Vorreau, P., Vallaitis, T., Dumon, P., Bogaerts, W., Baets, R., Esembeson, B., Biaggio, I.,

- Michinobu, T., Diederich, F., Freude, W., and Leuthold, J. (2009). All-optical high-speed signal

- processing with silicon–organic hybrid slot waveguides. Nature Photonics 3, 216-219. doi:

- 210 10.1038/nphoton.2009.25

- Baehr-Jones, T., Penkov, B., Huang, J., Sullivan, P., Davies, J., Takayesu, J., Luo, J., Kim, T. D.,

- Dalton, L., Jen, A., and Hochberg, M. (2008). Nonlinear polymer-clad silicon slot waveguide

- 213 modulator with a half wave voltage of 0.25 V. Applied Physics Letters 92, 163303. doi:

- 214 10.1063/1.2909656

- Chen, X., Chen, Y. S., Zhao, Y., Jiang, W., and Chen, R. T. (2009). Capacitor-embedded 0.54 pJ/bit

- silicon-slot photonic crystal waveguide modulator. Optics Letters 34, 602-604. doi:

- 217 10.1364/OL.34.000602

- Guo, R., Wang, B., Wang, X., Wang, L., Jiang, L., Zhou, Z. (2012). Optical amplification in Er/Yb

- 219 silicate slot waveguide. Optics Letters 37, 1427. doi: 10.1364/OL.37.001427

- Tengattini, A., Gandolfi, D., Prtljaga, N., Anopchenko, A., Ramírez, J.M., Lupi, F. F., Berencén, Y.,

- Navarro-Urrios, D., Rivallin, P., Surana, K., and Garrido, B. (2013). Toward a 1.54 m electrically

- driven erbium-doped silicon slot waveguide and optical amplifier. Journal of Lightwave Technology

- 223 31, 391-397. doi: 10.1109/JLT.2012.2231050

- Baehr-Jones, T., Hochberg, M., Walker, C., and Scherer, A. (2005). High-Q optical resonators in

- silicon-on-insulator-based slot waveguides. Applied Physics Letters 86, 081101. doi:

- 226 10.1063/1.1871360

- Ding, R., Baehr-Jones, T., Kim, W. J., Xiong, X., Bojko, R., Fedeli, J. M., Fournier, M., and

- Hochberg, M. (2010). Low-loss strip-loaded slot waveguides in silicon-on-insulator. Optics Express

- 229 18, 25061-25067. doi: 10.1364/OE.18.025061

- Spott, A., Baehr-Jones, T., Ding, R., Liu, Y., Bojko, R., O'Malley, T., Pomerene, A., Hill, C.,

- Reinhardt, W., and Hochberg, M. (2011). Photolithographically fabricated low-loss asymmetric

- 232 silicon slot waveguides. Optics Express 19, 10950-10958. doi: 10.1364/OE.19.010950

- Alasaarela, T., Korn, D., Alloatti, L., Säynätjoki, A., Tervonen, A., Palmer, R., Leuthold, J., Freude,

- W., and Honkanen, S. (2011). Reduced propagation loss in silicon strip and slot waveguides coated

- 235 by atomic layer deposition. Optics Express 19, 11529-11538. doi: 10.1364/OE.19.011529

- Debnath, K., Arimoto, H., Husain, M. K., Prasmusinto, A., Al-Attili, A., Petra, R., Chong, H. M. H.,

- Reed, G. T., and Saito, S. (2016). Low loss silicon waveguides and grating couplers fabricated using

- 238 anisotropic wet etching technique. Frontiers in Materials 3, 10. doi: 10.3389/fmats.2016.00010

- 239 Lee, K. K., Lim, D. R., and Kimerling, L. C. (2001). Fabrication of ultralow-loss Si/SiO<sub>2</sub> waveguides

- 240 by roughness reduction. *Optics Letters* 26, 1888-1890. doi: 10.1364/OL.26.001888

## **Running Title**

- 241 Covey, J. and Chen, R.T. (2013). Efficient perfectly vertical fiber-to-chip grating coupler for silicon

- 242 horizontal multiple slot waveguides. *Optics express* 21, 10886-10896. doi: 10.1364/OE.21.010886

- 243 Han, K., Kim, S., Wirth, J., Teng, M., Xuan, Y., Niu, B. and Qi, M. (2016). Strip-slot direct mode

- 244 coupler. *Optics express* 24, 6532-6541. doi: 10.1364/OE.24.006532

- Säynätjoki, A., Karvonen, L., Alasaarela, T., Tu, X., Liow, T.Y., Hiltunen, M., Tervonen, A., Lo,

- G.Q. and Honkanen, S. (2011). Low-loss silicon slot waveguides and couplers fabricated with optical

- 247 lithography and atomic layer deposition. *Optics express* 19, 26275-26282. doi:

- 248 10.1364/OE.19.026275

- 249 Passaro, V. and La Notte, M. (2012). Optimizing SOI slot waveguide fabrication tolerances and strip-

- slot coupling for very efficient optical sensing. Sensors 12, 2436-2455. doi: 10.3390/s120302436