# Single Carrier Trapping and De-trapping in Scaled Silicon Complementary Metal-Oxide-Semiconductor Field-Effect Transistors at Low Temperatures

Zuo Li<sup>1</sup>, Muhammad Khaled Husain<sup>1</sup>, James Byers<sup>1</sup>, Hiroyuki Yoshimoto<sup>2</sup>, Kazuki Tani<sup>2</sup>, Yoshitaka Sasago<sup>2</sup>, Digh Hisamoto<sup>2</sup>, Jonathan David Fletcher<sup>3</sup>, Masaya Kataoka<sup>3</sup>, Yoshishige Tsuchiya<sup>1</sup>, Shinichi Saito<sup>1</sup>

E-mail: S.Saito@soton.ac.uk

November 2016

#### Abstract.

The scaling of Silicon (Si) technology is approaching the physical limit, where various quantum effects such as direct tunnelling and quantum confinement are observed, even at room temperatures. We have measured standard Complementary Metal-Oxide-Semiconductor Field-Effect-Transistors (CMOSFETs) with wide and short channels at low temperatures to observe single electron/hole characteristics due to local structural disturbances such as roughness and defects. In fact, we observed Coulomb blockades in sub-threshold regimes of both p-type and n-type Si CMOSFETs, showing the presence of quantum dots in the channels. The stability diagrams for the Coulomb blockade were explained by the potential minima due to poly-Si grains. We have also observed sharp current peaks at narrow bias windows at the edges of the Coulomb diamonds, showing resonant tunnelling of single carriers through charge traps.

<sup>&</sup>lt;sup>1</sup>Nanoelectronics and nanoresearch group, Department of Electronics and Computer Science, Faculty of Physical Science and Engineering, University of Southampton, High field Campus, SO17 1BJ, UK.

$<sup>^2</sup>$ Research & Development Group, Hitachi, Ltd., 1-280 Higashikoigakubo, Kokubunji, Tokyo 185-8601, Japan.

$<sup>^3{\</sup>rm National}$  Physical Laboratory, Hampton Road, Teddington, Middlesex TW11 0LW, United Kingdom.

#### 1. Introduction

Silicon (Si) industry is seeking for a new disruptive application in quantum technologies by using the platform of existing infrastructure to fabricate scaled complementary-metal-oxide-semiconductor field-effect-transistors (CMOSFETs). According to International Technology Roadmap for Semiconductors 2.0 (ITRS 2.0) [1,2], which was issued in 2015 to replacethe previous ITRS, the single electron transistor (SET) is considered strong candidates for RF-mixers [1, 3, 4], which is an important part of RF front end. SETs are based on sequential single electron tunnelling [5] through two tunnelling barriers and a quantum dot with small self-capacitor [6, 7]. By changing the bias condition, the single electron sequential tunnelling is either unblocked or blocked, and SETs are controlled between on and off states, accordingly [8].

In the early stage of the research, scientists used metal [6,9] or III-V semiconductor [10,11] as materials to study the characteristics of SETs and single electron phenomena. From the manufacturing point of view, Silicon (Si) SETs have their advantages due to the compatibility with CMOS fabrication technology [12]. Si-based SETs have already been demonstrated [13– 15]. However, we must design complicated device structures with quantum confinement using dedicated processes, such as nanowire-defined dots [16], top gates [17], and side gates [18], which increases the complexity of fabrication. Besides complicated structures, the feature size must be comparable to or smaller than the thermal de Broglie length of single electrons to maintain a larger charging energy than thermal For the standard CMOSFETs, the fabrication processes are well established, and the minimum feature size of CMOSFETs were as small as 14nm [20] in 2014, which is already smaller than the thermal de Broglie length of 17nm for electrons in Si at 300K. Therefore, we should observe various quantum mechanical effects in conventional CMOSFETs. For example, random telegraph noise based on single electron trapping is a serious issue to secure reliabilities [21–24]. The purpose of this work is to investigate and establish the relationship between scaled Si CMOSFETs and Si SETs. Previously, the SET characteristics of Si nanowire FinFETs on SOI were observed at room temperatures [25, 26], and low temperatures [27–29]. But, the single electron phenomena in conventional CMOSFETs based on bulk Si at low temperatures has not been fully investigated.

# 2. Experiments

The MOSFETs were fabricated by using a standard 65nm technology node. The wide channel width of  $10\mu m$  was chosen to increase the chance to ob-

serve single carrier trapping and de-trapping phenomena. The channel length was 55 nm/75 nm for p MOSFET/n MOSFET, respectively. The gate electrode was made of doped poly-crystalline silicon (poly-Si). The gate dielectric material was SiON with the Equivalent Oxide Thickness (EOT),  $t_{\text{ox}}$ , of 2.4nm. The value of current at each bias was obtained by averaging over  $10^5$  data points each with a duration of  $2\mu \text{s}$ .

# 3. Results

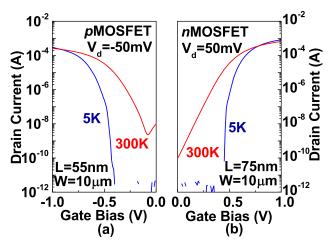

The drain current  $(I_d)$  on the gate bias  $(V_g)$  characteristics of the two MOSFETs were measured at 300K and 5K respectively, as shown in figure 1, at the drain bias  $(V_d)$  of  $\mp 50 \text{mV}$ .

Figure 1: Subthreshold characteristics for (a) pMOSFET and (b) nMOSFET at the temperatures 300K and 5K. The threshold voltages were shifted when the devices were cooled down.

The threshold voltages were -0.45V/0.47V at 300K and -0.60V/0.62V at 5K, for pMOSFET/nMOSFET, respectively (figure 1). The on-currents were larger for both pMOSFET and nMOSFET at 5K, because of the increase in mobility [30] and the increase of the saturation velocity [31]. The sub-threshold slopes were 14.9mV/decade for pMOSFET and 5.7mV/decade for nMOSFET at 5K, while they were 82.4mV/decade for pMOSFET and 80.3mV/decade for nMOSFET at 300K. The off-current was below our detection limit (~1pA) at 5K. In the sub-threshold regime at 5K, the channel resistance of both pMOSFET and nMOSFET were larger than 25.8k $\Omega$ , which was a necessary condition of observing single-electron effects in SETs.

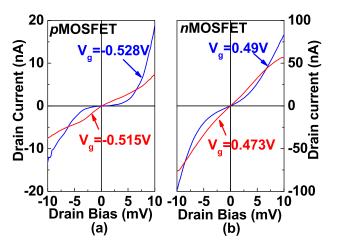

In fact, we observed typical SET characteristics at 5K, as shown in figure 2.

The dependences of the  $I_{\rm d}$ - $V_{\rm d}$  characteristics upon changing the  $V_{\rm g}$  implies the presence of a quantum dot in the channel of both devices. In figure 2 (a), at  $V_{\rm g}$

Figure 2: Coulomb blockade in (a) pMOSFET and (b) nMOSFET at 5K. The gate was biased at -0.528V (OFF state) and -0.515V (ON state) for pMOSFET, and was biased at 0.473V (ON state) and 0.49V (OFF state) for nMOSFET.

of -0.528V,  $I_{\rm d}$  of the pMOSFET was blocked in the  $V_{\rm d}$  range between -2.5mV and 2.5mV, while  $I_{\rm d}$  was not blocked at  $V_{\rm g}$  of -0.515V. The similar Coulomb blockade behaviour was also observed in nMOSFET (figure 2(b)).

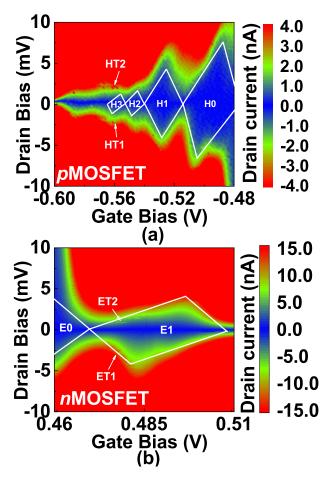

We measured  $I_{\rm d}$  in more detail by changing both  $V_{\rm g}$  and  $V_{\rm d}$  to check the single carrier trapping and de-trapping characteristics, as shown in the twodimensional (2D) contour plot of  $I_d$  (figure 3). Several Coulomb diamonds were found in pMOSFET while only one Coulomb diamond was found in nMOSFET. Different Coulomb diamonds, which corresponded to different hole/electron states in a quantum dot, are marked as H0, H1, H2, H3 in figure 3 (a) and E0, E1 in figure 3 (b). In figure 3 (a), the size of Coulomb diamond shrinks as  $|V_{\rm g}|$  was increased. It means that the coupling capacitance of quantum dot was changed as we changed  $V_{\rm g}$ . This is a marked difference from the standard characteristics predicted by the conventional mesoscopic model of metallic tunnelling junction [32], in which all coupling capacitance in equivalent circuit are fixed. In figure 3 (b), only one diamond was observed in the current map of nMOSFET. nMOSFET showed similar behaviour to p-MOSFET. The Coulomb diamond was observed when  $V_{\rm g}$  is between 0.47V and 0.51V. Above 0.51V where the coupling resistance becomes smaller than quantum resistance, no diamond was observed.

When  $V_{\rm g}$  was larger than 0.47V, the Coulomb diamond started to be observed. The diamond was not observed at 0.51V where the coupling resistance became smaller than quantum resistance.

By comparing pMOSFET with nMOSFET (figure 2), we found that  $I_{\rm d}$  in nMOSFET was almost

Figure 3: Contour plot of drain current versus gate voltage and drain voltage in (a) pMOSFET and (b) nMOSFET at 5K. The border of the Coulomb diamonds are determined by fitting with the standard mesoscopic model.

three times larger than that in pMOSFET. This may be explained by the mobility difference between the electrons and holes. The single electron/hole tunnelling event was only observable in corresponding sub-threshold region in the figure 1.

We also found that current peaks at the edges of Coulomb diamond for both devices. At narrow bias windows, which are marked as Hole Traps (HT1 and HT2) in figure 3 (a), and Electron Traps (ET1, ET2) in figure 3 (b), the current exhibited sharp peaks. The sharp current peaks were found at the edge of the Coulomb diamond blockade region in both figure 3 (a) and figure 3 (b).

### 4. Discussion

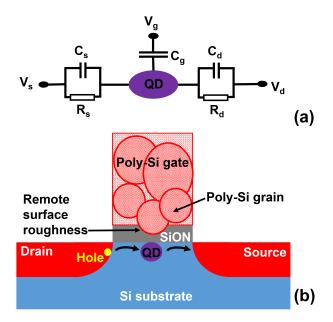

The standard mesoscopic model was used to estimate parameters for SETs [33], as shown in figure 4 (a). The carrier concentration was around  $10^{10} \sim 10^{12} \text{cm}^{-2}$  in Si

two-dimensional electron gas [34], which corresponds to  $10\sim100$ nm electron-electron distance. This is on the same magnitude as thermal de Broglie length of electron in Si at 5K, 133nm, and much larger than the Bohr radius in Si, 5.2nm. Under this condition, the electrons trapped in quantum dot can be treated as non-interactive electrons [35].

Figure 4: Circuit model and physical model of the quantum dot. (a) shows the standard equivalent circuit model and (b) shows a schematic diagram of the assumed remote poly-Si roughness for the quantum dot structure.

At the sub-threshold regime, the channel current is dominated by single hole/electron transistor current. Therefore, the carrier concentration can be approximately estimated:

$$N_{\text{channel}} = \frac{1}{WL} = 1.8 \times 10^8 \text{cm}^{-2}.$$

(1)

In this weakly inverted condition, the impact of poly-Si depletion layer is negligible.

However, the inversion layer thickness caused by quantum confinement near the SiON/Si interface cannot be neglected. The inversion layer thickness,  $t_{\rm inv}$ , is  $\sim 2 \text{nm} [34,36,37]$ . Therefore, the total capacitive effective thickness is

$$t_{\text{eff}} = t_{\text{ox}} + \frac{\varepsilon_{\text{ox}} t_{\text{inv}}}{\varepsilon_{\text{Si}}} = 3.1 \text{nm},$$

(2)

where  $\varepsilon_{ox}$  is the dielectric constant of SiO<sub>2</sub> and  $\varepsilon_{Si}$  is the dielectric constant of Si.

The coupling capacitances of each hole state shown in figure 3 (a) were different. As  $|V_{\rm g}|$  increased, more holes were occupied in the quantum dot. The gate coupling capacitance  $(C_{\rm g})$ , source coupling capacitance  $(C_{\rm d})$ , and drain coupling capacitances  $(C_{\rm d})$

to the quantum dot also increased. This implies that the coupling capacitances were connected to the inversion layer capacitance [38]. If  $|V_{\rm g}|$  increased after depletion layer reached its maximum width, the channel would start to be inverted. Therefore, both inversion layer capacitance per unit area [39],  $C_{\rm inv}$ , and oxide capacitance per unit area,  $C_{\rm ox}$ , contributed to  $C_{\rm g}$  as shown in

$$\frac{1}{C_{\rm g}} = \frac{1}{C_{\rm ox}S} + \frac{1}{C_{\rm inv}S},\tag{3}$$

where S was the area of the quantum dot. We can extract  $C_{\rm g}$  from the periodicity of Coulomb oscillations related to each Coulomb diamond,  $\Delta V_{\rm g}$ ,

$$C_{\rm g} = \frac{e}{\Delta V_{\rm g}}. (4)$$

The extracted capacitances of pMOSFET and nMOSFET are shown in table 1 and 2, respectively. In H3,  $V_{\rm g}$  was about -0.56V, which was quite close to the threshold voltage of pMOSFET. The carrier density in H3  $C_{\rm inv}$  was much higher than that in H0, H1 and H2. Therefore,  $C_{\rm inv}$  in H3 would be the largest compared with H0, H1 and H2. Since  $C_{\rm inv}$  was the largest, here we assume that the dominant contribution to  $C_{\rm g}$  would be  $C_{\rm ox}$  in H3, and neglect the contribution of  $C_{\rm inv}$ . We can estimate the size of the quantum dot from  $C_{\rm g}$  in H3,  $C_{\rm g}(H3)$ , based on this approximation. If we assume the quantum dot is a circle, we can caculate the diameter, d,

$$d = \sqrt{\frac{4C_{\rm g}(H3)}{\pi \varepsilon_{\rm ox}/t_{\rm eff}}} = 38.5$$

nm. (5)

The inversion layer capacitance in table 1 was extracted by assuming the diameter of the quantum dot in pMOSFET was 38.5nm.

Table 1: Coupling capacitance using mesoscopic model for pMOSFET

| 101 P111001 111                  |      |       |      |      |

|----------------------------------|------|-------|------|------|

| Diamond                          | Н3   | H2    | H1   | Н0   |

| Gate Capacitance (aF)            | 13.4 | 12.6  | 6.2  | 4.2  |

| Drain Capacitance (aF)           | 34.7 | 33.8  | 15.8 | 6.4  |

| Source Capacitance (aF)          | 62.0 | 52.8  | 22.8 | 10.7 |

| Inversion Layer Capacitance (aF) | N/A  | 211.1 | 11.5 | 6.1  |

| Charging Energy (meV)            | 1.5  | 1.6   | 3.6  | 7.5  |

Table 2: Coupling capacitance using mesoscopic model for nMOSFET

| Diamond                 | E1   |  |

|-------------------------|------|--|

| Gate Capacitance (aF)   | 4.2  |  |

| Drain Capacitance (aF)  | 11.6 |  |

| Source Capacitance (aF) | 23.5 |  |

| Charging Energy (meV)   | 4.1  |  |

The charging energy in H0 was 7.5meV for pMOSFET, much smaller than the value reported in single dopant transistor [26, 28, 40], which is roughly 30meV. Therefore, it is unlikely that the quantum dots were made of impurities in the channel due to the large size of the quantum dot. It implies that the quantum dots in both pMOSFET and nMOSFET come from physical structures defined by the surface roughness or poly-Si grains [41]. Grain boundaries of poly-Si cause remote surface roughness at poly-Si/SiON interface, as shown in figure 4 (b). The remote surface roughness at poly-Si/SiON interface results in local variations of equivalent oxide thickness [42,43]. This forms a dip of surface potential near the interface of grain boundary area, and single carriers would be confined near the peak region. The dimension of poly-Si grains can be around 50nm [44], which is comparable with the size of the quantum dot that we estimated from pMOSFET. If poly-Si grains were responsible for this Coulomb blockade phenomena, we should only be able to observe SET characteristics if the channel length is comparable with the size of poly-Si grains. Otherwise, the currents are superpositions of various channels through multiple connections of SETs.

The increase of drain and source coupling capacitance upon increasing  $|V_{\rm g}|$  (table 1) can be explained by the changes of tunnelling barrier height and the forming of an inversion layer. The barrier height was continuously reduced when we increased  $|V_{\rm g}|$ , and the capacitive coupling between source and drain also became stronger [45]. As a result, the Coulomb diamond shrinks significantly. The formation of inversion layer also contributed to the shrink of the Coulomb diamond. When  $|V_{\rm g}|$  was large enough to invert the channel, the inversion layer was initially formed around the source region [39]. When  $|V_{\rm g}|$  increased and the channel was inverted further, inversion layer started to expand from source to drain.

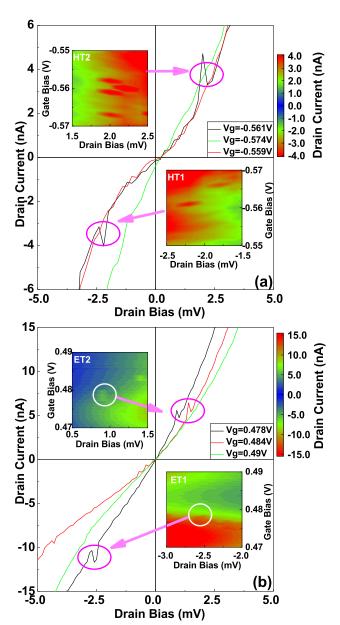

Next, we discuss about current peaks observed at the edges of the Coulomb diamond region. In order to analyse the current peak in detail, we plotted the  $I_{\rm d}$ - $V_{\rm d}$  characteristics and the current map near the noise region in figure 5.

The current peak was only observable at a very narrow window in bias condition. In figure 5 (a), at  $V_{\rm g}$  of -0.561V, a current peak is clearly observed if  $V_{\rm d}$  was at -4mV. When  $V_{\rm g}$  was at -0.559V and -0.574V, the peak was not observed. The fact that current peaks were found at the edge of the Coulomb diamonds implies that the current peaks were related to charge traps. The window of bias condition to observe this current peak is much narrower than the bias condition to observe Coulomb diamonds. This sharp current peak implies that the energy level broadening must be small in the charge trap, and resonant

Figure 5: Sharp current peaks observed at the edges of Coulomb diamond. The current peaks are shown in both current map and  $I_{\rm d}$  -  $V_{\rm d}$  characteristics. (a) indicates the influence of a single charge trap in pMOSFET with different gate bias. (b) shows the influence of a single charge trap in nMOSFET with different gate bias.

tunnelling was responsible for this phenomena. We were able to observe similar phenomenon in figure 5 (b), showing similar characteristics in the nMOSFET. More investigation is needed to identify the nature of these current peaks.

#### 5. Conclusion

We observed single carrier trapping and de-trapping phenomena by measuring standard short-channel MOSFETs at low temperatures. We observed single hole/electron tunnelling phenomena at sub-threshold regions in both standard p-type and n-type shortchannel MOSFETs. The size of the Coulomb diamond was shrinking with decreasing gate bias in p-MOSFET. The quantum dot corresponding to the Coulomb diamond was considered to have originated from the potential minimum created by the poly-Si grains. We also observed current peaks at the edge of Coulomb diamond at certain bias conditions. The current peaks were considered to have originated from the charge traps, which will potentially link reliability issues in advanced MOSFETs. Therefore, the low temperature measurements will be useful to investigate the single carrier trapping and de-trapping process in MOSFETs, which will help in understanding the quantum effects and pave the way to establish the relationship between scaled Si CMOSFETs and Si SETs.

# 6. Acknowledgement

The authors would like to thank Iridis, the supercomputing facility at the University of Southampton, for the supporting of servers to run simulation software. This work is supported by EPSRC Manufacturing Fellowship (EP/M008975/1), EU FP7 Marie-Curie Carrier-Integration-Grant (PCIG13-GA-2013-618116), and the University of Southampton. This work is also supported by the EMPIR programme co-financed by the Participating States and from the European Unions Horizon 2020 research and innovation programme. The data from the paper can be obtained from the University of Southampton ePrint research repository [46].

#### 7. Reference

- SI Association et al. International technology roadmap for semiconductors 2.0. Semiconductor Industry Association, Tech. Rep, 2015.

- [2] Carballo J A.and Chan W J, Gargini P A, Kahng A B, and Nath S. Itrs 2.0: Toward a re-framing of the semiconductor technology roadmap. In 2014 IEEE 32nd International Conference on Computer Design (ICCD), pages 139–146. IEEE, 2014.

- [3] Pierantoni L and Coccetti F. Radio-frequency nanoelectronics: A new paradigm in electronic systems design. In 2010 Asia-Pacific Microwave Conference, pages 1007– 1014. IEEE, 2010.

- [4] Knobel R, Yung C S, and Cleland A N. Single-electron transistor as a radio-frequency mixer. Appl. Phys. Lett, 81:532–534, 2002.

- [5] Kastner M A. The single-electron transistor. Rev. Mod. Phys., 64:849, 1992.

- [6] Averin D V and Likharev K K. Coulomb blockade of singleelectron tunneling, and coherent oscillations in small tunnel junctions. J. Low Temp. Phys., 62:345–373, 1986.

- [7] Meir Y, Wingreen N S, and Lee P A. Low-temperature transport through a quantum dot: The anderson model out of equilibrium. *Phys. Rev. Lett.*, 70:2601, 1993.

- [8] Chen R, Korotkov A N, and Likharev K K. Single-electron transistor logic. Appl. Phys. Lett., 68:1954–1956, 1996.

- [9] Schoelkopf R J, Wahlgren P, Kozhevnikov A A, Delsing P, and Prober D E. The radio-frequency single-electron transistor (rf-set): a fast and ultrasensitive electrometer. Science, 280:1238-1242, 1998.

- [10] Nakazato K, Thornton T J, White J, and Ahmed H. Singleelectron effects in a point contact using side-gating in delta-doped layers. Appl. Phys. Lett, 61:3145–3147, 1992.

- [11] Shilton J M, Talyanskii V I, Pepper M, D A Ritchie, Frost J E F, Ford C J B, Smith C G, and Jones G A C. High-frequency single-electron transport in a quasi-onedimensional gaas channel induced by surface acoustic waves. J. Phys. Condens. Matter, 8:L531, 1996.

- [12] Takahashi Y, Ono Y, Fujiwara A, and Inokawa H. Silicon single-electron devices. J. Phys.: Condens. Mat, 14:R995, 2002.

- [13] Dutta A, Oda S, Fu Y, and Willander M. Electron transport in nanocrystalline si based single electron transistors. Jpn. J. Appl. Phys, 39:4647, 2000.

- [14] Fujiwara A, Inokawa H, Yamazaki K, Namatsu H, Takahashi Y, Zimmerman N M, and Martin S B. Single electron tunneling transistor with tunable barriers using silicon nanowire metal-oxide-semiconductor field-effect transistor. Appl. Phys. Lett., 88:053121, 2006.

- [15] Takahashi N, Ishikuro H, and Hiramoto T. Control of coulomb blockade oscillations in silicon single electron transistors using silicon nanocrystal floating gates. Appl. Phys. Lett., 76:209–211, 2000.

- [16] Zhuang L, Guo L, and Chou S. Silicon single-electron quantum-dot transistor switch operating at room temperature. Appl. Phys. Lett., 72:1205–1207, 1998.

- [17] Matsuoka H and Kimura S. Transport properties of a silicon single-electron transistor at 4.2 k. Appl. Phys. Lett. 66:613–615, 1995.

- [18] Tan Y T, Kamiya T, Durrani Z A K, and Ahmed H. Room temperature nanocrystalline silicon single-electron transistors. J. Appl. Phys., 94:633–637, 2003.

- [19] Landau L D, Bell J S, Kearsley M J, Pitaevskii L P, Lifshitz E M, and Sykes J B. Electrodynamics of continuous media, volume 8. elsevier, 2013.

- [20] Natarajan S, Agostinelli M, Akbar S, Bost M, Bowonder A, Chikarmane V, Chouksey S, Dasgupta A, Fischer K, Fu Q, et al. A 14nm logic technology featuring 2 nd-generation finfet, air-gapped interconnects, self-aligned double patterning and a 0.0588 μm 2 sram cell size. In 2014 IEEE International Electron Devices Meeting, pages 3–7. IEEE, 2014.

- [21] Uren M J, Day D J, and Kirton M. 1/f and random telegraph noise in silicon metal-oxide-semiconductor field-effect transistors. Appl. Phys. Lett., 47:1195–1197, 1985.

- [22] Hung K K, Ko P K, Hu C, and Cheng Y C. Random telegraph noise of deep-submicrometer mosfets. *IEEE Trans. Electron Dev.*, 11:90–92, 1990.

- [23] Tega N, Miki H, Yamaoka M, Kume H, Mine T, Ishida T, Mori Y, Yamada R, and Torii K. Impact of threshold voltage fluctuation due to random telegraph noise on

- scaled-down sram. In Reliability Physics Symposium, 2008. IRPS 2008. IEEE International, pages 541-546. IEEE, 2008.

- [24] Luo M, Wang R, Guo S, Wang J, Zou J, and Huang R. Impacts of random telegraph noise (rtn) on digital circuits. IEEE Trans. Electron Dev., 62:1725–1732, 2015

- [25] Lavieville R, Barraud S, Corna A, Jehl X, Sanquer M, and Vinet M. 350k operating silicon nanowire single electron/hole transistors scaled down to 3.4 nm diameter and 10nm gate length. In EUROSOI-ULIS, 2015 Joint International EUROSOI Workshop and International Conference on, pages 9–12. IEEE, 2015.

- [26] Lavieville R, Triozon F, Barraud S, Corna A, Jehl X, Sanquer M, Li J, Abisset A, Duchemin I, and Niquet Y M. Quantum dot made in metal oxide silicon-nanowire field effect transistor working at room temperature. Nano Lett., 15:2958–2964, 2015.

- [27] Lansbergen G P, Rahman R, Wellard C J, Woo I, Caro J, Collaert N, Biesemans S, Klimeck G, L C L Hollenberg, and S. Rogge. Gate-induced quantum-confinement transition of a single dopant atom in a silicon finfet. Nature Phys., 4:656-661, 2008.

- [28] Pierre M, Wacquez R, Jehl X, Sanquer M, Vinet M, and Cueto O. Single-donor ionization energies in a nanoscale cmos channel. Nat. Nanotechnol., 5:133–137, 2010.

- [29] Wang C, Jones M E, and Durrani Z A K. Single-electron and quantum confinement limits in length-scaled silicon nanowires. *Nanotechnology*, 26:305203, 2015.

- [30] Klaassen D B M. A unified mobility model for device simulationii. temperature dependence of carrier mobility and lifetime. *Solid State Electron*, 35:961–967, 1992.

- [31] Quay R, Moglestue C, Palankovski V, and Selberherr S. A temperature dependent model for the saturation velocity in semiconductor materials. *Mater Sci Semicond Process*, 3:149–155, 2000.

- [32] Mahapatra S, Vaish V, Wasshuber C, Banerjee K, and Ionescu A M. Analytical modeling of single electron transistor for hybrid cmos-set analog ic design. *IEEE Trans. Electron Devices*, 51:1772–1782, 2004.

- [33] Pekola J P, Saira O P, Maisi V F, Kemppinen A, Möttönen M, Pashkin Y A, and Averin D V. Single-electron current sources: Toward a refined definition of the ampere. Rev. Mod. Phys, 85:1421, 2013.

- [34] Ando T, Fowler A B, and Stern F. Electronic properties of two-dimensional systems. Rev. Mod. Phys, 54:437, 1982.

- [35] Mahan G D. Many-particle physics. Springer Science & Business Media, 2013.

- [36] Hartstein A and Albert N F. Determination of the inversion-layer thickness from capacitance measurements of metal-oxide-semiconductor field-effect transistors with ultrathin oxide layers. Phys. Rev. B, 38:1235, 1988.

- [37] Saito S, Torii K, Hiratani M, and Onai T. Analytical quantum mechanical model for accumulation capacitance of mos structures. *IEEE Electron Device Lett.*, 23:348– 350, 2002.

- [38] Liang M S, Choi J Y, Ko P K, and Hu C. Inversion-layer capacitance and mobility of very thin gate-oxide mosfet's. IEEE Trans. Electron Dev., 33:409–413, 1986.

- [39] Sze S M. Semiconductor devices: physics and technology. John Wiley & Sons, 2008.

- [40] Sellier H, Lansbergen G P, Caro J, Rogge S, Collaert N, Ferain I, Jurczak M, and Biesemans S. Transport spectroscopy of a single dopant in a gated silicon nanowire. *Phys. Rev. Lett.*, 97:206805, 2006.

- [41] Jackson W B, Johnson N M, and Biegelsen D K. Density of gap states of silicon grain boundaries determined by optical absorption. Appl. Phys. Lett., 43:195–197, 1983.

- [42] Saito S, Torii K, Shimamoto Y, Tsujikawa S, Hamamura H, Tonomura O, Mine T, Hisamoto D, Onai T, Yugami J,

- et al. Effects of remote-surface-roughness scattering on carrier mobility in field-effect-transistors with ultrathin gate dielectrics. *Appl. Phys. Lett.*, 84:1395–1397, 2004.

- [43] Li J and Ma T P. Scattering of silicon inversion layer electrons by metal/oxide interface roughness. J. Appl. Phys., 62:4212–4215, 1987.

- [44] Yamauchi N, Hajjar J, and Reif R. Polysilicon thin-film transistors with channel length and width comparable to or smaller than the grain size of the thin film. *IEEE Trans. Electron Dev.*, 38:55–60, 1991.

- [45] Taur Y and Ning T H. Fundamentals of modern VLSI devices. Cambridge university press, 2013.

- [46] http://doi.org/10.5258/soton/403188.