# A Survey and Comparative Study of Hard and Soft Real-time Dynamic Resource Allocation Strategies for Multi/Many-core Systems

AMIT KUMAR SINGH, University of York and University of Southampton PIOTR DZIURZANSKI, University of York and Staffordshire University HASHAN ROSHANTHA MENDIS, University of York LEANDRO SOARES INDRUSIAK, University of York

Multi/Many-core systems are envisioned to satisfy the ever increasing performance requirements of complex applications in various domains such as embedded and high performance computing (HPC). Such systems need to cater for increasingly dynamic workloads, requiring efficient dynamic resource allocation strategies in order to satisfy hard or soft real-time constraints. This article provides an extensive survey of hard and soft real-time dynamic resource allocation strategies proposed over the last two decades and highlights the emerging trends for multi/many-core systems. The survey covers a taxonomy of the resource allocation strategies and considers their various optimization objectives, which have been used to provide comprehensive comparison. The strategies employ various principles such as market and biological concepts to perform the optimizations. The trend followed by the resource allocation strategies, open research challenges, and likely emerging research directions have also been provided.

${\tt CCS\ Concepts: \bullet\ Computer\ systems\ organization} \rightarrow {\tt Real-time\ systems; Embedded\ systems; Architectures:}$

Additional Key Words and Phrases: Many-core systems, hard real-time, soft real-time, design-space exploration, resource allocation, performance, energy consumption

## **ACM Reference format:**

Amit Kumar Singh, Piotr Dziurzanski, Hashan Roshantha Mendis, and Leandro Soares Indrusiak. 2017. A Survey and Comparative Study of Hard and Soft Real-time Dynamic Resource Allocation Strategies for Multi/Many-core Systems. *ACM Comput. Surv.* 9, 4, Article 39 (March 2017), 39 pages.

DOI: 0000001.0000001

#### 1 INTRODUCTION

A paradigm shift to the adoption of multi/many-core systems can be observed in various domains such as embedded and high performance computing (HPC). The reason behind such adoption lies in the fact that the performance requirements of applications cannot be satisfied by simply increasing the frequency of a single-core processor, which leads to high power and heat dissipation. In multi/many-core systems, chip manufactures are trying to overcome these bottlenecks by

This work has been funded in part by the EU FP7 project DreamCloud (project number 611411).

Author's addresses: A. K. Singh, (Current address) School of Electronics and Computer Science, University of Southampton; P. Dziurzanski, (Current address) School of Computing and Digital Tech, Staffordshire University; H. R. Mendis and L. S. Indrusiak, Department of Computer Science, University of York.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

© 2017 Copyright held by the owner/author(s). Publication rights licensed to ACM. 0360-0300/2017/3-ART39 \$15.00 DOI: 0000001.0000001

39:2 A. K. Singh et al.

integrating multiple cores operating at low frequencies, where the cores can cohesively communicate with each other [89] [22]. These systems provide increased parallelism that motivates us to partition applications into many small tasks and allocate them onto different cores in order to perform parallel executions towards satisfying the increased performance requirements [117].

The many-core processors have been designed by several chip manufactures. Some examples include Intel's Teraflop 80-core processor [183], Tilera's TILE-Gx family 100-core processor [181], AMD's Opteron 16-core processor [4], and Kalray's MPPA 256-core processor [50]. Recently, a joint effort between IBM and UCDavis has revealed KiloCore 1000-core chip [20]. The large number of cores are usually connected by an on-chip interconnection network [15, 18, 190]. These many-core processors are designed to be exploited in various application domains towards realizing different systems, referred to as many-core systems. Additionally, different types of cores have been integrated to exploit their distinct features towards meeting the functional and non-functional requirements [172]. The integration of different types of cores leads to the development of heterogeneous multi/many-core systems that become a formidable computing alternative where applications witness large improvement over their homogeneous (consisting of identical cores) counterpart. Further, the technological advancements will enable integration of higher number of cores in the same chip.

# 1.1 Resource Allocation for Multi/Many-core Systems

Resource allocation (mapping) process defines assignment and ordering of the tasks and their communications onto resources of multi/many-core system<sup>1</sup> in view of some optimization criteria such as compute performance and energy consumption. The many-core systems (contain relatively large number of cores) usually extend multi-core systems that contain small number of cores and thus resource allocation techniques for these systems can be interchangeably employed if they have architectural similarities [189]. However, to better exploit the many-core resources, the techniques tailored for multi-cores might need some modifications due to different interconnects. For these systems, usually, the applications need to be partitioned (parallelized) into multiple tasks that can be executed concurrently on different cores. Such partitioning is referred to as functional partitioning and can be furnished with the help of state-of-the-art application parallelization tools, e.g., MPSoC Application Programming Studio (MAPS) [34] and MNEMEE project tool-chain [115], and/or manual analysis. This procedure requires detailed application knowledge and involves finding the tasks, adding synchronization and inter-task communication in the tasks, management of the memory hierarchy communication and checking of the parallelized code (tasks) to ensure for correct functionality [122]. In case the multi/many-core system is heterogeneous, i.e. contains different types of cores, a task binding process that specifies the core types on them the task can be allocated along with the cost of allocation is required [172]. To compute the allocation cost, the binding process analyses the implementation costs (e.g., performance, power and resource utilization) of each task on different supported core types such as general purpose processor (GPP), digital signal processor (DSP) and coarse grain re-configurable hardware.

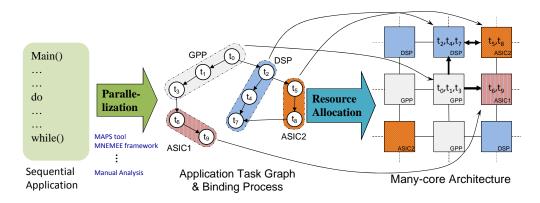

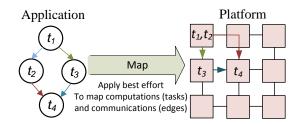

An example *resource allocation* along with the application *parallelization* is shown in Fig. 1. The *parallelization* procedure partitions a *sequential application* described in a high level programming language (e.g., C/C++) into various connected tasks. The connections between the tasks reflect the dependencies in the corresponding sequential application. The example partitioned application is shown as *Application Task Graph* that consists of ten tasks ( $t_0, t_1, ..., t_9$ ). For the *Application*

<sup>&</sup>lt;sup>1</sup>By multi/many-core system, we mean a system on a multi/many-core chip or several multi/many-core chips connected with each other, where each chip contains a set of connected cores.

Fig. 1. Resource allocation on many-core system.

Task Graph, the binding process has specified different core types for various tasks based on the implementation costs, e.g. GPP for tasks  $t_0$ ,  $t_1$  and  $t_3$ . The resource allocation process assigns tasks and their communications on part of a heterogeneous many-core system. The communicating tasks are mapped (allocated) on the same core or close to each other in order to optimize for the communication delay and energy. Differently from functional partitioning, data partitioning can also be employed to perform parallel processing of the data by the same function, e.g., applying a filter function on partitioned segments of an image.

The resource allocation process is carried out either at design-time (statically) or run-time (dynamically). Most of the existing literature for resource allocation fall under static resource allocation (e.g., [33, 39, 75, 86, 118, 129, 136, 180]). However, they cannot handle dynamic workloads and changing environments, e.g. adding a new application into the system at run-time.

Dynamic resource allocation approaches can handle aforementioned issues as the assignment of tasks and their communications on the multi/many-core system resources is done at run-time. In addition, they offer several other advantages such as adaptability to the available resources over time (in case performance requirements of a running application is changed or current allocation is not sufficiently close to optimal) and ability to avoid defective parts of multi/many-core systems and enable foreseeable upgrades [169]. The allocation has been handled either by performing all the processing at the run-time, i.e. on-the-fly processing, or by using previously analyzed results [81, 169]. The results have been analyzed by employing efficient design-time design space exploration (DSE) strategies to encounter for different run-time scenarios [120, 145, 159, 168, 175, 192, 195, 196]. For on-the-fly processing, efficient heuristics have been devised to assign new arriving tasks on the system resources [31, 37, 96, 133, 141, 158, 184]. These heuristics do not use any prior analysis results and thus provide rather low quality of resource allocations. However, since they do not use precomputed platform specific analysis results, they cope well to allocate unknown applications on any platform. In contrast, a better quality of resource allocations are achieved by using previously analyzed results, but the applications to be supported on a platform should be known in advance to perform analysis.

Real-time dynamic resource allocation is desired in systems where performance (timing) constraints need to be satisfied to fulfil safe system operations (e.g., in automotive engine management, operating medical equipments and flight control software) and end user demands (frame rate in video processing). This necessitates the development of efficient resource allocation strategies that take an application model, multi/many-core platform model, constraints (e.g., timing and power),

39:4 A. K. Singh et al.

performance model of inter-process communication (e.g., execution time and energy consumption) and estimate of the worst case execution time (WCET) of the process implementations on different cores (e.g., GPP, DSP, ASIC) as input and provide real-time performance guaranteeing resource allocations or optimized resource allocations. A significant amount of research for real-time dynamic resource allocation on single-core system was done in 1980s and 1990s [7]. For multi/many-core systems, it started at the same time, but huge attention was paid after the release of multi/many-core processors by the silicon vendors such as dual-core POWER4 processor by IBM in 2001. Despite the fact that several articles have been published and significant progress has been made for real-time allocation on multi/many-core systems, there still remains many open questions and research challenges.

# 1.2 Dynamic Resource Allocation Problem and Challenges

It has been well proven that resource allocation is one of the most complex problems in large many-core and distributed systems, and in general it is considered NP-hard [62]. It has also been identified as one of the most urgent problems to be solved for implementing multi/many-core based embedded systems [119] [123]. A well-tuned search algorithm may need to evaluate hundreds of thousands of distinct allocations before it finds one solution that meets the systemâĂŹs performance requirements [120, 145]. Since such evaluation is expected to take a long time, maybe hours to days, it cannot be applied to find the solution quickly, which is desired in the contexts of dynamic resource allocation. Further, it is difficult and challenging to identify the ways that can help to achieve accurate status of resources during run-time. This status may be utilization or memory usage of different cores into the system. An inaccurate status of resources may result in an allocation that might not be efficient at run-time.

It is also challenging to satisfy performance requirements of each application when various combinations of simultaneously active applications referred to as use-cases need to be supported into the system at run-time. For each use-case, since optimal solution cannot be explored at run-time due to limited computation power and evaluation time, it needs to be explored by advanced design-time DSE approaches and then to be used at run-time. However, an explosion in the number of use-cases is witnessed with increasing number of applications, e.g.,  $2^n$  use-cases for n applications. This makes analysis of all the possible use-cases infeasible for a large number of applications. In order to handle these situations, dynamic resource allocation employing on-the-fly processing needs to be applied even though optimal solutions are not guaranteed.

The resource allocation problem is being addressed by several research groups across the globe, which is evident from the massive available literature in this direction. Applications from various domains (e.g., automotive and video processing) are being targeted to allocate them on multi/many-core based systems in order to exploit their parallel processing capability. For a given domain, the knowledge of applications is used to devise an efficient resource allocation strategy. However, getting application domain knowledge might be time consuming and challenging. The research progress in the direction of dynamic resource allocation is being published in several top ranked conferences/journals to move beyond state-of-the-art.

# 1.3 Classification of Dynamic Resource Allocation Strategies

The dynamic resource allocation (DRA) strategies can be classified with a number of taxonomies, which could be based on optimization criteria (performance or energy), target architecture (homogeneous or heterogeneous), criticality (hard or soft real-time), etc. Broadly, the classification can be done based on criticality and other taxonomies can be included at some hierarchy in the criticality based classification. For example, hard real-time dynamic resource allocation can target

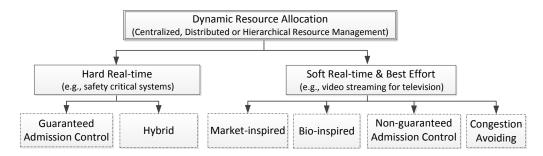

Fig. 2. A taxonomy of dynamic resource allocation strategies.

homogeneous or heterogeneous systems and carry out optimization for performance or energy. Fig. 2 shows a classification of the DRA strategies based on the criticality of the systems. The systems that need to guarantee the timing constraints (e.g., automotive engine management, operating medical equipments and flight control software, realized on a multi/many-core architecture) require *hard real-time* resource allocation approaches, whereas *soft real-time* & *best effort* resource allocation approaches are desired where deadline miss can be tolerated (e.g., video streaming for television and HPC systems).

For hard real-time resource allocation, the existing works reported in the literature can be classified into several categories. However, a careful observation of these works has led them to categorize broadly into *Guaranteed Admission Control* and *Hybrid* approaches, as shown in Fig. 2. In guaranteed admission control, concepts from scheduling theory are used to ensure that only requirement-satisfying applications are entered into the system during the course of resource allocation. The hybrid approaches utilize design-time computed allocations in order to identify a timing constraint satisfying allocation at run-time.

The existing soft real-time and best effort resource allocation approaches can be broadly categorized into Market-inspired, Bio-inspired, Non-guaranteed Admission Control and Congestion Avoiding strategies after observing the basic employed principles, as shown in Fig. 2. The strategies into different categories utilize some basic principles to optimize for one or several performance metrics in order to fulfil the end user demands.

The strategies under both the above categories perform computation either at both design-time and run-time or only at run-time depending upon the known system status at design-time. For example, if the applications to be executed in the platform are fixed and known at design-time, e.g., workloads of an application specific HPC data center, the allocations can be computed at design-time and used at run-time; otherwise, the allocations needs to be computed at run-time by applying best effort heuristics.

The resource dynamic management process is carried out by employing a *centralized* [31, 139, 141], *distributed* [32, 99, 144], or *hierarchical* [64, 149] approach. In centralized management, one core of the platform is used as the manager that handles the allocation process. For distributed management, the platform is divided into regions (clusters) and one core in each cluster manages the allocation process inside the cluster. The cluster managers communicate with each other through a global manager to find the best cluster for allocating an application. The hierarchical approach exploits the features of both the centralized and distributed approaches.

There are some resource allocation surveys reported in the literature, but they have several limitations, e.g., focus only on hard real-time resource allocation [48], cover strategies based on only one basic principle [194], focus on a specific domain [66, 79] or optimization criteria [69], and not

39:6 A. K. Singh et al.

explicitly and extensively covering hard and soft real-time aspects [111, 146, 153, 169, 200]. Based on the aforementioned taxonomy, this article presents an in-depth *survey* and *comparative study* of dynamic resource allocation strategies, which have been reported in the literature over the last two decades. The strategies that try to specifically optimize *compute performance*, *energy consumption*, or *both of them* have been considered towards focusing on the most important metrics of real-time multi/many-core based systems. They also might optimize for some other performance metrics such as reliability and temperature, but they are not considered to limit the scope of comparison. Optimizing for compute performance is of paramount importance in order to meet the timing deadlines or to minimize the time taken to finish some applications. The compute performance may refer to total *execution time*, *latency*, *delay*, *period*, *throughput*, *exploration time*, worst-case response time (WCRT), etc., which are related to timing information. Optimizing for the energy consumption of modern computing systems, e.g, embedded and high performance centers is important as they are usually operated by stand-alone power supply like battery or a huge amount of energy is required to operate such systems. The energy optimization needs to be performed in order to increase the operational time of the systems and reduce the energy costs.

To include aspects of other taxonomies, e.g., target architecture (homogeneous or heterogeneous) and resource control mechanism (centralized, distributed, or hierarchical), the strategies classified based on criticality (hard or soft real-time, as shown in Figure 2) are analyzed to highlight the considered *optimization goal*, *target architecture type*, *control mechanism*, and their consideration for *only computation or both computation and communication optimization*. The strategies have also been compared and analyzed to highlight their strengths and weaknesses. The above investigations have also enabled to observe the trend followed by the strategies and identify significant open issues and promising future research directions.

**Paper Organization:** Section 2 and Section 3 cover analysis and elaboration of hard real-time and soft real-time & best effort resource allocation strategies, respectively. A comparative study of strategies falling into different categories has been performed into Section 4. Section 5 provides the upcoming trends that could be followed as the future research and open research challenges. Finally, Section 6 provides some concluding remarks.

# 2 HARD REAL-TIME RESOURCE ALLOCATION

The majority of works reported in the literature for hard real-time resource allocation assume the workloads to be known in advance, i.e., the allocation decisions by taking the timing constraints are computed at design-time [21, 51, 67, 85, 154]. However, the main focus in this article has been on dynamic resource allocation that needs to compute allocations at run-time for dynamically arriving workloads. Based on the earlier classification as in Figure 2, hard real-time dynamic resource allocation approaches are described next along with the advantages and drawbacks of approaches in each category. Further, a combined discussion of all the approaches is provided.

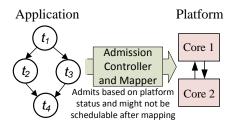

# 2.1 Guaranteed Admission Control based Resource Allocation

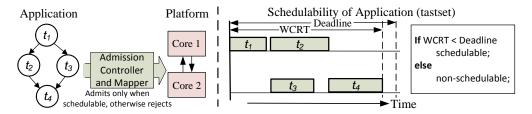

A guaranteed admission control ensures that all the admitted applications or tasks in a system will meet their respective deadlines without forcing other running applications/tasks to miss theirs. To achieve such a control, an admission controller that fully guarantees the schedulability of the admitted applications or tasks is desired. To ensure the schedulability of the application, schedulability analysis has been extensively used in order to determine whether the application or taskset is schedulable or not when to be allocated on platform core(s) [109]. Various kinds of schedulability tests have been employed in the literature, e.g., response time tests [6, 48, 80] and utilization tests [9, 112]. An application is schedulable if its end-to-end worst-case response time is

Fig. 3. Guaranteed admission control based resource allocation.

Table 1. Guaranteed admission control based resource allocation approaches that consider computation (Comp.) and/or communication (Comm.) for optimization.

|            | Optimization   | Comp. & Comm. |               |             |

|------------|----------------|---------------|---------------|-------------|

| References | Goal           | Consideration | Architecture  | Control     |

| [105]      | Execution time | Comp.         | Homogeneous   | Centralized |

| [84]       | Execution time | Comp.         | Homogeneous   | Centralized |

| [132]      | Execution time | Comp. & Comm. | Homogeneous   | Centralized |

| [134]      | Execution time | Comp. & Comm. | Heterogeneous | Centralized |

| [127]      | Execution time | Comp. & Comm. | Homogeneous   | Centralized |

| [126]      | Execution time | Comp. & Comm. | Homogeneous   | Centralized |

| [56]       | Execution time | Comp. & Comm. | Homogeneous   | Centralized |

less than or equal to its deadline [53]. Similarly, a taskset is schedulable if all its tasks are schedulable. The response time for each task can be estimated by employing widely available standard techniques that takes the interference of the tasks with higher priority into account. Fig. 3 provides an overview of the admission controller based resource allocation and schedulability analysis that determines the end-to-end worst-case response time (WCRT) by taking the interference with running tasks into account in order to identify if the taskset meets the deadline. First tasks are mapped by following an allocation policy. Then, schedulability analysis is performed to determine WCRT. If the WCRT is less than the application deadline, then it is considered to be schedulable and only then the admission controller admits it into the system. Once admitted, it is mapped on the platform cores by following the allocation policy used during the schedulability analysis.

The schedulability analysis is performed by taking the allocations of tasks and scheduling algorithm into account, where the former determines tasks to platform cores assignment and latter defines execution order of tasks assigned to a core. Therefore, the schedulability of a task or application (taskset) depends upon the employed allocation and scheduling algorithm. At run-time, the schedulability of a task considers the entire knowledge on the working scenario at that time, e.g., slack and utilization of cores [56]. The slack of a core is usually defined as the difference between worst-case execution time and actual execution time of the task currently running on the core. In case of a taskset, the scedulability analysis for each task is done when it arrives into the system. One can also perform worst-case schedulability tests which may be conservative, but safe, as a form of online admission test. In these instances, the real resource usage is unknown, but only the worst-case timing properties are used. For hard real-time systems, the schedulability tests ensuring timing guarantees, e.g., worst-case response time test [6, 127] and exact schedulability test [13, 49, 57] can be employed. Feedback-based admission controller originated from control theory can also be used to facilitate hard real-time allocation as more accurate system status is known by feedbacks [56, 113, 199]. Feedback mechanisms monitor the capacity of computing resources and

39:8 A. K. Singh et al.

quality-of-service levels in order to guarantee a bounded time response and stability even if the exact knowledge of a system workload and service capacity is not available a priori [173]. Thus, by careful fine-tuning of control parameters, they can be successfully applied even to systems with real-time constraints.

- 2.1.1 Existing Works. Table 1 lists works employing guaranteed (hard real-time) admission control based resource allocation of applications on multi/many-core systems. Such dynamic resource allocation works for multi/many-core systems are limited, unlike for single core systems, e.g. [199]. There has also been claims that some costly schedulability tests can be used for small task sets in on-line admission control [16]. These approaches try to find a schedulable allocation at run-time by taking limited available platform resources into account. They use assorted allocation and scheduling algorithms, e.g. highest priority task first and earliest deadline task first, and try to optimize only for the response time that has also been referred to as execution time. While optimizing for the execution time, they also try to optimize other real-time metrics, like schedulable applications, deadline misses, utilization, etc. In these approaches, all the computations are performed at run-time. A few works have been recently reported that utilize design-time computed results for dynamic resource allocation while applying schedulability analysis, but these fall in the category of hybrid resource allocations and are listed in the next subsection.

- 2.1.2 Advantages and Drawbacks. The schedulability analysis can be used to allocate time critical applications (e.g., avionics and medical) on required systems. Since such analysis can provide WCRT of an application in relatively short amount of time, it can be known whether the application is schedulable or not. In case the application is not schedulable (WCRT > deadline), a different allocation and scheduling algorithm can be tried. Further, if an application is rejected by an admission controller, the resource working time is not wasted with the application that will probably violate its deadline and a possibility of early signalling the lack of admittance can be employed by an outer system to perform an appropriate action (e.g., perform computation on a cloud) minimizing the negative impact of the task rejection. However, the drawback is that users need to have some knowledge of the application domain such that they can analyse the applications and well define the allocation and scheduling algorithms to be applied in order to meet the deadline. The scheduling analysis can also incur large computation (timing) overhead for a complex application/platform containing large number of tasks/cores, and complex dependencies to manage lots of data flows. Therefore, possibilities to reduce the analysis overhead for such complex scenarios can be explored [49, 102]. Another drawback is that the platform resources might be very little utilized as only deadline meeting applications are admitted and their number might be quite lower as hard real-time schedulability tests are pessimistic that take only the worst-case conditions into account.

# 2.2 Hybrid Resource Allocation

Depending upon the amount of computation involved at design-time and run-time, the existing literature for hybrid approaches can be classified into two categories: 1) Design-time Allocations Computation and Run-time Selection and 2) Design-time Deadline Distribution and Run-time Allocation. The details of these class of approaches are provided subsequently.

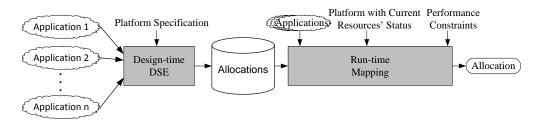

2.2.1 Design-time Allocations Computation and Run-time Selection. This kind of hybrid approaches utilize design-time computed allocations in order to identify a timing constraint satisfying allocation at run-time. In this approach, the applications to be supported on a platform should be known at design-time in order to perform advance design space exploration (DSE). Fig. 4 provides

Fig. 4. Hybrid resource allocation: Design-time allocations computation and run-time selection.

Table 2. Comparison of hybrid resource allocation approaches that consider computation (Comp.) and/or communication (Comm.) for optimizing execution time (ET) and/or energy consumption (EC).

| Optimization Comp. & Con |         | Comp. & Comm. |               |             |

|--------------------------|---------|---------------|---------------|-------------|

| References               | Goal    | Consideration | Architecture  | Control     |

| [77]                     | ET      | Comp. & Comm. | Heterogeneous | Centralized |

| [175]                    | ET      | Comp. & Comm. | Homogeneous   | Centralized |

| [187]                    | ET      | Comp. & Comm. | Heterogeneous | Centralized |

| [57]                     | ET      | Comp. & Comm. | Homogeneous   | Centralized |

| [42]                     | EC      | Comp. & Comm. | Homogeneous   | Centralized |

| [43]                     | EC      | Comp. & Comm. | Homogeneous   | Centralized |

| [159]                    | EC      | Comp.         | Heterogeneous | Centralized |

| [78]                     | EC      | Comp. & Comm. | Heterogeneous | Centralized |

| [163]                    | EC      | Comp. & Comm. | Homogeneous   | Centralized |

| [87]                     | EC      | Comp. & Comm. | Homogeneous   | Centralized |

| [55]                     | EC      | Comp. & Comm. | Homogeneous   | Centralized |

| [193]                    | ET & EC | Comp. & Comm. | Heterogeneous | Centralized |

| [195]                    | ET & EC | Comp. & Comm. | Heterogeneous | Centralized |

| [168]                    | ET & EC | Comp. & Comm. | Heterogeneous | Centralized |

| [93]                     | ET & EC | Comp. & Comm. | Homogeneous   | Centralized |

| [148]                    | ET & EC | Comp. & Comm. | Heterogeneous | Centralized |

| [171]                    | ET & EC | Comp. & Comm. | Homogeneous   | Centralized |

an overview of this hybrid resource allocation approach, which takes the advantages of both design-time and run-time computations. The heavy computations pertaining to mappings exploration are performed at design-time so that only light ones are left for run-time. At design-time, for each application, DSE is performed by taking the application and architecture specifications as input in order to explore *allocations* with some design objectives. The explored allocations are stored and used as guidelines to efficiently allocate the applications at run-time [103, 168]. The same DSE strategy can be applied to all the applications (Application 1 to Application n) one after another. For the applications to be allocated at run-time, light-weight heuristics are required to select the most efficient allocation for each of them from the storage (precomputed set) of allocations. The selection of an allocation is based on the user demands representing real-time performance constraints of the application and current status (availability) of the platform resources. The selected allocation is used to configure the platform in order to execute the application.

39:10 A. K. Singh et al.

Existing Works. Within the focus of this paper, the performance and energy optimizing existing resource allocation approaches have been considered. Table 2 lists the relevant approaches under this category that optimize performance, energy and both of them. For an application, all the approaches employ DSE to generate multiple allocations (operating points), which are used at run-time based on the platform status and user requirements. There has also been efforts just to develop DSE approaches optimizing for various metrics, such as execution time [5, 91, 145, 188], execution time and energy consumption [63, 196], and resource utilization [175, 192]. These efforts do not explore the ways to use the DSE results at run-time. However, they can be used to generate allocations to be used at run-time.

The DSE takes very long time if the application/platform size is large and hence the exploration may not finish within a limited time. Further, the exploration time increases with the heterogeneity in the platform (different types of cores) and number of optimization goals in order to find efficient allocations. To overcome the exploration time bottleneck, there have been efforts to accelerate the DSE process by incorporating estimations along with time consuming simulations to evaluate the allocations [71, 145, 164]. The accuracy of the results by these approaches depends upon the number of employed simulations. The exploration time could be further reduced by employing pure estimations [98, 131], but the evaluation results will not be accurate.

Along with efficient resource allocation, dynamic voltage and frequency scaling (DVFS) potential of cores has also been exploited to optimize energy consumption [42, 43, 163]. DVFS can be applied both at design-time and run-time based on the available time slack. At design-time, the slack is defined as the difference between applicationâĂŹs timing constraint and achieved execution time. At run-time, the slack is dynamically created due to tasks finishing earlier than their worst-case execution times (WCETs).

Advantages and Drawbacks. At run-time, since only selection of the allocation from the storage is required, a light-weight run-time platform manager can be employed to configure the applications efficiently. The hybrid approach allocates applications more efficiently than on-the-fly heuristics that perform all the computations at run-time. However, flexibility in these approaches is limited, since all potential applications must be known in entirety at design-time and analysis results will be applicable only to the analyzed platform. Therefore, design-time analysis needs to be repeated when the application set or platform changes. Further, storing analysis results introduces additional memory overhead.

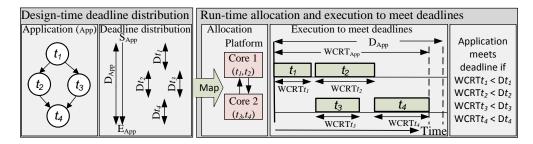

2.2.2 Design-time Deadline Distribution and Run-time Allocation. In order to meet a hard real-time (HRT) deadline, some researchers have tried to distribute deadlines to each task of the application at design-time and the resource management approach aims to meet these deadlines at run-time during the resource allocation and application execution process. There has also been efforts to distribute task's deadline further to its functional blocks [1]. Fig. 5 provides an overview of the design-time deadlines assignment to different tasks of an application and run-time resource allocation to meet the deadlines. Based on the application deadline ( $D_{App}$ ), the computation complexity of its tasks are evaluated and then deadline is assigned to each task based on its computation complexity. At run-time, the tasks are allocated to platform cores to perform execution. If individual tasks meet their deadlines, i.e. WCRT of each task is less than their respective deadline (D), the application meets its deadline.

Existing Works. Table 3 lists deadline distribution based resource allocation approaches reported in the literature. We would like to highlight that even though some of the reviewed techniques were not originally developed targeting multi/many-core systems, they are based on similar assumptions

Fig. 5. Design-time deadline distribution and run-time resource management.

Table 3. Deadline distribution based resource allocation approaches that consider computation (Comp.) and/or communication (Comm.) for optimization.

|            | Optimization   | Comp. & Comm. |              |             |

|------------|----------------|---------------|--------------|-------------|

| References | Goal           | Consideration | Architecture | Control     |

| [155]      | Execution time | Comp.         | Homogeneous  | Centralized |

| [92]       | Execution time | Comp.         | Homogeneous  | Centralized |

| [88]       | Execution time | Comp.         | Homogeneous  | Centralized |

| [160]      | Execution time | Comp.         | Homogeneous  | Centralized |

| [27]       | Execution time | Comp.         | Homogeneous  | Centralized |

| [108]      | Execution time | Comp.         | Homogeneous  | Centralized |

| [73]       | Execution time | Comp.         | Homogeneous  | Centralized |

and can or have been applied to the multi/many-core allocation problem. Similar to guaranteed-admission control based resource allocation approaches, these approaches also target to optimize only the execution time (response time) as their main focus is to meet deadlines. The deadline distribution considers mainly two types of deadlines, global and local, which define deadline for a taskset and individual tasks, respectively. With deadlines available for each task, the listed approaches apply various kinds of allocation and scheduling algorithms, e.g., earliest deadline first.

Advantages and Drawbacks. Deadline distribution enables to consider the allocation of individual application tasks independently by considering their deadlines and scheduling order. This facilitates optimization for each individual task in order to meet its local deadline towards meeting the global deadline of the application or taskset. Thus, only local deadlines need to be taken into account. However, this might lead to a situation where all the local deadlines are not met, but the end-to-end deadline might be met. A few drawbacks might be observed when the exact task properties are known, e.g., subtask deadline calculation might be wrong if exact execution time of task is not known and the calculation might be too pessimistic if only WCET is known. Further, in case of a complex application containing a large number of tasks, the deadline distribution to individual tasks considering dependencies amongst the tasks might be quite cumbersome. Additionally, the complexity of the run-time resource management to meet the deadlines also increases.

## 2.3 Discussions and Summary

These hard real-time approaches have been extensively studied in the literature and applied to meet the deadlines for time-critical applications. The concepts from one category of approaches can be used in another one as well in order to accomplish the aim in a particular category. For example, 39:12 A. K. Singh et al.

deadline distribution and schedulability analysis have been jointly exploited in [150], deadline distribution and admission control in [121], and hybrid and schedulability analysis is employed in [57]. For all the categories, it can also be deduced that complexity of the resource allocation increases with the complexity of the considered application. Out of the above categories, since hybrid resource allocation needs to perform computations at design-time, the taskset needs to be known in advance. However, most of the guaranteed admission control based approaches perform allocation and schedulability analysis directly at run-time as the analysis can be performed in a short amount of time [28].

#### 3 SOFT REAL-TIME AND BEST EFFORT RESOURCE ALLOCATION

Based on the classification as shown in Figure 2, soft real-time and best effort resource allocation approaches are described subsequently. Advantages and drawbacks of approaches in each category are also described. Further, a combined discussion of all the approaches is also provided.

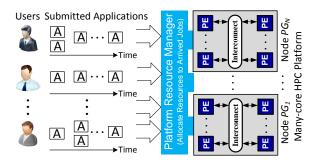

# 3.1 Market-inspired Resource Allocation

Market-inspired resource allocation mechanisms use market concepts to perform the allocation. These mechanisms use available platform capacity measured by low-level heuristics as bids within an auction-like allocation process in order to find the allocation that can provide guarantees to satisfy the required level of quality of service (QoS) and can maximize the overall system utility (profit). Fig. 6 demonstrates the process of market-inspired dynamic resource allocation where different applications need to be allocated into a many-core system representing a typical HPC data center. The shown system executes a set of *applications* submitted by various *users* at different moments of time. The applications are submitted to the *platform resource manager* that allocates resources to them. To incorporate market and value concepts in the allocation process, applications are assigned values and bids from resources are placed to the allocation engine (Manager Processor) in order to maximize the value/profit returned by a many-core system. The values of applications represent their importance level.

- 3.1.1 Existing Works. Table 4 lists some market-inspired resource allocation approaches that optimize for execution time, energy consumption, or both of them. The main goal of the execution time optimizing approaches is to maximize value (profit) by early completion of applications. Some researchers assume a fixed value of an application [179], whereas others consider values that can change with time, described with so-called value curve of the application [26, 36, 83, 97]. The changing value over time reflects the impact of the computation over the business processes and adds complexity to the allocation process. With changing value over time, an early completion leads to high value, whereas late completion results in a low value. An enormous literature exists for optimizing value as the main focus of cloud data centers have been to maximize the profit. However, since energy consumption of data centers is quite huge (around 1.5% of the worldwide electricity consumption [100]) and rapidly increasing, optimizing for energy consumption along with the value is of paramount importance and recently has been a focus point of various researchers. Along with allocation, DVFS potential has been exploited to achieve energy savings [29, 167].

- 3.1.2 Advantages and Drawbacks. These resource allocation approaches are proven to provide promising results in the overload situation where demand for available resources is higher than the supply. Such situation is normally encountered in HPC data centers [194]. The notion of values of applications and auction process facilitate in deciding to hold the low value applications for late allocation and allocating limited resources to the high value applications. However, with value curve associated with each application, the resource allocation becomes complex while considering

Fig. 6. Market-inspired resource allocation in a cloud data center that contains different nodes (servers) with dedicated cores (or Processing Elements, PEs) to execute applications submitted by multiple users.

Table 4. Market-inspired resource allocation approaches that consider computation (Comp.) and/or communication (Comm.) for optimizing execution time (ET) and/or energy consumption (EC).

|            | Optimization Comp. & Comm. |                      |               |             |

|------------|----------------------------|----------------------|---------------|-------------|

| References | Goal                       | Consideration        | Architecture  | Control     |

| [179]      | ET (Value)                 | Comp.                | Heterogeneous | Centralized |

| [11]       | ET (Value)                 | Comp.                | Homogeneous   | Centralized |

| [25]       | ET (Value)                 | Comp. & Comm.        | Homogeneous   | Centralized |

| [165]      | ET (Value)                 | Comp. & Comm.        | Homogeneous   | Centralized |

| [2]        | EC                         | Comp.                | Homogeneous   | Centralized |

| [29]       | EC                         | EC Comp. Homogeneous | Homogeneous   | Centralized |

| [186]      | EC                         | Comp.                | Homogeneous   | Centralized |

| [97]       | Value & EC                 | Comp.                | Homogeneous   | Centralized |

| [166]      | Value & EC                 | Comp. & Comm.        | Homogeneous   | Centralized |

| [167]      | Value & EC                 | Comp. & Comm.        | Homogeneous   | Centralized |

enormous number of applications arrived at the same time due to overload situation. Depending upon the arrival rate and value curve pattern of applications, appropriate resource allocation approach needs to be identified in order to perform optimization for desired metrics.

# 3.2 Bio-inspired Resource Allocation

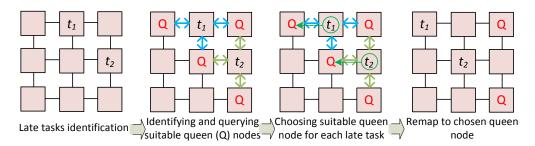

Biologically inspired resource allocation approaches draw inspiration from nature and apply the observed characteristics when solving specific computational problems [68]. They are often based on the characteristics of self-organizing biological systems where global patterns emerge from interactions at a lower-level in the system [8, 30]. This indicates that the resource allocations are changed, i.e. reallocations are performed based on observed biological phenomenon. They have been well explored to balance communication loads in networks and distributed systems [46, 140], communication loads in many-core systems [151], and both computation and communication loads in embedded systems [128]. These approaches usually employ distributed resource management to overcome the limitations of centralized and clustered (hierarchical distributed) managements for dynamic applications and large scale many-core systems. Fig. 7 illustrates an example to reallocate some late tasks in a 3×3 many-core system by employing biological inspiration that is based on pheromone signalling mechanism as seen in social insects (e.g honey bees) in order to improve the overall performance [128]. At each reallocation interval, *late tasks identification* is done on each node

39:14 A. K. Singh et al.

Fig. 7. Bio-inspired resource allocation. An example showing remapping of late tasks  $t_1$  and  $t_2$  on suitable queen nodes (cores) having higher resource availability.

Table 5. Bio-inspired resource allocation approaches that consider computation (Comp.) and/or communication (Comm.) for optimizing execution time (ET) and/or energy consumption (EC).

|            | Optimization | Comp. & Comm. |               |             |

|------------|--------------|---------------|---------------|-------------|

| References | Goal         | Consideration | Architecture  | Control     |

| [68]       | ET           | Comp.         | Homogeneous   | Distributed |

| [24]       | ET           | Comp.         | Heterogeneous | Distributed |

| [135]      | ET           | Comp.         | Homogeneous   | Distributed |

| [138]      | ET           | Comp.         | Heterogeneous | Distributed |

| [17]       | ET           | Comp.         | Homogeneous   | Distributed |

| [12]       | EC           | Comp.         | Homogeneous   | Distributed |

| [90]       | ET & EC      | Comp. & Comm. | Homogeneous   | Distributed |

| [128]      | ET & EC      | Comp. & Comm. | Homogeneous   | Distributed |

to find late tasks in their task queues. Then, for late tasks, e.g.  $t_1$  and  $t_2$ , the process of *identifying* and querying suitable queen (Q) nodes is carried out, where each Q node represents its pheromone level in terms of processing capability that is obtained periodically by executing light-weight set of rules on each node. Only the nodes having pheromone level greater than a threshold contribute to the Q nodes and suitable Q nodes are the ones in close proximity. Thereafter, suitability of each Q node is determined to reallocate the late tasks in order to *choose the most suitable queen node for each late task*. The neighbouring Q nodes are chosen to reallocate (remap) the late tasks such that they are still allocated close to each other in order to maintain low communication overhead in case the tasks communicate with each other.

- 3.2.1 Existing Works. Table 5 lists bio-inspired resource allocation approaches for many-core systems. It has been observed that they have been lesser explored for many-core systems than networks and distributed systems [46, 140]. These approaches have performed optimizations by considering several biological phenomenon, e.g., particle swarm optimization (PSO) [90], pheromone signalling (PS) [128], etc. In [128], energy consumption is not directly optimized, but communication overhead is reduced that leads to optimized communication energy consumption. These approaches have been studied to implement a fully distributed resource allocation in order to overcome the limitations of centralized and clustered (hierarchical) resource managements and have shown promising results in several scenarios.

- 3.2.2 Advantages and Drawbacks. The bio-inspired approaches perform allocation in a completely distributed and self-organizing way. Thus, they alleviate the limitations of centralized and

hierarchical (mixture of centralized and distributed) resource allocation approaches that suffer from the issues of scalability, huge monitoring traffic, hot-spots, etc. The main drawbacks of these approaches lie in the fact that they are difficult to implement, study and calibrate in real systems due to several assumptions on the running system. Additionally, in static environments with a small number of cores, they might lead to bad results as compared to other design-time (static) optimization approaches. Further, for a system of small size, they might perform worse than the centralized resource management approaches that have a better view of the system resources. For various system sizes, in [99], it has been shown that applications achieve better performance by centralized approach than the distributed approach.

#### 3.3 Non-guaranteed Admission Control based Resource Allocation

A non-guaranteed admission controller does not guarantee the schedulability of the admitted applications or tasks. Therefore, some of the admitted applications might not meet their deadlines. For guaranteed admission control, computation costly schedulability analysis (e.g., exact schedulability test) is employed, which takes several measures into account, e.g., computation/communication requirements of tasks and interference amongst tasks, such that timing guarantees are always fulfilled for the admitted and running tasks. The costly analysis might incur long delay between the application release (arrival) and its allocation process. Further, there might be very low utilization of system resources as the tasks are admitted only when the system can allocate a necessary resource budget to meet timing requirements. To overcome the issues of costly schedulability analysis and low utilization, low cost tests can be employed, which would let a higher number of tasks to enter into the system to increase the resources utilization, but some of them might miss their deadlines. Fig. 8 shows such a process, representing non-guaranteed admission control based resource allocation, where some of the admitted applications might miss their deadlines as light-weight schedulability tests are employed that are usually based on status of the platform resources and thus does not ensure schedulability. Feedback-based admission controller can also be used to provide monitored system information in order to facilitate for better admission control decisions.

- 3.3.1 Existing Works. Table 6 lists non-guaranteed admission control based resource allocation approaches and works applying light-weight schedulability tests for soft real-time systems. Some of the approaches also employ feedback concepts originated from control-theory. For overall execution time optimization, some approaches admit and allocate the tasks such that a load balance is achieved in the multi/many-core system in order to achieve high performance. The energy optimization is mainly based on the feedback utilized to perform dynamic voltage and frequency scaling (DVFS). Monitoring (feedback) information has also been used to perform adaptive resource allocation in order to improve performance [76, 107]. It has been observed that several works regarding feedback admission control exist for single-core systems, but we focus on multi/many-core systems. Additionally, admission control based approaches to jointly optimize both execution time and energy consumption are lacking.

- 3.3.2 Advantages and Drawbacks. The non-guaranteed admission control enables high system utilization by admitting a higher number of applications. Additionally, light-weight schedulability analysis reduces the delay between the start of schedulability test and time of admission into the system. This might lead to lower response time. However, in case of using feedback that is some monitored activity in the system, fast and accurate run-time monitoring is desired, which might not always be easily achievable. Further, monitoring activities can flood the network and increase energy consumption.

39:16 A. K. Singh et al.

Fig. 8. Non-guaranteed admission control based resource allocation.

Table 6. Non-guaranteed admission control based resource allocation approaches that consider computation (Comp.) and/or communication (Comm.) for optimization.

|            | Optimization       | Comp. & Comm. |              |             |

|------------|--------------------|---------------|--------------|-------------|

| References | Goal               | Consideration | Architecture | Control     |

| [104]      | Execution time     | Comp.         | Homogeneous  | Centralized |

| [101]      | Execution time     | Comp. & Comm. | Homogeneous  | Centralized |

| [127]      | Execution time     | Comp. & Comm. | Homogeneous  | Centralized |

| [110]      | Energy consumption | Comp.         | Homogeneous  | Centralized |

## 3.4 Congestion Avoiding Resource Allocation

The congestion avoiding heuristics assign new arriving tasks or application tasks on many-core system resources such that the congestion in the cores and links is minimized. This might lead to optimized overall execution time and energy consumption. These heuristics does not guarantee for a QoS requirement, but can be used to meet soft real-time requirements as they optimize congestion leading to optimized execution time. Fig. 9 shows an example mapping of the computations (tasks) and communications (edges) of an arrived application on a many-core system's cores and links, respectively, while trying to reduce congestion in the cores/links. Tasks  $t_1$  and  $t_2$  are mapped on one core assuming that they are highly communicating tasks (huge data needs to be transferred between them) and can fit on the core, i.e. the core has sufficient memory to allocate them. This reduces the communication overhead between the tasks as data transfer happens via shared local memory on the core. The other tasks are mapped in the close proximity assuming that higher amount of data needs to be transferred between  $t_3$  and  $t_4$  as compared to  $t_2$  and  $t_4$ , i.e.,  $t_3$  and  $t_4$  are mapped close to each other while trying to reduce the communication distance between  $t_2$  and  $t_4$  as well. The congestion on the cores is also reduced by homogeneously distributing loads of tasks on the cores.

- 3.4.1 Existing Works. Table 7 lists recent works applying congestion avoiding heuristics to allocate tasks/edges on the resources at run-time. The heuristics employ various fundamental principles based on the characteristics of the application and current status of system resources, e.g., map highly communicating tasks on the same core or neighbouring cores, edges on least utilized (highly available) links, and tasks on least utilized cores. These works optimize for one or several performance metrics. Further, these heuristics perform all the computations at run-time and thus can handle highly dynamic workloads.

- 3.4.2 Advantages and Drawbacks. The congestion avoiding heuristics cope well to map unknown applications (not available at design-time) on any platform as they do not use any platform specific analysis results computed in advance. However, these heuristics may not be able to guarantee

Fig. 9. Congestion avoiding resource allocation in a many-core system for an arrived application.

Table 7. Congestion avoiding resource allocation approaches that consider computation (Comp.) and/or communication (Comm.) for optimizing execution time (ET) and/or energy consumption (EC).

|            | Optimization   Comp. & Comm. |               |               |             |

|------------|------------------------------|---------------|---------------|-------------|

| References | Goal                         | Consideration | Architecture  | Control     |

| [133]      | ET                           | Comp. & Comm. | Homogeneous   | Centralized |

| [141]      | ET                           | Comp. & Comm. | Heterogeneous | Centralized |

| [3]        | ET                           | Comp. & Comm. | Heterogeneous | Distributed |

| [74]       | ET                           | Comp.         | Homogeneous   | Centralized |

| [162]      | ET                           | Comp.         | Homogeneous   | Centralized |

| [144]      | ET                           | Comp. & Comm. | Homogeneous   | Distributed |

| [178]      | ET                           | Comp.         | Heterogeneous | Centralized |

| [184]      | ET                           | Comp. & Comm. | Heterogeneous | Centralized |

| [19]       | ET                           | Comp.         | Heterogeneous | Centralized |

| [76]       | ET                           | Comp. & Comm. | Heterogeneous | Centralized |

| [99]       | ET                           | Comp. & Comm. | Heterogeneous | Distributed |

| [37]       | ET                           | Comp.         | Heterogeneous | Centralized |

| [40]       | EC                           | Comp. & Comm. | Homogeneous   | Centralized |

| [116]      | EC                           | Comp. & Comm. | Homogeneous   | Centralized |

| [176]      | EC                           | Comp. & Comm. | Homogeneous   | Centralized |

| [143]      | EC                           | Comp. & Comm. | Homogeneous   | Centralized |

| [172]      | ET & EC                      | Comp. & Comm. | Heterogeneous | Centralized |

| [125]      | ET & EC                      | Comp. & Comm. | Homogeneous   | Centralized |

| [23]       | ET & EC                      | Comp. & Comm. | Homogeneous   | Centralized |

| [41]       | ET & EC                      | Comp. & Comm. | Homogeneous   | Centralized |

| [158]      | ET & EC                      | Comp. & Comm. | Heterogeneous | Centralized |

| [31]       | ET & EC                      | Comp. & Comm. | Heterogeneous | Centralized |

| [177]      | ET & EC                      | Comp. & Comm. | Heterogeneous | Centralized |

| [32]       | ET & EC                      | Comp. & Comm. | Homogeneous   | Distributed |

| [130]      | ET & EC                      | Comp. & Comm. | Homogeneous   | Centralized |

| [59]       | ET & EC                      | Comp. & Comm. | Homogeneous   | Centralized |

| [139]      | ET & EC                      | Comp. & Comm. | Homogeneous   | Centralized |

for schedulability, i.e., for strict timing deadlines due to lack of any prior analysis and limited computational power at run-time.

39:18 A. K. Singh et al.

## 3.5 Discussions and Summary

The soft real-time and best effort resource allocation approaches can be applied to perform optimization for one or several performance metrics depending upon the need of the application domain. For example, in battery operated embedded systems, the timing constraints need to be fulfilled while optimizing for the energy consumption. These approaches employ different kinds of resource management, e.g., centralized, distributed or mix of both (hierarchical) depending upon the size of the many-core system and workload to be executed on it. It has been observed that distributed management leads to better results than centralized one when many-core systems of large sizes are considered [99]. However, in a relatively smaller system, the centralized management might perform better as the distributed approach incurs additional communication overhead amongst the several agents without offering significant advantages [94, 99]. In case the performance needs to be improved at run-time by employing adaptive resource allocation, task migrations are performed, where the tasks are migrated without completely stopping and restarting on the destination core [23, 144]. These approaches can also be modified to perform optimizations for other performance metrics, e.g., reliability, fault-tolerance, temperature, security, etc. by taking appropriate measures into account.

#### 4 COMPARATIVE STUDY AND SUMMARY

This section shows comparative results of various resource allocation approaches falling under hard real-time and soft real-time & best effort categories. We show some example comparisons, where mainly considered approaches are those that employ the same application and multi/many-core system model, or the application models that can be easily converted to a unified model such that the same evaluation tool can be used. It should be noted that a single tool chain is not used to evaluate approaches from various categories, but the tool chain to evaluate a set of approaches within a category is the same and taken from in-house/open-source tool chains. This enables a fair comparison of approaches within a category. Further, approaches within each category are compared separately, i.e., approaches across different categories are not compared as they try to achieve objectives by following different principles. This enables comparison of approaches following similar principles. It should also be noted that some approaches are not considered for comparison due to the reasons such as their well proven inferiority, lack of availability of application models, architecture models and tool chains. The used application model, architecture model and the tool chain are listed while presenting respective results in next subsections.

## 4.1 Hard Real-time Approaches

4.1.1 Guaranteed Admission Control based Approaches. The recently reported admission control based approaches that can be applied to applications represented as task graphs are considered for comparison and listed in Table 8. For the task graph, these approaches can use outputs from controllers to choose the core for critical path jobs or cores for the remaining jobs. The decision whether to use outputs from controllers or not for critical path and other jobs leads to four possible alternatives listed in Table 8 under column Approaches. We abbreviate them with four letter acronyms, where the two first letters denote whether the core selection for critical path jobs is done without (open loop - OL) or with (closed loop - CL) controllers and similarly the two remaining letters inform if the core selection for jobs outside the critical path is performed without (OL) or with (CL) controllers. Specifically, proportionalâĂŞintegralâĂŞderivative (PID) controllers are used to perform the comparative study. A Transaction-Level Modelling (TLM) simulation model developed in SystemC language has been used to evaluate the efficiency of the approaches. The controller

Table 8. Admission control based approaches considered for comparison with various open loop (OL) and closed loop (CL) combinations.

| References | Approaches                                                      | Abbreviation |

|------------|-----------------------------------------------------------------|--------------|

| [127]      | Open Loop for critical path jobs & Open Loop for other jobs     | OLOL         |

| [56]       | Open Loop for critical path jobs & Closed Loop for other jobs   | OLCL         |

| [56]       | Closed Loop for critical path jobs & Open Loop for other jobs   | CLOL         |

| [56]       | Closed Loop for critical path jobs & Closed Loop for other jobs | CLCL         |

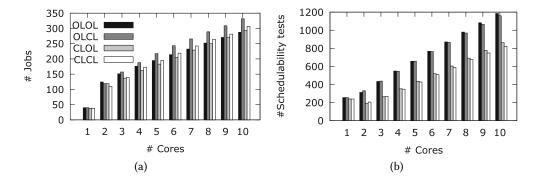

Fig. 10. Number of executed jobs and number of schedulability test executions.

components (proportional, integral, and derivative) are tuned by analysing the corresponding open-loop system response to a bursty workload.

Number of Executed Jobs and Number of Schedulability Test Executions. Figure 10 (a) and (b) show the number of jobs executed before their deadlines and number of schedulability tests when multi-core systems with different number of cores are considered. The shown results are for grid workload of an engineering design department of a large aircraft manufacturer that contains 100 tasks of 827 to 962 jobs in total, where job execution time varies from 1ms to 99ms, which has been scaled down for faster execution and was originally in the orders of hours. In the open-loop (OL) configuration, cores are scanned in a lexicographical order as long as the first one capable of executing the job satisfying its timing constraints is not found, whereas in the closed-loop (CL) configurations the tasks are checked with regards to the decreasing value of the corresponding controller outputs. A couple of observations can be made from Figure 10. 1) For the number of executed jobs, OLOL configuration approach seems to be particularly beneficial in the systems with lower number of cores (heavier loaded with jobs). However, in the systems with more than two cores, the OLCL configuration leads to the best results. Its superiority in comparison with CLCL stems from the fact that an over-pessimistic rejection of critical path jobs leads to fast rejection of the whole task. Thus, the cost of a false negative estimation is rather high. The OLCL configuration admits 11% more jobs than OLOL, whereas CLCL is only slightly (about 1.5%) better than the baseline OLOL. 2) For the number of schedulability tests, the difference between OLOL and OLCL is almost unnoticeable, but the configurations with control-theory-aided selection of a core for the critical path jobs, i.e. CLCL, leads to significant, over 30% reduction. This indicates the benefits of using the controller outputs. From the results, it follows that two configurations OLCL and CLCL dominate each other, the former in terms of number of executed jobs, the latter in terms of number 39:20 A. K. Singh et al.

Table 9. Hybrid approaches (design-time allocations computation and run-time selection) considered for comparison.

| References | Approaches                                                | Abbreviation |

|------------|-----------------------------------------------------------|--------------|

| [175]      | Hybrid Execution Time Optimization                        | HETOpt       |

| [42]       | Hybrid Energy Consumption Optimization 1                  | HECOpt1      |

| [163]      | Hybrid Energy Consumption Optimization 2                  | HECOpt2      |

| [193]      | Hybrid Execution Time & Energy Consumption Optimization 1 | HETECOpt1    |

| [168]      | Hybrid Execution Time & Energy Consumption Optimization 2 | HETECOpt2    |

| [171]      | Hybrid Execution Time & Energy Consumption Optimization 3 | HETECOpt3    |

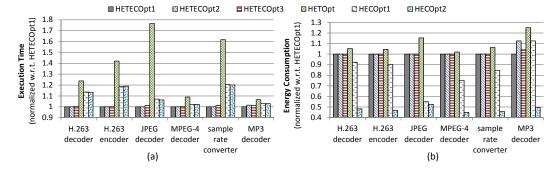

Fig. 11. Execution time and energy consumption comparison.

of schedulability tests. Depending upon which goal is more important, one of them is advised to be selected.

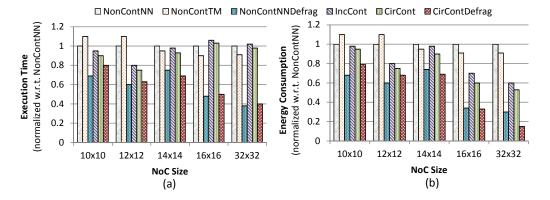

4.1.2 Hybrid Approaches: Design-time Allocations Computation and Run-time Selection. The compared hybrid approaches that perform design-time allocations computation and run-time selection are listed in Table 9. Some of these approaches optimize only execution time or energy consumption, and some of them optimize both the metrics. HETOpt tries to find a load balanced allocation to optimize execution time. The energy consumption optimization in HECOpt1 and HECOpt2 is performed by exploiting expected future slack and current slack, respectively. Appropriate voltage/frequency levels of used cores are identified to exploit the slack. In HETECOpt1, at design-time, exhaustive exploration is performed to identify the best allocation in terms of execution time and energy consumption, whereas HETECOpt2 prunes the design space to perform the exploration within a limited time. HETECOpt3 identifies the best allocation at run-time by exploiting the design-time extracted execution traces. To evaluate these approaches, they are implemented using publicly available SDF³ tool set [174] along with the required application and architecture models.

Execution Time and Energy Consumption Comparison. Figure 11 (a) and (b) show comparison of worst-case execution time and energy consumption for various streaming multimedia applications when different approaches tabulated in Table 9 are employed to map them on a 4×4 2D mesh multi-core chip. The multimedia applications are characterized by throughput constraints [10]. The results obtained by different approaches are normalized with respect to (w.r.t.) the result obtained by HETECOpt1. A couple of observations can be made from Figure 11 (a) and (b). 1) HETOpt leads to the worst result in terms of both execution time and energy consumption as it tries to perform load balanced resource allocation of tasks on cores without taking parallelism of tasks

Table 10. Hybrid approaches (design-time deadline distribution and run-time allocation) considered for comparison.

| References | Approaches                 | Abbreviation |

|------------|----------------------------|--------------|

| [88]       | Pipeline Delay Composition | PDC          |

| [27]       | Automatic Partitioning     | AP           |

| [73]       | Local-Deadline Assignment  | LDA          |

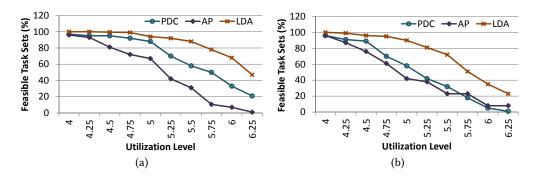

Fig. 12. Percentage of feasible task sets for (a) balanced and (b) imbalanced workloads.

and their communication overhead into account. 2) Both execution time and energy consumption optimization approaches HETECOpt1, HETECOpt2, and HETECOpt2 lead to similar results for most of the applications as all of them compute efficient allocations at design-time. 3) Energy consumption by HECOpt1 and HECOpt2 is lower than other approaches. The reason lies in the fact that HECOpt1 and HECOpt2 employ DVFS on cores to reduce the energy consumption while respecting the application deadlines, whereas, other approaches just try to find the best allocation and do not employ DVFS. 4) HECOpt2 leads to minimum energy consumption as DVFS is applied both at design-time and run-time while taking DVFS overhead and deadline into account.

4.1.3 Hybrid Approaches: Design-time Deadline Distribution and Run-time Allocation. The compared hybrid approaches that perform design-time deadline distribution and run-time allocation are listed in Table 10. These approaches distribute the end-to-end deadline of an application/job to its sub-functions and then perform resource allocation in order to meet the deadline. In PDC, end-to-end delay of a job in a multi-stage pipeline is bounded as a function of job execution times on different stages. The AP approach partitions a parallel real-time application into a set of sequential flows. In LDA, a locally optimal algorithm is employed to assign local deadlines to the jobs. The evaluation results for these approaches are employed from [73], where they are implemented in C++ and consider stream-type and general-type workloads to emulate different kinds of application scenarios.

Number of Executed Task Sets. Figure 12 (a) and (b) show comparison of feasible task sets at various utilization levels for balanced and imbalanced workloads when assorted approaches are employed. Each workload contains a total of 100 task sets of 50 tasks each, where individual instances of a task and sub-task are referred to as jobs and sub-jobs, respectively. A total of 8 cores are considered. In a balanced workload, the execution time of a job is randomly distributed along its execution path to balance the core loads, whereas cores' loads are imbalanced in an imbalanced

39:22 A. K. Singh et al.

workload. A couple of observations can be made from the figure. 1) LDA finds far more feasible sets than the other two methods for both the balanced and imbalanced workloads. 2) LDA performs much better than PDC and AP at high utilization levels where there are more jobs in the system. It should also be noted that sometimes LDA may not be able to find a feasible solution even though such solutions indeed exist, since LDA finds local sub-job deadlines for each core independently instead of using a global approach.

#### 4.2 Soft Real-time Approaches

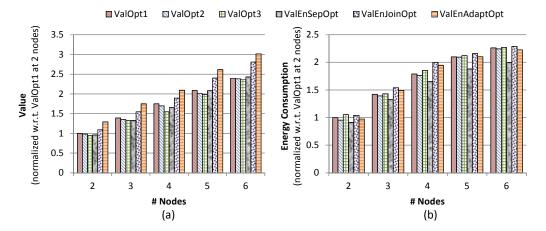

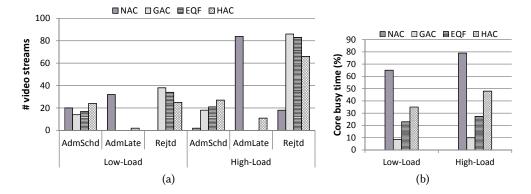

4.2.1 Market-inspired Approaches. We have considered mainly market-inspired and value based approaches for comparison. Table 11 lists the compared approaches that have been applied to applications containing dependent tasks. The value optimization approaches optimize only for value while applying various principles, e.g., ValOpt1 chooses the highest value application first, ValOpt2 first chooses the application having maximum value density computed as value over the amount of required computational resources, and ValOpt3 chooses the application with the minimum remaining value first. The approach in [163] optimizes only for energy and has been extended to optimize both value and energy consumption for a fair comparison, where first a value optimizing allocation is found and then DVFS is applied to optimize energy consumption. In ValEnJoinOpt, value and energy consumption are jointly optimized by employing a genetic algorithm. In ValEnAdaptOpt, in addition to joint optimization, adaptation (reallocation) is also performed based on the execution status of running applications and available system resources in order to explore the scope for further optimization. These approaches are implemented in a C++ prototype and integrated with a SystemC functional simulator. They are evaluated by considering job models from historical data of an industrial HPC data center at High Performance Computing Center Stuttgart (HLRS).

Value and Energy Consumption Comparison. Figure 13 (a) and (b) show the influence of the number of available nodes (servers) on the overall value and energy consumption when various approaches are employed. Each node contains a total of 10 cores. To sufficiently stress the platform, we consider all the applications arriving over a month. Further, to remain close to the reality, it is considered that higher number of applications arrives in peak times, i.e. weekdays and daytimes as compared to off-peak times, i.e. weekends and night times. The value and energy consumption results are normalized w.r.t. the value and energy by ValOpt1 approach at 2 nodes. A couple of observations can be made from Figure 13. 1) Overall value by all the approaches increases with the number of nodes due to increased processing capability leading to completion of a higher number of applications before their value becomes zero. 2) ValEnAdaptOpt approach achieves a higher overall value than other approaches. This is due to the fact that adaptation leads to early completion of executing applications and thus higher values for them. Further, earlier completion leaves resources for the queued applications to be allocated and completed sooner, leading to higher values. 3) The energy consumption is not the lowest by ValEnAdaptOpt as it completes execution of higher number of applications and energy is consumed for executing them. Further, if both the value and energy consumption metrics are to be jointly optimized as value achieved per unit of energy consumption, i.e. value divided by energy, ValEnAdaptOpt leads to the best results.

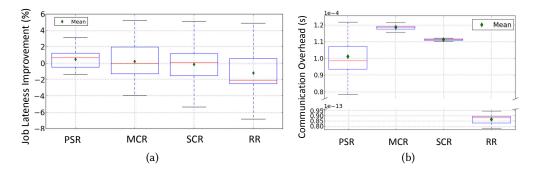

4.2.2 Bio-inspired Approaches. Table 12 lists the bio-inspired approaches considered for comparison. These approaches are applied to perform reallocation on top of an initial allocation done based on least utilized heuristic in order to improve average execution time and energy consumption. In RR, at every remapping interval, each core selects the most late task from its task queue and randomly selects another core to remap it. MCR partitions the whole many-core chip into virtual

| References | Approaches                             | Abbreviation  |

|------------|----------------------------------------|---------------|

| [179]      | Value Optimization 1                   | ValOpt1       |

| [11]       | Value Optimization 2                   | ValOpt2       |

| [25]       | Value Optimization 3                   | ValOpt3       |

| [163]      | Value and Energy Separate Optimization | ValEnSepOpt   |

| [166]      | Value and Energy Joint Optimization    | ValEnJoinOpt  |

| [167]      | Value and Energy Adaptive Optimization | ValEnAdaptOpt |

Table 11. Market-inspired and value based approaches considered for comparison.

Fig. 13. Value and energy consumption comparison.