## UNIVERSITY OF SOUTHAMPTON

### FACULTY OF PHYSICAL AND APPLIED SCIENCES

Electronics and Computer Science

# An Investigation into Event-B Methodologies and Timing Constraint ${\bf Modelling}$

by

Gintautas Sulskus

Thesis for the degree of Doctor of Philosophy

September 2017

#### UNIVERSITY OF SOUTHAMPTON

#### ABSTRACT

# FACULTY OF PHYSICAL AND APPLIED SCIENCES

Electronics and Computer Science

#### Doctor of Philosophy

# AN INVESTIGATION INTO EVENT-B METHODOLOGIES AND TIMING CONSTRAINT MODELLING

by Gintautas Sulskus

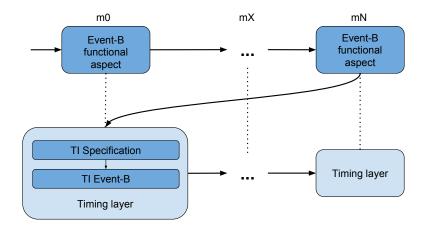

In the domain of formal modelling and verification of real-time safety-critical systems, our focus is on complex – i.e. nested, interdependent and cyclic – timing constraints. We strengthen the pallet of modelling tools and techniques to describe and verify timing properties in such real-time systems. Our contribution builds on Event-B – a formal language for systems modelling, based on set theory and predicate logic. This language has the advantage of mechanised proof and tackles system complexity through a stepwise refinement.

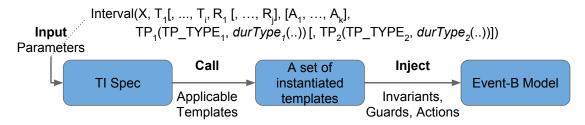

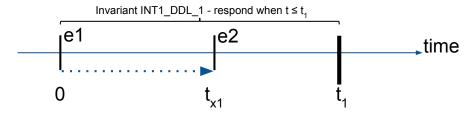

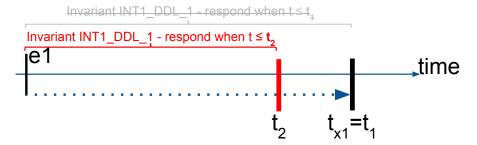

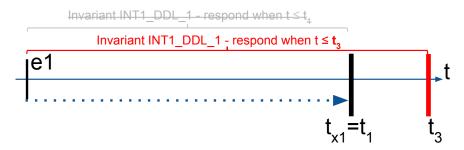

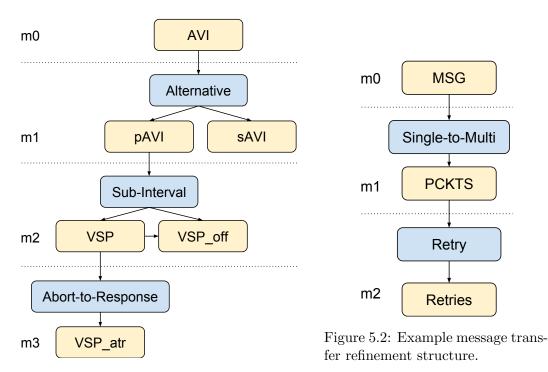

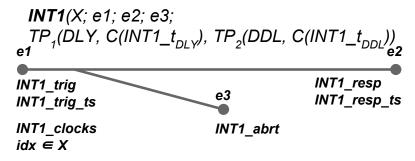

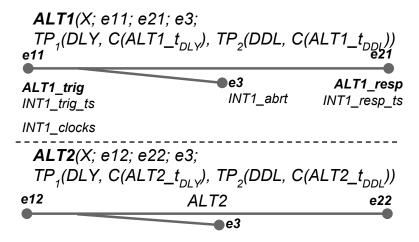

The foundation of our scheme – a notion of a timing interval – is a higher-level abstraction in terms of state machine and formal timing interval specification. It can formally bind together several related timing requirements, expressed in delay, deadline and expiry concepts. To support the timing interval abstraction through the Event-B based refinement method, we present five compositional refinement transformations: Sub-Interval, Alternative, Abort-to-Response, Single-to-Multi and Retry. The timing interval and its refinement transformations use a template-based generative scheme for the transformation of timed models – specified with state machines and timing interval – to Event-B. We provide a workflow and a recommended convention for modelling and graphically representing a timing interval and its refinement transformations in state machine diagrams. The modelling of a timing interval and its refinement transformations process is automated with our tool – tiGen.

Finally, we validate our approach and the recommended development workflow in three case studies. The results show that our timing interval can be developed through multiple levels of refinement. The process of modelling and proving is mostly automated.

# Contents

| D | eclar | ation of Authorship                             | xix |

|---|-------|-------------------------------------------------|-----|

| A | ckno  | wledgements                                     | xxi |

| 1 | Intr  | roduction                                       | 1   |

|   | 1.1   | Research Questions                              | 3   |

|   | 1.2   | Research Scope                                  | 4   |

|   | 1.3   | Contribution                                    | 4   |

|   | 1.4   | Outline                                         | 6   |

| 2 | Res   | earch Landscape                                 | 9   |

|   | 2.1   | Conventional Techniques                         | 9   |

|   |       | 2.1.1 Model-Based Development                   | 9   |

|   |       | 2.1.2 Verification                              | 10  |

|   | 2.2   | Formal Methods                                  | 12  |

|   |       | 2.2.1 Model Checking                            | 12  |

|   |       | 2.2.2 Deductive Verification                    | 13  |

|   |       | 2.2.3 Combination of Verification Methods       | 13  |

|   |       | 2.2.4 Practicality                              | 14  |

|   |       | 2.2.5 Dijkstra's Guarded Command Language       | 14  |

|   |       | 2.2.6 Refinement Calculus                       | 17  |

|   |       | 2.2.7 Temporal Logic                            | 19  |

|   |       | 2.2.8 Safety, Fairness and Liveness             | 21  |

|   | 2.3   | Timed Automata                                  | 22  |

|   |       | 2.3.1 Timed Automata Patterns                   | 23  |

|   |       | 2.3.2 UPPAAL                                    | 26  |

| 3 | Eve   | ent-B: Structure, Refinement and Time Modelling | 29  |

|   | 3.1   | Event-B                                         | 29  |

|   |       | 3.1.1 Event-B Modelling                         | 29  |

|   | 3.2   | Refinement                                      | 30  |

|   |       | 3.2.1 Superposition refinement                  | 30  |

|   |       | 3.2.2 Data refinement                           | 31  |

|   | 3.3   | Proving                                         | 31  |

|   | 3.4   | Example Model                                   | 32  |

|   | 3.5   | Tooling Support                                 | 34  |

|   |       | 3.5.1 iUML State Machines                       | 34  |

|   | 3.6   | Timing in Event-B                               | 36  |

vi CONTENTS

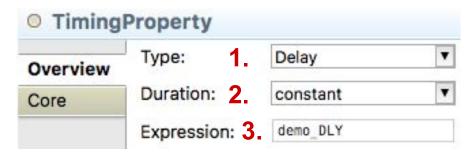

|   |         | 3.6.1   | Semantics of Sarshogh's Timing Properties                     | 8 |

|---|---------|---------|---------------------------------------------------------------|---|

|   |         |         | 3.6.1.1 Deadline Semantics                                    |   |

|   |         |         | 3.6.1.2 Delay and Expiry Semantics                            | 9 |

|   | 3.7     | Refine  | ement of Time in Event-B                                      | 0 |

|   |         |         |                                                               | _ |

| 4 |         |         | terval Approach 4                                             |   |

|   | 4.1     |         | ation                                                         |   |

|   | 4.2     |         | ified Example                                                 |   |

|   | 4.3     |         | g Interval Notation                                           |   |

|   | 4.4     |         | ntics of Interval                                             |   |

|   |         | 4.4.1   | Mapping Timing Interval to State Machine                      |   |

|   |         | 4.4.2   | Timing Interval Dynamics                                      |   |

|   | 4.5     |         | g Interval Templates                                          |   |

|   | 4.6     |         | mic Duration                                                  |   |

|   | 4.7     |         | ton Timing Interval                                           |   |

|   | 4.8     |         | tion and Verification                                         |   |

|   | 4.9     | Overv   | iew and Conclusions                                           | 6 |

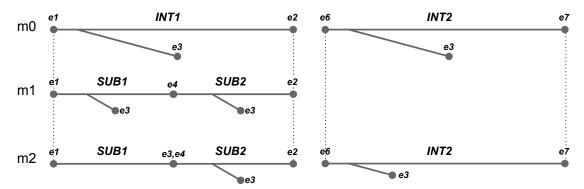

| 5 | Tin     | ning In | terval Refinement Patterns 6                                  | 7 |

|   | 5.1     | _       | g Interval Refinement                                         |   |

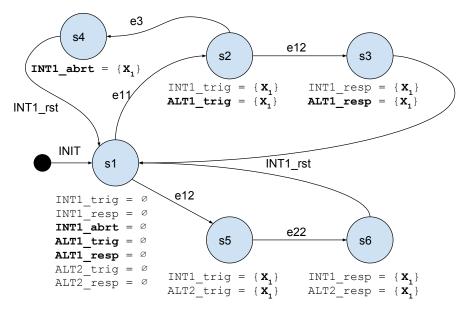

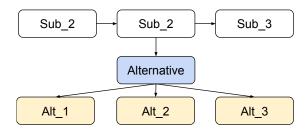

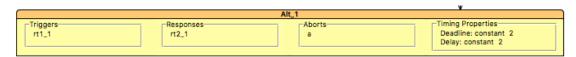

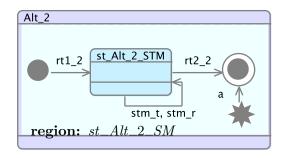

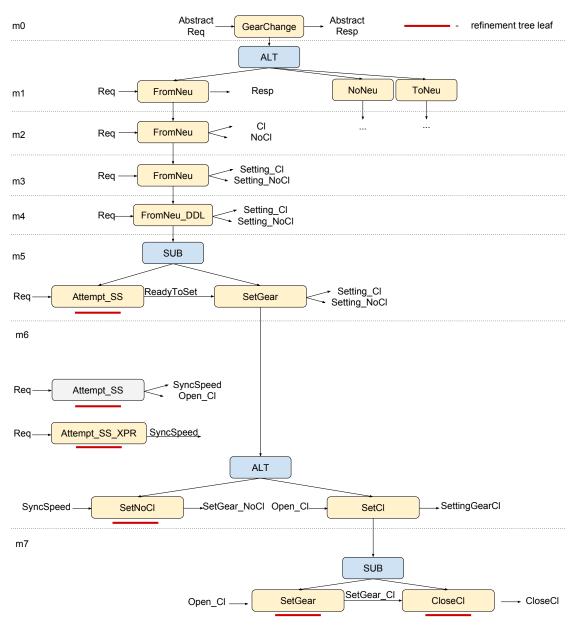

|   |         | 5.1.1   | Alternative Interval Transformation                           |   |

|   |         |         | 5.1.1.1 Dynamics of ALT1 and ALT2                             |   |

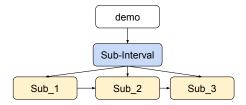

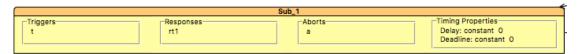

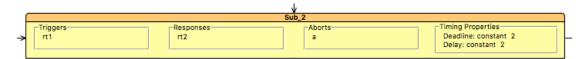

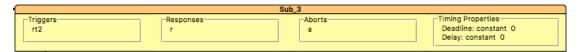

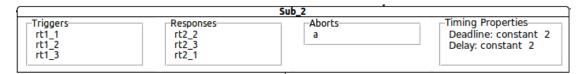

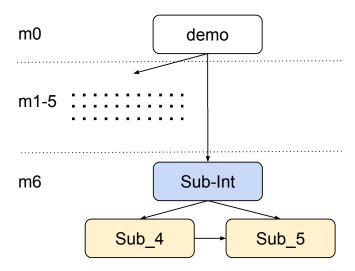

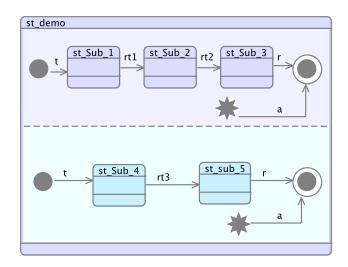

|   |         | 5.1.2   | Sub-Interval Transformation                                   |   |

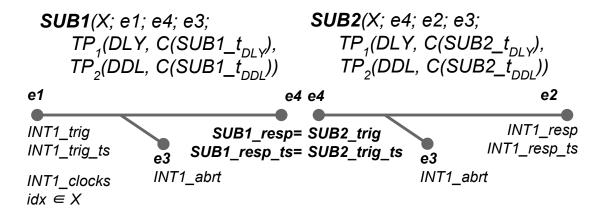

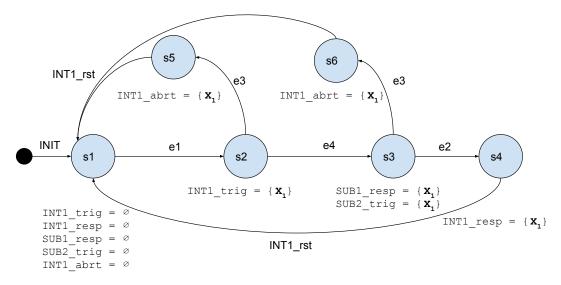

|   |         |         | 5.1.2.1 Dynamics of SUB1 and SUB2 8                           | 0 |

|   |         |         | 5.1.2.2 Special Case: Trigger-Abort Events for Adjacent Sub-  |   |

|   |         |         | Intervals                                                     | 1 |

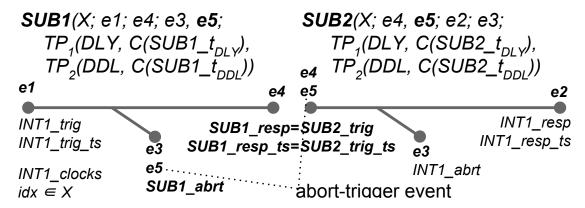

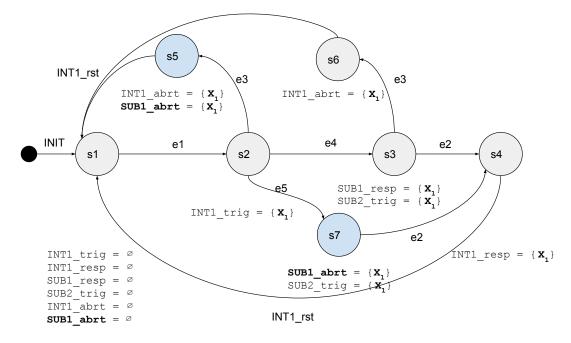

|   |         |         | 5.1.2.3 Dynamics of SUB1 with Abort-Trigger Event and SUB2. 8 | 7 |

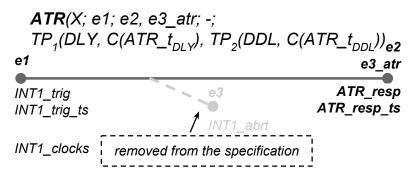

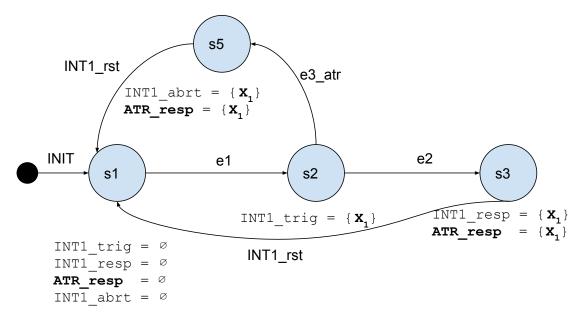

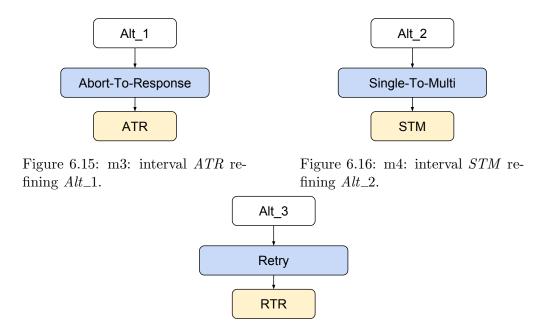

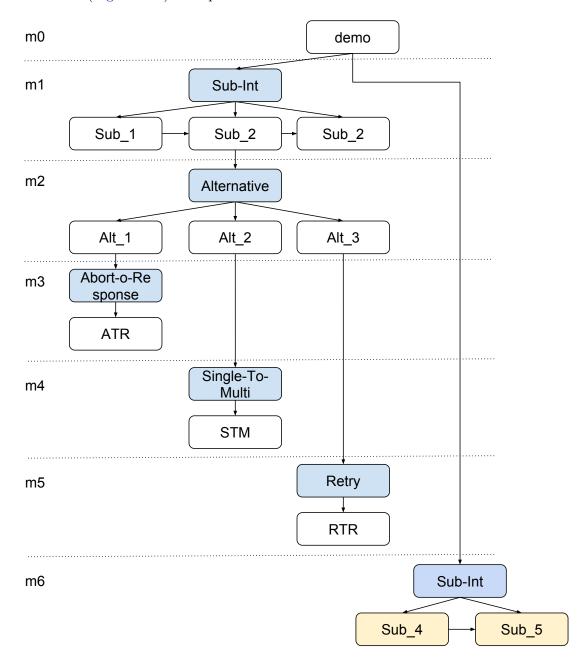

|   |         | 5.1.3   | Abort-To-Response Transformation                              | 7 |

|   |         |         | 5.1.3.1 Dynamics of the ATR Interval 9                        | 0 |

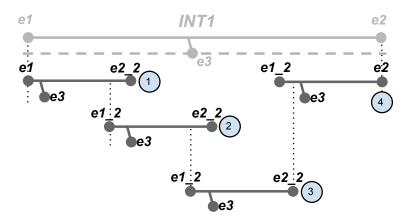

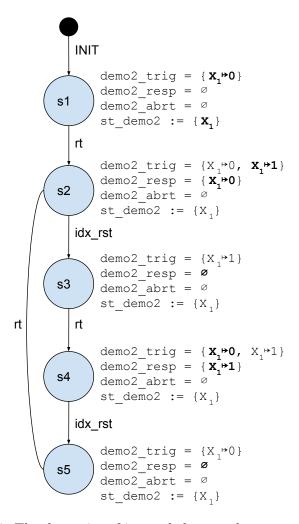

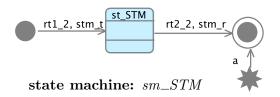

|   |         | 5.1.4   | Single-to-Multi Transformation                                | 1 |

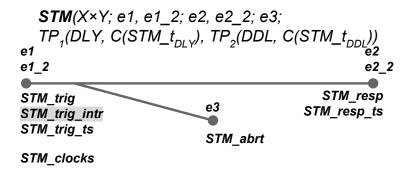

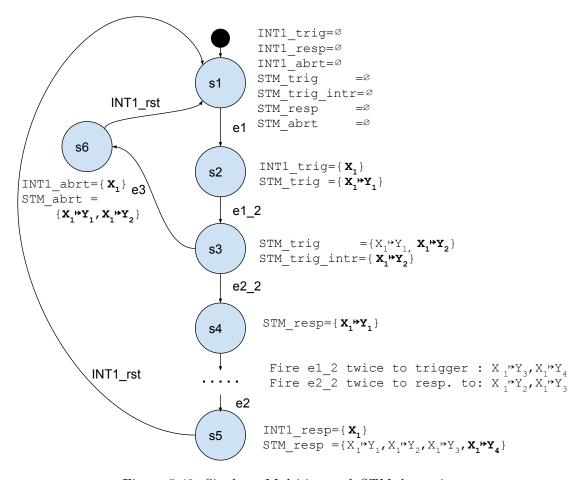

|   |         |         | 5.1.4.1 Dynamics of STM interval 9                            | 5 |

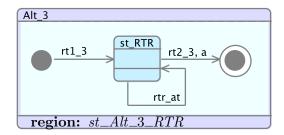

|   |         | 5.1.5   | Retry Transformation                                          | 5 |

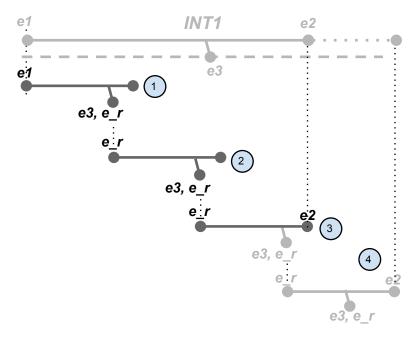

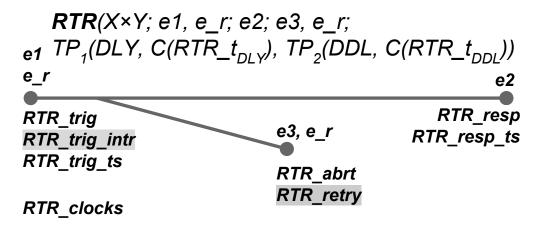

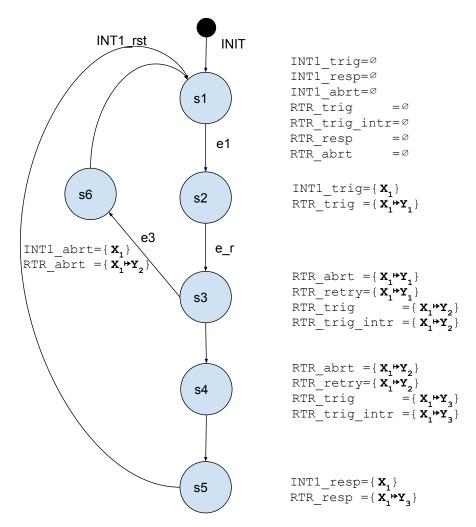

|   |         |         | 5.1.5.1 Interval RTR dynamics                                 | 1 |

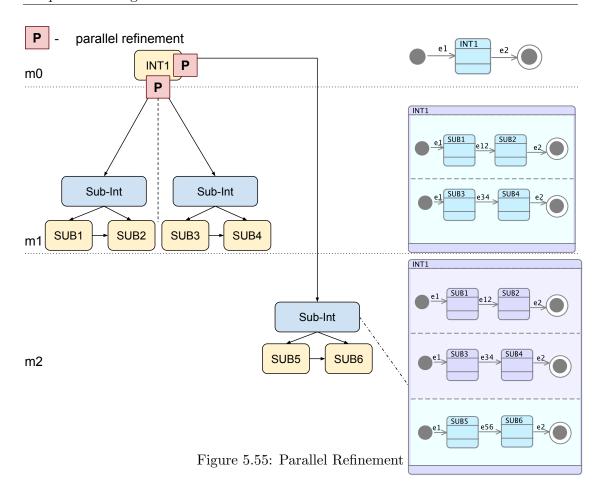

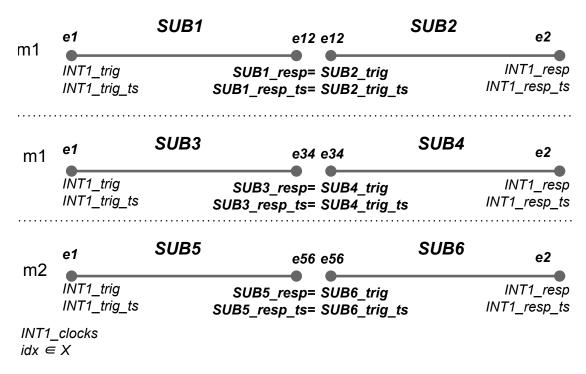

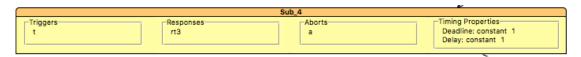

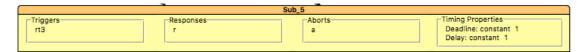

|   |         | 5.1.6   | Parallel Refinements                                          | 1 |

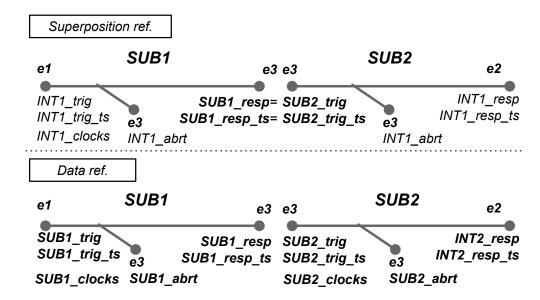

|   | 5.2     | Data 1  | Refinement of the Timing Interval                             | 4 |

|   | 5.3     | Overv   | iew and Conclusions                                           | 6 |

| • | <b></b> |         | 10                                                            | _ |

| 6 |         | _       | terval Automation 10                                          |   |

|   | 6.1     |         | Tool                                                          |   |

|   |         | 6.1.1   | What is Not Generated                                         |   |

|   |         | 6.1.2   | User Interface                                                |   |

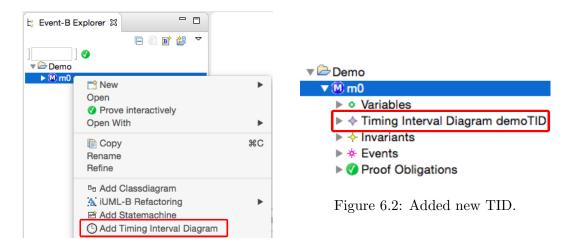

|   |         | 6.1.3   | Adding New Timing Interval                                    |   |

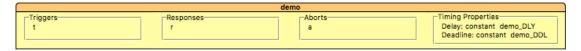

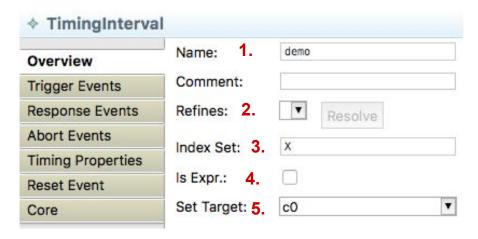

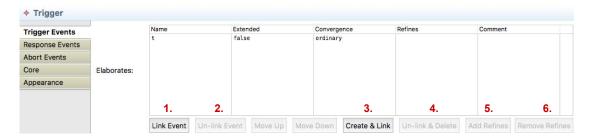

|   | 6.0     | 6.1.4   | Elaborating the Timing Interval                               |   |

|   | 6.2     | Overv   | iew and Conclusions                                           | O |

| 7 | Mo      | delling | Guidelines 11                                                 | 7 |

|   | 7.1     | _       | ling Work-Flow                                                | 7 |

|   | 7 2     |         | ing Timing Interval to State-Machine                          |   |

CONTENTS vii

|           | 7.3  | Mappin          | ng TI Refinement to a State Machine                      | 122 |

|-----------|------|-----------------|----------------------------------------------------------|-----|

|           | 7.4  | Deadlo          | ck Verification with ProB                                | 128 |

|           | 7.5  | Overvi          | ew and Conclusions                                       | 131 |

| 8         | Case | e <b>Stud</b> i | ies                                                      | 133 |

|           | 8.1  | Prover          | Optimisations                                            | 133 |

| 9         | Pace | emaker          | · Case Study                                             | 137 |

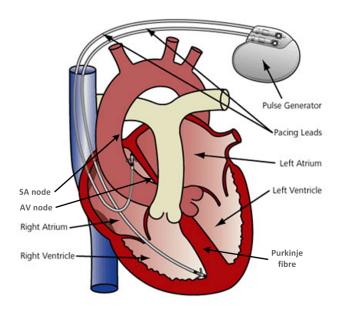

|           | 9.1  | Pacema          | aker                                                     | 137 |

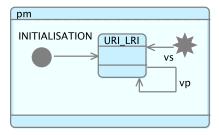

|           | 9.2  | Modell          | ing the Pacemaker                                        | 139 |

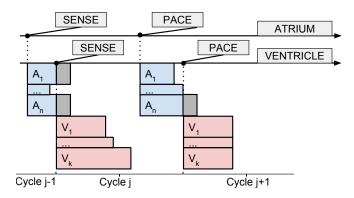

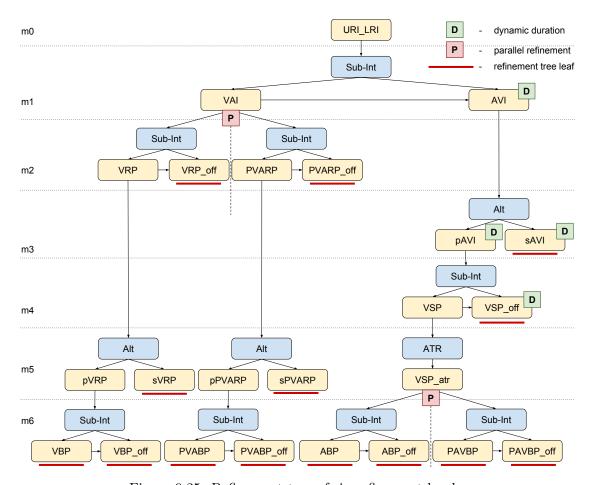

|           |      | 9.2.1           | Abstract Machine: Cardiac Cycle                          | 139 |

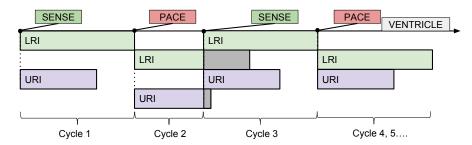

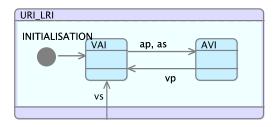

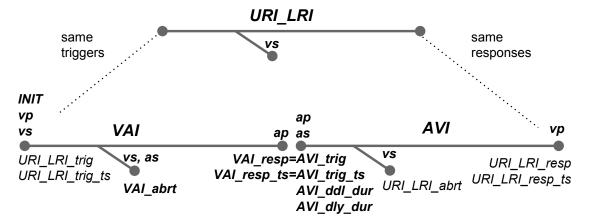

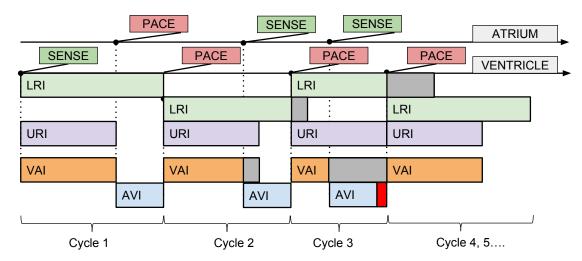

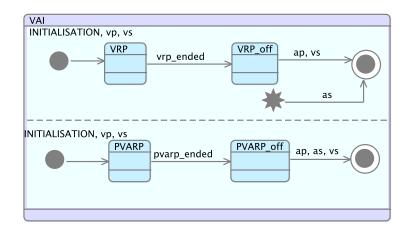

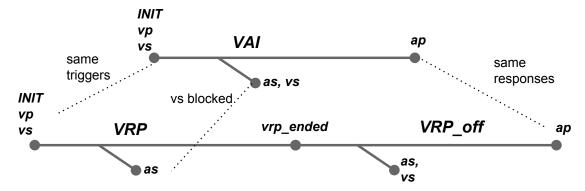

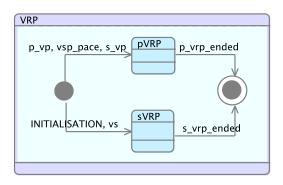

|           |      | 9.2.2           | First Refinement: Post- Ventricular and Atrial Intervals | 141 |

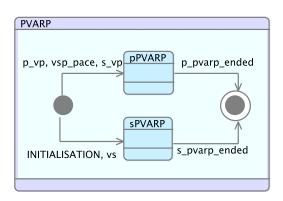

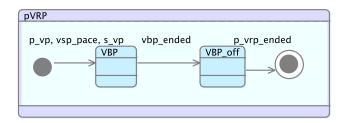

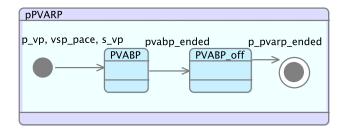

|           |      | 9.2.3           | Second Refinement: Post-Ventricular Refractory Intervals | 144 |

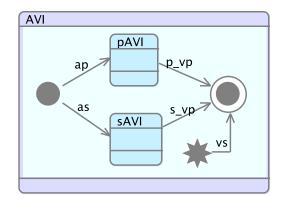

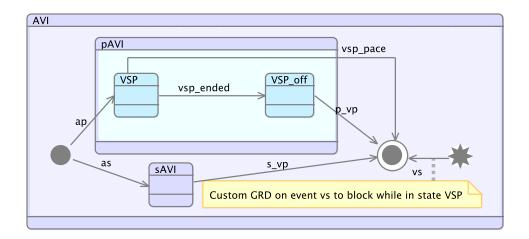

|           |      | 9.2.4           | Third Refinement: Sensed and Paced AVI                   | 146 |

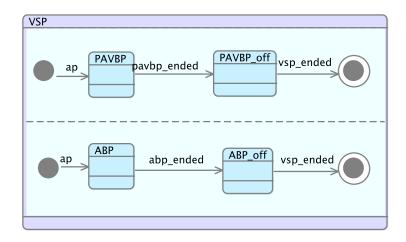

|           |      | 9.2.5           | Fourth Refinement: Ventricular Safety Period             | 147 |

|           |      | 9.2.6           | Fifth Refinement: Abort-To-Response Transformation       |     |

|           |      | 9.2.7           | Sixth Refinement: Blanking Periods                       | 149 |

|           | 9.3  | Overvi          | ew and Conclusions                                       |     |

| 10        | Mes  | sage P          | assing Case Study                                        | 155 |

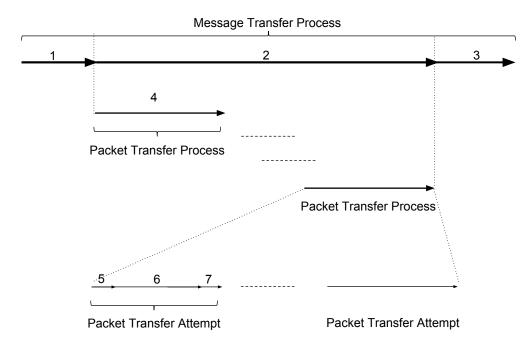

|           | 10.1 | Messag          | ge Transfer Protocol                                     | 155 |

|           |      | _               | ing Strategy and Highlights                              |     |

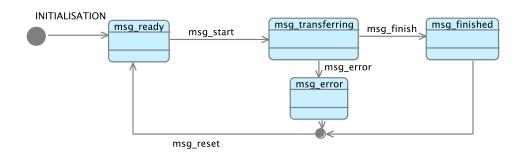

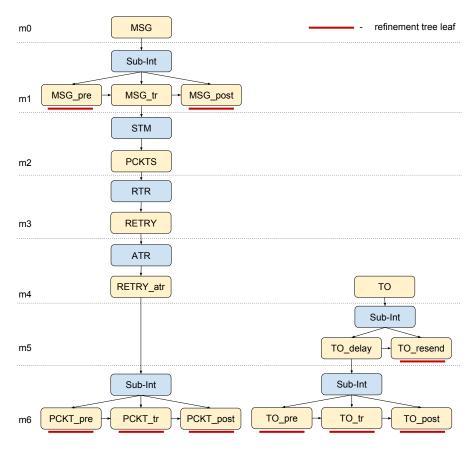

|           |      | 10.2.1          | Abstract Machine: Message Transfer                       | 157 |

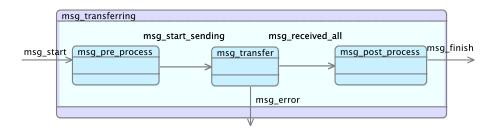

|           |      | 10.2.2          | First Refinement: Message Transfer Sub-tasks             | 159 |

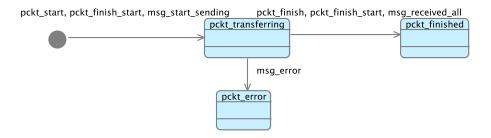

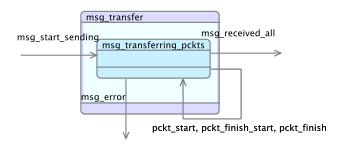

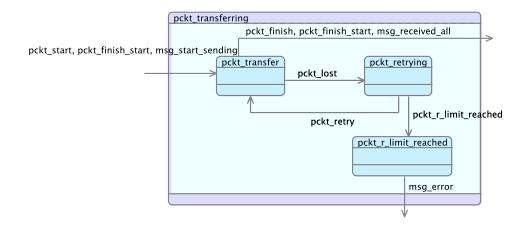

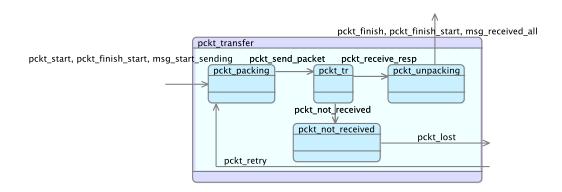

|           |      | 10.2.3          | Second Refinement: Packet Transfer                       | 160 |

|           |      | 10.2.4          | Third Refinement: Packet Retries                         | 162 |

|           |      | 10.2.5          | Fourth Refinement: Packet Time-out                       | 164 |

|           |      | 10.2.6          | Fifth Refinement: Packet Resend Constraint               | 165 |

|           |      | 10.2.7          | Sixth Refinement: Packet Pre and Post Processing         | 165 |

|           | 10.3 | Verifica        | ation and Validation                                     | 167 |

|           | 10.4 | Compa           | rison to Sarshogh's Message Passing Case Study           | 168 |

|           | 10.5 | Overvi          | ew and Conclusions                                       | 169 |

| 11        | Lan  | ding G          | ear Case Study                                           | 171 |

|           |      |                 | g Gear System                                            |     |

|           | 11.2 | Require         | ements                                                   | 172 |

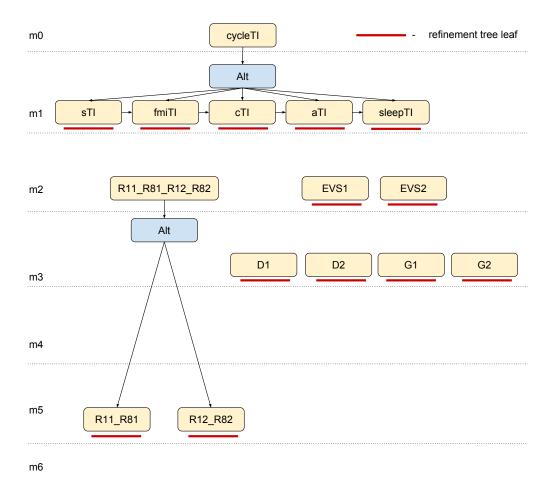

|           | 11.3 | Modell          | ing process                                              | 173 |

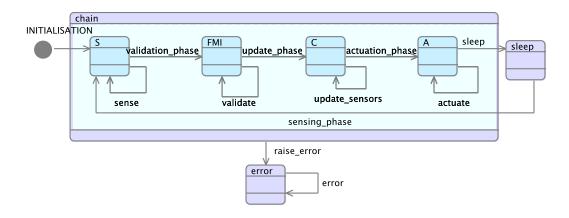

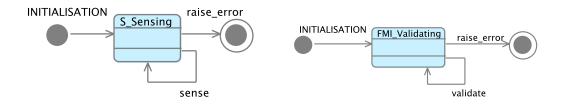

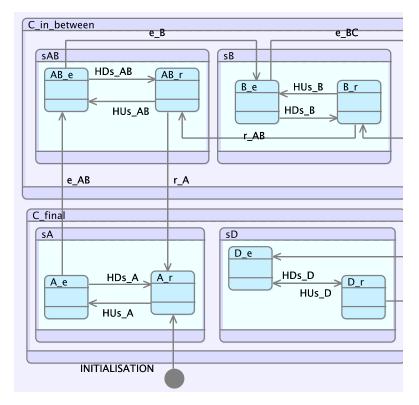

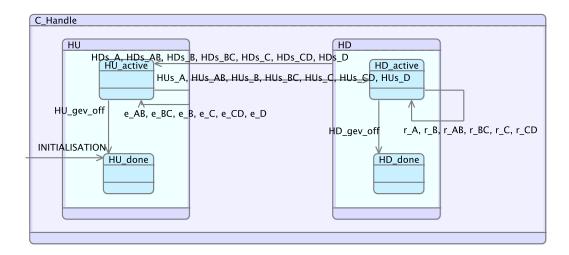

|           |      | 11.3.1          | Abstract Machine: Controller Cycle                       | 174 |

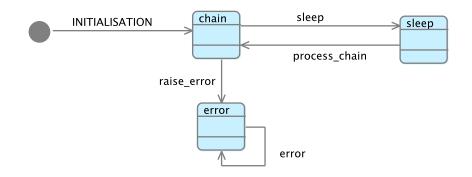

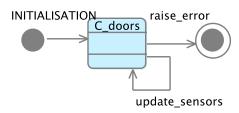

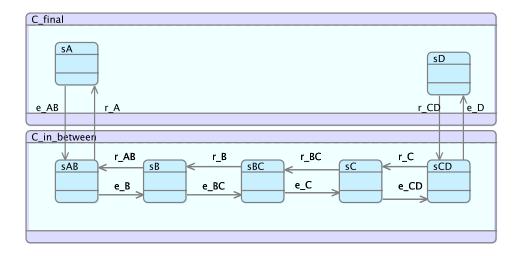

|           |      | 11.3.2          | First Refinement: Process Chain                          | 174 |

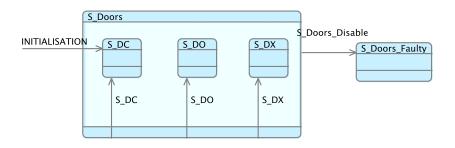

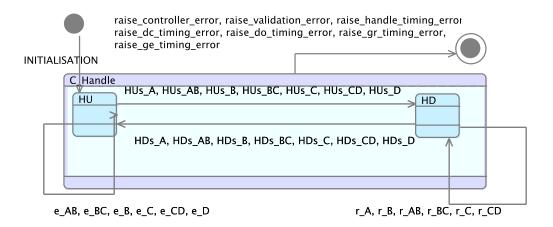

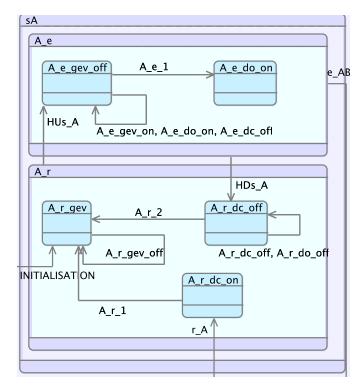

|           |      | 11.3.3          | Second Refinement: Elaborated Control Loop States        | 176 |

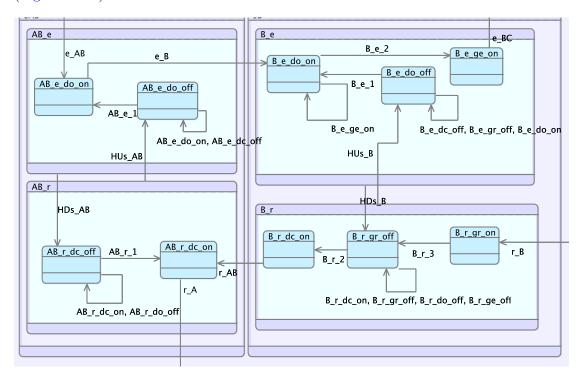

|           |      | 11.3.4          | Third Refinement                                         | 179 |

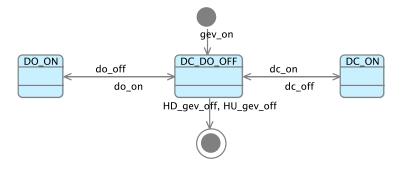

|           |      |                 | Fourth Refinement                                        |     |

|           |      | 11.3.6          | Fifth Refinement                                         | 180 |

|           |      |                 | Sixth Refinement                                         |     |

|           |      |                 | ation and Validation                                     |     |

|           | 11.5 | Overvi          | ew and Conclusions                                       | 184 |

| <b>12</b> | Con  | clusion         | ns and Future Work                                       | 187 |

viii *CONTENTS*

|              | 12.1 | Main (            | Contributions                            | . 187 |

|--------------|------|-------------------|------------------------------------------|-------|

|              | 12.2 | Scope             |                                          | . 189 |

|              | 12.3 | Scalabi           | ility                                    | . 190 |

|              |      |                   | d Work                                   |       |

|              | 12.5 | Related           | d Methodologies                          | . 192 |

|              |      |                   | tatic Gear Change Case Study             |       |

|              |      |                   | ial Optimisations of the Tool Chain      |       |

|              |      |                   | Work Directions                          |       |

|              |      |                   | Short-Term Goals                         |       |

|              |      |                   | Long-Term Goals                          |       |

| ٨            | Dof  | nomon             | at Transformation Templates              | 201   |

| A            | A.1  |                   | to-Response                              |       |

|              | A.1  |                   | Base Template                            |       |

|              |      |                   |                                          |       |

|              | 4.0  |                   | Transformed Event Template               |       |

|              | A.2  |                   | To-Multi Refinement Transformation       |       |

|              |      |                   | Base Template                            |       |

|              |      |                   | Delay Template                           |       |

|              |      | A.2.3             | Deadline Template                        |       |

|              |      | A.2.4             | Trigger Templates                        |       |

|              |      | A.2.5             | Response Templates                       |       |

|              | 4.0  | A.2.6             | Abort and Reset Event Templates          |       |

|              | A.3  |                   | Refinement Transformation                |       |

|              |      | A.3.1             | Base Template                            |       |

|              |      |                   | Event Templates                          |       |

|              |      | A.3.3             | Deadline Template                        |       |

|              |      | A.3.4             | Delay Template                           | . 211 |

| В            | Aut  | $\mathbf{omatic}$ | Prover Tactics Configuration             | 213   |

| $\mathbf{C}$ | Pac  | emaker            | r Test Case Scenarios                    | 215   |

| $\mathbf{D}$ | Case | e Stud            | y Requirement Documents                  | 219   |

|              |      | •                 | aker DDD Mode Requirements               | . 219 |

|              |      | D.1.1             | The Four Fundamental Timing Intervals    |       |

|              |      | D.1.2             | Lower Rate Interval                      |       |

|              |      | D.1.3             | Ventricular Refractory Period            | . 220 |

|              |      | D.1.4             | Atrioventricular Interval                | . 221 |

|              |      |                   | D.1.4.1 pAVI and sAVI                    | . 221 |

|              |      | D.1.5             | Postventricular Atrial Refractory Period | . 222 |

|              |      | D.1.6             | Derived Requirements                     | . 222 |

|              |      | D.1.7             | Atrial and Ventricular Blanking Periods  |       |

|              |      | D.1.8             | Ventricular Blanking Period              |       |

|              |      | D.1.9             | Postatrial Ventricular Blanking Period   |       |

|              |      |                   | Atrial Blanking Period                   |       |

|              |      |                   | Postventricular Atrial Blanking Period   |       |

|              |      |                   | Ventricular Safety Pacing                |       |

|              |      |                   | Value Ranges for Pacemaker Intervals     |       |

CONTENTS ix

|         |       | D.1.14 | Model-Checked Values                               | . 227 |

|---------|-------|--------|----------------------------------------------------|-------|

|         | D.2   | Messag | ge Passing Protocol Requirements                   | . 229 |

|         |       | D.2.1  | Environment Assumptions                            | . 229 |

|         |       | D.2.2  | Functional Requirements                            | . 229 |

|         |       | D.2.3  | Timing Constraints                                 | . 230 |

|         |       | D.2.4  | Error Detection                                    | . 231 |

|         | D.3   | Landir | ng Gear System Requirements                        | . 231 |

|         |       | D.3.1  | Environment Assumptions                            | . 231 |

|         |       | D.3.2  | Functional Requirements                            | . 232 |

|         |       | D.3.3  | Timing Constraints                                 | . 233 |

| ${f E}$ | tiGe  | en Sou | rce Code and Event-B Models                        | 235   |

|         | E.1   | tiGen  | Source Code                                        | . 235 |

|         | E.2   |        | B Model of the Pacemaker Passing Case Study        |       |

|         | E.3   |        | B Model of the Message Passing Protocol Case Study |       |

|         | E.4   | Event- | B Model of the Landing Gear System Case Study      | . 235 |

| R       | efere | nces   |                                                    | 237   |

|         |       |        |                                                    |       |

# List of Figures

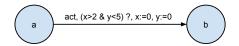

| 2.1  | An example of timed automaton                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

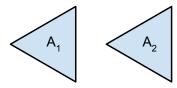

| 2.2  | Parallel composition pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24 |

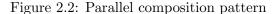

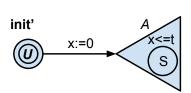

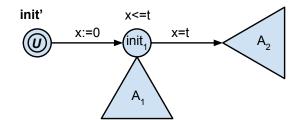

| 2.3  | Delay pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 24 |

| 2.4  | Deadline pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25 |

| 2.5  | Time-out pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25 |

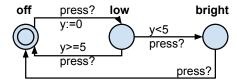

| 2.6  | Lamp example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27 |

| 2.7  | Lamp user example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27 |

| 9.1  | Contact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20 |

| 3.1  | Context                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30 |

| 3.2  | Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30 |

| 3.3  | Event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30 |

| 3.4  | Abstract machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33 |

| 3.5  | Refinement machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33 |

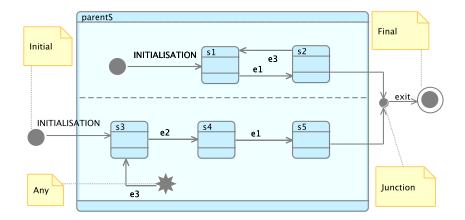

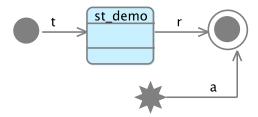

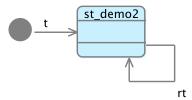

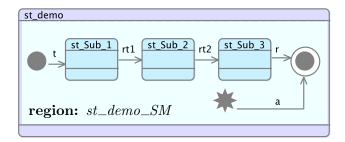

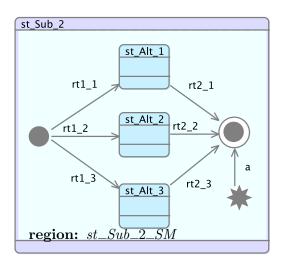

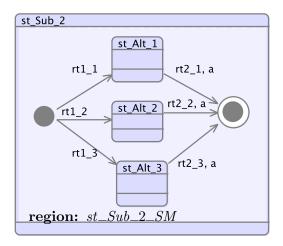

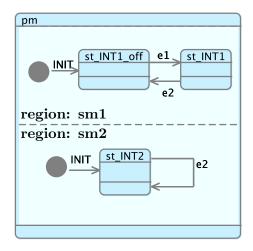

| 3.6  | iUML state machine exampleSM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35 |

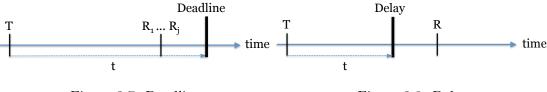

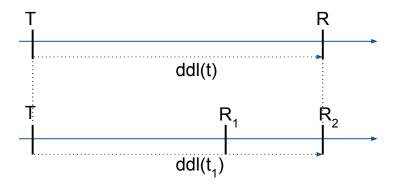

| 3.7  | Deadline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 38 |

| 3.8  | Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38 |

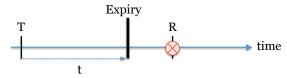

| 3.9  | Expiry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38 |

|      | The semantics of Sarshogh's deadline timing constraint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 39 |

|      | The semantics of Sarshogh's delay timing constraint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40 |

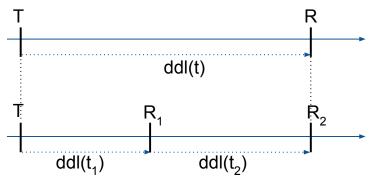

|      | Deadline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 41 |

| 3.13 | Deadline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 41 |

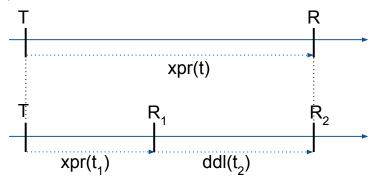

| 3.14 | Deadline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42 |

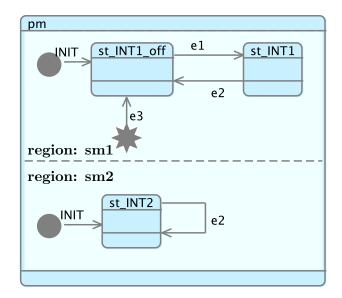

| 4.1  | Simplified pacemaker example. State machine $SM$ with two regions $sm1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 1.1  | and $sm2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45 |

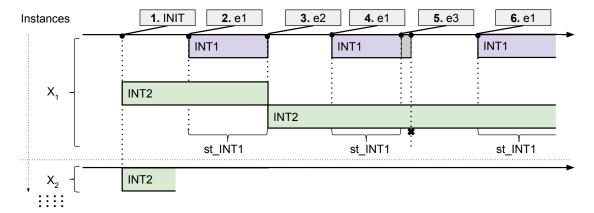

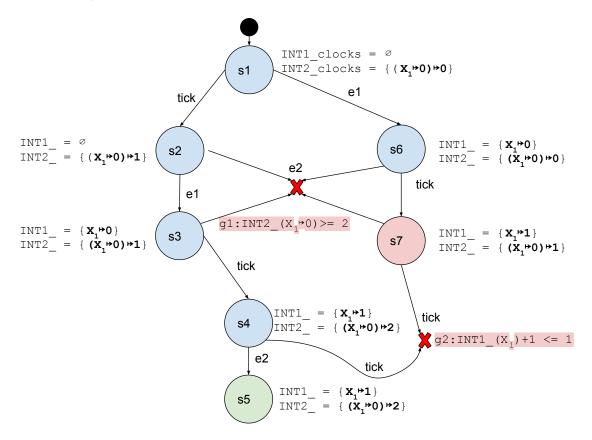

| 4.2  | Example execution scenario of the multi-instance state machines $sm1$ and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|      | sm2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46 |

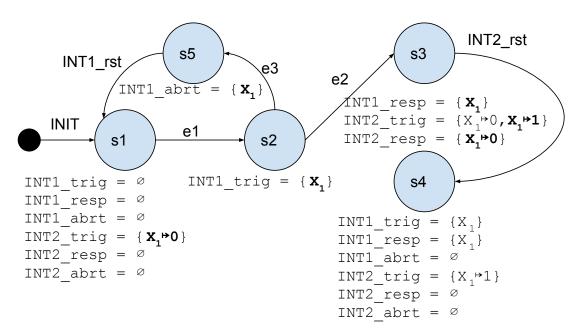

| 4.3  | INT1 variables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50 |