### UNIVERSITY OF SOUTHAMPTON

### FACULTY OF ENGINEERING AND THE ENVIRONMENT

Engineering of Science Mechatronics Research Group

### **Hybrid Modelling and Control for Switched-Mode Power Converters**

by **Xingda Yan**

Thesis for the degree of Doctor of Philosophy

Supervisor: Dr Zhan Shu

Prof Suleiman M Sharkh

November 8, 2017

#### UNIVERSITY OF SOUTHAMPTON

#### **ABSTRACT**

# FACULTY OF ENGINEERING AND THE ENVIRONMENT ENGINEERING OF SCIENCE MECHATRONICS RESEARCH GROUP

### Doctor of Philosophy

### **Hybrid Modelling and Control for Switched-Mode Power Converters**

by Xingda Yan

Switched-mode power converters are some of the most widely used power electronics circuits due to their advantages of high conversion efficiency, flexible output voltage, light weight. A variety of control methods have been developed for the switched-mode power converters. However, in many practical situation, additional constraints need to be considered, e.g., safety measurement, current limiting or soft-starting, gross changes of operation point with guaranteed system stability, which has not been fully addressed in the available research works. On the other hand, the majority of the control design for power converters are based on the state-space averaged approach which involves considerable approximation in analysis and synthesis. Hence, advanced control techniques are in demand, which should be more constraints friendly and based on more precise models.

In this thesis, much attention has been spent on designing controllers for both DC-DC converters and DC-AC inverters based on hybrid modelling and Lyapunov stability theory. Due to the existence of the power switches, switched-mode power converters are hybrid systems with both continuous dynamics and discrete transition events. Instead of linearizing the converter model around a specific operating point, hybrid modelling captures both dynamics, which results in more accurate models.

Firstly, a novel sampled-data control approach is proposed for DC-DC converters. DC-DC converters are modeled as sampled-data switched affine systems according to the status of the power switch. In order to avoid the delay of the switching signal, an on-line prediction method is adopted to estimate the system state at the next switching instant. Based on the switched affine model and the predicted system state, a novel switching control algorithm is synthesized by using the switched Lyapunov theory. The proposed approach is able to not only drive the output to a prescribed set point from any initial condition, but also track a varying reference signal, and the switching frequency can be adjusted online with guaranteed stability. In addition, with this approach, Continuous Conduction Mode (CCM) and Discontinuous Conduction Mode (DCM) operations can be treated in a unified way. Experimental verification has been carried out to test the effectiveness and merits of the proposed method.

Furthermore, to compensate the information loss due to limited access to the state, a multiple sampling scheme is employed to derive a discrete-time switched affine model with an augmented measurement output for DC-DC converters. Based on the model, an output-feedback switching control law, which drives the system state to a set of attainable switched equilibria, is synthesized by using a quadratic state-space partition. The multiple sampling scheme not only facilitates the controller synthesis, but also improves the energy efficiency of the converter by allowing a lower switching frequency.

In addition, hybrid modelling techniques have been extended to more complicated cases – DC-AC inverters as the increasing number of power switches and the time-variant nature of the references. A current controller based on the hybrid model of the three-phase two-level inverter has been developed, which can drive the inverter currents tracking the desired power references in realtime and keep a unity power factor at the same time. This method has been extended to three-phase NPC inverters later on. However, in order to solve the neutral point balancing issue, a capacitor voltages prediction algorithm, modified from model predictive control, has been adopted. It should also be mentioned that a novel hybrid model for a grid-connected single-phase NPC inverter also has been presented, which models not only the dynamic of the inverter but also the dynamic of the current reference. An experimental test platform including a three-phase NPC inverter and a FPGA control board has been designed to demonstrate the implementation of the proposed control scheme in practice.

# **Contents**

| Al             | Abstract                  |                                                                           |      |  |  |  |  |  |

|----------------|---------------------------|---------------------------------------------------------------------------|------|--|--|--|--|--|

| Li             | st of l                   | Figures                                                                   | xiii |  |  |  |  |  |

| Li             | st of '                   | Tables                                                                    | XV   |  |  |  |  |  |

| D              | Declaration of Authorship |                                                                           |      |  |  |  |  |  |

| A              | cknov                     | vledgements                                                               | xvii |  |  |  |  |  |

| 1 Introduction |                           |                                                                           |      |  |  |  |  |  |

|                | 1.1                       | Motivation                                                                | 1    |  |  |  |  |  |

|                | 1.2                       | Structure of the Thesis                                                   | 3    |  |  |  |  |  |

| 2              | Lite                      | rature Review                                                             | 5    |  |  |  |  |  |

|                | 2.1                       | Control Methods for DC-DC Converters                                      | 5    |  |  |  |  |  |

|                |                           | 2.1.1 DC-DC Converters Control in The Past                                | 5    |  |  |  |  |  |

|                |                           | 2.1.2 DC-DC Converters Control Today                                      | 8    |  |  |  |  |  |

|                |                           | 2.1.3 Current Issues                                                      | 15   |  |  |  |  |  |

|                | 2.2                       | Control Methods for DC-AC Inverters                                       | 16   |  |  |  |  |  |

|                |                           | 2.2.1 Linear Control                                                      | 16   |  |  |  |  |  |

|                |                           | 2.2.2 Hysteresis Control                                                  | 17   |  |  |  |  |  |

|                |                           | 2.2.3 Sliding Mode Control                                                | 18   |  |  |  |  |  |

|                |                           | 2.2.4 Model Predictive Control                                            | 19   |  |  |  |  |  |

|                | 2.3                       | Hybrid Modelling and Control                                              | 19   |  |  |  |  |  |

|                | 2.4                       | Summary                                                                   | 21   |  |  |  |  |  |

| I              | DC                        | -DC Converters                                                            | 23   |  |  |  |  |  |

| 3              | Rev                       | iew of Conventional Control Design for DC-DC Converters                   | 25   |  |  |  |  |  |

|                | 3.1                       | Linear Controller Design Based on the SSA Approach                        | 25   |  |  |  |  |  |

|                |                           | 3.1.1 Introduction of the DC-DC Buck Converter and Steady State Analysis. | 25   |  |  |  |  |  |

|                |                           | 3.1.2 Small Signal Analysis and State-Space Averaged Approach Modeling .  | 31   |  |  |  |  |  |

|                | 3.2                       | Hybrid Modeling and Model Predicative Control                             | 35   |  |  |  |  |  |

|                |                           | 3.2.1 Model Predictive Control                                            | 38   |  |  |  |  |  |

|                |                           | 3.2.2 Hybrid Modeling of the DC-DC Buck Converter                         | 38   |  |  |  |  |  |

|                |                           | 3.2.3 Modeling for Controller Design                                      | 41   |  |  |  |  |  |

|                |                           | 3.2.4 Model Predictive Controller Design                                  | 42   |  |  |  |  |  |

vi CONTENTS

|    | 3.3  | Summary                                                      | 43  |  |  |  |  |  |  |  |

|----|------|--------------------------------------------------------------|-----|--|--|--|--|--|--|--|

| 4  | Sam  | upled-Data Control with Adjustable Switching Frequency       | 45  |  |  |  |  |  |  |  |

|    | 4.1  | Hybrid Modelling in State-Space                              | 45  |  |  |  |  |  |  |  |

|    | 4.2  | Sampled-Data Control Scheme                                  | 48  |  |  |  |  |  |  |  |

|    |      | 4.2.1 Off-line Design of Switching Controller                | 49  |  |  |  |  |  |  |  |

|    |      | 4.2.2 Online Implementation                                  | 59  |  |  |  |  |  |  |  |

|    | 4.3  | Simulation Results                                           | 60  |  |  |  |  |  |  |  |

|    |      | 4.3.1 Model Normalization                                    | 60  |  |  |  |  |  |  |  |

|    |      | 4.3.2 Comparison with Other Control Schemes                  | 64  |  |  |  |  |  |  |  |

|    | 4.4  | Experiment Platform for Buck Converter Test                  | 65  |  |  |  |  |  |  |  |

|    |      | 4.4.1 The Buck Stage                                         | 65  |  |  |  |  |  |  |  |

|    |      | 4.4.2 Current Measurement                                    | 66  |  |  |  |  |  |  |  |

|    |      | 4.4.3 Voltage Measurement                                    | 68  |  |  |  |  |  |  |  |

|    |      | 4.4.4 MOSFET Gate Drive                                      | 70  |  |  |  |  |  |  |  |

|    | 4.5  | Experimental Results                                         | 72  |  |  |  |  |  |  |  |

|    | 1.0  | 4.5.1 Start Up and Close Down Response                       | 72  |  |  |  |  |  |  |  |

|    |      | 4.5.2 Continuous Conduction Mode (CCM)                       | 72  |  |  |  |  |  |  |  |

|    |      | 4.5.3 Discontinuous Conduction Mode (DCM)                    | 75  |  |  |  |  |  |  |  |

|    | 4.6  | Summary                                                      | 78  |  |  |  |  |  |  |  |

|    | 4.0  | Summary                                                      | 70  |  |  |  |  |  |  |  |

| 5  |      | tput Feedback Switching Control Using Multiple Sampling 79   |     |  |  |  |  |  |  |  |

|    | 5.1  | Problem Formulation                                          | 79  |  |  |  |  |  |  |  |

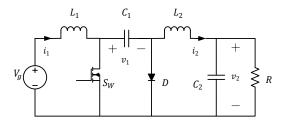

|    |      | 5.1.1 Switched Models for Different DC-DC Topologies         | 79  |  |  |  |  |  |  |  |

|    | 5.2  | A Discrete Model Under Multiple Sampling                     | 82  |  |  |  |  |  |  |  |

|    | 5.3  | Stabilization                                                | 84  |  |  |  |  |  |  |  |

|    | 5.4  | Simulation Results                                           | 90  |  |  |  |  |  |  |  |

|    |      | 5.4.1 Buck Converter                                         | 90  |  |  |  |  |  |  |  |

|    |      | 5.4.2 Ćuk Converter                                          | 98  |  |  |  |  |  |  |  |

|    | 5.5  | Summary                                                      | 103 |  |  |  |  |  |  |  |

|    |      |                                                              |     |  |  |  |  |  |  |  |

| II | DC   | C-AC Converters                                              | 105 |  |  |  |  |  |  |  |

| 6  | Swit | tching Control of Grid-Connected Three-Phase DC-AC Inverters | 107 |  |  |  |  |  |  |  |

|    | 6.1  | Hybrid Modelling of DC-AC Inverters                          | 107 |  |  |  |  |  |  |  |

|    | 6.2  | Current Control Law Design                                   | 110 |  |  |  |  |  |  |  |

|    |      | 6.2.1 Online Implementation                                  | 110 |  |  |  |  |  |  |  |

|    |      | 6.2.2 Current Reference Generation                           | 110 |  |  |  |  |  |  |  |

|    |      | 6.2.3 Stabilization of the Error System                      | 112 |  |  |  |  |  |  |  |

|    | 6.3  | Simulation Results                                           | 114 |  |  |  |  |  |  |  |

|    |      | 6.3.1 Nominal Operation                                      | 115 |  |  |  |  |  |  |  |

|    |      | 6.3.2 Active Power Tracking                                  | 116 |  |  |  |  |  |  |  |

|    | 6.4  | Summary                                                      | 118 |  |  |  |  |  |  |  |

|    | J. 1 |                                                              | 110 |  |  |  |  |  |  |  |

| 7  | Swit | tching Control of Grid-Connected Single-Phase NPC Inverters  | 119 |  |  |  |  |  |  |  |

|    | 7.1  | Switching States of Single-Phase Grid-Connected NPC Inverter | 119 |  |  |  |  |  |  |  |

|    | 7.2  | Hybrid Modelling and Switching Controller Design             | 121 |  |  |  |  |  |  |  |

*CONTENTS* vii

|     |                                                        | 7.2.1 Hybrid Model of the Filter Part               | 22        |  |  |  |  |  |  |  |

|-----|--------------------------------------------------------|-----------------------------------------------------|-----------|--|--|--|--|--|--|--|

|     |                                                        | 7.2.2 Switching Controller Design                   | 22        |  |  |  |  |  |  |  |

|     |                                                        | 7.2.3 Auxiliary Voltage Balancing Controller        | 25        |  |  |  |  |  |  |  |

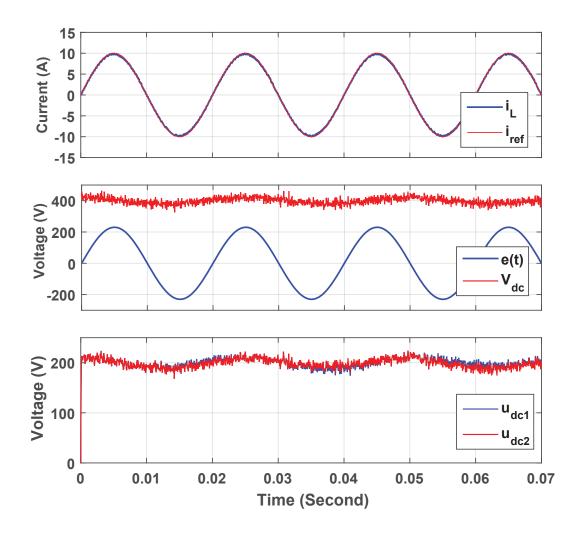

|     | 7.3                                                    | Simulation Results                                  | 26        |  |  |  |  |  |  |  |

|     |                                                        | 7.3.1 Nominal Operation                             | 26        |  |  |  |  |  |  |  |

|     |                                                        | 7.3.2 Reference Variation                           | 26        |  |  |  |  |  |  |  |

|     |                                                        | 7.3.3 DC-link Voltage Variation                     | 27        |  |  |  |  |  |  |  |

|     |                                                        | 7.3.4 Model Parameters Tolerances                   | 28        |  |  |  |  |  |  |  |

|     | 7.4                                                    | Summary                                             | 28        |  |  |  |  |  |  |  |

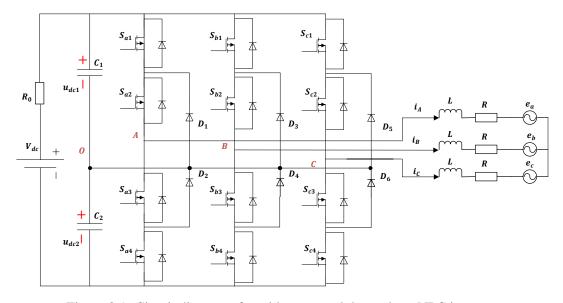

| 8   | C!4                                                    | ching Control of Three-Phase NPC Inverters 13       | 1         |  |  |  |  |  |  |  |

| 0   | 8.1                                                    | 0                                                   |           |  |  |  |  |  |  |  |

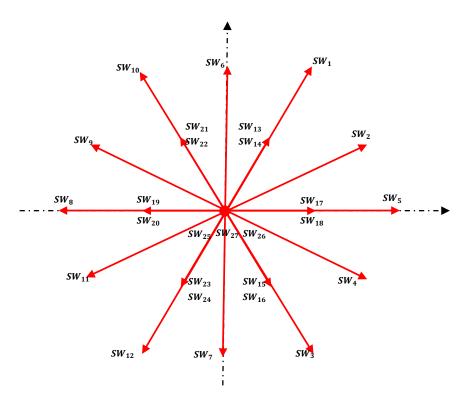

|     | 8.2                                                    | <b>,</b>                                            |           |  |  |  |  |  |  |  |

|     | 8.2                                                    |                                                     |           |  |  |  |  |  |  |  |

|     |                                                        |                                                     |           |  |  |  |  |  |  |  |

|     |                                                        | 8.2.2 Stabilization of the Error System             |           |  |  |  |  |  |  |  |

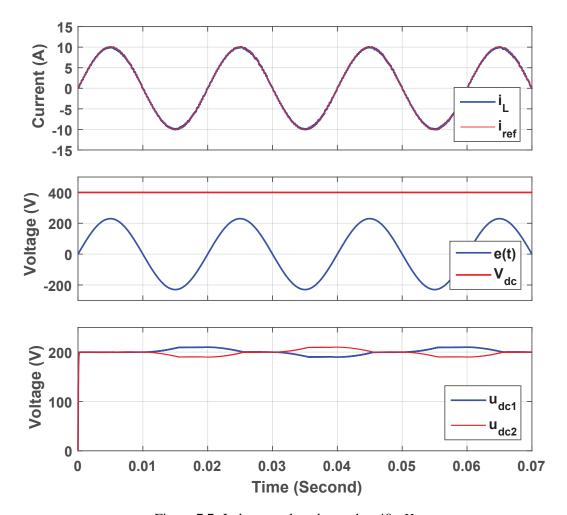

|     | 8.3                                                    | Simulation Results                                  |           |  |  |  |  |  |  |  |

|     | 8.4                                                    | Summary                                             |           |  |  |  |  |  |  |  |

|     | 0.4                                                    | Summary                                             | +2        |  |  |  |  |  |  |  |

| 9   | Experiment Validation on Three Phase NPC Inverters  14 |                                                     |           |  |  |  |  |  |  |  |

|     | 9.1                                                    | Switching Controller for NPC Inverters with RL Load | 13        |  |  |  |  |  |  |  |

|     |                                                        | 9.1.1 Phase Current Controller Design               | 13        |  |  |  |  |  |  |  |

|     |                                                        | 9.1.2 Capacitor Voltage Deviation Prediction        | 4         |  |  |  |  |  |  |  |

|     | 9.2                                                    | SEMIKRON Three Level Evaluation Inverter            | 15        |  |  |  |  |  |  |  |

|     | 9.3                                                    | Experimental Setup                                  | 15        |  |  |  |  |  |  |  |

|     | 9.4                                                    | Implementation based on FPGA                        | 6         |  |  |  |  |  |  |  |

|     |                                                        | 9.4.1 VHDL Modules                                  | 6         |  |  |  |  |  |  |  |

|     | 9.5                                                    | Experimental Results                                | <u>i2</u> |  |  |  |  |  |  |  |

|     | 9.6                                                    | Summary                                             | 5         |  |  |  |  |  |  |  |

| 10  | Conc                                                   | clusions and Future Research 15                     | 57        |  |  |  |  |  |  |  |

| - • |                                                        | Conclusions                                         | •         |  |  |  |  |  |  |  |

|     |                                                        | Future Research                                     |           |  |  |  |  |  |  |  |

| D - | feren                                                  | ces 16                                              | 3         |  |  |  |  |  |  |  |

| 1/G | ierell                                                 |                                                     | IJ        |  |  |  |  |  |  |  |

# **List of Figures**

| 1.1                               | Solar PV installations and average solar PV price in US [Source:Solar Energy Industries Association]                                                        |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1                               | Block diagram of a basic voltage mode controller                                                                                                            |

| 2.2                               | Block diagram of a basic current mode controller                                                                                                            |

| 2.3                               | The waveforms of the signal in a current controller in peak current mode control                                                                            |

| 2.4                               | Block diagram of a peak current controller with the slope compensation                                                                                      |

| <ul><li>2.5</li><li>2.6</li></ul> | Block diagram of the general structure of a digital current-mode controller Current waveform of the inductor and reference signal in a digital current-mode |

|                                   | controller                                                                                                                                                  |

| 2.7                               | Block diagram of DC-DC converters with a hysteresis controller                                                                                              |

| 2.8                               | Waveform of the output voltage and the gate signal used in a hysteresis controller                                                                          |

| 2.9                               | Sliding surface and state trajectory in the state-space                                                                                                     |

| 2.10                              | Field-oriented control diagram [1]                                                                                                                          |

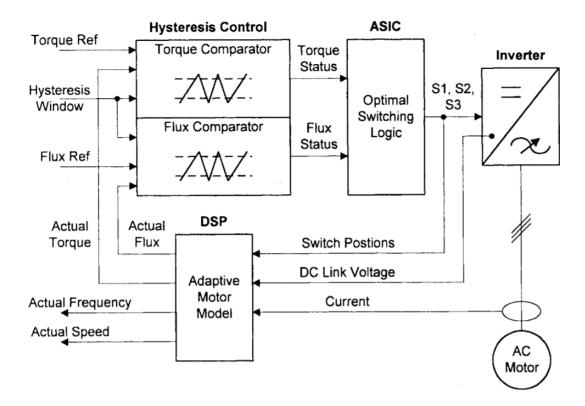

| 2.11                              | Direct torque control diagram [2]                                                                                                                           |

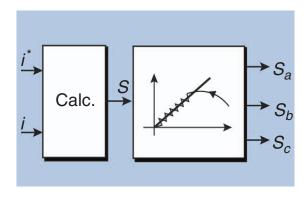

| 2.12                              | Sliding mode control diagram [3]                                                                                                                            |

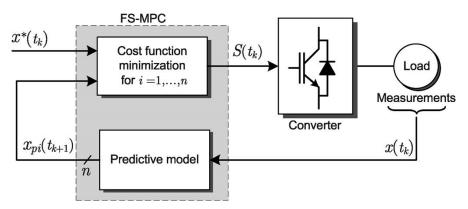

| 2.13                              | Model predictive control diagram [4]                                                                                                                        |

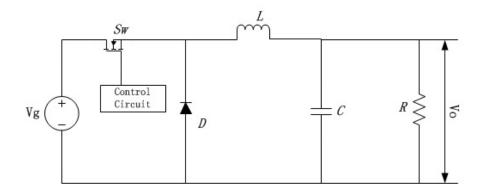

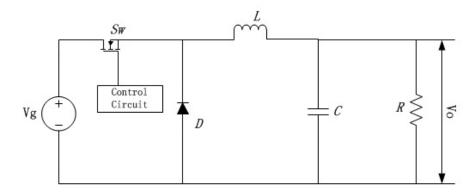

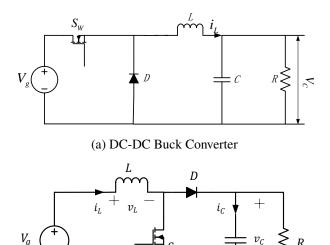

| 3.1                               | A buck converter topology                                                                                                                                   |

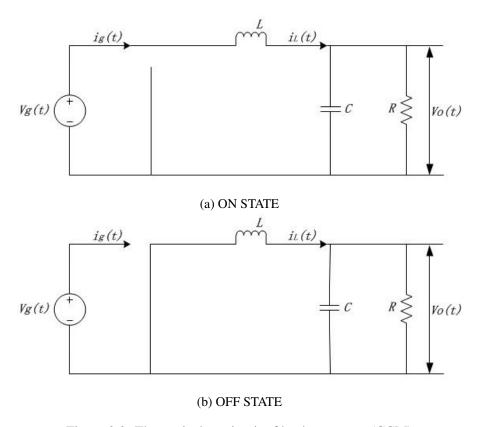

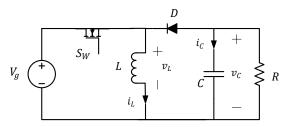

| 3.2                               | The equivalent circuit of buck converter (CCM)                                                                                                              |

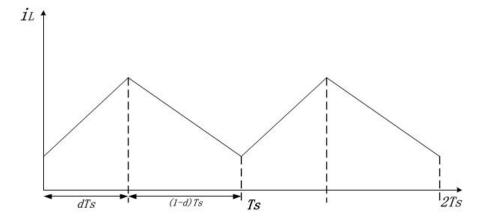

| 3.3                               | Inductor current waveform of the buck converter (CCM)                                                                                                       |

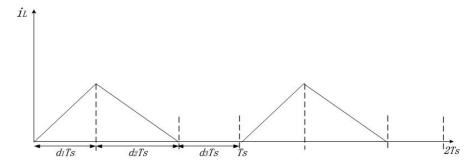

| 3.4                               | Inductor current waveform of the buck converter (DCM)                                                                                                       |

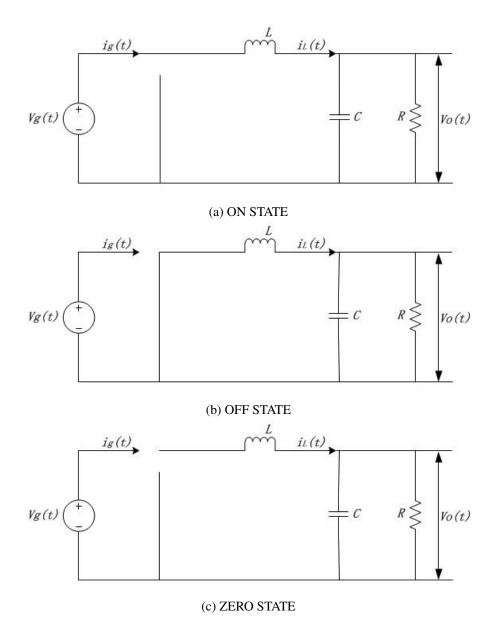

| 3.5                               | The equivalent circuit of the buck converter (DCM)                                                                                                          |

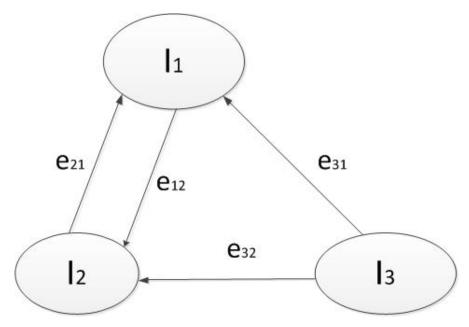

| 3.6                               | State diagram of hybrid system $(q = 1, 2, 3)$                                                                                                              |

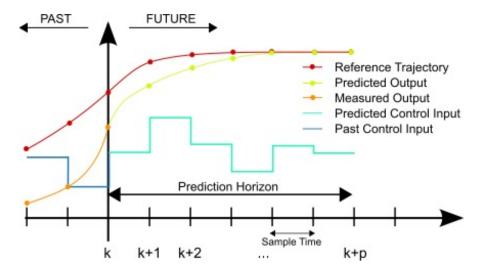

| 3.7                               | Receding horizon idea (image from wikipedia—licensed under the Creative                                                                                     |

|                                   | Commons Attribution-Share Alike 3.0 Unported)                                                                                                               |

| 3.8                               | A buck converter topology                                                                                                                                   |

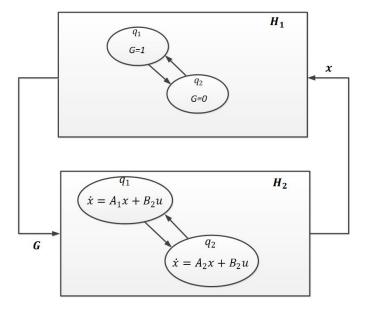

| 3.9                               | Hybrid automaton of the DC-DC buck converter                                                                                                                |

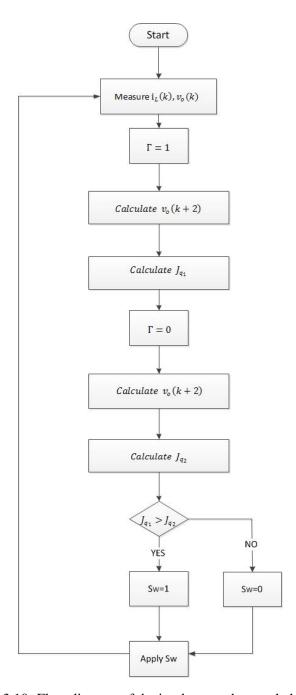

| 3.10                              | Flow diagram of the implemented control algorithm                                                                                                           |

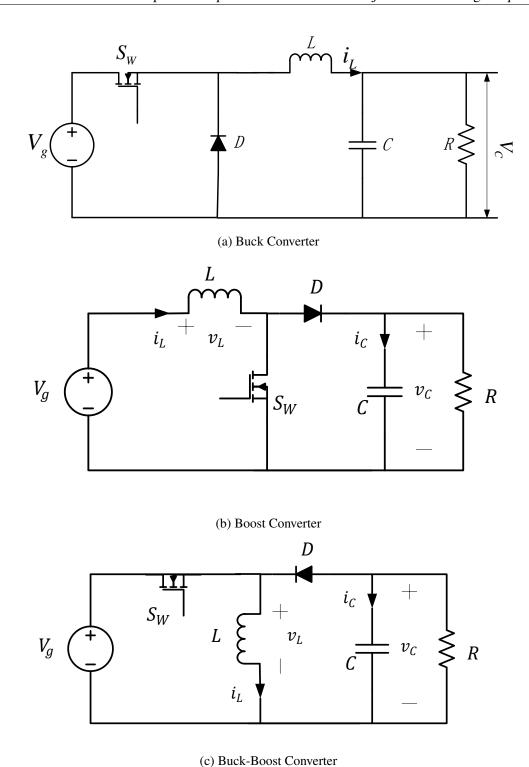

| 4.1                               | Topologies for different DC-DC Converters                                                                                                                   |

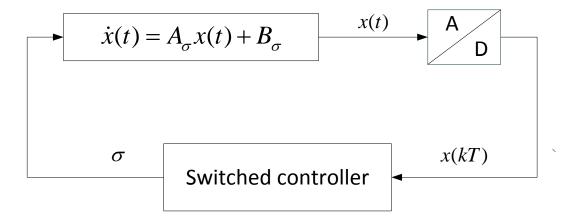

| 4.2                               | General sampled-data control structure for DC-DC buck converters                                                                                            |

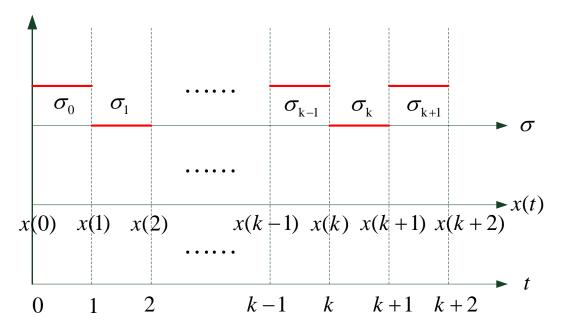

| 4.3                               | The time relationship among different variables                                                                                                             |

| 4.4                               | Flow chart of the proposed algorithm                                                                                                                        |

| 4.5                               | The start-up responses of $v_C$ and $i_L$ without switching frequency tuning (Simulation)                                                                   |

| 4.6                               | Switching surface for different reference points.                                                                                                           |

| 4.7                               | The responses of $v_C$ and $i_L$ with switching frequency tuning (Simulation)                                                                               |

x LIST OF FIGURES

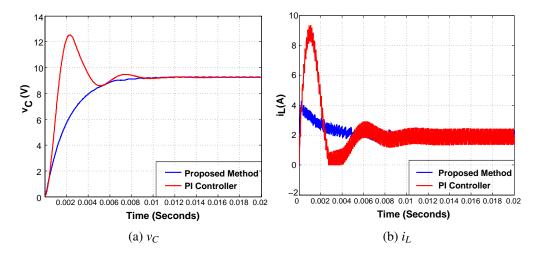

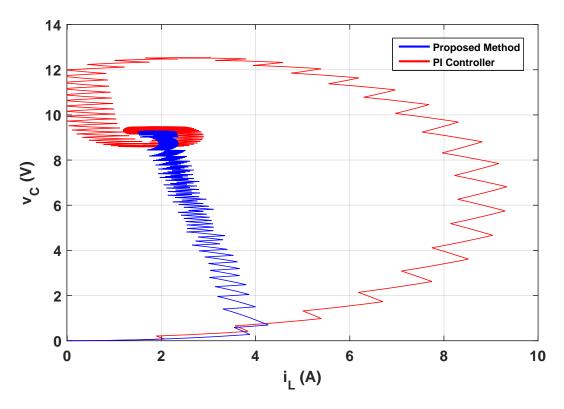

| 4.8  | The responses of $v_C$ and $i_L$ under proposed method and a PI controller (Simula-                                                                                          | . <del>.</del> |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 4.0  | tion)                                                                                                                                                                        | 65             |

| 4.9  | Phase diagrams of the proposed method and a PI controller                                                                                                                    | 65             |

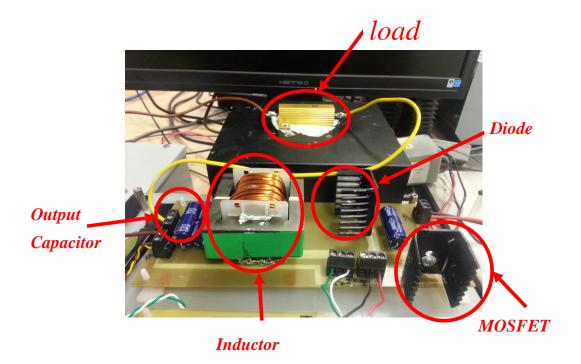

|      | Buck stage PCB board                                                                                                                                                         | 66             |

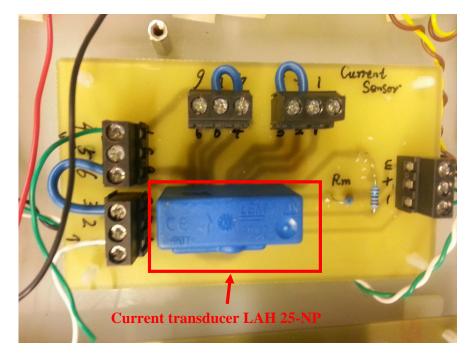

|      | Current measurement PCB board                                                                                                                                                | 67             |

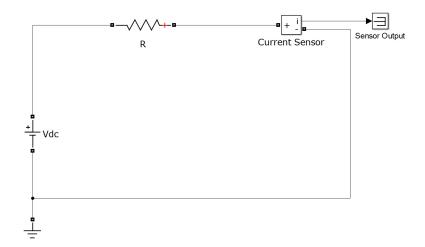

|      | Current calibration circuit                                                                                                                                                  | 67             |

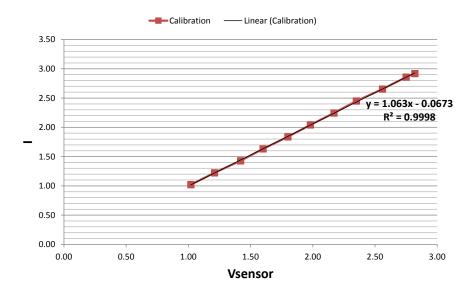

|      | Linear fitting of current sensor calibration                                                                                                                                 | 68             |

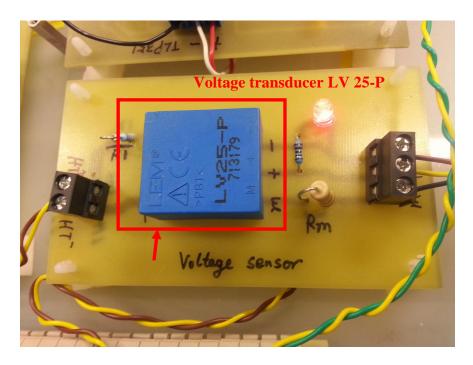

|      | Voltage measurement PCB board                                                                                                                                                | 69             |

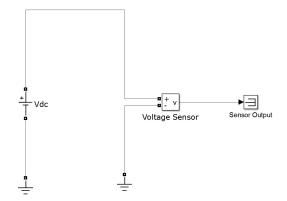

|      | Voltage calibration circuit                                                                                                                                                  | 69             |

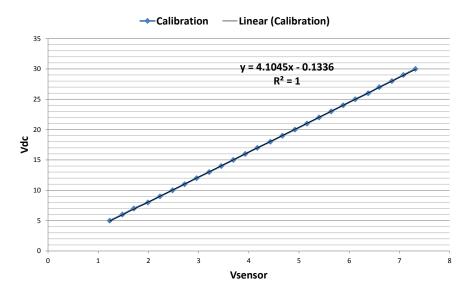

|      | Linear fitting of voltage sensor calibration                                                                                                                                 | 70             |

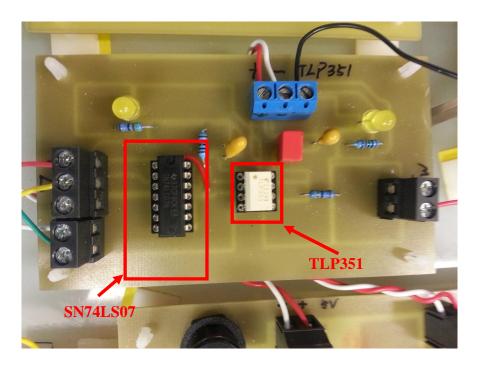

|      | MOSFET drive board                                                                                                                                                           | 71             |

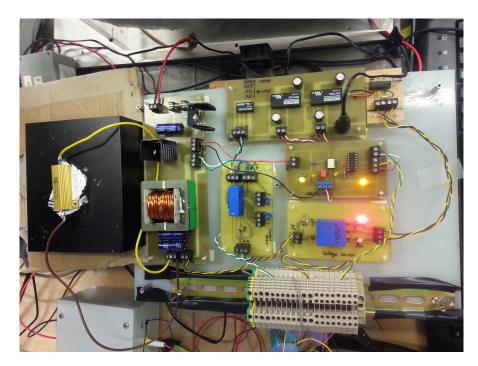

|      | Whole buck converter system without control platform                                                                                                                         | 71             |

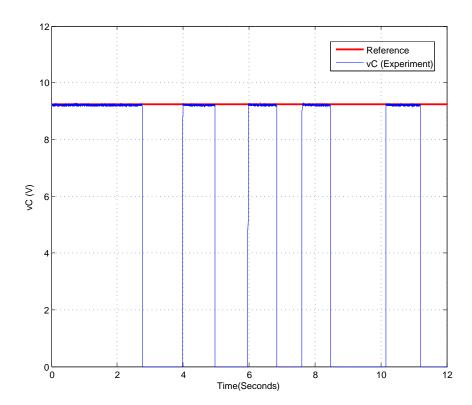

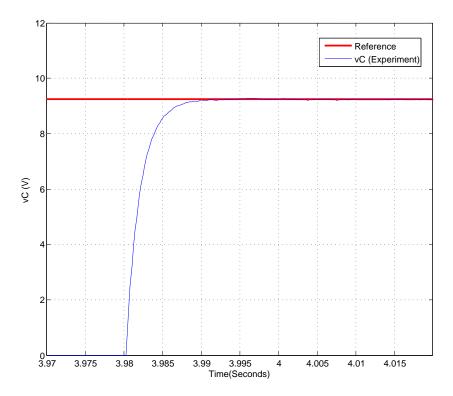

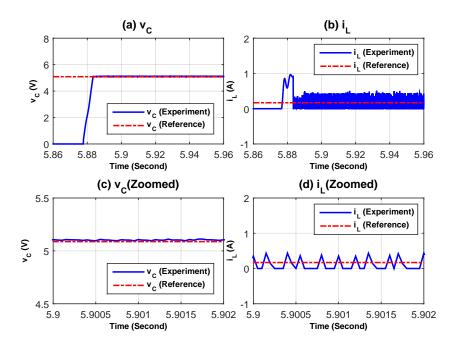

| 4.19 | The response of the output voltage $v_C$                                                                                                                                     | 72             |

| 4.20 | The zoomed response of the output voltage $v_C$                                                                                                                              | 73             |

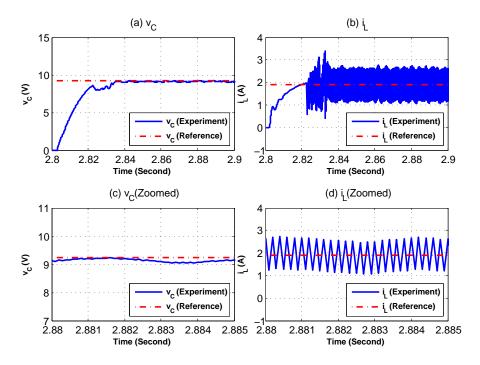

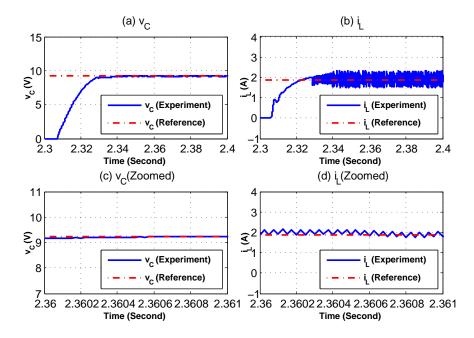

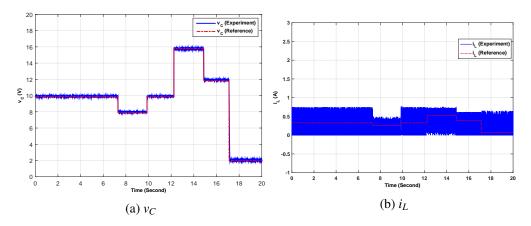

| 4.21 | The responses of $v_C$ and $i_L$ ( $f_s = 10 \text{ kHz}$ , CCM)                                                                                                             | 74             |

| 4.22 | The responses of $v_C$ and $i_L$ ( $f_s = 20 \text{ kHz}$ , CCM)                                                                                                             | 74             |

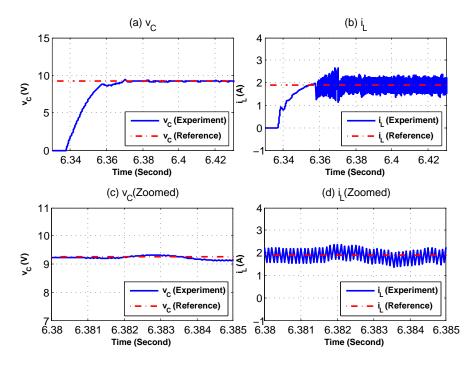

| 4.23 | The responses of $v_C$ and $i_L$ ( $f_s = 40 \text{ kHz}$ , CCM)                                                                                                             | 75             |

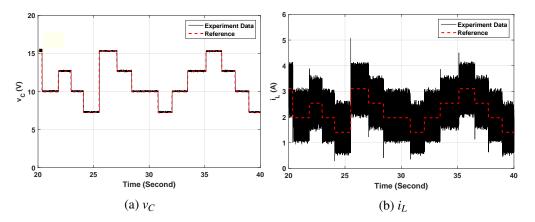

| 4.24 | The responses of $v_C$ and $i_L$ to different reference points (CCM mode)                                                                                                    | 75             |

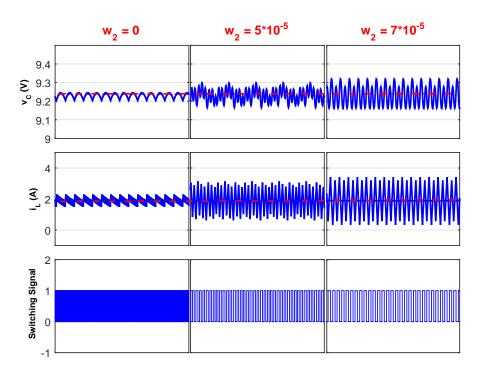

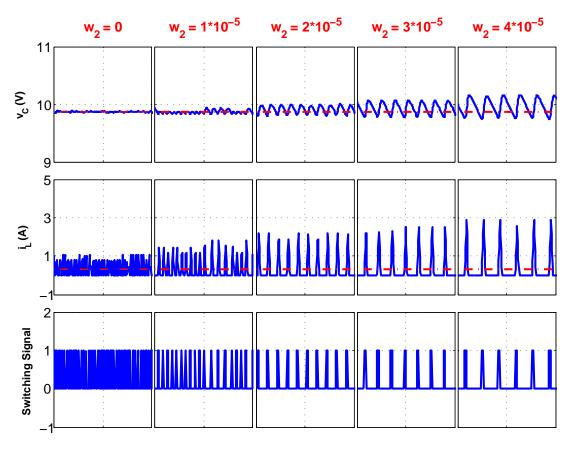

| 4.25 | Experimental behaviour of $v_C$ , $i_L$ and switching signal $\sigma$ when tuning the weight-                                                                                |                |

|      | ing factor $w_2$ (CCM mode)                                                                                                                                                  | 76             |

| 4.26 | The start-up responses of $v_C$ and $i_L$ (DCM mode)                                                                                                                         | 76             |

| 4.27 | The responses of $v_C$ and $i_L$ to different reference points (DCM mode)                                                                                                    | 77             |

| 4.28 | Experimental behaviour of $v_C$ , $i_L$ and switching signal $\sigma$ when tuning the weight-                                                                                |                |

|      | ing factor $w_2$ (DCM mode)                                                                                                                                                  | 77             |

| 5.1  | Topologies for different DC-DC Converters                                                                                                                                    | 80             |

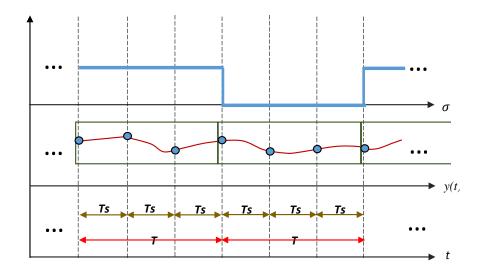

| 5.2  | Multiple sampling technique ( $h = 3, m = 1$ )                                                                                                                               | 82             |

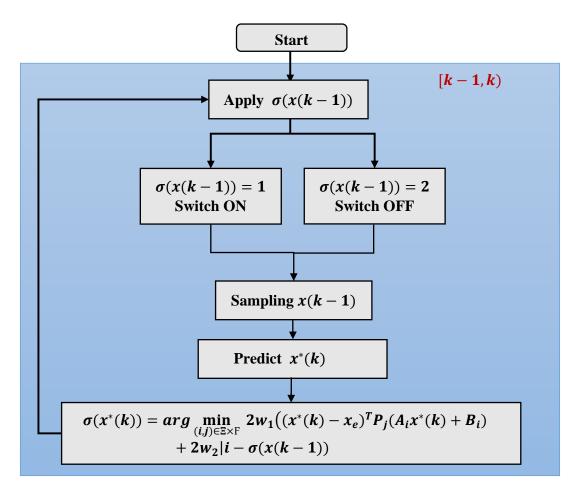

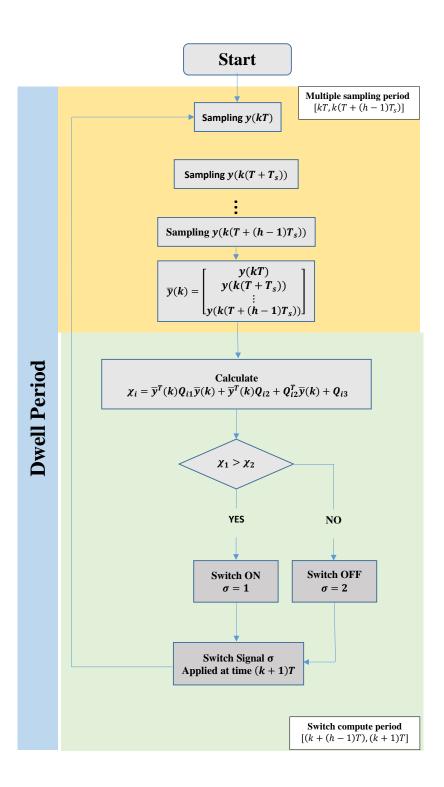

| 5.3  | Flowchart of the proposed output feedback control $\dots$                                                                                                                    | 89             |

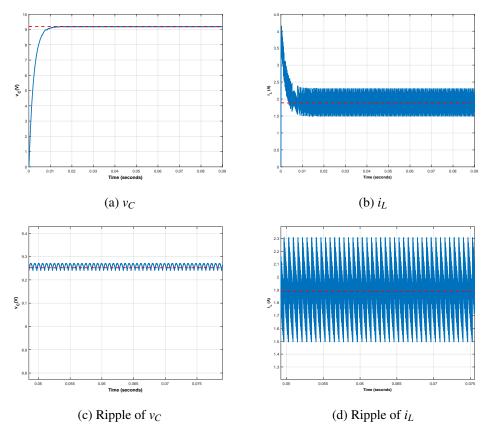

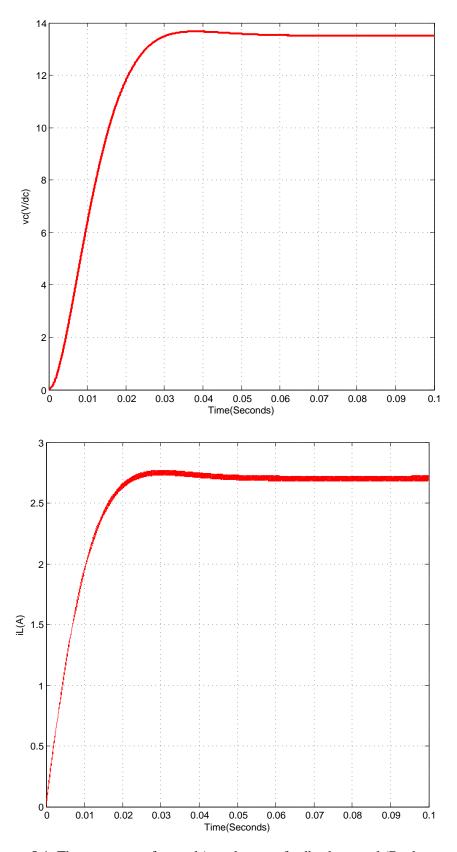

| 5.4  | The responses of $v_C$ and $i_L$ under state feedback control (Buck converter)                                                                                               | 94             |

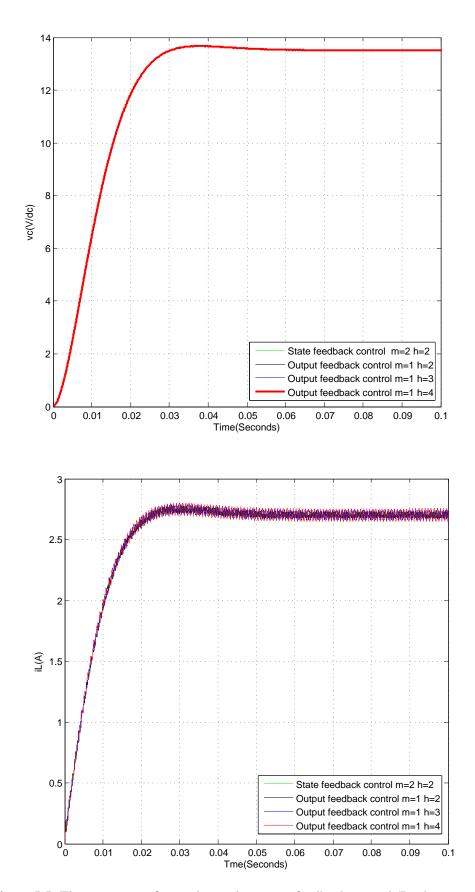

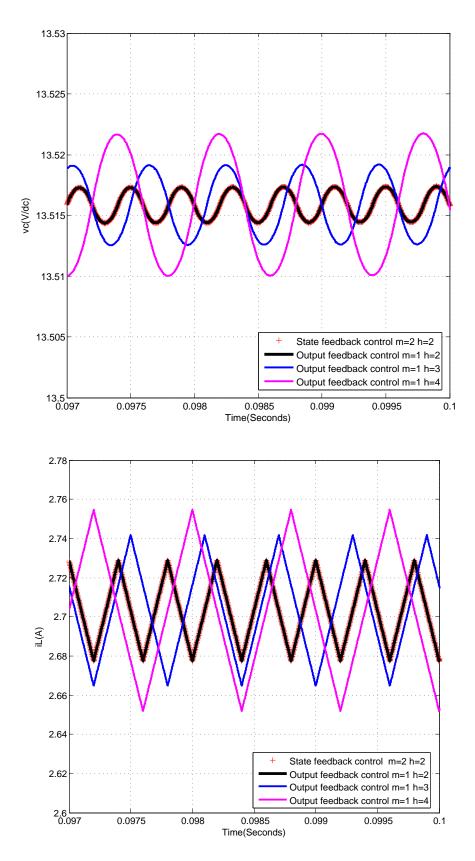

| 5.5  | The responses of $v_C$ and $i_L$ under output feedback control (Buck converter)                                                                                              | 95             |

| 5.6  | The zeomed responses of $v_C$ and $i_L$ under output feedback control(Buck converter). The zeomed responses of $v_C$ and $i_L$ under output feedback control(Buck converter) |                |

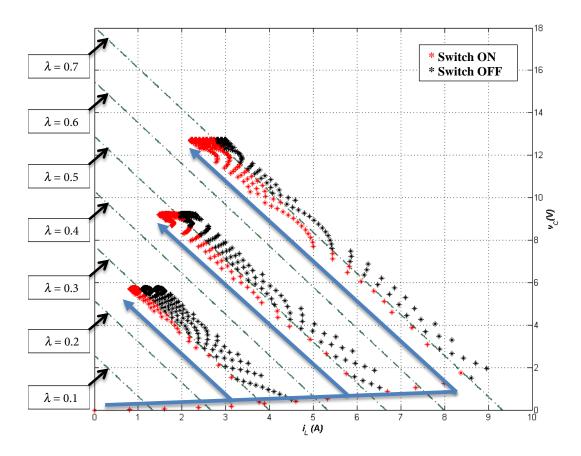

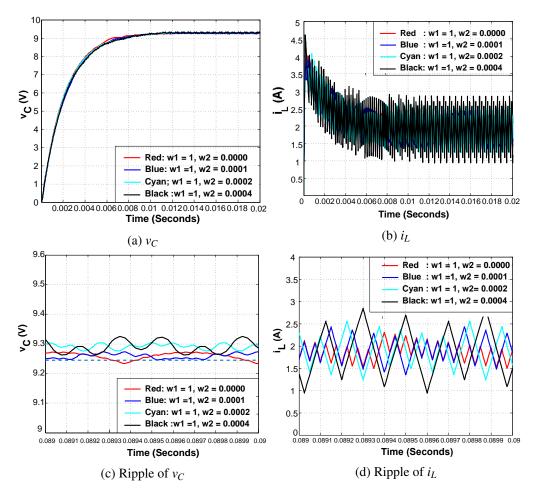

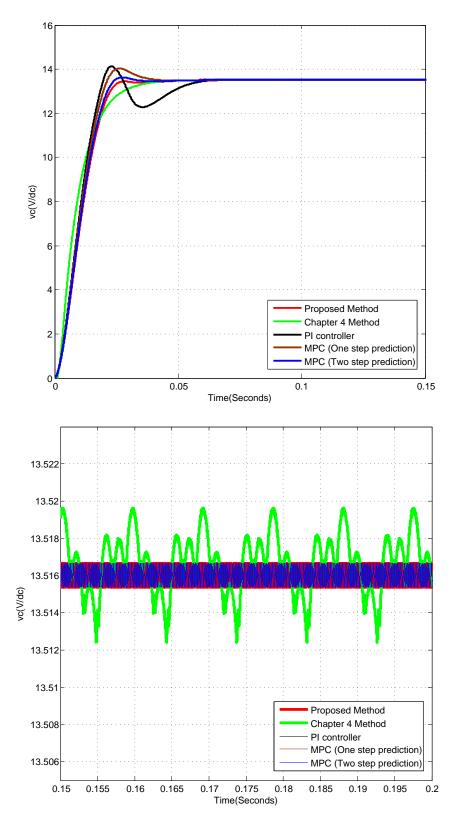

| 5.7  | The response of $v_C$ and zoomed under different control scheme (Buck converter)                                                                                             | 97             |

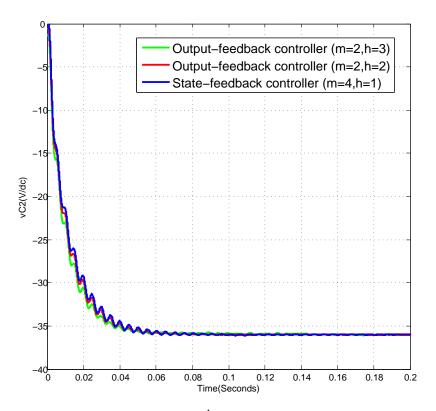

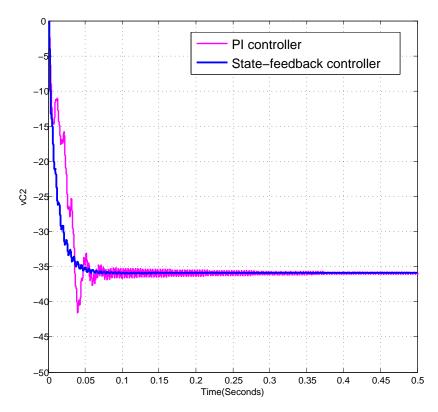

| 5.8  | The response of $v_{C2}$ for the Ćuk converters under output feedback control                                                                                                | 99             |

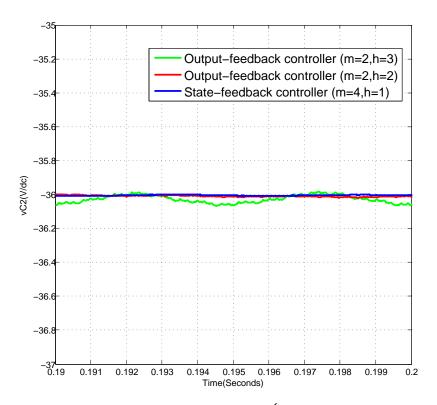

| 5.9  | Zoomed of the response of $v_{C2}$ for the Ćuk converters under output feedback                                                                                              |                |

| 3.7  |                                                                                                                                                                              | 100            |

| 5 10 |                                                                                                                                                                              | 102            |

| 3.10 | The responses of $v_{C2}$ under the proposed controller and a recontroller                                                                                                   | 102            |

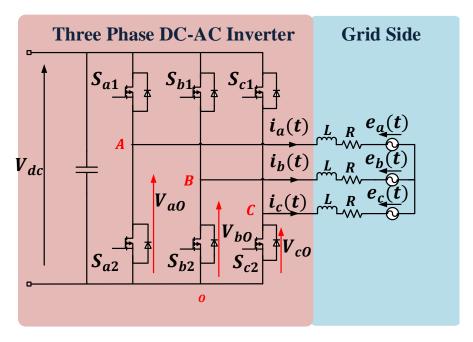

| 6.1  |                                                                                                                                                                              | 108            |

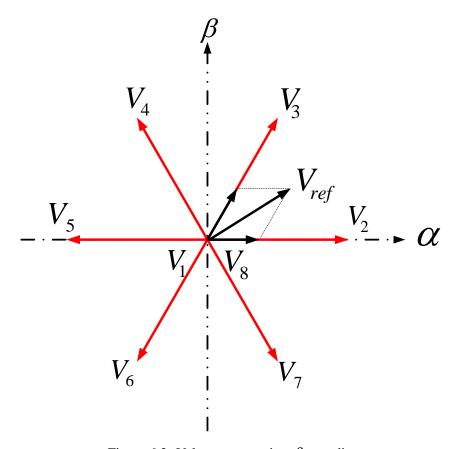

| 6.2  | Voltage vectors in $\alpha\beta$ coordinates                                                                                                                                 | 110            |

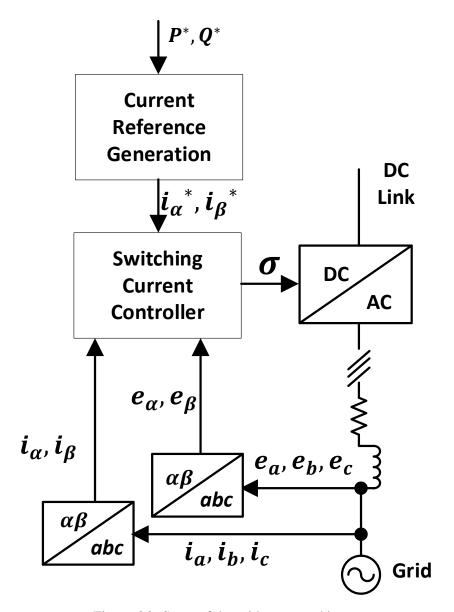

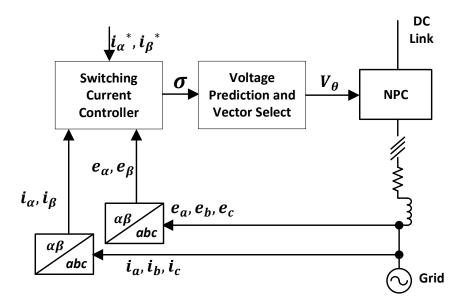

| 6.3  | Setup of the grid-connected inverter                                                                                                                                         | 111            |

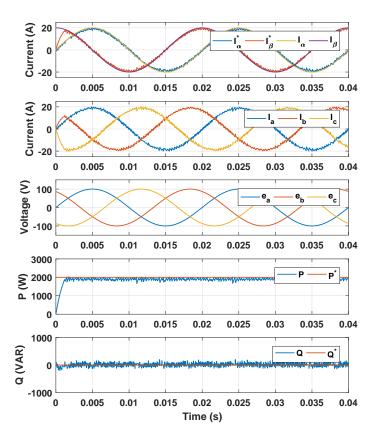

| 6.4  | The waveforms of the grid currents $i_{\alpha}$ , $i_{\beta}$ in $\alpha\beta$ -frame, $i_a$ , $i_b$ , $i_c$ in $abc$ -frame,                                                |                |

|      | grid voltages $e_a$ , $e_b$ , $e_c$ , active power and reactive power when the power refer-                                                                                  |                |

|      |                                                                                                                                                                              | 114            |

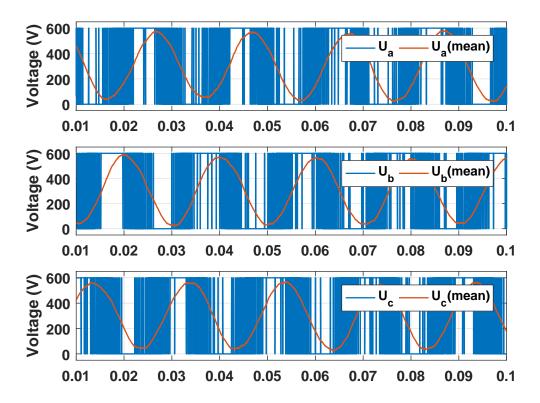

| 6.5  | The waveforms and the mean of the phase voltages $V_{aO}$ , $V_{bO}$ , $V_{cO}$ when the                                                                                     |                |

|      |                                                                                                                                                                              | 115            |

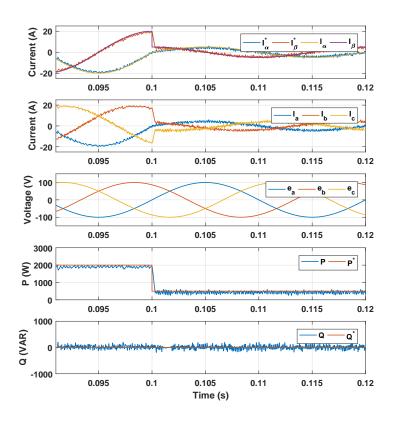

| 6.6  | The waveforms of the grid currents $i_{\alpha}$ , $i_{\beta}$ in $\alpha\beta$ -frame, $i_a$ , $i_b$ , $i_c$ in $abc$ -frame,                                                |                |

|      | grid voltages $e_a$ , $e_b$ , $e_c$ , active power and reactive power with various active                                                                                    |                |

|      | power steps.                                                                                                                                                                 | 116            |

LIST OF FIGURES xi

| 6.7  | The zoomed waveforms of the grid currents $i_{\alpha}$ , $i_{\beta}$ in $\alpha\beta$ -frame, $i_a$ , $i_b$ , $i_c$ in $abc$ -frame, grid voltages $e_a$ , $e_b$ , $e_c$ , active power and reactive power with various |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | active power steps.                                                                                                                                                                                                     | 117 |

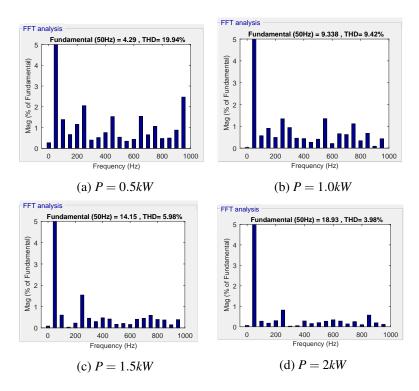

| 6.8  | Total Harmonic Distortion (THD) of grid current                                                                                                                                                                         | 117 |

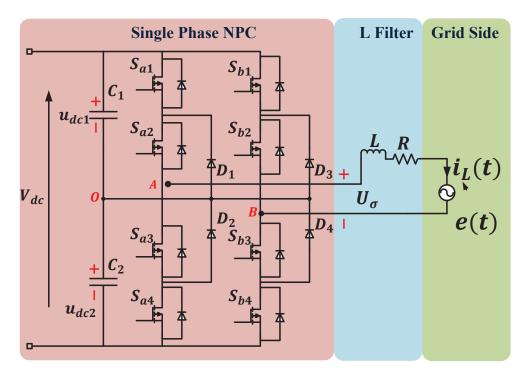

| 7.1  | Single-phase grid-connected NPC inverter for distributed energy source application                                                                                                                                      | 120 |

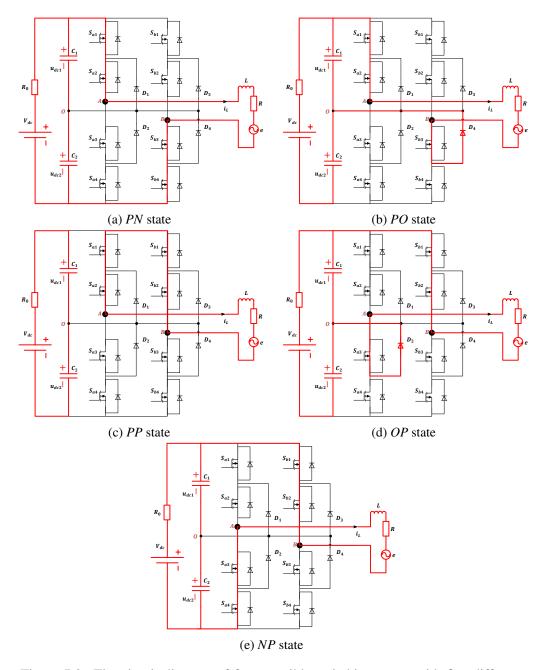

| 7.2  | The circuit diagram of four possible switching states with five different voltage level                                                                                                                                 | 121 |

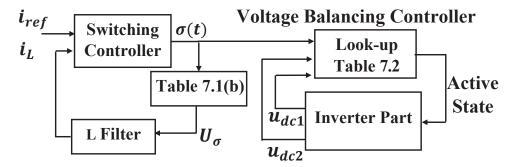

| 7.3  | A proposed control structure                                                                                                                                                                                            | 122 |

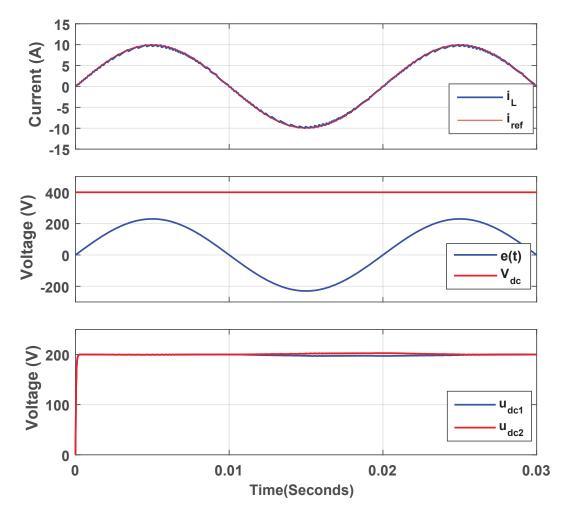

| 7.4  | Nominal operation                                                                                                                                                                                                       | 127 |

| 7.5  | Reference magnitude changed to 5V during 0.025s to 0.045s                                                                                                                                                               | 128 |

| 7.6  | DC-link voltage with large ripple and variation                                                                                                                                                                         | 129 |

| 7.7  | Inductor value changed to $40mH$                                                                                                                                                                                        | 130 |

| 8.1  | Circuit diagram of a grid-connected three-phase NPC inverter                                                                                                                                                            | 131 |

| 8.2  | Voltage vectors in $\alpha\beta$ coordinates                                                                                                                                                                            | 132 |

| 8.3  | Setup of the grid-connected inverter                                                                                                                                                                                    | 134 |

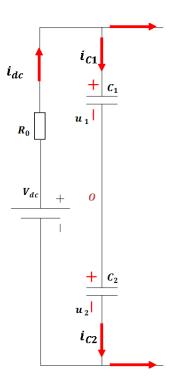

| 8.4  | Circuit diagram about DC side current follow of the NPC inverter                                                                                                                                                        | 137 |

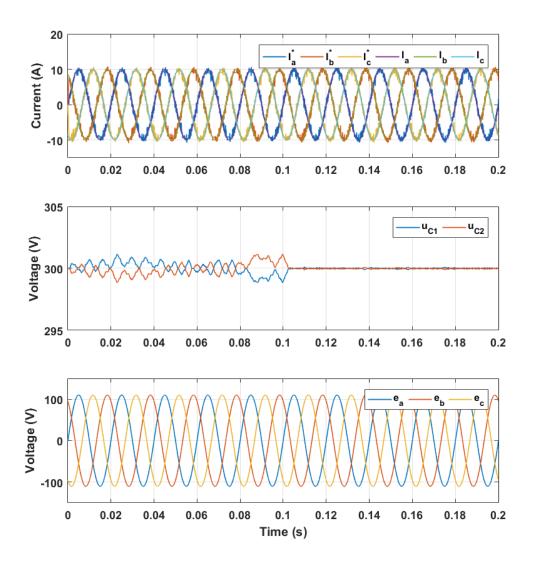

| 8.5  | The waveforms of the grid currents $i_a$ , $i_b$ , $i_c$ in $abc$ -frame as well as the current                                                                                                                         |     |

|      | references, the capacitor voltage $u_{C1}$ and $u_{C2}$ , grid voltages $e_a$ , $e_b$ , $e_c$                                                                                                                           | 140 |

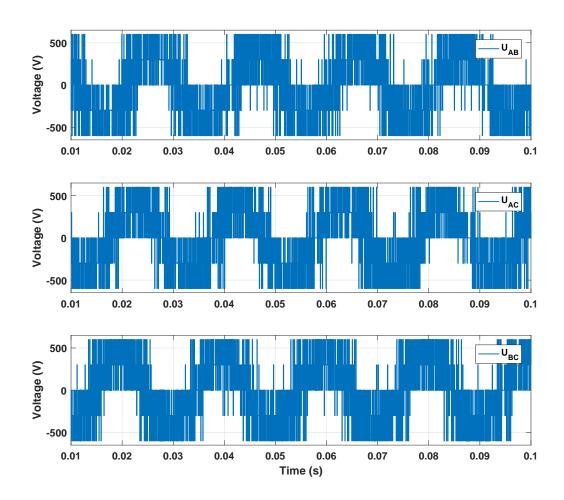

| 8.6  | The waveforms and the mean of the line voltages $U_{AB}$ , $U_{AC}$ , $U_{BC}$                                                                                                                                          | 141 |

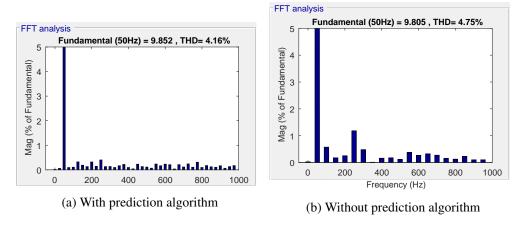

| 8.7  | Total Harmonic Distortion (THD) of Grid Current before and after capacitor voltage prediction enabled                                                                                                                   | 141 |

|      |                                                                                                                                                                                                                         |     |

| 9.1  | SEMIKRON three level evaluation inverter kit                                                                                                                                                                            | 145 |

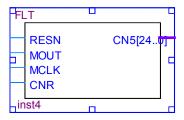

| 9.2  | VHDL Module: digital filter                                                                                                                                                                                             | 147 |

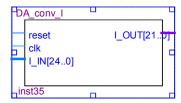

| 9.3  | VHDL Module: current sensor calibration                                                                                                                                                                                 | 148 |

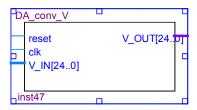

| 9.4  | VHDL Module: voltage sensor calibration                                                                                                                                                                                 | 148 |

| 9.5  | VHDL Module: current reference generation                                                                                                                                                                               | 149 |

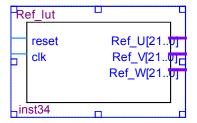

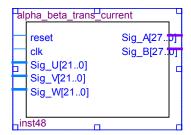

| 9.6  | VHDL Module: $\alpha\beta$ transformation                                                                                                                                                                               | 150 |

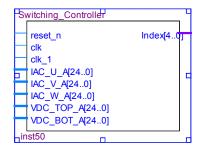

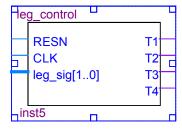

| 9.7  | VHDL Module: switching controller                                                                                                                                                                                       | 151 |

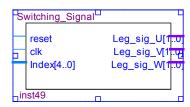

| 9.8  | VHDL Module: switching signal to leg signal                                                                                                                                                                             | 151 |

| 9.9  | VHDL Module: leg Signal to switches                                                                                                                                                                                     | 152 |

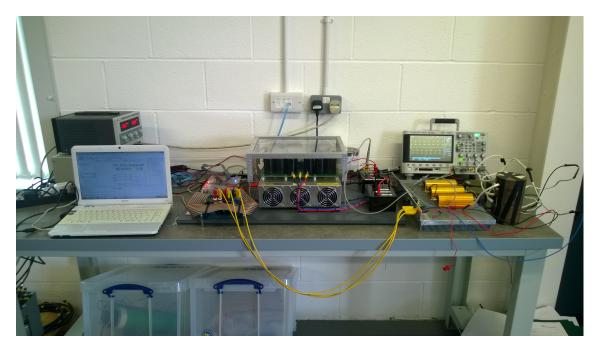

|      | Whole experiment setting up                                                                                                                                                                                             | 153 |

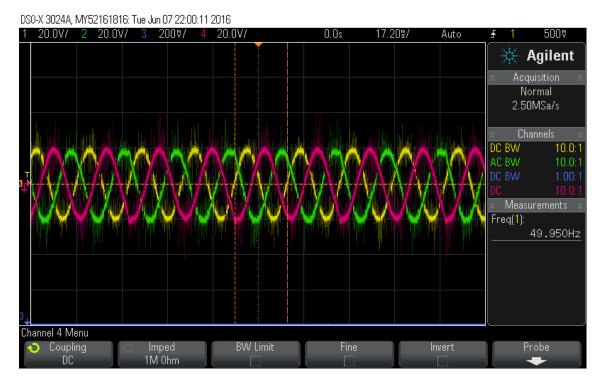

| 9.11 |                                                                                                                                                                                                                         | 153 |

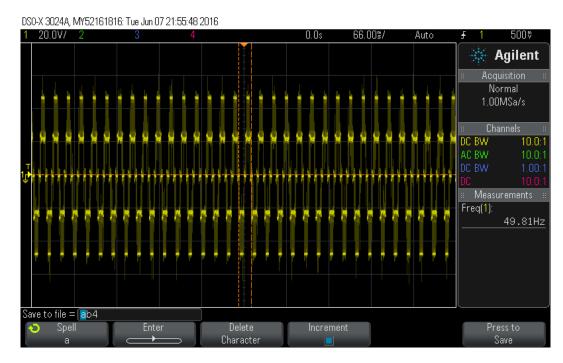

|      | Line A to B voltage                                                                                                                                                                                                     | 154 |

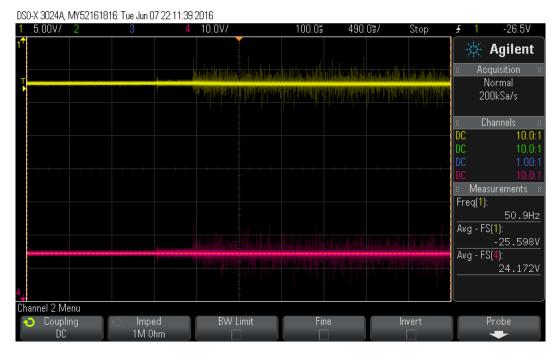

| 9.13 | Capacitor Voltages: top capacitor (Yellow) and bottom capacitor (Red)                                                                                                                                                   | 154 |

| 10.1 | Comparison among different control techniques discussed in the thesis                                                                                                                                                   | 158 |

## **List of Tables**

| 2.1 | Comparison between classical linear controller and hybrid control               | 21  |

|-----|---------------------------------------------------------------------------------|-----|

| 4.1 | State matrices of switched model for different topologies                       | 47  |

| 4.2 | The buck converter parameters                                                   | 60  |

| 4.3 | Converter parameters of the simulation results                                  | 61  |

| 4.4 | Weighting factors, average switching frequency and voltage ripple (Simulation). | 63  |

| 4.5 | System parameters and component values                                          | 66  |

| 4.6 | Current calibration data                                                        | 68  |

| 4.7 | Voltage calibration data                                                        | 69  |

| 5.1 | State matrices of switched model for different topologies                       | 81  |

| 5.2 | Results under different operation conditions                                    | 101 |

| 6.1 | State definition for each Phase                                                 | 108 |

| 6.2 | Switching modes and voltage vectors                                             | 108 |

| 6.3 | Grid-connected inverter parameters                                              | 114 |

| 7.1 | Switching states for each leg and the whole inverter                            | 120 |

| 7.2 | Auxiliary voltage balancing controller                                          | 126 |

| 7.3 | NPC inverter parameters                                                         | 126 |

| 8.1 | State definition for each Phase                                                 | 132 |

| 8.2 | Switching states and voltage vectors                                            | 133 |

| 8.3 | Grid-connected NPC inverter parameters                                          | 139 |

| 9.1 | NPC inverter experiment configuration                                           | 146 |

### **Declaration of Authorship**

- I, Xingda Yan, declare that the thesis entitled *Hybrid Modelling and Control for Switched-Mode Power Converters* and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research. I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as:

- Yan, Xingda, Zhan Shu, and Suleiman M. Sharkh. "Prediction-based sampled-data control for DC-DC buck converters." Smart Grid and Renewable Energy (SGRE), 2015 First Workshop on. IEEE, 2015.

- Yan, Xingda, Zhan Shu, and Suleiman M. Sharkh. "Output-feedback switching control of DC-DC cuk converters using multiple sampling." Automatic Control Conference (CACS), 2015 International. IEEE, 2015.

- 3. Yan, Xingda, Zhan Shu, and Suleiman M. Sharkh. "Hybrid modelling and control of single-phase grid-connected NPC inverters." Applied Power Electronics Conference and Exposition (APEC), 2016 IEEE. IEEE, 2016.

- 4. Yan, Xingda, Zhan Shu, Suleiman M. Sharkh, Zhengguang Wu, and Michael Z. Q. Chen. "A novel current control strategy for three-phase gird-connected inverters." Control Conference (CCC), 2016 35th Chinese. IEEE, 2016.

| Signed | d:    | <br> | <br> | <br> |      |

|--------|-------|------|------|------|------|

| υ      |       |      |      |      |      |

| _      | _     |      |      |      |      |

|        | )ate: | <br> | <br> | <br> | <br> |

### Acknowledgements

There are many people who deserve my sincere gratitute. Foremost, I would like to thank my two PhD superviosers: Dr Zhan Shu and Prof Suleiman M. Sharkh for your continuous support of my Ph.D study and research. During the past four years, both of them helped me to find the right direction of research and share their professional experience generously.

My sincere thanks also goes to Dr Mike Yuratich, the founder of TSL Technology Ltd. for offering me the intership opportunity in his company to carry out my experiment on NPC inverter. At the same time, I cannot forget the great help from Mr Liam Breathnath, who taught me FPGA programming hand by hand.

I would like to thank all the colleagues in mechatronics research group: ChinTeng Goh, Vorrapath Kokaew, Yu Zhang, just to name a few. Thanks for all the ideas and happiness shared over the everyday conversation. Particularly, I am very appreciated the support from Vorrapath Kokaew when I just started my experiment in the lab.

Xiaoru Sun and Mu Li are my closest friends at the University. I cannot forget the good memories with you during many weekends.

Last but not the least, I would like to thank my family; my parents Haifeng Li and Baolin Yan, my brother Wenda Yan, my wife Wenshu Zhang and my lovely daughter Scharlett for supporting me spiritually throughtout my PhD and my life in general.

### **Chapter 1**

### Introduction

### 1.1 Motivation

Since they were first developed through the introduction of power diode by Robert N. Hall in 1952, power semiconductor components have considerably ameliorated both in performance and price. Various power semiconductor components with good specifications for switching frequency and on-resistance, e.g., MOSFETs or IGBTs (Insulated Gate Bipolar Transistors) have become common. As a consequence, power converters, whose main functions are achieved by the switching property of power semiconductor components, have developed rapidly in recent years. A power converter is an electrical or electro-mechanical device for converting electric energy either converting between different forms like DC-AC/AC-DC or regulating voltage/frequency. Rectifiers are probably the most familiar example of power converters, and DC-DC converters and DC-AC/AC-DC inverters are also common applications [5][6] [7] [8].

Power converters exist almost in every kind of electronic device from industrial to residential applications. For DC-DC converters, one of the main applications is in power supplies, which contain DC-DC converters as their key parts. As the cost of electronic components declines dramatically, the power supply becomes a large fraction of system cost. Roughly speaking the power supply cost has almost reached 50% of a typical electronic product such as personal computers or hybrid electric vehicles. On the other hand, the specification requirements of power supplies are diversified as the development of electronic engineering. For example, a personal computer requires at least three different 5V supplies, two +12V supplies, a -12V supply and a 24V supply excluding supplies for peripheral devices. Therefore, development of high performance, low cost DC-DC converters is urgent.

Since a great number of household and industrial utilities needs AC supply, the DC-AC inverters could be found in a variety of applications. In order to adjusting the speed of AC motors, the DC-AC inverters are the essential part of AC motor drives [9][10]. For some situation, when only DC power sources, such as batteries or fuel cells, are available, the DC-AC

inverters could be used to drive the AC equipment [11][12]. Another important application of DC-AC inverters is the uninterruptible power supplies, which is widely used to protect vulnerable electrical equipment, such as data logging device, telecommunication equipment from an unexpected power disruption [13][14].

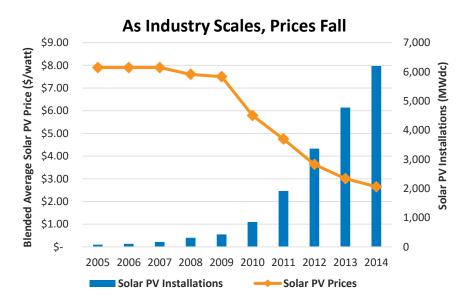

Due to the day-by-day increasing energy demand and the environmental problems caused by fossil fuel, alternative renewable and green distributed energy resources, such as solar power, wind energy, hydropower have drawn increasing attention to reduce the reliance on fossil fuel and cut emission [15][16]. As shown in Figure 1.1, the capacity of the utility-scale solar power has an exponential growth in the U.S during the last decade. In the meantime, the average price of the solar PV falls dramatically. A DC voltage is usually supplied by the distributed energy resources, such as photovoltaic (PV), fuel cells, and wind power. Hence, DC-AC inverters are used to interface these sources to the grid supplying high quality AC current in accordance with national standard [17][18][19][20].

Figure 1.1: Solar PV installations and average solar PV price in US [Source:Solar Energy Industries Association]

As for the design of power converters, one of the most important parts is the control system. The main challenge in controlling a power converter arises from their hybrid nature which is caused by the use of semiconductor components as power switches. From the control point of view, the power converters are nonlinear system which contains both continues and discrete dynamics. The conventional control approach to the modelling and controller design of power converters is the state-space averaged approach and the design of linear controllers. The disadvantages of the conventional methods are obvious.

- 1. The model is linearized around a specific operating point.

- 2. The tuning procedure of the controller is complicated, and the design is further complicated when the operating point is changed.

3. Practical experience is essential for the controller tuning.

On the other hand, the development of advanced hybrid system control theory together with more powerful control platform such as DSP, FPGA gives us the possibility of tackling the control problem from a new perspective. In view of this, more systematics modelling and control methods can be developed. In my research, the main goals are as follows.

- 1. Power converters are modeled as switched affine models, a specific type of hybrid systems, which describe the system dynamic across the whole operating range and determines the active continues dynamic by a switching law.

- 2. The Lypunov stability theory and robust control are main methodologies to derive the controller synthesis conditions.

- 3. There is no complicated tuning involved. A unified systematics design procedure will be given, which can be easily applied on different power converters with different topologies.

- 4. The practical limitation of power converters, such as switching frequency, ripple reduction, neutral point balanced, can be included easily by adding constrained conditions to the synthesis conditions.

- 5. Most importantly, all the design is done off-line which can highly release the computation burden.

- Experimental verification of the proposed control schemes will be carried out to demonstrate that these methods can be easily implemented in practice, which are not just methods on the papers.

Therefore, the main scope of this PhD project is to illustrate that advanced hybrid control methodologies can be applied on power converters conceivably and within reach. Two major types of power converters are considered in this thesis: DC-DC converters and DC-AC inverters.

### 1.2 Structure of the Thesis

This thesis generally includes three parts. First part is Chapter 1 and Chapter 2, which gives the motivation of this PhD project and reviews the modelling and control techniques for both DC-DC converters and DC-AC inverters.

The second part consists of Chapter 3, Chapter 4 and Chapter 5, which focuses on DC-DC converters. In Chapter 3, two conventional modelling and control techniques are reviewed in details, which are: linear controller design based on the state-space averaged model and model predictive control based on a hybrid model to act as benchmarks for the following chapters. In

Chapter 4, a novel sampled-data control approach is proposed, which not only guarantees the stability across all attainable operating points, but also has the ability to adjust the switching frequency. Experiments based on dSPACE control platform also have been carried out to verify the effectiveness of the proposed methods. In Chapter 5, a novel output feedback control approach is proposed. To compensate the information loss due to limited access to the state, a multiple sampling scheme is employed to derive a discrete-time switched affine model with an augmented measurement output. Based on the model, an output-feedback switching control law, which drives the system state to a set of attainable switched equilibria, is synthesized by using a quadratic state-space partition. The multiple sampling scheme not only facilitates the controller synthesis, but also improves the energy efficiency of the converter by allowing a lower switching frequency.

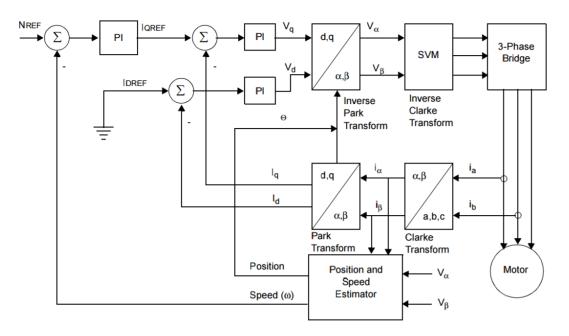

The third part of the thesis, which includes Chapter 6, Chapter 7, Chapter 8, and Chapter 9, deals with the hybrid modelling and control problems in DC-AC inverters. In Chapter 6, a grid-connected three-phase two-level inverter is studied. Hybrid models of the inverter are presented and a switching controller, which can stabilize the phase currents to the desired current references, is presented. In Chapter 7, a novel switching controller, which includes the current reference dynamics in the hybrid model, is proposed for a grid-connected single-phase Neutral Pointed Clamped (NPC) inverter. In Chapter 8, the control method developed in Chapter 6 is extended to a three-phase NPC inverter in conjunction with an additional capacitor voltage balancing controller. In Chapter 9, experimental work is presented to demonstrate how to implement the proposed switching control technique on a three-phase NPC inverter with RL load based on the DE-115 Field-Programmable Gate Array (FPGA) control board.

In the last Chapter 10, the proposed modelling and control schemes are compared with each others and also compared with the state-of-the-art modelling and control methods. In general, this PhD project gives a new perspective of modelling and control of switched-mode power converters. It demonstrates the advantages of the proposed methods over the traditional methods in several aspects. Firstly, the hybrid model captures both continuous and discrete dynamics which is more precise than the state-space averaged approach. Secondly, the proposed control approaches not only can guarantee the system stability within a much wider operation range, but also can be more constraints friendly. Last but not the least, the experiment verification carried out on both DC-DC converters and DC-AC inverters has proven that the proposed control scheme can be conveniently implemented on digital platforms with relatively low online computation burden.

### **Chapter 2**

### **Literature Review**

### 2.1 Control Methods for DC-DC Converters

There are numerous types of power converters. Among these, DC-DC converters, which convert a source of direct current (DC) from one voltage level to another, are one of the simplest power electronics devices. This type of converters have found widespread applications in practice, e.g., cellular phones, laptops, communication equipments, motor drives. A great number of control techniques based on different models have been employed for the control of DC-DC converters in industry including voltage-mode and current-mode control techniques [21]. Thus it is of interest to compare the dynamic response of these control approaches as well as their strength and weakness.

### 2.1.1 DC-DC Converters Control in The Past

A DC-DC converter consists a switching topology and the associated control circuit. The switching topology is a periodic time-varying circuit due to the discrete input and continuous output, and the control circuit is a hybrid circuit containing both nonlinear and linear stages. In order to use the classical control theory, approximations must be made to move from the time-varying nonlinear system to a time-invariant linear one. Thus the state-space averaged approach (SSA), a way to model DC-DC converter as a linear canonical circuit, was proposed [22, 23] and became one of the essential techniques for analyzing switched mode power conversion circuits. Based on the state-space averaged approach for the modeling of DC-DC converters, various control techniques have been adopted to investigate the dynamic responses of a DC-DC converter.

Generally, control techniques of DC-DC converters can be divided into voltage mode control and current mode control by the feedback signals. Both methods were initially implemented as analog approaches. For simplicity of explanation, in the following part, the different control methods are introduced based a typical buck converter.

Voltage mode control as shown in Figure 2.1 is a single loop control approach in which the output voltage is measured and compared to a reference voltage to generate an error signal. The duty ratio is regulated by comparing the error signal to a fixed frequency sawtooth waveform [24, 25]. Voltage mode control is still used in some industry applications because of following advantages: 1) Simple topology, single feedback loop, which is easy to design and low cost; 2) Less sensitive to noise; 3) Can work over a wide range of duty cycles. However, the drawbacks of voltage mode control are also obvious: 1) Loop gain proportional to input voltage leading to more complicated compensation; 2) The additional poles added by output filter may require Type III compensation (a three poles and two zeros compensation network); 3) Slow response to input voltage changes; 4) Current limiting must be done separately.

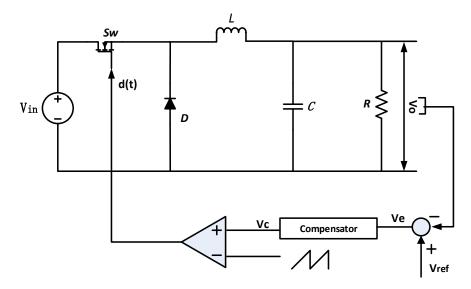

Figure 2.1: Block diagram of a basic voltage mode controller

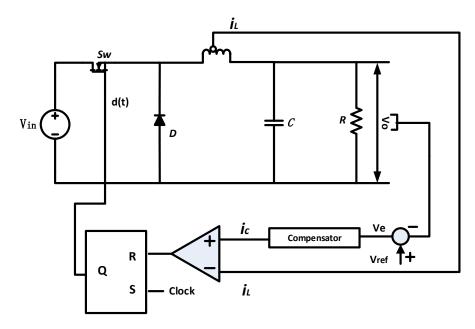

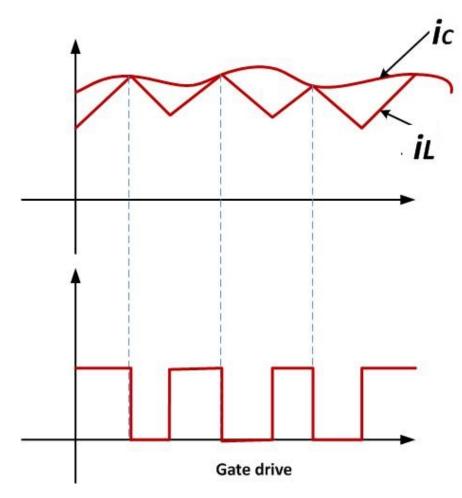

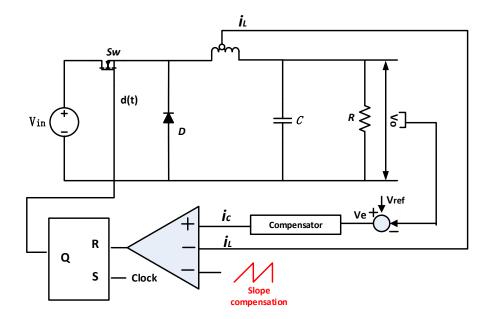

Due to the disadvantages of voltage mode control, current mode control [24, 25, 26] is used to alleviate all the weak points above. More specifically, the inductor current is measured and employed to control the duty ratio as shown in Figure 2.2. An error signal is produced in the same way as voltage mode control by comparing output voltage to the reference voltage, and acts as a reference signal for the current control loop after a compensator. Then inductor current is compared with the reference current signal to modulate the duty ratio. In 1978, the implementation of current mode control of DC-DC buck converters was first proposed with the so-called name "peak current control" [27], which means that during each cycle switch closure is ended when the sensed inductor current hits an adaptable threshold (Figure 2.3). After this, a series of related works on the peak current control was published [28, 29, 30, 31, 32]. However, when the duty ratio exceeds 50%, instability occurs resulting in period-doubling, sub-harmonic oscillations or chaotic behavior. In order to avoid this serious issue, slope compensation [24] was introduced —— the sum of inductor current and an external ramp is compared with the reference current signal as shown in Figure 2.4.

Figure 2.2: Block diagram of a basic current mode controller

Current mode control has several advantages over the classical voltage mode control: 1) The waveform of the inductor current responds promptly to the line voltage changes thus reducing the delayed response and gain variation with changes in the input voltage; 2) The output filter now offers only a single pole, hence compensation is simpler and higher gain bandwidth is obtained; 3) Cycle-by-cycle current limiting protection; 4) Ease of current sharing when converters operate in parallel. Although improvement has been made over the voltage mode control, the current mode control also comes with its unique set of challenges: 1) The two feedback loops brings more difficulty to the circuit analysis; 2) Oscillations appears when the duty cycle exceeds 50%; 3) Resonances from the power stage can insert noise into the control loop through the output current.

Initially, the implementation of both voltage mode and current mode control techniques for DC-DC converters was accomplished by analog circuits composed of passive components and amplifiers. Before the wide use of digital devices, using analog circuits was an essential approach to control power converters due to their simple structure and low cost. However, the disadvantages of analog circuit and components, such as bad flexibility, low reliability, and parameter deviation caused by the external influence (thermal, humidity, lifetime, etc), could not be neglected. In addition, linearized models of power converters are utilized in analog implementation which overlook the nonlinear properties.

Figure 2.3: The waveforms of the signal in a current controller in peak current mode control

### 2.1.2 DC-DC Converters Control Today

In recent decades, the use of microprocessors for the control of power electronics systems has become a common solution for full digital implementation of controllers. Several control techniques developed for analog control circuits have been replicated in a digital way. Moreover, modern control platforms with high computational capabilities such as digital signal processors (DSP), field-programmable gate array (FPGA) allow the possibility of implementation of more advanced control algorithms [33].

Based on the idea of the peak current control method, various digital techniques for DC-DC converters have been presented in recent years including Valley Current Control [34], Average Current Control [35], Delayed Valley Current Control [36], Delayed Peak Current Control [36], Delayed Average Current Control, Prediction Current-Mode Control With Delay Compensation, Compensated Digital Current-Mode Control [37, 38, 39, 40].

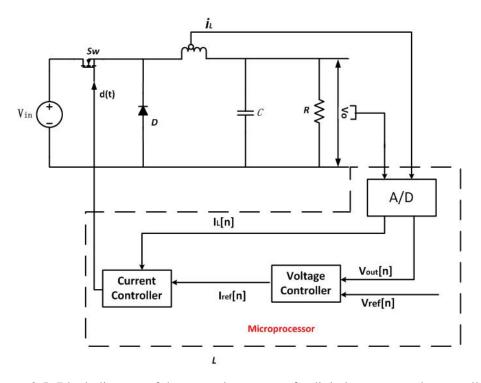

Figure 2.5 depicts the general structure of a digital current-mode controller implemented

Figure 2.4: Block diagram of a peak current controller with the slope compensation

Figure 2.5: Block diagram of the general structure of a digital current-mode controller

by a microprocessor. The microprocessor attempts to find the right value of the duty cycle to satisfy the control objective using the sampled data of input and output voltages and the inductor current. All of these approaches make an attempt to let the valley, average, or peak value of the inductor current to follow the current reference signal named  $i_{ref}$ , which is obtained from the voltage controller.

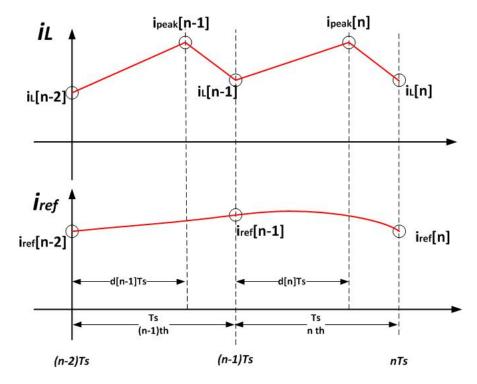

Figure 2.6: Current waveform of the inductor and reference signal in a digital current-mode controller

To compare the different digital control methods, a typical buck converter is considered. The inductor current waveform of a buck converter under continuous conduction mode is displayed in Figure 2.6. In order to make the following description about different techniques easy to access, notations are introduced first.  $T_s$  is the switching period of the DC-DC buck converter. d[n] is the duty ratio during the  $n^{th}$  switching period.  $i_L[n]$  is the sampled inductor current at time  $nT_s$ , which is the end of the  $n^{th}$  switching period, and  $i_{ref}[n]$  is the sampled current reference at time  $nT_s$ .  $V_{in}[n]$  and  $V_o[n]$  are the sampled input and output voltage, respectively. The input and output voltage are treated as constants during each switching period as they both vary slowly. Thus, we can write:

$$V_o[n] \approx V_o[n-1]$$

$$V_{in}[n] \approx V_{in}[n-1]$$

(2.1)

Valley current control is analog in nature [34]. However a digital controller can be obtained by changing the differential equations describing the dynamic of the power converter to difference equations. With this approach, the required value for the duty cycle is calculated in the ongoing period to make sure that

$$i_L[n] = i_{ref}[n-1] \tag{2.2}$$

To achieve the objective, the duty cycle of the  $n_{th}$  switching period can be calculated by (2.3) which is given in [34]:

$$d[n] = \frac{L}{V_{in}T_s}(i_{ref}[n-1] - i_L[n-1]) + \frac{V_o}{V_{in}}$$

(2.3)

In other words, the inductor current  $i_L$ , the reference current  $i_{ref}$  and the voltages are sampled at the beginning of each switching period. Then the duty ratio d[n] is obtained by (2.3) and applied so that the final value of inductor current at the beginning of each switching cycle will be equal to the reference current at the beginning of the switching cycle. One thing that must be mentioned is that microprocessor must be fast enough to compute and apply the duty cycle.

In [36], the method called delayed valley current control is presented. In this approach, the duty ratio is calculated in the previous period to guarantee that

$$i_L[n] = i_{ref}[n-2]$$

(2.4)

To fulfill the above control objective, the equation used to calculate the duty cycle has been given in (2.5).

$$d[n] = \frac{L}{V_{in}T_s}(i_{ref}[n-2] - i_L[n-2]) - d[n-1] + \frac{2V_o}{V_{in}}$$

(2.5)

This way, the inductor current and reference are sampled at the beginning of the previous switching period ((n-1)th) period) and used to calculated the duty ratio applied in next switching period (nth) period) to make the inductor current in the nth switching period following the current reference sampled at the beginning of the previous switching period. The advantage of this method is that the digital controller will have more time for the related computation at the cost of the introduction of an extra period of delay.

Average current control was first introduced in [35]. The control objective is that the average value of the inductor current in each switching period is equivalent to the current reference signal sampled at the start of the same cycle.

$$\frac{1}{T_s} \int_{(n-1)T_s}^{nT_s} i_L dt = i_{ref}[n-1]$$

(2.6)

According to [35], the duty ratio can be calculated as:

$$d[n] = \frac{L}{V_{in}T_s}(i_{ref}[n-1] - i_L[n-1] - \frac{T_sV_o}{2V_{in}} \cdot \frac{V_{in} - V_o}{L}) + \frac{V_o}{V_{in}}$$

(2.7)

The implementation procedure of this method is the same as the valley current control: inductor current, current reference and voltages are sampled at the beginning of each cycle and the duty ratio is calculated and applied using (2.7). It is proved in [35] that the control scheme

is stable for any value of the duty cycle without slope compensation.

A similar control method called "delay peak current control" is also proposed in [36]. Different from delay valley current control, the control scheme of this approach is to force the peak value of the inductor current during the coming period to be equivalent to the current reference sampled at the start of previous switching period.

$$i_{peak}[n] = i_{ref}[n-2]$$

(2.8)

Where  $i_{peak}[n]$  is the peak value of the inductor current in nth switching period.

From [36], the required duty ratio of the nth period can be described as

$$d[n] = \frac{L}{(V_{in} - V_o)T_s}(i_{ref}[n-2] - i_{peak}[n-2]) - \frac{V_{in}}{V_{in} - V_o}d[n-1] - \frac{V_o}{V_{in} - V_o}d[n-2] + \frac{2V_o}{V_{in} - V_o}d[n-2] - \frac{V_o}{(2.9)}d[n-2] + \frac{2V_o}{(2.9)}d[n-2] + \frac{2V_$$

For this method, the control objective has less than two period of time delay and when the duty cycle exceeds 50%, instability will occur. In addition, if the load change during the two period, as the sudden change of the current, the calculation of the duty ratio is invalid.

Prediction current mode control with delay compensation is introduced in [37, 39, 40, 38]. The control scheme is the same as the delay valley current control (2.4), however the duty ratio is updated every two switching periods. This would allocate more time for the microprocessor. The current reference is presumed to be constant during two switching period cycles.

$$i_{ref}[n] = i_{ref}[n-2] (2.10)$$

The current at the end of *nth* switching period is assumed to be calculated as

$$i_L[n] = 2i_L[n-1] - i_L[n-2]$$

(2.11)

According to [39], every other period the duty ratio can be calculated as (2.12) using the assumptions above.

$$d[n] = \frac{L}{2V_{in}T_s}(i_{ref}[n-2] - 4i_L[n-2] + 3i_L[n-3]) + d[n-2]$$

(2.12)

Therefore, the inductor current, reference and voltages sampled in the former three cycles are used to calculated the duty ratio. The computational overhead of digital control is decreased compared with the previous techniques. This method is suitable for fast systems such as high-performance DC switchmode power supplies.

For the sake of avoiding instability that may exist in valley current control, compensated

digital current-mode control is presented in [41, 42]. Slightly different from (2.2) slightly, the control scheme can be defined as

$$i_L[n] = i_{ref}[n-1] + m_c d[n]T_s$$

(2.13)

Where,  $m_c$  is a compensating ramp.

According to [42], the equation to calculate the duty ratio can be modified as

$$d[n] = \frac{1}{1 - \frac{Lm_c}{V_{in}}} \left( \frac{L}{V_{in}T_s} (i_{ref}[n-1] - i_L[n-1]) + \frac{V_o}{V_{in}} \right)$$

(2.14)

As for this method, the inductor current, reference and voltages are sampled at the beginning of every switching period and proper  $m_c$  is applied to calculate the duty ratio. According to [42], for buck converters, if  $m_c > \frac{V_{in}}{L}$ , the system is always stable.

To summarize, all of the control techniques described above are based on the state-space averaged approach and corresponding linearized approximate models. Most effort of these methods have been spent on finding a reasonable approach to calculate the duty ratio. However, the performance of these linear controllers would deteriorate under large parameter or load variations. Therefore, this has aroused a lot of interest in the development of nonlinear controllers for DC-DC converters. Some control schemes such as hysteresis control, sliding mode control are proposed in literature. By substituting the linear controllers with these nonlinear controllers in DC-DC converters, better regulation is achieved for a wider operating range.

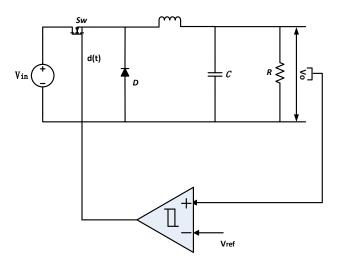

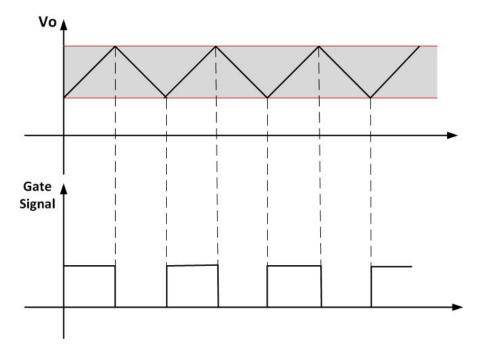

Hysteresis controllers were first implemented in boost converters [43]. Since this control scheme has an inherently fast response in addition to being robust with simple design and implementation, a lot of related work can be found [44, 45, 46, 47]. Figure 2.7 is the diagram of a DC-DC converter with a simple voltage hysteresis controller [48]. Figure 2.8 shows the waveform of the output voltage (with hysteresis band used in the hysteresis controller) and the gate signal. The implementation of the hysteresis controller is simple. The switching states of the power stage is determined by comparison of the output voltage to its reference, considering a given hysteresis width for the error. DC-DC converters with hysteresis controllers responds to disturbances and load change right after the transient takes place [49]. Moreover, a compensation network is not needed for closed loop control. Due to all the advantages above, hysteresis control would be a good choice for DC-DC converters. However, the main concern associated with this method is that the switching frequency changes when the input voltage changes. This is not acceptable in many applications especially when converters are operated in parallel. Some work have been reported to deal with this problems in [50, 51, 52].

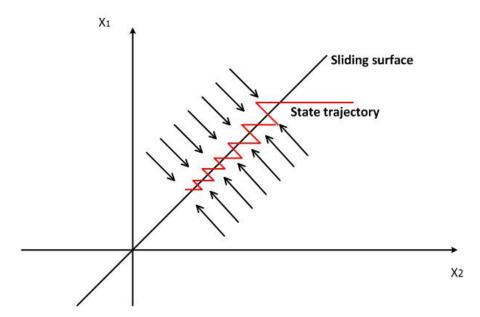

Sliding mode control (SM) is another nonlinear control strategy developed for controlling variable structure systems (VSSs) with good performance such as guaranteed stability and robustness against parameter, line, or load uncertainties [53, 54, 55]. The principle of SM control

Figure 2.7: Block diagram of DC-DC converters with a hysteresis controller

Figure 2.8: Waveform of the output voltage and the gate signal used in a hysteresis controller

is straightforward. A sliding surface is adopted as a reference path so that the controlled state variable can be directed towards the desired equilibrium as shown in Figure 2.9. DC-DC converters are inherently variable structure systems due to the switching property. Therefore, sliding control design and analysis for DC-DC converters has drawn lots of research interests. Bilalović *et al.* is the first group that worked on developing SM controller for DC-DC converters. In [56], a preliminary sliding mode controller was applied to a buck converter. Then SM control was applied to higher order converters such as second-order DC-DC converters by Venkataramanan *et al.* [57] and fourth-order Cuk converter by Huang *et al.* [58]. In 1997, a comparative study on buck converter's performance under different control scheme was presented by Raviraj and

Figure 2.9: Sliding surface and state trajectory in the state-space

Sen [59]. It was found that fuzzy-logic and SM controller show certain similarities in the system behavior. SM controllers were also developed for parallel connected converters [60, 61]. However, in spite of being a popular research topic, most of the literature focus on theoretical aspects. Seldom SM control has been adopted in practical DC-DC converters. The main reason is the high and variable switching frequency, which would result in excessive power losses, electromagnetic-interference generation and filter-design complication.

#### 2.1.3 Current Issues

Although these conventional control approaches may be adequate in some cases, the controller performance is quite limited, and the design involves a number of heuristic procedures, which lack theoretical guarantees. This motivates the study of advanced control technology for DC-DC power electronics converters, and a large number of control methods have been developed or tailored to control problems of DC-DC converters, e.g., sliding mode control [62, 63, 64, 65], fuzzy logic control [66], adaptive control [67], robust control [68] model predictive control [69, 38], artificial neural network control [70], Lyapunov-based control [71, 72, 73], to just mention a few.