# UNIVERSITY OF SOUTHAMPTON

# Fault Tolerance & Error Monitoring Techniques for Cost Constrained Systems

by

Mauricio Daniel Gutierrez Alcala

A thesis submitted in partial fulfillment for the degree of Doctor of Philosophy

in the Faculty of Physical Sciences and Engineering School of Electronics and Computer Science

September 2017

#### UNIVERSITY OF SOUTHAMPTON

## ABSTRACT

# FACULTY OF PHYSICAL SCIENCES AND ENGINEERING SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

## Doctor of Philosophy

by Mauricio Daniel Gutierrez Alcala

With technology scaling, the reliability of circuits is becoming a growing concern. The appearance of logic errors in-the-field caused by faults escaping manufacturing testing, single-event upsets, aging, or process variations is increasing. Traditional techniques for online testing and circuit protection often require a high design effort or result in high area overhead and power consumption and are unsuitable for low cost systems. This thesis presents three original contributions in the form of low cost techniques for online error detection and protection in cost constrained systems. The first contribution consists on low cost fault tolerance design technique, that protects the most susceptible workload on the most susceptible logic cones of a circuit, by targeting both timingindependent and timing-dependent errors. The susceptible workload is protected by a partial Triple Modular Redundancy (TMR) scheme. Protecting the 32 most susceptible patterns, an average error coverage improvement of 63.5% and 58.2% against errors induced by stuck-at and transition faults is achieved, respectively, compared an unranked pattern selection and protection. Additionally, this technique produces an average error coverage improvement of 163% and 96% against temporary erroneous output transition and errors induced by bit-flips, respectively. These error coverage improvements incur in an area/power cost in the range of 18.0-54.2\%, a 145.8-182.0\% reduction compared to TMR. The second contribution proposes a low cost probabilistic online error monitoring technique that produces an alarm signal when systematic erroneous behaviour has occurred over a pre-defined time interval. To detect systematic erroneous behaviour, the collected data is compared on-chip against the signature of error-free behaviour. Results demonstrate on the largest circuits, an average error coverage of 84.4% and 73.1% of errors induced by bit-flips and stuck-at faults, respectively, with an average area cost of 1.66%. The final contribution consists of a circuit approximation technique that can be used for low cost non-intrusive fault tolerance and concurrent error detection, based on finding functionality at the logic level that behaves similarly to single logic gates or constant values. An algorithm is proposed to select the input subsets to approximate. Results show an average coverage of 33.59% of all the input space with an average 7.43% area cost. Using this approximate circuits in a reduced TMR scheme results in significant area cost reductions compared to existing techniques.

# Contents

| N | omer       | ıclatur | re                                            | xiii |

|---|------------|---------|-----------------------------------------------|------|

| A | cknov      | wledge  | ements                                        | xv   |

| 1 | Intr       | oducti  |                                               | 1    |

|   | 1.1        |         | ation and Scope of this Research              |      |

|   | 1.2        |         | s Contributions and Organisation              |      |

|   | 1.3        | Public  | eations                                       | 4    |

| 2 | Bac        | kgroui  |                                               | 7    |

|   | 2.1        |         | Constrained Systems                           |      |

|   | 2.2        | Reliab  | oility challenges of Cost Constrained Systems |      |

|   |            | 2.2.1   | Technology scaling                            |      |

|   |            |         | 2.2.1.1 Process Variation                     |      |

|   |            |         | 2.2.1.2 Circuit Wearout                       |      |

|   |            | 2.2.2   | Power Management Techniques                   |      |

|   |            |         | 2.2.2.1 Power Gating                          |      |

|   |            |         | 2.2.2.2 Clock Gating                          |      |

|   |            |         | 2.2.2.3 Dynamic Voltage and Frequency Scaling |      |

|   |            | 2.2.3   | Faults in Cost Constrained Systems            |      |

|   |            |         | 2.2.3.1 Permanent Faults and Fault Models     |      |

|   |            |         | 2.2.3.2 Transient Faults                      |      |

|   |            |         | 2.2.3.3 Intermittent Faults                   |      |

|   | 2.3        |         | and error detection techniques                |      |

|   |            | 2.3.1   | Concurrent error detection (CED)              |      |

|   |            |         | 2.3.1.1 Hardware duplication                  |      |

|   |            |         | 2.3.1.2 Error Detecting Codes                 |      |

|   |            | 2.3.2   | Built-in Self Test (BIST)                     |      |

|   |            |         | 2.3.2.1 Online BIST                           |      |

|   | 2.4        | <b></b> | 2.3.2.2 Concurrent BIST                       |      |

|   | 2.4        |         | and Error protection techniques               |      |

|   |            | 2.4.1   | Hardware Redundancy                           |      |

|   |            | 2.4.2   | Error Correcting Codes                        |      |

|   | ~ <b>~</b> | 2.4.3   | Timing Redundancy and Software re-execution   |      |

|   | 2.5        |         | Cost Error Detection and Correction           |      |

|   | 2.6        |         | rch Objectives                                |      |

|   | 2.7        | Concli  | uding Remarks                                 | 23   |

vi CONTENTS

| 3 | $\mathbf{Pro}$ | babilistic Selective Fault Tolerance 25                                     |

|---|----------------|-----------------------------------------------------------------------------|

|   | 3.1            | Background                                                                  |

|   | 3.2            | Motivation                                                                  |

|   |                | 3.2.1 Selective Fault Tolerance                                             |

|   |                | 3.2.2 Probabilistic Fault Model: Output Deviations                          |

|   |                | 3.2.3 Workload types                                                        |

|   |                | 3.2.4 Motivational example                                                  |

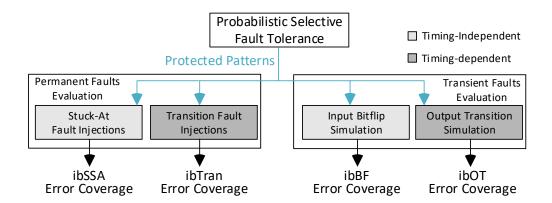

|   | 3.3            | Proposed Probabilistic Selective Fault Tolerance (PSFT) Design Technique 33 |

|   | 0.0            | 3.3.1 PSFT Design                                                           |

|   |                | 3.3.2 Proposed PSFT design flow                                             |

|   |                | 3.3.3 Process 1: Logic cone selection                                       |

|   |                | 3.3.4 Process 2: Pattern ranking and pattern selection                      |

|   |                | 3.3.4.1 Timing-independent pattern ranking for uncorrelated work-load       |

|   |                | 3.3.4.2 Timing-dependent pattern ranking for application-specific workload  |

|   | 3.4            | Experimental Validation                                                     |

|   | 0.1            | 3.4.1 Computational Effort Comparison                                       |

|   |                | 3.4.2 Simulation Setup                                                      |

|   |                | 3.4.3 Simulation Results                                                    |

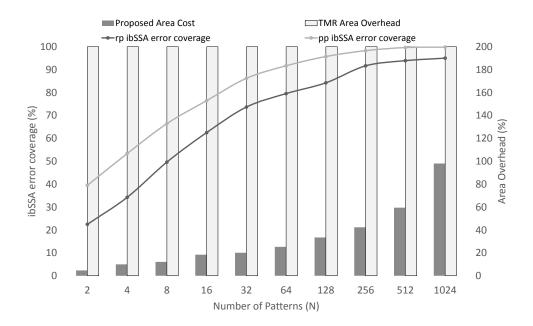

|   |                | 3.4.3.1 Errors Induced by Single Stuck-At Faults                            |

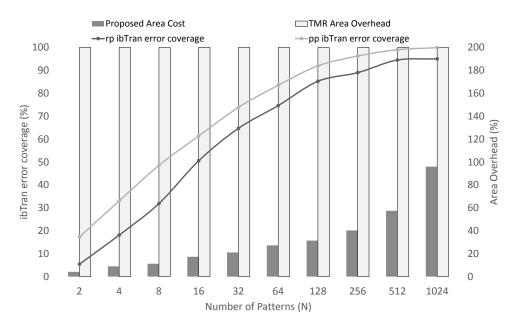

|   |                | 3.4.3.2 Errors Induced by Transition Faults                                 |

|   |                | 3.4.3.3 Overall Error Coverage Improvements and Area Cost                   |

|   |                | Trade-Off                                                                   |

|   | 3.5            | Concluding Remarks                                                          |

| 4 | Onl            | line Monitoring of Erroneous Behaviour in the Field 49                      |

|   | 4.1            | Background                                                                  |

|   | 4.2            | Analysis of Systematic Erroneous Behaviour using Online Signal Proba-       |

|   |                | bilities                                                                    |

|   |                | 4.2.1 Analysis                                                              |

|   |                | 4.2.2 Example: LGSynth'91 Benchmark t481                                    |

|   |                | 4.2.2.1 Probability of False Alarms                                         |

|   |                | 4.2.2.2 Signal Probabilities in the Presence of Faults 54                   |

|   |                | 4.2.2.3 Signal Probabilities and Errors                                     |

|   | 4.3            | On-Chip Monitoring Architecture                                             |

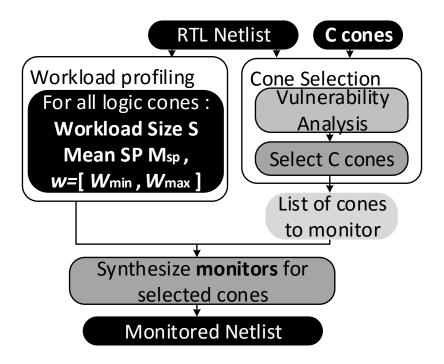

|   | 1.0            | 4.3.1 Monitoring architecture design flow                                   |

|   |                | 4.3.2 Monitoring architecture designs                                       |

|   |                | 4.3.2.1 Single counter design                                               |

|   |                | 4.3.2.2 Multiple counter design                                             |

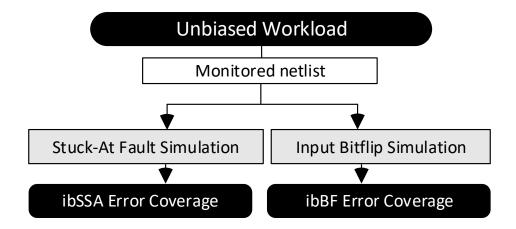

|   | 4.4            | Simulation Results                                                          |

|   | 4.4            |                                                                             |

|   |                | 1                                                                           |

|   | 4 -            | 4.4.2 Simulation Results                                                    |

|   | 4.5            | Discussion                                                                  |

|   | 4.6            | Concluding Remarks                                                          |

| 5 | Sing           | gle Gate Approximate Circuits 67                                            |

CONTENTS vii

| A | In-F | House Fault Injection Simulator                             | 97 |

|---|------|-------------------------------------------------------------|----|

|   | 6.2  | Future Research Directions                                  | 95 |

|   | 6.1  | Summary of Research Contributions                           |    |

| 6 | Con  | aclusions                                                   | 93 |

|   | 5.8  | Concluding remarks                                          | 92 |

|   | 5.7  | Discussion and Future Work                                  |    |

|   | 5.6  | Concurrent Error Detection using Approximate Logic Circuits |    |

|   | 5.5  | Selective Fault Tolerance using Approximate Logic Circuits  |    |

|   | 0.1  | Benchmark Results                                           |    |

|   | 5.4  |                                                             |    |

|   |      |                                                             |    |

|   | 0.0  | 5.3.1 Parallel Multiplier Examples                          |    |

|   | 5.3  | Input Subspace Selection Algorithm                          |    |

|   |      | 5.2.4 Types of Approximate Logic Circuits                   |    |

|   |      | 5.2.3 Second 4-input Example                                |    |

|   |      | 5.2.2 4-Input Circuit Example                               |    |

|   |      | 5.2.1 Full Adder Example                                    |    |

|   | 5.2  | Single Gate Approximation Premise                           |    |

|   | 5.1  | Background: Approximate logic circuits                      | 68 |

# List of Figures

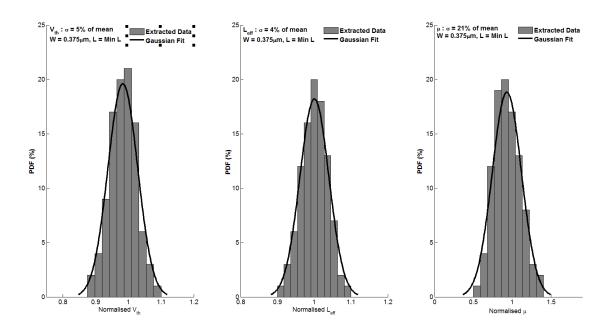

| 2.1  | Variations of $V_{th}$ , $L_{eff}$ & $\mu$ [30]                                                                               | 10 |

|------|-------------------------------------------------------------------------------------------------------------------------------|----|

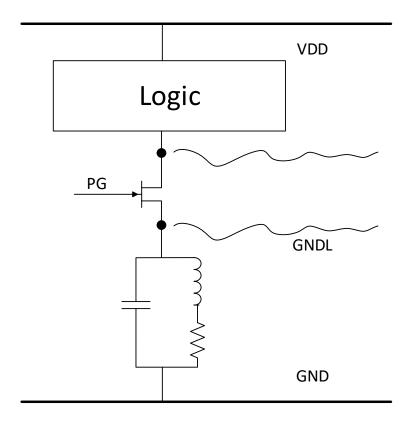

| 2.2  | Ground bounce noise in a power gated structure [39]                                                                           | 12 |

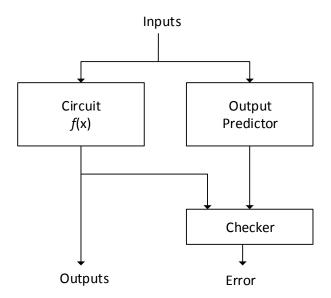

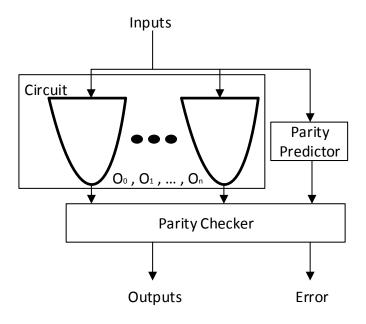

| 2.3  | General architecture of a CED mechanism [55]                                                                                  |    |

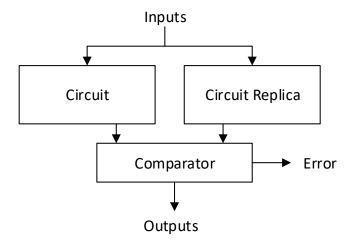

| 2.4  | Duplication with comparison CED [61]                                                                                          | 17 |

| 2.5  | Parity prediction with one parity bit [64]                                                                                    | 17 |

| 2.6  | Concurrent error detection with Berger codes [67]                                                                             | 18 |

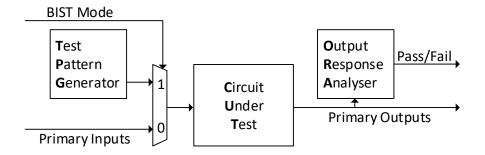

| 2.7  | Basic BIST architecture [68]                                                                                                  | 19 |

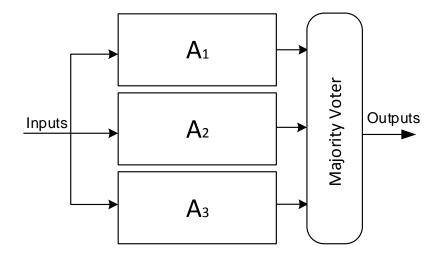

| 2.8  | Basic TMR scheme [8]                                                                                                          | 21 |

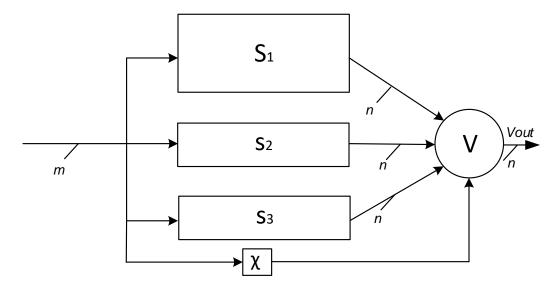

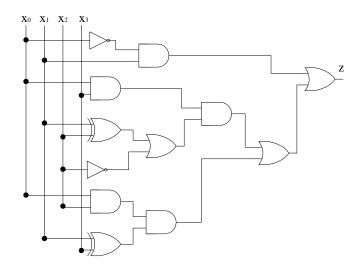

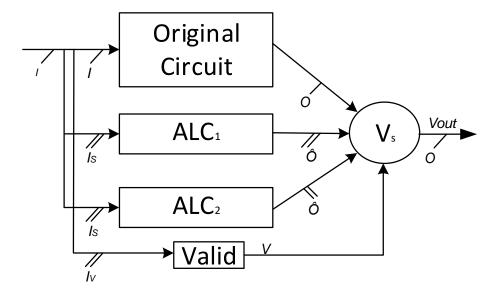

| 3.1  | Previous Selective Fault Tolerance design                                                                                     | 28 |

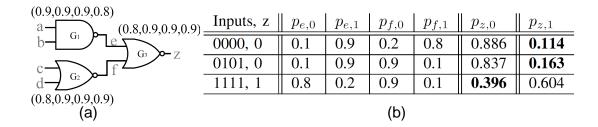

| 3.2  | Output deviations example [110]: (a) simple circuit with confidence level                                                     |    |

|      | vectors and (b) propagated output deviations                                                                                  | 29 |

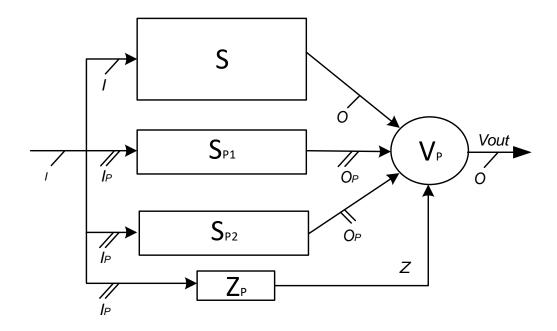

| 3.3  | Proposed Probabilistic Selective Fault Tolerance design                                                                       | 33 |

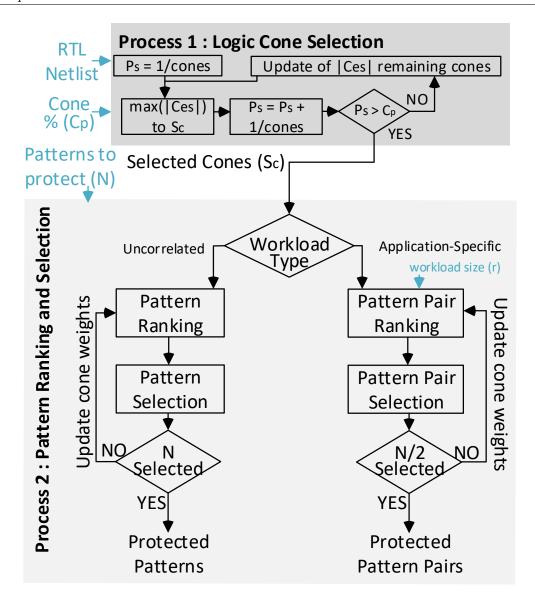

| 3.4  | Proposed design technique flow diagram                                                                                        | 35 |

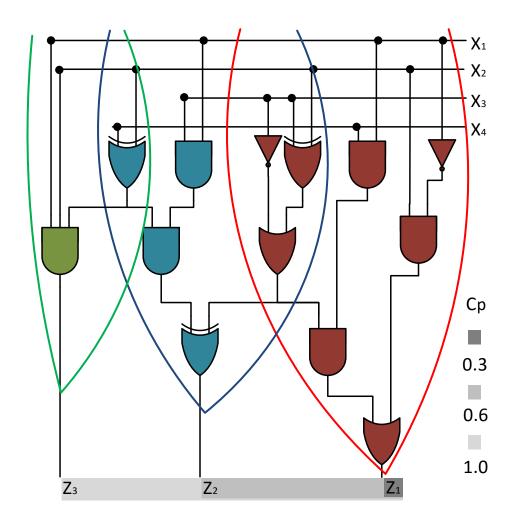

| 3.5  | Example of logic cone selection with different $C_p$                                                                          | 36 |

| 3.6  | Simulation Setup                                                                                                              | 40 |

| 3.7  | Area cost of Benchmark $c880$ and ibSSA EC for a selected cone percentage                                                     |    |

|      | $C_p = 0.1 \dots \dots$ | 42 |

| 3.8  | Area cost of Benchmark $c880$ and ibTran EC for a selected cone percent-                                                      |    |

|      | age $C_p = 0.1$                                                                                                               | 42 |

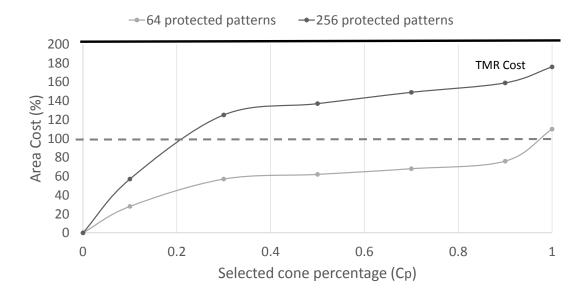

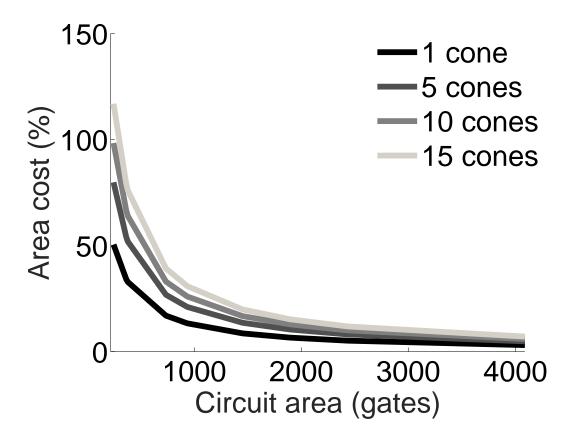

| 3.9  | Area cost of different $C_p$ for benchmark $pdc$                                                                              | 46 |

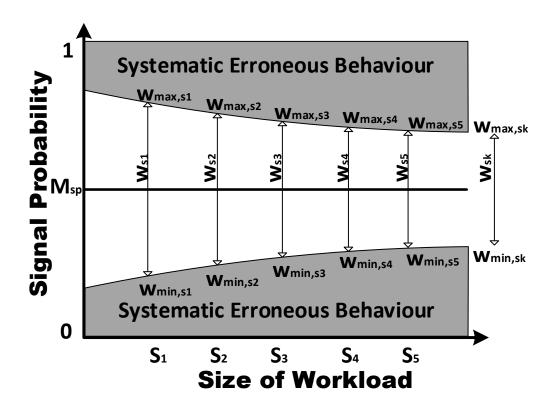

| 4.1  | Online signal probabilities                                                                                                   | 52 |

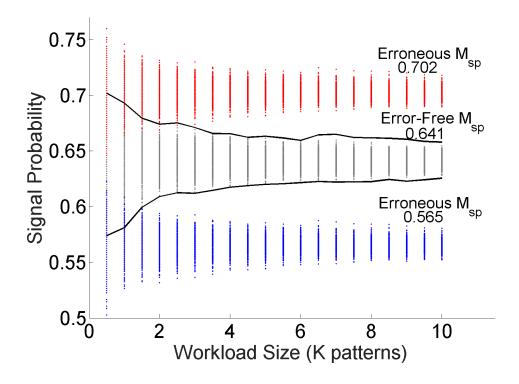

| 4.2  | Online signal probabilities of 1000 different workloads for circuit t481                                                      | 53 |

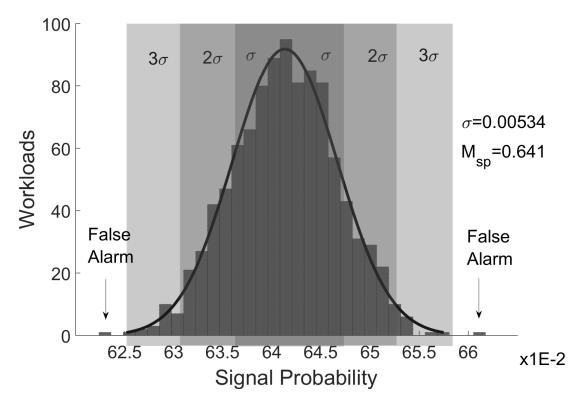

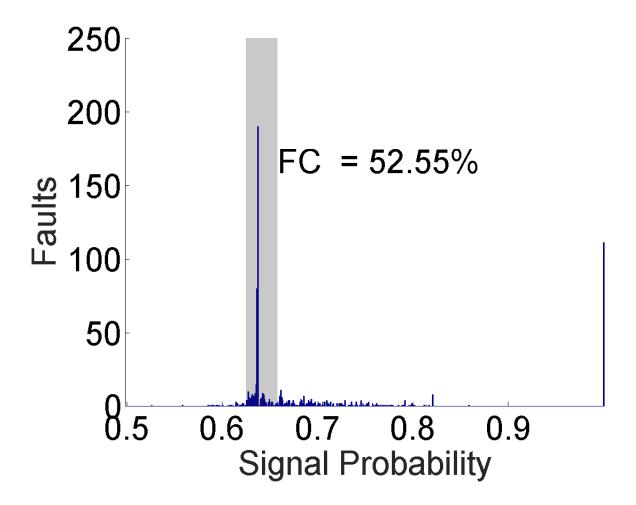

| 4.3  | Histogram of error-free online signal probabilities of circuit t481                                                           | 54 |

| 4.4  | Online signal probabilities of stuck-at faults for circuit t481 with $w=M_{sp}\pm$                                            |    |

|      | $3\sigma$                                                                                                                     | 55 |

| 4.5  | Online signal probabilities of propagated errors for circuit t481 with $w$                                                    |    |

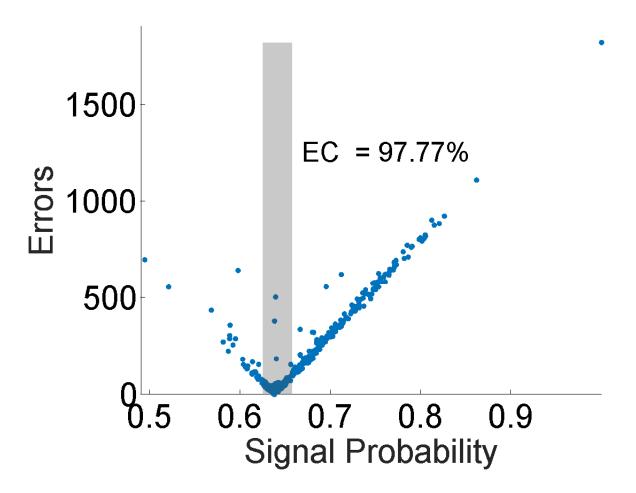

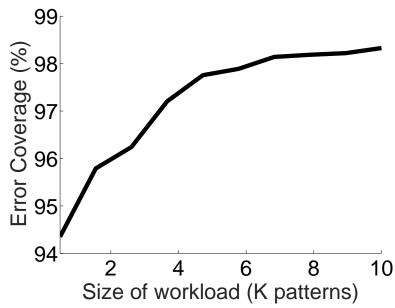

|      | $=M_{sp}\pm 3\sigma$                                                                                                          | 56 |

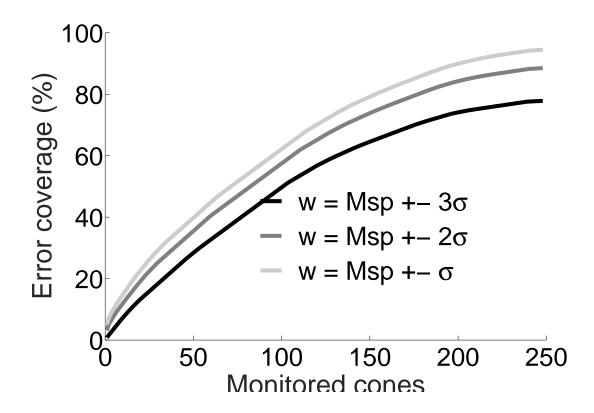

| 4.6  | Error Coverage for different workload sizes                                                                                   | 57 |

| 4.7  | Monitoring technique design flow                                                                                              | 58 |

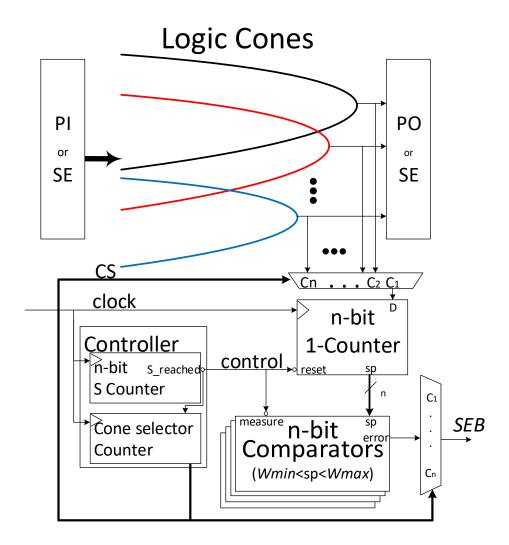

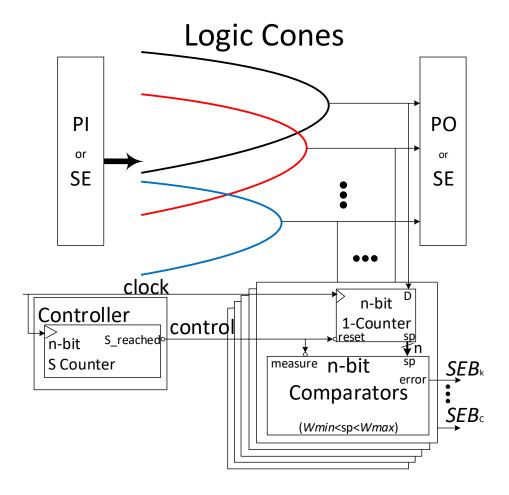

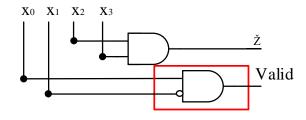

| 4.8  | Single counter design                                                                                                         | 59 |

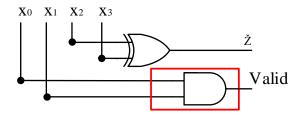

| 4.9  | Multiple counter design                                                                                                       | 60 |

|      | Simulation Setup                                                                                                              | 61 |

|      | ibSSA EC vs monitored cones with $S=7000$ for circuit s9234                                                                   | 64 |

| 4.12 | Area cost of single counter monitors compared to the size of the circuit $$ .                                                 | 65 |

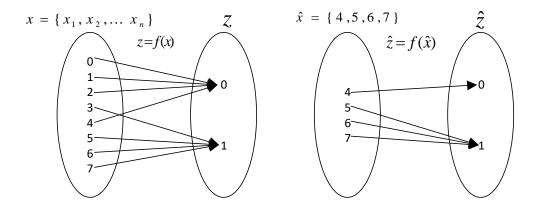

| 5.1  | Example of input subspace selection                                                                                           | 70 |

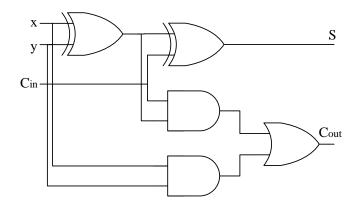

| 5.2  | Full adder circuit                                                                                                            | 71 |

x LIST OF FIGURES

| 5.3  | Karnaugh map for the approximation of $C_{out}$                              | 71 |

|------|------------------------------------------------------------------------------|----|

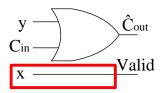

| 5.4  | ALC of the $C_{out}$ of a Full Adder                                         | 72 |

| 5.5  | Simplified circuit of a random 4-input 1-output circuit                      | 73 |

| 5.6  | AL for the random 4-input 1-output circuit using set A                       | 73 |

| 5.7  | AL for the random 4-input 1-output circuit using set B                       | 74 |

| 5.8  | AL for the random 4-input 1-output circuit using set I $\dots \dots \dots$ . | 75 |

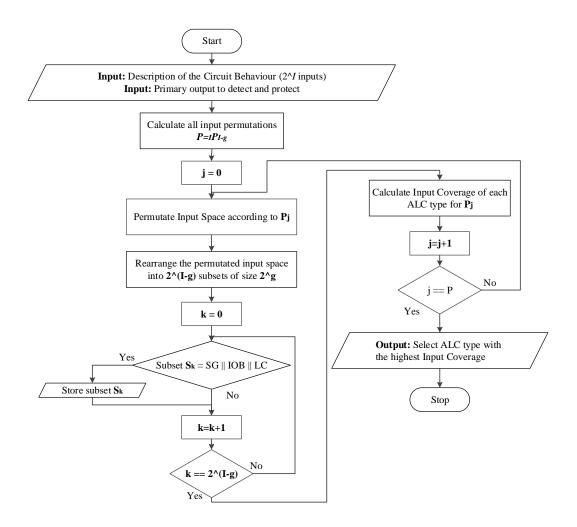

| 5.9  | Input subspace selection algorithm                                           | 77 |

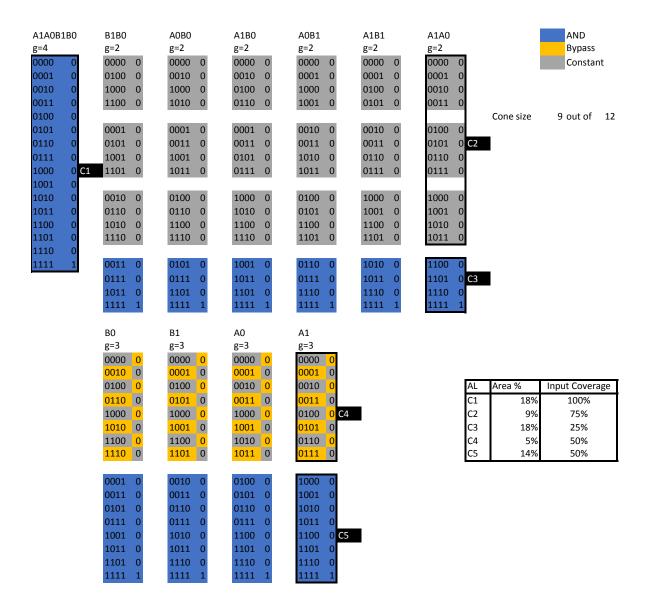

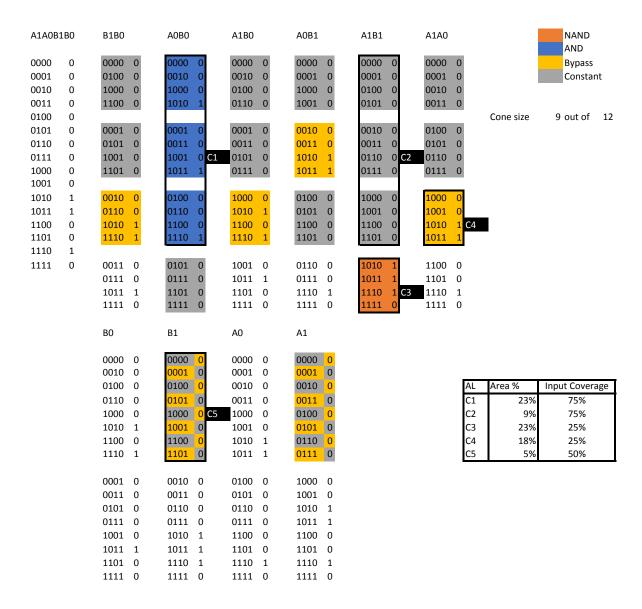

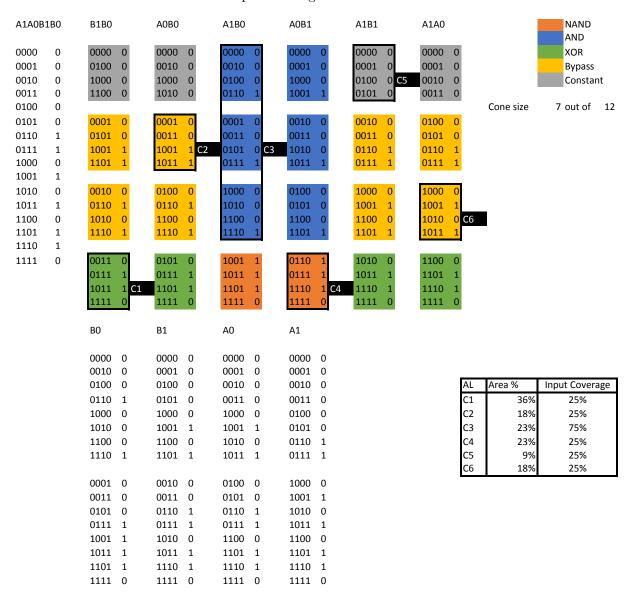

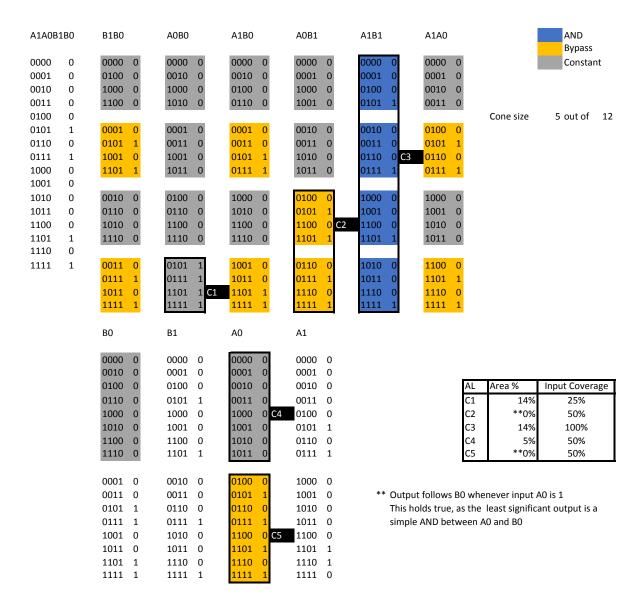

| 5.10 | Algorithm applied to the output $Z_3$ of the 2-bit parallel multiplier       | 79 |

| 5.11 | Algorithm applied to the output $Z_2$ of the 2-bit parallel multiplier       | 80 |

| 5.12 | Algorithm applied to the output $Z_1$ of the 2-bit parallel multiplier       | 81 |

| 5.13 | Algorithm applied to the output $Z_0$ of the 2-bit parallel multiplier       | 82 |

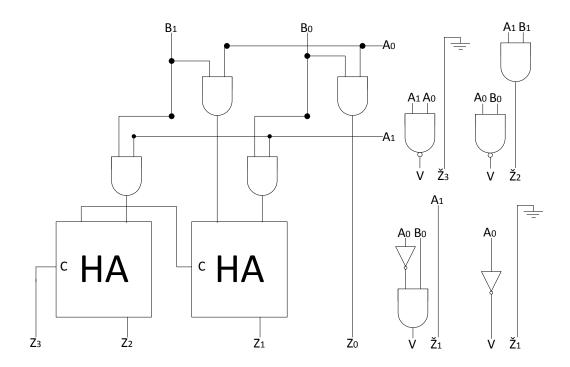

| 5.14 | 2-bit Parallel Multiplier and ALCs for each output                           | 84 |

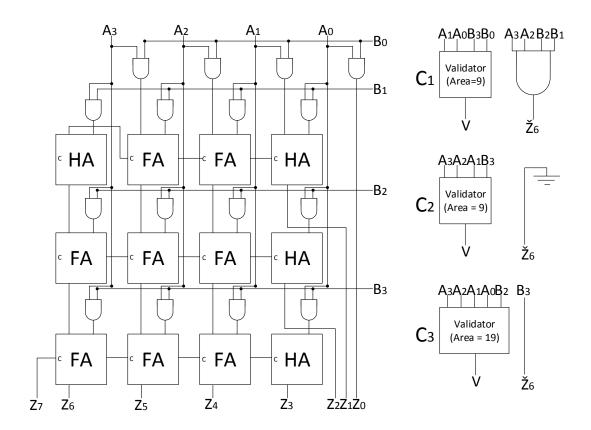

| 5.15 | Some AL candidates for the $Z_6$ output                                      | 85 |

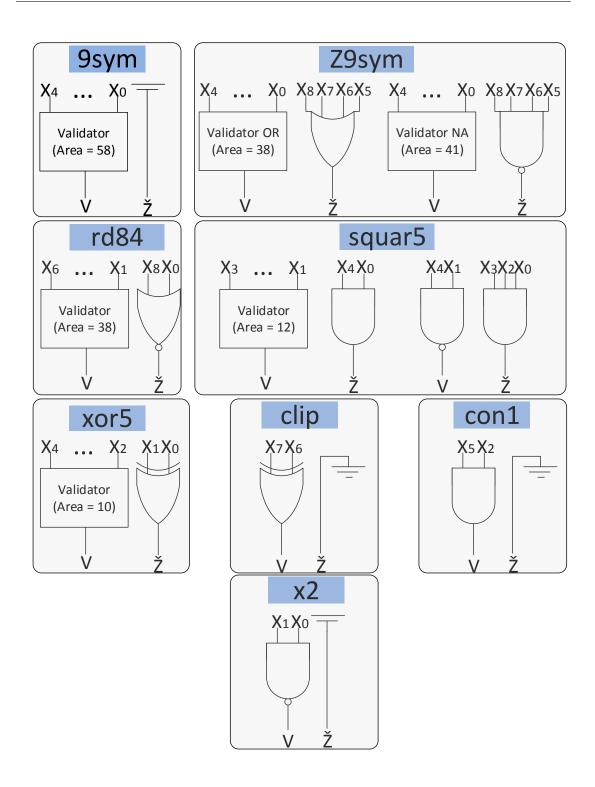

| 5.16 | Approximate Logic Circuits for the LGSynth91 benchmark circuits              | 89 |

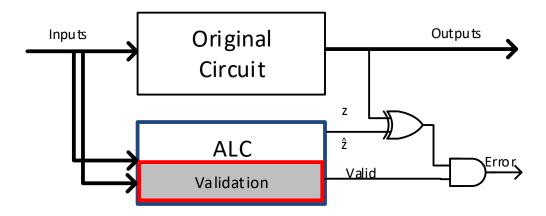

| 5.17 | Selective Fault Tolerance using Approximate Logic Circuits                   | 90 |

| 5.18 | Concurrent Error Detection using Approximate Logic Circuits                  | 91 |

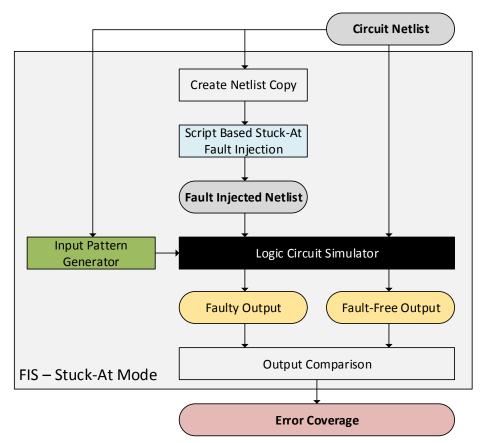

| A.1  | Fault Injection Simulator for Stuck-At Faults as used in Chapter 4           | 98 |

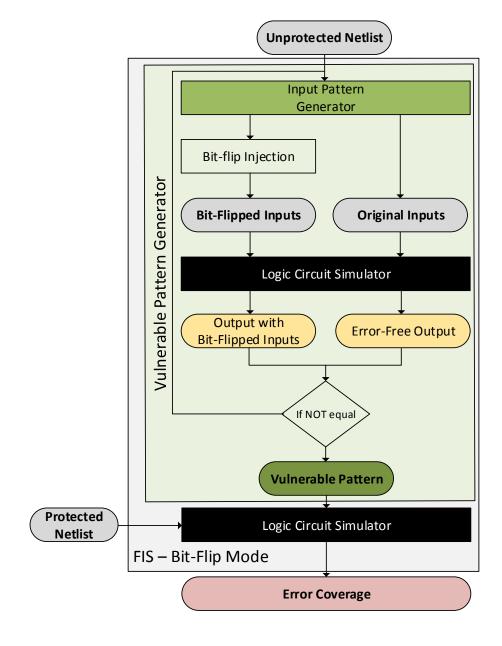

|      | Vulnerable Pattern Generator as used in Chapter 4 and Fault Injection        |    |

|      | Simulator for Bit-Flips injections as used in Chapter 3                      | 99 |

# List of Tables

| 3.1  | Measured SA fault coverage, transition fault coverage, susceptibility to                                                                         |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | bit-flips and temporary erroneous output transition between probabilistic and random patterns, for circuit $pdc$                                 | 32 |

| 3.2  | Benchmark circuit Inputs/Outputs and Gates                                                                                                       | 38 |

| 3.3  | CPU runtime of SFI and the proposed PSFT technique                                                                                               | 39 |

| 3.4  | Improvement of Error Coverage (EC) of errors induced by Single Stuck-At                                                                          | 00 |

| 0.1  | faults (ibSSA)                                                                                                                                   | 41 |

| 3.5  | Improvement of Error Coverage (EC) of errors induced by Transition                                                                               |    |

|      | faults (ibTran)                                                                                                                                  | 43 |

| 3.6  | Permanent (induced by single stuck-at and transition) and Transient (induced by erroneous output transitions and by bit-flips) EC, area cost and |    |

|      | the improvement over TMR of the proposed technique with $C_p=0.1$                                                                                | 44 |

| 4.1  | ibBF and ibSSA EC and area cost of different monitor designs $\ \ \ldots \ \ \ldots$                                                             | 62 |

| 5.1  | Example input subspace selection                                                                                                                 | 69 |

| 5.2  | Truth table of a Full Adder                                                                                                                      |    |

| 5.3  | Reduced Truth table of $C_{out}$                                                                                                                 | 71 |

| 5.4  | Truth table of a random 4-input 1-output circuit                                                                                                 | 72 |

| 5.5  | Truth table of set $A$                                                                                                                           | 73 |

| 5.6  | Truth table of $B$                                                                                                                               | 74 |

| 5.7  | Truth table of $I$                                                                                                                               | 74 |

| 5.8  | 2-bit Parallel Multiplier Truth Table                                                                                                            | 78 |

| 5.9  | Results of the selected ALC candidates for each output of a 2-bit parallel                                                                       |    |

|      | multiplier. *Logic cone consists of a single gate                                                                                                | 83 |

| 5.10 | Results of the selected ALC for the $Z_6$ output                                                                                                 | 84 |

| 5.11 | Results of each type of ALC for the t481 benchmark circuit                                                                                       | 87 |

| 5.12 | Results of applying the Input Subset Selection Algorithm on the LGSynth91 benchmark circuits                                                     | 88 |

| 5.13 | Comparison between SFT and this ALC technique                                                                                                    |    |

|      |                                                                                                                                                  |    |

# Nomenclature

IC Integrated Circuits

CMOS Complementary Metal-Oxide-Semiconductor

**CED** Concurrent Error Detection

**VDSM** Very Deep Sub-Micron

TMR Triple Modular Redundancy

**IoT** Internet of Things

$\alpha$  Switching activity

$C_L$  Load Capacitance

$V_{dd}$  Supply Voltage

$f_{clk}$  Operating Frequency

$P_{dynamic}$  Dynamic Power

$P_{leakage}$  Leakage Power

$T_{pd}$  Transistor Propagation Delay

$V_{th}$  Threshold Voltage

$I_{ds}$  Sub-threshold Leakage Current

PV Process Variation

$L_{eff}$  Effective Channel Length

$\mu$  Carrier Mobility

**NBTI** Negative Bias Temperature Instability

**HCI** Hot Carrier Injection

**PG** Power Gating

CG Clock Gating

**DVFS** Dynamic Voltage and Frequency Scaling

ATPG Automatic Test Pattern Generation

**SEU** Single-Event Upset

**CED** Concurrent Error Detection

**BIST** Built-in Self-Test

**DWC** Duplications With Comparison

**EDC** Error Detecting Codes

TPG Test Pattern Generator

CUT Circuit Under Test

**ORA** Output Response Analyser

xiv NOMENCLATURE

**ECC** Error Correcting Code

**SFT** Selective Fault Tolerance

OD Output deviations

**PSFT** Probabilistic Selective Fault Tolerance

**EC** Error Coverage

FC Fault Coverage

rp Random Pattern Set

pp Probabilistic Pattern Set

**TID** Timing-Independent Deviation

**TDD** Timing-Dependent Deviation

ibSSA Induced by Single Stuck-At

ibBF Induced by Bit-Flip

ibTran Induced by Transition

ibEOT Induced by Temporary Erroneous Output Transitions

SEB Systematic Erroneous Behaviour

**EDL** Error Detection Latency

$M_{sp}$  Mean Signal Probability

w Signature Window

$W_{max}$  Maximum Signature Window Bound

$W_{min}$  Minimum Signature Window Bound

ALC Approximate Logic Circuit

**SER** Soft Error Rate

**IOB** Input-Output Bypass

LC Logic Constant

IC Input Coverage

# Acknowledgements

I want to thank first and foremost my mother, whose unconditional support gives me an unbreakable foundation on the important matters. I would like to thank my siblings for their encouragement and support, always on point. I want to thank my supervisors, Bashir Al-Hashimi for the opportunity to pursue a PhD and Tom Kazmierski for providing assistance and helpful commentary throughout. My deep gratitude to examiners Jeff Reeve and Alex Yakovlev for their feedback. I would like to thank my sponsor the National Council of Science and Technology (CONACYT) in Mexico and to the mexican people for their trust and support. I want to express my gratitude to Dr. Daniele Rossi for his valuable insight and to Dr. Vasileios Tenentes for his continued feedback and significant input. I want to all friends and special people that have been with me through the road that is the PhD. My total gratitude for these wonderful experiences.

| To the loving men | nory of my father, whos<br>present and my future |  |

|-------------------|--------------------------------------------------|--|

|                   |                                                  |  |

# Chapter 1

# Introduction

As with every piece of machinery, integrated circuits (ICs) are prone to failure. With technology scaling, transistor sizes are reduced to open the way for increased functionality with reduced overall power dissipation, device dimensions and manufacturing costs. However, despite those advantages, the reliability of ICs has been affected [1]. The rising probability of circuit failure caused by increasing device complexity (i.e. transistor density) [2] and the errors caused by increased delay due to temperature rise in CMOS circuits, were well-known reliability concerns in the past. However until recently, achieving a high level of performance was the priority in IC design. With the introduction of very deep submicron (VDSM) CMOS technologies (sub-100nm feature size), the impact on circuit reliability caused by process variation along with other sources of signal instability has been steadily increasing [3]. Transistors in VDSM and nanoscale technologies operate within a small voltage range which makes them more susceptible to electrical noise or radiation induced instability than larger technologies [4]. Additionally, the variations in transistors cause each fabricated IC to possess different characteristics which may produce unknown behaviour and lead to errors under normal operation. Therefore, it is of utmost importance to address the impact of these reliability concerns or else the benefits provided by technology scaling will be severely outweighed by erroneous behaviour appearing in-the-field. However, traditional methodologies used to mitigate the impact of these reliability concerns often result expensive for low cost devices, and are therefore utilised primarily for safety-critical applications. On the other hand, low cost devices must be capable of producing error-free behaviour but the cost required to improve their reliability is constrained. This thesis describes novel low cost techniques to improve the reliability of cost constrained systems.

This chapter is organised as follows. Section 1.1 details the motivations and the scope of this research. Section 1.2 presents an overview of the contributions of each chapter and the organisation of this thesis, followed by the list of publications generated from this research in Section 1.3.

# 1.1 Motivation and Scope of this Research

The first design strategy used to reduce the impact of process variation was to define the worst-case scenarios to set noise margins or timing margins at which even the longest delay variations comply [5], [6], effectively setting the operating frequency of the IC as the one which will not violate those margins. As the effects of variability increased in VDSM technologies due to reduced feature sizes, the frequency of errors appearing in-the-field increased consistently [3], [7]. Faults escaping manufacturing testing manifesting as errors, single-event upsets caused by radiation induced charge deposition, temperature and voltage supply fluctuations causing gate and interconnect delay increase, and aging related problems increasing threshold voltage, have been observed to affect the functionality and performance of circuits and causing logic errors in-the-field at a higher rate than previous technologies.

The traditional solution for online mitigation of erroneous behaviour and reliable system design is hardware redundancy [8], [9]. It consists on the complete or partial replication. By replicating the circuit, the probability of failure is reduced, as it is highly unlikely an error would occur on every replica at the same time. Triple Modular Redundancy (TMR) is the best-known and most widely applied among the hardware redundancy techniques. TMR replicates original circuit so that there are three replicas whose outputs are passed on to a majority voter [10]. TMR is most widely used for safety-critical applications where robustness and data integrity are the top priority (e.g. aeronautics, medical equipment, transportation). Although TMR systems guarantee high level of reliability, its high area and power overhead, 200% of the original circuit, make it non-viable for cost constrained systems.

In recent years, there has been great interest in the development of cost-effective online testing and error monitoring design techniques to enhance the reliability of cost constrained systems. Most low cost techniques are based on a reliability assessment at the logic level of abstraction [11], [12]. At this abstraction level, low cost techniques are capable of leveraging the trade-off between error detection/circuit protection and the associated hardware cost. Example of cost-effective design techniques include partial replication using approximate logic of a slice of a circuit [13]–[15], enhanced reliability of flip-flops [16], [17] and low cost error detection to detect errors due to intermittent faults [18]. The aforementioned techniques are just a small sample of the methodologies that improve the reliability at a lower cost than traditional error detection and mitigation methods. The following chapters provide a larger review of the existing low cost techniques. However, at the logic abstraction level, there is a plethora of different approaches that can be taken to enhance circuit reliability of cost constrained systems.

Summarizing, the increased reliability concerns caused by process variability in VDSM technologies has a significant impact on the functionality and performance gains obtained by greater integration. Traditional solutions for concurrent error detection (CED) and

circuit protection used to enhance the reliability of modern ICs incur in a high cost and are unsuitable for cost constrained systems. Therefore, it is necessary to develop cost-efficient techniques to detect errors and protect circuits where the cost and power consumption are restricted.

# 1.2 Thesis Contributions and Organisation

This work presents three contributions all aimed to enhance the reliability of cost constrained systems by implementing three novel design techniques applicable at the logic level of abstraction. Aside from Chapter 2 which presents an overview of the theoretical background of this research, Chapters 3, 4 and 5 each present one of the novel reliability enhancing techniques. Finally, Chapter 6 presents the conclusions and the future work directions this research might lead to.

Chapter 3 presents the first contribution in the form of a novel low cost fault tolerance design technique applicable at the logic level, that selects and protects the most susceptible workload on the most susceptible logic cones of a circuit, by targeting both timing-independent and timing-dependent errors. The workload susceptibility is ranked as the likelihood of any error to bypass the inherent logic masking of the circuit and propagate an erroneous response to its outputs when that workload is executed. The susceptible workload is protected by a partial Triple Modular Redundancy (TMR) scheme. For the evaluation of the fault-tolerance ability of this technique, the surrogate error models of timing-independent errors induced by stuck-at faults and transient input bitflips are considered. Additionally considered are the timing-dependent errors induced by transition faults and temporary erroneous output transitions. This technique can achieve a similar error coverage when protecting the same number of patterns with an average 39.7% area/power cost reduction. Furthermore, it can improve by 95.1% on average the achieved error coverage with a similar area/power cost. Particularly, when protecting only the 32 most susceptible patterns, an average error coverage improvement of 63.5% and 58.2% against errors induced by stuck-at and transition faults is achieved, respectively, compared to the case where the same number of patterns are protected without any ranking. Additionally, this technique produces an average error coverage improvement of 163% and 96% against temporary erroneous output transition and errors induced by bit-flips, respectively. These error coverage improvements incur in an area/power cost in the range of 18.0-54.2\%, which corresponds to a 145.8-182.0\% reduction compared to TMR.

Chapter 4 presents the second contribution which consists of a novel low cost probabilistic online error monitoring technique that produces an alarm signal when systematic erroneous behaviour has occurred over a pre-defined time interval. Particularly, this technique monitors the signal probabilities at the outputs of the most vulnerable logic

cones of a circuit concurrently to its normal operation. To detect systematic erroneous behaviour, the collected data is compared on-chip against the signature of error-free behaviour. This technique is applied to a set of the EPFL and ISCAS benchmarks and results demonstrate that it achieves, on the largest circuits, an average error coverage of 84.4% and 73.1% of errors induced by intermittent bit-flips and intermittent stuck-at faults, respectively, with an average area cost of 1.66% and an error detection latency in the range of [0.01, 3.3] milliseconds.

Chapter 5 presents the last contribution consisting of a circuit approximation technique that can be used for low cost non-intrusive concurrent error detection and for selective fault tolerance. The circuit approximation is based on finding functionality at the logic level that behaves similarly to single logic gates or constant values. An algorithm is proposed to select the input subsets to approximate. This algorithm is applied to arithmetic circuits as a proof of concept. Furthermore, an application of this technique to a set of the LGSynth91 benchmark circuits shows an average input coverage of 33.59% of all the input space with an average 7.43% area cost. Additionally, using the generated approximate logic circuits for selective fault tolerance results in significant area cost reductions compared to existing techniques. In addition to that, it is shown that the generated approximate logic circuits can be used for low cost concurrent error detection.

# 1.3 Publications

The following peer-reviewed publications have been produced from the research presented in this thesis;

- M. D. Gutierrez, V. Tenentes, and T. Kazmierski, "Susceptible workload driven selective fault tolerance using a probabilistic fault model" in the 22th IEEE International Symposium on On-Line Testing and Robust System Design 2016. IOLTS. Proceedings, 2016.

- M. D. Gutierrez, V. Tenentes, D. Rossi and T. Kazmierski, "Low Power Probabilistic Online Monitoring of Systematic Erroneous Behaviour" in the 22th IEEE European Test Symposium 2017. ETS. Proceedings, 2017.

- M. D. Gutierrez, V. Tenentes, D. Rossi and T. Kazmierski, "Susceptible Workload Evaluation and Protection using Selective Fault Tolerance". Journal of Electronic Testing: Theory and Applications, August 2017, Vol 33, pp 463-477.

- M. D. Gutierrez, V. Tenentes, and T. Kazmierski, "Low Cost Error Monitoring for Improved Maintainability of IoT Applications" in the International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems. DFT. Proceedings. 2017.

The following research paper is under preparation:

M. D. Gutierrez and T. Kazmierski, "Single Gate Approximate Logic Circuits"

# Chapter 2

# Background

The appearance of faults in-the-field has been steadily rising with the reduction of technology nodes and increased integration density [19]. Online testing and monitoring techniques have been developed in the past to enhance the reliability of ICs by testing, monitoring and protecting circuits in-the-field. This chapter introduces the basic concepts related to this thesis and presents an overview of the previous research on this field. Additionally, chapters 3, 4 and 5 have their own background placing each of contribution in context of the relevant works in the field. This chapter is organised as follows. Section 2.1 reviews the concept of cost constrained systems. Section 2.2 presents the reliability challenges of cost constrained systems posed by technology scaling and power management techniques and describes the types of faults and errors that may appear as a result. Section 2.3 provides an overview of fault and error detection techniques such as concurrent error detection and built-in self test. Section 2.4 gives an overview of the circuit protection mechanisms most commonly deployed while Section 2.5 briefly describes the state if the art low cost error detection and protection techniques. Finally, Section 2.6 presents the objectives of the research presented in this thesis.

# 2.1 Cost Constrained Systems

The demand for cheap, mass produced integrated circuits (ICs) has risen significantly over the past years due to the exponential growth of personal devices and those connected to the Internet of Things (IoT). A few examples of such devices are tablets, smartphones, wearables, surveillance cameras, parking, environmental or geo-monitoring sensors. These kind of devices are designed to be cheap to implement, manufacture and operate, thus they are referred to as cost constrained systems.

In order for cost constrained systems to achieve a correct functionality while meeting its cost limitations, transistor sizes have been decreasing due to a process known as technology scaling. Additionally, to reduce operation costs, many low power design techniques have been developed in the past to achieve power consumption reduction. The goal of these techniques to minimize the power consumption as much as possible without having a significant impact on the performance of the system. The power consumption of a digital IC is calculated as follows [20] [21]:

$$P_{total} = \alpha \left( C_L \cdot V_{dd}^2 \cdot f_{clk} \right) + I_{leakage} \cdot V_{dd}$$

(2.1)

Which can be written as:

$$P_{total} = P_{dynamic} + P_{leakage} (2.2)$$

Where  $P_{dynamic}$  is the dynamic power dissipated by the switching activity  $(\alpha)$  of the transistors in the circuit, with load capacitance  $C_L$  and operating at frequency  $f_{clk}$  with a supply voltage  $V_{dd}$ .  $P_{leakage}$  is the leakage power which is the dissipated when the transistors are idle.

Low power design techniques aim to reduce either or both the  $P_{dynamic}$  and the  $P_{leakage}$  components of the overall power consumption in ICs. These techniques deploy a number of different tactics to achieve the targeted power reduction, albeit with a reliability cost that results in non-trivial challenges for modern IC technologies.

# 2.2 Reliability challenges of Cost Constrained Systems

The lifetime reliability of semiconductor devices in cost constrained systems may be affected by multiple sources [22], [23]. This section provides an overview of the reliability challenges of cost constrained systems posed by the scaling down of technology nodes and by power management techniques.

# 2.2.1 Technology scaling

The driving reason behind continuous reduction of technology nodes is fabrication costs. The cost of fabricating ICs is dependent primarily on the number of steps required by the technology node, therefore, including as many dies per wafer as possible is desirable. In addition of smaller transistor sizes occupying less physical space, they require less power to operate at the same frequencies, which also implies that a higher performance is possible with the same power consumption. An approximation of transistor propagation

delay is given by Equation 2.3 [24]:

$$T_{pd} \propto \frac{C_L \cdot V_{dd}}{\left(V_{dd} - V_{th}\right)^{\alpha}} \tag{2.3}$$

where  $T_{pd}$  is the transistor propagation delay,  $C_L$  is the load capacitance,  $V_{dd}$  is the supply voltage,  $V_{th}$  the threshold voltage and  $\alpha$  is used for modelling short channel effects [25]. Both  $C_L$  and  $V_{th}$  are proportional to the size of the transistor, therefore reducing sizes leads to shorter propagation delay, allowing for greater circuit performance. Incidentally, this behaviour also allows to reduce power consumption without increasing transistor delay by reducing the supply voltage.

On the other hand, reducing transistor sizes lowers the threshold voltage, which produces a significant increase in the leakage power. The primary contributor of leakage power is the sub-threshold leakage current that may be approximated as Equation 2.4 [24]:

$$I_{ds} \propto e^{\frac{V_{gs} - V_{th}}{n \cdot V_T}} \tag{2.4}$$

where  $V_{gs}$  is the gate-to-source voltage,  $V_{th}$  is the threshold voltage and  $V_T$  is the thermal voltage. The sub-threshold leakage current increases exponentially as the  $V_{th}$  is reduced. As a result, the leakage power also increases exponentially.

Scaling down of technology nodes has also had an impact on the reliability of cost constrained systems. As transistors get smaller, they become prone to all sources of instability. Additionally, the higher integration levels allowed by smaller transistors increase system complexity and power density, resulting in a higher probability of producing erroneous behaviour [7]. The main contributors to the impact of technology scaling on the reliability of cost constrained systems are process variation and circuit wearout. [3], [22], [26].

#### 2.2.1.1 Process Variation

The IC fabrication process is not exact and may produce variations in the characteristics of transistors within the same technology node. This problem is known as Process Variation (PV) [1], [27], [28]. Transistor sizes in very deep submicron (VDSM) technologies are significantly smaller than the light wavelength used in the lithography process to imprint the circuits on the silicon wafer which poses a challenge to modern manufacturing processes [27]. The imprinting can be imprecise leading to uneven surfaces on transistor channels thus creating differences in the electrical properties throughout the chip. In addition to that, sub-wavelength lithography suffers from printability issues like variations on the focus, pitch and light source exposure, whose effects can make the lines imprinted on the silicon wafer of a size different than the one designed on the mask [29]. These variations cause different threshold voltages in transistors on the same die,

which produces uncertainty in circuit delay of critical timing paths, and may lead to performance degradation.

Figure 2.1 illustrates the distribution of the extracted sub-threshold voltage  $V_{th}$ , effective channel length  $L_{eff}$ , and carrier mobility  $\mu$  of a 65nm chip [30]. The variation of the parameters of the transistors throughout the circuit follows a gaussian distribution whose standard deviations from the mean where of 5%, 4% and 21% respectively. These variations are expected to keep increasing as technology nodes scale down.

Figure 2.1: Variations of  $V_{th}$ ,  $L_{eff} \& \mu$  [30]

#### 2.2.1.2 Circuit Wearout

Semiconductor circuits degrade gradually due to normal operation. However, technology scaling allows a greater integration increasing power density which leads to accelerated circuit wearout and reduced lifetime of devices [31], [32]. Among the circuit wearout effects that have an impact on the reliability of a circuit are Negative bias temperature instability (NBTI) and Hot Carrier Injection (HCI)[33]. NBTI is generated by positive charge accumulating at  $SiO_2$  interface and the oxide while under negative bias, causing the threshold voltage to change, which decreases channel mobility thereby increasing the intrinsic delay of the transistor [31]. HCI is caused by carriers in the transistor channel (electrons or holes) gaining enough energy to tunnel through the oxide, manifesting as leakage current and changing transistor parameters gradually damaging the circuit [34].

# 2.2.2 Power Management Techniques

As shown by Equation (2.1), there are two components in the total power consumption: dynamic and leakage power. Various power management techniques have been developed to reduce power consumption, either dynamic or leakage in cost constrained systems [35]–[37]. Following is an overview of the most commonly used techniques.

#### 2.2.2.1 Power Gating

Leakage power has become a major concern regarding the overall power dissipation of nanoscale technologies [38]. One of the most commonly used leakage power reduction techniques is Power Gating (PG) [36]. This technique consists of completely turning off sections of the circuit that are expected to be idle for a certain amount of time, effectively preventing any leakage power consumption on the disabled sections. A drawback of this technique is that re-enabling the power-gated sections may take a long time period, in addition to the spike in power consumption that a re-initialization of the circuit may cause.

PG may cause a problem known as ground bounce noise, which is generated by the fluctuations on the power rails [39]. Figure 2.2 shows a power gated logic circuit affected by ground bounce noise. When the transition from sleep/off mode to active/on mode causes the sleep transistor (located at the bottom) to turn ON to saturation, a sudden discharge creates a current surge at the moment of the mode change, which results in voltage fluctuations across the power supply rails. These fluctuations may change the state of sequential elements in the circuit, potentially leading to unknown behaviour.

## 2.2.2.2 Clock Gating

In digital circuits, the high switching activity of the clock tree dissipates the most dynamic power compared to the rest of the system [40]. Clock gating (CG) techniques were developed to prevent the switching of the clock of sequential elements that are not required to update every clock cycle. The basic implementation requires the insertion of a clock gating module consisting of a latch and an AND gate, which controls the the switching of the clock signal. Similar to power gating, a section of the circuit that is clock-gated may not power up in time, generating glitches and affecting timing which lead to erroneous behaviour [38].

FIGURE 2.2: Ground bounce noise in a power gated structure [39]

#### 2.2.2.3 Dynamic Voltage and Frequency Scaling

As denoted by Equations (2.1) and (2.2), the dynamic power consumption is given as:

$$P_{dynamic} = \alpha \left( C_L \cdot V_{dd}^2 \cdot f_{clk} \right) \tag{2.5}$$

where  $\alpha$  is the switching activity,  $C_L$  is the load capacitance of the transistors Vdd is the supply voltage and  $f_{clk}$  is the frequency of the clock.

Notice from Equation (2.5) that  $V_{dd}$  has a quadratic relation to  $P_{dynamic}$ , therefore reducing it is the most effective means to decrease  $P_{dynamic}$ . Dynamic Voltage and Frequency Scaling (DVFS) is a power management technique which consists of reducing the supply voltage, to reduce dynamic power consumption. On the other hand, lowering  $V_{dd}$  increases the intrinsic transistor delay, which restricts the clock frequency at which the circuit can operate. This forces the reduction of the  $f_{clk}$  to prevent erroneous behaviour due to timing-related errors, which may occur if a task execution deadline of a time-constrained system is violated due to the slower clock frequency [41], [42]. Therefore, this technique may be be applied whenever there is slack time on the computation that allows a timely execution of the task with a slower  $f_{clk}$  [43]–[45].

## 2.2.3 Faults in Cost Constrained Systems

As discussed previously, technology scaling and low power design techniques may impose reliability challenges on cost constrained systems. The reliability of these systems may be affected by faults appearing in-the-field during normal operation. These faults can be classified into three categories according to their duration [46]: permanent, transient and intermittent faults.

#### 2.2.3.1 Permanent Faults and Fault Models

Permanent faults may appear due to defects escaping manufacturing testing, or by aging and circuit wearout effects caused by the gradual degradation of devices under typical operating conditions. These faults manifest continuously therefore having a lasting impact the system reliability.

The IC fabrication process is not perfect which may result in defective ICs being imprinted onto the silicon wafer. This process imperfection is exacerbated by the increased fabrication complexity as technology scales down. In order to verify that an IC was fabricated correctly, it is tested against manufacturing defects. However, due the diversity of possible defects in VDSM technologies, the generation of tests for real defects poses a significant challenge. Therefore, fault models were developed to emulate the effects that the different defects may have on the operation of the IC. These fault models should reflect the behaviour of defects with accuracy, and be computationally efficient. Various fault models have been proposed [47], of which the most widely used is the the stuck-at fault model.

Under the stuck-at fault model, a stuck-at fault is a logic-level (logic 0 or logic 1) defect which affects the logic value of the nets in a circuit. These nodes may belong to the primary inputs or outputs as well as any internal node in any gate. This type of faults force the value of the affected node to a constant logic 0 or logic 1, referred to as stuck-at-0 or stuck-at-1, respectively. Transistor-level stuck-at is another fault model [48] which targets transistor defects such as stuck-open (missing connection to ground) or a stuck-short (a conducting path between the power source and ground).

Other fault models target delay defects that affect the timing of the circuit. A delay fault produces an extra propagation delay in the affected path in such a way that the total delay is larger than the time limit required for a fault-free operation. Popular delay fault models include the gate-delay fault model, which models the gate interconnect and pin-to-pin delay, the path-delay fault model, which considers the delay distributed over a group of interconnected gates, and the transition fault model. The transition fault model is the most widely used delay fault model [49], [50]. The transition fault model requires the propagation of transitions in the circuit while operating at the desired frequency.

To propagate a transition, it is necessary to set apply two patterns at the inputs of the circuit, one for initialization of the relevant signals to known and controllable values, and one to produce the desired transition. This fault model works under the assumption that only a single gate is affected by a delay fault, and that the extra delay caused by the fault prohibits the correct transition from reaching a primary output or sequential element.

Fault models are then used by the Automatic Test Pattern Generation (ATPG) tools to generate test patterns of digital circuits [47]. ATPG tools define a list of faults depending on the fault model targeted an find those patterns that detect such faults. Then, they collect fault coverage statistics (the percentage of faults that may be detected) by deploying fault simulation campaigns. A fault simulation campaign consists of injecting modelled faults in a simulation environment and applying test patterns. The outputs of the circuit tested are compared against the values expected in the presence of the targeted faults to determine whether the fault is detected.

# 2.2.3.2 Transient Faults

Transient faults have a temporary impact on the reliability of ICs. These faults are caused by single-event upsets (SEU) or by other sources of instability and noise in modern ICs [51]. A SEU are produced by cosmic and alpha particle strikes. When a particle hits a node in the circuit, it may generate a short current pulse with enough magnitude that propagates through the node and reaches a storage element. If the current pulse has enough energy, the state of the storage element flips, effectively causing a bit-flip. The transistor sensitivity to SEUs is dependant on the transistor capacitance and supply voltage [7], which are both affected by technology scaling. The SEUs were known to cause bit-flips in storage elements for years, however, as technology scaled into VDSM technologies, they have also become a cause of temporary gate failures in combinational logic. This is due to the reduced threshold voltages of transistors in smaller technologies.

Another source of transient faults is the intrinsic noise in modern ICs. This noise is caused by inductive effects generated from the fast switching speed and high transistor density of modern ICs [52]. Process variation can also contribute to the generation of transient faults, due to the uneven threshold voltages on the transistors through out the chip.

#### 2.2.3.3 Intermittent Faults

Intermittent faults may appear and disappear repeatedly. These faults are activated in-the-field by defects that escaped manufacturing testing, by the systematic of power or thermal constrains, or by aging. Intermittent faults cause bursts of errors that repeat

FIGURE 2.3: General architecture of a CED mechanism [55]

periodically on the same places under specific operating conditions [53]. They manifest as multiple bit-flips on sequential or combinational logic, or exhibit a behaviour similar to permanent faults for a finite period of time.

Intermittent fault models were introduced as a variation of existing fault models [54], which include Intermittent stuck-at, Intermittent bit-flips and Intermittent delay. These fault models are based on the permanent fault models described previously, with the difference that the activation time of the intermittent faults is finite.

# 2.3 Fault and error detection techniques

Faults appearing in-the-field may impact the circuit reliability, producing an erroneous output. Therefore, it is of great interest to develop techniques in order to detect when errors, caused by permanent, transient or intermittent faults, have occurred.

The existing fault and error detection techniques can be classified into two categories: Concurrent Error Detection (CED) and Built-in Self-Test (BIST). CED targets the detection of logic errors occurring during normal operation. On the other hand, BIST mechanisms target the identification and diagnosis of faults in the circuit. An overview of both CED and BIST techniques is presented as follows.

# 2.3.1 Concurrent error detection (CED)

Concurrent error detection (CED) techniques are used to enhance system reliability [56]–[60]. The general architecture of a CED mechanism is shown in Figure 2.3 [55]. CED techniques operate according to the following principle: Consider a circuit that performs a function f on an input pattern  $x = (x_0, x_1, \dots, x_n,)$ . The CED mechanism consist of another circuit which concurrently predicts the output of the original circuit or a specific characteristic corresponding to such output for a given input pattern x. Finally, a checker determines whether the predicted output or its specific characteristic corresponds to the one produced by the original circuit given an input pattern x. If a mismatch occurs, an *error* signal is asserted indicating an error has occurred in the original circuit, the output predictor or in the checker.

The specific characteristic predicted by the output predictor circuits may consist of: the full or partial output itself, its parity or the number of 1's or 0's. Following is an overview of a number of CED techniques.

## 2.3.1.1 Hardware duplication

CED using hardware duplication with comparison (DWC), shown in Figure 2.4, is a technique in which the output predictor consists of a full or partial replica of the original circuit [61]. This replica performs the same logic function as the original circuit and it is expected to produce the same outputs. If the output predictor is only a partial replica, it is only capable of detecting errors on the outputs that are fully replicated [62]. A comparator is used to check if the outputs of both circuits match. In the case of a mismatch, the system indicates that an error has occurred.

A DWC system ensures an error-free operation only when both the original and the replica circuits do not generate identical errors, assuming that the comparator is also error-free. The most basic comparator consists of an array of XOR gates whose output is asserted when its inputs are different. However, since the comparator is essential to the error-free operation of the DWC system, self-checking comparators have been developed to guarantee an error-free comparison [63], [64].

# 2.3.1.2 Error Detecting Codes

CED techniques based on error detecting codes (EDCs) rely on encoding a characteristic of the output of a circuit along with the output itself. These characteristic may be the parity of the output, the number of logic 0's or 1's in the output, among others.

Of the EDCs, parity prediction is the most widely used CED technique. The parity of a set of binary digits is the number of logic 1's and it can be even or odd. Figure

Figure 2.4: Duplication with comparison CED [61]

FIGURE 2.5: Parity prediction with one parity bit [64]

2.5 presents the architecture of a single parity bit CED technique. The circuit with n outputs must be designed such that there is no logic sharing between its logic cones. Therefore, single faults can only affect one output at a given time. The parity of the outputs is predicted and passed on to the parity checker along with the outputs to check whether the actual parity of the outputs agrees with that of the predicted parity bit [64]–[66].

A major drawback of parity-based error detection is that it imposes the restriction on the

FIGURE 2.6: Concurrent error detection with Berger codes [67]

circuit that no logic sharing between the cones is allowed. This restriction often results in a high area cost. In order to reduce the area cost, multiple parity bits may be generated by partitioning the outputs into different parity groups, each with an associated parity bit. Logic sharing is only allowed between logic cones belonging to different groups, thus a single fault can affect at most one parity group.

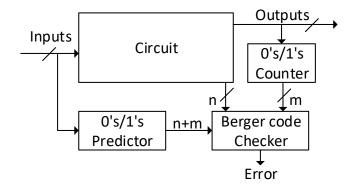

Other CED techniques using error detecting codes have been proposed that rely on unidirectional codes. Unidirectional codes are deployed under the assumption that only unidirectional logic errors may occur; i.e, either only  $0\rightarrow 1$  or  $1\rightarrow 0$ , but not both. The most widely known unidirectional cone is the Berger code [67], shown in Figure 2.6.

Using a Berger code, the encoded output is formed by the output of the circuit and checkbits containing the number of 0's (or 1's) in the output itself. Therefore, the length of the encoded output is calculated as n+m where n is the number of bits in the circuit output and m is the length of the checkbits, which is calculated is follows:

$$m = \lceil log_2(n) \rceil \tag{2.6}$$

This results in the minimum number of bits required to represent the number of 0's (or 1's) in the output.

## 2.3.2 Built-in Self Test (BIST)

Built-in Self-Test (BIST) techniques have been proposed in the past to test a circuit inthe-field [68], [69]. BIST mechanisms, illustrated in Figure 2.7, work under the following principle: A test pattern generator (TPG), typically implemented using a linear feedback shift-register, and an output response analyser (ORA) are integrated on-chip along with the circuit under test (CUT). The TPG generates test patterns in order to sensitize the

Figure 2.7: Basic BIST architecture [68]

CUT. This process is similar to the test-patterns generated by the ATPG and input into the circuit by the Automatic Test Equipment (ATE) deployed during manufacturing testing. The outputs of the CUT are examined by the ORA to detect if the circuit has become faulty. BIST mechanisms are tailored to a targeted fault model (stuck-at, transition, etc...) and thus are only capable of detecting specific types of faults. The cost of these BIST mechanism is often small, however, the design of BIST mechanisms is dependant on the nature of the logic of the CUT and the targeted fault model, which makes automating these mechanisms a difficult task. It is important to note that BIST mechanisms, are not designed to detect logic errors like CED techniques. These mechanisms are designed to test the circuit for faults, with no consideration if a fault is causing errors, or may cause an error in the future.

BIST mechanisms were originally developed to assist manufacturing testing by moving the test pattern generation and the analysis of the output response on-chip [70]–[73]. However, with the increased reliability concerns of modern VDSM technologies, BIST mechanisms have been adapted to perform tests online, after manufacturing testing and while the circuit is in-the-field. The efforts to use BIST mechanisms in-the-field can be categorized in two main directions: Online BIST and Concurrent BIST.

#### 2.3.2.1 Online BIST

Traditional BIST mechanisms were mainly used for quality assessment after the manufacturing process or prior shipping the circuit to a vendor [70]. However, the need to ensure system integrity during the lifetime of ICs, particularly for safety-critical applications, resulted in the design of BIST mechanisms capable of performing tests online and in-the-field.

Online BIST mechanisms, allow the detection of faults during the lifetime of digital systems [32], [46], [74]. The basic principle of offline BIST is preserved for the implementation of online BIST solutions (Figure 2.7). Online solutions however, apply

periodically to the CUT a heavily compressed deterministic test-set and checks the response to detect the presence of faults. The frequency at which this periodic test is applied may depend on an automatic process built in the circuit, the system software, or by an user input [75]–[77]. In order to apply the test, the state of the circuit must change to BIST (or test) mode, therefore being unable to perform concurrently to normal operation.

#### 2.3.2.2 Concurrent BIST

Concurrent BIST mechanisms were introduced to allow testing for faults in the circuit concurrently to normal operation [78]–[81]. These mechanisms use input patterns and responses generated off-line using ATPG, which are compacted and stored in on-chip memory. When one of the precomputed patterns is present at the primary inputs of the CUT during normal operation, the circuit response is checked against the stored expected response. These kinds of tests are non-intrusive, as they have no impact on circuit performance, however storing the sufficient patterns and responses may incur in a significant area and power cost. Additionally, the test times are unpredictable as in order to complete the test, all the required input patterns of the test must appear at the inputs, which may result in a long fault-detection latency.

## 2.4 Fault and Error protection techniques

To enhance the reliability of cost constrained systems, techniques that protect circuits against faults and errors have been developed in the past. In contrast to CED and BIST techniques which target only detection, these techniques have different targets: Preventing the appearance of faults or errors, or mitigating their effects to ensure correct functionality despite their presence. Protecting circuits indicates that some form of Fault Tolerance is included. Particularly, the protection against faults appearing in-the-field is commonly referred to as Hardening. Many hardening techniques developed in the past rely on providing extra resources to add some form of redundancy to the system. This redundancy may come from replicated hardware, intrinsic information redundancy in the outputs of the circuit or timing redundancy in re-execution methods and software recovery. Following is an overview of the most widely used techniques to protect a circuit against faults or errors.

#### 2.4.1 Hardware Redundancy

Hardware redundancy consists of fully or partially replicating a circuit. One of the classic hardware redundancy schemes is Triple Modular Redundancy (TMR) [8], [82], [83].

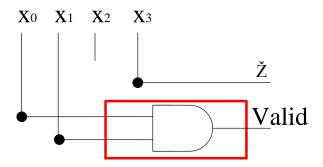

FIGURE 2.8: Basic TMR scheme [8]

TMR triplicates the system whose outputs are passed onto a majority voter circuits to compare them, selecting the majority values. TMR schemes may be applied to triplicate whole systems, blocks or even cells. The basic TMR scheme is illustrated in Figure 2.8.

#### 2.4.2 Error Correcting Codes

Error correcting codes (ECC) rely on introducing information redundancy in systems or using the one intrinsic to some applications in order to correct errors as they occur [84]. If an error appears, ECCs are designed in such a way that there is enough information at the encoded output to reconstruct the correct data from the faulty data. Many ECCs have been proposed as an extension of error detecting codes (section 2.3.1.2). Parity based techniques have been reported [85], [86] applied primarily in communication channels or storage elements. Hamming Codes extend the concept of parity checks to allow for single error correction and double error detection [87].

#### 2.4.3 Timing Redundancy and Software re-execution

Adding timing redundancy to a system consists of re-executing an instruction or reapplying an input when an error is detected [88]–[90]. This process often involves using the system software to issue a re-execution command which recomputes the last erroneous data [91]. The main advantage of implementing error correction using software is that it has no impact on design and area cost, although it imposes a high performance penalty.

#### 2.5 Low Cost Error Detection and Correction

Traditional CED and Hardening techniques are often expensive in terms of area or power for cost constrained systems. Therefore they have been used in circuits operating in harsh conditions or in safety-critical applications where data integrity is the top priority, such as aerospace electronics or medical devices. For instance, duplication with comparison CED often incurs in over 100% area cost [55] including the comparator. Furthermore, TMR entails an area and power cost greater than 200% of the original circuit. These costs result prohibitive for systems where low cost and low power consumption are the priority.

Low cost and low power techniques have been proposed to reduce the cost by trading off error detection and correction capabilities for a reduced area and power overhead. The main premise is the following: If providing CED or hardening a whole circuit is too expensive, then only the parts of the circuit or the application that are the most vulnerable to faults or errors must be checked or protected [92], [93]. Some methodologies to identify the vulnerable parts (soft spots) have been proposed [74], [94], [95], which allow low cost techniques to focus their efforts on those parts.

Selective Hardening techniques protect only the vulnerable parts of a circuit [96]. This protection may be done by localized TMR on the soft spots [97]. Other techniques require the analysis of specific workloads to find the sequential elements to harden [98], [99]. Additionally, selective hardening may also be applied at the gate level by duplicating [100] or resizing [101] vulnerable gates.

Instead of protecting particular parts of a circuit, Selective Fault Tolerance (SFT) has been proposed to reduce the cost of TMR by protecting only a specific subset of the input space in combinatorial circuits [102], [103]. SFT relies in an heuristic to arbitrarily select the input subset to protect, guaranteeing TMR-levels of protection for only those input vectors. This results in a reduced area cost compared to TMR.

## 2.6 Research Objectives

It is evident from the theoretical background presented in this chapter that low cost fault and error detection and correction techniques are and will continue to be a necessity. The reliability of modern ICs continues to be further aggravated by the consistent trend of scaling down technologies into the nanoscale. As discussed before, cost constrained systems are designed to be cheap to produce and often operate under strict power constrains. Many applications of cost constrained systems are not constrained by strict data integrity requirements, allowing a trade-off between cost and fault tolerance. Furthermore, some of the low cost solutions previously developed are tailored to a specific

type of faults (permanent or transient), or are dependent on the type of circuit they are targeting (datapath, control, sequential elements).

The aim of this thesis is to develop low cost and low power online testing & monitoring techniques that enhance the reliability of ICs in cost constrained systems. The techniques proposed in this thesis leverage the trade-off between fault and error coverage vs area overhead and power consumption in order to enable different levels of protection at various costs. Furthermore, the proposed techniques are applicable at the logic level to any circuit and are developed to be compatible with the standard electronic design automation (EDA) flow. This compatibility is of utmost importance to reduce the design effort associated with the implementation and inclusion of these techniques in existing and future designs. The techniques are compared qualitatively and whenever possible, quantitative, to existing concurrent error detection, selective hardening and selective fault tolerance techniques.

#### 2.7 Concluding Remarks

This chapter presented the basics of cost constrained systems. The reliability challenges posed by the design, design and operation of cost constrained systems were detailed. The types of faults that may appear during the normal operation of a cost constrained system, such as permanent, transient or intermittent faults, have been identified. The necessity of techniques that detect faults and errors in-the-field has been discussed and some of those techniques have been briefly described. Additionally, an overview of the various circuit protection techniques has been presented. Finally, the research objectives were laid out.

## Chapter 3

# Probabilistic Selective Fault Tolerance

Section 2.2 of Chapter 2 discusses the reliability challenges of cost constrained systems. These challenges indicate that circuits require protection against faults and errors appearing in-the-field. A number of fault and error protection techniques have been developed in the past to tackle this problem, as presented in Section 2.4. However traditional fault tolerance techniques are often expensive, thus low cost techniques were introduced to reduce the cost of circuit protection (Section 2.5). These techniques trade reliability to reduce the area cost and the power consumption of integrated circuits by protecting only a subset of their workload or their most vulnerable parts. The selection of the workload to protect is done randomly or arbitrarily [102], [103], without consideration if the patterns in the workload are the most susceptible to errors. Automatic Test Pattern Generation (ATPG) may be used to select the input patterns to protect (Section 2.2.3.1), however, the traditional fault models are biased towards the one specific type of fault they model (Section 2.2.3). Additionally, faults appearing in-the-field may not propagate errors, thus they will not affect the overall functionality of the system. Therefore, in the presence of faults not all workloads are equally susceptible to errors [104]. This motivates the need to develop low cost fault tolerance techniques that protect the workload against errors caused by any type of faults.

This chapter presents a novel low cost fault tolerance design technique that selects and protects the most susceptible workload on the most susceptible parts of the circuit by targeting faults that are both timing-independent (i.e. stuck-at) and timing-dependent (i.e transition) errors. The workload susceptibility is ranked as the likelihood of any error to bypass the inherent logic masking of the circuit and propagate an erroneous response to its outputs when that workload is executed. The susceptible workload is protected by a partial Triple Modular Redundancy (TMR) scheme.

This chapter is organized as follows. Section 3.2 presents an overview of previous works on Selective Fault Tolerance, reviews the probabilistic fault model of output deviations, introduces the concepts of uncorrelated and application-specific workloads and presents a motivational example. Section 3.3 describes the proposed probabilistic selective fault tolerance design technique and output deviation-based ranking metrics used for pattern ranking. Simulation results from the application of the proposed technique to a set of the LGSynth'91 and ISCAS'85 benchmarks are discussed in Section 3.4, Finally, the concluding remarks are given in Section 3.5.

#### 3.1 Background

Reliability of devices has been affected by technology scaling despite its advantages [19]. Devices manufactured using 32nm technologies and below are more prone to errors due to all sources of instability and noise [22] due to the elevated cost of mitigating process variability [105] and to the escalation of aging mechanisms [31]. As a result, transient and permanent faults can appear and generate errors in-the-field, therefore techniques to make Integrated Circuits (ICs) fault tolerant are required.

Fault tolerant IC design techniques such as hardware redundancy [106] and error correcting codes are utilized for enhancing circuit reliability. Hardware redundancy consists of the complete or partial replication of a circuit in order to ensure correct functionality. By replicating the circuit, the reliability is increased as it is highly unlikely that an error would occur on every replica at the same time. Triple Modular Redundancy (TMR) utilizes two replicas of the original circuit, whose outputs are passed on to a majority voter [106]. TMR has been widely used for safety-critical applications where robustness and data integrity are the top priority. Although TMR achieves a high level of reliability, it imposes a high area and power overhead, 200% of the original circuit plus the voter circuits, thus it is not viable for low power applications. Selective Fault Tolerance (SFT) and Selective hardening have been proposed to reduce area overhead and power consumption, by protecting only a subset of the workload of a circuit or its most vulnerable parts [102], [107].