University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

UNIVERSITY OF SOUTHAMPTON

# **Energy-Efficient Architectures for Multi-Gigabit MIMO Detection**

by

Ibrahim Ahmad Bello

A thesis submitted in partial fulfillment for the

degree of Doctor of Philosophy

in the

Faculty of Physical Sciences and Engineering

School of Electronics and Computer Science

July 2017

# Academic Thesis: Declaration of Authorship

I, **Ibrahim Bello**, declare that this thesis and the work presented in it are my own and has been generated by me as the result of my own original research.

## Energy-Efficient Architectures for Multi-Gigabit MIMO Detection

I confirm that:

1. This work was done wholly or mainly while in candidature for a research degree at this University;

2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

3. Where I have consulted the published work of others, this is always clearly attributed;

4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

5. I have acknowledged all main sources of help;

6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

7. Either none of this work has been published before submission, or parts of this work have been published as listed in Section 1.5 of this thesis.

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

by Ibrahim Ahmad Bello

The use of multiple antennas in wireless transmission, otherwise known as multiple-input multiple-output (MIMO), is an important technique for achieving the high data-rates required by future communication systems. Already, MIMO technology has been adopted by the 3rd Generation Partnership Project Long Term Evolution, WiMAX and by recent Wireless Local Area Network standards, such as the IEEE 802.11ac. It is envisaged that multi-antenna systems will play an even more prominent role in future as more diverse platforms become interconnected and user data rates requirements increase. Although MIMO offers numerous advantages to communication systems, it also presents a number of challenges, in particular to the receiver, where the complexity of the signal detection is exacerbated by the interferences from the multiple transmit antennas. In the worst-case scenario, the signal detection in MIMO systems is an NP-hard problem, which makes its application to real-time systems impractical. As a result, low-complexity detection algorithms, with near-optimal performance, have been extensively studied in the literature in the past decade.

In this thesis, a number of detection techniques for MIMO systems will be investigated, with particular focus on achieving high throughput and low power consumption. We begin by presenting the VLSI implementation of the sphere decoder (SD), which achieves the optimal maximum likelihood bit error rate (BER) performance. Although the SD has the potential of achieving a high throughput - specifically in high signal-to-noise ratios (SNR) - it also suffers a severe throughput degradation at low SNR, which is undesirable in a real-time system. This problem motivates us to investigate the  $K$ -best algorithm, which delivers a constant throughput irrespective of the channel condition. Two architectures for the  $K$ -best detector are considered: single and multi-stage architectures. The latter case is particularly interesting as the multiple stages can be utilised to achieve deeply pipelined detectors, which is attractive for high-throughput applications. The proposed multi-stage  $K$ -best detector is implemented in a 65 nm CMOS process, and achieves a throughput of 3.29 Gbps and a power consumption of 580 mW for a 64-QAM  $4 \times 4$  MIMO configuration, which compares favourably with recent implementations in the literature.

# Contents

|                                                                 |            |

|-----------------------------------------------------------------|------------|

| <b>Abbreviations</b>                                            | <b>x</b>   |

| <b>Nomenclature</b>                                             | <b>xi</b>  |

| <b>Acknowledgements</b>                                         | <b>xii</b> |

| <b>1 Introduction</b>                                           | <b>1</b>   |

| 1.1 Challenges of Multi-Antenna Communication Systems . . . . . | 2          |

| 1.2 Energy-Efficient Communications . . . . .                   | 3          |

| 1.3 Research Motivation . . . . .                               | 4          |

| 1.4 Research Objectives . . . . .                               | 5          |

| 1.5 Publications . . . . .                                      | 6          |

| 1.6 Organisation of the Thesis . . . . .                        | 6          |

| <b>2 Background</b>                                             | <b>8</b>   |

| 2.1 Introduction . . . . .                                      | 8          |

| 2.2 System Model . . . . .                                      | 8          |

| 2.3 MIMO Detection . . . . .                                    | 10         |

| 2.4 Linear Detection Algorithms . . . . .                       | 12         |

| 2.4.1 Zero-forcing . . . . .                                    | 12         |

| 2.4.2 Minimum Mean Square Error . . . . .                       | 13         |

| 2.4.3 Complexity Analysis . . . . .                             | 14         |

| 2.5 Successive Interference Cancellation . . . . .              | 15         |

| 2.6 Lattice Reduction . . . . .                                 | 16         |

| 2.7 Tree-Search Detection Algorithms . . . . .                  | 18         |

| 2.7.1 Sphere Decoding . . . . .                                 | 19         |

| 2.7.1.1 Complexity of the Sphere Decoder . . . . .              | 20         |

| 2.7.1.2 Partial Euclidean Distance Computation . . . . .        | 20         |

| 2.7.1.3 Real-valued Channel Decomposition . . . . .             | 21         |

| 2.7.1.4 Orthogonal Real-valued Decomposition . . . . .          | 22         |

| 2.7.1.5 Schnorr-Euchner Lattice Search . . . . .                | 23         |

| 2.7.2 K-Best Algorithm . . . . .                                | 25         |

| 2.7.3 Fixed-Complexity Sphere Decoder . . . . .                 | 26         |

| 2.7.4 Best-First Search Algorithm . . . . .                     | 27         |

| 2.7.5 Soft-Output Detection . . . . .                           | 27         |

| 2.8 Previous Work . . . . .                                     | 30         |

| 2.8.1 Performance Metrics . . . . .                             | 30         |

| 2.8.1.1 Impact of Technology Scaling . . . . .                  | 30         |

---

|          |                                                                       |           |

|----------|-----------------------------------------------------------------------|-----------|

| 2.8.1.2  | Area Consumption . . . . .                                            | 31        |

| 2.8.1.3  | Throughput . . . . .                                                  | 31        |

| 2.8.1.4  | Power Consumption . . . . .                                           | 32        |

| 2.8.2    | VLSI Implementations of the Sphere Decoder . . . . .                  | 33        |

| 2.8.3    | VLSI Implementations of the K-Best Algorithm . . . . .                | 34        |

| 2.8.4    | VLSI Implementations of the Fixed-Complexity Sphere Decoder . . . . . | 36        |

| 2.8.5    | VLSI Implementations of the Best-First Search Detector . . . . .      | 37        |

| 2.9      | Summary and Conclusion . . . . .                                      | 38        |

| <b>3</b> | <b>VLSI Implementation of the Sphere Decoder</b>                      | <b>39</b> |

| 3.1      | Introduction . . . . .                                                | 39        |

| 3.2      | Methodology . . . . .                                                 | 40        |

| 3.2.1    | High Level Analysis . . . . .                                         | 41        |

| 3.2.2    | Number Representation . . . . .                                       | 41        |

| 3.2.2.1  | Fixed-Point Number Representation . . . . .                           | 42        |

| 3.2.2.2  | Fixed-Point Simulation . . . . .                                      | 42        |

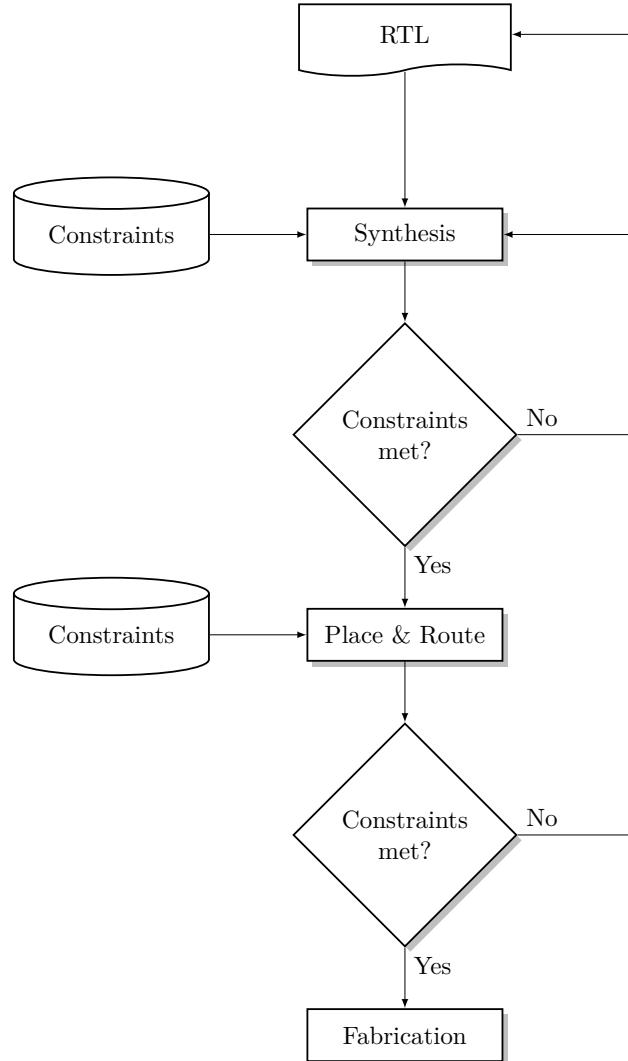

| 3.2.3    | ASIC Design Flow . . . . .                                            | 44        |

| 3.2.3.1  | RTL Implementation . . . . .                                          | 44        |

| 3.2.3.2  | Logic Synthesis . . . . .                                             | 46        |

| 3.2.3.3  | Place and Route . . . . .                                             | 46        |

| 3.2.4    | Power Estimation Flow . . . . .                                       | 47        |

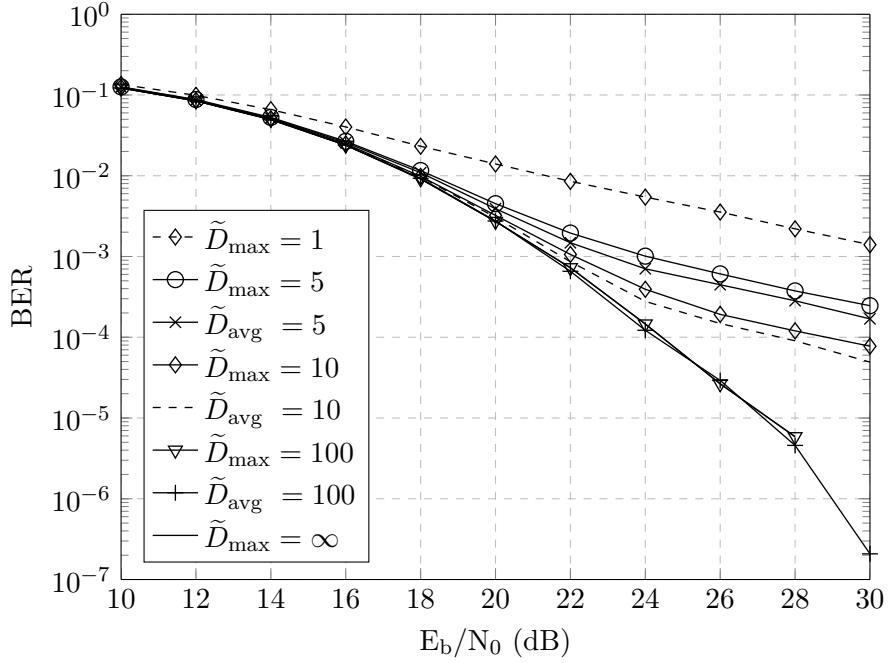

| 3.3      | Sphere Decoder with Runtime Constraints . . . . .                     | 48        |

| 3.3.1    | Sphere Decoder with Early Termination . . . . .                       | 48        |

| 3.3.2    | Sphere Decoder with Block Processing . . . . .                        | 48        |

| 3.3.3    | Simulation Results . . . . .                                          | 49        |

| 3.4      | Hardware Implementation . . . . .                                     | 50        |

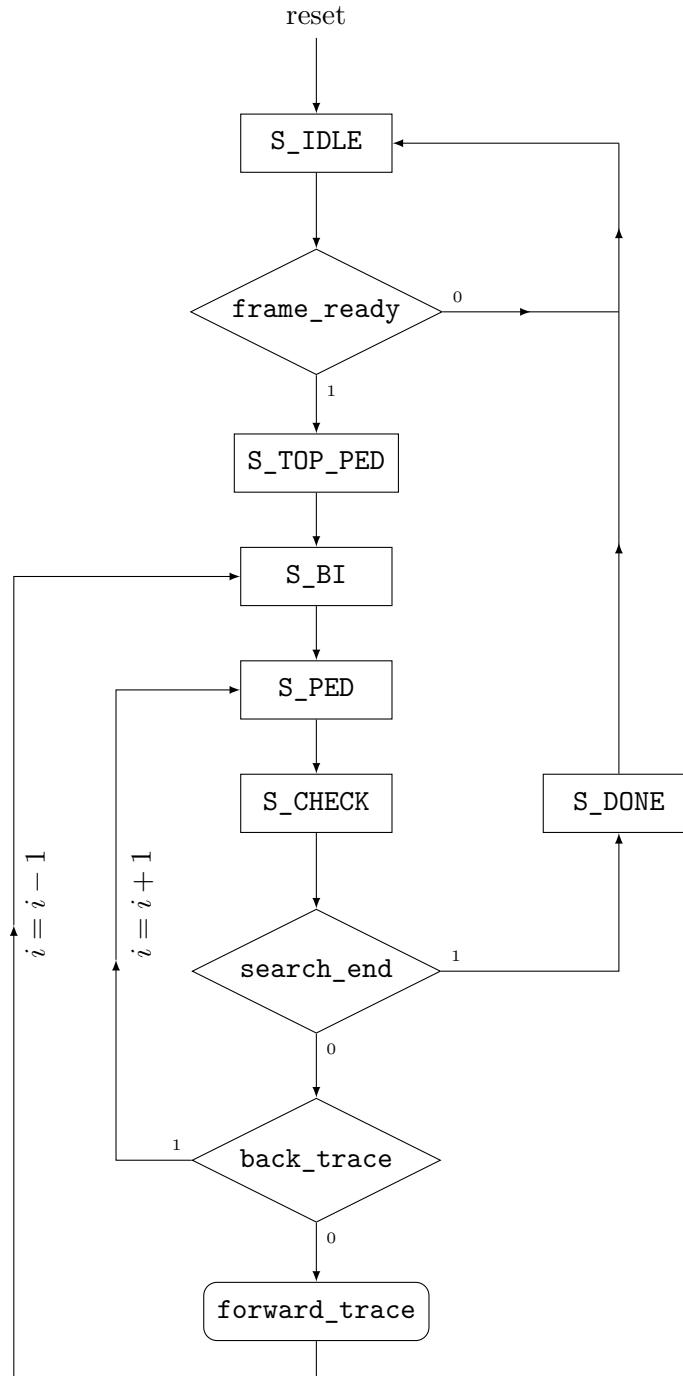

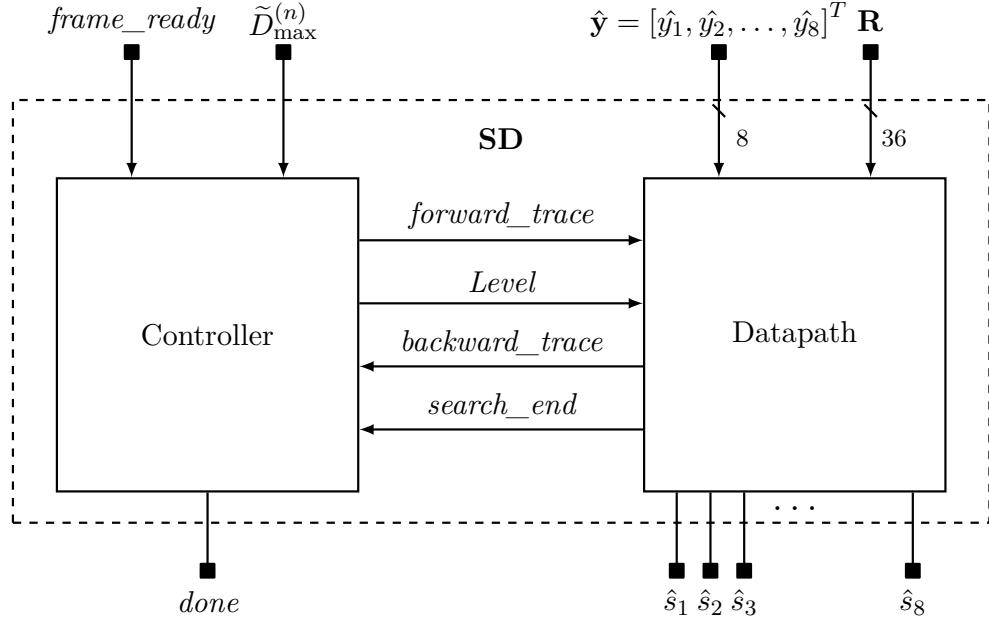

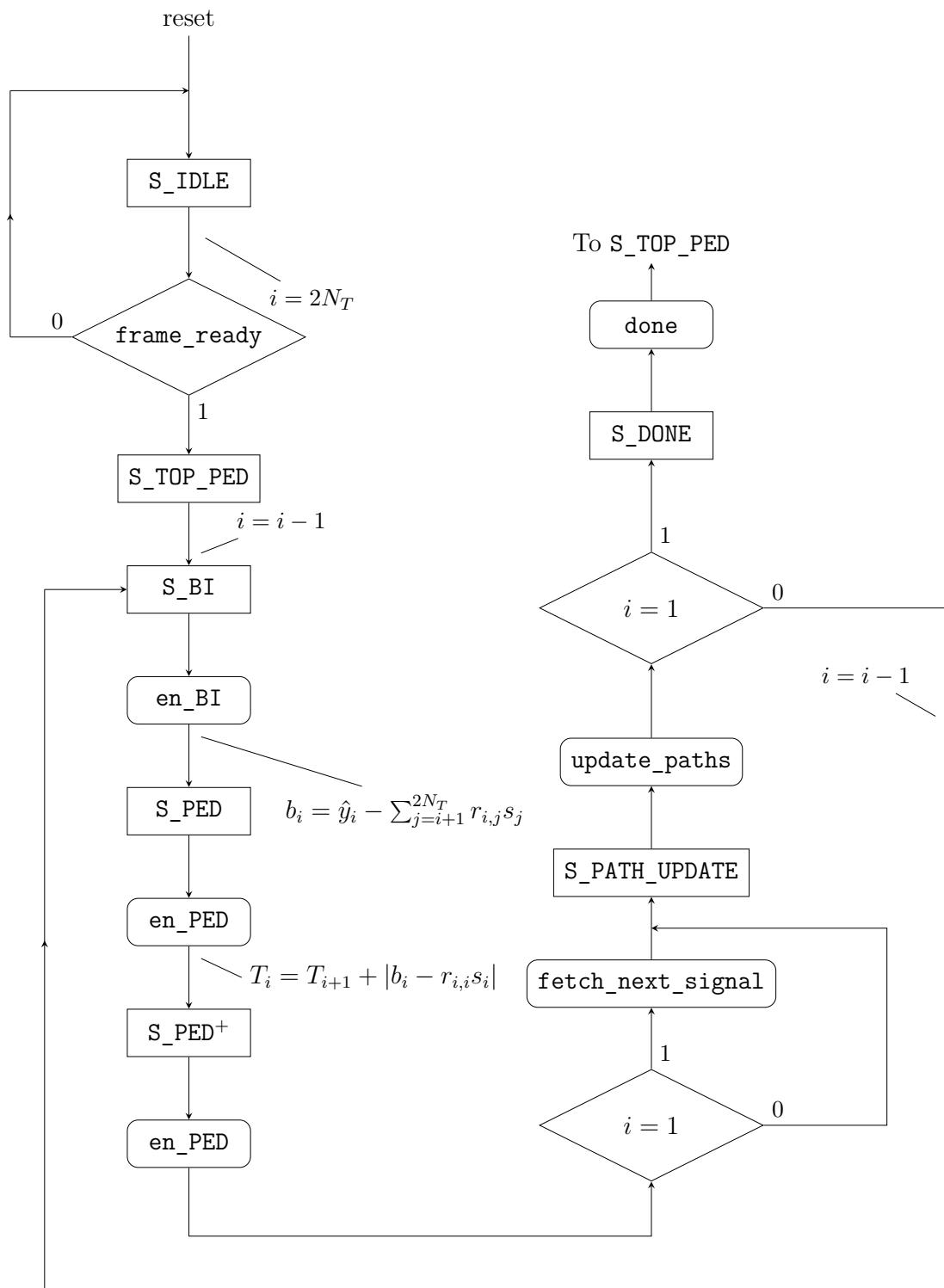

| 3.4.1    | Controller . . . . .                                                  | 50        |

| 3.4.2    | Controller with Look-Ahead . . . . .                                  | 54        |

| 3.4.3    | Datapath . . . . .                                                    | 56        |

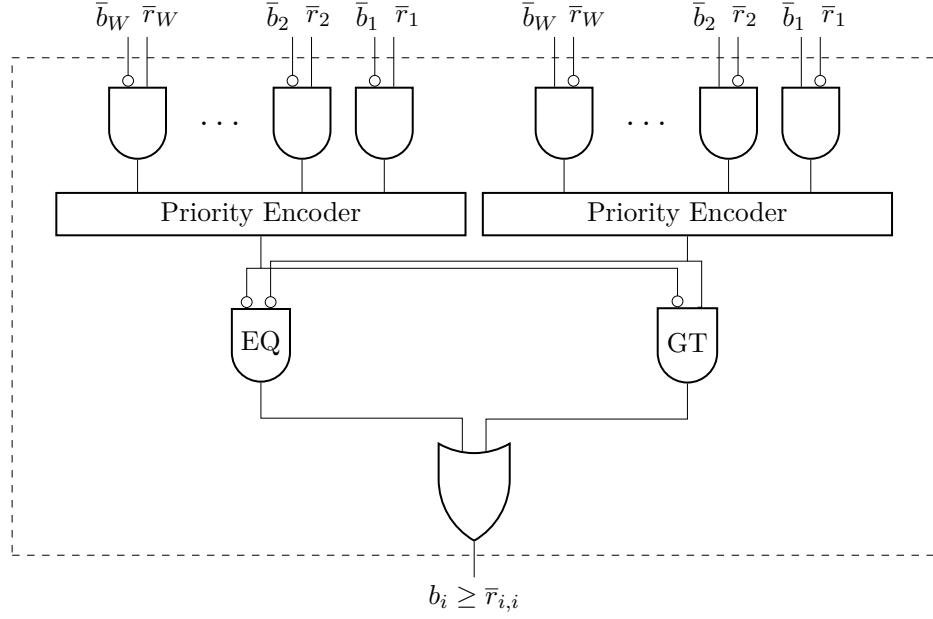

| 3.4.3.1  | Tabular Enumeration . . . . .                                         | 56        |

| 3.4.3.2  | Partial Euclidean Distance . . . . .                                  | 59        |

| 3.5      | Results and Discussion . . . . .                                      | 63        |

| 3.5.1    | Comparisons with State-of-the-Art . . . . .                           | 65        |

| 3.5.2    | Impact of Runtime Constraints . . . . .                               | 66        |

| 3.6      | Summary and Conclusion . . . . .                                      | 67        |

| <b>4</b> | <b>VLSI Implementation of a Single-Stage K-best Detector</b>          | <b>68</b> |

| 4.1      | Introduction . . . . .                                                | 68        |

| 4.2      | Performance Analysis . . . . .                                        | 69        |

| 4.2.1    | Comparison with the Sphere Decoder . . . . .                          | 69        |

| 4.2.2    | Reduced-Complexity K-best Detector . . . . .                          | 70        |

| 4.3      | Sorting . . . . .                                                     | 71        |

| 4.3.1    | Bubble Sort . . . . .                                                 | 72        |

| 4.3.2    | Distributed Sort . . . . .                                            | 72        |

| 4.3.3    | Relaxed Sort . . . . .                                                | 73        |

| 4.3.4    | Merge Algorithms . . . . .                                            | 74        |

| 4.3.4.1  | Odd-Even Merge . . . . .                                              | 74        |

---

|          |                                                                 |            |

|----------|-----------------------------------------------------------------|------------|

| 4.3.4.2  | Bitonic Merge . . . . .                                         | 75         |

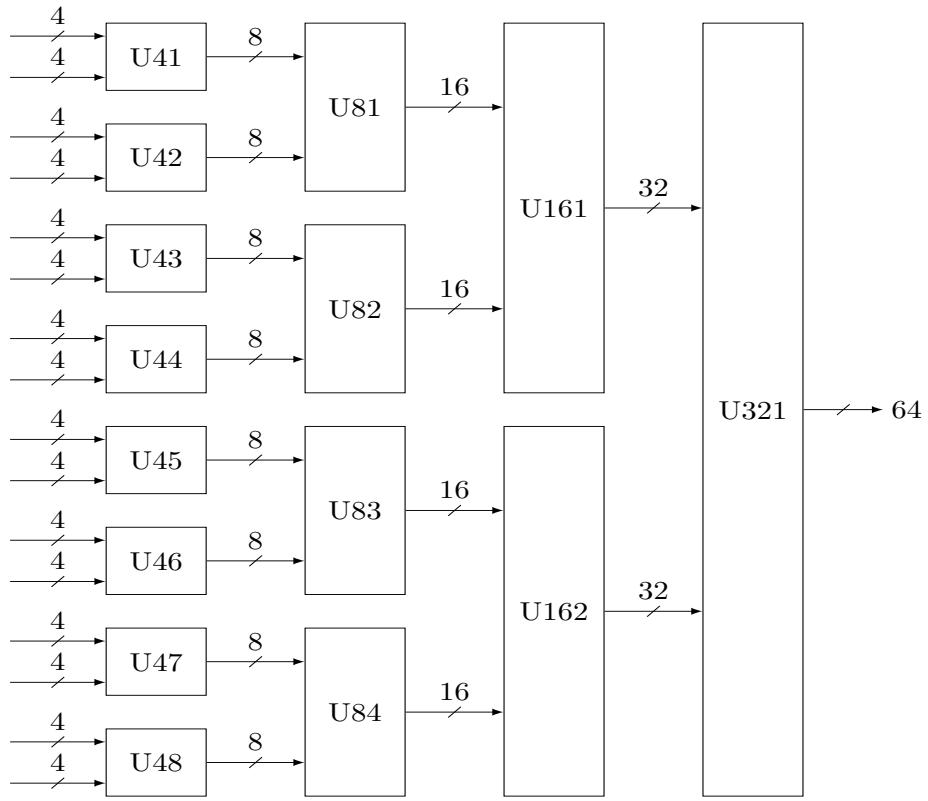

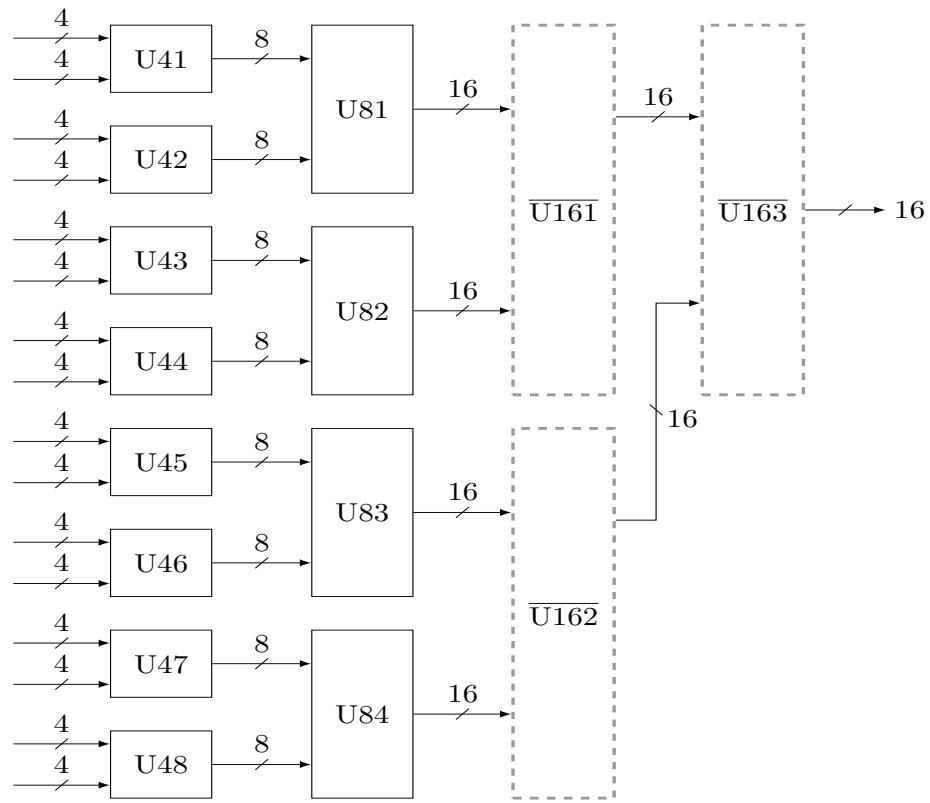

| 4.3.5    | Implementation of the Merge Network . . . . .                   | 76         |

| 4.3.5.1  | Area Optimisation . . . . .                                     | 77         |

| 4.3.5.2  | Pipelining the Merge Network . . . . .                          | 79         |

| 4.3.5.3  | Results and Discussion . . . . .                                | 80         |

| 4.4      | Hardware Implementation . . . . .                               | 81         |

| 4.4.1    | Single-Tree Single-Stage Architecture . . . . .                 | 81         |

| 4.4.2    | Controller . . . . .                                            | 83         |

| 4.4.3    | Datapath . . . . .                                              | 85         |

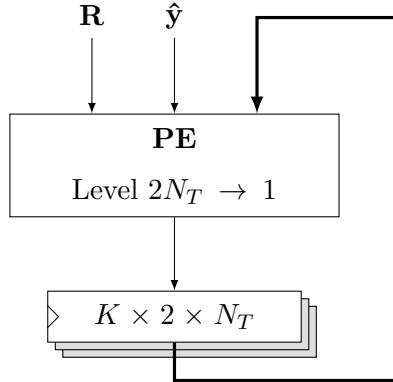

| 4.4.3.1  | Processing Element . . . . .                                    | 85         |

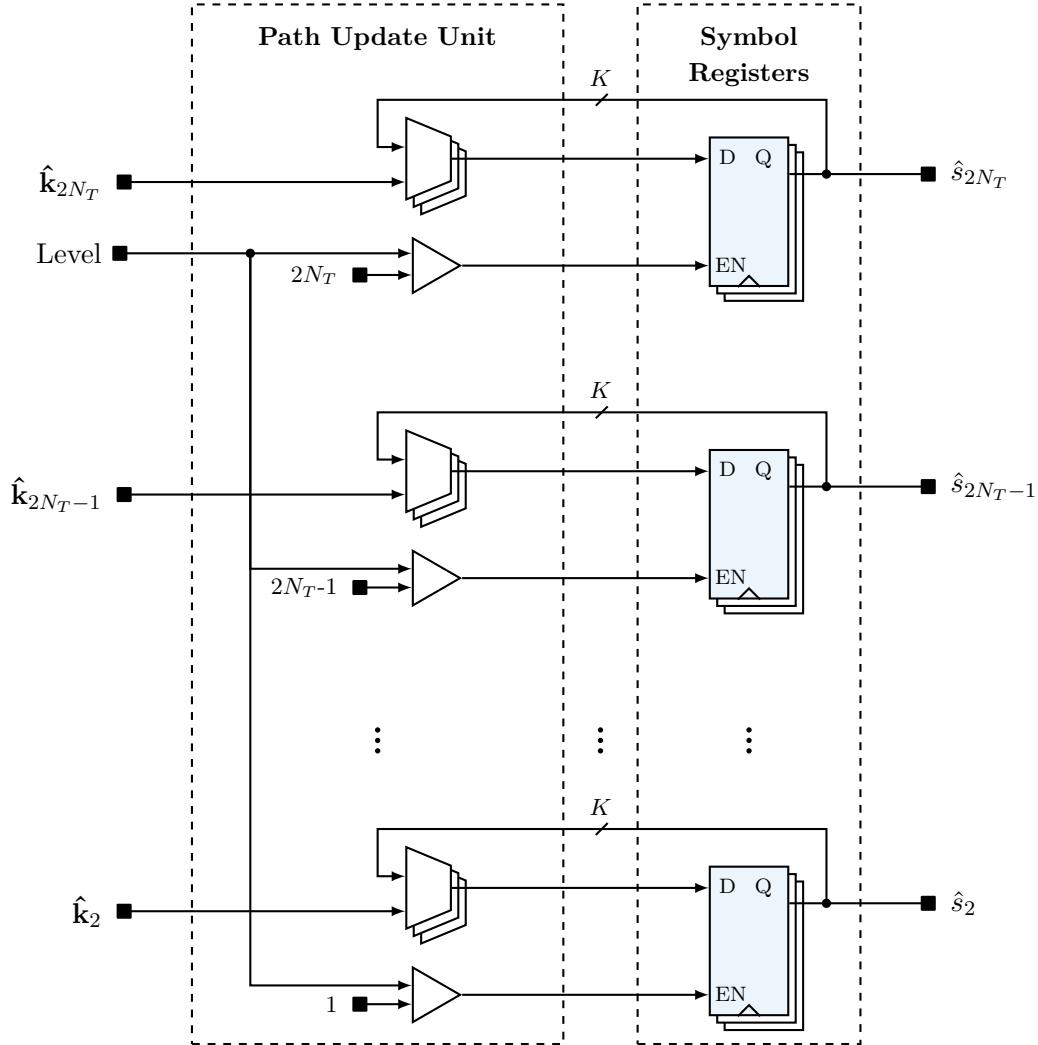

| 4.4.3.2  | Path Update Unit . . . . .                                      | 87         |

| 4.5      | Results and Discussion . . . . .                                | 87         |

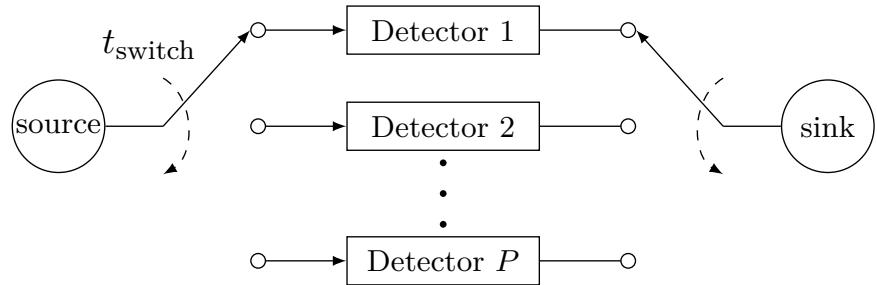

| 4.5.1    | Detector Interleaving . . . . .                                 | 89         |

| 4.5.2    | Comparison with the Sphere Decoder . . . . .                    | 89         |

| 4.5.3    | Comparison with State-of-the-Art . . . . .                      | 90         |

| 4.6      | Summary and Conclusion . . . . .                                | 92         |

| <b>5</b> | <b>VLSI Implementation of a Fully-Pipelined K-Best Detector</b> | <b>93</b>  |

| 5.1      | Introduction . . . . .                                          | 93         |

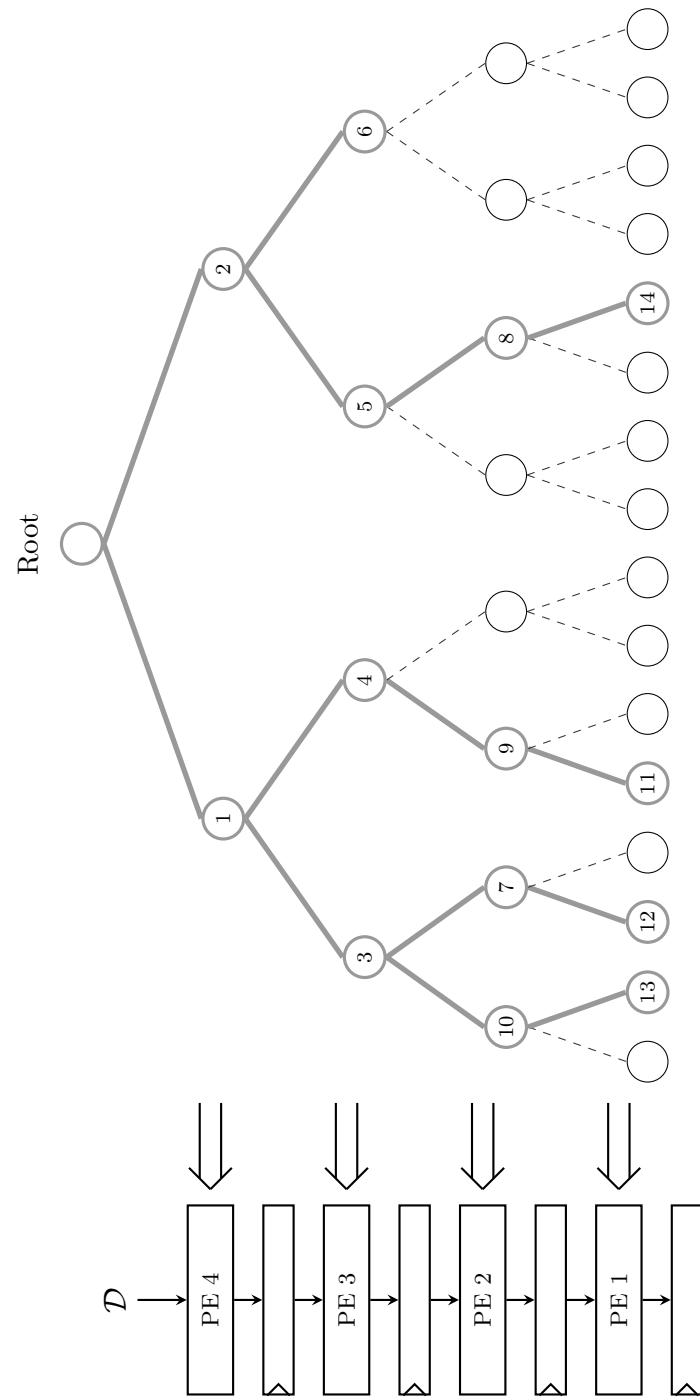

| 5.2      | Multiple-Tree Multi-Stage Architecture . . . . .                | 94         |

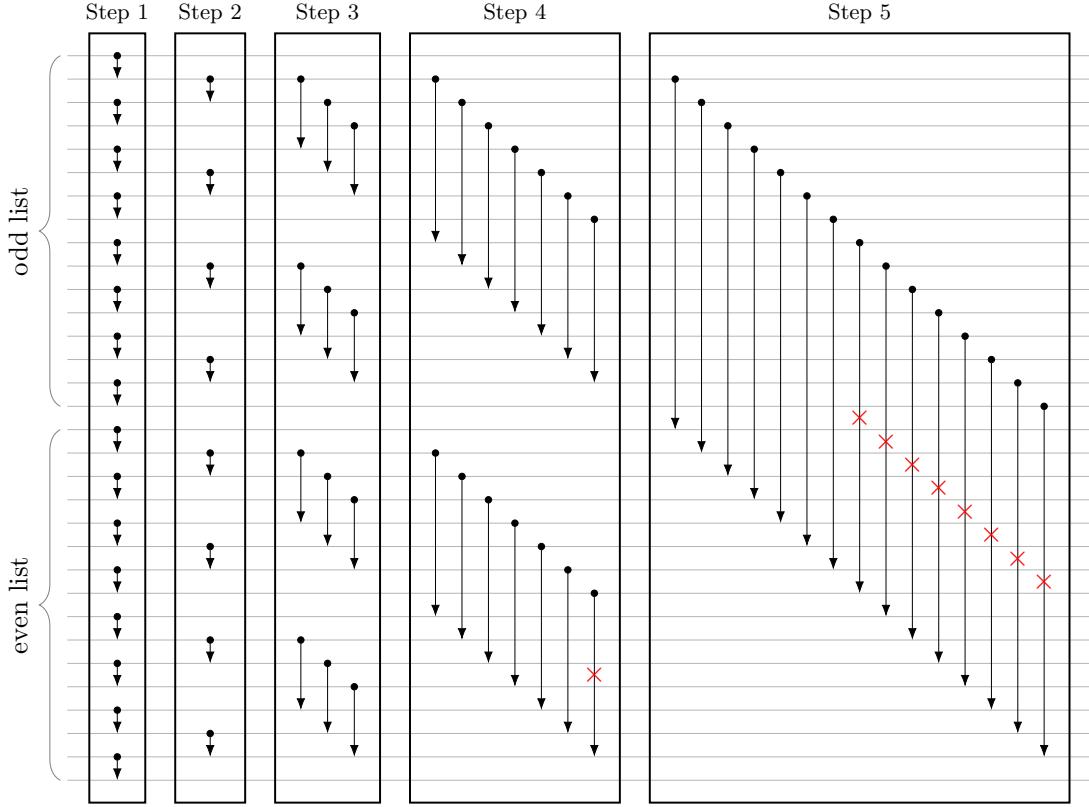

| 5.2.1    | Pipelining the K-Best Detector . . . . .                        | 94         |

| 5.2.1.1  | Fine-Grained Pipelining . . . . .                               | 96         |

| 5.2.1.2  | Coarse-Grained Pipelining . . . . .                             | 98         |

| 5.2.2    | Implementing the Fully-Pipelined K-Best Detector . . . . .      | 99         |

| 5.2.2.1  | Multiplexer-Based Pipelined K-Best Detector . . . . .           | 99         |

| 5.2.2.2  | Shift-Register-Based Pipelined K-Best Detector . . . . .        | 100        |

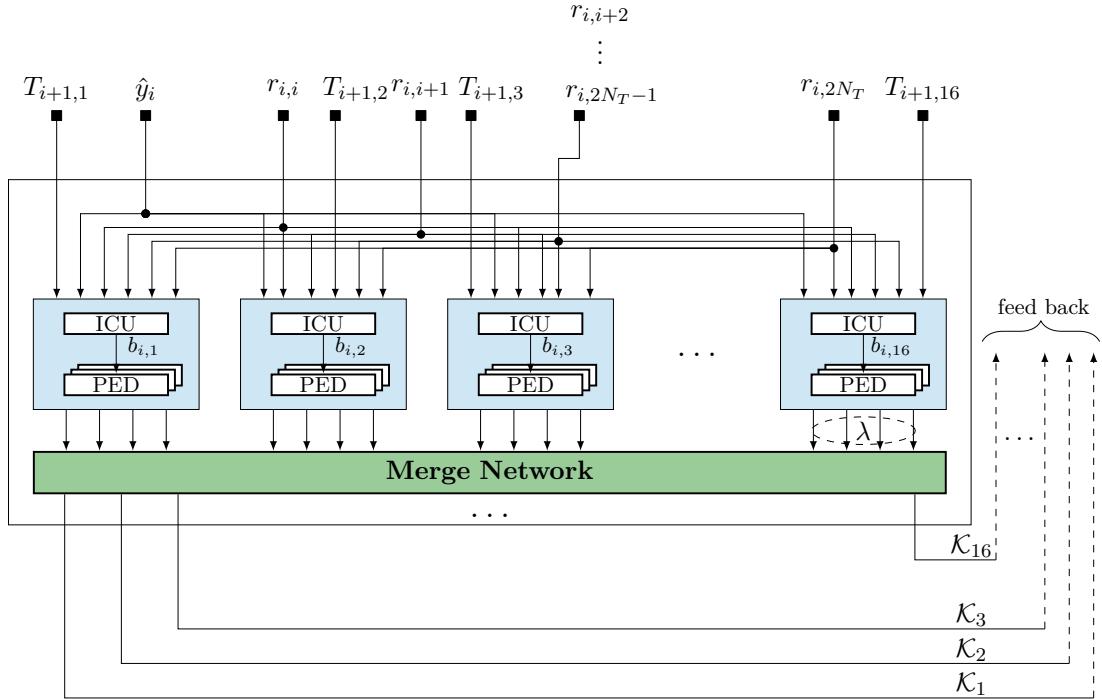

| 5.3      | Hardware Implementation . . . . .                               | 104        |

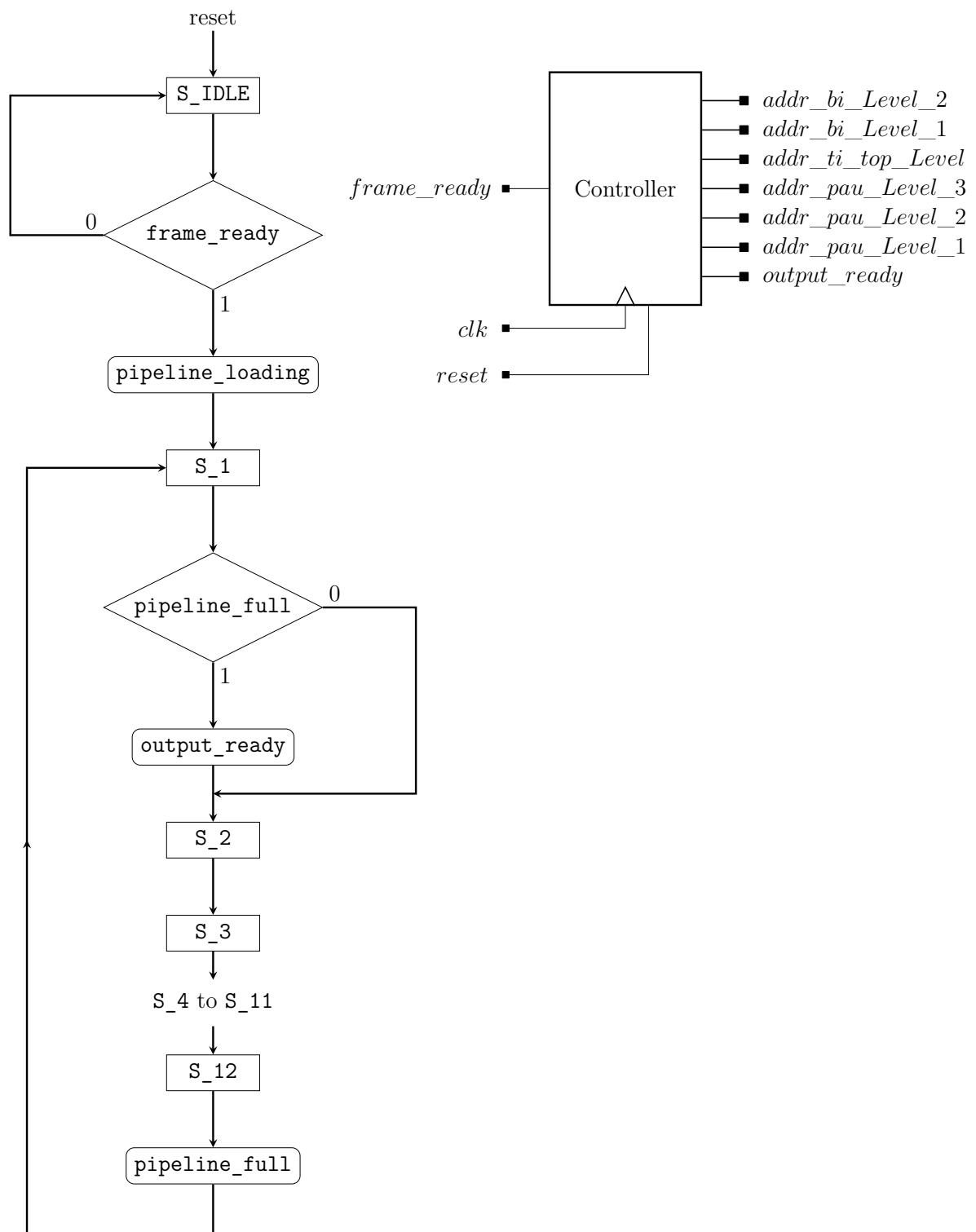

| 5.3.1    | Controller . . . . .                                            | 105        |

| 5.3.2    | Processing Element . . . . .                                    | 108        |

| 5.4      | Results and Discussion . . . . .                                | 109        |

| 5.4.1    | Cost of Pipelining . . . . .                                    | 109        |

| 5.4.2    | Pipelining versus Interleaving . . . . .                        | 111        |

| 5.4.3    | Comparison with State-of-the-Art . . . . .                      | 111        |

| 5.4.4    | Application to Current Wireless Standards . . . . .             | 113        |

| 5.4.4.1  | Throughput Considerations . . . . .                             | 113        |

| 5.4.4.2  | Performance Considerations . . . . .                            | 114        |

| 5.5      | Summary and Conclusion . . . . .                                | 115        |

| <b>6</b> | <b>Conclusions and Future Work</b>                              | <b>117</b> |

| 6.1      | Summary and Conclusions . . . . .                               | 117        |

| 6.2      | Design Guidelines . . . . .                                     | 118        |

| 6.3      | Future Work . . . . .                                           | 120        |

| <b>A</b> | <b>QR Decomposition</b>                                         | <b>122</b> |

| A.1      | Givens Rotation . . . . .                                       | 122        |

| A.2      | Gram-Schmidt Orthogonalisation . . . . .                        | 123        |

| A.3      | Householder Reflections . . . . .                               | 123        |

# List of Figures

|      |                                                                                                     |    |

|------|-----------------------------------------------------------------------------------------------------|----|

| 1.1  | Wireless trends in the past 20 years                                                                | 2  |

| 1.2  | Illustration of single and multiple antenna systems                                                 | 3  |

| 1.3  | Design trade-offs for MIMO detection                                                                | 5  |

| 2.1  | Block diagram of MIMO transmission and detection                                                    | 9  |

| 2.2  | 16-QAM constellation points and corresponding binary representation                                 | 10 |

| 2.3  | Classification of MIMO detection algorithms                                                         | 11 |

| 2.4  | Lattice search for the maximum likelihood detector                                                  | 12 |

| 2.5  | BER performance of ZF and MMSE detectors for 16-QAM and $N_T = 4$                                   | 17 |

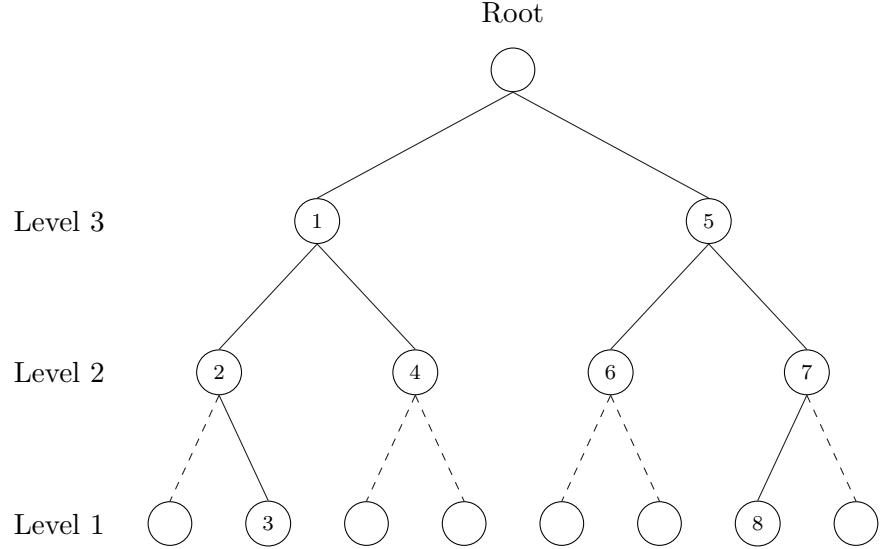

| 2.6  | Depth first tree search for a MIMO system with $N_T = 3$                                            | 18 |

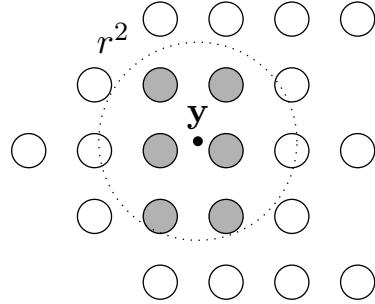

| 2.7  | Modified lattice search using the SD algorithm                                                      | 20 |

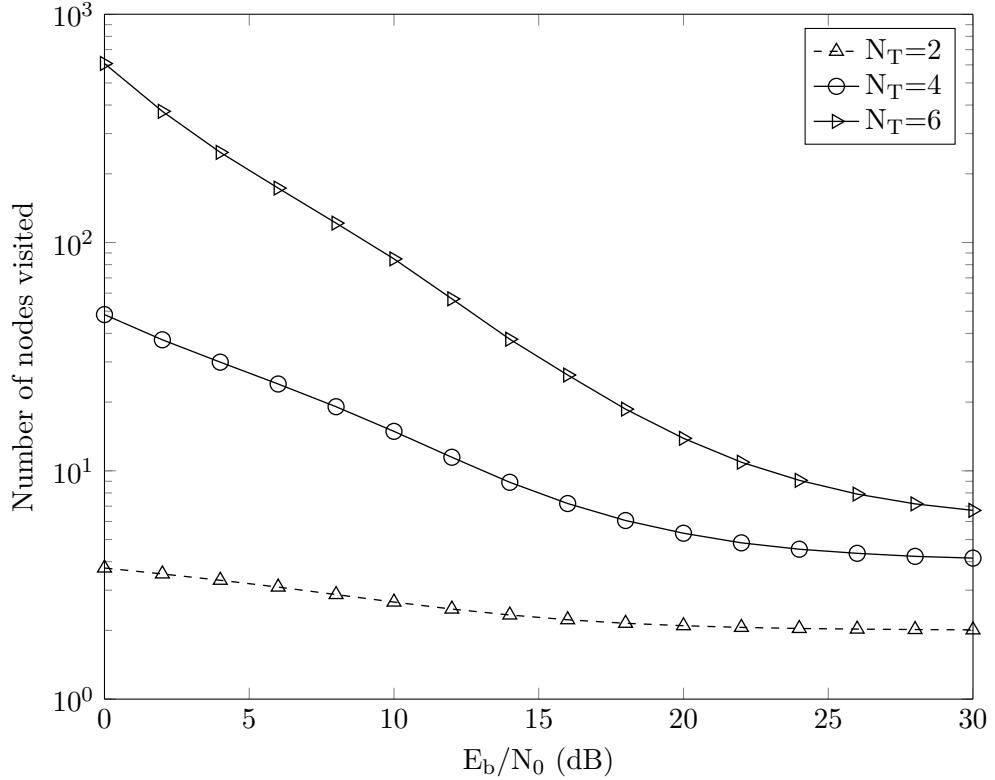

| 2.8  | Number of visited nodes for the SD versus SNR using 16-QAM                                          | 21 |

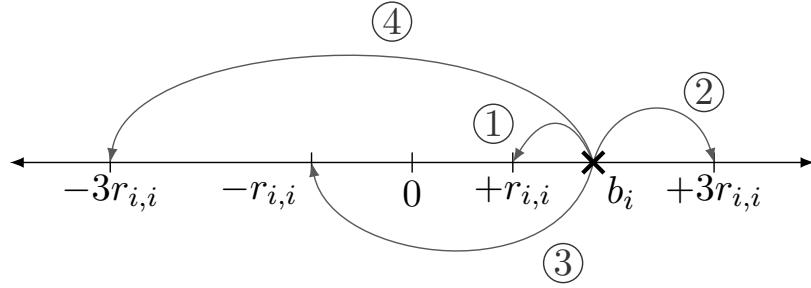

| 2.9  | SE enumeration based on a real axis for 16-QAM                                                      | 24 |

| 2.10 | Breadth first tree search for a MIMO system using BPSK and $N_T = 3$                                | 25 |

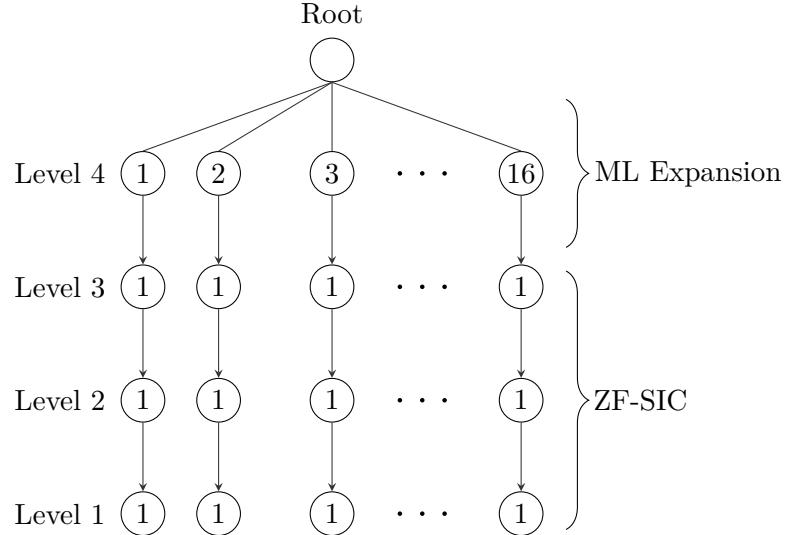

| 2.11 | FSD tree search using 16-QAM and $N_T = 4$                                                          | 26 |

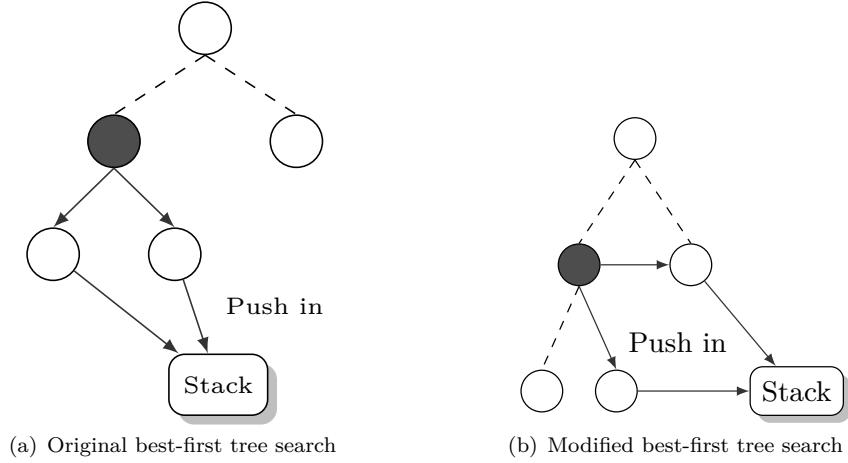

| 2.12 | Best-first tree search                                                                              | 28 |

| 2.13 | Block diagram of iterative MIMO detection                                                           | 29 |

| 2.14 | Illustration of tabular enumeration using 16-QAM                                                    | 34 |

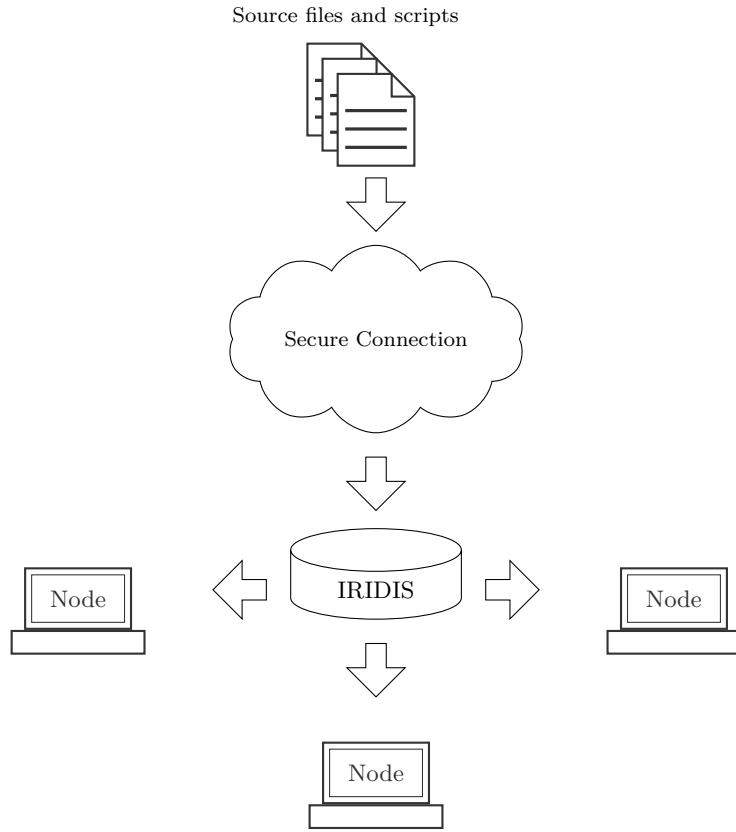

| 3.1  | High performance computing setup using the IRIDIS computer cluster                                  | 40 |

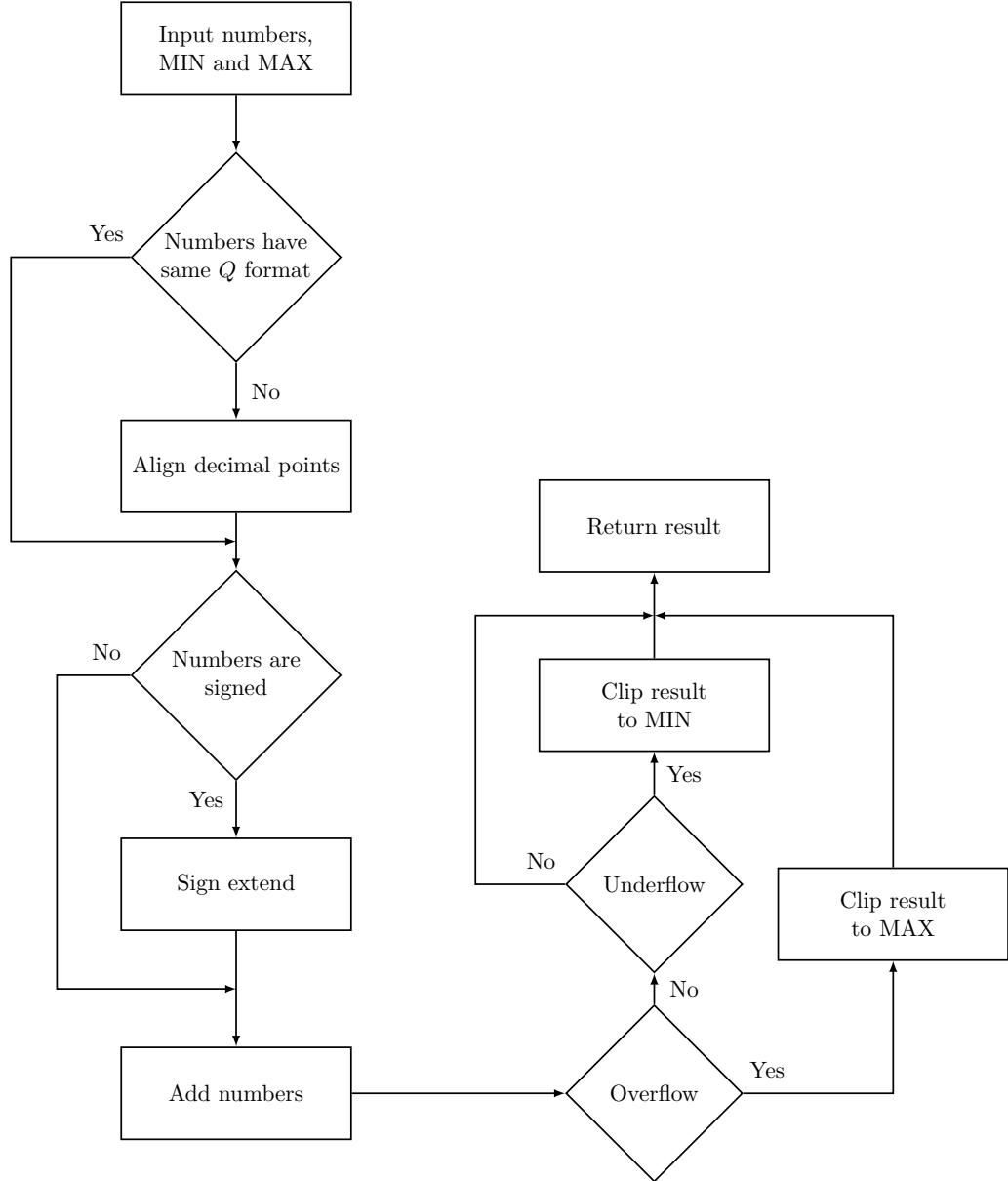

| 3.2  | Flowchart for adding two fixed-point numbers                                                        | 43 |

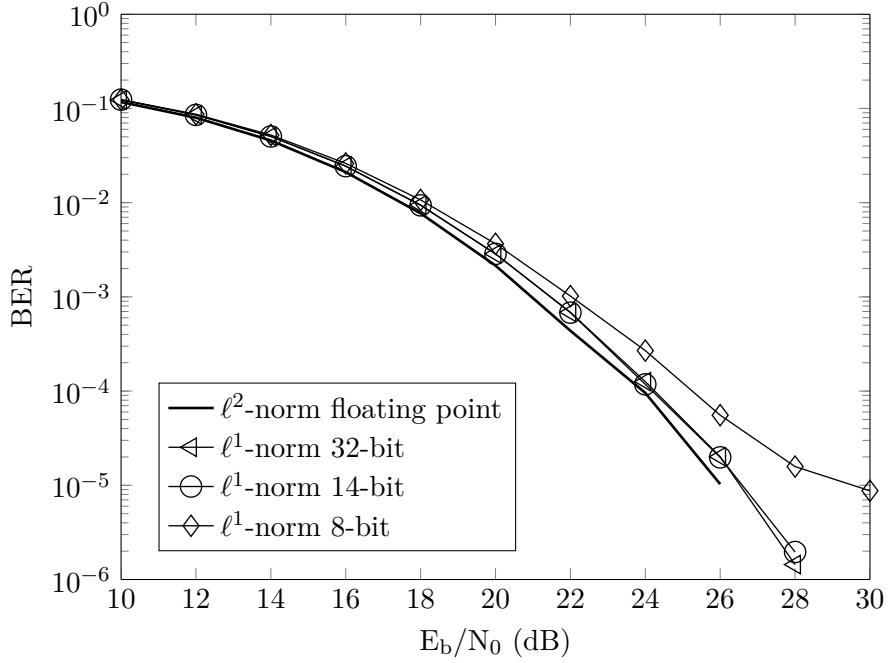

| 3.3  | BER versus SNR simulation for different word-lengths                                                | 44 |

| 3.4  | Simplified ASIC Design Flow                                                                         | 45 |

| 3.5  | BER versus SNR simulation for the sphere decoder using per-symbol and per-block runtime constraints | 50 |

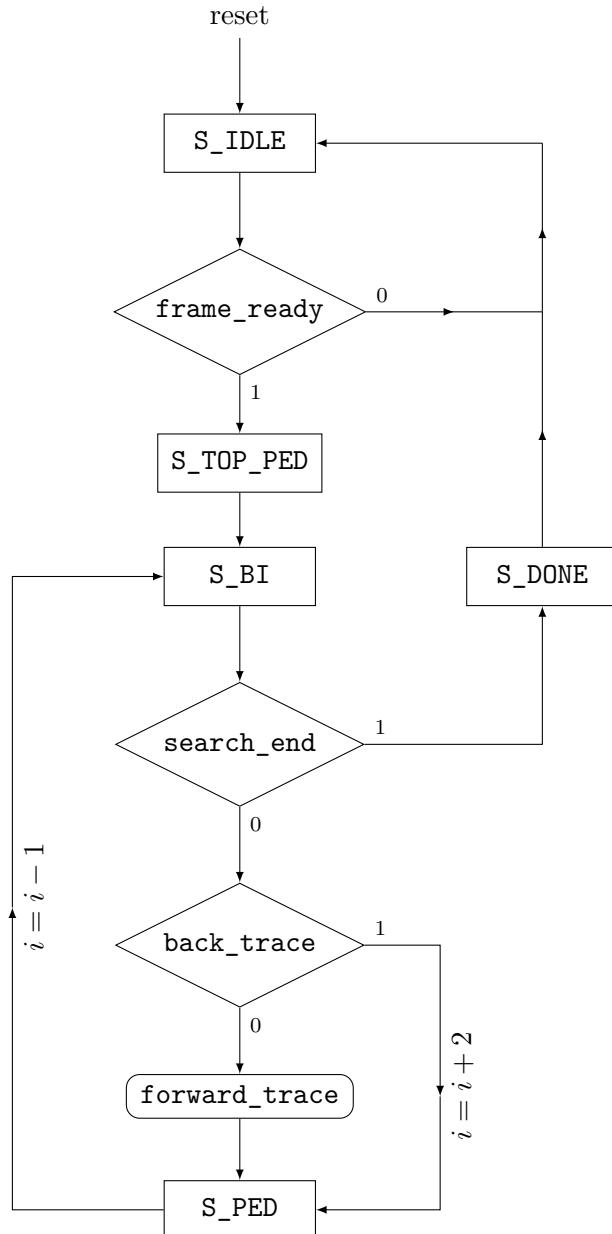

| 3.6  | ASM chart for the sphere decoder                                                                    | 51 |

| 3.7  | Sphere decoder architecture with controller and datapath                                            | 52 |

| 3.8  | Modified ASM chart for the sphere decoder with look ahead                                           | 54 |

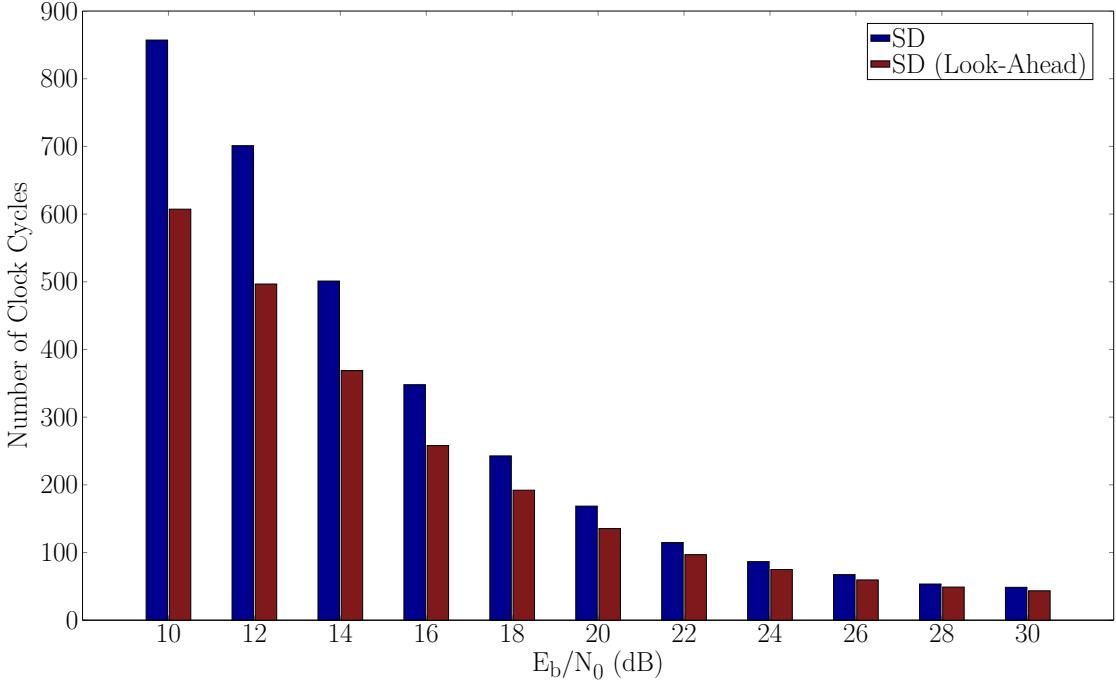

| 3.9  | Impact of “look-ahead” on the speed of the sphere decoder                                           | 55 |

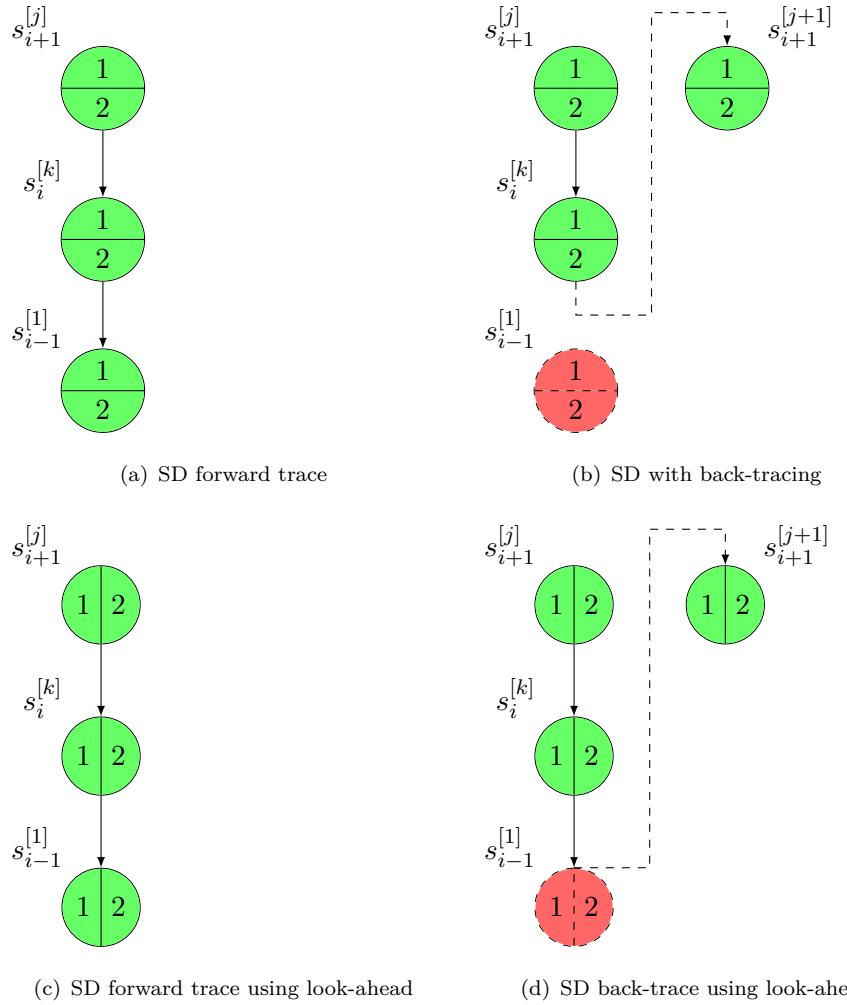

| 3.10 | Illustration of Sphere Decoder with Look-ahead Tree Traversal                                       | 57 |

| 3.11 | Determining enumeration region using bitwise comparisons                                            | 58 |

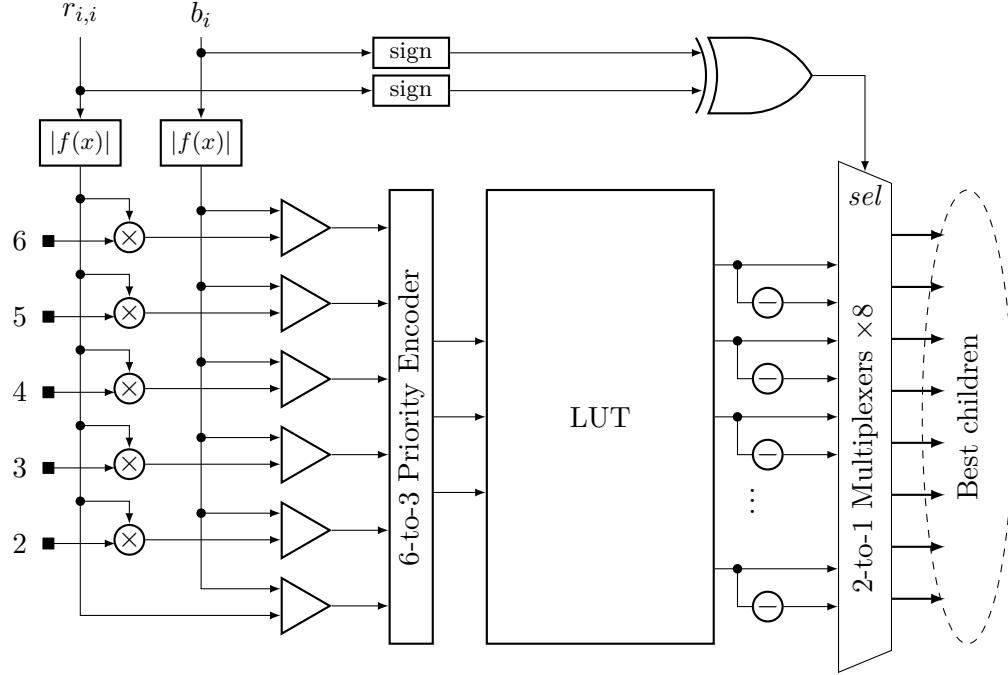

| 3.12 | Reduced-complexity SE enumeration computation unit for 64-QAM                                       | 60 |

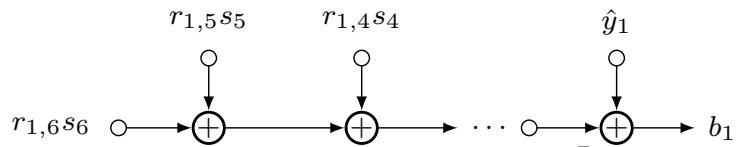

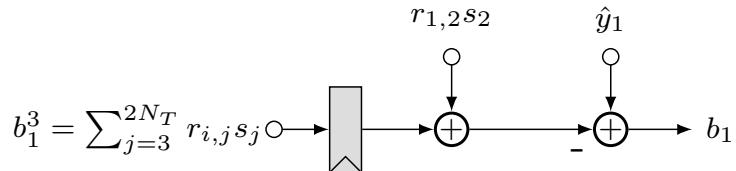

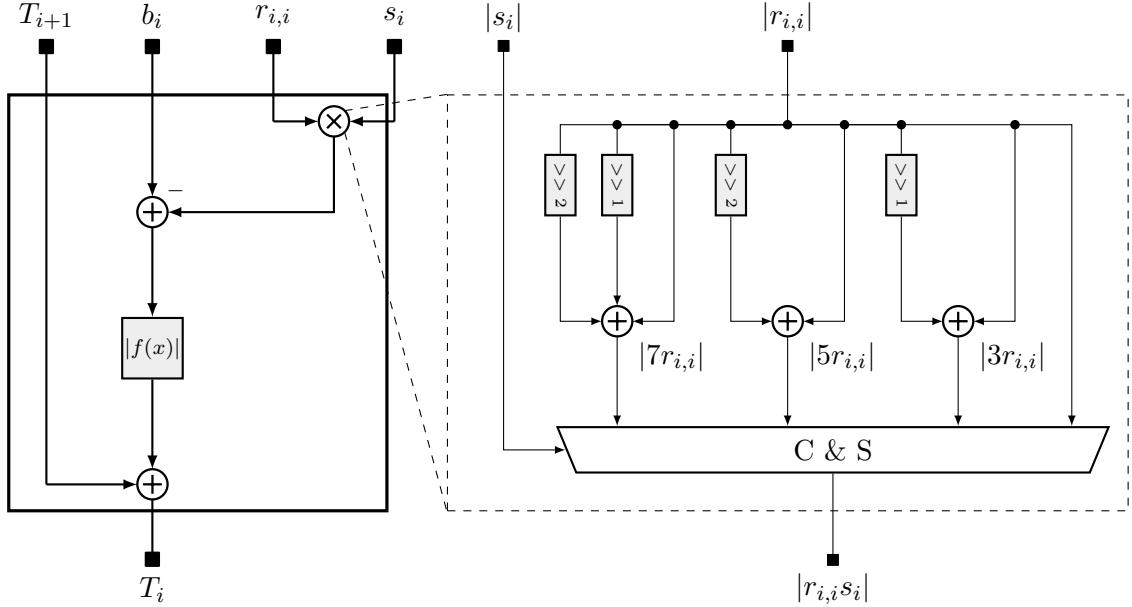

| 3.13 | Horizontal and vertical PED computation                                                             | 61 |

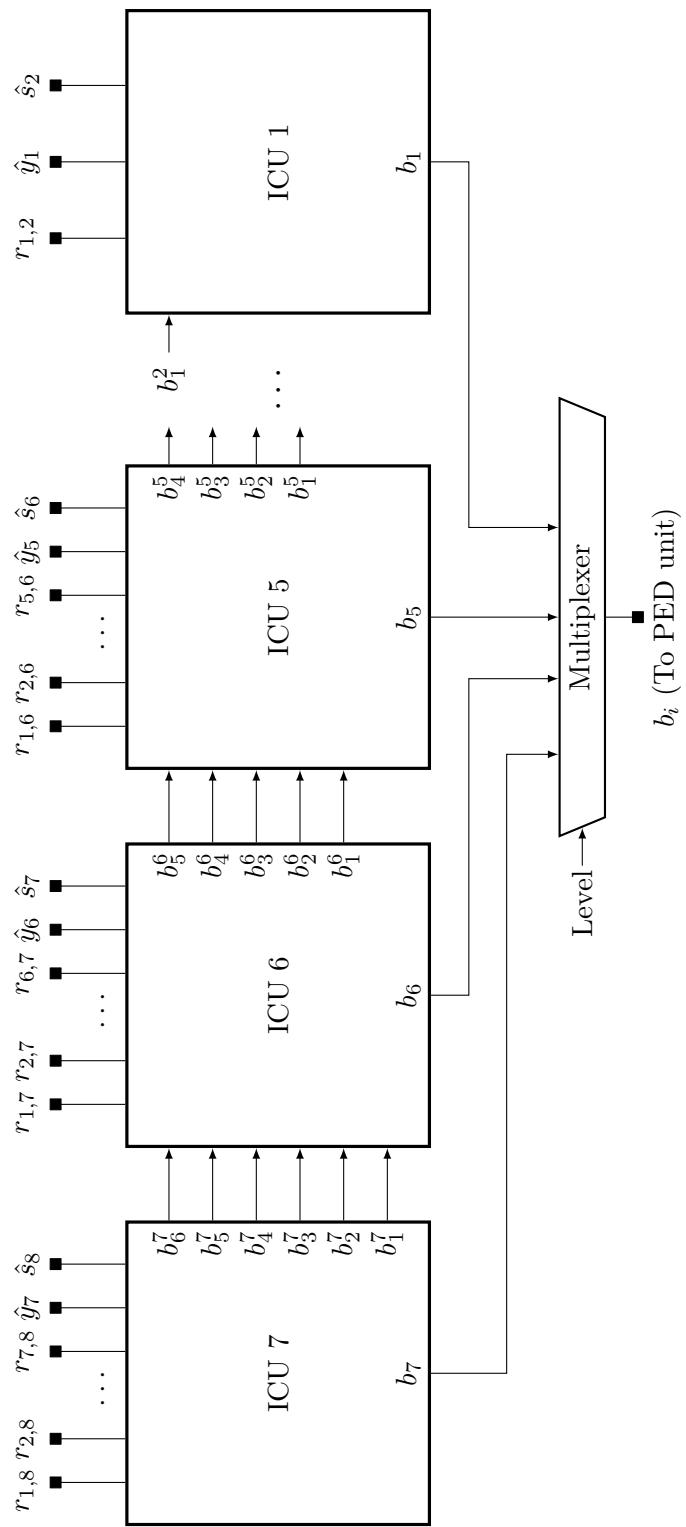

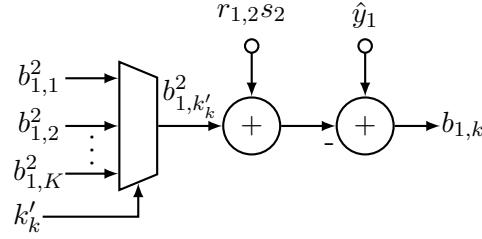

| 3.14 | Interference cancellation unit for the sphere decoder                                               | 62 |

| 3.15 | Architecture of the PED computation unit                                                            | 63 |

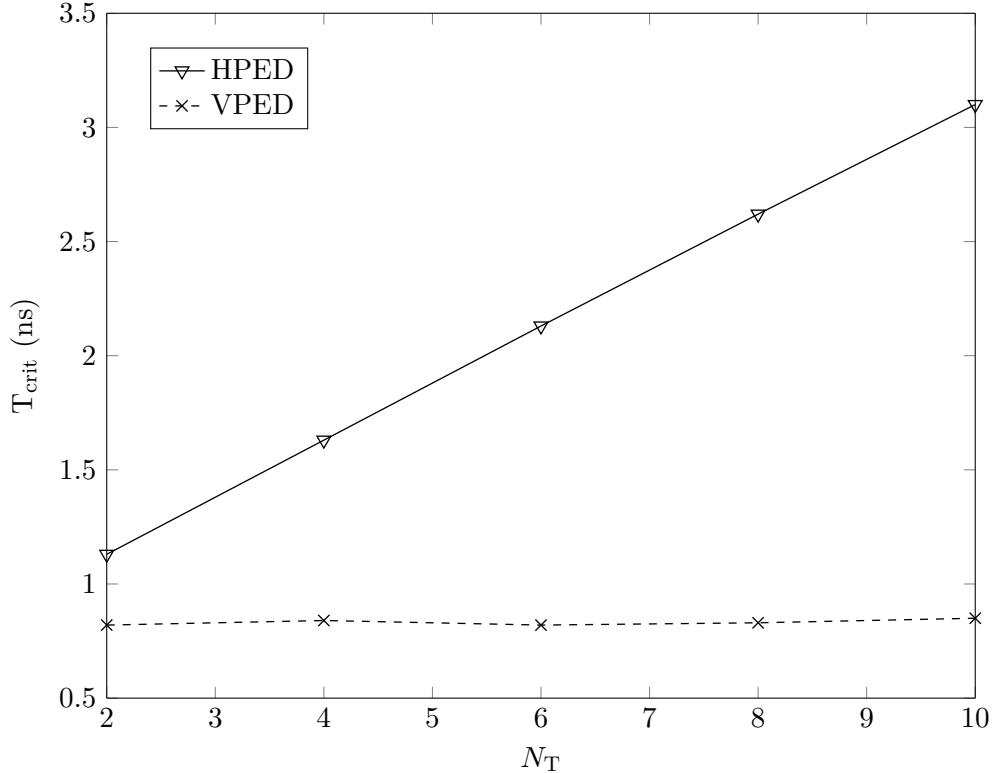

| 3.16 | Critical path delay of $b_i$ versus $N_T$                                                           | 65 |

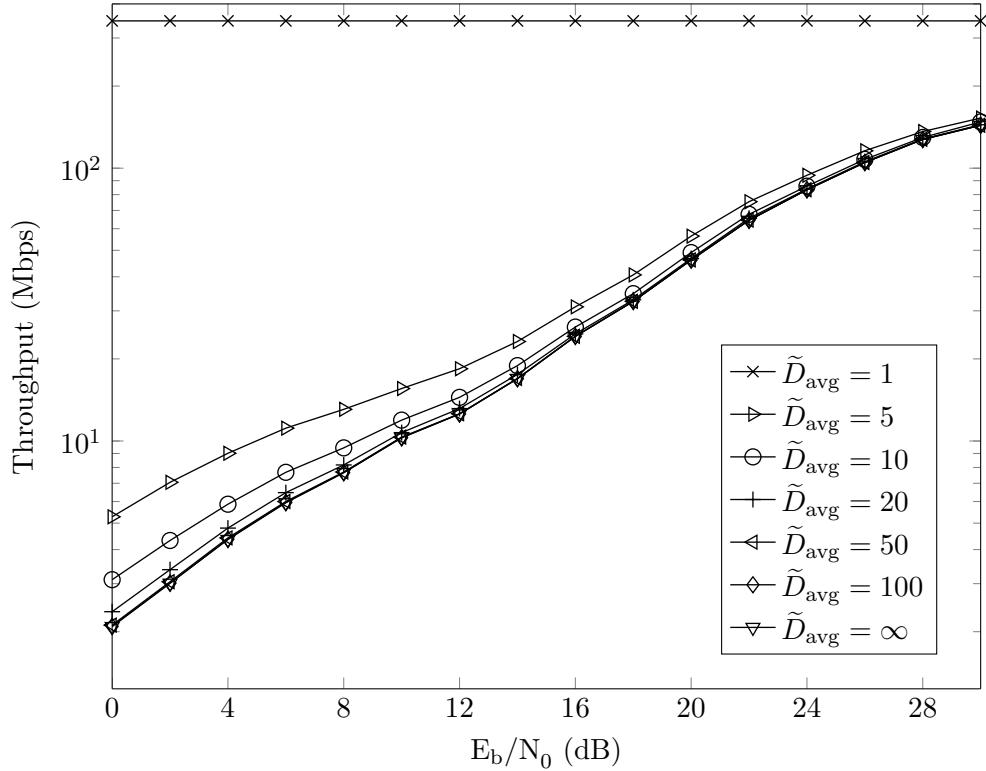

| 3.17 | Throughput versus SNR for the sphere decoder with different $\tilde{D}_{\text{avg}}$                | 66 |

---

|      |                                                                                              |     |

|------|----------------------------------------------------------------------------------------------|-----|

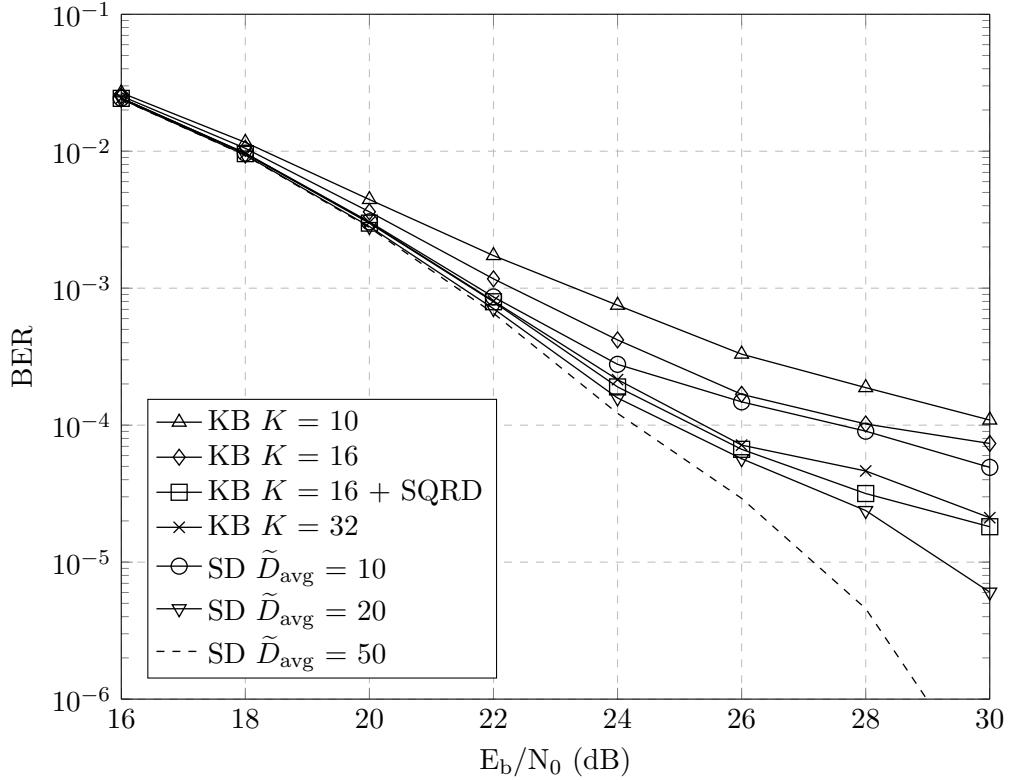

| 4.1  | BER performance of K-best versus SD for different values of $K$ and $\tilde{D}_{\text{avg}}$ | 70  |

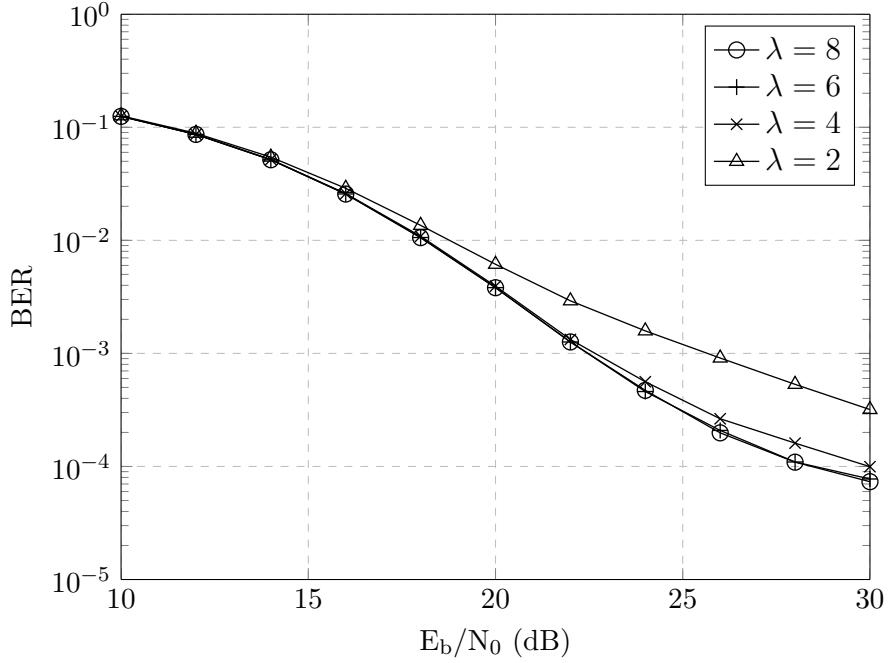

| 4.2  | BER performance of the K-best algorithm using different values of $\lambda$                  | 71  |

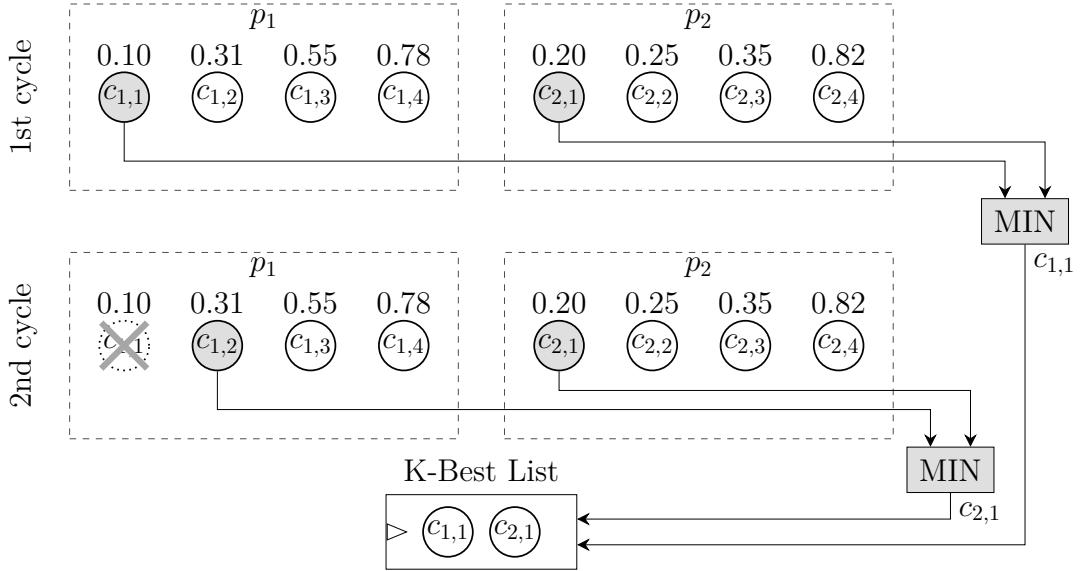

| 4.3  | Distributed K-best sorting for 16-QAM system with $K = 2$                                    | 73  |

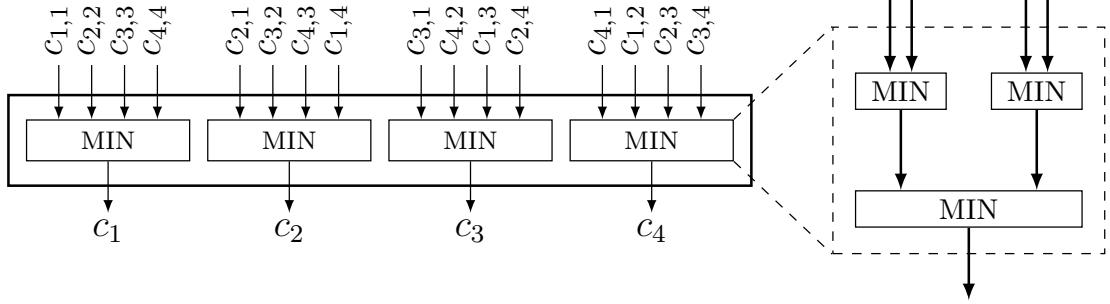

| 4.4  | Architecture for a relaxed sorter                                                            | 74  |

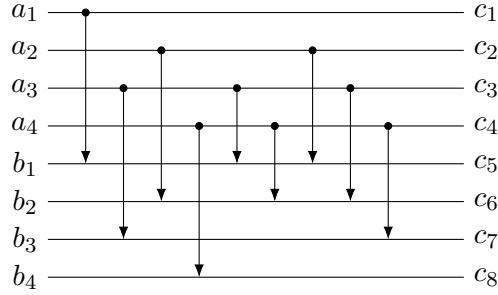

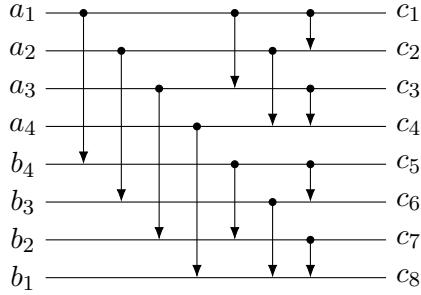

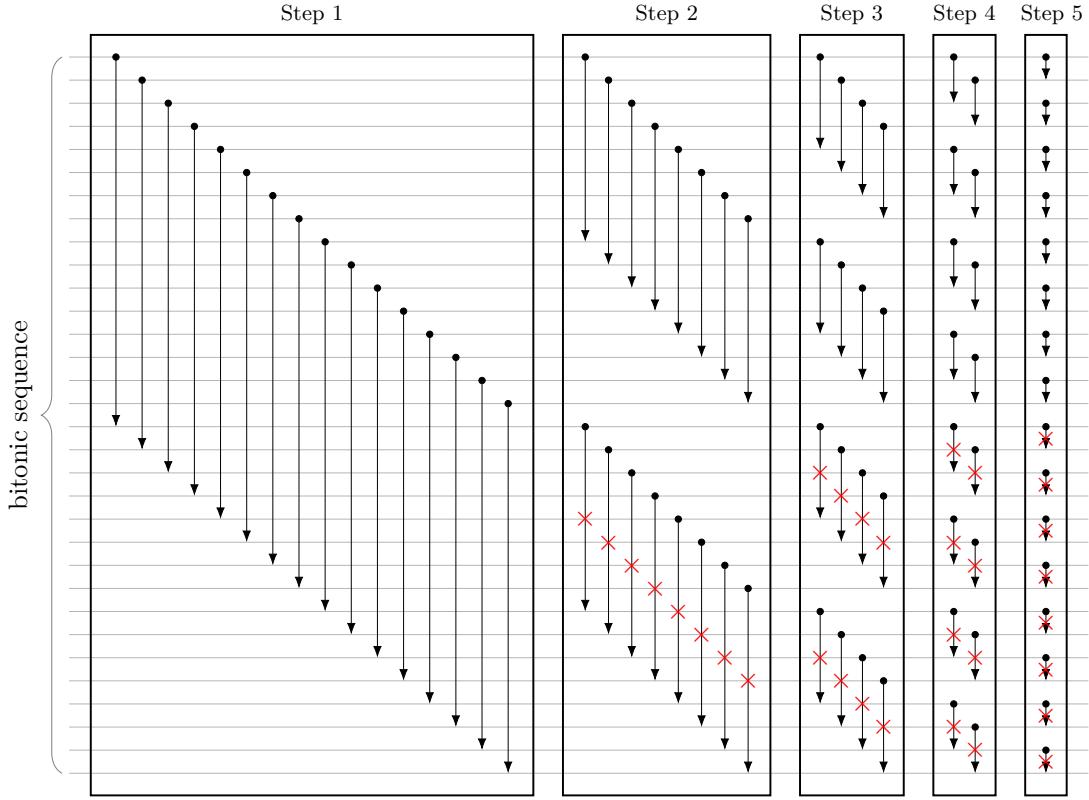

| 4.5  | Illustration of Batcher's merge algorithms                                                   | 75  |

| 4.6  | Full unoptimised merge network                                                               | 76  |

| 4.7  | Optimised merge network                                                                      | 77  |

| 4.8  | Modified U16 using the odd-even merge                                                        | 78  |

| 4.9  | Modified U16 using the bitonic merge                                                         | 79  |

| 4.10 | Single-tree single-stage architecture                                                        | 83  |

| 4.11 | Simplified ASMD chart for the single-stage K-best detector                                   | 84  |

| 4.12 | General architecture of a K-best processing element                                          | 86  |

| 4.13 | Vertical PED computation block for the K-best detector                                       | 87  |

| 4.14 | Path update operation for the K-best detector                                                | 88  |

| 4.15 | Illustration of detector interleaving                                                        | 89  |

| 5.1  | K-best multi-stage architecture with corresponding tree-mapping                              | 95  |

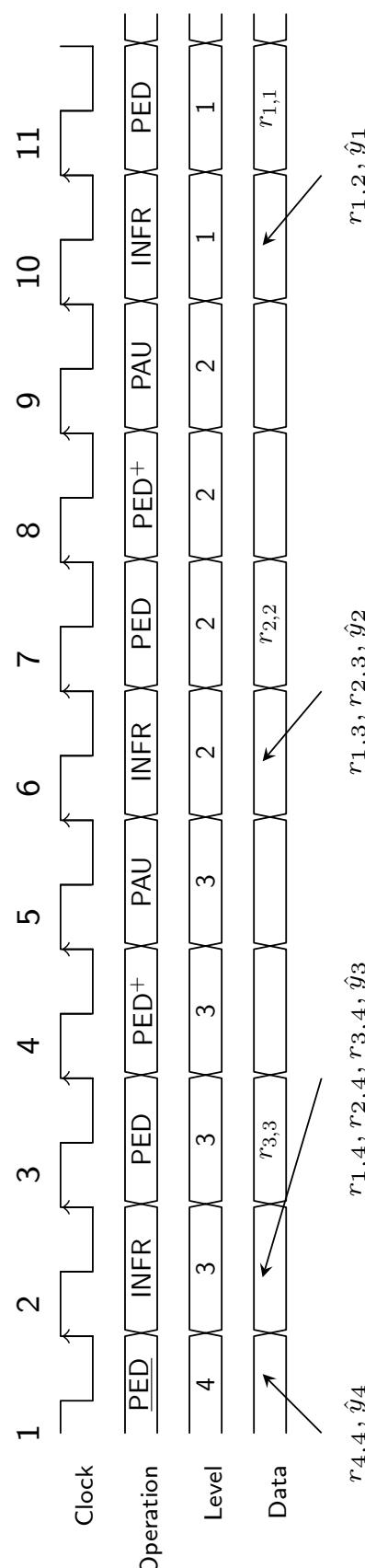

| 5.2  | Pipeline schedule for the K-best detector                                                    | 96  |

| 5.3  | Pipeline schedule using pipelined merge unit                                                 | 97  |

| 5.4  | Pipelining at tree level                                                                     | 98  |

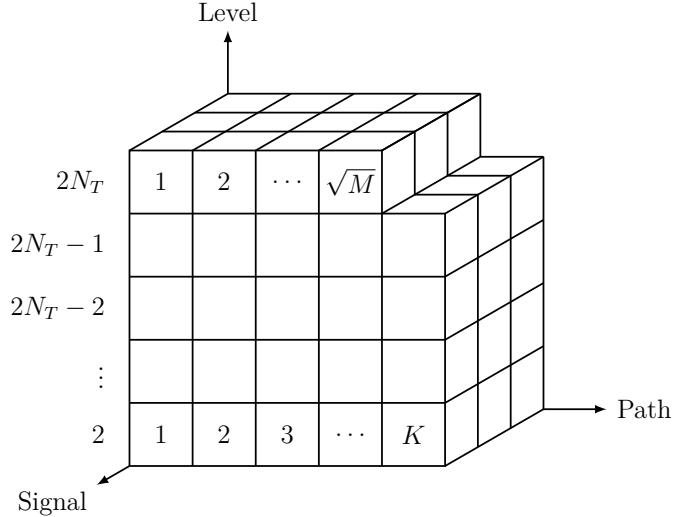

| 5.5  | Memory layout for $T_{i+1}$                                                                  | 99  |

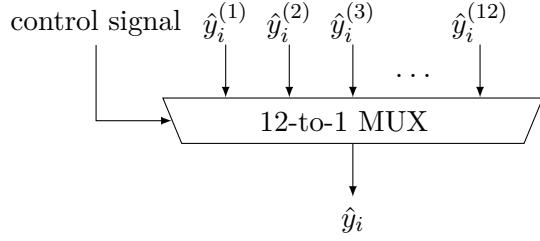

| 5.6  | Input selection using the MUX-based pipelined detector for $N_T = 2$                         | 100 |

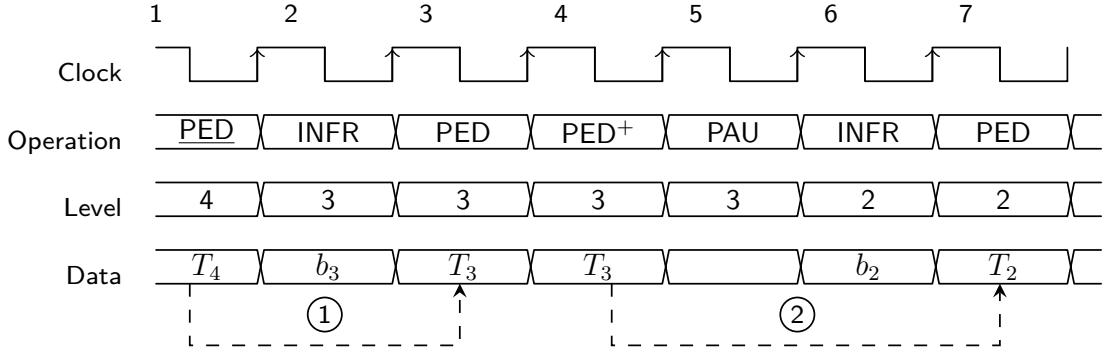

| 5.7  | Duration of K-best variables during pipeline operation                                       | 101 |

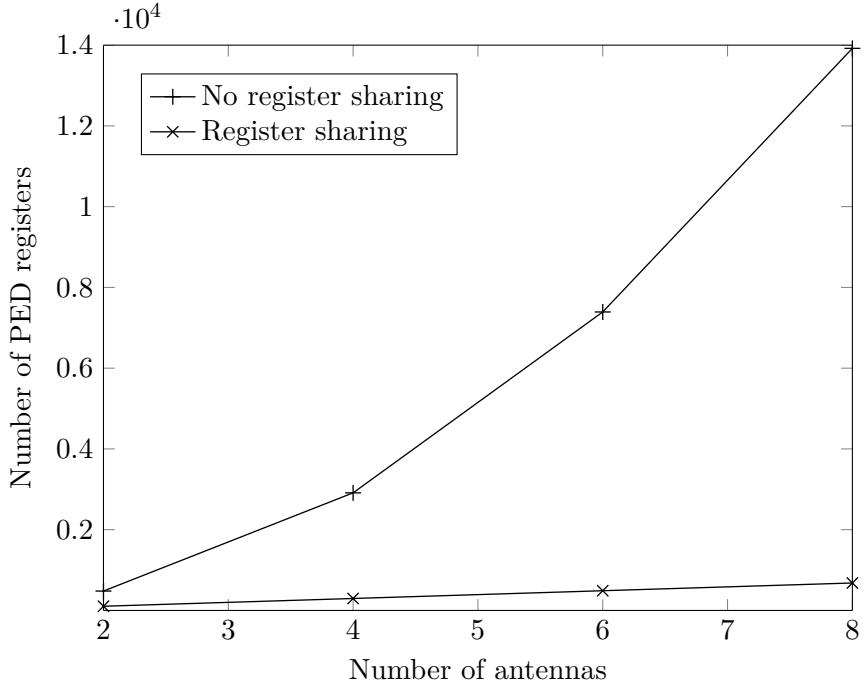

| 5.8  | Number of $T_{i+1}$ registers versus $N_T$                                                   | 102 |

| 5.9  | Data movement of channel and signal inputs in a $2 \times 2$ pipelined detector              | 103 |

| 5.10 | Overall architecture of the multiple-tree multi-stage architecture                           | 105 |

| 5.11 | ASM chart for the K-best MTMS controller                                                     | 106 |

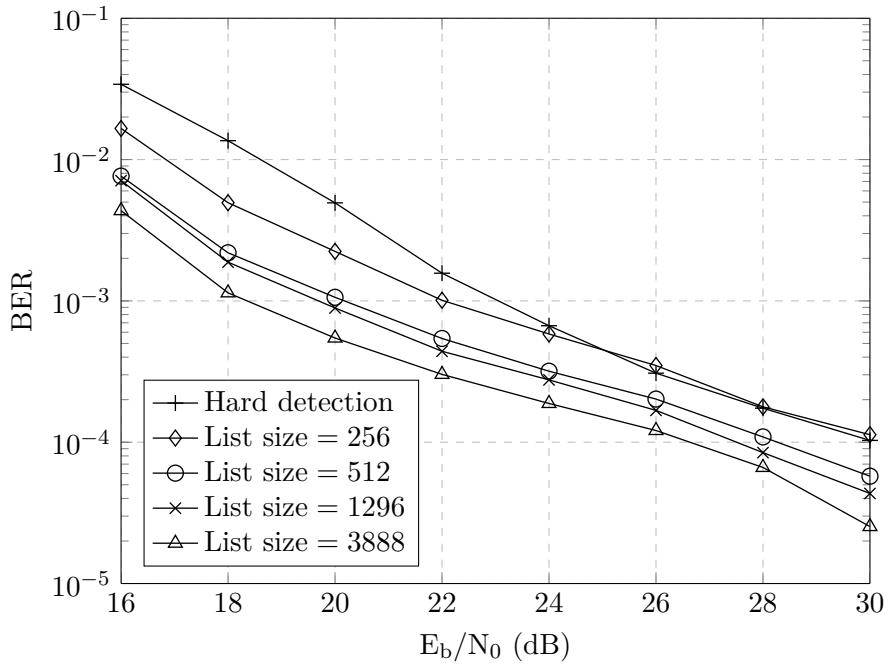

| 5.12 | BER vs SNR comparison of hard and soft K-best detectors                                      | 115 |

# List of Tables

|     |                                                                           |     |

|-----|---------------------------------------------------------------------------|-----|

| 2.1 | Numerical complexity of linear detectors versus the ML detector . . . . . | 14  |

| 2.2 | Simplification of $r_{i,i} \times s_i$ for 16-QAM . . . . .               | 23  |

| 3.1 | Fixed-point values of SD parameters . . . . .                             | 42  |

| 3.2 | Tabular enumeration for 64-QAM . . . . .                                  | 59  |

| 3.3 | Conventional interference computation for $N_T = 3$ . . . . .             | 61  |

| 3.4 | Implementation results for the sphere decoder . . . . .                   | 64  |

| 4.1 | Design trade-offs for different sorting algorithms . . . . .              | 72  |

| 4.2 | Comparison of full and optimised bitonic and odd-even merge units . . . . | 80  |

| 4.3 | Comparison of different sorting algorithms . . . . .                      | 81  |

| 4.4 | Classification of K-best MIMO detector architectures . . . . .            | 82  |

| 4.5 | Implementation results of single-stage K-best detectors for 64-QAM, MIMO  | 91  |

| 5.1 | Symbol register sharing for $N_T = 2$ . . . . .                           | 104 |

| 5.2 | Comparison of implementation results for different K-best architectures . | 110 |

| 5.3 | Comparison with 64-QAM $4 \times 4$ K-best Detectors . . . . .            | 112 |

| 5.4 | Optional and Mandatory Parameters for IEEE 802.11ac PHY Layer . . .       | 113 |

# Abbreviations

|                |                                               |

|----------------|-----------------------------------------------|

| <b>ASM</b>     | Algorithmic state machine                     |

| <b>ASMD</b>    | Algorithmic state machine with datapath       |

| <b>AWGN</b>    | Additive white Gaussian noise                 |

| <b>BER</b>     | Bit error rate                                |

| <b>CMOS</b>    | Complementary metal-oxide semiconductor       |

| <b>CORDIC</b>  | Coordinate rotation digital computer          |

| <b>FSD</b>     | Fixed-complexity sphere decoder               |

| <b>HDL</b>     | Hardware description language                 |

| <b>HPED</b>    | Horizontal partial Euclidean distance         |

| <b>ICU</b>     | Interference cancellation unit                |

| <b>kGE</b>     | Kilo gate equivalent                          |

| <b>MIMO</b>    | Multiple input multiple output                |

| <b>MIN</b>     | Minimum                                       |

| <b>ML</b>      | Maximum likelihood                            |

| <b>MMSE</b>    | Minimum mean square error                     |

| <b>MUX</b>     | Multiplexer                                   |

| <b>OFDM</b>    | Orthogonal frequency division multiplexing    |

| <b>ORVD</b>    | Orthogonal real-valued decomposition          |

| <b>PED</b>     | Partial Euclidean distance                    |

| <b>QAM</b>     | Quadrature amplitude modulation               |

| <b>QRD</b>     | QR decomposition                              |

| <b>RSV</b>     | Received signal vector                        |

| <b>RVD</b>     | Real-valued decomposition                     |

| <b>SE</b>      | Schnorr Euchner                               |

| <b>SD</b>      | Sphere decoder                                |

| <b>SQRD</b>    | Sorted QR decomposition                       |

| <b>SINR</b>    | Signal to interference and noise ratio        |

| <b>SNR</b>     | Signal to noise ratio                         |

| <b>TAR</b>     | Throughput to area ratio                      |

| <b>V-BLAST</b> | Vertical Bell Laboratories layered space time |

| <b>VPED</b>    | Vertical partial Euclidean distance           |

| <b>ZF</b>      | Zero forcing                                  |

# Nomenclature

|                         |                                                                    |

|-------------------------|--------------------------------------------------------------------|

| <b>A</b>                | Matrix                                                             |

| $a_{i,j}$               | Element at $i_{th}$ row and $j_{th}$ column of matrix <b>A</b>     |

| <b>H</b>                | Channel matrix                                                     |

| $\mathcal{S}$           | Complex constellation set                                          |

| $\mathcal{D}$           | Real constellation set                                             |

| $\langle \cdot \rangle$ | Expected Value                                                     |

| $\  \cdot \ $           | Euclidean norm                                                     |

| <b>I<sub>N</sub></b>    | $N \times N$ identity matrix                                       |

| $T_i$                   | Partial Euclidean distance at the $i$ th level                     |

| $T_{i,k}$               | Partial Euclidean distance at the $i$ th level for the $k$ th path |

| $\Re\{\cdot\}$          | Real part of a complex number                                      |

| $\Im\{\cdot\}$          | Imaginary part of a complex number                                 |

| $N_T$                   | Number of transmit antennas                                        |

| $N_R$                   | Number of receive antennas                                         |

| $N_0$                   | Noise spectral density                                             |

| $\sigma_n^2$            | Noise variance                                                     |

| $\mathbf{A}^T$          | Transpose of matrix <b>A</b>                                       |

| $\mathbf{A}^H$          | Hermitian transpose of matrix <b>A</b>                             |

| $ x $                   | Absolute value of $x$                                              |

| $\bar{x}$               | Complement of $x$                                                  |

| $ \mathbf{v} $          | Number of elements in the set <b>v</b>                             |

| $\lambda$               | Wavelength                                                         |

## Acknowledgements

Firstly, I will like to thank my supervisors, Prof Mark Zwolinski and Dr Basel Halak, for the regular discussions, feedbacks and guidance, which I found invaluable during my research. I will also like to acknowledge Dr Mohammed El-Hajjar for his advice on numerous aspects of my research. Thanks also to my examiners, Professors Koushik Maharatna and Tughrul Arslan (University of Edinburgh) for their comments and recommendations, which helped to improve the quality of this thesis.

I will also like to acknowledge my colleagues in Zepler Lab 4 including Haider Abbas, Illani Mohd, Syafiq Mispan, Yue Lu and others for the discussions and exchange of ideas, which made the PhD journey much more interesting. I had many fruitful discussions with Dr Dwaipayan Biswas and I will like to thank him for his helpful suggestions.

I will like to use this opportunity to thank my parents for supporting me throughout my education and for motivating me to always aim for the best. Thanks also to my brothers and sisters who provided plentiful support and encouragement throughout my studies.

Finally, I will like to thank my wife, Aishah, for her numerous sacrifices and support which made the PhD so much easier. Thanks also to my son, Abdurrahman, who provided welcome distraction while I worked on my thesis.

*The PhD was sponsored by the Petroleum Technology Development Fund, and their support is gratefully acknowledged. I will also like to acknowledge the use of the IRIDIS University of Southampton computer cluster, which was used in certain aspects of this work.*

*To my parents...*

# Chapter 1

## Introduction

The field of wireless communications has experienced quite spectacular advancements in recent years. From humble beginnings in radio telegraphy and Morse codes, wireless communications is now an indispensable part of daily life, present in applications as diverse as mobile phones to domestic electrical installations. In the next few years, it is estimated that tens to hundreds of billions of devices will become interconnected [1]. This development has instigated a significant amount of research work in developing new standards and techniques to power the next generation communication devices.

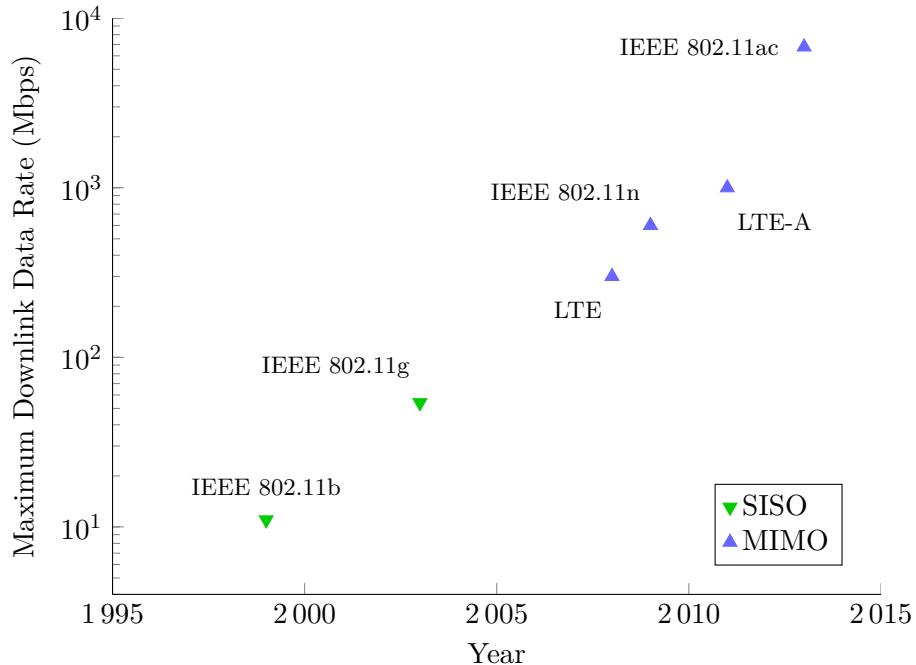

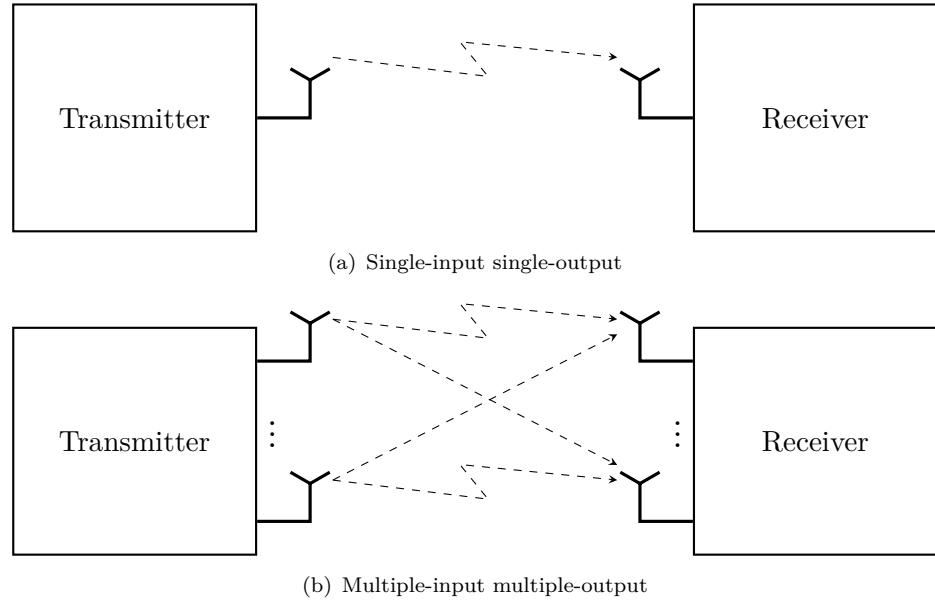

One of the most noticeable trends in wireless communications is the exponential increase in the data rate as illustrated in Fig. 1.1. Over time, this has been achieved by switching from analogue to digital signal processing, increasing the channel bandwidth, adopting more sophisticated modulation schemes and more recently, by employing multiple antennas at the transmitter and receiver. The latter case, which is the focus of this thesis, is also known as multiple-input multiple-output (MIMO), and it allows higher transmission rates to be achieved without increasing the bandwidth [2]. A MIMO communication system is illustrated in Fig. 1.2 and compared with a conventional single-antenna system.

MIMO can be employed in three major ways: spatial-multiplexing, diversity and beam-forming. In the *spatial-multiplexing* mode, the MIMO system aims to maximise the transmission rate by transmitting independent streams of data in parallel over multiple transmit antennas. In the absence of correlation between the parallel streams, the spatial-multiplexing MIMO system can increase the channel capacity in direct proportion to the number of transmit antennas [3]. Meanwhile, the MIMO system operating in the *diversity* mode aims to take advantage of the several antennas at the transmitter and receiver to improve the error rate of the transmission. The information bits are duplicated over the multiple antennas using one of a number of space-time block codes (STBC), such that multiple copies of the same data are available to the receiver, thereby, improving the performance. Diversity can be implemented both at the transmitter and receiver sides of the communication link; however, it is typically implemented at the transmitter since

**Figure 1.1:** Wireless trends in the past 20 years

implementing diversity techniques at the receiver-side could result in highly complex remote units due to their physical and computational limitations [4]. MIMO can also be utilised to provide a beamforming gain in a multi-user scenario, where the gain of a transmitter or receiver is increased in the direction of the desired user while suppressing the interferences from other users [5]. MIMO can also be used in conjunction with orthogonal frequency division multiplexing (OFDM), to combat inter-symbol interference at the receiver by transmitting independent streams on a tone-by-tone basis [6]. In spite of these benefits, MIMO also complicates the wireless transceiver, which is explained in more detail in the next section.

## 1.1 Challenges of Multi-Antenna Communication Systems

The use of multiple antennas at the transmitter and receiver presents a number of challenges as follows:

- **At the transmitter:** In spatial-multiplexing and diversity modes, the transmitter needs to transmit multiple data simultaneously over multiple antennas. In a multi-user scenario, the transmitter will also be equipped with user-selection capabilities based on certain criteria. All these impose additional complexity at the multi-antenna transmitter compared to a single-antenna transmitter.

- **At the receiver:** The signal detection at the receiver in a MIMO system is complicated as a result of interferences between the transmitted substreams on each

**Figure 1.2:** Illustration of single and multiple antenna systems

receive antenna. A straightforward detection using the maximum likelihood detector [7], results in an NP-hard problem, which is undesirable in a real-time communication system. This is particularly problematic when the receiver is a small hand-held device with limited power supply. This problem has inspired a significant amount of research into low-complexity alternatives to the maximum likelihood detector.

## 1.2 Energy-Efficient Communications

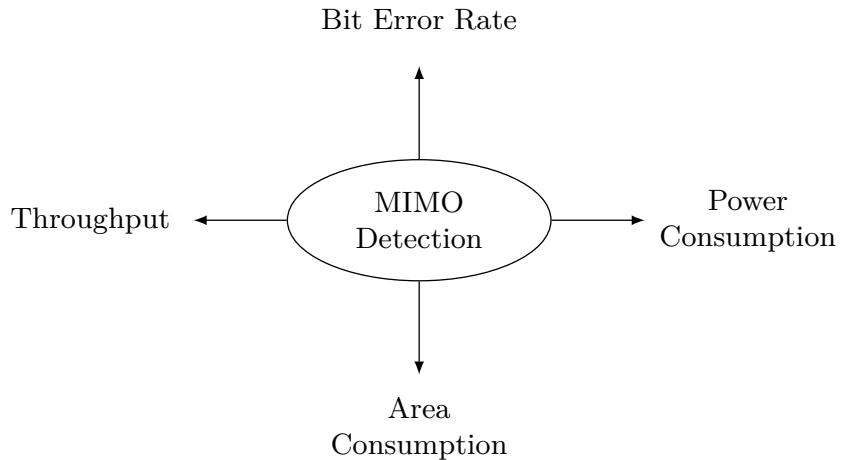

Energy efficiency refers to the ability of a digital circuit to meet its throughput target at a relatively low power consumption. Due to the increasing need for higher data rates, energy efficiency is expected to play a crucial role in future communication systems [8]. In this thesis, we will consider various strategies for achieving energy-efficient signal detection for MIMO communication systems. These design trade-offs are summarised in Fig. 1.3, which we elaborate as follows:

1. High throughput: Digital circuits that achieve a high throughput tend to be highly energy efficient, since they are operational over a short period, compared to slower digital circuits. However, a high throughput may also come at the expense of a higher power consumption.

2. Low power design techniques: These refer to circuit-level design techniques for reducing power consumption. Examples include well-established low power techniques such as power gating, clock gating and operand isolation. Optimising a

design for low power is a critical step in achieving highly energy-efficient digital circuits.

3. Low complexity: Complexity refers to different things depending on the context. In hardware design, this refers to the area consumption. A circuit with high complexity tends to incur a high power consumption due to the corresponding increase in the number of combinational and sequential elements. Thus, reducing the area of a design may lead to a more energy efficient system. Alternatively, complexity may refer to the number of operations required by an algorithm. This is usually measured in terms of floating-point operations per second (FLOPS). A circuit with a large number of FLOPS will tend to incur a high power consumption.

4. Error rate: This is the mismatch between the expected result of a computation and the *actual* output of a digital circuit. This is typically measured as the ratio of the number of correct information bits to the total number of bits transmitted. A relationship between the error rate and energy efficiency is less obvious than the previous three metrics. However, if a circuit does not meet its target error rate, this may increase the transmission power of the communication link [9]. Conversely, a system may deliberately aim for a lower error performance to reduce the power consumption.

### 1.3 Research Motivation

As already highlighted in Fig. 1.1, the data rates required by wireless communication systems have experienced an exponential growth in the past few decades. This phenomenon is expected to continue in the coming years with the introduction of 5G wireless systems. MIMO is a driving force of future wireless communication systems, and it is vital that the VLSI circuits for MIMO systems are designed as efficiently as possible to deliver the advantages promised by MIMO with high throughput and low power consumption. To achieve this, application specific integrated circuits (ASICs) are attractive as they have better potential for achieving low-power implementations compared to other platforms, such as field programmable gate arrays (FPGAs) [10] and digital signal processors (DSPs) [11].

In Section 1.1, the detector at the receiver-side was identified as a potential bottleneck in the MIMO communication system due to the high complexity required for detecting the transmitted data. Unfortunately, most of the existing VLSI implementations of MIMO detection in the literature do not achieve the high data-rates required by the next-generation communication systems, which now exceed the 1 Gbps mark [1]. Thus, more advanced circuit-level techniques are required to achieve the theoretic benefits promised by MIMO. The aim of this thesis is thus to fill this gap by presenting the

**Figure 1.3:** Design trade-offs for MIMO detection

VLSI implementations of different MIMO detector architectures and investigating numerous circuit-level strategies for achieving low complexity and high throughput MIMO detection.

## 1.4 Research Objectives

As highlighted in the previous sections, the signal detection in a MIMO receiver presents a major bottleneck in achieving the gains promised by MIMO technology. Several competing objectives come into play when implementing MIMO detection in hardware as illustrated in Fig. 1.3. Therefore, an efficient MIMO detector implementation should achieve a suitable trade-off among these objectives. This leads us to formulate a number of research questions as follows:

1. What is the impact of algorithm choice on the hardware implementation of a MIMO detector?

2. How do different architectural design choices of a particular algorithm impact the hardware implementation of the MIMO detector?

3. How do throughput optimisation strategies, such as pipelining and parallelism, compare with regards to achieving high data-rate MIMO detection?

To address these questions, we present a number of objectives for this thesis as follows:

1. Undertake a comprehensive survey of VLSI implementations of MIMO detection algorithms, which to the best of our knowledge is missing in the literature.

2. Investigate techniques for reducing the complexity of the sphere decoding algorithm [12] through critical path optimisations of the Euclidean distance computation. We will also implement a “look-ahead” strategy for reducing the number of clock cycles required by the sphere decoder for detecting the transmitted symbols.

3. Implement a high-speed sorting architecture, which will be applied to the  $K$ -best algorithm [13]. We will also study the impact of a reduced-complexity  $K$ -best algorithm on the BER performance compared with the original  $K$ -best algorithm.

4. Implement a fully-pipelined  $K$ -best architecture with a processing rate of 1 MIMO symbol per clock cycle. A novel pipeline scheduling technique will be implemented with the view of reducing the area consumption required by successive input signals. The fully-pipelined implementation will be compared with interleaved implementations (i.e. parallelism) of unpipelined  $K$ -best detectors.

5. Present a number of design guidelines for the hardware implementation of energy-efficient MIMO detectors, which will hopefully excite more research activity and innovations within this area.

## 1.5 Publications

The following papers have been published/submitted for publication as part of this research:

1. “A Survey of VLSI Implementations of Tree Search Algorithms for MIMO Detection,” *Circuits, Systems, and Signal Processing*, 2015 [14].

2. “VLSI Implementation of a Scalable  $K$ -best MIMO Detector,” in *2015 15th International Symposium on Communications and Information Technologies (ISCIT)*, Oct. 2015 [15].

3. “VLSI Implementation of a Low-Complexity Look-Ahead Sphere Decoder,” *submitted to Transactions on Circuits and Systems II: Express Briefs*.

## 1.6 Organisation of the Thesis

The thesis is organised as follows:

- **Chapter 2:** In this chapter, we tackle the first objective of the thesis as provided in Section 1.4. Firstly, the mathematical foundation for the MIMO communication

channel is presented. The complexity problem of the signal detection in a multi-antenna system is highlighted, and several low-complexity detection algorithms are presented. We pay particular attention to the class of detection algorithms that carry out the MIMO detection as a tree search, where each antenna corresponds with a level in the search-tree, and each branch of the tree corresponds to a possible solution. The chapter concludes by presenting a number of notable VLSI implementation results of tree-search detection algorithms from the literature.

- **Chapter 3:** This chapter addresses the second objective of the thesis. The sphere decoder is adopted for VLSI implementation due to its ML performance, which makes it useful in benchmarking other detection algorithms implemented in subsequent chapters of the thesis. We consider a number of strategies for improving the throughput of the sphere decoder, especially at low signal to noise ratios. We present and compare two implementations of the sphere decoder based on the conventional and proposed techniques for computing the partial Euclidean distance.

- **Chapter 4:** In this chapter, the implementation of a hybrid merge architecture is presented, which will be used in the  $K$ -best detector implementation, to meet the third objective of the thesis. Furthermore, a classification of  $K$ -best architectures is provided according to different criteria. The single-stage  $K$ -best architecture is selected due to its small area, and the VLSI implementation results are compared with that of the sphere decoder.

- **Chapter 5:** In this chapter, we tackle the fourth objective of the thesis by investigating pipelining as a technique for improving the throughput of the  $K$ -best detector. The pipeline schedules of a partial and fully-pipelined  $K$ -best detector are presented and analysed. A VLSI implementation of the fully-pipelined  $K$ -best detector is presented, and the results are compared with the interleaved single-stage  $K$ -best detector, as well as state-of-the-art implementations of  $K$ -best implementations from the literature. Finally, the potential application of the implemented fully-pipelined  $K$ -best architecture to recent high-throughput wireless communication standards is discussed.

- **Chapter 6:** The thesis is concluded in this chapter. A number of design guidelines are outlined, and possible topics are presented for future research.

# Chapter 2

## Background

### 2.1 Introduction

In Chapter 1, we provided an overview of MIMO technology and the impact it has had on wireless communications in the past few decades. In this chapter, we will provide a more in-depth discussion of MIMO technology, with particular focus on the signal detection at the receiver. The chapter is organised as follows. In Section 2.2, we will present the MIMO system model. In Section 2.3, we will provide an overview of the maximum likelihood MIMO detector. In Section 2.4, we will discuss linear detection algorithms. In Sections 2.5 and 2.6, we will present a number of non-linear techniques for improving the performance of linear detectors. In Section 2.7 a number of tree-search detection techniques will be presented. In Section 2.8, we will present a number of performance metrics for comparing hardware implementations of MIMO detectors. Furthermore, a number of notable results of tree-search VLSI implementations from the literature are provided. The chapter is concluded in Section 2.9.

### 2.2 System Model

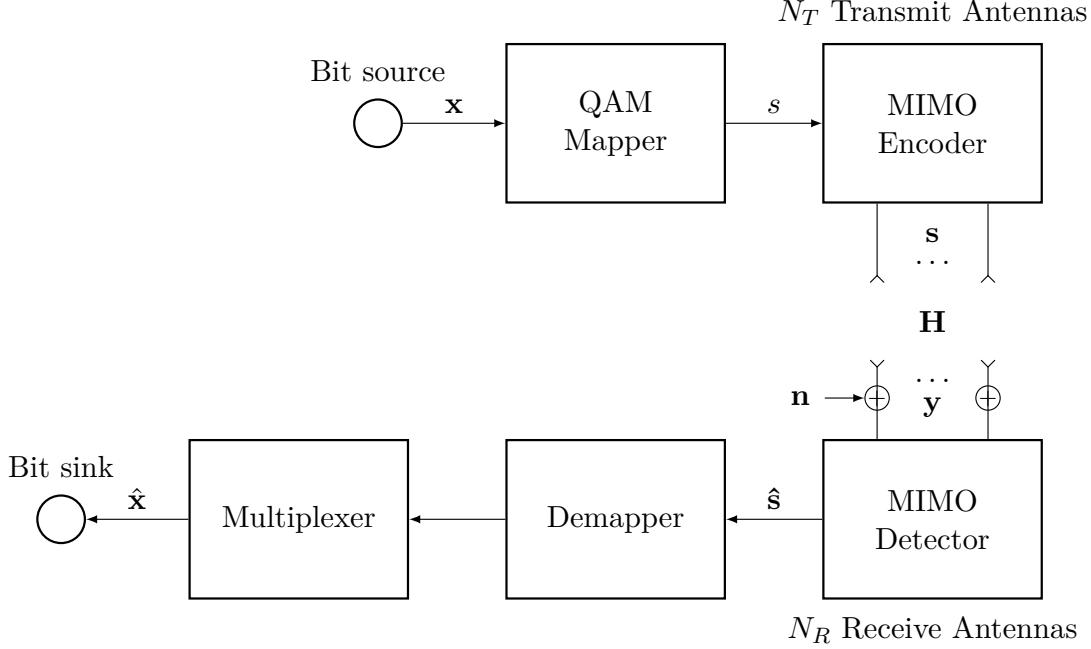

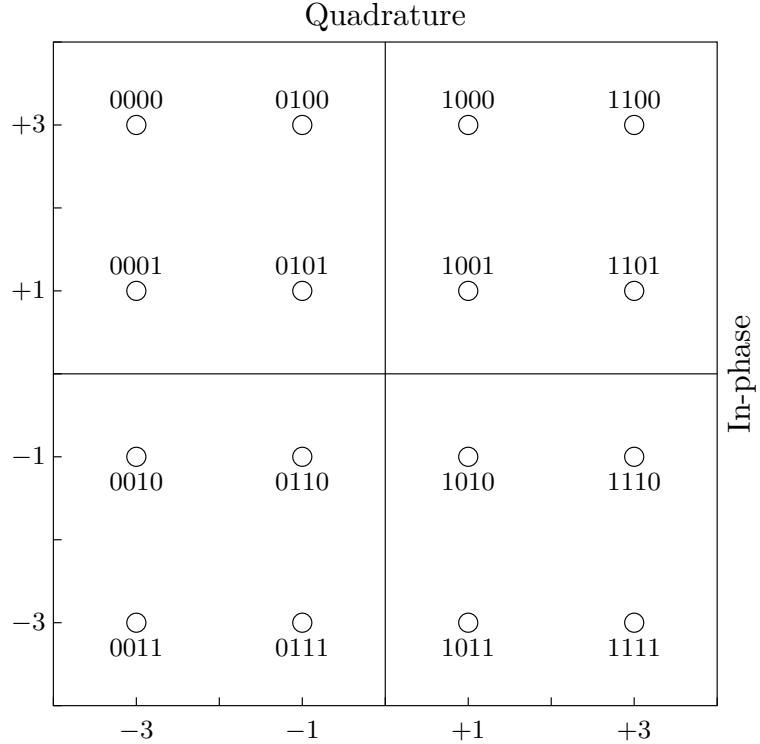

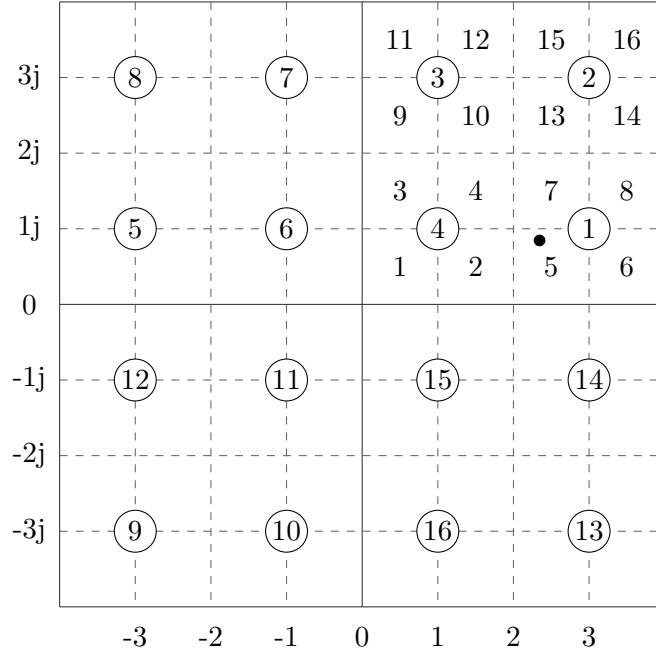

Figure 2.1 illustrates a MIMO system employing  $N_T$  and  $N_R$  antennas at the transmitter and receiver respectively. A stream of bits, denoted by  $\mathbf{x}$  is sent to a quadrature amplitude modulator (QAM), which maps  $Q$  bits to a QAM symbol, denoted by  $s$ , which is drawn from a constellation set of complex-valued symbols denoted by  $\mathcal{S}$ . The symbols for a 16-QAM scheme and their corresponding bit patterns are illustrated in Fig. 2.2. The QAM symbols are then demultiplexed over  $N_T$  transmit antennas to get an  $N_T \times 1$  MIMO symbol,  $\mathbf{s}$ , using one of several MIMO encoding schemes [16]. The wireless channel can be represented by the  $N_R \times N_T$  matrix,  $\mathbf{H}$ , whose elements represent the channel

**Figure 2.1:** Block diagram of MIMO transmission and detection

fading coefficient for each path between the transmit and receive antennas. That is,

$$\mathbf{H} = [\mathbf{h}_1 \mathbf{h}_2 \dots \mathbf{h}_{N_T}] = \begin{bmatrix} h_{1,1} & h_{1,2} & \dots & h_{1,N_T} \\ h_{2,1} & h_{2,2} & \dots & h_{2,N_T} \\ \vdots & \vdots & \ddots & \vdots \\ h_{N_R,1} & h_{N_R,2} & \dots & h_{N_R,N_T} \end{bmatrix}$$

where  $h_{ij}$  are complex-valued with normal distribution [3]. The  $i$ th column of the channel matrix,  $\mathbf{h}_i$ , represents the  $N_R \times 1$  vector of channel coefficients from the  $i$ th transmit antenna to all the  $N_R$  receive antennas. If the transmitted substreams are sufficiently decorrelated (which is achieved by separating the transmit antennas by a distance of at least  $\lambda/2$ ), then the entries of  $\mathbf{H}$  can be considered to be independent and identically distributed, which allows the maximum channel capacity<sup>1</sup> to be achieved [17].

The  $N_R \times 1$  received signal vector (RSV) at the receiver can be represented using the following linear equation:

$$\mathbf{y} = \mathbf{H}\mathbf{s} + \mathbf{n}, \quad (2.1)$$

where  $\mathbf{n}$  is the  $N_R \times 1$  additive white Gaussian noise (AWGN) experienced by the signal<sup>2</sup> at the receive antennas. At the receiver, a MIMO detector estimates the transmitted symbols by attempting to find the symbol,  $\hat{\mathbf{s}}$ , that minimises the error probability  $P(\hat{\mathbf{s}} \neq \mathbf{s})$ .

<sup>1</sup>Capacity, here, refers to the maximum data rate that the communication system can achieve at an arbitrarily small BER.

<sup>2</sup>The terms “signal” and “symbol” will be used frequently throughout the thesis. A symbol is scalar and is drawn from the complex constellation set, while a signal is a vector of complex numbers, obtained as a result of the attenuation and interferences experienced by the transmitted symbol vector in the channel.

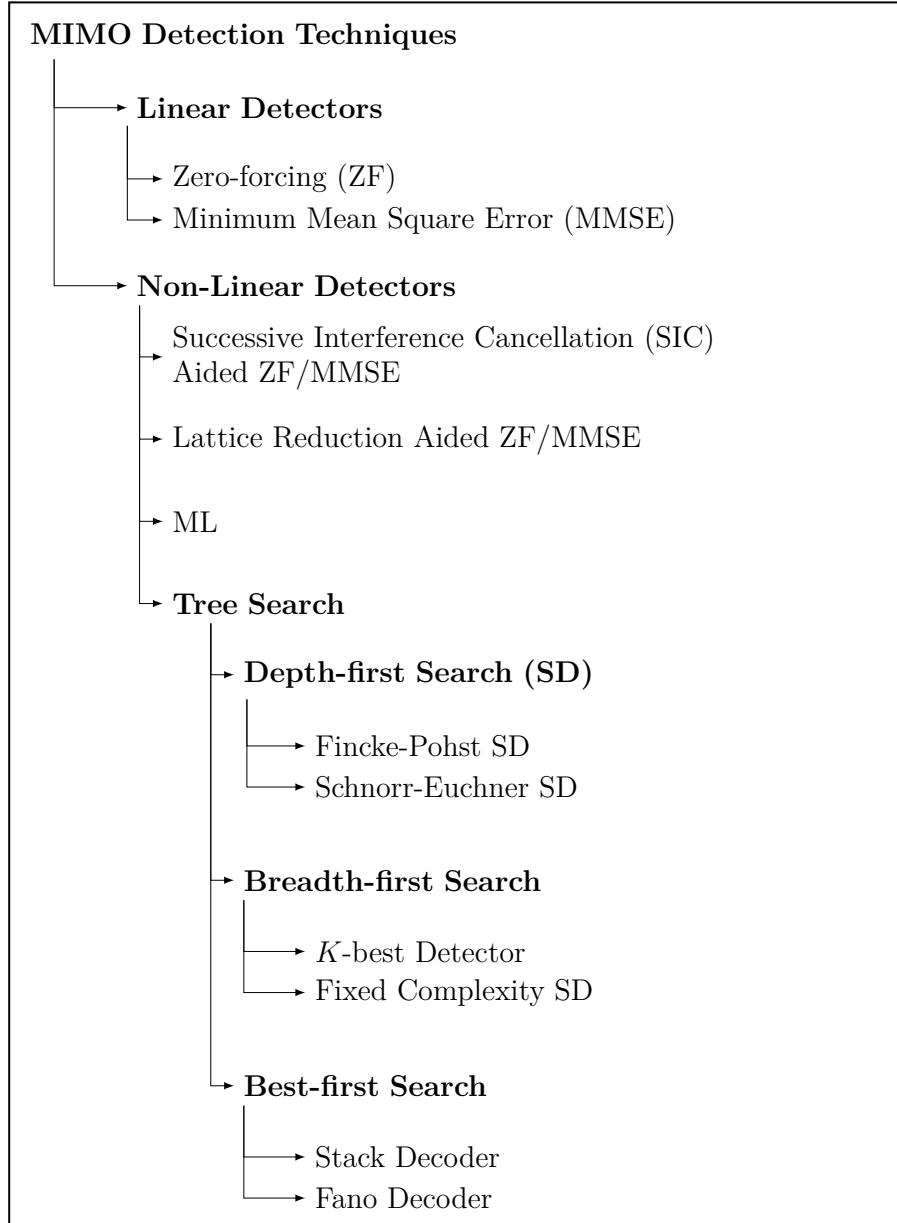

**Figure 2.2:** 16-QAM constellation points and corresponding binary representation

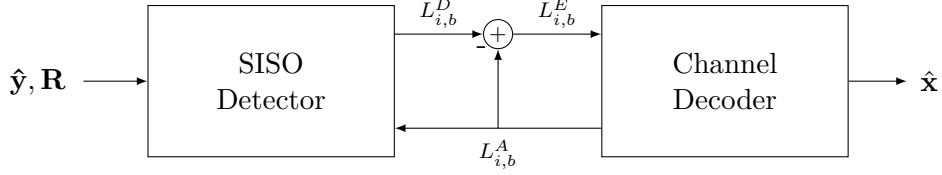

This procedure can be achieved in several ways as summarised in Fig. 2.3. After the signal has been detected, a demapper converts the symbols to their binary equivalent, according to the chosen modulation scheme, and a multiplexer converts the detected parallel bit streams into a single bit stream to recover the transmitted bits. A channel decoder may also be concatenated with the MIMO detector in a technique known as iterative decoding [18], in order to improve the BER. For the remainder of the thesis, we will assume an equal number of antennas at the transmitter and the receiver such that  $N_T = N_R$ .

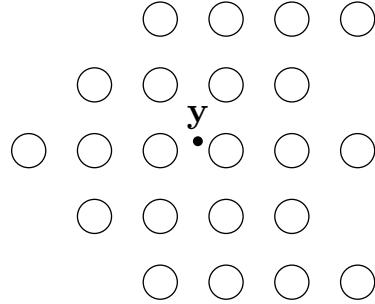

## 2.3 MIMO Detection

In Chapter 1, we highlighted the problem of the signal detection in a multi-antenna system, which is complicated by the mutual interferences between the transmitted substreams at each receive antenna. Essentially, the received substream at each antenna will need to be detected in the presence of  $N_T - 1$  interfering substreams. One approach of carrying out the signal detection is to consider all the possible transmitted symbol vectors as lattice points centred on the received signal,  $\mathbf{y}$ , as shown in Fig. 2.4. The detector exhaustively examines all the lattice points and determines the solution that minimises the Euclidean distance to the received signal. The maximum likelihood (ML) solution is obtained as follows:

**Figure 2.3:** Classification of MIMO detection algorithms

$$\mathbf{s}_{\text{ML}} = \arg \min_{\mathbf{s} \in \mathcal{S}^{N_T}} \|\mathbf{y} - \mathbf{H}\mathbf{s}\|^2, \quad (2.2)$$

where  $\mathcal{S}$  represents the complex QAM constellation set and  $\mathcal{S}^{N_T}$  is an  $N_T$  dimensional lattice with complex entries formed from all possible combinations of the  $N_T \times 1$  transmitted symbols. The total number of lattice points in the ML search is  $|\mathcal{S}|^{N_T}$  which requires  $N_T^2 + N_T$  complex multiplications per lattice point. Thus, the ML detector for a MIMO system employing binary phase shift keying (BPSK) modulation and 2 antennas will need to examine 4 lattice points and perform 12 complex multiplications, while 65,536 lattice points and 393,216 complex multiplications will be required in the case of 16-QAM with 4 antennas. This exponential complexity makes the ML detector

**Figure 2.4:** Lattice search for the maximum likelihood detector. Each of the circles represents a lattice point,  $\mathbf{H}\mathbf{s}$ .

unsuitable for implementation in real-time systems, especially at larger MIMO dimensions. As such, a number of low-complexity alternatives to the ML detector have been investigated in recent years, which we will discuss in the subsequent sections.

## 2.4 Linear Detection Algorithms

Linear detectors apply a linear filter,  $\mathbf{W}$ , to the received signal, which suppresses the mutual interference on each of the receive antennas. The received signal is multiplied by the filter matrix, and the symbol is detected by carrying out a parallel decision on all the layers [19]. Linear detection can be performed by applying either the zero-forcing (ZF) or the minimum mean square error (MMSE) criterion and is discussed in the following sections.

### 2.4.1 Zero-forcing

The ZF detector suppresses the mutual interferences between all the layers (i.e. the  $N_T$  transmitted data substreams [19]). In this detector, the filter matrix is computed as the pseudoinverse of the channel matrix and the ZF estimate is obtained as follows:

$$\begin{aligned}\mathbf{W}_{\text{ZF}} &= \mathbf{H}^\dagger = (\mathbf{H}^H \mathbf{H})^{-1} \mathbf{H}^H, \\ \tilde{\mathbf{s}}_{\text{ZF}} &= \mathbf{W}_{\text{ZF}} \mathbf{y}.\end{aligned}\tag{2.3}$$

The estimation errors of the different layers correspond to the main diagonal of the error covariance matrix given as follows [19]:

$$\Phi_{\text{ZF}} = \mathbb{E}\{(\tilde{\mathbf{s}}_{\text{ZF}} - \mathbf{s})(\tilde{\mathbf{s}}_{\text{ZF}} - \mathbf{s})^H\} = \sigma_n^2 (\mathbf{H}^H \mathbf{H})^{-1}.\tag{2.4}$$

The result of the multiplication in (2.3) is a vector of floating-point numbers, therefore, a quantiser is required in a final step to round off the ZF estimate to the nearest constellation point as follows:

$$\hat{\mathbf{s}}_{\text{ZF}} = \mathcal{Q}(\tilde{\mathbf{s}}_{\text{ZF}}),$$

where  $\mathcal{Q}$  is the *slicing* function corresponding to the modulation scheme adopted for the data transmission. Where  $N_T = N_R$  (i.e. when  $\mathbf{H}$  is square),  $\mathbf{W}_{\text{ZF}}$  can simply be computed as the ordinary inverse of  $\mathbf{H}$ , i.e.

$$\mathbf{W}_{\text{ZF}} = \mathbf{H}^{-1}, \quad (2.5)$$

which eliminates  $2N_T^3$  complex multiplications and  $2N_T^2(N_T - 1)$  complex additions,<sup>3</sup> compared to the pseudoinverse based computation in (2.3).

#### 2.4.2 Minimum Mean Square Error

In the computation of the error covariance matrix in (2.4) for the ZF detector, it can be observed that small eigenvalues of the matrix  $\mathbf{H}^H \mathbf{H}$  will result in large errors due to noise amplification, especially for large values of  $N_T$  [19]. The performance can be improved by incorporating the noise variance in the filter matrix, which results in a minimum mean square error criterion. The MMSE detection is carried out as follows:

$$\begin{aligned} \mathbf{W}_{\text{MMSE}} &= (\mathbf{H}^H \mathbf{H} + \sigma_n^2 \mathbf{I}_{N_T})^{-1} \mathbf{H}^H \\ \tilde{\mathbf{s}}_{\text{MMSE}} &= \mathbf{W}_{\text{MMSE}} \mathbf{y}, \end{aligned} \quad (2.6)$$

which results in a better estimate of the transmitted symbols. The estimation errors of the layers using the MMSE detector is given as follows:

$$\Phi_{\text{MMSE}} = E\{(\tilde{\mathbf{s}}_{\text{MMSE}} - \mathbf{s})(\tilde{\mathbf{s}}_{\text{MMSE}} - \mathbf{s})^H\} = \sigma_n^2 \left( \mathbf{H}^H \mathbf{H} + \sigma^2 \mathbf{I}_{N_T} \right)^{-1}.$$

Alternatively, the MMSE equalisation can be performed by substituting  $\mathbf{H}$  in (2.3) with an  $(N_T + N_R) \times N_T$  extended channel matrix  $\underline{\mathbf{H}}$  as follows [19]:

$$\underline{\mathbf{H}} = \begin{bmatrix} \mathbf{H} \\ \sigma_n \mathbf{I}_{N_T} \end{bmatrix}.$$

The received signal vector is extended as follows:

$$\underline{\mathbf{y}} = \begin{bmatrix} \mathbf{y} \\ \mathbf{0}_{N_T, 1} \end{bmatrix},$$

where  $\mathbf{0}_{N_T, 1}$  is a zero vector with  $N_T$  rows. Thus, the MMSE detection can be computed using (2.3), by simply replacing  $\mathbf{H}$  and  $\mathbf{y}$  with  $\underline{\mathbf{H}}$  and  $\underline{\mathbf{y}}$  respectively. The advantage of this approach is that the addition in (2.6) is eliminated and it is also convenient for the sorted QR decomposition MMSE detection described in [19].

---

<sup>3</sup>Two extra matrix multiplications are required if (2.3) is used to compute the ZF estimate compared to (2.5). Each matrix multiplication requires  $N_T^3$  complex multiplications and  $N_T^2(N_T - 1)$  complex additions.

**Table 2.1:** Numerical complexity of linear detectors versus the ML detector

| Detector                                         | ZF              | MMSE             | ML                                  |

|--------------------------------------------------|-----------------|------------------|-------------------------------------|

| $\mathbf{W}$                                     | $N_T^3$         | $3N_T^3$         | -                                   |

| $\mathbf{W} \cdot \mathbf{y}$                    | $N_T^2$         | $N_T^2$          | -                                   |

| $\mathbf{H} \cdot \mathbf{s}$                    | -               | -                | $N_T^2$                             |

| $\ \mathbf{y} - \mathbf{H} \cdot \mathbf{s}\ ^2$ | -               | -                | $N_T^2 + N_T$                       |

| Total CMs                                        | $N_T^3 + N_T^2$ | $3N_T^3 + N_T^2$ | $(N_T^2 + N_T)  \mathcal{S} ^{N_T}$ |

### 2.4.3 Complexity Analysis

The complexities of the ZF and MMSE detectors, in terms of the number of complex multiplications (CMs), are compared to the ML detector in Table 2.1. The number of CMs for the MMSE detector is determined according to (2.6). The Gauss-Jordan algorithm was considered for computing the matrix inverse, which has a polynomial complexity to the order of  $N_T^3$  [20]. The slicing operation and minimum Euclidean search required by the linear detectors and MLD respectively have not been considered. It is clear from the table that linear detectors have a much lower complexity compared to the ML detector. Furthermore, their complexities are independent of the constellation size employed. For example, the number of CMs required at 4-QAM for  $4 \times 4$  MIMO is 5120 for the ML detector and approximately  $1.3 \times 10^6$  at 16-QAM. Meanwhile, the number of CMs required for the ZF and MMSE for  $4 \times 4$  MIMO is 80 and 208 respectively, and remains the same irrespective of the modulation scheme employed.

The complexities of the linear detectors can also be reduced if the channel is relatively stationary. In this case, the computationally expensive matrix inverse operations need only be performed for  $1/\tau$  of the time on average [21]. The ZF and MMSE detectors require  $N_T^3$  and  $3N_T^3$  CMs respectively for computing the filter matrix (channel-rate processing).  $N_T^2$  CMs are required for the multiplication with  $\mathbf{y}$  (i.e. symbol rate processing). If the channel is sampled at the rate of  $1/\tau$ , it implies that the total number of CMs required for the ZF and MMSE detectors are  $N_T^3/\tau + N_T^2$  and  $3N_T^3/\tau + N_T^2$  respectively. On the other hand, there is no possibility to separate the ML detector into channel and symbol-rate processing. Unfortunately, this complexity advantage enjoyed by the ZF and MMSE detectors comes at the cost of a reduced diversity order compared to the ML detector, which limits their usefulness in practice. Non-linear techniques achieve an improved diversity order compared to linear detection techniques and will be discussed in the subsequent sections.

---

**Algorithm 1** Ordered SIC-aided ZF detection for V-BLAST spatial multiplexing

---

```

1:  $\mathbf{r}^{(1)} \leftarrow \hat{\mathbf{y}}$

2:  $\mathbf{H}^{(1)} \leftarrow \mathbf{H}$

3:

4: for  $k = 1$  to  $N_T$  do

5:    $\mathbf{W} \leftarrow \mathbf{H}^{(k)\dagger}$

6:    $i \leftarrow \arg \min_i \|\mathbf{w}_i\|, 1 \leq i \leq N_T$ , where substream  $i$  is yet to be detected

7:    $\hat{\mathbf{s}}_i \leftarrow \mathcal{Q}(\mathbf{w}_i^T \mathbf{r}_k)$

8:    $\mathbf{r}^{(k+1)} \leftarrow \mathbf{r}^{(k)} - \mathbf{h}_i \hat{\mathbf{s}}_i$

9:    $\mathbf{h}_i \leftarrow \mathbf{0}_{N_T \times 1}$

10: end for

11:

12: return  $\hat{\mathbf{s}}$

```

---

## 2.5 Successive Interference Cancellation

Linear detectors estimate the transmitted symbols by suppressing the interference on each of the layers. The performance can be improved by successively carrying out the detection layer by layer and cancelling out the interference of the already determined substreams on the currently detected symbol at every iteration. The successive interference cancellation algorithm (SIC) begins with the following initialisations:

$$\begin{aligned} \mathbf{r}^{(1)} &= \mathbf{y} \\ \mathbf{W} &= \mathbf{H}^\dagger, \end{aligned} \tag{2.7}$$

where the superscript indicates the current iteration of the algorithm. With this initialisation, the SIC-aided detection iteratively computes the signal at the  $k$ th iteration as follows:

$$\mathbf{r}^{(k+1)} = \mathbf{r}^{(k)} - \mathbf{h}_k \hat{\mathbf{s}}_k, \tag{2.8}$$

where  $\hat{\mathbf{s}}_k$  is obtained by quantising the product of the  $k$ th column of  $\mathbf{W}$  and the received signal vector in the current iteration as follows:

$$\hat{\mathbf{s}}_k = \mathcal{Q}(\mathbf{w}_k^T \mathbf{r}_k), \tag{2.9}$$

where  $\mathbf{w}_k$  is the  $k$ th column of  $\mathbf{W}$  and  $\mathcal{Q}(\cdot)$  is the quantisation function, which rounds the soft estimate,  $\hat{\mathbf{s}}_k$ , to the nearest constellation point in  $\mathcal{S}$ . It should be noted that  $\mathbf{w}_k$  is derived by taking the pseudoinverse of a deflated version of the channel matrix,  $\mathbf{H}$ , obtained by setting the  $k$ th column of  $\mathbf{H}$  to zero. The MMSE criterion can also be used to compute the weighting vectors in (2.7) for improved performance.

Although SIC improves the performance of linear detectors, the error propagation from previously detected symbols affects the overall performance of the detection. Essentially,

if a symbol is erroneously detected in previous iterations, then this will affect the reliability of the subsequent detections. The SIC detection proposed by Wolniansky, Foschini, Golden, *et al.* [22] for the vertical Bell Laboratories layered space-time (V-BLAST) communication system mitigates this problem by carrying out the detection starting with the layer with the maximum post-detection SNR, which is defined as:

$$\rho_k = \frac{\langle |s_k|^2 \rangle}{\sigma_n^2 \|\mathbf{w}_k\|^2}. \quad (2.10)$$

Since the values for  $\langle |s_k|^2 \rangle$  are not known prior, the optimal detection ordering can simply be estimated by detecting the symbols according to the ascending order of  $\|\mathbf{w}_k\|^2$ . An ordered SIC-aided ZF detection is illustrated in Algorithm 1.

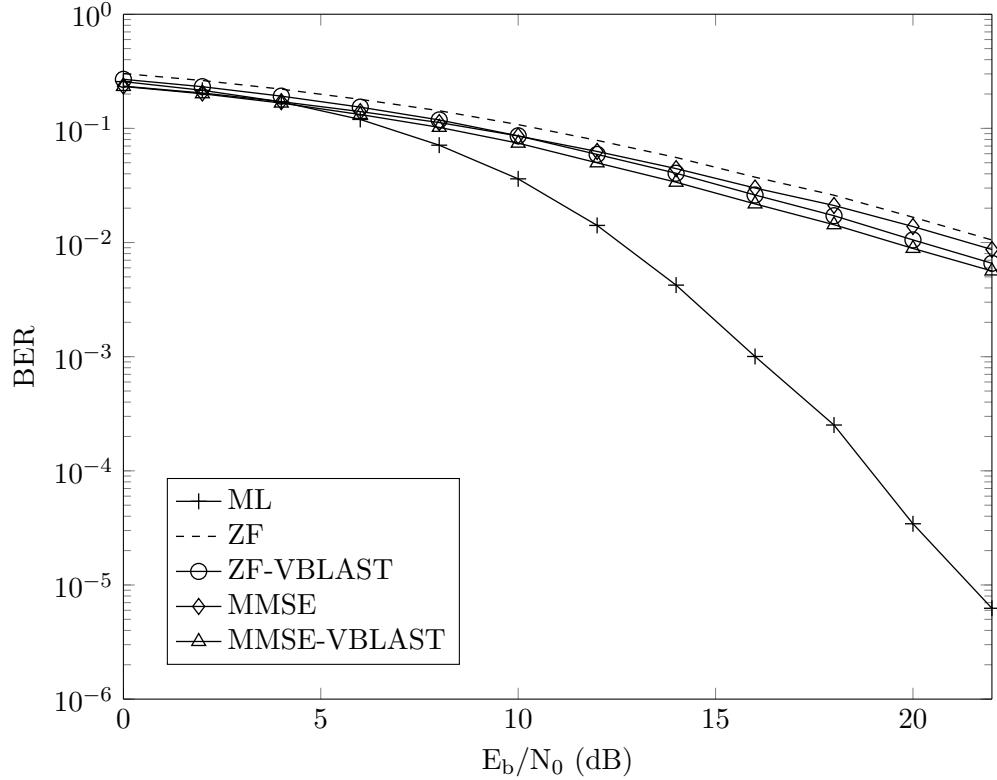

Figure 2.5 provide a comparison of the performances of linear detectors with the MLD. The BER plot is simulated for 16-QAM with  $N_T = 4$  based on 100, 000 randomly generated symbol vectors. The transmitter is assumed to employ spatial multiplexing in transmitting the symbol vectors over a Rayleigh fading channel. From the figure, it can be seen that the MMSE detector provides an improved performance compared to the ZF detector. Meanwhile, the use of V-BLAST ordering improves the BER in both cases. However, the performance still falls short of the diversity order delivered by the MLD. Another technique for improving the performance of linear detectors (as well as other sub-optimal algorithms) is lattice reduction, which is discussed in the next section.

## 2.6 Lattice Reduction

Although lattice reduction (LR) is originally applied in the field of linear algebra, it has also been successfully applied to MIMO detection [23]. If the matrix  $\mathbf{H}$  is considered to be a *basis* for the lattice  $\mathbf{H}\mathbf{s}$ , then lattice reduction techniques can be applied to make  $\mathbf{H}$  more orthogonal, which leads to better decision boundaries for the detection [24]. Linear detection techniques, as well as SIC-aided linear detectors, can then be applied to the reduced channel matrix to complete the detection.

The main operation of the LR-aided detector is to find a unimodular matrix,  $\mathbf{T}$  (i.e.  $\det(\mathbf{T}) = \pm 1$ ), such that  $\tilde{\mathbf{H}} = \mathbf{H}\mathbf{T}$  where  $\tilde{\mathbf{H}}$  spans the same lattice as  $\mathbf{H}$ . This transforms the channel equation as follows [24]:

$$\begin{aligned} \mathbf{y} &= (\mathbf{H}\mathbf{T})\mathbf{T}^{-1}\mathbf{s} + \mathbf{n} \\ \mathbf{y} &= (\tilde{\mathbf{H}}\mathbf{T}^{-1})\mathbf{s} + \mathbf{n}. \end{aligned}$$

The ZF (or MMSE) linear detection is then computed with respect to  $\tilde{\mathbf{H}}$ , rather than  $\mathbf{H}$ . After the output of the detector is quantised to the nearest constellation point, the detected symbol is computed as  $\hat{\mathbf{s}} = \mathbf{T}\hat{\mathbf{z}}$ , where  $\hat{\mathbf{z}} = \mathcal{Q}(\tilde{\mathbf{H}}^{-1}\mathbf{y})$ .

**Figure 2.5:** BER performance of ZF and MMSE detectors for 16-QAM and  $N_T = 4$

Unfortunately, the computation of  $\mathbf{T}$  for large matrix dimensions is NP hard, which results in a less than favourable detection complexity. Furthermore, the procedure is non-deterministic, which implies that different computation times will be required depending on the condition of the matrix. The most common method of finding the orthogonal matrix is using the Lenstra, Lenstra, Lovász (LLL) algorithm [25], which was originally formulated on real-valued lattices. This implies that a real-valued decomposition needs to be performed on the channel matrix [26]. A complex version of the LLL algorithm (CLLL) was proposed by Gan, Ling, and Mow [27], which implements the LLL algorithm on complex-valued lattices, which eliminates the need for an extra RVD step.

Like SIC, LR-aided detection has the attractive feature of having a complexity that is independent of the number of constellation points. Additionally, LR-aided detection is able to restore the full ML diversity order to the linear detectors [28]. However, LR has a variable complexity as the procedure is affected by the characteristics of the channel matrix which is random [29]. A particularly interesting result was by Shabany, Youssef, and Gulak [30], where a *fixed* complexity “hardware-optimized” CLLL (HOLLL) algorithm was realised. The implementation was able to achieve a fixed complexity by using a fixed number of iterations for its lattice reduction.

LR techniques can be used to improve the BER performance of the linear detectors and achieve ML diversity. However, the complexity is non-trivial, especially on larger matrix sizes [31]. The problem of a variable throughput has been resolved in [29] and [30] with

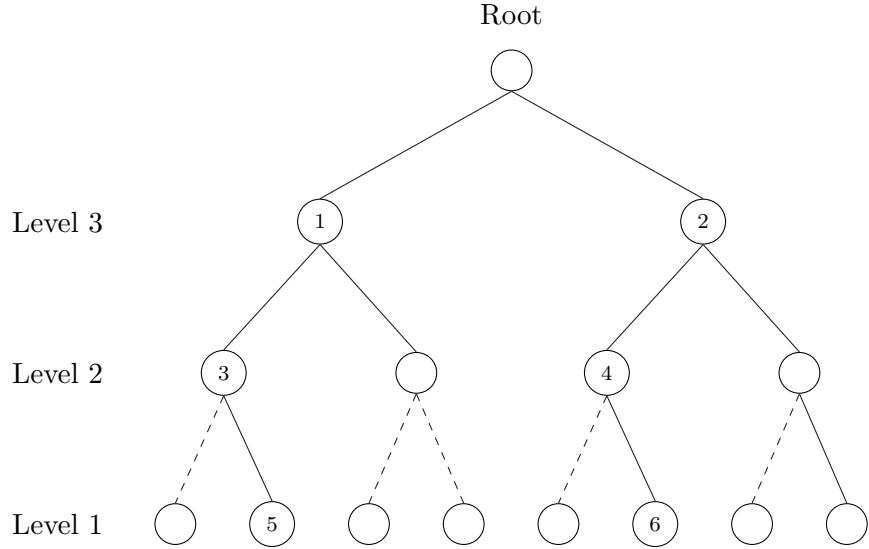

**Figure 2.6:** Depth first tree search for a MIMO system with  $N_T = 3$

some penalty to the BER performance. The sphere decoder is only slightly more complex than the LR-aided linear detector and achieves a better BER performance at a given SNR especially at lower order modulations [32]. A background on the sphere decoder and similar algorithms is provided in the next section.

## 2.7 Tree-Search Detection Algorithms

Tree search (TS) algorithms refer to a wide range of MIMO detection techniques that carry out the signal detection successively from one layer to another in a procedure somewhat similar to SIC-aided linear detection. Like the ML detector, TS algorithms are search-based methods that apply a branch-and-bound operation [33] to every candidate solution by keeping or discarding it depending on certain criteria. Unlike the ML detector, however, only a subset of the candidates is considered which allows performance-complexity trade-offs to be achieved. In the next sections, some well-known TS algorithms and notable VLSI implementations from the literature are discussed.

### 2.7.1 Sphere Decoding

The channel equation presented in (2.1) can be simplified by carrying out a QR decomposition<sup>4</sup> on the channel matrix to transform the channel equation (2.1) as follows:

$$\begin{aligned} \mathbf{y} &= \mathbf{QRs} + \mathbf{n}, \\ \mathbf{Q}^H \mathbf{y} &= \mathbf{Rs} + \mathbf{Q}^H \mathbf{n}, \end{aligned} \quad (2.11)$$

where  $\mathbf{Q}$  is an  $N_T \times N_T$  unitary matrix and  $\mathbf{R}$  is an  $N_R \times N_T$  triangular matrix. Due to the unitary nature of  $\mathbf{Q}$  (i.e.  $\mathbf{Q}^H \mathbf{Q} = \mathbf{I}$ ), the norm, and consequently the statistics of  $\mathbf{n}$ , is unchanged by multiplication with  $\mathbf{Q}^H$  and thus (2.11) can be rewritten as:

$$\mathbf{Q}^H \mathbf{y} = \mathbf{Rs} + \mathbf{n}. \quad (2.12)$$

For simplicity,  $\mathbf{Q}^H \mathbf{y}$  shall be denoted by  $\hat{\mathbf{y}}$ , and will refer to the “received signal vector” in subsequent discussions.

The triangular property of  $\mathbf{R}$  has interesting implications for the signal detection as only one symbol needs to be detected in each layer, while removing the interferences from previously detected symbols, unlike the ML detector where an  $N_T \times 1$  symbol vector is considered at a time. This results in an  $M$ -ary tree with  $N_T$  levels as shown in Fig. 2.6. The sphere decoder (SD) invented by Viterbo and Boutros [12] carries out a depth-first search (DFS), where the detection proceeds from level  $N_T$ , corresponding with the channel entry  $r_{N_T, N_T}$ , down to level 1 corresponding with  $r_{1,1}$ . At the top level, the detector selects a symbol from the QAM constellation points and proceeds iteratively down the tree until the cumulative metric of the selected path violates a pre-determined constraint. With respect to the ML lattice search, the SD only considers those lattice points that lie within a given radius from the filtered received signal,  $\hat{\mathbf{y}}$ , as shown in Fig. 2.7. This can be expressed mathematically as:

$$d(\mathbf{s}) = \|\hat{\mathbf{y}} - \mathbf{Rs}\|^2 < r^2, \quad (2.13)$$

where  $d(\mathbf{s})$  represents the Euclidean distance between the symbol vector,  $\mathbf{s}$ , and  $\hat{\mathbf{y}}$ . The radius constraint can be computed using a simple linear detector such as zero-forcing or as a measure of the noise variance [35]. In the next sections, we will present some important concepts and equations related to the sphere decoder.

<sup>4</sup>A Cholesky decomposition which decomposes the channel matrix into the product of an upper triangular matrix and its complex conjugate (i.e.  $\mathbf{H}^* \mathbf{H} = \mathbf{U}^* \mathbf{U}$ ) has also been applied to the SD [18]. However, the QR decomposition is attractive for hardware implementation as it can easily be realised using CORDIC rotations, which replace many complex arithmetic functions with shifts and additions [34]. A number of QR decomposition methods have been provided in Appendix A.

**Figure 2.7:** Modified lattice search using the sphere decoding algorithm. Only the lattice points that fall within the radius are considered in the search.

### 2.7.1.1 Complexity of the Sphere Decoder

The complexity of the SD is directly related to the number of nodes that are visited to arrive at a solution, which determines the number of times the Euclidean distance operation is invoked. Unlike the ML and ZF/MMSE detectors, it is difficult to derive a closed-form expression for the number of visited nodes, since the SD algorithm is highly recursive and has different termination times depending on the channel condition. Since the SD is essentially a reduced-complexity ML algorithm, we can assume there exists a number  $\gamma \in (0, 1]$ , which reduces the problem size of the SD compared to the ML detector, such that the complexity of the SD can be expressed as follows [36]:

$$C(N_T) = |\mathcal{S}|^{\gamma N_T},$$

where the value of  $\gamma$  is a function of the statistics of the channel matrix and the noise variance.

In the worst case, the SD can be expected to approach the exponential complexity of the MLD, while in high SNR, and for a small number of antennas, the SD exhibits a low complexity, which competes favourably with polynomial-time algorithms [36]. This result implies that at low SNR, the lattice points are more closely clustered around the received signal, than at high SNR, necessitating a much larger radius to ensure that a solution is found. Fig. 2.8 shows the number of visited nodes for the SD for different antenna sizes.

### 2.7.1.2 Partial Euclidean Distance Computation

The sequential nature of the depth-first search ensures that the Euclidean distance (2.13) cannot be calculated at once, instead, it must be computed incrementally as the detector progresses deeper into the tree. The Euclidean distance up to any level in the tree is thus known as the partial Euclidean distance (PED). By traversing the tree from level

**Figure 2.8:** Number of visited nodes for the SD versus SNR using 16-QAM

$i = N_T$  to  $i = 1$ , the PED  $T_i$ , up to the  $i_{th}$  level is given as

$$T_i = T_{i+1} + |e_i|^2, \quad (2.14)$$

where  $|e_i|^2$  is the PED increment at the  $i_{th}$  level and is given by

$$|e_i|^2 = |b_i - r_{i,i}s_i|^2, \quad (2.15)$$

where  $s_i$  represents a symbol at the  $i_{th}$  level and  $b_i$  is defined as

$$b_i = \hat{y}_i - \sum_{j=i+1}^{N_T} r_{i,j}s_j. \quad (2.16)$$

The summation term in (2.16) represents the interference of previously detected symbols which needs to be cancelled out from the currently detected symbol.

### 2.7.1.3 Real-valued Channel Decomposition

The original sphere decoder works on the basis of a complex constellation set and complex channel matrix. The channel equation described in (2.1) can also be decomposed

into the real and imaginary parts of the respective variables as follows [37]:

$$\begin{bmatrix} \Re\{\mathbf{y}\} \\ \Im\{\mathbf{y}\} \end{bmatrix} = \begin{bmatrix} \Re\{\mathbf{H}\} & -\Im\{\mathbf{H}\} \\ \Im\{\mathbf{H}\} & \Re\{\mathbf{H}\} \end{bmatrix} \begin{bmatrix} \Re\{\mathbf{s}\} \\ \Im\{\mathbf{s}\} \end{bmatrix} + \begin{bmatrix} \Re\{\mathbf{n}\} \\ \Im\{\mathbf{n}\} \end{bmatrix}, \quad (2.17)$$

where  $\Re\{\cdot\}$  and  $\Im\{\cdot\}$  denote the real and imaginary parts of a complex number respectively. This results in an equivalent tree with twice as many levels as the tree search based on the original complex-valued channel equation. Furthermore, the number of children per parent is reduced from  $M$  to  $\sqrt{M}$  resulting in a new constellation set of odd-valued integer symbols,  $\mathcal{D}$ , which is defined as:  $\{-\sqrt{M} + 1, \dots, \sqrt{M} - 1\}$ . It should be noted that as a result of the doubling of the tree depth, the summation in (2.16) now needs to be carried out up to  $j = 2N_T$ .

The conversion of the channel equation to a real model results in an attractive hardware implementation as it is generally easier to compute on real numbers than on complex numbers. The critical path of the multiplication in (2.16) is reduced from one real multiplier and adder in series to one real multiplier only, which results in a faster processing per node. However, the overall throughput of the real-valued detector suffers as a result of the longer time required to reach the leaf nodes.

#### 2.7.1.4 Orthogonal Real-valued Decomposition

In the previous section, a real-valued decomposition of the channel equation was presented, which generates an equivalent tree detection to the complex channel model, but which allows for a simpler hardware realisation. A different real-valued channel decomposition was proposed by Azzam and Ayanoglu [38], where the complex channel matrix is decomposed as follows:

$$\tilde{\mathbf{H}} = \begin{bmatrix} \Re\{h_{1,1}\} & -\Im\{h_{1,1}\} & \dots & \Re\{h_{1,N_T}\} & -\Im\{h_{1,N_T}\} \\ \Im\{h_{1,1}\} & \Re\{h_{1,1}\} & \dots & \Im\{h_{1,N_T}\} & \Re\{h_{1,N_T}\} \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ \Re\{h_{N_T,1}\} & -\Im\{h_{N_T,1}\} & \dots & \Re\{h_{N_T,N_T}\} & -\Im\{h_{N_T,N_T}\} \\ \Im\{h_{N_T,1}\} & \Re\{h_{N_T,1}\} & \dots & \Im\{h_{N_T,N_T}\} & \Re\{h_{N_T,N_T}\} \end{bmatrix}. \quad (2.18)$$

This new channel representation has the property that adjacent columns (i.e.  $\tilde{\mathbf{h}}_n$  and  $\tilde{\mathbf{h}}_{n+1}$ ) are orthogonal to each other, that is,  $\tilde{\mathbf{h}}_n \cdot \tilde{\mathbf{h}}_{n+1}^T = 0$  for odd values of  $n$  (i.e.  $1, 3, \dots, 2N_T - 1$ ). It can also be shown that the QR decomposition of the modified channel matrix results in  $\tilde{r}_{i,i+1} = 0$  for all odd values of  $i$ . Thus, setting  $\tilde{r}_{i,i+1}s_{i+1} = 0$ ,

**Table 2.2:** Simplification of  $r_{i,i} \times s_i$  for 16-QAM [40]

| Computation           | Equivalent                  |

|-----------------------|-----------------------------|

| $r_{i,i} \times (+3)$ | $r_{i,i} + (r_{i,i} << 1)$  |