# A 40-Gb/s 4-V<sub>pp</sub> Differential Modulator Driver in 90 nm CMOS

Yan-Feng Li, Po-Wei Chiu, Ke Li, David J. Thomson, Graham T. Reed, and Shawn S. H. Hsu

Abstract— In this letter, a 40-Gb/s optical modulator driver in 90 nm CMOS technology is presented. The design is based on the distributed amplifier (DA) topology with the proposed modified cascode stage to obtain high gain and large bandwidth, while also capable of protecting the MOS transistor under large output voltage swing. The modified cascode stage distributed amplifier (MCDA) with enhanced high voltage driving capability can reach an operating data rate up to 40 Gb/s with an differential output voltage swing of 4  $V_{pp}$  (~ 3 V eye amplitude), which can be used for driving 50-Ω silicon modulators.

Index Terms—Modulator driver, distributed amplifier, cascode amplifier, silicon photonics.

# I. INTRODUCTION

THE exponential growth of data communications over various networks is expected to continue in the near future. The high speed fiber network plays an essential role in this roadmap. Compared with data transmission via the electrical wires, optical communication features the advantages of an improved bandwidth, smaller power consumption, reduced propagation delay, and immunity from electromagnetic interference [1]-[4].

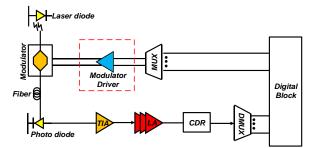

The optical modulator is essential for high speed fiber communication systems, because the direct modulation of laser has a limited bandwidth. Fig. 1 illustrates a typical optical communication system, where the modulator driver could be a bottleneck to limit the overall bandwidth for Electrical-to-Optical (E/O) signal conversion. One challenge for modulator driver design is the output voltage swing. The LiNbO<sub>3</sub> modulator typically requires a driving voltage up to 5-7 V, and the driver is normally based on the III-V technology to take the advantage of the higher breakdown voltage of transistors [4]. The CMOS compatible silicon modulator has attracted a significant attention recently, which can operate at a relatively lower voltage of 4-5 V. Also, the silicon modulator has been reported to achieve a bandwidth up to 50 Gb/s and beyond based on a Mach Zehnder interferometer (MZI) [5]. The reduced operating voltage makes it possible to realize the driving circuit in CMOS technology, which is also preferred for the silicon photonics platform. However, the breakdown voltage is still an issue in CMOS devices.

Manuscript received Aug. 21, 2017; accepted Nov. 08, 2017. This work was supported by the Ministry of Science and Technology (MOST), Taiwan, and Royal Society in the UK. Y.-F. Li, P.-W. Chiu, and S. S. H. Hsu are with the Department of Electrical Engineering, National Tsing Hua University, Hsinchu, Taiwan (e-mail: shhsu@ee.nthu.edu.tw). K. Li, D. J. Thomson, and G. T. Reed are with the Optoelectronics Research Centre, University of Southampton, UK.

Fig. 1. Block diagram of a typical optical communication system.

In this study, a 40-Gb/s  $4\text{-}V_{pp}$  differential modulator driver fabricated in 90-nm CMOS is demonstrated. The proposed modulator driver employs the distributed amplifier (DA) topology with the modified cascode stages to achieve a large output swing, whilst preventing transistor breakdown. In addition, the characteristics of high gain and large bandwidth can be obtained simultaneously.

## II. CIRCUIT DESIGN AND ANALYSIS

# A. Distributed Amplifier

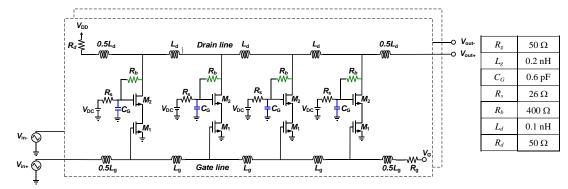

The distributed amplifier is a well-known and widely used topology for various applications. Based on the principle of transmission line (TML), the intrinsic parasitic capacitances of the active devices combine with the external inductive components to form the artificial TMLs, and a wide bandwidth can be obtained [6]-[9]. Fig. 2 shows the proposed DA in a differential configuration. Spiral inductors are used to form the gate and drain lines. The top metal layer with a thickness of 3 um is employed with the pattern ground for alleviated substrate effects and enhanced quality (O) factors. The cascode topology is used as the unit stage, which features higher input and output isolation, improved power gain, and increased output swing compared with the common-source (CS) stage. Note that the transistor sizes and stage numbers need to be design properly for wide bandwidth and high gain. A higher power gain can be achieved by selecting larger transistor sizes. However, this also requires the gate and drain lines to have increased inductance for maintaining the characteristic impedance of the line. The increased inductance will have a lower self-resonant frequency, which could ultimately limit the circuit bandwidth. In this design, the sizes of the cascode transistors are designed as 32 μm (CS) and 55 μm (common-gate, CG) with the four unit stages to achieve the desired bandwidth and gain. Also, both CS and CG transistors are the standard RF core device.

Fig. 2. Circuit topology of the proposed four modified cascode stage distributed amplifier (MCDA).

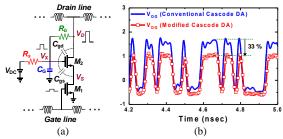

Fig. 3. (a) Modified cascode stage. (b) Comparison of voltage swing of conventional and modified cascode topologies.

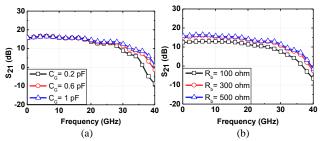

Fig. 4. Simulated  $S_{21}$  of the proposed DA as a function of (a)  $C_G$  (b)  $R_b$ .

# B. Modified Cascode Stage

As mentioned previously, the relatively low breakdown voltage of CMOS devices is the main limitation for the output swing of the modulator driver. The supply voltage suggested by the foundry for the adopted 90-nm RF CMOS is 1.2 V (maximum up to ~ 1.5 V) to avoid transistor breakdown and ensure long-term reliability. The cascode configuration is often used to enhance the output voltage swing [6]-[7]. However, the gate bias of the CG stage is fixed in a typical cascode gain cell, and hence the transistor could encounter the breakdown situation if a large swing appears at the drain node of the cascode cell. We propose the modified cascode configuration to resolve the problem as shown in Fig. 3(a), where a metalinsulator-metal (MIM) capacitor  $C_G$  is added between the gate of  $M_2$  and ground [10], and two resistors  $R_s$  and  $R_b$  are employed as feedback. As the circuit operates at relatively low frequencies (assuming the capacitances can be neglected), the voltage of  $V_X$  can be determined by the voltage divider of  $R_s$ and  $R_b$  as shown in (1), which allows  $V_X$  to swing with the drain voltage V<sub>D</sub> of M<sub>2</sub>. As a result, the difference of the drain-gate voltage reduces to prevent  $M_2$  breakdown. Similarly,  $V_X$  swings simultaneously with the AC signal at high frequencies because the capacitances including  $C_{\rm G}$ , and the parasitic capacitances  $C_{\rm gs}$  and  $C_{\rm gd}$  start to play important roles. Based on small-signal analysis,  $V_X$  can be obtained using (2) at high frequencies

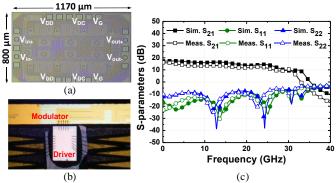

Fig. 5. (a) Chip micrograph of the proposed DA with modified cascode stage. (b) Photo of DA and silicon modulator connected by bond wires. (c) Comparison of measured and simulated S-parameters of the modulator driver.

$$V_{\rm X} = V_D \frac{R_s}{R + R} \tag{1}$$

$$V_{X} = V_{D} \frac{R_{s}}{R_{b} + R_{s}}$$

$$V_{X} = V_{D} \frac{Z_{G}Z_{gs}}{Z_{b}Z_{gs} + Z_{G}Z_{gs} + Z_{G}Z_{b}} + V_{S} \frac{Z_{b}Z_{G}}{Z_{b}Z_{gs} + Z_{G}Z_{gs} + Z_{G}Z_{b}}$$

(2)

where  $Z_G = R_s //C_G$ ,  $Z_b = R_b //C_{gd}$ ,  $Z_{gs} = 1/j \omega C_{gs}$ , and  $V_S$  is the source voltage of M2. The calculated results of (1) and (2) agree very well with the small-signal model simulation based on the actual circuit parameters.

As shown in Fig. 3(b), the simulated results indicate that the drain-gate voltage V<sub>DG</sub> of M<sub>2</sub> can be reduced by 33% compared with the conventional cascode stage for the same output swing of 2 V. However, the additional RC components may also degrade the bandwidth, and need to be designed carefully. Fig. 4(a) and 4(b) show how the bandwidth and gain vary with  $C_G$ and R<sub>b</sub>, respectively. Tradeoffs exist between gain bandwidth and transistors protection capability. For example, increasing  $C_{\rm G}$  can enhance the bandwidth. However, the voltage at the gate will not vary with the drain voltage if  $C_G$  becomes too large, and the transistor becomes vulnerable. In practical design,  $C_{\rm G}$ is chosen to limit the maximum  $V_{DG}$  of  $M_2$  at around 1 V. As mentioned, the suggested  $V_{\rm DD}$  is 1.2 V. With a typical gate bias of about 0.5 V, V<sub>DG</sub> is only 0.7 V. Considering the signal swing of transistor, a 1-V limit should be reasonable for proper operation of the proposed circuit. In contrast, decreasing  $R_b$  can reduce the drain-gate voltage of M<sub>2</sub> to prevent transistors from breakdown but at the expense of lowered gain and degraded output matching. The values of circuit parameters in our final design are shown in Fig. 2.

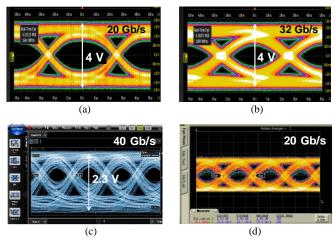

Fig. 6. Measured eye diagrams (a) 20 Gb/s (b) 32 Gb/s of differential output. (c) 40 Gb/s single-ended output. (d) Optical eye diagram at 20 Gb/s.

### III. RESULTS AND DISCUSSION

### A. Small-Signal Measurements

The proposed modulator driver using modified cascode stage distributed amplifier (MCDA) was implemented in the 90-nm CMOS. The micrograph of the chip and the chip connected to the silicon modulator by bond wires are shown in Fig. 5(a) and 5(b), respectively. The differential S-parameters were measured by the 4-port Keysight N5247A network analyzer, as shown in Fig. 5(c) (only 2-port results are shown due to symmetry). The circuit was biased at  $V_{\rm DD} = 5$  V,  $V_{\rm DC} = 1.8$  V, and  $V_{\rm G} = 0.5$  V (see Fig. 2) with a total power consumption of 650 mW. Note that most of the  $V_{\rm DD}$  voltage drops on  $R_{\rm d}$  (3.25 V), and the actual DC voltages at the drain nodes of  $M_2$  and  $M_1$  are only 1.75 V and 1.46 V, respectively. The driver achieves a high power gain of 17 dB and a 3-dB bandwidth of 28.2 GHz. The input and output reflection coefficients of the modulator driver remain below -10 dB within the bandwidth.

# B. Large-Signal Measurements

The large-signal measurements were performed using the Keysight N4974A pattern generator and the Keysight DSOZ504A Infiniium real time oscilloscope. Note that the differential eye diagram was measured only up to 32 Gb/s limited by the equipment. We also manage to obtain the singleended eye diagrams up to 40 Gb/s by the Anritsu MP1800A signal quality analyzer and the Keysight 86100D oscilloscope. Fig. 6(a) and 6(b) show the measured electrical eye diagrams of the modulator driver with differential output at 20 Gb/s and 32 Gb/s, respectively. Fig. 6(c) shows the measured single-ended eye at 40 Gb/s. The measured differential voltage swing can reach up to 4 V<sub>pp</sub> (about 3 V eye amplitude), whereas that for the single-ended eye can reach  $2.3 V_{pp}$  including the cable loss. Note that the achieved eye amplitude is still sufficient for the recently reported high speed silicon modulators with a reduced operating voltage [11]. Fig. 6(d) shows the measured optical eye diagram up to 20 Gb/s. The reduced speed can be mainly attributed to the loss and impedance mismatch introduced by the bond wires at the OE interface. Table I shows the comparison with previous works. Compared with [1] using 45 nm SOI CMOS, the proposed circuit based on the DA topology

has the advantage of a relatively flat gain over a wide bandwidth. Also, a high gain is achieved by a low cost 90 nm CMOS technology. On the other hand, the design in [1] using a single-stage stacked topology demonstrated a large output swing with a much smaller chip area and lower power consumption.

### IV. CONCLUSION

The modulator driver proposed in this study demonstrated high gain, large bandwidth, and excellent driving capability. With the proposed modified cascode stage in the distributed amplifier topology (MCDA), the common-gate transistor in the cascode stage can be protected from damage under a large output swing. The operating frequency reached up to 40 Gb/s, and an output differential swing can reach 4  $V_{pp}$  with an about 3 V eye amplitude.

TABLE I

COMPARISON OF PUBLISHED MODULATOR DRIVERS

| Ref.                    | This<br>work | [1]                 | [2]          | [3]            | [4]        |

|-------------------------|--------------|---------------------|--------------|----------------|------------|

| Technology              | 90nm<br>CMOS | 45nm<br>CMOS<br>SOI | 65nm<br>CMOS | 0.13µm<br>CMOS | InP<br>HBT |

| Data rate (Gb/s)        | 40           | 40                  | 25           | 20             | 40         |

| Gain (dB)               | 17           | 7.6                 | -            | -              | > 20       |

| BW (GHz)                | 28.2         | 33                  | -            | -              | 45         |

| Out. swing (V)          | 4*/3+        | 4.5*                | 3.3*         | 3.5*           | 2.4#       |

| Power (mW)              | 650          | 437                 | 480          | 900            | 1800       |

| Area (mm <sup>2</sup> ) | 0.936        | 0.38                | 0.029        | 0.72           | 2.81       |

\*Single-ended signal; \*differential signal; +eye amplitude.

### REFERENCES

- [1] J. Kim and J. F. Buckwalter, "A 40-Gb/s optical transceiver front-end in 45 nm SOI CMOS," *IEEE J. Solid-State Circuits*, vol.47, no. 3, pp. 615–626, March 2012.

- [2] S. Nakano et al., "A 25-Gb/s 480-mW CMOS modulator driver using area-efficient 3D inductor peaking," Proc. IEEE Asian Solid-State Circuits Conf., 2015, pp. 1–4.

- [3] M. S. Kao, F. T. Chen, Y.-H. Hsu, and J.-M. Wu, "20-Gb/s CMOS EA/MZ modulator driver with intrinsic parasitic feedback network," *IEEE Trans.* VLSI, vol. 22, no. 3, pp. 475–483, March 2014.

- [4] V. Radisic et al., "40 Gb/s differential traveling wave modulator driver," IEEE Microw. Wireless Compon. Lett., vol. 13, no. 8, pp. 332–334, Aug. 2003.

- [5] D. J. Thomson et al., "50-Gb/s silicon optical modulator," IEEE Photonics Tech. Lett., vol. 24, no. 4, pp. 234–236, Feb. 15, 2012.

- [6] C. Y. Hsiao, T. Y. Su, and S. S. H. Hsu, "CMOS distributed amplifiers using gate-drain transformer feedback technique," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 8, pp. 2901–2910, Aug. 2013.

- [7] K. Schneider et al., "Comparison of InP/InGaAs DHBT distributed amplifiers as modulator drivers for 80-Gbit/s operation," *IEEE Trans. Microw. Theory Techn.*, vol. 53, no. 11, pp. 3378–3387, Nov. 2005.

- [8] C. Lee, L. C. Cho, and S. I. Liu, "A 0.1–25.5-GHz differential cascaded-distributed amplifier in 0.18-μm CMOS technology," *Proc. IEEE Asian Solid-State Circuits Conf.*, 2005, pp. 129–132.

- [9] C. Yuen et al., "50 GHz high output voltage distributed amplifiers for 40 Gb/s EO modulator driver application," *IEEE Intl. Microwave Symp. Digest*, 2002, pp. 481–484.

- [10] S. Pornpromlikit et al., "A watt-level stacked-FET linear power amplifier in silicon-on-insulator CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 58, no. 1, pp. 57–64, Jan. 2010.

- [11] C. Tseng et al., "A dual-drive PAM-4 Si Mach-Zehnder modulator for 50Gb/s data transmission at 1550nm wavelength," CLEO, SM2O.7, San Jose, May 2017.