IEEE TRANSACTIONS ON ELECTRON DEVICES

# Total Ionizing Dose Hardened and Mitigation Strategies in Deep Submicrometer CMOS and Beyond

Eleni Chatzikyriakou<sup>®</sup>, Katrina Morgan<sup>®</sup>, *Member, IEEE*, and C. H. Kees de Groot<sup>®</sup>, *Senior Member, IEEE*

Abstract—From man-made satellites and interplanetary missions to fusion power plants, electronic equipment that needs to withstand various forms of irradiation is an essential part of their operation. Examination of total ionizing dose (TID) effects in electronic equipment can provide a thorough means to predict their reliability in conditions where ionizing dose becomes a serious hazard. In this paper, we provide a historical overview of logic and memory technologies that made the biggest impact both in terms of their competitive characteristics and their intrinsically hardened nature against TID. Further to this, we also provide guidelines for hardened device designs and present the cases where hardened alternatives have been implemented and tested in the lab. The technologies that we examine range from silicon-on-insulator and FinFET to 2-D semiconductor transistors and resistive random access memory.

Index Terms—2-D semiconductor, carbon, CMOS, deep submicrometer, FinFET, graphene, MoS2, resistive random access memory (RRAM), silicon-on-insulator (SOI), thin film, total ionizing dose (TID), ultrathin buried oxide (UTBOX).

### I. INTRODUCTION

N a radiation harsh environment, complex mechanisms take place which contribute to disturbances in the normal operation of electron devices. In space, energetic protons and other nuclei from galactic cosmic rays as well as energetic electrons and protons in the Van Allen belts impinge on space-craft equipment at fluxes dependent on the mission journey followed [1]. Solar flares can induce coronal mass ejections with fluxes of electrons and ions that can reach the earth a few days after an event is initiated. Aviation electronics could also be subjected to terrestrial gamma-ray flushes, emanating from thunderstorms, and carrying gamma rays of energies up to tens of megaelectronvolt [2], [3].

Manuscript received November 17, 2017; revised January 2, 2018; accepted January 8, 2018. The review of this paper was arranged by Editor B. Kaczer. (Corresponding author: Eleni Chatzikyriakou.)

- E. Chatzikyriakou is with the Department of Solid State Physics, Aristotle University of Thessaloniki, 541 24 Thessaloniki, Greece (e-mail: elchatz@auth.gr).

- K. Morgan is with the Optoelectronics Research Centre, University of Southampton, Southampton SO17 1BJ, U.K.

- C. H. K. de Groot is with the Department of Electronics and Computer Science, University of Southampton, Southampton SO17 1BJ, U.K.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2018.2792305

In high-energy physics establishments such as particle accelerators and nuclear power plants, energetic particles used for their operation and their ionizing products gradually degrade electronic devices operating close to areas of increased exposure [4], [5]. Sensory equipment, robotic control and telemetry, and data acquisition electronics can all be affected in such harsh environments [6].

One characteristic of the radiation that reaches on-board and other shielded electronics is that it is different than that found in the environment as a result of secondary particle emission from adjacent materials and equipment, as well as radioactivity that may be intrinsic to the materials used for shielding and packaging or resulting from radiation interactions [7].

Total ionizing dose (TID) describes the process by which degradation is gradually induced in the electronic devices as a function of the total dose incident in the device and is usually used to make a distinction between the dose-dependent mechanisms in which the effects of the total dose are more pronounced when the irradiation is taking place under low dose rate (enhanced low dose rate sensitivity) [8].

Particle interactions that can ionize matter are the photoelectric effect, Compton scattering, electron-positron pair production, and Bremsstrahlung and inelastic collisions. Photons, electrons, positrons, protons, and other ions all participate in such processes whose sequence is defined by the energies of the aforementioned particles [7].

Electrical equipment that is to be used in a radiation-harsh environment should be thoroughly tested. Radiation hardening is an elaborate process that involves many different layers of testing before the products are finally available. Radiation hardening can be of different types and at different levels. Hardening by process is performed at the technology level and involves changing materials and fabrication processes to suite particular needs for harsh environments. Hardening by design involves changing the structure of the integrated circuits (ICs) in ways that can mitigate the effects of radiation [9]–[11]. As a result of the extra production steps, the final technologies and circuits used for radiation applications lag behind the ITRS map [12].

In this paper, we explore deep submicrometer and beyond-CMOS technologies, and especially those that have exhibited an intrinsic hardness to TID effects. This includes off-the-shelf commercial solutions as well as other technologies that are still under research as replacements for Si CMOS. Initially, in Section II, we list terminology of TID effects on device characteristics that will be presented further in the text. Section III focuses on silicon-on-insulator (SOI) technologies, the effect of shallow trench isolation (STI), and the response of ultrathin body (UTB) and buried oxide (BOX) FETs. In Section IV, TID response of FinFETs and multigate technologies is described, and in Section V, nanowire (NW) as well as 3-D stacking of fins and NWs is described separately. In Section VI, the novel effects that arise in thin film and 2-D semiconductor FETs are described in detail along with those in carbon nanotube FETs, and last, in Section VII, TID effects in resistive random access memory (RRAM) are discussed. This paper is not an exhaustive listing of all the technologies that have been examined for their TID response; however, we hope that the reader will gain a general overview of the mechanisms that take place during TID exposure as well as insights toward TID resistant technology designs.

### II. TID EFFECTS ON DEVICE CHARACTERISTICS

Ionizing radiation causes electron-hole pairs to be produced inside the electronic components. These free carriers, when trapped in preexisting trapping sites in CMOS devices, can significantly alter the characteristics of the latter, causing temporary, or permanent failures in ICs. The magnitude of the electron-hole pairs produced is a function of: 1) the type of incident radiation and 2) the electric field that exists in the material at the time of irradiation [13]. The most important characteristic of this mechanism is that mainly positive charges are aggregated inside the bulk of the material, as electrons can escape much faster. This is translated to the effects of TID being more important in n-channel transistors, where the charges take on the role of positive bias and induce threshold voltage shifts ( $\Delta V_{\text{th}}$ ) and leakage paths which depend on the device architecture and manifest as OFF-state current ( $I_{\text{off}}$ ). Mobility degradation is also observed under TID, both in n-channel and p-channel devices and results from scattering centers created at and close to the semiconductor/oxide interfaces (interface traps) in the oxide [14].

The final changes in device characteristics are, however, separated from the underlying mechanisms that take place, which depend on the structure and materials used. In the following, we use the term scaling to refer to the concerted effort to reduce the final IC size as well as its power consumption either through reducing the size of the components, or from examination of alternative, novel technologies.

### III. SILICON-ON-INSULATOR AND SHALLOW TRENCH ISOLATION

Historically, SOI technologies were introduced in submicrometer gate lengths around 150 nm and involve the separation of the active silicon volume by an oxide layer (the BOX) which provided multiple advantages that assured increased performance in line with scaling. Research on radiation hardness of SOI was sparked by the idea that a smaller active silicon volume would, contrary to bulk transistors, reduce

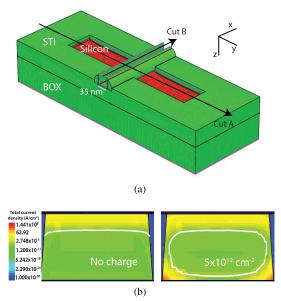

Fig. 1. (a) 3-D view of 45-nm PDSOI nMOSFET. (b) Cross section of the device along cut B in (a) showing the OFF-state leakage current formed in the bottom corners of the top silicon film for no oxide charge and effective areal oxide charge of  $5 \times 10^{12}$  cm<sup>-2</sup> in the field oxides (from [17]).

charge collection from traversing ions that cause single event effects. However, it was shown that in practice SOI transistor ICs were also susceptible to charged particle effects [15]. More recent scaled bulk devices have shown significant improvement in the effects caused by heavy ions, such as soft error rates in memory components, and especially some SOI technologies like the 28-nm FDSOI have achieved major improvement (up to 110×) compared to their bulk counterpart [16].

However, in terms of the TID hardness, the inclusion of the BOX increases the volume for charge trapping caused by ionizing radiation. Field oxides have in fact become the focus of all studies when, in order to satisfy scaling demands, thinning of the SiO<sub>2</sub> gate oxide increased quantum mechanical tunnelling of trapped charge. Thicker gate insulators of materials with a high dielectric constant (high-k) were introduced when SiO<sub>2</sub> had to be thinned down to dimensions that allowed electrons to tunnel through. But even in these cases, charge trapping in gate insulation was not a problem to their TID response [18]. Charges aggregated in the field oxides, namely, the intradevice isolation regions such as the BOX and the interdevice isolation such as the STI, induce drain-to-source  $I_{\text{off}}$ . In bulk transistors, the charges gathered at the STI contribute further to interdevice leakage current from n+ source/drain or n-well regions of adjacent transistors in a CMOS circuit [19].

TID hardness exhibited an increase with device scaling for specific SOI technologies until the 32-nm nodes [20]. Among the most notable commercial submicrometer transistor technologies to show an intrinsically hardened nature to TID were partially depleted SOI (PDSOI) MOSFETs, and especially at the 45-nm node and beyond [21]–[23]. A schematic of 45-nm PDSOI MOSFET is shown in Fig. 1(a). The positive charges that are gathered at the STI and BOX create what was initially termed a "back-gate" parasitic transistor [19].

Finite-elements method (FEM) simulations have revealed that the charges are mainly trapped at the bottom corner of

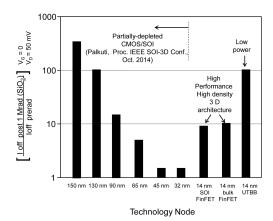

Fig. 2. TID hardness trend for commercial transistor technology nodes for irradiation at 1 MRad (SiO<sub>2</sub>). Reprinted with permission from [26]. Copyright 2015, IEEE.

the STI, adjacent to the BOX, and this creates leakage paths at the bottom silicon corners, as shown in Fig. 1(b) [24], [25]. However, further examination shows that the high body doping used in this device makes it immune to the formation of a leakage path up to very high total doses, and furthermore, that there exists a threshold above which no further charges are being trapped due to an equivalent positive charge density aggregating at the bottom of the BOX [17]. This reveals that, rounding the bottom STI/silicon corner can further increase the radiation hardness of the device as this would reduce the intensity of the electric field and prevent the creation of the corner leakage paths.

In fully depleted SOI, positive charge in the BOX can induce many complex mechanisms, such as coupling of the front with the parasitic transistor [27] and a total dose latch phenomenon [28]. This situation can be mitigated with the use of a back contact, or body doping schemes, which, however, increase device complexity.

The overall increased TID hardness of commercial transistor technologies down to the 32-nm nodes is reflected in Fig. 2 which shows the pre- to post- $I_{\rm off}$  percentage at 1 MRad (SiO<sub>2</sub>) as a function of transistor scaling [26]. The increased TID hardness trend stops after 32-nm technologies, where overcoming scaling issues creates a rich landscape of alternatives.

Another issue that arises in planar transistors at 50 nm and beyond is statistical variability from sources such as random dopant fluctuations (RDF), which can reach up to 50% of total variability [29]. Therefore, FDSOI transistors that include a doped silicon body to mitigate latch phenomena are susceptible to RDF. At the same time, the TID hardness of 45-nm PDSOI MOSFETs is reduced when RDF effects are taken into account, which could be a problem for some lower levels of doping [17].

Beyond 32-nm ultrathin BOX (UTBOX) devices for lower power applications were introduced. These devices feature a BOX of 25 nm down to a few nanometer that, when combined with UTB, results in very good electrostatic control of the gate and reduced variability originating from RDF effects [32]–[36]. UTB and BOX (UTBB) device performance is enhanced compared to extremely thin SOI (ETSOI) [37],

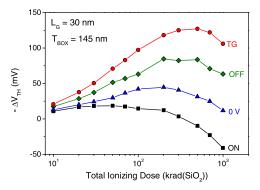

Fig. 3. Front gate  $\Delta V_{\text{th}}$  as a function of TID for an ETSOI device with  $L_g=30\,$  nm and BOX thickness of 145 nm, under different bias conditions. Reprinted with permission from [31]. Copyright 2013, IEEE.

both in terms of short channel effect control and S/D coupling due to the use of the thin BOX, and especially when combined with a ground plane doping scheme [38].

ETSOI device performance after TID exposure exhibits similar characteristics with that of FDSOI, namely, the electrostatic coupling between the front and back parasitic channels is the dominant effect. The front gate threshold voltage shift  $(\Delta V_{th\_front})$  in devices with BOX thickness,  $T_{BOX} = 145$  nm and Si film thickness,  $T_{Si} = 8$  nm, has shown a bias dependence during irradiation with transmission gate being the worst bias condition due to the distribution of the electric field lines in the BOX [30], [31].  $\Delta V_{\text{th front}}$  as a function of total dose for different bias conditions is shown in Fig. 3. In this case, the reduction in  $\Delta V_{\text{th\_front}}$  has been attributed to counterbalancing negative interface trap buildup at the interface of the silicon film with the gate and BOX. Throughout this paper, we examine cases where this characteristic can or has been used to increase the radiation hardness of different technologies.

UTBB transistors do not show a bias dependence on their TID characteristics as there is not enough space in the thin BOX for the electric field lines to assume varying directions. In these devices, although the leakage current is reduced, strong coupling between front and back transistors is induced, equivalent to ETSOI and FDSOI in general, and therefore there is no advantage in their use, while GP doping schemes do not alter the response significantly [30], [31].

The only exception to the previous rule is the case of  $T_{\rm BOX}=11$  nm that showed no significant  $\Delta V_{\rm th}$  up until 200 kRad(SiO<sub>2</sub>). This, combined with the information induced from Fig. 3, could mean that UTBB devices with very small BOX thickness, that may include passivated negative interface traps, could provide interesting postirradiation characteristics. Therefore, alumina BOX and composite SiO<sub>2</sub>/alumina UTBOX transistors such as those reported in [36] (Fig. 4) are very interesting for examination.

UTBOX configuration is also advantageous for the creation of low-power one-transistor DRAMs. Thus, floating body RAMs with UTBOX have been investigated for their TID response, and showed that exposure to TID reduces both the read window and the retention time [39]. Reduction of the memory window in the n-channel UTBOX MOSFETs is

Fig. 4. UTBB SOI architectures with  $Al_2O_3$  and composite BOX as reported in [36].

caused by the threshold voltage shifts of the front and back gate transistors and retention time is reduced when leakage current is induced in the device. The worst irradiation bias was found to be the HOLD DATA, with both the front and back gates biased at 1 V. This produced the highest shift in the memory window. However, it was also revealed that the back gate bias could be used to alleviate the effects of the irradiation by using a lower voltage. Due to the inherent operation of the device, decreasing the back-gate bias also increases retention time, and is therefore a useful way of reducing the TID effect on the final characteristics.

### IV. FINFETS AND OTHER MULTIGATE ARCHITECTURES

Multigate devices provided the answer to variability-induced problems in planar submicrometer transistors [40], [41] and were mainly introduced by manufacturers at 22-nm nodes and beyond. The FinFET has been established as the workhorse of the semiconductor industry for high performance down to 10-nm nodes [12]. Notably, the commercial 22-nm bulk tri-gate technology shows increased immunity against many reliability effects, including bias-temperature instability and stress-induced leakage current [41].

The TID response of multigate devices is slightly more complex than that of planar, as more factors come into play. Thorough reviews are provided in [42] and [43]. Here, we stress on the role that the distribution of trapped charge in the field oxide plays for the emergence of this complexity.

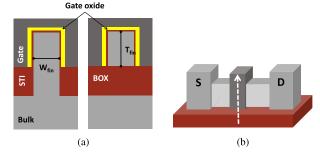

Fig. 5 shows a simplified schematic of bulk and SOI FinFETs with the directions that the width and thickness are measured. The introduction of multiple gates creates an environment where the control of the electrostatic potential induced in the fin and the isolation regions from the lateral gates largely defines the TID response of the whole device. Therefore, wide-fin devices have shown reduced hardness when compared to narrower fin SOI devices [44], [45]. By contrast, in bulk FinFETs, the opposite is true where wide fins increase the TID hardness [46]. Using FEM simulations, the latter has been shown to be due to the proximity of the STI sidewall closer to the middle of the fin, where it increases the electrostatic potential, thus increasing the effective width of the parasitic-channel transistor. Accordingly, the BOX introduced in SOI technologies defines the final characteristics of the parasitic channel formed adjacent to it. By reducing the width of the fin, the lateral gates move closer and the electric field lines inside the BOX are distorted so as the majority of the holes move away from the Si/BOX interface, thus protecting the back-channel region [47].

In terms of channel length, longer fins in bulk devices are also less susceptible to TID because the density of the charge

Fig. 5. Simplified (a) 2-D and (b) 3-D views of bulk and SOI FinFET structures. The width and thickness are measured perpendicularly to the gate length axis. The shape of the fin can vary significantly.

Fig. 6. (a) 3-D structure of 22-nm FinFET structure. (b) Trapped charge concentration in the STI with bulk donor trap density of  $8.2 \times 10^{17}$  cm<sup>-3</sup> (from [50]).

trapped does not depend on the channel length. As such, the electrostatic force experienced by the electrons in the leakage path is more intense with short-channel lengths [46]. In SOI FinFETs, the electrostatic potential of the gate reduces when the gate length decreases, and therefore charges trapped in the BOX dominate the TID response. Therefore, for gate lengths less than 40 nm, it is advised to use an SOI structure that gives more control over the channel, such as the gate-all-around (GAA) described in Section V [43].

The bias during irradiation influences the distribution of the charges in the isolation regions, with ON bias conditions for SOI nFinFETs inducing more pronounced TID effects due to the holes being trapped higher in the BOX, and closer to the active silicon region [48]. In four-gate 90-nm bulk FinFETs, the OFF state ( $V_D = 0.7 \text{ V}$ ) has been shown to be the worst bias condition for irradiation due to a higher electric field present at the STI corner compared to the rest of the bias conditions examined [49]. The TID response, however, also depends on the doping distribution in the neck region of the fin. In Fig. 6, the distribution of trapped charge in the STI is shown in a 22-nm bulk FinFET in the ALL-0 bias regime. This distribution is solely defined by the doping concentration in the silicon [50]. When the majority of the trapped charge is located deeper in the STI from the surface the path length of the electrons in the parasitic channel increases compared to when it is located at the vicinity of the S/D regions.

Fig. 7. Types of NWFET architectures. (a) GAA NW FET on bulk substrate. The 2-D cut is taken in the direction shown below. (b) 3-D view of NW FET that includes stacking tiers of NWs. (c) 2-D cut of stacked NWs in a 3-D architecture. The first NW is placed on top of the SOI. Subsequent tiers are fabricated in a GAA design [57].

At last, the type of architecture ( $\Pi$ -gate,  $\Omega$ -gate, and trigate) has also been shown to influence TID response, with increased "wrapping" around the channel providing higher immunity to TID [47].

### V. Nanowires and 3-D Stacking

NW FETs are extremely scaled FinFETs [51], [52]. In this case, the channel is fabricated either on an SOI substrate, or free standing by isotropic etching followed by deposition of the gate dielectric and the metal gate [Fig. 7(a)] [53]. In the latter case, the device is called GAA FET. Another option is to grow the NWs vertically using, for example, conformal chemical vapor deposition [54], dry etching with reduced oxidation techniques [55], or ion beam etching and the spacer etch technique presented in [56].

Stacking the NWs in tiers is also an efficient method of device integration, fully 3-D in nature [52]. NWs are stacked on top of each other with each channel being wrapped by a gate oxide stack and the gate. The first tier in this case could be implemented as in SOI architectures.

For NWs that are fabricated on SOI substrates, the width of the latter can affect the TID response of the device. In fact, threshold voltage shifts and subthreshold slope degradation have been observed in 30-nm gate-length nNWFETs, which was attributed to field oxide and interface trapped charges, respectively [57]. Furthermore, with FEM simulations, Gaillardin et al. [57] showed that the major influence in the leakage path formation originated from the BOX, instead of the S/D capping layer oxides. In the same work, the effect of changes in the gate length of the NW in the TID response were also examined. Longer nNWFETs exhibited increased TID hardness compared to the shorter gate counterparts. Overall, the geometric dependencies for these devices were similar to SOI multigate FinFET n-channel devices described earlier. It would be interesting to examine the response of stacked nNWFETs as having their channels wrapped completely by the gate, they could also prove hardened against TID effects.

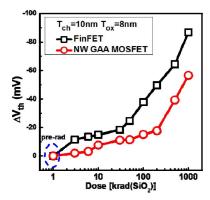

The scenery is different for GAA FETs. Originally, GAA FET architectures to be tested for their TID response featured thick gate isolation oxides, which aggregated trapped holes in bulk and border/interface traps [19]. The postrad device

Fig. 8.  $\Delta V_{\text{th}}$  of GAA NW FETs and FinFETs with 10- nm-thick NWs and fins respectively and  $t_{\text{OX}}=8$  nm. Reprinted with permission from [58]. Copyright 2015, IEEE.

characteristics were then dependent on the interplay of the trapping and annealing mechanisms of the latter [59], [60]. Modern GAA FETs, however, feature thin high-k/SiO2 gate stacks, which, combined with the complete "wrap" of the channel from the gate, eliminate the aforementioned problem, and making the GAA devices exceptionally hardened against TID (Fig. 8) [58], [61]. The devices in [58] feature 10- and 20-nm InGaAs NW channels with 8-nm Al<sub>2</sub>O<sub>3</sub> gate oxide. Using FEM simulations, it was shown that the electric field in the 20-nm NW FETs was stronger, which slightly aggravated the postirradiation device response. For thinner gate oxide thickness, high electric fields can also favor quantum mechanical tunnelling, and therefore reverse this situation. In the same study, the use of forming gas anneal has shown to increase radiation hardness by increasing the quality of the Al<sub>2</sub>O<sub>3</sub>/InGaAs interface.

For all the technologies described so far, the role of the thick field oxides in the postirradiation response is dominant. Although for further scaled devices more factors come into play, field oxides still contribute significantly with competing effects for positive bulk oxide and negative interface charge buildup. Therefore, FEM simulations can elucidate the role played from each and aid during device design [62], [63].

## VI. THIN FILM, 2-D MATERIAL, AND NANOTUBE TRANSISTORS

The 2-D and 1-D channels have become increasingly attractive solutions for highly scaled electronic devices. These materials exhibit a range of interesting properties. The high mobility of graphene was found suitable for high-frequency FETs [64], while low stand-by power transistors have been exhibited with single-layer MoS<sub>2</sub> [65]. CNT FETs have also shown superior mobility and threshold voltage variability characteristics due to the lower atomic dislocations present in the channel. Single wall (SW) CNT (SWCNT) FETs exchibit ballistic transport that makes these devices better candidates for RF performance [66]–[68].

Due to their large surface to volume ratios, 2-D and 1-D semiconductors undergo doping mechanisms during both the fabrication process and irradiation which dominate the final

device characteristics. Such mechanisms are more pronounced in ambient conditions, due to the large percentage of potential doping species that exist [69]. Postirradiation, secondary electrons, and protons that are released through Compton scattering processes have the potential to induce defects [70]. As a result, to understand the TID response and implement any hardening solutions, we need to be able to discriminate between intrinsic effects taking place in the 2-D channel and extrinsic effects taking place in the rest of the device, such as the dielectric layers. This is done in different ways, both analytically from the extracted device characteristics [71] and with the help of supplementary measurements, such as Raman spectroscopy [70]. When materials such as graphene and carbon nanotubes are used for the fabrication of TFTs, their postirradiation response shares many common features with 2-D and 1-D channel transistors. Unless otherwise stated, all devices described next have a back-gated configuration, for which we use  $V_g$  to denote the gate bias. The gate dielectrics in this case separate the thin film or 2-D channel from the

In p-type network channel SWCNT TFTs with 100-nm  $SiO_2$  gate dielectric and 32/32 W/L ratio, negative  $\Delta V_{th}$  of the order of 1 V was observed when irradiated in vacuum with a back gate voltage of 2 V, and was attributed to holes created during irradiation, migrating toward the SiO<sub>2</sub>/SWCNT interface, increasing the electrostatic potential, and therefore requiring more negative voltages to turn the transistor on [69]. Further irradiation of the same transistors in air resulted in positive  $\Delta V_{\text{th}}$  approximately 37 times greater and increased channel conductance. Raman spectra and mobility measurements showed that atomic lattice defects of the film were not the main cause of the postrad shifts, but rather the interactions of these defects with O<sub>2</sub>, H<sub>2</sub>O, and water-oxygen redox couples that were weakly adsorbed at the surfaces of the nanotubes and other charge trapping sites at their vicinity and at the surface of the SiO<sub>2</sub>.

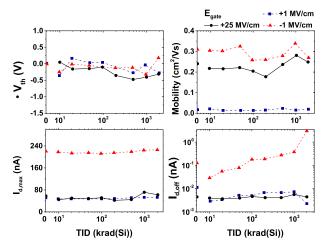

Similar results were obtained in another study for p-type SWCNT network TFTs irradiated in air [72], and furthermore revealed improved junction contact performance after irradiation. The density of the CNTs on the film also plays an important factor as higher density CNTs contribute to reduced adsorption mechanisms. N-type CNT TFTs of both array and network type were also examined in the same study, where the surfaces of the films were covered with Si<sub>3</sub>N<sub>4</sub>. Donors created in this insulating layer from the irradiation caused negative  $\Delta V_{\rm th}$ , but for network-type CNTs. The insulating layer also reduced the effect of irradiation, and therefore Zhao et al. [72] proposed covering the p-type devices with insulating layers that do not switch the polarity of the device, decreasing the thickness of the insulating layers to reduce the number of fixed charges introduced by them, and irradiating the device during fabrication to make the junctions saturated. Further to this, they exhibited TID-hardened logic inverters based on ambipolar TFTs by covering the p-type TFTs with Al<sub>2</sub>O<sub>3</sub>. SWCNT TFTs with a high degree of intrinsic TID hardness ( $\Delta V_{\text{th}} < 0.25 \text{ V}$ and no appreciable change in mobility and maximum drain current when irradiated in vacuum, as shown in Fig. 9) have been fabricated using a thin Si oxynitride gate dielectric, taking

Fig. 9. (a)  $\Delta V_{th}$  and changes in (b) mobility, (c) maximum drain current, and (d) OFF-state drain current of SWCNT TFTs with SiON gate dielectrics. Adapted with permission from [73].

advantage of the competing effect of holes trapped in the oxide and electrons at the interface to counterbalance the changes in the electric field [73]. This is the same mechanism that was described in Section III for hardened UTBB devices.

Mechanically exfoliated graphene ambipolar devices with 300-nm SiO<sub>2</sub> dielectrics exhibited increasing positive  $\Delta V_{th}$  with increasing dose when irradiated in air with 10 keV X-rays at  $V_g = -5$  V up to 300 kRad(SiO<sub>2</sub>) [74]. However, a dose greater than 1 MRad(SiO<sub>2</sub>) is required to induce  $\Delta V_{th}$  in suspended graphene sheet devices where the SiO<sub>2</sub> film has been removed. With the help of Raman spectra, the shifts in the device characteristics have been attributed to p-type doping effects from O<sub>2</sub> and H<sub>2</sub>O species that exist on the SiO<sub>2</sub> and in the ambient for the suspended devices. This can be further understood by the high formation energies that are required for displacement damage to take place in graphene [75].

On the contrary, when irradiated in vacuum, ambipolar graphene devices on 100-nm SiO2 exhibited negative  $\Delta V_{\text{th}}$  [76]. These devices, however, also included a trimethylsiloxy (TMS) monolayer between graphene and SiO<sub>2</sub> in order to stabilize the polarity of the electric field at the TMS/graphene interface and subsequently reduce gate hysteresis. This allowed Coulomb potential scattering mechanisms induced by the charges trapped at the SiO<sub>2</sub> dielectric to be examined. In another study, the memory window of nonvolatile FETs (NVFETs) with the graphene channel transferred onto 51 nm of lead-zirconate titanate (PZT), deposited on 100/10 nm Ti/Pt gate electrode and SiO<sub>2</sub>/Si substrate has shown to remain nearly stable after TID exposure up to 1 MRad(SiO<sub>2</sub>) [77] consistent with older studies on PZT thin film ferroelectric capacitors [78], [79] and polysiliconnitride-oxide-silicon nonvolatile memory transistors [80]. The PZT layer in this case introduced an antihysteretic behavior in the device whose response was dictated by trapping mechanisms at the interface with graphene that largely remained unaffected after TID exposure. CNT NVFETs, however, with similar counterclockwise hysteresis in their characteristics exhibited an increase in the memory window with increasing

total dose [81]. Generally, due to the sensitivity of graphene to dielectric and substrate charge accumulation effects, it is thought to be more appropriate for ionizing radiation sensor applications [70], although, a tunable TID response scheme has been proposed in [82] using hybrid organic-inorganic dielectrics of various thickness and composition, such as zirconia-based self-assembled nanodielectric. These schemes take advantage of the competing electron and hole charge accumulation to achieve stable device characteristics, much like the SWCNT TFTs with SiON dielectrics mentioned earlier.

In contrast to the increased contribution of Coulomb scattering mechanisms from oxide and interface trapped charges in graphene FETs, mobility in MoS<sub>2</sub> increases with total dose when irradiated in vacuum ultraviolet conditions [83]. Transfer characteristics also revealed negative  $\Delta V_{\text{th}}$  for all bias conditions. These two effects were attributed to charges trapped inside the gate oxide and at the interface of SiO<sub>2</sub> with MoS<sub>2</sub>. Furthermore, it was found that larger  $\Delta V$ th was produced in FETs with flakes of six-layer MoS2 than in monolayer MoS<sub>2</sub>, a phenomenon that was attributed to the differences in the proximity of the channel to the SiO2 interface. When irradiated in ambient, MoS2 transistors of similar structure exhibit positive  $\Delta V^{\text{th}}$  which, however, is observed at much lower doses than negative  $\Delta V^{\text{th}}$  when irradiated in vacuum [84]. Oxygen-induced surface traps on MoS2 are believed to be the cause of these shifts, which are also thought to cause scattering-related mobility degradation in the channel.

### VII. RESISTIVE RANDOM ACCESS MEMORY

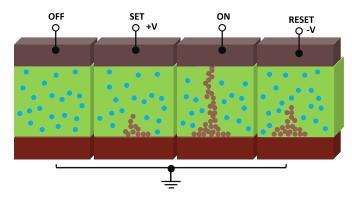

Resistive memory or RRAM is a promising next generation nonvolatile memory with properties superior to flash memory. Resistive memory improves as it scales and can be fabricated in a high-density cross-bar array, can operate at low power and has a very simple metal/switching-layer/metal structure [86]. The resistance of a RRAM cell can be changed between a high (HRS) and a low state (LRS), by altering an applied voltage, causing a conductive filament to reversibly connect and rupture between the two metal electrodes [87].

Resistive memory can be split into two types, dependent on the filament mechanism: 1) valence change memory (VCM) and 2) electrochemical metallization memory (ECM). VCM consists of a metal/oxide/metal structure where the conducting filament is constructed from oxygen vacancies and is known as anion memory [87]. A thorough review on its operation can be found in [88]. ECM, on the other hand, is a cation based memory with a soluble electrode leading to a metallic filament. Also known as conductive-bridging random access memory (CBRAM) or programmable metallization cells (PMC), ECM memories can have different types of switching layer materials such as metal-doped oxides, metal-doped chalcogenides, and solid electrolytes like SiC [89], [90]. The switching mechanism of an ECM cell depicted in Fig. 10 [85].

With very thin switching layers, often between 10–100 nm, and a switching mechanism based on conductive filaments rather than control of charge density, RRAM cells can be considered radiation hard by process [91]–[101]. However,

Fig. 10. Schematic representation of an ECM cell switching mechanism as suggested in [85]. During the OFF state, the Cu-doped ECM cell has no filaments present. During the SET operation, the Cu ions (blue dots) from the top electrode (Cu) dissolve into the switching layer and their number is reduced at the counter electrode (Pt) due to the applied bias. This continues until a complete metallic filament (gray dots) connects the top and bottom electrodes, resulting in the ON state. The process can be reversed by changing the applied bias, causing the filament to rupture (RESET).

such a large variety of materials, structures, and memory types leads to a variety of memory properties and radiation response.

In VCM, there are three main materials that have been the focus of research to date;  $TaO_x$ ,  $HfO_x$ , and  $TiO_x$  although some research into  $SiO_x$  has also been conducted [92]–[94], [96], [99], [101]–[109]. Over the years, variations in radiation responses between different or even the same materials has been reported. Whilst some indicate VCM memory to be either completely resistant to radiation effects, other research observes changes in memory properties, although typically only at Mrad dose levels or above.

Similar to  $SiO_2$  FETs, ionizing radiation of metal-oxides induces oxygen vacancies and charge. In the earlier work for  $HfO_x$  in particular, the lack of radiation response was attributed to the induced oxygen vacancies being too small in number comparable to the conductive filament, or that the induced charge was trapped in defect sites far from the conductive filament [107], [110].

A large amount of work, however, does report radiation effects in VCM memory at high doses which include changes in voltages, resistance, and in some cases, a complete switch of state [92], [93], [96], [102], [103], [106], [109], [111]–[114]. In these cases, it is thought that the induced charge and oxygen vacancies interfere with the conductive filament switching mechanism and/or the resistance of the oxide. Many mechanisms have been proposed. These mechanisms include trapping of radiation-induced charge at preexisting or radiation generated oxygen vacancies or defects and alteration or creation of internal electric fields and transient currents [92], [93], [96], [102], [104]–[106], [109], [111]–[114]. This can lead to obstruction of oxygen vacancy movement or joule heating which can, in turn, lead to the creation of additional oxygen vacancies [92], [102], [104], [115]. If field alterations or transient currents are large enough, state switching can occur [104], [112], [115].

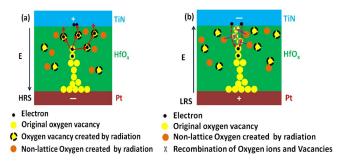

A possible radiation physical mechanism for a  $TiN/HfO_x/Pt$  cell is reported in [94]. It is proposed that Hf-O bonds are broken upon radiation leading to the creation of oxygen

Fig. 11. Schematic of radiation effect mechanism when device is in (a) HRS or (b) LRS during irradiation of gamma rays. Electrons follow the red line and oxygen follows the purple line. Reprinted from [94], with the permission of AIP Publishing.

vacancies and nonlattice oxygen (Fig. 11). Upon cycling after radiation, the radiation vacancies in  $HfO_x$ , located far from the filament, are not recovered, and therefore lead to an average decrease of HRS resistance. When in HRS [as shown in Fig. 11(a)], with a partial filament present, the induced oxygen vacancies aid connection of the filament upon SET. When in LRS [Fig. 11(b)], nonlattice oxygen can recombine with oxygen vacancies in the filament and cause rupturing. Changes in crystallisation phase, dependent on radiation dose, in  $TiO_x$  have been reported more recently [114]. The radiation effect on crystallisation is an interesting topic on its own right, and shedding light on this mechanism can further aid in choosing appropriate materials for TID hardened applications.

One of the challenges that arises when creating a complete model of radiation effects of RRAM memory originates from variation that occurs at device-to-device level. When forming a VCM memory cell, variations in oxygen vacancy density and distribution impacts the formation, location, and number of conductive filaments [104], [115]. As this variation exists device-to-device prior to radiation, differences after radiation will only worsen [92], [104], [115]. If radiation responses vary from device-to-device, this makes comparing the same materials from different sources very challenging. Further factoring in different materials makes a unified theory of VCM radiation effects extremely difficult and is still being actively studied.

Despite this, two dependencies of radiation hardness on VCM cells are well known: 1) circuit set up and 2) oxide thickness [93], [101], [104], [115]–[117]. Thinner devices that are not left floating are thought to be the ideal set up in a radiation environment and can be used to select radiation tolerant designs.

Whilst the mechanisms behind TID effects of VCM memory is still in discussion, VCM memory can be seen as a radiation hard memory where memory property alterations are usually only seen at Mrad dose levels which are much higher than required for space applications [115]. Thin oxide grounded VCM cells are promising for radiation environments, although evident switching of states indicates other types of RRAM may be preferable. This other type is ECM.

For metal-oxide ECM cells, e.g., Cu-doped HfO<sub>2</sub>, changes in HRS and  $V_{\text{set}}$  are reported [91], [93], [95], [107], [118]. Similar to VCM memory, oxygen ions, oxygen vacancies, and charge are induced in the oxide layer of oxide ECM

Fig. 12. Solid electrolyte SiC ECM memory cells exhibiting stable conduction mechanisms and resistance states following exposure to 2 Mrad of gamma radiation with (a) displaying LRS after pulsed and dc measurements with a gradient of 1.00+/-0.02, indicating Ohmic conduction and (b) displaying HRS and pristine state with a linear fit for  $LV^{1/2}$ , indicating Schottky emission [130].

memory. Radiation-induced oxygen vacancies can inhibit formation of metallic filament, resulting in increase in  $V_{\rm set}$ , attributed to either scattering of Cu ions or internal field reduction [91], [95], [93], [107]. Induced traps can also reduce HRS [95], [107], [118]. Unlike VCM memory, once a metallic filament is formed, the radiation induced oxygen vacancies have less impact on the filament, resulting in a higher radiation resilience when in LRS [91], [93].

For metal-doped chalcogenide ECM cells, e.g., Ag-doped Ge<sub>30</sub>Se<sub>70</sub>, a process known as photo doping can occur. Well known in the literature, electron hole generation in chalcogenides can lead to Ag diffusion in the chalcogenide matrix [119]–[121]. Applications such as sensors are made based on this photo-induced effect via thin film exposure to UV radiation [121], [122]. Electron-hole pairs generated by high energy ionizing radiation could also trigger photo-doping effects that then may lead to changes in the resistive state of a metal-doped chalcogenide ECM cell [123], [124].

Despite the photo-doping process, metal chalcogenide cells have shown a high radiation tolerance, although this is dependent upon the fabrication method and composition of the switching layer [97], [98], [124]–[128]. During fabrication, a sufficient UV/thermal doping step prior to radiation will leave the chalcogenide layer fully saturated with Ag, and thus further doping from radiation will not occur [124], [125], [129]. The structure, bonds, and arrangement of chalcogen atoms can also affect the ionic motion of silver, effecting the memory properties [129]. Therefore, differences in composition will result in further variation from radiation.

For the majority of metal chalcogenide ECM cells studied, LRS states are mainly unaffected whilst the pristine and HRS states have exhibited sensitivity to radiation, albeit at high doses [97], [98], [124]–[126]. It is hypothesized that when in the pristine state, nanosized clusters of highly conductive Ag ChG with a less conductive silver-doped ChG layer could occur due to ionizing radiation [117]. In the HRS state, it is thought that radiation induced electron holes activate

Ag surface agglomeration, reducing the Ag concentration in the layer below [98], [117], [125], [127]. Either way, careful selection of a fabrication process and chalcogenide material could possibly reduce these effects, leading to highly radiation tolerant RRAM cells.

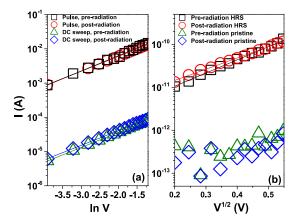

In 2015, high radiation tolerance of an un-doped solid electrolyte SiC ECM cell was reported [130]. Unlike a vast number of metal-oxide and chalcogenide ECM memories that report changes to HRS or pristine resistance states [95], [97], [98], [107], [118], [125], [127], [131], the SiC ECM cells showed no changes to any resistance states, nor conduction mechanisms, as seen in Fig. 12. The radiation stability could be attributed to a high diffusion barrier of SiC for Cu, meaning that photo doping from radiation-induced electronhole pairs is suppressed or it could be attributed to a large band gap, resulting in a lower number of radiation induced carriers. Selecting a nonoxide switching layer also removes any undesired effects caused by radiation induced oxygen vacancies. Further investigations into the radiation effects of other nonchalcogenide solid-state ECM could lead to the identification of a new type of radiation hard resistive memory.

### VIII. CONCLUSION

We have described TID response mechanisms in various CMOS technologies and beyond. Up until the latest Si-based CMOS commercial processes, the thick field oxides play a major role in the TID device characteristics, while for 2-D channel and thin film transistors, the focus shifts to the interplay between semiconductor surface, semiconductor/oxide interface, and bulk oxide charge trapping mechanisms.

Some technologies have shown exceptional hardness against TID radiation. These are the PDSOI MOSFET at the 45- and 35-nm nodes with high levels of body doping, bulk FinFETs of various gate lengths where the leakage paths are formed deep inside the neck region of the fin, GAA FETs where the channel is completely wrapped by the gate as well as NVFETs with single-layer graphene on PZT.

TID hardening solutions have also been proposed for CNT TFTs that include covering the film with a dielectric material to reduce surface adsorption mechanisms, reducing the thickness of the gate dielectric, and using alternative materials such as SiON. Organic-inorganic self-assembled nanodielectrics as gate insulation have also shown to increase radiation hardness of graphene back-gated transistors. This has been attributed to the competing mechanisms of aggregating interface and bulk oxide traps and charges, a process that can be proven useful for UTBB designs.

All RRAM cells, whether VCM and ECM, generally show very high tolerance to TID with negligible or no memory property changes seen until the Mrad regime. Compared to traditional memory or floating gate transistors, which can withstand 10–100 krad, RRAM is a superior radiation hard memory. Specifically, ECM cells show superior radiation hardness to VCM with no state switching seen, whilst solid-state electrolyte ECM cells could provide even more radiation resistant memory cells, with no changes to any memory properties.

It is generally expected that miniaturization will bring many interesting concepts on radiation hardened devices that include and take advantage of the many novel material properties and physical phenomena that arise from their combinations.

### **ACKNOWLEDGMENT**

The authors would like to thank Prof. S. Saito and Dr. I. Zeimpekis from the University of Southampton, U.K., for their useful comments.

#### REFERENCES

- [1] European Space Agency. SPace ENVironment Information System (SPENVIS). [Online]. Available: https://www.spenvis.oma.be/regulation.php

- [2] D. Smith, L. I. Lopez, R. P. Lin, and C. P. Barrington-Leigh, "Terrestrial gamma-ray flashes observed up to 20 MeV," *Science*, vol. 307, no. 5712, pp. 1085–1088, Feb. 2005.

- [3] O. J. Roberts et al., "Terrestrial gamma ray flashes due to particle acceleration in tropical storm systems," J. Geophys. Res., Atmos., vol. 122, no. 6, pp. 3374–3395, Mar. 2017. [Online]. Available: http://doi.wiley.com/10.1002/2016JD025799

- [4] V. Zoita et al., "Definition of the radiation fields for the JET gammaray spectrometer diagnostics," Fusion Eng. Design, vol. 88, nos. 6–8, pp. 1366–1370, Oct. 2013.

- [5] M. Gaillardin *et al.*, "High total ionizing dose and temperature effects on micro- and nano-electronic devices," *IEEE Trans. Nucl. Sci.*, vol. 62, no. 3, pp. 1226–1232, Jun. 2015.

- [6] R. Hull, J. Millard, and H. Brunnader, "Development of radiation hardened electronics," in *Proc. 2nd Int. Conf. CANDU Maintenance*, 1992, pp. 583–596.

- [7] G. Santin, "Chapter II radiation interaction physics and simulation," in *Radiation and its Effects on Components and Systems (RADECS)*. Oxford, U.K.: RADECS, 2013.

- [8] D. M. Fleetwood, "Total ionizing dose effects in MOS and low-dose-rate-sensitive linear-bipolar devices," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 3, pp. 1706–1730, Jun. 2013.

- [9] B. T. Pemberton, "A structured ASIC approach to a radiation hardened by design digital single sideband modulator for digital radio frequency memories," Ph.D. dissertation, Dept. Elect. Eng., Wright State Univ., Fairborn, OH, USA, 2008.

- [10] F. N. de Souza et al., "Boosting the total ionizing dose tolerance of digital switches by using OCTO SOI MOSFET," Semicond. Sci. Technol., vol. 30, no. 10, p. 105024, 2015.

- [11] L. E. Seixas et al., "Improving MOSFETs' TID tolerance through diamond layout style," *IEEE Trans. Device Mater. Rel.*, vol. 17, no. 3, pp. 593–595, Sep. 2017.

- [12] TTRS. (2015). The International Technology Roadmap for Semiconductors. [Online]. Available: http://www.itrs2.net

- [13] J. R. Schwank, "Basic mechanisms of radiation effects in the natural space radiation environment," presented at the 31st Annu. Int. Nucl. Space Radiat. Effects Conf., Tucson, AZ, USA, Jul. 1994.

- [14] K. F. Galloway and R. D. Schrimpf, "MOS device degradation due to total dose ionizing radiation in the natural space environment: A review," *Microelectron. J.*, vol. 21, no. 2, pp. 67–81, 1990.

- [15] J. R. Schwank, V. Ferlet-Cavrois, M. R. Shaneyfelt, P. Paillet, and P. E. Dodd, "Radiation effects in SOI technologies," *IEEE Trans. Nucl. Sci.*, vol. 50, no. 3, pp. 522–538, Jun. 2003.

- [16] P. Roche, J.-L. Autran, G. Gasiot, and D. Munteanu, "Technology downscaling worsening radiation effects in bulk: SOI to the rescue," in *IEDM Tech. Dig.*, Dec. 2013, pp. 766–769.

- [17] E. Chatzikyriakou, W. Redman-White, and C. H. De Groot, "Total ionizing dose, random dopant fluctuations, and its combined effect in the 45 nm PDSOI node," *Microelectron. Rel.*, vol. 68, pp. 21–29, Jan. 2017.

- [18] N. Rezzak et al., "The sensitivity of radiation-induced leakage to STI topology and sidewall doping," Microelectron. Rel., vol. 51, no. 5, pp. 889–894, May 2011.

- [19] H. J. Barnaby, "Total-ionizing-dose effects in modern CMOS technologies," *IEEE Trans. Nucl. Sci.*, vol. 53, no. 6, pp. 3103–3121, Dec. 2006.

- [20] S. T. Liu, A. Hurst, H. L. Hughes, P. McMarr, J. Benedito, and C. Capasso, "Total dose radiation response of a 45 nm SOI technology," in *Proc. IEEE Int. SOI Conf.*, Oct. 2010, pp. 5–6.

- [21] S. Narasimha et al., "High performance 45-nm SOI technology with enhanced strain, porous low-k BEOL, and immersion lithography," in IEDM Tech. Dig., Dec. 2006, pp. 1–4.

- [22] H. S. Yang et al., "Dual stress liner for high performance sub-45 nm gate length SOI CMOS manufacturing," in *IEDM Tech. Dig.*, Dec. 2004, pp. 1075–1077.

- [23] Y. Hirano et al., "A robust SOI SRAM architecture by using advanced ABC technology for 32 nm node and beyond LSTP devices," in Proc. IEEE Symp. VLSI Technol., Jun. 2007, pp. 78–79.

- [24] B. Ning et al., "Bias dependence of TID radiation responses of 0.13 μm partially depleted SOI NMOSFETs," Microelectron. Rel., vol. 53, no. 2, pp. 259–264, Feb. 2013.

- [25] M. L. Alles, H. L. Hughes, D. R. Ball, P. J. McMarr, and R. D. Schrimpf, "Total-ionizing-dose response of narrow, long channel 45 nm PDSOI transistors," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 6, pp. 2945–2950, Dec. 2014.

- [26] H. Hughes et al., "Total ionizing dose radiation effects on 14 nm FinFET and SOI UTBB technologies," in Proc. IEEE Radiat. Effects Data Workshop (REDW), Jul. 2015, pp. 1–6.

- [27] H.-K. Lim and J. G. Fossum, "Threshold voltage of thin-film silicon-on-insulator (SOI) MOSFET's," *IEEE Trans. Electron Devices*, vol. ED-30, no. 10, pp. 1244–1251, Oct. 1983.

- [28] P. Paillet et al., "Total ionizing dose effects on deca-nanometer fully depleted SOI devices," *IEEE Trans. Nucl. Sci.*, vol. 52, no. 6, pp. 2345–2352, Dec. 2005.

- [29] A. R. Brown, V. Huard, and A. Asenov, "Statistical simulation of progressive NBTI degradation in a 45-nm technology pMOSFET," *IEEE Trans. Electron Devices*, vol. 57, no. 9, pp. 2320–2323, Sep. 2010.

- [30] M. Gaillardin et al., "Radiation effects in advanced SOI devices: New insights into total ionizing dose and single-event effects," in Proc. IEEE SOI-3D-Subthreshold Microelectron. Technol. Unified Conf. (S3S), Oct. 2013, pp. 1–2.

- [31] M. Gaillardin et al., "Impact of SOI substrate on the radiation response of UltraThin transistors down to the 20 nm node," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 4, pp. 2583–2589, Aug. 2013.

- [32] C. Claeys, M. Aoulaiche, E. Simoen, T. Nicoletti, S. dos Santos, and J. A. Martino, "Potential and limitations of UTBB SOI for advanced CMOS technologies," in *Proc. Symp. Microelectron. Technol. Devices (SBMicro)*, Sep. 2013, pp. 1–6.

- [33] P. Perreau et al., "Parasitic bipolar impact in 32 nm undoped channel Ultra-Thin BOX (UTBOX) and biased ground plane FDSOI high-k/metal gate technology," in Proc. Eur. Solid-State Device Res. Conf. (ESSDERC), Sep. 2011, pp. 111–114.

- [34] P. Perreau et al., "Low power UTBOX and back plane (BP) FDSOI technology for 32 nm node and below," in Proc. IEEE Int. Conf. IC Design Technol. (ICICDT), May 2011, pp. 9–12.

- [35] C. Diaz-Llorente, C. Medina-Bailon, C. Sampedro, F. Gamiz, A. Godoy, and L. Donetti, "Sub-22 nm scaling of UTB2SOI devices for multi-V<sup>T</sup> applications," in *Proc. Joint Int. EUROSOI Work-shop Int. Conf. Ultimate Integr. Silicon (EUROSOI-ULIS)*, Jan. 2015, pp. 281–284.

- [36] D. Landru, F. Allibert, N. Daval, and O. Kononchuk, "UTBOX SOI substrate with composite insulating layer," ECS J. Solid State Sci. Technol., vol. 2, no. 6, pp. Q83–Q87, 2013.

- [37] K. Cheng et al., "Extremely thin SOI (ETSOI) technology: Past, present, and future," in Proc. IEEE Int. SOI Conf. (SOI), Oct. 2010, pp. 1–4.

- [38] Q. Liu et al., "Ultra-thin-body and BOX (UTBB) fully depleted (FD) device integration for 22 nm node and beyond," in Proc. Symp. VLSI Technol., Jun. 2010, pp. 61–62.

- [39] N. N. Mahatme et al., "Impact of back-gate bias and device geometry on the total ionizing dose response of 1-transistor floating body RAMs," *IEEE Trans. Nucl. Sci.*, vol. 59, no. 6, pp. 2966–2973, Dec. 2012.

- [40] X. Sun, V. Moroz, N. Damrongplasit, C. Shin, and T.-J. K. Liu, "Variation study of the planar ground-plane bulk MOSFET, SOI FinFET, and trigate bulk MOSFET designs," *IEEE Trans. Electron Devices*, vol. 58, no. 10, pp. 3294–3299, Oct. 2011.

- [41] S. Ramey et al., "Intrinsic transistor reliability improvements from 22 nm tri-gate technology," in Proc. IEEE Int. Rel. Phys. Symp. (IRPS), 2013, pp. 4–8.

- [42] E. Simoen et al., "Radiation effects in advanced multiple gate and silicon-on-insulator transistors," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 3, pp. 1970–1991, Jun. 2013.

- [43] M. Gaillardin et al., "Total ionizing dose effects in multiple-gate field-effect transistor," Semicond. Sci. Technol., vol. 32, no. 8, p. 83003, 2017

- [44] M. Gaillardin, P. Paillet, V. Ferlet-Cavrois, S. Cristoloveanu, O. Faynot, and C. Jahan, "High tolerance to total ionizing dose of Ω-shaped gate field-effect transistors," *Appl. Phys. Lett.*, vol. 88, no. 22, p. 223511, 2006.

- [45] J. P. Colinge et al., "Radiation dose effects in trigate SOI MOS transistors," *IEEE Trans. Nucl. Sci.*, vol. 53, no. 6, pp. 3237–3241, Dec. 2006.

- [46] I. Chatterjee et al., "Geometry dependence of total-dose effects in bulk FinFETs," IEEE Trans. Nucl. Sci., vol. 61, no. 6, pp. 2951–2958, Dec. 2014.

- [47] M. Gaillardin, P. Paillet, V. Ferlet-Cavrois, O. Faynot, C. Jahan, and S. Cristoloveanu, "Total ionizing dose effects on triple-gate FETs," *IEEE Trans. Nucl. Sci.*, vol. 53, no. 6, pp. 3158–3165, Dec. 2006.

- [48] J.-J. Song et al., "Fin width and bias dependence of the response of triple-gate MOSFETs to total dose irradiation," *IEEE Trans. Nucl. Sci.*, vol. 58, no. 6, pp. 2871–2875, Dec. 2011.

- [49] I. Chatterjee et al., "Bias dependence of total-dose effects in bulk FinFETs," IEEE Trans. Nucl. Sci., vol. 60, no. 6, pp. 4476–4482, Dec. 2013.

- [50] E. Chatzikyriakou, K. Potter, W. Redman-White, and C. H. De Groot, "Three-dimensional finite elements method simulation of total ionizing dose in 22 nm bulk nFinFETs," *Nucl. Instrum. Methods Phys. Res.*, Sec. B, Beam Interact. Mater. Atoms, vol. 393, pp. 39–43, Feb. 2017.

- [51] A. Hikavyy, I. Zyulkov, H. Mertens, L. Witters, R. Loo, and N. Horiguchi, "Use of high order precursors for manufacturing gate all around devices," *Mater. Sci. Semicond. Process.*, vol. 70, pp. 24–29, Nov. 2017.

- [52] A. Veloso, A. De Keersgieter, P. Matagne, N. Horiguchi, and N. Collaert, "Advances on doping strategies for triple-gate finFETs and lateral gate-all-around nanowire FETs and their impact on device performance," *Mater. Sci. Semicond. Process.*, vol. 62, pp. 2–12, May 2016.

- [53] J. Gu, Y. Liu, Y. Wu, R. Colby, R. Gordon, and P. Ye, "First experimental demonstration of gate-all-around III-V MOSFETs by top-down approach," in *IEDM Tech. Dig.*, Dec. 2011, no. 100, pp. 33.2.1–33.2.4, doi: 10.1109/IEDM.2011.6131662.

- [54] J. Sarkar, S. Dey, D. Shahrjerdi, and S. K. Banerjee, "Vertical flash memory cell with nanocrystal floating gate for ultradense integration and good retention," *IEEE Electron Device Lett.*, vol. 28, no. 5, pp. 449–451, May 2007.

- [55] B. Yang, K. D. Buddharaju, S. H. G. Teo, N. Singh, G. Q. Lo, and D. L. Kwong, "Vertical silicon-nanowire formation and gate-all-around MOSFET," *IEEE Electron Device Lett.*, vol. 29, no. 7, pp. 791–794, Jul. 2008.

- [56] K. Sun et al., "Low-cost top-down zinc oxide nanowire sensors through a highly transferable ion beam etching for healthcare applications," *Microelectron. Eng.*, vol. 153, pp. 96–100, Mar.2016.

- [57] M. Gaillardin et al., "Total ionizing dose response of multiple-gate nanowire field effect transistors," *IEEE Trans. Nucl. Sci.*, vol. 64, no. 8, pp. 2061–2068, Aug. 2017.

- [58] S. Ren et al., "Total ionizing dose (TID) effects in extremely scaled ultra-thin channel nanowire (NW) gate-all-around (GAA) InGaAs MOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 62, no. 6, pp. 2888–2893, Dec. 2015.

- [59] E. Simoen, C. Claeys, S. Coenen, and M. Decreton, "D.C. and low frequency noise characteristics of γ-irradiated gate-all-around siliconon-insulator MOS transistors," *Solid-State Electron.*, vol. 38, no. 1, pp. 1–8, Jan. 1995.

- [60] J. Colinge and A. Terao, "Effects of total-dose irradiation on gateall-around (GAA) devices," *IEEE Trans. Nucl. Sci.*, vol. 40, no. 2, pp. 78–82, Apr. 1993.

- [61] D.-I. Moon, J.-W. Han, and M. Meyyappan, "Fabrication of a silicon nanowire on a bulk substrate by use of a plasma etching and total ionizing dose effects on a gate-all-around field-effect transistor," Tech. Rep., 2016.

- [62] E. Patrick, N. Rowsey, and M. E. Law, "Total dose radiation damage: A simulation framework," *IEEE Trans. Nucl. Sci.*, vol. 62, no. 4, pp. 1650–1657, Aug. 2015.

- [63] E. Chatzikyriakou, K. Potter, and C. H. de Groot, "A systematic method for simulating total ionizing dose effects using the finite elements method," *J. Comput. Electron.*, vol. 16, no. 3, pp. 548–555, Sep. 2017.

- [64] Y.-M. Lin, C. Dimitrakopoulos, K. A. Jenkins, D. B. Farmer, H.-Y. Chiu, A. Grill, and P. Avouris, "100-GHz transistors from wafer-scale epitaxial graphene," *Science*, vol. 327, no. 5966, p. 662, Feb. 2010.

- [65] B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kis, "Single-layer MoS<sub>2</sub> transistors," *Nature Nanotechnol.*, vol. 6, no. 3, pp. 147–150, Mar. 2011.

- [66] L. Nougaret et al., "80 GHz field-effect transistors produced using high purity semiconducting single-walled carbon nanotubes," Appl. Phys. Lett., vol. 94, no. 24, pp. 2007–2010, 2009.

- [67] M. Schroter et al., "A 4" wafer photostepper-based carbon nanotube FET technology for RF applications," in *IEEE MTT-S Int. Microw.* Symp. Dig., Jun. 2011, pp. 4–7.

- [68] M. Schroter, M. Claus, P. Sakalas, M. Haferlach, and D. Wang, "Carbon nanotube FET technology for radio-frequency electronics: State-of-theart overview," *IEEE J. Electron Devices Soc.*, vol. 1, no. 1, pp. 9–20, Jan. 2013.

- [69] C. D. Cress, J. J. McMorrow, J. T. Robinson, A. L. Friedman, and B. J. Landi, "Radiation effects in single-walled carbon nanotube thinfilm-transistors," *IEEE Trans. Nucl. Sci.*, vol. 57, no. 6, pp. 3040–3045, Dec. 2010.

- [70] R. C. Walker, II, T. Shi, E. C. Silva, I. Jovanovic, and J. A. Robinson, "Radiation effects on two-dimensional materials," *Phys. Status Solidi A*, vol. 213, no. 12, pp. 3065–3077, Dec. 2016.

- [71] I. S. Esqueda, C. D. Cress, Y. Che, Y. Cao, and C. Zhou, "Charge trapping in aligned single-walled carbon nanotube arrays induced by ionizing radiation exposure," *J. Appl. Phys.*, vol. 115, no. 5, p. 054506, 2014.

- [72] Y. Zhao et al., "Radiation effects and radiation hardness solutions for single-walled carbon nanotube-based thin film transistors and logic devices," Carbon, vol. 108, pp. 363–371, Nov. 2016.

- [73] C. Cress et al., "Total ionizing dose-hardened carbon nanotube thinfilm transistors with silicon oxynitride gate dielectrics," MRS Commun., vol. 1, no. 1, pp. 27–31, Nov. 2011.

- [74] E. X. Zhang et al., "Low-energy X-ray and ozone-exposure induced defect formation in graphene materials and devices," *IEEE Trans. Nucl.* Sci., vol. 58, no. 6, pp. 2961–2967, Dec. 2011.

- [75] F. Banhart, J. Kotakoski, and A. V. Krasheninnikov, "Structural defects in graphene," ACS Nano, vol. 5, no. 1, pp. 26–41, 2011.

- [76] C. D. Cress, J. G. Champlain, I. S. Esqueda, J. T. Robinson, A. L. Friedman, and J. J. McMorrow, "Total ionizing dose induced charge carrier scattering in graphene devices," *IEEE Trans. Nucl. Sci.*, vol. 59, no. 6, pp. 3045–3053, Dec. 2012.

- [77] C. X. Zhang et al., "Electrical stress and total ionizing dose effects on graphene-based non-volatile memory devices," *IEEE Trans. Nucl. Sci.*, vol. 59, no. 6, pp. 2974–2978, Dec. 2012.

- [78] J. R. Schwank, R. D. Nasby, S. L. Miller, M. S. Rodgers, and P. V. Dressendorfer, "Total-dose radiation-induced degradation of thin film ferroelectric capacitors," *IEEE Trans. Nucl. Sci.*, vol. 37, no. 6, pp. 1703–1712, Dec. 1990.

- [79] S. C. Lee, G. Teowee, R. D. Schrimpf, D. P. Birnie, D. R. Uhlmann, and K. F. Galloway, "Total-dose radiation effects on sol-gel derived PZT thin films," *IEEE Trans. Nucl. Sci.*, vol. 39, no. 6, pp. 2036–2043, Dec. 1992.

- [80] P. J. McWhorter, S. L. Miller, and T. A. Dellin, "Radiation response of SNOS nonvolatile transistors," *IEEE Trans. Nucl. Sci.*, vol. NS-33, no. 6, pp. 1413–1419, Dec. 1986.

- [81] C. X. Zhang et al., "Total-ionizing-dose effects and reliability of carbon nanotube FET devices," Microelectron. Rel., vol. 54, no. 11, pp. 2355–2359, Nov. 2014.

- [82] H. N. Arnold et al., "Tunable radiation response in hybrid organic-inorganic gate dielectrics for low-voltage graphene electronics," ACS Appl. Mater. Interfaces, vol. 8, no. 8, pp. 5058–5064, 2016.

- [83] J. J. McMorrow et al., "Vacuum ultraviolet radiation effects on twodimensional MoS<sub>2</sub> field-effect transistors," Appl. Phys. Lett., vol. 110, no. 7, p. 073102, 2017.

- [84] C. X. Zhang et al., "Electrical stress and total ionizing dose effects on MoS<sub>2</sub> transistors," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 6, pp. 2862–2867, Dec. 2014.

- [85] I. Valov and M. N. Kozicki, "Cation-based resistance change memory," J. Phys. D, Appl. Phys., vol. 46, no. 7, p. 074005, Jan. 2013.

- [86] R. Waser, R. Dittmann, G. Staikov, and K. Szot, "Redox-based resistive switching memories—Nanoionic mechanisms, prospects, and challenges," Adv. Mater., vol. 21, nos. 25–26, pp. 2632–2663, Jul. 2009.

- [87] R. Waser and M. Aono, "Nanoionics-based resistive switching memories," *Nature Mater.*, vol. 6, no. 11, pp. 833–840, Nov. 2007.

- [88] H.-S. P. Wong et al., "Metal-oxide RRAM," Proc. IEEE, vol. 100, no. 6, pp. 1951–1970, Jun. 2012.

- [89] I. Valov, R. Waser, J. R. Jameson, and M. N. Kozicki, "Electrochemical metallization memories—Fundamentals, applications, prospects," *Nanotechnology*, vol. 22, no. 25, p. 254003, 2011.

- [90] K. A. Morgan et al., "Active counter electrode in a-SiC electrochemical metallization memory," J. Phys. D, Appl. Phys., vol. 50, no. 32, p. 325102, 2017.

- [91] Y. Wang et al., "Highly stable radiation-hardened resistive-switching memory," *IEEE Electron Device Lett.*, vol. 31, no. 12, pp. 1470–1472, Dec. 2010.

- [92] M. J. Marinella *et al.*, "Initial assessment of the effects of radiation on the electrical characteristics of TaO<sub>x</sub> memristive memories," *IEEE Trans. Nucl. Sci.*, vol. 59, no. 6, pp. 2987–2994, Dec. 2012.

- [93] L. Zhang et al., "Total ionizing dose (TID) effects on TaOx-based resistance change memory," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2800–2804, Aug. 2011.

- [94] R. Fang et al., "Total ionizing dose effect of γ-ray radiation on the switching characteristics and filament stability of HfOx resistive random access memory," AIP Adv., vol. 104, no. 18, p. 183507, 2014.

- [95] B. Butcher et al., "Proton-based total-dose irradiation effects on Cu/HfO<sub>2</sub>:Cu/Pt ReRAM devices," *Nanotechnology*, vol. 21, no. 47, p. 475206, 2010.

- [96] S. Kim, O. Yarimaga, S.-J. Choi, and Y.-K. Choi, "Highly durable and flexible memory based on resistance switching," *Solid-State Electron.*, vol. 54, no. 4, pp. 392–396, Apr. 2010.

- [97] J. L. Taggart et al., "Ionizing radiation effects on nonvolatile memory properties of programmable metallization cells," *IEEE Trans. Nucl.* Sci., vol. 61, no. 6, pp. 2985–2990, Dec. 2014.

- [98] P. Dandamudi, M. N. Kozicki, H. J. Barnaby, Y. Gonzalez-Velo, and K. E. Holbert, "Total ionizing dose tolerance of Ag-Ge<sub>40</sub>S<sub>60</sub> based programmable metallization cells," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 4, pp. 1726–1731, Aug. 2014.

- [99] K. A. Morgan, R. Huang, K. Potter, C. Shaw, W. Redman-White, and C. H. De Groot, "Total dose hardness of TiN/HfO<sub>x</sub>/TiN resistive random access memory," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 6, pp. 2991–2996, Dec. 2014.

- [100] J. Fan, L. Jiang, L. Zhong, R. P. Gowers, K. A. Morgan, and C. H. de Groot, "Microstructure and electrical properties of cosputtered Cu embedded amorphous SiC," *Mater. Lett.*, vol. 178, pp. 60–63, Sep. 2016.

- [101] J. Holt, N. Cady, and J. Yang-Scharlotta, "Radiation testing of tantalum oxide-based resistive memory," in *Proc. IEEE Int. Integr. Rel.* Workshop (IIRW), Oct. 2015, pp. 155–158.

- [102] C. Yaqing, L. Rongrong, T. Zhensen, and S. Ruiqiang, "Total ionizing dose effect on low on/off switching ratio TiO<sub>2</sub> memristive memories," in *Proc. 14th Eur. Conf. Radiat. Effects Compon. Syst. (RADECS)*, Sep. 2013, pp. 1–3.

- [103] D. R. Hughart *et al.*, "Radiation-induced resistance changes in  $TaO_X$  and  $TiO_2$  memristors," in *Proc. IEEE Aerosp. Conf.*, Mar. 2014, pp. 1–11.

- [104] M. L. McLain et al., "The susceptibility of TaO<sub>x</sub>-based memristors to high dose rate ionizing radiation and total ionizing dose," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 6, pp. 2997–3004, Dec. 2014.

- [105] M. McLain, D. Hughart, D. Hanson, and M. Marinella, "Effects of ionizing radiation on TaO<sub>x</sub>-based memristive devices," in *Proc. IEEE Aerosp. Conf.*, Mar. 2014, pp. 1–9.

- [106] D. Lee et al., "Proton irradiation effects on resistive random access memory with ZrO<sub>x</sub>/HfO<sub>x</sub> stacks," *IEEE Trans. Nucl. Sci.*, vol. 58, no. 6, pp. 3317–3320, Dec. 2011.

- [107] X. He, W. Wang, B. Butcher, S. Tanachutiwat, and R. E. Geer, "Superior TID hardness in TiN/HfO<sub>2</sub>/TiN ReRAMs after proton radiation," *IEEE Trans. Nucl. Sci.*, vol. 59, no. 5, pp. 2550–2555, Oct. 2012.

- [108] K. A. Morgan, R. Huang, S. Pearce, L. Zhong, L. Jiang, and C. H. de Groot, "Effect of stoichiometry of TiN electrode on the switching behavior of TiN/HfO<sub>x</sub>/TiN structures for resistive RAM," in *Proc. MRS*, vol. 1631. 2014.

- [109] D. S. Korolev *et al.*, "Influence of ion irradiation on the resistive switching parameters of SiO<sub>x</sub>-based thin-film structures," *J. Phys.*, *Conf. Ser.*, vol. 643, no. 1, p. 012094, 2015.

- [110] J. S. Bi et al., "The impact of X-ray and proton irradiation on HfO<sub>2</sub>/Hf-based bipolar resistive memories," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 6, pp. 4540–4546, Dec. 2013.

- [111] S.-H. Lin, Y.-L. Wu, Y.-H. Hwang, and J.-J. Lin, "Study of radiation hardness of HfO<sub>2</sub>-based resistive switching memory at nanoscale by conductive atomic force microscopy," *Microelectron. Rel.*, vol. 55, no. 11, pp. 2224–2228, Nov. 2015.

- [112] F. Yuan, S. Shen, and Z. Zhang, "γ-ray irradiation effects on TiN/HfO<sub>x</sub>/Pt resistive random access memory devices," in *Proc. IEEE Aerosp. Conf.*, Mar. 2015, pp. 1–7.

- [113] Y. Wang et al., "The TID effects of RRAM based oxide material," in Proc. 15th Eur. Conf. Radiat. Effects Compon. Syst. (RADECS), Sep. 2015, pp. 1–5.

- [114] K. Agashe *et al.*, "Effect of gamma irradiation on resistive switching of Al/TiO<sub>2</sub>/n<sup>+</sup>Si ReRAM," *Nucl. Instrum. Methods Phys. Res. B, Beam Interact. Mater. At.*, vol. 403, pp. 38–44, Jul. 2017.

- [115] M. L. McLain and M. J. Marinella, "Overview of the radiation response of anion-based memristive devices," in *Proc. IEEE Aerosp. Conf.*, Mar. 2015, pp. 1–11.

- [116] D. R. Hughart, Radiation-Induced Resistance Changes in Resistive Memory: Separating Displacement Damage and Ionization and Mapping Sensitive Areas. Washington, DC, USA: National Nuclear Security Administration, Mar. 2015.

- [117] Y. Gonzalez-Velo, H. J. Barnaby, and M. N. Kozicki, "Review of radiation effects on ReRAM devices and technology," *Semicond. Sci. Technol.*, vol. 32, no. 8, p. 083002, 2017.

- [118] W. Chen et al., "A study of gamma-ray exposure of Cu–SiO<sub>2</sub> programmable metallization cells," *IEEE Trans. Nucl. Sci.*, vol. 62, no. 6, pp. 2404–2411, Dec. 2015.

- [119] K. Shimakawa, A. Kolobov, and S. R. Elliott, "Photoinduced effects and metastability in amorphous semiconductors and insulators," Adv. Phys., vol. 44, no. 6, pp. 475–588, 1995.

- [120] H. Fritzsche, "The origin of reversible and irreversible photostructural changes in chalcogenide glasses," *Philos. Mag. B*, vol. 68, no. 4, pp. 561–572, 1993.

- [121] M. Frumar and T. Wagner, "Ag doped chalcogenide glasses and their applications," *Current Opinion Solid State Mater. Sci.*, vol. 7, no. 2, pp. 117–126, Apr. 2003.

- [122] P. Dandamudi et al., "Sensors based on radiation-induced diffusion of silver in germanium selenide glasses," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 6, pp. 4257–4264, Dec. 2013.

- [123] Y. Gonzalez-Velo et al., "Effects of cobalt-60 gamma-rays on Ge–Se chalcogenide glasses and Ag/Ge-Se test structures," *IEEE Trans. Nucl. Sci.*, vol. 59, no. 6, pp. 3093–3100, Dec. 2012.

- [124] Y. Gonzalez-Velo et al., "Total-ionizing-dose effects on the resistance switching characteristics of chalcogenide programmable metallization cells," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 6, pp. 4563–4569, Dec. 2013.

- [125] P. Dandamudi, "Resistance switching in chalcogenide based programmable metallization cells (PMC) and sensors under gamma-rays," Ph.D. dissertation, Arizona State Univ., Tempe, AZ, USA, 2013.

- [126] Y. Gonzalez-Velo, H. J. Barnaby, M. N. Kozicki, C. Gopalan, and K. Holbert, "Total ionizing dose retention capability of conductive bridging random access memory," *IEEE Electron Device Lett.*, vol. 35, no. 2, pp. 205–207, Feb. 2014.

- [127] Y. Gonzalez-Velo et al., "Radiation hardening by process of CBRAM resistance switching cells," IEEE Trans. Nucl. Sci., vol. 63, no. 4, pp. 2145–2151, Aug. 2016.

- [128] Y. Gonzalez-Velo et al., "TID impact on process modified CBRAM cells," in Proc. 15th Eur. Conf. Radiat. Effects Compon. Syst. (RADECS), Sep. 2015, pp. 1–4.

- [129] M. Marinella and H. Barnaby, Total Ionizing Dose and Displacement Damage Effects in Embedded Memory Technologies. Washington, DC, USA: National Nuclear Security Administration, Sep. 2013.

- [130] K. A. Morgan *et al.*, "Switching kinetics of SiC resistive memory for harsh environments," *AIP Adv.*, vol. 5, no. 7, p. 077121, 2015.

- [131] F. Yuan, Z. Zhang, J.-C. Wang, L. Pan, J. Xu, and C.-S. Lai, "Total ionizing dose (TID) effects of γ ray radiation on switching behaviors of Ag/AlO<sub>x</sub>/Pt RRAM device," *Nanosc. Res. Lett.*, vol. 9, no. 1, p. 452, Aug. 2014.

**Eleni Chatzikyriakou** received the Ph.D. degree from the Nanoelectronics and Nanotechnology Research Group, University of Southampton, Southampton, U.K., in 2016, where she examined total ionizing dose effects in field-effect transistors using computational methods.

She is currently with the Computational Physics Laboratory, Aristotle University of Thessaloniki, Thessaloniki, Greece, where she is involved in the first principles studies of transport and emergent physical phenomena at the nanoscale for next generation devices.

Katrina Morgan (S'11–M'14) received the Ph.D. degree in radiation effects of CMOS transistors and resistive memories from the Electronics and Computer Science Department, University of Southampton, Southampton, U.K.

She joined as a Research Fellow with the Optoelectronics Research Centre, University of Southampton, in 2016. She is currently developing advanced chalcogenide 2-D and thin films for a wide variety of optoelectronic applications.

**C. H. Kees de Groot** (SM'08) is currently a Professor of electronics and computer science with the University of Southampton, Southampton, U.K. His current research interests include the integration of novel nanomaterials and devices with silicon electronics processing with particular emphasis on the semiconducting properties of oxides, chalcogenides and carbides, including radiation hardness.