# Direct Off-Line Two-Switch Forward Converter with a Boost PFC Converter for Powering of DC Electromagnet Systems

### **Borislav Dimitrov**

University of Southampton, Southampton, UK

Abstract – In this paper a switch mode power supply design for electromagnet systems is presented. It is based on a boost converter with power factor correction and a two-switch forward converter. The powered electromagnetic systems in this research are part of various electrical contact apparatus such as electromagnetic contactors, relays, circuit breakers etc. The proposed schematic works in a wide input voltage range which solve the problem with the voltage sag occurring in the energy distribution system. The proposed solution ensures stable operation of the contact equipment and the relay circuits in their industrial application.

*Keywords* – Switch Mode Power Supply, Boost converter, Power Factor Correction, Forward Converter, Electromagnetic System.

### 1. Introduction

The voltage sag is a process that occurs in the electrical distribution system due to different transient processes such as switching operations associated with a temporary disconnection of supply, short circuits, inrush currents coursed of induction motors etc. It is defined as the decrease in the RMS voltage under 90% of the nominal value for a duration greater than 0.5 sec. but less than 1 min. Comprehensive descriptions of this process are given

DOI: 10.18421/TEM71-01 https://dx.doi.org/10.18421/TEM71-01

**Corresponding author:** Borislav Dimitrov, University of Southampton, Southampton, UK **Email:** b.h.dimitrov@soton.ac.uk

Received: 29 October 2017. Accepted: 07 December 2017. Published: 23 February 2018.

© 2018 Borislav Dimitrov; published by UIKTEN. This work is licensed under the Creative Commons Attribution-NonCommercial-NoDerivs 3.0 License.

The article is published with Open Access at <u>www.temjournal.com</u>

in [1, 2, 3, 4] and different methods for its measurement and mitigation are proposed in [5, 6, 7, 8]. Despite the proposed solutions the voltage sag is still a problem which broadly affects all electrical loads.

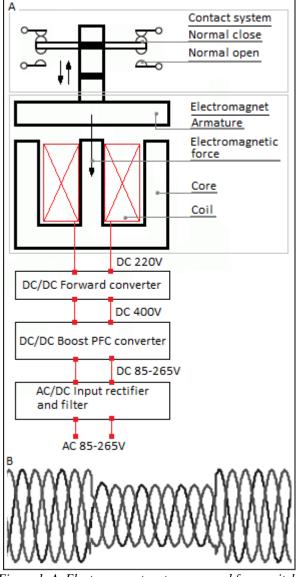

The proposed system is presented in Fig.1A. The electromagnet is part of an electromagnetic contactor which is powered from a switch mode power supply (SMPS), complete with the following elements: input rectifier and filter, boost converter with power factor correction (PFC) and forward converter. The input voltage can vary in the range 85-265V which covers the standards 110V and 230V without additional switching and prevents the voltage sag (Fig.1B) if the system works on 230V.

A two-switch forward converter is used here as it has some desirable advantages: galvanic disconnection between the primary and secondary side; the voltage across the MOSFETs is equal to the input voltage; simple driver circuit as the two transistors operate synchronously; operation in the power range around 1kW is possible.

The forward two-switch converter has been the object of significant research. In [9, 10] applications with multiple and variable outputs are presented. Some approaches for improving the efficiency based on zero voltage switching are given in [11, 12, 13]. The potential use as micro inverter [14] shows that an application for AC electromagnet systems is also possible with this schematic. A comparison between forward and flyback converters is shown in [15]. In this research the two-switch forward converter has been chosen because of its greater power rating. Several different specific applications are studied from [16, 17, 18, 19, 20, 21], respectively battery chargers, photovoltaic systems, supercapacitors power supply sources, hybrid electrical vehicle and arc welding power supplies. These applications show a significant flexibility and applicability of this type of forward converter.

Figure 1. A. Electromagnet system powered form switch mode power supply; B. Voltage sag.

For the experimental verification two platforms [22, 23] are used and the design is based on several established procedures and application manuals [24, 25, 26, 27, 28, 29]. The basic requirement to the input filter, the rectifier and the boost converter is operation in the proposed above voltage range with power factor correction. The design procedures are given in [30, 31, 32] which are applied for the proposed power supply system. Although the design of the powered electromagnet is not an object of this research its parameters have been considered according to [33, 34, 35].

The aim of this research is to propose a SMPS specifically designed for electromagnetic systems which are part of electrical apparatus. The wide input voltage range must prevent the voltage sag seen commonly occurred in any electrical distribution network.

The paper is organised as follows: part 2 gives an analysis of the proposed schematic where the basic parts of the proposed SMPS are described; part 3 presents the basic design of the proposed converter where the most important of the calculation procedure is given; the experimental verification of the entire system based on PFC boost converter, twoswitches forward converter and electromagnet as a load is shown in part 4; the conclusions are formulated in part 5.

### 2. Analysis of the proposed schematic

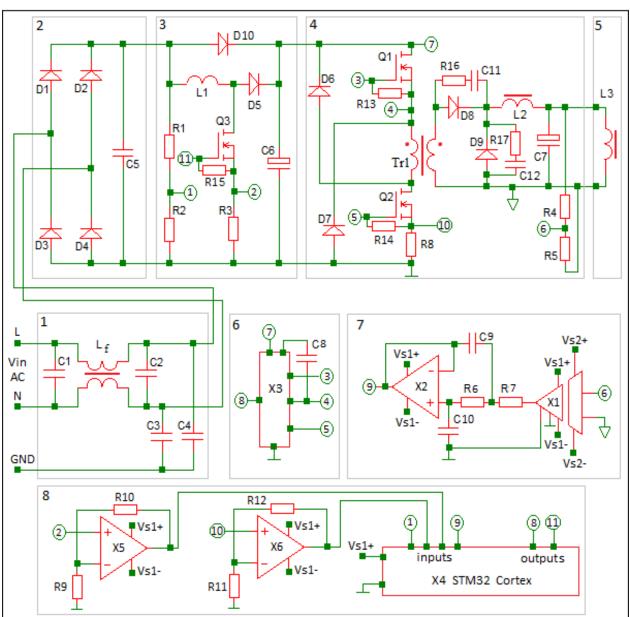

The basic parts of the proposed schematic are given in Fig.2 as follows:

- *Module 1. Input common mode filter.* It is comprised from X capacitors C1 and C2, Y capacitors C3 and, C4 and input filter Lf.

- *Module 2. Input rectifier.* The full bridge rectifier is comprised from diodes D1-D4 and filter capacitor C5. This capacitor is not the normal electrolytic boost capacitor because of the power factor correction operations. Normally here a ceramic capacitor is used with value between 220nF 470nF.

- *Module 3. Boost converter*. The boost converter schematic is comprised of transistor Q3, inductor L1 and diodes D5, D10 is an object of design. The input divider R1-R2 is connected directly to the input rectifier for zero detection in the input half wave voltage. The current sense resistor R3 measures the current through Q3. Respectively, the points 1 and 2 are voltage and current signals to the microcontroller and point 11 is the gate drive signal.

- *Module 4. Forward two-switch converter.* The schematic can be divided into the primary (transistors Q1, Q2, diodes D6, D7, the transformer Tr1) and secondary side (the rectifier D8, D9 and the filter L2, C7).

- *Module 5. DC Electromagnet as load of the power supply system.* An electromagnet has a significant inductance which must be taken into consideration in the design procedure. The maximum power of the proposed power supply system is 500W which can power a considerable range of low voltage contactors or circuit breakers. Examples are given in Tabl.1 according to [36, 37].

| Type of DC        | Power of the             |

|-------------------|--------------------------|

| contactors        | electromagnet system [W] |

| AL 9, 12, 16      | 3                        |

| AL 26, 30, 40     | 3,5                      |

| AE 45, 50, 63, 73 | 200                      |

| AF 45, 50, 63, 75 | 190                      |

| AE 95, 110        | 400                      |

| AF 95, 110        | 400                      |

| AF 145, 185       | 500                      |

| AF 210, 260, 300  | 520                      |

| AF 400, 460       | 990                      |

- *Module 6. Gate driver for the forward converter.* The gate drive schematic provides the pulse width modulation (PWM) signal to transistors Q1 (point 3) and Q3 (point 5).

- *Module 7. Feedback circuit.* The feedback circuit is based on a linear operational amplifier combined with an optocoupler X1 and additional active filter X2. The schematic gives the precise measurement of the output voltage over the divider R4-R5 (point 6) and options for its software digital control.

- *Module 8. Control system based on an STM32 Cortex microcontroller.* The control system is beyond the scope of the presented paper, but information about these types of microcontrollers can be found in [38, 39].

Figure 2. Schematic of of-line switch mode power supply for DC electromagnets

## **3.** Basic design of the power part of the proposed converter

The power stage of the boost converter follows the design procedures shown in [30, 31, 32], and the design of the forward converter is given in [21, 22, 23, 24, 25]. However, only a specific example is provided here in order to show the feasibility of the proposed schematic.

The parameters used in the design procedure are as follows:

- *I<sub>IN.nom.rms</sub>*, *I<sub>IN.max.rms</sub>*, *I<sub>IN.min.rms</sub>* are the input nominal, maximum and minimum RMS currents.

- *I<sub>OUT.avg</sub>*, *I<sub>OUT.min</sub>*, *I<sub>OUT.max</sub>*, *I<sub>OUT.ripple</sub>* are the average, minimum, maximum and ripple output DC currents.

- *I*<sub>D.rms.Q3</sub> is the Drain-Source current through the boost MOSFET transistor Q3.

- *I*<sub>D.Q1Q2.avg</sub>, *I*<sub>D.Q1Q2.min</sub>, *I*<sub>D.Q1Q2.max</sub> are the Drain-Source average, minimum and maximum current through the primary side MOSFET transistors Q1 and Q2.

- $P_{IN}$ ,  $P_{OUT}$  are the input and output power.

- $P_{BR1}$  is the dissipated power from the rectifier.

- *V*<sub>IN.nom.rms</sub>, *V*<sub>IN.min.rms</sub>, *V*<sub>IN.max.rms</sub>, *V*<sub>IN.pk</sub> are the nominal, minimum, maximum and peak input RMS voltages.

- *V<sub>out</sub>* is the output DC voltage.

- $V_{csR2}$ ,  $V_{csR8}$  are the voltages across the current sense resistors R2 and R8.

- $V_F$  is the forward drop over the input diodes;

- *V<sub>bus</sub>* is the voltage from the boost PFC converter.

- *V*<sub>bus.min</sub> is the minimum voltage from the boost PFC converter.

- $\eta$  is the efficiency.

- *DC*<sub>boost</sub> is the duty cycle of the boost converter.

- *DC<sub>forward</sub>* is the duty cycle of the forward converter.

- $t_{hold-up} = 20ms$  is the standard SMPS holdup time of 20 ms.

- $\Delta I_{L2}$  is the current ripple through the inductor L2.

- $\Delta V_{out\%}$  is the output voltage ripple over the load.

The input parameters of the designed converter are given in Tabl.2.

Table 2. Input parameters of the converter.

| Input voltage AC (minimum)        | 85 V    |  |

|-----------------------------------|---------|--|

| Input voltage AC (maximum)        | 265 V   |  |

| Input voltage AC (nominal)        | 230 V   |  |

| Output voltage DC                 | 230 V   |  |

| Voltage after the boost converter | 400 V   |  |

| Output power                      | 500 W   |  |

| Maximum switching frequency of    | 100 kHz |  |

| the boost and forward converters  |         |  |

The input power  $P_{IN}$  depends on the efficiency. For this design a reasonable assumption is  $\eta = 0.85$ :

$$P_{IN} = \frac{P_{OUT}}{\eta} \tag{1}$$

The input current is at a maximum when the input voltage is at a minimum  $V_{IN,min,rms}$ :

$$I_{IN.max.rms} = \frac{P_{IN}}{V_{IN.min.rms}}$$

(2)

From the same equation the nominal current is:

$$I_{IN.max.rms} = \frac{P_{IN}}{V_{IN.nom.rms}}$$

(3)

The power dissipated from the input bridge rectifier depends on the forward voltage drop  $V_F$ . If it is assumed  $V_F = 0.7V$  the power  $P_{BR1}$  is given from:

$$P_{BR1} = 2. V_F. I_{IN.max.rms} \tag{4}$$

The boost PFC converter must be designed at minimum input voltage  $V_{IN.min.rms}$ , maximum output power  $P_{OUT}$  and maximum input voltage.

The inductor L1 is chosen in order to provide 20% output ripples. The boost PFC converter operates at a constant frequency of 100 kHz, and variable duty cycle  $DC_{boost}$ :

$$DC_{boost} = 1 - \frac{V_{IN.min.rms} \times \eta}{V_{out}}$$

(5)

The inductor L1 value is calculated on the nominal values with 20% current ripple:

$$L_1 = \frac{V_{in.nom.rms} \times (V_{out} - V_{in.nom.rms})}{0.2 \times I_{in.nom.rms} \times F_{sw.boost} \times V_{out}}$$

(6)

The maximum current peak value  $I_{L1.max.pk}$ :

$$I_{L1.max.pk} = \frac{P_{out}.\sqrt{2}}{V_{IN.min.rms}}$$

(7)

The Q3 current can be calculated from:

$$I_{D.rms}^{2} = \frac{2}{T} \int_{0}^{\frac{T}{2}} DC_{boost}(t) . I_{IN.max.rms}^{2}(t) dt =$$

$$I_{D.rms}^{2} = \frac{2}{T} \int_{0}^{\frac{T}{2}} \left( 1 - \frac{V_{IN.pk}.\sin(\omega t)}{V_{bus}} \right) \times$$

(8)

$\times I_{IN.max.rms}^2$ .  $sin^2(\omega t)dt$

Eventually, the current  $I_{D.rms.Q3}$  is:

$$I_{D.rms.Q3} = I_{in.max.rms} \sqrt{\frac{1}{2} - \frac{4}{3\pi} \frac{V_{IN.pk}}{V_{bus}}}$$

(9)

The PFC current sense resistor R2 is:

$$R2 = \frac{V_{csR2}}{I_{L1.max.pk} + \frac{0.2 \times I_{L1.max.pk}}{2}},$$

(10)

but because in this design a standard value of 0.01 Ohm is chosen, the voltage over the resistor is:

$$V_{csR2} = R2. \left( I_{L1.max.pk} + \frac{0.2 \times I_{L1.max.pk}}{2} \right)$$

(11)

This voltage requires an additional operational amplifier X5 connected as a non-inverting amplifier.

In this case the power dissipation over R2 is:

$$P_{R2} = V_{csR2} I_{D.rms.03}$$

(12)

The last result shows that a 1W SMD resistor would be a possible choice.

The boost capacitor C6 must be calculated according to the standard hold-up time of 20ms. where the minimum capacitance can be derivated from:

$$\frac{1}{2}C_6(V_{bus}^2 - V_{bus.min}^2) \ge P_{out}.t_{hold-up}$$

(13)

It has been experimentally tested that during  $t_{hold-up}$  the bus voltage  $V_{bus}$  must not drop under 385V. In order to allow for stable operation, the fluctuation must not be greater than 15V. In this case the minimum capacitance is:

$$C_6 = \frac{P_{out} t_{hold-up}}{V_{bus}^2 - V_{bus.min}^2} \tag{14}$$

Two capacitors rated at  $470\mu F$ , 450V in parallel are a possible solution.

The forward converter also works with a constant switching frequency of 100 kHz. Normally, this type of converter works under a 50% duty cycle but here a safety margin of 10% is applied in order to stabilise the output voltage during the input voltage sag. With this assumption the maximum duty cycle is  $DC_{forward} = 40\%$ . The transformer turn ratio would be:

$$\frac{N_{sec}}{N_{prim}} = \frac{V_{out}}{V_{bus}.DC_{forward}}$$

(15)

The output secondary average current is given from:

$$I_{OUT.avg} = \frac{P_{out}}{V_{out}}$$

(16)

If 20% output current ripple is assumed:

$$I_{OUT.ripple} = 0.2 \times I_{OUT.avg} \tag{17}$$

From these values the primary side average current is given from:

$$I_{D.Q1Q2.avg} = I_{OUT.avg} \cdot \frac{N_{sec}}{N_{prim}}$$

(18)

If the current sense resistor R8 is a standard 0.01 Ohm 1% SMD, the voltage over it would be:

$$V_{csR8} = R8 \times I_{D.Q1Q2.max} \tag{19}$$

which must be amplified from the operational amplifier X6. The dissipated power is 0.12W.

The output inductor ripple is

$$\Delta I_{L2} = \frac{V_{out}}{L_2} \cdot \frac{(1 - DC_{forward})}{f_{sw}}$$

(20)

or if the  $\Delta I_{L2max}$  is the maximum output current:

$$L_2 = \frac{V_{out}}{\Delta I_{L2max}} \cdot \frac{(1 - DC_{forward})}{f_{sw}}$$

(21)

The output capacitor  $C_7$  is calculated from:

$$C7 = \frac{1}{8} \cdot \frac{1 - DC_{forward}}{L_s * f_{SW}^2} \cdot \frac{1}{\Delta V_{out\%}},$$

(22)

where, as a first assumption is taken the voltage output ripple 10% of the nominal output voltage.

The results according to the input parameters are given in Tabl.2.

Tabl.3 Results according to the input parameters given in Tabl.2.

| Equation | Parameter                                                                     | Value                      |

|----------|-------------------------------------------------------------------------------|----------------------------|

| 1        | $P_{IN}$                                                                      | 558 W                      |

| 2        | I <sub>IN.max.rms</sub>                                                       | 6.9 A                      |

| 3        | I <sub>IN.max.rms</sub>                                                       | 2.55 A                     |

| 4        | $P_{BR1}$                                                                     | 8.3 W                      |

| 5        | DC <sub>boost</sub>                                                           | 0.55                       |

| 6        | $L_1$                                                                         | 2.5 mH                     |

| 7        | I <sub>L1.max.pk</sub>                                                        | 8.32 A                     |

| 9        | I <sub>D.rms.Q3</sub>                                                         | 5.1 A                      |

| 11       | $V_{csR2}$                                                                    | 0.092 V                    |

| 12       | $P_{R2}$                                                                      | 0.47 W                     |

| 14       | <i>C</i> <sub>6</sub>                                                         | 849 µF                     |

| 15       | N <sub>sec</sub><br>N <sub>prim</sub>                                         | 1.5                        |

| 16       | I <sub>OUT.avg</sub>                                                          | 2.17 A                     |

| 17       | I <sub>OUT.ripple</sub><br>I <sub>OUT.min</sub><br>I <sub>OUT.max</sub>       | 0.43 A<br>1.95 A<br>2.39 A |

| 18       | I <sub>D.Q1Q2.avg</sub><br>I <sub>D.Q1Q2.min</sub><br>I <sub>D.Q1Q2.max</sub> | 3.2 A<br>2.8 A<br>3.5 A    |

| 19       | V <sub>csR8</sub>                                                             | 0.035 V                    |

| 21       | $L_2$                                                                         | 550 µH                     |

| 22       | C <sub>7</sub>                                                                | 1.5 μF                     |

### 4. Experimental results

The experimental results are shown as follows:

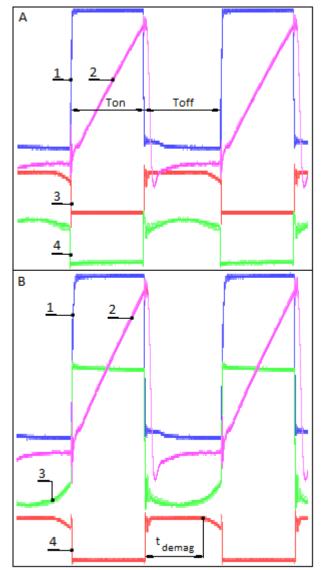

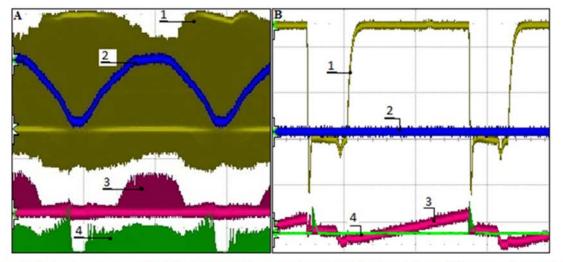

- Fig. 3. The primary side of the forward converter. Transistors **O**1 and Q3 are switched-on simultaneously with the gate drive signal (1). The current through (2) begins each cycle at zero value before reaching the peak. The voltages of the Drain-Source (Fig. 3A, graphics 3, 4) over Q1 and Q2 are equal to the bus voltage. During the gate drive OFF period the transformer is fully demagnetised through diodes D6 and D7. The time of the demagnetisation process is shown on fig. 3B as  $t_{demag}$ . It finishes before the next ON period which prevents the saturation of the transformer. This shows that the design is correct for the given frequency.

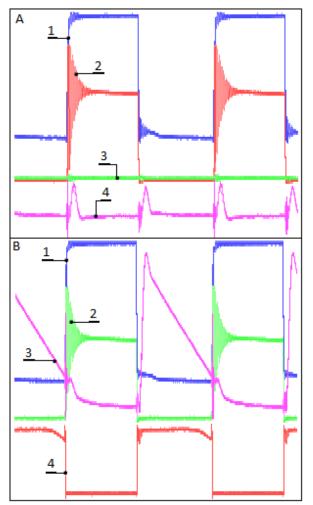

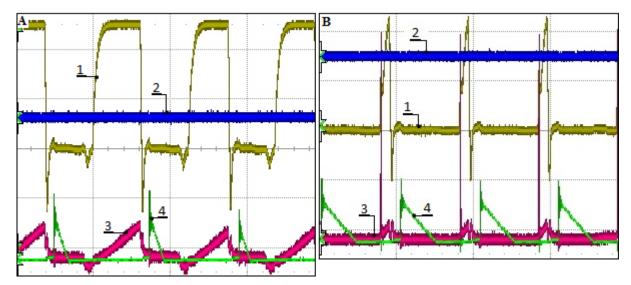

- *Fig. 4. The secondary side of the forward converter.* The output current through the load i.e. the electromagnetic system (Fig. 4A, graphic 4) shows the assumed 10% ripple, and the voltage over the electromagnet is filtered from the output filter. The current through D8 meets its maximum value. Moreover, the provided experiments showed that the two additional snubbers over the diodes D8 (R15, C11) and D9 (R17, C12) are mandatory (30 Ohm, 1nF, 400V). Their design requires experimental measurements and has been done according to [23].

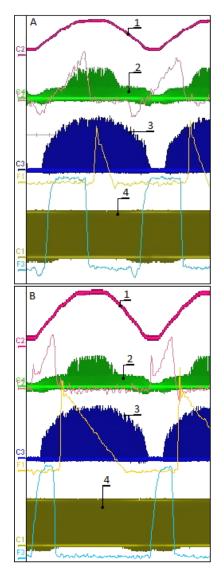

- Fig. 5. The boost converter with PFC and Fig.6 test of the PFC operation mode. The input full wave voltage (Fig. 5A, graphic 2) must have a clear zero crossing point. This means that the capacitor C5 must not smooth the input waveform. For the designed converter, this capacitor can be ceramic with a capacitance in the range 220-330nF. For this module, it was experimentally found that an additional diode D10 is necessary in order to mitigate the inrush current during the start-up transient process. The reason is that the designed converter for this specific application cannot have soft start and input inrush current limitation as such functions could affect the startup time of the electromagnetic system. The PFC operation mode is checked and depicted in three points of the input waveform: zero crossing point (Fig. 5B), 50% (Fig. 6A) and maximum point of the input waveform (Fig. 6B). The modulation of the gate drive PWM (graphic 1) shows that the boost converter works with PFC. Eventually, the power factor is 0.98.

Figure 3. The primary side of the forward converter. A: 1 Gate drive PWM; 2 Primary side current through the transformer; 3, 4, Voltages of the Drain-Source across Q1, Q2;

B: 3 Voltage across the primary side on the transformer.

Fig. 7. Experiment with an input voltage sag. The voltage sag is within 37% of the nominal voltage. If the voltage sag decreases below that value the PFC stage must be switched-off from the microcontroller. Fig. 7A shows the input waveform after the rectifier on the minimum input and Fig. 7B the same waveform on the nominal input. The average currents and PWM are also depicted. During the sag time the output voltage (Fig. 4A, graphic 3) has remained constant which shows the stable operation of the entire system. The presented experiments have been done with several types of electromagnets functioning as a propulsion system of electromagnetic contactors. A switching ON-OFF process on the contact system (Fig. 1A) has not been mentioned.

The conducted experiments showed that a stable operation under the minimum under voltage is also possible but these several additional steps must be considered: the boost converter stops the PFC operation and stabilises the bus voltage on the maximum possible value; the forward converter works with 50% duty cycle instead of the assumed (eq. 15) 40%. Alternatively, in the design procedure even smaller nominal duty cycle can be applied along with a higher transformer turn ratio. This would give an additional voltage margin.

Figure 4. The secondary side of the forward converter.

A: 1. Gate drive PWM; 2. Voltage across the inductor L2;

3. Output voltage across the electromagnet; 4. Output current through the electromagnet.

B: 1. Gate drive signal, 2. Voltage across the inductor L2,

3. Current across D9 during the freewheeling cycle,

4. Voltage across Q1.

Figure 5. The boost converter with PFC. A: 1. Gate drive signal on Q3 (100 kHz), 2. Input full-wave voltage after the rectifier (100 Hz). 3. Current through the Drain-Source of the transistor Q3. 4. Current through the diode D5. B: Testing the PFC. 1 Maximum duration of the gate drive signal (1) when the input voltage (2) is at zero point. 3. Current through Q3. 4. Current through D5.

Figure 6. Test of the PFC operation mode (continuation of Fig. 6). A: 1. 50% duration of the gate drive signal (1) when the input voltage (2) is at 50%. B: 1. Minimum duration of the gate drive signal (1) when the input voltage (2) is at maximum point. 3. Current through Q3. 4. Current through D5.

### 5. Conclusion

Generally, the designed and experimentally tested converter works steadily in the proposed application. The input boost converter stabilised the bus voltage on 400V during the PFC operation in the proposed input voltage range. The experimental verification shows that the PFC stage works normally (Fig. 5, Fig. 6) under the nominal input voltage and should be switched-off during the voltage sag.

The output boost voltage provides a safety margin for the next two-switch forward converter. This converter works steadily (Fig. 3, Fig. 4) under nominal condition with a safety margin on the maximum duty ratio.

Figure 7. A. Experiment with an input voltage sag voltage.

B. Nominal input voltage. 1 Input voltage after the rectifier; 2 Current through boost transistor Q3; 3.

Current through boost diode D5; 5. Gate drive on Q3.

#### References

- Dhend M., Chile R.(2007). Characterization of Fault using Voltage Sag Profile. *International Journal of Engineering Technology Science and Research*,4(5), 17-27.

- [2]. Kamble, S., & Thorat, C. (2014). Voltage Sag Characterization in a Distribution Systems: A Case Study. *Journal of Power and Energy Engineering*, 2(04), 546-553.

- [3]. Debdas, S., Paikra, S., & Choudhury, T. R. (2013). Voltage Sag Detection through Wavelet Energy Coefficient. *International Journal of Computer and Electrical Engineering*, 5(4), 383-386.

- [4]. Li, Y., Yue, T., Xie, H., & Wang, F. (2013). Study on Voltage Sag Detection of Wind Power System Based on HHT. *Energy and Power Engineering*, 5(04), 922-926.

- [5]. Omar, R., & Rahim, N. A. (2009, May). New control technique applied in dynamic voltage restorer for voltage sag mitigation. In *Industrial Electronics and Applications*, 2009. *ICIEA* 2009. 4th IEEE Conference on (pp. 848-852). IEEE.

- [6]. Nagendrababu V., Sreekanth G. Narender N. Srujana A.(2012). Series Compensation Technique for Voltage Sag Mitigation. *Journal of Engineering*, 2(8), 14-24.

- [7]. El-Gammal, M. A., Abou-Ghazala, A. Y., & El-Shennawy, T. I. (2011). Dynamic voltage restorer (DVR) for voltage sag mitigation. *International Journal on Electrical Engineering and Informatics*, 3(1), 1.

- [8]. Suresh, P., & Baskaran, B. (2017). Voltage sag compensation in multiline distribution system using closed loop controlled IDVR. *International Journal of Applied Engineering Research*, 12(8), 1576-83.

- [9]. Anjana S, Revathi H, Karthik R, Kavitha I. (2014). A Multiple Output Dc-Dc Converter Using Two Switch Forward Topology, *International Journal of* Advanced Research in Electrical, Electronics and Instrumentation Engineering, 3(5), 338-345.

- [10]. Patil, M. P. R., & Dinesh, M. M. (2013). Variable output AC-DC converter. *International Journal of Computer Trends and Technology*, 4(7), 2164-2169.

- [11]. Ghodke, D. V., & Muralikrishnan, K. (2002). ZVZCS, dual, two-transistor forward DC-DC converter with peak voltage of Vin/2, high input and high power application. In *Power Electronics Specialists Conference, 2002. pesc 02. 2002 IEEE* 33rd Annual (Vol. 4, pp. 1853-1858). IEEE.

- [12]. Lakshmi. R, Rajan K.(2014). Comparison of Two Switch And Three Switch Serial Input Interleaved Forward Converters, *International Journal of Innovative Research in Science, Engineering and Technology*, 3(2), 9349-9359.

- [13]. Huang, J. C., Wong, Y. S., & Kuo-Bin Liu, N. S. R. R. C. (2012). Zero Voltage Switching of Two-switch Flyback-Forward Converter. In *Conf. Proc.* (Vol. 1205201, No. IPAC-2012-THPPD063, pp. 3656-3658).

- [14]. Prakash, O., Chauhan A., Nadir A.(2015). Modeling and Analysis of Micro Inverter Using Dual Switch Forward Converter Push-Pull Topology, *International Journal of Engineering Science Invention Research & Development*, 1(12), 474-478.

- [15]. Perumal S, Sivanand K., Rajashekar J.(2015). Dual Switch Forward & Flyback Converter: A Comparison, International Journal of Innovative Science, Engineering & Technology, 2(4), 204-208.

- [16]. Sukesh A, Gururaj K.(2017). Two Switch Forward Converter for Charging of Battery through Hybrid Charging Technique, *International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering*, 5(2),37-41.

- [17]. Neelakrishnan G., Kannan M., Selvaraju S., Vijayraj K., Balaji M., Kalidass D.(2013). Transformer Less Boost DC-DC Converter with Photovoltaic Array, *IOSR Journal of Engineering*, 3(10), 30-37.

- [18]. Choi, W. Y., Yang, M. K., & Suh, Y. (2014). Highefficiency supercapacitor charger using an improved two-switch forward converter. *Journal of Power Electronics*, 14(1), 1-10.

- [19]. Kim, Y. S., Jung, D. W., & Lee, B. K. (2013). Advanced LDC test bed using energy recovery technique for HEVs. *Journal of Electrical Engineering & Technology (JEET)*, 8(4), 911-919.

- [20]. Birbir Y.(2017). Arc Welding Machine with Half-Bridge Forward Converter, *International Journal of Electronics and Electrical Engineering*, 5(2),106-109.

- [21]. ST Microelectronics, 2.5 kW MMA Welding Machine, Application Note AN3200, September 2010 <u>www.st.com</u>

- [22]. Analog Devices, Interleaved Two-Switch Forward Topology Featuring the ADP1046, Evaluation Board User Guide, UG-320, 2012, <u>www.analog.com</u>

- [23]. Infineon Technologies, 200W SMPS Demonstration Board II, Application Note AN-CoolMOS-09, Version 1.0, September 2004, http://www.infineon.com

- [24]. Intersil, A 50W, 48V-to-5V DC-DC Converter Using the HIP2100, Application Note AN96205, 1996, www.intersil.com

- [25]. Fairchild Semiconductor, Primary-Side Synchronous Rectifier (SR) Trigger Controller for Dual Forward Converter, Application Note FAN6210, Rev. 1.0.2. 2009, <u>www.fairchildsemi.com</u>

- [26]. Vishhay Siliconix, Two-Switch Forward Converter: Operation, FOM, and MOSFET Selection Guide, Application Note 91616, January 2014, www.vishay.com

- [27]. Linear Technology, 2-Switch Forward Controller and Gate Driver, LTC3705, 2006, <u>www.linear.com</u>

- [28]. Texas Instruments, LM5015 High Voltage Monolithic Two-Switch Forward DC-DC Regulator, Application Note SNVS538C, April 2013, www.ti.com

- [29]. Texas Instruments, ISO122 Precision Lowest-Cost Isolation Amplifier. Application note, January 2015, www.ti.com

- [30]. On Semiconductor. Implementing Power Factor Correction with the NCP1608. Application note AND8396/D, July 2009, <u>www.onsemi.com</u>

- [31]. Microchip Technology Inc., PFM/PWM Step-Up DC/DC Converter, TC115. Application note 2003. <u>http://www.microchip.com/</u>

- [32]. Microchip Technology Inc., Power Factor Correction in Power Conversion Applications Using the dsPIC DSC, Application note 2007, <u>http://www.microchip.com/</u>

- [33]. Balanis, C. A. (1999). Advanced engineering electromagnetics. ISBN 0-471-62194-3, John Wiley & Sons.,

- [34]. Bansal, R. (2006). Fundamentals of engineering electromagnetics. CRC press.

- [35]. Herbert P., Neff Jr.(1991). *Introductory Electromagnetics*, ISBN 0-471-60550-6, John Wiley & Sons, Inc.

- [36]. ABB. Contactors Motor Protection Accessories. 2007. www.abb.ca

- [37]. ABB. *Line contactors A9-AF1650.* 2015 <u>www.abb.ca</u>

- [38]. STMicroelectronics, Datasheet production data STM32F205xx, STM32F207xx, www.st.com. 2016

- [39]. Brown G, *Discovering the STM32 Microcontroller*. Indiana University, 2016.