# UNIVERSITY OF SOUTHAMPTON

# Separating Computation from Communication: A Design Approach for Concurrent Bug Finding

by

Ermenegildo Tomasco

A thesis submitted in partial fulfillment for the degree of Doctor of Philosophy

in the

Faculty of Engineering, Science and Mathematics School of Electronics and Computer Science

October 2017

#### UNIVERSITY OF SOUTHAMPTON

#### ABSTRACT

# FACULTY OF ENGINEERING, SCIENCE AND MATHEMATICS SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

#### Doctor of Philosophy

by Ermenegildo Tomasco

With the spread of multi-core systems, the need to write concurrent programs in order to take advantage of their multi-core processors continues to grow. Developing concurrent programs free of errors is very difficult, due to their often non-deterministic nature. Further, weak memory models (WMMs) implemented in modern multi-core hardware architectures introduce additional executions that can lead to seemingly counter-intuitive results which confound the developers' reasoning. Although testing is a widely used approach to finding program errors, testing-only approaches, such as stress testing, remain highly ineffective for concurrency errors that rarely manifest themselves and are difficult to reproduce.

Despite the substantial advancements in the field of analysis and verification of concurrent programs assuming the classical *Sequential Consistency* (SC) memory model, the state-of-the-art technology for other WMMs is quite unsatisfactory.

The main goal of this thesis is to extend existing successful techniques that have been implemented for SC to more general WMMs. This work describes a general approach that allows to combine different verification techniques with different memory models in the style of a plug-and-play architecture. Its main idea is to introduce an abstraction that allows us to separate the computation and communication concerns of concurrent programs, without loosing the efficiency of existing approaches. We start by introducing an abstract data type, called *shared memory abstraction* (SMA), that encapsulates the semantics of the underlying memory model and implements it under the simpler SC and assume that all the standard concurrency operations in multi-threaded programs are performed by invoking the corresponding calls to *API operations* over the SMA.

Furthermore, we implement efficient SMAs for *Total Store Ordering* (TSO) and *Partial Store Ordering* (PSO) semantics in our tool *LazySMA* and we experimentally demonstrate that it is very effective in finding bugs on a large set of benchmarks from the literature.

Then, we formally characterize the concept of thread-asynchronous transition systems that allows us to optimize intra-thread analysis by rearranging the operations of the threads. this thesis also shows that several concurrent verification techniques from the literature can easily be recast in our setting and thus be extended to weak memory models. We give thread-asynchronous SMA implementations for the SC, TSO, and PSO memory models that are based on the idea of individual memory unwinding. Finally, we instantiate our approach by developing a new, efficient BMC-based bug finding tool for multi-threaded C programs under SC, TSO, or PSO memory models, and experimentally demonstrate on the same set of benchmarks used for LazySMA that it is competitive with existing tools.

CONTENTS

# Contents

| 1 | Intr | oduction                                                           | 1  |  |  |  |  |  |

|---|------|--------------------------------------------------------------------|----|--|--|--|--|--|

|   | 1.1  | Problem Description                                                | 1  |  |  |  |  |  |

|   | 1.2  | Our Contributions                                                  | 3  |  |  |  |  |  |

|   | 1.3  | Structure of the thesis                                            | 6  |  |  |  |  |  |

| 2 | Bac  | kground                                                            | 7  |  |  |  |  |  |

|   | 2.1  | Alphabets, Words and Languages                                     |    |  |  |  |  |  |

|   | 2.2  | Transition systems                                                 |    |  |  |  |  |  |

|   | 2.3  | Multithreaded programs                                             |    |  |  |  |  |  |

|   |      | 2.3.1 Memory Models                                                | S  |  |  |  |  |  |

|   |      | Sequential Consistency (SC)                                        | 9  |  |  |  |  |  |

|   |      | Total Store Ordering (TSO)                                         | 6  |  |  |  |  |  |

|   |      | Partial Store Ordering (PSO)                                       | 10 |  |  |  |  |  |

|   |      | 2.3.2 Syntax of programs                                           | 10 |  |  |  |  |  |

|   |      | 2.3.3 Semantics of programs                                        | 11 |  |  |  |  |  |

|   |      | 2.3.4 Reachability problems                                        | 12 |  |  |  |  |  |

|   | 2.4  |                                                                    |    |  |  |  |  |  |

|   |      | 2.4.1 Boolean Satisfiability                                       | 13 |  |  |  |  |  |

|   | 2.5  | Bounded Model Checking                                             |    |  |  |  |  |  |

|   | 2.6  | Bounded Model Checking of Concurrent Programs                      |    |  |  |  |  |  |

|   |      | 2.6.1 Context-Bounded Analysis                                     | 15 |  |  |  |  |  |

|   |      | 2.6.2 Sequentialization                                            | 15 |  |  |  |  |  |

|   |      | 2.6.2.1 Eager Sequentialization                                    | 17 |  |  |  |  |  |

|   |      | MU-CSeq                                                            | 17 |  |  |  |  |  |

|   |      | 2.6.2.2 Lazy Sequentialization                                     | 22 |  |  |  |  |  |

|   |      | Lazy-CSeq                                                          | 23 |  |  |  |  |  |

|   |      | 2.6.3 CSeq framework                                               | 26 |  |  |  |  |  |

| 3 | Sep  | arating Computation from Communication                             | 29 |  |  |  |  |  |

|   | 3.1  | Introduction                                                       | 30 |  |  |  |  |  |

|   | 3.2  | Multi-Threaded Programms over Shared Memory Abstractions 31        |    |  |  |  |  |  |

|   |      | 3.2.1 Shared Memory Abstractions                                   | 32 |  |  |  |  |  |

|   |      | 3.2.2 Multi-threaded programs as composition of transition systems | 33 |  |  |  |  |  |

|   | 3.3  | Verification with thread-asynchronous SMAs                         | 34 |  |  |  |  |  |

vi CONTENTS

|          |     | 3.3.1    | Thread-asynchronous SMAs                               |

|----------|-----|----------|--------------------------------------------------------|

|          |     |          | 3.3.1.1 Thread-asynchronous SMAs for thread interfaces |

|          |     |          | 3.3.1.2 Extension to weak memory models                |

|          | 3.4 | Relate   | d Work                                                 |

|          | 3.5 | Conclu   | isions                                                 |

| 4        | Laz | y Sequ   | entialization for TSO and PSO via SMA                  |

|          | 4.1 | Introd   | uction                                                 |

|          | 4.2 | Design   | ing a TSO Shared Memory Abstraction                    |

|          |     | 4.2.1    | TSO-SMA                                                |

|          |     | 4.2.2    | Timestamping writes                                    |

|          |     | 4.2.3    | eTSO-SMA                                               |

|          |     | 4.2.4    | Temporal Circular Doubly Linked List                   |

|          | 4.3 | Impler   | mentation of eTSO-SMA                                  |

|          |     | 4.3.1    | Memory bounds                                          |

|          |     | 4.3.2    | Auxiliary data structures                              |

|          |     | 4.3.3    | Malloc and init                                        |

|          |     | 4.3.4    | Clock update                                           |

|          |     | 4.3.5    | Write operation                                        |

|          |     | 4.3.6    | Ind-write operation                                    |

|          |     | 4.3.7    | Read operations                                        |

|          |     | 4.3.8    | Fence operation                                        |

|          |     | 4.3.9    | Correctness                                            |

|          | 4.4 | Extens   | sion to the PSO memory model                           |

|          | 4.5 | LazySl   | MA Implementation and Evaluation                       |

|          | 4.6 | Relate   | d Work                                                 |

|          | 4.7 | Conclu   | isions                                                 |

| <b>5</b> | Bug | g findin | ng in Concurrent Programs by Memory Unwinding          |

|          | 5.1 | Introd   | uction                                                 |

|          | 5.2 | Memor    | ry unwinding.                                          |

|          |     | 5.2.1    | MU transition system                                   |

|          | 5.3 | Fine-g   | rained MU-based SMA                                    |

|          |     | 5.3.1    | Fine-grained MU-based SMA implementations              |

|          |     |          | 5.3.1.1 Data structures and invariants                 |

|          |     |          | 5.3.1.2 Simulation variables and auxiliary functions   |

|          |     |          | 5.3.1.3 Schema with Explicit Read Operations           |

|          |     |          | Memory initialization                                  |

|          |     |          | Thread creation, termination, join, and finish         |

|          |     |          | Read and write operations                              |

|          |     |          | Ind_read and ind_write operations                      |

|          |     |          | Address operation                                      |

CONTENTS vii

|    |        | Malloc operation                                               | 73  |

|----|--------|----------------------------------------------------------------|-----|

|    |        | Lock and unlock mutex variables                                | 73  |

|    |        | 5.3.2 Schema with Implicit Read Operations                     | 74  |

|    |        | Memory initialization.                                         | 75  |

|    |        | Read operation                                                 | 75  |

|    |        | 5.3.3 Hybrid Schema with Implicit and Explicit Read Operations | 76  |

|    | 5.4    | Coarse-grained MU-based SMA encodings                          | 76  |

|    |        | 5.4.1 Auxiliary Data Structures                                | 77  |

|    |        | 5.4.2 Shared memory procedures (Coarse-grained)                | 78  |

|    |        | Auxiliary functions                                            | 78  |

|    |        | Thread creation, termination, join, and finish                 | 79  |

|    |        | Read and write operations.                                     | 80  |

|    |        | Lock and unlock mutex variables                                | 81  |

|    | 5.5    | Mu-CSeq Implementation and Evaluation                          | 81  |

|    | 5.6    | Related work                                                   | 84  |

|    | 5.7    | Conclusions                                                    | 84  |

| 6  | Ind    | ividual Memory Location Unwindings                             | 87  |

|    | 6.1    | Introduction                                                   | 87  |

|    | 6.2    | IMU-based SMAs                                                 | 88  |

|    |        | IMU-based SMA for SC                                           | 88  |

|    |        | IMU-based SMA for TSO and PSO                                  | 89  |

|    |        | Verification by IMU                                            | 90  |

|    | 6.3    | IMU-based SMA implementations                                  | 90  |

|    |        | 6.3.1 IMU implementation for SC                                | 90  |

|    |        | Thread creation, termination, and join                         | 93  |

|    |        | Read and write operations                                      | 94  |

|    |        | Address and malloc operations                                  | 95  |

|    |        | Ind_read and ind_write operations                              | 95  |

|    |        | Lock and unlock mutex variables                                | 96  |

|    |        | 6.3.2 IMU implementation for TSO                               | 96  |

|    |        | 6.3.3 IMU implementation for PSO                               | 98  |

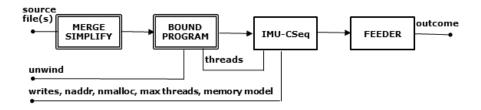

|    | 6.4    | IMU-CSeq Implementation and Evaluation                         | 98  |

|    | 6.5    | Conclusions                                                    | 102 |

| 7  | Cor    | nclusions                                                      | 103 |

|    | 7.1    | Summary of work                                                | 103 |

|    | 7.2    | Future work                                                    | 105 |

| Bi | ibliog | graphy                                                         | 107 |

viii LIST OF FIGURES

# List of Figures

| 2.1  | TSO architecture.                                                           | 9  |

|------|-----------------------------------------------------------------------------|----|

| 2.2  | Syntax of multi-threaded programs.                                          | 10 |

| 2.3  | Bounded model-checking: SSA form and VC generation of a simple program      | 14 |

| 2.4  | Multi-threaded Fibonacci: (a) C-code for 5 iterations, (b) translated code, |    |

|      | and sample memory unwindings: (c) fine-grained and (d) coarse-grained.      | 18 |

| 2.5  | $P_S$ : Mu main()                                                           | 20 |

| 2.6  | Mu-CSeq Rewriting rules                                                     | 21 |

| 2.7  | Producer/Consumer Example                                                   | 23 |

| 2.8  | Lazy-CSeq main driver                                                       | 24 |

| 2.9  | Lazy-CSeq translation of example program in Figure 2.7                      | 25 |

| 2.10 | Architecture of the CSeq framework                                          | 26 |

| 2.11 | Source transformation module: from $x++$ to $x=x+1$                         | 27 |

| 3.1  | Shared Memory Abstraction APIs                                              | 32 |

| 4.1  | T-CDLL example.                                                             | 46 |

| 4.2  | eTSO-SMA variable declarations                                              | 48 |

| 4.3  | eTSO-SMA clock_update function                                              | 49 |

| 4.4  | eTSO-SMA write and write_to_address functions                               | 50 |

| 4.5  | eTSO-SMA read and read_from_address functions.                              | 51 |

| 4.6  | eTSO-SMA fence function.                                                    | 52 |

| 4.7  | Architecture of the LazySMA tool                                            | 56 |

| 5.1  | Fine-grained MU: Auxiliary functions for MU implementation                  | 68 |

| 5.2  | Fine-grained MU: Constraints on memory structures                           | 69 |

| 5.3  | Fine-grained MU: init_address and init_malloc functions for MU implemen-    |    |

|      | tation.                                                                     | 69 |

| 5.4  | Fine-grained MU: Computation of array mem (explicit read-schema)            | 70 |

| 5.5  | Fine-grained MU: procedure init (explicit read schema)                      | 71 |

| 5.6  | Fine-grained MU: Function create                                            | 71 |

| 5.7  | Fine-grained MU: Procedure terminate                                        | 71 |

| 5.8  | Fine-grained MU: Procedures join and finish                                 | 72 |

| 5.9  | Fine-grained MU: Read and write functions (explicit read-schema)            | 73 |

| 5.10 | Functions address and malloc                                                | 73 |

| 5.11 | Mutex lock and unlock operations                                            | 74 |

LIST OF FIGURES  $\underline{\hspace{1cm}}$  ix

| 5.12 | Fine-grained MU: Computation of array var_next_write (implicit read-  |

|------|-----------------------------------------------------------------------|

|      | schema)                                                               |

| 5.13 | Fine-grained MU: Procedure init (implicit read schema)                |

| 5.14 | Fine-grained MU: Procedure read (implicit read schema)                |

| 5.15 | Coarse-grained MU: Constraints on memory structures                   |

| 5.16 | Coarse-grained MU: Auxiliary functions                                |

| 5.17 | Coarse-grained MU: Procedures create and terminate                    |

| 5.18 | Coarse-grained MU: Procedure join                                     |

| 5.19 | Coarse-grained MU: Procedure finish                                   |

| 5.20 | Coarse-grained MU: Procedures read and write                          |

| 5.21 | Coarse-grained MU: Procedures lock and unlock                         |

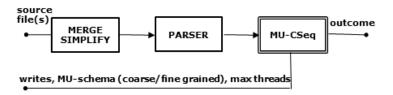

| 5.22 | Architecture of the MU-CSeq tool                                      |

| 6.1  | IMU initialization                                                    |

| 6.2  | IMU: init_address and init_malloc functions for IMU implementation 93 |

| 6.3  | IMU: Auxiliary functions for IMU implementation                       |

| 6.4  | IMU: Functions create, terminate and join 94                          |

| 6.5  | IMU: Read and write functions                                         |

| 6.6  | IMU: Functions address and malloc                                     |

| 6.7  | IMU: Mutex lock and unlock operations                                 |

| 6.8  | IMU: Functions read, fence and write for TSO                          |

| 6.9  | Architecture of the IMU tool                                          |

x LIST OF TABLES

# List of Tables

| 4.1 | Analysis runtimes under TSO and PSO                                                                                       | 57  |

|-----|---------------------------------------------------------------------------------------------------------------------------|-----|

| 4.2 | Analysis runtimes for SafeStack under TSO and PSO                                                                         | 59  |

| 5.1 | Performance comparison among different tools on the unsafe instances of the SV-COMP15 Concurrency category                | 83  |

| 6.1 | Performance comparison among different tools for SC semantics on unsafe instances from the SV-COMP16 Concurrency category | 100 |

| 6.2 | Analysis runtime under TSO/PSO                                                                                            | 101 |

To my wonderful daughter Desiree T....

# Chapter 1

# Introduction

# 1.1 Problem Description

Modern computer architectures use several cores that work in parallel in order to increase their computational power. With the spread of these architectures, the need to write multithreaded programs in order to take advantage of their multi-core processors continues to grow.

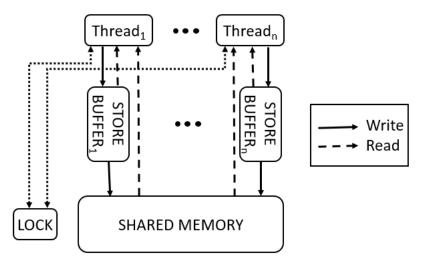

Typically, multithreaded programs consist of several components, called threads, which run in parallel and communicate with each other through shared memory. A shared memory is a sequence of memory locations of fixed size. The content of each location can be read or written using an explicit memory operation. The semantics of read and write operations depend upon the adopted memory model<sup>1</sup>. In the classical Sequential Consistency (SC) memory model [Lam79] when a shared memory location is written by a thread, its new valuation is immediately visible to all the other threads. For performance reasons, due to the gap between CPU and memory speeds, modern multi-core hardware architectures implement weak memory models (WMMs), that allows optimizations such as instruction reordering, store buffering or write atomicity relaxation [AG96]. For example, the total store ordering (TSO) memory model [MA15, SSO+10a] uses buffering to speed up execution time of multi-threaded programs. Each thread t is equipped with a local store buffer that is used to cache the write operations performed by t. Updates to the shared memory occur nondeterministically along the computation. Before updating, the effect of a cached write is visible only to the thread that has performed it. For partial store ordering (PSO) each thread is endowed with a store buffer for each shared memory location. In the rest of this chapter and throughout the thesis we use the terms shared-memory multithreaded programs, multithreaded programs and concurrent programs interchangeably.

<sup>&</sup>lt;sup>1</sup>To provide semantics to concurrent programs, we reason at the programming level (as in [SSO<sup>+</sup>10a]), by replacing each memory access with a composition of read-and-write operations that are executed atomically and whose semantics is given in Section 2.3.1.

Developing concurrent programs free of errors is already hard when assuming the SC memory model, due to the large number of possible ways in which the different elements of a concurrent program can interact with each other. The reordering allowed by WMMs has made this task even harder, because they introduce additional executions that can lead to seemingly counter-intuitive results that confound the developers' reasoning. Thus, automatic verification tools that enable detection of errors in a systematic and symbolic way are essential.

Testing remains the most widely used approach to finding program errors. It is useful when a high percentage of the selected executions lead to a violation of the program specification. However, testing-only approaches, such as stress testing, remain highly ineffective for concurrency errors that manifest themselves rarely and are difficult to reproduce and repair [TDB14]. Such "Heisenbugs" [MQB+08] have become more prevalent on modern hardware architectures that use weak memory models, because WMMs introduce additional non-determinism that remains outside the control of the testing environment. Consequently, testing needs to be complemented by automated verification techniques that can handle concurrency (and the non-determinism it introduces) symbolically.

However, it is difficult to build efficient symbolic verification tools for realistic programming languages like C, and harder yet to extend them to handle concurrency. Concurrent programs are very different in nature from sequential programs. The large number of possible ways in which the different components of a concurrent program can interact (e.g., the different interleavings of a multi-threaded program) makes it diffcult to scale up approaches that explicitly explore individual interactions (e.g., ESBMC [CF11] or CHESS [MQB07]). Therefore, symbolic approaches to handling concurrency, where all possible interactions are analyzed simultaneously, are desirable, but these approaches still face the problem of exponentially growing symbolic state spaces.

Tools often compromise generality to achieve efficiency, by focusing on a specific memory model, typically sequential consistency (SC), and by folding the concurrency handling deep into their general verification approaches (see [AAA<sup>+</sup>15, AKT13, ABP11, BCDM15, WT15, ZKW15]). This in turn introduces a strong coupling between the two, which makes it hard to reuse existing tools and to generalize solutions to other memory models.

Despite the substantial advancements in the field of analysis and verification of concurrent programs assuming the SC memory model, the state-of-the-art technology for other WMMs is quite unsatisfactory. The starting point of our research is thus to extend existing successful approaches that have been implemented for the simpler SC memory model to WMMs, without loosing their efficiency and preserving their correctness.

SAT/SMT-based bounded model checking (BMC) [CGP99] is a technique which, given a program, a property, and a bound k, translates the program into a SAT or SMT (quantified free) formula that is satisfiable if and only if the property has a counterexample whose size is less than k. It has been used successfully to discover subtle errors in sequential

software, even at large scale [KT14, SKB<sup>+</sup>15]. Sequential BMC tools can be extended symbolically to the concurrent case by conjoining the formulae representing the effect of each individual thread in isolation with an additional formula representing the possible interferences caused by concurrent accesses to the shared memory [SW11, AKT13]. Since this additional formula effectively includes an axiomatization of the underlying memory model, this approach can in principle work for both sequential consistency (SC) and different WMMs. However, embodying a memory model at the formula level requires extensive (and non-reusable) modifications of the underlying sequential BMC tool, and can affect scalability since the resulting expressions are large and complex.

An alternative approach is *sequentialization*, which translates concurrent programs into sequential programs with data non-determinism that (under certain assumptions) behave equivalently, so that the different interleavings do not need to be treated explicitly during the analysis. This allows the reuse of existing sequential BMC tools. The idea of sequentialization was proposed by Qadeer and Wu [QW04], but the most popular sequentialization that could handle an arbitrary but bounded number of context switches was proposed by Lal and Reps [LR09].

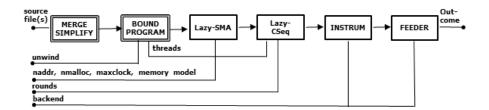

Sequentializations can be used as basis of very effective bug finding tools, such as our MU-CSeq [TIF+15b] and Lazy-CSeq [ITF+14a]. This is witnessed by our tools' top rankings in recent software verification competitions but is also borne out in practice: for example, using Lazy-CSeq we discovered in 30 minutes a bug in the safestack benchmark [Vyu10], while all other approaches, including testing, failed [TDB14]. However, to the best of our knowledge, sequentializations have been developed only for SC, and not for any of the WMMs that are prevalent in modern computer architectures.

## 1.2 Our Contributions

The main goal of this thesis is to extend existing successful bug finding techniques that have been implemented for SC to more general WMMs. We describe a general approach that allows to combine different verification techniques with different memory models in the style of a plug-and-play architecture. We also instantiate our approach by developing new efficient BMC-based bug finding tools for multi-threaded C programs under SC, TSO, or PSO memory models, and show experimentally that they are very effective in finding bugs on a large set of benchmarks from the literature.

**Separating Computation from Communication**. Our main idea is to introduce an abstraction that allows us to separate the computation and the communication concerns of concurrent programs, without loosing the efficiency of existing approaches.

**Shared Memory Abstraction**. We introduce an abstract data type that encapsulates the semantics of the underlying memory model and implements it under the simpler

SC. We call this abstract data type shared memory abstraction (SMA). In particular, we assume that all the standard concurrency operations in multi-threaded programs are performed by invoking the corresponding calls to API operations over a shared memory abstraction. Introducing the SMA provides a separation of concerns between the shared memory and the control-flow related aspects of concurrent programs, such that the verifier design can focus on each of these aspects in isolation. Our approach bears some similarity to the axiomatic representation of memory models [SW11, AKT13] but the fundamental difference is that we work at the code level. We replace all accesses to shared memory items (i.e., reads from and writes to shared memory locations, and synchronization primitives like lock and unlock) by explicit calls to API operations over the given shared memory abstraction. For example, if x and y are two shared scalar variables then the statement x = y + x + 3 is translated into write(x, read(y) + read(x) + 3).

Extending Lazy-CSeq to handle TSO and PSO. Following this approach, we propose novel SMA implementations for TSO and PSO that are carefully designed to optimize some parameters that lead, in combination with a lazy sequentialization targeting BMC tools, to efficient SAT/SMT encodings. We implement this approach by extending our Lazy-CSeq tool, that implements our Lazy Sequentialization for SC [ITF<sup>+</sup>14a]. We compare our implementation, called LazySMA, with other verification tools for WMMs. The experiments show that our approach delivers a comparable performance on simple benchmarks, but outperforms these tools on more complex problems.

Our general approach. Although this approach has been successful in combination with Lazy-CSeq, extending verification methods to other memory models by simply replacing the SMA implementation might not result in scalable verification tools, for the following reason. To preserve the correct semantics of the memory operations, these must be invoked in the same order as they appear along the run, which may be a bottleneck when we explore the state space of the program, both in case of the analysis based on summaries (e.g., BDD-based model checking) or bounded model checking. In the former, we must keep a cross-product of the states of all threads in the configurations; this is a well-known problem that leads to state-space explosion. In the latter, since context-switches can happen at any point, we must encode into the SAT/SMT formula the code of all threads for each of the context-switch points in the underlying bounded multi-threaded program, which leads to large formulas.

Some approaches from the literature instead explore the program executions by rearranging the order in which the memory operations of the different threads are executed, e.g., by simulating each thread to completion [LMP10, LR09]. More generally, the approach of verifying each thread in isolation is also the essence of the compositional approaches based on assume-guarantee reasoning [MC81, Jon83].

We generalize the ad-hoc approaches above, in our SMA framework where now intrathread analysis can be optimized by rearranging the operations of the threads. This requires that the used SMA implementation is thread-asynchronous, that is that its behaviours are insensitive to how the threads are interleaved. This allows us to transform freely the threads as long as we stay within the class of thread-wise equivalent programs, that is programs where the intra-thread ordering of the statements remains the same. We formalize the correctness of the derived design approach and also discuss how previous successful approaches from the literature fit into our setting, yielding correctness proofs for free; then we extend them to other more realistic memory models.

Thread-asynchronous SMA implementations. We also develop thread-asynchronous shared memory abstraction implementations for SC, TSO and PSO memory models, based on the idea of individual shared memory location unwinding (IMU for short), that extends the simpler concept of memory unwinding (MU for short), i.e. an explicit representation of the sequence of write operations into the shared memory, that we have introduced in [TIF<sup>+</sup>15b].

More specifically, we first give a novel implementation of thread-asynchronous shared memory abstraction based on the idea of memory unwinding for SC memory model. For the verification, we nondeterministically guess this unwinding and then explore all the executions of the program that respect this guess; each thread is simulated in isolation in according with the initially guessed memory unwinding. This approach is complementary to other approaches [FIP13a, LR09, LMP10] and explores an orthogonal dimension, i.e., the number of write operations of the shared memory. We follow up on the observation of Lu et al. [LPSZ08], that only a few memory accesses are relevant to finding concurrency bugs.

We implement our MU-based thread-asynchronous SMAs for SC in our prototype tool MU-CSeq and combine them with our eager sequentialization [TIF<sup>+</sup>15b]. We evaluate MU-CSeq over the set of concurrency benchmarks from the SV-COMP benchmark suite and we show that our tool compares well with existing tools with built-in concurrency handling as well as other sequentializations.

Finally, we extend the idea of memory unwinding to individual shared memory location unwinding and implement thread-asynchronous SMA implementations for the SC, TSO and PSO memory models that are based on this new concept. In particular, IMU splits the sequence of write operations of the shared memory into different sequences, one for each individual shared memory location. This simplifies the handling of store buffers in WMM and further leads to smaller formula sizes when used in combination with BMC verification tools.

We combine our IMU-based thread-asynchronous SMAs with our sequentialization [TIF $^+$ 15b] in the protoppe tool IMU-CSeq. We show experimentally, that this approach is very effective in finding bugs under TSO and PSO on the same set of benchmarks we use to evaluate LazySMA.

The material we use in this thesis is largely based on our published works [ITF<sup>+</sup>14a, ITF<sup>+</sup>14b, TNI<sup>+</sup>16a, TIF<sup>+</sup>15a, TNI<sup>+</sup>15b, TIF<sup>+</sup>15b, TNF<sup>+</sup>17]. With our tools, we have entered the last three editions of the Software Verification Competition SV-COMP in the concurrency category, where MU-CSeq [TIF<sup>+</sup>14, TIF<sup>+</sup>15a] has won two silver medals in the first two editions whereas IMU-CSeq [TNI<sup>+</sup>16b] has won the gold medal in the last edition.

# 1.3 Structure of the thesis

In Chapter 2, we provide a short background overview over the information useful to understand the material proposed in this thesis.

In Chapter 3, we describe our novel approach to design static analysis and bug finding tools for concurrent programs.

In Chapter 4, we give efficient SMA implementations for TSO and PSO and combine them with our Lazy sequentialization for SC memory model [ITF<sup>+</sup>14a]; in this way we obtain an efficient tool for the bug finding in concurrent programs under TSO and PSO memory model based on lazy sequentialization.

In Chapter 5, we give efficient thread-asynchronous SMA implementations for SC memory model, based on the idea of memory unwinding; we combine them with our eager sequentialization from [TIF<sup>+</sup>15b] for SC memory model in the tool MU-CSeq and we evaluate it over a set of concurrent benchmarks from SV-COMP.

In Chapter 6, we give efficient thread-asynchronous SMA implementations for SC, TSO and PSO memory model, based on the idea of individual shared memory location unwinding; we combine them with our eager sequentialization from [TIF+15b] for SC memory model in the tool IMU-CSeq and we evaluate it against the state of the art tool for concurrent programs under week memory models.

# Chapter 2

# Background

# 2.1 Alphabets, Words and Languages.

An alphabet  $\Sigma$  is a set of symbols. For an alphabet  $\Sigma$ , a word over  $\Sigma$  is a sequence of zero or more symbols from  $\Sigma$ . The empty word, denoted by  $\varepsilon$ , is the word formed of zero symbols. Recall that  $w\varepsilon = \varepsilon w = w$  for any word w.

A language L over an alphabet  $\Sigma$  is a set of finite-length words over  $\Sigma$ .

# 2.2 Transition systems.

A transition system  $\mathcal{A}$  is a tuple  $(Q, \Sigma, \Delta, Q_0, F)$  where Q is a set of states,  $\Sigma$  is an alphabet,  $\Delta \subseteq Q \times (\Sigma \cup \{\varepsilon\}) \times Q$  is a transition relation,  $Q_0 \subseteq Q$  is a set of initial states, and  $F \subseteq Q$  is a set of final states.

A run  $\pi$  of  $\mathcal{A}$  is a sequence  $q_0 \stackrel{\sigma_1}{\to} q_1 \stackrel{\sigma_2}{\to} q_2 \dots \stackrel{\sigma_d}{\to} q_d$  where  $q_0 \in Q_0$  and  $(q_{i-1}, \sigma_i, q_i) \in \Delta$  for each  $i \in [1, d]$ . Moreover,  $\pi$  is accepting if  $q_d \in F$  and  $\sigma_1 \dots \sigma_d$  is the corresponding word. We denote by  $L(\mathcal{A})$  the set of all words that correspond to accepting runs of  $\mathcal{A}$ .

Let  $A_i = (Q_i, \Sigma, \Delta_i, Q_{0,i}, F_i)$  be a transition system for  $i \in \{1, 2\}$ . The composition of  $A_1$  and  $A_2$ , denoted  $A_1|A_2$ , is the standard cross product, i.e.,  $A_1|A_2$  is the transition system  $(Q_1 \times Q_2, \Sigma, \Delta, Q_{0,1} \times Q_{0,2}, F_1 \times F_2)$  where  $\Delta$  is the minimal set containing all tuples  $((q_1, q_2), \sigma, (q'_1, q'_2))$  such that either one of the following cases hold: 1.  $\sigma = \varepsilon$ ,  $(q_1, \varepsilon, q'_1) \in \Delta_1$ ,  $q_2 = q'_2$ ; or, 2.  $\sigma = \varepsilon$ ,  $q_1 = q'_1$ ,  $(q_2, \varepsilon, q'_2) \in \Delta_2$ ; or, 3.  $\sigma \neq \varepsilon$ , and  $(q_i, \sigma, q'_i) \in \Delta_i$  for  $i \in \{1, 2\}$ .

# 2.3 Multithreaded programs

A multithreaded program  $\mathcal{P}$  consists of several components, called threads, which run in parallel and communicate with each other by using shared memory. A *shared memory* is a sequence of memory locations of fixed size. The content of each location can be read or written using an explicit memory operation. The semantics of read and write operations depend upon the adopted memory model.

Sequential Consistency (SC) is the classical memory model for concurrent programs with shared memory. However, modern multi-core hardware architectures do not implement the SC memory model; instead, they implement weak memory models (WMMs), that allow optimizations such as instruction reordering, store buffering or write atomicity relaxation [AG96]. Such optimizations introduce additional executions which are not captured by naively interleaving the sequential code. To describe what programmers can rely on with these architectures, vendors give architecture specifications which are full of hardware-level details and are difficult to understand at the programming language level. Further, some of these specifications are often ambiguous, and are sometimes incomplete and unsound, as observed by Sewl et al. [SSO+10a]. To provide semantics to concurrent programs, we then lift hardware models to the programming level, as in [SSO+10a], by replacing each memory access with a composition of read-and-write operations that are executed atomically and whose semantics is given below.

We consider multi-threaded programs with a simple C-like syntax including pointer arithmetics and dynamic memory allocation. We further consider POSIX-like threads with dynamic thread creation, thread join, and mutex locking and unlocking operations for thread synchronization. Thread communication is implemented via shared memory in the form of global variables. The exact program syntax is defined in Section 2.3.2 by the grammar shown in Figure 2.2. We assume that all shared memory and synchronization operations are performed through an abstract data type, called *shared memory abstraction* (SMA for short), whose APIs are described in Section 3.2.2.

In this thesis, we describe a general approach that allows to combine different verification techniques with different memory models in the style of a plug-and-play architecture. We implemented our approach developing new efficient BMC-based bug finding tools for multi-threaded C programs under different memory models.

We remark that in our implementations we consider a simplified syntax and semantics of C. We allow for a restricted grammar with respect to the standard C [ISO11] and also introduce several assumptions; for instance, we assume atomicity of statements and non-deterministic values for initialized local variables. Our grammar and assumptions are even more restricted in comparison with multi-threaded C programs using POSIX threads [ISO09]. We examine only SC, TSO and PSO memory models, but there are many other more powerful memory models where the number of possible reorderings of

memory operations increase significantly. Further, we do not support the complex notion of sequence points in C and assume in-order instruction execution within threads.

These restrictions allow us to cover the Competition on Software Verification (SV-COMP)'s requirements, but exclude many subtle circumstances that actually do occur in practice [Boe05]. We could remove such limitations in order to design industrial-strength bug-finding tools, but it is to be left as future work.

# 2.3.1 Memory Models

In this thesis, beside SC, we also consider TSO and PSO; these models use buffering to speed up execution time of multi-threaded programs.

Sequential Consistency (SC). SC is the "standard model", where a write into the shared memory is performed directly on the memory location. This has the effect that the newly written value is instantaneously visible to all the other threads [Lam79]. A configuration of this model consists of a valuation of the shared locations, the addresses of such locations, the status of each created thread (i.e., if the thread is active, ready, suspended or terminated) and the status of each mutex (i.e., if it is locked or unlocked).

**Total Store Ordering (TSO).** The behaviour of the TSO memory model can be described using the simplified architecture shown in Figure 2.1 (cf. [SSO<sup>+</sup>10a]).

FIGURE 2.1: TSO architecture.

Each thread t is equipped with a local *store buffer* that is used to cache the write operations performed by t according to a FIFO policy. Updates to the shared memory occur nondeterministically along the computation, by selecting a thread, removing the oldest write operation from its store buffer, and then updating the shared memory

valuation accordingly. Before updating, the effect of a cached write is visible only to the thread that has performed it. A read by t of a variable y retrieves the value from the shared memory unless there is a cached write to y pending in its store buffer; in that case, the value of the *most recent* write in t's store buffer is returned. A thread can also execute a *fence*-operation to block its execution until its store buffer has been emptied.

Partial Store Ordering (PSO). The semantics of PSO is the same as for TSO except that each thread is endowed with a store buffer for each shared memory location.

We represent memory models as state transition systems whose configurations keep track of the valuation of the shared locations, the state of the store buffers (if any), the status of each created thread (i.e., active, ready, suspended or terminated) and the status of each mutex (i.e., locked or unlocked).

# 2.3.2 Syntax of programs.

The syntax of programs is defined by the grammar shown in Figure 2.2. Terminal symbols are set in typewriter font.  $\langle n \, \mathbf{t} \rangle^*$  represents a possibly empty list of non-terminals n that are separated by terminals  $\mathbf{t}$ ; x denotes a local variable, y an identifier of a shared variable, p an identifier of a pointer variable, m a mutex identifier, t a thread identifier and f a function name. We assume expressions e to be local variables, pointer values (returned by a read of a pointer variable), or integer constants that can be combined using mathematical operators. Boolean expressions b comprise the constants true, false, and Boolean variables, and can be combined using standard Boolean operations.

```

\begin{array}{lll} P & ::= & \text{init()}; \ (type \ f \ (\langle dec, \rangle^*) \ \{(dec;)^*stm\})^* \\ \\ dec & ::= & type \ z \ | \ type * \ p \\ \\ type & ::= & \text{bool} \ | \ \text{int} \ | \ \text{void} \\ \\ stm & ::= & seq \ | \ conc \ | \ \{\langle stm; \rangle^*\} \\ \\ seq & ::= & \text{assume}(b) \ | \ \text{assert}(b) \ | \ x = e \ | \ x = f(\langle e, \rangle^*) \ | \ \text{return} \ e \\ & | \ | \ if(b) \ stm \ | \ \text{while}(b) \ stm \\ \\ conc & ::= & p = \text{address}(y,t) \ | \ p = \text{malloc}(e,t) \\ & | \ x = \text{read}(y,t) \ | \ x = \text{ind}.\text{read}(p,t) \ | \ \text{write}(y,x,t) \ | \ \text{ind}.\text{write}(p,x,t) \\ & | \ t = \text{create}(f,pt) \ | \ \text{join}(t_1,t_2) \ | \ \text{terminate}(t) \\ & | \ fence(t) \ | \ \text{lock}(m,t) \ | \ \text{unlock}(m,t) \\ \end{array}

```

FIGURE 2.2: Syntax of multi-threaded programs.

A multi-threaded program consists of an init() invocation followed by a list of functions. init() instantiates a shared memory abstraction that captures a number of shared locations. Each function has a list of zero or more typed parameters, and its body has a declaration of local variables followed by a statement.

A statement is either a sequential or a concurrent statement, or a sequence of statements enclosed in braces (*compound statement*).

A sequential statement can be an assume- or assert-statement, an assignment, a call to a function that takes multiple parameters (with an implicit call-by-reference parameter passing semantics), a return-statement, a conditional statement, or a loop. All variables involved in a sequential statement are local. Local variables are considered uninitialised right after their declaration, which means that they can take any value from their domains. Therefore, until not explicitly set by an appropriate assignment statement, they can nondeterministically assume any value allowed by their type.

A concurrent statement involves an interaction with the shared memory abstraction and thus we have a different concurrent statement for each of the functions of the SMA API (other than init that is invoked only in the beginning).

We assume that a valid program P satisfies the usual well-formedness and type-correctness conditions. We also assume that P contains a function main, which is the starting function of the only thread that exists in the beginning. We call this the  $main\ thread$ . We further assume that there are no calls to main in P and that no other thread can be created that uses main as starting function.

## 2.3.3 Semantics of programs.

We adopt an interleaving semantics where only one of the *enabled* threads can be *active* at any given time. A computation of a *multi-threaded* program  $\mathcal{P}$  is obtained by interleaving the computations of its threads.

Initially, only the main thread is active; new threads can be spawned from any thread by a call to the create function. Once created, a thread is added to the pool of inactive threads. A step is either the execution of a step of the active thread or is a context-switch that replaces the active thread with one of the inactive threads. At a context switch the current thread is suspended and becomes inactive, and one of the inactive threads is resumed and becomes the new active thread. When a thread is resumed its execution continues either from the point where it was suspended or, if it becomes active for the first time, from the beginning. A thread can pause its execution until another thread terminates, or it can acquire and release a mutex. Since threads can allocate memory dynamically using malloc, different threads can simultaneously access and alter shared dynamic data structures. A thread will no longer be available when its execution is terminated, i.e., there are no more steps that it can take.

For ease of presentation, we assume that each statement is atomic. Note that, this is not a restriction, in fact it is always possible to decompose a statement in a sequence of statements, each involving at most one shared variable [Mül06].

A thread configuration is a triple  $\langle locals, pc, stack \rangle$ , where locals is a valuation of the local variables, pc is the program counter that tracks the currently executing statement, and stack is a stack of function calls that works as usual. In the SC memory model a configuration of a multithreaded program is a tuple of thread configurations along with valuation of the global variables that are shared by all threads. In the TSO and PSO memory models the notion of configuration is extended to include the valuations of the store buffers.

In Section 3.2, we give a formal semantics of multi-threaded programs by the composition of two transition systems  $\mathcal{C}|\mathcal{M}$ , where  $\mathcal{C}$  is the control-flow transition system that captures the control flow of the program and  $\mathcal{M}$  is the shared memory abstraction transition system that implements the behaviours of the SMA.

## 2.3.4 Reachability problems

Let P be a concurrent program. The reachability problem asks whether there is a reachable assertion-failure configuration of P. For concurrent programs, reachability is undecidable [Ram00]. By restricting to only computations with a bounded number of context switches, not only the problem becomes decidable but it has shown to be an effective method to finding bugs in concurrent programs.

# 2.4 Propositional Logic

The alphabet of propositional logic consists of:

- a countably-infinite set  $Lp = (x_1, x_2, ...)$  of propositional variables

- the logical connectives NOT  $(\neg)$ , OR  $(\lor)$

- parentheses ( and ).

Further logical connectives, such as AND ( $\wedge$ ), IMPLIES ( $\rightarrow$ ) and EQUIVALENT TO ( $\leftrightarrow$ ), are derived from the standard connectives ( $\neg$ , $\vee$ ) in the usual way.

The set WFF of well-formed formulae of propositional logic is inductively defined as follows:

- $\forall x$ , if  $x \in Lp \implies x \in WFF$

- if  $\alpha, \beta \in WFF \implies \alpha \vee \beta \in WFF$

- if  $\alpha \in WFF \implies \neg \alpha \in WFF$

- if  $\alpha \in WFF \implies (\alpha) \in WFF$

- nothing else  $\in WFF$

An interpretation is a function  $Int: WFF \to \{\bot, \top\}$  that assigns either TRUE  $(\top)$  or FALSE  $(\bot)$  to every propositional symbol in WFF.

Given a well-formed formula  $\varphi$  and an interpretation Int, either Int satisfies  $\varphi$  or not. This is indicated with  $Int \models \varphi$  or  $Int \not\models \varphi$ , respectively, and inductively defined by the following rules:

- if  $\varphi = x$ , with  $x \in Lp$ , then  $Int \models \varphi$  if and only if  $Int(x) = \top$

- if  $\varphi = \neg \psi$ , with  $\psi \in WFF$ , then  $Int \models \varphi$  if and only if  $Int \not\models \psi$

- if  $\varphi = \psi_1 \vee \psi_2$ , with  $\psi_1, \psi_2 \in WFF$ , then  $Int \models \varphi$  if and only if  $Int \models \psi_1$  or  $Int \models \psi_2$ .

A formula  $\varphi$  is satisfiable if there exists an interpretation Int under which the formula is true; if no such interpretation exists,  $\varphi$  is unsatisfiable, or a contradiction. A formula that evaluates to true under all possible assignments is valid, or a tautology.

#### 2.4.1 Boolean Satisfiability

The boolean satisfiability problem, also known as SAT (for short), consists in determining whether a given propositional formula is satisfiable.

A SAT solver is a decision procedure that takes as input a given formula  $\varphi$  and returns as output an assignment Int of the variables of  $\varphi$  that satisfies  $\varphi$ , or FALSE if the  $\varphi$  is unsatisfiable.

In general, SAT is an NP-complete problem [Coo71] and no one knows a polynomial algorithm that could solve it. However, modern SAT solvers use sophisticated heuristics developed in the last 40 years that are very effective on several big real world instances. In general, it is hard to predict what a good SAT encoding is [KSMS11]. However, as a rule of thumb, it is desirable to produce SAT formulas of small sizes as it often leads to better performance in modern SAT solvers.

# 2.5 Bounded Model Checking

Bounded model-checking (BMC) is a technique where a program is first transformed into a bounded program by unrolling all loops up to a given bound, and inlining functions

```

(b) SSA form

(c) verification condition

(a) input program

x1:=x0-y0;

x := x - y;

\varphi_C :=

x_1 = x_0 - y_0 \wedge

x_2 = 2 \wedge

x_3 = (x_1 + 1) \wedge

if(x==1) then

x := 2;

x2:=2;

x_4 = (x_1 = 1)?x_2 : x_3

else

x3=x1+1;

x4=(x1==1)?x2:x3

x := x+1:

assert(x==6);

assert(x4==6);

x_4 = 6

\varphi_P :=

```

Figure 2.3: Bounded model-checking: (a) simple input program, (b) static single assignment (SSA) form and (c) verification condition

(if a function is recursive, it is inlined up to the given bound). Conceptually, a loop statement is removed by replicating its body k times, where each such copy is guarded using an if-statement that uses the loop condition, and a loop unwinding assertion with the negated loop condition is added after the last copy (loop unwinding). A function call is removed by inlining its code, and replacing the return statements with an assignment for the return value (if any) and a goto to the end of the function. Recursive calls are handled similarly to the case of loop unwinding by asserting in the end that the recursion does not pass the bound (function-call unwinding).

Thus, the resulting program captures all possible computations of the original program for a bounded number of steps. Then the program is transformed into SSA (static single assignment) form [AKT13]; this guarantees that each variable is assigned at most once (see Figure 2.3(b)).

Then the intermediate program in SSA form is translated into a SAT or SMT (quantified free) formula (see Figure 2.3(c)). This formula is checked for satisfiability. A satisfiability assignment for variables is then used to build a counter-example of the program. If the formula is not satisfiable, it means that no error is found in the given bound. Therefore, BMC techniques are appealing only for discovering shallow bugs (as is often the case for concurrent programs [MQB+08]). The success of BMC techniques is borrowed by efficient SAT/SMT solvers that can nowadays handle formulas with several millions of variables [JLBRS12, CGBD12].

BMC is an under-approximation technique and can thus be used only to find violations of the property up to the bound k (i.e., bug finding). In order to prove properties we can either select a bound k that is "big enough" (i.e., exceeds the *completeness threshold* [Bie09]) or uses techniques like k-induction [SSS00] that build on top of BMC.

# 2.6 Bounded Model Checking of Concurrent Programs

We recall that a **Concurrent program**  $\mathcal{P}$  consists of several components, called threads, which run in parallel and communicate with each other by using shared memory. A computation of  $\mathcal{P}$  is obtained by interleaving the computations of its threads. The number of possible interleavings grows exponentially with the number of threads and statements in the program.

Attempts to extend BMC to the analysis of concurrent programs face the problem of state space explosion. There are two main approaches to address this problem: *context bounding* limits the analysis to a given number of context switches and *partial-order reduction* prunes the search space by avoiding the exploration of multiple executions leading to the same state.

## 2.6.1 Context-Bounded Analysis

State space explosion can be reduced by limiting the number of interactions that are analyzed by a verification tool. Context-bounded analysis (CBA) is a technique that bounds the number of context switches [QR05, LR09, LMP09a]. In [MQ07, QW04], it was empirically shown that most of the errors in concurrent programs manifested themselves in a few context-switches.

A context-bounded analysis can be implemented as SAT/SMT-based bounded model checking (BMC), which has been used successfully to discover subtle errors in sequential software, even at large scale [KT14, SKB+15]. Sequential BMC tools can be extended symbolically to the concurrent case by conjoining the formula representing the effect of each individual thread in isolation with a second formula representing the possible interferences caused by concurrent accesses to the shared memory [SW11, AKT13]. Since this second formula effectively includes an axiomatization of the underlying memory model, this approach can in principle handle sequential consistency (SC) as well as different WMMs.

An alternative approach is based on *sequentialization*, which translates concurrent programs into sequential programs with data non-determinism that (under certain assumptions) behave equivalently, so that the different interleavings do not need to be treated explicitly during the analysis. This allows the reuse of existing sequential BMC tools.

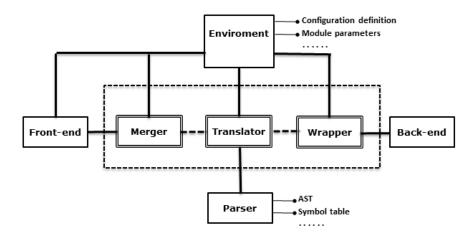

#### 2.6.2 Sequentialization

A sequentialization translates a concurrent program P into a non-deterministic sequential program  $P_{seq}$  that (under certain assumptions) behaves equivalently. Sequentialization

can be seen as a kind of pre-processing for existing mature sequential program verification tools.

A first attempt of sequentialization could be to implement it as an interpreter which simulates the concurrent program tracking at all times the cross product of the local states of each thread. For theoretical reasons, this kind of solution is ineffective due to the state-space explosion. To make the approach effective,  $P_{seq}$  should not track the whole state-space of the concurrent program, as in the cross product of the thread states. All sequentializations that have been proposed in literature only track one local state at a time and use 2k copies of the shared variables [LR09, LMP09a, LMP12], for a given parameter k. Under these restrictions, such approaches can only cover a subset of computations in which each thread can at most interact k times with the other threads. By increasing the parameter k, we can capture more computations, but this of course comes with a cost in terms of computational resources.

The first sequentialization of concurrent programs was proposed in the KISS paper (Keep It Simple and Sequential) by Qadeer and Wu in 2004 [QW04]. The sequentialization is bounded on a finite number of threads and two context-switches, while the length of the runs is unbounded. The resulting sequential program  $P_{seq}$  uses only one stack which is partitioned into contiguous blocks where each of them corresponds to the local stack of one thread. On the top of the stack we have the local stack of the thread that is executing currently. The scheduler non-deterministically can do, at any time, one of the following options:

- 1. terminate the thread currently executing and popping its contiguous block; then the thread whose block is just below is resumed;

- 2. schedule another thread by calling its starting function.

The authors have also implemented their technique in a tool called KISS which is a pre-processing for the SLAM [BR] model checker for sequential C programs. They used KISS to finding several bugs in Windows NT device drivers.

In 2007, Qadeer and Masuvathi empirically showed that most of the errors in concurrent programs manifest themselves in a few preempting context-switches [MQ07]. In the same paper, the authors showed that a fair percentage of state-space is reached through executions with a few preemptions.

Sequentializations can be classified in *eager* and *lazy*. Eager sequentializations guess the different values of the shared memory before the verification, which means that they can explore infeasible computations that need to be pruned away afterwards. In contrast, lazy sequentializations [LMP09a] only explore feasible computations.

## 2.6.2.1 Eager Sequentialization

Lal and Reps in 2009 proposed a sequentialization (LR) [LR09] which allows the handling of a fixed number of context-switches between a statically-created set of threads.

The LR sequentialization translates a concurrent program P into a sequential program  $P_{seq}$ , which non-deterministically simulates a round-robin schedule.  $P_{seq}$  simulates each thread to completion and uses a copy of the shared global memory for each round. The initial values of all memory copies are nondeterministically guessed in the beginning (eager exploration). At the end a checker prunes away all infeasible runs where the initial values guessed for one round do not match the values computed at the end of the previous round.

Lal and Reps' technique has been implemented in several tools. Rek [CGS11] is targeted to real-time systems. STORM [LQR09], Poirot [Qad11] and Corral first translate concurrent C programs into Boogie and then implement Lal and Reps at the Boogie level. Corral also integrates Lal and Reps into a CEGAR approach. CSeq [FIP13b, FIP13a] implements Lal and Reps directly on concurrent C programs and it also handles dynamic thread creation. CSeq can use several BMC back-ends, like CBMC, ESMBC and LLBMC.

In 2012, Bouajjani and Emmi proposed a sequentialization for distributed applications where threads communicate through FIFO channels [BE12].

MU-CSeq. In our paper [TIF+15b], we describe a new sequentialization-based approach to the symbolic verification of multithreaded programs with shared memory and dynamic thread creation, whose main novelty is the idea of *memory unwinding* (MU), i.e., an explicit representation of the sequence of write operations into the shared memory.

Recent empirical studies have pointed out other common features for concurrency errors, but these have not yet been exploited for practical verification algorithms. In particular, Lu et al. [LPSZ08] observed that "almost all [...] concurrency bugs are guaranteed to manifest if certain partial order among no more than 4 memory accesses is enforced."

In [TIF<sup>+</sup>15b], we follow up on their observation that only a few memory accesses are relevant, and propose a corresponding new approach to the automated bug finding in concurrent programs. The proposed approach simulates the executions of a multithreaded program but bounds the total number of write operations into the shared memory that can be read by threads other than the one performing the writing. It is related to context-bounded analyses [QR05, LR09, LMP09a] but the bounding parameter is different, which allows an orthogonal exploration of the search space.

Figure 2.4(a) shows the C-code of a multi-threaded implementation of a nondeterministic Fibonacci-function. This example from the SV-COMP benchmark suite uses two threads

```

int i = 1, j = 1;

int i = 1, j = 1;

int ct; bool \_error = F;

int th_pos[3];

void f1() {

\verb"void" <math>f1_S()\ \{

i = i + j;

write(\langle i \rangle, read(\langle i \rangle, ct) + read(\langle j \rangle, ct), ct);

i = i + j;

write(\langle i \rangle, read(\langle i \rangle, ct) + read(\langle j \rangle, ct), ct);

\mathtt{write}(\langle i \rangle, \mathtt{read}(\langle i \rangle, ct) + \mathtt{read}(\langle j \rangle, ct), ct);

i = i + j;

\mathtt{write}(\langle i \rangle, \mathtt{read}(\langle i \rangle, ct) + \mathtt{read}(\langle j \rangle, ct), ct);

i=i+j;

write(\langle i \rangle, read(\langle i \rangle, ct) + read(\langle j \rangle, ct), ct);

\operatorname{void}\ f2()\ \{

void f2_S() {

j = j + i;

write(\langle j \rangle, read(\langle j \rangle, ct) + read(\langle i \rangle, ct), ct);

j = j + i;

write(\langle j \rangle, read(\langle j \rangle, ct) + read(\langle i \rangle, ct), ct);

j = j + i;

\mathtt{write}(\langle j \rangle, \mathtt{read}(\langle j \rangle, ct) + \mathtt{read}(\langle i \rangle, ct), ct);

j = j + i;

write(\langle j \rangle, read(\langle j \rangle, ct) + read(\langle i \rangle, ct), ct);

j = j + i;

\mathtt{write}(\langle j \rangle,\, \mathtt{read}(\langle j \rangle,\, ct) + \mathtt{read}(\langle i \rangle,\, ct)\,,\, ct);

void main_S() {

void main() {

int t1, t2;

pthread_t t1, t2;

t1 = \mathtt{CREATE}(f1_S, ct);

pthread_create(&t1,((void*)0),f1,((void*)0));

t2 = \mathtt{CREATE}(f2_S, ct);

\texttt{pthread\_create}(\&t2,((void*)0),f2,((void*)0));

check_return;

assert(j < 144);

if(read(\langle j \rangle, ct) >= 144) {

error:=T; return 0;

void main(void) \{...\}

(a)

(b)

exposed writes

threads

pos

pos

val

var

\{2\}\{2,3\}

0

\{(i=4)\}

0

2

2

i

=5), (j=10)

1

1

2

3

\frac{(j=15)}{\{(j=15)\}}

2

{3}

\frac{2}{3}

3

\{2,3\}

=15), (j=45)

2

5

(d)

3

5

5

3

10

6

3

15

7

2

8

3

30

9

3

45

(c)

```

FIGURE 2.4: Multi-threaded Fibonacci: (a) C-code for 5 iterations, (b) translated code, and sample memory unwindings: (c) fine-grained and (d) coarse-grained.

f1 and f2 to repeatedly increment the shared variables i and j by j and i, respectively. With a perfect interleaving (i.e., a round-robin schedule with context switches after each assignment) the variables i and j take on the consecutive values from the Fibonacciseries, and the program terminates with i = fib(11) = 89 and j = fib(12) = 144 if this interleaving starts with f1. Any other schedule will lead to smaller values for i or j. The main function first creates the two threads f1 and f2, then uses two join statements to ensure that both threads run to completion, and finally checks the outcome of the choosen interleaving.

Here, we first give a general overview of the main concepts of our approach, namely the memory unwinding and the simulation of the read and write operations, before we describe the sequentialization translation. We use the Fibonacci-example above to illustrate the concepts.

High-level description. Our approach is based on a code-to-code translation of any concurrent program P into a corresponding sequential program  $P_{W,T,V}$  that captures all the executions of P involving at most W write operations in the shared memory, T threads and V memory locations. We denote the original concurrent program with P and the sequentialized program  $P_{W,T,V}$  with  $P_S$  in the rest of this section.

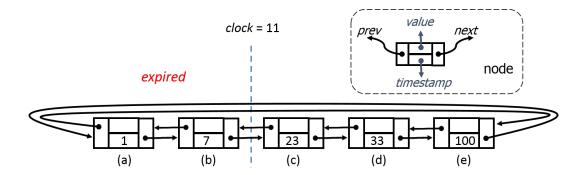

A core concept in this translation is the memory unwinding. A W-memory unwinding  $\mathcal{M}$  of P is a sequence of writes  $w_0 \dots w_{W-1}$  of P's shared variables; each  $w_i$  is a triple  $(t_i, var_i, val_i)$  where  $t_i$  is the identifier of the thread that has performed the write operation,  $var_i$  is the name of the written variable and  $val_i$  is the new value of  $var_i$ . A position in an W-memory unwinding  $\mathcal{M}$  is an index in the interval [0, W-1]. An execution of P conforms to a memory unwinding  $\mathcal{M}$  if the sequence of its writes in the shared memory exactly matches  $\mathcal{M}$ .

The approach allows us to vary which write operations are represented and thus exposed to the other threads. This leads to different strategies with different performance characteristics. In a *fine-grained* MU (see Figure 2.4(c)) every write operation is represented explicitly and individually while coarse-grained MU only represents a subset of the writes, but group together multiple writes. In a coarse-grained MU (see Figure 2.4(d)) we store at each position a partial mapping from the shared variables to values, with the meaning that the variables in the domain of the mapping are modified from the previous position and the value given by the mapping is their value at this position.

Fig. 2.4(c) gives a fine-grained memory unwinding that conforms to an execution of the multithreaded program given in Fig. 2.4(a), namely the execution given by (we omit the main thread): the first three assignments of f1, followed by a read of i by f2, then the fourth assignment of f1, the completion of the first two assignments of f2, the read of f by f, the third assignment of f, the last assignment of f and the remaining assignments of f. Note that a memory unwinding can be unfeasible for a program, in the sense that no execution of the program conforms to it. Conversely, multiple executions can also conform to one memory unwinding, although this is not the case for the Fibonacci-example. Fig. 2.4(d) gives a coarse-grained memory unwinding that conforms to the same execution described above.

We use a memory unwinding  $\mathcal{M}$  to explore the runs of P that conform to it by running each thread t separately. The idea is to use the memory unwinding for the concurrent statements (which involve the shared memory) and execute the sequential statements directly. In particular, when we execute a write of t in the shared memory, we check that it matches the next write of t in  $\mathcal{M}$ . However, a read of t in the shared memory is more involved, since the sequence of reads is not explicitly stored in the memory unwinding. We therefore need to guess nondeterministically the position in the unwinding from which

we read. Admissible values are all the positions that are in the range from the current position (determined by previous operations on the shared memory) to the position of t's next write in  $\mathcal{M}$ . The nondeterministic guess ensures that we are accounting for all possible interleavings of thread executions that conform to the memory unwinding.

For example, consider again the 10-memory unwinding of Fig. 2.4(c). The execution of f1 is simulated over this as follows. The first four writes are matched with the first four positions of the unwinding; moreover, the related reads are positioned at the current index since they are each followed by the write which is at the next position in the memory unwinding. The fifth write is matched with position 7. The corresponding read operations can be assigned nondeterministically to any position from 3 to 6. However, in order to match the value 15 with the write, the read of j must be positioned at 5. Note that the read of j can be positioned anywhere in this range since it was written last time at position 3.

When simulating one thread, we assume that all the writes executed by the other threads, and stored in the memory unwinding, indeed all occur and, moreover, in the ordering shown in  $\mathcal{M}$ . Thus, for the correctness of the simulation, for each thread t we must ensure not only that each of its writes involving the shared variables conforms to the write sequence in the guessed memory unwinding, but also that all the writes claimed in the unwinding are actually executed. Further, t should not contribute to the computation before the statement that creates it has been simulated. This can be easily enforced by making the starting position of the child thread to coincide with the current position in  $\mathcal{M}$  of the parent thread when its creation is simulated.

Construction of  $P_S$ . The program  $P_S$  first guesses an W-memory unwinding  $\mathcal{M}$  and then simulates a run of P that conforms to  $\mathcal{M}$ . The simulation starts from the main thread (which is the only active thread when P starts) and then calls the other threads one by one, as soon as their thread creation statements are reached. Thus, the execution of the parent thread is suspended and then resumed after the simulation of the child thread has completed. Essentially, dynamic thread creation in P is modeled by function calls in  $P_S$ .  $P_S$  is formed by a main, and a new procedure  $P_S$  for each procedure  $P_S$  of  $P_S$ . It uses some additional global variables:  $P_S$  is initialized to false and stores whether an assertion failure in  $P_S$  has occurred;  $P_S$  stores the current thread; the array th-pos stores the current position in the memory unwinding for each thread.

The main procedure of  $P_S$  is given in Fig. 2.5. First, we call  $\operatorname{init}(V, W, T)$  that guesses an W-memory unwinding with V variables and T threads, and then  $\operatorname{create}(main_S, 0)$  that registers the main thread and returns its id. Note that we encode each of P's shared variables y with a different integer  $\langle y \rangle$  in the interval [0, V-1] and each thread

```

\label{eq:void_main} \begin{split} & \text{void_main}(\text{void}) \; \{ \\ & \text{init}(\text{V}, \text{W}, \text{T}); \\ & ct := \text{create}(main_S, 0); \\ & \text{main}_S(x_1, \dots, x_k); \\ & \text{terminate}(ct); \\ & \text{finish}(); \\ & \text{assert}(\_\text{error} \neq 1) \quad \} \end{split}

```

FIGURE 2.5:  $P_S$ : Mu main().

with a different integer  $\langle t \rangle$  in [0, T-1]; once T threads are created create returns -1 (an

invalid id) that causes the thread not to be executed. The parameter passed to create is the id of the thread that is invoking the thread creation. For the creation of the main thread we thus pass 0 to denote that this is the first created thread. The call to  $\mathtt{main}_S$  starts the simulation of the main thread. Then, we check that all the write operations guessed for the main thread have been executed (by  $\mathtt{terminate}$ ), and all the threads involved in the guessed writes have been indeed simulated (by  $\mathtt{finish}$ ). If either one of the above checks fails, the simulation is considered infeasible and thus aborted. The global variable  $\_\mathtt{error}$  is used to check whether an assertion has been violated. It is set to T in the simulation of the threads of P whenever an assertion gets violated and is never reset.

Each  $p_S$  is obtained from p according to the transformation function  $[\cdot]$  defined inductively over the programs syntax by the rules given in Fig. 2.6. For example, Fig. 2.4(b) gives the transformations for the functions of the Fibonacci program from Fig. 2.4(a). There we use the macro CREATE as a shorthand for the code given in the translation rules for the create statement. Also, we have omitted the declaration of tmp in the functions  $f1_S$  and  $f2_S$  since it is not used there, and reported the translation of the assignments in a compact form.

```

1. [type \ p\ (par^*)\{dec^*\ stm\}] ::= type \ p_S\ (par^*)\{dec^*\ ; \ uint \ tmp\ ; \ [stm]\}

2. [\{\langle stm; \rangle^*\}] ::= \{\langle [stm]; \rangle^*\}

Sequential statements: (x \text{ is local})

3. [assume(b)] ::= check_return; assume(b)

[assert(b)] ::= check_return; if(\neg b) {_error:= T; return 0}

5. [return e] ::= return e

6. [x = e] ::= x = e

7. [x = f(e_1, ..., e_n)] ::= x = f_S(e_1, ..., e_n); check_return;

8. [if(b) stm else stm] ::= if(b) [stm] else [stm]

9. [while (b) { stm } ::= while (b) { check_return; [stm] }

Concurrent statements: (x is local, y is shared, ct contains the current tread id)

10. \ [p:=address(y,t)] \ ::= \ \ p:=address(\langle y \rangle,t);

11. [p := malloc(e, t)] ::= p := malloc(e, t);

12. [x = read(y, t)] ::= x = read(\langle y \rangle, t);

13. [x = ind\_read(p, t)] ::= x = ind\_read(\langle p \rangle, t);

14. [write(y, x, t)] ::= write(\langle y \rangle, x, t);

15. [ind\_write(p, x, t)] ::= write(\langle p \rangle, x, t);

16. \ [t = \mathtt{create} \ (p(e_1, \ldots, e_n), pt)] \ ::= \ \mathtt{check\_return}; \ tmp = ct; \quad t := \mathtt{create}(p_S, ct);

if(t > 0) { ct = t; p_S(e_1, ..., e_n); };

ct = tmp;

17. [join(ct, t)] ::= join(ct, t);

18. [terminate(t)] := terminate(t);

19. [fence(t)] := fence(t);

20. [lock (v, ct)] ::= lock(\langle v \rangle, ct);

[unlock (v, ct)] ::= unlock (\langle v \rangle, ct);

```

FIGURE 2.6: Mu-CSeq Rewriting rules.

The transformation adds a local variable tmp that is used to store the current thread id when a newly created thread is simulated. The sequential statements are left unchanged except for the injection of the macro check\_return that is defined as "if(is\_th\_terminated(t)) then return 0;". Function is\_th\_terminated(t) returns true either when the thread t has previously been interrupted, or it is non-deterministically interrupted now. The macro is injected after each function call, as a first statement of a

loop, and before any assume- and assert-statement; in this way, when the simulation of the current thread has finished or is aborted, we resume the simulation of the parent thread.