### UNIVERSITY OF SOUTHAMPTON

### FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

Department of Electronics and Computer Science

## A Joint Algorithm and Architecture Design Approach to Joint Source and Channel Coding Schemes

by

### Matthew Brejza

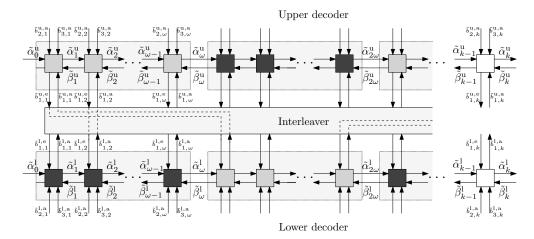

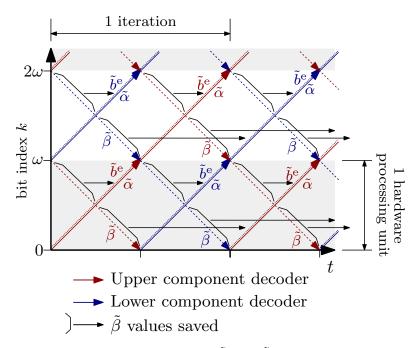

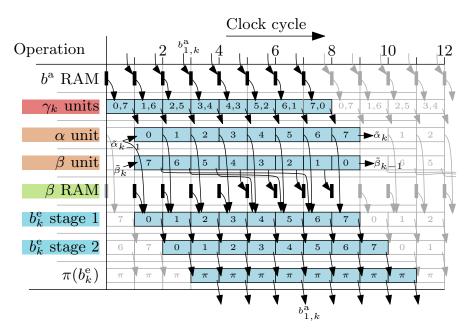

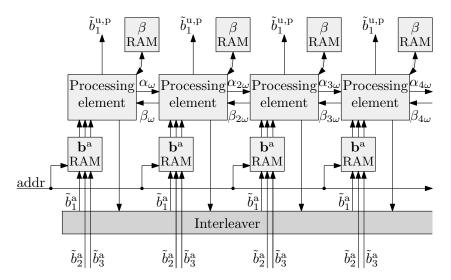

Thesis for the degree of Doctor of Philosophy

Supervisors:

Professor Lajos Hanzo, Dr Robert G. Maunder, Professor Bashir M. Al-Hashimi

December 2016

© Matthew Brejza 2016

#### UNIVERSITY OF SOUTHAMPTON

#### ABSTRACT

# FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

Department of Electronics and Computer Science

### Doctor of Philosophy

# A JOINT ALGORITHM AND ARCHITECTURE DESIGN APPROACH TO JOINT SOURCE AND CHANNEL CODING SCHEMES

by Matthew Brejza

Shannon's separate source and channel coding theorem suggests that communication of throughputs closely approaching the capacity of the channel can be achieved using an near-entropy source code to compress a source by removing all redundancy, combined with a near-capacity channel code which adds redundancy to increase the resilience to transmission errors. However, in practice, Separate Source and Channel Coding (SSCC) can impose excessive delay and complexity, or cannot tolerate any transmission errors without causing an endless cascade of errors. This motives Joint Source and Channel Coding (JSCC), where the residual redundancy from a non-optimal source code is used by the channel code in order to increase the error correction capability. In particular, the recently proposed Unary Error Correction (UEC) code is an example of a JSCC scheme, which is well suited to encoding symbols generated during multimedia transmission, such as a H.264 or H.265 video encoder. Despite this, the UEC is only suitable for encoding symbols that are generated according to a limited range of probability distributions. Furthermore, due to their computational complexity, iterative decoder components such as source and channel decoders are usually implemented using specialized dedicated hardware. Despite this, there is little work in the open literature on the hardware implementation of JSCC schemes. Against this background, this thesis jointly considers the algorithm and architecture design of joint source and channel codes for the first time, in order to achieve an increased error correction performance and an improved hardware efficiency.

This thesis begins by proposing improvements to the UEC JSCC scheme. Firstly, an adaptive activation order algorithm is extended for use with a more complex UEC scheme, which comprises four iterative components, including a demodulator. This adaptive activation order algorithm facilitates an improved error correction performance, using a reduced number of iterations. Following this, in order to increase the applicability of the UEC code, it is extended and generalized to obtain the novel RiceEC and ExpGEC codes. These codes can be applied to any arbitrary unbound monotonic symbol distribution, including the symbols produced by the H.265 video codec and the letters of

the English alphabet. Furthermore, the practicality of the proposed codes is enhanced to allow a continuous stream of symbol values to be encoded and decoded using only fixed-length system components.

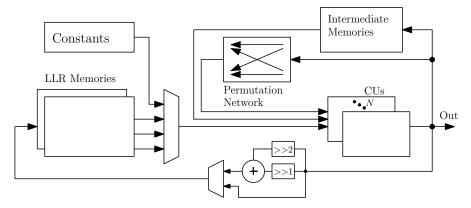

This thesis also provides the first hardware implementations of UEC schemes. Owing to their relatively high complexity, many capacity-approaching techniques proposed in the literature have not yet been invoked in Wireless Sensor Network (WSN) applications, despite their potential benefits of facilitating a reduced transmission power or extended communication range. Against this background, this thesis proposes an energy-efficient architecture comprised of multiple Calculation Units (CUs), which is sufficiently flexible for accommodating different iterative decoder components of a UEC-based JSCC scheme, using the same hardware. This architecture achieves a throughput suitable for low-speed video applications, while achieving high hardware utilisation, which is important in cost- and energy-sensitive applications.

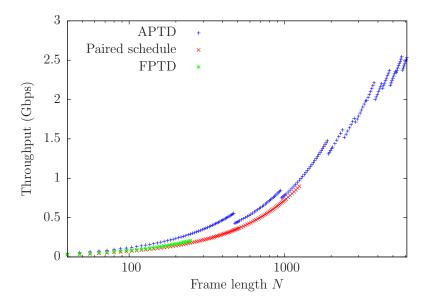

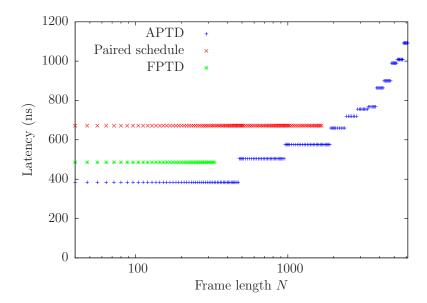

Following this, a UEC scheme is implemented for very high throughput applications, by extending the philosophy of the Fully Parallel Turbo Decoder (FPTD). More specifically, in the wireless transmission of multimedia information, the achievable transmission throughput and latency may be limited by the processing throughput and latency associated with source and channel coding. For example, ultra-high throughput and ultra-low latency processing of source and channel coding is required by the emerging new video transmission applications, such as the first-person remote control of unmanned vehicles. Here, a new architecture is developed by jointly considering the algorithm and hardware implementation, in order to achieve an improved hardware efficiency, high throughput, and low latency. This thesis will demonstrate the application of these improvements to both the LTE turbo code and the UEC code, where the proposed design achieves a throughput of 450 Mbps on a mid-range FPGA, as well as a factor of 2.4 hardware efficiency improvement over previous implementations of the FPTD.

# List of publications

- M. F. Brejza, L. Li, R. G. Maunder, B. Al-Hashimi, C. Berrou and L. Hanzo (2016). 20 Years of Turbo Coding and Energy-Aware Design Guidelines for Energy-Constrained Wireless Applications. *IEEE Communications Surveys & Tutorials*, 18(1), 8–28.

- M. F. Brejza, T. Wang, W. Zhang, R. G. Maunder, B. Al-Hashimi and L. Hanzo (2016). Exponential Golomb and Rice Error Correction Codes for Generalized Near-Capacity Joint Source and Channel Coding. *IEEE Access*, 4, 7154–7175.

- M. F. Brejza, R. G. Maunder, B. Al-Hashimi and L. Hanzo. A High-Throughput FPGA Architecture for Fully-Parallel Joint Source and Channel Decoding. *IEEE Access*, PP(99), 1–1.

- M. F. Brejza, R. G. Maunder, B. Al-Hashimi and L. Hanzo. Flexible Iterative Receiver Architecture for Wireless Sensor Networks: A Joint Source and Channel Coding Design Example. Accepted by *IET Wireless Sensor Systems*.

- M. F. Brejza, W. Zhang, R. G. Maunder, B. Al-Hashimi and L. Hanzo (2015). Adaptive iterative detection for expediting the convergence of a serially concatenated unary error correction decoder, turbo decoder and an iterative demodulator. In *IEEE International Conference on Communications (ICC)*, 2015 (pp. 2603–2608).

- M. F. Brejza, J. Hooker, J. Sowman, D. Oakley and R. G. Maunder (2016). Design of Digital Testbeds for Undergraduate Microelectronics Teaching. In 11th European Workshop on Microelectronics Education.

- W. Zhang, M. F. Brejza, T. Wang, R. G. Maunder, and L. Hanzo (2015). Irregular Trellis for the Near-Capacity Unary Error Correction Coding of Symbol Values From an Infinite Set. *IEEE Transactions on Communications*, 63(12), 5073–5088.

- W. Zhang, Y. Jia, X, Meng, M. F. Brejza, R. G. Maunder and L. Hanzo (2015). Adaptive iterative decoding for expediting the convergence of unary error correction codes. *IEEE Transactions on Vehicular Technology*, 64(2), 621–635.

- W. Zhang, Z. Song, M. F. Brejza, T. Wang, R. G. Maunder and L. Hanzo (2016). Learning-aided unary error correction codes for non-stationary and unknown sources. *IEEE Access*, 4, 2408–2428.

- T. Wang, M. F. Brejza, W. Zhang, R. G. Maunder and L. Hanzo (2016), Reordered Elias Gamma Error Correction Codes for the Near-Capacity Transmission of Multimedia Information. *IEEE Access*, 4, 5948–5970.

# Contents

| Li           | st of | public  | cations                                                 |   | iv   |

|--------------|-------|---------|---------------------------------------------------------|---|------|

| $\mathbf{D}$ | eclar | ation o | of Authorship                                           |   | xi   |

| $\mathbf{A}$ | cknov | wledge  | ements                                                  |   | xiii |

| N            | omer  | ıclatur | re                                                      |   | xv   |

| 1            | Intr  | oducti  |                                                         |   | 1    |

|              | 1.1   | Source  | e coding                                                |   | . 2  |

|              | 1.2   | Chann   | nel coding                                              |   | . 3  |

|              | 1.3   | Joint s | source and coding                                       |   | . 5  |

|              | 1.4   | Joint a | algorithm and hardware design                           |   | . 6  |

|              | 1.5   | Outlin  | ne and novel contributions                              | • | . 7  |

| 2            | Bac   | kgroui  | nd                                                      |   | 11   |

|              | 2.1   | Turbo   | ocoding $\ldots$                                        |   | . 12 |

|              |       | 2.1.1   | Convolutional encoder                                   |   | . 13 |

|              |       | 2.1.2   | Turbo coded transmitter                                 |   | . 14 |

|              |       | 2.1.3   | Channel                                                 |   | . 14 |

|              |       | 2.1.4   | Turbo coded receiver                                    |   | . 15 |

|              |       | 2.1.5   | Logarithmic Bahl-Cocke-Jelinek-Raviv (Log-BCJR) decoder |   | . 17 |

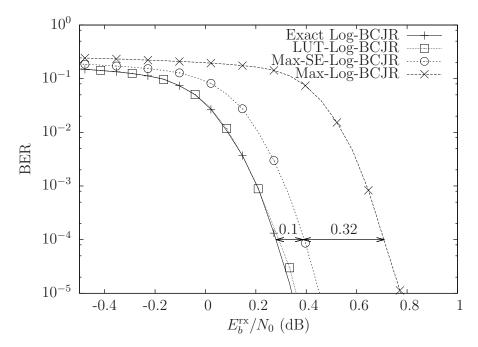

|              |       | 2.1.6   | Algorithmic modifications to the Log-BCJR decoder       |   | . 21 |

|              |       | 2.1.7   | Turbo code performance                                  |   | . 23 |

|              | 2.2   | Turbo   | decoder architectures                                   |   | . 24 |

|              |       | 2.2.1   | Datapath considerations                                 |   | . 27 |

|              |       | 2.2.2   | Algorithm control                                       |   | . 28 |

|              |       | 2.2.3   | Memory considerations                                   |   | . 31 |

|              | 2.3   | Holisti | ic design characterization                              |   | . 33 |

|              |       | 2.3.1   | Methodology                                             |   | . 36 |

|              |       | 2.3.2   | Results                                                 |   | . 37 |

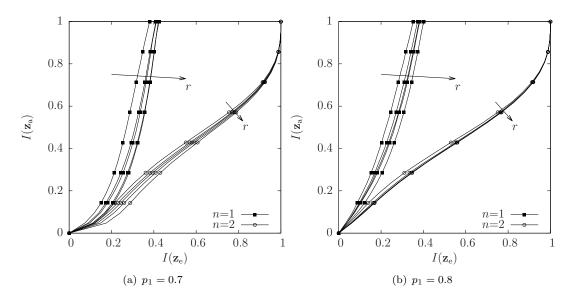

|              | 2.4   | EXIT    | functions                                               |   | . 40 |

|              |       | 2.4.1   | Theory                                                  |   | . 40 |

|              |       | 2.4.2   | Near-capacity operation                                 |   | . 44 |

|              | 2.5   | Unary   | r error correction                                      |   |      |

|              |       | 2.5.1   | Zeta distribution                                       |   | . 47 |

|              |       | 2.5.2   | Unary encoder                                           |   | . 49 |

|              |       | 252     | HEC 411: 1                                              |   | 40   |

viii CONTENTS

|   |     | 2.5.4  | UEC trellis decoder                                       | . 51  |

|---|-----|--------|-----------------------------------------------------------|-------|

|   | 2.6 | Backg  | round summary                                             | . 53  |

| 3 | Ada | ptive  | unary error correction decoder                            | 55    |

|   | 3.1 | Introd | uction                                                    | . 55  |

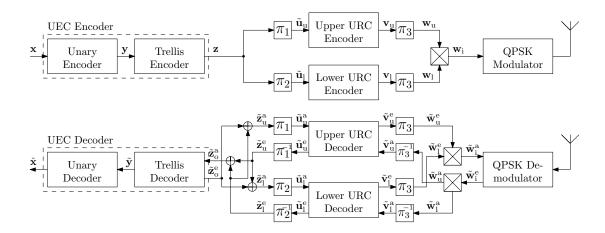

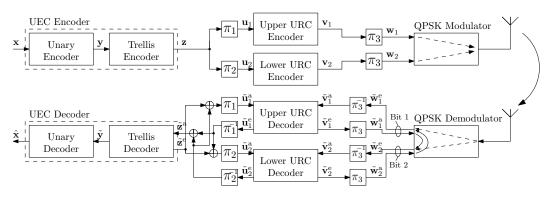

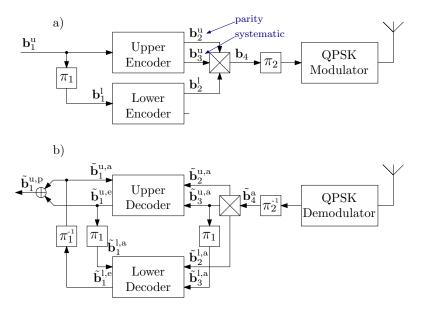

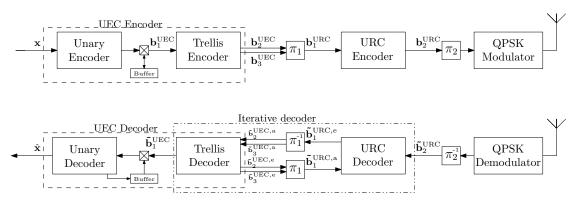

|   | 3.2 | Transı | mitter and receiver scheme                                | . 57  |

|   |     | 3.2.1  | Transmitter                                               | . 57  |

|   |     | 3.2.2  | Receiver                                                  | . 58  |

|   | 3.3 | Adapt  | ive decoder activation order algorithm                    | . 60  |

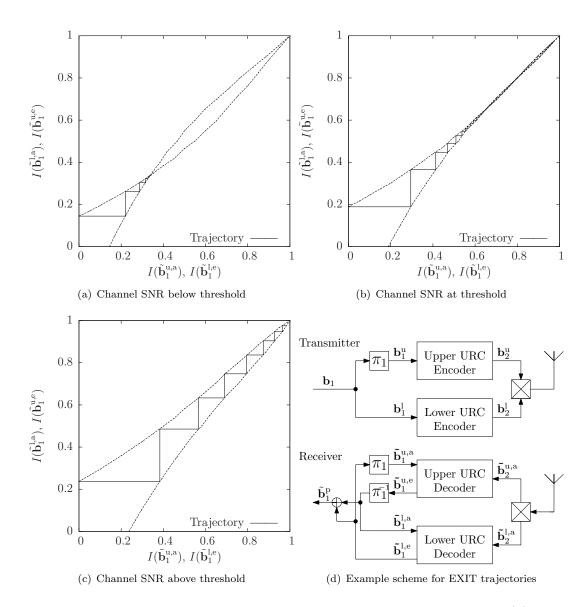

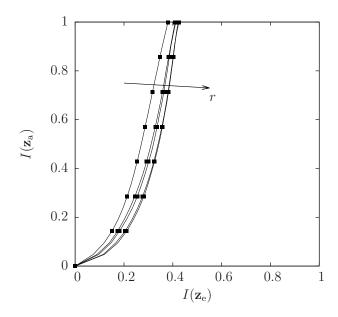

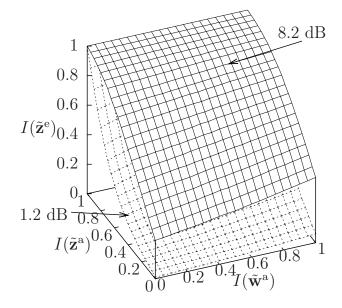

|   |     | 3.3.1  | EXIT function analysis                                    | . 60  |

|   |     | 3.3.2  | Adaptive activation algorithm                             | . 62  |

|   |     | 3.3.3  | Storage requirements                                      | . 64  |

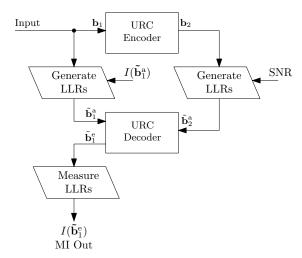

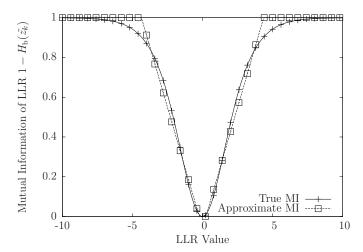

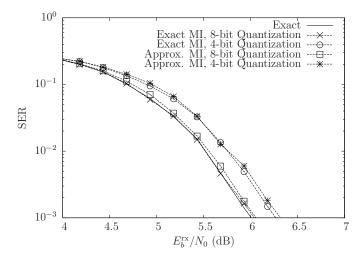

|   |     | 3.3.4  | MI measurement                                            | . 64  |

|   | 3.4 | Result | S                                                         | . 65  |

|   |     | 3.4.1  | Considered schemes                                        | . 66  |

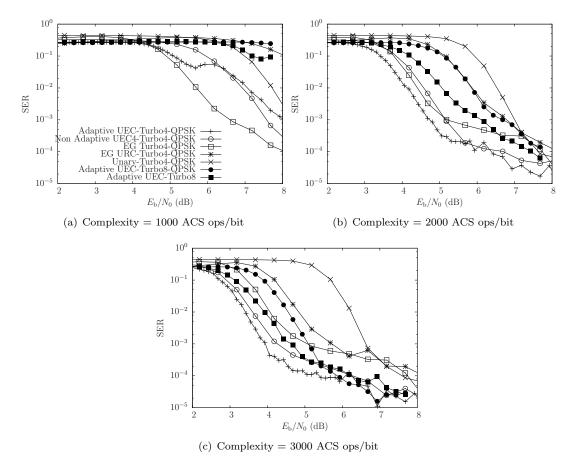

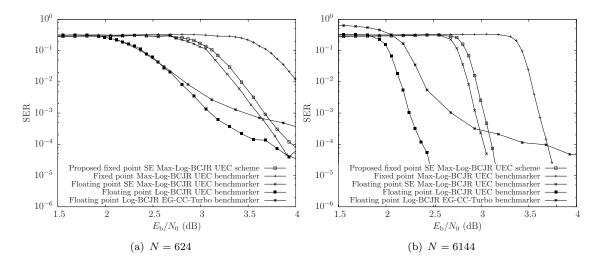

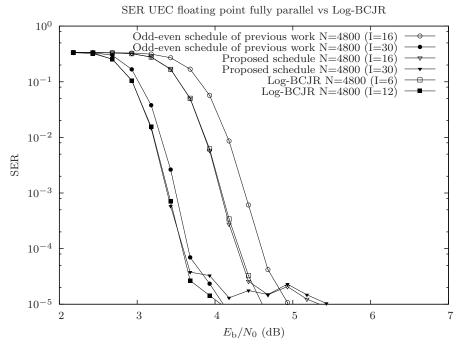

|   |     | 3.4.2  | SER performance                                           | . 67  |

|   | 3.5 | Conclu | usions                                                    | . 70  |

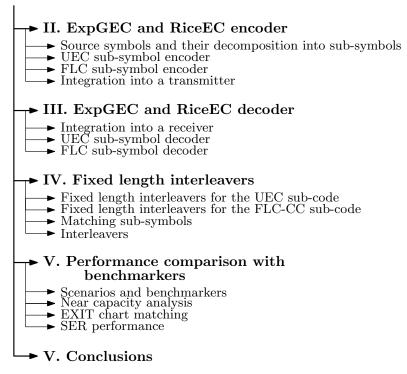

| 4 | Imp | roving | g the applicability of UEC using RiceEC and ExpGEC coding | g 71  |

|   | 4.1 | Introd | luction                                                   | . 71  |

|   | 4.2 | ExpG   | EC and RiceEC encoder                                     | . 75  |

|   |     | 4.2.1  | Source symbols and their decomposition into sub-symbols   | . 75  |

|   |     | 4.2.2  | UEC sub-symbol encoder                                    | . 78  |

|   |     | 4.2.3  | FLC-CC sub-symbol encoder                                 |       |

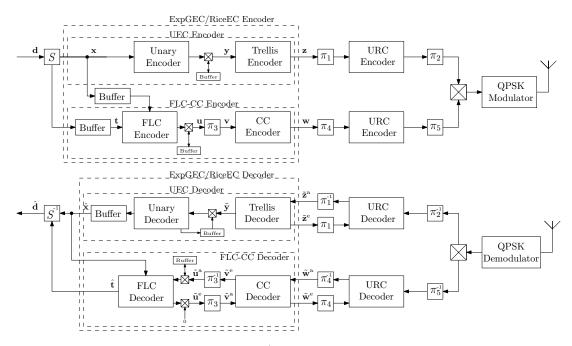

|   |     | 4.2.4  | Integration into a transmitter                            |       |

|   | 4.3 | ExpG   | EC and RiceEC decoder                                     | . 83  |

|   |     | 4.3.1  | Integration into a receiver                               | . 83  |

|   |     | 4.3.2  | UEC sub-symbol decoder                                    | . 85  |

|   |     | 4.3.3  | FLC sub-symbol decoder                                    | . 86  |

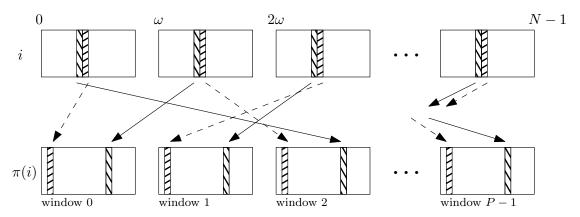

|   | 4.4 | Fixed- | length interleavers                                       | . 88  |

|   |     | 4.4.1  | Fixed-length interleavers for the UEC sub-code            | . 89  |

|   |     | 4.4.2  | Fixed-length interleavers for the FLC-CC sub-code         |       |

|   |     | 4.4.3  | Matching sub-symbols                                      | . 92  |

|   |     | 4.4.4  | Interleavers                                              |       |

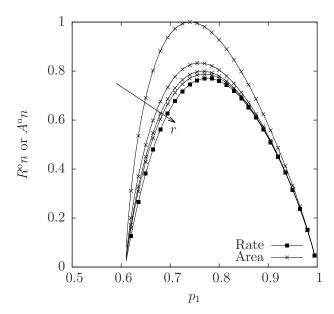

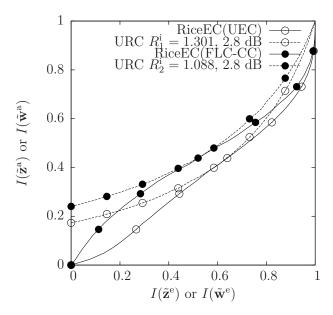

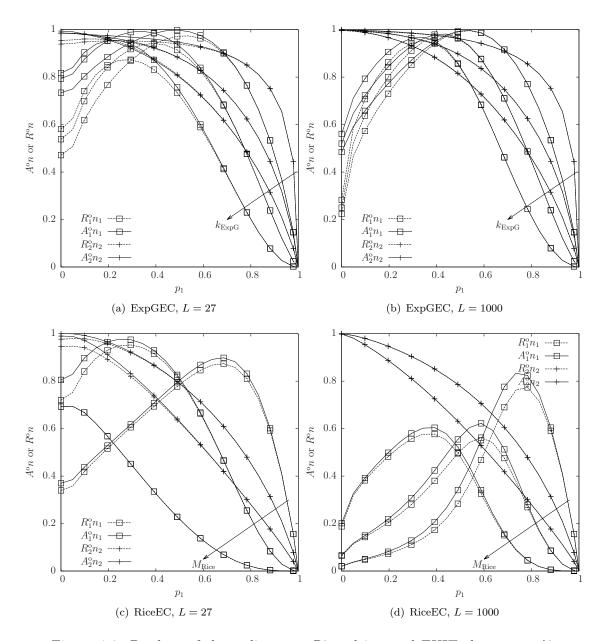

|   | 4.5 | Perfor | mance comparison with benchmarkers                        |       |

|   |     | 4.5.1  | Scenarios and benchmarkers                                |       |

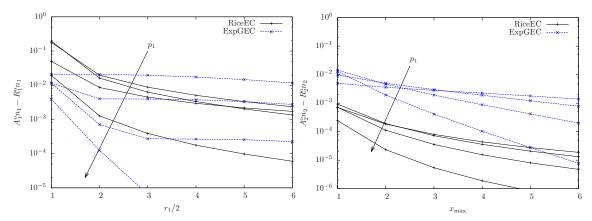

|   |     | 4.5.2  | Near capacity analysis                                    |       |

|   |     | 4.5.3  | EXIT chart matching                                       |       |

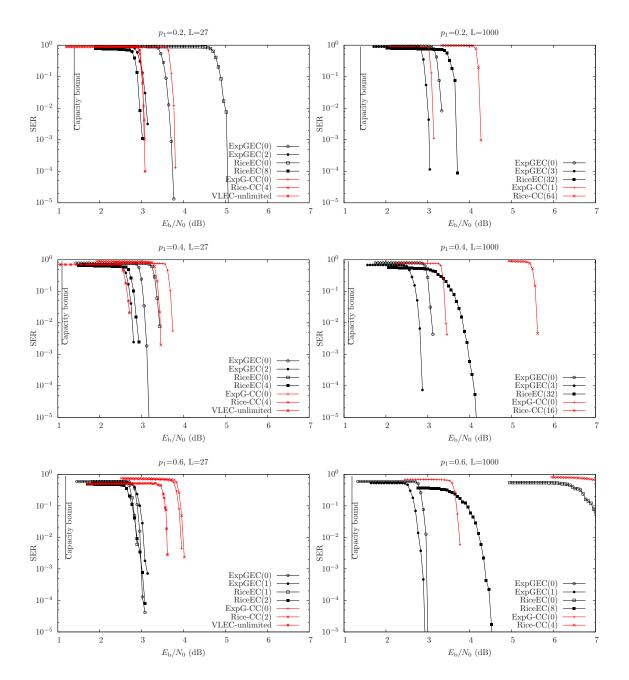

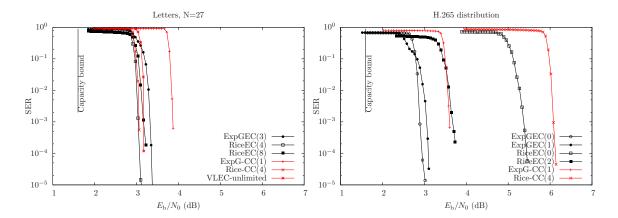

|   |     | 4.5.4  | SER performance                                           |       |

|   | 4.6 |        | usions                                                    |       |

|   |     | 4.6.1  | Design guidelines                                         | . 105 |

| 5 | A t |        | ecoder architecture for wireless sensor networks          | 107   |

|   | 5.1 |        | uction                                                    |       |

|   | 5.2 | _      | ammable ASIC architecture                                 |       |

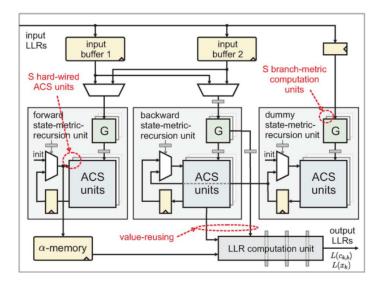

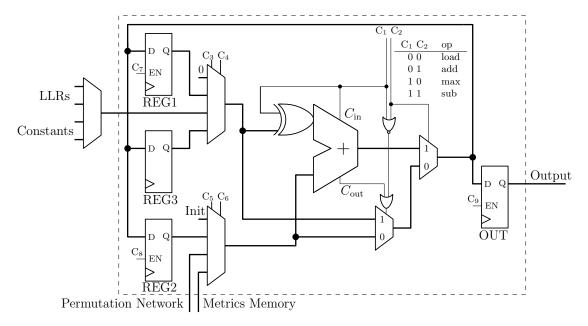

|   |     | 5.2.1  | The BCJR algorithm                                        |       |

|   |     | 5.2.2  | The decoder top level                                     | . 112 |

CONTENTS ix

|   |     | 5.2.3   | The Computation Unit                                                   | 114 |

|---|-----|---------|------------------------------------------------------------------------|-----|

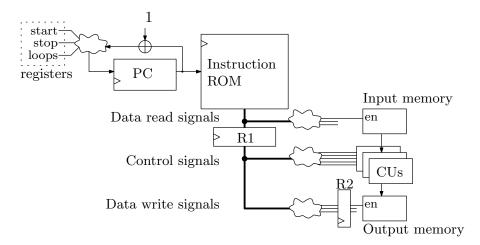

|   |     |         | Controller                                                             |     |

|   | 5.3 |         | ation to a joint source coding, channel coding and modulation sch      |     |

|   |     |         | Transmitter design                                                     |     |

|   |     | 5.3.2   | Receiver design                                                        | 117 |

|   |     | 5.3.3   | Mapping of the receiver design to the proposed architecture.           | 118 |

|   | 5.4 |         |                                                                        |     |

|   | 5.5 | Conclus | sions                                                                  | 124 |

| 6 |     | _       | oughput FPGA architecture for UEC and LTE                              | 127 |

|   | 6.1 |         | $\operatorname{ction}$                                                 |     |

|   | 6.2 | _       | ound                                                                   |     |

|   |     |         | LTE turbo code scheme                                                  |     |

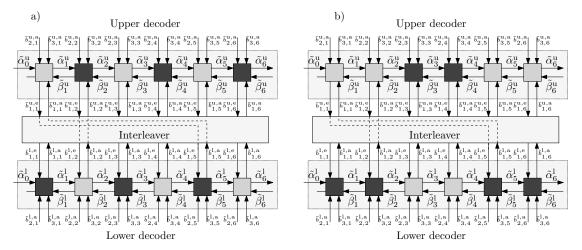

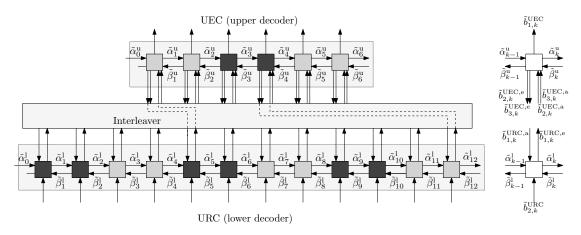

|   |     |         | UEC-URC JSCC scheme                                                    |     |

|   |     |         | Fully parallel decoding algorithm                                      |     |

|   | 6.3 |         | hm adaptations                                                         |     |

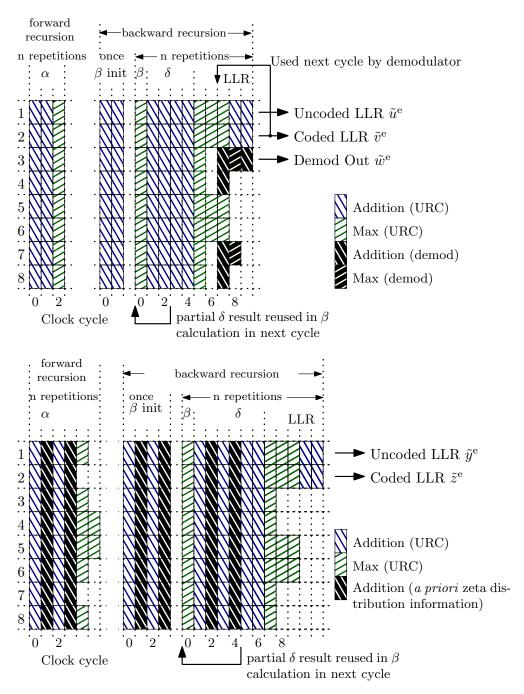

|   |     |         | Scheduling                                                             | 141 |

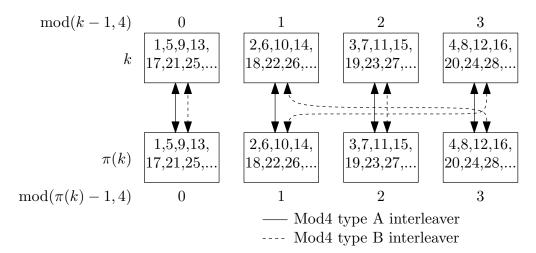

|   |     |         | Interleaver                                                            |     |

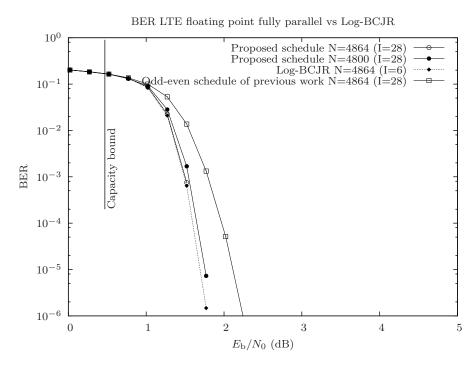

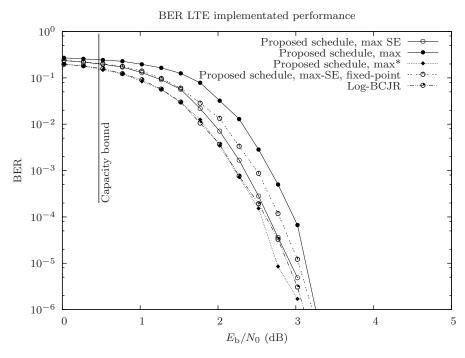

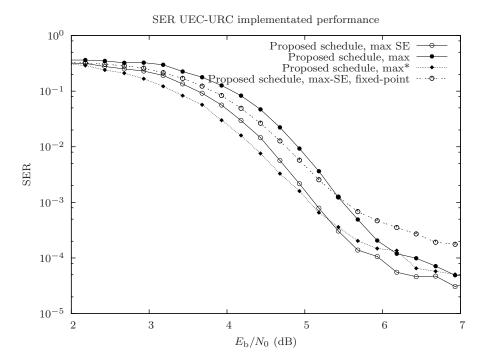

|   |     |         | Error correction performance                                           |     |

|   |     | 6.3.4   | Extrinsic scaling                                                      | 148 |

|   |     | 6.3.5   | Number representation                                                  | 149 |

|   | 6.4 | FPGA    | implementation                                                         | 151 |

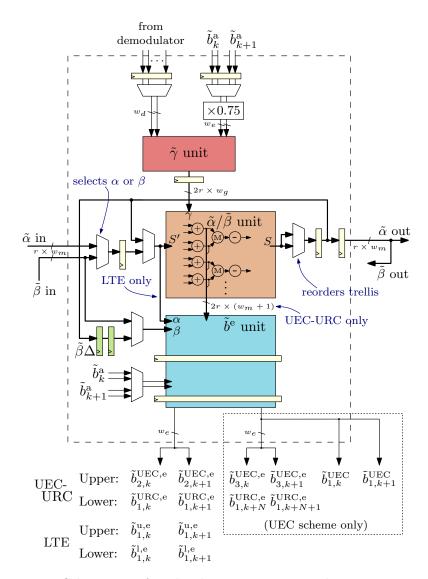

|   |     | 6.4.1   | Decoding block top level                                               | 152 |

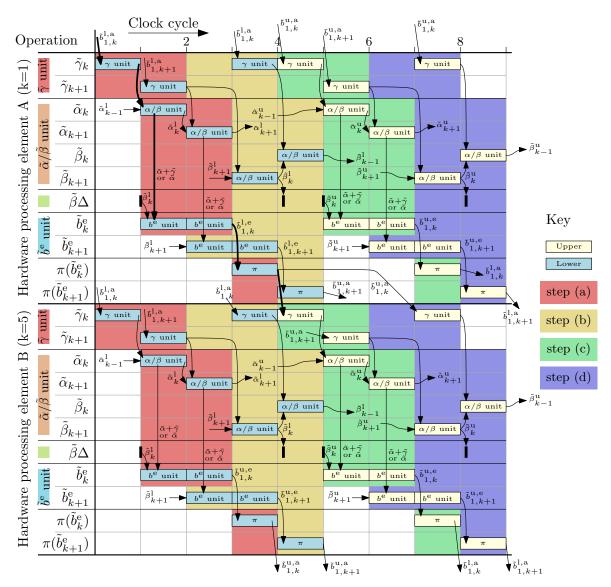

|   |     | 6.4.2   | Scheduling                                                             | 156 |

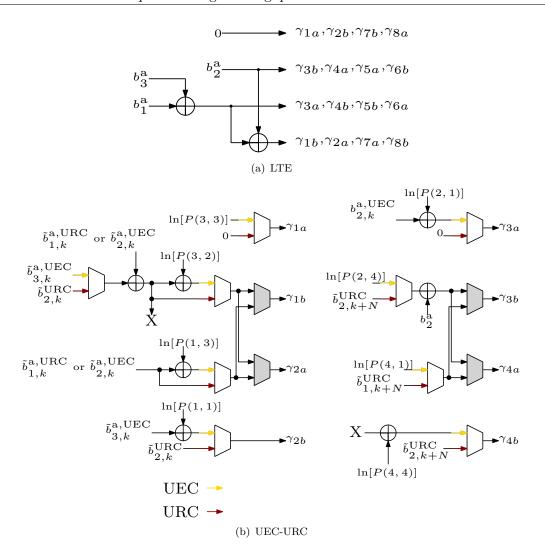

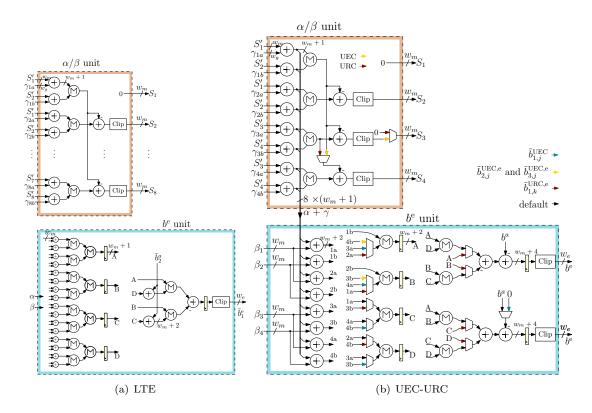

|   |     |         | Scheme-specific implementation                                         |     |

|   |     |         | Comparison to scheduling in the existing state-of-the-art importations |     |

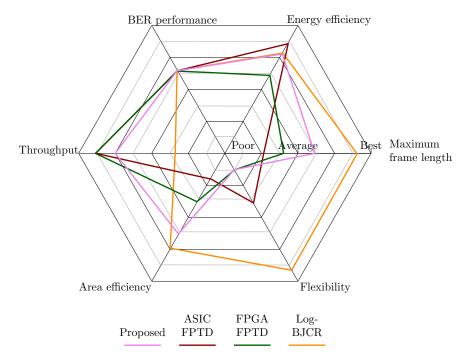

|   | 6.5 |         |                                                                        |     |

|   | 6.6 |         | sions                                                                  |     |

| _ |     |         |                                                                        |     |

| 7 |     |         | velopment of a high throughput decoder                                 | 169 |

|   |     |         | ction                                                                  |     |

|   | 7.2 | _       | hm modifications                                                       |     |

|   |     |         | Arbitrarily Parallel Turbo Decoder (APTD) top level                    |     |

|   | 7.0 |         | APTD scheduling                                                        |     |

|   | 7.3 |         | re implementation                                                      |     |

|   |     |         | Hardware scheduling                                                    |     |

|   |     |         | Proposed APTD hardware architecture                                    |     |

|   | - 4 |         | Interleaver requirements                                               |     |

|   | 7.4 |         | nance characteristics                                                  |     |

|   |     |         | BER performance                                                        |     |

|   |     |         | Implementation results                                                 |     |

|   | 7.5 | Conclus | sions                                                                  | 185 |

| 8 | Cor |         | s and future work                                                      | 187 |

|   | 8.1 |         | sions                                                                  |     |

|   |     | 8.1.1   | Design guidelines                                                      | 190 |

|        | Future work |     |

|--------|-------------|-----|

| Refere | nces        | 195 |

| Index  |             | 207 |

### **Declaration of Authorship**

I, Matthew Brejza , declare that the thesis entitled A Joint Algorithm and Architecture Design Approach to Joint Source and Channel Coding Schemes and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research. I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published, as seen in the list of publications

| Signed: | <br> | <br> |  |

|---------|------|------|--|

| 0       |      |      |  |

|         |      |      |  |

| Dato    |      |      |  |

## Acknowledgements

I would like to thank my supervisors Dr Rob Maunder, Professor Lajos Hanzo and Professor Bashir Al-Hashimi for their outstanding help and support, as well as sharing their knowledge and experience during the course of my studies. In particular, this thesis has benefited immensely from their quick feedback, useful insight and guidance. I would also like to extend my gratitude to my colleagues for their valuable input during our discussions over the past four years.

# Nomenclature

A Area beneath the inverted EXIT function.

$A_{\text{Amp}}$  Power amplifier efficiency. a, b, c Bit or LLR vector lengths.

d, x, t Stream of symbols or sub-symbols at the transmitter.

b, y, z, u, v, w Bit vectors at the transmitter.

$\hat{\mathbf{d}}, \hat{\mathbf{x}}, \hat{\mathbf{t}}$  Stream of decoded symbols or sub-symbols.  $\tilde{\mathbf{y}}$  Vector of a posteriori LLRs at the receiver.  $\tilde{\mathbf{b}}^{a}, \tilde{\mathbf{z}}^{a}, \tilde{\mathbf{u}}^{a}, \tilde{\mathbf{v}}^{a}, \tilde{\mathbf{w}}^{a}$  Vector of a priori LLRs at the receiver.  $\tilde{\mathbf{b}}^{e}, \tilde{\mathbf{z}}^{e}, \tilde{\mathbf{u}}^{e}, \tilde{\mathbf{v}}^{e}, \tilde{\mathbf{w}}^{e}$  Vector of extrinsic LLRs at the receiver.

H Symbol entropy.

I Number of decoding iterations.

i,j,k Bit or symbol indices.

$k_{\mathrm{ExpG}}$  Parameter of the ExpG code. l Average codeword length. L Symbol alphabet cardinality.  $M_{\mathrm{Rice}}$  Parameter of the Rice code.  $M_{\mathrm{Mod}}$  Number of constellation points.

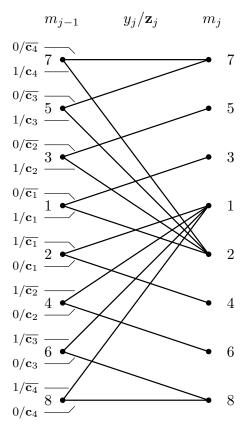

m Trellis state.

$\mathbb{N}_1$  The set of natural numbers,  $\mathbb{N}_1 = \{1, 2, 3, ...\}.$

N Frame length. n Codeword length.

P Number of hardware processing elements.

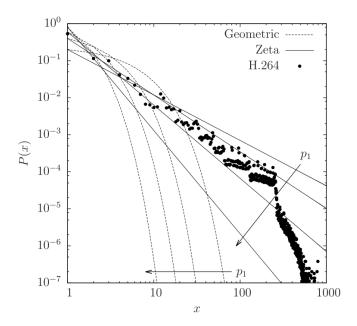

$p_1$  Probability of the value 1 in a zeta distribution.

R Coding, puncturing or doping rate.

r Number of states in a trellis. s Parameter of the zeta function.

T Trellis transition.

$x_{\text{max}}, d_{\text{max}}$  Maximum value of sub-symbol considered by the FLC decoder.

xvi NOMENCLATURE

$\alpha, \beta, \gamma, \delta$   $\alpha, \beta, \gamma$  and  $\delta$  calculations of the BCJR algorithm.

$\begin{array}{ll} \eta & & \text{Effective throughput.} \\ \omega & & \text{Window length.} \end{array}$

**3GPP** 3rd Generation Partnership Project

ACS Add-Compare-Select

ALM Adaptive Logic Module

ALUT Adaptive Look-Up Table

APTD Arbitrarily Parallel Turbo Decoder

ASIC Application-Specific Integrated Circuit

AWGN Additive White Gaussian Noise

BCJR Bahl-Cocke-Jelinek-Raviv

**BER** Bit Error Ratio

BPSK Binary Phase-Shift Keying

**CC** Convolutional Code

CRC Cyclic Redundancy Check

CU Calculation Unit

DCMC Discrete-Input Continuous-Output Memoryless Channel

**EC** Energy Consumption

EG Elias Gamma

EGEC Elias Gamma Error Correction

EXIT EXtrinsic Information Transfer

**ExpG** Exponential Golomb

**ExpGEC** Exponential Golomb Error Correction

FLC Fixed Length Code

**FLC-CC** Fixed Length Code-Convolutional Code

FPGA Field Programmable Gate Array

FPTD Fully Parallel Turbo Decoder

IID Independent and Identically Distributed

**IoT** 'Internet of Things'

**JSCC** Joint Source and Channel Coding

LDPC Low-Density Parity-Check

LLR Logarithmic Likelihood Ratio

Log-BCJR Logarithmic Bahl-Cocke-Jelinek-Raviv

LTE Long Term Evolution

LUT Look-Up Table

LUT-Log-BCJR Look-Up-Table based Log-BCJR

Max-Log-BCJR Maximum Log-BCJR

Max-SE-Log-BCJR Maximum with Scaled Extrinsic Log-BCJR

MCTC Multiple-Component Turbo Code

MI Mutual Information

ML Maximum Likelihood

NOMENCLATURE xvii

PA Power Amplifier

PIVI Previous Iteration Value Initialization

QAM Quadrature Amplitude Modulation

QPSK Quadrature Phase Shift Keying

RAM Random Access Memory

RiceEC Rice Error Correction

RNF Receiver Noise Figure

RS Reed-Solomon

RV Random Variable

SBSD Soft Bit Source Decoding

SER Symbol Error Rate

SIMD Single Instruction, Multiple Data

SISO Soft-In Soft-Out

SMP State-Metric Propagation SNR Signal-to-Noise Ratio

SSCC Separate Source and Channel Coding

TC Turbo Code

TCTC Twin-Component Turbo Code

TSMC Taiwan Semiconductor Manufacturing Company

UEC Unary Error CorrectionURC Unity Rate Convolutional

VLEC Variable Length Error-Correction

WSN Wireless Sensor Network

## Chapter 1

# Introduction

In modern telecommunication systems, there is a desire to achieve ever increasing transmission throughputs, while maintaining reasonable transmit power and receiver complexity. Over the previous two decades, the high performance turbo [1] and Low-Density Parity-Check (LDPC) [2] error correction codes have been adopted extensively, since they have the ability to reduce the transmit power required to achieve reliable communications, and/or increase the transmission throughput. In addition to this, high efficiency source codes have been developed to reduce the number of bits required to convey a message, which increases the efficiency of the system. To enable the practical use of these high complexity techniques, Application-Specific Integrated Circuit (ASIC) or Field Programmable Gate Array (FPGA) implementation is generally required to achieve high processing throughputs, which match the high transmission throughputs that they afford.

Improvements to the overall system performance can be achieved by jointly designing the various parts of the system together. In particular, Joint Source and Channel Coding (JSCC) [3] takes advantage of inefficiencies in the source code in order to increase the performance of the error correction code. Likewise, by considering the algorithm and hardware implementation jointly, a reduction in the architecture's power consumption or hardware resource usage can be achieved [4].

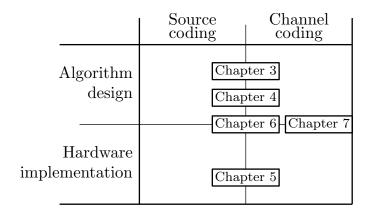

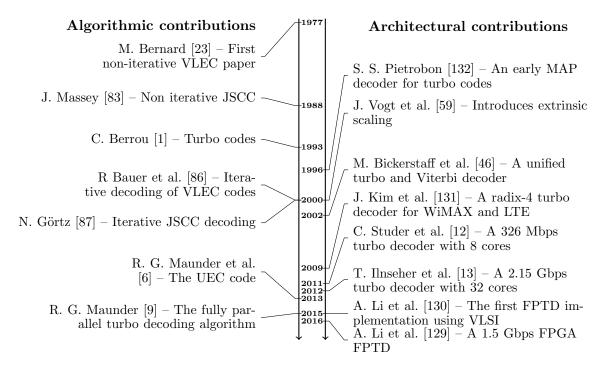

Figure 1.1 and Table 1.1 characterises a selection of work relating to the topics of source coding and channel coding. These are categorised into algorithm design or hardware implementation, where an overlap between topics identifies papers which consider these topics jointly. Against this background, this thesis considers the algorithmic design and hardware implementation of joint source and channel coding schemes. By considering these topics together, this thesis aims to achieve an increased performance with a reduction in hardware resources, compared to an approach where the source coding and channel coding algorithms and their implementation are developed in isolation. To build upon this further, the following sections briefly outline the key topics which constitute

this thesis. Following this, Section 1.5 summarises the novel contributions and structure of this thesis.

|                              | Source<br>coding | Channel coding                        |

|------------------------------|------------------|---------------------------------------|

| Algorithm<br>design          | [7]<br>[8]       | [6]<br>[5]<br>[5]<br>[2]<br>Chis [10] |

| <br>rdware im-<br>ementation | th               | lesis — [10] —<br>                    |

Figure 1.1: Topic map for some existing work in the topics considered by this thesis

- [7] Arithmetic code

- [8] Lempel-Ziv code

- [1] Turbo codes

- [9] Fully parallel turbo decoder

- [2] LDPC

- [6] Unary Error Correction (UEC) code

- [5] Variable Length Error-Correction (VLEC) code

- [11] A JSCC ASIC

- [12] Long Term Evolution (LTE) ASIC

- [13] 2.15 Gbps turbo decoder

- [14] Arithmetic code ASIC

- [10] Turbo decoder memory optimisation

Table 1.1: Some existing work in the topics considered by this thesis

### 1.1 Source coding

Source coding is used for the conversion of symbols provided by a source such as a video encoder into a series of bits, which can then be transmitted over a digital wireless link. Figure 1.1 shows some examples of sophisticated source codes from the literature. Each symbol source emits symbols from a particular set of values, where each symbol value has a particular probability of occurring. For example, a particular source may emit symbols having values selected from the set  $\{1, 2, 3, 4, 5, 6\}$ , with the corresponding probabilities  $\{0.30, 0.25, 0.15, 0.15, 0.10, 0.05\}$ .

Table 1.2: Example codewords for different source codes

| Symbol            | 1    | 2    | 3    | 4    | 5     | 6      |

|-------------------|------|------|------|------|-------|--------|

| Probability       | 0.30 | 0.25 | 0.15 | 0.15 | 0.10  | 0.05   |

| Binary codewords  | 000  | 001  | 010  | 011  | 100   | 101    |

| Huffman codewords | 11   | 01   | 101  | 100  | 001   | 000    |

| Unary codewords   | 1    | 01   | 001  | 0001 | 00001 | 000001 |

With this example, the most simple source code would represent each symbol using its binary representation, where  $\lceil \log_2(6) \rceil = 3$  bits are required for the 6 different symbols, as shown in Table 1.2. This is an inefficient source code, since it does not take into account the probabilities of each symbol. Since each codeword in the binary scheme has the same length of 3 bits, the average codeword length is  $l_{\text{Bin}} = 3$  bits. An improvement is offered by the Huffman code [15], which produces variable length binary representations

of each possible symbol value, as shown in Table 1.2. More specifically, the Huffman code allocates shorter codewords to more frequently occurring symbols and longer codewords to the rarer codewords. In this way the average codeword length of the Huffman code is reduced to  $l_{\rm Huff}=2.45$  bits. The entropy of a symbol source defines the minimum theoretical number of bits needed to represent a set of source symbols [16]. In the example of Table 1.2, the entropy of the source symbols is H=2.39 bits, showing the Huffman code achieves close to the theoretical limit.

In the example of Table 1.2, the number of symbols in the set is limited to 6. However, much larger alphabets may be encountered in practical schemes. In this thesis, the infinite symbol set will be explored, where an arbitrarily high symbol value could be produced, but with successively lower probabilities for increasing symbol value. When the size of symbol set is large, or when the probabilities of occurrence change over time, source codes such as the Huffman code become impractical. In this case, a code such as the unary code of Table 1.2 may be preferred, owing to its simpler structure, which does not require a codeword to be specifically designed to match the probability of occurrence of each symbol. However, this simplicity is typically at the cost of an increased average codeword length, where  $l_{\rm Unary} = 2.65$  results for the example of Table 1.2.

## 1.2 Channel coding

In contrast to source coding which aims to remove redundancy from a message, the channel code intentionally adds redundant bits to a message before its transmission over a noisy channel. Since the value of the bits received may be changed by errors induced by the channel, a channel decoder uses these redundant bits to attempt to recover the original message. This avoids the requirement for the transmitter to re-transmit the message, or increase the transmit power for subsequent messages to avoid errors occurring. However, the redundant bits transmitted by the error correction code will also consume additional energy at the transmitter. Owing to this, different schemes are compared according to how much energy per message bit  $(E_b)$  is required for reliable communication.

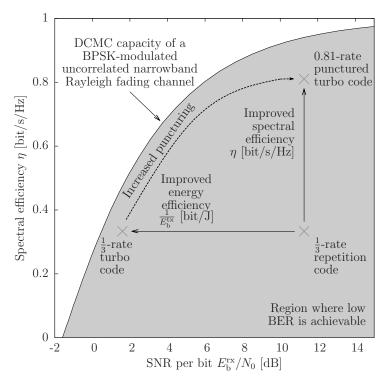

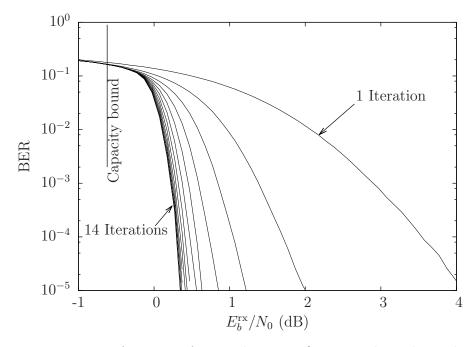

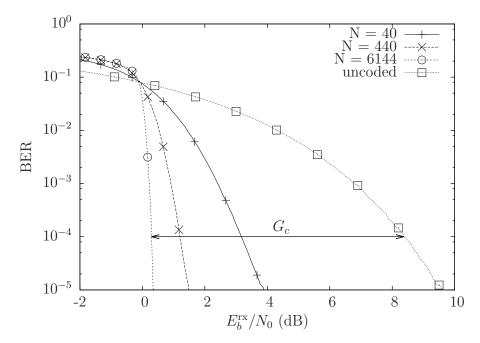

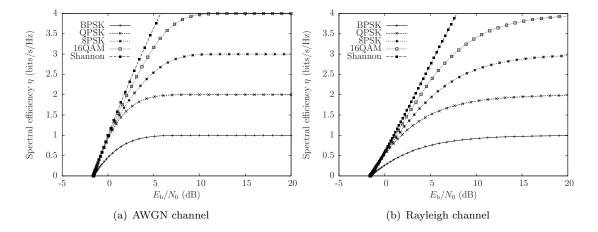

The performance of an error correction code can be characterised by how close it performs compared to the theoretical limit. More specifically, the Shannon limit [16] specifies the maximum achievable spectral efficiency, given the Signal-to-Noise Ratio (SNR) at the receiver  $E_{\rm b}^{\rm rx}/N_0$ , where  $N_0$  is the noise power spectral density. Figure 1.2 graphically illustrates the theoretical limit, in the case where BPSK modulation is used to transmit bits over an uncorrelated narrowband Rayleigh fading channel. Figure 1.2 characterises a 1/3-rate repetition code which is a simple error correction code that duplicates the transmission of each bit three times. The error correction capability relies on at least two copies of each bit being received without corruption, allowing the third corrupted

Figure 1.2: Performance of error correction codes compared to the theoretical limit for BPSK communication over an uncorrelated narrowband Rayleigh fading channel. From ©IEEE [17].

bit to be out voted. Here, the coding 'rate' refers to the fraction of the transmitted bits that are message bits. Figure 1.2 shows that the 1/3-rate repetition code has a spectral efficiency of 1/3 bit/s/Hz when employing BPSK, and requires an SNR of about 11 dB in order to achieve reliable communication. By contrast, turbo codes [1] are sophisticated error correction codes, used by modern communication standards such as LTE [18]. Figure 1.2 characterises a 1/3-rate turbo code, which has the same coding rate as the repetition code, but owing to the turbo code's increased error correction capability, the required SNR at the receiver is now only about 1 dB. The turbo code may be considered to be a near-capacity code, since it requires an SNR that is only about 1 dB greater than the theoretical limit. Alternatively, the turbo code may operate by transmitting only a reduced selection of its redundant bits, using a technique known as puncturing. Figure 1.2 shows how a punctured 0.81-rate turbo code requires the same receive SNR as the 1/3-rate repetition code, but achieves a significantly improved spectral efficiency of 0.81 bit/s/Hz.

As shown on Figure 1.1, turbo codes and LDPC codes [2] are examples of near-capacity iterative error correction codes. At the receiver, the turbo or LDPC decoder relies on two or more component decoders, which iteratively exchange information between themselves, such that each decoder aids the other to achieve successful decoding. This iterative approach leads to an attractive tradeoff between performance and complexity.

However, despite the complexity reduction offered by the iterative decoding methods relative to powerful non-iterative codes, turbo and LDPC decoders still have a high decoding complexity. For example, the LDPC code was originally proposed by Gallager in 1962 [2], however it was not until 1997 [19] when they were first considered suitable for use. More specifically, the authors of [20] considered the power consumption of the various components of a transceiver, finding that for the range of LTE base-stations which were considered, the turbo code consumes approximately the same power as all the other baseband radio components combined. Additionally, it was found for the smallest 'femto' base-stations that the turbo code also consumes approximately the same power as the Power Amplifier (PA) components. This demonstrates that the energy consumption required for error correction decoding is significant, especially for battery powered devices. Since error correction codes also have high complexity, the associated hardware cost required for high speed implementation is also a concern for wireless devices.

### 1.3 Joint source and coding

In Separate Source and Channel Coding (SSCC), a source code is combined with a channel code, as discussed in Sections 1.1 and 1.2, respectively. Here, the source code aims to remove as much redundancy as possible, while the channel code adds redundancy to allow error correction to be performed at the receiver. In contrast, JSCC [3] considers the source coding and channel coding jointly, which enables the channel code to take advantage of any residual redundancy that remains after source encoding, in order to enhance the error correction. Typically, a simple source code will be used, which may be intentionally chosen to give more excess redundancy, so that it can be used by the channel code. For example, Table 1.2 shows the unary source code [21] alongside the Huffman code. In this example, the unary source code has an average length of  $l_{\rm Unary} = 2.65$ , which compares to  $l_{\rm Huff} = 2.45$  for the Huffman code, as discussed in Section 1.1. Of these two options, the Huffman code would be the best choice for SSCC, since it removes most of the redundancy. However, the unary code may be the best choice for JSCC since the channel code can exploit the extra redundancy, in order to improve error correction.

Figure 1.1 shows a selection of papers on JSCC, which consider the source code and channel code together, in order to offer performance enhancements over the equivalent SSCC schemes. In particular, the UEC code [6] is an example of JSCC which can encode source symbols from a large or infinite set, such as those generated by a H.265 video encoder. This code achieves near capacity operation, without requiring knowledge of all source symbol probabilities, and without requiring careful synchronisation between the encoder and decoder. By contrast, near-entropy source codes such as the arithmetic code and Lempl-Ziv [8] code require both the transmitter and receiver to have accurate

knowledge of the probability of each symbol, which can impose large memory requirements when using large symbol sets. In these schemes, if the transmitter and receiver learn the symbol probabilities to avoid the transmitter having to convey them to the receiver, then any transmission errors will lead to the receiver becoming de-synchronised from the transmitter, which may introduce a large number of errors thereon [22].

However, the UEC code is not a universal code, which means that it cannot be applied for all symbol set probabilities. Motivated by this, this thesis proposes the Exponential Golomb Error Correction (ExpGEC) and Rice Error Correction (RiceEC) codes, which extend and improve the applicability of the UEC code. In particular, this thesis aims to offer performance gains without increasing the complexity required to achieve these gains. In contrast, the VLEC [23] code is an example of JSCC which offers a performance improvement compared to SSCC schemes, but requires an order of magnitude more complexity than SSCC schemes. This thesis shows that the ExpGEC and RiceEC schemes can offer the same performance improvements as the VLEC code, while using the same complexity as the SSCC schemes.

### 1.4 Joint algorithm and hardware design

This introduction has so far described the algorithmic methods which can be employed for reduced transmit power and increased throughput applications. However, in order to enable their practical use, the hardware implementation of these techniques must be considered.

When implementing an algorithm in hardware, there are tradeoffs which have to be made. For example, the algorithm may have originally been designed using floating point and high complexity mathematical operations. In order to reduce the complexity, the hardware implementation may use fixed point numbers with a more limited precision, and approximations of the mathematical operations, which typically lead to a performance degradation. In the case of an iterative decoder, such as those used by channel codes discussed in Section 1.2, these approximations may still approach the performance of the original algorithm, but requiring an increased number of iterations. Therefore, tradeoffs must be made between the complexity reduction achieved and the performance impairments associated with techniques such as using fixed point numbers.

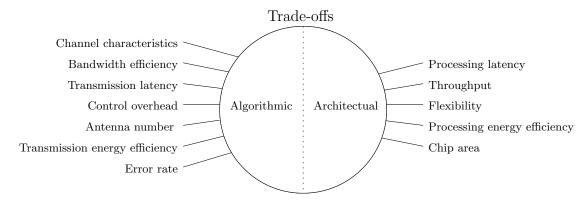

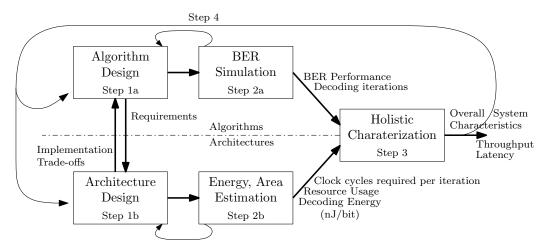

In order to improve the overall performance of an implemented design, techniques must be developed which consider both the algorithm and hardware, some of which are shown in Figure 1.1. For example, techniques such as extrinsic scaling [24, 25] reduce the performance impact of the complexity reducing approximations made within an error correction decoder. Understanding how the algorithm works, and considering algorithmic aspects is also important when attempting to increase the throughput of an implementation. In particular, each iterative component of the turbo decoder is comprised of long serial operations, which imposes restrictions upon its parallelism and hence its throughput. In the case of a turbo decoder, the highly serial processing also increases the Random Access Memory (RAM) requirement of a decoder. Motivated by these limitations, various techniques have been proposed to modify the turbo decoding algorithm, in order to achieve a considerably greater degree of parallelism, and therefore throughput. However, these techniques may also impact upon the performance of the algorithm, which must also be considered during the joint algorithm and hardware design. The various algorithmic and architectural factors are shown in Figure 1.3, characterising the design trade-offs that must be considered.

As shown in Figure 1.1, the majority of previous work on the joint design of algorithms and hardware implementations has considered only the channel code, or only the source code, with no papers jointly considering the algorithm and hardware implementation of a JSCC scheme. Upon this background, this thesis jointly considers the algorithm and hardware design of JSCC schemes, for the first time. Furthermore, this thesis will show how the high performance implementation techniques that have been previously developed for channel codes can also be applied to JSCC schemes.

Figure 1.3: Design trade-offs in a communication system.

### 1.5 Outline and novel contributions

This section details the structure of the thesis, and lists the novel contributions of each chapter. Figure 1.4 shows which of the topics discussed in this introduction are considered by each of the chapters.

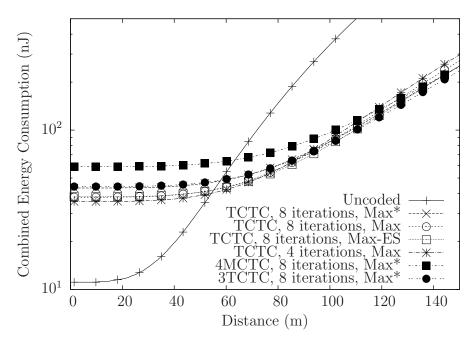

This thesis will continue in Chapter 2 with a background review. This will introduce and discuss the Log-BCJR error correction algorithm [17] and its implementation, which forms the basis of the iterative component decoders within the turbo code. An example of holistic design is provided, which applies the joint hardware and algorithm design philosophy of Section 1.4 to characterise the overall energy consumption in various example scenarios. This is followed by a discussion of EXtrinsic Information Transfer (EXIT)

Figure 1.4: The topics covered by the chapters in this thesis.

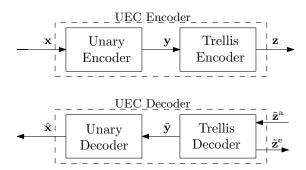

functions [26], which may be used to characterise iterative decoders. Finally, the operation of the UEC code and its encoder and decoder will be discussed.

Chapter 3 will detail the adaptive activation algorithm for a UEC scheme. Here, EXIT charts are used in an on-line fashion for deciding in which order to activate each of the iterative decoding blocks, allowing decoding to be completed with fewer iterations. This chapter shows that for a fixed complexity, the adaptive UEC scheme offers a performance improvement over the non-adaptive schemes, including SSCC benchmarkers. As shown in Figure 1.4, this chapter considers primarily the algorithmic aspects of a joint source and channel code, however some consideration is given to the ease of implementation, specifically by limiting the complexity, and by applying approximations to reduce the adaptive algorithm's complexity. The novel contributions of this chapter are as follows.

- The adaptive algorithm of [27] is extended to a UEC scheme having four iterative components, including an iterative demodulator. This requires the adaptive algorithm to be modified in order to operate on a scheme featuring both parallel and serial concatenations.

- We reduce the complexity of the Mutual Information (MI) measuring operation, that is used to decide which decoding block to activate next, by removing the need for exponential and logarithmic functions.

- The inclusion of the demodulator into the iterative decoding process is shown to reduce the overall complexity of the scheme, since it provides a more complementary match between lower complexity decoder components.

In Chapter 4, the applicability of the UEC code is increased. As discussed in Section 1.3, the UEC code cannot be applied to all symbol set probabilities, and performs poorly in some others. The work of [28] proposed the Elias Gamma Error Correction (EGEC) code, which splits each input symbol into two sub-symbols, one of which exploits the UEC code. This chapter extends the work of [28], where the ExpGEC and RiceEC codes

are proposed. These family of codes are shown to have greater applicability than the UEC or EGEC codes. Figure 1.4 shows that the work of this chapter mainly concerns the algorithmic aspects of the proposed JSCC schemes, however the implementational aspects are also considered. A complexity limit is imposed in order to demonstrate that the offered improvements do not come at the cost of extra complexity, while the practicality of the interleavers is also considered. The novel contributions of this chapter are as follows.

- The RiceEC and ExpGEC codes are proposed, which extend the EGEC of [28]. These codes use the UEC for near-capacity operation.

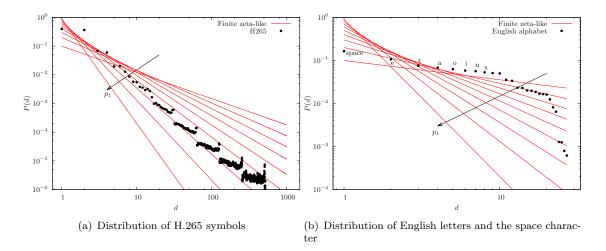

- The performance of the RiceEC, ExpGEC, UEC and EGEC schemes are characterised for a wide range of symbol sets, including the English alphabet and H.265 video data. The results show that the proposed family of codes can offer near-capacity performance for a wide range of symbol sets, where symbol sets with both large and small cardinality are considered.

- The wide range of considered symbol sets are analysed for each of the proposed codes, and the key aspects which impact upon the performance are discussed.

- A novel method is proposed to allow symbols and their variable-length codeword representations to be streamed through the encoder with fixed-length interleavers.

This method is shown to be immune to synchronisation issues that might otherwise occur with transmission errors.

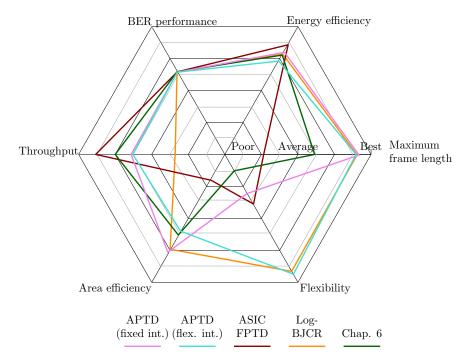

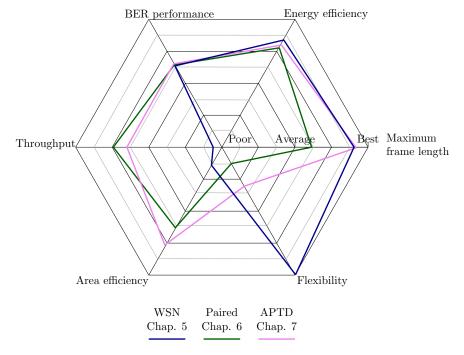

As shown in Figure 1.4, Chapter 5 details the implementation of a decoder for a JSCC scheme. This decoder is designed to be flexible, such that the same hardware can be used for the different constituent decoders of the JSCC scheme. This scheme is similar to that of Chapter 3, where a UEC scheme is used in conjunction with an iterative demodulator. The implementation is targetted towards Wireless Sensor Network (WSN) applications, hence the architecture has a low power consumption and small chip area. The novel contributions of this chapter are as follows.

- The same hardware is used for the different parts of the receiver, namely the UEC decoder, the two Unity Rate Convolutional (URC) decoders, and the demodulator.

- A controller was developed to handle the scheduling of the three different types of decoder, and to ensure that the hardware is kept as busy as possible, in order to achieve a high utility and hardware efficiency.

Chapter 6 also details the implementation of a UEC scheme. In contrast to Chapter 5, this implementation targets high throughputs and low latencies by vastly increasing the parallelism of the decoder, while offering a hardware efficiency improvement over similar

implementations. As shown in Figure 1.4, this chapter also considers the algorithm alongside the implementation. More specifically, the decoding algorithm is modified while considering how it will be implemented, allowing the hardware to achieve higher throughputs and lower latencies than would otherwise be achievable by simply using the Log-BCJR. The novel contributions of this chapter are as follows.

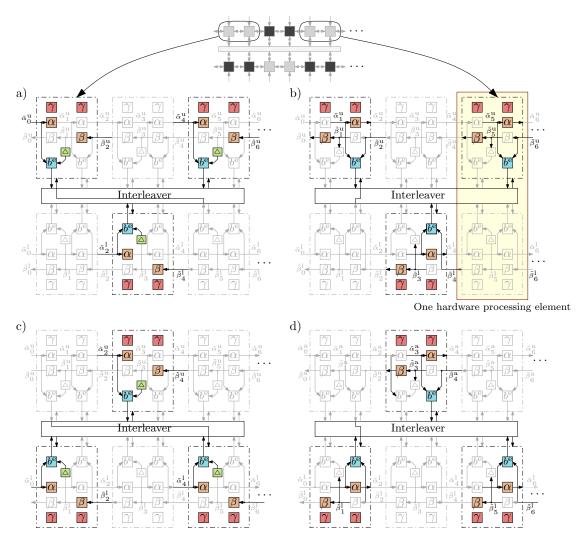

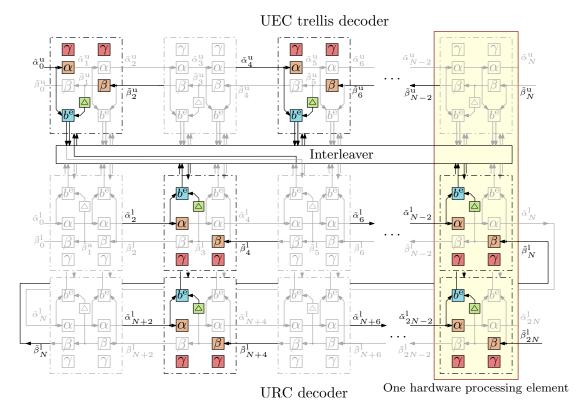

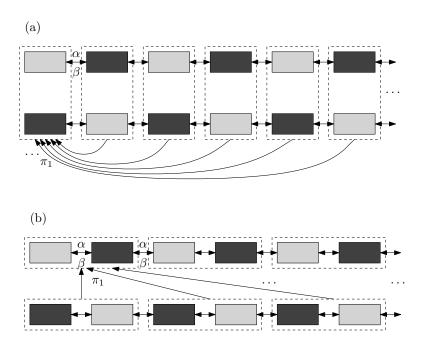

- A novel 'paired scheduling' decoder, derived from the fully parallel decoder of [9],

is used to achieve high throughputs and low latencies. This paired scheduling was

designed while jointly taking into consideration the algorithm and the hardware

implementation, in order to ensure improved error correction performance, and an

increased hardware efficiency.

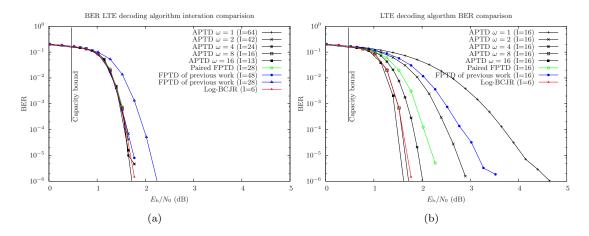

- The implementation of this chapter offers several improvements over previous fully parallel implementations. Increased pipelining allows a higher clock frequency, and the modified paired scheduling requires fewer iterations to achieve the same performance as the original fully parallel decoder of [9].

- Due to the increased hardware efficiency, the paired scheduling increases the frame length that can be decoded within a given hardware size, compared to the previous fully parallel implementations.

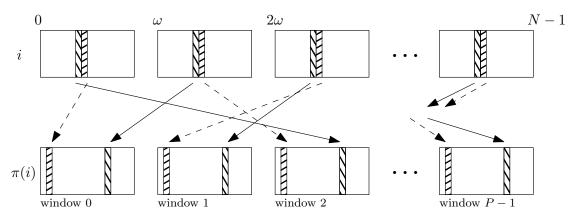

Chapter 7 extends the work of Chapter 6, where a potential future architecture is discussed. The paired scheduling is extended such that each of the parallel hardware processing elements can vary how many bits they each decode, depending on the frame length. Figure 1.4 shows that this chapter also considers the algorithm design and hardware implementation jointly, in order to offer increased performance. While a JSCC scheme is not considered by this chapter, the work of Chapter 6 shows how the techniques of this chapter may be extended to a UEC scheme. The novel contributions of this chapter are as follows.

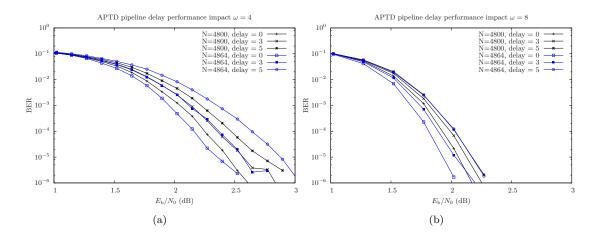

- The proposed architecture is compatible with all LTE frame lengths within any given hardware resource limit, where the decoder is flexible in its operation and offers a higher degree of parallelism compared to conventional Log-BCJR decoders.

- Since practical interleavers impose a few clock cycles of delay, the corresponding performance degradation is investigated.

This thesis will conclude in Chapter 8 by evaluating the completed work, and suggest future work and improvements.

# Chapter 2

# Background

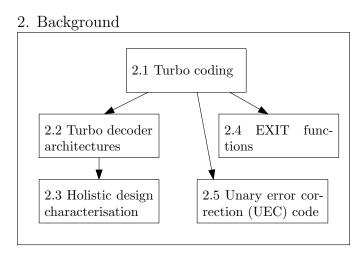

Figure 2.1: The outline for the background chapter

The outline for this chapter is shown in Figure 2.1. This chapter commences in Section 2.1 by describing the operation of turbo codes [1] in a typical communication system, which provides key a foundation to the rest of this thesis, as well as the other background sections. Following this, Section 2.2 investigates the challenges and solutions when implementing the turbo decoder of Section 2.1 in hardware. Section 2.3 provides an example of joint algorithm and hardware design, by jointly optimizing the energy consumption of the wireless system. Here the transmitter's energy consumption is considered alongside the receiver's energy consumption, to allow the most energy efficient option to be chosen. In Section 2.4, EXIT functions are discussed, which are used to characterise and predict the operation of individual blocks of iterative decoders. Finally, Section 2.5 discusses Unary Error Correction (UEC) codes, which can be combined with turbo codes of Section 2.1 to form Joint Source and Channel Coding (JSCC)

This chapter is partially based on the following publication.

**M. F. Brejza**, L. Li, R. G. Maunder, B. Al-Hashimi, C. Berrou and L. Hanzo (2016). 20 Years of Turbo Coding and Energy-Aware Design Guidelines for Energy-Constrained Wireless Applications. *IEEE Communications Surveys & Tutorials*, 18(1), 8–28.

schemes, which yields improved performance compared to conventional Separate Source and Channel Coding (SSCC) schemes.

## 2.1 Turbo coding

In this section, the Turbo Code (TC) scheme of Figure 2.2 is introduced. More specifically, the topic of Figure 1.1 covered by this section is mostly the algorithm design of the channel code. Section 2.1.1 begins by describing the convolutional encoders, which

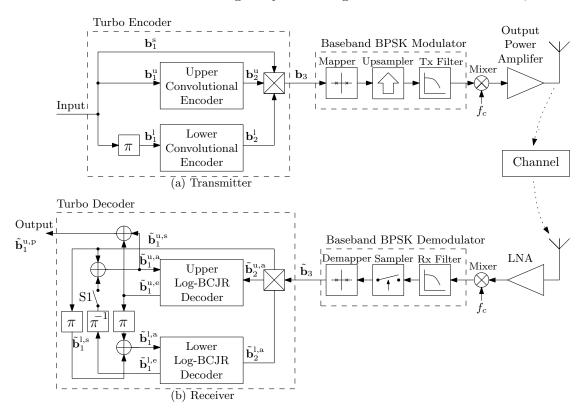

Figure 2.2: A BPSK-modulated R = 1/3 TC scheme.

are concatenated in parallel in order to form the turbo encoder of Figure 2.2. The integration of the turbo encoder into a BPSK transmitter is discussed in Section 2.1.2. Following this, Section 2.1.3 describes the modelling of transmission over an Additive White Gaussian Noise (AWGN) channel, subject to a certain path loss. Section 2.1.4 discusses the operation of the turbo-coded BPSK receiver of Figure 2.2. This operates on the basis of the most frequently used variant of the BCJR decoder, namely the Logarithmic Bahl-Cocke-Jelinek-Raviv (Log-BCJR) decoder, which is detailed in Section 2.1.5. Modifications of the Log-BCJR algorithm are conceived for the practical implementations, which are discussed in Section 2.1.7, before the TC's error correction performance is characterized in Section 2.1.6.

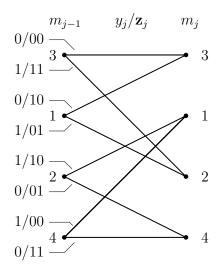

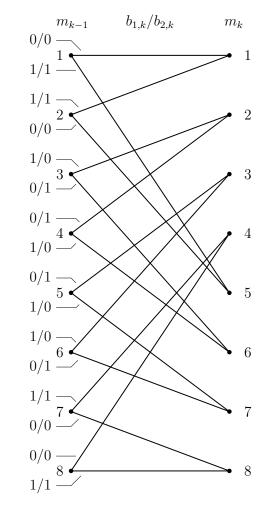

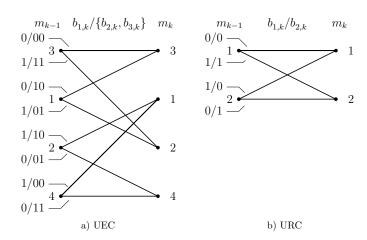

#### 2.1.1 Convolutional encoder

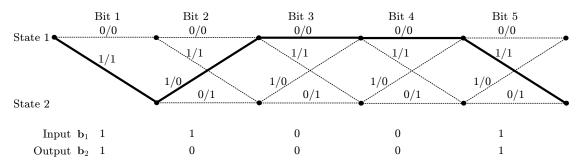

The convolutional encoder [29] is a widely adopted component in sophisticated error correcting schemes, forming the basis of the turbo encoder, as shown in Figure 2.2. In this application, the input of the convolutional encoder is a message frame  $\mathbf{b}_1$  $[b_{1,k}]_{k=1}^N$  comprising N bits, while the output is an N-bit encoded frame  $\mathbf{b}_2 = [b_{2,k}]_{k=1}^N$ . The parametrization of a convolutional encoder may be specified by a trellis, which graphically illustrates the relationship between the frames  $\mathbf{b}_1$  and  $\mathbf{b}_2$ . The example trellis of Figure 2.3 corresponds to a simple convolutional encoder, which may be used for encoding a message frame  $\mathbf{b}_1$  comprising N=5 bits. This encoder adopts one of two possible states following the encoding of each bit  $b_{1,k}$  in the frame, as represented by the dots in Figure 2.3. Depending on the value of this bit, the encoder state is selected by following one of two possible transitions from the previous state, as represented by the lines in Figure 2.3. As shown in Figure 2.3, the convolutional encoder is initialized in state 1 before encoding the first bit in the message frame  $\mathbf{b}_1$ . Each selected transition identifies a bit value for the encoded frame  $\mathbf{b}_2$ . For example, the message frame  $\mathbf{b}_1 =$ [1, 1, 0, 0, 1] corresponds to the sequence of transitions that is highlighted in bold in Figure 2.3. In turn, this sequence identifies the encoded frame  $\mathbf{b}_2 = [1, 0, 0, 0, 1]$ .

Figure 2.3: An example convolutional code trellis having two possible states. Each transition T is labelled with the notation  $a_1(T)/a_2(T)$ . A particular transition T from the current state will be selected if the corresponding bit in the message frame  $\mathbf{b}_1$  has the value  $a_1(T)$ , while  $a_2(T)$  is the value that will be output for the corresponding bit in the encoded frame  $\mathbf{b}_2$ .

Note that the convolutional code's trellis of Figure 2.3 has r=2 states, which corresponds to a shift register having one memory element. Furthermore, each transition between states is selected based on the value of one message bit, resulting in the generation of n=1 encoded bit. This results in a coding rate for this convolutional encoder of R=1, and an overall coding rate for the turbo code of Figure 2.2 of R=1/3. However, the convolutional codes of generalized TCs may employ a shift register having any number of memory elements. The TC of the Long Term Evolution (LTE) standard in cellular telephony [18] employs a trellis having  $r_{\rm LTE}=8$  states and n=1 encoded bits, where the mapping of message and encoded bit values to each transition in the LTE TC trellis is specified by its generator polynomials. Furthermore, the LTE TC appends three additional termination bits to each message frame  $\mathbf{b}_1$ , in order to guarantee that

the convolutional encoder always reaches the same particular state at the end of the encoding process.

#### 2.1.2 Turbo coded transmitter

As shown in Figure 2.2, the turbo encoder comprises a parallel concatenation of two convolutional encoders, which are referred to as the upper and lower encoders. The upper encoder processes the frame of message bits  $\mathbf{b}_1^{\mathrm{u}} = [b_{1,k}^{\mathrm{u}}]_{k=1}^N$  in order of increasing increasing k, while the lower encoder processes the same bits, but in a different order. This reordering is performed by the interleaver  $\pi$  of Figure 2.2, which outputs the interleaved message frame  $\mathbf{b}_1^{\mathrm{l}} = [b_{1,k}^{\mathrm{l}}]_{k=1}^N$ . The upper and lower convolutional encoders produce the N-bit encoded frames  $\mathbf{b}_2^{\mathrm{u}} = [b_{2,k}^{\mathrm{u}}]_{k=1}^N$  and  $\mathbf{b}_2^{\mathrm{l}} = [b_{2,k}^{\mathrm{l}}]_{k=1}^N$ , respectively. These encoded frames provide 2N parity bits, which are multiplexed in the crossed block of Figure 2.2 with N systematic bits, which are provided by the N-bit message frame  $\mathbf{b}_1^{\mathrm{u}}$ . The resultant transmission frame  $\mathbf{b}_3$  comprises 3N bits, corresponding to a coding rate of R = N/(3N) = 1/3.

Following turbo encoding, the transmitter of Figure 2.2 employs BPSK modulation, upsampling, pulse shaping, Radio Frequency (RF) mixing and power amplification. These are employed in order to transmit the frame  $\mathbf{b}_3$  using the desired carrier frequency  $f_c$  at a desired transmission energy per bit  $E_{\rm b}^{\rm tx}$ . Here,  $E_{\rm b}^{\rm tx}$  is related to the energy  $E_{\rm s}^{\rm tx}$  dissipated per modulated symbol according to  $E_{\rm b}^{\rm tx}[{\rm dBJ}] = E_{\rm s}^{\rm tx} - 10\log_{10}(\eta)$ , where  $\eta = R\log_2(M_{\rm mod})$ , R is the coding rate and  $M_{\rm mod}$  is the modulation order of the modulation scheme, with  $M_{\rm mod} = 2$  in the case of BPSK. Note that the employment of  $E_{\rm b}^{\rm tx}$  is typically preferable to  $E_{\rm s}^{\rm tx}$ , since this allows a fair comparison amongst schemes having different coding rates R and modulation orders M in terms of their transmission energy consumption.

#### 2.1.3 Channel

The wireless channel of Figure 2.2 conveys the BPSK-modulated signal between the transmitter and receiver antennas, but imposes degradation. These antennas can be characterized by their gain ( $G_{\rm tx}$  and  $G_{\rm rx}$ ) for the intended direction of propagation. In the scenario where there is a dominant line-of-sight (LOS) path between these antennas, the degradation may be modelled by the inverse-second-power free space path loss and AWGN. Here, the path loss is imposed by the attenuation of the BPSK-modulated signal as it propagates through free space. This depends on the distance between the transmit and receive antennas d (in m) and the carrier frequency  $f_c$  (in Hz) [30], according to

$$P_{\rm I}(d)[{\rm dB}] = 20\log_{10}(d) + 20\log_{10}(f_c) + 20\log_{10}\left(\frac{4\pi}{c}\right),$$

(2.1)

where  $c = 2.998 \times 10^8$  m/s is the speed of light, resulting in the last term of (2.1) having a constant value of -147.55 dB. However, the free space path loss model may be optimistic, since often there are multiple paths between the transmitter and receiver but the LOS path might be absent. In order to account for this, the path loss equation can be generalized by parameterising the path loss exponent p [31,32], according to

$$P_1(d)[dB] = 10p \log_{10}(d) + 20 \log_{10}(f) - 147.55.$$

(2.2)

Path loss exponents between p=2 and p=4 can be expected in the diverse environments encountered. The AWGN is imposed by the Brownian motion of electrons, resulting in thermal noise at the receiver, which has the power spectral density of  $N_0[\mathrm{dBJ}] = 10 \times \log(k \cdot T)$ , where  $k=1.3806503 \times 10^{-23} J K^{-1}$  is the Boltzmann constant. For the case of the room temperature T=300K, we obtain  $N_0=-203.8$  dBJ. Note that depending on the operating conditions, co-user interference is often more significant than the thermal noise. To model this,  $N_0$  can instead be replaced with the noise power spectral density that is expected in the operating conditions of the wireless link [33].

Considering the above channel effects, we can therefore relate the energy per bit at the receiver  $E_{\rm b}$  in terms of the energy dissipated at the transmitter  $E_{\rm b}^{\rm tx}$  and the channel conditions, according to

$$E_{\rm b}[{\rm dBJ}] = 10 \log_{10}(E_{\rm b}^{\rm tx}) - A_{\rm Amp} - P_{\rm l}(d) + G_{\rm tx} + G_{\rm rx},$$

(2.3)

where  $A_{\rm Amp}$  is the power amplifier efficiency, and where all quantities are expressed in dB, except  $E_{\rm b}^{\rm tx}$  which is expressed in Joules. Note that if shadowing or fading is prevalent in the particular wireless environment considered, then (2.3) can be modified to model this by additionally subtracting corresponding fading margins [34]. In particular, narrowband uncorrelated Rayleigh fading [35] channels are explored in this thesis.

#### 2.1.4 Turbo coded receiver

In the receiver of Figure 2.2, the BPSK-modulated signal provided by the receive antenna is passed to a Low Noise Amplifier (LNA). This is employed to boost the weak received signals, while introducing only a minimal amount of additional noise, which is quantified by its Receiver Noise Figure (RNF). The amplified signal is mixed down from the RF range to the baseband, where it is filtered to remove the out-of-band noise, down-sampled and provided to the BPSK demodulator.

The role of the BPSK demodulator is to extract information pertaining to the turboencoded bits from the received signal. However, the BPSK demodulator can never be certain of the correct value for each bit, owing to the unpredictable nature of the degradation imposed by the channel. Rather than making a binary *hard decision* of '1' or '0' for each bit, superior error correction performance can be obtained if the demodulator makes a soft decision. Here, a soft decision expresses not only what the most likely value of the bit is, but also how likely this value is. More specifically, the demodulator, which is also often referred to as a demapper, can express the soft information pertaining to a particular bit using a Logarithmic Likelihood Ratio (LLR), which represents the probabilities associated with the value of the bit b according to  $b = \ln[\Pr(b=1)/\Pr(b=0)]$ . Here, the sign of an LLR expresses whether a value of '1' or '0' is more likely for the corresponding bit, while the magnitude of the LLR is commensurate with how likely this value is. When employing BPSK modulation, it can be shown that each LLR is directly proportional to the corresponding sample provided by the down-sampler [36]. As shown in Figure 2.2, the BPSK demodulator generates the LLR sequences  $\tilde{\mathbf{b}}_1^{\mathrm{u,s}}$ ,  $\tilde{\mathbf{b}}_2^{\mathrm{u,a}}$  and  $\tilde{\mathbf{b}}_2^{\mathrm{l,a}}$ , which pertain to the bit sequences  $\mathbf{b}_1^{\mathrm{u}}$ ,  $\mathbf{b}_2^{\mathrm{u}}$  and  $\mathbf{b}_2^{\mathrm{l}}$  respectively. Furthermore, an interleaver  $\pi$  is employed for converting  $\tilde{\mathbf{b}}_1^{\mathrm{u,s}}$  into the LLR sequence  $\tilde{\mathbf{b}}_{1}^{l,s}$ , which pertains to the bit sequence  $\mathbf{b}_{1}^{l}$ . These LLR sequences are then provided to the turbo decoder, which is invoked for mitigating the corresponding uncertainty and for eliminating transmission errors. As shown in Figure 2.2, the turbo decoder comprises two Log-BCJR decoders, which correspond to the two convolutional encoders of the turbo encoder.

The turbo decoder is operated in an iterative manner, with the switch labelled 'S1' in Figure 2.2 being left open during the first decoding iteration. This enters the LLR sequence  $\tilde{\mathbf{b}}_1^{\mathrm{u,s}}$  provided by the BPSK demodulator directly into the upper Log-BCJR decoder  $\tilde{\mathbf{b}}_{1}^{\mathrm{u,a}}$ . As shown in Figure 2.2, the upper Log-BCJR decoder's other input  $\tilde{\mathbf{b}}_{2}^{\mathrm{u,a}}$ is supplied by the BPSK demodulator. The upper Log-BCJR decoder combines the old (or "a priori") information provided by its two input LLR sequences, in order to extract new (or "extrinsic") information for the output LLR sequence  $\tilde{\mathbf{b}}_{1}^{\mathrm{u,e}}$ . Since this LLR sequence pertains to the uncoded bit sequence  $\mathbf{b}_1^{\mathrm{u}}$ , the interleaver  $\pi$  may be used for converting it into information pertaining to the bit sequence  $\mathbf{b}_1^1$ . Following this, the resultant interleaved LLR sequence may be added on a bit-by-bit basis to the values in the LLR sequence  $\tilde{\mathbf{b}}_{1,s}^{l}$  provided by the BPSK demodulator, which also pertains to  $\mathbf{b}_1^l$ . The resultant LLR sequence is then forwarded to the lower Log-BCJR decoder's input  $\tilde{\mathbf{b}}_{1}^{\mathrm{l,a}}$ , as shown in Figure 2.2. Meanwhile, the lower Log-BCJR decoder's other input  $\tilde{\mathbf{b}}_{2}^{\mathrm{l,a}}$  is supplied by the BPSK demodulator. In turn, the lower Log-BCJR decoder combines these a priori LLR sequences, in order to obtain the extrinsic LLR sequence  $\mathbf{b}_{1}^{1,e}$ , completing the first decoding iteration.

In the second and in all subsequent decoding iterations, the switch labelled 'S1' in Figure 2.2 is closed. This allows the extrinsic LLR sequence  $\tilde{\mathbf{b}}_{1}^{l,e}$  to be deinterleaved  $\pi^{-1}$  and added on a bit-by-bit basis to the values in the LLR sequence  $\tilde{\mathbf{b}}_{1}^{u,s}$ , in order to generate an improved a priori LLR sequence  $\tilde{\mathbf{b}}_{1}^{u,a}$  for the upper Log-BCJR decoder. This motivates the repeated operation of the upper Log-BCJR decoder, in order to produce an improved extrinsic LLR sequence  $\tilde{\mathbf{b}}_{1}^{u,e}$ . In turn, this may be interleaved and added on a bit-by-bit basis to the values in the LLR sequence  $\tilde{\mathbf{b}}_{1}^{l,s}$ , in order to generate an improved

a priori LLR sequence  $\tilde{\mathbf{b}}_{1}^{l,a}$  for the lower Log-BCJR decoder. Likewise, the operation of the lower Log-BCJR decoder may be repeated for obtaining an improved extrinsic LLR sequence  $\tilde{\mathbf{b}}_{1}^{l,e}$ . This process may be repeated during the third iteration and during all further iterations, in order to gradually improve the quality of the iteratively exchanged LLR sequences. However, as will be show in Section 2.1.7, each additional iteration yields a diminishing return, until convergence is eventually achieved, whereupon additional iterations provide no further improvement. Once a sufficient number I of iterations has been performed, a final output may be obtained by adding the LLR sequences  $\tilde{\mathbf{b}}_{1}^{u,a}$  and  $\tilde{\mathbf{b}}_{1}^{u,e}$  on a bit-by-bit basis. The resultant LLR sequence  $\tilde{\mathbf{b}}_{1}^{u,p}$  contains all (or "a posteriori") information pertaining to the turbo encoder's input bit sequence  $\mathbf{b}_{1}^{u}$ . Finally, these soft-valued LLRs may be converted into hard-valued bits by considering the sign of each LLR, where a positive value corresponds to a '1' and a negative value corresponds to a '0'.

### 2.1.5 Log-BCJR decoder

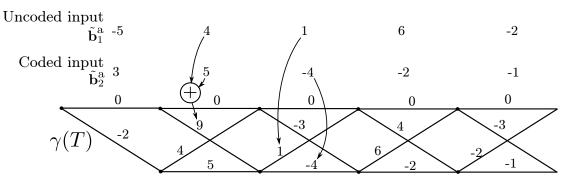

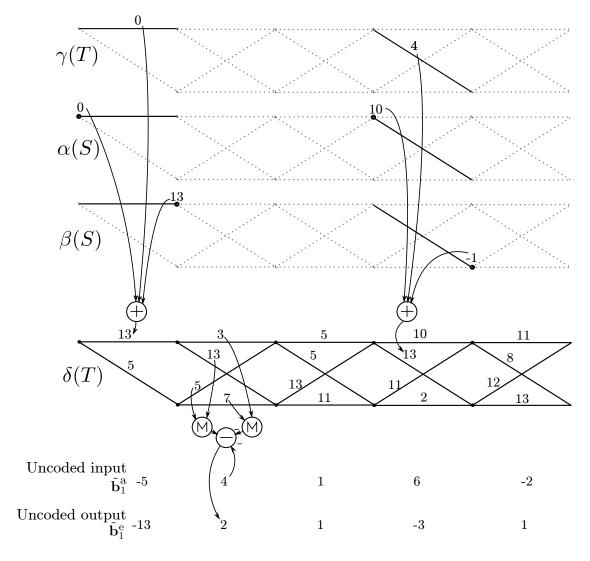

In this section, this thesis provides an overview of the Log-BCJR algorithm [37], which is employed both by the upper and lower Log-BCJR decoders of Figure 2.2. Note that the Log-BCJR algorithm is a reduced-complexity version of the BCJR algorithm, as will be discussed in greater detail in Section 2.1.6, together with a discussion of other variants of the Bahl-Cocke-Jelinek-Raviv (BCJR) algorithm. Here, as an example, the trellis of Figure 2.3 is imposed for combining the example a priori LLR sequences  $\tilde{\mathbf{b}}_1^a = [-5, 4, 1, 6, -2]$  and  $\tilde{\mathbf{b}}_2^a = [3, 5, -4, -2, -1]$ , in order to obtain the extrinsic LLR sequence  $\tilde{\mathbf{b}}_1^e$ . Note that these example LLRs have been rounded to the nearest integer, for the sake of simplicity. The Log-BCJR algorithm comprises four intermediate steps, in which four sets of metrics are calculated, namely the  $\tilde{\gamma}(T)$ ,  $\tilde{\alpha}(m)$ ,  $\tilde{\beta}(m)$  and  $\tilde{\delta}(T)$  values, where T refers to a particular transition in the trellis and m refers to a particular state, as detailed in the following discussion. This thesis will show that the calculations of each step can be approximately decomposed into simple Add-Compare-Select (ACS) operations. Further detailed discussions are available in [38,39].

In the first step of the Log-BCJR algorithm, a  $\tilde{\gamma}(T)$  value is calculated for each transition in the trellis of Figure 2.3. This  $\tilde{\gamma}(T)$  value represents the *a priori* probability that the transition T was selected during the convolutional encoding process. The  $\tilde{\gamma}(T)$  value for a particular transition T in the trellis of Figure 2.3 is calculated according to

$$\tilde{\gamma}(T) = a_1(T) \cdot \tilde{b}_{1,i(T)}^{a} + a_2(T) \cdot \tilde{b}_{2,i(T)}^{a},$$

(2.4)

where  $a_1(T)$  and  $a_2(T)$  are described in Figure 2.3. Here, i(T) is the index of the bits that are represented by the transition T, while  $\tilde{b}_{1,i(T)}^{\rm a}$  is the LLR having that specific index i(T) in the sequence  $\tilde{\mathbf{b}}_1^{\rm a}$ . Likewise,  $\tilde{b}_{2,i(T)}^{\rm a}$  is the corresponding LLR in the sequence  $\tilde{\mathbf{b}}_2^{\rm a}$ . In Figure 2.4 each transition is labelled with the particular  $\tilde{\gamma}(T)$  value that results

for our example. Note that relatively high  $\tilde{\gamma}(T)$  values result for transitions where the *a priori* LLRs match with that transition's  $a_1(T)$  and  $a_2(T)$  combination. Since  $a_1(T)$  and  $a_2(T)$  have binary values, each  $\tilde{\gamma}(T)$  value is given by 0,  $\tilde{b}_{1,i(T)}^{\rm a}$ ,  $\tilde{b}_{2,i(T)}^{\rm a}$  or  $\tilde{b}_{1,i(T)}^{\rm a} + \tilde{b}_{2,i(T)}^{\rm a}$ . Therefore, the entire set of  $\tilde{\gamma}(T)$  values can be calculated using only addition and selection operations.

Figure 2.4: Calculating the  $\tilde{\gamma}(T)$  values for some example a priori LLRs.

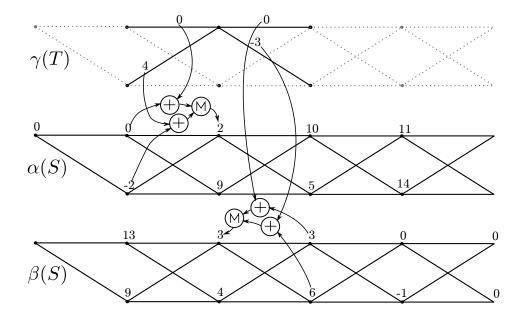

The second step of the Log-BCJR algorithm is to calculate an  $\tilde{\alpha}(m)$  value for each state m in the trellis. These  $\tilde{\alpha}(m)$  values represent the probability that a particular state was entered into during the encoding process. This is obtained by considering the probabilities of the previous states having been entered into during encoding, as well as the probabilities that the transitions between these pairs of states have been taken. Owing to these dependencies between the probabilities associated with consecutive states, a forward recursion is required in order to calculate the  $\tilde{\alpha}(m)$  values for the states of the trellis in a specific order, evolving from left to right. The calculation for an  $\tilde{\alpha}(m)$  for a particular state m is given by

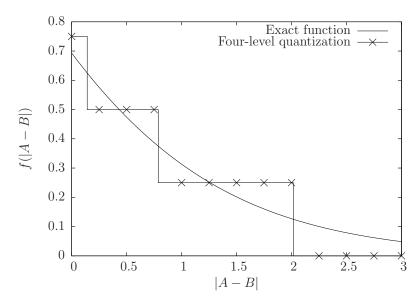

$$\tilde{\alpha}(m) = \max_{T \in to[m]}^{*} \left[ \tilde{\gamma}(T) + \tilde{\alpha}(fr[T]) \right], \tag{2.5}$$

where to[m] returns the set of all transitions merging into the state m, while fr[T] returns the particular state that the transition T emerges from. The operation  $\max^*$  for two inputs A and B is defined as  $\max^*(A,B) = \max(A,B) + \ln(1+e^{-|A-B|})$ . Since this operation is associative, it can be readily extended to more inputs. In the example of Figure 2.5, each state in the trellis is labeled with its  $\tilde{\alpha}(m)$  value, where the  $\max^*$  operator has been approximated using the max operation for simplicity. As shown in Figure 2.5, the forward recursion is initialized by setting the  $\tilde{\alpha}(m)$  value of the state at the far left of the trellis to zero. Note that the  $\tilde{\alpha}(m)$  values are calculated using only addition and  $\max^*$  operations, which can be further decomposed into only ACS operations, as will shall show in Section 2.1.6.

In the third step of the Log-BCJR algorithm, a  $\tilde{\beta}(m)$  value is calculated for each state in the trellis, using a similar process to that of the  $\tilde{\alpha}(m)$  values. While the  $\tilde{\alpha}(m)$  values depend on the previous  $\tilde{\alpha}(m)$  values in the trellis, the  $\tilde{\beta}(m)$  value of a particular state

Figure 2.5: Calculating the  $\tilde{\alpha}(m)$  and  $\tilde{\beta}(m)$  values. The previous  $\tilde{\gamma}(T)$  trellis is shown for reference. The circled 'M' represents the max\* operation, which has been approximated using the max operation in the presented calculations, to maintain integer values for simplicity.

depends on those of the next states in the trellis. Therefore the  $\tilde{\beta}(m)$  values must be calculated in order, using a backward recursion order, evolving from the right end of the trellis to the left end. This is achieved according to

$$\tilde{\beta}(m) = \max_{T \in fr[m]}^{*} \left[ \tilde{\gamma}(T) + \tilde{\beta}(to[T]) \right], \tag{2.6}$$

where fr[m] returns the set of all transitions that emerge from the state m, while to[T] returns the particular state that the transition T merges into. Once again, the  $\tilde{\beta}(m)$  values for our example are shown on the states of Figure 2.5, where the max\* operator has been approximated using the max operation for simplicity. As shown in Figure 2.5, the backward recursion is initialized by setting the  $\tilde{\beta}(m)$  values of the states at the far right of the trellis to zero. Like the  $\tilde{\alpha}(m)$  values, the  $\tilde{\beta}(m)$  values can be calculated using only ACS calculations.

The fourth set of metrics required for the Log-BCJR algorithm are the  $\tilde{\delta}(T)$  values, which combine the results from previous metrics in order to represent the *a posteriori* probabilities that the transitions were followed in the encoder. The  $\tilde{\delta}(T)$  value of a particular transition T is calculated by adding its  $\tilde{\gamma}(T)$  value to the  $\tilde{\alpha}(m)$  value of the state it emerges from and the  $\tilde{\beta}(m)$  value of the state it merges into, according to

$$\tilde{\delta}(T) = \tilde{\alpha}(fr[T]) + \tilde{\gamma}(T) + \tilde{\beta}(to[T]). \tag{2.7}$$

The  $\tilde{\delta}(T)$  calculations detailed for our example can be seen in Figure 2.6. Since the  $\tilde{\delta}(T)$  values are calculated using only additions, they can be decomposed into ACS operations.

Figure 2.6: Calculating the  $\tilde{\delta}(T)$  values and the extrinsic LLRs. The circled 'M' represents the max<sup>\*</sup> operation, which has been approximated using the max operation in the presented calculations, to maintain integer values for simplicity.

Finally, the Log-BCJR algorithm can combine the  $\tilde{\delta}(T)$  values in order to calculate the output extrinsic LLRs. This is achieved according to

$$\tilde{b}_{1,i}^{e} = \max_{T \mid a_{1}(T)=1 \atop i(T)=i}^{*} \left[ \tilde{\delta}(T) \right] - \max_{T \mid a_{1}(T)=0 \atop i(T)=i}^{*} \left[ \tilde{\delta}(T) \right] - \tilde{b}_{1,i}^{a}, \tag{2.8}$$

where  $T \begin{vmatrix} a_1(T)=0 \\ i(T)=i \end{vmatrix}$  is the set of all transitions for which the represented uncoded bit value  $a_1(T)$  is zero and the index i(T) of that uncoded bit is i. As shown in the example of Figure 2.6, this corresponds to the grouping of the  $\tilde{\delta}(T)$  values into two sets, which are then combined using max\* operations. Following this, the *a priori* LLR  $\tilde{b}_{1,i}^a$  is subtracted from the difference between these two max\* calculations. Note that the

extrinsic LLRs are calculated using only subtraction and max\* operations, which can be further decomposed into only ACS operations, as will be shown in Section 2.1.6. This completes the Log-BCJR decoding process.

## 2.1.6 Algorithmic modifications to the Log-BCJR decoder

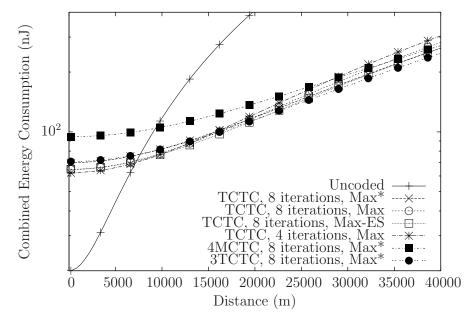

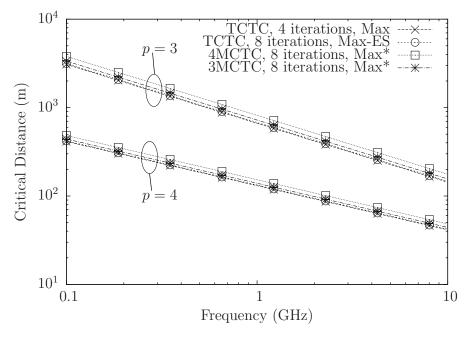

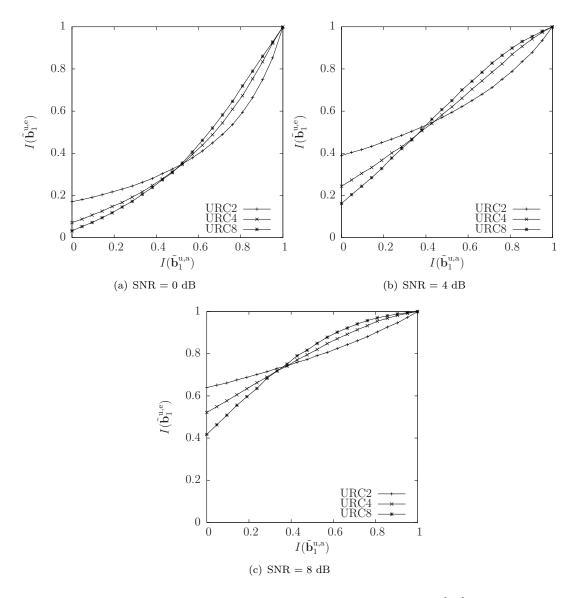

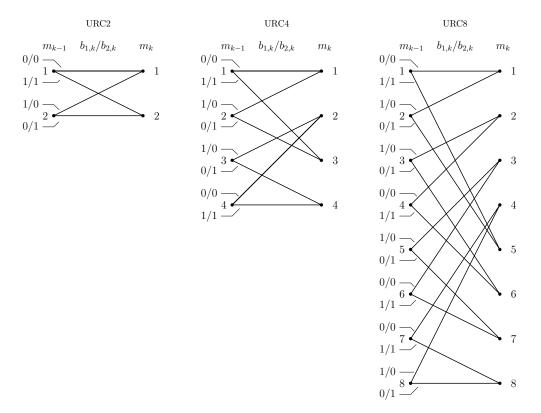

The Log-BCJR algorithm is universally preferred for implementation over the BCJR algorithm owing to its reduced computational complexity. More specially, the BCJR algorithm operates in the normal domain, requiring addition and multiplication operations for calculating the bit probabilities. Since these probabilities have a high dynamic range, a large number of bits are required for their digital representation. By converting the equations of the BCJR algorithm into the logarithmic domain, the Log-BCJR algorithm replaces multiplications with additions, and replaces additions with the max\* operation. These operations have a lower computational complexity, and representing the probabilities in the logarithmic domain requires fewer bits.