# Live Demonstration: Benchmarking Analogue Performance of Emerging Random Access Memory Technologies

Spyros Stathopoulos\*†, Ali Khiat†, Alexantrou Serb\*† *Member*, *IEEE*, Themis Prodromakis\*† *Senior Member*, *IEEE*

\*ArC Instruments Ltd., 75 Sirocco, 33 Channel Way, Southampton, SO143JF, UK.

†Nanoelectronics and Nanotechnology Research Group, Electronics and Computer Science Department,

University of Southampton, Southampton, SO17 1BJ, UK

t.prodromakis@soton.ac.uk

Abstract—In this demo we present a comprehensive solution for benchmarking the multibit capabilities of resistive memory cells using sequential programming pulses. The algorithm is presented through a rich graphical user interface that allows the user to fully tune the benchmarking parameters

Keywords—memristors, RRAM, multibit memory, analogue memory, non-volatile, characterization

#### I. Introduction

Resistive memory cells exhibiting memristive behavior [1], [2] have attracted particular scientific attention due to their increased array of potential applications. Of particular interest is the application in developing non-volatile memories and on-memory computing nodes in the form of neuroinspired circuits. Key parameter for these applications is the ability to maximize the available resistive state of a memristive cell. For this purpose we developed a comprehensive evaluation algorithm [3] to assess the number of available resistive levels in a given cell.

### II. DEMONSTRATION SETUP

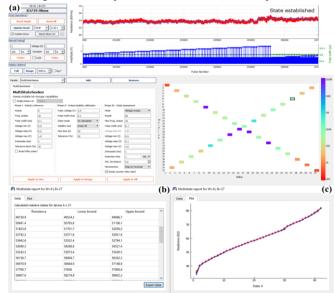

The setup consists of a laptop connected to our in-house developed memristor characterization platform [4], ArC ONE<sup>™</sup> (fig. 1) running an implementation of the proposed evaluation algorithm. TiO<sub>2</sub>-based resistive memory devices packaged in PLCC68 housing will be available for in-situ assessment through the developed graphical user interface (fig. 2).

## III. VISITOR EXPERIENCE

The visitor can use the demonstrated software to characterize the packaged devices, manually tune the various parameters and observe their effect in partitioning the operating range of the device into discrete resistive levels. All tunable parameters described in the characterization method are exposed to the user through an easy to use graphical interface while the different phases of the algorithm can be run independently. The results are presented either in a tabular or graphical format and can be extracted for further analysis.

### REFERENCES

- [1] L. Chua, "Memristor-The missing circuit element," *IEEE Transactions on Circuit Theory*, vol. 18, no. 5, pp. 507–519, Sep. 1971.

- [2] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," *Nature*, vol. 453, no. 7191, pp. 80–83, May 2008

Fig 1: ArC ONE™ parallel memristor characterization platform

Fig 2: Graphical interface of the implemented algorithm: (a) Device map and current state; list (b) and plot (c) of the extracted resistive states

- [3] S. Stathopoulos, A. Khiat, A. Serb, and T. Prodromakis, "Benchmarking Analogue Performance of Emerging Random Access Memory Technologies," 2018 IEEE International Symposium on Circuits and Systems, 2018.

- [4] R. Berdan, A. Serb, A. Khiat, A. Regoutz, C. Papavassiliou, and T. Prodromakis, "A μ-Controller-Based System for Interfacing Selectorless RRAM Crossbar Arrays," *IEEE Transactions on Electron Devices*, vol. 62, no. 7, pp. 2190–2196, Jul. 2015.