# **UNIVERSITY OF SOUTHAMPTON**

### FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

Optoelectronics Research Centre

# PASSIVELY ALIGNED PACKAGING SOLUTIONS FOR SILICON PHOTONICS

by

Scott Reynolds

Thesis for the degree of Doctor of Philosophy

#### UNIVERISITY OF SOUTHAMPTON

# **ABSTRACT**

#### FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

**Optoelectronics Research Centre**

#### <u>Doctor of Philosophy</u>

#### PASSIVELY ALIGNED PACKAGING SOLUTIONS FOR SILICON PHOTONICS

### by Scott Reynolds

Packaging is a critical component in bringing silicon photonics to application. Without low cost, high throughput packaging, the per-unit cost of silicon photonic integrated circuits will be too high for mass markets.

Passive alignment of optical fibres to silicon photonic waveguides would significantly reduce the assembly time currently required where active alignment is labour intensive and time consuming.

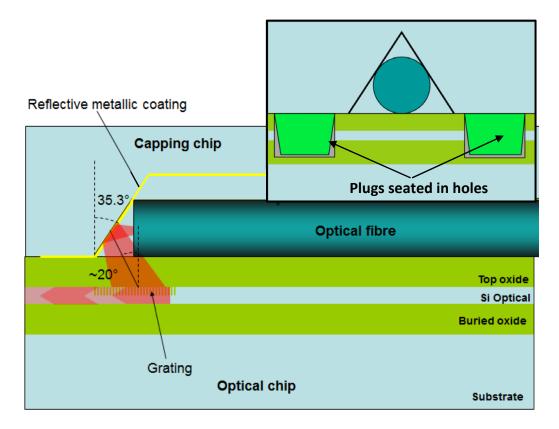

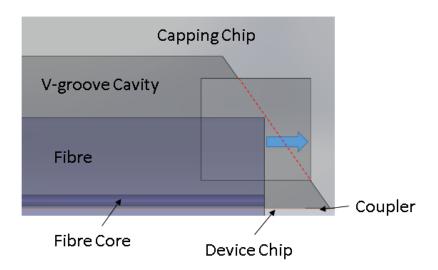

In this work a design is presented that has the potential for high volume cost effective packaging. The design accomplishes this by supporting and positioning multiple fibres relative to a silicon photonic integrated circuit. The capping chip passively aligns the fibres to silicon nanowires via a grating couplers. V-groove structures in the capping chip are used to support and position the fibres and the end facet of the v-groove reflects the light down on to the grating coupler. Plugs on the capping chip align with holes on the photonic chip assuring accurate positioning and optimal coupling.

The processing required has been detailed and demonstrated, including a hybrid lithography process, crystallographically aligned v-grooves and highly accurate alignment structures. Once combined these processes will passively align fibre optic cables with silicon photonic waveguide gratings with a misalignment less than 2um which in theory will produce an added loss less than 1dB, grating couplers have been produced based on a bespoke design fitting the demands of the packaging solution and show a loss of 2.7dB with room for improvement compared to a simulated result of 1.67dB.

i

# Academic Thesis: Declaration of Authorship

### I, SCOTT REYNOLDS,

declare that this thesis and the work presented in it are my own and has been generated by me as the result of my own original research.

#### PASSIVELY ALLIGNED PACKAGING SOLUTIONS FOR SILICON PHOTONICS

#### I confirm that:

- 1. This work was done wholly or mainly while in candidature for a research degree at this University;

- 2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- 3. Where I have consulted the published work of others, this is always clearly attributed;

- 4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- 5. I have acknowledged all main sources of help;

- 6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- 7. Either none of this work has been published before submission, or parts of this work have been published as: [please list references below]:

### Journal papers

- [1] C. G. Littlejohns, A. Z. Khokhar, D. J. Thomson, Y. Hu, L. Basset, S. A. Reynolds, G. Z. Mashanovich, G. T. Reed, and F. Y. Gardes, "Ge-on-Si Plasma-Enhanced Chemical Vapor Deposition for Low-Cost Photodetectors," Photonics Journal, IEEE, vol. 7, pp. 1-8, 2015.

- [2] B. Troia, A. Khokhar, M. Nedeljkovic, S. Reynolds, Y. Hu, G. Mashanovich, and V. Passaro, "Design Procedure and Fabrication of Reproducible Silicon Vernier Devices for High-Performance Refractive Index Sensing," Sensors, vol. 15, p. 13548, 2015.

- [3] G. Z. Mashanovich, F. Y. Gardes, D. J. Thomson, H. Youfang, L. Ke, M. Nedeljkovic, J. Soler Penades, A. Z. Khokhar, C. J. Mitchell, S. Stankovic, R. Topley, S. A. Reynolds, W. Yun, B. Troia, V. M. N. Passaro, C. G. Littlejohns, T. Dominguez Bucio, P. R. Wilson, and G. T. Reed, "Silicon Photonic Waveguides and Devices for Near- and Mid-IR Applications," Selected Topics in Quantum Electronics, IEEE Journal of, vol. 21, pp. 407-418, 2015.

- [4] M. Nedeljkovic, S. Stankovic, C. J. Mitchell, A. Z. Khokhar, S. A. Reynolds, D. J. Thomson, F. Y. Gardes, C. G. Littlejohns, G. T. Reed, and G. Z. Mashanovich, "Mid-Infrared Thermo-Optic Modulators in Sol," Photonics Technology Letters, IEEE, vol. 26, pp. 1352-1355, 2014.

- [5] C. G. Littlejohns, H. Youfang, F. Y. Gardes, D. J. Thomson, S. A. Reynolds, G. Z. Mashanovich, and G. T. Reed, "50 Gb/s Silicon Photonics Receiver With Low Insertion Loss," Photonics Technology Letters, IEEE, vol. 26, pp. 714-717, 2014.

### Conference Papers

- [1] G T Reed, R Topley, A Z. Khokhar, D J. Thomson, S Stanković, S Reynolds, N Soper, C J Mitchell, Y Hu, L. Shen, G Martinez-Jimenez, N Healy, S Mailis, A C Peacock, M Nedeljkovic, J. Soler Penades and G Z Mashanovich, "Silicon photonics: some remaining challenges" Photonics West 2016, Proceedings SPIE 9751, 2016 (invited).

- [2] G T Reed, R Topley, D J Thomson, A Z Khokhar, S Stanković, S Reynolds, N Soper, C J Mitchell, G Martinez-Jimenez, N Healy, S Mailis, A C Peacock, and G Z Mashanovich, "Future Challenges for Silicon Photonics", The 5th International Symposium on Photonics and Electronics Convergence-Advanced Nanophotonics and Silicon Device Systems, (ISPEC2015), Tokyo, Japan on 30 November 2 December, 2015, (invited).

- [3] D. J. Thomson, K. Li, F. Y. Gardes, Y. Hu, M. Nedeljkovic, C. Littlejohns, R. Topley, A. Z. Khokhar, S. Stanković, J. S. Penades, C. J. Mitchell, S. A. Reynolds, G. Z. Mashanovich, P. R. Wilson, and G. T. Reed, "Silicon photonics at the University of Southampton," presented at the PIERS 2015, Prague, Czech Republic, 2015.

- [4] G. T. Reed, Y. Hu, G. Z. Mashanovich, F. Y. Gardes, D. J. Thomson, J. Soler-Penades, M. Nedeljkovic, A. Z. Khokhar, P. Thomas, C. G. Littlejohns, A. Ahmed, S. A. Reynolds, R. Topley, C. J. Mitchell, S. Stankovic, T. Dominguez-Bucio, P. R. Wilson, L. Ke, T. M. Ben Masaud, A. Tarazona, H. M. H. Chong, D. J. Richardson, and P. Petropoulos, "Silicon Photonics for the near infrared and the mid infrared" presented at Photonics Asia, Beijing, China, 9 11 Oct 2015 (invited).

- [5] G. T. Reed, C. G. Littlejohns, K. Li, D. J. Thomson, S. Liu, P. R. Wilson, Y. Hu, R. Topley, F. Y. Gardes, A. Z. Khokhar, S. Stanković, S. A. Reynolds, C. J. Mitchell, G. Martinez-Jimenez, L. O'Faolain, N. Healy, S. Mailis, A. C. Peacock, and G. Z. Mashanovich, "Facilitating an integrated Silicon Photonics platform," presented at Asia Communications and Photonics (ACP), Hong Kong. 19 23 Nov 2015 (Invited).

- [6] G. T. Reed, Y. Hu, R. Topley, D. J. Thomson, A. Z. Khokhar, S. Stanković, S. Reynolds, C. J. Mitchell, F. Y. Gardes, G. Martinez-Jimenez, L. O'Faolain, N. Healy, S. Mailis, A. C. Peacock, and G. Z. Mashanovich, "Silicon photonics devices for systems and testing," presented at the EOCC 2015, Shanghai, China, 2015.

- [7] G. T. Reed, Y. Hu, R. Topley, D. J. Thomson, A. Z. Khokhar, S. Stanković, S. Reynolds, C. J. Mitchell, F. Y. Gardes, G. Martinez-Jimenez, N. Healy, S. Mailis, A. C. Peacock, and G. Z. Mashanovich, "Silicon Photonics based optical devices and circuits," presented at the Energy Materials Technology, Phuket, Thailand, 2015.

- [8] D. J. Thomson, K. Li, F. Y. Gardes, Y. Hu, C. Littlejohns, S. A. Reynolds, P.-W. Chiu, S.-W. Chen, S. H. Hsu, G. Z. Mashanovich, P. Wilson, and G. T. Reed, "High speed silicon photonic devices," presented at the Energy Materials Nanotechnology conference, Beijing, China, 2015.

- [9] G. Z. Mashanovich, M. Nedeljkovic, J. S. Penades, C. J. Mitchell, A. Z. Khokhar, C. J. Littlejohns, S. Stankovic, B. Troia, Y. Wang, S. Reynolds, V. M. N. Passaro, L. Shen, N. Healy, A. C. Peacock, C. Alonso-Ramos, A. Ortega-Monux, G. Wanguemert-Perez, I. Molina-Fernandez, D. J. Rowe, J. S. Wilkinson, P. Cheben, J. J. Ackert, A. P. Knights, D. J. Thomson, and F. Y. Gardes, "Mid-IR group IV photonics," presented at the SPIE Photonics West 2015, San Francisco, CA, USA, 2015.

- [10] G. T. Reed, Y. Hu, G. Z. Mashanovich, F. Y. Gardes, D. J. Thomson, J. Soler-Penades, M. Nedeljkovic, A. Khokar, P. Thomas, C. Littlejohns, A. Ahmad, S. Reynolds, R. Topley, C. Mitchell, S. Stankovic, D. J. Richardson, P. Petropoulos, P. R. Wilson, L. Ke, T. M. Ben Masaud, A. Tarazona, and H. Chong, "Near infrared and the mid infrared silicon photonic devices," presented at the Nano Korea 2014 Symposium, Seoul, South Korea, 2014.

- [11] G. T. Reed, G. Z. Mashanovich, F. Y. Gardes, D. J. Thomson, Y. Hu, J. Soler-Penades, M. Nedeljkovic, A. Khokar, P. Thomas, C. Littlejohns, A. Ahmad, S. Reynolds, R. Topley, C. Mitchell, S. Stankovic, X. Chen, P. R. Wilson, L. Ke, T. M. Ben Masaud, A. Tarazona, and H. Chong, "Silicon Photonics," presented at the 7th International Silicon-Germanium Technology and Device Meeting, Singapore, 2014.

- [12] C. G. Littlejohns, Y. Hu, J. Soler Penades, A. Z. Khokhar, S. Stankovic, S. A. Reynolds, C. J. Mitchell, F. Y. Gardes, and D. J. Thomson, "Multichannel silicon photonic devices based on angled multimode interferometers," presented at the Photonics North 2014, Montreal, Canada, 2014.

- [13] G. T. Reed, G. Z. Mashanovich, F. Y. Gardes, D. J. Thomson, Y. Hu, J. Soler-Penades, M. Nedeljkovic, A. Z. Khokhar, P. Thomas, C. Littlejohns, A. Ahmed, S. Reynolds, R. Topley, C. Mitchell, S. Stankovic, P. R. Wilson, L. Ke, T. M. Ben Masaud, A. Tarazona, and H. M. H. Chong, "Silicon photonic devices for the near and mid-infrared wavelength ranges," presented at the Mediterranean Photonics Conference, Trani, Italy, 2014.

- [14] G. T. Reed, G. Z. Mashanovich, F. Y. Gardes, D. J. Thomson, Y. Hu, J. Soler-Penades, M. Nedeljkovic, A. Khokhar, P. Thomas, C. Littlejohns, A. Ahmad, S. Reynolds, R. Topley, C. Mitchell, S. Stankovic, N. Owens, X. Chen, P. R. Wilson, L. Ke, T. Ben Masaud, A. Tarazona, and H. M. H. Chong, "Recent results in Silicon Photonics at the University of Southampton," presented at the Photonics West 2014, San Francisco, USA, 2014.

### **Patents**

[1] F. Gardes, D. Thomson, G. Reed, and S. Reynolds, "Apparatus comprising at least one optical device optically coupled to at least one waveguide on an optical chip ", 04/12/2012, 2012.

Academic Thesis: Declaration of Authorship

# **Book Sections**

| [1] D. J. Thomson, C. G. Littlejohns, S. Stankovic, M. Nedeljkovic, and S. A. Reynolds,    |

|--------------------------------------------------------------------------------------------|

| "Silicon Photonics," in The Wiley Encyclopedia in Electronic and Photonic Engineering, ed, |

| 2015.                                                                                      |

| Cianad.                                                                                    |

| Signed:                                                                                    |

|                                                                                            |

| Date:                                                                                      |

# Contents

| ABSTRACT        |                              | i    |

|-----------------|------------------------------|------|

| Academic Thesis | s: Declaration Of Authorship | iii  |

| Contents        |                              | vii  |

| List of Figures |                              | xi   |

| List of Tables  |                              | xvii |

| Acknowledgme    | nts                          | xix  |

| Chapter 1: In   | troduction                   | 1    |

| 1.1: Silicon Ph | notonics                     | 1    |

| 1.2: Motivation | on                           | 1    |

| 1.3: Techniqu   | es                           | 2    |

| 1.4: Thesis La  | yout                         | 3    |

| Chapter 2: Ba   | ckground                     | 5    |

| 2.1: Fundame    | entals                       | 6    |

| 2.1.1: Fibre    | 2S                           | 6    |

| 2.1.2: Wav      | eguides                      | 8    |

| 2.1.3: Coup     | oling                        | 9    |

| 2.1.4: Tape     | ring                         | 10   |

| 2.2: Coupling   | Methodologies                | 14   |

| 2.2.1: In pla   | ane coupling                 | 14   |

| 2.2.2: Verti    | ical Coupling                | 16   |

| 2.2.3: Com      | parison                      | 21   |

| 2.2.4: Antir    | reflection                   | 22   |

| 2.3: Literatur  | e Review                     | 22   |

| 2.3.1: Out      | of Plane Solutions           | 23   |

| 2.3.2: In Pla   | ane Coupling Solutions       | 24   |

### Contents

| 2.4: Design Process                                | 32 |

|----------------------------------------------------|----|

| 2.4.1: Solution 1                                  | 32 |

| 2.4.2: Solution 2: Deep Device Chip Etch           | 33 |

| 2.4.3: Solution 3: Through Wafer Optical Chip Etch | 35 |

| Chapter 3: Tools and Equipment                     | 37 |

| 3.1: Cleanroom Equipment                           | 38 |

| 3.1.1: Mask Design                                 | 38 |

| 3.1.2: Lithography                                 | 38 |

| 3.1.3: Etching                                     | 41 |

| 3.1.4: Chemical Vapour Deposition                  | 47 |

| 3.1.5: Plasma Ashing                               | 48 |

| 3.1.6: Metrology                                   | 48 |

| 3.2: Laboratory equipment                          | 50 |

| 3.2.1: Fibre Holders                               | 52 |

| 3.2.2: Fibre Stages                                | 56 |

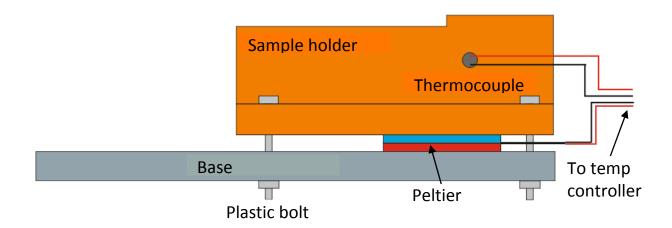

| 3.2.3: Sample stage                                | 56 |

| 3.2.4: Optical bench                               | 57 |

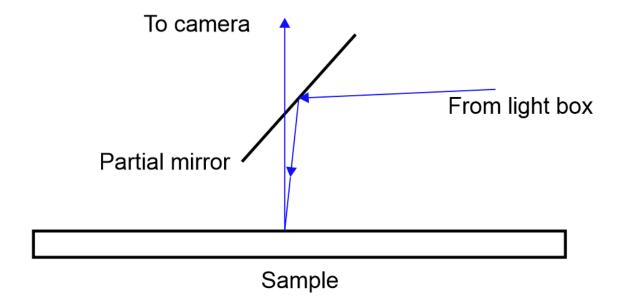

| 3.2.5: Imaging                                     | 57 |

| 3.2.6: LASER and Detector                          | 58 |

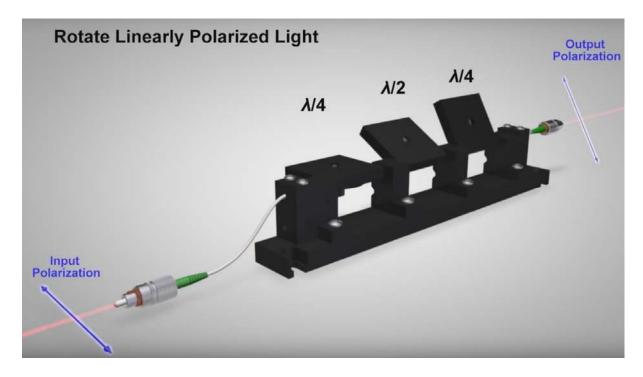

| 3.2.7: Polarization Control                        | 59 |

| Chapter 4: Fabrication                             | 61 |

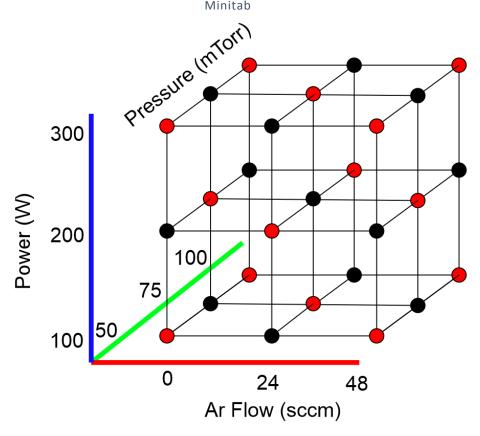

| 4.1: Design of Experiment (DOE)                    | 62 |

| 4.2: Optical Wafer                                 | 67 |

| 4.2.1: Process Flow                                | 67 |

| 4.2.2: Alignment Marks                             | 68 |

| 4.2.3: Optical components                          | 69 |

| 4.2.4: Fibre Cavity and Alignment Holes            | 70 |

| 4.2.5: Backside SiO <sub>2</sub> Removal           | 78 |

| 4.2.6: Final Process flow                          | 79 |

| 4.3: V-Grooves and Alignment Plugs                 | 81 |

| 131. Process Flow                                  | 82 |

| 4.3.2: Crystallographic Alignment and V-grooves Process | 82  |

|---------------------------------------------------------|-----|

| 4.3.3: Plug Protect and Strip Process                   | 85  |

| 4.3.4: V-groove Fabrication                             | 85  |

| 4.3.5: Plug Protection Fabrication                      | 94  |

| 4.3.6: Pyramid structures                               | 95  |

| 4.3.7: Final Process Flow                               | 96  |

| 4.4: Grating Coupler Design                             | 97  |

| 4.4.1: Uniform Grating Couplers                         | 98  |

| 4.4.2: Apodized Grating Couplers                        | 101 |

| 4.5: Fabrication Discussion                             | 102 |

| Chapter 5: Summary, Conclusion and Future Work          | 105 |

| 5.1: Summary and Conclusion                             | 105 |

| 5.2: Future Work                                        | 108 |

| 5.2.1: Segmented V Grooves                              | 108 |

| 5.2.2: Mirror Improvement                               | 109 |

| 5.2.3: Assembly                                         | 109 |

| 5.2.4: Wafer Scale Assembly                             | 109 |

| 5.2.5: Etching of Redundant V Groove Mirror             | 110 |

| 5.2.6: Grating Coupler Improvements                     | 110 |

| 5.2.7: Silicon Nitride Deposition                       | 111 |

| 5.2.8: Minor Improvements                               | 111 |

| References                                              | 113 |

| Appendix 1. Process Flow Diagram                        | 119 |

# List of Figures

| Figure 2.1 An optical fibre showing the core and cladding which confines transmi     | _             |

|--------------------------------------------------------------------------------------|---------------|

| Figure 2.2 A chart displaying different fibre technologies, their speeds and distar  |               |

| Figure 2.3 (a) a representation of a slot waveguide with a simulated guided most     |               |

| schematic drawing of a suspended waveguide[6]. (c) A schematic drawing               |               |

| waveguide[10]. (d) A schematic drawingof a rib waveguide[10]. (e) A schematic        |               |

| photonic crystal waveguide                                                           |               |

| Figure 2.4 Displaying the large field profile mismatch between an SMF-28 optical     |               |

| photonic nanowire. Figure reproduced from[11]                                        |               |

| Figure 2.5 A one dimensional taper                                                   |               |

| Figure 2.6 A two dimensional taper                                                   |               |

| Figure 2.7 Inverted taper structure (left) and field intensity image of the mod      |               |

| polymer waveguide (right)[12]                                                        |               |

| Figure 2.8 A graph showing the mode conversion loss with respect to tip width,       |               |

| need for a small tip[14]                                                             | 13            |

| Figure 2.9 An example of a parabolic taper (a) and a transmission comparison with    | th respect to |

| taper length for parabolic, linear and exponential tapers (b) presented by Tong      | Ye et al [17] |

|                                                                                      | 14            |

| Figure 2.10 An example of Butt Coupling where light from a fibre is being laur       | nched into a  |

| waveguide. The fibre cladding has been omitted for clarity                           | 15            |

| Figure 2.11 Loss verses displacement characteristics of a lensed optical fibre beir  | ng aligned to |

| a 3x3µm facet [11]                                                                   | 16            |

| Figure 2.12 A diagram of an incident ray on the surface of a waveguide[2]            | 17            |

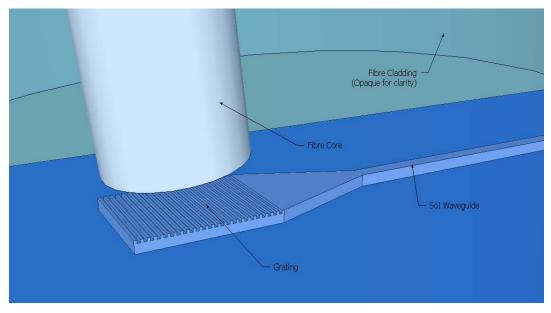

| Figure 2.13 A diagram of a fibre being aligned to a grating coupler                  | 20            |

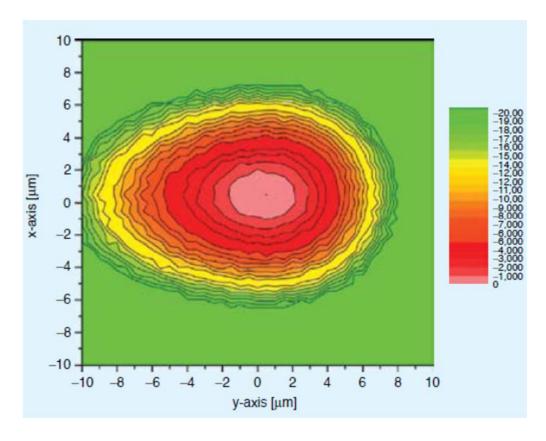

| Figure 2.14 Miss-alignment characteristics of a grating coupler, the key on the rigi | ht shows the  |

| loss in dB [11]                                                                      | 21            |

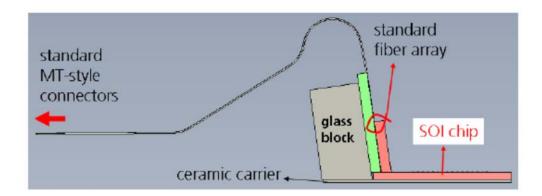

| Figure 2.15 Multi-channel fibre array grating coupled to an SOI chip using v-gr      | oove etched   |

| blocks as support [25]                                                               | 23            |

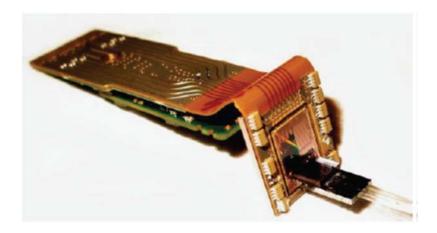

| Figure 2.16 Luxtera 40Gb/s transceiver using grating coupled fibre arrays [26]       |               |

| Figure 2.17 Shows a laser chip, fibre carrier and capping chip allowing passive ali  |               |

|                                                                                      |               |

| Figure 2.18 Low profile silicon photonic package utilising a sub-mount carried to    |               |

| Figure 2.18 Low profile silicon photonic backage utilising a sub-mount carried to    | support ICs   |

| Figure 2.19 Butt coupling using v-grooves and a novel undercut solution to avoid cleavir polishing [29]. |         |

|----------------------------------------------------------------------------------------------------------|---------|

| Figure 2.20 "Schematic of metamaterial fiber interface with integrated v-groove fibe                     |         |

| alignment structure. (a) top-view, (b) cross-section through the suspended metama                        |         |

| converter, (c) cross-section through the v-groove and fiber"[31]                                         |         |

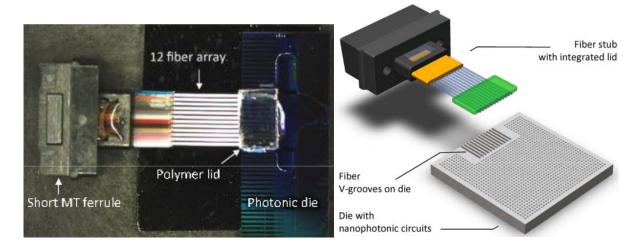

| Figure 2.21 (Left) "Top-down optical micrograph of a fiber stub assembled to a photon                    |         |

| The length of the fibers can be customized to a given application" (Right) A schematic sh                |         |

| the fibres held by a polymer lid and the optical chip with v-grooves.[32]                                |         |

| Figure 2.22 Combining the advantages of in plane coupling and grating couplers for a                     |         |

| packaging solution [33]                                                                                  |         |

| Figure 2.23 ePIXfab's packaging solution utilising angled fibre tips to reflect light down               |         |

| a grating coupler single channel (top) and multi-channel (bottom)[34]                                    |         |

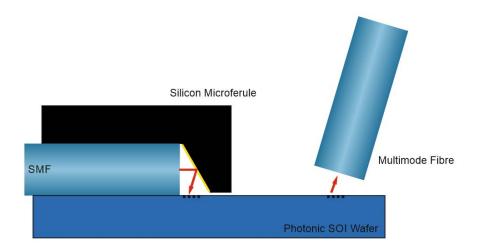

| Figure 2.24 The combination of a silicon micro ferule as a mirror to reflect light down of               |         |

| PIC. Reproduced from[35]                                                                                 |         |

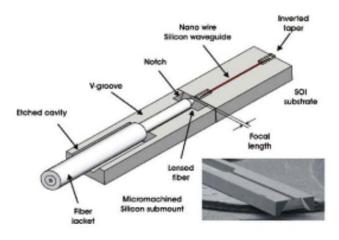

| Figure 2.25 A lensed fibre supported by a v-groove semi passively aligned to a PIC                       |         |

| inverted tapers[35]                                                                                      |         |

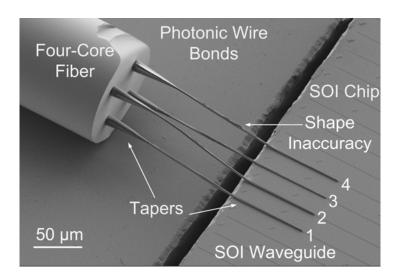

| Figure 2.26 photonic wire bonds between a four core fibre and silicon photonic chip[36                   |         |

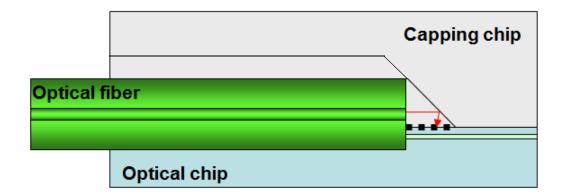

| Figure 2.27 Initial design concept showing a fibre being positioned and secured by                       | _       |

| groove of a capping chip which reflects light down towards the optical chip using a                      | metal   |

| coated angled surface as a reflector which can be produced by the v-groove etching p                     |         |

| (inset) shows the concept of plugs and holes being used to position the capping chip (                   | not to  |

| scale)                                                                                                   |         |

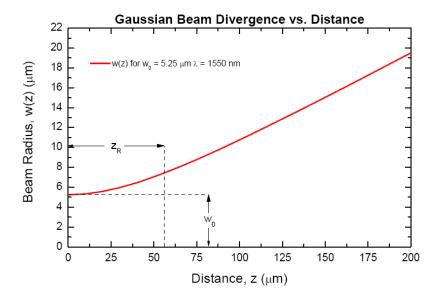

| Figure 2.28 The Gaussian beam divergence vs. distance after being launched from an SI                    | MF-28   |

| optical fibre [39]                                                                                       | 34      |

| Figure 2.29 A revised concept design with the fibre embedded in the optical chip, rec                    | ducing  |

| the distance from the fibre facet to the grating coupler, in turn reducing divergence                    | 34      |

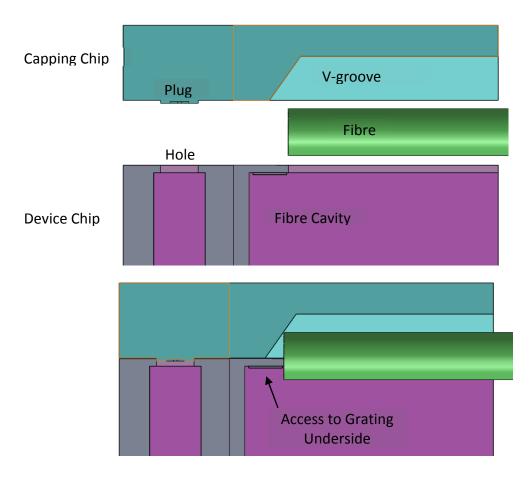

| Figure 2.30 A cross section diagram of the packaging design in an exploded view (top                     | p) and  |

| assembled (bottom)                                                                                       | 35      |

| Figure 2.31 Shows the packaging design with a through wafer process allowing vision                      | of the  |

| capping chip through the device chip which makes alignment easier during assembly                        | y. The  |

| fibre can also be inserted after chip assembly                                                           | 36      |

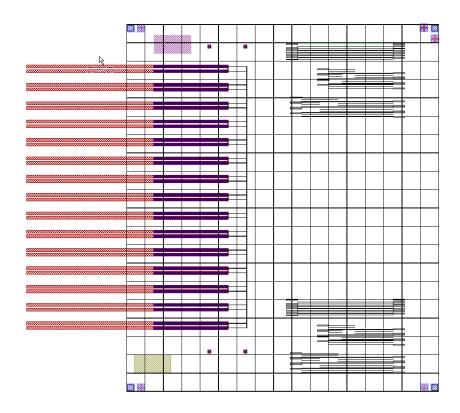

| Figure 3.1 The complete mask design used for this project. Each colour corresponds                       | to an   |

| individual layer or fabrication step                                                                     | 38      |

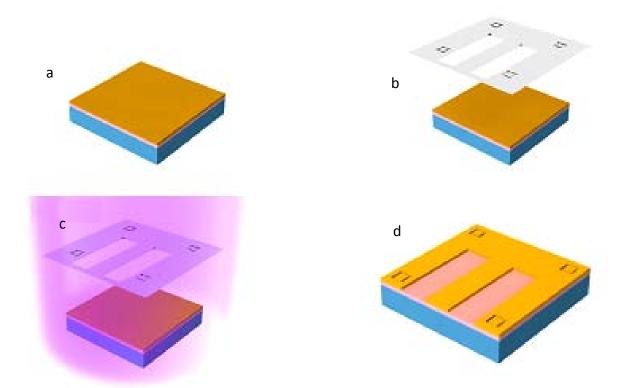

| Figure 3.2 A diagram of the photolithography process a) deposition of resist. b) Position                | ning of |

| chrome mask. c) Exposure of UV light. d) Development to form features                                    | 40      |

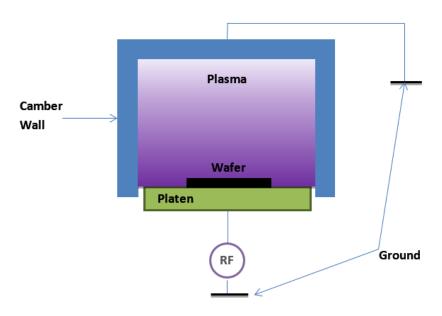

| Figure 3.3 A schematic diagram of a reactive ion etcher.                                                 | 41      |

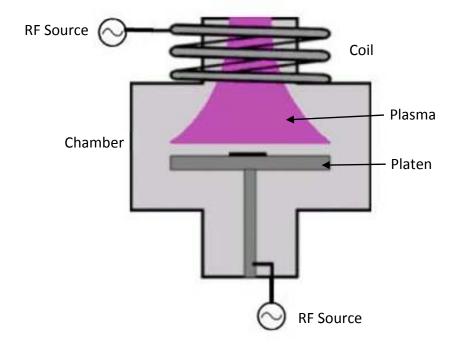

| Figure 3.4 A diagram of an ICPRIE (left) showing a similar construction to a standard R                  | IE but  |

| with a large inductive coil encapsulating the chamber                                                    | 43      |

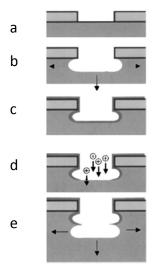

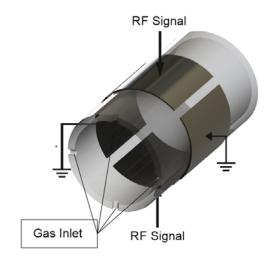

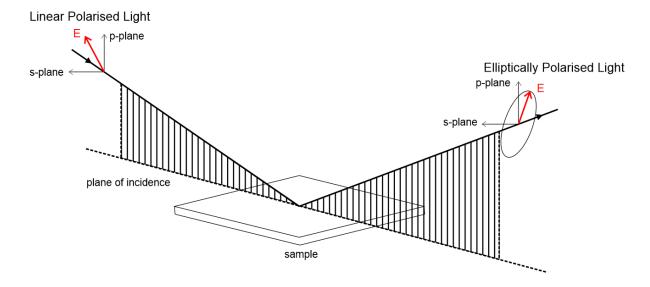

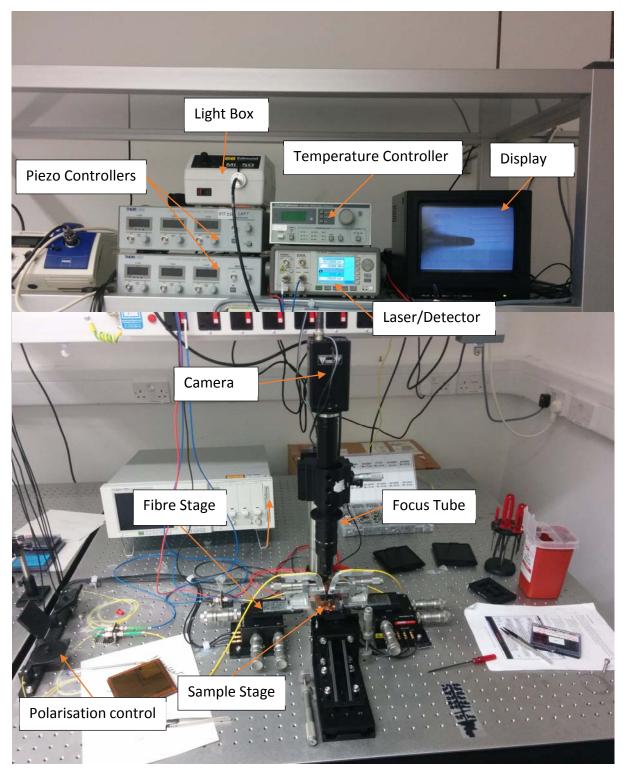

| Figure 3.5 A diagram showing each phase of the DRIE etch process starting with a masked substrate (a) then submitted to an isotropic etch(b), followed by polymer passivation (c), anisotropic ion bombardment removes the polymer from the horizontal surfaces (d) which allows access for the isotropic etch to start again(e)[46] |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

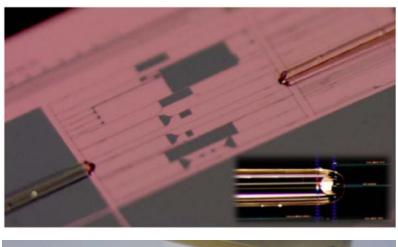

| Figure 3.9 The setup for measuring passive grating coupler based devices                                                                                                                                                                                                                                                             |

| Figure 3.12 A 3D printed fibre arm prototype with a 3D printed stand to keep it level when not secured to a movement stage                                                                                                                                                                                                           |

| Figure 3.13 machined aluminium fibre arms                                                                                                                                                                                                                                                                                            |

| Figure 3.18 A diagram of a three paddle polarization controller showing the quarter half quarter waveplate configuration, taken from a video at thorlabs.de [58]                                                                                                                                                                     |

| Figure 4.1 A screenshot of the table to be filled out for a three parameter Box-Behnken DOI within Minitab63                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.2 The 3D experiment space generated by a box Box-Behnken DoE where the rec                                                                                                                                                                           |

| points are ommited to reduce the number of experiments63                                                                                                                                                                                                      |

| Figure 4.3 A screenshot of the Box-Behnken experiment in Minitab showing the paramete combinations, the order they should be tested in and the results attributed to then highlighted on the right.                                                           |

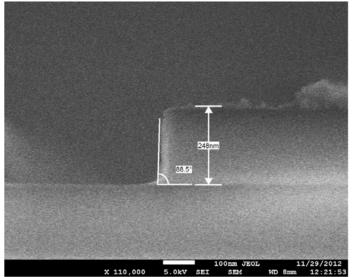

| Figure 4.4 A cross section SEM image of the SiO <sub>2</sub> etch sample showing near vertical side walls                                                                                                                                                     |

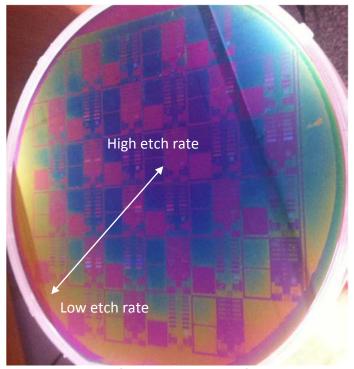

| Figure 4.5 The 6 inch $SiO_2$ etch test wafer showing poor uniformity with a higher etch rate in the centre transitioning to a low etch rate towards the edge.                                                                                                |

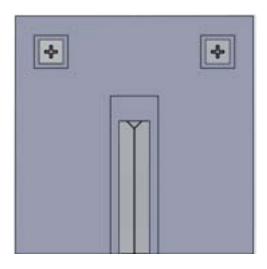

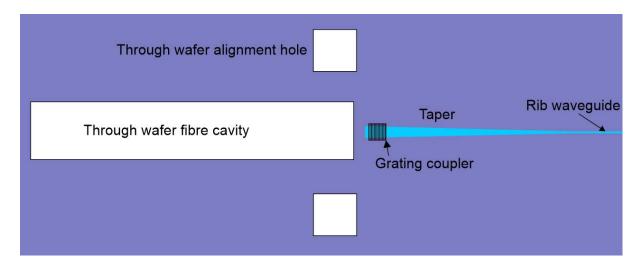

| Figure 4.6 Top down diagram showing the main components of the optical wafer                                                                                                                                                                                  |

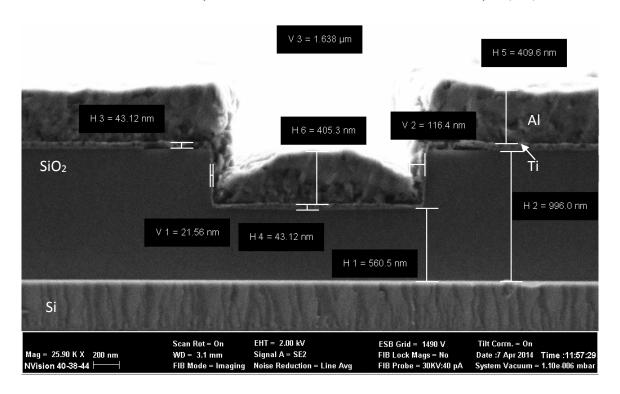

| Figure 4.8 An example of the $SiO_2$ etch in the DRIE showing its ability to produce a vertical sidewall $SiO_2$ etch. Image credit; Callum Littlejohns                                                                                                       |

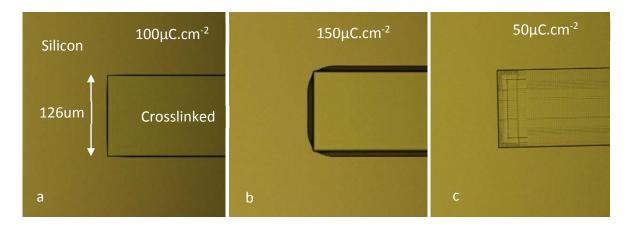

| and 50μC.cm-2 which shows underexposure(c)72                                                                                                                                                                                                                  |

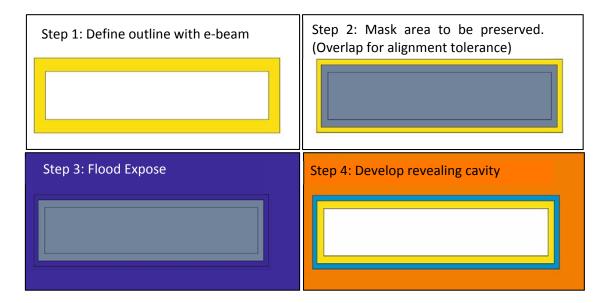

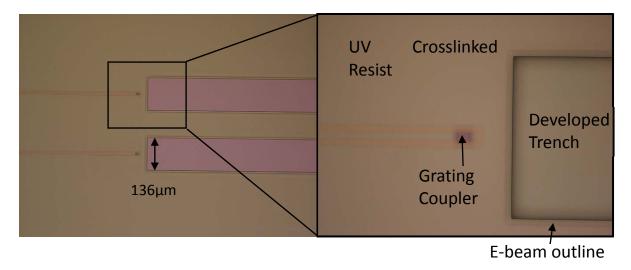

| Figure 4.10 A diagram showing the hybrid lithography process using e-beam lithography to define an outline and contact lithography to reduce write time by exposing non critical areas                                                                        |

| Figure 4.11 The completed hybrid lithography process74                                                                                                                                                                                                        |

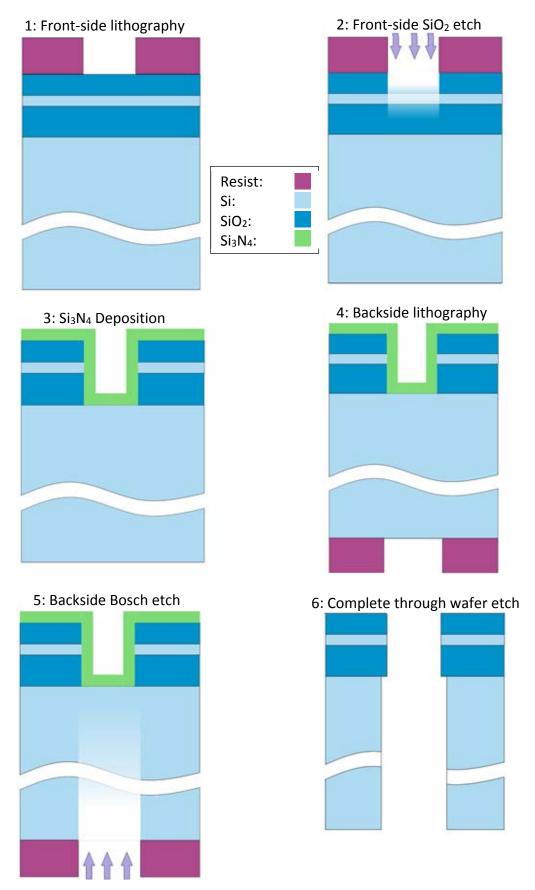

| Figure 4.12 Diagrams of the device wafer, through wafer etch process depicting lithography and etching of the front side down to the substrate, depositing nitride to protect the plater and then lithography and etching of the substrate from the back side |

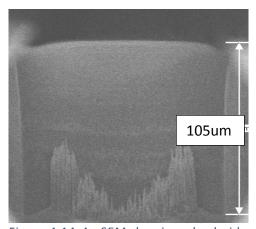

| Figure 4.14 An SEM showing a back side deep etch trench with grassing at the bottom caused by a lack of power as the etch gets deeper, preventing the complete removal of the passivation layer deposited previously                                          |

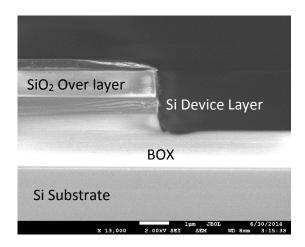

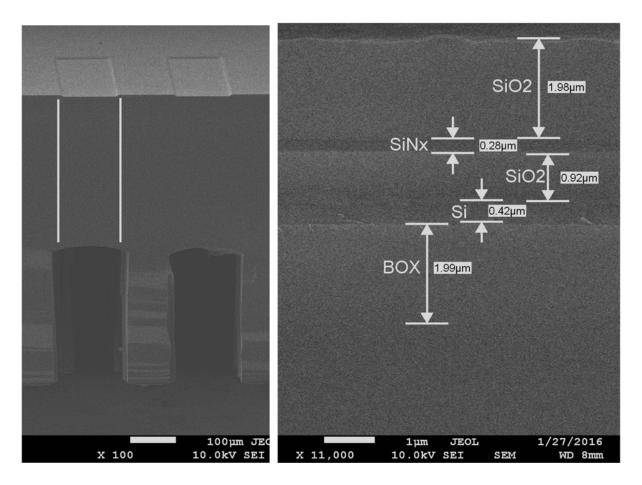

| Figure 4.15 SEM cross section images of an optical chip showing (left) the complete front side                                                                                                                                                                |

| etch and partial backside etch showing backside alignment within the $\pm 5 \mu m$ tolerance. Some                                                                                                                                                            |

| lateral etching is observed but is not critical and poor development needs addressing. (right                                                                                                                                                                 |

| The complete stack before stripping the front protection layers                                                                                                                                                                                               |

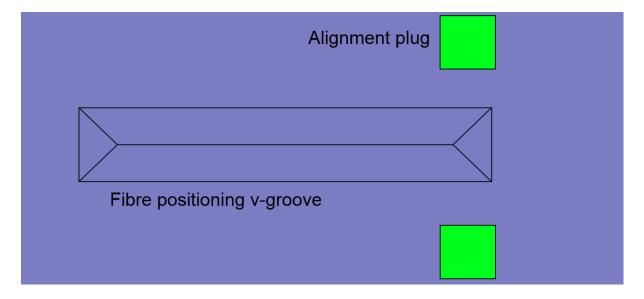

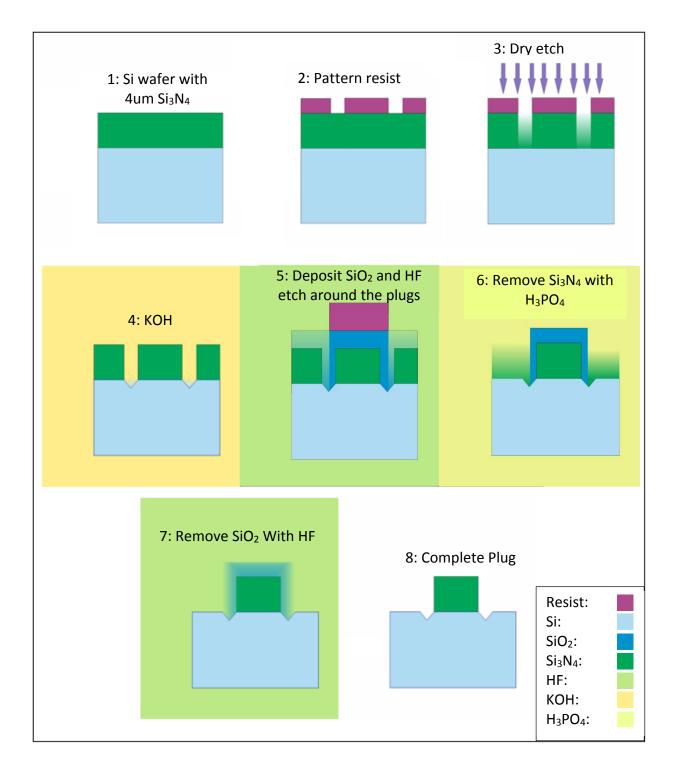

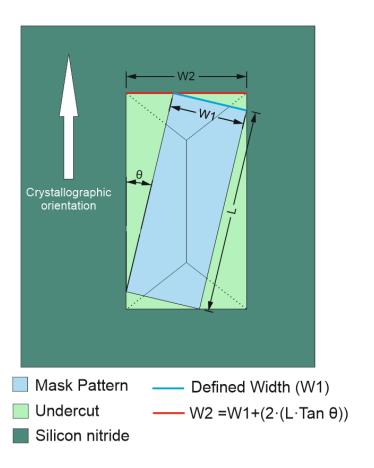

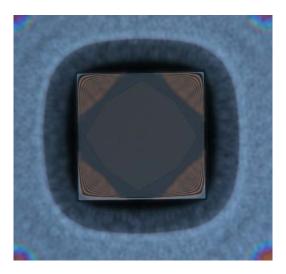

| Figure 4.16 A diagram showing the layout of the capping chip with a v-groove to support a fibre and plugs for passive alignment82                                                                                                                             |

| Figure 4.17 An illustration of the initial process flow                                                                                                                                                                                                       |

| Figure 4.18 a SEM image showing significant undercut on one of the first KOH experiments.         |

|---------------------------------------------------------------------------------------------------|

| Figure 4.19 If a mask is rotated away from the crystal plane the resulting KOH groove will be     |

| larger by a function of the rotation and size                                                     |

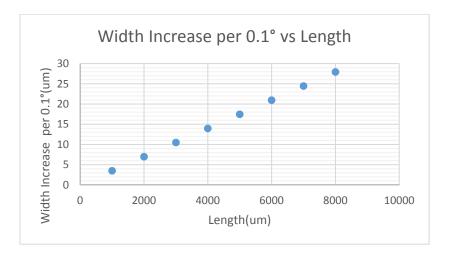

| Figure 4.20 Graph showing the calculated increased width per 0.1° of KOH etched v-grooves         |

| for various lengths based on equation W2 in Figure 4.19                                           |

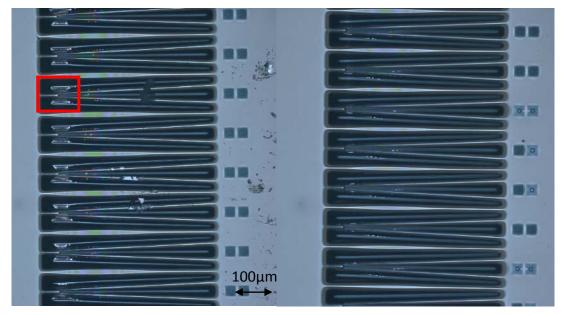

| Figure 4.21 Crystallographic alignment forks after KOH etching that show symmetric patterns       |

| on the left and asymmetric on the right88                                                         |

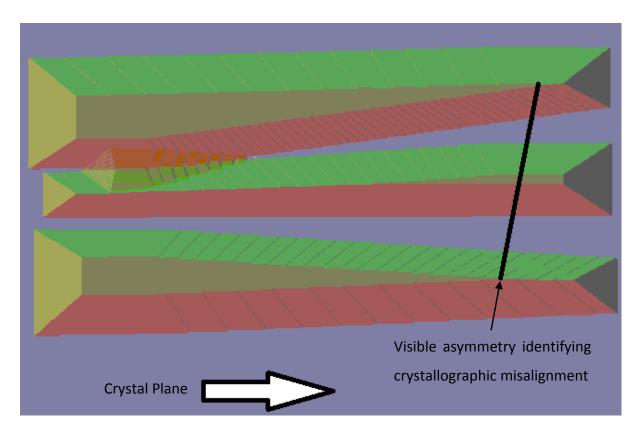

| Figure 4.22 Simulated KOH etch of a crystallographic alignment fork rotated 2 degrees away        |

| from the crystal plane using ACES simulation tool89                                               |

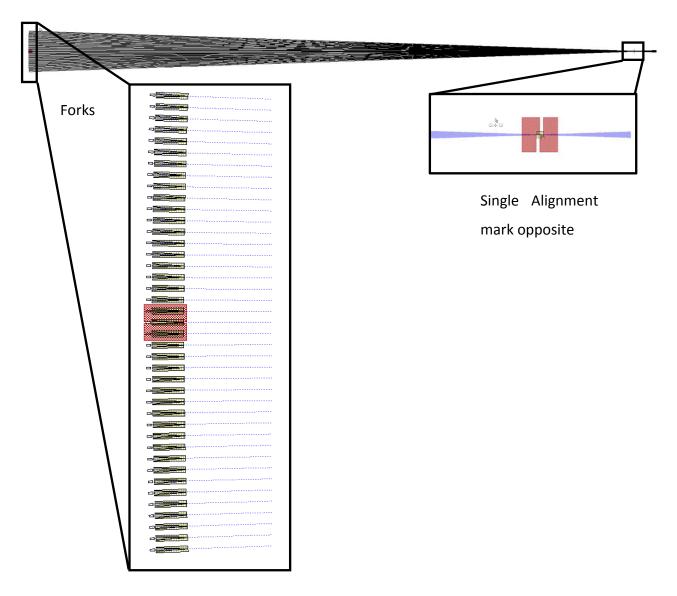

| Figure 4.23 The LEdit cell showing the crystallographic alignment marks with lines added to       |

| show the focus point on the opposite side of the wafer90                                          |

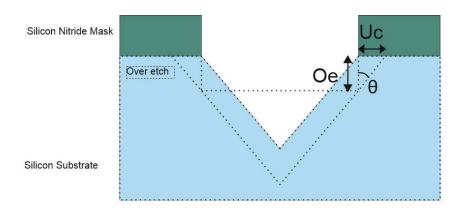

| Figure 4.24 How over etching effects the v-groove structure91                                     |

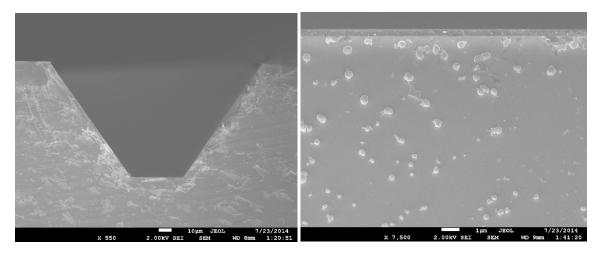

| Figure 4.25 (Left) Large channel over etched at the silicon nitride edge. (Right) the point at    |

| which the nitride etch broke through at the edge prematurely92                                    |

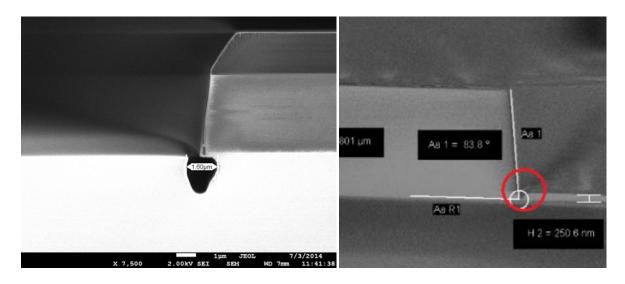

| Figure 4.26 SEM images of (left) a cross section of a v-groove etched in KOH and (right) of the   |

| sidewall of a KOH etch facet showing $\sim$ 500nm size particles assumed to be caused during      |

| dicing process93                                                                                  |

| Figure 4.27 KOH etch model showing undercut of the nitride plugs using ACES wet etch              |

| modeling software [53]94                                                                          |

| Figure 4.28 Pyramid structures trialled for fibre positioning and support showing under           |

| etching of the (111) plane96                                                                      |

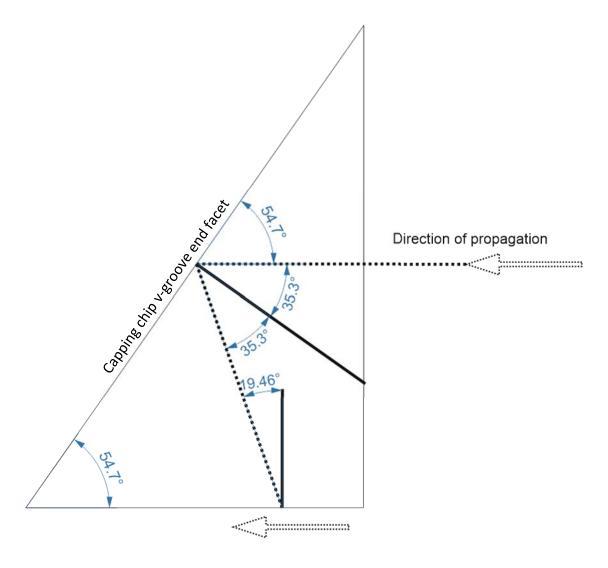

| Figure 4.29 A diagram showing how light will be reflected from the capping chip mirror,           |

| resulting in a 19.5° coupling angle in the reverse direction97                                    |

| Figure 4.30 A schematic diagram of a uniform grating coupler with a fibre set to an angle to      |

| avoid back reflections99                                                                          |

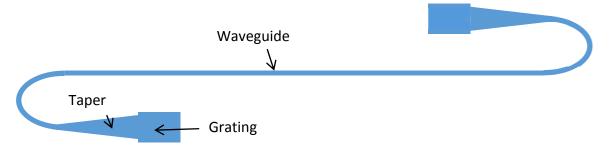

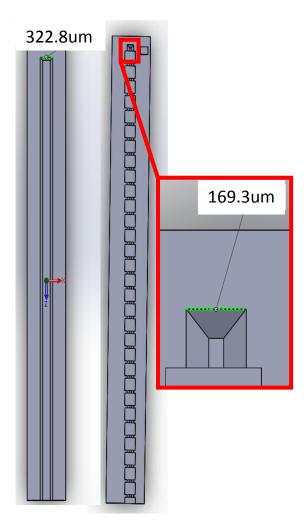

| Figure 4.31 The reverse coupled grating couplers configured for coupling with out of plane        |

| fibres                                                                                            |

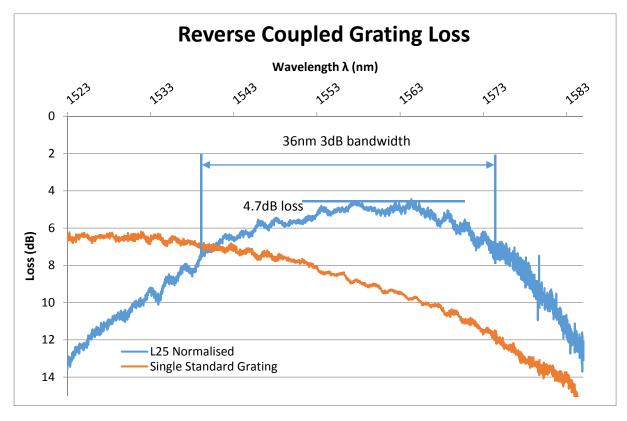

| Figure 4.32 A graph showing the normalised grating coupler loss for gratings with a period of     |

| 483nm and aspect ratio of 0.45 measured with a fibre angle of -20 $^{\circ}$ (L25) and a standard |

| uniform grating coupler measured at 10°                                                           |

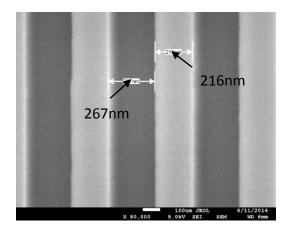

| Figure 4.33 An SEM image of a grating coupler showing a period of 483nm and aspect ratio of       |

| 0.45                                                                                              |

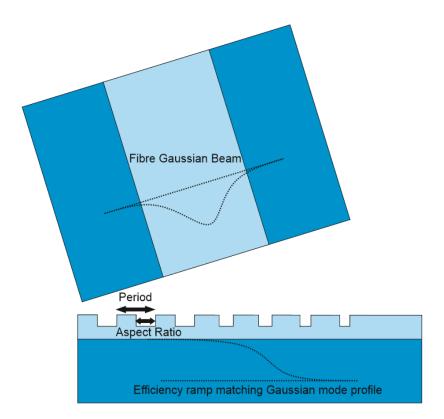

| Figure 4.34 a schematic diagram showing the Gaussian mode field profile of the fibre and how      |

| an apodized grating coupler tries to match it101                                                  |

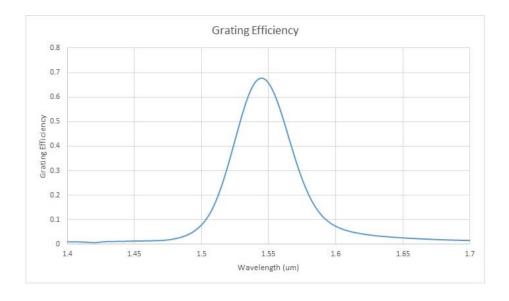

| Figure 4.35 A graph showing the simulated grating coupler efficiency of 68%102                    |

| Figure 5.1 A diagram showing how segmented v-grooves can minimise the effect of                   |

| crystallographic misalignment. Both v-grooves represent a groove defined as 9mm long and          |

### List of Figures

| $165.8 \mu m$ wide, rotated $1^\circ$ away from the crystal plane. This is an exaggeration to $d$ | lisplay the |

|---------------------------------------------------------------------------------------------------|-------------|

| effect                                                                                            | 108         |

| Figure 5.2 A schematic diagram depicting how removal of the redundant mirror co                   | ould move   |

| the fibre closer to the grating coupler, reducing divergence                                      | 110         |

# List of Tables

| Table 2.1 A Comparison showing the advantages and disadvantages of butt co                                      | upling and  |

|-----------------------------------------------------------------------------------------------------------------|-------------|

| grating coupling                                                                                                | 22          |

| Table 2.2 Summary of the state of the art in silicon photonics                                                  | 31          |

| Table 2.3 The predicted missalignment causes which could affect coupling accuracy                               | y and their |

| potential remedies                                                                                              | 36          |

| Table 3.1 The etch rates and selectivity of silicon crystal planes and common mask                              | clayers45   |

| Table 4.1 The optical wafer process flow.                                                                       | 68          |

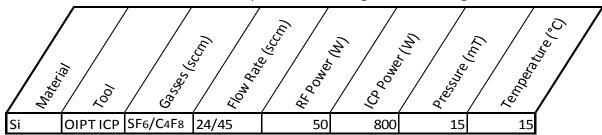

| Table 4.2 OIPT ICPRIE Si etch recipe used for etching devices and alignment marks                               | 69          |

| Table 4.3 Lithography process table                                                                             | 69          |

| Table 4.4 PECVD process table.                                                                                  | 69          |

| Table 4.5 Plasmatherm Versaline etch process table                                                              | 74          |

| Table 4.6 Wet etch process table                                                                                | 78          |

| Table 4.7 The final process flow                                                                                | 79          |

| Table 4.8 is an excerpt from the spreadsheet used to track development progress.                                | Every step  |

| in the process is represented                                                                                   | 82          |

| Table 4.9 Lithography processes used for the capping wafer                                                      | 83          |

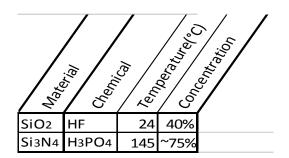

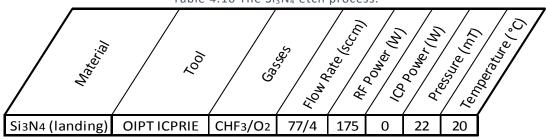

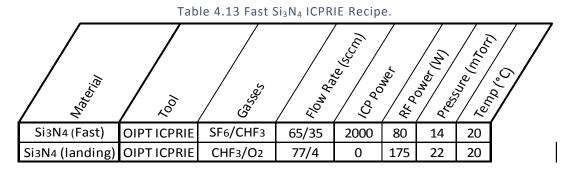

| Table 4.10 The Si <sub>3</sub> N <sub>4</sub> etch process.                                                     | 83          |

| Table 4.11 The wet etch process used for making the capping wafer                                               | 83          |

| Table 4.12 PECVD process table                                                                                  | 85          |

| Table 4.13 Fast Si₃N₄ ICPRIE Recipe                                                                             | 91          |

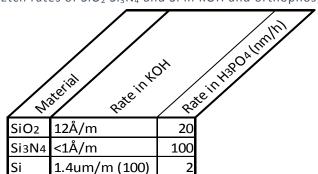

| Table 4.14 Etch rates of SiO <sub>2</sub> Si <sub>3</sub> N <sub>4</sub> and Si in KOH and orthophosphoric acid | 95          |

| Table 4.15 The finalised process flow incorporating the changes in process compa                                | ared to the |

| table produced at the start of the project                                                                      | 96          |

# Acknowledgments

This thesis would not have been possible without the guidance and support of several individuals who in one way or another contributed advice, support or assistance in the development of this work.

Firstly, I would like to thank Professor Graham Reed, Dr Goran Mashonovich and Dr David Thomson, my supervisors, for their valuable advice, endless support and brilliant leadership.

Dr Ali Khokhar, for continually finding e-beam time and working all hours to get my work through as quickly as possible.

Mike Perry, Dr Owain Clark and Dr Kian Kiang for tirelessly working to keep the tools in the cleanroom working and selflessly sharing their expertise.

Dr Milos Nedeljkovic and Dr Taha Ben Masaud for their academic insight and always being available for any question.

Mr Nathan Soper has worked very hard to help produce results both in simulations and in the cleanroom.

Dr Callum Littlejohns for being a good friend as well as a helpful colleague. Particular thanks for keeping moral high with numerous outings and keeping fantasy football entertaining.

Many colleagues across the ORC and ECS at the University of Southampton have helped me at one time or another, thank you to Dr Frédéric Gardès, Dr Colin Mitchell, Dr Youfang Hu, Dr Xia Chen, Dr Nathan Owens, Paul Thomas, Jordi Soler Penades, Dr Arifa Ahmed, Qu Zhibo, Dr Milan Milosevic, Dr Robert Topley, Dr Antulio Tarazona, Dr Harold Chong, Dr Ke Li, Dr James Gates, Prof James Wilkinson, Dr Katrina Morgan, Jonathan Butement, Thalia Dominguez Bucio and many more that I may have missed.

Extra thanks to Dr David Thomson, his wife Zoe and children William and Lewis for sharing their home with me and feeding me.

### Acknowledgments

There are so many other friends I could thank and I hold a huge amount of gratitude for their friendship, kind words and support. Particularly Tom, Daisy, Nick and Nicola for always showing interest in my progress.

I would like to thank Sophie Burnett for her faultless love and friendship.

A special thanks to my family; my Mum for never doubting my abilities and giving me the confidence to succeed and my sister for her unique brand of encouragement.

My Dad for showing great pride which served to be a source of endless reassurance, not to mention keeping me on the road all these years. My Nan and Grandpa for being so welcoming and offering me their home for much needed respite.

# Chapter 1: Introduction

### 1.1: Silicon Photonics

Photonics itself is a huge industry that encompasses a wide variety of fields from high power industrial lasers through to medicine. Traditionally these industries tend toward using exotic compounds produced from group III elements such as Gallium and group V elements such Arsenic. These are combined to produce III-V compounds for example, Gallium Arsenide or Indium Phosphide. These compounds are used in order to exploit their direct bandgap which makes lasing possible. Silicon has been successful within the electronics industry mostly due its low cost, ease of processing, excellent native oxide and abundance. Although not direct bandgap, it has many promising attributes that gives it great potential within photonics. What is seen as its greatest advantage is its compatibility with the very large scale integration (VLSI) involved in electronics manufacture; III-V materials are inherently incompatible due to them being contaminants within a CMOS (Complementary Metal Oxide Semiconductor) fabrication facility. Furthermore, photonic concepts using silicon can benefit from the many years of development of silicon electronics processing techniques. Silicon has the potential for truly monolithic integration allowing for low cost optical communications in many areas such as: fibre optic communications to the home, short reach optical interconnects or even intra-chip optical communications.

# 1.2: Motivation

In the context of photonics and electronics, packaging is the process of taking a fabricated device and its relevant I/O peripherals and wrapping it all up in to a marketable product that is reliable, robust, and easy to use. Common integrated circuits (ICs) are a good example of this, where a silicon chip's input and output lines are attached to easy to use pins or pads and the whole device is encapsulated in plastic or ceramic for protection and usability. This is a small sample of many electronic packaging methods that have a wide variation depending on the application. When considering photonic circuits, the goals are the same e.g. convenience

and protection; however, the approaches are significantly different. Unlike electronics, light must be accurately directed, or coupled, into an on-chip waveguide which is no easy task. In fact, this is the primary issue in packaging photonic circuits where often fibre to coupler alignment accuracies are less than one micrometre compared to the sub ten micrometre requirements for electronics.

Previously, production of optical devices has not been on a mass scale and so ultra-low cost packaging has not been required. Therefore, current solutions are usually labour intensive, costly, and slow due to the requirement of active alignment techniques. Active alignment is a process whereby light is launched into a device and monitored at the output, the input and output fibres are then adjusted to maximise the transmitted power. Although this is the best way to ensure maximum transmitted efficiency, the process is not cost effective for mass market devices. In fact, this process can amount to a third of the cost of developing a photonic integrated circuit (PIC)[1]. The preferred method of alignment uses passive techniques where structures produced through manufacture align the fibre automatically, vastly improving development time and cost.

# 1.3: Techniques

In this work, in order to produce a reliable, passive packaging solution, two separate chips will be used; a device chip complete with waveguides, devices and grating couplers combined with a capping chip utilising alignment V-grooves. These two chips will sandwich optical fibres, securing them and allowing precise alignment. The V-grooves will also provide a reflecting surface allowing in plane coupling from fibre to device and vice versa.

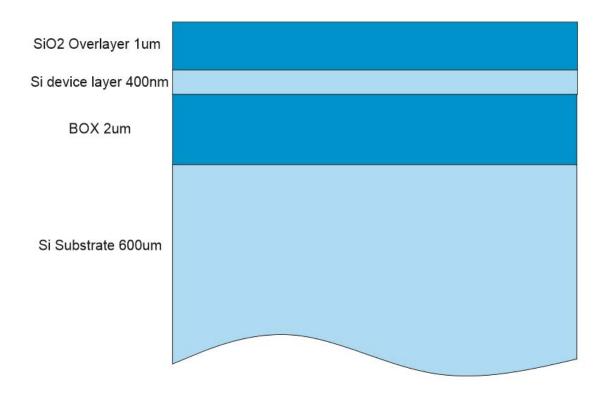

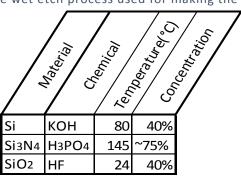

The device chip for testing purposes will have waveguides and bespoke grating couplers, produced on an SOI (Silicon on Insulator) platform. They will be produced using e-beam lithography and dry plasma etching. The capping chip will utilise a thick silicon nitride ( $Si_3N_4$ ) layer on silicon wafer where the  $Si_3N_4$  will be formed in to alignment plugs, also using dry plasma etching, and the V-grooves will be formed using wet KOH (potassium hydroxide) etching. Whilst e-beam lithography is not a production tool, the tolerance analysis implemented in this work has assumed the tolerances associated with high quality commercial lithography systems, thereby making the work compatible and transferable to real applications.

Full assembly and testing is beyond the scope of this project but will be considered and discussed in future work.

# 1.4: Thesis Layout

Chapter 2 of this thesis begins by introducing the fundamentals regarding coupling and describes fundamental packaging concepts and methods. It then goes on to describe how these are implemented in the state of the art, at the time of writing. This is followed by a description of designs which are considered to improve on the current state of the art. Chapter 3 describes the tools, equipment and how they are set up to familiarise the reader with their basic function before describing the recipes and processes used in chapter 4. Chapter 4 discusses the development of the processes required for producing the solutions laid out at the end of chapter 2, including the final process flows for producing samples ready for assembly. Finally, chapter 5 summarises and concludes the thesis and goes on to outline further work that can be completed to improve the concept further.

# Chapter 2: Background

The background chapter will start by broadly discussing the fundamentals required to undertake the project; explaining coupling and packaging, and why it is necessary. This leads on to a discussion of what has been accomplished in the state of the art, identifying the limits in current research that will be tackled in this project, thereby setting this work into context.

### 2.1: Fundamentals

### 2.1.1: Fibres

Optical fibres are made of strands of glass of the order of  $125\mu m$  in diameter, approximately the thickness of a human hair. They transmit data in the form of light which is confined within the fibre by multiple layers of glass with different optical qualities [2](Figure 2.1). Fibres hold significant value in the sphere of communications as they can transmit large amounts of data quickly, over long distances compared to its predecessor, copper.

Figure 2.1 An optical fibre showing the core and cladding which confines transmitted light.

Fibres mainly come in two forms, multimode and single mode, the main difference between them is the size of the core which affects the constraints for propagation. Multimode fibres allow multiple modes of light to propagate due to a larger core size compared to that of a single mode fibre, which as the name suggests only allows propagation of a single mode. Multimode fibres are finding application in next generations of communications systems as they can allow higher data rates. They are, however, susceptible to modal dispersion which is attributed to the individual modes propagating at different effective velocities along a given length of fibre thus resulting in the spreading a pulse or bit of data in the time domain. Dispersion limits the speed of transmission or length of the cable as eventually the pulses overlap rendering the data undecipherable. This means that multimode systems are used for

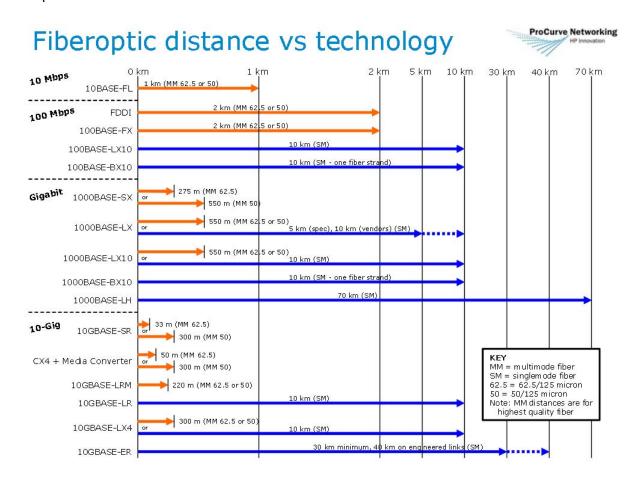

short range interconnects. Figure 2.2 shows the ranges and speeds that single mode and multimode fibre technologies operate over[3].

The larger core size of a multimode fibres also complicates the coupling of light between the fibre and the small waveguides used in silicon photonics, which will be discussed later in this chapter.

Figure 2.2 A chart displaying different fibre technologies, their speeds and distances[3].

Single mode fibres are used for long distance communications and are more common than multimode fibres. They are also more common within silicon photonics, even though silicon photonics is focused towards short range interconnects this is somewhat a misnomer, the networks that silicon photonics needs to penetrate are those that are too short for long haul communications to address due to their current high cost. This boundary lies around 10km and the distances between racks within a data centre can be as far as this, which prevents multimode from being desirable because of its limited range of 2km (Figure 2.2). Single mode methodologies allow easier coupling to silicon photonic circuits with sub micrometre

waveguides and also allow higher aggregate transmission rates per fibre via wavelength division multiplexing (WDM) which is also possible in multimode fibre, but is limited by its high modal dispersion[4]. Due to these advantages and the broad use of single mode fibres, this project will only use single mode fibres, specifically SMF28 fibres made by Corning. This is a commonly used optical fibre, and therefore has widespread application.

# 2.1.2: Waveguides

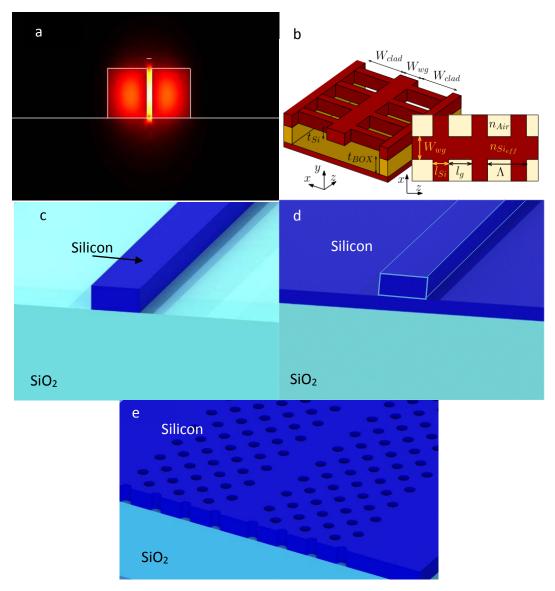

Waveguides perform the same routing function as an optical fibre, except they route light on a photonic circuit rather than along a cable. There are many different waveguide structures both in single mode and multimode configurations. However, due to the constraints mentioned previously and the fact that many optical devices used in silicon photonics are not compatible with multimode operation, only single mode waveguide structures will be considered here. Even with this restriction, there are still many structures to consider. Photonic crystal, suspended, strip, and slot waveguides have all been demonstrated in the photonics community [5-8](Figure 2.3). However, frequently when designing near infrared devices, rib waveguides are used, due to their lower loss[2], and potential advantages when creating active devices[9]. Rib waveguides can also be defined and etched in the same process step as grating couplers which have been shown to work well, further details of this are reported in section 4.3: Grating Couplers. Therefore, in order to conform to common processes, rib waveguides will be used for this project. It is important to note that this decision does not rule out other methods and minor modifications are required to scale the project design to operate with a range of waveguide types.

Figure 2.3 (a) a representation of a slot waveguide with a simulated guided mode[5]. (b) A schematic drawing of a suspended waveguide[6]. (c) A schematic drawing of a strip waveguide[10]. (d) A schematic drawing of a photonic crystal waveguide.

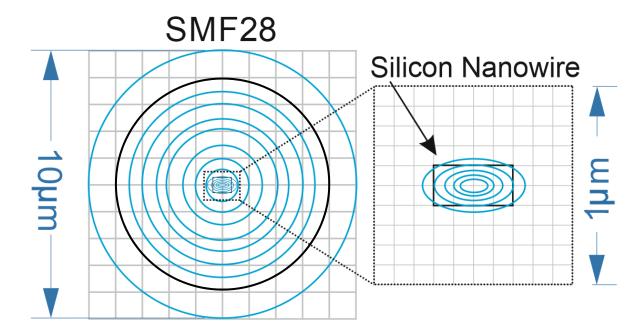

# 2.1.3: Coupling

Coupling from an optical fibre to a silicon nanowire is difficult for a number of reasons, predominantly due to the dimensions of the fibre core being much larger than the dimensions of a silicon waveguide, producing significant differences in mode field profile as shown in Figure 2.4[11]. This figure shows the single mode fibre to have a core diameter of 8m and the waveguide to have dimensions of around 400 x 200nm. Without manipulation of this field profile, severe coupling losses can be expected, up to -16dB [11]. Light transmission is also sensitive to refractive index differences between waveguides making coupling from one medium to another a challenge.

Figure 2.4 Displaying the large field profile mismatch between an SMF-28 optical fibre and a photonic nanowire. Figure reproduced from[11]

### 2.1.4: Tapering

Waveguide tapering is the method wherein the field profile is manipulated allowing for easier transmission from one medium to another. This improves coupling efficiencies as the field profile is usually manipulated with the receiving medium in mind typically a fibre. There are a number of methods of tapering and the primary ones are discussed in this section.

### One Dimensional Tapers

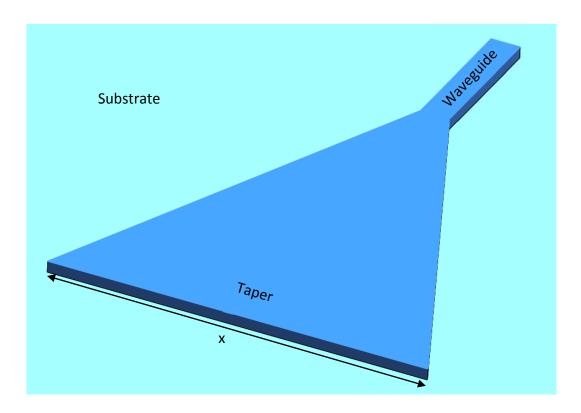

In One Dimensional (1D) tapering the waveguide is extended in one direction in order to expand the mode field profile laterally (Figure 2.5). This is a reciprocal process, so propagation in the opposite direction would reduce the mode field profile. These tapers are very simple to manufacture if the taper is only varied in a horizontal plane, as this is merely a function of the photolithography mask used for the device, and 1D tapers therefore allow rudimentary field profile manipulation. Although the resulting profile can be as wide as desired it is still restricted in the vertical direction. Whilst this can improve the coupling efficiency, it results in a method that is still very inefficient, and is inadequate for commercial applications.

Figure 2.5 A one dimensional taper

### Two Dimensional Tapers

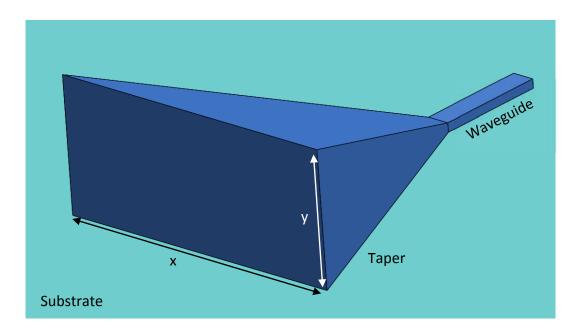

Similar to single dimension tapers, the waveguide is expanded to increase the field profile to better match that of an optical fibre. In this case the waveguide is also increased in size both horizontally and vertically allowing the field profile to expand (Figure 2.6). Two dimensional tapers (2D) are very advantageous as the resulting spot size can easily be made to match that of a fibre. However, 2D tapers are generally difficult to produce as the vertical dimension of the waveguide needs to be in the order of 10 microns. From a manufacturing point of view this is a challenge as it requires a thick layer in the locality of the taper, which in turn requires either specialist wafers or deposited materials which both require specialised manufacturing techniques that can limit subsequent development.[12][13]. Furthermore, it is extremely difficult to produce smooth vertical waveguide sidewalls as the taper dimensions reach a few hundred nanometres, resulting in high scattering loss. In addition, 1D and 2D taper require antireflection coatings (ARC) to be applied to reduce Fresnel reflection at the silicon-air interface.

Figure 2.6 A two dimensional taper

### **Inverted Taper**

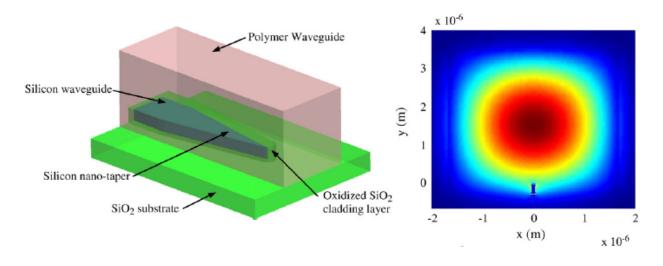

Inverted tapers, in contrast to the multi-dimensional tapers discussed previously, narrow the waveguide to a point which squeezes the mode out of the waveguide. This allows the field profile to spread out into a surrounding medium that forms a cladding waveguide. In a typical example Pu et al. [14] have shown that if the taper is created inside a polymer block that is  $3x3\mu m$  in dimension, then the field profile expands to this size and allows low loss coupling of 0.36dB to a lensed fibre (Figure 2.7).

Figure 2.7 Inverted taper structure (left) and field intensity image of the mode inside the polymer waveguide (right)[12].

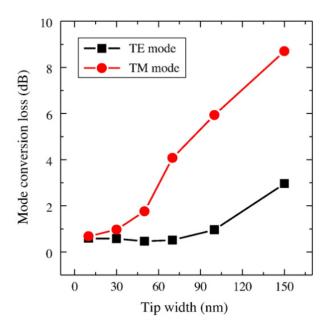

B. Ben Bakir et al[15] produced a similar structure using silicon dioxide as a cladding waveguide coupled to a lensed fibre with losses of 0.25dB and a 3dB spectral range of more than 300nm. Due to the restrictions in deposition of cladding waveguide materials, the spot size conversion is limited, these examples along with most other inverted tapers rely on lensed fibres to reduce the spot size which increases misalignment penalties and reduces their desirability as a packaging component. Further to this, fabrication is complicated by the need for a very small tip at the end of the waveguide taper, typically less than 100nm (Figure 2.8), with fabrication tolerances that are difficult to meet. This is observed by T. Barwicz et al who avoid using a tip in their inverted taper packaging solution by using metamaterials, which will be discussed further in section 2.3.2.

Figure 2.8 A graph showing the mode conversion loss with respect to tip width, showing the need for a small tip[14].

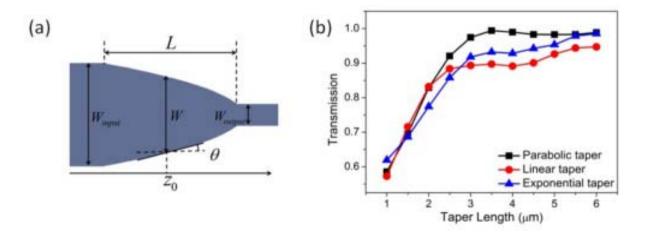

### Taper Transition and Footprint

Regardless of the tapering method the footprint and transition are both an important consideration. The length of the taper is associated with its efficiency, where a shorter taper will exhibit more loss than a longer one and so a compromise must be made between having a larger footprint and a low loss taper. Linear tapers are easy to produce but need to be very long to achieve an adiabatic transition in which case propagation loss can become a factor. Non-linear tapers smooth the taper transition, reducing loss and has been shown to reduce taper length by over 50% while maintaining a consistent loss[16]. A good example of a

nonlinear taper is shown in Figure 2.9 where the paper also compares the transmission loss of linear and different nonlinear tapers.

Figure 2.9 An example of a parabolic taper (a) and a transmission comparison with respect to taper length for parabolic, linear and exponential tapers (b) presented by Tong Ye et al [17]

# 2.2: Coupling Methodologies

Different coupling methodologies require different tapers. Before deciding which taper could be used, the type of coupling must be considered. Within photonics there are two coupling methods that are widely used; in plane coupling and out of plane coupling, both of which will be discussed in the following section.

# 2.2.1: In plane coupling

In plane, is performed by simply aligning a fibre to the facet of a waveguide (Figure 2.10). The waveguides have usually been subjected to field profile manipulation methods as mentioned previously. The alignment is, in theory a simple concept, however in practice there can be many complications. For example; the facet that will receive or transmit the light must be as smooth and as clean as possible. In order to accomplish this, the device chip must be perfectly cleaved and if that is not possible, typically many hours of polishing are required. In itself polishing is a labour intensive process and can produce problems of its own such as debris damaging the device chip or causing additional scattering. Etched facets are also an option, an example of this is shown later in this chapter in section 2.3.2. Chips can also be cleaved but that results in inconsistent facet quality.

Further disadvantages are apparent with aligning to the edge of a sample as dicing the wafer removes the possibility for wafer scale testing.

In plane coupling can take advantage of all of the field profile manipulation techniques discussed previously and, even though there are still significant field profile mismatches after manipulation, very low coupling losses can be achieved with sub-micron alignment precision.

Figure 2.10 An example of Butt Coupling where light from a fibre is being launched into a waveguide. The fibre cladding has been omitted for clarity

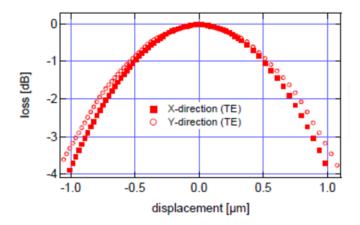

Because of the small feature sizes, the misalignment penalties are severe. Typically, different device chips have different structures, depending on size and geometry, so there are no generic loss characteristics to quote. However as an example, Figure 2.11[11] shows the loss as a function of displacement of a lensed fibre to a  $3x3\mu m$  waveguide which is typically the size of an expanded inverted taper waveguide.

It can be seen that  $\pm 0.5 \mu m$  gives a 1dB loss, which shows how difficult a fibre can be to align even after modal expiation techniques such as inverted tapers.

Figure 2.11 Loss verses displacement characteristics of a lensed optical fibre being aligned to a  $3x3\mu m$  facet [11].

All things considered, butt coupling does have a key advantage as it utilises an in plane approach which allows the fibres to be supported easily. Potentially, passive alignment techniques, with the use of v-grooves, can also be combined with butt coupling. These will be discussed in further detail later. Most significant of all its advantages are polarisation diversity and optical bandwidth which allow very high data rates through wavelength division multiplexing because more wavelengths are available.

# 2.2.2: Vertical Coupling

In order to avoid the difficulties of butt coupling, light could be introduced from anywhere on the device surface; however, the basic concept is fundamentally flawed.

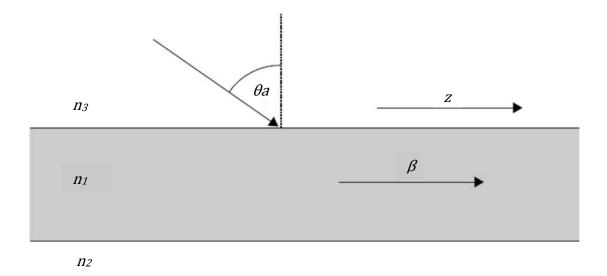

### For example

Figure 2.12[2] shows a waveguide cross section and an incident beam on the surface at an angle of  $\theta a$ . z is the direction of intended propagation,  $\beta$  is the waveguide propagation constant and  $n_1$ ,  $n_2$  and  $n_3$  are the respective refractive indices of each of the three materials. In order for light to travel in the z direction within the medium  $n_1$ , the propagation constants in the z direction must be the same. The beam will propagate in the medium  $n_3$  with a propagation constant of  $k_0 n_3$  in the direction of propagation (where the arrow is pointing).

Figure 2.12 A diagram of an incident ray on the surface of a waveguide[2].

In order for the light to propagate in the z direction in this medium the propagation constant  $k_z$  must be equal to 2.1:

$$k_z = k_0 n_3 \sin \theta_a \tag{2.1}$$

So we now know the propagation constant in z for  $n_3$  and this must match  $\beta$ , the propagation constant in z, within the waveguide:

$$\beta = k_z = k_0 n_3 \sin \theta_a \tag{2.2}$$

Now this is where a flaw appears;  $\beta$  is determined by the critical angles of the upper and lower claddings of the waveguide. The critical angles are the angles at which light will be totally internally reflected within the waveguide allowing propagation to occur. The maths of the critical angle will not be discussed here but the critical angle limits  $\beta$  to be:

$$\beta \ge k_0 n_3 \tag{2.3}$$

This means that the condition in 2.3 can never be met as  $sin\ \theta_a$  will never be unity (i.e.  $\theta_a$  = 90°) and coupling will not occur. Hence something is required in order to make vertical coupling possible. There are two preferred methods for this, one being prism coupling which introduces a prism to the top of the waveguide and reduces the refractive index change between  $n_3$  and  $n_1$  and allows the phase match condition to be true. Prism coupling does show potential, however the development steps are more complex than grating couplers, which also satisfy the phase match condition. The difficulties are due to the requirement of a

thick layer of a high refractive index material in the region of the coupler, similar to the problems seen when trying to create two dimensional tapers[2].

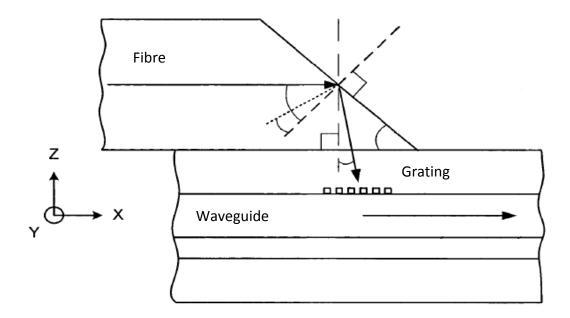

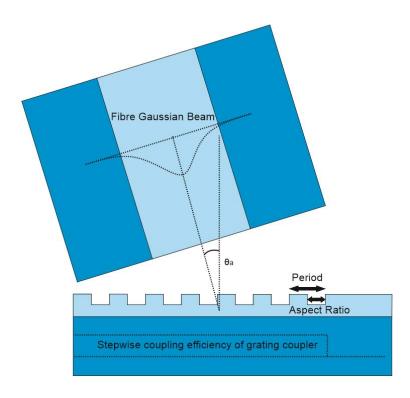

Grating couplers (Figure 2.13) utilise periodic recesses on the top surface of the waveguide. The recesses create a periodic modulation of the effective refractive index of the waveguide with respect to the wavelength of light, satisfying the phase match condition. Careful design of the recess depth, period and mark/space ratio allow precise optimisation for a given fibre approach angle[2, 18].

As mentioned previously the propagation constant of the waveguide is,  $\beta$ , however the periodic nature of the grating now permits a number of added propagation constants, shown as:

$$\beta_p = \beta_w + \frac{2p\pi}{\Lambda}$$

2.4

where  $\Lambda$  is the period of the grating and  $p=\pm 1, \pm 2, \pm 3, etc$ . is a series of diffraction orders for the diffraction grating. In order for the phase match condition to be true a number of changes need to be made; firstly, in order for  $\beta_p$  to be higher than  $k_0n_3$ , p must be negative. It is also normal to design the gratings such that there is only a single phase match with a waveguide mode, therefore p=-1 and the waveguide propagation becomes:

$$\beta_p = \beta_w - \frac{2\pi}{\Lambda}$$

2.5

and the phase match condition becomes:

$$\beta_w - \frac{2\pi}{\Lambda} = k_0 n_3 \sin \theta_a \tag{2.6}$$

Writing  $\beta w$  in terms of the effective index N, 2.6 becomes:

$$k_0 N - \frac{2\pi}{\Lambda} = k_0 n_3 \sin \theta_a \tag{2.7}$$

and on substituting for  $k_0$  we obtain:

$$\Lambda = \frac{\lambda}{N - n_3 \sin \theta_a}$$

2.8

This allows the design of a grating with a period for a desired coupling angle and wavelength, but this doesn't necessarily provide an efficient grating coupler. Many variables complicate grating design such as the size of the waveguide, the thickness of the buried oxide, the thickness and makeup of a cladding layer, the field profile of the coupled light and the etch depth of the grating coupler. As there are so many variables, a complex study is required to understand if a grating coupler is likely to be efficient and so simulations are regularly carried out to model ideal grating couplers under specific conditions. Often waveguide structures, buried oxide (BOX) and cladding thicknesses etc. are already defined due to their own efficiencies and so these can remain constant to reduce simulation complexity. Tuning the remaining variables e.g. aspect ratio, period and etch depth, is still a laborious task and so simulation tools such as the Lumerical FTDT solutions have convenient built-in features to aid in designing the most efficient grating coupler for a given scenario. For this project, the particle swarm optimisation was particularly useful as it allows the optimisation of multiple variable ranges and the software will complete a large number of simulations converging to the best performance[19]. This will be discussed further in section 4.4: Grating Coupler Design.

Adding complexity to the design of a grating coupler can yield higher efficiency, for example non-uniform gratings can be used to minimise the difference in mode field profile[20], and will be discussed later in this thesis.

When using grating couplers with SOI waveguides, some light is directed downwards and is lost to the substrate, so buried reflectors can be used to reflect the light back up and subsequently improve efficiency. An example of this has been demonstrated by D. Taillaert et al who improved grating efficiency by 31% [21].

A combination of a non-uniform grating with a metal backside mirror was presented by Y. Ding et al[22], boasting a record coupling efficiency of -0.58dB with a 3dB bandwidth of 71nm.

Footprint can be an issue for grating couplers as tapering structures can be very long. Focused gratings can be used to reduce taper lengths and F. van Laere showed an eight fold reduction in taper length with no added loss[23].

In order to address the lack of polarisation diversity in grating couplers two dimensional couplers have been created that split transverse electric (TE) and transverse magnetic (TM)

polarisations at the point of coupling. L. Carroll et al. showed the best example of this in terms of loss with 0.95dB of coupling loss and low polarization dependant losses of 0.3dB[24].

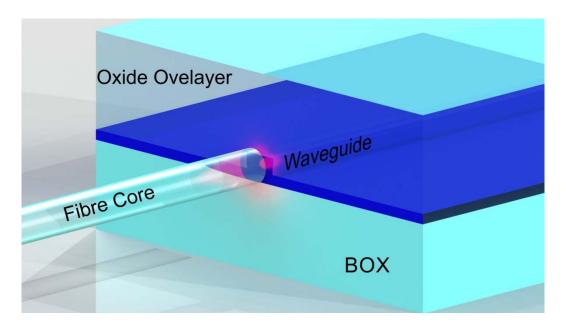

The surface grating approach (Figure 2.13) avoids having to cleave the chip and makes gratings specifically beneficial to wafer scale test procedures. More importantly however, the grating design allows for a much larger acceptance area as the dimensions are not restricted by the thickness of the silicon over layer. This means alignment tolerances are significantly increased as shown in Figure 2.14[11] where this example demonstrates only 1dB of loss for over 2µm of displacement in both the x and the y axis. Although advantageous in many ways, a vertical approach is not ideal for packaging; it makes securing the fibre problematic as it must be adhered and supported robustly enough for commercial applications. It also cannot utilise any well-developed forms of passive alignment. In many cases these gratings can be produced in a single etch step, where waveguides and grating couplers are defined in the same lithography step[21] which streamlines production in comparison to any butt coupling technique or prism coupling.

Figure 2.13 A diagram of a fibre being aligned to a grating coupler.

Figure 2.14 Miss-alignment characteristics of a grating coupler, the key on the right shows the loss in dB [11]

# 2.2.3: Comparison

Different coupling methodologies have their pros and cons, whenever an approach is considered, compromises are necessary (Table 2.1). Grating couplers are limited in their spectral range (70nm -3dB[22]) and polarisation diversity[24] and can be perceived as inefficient with efficiencies ranging from 30-46%[20]. This can be improved significantly up to 88%[22] with the addition of features such as backside mirrors and anodization, however this typically increases fabrication complexity. A vertical approach does not align to traditional packaging methodologies but in their simplest form gratings make PIC development, testing and packaging simpler and cost effective. Their relatively large alignment tolerance[11] and ease of access make them a strong choice from a packaging perspective.

Table 2.1 A Comparison showing the advantages and disadvantages of butt coupling and grating coupling

|                     | <b>Grating Coupling</b> | <b>Butt Coupling</b> |

|---------------------|-------------------------|----------------------|

| Spectral Range      | Low -                   | High ++              |

| Efficiency          | Low -                   | High ++              |

| Approach            | Out Of Plane -          | In Plane +           |

| Wafer Scale Testing | Yes +                   | No-                  |

| Sample Prep         | Low ++                  | High                 |

| Alignment Tolleranc | High +++                | Low                  |

In plane coupling is reported to accomplish up to 92% efficiency[14], has wide spectral bandwidth (300nm)[15] and are polarisation diverse compared to grating couplers. However, requiring access to the edge of the chip is limiting, chip preparation is time consuming and misalignment tolerances are high. The in plane angle of approach for butt coupling does make it ideal for packaging but misalignment tolerances make passive alignment particularly difficult.

# 2.2.4: Antireflection

When coupling from one medium to another there is always some undesired reflection due to a change in refractive index. This reflection is approximately 31% for a silicon to air interface at normal incidence and can induce a loss of 1.6dB[2]; to combat this, antireflection coatings can be used. The fundamentals behind antireflective coatings are beyond this text, however they comprise a layer deposited on the facet of a waveguide to reduce reflection. Antireflection coatings are rarely used for silicon photonic packaging because index matching fluids or adhesives are more often used to ease the refractive index change between the fibre and waveguide.

# 2.3: Literature Review

Although limited, there have been advances in silicon photonics packaging, some of which have been implemented in production. This section will outline some of those demonstrated products. Inspiration can also be obtained from other areas of photonics which use similar techniques and technology to exhibit the same goals. These examples can be split into two different groups and will be described in the following sections. The first of these will be solutions based on an out of plane approach and the second on in-plane couplers.

# 2.3.1: Out of Plane Solutions

Approach angle is a key component in packaging, and an out of plane approach is not often desirable as it makes securing and supporting the fibres problematic. The following solutions have tackled this problem, creating both commercial and research based applications.

Figure 2.15 Multi-channel fibre array grating coupled to an SOI chip using v-groove etched blocks as support [25].

Zimmermann et al have produced a range of solutions based on waveguide gratings[25], for example, Figure 2.15 shows a solution using fibre arrays vertically aligned to an SOI chip that have been sandwiched between two blocks for support. One of the blocks supports the fibres with v-grooves, positioning them to the correct pitch and alignment with a  $\pm 1\mu$ m tolerance, whilst the other block holds the fibres in the v-grooves. The assembled block is then polished to an angle reducing back reflections and allowing the fibres to sit directly on the gratings. Once positioned the block is secured using UV epoxy. This method is actively aligned and the additional loss caused by the packaging process is 2dB  $\pm 1$ dB. These losses are high considering that it is actively aligned.

Luxtera have used a similar solution to develop a wavelength division multiplexing (WDM) transceiver [26] which demonstrates 40Gb/s data rate over four channels (Figure 2.16). The packaging process is not described in detail in the article.

These solutions show that with improvement, grating couplers could be used in the process of packing. However, current solutions are still bulky, lossy and actively aligned. They do not fit into traditional packaging schemes, and although they demonstrate the potential for grating couplers within photonic packaging, much improvement is needed before true mass production can be realised.

Figure 2.16 Luxtera 40Gb/s transceiver using grating coupled fibre arrays [26].

# 2.3.2: In Plane Coupling Solutions

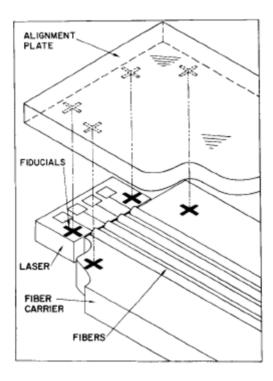

Photonic packaging is not limited to silicon. The packaging of lasers has often had to overcome the same difficulties when trying to couple to photonic waveguides, especially when trying to realise passive alignment. M. S. Cohen et al developed the approach shown in Figure 2.17; it shows an in-plane coupling method, utilising v-grooves and a capping chip for passive alignment [27]. The experiment used four separate parts; a v-groove chip for fibre support, a LASER chip, a substrate to hold them together and a glass alignment plate. The fibre and laser chips have alignment marks defined by lithography that match alignment marks on the alignment plate. The v-groove chip and laser chip are moved in to position while being viewed through the alignment plate, once positioned they were held against the alignment plate by a vacuum applied through the alignment plate itself. Solder is applied to metal pads on the substrate, it is heated and raised under the other two chips that have matching metal pads on their underside. When they come in to contact, the solder is cooled and the device is secure.

This is a long, complex process and is technically passive alignment but too lengthy for high throughput production.

Figure 2.17 Shows a laser chip, fibre carrier and capping chip allowing passive alignment [27]

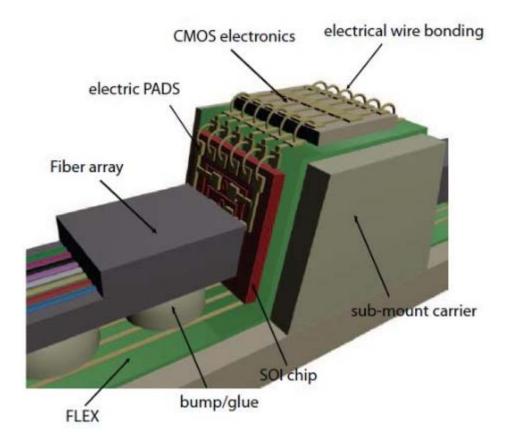

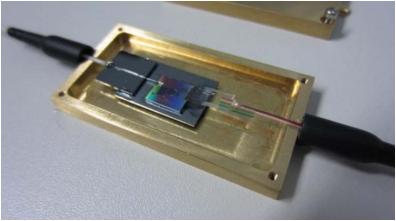

J.V. Galan et al[28] have attempted to make an in-plane version of the fibre blocks from the previous section. They have mounted electronic and photonic circuits on a sub-mount carrier, and a fibre block is aligned to the photonic chip which is secured by glue (Figure 2.18). Single grating efficiency of 24% is reported but the additional loss of the packaging approach is not specified.

Figure 2.18 Low profile silicon photonic package utilising a sub-mount carried to support ICs and fibres[28].

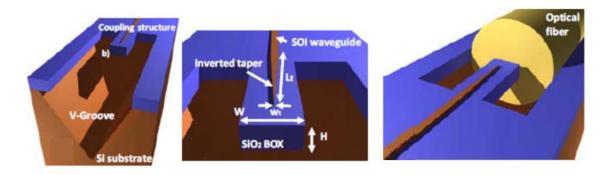

A solution which utilises V-grooves to allow passive alignment was also produced by J. V. Galan et al[29](Figure 2.19). It boasts  $\pm 300$ nm alignment tolerances which are crucial for this type of packaging. 400nm wide strip waveguides are etched in to a 220nm/2 $\mu$ m silicon (Si)/silicon dioxide (SiO<sub>2</sub>) SOI wafer, inverted tapers are used to couple adiabatically in to a SiO<sub>2</sub> waveguide etched in to the BOX. This waveguide is then under etched using potassium hydroxide (KOH) which also creates a v-groove to support a fibre. Losses of 7.5dB are reported partially due to the lack of an upper cladding. Coupling losses of ~1-2dB could be expected here but an upper cladding would make fabrication troublesome.

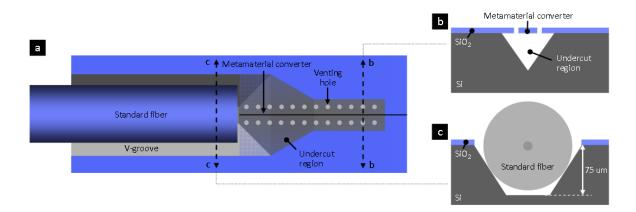

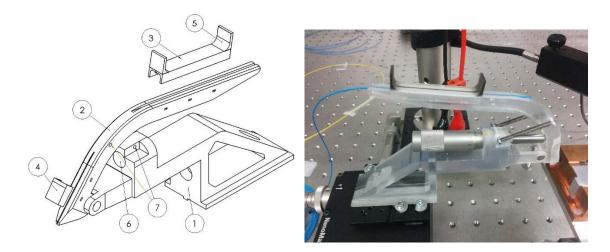

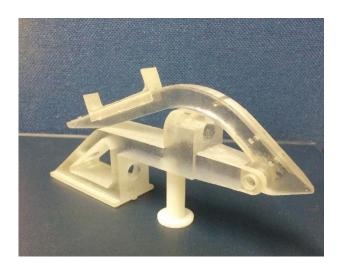

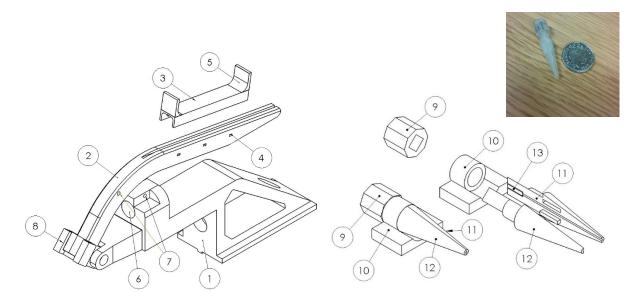

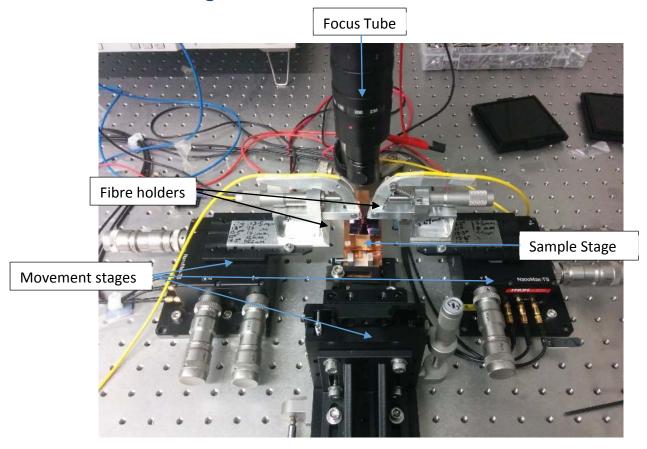

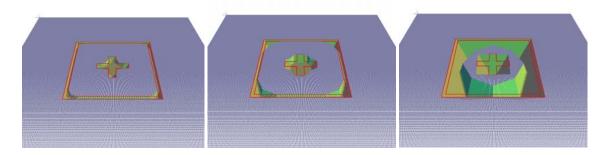

Figure 2.19 Butt coupling using v-grooves and a novel undercut solution to avoid cleaving and polishing [29].