### UNIVERSITY OF SOUTHAMPTON

# Runtime Energy Management of Multi-core Processors

by

Charles Leech

Thesis submitted for the degree of Doctor of Philosophy

in the Faculty of Physical Sciences and Engineering Electronics and Computer Science

May 2018

# UNIVERSITY OF SOUTHAMPTON ABSTRACT

# FACULTY OF PHYSICAL SCIENCES AND ENGINEERING ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

#### RUNTIME ENERGY MANAGEMENT OF MULTI-CORE PROCESSORS

by Charles Leech

Performance requirements of emerging applications and tighter power consumption constraints of mobile and embedded platforms mean that runtime management software is required to control these systems efficiently. In order for embedded systems to maintain their optimality, especially in dynamic environments, runtime software must be capable of learning and adaptability. This thesis investigates and develops runtime modelling methods, including their experimental validation, to reduce energy consumption in homogenous and heterogeneous multi-core processors. A multiple linear regression model is established to predict power and performance and drive runtime adaptations of an application and platform to maximise energy efficiency whilst meeting performance targets.

The proposed method is further validated with a parallel stereo matching application, which is developed to investigate the use of core scaling and analyse trade-offs between power and performance through runtime adaptation for energy saving. Experimental results obtained from a 61-core Intel Xeon-Phi platform show that the same performance can be achieved with an average reduction in power consumption of 27.8% and increased energy efficiency by 30.0%, in comparison to baseline dynamic power management techniques.

To make energy management independent of the application and platform, this thesis presents a holistic approach to runtime management in the form of a runtime framework that is both application- and platform-agnostic. The framework unites the hardware and software layers by embedding the runtime management layer at the centre and enables cross-layer interactions through an API and dynamic *knobs* and *monitors*. The framework is demonstrated experimentally across multiple applications and two heterogeneous platforms, the Odroid-XU3 and Cyclone V. Two state-of-the-art runtime management approaches are validated that reduce the energy consumption of application execution by 18.2% and 17.2%. Trade-offs between power, performance and accuracy are presented in three application-platform scenarios.

# Contents

| Li | st of | Figure        | es                                            | g        |

|----|-------|---------------|-----------------------------------------------|----------|

| Li | st of | Tables        | 5                                             | 13       |

| Li | st of | Algor         | ithms                                         | 15       |

| Li | st of | Acron         | ıyms                                          | 17       |

| D  | eclar | ation o       | of Authorship                                 | 19       |

| A  | cknov | wledge        | ements                                        | 23       |

| 1  | Intr  | oducti        | ion                                           | 25       |

|    | 1.1   | Resear        | rch Challenges                                | 27       |

|    | 1.2   | Resear        | rch Questions                                 | 28       |

|    | 1.3   | Resear        | rch Contributions                             | 28       |

|    |       | 1.3.1         | Software Contributions                        | 29       |

|    |       | 1.3.2         | Publications                                  | 30       |

|    | 1.4   | Thesis        | Structure                                     | 31       |

| 2  | Lite  | erature       | Review                                        | 33       |

|    | 2.1   | Multip        | processor Systems                             | 33       |

|    |       | 2.1.1         | Symmetric Multiprocessors                     | 34       |

|    |       | 2.1.2         | Circuit-level Technologies                    | 34       |

|    |       |               | 2.1.2.1 Dynamic Voltage and Frequency Scaling | 35       |

|    |       |               | 2.1.2.2 Power Domains                         | 35       |

|    |       |               | 2.1.2.3 Caches and Interconnects              | 36       |

|    |       | 2.1.3         | Heterogeneous Multiprocessor Architectures    | 37       |

|    |       |               | 2.1.3.1 ARM big.LITTLE                        | 38       |

|    |       |               | 2.1.3.2 Composite Cores                       | 39       |

|    |       | ~ •           | 2.1.3.3 Dynamic Core Morphing                 | 40       |

|    | 2.2   |               | are for Heterogeneous Multiprocessor Systems  | 41       |

|    |       | 2.2.1         | Dynamic Power Management Software             | 41       |

|    | 0.0   | 2.2.2         | Task Assignment and Allocation                | 42       |

|    | 2.3   |               | cation Characterisation for HMP Systems       | 43       |

|    |       | 2.3.1         | Intel RMS Applications                        | 44       |

|    |       | 2.3.2         | Berkeley Motifs                               | 45       |

|    | 0.4   | 2.3.3         | The Stereo Matching Application               | 45       |

|    | 2.4   |               | me Management                                 | 47       |

|    |       | 2.4.1         | Runtime Management Algorithms                 | 47       |

|    |       | 2.4.2 $2.4.3$ | Machine Learning for Runtime Management       | 49<br>49 |

|    |       | 4.4.3         | 2.4.3.1 Generalised Linear Models             | 49<br>50 |

|    |       |               | 2.4.0.1 Generalised linear models             | O(       |

6 CONTENTS

|   |      | 2.4.3.2 Support Vector Machines                                            |

|---|------|----------------------------------------------------------------------------|

|   |      | 2.4.3.3 Naive Bayes                                                        |

|   |      | 2.4.3.4 Neural Networks                                                    |

|   |      | 2.4.4 Model-based learning for Runtime Management                          |

|   |      | 2.4.4.1 Task Mapping and Parallelism                                       |

|   |      | 2.4.4.2 DVFS in Runtime Management                                         |

|   |      | 2.4.4.3 DPM in Runtime Management                                          |

|   |      | 2.4.5 Comparison of Model-based learning Approaches                        |

|   | 2.5  | Runtime Management Frameworks                                              |

|   | 2.6  | Experimental Platforms                                                     |

|   |      | 2.6.1 Intel Xeon Phi 7120P                                                 |

|   |      | 2.6.2 Odroid-XU3                                                           |

|   |      | 2.6.3 Cyclone V SoC Development Board                                      |

|   | 2.7  | Summary                                                                    |

| 3 | Line | ear regression modelling for runtime power and performance optimisation 63 |

|   | 3.1  | Linear Modelling                                                           |

|   | 3.2  | Runtime Power and Performance Model                                        |

|   | 3.3  | Runtime Model Validation                                                   |

|   | 3.4  | Gradient Decent for Runtime Optimisation                                   |

|   | 3.5  | Runtime Manager Overheads                                                  |

|   | 3.6  | Summary                                                                    |

| 4 | Rur  | ntime Management of a Parallel Stereo Matching Algorithm 81                |

|   | 4.1  | Geometric Model of a Stereo Vision System                                  |

|   |      | 4.1.1 Pinhole Camera Model                                                 |

|   |      | 4.1.2 Distortion                                                           |

|   |      | 4.1.3 Epipolar Geometry                                                    |

|   |      | 4.1.4 Stereo Geometry                                                      |

|   | 4.2  | Disparity Estimation                                                       |

|   |      | 4.2.1 Algorithm                                                            |

|   |      | 4.2.1.1 Pre-processing                                                     |

|   |      | 4.2.1.2 Cost Volume Construction                                           |

|   |      | 4.2.1.3 Cost Volume Filtering                                              |

|   |      | 4.2.1.4 Disparity Selection                                                |

|   |      | 4.2.1.5 Post Processing                                                    |

|   |      | 4.2.2 Quantitative Evaluation of Accuracy                                  |

|   |      | 4.2.3 Multi-threaded Software Implementation                               |

|   | 4.3  | Experimental Characterisation of Performance and                           |

|   |      | Power Consumption                                                          |

|   | 4.4  | Runtime Management of Stereo Matching                                      |

|   | 4.5  | Experimental Results of Online Adaptation                                  |

|   | 4.6  | Summary                                                                    |

| 5 | A F  | ramework for Application- and Platform-agnostic Runtime Management 107     |

|   | 5.1  | Fundamental Concepts of the Cross-layer Framework                          |

|   |      | 5.1.1 System Layers                                                        |

|   |      | 5.1.2 Cross-layer Connections                                              |

|   |      | 5.1.3 The Optimisation of Targets and Constraints                          |

|   |      | 5.1.4 Monitor and Application Weighting                                    |

|   |      | 5.1.5 Knob and Monitor Types                                               |

|   |      | 5.1.6 Runtime Adaptability                                                 |

|   | 5.2  | Framework Specification                                                    |

|   | 0.4  | - 11amcwork DD5CHCauloff                                                   |

CONTENTS 7

|               |       | 5.2.1  | Knobs and Monitors                                               | 115 |

|---------------|-------|--------|------------------------------------------------------------------|-----|

|               |       | 5.2.2  | Cross-layer APIs                                                 | 115 |

|               |       |        | 5.2.2.1 Application-RTM Interaction                              | 116 |

|               |       |        | 5.2.2.2 RTM-Device Interaction                                   | 119 |

|               | 5.3   | Frame  | work Software Implementation                                     | 120 |

|               |       | 5.3.1  | Namespaces                                                       | 121 |

|               |       | 5.3.2  | API Interfaces                                                   | 121 |

|               |       | 5.3.3  | Interprocess Communication                                       | 122 |

|               |       | 5.3.4  | Component Classes                                                | 123 |

|               | 5.4   | Bench  | marks                                                            | 124 |

|               |       | 5.4.1  | Applications                                                     | 124 |

|               |       |        | 5.4.1.1 Jacobi Iterative Method                                  | 124 |

|               |       |        | 5.4.1.2 Video Decoder                                            | 125 |

|               |       |        | 5.4.1.3 Whetstone Benchmark                                      | 125 |

|               |       | 5.4.2  | Runtime Managers                                                 | 126 |

|               |       |        | 5.4.2.1 Profiler Runtime Manager                                 | 126 |

|               |       |        | 5.4.2.2 Q-Learning Runtime Manager                               | 126 |

|               |       |        | 5.4.2.3 PMC-based Runtime Manager                                | 128 |

|               |       | 5.4.3  | Devices                                                          | 128 |

|               |       |        | 5.4.3.1 Odroid XU3                                               | 128 |

|               |       |        | 5.4.3.2 Cyclone V                                                | 130 |

|               | 5.5   | Frame  | ework Experimentation Tools                                      | 130 |

|               |       | 5.5.1  | User Interface                                                   | 131 |

|               |       | 5.5.2  | Logger                                                           | 132 |

|               | 5.6   | Exper  | imental Evaluation and Results                                   | 133 |

|               |       | 5.6.1  | System Profiling and Trade-off Analysis                          | 133 |

|               |       | 5.6.2  | Runtime Manager Validation                                       | 135 |

|               |       |        | 5.6.2.1 Q-Learning RTM                                           | 137 |

|               |       |        | 5.6.2.2 PMC-based RTM                                            | 138 |

|               | 5.7   | Summ   | ary                                                              | 139 |

| 6             | Con   |        | n and Future Directions                                          | 141 |

|               | 6.1   |        | usions                                                           |     |

|               | 6.2   | Resear | rch Questions                                                    | 143 |

|               | 6.3   | Future | e Investigations                                                 | 144 |

| Αp            | pen   | dix A  | RTM Modelling and Analysis Scripts                               | 147 |

| Αp            | pen   | dix B  | RTM Experimental Data                                            | 157 |

| Αp            | pen   | dix C  | Stereo Matching Algorithm Code                                   | 159 |

| An            | ppen  | dix D  | Stereo Matching Algorithm Data Analysis Scripts                  | 169 |

| -             | -     |        | Framework Code                                                   | 175 |

| -             | -     |        |                                                                  | 181 |

| Ī             | _     |        | Framework Data Analysis Scripts  Departs Dublished and Submitted |     |

| _             | _     |        | Papers Published and Submitted                                   | 189 |

| $\mathbf{Bi}$ | bliog | graphy |                                                                  | 281 |

# List of Figures

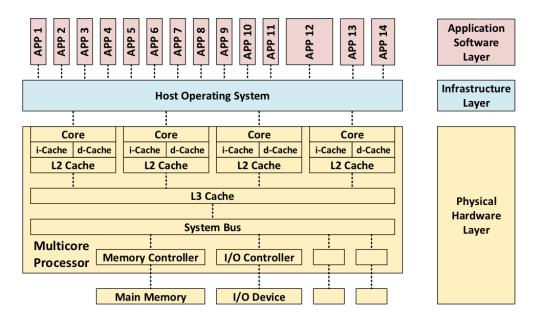

| 2.1        | System block diagram of a theoretical homogeneous/symmetric multiprocessor, reprinted from [1]                                                                                                                                                                                                                        |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

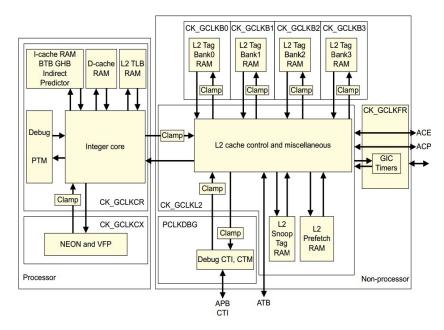

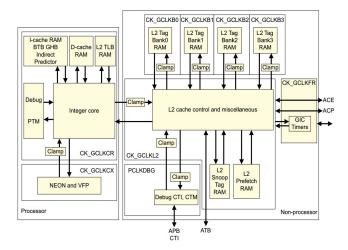

| 2.2        | The ARM Cortex-A15 features multiple power domains for the core and surrounding logic, reprinted from [2]                                                                                                                                                                                                             |

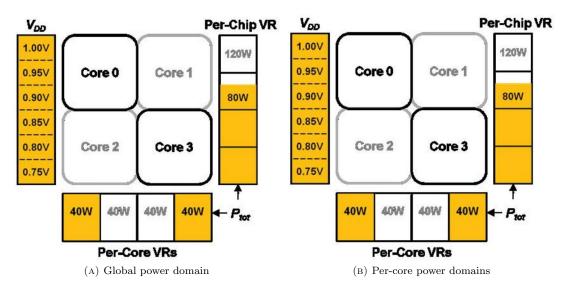

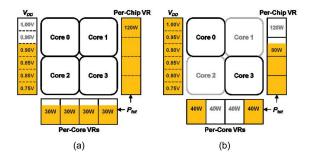

| 2.3        | Per-core power domains can reduce power consumption and provide higher per-                                                                                                                                                                                                                                           |

|            | formance levels, reprinted from [3]                                                                                                                                                                                                                                                                                   |

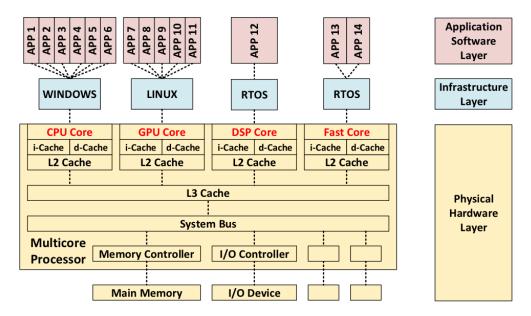

| 2.4        | System block diagram of a theoretical Heterogeneous Multiprocessor (HMP), reprinted from [1]                                                                                                                                                                                                                          |

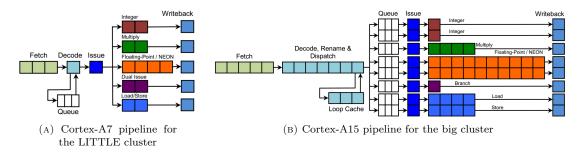

| 2.5        | ARM microarchitectural pipelines of the big.<br>LITTLE HMP, reprinted from $[4]$                                                                                                                                                                                                                                      |

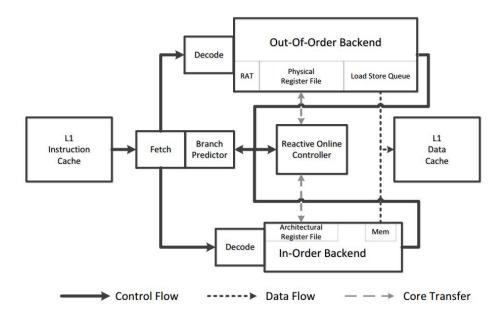

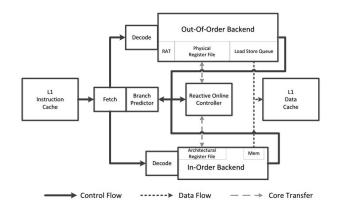

| 2.6        | Microarchitecture of a Composite Core featuring two backend modules called $\mu$ Engines, reprinted from [5]                                                                                                                                                                                                          |

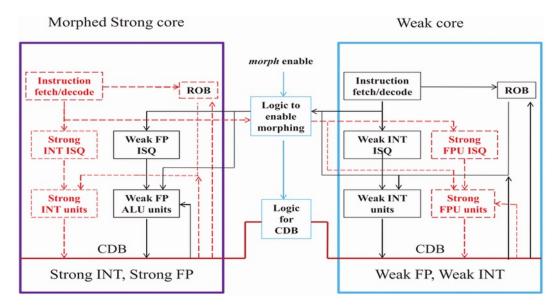

| 2.7        | The process of dynamic core morphing, reprinted from [6]                                                                                                                                                                                                                                                              |

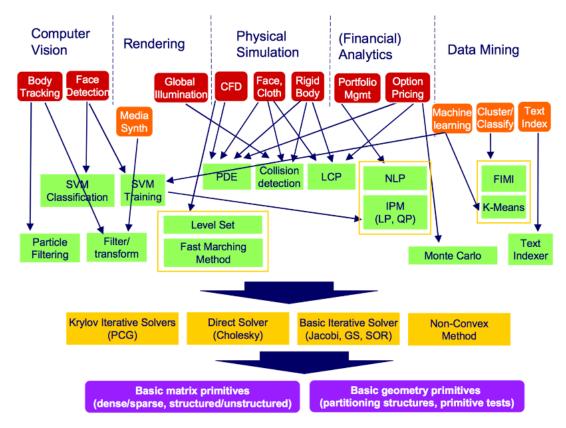

| 2.8        | Workload Convergence from applications (red) to computational kernels (green) to algorithms (yellow) and finally to mathematical primitives (purple), reprinted from [7]. Arrows show how applications can be derived from a common set of computational kernels                                                      |

| 2.9        | Illustration of how an application can be composed of RMS stages, reprinted from [8]                                                                                                                                                                                                                                  |

| 2.10       | The Berkeley Motifs and their association with particular applications and application domains, reprinted from [9]. The three levels of need (green=low, yellow=medium, red=high) relate to the rate of occurrence of the motif within the                                                                            |

| 2.11       | application                                                                                                                                                                                                                                                                                                           |

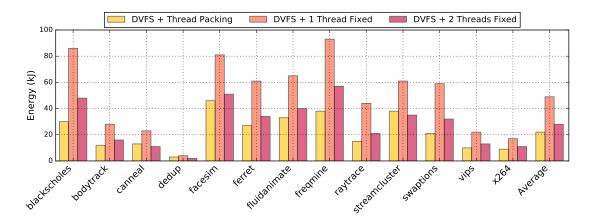

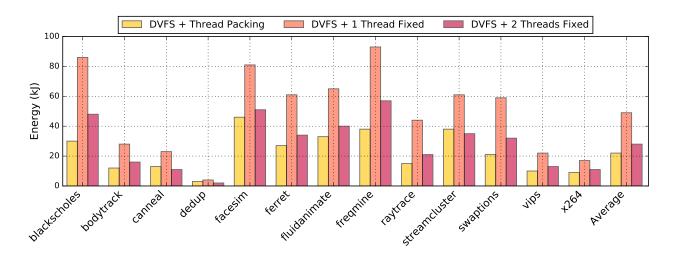

| 2.12       | Comparison of energy consumption for benchmarks with and without thread-packing on a homogeneous CMP, reprinted from [10]                                                                                                                                                                                             |

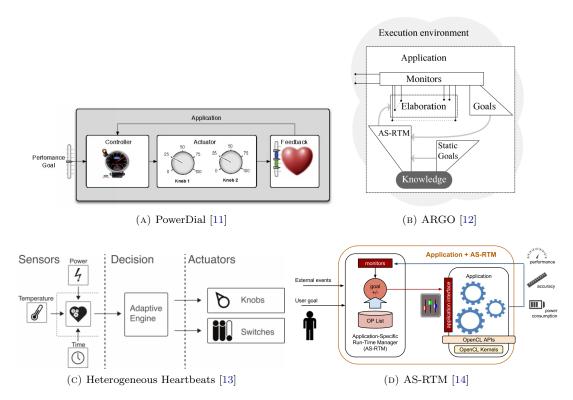

| 2.13       | Conceptual overviews of frameworks proposed in literature, reprinted from [11,                                                                                                                                                                                                                                        |

|            | 12, 13, 14]                                                                                                                                                                                                                                                                                                           |

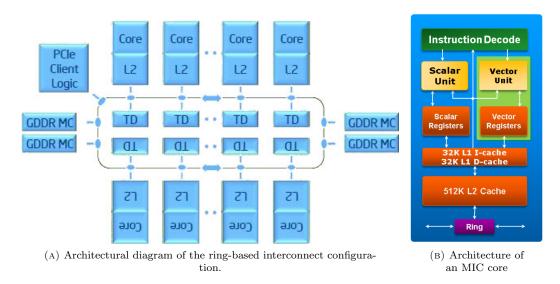

|            | Intel Xeon Phi diagrams, adapted from [15] and reprinted from [16]                                                                                                                                                                                                                                                    |

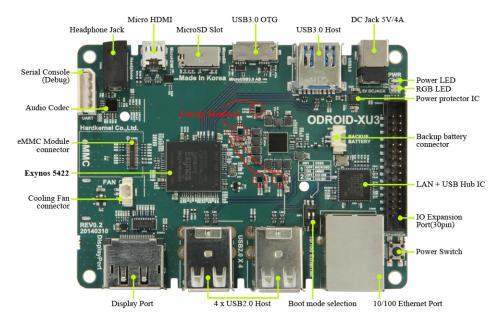

|            | Odroid-XU3 Board Image, reprinted from [17]                                                                                                                                                                                                                                                                           |

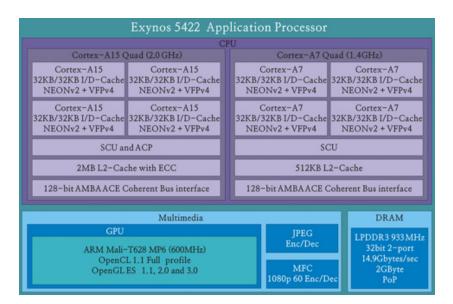

|            | Odroid-XU3 system block diagram, adapted from [17]                                                                                                                                                                                                                                                                    |

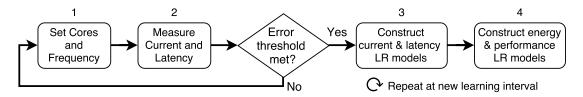

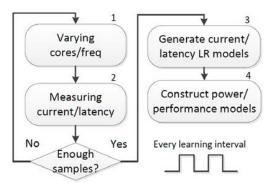

| 3.1        | Flowchart of the runtime power and performance model generation process                                                                                                                                                                                                                                               |

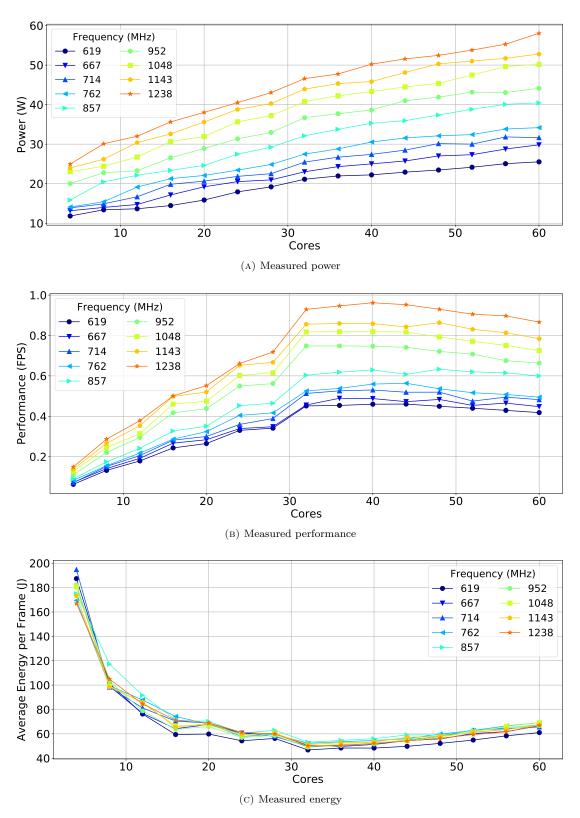

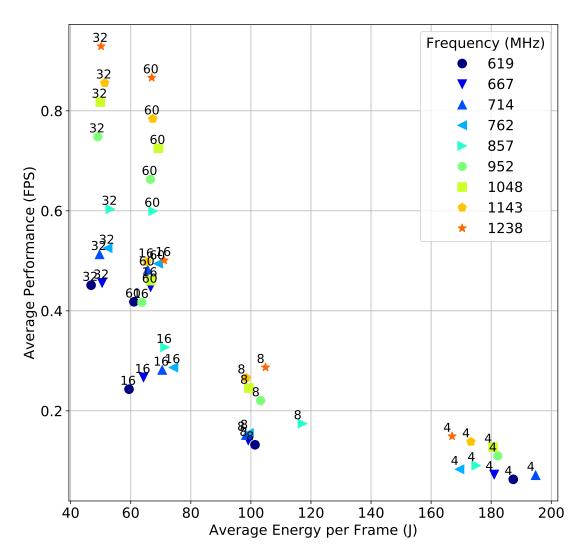

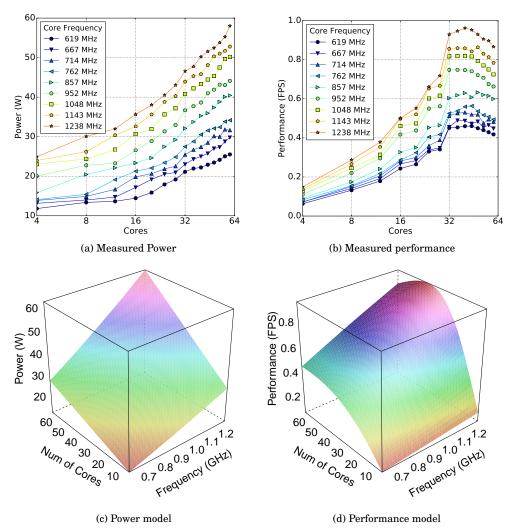

| 3.2        | Plots of measured power (a), performance (b) and energy (c), for the stereo matching application executing on the Xeon Phi, across a range of frequencies and number of cores. Each point is an average of four measurements. Data is listed in                                                                       |

|            | Appendix B                                                                                                                                                                                                                                                                                                            |

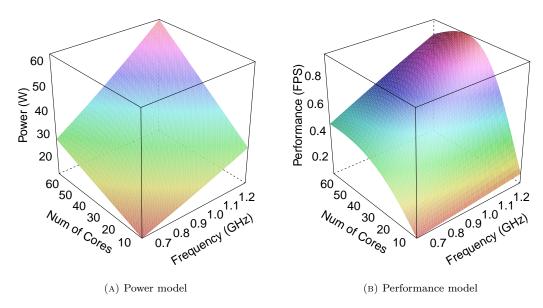

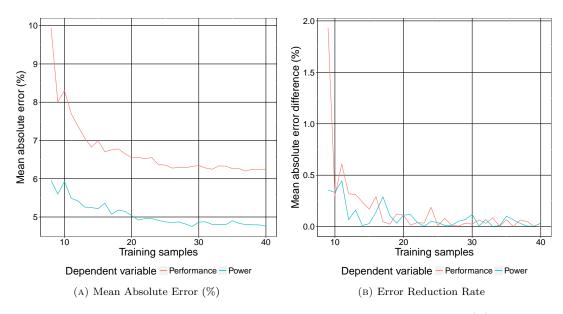

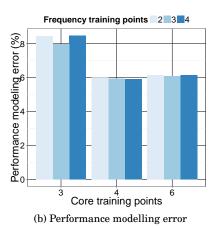

| 3.3<br>3.4 | Runtime models for power (a) and performance (b) generated from training data. Effect of the number of training samples on the mean absolute error (A) and the rate of reduction of the error (B) of the power and performance models. Error is the difference between predictions using the models and the remaining |

|            | experimental characterisation data                                                                                                                                                                                                                                                                                    |

10 LIST OF FIGURES

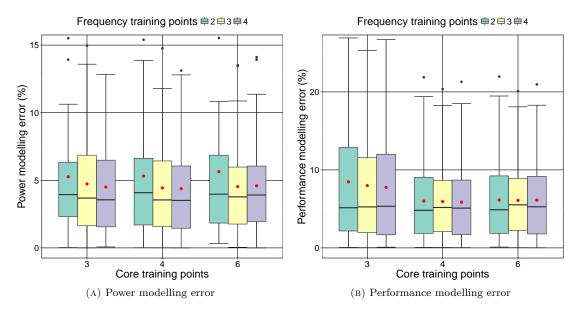

| 3.5   | Increasing the number of training samples for both core count and frequency reduces the power and performance modelling error. Mean error is show in red, boxes extend from the first to third quartile with the median line marked | 7  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

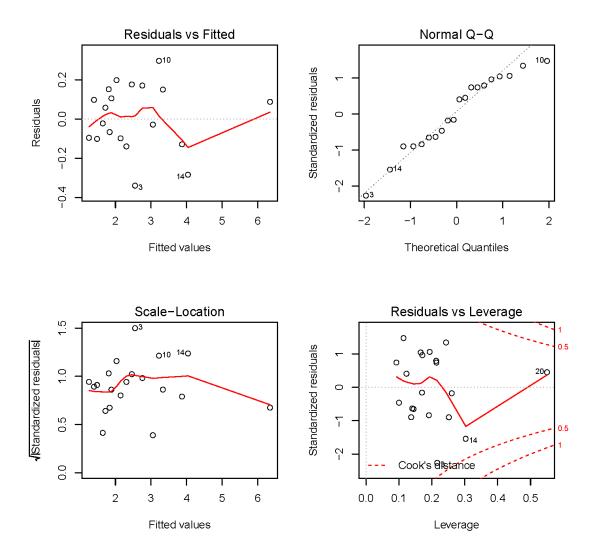

| 3.6   | Analysis of Variance for the latency model                                                                                                                                                                                          | 7  |

| 3.7   | Analysis of Variance for the current model                                                                                                                                                                                          | 7  |

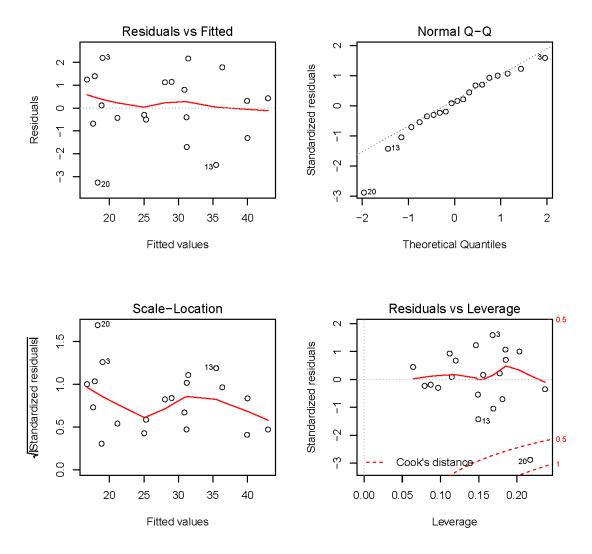

| 3.8   | Backtracking line search for the step size of gradient descent, reprinted from [18].                                                                                                                                                | 70 |

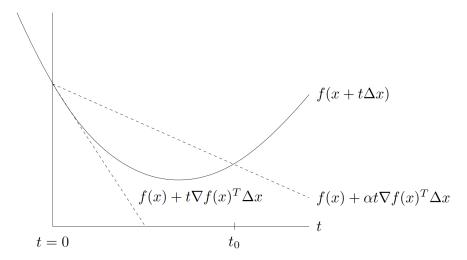

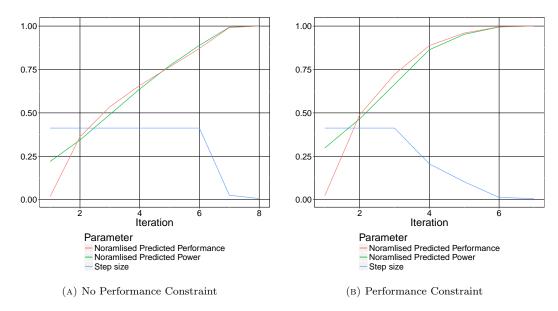

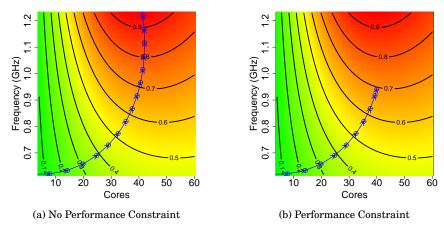

| 3.9   | Runtime optimisation examples (a) without performance constraint and (b) with                                                                                                                                                       |    |

| 0.0   | performance constraint. Power consumption is shown using an overlaid colour                                                                                                                                                         |    |

|       | map and the performance level is shown with contour lines                                                                                                                                                                           | 7  |

| 3 10  | Step size, normalised power and normalised performance over the gradient descent                                                                                                                                                    | •  |

| 0.10  | iterations                                                                                                                                                                                                                          | 7  |

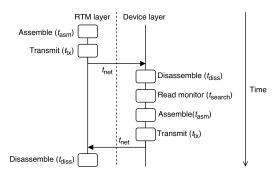

| 3.11  | Timing diagram of the optimisation and measurement overheads of the runtime management processes during application execution.                                                                                                      | 7  |

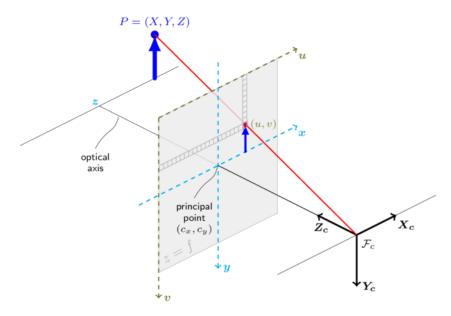

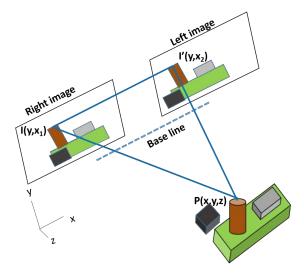

| 4.1   | Pinhole camera model illustrating the projection of a Three Dimensional (3D)                                                                                                                                                        |    |

|       | point in space to the image plane, reprinted from [19]                                                                                                                                                                              | 8  |

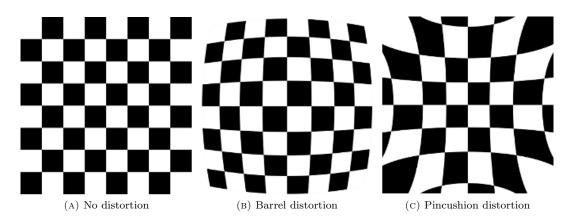

| 4.2   | The two modes of radial distortion, reprinted from [19]                                                                                                                                                                             | 8  |

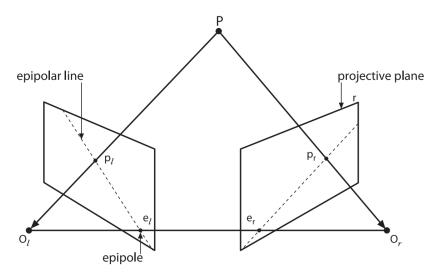

| 4.3   | Epipolar geometry of a stereo imaging system, reprinted from [20]                                                                                                                                                                   | 8  |

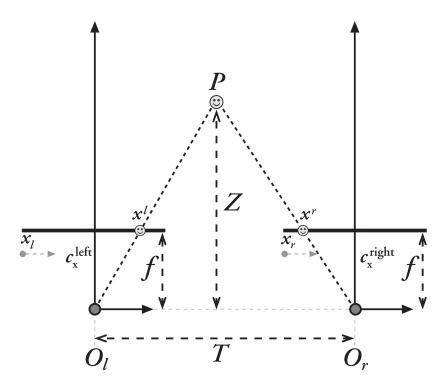

| 4.4   | Coplanar geometry of a calibrated stereo imaging setup reprinted from [20]                                                                                                                                                          | 8  |

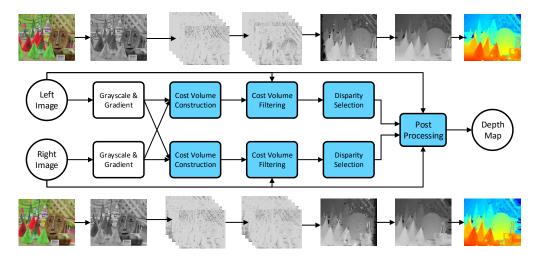

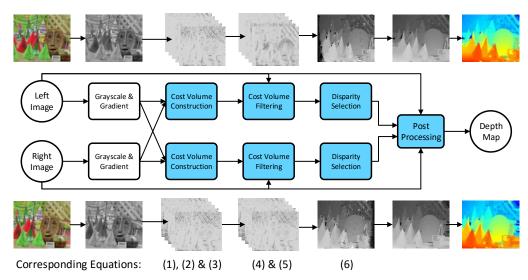

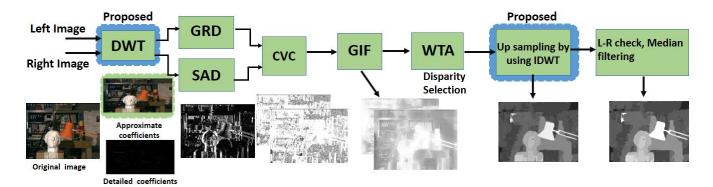

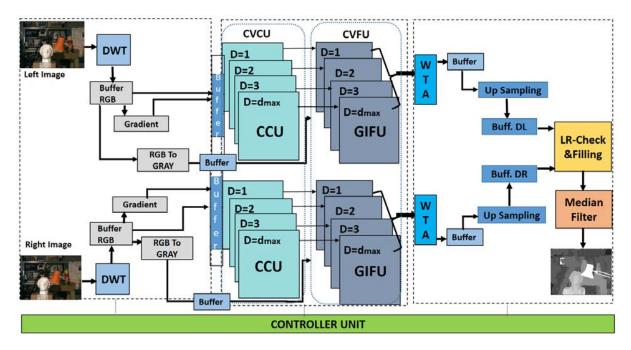

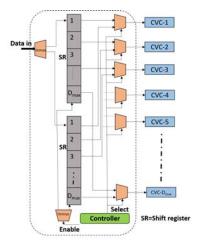

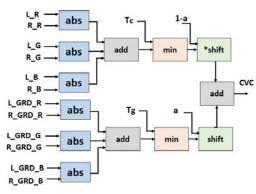

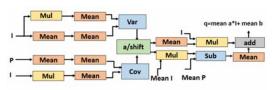

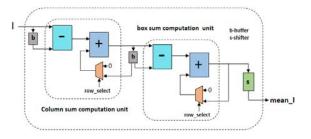

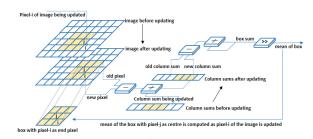

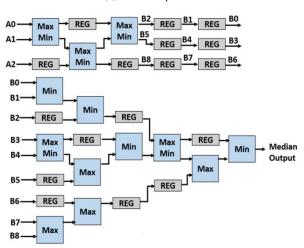

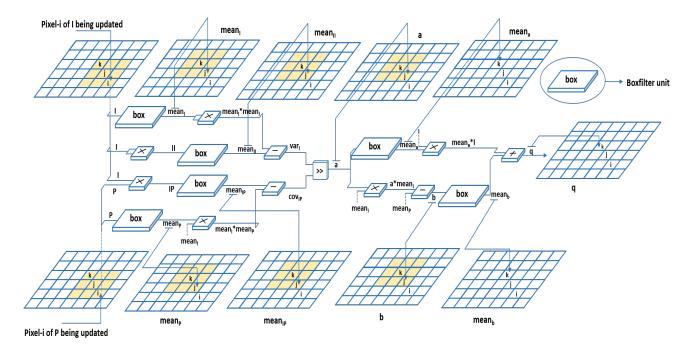

| 4.5   | Block diagram of the DE algorithm composed of CVC, CVF, DS and PP stages.                                                                                                                                                           |    |

|       | The cost volume is created in CVC, with $D$ slides, each slice is filtered in CVF                                                                                                                                                   |    |

|       | and then combined in DS. The shaded regions are the enhanced parallel stages                                                                                                                                                        |    |

|       | which offer opportunity for runtime tuning of the threading level                                                                                                                                                                   | 8  |

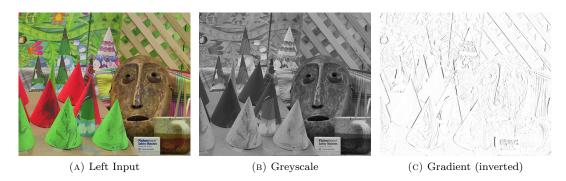

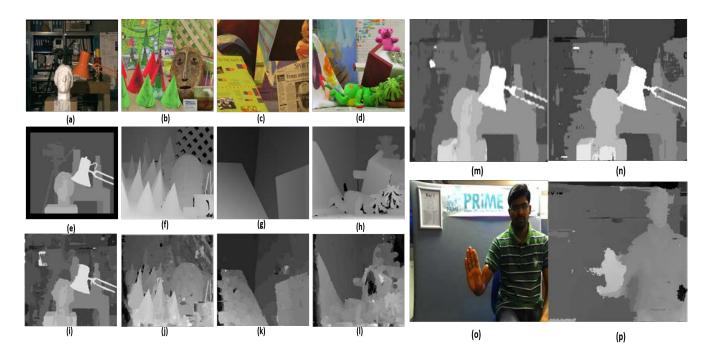

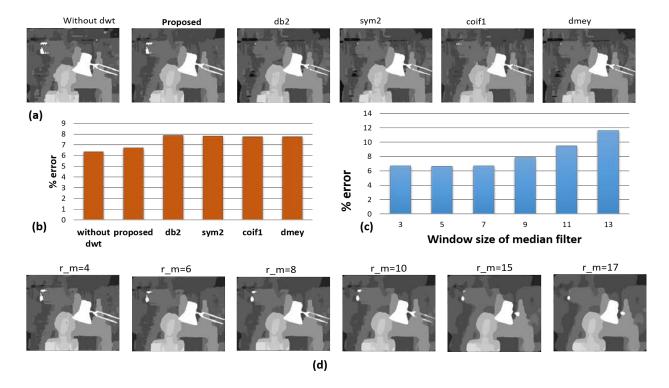

| 4.6   | Left input image, greyscale and x-gradient images produced from pre-processing.                                                                                                                                                     | 8  |

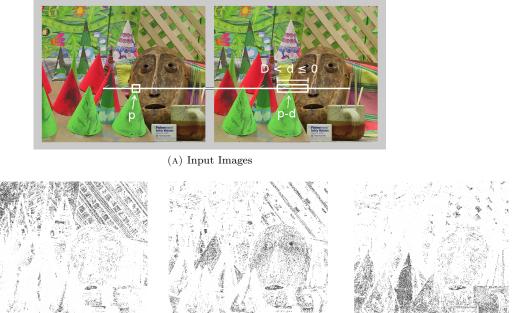

| 4.7   | (A) Left and right input images with illustration of the matching process, (B - D)                                                                                                                                                  |    |

|       | slices through the cost volume after construction with Equation $4.14$ at $d = 19$ ,                                                                                                                                                | 0  |

| 4.0   | 33 and 46                                                                                                                                                                                                                           | 8  |

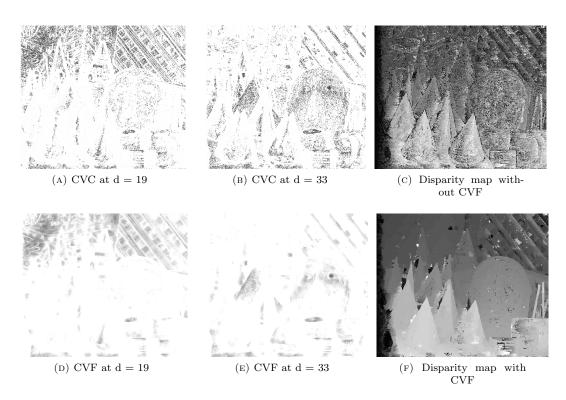

| 4.8   | Cost volume slices before (A - B) and after (D - E) filtering with Equation 4.15 at disparities d = 19 and 33. The disparity map built from an unfiltered (C) and filtered (F) cost volume.                                         | 9  |

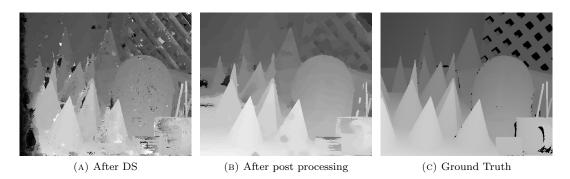

| 4.9   | The affect of post processing illustrated with a comparison between the disparity map (A) after the selection stage, (B) after post processing and (C) the ground                                                                   |    |

|       | truth map from the dataset source                                                                                                                                                                                                   | 9  |

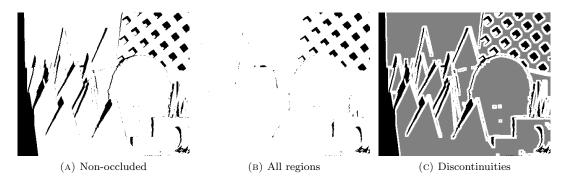

| 4.10  | Masks used to evaluate the accuracy of the disparity map in reference to the                                                                                                                                                        |    |

|       | ground truth. These are; non-occluded regions (nonocc), all known regions (all)                                                                                                                                                     | 0  |

| 4 1 1 | and regions near depth discontinuities (disc)                                                                                                                                                                                       | 9  |

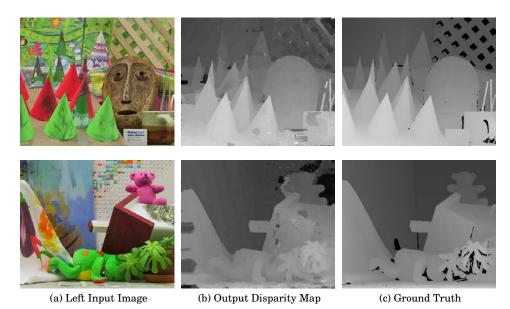

| 4.11  | Comparison of the depth map output from our algorithm and the ground truth                                                                                                                                                          | 0  |

| 4 10  | depth map provided with the dataset.                                                                                                                                                                                                | 9  |

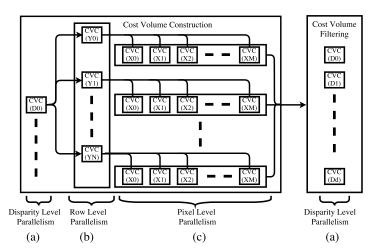

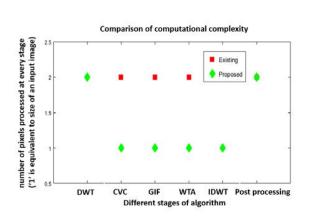

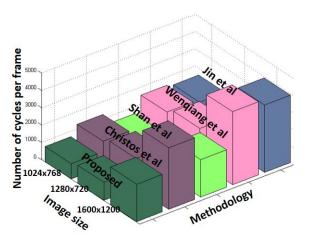

| 4.12  | The dimensions of parallelism introduced to each stage of this implementation of the Disparity Estimation (DE) algorithm                                                                                                            | 9  |

| 1 19  | - • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                             | 9  |

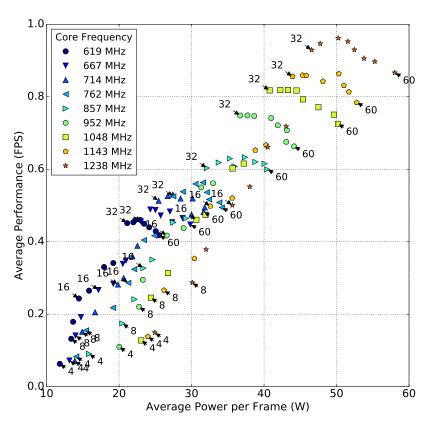

| 4.13  | Power and performance operating points for the range of cores and frequencies of<br>the Xeon Phi when executing the DE algorithm. The power and performance of                                                                      |    |

|       | each point is an average of four measurements, collected by cycling the algorithm                                                                                                                                                   |    |

|       | with the image pair from Section 4.2                                                                                                                                                                                                | 9  |

| 4 14  | Optimisation and scaling actions made in the DE algorithm's operating space on                                                                                                                                                      | J  |

| 1.11  | the Xeon Phi platform                                                                                                                                                                                                               | 9  |

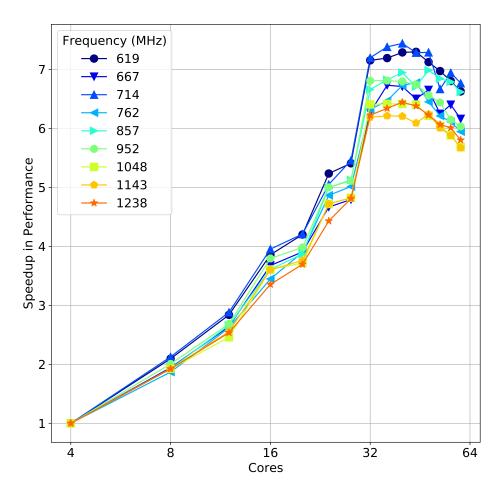

| 4.15  | Energy and performance trade-offs for $2^x$ , $(2 \le x \le 5)$ and 60 cores over the range                                                                                                                                         | 9  |

| 1.10  | of operating frequencies when executing the DE algorithm on the Xeon Phi                                                                                                                                                            | 9  |

| 4.16  | Speed-up in performance of the DE algorithm as a result of core scaling. Speed-up                                                                                                                                                   | ,  |

| 0     | is in relation to the performance at four cores                                                                                                                                                                                     | 10 |

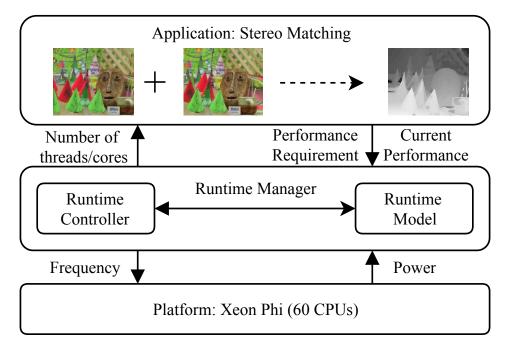

| 4.17  | Block diagram of the stereo matching run-time optimisation approach                                                                                                                                                                 | 10 |

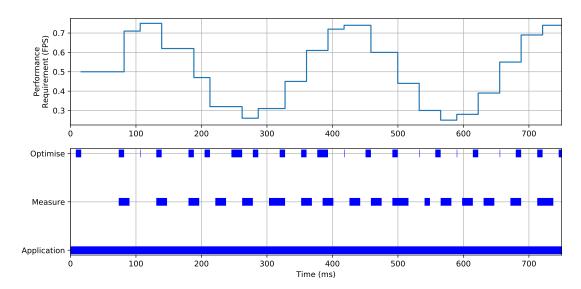

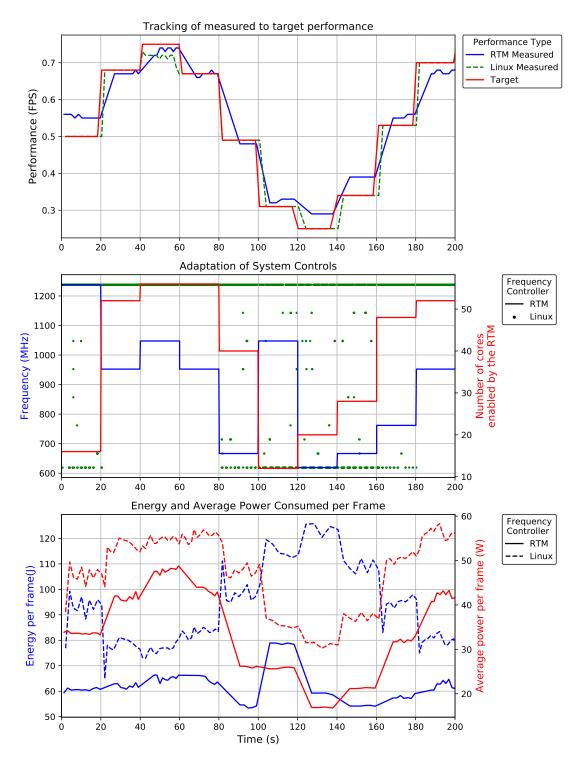

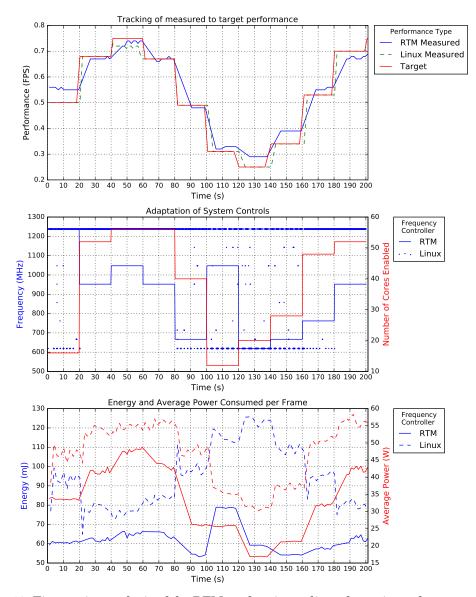

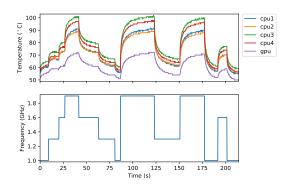

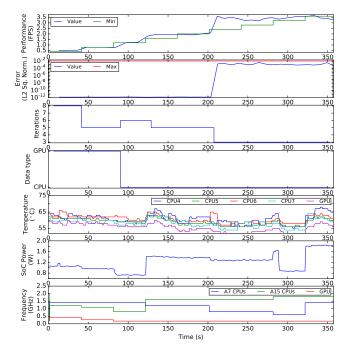

|       | Time series analysis of the Runtime Manager (RTM) performing online adapta-                                                                                                                                                         | -0 |

| _,_   | tions of core number and frequency to optimise power and energy whilst meeting                                                                                                                                                      |    |

|       | a target performance.                                                                                                                                                                                                               | 10 |

|       |                                                                                                                                                                                                                                     |    |

LIST OF FIGURES 11

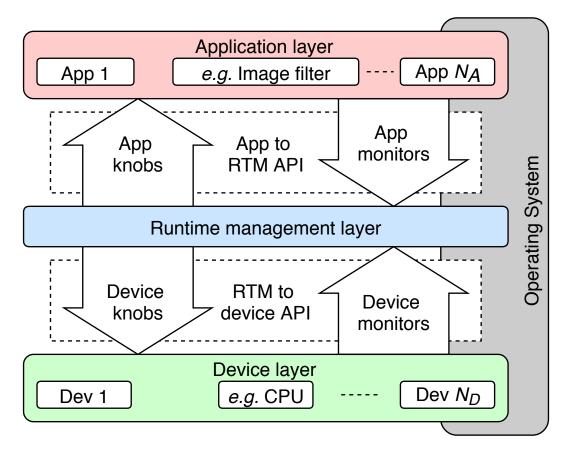

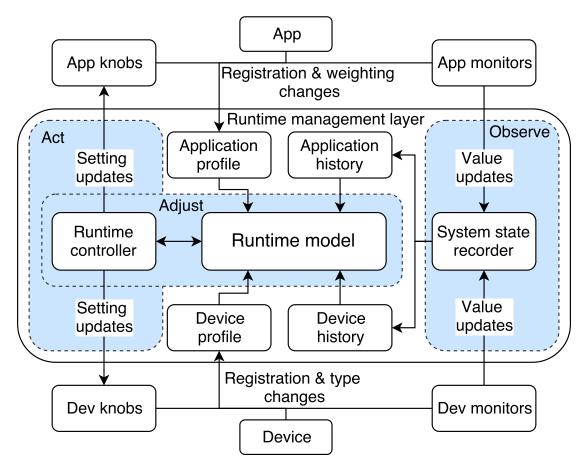

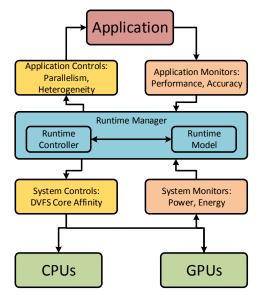

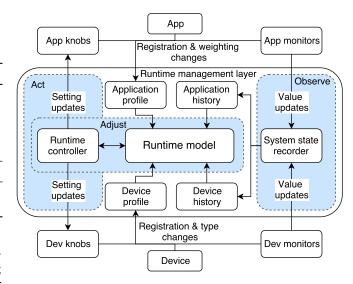

| 5.1        | Cross-layer framework and APIs enabling communication between the application, runtime management and device layers using knobs and monitors. The operating system spans all three layers and hosts the execution of each | 110 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

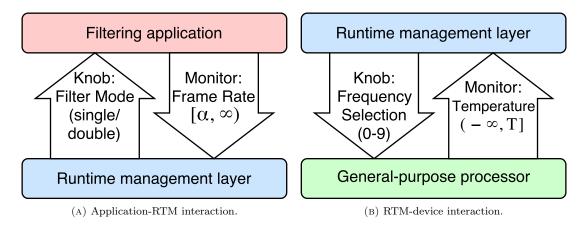

| 5.2        | Cross-platform and application-agnostic knob and monitor examples used within                                                                                                                                             |     |

| <b>-</b> 0 | the framework                                                                                                                                                                                                             | 111 |

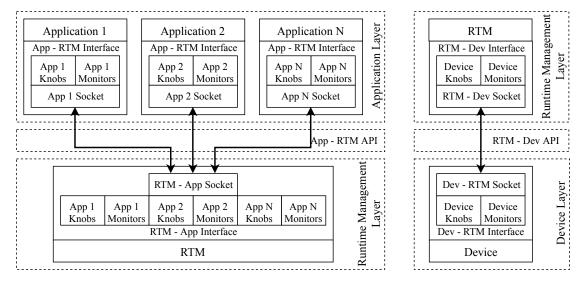

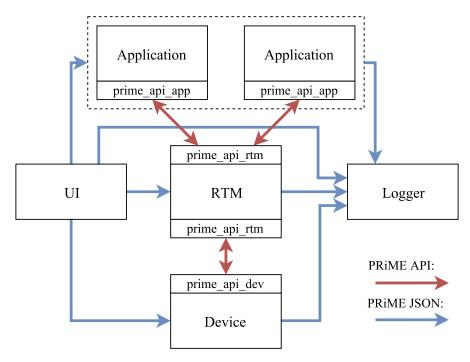

| 5.3        | Implementation of the framework from a software-component perspective, including the location of knobs and monitors, interfaces and sockets in each layer                                                                 | 121 |

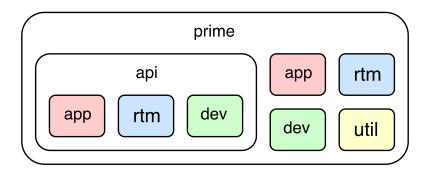

| 5.4        | Namespaces in this implementation of the framework to provided code separation.                                                                                                                                           |     |

| 5.5        | Example structure of the runtime management layer with the act-observe-adjust                                                                                                                                             |     |

| 0.0        | phases highlighted                                                                                                                                                                                                        | 127 |

| 5.6        | Block digram of the tools (UI and Logger) integrated into the framework to aid                                                                                                                                            |     |

|            | experimentation                                                                                                                                                                                                           | 130 |

| 5.7        | Main menu of the UI                                                                                                                                                                                                       | 131 |

| 5.8        | Demo mode of the UI                                                                                                                                                                                                       | 132 |

| 5.9        | Auto mode of the UI                                                                                                                                                                                                       | 132 |

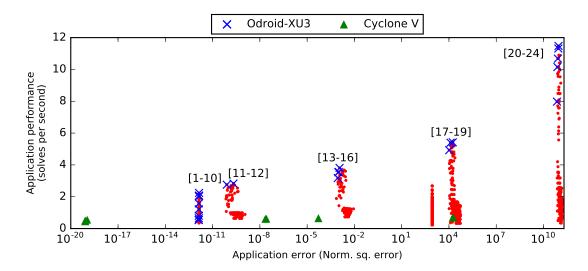

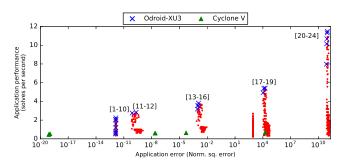

| 5.10       | Pareto-optimal states for the error and performance trade-off of the Jacobi ap-                                                                                                                                           |     |

|            | plication on the Odroid-XU3 and Cyclone V. Label numbers link each operating                                                                                                                                              |     |

|            | point to the rows of Table 5.7, which show the knob and monitor values that each                                                                                                                                          | 104 |

| F 11       | point encodes                                                                                                                                                                                                             | 134 |

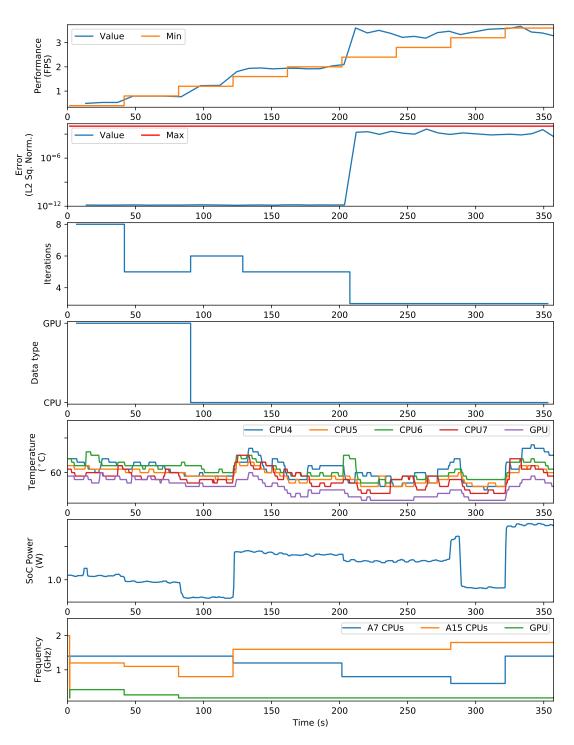

| 5.11       | sponse to step increases in the performance monitor minimum bound of the Jacobi                                                                                                                                           |     |

|            | application running on the Odroid platform. Application monitors and knobs are                                                                                                                                            |     |

|            | shown in graphs 1-2 and 3-4, respectively, with device monitors and knobs shown                                                                                                                                           |     |

|            | in 5-6 and 7, respectively. The RTM uses a look-up table with a control loop that                                                                                                                                         |     |

|            | filters it based on the monitor bounds                                                                                                                                                                                    | 136 |

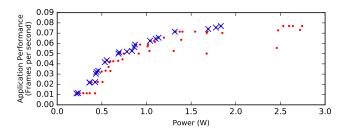

| 5.12       | Pareto-optimal states identified by the RTM for the power and performance trade-                                                                                                                                          |     |

|            | off of the video decoder application on the Odroid-XU3                                                                                                                                                                    | 137 |

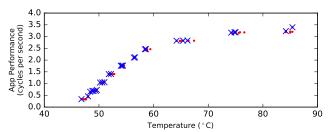

| 5.13       | Pareto-optimal states identified by the RTM for the temperature and performance                                                                                                                                           |     |

| - 11       | trade-off of the Whetstone application on the Odroid-XU3                                                                                                                                                                  | 137 |

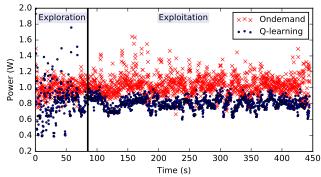

| 5.14       | Comparison between Q-learning RTM and Ondemand governor for the power                                                                                                                                                     | 138 |

| E 1E       | consumption of the video decoder executing on the Odroid                                                                                                                                                                  | 190 |

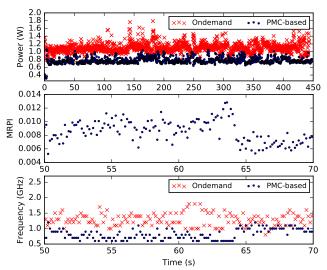

| 5.15       | power consumption of the video decoder executing on the Odroid. Middle and                                                                                                                                                |     |

|            | lower: the MRPI metric and the frequency choices of the PMC-based RTM and                                                                                                                                                 |     |

|            | Ondemand governor                                                                                                                                                                                                         | 139 |

# List of Tables

| 2.1        | Governors available in the Linux kernel since version 2.6 [21]                                                                                                 | 41  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2<br>2.3 | Summary of runtime management algorithms published in the literature Grouping of existing model-based runtime learning techniques for power and en-            | 48  |

|            | ergy management                                                                                                                                                | 52  |

| 2.4        | Voltage and frequency scaling steps of the Xeon Phi processors                                                                                                 | 59  |

| 3.1        | MLR modelling hypotheses                                                                                                                                       | 65  |

| 3.2        | Summary of the statistical properties of the latency model                                                                                                     | 72  |

| 3.3        | Summary of the statistical properties of the current model                                                                                                     | 72  |

| 3.4        | Data for each step in the gradient descent search for performance optimisation of<br>the stereo matching application executing on the Xeon Phi platform        | 77  |

| 3.5        | Gradient descent search data for optimisation of the stereo matching application with a                                                                        |     |

|            | performance constraint, executing on the Xeon Phi platform                                                                                                     | 78  |

| 4.1        | Comparison of the accuracy of related stereo matching algorithms using standard image pairs from the Middlebury database [22]                                  | 94  |

| 4.2        | Normalised power and performance operating points. Traversing between these                                                                                    |     |

|            | performs optimisation or scaling actions                                                                                                                       | 98  |

| 4.3        | Optimised operating points, sampled from Figure 4.18, that minimised power consumption under each performance target                                           | 104 |

| 5.1        | Structure of application and device knobs in the cross-layer framework                                                                                         | 114 |

| 5.2        | Structure of application and device monitors in the cross-layer framework                                                                                      | 115 |

| 5.3        | Complete set of framework API functions                                                                                                                        | 117 |

| 5.4        | Application-level knobs and monitors present in Jacobi (Section 5.4.1.1), video                                                                                |     |

|            | decoder $(5.4.1.2)$ and Whetstone $(5.4.1.3)$                                                                                                                  | 125 |

| 5.5        | Available device-level knob and monitor types                                                                                                                  | 129 |

| 5.6        | Device-level knobs and monitors for Odroid-XU3 (Section 5.4.3.1) and Cyclone V                                                                                 |     |

|            | (5.4.3.2) platforms                                                                                                                                            | 129 |

| 5.7        | Knob and monitor values for Pareto-optimal points of the Odroid platform in Figure 5.10                                                                        | 134 |

| B.1        | Characterisation data for a multi-core platform and multi-threaded application, including the power consumption and performance, in FPS, resulting from a par- |     |

|            | ticular frequency and number of active cores                                                                                                                   | 157 |

| B.2        | Characterisation data continued from Table B.1                                                                                                                 | 158 |

# List of Algorithms

| 3.1 | R code to generate the power and performance models of Figure $3.3a$ and $3.3b$      | 69   |

|-----|--------------------------------------------------------------------------------------|------|

| 3.2 | R code to test the number of training samples required for error convergence. The    |      |

|     | full script can be found in Listing A.2 of Appendix A                                | 70   |

| 4.1 | Block threading approach to throttle parallelism at the disparity level              | 95   |

| 5.1 | API functions required to register an application (presented in Section 5.4.1.1)     |      |

|     | and create application-level knobs and monitors                                      | 116  |

| 5.2 | API functions required to get updated values of application knobs and set updated    |      |

|     | monitor values through the framework                                                 | 118  |

| 5.3 | API functions required to deregister an application and its knobs and monitors       |      |

|     | from the framework                                                                   | 119  |

| 5.4 | API functions for the RTM to register the device and its knobs and monitors          | 119  |

| 5.5 | The RTM pulling monitor values from the device and pushing device knob settings      |      |

|     | through the API                                                                      | 120  |

| 5.6 | Example JSON code for an application knob registration message                       | 122  |

| 5.7 | Discrete knob registration case in the message handler function of the app interface |      |

|     | of the RTM layer                                                                     | 123  |

| 5.8 | Extract from the logger output of an experiment using the framework                  | 132  |

| A.1 | R code for Multiple Linear Regression (MLR) analysis and the plotting of Figure 3.3  | .147 |

| A.2 | R code for MLR error conergence analysis and the plotting of Figure 3.4              | 148  |

| A.3 | Complete R code for gradient decent analysis and the plotting of Figure 3.9 and      |      |

|     | 3.10                                                                                 | 150  |

| A.4 | Python script to plot experimental characterisation data for Figure 3.2, 4.15 and    |      |

|     | 4.16                                                                                 | 153  |

| C.1 | Top-level code for the disparity estimation algorithm                                | 159  |

| C.2 | Power measurement and energy recording code for the Xeon Phi platform                | 162  |

| C.3 | RTM code for modelling and optimisation of the stereo matching application and       |      |

|     | Xeon Phi platform                                                                    | 164  |

| D.1 | Python script to generate power, performance and energy operating points from        |      |

|     | experimental data for Figure 4.13 and 4.14                                           | 169  |

| D.2 | Python script to plot experimental data for the RTM optimisation in response to      |      |

|     | changing performance targets in Figure 4.18                                          | 172  |

| E.1 | V 1                                                                                  | 175  |

| E.2 | Common application types API header                                                  | 175  |

| E.3 | Common device types API header                                                       | 176  |

| E.4 | Application API header, containing the rtm_interface                                 | 177  |

| F.1 | Time series plotting and processing script for standard logger output. Used to       |      |

|     | plot Figure 5.11                                                                     | 181  |

| F.2 | Python class mon_ops used to store and calculate monitor operating points            | 185  |

# List of Acronyms

**2D** Two Dimensional.

**3D** Three Dimensional.

ADSW Adaptive Support Weight.

**ANOVA** Analysis of Variance.

**API** Application Programming Interface.

**CFS** Completely Fair Scheduler.

**CMP** Chip Multiprocessor.

**CPU** Central Processing Unit.

**CVC** Cost Volume Construction.

**CVF** Cost Volume Filtering.

**DCM** Dynamic Core Morphing.

**DCT** Dynamic Concurrency Throttling.

**DE** Disparity Estimation.

**DPM** Dynamic Power Management.

**DS** Disparity Selection.

**DSP** Digital Signal Processor.

**DVFS** Dynamic Voltage and Frequency Scaling.

**EAS** Energy Aware Scheduler.

**FPGA** Field-Programmable Gate Array.

**FPS** Frames Per Second.

**GIF** Guided Image Filtering.

**GLM** Generalized Linear Models.

18 List of Acronyms

**GPU** Graphics Processing Unit.

**HD** High Definition.

**HMP** Heterogeneous Multiprocessor.

**HPC** High Performance Computing.

IO Input/Output.

**IPC** Instructions per Cycle.

**ISA** Instruction Set Architecture.

JSON JavaScript Object Notation.

MIC Many Integrated Core.

ML Machine Learning.

MLR Multiple Linear Regression.

MRPI Memory Reads Per Instruction.

NN Neural Network.

**OLS** Ordinary Least Squares.

OpenCL Open Compute Language.

**OS** Operating System.

**PID** Process Identifier.

**PMC** Performance-monitoring Counter.

**PP** Post Processing.

**pthreads** POSIX threads.

**QoE** Quality of Experience.

**QoS** Quality of Service.

**RMS** Recognition, Mining and Synthesis.

**RTM** Runtime Manager.

**SBC** Single Board Computer.

**SGM** Semi Global Matching.

**SMP** Symmetric Multiprocessor.

**SoC** System on Chip.

**SVC** Support Vector Classification.

List of Acronyms 19

${\bf SVM} \qquad \text{Support Vector Machines}.$

**SVR** Support Vector Regression.

$\mathbf{TDP} \qquad \text{Thermal Design Power.}$

**UDS** Unix Domain Socket.

UI User Interface.

VR Virtual Reality.

## **Declaration of Authorship**

I, Charles Leech, declare that this thesis entitled Runtime Energy Management of Multi-core Processors and the work presented in it are my own and has been generated by me as the result of my own original research.

#### I confirm that:

- 1. This work was done wholly or mainly while in candidature for a research degree at this University;

- 2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- 3. Where I have consulted the published work of others, this is always clearly attributed;

- 4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- 5. I have acknowledged all main sources of help;

- 6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- 7. Parts of this work that have been published are listed under the research contributions.

| Signed: | <br> | <br> | <br> | <br> | • • | <br> | <br>• • | <br> | <br> | <br> | <br> | <br>• • | <br> | <br> | <br> | <br> |

|---------|------|------|------|------|-----|------|---------|------|------|------|------|---------|------|------|------|------|

| Date:   | <br> | <br> | <br> | <br> |     | <br> | <br>    | <br> | <br> | <br> | <br> | <br>    | <br> | <br> | <br> | <br> |

### Acknowledgements

I would firstly like to extend my thanks to my supervisors; principally Professor Bashir M. Al-Hashimi for his guidance and direction throughout my PhD, Dr Geoff V. Merrett for his supervision and advice at many times and Dr Tom J. Kazmierski for providing me with the opportunity to undertake this research. My thanks also go to the Engineering and Physical Sciences Research Council (EPSRC) for funding my work over the course of the PhD.

A great amount of time has been spent in the presence of a unique group of colleagues within and around the PRiME Project, both past and present. Some notable individuals include; Dr Graeme Bragg, Dr Domenico Balsamo, Dr Monica Glanc-Gostkiewicz, Matt Walker, Dr James Davis, Dr Sheng Yang, Dr Josh Levine and many more. It has been fantastic to work with such a charismatic group of people. In addition, I am thankful to all the members of the wider PRiME Project for creating a stimulating environment for ideas and discussion, as well as to all those who contributed to multiple productive collaborations.

Thank you to all my friends who have been around for entertainment, relaxation and plenty of special life events; Alex and Rachel Clayton for being great housemates, good cooks and the best friends; Jon New and Kate Rawlings for the impromptu chats, films and welcome distractions; Matthew Posner and Becky Bellworthy for getting me into cycling, pioneering the best cycling club in town and having great taste in coffee; and Rhys Thomas and Laurie Pestana for their passion for cycling, their warm friendship and all the cafe stops. A few more special mentions to some influential figures in my brief cycling career go to Tj Key and Trevor Allen, for bringing out the competitive side in me and James Robards and Chris Brooks for both having impeccable style. Thank you all for the miles and smiles along the way.

I would like to say a big thank you to my parents; Diana and Roger and my brother James, for shaping my upbringing, making me into who I am today, and providing many welcome escapes.

Finally, the greatest thanks are reserved for my wife, Rachel who has always believed in me and given me her endless love, support and understanding through our life-long journey together.

## Chapter 1

## Introduction

Processors have evolved over the decades due to a complex combination of influences and driving forces. From advancements in fabrication technology and improvements in software capabilities, to the emergence of new computing platforms, next-generation applications and changes in the demands of users.

The development of processor architectures can be characterised into three distinct eras. From the 1970s, a single-threaded era focused on the primary target of improving performance of a single processor, achieved through transistor scaling, improvements in fabrication and increased processor clock speeds. For many years, these techniques maintained the pursuit of Moore's Law and satisfied the demands of applications at the time. Dubbed "the free lunch", these applications benefited from uncompromising improvements in performance and processing speed with each generation of processors [23].

However, with technological advancements pushing to the boundaries of physics, a lack of clock scaling stalled the previously freely-available performance improvements. Subsequently, the second multi-core era exploited advances in fabrication techniques to allow the integration of multiple processors within a single chip. From then on developments in processor technology focused on core scaling as a priority. In reaction, the advent of parallel processing brought about changes throughout the entire software stack, with new programming models and paradigms designed to extract parallelism from applications.

This trend stalled due to an exponential increase in the power density of chip multiprocessors. High power consumption from fast clock rates combined with increasing transistor densities pushed thermal dissipation rates in excess of operating levels. As a result, only portions of a chip could function at any one time, in order to manage thermal levels and prevent damage to circuitry. This phenomenon has been nicknamed *dark silicon*, in a similar manner to the inactivity of dark energy, because the inactive parts of the chip exist but cannot operate due to thermal implications [24].

In the current era of processor development, the electronics industry looks to new innovations to continue delivering improved performance with each generation of devices. The focus now is on

achieving the best balance between energy and performance, a target that is being most successfully achieved through heterogeneous architectures containing asymmetric processors. Heterogeneous multiprocessor architectures have the potential to deliver both speed and energy efficiency through adaptability and targeted execution. With performance asymmetry, a heterogeneous multiprocessor implements a different trade-off between energy efficiency and performance for each processing resource or core. Smaller cores are used to process simple tasks in an energy-efficient way while larger cores provide higher-performance processing for more compute-intensive tasks. The introduction of functional asymmetry further expands the range of compute modes to highly-parallel and custom-accelerator processors. The mix of compute resources now supports a diverse collection of programming models, code structures and application types.

Furthermore, advances in system-on-chip integration and transistor scaling have successfully driven the reduction in size of electronic systems, leading to the emergence of entirely new platforms and environments in mobile and embedded computing. Devices operating in these domains are fundamentally governed by their energy efficiency, which is now considered as a design priory rather than an afterthought or side-affect. Moreover, the performance capability of processors has increased far in excess of the developments in battery capacity. This has led to a large reduction in the usage time for mobile devices from the order of days to hours. In addition, consumers demand an ever-improving user experience, with higher-performance and more graphically-intensive mobile applications, necessitating the use of high frequency multi-core processors to meet tighter performance deadlines. Now the prominent design challenge for these devices has become the development of effective methods for minimising power consumption as the energy efficiency of processors and embedded systems must be maximised in order to maintain battery life.

The increase in performance capability of mobile devices, due to heterogeneous multiprocessor architectures, has opened up this sector to applications that require the variety of processing resources available to compute tasks. The array of technological features and sensors now embedded on these devices allows them to deliver a rich and immersive experience that is interactive and connected to the user. A notable example is Virtual Reality (VR) where the user experiences a simulated environment different from that of their current surroundings. Primarily used as an entertainment experience, for example, to complete puzzles or play games. The experience requires a user to wear a headset projecting 3D visuals and headphones providing surroundsound. Accelerometer-based motion sensors in the headset track movement of the head in all directions and update the display and sound perspective to match. For this application, highlyeffective real-time processing is required to deliver an adequate Quality of Experience (QoE) to the user. Otherwise, any lag in the display or sound will render the entire experience invalid as the conflicting sensual environment is unpleasant for the user. Moreover, as a mobile device, that must be ergonomic and lightweight, a constraint is placed on the power consumption and form factor of the embedded electronics. These factors combine to require a system that is highly-electronically advanced, involving high-speed sensing, complex interpretation and High Definition (HD) video streaming, but must also be lightweight, comfortable and energy efficient, presenting a significant engineering challenge.

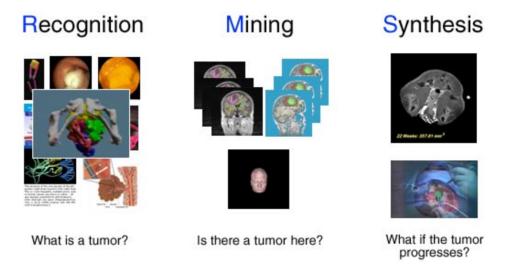

With the development of heterogeneous architectures comes the need to identify and characterise the properties of applications, in order to most effectively execute them across the multitude of specialised resources. Intel's Recognition, Mining and Synthesis (RMS) and the Berkeley Motifs are two prominent taxonomies that have emerged to meet this need, with differing approaches that are explored in more detail in Section 2.3. The taxonomies provide a framework for characterisation so that the constituent elements of applications such as computer vision and data analytics can be identified and consolidated.

To ensure that characterised applications execute on the necessary processing resources, given the asymmetry in heterogeneous architectures, runtime management software is an essential component in the system stack. The Runtime Manager (RTM) is responsible for ensuring that the performance requirements of all the applications executing on the platform are met, whilst minimising physical quantities of the platform such as energy consumption or temperature. The degree to which the RTM achieves the balance between these orthogonal objectives is known as the Quality of Service (QoS) delivered.

Runtime management can be achieved by any process that controls and adapts the behaviour of a platform and/or application during execution. Approaches can be classified using the mathematical techniques that they use, from closed-loop control to machine learning, or the power management technologies that they control, including frequency scaling and task allocation. RTM approaches that have been implemented in the literature are presented and evaluated in Section 2.4, with a focus on machine learning methods, which show greatest suitability to this task due to their high accuracy and adaptability.

Balancing accuracy with adaptability is an important consideration when developing a runtime management approach, due to the wide range of heterogeneous platforms and applications. For any approach to be suitable for the mobile and embedded domains it must be able to adapt to changes in application requirements as well as operate with unknown applications and platforms. Learning at runtime is therefore essential under these circumstances.

A cross-layer framework is proposed in this thesis to support runtime learning and promote properties such as adaptability, application-agnosticism and ensure that runtime software is cross-platform. Platform and application hooks that control tunable parameters are captured as generic constructs called *knobs* and important performance metrics or physical quantities are captured as *monitors*. Monitors allow observation and learning of system behaviour, to ensure that performance requirements are met and energy is optimised. Knobs enable the RTM to be adaptive and control both the platform and applications in an agnostic manner. An Application Programming Interface (API) is defined as a specification of the concepts encompassed by the framework. This can be used by application, RTM and platform developers so that their components may be used in any circumstance.

The challenges associated with developing a runtime energy management approach, optimising complex applications and formulating a framework for runtime management are discussed in the following section.

## 1.1 Research Challenges

The energy consumption optimisation of multi-core systems at runtime is an established area of research, with Dynamic Power Management (DPM) technologies being implemented in many

mobile and embedded devices. These approaches can respond to fluctuations in the load of the system, however they are limited in that they possess no predictive capabilities. This is a requirement in order to manage energy and performance trade-offs due to the fact that knowledge of the potential operating space is necessary, *i.e.* what energy savings exist and how to achieve them. Modelling energy-performance trade-offs in multi-core systems at runtime is therefore necessary in order to identify optimisation opportunities. Moreover, the continuous optimisation and prediction of energy consumption becomes increasingly difficult in the presence of dynamic application requirements, behaviour that is common in mobile and embedded workloads.

Furthermore, the majority of runtime management approaches are specific to a single, group or domain of applications and/or devices, which limits their applicability in the general case. In order to generalise these approaches, an environment must be established where the mechanisms for runtime management are exposed in a standardised way. However, this environment must still meet the prerequisite that the runtime management approach remains able to operate as effectively as it did in the specific case.

### 1.2 Research Questions

To overcome the challenges outlined, the need for runtime energy management in multi-core systems is evident and motivates this research to address the following questions:

- 1. How can a multi-core system be modelled at runtime to optimise energy efficiency and performance requirements?

- 2. What are the potential energy and performance trade-offs when applying runtime energy management to next-generation mobile and embedded applications?

- 3. How can the runtime management of energy and performance be made more cross-platform and application-agnostic? How can this be extended to the management of other properties?

### 1.3 Research Contributions

In seeking to address the research questions posed, this thesis makes several contributions to the research in this area.

1. The development and validation of a modelling approach, based on MLR, that can be trained at runtime using a minimum number of samples to predict the power and performance of a multi-core system and multi-threaded application. This is coupled with a runtime optimisation method based on gradient descent to optimise platform and application settings under a performance target. This contribution has been published in ACM TECS as Leech et al. [25]

- 2. Deployment of the runtime management approach to optimise the execution of a multi-threaded implementation of the disparity estimation algorithm for stereo matching, including characterisation of the operating space of the application on a multi-core platform with scaling and trade-off analysis. Moreover, runtime modelling and optimisation of the application is carried out in response to specified performance targets. This contribution has also been published in ACM TECS as Leech et al. [25]

- 3. The creation of a cross-layer framework for application- and platform-agnostic runtime management. Specification of an API for cross-layer communication of information through knobs and monitors exposed by applications and platforms. The realisation of a software implementation of the framework including experimentation tools and data analysis methods. The validation of the framework with three applications, two RTMs and two heterogeneous multi-core platforms.

The work presented in this thesis is aligned with the objectives of the PRiME Project (Power-efficient, Reliable, Many-core Embedded systems), with which the author is a member. The PRiME Project is an EPSRC funded research programme developing the theory and practices for future high-performance embedded systems utilising many-core processors. PRiME's objective is to enable processor core scaling with sustainable energy consumption and reliability.

This thesis has addressed aspects of these objectives through the runtime energy management approach that is present in Chapter 3. The application presented in Chapter 4 and the platforms in Chapter 5 are examples of next-generation applications and high-performance embedded systems, for which new optimisation practices have been developed. Due to the collaborative nature of the project, some of the contributions stated were made as part of team projects. The development of the cross-layer framework was a collaborative effort with researchers from within the project at both the University of Southampton and Imperial College London. As a result, the author was at least significantly involved in the work for any contributions stated. In addition, it is possible that the code shown in some listing was not written wholly by the author, as this is the nature of collaborative software development, however it is required in order to ensure the clarity of the listing. A detailed breakdown of the contributions made by the author to the development of the framework is given in the introduction to Chapter 5.

#### 1.3.1 Software Contributions

Two significant software contributions have been made during the course of the PhD and are described here.

**PRIMEStereoMatch:** The stereo matching application, containing the disparity estimation algorithm, was developed to perform the experimentation presented in Chapter 4. This was extended during the course of the project into a significant software program. To enable others to use this software and provide a contribution to the research community, the application has been made publicly available under an open-source license through a GitHub repository. This can be accessed at the address: https://github.com/PRiME-project/PRiMEStereoMatch

**PRIME\_Framework:** The software implementation of the cross-layer framework, which was used to perform the experimentation in Chapter 5, has also been made publicly available under

an open-source license in the same manner. One of the fundamental purposes of the framework is to encourage research into runtime management to be conducted in an application- and platform-agnostic environment that enables the comparison and evaluation of the effectiveness of different approaches. The framework also represents a research enablement tool, allowing researchers to focus on solving runtime management challenges by separating the development process into layers, connected using the API. The project is released as the PRiME Framework as is it a collaborative project within the PRiME Project. The framework can be accessed at the address: https://github.com/PRiME-project/PRiME\_Framework

### 1.3.2 Publications

The contributions of the research presented in this thesis have also been published as follows:

- Leech, Charles, Vala, Charan Kumar, Acharyya, Amit, Yang, Sheng, Merrett, Geoff V. and Al-Hashimi, Bashir (2017) Run-time performance and power optimization of parallel disparity estimation on many-core platforms *ACM Transactions on Embedded Computing Systems* [25]

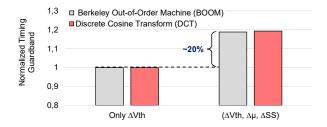

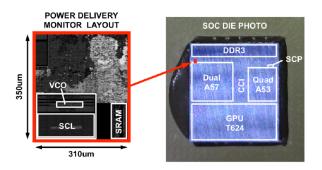

- Tenentes, Vasileios, Leech, Charles, Bragg, Graeme, Merrett, Geoff V., Al-Hashimi, Bashir, Amrouch, Hussam, Henkel, Jörg and Das, Shidhartha (2017) Hardware and software innovations in energy-efficient system-reliability monitoring In *IEEE International Symposium* on Defect and Fault Tolerance in VLSI and Nanotechnology Systems. IEEE. 5 pp. [26]

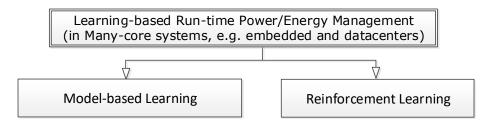

- Singh, Amit, Leech, Charles, Basireddy, Karunakar Reddy, Al-Hashimi, Bashir and Merrett, Geoff V. (2017) Learning-based run-time power and energy management of multi/many-core systems: current and future trends *Journal of Low Power Electronics* [27]

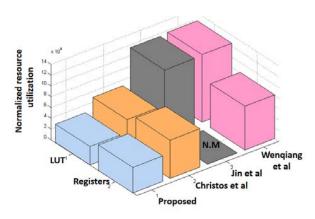

- Vala, Charan Kumar, Immadisetty, Koushik, Acharyya, Amit, Leech, Charles, Balagopal, Vibishna, Merrett, Geoff V. and Al-Hashimi, Bashir (2017) High-speed low-complexity guided image filtering-based disparity estimation IEEE Transactions on Circuits and Systems I: Regular Papers. [28]

- Leech, Charles and Kazmierski, T J (2014) Energy Efficient Multi-Core Processing ELEC-TRONICS, 18, (1), pp. 3-10. [29]

- Leech, Charles, Bragg, Graeme, Davis, James, Constantinides, George, Merrett, Geoff V. and Al-Hashimi, Bashir (2018) The PRiME Framework: Application- and Platformagnostic Runtime Management Transactions on Computer-Aided Design of Integrated Circuits and Systems (Under Review)

The following publications were also made during the course of the PhD, but are not directly reported as contributions in this thesis:

• Leech, Charles, Raykov, Yordan P., Ozer, Emre and Merrett, Geoff V. (2017) Real-time room occupancy estimation with Bayesian machine learning using a single PIR sensor and microcontroller At *IEEE Sensors Applications Symposium (SAS)*, Glassboro, NJ, 2017, pp. [30]

### 1.4 Thesis Structure

The thesis is structured as follows. Chapter 2 presents a review of research into hardware and software innovations around homogeneous and heterogeneous multiprocessor systems. Furthermore, it explores emerging applications and methods to support their implementation on these platforms. The chapter presents model-based machine learning approaches and their applicability to the runtime energy management of multi-core systems. In addition, the chapter looks beyond these to runtime management frameworks, which aim to provide a common approach to runtime management. The chapter concludes with information on the platforms used for experimentation in chapters 3 to 5.

Chapter 3 presents an MLR model-based runtime management approach applicable to multicore systems. The effectiveness of the model is validated empirically and a gradient-descent optimisation approach is proposed to utilise the model at runtime and select optimal operating settings.

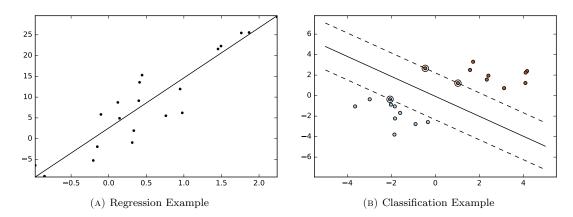

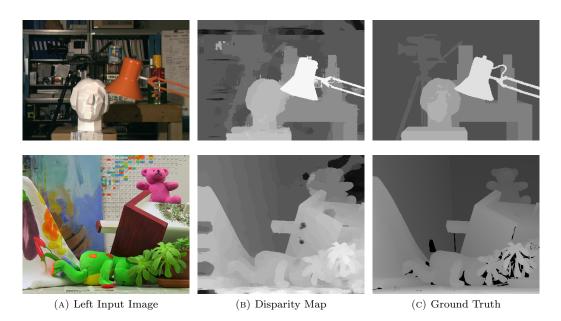

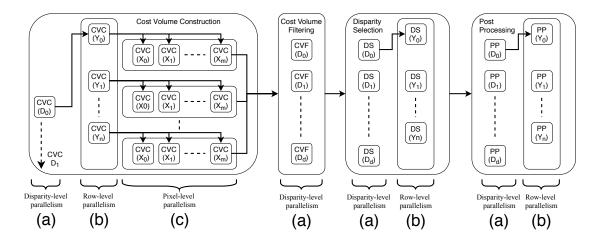

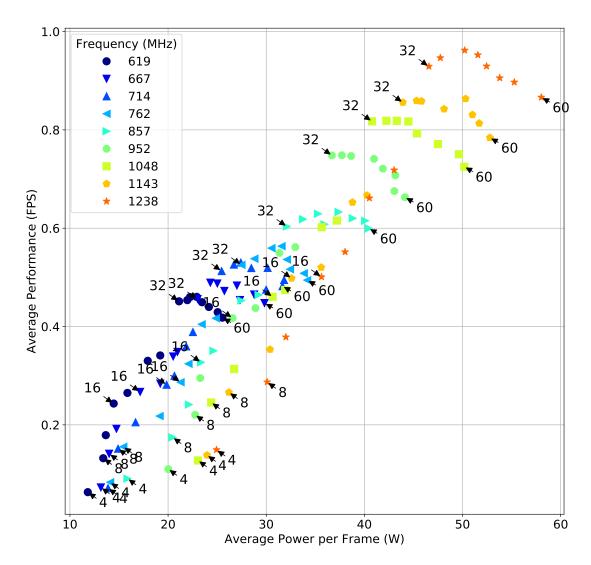

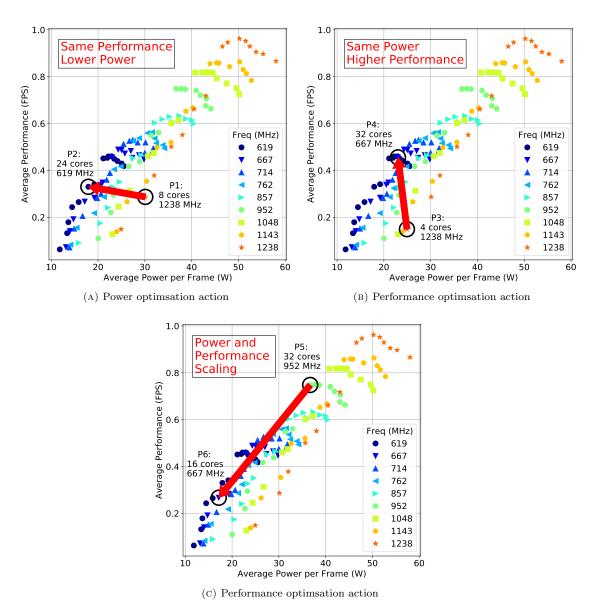

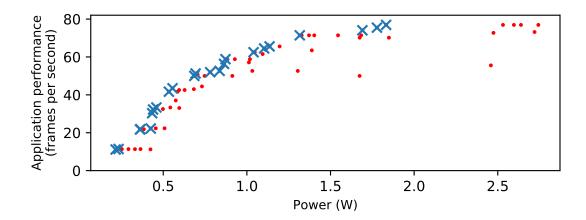

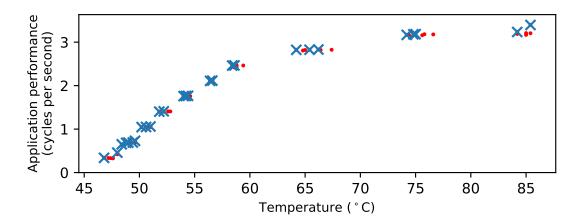

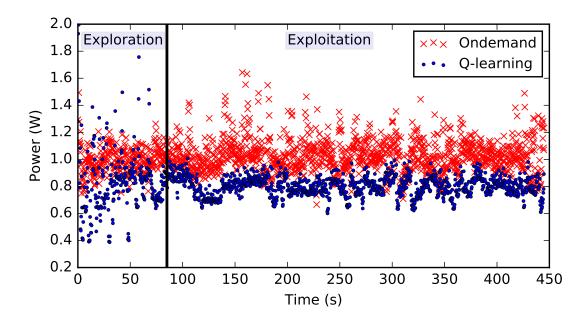

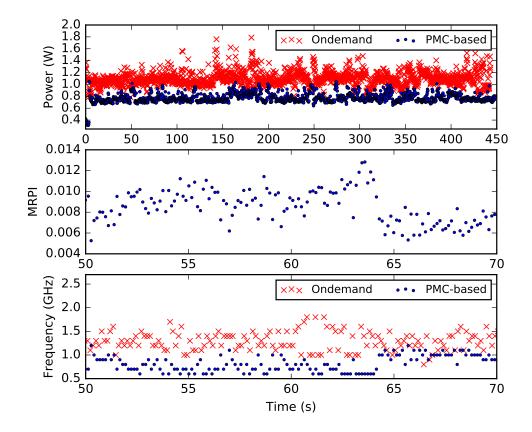

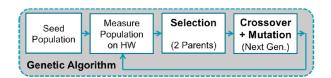

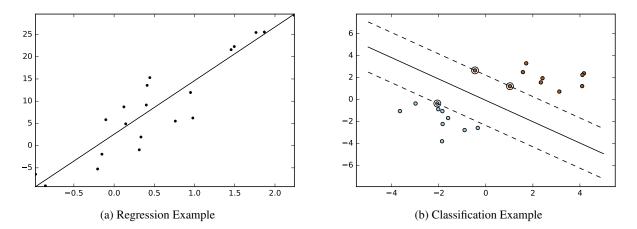

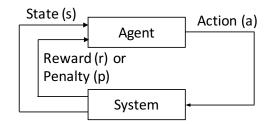

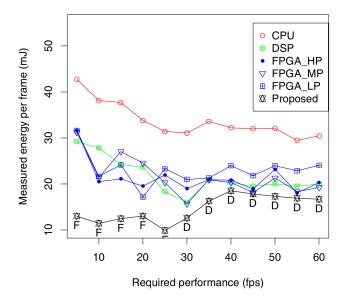

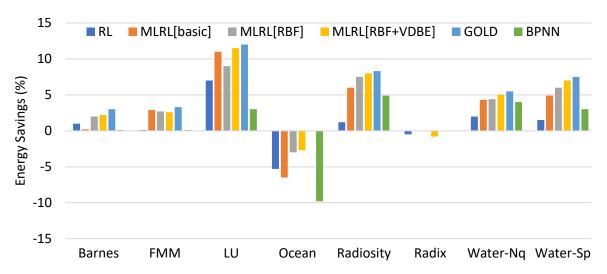

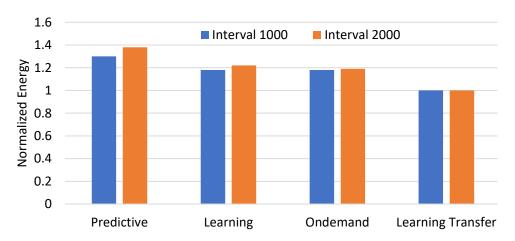

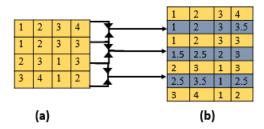

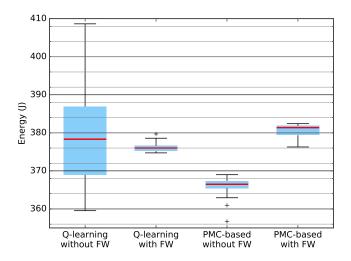

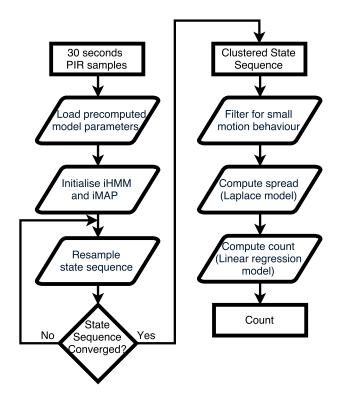

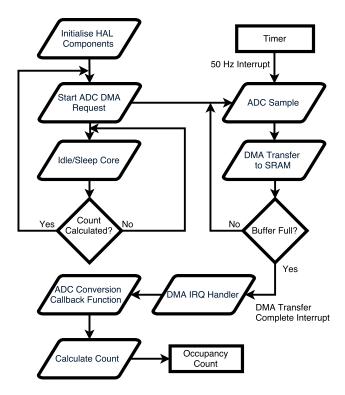

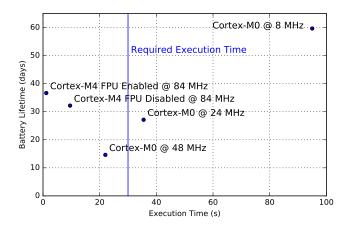

Leading on from this, Chapter 4 documents the development of a stereo matching application, based on the disparity estimation algorithm, for depth calculation using a stereoscopic camera. The objective is to develop a scalable application that is amenable to runtime management on multi-core platforms, to deliver both energy-efficient and high-performance operation. This chapter covers exploration of the application's operating space on a homogeneous many-core platform, which motivates the need for runtime management. Runtime modelling and adaptation is demonstrated using the approach developed in the previous chapter.