Back-end-of-line a-SiO<sub>x</sub>C<sub>v</sub>:H dielectrics for resistive memory

J. Fan, <sup>1,a)</sup> O. Kapur, <sup>2</sup> R. Huang, <sup>2</sup> S.W. King, <sup>3</sup> C.H. de Groot, <sup>2</sup> L. Jiang <sup>1</sup>

<sup>1</sup>School of Engineering, <sup>2</sup>School of Electronics and Computer Science, Faculty of Engineering and Physical

Sciences, University of Southampton, Southampton, SO17 1BJ, United Kingdom

<sup>3</sup>Logic Technology Development, Intel Corporation, Hillsboro, OR 97124, USA

**Abstract**

Resistive switching of W/amorphous (a)-SiO<sub>x</sub>C<sub>y</sub>:H/Cu resistive memories incorporating solely native back-end-

of-line (BEOL) materials were studied. A-SiC<sub>1.1</sub>:H, a-SiO<sub>0.9</sub>C<sub>0.7</sub>:H, and a-SiO<sub>1.5</sub>C<sub>0.2</sub>:H were exploited as switching

layers for resistive memories which all show resistive-switching characteristics with ultrahigh ON/OFF ratios in

the range of 10<sup>6</sup> to 10<sup>10</sup>. Ohmic conduction in the low resistance state is attributed to the formation of Cu

conductive filament inside the a-SiO<sub>x</sub>C<sub>y</sub>:H switching layer. Rupture of the conductive filament leads to current

conduction dominated by Schottky emission through a-SiO<sub>x</sub>C<sub>v</sub>:H Schottky contacts. Comparison of the switching

characteristics suggests composition of the a-SiO<sub>x</sub>C<sub>y</sub>:H has influences on V<sub>FORM</sub> and V<sub>SET</sub>, and current conduction

mechanisms. These results demonstrate the capability to achieve functional W/a-SiO<sub>x</sub>C<sub>v</sub>:H/Cu using entirely

BEOL native materials for future embedded resistive memories.

Introduction

Conductive bridge resistive memories (RMs) have attracted great research interest for next-generation non-

volatile memories due to potentials for down-scaling<sup>1</sup> and superior switching performance<sup>2</sup> as well as

compatibility with CMOS back-end-of-line (BEOL) processes<sup>3</sup>. RMs have a Metal-Insulator-Metal (MIM)

structure where an insulator switching layer is sandwiched between two metal layers acting as an active and an

inert electrode, respectively. It was reported that the formation and disruption of nanometer-scale metal filaments<sup>4</sup>.

<sup>5</sup> in the switching layer lead to the low resistance state (LRS) and high resistance state (HRS), respectively. Many

metal materials have been exploited for electrodes including Cu<sup>6</sup> and W<sup>7</sup>. Cu and W are advantageous due to their

widespread use in BEOL interconnects3. By also including native BEOL dielectrics such as a-SiOC:H as the

middle insulator switching layer, it is possible to fabricate RMs that could be integrated into the BEOL

interconnects with the advantages of being low cost and easy implementation<sup>8</sup>. These RM memory cells could be

potentially positioned on top of transistors based control or logic layers and thus help shorten the interconnect

delay, and at the same time could also help to achieve the 3D stacked configuration for high memory capacity<sup>9</sup>.

a)Email: jf3g12@soton.ac.uk

Amorphous (a)-SiC based dielectrics have attracted significant interest because of their recent success in BEOL applications  $^{10,11}$  due to their low dielectric constant (k) as compared to conventional SiO<sub>2</sub> and SiN<sup>12</sup>. In particular, a-SiOC:H with k values of 3.1-4.8 has replaced SiO<sub>2</sub> (k≈4-4.2) as the typical interlayer dielectric and also shown promise to replace a-SiN:H (k≈6.5-7.0) in etch stop and Cu diffusion barrier applications  $^{12}$ . Excellent endurance of RMs using a-SiC as the switching layer has been reported  $^{13}$ . Our previous studies  $^{14-16}$  also led to a-SiC based RMs with ultrahigh ON/OFF ratios of up to  $^{10}$ 9. Ultrahigh ON/OFF ratios present great advantages in future applications as it not only enables fast and reliable detection of the states of memory cells, simplifies the periphery circuit to distinguish the storage information  $^{14, 15}$ , but also provide a promising chance to achieve multilevel storage, e.g. five stable states in  $^{106}$  ON/OFF ratios was reported  $^{17}$ . However, there is little study on RMs using native BEOL a-SiO<sub>x</sub>C<sub>y</sub>:H dielectrics as switching layers. Fan et al.  $^8$  reported preliminary work of RMs using porous a-SiOC:H. However, low yield and high switching currents, i.e. in mA range, and also relatively low ON/OFF ratio were reported. There are no comprehensive studies on RMs incorporating BEOL dielectrics a-SiO<sub>x</sub>C<sub>y</sub>:H with different compositions. It is envisaged that different compositions may affect the k-values and Schottky barrier height (SBH) at the metal/dielectric interface, all of which may play an important role in the RM performance.

In this paper, we report RMs incorporating native BEOL dielectrics, i.e.  $a\text{-SiO}_xC_y$ :H as switching layers, Cu as active electrodes and W as inert electrodes, thus fully compatible with potential BEOL processes. Three compositions of  $a\text{-SiO}_xC_y$ :H, i.e.  $a\text{-SiC}_{1.1}$ :H,  $a\text{-SiO}_{0.9}C_{0.7}$ :H, and  $a\text{-SiO}_{1.5}C_{0.2}$ :H were studied. Material characterisations to determine compositions, k values, and SBHs of the corresponding metal/dielectric interfaces were conducted. Subsequently, W/a-SiO<sub>x</sub>C<sub>y</sub>:H/Cu RMs were fabricated, and typical switching characteristics were studied and compared as a function of the composition.

# **Experiment**

The a-SiO<sub>x</sub>C<sub>y</sub>:H thin films were deposited on 300 mm diameter substrates using standard BEOL processes. The bottom Si (001) wafers were initially coated with 100 nm thermal oxide (SiO<sub>2</sub>), followed by 100 nm SiN, a thin TaN/Ta adhesion layer, and finally, an electroplated Cu layer chemically mechanically polished to a final thickness of 300 nm.<sup>10</sup> The Cu layers were embedded here with an intention to be used later on as active electrodes in the a-SiO<sub>x</sub>C<sub>y</sub>:H RMs. The a-SiO<sub>x</sub>C<sub>y</sub>:H layers with thicknesses of 20 nm and 40 nm, respectively were deposited on top of the Cu layer using Plasma enhanced chemical vapor deposition (PECVD). Different compositions were achieved by adjusting the organosilicon/oxidizer and reactant diluent ratios, deposition pressure, and radio

frequency power<sup>18</sup>, as details described in previous publications<sup>10, 11</sup>. Thus, the final stacked layers were a- $SiO_xC_v$ :H/Cu/Ta/TaN/SiN/SiO<sub>2</sub>/Si.

X-ray photoelectron spectroscopy (XPS) measurement was performed on a-SiO<sub>x</sub>C<sub>y</sub>:H films using a Theta probe in order to determine relative atomic% (at%) of the Si, C, and O elements in a-SiO<sub>x</sub>C<sub>y</sub>:H, whereby x and y are the at% ratio of O/Si and C/Si, respectively. A 40 s surface sputtering was performed before XPS measurements to remove any possible native oxide or contaminations. The mass density of the a-SiO<sub>x</sub>C<sub>y</sub>:H films was determined from a previous work using X-ray reflectivity measurements on the same films<sup>19</sup>. Terminal hydrogen groups were intentionally incorporated during film deposition to introduce controlled levels of nano-porosity<sup>12</sup>, while this work focuses on the effect of the different compositions of O and C across the three typical BEOL materials. Porosity analysis based on ellipsometric porosimetry measurements<sup>20</sup> and Positronium annihilation lifetime spectroscopy (PALS)<sup>19</sup> have also been included here to assist material characterisation.

To fabricate W/a-SiO<sub>x</sub>C<sub>y</sub>:H/Cu resistive memories, photolithography process was conducted to pattern photoresist on the substrates, followed by W metal deposition and subsequent lift-off. This process led to W/a-SiO<sub>x</sub>C<sub>y</sub>:H/Cu resistive memories with a range of device areas from 20  $\mu$ m × 20  $\mu$ m to 100  $\mu$ m × 100  $\mu$ m. Cu contact windows were exposed on the side of each device chip by scratching-off the top a-SiO<sub>x</sub>C<sub>y</sub>:H layer using a razor blade. Before any switching studies, the capacitance of the original W/a-SiO<sub>x</sub>C<sub>y</sub>:H/Cu stacking structure was measured using an Agilent 4279 C-V meter at 1 MHz. The k values of corresponding a-SiO<sub>x</sub>C<sub>y</sub>:H materials was then calculated from the capacitance with known device areas and insulator thicknesses<sup>21</sup>. The current-voltage (I-V) characteristics of the a-SiO<sub>x</sub>C<sub>y</sub>:H RMs were measured using an Agilent 4155C parameter analyser and a Cascade REL-3200 probe station. In all the I-V measurements, +/-V was applied to the W electrodes while the Cu electrodes have always been grounded. Since Cu was acting as the active electrode, for clarity and ease of understanding, all the I-V plots in this paper were plotted with +V applied to Cu during SET and -V applied to Cu during RESET. A 5 mV/50 ms voltage ramping rate was applied for all the switching measurements in this paper.

## Results and discussion

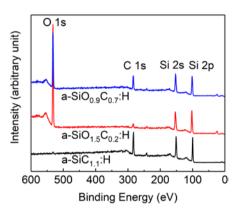

XPS survey spectra of a-SiO<sub>x</sub>C<sub>y</sub>:H in Figure 1 show Si 2p, C 1s, and O 1s peaks at approximately 101 eV, 283 eV, and 532 eV, respectively, aligning with Si-C, C-Si, and Si-O bonding.<sup>22</sup> Relative at% of Si, C, and O elements were estimated using the areas of the Si 2p, C 1s, and O 1s peaks and sensitivity factors of 0.27, 0.25, and 0.66,

respectively.<sup>23</sup> Three compositions were thus determined as a-SiC<sub>1.1</sub>:H, a-SiO<sub>0.9</sub>C<sub>0.7</sub>:H, and a-SiO<sub>1.5</sub>C<sub>0.2</sub>:H, corresponding to 0 at%, 35 at% and 55 at%. Previous work on these a-SiO<sub>x</sub>C<sub>y</sub>:H films<sup>19</sup> reported higher mass densities of 2-2.4 g/cm<sup>3</sup> as compared with 0.7-1.3 g/cm<sup>3</sup> of porous a-SiO<sub>x</sub>C<sub>y</sub>:H<sup>24</sup>. Furthermore, ellipsometry and PALS have also confirmed there is no inter-connected porosity in these a-SiO<sub>x</sub>C<sub>y</sub>:H films.

FIG. 1. XPS survey spectra of a-SiO<sub>x</sub>C<sub>v</sub>:H films.

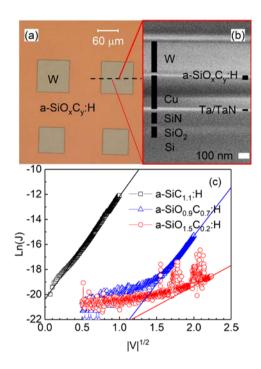

Figure 2 shows a top view (FIG. 2a) and a Scanning electron microscope (SEM) cross-section image (FIG. 2b) of W/a-SiO<sub>x</sub>C<sub>y</sub>:H/Cu RM devices with stacking layers. K values of 5.2, 4.4, 4.3 for a-SiC<sub>1.1</sub>:H, a-SiO<sub>0.9</sub>C<sub>0.7</sub>:H, and a-SiO<sub>1.5</sub>C<sub>0.2</sub>:H, respectively were obtained from capacitance measurements of pristine W/a-SiO<sub>x</sub>C<sub>y</sub>:H/Cu devices, which align with the range of 4.1-6.9 reported for non-porous a-SiO<sub>x</sub>C<sub>y</sub>:H materials<sup>19</sup>. Moreover, the decrease of k with the decrease of C content is consistent with the reported trend<sup>25</sup> as more Si-C bonds are likely to be replaced with Si-O bonds.<sup>19</sup> Figure 2(c) shows the current density (J) as a function of  $|V|^{1/2}$  obtained from pristine W/a-SiO<sub>x</sub>C<sub>y</sub>:H/Cu devices. The linear fits suggest possible Schottky emission conduction mechanisms in the specific fitting range which follows:<sup>26</sup>

$$J = I/A = A^*T^2 \exp(\frac{-q\Phi_B}{kT} + \frac{q}{kT} \sqrt{\frac{qE}{4\pi\varepsilon}}),\tag{1}$$

where A is the device area,  $A^*$  is the Richardson constant, T is the temperature,  $\Phi_B$  is the SBH, E is the electric field, k is the Boltzmann constant, and  $\varepsilon$  is permittivity of the dielectric layer. It is worth noting that symmetrical J-V characteristics were observed across –V and +V regions (not shown here). This may be due to the existence of Fermi level pinning effect which can play a dominating role in SBHs<sup>21</sup>. Thus,  $\Phi_B$  can be estimated from these linear fits to be 0.94 eV, 1.21 eV, and 1.09 eV for pristine a-SiC<sub>1.1</sub>:H, a-SiO<sub>0.9</sub>C<sub>0.7</sub>:H, and a-SiO<sub>1.5</sub>C<sub>0.2</sub>:H respectively. The slightly higher  $\Phi_B$  for a-SiO<sub>0.9</sub>C<sub>0.7</sub>:H and a-SiO<sub>1.5</sub>C<sub>0.2</sub>:H as compared with that of a-SiC<sub>1.1</sub>:H may be attributable to relatively higher C at% in a-SiC<sub>1.1</sub>:H which may promote electronic states into the band

gap of the a-SiOC:H, reducing  $\Phi_B^{-11}$ . It is worth noting that these SBHs are lower than previous reported SBHs (1.45-1.65 eV) estimated from XPS measurements<sup>10,11</sup>. This may be due to XPS being more sensitive to the energy gap between the dielectric conduction band edge (E<sub>C</sub>) and the metal Fermi level (E<sub>f</sub>), whereas the electrical SBH measurement is more sensitive to defects and traps within the bandgaps, leading to reduced SBH.<sup>27</sup> All key material characteristics are summarized in Table I.

FIG. 2. (a) Top-view image and (b) SEM cross-section image of W/a-SiO<sub>x</sub>C<sub>y</sub>:H/Cu RMs. (c)  $Ln(J)-|V|^{1/2}$  curves of pristine W/a-SiO<sub>x</sub>C<sub>y</sub>:H (20 nm)/Cu RMs, with respective linear fits.

TABLE I. Key material characteristics of a-SiO<sub>x</sub>C<sub>y</sub>:H.

| Switching layer                          | Mass density (g/cm <sup>3</sup> ) | k           | SBH (eV) |

|------------------------------------------|-----------------------------------|-------------|----------|

| a-SiC <sub>1.1</sub> :H                  | 2                                 | 5.2±0.1     | 0.94     |

| $a-SiO_{0.9}C_{0.7}:H$                   | 2                                 | $4.4\pm0.2$ | 1.21     |

| a-SiO <sub>1.5</sub> C <sub>0.2</sub> :H | 2.4                               | $4.3\pm0.2$ | 1.09     |

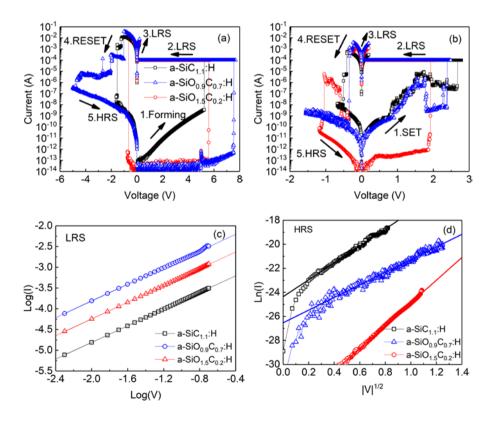

Figure 3 shows the typical forming (i.e. the first) and subsequent switching cycles of W/a-SiO<sub>x</sub>C<sub>y</sub>:H/Cu RMs with the voltage sweep sequence indicated by the arrows, respectively. All the switching cycles start at the high resistance state (HRS). The resistance of the devices at HRS is noted as  $R_{OFF}$  and was measured at 0.1 V. An applied +V sweep can induce a sharp transition from HRS to low resistance state (LRS) at the  $V_{FORM}$  (for the first cycle in FIG. 3a) and  $V_{SET}$  (for subsequent cycles in FIG. 3b), respectively. Subsequently, an applied -V sweep

induces a sharp transition from LRS to HRS at  $V_{RESET}$ . We believe the resistive-switching observed in Figure 3 is likely due to formation and rupture of Cu filaments in the a-SiO<sub>x</sub>C<sub>y</sub>:H dielectric layer. This is because we observed lower  $V_{FORM}$  in the +V regime than  $V_{FORM}$  in the -V regime (not shown here), which may correspond to formation of Cu and W filaments, respectively, when applying different  $V_{FORM}$  polarities. This is different from switching behaviour observed in  $SiO_x^{28-33}$  based RMs whereby symmetrical  $V_{FORM}$  was mostly reported, supporting intrinsically filament mechanism. Linear fits in I-V characteristics as shown in Figure 3(c) provide further support to this with details discussed below.

Higher  $V_{FORM}$  (4.2-7.4V) as compared with  $V_{SET}$  (2.2-4.2V) is observed which has been frequently reported for RMs due to the initial formation of the metal filament in the pristine device. <sup>1, 16</sup> During the forming and SET processes, a 100  $\mu$ A current compliance was adopted to avoid permanent dielectric breakdown of the device. The resistance of the devices at LRS is noted as  $R_{ON}$  and was measured at 0.1 V. All RMs have shown ultrahigh ON/OFF current ratio (equivalent to  $R_{OFF}/R_{ON}$  at 0.1 V) in the range of  $10^6$  to  $10^{10}$ , which demonstrate significant improvement as compared with the reported ratio of  $10^3$  in literatures<sup>8</sup>. All key switching characteristics are summarized in Table II.

FIG. 3. I-V characteristics of the (a) first forming and (b) subsequent switching cycles of W/a-SiO<sub>x</sub>C<sub>y</sub>:H/Cu RMs. The labelled arrows indicate the direction and sequence of I-V sweeps. Forming, SET, RESET and corresponding

LRS, HRS are also labelled. (c) Log(I)-Log(V) curves for LRS obtained from W/a-SiO<sub>x</sub>C<sub>y</sub>:H/Cu RMs, with respective linear fits. (d) Ln(I)- $\sqrt{V}$  curves for HRS obtained from W/a-SiO<sub>x</sub>C<sub>y</sub>:H/Cu RMs, with respective linear fits.

It is worth noting that our  $V_{FORM}$  values (4.2-7.4V) are generally higher than those reported (1-2 V) from RMs using porous a-SiOC:H<sup>8</sup>. This is likely due to the existence of interconnected pores in porous a-SiOC:H (1.2 g/cm<sup>3</sup>) which require lower diffusion energy for Cu ions as compared with denser (2-2.4 g/cm<sup>3</sup>) a-SiO<sub>x</sub>C<sub>y</sub>:H dielectrics used in this study. It has also been reported the activation energy of Cu diffusion in dense dielectrics is inversely proportional to their dielectric properties<sup>34</sup>. Therefore,  $V_{FORM}$  and  $V_{SET}$  (Table II) obtained from RMs having a-SiO<sub>0.9</sub>C<sub>0.7</sub>:H and a-SiO<sub>1.5</sub>C<sub>0.2</sub>:H with lower k values (Table I) are generally higher than those from W/a-SiC<sub>1.1</sub>:H/Cu RMs. No clear dependence of  $V_{RESET}$  on the composition of a-SiO<sub>x</sub>C<sub>y</sub>:H is identified.

TABLE II. V<sub>FORM</sub>, V<sub>SET</sub>, V<sub>RESET</sub>, and ON/OFF ratio of W/a-SiO<sub>x</sub>C<sub>v</sub>:H/Cu RMs.

| Switching layer         | $V_{FORM}(V)$ | $V_{SET}(V)$  | V <sub>RESET</sub> (V) | ON/OFF ratio         |

|-------------------------|---------------|---------------|------------------------|----------------------|

| a-SiC <sub>1.1</sub> :H | $4.2\pm1.7$   | $2.2 \pm 1.5$ | -2.0±1.1               | $6.0 \times 10^{6}$  |

| $a-SiO_{0.9}C_{0.7}:H$  | $7.4 \pm 2.1$ | $4.2\pm2.6$   | $-1.7 \pm 1.1$         | $8.5 \times 10^{7}$  |

| $a-SiO_{1.5}C_{0.2}:H$  | $6.5 \pm 3.4$ | $3.5\pm2.6$   | $-1.3\pm0.8$           | $3.0 \times 10^{10}$ |

Figure 3(c) shows detailed I-V characteristics for LRS in a double logarithmic plot for the RMs. The slopes of the linear fits are all close to 1, indicating Ohmic conduction which attributes to the conduction through Cu filaments.

14. The formation process of the Cu conductive filaments can be explained as when Cu active electrode is subject to a positive electric field (i.e. +V applied on Cu), Cu atoms from the Cu electrode oxidize into Cu cations and drift toward the negatively charged W electrode. The Cu cations inside the a-SiO<sub>x</sub>C<sub>y</sub>:H layer then reduce back to Cu atoms and these Cu atoms inside the a-SiO<sub>x</sub>C<sub>y</sub>:H layer then accumulate and form Cu conductive filament.

Figure 3(d) shows the HRS Ln(I) vs |V|<sup>1/2</sup> of a-SiO<sub>x</sub>C<sub>y</sub>:H RMs, which follow Schottky emission conduction mechanism aligning with Equation (1). The RESET mechanism has been reported as the disruption of the Cu filaments in the switching layer upon application of –V at active (i.e. Cu) electrodes. The negative electric field induces oxidation process for Cu atoms to transform into Cu cations, which subsequently drift back toward the Cu electrode<sup>1, 16</sup>. This could form an interface between the metal filament and a-SiO<sub>x</sub>C<sub>y</sub>:H at the HRS. This interface is different from the interface configuration between a-SiO<sub>x</sub>C<sub>y</sub>:H and metal electrodes as in the pristine state.

14 The SBH at the HRS were calculated based on the linear fits in Figure 3(d) and 0.78 eV, 0.84 eV, and 1.05 eV are obtained for RMs incorporating a-SiC<sub>1,1</sub>:H, a-SiO<sub>0,9</sub>C<sub>0,7</sub>:H, and a-SiO<sub>1,5</sub>C<sub>0,2</sub>:H, respectively. These SBHs

in the HRS are lower than those of the pristine devices as shown in Table I. This may be attributable to the possible existence of residual Cu nanoclusters in the a-SiO<sub>x</sub>C<sub>y</sub>:H where the conductive filament ruptured. This may have altered the local defect charges and work functions in a-SiO<sub>x</sub>C<sub>y</sub>:H, thus lowering SBH.<sup>14</sup> SBH in HRS of a-SiO<sub>0.9</sub>C<sub>0.7</sub>:H and a-SiO<sub>1.5</sub>C<sub>0.2</sub>:H RMs (0.84-1.05 eV) is slightly higher than that of the a-SiC<sub>1.1</sub>:H RM (0.78 eV), following a similar trend as in the pristine state. This may again be due to the relatively higher C at% in a-SiC<sub>1.1</sub>:H introducing electronic states in the band gaps of a-SiOC:H<sup>11</sup>.

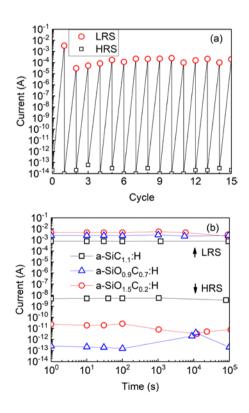

Figure 4(a) shows the HRS and LRS current in successive switching cycles of a typical a-SiO<sub>1.5</sub>C<sub>0.2</sub>:H RM. Ultrahigh and stable ON/OFF ratios of approximately  $10^8$  were observed. Retention characteristic was measured at 0.1 V and room temperature, as shown in Figure 4(b). Although a-SiC<sub>1.1</sub>:H and a-SiO<sub>0.9</sub>C<sub>0.7</sub>:H RMs have also been successfully switched multiple cycles with ultrahigh ON/OFF ratios in the range of  $10^5$  to  $10^8$  (not shown here), we observed in this work that a-SiO<sub>1.5</sub>C<sub>0.2</sub>:H RMs were relatively more stable over switching cycles. Promising retention in both LRS and HRS with negligible change in  $10^5$  s are observed aligning with many reported RMs<sup>35, 36</sup>. The stability<sup>37</sup> and promising retention may be attributable to the stable chemical properties of non-porous a-SiO<sub>x</sub>C<sub>v</sub>:H materials<sup>12</sup> as well as the ability of non-porous a-SiO<sub>x</sub>C<sub>v</sub>:H to act as Cu barriers<sup>19</sup>.

FIG. 4. (a) LRS and HRS currents in switching cycles of a W/a-SiO $_{1.5}$ C $_{0.2}$ :H/Cu RM. (b) Retention obtained from W/a-SiO $_x$ C $_y$ H/Cu.

#### Conclusion

W/a-SiO<sub>x</sub>C<sub>y</sub>:H/Cu RMs composed entirely of native BEOL materials were fabricated. Resistive switching with ultrahigh ON/OFF ratios in the range 10<sup>6</sup> to 10<sup>10</sup> were observed. The analysis of detailed I-V characteristics suggests the Ohmic conduction in the LRS are attributed to the formation of Cu filament. Also, the a-SiO<sub>x</sub>C<sub>y</sub>:H Schottky contacts in pristine state and HRS lead to Schottky emission conduction mechanisms and ultrahigh resistance. 10<sup>5</sup> s retention at room temperature were measured. Long retention, supreme BEOL compatibility, and high ON/OFF ratios suggest promising application potentials of W/a-SiO<sub>x</sub>C<sub>y</sub>:H/Cu RMs. Moreover, the composition of the a-SiO<sub>x</sub>C<sub>y</sub>:H switching layer has shown influences on V<sub>FORM</sub> and V<sub>SET</sub>, and current conduction mechanisms.

## Acknowledgements

All data supporting this study are openly available from the University of Southampton repository at https://doi.org/10.5258/SOTON/D0641. O.K would like to acknowledge an EPSRC ICASE scheme award 16000087 in collaboration with AWE. The authors acknowledge Intel for the in-kind support of low-k/Cu samples.

#### Reference

- <sup>1</sup>I. Valov, R. Waser, J. R. Jameson, and M. N. Kozicki, Nanotechnol. **22**, 254003 (2011).

- <sup>2</sup>Y. C. Yang, F. Pan, Q. Liu, M. Liu, and F. Zeng, Nano Lett. **9**, 1636 (2009).

- <sup>3</sup>L. Goux and I. Valov, Phys. Status Solidi A **213**, 274 (2016).

- <sup>4</sup>S. Rahaman, S. Maikap, W. Chen, H. Lee, F. Chen, M. Kao, and M. Tsai, Appl. Phys. Lett. **101**, 073106 (2012).

- <sup>5</sup>U. Celano, L. Goux, A. Belmonte, K. Opsomer, A. Franquet, A. Schulze, C. Detavernier, O. Richard, H. Bender, M. Jurczak, and W. Vandervorst, Nano Lett. **14**, 2401 (2014).

- <sup>6</sup>T. Sakamoto, H. Sunamura, H. Kawaura, T. Hasegawa, T. Nakayama, and M. Aono, Appl. Phys. Lett. **82**, 3032 (2003).

- <sup>7</sup>C. Schindler, S. C. P. Thermadam, R. Waser, and M. N. Kozicki, IEEE Trans. Electron Devices **54**, 2762 (2007).

- <sup>8</sup>Y. Fan, S. W. King, J. Bielefeld, and M. K. Orlowski, ECS Trans. **72**, 35 (2016).

- <sup>9</sup>H.-S. P. Wong and S. Salahuddin, Nat. Nanotechnol. **10**, 191 (2015).

- <sup>10</sup>S. W. King, M. French, M. Jaehnig, M. Kuhn, B. Boyanov, and B. French, J. Vac. Sci. Technol., B **29**, 051207 (2011).

- <sup>11</sup>S. King, M. French, M. Jaehnig, M. Kuhn, and B. French, Appl. Phys. Lett. **99**, 202903 (2011).

- <sup>12</sup>S. W. King, ECS J. Solid State Sci. Technol. **4**, N3029 (2015).

- <sup>13</sup>W. Lee, M. Siddik, S. Jung, J. Park, S. Kim, J. Shin, J. Lee, S. Park, M. Son, and H. Hwang, IEEE Electron Device Lett. **32**, 1573 (2011).

- <sup>14</sup>L. Zhong, P. Reed, R. Huang, C. H. de Groot, and L. Jiang, Solid-State Electron. **94**, 98 (2014).

- <sup>15</sup>L. Zhong, P. Reed, R. Huang, C. H. de Groot, and L. Jiang, Microelectron. Eng. **119**, 61 (2014).

- <sup>16</sup>L. Zhong, L. Jiang, R. Huang, and C. H. de Groot, Appl. Phys. Lett. **104**, 093507 (2014).

- <sup>17</sup>G. Ma, X. Tang, H. Zhang, Z. Zhong, X. Li, J. Li, and H. Su, J. Mater. Sci. **52**, 238 (2017).

- <sup>18</sup>S. W. King and J. Gradner, Microelectron. Reliab. **49**, 721 (2009).

- <sup>19</sup>S. King, D. Jacob, D. Vanleuven, B. Colvin, J. Kelly, M. French, J. Bielefeld, D. Dutta, M. Liu, and D. Gidley, ECS J. Solid State Sci. Technol. **1**, N115 (2012).

- <sup>20</sup>M. Baklanov, K. Mogilnikov, V. Polovinkin, and F. Dultsev, J. Vac. Sci. Technol., B **18**, 1385 (2000).

- <sup>21</sup>J. Fan, L. Jiang, L. Zhong, R. P. Gowers, K. A. Morgan, and C. H. de Groot, Mater. Lett. **178**, 60 (2016).

- <sup>22</sup>Y. Wang, M. Moitreyee, R. Kumar, L. Shen, K. Zeng, J. Chai, and J. Pan, Thin Solid Films **460**, 211 (2004).

- <sup>23</sup>L. Jiang, R. Cheung, R. Brown, and A. Mount, J. Appl. Phys. **93**, 1376 (2003).

- <sup>24</sup>T. Pomorski, B. Bittel, P. Lenahan, E. Mays, C. Ege, J. Bielefeld, D. Michalak, and S. King, J. Appl. Phys. **115**, 234508 (2014).

- <sup>25</sup>H. J. Kim, Q. Shao, and Y.-H. Kim, Surf. Coat. technol. **171**, 39 (2003).

- <sup>26</sup>S. M. Sze and K. K. Ng, *Physics of semiconductor devices, 2nd ed.* (John wiley & sons, New Jersey, 2006) p.197-240.

- <sup>27</sup>M. J. Mutch, T. Pomorski, B. C. Bittel, C. J. Cochrane, P. M. Lenahan, X. Liu, R. J. Nemanich, J. Brockman, M. French, M. Kuhn, B. French, and S. W. King, Microelectron. Reliab. **63**, 201 (2016).

- <sup>28</sup>Y.F. Chang, P.Y. Chen, B. Fowler, Y.T. Chen, F. Xue, Y. Wang, F. Zhou, and J.C. Lee, J. Appl. Phys. **112**, 123702 (2012).

- <sup>29</sup>Y. Wang, Y.T. Chen, F. Xue, F. Zhou, Y.F. Chang, B. Fowler, and J.C. Lee, Appl. Phys. Lett. **100**, 083502 (2012).

- <sup>30</sup>Y.F. Chang, B. Fowler, Y.C. Chen, Y.T. Chen, Y. Wang, F. Xue, F. Zhou, and J.C. Lee, J. Appl. Phys. **116**, 043708 (2014).

- <sup>31</sup>Y. Wang, B. Fowler, Y.T. Chen, F. Xue, F. Zhou, Y.F. Chang, and J.C. Lee, Appl. Phys. Lett. **101**, 183505 (2012).

- <sup>32</sup>K.C. Chang, T.C. Chang, T.M. Tsai, R. Zhang, Y.C. Hung, Y.E. Syu, Y.F. Chang, M.C. Chen, T.J. Chu, H.L. Chen, C.H. Pan, C.C. Shih, J.C. Zheng, and S.M. Sze, Nanoscale Res. Lett. **10**, 120 (2015).

- <sup>33</sup>L.W. Feng, C.Y. Chang, Y.F. Chang, W.R. Chen, S.Y. Wang, P.W. Chiang, and T.C. Chang, Appl. Phys. Lett. **96**, 052111 (2010).

- <sup>34</sup>K.-S. Kim, Y.-C. Joo, K.-B. Kim, and J.-Y. Kwon, J. Appl. Phys. **100**, 063517 (2006)

- <sup>35</sup>M. Kund, G. Beitel, C.-U. Pinnow, T. Rohr, J. Schumann, R. Symanczyk, K. Ufert, and G. Muller, in *IEDM Technical Digest. IEEE International 2005, Electron Devices Meeting* (2005), pp. 754.

- <sup>36</sup>K. Tsunoda, Y. Fukuzumi, J. Jameson, Z. Wang, P. Griffin, and Y. Nishi, Appl. Phys. Lett. **90**, 113501 (2007).

- <sup>37</sup>K. A. Morgan, J. Fan, R. Huang, L. Zhong, R. Gowers, L. Jiang, and C. H. de Groot, AIP Adv. **5**, 077121 (2015).