| I   | NI | VER | SITY | $\mathbf{OF}$ | SOI      | TTH | M        | PT | O | V |

|-----|----|-----|------|---------------|----------|-----|----------|----|---|---|

| • , |    | •   |      |               | . 74 / 4 | . , | <b>~</b> |    |   |   |

FACULTY OF FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

School of Optoelectronics Research Centre

**Clock Generation for Silicon Photonics based Optical Communication Systems**

by

## **Fanfan Meng**

Thesis for the degree of Doctor of Philosophy

Feb, 2018

#### UNIVERSITY OF SOUTHAMPTON

## **ABSTRACT**

#### FACULTY OF OF PHYSICAL SCIENCES AND ENGINEERING

### ELECTRONIC AND ELECTRICAL ENGINEERING

Thesis for the degree of Doctor of Philosophy

## **Clock Generation for Silicon Photonics based Optical Communication Systems**

### By Fanfan Meng

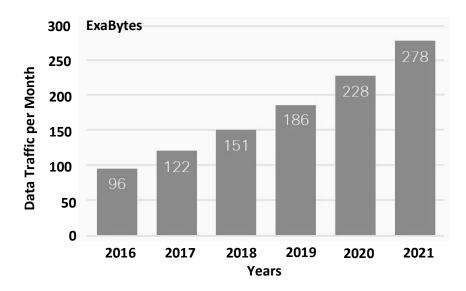

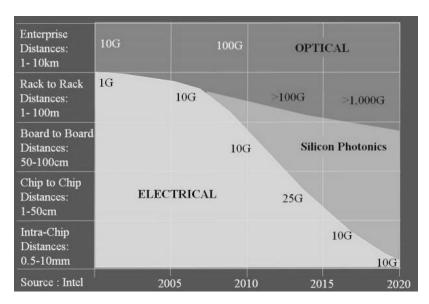

As communications data traffic continues to increase, electronic interconnects over short reaches are struggling to keep up with the bandwidth and power consumption requirements. One of the technology trends is to migrate from copper to optical based interconnects where silicon Photonics (SiP) technology has emerged as an excellent technical solution to meet the performance and cost requirements of these short-reach applications.

The clock generation system is a critical module that none of the communication systems can overlook. However, the reported clock generation solutions utilized in SiP transceivers inherit limitations from traditional electronic interconnects, where the clock signals are limited by the frequency tuning range, system settling time and the number of clock phases. The motivation for this PhD project is to build a novel clock generation system that can be fully integrated with future SiP transceiver and the innovation has been realized in various aspects of the work.

Firstly, a novel high-speed ring-based voltage-controlled oscillator (VCO) is proposed using inductor peaking. The proposed VCO topology was validated with four design examples fabricated in different CMOS processes nodes (130nm and 65nm) and measured results show close agreement with theoretical analysis. The figure of merit (FOM) of 203 is the best combination of frequency and tuning range currently.

Secondly, a dedicated phase locked loop (PLL) structure combined with the inductor peaking VCO was created, focusing on the requirements of frequency controllability and system settling time for SiP communication system. A programmable frequency

range of more than 25GHz has been achieved using a 40nm process while the measured phase locking time is always less than half of a microsecond.

Finally, with the mainstream CMOS process for analogue circuits design migrating towards to 28nm High-k/Metal Gate (HKMG), design methodologies on the proposed VCO have been realized in order to adapt this evolution. Two specific design cases have been implemented to fully utilize the advantages of new CMOS process and mitigate the side-effects of 28nm HKMG process.

# **Contents**

| Contents  | i                                                |

|-----------|--------------------------------------------------|

| List of F | iguresv                                          |

| List of T | ables xiii                                       |

| Academi   | c Thesis: Declaration Of Authorshipxiv           |

| Acknowl   | edgementsxv                                      |

| Definitio | ns and Abbreviationsxvi                          |

| Publicati | ons xviii                                        |

| Chapter   | 1 Introduction1                                  |

| 1.1       | Background of Silicon Photonics                  |

| 1.2       | Project Motivations4                             |

| 1.2.1     | Technology Trend of Electro-Optics Interconnect4 |

| 1.2.2     | 2 Targeting Demands for Clock Generation System6 |

| 1.3       | Design Challenges                                |

| 1.4       | Thesis Outline9                                  |

| 1.5       | Summary11                                        |

| Chapter   | 2 Literature Review12                            |

| 2.1       | Introduction                                     |

| 2.2       | Traditional Broadband Serializer-Deserializers   |

| 2.2.1     | Electrical Transceiver Links                     |

| 2.2.2     | 2 Optical Transceiver Link14                     |

| 2.3       | Voltage Controlled Oscillator (VCO)              |

| 2.3.1     | Conventional VCO Structure                       |

| 2.3.2     | 2 Broadband VCO                                  |

| 2.3.3     | B Low Noise VCO                                  |

| 2.4       | Conventional Phase Locked Loop (PLL)             |

| 2.     | .4.1 Type I PLL |                                                         | 28     |  |

|--------|-----------------|---------------------------------------------------------|--------|--|

| 2.     | 4.2             | Type II PLL                                             | 30     |  |

| 2.5    | Alt             | ternative PLL Topologies                                | 33     |  |

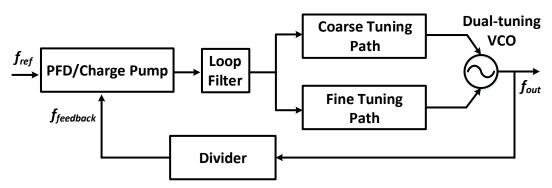

| 2.     | 5.1             | Dual Tuning PLL                                         | 33     |  |

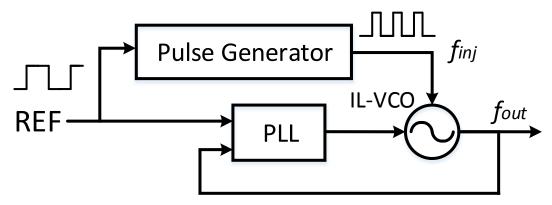

| 2.     | 5.2             | Multiple Loop PLLs                                      | 36     |  |

| 2.     | 5.3             | Multiplying Delay Locked PLL                            | 39     |  |

| 2.     | 5.4             | PLL-based CDR                                           | 40     |  |

| 2.6    | Su              | mmary                                                   | 44     |  |

| Chapt  | er 3            | Ultra-wide Tuning Range CMOS Ring-based VCO with In     | ductor |  |

| Peakir | ıg              |                                                         | 46     |  |

| 3.1    | Int             | roduction                                               | 46     |  |

| 3.2    | An              | alysis on Bandwidth Enhancement of VCO                  | 47     |  |

| 3.     | 2.1             | Analysis on Transistor Sizing to Frequency              | 48     |  |

| 3.     | 2.2             | Analysis on Noise Contribution                          | 49     |  |

| 3.     | 2.3             | Analysis on Voltage Tuning Range                        | 50     |  |

| 3.3    | Co              | mmon Source RO-VCO with Inductor Peaking                | 52     |  |

| 3.4    | Inc             | luctive Peaking VCO Design Application                  | 55     |  |

| 3.     | 4.1             | The Research Purposes of Implementation                 | 55     |  |

| 3.     | 4.2             | Chip Level Design                                       | 55     |  |

| 3.     | 4.3             | Testing and Experimental Results                        | 58     |  |

| 3.5    | Su              | mmary                                                   | 63     |  |

| Chapt  | er 4 ]          | Theoretical Analysis of Dual-Loop Triple-Controlled PLL | 65     |  |

| 4.1    | Int             | roduction                                               | 65     |  |

| 4.2    | Co              | nsiderations of Inductor Peaking VCO in PLL             | 66     |  |

| 4.3    | Inv             | vestigation of Classic PLL with Inductor Peaking VCO    | 67     |  |

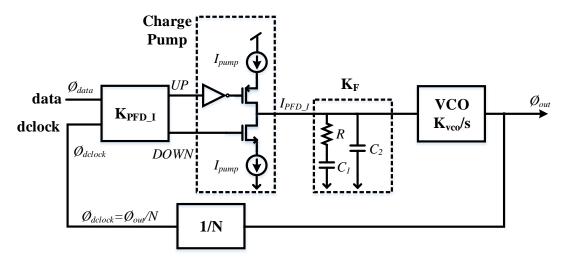

| 4.     | 3.1             | Charge-pump PLL with Inductor Peaking VCO               | 67     |  |

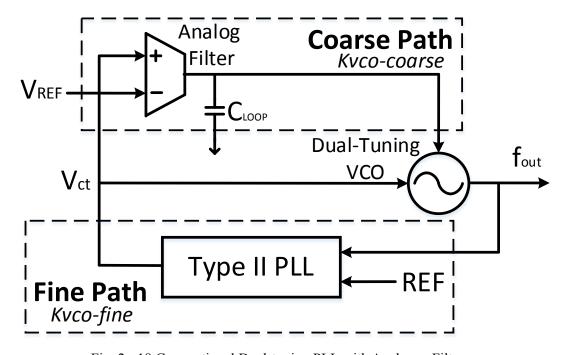

| 4      | 3.2             | Dual-tuning PLL with Inductive Peaking VCO              | 72     |  |

| 4.4    | Pro                                                      | Proposed Dual-loop Triple-controlled PLL                    |    |

|--------|----------------------------------------------------------|-------------------------------------------------------------|----|

| 4.4    | 4.4.1 Trade-off between Loop Bandwidth and Settling Time |                                                             | 78 |

| 4.4    | 4.2                                                      | Bandwidth Enhancement                                       | 79 |

| 4.5    | Per                                                      | formance Comparison                                         | 85 |

| 4.6    | Sui                                                      | mmary                                                       | 86 |

| Chapte | er 5 I                                                   | Practical Implementation of Dual-Loop Triple-Controlled PLL | 87 |

| 5.1    | Int                                                      | roduction                                                   | 87 |

| 5.2    | Toj                                                      | p level System Design                                       | 88 |

| 5.3    | Arc                                                      | chitecture of DLTC-PLL                                      | 89 |

| 5.3    | 3.1                                                      | Inductor Peaking VCO with Voltage Tuning Range Enhancement  | 90 |

| 5.3    | 3.2                                                      | Adaptive DC Shifting Unit                                   | 94 |

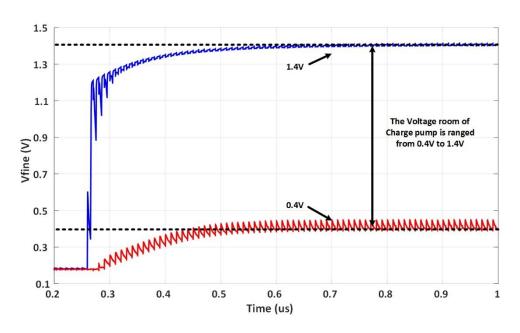

| 5.3    | 3.3                                                      | Charge Pump with Voltage Protection                         | 96 |

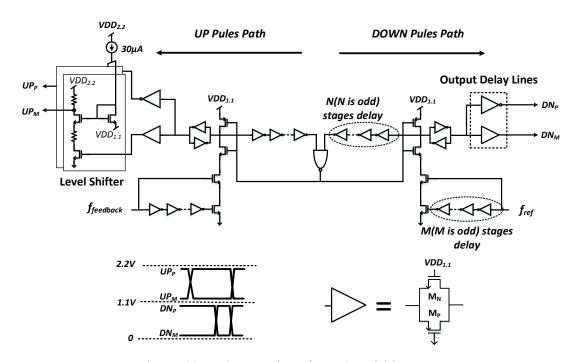

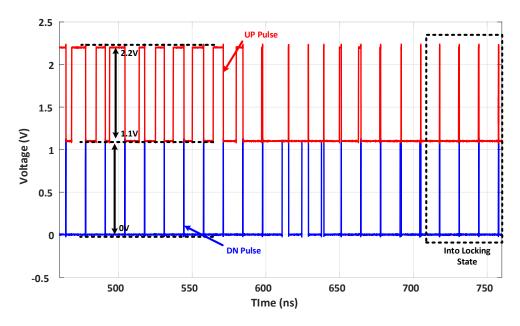

| 5.3    | 3.4                                                      | Fast Acquisition PFD                                        | 99 |

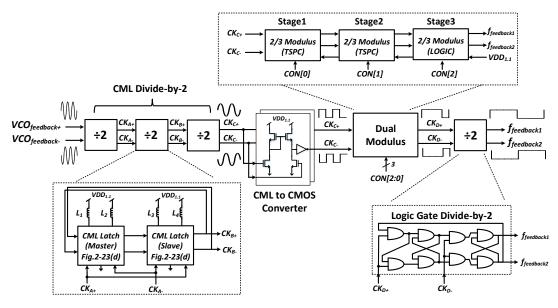

| 5.3    | 3.5                                                      | Integer-N Frequency Pre-scaler10                            | 00 |

| 5      | 3.6                                                      | Reference Clock Scheme10                                    | 02 |

| 5.4    | Ou                                                       | tput Buffer Stages10                                        | 03 |

| 5.4    | 4.1                                                      | Output Buffer 110                                           | 04 |

| 5.4    | 4.2                                                      | Output Buffer 2                                             | 04 |

| 5.5    | Ful                                                      | l Chip Layout10                                             | 05 |

| 5.6    | Sin                                                      | nulation and Testing10                                      | 07 |

| 5.0    | 6.1                                                      | Simulation Environment10                                    | 07 |

| 5.0    | 6.2                                                      | Simulation Results                                          | 08 |

| 5.0    | 6.3                                                      | Testing Measurements                                        | 10 |

| 5.7    | Sui                                                      | mmary1                                                      | 18 |

| Chapte | er 6 I                                                   | Design Methodology and Enhancement for Ultra-small Process1 | 19 |

| 6.1.   | Int                                                      | roduction1                                                  | 19 |

| 6.2.   | Design Case I: Advanced Layout Techniques for High-speed      | Analogue   |

|--------|---------------------------------------------------------------|------------|

| Circu  | ıits                                                          | 120        |

| 6.2    | 2.1. Circuits Details                                         | 121        |

| 6.2    | 2.2. Experimental Results                                     | 125        |

| 6.3.   | Design Case II: Inductive Peaking VCO with Cascode Noise Redu | iction 130 |

| 6.3    | 3.1. Inductive Peaking VCO with Cascode Noise Reduction       | 130        |

| 6.3    | 3.2. Design Example                                           | 136        |

| 6.3    | 3.3. Simulation Results                                       | 138        |

| 6.4.   | Summary                                                       | 141        |

| Chapte | er 7 Conclusions and Future                                   | 143        |

| 7.1    | Conclusions                                                   | 143        |

| 7.2    | Future Work                                                   | 146        |

| Appen  | dix. A Basic Concepts                                         | 151        |

| A.1    | General Theory of Oscillation                                 | 151        |

| A.2    | RC and LC based Oscillator                                    | 152        |

| Α.     | 2.1 RC based Oscillator                                       | 152        |

| A.     | 2.2 LC based Oscillator                                       | 154        |

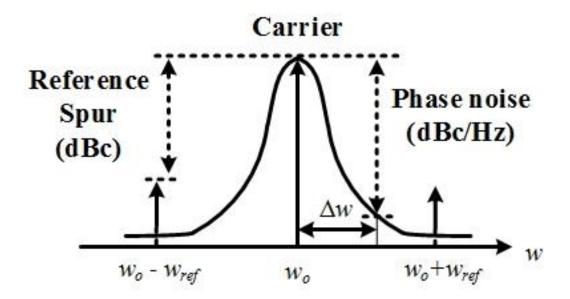

| A.3    | Phase Noise and Reference Spur                                | 156        |

| Appen  | dix. B Necessary Building Blocks                              | 161        |

| B.1    | Phase (Frequency) Detector (PD/PFD)                           | 161        |

| B.2    | Charge Pump                                                   | 166        |

| B.3    | Loop Filter                                                   | 170        |

| B.4    | Frequency Division                                            | 172        |

| Appen  | dix. C Additional Results of Simulations and Measurements     | 176        |

| Appen  | dix. D Design Methodology for High-speed Analogue Circuit     | 178        |

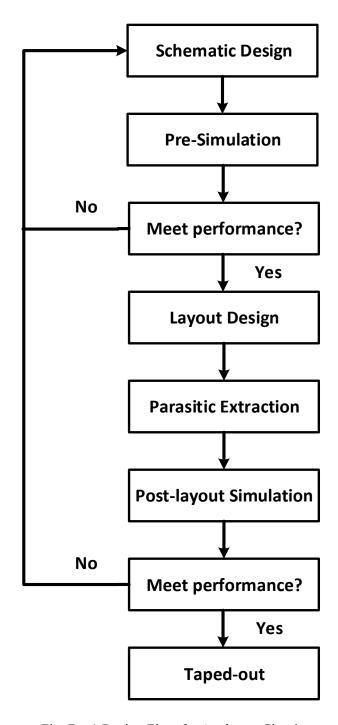

| D.1    | Design flow of High-speed Analogue Circuit                    | 178        |

| D.2    | Design Example                                                | 180        |

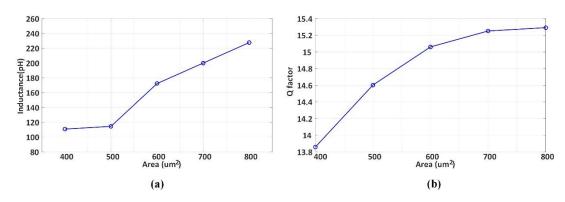

| Append  | lix. E Inductor Modelling                | 187 |

|---------|------------------------------------------|-----|

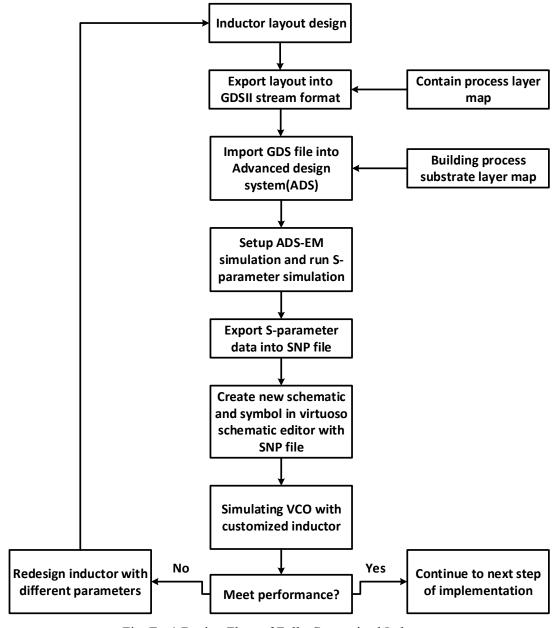

| E.1.    | Design Flow of fully customized inductor | 187 |

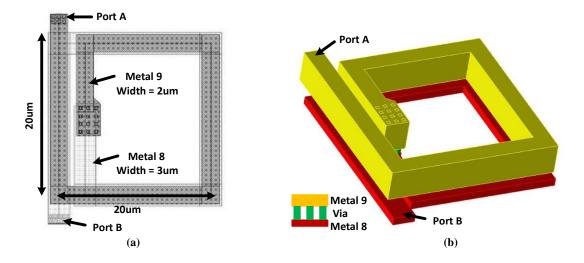

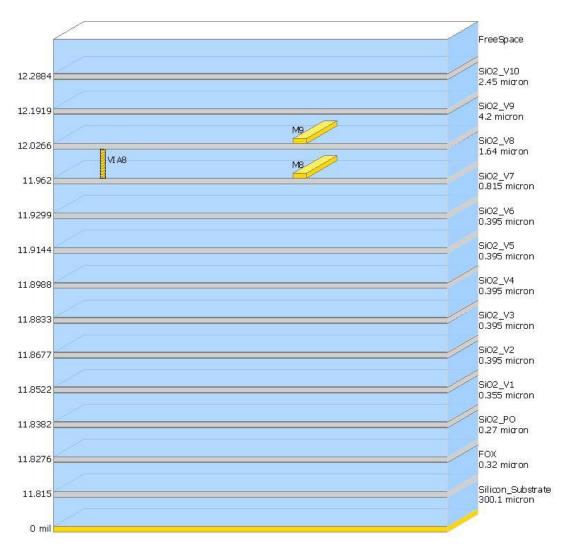

| E.2.    | Design Example                           | 189 |

| Referei | nces                                     | 193 |

# **List of Figures**

| Fig. 1- 1 The Past and Predicted Growth of the Total Internet Traffic [1]                                                                              | 1    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 1- 2 Data Rate Limits for Different Data Communication Distances [5]                                                                              | 2    |

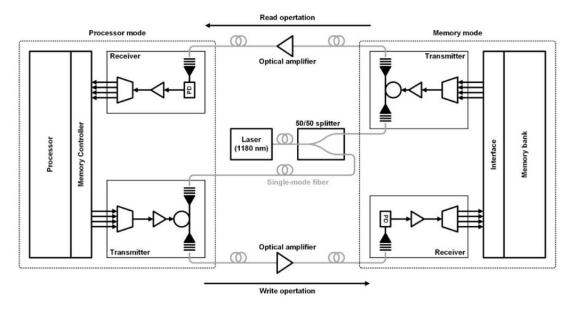

| Fig. 1- 3 Realization of Processor-memory Optical Link [10]                                                                                            | 3    |

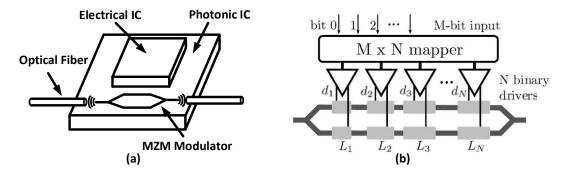

| Fig. 1-4 (a) Conceptual View of Silicon Photonics IC integrated with Electrical IC Hybrid Integration. (b) The Principle of Segmented Optical DAC [17] | -    |

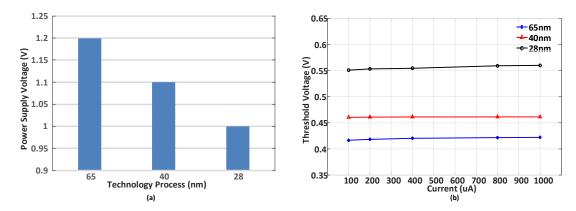

| Fig. 1- 5 Technology Process Scaling (a) Power Supply Voltage (b) Threshology of Single Transistor                                                     |      |

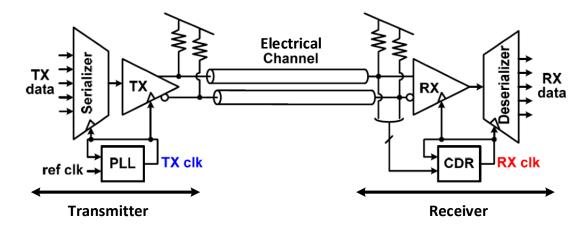

| Fig. 2 - 1Typical High-speed Electrical Link System                                                                                                    | .13  |

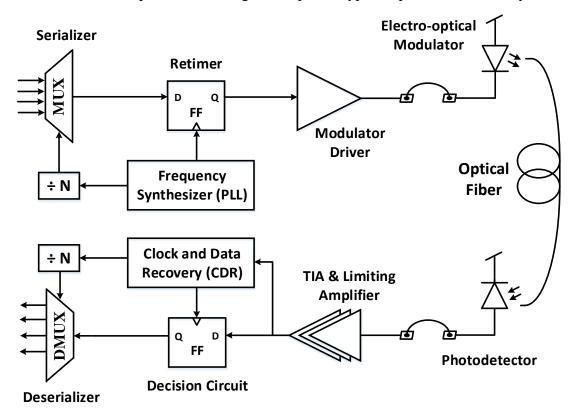

| Fig. 2 - 2 Typical Optical Transceiver System                                                                                                          | . 15 |

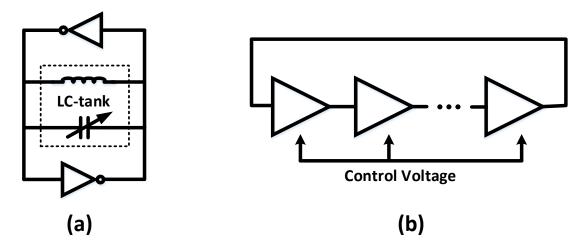

| Fig. 2 - 3 Topology of VCO (a) LC Tank (b) Ring Based                                                                                                  | .17  |

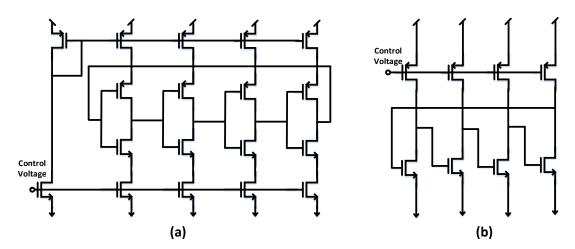

| Fig. 2 - 4 Common Used RO-VCO (a) Current Starved (b) Common Source                                                                                    | .18  |

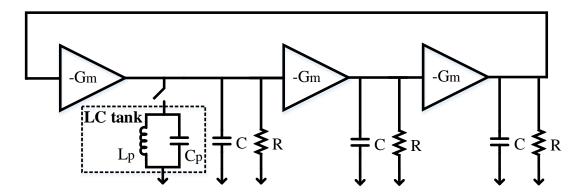

| Fig. 2 - 5 Block Diagram of 3-stages Ring Oscillator with LC Tank                                                                                      | .20  |

| Fig. 2 - 6 RO-VCO with Multiple Pass Loop [59]                                                                                                         | .21  |

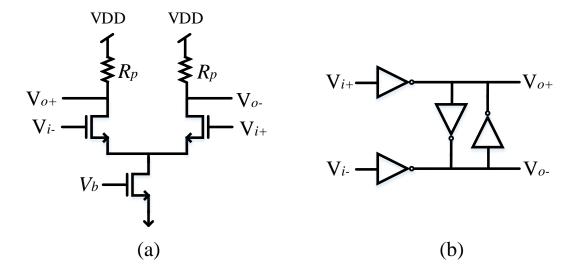

| Fig. 2 - 7 (a) Rail-to-rail Voltage Tuning Delay Cell (b) Bias-level-shift Circuit                                                                     | .22  |

| Fig. 2 - 8 Linear Tuning Delay Cell                                                                                                                    | .23  |

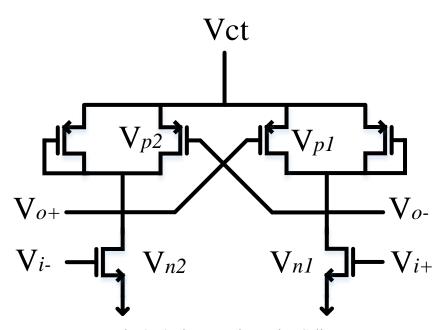

| Fig. 2 - 9 (a) Full Differential (FD) Delay Cell (b) Pseudo-differential Delay Cell                                                                    | .24  |

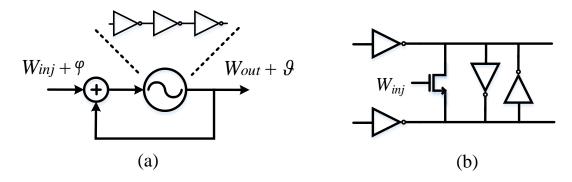

| Fig. 2 - 10 (a) Model of Injection in a Ring Oscillator (b) Pseudo Differential De Cell with Injection Locking                                         |      |

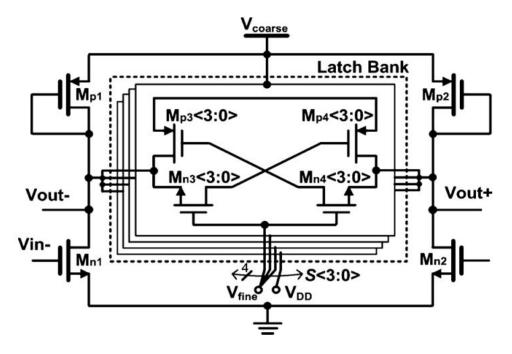

| Fig. 2 - 11 Diagram of Scaling Kvco Delay Cell [64]                                                                                                    | .27  |

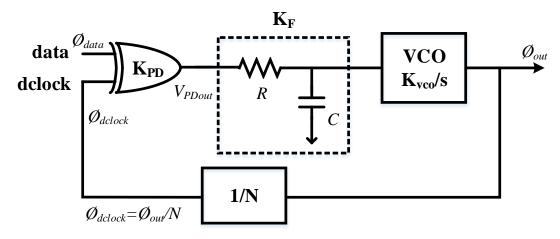

| Fig. 2 - 12 Linear Model of PLL                                                                                                                        | .28  |

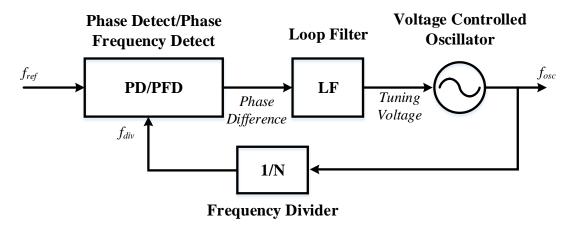

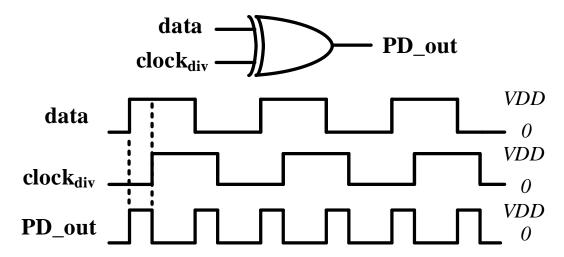

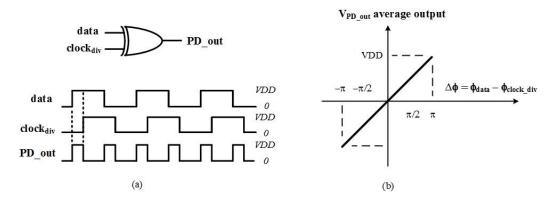

| Fig. 2 - 13 Operation of XOR Phase Detector                                                                                                            | . 29 |

| Fig. 2 - 14 Conventional Type I PLL                                                                                                                    | .29  |

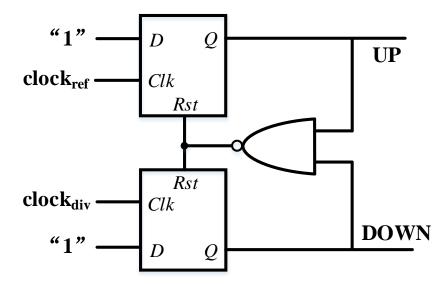

| Fig. 2 - 15 Schematic Diagram of Phase Frequency Detector (PFD)                                                                                        | .31  |

| Fig. 2 - 16 Block Diagram of Conventional Type II PLL                                                                                                  | .31  |

| Fig. 2 - 17 Topology of Dual Control PLL                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 2 - 18 Conventional Dual-tuning PLL with Analogue Filter                                                                                     |

| Fig. 2 - 19 Conventional Injection Locking PLL                                                                                                    |

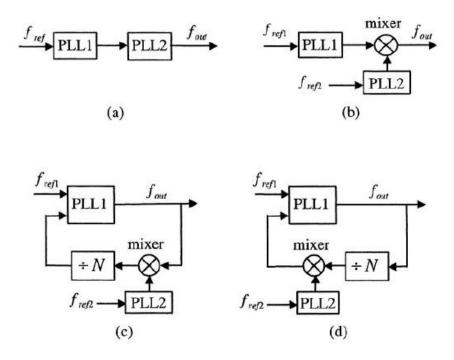

| Fig. 2 - 20 Several Topologies of Multiple-loop PLL                                                                                               |

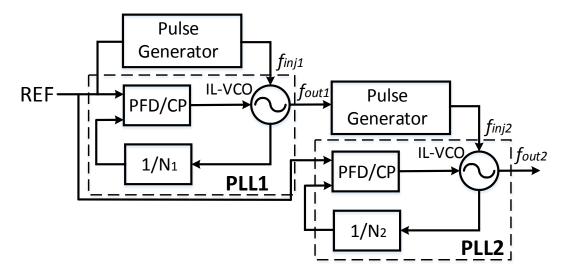

| Fig. 2 - 21 Multiple Loop PLL with Cascaded Injection Locking                                                                                     |

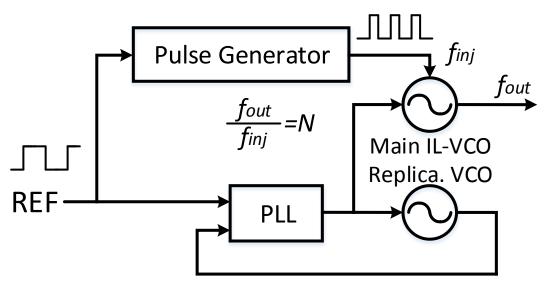

| Fig. 2 - 22 Multiple Loop PLL with Two Identical VCOs                                                                                             |

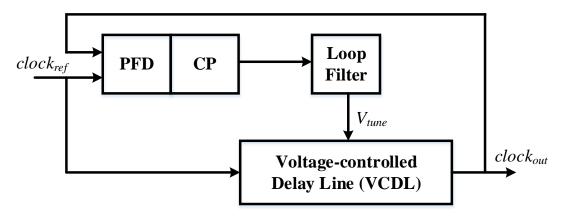

| Fig. 2 - 23 Block Diagram of Typical DLL                                                                                                          |

| Fig. 2 - 24 DLL with Multiple Loop                                                                                                                |

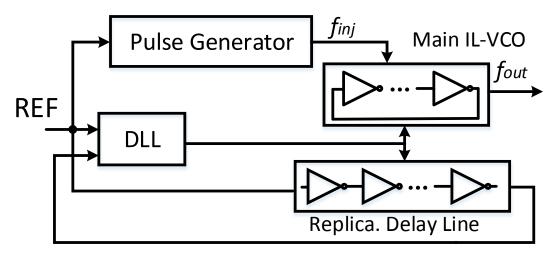

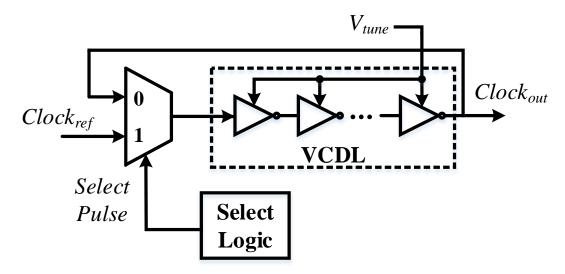

| Fig. 2 - 25 Multiplying Delay-locked Loop (MDLL)                                                                                                  |

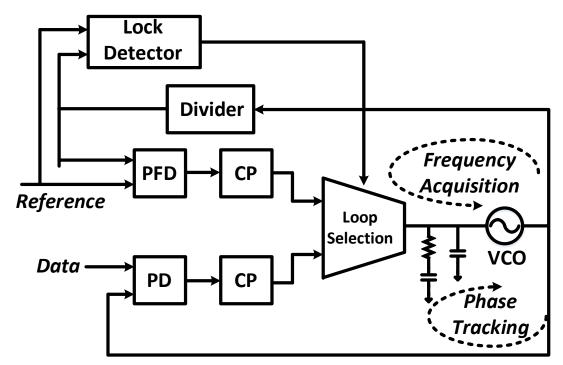

| Fig. 2 - 26 Traditional CDR Topology41                                                                                                            |

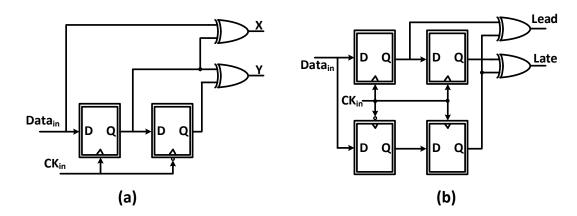

| Fig. 2 - 27 (a) Hogge PD (b) Alexander PD (Bang-Bang PD)                                                                                          |

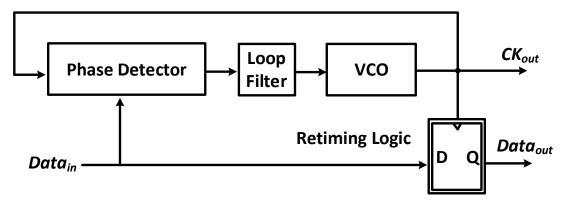

| Fig. 2 - 28 Conventional PLL-based CDR                                                                                                            |

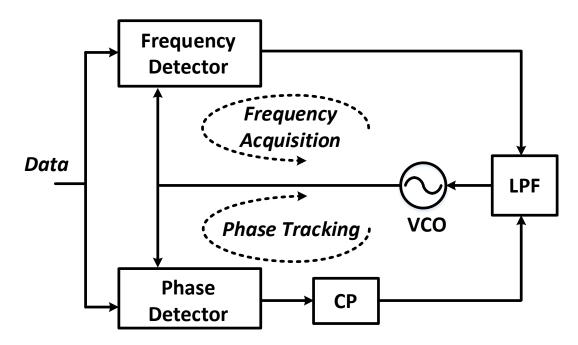

| Fig. 2 - 29 Full Rate Referenceless CDR                                                                                                           |

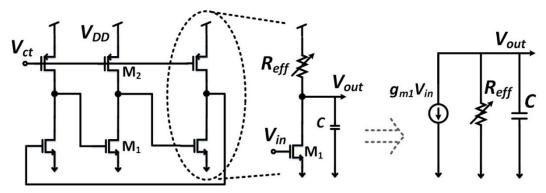

| Fig. 3 - 1 Typical Three Stage RO-VCO                                                                                                             |

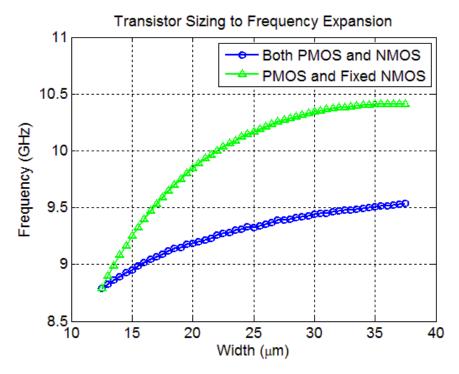

| Fig. 3 - 2 Transistor Sizing to Frequency Expansion                                                                                               |

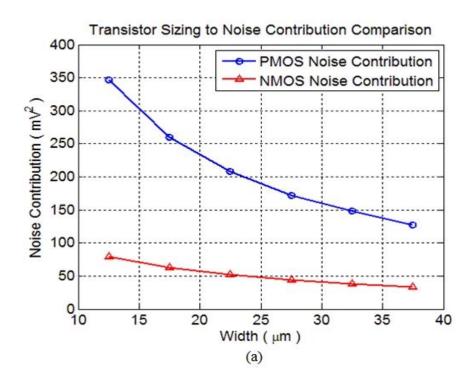

| Fig. 3 - 3 Noise Contribution Comparison (a) Transistor Sizing to Noise Contribution (b) Noise Contribution Scaling with Size Ratio               |

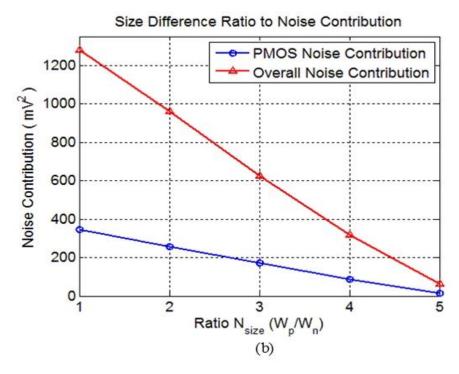

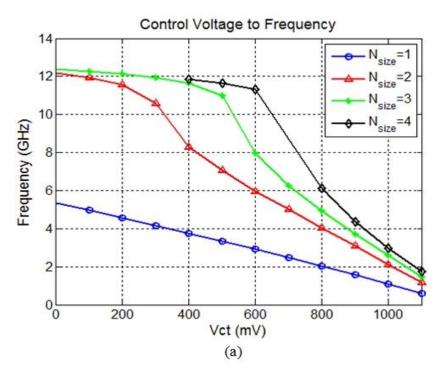

| Fig. 3 - 4 (a) Control Voltage to Frequency Range (b) Gain-Frequency Response with <i>Nsize</i> =3                                                |

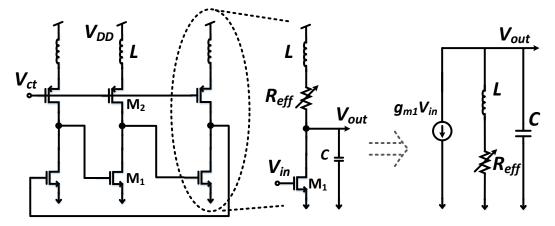

| Fig. 3 - 5 RO-VCO with Peaking Inductor                                                                                                           |

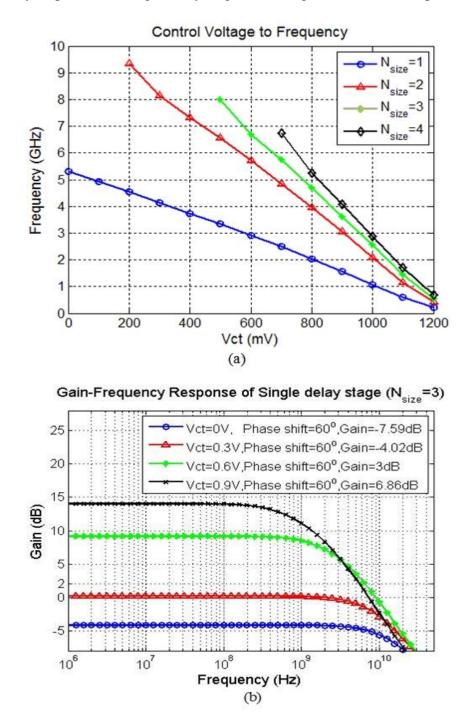

| Fig. 3 - 6 (a) Control Voltage to Frequency Response (b) Gain-Frequency Response with <i>Nsize</i> =3                                             |

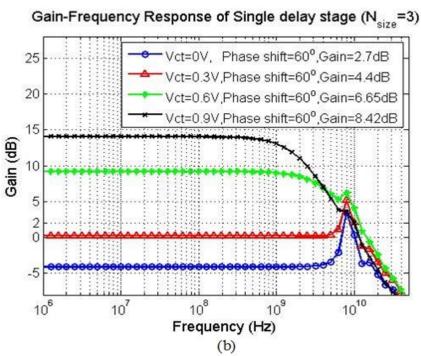

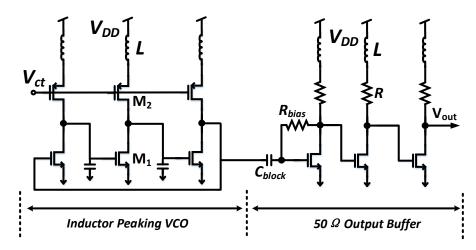

| Fig. 3 - 7 Proposed Structure of Design Example (a) Top Circuit Topology (b) Proposed VCO Structure with Inductor Peaking (c) 50Ω Output Buffer55 |

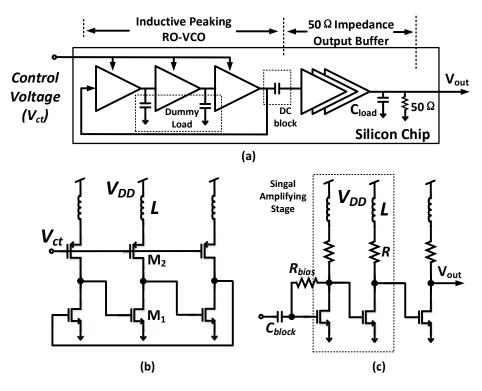

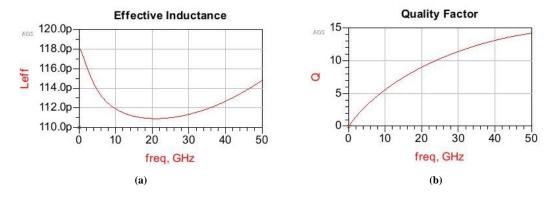

| Fig. 3 - 8 Layout View of the Inductors used with (a) VCO-3 and (b) VCO-457                                                                       |

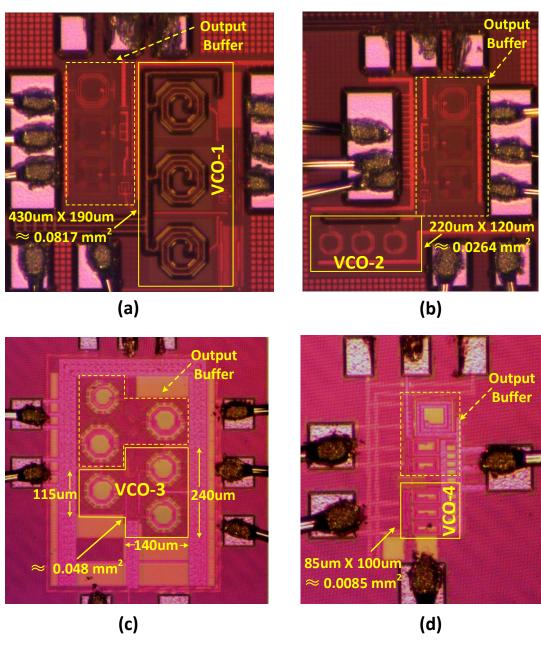

| Fig. 3 - 9 Microscope View of the Proposed Four RO-VCO (a) VCO-1 (b) VCO-2 (c)                                      |

|---------------------------------------------------------------------------------------------------------------------|

| VCO-3 (d) VCO-457                                                                                                   |

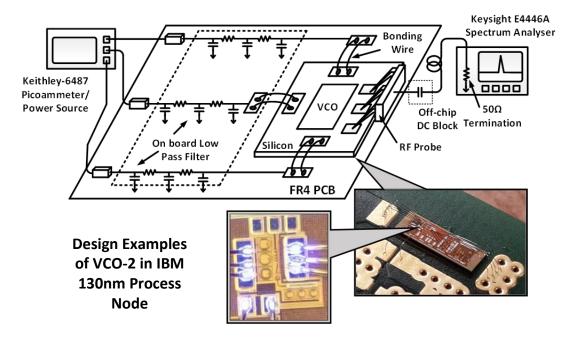

| Fig. 3 - 10 Testing Bench for Four Design Examples                                                                  |

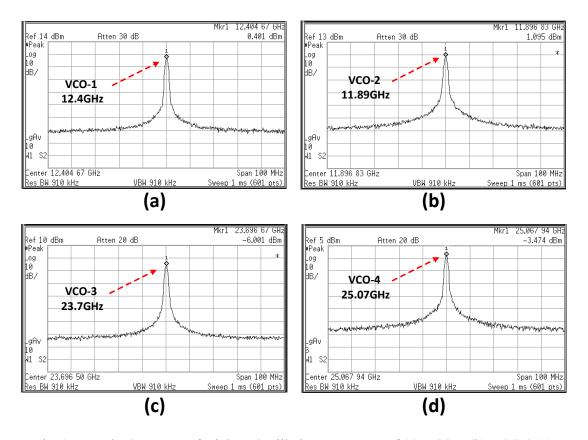

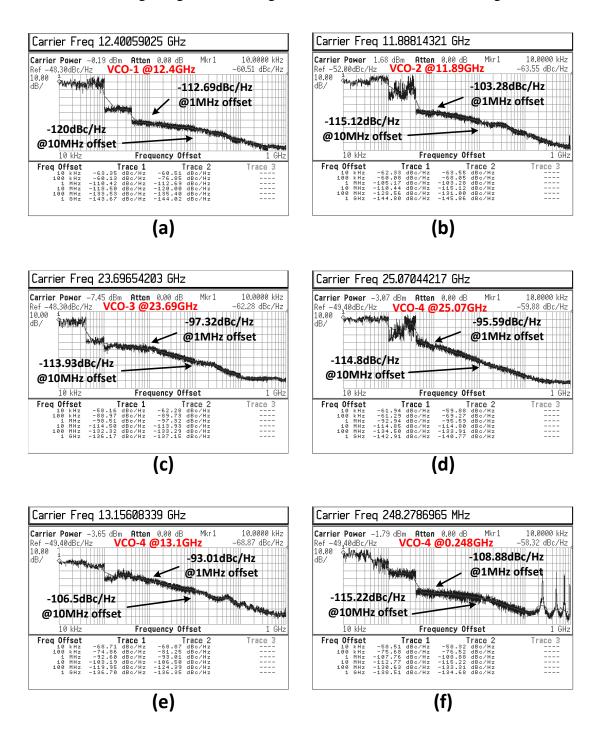

| Fig. 3 - 11. The Spectrum of Highest Oscillation Frequency of (a) VCO-1 (b) VCO-2 (c) VCO-3 (d) VCO-4               |

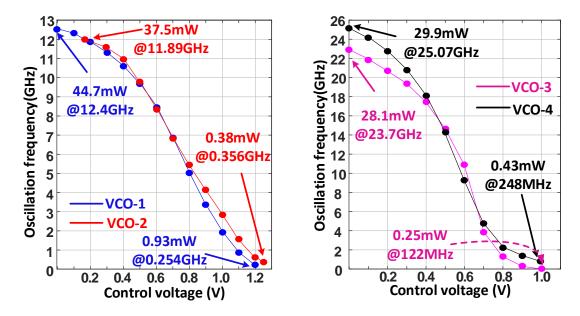

| Fig. 3 - 12 Measured Frequency Tuning Characteristics                                                               |

| Fig. 3 - 13 Measured Phase Noise Results of Each Design Examples61                                                  |

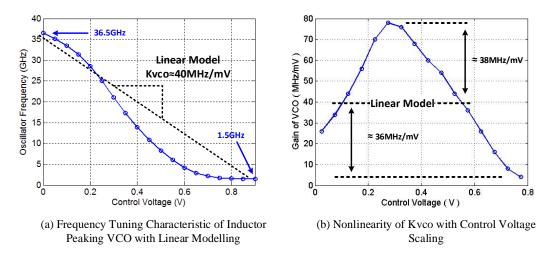

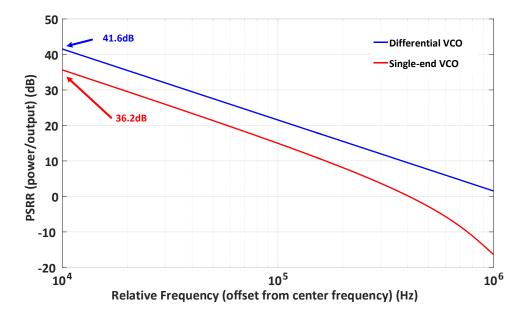

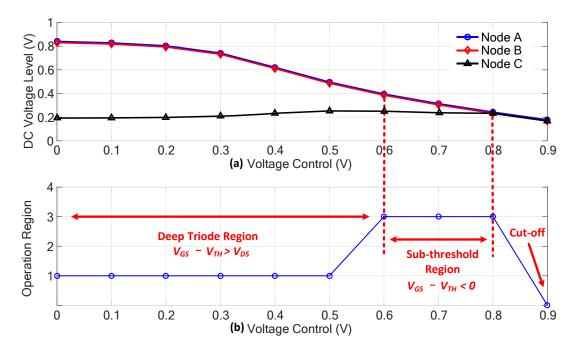

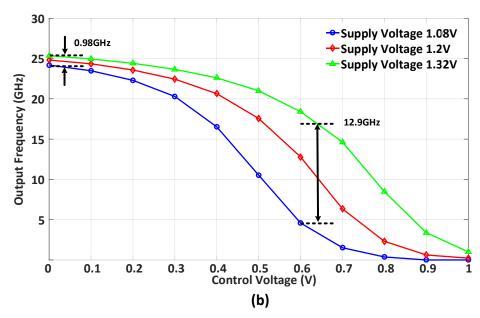

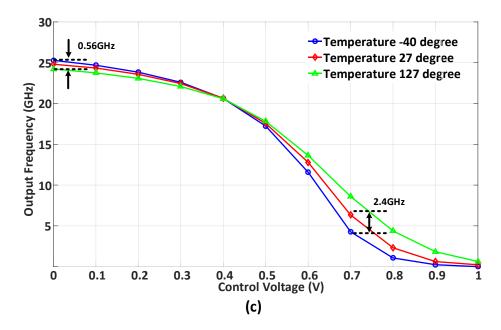

| Fig. 4 - 1 (a) Frequency Tuning Characteristics of Inductor Peaking VCO (b)  Nonlinear Behaviour of the Gain of VCO |

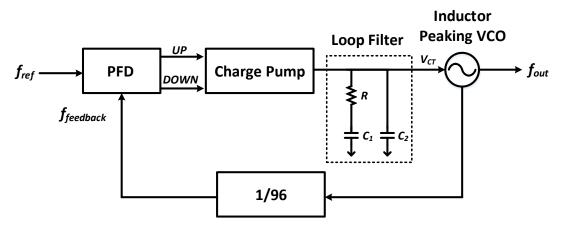

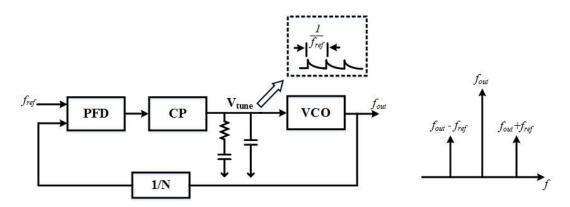

| Fig. 4 - 2 Block Diagram of Charge Pump PLL (CP-PLL)67                                                              |

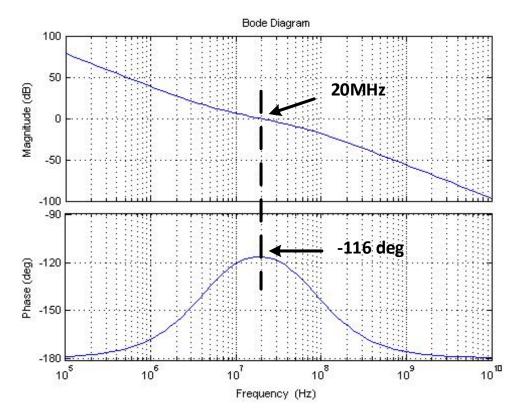

| Fig. 4 - 3 Bode Plot of Open Loop Transfer Function                                                                 |

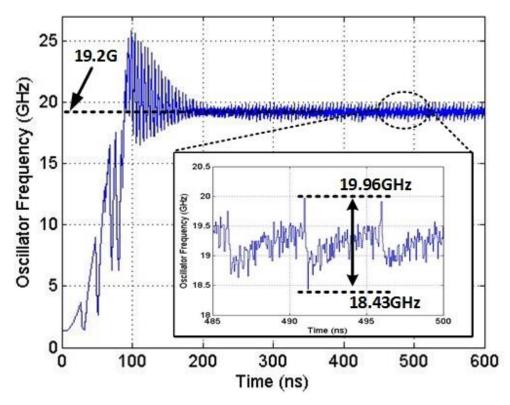

| Fig. 4 - 4 Frequency Output of CP-PLL                                                                               |

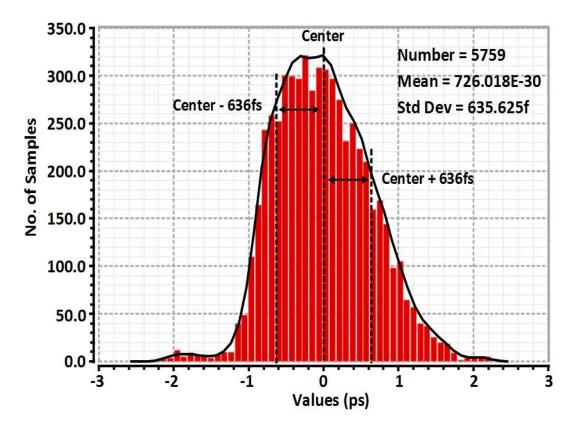

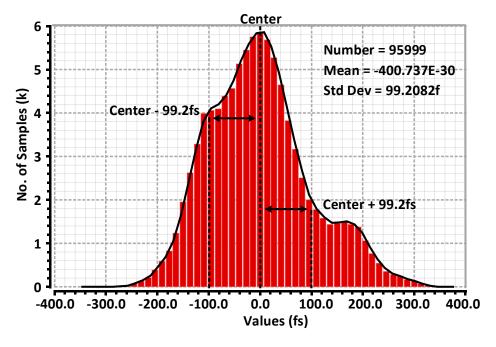

| Fig. 4 - 5 Period Jitter Performance of CP-PLL70                                                                    |

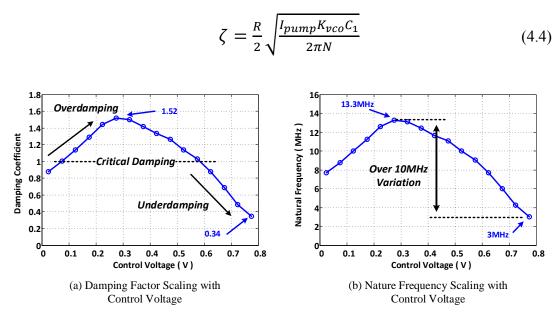

| Fig. 4 - 6 Influences of Nonlinear Behaviours (a) Damping Factor (b) Natural Frequency                              |

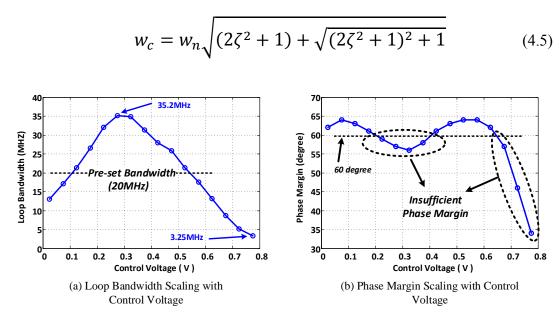

| Fig. 4 - 7 Tendency under Nonlinear Behaviours (a) Loop Bandwidth (b) Phase Margin                                  |

| Fig. 4 - 8 Block Diagram of Dual Tuning PLL (DT-PLL)72                                                              |

| Fig. 4 - 9 Applied Structure of Dual Tuning VCO                                                                     |

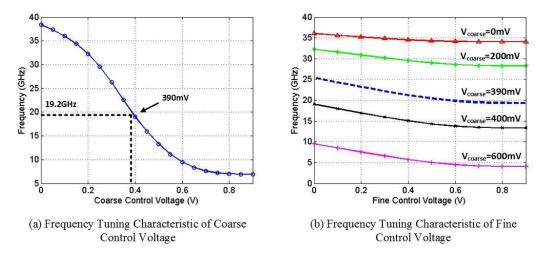

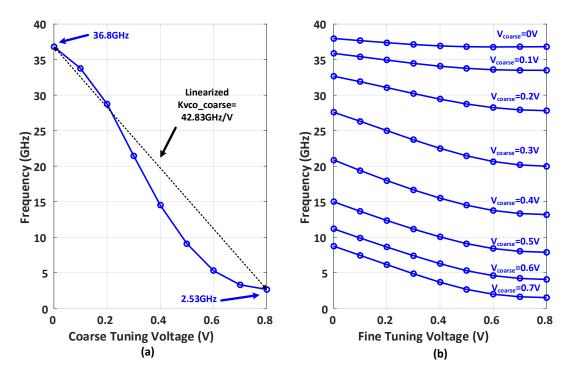

| Fig. 4 - 10 Frequency Tuning Characteristics of (a) Coarse Tuning Voltage (b) Fine Tuning Voltage                   |

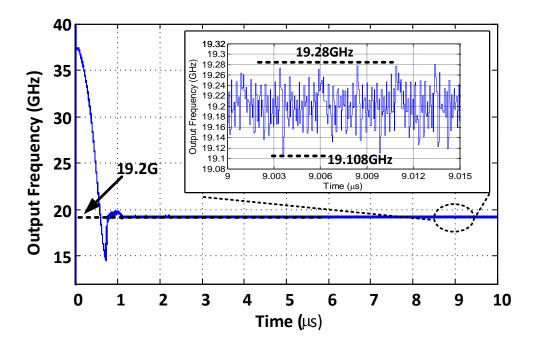

| Fig. 4 - 11 Frequency Output of DT-PLL                                                                              |

| Fig. 4 - 12 Period Jitter Performance of DT-PLL                                                                     |

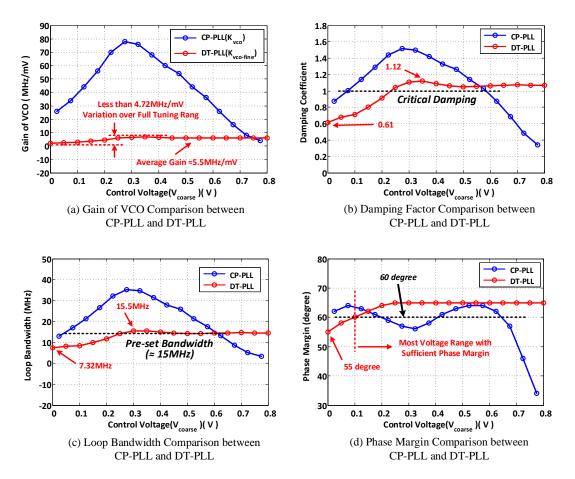

| Fig. 4 - 13 Nonlinear Behaviours of (a) Gain on $V_{coarse}$ (b) Damping Factor (c) Loop Bandwidth (d) Phase Margin |

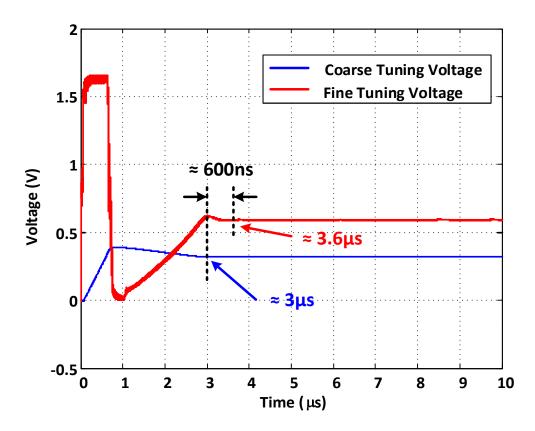

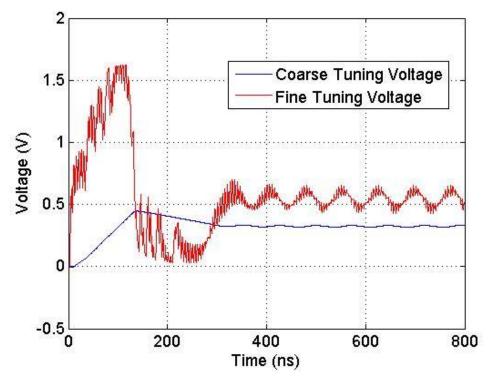

| Fig. 4 - 14 Setting Time in DT-PLL.                                                                                 |

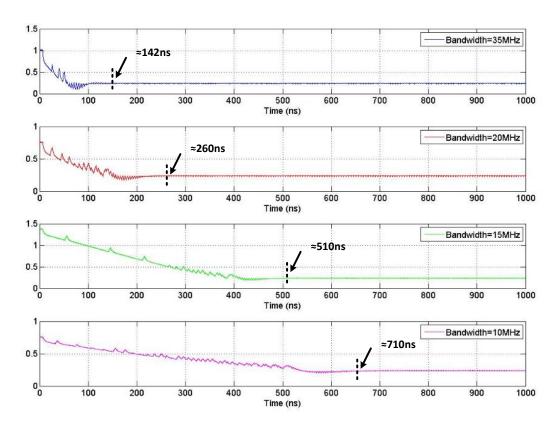

| Fig. 4 - 15 Trade-off between Loop Bandwidth and Settling Time                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 4 - 16 Instability Issue in DT-PLL                                                                                                                                                                                        |

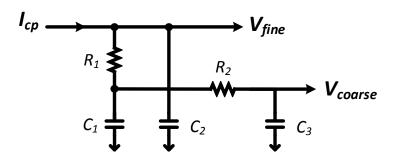

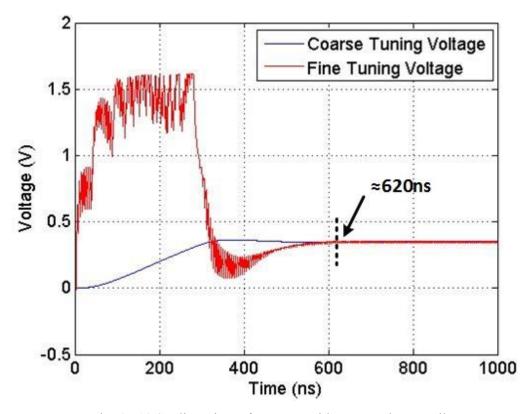

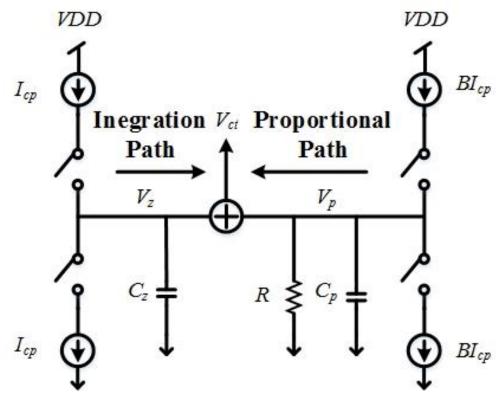

| Fig. 4 - 17 Proposed Structure of Loop Filter                                                                                                                                                                                  |

| Fig. 4 - 18 Equivalent Structure of Proposed Loop Filter                                                                                                                                                                       |

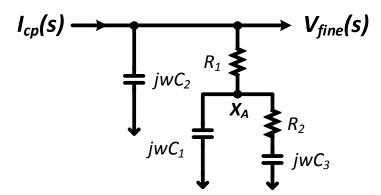

| Fig. 4 - 19 Settling Time of DT-PLL with Proposed Loop Filter                                                                                                                                                                  |

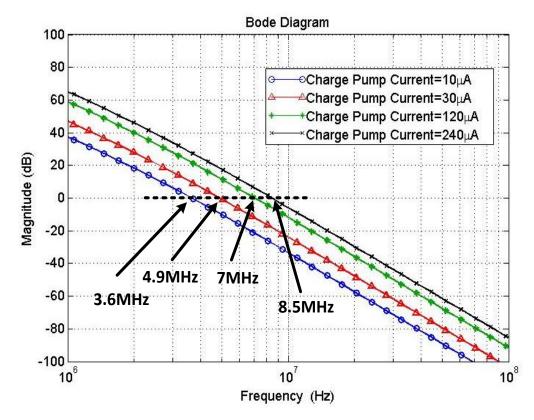

| Fig. 4 - 20 Loop Bandwidth with Different Charge Pump Current                                                                                                                                                                  |

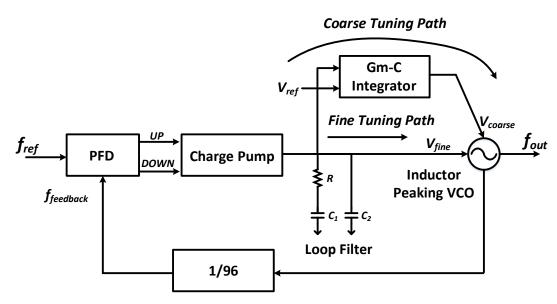

| Fig. 4 - 21 Block Diagram of Proposed Dual-loop Triple-Control PLL (DLTC-PLL)                                                                                                                                                  |

| Fig. 4 - 22 Settling Response of Proposed DLTC-PLL                                                                                                                                                                             |

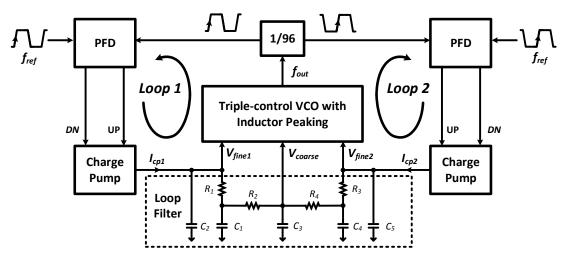

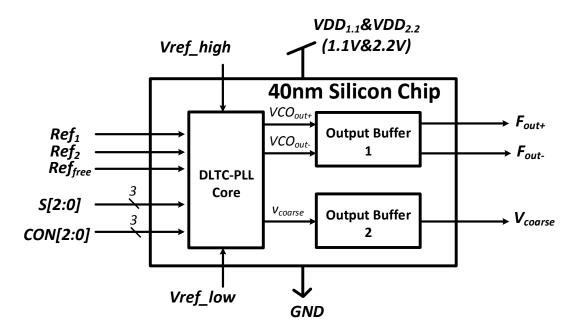

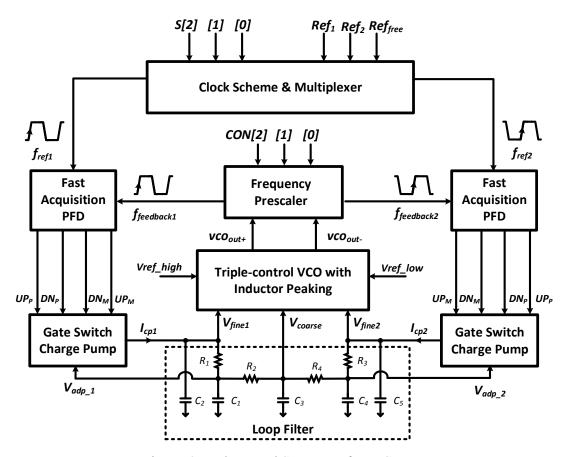

| Fig. 5 - 1 Top Level Structure of DLTC-PLL                                                                                                                                                                                     |

| Fig. 5 - 2 Implemented Structure of DLTC-PLL                                                                                                                                                                                   |

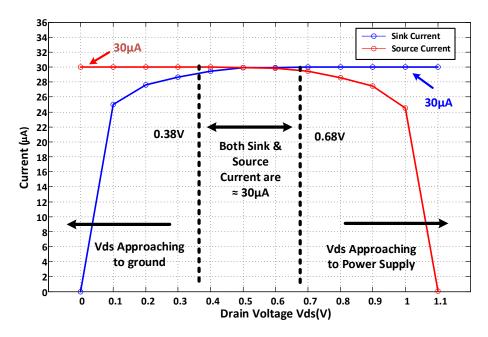

| Fig. 5 - 3 Source (Sink) Current Scaling with Drain-source Voltage of MOSFET90                                                                                                                                                 |

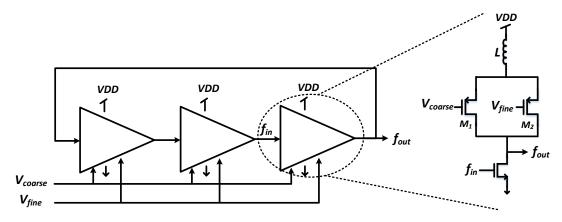

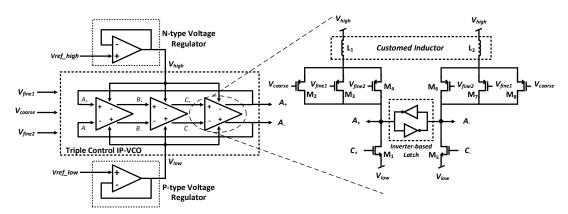

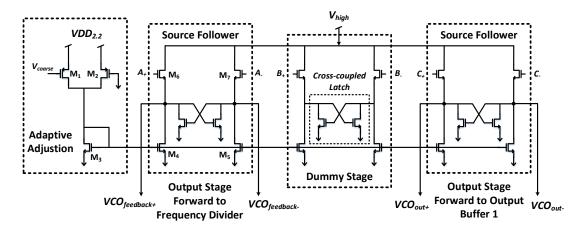

| Fig. 5 - 4 Implemented Inductor Peaking VCO with Voltage Regulation91                                                                                                                                                          |

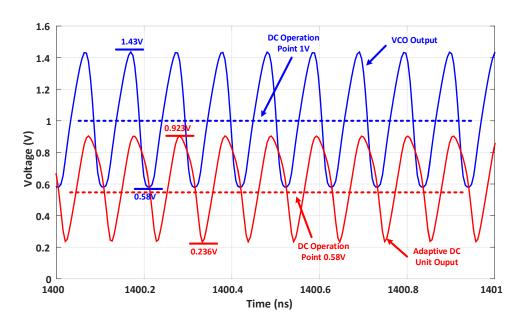

| Fig. 5 - 5 Implementation of Adaptive DC Shifting Unit95                                                                                                                                                                       |

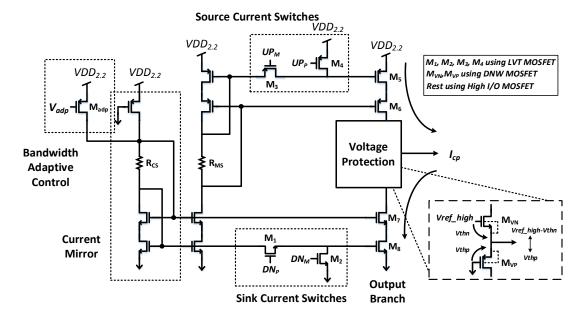

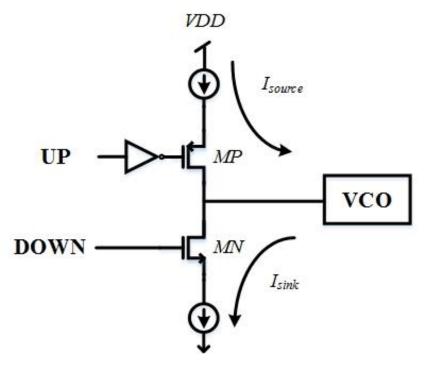

| Fig. 5 - 6 Implementation of Gate Switch Charge Pump with Voltage Protection 97                                                                                                                                                |

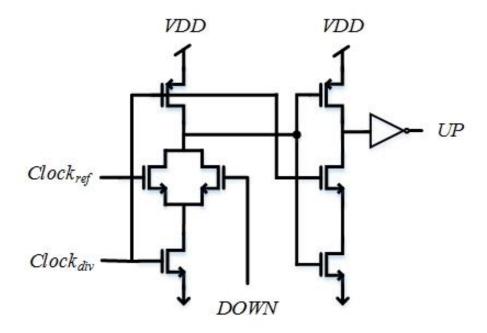

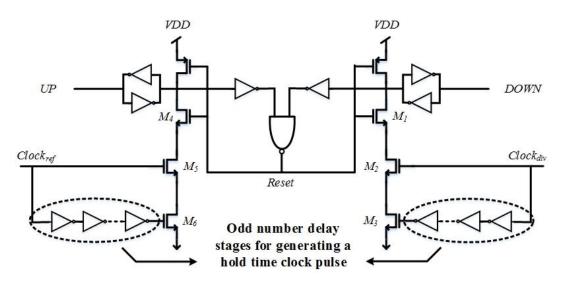

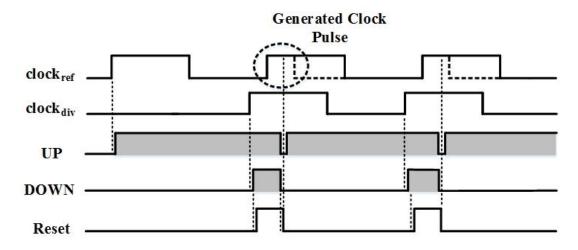

| Fig. 5 - 7 Implementation of Fast Acquisition PFD Error! Bookmark not defined.                                                                                                                                                 |

| Fig. 5 - 8 Implementation of Integer-N Frequency Pre-scaler                                                                                                                                                                    |

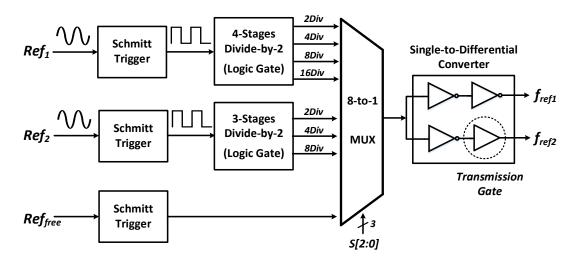

| Fig. 5 - 9 Implementation of Reference Clock Scheme                                                                                                                                                                            |

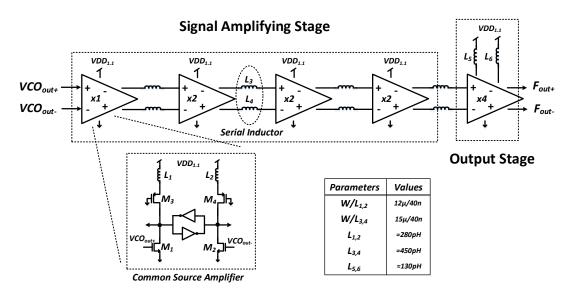

| Fig. 5 - 10 Implemented Structure of Output Buffer 1                                                                                                                                                                           |

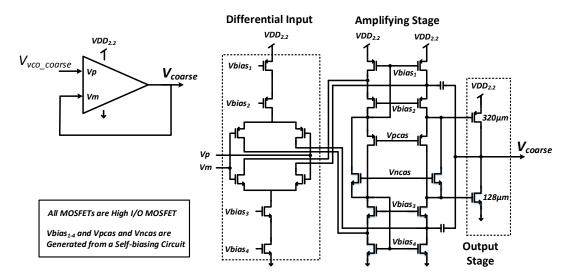

| Fig. 5 - 11 Implemented Structure of Output Buffer 2                                                                                                                                                                           |

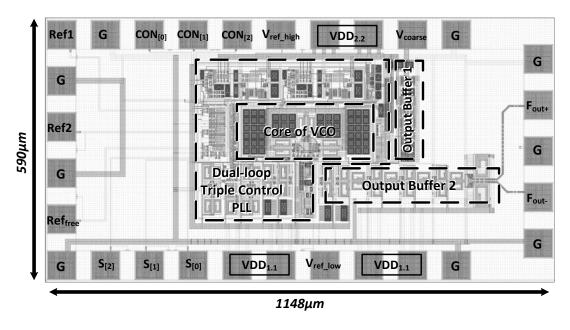

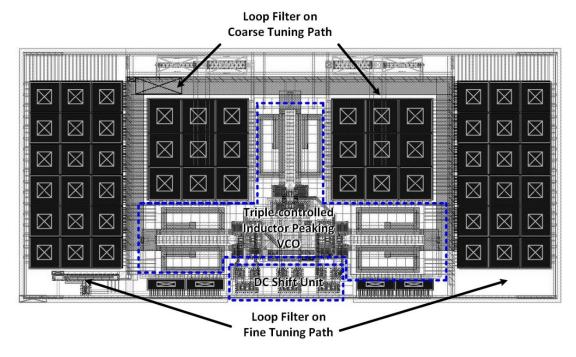

| Fig. 5 - 12 Full Chip Layout of DLTC-PLL in 40nm Process                                                                                                                                                                       |

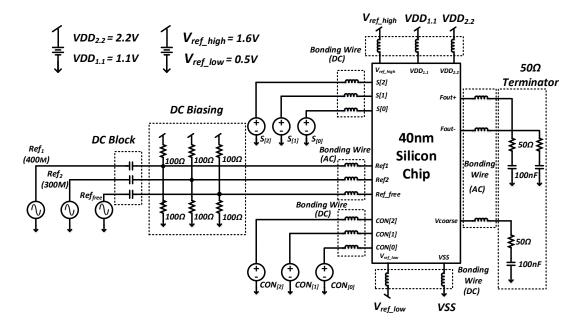

| Fig. 5 - 13 Simulation Test Bench for 40nm DLTC-PLL 108                                                                                                                                                                        |

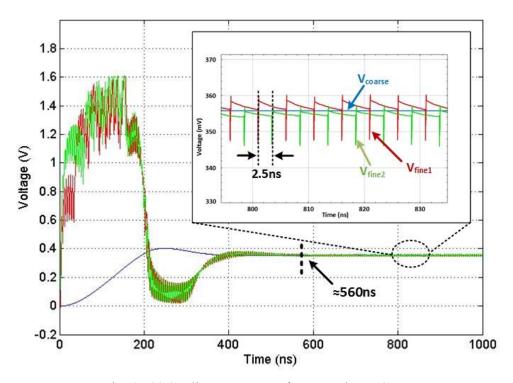

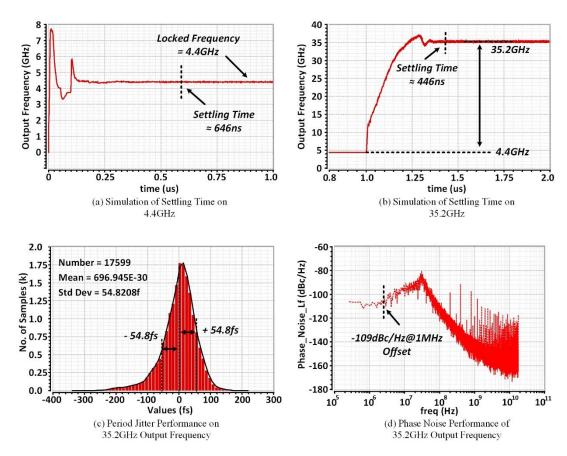

| Fig. 5 - 14 Post Layout Results (a) Transient Respond of 4.4GHz Lock-up Time (b) Transient Respond of 35.2GHz Lock-up Time (c) Period Performance of 35.2GHz Output Frequency (d) Phase Noise Performance of 35.2GHz Frequency |

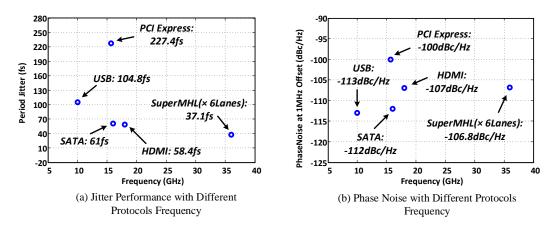

| Fig. 5 - 15 Performance with Different Protocols Frequency (a) Jitter (b) Phase Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

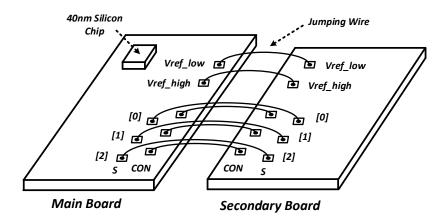

| Fig. 5 - 16 Concept View of PCB Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

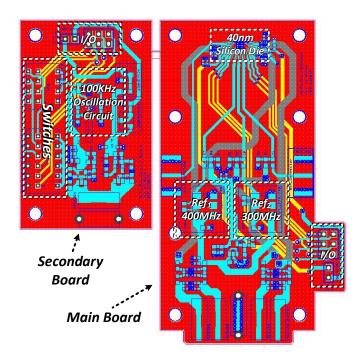

| Fig. 5 - 17 PCBs Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

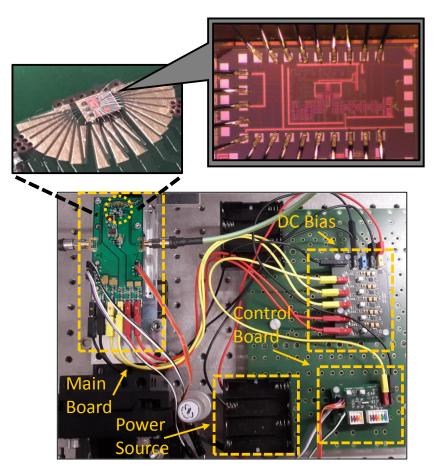

| Fig. 5 - 18 Measurement Environment with Photography of 40nm Silicon Die111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

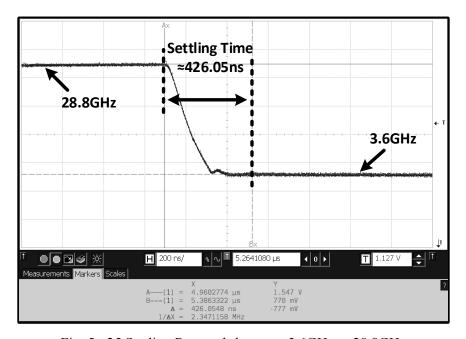

| Fig. 5 - 19 Settling Responds between 3.6GHz to 28.8GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

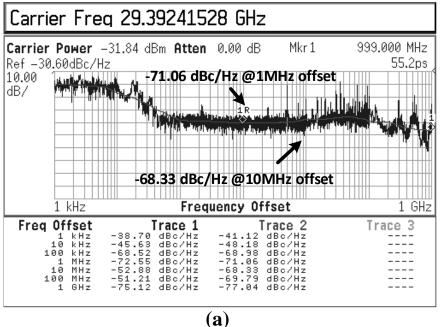

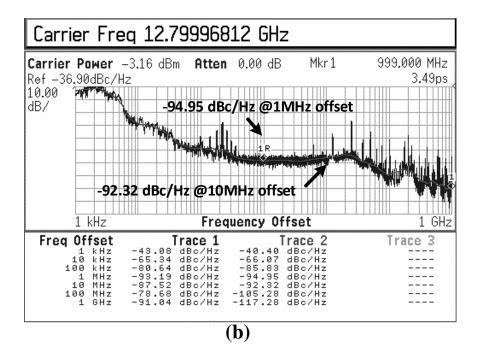

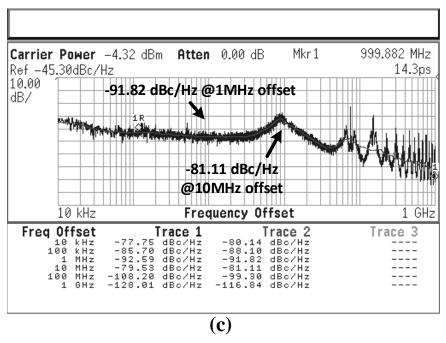

| Fig. 5 - 20 Phase Noise Performance (a) High-frequency Band (b) Middle-frequency Band (c) Low-frequency Band (c) Low-frequency Band (d) Low-frequency Band (e) Low-frequency Band (e) Low-frequency Band (f) L |

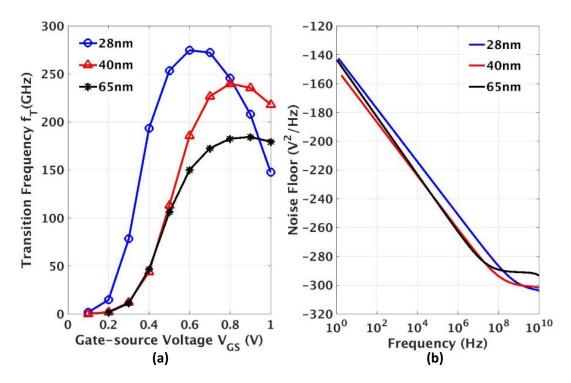

| Fig. 6 - 1 Comparison in Different Process Node (a) Transition Frequency $f_T$ (b) Noise Floor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

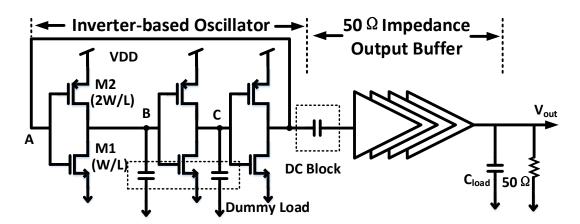

| Fig. 6 - 2 Implemented Inverter-based Oscillator Example Structure with 50Ω Impedance Output Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

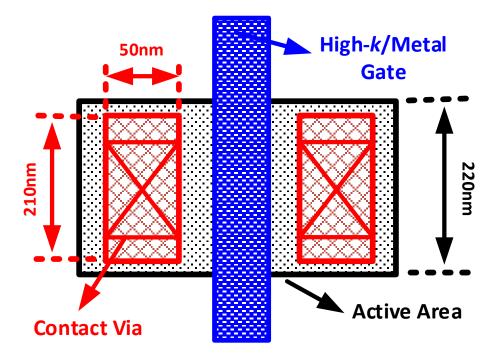

| Fig. 6 - 3 Single Transistor with Minimum Finger Width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

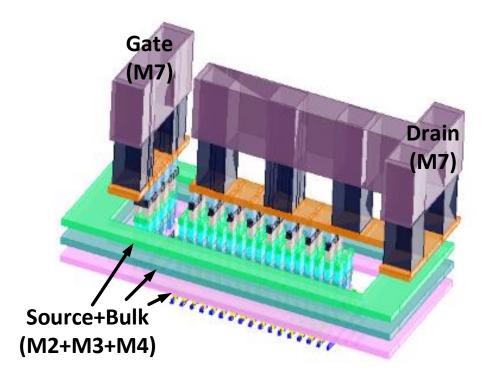

| Fig. 6 - 4 Optimal Transistor Layout with a Finger Width of 440nm123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

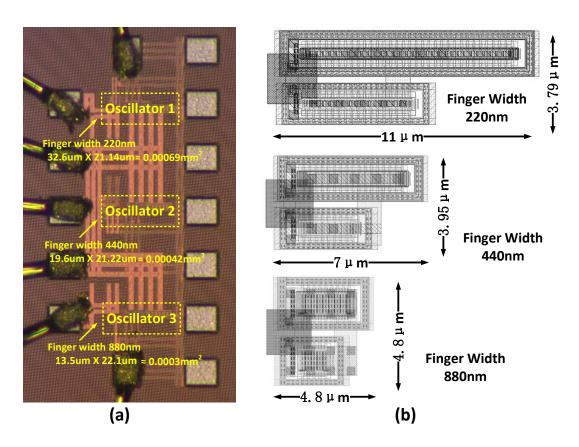

| Fig. 6 - 5 (a) Microscope View of Three Oscillator Examples (b) Layout View of Delay Cell of Three Oscillator Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

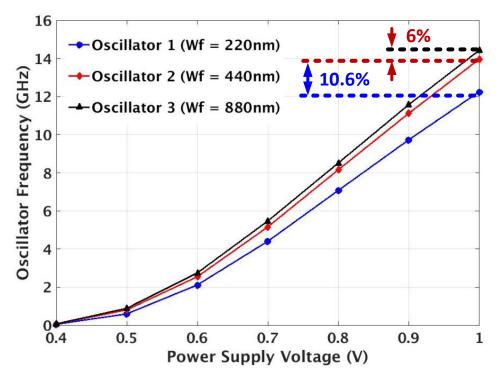

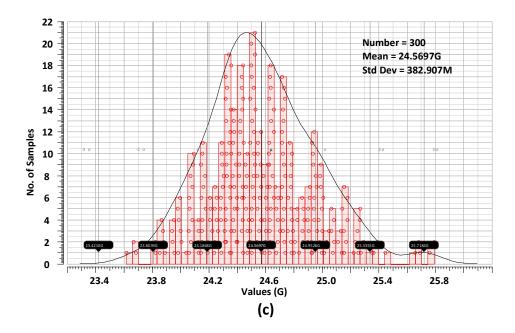

| Fig. 6 - 6 Averaged Measurement Results of Oscillation Frequency of Three Oscillator Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

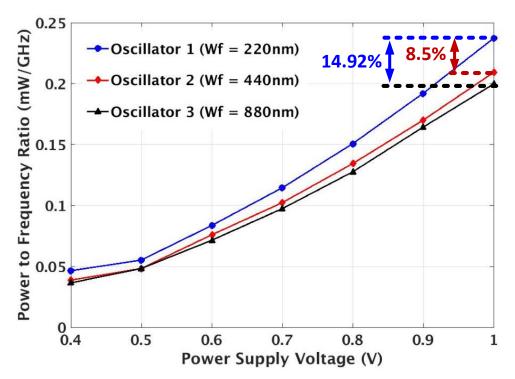

| Fig. 6 - 7Averaged Measurement Results of Power to Frequency Efficiency of Three Oscillator Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

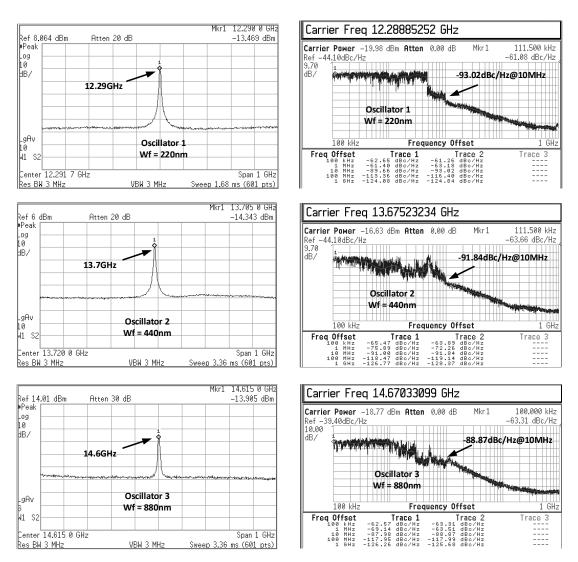

| Fig. 6 - 8 Measured Frequency Spectrum and Phase Noise Results at 1MHz Offset Frequency of Three Oscillator Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

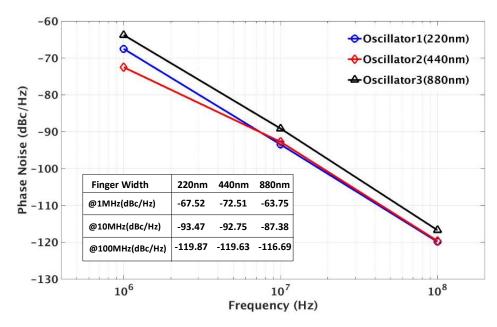

| Fig. 6 - 9 Averaged Phase Noise Performance of Three Oscillator Examples129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

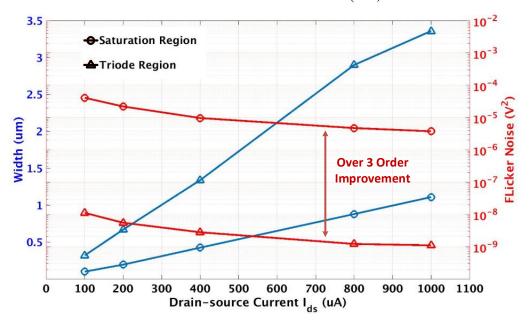

| Fig. 6 - 10 Comparison of Width versus Flicker Noise in Triode and Saturation Region                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

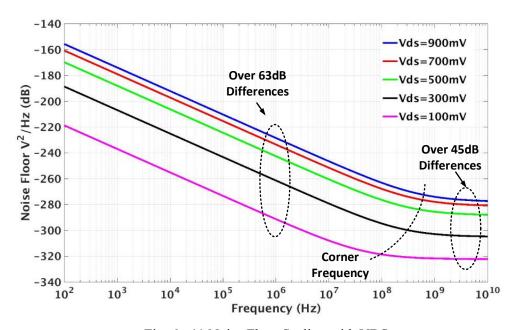

| Fig. 6 - 11 Noise Floor Scaling with VDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

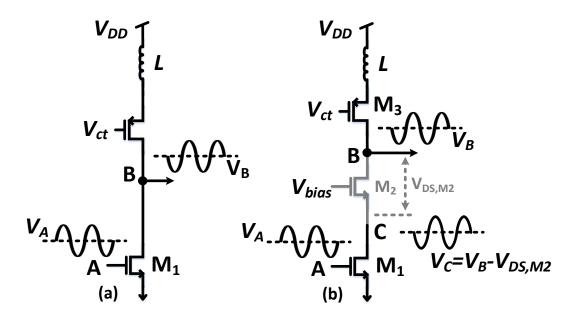

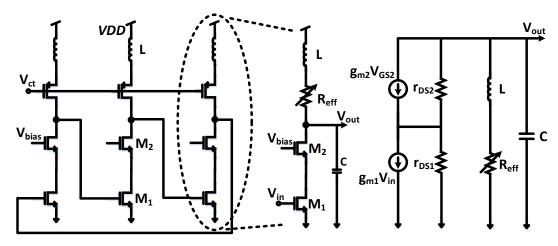

| Fig. 6 - 12 Delay Cell of Inductive Peaking VCO (a) Conventional (b) Proposed wit                                                                                                                                                                   |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Cascode Noise Reduction                                                                                                                                                                                                                             |  |  |  |

| Fig. 6 - 13 Proposed Three Stages Inductive Peaking VCO with Cascode Noise Reduction                                                                                                                                                                |  |  |  |

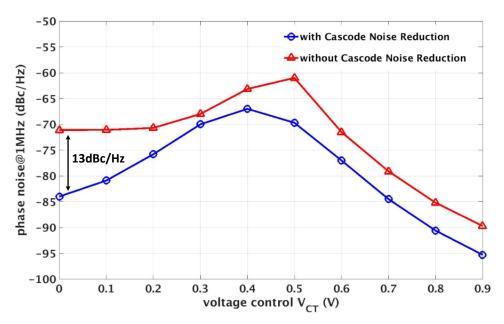

| Fig. 6 - 14 Phase Noise Comparison between Conventional Inductive Peaking VCO                                                                                                                                                                       |  |  |  |

| and Proposed Cascode Noise Reduction VCO during All Frequency Tuning Range                                                                                                                                                                          |  |  |  |

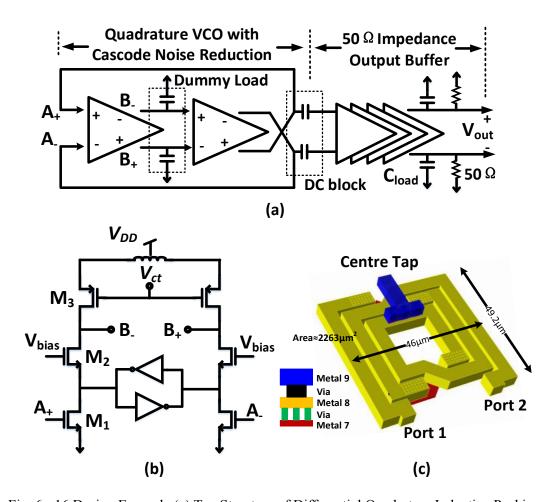

| Fig. 6 - 15 Design Example (a) Top Structure of Differential Quadrature Inductive<br>Peaking VCO with Cascode Noise Reduction and its Output Buffer (b) Differential<br>Delay Cell of Proposed VCO with Symmetric Inductor (c) Layout View of Fully |  |  |  |

| Customized Symmetrical Inductor                                                                                                                                                                                                                     |  |  |  |

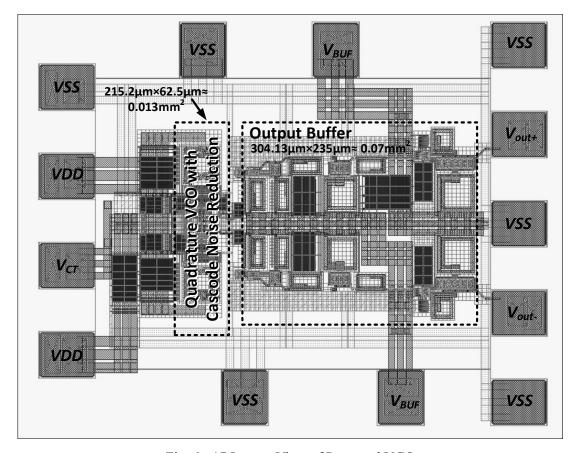

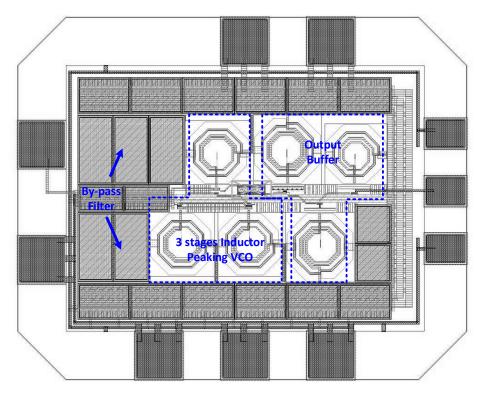

| Fig. 6 - 16 Layout View of Proposed VCO                                                                                                                                                                                                             |  |  |  |

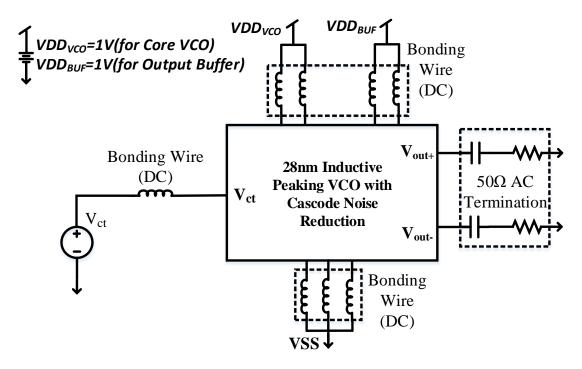

| Fig. 6 - 17 Simulation Testbench 139                                                                                                                                                                                                                |  |  |  |

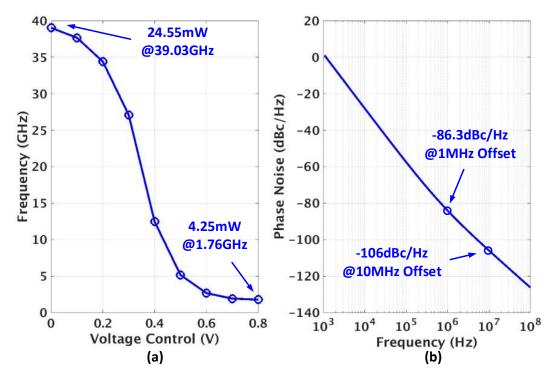

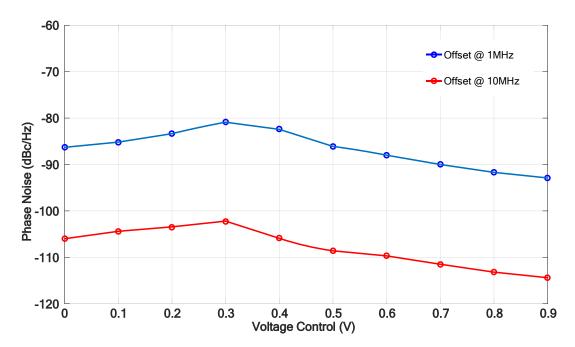

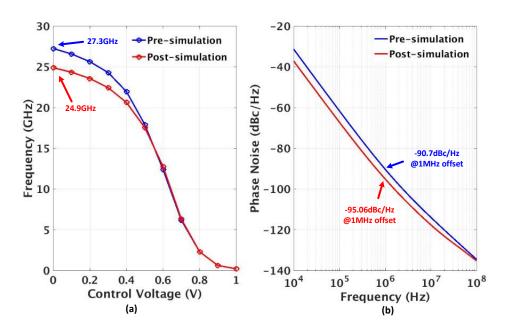

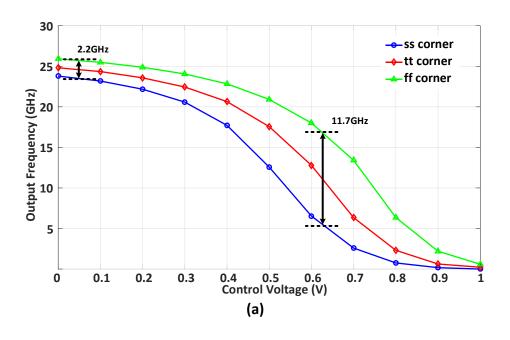

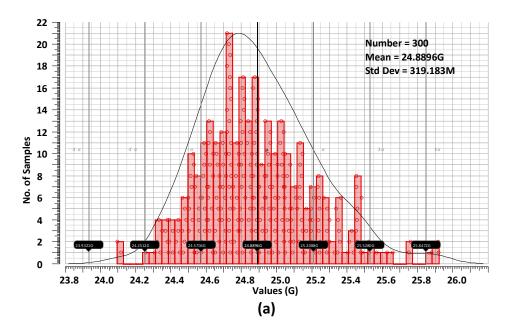

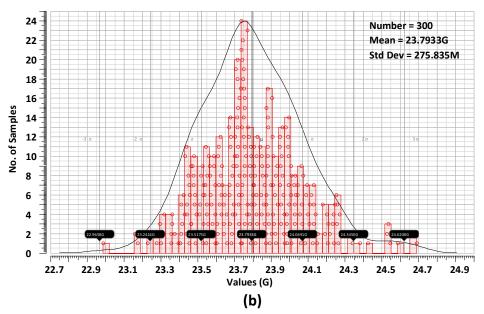

| Fig. 6 - 18 Post-layout Simulation Results (a) Frequency Tuning Range (b) Phase Noise                                                                                                                                                               |  |  |  |

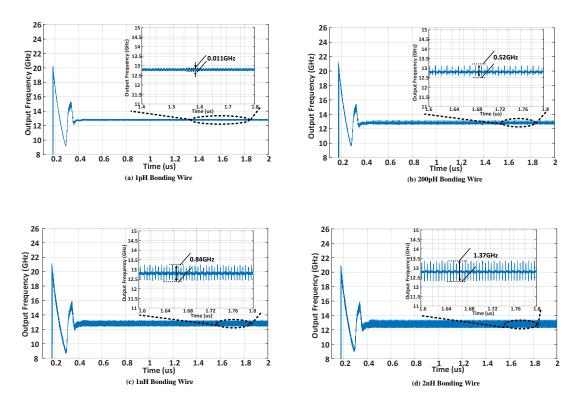

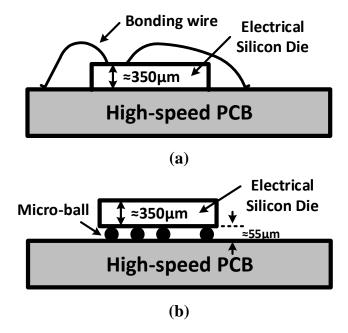

| Fig. 7- 1 Illustrations of Integration (a) Wire Bonding (b) Flip-chip Bonding 146                                                                                                                                                                   |  |  |  |

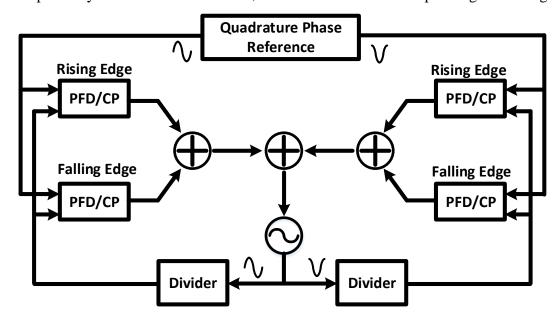

| Fig. 7- 2 Potential Circuit Design based on DLTC-PLL                                                                                                                                                                                                |  |  |  |

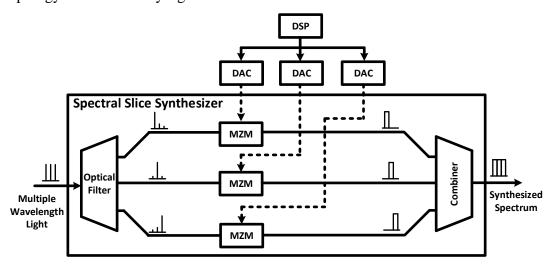

| Fig. 7- 3 Topology of Spectral Slice Synthesizer                                                                                                                                                                                                    |  |  |  |

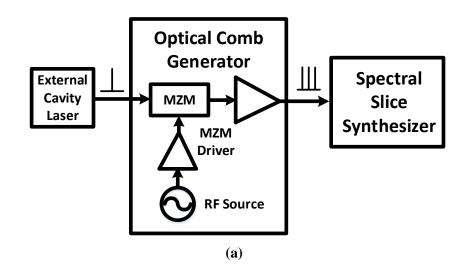

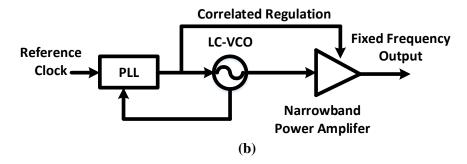

| Fig. 7- 4 (a) Optical Comb Generator (b) Narrowband Clock Generation System for Optical Comb                                                                                                                                                        |  |  |  |

| Fig. A - 1 Oscillatory Changing in Feedback System with Time                                                                                                                                                                                        |  |  |  |

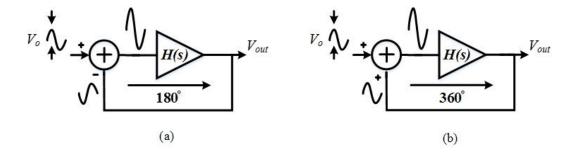

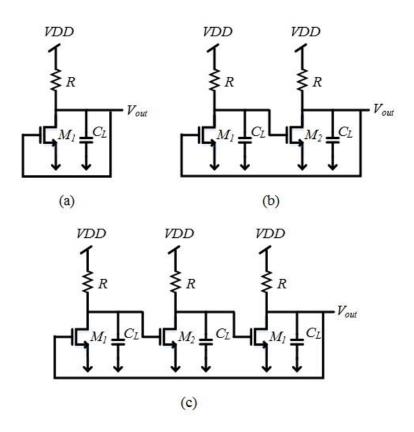

| Fig. A - 2 Common Source Amplifier in Loop with Different Stages: (a) single stage common source amplifier (b) two-stages (c) three stages                                                                                                          |  |  |  |

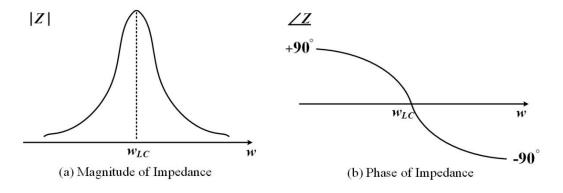

| Fig. A - 3 Magnitude and Phase of the Impedance of an LC Tank                                                                                                                                                                                       |  |  |  |

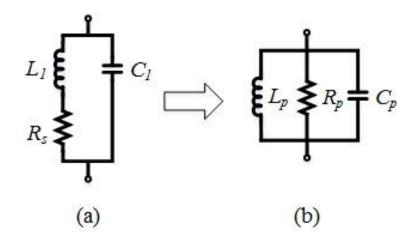

| Fig. A - 4 Conversion of a Tank to Three Parallel Components: (a) Practical LC Tank Configuration. (b) Equivalent Parallel LC Tank Configuration                                                                                                    |  |  |  |

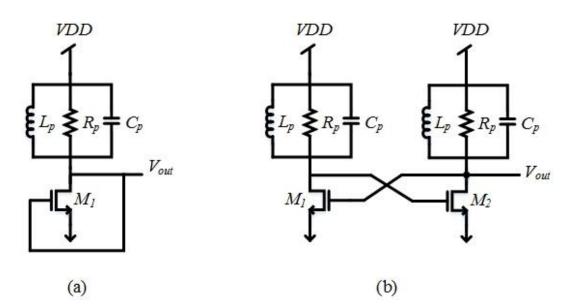

| Fig. A - 5 (a) Single Tuned Stage with LC Load. (b) Two Tuned Stages in a Feedback                                                                                                                                                                  |  |  |  |

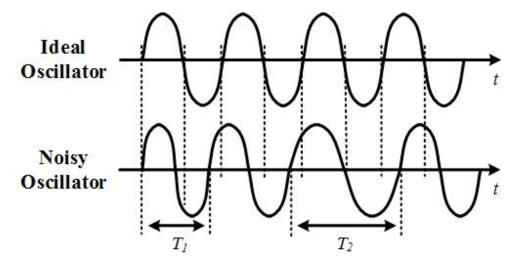

| Fig. A - 6 Noise Interference on Zero Crossing                                                                       |

|----------------------------------------------------------------------------------------------------------------------|

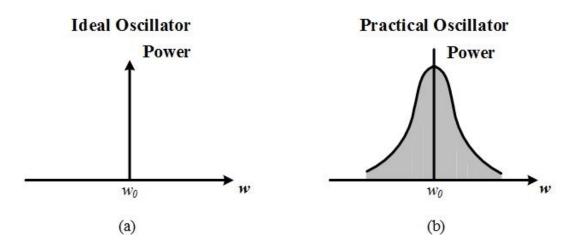

| Fig. A - 7 Power Spectrum Density of Oscillator (a) Ideal Oscillator (b) Practical Oscillator                        |

| Fig. A - 8 Reference Spur on VCO's Tuning Node                                                                       |

| Fig. A - 9 Phase Noise and Reference Spur in Power Spectrum                                                          |

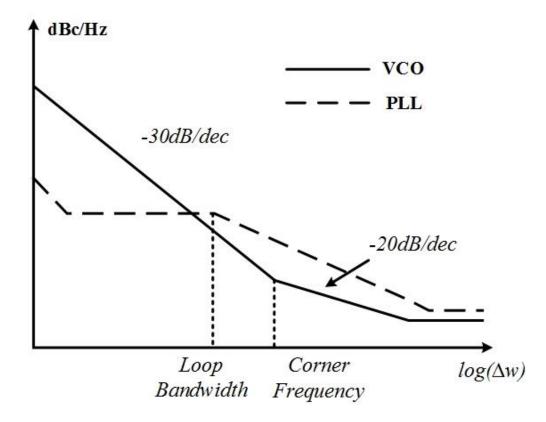

| Fig. A - 10 Phase Noise Comparison between VCO and PLL                                                               |

| Fig. B - 1 (a) Operation of XOR PD (b) The Characteristics of XOR PD161                                              |

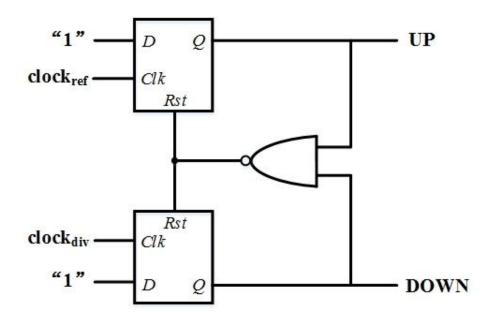

| Fig. B - 2 Common Linear PFD Structure                                                                               |

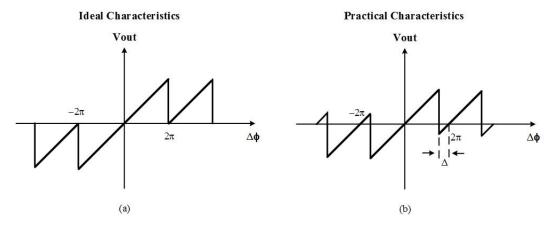

| Fig. B - 3 Characteristics of PFD (a) Ideal (b) Parctical                                                            |

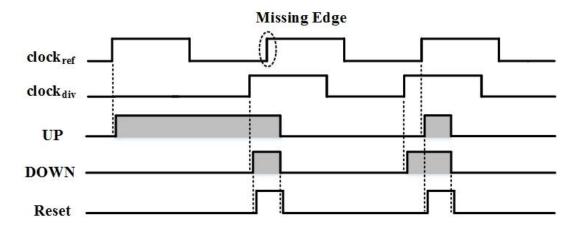

| Fig. B - 4 Non-ideal Behavior of Missing Clock Edge                                                                  |

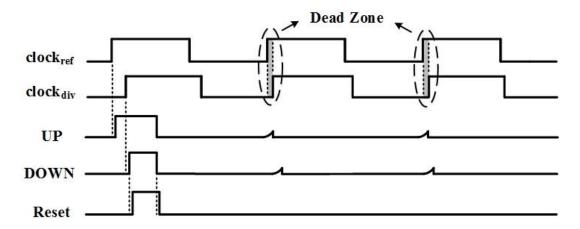

| Fig. B - 5 Non-ideal Behavior of Dead Zone                                                                           |

| Fig. B - 6 Basic Block Diagram of Pre-charge PFD                                                                     |

| Fig. B - 7 Structure of Fast Acquisition Latch-based PFD                                                             |

| Fig. B - 8 Missing Clock Edge Elimination                                                                            |

| Fig. B - 9 Basic Concept of Charge Pump                                                                              |

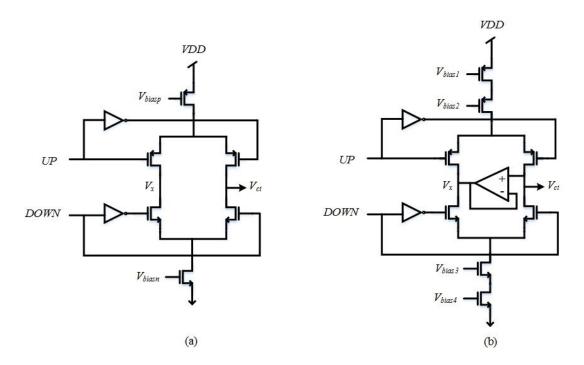

| Fig. B - 10 Practical Implementation of Charge Pump (a) without mismatch cancellation (b) with mismatch cancellation |

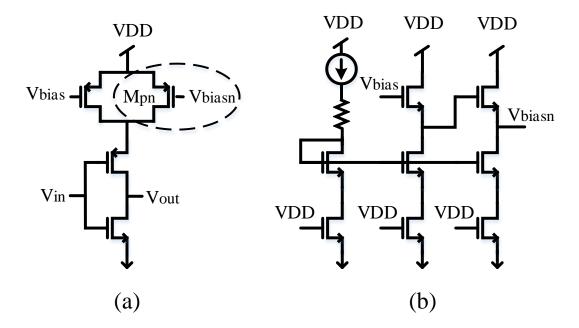

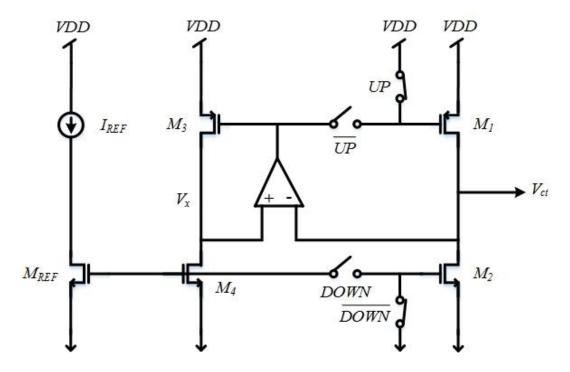

| Fig. B - 11 (a) Regulated Cascade Charge Pump (b) Op-amp Regulated Charge Pump                                       |

|                                                                                                                      |

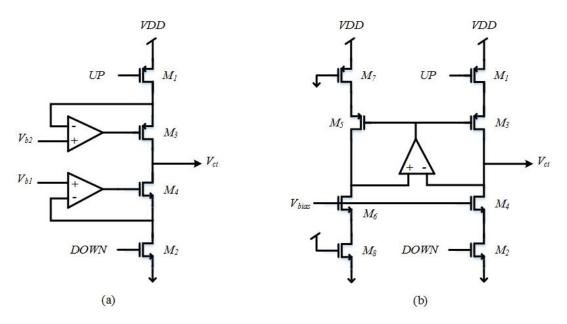

| Fig. B - 12 Gate Switching Charge Pump                                                                               |

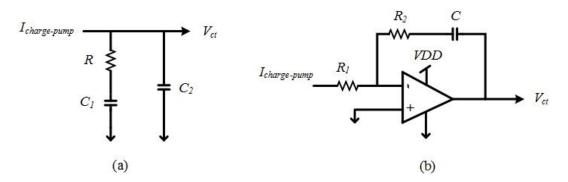

| Fig. B - 13 (a) Passive Loop Filter (b) Active Loop Filter170                                                        |

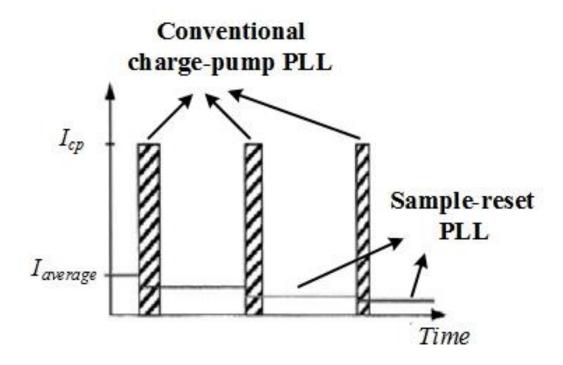

| Fig. B - 14 Dual-path Loop Filter                                                                                    |

| Fig. B - 15 Behavior of Sample-reset Charge Pump                                                                     |

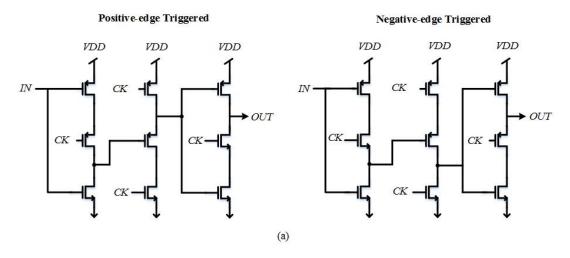

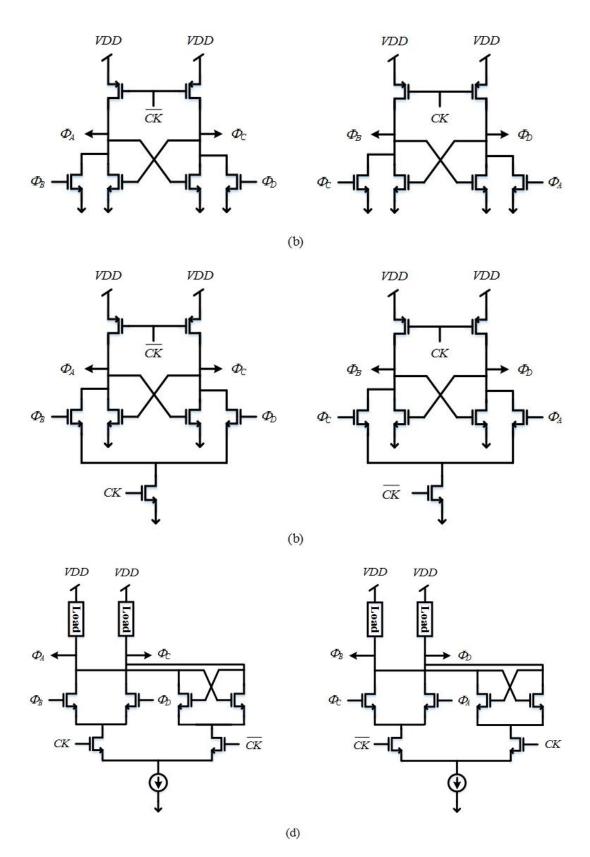

| Fig. B - 16 Alternative Register Structure for Divide-by-2 Frequency Divider (a) True                                |

| Single Phase Clocked (TSPC) (b) Razavi Divider (c) Wang's Topology (d) Current                                       |

| Mode Latch (CML)                                                                                                     |

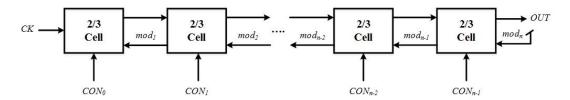

| Fig. B - 17 Architecture of High Dividing Order Programmable Pre-scaler with 2/3 |  |

|----------------------------------------------------------------------------------|--|

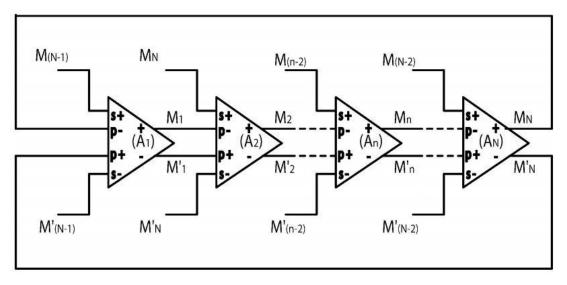

| Dual-modulus Divider                                                             |  |

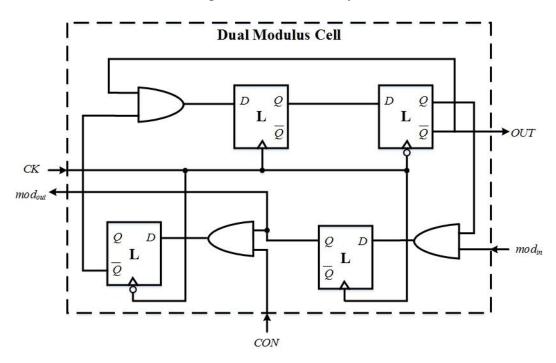

| Fig. B - 18 Structure Diagram of Dual Modulus Cell                               |  |

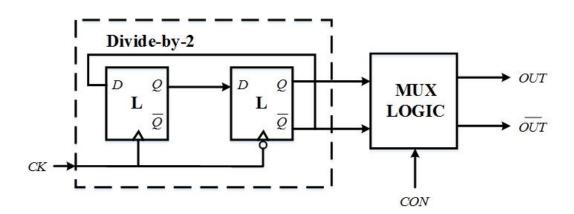

| Fig. B - 19 Divide-by-2/3 Dual Modulus by Multiplexing Logic                     |  |

# **List of Tables**

| Table 1- 1 Widely Applied Communication Protocols and Corresponding Data Rate6         |

|----------------------------------------------------------------------------------------|

| Table 2 - 1 Examples of Transceiver with Corresponding Clock in Present Research Works |

| Table 3 - 1 Key Parameters of Four Design Examples                                     |

| Table 3 - 2 Performance Summary and Comparison                                         |

| Table. 4 - 1 Parameter's Configuration Values of CP-PLL                                |

| Table. 4 - 2 Parameter's Configuration Values of DT-PLL74                              |

| Table. 4 - 3 Performance Comparison between CP-PLL, DT-PLL and Proposed DLTC-PLL       |

| Table 5 - 1 Detailed Parameters of Inductor Peaking VCO in DLTC-PLL92                  |

| Table 5 - 2 Detailed Parameters in Adaptive DC Shifting Unit96                         |

| Table 5 - 3 Look-up Table of Potential Output Frequencies                              |

| Table 5 - 4 Chip Details                                                               |

| Table 5 - 5 Parameters of Testing for High, Middle and Low Frequency Band113           |

| Table 5 - 6 Performance Comparison of DLTC-PLL with Recent Works115                    |

| Table 6 - 1 Key Parameters of Three Oscillator Examples                                |

| Table 6 - 2 Cell Area and Parasitic Parameters of Three Oscillator Examples124         |

| Table 6 - 3 Averaged FOM of Three Oscillator Design Examples                           |

| Table 6 - 4 Key Parameters of Design Example                                           |

| Table 6 - 5 Performance Summary and Comparisons                                        |

| Table C - 1 Measurement Results from 6 Different Wafers                                |

# **Academic Thesis: Declaration Of Authorship**

| <b>I</b> , ] | Fanfan Meng, declare that this thesis and the work presented in it are my own and        |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------|--|--|--|--|

| ha           | has been generated by me as the result of my own original research.                      |  |  |  |  |

|              | Clock Generation for Silicon Photonics based Optical Communication Systems.              |  |  |  |  |

|              | onfirm that:                                                                             |  |  |  |  |

| 1.           | This work was done wholly or mainly while in candidature for a research degree at this   |  |  |  |  |

|              | University;                                                                              |  |  |  |  |

| 2.           | Where any part of this thesis has previously been submitted for a degree or any other    |  |  |  |  |

|              | qualification at this University or any other institution, this has been clearly stated; |  |  |  |  |

| 3.           | Where I have consulted the published work of others, this is always clearly attributed;  |  |  |  |  |

| 4.           | Where I have quoted from the work of others, the source is always given. With the        |  |  |  |  |

|              | exception of such quotations, this thesis is entirely my own work;                       |  |  |  |  |

| 5.           | I have acknowledged all main sources of help;                                            |  |  |  |  |

| 6.           | Where the thesis is based on work done by myself jointly with others, I have made        |  |  |  |  |

|              | clear exactly what was done by others and what I have contributed myself;                |  |  |  |  |

| 7.           | Parts of this work have been published as listed in Chapter 3 and Chapter 6.             |  |  |  |  |

| Sig          | gned: Fanfan Meng                                                                        |  |  |  |  |

| Da           | nte: 02/03/2018                                                                          |  |  |  |  |

# Acknowledgements

First and foremost, I would like to take this opportunity to thank all my supervisors, Professor Graham Reed, for providing me with a chance to participate in silicon photonics projects and the supports of practical experiments. Without it, I would not have built up my skills and experiences, and all the ideas will not come into solid achievements. Professor Peter Wilson, for giving me an opportunity to start my PhD journey and all the advice throughout my PhD study. Without his help, this thesis would not have been possible. Dr. Ke, Li, for enlightening my mind in this area, with his knowledge and patient guidance I am able to establish my learning curve in various aspects within each step of the project.

I would also like to thank all the colleagues in the silicon photonics group, especially, Dr. David Thomson and Dr. Cosimo Lacava, for their precious advice and support during the experiment testing. Furthermore, special thanks also go to my colleague, Shenghao Liu, for all his encouragement and help from the first day of my PhD.

Finally, I want to acknowledge my parents, who gave me the financial support and strength during my PhD studying life. I will always owe them for their support, which cannot be counted and redeemed. In addition, further thanks goes to my girlfriend for her encouragement and company in my most frustrated moment.

This thesis records the journey and accomplishment in my PhD life over the past four years. I would like to dedicate this thesis to my parents and my friends for appreciating all the company and strength they have given me.

## **Definitions and Abbreviations**

AAC Automatic amplitude control

ADC Analogue-to-digital converter

AWG Arbitrary waveform generator

BPG Bit pattern generator