#### UNIVERSITY OF SOUTHAMPTON

#### FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

Electronics and Computer Science

Reliability of Analogue Circuits

by

Illani Mohd Nawi

Thesis for the degree of Doctor of Philosophy

September 2018

Academic Thesis: Declaration of

Copyright

Copyright © and Moral Rights for this thesis, and, where applicable, any accompanying data are retained by author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Author (Year of Submission) "Full thesis title", University of Southampton, name of the University Faculty or School or Department, PhD Thesis, pagination.

Data: Author (Year) Title: URI [dataset]

# Academic Thesis: Declaration of Authorship

I, Illani Mohd Nawi, declare that this thesis and the work presented in it are my own and have been generated by me as the result of my own original research.

#### Reliability of Analogue Circuits

#### I confirm that:

- 1. This work was done wholly or mainly while in candidature for a research degree at this University;

- 2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- 3. Where I have consulted the published work of others, this is always clearly attributed;

- 4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- 5. I have acknowledged all main sources of help;

- 6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- 7. Either none of this work has been published before submission, or parts of this work have been published as listed in Section 1.8 of this thesis.

#### UNIVERSITY OF SOUTHAMPTON

#### ABSTRACT

#### FACULTY OF PHYSICAL SCIENCES AND ENGINEERING Electronics and Computer Science

Doctor of Philosophy

#### RELIABILITY OF ANALOGUE CIRCUITS

by Illani Mohd Nawi

The reliability of CMOS circuits has worsened due to technology scaling. From the review of previous work on reliability study for CMOS circuits, it has been found that both digital and analogue circuits were susceptible to single event effects. Single event effects although causing non-permanent errors have already been identified to have caused billion of dollars worth of lost. Single event transients have been established as one of the single event effects which may reduce the reliability of analogue circuits and safety critical systems, in general. The impact of radiation effects on analogue circuits has been investigated in this thesis using circuit-level single event transient modelling. The characterization of impact of single event transient has been investigated for several analogue circuits. These analogue circuits; namely operational amplifier and comparator, have been recognized to be susceptible to single event transients. Several influencing factors have been associated with previous works and this study to have impacts on the severity of the single event transients to these circuits. Sensitivity analysis has been completed to determine the most and the least sensitive transistor to be used in the variability analysis. The variability analysis addresses the impact of the influencing factors and this information may be used in finding the trade-off which exists between the influencing factors and single event transient. These trade-offs may also be used in mitigating the single event transient. A simple mitigation technique still at preliminary stage has also been included, as part of this study.

# Contents

| A | ckno | wledge       | ments      |                                                                     | xiii |  |  |

|---|------|--------------|------------|---------------------------------------------------------------------|------|--|--|

| N | omer | ıclatur      | e          |                                                                     | xxi  |  |  |

| 1 | Intr | Introduction |            |                                                                     |      |  |  |

|   | 1.1  | Radia        | tion Effec | ets in Safety-Critical Systems                                      | . 2  |  |  |

|   | 1.2  | Soft E       | rrors in V | VLSI Circuits                                                       | . 4  |  |  |

|   | 1.3  | Single       | Event Tr   | ransients in Analogue Circuits                                      | . 4  |  |  |

|   | 1.4  | Curre        | nt Trends  | in Soft Error Mitigations                                           | . 6  |  |  |

|   | 1.5  | Resear       | ch Motiv   | rations and Objectives                                              | . 7  |  |  |

|   | 1.6  | Contri       | butions .  |                                                                     | . 8  |  |  |

|   | 1.7  | Thesis       | Organiza   | ation                                                               | . 8  |  |  |

|   | 1.8  | List of      | Publicat   | zions                                                               | . 9  |  |  |

| 2 | Lite | erature      | Review     | 7                                                                   | 11   |  |  |

|   | 2.1  | Radia        | tion-indu  | ced Faults                                                          | . 11 |  |  |

|   | 2.2  | Dynan        | nic Mitig  | ation Design Flow                                                   | . 12 |  |  |

|   | 2.3  | Single       | Event Tr   | ransients Characterization in Analogue Circuits                     | . 14 |  |  |

|   |      | 2.3.1        | Single E   | Event Transients in Operational Amplifiers                          | . 14 |  |  |

|   |      | 2.3.2        | Single E   | Event Transients in Comparators                                     | . 15 |  |  |

|   |      |              | 2.3.2.1    | Single Event Transients in High Sampling Circuits                   | . 18 |  |  |

|   |      | 2.3.3        | SETs in    | Analogue Circuits with Memory Mechanisms                            | . 18 |  |  |

|   |      | 2.3.4        | Selected   | Analogue Circuits for Investigations                                | . 20 |  |  |

|   | 2.4  | Genera       | al Operat  | ions and Topology of Selected Analogue Circuits                     | . 21 |  |  |

|   |      | 2.4.1        | Operation  | onal Amplifier Operations                                           | . 21 |  |  |

|   |      | 2.4.2        | Operation  | onal Amplifiers Topology                                            | . 22 |  |  |

|   |      | 2.4.3        | Compar     | ator Operations                                                     | . 23 |  |  |

|   |      | 2.4.4        | Compar     | ator Topology                                                       | . 25 |  |  |

|   | 2.5  | Chara        | cterizing  | Soft Errors                                                         | . 25 |  |  |

|   |      | 2.5.1        | Charact    | erizations at Physical-level                                        | . 26 |  |  |

|   |      | 2.5.2        | Charact    | erizations at Device-level                                          | . 28 |  |  |

|   |      | 2.5.3        | Charact    | erizations at Circuit-level                                         | . 29 |  |  |

|   |      |              | 2.5.3.1    | Modelling critical charge using double exponential model            | 32   |  |  |

|   |      |              | 2.5.3.2    | Modelling critical charge using simplified double exponential model | . 34 |  |  |

|   |      |              | 2.5.3.3    | Modelling critical charge using dual-double exponential model       | . 34 |  |  |

|   |      |              | 2.5.3.4    | Limitations in modelling critical charge at circuit-level .         | . 37 |  |  |

X CONTENTS

|   |     | 2.5.4   | Soft Error Rate, SER                                             | 37    |

|---|-----|---------|------------------------------------------------------------------|-------|

|   | 2.6 | Factor  | s influencing Single Event Transients                            | 38    |

|   |     | 2.6.1   | Device-related Factors                                           | 39    |

|   |     |         | 2.6.1.1 Technology scaling                                       | 39    |

|   |     |         | 2.6.1.2 Parasitics                                               | . 41  |

|   |     | 2.6.2   | Environmental Factor                                             | . 41  |

|   |     |         | 2.6.2.1 Temperature                                              | 41    |

|   |     | 2.6.3   | Device's Parameter and Topology Factor                           | 42    |

|   |     |         | 2.6.3.1 Biasing conditions                                       | 42    |

|   |     |         | 2.6.3.2 Positive feedback                                        | . 42  |

|   |     | 2.6.4   | Temporal Unreliability Effects Factor                            | 43    |

|   |     |         | 2.6.4.1 Ageing - NBTI                                            | 43    |

|   | 2.7 | Design  | of Experiments Methodology                                       | 43    |

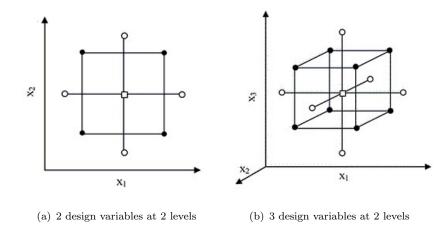

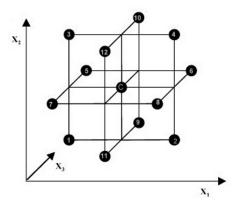

|   |     | 2.7.1   | Full factorial                                                   | 44    |

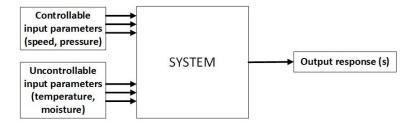

|   |     | 2.7.2   | Response Surface Methodology                                     | 48    |

|   |     | 2.7.3   | General Steps in Completing Design of Experiments                | 49    |

|   |     | 2.7.4   | Planning Phase                                                   |       |

|   |     | 2.7.5   | Designing Phase                                                  |       |

|   |     | 2.7.6   | Conducting Phase                                                 |       |

|   |     | 2.7.7   | Analyzing Phase                                                  |       |

|   | 2.8 | Mitiga  | tions of Single Event Transients                                 |       |

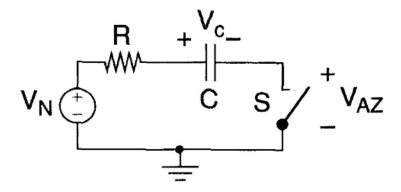

|   |     | 2.8.1   | Auto-zeroing Technique                                           |       |

|   |     | 2.8.2   | Analogue Voting                                                  |       |

|   | 2.9 | Summ    | ary                                                              | 58    |

| 3 | Cha | ractor  | ization of CMOS Analogue Electronic Circuits                     | 61    |

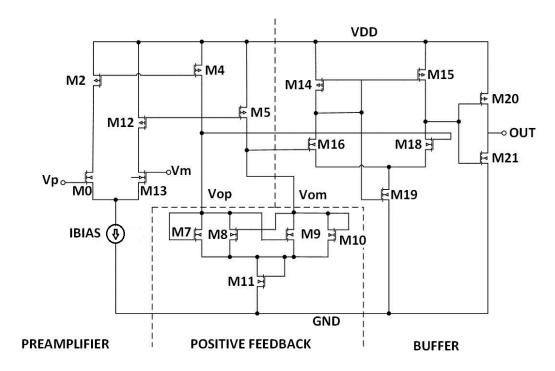

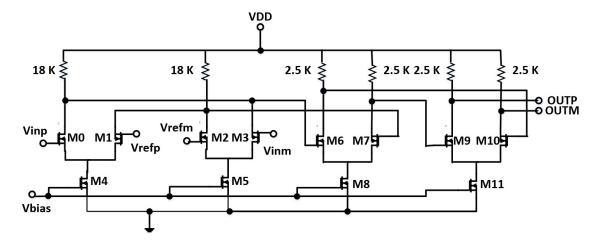

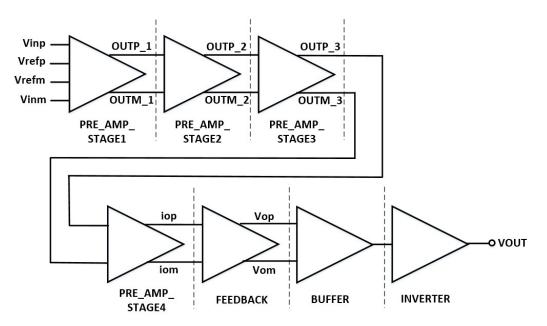

| J | 3.1 |         | resis-free Comparator Design                                     |       |

|   | 5.1 | 3.1.1   | Designing the input stage: pre-amplification                     |       |

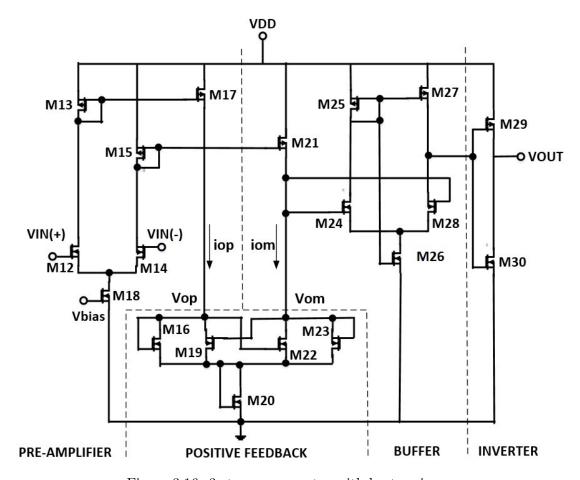

|   |     | 3.1.2   | Designing the decision stage: decision circuit                   |       |

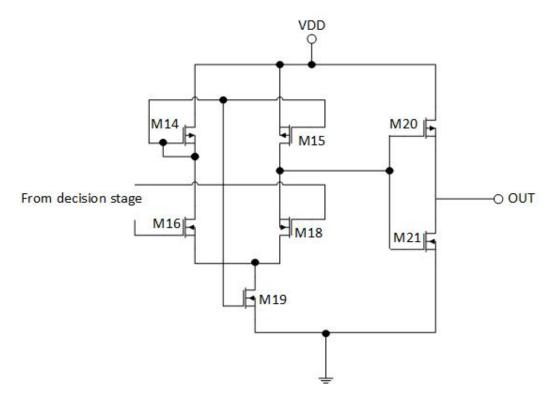

|   |     | 3.1.3   | Designing the output stage: post-amplification                   |       |

|   | 3.2 |         | Circuit-level Characterizations for Hysteresis-free Comparator   |       |

|   | J   | 3.2.1   | Standard Testing Parameters for SET Characterizations            |       |

|   |     | 3.2.2   | Preliminary SET Characterizations                                |       |

|   |     | 3.2.3   | Sensitivity Analysis on Hysteresis-free Comparator               |       |

|   | 3.3 |         | arator-with-hysteresis Design                                    |       |

|   |     | 3.3.1   | Hysteresis                                                       |       |

|   | 3.4 |         | Circuit-level Characterizations for Comparator-with-hysteresis   |       |

|   |     | 3.4.1   | Preliminary SET characterizations                                |       |

|   |     | 3.4.2   | Sensitivity Analysis on Comparator-with-hysteresis               |       |

|   | 3.5 | 2-stage | e Operational Amplifier Design                                   |       |

|   |     | 3.5.1   | Designing stage 1: input stage                                   |       |

|   |     | 3.5.2   | Designing stage 2: output stage                                  |       |

|   | 3.6 | SET C   | Circuit-level Characterizations of 2-stage Operational Amplifier |       |

|   |     | 3.6.1   | Preliminary SET characterizations                                |       |

|   |     | 3.6.2   | Sensitivity Analysis on 2-stage Operational Amplifier            |       |

|   | 3.7 | Using   | Different SET Model Parameters                                   |       |

|   | 3.8 | Summ    | ary                                                              | . 105 |

CONTENTS xi

| 4            | Var          | iability           | Analysis of CMOS Comparators                                        | 107    |

|--------------|--------------|--------------------|---------------------------------------------------------------------|--------|

|              | 4.1          | Variab             | oility Analysis of Hysteresis-free Comparator                       | . 107  |

|              |              | 4.1.1              | Response Surface Methodology In Optimizing No. of Experiment        | s 107  |

|              |              | 4.1.2              | Modelling and Impact of Variability for Radiation-free Hysteresis-  |        |

|              |              |                    | free Comparator                                                     | . 108  |

|              |              | 4.1.3              | Modelling and Impact of Variability on Most Vulnerable Transist     | or 110 |

|              |              | 4.1.4              | Modelling and Impact of Variability on Least Vulnerable Transist    | or 114 |

|              | 4.2          |                    | t of Selected Influencing Factors on SET for Irradiated Comparator- |        |

|              |              | with-h             | ysteresis                                                           | . 115  |

|              |              | 4.2.1              |                                                                     |        |

|              |              | 4.0.0              | voltage                                                             |        |

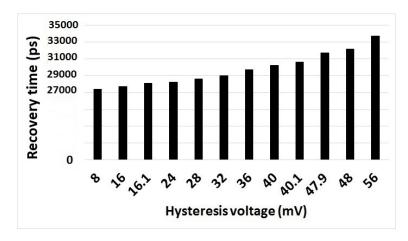

|              |              | 4.2.2              | Impact of hysteresis voltage                                        |        |

|              | 4.0          | 4.2.3              | Impact of NBTI                                                      |        |

|              | 4.3          |                    | Capacitance to Mitigate Single Event Transients for Comparator-     |        |

|              | 4.4          |                    | ysteresis                                                           |        |

|              | 4.4          | Summ               | ary                                                                 | . 124  |

| 5            | Con          | clusio             | ns and Future Work                                                  | 127    |

|              | 5.1          | Conch              | usions                                                              | . 127  |

|              |              | 5.1.1              | Objective 1                                                         | . 127  |

|              |              | 5.1.2              | Objective 2                                                         | . 129  |

|              |              | 5.1.3              | Objective 3                                                         | . 130  |

|              | 5.2          | Descri             | ption of Publications                                               | . 131  |

|              |              | 5.2.1              | Reliability Analysis of Comparators                                 | . 131  |

|              |              | 5.2.2              | Ageing Impact on a High Speed Voltage Comparator                    | . 132  |

|              |              | 5.2.3              | The Influence of Hysteresis Voltage on Single Event Transients in   |        |

|              |              |                    | a 65 nm CMOS High Speed Comparators                                 |        |

|              | 5.3          | Potent             | tial Journal Publication                                            | . 132  |

|              | 5.4          | Limita             | ations                                                              | . 133  |

|              | 5.5          |                    | oility of the Dynamic Mitigation Flowchart used throughout the the  |        |

|              | 5.6          |                    | e Works                                                             |        |

|              |              |                    | Using Actual Radiation Data for 120-nm and 65-nm CMOS Device        | es 135 |

|              |              | 5.6.2              | Extending The Correlation Investigations for Other Design Facto     | rs 135 |

|              |              | 5.6.3              | Extending The Impact of Ageing On Sensitivity of Circuits to SE     |        |

|              |              | 5.6.4              | Extending The Preliminary Mitigation Technique using Capaci-        |        |

|              |              |                    | tors Connected to Transistor Terminals                              |        |

|              |              | 5.6.5              | Redesigning The Comparators under Parasitics Considerations .       | . 136  |

| A            | Hys          | teresis            | s-free Comparator Analysis                                          | 137    |

| В            | Con          | nparat             | or-with-hysteresis Analysis                                         | 143    |

| $\mathbf{C}$ | <b>2</b> -st | age O <sub>l</sub> | perational Amplifier Analysis                                       | 149    |

| Re           | efere        | nces               |                                                                     | 153    |

#### Acknowledgements

To Prof Mark Zwolinski and Dr Basel Halak, for supervising and being understanding throughout the journey. Thank you for showing me that PhD is not just getting to the end but more of the journey itself.

To Dr Alex Weddell, my internal examiner, and Prof Franco Fummi, my external examiner; thank you for the feedbacks throughout my PhD journey.

To Dr Andy Gravell, thank you for the support towards the end of my PhD journey. To Mr Eric Cooke and the tutor team of the Electronics and Computer Science department, I thank you. To the Financial Assistance office for providing my daughter's childcare fees and the Counselling and Advise centre; especially to Ms Liz Mace and Mr Krishan Mistry, I cannot thank both of you enough for saving me.

To Majlis Amanah Rakyat (MARA), the Malaysian government agency for the study loan awarded and for providing this lifetime opportunity.

To my late father and mother, I miss both of you so much and I dedicate this to both of you. To Umi, thank you for every prayers. I love you.

To my spouse, things have been rough for the past 7 years. I hope the gap left between us would be able to be patched in time.

To my darling daughter, to the better days for our little family. Mama loves you so much.

To my siblings and their family, as a part of the entity who made me what I am today.

To fellow colleagues, especially Ibrahim, Syafiq, Radi, Sabirah, Hazrin, Izzati, Fara, Azlin, Alisa, Hazlina, Azura, Huda, Zetty, Yang Lin and Haider; a big thank you. To my other fellow Malaysians, especially Marinah, Asma, Fiza, Husna, Siti, Zawana, Azura, Mas, Syafiqah, Edora, Rahimah, Asidah, Rasidah, Ira and many more. I am glad that I knew each and every one of you.

To newly acquainted friends and now, my lifetime buddies, Durra Abdul Razak and Rusniza Abdul Rahman, thank you for giving your ears, eyes and shoulders to cry on.

To Tracy and Christelle, I wish our friendship will not end here.

This is to the start of a new journey.

# List of Figures

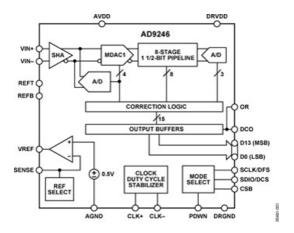

| 1.1  | Analog Devices AD9246 Analogue to Digital Converter                                                                                                              | -  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

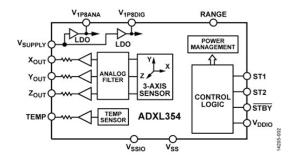

| 1.2  | Analog Devices ADXL354 Accelerometer with Analogue Output                                                                                                        | Ē  |

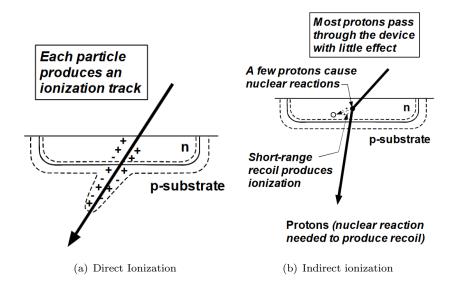

| 2.1  | Radiation-induced elements hit the silicon layers and produces ion tracks either by direct or indirect mechanisms                                                | 12 |

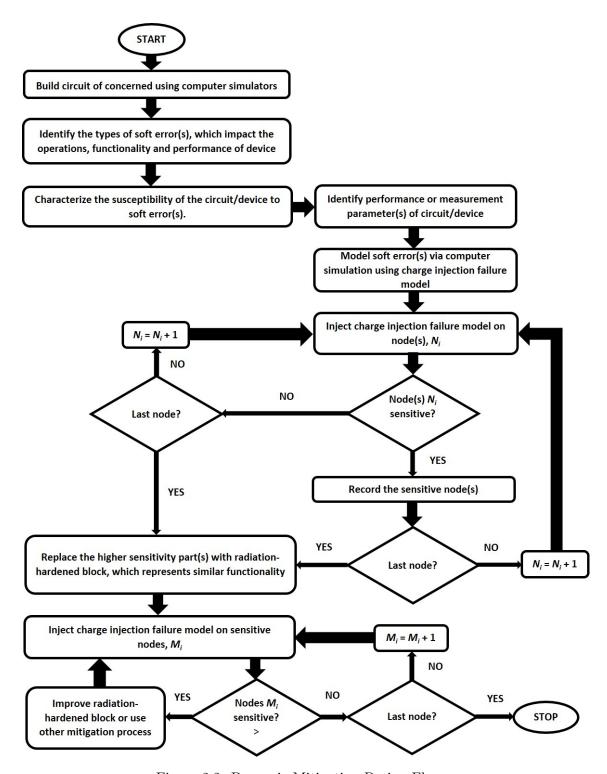

| 2.2  | Dynamic Mitigation Design Flow                                                                                                                                   | 13 |

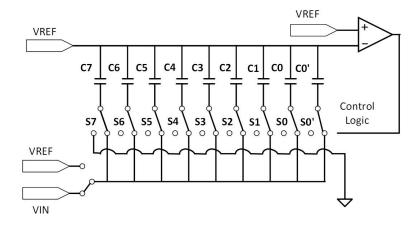

| 2.3  | Charge redistribution architecture                                                                                                                               |    |

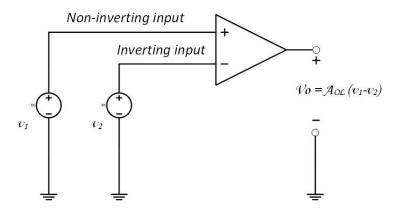

| 2.4  | Ideal operational amplifier symbol                                                                                                                               |    |

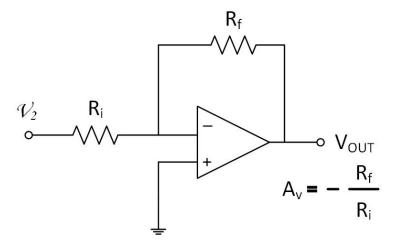

| 2.5  | Inverting amplifier                                                                                                                                              |    |

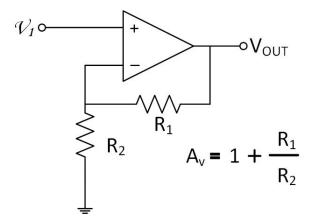

| 2.6  | Non-inverting amplifier                                                                                                                                          |    |

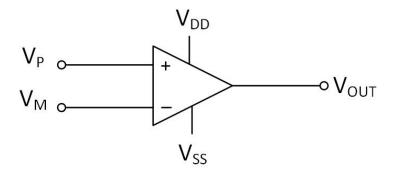

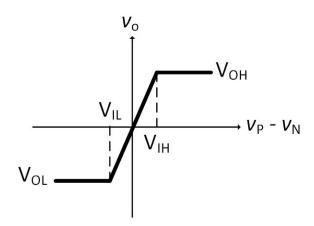

| 2.7  | Comparator symbol                                                                                                                                                | 24 |

| 2.8  | Comparator's ideal transfer characteristic                                                                                                                       | 24 |

| 2.9  | Comparator's first-order transfer characteristic                                                                                                                 | 24 |

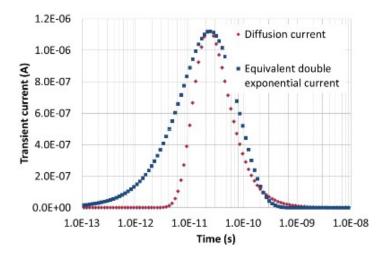

| 2.10 | Diffusion transient current plotted in log-log scale with the corresponding double exponential representation                                                    | 33 |

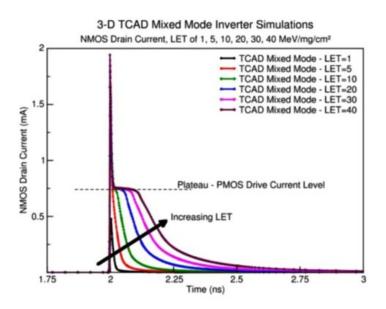

| 2.11 | NMOS TCAD simulation results portraying both short and high current peaks                                                                                        | 35 |

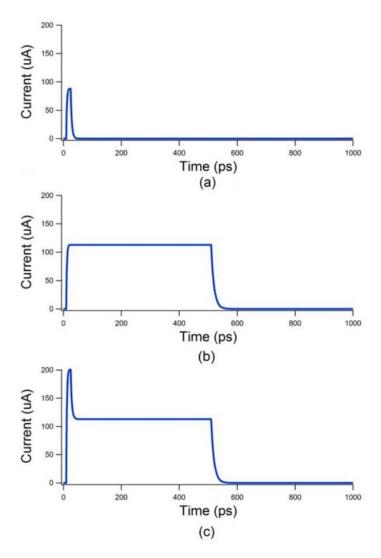

| 2.12 | Combination of (a) short double exponential current source and (b) long double exponential current source producing (c) a dual double exponential current source | 36 |

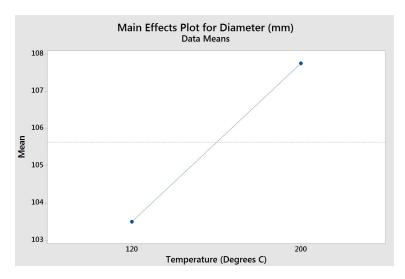

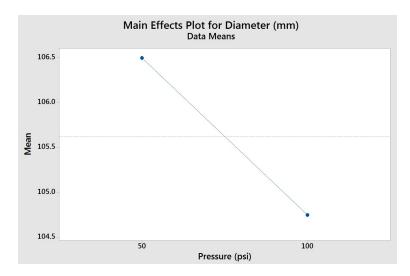

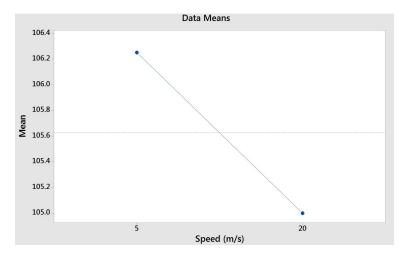

| 9 12 | Main effects plot for temperature on the drilled hole's diameter                                                                                                 |    |

|      | Main effects plot for pressure on the drilled hole's diameter                                                                                                    |    |

|      | Main effects plot for speed on the drilled hole's diameter                                                                                                       |    |

|      | Central composite design model                                                                                                                                   |    |

|      | Box-Behnken design for 2 variables                                                                                                                               | 49 |

|      | A system's process, design variables and response under DOE considerations                                                                                       |    |

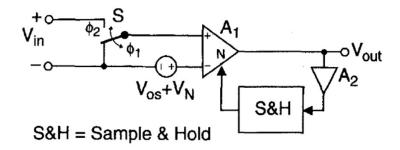

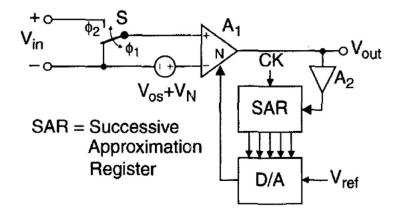

|      | Basic auto-zeroing circuit                                                                                                                                       |    |

|      | Auto-zeroing technique with an analogue offset control storage                                                                                                   |    |

|      | Auto-zeroing technique with a digital offset control storage                                                                                                     |    |

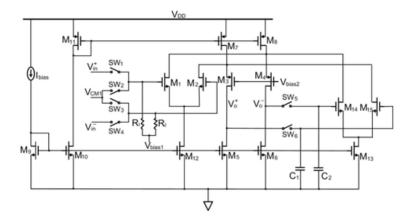

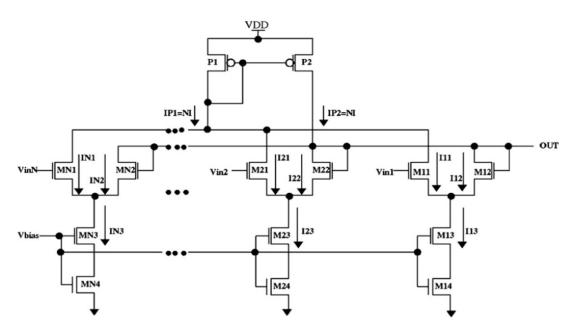

|      | Auxiliary offset storage folded cascode comparator                                                                                                               |    |

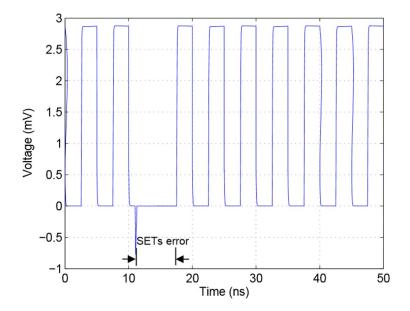

|      | Differential output voltage with AOS folded cascode comparator with                                                                                              |    |

|      | SET effect for only 1 clock cycle                                                                                                                                | 55 |

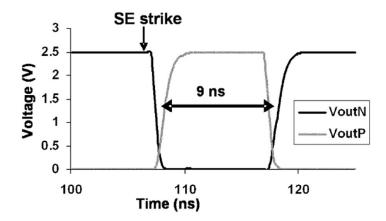

| 2.24 | SET for auto-zeroed inverter comparator only prolongs for as long as 9                                                                                           |    |

|      | ns, less than 1 clock period                                                                                                                                     | 55 |

| 2.25 | N-mean voter circuit                                                                                                                                             | 57 |

| 2.26 | Redundancy factor determination algorithm                                                                                                                        | 59 |

| 3.1  | 3-stage pre-amplifier comparator                                                                                                                                 | 62 |

xvi LIST OF FIGURES

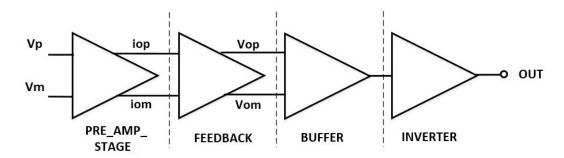

| 3.2         | Simplified block diagram for 3-stage comparator                                                                                                   | 62    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|

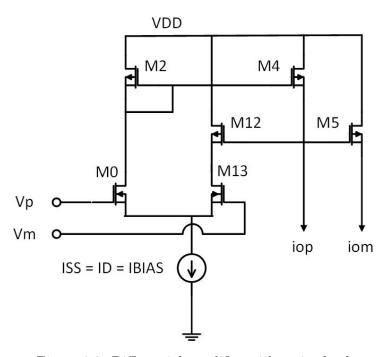

| 3.3         | Differential amplifier with active load                                                                                                           | 64    |

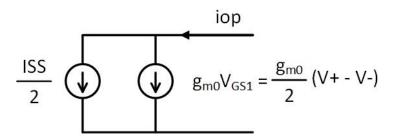

| 3.4         | The small signal equivalent circuit for M0, with symmetrical assumptions                                                                          | 66    |

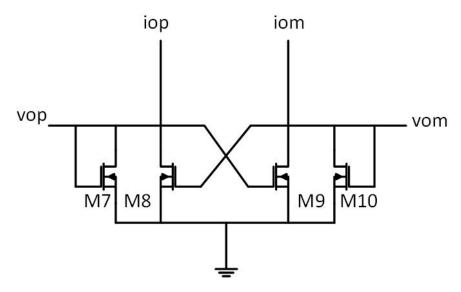

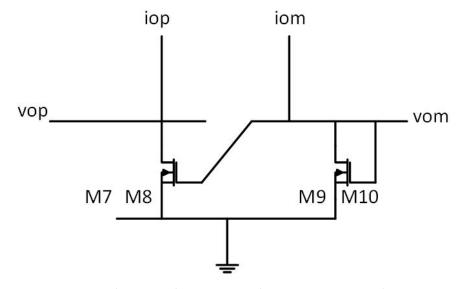

| 3.5         | Positive feedback circuit as decision making stage                                                                                                | 67    |

| 3.6         | The equivalent circuit when $V_{op}$ is greater than $V_{om}$                                                                                     |       |

| 3.7         | The equivalent circuit when $V_{om}$ is greater than $V_{op}$                                                                                     |       |

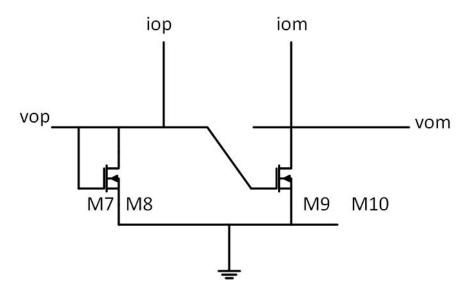

| 3.8         | Self bias differential amplifier as buffer                                                                                                        |       |

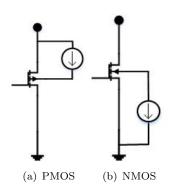

| 3.9         | SET modelling for PMOS and NMOS transistors                                                                                                       | . 72  |

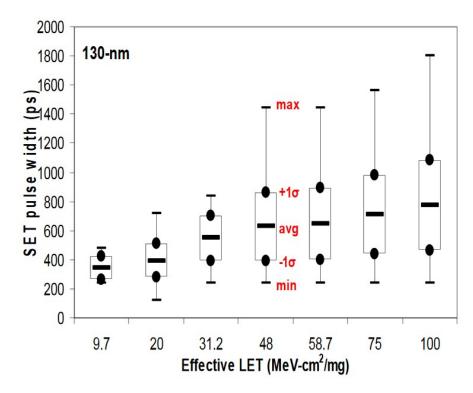

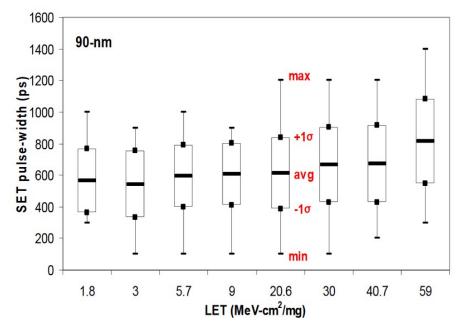

| 3.10        | SET pulse widths from heavy ion tests under 130-nm CMOS technology                                                                                | . 75  |

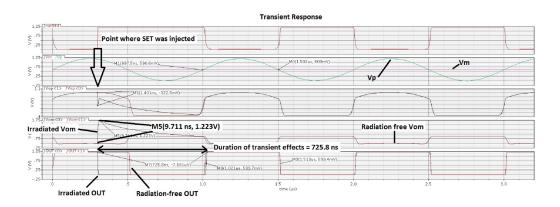

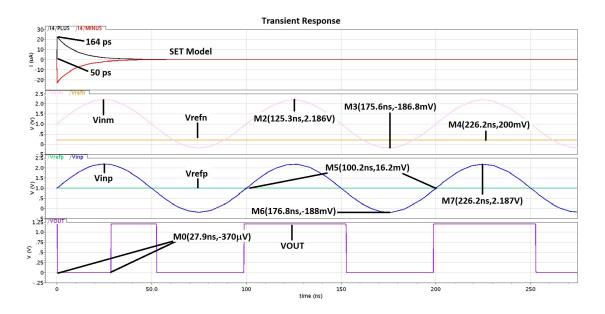

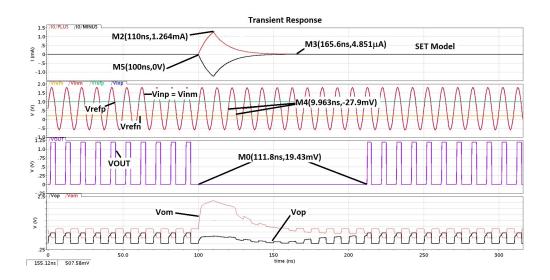

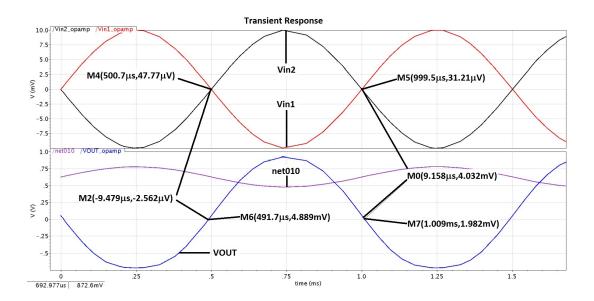

| 3.11        | Transient effects exhibited from injecting SET to transistor M5                                                                                   | . 75  |

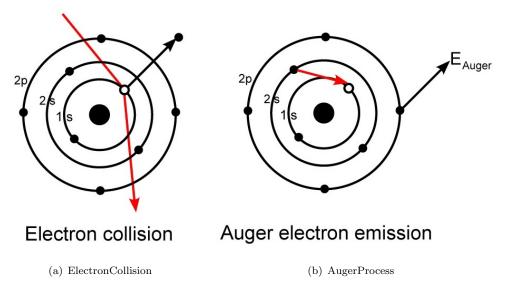

| 3.12        | Auger Effect in Semiconductors                                                                                                                    | . 76  |

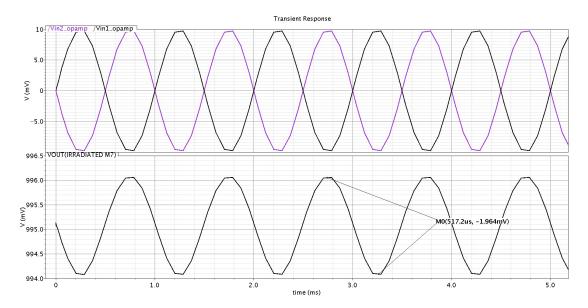

| 3.13        | Maximum voltage variation displayed by transistor M7                                                                                              | . 77  |

| 3.14        | Worst transient effects                                                                                                                           | . 77  |

| 3.15        | 3-stage preamplifier                                                                                                                              | . 79  |

| 3.16        | 3-stage comparator-with-hysteresis                                                                                                                | . 80  |

| 3.17        | Overall block diagram of improved comparator-with-hysteresis                                                                                      | . 80  |

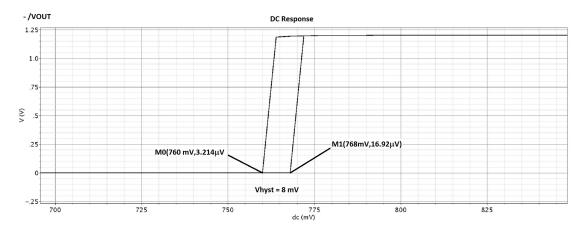

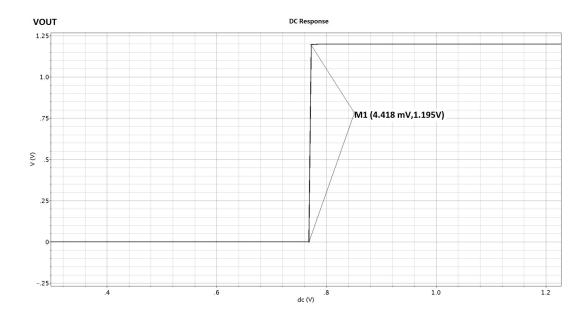

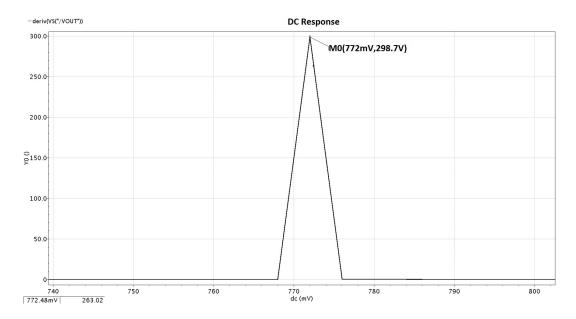

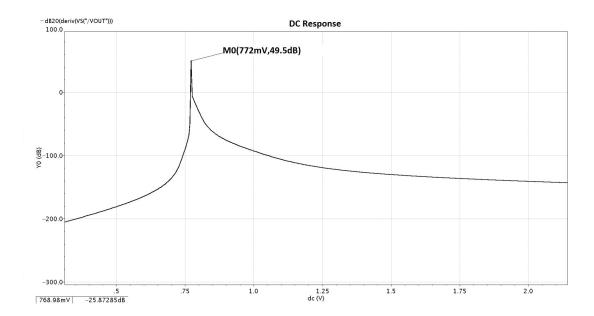

| 3.18        | Measured hysteresis voltage                                                                                                                       | . 82  |

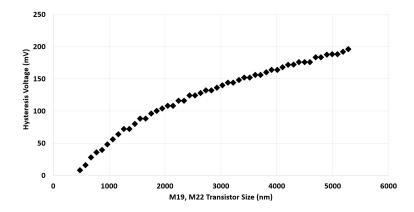

| 3.19        | Variations of transistor sizing of positive feedback's transistor, M19 and                                                                        |       |

|             | M22 with matching hysteresis voltage (mV)                                                                                                         |       |

|             | SET pulse widths from heavy ion tests under 90-nm CMOS technology.                                                                                |       |

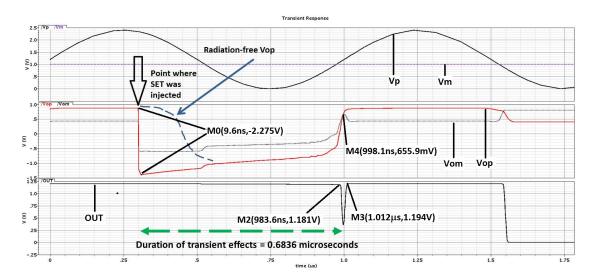

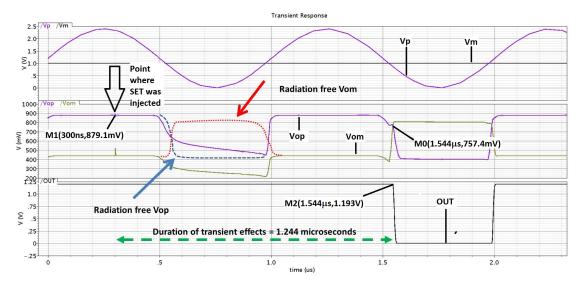

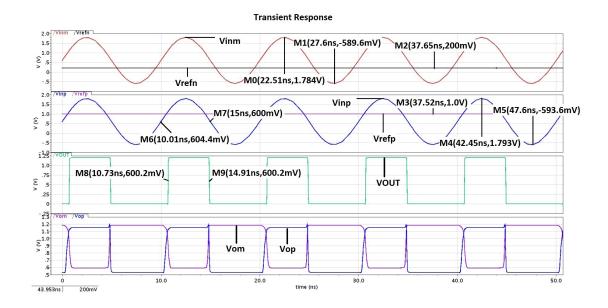

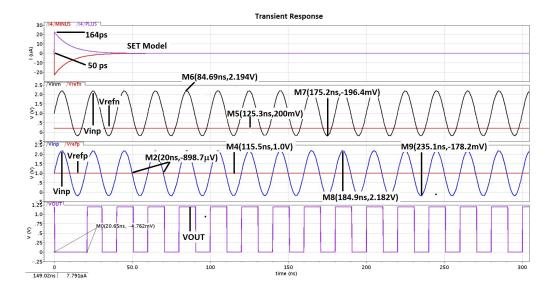

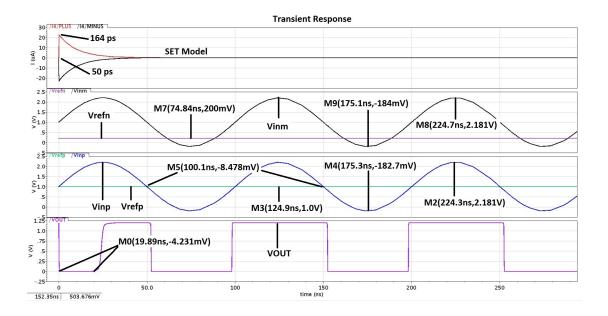

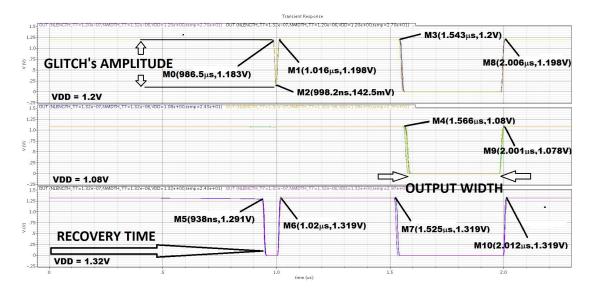

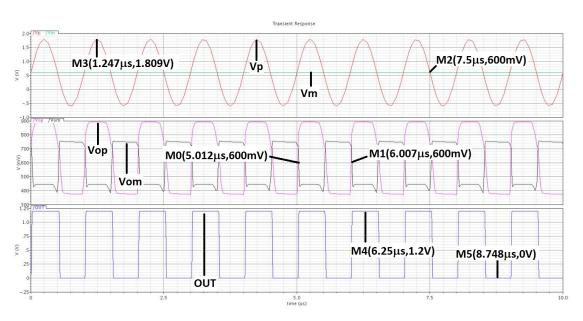

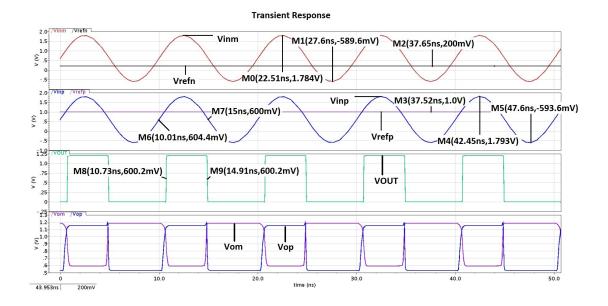

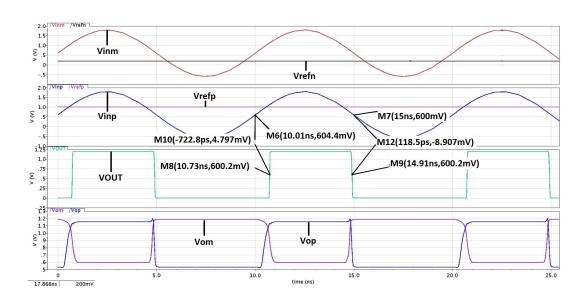

|             | Transient response of the output of comparator-with-hysteresis                                                                                    | . 84  |

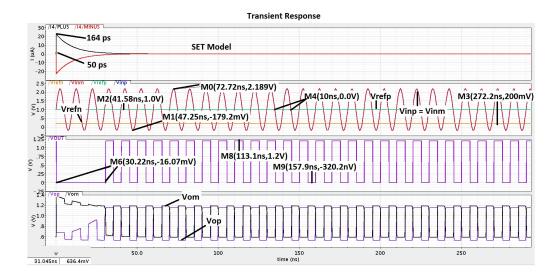

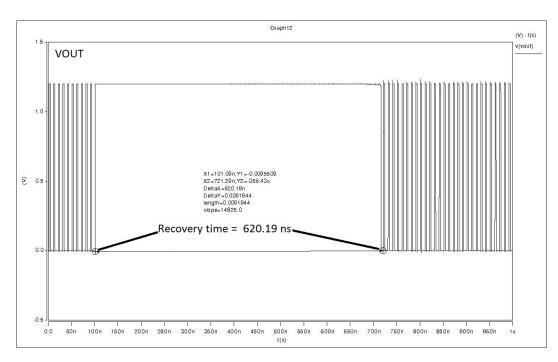

| 3.22        | Recovery time exhibited by transistor M16 at input voltage frequency of                                                                           |       |

|             | 50 MHz and hysteresis voltage of 8 mV, using Wrobel's parameter values                                                                            | 85    |

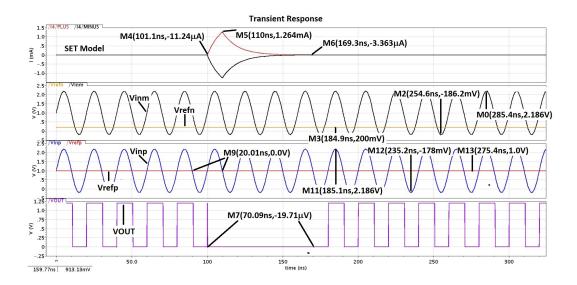

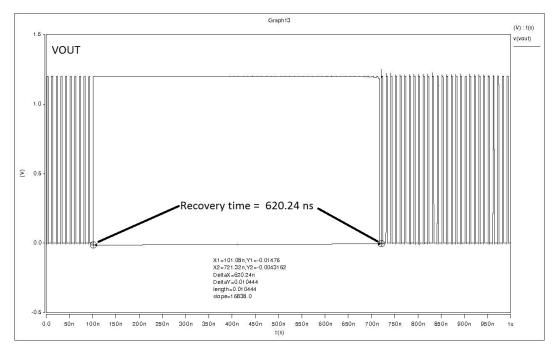

| 3.23        | Recovery time exhibited by transistor M16 at input voltage frequency of                                                                           | 0.0   |

| 2.04        | 50 MHz and hysteresis voltage of 8 mV, using Duran's parameter values                                                                             | . 86  |

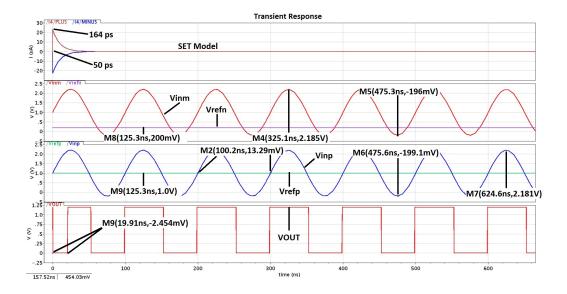

| 3.24        | Recovery time exhibited by transistor M16 at input voltage frequency of                                                                           | 86    |

| 2 25        | 10 MHz and hysteresis voltage of 8 mV, using Wrobel's parameter values<br>Recovery time exhibited by transistor M16 at input voltage frequency of | 00    |

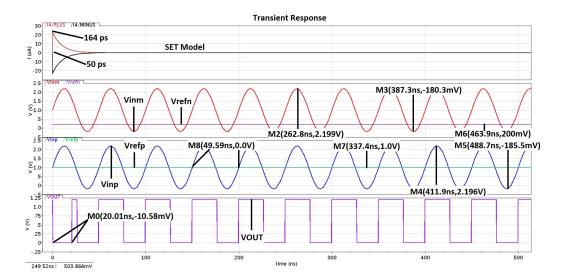

| 3.23        | 20 MHz and hysteresis voltage of 8 mV, using Wrobel's parameter values                                                                            | 87    |

| 3 26        | Maximum voltage variation displayed by transistor M21, for hysteresis                                                                             | 01    |

| 0.20        | voltage of 8 mV under input signal frequency of 10 MHz                                                                                            | . 88  |

| 3.27        | Maximum voltage variation displayed by transistor M21, for zero hystere-                                                                          |       |

|             | sis voltage under signal frequency of 10 MHz                                                                                                      | . 88  |

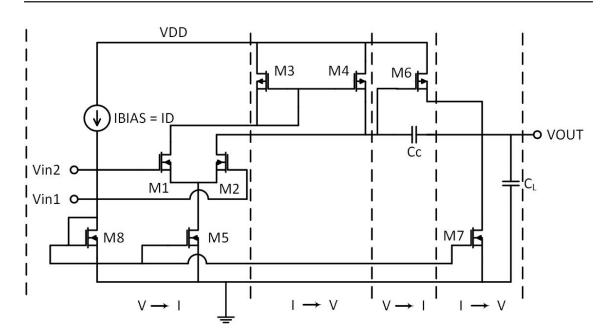

| 3.28        | 2 stage amplifier                                                                                                                                 | . 89  |

| 3.29        | The simulated DC operating points illustrating the saturation conditions                                                                          |       |

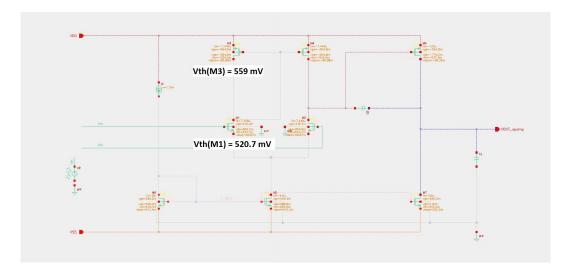

|             | experienced by all transistors of 2-stage operational amplifier                                                                                   | 93    |

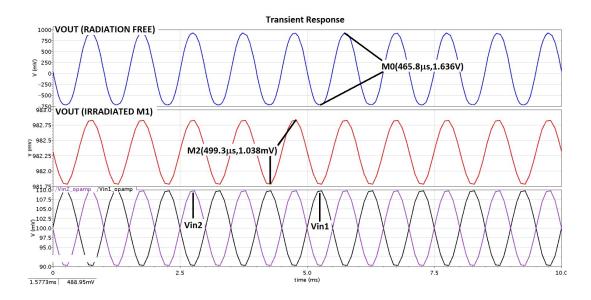

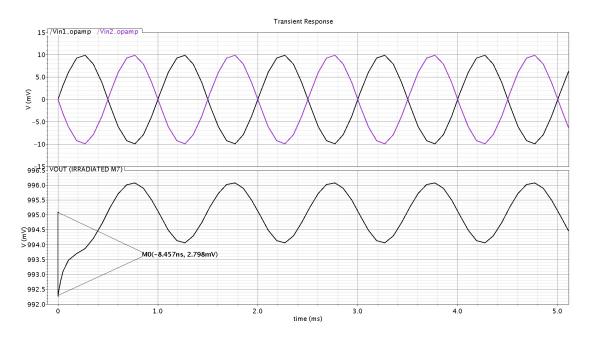

| 3.30        | Reduced voltage swing has been observed for irradiation at transistor M1                                                                          |       |

|             | of 2-stage operational amplifier                                                                                                                  | 100   |

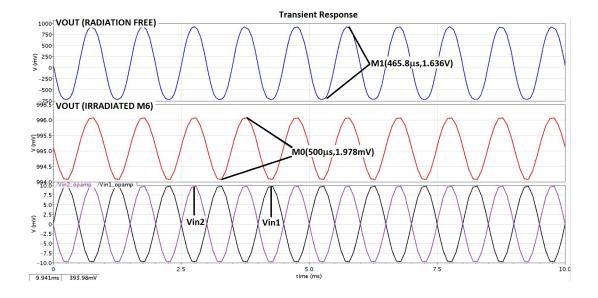

| 3.31        | Reduced voltage swing has been observed for irradiation at transistor M6                                                                          |       |

|             | of 2-stage operational amplifier                                                                                                                  | 100   |

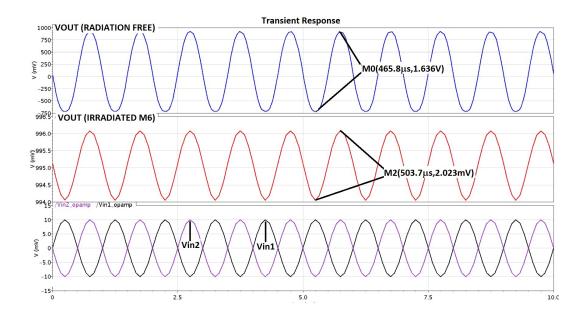

| 3.32        | Reduced voltage swing has been observed for irradiation at transistor M6                                                                          |       |

|             | of 2-stage operational amplifier using Duran's SET model                                                                                          | . 101 |

| 3.33        | Observation of largest effect which corresponds to SET injected at one of                                                                         | 101   |

| 0.04        | the transistor, M3 for folded cascode comparator                                                                                                  | . 101 |

| <b>3.34</b> | Reduced voltage swing has been observed for irradiation at transistor M7                                                                          | 100   |

| 2 25        | of 2-stage operational amplifier using 95 mA current pulse                                                                                        | . 102 |

| 0.00        | of 2-stage operational amplifier using 25 A current pulse                                                                                         | 109   |

|             | of 2 brase operational amplifier using 20 A current pulse                                                                                         | 102   |

LIST OF FIGURES xvii

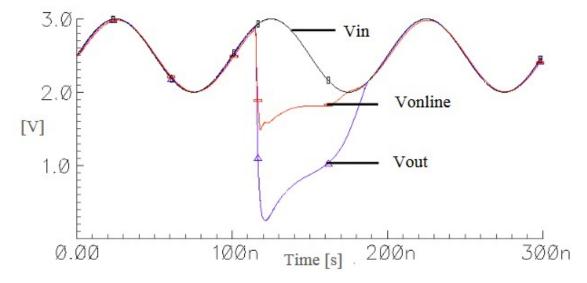

| 3.36 | Observed output from radiation effect analysis on comparator-with-hysteresis with input signal frequency of 100 MHz, using Duran's SET model                                                                          |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.37 | Observed output from radiation effect analysis on comparator-with-hysteresi with input signal frequency of 100 MHz using Wrobel's SET model                                                                           | is, |

| 4.1  | The measurement of output responses                                                                                                                                                                                   |     |

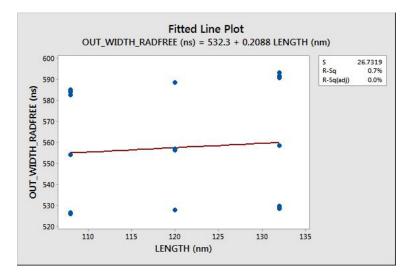

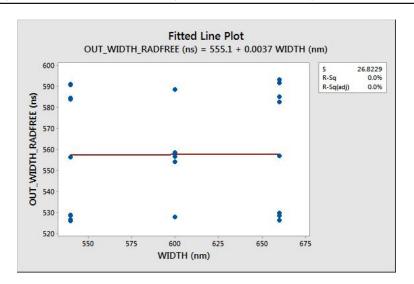

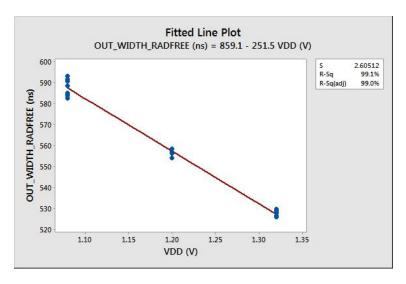

| 4.2  | Fitted line plot for impact of transistor's length to output width of radiation-free hysteresis-free comparator $\dots$                                                                                               |     |

| 4.3  | Fitted line plot for impact of transistor's width to output width of radiation-free hysteresis-free comparator                                                                                                        | 111 |

| 4.4  | Fitted line plot for impact of VDD to output width of radiation-free hysteresis-free comparator                                                                                                                       | 112 |

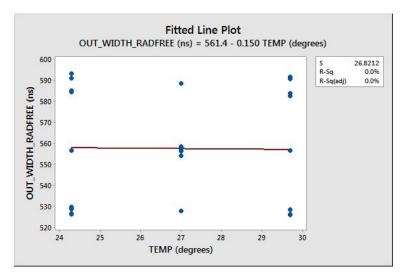

| 4.5  | Fitted line plot for impact of temperature to output width of radiation-free hysteresis-free comparator                                                                                                               | 112 |

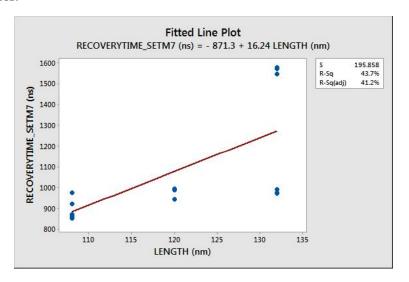

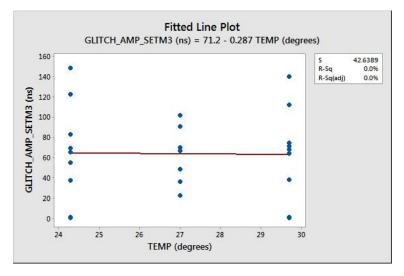

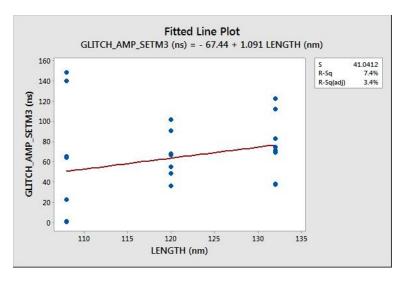

| 4.6  | Fitted line plot for impact of transistor's length to recovery time for irradiated most sensitive transistor in hysteresis-free comparator                                                                            | 113 |

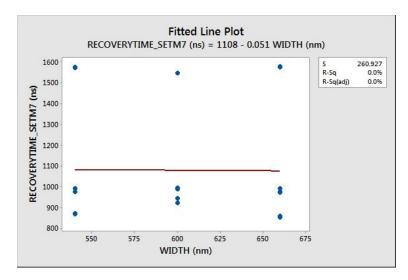

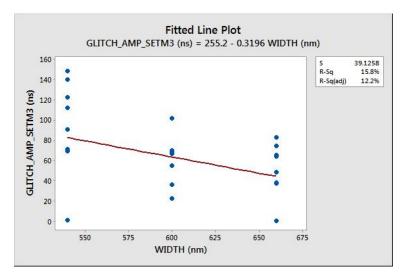

| 4.7  | Fitted line plot for impact of transistor's width to recovery time for irradiated most sensitive transistor in hysteresis-free comparator                                                                             | 113 |

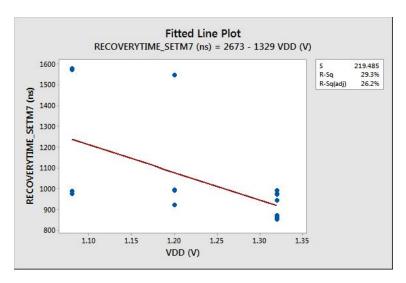

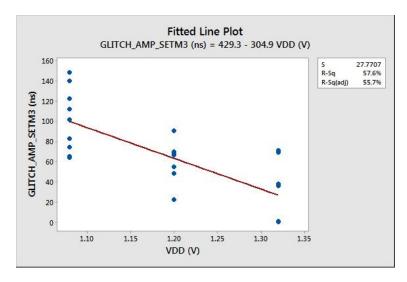

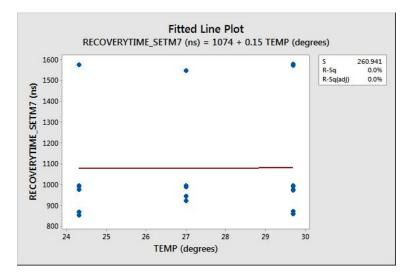

| 4.8  | Fitted line plot for impact of VDD to recovery time for irradiated most sensitive transistor in hysteresis-free comparator                                                                                            | 114 |

| 4.9  | Fitted line plot for impact of temperature to recovery time for irradiated most sensitive transistor in hysteresis-free comparator                                                                                    | 114 |

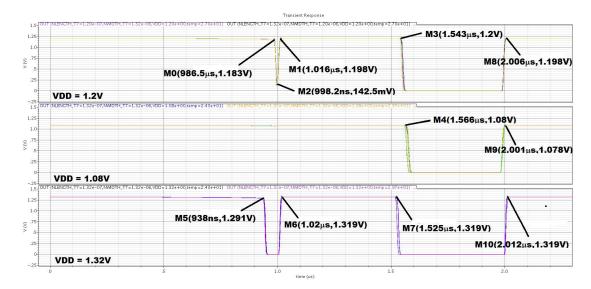

|      | Observed output of comparator under variability during SET injection to M7                                                                                                                                            | 115 |

|      | Fitted line plot for impact of transistor's length to glitch's amplitude for irradiated least sensitive transistor hysteresis-free comparator                                                                         | 116 |

|      | Fitted line plot for impact of transistor's width to glitch's amplitude for irradiated least sensitive transistor hysteresis-free comparatorr Fitted line plot for impact of VDD to glitch's amplitude for irradiated | 116 |

|      | least sensitive transistor hysteresis-free comparator                                                                                                                                                                 | 117 |

|      | diated least sensitive transistor hysteresis-free comparator                                                                                                                                                          | 117 |

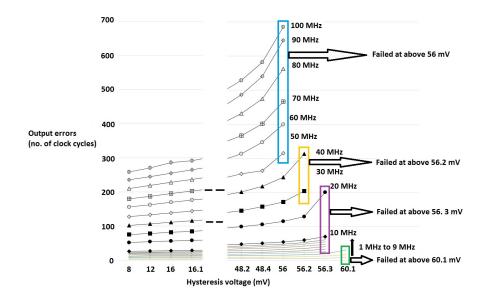

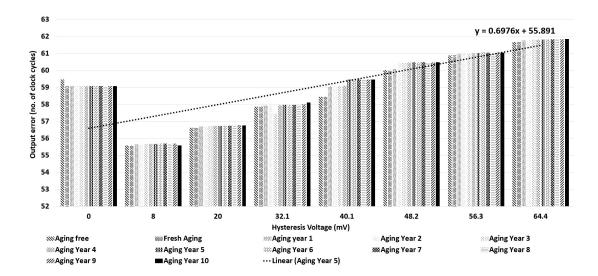

|      | with-hysteresis to SETs                                                                                                                                                                                               | 118 |

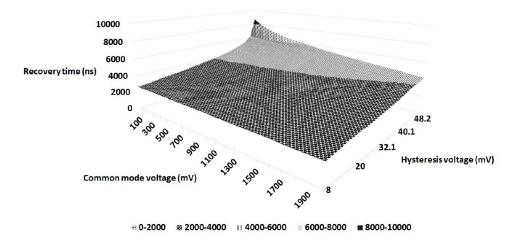

|      | hysteresis to SETs                                                                                                                                                                                                    | 119 |

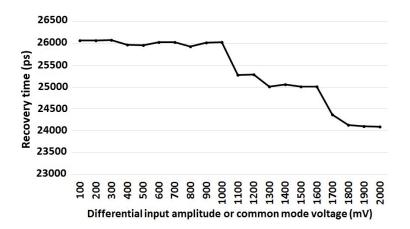

|      | frequencies                                                                                                                                                                                                           | 120 |

| 4.19 | plitude or common mode voltage                                                                                                                                                                                        | 120 |

| 4.20 | mV, under radiation and under ageing                                                                                                                                                                                  |     |

| 4.21 | with Vhyst = $64$ mV, under radiation and under ageing Output error versus hysteresis voltage under ageing impact, including                                                                                          |     |

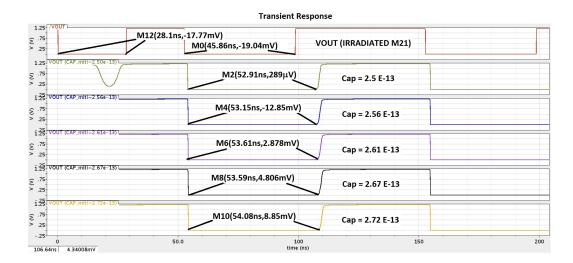

| 4.22 | ageing-free for freq = 100 MHz $\dots$ Observed outputs responses for different capacitor values $\dots$ .                                                                                                            |     |

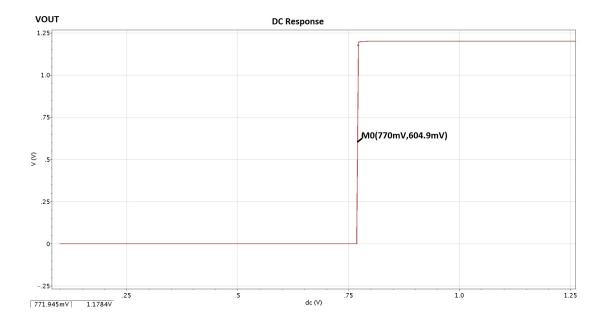

| A1   | DC response to obtain input offset voltage for hysteresis-free comparator .                                                                                                                                           | 138 |

xviii LIST OF FIGURES

| <b>A2</b>     | The derivatives of the DC response to obtain voltage gain for hysteresis-     |

|---------------|-------------------------------------------------------------------------------|

|               | free comparator                                                               |

| <b>A</b> 3    | Voltage gain in decibel for hysteresis-free comparator                        |

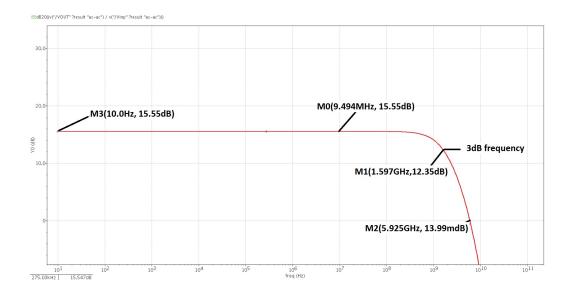

| $\mathbf{A4}$ | Frequency response highlighting the 3dB frequency for hysteresis-free         |

|               | comparator                                                                    |

| A5            | Propagation delay time for rising and falling edge of comparator 140          |

| <b>A</b> 6    | Rise and fall time of comparator                                              |

| A7            | Transient response of the output of comparator                                |

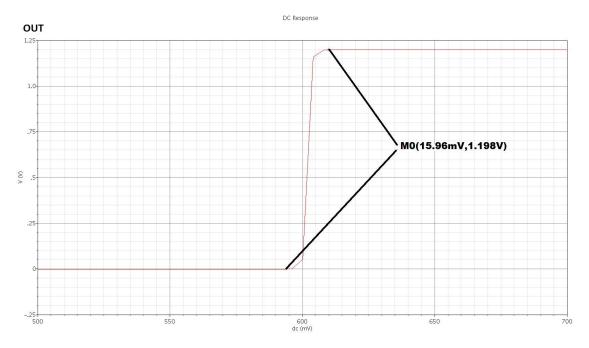

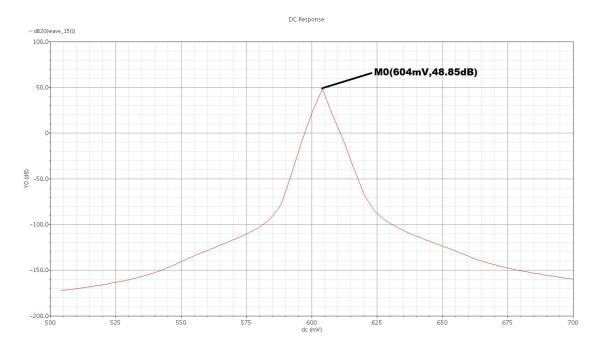

| B1            | DC response to obtain input offset voltage for comparator-with-hysteresis 144 |

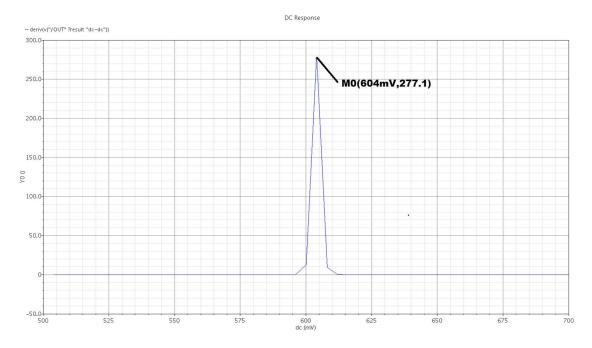

| B2            | The derivatives of the DC response to obtain voltage gain for comparator-     |

|               | with-hysteresis                                                               |

| B3            | Voltage gain in decibel for comparator-with-hysteresis                        |

| B4            | Identifying $V_{bias}$ for AC analysis                                        |

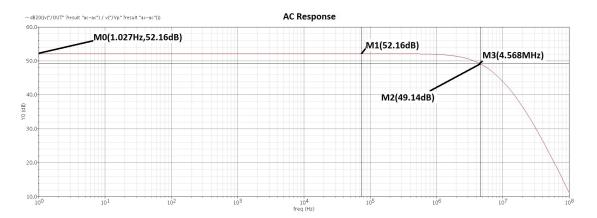

| B5            | Frequency response highlighting the 3db frequency and bandwidth 146           |

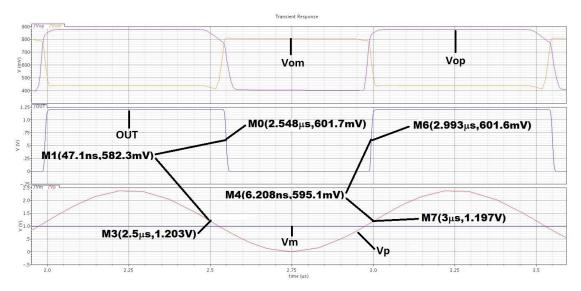

| B6            | Transient response of the output of comparator-with-hysteresis 146            |

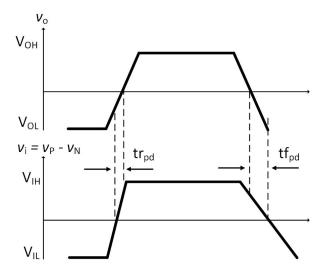

| B7            | Rise and fall time of comparator                                              |

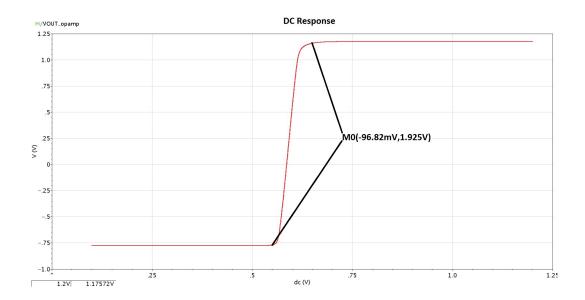

| C1            | DC response illustrating the input offset voltage for 2-stage amplifier 150   |

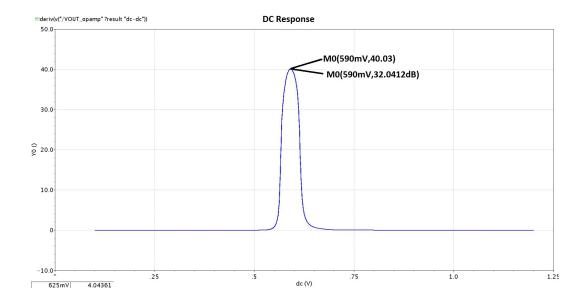

| C2            | The derivatives of the DC response illustrating the voltage gain for 2-stage  |

|               | amplifier                                                                     |

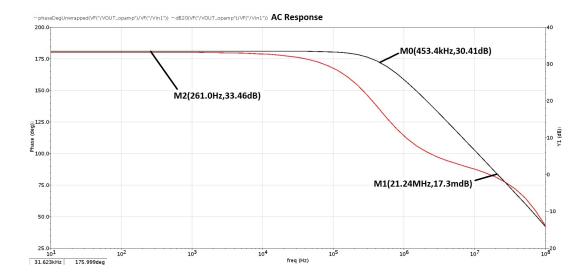

| C3            | Frequency response of 2-stage operational amplifier                           |

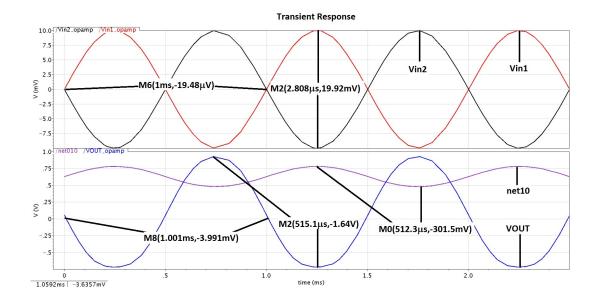

| C4            | Transient response of 2-stage operational amplifier                           |

| C5            | Transient response of 2-stage operational amplifier for measurements of       |

|               | propagation delay                                                             |

# List of Tables

| 2.1  | The total number of experiments from 3 factors                                   | 5 |

|------|----------------------------------------------------------------------------------|---|

| 2.2  | Factors under investigation and realistic high and low-level values 4            | 5 |

| 2.3  | Possible experimental combination for evaluation testing of machining            |   |

|      | device                                                                           | 6 |

| 2.4  | Evaluation testing based on the diameter of a drilled hole by the machin-        |   |

|      | ing device                                                                       | 6 |

| 3.1  | Process parameters for hysteresis-free comparator 6                              | 3 |

| 3.2  | Design specifications for hysteresis-free comparator 6                           | 3 |

| 3.3  | Performance specification of hysteresis-free comparator                          | 2 |

| 3.4  | Relevant effects for sensitivity analysis for hysteresis-free comparator $7$     | 8 |

| 3.5  | Transistor sizing                                                                | 9 |

| 3.6  | Performance specifications for comparator-with-hysteresis 8                      | 1 |

| 3.7  | Relevant effects of sensitivity analysis for comparator-with-hysteresis 8        | 9 |

| 3.8  | Design specifications and process parameters for 2-stage amplifier $9$           | C |

| 3.9  | Transistor sizing and related calculated currents                                | 7 |

| 3.10 | Performance specification of 2-stage amplifier                                   | 8 |

| 3.11 | Relevant effects of sensitivity analysis for 2-stage operational amplifier $$ 10 | 3 |

| 4.1  | Design variable parameters                                                       | 8 |

| 4.2  | Experimental runs                                                                | 9 |

| 4.3  | Measurement results for variability analysis                                     | 1 |

## Nomenclature

AC Alternating Current

ADC Analogue-to-Digital Converter

AOS Auxiliary Offset Storage

BiCMOS Bipolar Complementary Metal-Oxide-Semiconductor

BICS Bulk Built-In Current Sensor

BWCA Binary Weighted Capacitor Array

CERN European Organization for Nuclear Research

CMOS Complementary Metal-Oxide-Semiconductor

COTS Commercial-On-the-Shelf CPU Central Processing Unit

DAC Digital-To-Analogue Converter

DC Direct Current

DCE Digital Communications Experiment

DOE Design of Experiments

DRAM Dynamic Random Access Memory

DSR Digital Store and Read Experiment

EDAC Error Detection and Correction Circuit

EEPROM Electrically Erasable Programmable Read-only Memory

EOC End-of-Conversion FIT Failures-In-Time

FPGA Field Programmable Gate Array

FSR Full Scale Voltage Range GPS Global Positioning System HCS High-Conduction-State

IBM International Business Machines Corporation

IC Integrated Circuit

ICARE Influence of Space Radiation on Advanced Components

ICMR International Commission on Radiological Units and Measurements

ICS Intermediate-Conduction-State

IOS Input Offset Storage

LCS Low-Conduction-State

LET Linear Energy Transfer

xxii NOMENCLATURE

LSB Least Significant Bit

MTF Multiple Transient Fault

MOS Metal-Oxide-Semiconductor

MOSFET Metal-Oxide-Semiconductor-Field-Effect-Transistor MOSRA Metal-Oxide-Semiconductor Reliability Analysis

MSI Medium Scale Integrated

NBTI Negative-Bias Temperature Instability NMOS N-type Metal-Oxide-Semiconductor

Op Amp Operational Amplifier

OOS Output Offset Storage

PMOS P-type Metal-Oxide-Semiconductor

PWL Pulse-Width-Length

RAL Rutherford Appleton Laboratory

RDF Random Dopant Fluctuations

RE Relative Error

RHBD Radiation-Hardening-by-Design SAR Successive Approximation Register

SEE Single Event Effect SER Soft Error Rate

SET Single Event Transient

SEU Single Event Upset

SiGe Silicon Germanium

SNR Signal to Noise Ratio

SOI Silicon-On-Insulator

SPICE Simulation Program with Integrated Circuit Emphasis

SRAM Static Random Access Memory

ST STMicroelectronics, Inc.

STFC Science and Technology Facilities

TCAD Technology Computer Aided Design

TID Total Ionizing Dose

TMR Triple Modular Redundancy

TSMC Taiwan Semiconductor Manufacturing Company

VLSI Very-Large-Scale-Integration

$Q_{crit}$  Critical Charge

$Q_s$  Charge Collection Efficiency

### Chapter 1

## Introduction

CMOS reliability issues emerge from the increasing scaling rate of CMOS technology. The scaling trend is in demand due to the increasing performance requirements and competition for better electronic products. These products required improved performance for meeting the speed, complexity, circuit density and size, power consumption and cost requirements, with some drawbacks. This motivates the sudden increase in the study of reliability and variability of CMOS circuits, both at pre- and post-fabrications stages.

With these scaling advancements, comes more technical challenges in the form of CMOS reliability issues as further classified by Maricau [1], the spatial and temporal unreliability effects. Spatial effects exist immediately after productions and fixed in time while temporal effects are time-varying effects, which changes based on the operating conditions of the transistor or circuit, such as the operating voltage, temperature, switching activity, presence and activities of neighbouring circuits. These spatial effects also known as hard errors, could be corrected much earlier during the fabrication process while temporal effects or soft errors may need innovative mitigating solutions. At the same time, these solutions although may reduce the soft errors, it may not satisfy the design constraints specified by users. Design trade-offs as one of the mitigation technique may be helpful in reducing the sensitivity of a particular circuit to these errors, however, there are cases where these issues are no longer preventable and have to be corrected with state-of-the-art mitigation techniques. Some of these techniques, unfortunately, are very costly.

In soft errors, new electron-hole pairs are generated from the particle strikes initiated from the radiation source. This new electron-hole pairs would not affect the circuit permanently, thus termed as 'soft' errors; as opposed to hard errors [2]. Soft errors are also termed as transient faults or single event effects (SEEs). Although soft errors are a non-permanent causal of malfunction; it has been reported that a single soft error has

caused an interleaved system farm to fail and in a different incident, halted a billion-dollar automotive factory operation; which has raised a major concern [2].

Backgrounds on the radiation effects in safety-critical systems and its impact to VLSI and analogue circuits were briefly reported in this chapter. Section 1.1 outlines the radiation effects occurring in safety-critical systems, which have been the cause of failures and potential-failures as reported by various sources. Section 1.2 briefly describes soft errors and discusses the existence of soft errors in VLSI circuits while Section 1.3 discusses the observation of single event transients for analogue circuits. On the other hand, Section 1.4 provides the overview of some of the existing soft error mitigation techniques and the current trends. Motivations and research objectives have been described in Section 1.5. The thesis organization has been described in Section 1.7. And finally, Section 1.8 listed the parts of completed work which have been submitted for publications and workshops.

#### 1.1 Radiation Effects in Safety-Critical Systems

In this thesis, focus is only given on radiation effects which are caused by alpha particles and neutrons. This is due to the fact that soft errors caused by radiation effects contributed by alpha particles and neutrons have a higher contribution towards overall soft error rate as opposed to soft errors which were generated from electrical noise from cross talk and interference in power supply [1]. The alpha particles come from the decaying packaging and bonding materials while neutrons come from the atmosphere and its environment [2]. Further descriptions of the radiation-induced faults have been elaborated in Section 2.1.

The impact of radiation effects caused by in-orbit sources has been well documented as reported by Ecoffet in his work [3]. He mentioned that radiation effects have become a major contributor towards space anomalies, as reported by The Satellite News Digest [4]. The Satellite News Digest reported on a weekly basis, any incidents and failures both on-board electronics on satellites and on ground controllers. Although the digest is a non-official collection of satellite failures reported, the author, Klanowski [4] claimed the sources referred to are believed to be reliable. Ecoffet [3] in his work, highlighted the intense solar activity reported by [4] during October to November of 2003; which has caused at least 2 space anomalies per day from 23rd of October 2003 to 6th of November 2003. These space anomalies are caused by various radiation sources which are the protons and electrons from the radiation belts, ions and protons from solar flares and ions from cosmic rays [3]. The latest reported satellite failure caused by radiation effects was to EchoStar 8 in January 2011. The satellite has temporarily been off its course after a single event upset being detected [4]. No other satellite failures are declared

to be caused by radiation effects based on the latest weekly update checked on February 20th, 2018.

Based on the reported high degree of space anomalies in 2003, up to 10% satellites will experience operational outages from hours to days from a modest solar storm as judged by The Royal Academy of Engineering [5]. Solar storm or also known as solar flares, is a sudden eruption of matter and energy on the sun above a sunspot, believed to be caused by sudden release of magnetic energy [6, 7]. In easier definition, solar flares are high intensity radiation bursts [8]. Within few minutes, the flares will be able to reach its maximum brightness and may last for hours [6]. These flares are believed to be incapable in affecting humans on ground levels, however extreme solar flare may affect the atmosphere layer where GPS and communication signals travel [8]. The solar flare strength fluctuates in 11-year cycle, with 4 quiet years followed by 7 active years [9]. 11-year cycle is taken as the duration of a solar cycle as the sun's geomagnetic poles change direction in successive 11-year cycles [9]. The solar storm will not only trigger the outages but also increases the ageing of the satellites. Although the phenomenon of a super storm, which is the extreme solar flare event has never been encountered, the highest recorded radiation effects measured on spacecraft in October 2003 has already caused major damage to spacecraft, as reported earlier by [3, 4]. The highest intensity solar flare reported by [3, 4], was recorded by astronomers using the Solar and Heliosphere Observatory (SOHO) satellite [6]. The most recent significant solar flare has been detected on September 10th, 2017 [8]. With the limited knowledge and still ongoing research work such as by Engell et al., [10] and Murray et al., [11] in predicting the solar storm's occurrence and its impact, efforts shall be made on improving the susceptibilities of spacecraft and avionic electronics towards radiation effects.

These satellites if being used for projecting TV channels i.e. trivial communication data, non-permanent error suffered by these satellites may not be as significant as compared to being used in, for example, a real-time emergency alert system for earthquake [12] or tsunami [13]. The Great Tohoku earthquake which happened on the 11th of March 2011, has been considered a massive disaster and heartbreaking; thus a real-time emergency alert system which uses efficient, fault-free and dependable real-time GPS geophysical system may be helpful to encounter future events.

Soft errors caused by radiation sources are not only known to impact electronic devices for aerospace and avionic applications but also has given a significant impact on electronics at earth level. These devices in applications such as aerospace, avionics, automotive, medical, weaponry and nuclear systems are all classified as safety-critical systems [14]. The impact will worsen by orders of magnitude when the electronic devices are implemented in aerospace applications and in both commercial and military aircraft due to the higher atmospheric neutron flux [15]. Nevertheless, devices located at the earth level may be exposed to higher radiation effects. The sensitivity of devices may also be influenced by several factors, which have been further elaborated in Section 2.6.

#### 1.2 Soft Errors in VLSI Circuits

Soft errors in VLSI circuits exists due to the radiation-induced particles; such as neutron in the atmosphere due to the cosmic rays and the alpha particles from the packaging materials [2]. These particles generate new electron-hole pairs which are later collected by transistor source and diffusion nodes; where a sufficient accumulated charge will invert the logic device's state, from a 1 to 0 and vice versa. This is particularly true in digital circuits. Analogue circuits on the other hand experience different effects. Studies made by injecting single transient error into analogue circuits concludes soft error will effect the analogue circuit's performance [16]. Even though analogue circuits experience different effects, the physics of charge generation, transport and collection of soft errors characterized from digital circuits, are deemed similar in any types of circuit, thus it's theoretical knowledge can also be applied to analogue circuits [17]. Koga [17] also mentioned that it is reasonable to also designate the upsets in analogue circuit as single event upsets (SEUs), similar to digital circuits. Due to this justification, the modelling of single event effects used in digital circuits is also commonly used for modelling single events in analogue circuits, as further elaborated in Section 2.5.3.

Soft errors can sometimes be mistakenly identified as a single data which may cause non-permanent changes to the circuit operation. The errors which are successfully being detected may be corrected using error correction method. It is sometimes impossible to detect the existence of these errors or to determine the actual data to be compared with, thus fault tolerant circuit is implemented. Soft errors caused at device level may have little effect due to the advancements of the packaging materials; however, as the technology being vigorously scaled down, VLSI circuits are returning to become more vulnerable [18]. Similar to the device level mitigation using packaging materials, circuit and architectural level techniques developed earlier may or may not be able to tolerate the soft errors which have increasingly become more aggressive.

#### 1.3 Single Event Transients in Analogue Circuits

One of the types of soft errors is the single event transients (SETs). SETs in digital circuits are only visible when they are converted into single event upset; for example when the SET change the supposed output or information in a memory circuit, while SETs in an analogue circuit must be propagated to usually its digital counterparts in order to be detected as an error [19]. Comparators are commonly used in analogue to digital converters (ADCs) and sensors, as highlighted in one of the application presented by Analog Devices for space applications in Figure 1.1. Operational amplifiers on the other hand are used mostly in sensors, such as the accelerometer in Figure 1.2 developed by Analog Device, suitable for space applications. Most of the time, the SETs detected in analogue circuits will not produce any long term or continuous effects on the analogue

device but may initiate prolonged effect on the follow-on circuit especially if the error has been latched and used for consequent stages. An irradiated comparator has been observed to experience disturbance pulses which are visible at the intermediate nodes, but only being reflected either by a missing bit or having additional bit at the comparator's output. As opposed to operational amplifiers, comparators are much easier to be identified as a failure; due to the dimensionless bits.

Figure 1.1: Analog Devices AD9246 Analogue to Digital Converter [20]

Figure 1.2: Analog Devices ADXL354 Accelerometer with Analogue Output [21]

While [16] mentioned that soft errors in particular single event transients will affect the circuit's performance, [17] has observed that operational amplifiers exhibited a short-duration disturbance pulses. In particular, Koga et al. [17] has observed single event upsets in several bipolar analogue devices; the HS3530RH, OP-05 and OP-15 operational amplifiers irradiated with heavy ions and concluded these devices have experienced either positive or negative-going short-duration disturbance pulses. The difference in pulse's amplitude values suggests that even for the same type of circuit i.e. operational amplifiers, the impact of SET to these devices varies. The differences may be due to the topology of the operational amplifier under investigation, or other influencing factors, which are discussed in Section 2.6. The varying amplitude values yield that the type of circuit alone does not guarantee the level of sensitivity a circuit portrays.

SETs are considered a threat for space electronics as transient pulses, if not corrected or filtered, will propagate from the sensitive device into the overall system and later cause either temporary or permanent failure of the electronic systems [22]. As electronic systems control most of the operations in spacecraft and other safety-critical systems, this will cause a part or the whole operation to halt. Although no official report has been published on the actual failures or serious operational problems caused by SETs in analogue electronics in other safety critical systems such as for automotive or biomedical applications; the prediction of a super storm has initiated efforts in improving the susceptibilities of other safety-critical systems, as mentioned earlier in Section 1.1.

#### 1.4 Current Trends in Soft Error Mitigations

The mitigations of soft errors or single event effects may be repaired by error detection and correction (EDAC) circuits or algorithm in a system's software. A well-known example of EDAC is triple modular redundancy (TMR). TMR is based on the concept of using 3 similar designed circuit which is made to be able to run in parallel and compared with each other. This concept is termed as redundancy. For example, after the processing is completed for all three circuits, if one circuit provides a different answer than the other two, it is believed that the two other circuits produce the correct answer. Hence, the answer to this particular calculation or algorithm is loaded from the correct answer. The one circuit or system which produces a different answer is reset or corrected [23]. Redundancy, although proven to cost more, is commonly used in digital circuits. On the other hand, examples for error correction for analogue circuits at design or circuit-level, are the usage of analogue redundancy in the form of majority or mean voter to eliminate the error found [24, 25] or applying trade-offs such as modifications of the bandwidth and gain of an amplifier circuit using feedback resistor to reduce the sensitivity of the analogue circuit [26]. Other mitigation methods which have been used is by using the circuit techniques for reducing the imperfection of amplifier such as autozeroing suggested by [27] and has been implemented by [28] and [29] into comparators. In general, both digital and analogue circuits can be mitigated using a device, circuit, layout or packaging techniques; which is commonly practiced in the industry. A comparator circuit identified for characterization of its radiation effects is said to be problematic when the transient effect is latched by some memory mechanism. The latched signal may be propagated to its digital counterparts or subsequent circuit which later causes the whole system to fail or produces the wrong data. If this particular signal is unable to be detected by the error correction circuit at system-level, a lower level mitigation circuit must be implemented. The importance of finding circuit-level mitigation techniques for the selected circuits in this thesis has been further justified in Section 2.3.3.

#### 1.5 Research Motivations and Objectives

The increasing reliability concerns motivate the study of radiation effects, particularly on CMOS circuit. The majority of radiation effects analyses are performed on commercial-on-the-shelf components (COTS) and in particular, analogue circuits; are built on bipolar technologies. Only recently, analogue electronic circuits are built on CMOS or other material such as BiCMOS or SiGe. And only recently, radiation testing has been performed on these devices. Studies made on analogue electronics under radiation effects suggested that SETs affect the performance of the analogue circuit or in some cases, exhibited short-duration disturbance pulses; which in most cases fades away during operation. The reported variations of the shape and duration of these disturbance pulses have sparked the motivation to study the impact of SETs on several selected analogue circuits, especially on influencing factors which may have impacts to the sensitivity of the circuits to SETs and may have caused the increase in failures. Based on these motivations, the following objectives have been set.

- Firstly, to clarify whether all analogue circuits suffer the same impact to the susceptibility of the circuits to radiation effects, and how SETs affect the comparator's behaviour and eventually cause failures to the device or the overall system. In general, all analogue circuits have been identified to be sensitive to single event transients, however as the disturbance pulses exhibited at the output varies for even the same type of analogue circuit; further investigations shall be made on selected circuits. Several different analogue circuits need to be selected with proper justifications. These circuits are to be characterized using circuit-level modelling.

- Secondly, to investigate whether the analogue circuit's sensitivity to single event transient worsens under variability. Variability relates to design factors which may or may not influence the sensitivity of the selected analogue circuits. From literature reviews, these factors are identified to be influencing the sensitivity of the similar circuits, either in a positive or negative way. From observing the impact of these factors, some trade-offs between these factors and performance parameters may be summarized; which later may be used in mitigating the single event transients.

- Finally, for circuits which have been identified to be sensitive to single event transients and may cause malfunctions to adjacent circuits; a simple mitigation technique shall be suggested. Mitigation technique suggested can be in the form of trade-offs between the design factors and performance parameters or corrections of the single event transients.

#### 1.6 Contributions

The main objective of this thesis completion is to suggest on methods on improving the sensitivity of circuits or a system to soft errors by means of mitigations. There is no actual dynamic design flow or methodology in soft error mitigation published by any, however, the common practices by researchers in mitigating digital circuits using computer simulations has been summarized and reported, in Section 2.2. This thesis has been completed based on the summarized dynamic mitigation design flow.

This thesis has also concluded that

- All analogue circuits studied in this work have been identified to be sensitive to single event transients, however to different level of sensitivity.

- Certain factors have significant impact on the sensitivity of the selected circuits based on completed characterization study.

- A simple mitigation technique using capacitors on the sensitive nodes has improved the sensitivity of the overall circuit to soft errors, particularly single event transient.

#### 1.7 Thesis Organization

Chapter 2 provides the literature and background which have been reviewed in order to complete this research. Chapter 2 further elaborates the phenomenon of radiation-induced faults and in quantifying soft errors. Some of the important terms in physical-level modelling have been introduced here. Chapter 2 reported the characterization of COTS devices and also, several non-COTS devices. The general operations of selected analogue circuits with selected topology are described in Chapter 2. Chapter 2 has also included the initial design stages for the 2-stage operational amplifier and the two comparators with some performance specifications obtained from preliminary simulations.

In Chapter 2, the chosen circuit-level modelling for single event effect is further described, together with some recently improved models. In addition to these subjects, the factors which are deemed influential to the sensitivity of a device to SETs have been described. The statistical tool used for investigating the impact of variability is also described in Chapter 2. Several circuit-level mitigation techniques have been reported briefly in Chapter 2, although not being tested on implemented device in this thesis.

Upon completion of implementation and design of amplifier and comparators, each device has been tested for its sensitivity to single event effects as reported in Chapter 3. The initial design for 2-stage operational amplifier and the two comparators are included in Chapter 3. A simple SPICE level single event modelling is described and used to model the particle strike to these circuits. A sensitivity analysis has been performed on each device in order to identify both the most and the least sensitive transistors. The result from the sensitivity analysis is used for variability analysis in Chapter 4.

Variability analyses are performed on the two variations of comparators, hysteresis-free comparator and comparator-with hysteresis in Chapter 4. The correlations between several factors, such as scaling and impact of temperature on the severity of single event effects have been reported and presented based on Design of Experiment(DOE) technique, particularly for a hysteresis-free comparator. On the other hand, several influencing factors for comparator-with-hysteresis characterization, such as differential input voltage, hysteresis and ageing are also analyzed and reported in Chapter 4. A preliminary mitigation to the circuits using capacitor has also been reported in Chapter 4.

Chapter 5 acts as the concluding chapter on the findings from the work completed for this thesis. Future work has been suggested focusing on the influencing factors that may be used as trade-offs in the mitigation process of the circuits. On top of that, further investigations as part of future work must be performed as a continuation to the preliminary mitigation technique applied in Chapter 4.

#### 1.8 List of Publications

Parts of this thesis have been published in the following:

Nawi, I.M, B.Halak, and M. Zwolinski, "Reliability Analysis of Comparators", Designing with Uncertainty: Opportunities and Challenges Workshop, 13th March 2015, Grenoble, France.

Nawi, I.M, B. Halak, and M. Zwolinski, "Reliability Analysis of Comparators", PhD Research in Microelectronics and Electronics (PRIME), 29th June to 2nd July 2015, Glasgow, Scotland.

Nawi, I.M, B.Halak, and M. Zwolinski, "Ageing Impact on a High Speed Comparator with Hysteresis", Workshop on Early Reliability Modelling for Ageing and Variability in Silicon Systems (ERMAVSS), 18th March 2016, Dresden, Germany.

Nawi, I.M, B.Halak, and M. Zwolinski, "The Influence of Hysteresis Voltage on Single Event Transients in a 65nm CMOS High Speed Comparator", IEEE European Test Symposium, 24 to 27th May 2016, Amsterdam, The Netherlands.

### Chapter 2

## Literature Review

This chapter includes the literature reviewed and background study taken to understand the basic concepts on soft errors caused by radiation sources. The impact of soft errors on analogue circuits have been reviewed and the existing characterization, modelling and mitigation of selected soft errors have also been reported. On top of that, the general operations of selected analogue circuits have also been included.

#### 2.1 Radiation-induced Faults

Radiation-induced faults are caused by two sources, which are alpha particles and neutrons. These two particles introduce errors in the silicon chips in the same way for both analogue and digital circuits. However, the effect of particle strikes on the digital and analogue circuits may be different [2]. Alpha particles affect the semiconductor devices by creating a track of electron-hole pairs as the particles pass through the substrate of the transistor which results in ionization as illustrated as in Figure 2.1(a). If this ionization come in close contact with the depletion region of the gate, it will cause the electric field to rapidly collect the carriers; which later create a voltage or current glitch at the gate's node. If the track of electron-hole pairs is further away from the depletion region, a smaller charge will be collected hence very unlikely this will cause a current or voltage glitch [30]. But, as the distance between the track and the depletion region is reduced, the higher the charge being collected. A minimum point at which the charge required to disturb a chip's reliability or to cause a circuit to malfunction is termed as the critical charge,  $Q_{crit}$ . This value is estimated by repeatedly running a circuit with different current pulses injected until the circuit fails. If the collected charge exceeds the critical charge, then the chip may experience soft errors. A higher critical charge may reduce the soft error rate, but the chip will experience slower operation and higher power dissipation.

Figure 2.1: Radiation-induced elements hit the silicon layers and produces ion tracks either by direct or indirect mechanisms [31]

On the other hand, neutrons do not have a direct impact on electrons to create similar ionization. When the neutrons hit the silicon layers or other atoms, secondary particles such as protons, neutrons, pions, are created [32], and later may create similar ionization track of sufficient electron-hole pairs. These secondary particles are capable of producing electron-hole pairs which may cause transient faults in a device, however, such a collision has a very low probability as compared with alpha particles. The collisions of neutrons with other heavier atoms may also create a reaction energy that being deposited along their travelling path, thus resembles direct ionization caused by alpha particles as illustrated in Figure 2.1(b). This ionization is termed as indirect ionization [32]. In addition to this, higher volumes of neutrons are required to produce the same number of transient faults exhibited by a device affected by alpha particles. In other words, alpha particles may have a greater effect in contributing towards soft errors.

#### 2.2 Dynamic Mitigation Design Flow

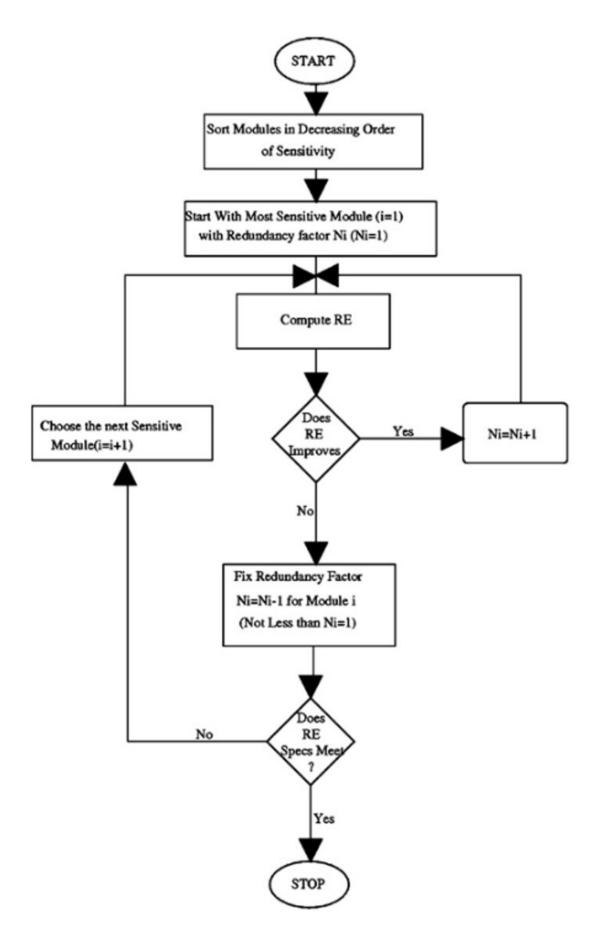

Before proceeding with the mitigation process of selected circuits, a methodology needs to be properly outlined. As already stated in Section 1.6, there is no actual overall dynamic mitigation design flow published by any either in digital, analogue or mixed signal design community. Stamenkovic et al., [33] only reported the design flow focuses on applying suggested fault tolerant techniques particularly for ASICs, while Pontes et al. [34], proposed a design flow focusing on modelling single event effects at system level for digital circuits. However, after reviewing the majority of work completed by digital designers, a summary comprising the methodology normally practised in mitigating circuits under radiation; the following design flow in Figure 2.2 has been produced.

Figure 2.2: Dynamic Mitigation Design Flow

The mitigation process of selected circuits has been summarized based on a mitigation design steps on correcting digital circuits, as reported by [35, 36, 37, 2, 38] The dynamic mitigation design flow as shown in Figure 2.2, although summarized based on digital circuits, has also been used for mitigating analogue and mixed signal circuits as described by Askari and Nourani [25]. In [25] however, the improvements of sensitive parts has been

established by expanding the sensitivity analysis followed by systematic optimization of the number of redundancy blocks, as part of improving sensitivity of the mixed-signal circuit.

The mitigation methodology commonly used in improving the sensitivity of digital, analogue and mixed signal circuits has initiated several automation tools in characterization selected soft errors. [39] reported there are several tools available in analyzing the soft errors in VLSI circuits, such as GRAS (Geant4 Radiation Analysis for Space) [40] and MRED (Monte Carlo Radiative Energy Deposition) [41]. These tools have been used to analyze radiation at system level while Marquez et al. [39] proposes a fault tolerant debugging tool for analogue and mixed-signal circuits at transistor level, designated as AFTU (Analogue Fault Tolerant University of Seville Debugging System).

# 2.3 Single Event Transients Characterization in Analogue Circuits

Analogue circuits consist of operational amplifiers and comparators. These circuits are identified to be the components commonly used for safety-critical systems [2, 16]. Thus, it is essential to review work completed on the characterization of SETs for circuits such as amplifiers and comparators for the past few decades. Section 2.3.1 and Section 2.3.2 describes the characterizations made on operational amplifiers and comparators; which mostly are bipolar circuits. Section 2.3.3 explained on a particular topology of comparators which are deemed problematic due to its feedback mechanism. Section 2.3.3 also described an application where the comparators seemingly are liable to cause a system's failure if the comparator has been struck with the radiation fault.

#### 2.3.1 Single Event Transients in Operational Amplifiers