## University of Southampton Research Repository

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Author (Year of Submission) "Full thesis title", University of Southampton, name of the University Faculty or School or Department, PhD Thesis, pagination.

UNIVERSITY OF SOUTHAMPTON

FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

Electronics and Computer Science

**Towards Reliable and Secure Physical Unclonable Functions**

by

**Mohd Syafiq Mispan**

Thesis for the degree of Doctor of Philosophy

July 2018

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

Electronics and Computer Science

Doctor of Philosophy

TOWARDS RELIABLE AND SECURE PHYSICAL UNCLONABLE FUNCTIONS

by **Mohd Syafiq Mispan**

Physical Unclonable Functions (PUFs) have emerged as a promising primitive that can be used to provide a hardware root of trust for integrated circuit (IC) applications. PUFs exploit the random intrinsic manufacturing process variations that map a set of challenges to a set of responses. The mapping of challenge-response pairs (CRPs) is unique and random to each PUF instance, which makes PUFs a very promising technology for robust security devices. PUFs have been proposed for lightweight IC identification and authentication, and cryptographic key generation. However, as CMOS technology scales down, device ageing becomes more pronounced and introduces reliability issues for PUF circuits. When PUFs undergo ageing, the response changes. As a consequence, the trustworthy identity of the ICs can be violated. The area overhead of an error correction code (ECC) in a PUF-based system needed to generate error-free cryptographic keys also increases. Furthermore, a PUF is physically unclonable but its function is susceptible to modelling attacks from machine learning (ML) techniques. Therefore, providing reliable and secure PUFs for lightweight applications is a major challenge. This thesis studies the reliability of PUFs for lightweight applications under ageing. It also considers the susceptibility of PUFs to ML-based attacks.

This thesis presents three major contributions. The context of the first and second contributions is within the lightweight IC identification and authentication, and the third contribution is within the cryptographic key generation. The first contribution presents an analysis of the impact of ageing on PUF-based differential architectures. The simulation results demonstrate that a differential design technique to build a PUF can be a mechanism to mitigate the first-order dependencies of ageing such as the duty cycle and supply voltage. The second contribution proposes a challenge permutation technique to increase the complexity of the CRP mapping. The technique has been implemented on an Arbiter-PUF using a TSMC 65-nm technology. The simulation results show that using a challenge permutation technique can alter the output transition probability of Arbiter-PUF, resulting in the reduction of its predictability from  $\approx 99\%$  to  $\approx 65\%$ . The challenge permutation technique introduces no extra overhead as it can be implemented by routing obfuscation. Finally, the third contribution proposes a bit selection technique in a dual use of SRAM as a memory and PUF to mitigate the ageing impact and reduce the area overhead of the ECC. The results show that the proposed technique can effectively reduce the bit errors due to ageing and the area overhead of the ECC is reduced by about 6 times compared to that without bit selection.

# Contents

|                                                            |             |

|------------------------------------------------------------|-------------|

| <b>Declaration of Authorship</b>                           | <b>xv</b>   |

| <b>Acknowledgements</b>                                    | <b>xvii</b> |

| <b>Abbreviations</b>                                       | <b>xix</b>  |

| <b>Nomenclature</b>                                        | <b>xxi</b>  |

| <b>1 Introduction</b>                                      | <b>1</b>    |

| 1.1 Cryptographic Key Storage Technologies . . . . .       | 1           |

| 1.2 Physical Unclonable Function . . . . .                 | 3           |

| 1.3 Motivations For Research . . . . .                     | 4           |

| 1.4 Objectives . . . . .                                   | 5           |

| 1.5 Thesis Structure . . . . .                             | 5           |

| 1.6 Publications . . . . .                                 | 6           |

| <b>2 Physical Unclonable Function</b>                      | <b>9</b>    |

| 2.1 Definition of a PUF . . . . .                          | 9           |

| 2.2 Variability in Integrated Circuits . . . . .           | 10          |

| 2.3 Types of PUFs . . . . .                                | 11          |

| 2.3.1 Non-Silicon and Silicon PUFs . . . . .               | 11          |

| 2.3.2 Strong, Weak and Controlled PUFs . . . . .           | 12          |

| 2.4 Silicon PUF Constructions . . . . .                    | 13          |

| 2.4.1 Arbiter-PUF . . . . .                                | 14          |

| 2.4.2 Ring Oscillator PUF . . . . .                        | 17          |

| 2.4.3 SRAM-PUF . . . . .                                   | 18          |

| 2.4.4 Flip-flop, Latch and Buskeeper PUFs . . . . .        | 20          |

| 2.4.5 Mixed-Signal PUFs . . . . .                          | 21          |

| 2.4.6 Emerging Nanotechnology-based PUFs . . . . .         | 23          |

| 2.5 PUF Quality Metrics . . . . .                          | 24          |

| 2.5.1 Uniqueness . . . . .                                 | 24          |

| 2.5.2 Reliability . . . . .                                | 25          |

| 2.5.3 Uniformity . . . . .                                 | 25          |

| 2.6 The Effect of Ageing on PUFs . . . . .                 | 29          |

| 2.6.1 CMOS Device Ageing . . . . .                         | 29          |

| 2.6.2 Related Works of Ageing on PUFs . . . . .            | 31          |

| 2.7 PUF Applications . . . . .                             | 33          |

| 2.7.1 Low-Cost Identification and Authentication . . . . . | 33          |

---

|          |                                                             |           |

|----------|-------------------------------------------------------------|-----------|

| 2.7.2    | Cryptographic Key Generation                                | 36        |

| 2.8      | Known Attacks to PUFs                                       | 38        |

| 2.8.1    | Invasive Attacks                                            | 38        |

| 2.8.2    | Semi-invasive Attacks                                       | 38        |

| 2.8.3    | Non-invasive Attacks                                        | 39        |

| 2.8.4    | Challenges                                                  | 41        |

| 2.9      | Advantages of PUFs                                          | 42        |

| 2.10     | Summary                                                     | 43        |

| <b>3</b> | <b>PUF Implementation and Evaluation</b>                    | <b>45</b> |

| 3.1      | Motivation                                                  | 46        |

| 3.2      | MOSFET in Subthreshold Region                               | 47        |

| 3.3      | TCO-PUF Architecture                                        | 49        |

| 3.3.1    | Design of Transistor Arrays                                 | 49        |

| 3.3.2    | Design of Voltage Sense Amplifier                           | 51        |

| 3.4      | Simulation Results and Analysis                             | 53        |

| 3.4.1    | Setup                                                       | 53        |

| 3.4.2    | Analysis of Transistor Arrays                               | 54        |

| 3.4.3    | PUF Metrics Evaluation                                      | 54        |

| 3.4.3.1  | Uniqueness                                                  | 54        |

| 3.4.3.2  | Reliability                                                 | 55        |

| 3.4.3.3  | Uniformity                                                  | 56        |

| 3.5      | ML-Attack Susceptibility                                    | 57        |

| 3.6      | Impact of NBTI on PUFs                                      | 59        |

| 3.6.1    | Ageing Evaluation Methodology                               | 59        |

| 3.6.2    | NBTI Impact on RO-PUF                                       | 60        |

| 3.6.3    | NBTI Impact on PUF-based Differential Architectures         | 62        |

| 3.7      | Summary                                                     | 69        |

| <b>4</b> | <b>A Lightweight Technique for ML-Attack Resistant PUFs</b> | <b>71</b> |

| 4.1      | Motivation                                                  | 72        |

| 4.2      | Methodology                                                 | 75        |

| 4.2.1    | CRP Generation                                              | 75        |

| 4.2.2    | PUF Configuration                                           | 76        |

| 4.2.3    | Artificial Neural Network                                   | 76        |

| 4.2.4    | Threat Model                                                | 78        |

| 4.3      | Arbiter-PUF Properties                                      | 79        |

| 4.3.1    | Functionality Description                                   | 79        |

| 4.3.2    | Output Transition Probability                               | 80        |

| 4.4      | Analysis                                                    | 82        |

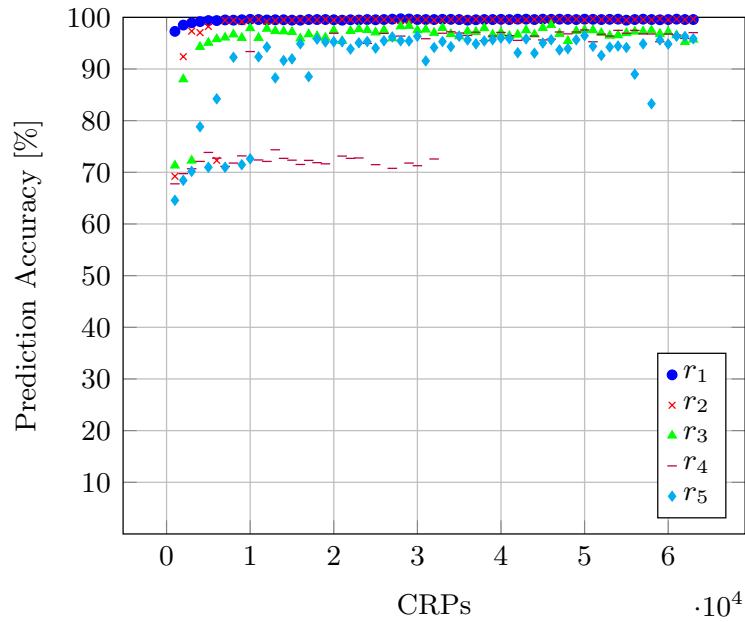

| 4.4.1    | ML-attack on Arbiter-PUF                                    | 82        |

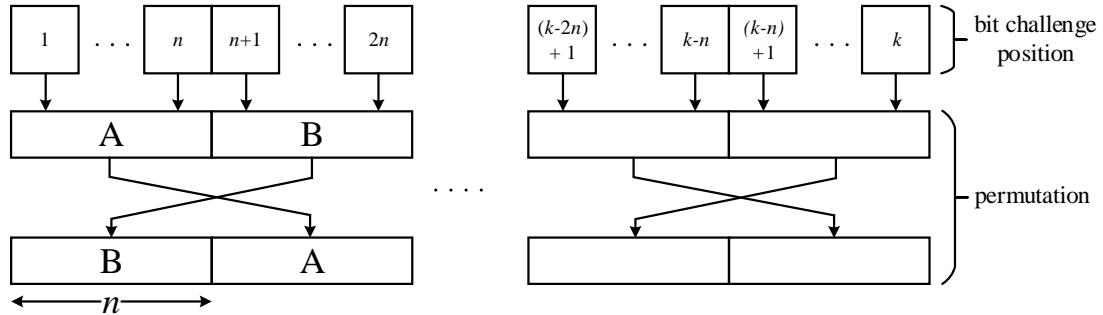

| 4.4.2    | Challenge Permutation Technique                             | 84        |

| 4.4.3    | Random Challenge Permutation                                | 86        |

| 4.4.4    | Hardware Implementation                                     | 89        |

| 4.4.5    | Predictability Comparison                                   | 91        |

| 4.5      | Summary                                                     | 92        |

---

|                                                               |            |

|---------------------------------------------------------------|------------|

| <b>5 A Reliable PUF in a Dual Function SRAM</b>               | <b>95</b>  |

| 5.1 Motivation . . . . .                                      | 96         |

| 5.1.1 A Dual Function SRAM . . . . .                          | 96         |

| 5.1.2 Ageing Mitigation in SRAM-PUFs . . . . .                | 97         |

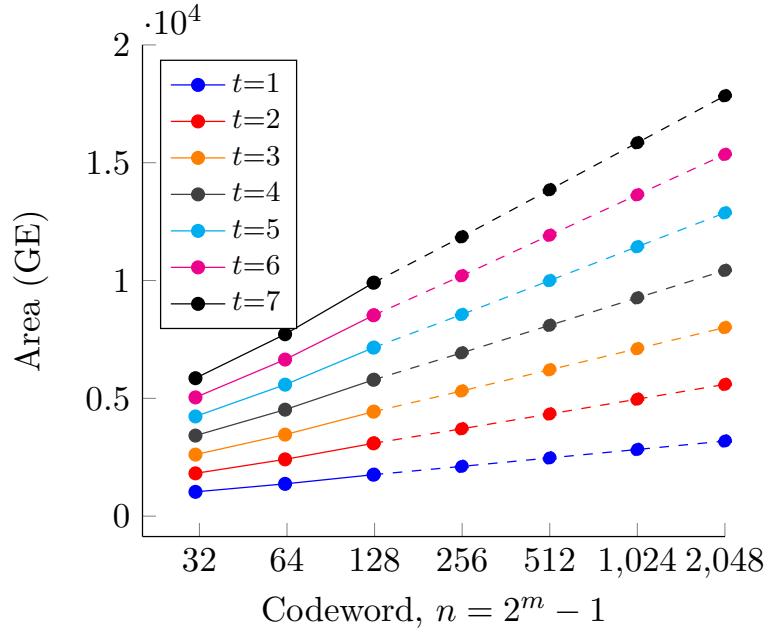

| 5.1.3 Area Estimation of ECC . . . . .                        | 98         |

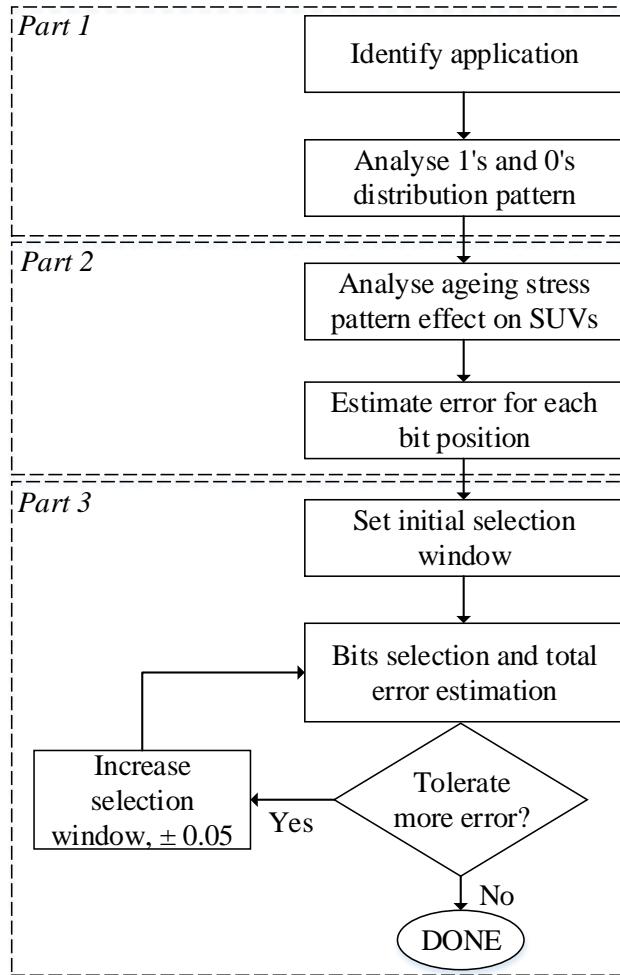

| 5.2 Pre-processing Approaches . . . . .                       | 99         |

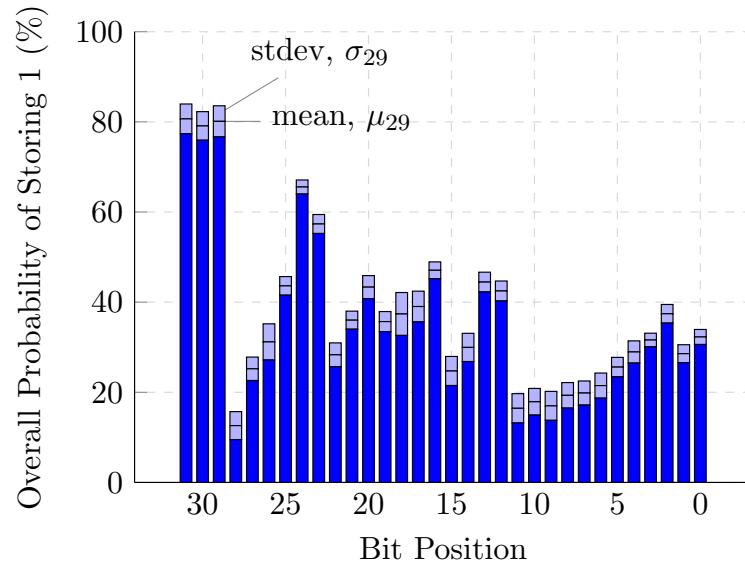

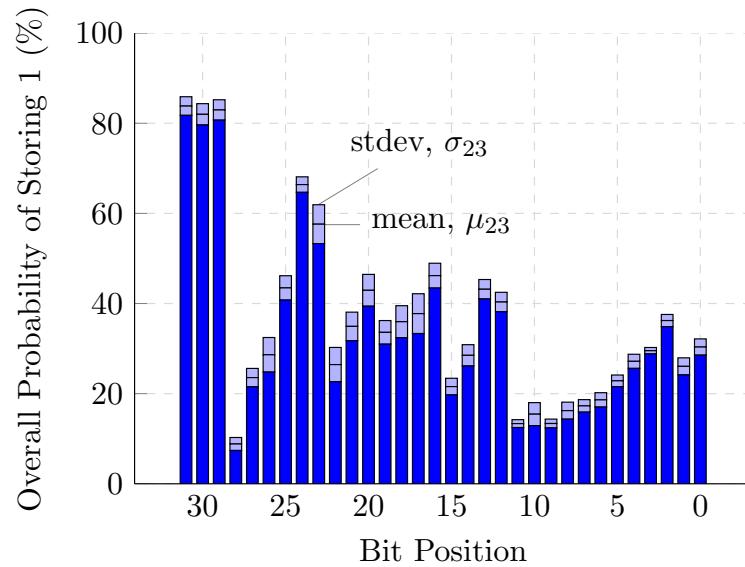

| 5.3 Signal Probability Pattern in SRAM Caches . . . . .       | 100        |

| 5.4 NBTI Impact on SUVs . . . . .                             | 104        |

| 5.4.1 Simulation Setup . . . . .                              | 104        |

| 5.4.2 Bit Error Analysis Under NBTI Effect . . . . .          | 104        |

| 5.5 Bit Selections . . . . .                                  | 106        |

| 5.5.1 Temperature and Voltage Variations . . . . .            | 110        |

| 5.5.2 Uniqueness and Uniformity . . . . .                     | 111        |

| 5.6 Hardware Cost and Implementation . . . . .                | 113        |

| 5.6.1 Area Overhead of Bit Select Configurations . . . . .    | 113        |

| 5.6.2 Area Overhead of ECC . . . . .                          | 114        |

| 5.7 Summary . . . . .                                         | 116        |

| <b>6 Conclusions and Future Work</b>                          | <b>117</b> |

| 6.1 Conclusions . . . . .                                     | 117        |

| 6.2 Future Work . . . . .                                     | 119        |

| <b>A MATLAB Code</b>                                          | <b>121</b> |

| A.1 Uniqueness . . . . .                                      | 121        |

| A.2 Uniformity . . . . .                                      | 122        |

| A.3 Optimum Size of BCH scheme . . . . .                      | 123        |

| A.4 Linear Feedback Shift Register (LFSR) Fibonacci . . . . . | 124        |

| A.5 Output Transition Probability . . . . .                   | 126        |

| A.5.1 Non-permuted and Permutated CRPs . . . . .              | 126        |

| A.5.2 Iterative Permutation . . . . .                         | 128        |

| A.6 ML-attack . . . . .                                       | 130        |

| <b>B Verilog Code</b>                                         | <b>133</b> |

| B.1 Hardware Implementation of Figure 4.13 . . . . .          | 133        |

| <b>C Miscellaneous</b>                                        | <b>139</b> |

| C.1 Reliability of 2-XOR Arbiter-PUF . . . . .                | 139        |

| C.2 BCH code . . . . .                                        | 140        |

| <b>References</b>                                             | <b>143</b> |

# List of Figures

|      |                                                                                                                                                                                                 |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Plaintext encryption using a XOR function. . . . .                                                                                                                                              | 2  |

| 1.2  | Security-cost positioning of permanent key storage technologies [9]. . . . .                                                                                                                    | 2  |

| 2.1  | Basic functionality of PUF. . . . .                                                                                                                                                             | 10 |

| 2.2  | Scaling trend of $V_{th}$ variations due to RDF [20]. . . . .                                                                                                                                   | 11 |

| 2.3  | The construction of Arbiter-PUF as proposed in [36]. . . . .                                                                                                                                    | 14 |

| 2.4  | The construction of Feed-Forward Arbiter-PUF as proposed in [30]. . . . .                                                                                                                       | 15 |

| 2.5  | The construction of Lightweight-PUF as proposed in [31] for $l=4$ . . . . .                                                                                                                     | 16 |

| 2.6  | The construction of the $l$ -XOR Arbiter-PUF as proposed in [22]. . . . .                                                                                                                       | 17 |

| 2.7  | The construction of an RO-PUF as proposed in [22]. . . . .                                                                                                                                      | 18 |

| 2.8  | 6-T SRAM cell circuit. . . . .                                                                                                                                                                  | 19 |

| 2.10 | The construction of Butterfly PUF [25], D Flip-flop PUF [32], SR-NOR latch PUF [33] and Buskeeper PUF [26]. . . . .                                                                             | 21 |

| 2.11 | The construction of VTC-PUF [34]. . . . .                                                                                                                                                       | 22 |

| 2.12 | The construction of the current mirror circuit in the Current Mirror-PUF [35]. . . . .                                                                                                          | 22 |

| 2.13 | 3-T pixel circuit. . . . .                                                                                                                                                                      | 23 |

| 2.14 | The construction of $n$ cascaded transistors of one block in TV-PUF [41]. . . . .                                                                                                               | 24 |

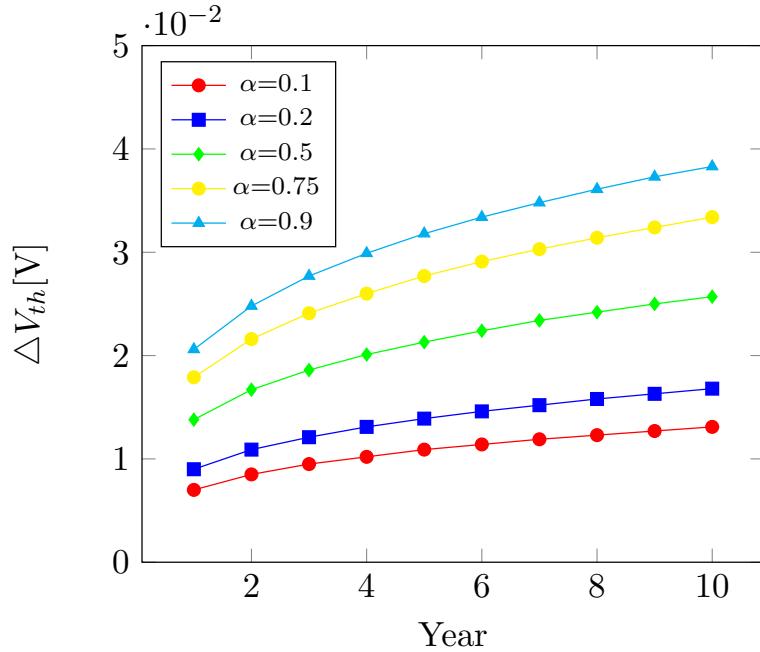

| 2.15 | Threshold voltage degradation ( $\Delta V_{th}$ ) over the time for CMOS inverter at different duty cycle due to NBTI effect. . . . .                                                           | 30 |

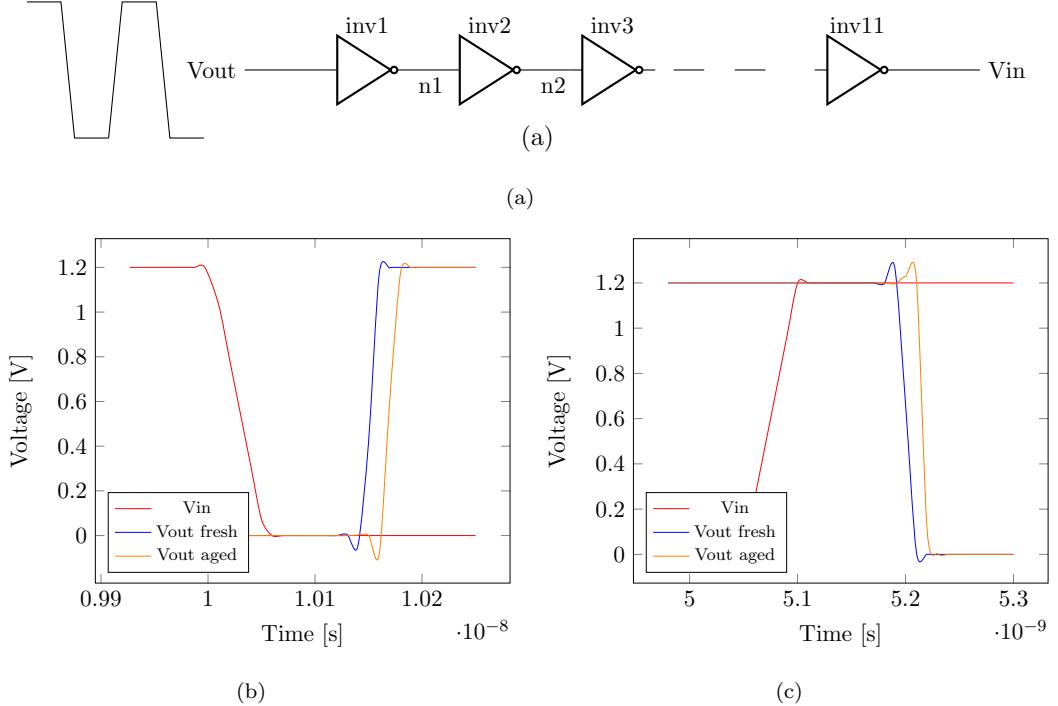

| 2.16 | Transient behaviour of CMOS inverter under NBTI (a) a chain of 11 inverters, (b) assertion of falling signal at the primary input, (c) assertion of rising signal at the primary input. . . . . | 31 |

| 2.17 | Low-cost PUF-based identification and authentication [22, 10]. . . . .                                                                                                                          | 34 |

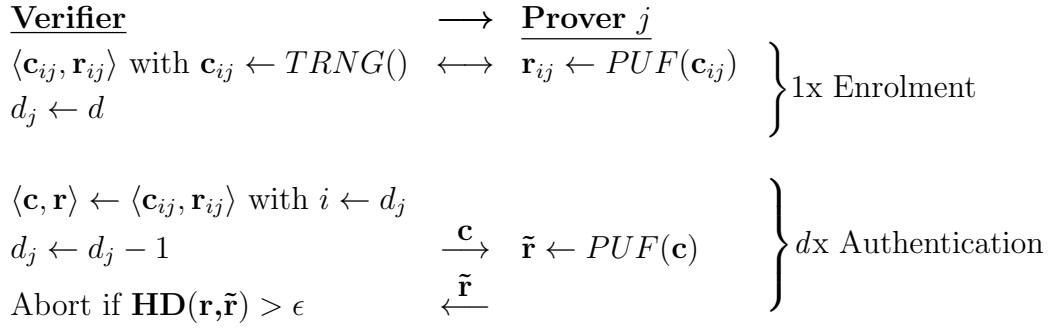

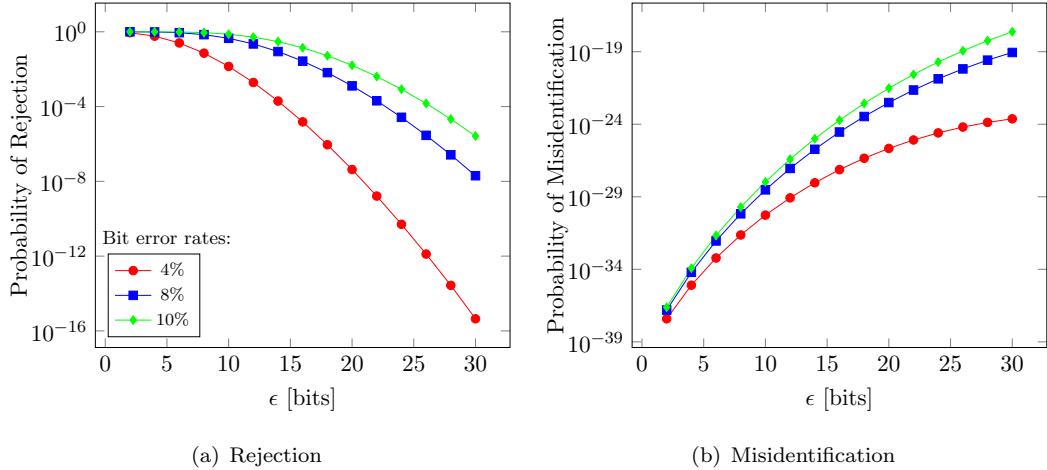

| 2.18 | Probability of rejection and misidentification at different bit error rates and $\epsilon$ for $n=128$ -bit and $p_{inter}=0.5$ . . . . .                                                       | 35 |

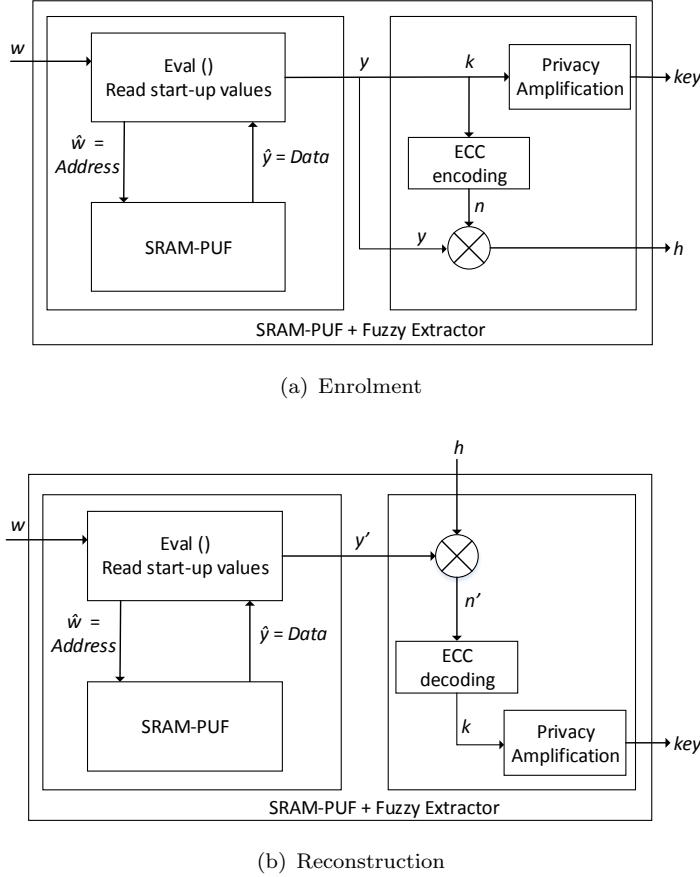

| 2.19 | The procedure of cryptographic key generation based on SRAM-PUF [26]. . . . .                                                                                                                   | 37 |

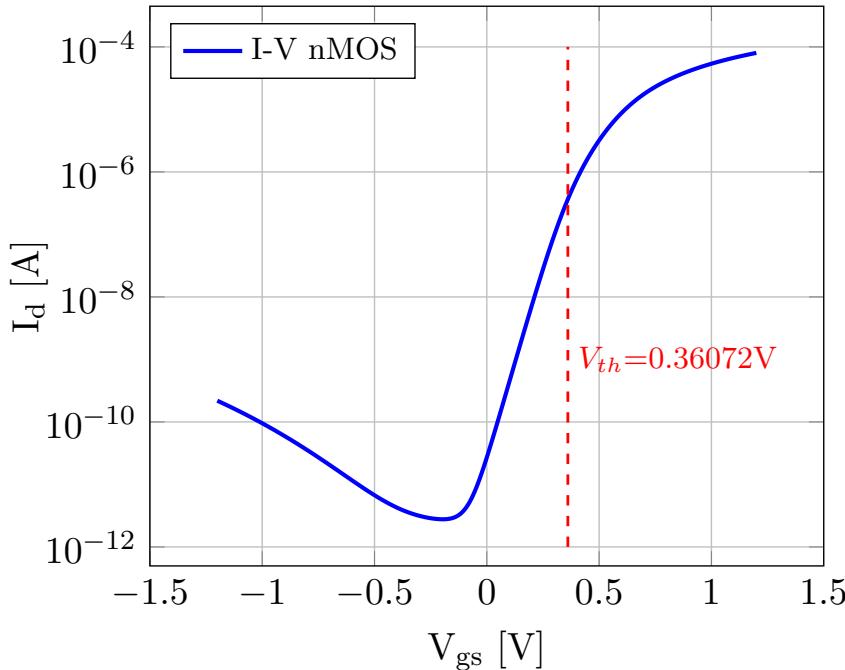

| 3.1  | I-V characterisation for nMOS using a low- $k$ TSMC 65-nm CMOS technology node. . . . .                                                                                                         | 48 |

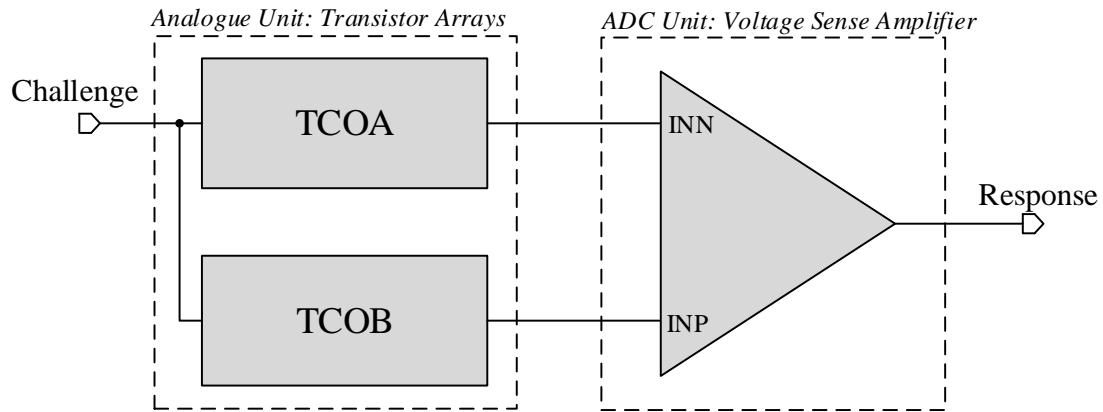

| 3.2  | Top level of TCO-PUF architecture. . . . .                                                                                                                                                      | 49 |

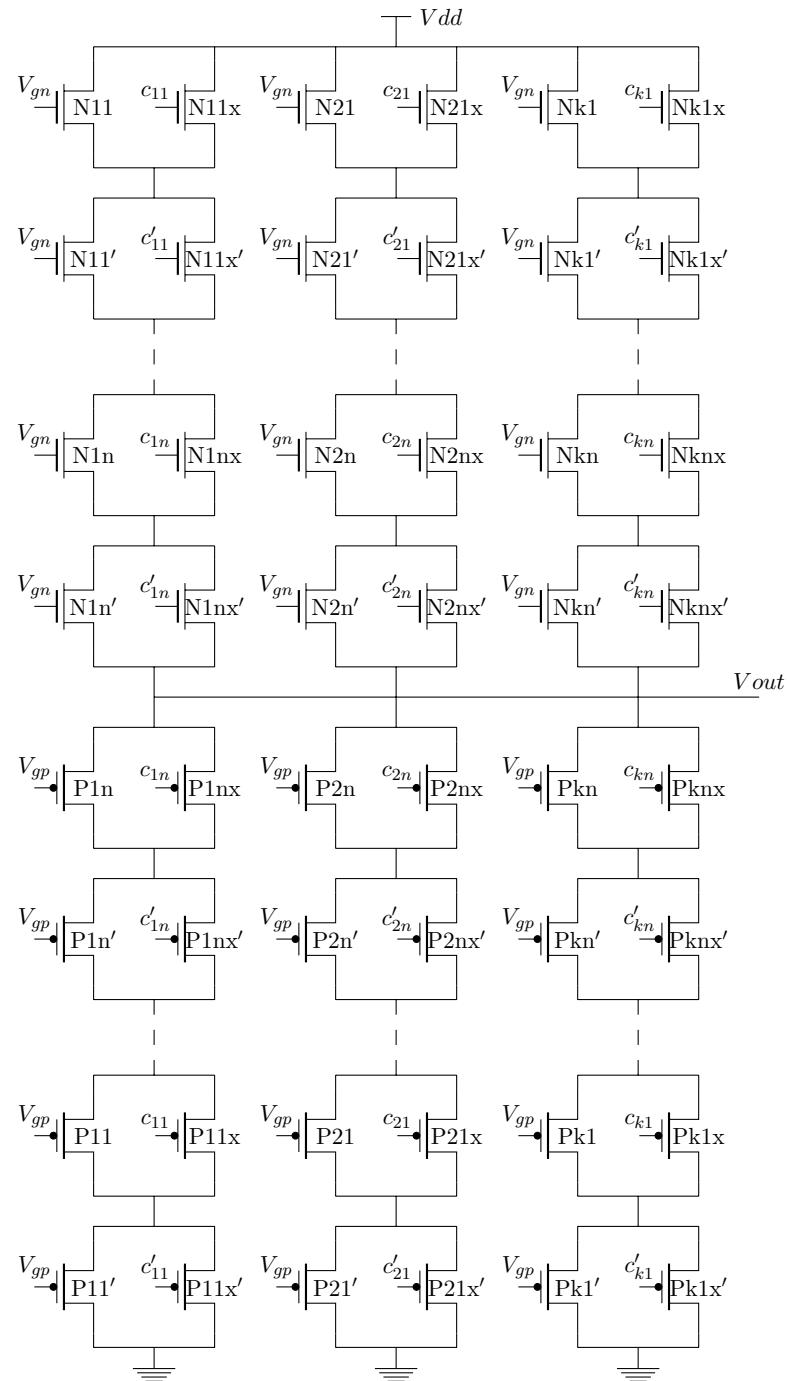

| 3.3  | The construction of the transistor array of TCO-PUF. . . . .                                                                                                                                    | 50 |

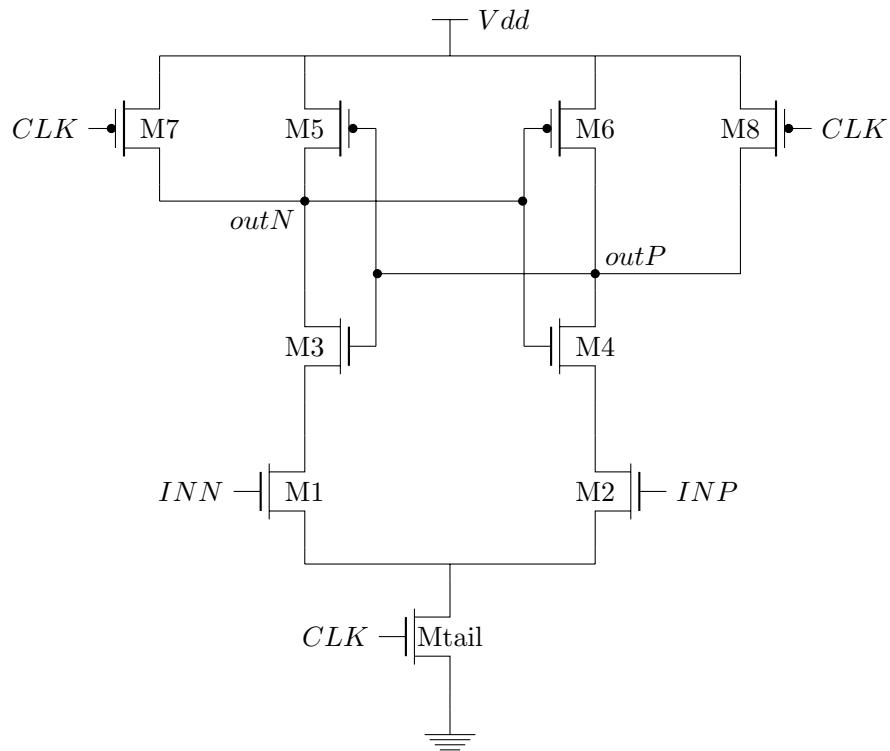

| 3.4  | The construction of the voltage sense amplifier. . . . .                                                                                                                                        | 52 |

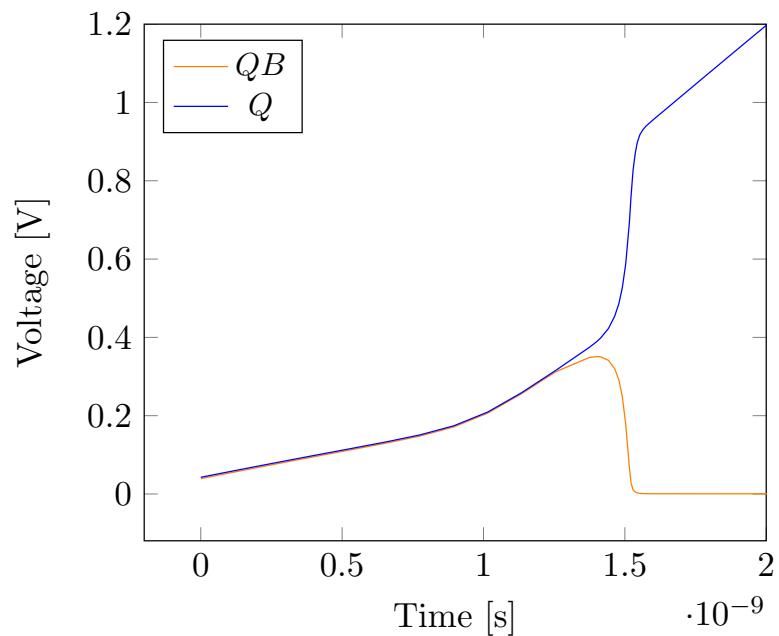

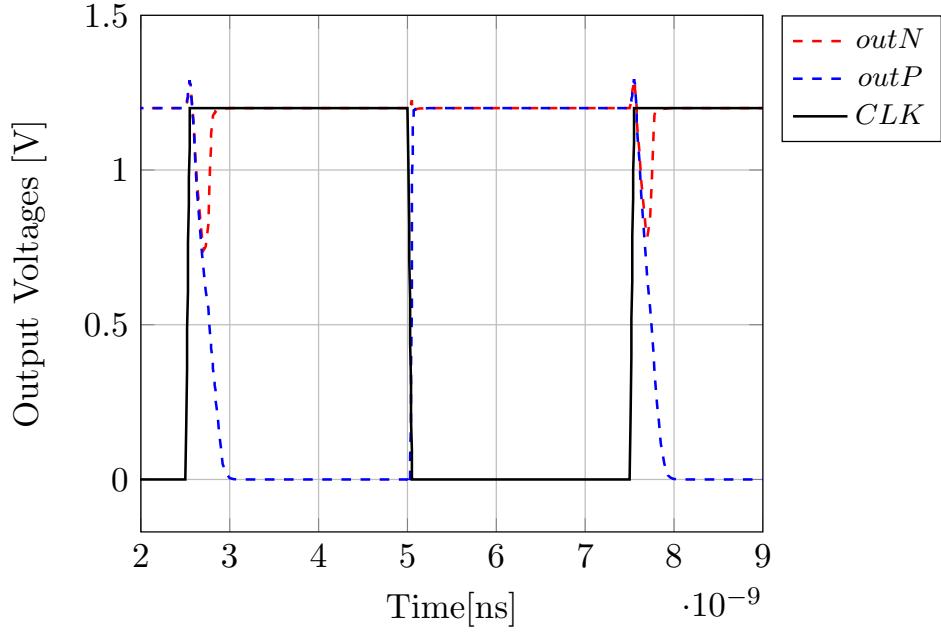

| 3.5  | Transient simulation of the voltage sense amplifier for input voltage difference $\Delta V_{in} = 5\text{mV}$ and $V_{dd} = 1.2\text{V}$ . . . . .                                              | 53 |

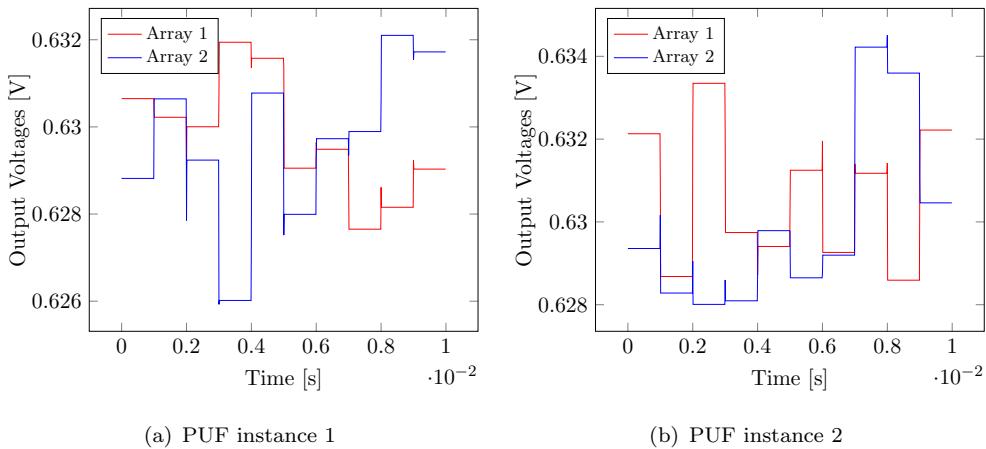

| 3.6  | Output voltages from transistor arrays of two TCO-PUF instances. . . . .                                                                                                                        | 54 |

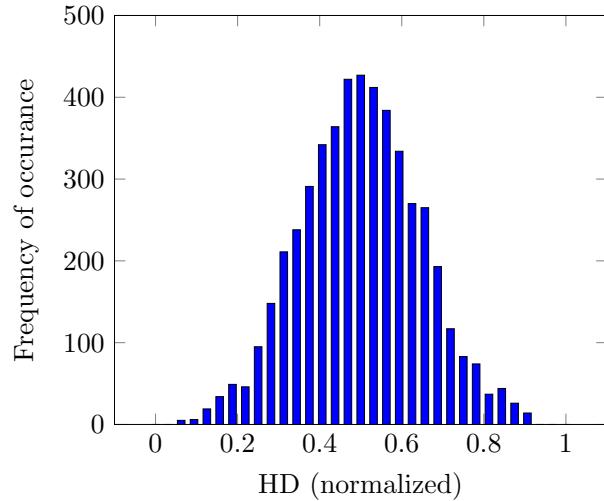

| 3.7  | Uniqueness of 32-bit TCO-PUF for 100 instances. . . . .                                                                                                                                         | 55 |

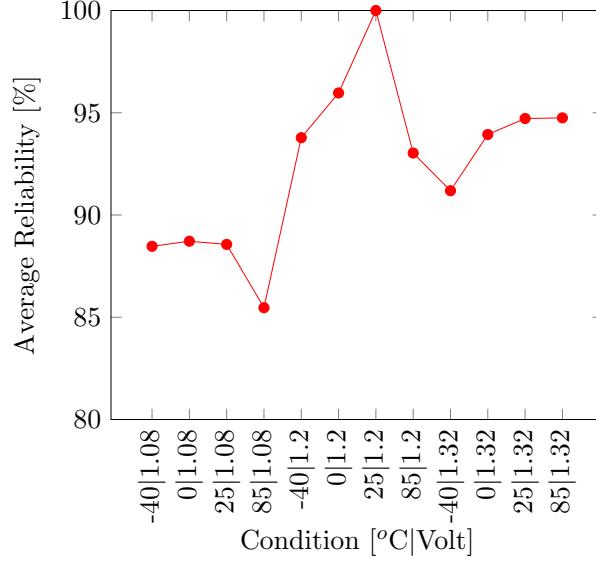

| 3.8  | Reliability for 32-bit TCO-PUF under temperature variations of $-40^\circ\text{C}$ to $85^\circ\text{C}$ and a supply voltage of $1.2\text{V} \pm 10\%$ . . . . .                               | 56 |

|      |                                                                                                                                      |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

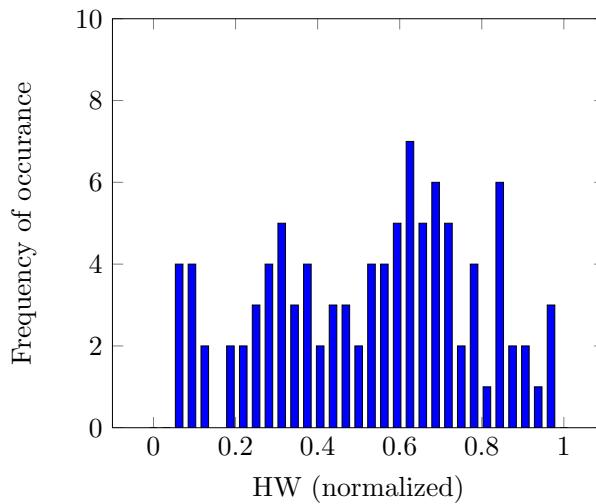

| 3.9  | Uniformity of 32-bit TCO-PUF for 100 instances. . . . .                                                                              | 56  |

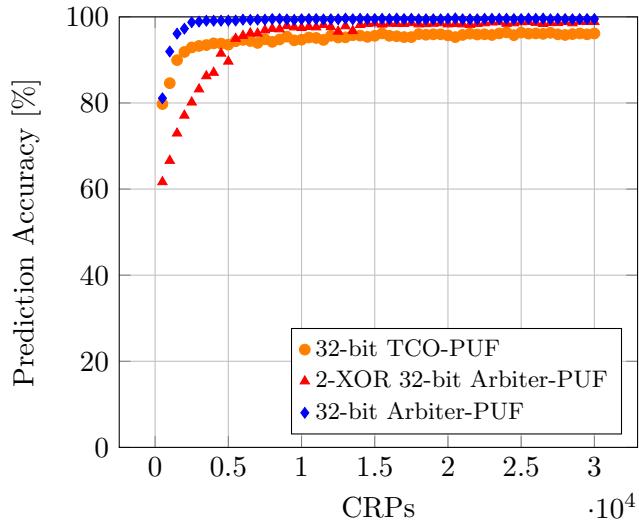

| 3.10 | ML-attack on 32-bit TCO-PUF and comparison with other PUFs. . . . .                                                                  | 57  |

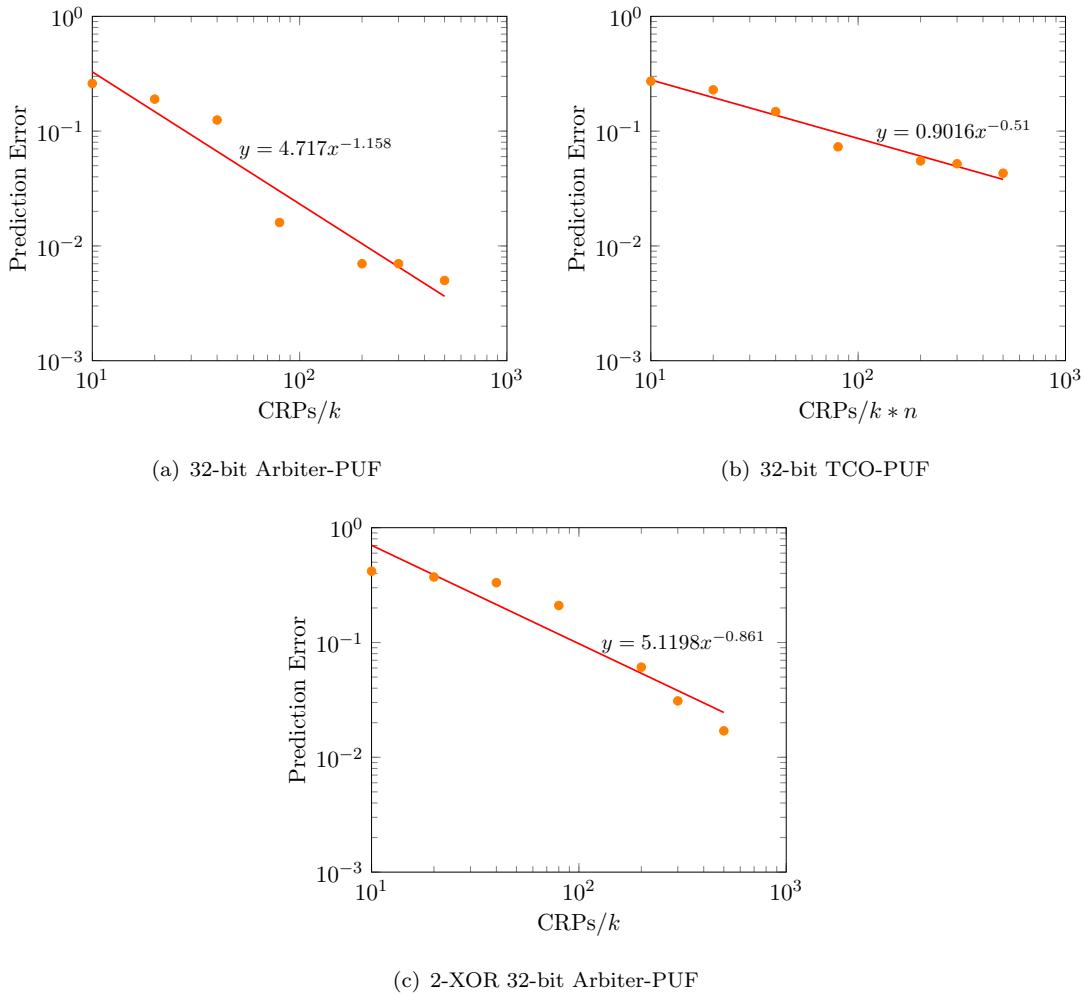

| 3.11 | Prediction error rate on the ratio of training CRPs and bit-length of the challenge. . . . .                                         | 58  |

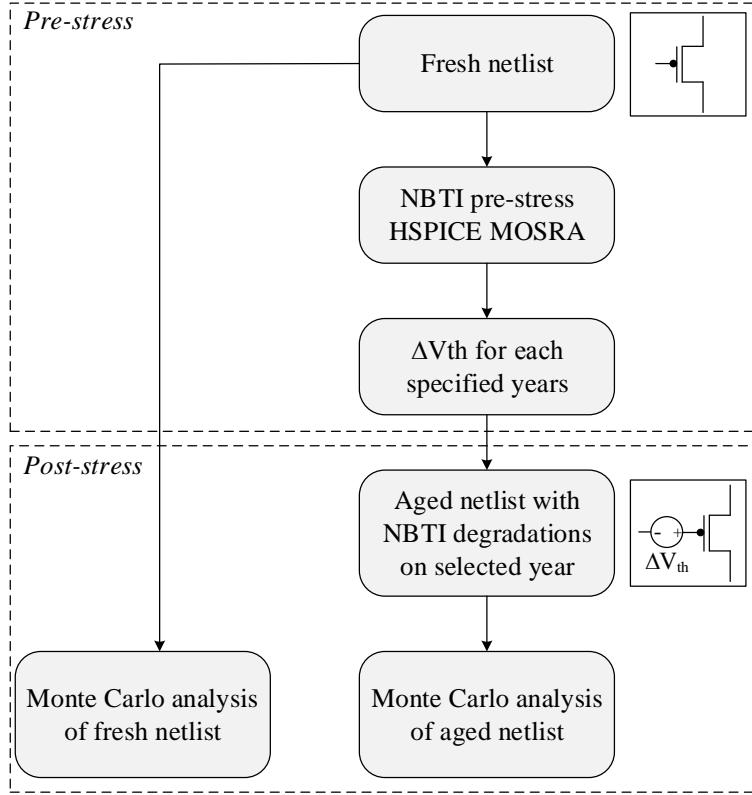

| 3.12 | NBTI simulation strategy. . . . .                                                                                                    | 60  |

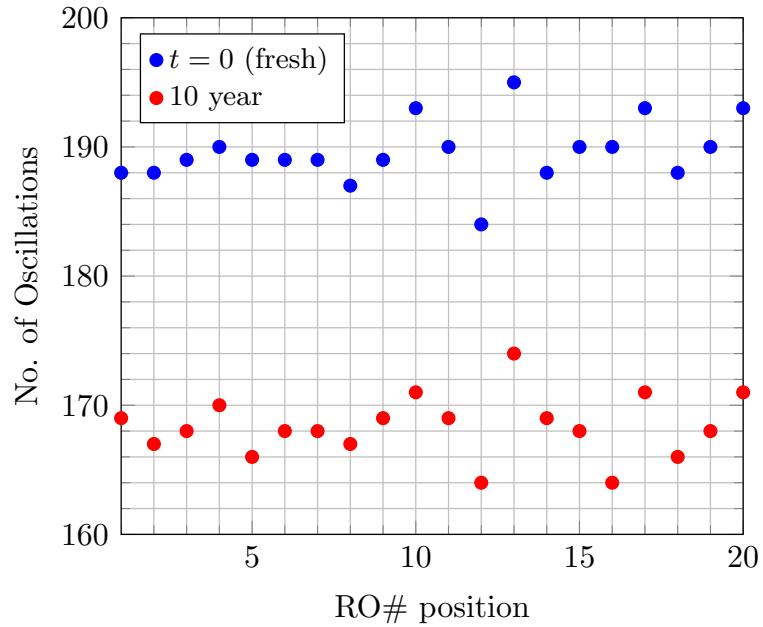

| 3.13 | RO oscillation degradation under NBTI stress. . . . .                                                                                | 61  |

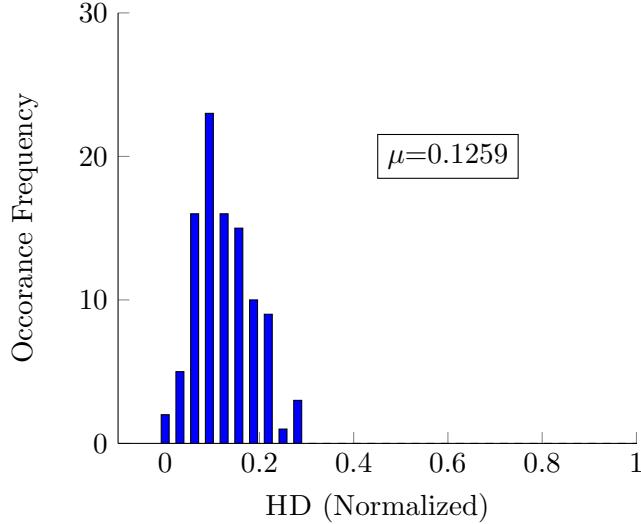

| 3.14 | Distribution of bit errors due to NBTI for 100 RO-PUFs in 10 years with 20% activity factor. . . . .                                 | 62  |

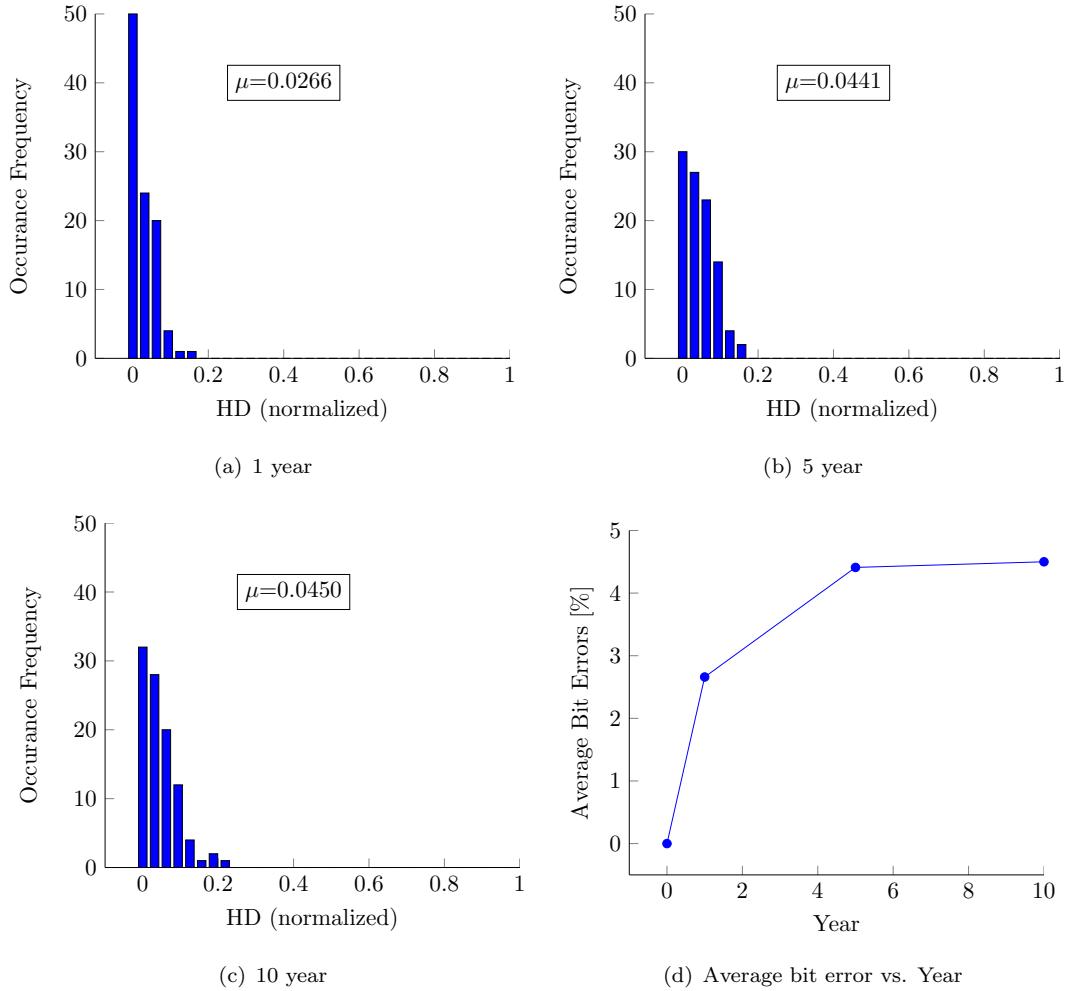

| 3.15 | Distribution of bit errors due to NBTI for 100 TCO-PUFs in 1, 5, and 10 years with 20% activity factor. . . . .                      | 63  |

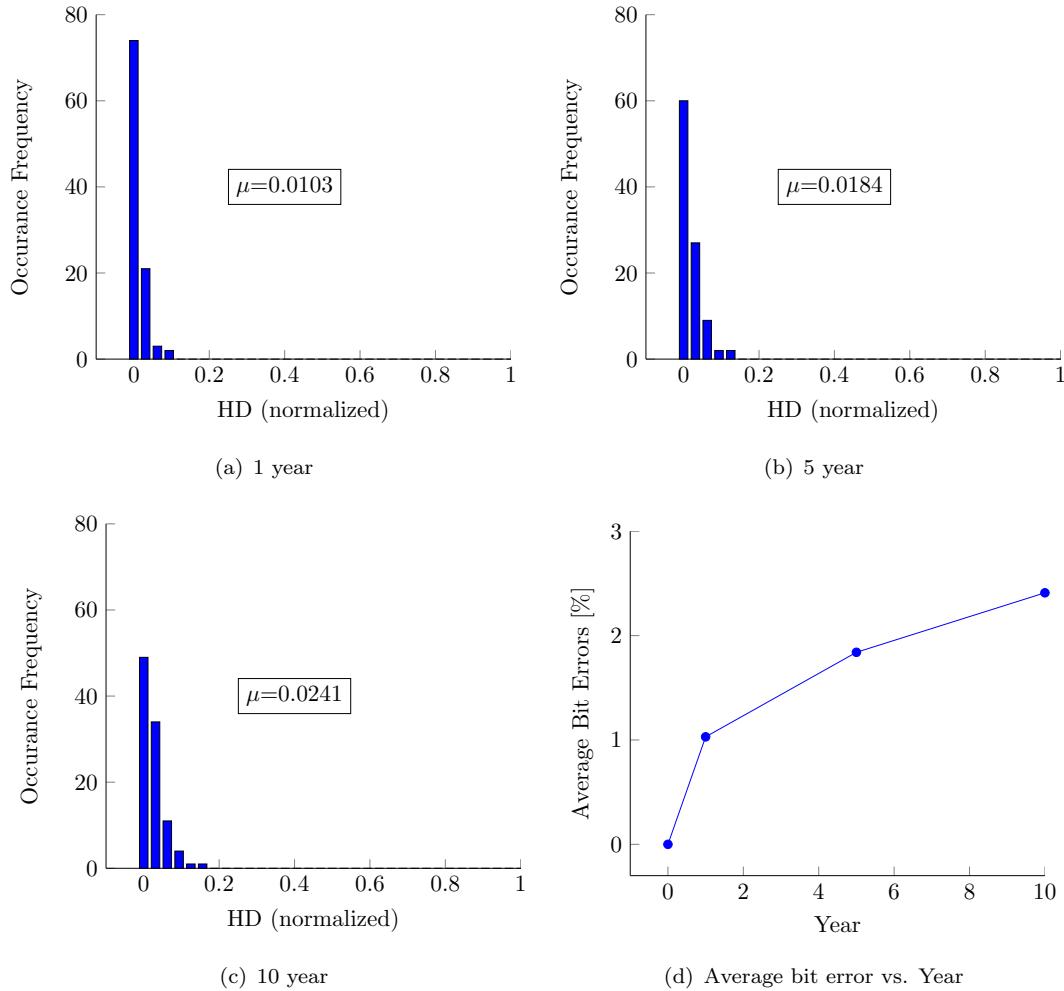

| 3.16 | Distribution of bit errors due to NBTI for 100 Arbiter-PUFs in 1, 5, and 10 years with 20% activity factor. . . . .                  | 64  |

| 3.17 | Path propagation in switching component [3]. . . . .                                                                                 | 65  |

| 3.18 | Simplified circuit of Arbiter-PUF. . . . .                                                                                           | 66  |

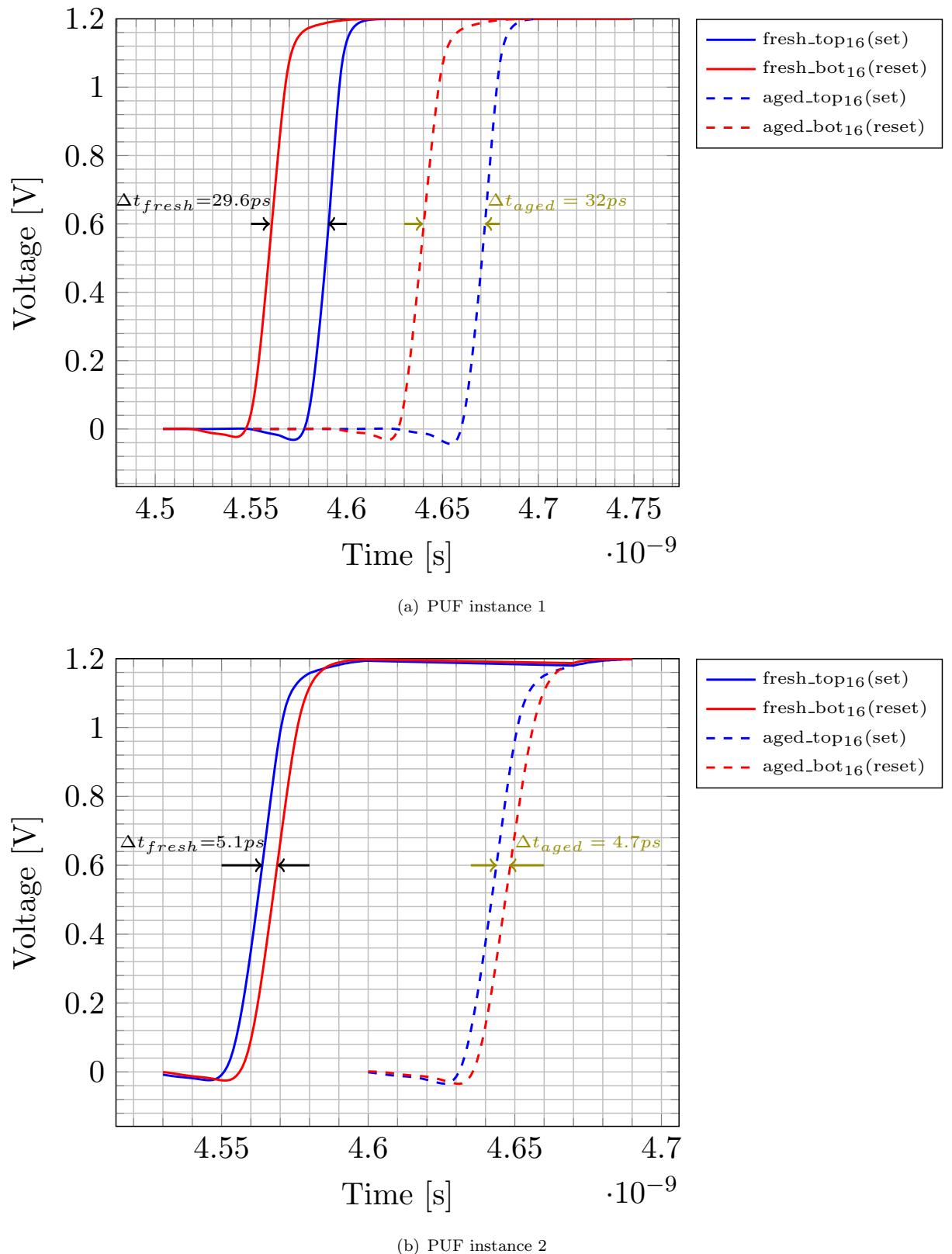

| 3.19 | Arrival time of a rising pulse before the SR-latch under NBTI stress for two Arbiter-PUF instances with a similar challenge. . . . . | 67  |

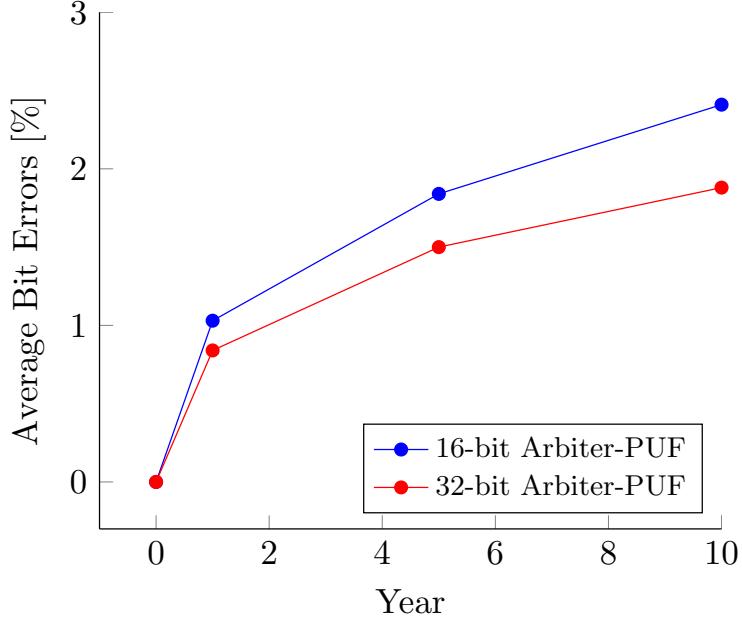

| 3.20 | Average bit error rates for 16-bit and 32-bit Arbiter-PUFs. . . . .                                                                  | 68  |

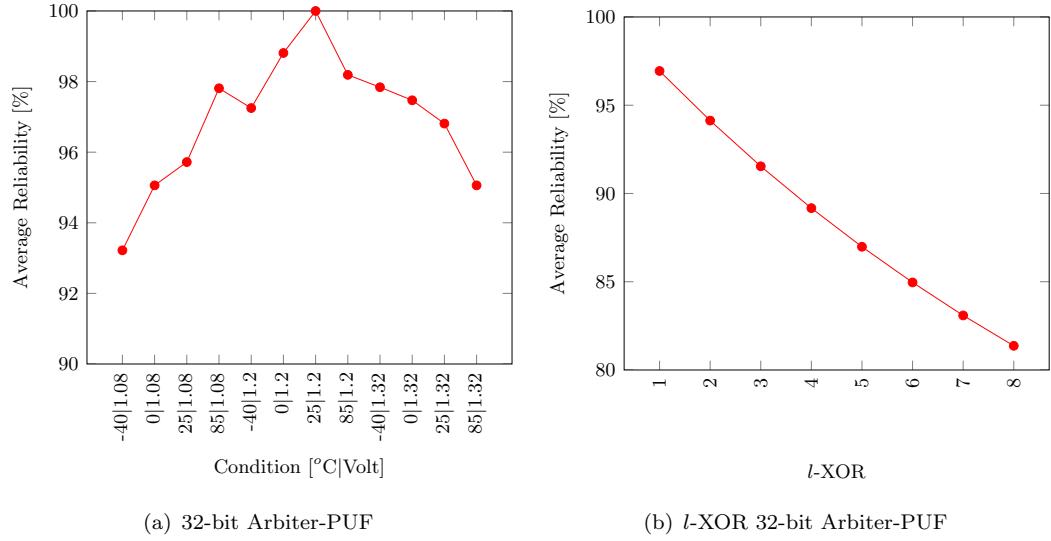

| 4.1  | Reliability for 32-bit Arbiter-PUF under temperature and supply voltage variations. . . . .                                          | 73  |

| 4.2  | The concept of Controlled PUF [27]. . . . .                                                                                          | 74  |

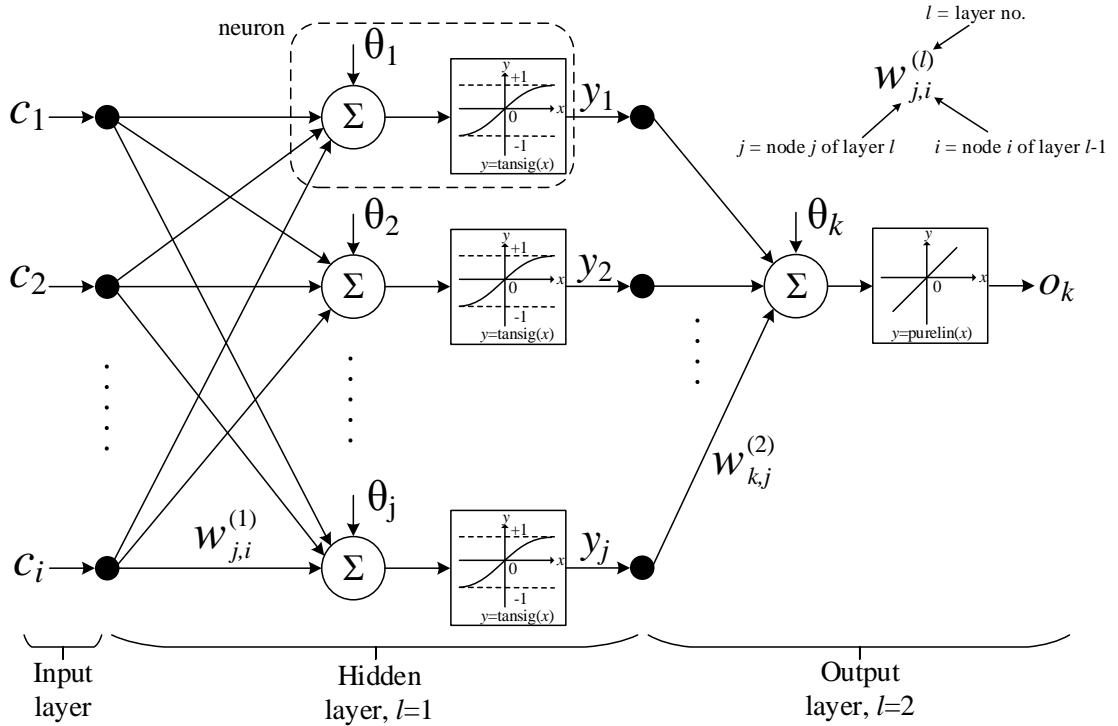

| 4.3  | MLP feed-forward network structure for binary classification problem. . . . .                                                        | 77  |

| 4.4  | $k$ -bit Arbiter-PUF. . . . .                                                                                                        | 79  |

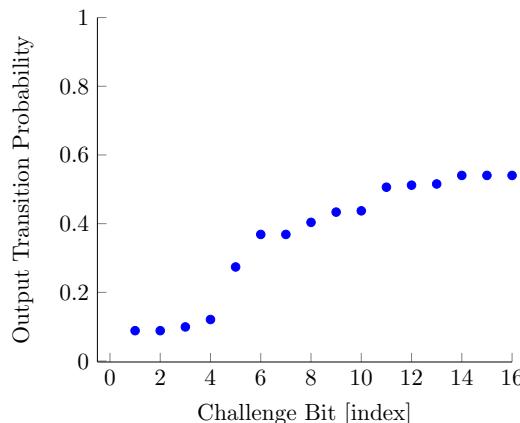

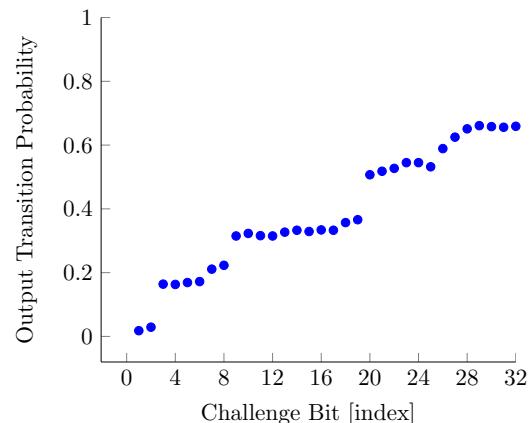

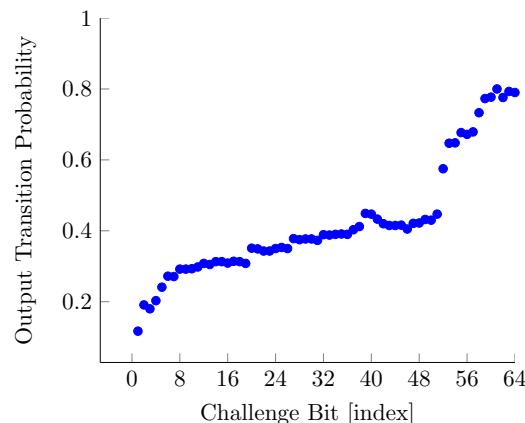

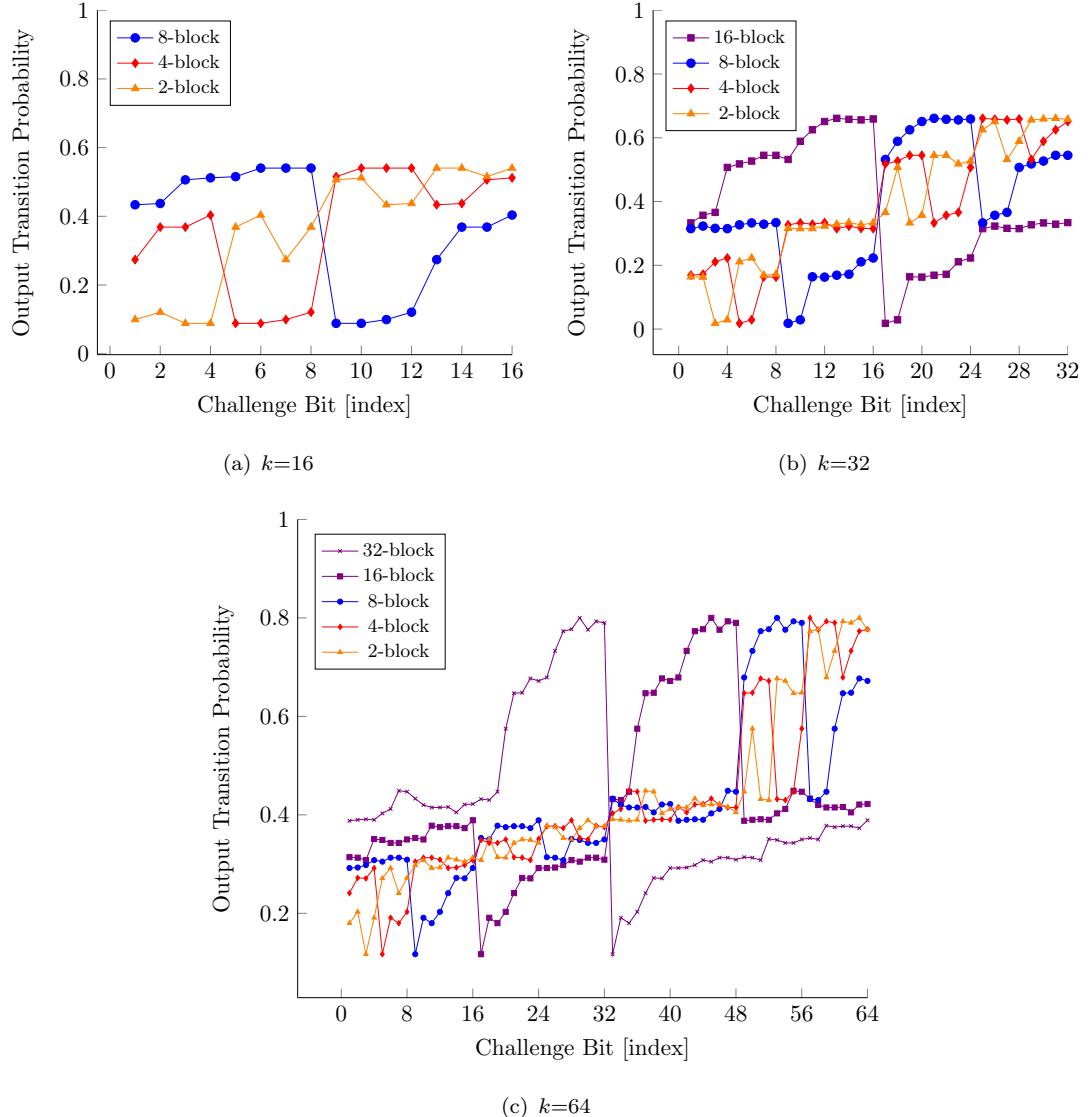

| 4.5  | Output transition probability for $k$ -bit Arbiter-PUF. . . . .                                                                      | 81  |

| 4.6  | ML-attack on 16-bit LFSR plus 16-bit Arbiter-PUF configuration using ANN. . . . .                                                    | 83  |

| 4.7  | $n$ -block permutation scheme. . . . .                                                                                               | 84  |

| 4.8  | Output transition probability for $k$ -bit Arbiter-PUF with $n$ -block permutation. . . . .                                          | 85  |

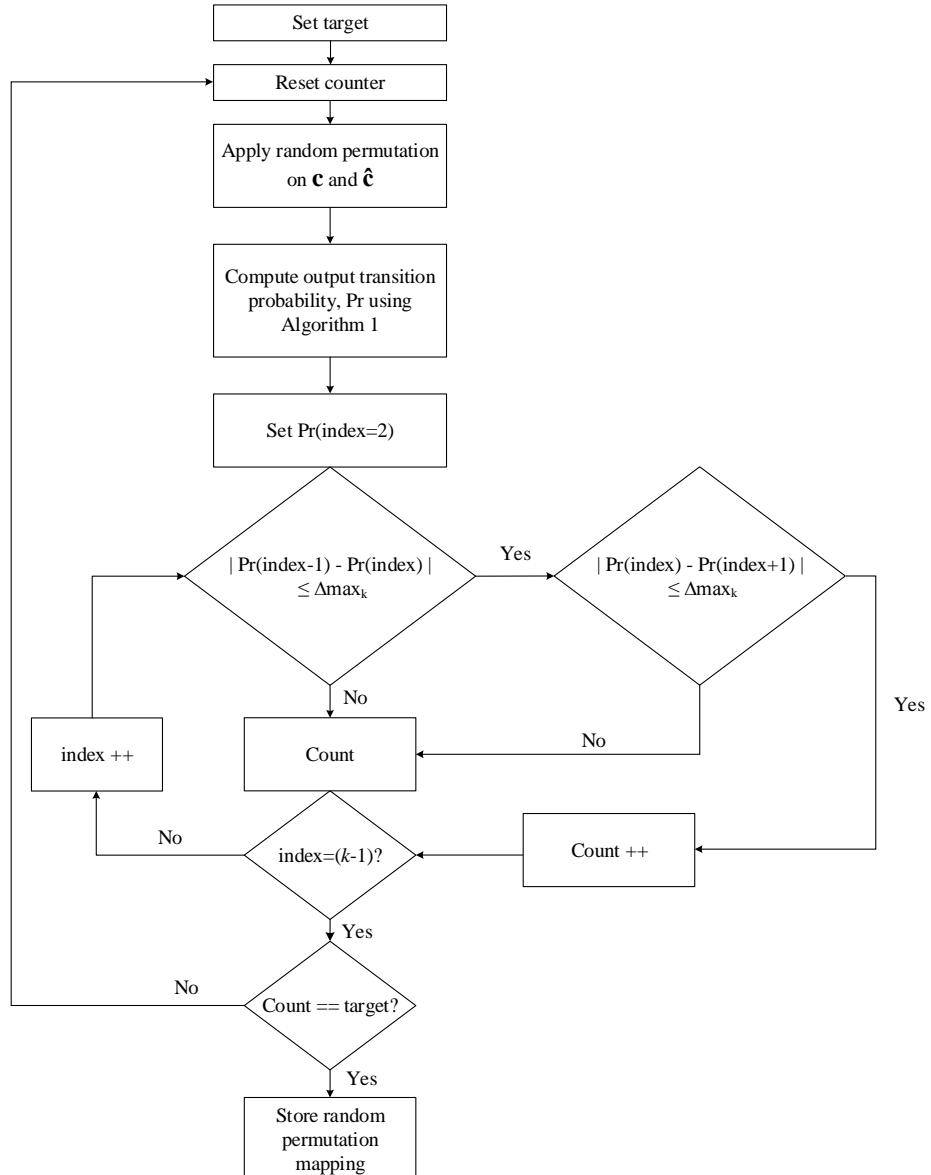

| 4.9  | Iteratively finding a random challenge permutation mapping. . . . .                                                                  | 87  |

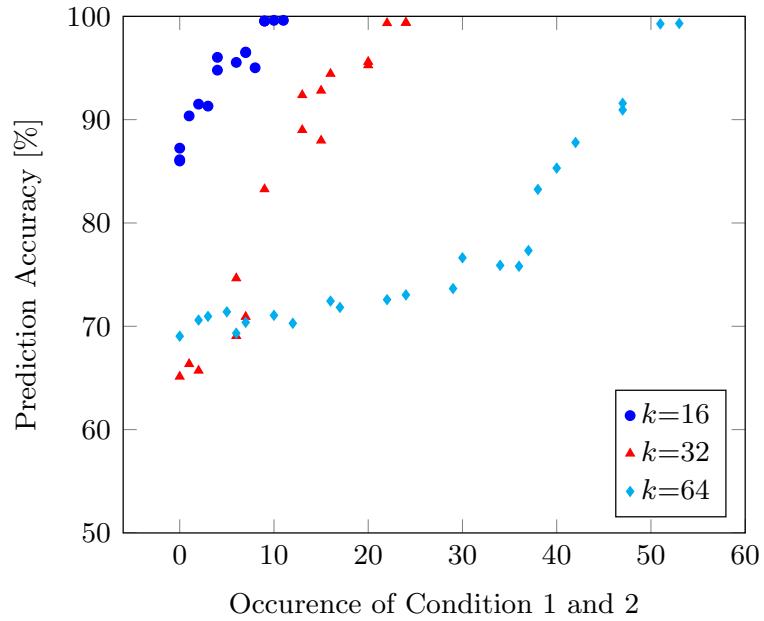

| 4.10 | Correlation between the ML prediction and the occurrence of condition 1 and 2 for $k$ -bit Arbiter-PUF. . . . .                      | 88  |

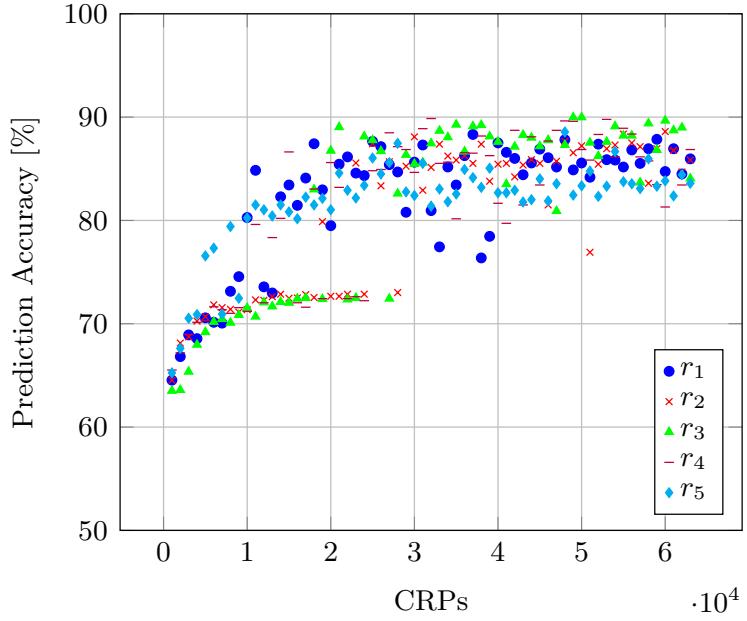

| 4.11 | ML-attack on 16-bit LFSR plus 16-bit Arbiter-PUF configuration with permuted challenge using ANN. . . . .                            | 89  |

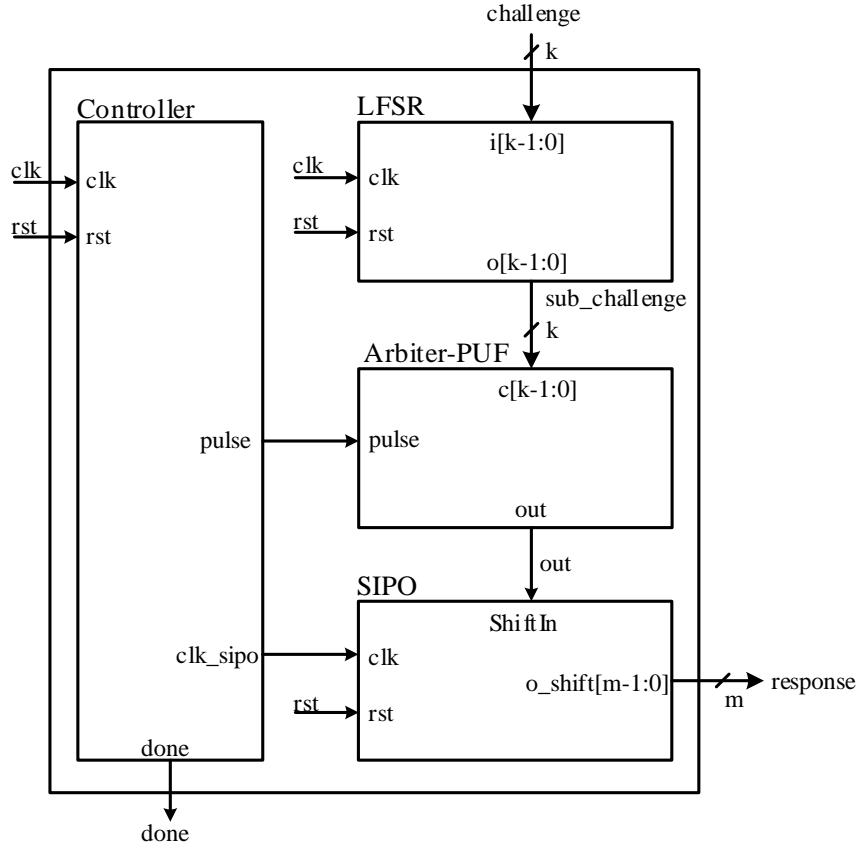

| 4.12 | Top level architecture of $k$ -bit Arbiter-PUF. . . . .                                                                              | 90  |

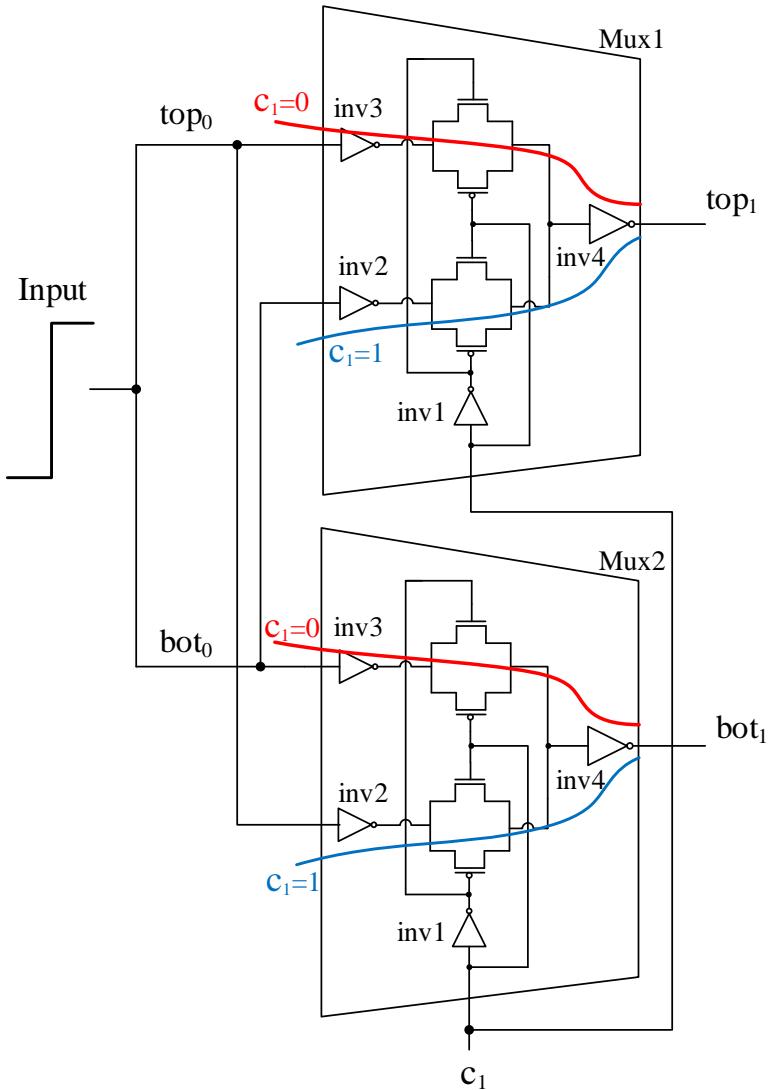

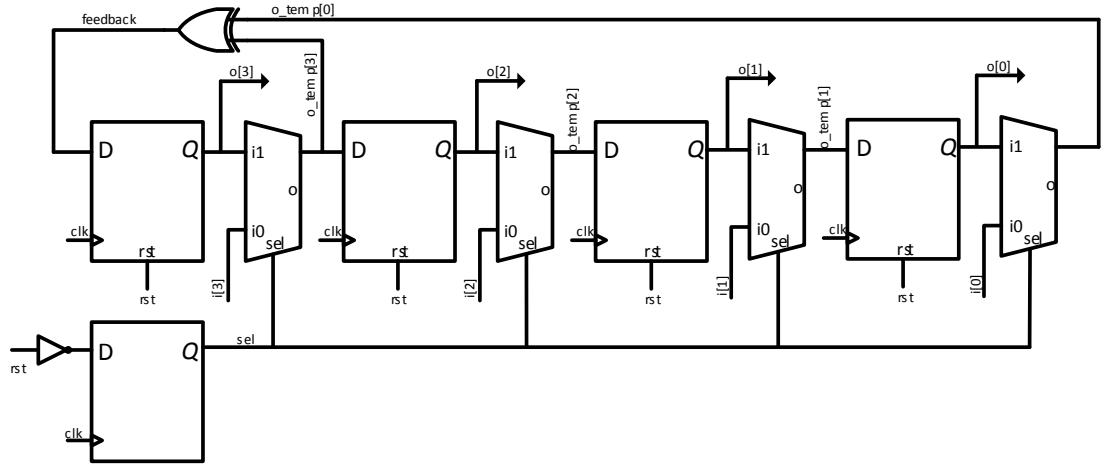

| 4.13 | Example: 4-bit Fibonacci LFSR with 2-to-1 multiplexer. . . . .                                                                       | 91  |

| 5.1  | NBTI impact on a 6-T SRAM cell circuit. . . . .                                                                                      | 98  |

| 5.2  | Area (GE) of the BCH scheme. . . . .                                                                                                 | 99  |

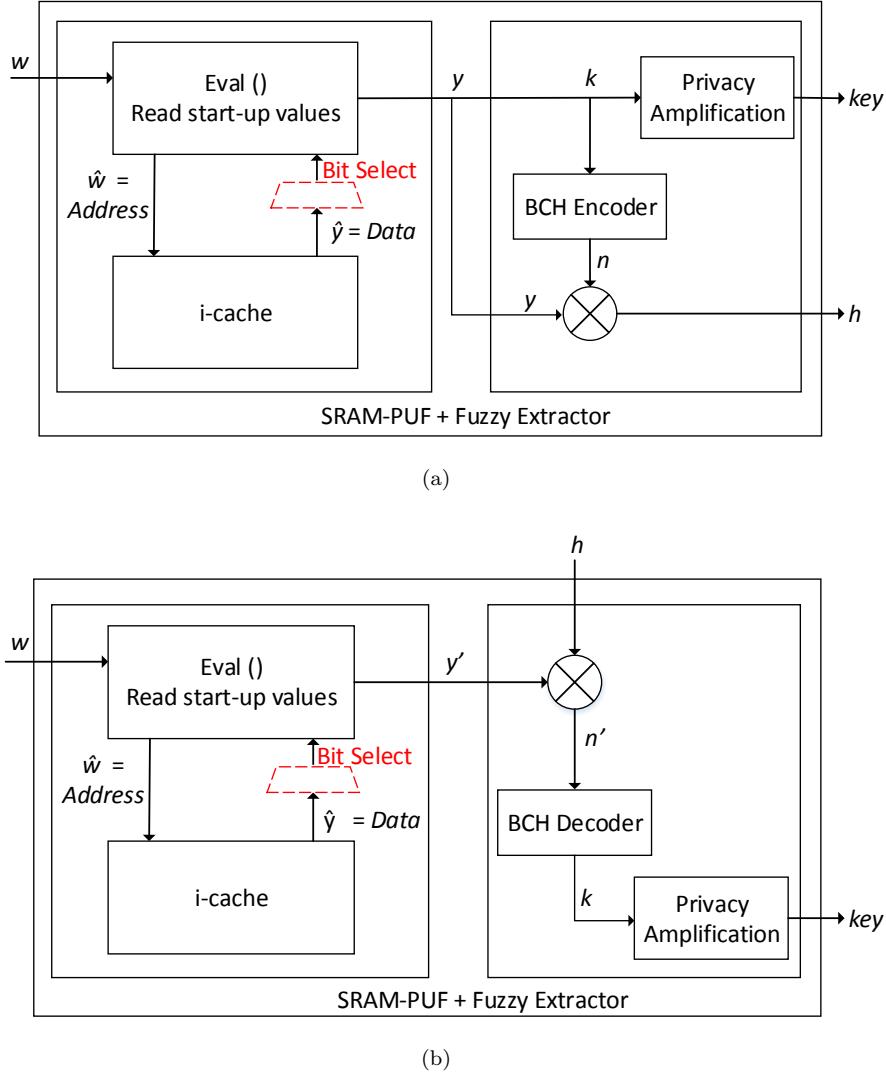

| 5.3  | Overview of a bit selection technique. . . . .                                                                                       | 100 |

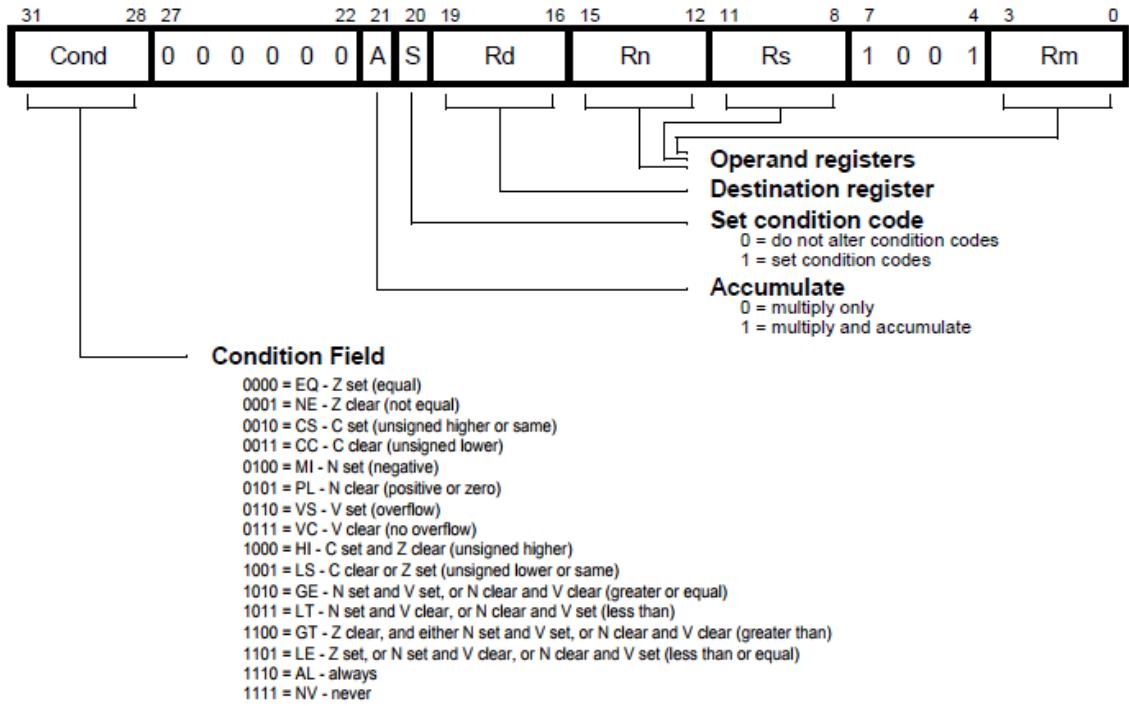

| 5.4  | Multiply and multiply-accumulate instruction format for 32-bit ARM [108]. . . . .                                                    | 101 |

| 5.5  | Mean and standard deviation values for the probability of storing a '1' in i-cache over 16 benchmarks. . . . .                       | 102 |

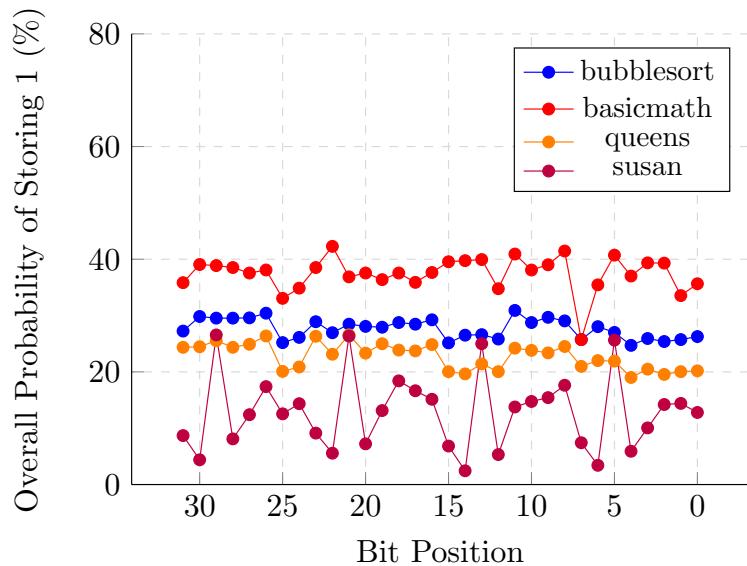

| 5.6  | Mean values for probability of storing '1' in d-cache running four benchmarks. . . . .                                               | 103 |

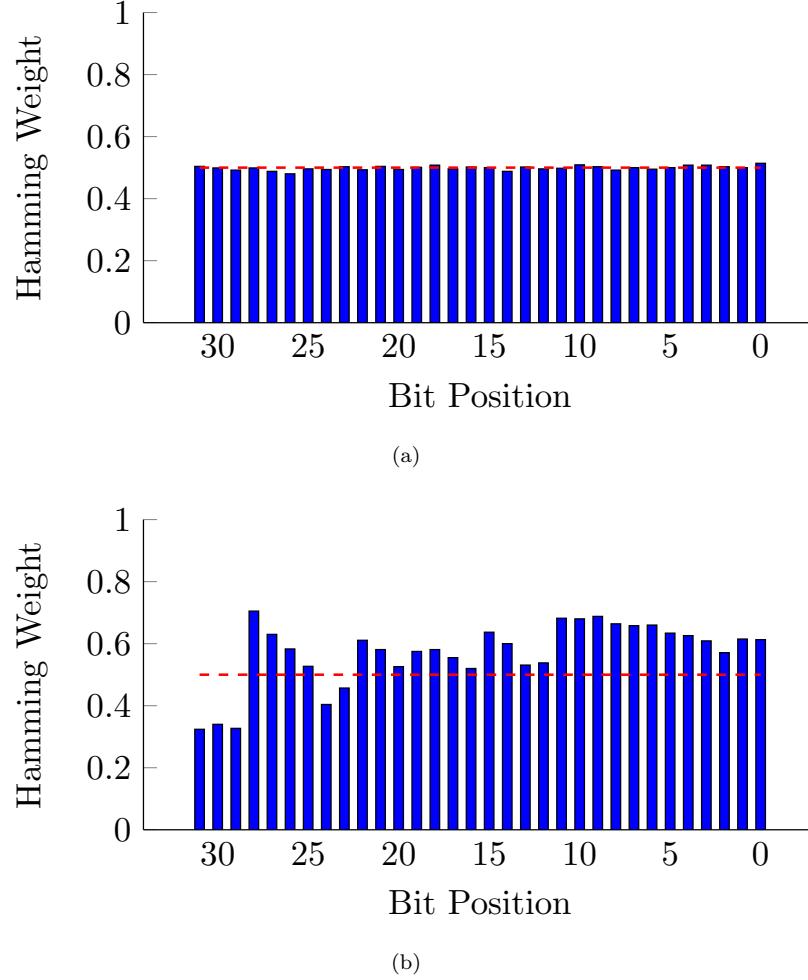

| 5.7  | Distribution of '1' and '0' (a) fresh (b) 5 years ageing based on the mean probability of storing '1'. . . . .                       | 105 |

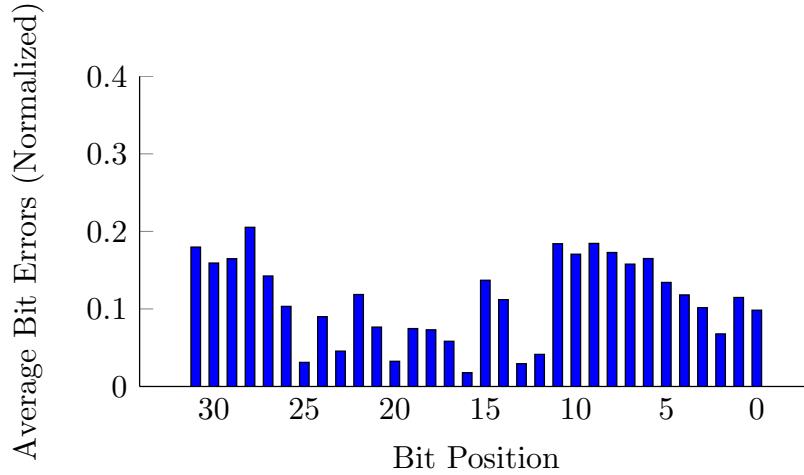

| 5.8  | Average bit errors based on the mean probability of storing '1'. . . . .                                                             | 106 |

|      |                                                                                                  |     |

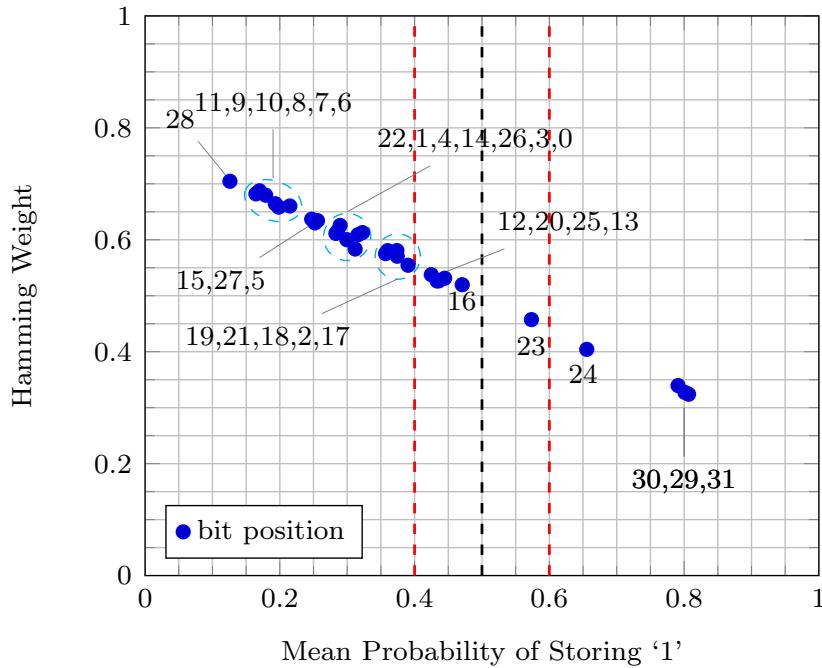

|------|--------------------------------------------------------------------------------------------------|-----|

| 5.9  | The relationship between the HW and the mean probability of storing ‘1’ for all 32 bits. . . . . | 107 |

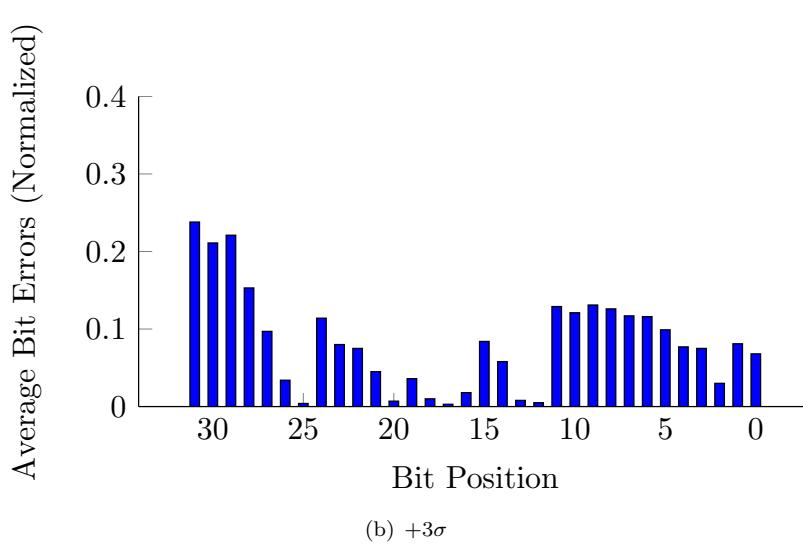

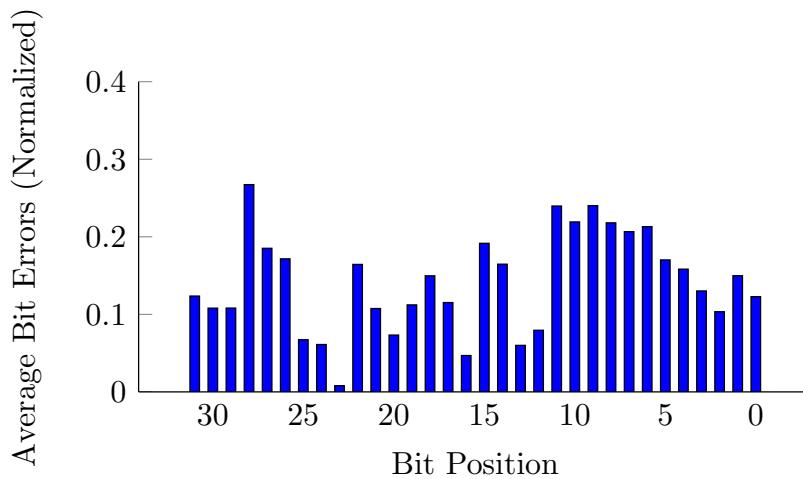

| 5.10 | Average bit errors based on the $\pm 3\sigma$ probability of storing ‘1’. . . . .                | 108 |

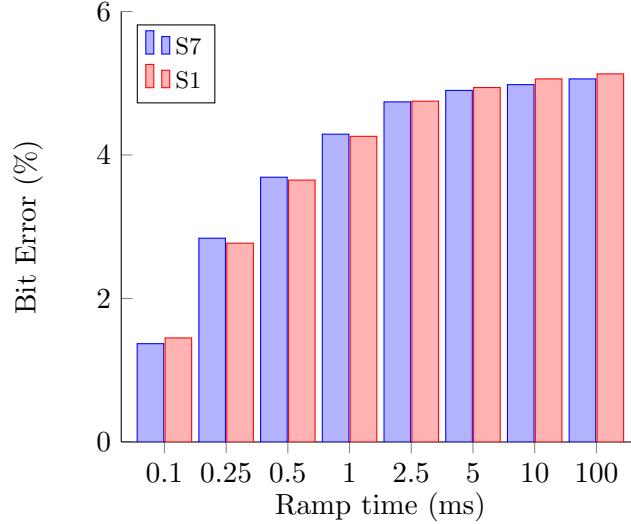

| 5.11 | Bit error rate at different ramp-up time. . . . .                                                | 111 |

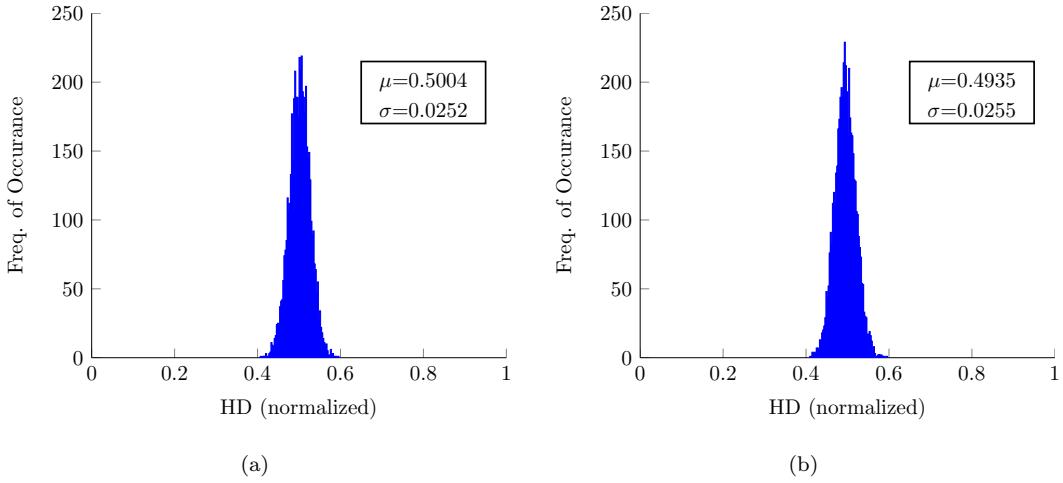

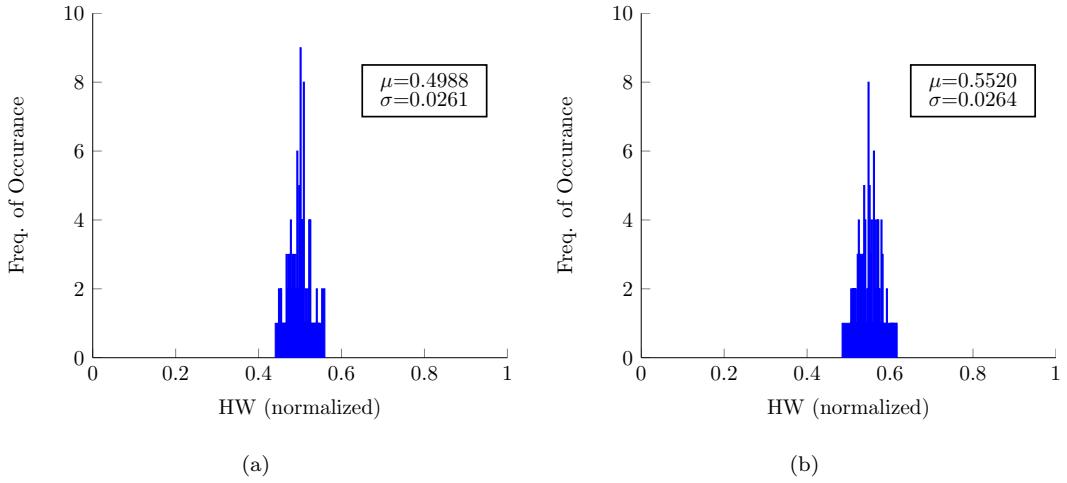

| 5.12 | Uniqueness for S1 set (a) fresh (b) 5 years ageing at the $-3\sigma$ probability. .              | 112 |

| 5.13 | Uniformity for S1 set (a) fresh (b) 5 years ageing at the $-3\sigma$ probability. .              | 113 |

| 5.14 | Implementation of a bit selection technique. . . . .                                             | 114 |

# List of Tables

|     |                                                                                                                               |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Performance of surveyed silicon PUF constructions in Section 2.4 . . . . .                                                    | 27  |

| 2.2 | Summary of known attacks to PUFs. . . . .                                                                                     | 42  |

| 3.1 | Ageing impact comparison . . . . .                                                                                            | 69  |

| 4.1 | Area and power of hash function . . . . .                                                                                     | 74  |

| 4.2 | Generator polynomials for maximal-length sequences . . . . .                                                                  | 76  |

| 4.3 | Prediction accuracy of $k$ -bit Arbiter-PUF with $n$ -block permutation scheme                                                | 86  |

| 4.4 | Area and power estimation . . . . .                                                                                           | 91  |

| 4.5 | Comparison of prediction accuracy . . . . .                                                                                   | 92  |

| 5.1 | Cache configuration . . . . .                                                                                                 | 102 |

| 5.2 | Bit error (%) of bit selection combination based on mean probability of storing ‘1’ . . . . .                                 | 108 |

| 5.3 | Bit error (%) of bit selection combination based on mean and $\pm 3\sigma$ probability of storing ‘1’ after 5 years . . . . . | 109 |

| 5.4 | Bit error (%) comparison at different temperatures and supply voltages .                                                      | 110 |

| 5.5 | Area comparison . . . . .                                                                                                     | 115 |

| C.1 | Simplification of input-output transition probability . . . . .                                                               | 139 |

| C.2 | Number of correctable errors in the BCH Code for $n=127$ . . . . .                                                            | 140 |

| C.3 | Number of correctable errors in the BCH Code for $n=255$ . . . . .                                                            | 141 |

| C.4 | Number of correctable errors in the BCH Code for $n=511$ . . . . .                                                            | 142 |

## Declaration of Authorship

I, **Mohd Syafiq Mispan**, declare that the thesis entitled *Towards Reliable and Secure Physical Unclonable Functions* and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research. I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as: [1],[2],[3],[4],[5],[6],[7]

Signed:.....

Date:..... 17/07/2018

## **Acknowledgements**

I owe my deepest gratitude to my supervisors, Professor Mark Zwolinski and Dr. Basel Halak, for their precious support and guidance through my research project. Their vision and wisdom in approaching a problem is the greatest thing I have learned. They have been a great mentor and a source of inspiration throughout my Ph.D. journey.

Also, I would like to thank Professor CH Kees De Groot and Dr. Jeff Reeve, for their revision of my work and their valuable advice for my first-year and second-year reports. I would also like to offer my thank to the Ministry of Education Malaysia and the Technical University of Malaysia Malacca, for the financial support. This Ph.D. project would not have been possible without this support.

Finally, my lovely wife, my daughters, my late parents, my parents-in-law and the rest of my immediate family which have always been my strongest supporters. I am greatly thankful for their love and faith in me, and I would like to dedicate this work to them.

# Abbreviations

|        |                                                      |

|--------|------------------------------------------------------|

| ADC    | Analogue-to-digital Converter.                       |

| ALU    | Arithmetic Logic Unit.                               |

| ANN    | Artificial Neural Network.                           |

| ASIC   | Application-specific Integrated Circuit.             |

| BCH    | Bose-Chaudhuri-Hocquenghem.                          |

| BTI    | Bias Temperature Instability.                        |

| CPLD   | Complex Programmable Logic Device.                   |

| CRP    | Challenge-response Pair.                             |

| DAA    | Direct Accelerated Ageing.                           |

| DIBL   | Drain-Induced Barrier Lowering.                      |

| DOS    | Denial Of Service.                                   |

| ECC    | Error Correction Code.                               |

| EEPROM | Electrically Erasable Programmable Read-only Memory. |

| ES     | Evolution Strategies.                                |

| FIB    | Focus Ion Beam.                                      |

| FPGA   | Field-Programmable Gate Array.                       |

| GE     | Gate Equivalent.                                     |

| HCI    | Hot Carrier Injection.                               |

| HD     | Hamming Distance.                                    |

| HW     | Hamming Weight.                                      |

| IC     | Integrated Circuit.                                  |

| IOT    | Internet-of-Things.                                  |

| IP     | Intellectual Property.                               |

| LFSR   | Linear Feedback Shift Register.                      |

| LR     | Logistic Regression.                                 |

| LS     | Laser Stimulation.                                   |

| MAC    | Message Authentication Code.                         |

| ML     | Machine Learning.                                    |

| MLP    | Multilayer Perceptron.                               |

| MTP    | Multiple-Time Programmable.                          |

| NBTI   | Negative Bias Temperature Instability.               |

|      |                                        |

|------|----------------------------------------|

| NVM  | Non-volatile Memory.                   |

| OTP  | One-Time Programmable.                 |

| PBTI | Positive Bias Temperature Instability. |

| PEA  | Photonic Emission Analysis.            |

| POWF | Physical One-way Function.             |

| PUF  | Physical Unclonable Function.          |

| RDF  | Random Dopant Fluctuations.            |

| RFID | Radio Frequency Identification.        |

| RNG  | Random Number Generator.               |

| RO   | Ring Oscillator.                       |

| ROM  | Read-Only Memory.                      |

| SAC  | Strict Avalanche Criteria.             |

| SEM  | Scanning Electron Microscope.          |

| SLP  | Single-layer Perceptron.               |

| SOC  | System-on-a-chip.                      |

| SRAM | Static Random-access Memory.           |

| SUV  | Start-up Value.                        |

| SVM  | Support Vector Machine.                |

| T-D  | Trapping/de-trapping.                  |

# Nomenclature

|            |                               |

|------------|-------------------------------|

| $C_{ox}$   | Gate-oxide capacitance        |

| $C_d$      | Depletion layer capacitance   |

| $\epsilon$ | Hamming Distance threshold    |

| $k_B$      | Boltzmann constant            |

| $L$        | Channel length                |

| $\mu_o$    | Electron or hole mobility     |

| $\mu$      | Mean                          |

| $q$        | Electrical charge of electron |

| $\sigma$   | Standard deviation            |

| $SiON$     | Silicon oxynitride            |

| $T$        | Absolute temperature          |

| $V_{th}$   | Threshold voltage             |

| $V_t$      | Thermal voltage               |

| $W$        | Channel width                 |

# Chapter 1

## Introduction

Nowadays, electronic devices are becoming ubiquitous. The inception of a network of physical objects or the so-called Internet-of-Things (IoT) allows these electronic devices to be interconnected, operated, and controlled remotely through the internet infrastructure. Examples of these applications include secure access, mobile payment, electronic passports, smart meters, and smart homes. With this wide range of applications, they process sensitive, user-specific data, by which if disclosed, may lead to loss of privacy and other unwanted implications. Low-cost pervasive devices, such as Radio Frequency Identification (RFID) devices and wireless sensor nodes are the foundations for building the next generation of ubiquitous networks, IoT [8]. Such devices typically have limited area and energy resources which introduce a significant challenge in providing fundamental security services, such as device authentication and cryptographic key storage/generation.

### 1.1 Cryptographic Key Storage Technologies

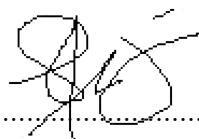

Cryptography is the study and practice of securing communication in the presence of adversaries or third parties. Cryptography can ensure the confidentiality, integrity, authenticity, and acknowledgement of the user data. Cryptographic primitives are low-level algorithms which are used to build secure protocols. These include but not limited to the authentication, digital signatures, one-way functions, encryption, and decryption. Figure 1.1 shows a basic cryptographic algorithm which is an encryption of a plaintext XORed with a secret key.

Figure 1.1: Plaintext encryption using a XOR function.

Implementation of current security solutions relies on the secret keys stored in the on-chip non-volatile memory (NVM) or battery-backed static random-access memory (SRAM) [9, 10]. These approaches introduce critical security-related issues. By storing the secret keys in NVM or battery-backed SRAM, the keys are always available. Therefore, they are susceptible to read-out or tampering through invasive or semi-invasive attacks based on techniques derived from integrated circuit (IC) failure analysis. The resilience against these physical attacks can be improved through a tamper-sensing environment which would further increase the cost of implementation. Moreover, the secret keys need to be programmed which often relies on the IC manufacturer or system owner. Hence, there is a possibility that the secret keys can be compromised by an untrusted third party within the product supply chain.

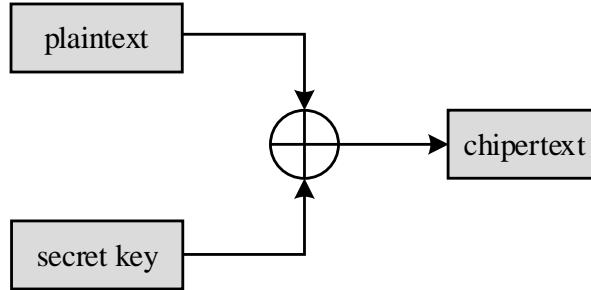

Figure 1.2: Security-cost positioning of permanent key storage technologies [9].

The relative cost of implementation of the aforementioned key storage solutions is depicted in Figure 1.2. Different technologies can be deployed for the key storage on NVM

such as Read-Only Memory (ROM), One-Time Programmable (OTP), and Multiple-Time Programmable (MTP). A lightweight method of storing keys in NVM is by using ROM when large-quantities and low-cost are required. However, this approach has low security and is very inflexible as the secret keys are mask defined and shared by each device [10]. The secret keys, however, can be programmed once through the OTP NVM using fuse or anti-fuse technologies. Reprogramming can be emulated via the partitioning of a large OTP NVM which further increases the cost. Instead, it is more efficient to use MTP NVM, such as electrically erasable programmable read-only memory (EEPROM) which offer more flexibility as the secret keys can be re-programmed many times but still, the cost is high. Battery-backed SRAM requires a standard CMOS SRAM, but the battery that is needed to retain the secret keys in a volatile memory is considered to be costly and bulky (i.e., space overhead), particularly for resource-constrained applications.

## 1.2 Physical Unclonable Function

A Physical Unclonable Function (PUF) is an emerging technology which offers a promising solution to the critical security-related issues as discussed above with a relatively low cost. PUF maps a set of challenges to a set of responses. Its challenge-response relationship is determined by the intrinsic process variations in the transistor and interconnects of a silicon chip. The intrinsic process variations are caused by uncontrollable deviations in the chip manufacturing process, which are unique and random from die to die and wafer to wafer. Therefore, a PUF can be used to generate a unique and random key or identifier. Furthermore, the complex and random nature of the manufacturing process variations makes a PUF practically and physically impossible to clone [11]. A PUF is considered as secure and low-cost technology since the identifier or the key can only be generated during power-on state and is wiped-out in the power-off state. A PUF can be implemented using a standard CMOS circuit design technique which requires no special fabrication process. Besides, a physically invasive attack to recover the identifier or key, which is only available during the power-on state by a micro-probing technique, is most likely to destroy the unique delay characteristics, effectively destroying the identifier or key [12]. This makes a PUF a tamper-resistance solution.

All of the above show that PUFs provide uniqueness, randomness, unclonability, security, low-cost, and tamper resistance which make them very suitable candidates for robust hardware-based intrinsic security devices. With these advantages, PUFs have been proposed for lightweight device identification and authentication, and cryptographic key generation. Now, PUFs are transforming from research to commercial products as the results of the huge potential of PUFs observed by the industry [13, 14].

### 1.3 Motivations For Research

In order for a PUF to be usable, the response of the PUF, which later will be used for an identifier or a key must be reproducible and reliable over multiple authentication or key generation processes. However, as the PUF is implemented using CMOS circuit design techniques, it is susceptible to environmental variations such as temperature and supply voltage, and also CMOS ageing effects. Although the environmental variation is a concern, it is a reversible effect. For example, the operating frequency of a CMOS circuit is slower than normal at an elevated temperature, but its normal operating frequency is restored once it is cooled down to its normal operating temperature. On the contrary, the impact of ageing is irreversible over an extended period, leading to a permanent shift in the circuit behaviour. Generally, the effect of CMOS device ageing mechanisms such as Bias Temperature Instability (BTI) and Hot Carrier Injection (HCI) can be manifested as a degradation in the threshold voltage,  $V_{th}$  [15]. This reduces the drive currents and leads to a performance (e.g., speed) degradation of the CMOS circuit. When a PUF ages, the response of the PUF is not 100% reliable. As a consequence, there may be two possible errors in the device authentication, either a false negative or a false positive. A false negative means that the response of a PUF deviates significantly from its initial state, and it might be deemed as a different PUF and rejected during an authentication process. On the other hand, a false positive occurs when the response of a PUF deviates and become nearly same as another PUF's response, and it might be accepted during an authentication process as another device. For a cryptographic key generation, inherently noisy PUF response must be corrected with an error correction mechanism before it can be used as a secret key. Due to the impact of ageing, the number of errors in PUF response increases. As a consequence, the complexity (i.e., area) of an error correction code (ECC) to generate error-free cryptographic keys increases. An increase in the area can be seen as a disadvantage for a PUF to be used in resource-constraint security devices.

As discussed in Section 1.2, the mapping between the challenge-response pairs (CRPs) of a given PUF is determined by its process variations. The impact of process variations remains static. Therefore, although it is impossible to physically clone the PUF through the fabrication process, the relationship of its CRPs can be modelled or software-cloned using machine learning (ML) techniques. From all of the above, the two keywords that summarise the open problems are reliability (i.e., due to ageing) and security (i.e., susceptibility to ML-attack). The aim of this project is to study the reliability and security aspects of PUFs with regard to the ageing and susceptibility to ML-attack, respectively, in the context of resource-constrained security devices.

## 1.4 Objectives

The objectives of the research presented in this thesis are summarised as follows:

- To implement and characterise a PUF using a 65-nm CMOS fabrication technology.

- To investigate the impact of ageing on PUFs and proposed mitigation techniques, if necessary.

- To develop a lightweight technique to increase the robustness of PUFs against ML attacks and to validate the technique using a suitable machine learning algorithm.

## 1.5 Thesis Structure

Chapter 2 provides an overview of the literature and the essential background related to the work in this thesis. The types of PUFs, related PUFs construction, and PUF quality metrics are discussed. The CMOS ageing process is then described and its potential impact on the reliability of PUFs is discussed. The proposed use of PUFs in cryptographic key generation and low-cost identification and authentication are summarised. The known attacks on PUFs are discussed, including invasive, semi-invasive, and non-invasive attacks. Despite the potential issues in reliability and security, the advantages of PUFs as compared to a conventional method of storing a key in NVM are discussed.

Chapter 3 presents the first contribution of the thesis. We demonstrate that a differential design technique to build a PUF can be a mechanism to mitigate the first-order dependencies of ageing, such as signal probability/duty cycle and supply voltage. A “Two Chooses One” PUF or TCO-PUF is introduced and the circuit-level implementation is detailed using a TSMC 65-nm CMOS technology. The quality metrics of TCO-PUF such as the uniqueness, reliability, and uniformity are analysed. The susceptibility to an ML-attack is further analysed. An evaluation of the impact of ageing on PUF-based differential architectures which include TCO-PUF and Arbiter-PUF (both implemented using a 65-nm CMOS fabrication technology) is carried out. The results show that a differential design technique is desirable for PUF implementation to achieve high reliability under device ageing.

Chapter 4 describes the second contribution, which is a challenge permutation technique to increase the resiliency of an Arbiter-PUF against an ML-attack. An Arbiter-PUF has been implemented using a TSMC 65-nm CMOS technology. An artificial neural network (ANN) has been used to evaluate the vulnerability of the Arbiter-PUF to an ML-attack. The results show that a challenge permutation technique can alter the output transition probability of the Arbiter-PUF, resulting in an increase of the resilience to an ML-attack. Moreover, the results show that a random challenge permutation is required to maximise

the complexity of the output transition probability of the Arbiter-PUF. Hence, a high unpredictability for an Arbiter-PUF can be achieved. A challenge permutation technique can be implemented by routing obfuscation which introduces no extra overhead.

Chapter 5 presents the third contribution. A bit selection technique is proposed to reduce the bit error rates due to ageing in a dual function SRAM used as a memory and PUF, which results in a reduction in the area overhead of the ECC. The effect of ageing on SRAM used as a PUF is not uniform, but is dependent on the patterns of the data stored in the memory. The distribution pattern of a 32-bit ARM instruction cache (i-cache) is found to be predictable as in the impact of ageing. Based on these analyses, a bit selection technique is proposed to select only SRAM cells that have close to a 50% probability of storing a value of ‘1’. By using a bit selection technique, a reduction in the bit error rates is achieved and the area overhead of the ECC is reduced by 6 times compared to that without a bit selection technique. Meanwhile, the proposed technique requires a negligible area overhead with respect to the reduction in the area overhead of the ECC.

Chapter 6 concludes the findings and contributions of the work in this thesis. Suggestions for future work directions are also provided.

## 1.6 Publications

A list of publications related to this research is as follows:

1. B. Halak, Y. Hu, and M. S. Mispan, “Area efficient configurable physical unclonable functions for FPGAs identification,” in IEEE International Symposium on Circuits and Systems, 2015, pp. 946-949.

2. M. S. Mispan, B. Halak, Z. Chen, and M. Zwolinski, “TCO-PUF : A subthreshold physical unclonable function,” in 11th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), 2015, pp. 105-108.

3. M. S. Mispan, B. Halak, and M. Zwolinski, “NBTI aging evaluation of PUF-based differential architectures,” in IEEE International Symposium on On-Line Testing and Robust System Design, 2016, pp. 103-108.

4. B. Halak, M. Zwolinski, and M. S. Mispan, “Overview of PUF-based hardware security solutions for the Internet of Things,” in IEEE Midwest Symposium on Circuits and Systems, 2016, pp. 1-4.

5. M. S. Mispan, B. Halak, and M. Zwolinski, “Lightweight obfuscation techniques for modeling attacks resistant PUFs,” in IEEE International Verification and Security Workshop, 2017, pp. 19-24.

6. M. S. Mispan, B. Halak, and M. Zwolinski, “Extended abstract: SRAM-PUF based on selective power-up and non-destructive scheme,” in International Workshop on Microprocessor/SoC Test and Verification, 2016, pp. 1-2 (**unpublished**).

7. M. S. Mispan, H. Su, and M. Zwolinski, and B. Halak, “Cost-efficient designs for modeling attacks resistant PUFs,” in Design, Automation & Test in Europe Conference & Exhibition, 2018, pp. 467-472.

8. M. S. Mispan, S. Duan, B. Halak, and M. Zwolinski, “A reliable PUF in a dual function SRAM,” in International Symposium on Power and Timing Modeling, Optimization and Simulation, 2018, pp. 1-6.

## Chapter 2

# Physical Unclonable Function

This chapter provides a broad overview of the research related to the topic in this thesis. The literature relevant to Chapters 3, 4, and 5 is separately introduced, to describe the contributions in these chapters in the relevant research context. Section 2.1 describes the general definition of a PUF. Section 2.2 explains the process variations in ICs which are exploited by a PUF. The types of PUFs are discussed in Section 2.3. Section 2.4 summarises the existing proposed techniques of silicon PUFs, in which some of the proposed PUFs are used as a case study in Chapter 3, 4, and 5. The metrics to quantify the quality of PUFs are discussed in Section 2.5. Section 2.6 introduces the effect of ageing on PUFs, which are related to the ageing evaluation on differential PUF architecture discussed in Chapter 3 and the proposed ageing mitigation technique described in Chapter 5. In addition, two primary applications of PUFs are discussed in Section 2.7, while Section 2.8 describes the known attacks on PUFs, in which a countermeasure for one of the known attacks is proposed in Chapter 4. Despite the known attacks on PUFs, Section 2.9 describes the advantages of PUFs. Finally, Section 2.10 summarises the literature reviewed in this chapter.

### 2.1 Definition of a PUF

A PUF is defined as a function that maps challenges to responses and that function is embodied by the physical material of the device [16]. As opposed to a mathematical function which is deterministic in nature and that generates a fixed output for the same input, a function embodied in a physical device is non-deterministic and varies from one instance to another [17]. Based on this notion, in our study, we have focused on silicon PUFs, which exploit the intrinsic and random variations in CMOS devices due to the manufacturing process, as described briefly in Section 1.2. Nevertheless, generally a PUF can be constructed using a non-silicon material, as described later in Section 2.3. For a silicon PUF, the complex statistical variations of devices and interconnects can be

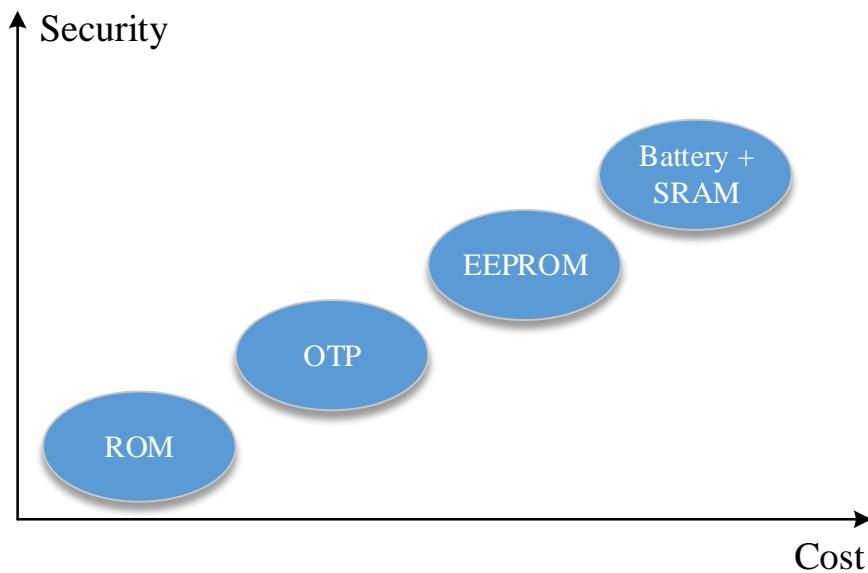

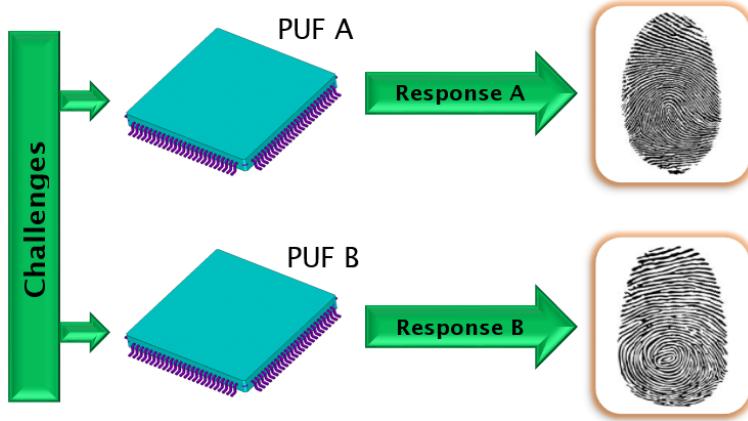

used to map a set of challenges to a set of responses in one instance of a PUF and the mapping changes from one instance to another, stochastically. The set of CRPs for a PUF can be defined as  $(C_i, R_i)$ ,  $i = 1, \dots, N$ . Depending on the types of PUFs, however, generally a challenge  $C$  can be described as a  $k$ -bit input. Challenges are used to control the behaviour of a PUF and based on the challenges applied, corresponding responses are generated. As shown in Figure 2.1, when a challenge is applied to two different PUFs (PUF A and PUF B), the respective responses were produced where Response A  $\neq$  Response B.

Figure 2.1: Basic functionality of PUF.

A unique response is like an electronic fingerprint which uniquely identifies each PUF. Therefore, there is no need to store a secret key in any memory devices, unlike the conventional method of IC security as discussed in Section 1.1. Instead, a secret key only needs to be generated when it is required, by applying a challenge. Thus, a PUF provides unclonable, random, and secure features, which make it a very promising technology as a replacement for current security solutions.

## 2.2 Variability in Integrated Circuits

Manufacturing process variation is a fundamental limitation of the control of the device's physical features and interconnects during fabrication [18]. Process variations can be divided into two categories [19]. The first category is inter-die variations where the same device on a die can have different characteristics across various dies. The second category is intra-die variations where similar transistors within a single die can have different characteristics. The aggressive scaling of CMOS technology has led to a drastic increase in process variations such as oxide thickness and random dopant fluctuations (RDF) which causes a direct impact on the electrical behaviour of MOSFETs. One of the fundamental challenges for CMOS device performance is RDF which is caused

by the randomness in the amount and position of dopants during dopant implantation, resulting in a fluctuation of the total number of dopants in the transistor channel [20].

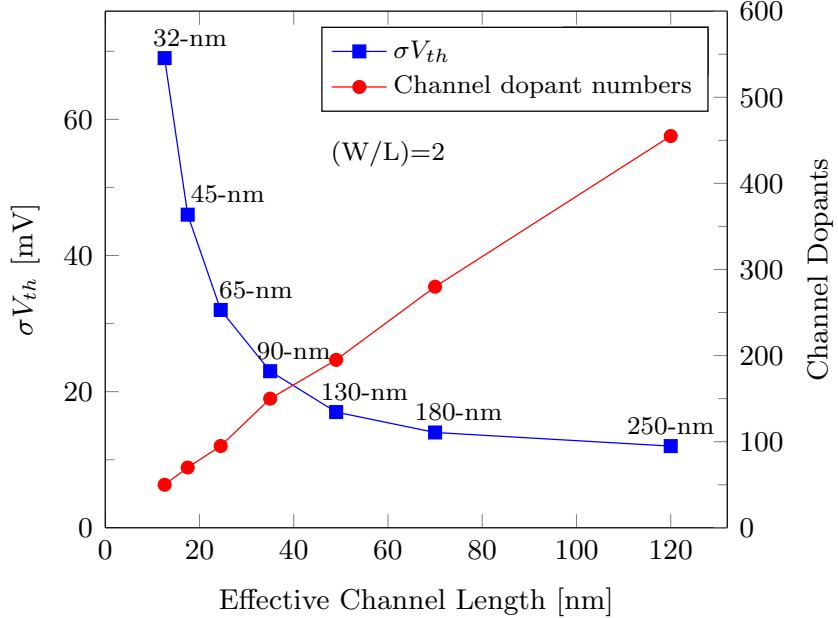

Figure 2.2: Scaling trend of  $V_{th}$  variations due to RDF [20].

The  $V_{th}$  of MOSFETs is significantly determined by the dopant density in the transistor channel. As devices scale down, the channel volume decreases and the total number of channel dopants decreases. As a result, the relative effect of a single change in dopant number increases and the variations in the  $V_{th}$  becomes significant [20]. The effect of RDF on device scaling from 250-nm to 32-nm technology node can be seen in Figure 2.2. Although process variation is an unwanted effect for CMOS circuitry, it is the desired effect for PUFs.

## 2.3 Types of PUFs

### 2.3.1 Non-Silicon and Silicon PUFs

The idea of a PUF was introduced when Pappu *et al.* proposed the concept of physical one-way functions (POWFs) which are based on an optical principle of operation [21]. The speckle patterns resulted from applying laser lights (at the different angle, distance, and wavelength) on a transparent optical medium, which contains scattering particles, are found to be unique and unpredictable. Following Pappu's works, the concept of a silicon PUF was first introduced [16]. In this study, Gassend *et al.* argued that a complex IC can be viewed as a silicon PUF and described a technique to identify

and authenticate individual ICs. Further, the PUF was realized in a real silicon and called an Arbiter-PUF [12]. The Arbiter-PUF exploits the delay mismatch between two nominally identical delay paths. Another delay-based PUF called the Ring Oscillator-PUF (RO-PUF) was proposed in [22], where the output response is generated based on the frequency mismatch between a pair of ring oscillators (ROs). In [23], a memory-based PUF, which is based on the random start-up values (SUVs) of SRAM cells was proposed. The power-up SRAM state as an identifying fingerprint was also concurrently proposed in [24]. A PUF based on cross-coupled latches was proposed in [25], namely the Butterfly-PUF, targeted at protecting intellectual property (IP) designs in Field-Programmable Gate Arrays (FPGAs). Another memory-based PUF was proposed in [26] which uses a known cell structure of data bus keeper or data bus holder (i.e., cross-coupled inverters) as a PUF, namely the Buskeeper-PUF.

### 2.3.2 Strong, Weak and Controlled PUFs

Silicon PUFs can be categorised into three sub-types according to the security properties of their challenge-response behaviours, each with their own preferred applications. Three established types are the Strong PUFs [23], the Weak PUFs [23], and the Controlled PUFs [27].

1. Strong PUFs: Strong PUFs are PUFs with a very large number of CRPs ( $C_i, R_i$ ),  $i = 1, \dots, N$  [23]. The number of CRPs of the considered PUFs grows exponentially as the number of bit challenges increases. The challenge-response interface is directly accessible without a protection mechanism in which the CRPs can be collected using a non-invasive CRPs measurement. Rührmair *et al.*, [28] refined the Strong PUF definition in which it must also be infeasible to be numerically modelled with a high prediction accuracy based on the observed CRPs (i.e., the PUF response is unpredictable).

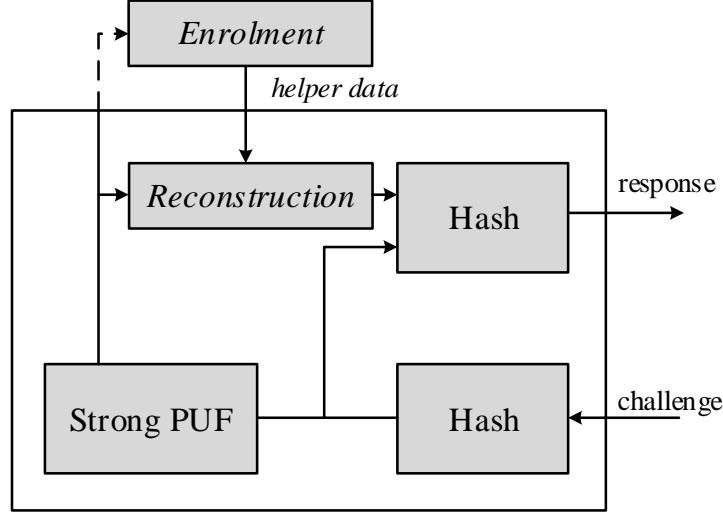

2. Controlled PUFs: Controlled PUFs are improved Strong PUFs where the challenge-response interface is not directly accessible but it is protected by a logic processing unit using techniques such as random hash function, permutation, obfuscation and etc. Gassend *et al.*, [27] used random hash function technique for the pre-processing of challenges before being input to the Strong PUF. In a similar way, the responses of the Strong PUF are post-processed by the random hash function before being output by the Controlled PUF.

A model-building attack is one of the plausible attacks on strong PUFs [28, 27], where the adversary builds a numerical model of the PUF by measuring a number of CRPs. The introduction of an extra pre and post-processing steps for the Controlled PUFs increases the level of difficulty to measure and collect the CRPs. Hence, this reduces the vulnerability to a model-building attack [27].

3. Weak PUFs: Weak PUFs are PUFs with a very small number of CRPs, fixed challenges, and in the extreme case with just only a single challenge [23, 28].

Based on the above definition, the main distinction between Strong and Weak PUFs is the number of generated CRPs. As Strong-PUFs can support a large number of CRPs, they can provide authentication capabilities, particularly using a challenge-response protocol without having to store a secret key as a unique identifier. For Weak-PUFs, a limited number of CRPs meant that these CRPs must be kept secret. For this reason, Weak PUFs are well suited for a secret key generation for any cryptographic process such as encryption/decryption and message authentication code (MAC). The preferred applications based on the categorisation above are further discussed later in Section 2.7.

## 2.4 Silicon PUF Constructions

Since the first idea of silicon PUF, as been described in [16], which was motivated by the Pappu's works [29], an enormous number of PUF techniques have been proposed in the past decade. In this section, silicon PUFs are classified based on their construction and operating principles:

1. The first class of construction consists of delay-based PUFs, which are often constructed from simple digital circuit structures and exploit the intrinsic variations in the logic gate and interconnect delays to produce device-specific random signatures. Delay-based PUFs include Arbiter-PUFs [12, 30, 22, 31] and RO-PUFs [16, 22].

2. The second class of construction is memory-based PUFs, which exploit intrinsic variations in bi-stable memory elements such as SRAM PUFs [23, 24], D Flip-flop PUF [32], Butterfly PUF [25], SR-NOR latch PUF [33], and Buskeeper PUF [26].

3. The third class of construction is mixed-signal PUFs in which the PUF behaviour is inherently of an analogue nature and require analogue-to-digital converter (ADC) to digitise the measured analogue responses. A mixed-signal PUF typically exploits the variability of minimum size MOSFETs to enhance the threshold voltage mismatches, such as in the Voltage Transfer Characteristic PUF (VTC-PUF) [34] and Current Mirror-PUF [35].

4. The final class of construction is PUF built from emerging nanotechnology devices in order to further achieve secure, robust, and lightweight PUF designs [11].

The following sections discuss in detail the construction of each PUF that are mentioned above. Though this is not a comprehensive discussion on different PUFs proposed so far, it gives an overview of PUF development in general.

### 2.4.1 Arbiter-PUF

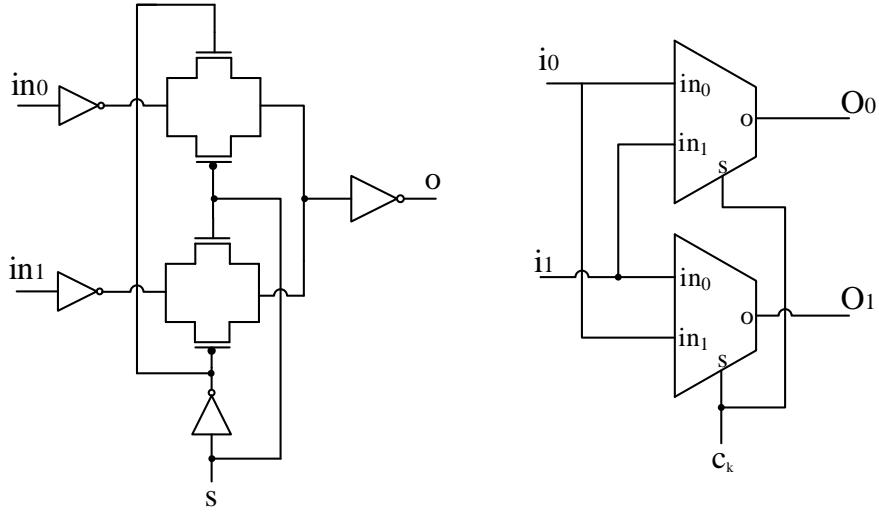

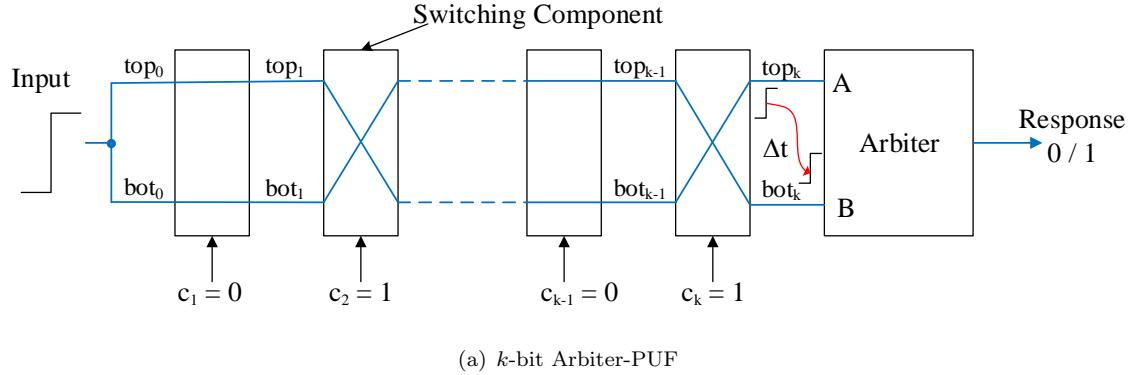

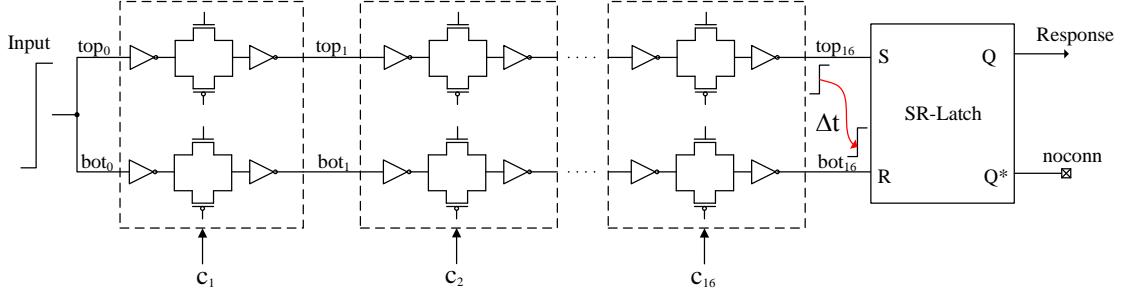

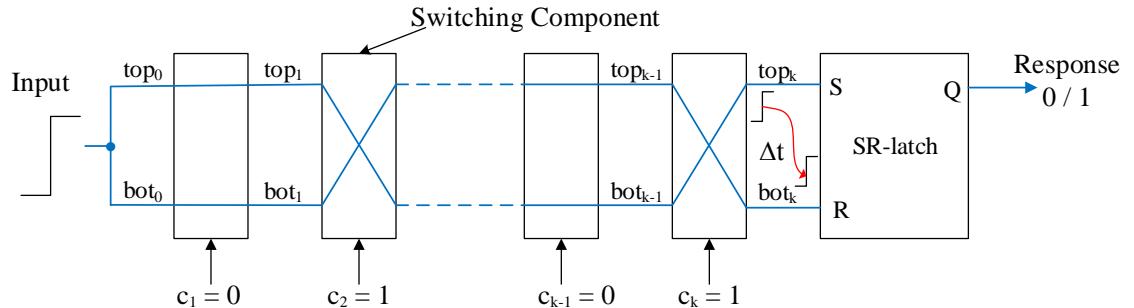

Lee *et al.* presented the first PUF which was fabricated on silicon using a TSMC 180-nm CMOS technology, namely an Arbiter-PUF [12]. This PUF circuit exploits the logic gate delays and interconnect variations which are affected by the process variations. The Arbiter-PUF consists of  $k$  stages or switching component where each stage is composed of two 2-to-1 multiplexers as shown in Figure 2.3 [36]. A rising pulse at an input propagates through two nominally identical delay paths. The paths for the input pulse are controlled by the switching elements, which are set by the bits of the challenge,  $C = \{c_1, c_0, \dots, c_k\}$ . For  $c_k = 0$ , the paths go straight through, while for  $c_k = 1$ , they are crossed. Because of manufacturing variations, there is a delay difference of  $\Delta t$  between the paths. An arbiter at the end generates a random response, ‘0’ or ‘1’, depending on the difference in arrival times.

Figure 2.3: The construction of Arbiter-PUF as proposed in [36].

Ideally, an Arbiter-PUF response is equally likely to be ‘0’ or ‘1’ in which it is solely dependent on the randomness in process variations. However, the response could be

biased to be either ‘0’ or ‘1’. A large bias reduces the uniqueness and randomness of Arbiter-PUF responses. To avoid the bias, two important criteria must be fulfilled at the design stage:

1. The highest degree of symmetry in the layout is required to ensure the unbiased response of the Arbiter-PUF. The symmetry routing includes the routing before the first switching element, inside the switching element, in between stages, before and inside the arbiter circuit. Although it is non-trivial, it is possible to achieve a symmetrical routing in application-specific integrated circuits (ASICs) [12], while implementations on FPGAs seem to be difficult due to the placement and routing constraints of the general FPGA hardware architecture [37].

2. An unbiased arbiter circuit must be used for digitisation of the delay difference. According to [38], fair arbitration can be achieved by using an SR-latch which has a symmetric circuit topology.

For an Arbiter-PUF, although the effect of process variations on the logic gates and interconnect delays is random, there is a small yet non-negligible probability that metastability could happen if the rising edges at the inputs  $A$  and  $B$  of the arbiter circuit have a very small timing difference. A fair arbiter circuit such as an SR-latch which has a symmetric circuit topology is desired to minimise the arbiter bias and the metastability effects [39].

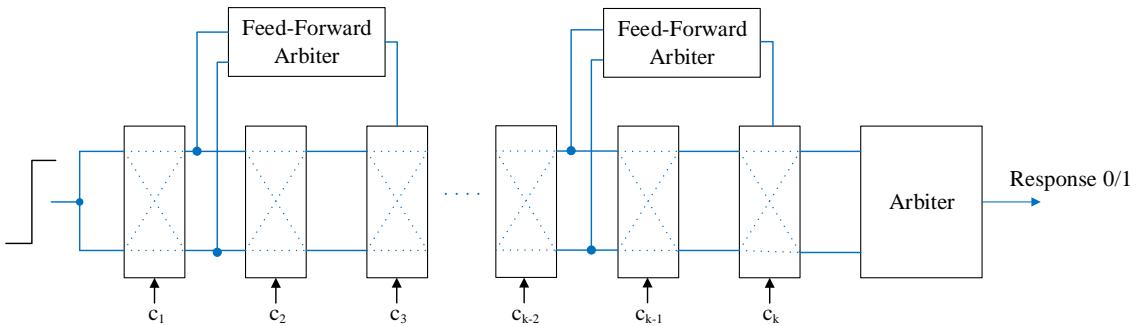

Figure 2.4: The construction of Feed-Forward Arbiter-PUF as proposed in [30].

The construction of an Arbiter-PUF, as in Figure 2.3, is based on additive delays caused by the individual switching components which have linear characteristics [36]. Therefore, the complexity of the CRPs mapping is minimal which enables the model building attacks using ML techniques. A few derivatives of the Arbiter-PUF have been proposed with the aim in introducing the non-linearity into it. Lim *et al.*, [30] presented the Feed-Forward Arbiter-PUF which uses the output of intermediate arbiters to configure the subsequent switching components as depicted in Figure 2.4. However, the intermediate arbiters increase the probability of metastability states, which would result in more errors in the PUF response.

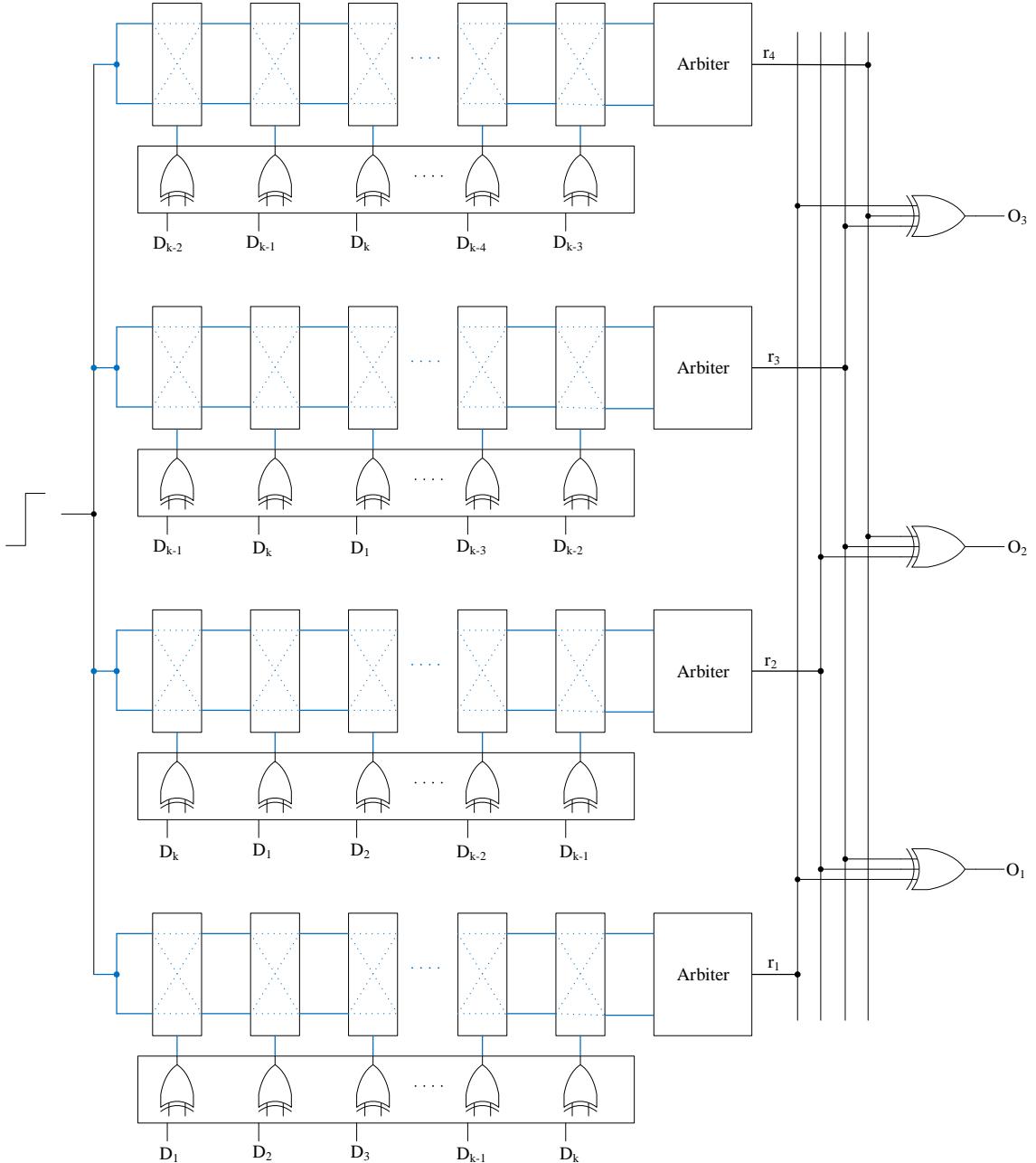

Figure 2.5: The construction of Lightweight-PUF as proposed in [31] for  $l=4$ .

Elsewhere, Majzoobi *et al.*, [31] proposed a Lightweight-PUF which consists of  $l$  parallel Arbiter-PUFs. The outputs of the Arbiter-PUFs are XORed to generate an overall PUF response  $O_1, O_2$ , and  $O_3$  as shown in Figure 2.5. The input XOR network in the Lightweight-PUF is expected to further increase the non-linearity in the CRPs mapping. Earlier,  $l$ -XOR Arbiter-PUF was proposed in [22] which consists of  $l$  parallel Arbiter-PUFs as illustrated in Figure 2.6. The susceptibility of the Arbiter-PUF and its derivatives to ML-attacks will be discussed in detail in Section 2.8.3.

Figure 2.6: The construction of the  $l$ -XOR Arbiter-PUF as proposed in [22].

### 2.4.2 Ring Oscillator PUF

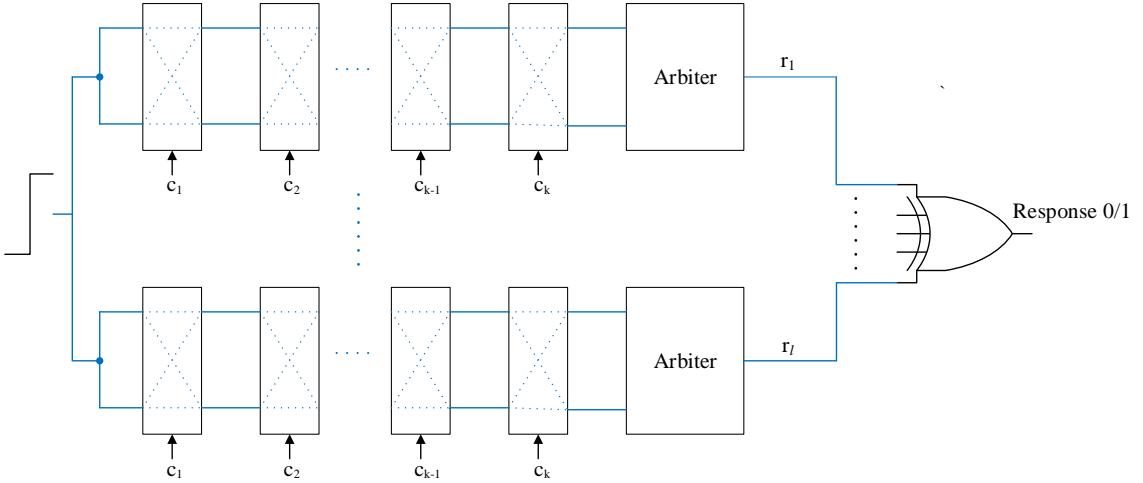

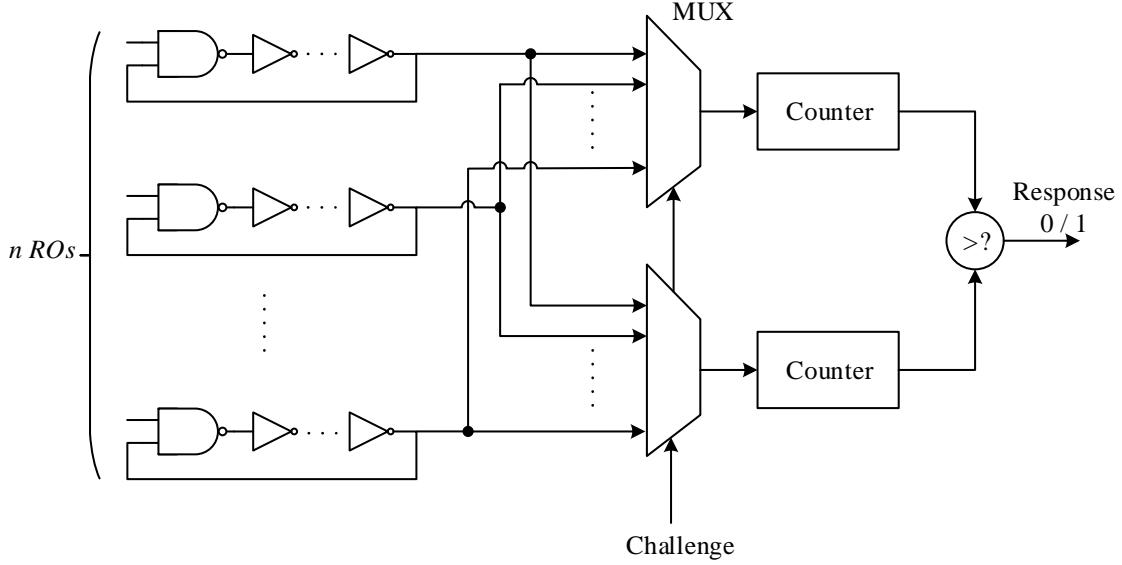

Another type of delay-based PUF is the ring oscillator PUF (RO-PUF). The working principle of the RO-PUF is that by measuring the frequencies of digital oscillating circuits that randomly vary due to the uncontrollable effects of silicon process variations on the logic gates and interconnect delays. The notion of a PUF which uses an oscillating circuit was first proposed by Gassend *et al.*, [16]. Further, Suh *et al.*, [22] proposed an RO-PUF architecture which consists of an array of  $n$  nominally identical ROs. The architecture also contains two frequency counters to count the number of rising edges at the selected RO pairs. Two  $n$ -to-1 multiplexers control which pair of ROs is currently applied to both counters. Hence, the selection signals of these multiplexers become the PUF's challenge. The construction of an RO-PUF is depicted in Figure 2.7. Both frequency counters are enabled for a fixed time interval and the resulting counter values are compared to generate a response, '0' or '1', based on which oscillator from the selected RO pair is faster. Since the process variations affect the frequencies of the  $n$  RO arrays, the resulting comparison bit will be random and device-specific.

Each comparison of a pair of oscillators generates a bit. Therefore, given an array of  $n$  oscillators, a total of  $\binom{n}{2} = \frac{n(n-1)}{2}$  pairs can be compared. However, the number of independent bits that can be produced is less than  $\frac{n(n-1)}{2}$ . For example, if oscillator A is faster than B and B is faster than C, clearly that A will also be faster than C which results in a correlated pair-wise comparison. Suh and Devadas [22] concluded that the maximum number of uncorrelated comparisons is limited by the number of possible orderings in which the oscillators can be ordered. Given  $n$  oscillator frequencies which are independent and equally distributed, there exist  $n!$  equally likely possible orderings. Hence, the maximum entropy (i.e., uncorrelated pair-wise comparisons) of an RO-PUF is  $\log_2 n!$ . It is also possible to avoid any correlation by simply comparing a pair of ROs once, resulting in only  $\frac{n}{2}$  response bits.

Figure 2.7: The construction of an RO-PUF as proposed in [22].

### 2.4.3 SRAM-PUF

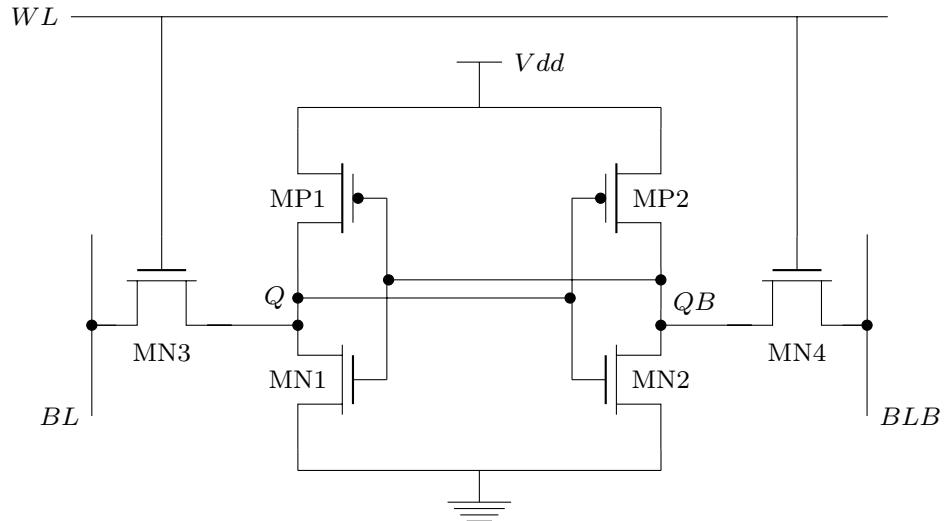

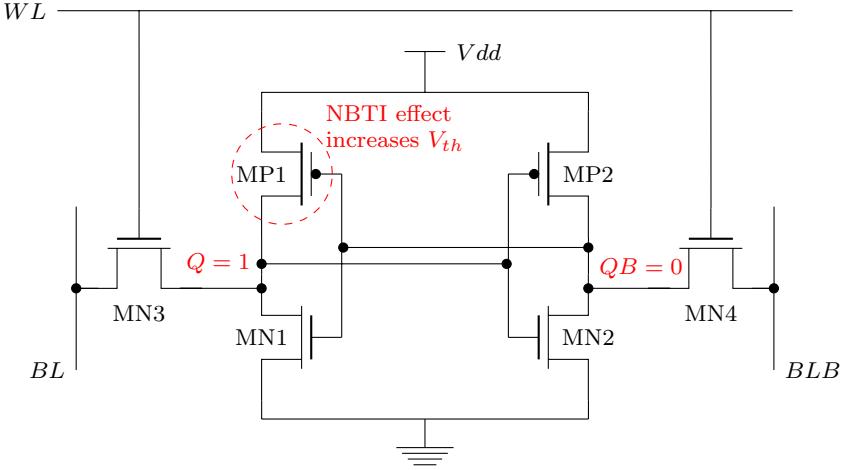

The previously discussed PUFs are all delay-based PUFs which require additional circuitry to use them as on-chip hardware security. Another idea is to use on-chip resources as a PUF, particularly using SRAM, which is available in any computing system [23, 24]. Guajardo *et al.*, [23] exploited SRAM memory as an intrinsic PUF for use as a secret key generator for FPGA bitstream encryption/decryption to support an IP protection. Holcomb *et al.* [24], targeted wider applications of SRAM as PUFs to support resource-constrained security-critical applications such as contactless credit cards etc. Generally, SRAM memory is constructed based on rows and columns of bit cells. The number of available bit cells in an SRAM represents its storage size. Each bit cell of SRAM is typically a six-transistor CMOS circuit which consists of two cross-coupled inverters (MP1, MP2, MN1, and MN2) and two access transistors (MN3 and MN4), as illustrated in Figure 2.8.

The transistors forming the cross-coupled inverters are also known as a bi-stable element, in which each node  $Q$  and  $QB$  can be in either of two states, '0' or '1'. The power-up or SUVs of bi-stable elements depend on the device mismatches, which result from process variations. During power-up of an SRAM cell, as the supply voltage increases, the current flowing through MN1 and MN2 will slowly pull up the voltage at nodes  $Q$  and  $QB$ . Because of the random process variations, transistor MP2 has a slightly higher threshold voltage compared to that of MP1. Therefore, the current that flows through MN1 is slightly higher than through MN2, thus turning ON the MN2 and pulling down node  $QB$  to  $GND$ . At the same time when node  $QB$  is discharging, MP1 is turned ON and pulls up node  $Q$  to  $V_{dd}$ . As shown in Figure 2.9, the nodes  $Q$  and  $QB$  settle at '0'

Figure 2.8: 6-T SRAM cell circuit.

Figure 2.9: Bi-stable SRAM internal nodes,  $Q$  and  $QB$  resolving to '1' and '0' during power-up process.

and ‘1’, respectively. When powering-up the SRAM, the SUVs across different memory blocks within an SRAM and across multiple SRAMs show device-specific and random patterns, which are the desired qualities to be used as a PUF [23, 24].

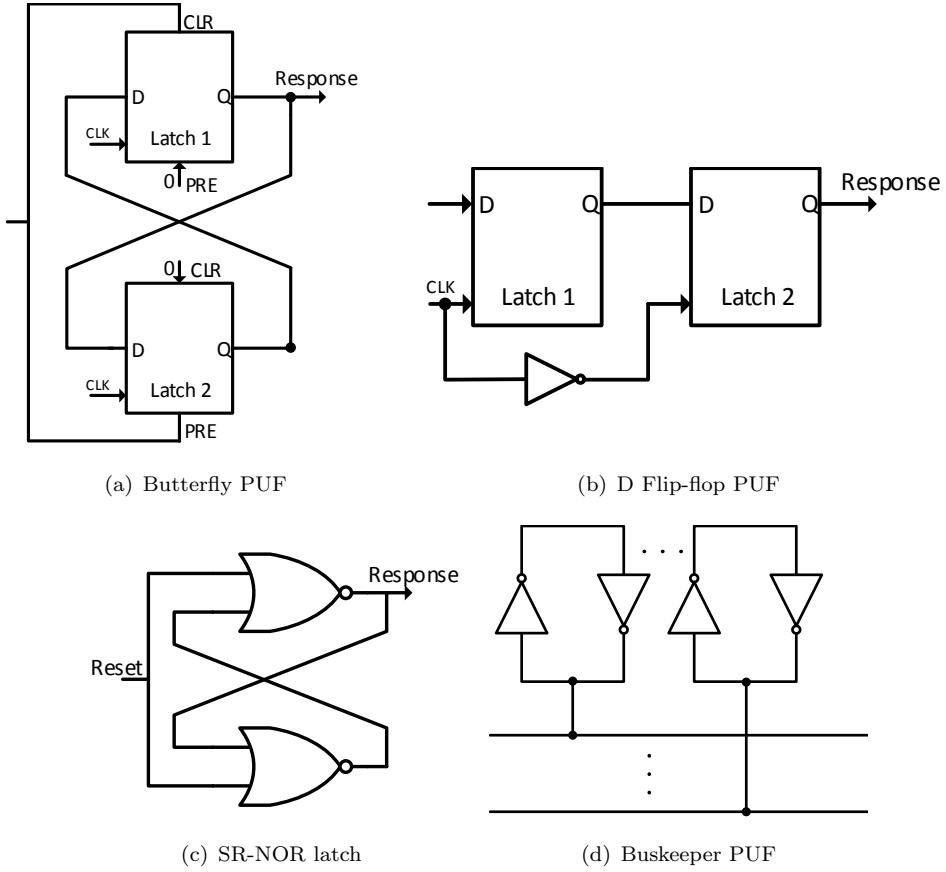

#### 2.4.4 Flip-flop, Latch and Buskeeper PUFs

PUFs based on flip-flops and latches are derived from the same working principles and physical effects as SRAM-PUFs. Kumar *et al.*, [25] proposed a Butterfly PUF which consists of a pair of cross-coupled latches, forming a bi-stable circuit as illustrated in Figure 2.10(a). When the preset (PRE) and clear (CLR) signals are simultaneously set to high, the Butterfly PUF can be forced into an unstable state and converges into a stable state when both signals are set low after a few clock cycles. The Butterfly PUF was proposed to overcome the disadvantage of the SRAM-PUF on FPGA platforms, whereby the SRAM on most commercial FPGAs is cleared after power-up. However, the Butterfly PUF requires symmetrical routing to minimise the impact of design mismatch which is not trivial to achieve due to the routing constraints on FPGAs [37]. Elsewhere, a PUF based on the power-up behaviour (i.e., similar to the SRAM PUF) of clocked D flip-flops is proposed by van der Leest *et al.*, [32]. Most D flip-flops are based on two latches as depicted in Figure 2.10(b). The advantage of D Flip-flop PUF is that the location of the individual flip-flop can be randomly spread across a design and their signal lines connecting them to the read-out circuitry can be obfuscated which increases the defence against invasive attacks such as probing attacks.

Su *et al.*, [33] proposed a device identification technique based on the two cross-coupled NOR-gates which constitute a simple SR-NOR latch as shown in Figure 2.10(c). When the reset signal is high, the SR-NOR latch enters an undefined state and converges to a stable state depending on the internal mismatch between the NOR gates when the reset signal is low. The SR-NOR latch uses the same working principle as SRAM-PUF, however does not rely on a power-up state that depends on the supply voltage. Therefore, it provides more flexibility because it can generate unpredictable and reproducible responses when the reset signal is (re)asserted any time that the secret key is required during the on-time of the device. Another variant of latch-based PUF is the Buskeeper PUF, proposed in [26], which is constructed using bus keeper cells. The basic structure of a bus keeper cell is a cross-coupled inverter with a weak drive-strength, connected to a bus line, as shown in Figure 2.10(d). A bus keeper cell is used to maintain the last driven state on the bus line and prevents the bus line from floating. Similar to SRAM cells, the power-up state of bus keeper cells is determined by the device mismatches which result from process variations. An advantage of the Buskeeper PUF is the low area overhead in comparison to other types of memory based-PUFs such as D Flip-flop PUFs.

Figure 2.10: The construction of Butterfly PUF [25], D Flip-flop PUF [32], SR-NOR latch PUF [33] and Buskeeper PUF [26].

#### 2.4.5 Mixed-Signal PUFs

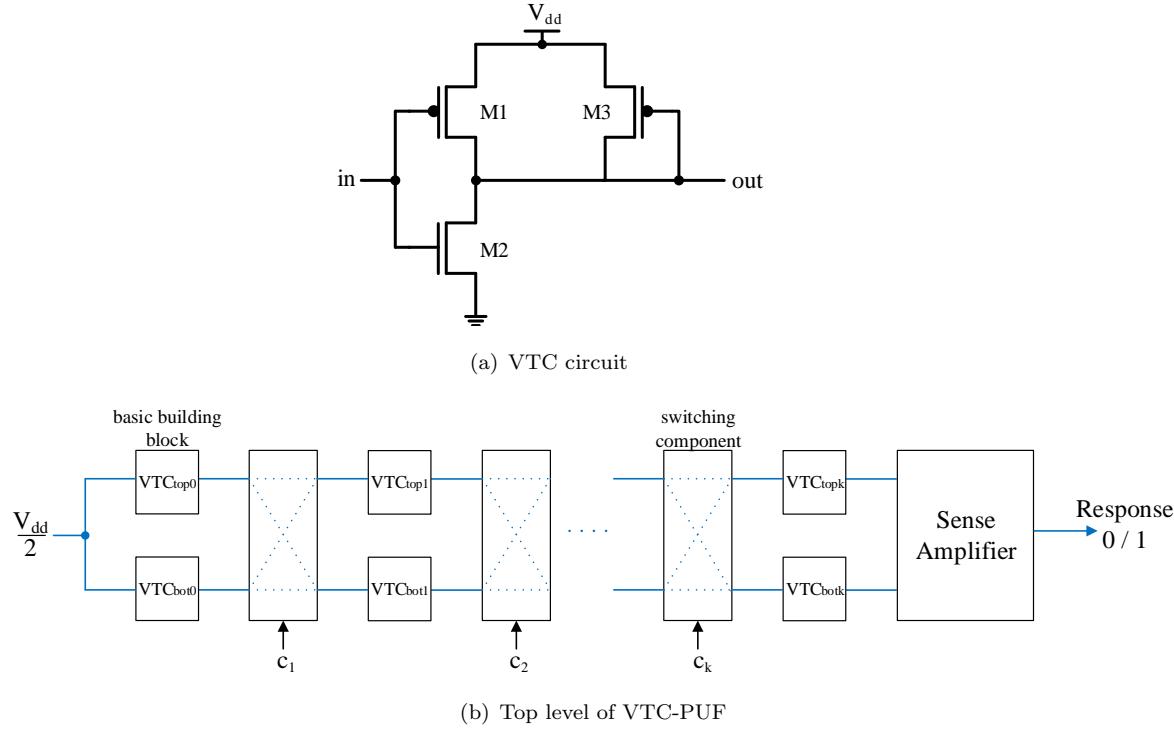

A PUF with a mixed-signal structure, namely the VTC-PUF, was proposed by Vijayakumar *et al.*, [34], which exploits the variability in a voltage transfer characteristic (VTC) circuit as shown in Figure 2.11(a). The VTC circuit has a non-linear relationship between input and output voltages in which the non-linearity is controlled by the feedback transistor, M3. Adapted from the architecture of Arbiter-PUF, the VTC circuit is used as a basic building block in which it is coupled with a switching component in each stage, creating a cascaded circuit as depicted in Figure 2.11(b). The switching components are created from a simple transmission gate based circuit. The input node is connected to  $\frac{V_{dd}}{2}$ . A voltage sense amplifier is used to sense the difference of the propagated input voltages and generate a response, '1' or '0', based on the sign of the differential output at the final stage.

Figure 2.11: The construction of VTC-PUF [34].

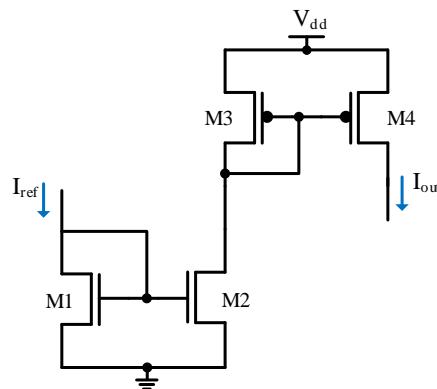

Kumar *et al.*, [35] proposed a Current Mirror-PUF which is also adapted from the Arbiter-PUF architecture, as in Figure 2.11. However, the basic building block is the current mirror circuit illustrated in Figure 2.12.  $I_{out}$  is the mirrored current of  $I_{ref}$  which will be varied slightly due to the process variations experienced by the transistors, M1-M4. Similar to the VTC-PUF, the switching components are created by a simple transmission gate based circuit, but the input is connected to a constant current source. A current sense amplifier is used to sense the difference of the propagated input currents and generate a response, ‘1’ or ‘0’, based on the sign of the differential output at the final stage.

Figure 2.12: The construction of the current mirror circuit in the Current Mirror-PUF [35].

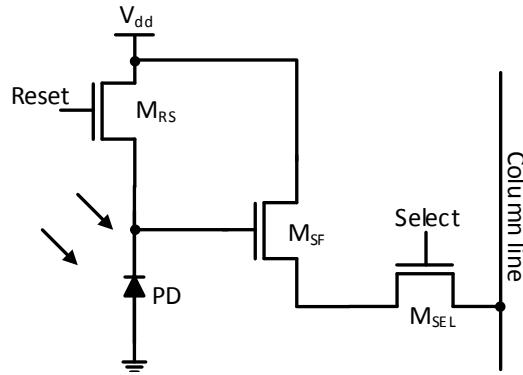

Elsewhere, Cao *et al.*, [40] proposed a mixed-signal PUF based on a CMOS image sensor circuit. The image sensor function is not affected when operated in a PUF mode. The core of a CMOS image sensor is a pixel array, where its typical structure is depicted in Figure 2.13. This PUF exploits the variations of the pixel output voltage during the reset phase which varies due to the variations in the threshold voltages of transistors  $M_{RS}$  and  $M_{SF}$ . The two reset voltages of two pixels are compared to generate a response, ‘0’ or ‘1’, based on which reset voltage is larger. A predefined threshold is introduced during the comparison of reset voltages which effectively increases the reliability of the response by about 10.8%.

Figure 2.13: 3-T pixel circuit.

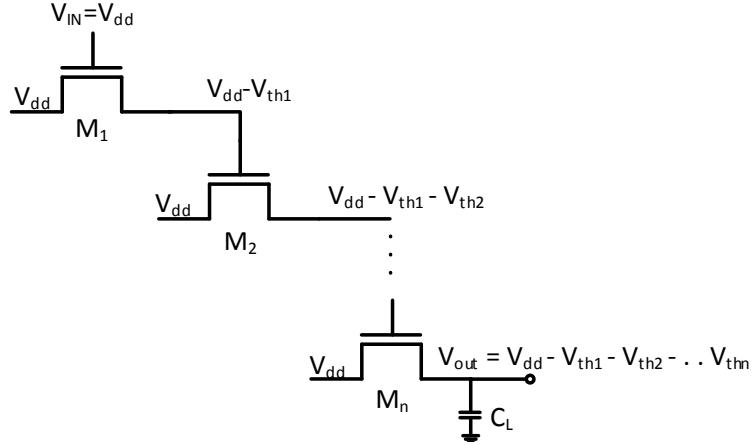

Saha *et al.*, [41] proposed a fast and lightweight mixed-signal PUF which exploits the susceptibility of the threshold voltage of MOSFETs to process variations, hence, the name “Threshold Voltage PUF” or TV-PUF. The core circuit in the TV-PUF is a block consisting of  $n$  cascaded transistors as depicted in Figure 2.14. When  $V_{IN}=V_{dd}$ , the output voltage at the source terminal of the cascaded series of transistors becomes  $V_{out} = V_{dd} - V_{th1} - V_{th2} - \dots - V_{thn}$ . Clearly, the output voltage depends on the threshold voltages of  $n$  cascaded transistors which are susceptible to random process variations. Due to this, the output voltages of two nominally identical blocks are different and are compared using the sense amplifier to generate a 1-bit response. A decoder circuit is used to set the level of  $V_{IN}$  to *HIGH* ( $V_{dd}$ ). For a unique challenge (i.e., an input decoder), only one decoder output is *HIGH*, which is connected to two blocks of  $n$  cascaded transistors.

#### 2.4.6 Emerging Nanotechnology-based PUFs

All of the above PUF designs focus on exploiting process variations intrinsic to CMOS technology. Recently, nanotechnology-based PUFs have made some progress since the scaling down to the nano-region has resulted in an increased variability in nanoelectronic devices. PUFs that have been proposed include the Carbon-nanotube field-effect transistors (CNFET) based PUF [42], the phase change memory (PCM) based PUF [43],

Figure 2.14: The construction of  $n$  cascaded transistors of one block in TV-PUF [41]

and the Memristor-based PUF [44]. Nanotechnology-based PUFs offer a few advantages over CMOS based PUFs, such as substantial process variations, small foot-prints, and lower energy consumption [11]. Since this study focuses on CMOS silicon-based PUFs, one may refer to [11] for a comprehensive discussion on PUFs based on emerging nanotechnology devices.

## 2.5 PUF Quality Metrics

All of the above discussed the proposed techniques for different types of PUFs implementations. Several parameters were defined to quantify the performance of the proposed PUFs, but the parameter or evaluation criteria differ for each implementation. Therefore, a standard set of parameters is needed to quantify the performance of these PUFs. Maiti *et al.*, [45] has systematically refined the quality parameters to evaluate and compare the performance of PUFs. These parameters are uniqueness, reliability, and uniformity. Next, the definition of these parameters are described and later in this section, the quality metrics for PUFs discussed in Section 2.4 are summarised in a performance table.

### 2.5.1 Uniqueness