### UNIVERSITY OF SOUTHAMPTON

# Single Electron Manipulation in Silicon Nanowires for Quantum Technologies

by

### Zuo Li

A thesis submitted for the degree of Doctor of Philosophy Primary Supervisor: Prof. Shinichi Saito Second Supervisor: Dr. Yoshishige Tsuchiya

in the

Faculty of Physical Science and Engineering School of Electronics and Computer Science

June 2018

#### UNIVERSITY OF SOUTHAMPTON

### ABSTRACT

# FACULTY OF PHYSICAL SCIENCE AND ENGINEERING SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

### Doctor of Philosophy

by Zuo Li

A redefinition of the Ampere based on the quantum metrology triangle is required to improve the accuracy of the unit. The Si single electron pump is considered a promising candidate for the single electron source in the quantum metrology triangle due to its compatibility with the state-of-art CMOS manufacturing platform. However, the fabrication processes have not been fully established, and the performance impact factors and reliability of Si single electron pumps have not been fully addressed.

In this project, I successfully fabricated Si electron pumps with atomically flat surfaces, using the advanced facilities in Southampton Nanofabrication Centre. I observed current plateaus with the width of 18 meV and uncertainty of 0.828% when the single electron pump is operated at 125 MHz in the National Physical Laboratory, showing the possibilities for the applications of current calibration. The reliability issues were investigated by measuring Si quantum dot devices and the single electron pumps fabricated. The impact of charge traps in quantum devices were addressed by investigating the random telegraph noise in the devices. I demonstrated that the charge traps can impact the device reliability by resonant tunnelling, which will help scientists to understand further about the reliability impact factors of silicon quantum devices.

### **Academic Thesis: Declaration Of Authorship**

I, Zuo Li, declare that this thesis and the work presented in it are my own and has been generated by me as the result of my own original research, *Single Electron Manipulation in Silicon Nanowires for Quantum Technologies*.

#### I confirm that:

- 1. This work was done wholly or mainly while in candidature for a research degree at this University;

- 2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- 3. Where I have consulted the published work of others, this is always clearly attributed;

- 4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- 5. I have acknowledged all main sources of help;

- 6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- 7. Either none of this work has been published before submission, or parts of this work have been published as:

- Li, Z., Husain, M.K., Yoshimoto, H., Tani, K., Sasago, Y., Hisamoto, D., Fletcher, J.D., Kataoka, M., Tsuchiya, Y. and Saito, S., 2017. Single carrier trapping and de-trapping in scaled silicon complementary metal-oxide-semiconductor field-effect transistors at low temperatures. *Semiconductor Science and Technology*, **32(7)**, p.075001.

- Li, Z., Sotto, M., Liu, F., Husain, M.K., Yoshimoto, H., Sasago, Y., Hisamoto, D., Tomita, I., Tsuchiya, Y. and Saito, S., 2018. Random telegraph noise from resonant tunnelling at low temperatures. *Scientific reports*, **8(1)**, p.250.

- Li, Z., Sotto, M., Liu, F., Husain, M.K., Zeimpekis, I., Yoshimoto, H., Tani, K., Sasago, Y., Hisamoto, D., Fletcher, J.D. and Kataoka, M., 2017, February. Random-telegraph-noise by resonant tunnelling at low temperatures. In Electron Devices Technology and Manufacturing Conference (EDTM), 2017 IEEE (pp. 172-174). IEEE.

| Signed: | <br> | <br> | <br> |

|---------|------|------|------|

|         |      |      |      |

|         |      |      |      |

| Date:   | <br> | <br> | <br> |

## Contents

| A            | cknov | wledgements                                                        | xvii |

|--------------|-------|--------------------------------------------------------------------|------|

| 1            | Intr  | roduction                                                          | 1    |

| 2            | Bac   | kground Research                                                   | 5    |

|              | 2.1   | Quantum Metrology Triangle                                         | . 5  |

|              | 2.2   | Device Physics: Single electron transport                          | . 7  |

|              |       | 2.2.1 Fundamental Physics for Single Electron Transport            | . 7  |

|              |       | 2.2.2 Single Electron Transport in Metal Oxide Tunnelling Junction | . 9  |

|              |       | 2.2.3 Single Electron Transport in Semiconductor                   | . 14 |

|              | 2.3   | Single Electron Pump: Design and Realisation                       | . 18 |

|              |       | 2.3.1 Adiabatic Pumping                                            | . 18 |

|              |       | 2.3.2 Non-adiabatic Pumping                                        | . 19 |

|              |       | 2.3.3 Variations of Designs                                        | . 26 |

|              | 2.4   | Fabrication of Si nanowire device                                  | . 34 |

| 3            | Fab   | rication of Single Electron Pump                                   | 39   |

|              | 3.1   | Overview of the device layout design                               | 39   |

|              | 3.2   | Fabrication Process Flow                                           |      |

|              |       | 3.2.1 Nanowire definition                                          |      |

|              |       | 3.2.2 Dopant diffusion Window                                      |      |

|              |       | 3.2.3 First gates definition                                       |      |

|              |       | 3.2.4 Top gates definition                                         | 49   |

|              |       | 3.2.5 Contact Opening                                              | 49   |

|              |       | 3.2.6 Metallisation                                                | 50   |

|              | 3.3   | Yield Analysation and summary                                      | . 52 |

| 4            | Mea   | asurement of Single Electron Devices                               | 59   |

|              | 4.1   | Measurement of Si quantum dots in advanced MOSFETs                 | . 59 |

|              |       | 4.1.1 SET Characteristics and Investigation                        | 60   |

|              |       | 4.1.2 RTN Characteristics and Investigation                        | 67   |

|              | 4.2   | Measurement of single electron pump devices                        | . 80 |

| 5            | Con   | aclusions                                                          | 91   |

| A            | Gat   | e dry etching recipe development                                   | 93   |

| $\mathbf{R}$ | Dor   | pant diffusion test                                                | 97   |

vi CONTENTS

| $\mathbf{C}$ | L- $E$ | dit La   | yout for the device design                       | 101   |

|--------------|--------|----------|--------------------------------------------------|-------|

|              | C.1    | Mask     | Layout Design                                    | . 101 |

|              |        | C.1.1    | Main Design (a): 2 First Gates                   | . 101 |

|              |        | C.1.2    | Main Design (b): 3 First Gates                   | . 103 |

|              |        | C.1.3    | Main Design (c): 2 First Gates+ 1QD              | . 106 |

|              |        | C.1.4    | Main Design (d): 3 First Gates+ 1QD              | . 108 |

|              |        |          | Secondary Design (e): 2 First Gates              |       |

|              |        |          | Secondary Design (f): 2 First Gates              |       |

|              |        |          | Secondary Design (g): 2 First Gates              |       |

|              |        |          | Secondary Design (h): 2 First Gates              |       |

| D            | Pub    | olicatio | on List                                          | 121   |

|              | D.1    | Journa   | al Publication: As first author                  | . 121 |

|              | D.2    | Intern   | ational Conference Publication: As first author  | . 121 |

|              | D.3    | Journa   | al Publication: As other authors                 | . 121 |

|              | D.4    | Intern   | ational Conference Publication: As other authors | . 122 |

| Bi           | bliog  | graphy   |                                                  | 123   |

# List of Figures

| 2.1  | Schematic Diagram of Quantum Metrology Triangle. The links between                                                                             | _   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | the three parameters, frequency $f$ , current $I$ and voltage $U$ are shown                                                                    | 5   |

| 2.2  | Quantum Metrology Triangle Experimental Set-up                                                                                                 | 6   |

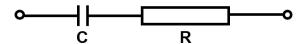

| 2.3  | The schematic RC circuit model to describe the coupling between the                                                                            | _   |

|      | electron to the ambient. Resistance and Capacitance are in series                                                                              | 8   |

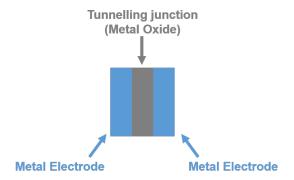

| 2.4  | Schematic Diagram of a Metallic Tunnelling Junction                                                                                            | 9   |

| 2.5  | Schematic Diagram of a Single Electron Box                                                                                                     | 10  |

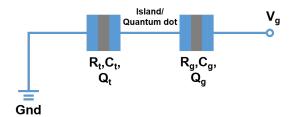

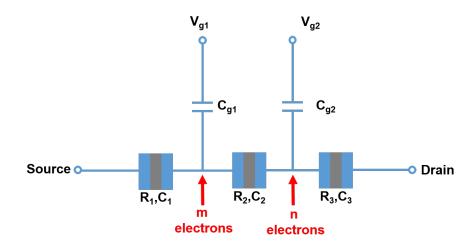

| 2.6  | Equivalent Circuit Diagram of a Single Electron Transistor                                                                                     | 11  |

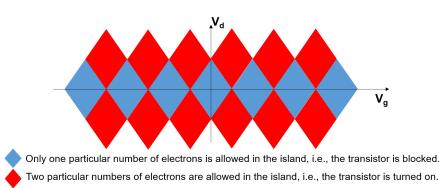

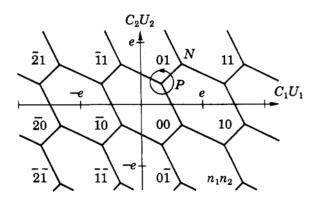

| 2.7  | Ideal Stability Diagram of a Metallic Single Electron Transistor                                                                               | 12  |

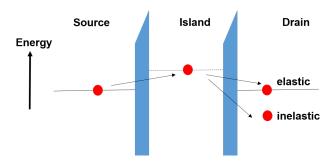

| 2.8  | A schematic diagram of the Co-tunnelling Process. Electrons tunnel from                                                                        |     |

|      | the source to the drain through a virtual state                                                                                                | 13  |

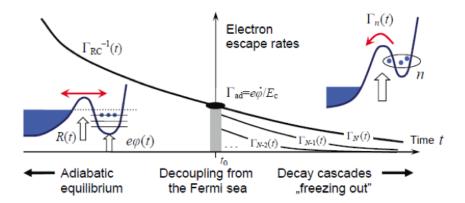

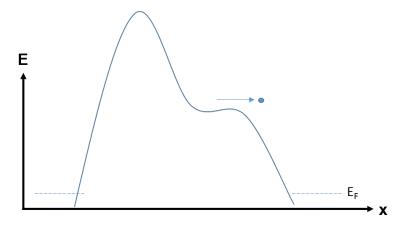

| 2.9  | Decay-Cascade Process in the non-adiabatic single electron transfer.[55] .                                                                     | 15  |

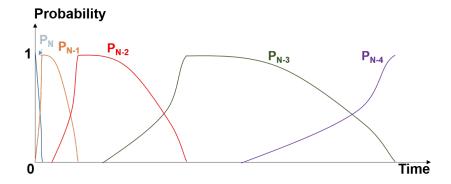

| 2.10 |                                                                                                                                                |     |

|      | tunnels out the quantum dot is much smaller than the (N-1)th electron                                                                          | 17  |

|      | Schematic diagram of a metallic single electron pump                                                                                           | 18  |

|      | Stability diagram of a metallic single electron pump at 0 drain bias.[57] .                                                                    | 18  |

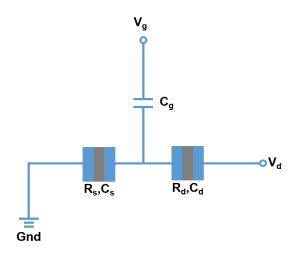

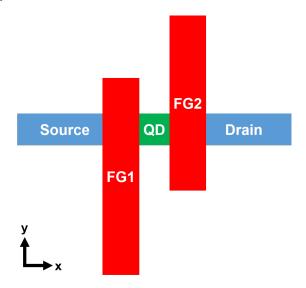

|      | General schematic model of semiconductor single electron pump                                                                                  | 19  |

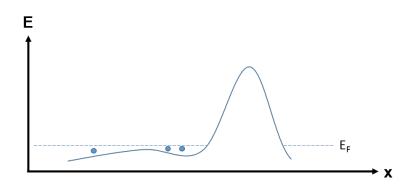

| 2.14 | Loading Process of the non-adiabatic single electron pump. The source                                                                          |     |

|      | and quantum dot are metallically connected                                                                                                     | 20  |

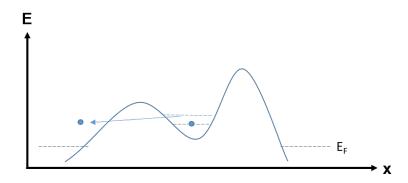

| 2.15 | Initialisation Process of the non-adiabatic single electron pump. The                                                                          |     |

|      | electrons in the quantum dot back-tunnel to the source through quantum-                                                                        |     |

|      | mechanical processes                                                                                                                           | 20  |

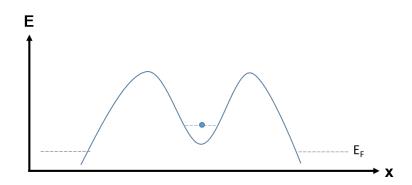

| 2.16 | Trapping Process of the non-adiabatic single electron pump. One single                                                                         |     |

|      | electron is trapped in the quantum dot, and decoupled from both source                                                                         | 0.1 |

| 0.15 | and drain.                                                                                                                                     | 21  |

| 2.17 |                                                                                                                                                |     |

|      | trapped in the quantum dot is ejected to the drain reservoir, and the                                                                          | า1  |

| 9.10 | single electron transfer process is completed                                                                                                  | 21  |

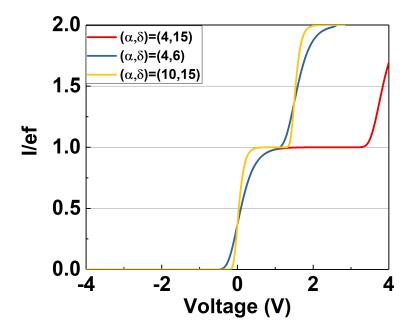

|      | Simulation of decay cascade model with different fitting parameters $\alpha$ and $\delta$ .                                                    | 23  |

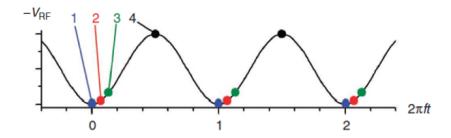

| 2.19 | The timescale of the loading, initialisation, trapping and ejection event of non-adiabatic pumping while operating with a sine wave. The 1, 2, |     |

|      | 3, 4 points shown in the figure correspond to the loading, initialisation,                                                                     |     |

|      | trapping and ejection event, respectively.[30]                                                                                                 | 24  |

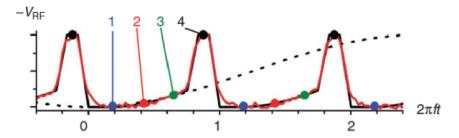

| 2.20 |                                                                                                                                                | 24  |

| 2.20 | of non-adiabatic pumping while operating with a specially-designed arbi-                                                                       |     |

|      | trary wave. The 1, 2, 3, 4 points shown in the figure correspond to the                                                                        |     |

|      | loading, initialisation, trapping and ejection event, respectively.[30]                                                                        | 25  |

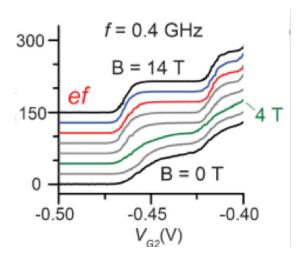

| 2.21 | Influence of Magnetic Field on the current-voltage characteristics of the                                                                      |     |

|      | single electron pump.[65]                                                                                                                      | 25  |

|      | - O r r r (**)                                                                                                                                 |     |

viii LIST OF FIGURES

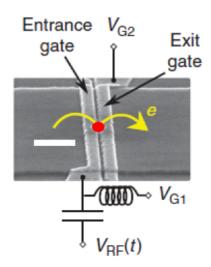

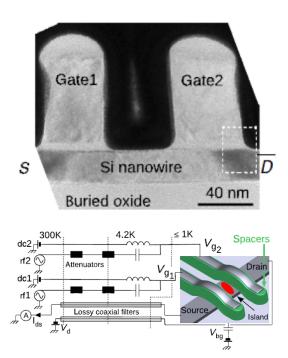

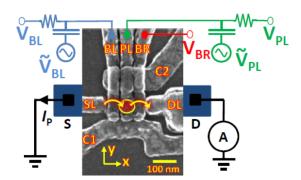

| 2.22 | as a red spot in the figure. The RF signal is connected to the entrance gate.[30]                                                                                                                                                                                               | 27       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

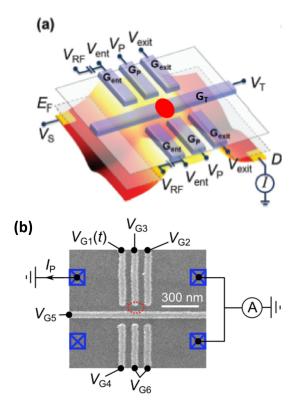

| 2.23 | A GaAs pump design from South Korea. The quantum dot is drawn as a red spot in (a). The RF signal is connected to the entrance gate. (a) shows the schematic diagram while (b) shows the SEM image of the device. The quantum dot is modulated by both trench gate and the side |          |

| 2.24 | gate.[69,70]                                                                                                                                                                                                                                                                    | 28       |

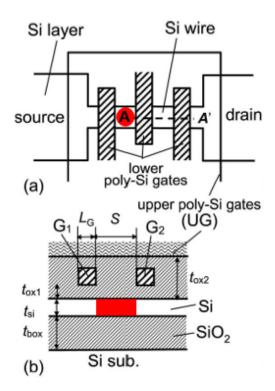

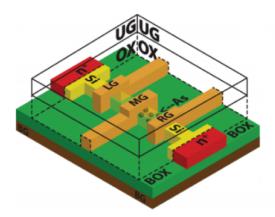

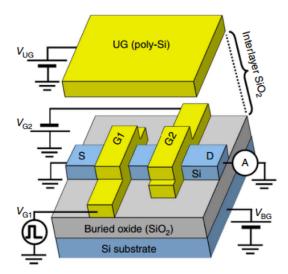

| 2.25 | upper poly-Si gate.[73]                                                                                                                                                                                                                                                         | 29       |

| 2.26 | substrate.[75]                                                                                                                                                                                                                                                                  | 30<br>30 |

| 2.27 | A Si dopant pump design from NTT. The quantum dot is the As dopants between MG and RG. The quantum dot is modulated by the upper poly-                                                                                                                                          |          |

| 2.28 | Si gate. [78]                                                                                                                                                                                                                                                                   | 31<br>31 |

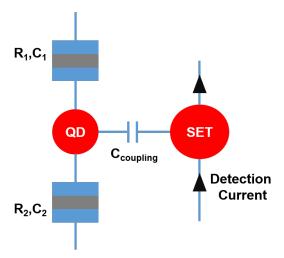

| 2.29 | Schematic of circuit diagram for charge detection scheme. The SET is used as a current sensor.                                                                                                                                                                                  | 32       |

| 2.30 | A Si pump design with charge-detection scheme from NTT. The charge detection scheme is a Si single electron transistor capacitively coupled to                                                                                                                                  |          |

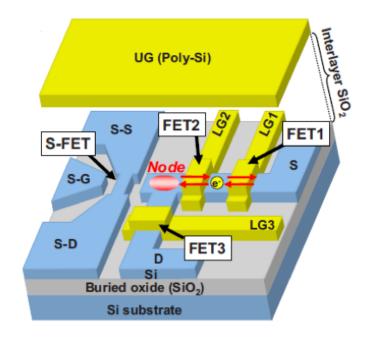

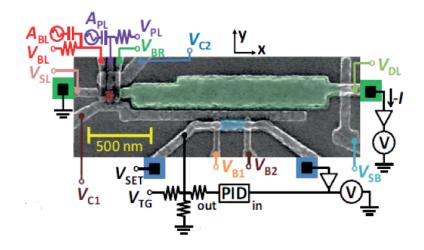

| 2.31 | A Si pump design with charge-detection scheme from UNSW. The charge detection scheme is a Si single electron transistor, controlled by B1 and B2, and connectively coupled to the electron node [01]                                                                            | 33<br>33 |

| 2.32 | B2, and capacitively coupled to the electron node.[91]                                                                                                                                                                                                                          | აა       |

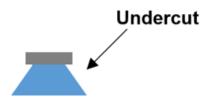

|      | anisotropic etching process.                                                                                                                                                                                                                                                    |          |

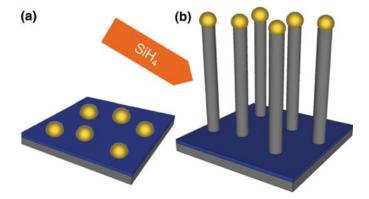

|      | Schematic Diagram of TMAH Undercut in a $<100>$ -oriented SOI wafer. Schematic Diagram of Bottom-up Process. The nanowire is grown by                                                                                                                                           | 35       |

| 2.04 | using gold particle as catalyst.[105]                                                                                                                                                                                                                                           | 35       |

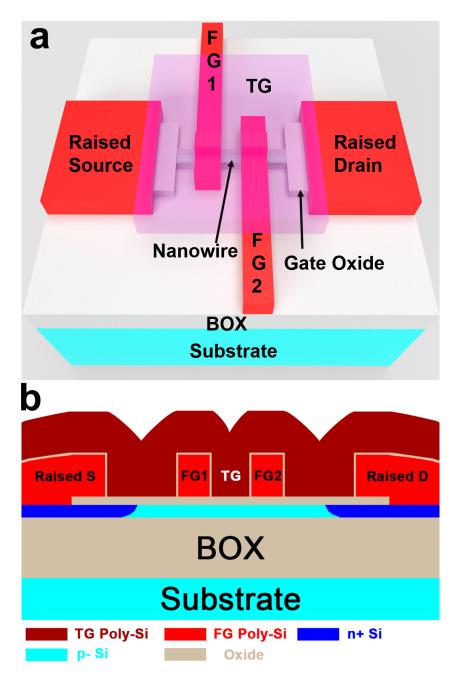

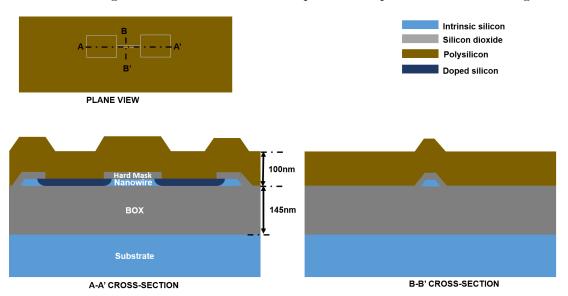

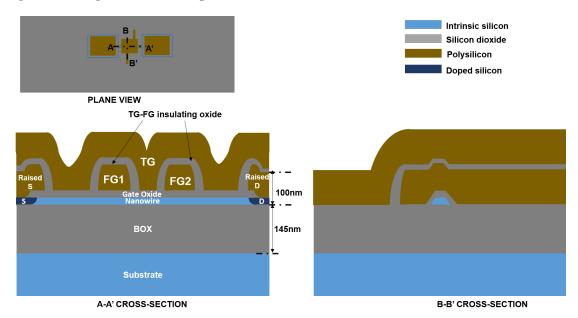

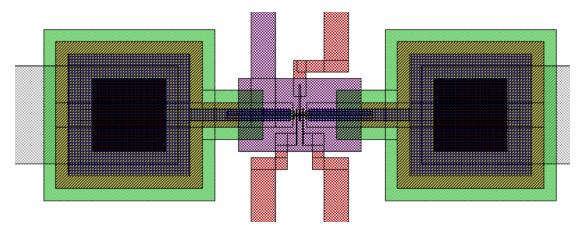

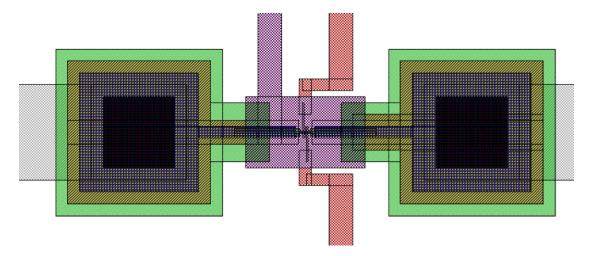

| 3.1  | Schematic diagram of the device design in the key operation region. (a) shows the 3-D view of the proposed device structure, while (b) shows the ideal cross-sectional structure of the device. The metal connection part                                                       |          |

|      | is not shown in the schematic diagram                                                                                                                                                                                                                                           | 40       |

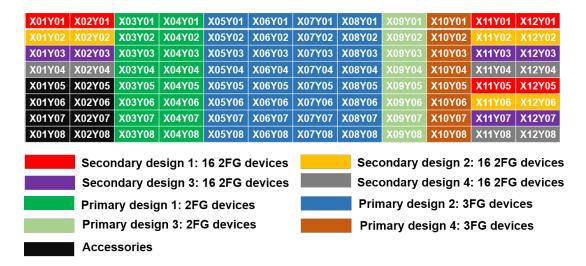

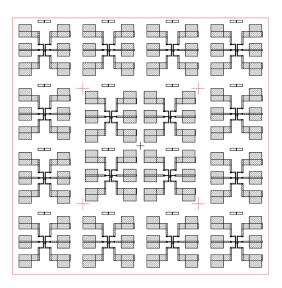

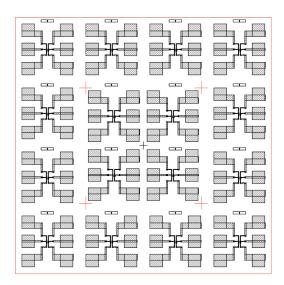

| 3.2  | Layout arrangement of the mask design. The designs that each sub-chip                                                                                                                                                                                                           | 41       |

| 3.3  | will carry is shown in the figure                                                                                                                                                                                                                                               |          |

| 3.4  | Position of dies on a single wafer                                                                                                                                                                                                                                              |          |

LIST OF FIGURES \_\_\_\_\_\_ix

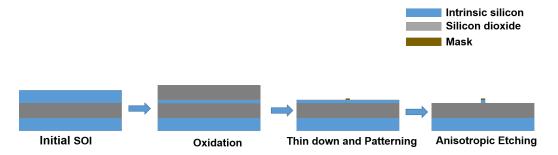

| 3.5  | General fabrication process flow of the device designs, based on the e-                                                                | 40 |

|------|----------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.0  | beam lithography required                                                                                                              | 43 |

| 3.6  | Schematic diagram in the nanowire definition step. Atomically-flat <111> nanowire surfaces are formed by TMAH etching                  | 44 |

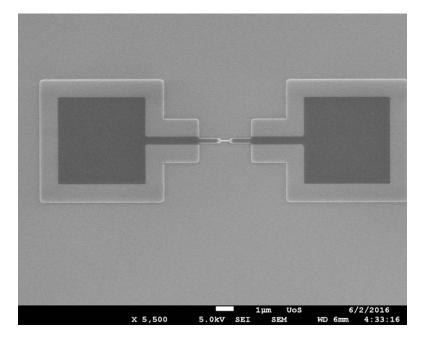

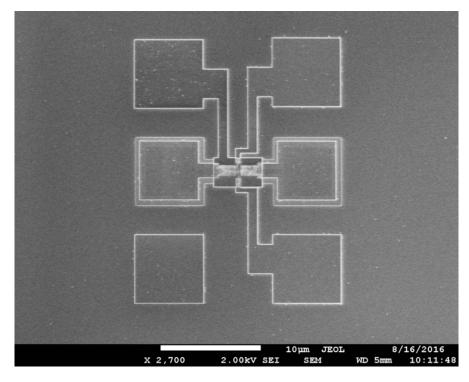

| 2.7  | SEM image in the nanowire definition step. The HSQ mask is still cover-                                                                | 44 |

| 3.7  | ing the Si nanowires, and the width of Si nanowire is measured                                                                         | 44 |

| 3.8  | SEM image of a device before the dopant window opening step. The                                                                       | 44 |

| 3.0  | dopant window is shown as dark region in the SEM image                                                                                 | 45 |

| 2.0  |                                                                                                                                        | 40 |

| 3.9  | Schematic diagram of the device after the polysilicon deposition step.                                                                 |    |

|      | Direct connection between metallised poly-Si and crystalline-Si are made                                                               | 46 |

| 9.10 | to allow the dopant diffusion.                                                                                                         | 40 |

| 3.10 | •                                                                                                                                      | 47 |

| 0.11 | gates are formed by ICP dry etching.                                                                                                   | 47 |

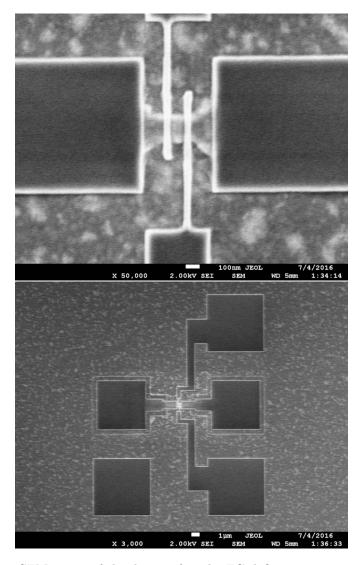

| 3.11 | SEM image of the device after the FG definition step. Two first gates                                                                  | 40 |

| 0.40 | were clearly observed in the SEM image                                                                                                 | 48 |

| 3.12 | Schematic diagram of a device after the TG definition step. The insulating                                                             | 40 |

| 0.40 | oxide is created by RTA thermal oxidation.                                                                                             | 49 |

| 3.13 | SEM image of a device after the TG definition step. Clearly-defined TG                                                                 |    |

|      | were observed.                                                                                                                         | 50 |

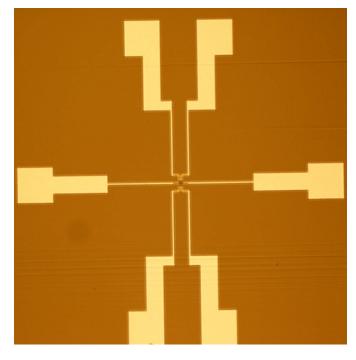

| 3.14 | Optical image of the device after the Contact opening step. Wet-etched                                                                 |    |

|      | round contacts can be observed                                                                                                         | 51 |

| 3.15 | Optical image of the device after the metallisation. Metal layers can be                                                               |    |

|      | observed                                                                                                                               | 51 |

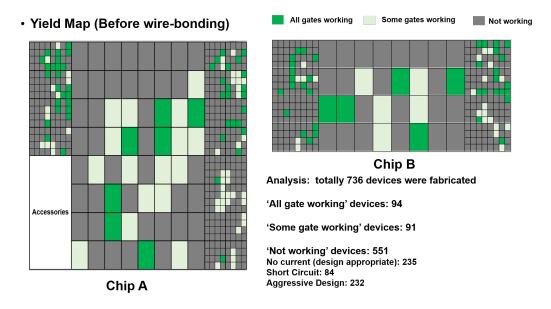

| 3.16 | Yield summary of the wafer W4. The functionalities of each individual                                                                  |    |

|      | device are marked in a schematic die layout. 94 devices show complete                                                                  |    |

|      | functionalities.                                                                                                                       | 52 |

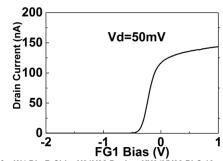

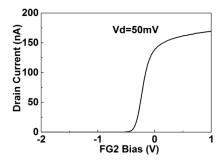

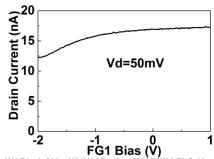

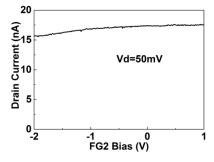

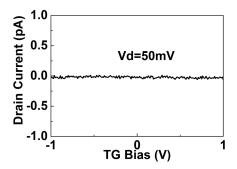

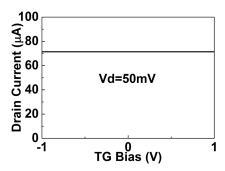

| 3.17 | A demonstration of a fully-working device. All the gates are able to turn                                                              |    |

|      | ON/OFF the transistor, showing ability to modulate the potential in the                                                                |    |

|      | device channel.                                                                                                                        | 53 |

| 3.18 | A demonstration of a partially-working device. The top gate is able to                                                                 |    |

|      | turn ON/OFF the transistor while both first gates are difficult to turn                                                                | ٠. |

|      | OFF the transistor.                                                                                                                    | 54 |

| 3.19 | Failure mode: broken metal. The metal parts were broken due to the                                                                     |    |

|      | ultrasonic wave used in the lift-off process                                                                                           | 55 |

| 3.20 | A demonstration of an open-circuit device. No current was detected in                                                                  |    |

|      | the device                                                                                                                             | 56 |

| 3.21 | A demonstration of a short-circuit device. Large current was detected in                                                               |    |

|      | the device                                                                                                                             | 56 |

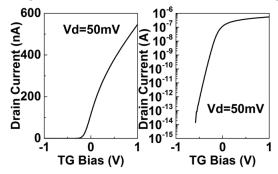

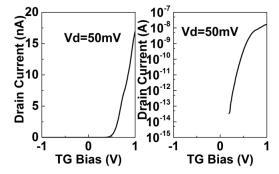

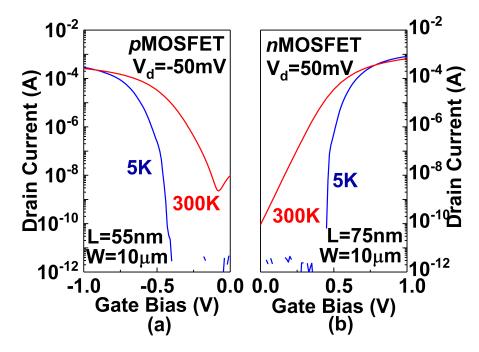

| 4.1  | $I_{\rm d}$ - $V_{\rm g}$ characteristics of device 1 at cryogenic and room temperatures.[118]                                         | 60 |

|      | $I_{\text{d}}$ - $V_{\text{g}}$ characteristics of device 1 at cryogenic and room temperatures.[118]                                   | 61 |

| 4.2  | Contour plot of drain current versus gate voltage and drain voltage in (a)                                                             | UΙ |

| 4.3  |                                                                                                                                        |    |

|      | pMOSFET and (b) nMOSFET at 5 K. The border of the Coulomb diamonds were extracted by fitting with the standard messescopic model [118] | 69 |

| 1 1  | monds were extracted by fitting with the standard mesoscopic model.[118]                                                               | 62 |

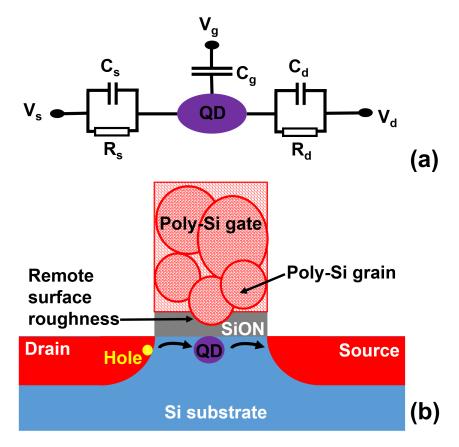

| 4.4  | Circuit model and physical model of the quantum dot. (a) shows the                                                                     |    |

|      | standard equivalent circuit model and (b) shows a schematic diagram of                                                                 | 62 |

|      | the assumed remote poly-Si roughness for the quantum dot structure. [118]                                                              | 63 |

x LIST OF FIGURES

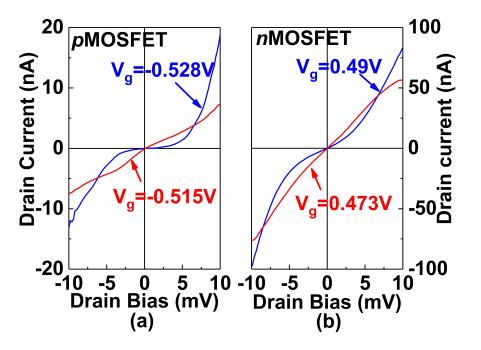

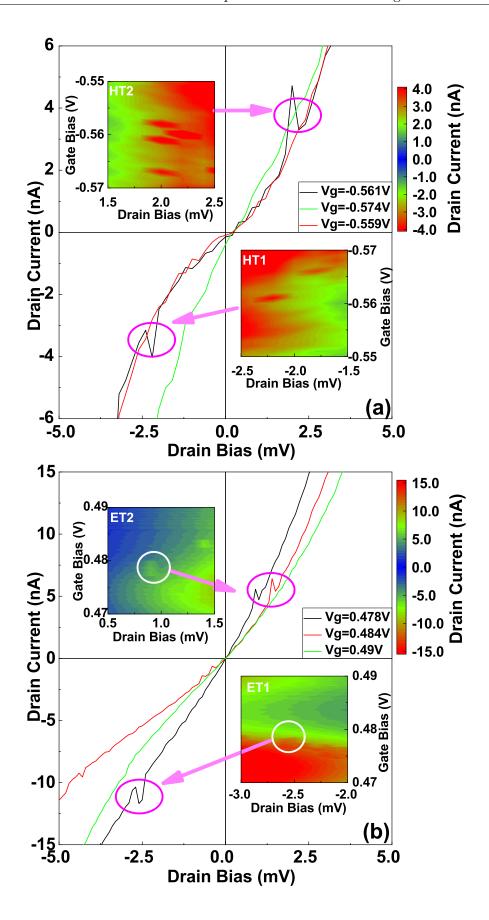

| 4.5  | Sharp current peaks observed at the edges of Coulomb diamond. The current peaks are shown in both current map and $I_{\rm d}$ - $V_{\rm d}$ characteristics. (a) indicates the influence of a single charge trap in pMOSFET with                                                                                                                                                                                                                                                                                                                                                   |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | different gate bias. (b) shows the influence of a single charge trap in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66 |

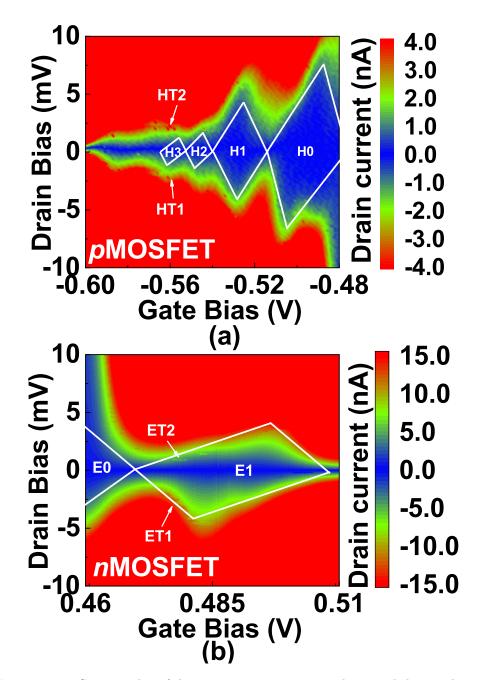

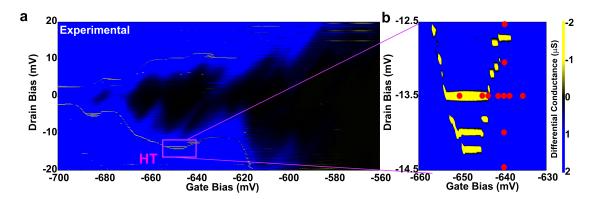

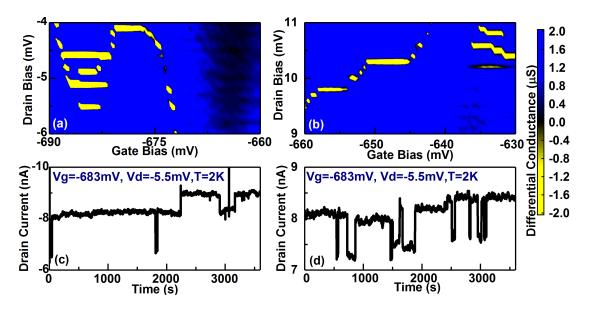

| 4.6  | Bias condition to observe current peaks. (a) shows the stability diagram of the $p$ MOSFET at 2 K. The regime where current peaks can be observed (negative differential conductance) was shown. (b) shows the extended view of HT region and the bias conditions where RTNs were measured.[132]                                                                                                                                                                                                                                                                                   | 68 |

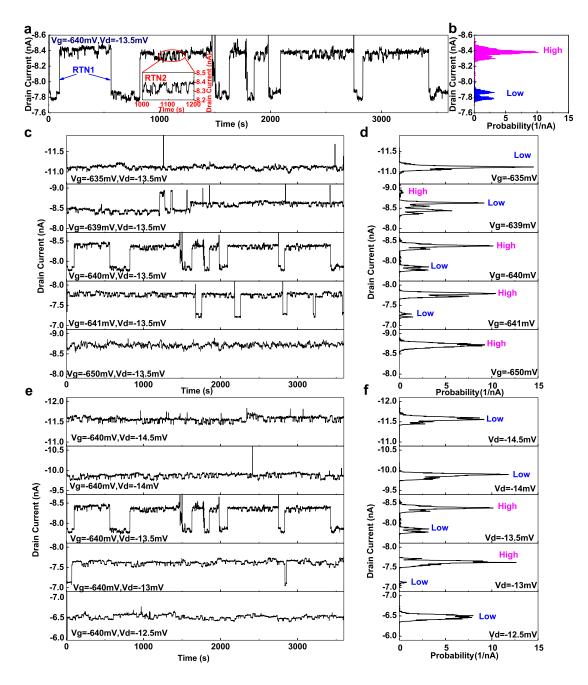

| 4.7  | Time domain characteristics of $I_{\rm d}$ . (a) shows the time domain characteristics of $I_{\rm d}$ measured at $V_{\rm g}$ of -640 mV and $V_{\rm d}$ of -13.5 mV. RTN1 and RTN2 are marked. (b) shows the probability distribution of current versus its value. The state 'High' and 'Low' regarding RTN1 is marked. (c) shows the dependence of RTN on $V_{\rm g}$ if $V_{\rm d}$ is biased at -13.5 mV, and (d) shows the probability distribution of current accordingly. (e) shows the dependence of RTN on $V_{\rm d}$ if $V_{\rm g}$ is biased at -640 mV, and (f) shows |    |

|      | the probability distribution of current accordingly.[132]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 69 |

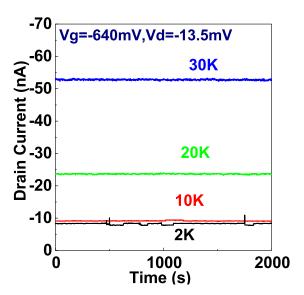

| 4.8  | Temperature dependence of RTN1. The RTN1 was not observed at temperatures higher than 10 K.[132]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 70 |

| 4.9  | RTN characteristics at other bias conditions.[132]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 71 |

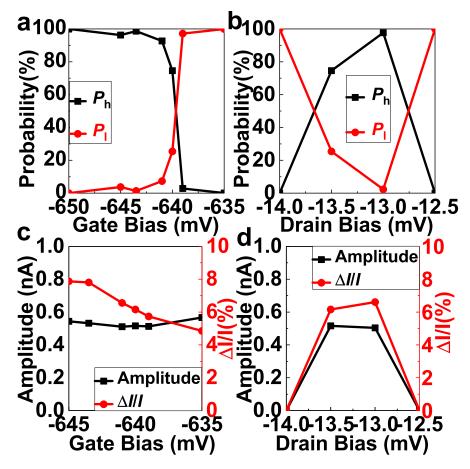

| 4.10 | The bias dependence of RTN1. (a) and (b) shows the dependence of $P_{\rm h}$ and $P_{\rm l}$ on $V_{\rm g}$ and $V_{\rm d}$ , respectively. (c) and (d) shows the dependence of RTN1 amplitude on $V_{\rm g}$ and $V_{\rm d}$ , respectively.[132]                                                                                                                                                                                                                                                                                                                                 | 72 |

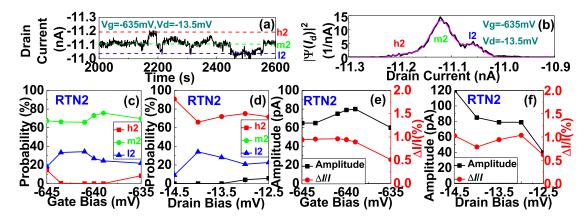

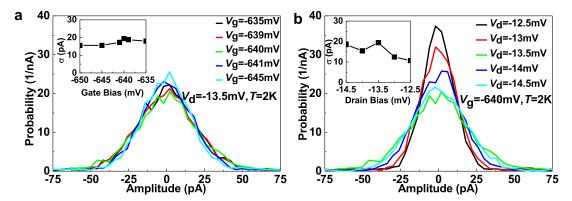

| 4.11 | Investigation on RTN2. (a) shows the time domain characteristics of $I_{\rm d}$ at certain time range if $V_{\rm g}$ was biased at -635 mV and $V_{\rm d}$ was biased at -13.5 mV and (b) shows the corresponding wavefunction. The three current states, h2, m2 and l2, corresponding to RTN2, are marked in (b). (c) and (d) shows the dependence of probability on $V_{\rm g}$ and $V_{\rm d}$ , respectively. (e) and (f) shows the dependence of RTN2 amplitude on $V_{\rm g}$ and $V_{\rm d}$ , respectively.[132]                                                           | 73 |

| 4.12 | The dependence of experimental parameters on wavefunction broadening. (a) and (b) shows the dependence of wave function broadening on $V_g$ and $V_d$ , respectively. The $V_g$ and $V_d$ dependence on standard deviation of the corresponding Gaussian wave function, $\sigma$ , is shown in subfigures inside (a) and (b), respectively.[132]                                                                                                                                                                                                                                   | 73 |

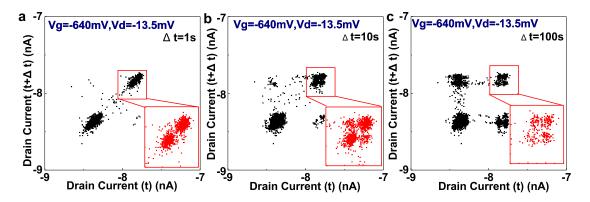

| 4.13 | Fractal nature of the charge traps. The lag plot of $I_d$ with different                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10 |

| _3   | time lag shows fracture nature of charge traps. (a), (b) and (c) shows the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 74 |

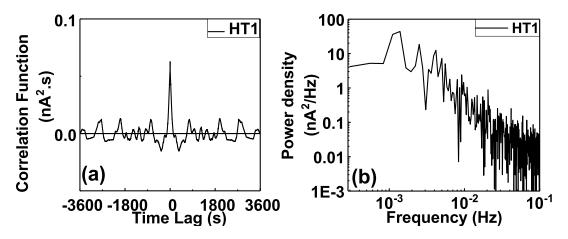

| 4.14 | The correlation function of the $I_{\rm d}$ . The time domain characteristics were                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|      | shown in (a) while (b) gives information about the power density obtained from Fourier transformation [132]                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 74 |

LIST OF FIGURES xi

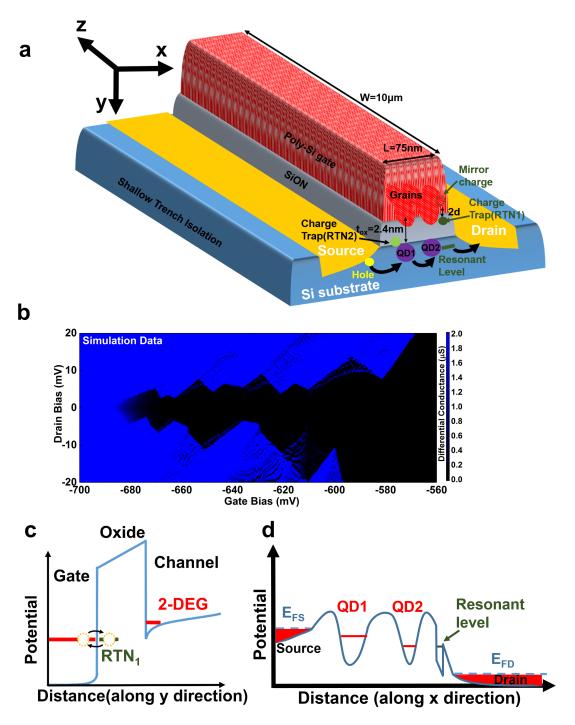

| of the device. Series quantum dots are assumed to be responsible for the drain current, and the resonant level was formed by the trap 1, presumably a Boron ion. (b) shows the simulated stability diagram based on the series quantum dots model. (c) shows the schematic potential diagram across the oxide layer associated with the charge trapping and de-trapping |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| channel. The deep and sharp potential well is formed by the electron dipole in the SiON layer                                                                                                                                                                                                                                                                           | . 77                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

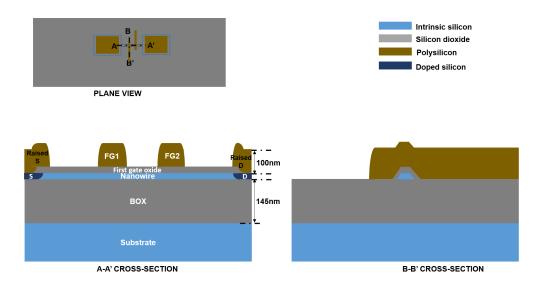

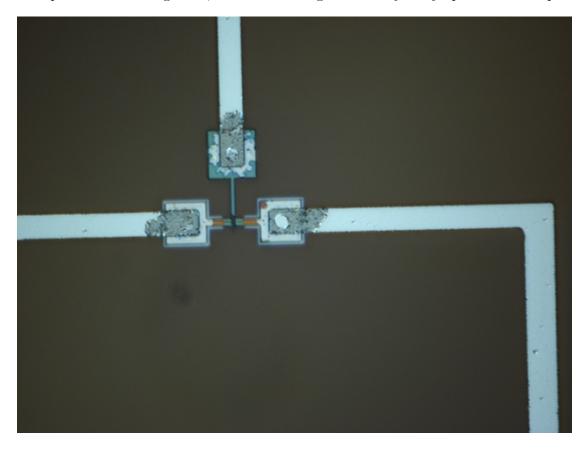

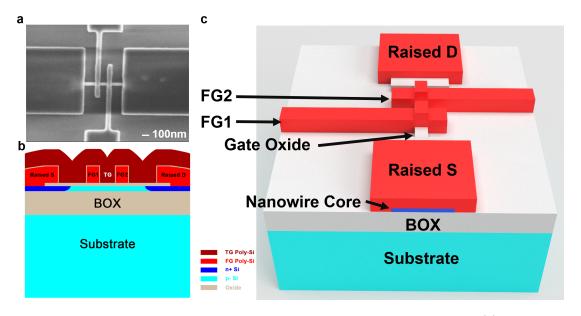

| the SEM image of the plane view before the top gate was patterning. (b) shows the schematic cross-secton image of the device. (c) shows the schematic diagram of the device 3-D structure before the top gate was                                                                                                                                                       | . 80                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

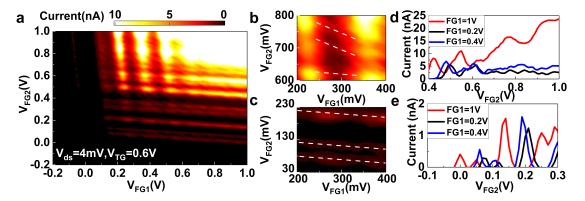

| Investigation on the spectrum of Si quantum dots. (a) shows the energy spectrum measurement result of the quantum dots. (b) shows the transition between localised quantum dots and strongly coupled quantum dots. (c) shows the spectrum of the quantum dot measurement. (d) shows the vanish of resonant tunnelling at large FG1 bias. (e) shows the current          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| peaks from resonant tunnelling                                                                                                                                                                                                                                                                                                                                          | . 81                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

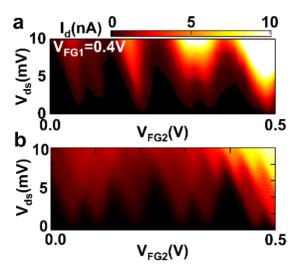

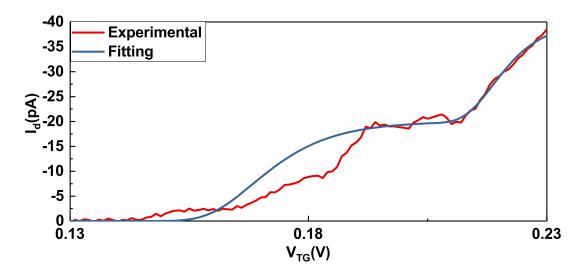

| data                                                                                                                                                                                                                                                                                                                                                                    | . 82                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

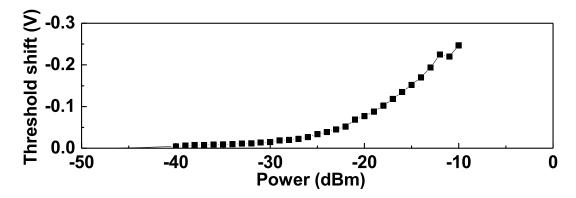

| Shift of threshold voltage versus the RF power                                                                                                                                                                                                                                                                                                                          | . 82                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

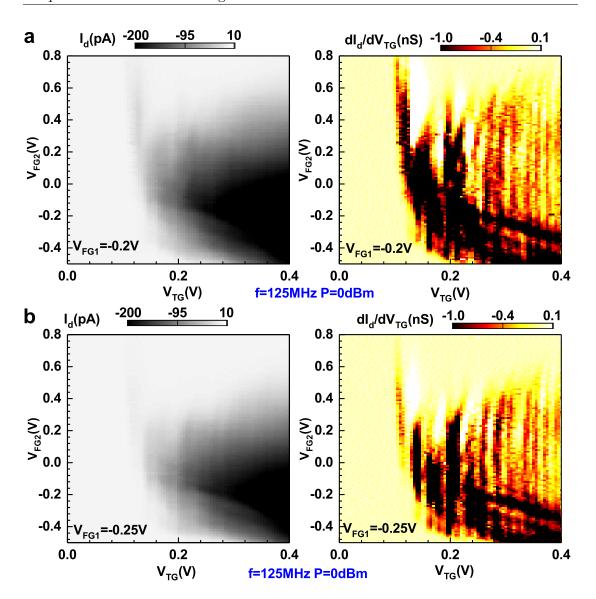

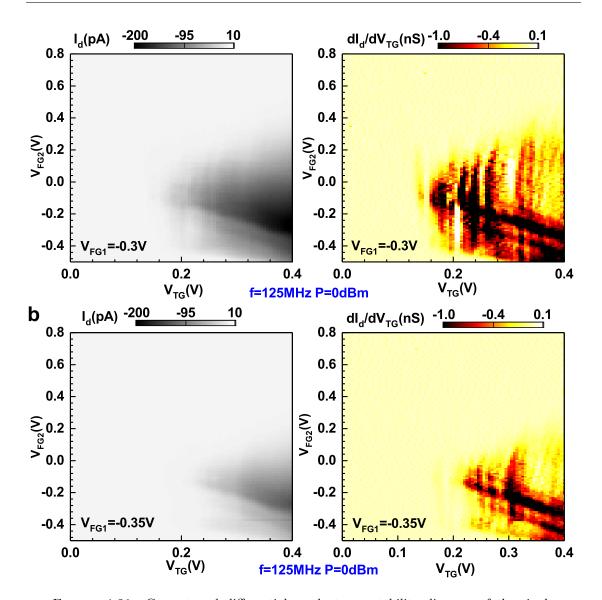

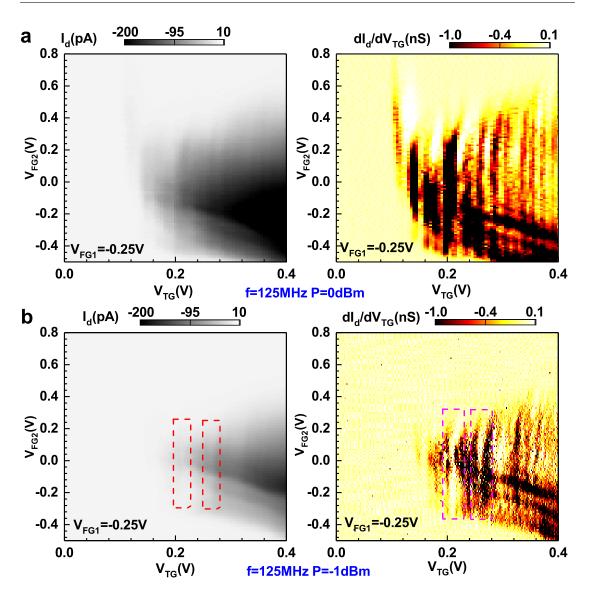

| Current and differential conductance stability diagram of the single elec-                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| FG1 was biased at -0.25V                                                                                                                                                                                                                                                                                                                                                | . 83                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| tron pump with RF signal on FG2. In (a) FG1 was biased at -0.3V, (b)                                                                                                                                                                                                                                                                                                    | . 84                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Current and differential conductance stability diagram of the single elec-                                                                                                                                                                                                                                                                                              | . 04                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

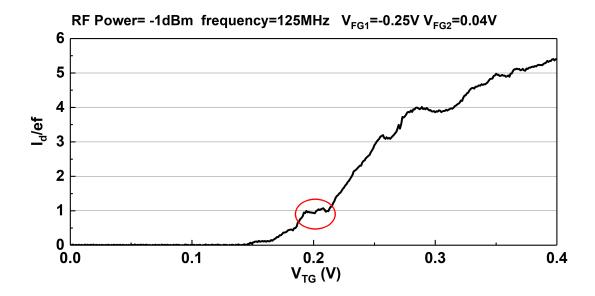

|                                                                                                                                                                                                                                                                                                                                                                         | . 85                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Plateau characteristics of the drain current                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| The fitting of decay cascade model with the experimental data                                                                                                                                                                                                                                                                                                           | . 86                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

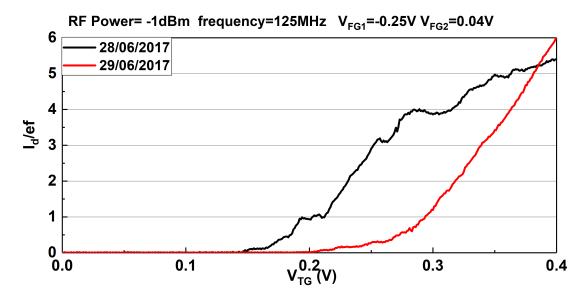

| Repeatability test of the plateau                                                                                                                                                                                                                                                                                                                                       | . 87                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

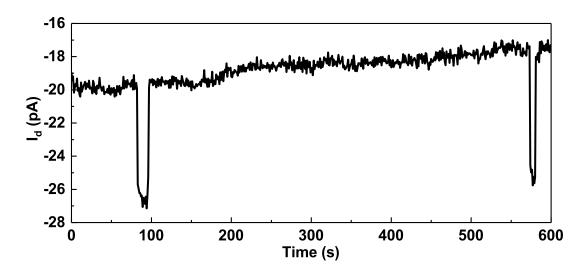

| Time domain characteristics of drain current                                                                                                                                                                                                                                                                                                                            | . 87                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

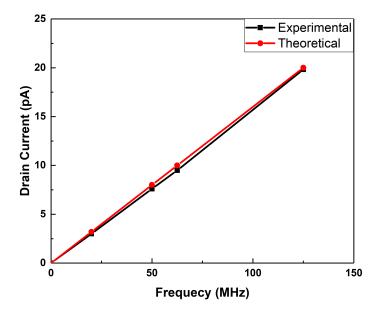

| The RF response of the drain current. The drain current shows a rough                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| found at frequencies above 125MHz                                                                                                                                                                                                                                                                                                                                       | . 88                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

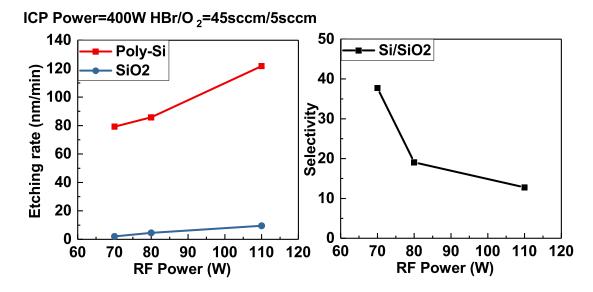

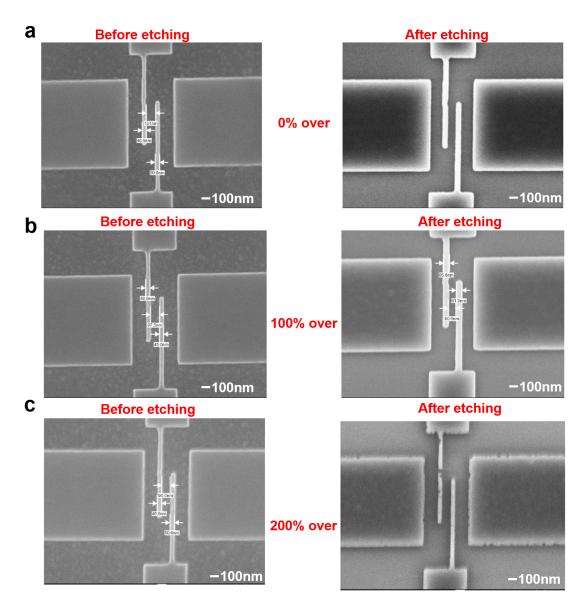

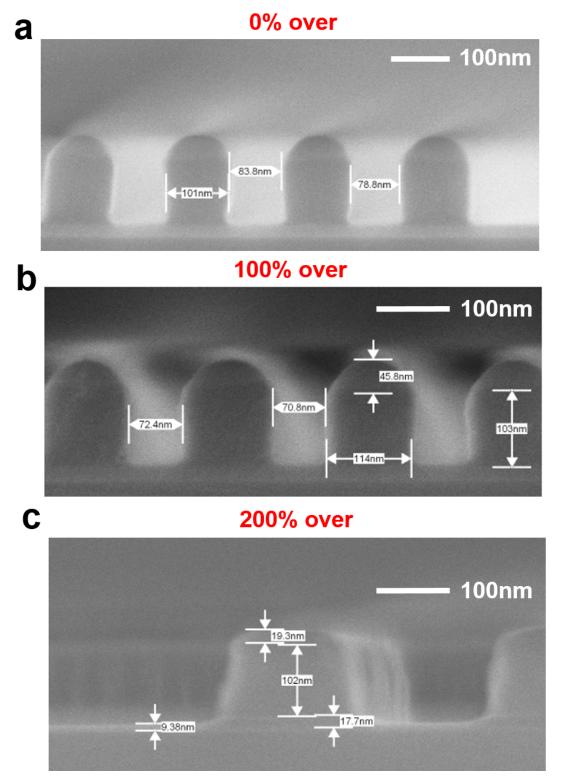

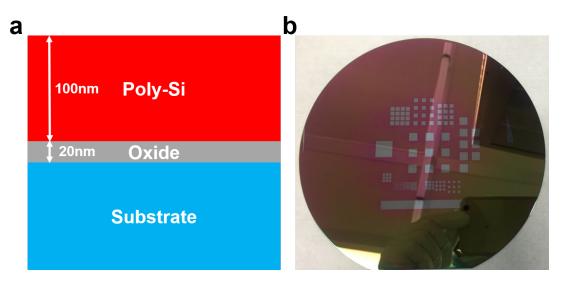

| Dependence of the dry etching rate and selectivity on the RF power for $HBr/O_2$ recipe                                                                                                                                                                                                                                                                                 | . 94                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Dependence of the dry etching rate and selectivity on the RF power for $HBr/O_2$ recipe                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Dependence of the dry etching rate and selectivity on the RF power for $HBr/O_2$ recipe                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                         | drain current, and the resonant level was formed by the trap 1, presumably a Boron ion. (b) shows the simulated stability diagram based on the series quantum dots model. (c) shows the schematic potential diagram across the oxide layer associated with the charge trapping and de-trapping process. (d) shows the schematic diagram of the potential across the channel. The deep and sharp potential well is formed by the electron dipole in the SiON layer |

xii LIST OF FIGURES

| D 1  | The ashamatic diagram of areas section and most levent of the conscitors                                                                          |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

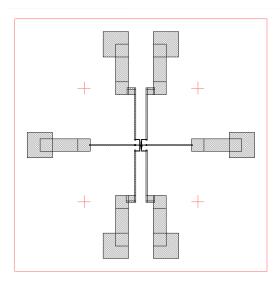

| B.1  | The schematic diagram of cross-section and mask layout of the capacitors.  (a) shows the cross-section while (b) shows the mask layout            |

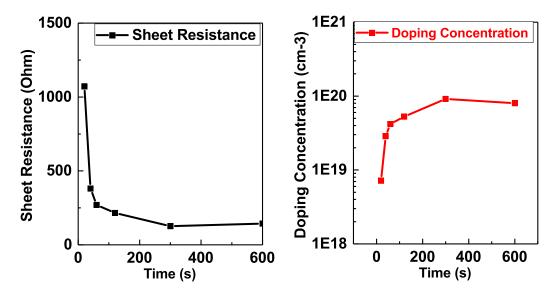

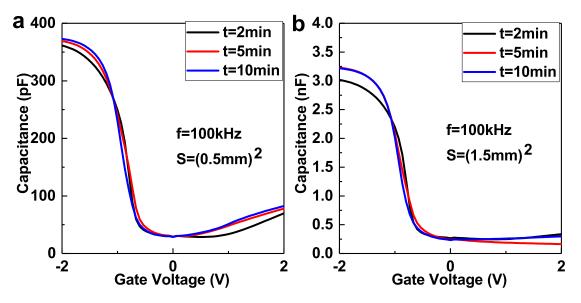

| B.2  | Sheet resistance and doping concentration versus time. (a) shows the measured sheet resistance while (b) shows the extracted doping concentration |

| B.3  | Sheet resistance and doping concentration versus time. (a) shows the measured sheet resistance while (b) shows the extracted doping concentration |

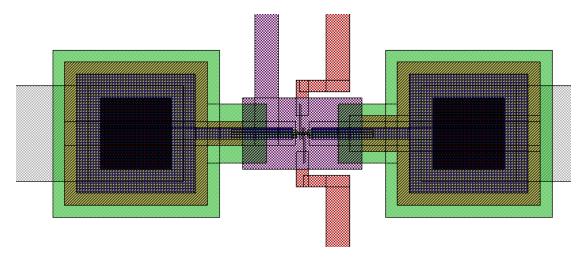

| C.1  | Colours of different layers in the mask design layout                                                                                             |

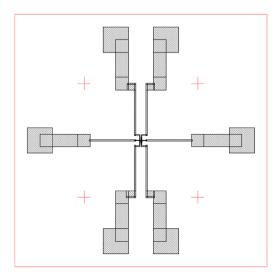

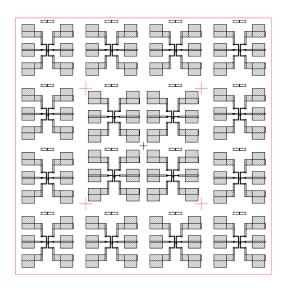

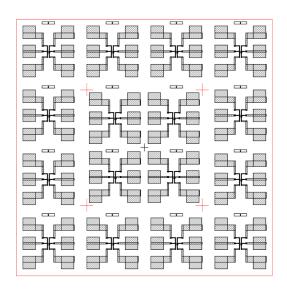

| C.2  | Brief View of Design (a). This shows the metal-layer layout of the design. $102$                                                                  |

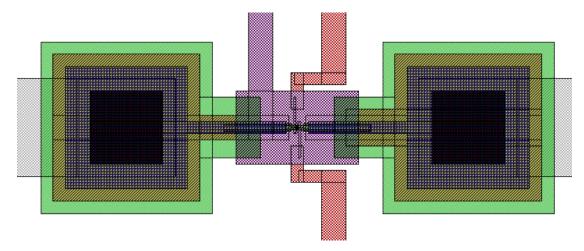

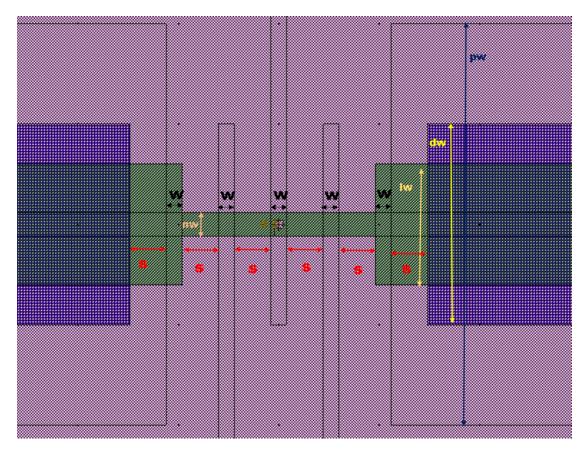

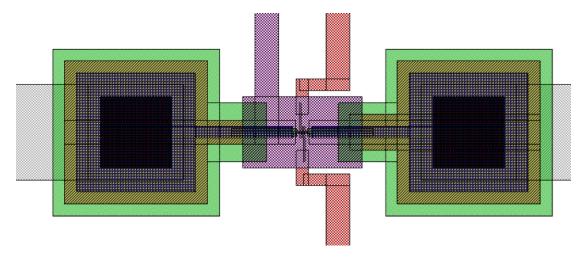

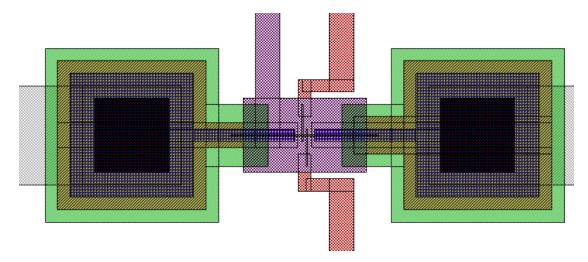

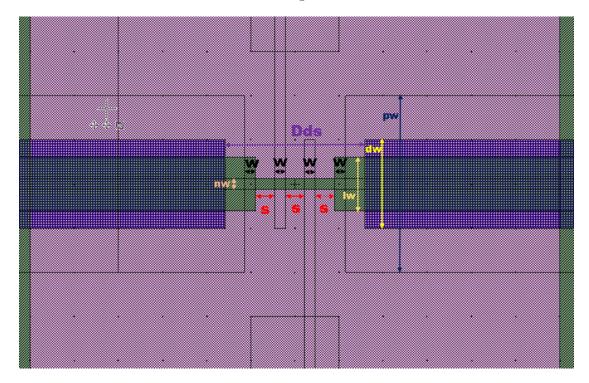

| C.3  | Detailed View of Design (a). This shows the source/drain layout of the                                                                            |

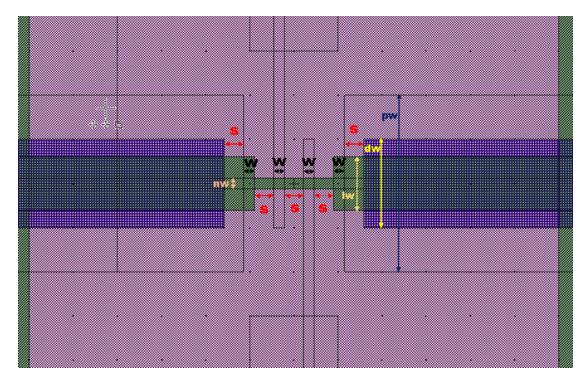

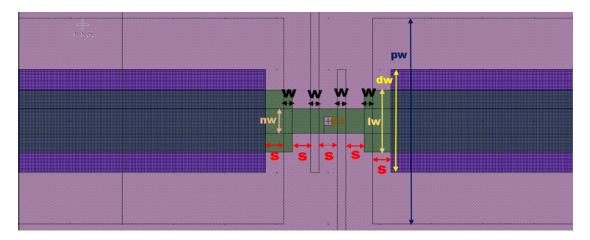

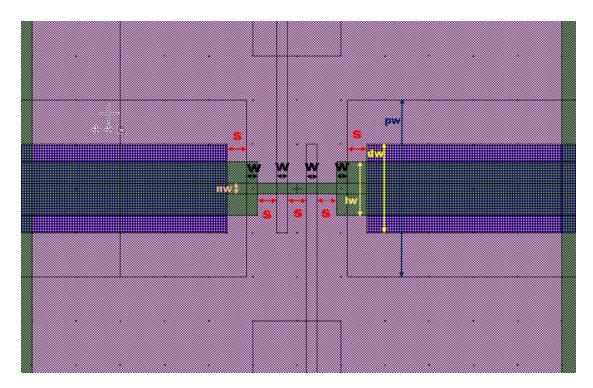

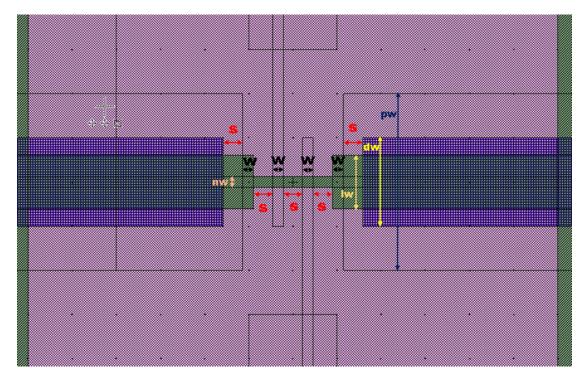

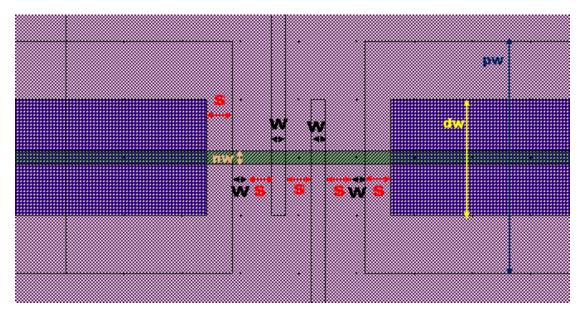

| C.4  | design                                                                                                                                            |

| 0.4  | dot region of the design                                                                                                                          |

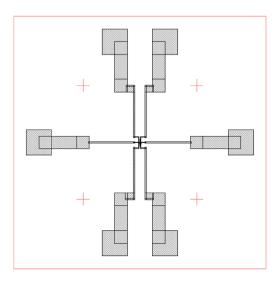

| C.5  | Brief View of Design (b). This shows the metal-layer layout of the design. 104                                                                    |

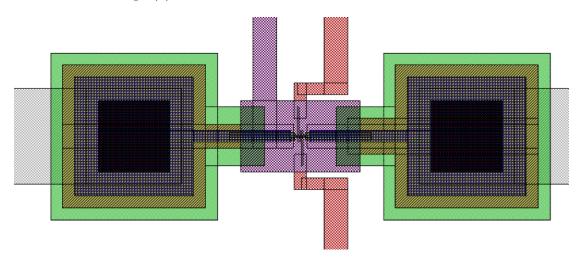

| C.6  | Detailed View of Design (b). This shows the source/drain layout of the design                                                                     |

| C.7  | Focusing View of Design (b). This shows the layout near the quantum dot region of the design                                                      |

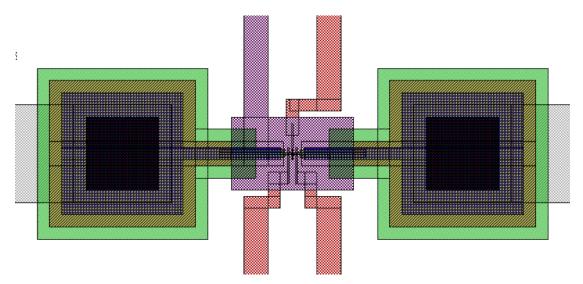

| C.8  | Brief View of Design (c). This shows the metal-layer layout of the design. 107                                                                    |

| C.9  | Detailed View of Design (c). This shows the source/drain layout of the design                                                                     |

| C.10 | Focusing View of Design (c). This shows the layout near the quantum                                                                               |

|      | dot region of the design                                                                                                                          |

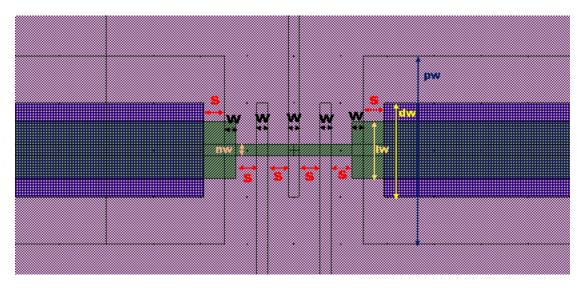

|      | Brief View of Design (d). This shows the metal-layer layout of the design. 109                                                                    |

| C.12 | Detailed View of Design (d). This shows the source/drain layout of the design                                                                     |

| C.13 | Focusing View of Design (d). This shows the layout near the quantum dot region of the design                                                      |

| C.14 | Brief View of Design (e). This shows the metal-layer layout of the design. 111                                                                    |

| C.15 | Detailed View of Design (e). This shows the source/drain layout of the design                                                                     |

| C.16 | Focusing View of Design (e). This shows the layout near the quantum dot region of the design                                                      |

| C.17 | Brief View of Design (f). This shows the metal-layer layout of the design. 113                                                                    |

|      | Detailed View of Design (f). This shows the source/drain layout of the design                                                                     |

| C.19 | Focusing View of Design (f). This shows the layout near the quantum dot region of the design                                                      |

| C.20 | Brief View of Design (g). This shows the metal-layer layout of the design. 116                                                                    |

|      | Detailed View of Design (g). This shows the source/drain layout of the design                                                                     |

| C.22 | Focusing View of Design (g). This shows the layout near the quantum dot region of the design                                                      |

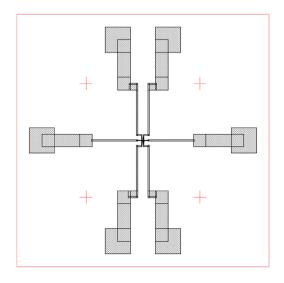

| C.23 | Brief View of Design (h). This shows the metal-layer layout of the design. 118                                                                    |

|      | Detailed View of Design (h). This shows the source/drain layout of the design                                                                     |

LIST OF FIGURES xiii

| C.25 Focusing View of Design (h). | This shows the layout near the quantum |       |

|-----------------------------------|----------------------------------------|-------|

| dot region of the design          |                                        | . 119 |

## List of Tables

| 4.1  | Successfully measured devices                                                                                                                                           |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.2  | Coupling Capacitances for device 1                                                                                                                                      |

| 4.3  | Coupling Capacitances for device 2                                                                                                                                      |

| 4.4  | Extracted coupling capacitances of single-hole states in QD1 78                                                                                                         |

| 4.5  | Extracted coupling capacitances of single-hole states in QD2 78                                                                                                         |

| C.1  | Design parameter variables for the design style (a)                                                                                                                     |

| C.2  | Design parameter variables for the design style (b)                                                                                                                     |

| C.3  | Design parameter variables for the design style (c) $\dots \dots \dots$ |

| C.4  | Design parameter variables for the design style (d) $\dots \dots \dots$ |

| C.5  | Design parameter variables for the design style (e)                                                                                                                     |

| C.6  | Design parameter variables for the design style (e)                                                                                                                     |

| C.7  | Design parameter variables for the design style (f) $\dots \dots \dots$ |

| C.8  | Design parameter variables for the design style (f)                                                                                                                     |

| C.9  | Design parameter variables for the design style (g)                                                                                                                     |

| C.10 | Design parameter variables for the design style (g)                                                                                                                     |

| C.11 | Design parameter variables for the design style (h)                                                                                                                     |

| C 12 | Design parameter variables for the design style (h)                                                                                                                     |

### Acknowledgements

I would like to thank Prof. Shinichi Saito, and Dr. Yoshishige Tsuchiya, for their help and supervision in the University of Southampton. It is an honour for me to be guided by them in this research project.

I would like to thank Dr. Jonathan Fletcher, Dr. Stephen Giblin and Dr. Masaya Kataoka for their supervision in NPL. I really have learned a lot through my experience in NPL, and they are always very kind to help.

I would like to thank Dr. Muhammad Khaled Husain and Mr. Fayong Liu for their hard work and help in device fabrication and packaging. I would also like to thank all the colleagues in our group for sharing ideas.

I would like to thank all the staffs in Southampton Nanofabrication Centre and Sustainable Electronic Technology group for their help and training.

This work is supported by EPSRC Manufacturing Fellowship (EP/M008975/1), EU FP7 Marie-Curie Carrier-Integration-Grant (PCIG13-GA-2013-618116), and the University of Southampton. This work is also supported by the EMPIR programme co-financed by the Participating States and from the European Unions Horizon 2020 research and innovation programme.

## Chapter 1

## Introduction

The accurate calibration is significant for the state-of-the-art industry, especially when more and more components are integrated into a product. The fundamental science associated with the accuracy and calibration is metrology. The concept of metrology is defined by the International Bureau of Weights and Measures (BIPM) as the science of measurement, embracing both experimental and theoretical determinations at any level of uncertainty in any field of science and technology[1].

The classical metrology is based on SI (Le Systme International d'Units) units, which are considered as international standards worldwide[2]. SI units are established on the MKS system, in which metre, kilogram and second are considered as fundamental units to derive all other mechanical units[3]. However, some original definitions of these units limit the intrinsic achievable accuracy. For example, in 1956, the definition of second was initially based on the tropical year. The best accuracy ever achieved using this definition was only 1 ppm[4]. Today, with the help of quantum mechanics, the definition of second is based on optical atomic clock and the relative uncertainty is as small as  $2.5 \times 10^{-11}$ [5]. The accuracy has been improved by almost one million times compared with the original definition.

The electronic industries are basically based on the electricity. High resolutions of the electrical current are often required in the sensors to ensure the stability of the system. Therefore, calibration of ampere, the unit of electrical current, is very important. The definition of ampere is 'The ampere is that constant current which, if maintained in two straight parallel conductors of infinite length, of negligible circular cross section, and placed 1 metre apart in vacuum, would produce between these conductors a force equal to  $2 \times 10^{-7}$  newton per metre of length. [6]' The classical realisation of this definition is by measuring forces between two conductive coils. There are many limiting factors that put caps on the accuracy, for example, the difficulty to calculate the actual distribution of current flowing through a wire with definite diameter. The best accuracy ever achieved so far with this conventional definition

was 0.3 ppm[7], which is far below the accuracy already achieved by the definition of second and metre, with the help of quantum mechanics.

As a result, scientists began searching for a new definition of ampere connecting to a natural constant. The idea is called quantum metrology, which is defined as 'the study of making high-resolution and highly sensitive measurements of physical parameters using quantum theory to describe the physical systems, particularly exploiting quantum entanglement [8]'. A natural idea is associating the current with the elementary charge. In the quantised current, integer number of electrons flow through a circuit in a certain period of time. As a result, quantised current source with high accuracy is required. One of the most attractive and promising quantised current sources is the single electron pump[9], which is modulated by an AC signal. In this device, only one single electron is pumped through the circuit within a period of tuning AC signal. There are mainly two kinds of single electron pumps, which are based on metallic island and semiconductor quantum dot respectively. Metallic single electron pump has been investigated since 1990s, and accuracy up to 0.02 ppm has been achieved[10]. However, it is extremely hard to achieve high current in metallic single electron pump because the operation frequency of adiabatic pumping is limited by the RC constant of the oxide tunnelling junctions. It is almost impossible to overcome the large RC time constants of the tunnelling junctions[11].

With non-adiabatic pumping, which is only achievable in semiconductor quantum dot pumps, it is possible to achieve high-speed operation to overcome this frequency limit. Due to the compatibility with the state-of-the-art CMOS fabrication platform, the Si single electron pumps have the potential to realise mass reliable fabrication and parallel operations to enhance the current. These advantages make the Si single electron pump be a promising candidate to achieve the quantum standard of ampere.

There are still many issues need to be solved to achieve the accurate quantum current source. Single electron transport can only be observed at cryogenic condition (usually below 20 K) in nano-scale structure (usually less than 100 nm), and high magnetic field (usually in the level of 10 T) is often required to achieve high accuracy[12]. The small scale induce challenges in the fabrication of single electron pumps, and the extreme operation environment makes the measurement difficult. Besides, the device physics to explain the transportation is still not very clear at the moment. Some models have been introduced, but the deviation still exists especially when the temperature is as low as 100 mK[13]. As a result, the performance limiting factor of Si single electron pumps has not been fully investigated yet. Much work is still required in this research field.

The aim of my PhD project is to understand the operation of single electron devices, learn the fabrication processes of the Si single electron pumps, and measure the pumps in National Physical Laboratory to address the reliability limiting factors of single electron pumps. Practically, I would like to

- (a) Fabricate a batch of silicon single electron pumps, using the facilities from Southampton Nanofabrication Centre.

- (b) Demonstrate a successful operation of the single electron pump, showing the ability for the device to calibrate the current.

- (c) Understand the reliability impact factors of the silicon single electron pumps and other related silicon quantum dot devices.

In order to achieve this target, in my PhD project, I have read literatures to understand the operation of single electron transistors and previous work in single electron pumps by other groups, which are summarised in chapter 2. The fabrication of our single electron pump lot will be introduced in Chapter 3. I designed all the e-beam lithography masks for the single electron pumps, have successfully fabricated single electron pumps together with Dr. Muhammad Khaled Husain, the research fellow in our group, and tested the devices at room temperatures to analyse the yield. The measurement results of single electron devices are summarised in Chapter 4. I have measured some Si devices at low temperatures to investigate on the characteristics and performance limiting factor for the Si single electron devices based on quantum dots. I observed single electron transistor characteristics and current peaks in advanced conventional MOSFETs, and investigate on the current peaks observed in the experiment to study the impact of charge traps on the devices. I also measured our single electron pumps in NPL, and observed unstable single electron pump characteristics. I investigated on the spectrum of quantum dot and identified the impact of charge traps to understand the performance limiting factor in Si single electron pumps. Conclusions of the researches in my PhD study have been made in Chapter 5. Some of the work I have done, such as processes development, are introduced in the appendix.

In total, I have successfully fabricated Si single electron pumps, using the facilities in the University of Southampton Nanofabrication Centre. I have investigated on the characteristics and performance limiting factors in Si quantum dot devices, and the results were published in full article in *IOP Semiconductor Science Technology* and *Nature Scientific Reports*, respectively. Based on the knowledge obtained in these measurements and devices fabricated, I measured our single electron pumps in National Physical Laboratory, observed unstable pumping characteristics, and investigated the performance limiting factor in detail. The results have been summarised, and submitted for publication.

## Chapter 2

## Background Research

### 2.1 Quantum Metrology Triangle

In order to redefine ampere with the quantised single electron source, logically, existing ammeters cannot be used to calibrate the generated current. As a result, a null-current circuit is required. In the null-current circuit, I only use null-current detector to identify the presence of the current. Therefore, an accurate voltage source and a precise resistor are both mandatory for its realisation.

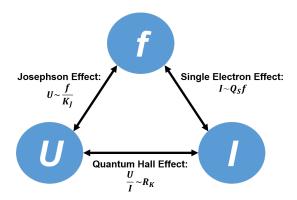

After both Josephson effect [14] and Quantum Hall effect [15] had been observed, people began to establish the practical realisation of the current redefinition. Likrahev and Zolin proposed an idea [16] to build a standard voltage source with the help of Josephson effect [17], calibrate an accurate resistor using Quantum Hall Effect [18], and use a single electron current source [19] with an error-counting scheme [20] in the null-current circuit in order to balance the current flowing through the accurate resistor. The idea was given the name of Quantum Metrology Triangle [21]. The schematic set-up of the quantum metrology triangle is shown in Fig. 2.1.

FIGURE 2.1: Schematic Diagram of Quantum Metrology Triangle. The links between the three parameters, frequency f, current I and voltage U are shown.

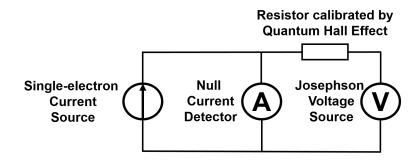

In order to realise this schematic set up, a practical circuit diagram is required. A typical circuit diagram of experimental quantum metrology triangle is shown in Fig. 2.2.

FIGURE 2.2: Quantum Metrology Triangle Experimental Set-up.

In this null-current circuit, the current generated by Josephson voltage source will be balanced by the single-electron current source. If there is no current flowing through the null-current detector, a balance is achieved, and I can establish the quantum standards of electrical units based on this circuit.

A practical issue with this design is the low current level of single-electron current source, which is usually  $\sim$ nA level in practical. It is normally not enough to balance the current generated by Josephson Voltage source (usually  $\sim$ mV) and a resistor with the exact quantum hall resistance( $\sim$ k $\Omega$ ), which is about  $\mu$ A level. In order to solve the problem, a high-precision amplifier is used to enhance the current generated by single electron source[22, 23] or a larger cryogenic resistor calibrated by quantum hall resistance is required[24, 25].

In order to make the redefinition practical and reasonable, the single electron source need to reach two certain limits in accuracy and current level (equivalent to operation frequency):

# (1) The error of the single-electron current source should be no more than 0.05ppm.

It is an agreement made by metrologists [26]. The definition of electric current should only be changed when the uncertainty of one parameter in quantum metrology triangle is less than 0.02 ppm and the rest two are less than 0.05 ppm. Since the uncertainty in Josephson voltage source and Quantum Hall Resistance have both met the requirement of 0.02 ppm, the uncertainty in single-electron current source, therefore, should be less than 0.05 ppm.

# (2) The current level of current source should be at least in the magnitude of 100 pA, i.e., the pump must be able to operate with gigahertz-level frequency.

The level of current generated by single-electron source should be large enough, so that the Johnson Noise[27] (coming from thermal agitation of charge carriers) would not have significant impact on the measurement result.

Idefine the total current as  $I_{\rm S}$ . The error created by Johnson Noise,  $\delta I_{\rm S}$ , can be expressed by

$$\delta I_{\rm S} = \sqrt{\frac{4k_{\rm B}T}{tR}},\tag{2.1}$$

where T is the ambient temperature,  $k_{\rm B}$  is the Boltzmann constant, t is the time taken for each point in the measurement, and R is the total coupling resistance of the system. Therefore, the related error is:

$$\frac{\delta I_{\rm S}}{I_{\rm S}} = \sqrt{\frac{4k_{\rm B}T}{tRI_{\rm S}^2}}.$$

(2.2)

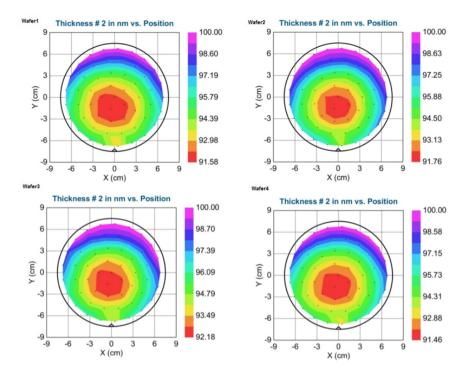

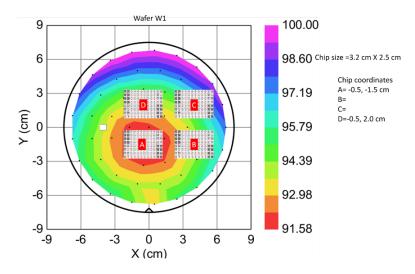

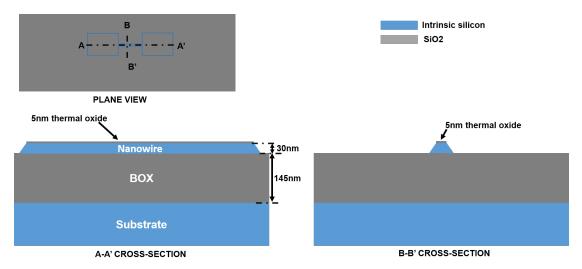

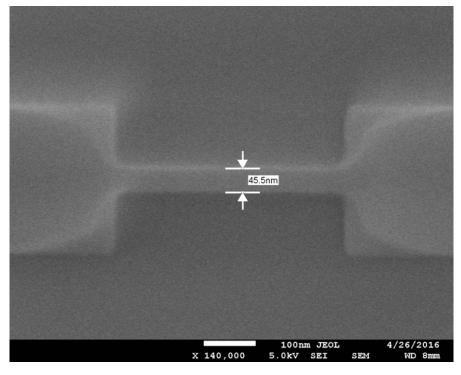

In a practical quantum metrology measurement, I can assume  $R \sim R_K$ , which is the quantum resistance,  $25.\text{k}\Omega$ . The related error of the system,  $\delta I_S/I_S$ , should be less than  $5\times10^{-8}$ , t=24 h and T=10 mK. As a result, the current level must be larger than 314.7 pA according to equation (2.2), which is equivalent to 2 GHz operation frequency.