# University of Southampton Research Repository

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Author (Year of Submission) "Full thesis title", University of Southampton, name of the University Faculty or School or Department, PhD Thesis, pagination.

Data: Author (Year) Title. URI [dataset]

# UNIVERSITY OF SOUTHAMPTON

#### FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

Electronic and Computer Science

Nano Research Group

# Design, Fabrication and Characterization of High Performance Zinc Oxide Nanowire Field-Effect Transistors

by

#### Nor Azlin Ghazali

Thesis for the degree of Doctor of Philosophy

March 2018

#### UNIVERSITY OF SOUTHAMPTON

# **ABSTRACT**

FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

#### SCHOOL OF ELECTRONICS AND COMPUTER SCIENCES

#### **Doctor of Philosophy**

## DESIGN, FABRICATION AND CHARACTERIZATION OF HIGH PERFORMANCE ZINC OXIDE NANOWIRE FIELD-EFFECT TRANSISTORS

#### Nor Azlin Ghazali

This research project is focused on the optimization and electrical enhancement of zinc oxide (ZnO) nanowire field-effect transistors by remote plasma atomic layer deposition. Three device configurations have been fabricated based on a top-down fabrication method with channel lengths in the range of 18.6 µm to 1.3 µm. These devices were produced in well-defined locations on a 150 mm diameter silicon wafer. Controllable nanowire FET dimensions and locations are seen as fundamental to wafer-scale nanowire integrated circuit fabrication. Measured electrical results show n-type depletion behaviour with good electrical characteristics for all device configurations.

The first device configuration was fabricated with optimization of a top-down process based on a spacer method, aiming to reduce the sidewall roughness of the nanowire. The approach included the top-down nanowire process with reduced sidewall roughness during pattern transfer and the improvement of the electrical characteristics. The process involved a photoresist reflow technique and dry oxidation of the etched silicon sidewalls. The optimized top-down fabrication and sidewall resist smoothing were shown to produce ZnO nanowire FETs with good electrical characteristics for channel length devices of 1.3  $\mu$ m, 8.6  $\mu$ m, and 18.6  $\mu$ m. The optimized device is able to produce a high output drain current by a factor of three, steep subthreshold slope of 800 mV/decade and a transconductance value of 5.9 nS, which is two times higher than the device from an un-optimized fabrication process.

In the second device configuration, the aim was to improve the contact resistance between the ZnO nanowire channel and source/drain contact as well as the mobility of the ZnO nanowire FET. Enhanced performance of the ZnO nanowire FET is demonstrated by depositing an Al-doped ZnO (AZO) thin film between the ZnO nanowires and the source/drain aluminium contact. This highly conductive AZO thin film is deposited via a thermal atomic layer deposition (ALD) at 200 °C and forms a bi-layer source/drain contact. The contact resistance was reduced from 194.1  $\Omega$  with aluminium contact to only 9.6  $\Omega$  using AZO. The field-effect mobility of ZnO nanowire FETs with AZO increases from 3.5 cm²/Vs to 85.7 cm²/Vs in dual nanowires. The AZO layer is seen as a promising source/drain contact material for the fabrication of high performance ZnO nanowire FETs. The ZnO nanowire FET with AZO thin film as the source/drain contact is further investigated by measuring the temperature-dependant electrical characteristics. The transfer curves shows a parallel shift toward negative voltage as the temperature increased from 200 K to 300 K.

In the third device configuration, the new fabrication method using direct photolithography and lateral wet etching was used to simplify the fabrication of top-down ZnO nanowire FETs and to avoid the disadvantage of the spacer method. This particular method is a preliminary attempt towards achieving high electrical performance in ZnO nanowire FETs for RF and logic circuit applications. This novel technique allows for the formation of nanowire FET with minimal impact from ions and chemical radicals during the anisotropic dry etching process. Except for the low field-effect mobility, this experiment demonstrated desirable electrical characteristics. Bottom-gate ZnO nanowire FETs with different gate lengths show a threshold voltage between -0.7 V to 1.5 V, on/off current ratio up to  $10^7$  and a subthreshold swing between 200 mV/decade to 300 mV/decade. This top-down fabrication method with low temperature film deposition encourages further research regarding the RF characterization of ZnO nanowire FETs and the adaptability of a RF device using ZnO nanowire FETs.

# **Table of Contents**

| 1 able ( | or Conter | 1ts                                                | 1    |

|----------|-----------|----------------------------------------------------|------|

| List of  | Tables    | v                                                  |      |

| List of  | Figures   | vii                                                |      |

| DECL     | ARATIO    | N OF AUTHORSHIP                                    | XV   |

| List of  | Publicat  | ions                                               | xvii |

| Jour     | nals      |                                                    | xvii |

| Con      | ferences  |                                                    | xvii |

| Acknow   | wledgem   | ents                                               | viv  |

|          | C         | Abbreviations                                      |      |

| Chapte   |           | Introduction                                       |      |

| 1.1      | Overvie   | ew                                                 | 1    |

| 1.2      |           | ion                                                |      |

| 1.3      |           | ves                                                |      |

| 1.4      |           | Outline                                            |      |

| 1.5      | Referen   | ices                                               | 6    |

| Chapte   | er 2:     | Literature Review                                  | 9    |

| 2.1      | Introduc  | ction                                              | 9    |

| 2.1.1    |           | Depletion                                          | 10   |

| 2.1.2    |           | Inversion                                          |      |

| 2.1.3    |           | Accumulation                                       |      |

| 2.2      | Electric  | al Characterization of Nanowire FET                | 13   |

| 2.2.1    |           | Flat Band Voltage                                  | 13   |

| 2.2.2    |           | Current-Voltage Relationship Concepts              |      |

| 2.2.3    |           | Threshold Voltage, $V_{TH}$                        |      |

| 2.2.4    |           | The Subthreshold Region                            |      |

| 2.3      | Zinc ox   | ide material system                                | 17   |

| 2.4      |           | al properties of Zinc Oxide                        |      |

| 2.5      |           | tion of ZnO nanowire field-effect transistor (FET) |      |

| 2.5.1    |           | Benchmarking the ZnO nanowire FETs                 | 25   |

| 2.6    | Conclusion                                                           | 31     |

|--------|----------------------------------------------------------------------|--------|

| 2.7    | References                                                           | 32     |

| Chapte | er 3: Theoretical Background                                         | 39     |

| 3.1    | ZnO Nanowire FET Electrical Characteristics                          | 39     |

| 3.1.1  | Oxide Capacitance                                                    | 40     |

| 3.1.2  | Threshold Voltage, V <sub>TH</sub>                                   | 41     |

| 3.1.3  | Subthreshold Swing, SS                                               | 44     |

| 3.1.4  | Transconductance                                                     | 44     |

| 3.1.5  | Field-Effect Mobility, µFE                                           | 45     |

| 3.1.6  | On/Off Current Ratio                                                 | 47     |

| 3.2    | Comparing ZnO TFT Simulation with Sultan Experiment                  | 47     |

| 3.3    | Conclusion                                                           | 53     |

| 3.4    | References                                                           | 53     |

| Chapte | er 4: Fabrication of Top-down Zinc Oxide Nanowire FETs               | 55     |

| 4.1    | Introduction                                                         | 55     |

| 4.2    | Deposition of ZnO Film by remote plasma ALD                          | 57     |

| 4.3    | ZnO nanowire FETs fabrication                                        | 59     |

| 4.3.1  | Fabrication of ZnO nanowire-FET by sidewall smoothing                | 59     |

| 4.3.2  | Fabrication of ZnO nanowire FET with AZO and Al heteroju             | nction |

|        | source/drain contacts                                                | 64     |

| 4.3.3  | The fabrication of top-down ZnO nanowire FET by lateral wet etch     | ing 67 |

| 4.4    | Conclusion                                                           | 70     |

| 4.5    | References                                                           | 71     |

| Chapte | er 5: Characterization of ZnO Nanowire FETs by Sidewall smoothin     | g73    |

| 5.1    | Introduction                                                         | 73     |

| 5.2    | Effect of gate dielectric thickness                                  | 74     |

| 5.3    | Sidewall roughness measurement                                       | 78     |

| 5.4    | Electrical Characteristics of ZnO nanowire FET by sidewall smoothing | 81     |

| 5.5    | Conclusion                                                           | 86     |

| 5.6    | References                                                           | 87     |

| Chapte | er 6: Improving Performance of Top-down Zinc Oxide N           | anowire FETs     |

|--------|----------------------------------------------------------------|------------------|

|        | with AZO and Al bi-layer source/drain contacts                 | 91               |

| 6.1    | Introduction                                                   | 91               |

| 6.2    | Contact Resistance, R <sub>C</sub>                             | 93               |

| 6.3    | Characterization of ZnO nanowire FETs with AZO and Al source/d | lrain contacts95 |

| 6.4    | Temperature-Dependent Electrical Characterization of ZnO Nanov | wire FETs with   |

|        | AZO and Al Source/Drain Contacts                               | 100              |

| 6.5    | Conclusions                                                    | 105              |

| 6.6    | References                                                     | 106              |

| Chapte | er 7: Towards RF Characteristics of ZnO Nanowire FETs          | 111              |

| 7.1    | Introduction                                                   | 111              |

| 7.2    | Electrical Characterization                                    | 112              |

| 7.3    | Conclusions                                                    | 117              |

| 7.4    | References                                                     | 118              |

| Chapte | er 8: Conclusions and Future Outlook                           | 121              |

| 8.1    | Conclusions                                                    | 121              |

| 8.2    | Future Outlook                                                 | 123              |

| 8.3    | References                                                     | 124              |

# **List of Tables**

| Table 2-1: Electrical characteristics of ZnO bulk and thin film from various literature [18], |

|-----------------------------------------------------------------------------------------------|

| [33]–[41]                                                                                     |

| Table 2-2 Review of high performance transistors based on various structures of ZnO.28        |

| Table 2-3 Review of high performance transistors based on ZnO competing materials 29          |

| Table 3-1: Material parameters (constants) of ZnO thin film for 2D device simulation 47       |

| Table 3-2 Parameter used for ZnO TFT simulation                                               |

| Table 6-1 Comparison of device performance characteristics of ZnO nanowire FETs with          |

| and without AZO and the device without the gate insulator stack                               |

| Table 7-1 Electrical characteristics of ZnO nanowire FETs with gate lengths varies from       |

| 2.5 $\mu$ m to 4 $\mu$ m at $V_{DS} = 1.0 \text{ V}$                                          |

| Table 7-2 Comparison of electrical characteristics of ZnO nanowire FETs by lateral wet        |

| etching and device with AZO/Al source drain contacts                                          |

# **List of Figures**

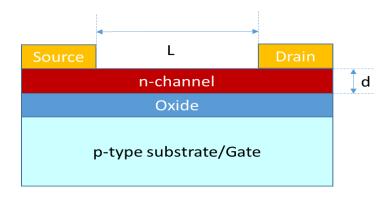

| Figure 2.1 Cross-section of an n-type nanowire FET with bottom-gate structure 10                              |

|---------------------------------------------------------------------------------------------------------------|

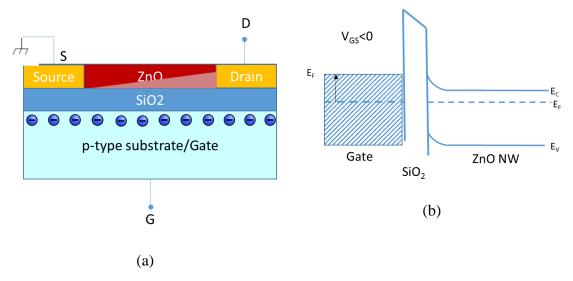

| Figure 2.2 (a) Schematic of ZnO nanowire FET when negative voltage is applied (b)                             |

| Energy band diagram of n-type ZnO nanowire FET in depletion conditions11                                      |

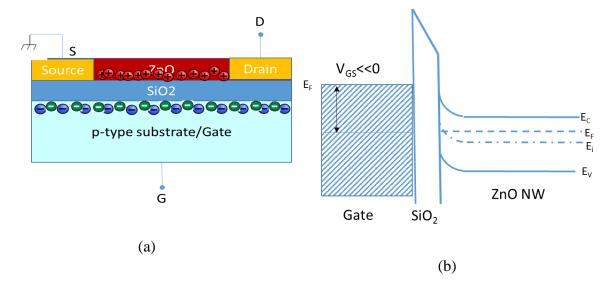

| Figure 2.3 (a) Schematic of ZnO nanowire FET when negative voltage is applied (b)                             |

| Energy band diagram of ZnO nanowire FET in inversion                                                          |

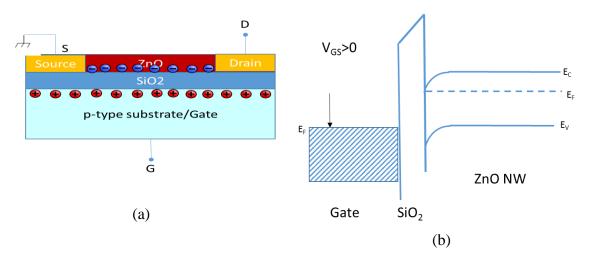

| Figure 2.4 (a) Schematic of ZnO nanowire FET when positive voltage is applied (b)                             |

| Energy band diagram of ZnO nanowire FET in accumulation                                                       |

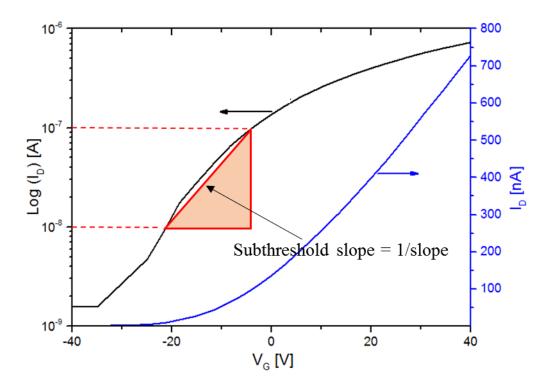

| Figure 2.5 $I_{DS}$ - $V_{GS}$ curve in linear (blue) and semi-logarithmic scale of $I_{DS}$                  |

| Figure 2.6 Stick and ball representation of ZnO crystal structures: (a) cubic rocksalt (B1),                  |

| (b) cubic zinc blende (B3), and (c) hexagonal wurtzite (B4). The shaded gray and black                        |

| spheres denote Zn and O atoms, respectively. Figure reproduced from Ref. [12] 18                              |

| Figure 2.7 A sketch of top-down and bottom-up paradigm applied to nanowires fabrication.                      |

| Figure reproduced from Ref. [49]                                                                              |

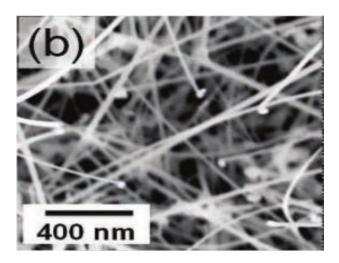

| Figure 2.8 An SEM image of entangled mesh of ZnO nanowire. Figure adapted from Ref.                           |

| [50]24                                                                                                        |

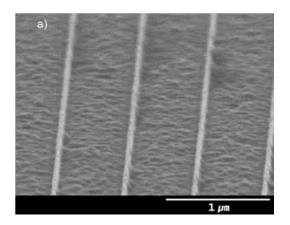

| Figure 2.9 SEM image of ZnO nanowire fabricated by top-down fabrication using spacer                          |

| method. Figure reproduced from Ref. [63]                                                                      |

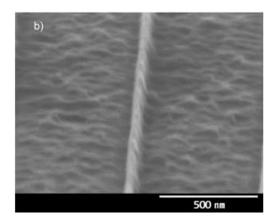

| Figure 2.10 Survey on ZnO nanowires looking at field-effect mobility versus subthreshold                      |

| slope                                                                                                         |

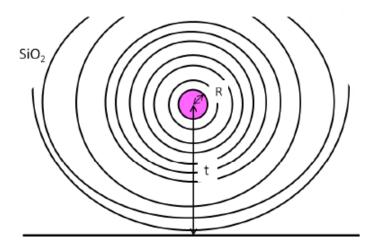

| Figure 3.1 Cross-sectional view of the ZnO nanowire                                                           |

| Figure 3.2 Cross section geometry of back-gated NWFETs of embedded NW with t/R =6.                            |

| The lines are equally separated constant potentials obtained by finite element method                         |

| (FEM) calculations. Figure reproduce from [2]                                                                 |

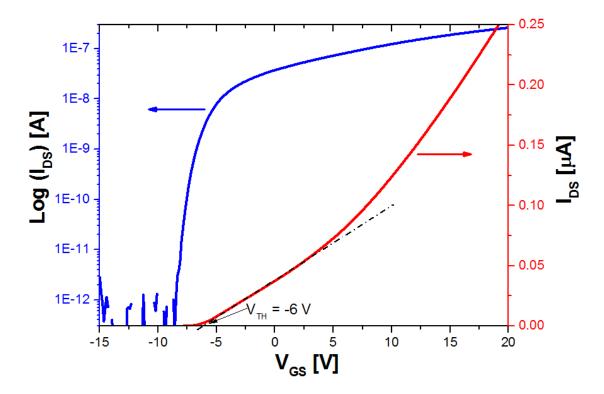

| Figure 3.3 $I_{DS}$ - $V_{GS}$ curve at $V_{DS} = 1$ V of ZnO nanowire FET with channel length, L=8.6         |

| μm. Linear curve (red) and subthreshold characteristics (blue)                                                |

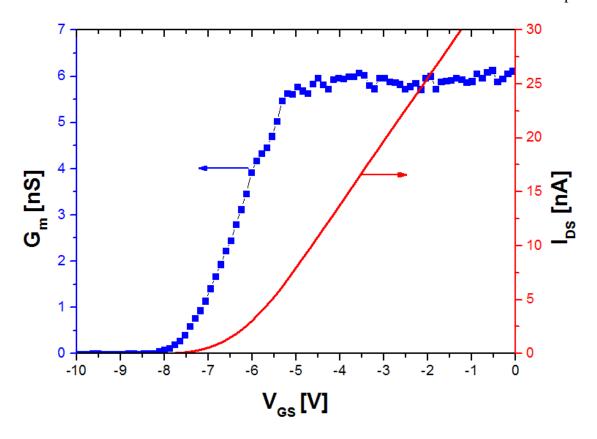

| Figure 3.4 $I_{DS}$ - $V_{GS}$ curve (red) and resulting transconductance (blue) at $V_{DS} = 1 \text{ V}$ 45 |

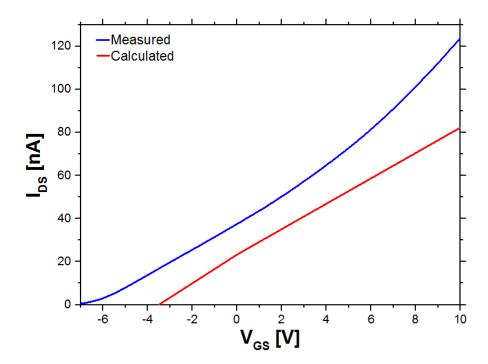

| Figure 3.5 Linear $I_{DS}$ - $V_{GS}$ curve of measured (blue) and calculated (red) ZnO nanowire FET at $V_{DS} = 1 \text{ V}$                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

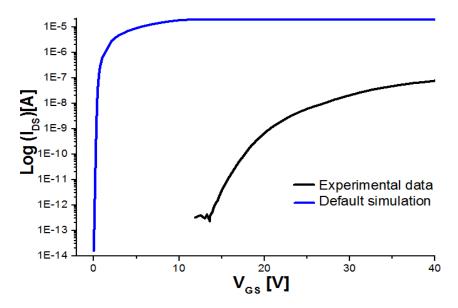

| Figure 3.6 Initial simulation using default parameters derived from literature [12]-[14]49                                                                                                                                                                                                  |

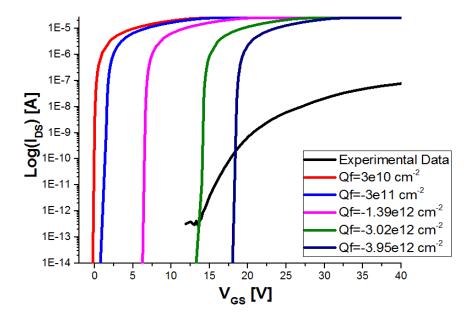

| Figure 3.7 Subthreshold plot- Investigating the effect of interface charge 50                                                                                                                                                                                                               |

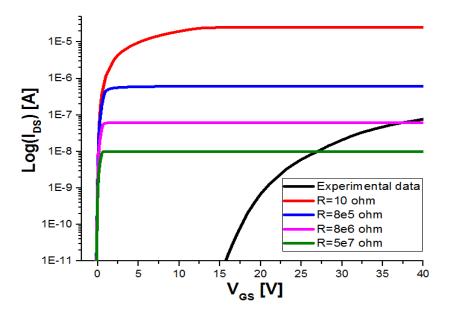

| Figure 3.8 Subthreshold plot- Investigating the effect contact resistance                                                                                                                                                                                                                   |

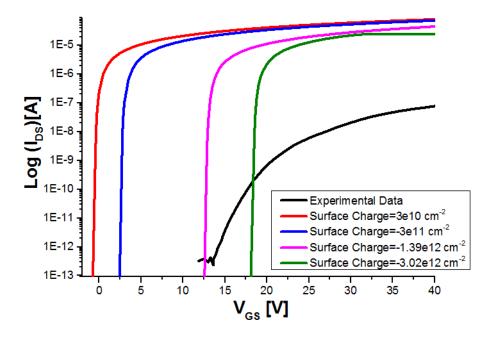

| Figure 3.9 Subthreshold plot- Investigating the effect of surface charge                                                                                                                                                                                                                    |

| Figure 3.10 Subthreshold plot- Comparing simulation with experimental data (best fit)52                                                                                                                                                                                                     |

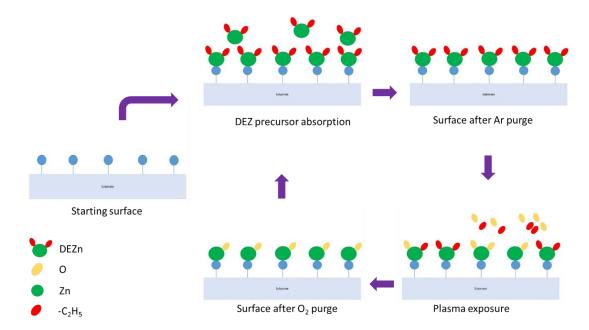

| Figure 4.1 Illustration of ALD ZnO film reaction showing the DEZ – zinc monolayer deposition followed by argon purge and oxidation step of the zinc with the oxygen plasma.  Adapted from [14]                                                                                              |

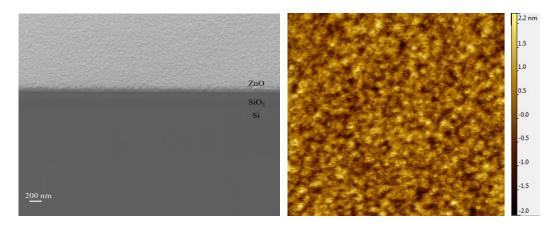

| Figure 4.2 Cross-sectional SEM (right) and top-view of AFM image of as-deposited remote plasma ALD ZnO film (left)                                                                                                                                                                          |

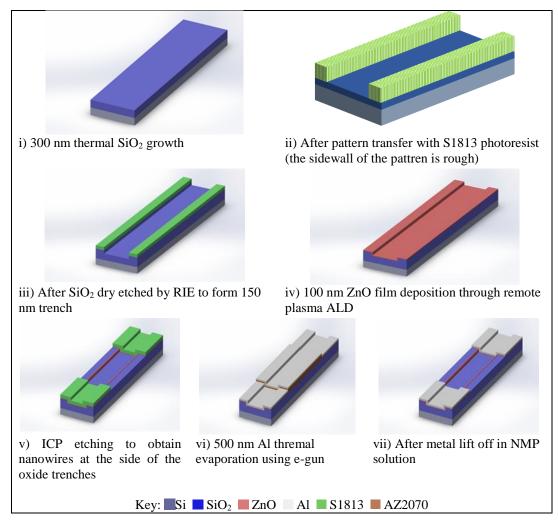

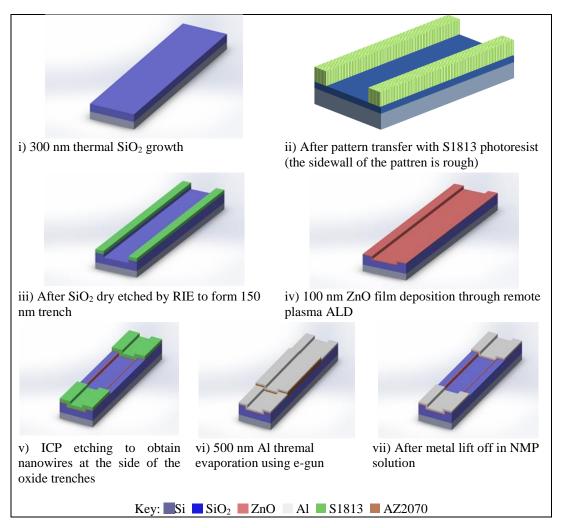

| Figure 4.3 Schematic of the fabrication process for non-reflow photoresist spacer method                                                                                                                                                                                                    |

| Figure 4.4 Schematic of the fabrication process reflow photoresist spacer method 61                                                                                                                                                                                                         |

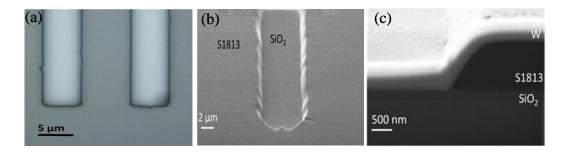

| Figure 4.5 (a) Optical microscope image (b) Scanning electron micrograph of the trench top surface and (c) cross section of the of the pattern from non-reflow photoresist spacer method process.                                                                                           |

| Figure 4.6 (a) Optical microscope image (b) Scanning electron micrograph of the trench top surface and (c) cross section of the of the pattern from reflow photoresist spacer method process.                                                                                               |

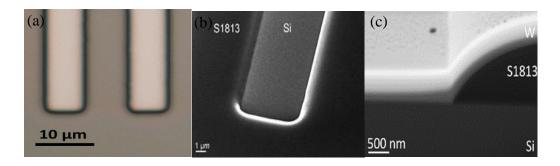

| Figure 4.7 Scanning electron micrograph of the trench cross section after thermal oxidation of reflow (left) and non-reflow process (right). The tungsten (W) layer is to protect the SiO <sub>2</sub> layer during focused ion beam cross-sectioning and provide contrast to the SEM image |

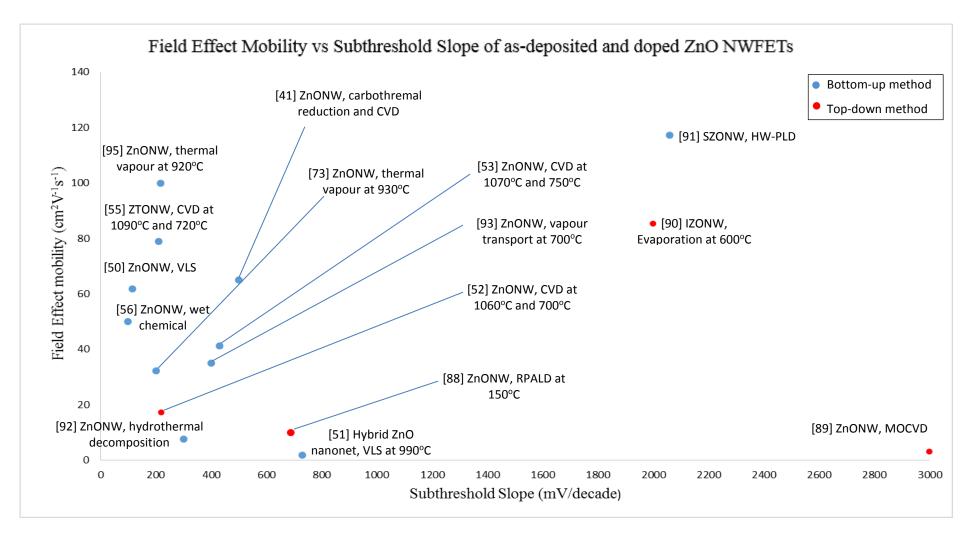

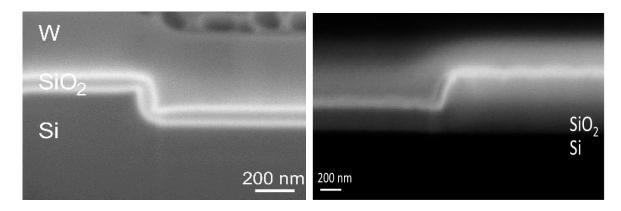

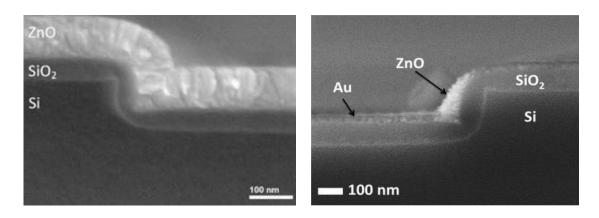

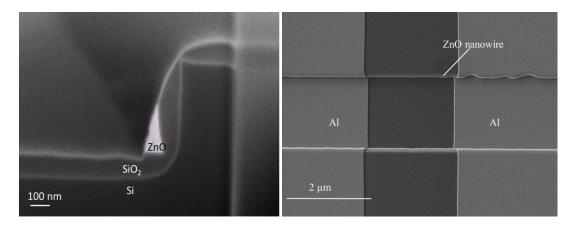

| Figure 4.8 SEM cross-section of ZnO layer after remote plasma ALD deposition (left) and                                                                                                                                                                                                     |

| 7nO nanowire on the sidewall with sputtered Au for imaging (right) 63                                                                                                                                                                                                                       |

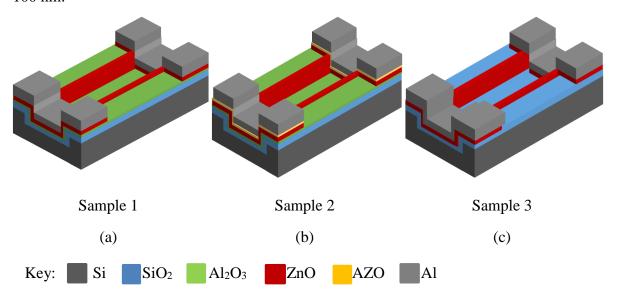

| Figure 4.9 Cross-sectional schematic diagram of the ZnO nanowire FET us                                  | ing ZnO    |

|----------------------------------------------------------------------------------------------------------|------------|

| nanowire as channel layer: (a) with bilayer gate insulator and Al source/drain con                       | ntact, (b) |

| with bilayer gate insulator and Al/AZO source/drain contact, and (c) with SiO                            | 2 as gate  |

| insulator and Al source/drain contact                                                                    | 66         |

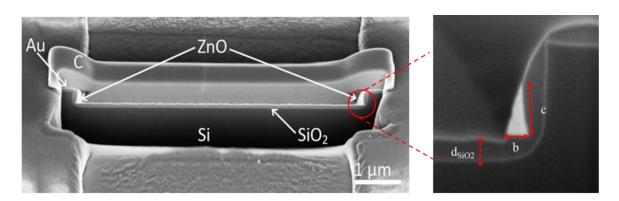

| Figure 4.10. Cross-section and top view scanning electron micrograph of sample 3                         | with the   |

| ZnO nanowire at the edge of SiO <sub>2</sub> trench after ICP etching.                                   | 67         |

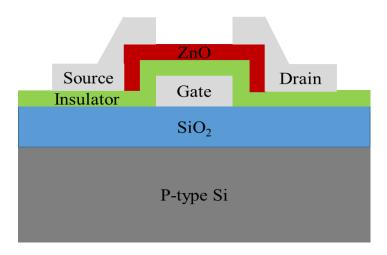

| Figure 4.11 Schematic cross-section view of bottom-gate ZnO nanowire FETs                                | 67         |

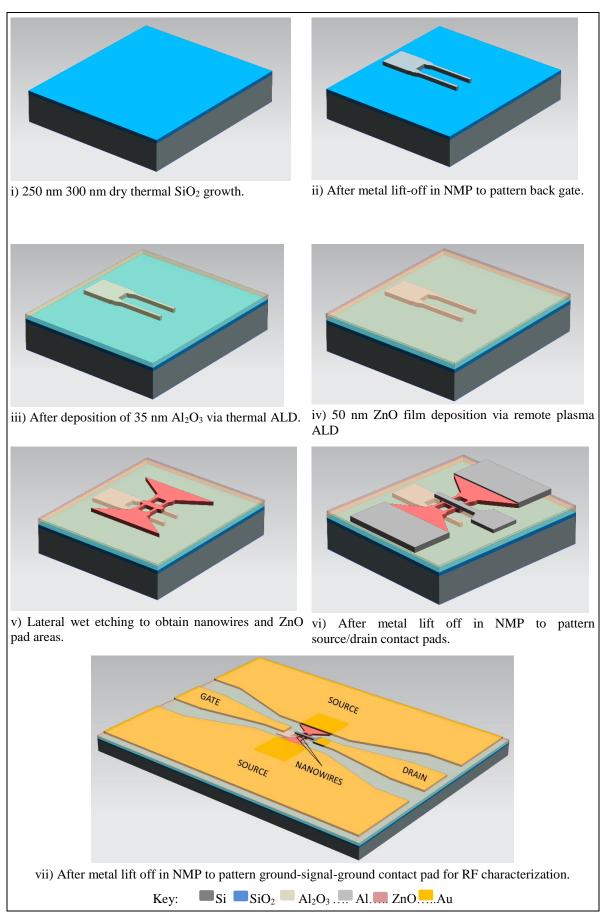

| Figure 4.12 Schematic of the fabrication process for ZnO nanowire FETs wi                                | th direct  |

| photolithography and lateral wet etch.                                                                   | 68         |

| Figure 4.13 A top view of ZnO nanowire FET with patterned Al metal pads                                  | 70         |

| Figure 4.14 A top view of ZnO nanowire FET with Au bond pads                                             | 70         |

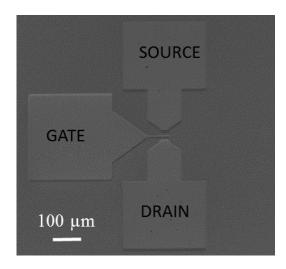

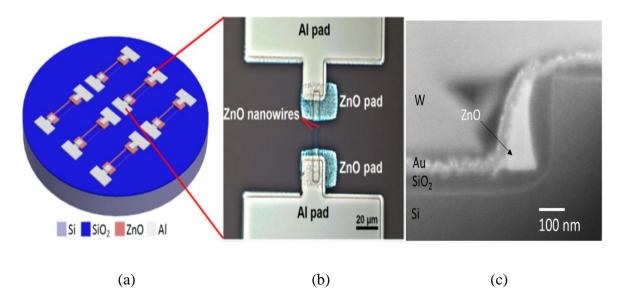

| Figure 5.1 (a) Schematic drawing of the processed nanowire FET array (b                                  | ) optical  |

| microscope image of dual nanowires (c) scanning electron micrograph of the trenc                         | h section  |

| of the fabricated nanowire FETs (Au= gold coating, W= tungsten coating for foc                           | cused ion  |

| beam cross-sectioning)                                                                                   | 74         |

| Figure 5.2 $I_{DS}$ - $V_{DS}$ characteristics of different thickness of SiO <sub>2</sub> gate dielect   | tric ZnO   |

| nanowire FETs (a) 50 nm (b) 75 nm (c) 100nm.                                                             | 75         |

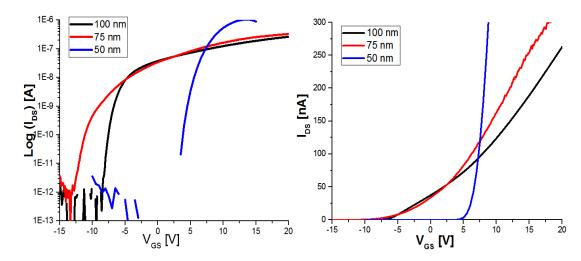

| Figure 5.3 Semi-logarithmic (left) and linear (right) $I_{DS}$ - $V_{GS}$ characteristic of              | the ZnO    |

| nanowire FETs with different thickness of $SiO_2$ at $V_{DS} = 1.0 \text{ V}.$                           | 76         |

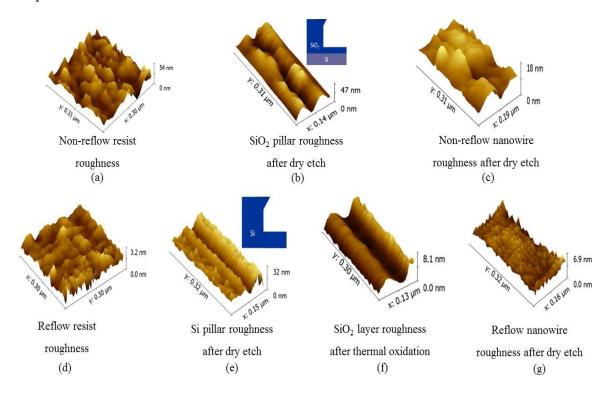

| Figure 5.4 Transconductance $(g_m)$ and field effect mobility $(\mu_{FE})$ as a function of              | gate bias  |

| at $V_{DS} = 1.0 \text{ V}$ for ZnO nanowire FETs with SiO <sub>2</sub> thickness of (a) 50 nm (b) 75 nr | n and (c)  |

| 100 nm                                                                                                   | 77         |

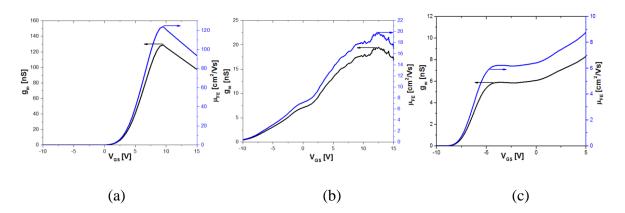

| Figure 5.5 Position of the AFM tip and scan directions.                                                  | 79         |

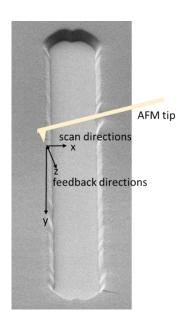

| Figure 5.6 AFM image of surface sidewall profile of the device fabrication base                          | ed on (a)  |

| non-reflow process (b) reflow process                                                                    | 80         |

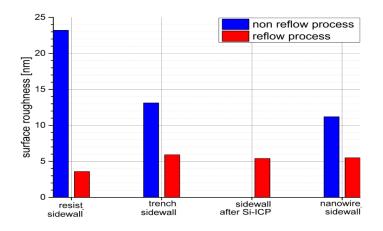

| Figure 5.7 Comparison of the nanowire surface roughness between the non-reflow                           | v process  |

| and the new reflow fabrication design measured by AFM.                                                   | 81         |

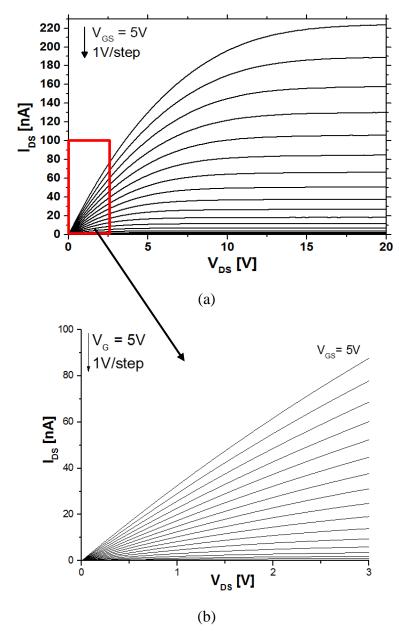

| Figure 5.8 (a) $I_{DS}$ - $V_{DS}$ characteristics with a $V_{GS}$ drive from -10 V to 5 V with ste      | ps of 1.0  |

| V and (h) Zoomed area of Inc. Vnc characteristics from Vnc 0 V to 3 V                                    | 82         |

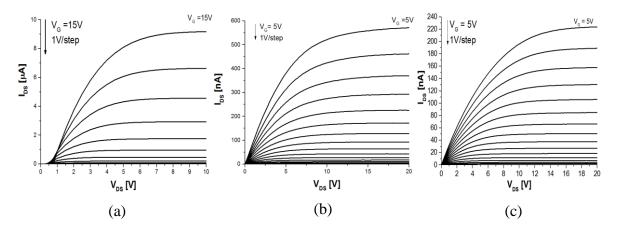

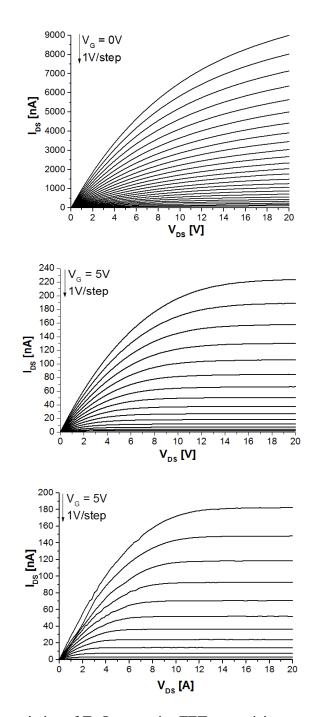

| Figure 5.9 Output characteristics of ZnO nanowire FET comprising two parallel nanow                                                                                                                                                                                                                                                                                                | vires        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| with channel lengths, L of (a) 1.3 μm (b) 8.6 μm (c) 18.6 μm                                                                                                                                                                                                                                                                                                                       | 3            |

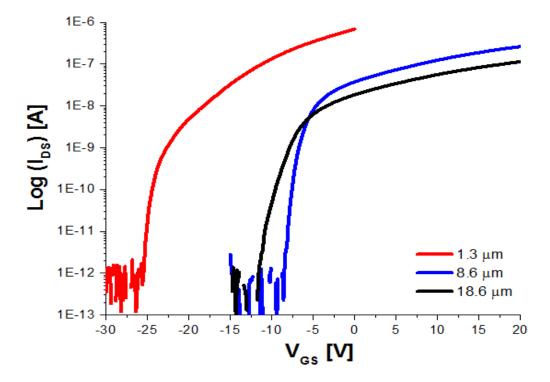

| Figure 5.10 Transfer characteristics for devices with different channel lengths at $V_{DS}$ = V                                                                                                                                                                                                                                                                                    |              |

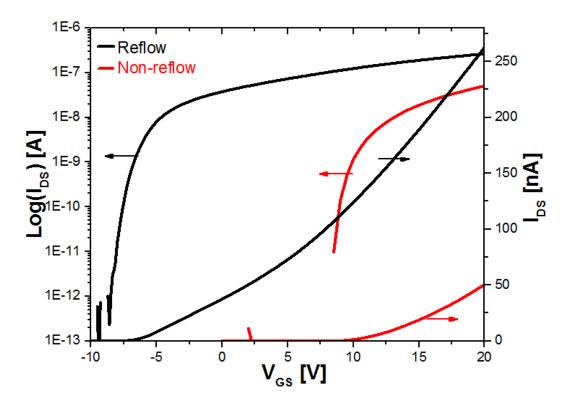

| Figure 5.11 Semi-logarithmic and linear $I_{DS}$ - $V_{GS}$ characteristic of the reflow (black)                                                                                                                                                                                                                                                                                   | and          |

| non-reflow (red) fabricated nanowire FET at $V_{DS}$ = 1.0 V                                                                                                                                                                                                                                                                                                                       | 5            |

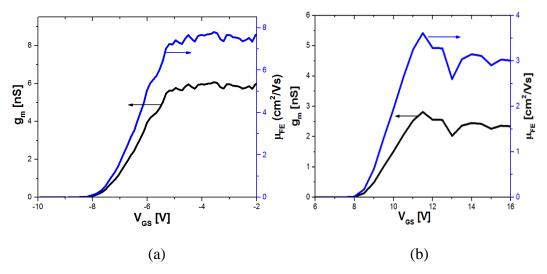

| Figure 5.12 Transconductance ( $gm$ ) and field-effect mobility ( $\mu_{FE}$ ) as a function of bias at $V_{DS}$ =1.0 V for ZnO nanowire FET of (a) reflow and (b) non-reflow                                                                                                                                                                                                      | _            |

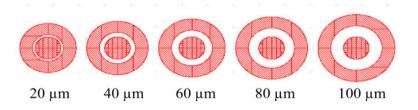

| Figure 6.1. Mask layout of the CTLM structures used to determine the contact resista                                                                                                                                                                                                                                                                                               |              |

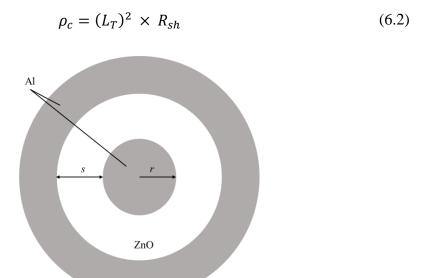

| Figure 6.2 The schematic of top view of the CTLM which indicate the radius radius of inner circular contact, r and the gap between inner and outer circular, s                                                                                                                                                                                                                     |              |

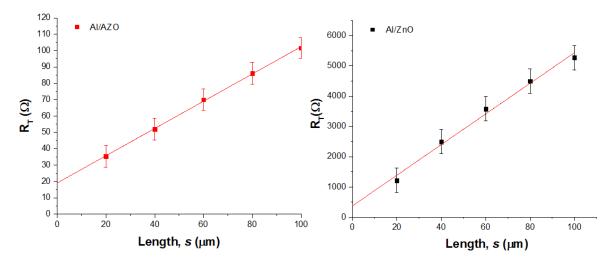

| Figure 6.3 Resistance as a function of the distance between aluminum contact on AZO ZnO                                                                                                                                                                                                                                                                                            |              |

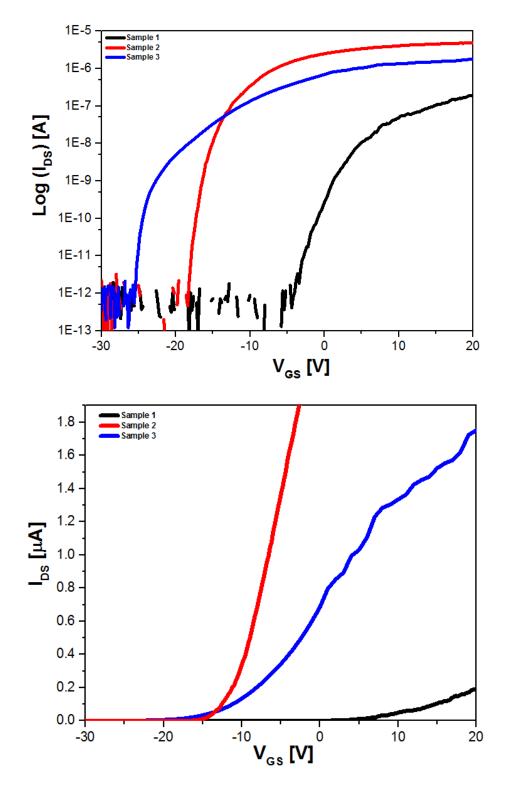

| Figure 6.4 Semi-logarithmic (top) and linear (bottom) transfer characteristics of the NWFETs with and without AZO and with and without gate oxide stack at $V_{DS} = 1.0 \text{ V}$ .                                                                                                                                                                                              |              |

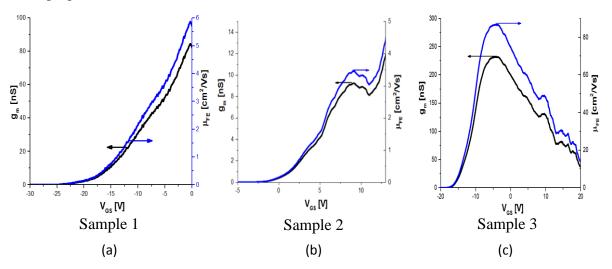

| Figure 6.5 Transconductance $(g_m)$ and field-effect mobility $(\mu_{FE})$ as a function of gate at $V_{DS} = 1.0 \text{ V}$ for ZnO nanowire FETs (a) with Al electrodes and SiO <sub>2</sub> gate oxide (b) Al electrodes and Al <sub>2</sub> O <sub>3</sub> /SiO <sub>2</sub> gate oxide (c) with Al/AZO electrodes and Al <sub>2</sub> O <sub>3</sub> /SiO <sub>2</sub> oxide. | with<br>gate |

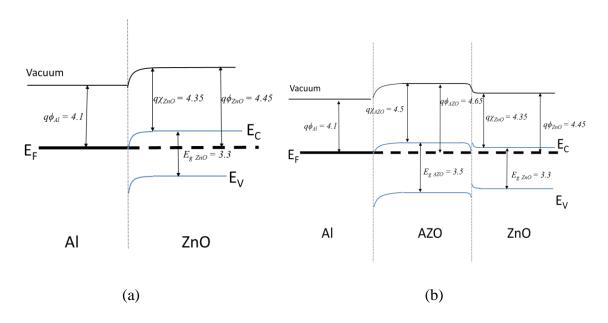

| Figure 6.6 Energy band diagram of contact system in the case of the ZnO nanowire F with and without AZO.                                                                                                                                                                                                                                                                           |              |

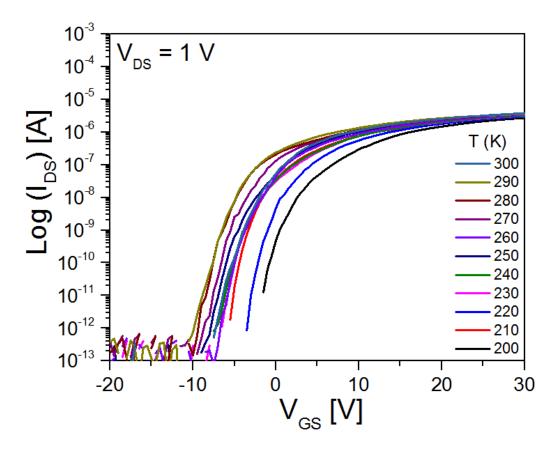

| Figure 6.7 Transfer characteristics of ZnO nanowire FET in the temperature range f $200 \text{ K}$ to $300 \text{ K}$ measured at $V_{DS} = 1.0 \text{ V}$ .                                                                                                                                                                                                                       |              |

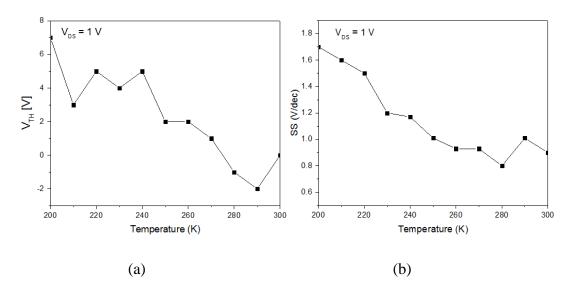

| Figure 6.8 Temperature dependence of a) threshold voltage and b) subthreshold slope = 1.0 V                                                                                                                                                                                                                                                                                        |              |

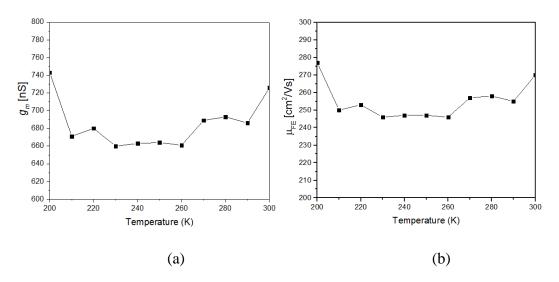

| Figure 6.9 (a) Transconductance peak vs. temperature and b) extracted field-effect mob                                                                                                                                                                                                                                                                                             | oility       |

| vs. temperature at $V_{DS} = 5.0 \text{ V}$                                                                                                                                                                                                                                                                                                                                        | 13           |

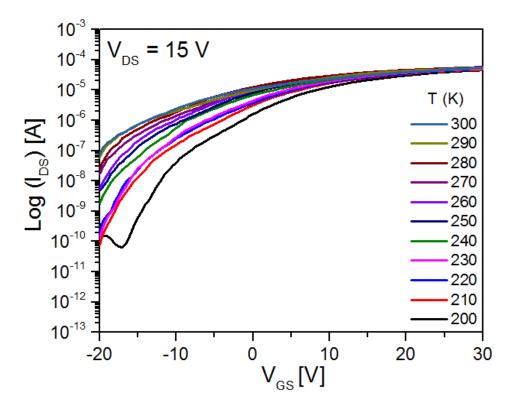

| Figure 6.10 Transfer characteristic at $V_{DS} = 15.0 \text{ V}$ in the temperature range from 200 K to                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 300 K in semi-logarithmic plot                                                                                                                           |

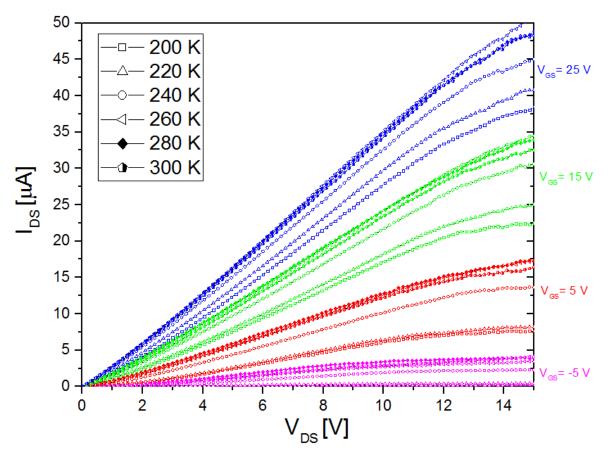

| Figure 6.11 Output characteristics in the temperature range from 200 K to 300 K at different $V_{GS}$ .                                                  |

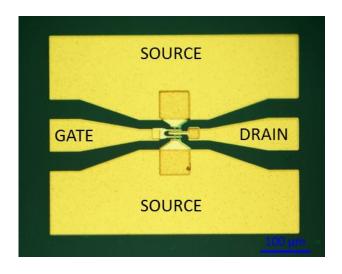

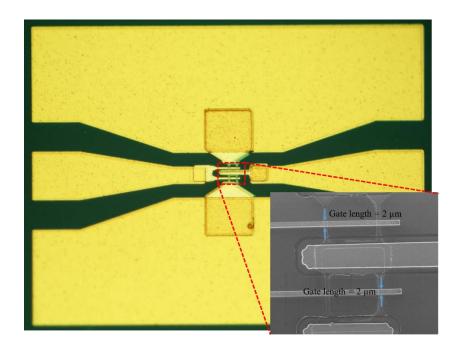

| Figure 7.1 Top-view image of the ZnO nanowire FET with gate length = $2 \mu m$ 112                                                                       |

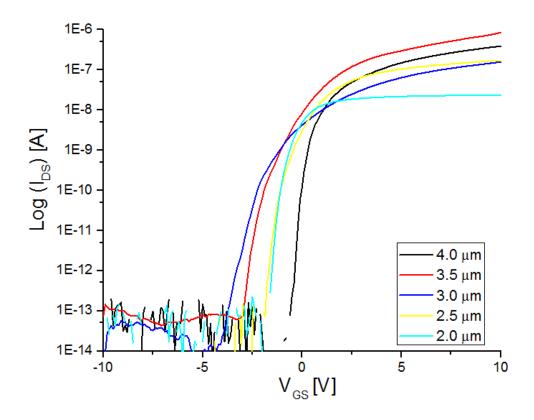

| Figure 7.2 Transfer characteristics of ZnO nanowire FETs with gate lengths between 2.5 $\mu$ m to 4 $\mu$ m at $V_{DS} = 1.0$ V in semi-logarithmic plot |

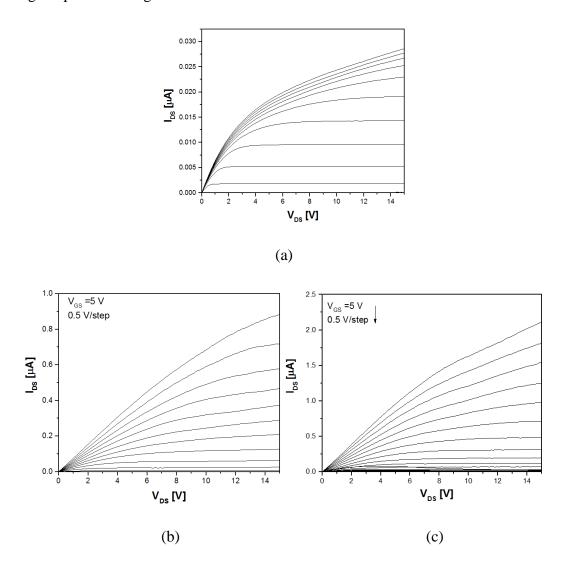

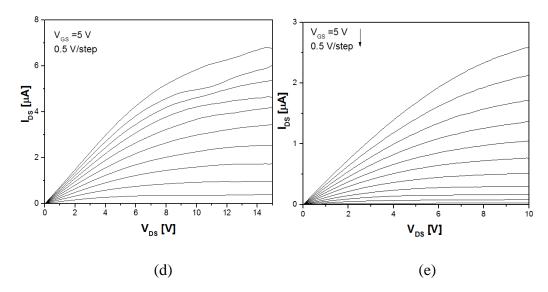

| Figure 7.3 Output characteristics of nanowire transistor with gate length of a) 2 µm, b) 2.5                                                             |

| μm, c) 3 μm, d) 3.5 μm, and e) 4 μm                                                                                                                      |

### **DECLARATION OF AUTHORSHIP**

I,Nor Azlin Ghazali, declare that this thesis entitles Design, Fabrication, and characterization of High Performance Zinc Oxide Nanowire Field-Effect Transistors, and the work presented in it are my own and has been generated by me as the result of my own original research.

#### I confirm that:

- 1. This work was done wholly or mainly while in candidature for a research degree at this University;

- 2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- 3. Where I have consulted the published work of others, this is always clearly attributed;

- 4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- 5. I have acknowledged all main sources of help;

- 6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- 7. Parts of this work have been published as shown in the List of Publications that follows:

| Signed: | AST        |      |       | <br> | ••••• |

|---------|------------|------|-------|------|-------|

| Date    | 02/08/2018 | •••• | ••••• | <br> |       |

### **List of Publications**

#### **Journals**

#### Top- down fabrication optimisation of ZnO nanowire-FET by sidewall smoothing

N. A. B. Ghazali, M. Ebert, N. M. J. Ditshego, M. R. R. De Planque, and H. M. H. Chong, "Top-down fabrication optimisation of ZnO nanowire-FET by sidewall smoothing," *Microelectron. Eng.*, vol. 159, pp. 121–126, Jun. 2016.

# Multichannel ZnO nanowire field effect transistors by lift-off process (accepted for publication)

M. Ebert, N. A. B. Ghazali, K.S. Kiang, I. Zeimpekis, B. Maerz, M. R. R. de Planque, and H. M. H. Chong, *Nanotechnology*.

#### Effect of AZO ohmic layer on ZnO nanowire field-effect transistors (in preparation)

N. A. B. Ghazali, M. Ebert, K.Kalna, M. R. R. De Planque, and H. M. H. Chong, *Applied Surface Science*.

#### **Conferences**

#### ZnO nanowire-FET for charge-based sensing of protein biomolecules

N.M.J. Ditshego, N.A.B. Ghazali, M. Ebert, K. Sun, I. Zeimpekis, P. Ashburn, M.R.R. de Planque, H.M.H. Chong. IEEE NANO 2015, 15th International Conference on Nanotechnology (accepted for publication), 27 – 30 July 2015, Rome (Italy).

#### Top- down fabrication optimisation of ZnO nanowire-FET by sidewall smoothing

N. A.B. Ghazali, M. Ebert, N. M. J. Ditshego, M. R. R. de Planque, and H. M. H. Chong, 41<sup>st</sup> International Conference on Micro and Nano Engineering (MNE2015), The Hague, 21<sup>st</sup>-24<sup>th</sup> September 2015.

# Novel top-down fabrication of ZnO nanowires by atomic layer deposition and anisotropic dry etch process

Ebert M., Ghazali N. A.B., Kiang K.S., de Planque M.R.R., and Chong H. M. H., 29<sup>th</sup> *International Microprocesses and Nanotechnology Conference (MNC 2016)*, Kyoto, 8<sup>th</sup>-11<sup>th</sup> November 2016.

# Novel top-down bilayer photoresist fabrication of ZnO nanowire Field effect transistors

Ebert M., Ghazali N. A.B., Kiang K.S., Zeimpekis I., de Planque M.R.R., and Chong H. M. H., *43<sup>rd</sup> International Conference on Micro and Nano Engineering (MNE2017)*, Braga, 18<sup>th</sup>-22<sup>th</sup> September 2017.

# Acknowledgements

My humble gratitude towards Almighty who created the whole universe for blessing me with opportunities and gratitude. I would like to take this opportunity as a privilege to thank all individuals without whose support and guidance I could not have completed this work within stipulated time.

First and foremost, I want to express my sincere gratitude to my supervisor, Professor Harold M. H. Chong, for the tremendous amount of guidance and support in completing my PhD. His patience, encouragement, enthusiasms and commitments are much appreciated without which this thesis would not have been possible. I extremely lucky to work under his supervision. He always blown me away with her vision, consideration, knowledge, and cheers.

I spent more hours than I care to remember in cleanroom facilities over the past 3 years. In particular I would like to thank the cleanroom engineers and technicians who made my work possible and even enjoyable. A special thanks goes to Martin Ebert for helping me in fabrication process. His ideas and advice in my entire work are so much appreciated. In addition, I am very grateful to Dr Kian Kiang for the yellow room trainings and for being supportive in part of my work. I'm also thankful to Zhen and Jamie for the ideas and advice in my mask design. Special thanks also goes Swe Zin Oo and Rafidah Petra for always be there to helped me during my hard times, accompany me during odd hours in the cleanroom and office and being my loyal friends. Both of you were always helped me from the very start of my PhD journey, right until the very end of the journey. You showed me the ropes of the cleanroom as a colleague and as a friend.

Special thanks to Takuya Iwasaki from Mizuta Laboratory, JAIST for helping me in low temperature measurements. The measurements results gave a big impact in my thesis.

I would also like to thank the Ministry of Higher Education Malaysia and Universiti Sains Malaysia (USM) for providing financial support for me and my family during my PhD study in Southampton.

Now I can write a few paragraphs to thank the family and friends who put up with me and my cleanroom-induced melancholy for so long and made it possible not only for me to finish graduate school, but to even get here in the first place. These people encouraged, loved, cajoled, and disciplined me into the person, student, and researcher that I am today.

To the Malaysian community in Southampton, you have made Southampton feel like home from the first day I've arrived until the last day my family and I were there. I will miss you all dearly and will see you all again sooner or later. Rusniza, Siti, Alisa, Syafiqah, Aida, Dilla, and Ain you all are more than friends. We shared so much together. I will never forget the happy and hard time when we were in Southampton. You all know what it is like to slog through PhD. Thank you so much for the comfort, advice, joys and love that made the trek a little easier for me.

To my whole family in Malaysia that I have left physically for years, I would like to express guilt for the missing years in important family matters. You are always in my thoughts although I'm not there. Thanks Mom and Dad for teaching me to love learning and to never be finished with it. Thank you both for your blessing to me to get here even you don't really like when I'm away from you. I'm so sorry for the years spent worrying about me and my kids who's been miles away from you. Special recognition to my sibling Azliza, Hafizuddin, Hisyamuddin, Athirah and Syafinaz for helping me take care of personal matters and made our parents comfort during my absent. From the bottom of my heart, thank you.

Last but not least, my heartiest appreciation goes to my husband, Ahmad Suffian and my kids, Aqil and Akif who has been patiently waiting for this day to come. Because of their endless encouragement, love, patience and forgiveness I made it through without too many scars. This thesis is dedicated especially to three of you.

# **Definitions and Abbreviations**

AFM Atomic Force Microscope

Al<sub>2</sub>O<sub>3</sub> Aluminium Oxide

ALD Atomic Layer Deposition

AZO Aluminium-Doped Zinc Oxide

CHF<sub>3</sub> Fluoroform

CTLM Circular Transmission Line Measurement

CO<sub>2</sub> Carbon Dioxide

CVD Chemical Vapour Deposition

DC Direct Current

DEZ diethyl zinc

FEGSEM Field Emission Scanning Electron Microscopy

FET Field-Effect Transistor

FIB Focused Ion Beam

HCl Hydrochloric Acid

HF Hydrofluoric Acid

IBE Ion Beam Etcher

ICP Inductively Coupled Plasma

IPA Isopropyl Alcohol

MOS Metal-Oxide-Semiconductor

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

NMP 1-Methyl-2-pyrrolidon

NW Nanowire

NWFET Nanowire Field-Effect Transistor

O<sub>2</sub> Oxygen

PEALD Plasma Enhance Atomic Layer Deposition

PECVD Plasma Enhanced Chemical Vapour Deposition

PMMA Poly(methyl methacrylate)

RF Radio Frequency

RIE Reactive Ion Etch

RMS Root-Mean-Square

RPALD Remote Plasma Atomic Layer Deposition

SEM Scanning Electron Microscopy

SS Subthreshold Slope

TLM Transmission Line Measurement

TMA Trimethylaluminum

TMAH Tetramethylammonium Hydroxide

VLS Vapour-Liquid-Solid

ZnO Zinc Oxide

# Chapter 1:

### Introduction

This chapter provides an introduction to the research work presented in this report. It describes the motivation and objectives of the research work and finally, it introduces the structure of the report.

#### 1.1 Overview

It is undeniable that semiconductors changed the world beyond anything that could have been imagined since the first transistor was invented at Bell Laboratories, United States of America in 1947 [1]. Further development of the transistors has lead to devices using different type of semiconducting materials. Transistor technology developments have sustained the research of new semiconductor material and new structures of modern nanostructured semiconductor devices such as nanowires. Nanowires (NWs) made from different semiconductor material systems (gallium arsenic, zinc oxide) have been studied extensively over the past two decades and developments in this field continue. This is due to their novel electronic, photonic and sensing properties.

Zinc oxide (ZnO) as a semiconductor has attracted considerable research effort due to its unique properties such as its high electron mobility and its high crystalline quality as well as its versatile applications in fabricating electronic devices and sensors of nanoscale dimensions [2]. ZnO is an II-VI compound which crystallizes in the wurtize phase and has a wide direct bandgap of 3.4 eV at room temperature with a high breakdown voltage and large saturation velocity [2]. It also has several advantage over the GaN including larger exciton binding energy (60 meV versus 25 meV for GaN), low temperature epitaxial growth and the possibility of a wet etching process leading to potential low cost ZnO based devices. It is also a promising semiconductor material with several exciting applications and a robust tendency to grow in nanostructured form.

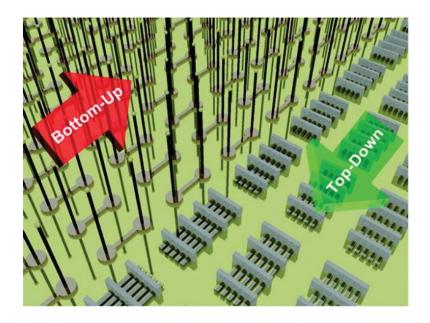

Generally, there are two methods to manufacture ZnO nanowires. The most common method is by a bottom-up process such as chemical vapour deposition (CVD), vapour-liquid-solid (VLS) or a wet chemical synthesis [3]–[5]. Based on these methods, high quality nanowires with excellent mobility can be fabricated but because the nanowire is scattered on the substrate, there is a need for a good pick and place method to align the

#### Chapter 1

nanowire. Furthermore, many variables such as the different sizes of the grown nanowires as well as alignment issues and the issues of the alignment attest to how difficult it is to make nanowire-based devices.

The top-down process is conventional scaling, it is a straightforward process to pattern and etch the nanowires' structure. The top-down process is seen as the best candidate to overcome the drawbacks of the bottom-up process [6]. The top-down process offers nanowires a well-defined location on substrates and allows nanowires with various length to be fabricated on the same wafer. Although ZnO-based nanowires fabricated by top-down methods do not exhibit excellent mobility compared to nanowires fabricated by the bottom-up process, in Ref. [6] shows a potential of top-down methods fabricating a device with field-effect mobility > 10 cm<sup>2</sup>/Vs with excellent crystallinity.

The nanowires are the best candidates for the realization of field-effect transistors (FETs) owing opportunity to construct a wrapping gate that offers an improvement of electrostatic control of the channel, with in parallel good on/off current ratio which are necessary for various applications [7]. The ZnO nanowires are also suitable to create high performance FETs in large-area electronics and active-matrix display or sensor arrays, which involve less complex circuitry and smaller FET densities [8].

In general, research on high performance ZnO nanowires FETs is ongoing, and there are still a number of gaps to be filled. The aim of this research work is the development of high performance FETs with high mobility based on ZnO nanowires that can be fabricated at low temperature and can therefore be implemented on silicon or polymer-based substrates.

#### 1.2 Motivation

ZnO has been widely used in sunscreen lotions, paints, ceramics, and food supplements for quite a long time. Aside from its common uses, it also a very promising material for semiconductor devices such as transistors and diodes. The main advantages of ZnO are abundance, low price and it is non-toxic in small amounts. In recent years, ZnO has been considered a favourable candidates as metal oxide materials because of its low-cost fabrication, ideal conductivity and efficient visible transmittance [9].

Stoichiometric ZnO is a semicondcutor that crystallizes with a wurtzite structure [9]. The ZnO crystal is naturally n-type due to the native defect such as zinc interstitials and

oxygen vacancies. The research of the p-type ZnO is still an ongoing research area and the lack of p-type material has hindered the development of transistors based on ZnO. Although there are several reports on p-type measurements in ZnO [10], there is still ongoing research seeking to discover a good quality p-type ZnO. While the p-type is still mysterious, the advantages of the n-type ZnO are being utilized by using it as an active layer on p-type materials and by utilizing heteroepitaxy structures [11].

The typical Hall mobility of single crystals of ZnO at room temperature are about 100 cm<sup>2</sup>/Vs –200 cm<sup>2</sup>/Vs [12]. These properties make ZnO attractive for nanowires, which have been produced by a various methods that generally produce single-crystal material [13]. However, improving the quality of the crystal growth and device fabrication process may increase the mobility of ZnO nanowires to thousands of cm<sup>2</sup>/Vs [14]. Additionally, nanowires have been found to have superior electrical and mechanical properties compared to bulk ZnO, because of their confined dimensions.

Initial studies of top-down ZnO nanowire field-effect transistors (NWFETs) showed a significant variation of electrical characteristics, such as output drain current, threshold voltage and field-effect mobility [6]. One of the possible causes is the nanowire surface roughness from the fabrication process, which can induce a high trap charge density and influence the device characteristics [15]. The other possible reason for the variation, especially the mobility, is due the existence of contact resistance. Contact resistance might decrease the voltage drop across the channel and limit the injected current [16]. In semiconductor devices, high contact resistance could lead to the deterioration of device performance caused by thermal stress, likely resulting in device failures. In addition, the ZnO nanowire FET also exhibits a relatively large operating voltage, which makes it unsuitable for low power device application. This problem can be avoided by modulating the gate insulator and carrier concentration of the ZnO channel layer [17]. In order to drive a high output current at low voltage, the capacitive coupling between the active channel and the gate electrode must be increase by reducing the gate insulator thickness or using a high dielectric constant material [18][19]. On the other hand, carrier concentration of the ZnO nanowire also related to its resistance. The large number of free carriers in the ZnO nanowire can decrease the resistance of the ZnO channel, triggering a high flow of electrons to pass through the source and drain.

In this work, the ZnO nanowire FETs will be fabricated by optimising process steps based on [6] with a focus on improving the surface roughness of the nanowire and reduce

#### Chapter 1

the contact resistance between the contact pad and the active channels. Moreover, in order to increase the speed of the transistor, it is necessary to reduce the gate length specifically top-gate configuration. These strategies have the potential to produce high performance ZnO nanowire FETs in terms of low subthreshold swing, large on/off current ratio, high carrier mobility and threshold voltage stability.

The main focus of this research is the n-type ZnO nanowire based FET fabricated using a top-down fabrication method, which can demonstrate high performance transistor characteristic for radio frequency (RF) and logic circuit applications. Based on Franklin's high performance transistor review by, high performance transistors should have a low operating voltage of <1 V, high drive current of >1 mA/ $\mu$ m and the channel length of <20nm [20]. Although mobility is one of the most widely used metrics for describing carrier transport through a semiconductor, mobility in no longer meaningful for high performance transistors with short channel variety [20]. This is because if the channel length is falls below the average length between scattering events or the channel is ballistic, the carrier transport is no longer limited by scattering in the channel [20]. Mobility remains a useful parameter for a high performance devices with long channel variety. Thus, the aim of this research work to fabricate a high performance FET based on the n-type ZnO nanowire with aforementioned high performance characteristics. So, this work aims to achieve on/off current ratio of ~ 10<sup>6</sup> because it is an acceptable on/off current ratio for RF applications [21], low threshold voltage between -5 V to 5 V, subthreshold swing of 200 mV/decade and mobility of ~ 100 cm<sup>2</sup>/Vs. Instead of focussing on a channel length criteria specified by Franklin, to achieved high performance ZnO nanowire FETs, this study will focus on fabrication of a high performance transistor with gate lengths varying from 2 µm to 4 µm. In order to achieve small gate length of up to 20 nm, the electron beam (e-beam) lithography need to be used and the etching selectivity becomes critical since the most commonly used etching mask material in e-beam lithography is a thin layer of a poly(methyl methacrylate) (PMMA) [22]. Since, the deposited ZnO thin film has a grain issue, the wet etching of the nanowire could not be accurately achieved and the dry etching also not possible because the PMMA is not compatible with ZnO etching process.

### 1.3 Objectives

This work aims to address the following research objectives:

• To fabricate the ZnO nanowire FETs with an optimized process step to improve the surface roughness of the ZnO nanowires. Surface roughness is shown to have

- significant effects in electrical properties. Therefore, improving the surface roughness, could improve the electrical characteristics of the device.

- To further optimize the device by investigating different SiO<sub>2</sub> thickness and using Al<sub>2</sub>O<sub>3</sub> as the gate oxide to reduce the leakage current.

- To fabricate the ZnO nanowire FETs with an optimized process step of improving contact between ZnO nanowires and Al source drain pads by using the AZO.

- To fabricate a new structure of ZnO nanowire FETs using photolithography and lateral wet etch for RF applications. This experiment aim to simplify the top-down fabrication process using a wet etch method for nanowire FETs.

#### 1.4 Thesis Outline

This thesis is structured and divided into several background and experimental chapters. This section summarises and cover the necessary scientific theory required to understand the aim and the scope of the study as well as the experimental evidence needed to justify the approach.

Chapter 2 provides an introduction and discusses the fundamental theory of the research in detail. The chapters start by discussing the operation of a metal-oxide semiconductor field-effect transistor (MOSFET). The discussion is based on the n-type definitions and the expression of the electrical parameters of the devices. It also presents a summary of existing ZnO-based field-effect transistor technologies, as well as the current research. Firstly, ZnO material will be discussed and this will be followed by a comparison ZnO nanowire FETs in terms of their fabrication processes and electrical characteristics.

Chapter 3 explains the capacitance model used for the fabricated ZnO nanowire FETs. It also discussed about the extraction method of the electrical characteristics of the ZnO nanowire FET such as threshold voltage, subthreshold slope, and field-effect mobility and verify these measured values with calculation based on analytical model and simulation model.

Chapter 4 describes the deposition of the ZnO thin film, design, and fabrication method in ZnO nanowire FET fabrication, together with the potential advantages of each technique.

Chapter 5 presents a characterization of a top-down ZnO nanowire FET made using the sidewall smoothing technique from Chapter 4. In the first phase, the effect of gate

#### Chapter 1

dielectric thickness has been discussed. After the optimum gate dielectric thickness has been identified, the effect of nanowire surface roughness is explained. The sidewall smoothing technique reduced the nanowire roughness and improved the electrical characteristics of ZnO nanowire FET. The electrical characteristics of the ZnO nanowire FETs from the non-reflow and reflow resist processes were then compared to give an insight of the effect of surface roughness.

Chapter 6 explains the enhanced performance of ZnO nanowire FETs by depositing AZO thin film between the ZnO nanowire FET and the source/drain Al contact. The properties of AZO film, field-effect mobility, on/off current ratio, threshold voltage and subthreshold slope of the ZnO nanowire FETs with and without the AZO layer were systematically investigated. The electrical characteristics measured at various temperatures ranging from 200 K-300 K was then discussed.

Chapter 7. The preliminary electrical characteristics of the ZnO nanowire FET for RF applications is discussed in this chapter as well as the results based on the prototype device for RF characterization with ground-signal-ground contact pads.

Chapter 8 concludes this study with an overview of what have been achieved, and a discussion of the important contribution of this work. It suggest how to characterize this device for RF performance evaluation as future extension to this work. Further optimization processes are also described.

#### 1.5 References

- [1] W. Shockley, "The path to the conception of the junction transistor," *Electron Devices, IEEE Transactions on*, vol. 23, no. 7. pp. 597–620, 1976.

- [2] P.-C. Chang, Z. Fan, C.-J. Chien, D. Stichtenoth, C. Ronning, and J. G. Lu, "High-performance ZnO nanowire field effect transistors," *Appl. Phys. Lett.*, vol. 89, no. 13, p. 133113, 2006.

- [3] S. Lee, S. Kim, D. B. Janes, M. Meyyappan, and S. Ju, "Red-green-blue light sensitivity of oxide nanowire transistors for transparent display applications," *AIP Adv.*, vol. 3, no. 1, p. 12112, 2013.

- [4] J. Yang, M. S. Lee, H.-J. Lee, and H. Kim, "Hybrid ZnO nanowire networked field-effect transistor with solution-processed InGaZnO film," *Appl. Phys. Lett.*, vol. 98, no. 25, p. 253106, 2011.

- [5] D. Kälblein, H. Ryu, F. Ante, B. Fenk, K. Hahn, K. Kern, and H. Klauk, "High-Performance ZnO Nanowire Transistors with Aluminum Top-Gate Electrodes and Naturally Formed Hybrid Self-Assembled Monolayer/AlOx Gate Dielectric," *ACS Nano.*, vol. 8, no. 7, pp. 6840–6848, Jun. 2014.

- [6] S. M. Sultan, N. J. Ditshego, R. Gunn, P. Ashburn, and H. M. Chong, "Effect of atomic layer deposition temperature on the performance of top-down ZnO nanowire transistors.," *Nanoscale Res. Lett.*, vol. 9, no. 1, p. 517, Jan. 2014.

- [7] G. Rosaz, B. Salem, N. Pauc, P. Gentile, A. Potié, A. Solanki, and T. Baron, "High-performance silicon nanowire field-effect transistor with silicided contacts," *Semicond. Sci. Technol.*, vol. 26, no. 8, p. 85020, 2011.

- [8] S. Ju, J. Li, J. Liu, P.-C. Chen, Y. Ha, F. Ishikawa, H. Chang, C. Zhou, A. Facchetti, D. B. Janes, and T. J. Marks, "Transparent Active Matrix Organic Light-Emitting Diode Displays Driven by Nanowire Transistor Circuitry," *Nano Lett.*, vol. 8, no. 4, pp. 997–1004, 2008.

- [9] Ü. Özgür, Y. I. Alivov, C. Liu, A. Teke, M. A. Reshchikov, S. Doğan, V. Avrutin, S.-J. Cho, and H. Morkoç, "A comprehensive review of ZnO materials and devices," *J. Appl. Phys.*, vol. 98, no. 4, p. 41301, 2005.

- [10] M. Ding, D. Zhao, B. Yao, B. Li, Z. Zhang, and D. Shen, "The p-type ZnO film realized by a hydrothermal treatment method," *Appl. Phys. Lett.*, vol. 98, no. 6, p., 2011.

- [11] F. M. Li, G.-W. Hsieh, S. Dalal, M. C. Newton, J. E. Stott, P. Hiralal, A. Nathan, P. A. Warburton, H. E. Unalan, P. Beecher, A. J. Flewitt, I. Robinson, G. Amaratunga, and W. I. Milne, "Zinc Oxide Nanostructures and High Electron Mobility Nanocomposite Thin Film Transistors," *Electron Devices, IEEE Transactions on*, vol. 55, no. 11. pp. 3001–3011, 2008.

- [12] V. A. Coleman and C. Jagadish, *Zinc Oxide Bulk, Thin Films and Nanostructures*. Elsevier, 2006.

- [13] S. J. Pearton, D. P. Norton, L.-C. Tien, and J. Guo, "Modeling and Fabrication of ZnO Nanowire Transistors," *Electron Devices, IEEE Transactions on*, vol. 55, no. 11. pp. 3012–3019, 2008.

- [14] H. Liu, R. Peng, S. Chu, and S. Chu, "High mobility ZnO nanowires for terahertz detection applications," *Appl. Phys. Lett.*, vol. 105, no. 4, p. 43507, 2014.

- [15] W.-K. Hong, S. Song, D.-K. Hwang, S.-S. Kwon, G. Jo, S.-J. Park, and T. Lee, "Effects of surface roughness on the electrical characteristics of ZnO nanowire field effect transistors," *Appl. Surf. Sci.*, vol. 254, no. 23, pp. 7559–7564, Sep. 2008.

- [16] A. Ahnood, K. Ghaffarzadeh, A. Nathan, P. Servati, F. Li, M. R. Esmaeili-Rad, and A. Sazonov, "Non-ohmic contact resistance and field-effect mobility in nanocrystalline silicon thin film transistors," *Appl. Phys. Lett.*, vol. 93, no. 16, p. 163503, 2008.

- [17] S. Bang, S. Lee, J. Park, S. Park, W. Jeong, and H. Jeon, "Investigation of the effects of interface carrier concentration on ZnO thin film transistors fabricated by atomic layer deposition," *J. Phys. D. Appl. Phys.*, vol. 42, no. 23, p. 235102, 2009.

- [18] K. Kang, M.-H. Lim, H.-G. Kim, I.-D. Kim, and J.-M. Hong, "High field-effect mobility ZnO thin-film transistors with Mg-doped Ba<sub>0.6</sub> Sr<sub>0.4</sub> TiO<sub>3</sub> gate insulator on plastic substrates," *Appl. Phys. Lett.*, vol. 90, no. 4, p. 43502, 2007.

- [19] P. F. Carcia, R. S. McLean, and M. H. Reilly, "High-performance ZnO thin-film transistors on gate dielectrics grown by atomic layer deposition," Appl. Phys. Lett., vol. 88, no. 12, p. 123509, 2006.

- [20] A. D. Franklin, "Nanomaterials in transistors: From high-performance to thin-film applications," *Sci.*, vol. 349, no. 6249, Aug. 2015.

- [21] C. Rutherglen, D. Jain, and P. Burke, "Nanotube electronics for radiofrequency applications," *Nat. Nanotechnol.*, vol. 4, p. 811, Nov. 2009.

- [22] K. K. Lee, Y. Luo, X. Lu, P. Bao, and A. M. Song, "Development of Reactive-Ion Etching for ZnO-Based Nanodevices," IEEE Trans. Nanotechnol., vol. 10, no. 4, pp. 839–843, 2011.

# Chapter 2:

### Literature Review

This chapter presents the quantitative details of depletion-mode n-type ZnO nanowire FET with bottom gate structure and theory of field effect transistor (FET) upon the standard MOSFET approach. This chapter also discusses the literature on zinc oxide (ZnO) material, various ZnO nanowire deposition techniques and respective electrical properties. Its aim is to grasp the best method to fabricate high performance ZnO nanowire field-effect transistors (FETs) with excellent electrical characteristics.

### 2.1 Introduction

The electrical characteristics of nanowire-based FETs will be discussed in this chapter. FETs are a fundamental component in modern electronics, and are used in a wide variety of applications. The term FET indicates a three-terminal device where the current flow between source and drain is monitored by the electric field from the gate electrode. Nanowire FET have can be fabricated based on top-gate [1][2], bottom-gate [3][4] and surround-gate [5][6] geometries and all types of geometries show a promising FET characteristics. Mostly, nanowire FET are operated in an accumulation or depletion mode. The specific theory discussed in this chapter is based on depletion-mode n-channel fieldeffect transistors. The semiconductor employed in this study is ZnO and usually shows ntype conductivity. Thus the following discussion on FET mode of operation will focus on the FET structure with an n-type channel. Figure 2.1 shows the cross-sectional view of an n-type nanowire FET channel with a bottom-gate structure. It is assumed that the crosssection of the nanowire used in this section is a square shape rather than a circular, hexagonal or triangular nanowire shape to simplify the analytical calculation method based on thin film transistor (TFT) operation principles. This is because the fabricated ZnO nanowire FETs is technically a TFT and the conduction through ZnO nanowires is surfacecentred rather than bulk-centred. The nanowire is a semiconductor with n-type impurities and the metals are used for ohmic contacts of the source and drain. Here, L and d, represent the length and thickness of the nanowire, respectively.

Figure 2.1 Cross-section of an n-type nanowire FET with bottom-gate structure.

Typically, nanowire FET is treated using metal-oxide-semiconductor (MOSFET) equations. However, it is important to note that the nanowire FET structure owns some dissimilarities as compared to the widely studied. In a nanowire FET, the source and drain is made from metal electrode and it contact with the channel. In contrast, the source and drain regions of the MOSFET are made up of degenerately doped semiconductor. An additional property of nanowire FETs to consider is that usually the nanowire is uniformly doped along its axial length. In MOSFET, the channel have varies dopant profiles along its axial length in order to improve the performance.

Depletion-mode FETs are normally-on-state devices. Unlike a normally-off-state FET (enhancement-mode FET), a depletion mode FET have a conductive channel and current flow strongly between the drain and source when applying zero voltage gate. When a voltage gate is applied to the gate, the bands of the semiconductor bend and electron are either depleted or accumulated underneath the gate depending on the bias this concept is the basis for the operation of the nanowire FET.

### 2.1.1 Depletion

In the n-channel device, when the negative voltage  $V_{GS}$  is applied to the gate, the current from drain to source,  $I_{DS}$ , is turned off because the electric field created underneath the gate repels electrons and a depletion region form at the gate-insulator surface. Therefore, the bands near the ZnO surface are bend upward. As the negative bias increases, the depletion region expand because more electrons are withdrawn. The device is said to be in off-state since no conducting channel is present. Figure 2.2 shows a diagram of how a ZnO nanowire FET operates in depletion.

Figure 2.2 (a) Schematic of ZnO nanowire FET when negative voltage is applied (b) Energy band diagram of n-type ZnO nanowire FET in depletion conditions.

### 2.1.2 Inversion

When the negative voltage applied is further increased, a large number of holes were induced at SiO<sub>2</sub>/ZnO interface. Accordingly, the bands bend upwards even more so that the intrinsic level at the surface crosses over the Fermi level as shown in Figure 2.3. There is an additional electron at the SiO<sub>2</sub>/ZnO interface due to the minority carriers from the gate. In accordance with the charge in character observation, the condition where the number of minority carrier exceeds the number of majority carriers is referred to as inversion. However, in the case of a ZnO nanowire FET with the background n-type doping present in the material system, the inversion condition is difficult to realize under practical conditions because the ZnO based material is a wide band gap semiconductor [7].

Figure 2.3 (a) Schematic of ZnO nanowire FET when negative voltage is applied (b) Energy band diagram of ZnO nanowire FET in inversion.

### 2.1.3 Accumulation

The unique features of depletion-mode FETs is that they can also be made to operate in the enhancement-mode. This mode can be achieved by applying a positive bias to the gate. When the gate voltage is increased above the threshold voltage,  $V_{TH}$ , ( $V_{GS} > V_{TH}$ ), the free electron is accumulated at the  $SiO_2/ZnO$  interface. Therefore, the bands near the ZnO surface are bent downwards and the conduction band edge becomes closer to the Fermi level. The schematic band diagram is shown in Figure 2.4.

Figure 2.4 (a) Schematic of ZnO nanowire FET when positive voltage is applied (b) Energy band diagram of ZnO nanowire FET in accumulation.

If the gate voltage is keep on increased, the voltage drop across the ZnO channel and the corresponding potential difference leads to an expansion of the depletion layer at the drain side of the ZnO channel. When the drain bias equal to the gate bias ( $V_{DS} = V_{GS}$ ), the width of the depletion layer equals to the thickness of the ZnO channel resulting in the onset of pinch-off and the drain current start to saturates. An excessive increase of the gate voltage lead to the increase of the  $V_{DS}$  result in the breakdown of the channel.

### 2.2 Electrical Characterization of Nanowire FET

The term FET indicates a three terminal device where the transverse electric-field imparted by the gate electrode controls the resistance of a ZnO channel between the source and drain terminals. In the fabrication of high performance FETs, feedback between device fabrication and characterization is important for the device optimization. Hence, accurate parameter extraction is essential in the high performance FETs. Based on the operation principle discussed previously, electrical characteristics of nanowire FETs will be discussed in this section.

#### 2.2.1 Flat Band Voltage

The transfer from accumulation to depletion regions occurs at a finite voltage,  $V_{FB}$  called flat band voltage. It is the voltage at which the bands in the semiconductor are flat, which implies that no charge exists in the semiconductor. The flat band voltage basically equals the difference between the gate metal work function,  $q\mathcal{O}_m$ , and the semiconductor work function,  $q\mathcal{O}_s$ . This is the condition when there is no charge is present in the oxide or at the oxide-semiconductor interface and is referred to as the ideal flat band condition.

$$V_{FB} = q \emptyset_{ms} = q \emptyset_m - q \emptyset_s \tag{1}$$

The work function is the energy difference between the vacuum level and the Fermi level, which varies with the doping concentration.

### 2.2.2 Current-Voltage Relationship Concepts

In the linear region, the drain current  $(I_D)$  is dependent on both  $V_{GS}$  and  $V_{DS}$ . The  $I_D$  is a mixture of drift and diffusion currents. In the linear region operation the drift current becomes prominent and diffusion is negligible due to uniformity of the channel charge

from source to drain. Considering a differential drain voltage for an elemental section dy of conducting channel given by [8].

$$dV = I_D dR = \frac{I_D dy}{\mu_{FE} W |Q_{acc}(y)|}$$

(2)

Where  $\mu_{FE}$  is the field-effect mobility and  $Q_{acc}(y)$  is the total accumulation charge per unit area induced at position y within the channel given by:

$$Q_{acc}(y) = C_{ox}|V_G - V_{TH} - V(y)|$$

(3)

Separating the current from the voltage in Eq.3 gives:

$$I_D dy = \mu_{FE} W |Q_{acc}(y)| dV \tag{4}$$

Substituting Eq. 3 into Eq.4 and integrating from the source (y = 0, V = 0) to the drain (y = 0, V = 0)L,  $V = V_D$ ) gives

$$I_D \int_0^L dy = \mu_{FE} W \int_0^{V_D} [C_{ox}(V_G - V_{TH} - V(y))] dV$$

(5)

Then Eq.5 yields

$$I_D = \frac{W}{L} C_{ox} \mu_{FE} \left\{ (V_G - V_{TH}) V_D - \frac{1}{2} V_D^2 \right\}$$

(6)

Since

$$V_D << V_G - V_{TH}$$

, Eq.6 is normally simplified into

$$I_D = \frac{W}{L} C_{ox} \mu_{FE} (V_G - V_{TH}) V_D$$

(7)

When  $V_D \ge (V_G - V_{TH})$  channel pinches off. The channel actually ends before the drain edge. The drain current will saturate once the channel pinches off and become constant irrespective of any further increase in  $V_{D}$ . The resulting equation for  $I_D$  is as follows:

$$I_{Dsat} = \frac{W}{2L} C_{ox} \mu_{sat} (V_G - V_{TH})^2$$

(8)

#### 2.2.3 Threshold Voltage, $V_{TH}$

Threshold voltage,  $V_{TH}$  is defined as the minimum applied gate bias which can conduct a channel between the source and drain that is needed to turn the device on for linear and saturation regions of operation. The discussion in this section will focus mainly

the derivation of the threshold voltage for depletion mode n-type ZnO nanowire FET. In this type of device, a negative gate bias will induce a space charge region under the oxide, reducing the thickness of the n-channel. A positive gate bias will create an electron accumulation layer, which increases the drain current. At threshold, it can be defined that the gate voltage,  $V_G = V_{TH}$  where  $V_{TH}$  is the threshold voltage. The threshold voltage equals the sum of the flatband voltage, twice the bulk potential and the voltage across the oxide due to the depletion layer charge. The threshold voltage for the depletion mode n-type ZnO nanowire FET can be written as [9]:

$$V_{TH} = V_{FB} + 2\Psi_B + V_{DEP} \tag{9}$$

The potential due to the uncovered depletion layer charge is given by:

$$V_{DEP} = \frac{Q_{DEP}}{C_o} \tag{10}$$

The uncovered charge per unit area in the depletion region is simply

$$Q_{DEP} = -qN_DW (11)$$

In the n-channel depletion mode nanowire FET, the bulk potential is negative (the band diagram bends upwards). By tying all the equation above it gives:

$$V_{TH} = V_{FB} - \frac{qN_DW}{C_0} - 2\Psi_B \tag{12}$$

### 2.2.4 The Subthreshold Region

When  $V_G$  is significantly larger than  $V_{TH}$ , the channel has plenty of mobile electrons and the current has limited drift due to  $V_D$ . However, when  $V_G$  is around  $V_{TH}$  or less than  $V_{TH}$ , the current is mainly due to diffusion current. The drain current in this region, is called the subthreshold current, and it is a critical characteristic for transistors operating at low voltage for low power applications. The subthreshold region reflects how fast the device can switch. The subthreshold current is given by:

$$I_D = I_{DI} \left( e^{\frac{q(V_G - V_{TH})}{nkT}} \right) \left( 1 - e^{\frac{qV_D}{kT}} \right) \tag{13}$$

where  $I_{DI}$  is a dependent on temperature, device dimensions and channel doping. The term n in the equation is given by:

$$n = 1 + \frac{C_{DEP}}{C_{ox}} \tag{14}$$

$C_{DEP}$  is the depletion capacitance per unit area and it is defined as:

$$C_{DEP} = \frac{\varepsilon_{ZnO}}{W_{DEP}} \tag{15}$$

The depletion width  $W_{DEP}$  may be derived to be:

$$W_{DEP} = W_m = \sqrt{\frac{\varepsilon_{ZnO}\varepsilon_o kT ln \frac{N_A}{n_i}}{qN_A}}$$

(16)

Subthreshold swing is another important device characteristic in the subthreshold region. The subthreshold swing, SS is defined as the change in the gate voltage required to reduce subthreshold current by one decade [5]. The subthreshold swing of a device is a measure of how fast the FET switches from the off state to the on state. This happens over the subthreshold regime of the transfer characteristics, which happens at gate voltages slightly below the threshold voltage. The logarithm is taken off the transfer characteristics, and the subthreshold swing is then the inverse of the gradient of the subthreshold regime. It is usually given in mV/decade, where the decade refers to an order of magnitude of source-drain current.

$$SS = \frac{dV_G}{d(logI_D)} \tag{17}$$

When  $V_D$  is larger than kT/q, the last term in Eq.13 can be ignored. Hence, the subthreshold swing varies exponentially with gate voltage. Thus, a curve of log  $(I_D)$  versus  $V_G$  is linear in the subthreshold region as shown in Figure 2.5, such a plot has a subthreshold swing of [10],

$$SS = n \frac{kT}{q} \ln 10 \, V/decade \tag{18}$$

Figure 2.5  $I_{DS}$ - $V_{GS}$  curve in linear (blue) and semi-logarithmic scale of  $I_{DS}$ .

Theoretically, the subthreshold swing of 60 mV/decade is considered to be the lowest subthreshold swing achievable by a typical FETs [11]. A good device should have a steeper subthreshold swing in order for the device to be turned on using lower voltage.

## 2.3 Zinc oxide material system

Zinc oxide (ZnO) is an inorganic binary compound belonging to the II-VI semiconductor material group whose ionicity resides at the borderlines between the ionic and covalent semiconductor [12]. Research on ZnO has been being conducted since the early 1930 s [13][14]. In the last few years, we have seen the overwhelming interest in the material system possibilities of growing high quality ZnO single crystal and ZnO nanostructures. The ZnO is an excellent candidate for application in several different areas because it has a number of superior attributes when compared to other material such as GaN.

ZnO is an environmentally friendly material, wide band gap semiconductor with a direct gap of  $E_g \sim 3.4 \text{eV}$  at 300 K which has been the focus of intense materials research and device development. The ZnO has fairly high quality bulk single crystal and a large exciton binding energy ( $\sim 60 \text{meV}$ ) [13]. The electron Hall mobility of single crystalline ZnO using Monte Carlo simulation is estimated to be around 300 cm<sup>2</sup>/Vs at room temperature [15] and its density is 5.6 gcm<sup>-3</sup> [16] Moreover, ZnO can easily be etched in

acidic or alkaline solution at low temperatures. Another beneficial factor of ZnO in an electronic device is the possibility of patterning by wet etching [16].

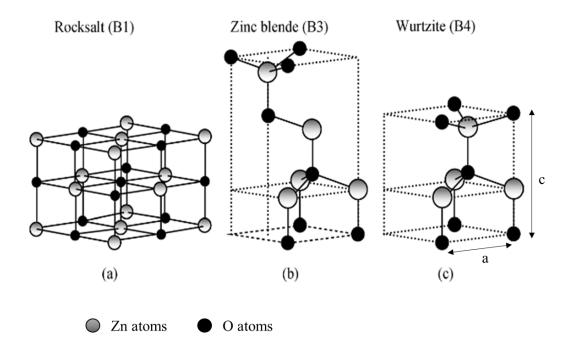

ZnO can crystallize in three different crystals; wurtize (B4), zinc blende (B3) or rarely observed rocksalt (B1) as shown in Figure 2.6. However, ZnO preferentially crystallizes in the hexagonal wurtize-type, which is the stable phase of ZnO at 300 K and is most common form [12]. The zinc blend form can be stabilized by growing ZnO on substrate with cubic lattice structure. In both wurtize and zinc blends, the zinc and oxide centres are tetrahedral. The rocksalt (NaCl-type) structure is only observed at relatively high pressures of about 10 GPa [12]. The ZnO crystal is a hexagonal wurtize structure and exhibits partial polar characteristics with lattice parameters a = 0.3296, and c = 0.52065 nm, where the  $O^{2-}$  and the  $Zn^{2+}$  create alternating planes of tetrahedral coordinated units [13].

Most of the II-VI material show largely ionic bonding, which explains its strong piezoelectricity. Owing to the polar Zn-O bonds, zinc and oxygen planes bear positive and negative charges. In most similar materials, in order to keep electrical neutrality, those planes restructure at the atomic level. However in ZnO, its surfaces are atomically flat, stable and exhibit no reconstruction. This irregularity of ZnO has not yet been fully explained [3].

Figure 2.6 Stick and ball representation of ZnO crystal structures: (a) cubic rocksalt (B1), (b) cubic zinc blende (B3), and (c) hexagonal wurtzite (B4). The shaded gray and black spheres denote Zn and O atoms, respectively. Figure reproduced from Ref. [12].

Research interest in ZnO includes a diverse set of fields and each of them is inspired with respect to different applications. ZnO is used at the cutting edge of research in transparent electronics, optoelectronics, photovoltaics, diluted ferromagnets, sensors and solar cells [13][14][16]–[18].

### 2.4 Electrical properties of Zinc Oxide