# UNIVERSITY OF SOUTHAMPTON FACULTY OF ENGINEERING AND APPLIED SCIENCE ELECTRONICS DEPARTMENT

## LASER TESTING OF INTEGRATED CIRCUITS

A thesis submitted for the degree of

Doctor of Philosophy of the University of Southampton

Ъy

Harry Edward Oldham

- August 1977 -

#### UNIVERSITY OF SOUTHAMPTON

#### ABSTRACT

#### FACULTY OF ENGINEERING AND APPLIED SCIENCE

#### ELECTRONICS

#### Doctor of Philosophy

#### LASER TESTING OF INTEGRATED CIRCUITS

by Harry Edward Oldham

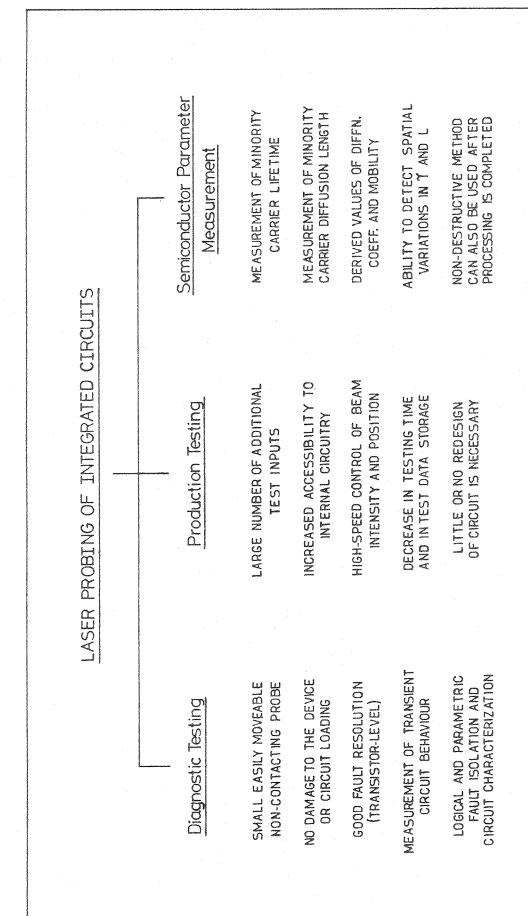

Comprehensive testing is one of the major problems in the production of l.s.i.: principally this is because of the small number of circuit nodes which are directly accessible to the tester and the extremely long input sequences needed for exhaustive testing.

A technique is presented in which information is injected directly into the internal circuitry of an integrated circuit via a finely focussed laser beam. The intensity of the light input is controlled by an electro-optic modulator, enabling data patterns to be inserted at high speed. The laser beam power necessary to achieve this task in an i.c. is dependent upon the circuit implementation: a small 2mW laser has proved to be adequate for the testing of M.O.S. and I<sup>2</sup>L circuitry but more than 10mW is needed for some forms of T.T.L., E.C.L. and C.M.O.S.

The non-contacting, non-destructive laser probe has also been used to determine some features of the operation of the internal circuitry, including measurement of transient waveforms, and two important semiconductor parameters — diffusion length and lifetime.

Fault diagnosis with improved resolution can be performed quickly and easily by using the moveable laser input and large savings in the time taken for fault detection are also envisaged from this technique, especially when used in conjunction with conventional automatic test equipment.

#### ACKNOWLEDGEMENTS

I would like to thank my supervisor, Mr J.G. Smith, for his continuing support and encouragement and the other members of the Microelectronics Group, in particular Mr H.A. Kemhadjian and Dr. A. Brunnschweiler, for helpful discussions and comments throughout this work. It is also a pleasure to acknowledge the invaluable assistance and enthusiasm of my colleague Mr J.C. White at all levels and on many topics during the past three years.

H.E. Oldham

# CONTENTS

|              |                                               | Page |

|--------------|-----------------------------------------------|------|

| Chapter      | 1. Introduction                               | 1    |

|              |                                               |      |

| Chapter      | 2. A Background to Integrated Circuit Testing | 4    |

| 2.1          | Faults and Failure Mechanisms                 | 5    |

| 2.2          | Methods used in I.C. Testing                  | 6    |

|              |                                               |      |

| 2.3          | Fault Detection in Digital I.C.'s             | 7    |

| 2.4          | L.S.I. Testing Problems                       | 8    |

| 2.5          | Testability of Integrated Circuits            | 11   |

| 2.6          | Provision of Extra Circuit Inputs             | 15   |

|              |                                               |      |

| Chapter      | 3. The Laser Probe                            | 17   |

| 3.1          | Optical Illumination of a semiconductor       | 18   |

|              | 3.1.1 Photoconductivity                       | 18   |

|              | 3.1.2 The photovoltaic effect                 | 20   |

| 3.2          | The Light Source                              | 23   |

| 3.3          | Characteristics of the Laser                  | 24   |

| 3.4          | Production of the Laser Probe                 | 25   |

|              | 3.4.1 Beam focussing                          | 25   |

|              | 3.4.2 Other aspects of the optical system     | 29   |

| 3.5          | Laser Probing of a Silicon Integrated Circuit | 29   |

|              | 3.5.1 Circuit preparation and mounting        | 29   |

|              | 3.5.2 Laser damage to the i.c.                | 30   |

| 3.6          | Light Beam Modulation                         | 31   |

|              | 3.6.1 The electro-optic modulator             | 32   |

|              | 3.6.2 Experimental arrangement                | 34   |

| 3 <b>.</b> 7 | The Laser Input                               | 35   |

|              | 3.7.1 Electronic control system               | 35   |

|              | 3.7.2 Overall system performance              | 35   |

|                                                     | Page |

|-----------------------------------------------------|------|

| Chapter 4. Laser Beam Evaluation of a Semiconductor | 39   |

|                                                     |      |

| 4.1 Quantum Efficiency                              | 40   |

| 4.1.1 Introduction                                  | 40   |

| 4.1.2 Results                                       | 41   |

| 4.1.3 Analysis                                      | 43   |

| 4.2 Carrier Injection Levels                        | 49   |

| 4.3 Diffusion Length                                | 53   |

| 4.3.1 Elementary theory                             | 53   |

| 4.3.2 Measurements                                  | 55   |

| 4.3.3 Analysis of the results                       | 58   |

| 4.3.4 Interference from other junctions             | 64   |

| 4.4 Lifetime                                        | 70   |

| 4.4.1 Elementary theory                             | 70   |

| 4.4.2 Measurements                                  | 71   |

| 4.4.3 Analysis of the results                       | 76   |

| 4.4.4 The effect of lifetime upon the               | 82   |

| laser testing rate                                  |      |

| 4.5 Semiconductor Substrate Characterization        | 82   |

|                                                     |      |

|                                                     | 85   |

| Chapter 5. Laser Probing of I.C.'s                  | 05   |

| 5.1 Photoeffects in Simple Circuits                 | 86   |

| 5.2 Illumination of Linear Integrated Circuits      | 92   |

| 5.2.1 The 709 op. amp.                              | 92   |

| 5.2.2 The 741 op. amp.                              | 95   |

| 5.2.3 The CA3130 op. amp.                           | 99   |

| 5.3 Laser Probing of Shift Registers                | 102  |

| 5.3.1 The shift register                            | 102  |

| 5.3.2 Optical data insertion                        | 108  |

| 5.4 Laser Probing of Different I.C. Families        | 111  |

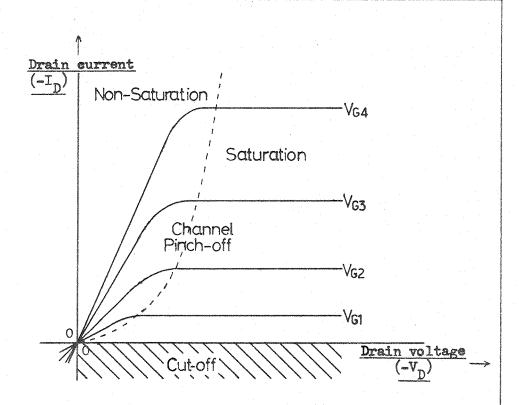

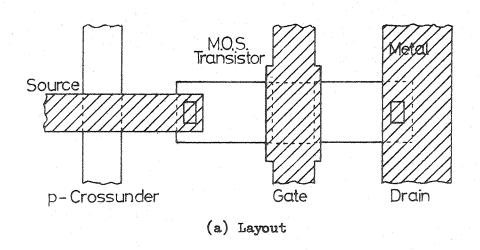

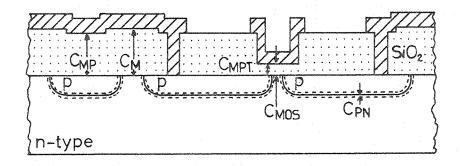

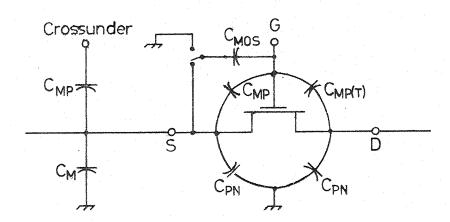

| 5.4.1 p-Channel static M.O.S. logic                 | 112  |

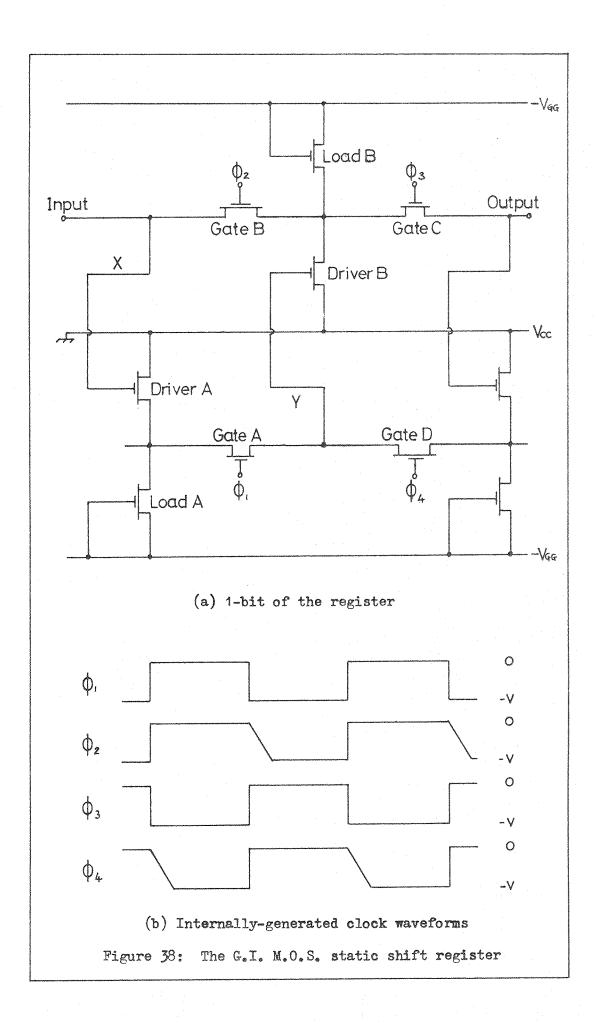

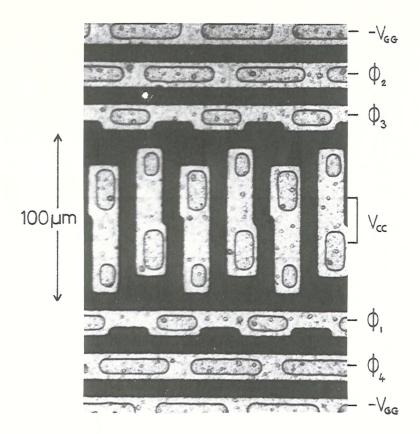

| 5.4.1.1 The M.O.S. static shift register            | 112  |

| 5.4.1.2 The ML232B T.V. touch tuner                 | 116  |

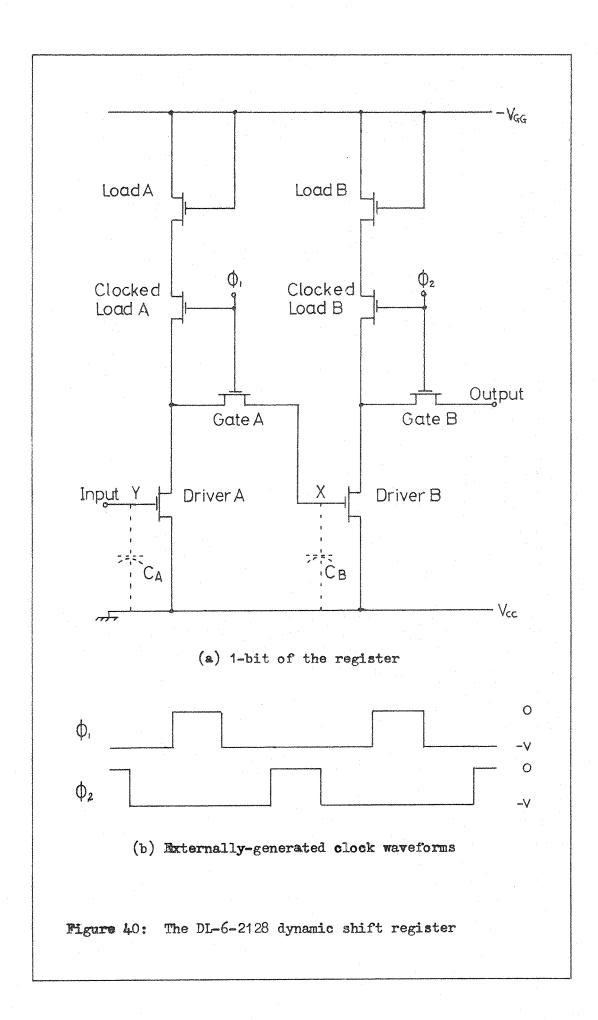

| 5.4.2 p-Channel dynamic M.O.S. logic                | 120  |

|                                                     | 122  |

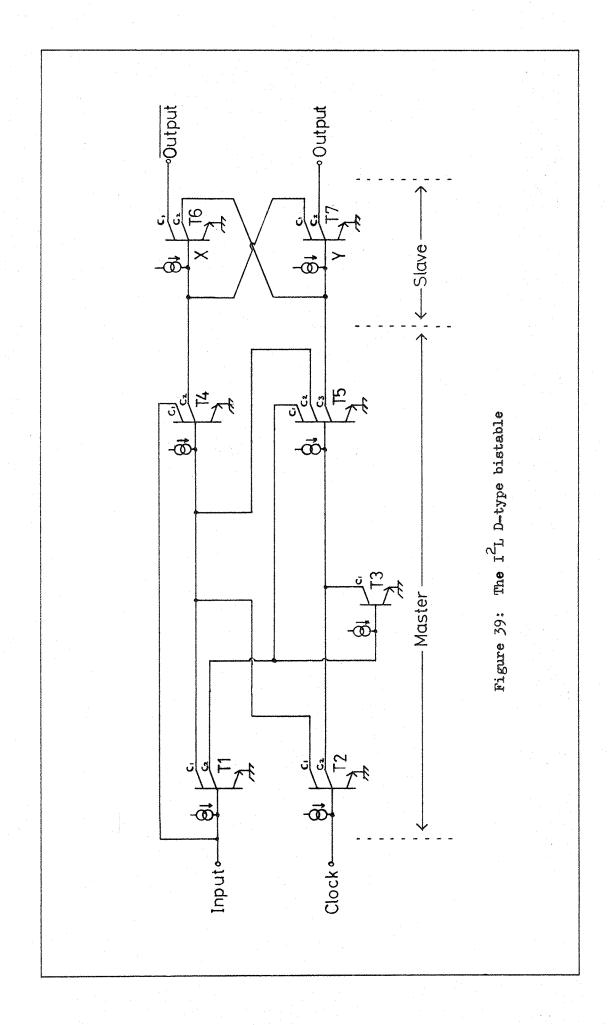

| 5.4.3 Integrated injection logic                    | 126  |

| 5.4.4 Low power schottky T.T.L.                     | 120  |

|         |               |                                                     |   | Page |

|---------|---------------|-----------------------------------------------------|---|------|

|         | 5.4.5         | Standard T.T.L.                                     |   | 131  |

|         | 5.4.6         | Complementary M.O.S. logic                          |   | 134  |

|         | 5.4.7         | Laser testing of other i.c.'s                       |   | 137  |

|         |               | 5.4.7.1 M.O.S. circuits and insulating              |   | 139  |

|         |               | substrate devices                                   |   |      |

|         |               | 5.4.7.2 Bipolar i.c.'s                              |   | 140  |

|         |               | 5.4.7.3 Charge coupled devices                      |   | 144  |

|         |               | 5.4.7.4 Summary                                     |   | 144  |

| 5.5     | Measur        | rement of the Internal Circuit Operation            |   | 146  |

|         | 5.5.1         | Parametric testing with the laser probe             |   | 146  |

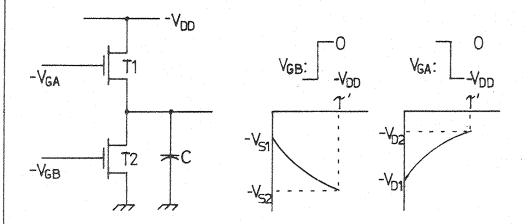

|         | 5.5.2         | M.O.S. static shift register transfer               |   | 147  |

|         |               | gate response                                       |   |      |

|         | 5.5.3         | M.O.S. dynamic shift register transfer              |   | 152  |

|         |               | gate response                                       |   |      |

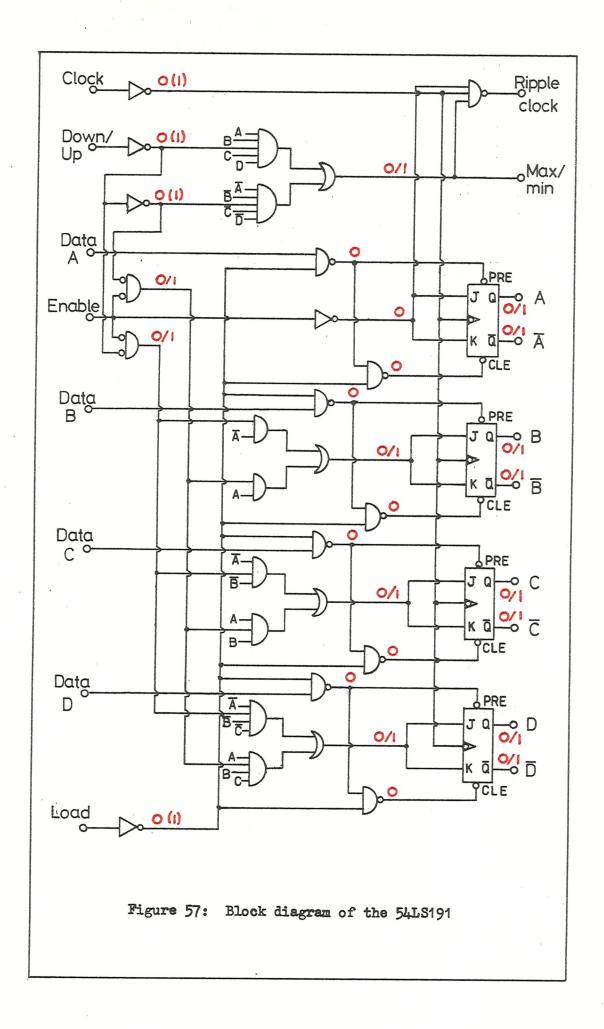

| 5.6     | Laser         | Testing of the SN54LS191                            |   | 152  |

|         |               |                                                     |   |      |

| Chanter | 6 De          | evelopment of a Commercial Laser I.C. Test System   |   | 159  |

| onapter | 0. <u>D</u> 0 | veriophenic of a commercial basel 1,0, 1050 by boom |   | ינעו |

| 6.1     | Test S        | trategy using the Laser Probe                       |   | 160  |

|         | 6.1.1         | Laser probing at the transistor level               |   | 160  |

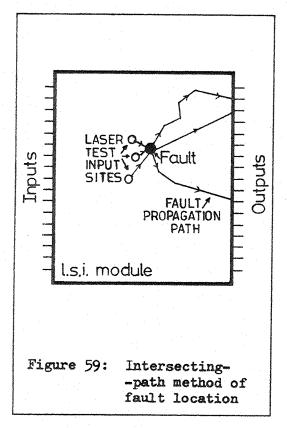

|         | 6.1.2         | Fault diagnosis                                     |   | 161  |

|         | 6.1.3         | High-speed fault detection                          |   | 162  |

| 6.2     | Practi        | cal I.C. Testing using a Laser                      |   | 163  |

|         | 6.2.1         | Diagnostic testing                                  |   | 163  |

|         | 6.2.2         | Production (go/no-go) testing                       |   | 165  |

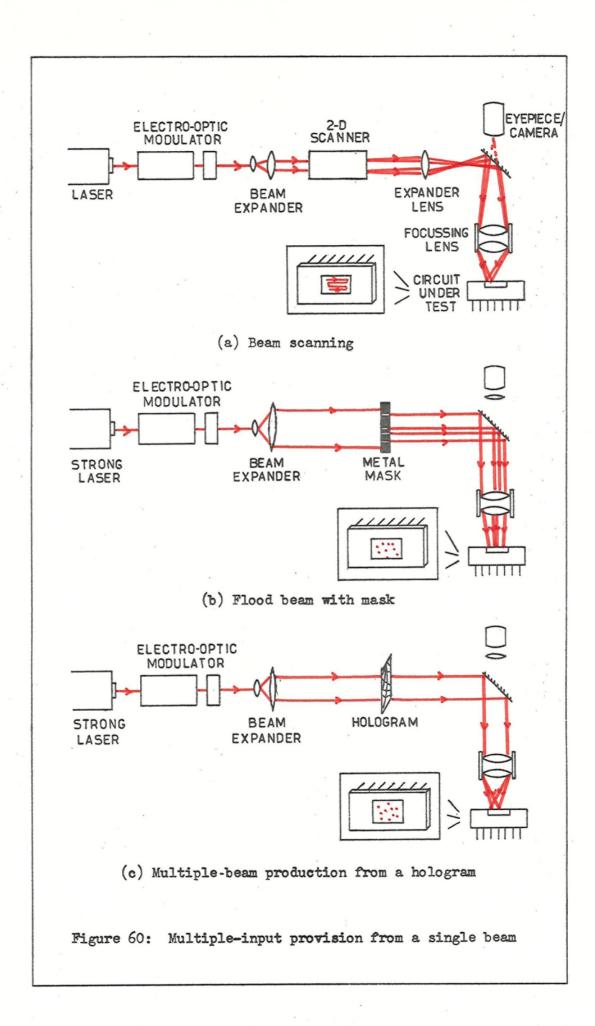

|         |               | 6.2.2.1 Provision of multiple inputs                | , | 166  |

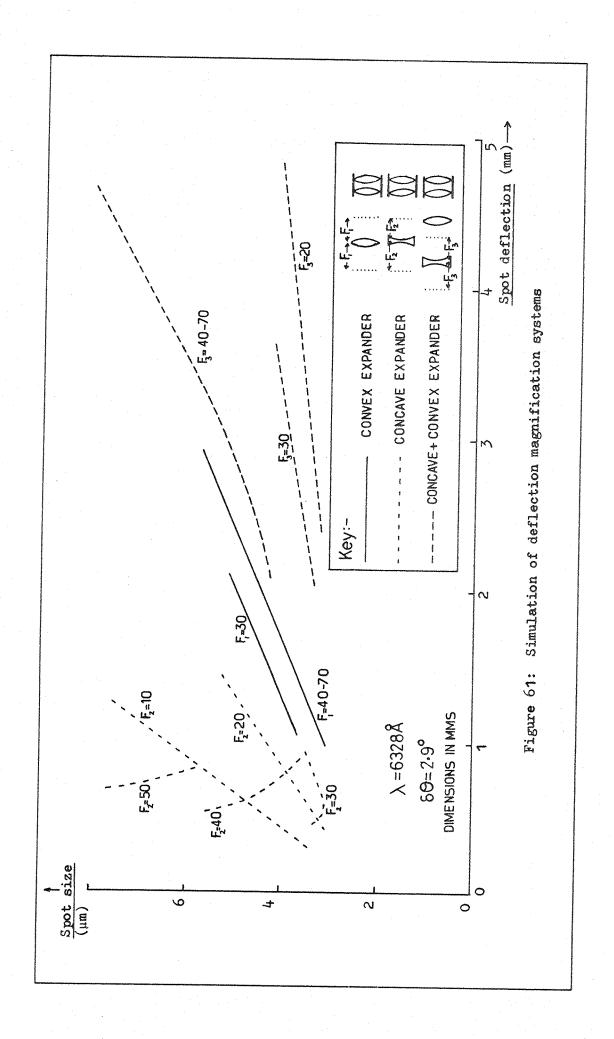

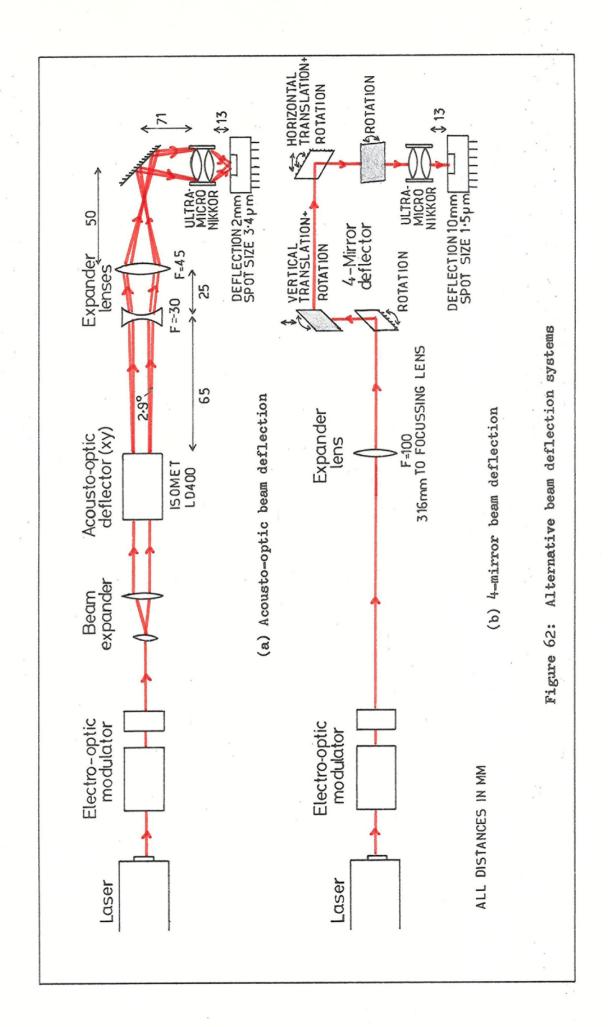

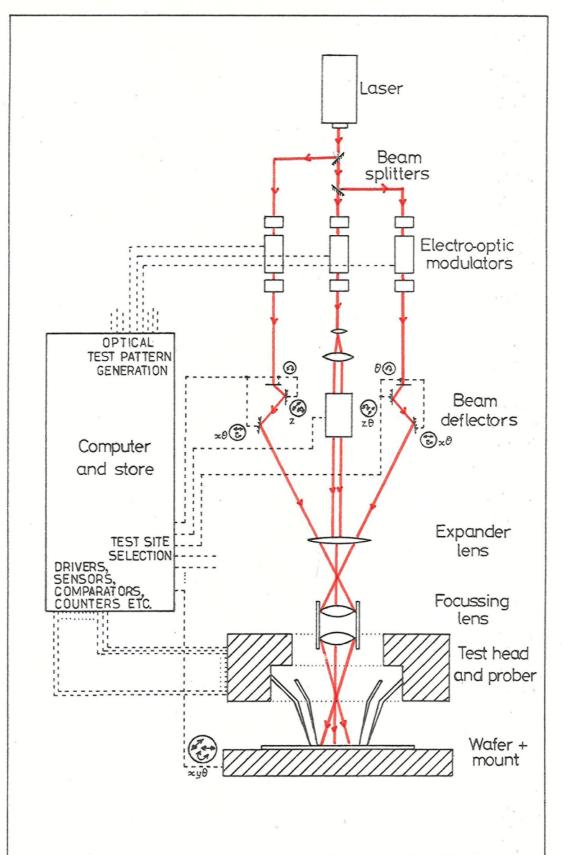

|         |               | 6.2.2.2 Automatic beam deflection                   |   | 169  |

|         |               | 6.2.2.3 Beam alignment                              |   | 174  |

|         |               | 6.2.2.4 Integration with a conventional             |   | 175  |

|         |               | i.c. tester                                         |   |      |

| 6.3     | Design        | of Laser-Testable Circuits                          |   | 177  |

| 6.4     | Future        | Possibilities                                       |   | 180  |

|         |               |                                                     |   |      |

| Chanton | 7 C-          | nelusion                                            |   | 181  |

| onapter | /• <u>uo</u>  | nclusion                                            |   | 101  |

|         |               |                                                     |   |      |

| Referen | ces Cit       | ed                                                  |   | 186  |

|             |                               | Page |

|-------------|-------------------------------|------|

| Appendices  |                               | 194  |

| Appendix 1. | Gaussian Beams                | 195  |

| Appendix 2. | Reflection and Interference   | 198  |

| Appendix 3. | Injection Levels and Excess   | 201  |

|             | Carrier Distribution          |      |

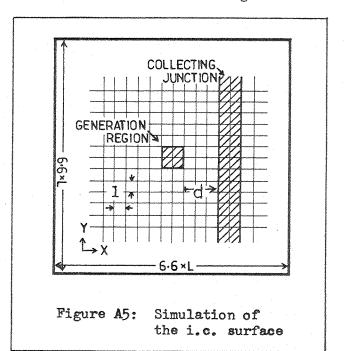

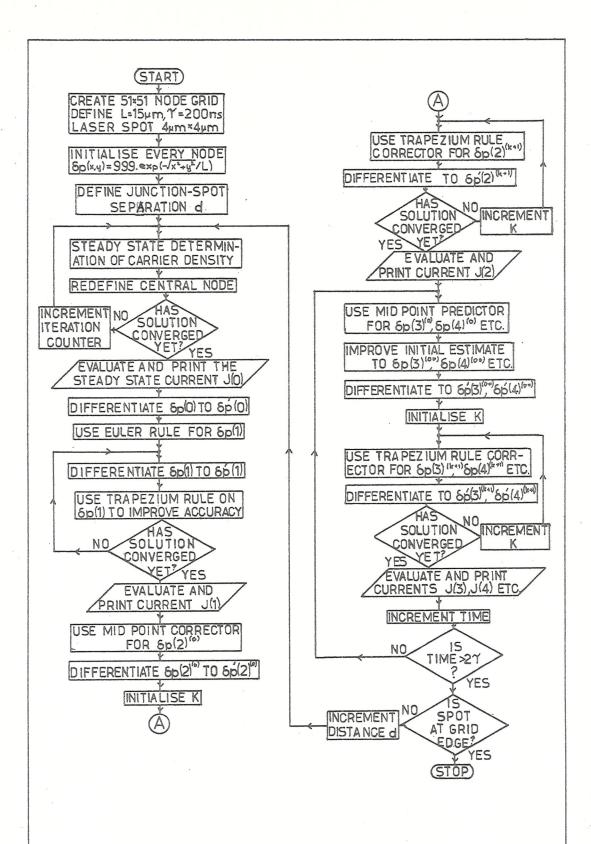

| Appendix 4. | Computer Simulation of Excess | 211  |

|             | Carrier Distribution          |      |

| Appendix 5. | Nodal Isolation               | 218  |

| Appendix 6. | M.O.S. Circuit Analysis       | 220  |

| Appendix 7. | Laser I.C. Test Equipment     | 226  |

| Appendix 8. | Published Paper               | 229  |

# CHAPTER 1

# INTRODUCTION

#### 1. INTRODUCTION

Electronic circuits have been shrunk by modern technology to a fraction of the size occupied by their predecessors, particularly since the introduction of integrated circuits. The reliability of these devices is very high, they are relatively cheap and in many cases can operate faster and with less power dissipation than previous circuits.

However, as they increase in complexity, it becomes much harder to ensure that they are working correctly in every detail. evolutionary refinements in circuit design and manufacturing techniques have outpaced testing methods so that today very large scale integrated circuits (vlsi) are being produced which cannot be tested economically, because the test routines can only cope efficiently with medium scale integration (msi) where the ratio of input and outputs to the circuit interior is much larger. The only way to test large complicated circuits has been to apply extremely long test sequences to the devices' inputs in order to exercise them through all, or most of, the possible conditions they may encounter in service. This process may take so much time and involve such vast amounts of information storage that the cost of testing becomes much larger than the cost of producing the device; thus the problem of quick and efficient integrated circuit testing must be solved if the trend towards cheaper and more comprehensive circuitry is to be maintained.

A technique is presented in this thesis which can be used to speed up the test process and improve the testability of a circuit by introducing extra inputs without the need for major redesign of the circuit itself. The method is based upon the fact that a laser beam produces a current when it hits the surface of an integrated circuit: this behaves in the same way to a current injected by a conventional probe positioned at the same point, but the laser 'probe' has the advantage of being non-contacting, very small and easily moved from site to site.

The operation, characteristics and capabilities of the laser probe are detailed in sections 3 and 5 and another use of the method is described in section 4, under the heading 'Evaluation of the semiconductor substrate'. Present methods of integrated circuit testing are described in section 2, and the advantages and changes which laser probing would bring in this context are discussed in the penultimate section.

A summary of the results is presented in section 7, by which stage it is to be hoped that laser testing of integrated circuits will be seen to be useful in counteracting the situation where testing integrated circuits is often more of a problem than making them.

#### CHAPTER 2

### A BACKGROUND TO INTEGRATED CIRCUIT TESTING

- Faults and failure mechanisms

- m Methods used in i.c. testing

- Fault detection in digital i.c.'s

- L.S.I. testing problems

- Testability of integrated circuits

- Provision of extra circuit inputs

#### 2. A BACKGROUND TO INTEGRATED CIRCUIT TESTING

In the most general sense, i.c. testing means an application of an input sequence to a device followed by a comparison between the precomputed 'expected' output sequence and the one actually observed. Any discrepancy implies a failure, the cause of which is a fault.

#### 2.1 Faults and Failure Mechanisms

Faults can be categorised into two broad groups: logical and parametric. A logical fault is one which causes the logical operation of a circuit to be changed to some other function, but a parametric fault alters the magnitude of a circuit parameter, such as speed, current or voltage, without necessarily changing the logical behaviour of the circuit. For example, a short would probably be a logical fault whereas a 'leaky' reverse characteristic of a transistor could be a parametric fault.

A fault may occur at any time during the life of an integrated circuit: in the manufacturing process or during assembly, testing, storage and in service. The nature of the faults encountered in each of these periods is different, so consequently the type of testing which is performed at each stage differs. A mixture of logical and parametric faults may occur during manufacture (such as masking defects and bulk shorts) then further failure modes can be introduced during the assembly and testing processes (for example, open bonds or shorting leads). Factors such as high temperature and humidity may produce parametric faults during the storage phase and finally when the circuit is actually used, more failures can be introduced because of heat dissipation, vibration, voltage stress and ageing. A typical graph of failure rate against time for an integrated circuit family shows a 'bathtub' distribution with a high initial failure rate, reaching a low value after the early failures are discarded and finally rising again when component ageing becomes significant.

Failures are caused by an imperfect manufacturing process or an unsatisfactory operating environment; thus not only does a fault have to be found, but its location and cause needs to be determined in order to prevent its recurrence in future devices. Emphasis is therefore given to diagnostic testing during the initial stages of the manufacture of a new circuit but when the 'teething troubles' are overcome and production begins on a large scale, then commonly fault detection alone is used (a go/no-go test).

#### 2.2 Methods used in I.C. Testing

The performance of an integrated circuit is monitored at each stage of its life in order to discover any failures as soon as they arise<sup>3</sup>. A typical test routine is as follows<sup>4</sup>:

- (i) In-process inspection: this is a sampling test made to a specific acceptable quality level which is performed throughout the processing of the device, for example slice inspection after the oxide etch prior to diffusion. The final test is often a visual screen.

- (ii) Wafer test: some manufacturers perform only a minimal test at the wafer stage, usually a simple continuity test, when the faults introduced during assembly are considered to be significant, but others give a full test of type (iv) before bonding. Clock rate testing may not be possible for very high speed circuits because of probe loading.

- (iii) Accelerated ageing: the circuit is stressed to precipate any time-related failure modes and weed out any latent early failures. This process, which may last for up to 1000 hours, usually includes thermal shock and thermal cycling, electrical and mechanical stressing and a hermiticity check.

- (iv) Functional, parametric and clock rate testing:

these tests are to ensure that the device performs

according to its electrical specifications. Only

simple d.c. tests are used if a full wafer test

has been performed prior to bonding.

- (v) Incoming inspection: many i.c. users perform their own tests (of type (iv)) upon bought devices before incorporation into a final system.

Of these classifications, by far the most effort, time and money is spent on categories (ii) and (iv), but only full wafer testing will be considered in this work.

# 2.3 Fault Detection in Digital I.C.'s

Analogue circuit tests are usually specifically designed for the particular type of circuit being tested, so no generalizations can be made for testing this type of device.

Digital circuits are characterized by the feature that the steadystate circuit responses can only assume one of two values. They may be studied at the circuit level where the analysis is concerned with waveforms and currents etc., or at the logic level when only two states, logical 'O' and '1', are possible.

Digital circuit tests can be sub-divided into three branches<sup>5</sup>:

- (a) Functional (DC) testing in which all parts of the circuit are exercised by applying binary input patterns and analysing the corresponding steady-state outputs to check the functional operation of the device. This type of testing usually involves a large number of tests and is performed as fast as possible.

- (b) Parametric (AC) testing is used to check the timerelated behaviour of the circuit and involves the measurement of actual voltage and current levels to high accuracy, but the test rate is usually low.

(c) Clock rate testing is similar to functional testing, but is performed at rates near the maximum and minimum clock speed of the circuit under test.

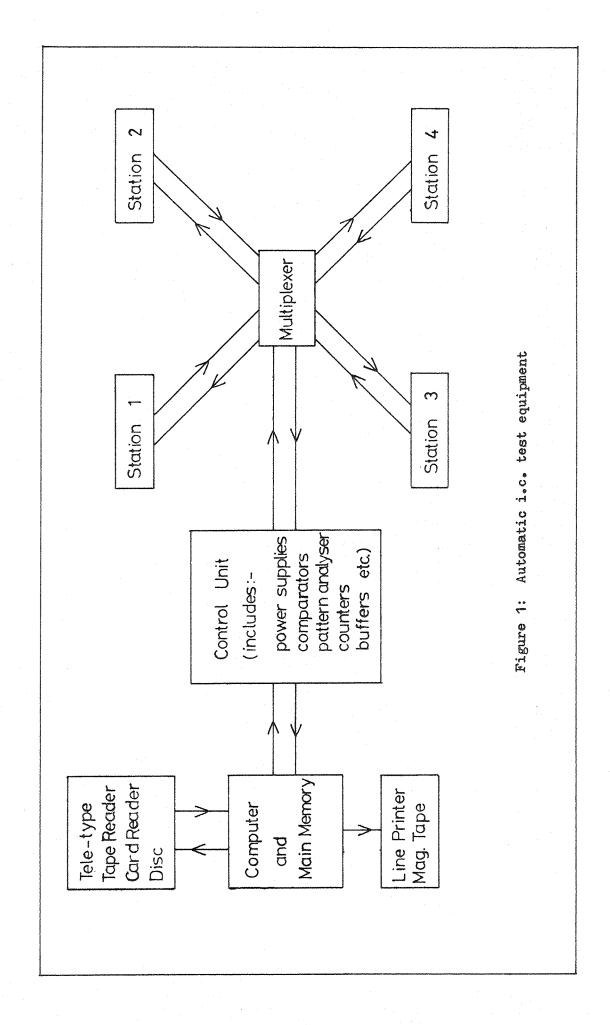

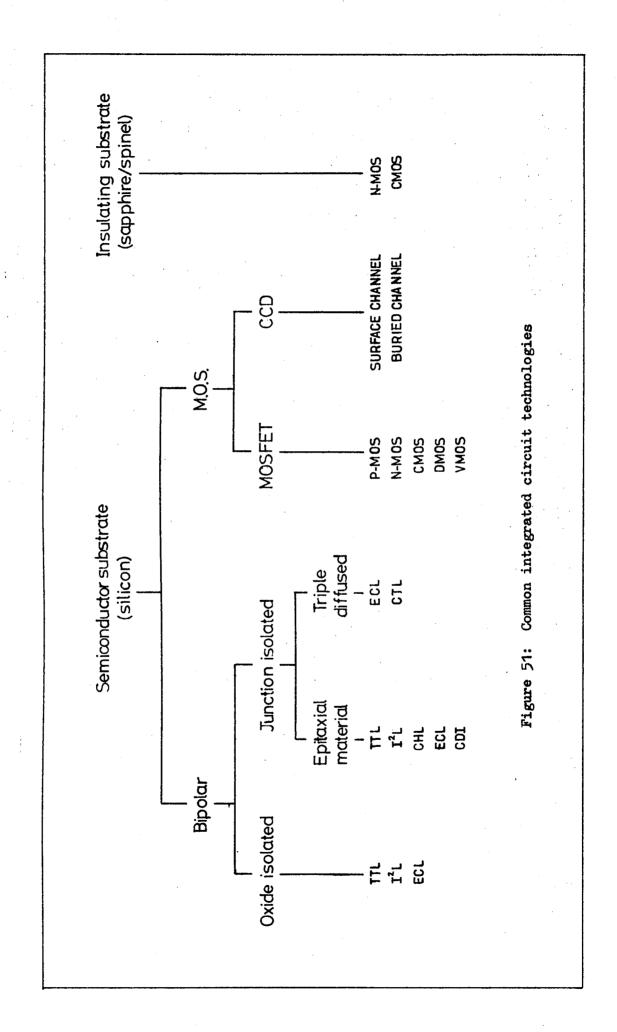

Integrated circuit testers range in complexity from a simple comparison tester which can perform some limited functional tests to fully computerised automatic systems with multiple test stations which can perform all of the above tests on i.c.'s fabricated using many different technologies. A schematic diagram of a comprehensive computer-controlled system is shown in figure 1. Typical specifications of a commercial general purpose tester at the top end of its class? include functional tests at a 10MHz rate, parametric tests to 160psec resolution, the ability to test TTL, DTL, ECL, MOS and CMOS devices in all types of package up to 120pin and a computer with 16k words of main memory and an 18Mbit disc store. The price is over \$200,000.

#### 2.4 L.S.I. Testing Problems

Even with such versatile and powerful testers of the type mentioned in the previous section, every user of automatic test equipment interviewed in a 1976 survey was dissatisfied with the systems presently available. The main trouble has arisen from the introduction of l.s.i., which is being closely followed by v.l.s.i. (over 1000 gates on a single chip): as the circuits become more complicated, the time taken to test them becomes much longer so the contribution of testing costs to the price of the final product becomes proportionally larger. The percentage of the cost which arises from the testing alone has not been determined for l.s.i. circuits in general, but the trend can be followed from the change from discrete transistors through s.s.i. to m.s.i. circuits, where the testing cost was 5 percent, 15percent and 30percent respectively of the total.

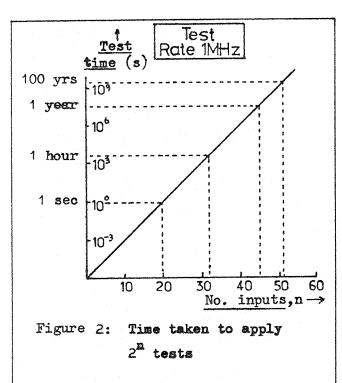

Most of this increase arises because more time is needed to apply the functional tests, when the number of input patterns needed to check every aspect of the circuit operation becomes astronomically large. For

the case of a combinational circuit (i.e. no feedback loops) with n active inputs, the nu--mber of tests needed to cover every combination is 2<sup>n</sup>. The time taken to apply these tests for various values of n is shown in figure 2, assuming a test rate of a million tests per second. If sequential circuits are considered, the presence of feedback loops and storage elements can increase the test time by many orders of magnitude: if m, the number of internal storage

states, can be defined, then the number of tests rises to 2<sup>n+m</sup>. Not only does the time taken to apply the test patterns pose a problem, but the patterns, which may be many millions of bits in length, have to be generated then the outputs compared with the computed 'expected' response, so vast amounts of data must be stored in some memory system. This process can be reduced by techniques such as pseudo-random sequence generation or transition counting but still a very large and expensive store is required.

Circuits are often built which cannot be tested comprehensively in a reasonable time, so 'adequate' testing is then used, where the intention is to cover perhaps 90percent of all possible faults. It is necessary to ensure that worst-case conditions are fully covered, as are all the common failure modes, so the fault diagnosis which is performed during the initial stages in the production of a new circuit is of great importance.

#### 2.5 Testability of Integrated Circuits

Modern i.c.'s are becoming harder to test because there is less access to the internal circuitry than with the earlier, smaller circuits. Package and chip size is kept to the minimum for yield and economic reasons, so as the devices become more complex, the proportion of the circuitry which can be directly reached from the external pins decreases rapidly. If more observation points 10 (i.e. extra outputs) or control points 11 (extra inputs) were provided then testing could be performed more easily and significantly faster.

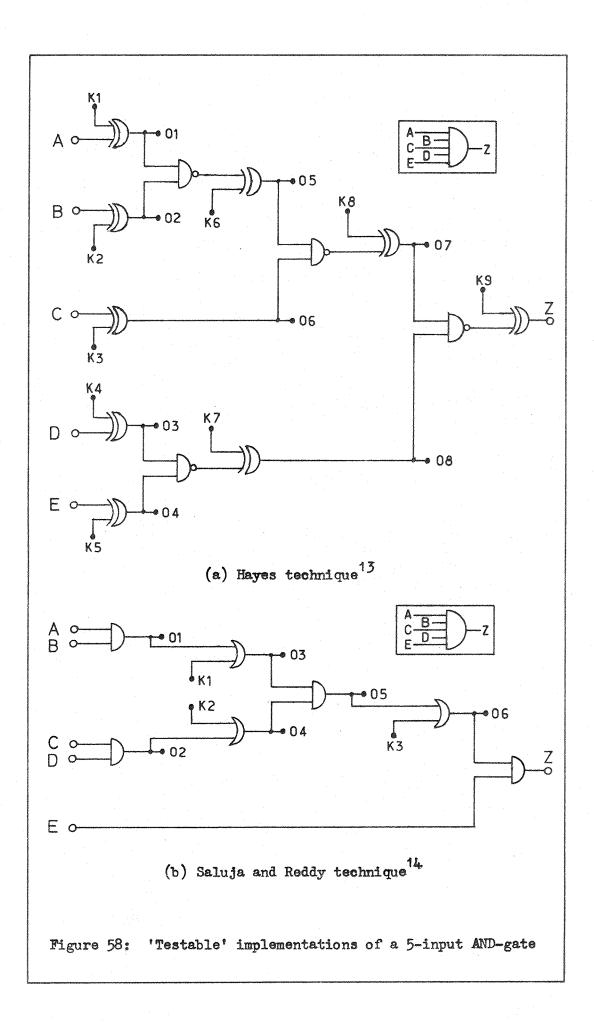

Theoretical work in the field of circuit design for maximum testability has produced schemes which provide 100percent fault cover with excellent diagnostibility in a very small number of tests (down to three) 12,13,14 by implementing the circuit function in terms of simple units and using a large number of extra input and output pins. In practice such methods are unworkable 15: for example a 16 pin m.s.i. circuit is transformed to a 180 pin l.s.i. device with a chip area four times larger than previously, in order to reduce the number of tests from ten to six and enable each failure mechanism to be uniquely determined (section 5.6).

Between the two extremes of circuits designed specifically from the testing viewpoint (as in the above example) and those built with no consideration of testing problems (as the vast majority now are), large benefits can arise from the provision of a few test sites <sup>16</sup>. In the following examples of actual circuits, one or more extra inputs have been added to improve the testability. More output points would be beneficial for diagnostic testing and to determine the states of internal sites, but have not been included here.

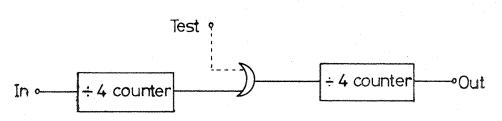

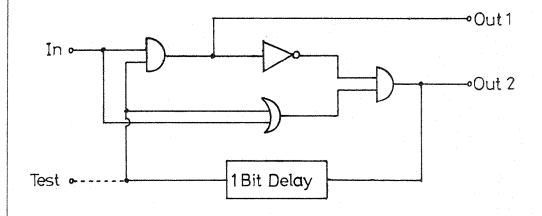

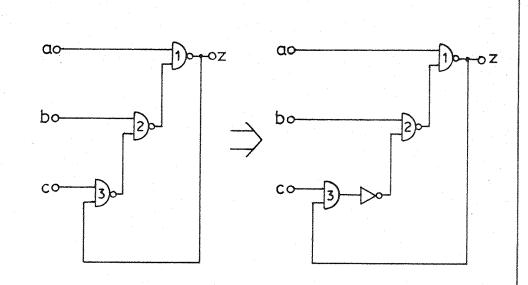

Figure 3(a) shows a simple 16-bit counter in which the test pattern length can easily be shortened by adding the test input as shown. Pulses via this test input will force the second half of the counter to advance at a faster rate than normal, so the total number of tests can be reduced from 16 to 7 (4 at the normal input and 3 at the test input). Any fault can obviously be isolated to either the first or the second counter blocks.

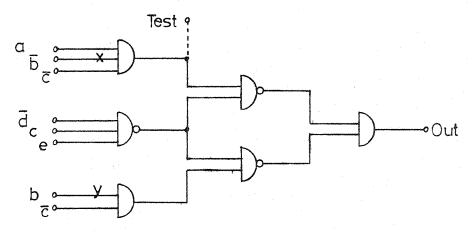

Circuits are commonly designed with some logical redundancy which is introduced in order to eliminate certain potential hazard conditions or improve reliability. In such cases, failures often cannot even be detected and fault diagnosis proves to be almost impossible. The effect of a fault in the redundant branch of a circuit could be to reintroduce the hazard or even to mask the detection of a normally detectable logical fault on a non-redundant connection.

Such a situation can arise with the circuit shown in figure 3(b). A stuck-at-1 fault at point X is not detectable at all, but if Y was stuck-at-0 at the same time, then the output would give the correct response to the normal node Y test (a = b = e = '1', c = d = '0'). The inclusion of the test input as shown would enable the whole circuit to be tested, including point X, and similarly all redundant paths in other circuitry can be isolated and tested individually with a suitable choice of test input site.

A small sequential circuit is given as figure 3(c). The state table of simple circuits of this type can be very large, but if the feedback loop is disabled then the circuit reduces to a much simpler one; in this case the test sequence can be reduced from 16 to 5 bits in length by using the extra input shown.

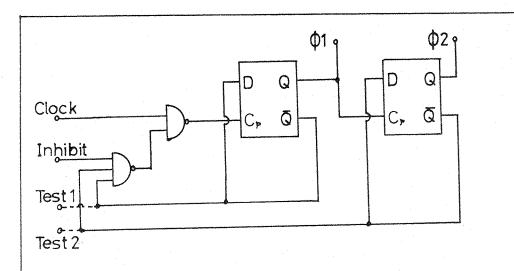

A common difficulty encountered in testing large circuits is that the initial state of certain parts of the circuit needs to be determined before the test pattern can usefully be applied. The common clock generation circuit shown in figure 3(d) illustrates this problem: it is self-initialising but there is no direct reset control, so between 0 and 3 clock pulses (depending upon the present state of the system) must be applied after the inhibit control goes high before both 4 and 4 are held at '0' and the test pattern could be meaningfully applied. If a cascade of such circuits is used or if the clock and inhibit controls are derived functions, then the initialisation sequence can become very large. This could be reduced by the provision of extra inputs as shown; an additional advantage of these extra controls is that any faults present in the initialisation circuitry itself can be isolated - this may otherwise be impossible because the starting conditions for the test sequence would not be repeatable.

(a) Test sequence reduction (16-bit counter)

(b) Testing of logically redundant circuitry

(c) Simplification of sequential circuitry

(d) Circuit initialisation (clock generator)

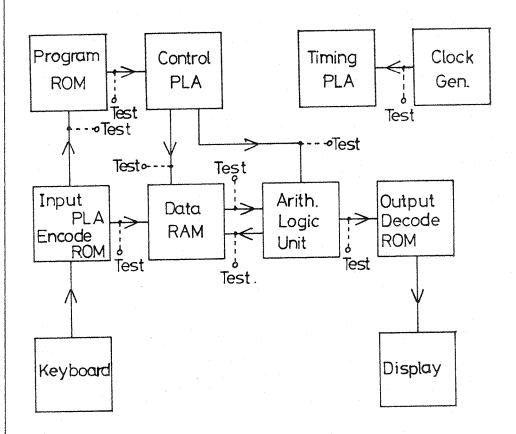

(e) Partitioning into modules (TMSO100 calculator)

Figure 3: Improving testability by the addition of extra inputs

The more complicated 1-chip calculator circuit of figure 3(e) is used to demonstrate a very important benefit which extra inputs can bring. If the interconnections between the various circuit blocks or modules were accessible then each could be isolated and tested individually with a relatively simple sequence. This partitioning method is presently used for microprocessor testing <sup>17</sup>.

The addition of extra test inputs to key circuit nodes can therefore be used to speed up the testing process and improve the chances of locating any fault which may occur. Greatest benefit will be gained if a large number of inputs is available, but a compromise between the enhanced testability and the difficulty and expense involved in the provision of these controls will have to be reached.

#### 2.6 Provision of Extra Circuit Inputs

Integrated circuit chip area and package size is at a premium, so any increase in the number of contact pads and internal connections, together with the associated rise in failure rate, is not favoured by manufacturers. Some efforts have been made to give the existing contacts a bifunctional role, with 'can't happen' input conditions used for test purposes or by adding a control signal which modifies the logical behaviour slightly to allow access to different parts of the circuit, but such systems are often complicated and the extra control circuitry itself is often extremely hard to test.

Another method occasionally used is to have a separate metallization mask for one chip on a slice, in which certain internal nodes are brought out to the contact pads instead of the normal inputs and outputs. Only one device per slice is lost in this way but the technique is only useful in diagnostic testing. The usual method of fault diagnosis is to delve into the internal circuitry with a needle probe, typically about 10-20µm wide <sup>18</sup>. This can give accurate dclevel measurements but its capacitance loads down most internal nodes so that meaningful transient readings cannot be taken. The relatively large size of these probes and their clumsiness is very likely to result in some damage to the circuit <sup>19</sup>.

Information can be introduced into a circuit via a non-contacting probe, which has the advantage of being non-destructive and easily and accurately moveable. Electron beams have been used to scan the surface 20,21 but in the present study a focussed optical beam is used 22,23 as an active probe. The production and operation of the light probe are described in the following section.

#### CHAPTER 3

#### THE LASER PROBE

- Optical illumination of a semiconductor

- The light source

- Characteristics of the laser

- Production of the laser probe

- Laser probing of a silicon integrated circuit

- Light beam modulation

- The laser input

#### 3. THE LASER PROBE

# 3.1 Optical Illumination of a Semiconductor

Radiation in the visible region of the electromagnetic spectrum can affect the properties of a monolithic integrated circuit. Two mechanisms of importance in relation to this phenomenon are photo--conductivity in the semiconductor and the photovoltaic effect 24.

# 3.1.1 Photoconductivity

At room temperature, a number of free carriers are present in all intrinsic semiconductors, so a current will flow when a field is applied. If the material is exposed to sufficiently intense radiation of a suitable energy, then a larger current will flow until the radiation is removed. The change in conductivity results from a transfer of energy from the incident photons to the valence band electrons, which can then be excited into the conduction band energy states. In the steady-state, the rate of free carrier generation is balanced by recombination, and when the source of illumination is removed, it is the recombination process that determines the rate of decay of the excess carriers.

The energy of the incident photons must be greater than the energy gap  $(E_g)$  of the semiconductor for the photoconductive effect to become significant, so

$$hv \ge E_g$$

... (3.1)

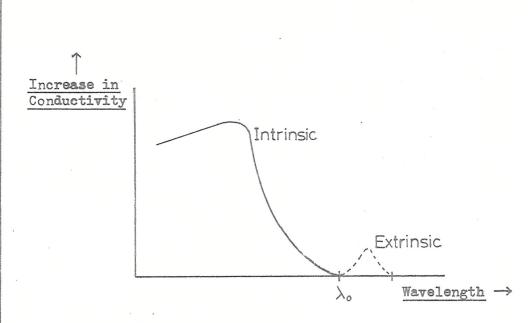

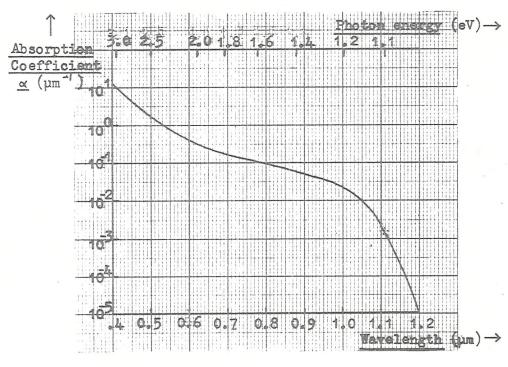

where h is Planck's constant and  $\nu$  is the frequency of the illumination. There is therefore a wavelength  $\lambda_{\rm O}$  above which no change in conductivity is noted, as shown in figure 4(a).

In an extrinsic semiconductor, some conductivity change is noted at wavelengths larger than  $\lambda_0$  since the difference in energy between impurity levels and the valence and conduction bands becomes the effective energy gap; the photon energy may also be absorbed by free carriers and

(a) Photoconductivity in silicon

. (b) Absorption coefficient in silicon 25

Figure 4: Photo-effects in silicon

excitons or create multiple electron-hole pairs, so equation (3.1) is only approximately true in practice.

The light intensity (I) drops by a factor  $\alpha$  per unit distance of travel inside the semiconductor because of absorption:

$$\frac{dI}{dz} = -\alpha I \qquad (3.2)$$

If the absorption coefficient,  $\alpha$ , is not a function of the intensity then at a depth z the intensity is

$$I(z) = I_0 \cdot \exp(-\alpha z) \qquad (3.3)$$

where  $I_o$  is the intensity just inside the surface, at z=0. The characteristic length,  $1/\alpha$ , is called the penetration depth, and nearly 90percent of the incident illumination is absorbed within two penetration depths. The variation of absorption coefficient with the wavelength of the incident light is shown in figure 4(b) for silicon at room temperature  $^{25}$ .

The rate of carrier generation per unit volume is dependent upon the light intensity, as shown by the equation

$$g = \frac{\alpha I}{h\nu} = \frac{\alpha I_o \cdot \exp(-\alpha z)}{h\nu} \qquad ... (3.4)$$

assuming that every absorbed photon produces an electron-hole pair.

#### 3.1.2 The photovoltaic effect

Photocurrents can be detected in a homogeneous semiconductor when an electric field is applied, but they also can be found in the absence of an applied field in an inhomogeneous semiconductor, due to the existence of localised 'built-in' fields. The light produces an excess of free carriers which move in response to these electric fields and accumulate in regions where they produce a net space charge. This generation of a voltage across a portion of the semiconductor by light is called the photovoltaic effect.

The internal field arising from a variation in the semiconductor doping at a pn-junction will be considered here, but discontinuities such as a heterojunction, and strains or impurities can also give rise to local fields. The built-in field at the junction drives the free electrons

and holes generated by the light in opposite directions, with the electrons moving to the n-type and holes to the p-type region; this charge separation results in the appearance of a potential difference across the junction with the p-region becoming positive with respect to the n-type. The pn-junction is therefore biassed in the forward direction, so more carriers will overcome the lowered potential barrier and be injected into the opposite region, where they become minority carriers and recombine.

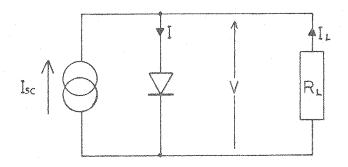

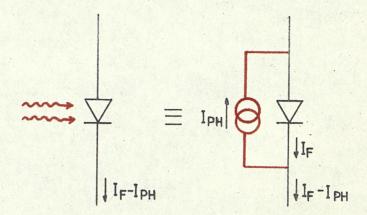

If an external circuit is connected across the junction, then either a photovoltage or, if the load resistance is low, a photocurrent will be detected, with the illuminated pn-junction behaving like a battery. The effect of light upon the junction characteristic is shown schematically in figure 5. The photocurrent adds to the reverse saturation current (I<sub>S</sub>), so if the light generates a current I<sub>S</sub> with the junction short-circuited, then the normal diode equation is modified to

$$I_{L} = I_{S}(\exp(qV/kT) - 1) - I_{SC}$$

... (3.5)

where  $I_L$  is the current through the load, k is Boltzmann's constant, V is the voltage across the junction, q is the electronic charge and T the temperature. For an open-circuited diode,  $I_L=0$  and

$$v_{oc} = \frac{kT}{a} \log_e(I_{sc}/I_s + 1) \qquad ... (3.6)$$

where V is the voltage appearing across the junction in the absence of current flow.

The value of I is related to the light power (P), the photon energy (hv) and quantum efficiency  $(\gamma)$  i.e. the number of electron-hole pairs generated per incident photon, by the equation

$$I_{sc} = \frac{P}{hv} \cdot q \cdot \gamma \qquad (3.7)$$

$$I_{sc} = \frac{qP\eta}{h\nu} \qquad I_L = I_s[\exp(qV/kT) - 1] - I_{sc}$$

(a) Equivalent circuit

(b) Diode characteristic

Figure 5: Illumination of a pn-junction

#### 3.2 The Light Source

'Probe' diameters of well under a micron have been obtained using focussed electron beams, with beam energy and penetration capable of accurate control, 26,27,28 but such systems must have the semiconductor sample enclosed in a vacuum chamber and the 'charged' probe can itself influence the properties of the material under test 29,30. Optical beams cannot be focussed to such a small size but are much easier to use and cheaper, neither do they interact detrimentally with the illuminated semiconductor: as a result, an optical source has been considered to be more suitable for the present system.

Semiconductor silicon is the most widely used material in modern integrated circuits, so the choice of the source has been governed by its properties. At room temperature, the energy gap is about 1.1eV, so the critical wavelength  $\lambda_0$  is 1.1µm. The region of most interest in an i.c. is the surface and the layer immediately below it, down to the junction depth which is typically up to 3µm deep. The radiation should therefore be mainly absorbed within this region: from figure 4(b) it can be seen that the penetration depth ( $\alpha^{-1}$ ) is 3µm when the wavelength is 6440Å, and over 90percent of the light is absorbed within this depth if the wavelength is less than 5340Å.

A strong light source is needed so that the focussed beam will produce a significant number of excess carriers in the semiconductor. Quartz-halogen lamps with a monochromator have been used for this purpose  $^{31}$ , but a large part of the power output is lost in focussing down to a small spot. The advent of the laser has brought the opportunity to use a collimated beam with high power density, but in general the output wavelength is fixed. A common laser whose wavelength satisfies the criteria mentioned above is the helium-neon laser with  $\lambda = 6328 \text{Å}$ . Other suitable choices would include the krypton laser ( $\lambda = 4131$ , 5309, 5681, 6471, 7525 Å) and Nd:YAG ( $\lambda = 5320 \text{Å}$ ,  $\alpha^{-1} = 1.28 \mu\text{m}$ ). By using different or multiple-wavelength lasers, the penetration depth could be varied from 0.2  $\mu$ m to  $\mu$ m, but for the present work, the cheap HeNe c.w. laser has proved satisfactory. At this particular wavelength the photon energy is 1.96eV and the penetration depth is 2.4  $\mu$ m.

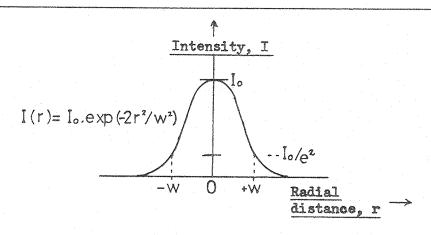

#### 3.3 Characteristics of the Laser

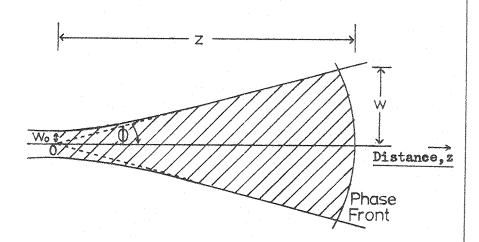

The beam of light emerging from a laser has a gaussian intensity distribution if it is operated in the TEM mode<sup>32</sup>. The properties of these beams and the equations governing their propagation are detailed in Appendix 1.

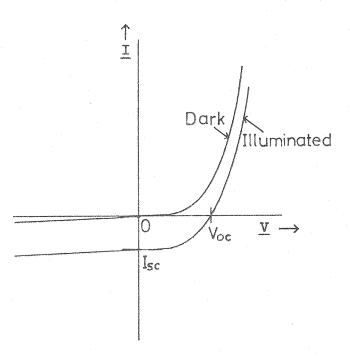

The width of the beam must be determined at various points along the optical path in order to calculate the size and position of the focus; however a gaussian beam width, which is defined as the distance over which the intensity drops to e<sup>-2</sup> of its peak value, cannot simply be measured from visual observation because of the non-uniform intensity across the beam. Two methods have been used to measure this parameter:-

- (i) a pinhole is scanned across the beam and the intensity measured at each point

- and (ii) an iris is used to restrict the beam and its aperture adjusted until its radius is equal to the beam width.

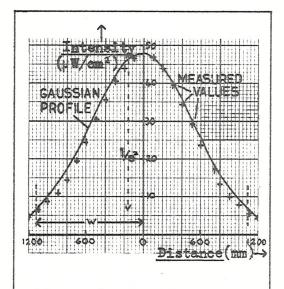

A 0.4mm diameter pinhole has been used to measure beam widths of greater than 1mm, and the results of a scan across the beam at a distance 2000mm from the laser are shown in figure 6, from which the

beam width can be calculated to be

1.11mm; a gaussian curve is superimposed upon the plot to demonstrate

that the laser is operating in the

TEM mode.

The proportion of the power intercepted by a circular iris of radius a is

$$P_{iris} = P.(1-exp(-2a/w^2))$$

... (3.8)

where w is the beam width, so by adjusting the aperture till

Figure 6: Gaussian beam intensity distribution

13.5percent of the power is lost, the beam width can be found directly by measuring the iris radius. The diameter of the aperture could be measured to within 50µm and this method was used for beam

widths up to 5mm; the values obtained agreed well with those from the intensity scan using the pinhole.

After the radius has been found at various positions along the beam, an iterative procedure is used with equation (Al.2) in Appendix 1 to find the beam focus and its position. Measurement of the beam transformation by lenses has been found to be usually in good agreement with the theory outlined in the Appendix.

Both a 1mw and a 7.5mw laser have been used in the present study, and each produced a vertically polarized output beam. For the larger laser, the untransformed beam waist was measured to be 0.56mm at a position 200mm behind the output mirror; its far field divergence angle is 0.36mrad.

Laser power levels have been measured in radiometric units using a silicon pin diode of 1cm<sup>2</sup> active area<sup>‡</sup>, but conversion can be made to photometric units by using the identity

Flux (lumens) =

$$137 \times Power$$

(watts) ... (3.9)

The stability of the laser output has also been investigated: after a warm-up period of about two hours, only a 4percent drift in the output power has been observed during a five hour period, and in the short term (under 1 minute), less than 0.8percent variation was noted.

#### 3.4 Production of the Laser Probe

#### 3.4.1 Beam focussing

The laser beam must be focussed so that it is smaller than the inter-element spacing of the integrated circuit which is to be probed, so a beam diameter of typically less than 10µm will be required.

- \* Spectra Physics model 132

- + Scientifica and Cook model SLH/7.5

- † United Detector Technology type 40X Optometer

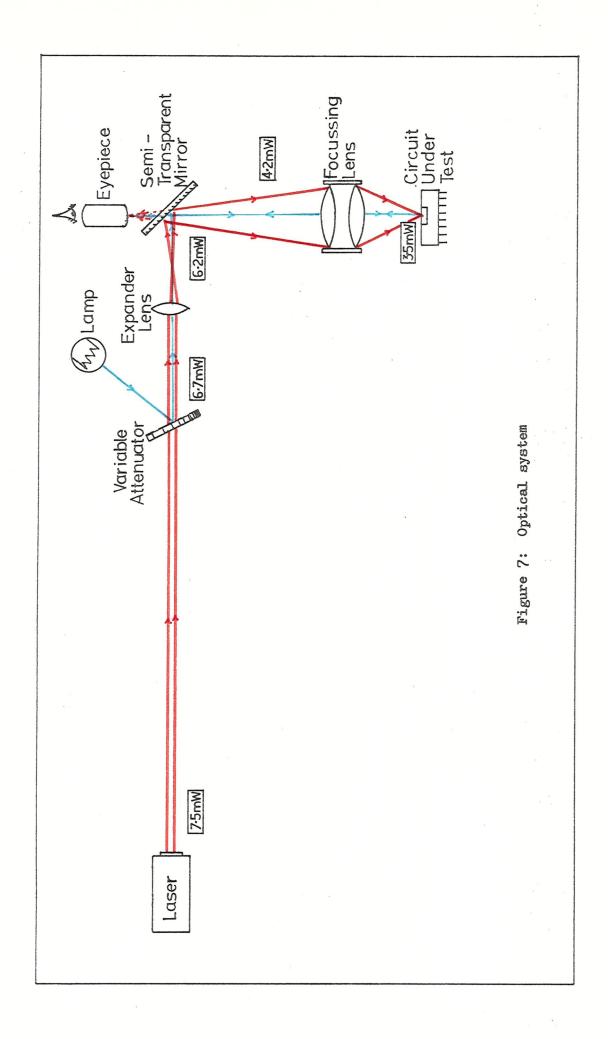

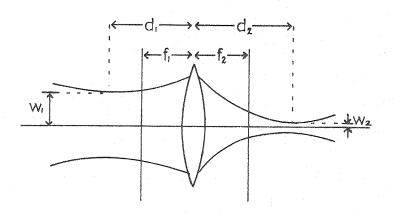

The wavelength of light is the limiting factor in the focussed spot size (see Appendix 1), and since this is 0.63µm for the HeNe laser, a near diffraction-limited spot will be needed. For convenience the light spot should also be visible upon the i.c. surface, so a microscope system has been chosen to meet both needs; in one configuration the laser entered the microscope via an eyepiece 33 but the arrangement illustrated in figure 7 has proved to be the most convenient.

The beam focussing is achieved in two stages: an intermediate focus is formed by a low-powered lens then this is transformed by a second, stronger lens to produce the final small laser spot. The initial focussing is necessary to increase the beam divergence so that the aperture of the second lens is filled (to produce a diffraction-limited spot) and also to allow the image of the focussed beam and circuit surface to appear in focus together when viewed through the eyepiece.

In order to produce a small undistorted laser spot, the second focussing lens must be of good quality and have a large numerical aperture (see equation (A1.9), Appendix 1); in addition the aperture stop and working distance of the lens should be as big as possible (see sections 6.2.1 and 6.2.2) The lenses which have been used for this task are detailed in table 1; all but one are microscope objectives, the exception being a high-quality camera lens designed for use in mask-making equipment. This lens has a much larger working distance than the objectives of similar power.

The choice of the first lens is not so critical and the two whose properties are listed in table 1 have proved satisfactory. Beam expansion by the 43mm focal length lens was not quite sufficient to fill the aperture of any of the focussing lenses, but the slightly larger spot size was considered to be preferable to the power loss resulting from the over-expansion of the more powerful lens. This x 6 objective was used in conjunction with the Ultra-Micro Nikkor camera lens though, where the input aperture was much larger.

The combination of lenses most commonly used was the 43mm expander lens followed by either the x10 or x20 microscope objectives. This resulted in final spot diameters of 2.5µm and 1.5µm respectively.

| Focussing lens             | Numerical<br>aperture | Working<br>distance (mm) | Focal<br>length (mm) | Optical tran-<br>-smission (%) |

|----------------------------|-----------------------|--------------------------|----------------------|--------------------------------|

| x5 Objective               | 0.15                  | 17.0                     | 11.7                 | 93                             |

| x10 Objective              | 0.25                  | 5.0                      | 4.55                 | 93                             |

| x20 Objective              | 0.50                  | 1.2                      | 1.14                 | 83                             |

| x40 Objective              | 0.65                  | 0.68                     | 0.66                 | 77                             |

| Ultra-Micro<br>Nikkor lens | 0.28                  | 13.6                     | 28.2                 | 77                             |

# (a) Focussing lenses ( $\lambda=6328\text{\AA}$ )

| Expander<br>lens | Numerical<br>aperture | Aperture (mm) | Focal<br>length (mm) | Optical tran-<br>-smission (%) |

|------------------|-----------------------|---------------|----------------------|--------------------------------|

| Biconvex         | 0.06                  | 15.0          | 43.0                 | 93                             |

| x6 Objective     | 0.12                  | 7.5           | 12,0                 | 91                             |

(b) Expander lenses  $(\lambda = 6328\text{Å})$

Table 1: Lenses used for beam focussing

# 3.4.2 Other aspects of the optical system

The light power is controlled by neutral density filters and a variable attenuator (density range 0 to 2, or 100percent to 1percent transmission), which is used both as a fine power control and as a reflector for the light from an external 60W lamp which illuminates the integrated circuit around the laser spot.

The chassis of a microscope has been used to hold the focussing lens and circuit under test. The expanding laser beam from the intermediate focus enters through the illumination porthole and is then deflected onto the second lens by a specially prepared front-silvered 70percent-reflecting mirror; this arrangement is used to reduce multiple reflections, to divert most of the power onto the final lens and prevent too much reaching the eyepiece. Some secondary images can be observed, but over 97percent of the total power is concentrated in the primary focus so these other 'probes' will not affect the operation of the overall system. In an effort to eradicate this problem, a small piece of aluminium has been tried in place of the mirror, but the distorted image which resulted when viewed through the eye-piece was found to be more of a drawback.

#### 3.5 Laser Probing of a Silicon Integrated Circuit

#### 3.5.1 Circuit preparation and mounting

All the integrated circuits probed by the laser beam have come from the manufacturer in a fully passivated and packaged form. The silicon chips are exposed to view by decapping the dual-in-line or TO-type packages, but in some cases it has been necessary to rebond the device in a new pack because of damage to the original. Often the chip is recessed well below the upper surface of the package, so a working distance of 1mm or more has to be allowed in order to bring it into focus; this factor has restricted the use of the higher-powered microscope objectives.

The circuit is mounted in a holder which is situated on the manual xy stage of the microscope, and connections to the power rails, clocks and conventional inputs and outputs are made by shielded cables. The light spot position on the chip surface is adjusted by moving the circuit and holder with the stage vernier controls.

# 3.5.2 Laser damage to the i.c.

An indication of the maximum power levels reached at each point in the optical system is given in figure 7. The power density is always well below the threshold level for damage to the optical components but at the final focus a very large density is attained (200kW/cm²), so the physical interaction between this high energy beam and the silicon surface must be studied.

The temperature rise of the chip in the steady-state has been calculated by using a simple hemispherical model of heat distribution. From a point source, the thermal energy spreads a distance d, where

$$d = \sqrt{\frac{4 K \Upsilon_t}{\rho c_p}} \qquad ... (3.10)$$

and K is the thermal conductivity (1.5W/cm°K for silicon),  $\Upsilon_{t}$  is a thermal time constant,  $\rho$  is the density and  $C_{p}$  is the specific heat of the material  $^{35}$ . This distance is calculated to be 15mm in silicon (assuming a time constant of 1 second), considerably larger than the integrated circuit dimensions. The radial heat flow in the steady-state is

$$q_{r} = -K.A. \frac{dT}{dr} \qquad ... (3.11)$$

where A is the area and dT/dr is the radial temperature gradient.

Assuming a hemispherical distribution of heat, the thermal resistance

R is found to be

$$R_{j} = \frac{1}{2\pi Kw} \qquad ... (3.12)$$

where w is the radius of the generation region. For the case of laser beam illumination with a power of 3.5mW and beam width of 0.75mm. the maximum temperature rise is calculated to be 5°C. The model does not take into account the fact that the chip is bonded down to a kovar header which will act as a heat sink, so this value should be an over-estimate. Measurements on a thermally insulated chip using a similar system have shown that the maximum temperature rise was 9.2 ± 1°C, 36 so the increase is not very significant. Reported results 37 on the irradiation of a silicon pin diode with ruby laser light (wavelength 0.69µm) have shown that a power of the order 50-200W is needed to produce any permanent damage to the device when long light pulses are used (approaching the limiting case of the steady-state assumption); in addition, observable characteristics such as craters and surface charring or a degraded diode response are always found once the damage threshold is crossed. No such surface damage or effect upon the device performance has been noted with the present system, confirming the calculation of a low temperature increase, so it may be assumed that the focussed laser spot will not damage the circuit under test and the method is truly non-destructive. The retina of the eye is more prone to damage though, so safety precautions have had to be carefully observed.

#### 3.6 Light Beam Modulation

The intensity of the laser probe must be accurately controlled if it is to be used to inject time-varying information into an i.c. High speed operation is also required (1-10MHz) for integrated circuit testing applications, so an electro-optic modulator has been chosen for use in this system.

Other modulators include mechanical systems, such as rotating and oscillating blades or multi-faceted spinning mirrors which can only operate up to about 10kHz and offer limited control of the light intensity pattern, and acousto-optic devices 39, which consist of a piezoelectric transducer bonded to a high quality, low opticalloss material and can operate up to about 1MHz. The solid state electro-optic modulator has an upper frequency limit of over 100MHz and is

cheaper than the acoustic wave version. The output intensity is approximately a linear function of applied voltage and can be easily synchronised with other equipment, so this system has proved to be very suitable for purposes of this study.

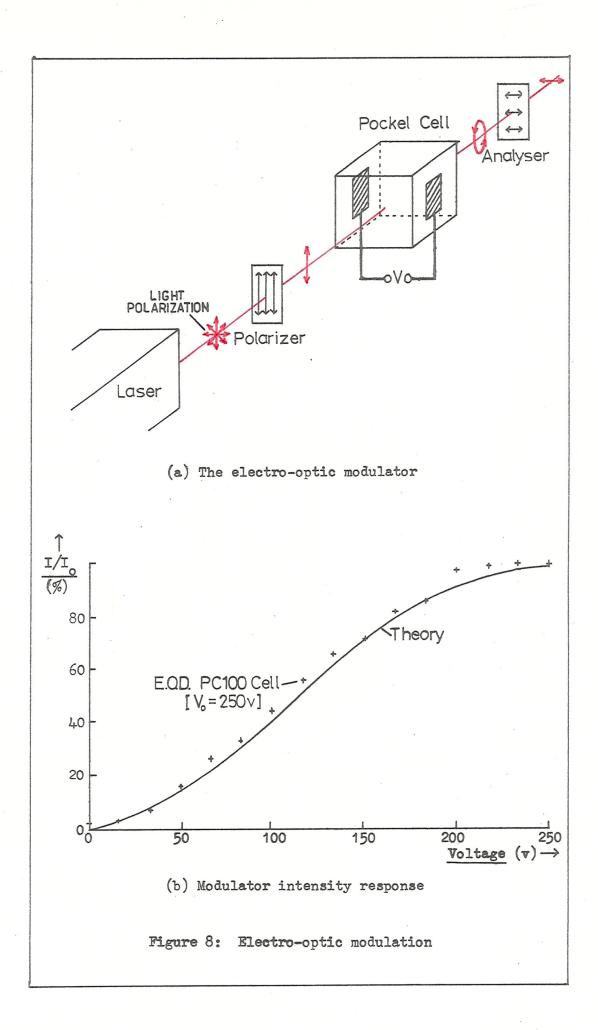

# 3.6.1 The electro-optic modulator

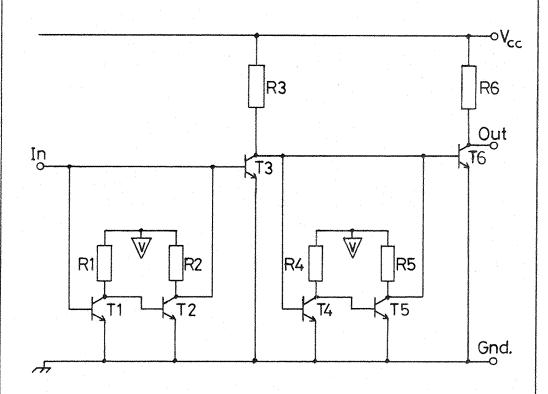

The basic element in an electro-optic modulator is the pockel cell, which is a crystal that undergoes an index of refraction change with the application of an electric field, i.e. it is birefringent. The incident light beam is split into two mutually perpendicular components which meet different indices of refraction within the crystal and therefore travel with different velocities, resulting in the introduction of a phase difference between the two parts at the output face of the cell. If the cell is positioned between crossed polarizers then the phase-modulated light can be converted into amplitude-modulated light, with the light transmission through the system controlled by the application of a voltage along the crystal axis. The modulator is shown schematically in figure 8(a).

The electro-optic effect may be described mathematically by

$$\Delta(1/n^2) = r_p E + P_K E^2$$

... (3.13)

where n is the refractive index, E the applied field,  $r_p$  the linear electro-optic coefficient and  $P_K$  is a coefficient associated with the quadratic (Kerr) effect. The linear variation of the index term  $r_p E$  is known as the Pockels Effect and will be the only one considered here. The operation of the modulator is based on two factors:

- (i) a phase retardation is introduced between the two polarized components of the incident beam

- and (ii) the two waves interfere with each other.

The intensity of the light output is

$$I = I_0 \cdot \sin^2(\phi/2)$$

... (3.14)

where  $\emptyset$  is the total phase difference between the two waves traversing the electro-optic crystal and  $I_o$  is the incident light intensity; since the phase retardation in the linear Pockels Effect is proportional to the voltage, then

$$I = I_0 \cdot \sin^2\left(\frac{\pi}{2} \cdot \frac{V}{V_0}\right) \qquad ... (3.15)$$

where  $V_o$  is the voltage needed to produce maximum transmission  $(I=I_o)$ , often called the half-wave voltage. The operating point on this characteristic can be shifted to the near-linear central region of the  $\sin^2$  curve by the application of a d.c. bias, so that any superimposed time-varying voltage will be faithfully reproduced in the light-intensity domain.

Mechanical strains in the crystal can produce variations in the refractive index and in the birefringence. Changes in the former cause scattering of the incident light and distort the wavefronts and variations in the birefringence tend to reduce the degree of modulation and degrade the optimum optical bias 41. By restricting the output aperture of the crystal, the modulator response can be improved by confining the light beam to the relatively strain-free central region of the crystal.

### 3.6.2 Experimental arrangement

A transverse modulator system has been used in the final arrangement, which includes an ammonium dihydrogen phosphate (ADP) pockel cell with a half-wave voltage of 250v. This voltage is supplied by a high power video amplifier, which can operate up to 7MHz with a 10-90percent response time of 150nsec and also provide a d.c. bias of ±280v to the cell. The need for a separate polarizer is obviated by the vertically polarized laser output, but a calcite prism, mounted in a precision rotary unit, is used as the analyser.

The crystal alignment is highly critical, so a special pin--mounted gimbal cell holder has been built so that the crystal axis and light beam can be matched to within 0.1°. A 1mm diameter pinhole

<sup>\*</sup>Electro-optic Developments PC100 Pockel Cell and VLA30 video linear amplifier

has been used to restrict the output beam from the modulator in order to improve the response of the system; by careful adjustment, the extinction ratio (maximum to minimum transmission) can be raised from 30 to about 60. The modulator response is shown in figure 8(b).

#### 3.7 The Laser Input

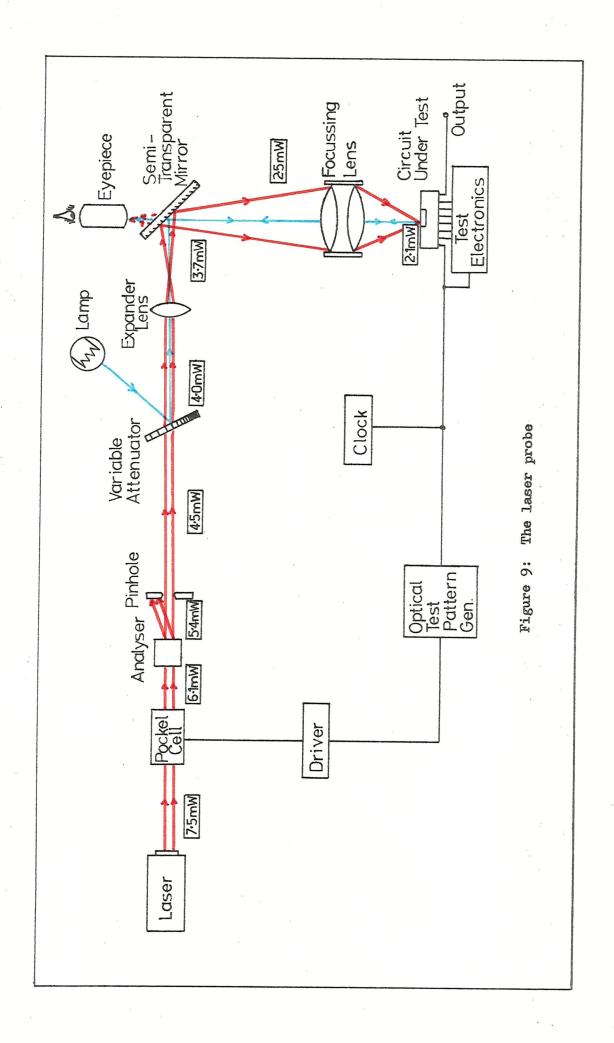

### 3.7.1 Electronic control system

The modulated light beam must be synchronised with the integrated circuit clocks and other time-dependent controls if it is to be used as an extra input. In the system shown in figure 9, this has been achieved by using the same clock generator to control both the circuit under test and the pockel cell driver. An intermediate pattern generation and bias adjusting network has also been used; this consisted of a 32-bit shift register with associated loading circuitry and a buffer stage to provide the 2v into 50n amplifier input. This test system configuration has proved useful for work with the various shift registers which have been probed with the laser, where the 'prog--rammable' 32-bit digital light input sequence (with '1' equivalent to the light GN and '0' to the no-light condition) has helped to determine the properties of the laser probe, but more sophisticated systems have had to be used for i.c.'s which use multi-phase clocks or need an analogue form of light input.

#### 3.7.2 Overall system performance

From figures 7 and 9 it can be seen that the maximum laser powers incident upon the circuit surface are 3.5mW and 2.1mW for the unmodulated and modulated cases respectively. Using equation (3.7) and assuming a quantum efficiency of 70percent (see section 4.1), these values can be related to the photocurrent which would flow across a pn-junction lying under the incident light beam - numerically these currents are 1.25mA and 0.75mA.

The laser beam input can therefore supply a current of 0.75mA at a maximum repetition rate of 7MHz or in 0.2µsec pulses via a non-contacting, non-destructive probe of diameter 2µm.

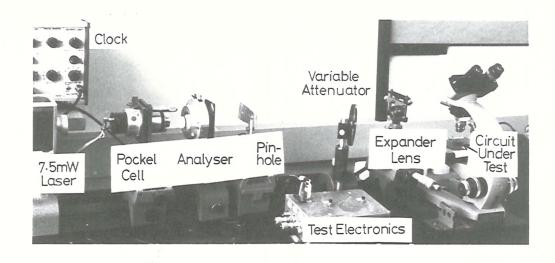

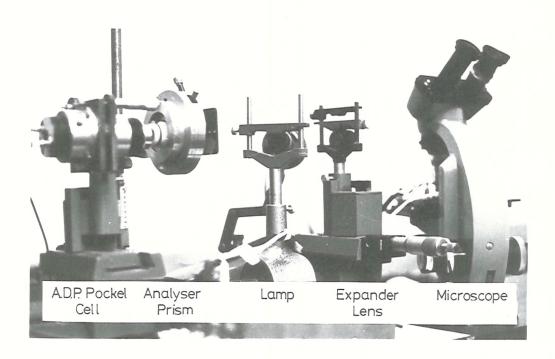

A photograph of the complete system is shown in figure 10(a), in which the external lamp and safety cover have been removed; the x5 microscope objective is used as the focussing lens and this can be seen just above the circuit under test. In the close-up of the optical system, figure 10(b), the pockel cell and analyser holders can be clearly seen, and in addition the accurate expander lens movement apparatus (section 4.3.2) is also visible. A glass plate has replaced the variable attenuator in order to show the 60W lamp.

(a) Overall view

(b) Modulator and optical system

Figure 10: Experimental arrangement

# CHAPTER 4

### LASER BEAM EVALUATION OF A SEMICONDUCTOR

- Quantum efficiency

- Carrier injection levels

- Diffusion length

- Lifetime

- Semiconductor substrate characterization

### 4. LASER BEAM EVALUATION OF A SEMICONDUCTOR

### 4.1 Quantum Efficiency

### 4.1.1. <u>Introduction</u>

For a given incident light power, the magnitude of the photocurrent flowing across an illuminated pn-junction is dependent upon the quantum efficiency (the number of electron-hole pairs generated per incident photon) and the photon energy, as described by equation (3.7) which is repeated here:

$$I_{SC} = \frac{P}{hv} \cdot q \cdot \gamma \qquad ...(4.1)$$

therefore in S.I. units,

$$\gamma = \frac{I_{SC}}{P} \times 1.96 \times 100\%$$

...(4.2)

for the helium-neon laser light.

The value of quantum efficiency (n) is determined by several factors, which include reflection, absorption and interference of the light in the surface layers or at the various interfaces and also device parameters such as junction depth and diffusion length.

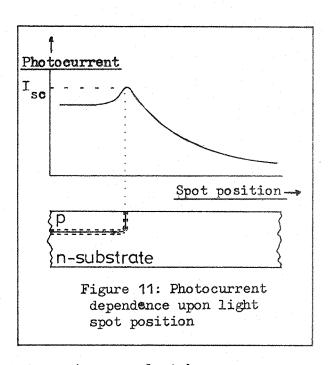

The position and size of the focussed laser beam can play an important part in the deter—mination of the effective quantum efficiency. This is illustrated in figure 11 which shows the variation in photocurrent as a very small laser spot of constant power is moved along the upper surface of the semiconductor and across a pn-junction. A maximum value is reached when the beam is directly over the junction, but on each side

of this position some of the generated carriers are lost by recombination. If the laser 'spot' overlaps the depletion layer, then

again not every one of the photo-carriers is collected by the junction, even when the centre of the generation region is coincident with the junction edge. Therefore for measurements of quantum efficiency, care must be taken to accurately position the beam and use as small a laser beam width as possible.

# 4.1.2 Results

Measurements of quantum efficiency have been made on a variety of devices, and in each case a reverse-biassed pn-junction which is directly accessible from contact pads has been used as a photocurrent monitor. A 3v bias has been found to be necessary to prevent the self-biassing of the junction in the forward direction, which arises because of the voltage drop in the substrate; if not prevented, this would result in the measured photocurrent being too low (see figure 5).

The values of quantum efficiency which have been measured are listed in table 2: each quoted result refers to a separate device, and the average for each class is shown bracketed. The minimum laser power needed to produce a photocurrent of 0.5mA has been measured, from which the value for  $\eta$  has been calculated. No dependence of this value upon the light power level in a 10 $\mu$ W-1mW range has been noted, and the choice of focusing lens did not have a significant influence upon the readings, except when the smallest x5 objective was used - here the larger diameter laser spot caused an apparent reduction in quantum efficiency by up to 6percent; for the other lenses, less than 0.5percent variation was noted.

The majority of the devices tested have been M.O.S. i.c.'s but some bipolar types have been studied. Three conclusions can be drawn from the results obtained:

- (i) the variation in quantum efficiency from one region to another region on the same device is small

- (ii) between different devices of the same type there is also little change in the results

- (iii) there is a correlation between the quantum efficiency values and the circuit manufacturer.

| I.C.family                       | Manufacturer              | Device type       | Quantum efficiency (%)                        |  |

|----------------------------------|---------------------------|-------------------|-----------------------------------------------|--|

| M.N.O.S.<br>p-channel<br>Al-gate | General<br>Instruments    | SS-6-1032         | 69.6,72.0 (70.8)                              |  |

|                                  |                           | SI-6-4025         | 67.0                                          |  |

|                                  |                           | <b>SI-6-403</b> 2 | 66.1,62.8 (64.5)                              |  |

|                                  |                           | SL-6-2064         | 69.3,63.9 (66.6)                              |  |

|                                  |                           | DL-6-2128         | 62.8                                          |  |

|                                  |                           | AX-6-8591         | 73.5,69.3 (71.4)                              |  |

|                                  |                           | Q2-2              | 72.8                                          |  |

| M.O.S.<br>p-channel<br>Al-gate   | Plessey                   | ML232B            | 81.5,79.6,76.5<br>82.3 (80.0)                 |  |

| M.O.S.<br>p-channel<br>Si-gate   | Mullard                   | GYN111            | 66.6,63.5 (65.1)                              |  |

|                                  |                           | GYN141            | 67.0,64.8 (65.9)                              |  |

|                                  |                           | GYQ101            | 72.7,76.1,76.5,74.0,<br>75.3,73.0,76.9 (74.9) |  |

| C.M.O.S.                         | R.C.A.                    | CD4012            | 81.4                                          |  |

|                                  |                           | СD4013            | 68.0                                          |  |

| Bi <b>p</b> olar                 | Fairchild                 | 70 <b>9C</b>      | 70.7,70.3,76.1 (71.5)                         |  |

|                                  | Southampton<br>University | 142 ABAB          | 60.9,63.3,55.6,51.4,<br>55.0,55.6,57.5 (57.0) |  |

|                                  |                           | 166 JGSJCW        | 54.2,53.5 (53.9)                              |  |

| Bipolar<br>(n-sub)               | Southampton<br>University | 166 JGSJCW        | 68.1,71.5,71.1 (70.2)                         |  |

Table 2: Quantum efficiency

From measurements on a single SS-6-1032 circuit with seven accessible pn-junctions, a 2percent difference between the values of  $\eta$  measured at each site was found, and similarly from the results of tests performed on seven GYQ101 memories, only a small (3percent) variation was noted. This close agreement is to be expected since in each case the manufacturing process should be identical and so the factors influencing the quantum efficiency should also be the same; in addition it is probable that devices in the same family, for example the G.I. static shift register series SS-6-1032, SL-6-4025, SL-6-4032 and SL-6-2064, will also have similar quantum efficiencies.

Different manufacturers will not use the same processing methods, so variations in passivation layer thickness or junction depth for example will be found, and this could explain the significant differences in values of quantum efficiency, such as the 80percent for Plessey M.O.S. and 65percent for General Instrument devices. Similarly a modification of the processing steps used by one producer can also have a large effect: this has been noted for two sets of 166 JGSJCW devices in which a change from 0.46µm to 0.52µm oxide thickness produced a corresponding change in quantum efficiency from 53percent to 70percent.

All the measured values of  $\eta$  lie in the range 55-85percent, but differences of this magnitude are not very significant for the application of integrated circuit testing, where the power requirements can vary over many decades; however in the following section an attempt is made to predict the quantum efficiency theoretically, which will be useful for circuits in which it cannot be directly measured.

# 4.1.3 Analysis

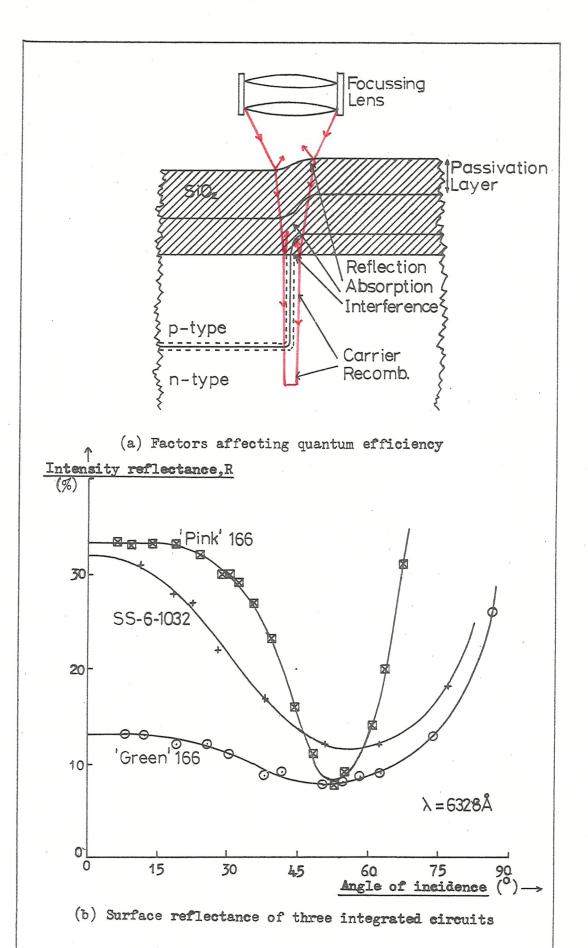

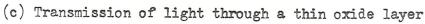

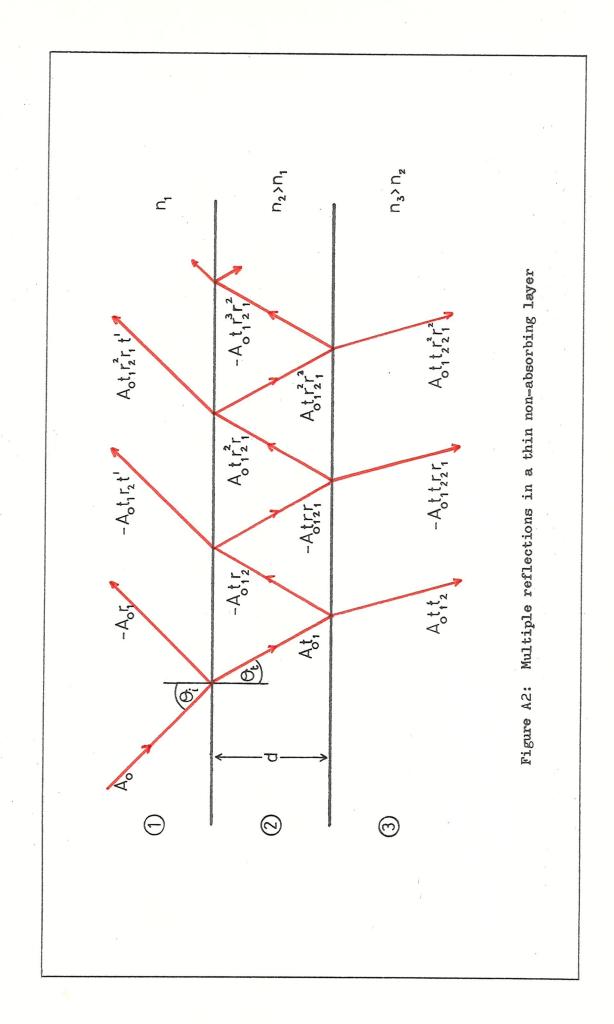

Interference, reflection and absorption of light in the silicon dioxide layers and at the air-oxide and oxide-silicon interfaces are expected to be the most significant factors which govern the value of the quantum efficiency, but photo-carrier loss mechanisms in the bulk semiconductor may also play an important part, as shown schematically in figure 12(a).

The theoretical analysis of this problem will be treated in two parts, where first the optical parameters and secondly the effects

inside the semiconductor are considered. It will be assumed that only a negligible fraction of the photon energy is absorbed by free carriers or excitons for illumination at this laser wavelength, so that each photon reaching the silicon will produce one electron—hole pair.

Details of oxide thickness, junction depth and doping profile are known for two devices, and measurements from these have been used to justify the theoretical calculations. Both were 166 JGSJCW bipolar circuits fabricated at this university: one was pink in colour when viewed vertically and had an oxide thickness of 0.46µm, a p-type substrate and an epitaxial layer 6µm deep; the other was a green colour (thickness 0.52µm) but it had an n-type substrate. The diode used for quantum efficiency measurements was formed between a p-type diffusion (junction depth 2.6µm) and the n-type 'collector' material, and the values for my were found to be 53percent for the 'pink' device and 70percent for the 'green' one (table 2).

# (a) Absorption, reflection and interference

The oxide thickness on each circuit tested will be less than  $2\mu\text{m}^{42}$ , and since extrapolation from results quoted by Wolf gives a penetration depth in the oxide at the laser wavelength of 1mm, absorption losses here can be ignored.

Reflection will be significant at both the air-oxide and oxide-silicon boundaries. The reflectance, R, at an interface between two

non-absorbing dielectrics can be determined from the Fresnel

relationships which are given in Appendix 2: for a simple air-silicon

dioxide system with light incident normally, the intensity reflectance

is calculated to be 13percent; and for light polarization parallel to

the plane of incidence, the reflectance drops as the angle of incidence

is increased, reaching zero at the Brewster angle (55°) then rising

again for larger angles.

Measurements using the laser, which is polarized in this plane, have been taken with three devices to determine the variation of reflectance with angle of incidence for an air-oxide-silicon system.

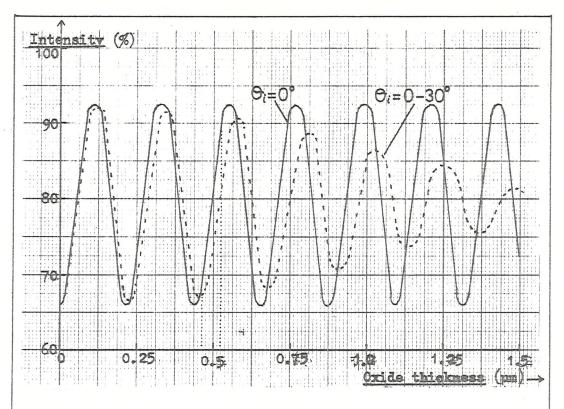

The laser (assumed to be producing a parallel beam) is directed at a metal-free oxide area, and the reflected light intensity measured as a function of incident beam angle with the results as shown in figure 12(b). The devices tested were the pink and green 166's and a passivated shift register cirucit, which was dull grey in appearance. A dip in the response around the oxide Brewster angle is found in each case, but the magnitudes of the reflectance are significantly different from the simple air-oxide prediction, and each other. This can only be explained by a consideration of the interference between the various reflections at the two boundaries, a factor which is strongly dependent upon oxide thickness. It has been shown in Appendix 2 that in an air-oxide-silicon system with a zero angle of light incidence, a plot of the transmission into the silicon (or alternatively total reflectance) shows a periodic variation as the oxide thickness is increased (figure 12(c), solid line). However the lenses used to focus the beam do not produce a single angle of incidence, so this periodic response will be 'smeared' out, particularly for thick oxide layers and large numerical aperture lenses. A simple calculation has been made to estimate the net transmission/oxide thickness variation which would be obtained if the x20 microscope objective was used (half angle 30°), and this is the dotted line shown in figure 12(c). For large oxide thickness, the transmittance is tending to a limit of 79percent.

The overall reflectance of the two 166 devices has been measured, so a check upon the theoretical curve can be made. For oxide thicknesses of  $0.46\mu m$  and  $0.52\mu m$ , the theory predicts a **reflectance** of 32percent and 11percent, which compares very well with the measured 33percent and 13percent respectively (assuming no absorption).

The proportion of the incident light intensity which reaches the silicon is therefore heavily dependent upon the thickness of the oxide layer, but this could be calculated if the depth of oxide is known or can be determined from its colour. However transmission losses alone do not give rise to the quantum efficiency value, and so effects inside the semiconductor must also be studied.

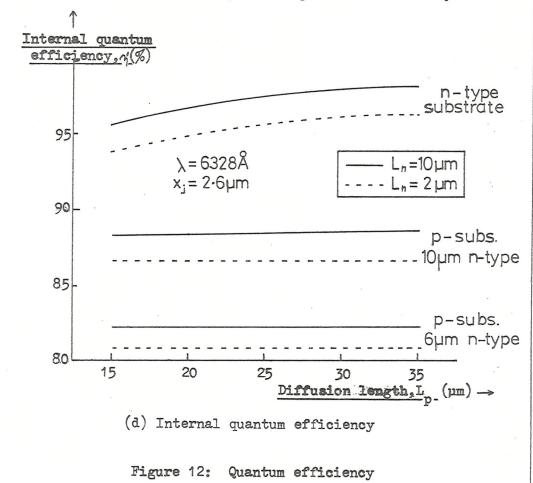

#### (b) Losses in the semiconductor

An internal quantum efficiency,  $\eta'$ , is defined to be the number of carriers which cross the pn-junction per each incident photon in the semiconductor. Its value will be influenced by surface recombination velocity, junction and penetration depths, carrier diffusion lengths, doping profile with associated drift field and the substrate thickness, but a one-dimensional analysis of the problem has been made 44 from which it has been found that only the penetration, junction and epitaxial layer depths are significant. Three sets of curves have been calculated (figure 12(d)) assuming a junction depth of 2.6µm and radiation of 6328A: diffusion length has been plotted as the variable, and the cases of n-type substrate and p-type substrate with epitaxial layer of 6µm and 10µm have been chosen to illustrate the influence of a second pn-junction below the surface. The pink 166 device had a 6µm deep n-type layer, and the diffusion length is known (see section 4.3.2), so a value for m' of 82percent is predicted; similarly for the 'green' device  $\eta'$  is expected to be 95percent. The contribution of the m factor to the total quantum efficiency is therefore much less than the losses from interference and reflection.

It has been assumed that all the photon energy which reaches the bulk semiconductor is used to generate electron-hole pairs at this particular wavelength. The validity of this assumption can be roughly checked by comparing the overall quantum efficiency predicted from the above analyses with actual measurements for the two 166 circuits. For the p-substrate pink device, the true value of 53 percent is very close to the calculated 56 percent and similarly for the n-substrate chip, 70 percent was measured and 75 percent predicted. Thus it seems probable that within the accuracy limits of the present experiments, all the photon energy is used to generate free carriers.

The theoretical treatment of quantum efficiency does give a reasonable agreement with measured results in two cases, but it is possible that if any dielectric layers as well as the oxide are used in the processing then the model will not give the correct answer. However to a first approximation, for thick passivation layers the

quantum efficiency will tend towards a value of about 77percent for n-substrate devices or 65percent for 6µm deep epi-layer on a p-substrate (with thicker layers giving a higher  $\gamma$  value). These relatively small differences will not be very significant in the context of integrated circuit testing but an average value of 70percent will be assumed throughout this work in all calculations involving photocurrent in which the true value has not been measured.

# 4.2 Carrier Injection Levels

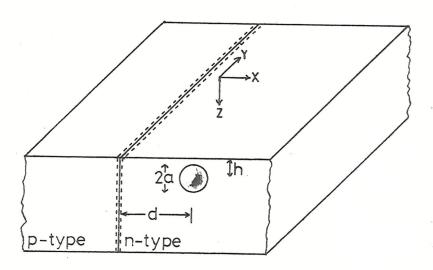

Approximately 70 percent of the incident photons produce electron--hole pairs inside the silicon semiconductor, so by using a very powerful light source it is possible that the injected carrier concentration could be greater than the substrate doping concentration, and high level injection conditions (conductivity modulation of the semiconductor) would prevail. A knowledge of the laser powers necessary to reach this state and the boundaries of the region over which it occurs is therefore essential if measurement of minority carrier diffusion length and lifetime is to be made with the laser probe. These parameters vary as a function of injection level 45 (see Appendix 3(a)) and experimental measurements 46 have shown that the lifetime can change by a factor of up to 20 as the injection conditions are altered. The transition between the high and low level injection limits has been found to take place over a two-decade range of injected carrier concentration, centred on the initial substrate concentration level; for carrier concentrations outside this range, the lifetime and diffusion length remain constant at either the high or low injection value.

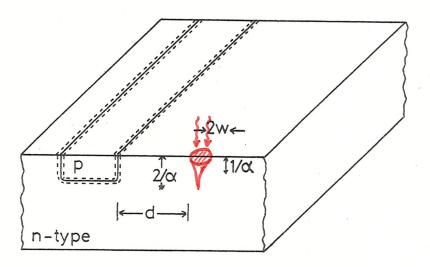

Delineation of the injection levels as a function of incident light power is complicated by the fact that the carrier generation occurs in a finite volume close to the illuminated portion of the semiconductor surface, whose dimensions are determined by the penetration depth in the material and the gaussian laser beam profile, and away from this source the excess carrier concentration decreases as a function of distance and diffusion length. As a result, a localised high injection regime could be formed around the generation region, but at a pn-junction some distance away, low injection conditions may still hold.

Theoretical analysis of this problem has been based upon the published work of Berz and Kuiken 47. Their treatment is more comprehensive than other analyses 48,49 and considers both a finite generation volume (not simply a point or line source) and the effects of non-zero surface recombination. Only slight modifications are needed to adapt this theory to the case of laser beam carrier-generation, and experimental measurements give satisfactory agreement with its predictions. Mathematical details are given in Appendix 3(b): three simple approximations to the shape of the generation volume have been attempted and compared with a measured value of injected carrier concentration in order to obtain the best analytical solution of the differential equations.

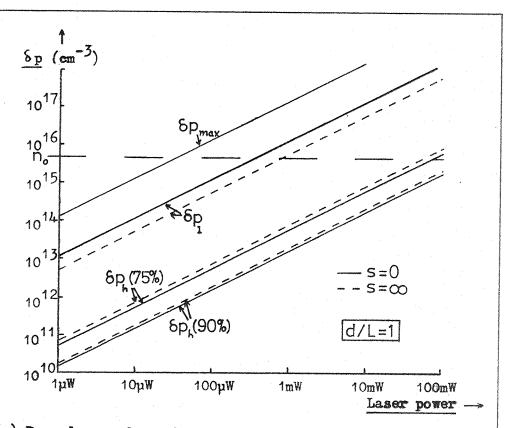

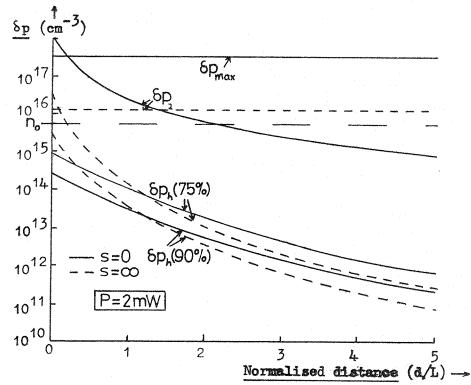

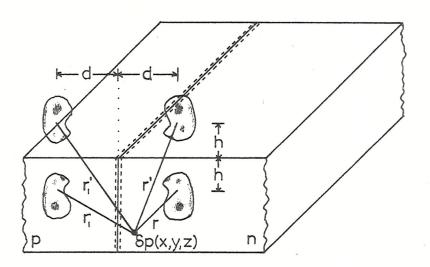

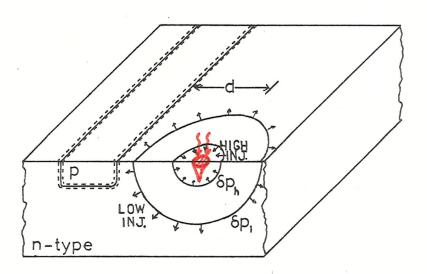

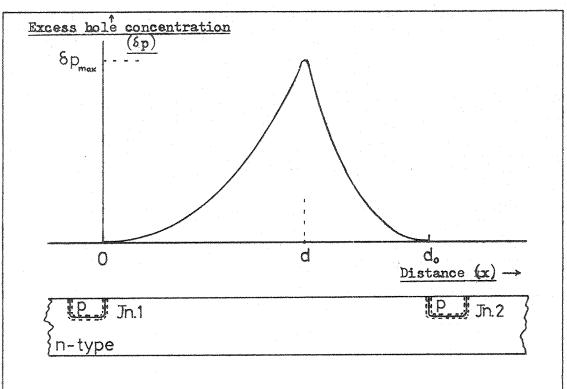

The results obtained from an application of the theory are shown in figure 13. Three regions of excess carrier concentration have been defined:-  $\delta p_{max}$  is the maximum carrier concentration which is found within the generation volume,  $\delta p_1$  is the low level injection boundary, i.e. if  $\delta p_1$  is less than the substrate doping concentration at a certain point, then low injection conditions apply at that point, and similarly  $\delta p_h$  is the high injection limit where a substrate doping level less than  $\delta p_h$  indicates high level carrier injection. Two definitions of the high injection region have been used (see Appendix 3) so two  $\delta p_h$  values have been shown and these are denoted  $\delta p_h(75\%)$  and  $\delta p_h(90\%)$ .

Device parameters which apply to the SS-6-1032 shift register have been used to calculate the family of curves shown in figure 13 but these are typical of most of the devices tested. The substrate doping concentration (n-type) is  $5 \times 10^{15}$  cm<sup>-3</sup>.

The first graph shows the variation of excess carrier concentration with laser beam power, where the pn-current-collecting junction has been assumed to be one diffusion length away from the 2µm wide laser spot. At the junction under these conditions, low injection applies for laser powers of below 0.4mW and high injection for powers above 100mW.

(a) Dependence of carrier concentration upon laser power

(b) Carrier concentration at a distance d from the source

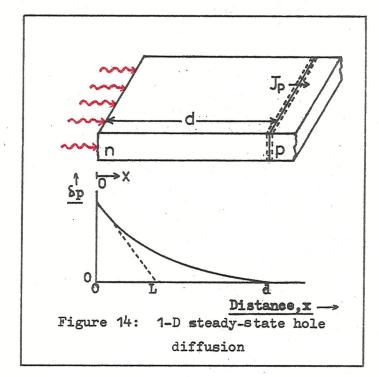

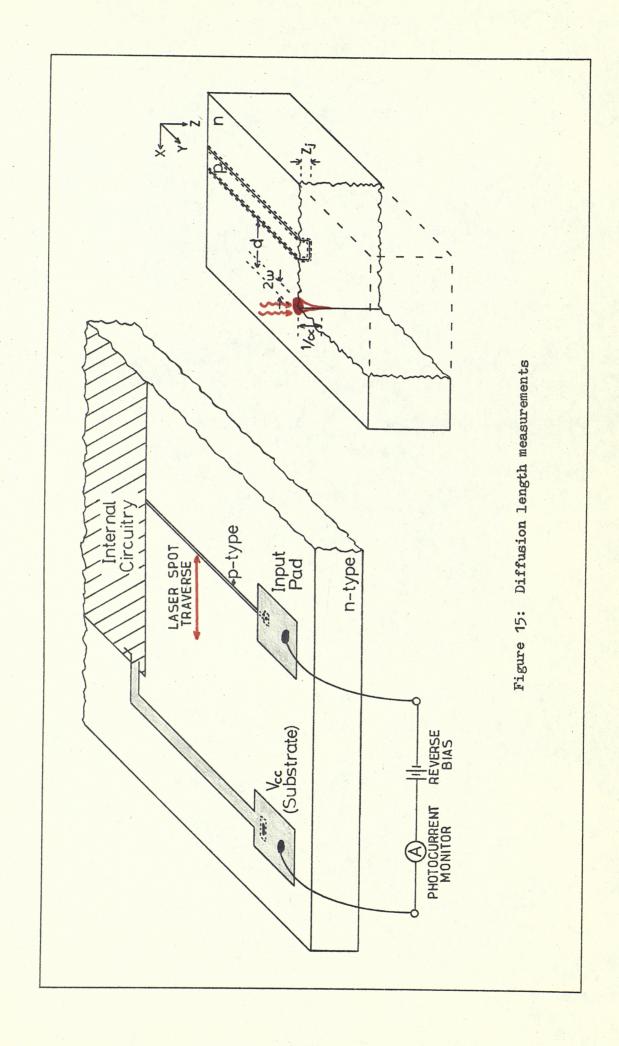

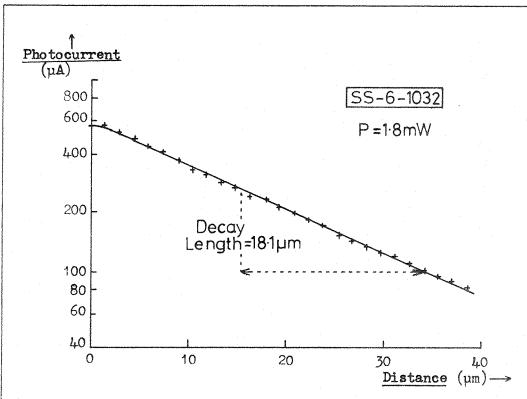

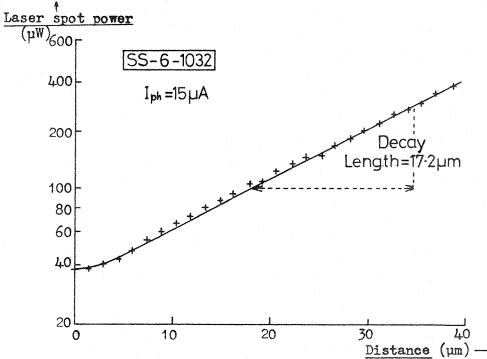

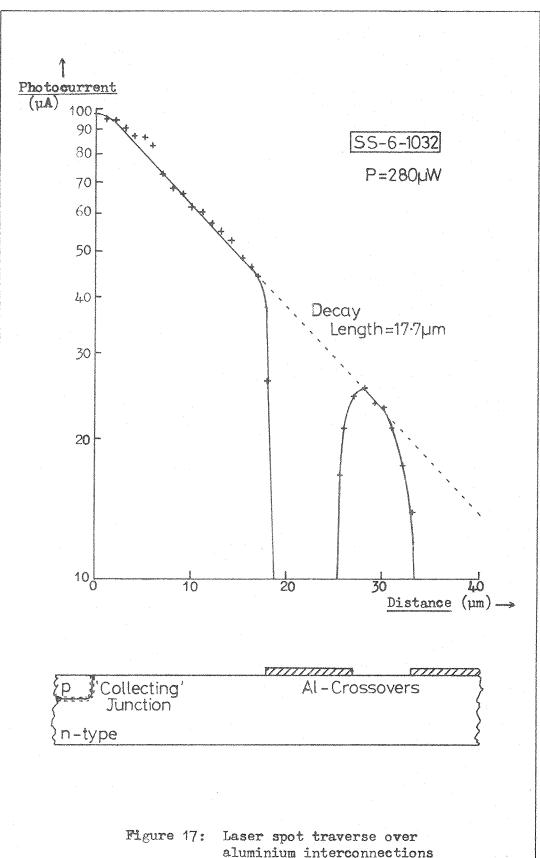

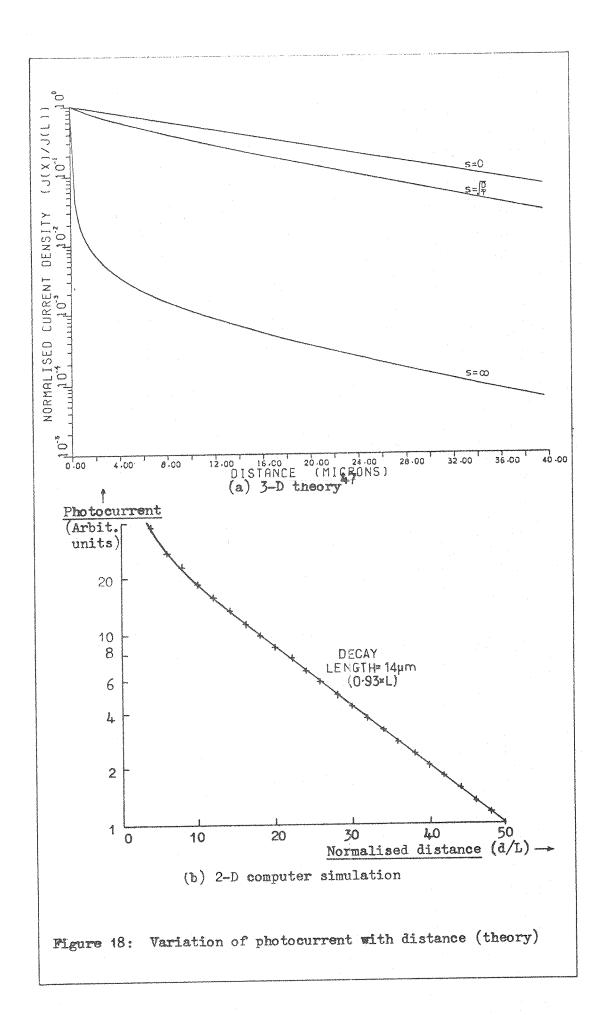

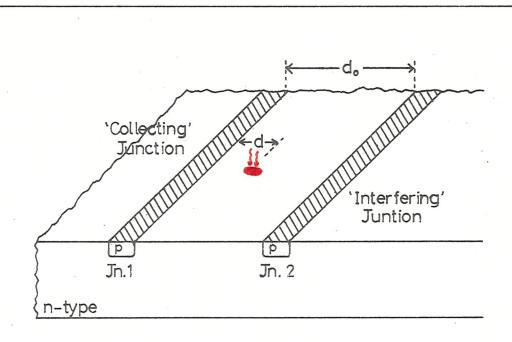

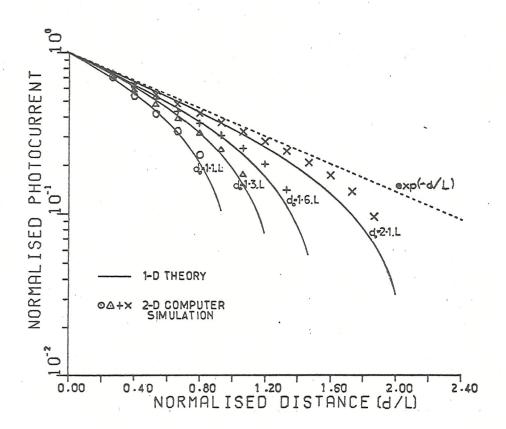

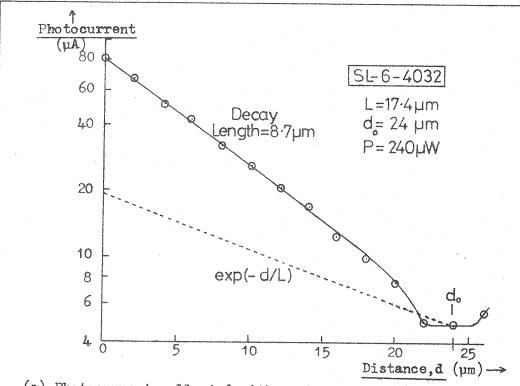

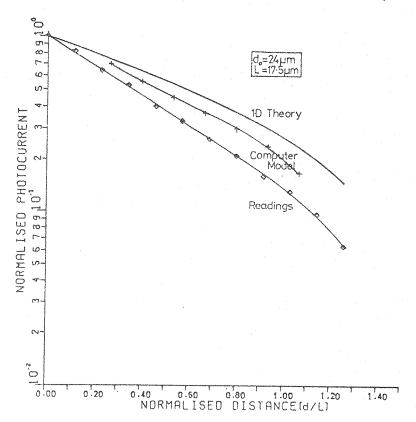

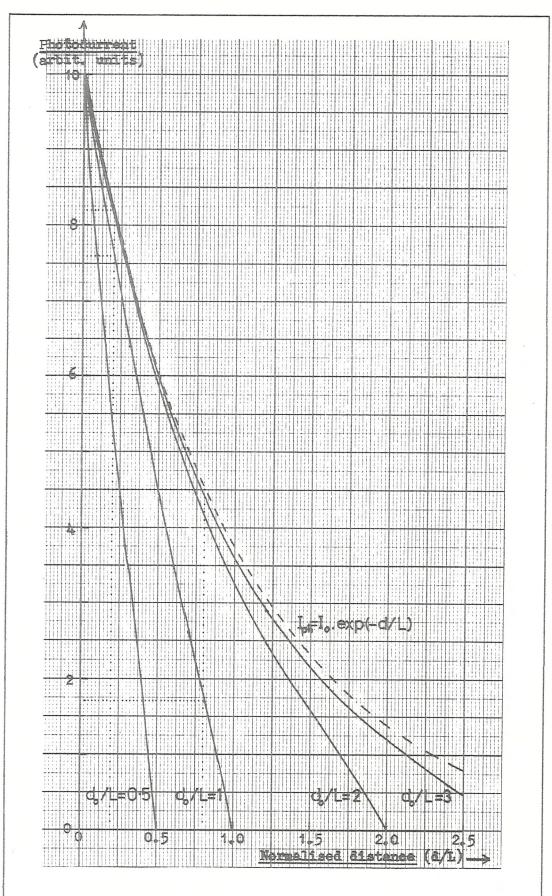

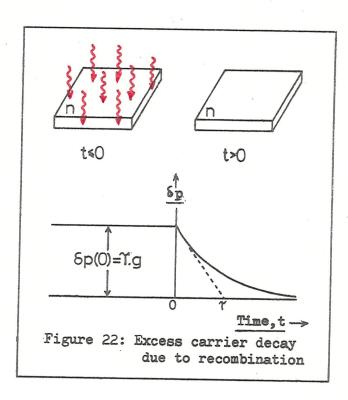

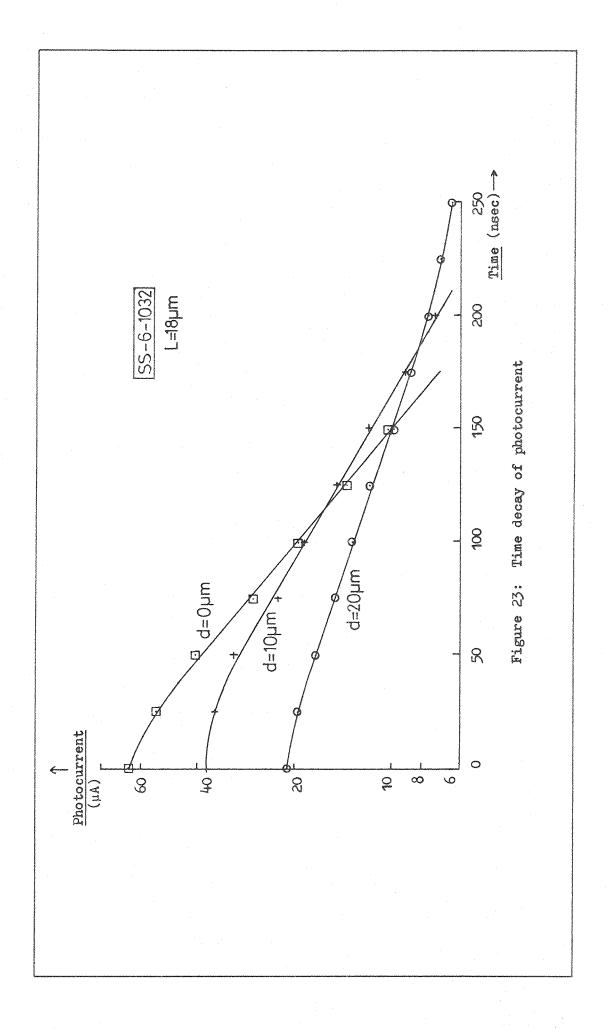

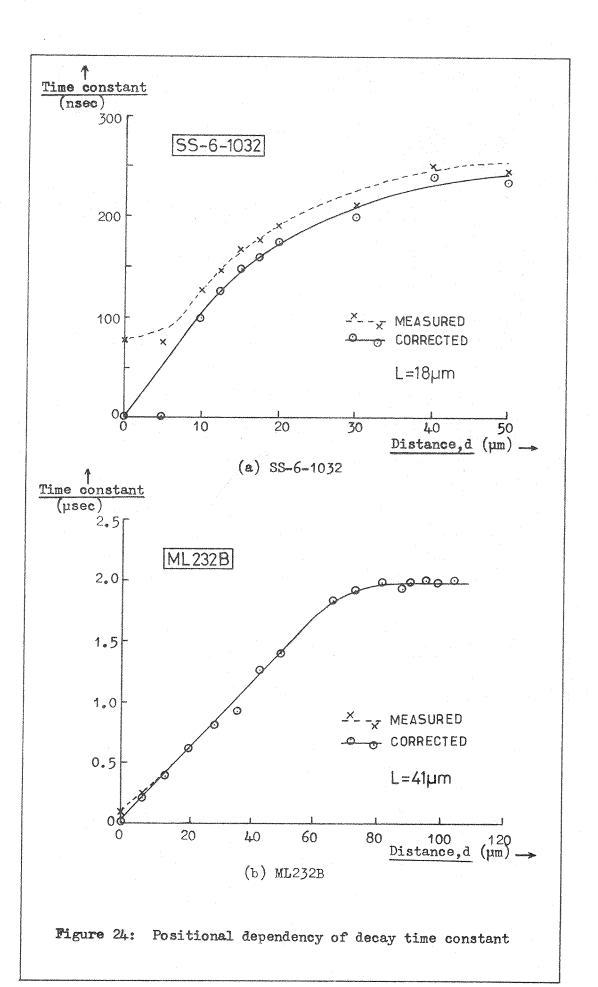

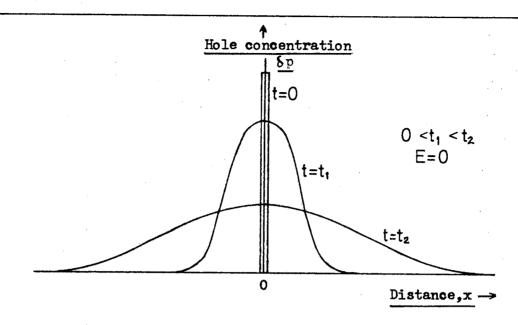

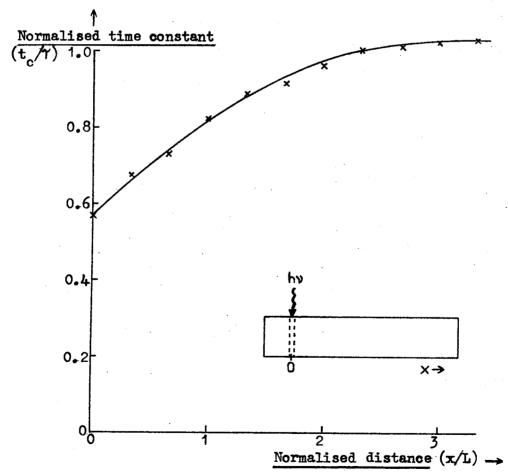

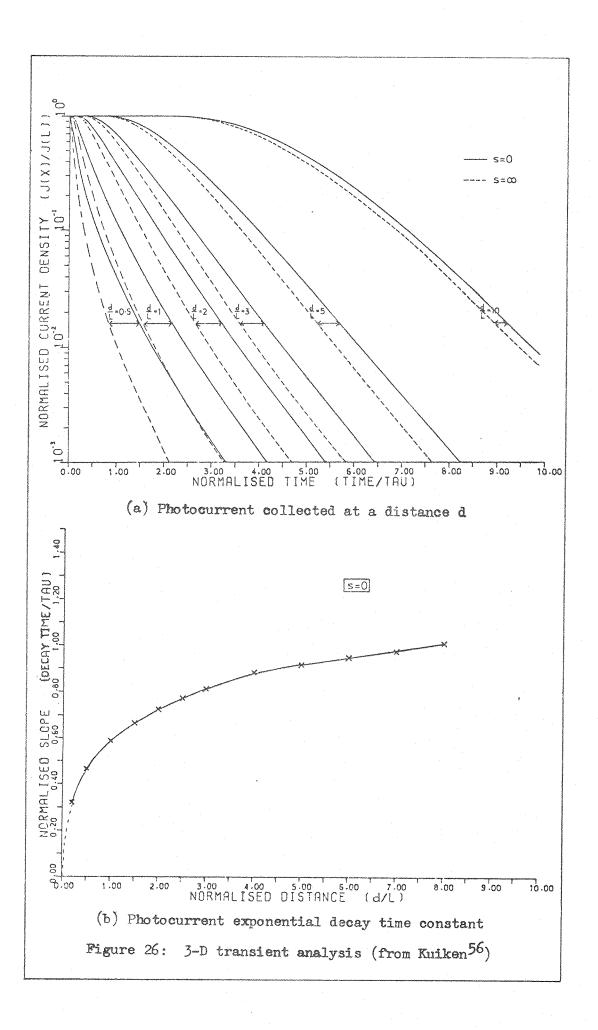

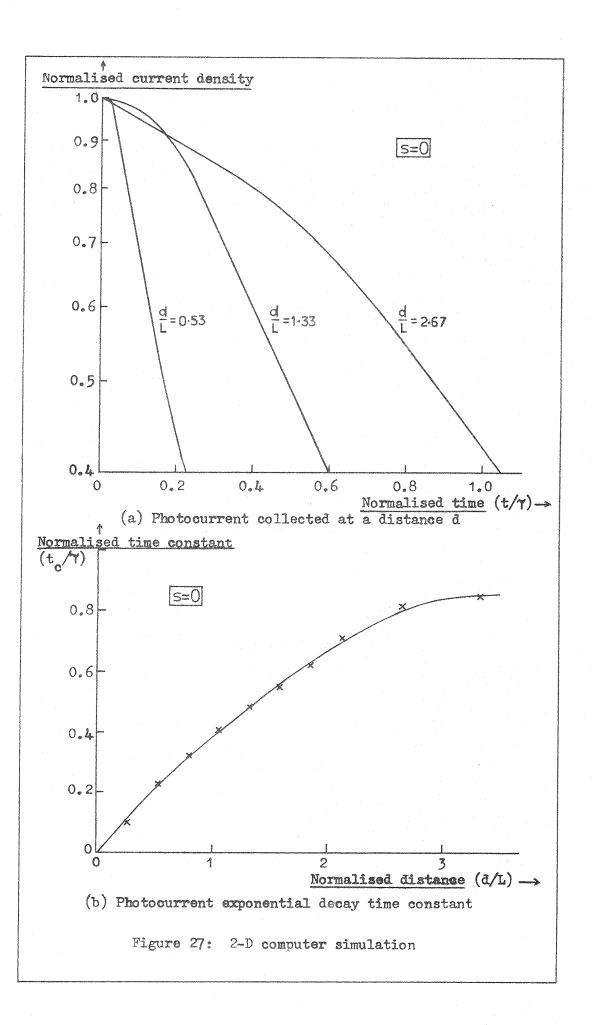

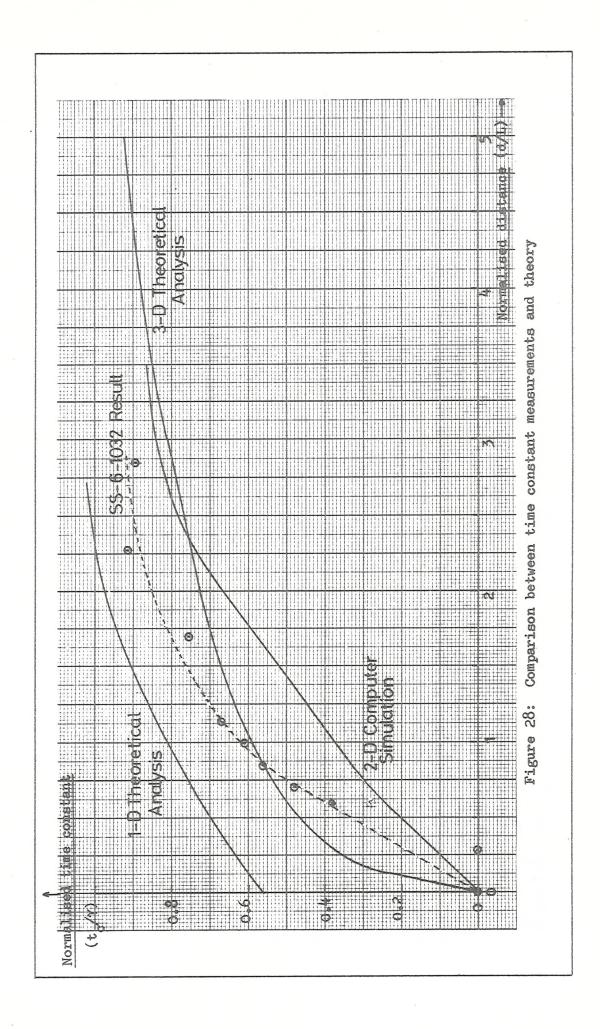

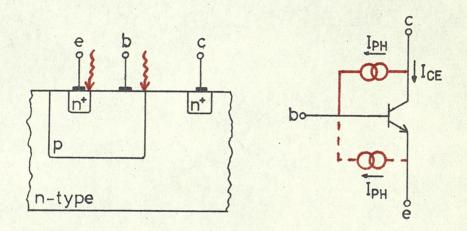

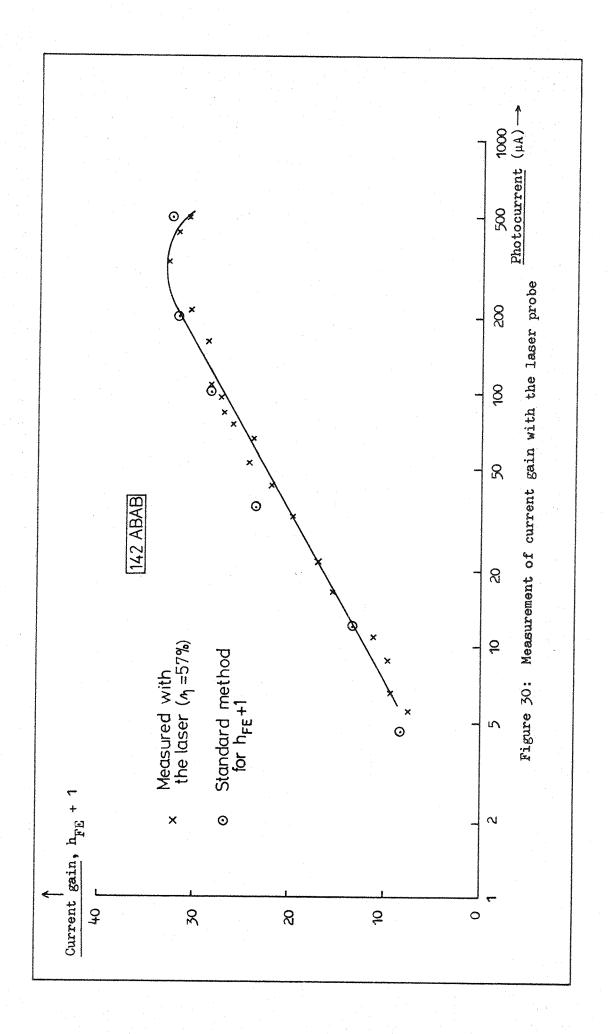

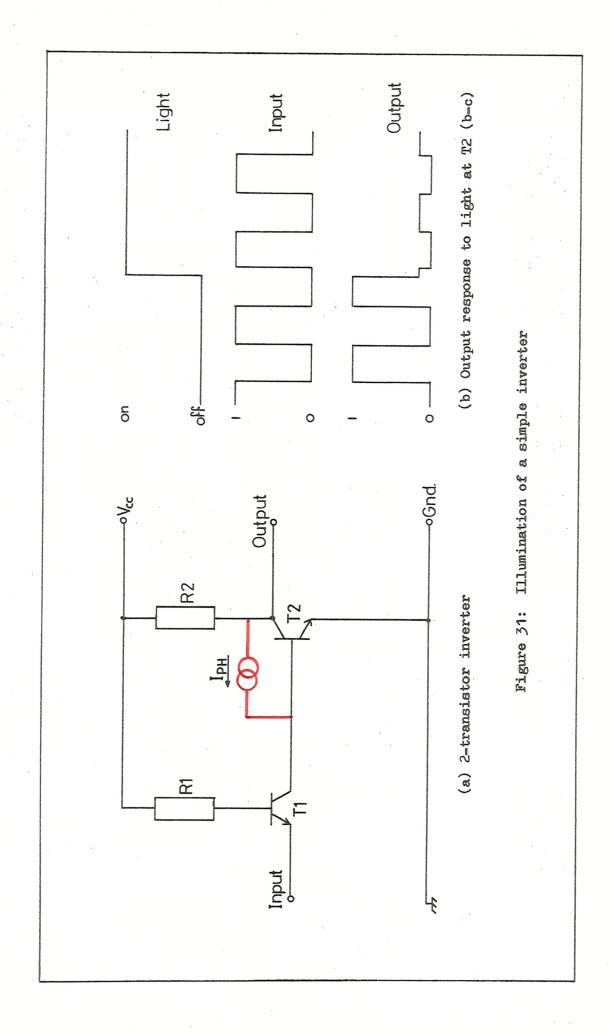

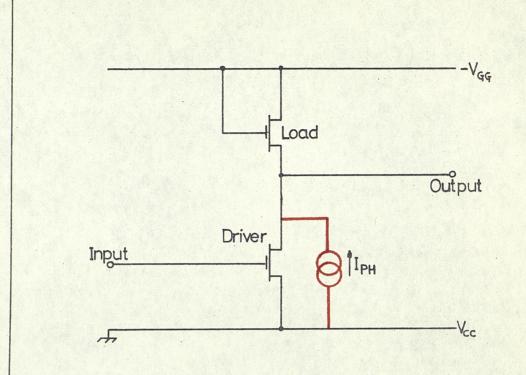

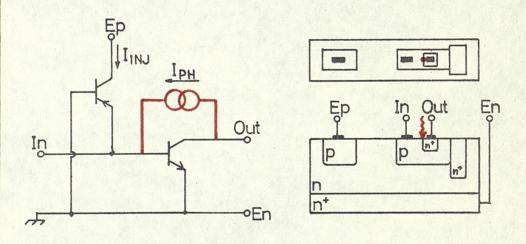

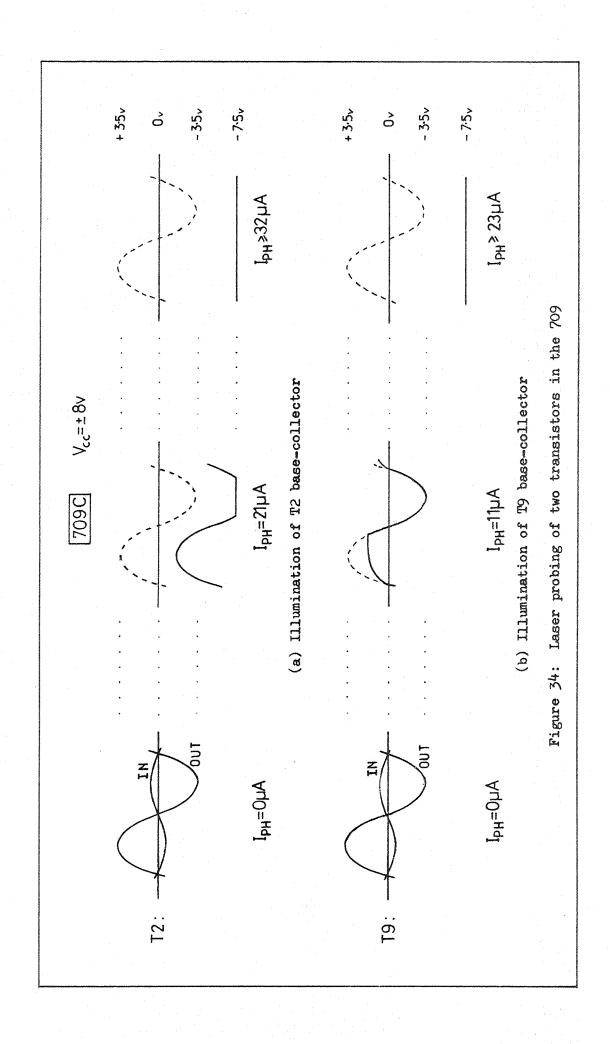

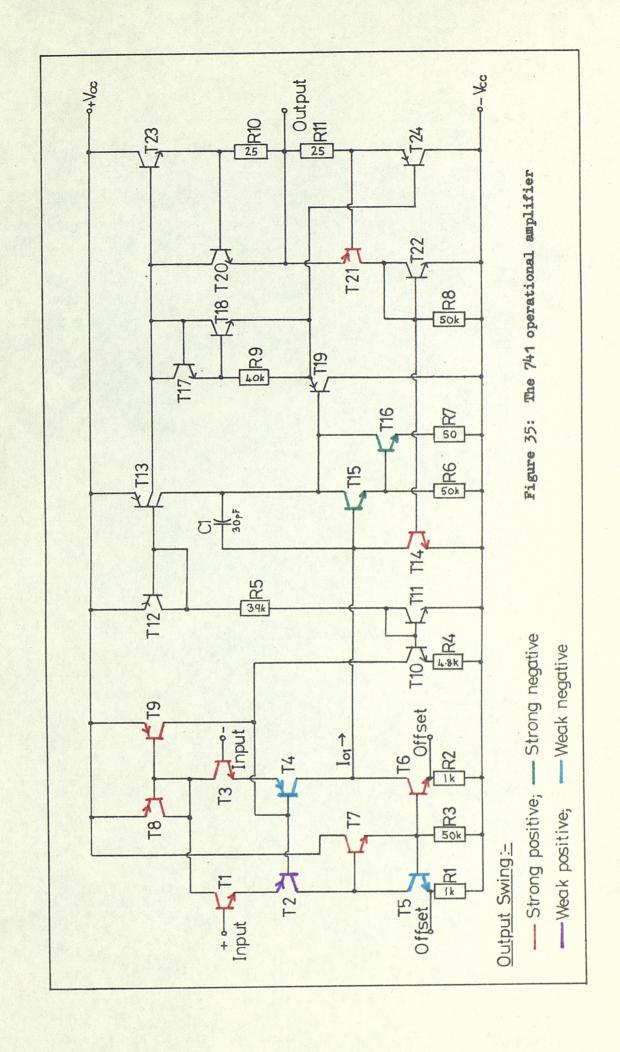

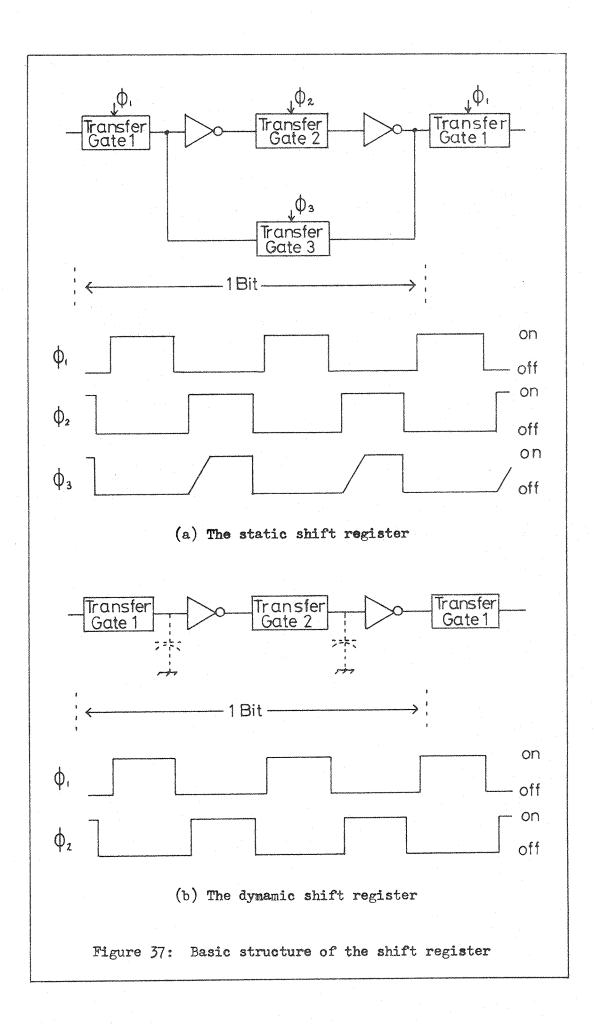

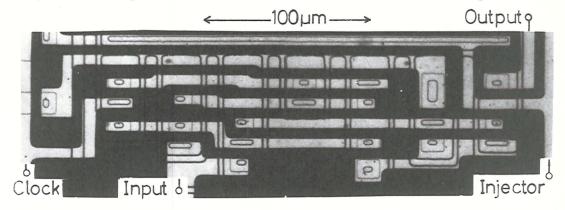

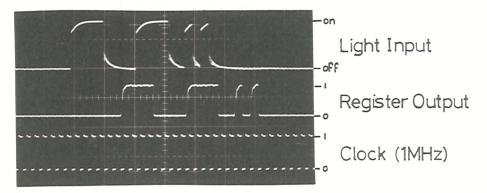

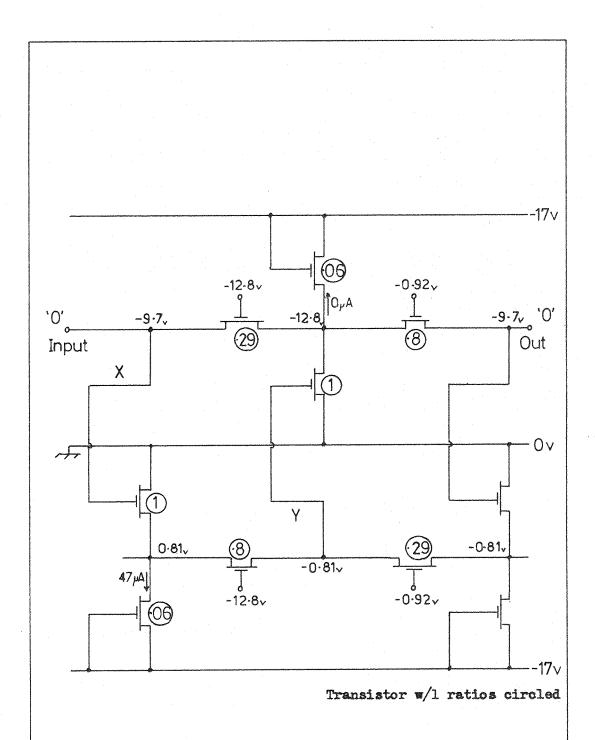

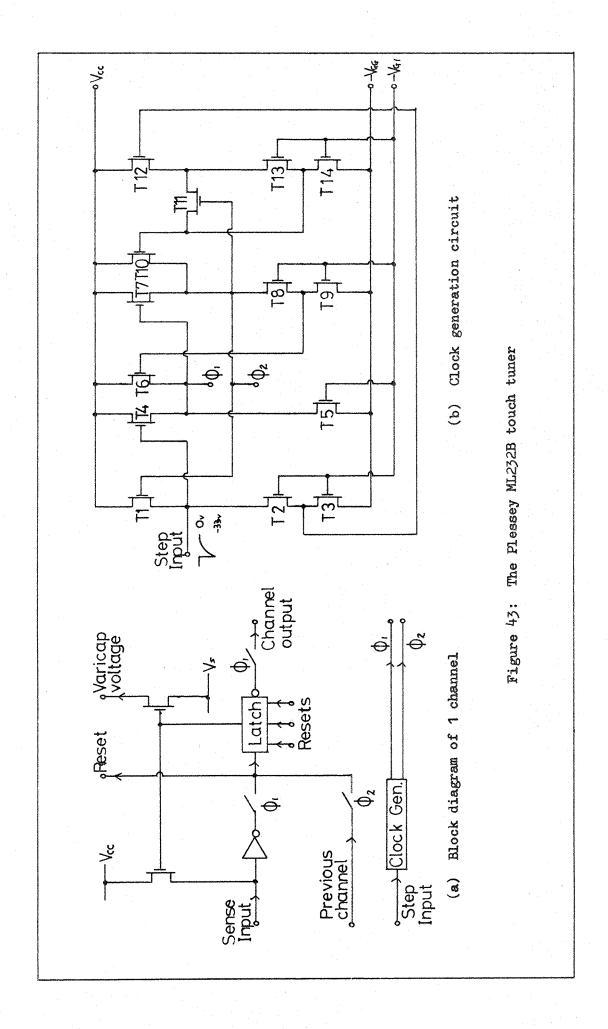

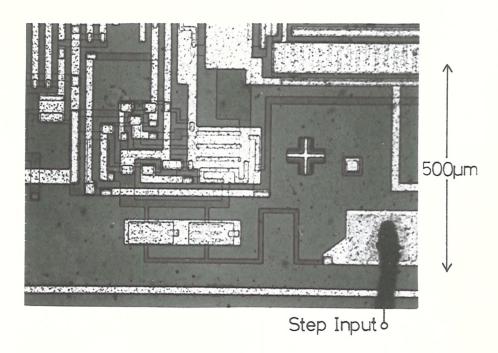

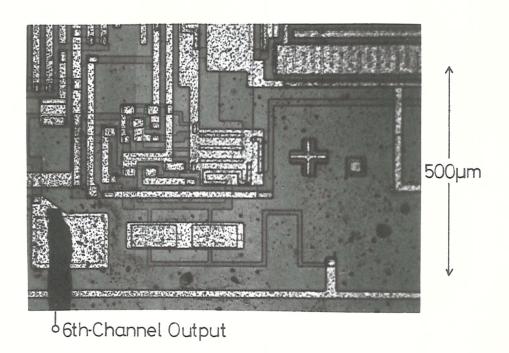

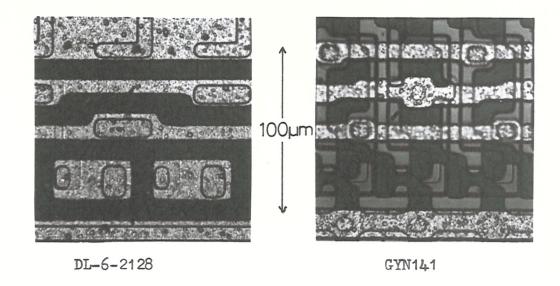

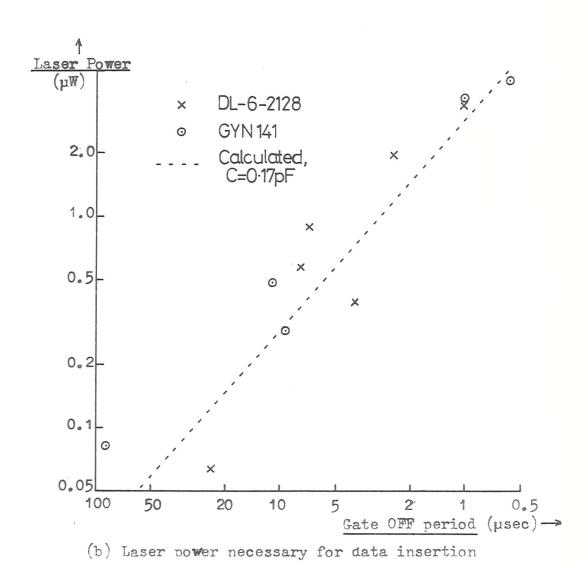

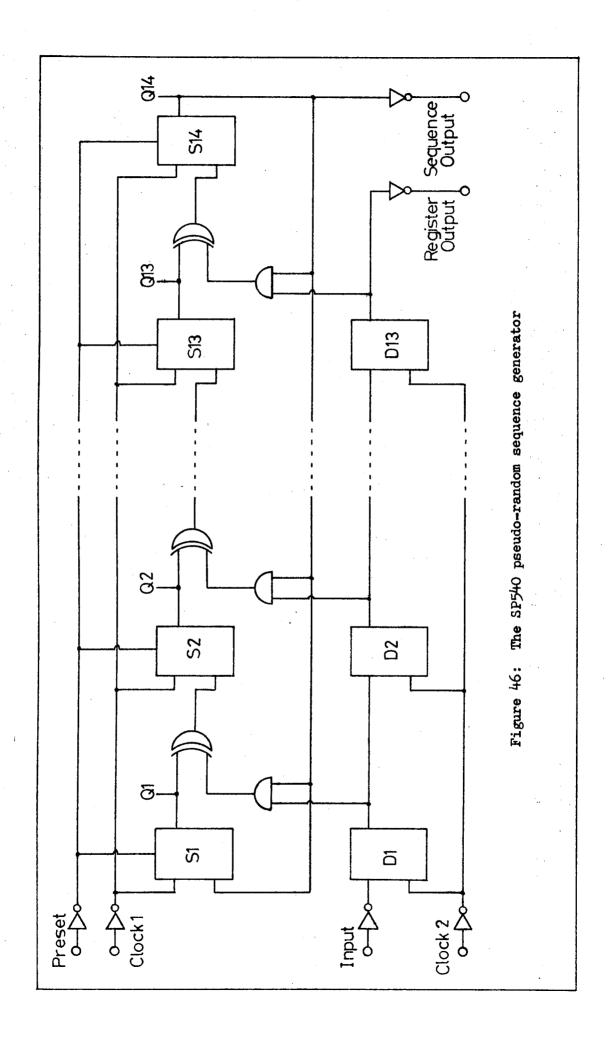

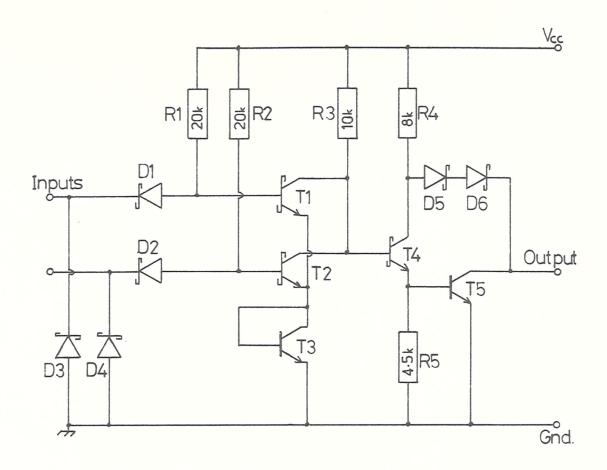

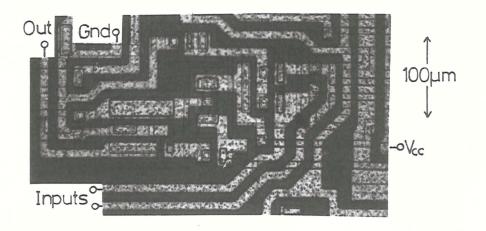

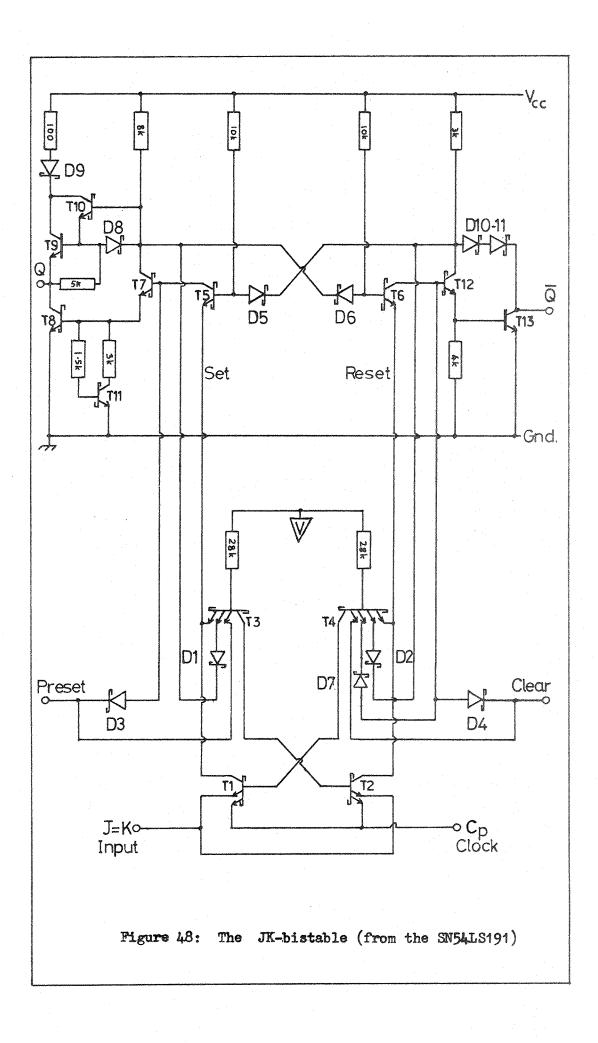

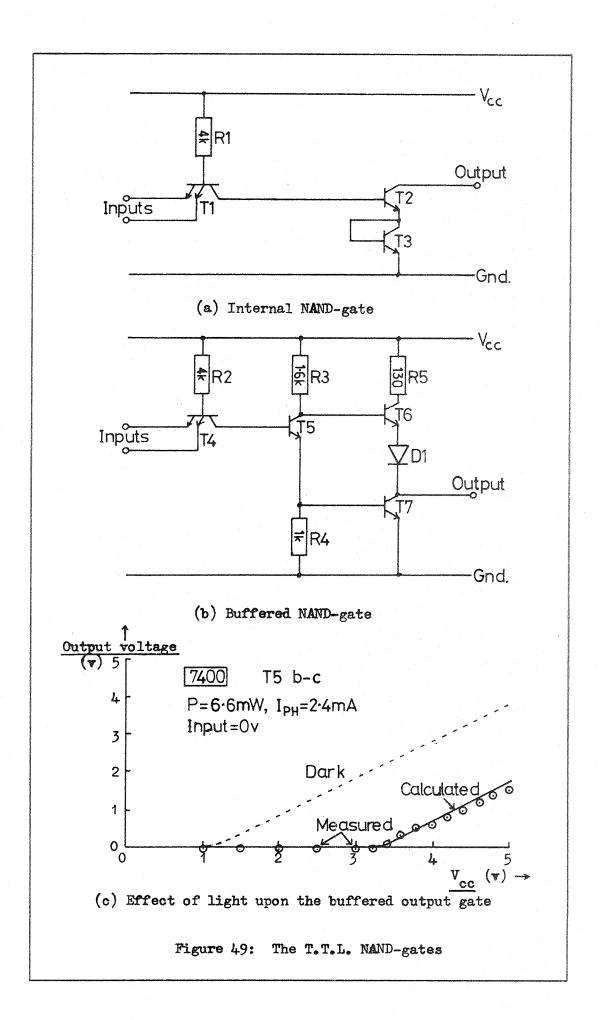

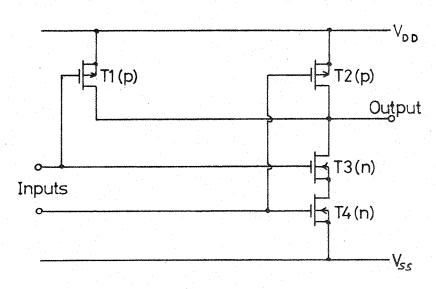

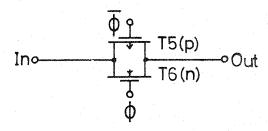

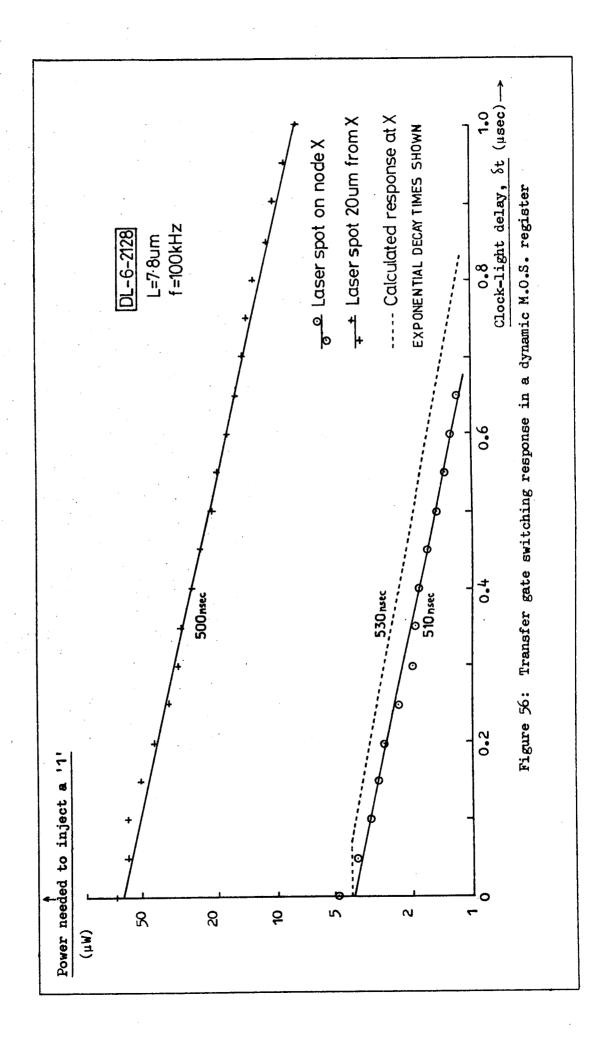

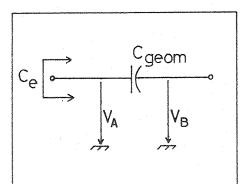

Figure 13: Injected carrier density