# A Systematic Approach to Process Selection in MEMS

David J. Quinn, ASME, Member, S. Mark Spearing, ASME, Member, Mike F. Ashby, and Norman A. Fleck

Abstract—A systematic approach is developed to select manufacturing Process Chains for the generic elements of a MEMS device. A database of MEMS Process Chains and their attendant process attributes is developed from an extensive review of the literature, and used to construct Process Attribute charts. The performance requirements of MEMS beams and trenches are translated into the same set of Process Attributes. This allows for a screening of the Process Chains to obtain a list of candidate manufacturing methods. This method is illustrated in a brief design example.

### I. INTRODUCTION

THE design of any mechanical device requires knowledge of the constraints imposed by material properties and manufacturing processes. In microelectromechanical systems (MEMS) the currently available set of manufacturing processes is much smaller than that for traditional mechanical design, and they impose limits on achievable dimensions, tolerances and performance. At present, the selection of materials and processes in MEMS is often done heuristically using processing capabilities available "in house," rather than by a systematic approach that considers all possible materials and fabrication routes. In the current state of micromechanical design, this may be acceptable, particularly as the introduction of new materials and processes carries a cost penalty. However, as the number of materials and processes available for microfabrication increases, a more systematic approach to material and process selection is needed to avoid cost penalties associated with changing fabrication plans at later stages in the design process. The present study outlines a design tool for the selection of MEMS fabrication routes, both to help the designer and to educate the student.

A major difference between traditional manufacturing processes and microfabrication lies in the level of complexity of shape that can be achieved. In the manufacture of macroscale devices, complex three-dimensional (3-D) shapes are routine. In microfabrication, almost all structures are defined by a combination of deposition, lithographic patterning and etching. Consequently, the complexity of shape is limited to projections of two-dimensional patterns, and most structures take on a limited variety of shape in the through-thickness direction. As a result, most MEMS structural elements can be broadly classified as

ces, complex three-dimensional (3-D) shapes are routine. In rofabrication, almost all structures are defined by a combinently, the complexity of shape is limited to projections of dimensional patterns, and most structures take on a limited dimensional patterns, and most structures take on a limited.

for currently available MEMS processing routes and their use is illustrated in a design example.

Manuscript received November 18, 2003; revised November 25, 2005. Subject Editor T. J. Kenny.

D. J. Quinn is with the Massachusetts Institute of Technology, Cambridge, MA 02139 USA (e-mail: djquinn@mit.edu).

S. M. Spearing is with the Massachusetts Institute of Technology, Cambridge, MA 02139 USA and also with the School of Engineering Sciences, Southampton University, Southampton, SO17 1BJ, U.K.

M. F. Ashby and N. A. Fleck are with the Engineering Department, Cambridge University, Cambridge, CB2 1PZ, U.K.

Digital Object Identifier 10.1109/JMEMS.2006.880292

# II. MEMS PROCESS SELECTION ATTRIBUTES

of beams and trenches. Process selection charts are constructed

beam or trench structures. In this broad classification beam in-

cludes the beams and plates of macro design, and trench refers to

fully enclosed channels and can also define pillars or post struc-

tures. Fabrication is generally achieved by a sequence of steps

using different technologies and procedures, rather than a single

manufacturing process. Understanding these Process Chains is

The strategy adopted here is to construct a database of MEMS

Process Chains, and to ascribe to each chain a set of process attributes. A general framework has been developed by Ashby [1], [2] for process selection, and this is adopted here. In the language of biological classification, the *kingdom* of manufacturing

processes for MEMS beams and trenches is divided into fami-

lies (such as bulk micromachining). Each family contains classes

(such as wet etch) and members (such as anisotropic wet etching

of (100) Si using KOH). The members of this process kingdom

are each quantified by a set of attributes, which include the ma-

terials it can process, the dimensions and tolerances of which it

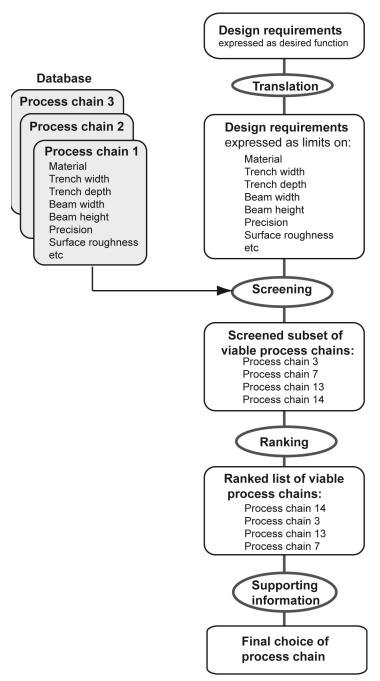

The database is used for process selection via the strategy illus-

trated in Fig. 1. The performance of the planned MEMS design

is translated into a set of desired feature-attributes such as ma-

terial, shape, dimensions, precision etc drawn from the list used

to characterize the Process Chains. The library of Process Chains

is then screened, rejecting those incapable of making the desired

feature from the desired material, with the desired dimensions

and precision, leaving a subset of candidates that could be used

to manufacture the MEMS device. Screening is done either man-

ually using process selection maps or done electronically using an

appropriately constructed database and software tool, such as the

CES<sup>1</sup> Constructor and Selector system. The screened subset of

processes are then ranked, using approximate economic criteria,

the most obvious of which is time. The final step is to search for

detailed supporting information for the top-ranked candidates, al-

is capable and the processing temperature and pressure.

of the greatest importance for MEMS design.

An appropriate set of Process Attributes must first be identified in order to construct a library of MEMS Process Chains. The discriminating attributes for MEMS identified here include

<sup>1</sup>Granta Design Ltd., Rustat House, 62 Clifton Road, Cambridge, CB1 7EG, U.K.

1057-7157/\$20.00 © 2006 IEEE

Fig. 1. Flow chart for process selection scheme.

material, shape (including tolerance and surface quality), and processing temperature and pressure.

## A. Material Attributes

Until recently, the set of candidate materials for MEMS has been relatively limited and centred on silicon, Si [3]. As the set expands, it becomes important to identify the spectrum of materials which can be processed by each Process Chain [4]. Furthermore, in any MEMS fabrication sequence, several materials are used sacrificially. For example a material may be deposited and then etched away later in the sequence of process steps. To address this, one can classify a material used in a fabrication sequence as either *primary* or *secondary*. A primary material is the

main structural material used, while secondary materials either no longer exist in the device after completion of the fabrication sequence or serve a nonstructural purpose, such as metallization or insulation layers.

### B. Shape, Tolerance, and Surface Attributes

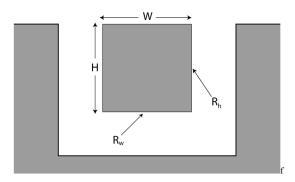

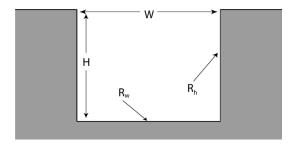

A number of geometric attributes can be ascribed to the beam or trench. They include the in-plane leading dimension w, the out-of-plane height h, the achievable tolerances  $\Delta w$  and  $\Delta h$ , and the root-mean square surface roughnesses  $R_w$  and  $R_h$ . This set of attributes is shown in Fig. 2 for the beam and in Fig. 3 for the trench; they are also listed in Tables I and II. The relative importance of each attribute varies from application to application. For example, the roughness  $R_w$  is particularly important in

Fig. 2. Beam geometry. For the purposes of this paper the key dimensions of a beam are its width and height, and the tolerances associated with them.

Fig. 3. Trench geometry. For the purpose of this paper the key dimensions of a trench are its width and depth and the tolerances associated with them.

TABLE I GEOMETRIC ATTRIBUTES OF BEAM

| BEAM - Geometric and Surface Attributes |                                                         |  |  |  |

|-----------------------------------------|---------------------------------------------------------|--|--|--|

| Dimension                               | Description                                             |  |  |  |

| W                                       | Beam width                                              |  |  |  |

| $\Delta w$                              | Tolerance on beam width dimension (+/-)                 |  |  |  |

| $R_{\rm w}$                             | R <sub>w</sub> In-plane rurface roughness of beam (RMS) |  |  |  |

| h                                       | h Beam height                                           |  |  |  |

| Δh                                      | Δh Tolerance on beam height dimension (+/-)             |  |  |  |

| $R_h$                                   | Out of plane / wall roughness of beam (RMS)             |  |  |  |

TABLE II

GEOMETRIC ATTRIBUTES OF TRENCH

| TRENCH - Geometric and Surface Attributes |                                                                               |  |  |  |

|-------------------------------------------|-------------------------------------------------------------------------------|--|--|--|

| Dimension                                 | Description                                                                   |  |  |  |

| w                                         | Trench width                                                                  |  |  |  |

| $\Delta \mathrm{w}$                       | Tolerance on trench width dimension (+/-)                                     |  |  |  |

| $R_{\rm w}$                               | Roughness of trench bottom (RMS)                                              |  |  |  |

| h                                         | Trench height                                                                 |  |  |  |

| Δh                                        | Tolerance on trench height dimension (+/-) Roughness of trench sidewall (RMS) |  |  |  |

| $R_h$                                     |                                                                               |  |  |  |

the design of mirrors and in the avoidance of stiction [5]–[11]. These geometric features of the beam or trench structure are also process attributes and their achievable values depend upon the Process Chain employed.

# C. Processing Attributes

A number of processing attributes dictate the subsequent performance of a part. For example, the maximum processing temperature has an effect upon the subsequent operating temperature. Here we include as representative process attributes the maximum processing temperature and the minimum processing pressure. These two parameters, in conjunction with knowledge

of primary and secondary materials, can help serve as a cost indicator and help in the development of full device fabrication process flows as they help establish the compatibility of process chains

In macroscale manufacture, it is usually the economic attributes of a process that ultimately distinguish it for selection over other processes with similar capabilities [1]. This is also true to a large degree in MEMS design, as the value of MEMS devices frequently lies in their ability to be mass-produced, such that large capital investments can be written off over time. However, the work presented here has focused on a preliminary evaluation of systematic process selection routines and tools based on performance attributes, not on their economics, for which reliable data are difficult to determine. Thus, no direct cost attributes are developed in the current study.

### III. THE CONSTRUCTION OF PROCESS ATTRIBUTE CHARTS

A literature survey has been conducted to construct a representative set of Process Chains for MEMS structures. These fabrication sequences, along with a summary of the process flow and primary references, are listed in Table III. The geometric and processing attributes of these Process Chains have been assembled from the literature and stored in an electronic database. In cases where the data are sparse, estimates have been made from a knowledge of physical limitations and of the capabilities of similar processes. It is helpful to display these data in charts using process attributes as axes. The charts are of direct use in matching the requirements of beam and trench structures to a candidate set of Process Chains.

# A. Dimensions

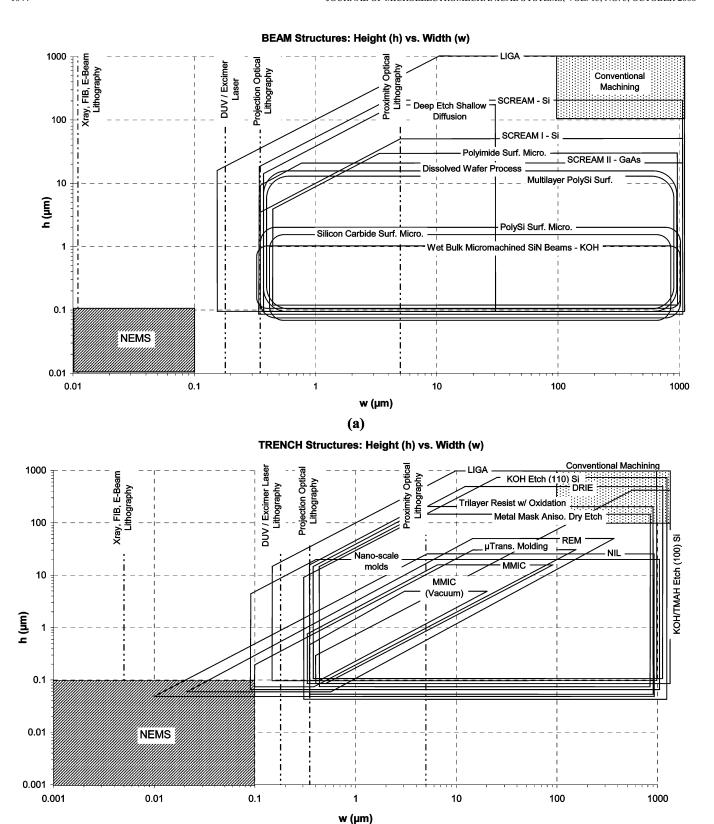

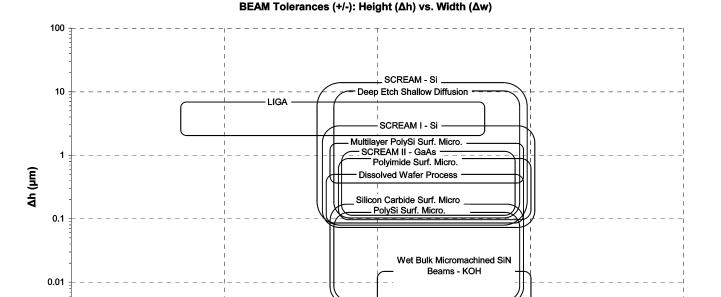

Fig. 4 presents the range of achievable out-of-plane (height) and in-plane (width) dimensions of microfabricated beam and trench structures. Minimum achievable dimensions are important for determining the compactness, natural frequency and thermal time constants of devices and can determine the sensitivity limits for sensors and actuators. In some cases upper limits on fabricated dimensions can also be important, particularly when deep etched features or thick deposited layers are required for high force or power applications. Where there is not a well-defined upper limit for a particular dimension, a nominal upper limit of 1mm has been used.

A high degree of overlap of processing capabilities is evident for the width dimension of both beams and trenches. This dimension is generally dictated by lithographic limits. LIGA, and soft-lithography processes such as Nano-imprint lithography (NIL) and replica molding (REM), are outliers on the h versus w plots because they use high resolution lithographic technologies such as X-ray and E-beam lithography. The deep etch, shallow diffusion process is limited by the width across which one can boron dope silicon by diffusion [26], [29].

The upper limits on the out-of-plane dimensions for both beam and trench structures are limited by practical limits of the etching or deposition processes. When deposition defines the out-of-plane dimension, as with surface micromachining, the upper limit is set by the ability of the structural material to be deposited without significant degradation of film quality, and without excessive residual stress [6], [7]. This limitation has

TABLE III PROCESS CHAINS

| Process Chain Fa                         | mily                                      | Process Chain Name                                                          | Fabrication Sequence Summary                                                                                                                                                                                                                                                                      | Primary Material                | Secondary<br>Material(s)           | References                                                 |

|------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------------------|------------------------------------------------------------|

|                                          |                                           | Anisotropic Wet Etching of (100) Si - KOH                                   | Deposit mask material; pattern; etch; remove mask material (if desired)                                                                                                                                                                                                                           | Si                              | SiO <sub>2</sub> , SiN             |                                                            |

| Wet Etch  Bulk Micromachining  Dry Etch  | Anisotropic Wet Etching of (110) Si - KOH | Deposit mask material; pattern; etch; remove mask material (if desired)     | Si                                                                                                                                                                                                                                                                                                | SiO <sub>2</sub> , SiN          | [8, 12-22]                         |                                                            |

|                                          | Wet Etch                                  | Anisotropic Wet Etching of (100) Si - TMAH                                  | Deposit mask material; pattern; etch; remove mask material (if desired)                                                                                                                                                                                                                           | Si                              | SiO <sub>2</sub> , SiN             |                                                            |

|                                          | Anisotropic Etched Beam in (100) Si - KOH | Deposit mask material; pattern; underetch / release beam                    | SiN                                                                                                                                                                                                                                                                                               | Si                              | [8, 12-21, 23-25]                  |                                                            |

|                                          |                                           | Anisotropic Wet Etching of (100) Si - EDP with<br>P++ Etch Stop             | Thin wafer; boron diffuse and drive in; define mask and pattern; etch                                                                                                                                                                                                                             | Si                              | SiO <sub>2</sub> , SiN             | [5, 8, 9, 12-14, 16, 17, 19, 26-29                         |

|                                          |                                           | Anisotropic Dry Etching (RIE) of Si - Metal<br>Mask                         | Deposit (electroplate) metal mask and pattern; RIE; remove mask                                                                                                                                                                                                                                   | Si                              | Metal (Ni)                         | [5, 8, 9, 12-14, 16, 17, 22, 24, 26<br>30-35]              |

|                                          |                                           | Deep Etch, Shallow Diffusion Process                                        | Deposit mask material; RIE; boron diffuse; short RIE; release OR bond to glass, thin and release                                                                                                                                                                                                  | Si                              | Metal (Ni)                         | [5, 8, 9, 12-14, 16, 17, 22, 24, 26<br>28, 29, 31, 34, 35] |

|                                          |                                           | Dissolved Wafer Process                                                     | Etch anchor recesses; boron diffuse and drive in; pattern structure; etch recess in glass; bond Si wafer to glass; thin wafer; EDP etch                                                                                                                                                           | Si                              | Glass                              | [5, 8, 9, 12, 28, 34]                                      |

|                                          |                                           | SCREAM - Si (Thick Oxide Mask)                                              | Short thermal oxidation and pattern; RIE; long (thick) thermal oxidation; RIE; thermal oxidation of sidewalls; deposit metal; deposit resist; isotropic release etch                                                                                                                              | Si                              | SiO <sub>2</sub>                   | [5, 8, 9, 12, 25, 34, 36-42]                               |

|                                          | Dry Etch                                  | SCREAM I - Si (Deposited Oxide Mask)                                        | Deposit mask oxide and pattern; long RIE; deposit sidewall oxide; short RIE; long RIE; isotropic release etch; deposit metal                                                                                                                                                                      | Si                              | SiO <sub>2</sub>                   | [5, 8, 9, 12, 25, 34, 36-43]                               |

|                                          |                                           | SCREAM II - GaAs                                                            | Deposit nitride mask and pattern; RIE; deposit nitride layer; deposit metal; spin on resist, bake and remove; RIE exposed metal; RIE nitride; isotropic release etch                                                                                                                              | GaAs                            | SiN                                | [5, 8, 9, 12, 25, 34, 36-43]                               |

|                                          |                                           | Deep Reactive Ion Etching (DRIE - Bosch<br>Process)                         | Deposit mask and pattern; short isotropic etch (SF6); passivate sidewalls (C4F8); repeat to desired depth                                                                                                                                                                                         | Si                              | C <sub>4</sub> F <sub>8</sub>      | [8, 30, 32, 44-48]                                         |

|                                          |                                           | Trilayer Mask Dry Etch Process with Thermal<br>Oxidation Finishing          | Deposit mask layer #1 (metal); deposit mask layer #2 (resist and bake); deposit mask layer #3 (metal);<br>pattern trilayer mask (RIE); RIE; thermal oxidize sidewalls; isotropic wet (finishing) etch of sidewalls                                                                                | Si                              | Ni, SiO <sub>2</sub>               | [5, 8, 12, 13, 32, 36, 49]                                 |

| Surface Micromachining  Poly  Multilayer |                                           | Polysilicon Surface Micromachining                                          | Deposit isolation layer (if desired); deposit sacrificial layer (densification bake if necessary); open up anchors in sacrificial layer; deposit structural (polysilicon layer) and anneal (if necessary); pattern structure (RIE); wet isotropic release etch of sacrificial layer               | PolySi                          | PSG, SiO <sub>2</sub>              | [7, 8, 11, 12, 34, 37, 50-53]                              |

|                                          |                                           | Silicon Carbide Surface Micromachining                                      | Deposit isolation layer (if desired); deposit sacrificial layer; open up anchors in sacrificial layer; deposit structural (Silicon Carbide); pattern structure (RIE); wet isotropic release etch of sacrificial layer                                                                             | SiC                             | Si, PSG, SiO <sub>2</sub>          | [7, 8, 11, 12, 34, 37, 50, 51, 54-5                        |

|                                          |                                           | Polyimide Surface Micromachining                                            | Deposit isolation layer; deposit sacrificial layer; spin-on thin polyimide layer and partial cure; deposit conductor layer (if necessary), alternate spin casting and soft baking for remaining structural depth; final cure; deposit metal mask and pattern; plasma etch; isotropic release etch | Polyimide                       | PSG, SiO₂                          | [7, 8, 11, 12, 34, 37, 50, 51, 59-6                        |

|                                          |                                           | Multilayer Polysilicon Surface Micromachining<br>(Sandia SUMMIT / SUMMIT V) | Deposit buffer/isolation layer; deposit sacrificial layer; deposit structural (polysilicon) layer; planarize<br>using CMP; repeat to desired height up to 5 structural layers; wet isotropic release structure                                                                                    | PolySi                          | PSG, SiO <sub>2</sub>              | [7, 8, 11, 12, 34, 37, 50-53, 62]                          |

| Soft Lithography Processes Micro         |                                           | E-beam Defined, Hard Master Mold Making<br>(Nano-scale Molds)               | Thermal oxidize layer and pattern (e-beam); RIE                                                                                                                                                                                                                                                   | Si, SiO <sub>2</sub>            | SiO <sub>2</sub>                   | [8, 12, 24, 43, 63-67]                                     |

|                                          |                                           | Micro-contact Printing (μCP)                                                | Ink master stamp with pattern material; transfer patter to target material (press); use pattern as etch or deposition mask (if desired)                                                                                                                                                           | "Inks" (polymers,<br>SAMs etc.) | PDMS<br>(Master Material)          | [8, 63, 64, 68]                                            |

|                                          |                                           | Micro-molding in Capillaries (MMIC)                                         | Press PDMS master mold against target substrate; insert liquid polymer via capillary action and cure; remove mold                                                                                                                                                                                 | Polymers                        | PDMS<br>(Master Material)          | [8, 63, 64, 66, 69, 70]                                    |

|                                          |                                           | Micro-molding in Capillaries (MMIC) - Vacuum<br>Assisted                    | Press PDMS master mold against target substrate; insert liquid polymer via vacuum action and cure; remove mold                                                                                                                                                                                    | Polymers                        | PDMS<br>(Master Material)          | [8, 63, 64, 66, 69, 70]                                    |

|                                          |                                           | Micro Replica Molding (REM)                                                 | Cast and cure PDMS against hard master mold (Si, SiO <sub>2</sub> , or SU8) and remove                                                                                                                                                                                                            | PDMS                            | PDMS, SU8, Si<br>(Master Material) | [8, 24, 63, 64, 66, 67]                                    |

|                                          |                                           | Micro Transfer Molding (μTM)                                                | Fill master PDMS mold with liquid polymer; press / pattern against substrate; remove excess polymer<br>and cure; remove mold                                                                                                                                                                      | Polymers                        | PDMS<br>(Master Material)          | [8, 63, 64, 66, 67]                                        |

|                                          |                                           | Hard Master Embossing / Nano-Imprint<br>Lithography (NIL)                   | Deposit polymer; imprint pattern into deposited polymer and cure; complete pattern transfer with RIE;<br>deposit metal on patterned polymer and lift off                                                                                                                                          | Polymers                        | SiO <sub>2</sub>                   | [8, 63-65, 71, 72]                                         |

| LIGA                                     |                                           | LIGA                                                                        | Deposit thick resist layer (PMMA); X-Ray pattern and develop; electroplate metal and release                                                                                                                                                                                                      | Metal (Ni)                      | PMMA                               | [8, 12, 73, 74]                                            |

been largely overcome for polysilicon structures by the Sandia SUMMIT process (multilayer polysilicon surface micromachining), where a proprietary low-stress deposition process, combined with intermediate planarization steps by chemical mechanical polishing (CMP) have been used to produce moderately thick structures,  $h \approx 14~\mu \mathrm{m}$  [62].

Virtually all etching used in microfabrication has a limiting height to width aspect ratio, as for a given width, there is a depth beyond which reaction products cannot be removed from the trench, thus halting the etch process. In fabrication sequences utilizing wet anisotropic etching of Si to define height dimensions, aspect ratio limits are dictated by the orientation of crystallographic planes [14], [17]. That is, when etching (100) silicon, etching is terminated on  $\{111\}$  planes oriented at an angle of  $54.74^{\circ}$  to the  $\{100\}$  planes; consequently, the maximum aspect ratios is less than unity.

Dry etching also produces a restricted aspect ratio due to the limited removal of reaction products and due to ion bowing: ions impact the side walls as etching proceeds. The aspect ratio is further limited by the durability of mask materials. The solubility of the mask material by the etchant not only limits the overall depth that can be achieved before the mask completely erodes but also limits the straightness of the sidewall: the mask material may become redeposited on the sidewalls of the etched features [8], [17], [22], [24], [31], [35].

The use of metal, trilayer resist and thick thermal oxide masks (as in SCREAM) allow for the highest aspect ratio of the dry etch Process Chains [42], [49], [75]. DRIE uses these same principles and repeated isotropic and sidewall passivation/protection steps to achieve not only a high aspect ratio, but also higher etch rates, thus allowing structures to be fabricated with dimensions comparable to the wafer thickness [47], [48], [76].

Limitations in aspect ratio can arise from physical effects in addition to the etching process. LIGA, for example, uses X-ray lithography to define the height of structures, and the aspect ratio limitations are attributed, in part, to diffraction of the X-ray beam [8]. In several soft lithography processes, such as nanoscale hard embossing (nano-imprint lithography—NIL) and replica molding (REM), the use of polymeric materials and moulds dictate minimum and maximum aspect ratios for patterns to be transferred with acceptable fidelity. The rheology of fluids in moulds and the deformation of master stamps overlarge surface areas limit the range of achievable aspect ratio [63], [64], [69], [77].

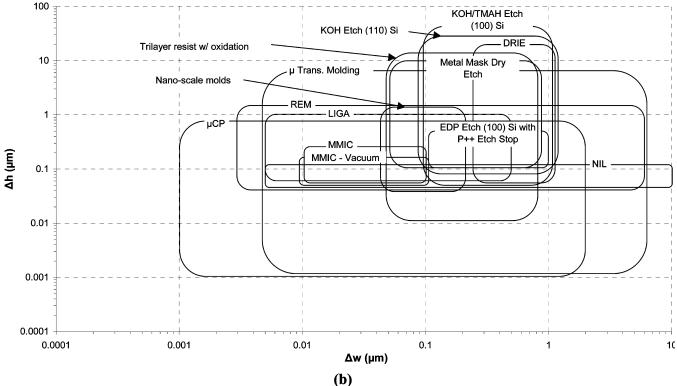

# B. Tolerance

The  $\pm$  amplitude of tolerances on height  $\Delta h$ , and on width,  $\Delta w$ , are important in the design of MEMS. The ability to manufacture to tolerances controls the precision and accuracy of the devices and also has economic consequences if subsequent "tuning"

or rework steps are required to compensate for poor tolerances. Tolerances, expressed as absolute dimensions, are plotted in the tolerance maps of Fig. 4 for the library of Process Chains.

Typically, the lithographic step dictates the width tolerance. This is reflected in the Process Chains using high-resolution lithographic steps such as LIGA and various soft-lithography processes. In addition to lithography, one must consider the subsequent etch steps of the fabrication sequence. If the etch gives significant mask undercutting, the tolerance on the width dimension increases. This is reflected by the relative width tolerance for anisotropic wet and dry etch based processes: the occurrence of mask misalignment and crystallographic etching in wet etch based processes leads to a greater width tolerance than anisotropic dry etch based processes, assuming the use of durable mask materials in the dry etch process [8], [14], [17]. Similarly, in DRIE, isotropic dry etching gives mask undercutting and a consequent increase in width tolerance [35].

Several soft lithography processes involve the casting and curing of polymers in a moulding or stamping process. The resulting shrinkage and expansion by 1–3% contribute to the tolerances that can be held in the in-plane dimensions [63], [64], [77]–[79].

Tolerances in the height dimension are generally dictated by the etching or deposition processes used in the fabrication sequence. Where deposition steps define the height of a structure, as in surface micromachining, the out-of-plane dimension can be controlled down to nanometer level. Poorer tolerances are achieved by multilayer surface micromachining where the tolerance on the out-of-plane dimension is cumulative over multiple deposition steps, and by polyimide surface micromachining where the use of spin casting is less accurate than other deposition techniques [59], [60].

Next, consider a structure of height dictated by a single etch step. Structures whose height is defined by a single etch step generally have tighter tolerances using dry etching than wet etching. In standard anisotropic wet etch processes, even if one has accurate control over the concentration, stirring and reactant removal, it is difficult to control the depth of etch to better than 10% of the nominal depth [17]. This is unacceptable when making structures requiring depths of etch in excess of a couple of hundred microns, such as in the fabrication of thin membranes, where control of the thickness of the membrane is critical. Tighter tolerances on depth dimensions can be attained by anisotropic dry etching due to close control over the pressure, bias, gas flow and other process variables [22].

The use of an etch stop in wet bulk micromachining allows for a tight tolerance on the depth dimension, see Fig. 5. For example, a diffused and driven-in boron layer (p++ doped) can be used to define the depth of etch. This diffusion layer is largely resistant to EDP etching, allowing for depth control in the submicron domain [8], [28]. Other etch stop procedures, such as electrochemical and material stops, particularly buried oxide layers in silicon on insulator wafers, have a similar performance [17], [27].

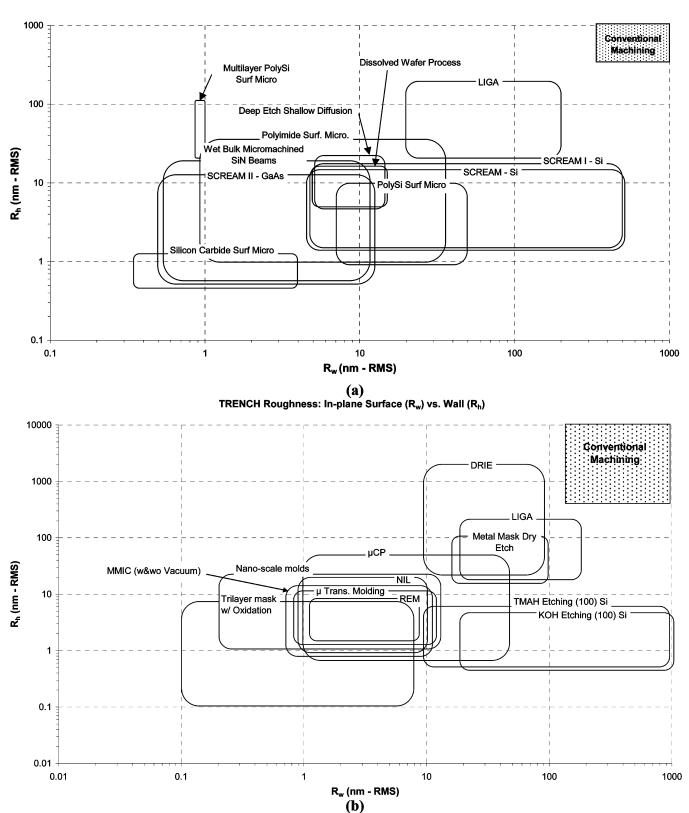

### C. Roughness

Fig. 6 presents Process Attribute maps for in-plane surface roughness and side-wall roughness, given as the

root-mean-square (rms) values. Roughness is important for optical applications where reflectivity is required. High roughness is undesirable in tribological applications, but may be desirable if stiction is to be avoided. Roughness also plays a role in dictating the strength of the resulting structure. Again, the roughness characteristics are dictated mainly by the combination of etching and deposition used in each Process Chain.

Dry etch processes have the potential for attaining very low surface roughness both in-plane and in the side-wall direction. An exception is DRIE, where the alternating etch and passivation steps creates a scalloping of the sidewalls and roughness up to the micron level [47], [48]. In anisotropic wet etching, the side-walls can be aligned with crystallographic planes and the resulting roughness can be of atomic magnitude. Wet etching also has the potential to leave extremely rough in-plane surfaces: the roughness of {110} planes exceeds that of {100} planes [15]. Improved surface roughnesses are achieved in doped silicon through the use of an etch stop or a deep etch shallow diffusion sequence.

The use of finishing steps to improve surface and side-wall roughness in Process Chains is included in Fig. 6. In-plane roughness can be improved dramatically by the use of CMP steps, as illustrated by multilayer surface micromachining. Another common technique for reducing both in-plane and sidewall roughness, shown here in combination with a trilayer resist mask dry etch process, is the use of an oxidation finishing step, where thermal oxidation followed by a wet etch dramatically reduces the roughness of the as-etched or oxidized surface [5], [19].

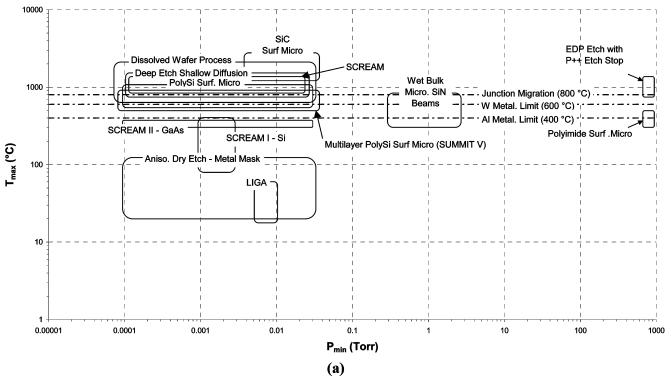

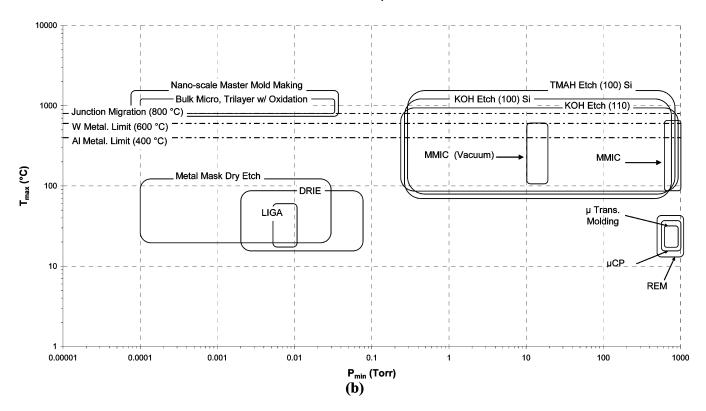

# D. Pressure and Temperature

Fig. 7 presents a chart of the maximum process temperature versus minimum processing pressure for the MEMS Process Chains. These two parameters are important for several reasons. First, they are often indicative of the cost and time of a Process Chain, such as the capital cost of high temperature or vacuum equipment, and the time necessary to carry out high temperature or high vacuum steps. Second, these attributes allow the designer to discriminate between those candidate process chains that can be carried out "in-house" and those that must be outsourced for fabrication. This is an indirect cost indicator. And third, these parameters determine the compatibility of different Process Chains and materials. That is, if one wanted to fabricate a complete device using a series of Process Chains, compatibility can only be assured if the maximum temperature of the Process Chain considered does not exceed the melting temperature of the materials present in an early fabrication sequence. Similarly, one could not use a high vacuum fabrication sequence following a fabrication sequence that leaves potentially contaminating materials.

The maximum process temperature and minimum processing pressure also dictate whether these process sequences can be carried out on IC circuitry. The integration of mechanical and electronic subsystems is part of the more general issue of packaging, an important issue which must be addressed at the earliest stages of design [80]. Junction migration will occur at approximately 800 °C for shallow junctions. Thus, temperatures in excess of this limit should be avoided for integration with IC circuitry. In addition, aluminium and tungsten, common metals

Fig. 4. Height versus width attribute charts for (a) beams and (b) trenches. The "envelopes" for each process chain are derived from the literature according to Table III. The height and width are arbitrarily limited to  $1000 \, \mu \mathrm{m}$  as a practical upper limit to microfabrication.

**(b)**

used in CMOS fabrication, generally begin to degrade when subjected to temperatures in excess of 400 °C and 600 °C, respectively. Thus, process chains that require temperatures in excess of these limits require careful consideration of the full fab-

rication sequence. Where high temperature steps, such as deposition and annealing steps, of a given process chain follow the IC fabrication steps, appropriate analyses must be performed to ensure that the integrated circuitry is sufficiently insulated.

0.01

0.001

10

TRENCH Tolerances (+/-): Height (Δh) vs Width (Δw)

0.1

Δw (μm)

(a)

Fig. 5. Height and width tolerance attribute charts for (a) beams and (b) trenches. This data is derived from the literature according to Table III.

# IV. APPLICATON OF THE PROCESS ATTRIBUTE CHARTS

How can the Process Attribute charts help in the design of a MEMS device? Conceptually, this is straightforward: upon translating device performance into a set of process attributes of each beam and trench, one can filter out the potential process sequences for use in fabrication. A detailed search for support information is then used to rank the list of

# BEAM Roughness: In-plane surface (R<sub>w</sub>) vs. Wall Roughness (R<sub>h</sub>)

Fig. 6. In-plane surface and wall roughness attribute charts for (a) beams and (b) trenches. Data is derived from the literature according to Table III.

candidate Process chains and to select the most appropriate for the task. Subsequently, a detailed review of the process must be undertaken to understand additional limitations and secondary considerations. As an illustrative example, consider a MEMS device with a pressure diaphragm comprising a Si plate with doped in piezoresistors. A detailed case study of such a device is provided in [80, Ch. 18]. In order to compete with existing devices

### BEAM Structures: Max. Process Temp vs. Min. Process Pressure

TRENCH Structures: Max. Process Temp vs. Min. Process Pressure

Fig. 7. Maximum process temp versus minimum process pressure attribute charts for (a) beams and (b) trenches.

the pressure sensitivity,  $K_P$ , must be better than 0.1 mv/V-kPa. From [80, eq. 18.46], given typical piezoresistor dimensions and piezoelectric coefficients it can be shown that for a square

diaphragm  $K_P$  is given by

$$K_P = 39 \times 10^{-6} \left(\frac{L}{H}\right)^2 \tag{1}$$

where  $K_P$  is in units of mv/V-kPa, and where L and H are the in-plane dimension (width) and thickness of the diaphragm respectively. Thus to achieve the required sensitivity, L/H must exceed 50. Since the diaphragm is essentially a beam structure, this design constraint can be plotted on Fig. 4(a). It creates a triangular area in the bottom right-hand corner of most of the process lozenges. By this metric most of the bulk micromachining processes appear as candidates, capable of creating membranes with dimensions of  $1000~\mu m$  by  $20~\mu m$  thick down to  $10~\mu m$  by  $0.2~\mu m$  thick.

A second important consideration is the accuracy of the sensor. Currently piezoresistive pressure sensors require electrical calibration using laser trimming of the resistors. One contribution to this is the tolerances on the microfabrication of the diaphragm. An accuracy of better than 1% is required for automotive applications (see [80, Table 17.1, Ch. 17]). If this step could be avoided, by choice of a suitable process chain, then it would have considerable impact on the cost of fabrication of such sensors. Consider a large diaphragm, 1000  $\mu m$ by 20  $\mu m$  thick. In the absence of any thickness variation, a width (L) variation of 5  $\mu m$  is permissible according to (1). This is clearly achieved, see Fig. 5(a). However, in the absence of any width variation, a thickness tolerance of 0.1  $\mu m$  must be held. From Fig. 5(a), this is marginal for bulk micromachining processes, and given other sources of error, it is clear that microfabrication alone cannot be relied upon to achieve the required accuracy. Greater inaccuracies are anticipated for smaller pressure sensors in their as-processed state. We also note in passing that temperature compensation and packaging introduced stresses are additional drivers for the laser trimming step.

Pursuing the pressure sensor example further, accepting the need to use laser trimming to compensate for the limits in manufacturing tolerances, if the device is to have embedded IC circuitry with aluminium metallization, this requires the processing temperature not to exceed 400 °C, On referring to Fig. 7(a), this would eliminate some process chains involving bonding or doping. From Figs. 5(a) and 7(a) it can be seen that the principal candidate process chains are: DRIE, Anisotropic KOH etching or TMAH etching of (110) Si. In all cases the diaphragm would be formed by etching down from the backside of the wafer, either as a timed etch, or to an etch stop. Additional considerations of cost and process sequence compatibility are needed to identify the best choice. It is clear from this example that a systematic consideration of the functional requirements helps to narrow the process selection substantially.

### V. CONCLUDING REMARKS

The most obvious limitation of the work presented here is that due to the accuracy and availability of processing data. Typically, the focus of much of the literature on fabrication sequences is neither on process control nor on absolute limits of the Process Chains but on particular devices fabricated using these Process Chains. Few, if any, statistical measures are given to indicate the distribution of the data. Nevertheless, for the purposes of evaluating the use of a systematic approach to MEMS process selection and its associated tools, the data presented here

are considered to be adequate. An additional limitation is the lack of economic and time data presented here; this is the subject of future work.

A systematic approach to process selection in MEMS has been presented. Process Attribute maps have been constructed and used to quantify the relative merit of existing Process Chains for MEMS fabrication. In discussing the construction of these maps the process steps of lithography, deposition and etching have been highlighted as controlling the overall performance of MEMS fabrication sequences. The Process Attribute maps have additional value as educational tools and in motivating the further development of MEMS fabrication techniques to extend the coverage of processing space.

### REFERENCES

- M. F. Ashby, Materials Selection in Mechanical Design. Boston, MA: Butterworth Heinemann, 1999.

- [2] A. M. K. Esawi and M. F. Ashby, Computer-Based Selection of Manufacturing Processes Cambridge Univ. Eng. Dept., Cambridge, 1997, CUED Report TR50.

- [3] S. M. Spearing, Materials Issues in Microelectromechanical Systems (MEMS). New York: Acta Materiala, 2000, vol. 48, pp. 179–196.

- [4] V. T. Srikar and S. M. Spearing, "Materials selection in micromechanical design: An application of the Ashby approach," *J. Microelec*tromech. Syst., vol. 12, pp. 3–10, 2003.

- [5] W. H. Juan and S. W. Pang, "Controlling sidewall smoothness for micromachined Si mirrors and lenses," *J. Vacuum Sci. Technol. B*, vol. 14, pp. 4080–4084, 1996.

- [6] R. T. Howe, "Surface micromachining for microsensors and microactuators," J. Vacuum Sci. Technol. B, vol. 6, pp. 1809–1813, 1988.

- [7] J. Bustillo, R. Howe, and R. Muller, "Surface micromachining for microelectromechanical systems," *Proc. IEEE*, vol. 86, pp. 1552–1574, 1998

- [8] M. Madou, Fundamentals of Microfabrication, 2 ed. Boca Raton, FL: CRC Press, 2002.

- [9] W. H. Juan and S. W. Pang, "High-Aspect-Ratio Si vertical micromirror arrays for optical switching," J. Microelectromech. Syst., vol. 7, pp. 207–213, 1998.

- [10] H. Toshiyoshi and H. Fujita, "Electrostatic micro torsion mirrors for an optical switch matrix," J. Microelectromech. Syst., vol. 5, pp. 231–237, 1996

- [11] J. Zou, M. Balberg, C. Byrne, C. Liu, and D. Brady, "Optical properties of surface micromachined mirrors with etch holes," *J. Microelectromech. Syst.*, vol. 8, pp. 506–513, 1999.

- [12] The MEMS Exchange [Online]. Available: http://www.mems-exchange.net

- [13] G. Kaminsky, "Micromachining of silicon mechanical structures," J. Vacuum Sci. Technol. B, vol. 3, pp. 1015–1024, 1985.

- [14] G. Kovacs, N. I. Maluf, and K. Petersen, "Bulk micromachining of silicon," *Proc. IEEE*, vol. 86, pp. 1536–1551, 1998.

- [15] E. D. Palik, O. J. Glmbocki, I. Heard, P. S. Burno, and L. Tenerz, "Etching roughness for (100) silicon surfaces in Aqueous KOH," J. Appl. Phys., vol. 70, pp. 3291–3300, 1991.

- [16] N. I. Maluf, An Introduction to Microelectromechanical Systems (MEMS). Boston, MA: Artech House, 2000.

- [17] M. Elwenspoek and H. V. Jansen, Silicon Micromachining. Cambridge, U.K.: Cambridge University Press, 1998.

- [18] P. Krause and E. Obermeier, "Etch rate and surface roughness of deep narrow U- grooves in (110)-oriented silicon," *J. Micromech. Microeng.*, vol. 5, pp. 112–114, 1995.

- [19] K. Lee, D. Lim, and L. Kimerling, "Fabrication of ultralow-loss Si/SiO<sub>2</sub> waveguides by roughness reduction," *Opt. Lett.*, vol. 26, pp. 1888–1890, 2001.

- [20] D. Resnik, D. Vrtacnik, U. Aljancic, and S. Amon, "Effective roughness reduction of {100} and {311} planes in anisotropic etching of {100} silicon in 5% TMAH," *J. Micromech. Microeng.*, vol. 13, pp. 26–34, 2003.

- [21] M. Lambrechts and W. Sansen, Biosensors: Microelectrical Devices. Philadelphia, PA: Institute of Physics Publishers, 1992.

- [22] D. Manos and D. Flamm, Plasma Etching—An Introduction. Boston, MA: Academic, 1989.

- [23] Y. B. Park and S. W. Rhee, "Bulk and interface properties of low-temperature silicon nitride films deposited by remote plasma enhanced chemical vapor deposition," *J. Mater. Sci.: Mater. Electron.*, vol. 12, pp. 515–522, 2001.

- [24] R. G. Poulsen, "Plasma etching in integrated circuit manufacture—A review," J. Vacuum Sci. Technol. B, vol. 14, pp. 266–274, 1977.

- [25] C. Reyes-Betanzo, S. A. Moshkalyov, M. A. Cotta, M. A. Pavanello, A. C. S. Ramos, and J. W. Swart, "Plasma etching of silicon nitride with high selectivity over silicon oxide and silicon in fluorine containing plasmas," *J. Vacuum Sci. Technol. A*, vol. 17, pp. 3179–3179, 1999.

- [26] W. H. Juan and S. W. Pang, "Released Si microstructures fabricated by deep etching and shallow diffusion," *J. Microelectromech. Syst.*, vol. 5, pp. 18–23, 1996.

- [27] B. Kloeck, S. Collins, N. D. Rooij, and R. Smith, "Study of electrochemical etch-stop for high-precision thickness control of silicon membranes," *IEEE Trans. Electron Devices*, vol. 36, pp. 663–669, 1989.

- [28] C. Huang and K. Najafi, "Fabrication of ultrathin p++ silicon microstructures using ion implantation and boron etch-stop," J. Microelectromech. Syst., vol. 10, pp. 532–537, 2001.

- [29] J. W. Weigold and S. W. Pang, "Fabrication of thick Si resonators with a frontside-release etch-diffusion process," *J. Microelectromech. Syst.*, vol. 7, pp. 201–206, 1998.

- [30] J. Bhardwaj, H. Ashraf, and A. McQuarrie, "Dry silicon etching for MEMS," in *Proc. Annu. Meeting Electrochem. Soc.*, Montreal, QC, Canada, 1997

- [31] H. Jansen, H. Gardeniers, M. d. Boer, M. Elwenspoek, and J. Fluitman, "A survey on the reactive ion etching of silicon in microtechnology," *J. Micromech. Microeng.*, vol. 6, pp. 14–28, 1996.

- [32] C. Zhao, Y. Z. Hu, T. Labayen, L. Lai, and E. A. Irene, "Comparison of Si/SiO<sub>2</sub> interface roughness from electron cyclotron resonance plasma and thermal oxidation," *J. Vacuum Sci. Technol. A*, vol. 16, pp. 57–62, 1998

- [33] M. R. Rakhshandehroo, J. W. Weigold, W. C. Tian, and S. W. Pang, "Dry etching of Si field emitters and high aspect ratio resonators using an inductively coupled plasma source," *J. Vacuum Sci. Technol. B*, vol. 16, pp. 2849–2854, 1998.

- [34] W. H. Juan and S. W. Pang, "Control of etch profile for fabrication of Si microsensors," J. Vacuum Sci. Technol. A, vol. 14, pp. 1189–1193, 1996

- [35] W. C. Tian, J. W. Weigold, and S. W. Pang, "Comparison of Cl2 and F-based dry etching for high aspect raio Si microstructures etched with an inductively coupled plasma source," *J. Vacuum Sci. Technol. B*, vol. 18, pp. 1890–1896, 2000.

- [36] Z. L. Zhang and N. MacDonald, "Fabrication of submicron high-aspect-ratio GaAs actuators," *J. Microelectromech. Syst.*, vol. 2, pp. 66–73, 1993.

- [37] Handbook of Micro/Nano Tribology2 ed. Boca Raton, FL, CRC Press, 1995.

- [38] Dry Etching of Silicon Obermeier. MAT, Berlin [Online]. Available: http://www-mat.ee.tu-berlin.de/research/dryetch/dryetch.htm

- [39] R. Petri, P. Brault, O. Vatel, D. Henry, E. Andre, P. Dumas, and F. Salvan, "Silicon roughness induced by plasma etching," *J. Appl. Phys.*, vol. 75, pp. 7498–7506, 1994.

- [40] N. C. MacDonald, MicroElectomechanical Systems Module: Single Crystal Reactive Etching and Metallization (SCREAM) Process [Online]. Available: http://designstudio.mae.cornell.edu/realization/mems-module

- [41] Z. L. Zhang and N. MacDonald, "A rie process for submicron, silicon electromechanical structures," *J. Micromech. Microeng.*, vol. 2, pp. 31–38, 1992.

- [42] N. C. MacDonald, "SCREAM microelectromechanical systems," Microelectron. Eng., vol. 32, pp. 49–73, 1996.

- [43] Microelectronics Fabrication Facility Hong Kong Institute of Science and Technology [Online]. Available: http://www.mff.ust.hk

- [44] High Aspect Ratio Etching Protron Mikrotechnik [Online]. Available: http://www.protron-mikrotechnik.de/technology/technology\_ase\_e\_2.htm

- [45] L. Chen, H. Neves, and T. Kudrle, Cornell Nanofabrication Facility: National Nanofabrication Users Network. Process Development for the Integration of MEMS and RF Devices [Online]. Available: http://www.nnf.cornell.edu/1999REU/ra/Chen.pdf

- [46] W. C. Tian and S. W. Pang, "Freestanding microheaters in Si with high aspect ratio microstructures," *J. Vacuum Sci. Technol. B*, vol. 20, pp. 1008–1012, 2002.

- [47] A. A. Ayon, R. A. Braff, R. Bayt, H. H. Sawin, and M. A. Schmidt, "Characterization of a time multiplexed inductively coupled plasma etcher," *J. Electrochem. Soc.*, vol. 146, pp. 339–349, 1999.

- [48] —, "Influence of coil power on the etching characteristics in a high density plasma etcher," J. Electrochem. Soc., vol. 146, pp. 2730–2736, 1999.

- [49] F. Eberhard and E. Deichsel, Fabrication of Vertical Facets in AlGaAs Using Chemically-Assisted Ion-Beam Etching Univ. of Ulm, Dept. Optoelectronics, 1997, Annual Report.

- [50] PHS MEMS [Online]. Available: www.phsmems.com

- [51] P. Chabert, "Deep etching of silicon carbide for micromachining applications: Etch rates and etch mechanisms," *J. Vacuum Sci. Technol. B*, vol. 19, pp. 1339–1345, 2001.

- [52] G. F. Cardinale, C. C. Henderson, J. E. M. Goldsmith, P. J. S. Mangat, J. Cobb, and S. D. Hector, "Demonstration of pattern transfer into sub-100nm polysilicon line/space features patterned with extreme ultraviolet lithography," *J. Vacuum Sci. Technol. A*, vol. 17, pp. 2970–2974, 1999.

- [53] R. Hegde, W. Paulson, and P. Tobin, "Surface topography of phosphorous doped polysilicon," *J. Vacuum Sci. Technol. B*, vol. 13, pp. 1434–1441, 1995.

- [54] B. Kim, H. Choi, and B. Lee, "Surface roughness of silicon carbide etched in a  $\rm C_2F_6/\rm O_2$  inductively coupled plasma," *J. Vacuum Sci. Technol. A*, vol. 20, pp. 424–429, 2002.

- [55] A. R. Shrimkunas, P. E. Mauger, L. P. Bourget, R. S. Post, L. Smith, R. F. Davis, G. M. Wells, F. Cerrina, and R. B. McIntosh, "Advanced electron cylcotron resonance chemical vapor deposition sic coatings and x-ray mask membranes," *J. Vacuum Sci. Technol. B*, vol. 9, pp. 3258–3261, 1991.

- [56] N. Agarwal, S. Ponoth, J. Plawsky, and P. Persans, "Optimized oxygen plasma etching of polyimide films for low loss optical waveguides," *J. Vacuum Sci. Technol. A*, vol. 20, pp. 1587–1591, 2002.

- [57] P. Neudeck, Recent Progress in Silicon Carbide Semiconductor Electronics Technology NASA Glenn Research Center, 2001 [Online]. Available: http://www.grc.nasa.gov/www/SiC/SiCReview.html

- [58] SiC MEMS at CWRU Case Western Reserve University [Online]. Available: http://mems.cwru.edu/SiC

- [59] M. A. Schmidt, R. T. Howe, S. Senturia, and J. Haritonidis, "Design and calibration of a microfabricated floating-element shear-stress sensor," *IEEE Trans. Electron Devices*, vol. 35, pp. 750–757, 1988.

- [60] S. Bagen, Photoresist Coating Methods MEMS Exchange, 1997 [Online]. Available: http://mail.mems-exchange.org/pipermail/mems-talk/ 1997-September/001056.html

- [61] K. Suzuki and I. Shimoyama, "Insect-Model based microrobot with elastic hinges," J. Microelectromech. Syst., vol. 3, pp. 4–9, 1994.

- [62] SUMMIT V Sandia National Laboratories [Online]. Available: http:// www.sandia.gov

- [63] Y. Xia and G. Whitesides, Soft Lithography. : Angewandte Chemie—International Edition, 1998, vol. 37, pp. 550–575.

- [64] —, "Soft lithography," Annu. Rev. Mater. Sci., vol. 28, pp. 153–184, 1998.

- [65] S. Chou, P. Krauss, and P. Renstrom, "Imprint lithography with 25-nanometer resolution," *Science*, vol. 272, pp. 85–87, 1996.

- [66] B. D. Terris, H. J. Mamin, M. E. Best, J. A. Logan, D. Rugar, and S. A. Rishton, "Nanoscale replication for scanning probe data storage," *Appl. Phys. Lett.*, vol. 69, pp. 4262–4264, 1996.

- [67] Y. Z. Hu, P. P. Buaud, L. Spanos, Y. Q. Wang, M. Li, and E. A. Irene, "In situ electron cyclotron resonance plasma surface cleaning of silicon," *J. Vacuum Sci. Technol. A*, vol. 12, pp. 1315–1321, 1994.

- [68] M. J. Lercel, C. S. Whelan, H. G. Craighead, K. Seshadri, and D. L. Allara, "High-Resolution silicon patterning with self-assembled monolayer resists," *J. Vacuum Sci. Technol. B*, vol. 14, pp. 4085–4090, 1996.

- [69] N. L. Jeon, I. S. Choi, B. Zu, and G. Whitesides, "Large area patterning by vacuum-assisted micromolding," *Adv. Mater.*, vol. 11, pp. 946–950, 1999.

- [70] J. Rogers, Z. Bao, and V. R. Raju, "Nonphotolithographic fabrication of organic transistors with micron feature sizes," *Appl. Phys. Lett.*, vol. 72, pp. 2716–2718, 1998.

- [71] P. Krauss and S. Y. Chou, "Nano-compact disks with 400 Gbit/in2 storage density fabricated using nanoimprint lithography and read with proximal probe," Appl. Phys. Lett., vol. 71, pp. 3174–3176, 1997.

- [72] S. Chou, P. Krauss, and P. Renstrom, "Imprint of sub-25 nm vias and trenches in polymers," *Appl. Phys. Lett.*, vol. 67, pp. 3114–3116, 1995.

- [73] A. B. Frazier and M. G. Allen, "Metallic microstructures fabricated using photosensitive polyimide electroplating molds," *J. Microelectromech. Syst.*, vol. 2, pp. 87–94, 1993.

- [74] A. Rogner, J. Eicher, D. Munchmeyer, R. Peters, and J. Mohr, "The ligatechnique—What are the new opportunities," *J. Micromech. Microeng.*, vol. 2, pp. 133–140, 1992.

- [75] A. Mehra, X. Zhang, A. Ayon, I. Waitz, M. Schmidt, and C. Spadaccini, "A six-wafer combustion system for a silicon micro gas turbine engine," J. Microelectromech. Syst., vol. 9, pp. 517-527, 2000.

- [76] K. Ishihara, C. Yung, A. Ayon, and M. Schmidt, "An intertial sensor technology using drie and wafer bonding with interonnecting capability," J. Microelectromech. Syst., vol. 8, pp. 403-408, 1999.

- [77] J. Rogers, K. Paul, and G. Whitesides, "Quantifying distortions in soft lithography," J. Vacuum Sci. Technol. B, vol. 16, pp. 88–97, 1997.

- [78] Y. Xia, E. Kim, X. Zhao, J. Rogers, M. Prentiss, and G. Whitesides, "Complex optical surfaces formed by replica molding against eleastomeric masters," Science, vol. 273, pp. 347-349, 1996.

- [79] Y. Xia, J. Rogers, K. Paul, and G. Whitesides, "Unconventional methods for fabricating and patterning nanostructures," Chem. Rev., vol. 99, pp. 1823-1848, 1999.

- [80] S. Senturia, Microsystem Design. Boston, MA: Kluwer Academic,

S. Mark Spearing received the Ph.D. degree from Cambridge University Engineering Department, U.K., in 1990.

In 2004, he was appointed Professor of Engineering Materials in the School of Engineering Sciences at The University of Southampton, U.K. Prior to this, he spent 10 years as Professor of Aeronautics and Astronautics at the Massachusetts Institute of Technology (MIT), Cambridge. His technical interests include materials characterization and structural analysis and design of MEMS, devel-

opment of wafer bonding-technologies, microelectronic and MEMS packaging, and advanced composites. From 1995 to 2005, he was responsible for materials, structural design, and packaging tasks of the MIT MicroEngine, MicroRocket, Micro-Chemical Power, and MicroHydraulic Transducer projects as well as conducting cross-cutting underpinning technology development.

Dr. Spearing is an Associate Editor of the JOURNAL OF MICROELECTROMECHANICAL SYSTEMS and Member of the American Society of Mechanical Engineers (ASME). In 2004, he received a Royal Society Wolfson Research Merit Award.

Ph.D. degree at the Massachusetts Institute of Technology (MIT), Cambridge, where he received the M.Sc. degree in mechanical engineering in 2006. Prior to attending MIT, he received the M.Phil. degree in engineering by research from Cambridge University, Cambridge, U.K., in 2003 and the B.Sc. degree in mechanical engineering at Villanova University, Villanova, PA.

His technical interests include mechanical behavior of materials and structural design and analysis

of MEMS. He has been awarded the Fulbright and Gates Cambridge Scholarships as well as the National Defense Science and Engineering and National Science Foundation Graduate Research Fellowships.

Mr. Quinn is a member of the American Society of Mechanical Engineers (ASME).

Mike Ashby is a Royal Society Research Professor at the University of Cambridge, U.K., and a Royal Academy of Engineering Visiting Professor at the Royal College of Art in London. He is the author of a number of books on materials. Among the more recent are Engineering Materials, Volumes 1 and 2 (3rd edition 2005), Cellular Solids (1988, 2nd edition 1997), Materials Selection in Mechanical Design (1992, 3rd edition 2005), "Metal Foams-A Design Guide (2000), and Materials and Design-the Art and Science of Materials Selection in Product

Design (2002). His interests are in design, and in the role materials play in it.

Norman A. Fleck is Head of Mechanics, Materials and Design at Cambridge University, Engineering Department. He did his undergraduate and graduate work at the University of Cambridge, and was a Postdoctoral Researcher at Harvard University before returning to the staff at Cambridge University. His research interests are in the mechanics of materials, and is currently researching the mechanics of MEMS, lattice materials, thermal barrier coatings, and skin.