#### UNIVERSITY OF SOUTHAMPTON

# FACULTY OF PHYSICAL SCIENCES & ENGINEERING Department of Electronics and Computer Science

# Design and implementation of flexible FPGA-based LDPC decoders

by

Peter Hailes

A thesis submitted in partial fulfillment for the degree of Doctor of Philosophy

June 19, 2018

Supervisors:

Professor Robert G. Maunder, Professor Bashir M. Al-Hashimi, and Professor Lajos Hanzo

© Peter Hailes 2018

#### UNIVERSITY OF SOUTHAMPTON

#### ABSTRACT

#### FACULTY OF PHYSICAL SCIENCES & ENGINEERING

Department of Electronics and Computer Science

#### Doctor of Philosophy

#### Design and implementation of flexible FPGA-based LDPC decoders

by Peter Hailes

Since their rediscovery in the mid-1990s, Low-Density Parity Check (LDPC) error correction decoders have been the focus of a great deal of research within the communications community. They have also become popular channel coding schemes in a plethora of diverse communications standards, as a benefit of their strong error correction performance, low-complexity computations, and their suitability to parallel hardware implementation. Meanwhile, a great deal of research effort has been invested into LDPC decoder designs that exploit the high processing speed and parallelism of Field-Programmable Gate Array (FPGA) devices, which now constitute a cost-effective alternative to Application-Specific Integrated Circuit (ASIC) platforms for LDPC decoder implementations. However, the FPGA-based LDPC decoder designs published in the open literature vary greatly in terms of design choices and performance criteria, making them a challenge to compare and even more challenging to implement.

In this thesis, we explore the key factors involved in FPGA-based LDPC decoder design and present an extensive review of the current literature, analysing and characterising the performance tradeoffs demonstrated across over 140 competing designs. From this survey, we conclude that high-performance FPGA-based LDPC decoder designs supporting the ability to dynamically alter their decoding parameters at run-time are under-represented within the state-of-the-art, despite their necessity in order to comply with many modern communications standards.

Accordingly, this thesis therefore proposes two parameterised FPGA-based LDPC decoder architectures, which both support run-time flexibility over any arbitrary set of one or more Quasi-Cyclic (QC) LDPC codes. Our first architecture adopts a traditional fixed-point message decoding algorithm, but features a variety of design optimisations which reduce the costs of supporting multiple diverse codes. Implementation results of this decoder indicate that it is capable of achieving throughputs that are higher than previous flexible FPGA-based LDPC decoders, even whilst achieving the desired level of flexibility and satisfactorily high error correction performance.

Our second decoder architecture utilises stochastic computing in order to achieve a reduced hardware resource requirement. We demonstrate the first stochastic LDPC decoder to exhibit true run-time flexibility, and detail the numerous novel optimisations that support this feature. Finally, we also propose an offline design flow, which may be used to automatically generate an optimised decoder having either of the two proposed architectures, for any chosen selection of QC codes. This added design-time flexibility greatly enhances the usefulness of the proposed architectures in real applications, facilitating easier experimental investigations of the trade-offs discussed previously.

### Academic Thesis: Declaration Of Authorship

| I. | Peter  | Hail  | es. |

|----|--------|-------|-----|

| -, | 1 0001 | 22012 |     |

declare that this thesis and the work presented in it are my own and has been generated by me as the result of my own original research.

Title of thesis: Design and implementation of flexible FPGA-based LDPC decoders

I confirm that:

- 1. This work was done wholly or mainly while in candidature for a research degree at this University;

- 2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- 3. Where I have consulted the published work of others, this is always clearly attributed;

- 4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- 5. I have acknowledged all main sources of help;

- 6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- 7. Either none of this work has been published before submission, or parts of this work have been published in the listed publications.

| Signed: | , е   |      | •• |

|---------|-------|------|----|

| Date:   | 19/6, | / 18 |    |

# Contents

| A                | cknov | wledge  | ments                               | xv   |

|------------------|-------|---------|-------------------------------------|------|

| N                | omer  | ıclatur | e                                   | xvii |

| $\mathbf{C}_{0}$ | omm   | only u  | sed symbols                         | xix  |

| 1                | Intr  | oducti  | on                                  | 1    |

|                  | 1.1   | Struct  | ure of the thesis                   | . 3  |

|                  | 1.2   | Novel   | contributions of the thesis         | . 5  |

| 2                | Bac   | kgrour  | nd                                  | 7    |

|                  | 2.1   | Forwar  | rd error correction                 | . 7  |

|                  | 2.2   | LDPC    | codes                               | . 9  |

|                  |       | 2.2.1   | Encoding                            | . 9  |

|                  |       | 2.2.2   | Parity-check matrix                 | . 11 |

|                  |       | 2.2.3   | Factor graphs                       |      |

|                  | 2.3   |         | code construction                   |      |

|                  |       | 2.3.1   | Random codes                        |      |

|                  |       | 2.3.2   | Pseudorandom codes                  |      |

|                  |       | 2.3.3   | Quasi-cyclic codes                  |      |

|                  |       | 2.3.4   | Repeat-accumulate codes             |      |

|                  |       | 2.3.5   | Progressive edge growth algorithm   |      |

|                  | 2.4   |         | decoding                            |      |

|                  |       | 2.4.1   | Scheduling                          |      |

|                  |       |         | 2.4.1.1 Flooding                    |      |

|                  |       |         | 2.4.1.2 Layered belief propagation  |      |

|                  |       |         | 2.4.1.3 Informed dynamic scheduling |      |

|                  |       | 2.4.2   | Check node calculations             |      |

|                  |       | 2.4.3   | Variable node calculations          |      |

|                  | 2.5   |         | decoding architectures              |      |

|                  |       | 2.5.1   | Parallelism                         |      |

|                  |       | 2.5.2   | Representation of messages          |      |

|                  |       | 2.5.3   | Pipelining                          |      |

|                  | 0.0   | 2.5.4   | Stopping criteria                   |      |

|                  | 26    | EDC V   |                                     | 26   |

viii CONTENTS

|   |     | 2.6.1  | Structure                                                         | 26 |

|---|-----|--------|-------------------------------------------------------------------|----|

|   |     | 2.6.2  | FPGA vendor conventions                                           | 28 |

|   |     | 2.6.3  | Comparing FPGAs                                                   | 28 |

|   | 2.7 | Stocha | astic LDPC decoding                                               | 29 |

|   |     | 2.7.1  | Stochastic arithmetic                                             | 30 |

|   |     | 2.7.2  | Stochastic LDPC computations                                      | 31 |

|   |     | 2.7.3  | Issues with stochastic decoding                                   |    |

|   |     |        | 2.7.3.1 Scaling the channel probabilities                         |    |

|   |     |        | 2.7.3.2 Edge memories and internal memories                       |    |

|   | 2.8 | Conclu | usion                                                             |    |

| 3 | A s | urvev  | of FPGA-based LDPC decoders                                       | 37 |

|   | 3.1 |        | luction                                                           | 37 |

|   | 3.2 |        | arison of decoders                                                |    |

|   |     | 3.2.1  |                                                                   |    |

|   |     |        | 3.2.1.1 LDPC PCMs                                                 |    |

|   |     |        | 3.2.1.2 Architecture                                              |    |

|   |     |        | 3.2.1.3 Algorithm                                                 |    |

|   |     |        | 3.2.1.4 Iterations                                                |    |

|   |     | 3.2.2  | Characteristics                                                   |    |

|   |     | 9.2.2  | 3.2.2.1 Processing throughput                                     |    |

|   |     |        | 3.2.2.2 Processing latency                                        |    |

|   |     |        | 3.2.2.3 Hardware requirements                                     |    |

|   |     |        | 3.2.2.4 Transmission energy efficiency                            |    |

|   |     |        | 3.2.2.5 Processing energy efficiency                              |    |

|   |     |        | 3.2.2.6 Bandwidth efficiency                                      |    |

|   |     |        | 3.2.2.7 Flexibility                                               |    |

|   | 3.3 | Discus | ssions                                                            |    |

|   | 0.0 | 3.3.1  | Trade-offs                                                        |    |

|   |     | 3.3.2  | Relationships between parameters and each characteristic          |    |

|   |     |        | 3.3.2.1 Processing throughput                                     |    |

|   |     |        | 3.3.2.2 Processing latency                                        |    |

|   |     |        | 3.3.2.3 Hardware requirements                                     |    |

|   |     |        | 3.3.2.4 Transmission energy efficiency and bandwidth efficiency . |    |

|   | 3.4 | Design | n recommendations                                                 |    |

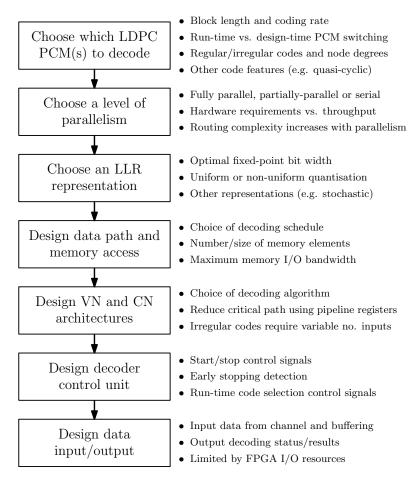

|   |     | 3.4.1  | Recommended design methodology                                    |    |

|   |     | 3.4.2  | Recommendations for enhancing future comparisons                  | 57 |

|   | 3.5 | Conclu |                                                                   |    |

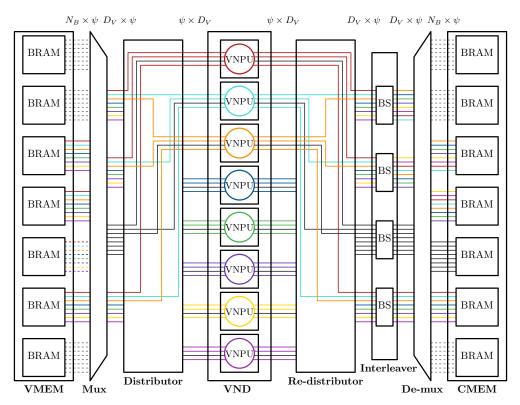

| 4 | ΔЯ  | evible | fixed-point Quasi-Cyclic LDPC decoder architecture                | 61 |

| _ | 4.1 |        | luction                                                           |    |

|   | 4.2 |        | ally-parallel decoding of quasi-cyclic codes                      |    |

|   | 1.2 | 4.2.1  | Quasi-cyclic LDPC codes                                           |    |

|   |     | 4.2.2  | Partially-parallel decoder architectures                          |    |

|   | 4.3 |        | roposed decoder architecture                                      |    |

|   | 1.0 | 4.3.1  | Overview of parallelised decoding in the proposed architecture    |    |

|   |     | 3.1    | 4.3.1.1 Level of parallelism                                      |    |

|   |     |        |                                                                   |    |

CONTENTS ix

|   |     |                | 4.3.1.2            | Decoding schedule                         | 70  |

|---|-----|----------------|--------------------|-------------------------------------------|-----|

|   |     |                | 4.3.1.3            | PCM ROMs                                  | 71  |

|   |     | 4.3.2          | BRAM a             | urrangement                               | 71  |

|   |     | 4.3.3          | Datapatl           | h                                         | 73  |

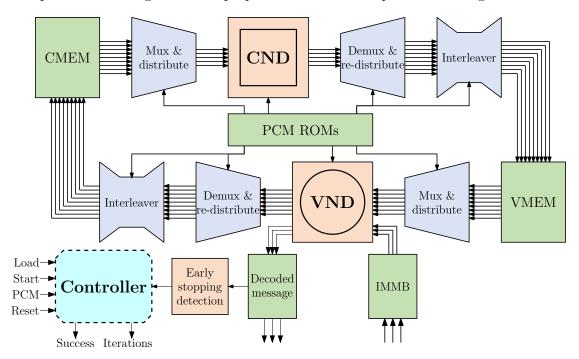

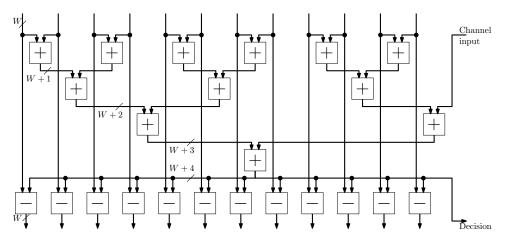

|   |     |                | 4.3.3.1            | VND datapath                              | 74  |

|   |     |                | 4.3.3.2            | CND datapath                              | 75  |

|   |     |                | 4.3.3.3            | Programmable barrel shifters              |     |

|   |     | 4.3.4          | NPU arc            | hitectures                                | 80  |

|   |     |                | 4.3.4.1            | VNPU architecture                         |     |

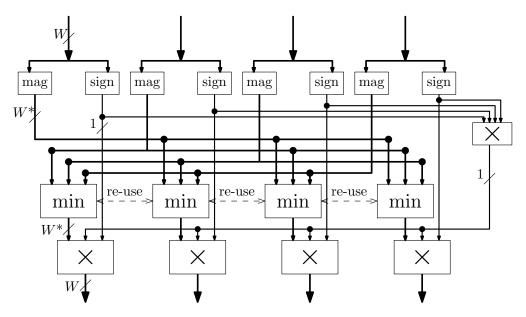

|   |     |                | 4.3.4.2            | CNPU architecture                         |     |

|   |     |                | 4.3.4.3            | Flexible CNPUs                            | 84  |

|   |     | 4.3.5          | Controlle          | er                                        | 84  |

|   |     |                | 4.3.5.1            | Control signals                           | 85  |

|   |     |                | 4.3.5.2            | Early stopping detection                  |     |

|   | 4.4 | Imple          | mentation          | results                                   |     |

|   |     | 4.4.1          | Method             |                                           | 87  |

|   |     | 4.4.2          |                    | s targeted at WiFi LDPC PCMs              |     |

|   |     | 4.4.3          | Decoders           | s targeted at WiMAX LDPC PCMs             | 91  |

|   |     | 4.4.4          | Decoders           | s targeted at WPAN LDPC PCMs              | 95  |

|   |     | 4.4.5          | Decoders           | s targeted at WiGig LDPC PCMs             | 97  |

|   |     | 4.4.6          | Decoders           | s targeted at PCMs from multiple families | 99  |

|   | 4.5 | Concl          | usion              |                                           | 103 |

|   |     |                | _                  |                                           |     |

| 5 |     |                |                    | ic Quasi-Cyclic LDPC decoder architecture | 105 |

|   | 5.1 |                |                    |                                           |     |

|   | 5.2 |                |                    | ling                                      |     |

|   |     | 5.2.1          |                    | ic computation                            |     |

|   |     | 5.2.2          |                    | stochastic decoding                       |     |

|   | 5.3 | _              | -                  | cochastic decoder architecture            |     |

|   |     | 5.3.1          |                    | sm and decoding schedule                  |     |

|   |     |                |                    | Schedule                                  |     |

|   |     |                | 5.3.1.2            | Pipelining                                |     |

|   |     | <b>.</b>       | 5.3.1.3            | PCM ROMs                                  |     |

|   |     | 5.3.2          | Datapatl           |                                           |     |

|   |     | 5.3.3          |                    | node decoder                              |     |

|   |     |                | 5.3.3.1            | VNPU inputs and outputs                   |     |

|   |     |                | 5.3.3.2            | Node processing unit architecture         |     |

|   |     |                | 5.3.3.3            | Flexible stochastic subnodes              |     |

|   |     |                | 5.3.3.4            | Distributed randomisation engine          |     |

|   |     | 5.3.4          |                    | er                                        |     |

|   |     |                | 5.3.4.1            | Control signals                           |     |

|   |     | _              | 5.3.4.2            | Early stopping detection                  |     |

|   | 5.4 | -              | mentation          | results                                   |     |

|   |     |                |                    |                                           |     |

|   |     | 5.4.1          | Method             |                                           |     |

|   |     | 5.4.1          | 5.4.1.1            | Use of pipelining                         | 127 |

|   |     | 5.4.1<br>5.4.2 | 5.4.1.1<br>5.4.1.2 |                                           | 127 |

X CONTENTS

|    |       | 5.4.3  | Decoders targeted at WiMAX LDPC PCMs             | . 132 |

|----|-------|--------|--------------------------------------------------|-------|

|    |       | 5.4.4  | Decoders targeted at WPAN LDPC PCMs              | . 135 |

|    |       | 5.4.5  | Decoders targeted at WiGig LDPC PCMs             | . 137 |

|    |       | 5.4.6  | Decoders targeted at PCMs from multiple families | . 138 |

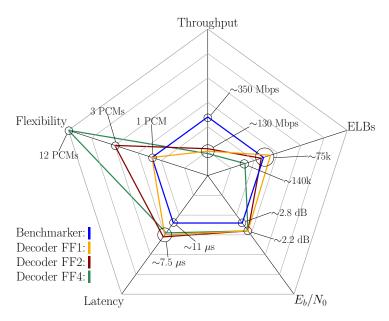

|    |       | 5.4.7  | Comparison of the proposed architectures         |       |

|    | 5.5   | Conclu | asion                                            | . 143 |

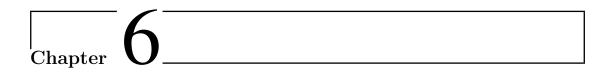

| 6  | The   | propo  | osed offline design flow                         | 145   |

|    | 6.1   | Introd | $\operatorname{uction}$                          | . 145 |

|    | 6.2   | PCM    | interpretation                                   | . 146 |

|    |       | 6.2.1  | Calculating parameters                           | . 147 |

|    |       | 6.2.2  | PCM ROMs                                         | . 148 |

|    | 6.3   | HDL 8  | generation                                       | . 149 |

|    | 6.4   | Modul  | le descriptions                                  | . 150 |

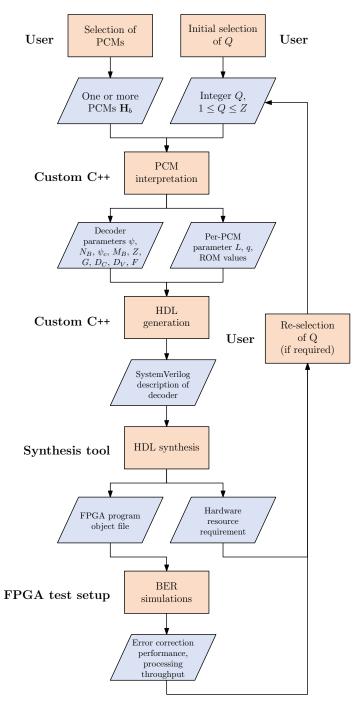

|    |       | 6.4.1  | Binary tree NPU generation                       | . 150 |

|    |       | 6.4.2  | Dual-tree NPU generation                         | . 151 |

|    |       |        | 6.4.2.1 Flexible stochastic subnode generation   | . 154 |

|    |       | 6.4.3  | Programmable barrel shifter generation           | . 154 |

|    | 6.5   | Conclu | asion                                            | . 155 |

| 7  | Con   | clusio | ns and future work                               | 157   |

|    | 7.1   | Summ   | ary and conclusions                              | . 157 |

|    | 7.2   | Future | e work                                           | . 160 |

|    | 7.3   | Conclu | ading remarks                                    | . 162 |

| Bi | bliog | raphy  |                                                  | 163   |

# List of Figures

| 2.1  | A communications system                                                                                      |

|------|--------------------------------------------------------------------------------------------------------------|

| 2.2  | A factor graph for an example LDPC code                                                                      |

| 2.3  | An example of the flooding schedule                                                                          |

| 2.4  | An example of the layered belief propagation schedule                                                        |

| 2.5  | An example of informed dynamic scheduling                                                                    |

| 2.6  | Example FPGA structure                                                                                       |

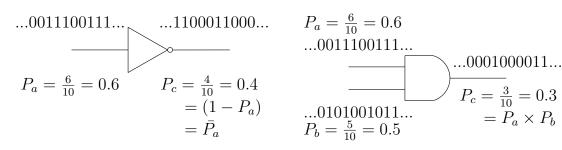

| 2.7  | Examples of stochastic bit stream generation and computations $31$                                           |

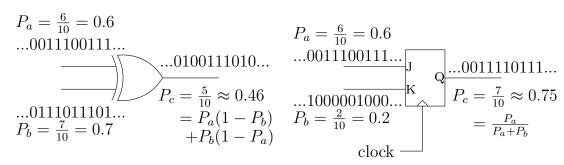

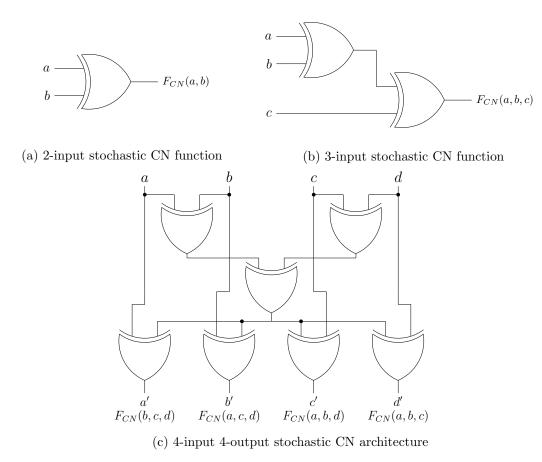

| 2.8  | Stochastic realisations of the CN function                                                                   |

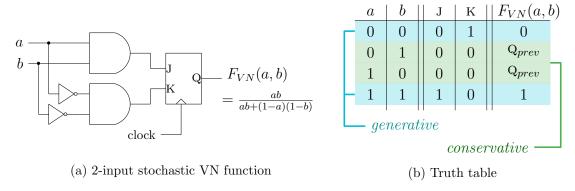

| 2.9  | Stochastic realisation of the VN function                                                                    |

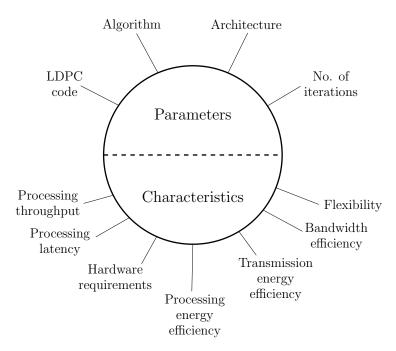

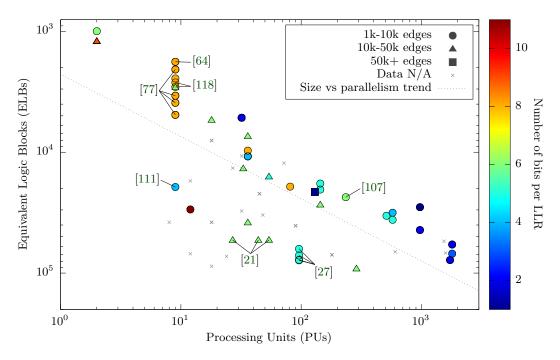

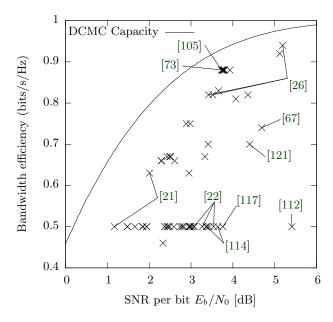

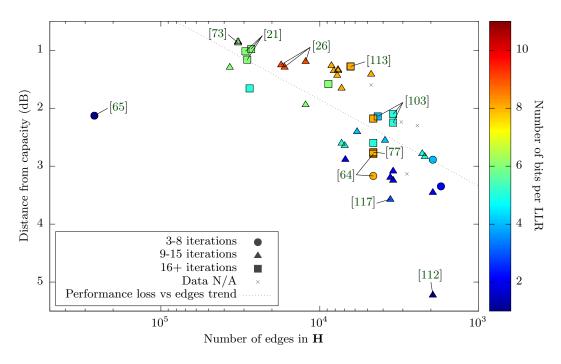

| 3.1  | FPGA-based LDPC decoder system parameters and characteristics 38                                             |

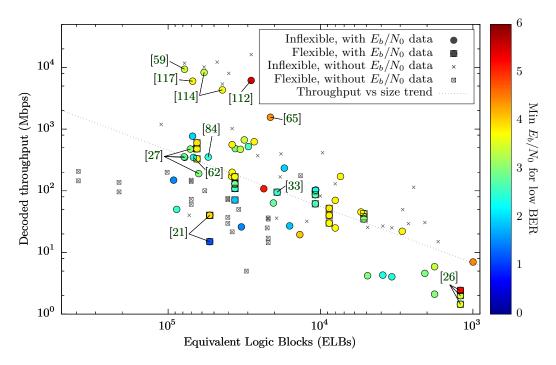

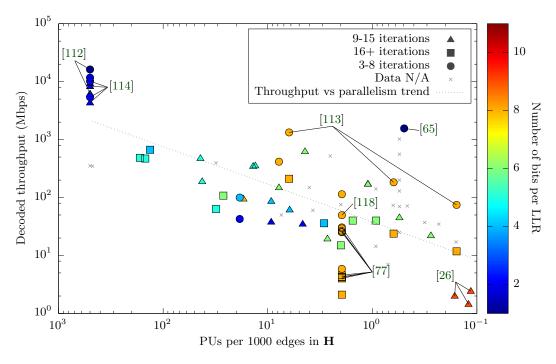

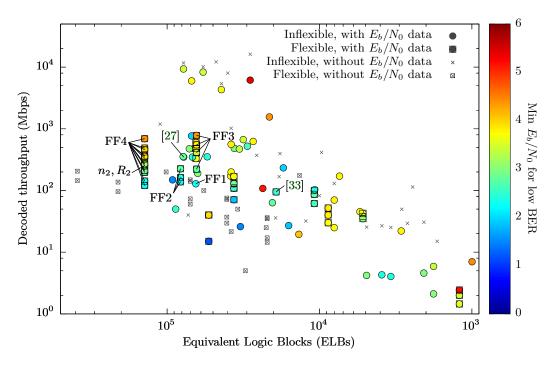

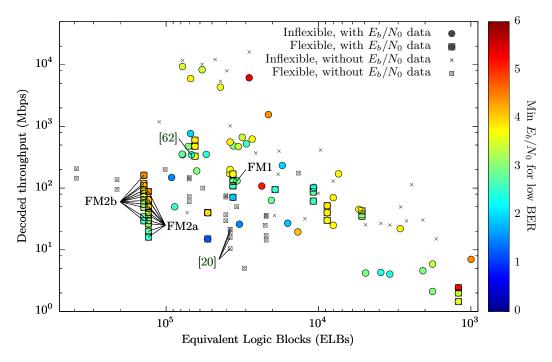

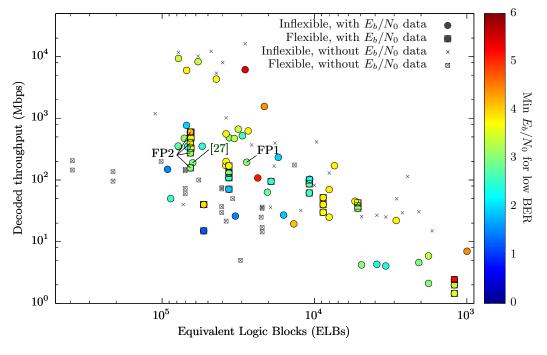

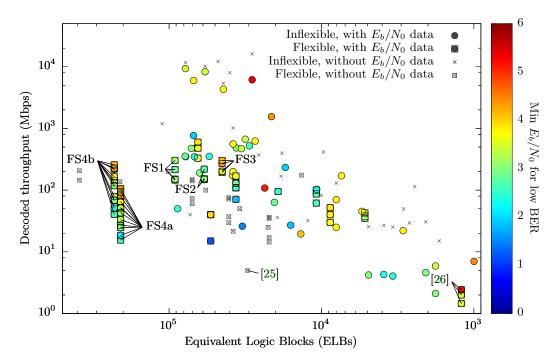

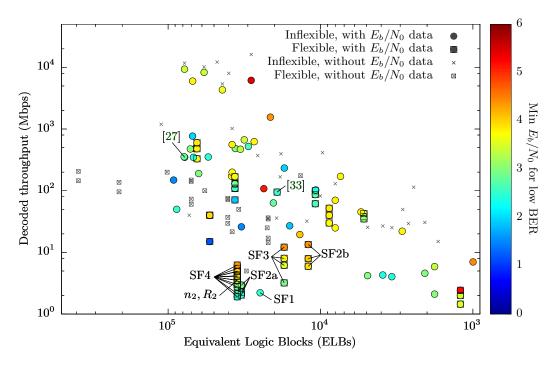

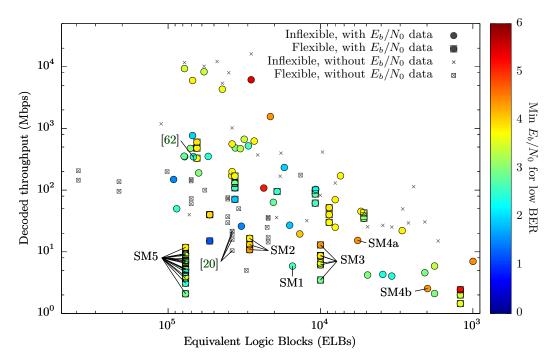

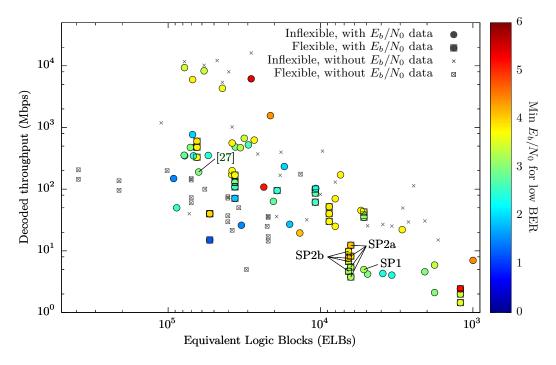

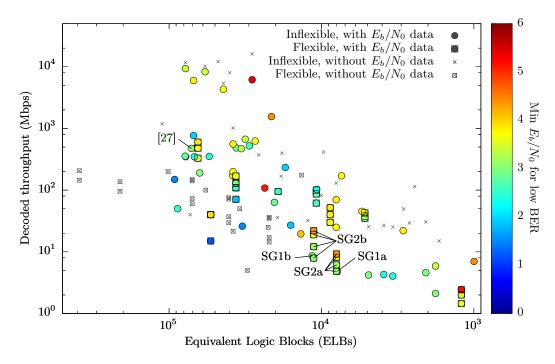

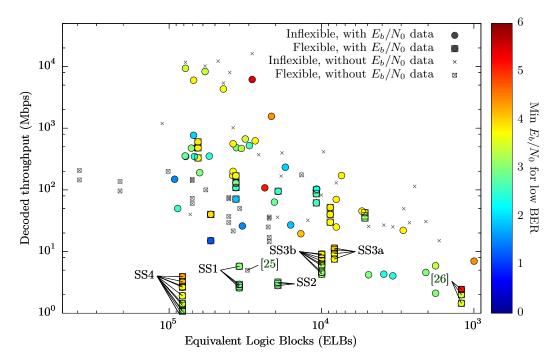

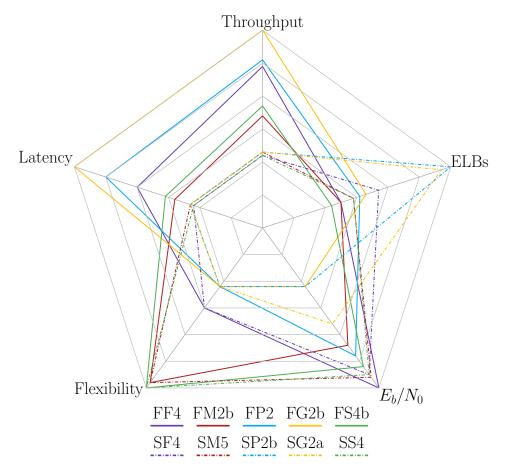

| 3.2  | Trade-offs of the surveyed decoders                                                                          |

| 3.3  | Factors affecting the processing throughput                                                                  |

| 3.4  | Factors affecting the hardware requirements                                                                  |

| 3.5  | Decoder performance loss from capacity                                                                       |

| 3.6  | Factors affecting the error correction performance                                                           |

| 3.7  | Recommended LDPC decoder design methodology                                                                  |

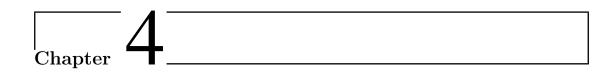

| 4.1  | Demonstration of using submatrix shift values to optimise storage 65                                         |

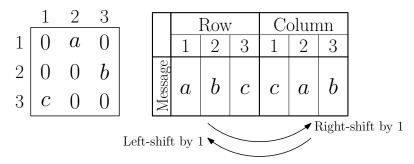

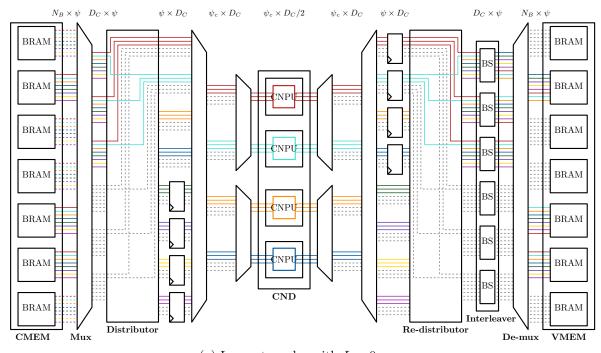

| 4.2  | Block diagram of the proposed fixed-point flexible architecure 67                                            |

| 4.3  | VMEM and CMEM locations of submatrices                                                                       |

| 4.4  | Example of a VND datapath                                                                                    |

| 4.5  | Example of a CND datapath                                                                                    |

| 4.6  | Tree SM VNPU structure                                                                                       |

| 4.7  | Min Tree CNPU structure                                                                                      |

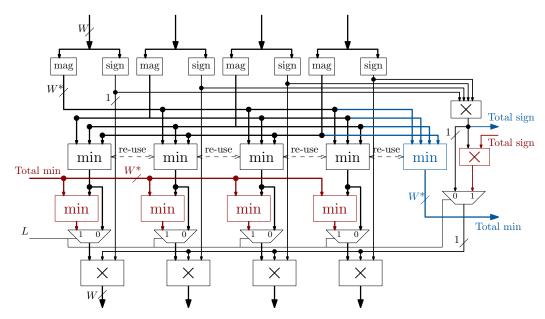

| 4.8  | Flexible Min Tree CNPU structure                                                                             |

| 4.9  | WiFi characterisation of the proposed fixed-point architecture 89                                            |

| 4.10 | Comparison of decoders targeted at WiFi PCMs                                                                 |

| 4.11 | WiMAX characterisation of the proposed fixed-point architecture 95 $$                                        |

| 4.12 | WPAN characterisation of the proposed fixed-point architecture 96                                            |

| 4.13 | WiGig characterisation of the proposed fixed-point architecture 98                                           |

| 4.14 | Multiple-family characterisation of the proposed fixed-point architecture $% \left( 102\right) =100$ . $102$ |

| 5.1  | Comparison of flooding and layered stochastic decoding schedules 109                                         |

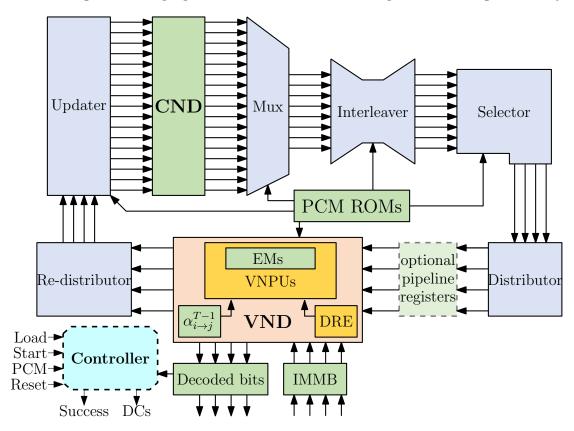

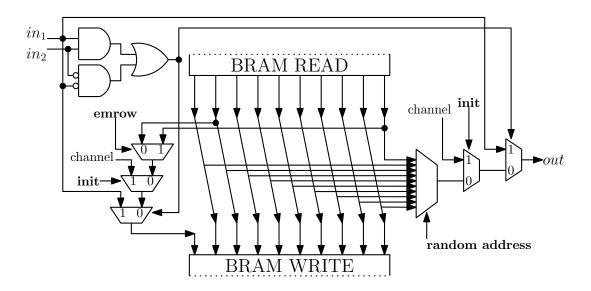

| 5.2  | Block diagram of the proposed stochastic flexible architecture $110$                                         |

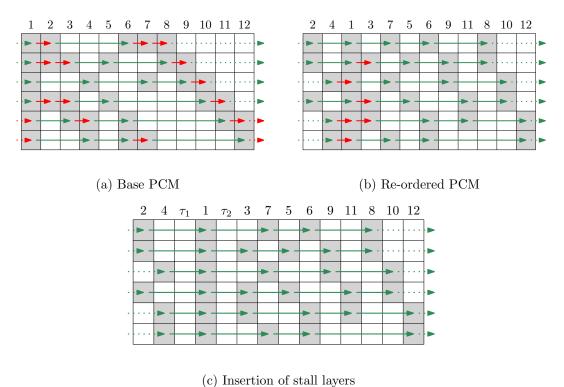

| 5.3  | Example of modifying a PCM to make it column-orthogonal                                                      |

xii LIST OF FIGURES

| 5.4  | Optimisations to the mux module in the stochastic datapath 116                 |

|------|--------------------------------------------------------------------------------|

| 5.5  | Calculation of inputs and outputs for an LBP stochastic VNPU 118               |

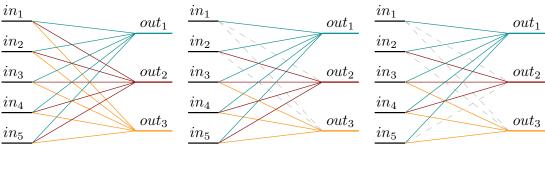

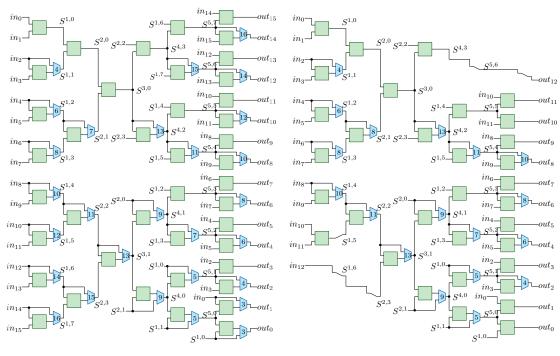

| 5.6  | Examples of the proposed flexible dual-tree NPU architecture 120               |

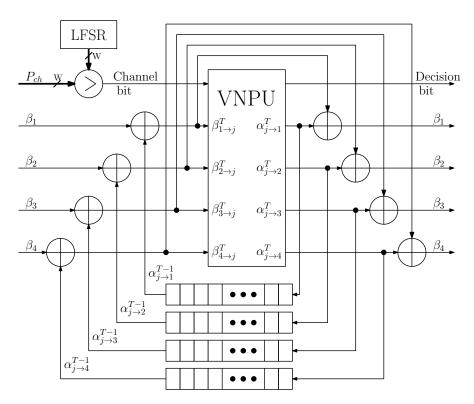

| 5.7  | VNPU subnode design for the proposed flexible stochastic architecture $122$    |

| 5.8  | Comparison of EM initialisation methods                                        |

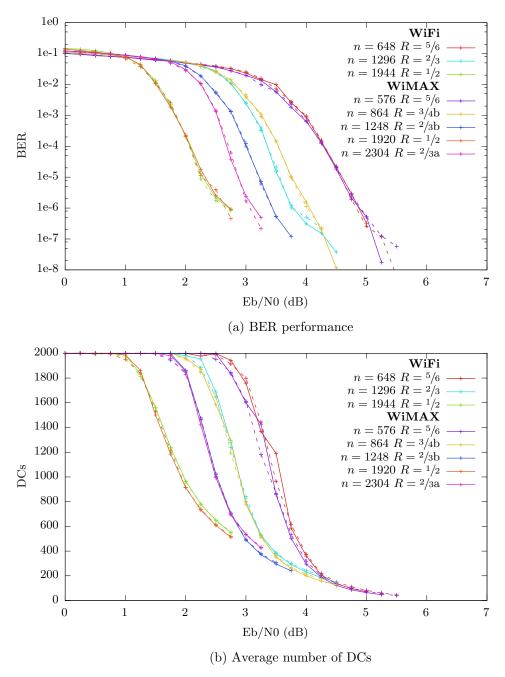

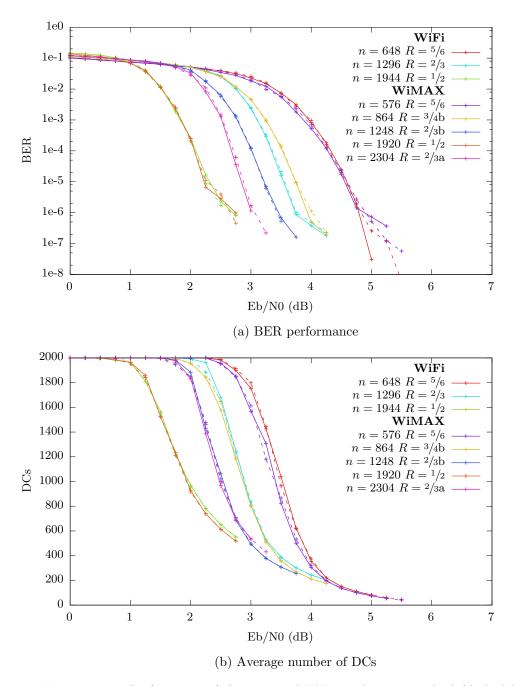

| 5.9  | WiFi characterisation of the proposed stochastic architecture                  |

| 5.10 | WiMAX characterisation of the proposed stochastic architecture 134             |

| 5.11 | WPAN characterisation of the proposed stochastic architecture 135              |

| 5.12 | WiGig characterisation of the proposed stochastic architecture 138             |

| 5.13 | Multiple-family characterisation of the proposed stochastic architecture . 139 |

| 5.14 | Comparison of the proposed architectures                                       |

| 6.1  | The proposed automated offline design flow                                     |

| 6.2  | Examples of the tree generation algorithm                                      |

| 6.3  | Construction of a flexible dual-tree NPU                                       |

# List of Tables

| 2.1 | Comparison of FPGAs available from Intel and Xilinx                                                                       |

|-----|---------------------------------------------------------------------------------------------------------------------------|

| 3.1 | Comparison of FPGA-based LDPC decoders                                                                                    |

| 4.1 | Decoding schedule for one iteration of an example QC PCM 70                                                               |

| 4.2 | Comparison of VNPU architectures                                                                                          |

| 4.3 | Comparison of CNPU architectures                                                                                          |

| 4.4 | WiFi characterisation of the proposed fixed-point architecture 90                                                         |

| 4.5 | WiMAX characterisation of the proposed fixed-point architecture 94                                                        |

| 4.6 | WPAN characterisation of the proposed fixed-point architecture 96                                                         |

| 4.7 | WiGig characterisation of the proposed fixed-point architecture 98                                                        |

| 4.8 | Multiple-family characterisation of the proposed fixed-point architecture $% \left( 100000000000000000000000000000000000$ |

| 5.1 | Number of pipeline stalls required by the featured PCMs                                                                   |

| 5.2 | Values of $\gamma$ used in the simulations of the proposed decoder                                                        |

| 5.3 | WiFi characterisation of the proposed stochastic architecture 130                                                         |

| 5.4 | WiMAX characterisation of the proposed stochastic architecture 133                                                        |

| 5.5 | WPAN characterisation of the proposed stochastic architecture 136                                                         |

| 5.6 | WiGig characterisation of the proposed stochastic architecture 137                                                        |

| 5.7 | Multiple-family characterisation of the proposed stochastic architecture . 140                                            |

#### Acknowledgements

First and foremost, I would like to express my sincere thanks to my primary supervisor, Professor Rob Maunder, for all of the guidance and support he has provided over the course of this Ph.D.; for his tireless work ethic and unrelenting optimism that have always helped to keep things moving.

I would also like to thank my other supervisors, Professor Lajos Hanzo and Professor Bashir M. Al-Hashimi, for lending their considerable wisdom and experience when required. Thanks also to Lei Xu at Intel for providing the means for this Ph.D. to come about in the first place, and for offering his valuable commercial perspectives to various questions of direction or focus along the way.

Last but by no means least, I would like to express my deep gratitude to my loving wife, Alethia, whose unconditional support and gentle encouragement have been so instrumental in helping me to get this far, and who continues to be a blessing to me every day of my life.

### Nomenclature

4LUT 4-input Lookup Table6LUT 6-input Lookup TableALM Adaptive Logic Module

ASIC Application-Specific Integrated Circuit

AWGN Additive White Gaussian Noise

BER Bit Error Rate

BPSK Binary Phase-Shift Keying

BRAM Block RAM

BS Barrel Shifter

CLB Configurable Logic Block

CN Check Node

CND Check Node Decoder

CNPU Check Node Processing Unit

C-RAN Centralised Radio Access Network

DC Decoding Cycle

DCMC Discrete-input Continuous-output Memoryless Channel

DFF D-type Flip-Flop

DRE Distributed Randomisation Engine

ELB Equivalent Logic Block

EM Edge Memory

eMBB enhanced Mobile Broadband EXIT Extrinsic Information Transfer

FEC Forward Error Correction

FER Frame Error Rate

FPGA Field-Programmable Gate Array HDL Hardware Description Language

HLS High-Level Synthesis

IDS Informed Dynamic Scheduling

IM Internal Memory

IMMB Intrinsic Message Memory Bank

xviii NOMENCLATURE

JKFF JK-type Flip-Flop LAB Logic Array Block

LBP Layered Belief Propagation LDPC Low-Density Parity Check

LE Logic Element

LFSR Linear Feedback Shift Register LLR Logarithmic-Likelihood Ratio

LUT Lookup Table

MSA Min-Sum Algorithm

NDS Noise-Dependent Scaling

NPU Node Processing Unit

NR New Radio

PCM Parity-Check Matrix

PEG Progressive Edge Growth

PU Processing Unit QC Quasi-Cyclic

SNR Signal to Noise Ratio SPA Sum-Product Algorithm

VN Variable Node

VND Variable Node Decoder

VNPU Variable Node Processing Unit

# Commonly used symbols

#### Forward Error Correction vector of original information bits $\mathbf{m}$ vector of transmitted codeword bits $\mathbf{c}$ vector of transmitted BPSK symbols $\mathbf{x}$ $E_s$ transmission energy per symbol transmission energy per bit $E_b$ $N_0$ noise power spectral density vector of received BPSK symbols $\mathbf{y}$ $\tilde{\mathbf{c}}$ vector of received codeword LLRs $\mathbf{\tilde{c}}'$ vector of decoded codeword LLRs vector of decoded codeword bits ĉ m̂ vector of recovered information bits vector of syndrome bits $\mathbf{s}$ Parity-Check Matrices knumber of information bits for a particular PCM number of parity bits (rows) in a particular PCM mnumber of codeword bits (columns) in a particular PCM nRcoding rate $\mathbf{G}$ generator matrix Н parity-check matrix variable node degree for a particular PCM $d_v$ $d_c$ check node degree for a particular PCM Quasi-Cyclic Parity-Check Matrices $\mathbf{H}_{b}$ quasi-cyclic base parity-check matrix number of block-rows within a particular QC PCM $m_b$ number of block-columns within a particular QC PCM $n_b$ quasi-cyclic submatrix expansion factor in a particular QC PCM zquasi-cyclic submatrix shift amount s

#### Parity-Check Matrix sets

K maximum number of information bits in a set of PCMs

M maximum number of parity bits (rows) in a set of PCMs

N maximum number of codeword bits (columns) in a set of PCMs

$M_B$  maximum number of block-rows in a set of QC PCMs

$N_B$  maximum number of block-columns in a set of PCMs

$D_V$  maximum variable node degree in a set of PCMs

$D_C$  maximum check node degree in a set of PCMs

Z maximum quasi-cyclic submatrix expansion factor in a set of QC PCMs

#### LDPC decoding

$\alpha$  VN to CN messages

$\beta$  CN to VN messages

$F_{VN}$  VN update function

$F_{CN}$  CN update function

#### LDPC decoders

$\psi$  decoder degree of parallelism

$\psi_c$  decoder degree of CNPU parallelism

Q decoder parallelism reduction factor

q number of subblocks per block for a particular PCM

W bit width of binary messages

F employment of linked CNPUs in a decoder

l employment of linked CNPUs for a particular PCM

f clock frequency

$f_{max}$  maximum clock frequency

$t_i$  clock cycles required per iteration

$t_{DC}$  clock cycles required per DC

$T_a$  average number of iterations/DCs required per frame

#### NPU architecture

$N_{sub}$  number of 2-input 1-output subnodes in an NPU

$\Lambda$  maximum number of NPU inputs/outputs

$\lambda_a$  current active number of NPU inputs/outputs

$\lambda_n^{y,x}$  minimum value of  $\lambda_a$  to use a node for term x at stage y

$\lambda_c^{y,x}$  minimum value of  $\lambda_a$  for term x at stage y to be connected

$S^{y,x}$  intermediate signal x at stage y of dual-tree NPU

$L_E$  ring buffer length for each EM

$L_I$  ring buffer length for each IM

## List of publications

- **P.** Hailes, L. Xu, R. G. Maunder, B. M. Al-Hashimi, and L. Hanzo, "A Survey of FPGA-Based LDPC Decoders," in *IEEE Commun. Surveys Tuts.*, vol. 18, no. 2, pp. 1098–1122, jan 2016.

- **P. Hailes**, L. Xu, R. G. Maunder, B. M. Al-Hashimi, and L. Hanzo, "A Flexible FPGA-Based Quasi-Cyclic LDPC Decoder," in *IEEE Access*, vol. 5, pp. 20965–20984, mar 2017.

- **P. Hailes**, L. Xu, R. G. Maunder, B. M. Al-Hashimi, and L. Hanzo, "Hardware-efficient Node Processing Unit Architectures for Flexible LDPC Decoder Implementations," in *IEEE Trans. Circuits Syst. II, Exp. Briefs*.

- **P.** Hailes, L. Xu, R. G. Maunder, B. M. Al-Hashimi, and L. Hanzo, "A Flexible Stochastic LDPC Decoder Architecture," in preparation for *IEEE Access*.

- A. Li, **P. Hailes**, R. G. Maunder, B. M. Al-Hashimi, and L. Hanzo, "1.5 Gbit/s FPGA implementation of a fully-parallel turbo decoder designed for mission-critical machine-type communication applications," in *IEEE Access*, vol. 4, pp. 5452–5473, aug. 2016.

- S. Shao, **P. Hailes**, R. G. Maunder, T. Wang, J.-Y. Wu, B. M. Al-Hashimi, and L. Hanzo, "Survey of Turbo, LDPC and Polar Decoder ASIC Implementations," in preparation for *IEEE Commun. Surveys Tuts.*.

### Introduction

Low-Density Parity Check (LDPC) codes represent a class of Forward Error Correction (FEC) codes that may be employed for providing near-theoretical-limit error correction of transmission errors in communication systems. They were first proposed by Gallager in 1962 [1], but were considered to be too complex for practical simulation and implementation at the time of their conception, hence they were left largely untouched for decades. Subsequently, and perhaps partially motivated by the fact that the turbo codes patented during the early 1990s attracted a license-fee, in 1996 LDPC codes were rediscovered by Mackay and Neal [2]. They have since enjoyed a renaissance, becoming the focus of much research within the communications community and demonstrating the potential for excellent practical performance. Given the increased computing power available today, LDPC codes have been adopted in many modern communications standards, including IEEE 802.11n [3], IEEE 802.16e [4], DVB-S2 [5], CCSDS [6], ITU G.hn [7], and enhanced Mobile Broadband (eMBB) data in the forthcoming 3GPP 5G New Radio (NR) [8].

LDPC codes benefit from a number of appealing features that make them very attractive for implementation. The LDPC decoding algorithm can be implemented using low-complexity calculations, resulting in a relatively low design and implementation cost for the processing hardware. The inherent parallelism of the LDPC decoding algorithm also maps intuitively to distributed parallel computation units for high-throughput low-latency implementations. Furthermore, like turbo codes, LDPC codes are decoded iteratively, achieving an error correction performance that is close to the theoretical limit when decoding messages that have large block lengths [9]. However, in contrast to turbo codes, there is a wide variety of possible algorithms and levels of parallelisation that may be considered for the design of LDPC decoders, presenting designers with a range of options that may be selected from in order to achieve the desired characteristics.

However, while the design of the individual processing components is relatively simple, the design of a complete LDPC decoder is subject to a complex interplay between a number of system characteristics, namely the processing throughput, processing latency, hardware resource requirements, error correction capability, processing energy efficiency, bandwidth efficiency and flexibility. These characteristics depend on a number of system parameters, namely the architecture, the LDPC code employed, the algorithm used, and the number of decoding iterations. The complex nature of the relationships between all of these parameters and characteristics makes the process of designing and implementing an efficient LDPC decoder a very challenging and time-consuming task.

During this process, it is often desirable for a designer to have the capability to implement design prototypes at various stages, in order to physcially measure their achievable performance in realistic conditions. This may be readily achieved through the use of a Field-Programmable Gate Array (FPGA) device, which facilitates rapid prototyping and fast parallel logic processing. These advantages are evident from the sheer number of published FPGA-based LDPC decoder designs that exist in the open literature, which will be compared later in this thesis. Furthermore, the decoding techniques and implementation-oriented research presented alongside these designs has been of significant benefit to the wider communications research community [10–15]. In particular, the implementational characteristics of these FPGA-based LDPC decoders are increasingly informing the holistic design of communication systems.

Another very practical use of FPGA-based LDPC decoders is in the research environment, where the very fast and highly-parallel logic resources available on an FPGA are very useful for measuring the Bit Error Rate (BER) performance of various codes [16]. More explicitly, simulations that would take days on a computer can be completed in only hours when using a custom FPGA implementation [17]. However, the majority of published FPGA-based LDPC decoder designs are tailored specifically to one code. This means that they would require a great deal of extra design work in order to modify the architecture every time a new LDPC code is to be investigated. This design work would then have to be re-synthesised to produce another FPGA configuration file, which would then have to be downloaded onto the FPGA before any decoding of the new code could commence.

In addition to their suitability for prototyping and research measurements, FPGAs constitute a viable alternative to Application-Specific Integrated Circuits (ASICs) for the LDPC decoders of small-production-run communication devices, while their programmability has made them attractive for software-defined radios. In these cases, a decoder having the ability to switch between different LDPC codes at run-time is necessary to fully support all of the codes within many standards [3–5], in which the coding rate and frame length may be dynamically adjusted in order to suit the prevailing channel conditions [18]. Furthermore, decoders having the ability to support LDPC codes from multiple families may be used to facilitate Centralised Radio Access Networks (C-RAN).

Here, LDPC decoding for multiple remote basestations (often serving multiple different standards) is performed by cloud-based digital function units (DFUs), allowing more efficient use of resources, and effectively combining multiple independent cells together to reduce inter-cell interference. When each LDPC decoder in these DFUs has the ability to process LDPC codes from any of the supported standards, the flexibility (and hence efficiency through pooling resources) of the associated C-RAN is increased.

It is therefore desirable to have a generalised FPGA-based LDPC decoder architecture capable of supporting multiple LDPC codes, from within a single family or from multiple families, with the ability to rapidly switch the code that is currently being decoded at run-time. Some prior research into run-time flexible FPGA-based LDPC decoder designs has been performed, however they are all either constrained to a very limited set of related codes [19–24] or achieve a very low processing throughput [25, 26]. It is also desirable that decoder instances having this architecture could be generated automatically, based on the selection of which LDPC codes they are expected to support. This enables a more comprehensive design-time parsing and analysis of the features of the target code set, facilitating greater automated optimisations to the decoder design, without requiring any prior knowledge of its operation. This design flow would hence grant automated design-time flexibility to a decoder design already having run-time flexibility, greatly extending its usefulness to a variety of parties. Again, some previous works have proposed similar automated design flows for the generation of LDPC decoders [27–31], however these do not produce designs with the run-time flexibility described above.

This work has three main aims. Firstly, we provide a comprehensive comparison of all of the implementations of FPGA-based LDPC decoders that we are aware of. In doing so, we observe, explain, and characterise the fundamental trade-offs and relationships between the associated parameters and characteristics of these decoders. Secondly, we use these findings to propose two new generalised architectures for FPGA-based decoders that are capable of supporting any set of one or more quasi-cyclic LDPC codes, with the ability to switch from one code to another in a single clock cycle. Thirdly, to improve the usefulness of these architectures in real-world situations, we present an automated design flow which generates the full specific hardware description of decoders having the proposed architecture, based on a chosen selection of codes.

#### 1.1 Structure of the thesis

This thesis is structured as follows.

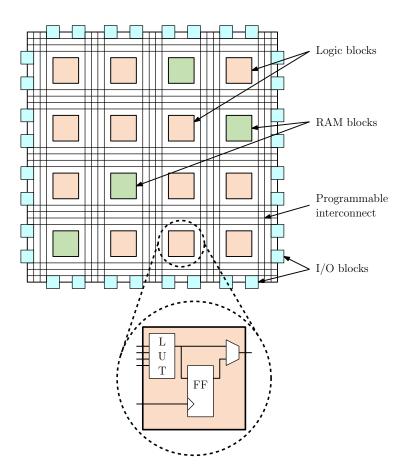

In **Chapter 2**, we present a detailed tutorial-style introduction to LDPC codes and the associated encoding and decoding processes. In doing so, we introduce many of the implementational factors that affect the design and performance of FPGA-based LDPC decoders, and provide a brief explanation of the key features of FPGAs. We also

introduce the relatively recent concept of stochastic LDPC code decoding, discussing the various ways in which it differs from traditional fixed-point decoding, as well as the associated advantages and disadvantages.

Following this, Chapter 3 presents a comprehensive survey of published FPGA-based LDPC decoders. This facilitates a detailed discussion of the selectable parameters and measurable characteristics which must be considered when designing an FPGA-based LDPC decoder, before characterising the trade-offs and relationships between them. In this chapter we also use the experience gained as a result of conducting this survey to present a set of recommendations for future authors of FPGA-based LDPC decoder implementation publications to follow, in order to simplify the process of comparing designs in future.

Chapter 4 then presents our generalised flexible fixed-point FPGA-based LDPC decoder architecture. We firstly explain our reasons for targeting quasi-cyclic LDPC codes, and present the associated advantages. We then describe each part of the decoder architecture in detail, including the degree of parallelism, the memory management scheme, the flexible datapath, the node processing units, and the control unit. In doing so we present several optimisations which improve the implementation characteristics of decoders having the proposed architecture, without making it specific to any particular code family. Implementation results presented at the end of this chapter indicate that certain parametrisations of the proposed architecture are capable of achieving throughputs that are greater than any previous flexible FPGA-based LDPC decoder. Meanwhile, instances targeting larger sets of supported codes maintain throughputs that are comparable to the majority of other decoders, but at the expense of higher hardware resource requirements.

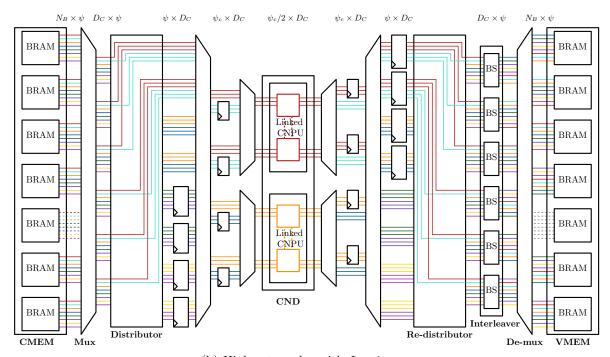

Motivated by the findings of Chapter 4, the alternative generalised flexible FPGA-based LDPC decoder architecture presented in **Chapter 5** employs stochastic computations, in an effort to achieve a smaller hardware resource consumption than its fixed-point counterpart. In order to achieve the desired level of flexibility, this architecture employs a structure and decoding algorithm that have not been demonstrated by stochastic decoders previously. Consequently, this architecture also represents the first stochastic LDPC decoder to support run-time flexibility over multiple code sets. Chapter 5 describes the ways in which the design of the stochastic decoder architecture facilitates these aspects, whilst also briefly describing the ways in which it is similar to previous stochastic decoders and the architecture of Chapter 4. Finally, the performance of decoders having this architecture are characterised, and its strengths and weaknesses are described and explained.

Following this, an explanation of our automated design flow is presented in **Chapter 6**. This includes a description of the ways in which it parses the target set of supported LDPC codes to extract and generate the range of decoder parameters required by the

architectures of Chapters 4 and 5, and also a brief description of the methods employed to automatically generate the hardware description language design files. Finally, Chapter 6 also provides a description of the ways in which some of the most highly-optimised elements of the proposed architectures are carefully automatically generated at designtime, in order to increase the achievable performance characteristics.

Finally, **Chapter 7** summarises the main findings of this thesis and provides some concluding remarks, alongside suggestions for possible avenues of future work which may improve the proposed designs further.

#### 1.2 Novel contributions of the thesis

In summary, the novel contributions presented in this thesis are:

- an extensive survey of over 140 published FPGA-based LDPC decoders, including novel methods of measuring and comparing performance characteristics across diverse designs and architectures;

- a detailed analysis and graphical depiction of the trade-offs inherent to FPGAbased LDPC decoder design;

- a generalised architecture of a parametrisable fixed-point FPGA-based LDPC decoder, having both design-time and single-clock-cycle run-time flexibility over an arbitrary set of supported LDPC codes;

- parametrisations of the proposed fixed-point architecture exhibiting the highest throughputs achieved by flexible FPGA-based LDPC decoders;

- the first stochastic LDPC decoder to support a partially-parallel architecture, including adaptations to the traditional stochastic processing elements to make them compliant with processing multiple time-multiplexed nodes;

- a novel variation of the traditional multicast layered belief propagation decoding schedule that is compatible with stochastic processing units;

- the first stochastic LDPC decoder supporting run-time flexibility over more than one code family:

- a generalised algorithm for constructing a hardware-efficient and implementationagnostic node processing unit, along with a novel method of adding run-time flexibility over any set of supported numbers of inputs and outputs;

- a novel design flow that automatically generates optimised hardware descriptions of decoders having either of the proposed architectures, targeted at any desired set of quasi-cyclic LDPC codes, and with a customisable degree of parallelism.

$_{ ext{Chapter}} 2$

### Background

Before commencing the presentation of our survey results and novel designs in later chapters, this chapter presents a tutorial on FPGA-based LDPC decoders. In doing so, we introduce the concepts and notations used throughout the rest of this work. Section 2.1 commences by discussing Forward Error Correction (FEC) in general terms, before LDPC codes are introduced in Section 2.2. This is followed by a discussion of how LDPC codes may be designed and decoded in Sections 2.3 and 2.4, respectively. The practicalities of LDPC decoder implementations are then discussed in Section 2.5, which is followed by a brief introduction to FPGAs in Section 2.6. Finally, Section 2.7 provides an introduction and explanation of stochastic LDPC decoding, which is necessary to understand the design decisions motivating the novel architecture proposed in Chapter 5.

#### 2.1 Forward error correction

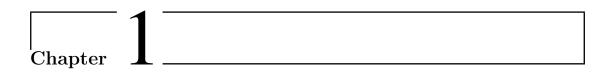

Figure 2.1 shows a schematic of a simplified communications system, where the information message word  $\mathbf{m} = \{m_i\}_{i=1}^k$  is a vector of k bits, which is FEC encoded in order to obtain the codeword  $\mathbf{c} = \{c_j\}_{j=1}^n$ , which is a vector of n > k bits. The FEC encoder converts the k-bit message word  $\mathbf{m}$  into the n-bit codeword  $\mathbf{c}$  by adding m = n - k parity bits to the message. The ratio of the message length k to the total codeword length n is referred to as the coding rate R,

$$R = \frac{k}{n} = \frac{n-m}{n}. (2.1)$$

The m additional parity bits are derived from the k message bits and hence they do not carry any information of their own. However, they are used during the FEC decoding process to allow transmission errors to be detected and even corrected, depending on the specific scheme used and on the severity of the corruption, as will be discussed below.

Figure 2.1: A communication system

Various modulation schemes can be used for modulating the codeword **c** onto the channel. As we shall show in Section 3.3.2.4, Binary Phase-Shift Keying (BPSK) modulation is assumed for nearly all FPGA-based LDPC decoder research. For this reason, we also assume the employment of BPSK modulation throughout this tutorial discussion. It is important to note however, that BPSK is a very simple modulation scheme, which is rarely employed alone in practical communication schemes. Therefore, considering BPSK modulation exclusively during the design phase could result in an LDPC decoder which does not necessarily work satisfactorily in practical systems, where higher-order modulation schemes are employed. Note that our analysis in Section 3.3 will take the specific modulation scheme that was used into consideration, when comparing the error correction performance of various FPGA-based LDPC decoders.

BPSK generates the modulated symbol vector  $\mathbf{x} = \{x_j\}_{j=1}^n$  according to  $x_j = +\sqrt{E_s}$  when  $c_j = 0$  and  $x_j = -\sqrt{E_s}$  when  $c_j = 1$ , where  $E_s$  is the transmission energy per symbol. Similarly, there are several different ways of modelling the random corruption that is imposed by the channel upon the signal  $\mathbf{x}$  as it is transformed into the received signal  $\mathbf{y} = \{y_j\}_{j=1}^n$ . In common with most FPGA-based LDPC research, we assume the Additive White Gaussian Noise (AWGN) channel model, in which a random noise signal is added to the transmitted signal,

$$y_i = x_i + \mathcal{CN}(0, N_0), \tag{2.2}$$

where  $\mathcal{CN}(\cdot)$  is the complex normal distribution and  $N_0$  is the noise power spectral density. The Signal to Noise Ratio (SNR) is given by  $E_s/N_0$ , and may also be expressed as the SNR per bit according to

$$\frac{E_b}{N_0} = \frac{1}{R} \times \frac{E_s}{N_0}.\tag{2.3}$$

The corruption imposed by the channel causes  $\mathbf{y}$  to differ from  $\mathbf{x}$  in an unpredictable manner, potentially resulting in the demodulation of a perturbed received codeword  $\hat{\mathbf{c}}$ , potentially including some transmission errors. The decoder of Figure 2.1 is employed

to recover the message word  $\hat{\mathbf{m}}$ , and without this there would be no way of correcting (or even detecting the presence of) these errors.

The error correction capability of a FEC decoder is affected by the form of the information provided by the demodulator. Rather than using hard decisions to convert received symbols into demodulated bits, superior error correction capability can be obtained if the demodulator provides soft decisions. These may be represented in the form of probabilities, but are are far more commonly expressed using the *Logarithmic-Likelihood Ratio* (LLR) [32]. The sign of an LLR (positive or negative) expresses what the most likely value for the corresponding bit is (0 or 1, respectively). Meanwhile, the magnitude of an LLR expresses how likely this value is, where 0 represents complete uncertainty and  $\infty$  represents absolute certainty. The value of an LLR is calculated as

$$\tilde{c}_i = \log \frac{P(c_i = 0 \mid y_i)}{P(c_i = 1 \mid y_i)},$$

(2.4)

where  $\tilde{c}_i$  is the output LLR,  $c_i$  is the transmitted bit being represented by the LLR, and  $y_i$  is the received symbol.

Here, the logarithm is used because it reduces the dynamic range of the likelihood ratio, tending to produce values in the range of -10 to +10, rather than 0.0001 to 10,000. This also allows probability intersections to be calculated using additions, rather than hardware-intensive multiplication operations. LLRs are extensively used throughout the LDPC decoding process for the majority of LDPC decoders, as will be detailed below.

When using BPSK modulation over an AWGN channel, the demodulator can convert the received signals into LLRs directly, according to

$$\tilde{c}_i = 4 \times R \times \frac{E_b}{N_0} \times \text{Re}(y_i).$$

(2.5)

#### 2.2 LDPC codes

This section provides an introduction to LDPC codes, commencing with their structure and the encoding process in Section 2.2.1. Following this, the decoder's Parity-Check Matrix (PCM) is introduced in Section 2.2.2, together with its graphical representation using factor graphs in Section 2.2.3.

#### 2.2.1 Encoding

Decoding an LDPC codeword is associated with a significantly higher complexity than the encoding process, because the decoder must consider every possible message word simultaneously, while operating on the basis of soft decision LLRs rather than hard message bits. For this reason, we focus our attention on LDPC decoders in this thesis, but the encoding process is explained briefly here for the sake of completeness.

As described previously, LDPC codes permit the correction of transmission errors by supplementing each k-bit message word with m parity bits in order to produce an n-bit codeword, where n = k + m [33]. Codes which include the k bits of the message word within the n bits of the codeword are referred to as systematic, while non-systematic codes have codewords which do not directly contain the original message bits. There are  $2^k$  possible permutations of the k-bit message word, each of which is mapped by the LDPC encoder to a corresponding one of  $2^k$  legitimate codeword permutations. The error correction capability of the LDPC code depends on the minimum Hamming distance between any pair of these  $2^k$  legitimate codeword permutations. Naturally high minimum distances are preferred, since these make it unlikely for a legitimate codeword to be transformed into another by the distortion introduced during transmission.

For example, a code with a message word length of k = 6 and a codeword length of n = 10 employs m = n - k = 4 parity bits and has a coding rate of R = k/n = 3/5. In the case where the code is systematic, each codeword **c** may be of the form

$$\mathbf{c} = [c_1, c_2, c_3, c_4, c_5, c_6, c_7, c_8, c_9, c_{10}], \tag{2.6}$$

where  $c_1

ldots c_6$  are the k = 6 bits of the message word  $\mathbf{m}$  and  $c_7

ldots c_{10}$  are the m = 4 parity bits. Each of the parity bits represents a parity check covering a specific subset of the message bits. As an example, the parity check bits may be obtained according to the following modulo-2 summations of message bits:

$$c_7 = c_4 \oplus c_6 \tag{2.7a}$$

$$c_8 = c_1 \oplus c_3 \oplus c_5 \oplus c_6 \tag{2.7b}$$

$$c_9 = c_2 \oplus c_5 \tag{2.7c}$$

$$c_{10} = c_1 \oplus c_2 \oplus c_6.$$

(2.7d)

The design of an LDPC code's parity check equations is subject to many complex factors, as will be briefly described in Section 2.3. Using these equations, a  $(k \times n)$ -element generator matrix  $\mathbf{G}$  can be constructed to efficiently describe the encoding process. In a systematic code,  $\mathbf{G}$  may adopt the form

$$\mathbf{G} = \begin{bmatrix} \mathbf{I}_k & \mathbf{A} \end{bmatrix}, \tag{2.8}$$

where  $\mathbf{I}_k$  is the  $(k \times k)$ -element identity matrix and the columns of  $\mathbf{A}$  represent each of the parity checks. The generator matrix of the systematic code described above would

therefore be

$$\mathbf{G} = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 1 & 0 & 1 \\ 0 & 1 & 0 & 0 & 0 & 0 & 0 & 1 & 1 \\ 0 & 0 & 1 & 0 & 0 & 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 & 0 & 1 & 1 & 0 \\ 0 & 0 & 0 & 0 & 0 & 1 & 1 & 1 & 0 & 1 \end{bmatrix}.$$

$$(2.9)$$

Codewords can be calculated using this matrix by finding the modulo-2 matrix product of the message  $\mathbf{m}$  and the generator matrix  $\mathbf{G}$ , according to  $\mathbf{c} = \mathbf{m} \times \mathbf{G}$ . For example, it may be readily verified that the message  $\mathbf{m} = [0\ 1\ 1\ 1\ 0\ 1]$  has the corresponding codeword  $\mathbf{c} = \mathbf{m} \times \mathbf{G} = [0\ 1\ 1\ 1\ 0\ 1\ 0\ 1\ 0]$ .

#### 2.2.2 Parity-check matrix

In the decoder, the parity checks are used to detect the presence of transmission errors in the received codeword  $\hat{\mathbf{c}}$ . Since all of the codeword bits involved in a parity check (including the parity bit itself) should have a modulo-2 summation of 0, Equations (2.7a)–(2.7d) can be re-written as follows:

$$c_4 \oplus c_6 \oplus c_7 = 0 \tag{2.10a}$$

$$c_1 \oplus c_3 \oplus c_4 \oplus c_6 \oplus c_8 = 0 \tag{2.10b}$$

$$c_2 \oplus c_5 \oplus c_9 = 0 \tag{2.10c}$$

$$c_1 \oplus c_2 \oplus c_6 \oplus c_{10} = 0.$$

(2.10d)

These equations are more commonly viewed as a PCM  $\mathbf{H}$ , which has n columns corresponding to the bits of the codeword and m rows corresponding to the parity checks. A non-zero entry in any position  $H_{ij}$  indicates that the j-th bit  $c_j$  takes part in the i-th parity check. In the case of systematic codes  $\mathbf{H}$  is related to  $\mathbf{G}$  according to

$$\mathbf{H} = \begin{bmatrix} \mathbf{A}^T & \mathbf{I}_m \end{bmatrix}. \tag{2.11}$$

Continuing our example from above, we have

$$\mathbf{H} = \begin{bmatrix} 0 & 0 & 0 & 1 & 0 & 1 & 1 & 0 & 0 & 0 \\ 1 & 0 & 1 & 0 & 1 & 1 & 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 0 & 1 & 0 & 0 & 0 & 1 & 0 \\ 1 & 1 & 0 & 0 & 0 & 1 & 0 & 0 & 0 & 1 \end{bmatrix}. \tag{2.12}$$

Upon obtaining a received codeword  $\hat{\mathbf{c}}$ , the syndrome  $\mathbf{s}$  can be calculated according to  $\mathbf{s} = \hat{\mathbf{c}} \times \mathbf{H}^T$ . In the case where  $\hat{\mathbf{c}}$  is a legitimate codeword permutation, the syndrome will equate to a vector of zeros. This may be demonstrated by re-using the codeword

calculated in the previous subsection, which equates to a  $(1 \times m)$ -element vector of 0s when multiplied by  $\mathbf{H}^T$ .

Note however that an LDPC **H** matrix of the form shown in (2.12) is very unusual in practice. As it will be explained in Section 2.4, the decoder's error correction ability is dictated by the number of non-zero entries in each row or column, which is referred to as its *weight*. More specifically, columns with a weight of 1 can result in the decoder being unable to correct some transmission errors. This can be avoided by modifying the PCM **H** using elementary row operations (modulo-2 additions and swaps). In the case of the above example, this may lead to:

$$\mathbf{H} = \begin{bmatrix} 1 & 0 & 0 & 1 & 1 & 0 & 1 & 0 & 1 & 1 \\ 0 & 1 & 1 & 0 & 1 & 0 & 0 & 1 & 0 & 1 \\ 1 & 1 & 1 & 0 & 0 & 1 & 0 & 1 & 1 & 0 \\ 0 & 1 & 0 & 1 & 1 & 1 & 1 & 0 & 1 & 0 \end{bmatrix}. \tag{2.13}$$

This modified  $\mathbf{H}$  avoids any weight-1 columns, while still checking the same distribution of parity bits that was added to codewords by the generator matrix  $\mathbf{G}$  of (2.9). Note however that this toy-example PCM is still unusual for a realistic LDPC code. Specifically, the PCM used in LDPC decoding should be sparse, containing far fewer non-zero entries than 0s. Clearly, the  $\mathbf{H}$  of (2.13) does not satisfy this constraint, owing to its codeword length of n = 10, which is very short compared to practical LDPC codewords, which tend to be hundreds or even thousands of bits long.

Owing to its significance in the decoding process, the PCM **H** is commonly used to define a particular LDPC code design. As discussed later in Section 2.3, creating a **H** matrix that achieves a strong error correction capability is a complex task, so this is usually the first aspect of the code to be designed. Following this, the generator matrix **G** can be derived from **H**, by following the reverse of the process described above.

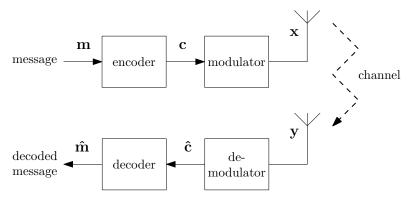

#### 2.2.3 Factor graphs

The PCM  $\mathbf{H}$  can also be visualised graphically using a factor graph, which is also known as a  $Tanner\ graph\ [34]$ . This is exemplified in Figure 2.2 for the PCM of (2.13). A factor graph is comprised of two sets of connected nodes, namely n Variable Nodes (VNs) for representing the columns of  $\mathbf{H}$  and m Check Nodes (CNs) for representing the rows.

The connections  $\tilde{c}_j$  above each VN in Figure 2.2 pertain to the channel messages (i.e. LLRs or probabilities) associated with the n codeword bits of  $\hat{\mathbf{c}}$ . An edge connects the j-th VN  $V_j$  to the i-th CN  $C_i$  if there is a non-zero element in the j-th column and i-th row of  $\mathbf{H}$ ,  $H_{ij}=1$ . To illustrate this, all of the edges that are connected to the  $1^{\text{st}}$  CN  $C_1$  in Figure 2.2 are shown with thicker lines. These edges are connected to the  $1^{\text{st}}$ ,  $4^{\text{th}}$ ,

FIGURE 2.2: A factor graph for an example LDPC code

$5^{\rm th}$ ,  $9^{\rm th}$ , and  $10^{\rm th}$  VNs, in accordance to the position of the 1s in the top row of **H** in (2.13).

The degree of a node is defined as the number of other nodes that it is connected to and is equal to the corresponding row or column weight in **H**. The degree of the CNs  $d_c$  and the degree of the VNs  $d_v$  are important parameters in an LDPC code. If all CNs have the same degree  $d_c$  and all VNs have the same degree  $d_v$ , the LDPC code is said to be regular. If either value varies from node to node, the code is said to be irregular and  $d_c$  and  $d_v$  can be expressed as the average degree over all nodes. For example, the factor graph of Figure 2.2 is irregular with  $d_c = 5.75$  and  $d_v = 2.3$ . In any case, the number of 1s in the PCM **H** must be the same regardless, whether it is viewed row-by-row or column-by-column, giving  $d_c \times m = d_v \times n$ , with  $d_v = d_c \times (1 - R)$ .

#### 2.3 LDPC code construction

In addition to the size of the factor graph and the degrees of its nodes, the position of the edges within the factor graph also has a significant impact on the associated error correction performance, as well as upon the decoding complexity. Some of the main objectives when designing the PCM **H** is to avoid creating stopping sets [35] and short cycles [36] in the corresponding factor graph, which are associated with an eroded error correction performance. A number of techniques have been proposed for placing edges within the factor graph have been proposed, as summarised in the following subsections.

#### 2.3.1 Random codes

Unstructured randomly-designed codes potentially achieve the best LDPC error correction performance, owing to the maximised degree of freedom that is afforded when

placing edges in this manner [37]. However, this is achieved at the cost of having to implement complex unstructured routing or memory lookup tables, in order to exchange messages between the VNs and CNs. A straightforward recursive algorithm for creating unstructured PCMs of this form involves placing a 1 at a random unfilled location in **H**, then checking to see whether doing so has violated any design constraints, such as the maximum node degrees, stopping sets or cycle lengths. If the placement is valid, the algorithm will continue and repeat the process for the next randomly placed 1. This is repeated until the desired number of edges have been positioned. If a randomly placed 1 is not valid, then it will be rejected and a new location will be tried instead. This algorithm is conceptually very simple, but whether the process can successfully complete and how quickly is unpredictable.

#### 2.3.2 Pseudorandom codes

The original LDPC code construction method proposed by Gallager [1] involves stacking  $d_c$  number of submatrices on top of each other. Each submatrix has the dimensions  $m/d_c \times n$ , with each column having a weight of 1 and each row having a weight of  $d_v$ . The top matrix is pseudo-randomly generated, and random column permutations are applied to it in order to obtain all other submatrices.

Similarly to this, Mackay [2] proposed a code construction method, which involves constructing the PCM  $\mathbf{H}$  on a column-by-column basis, where the columns are generated pseudorandomly with appropriate weight, before being concatenated horizontally. Again, this process must be performed in a recursive manner, so that the row weights can be checked after each column is added. If  $d_c$  has been exceeded for any row, then the current column is regenerated.

#### 2.3.3 Quasi-cyclic codes

The PCM  $\mathbf{H}$  of a QC code is semi-structured, based on an upper matrix  $\mathbf{H}_b$  of elements which each represent a square submatrix of size  $z \times z$  [38]. If a particular element in  $\mathbf{H}_b$  has a value of -1, then the corresponding submatrix of  $\mathbf{H}$  is a null matrix. Otherwise, the submatrix is an identity matrix, which has been cyclically shifted a number of times according to the corresponding value in the upper matrix [39]. Adopting this structure provides a range of benefits for LDPC decoders without incurring a significant sacrifice in error correction performance, and hence QC LDPC codes are employed by a number of communications standards, including DVB-S2 [5], IEEE 802.11 (WiFi) [3] and IEEE 802.16 (Mobile WiMAX) [4]. Owing to this wide-spread adoption, the decoder architectures described in Chapters 4 and 5 target any LDPC code having a QC structure, in order to take advantage of the associated benefits. A full discussion of the nature and causes of these benefits is hence presented in Section 4.2.1.

# 2.3.4 Repeat-accumulate codes

Repeat-accumulate (RA) codes constitute another type of semi-structured codes. Like QC codes, RA codes benefit from simpler encoding/decoding than random codes, without imposing an unacceptable loss in error correction performance. The PCMs of RA codes are composed of two horizontally-concatenated submatrices  $\mathbf{H}_1$  and  $\mathbf{H}_2$ , where  $\mathbf{H}_2$  is an  $(m \times m)$ -element dual-diagonal matrix. This structure allows each parity bit to be calculated using only the previous parity bit and a subset of the message bits, leading to the accumulation alluded to in the code's name.

# 2.3.5 Progressive edge growth algorithm

Whilst not a code structure itself, the Progressive Edge Growth (PEG) algorithm [40] is an important technique for constructing codes having an excellent error correction performance. The operation of the PEG algorithm is VN-centric, focusing on each VN in turn in order to place edges. The algorithm repeatedly constructs a set of CNs as candidates for the VN to connect to. From this set, the subset of nodes having the lowest degree is extracted and one of these is randomly selected. This approach results in LDPC codes that have approximately regular degree distributions.

The PEG algorithm constructs a tree structure, alternating between the connection of VNs to CNs and vice versa. At each stage only nodes that are not already in the tree are considered for inclusion. This process continues until there are no remaining options meeting this constraint. The PEG algorithm then places an edge in the location that is identified as maximising the length of the resultant cycle within the graph, before continuing the algorithm with the selection of a different VN. In this way, a factor graph having no short cycles can be created, yielding a strong error correction performance.

# 2.4 LDPC decoding

LDPC codes are typically decoded using a belief propagation (BP) algorithm in which messages are iteratively passed in both directions along the edges between connected nodes [41]. For example, Figure 2.2 illustrates a message  $\alpha_{4\to 1}$  sent from the 4<sup>th</sup> VN  $V_4$  to the 1<sup>st</sup> CN  $C_1$ , while the message  $\beta_{4\to 9}$  is sent from the 4<sup>th</sup> CN  $C_4$  to the 9<sup>th</sup> VN  $V_9$ . The messages provided as inputs to a node are processed by activating that node, causing it to create new output messages that are sent back to the nodes it is connected to. Thus the processing of the LDPC decoder is delegated to the many individual calculations performed by the individual nodes, rather than being a single monolithic global equation. An important facet of the belief propagation algorithm is that any message sent to a particular node does not depend on the message received from that

node. For example, CN  $C_2$  is connected to VNs  $V_2$ ,  $V_3$ ,  $V_5$ ,  $V_8$ , and  $V_{10}$ ; however, the message  $\beta_{2\to 5}$  it sends to  $V_5$  will be calculated based only on the messages it has received from  $V_2$ ,  $V_3$ ,  $V_8$ , and  $V_{10}$ .

Nodes are activated in an order determined by the LDPC decoder's *schedule*. This has a significant effect upon the LDPC decoder's error correction capability, as well as on its other characteristics. Many different schedules exist, and the most common options will be outlined in Section 2.4.1. Following this, variations of the specific calculations performed within CNs and VNs will be presented in Sections 2.4.2 and 2.4.3 respectively.

# 2.4.1 Scheduling

The schedule of the LDPC decoding process determines the order in which VNs and CNs are processed, as well as whether multiple nodes are processed in parallel. Many scheduling variations exist, but the three most common schedules are described here, namely flooding [42], Layered Belief Propagation (LBP) [43], and Informed Dynamic Scheduling (IDS) [44].

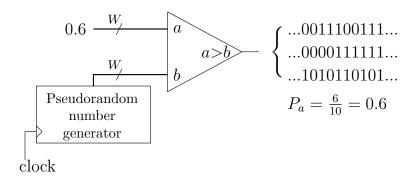

# 2.4.1.1 Flooding

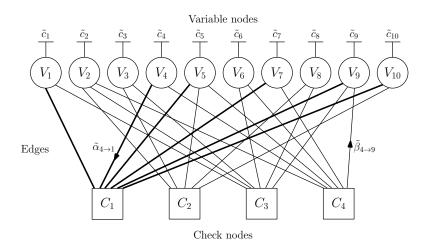

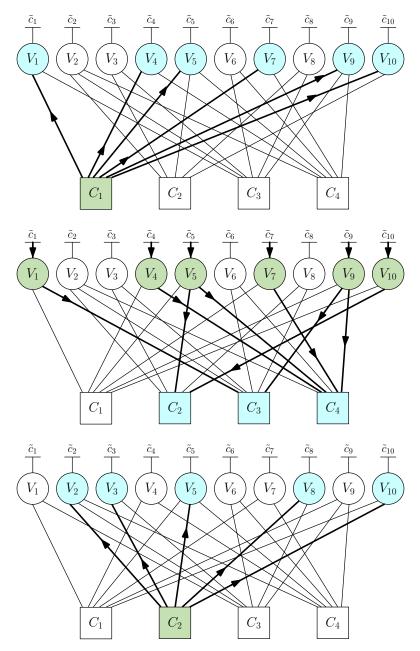

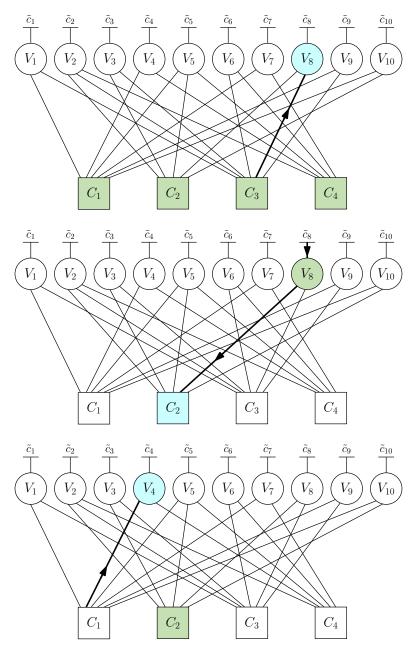

FIGURE 2.3: An example of the flooding schedule

Flooding is perhaps the most conceptually simple LDPC decoding schedule. Here, the factor graph is processed in an iterative manner, where each iteration comprises the simultaneous activation of all CNs, followed by the simultaneous activation of all VNs [41]. An example of this schedule is depicted in Figure 2.3. It can be seen that at first the CNs  $C_1$ – $C_4$  (shown in green) calculate their messages  $\beta_{j\to i}$ , which are then sent along every edge (in bold) to every receiving VN (shown in blue). In the second half-iteration, the VNs are shown in green to indicate that they are performing calculations and sending messages  $\alpha_{i\to j}$ , while the CNs are shown in blue to indicate that they are receiving messages.

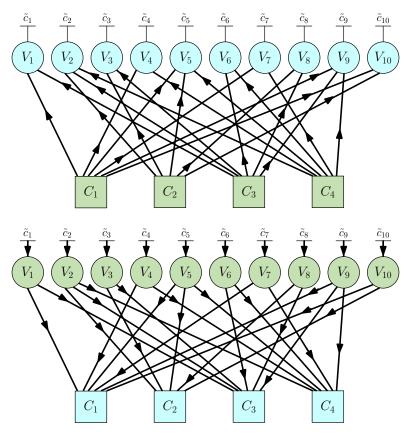

## 2.4.1.2 Layered belief propagation

While LBP [43] also operates in an iterative manner, within each iteration it breaks the factor graph up into a series of layers, which it processes sequentially [29]. Note that the following explanation focuses on a row-centric interpretation, which is the most common way of implementing LBP [45], though column-centric representations also exist [46]. Each layer comprises a number  $\phi$  of check-nodes, where  $1 \leq \phi \ll m$ . The value of  $\phi$  must be chosen such that no column within the layer has a column-weight that is greater than 1 (i.e. no VN connects to more than one CN within a single layer) [47]. The processing of each layer begins with the simultaneous activation of all of its CNs. Once the CNs have been activated, all of their connected VNs are then activated, before moving on to the next layer. Once every layer has been processed, the iteration is complete.

This process is exemplified in Figure 2.4, for a layer size of  $\phi = 1$  CN. Here, the LBP decoding iteration begins with the activation of the first layer, which is comprised of CN  $C_1$ . Once it has been activated,  $C_1$  then sends messages  $\beta_{1\to j}$  to each of its connected VNs  $V_j$ ,  $j \in \{1, 4, 5, 7, 9, 10\}$ . Each of these VNs are then activated, sending new messages  $\alpha_{j\to i}$  to each of their connected CNs  $C_i$ , except  $C_1$ . Following this, the next layer (containing  $C_2$ ) may be activated, allowing it to make use of the new information received from  $V_5$  and  $V_{10}$  alongside the information previously received from its other connected VNs. This process continues until every layer has been activated, which then marks the end of one decoding iteration.

LBP has the advantage that the information obtained during an iteration is available to aid the remainder of the iteration [48]. Owing to this however, it does not have the same high level of parallelism as the flooding schedule, possibly resulting in a lower processing throughput and a higher processing latency. It can also be seen that m CN activations and  $d_c \times m$  VN activations occur per iteration, resulting in a higher computational complexity per iteration, when compared to the flooding schedule. However, it will also be shown in Section 2.4.2 that CN activations can be significantly more computationally expensive than the VN activations, hence the increased cost is manageable. Additionally,

FIGURE 2.4: An example of the layered belief propagation schedule

LBP tends to converge to the correct codeword using fewer iterations and therefore with lower overall computational complexity than flooding [33,48].

A common method for implementing LBP decoding is by also taking advantage of the multicast-style messages proposed in [49, 50]. Here, the VNs function simply as memories, where each VN  $V_j$  stores a single message  $\alpha_j$ , which it broadcasts to all of its connected CNs [47]. When CN  $C_i$  is activated at iteration T, for each connected VN  $V_j$ , it first subtracts the check-to-variable message calculated during the previous iteration from the incoming broadcast VN message,

$$\alpha_{j \to i}^T = \alpha_j - \beta_{i \to j}^{T-1}. \tag{2.14}$$

Once the current values of  $\alpha_{j\to i}^T$  have been calculated, they may then be used to activate  $C_i$  as normal,

$$\beta_{i \to j}^T = F_{CN}(\alpha_{j \to i}^T), \tag{2.15}$$

where the CN update function  $F_{CN}(\cdot)$  is defined for varying algorithms and message representations in Section 2.4.2. The new values of  $\beta_{i\to j}^T$  must then be stored to be used at iteration T+1, and are used to calculate the updated value of the broadcast message for  $V_i$ ,

$$\alpha_j = \beta_{i \to j}^T + \alpha_{i \to i}^T. \tag{2.16}$$

This variation of the layered decoding schedule requires a slightly greater amount of storage at each node, but benefits from greatly reduced routing complexity for the VN messages.

## 2.4.1.3 Informed dynamic scheduling

Informed Dynamic Scheduling [51, 52] inspects the messages that are passed between the various nodes, selecting to activate whichever node is expected to offer the greatest improvement in belief. This requires IDS to perform additional calculations in order to determine which node to activate at each stage of the decoding process. However, IDS facilitates convergence using fewer node activations than in either flooding or LBP, which may lead to a lower complexity overall [53].

During IDS, the difference between the previous message sent over an edge and the message that is obtained using recently-updated information [44] is calculated. This difference is termed the residual [52], and represents the improvement in belief that is achieved by the new message. Like the LBP schedule, IDS is commonly centred on the CNs. At the start of the iterative decoding process, the residual for each output of each CN is calculated as the magnitude of the message to be sent over that edge. The message with the greatest residual is identified, and the receiving VN is then activated, sending updated messages to each of its connected CNs. These CNs then calculate new residuals for each of their edges as the difference between its new message and its previous message. All of the residuals in the graph are then compared for the sake of identifying the new maximum, before the process is repeated.

Using Figure 2.5 as before, suppose that at the start of the iterative decoding process, the message  $\tilde{\beta}_{3\to 8}$  from CN  $C_3$  is identified as having the highest magnitude of all the check-to-variable messages in the graph. Owing to this,  $\tilde{\beta}_{3\to 8}$  is passed to the VN  $V_8$ , which is then activated, in order to obtain the message  $\tilde{\beta}_{8\to 2}$  which is then passed to  $C_2$ . The CN  $C_2$  can then be activated to calculate new residuals for its other four edges, as the difference between their previous messages and their new messages that have been obtained using the updated information from  $V_8$ . These new residuals are then compared with the others from the previous step, allowing a new global maximum to be

FIGURE 2.5: An example of informed dynamic scheduling