# HWCVD a-Si:H interlayer slope waveguide coupler for multilayer silicon photonics platform

RAFIDAH PETRA,<sup>1</sup> SWE ZIN OO,<sup>1,2</sup> ANTULIO TARAZONA,<sup>2</sup> ROBERT CERNANSKY,<sup>3</sup> SCOTT A. REYNOLDS,<sup>2</sup> ALI Z. KHOKHAR,<sup>2</sup> VINITA MITTAL,<sup>2</sup> DAVID J. THOMSON,<sup>2</sup> ALBERTO POLITI,<sup>3</sup> GORAN Z. MASHANOVICH,<sup>2</sup> GRAHAM T. REED,<sup>2</sup> AND HAROLD M. H. CHONG,<sup>1,4,\*</sup>

**Abstract:** We present interlayer slope waveguides, designed to guide light from one level to another in a multi-layer silicon photonics platform. The waveguide is fabricated from hydrogenated amorphous silicon (a-Si:H) film, deposited using hot-wire chemical vapor deposition (HWCVD) at a temperature of 230°C. The interlayer slope waveguide is comprises of a lower level input waveguide and an upper level output waveguide, connected by a waveguide on a slope, with vertical separation to isolate other crossing waveguides. Measured loss of 0.17 dB/slope was obtained for waveguide dimensions of 600 nm waveguide width (w) and 400 nm core thickness (h) at a wavelength of 1550 nm and for transverse electric (TE) mode polarization.

Published by The Optical Society under the terms of the Creative Commons Attribution 4.0 License. Further distribution of this work must maintain attribution to the author(s) and the published article's title, journal citation, and DOI.

## 1. Introduction

Wafer space on an optical chip is seen as the next challenge to bring silicon photonics (SiP) to mass market. Multiple stacking of optical layers and electronic layers in a three-dimensional (3D) multilayer integration can resolve this issue, offering dense footprint and computational system with new functionality and greater optical data processing capability [1–3]. However, the challenge in realizing multilayer technology is making 3D vertical optical vias to connect vertically stacked optical components through depositable material that is compatible with CMOS processes. Thus, researchers have proposed various structures to tackle this matter. Several groups have reported ways for vertical coupling. This include Takei et al. [4], Shang et al. [5] and Itoh et al. [6] who utilized evanescent field and Zhang et al. [7] who utilized phase-matching conditions, all based on silicon (Si) thin films to couple light vertically. They reported coupling loss of 0.87 dB, 0.01 dB and 0.49 dB, respectively. Other interlayer coupling methods using polymeric-based material are demonstrated by Garner et al. [8] and Ni et al. [9] by direct coupling through vertical S-bend waveguide, demonstrating an excess loss of 0.3 dB and propagation loss of 1.1 dB/cm, respectively. These reported 3D interconnect structures [4-9] have demonstrated vertical coupling capability suitable for multilayer integration. With regard to the vertical S-bend coupler used to guide light from one layer to another layer through direct coupling, there is still limited report on direct waveguide coupling between optical layers and use of CMOS process compatible silicon materials at 1550 nm wavelength.

<sup>&</sup>lt;sup>1</sup>Sustainable Electronics Technology Group, School of Electronics and Computer Science, University of Southampton, Southampton SO17 1BJ, UK

<sup>&</sup>lt;sup>2</sup>Optoelectronics Research Centre, University of Southampton, Southampton SO17 1BJ, UK

<sup>&</sup>lt;sup>3</sup>Department of Physics and Astronomy, University of Southampton, Southampton SO17 1BJ, UK

<sup>&</sup>lt;sup>4</sup>Japan Advanced Institute of Science and Technology, Nomi, Ishikawa 923-1211, Japan

<sup>\*</sup>hmhc@ecs.soton.ac.uk

Thus, in this paper we proposed an interlayer slope waveguide, fabricated from hydrogenated amorphous silicon (a-Si:H) film deposited at low temperature using a hot-wire chemical vapour deposition (HWCVD) tool [10]. The interlayer coupler is designed to achieve vertical freedom for direct coupling, allowing transport of light up or down the multilayer SiP platform over a relatively large cladding height. The device design is simple and robust in terms of fabrication, making it feasible to control the waveguide dimensions during fabrication. The ability to control the waveguide dimensions is advantageous in minimizing the fluctuation of effective index of the optical mode ( $n_{eff}$ ) across the slope waveguide. In addition, the nature of direct coupling of the interlayer slope waveguide makes the device adaptable to polarization change, while offering a broad bandwidth similar to any planar waveguides [11,12].

The use of a-Si:H film is promising because of its compatibility with CMOS back-end processes, enabling device fabrication on the electronic circuit layers. Also, the material exhibits low absorption loss having an energy bandgap of ~1.7 eV [13], allowing near infrared photons with  $\sim 0.79$  eV (hv) energy to be transmitted. In addition, the high refractive index exhibits strong confinement of the optical mode within the waveguide facilitating ultracompact interconnect devices. To date, several groups such as Selvaraja et al. [14], Zhu et al. [15], Furuya et al. [16] and Takei et al. [17] have reported high-quality plasma enhanced chemical vapour deposition (PECVD) a-Si:H film. These groups have demonstrated submicron sized waveguide structure with propagation losses between 0.6 dB/cm and 3.45 dB/cm, which is fundamental for the realization of 3D interconnect [18]. The main advantage of using the HWCVD tool in our work over plasma-enhanced chemical vapour deposition (PECVD) is the effective dissociation of the precursor gas, i.e., silane (SiH<sub>4</sub>), into atomic silicon (Si) and hydrogen (H<sub>2</sub>) molecules, by the hot filaments which reduces film stress due to the absence of plasma ion bombardment [19]. Thus, this allows high quality HWCVD a-Si:H thin film to be attainable at low temperature below 400°C for Back End of Line (BEOL) process compatibility [20]. In this paper, we demonstrate the fabrication and characterization of HWCVD a-Si:H interlayer slope waveguides. The a-Si:H film is deposited at a low deposition temperature of 230°C and supplied with sufficient hydrogen radicals to passivate the dangling bonds of the silicon atoms [21]. Although the device is not restricted to any propagation modes, transverse electric (TE) mode polarization at a wavelength of 1550 nm is used for our device characterization as it is commonly used for silicon-on-insulator (SOI) platforms in silicon photonic integrated circuits (Si-PICs) due to its use as a standard telecom wavelength [12].

# 2. Interlayer slope waveguide

#### 2.1. Device structure and design

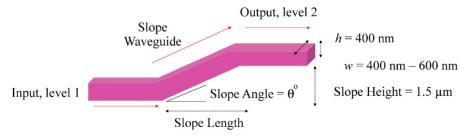

The schematic structure of the interlayer slope waveguide is shown in Fig. 1. The device comprises of a lower level waveguide as the input and an upper level waveguide as the output connected by a waveguide on the slope. In our design, the core thickness (h) is 400 nm with the width (w) of the waveguide varied from 400 nm to 600 nm, with both ends tapered out to grating couplers. A large slope height of 1.5  $\mu$ m is designed with a corresponding calculated slope length. This height is adjustable depending on the required etching parameters.

Fig. 1. Schematic design of the HWCVD a-Si:H interlayer slope waveguide.

The slope structure was designed so that the device was well adapted for practical use and integration into the multilayer SiP platform. Two important criteria were considered:

- 1) The functionality of the waveguide to guide light from one layer to another with the highest transmission possible.

- 2) The compactness of the device to increase circuit density in terms of footprint.

#### 2.2. Mask design

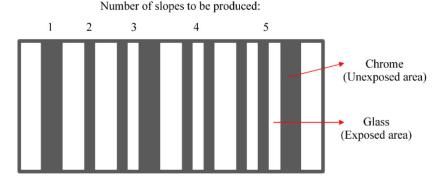

The interlayer slope waveguide is characterized in terms of loss in dB per slope. Thus, in characterizing the interlayer slope waveguide, many slopes are required to be fabricated as a platform for the interlayer waveguide. Two masks were mainly used: optical mask and electron-beam (e-beam) mask. The optical mask is designed with multiple bars that are used to define the slopes structure, as shown in Fig. 2. This designed structure was the first layer to be fabricated.

Fig. 2. Schematic diagram of the optical mask design illustrating the multiple bars used to define the slope platform.

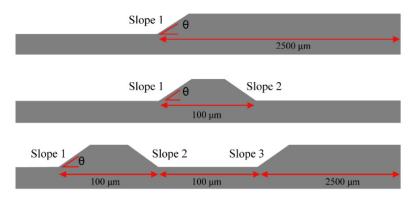

Positive photoresist, S1813, was used to transfer the pattern from the optical mask. In performing optical lithography, the exposed part of S1813 photoresist that is exposed to UV light becomes weakened on radiation and is dissolved during development. This produces structures as shown in Fig. 3, after the process of wet etching. Figure 3 illustrates the etched slope profiles for (a) a 1 slope platform, (b) 2 slopes platform, and (c) 3 slopes platform.

Fig. 3. Schematic diagrams of cross-sectional views of the slope platform after wet etching, with pattern transferred using the optical mask.

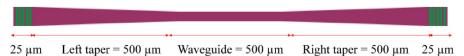

Having used the optical mask to produce the slope platform, the e-beam mask was then used to generate the waveguide structures. Figure 4 illustrates the schematic drawing of the waveguide containing tapers and gratings attached at both ends of the waveguide. This structure was the second layer to be fabricated. Here, the total length of the waveguide including the tapers and the gratings was  $1550 \, \mu m$ .

Fig. 4. Schematic diagram of the waveguide structure.

#### 2.3. Modelling of the interlayer slope waveguide

In the design of the interlayer slope waveguide, the slope angle plays a major role in obtaining high transmission. Based on the waveguide bend theory, the angle must be sufficiently small to avoid large changes in the effective propagation constant  $(\beta)$  of the mode propagating across the waveguide.

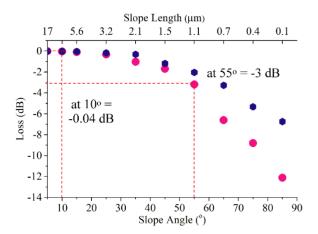

Lumerical FDTD software was used to simulate the transmission characteristics of the interlayer slope waveguide with a varying slope angle from  $5^{\circ}$  to  $85^{\circ}$ . Here, the slope height was kept constant at 1.5  $\mu$ m to allow sufficient isolation between the input and output waveguides and other crossing waveguides, with the slope length varying according to the slope angle. The slope length was calculated based on Pythagoras' theorem, using a known slope height and angle. The simulation results are shown in Fig. 5.

Fig. 5. Transmission characteristics on varying the slope angle and the corresponding slope length of the a-Si:H interlayer slope waveguide at 1550 nm wavelength with TE polarized mode;  $\bullet$  are the simulated losses for 400 nm (w) by 400 nm (h) waveguide dimensions, and  $\bullet$  are the losses for 600 nm (w) by 400 nm (h) waveguide dimensions.

The pink circles are for 400 nm (w) by 400 nm (h) waveguide dimensions, and the blue circles are for 600 nm (w) by 400 nm (h) waveguide dimensions. An optimized slope angle between 5° and 20° has shown to have the lowest transmission loss below 0.1 dB. The losses increased gradually with an increase in slope angle, and increased rapidly when the slope angle was made higher. Additionally, Fig. 5 shows that the loss in the wider waveguide (600 nm (w) by 400 nm (h)) increased more slowly than in the narrower waveguide (400 nm (w) by 400 nm (h)). This suggests that the mode in the wider waveguide was largely confined within the waveguide core and was more susceptible to bend losses.

The higher loss present for the larger slope angle of 55°, as shown in Fig. 5, is caused by mode-mismatch through the bend at the slope interface. At higher slope angles, the launched single mode experiences a significant phase shift as it interacts with the slope interface, where some of the mode field penetrates into the substrate and is lost through radiation [22].

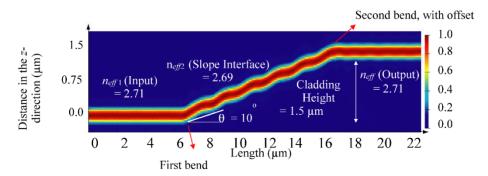

Figure 6 illustrates a 2D simulation of the interlayer slope waveguide at  $10^{\circ}$  slope angle, with waveguide dimensions of 400 nm (w) by 400 nm (h) at a wavelength of 1550 nm with TE mode polarization. It can be observed that the optical mode is coupled to the upper level via the  $10^{\circ}$  slope waveguide with 0.04 dB transmission loss. Compared to a straight waveguide, the loss contributed from the  $10^{\circ}$  slope waveguide is small with only 1% of the optical mode radiated into the substrate. The simulation profile shows that mode propagating the slope waveguide (after being perturbed at the first slope interface) appear to show mode beating. The introduction of transition offset to the second slope interface suppresses the higher-order mode, reconstructing it back to fundamental mode [23,24].

Fig. 6. Simulation profile of the a-Si:H interlayer slope waveguide with 10° slope angle at 1550 nm wavelength with TE polarized mode.

#### 2.4. Fabrication

Device fabrication started with PECVD deposition of 4.5 μm thick SiO<sub>2</sub> at 350°C on a silicon wafer. Four samples were prepared, Sample A, Sample B, Sample C and Sample D.

#### 2.4.1. Formation of slope platform

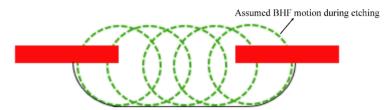

The next step was to pattern the four samples by optical lithography using S1813 as the photoresist to define the slope platform. In this work, the formation of the slope profile with controllable slope angle is the core step in fabricating the interlayer slope waveguide. By varying the properties of the photoresist through the addition of primer and subjecting the sample to thermal treatment, allow the adhesion strength between the photoresist and the etching material (PECVD SiO<sub>2</sub>) to be increased. This is caused by the physical linkages of bonding network between the atoms of the photoresist and SiO<sub>2</sub>, which increases the intermolecular forces between the two interfaces. Increasing the adhesion strength would mean that the photoresist sticks very well to the surface of the etching material [25]. The stickiness allows the etching profile to be controlled. The isotropic profile is the most commonly encountered etch profile for both wet and dry etching. This includes SiO<sub>2</sub> etched in aqueous hydrofluoric (HF) acid solutions where a curved sidewall is formed, as shown in Fig. 7. This isotropic etching profile is created when the adhesion between the resist and the SiO<sub>2</sub> surface is high [25,26].

Fig. 7. Cross-sectional view of the contour of the wall of wet etching silicon dioxide (SiO<sub>2</sub>) in hydrofluoric (HF) acid solution, with strong adhesion of resist onto silicon dioxide (SiO<sub>2</sub>) surface [25,26].

In the case when the adhesion is poor, delamination of the resist occurs. The aqueous HF solutions easily attack the etching material underneath the resist due to the weak bonding network between the two interfaces. This results in the  $SiO_2$  at the surface having higher etch rate and causing the top film to get etched faster. The film continued to be etched both in the horizontal and vertical directions forming the tapered-like wall structure with sharp bends. The profile evolution and the resulting etch profile is shown in Fig. 8 [26,27].

Fig. 8. Profile evolution of the fast etching of the top surface of the silicon dioxide (SiO<sub>2</sub>) in hydrofluoric (HF) acid solution, due to weak adhesion of resist onto silicon dioxide (SiO<sub>2</sub>) surface [26,27].

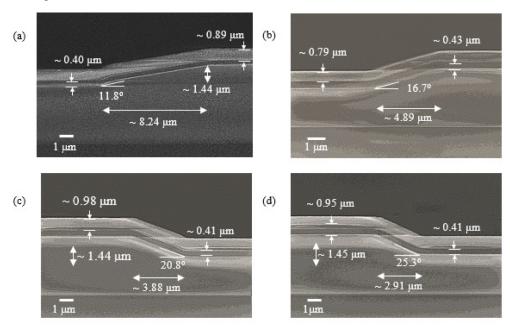

All four samples were patterned using photolithography with S1813 as the photoresist to define the slope platform. In this work, two types of S1813 were used in the optical lithography, S1813 without adhesion primer and S1813 with adhesion primer. The addition of adhesion primer and further baking of the S1813 increases the adhesion strength between the photoresist and the SiO<sub>2</sub> film and allows the slope etching profile to be controlled [26]. Sample A and Sample B were spun with S1813 without adhesion primer. Sample C and Sample D were spun with S1813 with adhesion primer. Then the four samples were exposed to UV light using an EVG620TB mask aligner system. After the photoresist was developed, Samples B and D were post-baked at 130°C for 60 seconds to increase the adhesion between the photoresist and the SiO<sub>2</sub> interface. Figure 9 illustrates the photolithography steps for the four samples. Then, all the four samples were wet-etched in buffered hydrofluoric acid, NH<sub>4</sub>F:HF (7:1), at room temperature to define the slope profile [28, 29]. With a five minute wet-etch, Sample A, Sample B, Sample C and Sample D produces slope angle equal to 11.8°, 16.7°, 20.8° and 25.3°. Table. 1 shows the slope profiles for all four samples with the five minute wet-etch.

Fig. 9. Illustration of photolithography steps for the four samples.

Table 1. Slope profile with a five minute wet-etching.

|                  | Photoresist S1813 |              | Photoresist S1813 + Adhesion primer |              |

|------------------|-------------------|--------------|-------------------------------------|--------------|

| Slope parameters | Sample A          | Sample B     | Sample C                            | Sample D     |

|                  | (No post-bake)    | (Post-baked) | (No post-bake)                      | (Post-baked) |

| Angle (°)        | 11.8              | 16.7         | 20.8                                | 25.3         |

| Height (µm)      | 1.44              | 1.51         | 1.44                                | 1.45         |

| Length (μm)      | 8.24              | 4.89         | 3.88                                | 2.91         |

Then, the process was followed by the deposition of a 400 nm thick a-Si:H film by HWCVD system. A silane (SiH<sub>4</sub>) gas flow of 40 sccm and a hydrogen (H<sub>2</sub>) gas flow of 30 sccm were used for the deposition process. The substrate temperature was regulated at 230°C

at a pressure of 7.5 mTorr. Submicron sized waveguides with widths (w) of 400 nm and 600 nm and grating couplers with varied periods from 0.5  $\mu$ m to 1.0  $\mu$ m were patterned using ebeam lithography and dry etched in an inductively coupled plasma (ICP) tool with fluorine-based gas to form a strip waveguide. The grating couplers were varied to take into account of fabrication errors.

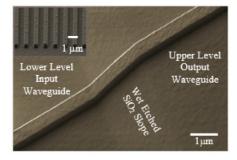

Finally, the waveguides were covered with 1  $\mu$ m thick PECVD SiO<sub>2</sub> layer as the top cladding. Figures 10(a)–10(d) show the SEM images of the cross-sectional view of the interlayer slope waveguide for the four samples. Figure 11 shows the SEM image of the fabricated and un-cladded interlayer slope waveguide with 400 nm width and 400 nm core thickness, with inset picture of fully-etched grating couplers used for measurement.

The above fabrication method can be used to build a new photonic integrated circuit layer by deposition of new  $SiO_2$  after the slope waveguides and planarization with chemical mechanical polishing (CMP). The planarized  $SiO_2$  surface will provide the new photonic device platform.

Fig. 10. SEM images of cross-sectional view of the interlayer slope waveguide for, (a) Sample A, (b) Sample B, (c) Sample C, and (d) Sample D.

Fig. 11. SEM image of: Top-view of the interlayer slope waveguide for 400 nm core thickness and 400 nm width, inset: Fully-etched grating couplers connected at both ends of the interlayer slope waveguide.

#### 2.5. Measurement results and discussion

The transmission properties of the interlayer slope waveguides were measured in dB per slope (dB/slope) through averaging of up to five slopes. A tunable Agilent 81940A laser source and Agilent 81634B power sensor were used for the measurements at the wavelength of 1550 nm in transverse electric (TE) mode polarization. Single mode SMF-28-J9 fiber was used to couple light at the input and output of the slope waveguides via fully etched grating couplers. The size of the grating couplers is 13  $\mu$ m by 13  $\mu$ m, sufficient to collect light from the single mode core fibre with mode field diameter of 10.4  $\mu$ m. The design of the grating couplers allowed coupling of TE mode polarization only. Our measured propagation loss for a straight a-Si:H waveguide for 650 nm (w) by 400 nm (h) waveguide dimensions is 0.8 dB/cm [20].

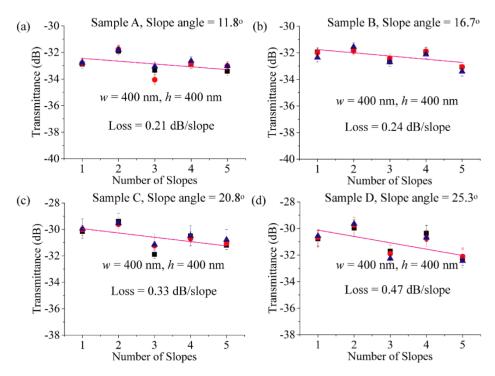

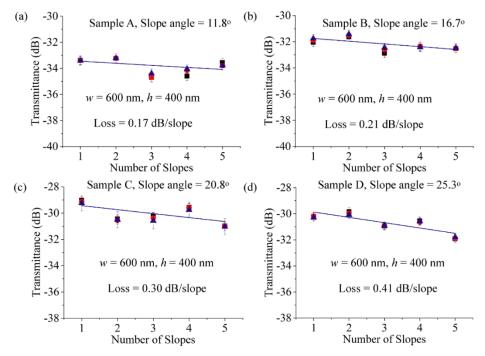

The fabricated interlayer slope waveguides have a varied width (w) of 400 nm and 600 nm, and fixed height (h) of 400 nm. Figures 12 and 13 shows the slope loss characteristics of Samples A, B, C and D. The transmission measurements at each number of slopes (1, 2, 3, 4 and 5 slopes) for all the devices were repeated 3 times and has an average tolerance of 0.1 dB. In scanning the transmission across a range of wavelengths, it was observed that the output power fluctuated. Thus, each data point of the loss measurements was the results of averaging the transmission (dB) to up to a 20 nm wavelength interval, centred at 1550 nm in TE mode polarization. The 3 repeated measurements were represented by 3 different point symbols with 3 different colours, which are blue triangle, red circle and black square. In measuring the transmission properties of the interlayer slope waveguides which are measured in dB per slope, regression line fitting was done across the 5 slopes of each graph. Because the data points are scattered with uncertainties due to fabrication and experimental errors, error bars were added to each data points to increase accuracy in the line fitting.

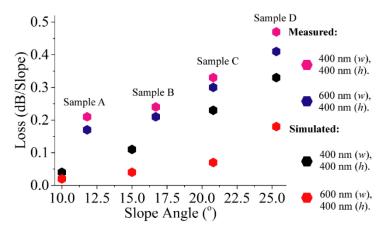

The measured slope loss in Figs. 12(a) and 12(b) is 0.21 dB/slope and 0.24 dB/slope, which the small loss difference is expected for the angle 11.8° and 16.7°. Similar slope loss characteristics are obtained in Figs. 13(a) and 13(b) of 0.17 dB/slope and 0.21/slope. However, the measured slope loss starts to deviate when the slope angle becomes greater than 20°, which was also shown in Fig. 5 simulation. Figures 12(c) and 12(d) demonstrate slope loss of 0.33 dB/slope and 0.47 dB/slope for angle of 20.8° and 25.3°. The slope loss for the 600 nm wide waveguide in Figs. 13(c) and 13(d) is 0.30 dB/slope and 0.41 dB/cm. The difference in the simulated slope loss of less than 0.1 dB for angle between 5° to 20° compared to the measured slope losses of greater than 0.2 dB/slope suggests contribution of the vertical bends and surface roughness due to fabrication. The losses from the four different slope angles of the measurements as shown in Figs. 12(a)–12(d) and 13(a)–13(d) are compared with simulations as presented in Fig. 14.

It was noted that the insertion loss is large because of the inputs and outputs of the grating couplers are at different levels, which pose a challenge for vertical alignment of the optical fibers.

Fig. 12. (a) -12(d) Transmission characteristics of the interlayer slope waveguide for 400 nm (w) by 400 nm (h) waveguide, at 1550 nm in TE mode polarization.

Fig. 13. (a) -13(d) Transmission characteristics of the interlayer slope waveguide for 600 nm (w) by 400 nm (h) waveguide, at 1550 nm in TE mode polarization.

Fig. 14. Measured and simulated losses for four different slope angles and varied waveguide dimensions.

### 2.5.1. Effect of bending structure

The losses of the four samples indicate that the majority of the losses in the interlayer slope waveguide were attributed to a higher slope angle. The interface between the input waveguide and the slope waveguide is analogous to a waveguide bend, for which the loss mechanics are well described [22]. Fundamentally, when the optical mode travels from a straight waveguide into the slope interface, which it encounters as surface perturbation, it changes the direction of propagation with respect to the interface curvature. The change in direction of propagation changes the effective index  $(n_{eff})$  and thus the effective propagation constant  $(\beta)$  of the propagating mode. The slight variation of n<sub>eff</sub> values were noted as shown in Fig. 6. In Fig. 6, the value of  $n_{eff}$  on the straight section of the waveguide reduces from  $n_{eff1} = 2.71$  to  $n_{eff2} =$ 2.69 at the slope interface. At the straight section of the waveguide, fundamental mode propagates with its respective propagation constant,  $\beta_l$ , regarded as the input field. The propagation changes of the fundamental mode from straight to the slope junction would excite bending mode travelling at a different propagation constant,  $\beta_2$ , regarded as the coupled field. The input field and the coupled field are dissimilar, resulting in modal overlap mismatch which can be evaluated through calculation of the overlap integral between the two individual mode solutions (the input field and the coupled field). With an overlap integral fraction of less than 1, induces interface loss at the transition region occurring between the straight and the bent section of the waveguide [22,23]. The losses of the slope junction would become more obvious if there was a sharp interface between the two waveguides.

The measurement results conform to the simulation shown in Fig. 5, where it shows high loss at higher slope angle. In the measurement, the 25.3° slope angle exhibits loss of 0.47 dB/slope, and the 11.8° slope angle has a loss equal to 0.21 dB/slope. This implies that mode propagating in the 25.3° slope angle, experiences significant modal overlap mismatch and thus, increases the loss. In contrast, mode propagating in the 11.8° slope angle, underwent smoother transition during the mode conversion.

## 2.5.2. Effect of surface roughness of the film

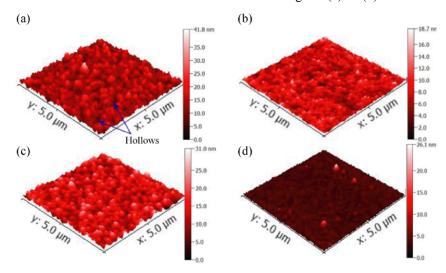

Another loss contribution can be attributed to scattering loss due to roughness between the waveguide surface and cladding layers. The surface roughness of the HWCVD a-Si:H film and the underlying PECVD SiO<sub>2</sub> were evaluated using Bruker Nanoscope Veeco tapping mode of an atomic force microscope (AFM).

The structure of the interlayer slope waveguide comprises of two-level platforms with two bottom cladding  $SiO_2$  thicknesses. As described in the fabrication process in section 2.2, the fabrication of the device involves wet etching the PECVD  $SiO_2$  to produce the slope platform,

resulting in two distinct surface profiles. Thus, it is necessary to characterize the surface roughness of both the upper and lower layer SiO<sub>2</sub>, and the corresponding surface roughness of the upper and lower layer HWCVD a-Si:H film. The AFM results of both the upper and lower layer SiO<sub>2</sub>, and the corresponding surface roughness of the upper and lower layer HWCVD a-Si:H films are tabulated in Table. 2.

Table 2. RMS surface roughness of upper and lower level PECVD SiO<sub>2</sub> and HWCVD a-Si:H waveguide.

| Material                           | RMS surface roughness (nm) |

|------------------------------------|----------------------------|

| Upper layer PECVD SiO <sub>2</sub> | 4.2                        |

| Lower layer PECVD SiO <sub>2</sub> | 2.1                        |

| Upper layer HWCVD a-Si;H           | 3.99                       |

| Lower laver HWCVD a-Si:H           | 1 35                       |

The surface topography of the upper and lower layer PECVD SiO<sub>2</sub> and HWCVD a-Si:H films extracted from the AFM measurement are shown in Figs. 15(a)–15(d).

Fig. 15. Topographical AFM image of: (a) Upper layer PECVD SiO2, (b) Lower layer PECVD SiO2, (c) Upper layer HWCVD a-Si:H and (d) Lower layer HWCVD a-Si:H.

As part of the analysis, Lumerical FDTD was used to simulate the effect of having surface roughness to the loss of the interlayer slope waveguide. The material-induced absorption loss was excluded from the model. The loss was estimated by introducing surface roughness to the top and bottom interfaces and the waveguide sidewalls. As an approximation, the roughness for the top interface was set to 3.99 nm, and the underlying bottom roughness was equal to 4.2 nm. The exact roughness of the waveguide sidewalls could not be evaluated due to the limitations of the AFM tool. However, for analysis purposes it is assumed that the sidewall roughness of the interlayer slope waveguide was the same as the roughness set to the top interface, which is 3.99 nm. In the simulation, the resolution of the mesh was set to 2 nm with an autocorrelation length of 120 nm. The value of the autocorrelation length was extracted from the AFM measurement. The simulation was run at a wavelength of 1550 nm with TE mode polarization. Simulation results show the increase in the loss for the four different slope angles with the added roughness. The results are shown in Table. 3, with the simulation loss results tabulated with the measured loss results for comparison.

| (v) wavegute unionsons |                                           |                                           |        |                 |  |  |  |

|------------------------|-------------------------------------------|-------------------------------------------|--------|-----------------|--|--|--|

|                        | Simulated loss                            |                                           | Me     | Measured loss   |  |  |  |

| Slope angle (°)        | Loss (dB/Slope) without surface roughness | Loss (dB/Slope)<br>with surface roughness | Sample | Loss (dB/Slope) |  |  |  |

| 10                     | 0.04                                      | 0.11                                      | A      | 0.21            |  |  |  |

| 15                     | 0.11                                      | 0.19                                      | В      | 0.24            |  |  |  |

| 20                     | 0.23                                      | 0.28                                      | С      | 0.33            |  |  |  |

| 25                     | 0.33                                      | 0.40                                      | D      | 0.47            |  |  |  |

Table 3. Simulated and measured loss for different slope angles (°) for 400 nm (w) by 400 nm (h) waveguide dimensions.

The simulation was designed for the interlayer waveguide coupler to have top, bottom and sidewall interfaces to have surface roughness equal to 3.99 nm. The addition of surface roughness in the simulation increases the loss of the slope. However, it is observed that the contribution to the loss with a 3.99 nm RMS surface roughness is very minimal, as shown in Table. 3. This is because the overlap of the evanescent field with the surface roughness is small, and therefore, loss is minimal at the interlayer coupler.

In addition, because the interlayer slope waveguide was cascaded and fabricated on two different SiO<sub>2</sub> level, it was expected that the varying RMS surface roughness would affect the transmission characteristics. This would be due to the films on the upper and lower layers having different surface roughness. The measurements of the interlayer slope waveguide are shown in Figs. 12(a)–12(d) and 13(a)–13(d). The transmission for each number of slopes decreased at every odd slope numbers. For example, the transmission for the 1 slope structure is slightly lower compare to the 2 slope structure. This was the result of varied surface roughness of the two-level SiO<sub>2</sub> films. Optical mode propagating at the output taper of the 1 slope, 3 slopes and 5 slopes devices interacted mainly with the upper level SiO<sub>2</sub> film with RMS surface roughness of 4.2 nm. Optical mode propagating at the input and output tapers of the 2 slopes and 4 slopes devices interacted more with the lower level SiO<sub>2</sub> film with RMS surface roughness equal to 2.1 nm. However, the varied surface roughness had minimal effect of the loss of the slope, since the mode interacting at the slope interfaces with respect to varied roughness was minimal.

# 3. Conclusion

In summary, we demonstrated a-Si:H interlayer slope waveguide loss of 0.17 dB/slope for a 600 nm (w) by 400 nm (h) waveguide dimensions, with 1550 nm wavelength TE polarized light. HWCVD deposition at 230°C was used during fabrication. All fabrication processes were regulated below 400°C for BEOL compatibility. The design of the interlayer slope waveguide coupler is compact due to a high index contrast, low slope angle of 11.8°, short slope length of ~8.24  $\mu$ m, and a cladding height of 1.44  $\mu$ m.

The RMS surface roughness of the upper and lower layer HWCVD a-Si:H closely follow the RMS surface roughness of the corresponding PECVD SiO<sub>2</sub>. This is due to the surface roughness of the underlying PECVD SiO<sub>2</sub> film being transferred to the upper film layer. In the future, the work will focus on the fabrication at lower deposition temperatures and improving the surface roughness of the deposited PECVD SiO<sub>2</sub> film either by chemical mechanical polishing (CMP) or immersing the sample in NH<sub>4</sub>:HF (7:1) before pattern generation and slope etching processes. In addition, the design of the interlayer slope waveguide will be further optimized by having tapered structure at the slope interfaces. Effectively, this would allow gradual transition of the optical mode, which consequently would reduce the insertion loss value of the interlayer slope waveguide.

## **Funding**

Universiti Teknologi Brunei PhD scholarship scheme; EPSRC Silicon Photonics for Future Systems Programme Grant (EP/L00044X/1); EPSRC Electronic-Photonic Convergence Platform grant (EP/N013247/1); EPSRC Laser-Engineered Silicon Grant (EP/M022757/1); Royal Society for David J. Thomson's University Research Fellowship.

### **Acknowledgments**

The author would like to acknowledge the Universiti Teknologi Brunei PhD scholarship scheme. The authors would like to acknowledge the EPSRC Silicon Photonics for Future Systems Programme Grant (EP/L00044X/1), EPSRC Electronic-Photonic Convergence Platform grant (EP/N013247/1), EPSRC Laser-Engineered Silicon Grant (EP/M022757/1) and the Southampton Nanofabrication Centre. Thomson acknowledges funding from the Royal Society for his University Research Fellowship.

#### References

- 1. N. Sherwood-Droz and M. Lipson, "Scalable 3D dense integration of photonics on bulk silicon," Opt. Express 19(18), 17758–17765 (2011).

- P. Koonath and B. Jalali, "Multilayer 3-D photonics in silicon," Opt. Express 15(20), 12686–12691 (2007).

- S. J. Ben Yoo, B. Guan, and R. P. Scott, "Heterogeneous 2D/3D photonic integrated microsystems," Microsyst. Nanoeng. 2, 16030 (2016).

- R. Takei, Y. Maegami, E. Omoda, Y. Sakakibara, M. Mori, and T. Kamei, "Low-Loss and Low Wavelength-Dependence Vertical Interlayer Transition for 3D Silicon Photonics," Opt. Express 23(14), 18602–18610 (2015).

- K. Shang, S. Pathak, B. Guan, G. Liu, and S. J. B. Yoo, "Low-Loss Compact Multilayer Silicon Nitride Platform for 3D Photonic Integrated Circuits," Opt. Express 23(16), 21334–21342 (2015).

- K. Itoh, Y. Kuno, Y. Hayashi, J. Suzuki, N. Hojo, T. Amemiya, N. Nishiyama, and S. Arai, "Crystalline/Amorphous Si Integrated Optical Couplers for 2D/3D Interconnection," IEEE J. Sel. Top. Quantum Electron. 22(6), 255–263 (2016).

- Y. Zhang, D. Kwong, X. Xu, A. Hosseini, S. Y. Yang, J. A. Rogers, and R. T. Chen, "On-Chip Intra- and Inter-Layer Grating Couplers for Three-Dimensional Integration of Silicon Photonics," Appl. Phys. Lett. 102(21), 211109 (2013).

- S. M. Garner, L. Shang-Shin, V. Chuyanov, A. Chen, A. Yacoubian, W. H. Steier, and L. R. Dalton, "Three-Dimensional Integrated Optics Using Polymers," IEEE J. Quantum Electron. 35(8), 1146–1155 (1999).

- W. Ni, X. Wu, and J. Wu, "Layer-to-Layer Optical Interconnect Coupling by Soft-Lithographic Stamping," Opt. Express 17(3), 1194–1202 (2009).

- T. M. B. Masaud, A. Tarazona, E. Jaberansary, X. Chen, G. T. Reed, G. Z. Mashanovich, and H. M. H. Chong, "Hot-Wire Polysilicon Waveguides with Low Deposition Temperature," Opt. Lett. 38(20), 4030–4032 (2013).

- 11. H. P. Zappe, Introduction to Semiconductor Integrated Optics (Artech House, 1995).

- D. Thomson, A. Zilkie, J. E. Bowers, T. Komljenovic, G. T. Reed, L. Vivien, D. Marris-Morini, E. Cassan, L. Virot, J. M. Fedeli, J. M. Hartmann, J. H. Schmid, D. X. Xu, F. Boeuf, P. O'Brien, G. Z. Mashanovich, and M. Nedeljkovic, "Roadmap on silicon photonics," J. Opt. 18(7), 073003 (2016).

- 13. S. H. Lin, Y. C. Chan, D. P. Webb, and Y. W. Lam, "Optical characterization of Hydrogenated Amorphous Silicon Thin Films Deposited at High Rate," J. Electron. Mater. 28(12), 1452–1456 (1999).

- S. K. Selvaraja, E. Sleeckx, M. Schaekers, W. Bogaerts, D. V. Thourhout, P. Dumon, and R. Baets, "Low-loss amorphous silicon-on-insulator technology for photonic integrated circuitry," Opt. Commun. 282(9), 1767–1770 (2009).

- S. Zhu, G. Q. Lo, and D. L. Kwong, "Low-loss amorphous silicon wire waveguide for integrated photonics: effect of fabrication process and the thermal stability," Opt. Express 18(24), 25283–25291 (2010).

- K. Furuya, K. Nakanishi, R. Takei, E. Omoda, M. Suzuki, M. Okano, T. Kamei, M. Mori, and Y. Sakakibara, "Nanometer-scale thickness control of amorphous silicon using isotropic wet-etching and low loss wire waveguide fabrication with the etched material," Appl. Phys. Lett. 100(25), 251108 (2012).

- R. Takei, S. Manako, E. Omoda, Y. Sakakibara, M. Mori, and T. Kamei, "Sub-1 dB/cm submicrometer-scale amorphous silicon waveguide for backend on-chip optical interconnect," Opt. Express 22(4), 4779

–4788 (2014).

- 18. B. Jalali and S. Fathpour, "Silicon Photonics," J. Lightwave Technol. 24(12), 4600–4615 (2006).

- R. E. I. Schropp, "Industrialization of hot wire chemical vapor deposition for thin film applications," Thin Solid Films 595, 272–283 (2015).

- 20. S. Z. Oo, A. Tarazona, A. Z. Khokhar, R. Petra, Y. Franz, G. Z. Mashanovich, G. T. Reed, A. C. Peacock, and H. M. H. Chong, "Hot-wire CVD low-loss a-Si:H waveguides for silicon photonic devices," Photon. Res. 7(2), 193–200 (2019).

- A. A. Onischuk and V. N. Panfilov, "Mechanism of thermal decomposition of silanes," Russ. Chem. Rev. 70(4), 321–332 (2001).

- 22. G. T. Reed, and A. P. Knights, Silicon Photonics an Introduction (John Wiley & Sons, Ltd, 2005).

- 23. R. G. Hunsperger, Integrated Optics, Theory and Technology, 6th ed. (Springer, 2009).

- A. Melloni, P. Monguzzi, R. Costa, and M. Martinelli, "Design of curved waveguides: the matched bend," J. Opt. Soc. Am. A 20, 130–137 (2003).

- 25. S. Franssila, Introduction to Micro Fabrication (John Wiley & Sons, 2004).

- G. A. C. M. Spierings, "Wet chemical etching of silicate glasses in hydrofluoric acid based solutions," J. Mater. Sci. 28(23), 6261–6273 (1993).

- S. Ponoth, N. T. Agarwal, P. D. Persans, and J. L. Plawsky, "Fabrication of controlled sidewall angles in thin films using isotropic etches," J. Vac. Sci. Technol., B: Microelectron. Nanometer Struct.--Process., Meas., Phenom. 21, 1240 (2003).

- 28. S. Kal, S. Haldar, and S. K. Lahiri, "Slope Etching of Silicon Dioxide," Microelectron. Reliab. 30(4), 719–722 (1990).

- 29. H. M. H. Chong, R. Petra, S. Z. Oo, A. Tarazona, and G. T. Reed, "Waveguide for an integrated photonic device." U.S. Patent 15/999071, Aug. 17, 2018.