## University of Southampton Research Repository

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Author (Year of Submission) "Full thesis title", University of Southampton, name of the University Faculty or School or Department, PhD Thesis, pagination.

Data: Author (Year) Title. URI [dataset]

UNIVERSITY OF SOUTHAMPTON

FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

School of Electronics and Computer Science

**Hardware-Validated Performance and Power Modelling of

Heterogeneous Multi-Processing Architectures**

by

Matthew James Walker

ORCID ID: 0000-0001-6368-3644

Thesis for the degree of Doctor of Philosophy

June 2019

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

School of Electronics and Computer Science

Doctor of Philosophy

**Hardware-Validated Performance and Power Modelling of Heterogeneous

Multi-Processing Architectures**

by Matthew James Walker

Modern processors are becoming increasingly more complex and utilise higher numbers of Heterogeneous Multi-Processing (HMP) cores. Energy-efficiency has become the primary design constraint in recent years, and improvements enable battery-powered devices to run longer and reduce the energy and cooling costs in data centres. Moreover, increased energy-efficiency enables greater peak performance under the thermal and power constraints, enabling innovative new uses and applications. Accurate run-time power estimations are critical in guiding online energy-saving techniques and energy-aware scheduling decisions to find the optimum performance, power and energy trade-off. This thesis presents a statistically-rigorous methodology for developing accurate and stable empirical power models for providing run-time power estimations to a run-time manager (RTM) while considering thermal variation, coefficient stability, heteroscedasticity, robust model specification, and non-ideal voltage regulation. The novel methodology ensures that the models perform significantly more accurately across a wider range of workloads when compared with existing run-time power modelling methodologies, achieving average errors lower than four percent. Practical considerations and shortcomings in existing approaches are also identified and addressed.

Furthermore, the recent slowdown in technology scaling has forced researchers and engineers to rely on micro-architectural advances and system-level optimisations to drive performance improvement, the development of which is underpinned by simulation tools. However, such simulation tools inevitably have limitations and contain sources of error which, if not understood by the user, can lead to inaccurate results and incorrect conclusions. This thesis presents a methodology for evaluating CPU performance models and identifying specific sources of error, allowing such models to be improved; extended to other CPUs; validated after changes; and tested for suitability to a specific use case. These hardware-validated performance models are combined with the empirical power models to enable accurate and reliable performance, power and energy simulation.

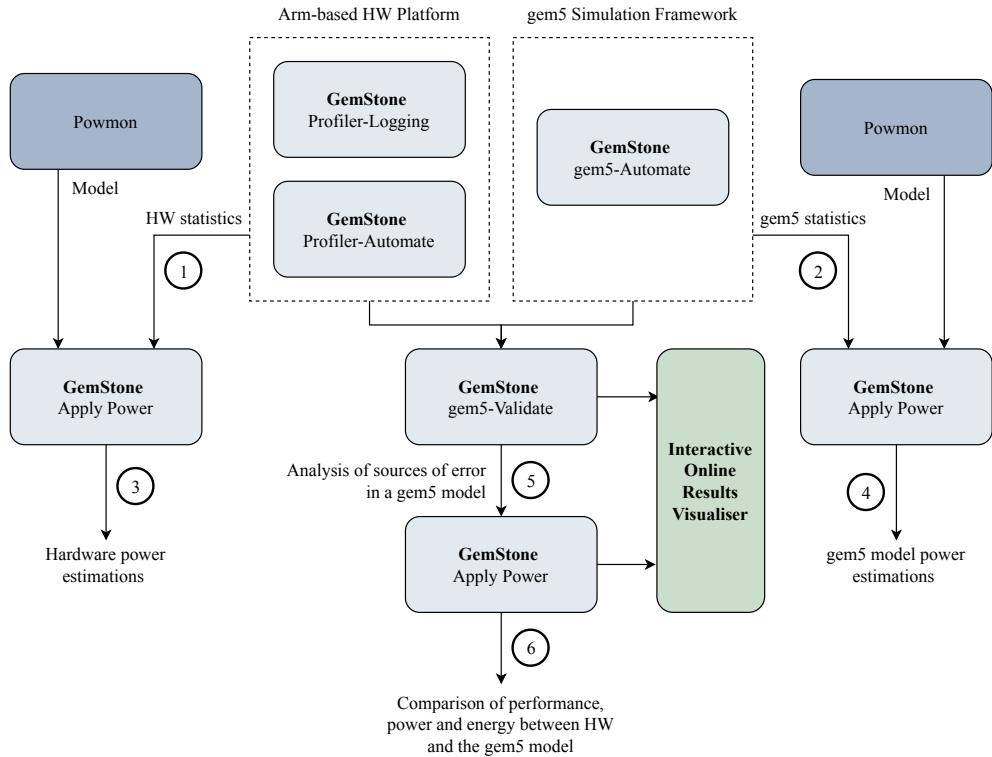

Moreover, the *Powmon* and *GemStone* software tools are presented, which implement the methodologies for developing power models and validating performance models, respectively.

# Contents

|                                                         |      |

|---------------------------------------------------------|------|

| <b>Contents</b>                                         | iii  |

| <b>List of Figures</b>                                  | vii  |

| <b>List of Tables</b>                                   | xiii |

| <b>Accompanying Material</b>                            | xv   |

| <b>Declaration of Authorship</b>                        | xvii |

| <b>Acknowledgements</b>                                 | xix  |

| <b>Nomenclature</b>                                     | xxi  |

| <b>1 Introduction</b>                                   | 1    |

| 1.1 Research Questions . . . . .                        | 2    |

| 1.2 Energy Efficiency and Run-Time Management . . . . . | 3    |

| 1.3 Power Modelling . . . . .                           | 3    |

| 1.4 Simulation Tools . . . . .                          | 4    |

| 1.5 Contributions . . . . .                             | 6    |

| 1.6 Authored Publications . . . . .                     | 6    |

| 1.6.1 Journals . . . . .                                | 6    |

| 1.6.2 Conferences . . . . .                             | 6    |

| 1.6.3 Workshops . . . . .                               | 7    |

| 1.6.4 Tutorials . . . . .                               | 7    |

| 1.6.5 Poster Presentations . . . . .                    | 7    |

| 1.7 Authored Software Tools . . . . .                   | 8    |

| 1.7.1 Powmon . . . . .                                  | 8    |

| 1.7.2 GemStone . . . . .                                | 8    |

| 1.8 Thesis Outline . . . . .                            | 10   |

| <b>2 Background and Literature Review</b>               | 11   |

| 2.1 CPU Power Consumption . . . . .                     | 12   |

| 2.2 Techniques for CMOS Power Reduction . . . . .       | 14   |

| 2.2.1 Dynamic Power Reduction . . . . .                 | 14   |

| 2.2.2 Static Power Reduction . . . . .                  | 15   |

| 2.3 System-Level Power Management . . . . .             | 17   |

| 2.3.1 Dynamic Voltage and Frequency Scaling . . . . .   | 17   |

---

|          |                                                                 |           |

|----------|-----------------------------------------------------------------|-----------|

| 2.3.2    | Dynamic Power Management . . . . .                              | 17        |

| 2.3.3    | Heterogeneous Multi-Processing Architectures . . . . .          | 18        |

| 2.3.4    | Energy-Aware Scheduling . . . . .                               | 18        |

| 2.3.5    | Maximum Deliverable Power . . . . .                             | 19        |

| 2.3.6    | Thermal Operating Envelope . . . . .                            | 19        |

| 2.3.7    | Lifetime Reliability . . . . .                                  | 19        |

| 2.3.8    | Energy-Delay Product . . . . .                                  | 20        |

| 2.4      | Mobile CPU Architecture and Micro-Architecture . . . . .        | 20        |

| 2.5      | Power Modelling Approaches . . . . .                            | 24        |

| 2.5.1    | Power Measurement . . . . .                                     | 24        |

| 2.5.2    | Top-Down Modelling Approaches . . . . .                         | 24        |

| 2.5.3    | Circuit, Gate, and Register-Transfer Level Approaches . . . . . | 25        |

| 2.5.4    | Bottom-Up Modelling Approaches . . . . .                        | 26        |

| 2.5.5    | Comparison of Power Modelling Approaches . . . . .              | 26        |

| 2.6      | Empirical CPU Power Modelling . . . . .                         | 27        |

| 2.7      | Full-System Performance and Energy Simulation . . . . .         | 29        |

| 2.7.1    | Performance Modelling Frameworks . . . . .                      | 30        |

| 2.7.2    | Power Modelling Frameworks . . . . .                            | 31        |

| 2.7.3    | Accuracy and Validation of Simulation Tools . . . . .           | 31        |

| 2.8      | Discussion . . . . .                                            | 32        |

| <b>3</b> | <b>Run-Time Power Modelling of Mobile CPUs</b>                  | <b>35</b> |

| 3.1      | Multivariate Linear Regression . . . . .                        | 36        |

| 3.1.1    | Definition . . . . .                                            | 36        |

| 3.1.2    | Estimating Coefficients . . . . .                               | 37        |

| 3.1.3    | Fitting Values . . . . .                                        | 39        |

| 3.1.4    | Analysis of Variance . . . . .                                  | 40        |

| 3.1.5    | Coefficient of Determination . . . . .                          | 40        |

| 3.1.6    | Assumptions of OLS . . . . .                                    | 41        |

| 3.1.7    | Alternative Modelling Methods . . . . .                         | 42        |

| 3.2      | Extracting PMCs on Mobile Systems . . . . .                     | 45        |

| 3.3      | Experimental Platform . . . . .                                 | 46        |

| 3.4      | Recording Run-Time Power Measurements . . . . .                 | 47        |

| 3.5      | Experimental Setup . . . . .                                    | 47        |

| 3.6      | Methodology Overview . . . . .                                  | 48        |

| 3.7      | Post-Processing and Phase Detection . . . . .                   | 49        |

| 3.8      | Feature Selection . . . . .                                     | 56        |

| 3.9      | Model Specification and Validation . . . . .                    | 59        |

| 3.10     | Inspection of Coefficients . . . . .                            | 65        |

| 3.11     | Conclusion . . . . .                                            | 65        |

| <b>4</b> | <b>Accurate and Stable Run-Time Power Modelling</b>             | <b>71</b> |

| 4.1      | Proposed Methodology . . . . .                                  | 72        |

| 4.2      | Data Acquisition . . . . .                                      | 74        |

| 4.2.1    | Experimental Platform . . . . .                                 | 74        |

| 4.2.2    | Experiment Workflow . . . . .                                   | 74        |

|          |                                                            |            |

|----------|------------------------------------------------------------|------------|

| 4.2.3    | Workloads . . . . .                                        | 76         |

| 4.2.4    | Power Variation . . . . .                                  | 76         |

| 4.2.5    | Feature Conditioning . . . . .                             | 77         |

| 4.3      | Feature Selection . . . . .                                | 78         |

| 4.3.1    | Model Stability . . . . .                                  | 78         |

| 4.3.2    | Multicollinearity . . . . .                                | 82         |

| 4.3.3    | Principle Component Analysis . . . . .                     | 82         |

| 4.3.4    | Event Clustering . . . . .                                 | 87         |

| 4.3.5    | Variance Inflation Factor . . . . .                        | 92         |

| 4.3.6    | Automated PMC Event Selection Method . . . . .             | 92         |

| 4.3.7    | Demonstration of Model Stability . . . . .                 | 95         |

| 4.3.8    | Monte Carlo Validation . . . . .                           | 97         |

| 4.4      | Model Formulation and Validation . . . . .                 | 97         |

| 4.4.1    | Model Specification . . . . .                              | 98         |

| 4.4.2    | Analysis of Residuals . . . . .                            | 101        |

| 4.4.3    | Model Evaluation . . . . .                                 | 110        |

| 4.4.4    | Model Coefficients . . . . .                               | 112        |

| 4.4.5    | Cross-Fold Validation . . . . .                            | 112        |

| 4.4.6    | Model Decomposition . . . . .                              | 113        |

| 4.4.7    | Sensitivity to Sampling Frequency . . . . .                | 113        |

| 4.5      | Comparison with Existing Works . . . . .                   | 115        |

| 4.6      | CPU Voltage Model . . . . .                                | 118        |

| 4.7      | Conclusion . . . . .                                       | 119        |

| <b>5</b> | <b>Thermally-Aware Composite Run-Time CPU Power Models</b> | <b>121</b> |

| 5.1      | Introduction . . . . .                                     | 121        |

| 5.2      | Experimental Setup . . . . .                               | 122        |

| 5.3      | Regression-Based Modelling Methodology . . . . .           | 123        |

| 5.4      | Temperature Compensation . . . . .                         | 124        |

| 5.5      | Model Decomposition and Offline Cores . . . . .            | 127        |

| 5.6      | Thermal Modelling . . . . .                                | 131        |

| 5.7      | Energy Cost in the Memory Hierarchy . . . . .              | 133        |

| 5.8      | Conclusion . . . . .                                       | 136        |

| <b>6</b> | <b>Hardware-Validated Performance and Energy Modelling</b> | <b>141</b> |

| 6.1      | Introduction and Literature Review . . . . .               | 142        |

| 6.1.1    | Simulation Use Cases and Baseline Models . . . . .         | 142        |

| 6.1.2    | Performance Simulation Error . . . . .                     | 144        |

| 6.1.3    | Contributions of this Chapter . . . . .                    | 145        |

| 6.2      | Methodology Overview . . . . .                             | 145        |

| 6.3      | Experimental Setup and Workflow . . . . .                  | 146        |

| 6.4      | Identifying Sources of Errors in gem5 . . . . .            | 148        |

| 6.4.1    | Micro-Benchmarks . . . . .                                 | 150        |

| 6.4.2    | Cluster and Correlation Analysis (HW PMC Events) . . . . . | 151        |

| 6.4.3    | Cluster and Correlation Analysis (gem5 Events) . . . . .   | 152        |

| 6.4.4    | Regression Analysis . . . . .                              | 153        |

|                   |                                                                          |            |

|-------------------|--------------------------------------------------------------------------|------------|

| 6.4.5             | Event Comparison . . . . .                                               | 154        |

| 6.4.6             | Summary . . . . .                                                        | 155        |

| 6.5               | Power Modelling . . . . .                                                | 157        |

| 6.5.1             | Alternative Approach . . . . .                                           | 160        |

| 6.6               | Performance, Power and Energy Evaluation . . . . .                       | 160        |

| 6.7               | Improvements to the gem5 Models . . . . .                                | 163        |

| 6.8               | Conclusion . . . . .                                                     | 167        |

| <b>7</b>          | <b>Conclusion and Future Work</b>                                        | <b>169</b> |

| 7.1               | Research Questions . . . . .                                             | 174        |

| 7.2               | Future Work . . . . .                                                    | 178        |

| 7.2.1             | Adaptive Training Workloads and Enhanced Stability . . . . .             | 178        |

| 7.2.2             | Effects of Voltage Regulation on Power Consumption and RTM Decisions . . | 179        |

| 7.2.3             | Combining Top-Down and Low-Level Bottom-Up Techniques . . . . .          | 180        |

| 7.2.4             | Power Estimation in Diverse Thermal Environments . . . . .               | 180        |

| 7.2.5             | Event Forecasting for Performance, Power and Energy Prediction . . . . . | 180        |

| 7.2.6             | Using Workload Classification in Power Estimation . . . . .              | 182        |

| 7.2.7             | Dynamic Micro-Architectural Feature Extraction . . . . .                 | 184        |

| 7.2.8             | Validating Newer CPU Performance and Energy Models . . . . .             | 184        |

| 7.2.9             | Applying Power Modelling to New Systems . . . . .                        | 184        |

| <b>References</b> |                                                                          | <b>185</b> |

# List of Figures

|      |                                                                                                                                                                                                                                               |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Overview of the GemStone suite of software tools . . . . .                                                                                                                                                                                    | 9  |

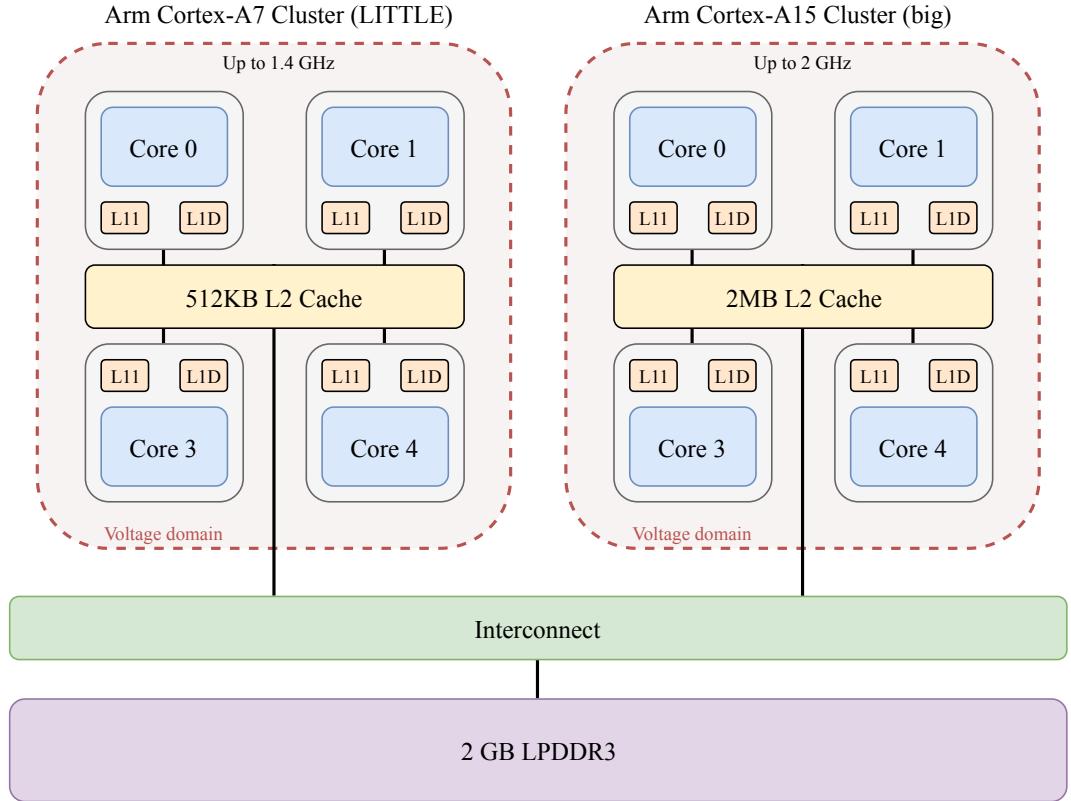

| 2.1  | Hardkernel ODROID-XU3 CPU Block Diagram . . . . .                                                                                                                                                                                             | 21 |

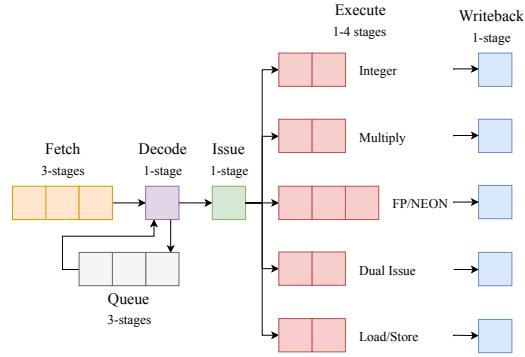

| 2.2  | The Arm Cortex-A7 Pipeline [139] . . . . .                                                                                                                                                                                                    | 22 |

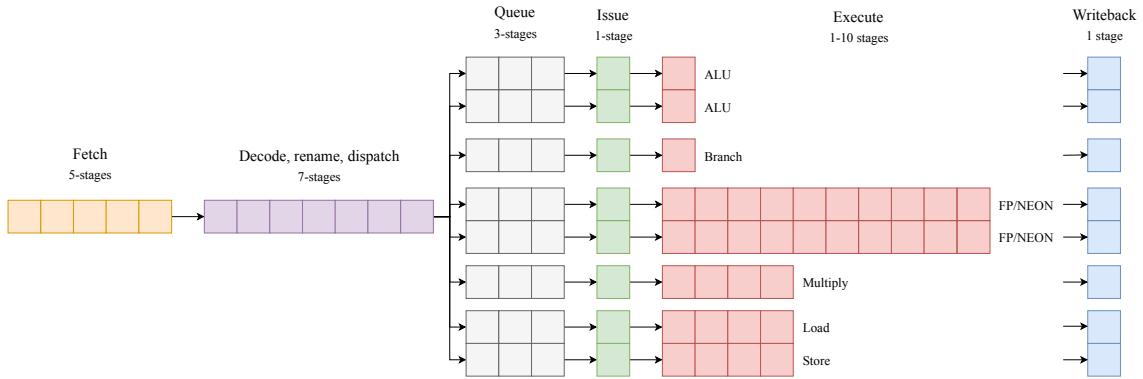

| 2.3  | The Arm Cortex-A15 Pipeline [112] . . . . .                                                                                                                                                                                                   | 22 |

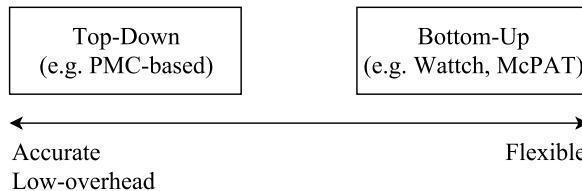

| 2.4  | Top-down vs. Bottom-Up Power Modelling . . . . .                                                                                                                                                                                              | 26 |

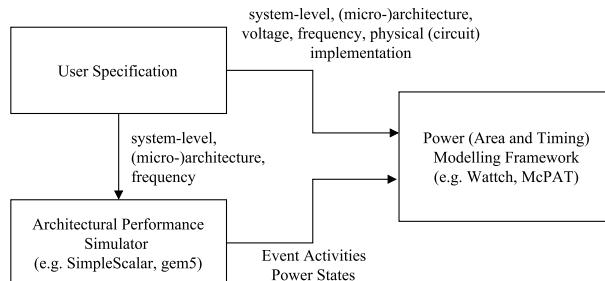

| 2.5  | Bottom-Up Simulation Workflow . . . . .                                                                                                                                                                                                       | 30 |

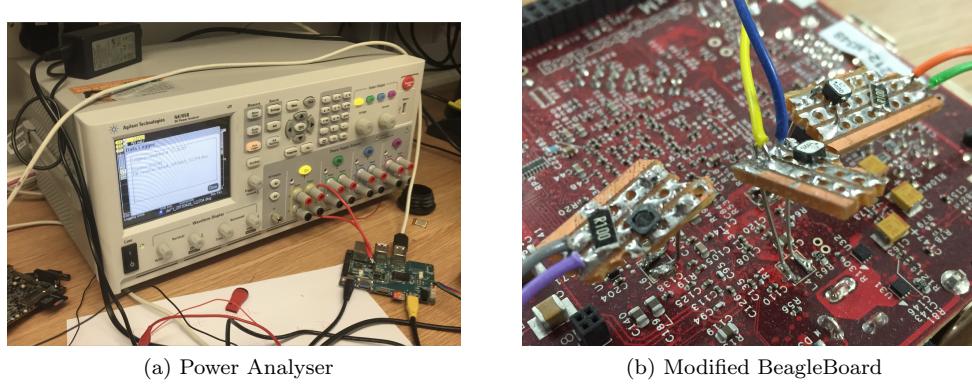

| 3.1  | BeagleBoard-xM development board . . . . .                                                                                                                                                                                                    | 47 |

| 3.2  | Power measurement setup . . . . .                                                                                                                                                                                                             | 47 |

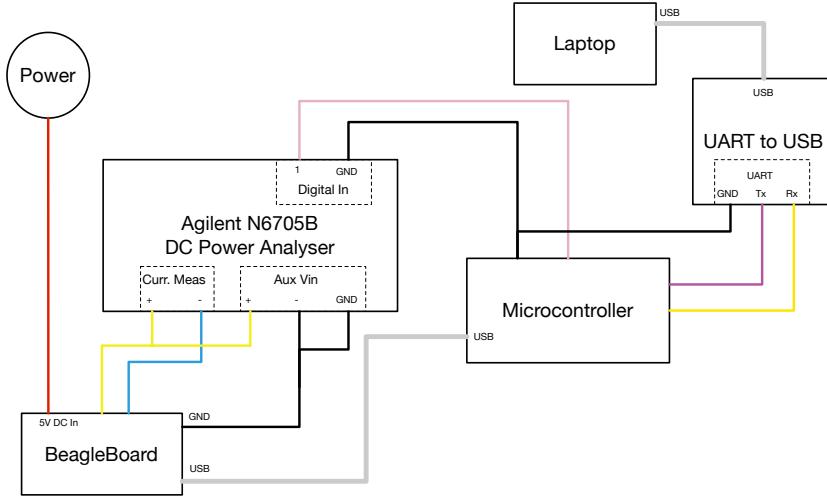

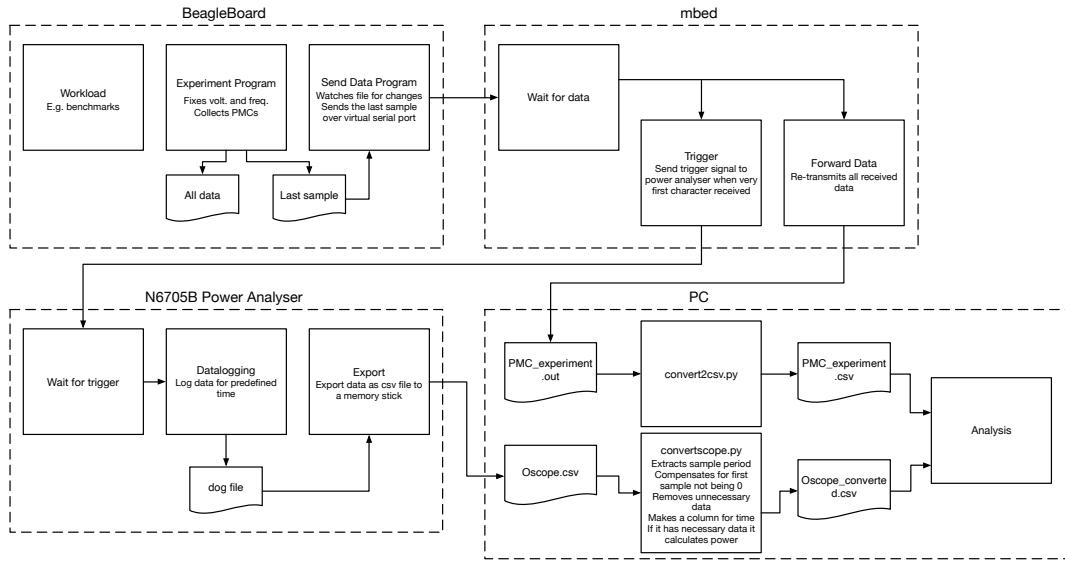

| 3.3  | Experimental setup used for characterising and validating the PMC-based power model                                                                                                                                                           | 48 |

| 3.4  | Experiment workflow . . . . .                                                                                                                                                                                                                 | 48 |

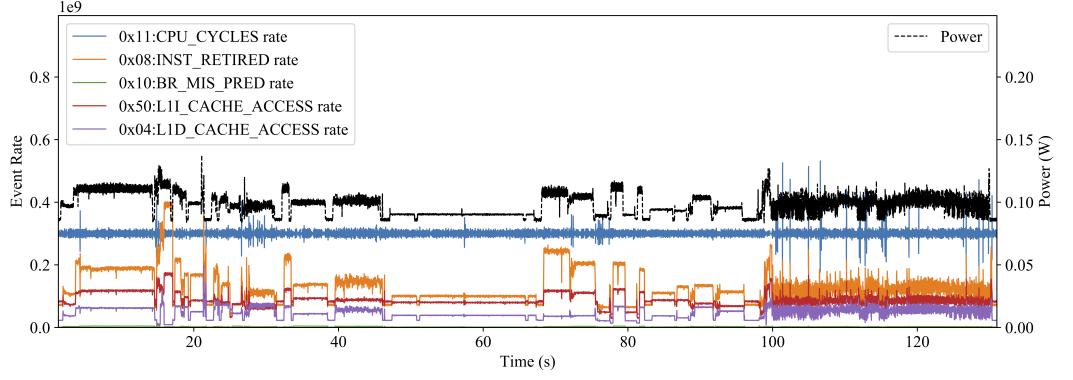

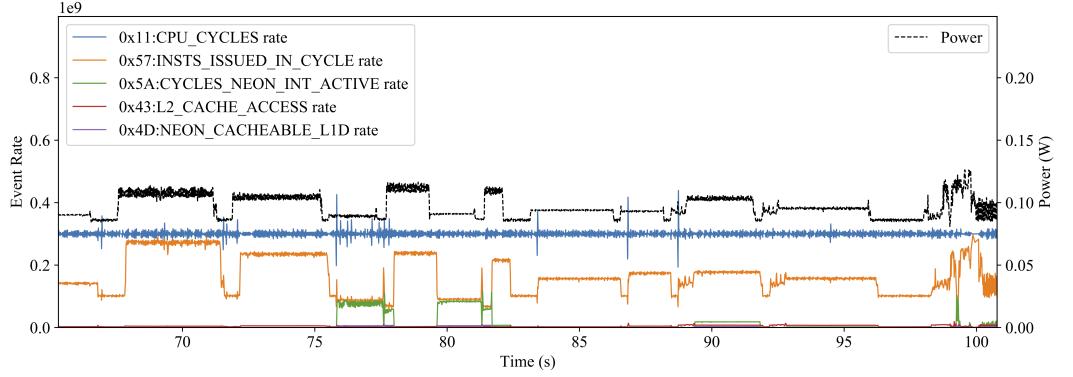

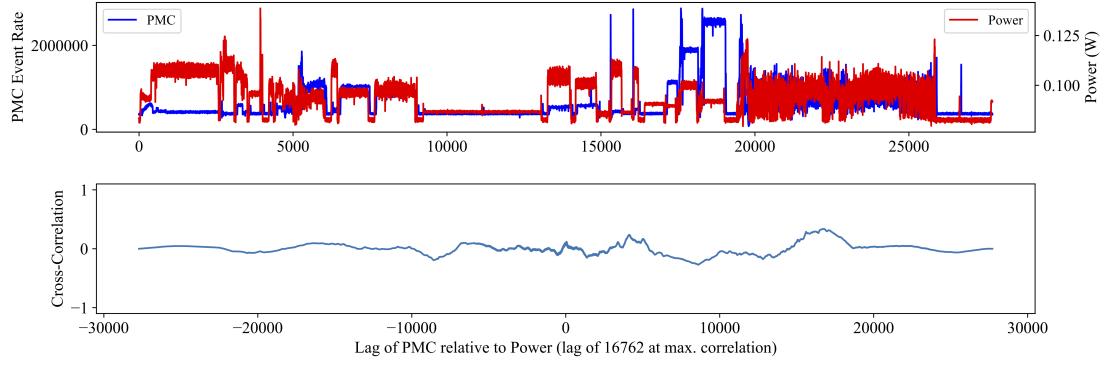

| 3.5  | Raw PMC events and corresponding power consumption (before synchronisation).<br>$f_{clk} = 300$ MHz. . . . .                                                                                                                                  | 49 |

| 3.6  | NEON SIMD and integer events (before synchronisation). $f_{clk} = 300$ MHz . . . . .                                                                                                                                                          | 49 |

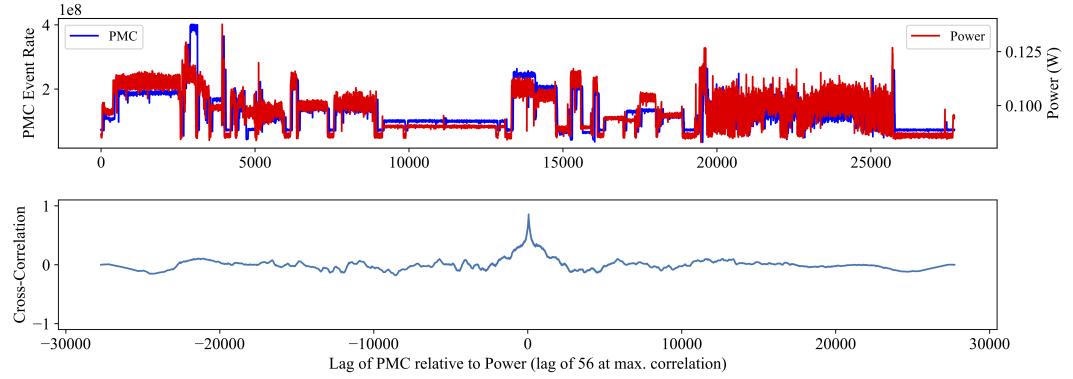

| 3.7  | Cross-correlation of Event 0x08 (INST_RETIRE) and the power. The lag is accurately calculated. . . . .                                                                                                                                        | 51 |

| 3.8  | Cross-correlation of Event 0x05 (L1D_TLB_REFILL) and the power. The lag is not correctly derived. . . . .                                                                                                                                     | 51 |

| 3.9  | Cross-correlation of the absolute of the derivative of the Event 0x05 (L1D_TLB_REFILL) rate and the absolute of the derivative of the power measurements. The lag is accurately calculated. . . . .                                           | 51 |

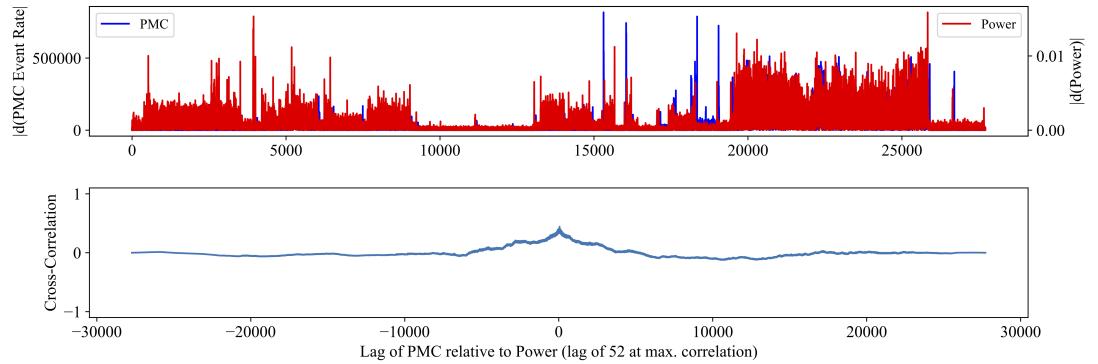

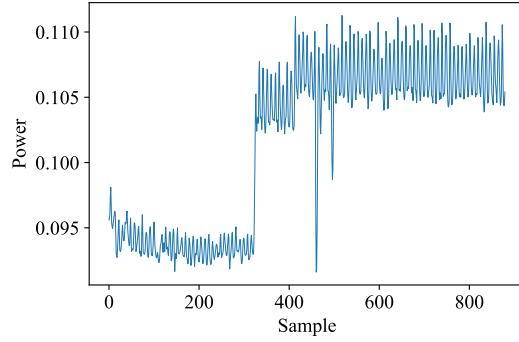

| 3.10 | Example segment of the power trace with a clear, abrupt phase change . . . . .                                                                                                                                                                | 54 |

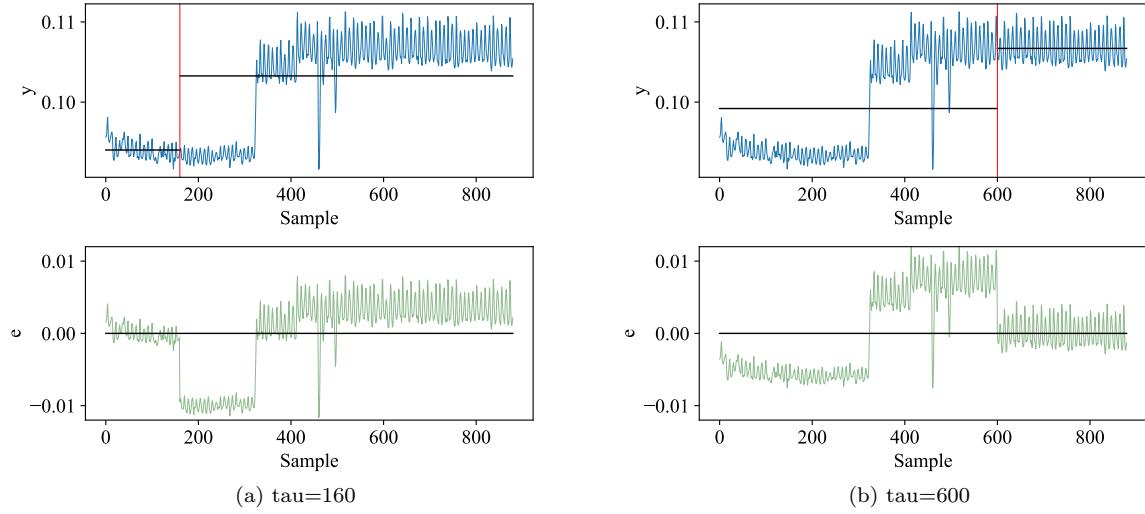

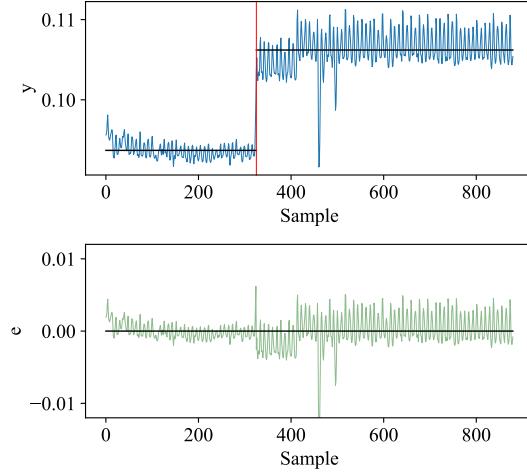

| 3.11 | Upper plot shows the example power trace. $\tau_k$ (selected manually for this example) and the horizontal black lines show $\mu_k - 1$ and $\mu_k$ . The lower plot shows the resulting residuals for the chosen value of $\tau_k$ . . . . . | 54 |

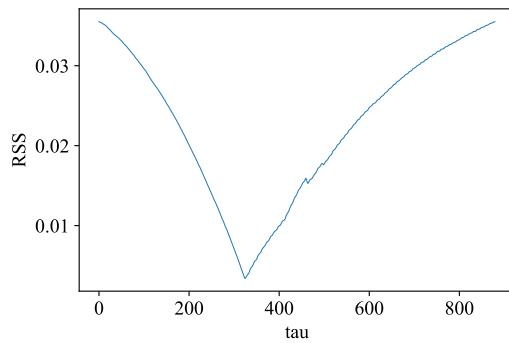

| 3.12 | RSS plot across all values of $\tau$ (tau) . . . . .                                                                                                                                                                                          | 54 |

| 3.13 | The power trace (upper plot) and residuals (lower plot) at the automatically identified change point ( $\tau = 325$ ) . . . . .                                                                                                               | 55 |

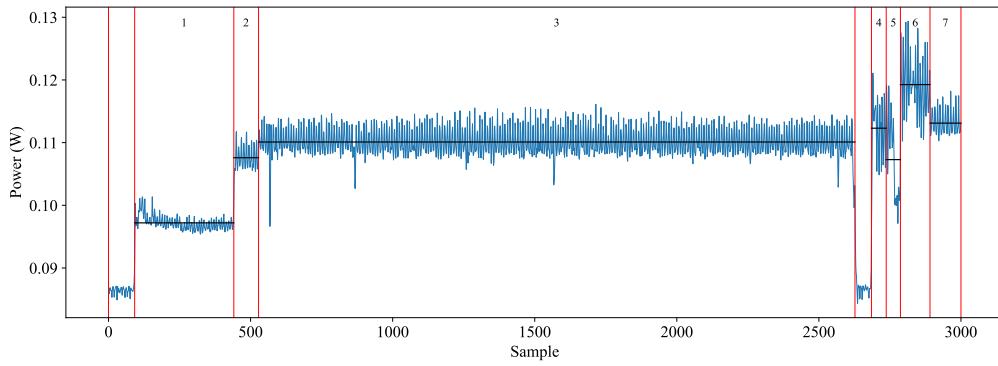

| 3.14 | Automatic workload and workload phase detection . . . . .                                                                                                                                                                                     | 56 |

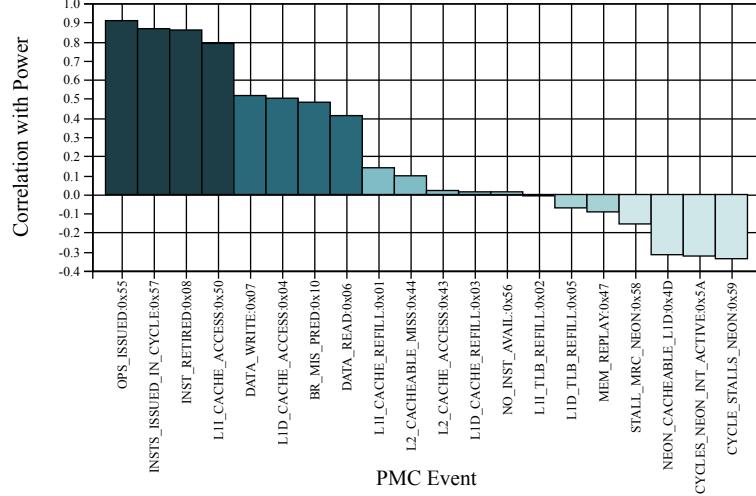

| 3.15 | Correlation of each PMC Event with the measured power consumption . . . . .                                                                                                                                                                   | 57 |

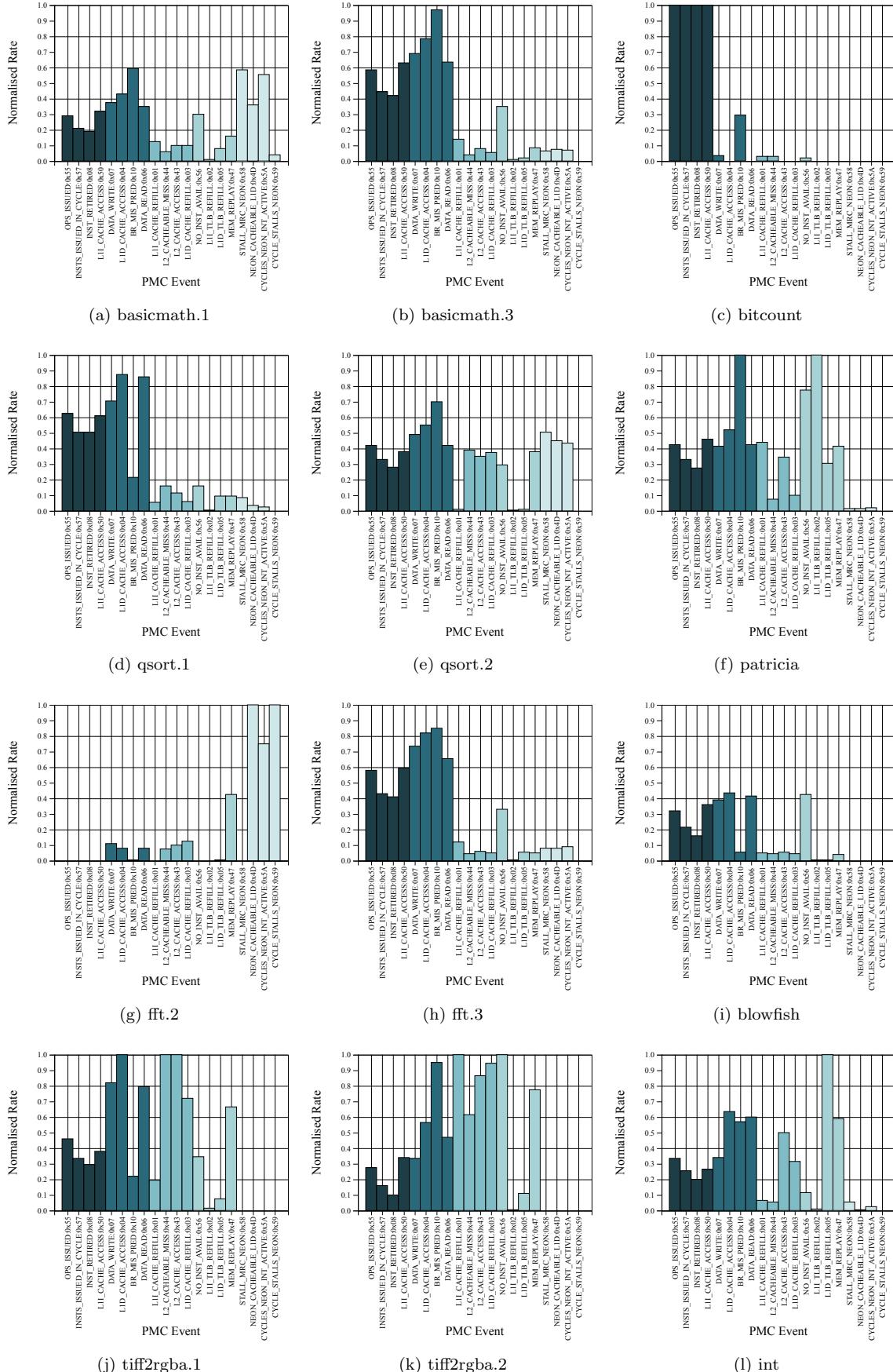

| 3.16 | Min-max normalised PMC event rate for selected workloads . . . . .                                                                                                                                                                            | 58 |

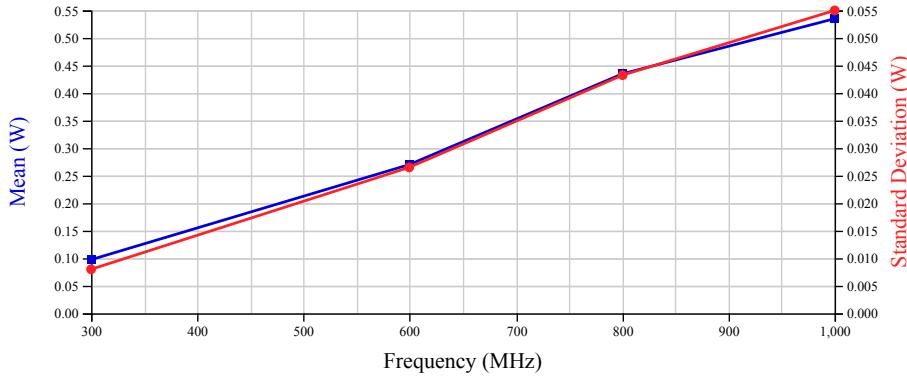

| 3.17 | Power mean and standard deviation . . . . .                                                                                                                                                                                                   | 60 |

|      |                                                                                                                                                                                                                                                                                                                                                 |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

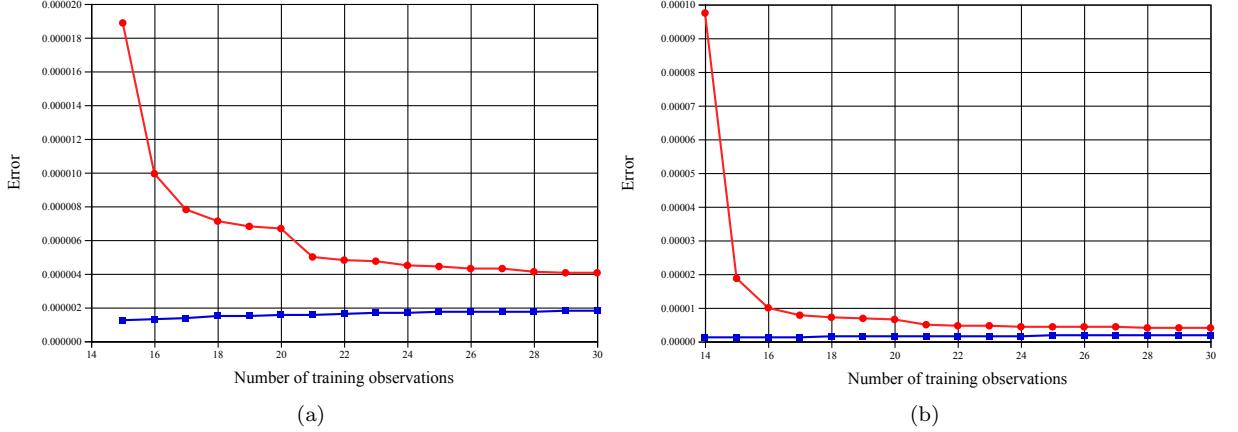

| 3.18 | Training and testing set error (MSE) for using different numbers of training observations (number of testing observations is 18). Values shown are the mean of 500 iterations, with both the training and testing workloads being randomized on each iteration. The same plot with two different scales on the <i>y</i> axis are shown. . . . . | 61 |

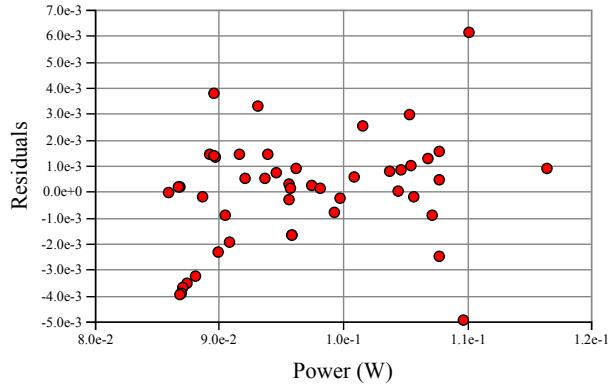

| 3.19 | Model Power Residuals . . . . .                                                                                                                                                                                                                                                                                                                 | 61 |

| 3.20 | Residuals (shown for $f_{clk} = 300$ MHz) . . . . .                                                                                                                                                                                                                                                                                             | 62 |

| 3.21 | Model performance for different DVFS levels (trained and tested with all observations)                                                                                                                                                                                                                                                          | 63 |

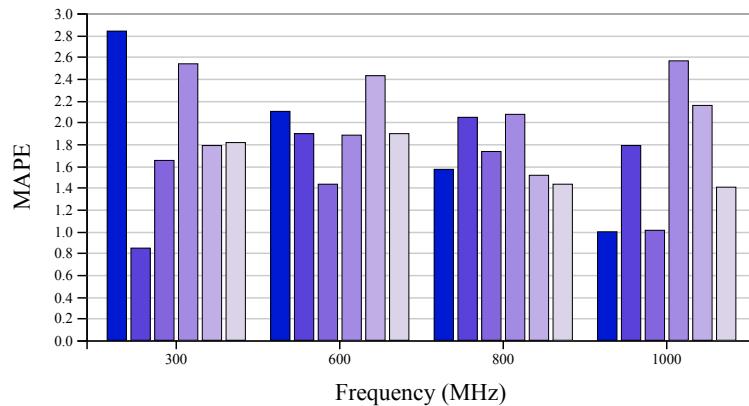

| 3.22 | Testing set MAPE for each fold of 6-fold cross-validation . . . . .                                                                                                                                                                                                                                                                             | 63 |

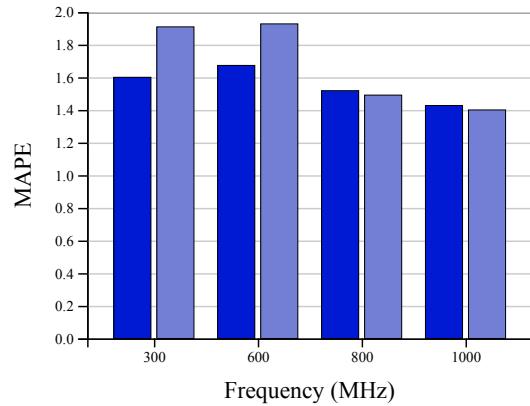

| 3.23 | MAPE of model trained with all observations (left bars) vs. MAPE of models trained and tested with cross-validation (right bars) . . . . .                                                                                                                                                                                                      | 63 |

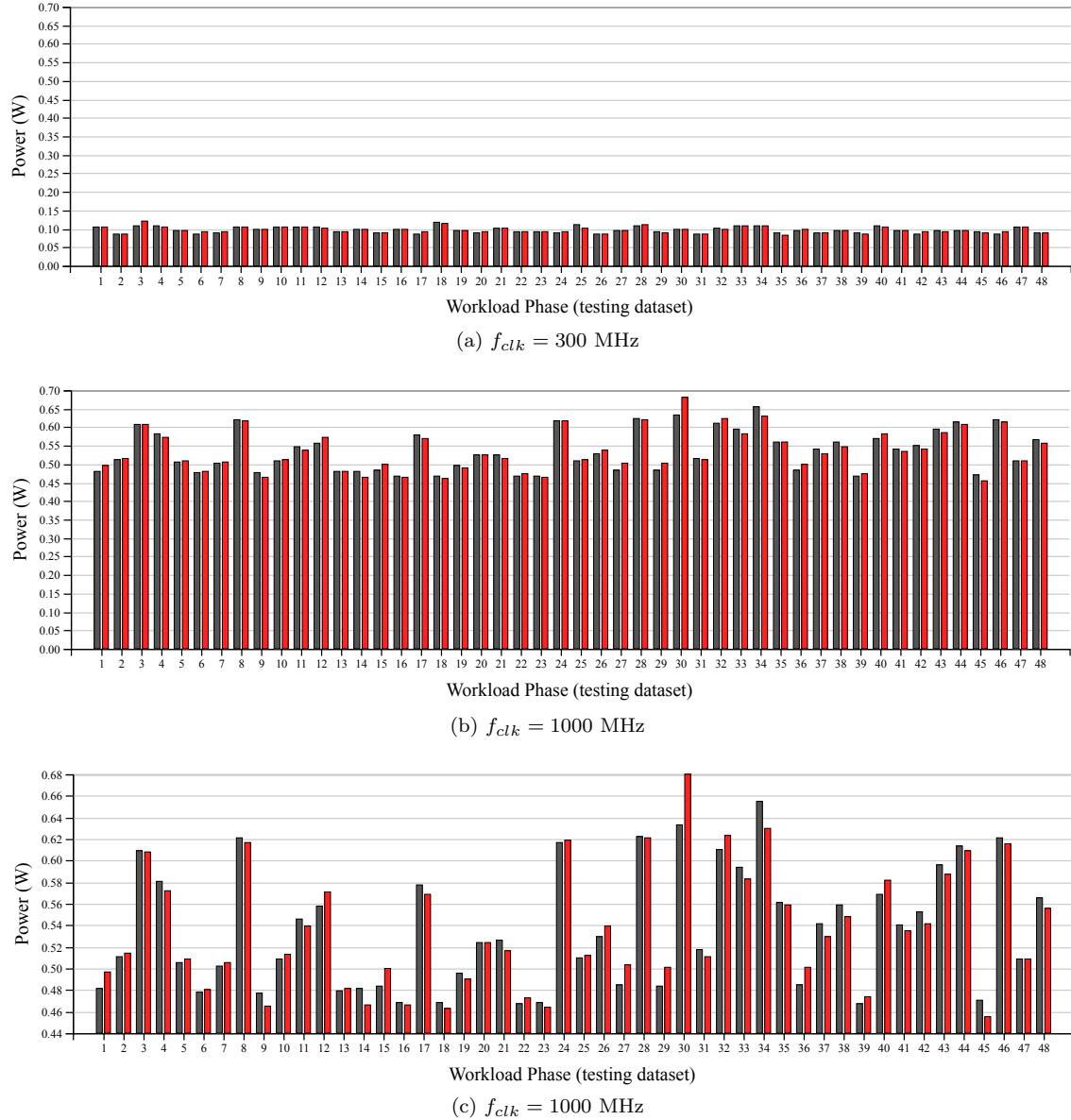

| 3.24 | Cross-fold validation across all testing observations (Note that the observations are not consistent between plots of different DVFS levels as the workload phase selections are randomised). . . . .                                                                                                                                           | 64 |

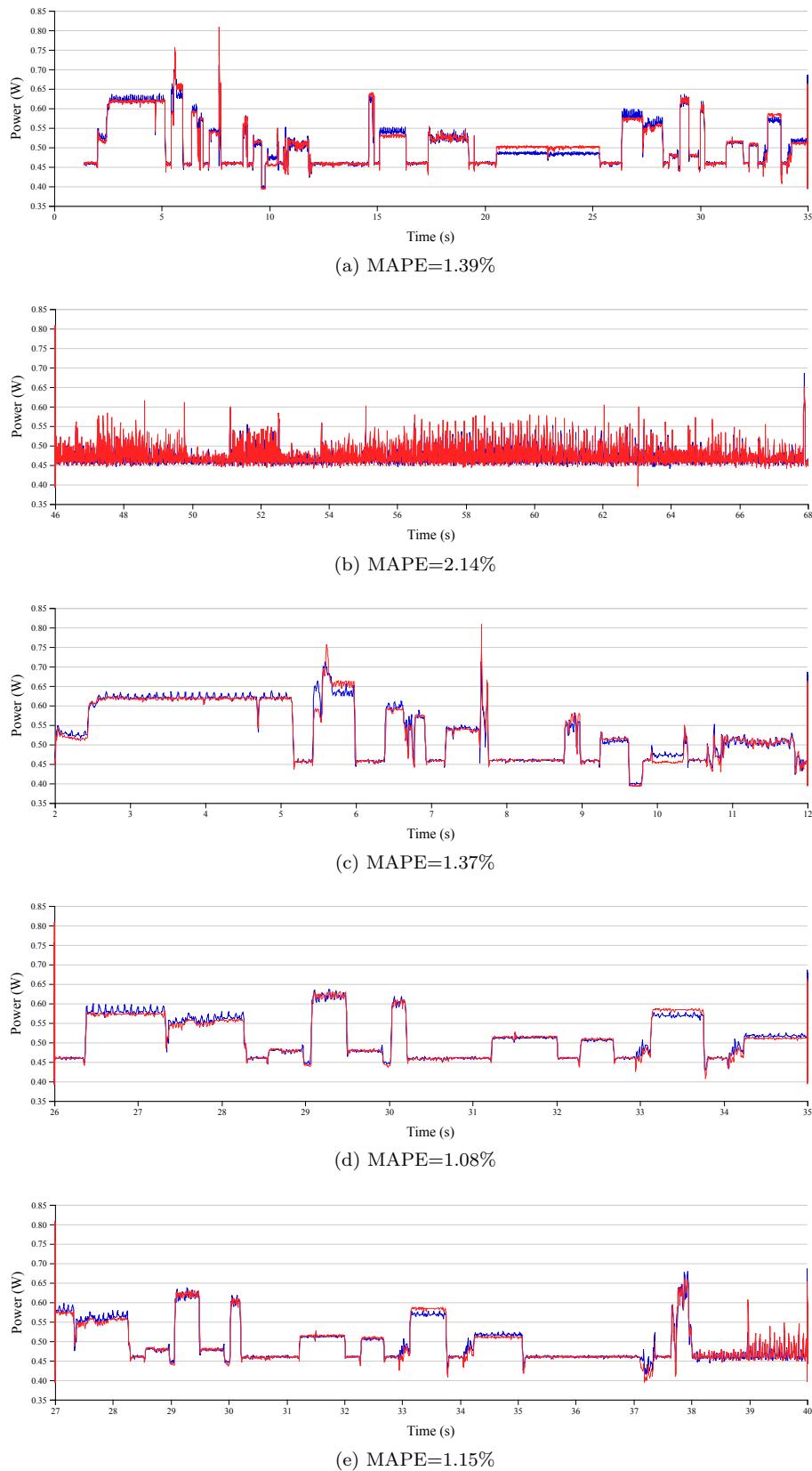

| 3.25 | Measured power (dark, blue) and predicted power (light, red). $f_{clk} = 1000$ MHz . . . . .                                                                                                                                                                                                                                                    | 66 |

| 3.26 | Measured power (dark, blue) and predicted power (light, red) after moving average (window size of 20 samples). $f_{clk} = 1000$ MHz . . . . .                                                                                                                                                                                                   | 67 |

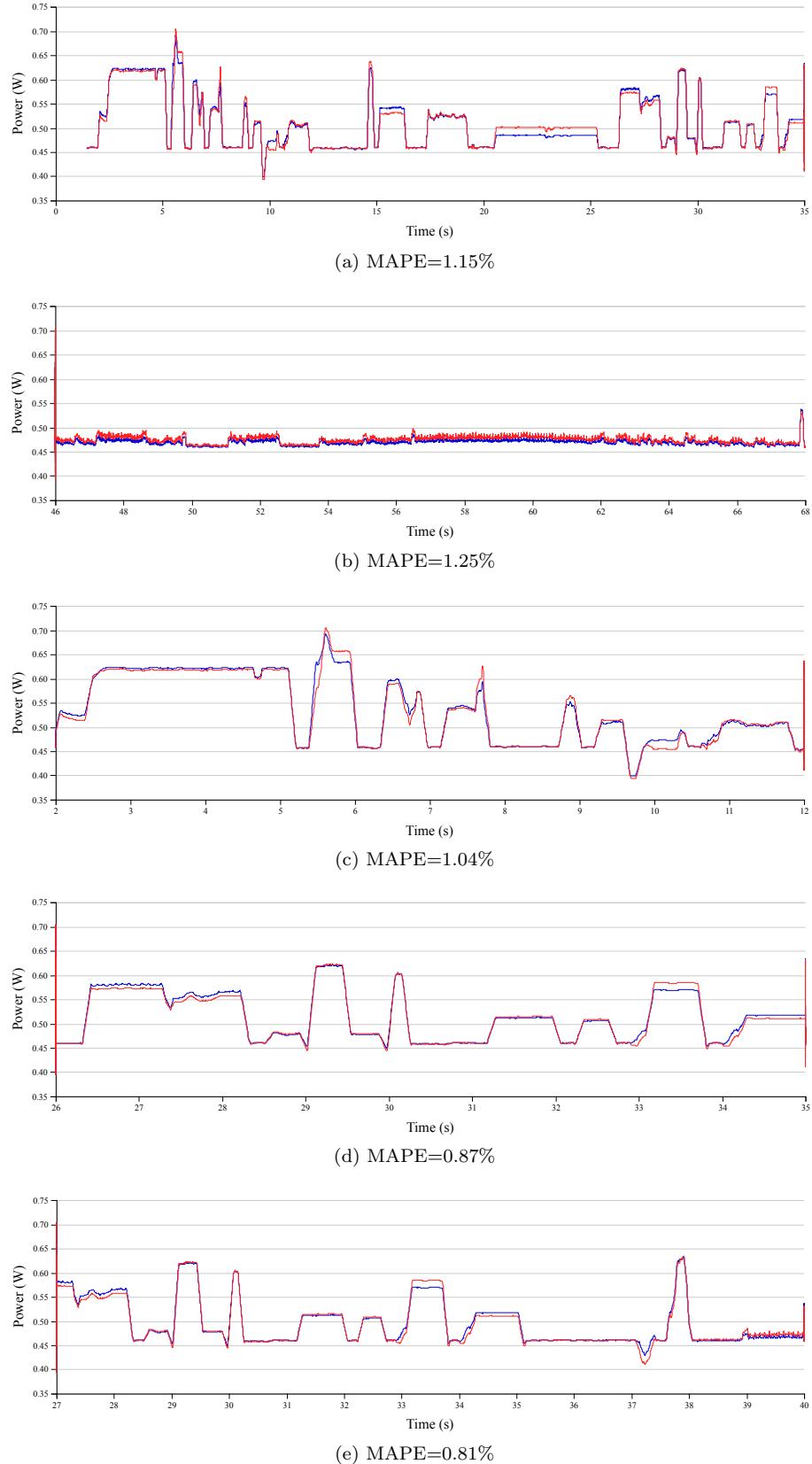

| 4.1  | Steps of the proposed power modelling methodology . . . . .                                                                                                                                                                                                                                                                                     | 73 |

| 4.2  | Hardkernel ODROID-XU3 Development Board . . . . .                                                                                                                                                                                                                                                                                               | 74 |

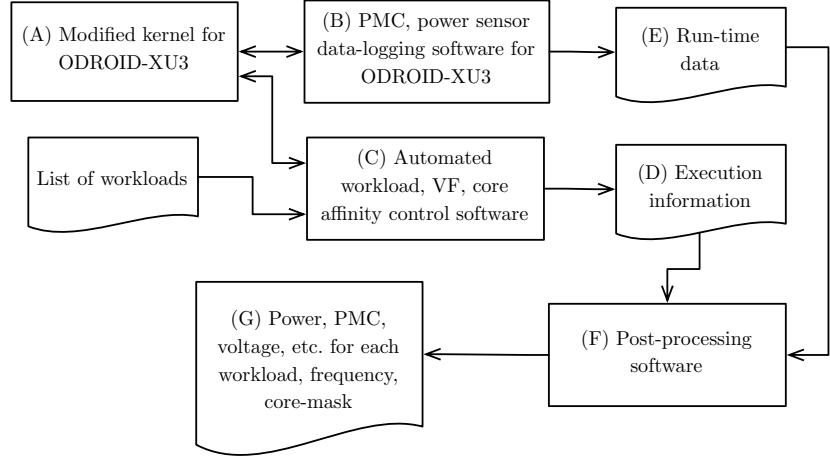

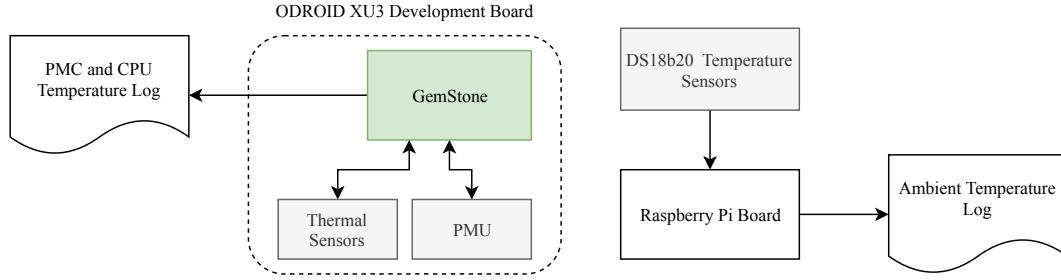

| 4.3  | Simplified overview of the experimental platform software (corresponding to Step 1 in Figure 4.1). . . . .                                                                                                                                                                                                                                      | 75 |

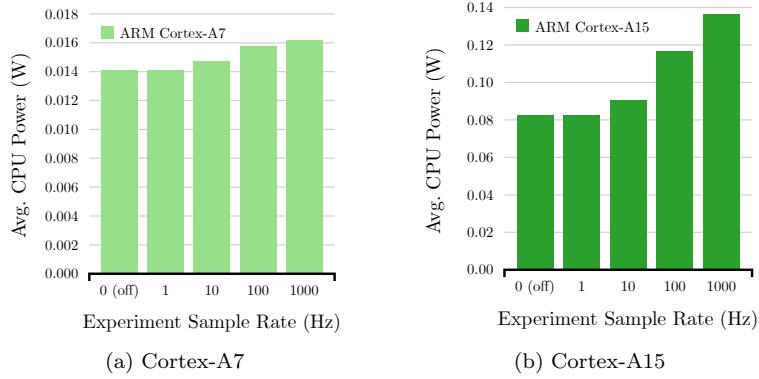

| 4.4  | Power overhead of experimental platform (@200 MHz, worst-case) . . . . .                                                                                                                                                                                                                                                                        | 75 |

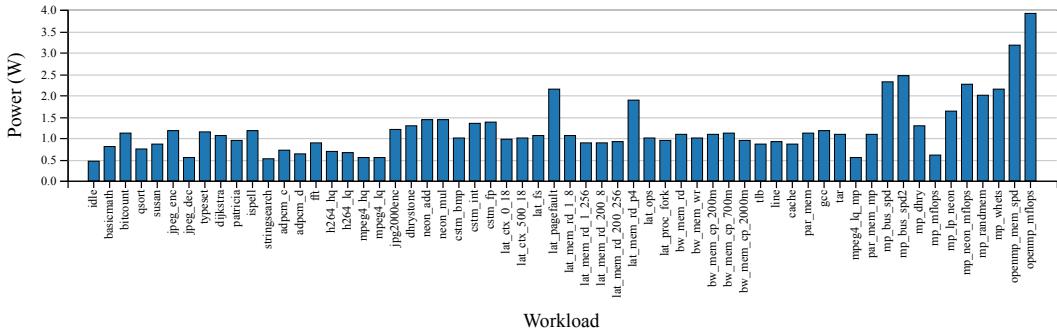

| 4.5  | Power consumption of each workload at 1.6 GHz with one workload instance running on one core . . . . .                                                                                                                                                                                                                                          | 77 |

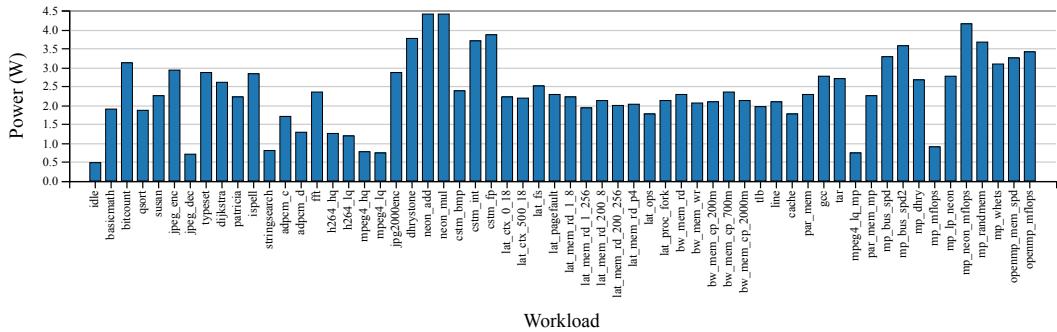

| 4.6  | Power consumption of each workload at 1.6 GHz with four workload instances running across the four cores . . . . .                                                                                                                                                                                                                              | 77 |

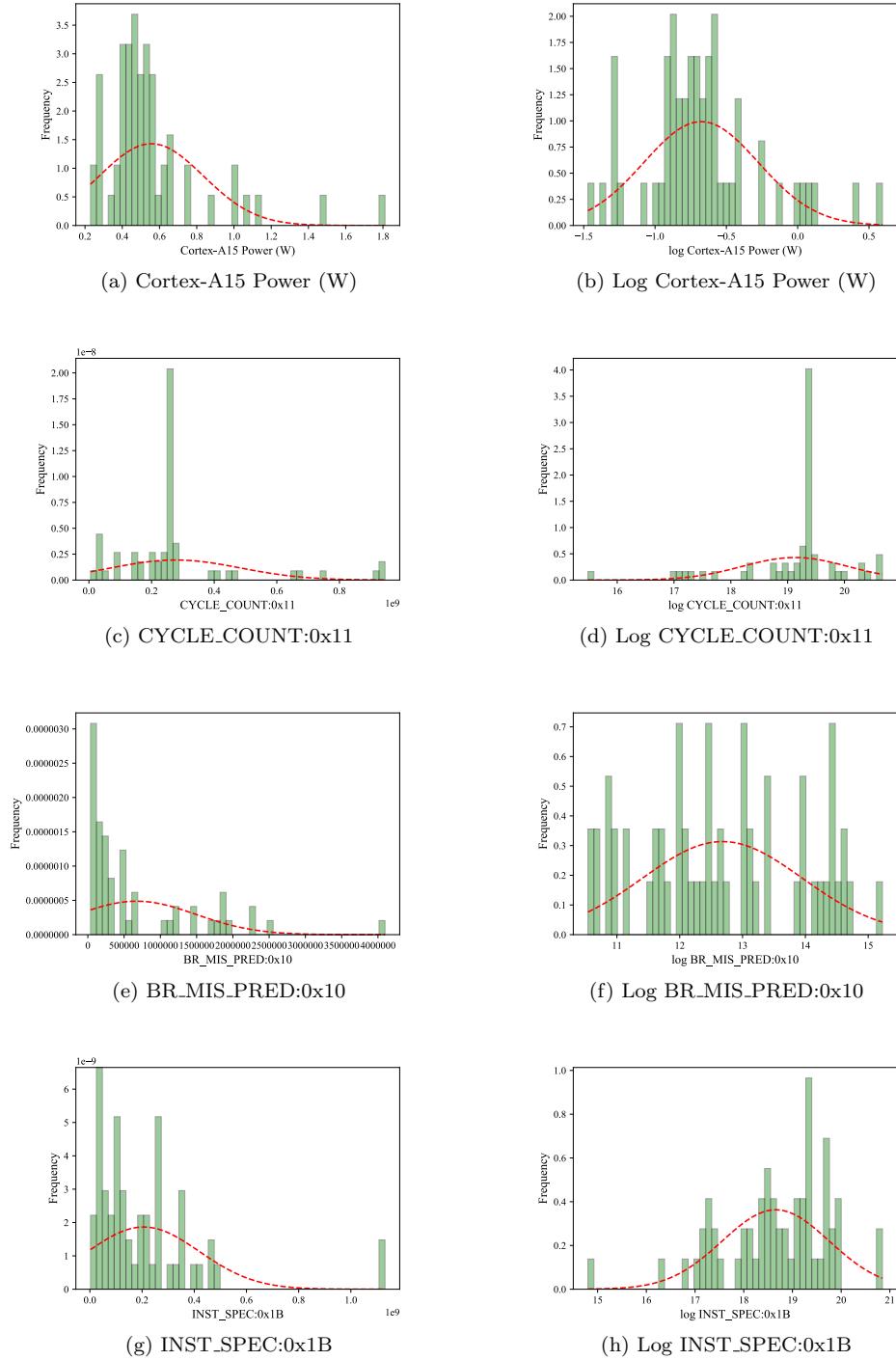

| 4.7  | Distribution of the independent variable and PMC event rates both without any transformation and with a log transform. A normal distribution is superimposed. . . . .                                                                                                                                                                           | 79 |

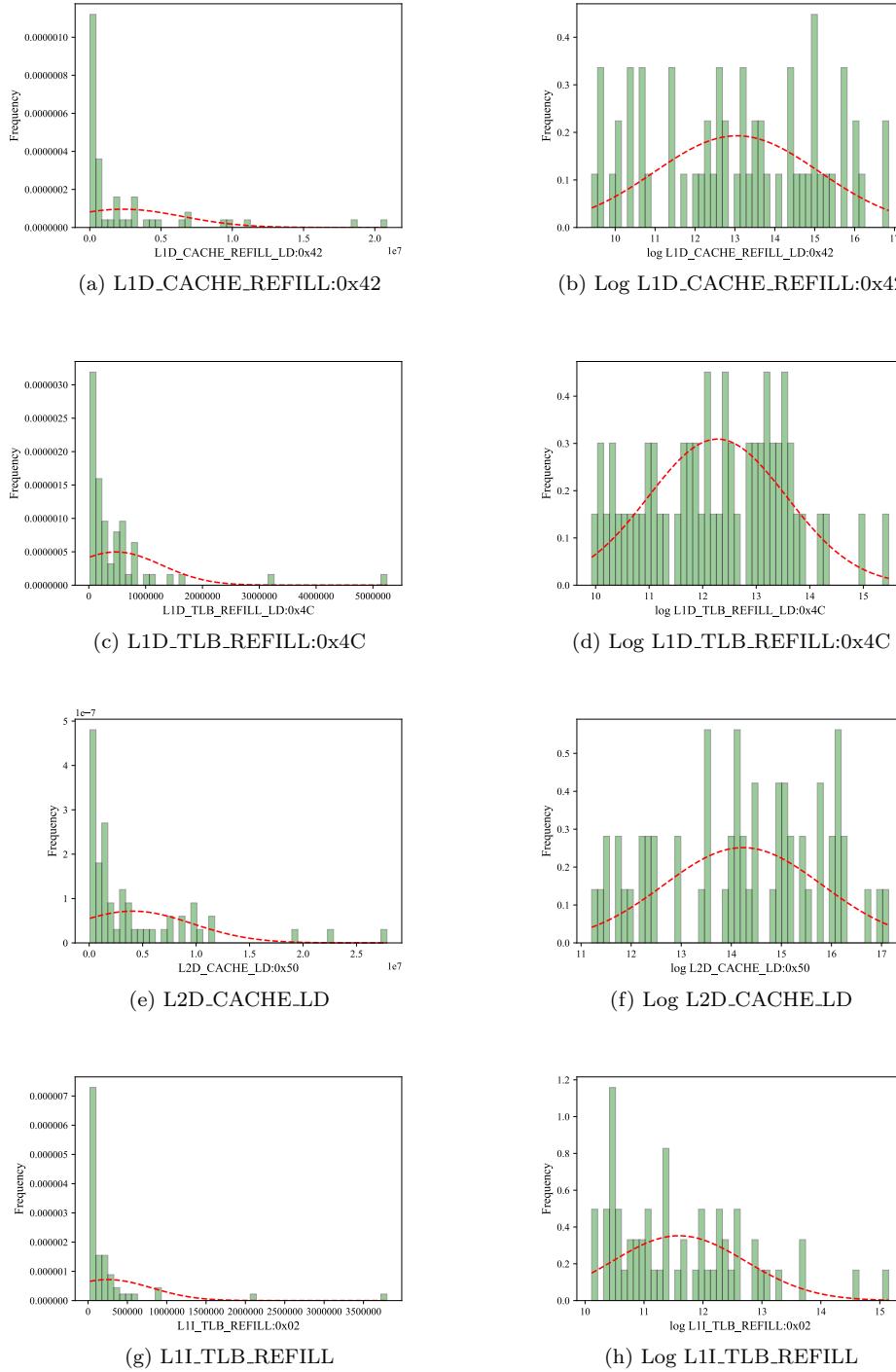

| 4.8  | Distribution of PMC event rates both without any transformation and with a log transform. A normal distribution is superimposed. . . . .                                                                                                                                                                                                        | 80 |

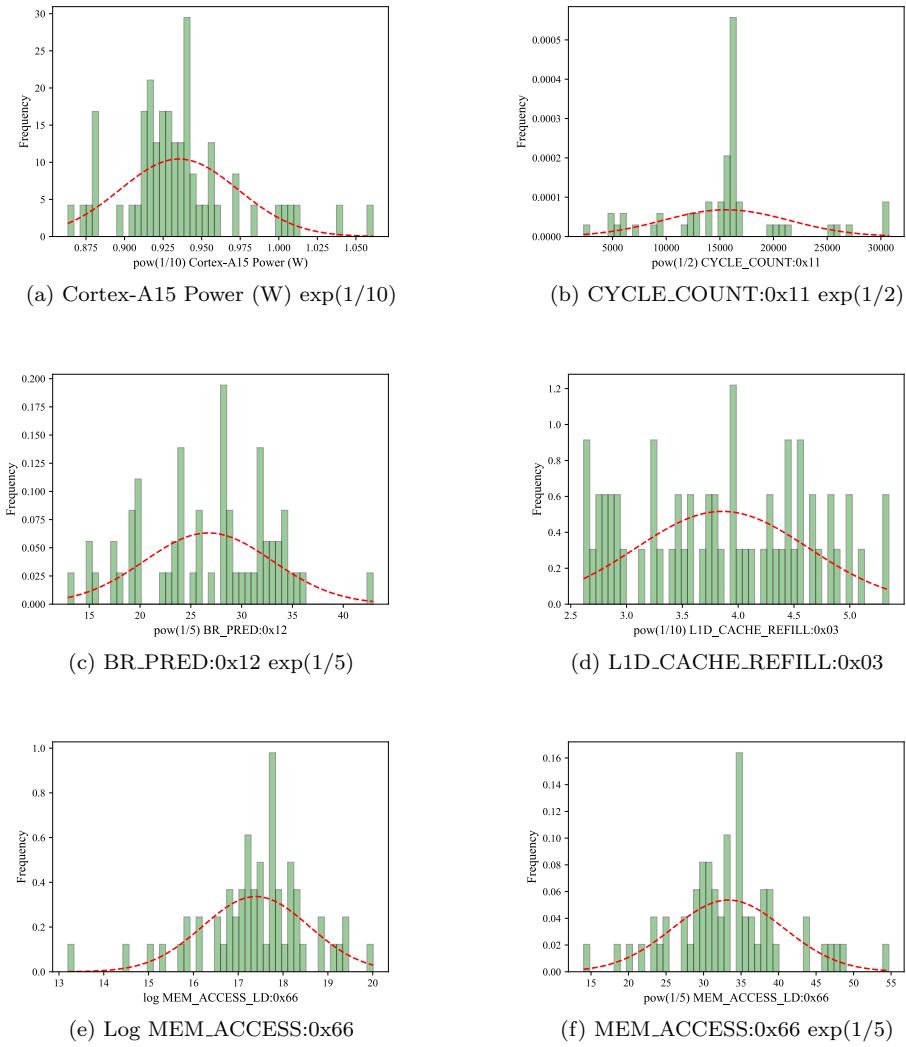

| 4.9  | Distribution of PMC event rates with various exponential transforms . . . . .                                                                                                                                                                                                                                                                   | 81 |

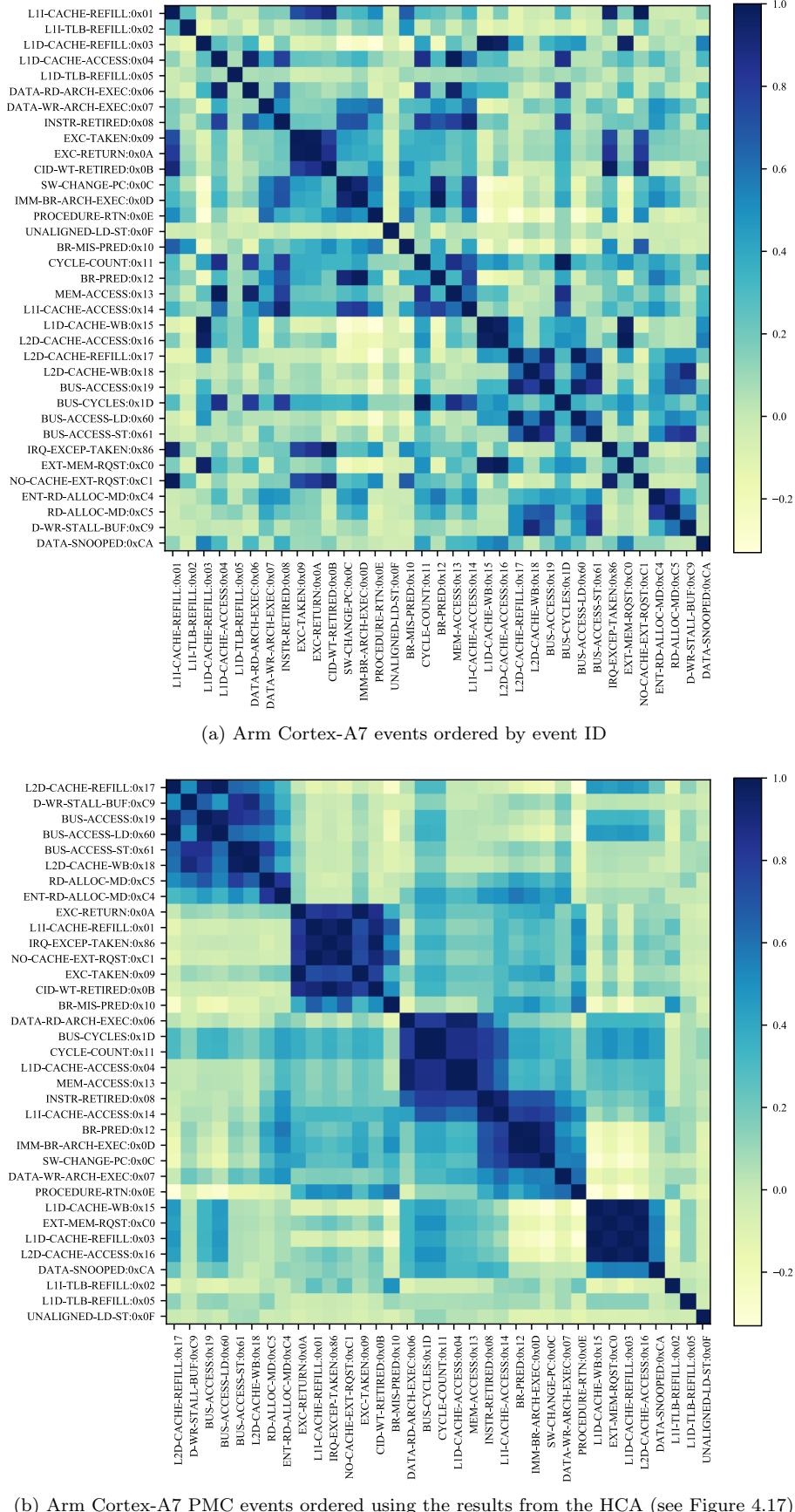

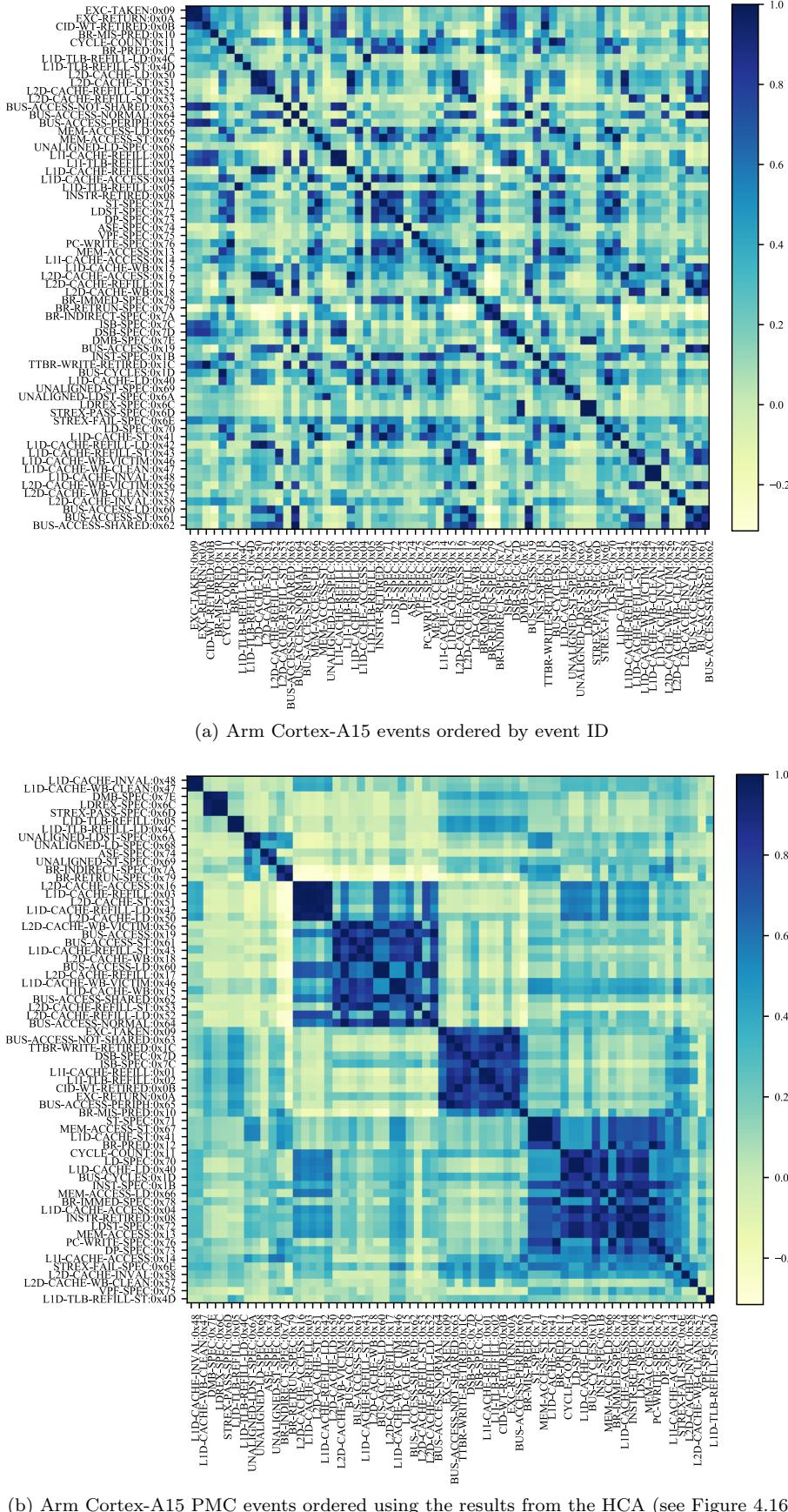

| 4.10 | Arm Cortex-A7 PMC event correlation matrices. Shading shows the event correlation.                                                                                                                                                                                                                                                              | 83 |

| 4.11 | Arm Cortex-A15 PMC event correlation matrices. Shading shows the event correlation.                                                                                                                                                                                                                                                             | 84 |

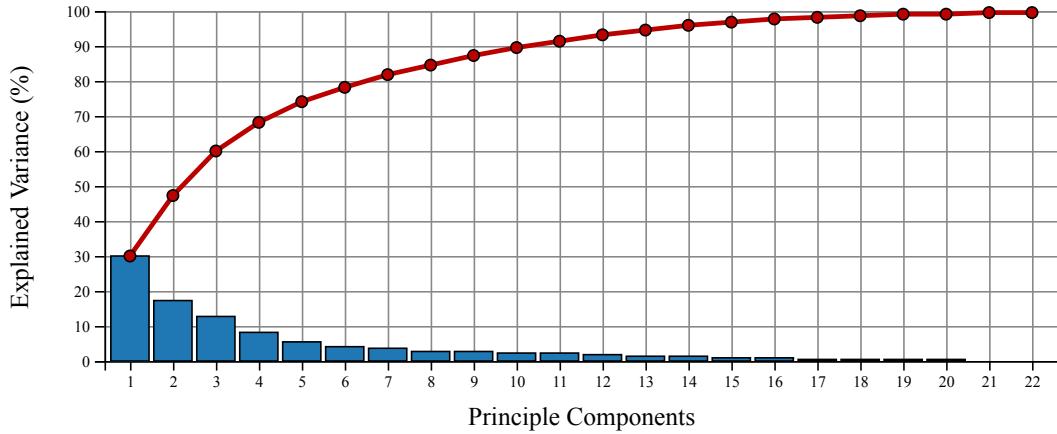

| 4.12 | Explained variance and cumulative explained variance for each principle component                                                                                                                                                                                                                                                               | 86 |

| 4.13 | Explained variance and cumulative explained variance for each principle component                                                                                                                                                                                                                                                               | 86 |

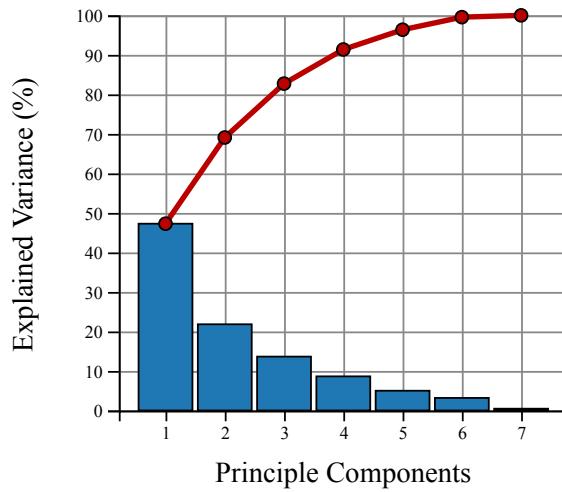

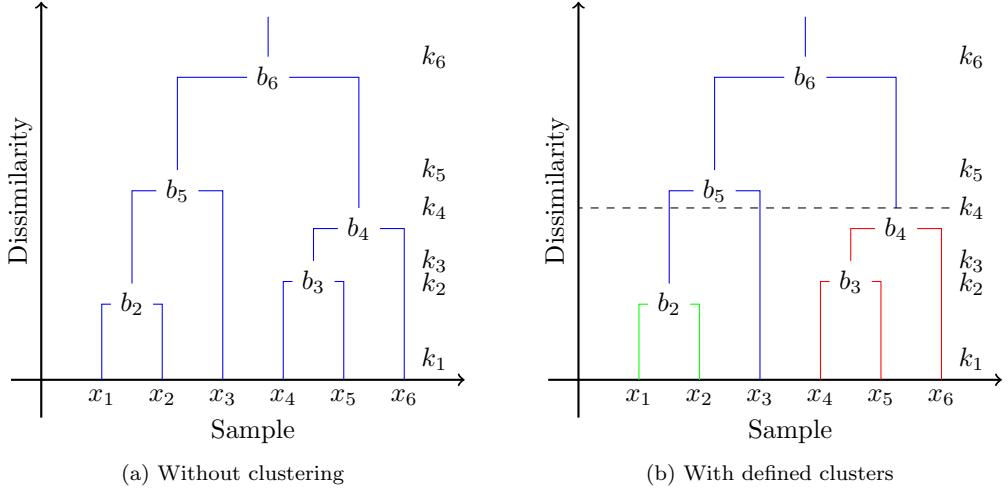

| 4.14 | Dendrogram Example . . . . .                                                                                                                                                                                                                                                                                                                    | 89 |

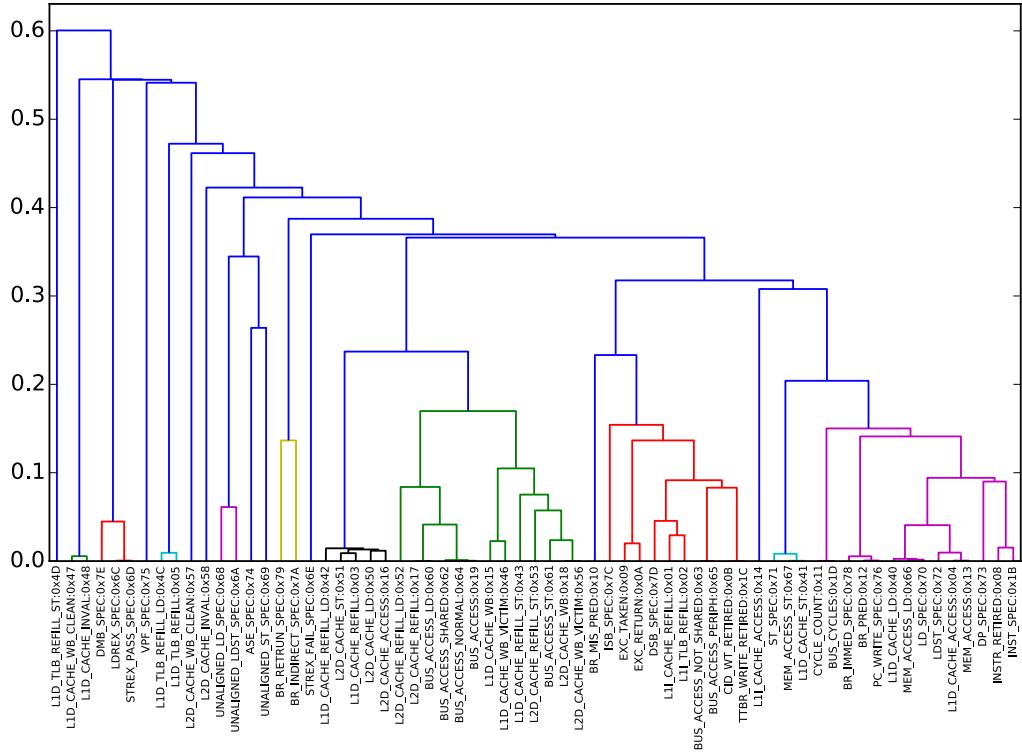

| 4.15 | Dendrogram showing PMC Event clustering. Clusters formed by “cutting” the dendrogram at a similarity metric of 0.18. . . . .                                                                                                                                                                                                                    | 89 |

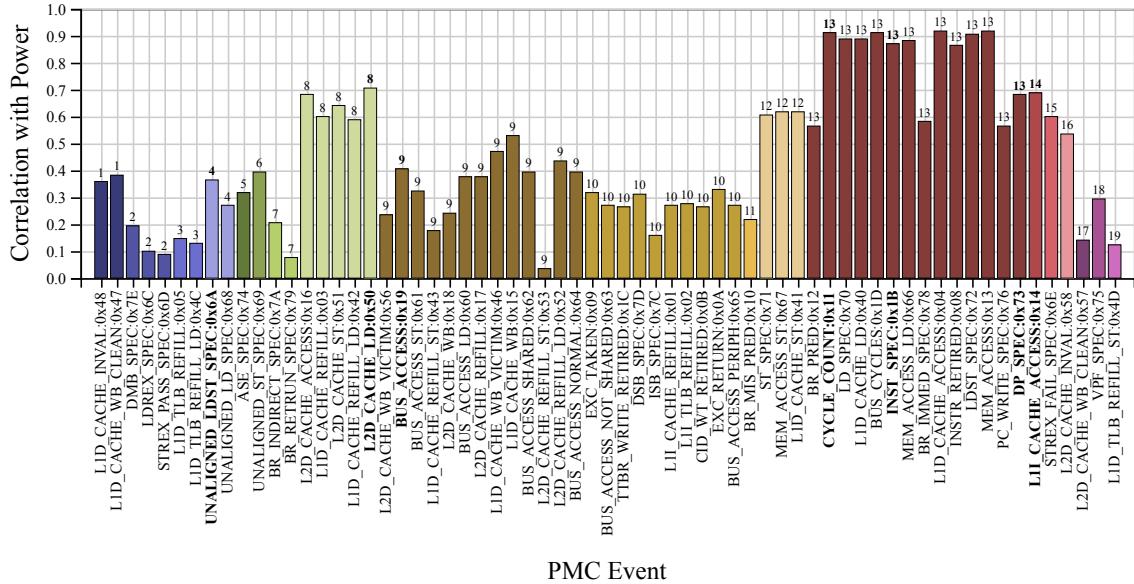

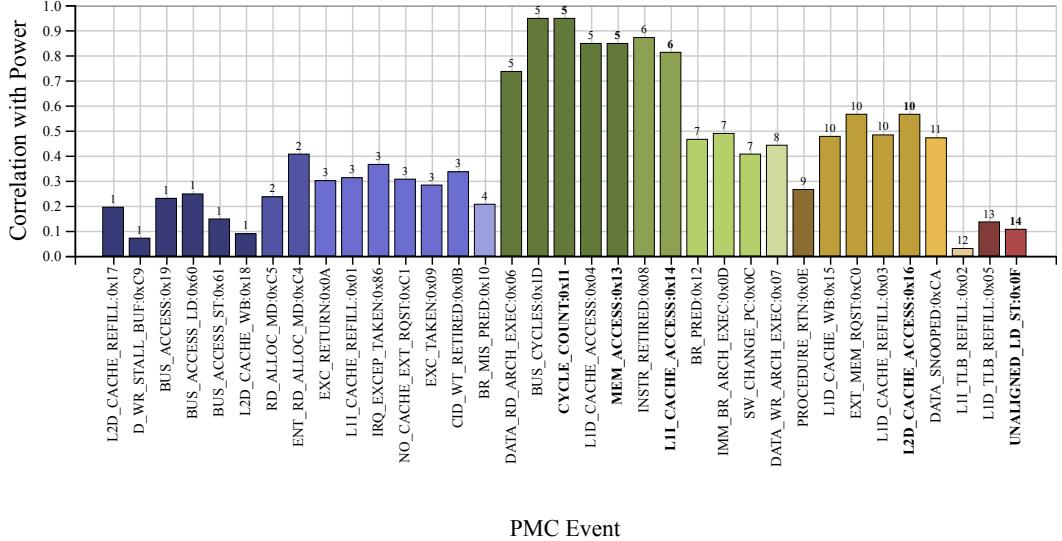

| 4.16 | Correlation of each Arm Cortex-A15 PMC event with power, grouped, coloured and labelled by cluster number, with PMC events chosen by the automated algorithm labelled in bold font . . . . .                                                                                                                                                    | 90 |

| 4.17 | Correlation of each Arm Cortex-A7 PMC event with power, grouped, coloured and labelled by cluster number, with PMC events chosen by the automated algorithm labelled in bold font . . . . .                                                                                                                                                     | 91 |

| 4.18 | Algorithm of the first stage of the PMC event selection method . . . . .                                                                                                                                                                                                                                                                        | 91 |

|      |                                                                                                                                                                                                                                                               |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

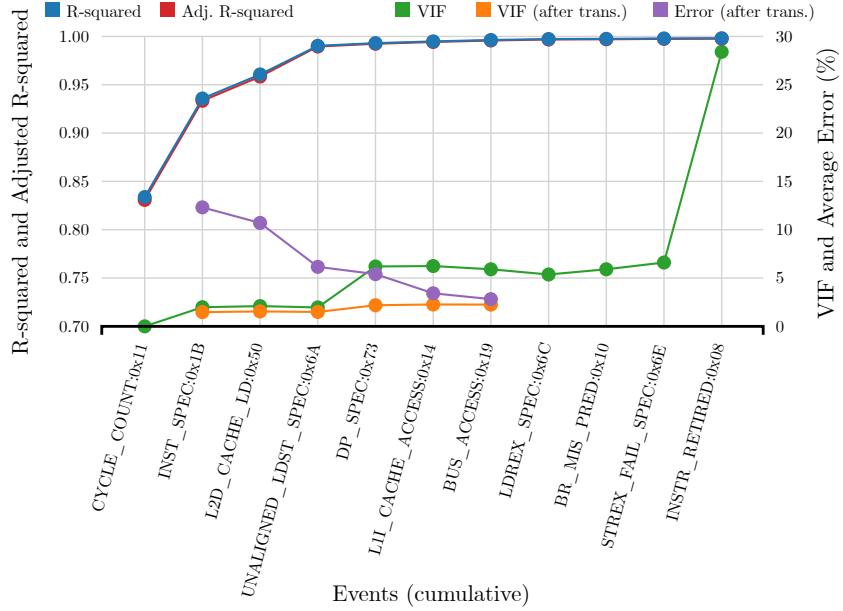

| 4.19 | $R^2$ , Adj. $R^2$ , VIF of selected PMC events (cumulative) from Stage 1. Also shows error and VIF after transformation in Stage 2 . . . . .                                                                                                                 | 93  |

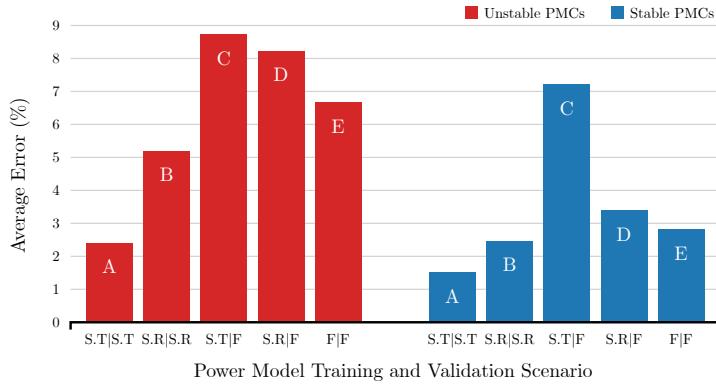

| 4.20 | Comparison of a model with unstable PMC events and one with stable PMC events selected with the proposed methodology. Tested with different training and testing data sets. (S.T = small typical, S.R = small random, F = full set of 60 workloads) . . . . . | 96  |

| 4.21 | PMC event selection cross-validation procedure . . . . .                                                                                                                                                                                                      | 97  |

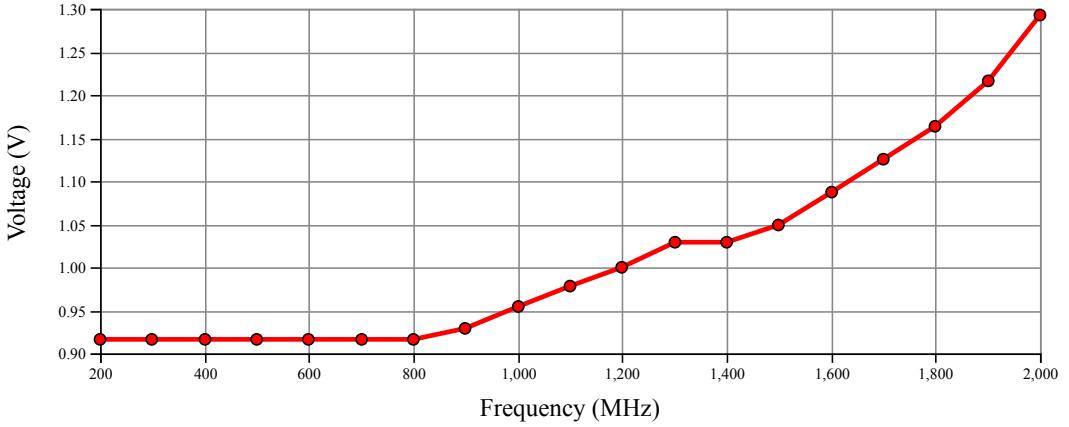

| 4.22 | Voltage (V) at each DVFS level . . . . .                                                                                                                                                                                                                      | 99  |

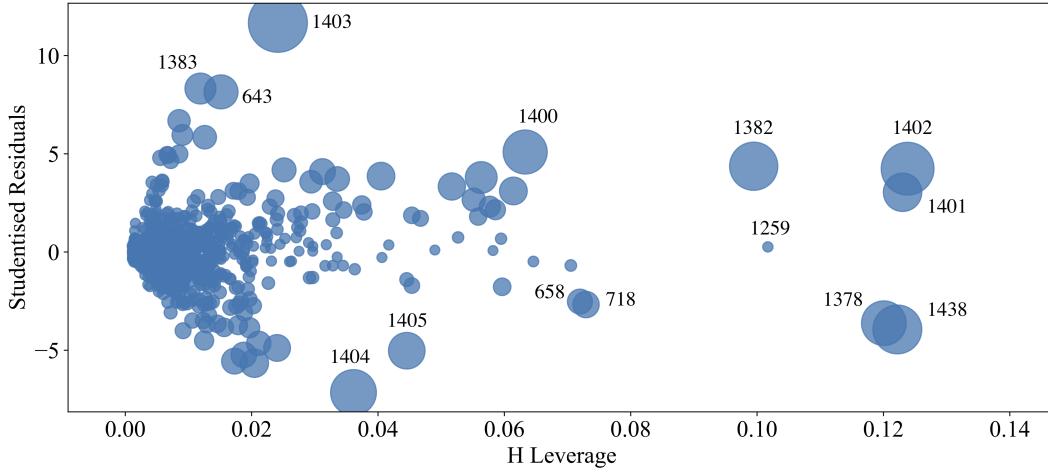

| 4.23 | Influence plot. Point diameter is proportional to Cook's distance . . . . .                                                                                                                                                                                   | 104 |

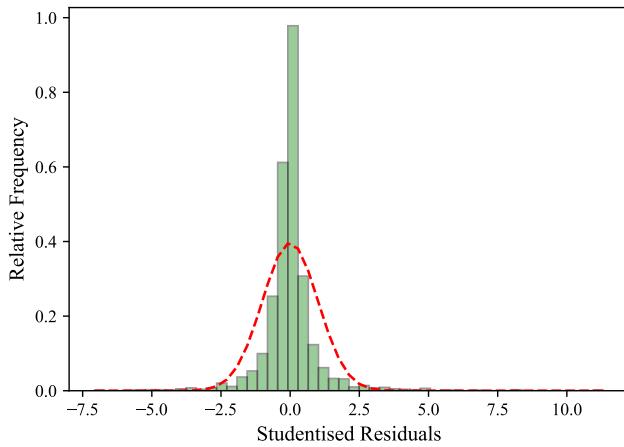

| 4.24 | A histogram plot of the (internal) studentised residuals with a modelled Gaussian distribution superimposed . . . . .                                                                                                                                         | 105 |

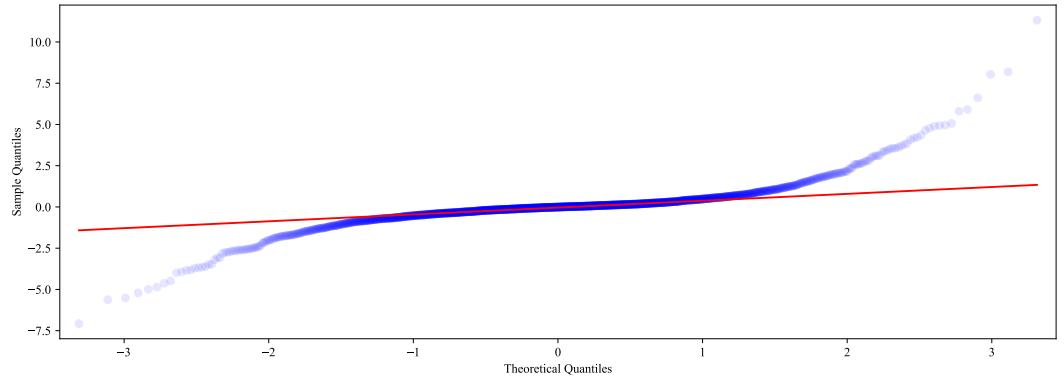

| 4.25 | Normal probability plot of the studentised residuals . . . . .                                                                                                                                                                                                | 105 |

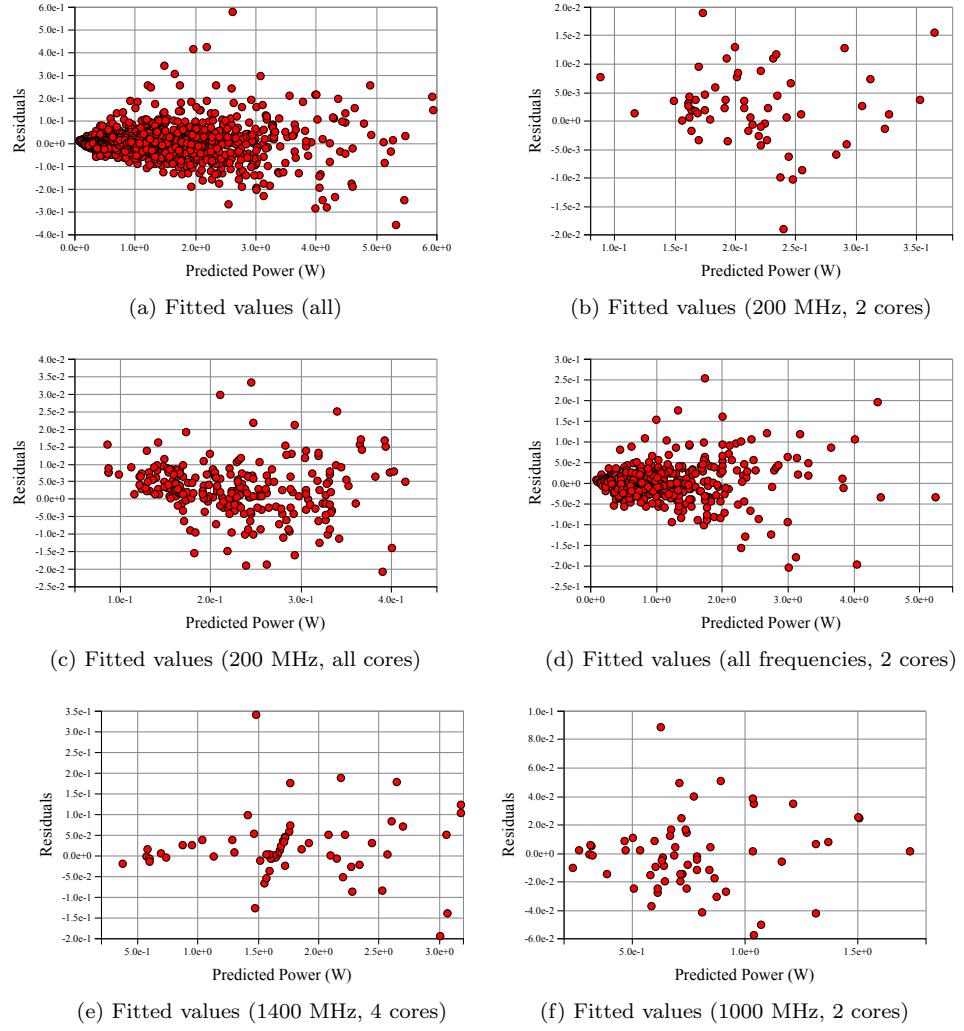

| 4.26 | Residuals plotted against the fitted values . . . . .                                                                                                                                                                                                         | 107 |

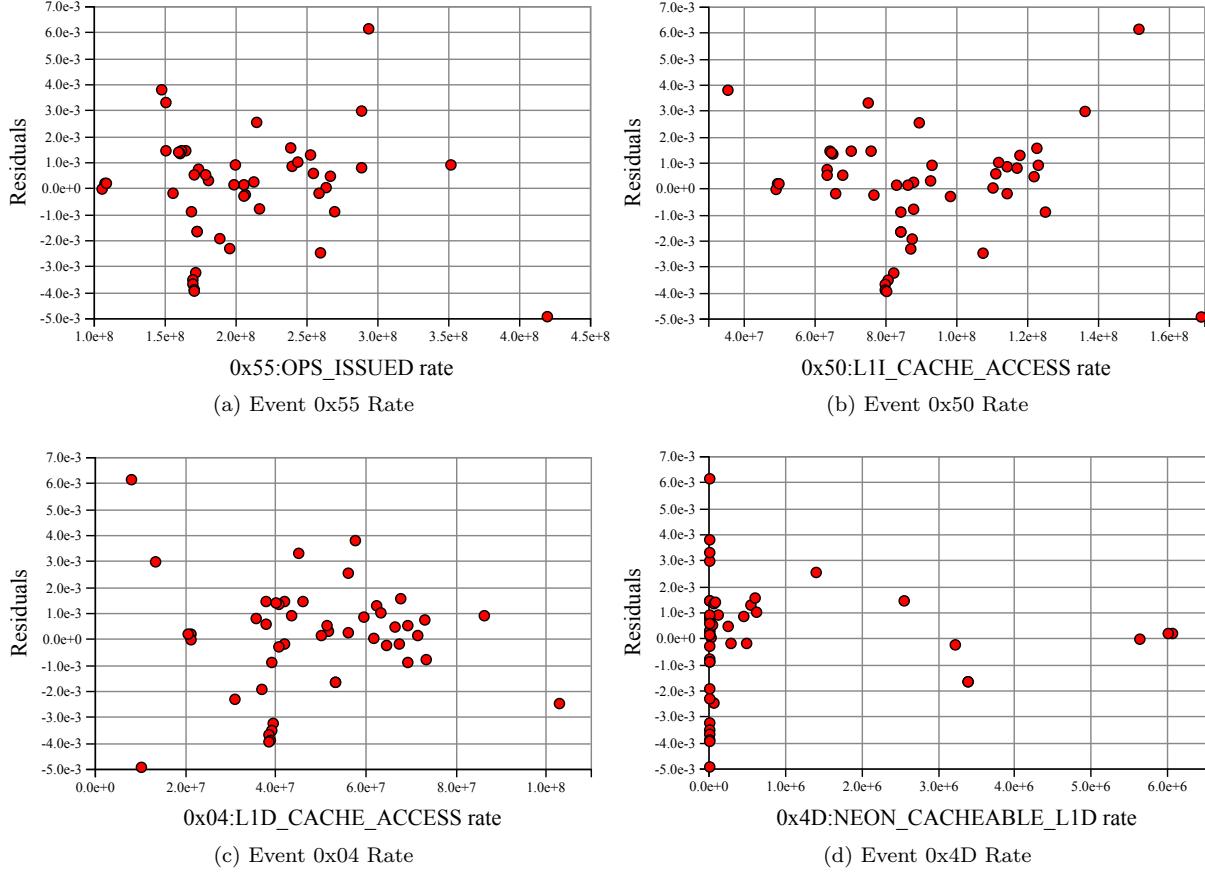

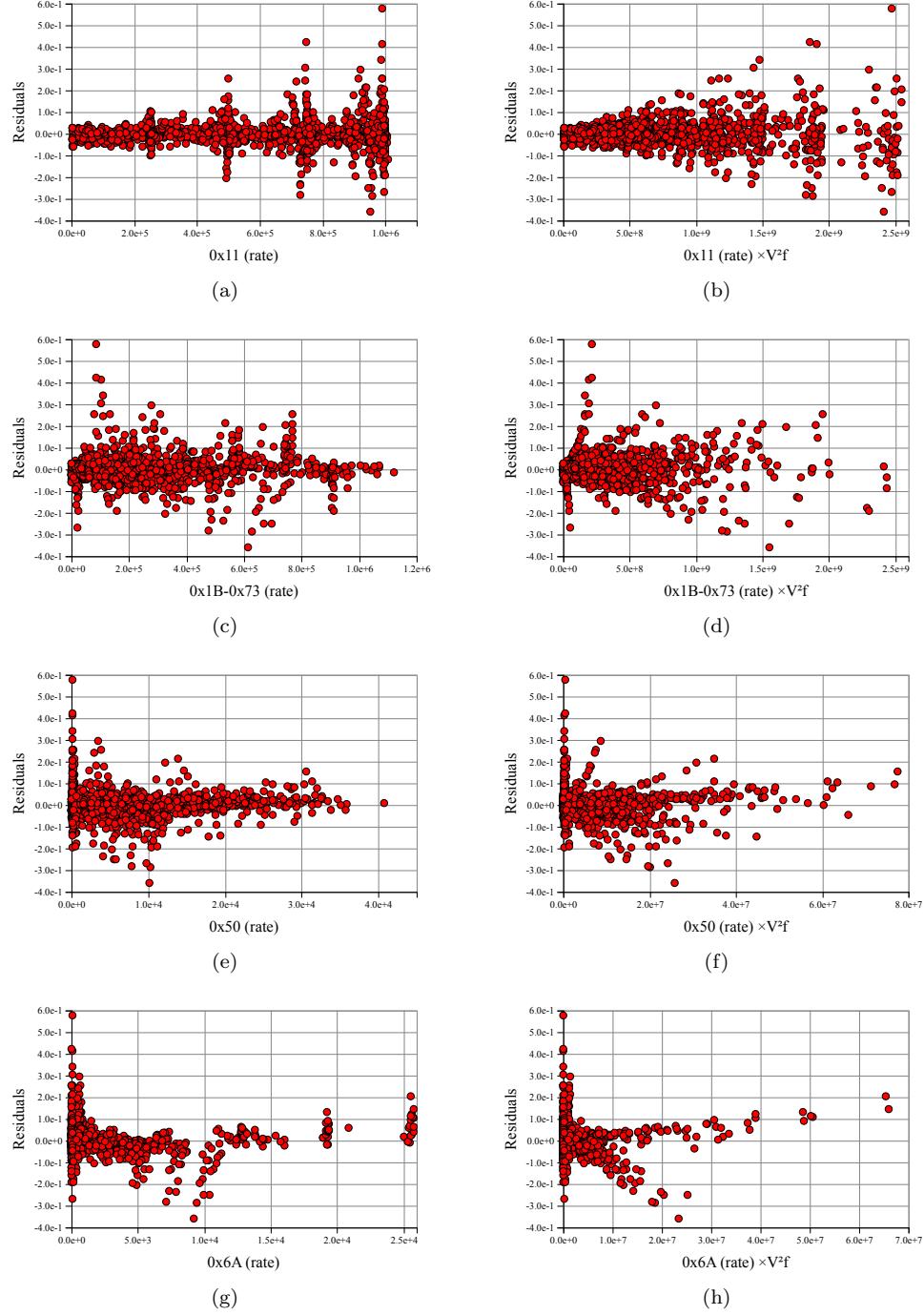

| 4.27 | Residuals plotted against PMC event rates . . . . .                                                                                                                                                                                                           | 108 |

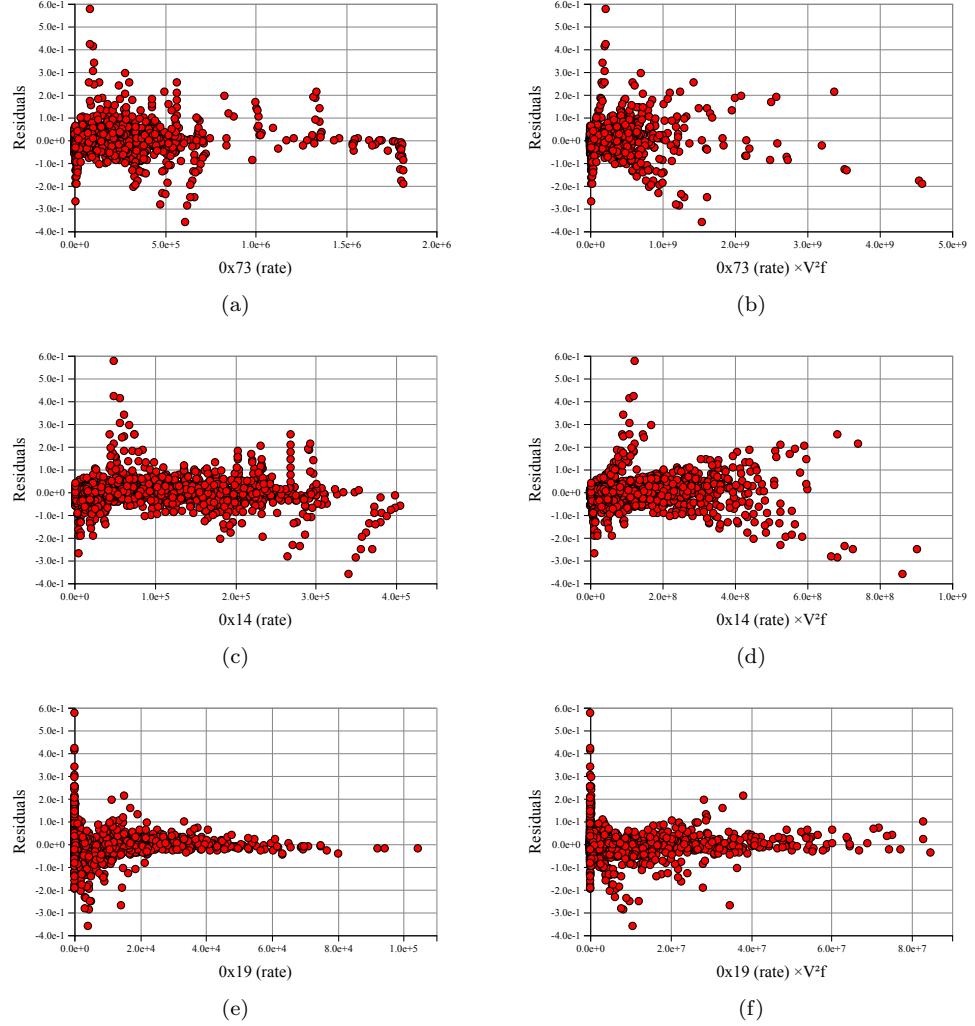

| 4.28 | Residuals plotted against PMC event rates . . . . .                                                                                                                                                                                                           | 109 |

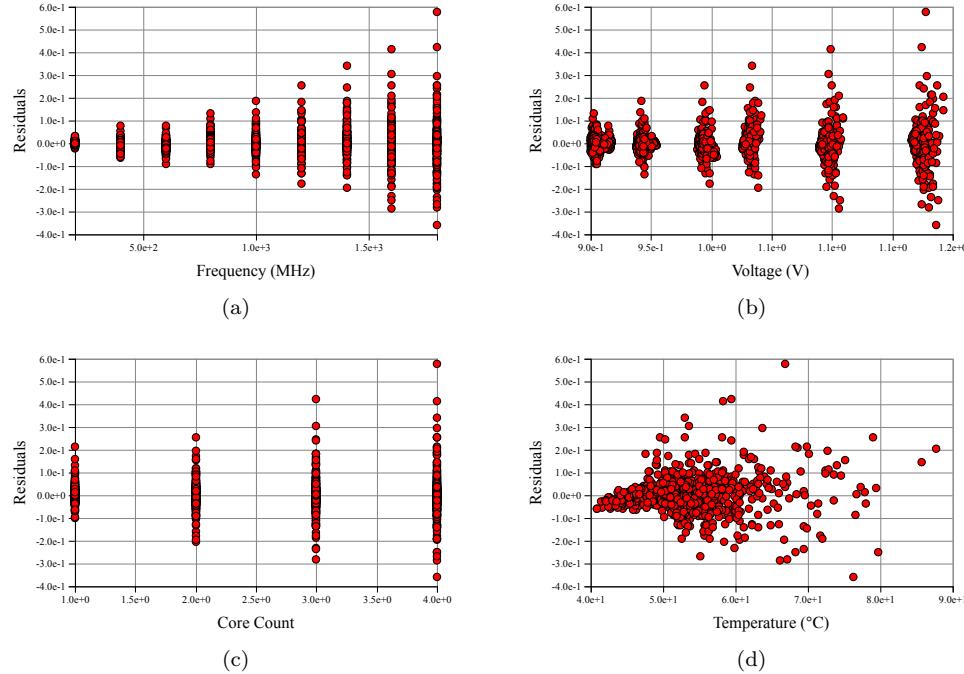

| 4.29 | Residuals plotted against the frequency, voltage, number of active cores and the temperature . . . . .                                                                                                                                                        | 110 |

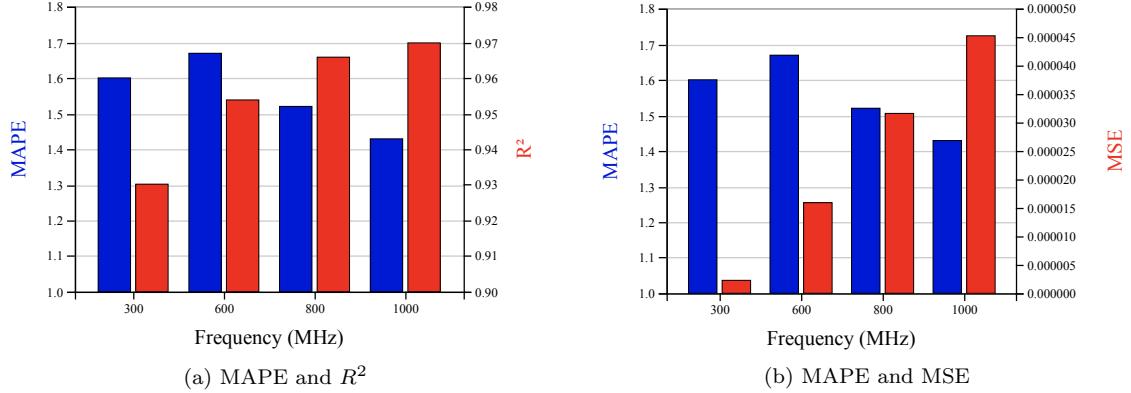

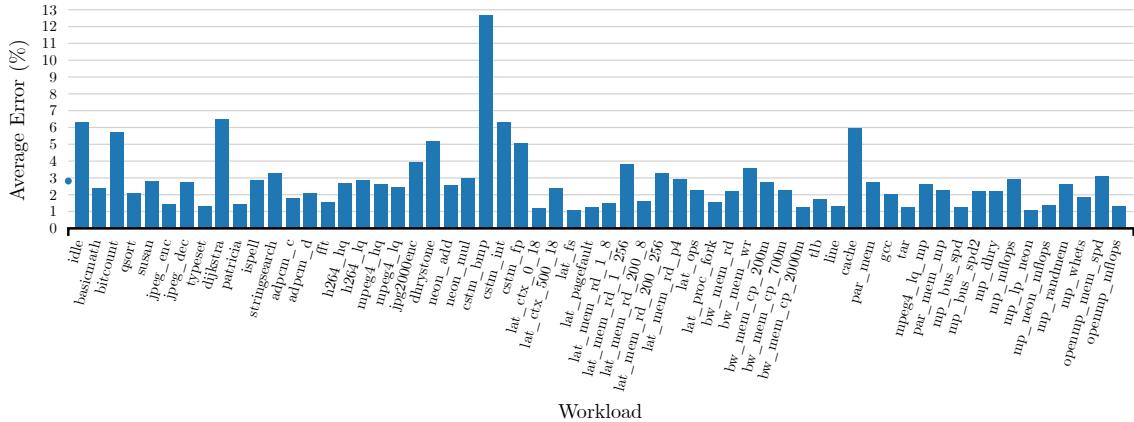

| 4.30 | Average error (mean absolute percentage error [MAPE]) across each DVFS level for all 60 workloads (Cortex-A15 CPU model) . . . . .                                                                                                                            | 114 |

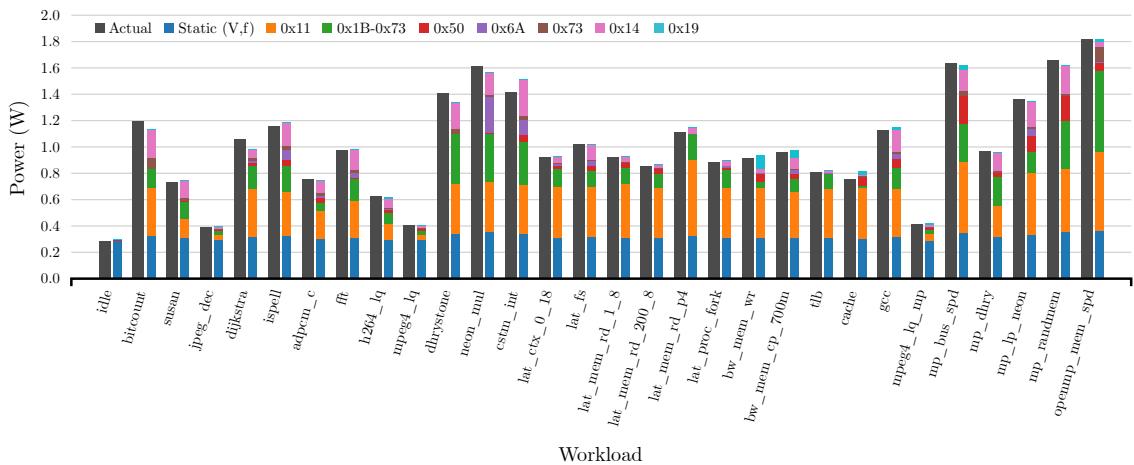

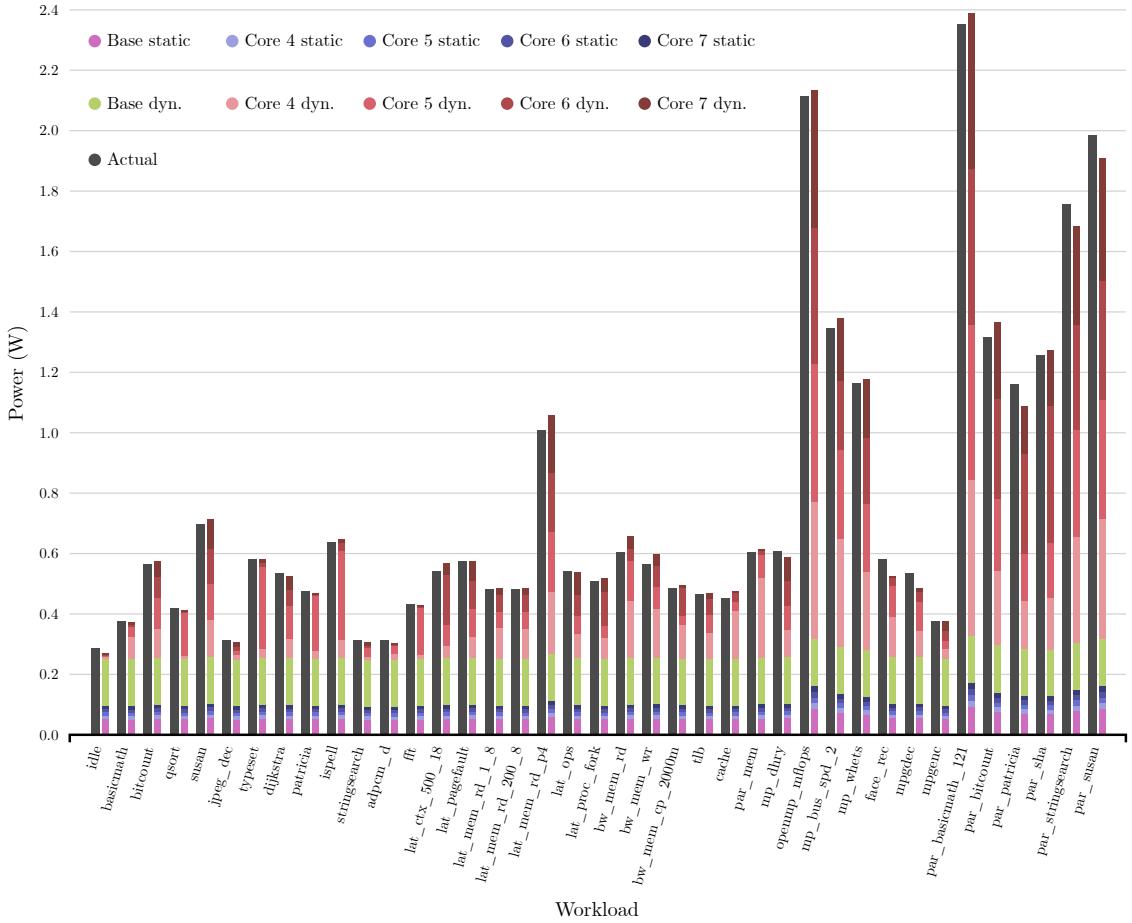

| 4.31 | Actual (measured) power vs. the predicted power for half of the considered workloads, with the predicted power broken down into its constituting parts (Cortex-A15 CPU model) . . . . .                                                                       | 114 |

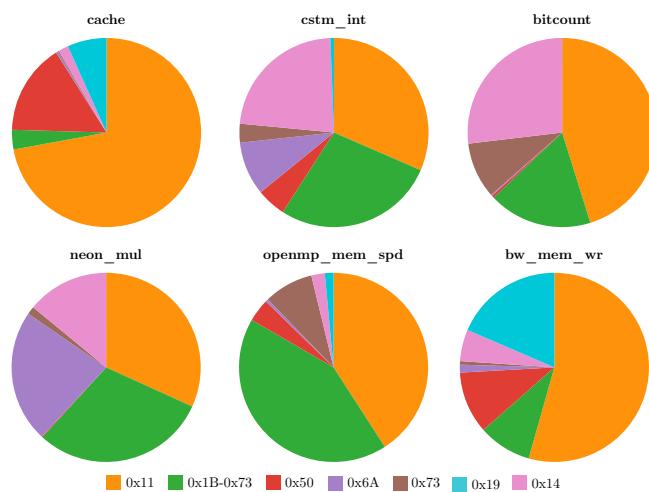

| 4.32 | Contribution of each PMC event to the dynamic power prediction for six different workloads . . . . .                                                                                                                                                          | 114 |

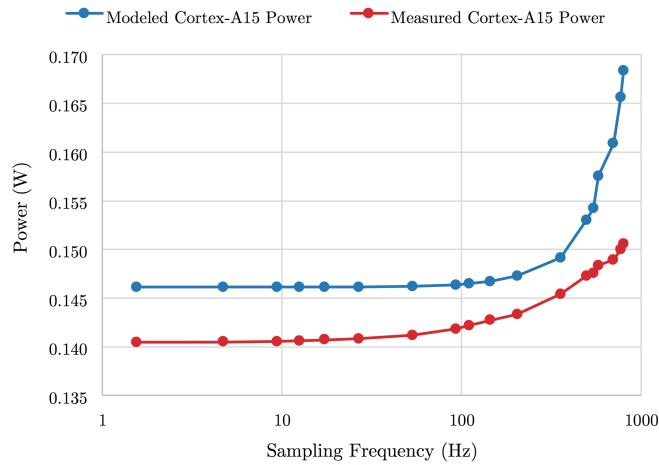

| 4.33 | Modelled power and measured power for the Arm Cortex-A15 cluster running at 200 MHz with various sampling frequencies and no other workloads . . . . .                                                                                                        | 115 |

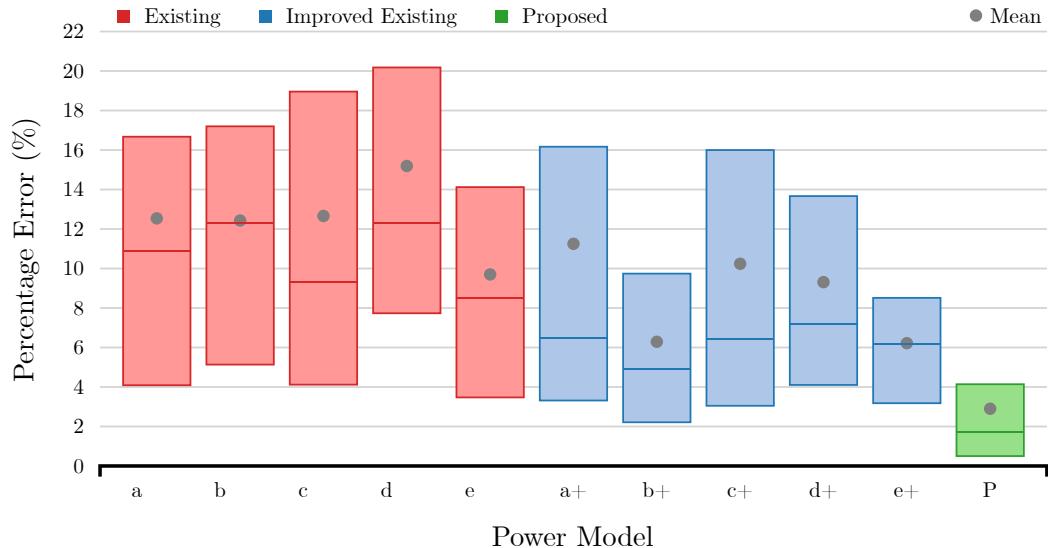

| 4.34 | Box plot of error distribution for each model, trained with 20 diverse workloads and validated with 60 workloads, showing the median, lower quartile, upper quartile and arithmetic mean . . . . .                                                            | 117 |

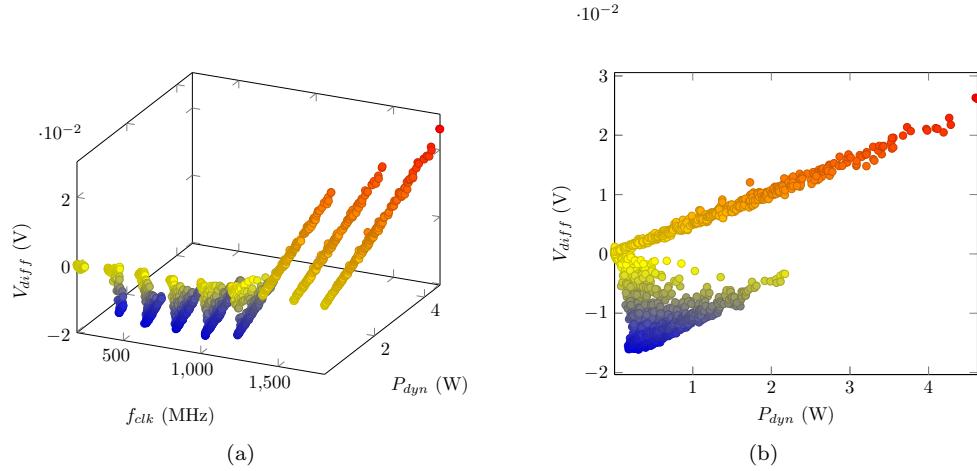

| 4.35 | The difference between the CPU idle voltage and the measured voltage, $V_{diff}$ , against the CPU dynamic power consumption, $P_{dyn}$ , for workloads running at various DVFS levels, $f_{clk}$ . . . . .                                                   | 118 |

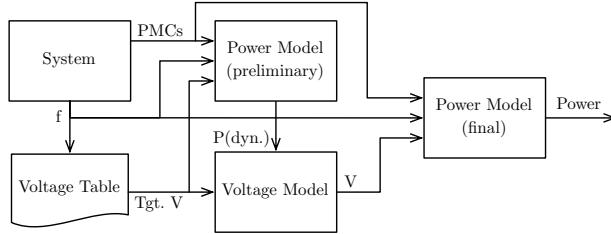

| 4.36 | Run-time power estimation setup with the voltage model . . . . .                                                                                                                                                                                              | 119 |

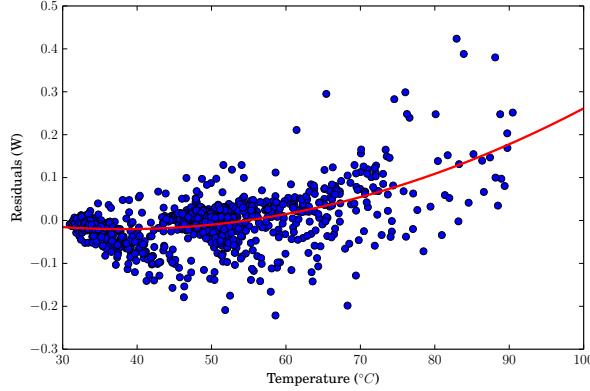

| 5.1  | Residuals of model <i>b</i> plotted against temperature. Red line shows an equation predicting this trend. . . . .                                                                                                                                            | 126 |

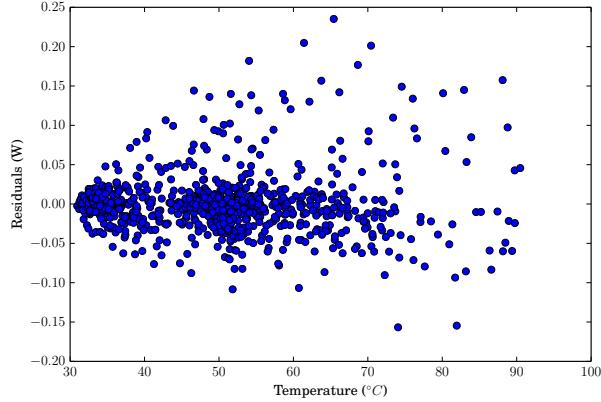

| 5.2  | Residuals of model <i>c</i> (temperature-compensated) plotted against temperature. Red line shows an equation predicting this trend. . . . .                                                                                                                  | 127 |

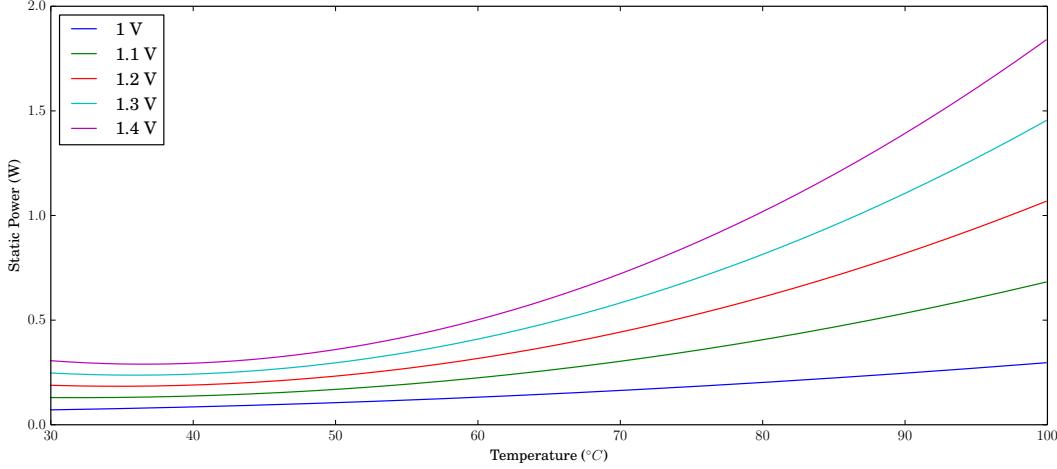

| 5.3  | Model output response when varying the temperature input at various cluster voltage points. . . . .                                                                                                                                                           | 128 |

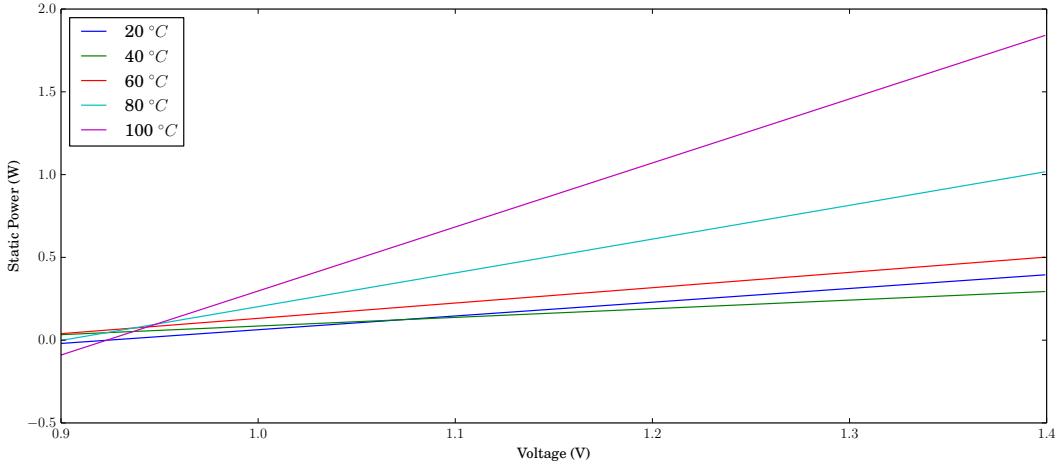

| 5.4  | Model output response when varying the voltage input at various temperature points. . . . .                                                                                                                                                                   | 128 |

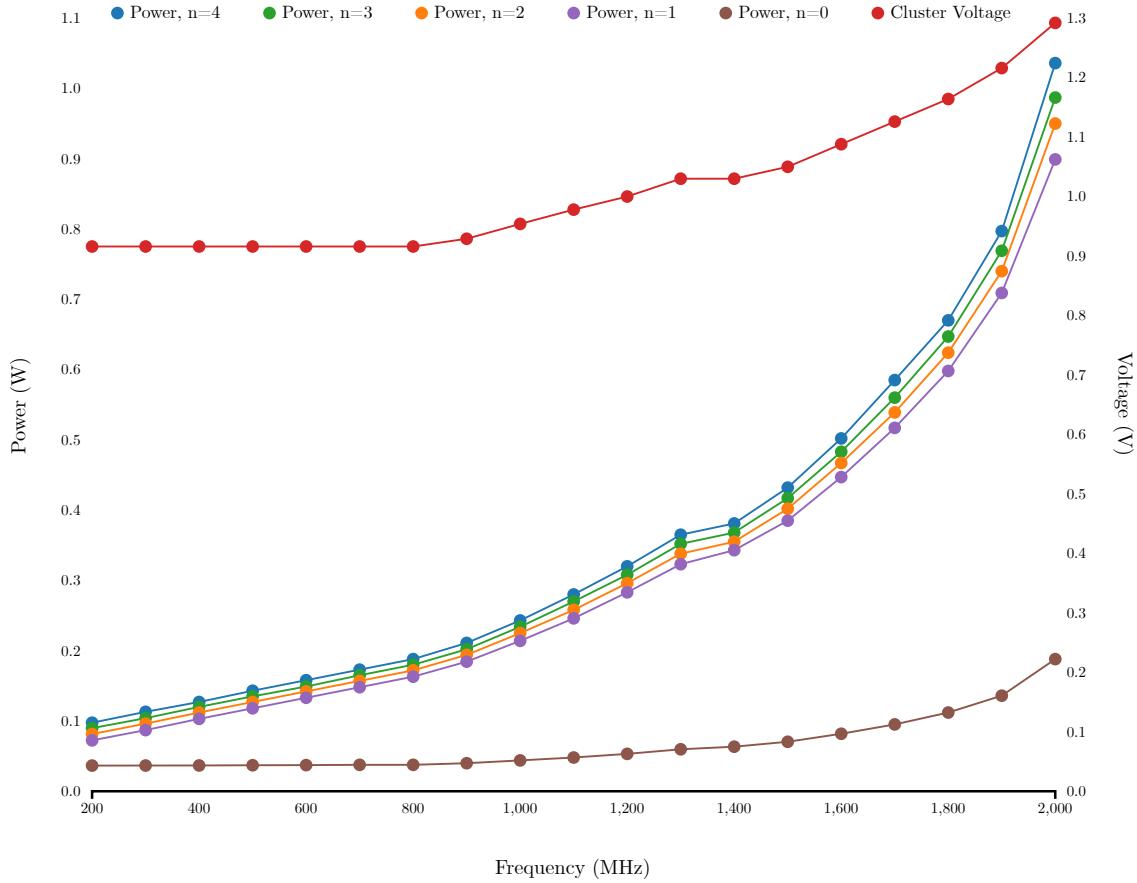

| 5.5  | The measured idle quad-core Cortex-A15 cluster power at various clock frequencies ( $f_{clk}$ ) when all four cores are online (n=4) and switching each off in turn until no core is online (n=0). The cluster voltage is also shown. . . . .                 | 130 |

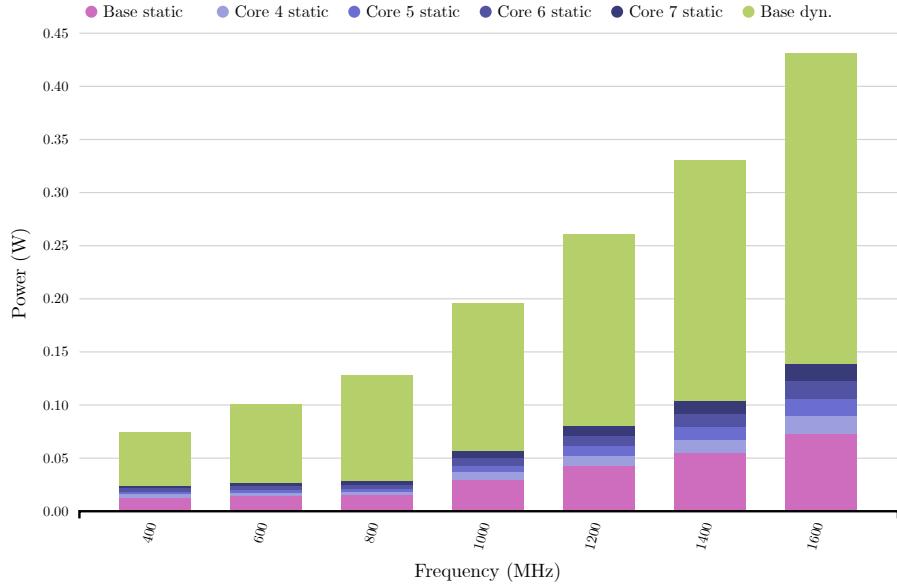

| 5.6  | Idle power consumption across different clock frequencies, showing the contribution from the static power and BG dynamic power. Fan switched on. Average temperature is 35.5 °C. . . . .                                                                      | 131 |

|      |                                                                                                                                                                                                                                                                                                                                                                                      |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

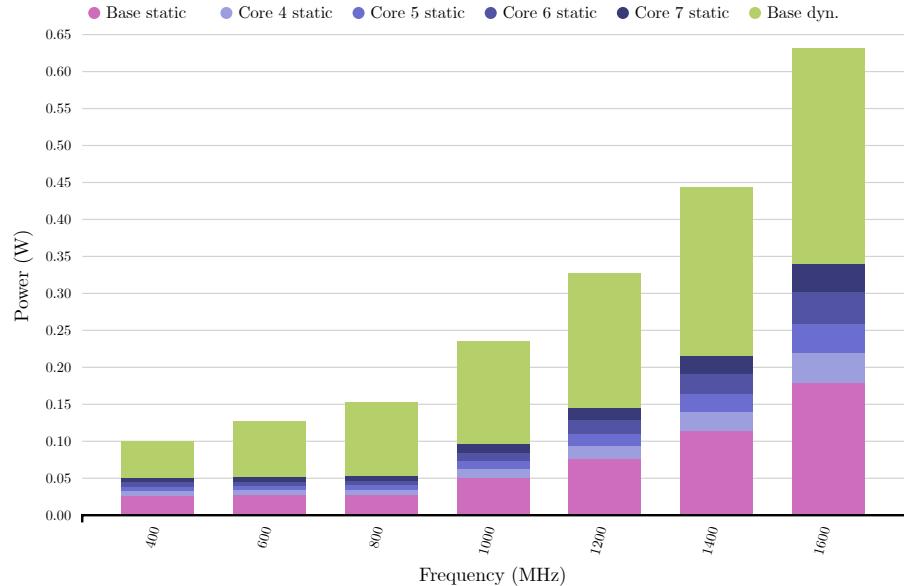

| 5.7  | Idle power consumption across different clock frequencies, showing the contribution from the static power and BG dynamic power. Fan switched off. Average temperature is 60.1 °C. . . . .                                                                                                                                                                                            | 131 |

| 5.8  | Average error (mean absolute percentage error [MAPE]) for all 39 workloads, aggregated across each DVFS level and three fan settings . . . . .                                                                                                                                                                                                                                       | 132 |

| 5.9  | Power breakdown for all 39 workloads, aggregated over every DVFS level and three different fan settings . . . . .                                                                                                                                                                                                                                                                    | 132 |

| 5.10 | Overview of the thermal characterisation setup . . . . .                                                                                                                                                                                                                                                                                                                             | 134 |

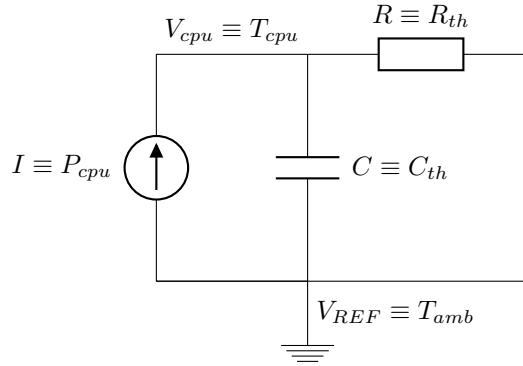

| 5.11 | Example of the most basic form of an equivalent circuit CPU temperature model . .                                                                                                                                                                                                                                                                                                    | 134 |

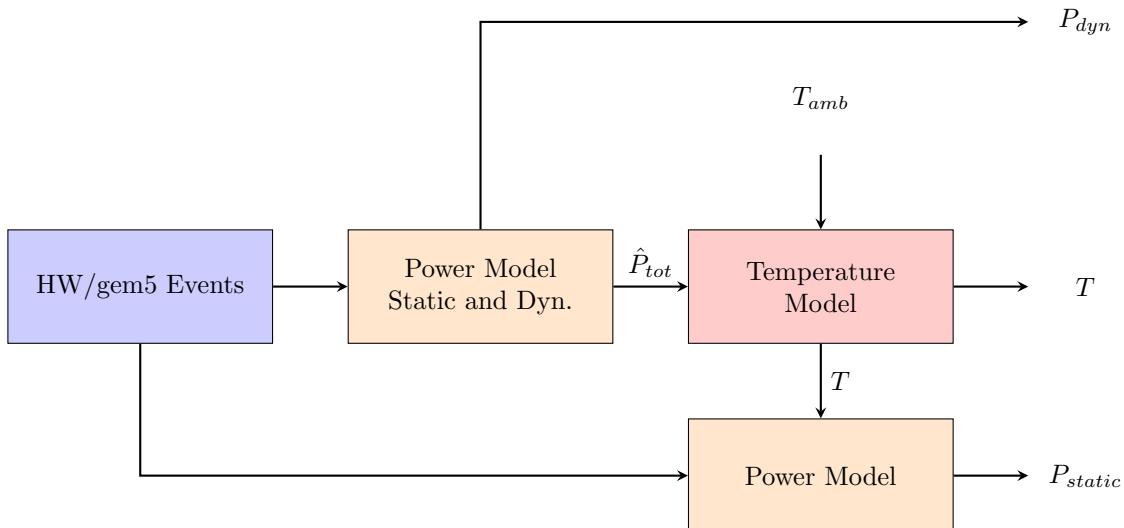

| 5.12 | Online thermal and power prediction block diagram . . . . .                                                                                                                                                                                                                                                                                                                          | 134 |

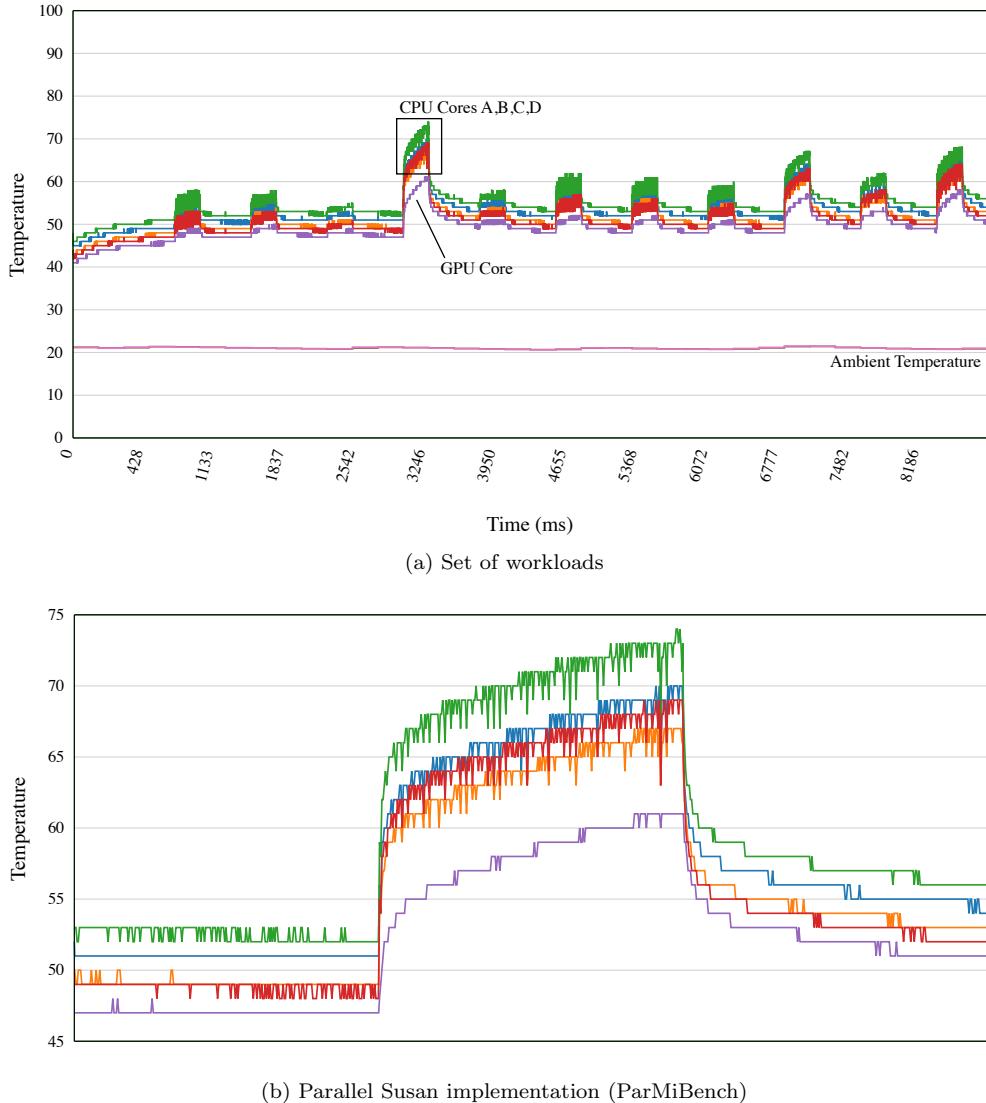

| 5.13 | Temperature (degrees Celsius) readings from the four CPU core sensors, a GPU core sensor, and an ambient temperature sensor while running selected workloads on the Arm Cortex-A15 cluster . . . . .                                                                                                                                                                                 | 135 |

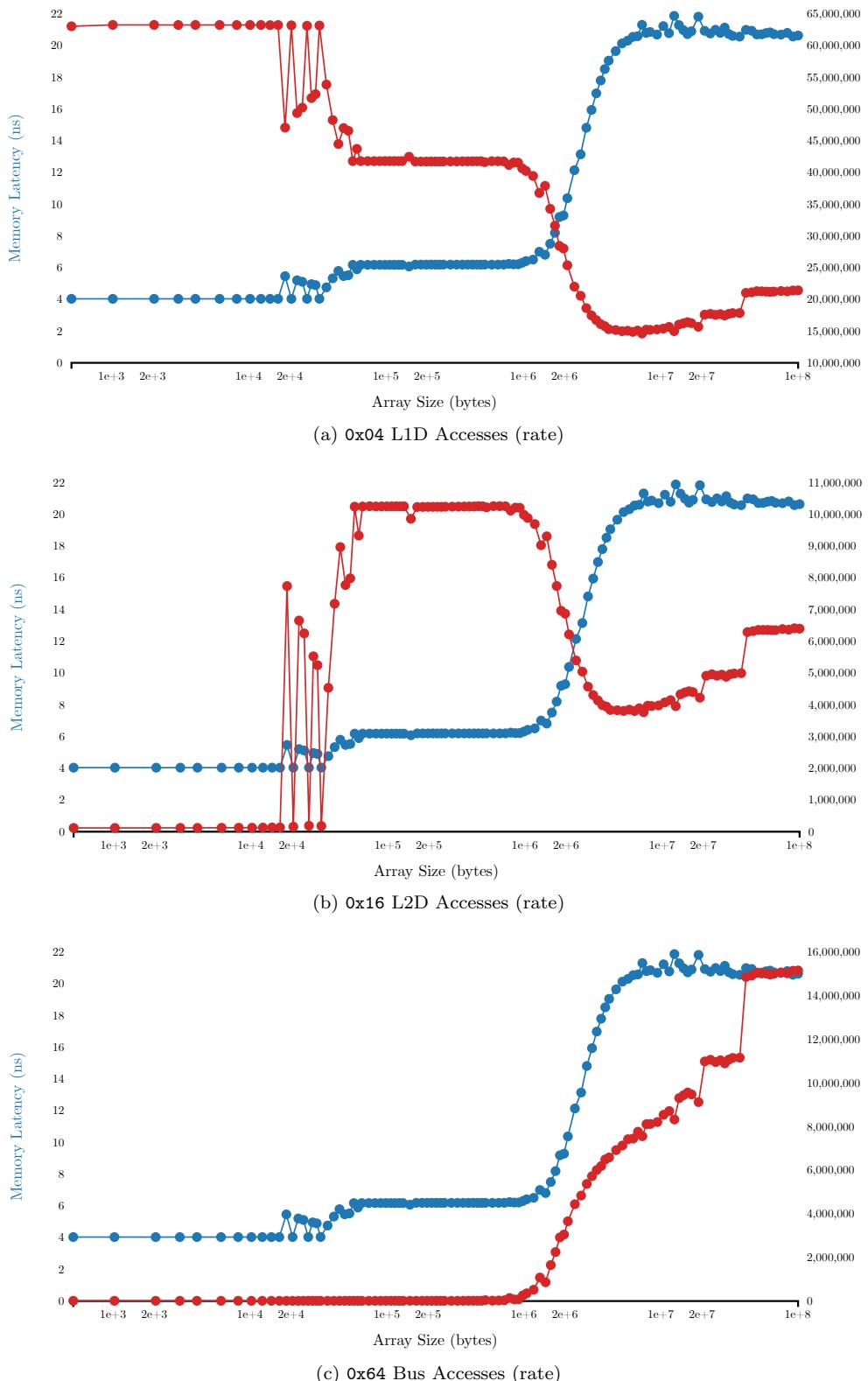

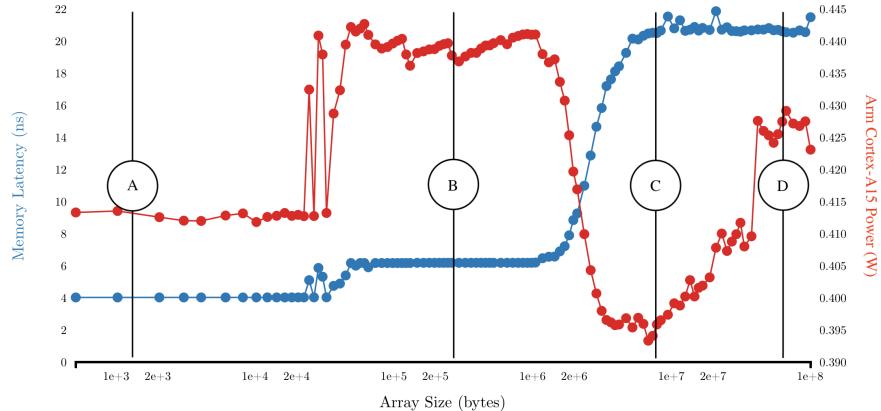

| 5.14 | Memory latency (left axis) plotted with Cortex-A15 power consumption (right axis). Maximum array length of 100 MB and a stride of 8 bytes. . . . .                                                                                                                                                                                                                                   | 136 |

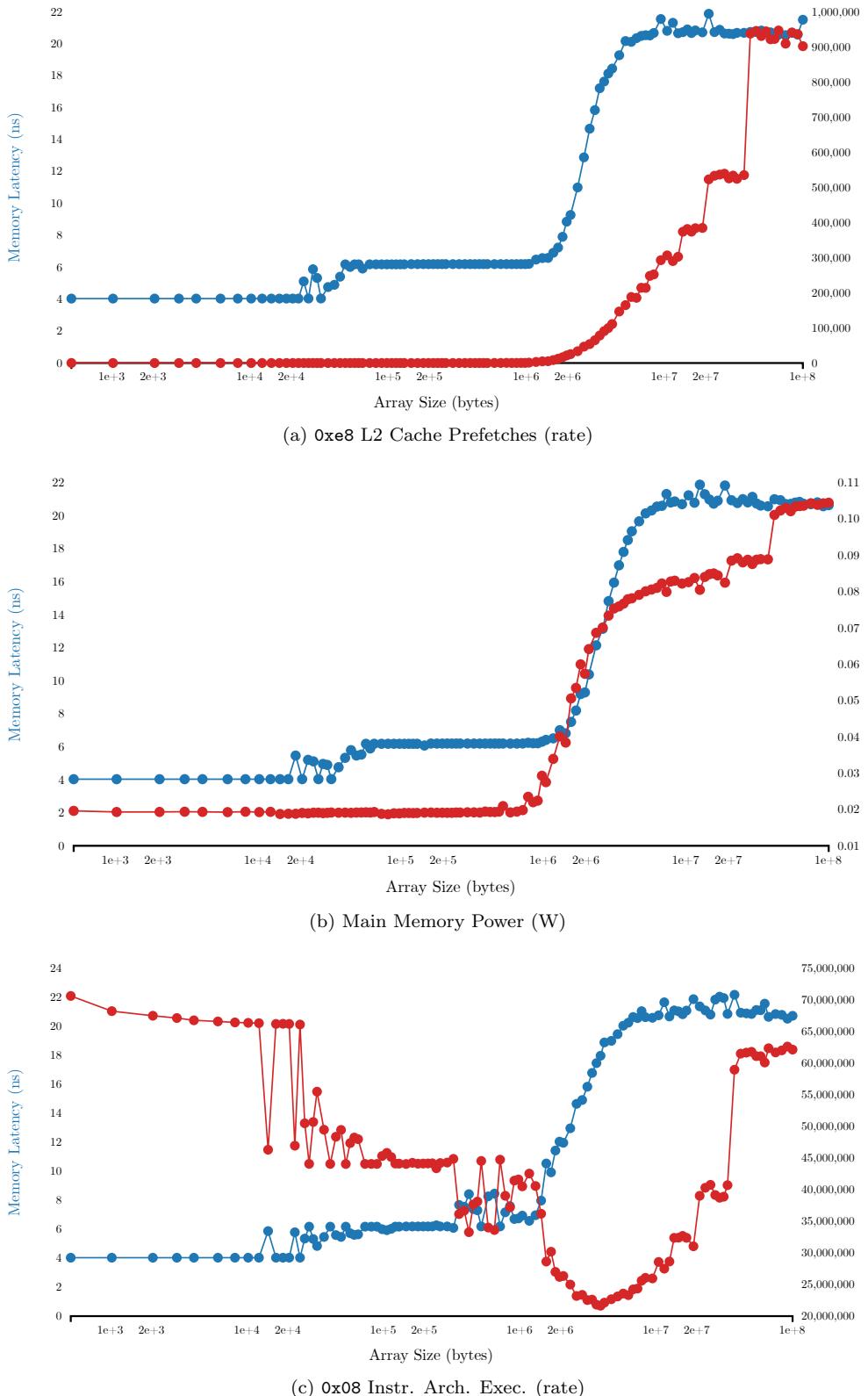

| 5.15 | (continued) Memory latency (left axis) plotted with various PMC event rates (right axis). Maximum array length of 100 MB and a stride of 8 bytes. . . . .                                                                                                                                                                                                                            | 137 |

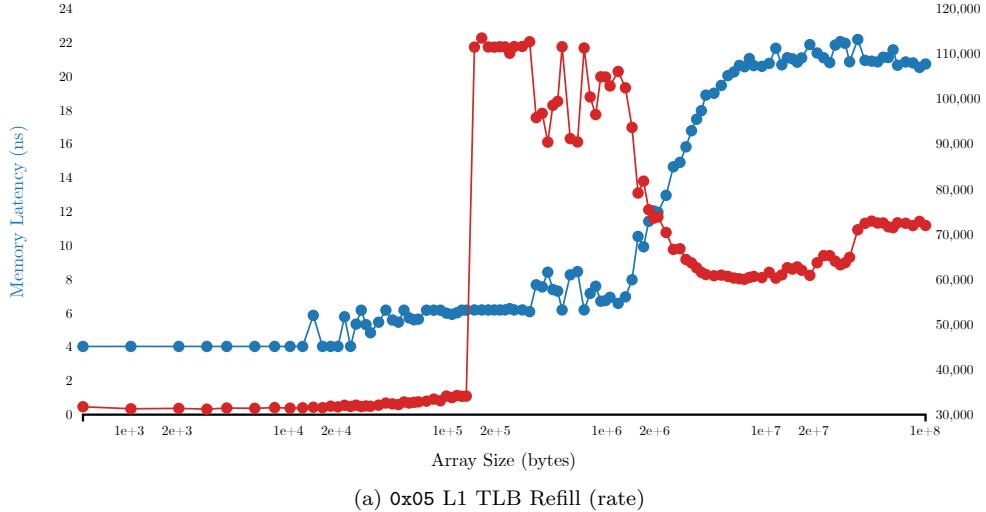

| 5.16 | (continued) Memory latency (left axis) plotted with PMC event rates and memory power consumption (right axis). Maximum array length of 100 MB and a stride of 8 bytes. . . . .                                                                                                                                                                                                       | 138 |

| 5.17 | (continued) Memory latency (left axis) plotted with a PMC event rate (right axis). Maximum array length of 100 MB and a stride of 8 bytes. . . . .                                                                                                                                                                                                                                   | 139 |

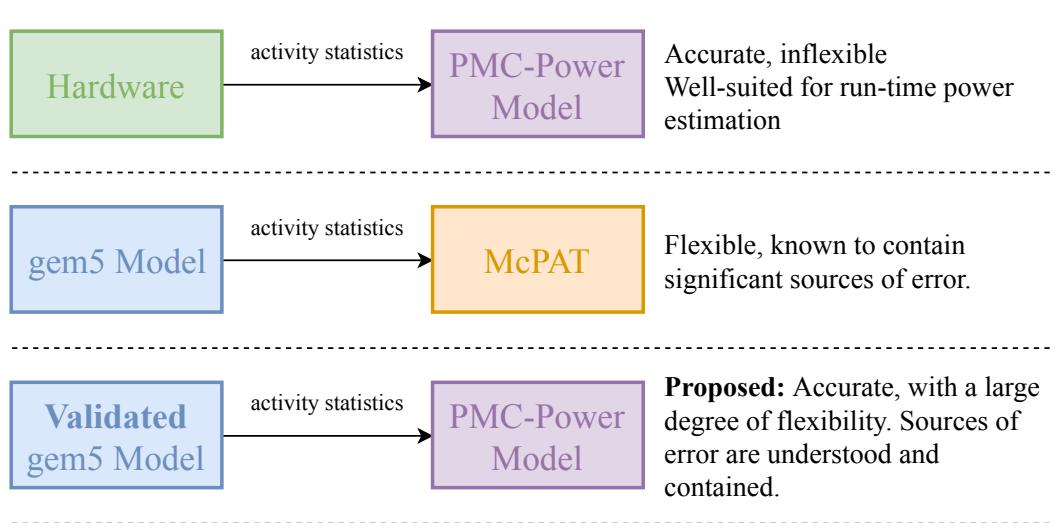

| 6.1  | Proposed simulation methodology . . . . .                                                                                                                                                                                                                                                                                                                                            | 142 |

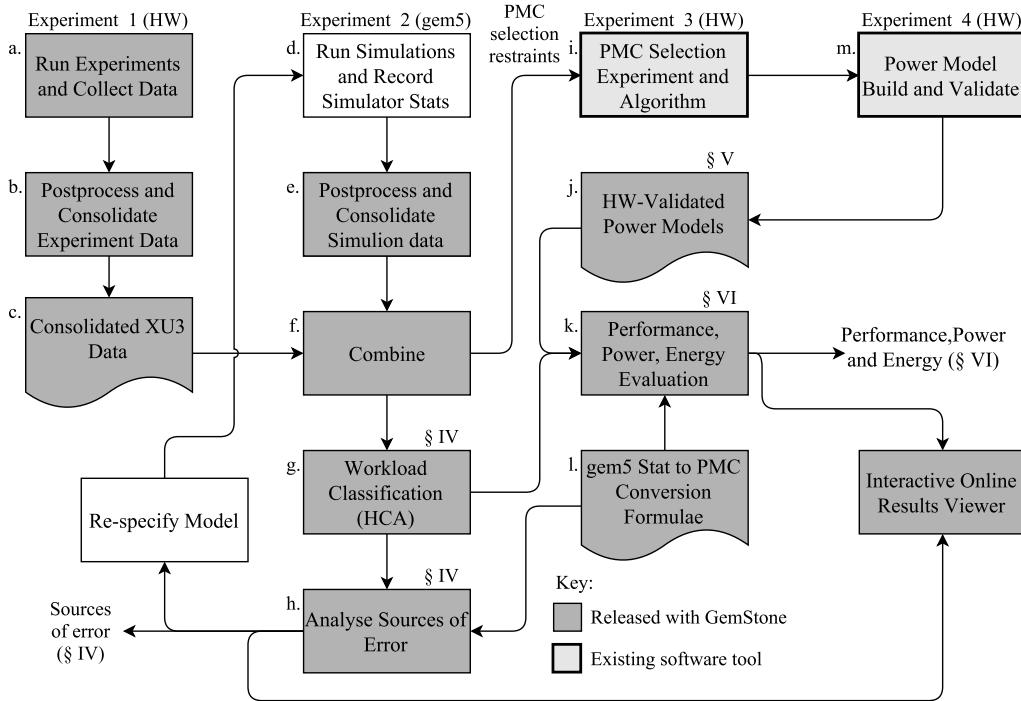

| 6.2  | Experimental setup and methodology overview . . . . .                                                                                                                                                                                                                                                                                                                                | 146 |

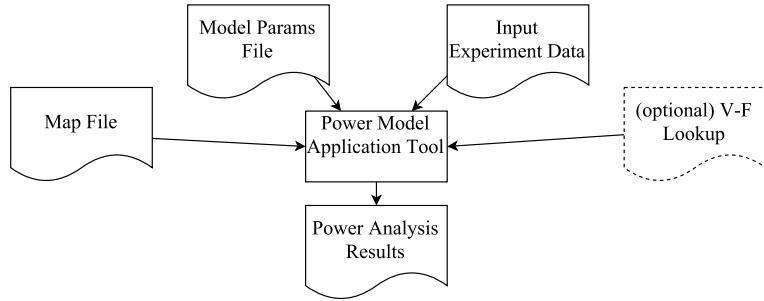

| 6.3  | Software tool for applying power models to either hardware collected data or gem5 data . . . . .                                                                                                                                                                                                                                                                                     | 147 |

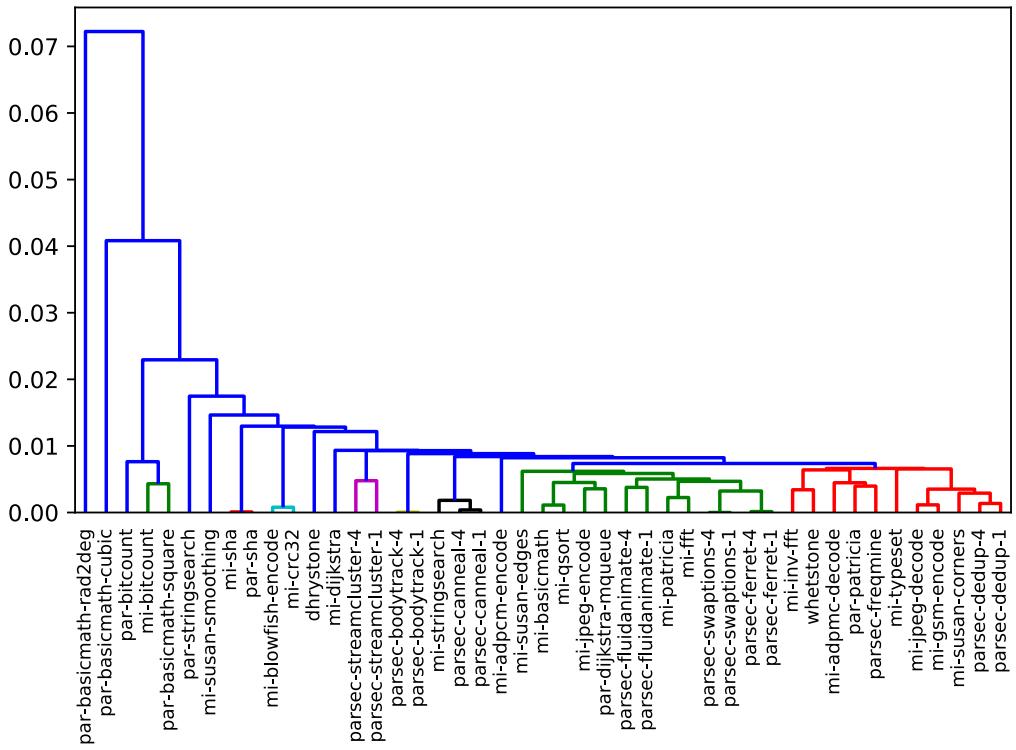

| 6.4  | Dendrogram of workload clustering. (MiBench prefix: <i>mi</i> , ParMiBench prefix: <i>par</i> , PARSEC prefix: <i>parsec</i> ) . . . . .                                                                                                                                                                                                                                             | 149 |

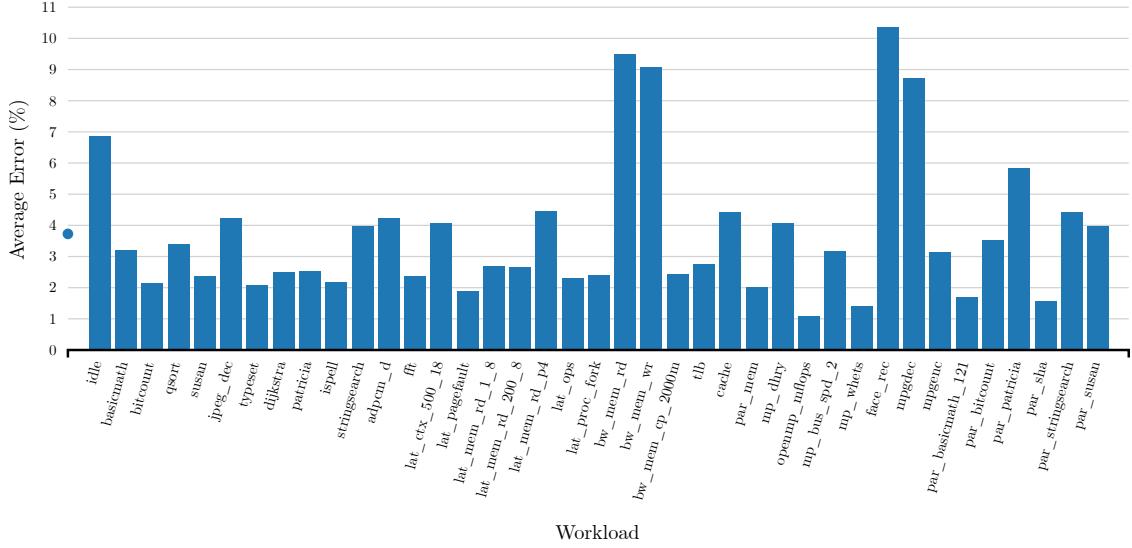

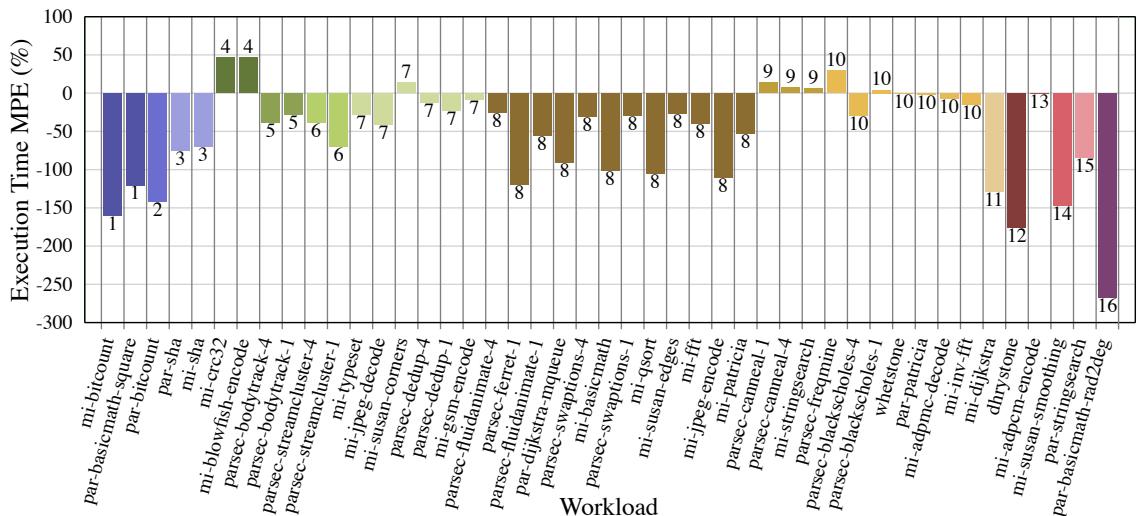

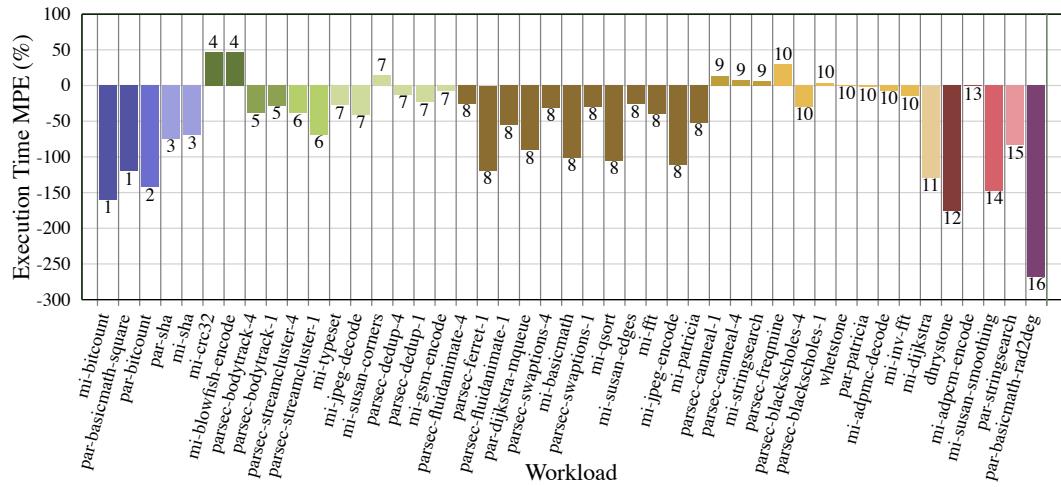

| 6.5  | Execution time Mean Percentage Error (MPE) for each workload running at 1 GHz on the Cortex-A15 cluster. Workloads are ordered, coloured and labelled (above bars) by cluster designation from Hierarchical Cluster Analysis (HCA) of the hardware PMC correlation. A positive error indicates an overestimation of the performance (underestimation of the execution time). . . . . | 149 |

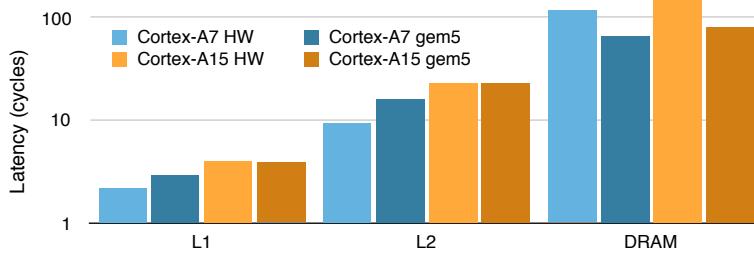

| 6.6  | Measured memory latency with a stride of 256 . . . . .                                                                                                                                                                                                                                                                                                                               | 150 |

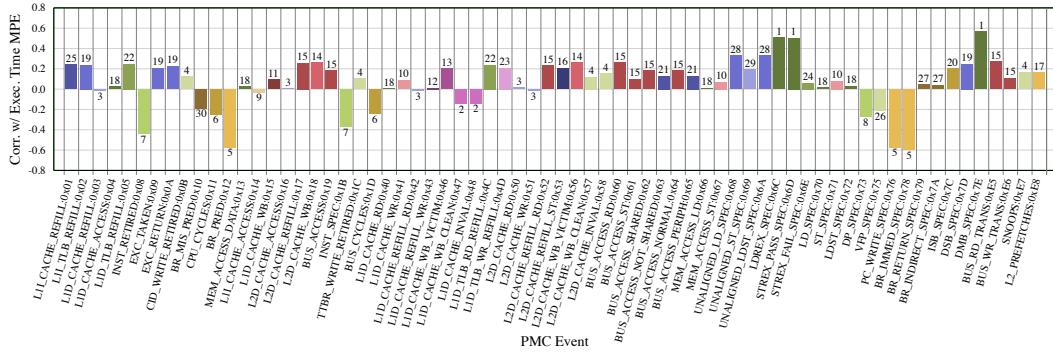

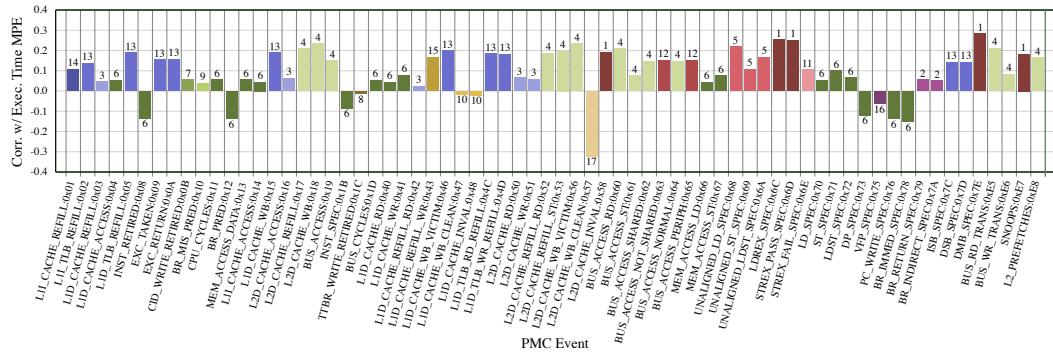

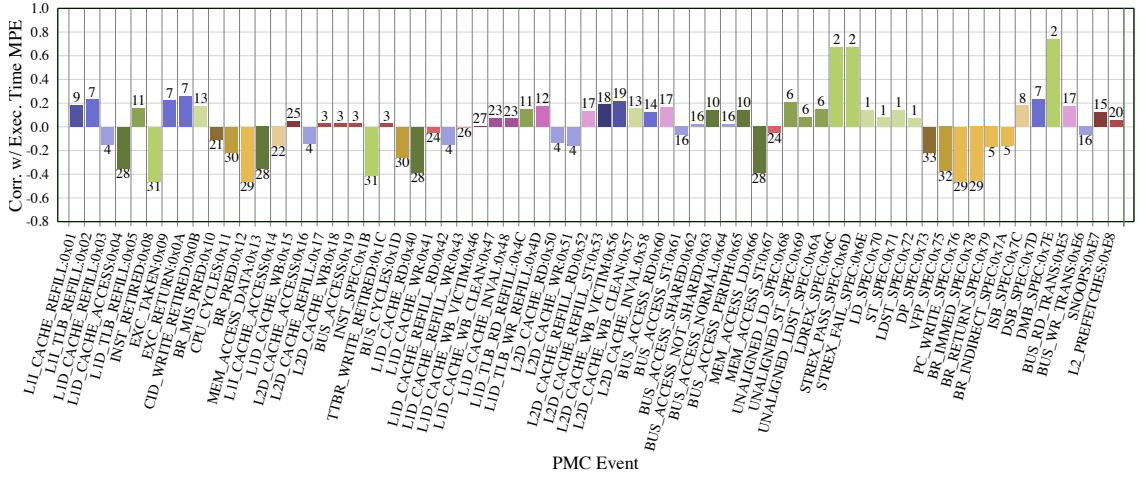

| 6.7  | Correlation of each HW PMC (rate) with the execution time MPE, labelled and coloured by clusters derived from HCA of the correlation between PMC events across different workloads. . . . .                                                                                                                                                                                          | 151 |

| 6.8  | Correlation of each HW PMC (total) with the execution time MPE, labelled and coloured by clusters derived from HCA of the correlation between PMC events across different workloads. . . . .                                                                                                                                                                                         | 151 |

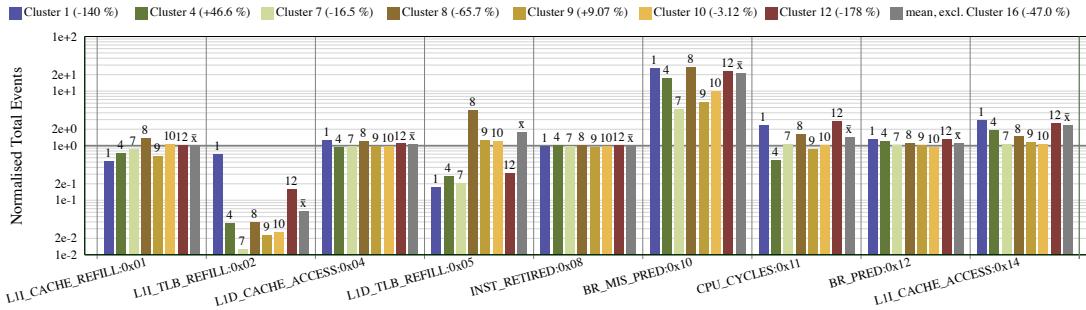

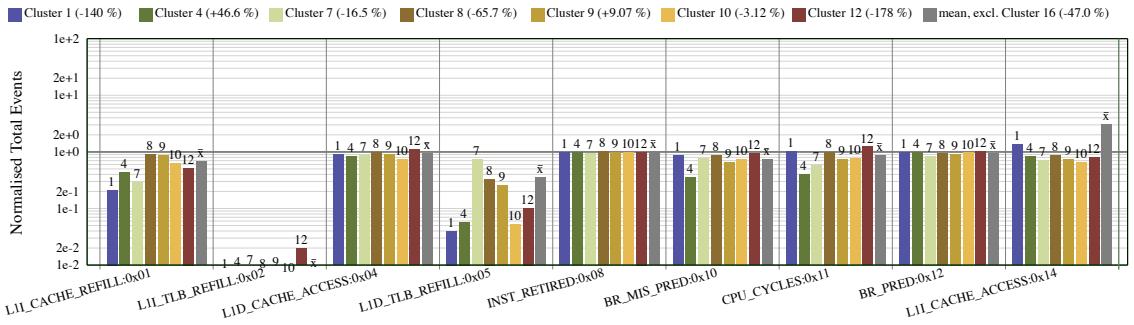

| 6.9  | Total gem5 events normalised with their HW PMC equivalent (bars over 1 indicate that gem5 overestimates the PMC event). Results shown for selected clusters. The mean bars exclude Cluster 16. . . . .                                                                                                                                                                               | 154 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

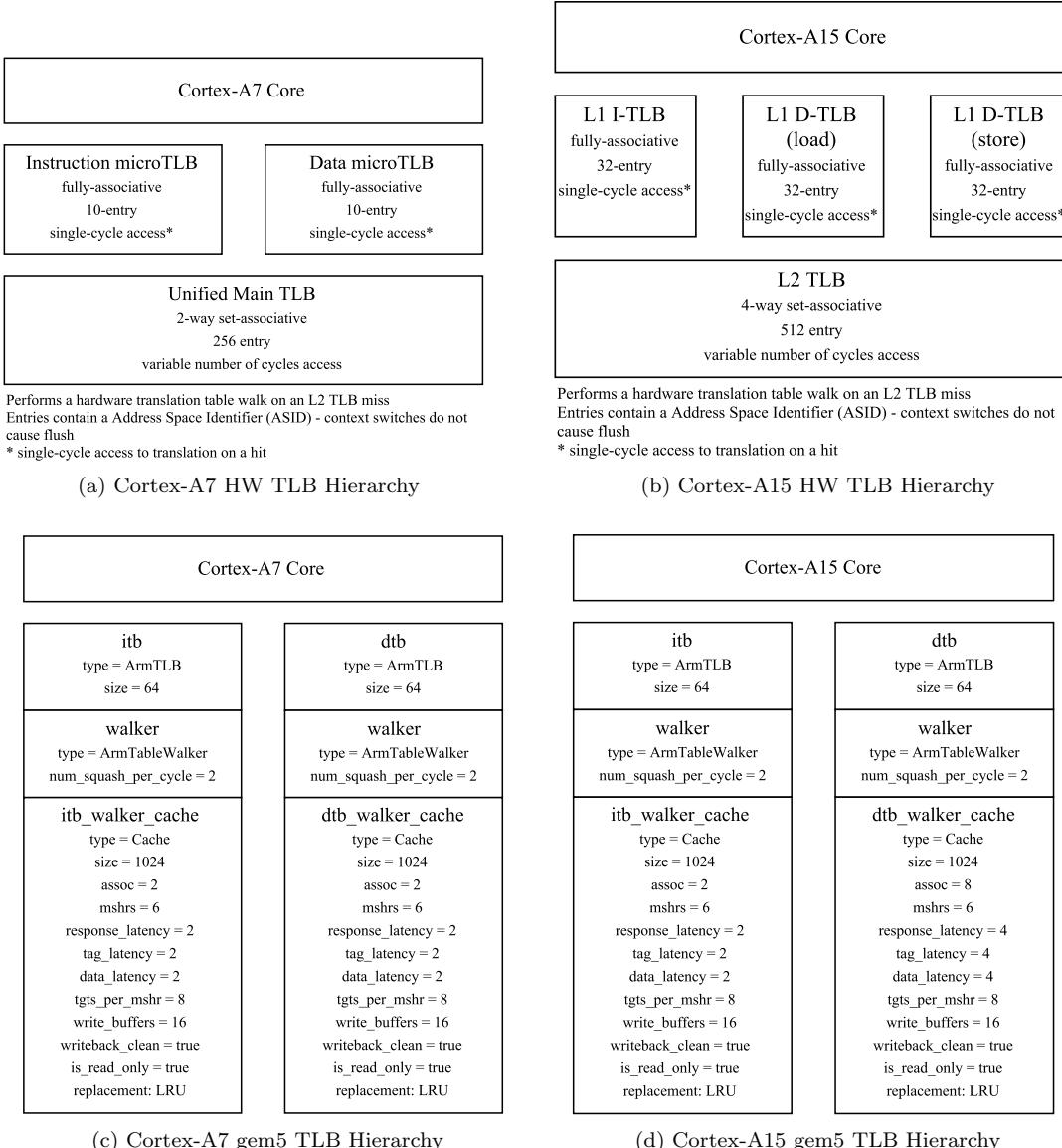

| 6.10 Comparison of the Translate Lookaside Buffer (TLB) Hierarchy between HW and the gem5 for both the Arm Cortex-A7 and Arm Cortex-A15 CPUs in the Samsung Exynos-5422 . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                           | 156 |

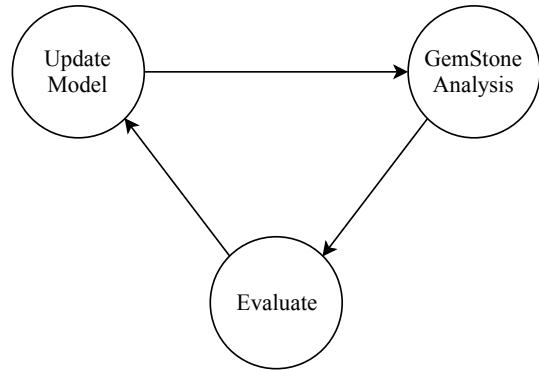

| 6.11 Iterative model improvement . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 157 |

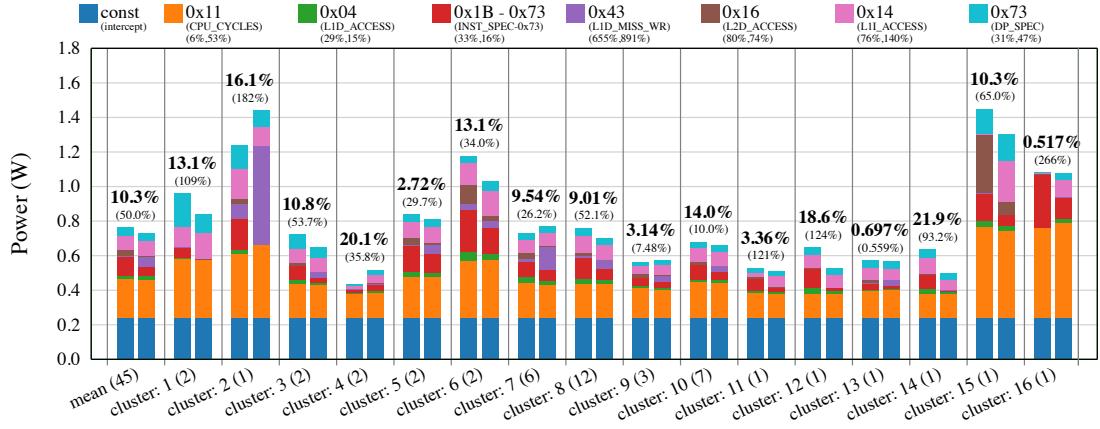

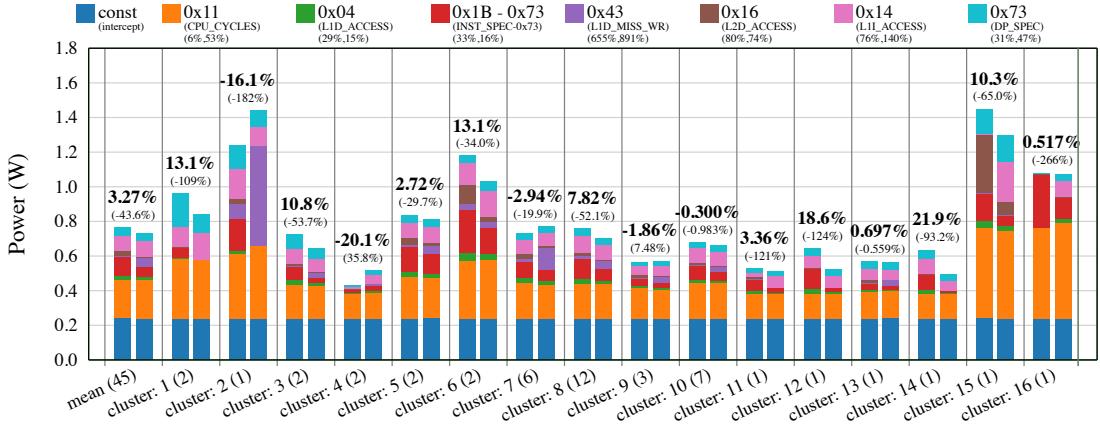

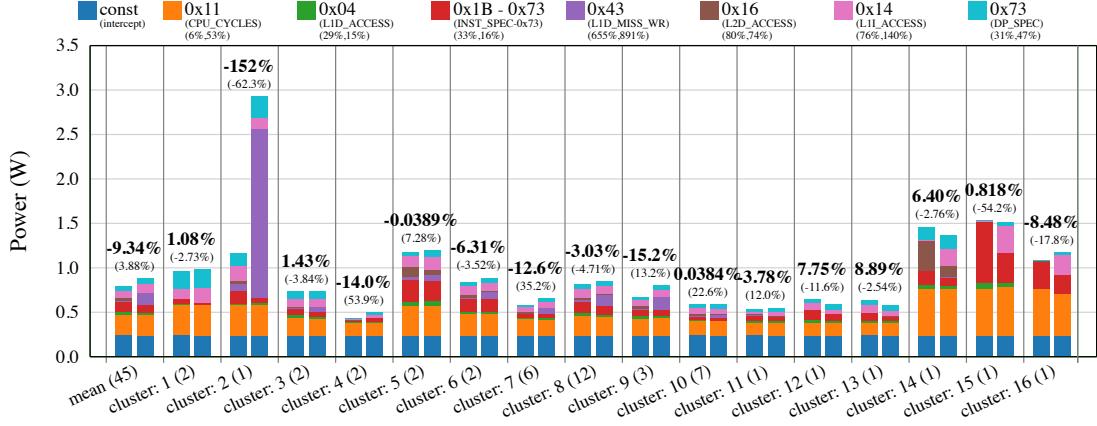

| 6.12 Comparison of estimated power between using the HW PMC events (left bar) and the gem5 events (right bar) for each cluster (number of workloads in cluster in brackets in X-Axis labels) as per Figure 6.5 (Cortex-A15 CPU). The power MAPE is above each bar pair in bold, with the energy MAPE below it in brackets. The bars are colour-coded to show the power contribution from each model component. $f_{clk} = 1$ GHz . . . . .                                                                                                                                                                                  | 158 |

| 6.13 The same graph as shown in Figure 6.12 but with the Power MPEs (bold typeface) and energy MPEs show above the bars. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 158 |

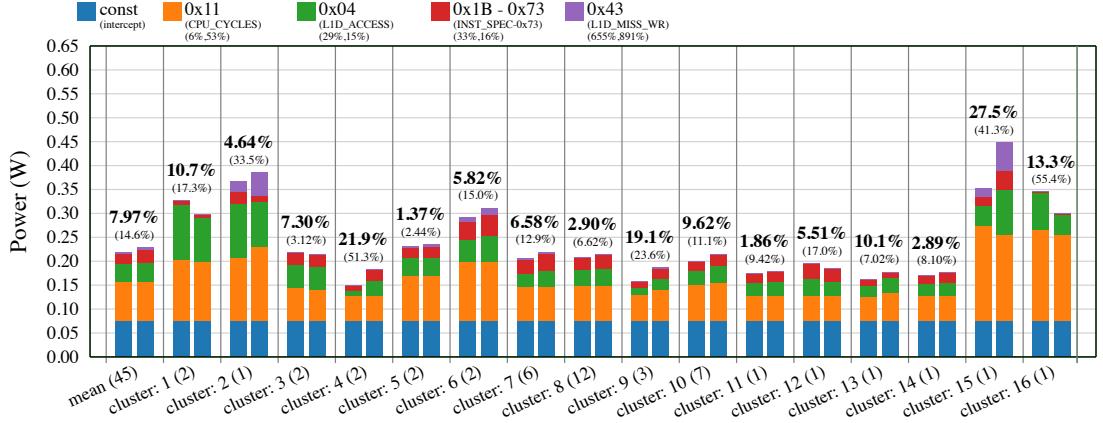

| 6.14 Comparison of estimated power between using the HW PMC events (left bar) and the gem5 events (right bar) for each cluster (number of workloads in cluster in brackets in X-Axis labels) as per Figure 6.5 (Cortex-A7 CPU). The power MAPE is above each bar pair in bold, with the energy MAPE below it in brackets. The bars are colour-coded to show the power contribution from each model component. $f_{clk} = 1$ GHz . . . . .                                                                                                                                                                                   | 159 |

| 6.15 The same graph as shown in Figure 6.15 but with the Power MPEs (bold typeface) and energy MPEs show above the bars. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 159 |

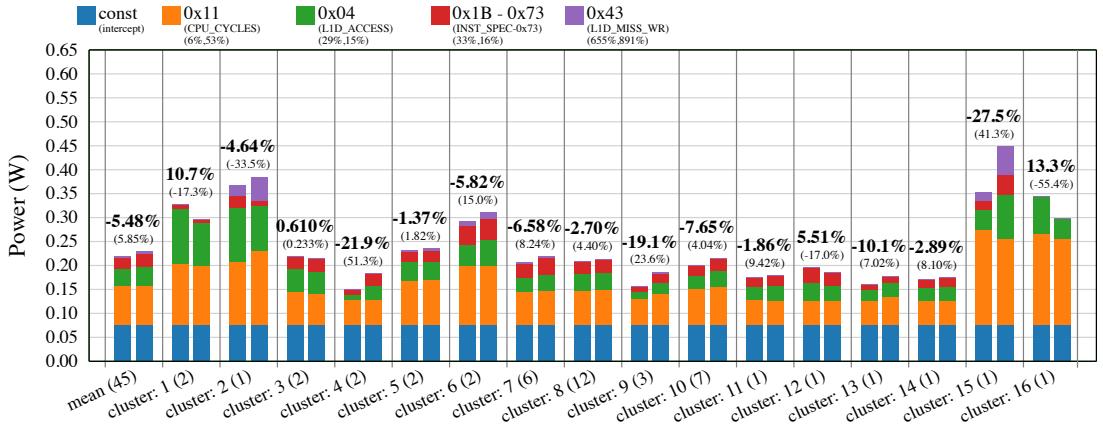

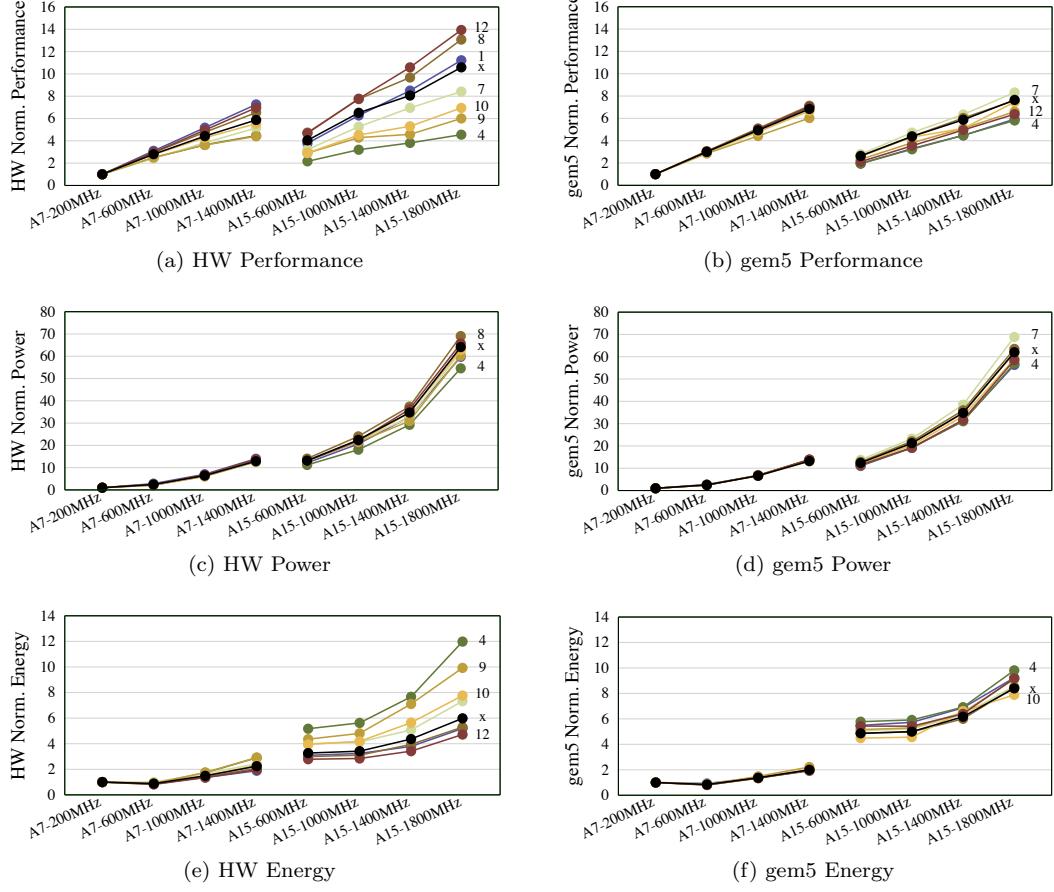

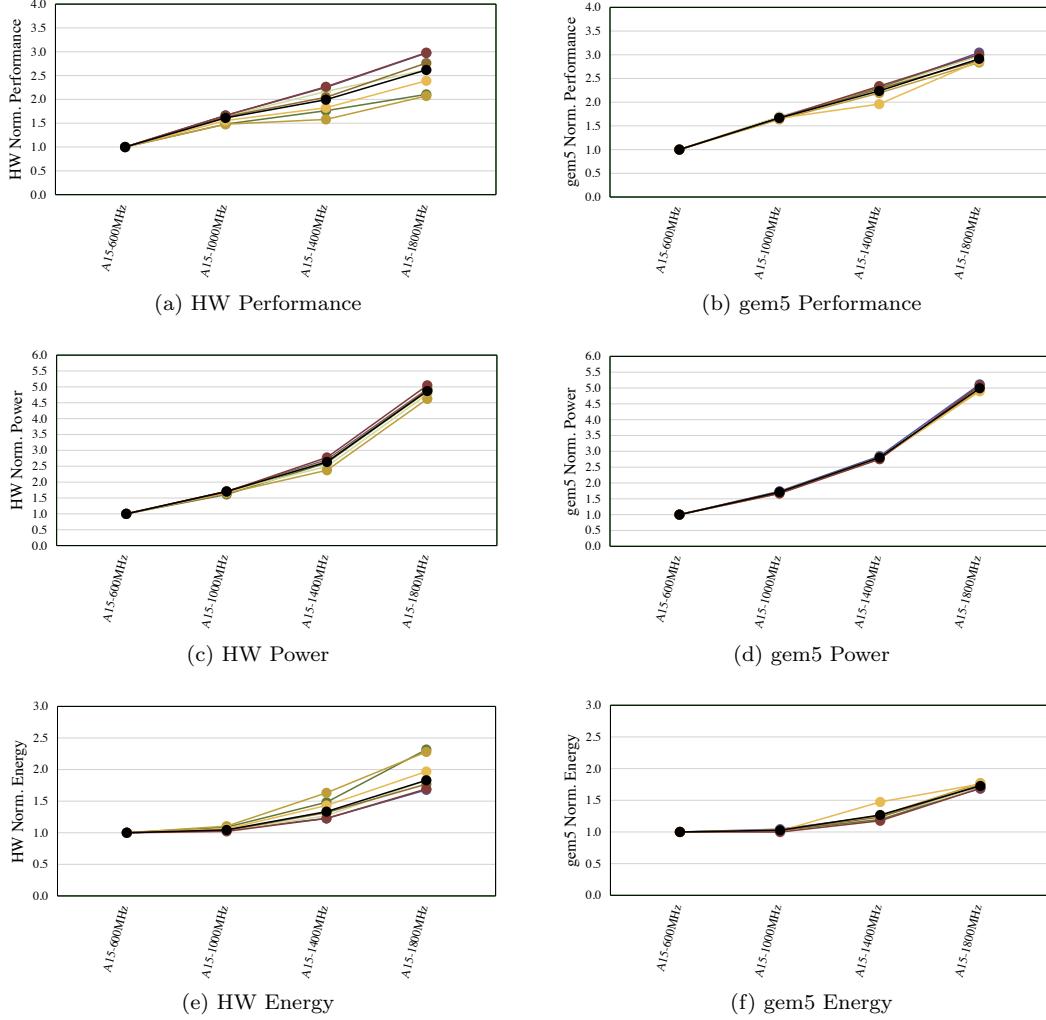

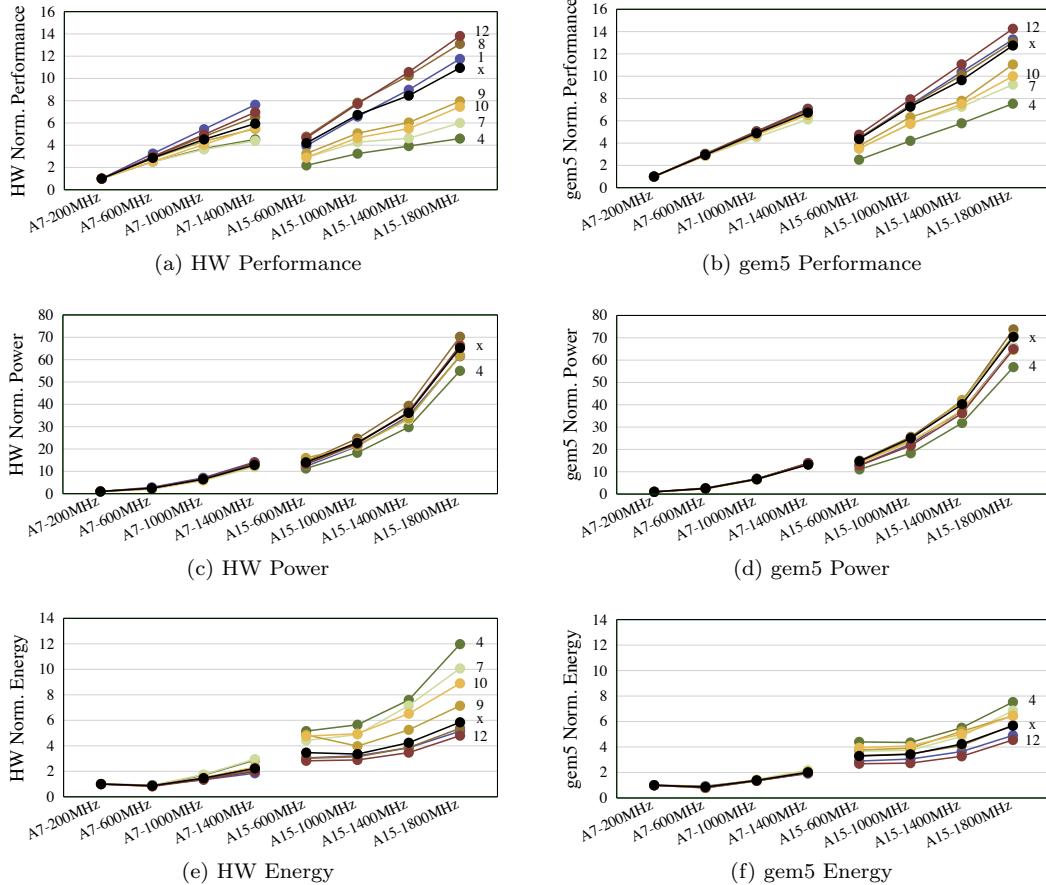

| 6.16 Performance, power and energy scaling normalised to 200 MHz on the Cortex-A7 CPU. Cluster numbers and colours correspond to Figure 6.5. Line x (black line) is the mean of all clusters (excluding cluster 16) . . . . .                                                                                                                                                                                                                                                                                                                                                                                               | 161 |

| 6.17 Performance, power and energy scaling normalised to 600 MHz on the Cortex-A15 CPU. Cluster numbers and colours correspond to Figure 6.5. Line x (black line) is the mean of all clusters (excluding cluster 16) . . . . .                                                                                                                                                                                                                                                                                                                                                                                              | 162 |

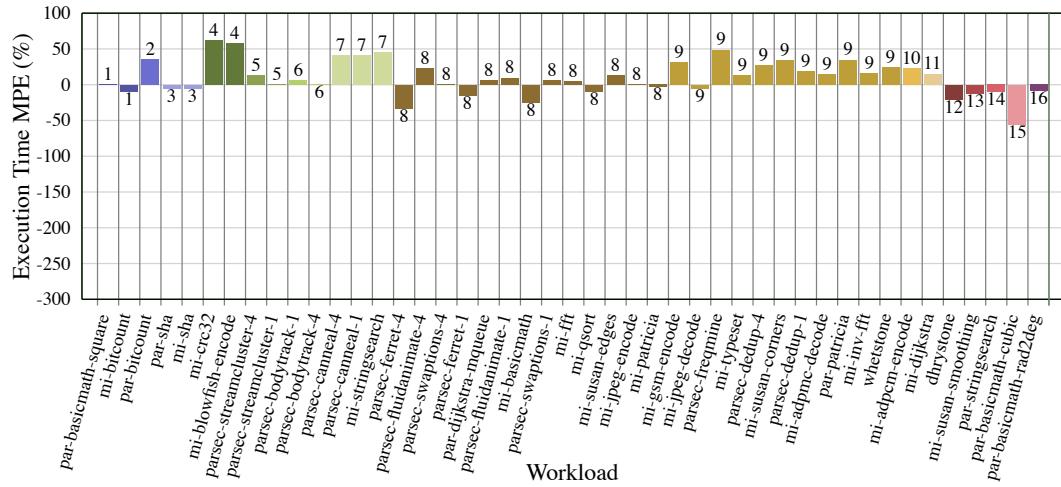

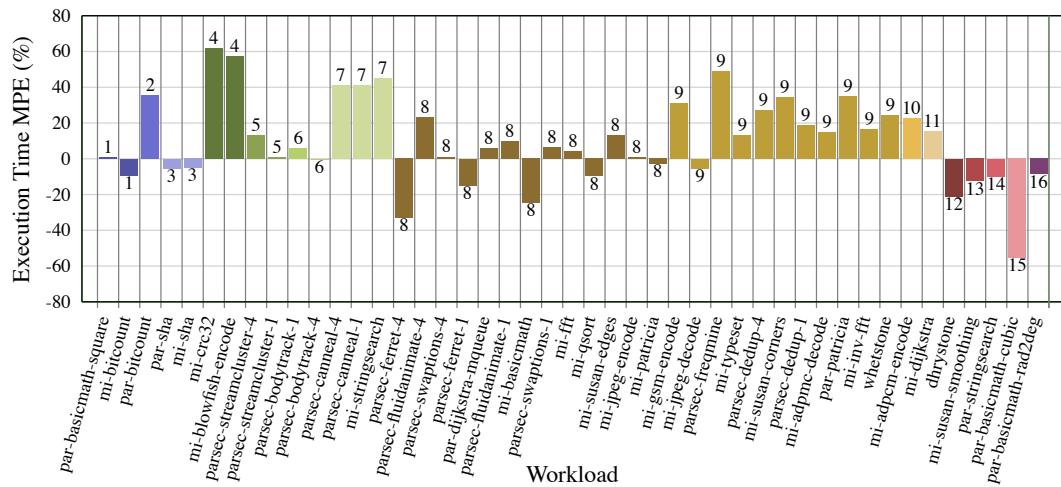

| 6.18 Execution time MPE for each workload running at 1 GHz on the Cortex-A15 (grouped and labelled by workload cluster allocation) before branch predictor modification (reproduction of Figure 6.5 for comparison purposes) . . . . .                                                                                                                                                                                                                                                                                                                                                                                      | 164 |

| 6.19 Equivalent to Figure 6.18 but after branch predictor modification . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 164 |

| 6.20 Equivalent to Figure 6.19 but with adjusted axis scaling for closer inspection of MPE . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 164 |

| 6.21 Correlation of each HW PMC (rate) with the execution time MPE (after branch predictor change), labelled and coloured by clusters derived from HCA of the correlation between PMC events across different workloads . . . . .                                                                                                                                                                                                                                                                                                                                                                                           | 165 |

| 6.22 Total gem5 events normalised with their HW PMC equivalent (bars over 1 indicate that gem5 overestimates the PMC event). Results shown for selected clusters. The mean bars exclude Cluster 16 . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                | 165 |

| 6.23 Comparison of estimated power between using the HW PMC events (left bar) and the gem5 events (right bar) for each cluster (number of workloads in cluster in brackets in X-Axis labels) as per Figure 6.5 (Cortex-A15 CPU, after branch predictor change). The power MAPE is above each bar pair in bold, with the energy MAPE below it in brackets. The bars are colour-coded to show the power contribution from each model component. $f_{clk} = 1$ GHz. Note that the workloads in some clusters have changed and so Figure 6.20 must be checked before comparing with clusters in Figures 6.13 and 6.12 . . . . . | 166 |

| 6.24 Performance, power and energy scaling normalised to 200 MHz on the Cortex-A7 CPU. Cluster numbers correspond to Figure 6.5 . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 166 |

|     |                                                                                                                                         |     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.1 | Diverse observation from memory latency experiments of Section 5.7 . . . . .                                                            | 179 |

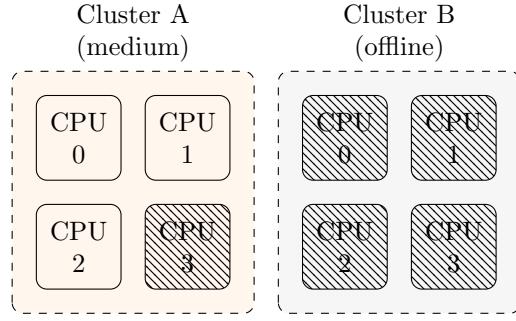

| 7.2 | EAS Motivation: Cluster A at a medium DVFS level with three tasks running on<br>three active cores, while Cluster B is offline. . . . . | 181 |

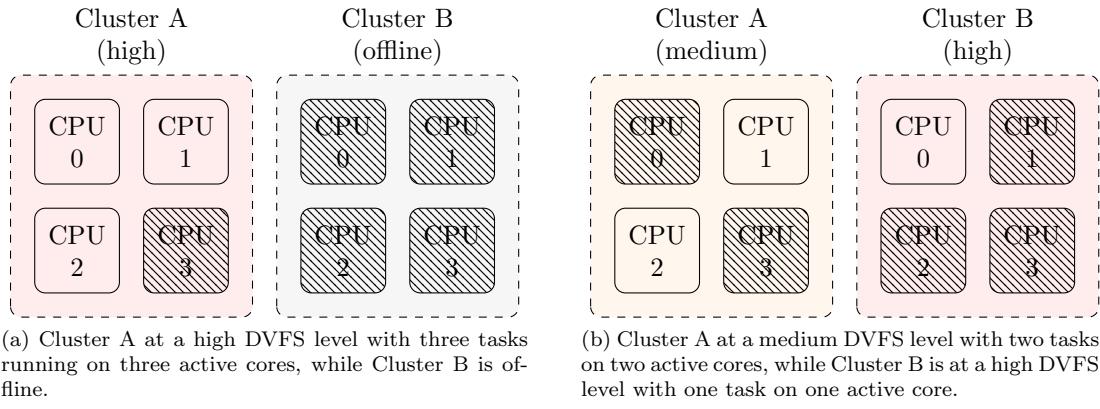

| 7.3 | Two scheduling options to the situation where the task running on CPU0 in Cluster<br>A requires a higher performance. . . . .           | 181 |

# List of Tables

|     |                                                                                                                                                                                       |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | A selection of Arm Cortex-A series processors and the corresponding number of PMU counters . . . . .                                                                                  | 45  |

| 3.2 | Mean, standard deviation and coefficient of variance of all observations for each DVFS level . . . . .                                                                                | 59  |

| 3.3 | Model Coefficients . . . . .                                                                                                                                                          | 62  |

| 3.4 | Model coefficients for the different folds . . . . .                                                                                                                                  | 65  |

| 3.5 | Model coefficients for the different folds with a variable removed . . . . .                                                                                                          | 68  |

| 4.1 | First seven selected events for the Cortex-A15 with their corresponding cluster number and VIF from Stage 1 . . . . .                                                                 | 94  |

| 4.2 | First seven selected events for the Cortex-A15 after Stage 2 transformations . . . . .                                                                                                | 95  |

| 4.3 | First five selected events for the Cortex-A7 with their corresponding cluster number and VIF from Stage 1 . . . . .                                                                   | 95  |

| 4.4 | Cortex-A15 CPU model coefficients, $d = V^2f$ . . . . .                                                                                                                               | 101 |

| 4.5 | Model formulation experiment speedup when exploiting smart model formulation and enhanced stability . . . . .                                                                         | 101 |

| 4.6 | Results for the Cortex-A7 and Cortex-A15 CPU models (final model, trained on all workloads) . . . . .                                                                                 | 111 |

| 4.7 | Cortex-A7 Model Coefficients . . . . .                                                                                                                                                | 112 |

| 4.8 | Model results from k-fold cross-validation . . . . .                                                                                                                                  | 112 |

| 4.9 | Parameters of models included in this comparison . . . . .                                                                                                                            | 116 |

| 5.1 | Comparison of three models using different model equations and under different thermal conditions. . . . .                                                                            | 125 |

| 5.2 | Cortex-A15 Model Coefficients and p-values, grouped into three components: dynamic activity (Dyn. act.) power; constant background dynamic power (BG Dyn.); and static power. . . . . | 126 |

| 5.3 | Model results . . . . .                                                                                                                                                               | 127 |

| 5.4 | Model results from k-fold cross-validation . . . . .                                                                                                                                  | 128 |

| 5.5 | Thermal variables with their electrical equivalents . . . . .                                                                                                                         | 134 |

# Accompanying Material

All data supporting this study are openly available from the University of Southampton repository at <https://doi.org/10.5258/SOTON/D0979>

A website containing information, software tools and experimental data supporting Chapter 4 and Chapter 5 is at <http://www.powmon.ecs.soton.ac.uk>

A website containing information, software tools and experimental data supporting Chapter 6 is at <http://gemstone.ecs.soton.ac.uk>

# Declaration of Authorship

I, Matthew J. Walker, declare that the thesis entitled *Hardware-Validated Performance and Power Modelling of Heterogeneous Multi-Processing Architectures* and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research. I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as: [305, 309, 308, 304, 310].

Signed: \_\_\_\_\_

Date: \_\_\_\_\_

## Acknowledgements

I would, first and foremost, like to thank my supervisors, Bashir Al-Hashimi and Geoff Merrett, for their support, encouragement and valuable feedback throughout the many long years of my PhD studies. I would also like to thank Stephan Diestelhorst and Andreas Hansson for their invaluable guidance and technical insights both during and after my internships in Arm Ltd.

This work would not be possible without the funding and support from the Engineering and Physical Sciences Research Council (EPSRC), Arm Research, the Arm-ECS Research Centre, and the University of Southampton.

I am also grateful to my colleagues for their invaluable support, stimulating discussion, and their company when working at unsociable hours. These include, but are not limited to: Karunakar Reddy Basireddy, Sascha Bischoff, Graeme Bragg, Anup Das, Mauricio Gutierrez Alcala, Kath Kerr, Andy Kufel, Charlie Leech, Luis Maeda-Nunez, Bassem Ouni, Ghaithaa Manla, Andy Mallett, Rishad Shafik, Sheng Yang and Ilias Vougioukas.

With many long days and weekends spent in the office, I am particularly grateful to friends and family for being patient and providing support and reassurance through the most difficult times. In particular, I would like to mention Domenico, Benedetta, Ananya, my brother Rob, and my sister-in-law Liz. Finally, I would like to thank my parents, Catherine and Graham, for their love, support and encouragement, without which I would not have been able to complete this work. I would like to dedicate this thesis to the memory of my grandfather, Anthony Billson, who inspired me to pursue a career in engineering.

# Nomenclature

|          |                                         |

|----------|-----------------------------------------|

| $\ A\ $  | Determinant of Matrix A                 |

| $A^*$    | Conjugate Transpose of Matrix A         |

| $A^+$    | Pseudo-Inverse of Matrix A              |

| $A^T$    | Transpose of Matrix A                   |

| $A^{-1}$ | Inverse of Matrix A                     |

| ANN      | Artificial Neural Network               |

| API      | Application Programming Interface       |

| $\beta$  | Coefficient Vector                      |

| BLUE     | Best Linear Unbiased Estimator          |

| BTB      | Branch Target Buffer                    |

| CMT      | Chip-level Multiprocessing              |

| CPD      | Change Point Detection                  |

| CPI      | Cycles Per Instruction                  |

| CPU      | Central Processing Unit                 |

| CV       | Coefficient of Variation                |

| $D$      | Cook's Distance                         |

| DPM      | Dynamic Power Management                |

| DRAM     | Dynamic Random Access Memory            |

| DVFS     | Dynamic Voltage and Frequency Scaling   |

| $e$      | Residuals Vector                        |

| $E$      | PMC Event Rate divided by CPU Frequency |

| EAS      | Energy-Aware Scheduling                 |

| EDP      | Energy-Delay Product                    |

---

|                       |                                 |

|-----------------------|---------------------------------|

| EPC                   | Energy per Cycle                |

| ESS                   | Explained Sum of Squares        |

| $f_{clk}$             | CPU Frequency                   |

| FPU                   | Floating Point Unit             |

| FS                    | Full-System                     |

| GPU                   | Graphics Processing Unit        |

| GTS                   | Global Task Scheduling          |

| <b><math>H</math></b> | Hat Matrix                      |

| HCA                   | Hierarchical Cluster Analysis   |

| HMP                   | Heterogeneous Multi-Processing  |

| HW                    | Hardware                        |

| <b><math>I</math></b> | Identity Matrix                 |

| $I_{bibt}$            | Band-to-Band Tunnelling Current |

| $I_{leak}$            | Leakage Current                 |

| $I_{ox}$              | Gate-Oxide Current              |

| $I_{sub}$             | Sub-Threshold Current           |

| InO                   | In-Order                        |

| IoT                   | Internet of Things              |

| IP                    | Intellectual Property           |

| IPC                   | Instructions Per Cycle          |

| ISA                   | Instruction Set Architecture    |

| k-NN                  | k-Nearest Neighbours            |

| L1D                   | Level 1 Data                    |

| L1I                   | Level 1 Instruction             |

| L2                    | Level 2                         |

| LRU                   | Least Recently Used             |

| <b><math>M</math></b> | Annihilator Matrix              |

| MAPE                  | Mean Absolute Percentage Error  |

| ML                    | Maximum-Likelihood              |

| MLE                   | Maximum-Likelihood Estimation   |

|              |                                                                 |

|--------------|-----------------------------------------------------------------|

| MOESI        | Modified Owned Exclusive Shared Invalid                         |

| MPE          | Mean Percentage Error                                           |

| MSE          | Mean Squared Error                                              |

| MTTF         | Mean Time to Failure                                            |

| $n$          | Number of observations                                          |

| NN           | Neural Network                                                  |

| NoC          | Network on Chip                                                 |

| OLS          | Ordinary Least Squares                                          |

| OoO          | Out-of-Order                                                    |

| OS           | Operating System                                                |

| $p$          | Number of predictors (features)                                 |

| $\mathbf{P}$ | Projection Matrix (also known as the hat matrix, $\mathbf{H}$ ) |

| $P_{CPU}$    | CPU Power Consumption                                           |

| $P_{dyn}$    | Dynamic Power Consumption                                       |

| $P_{sc}$     | Short-Circuit Power Consumption                                 |

| $P_{static}$ | Static Power Consumption                                        |

| P.I.         | Prediction Interval                                             |

| PCA          | Principle Component Analysis                                    |

| PMC          | Performance Monitoring Counter                                  |

| PMU          | Performance Monitoring Unit                                     |

| PPA          | Performance, Power, Area                                        |

| QoE          | Quality of Experience                                           |

| QoS          | Quality of Service                                              |

| $r$          | Internally Studentised Residuals                                |

| $R^2$        | Coefficient of Determination                                    |

| $\bar{R}^2$  | Adjusted Coefficient of Determination                           |

| RMSE         | Root Mean Squared Error                                         |

| RSS          | Residual Sum of Squares                                         |

| RTL          | Register Transfer Level                                         |

| RTM          | Run-Time Management                                             |

|          |                                                     |

|----------|-----------------------------------------------------|

| $\Sigma$ | Covariance Matrix                                   |

| SER      | Standard Error of Regression                        |

| SMT      | Simultaneous Multithreading                         |

| SoC      | System-on-Chip                                      |

| SPICE    | Simulation Program with Integrated Circuit Emphasis |

| SRAM     | Static Random Access Memory                         |

| SVM      | Support Vector Machine                              |

| T        | Temperature                                         |

| $t$      | Externally Studentised (Deleted) Residuals          |

| TDP      | Thermal Design Power                                |

| TLB      | Translation Lookaside Buffer                        |

| TSS      | Total Sum of Squares                                |

| $V_{DD}$ | CPU Voltage                                         |

| VIF      | Variance Inflation Factor                           |

| VLSI     | Very Large Scale Integration                        |

| WAPE     | Weighted Absolute Percentage Error                  |

| WLS      | Weighted Least Squares                              |

| $X$      | Design Matrix                                       |

| $y$      | Dependent Variable Vector                           |

# Chapter 1

## Introduction

The primary design goal for computer processors has historically been performance, which has reliably improved for many years with the aid of technology scaling. However, technology scaling has slowed and physical limits have caused a reduction in performance improvement and have led to challenges with heat dissipation. This has forced processor architects to look elsewhere for performance gains in order to keep up with industry expectations derived from Moore's Law [256]. Modern processors are therefore heavily optimised towards performance and have complex designs that utilise deep pipelines, memory hierarchies, speculative execution, multiple execution units (superscalar design), out-of-order execution, single instruction, multiple data (SIMD) co-processors, and multi-core designs.

In the last decade there has been a shift in emphasis from performance towards energy efficiency due to the emergence of mobile devices, such as smartphones, tablets, thinner fan-less laptops and, more recently, smart watches. Such devices have limited thermal dissipation and are typically powered from batteries with limited capacity.

By improving CPU energy-efficiency through novel design and careful online management, a mobile processor can achieve higher performance while respecting its Thermal Design Power (TDP), which enables emerging mobile applications such as augmented reality, machine learning, artificial intelligence and 3D photography. Energy-efficient processor designs, initially targeted towards mobile devices, are now also being utilised in data centres to reduce energy bills and the cost spent on cooling systems.

The following two key areas provide opportunities for improving performance and energy efficiency despite the challenges in technology scaling:

1. Run-time system optimisation that controls task scheduling and online energy management mechanisms effectively to achieve the desired level of user experience while simultaneously respecting thermal and power constraints, and maximising energy-efficiency;

2. Architectural, micro-architectural and system-level design innovations that optimise for modern workload demands and exploit new technologies.

Accurate performance, power, thermal, and energy models are required for both guiding run-time system optimisation and exploring innovative software and hardware improvements.