UNIVERSITY OF SOUTHAMPTON

FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

Electronics and Computer Science

**Ultra-Low-Power Sequential Circuit Design for Near-Threshold

Voltage System**

by

**Cai Yunpeng**

Thesis for the degree of Doctor of Philosophy

Supervisor: Dr Tom J Kazmierski

Dr Alex Weddell

March 7, 2019

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

Electronics and Computer Science

Doctor of Philosophy

ULTRA-LOW-POWER SEQUENTIAL CIRCUIT DESIGN FOR

NEAR-THRESHOLD VOLTAGE SYSTEM

by **Cai Yunpeng**

Near-Threshold Voltage (NTV) techniques have been demonstrated to reduce energy consumption significantly by decreasing the supply voltage approaching the threshold voltage while maintaining the scaling characteristics of Super-Threshold operation. The primary challenge in applications of NTV operation is to ensure robustness, tolerance against variability and resilience against error issues at low voltage. This research focuses on addressing the design challenges in sequential logic at NTV by providing various novel circuits, for improving the SoA designs regarding power, area, robustness, and reliability at NTV.

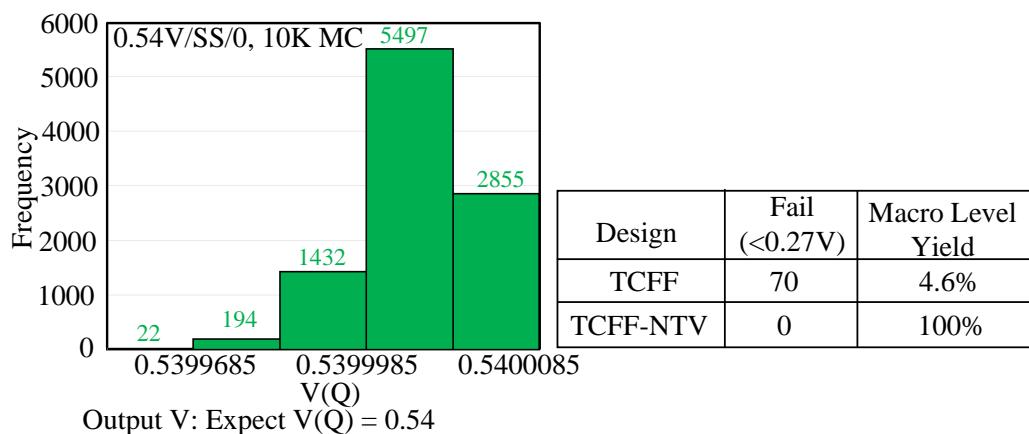

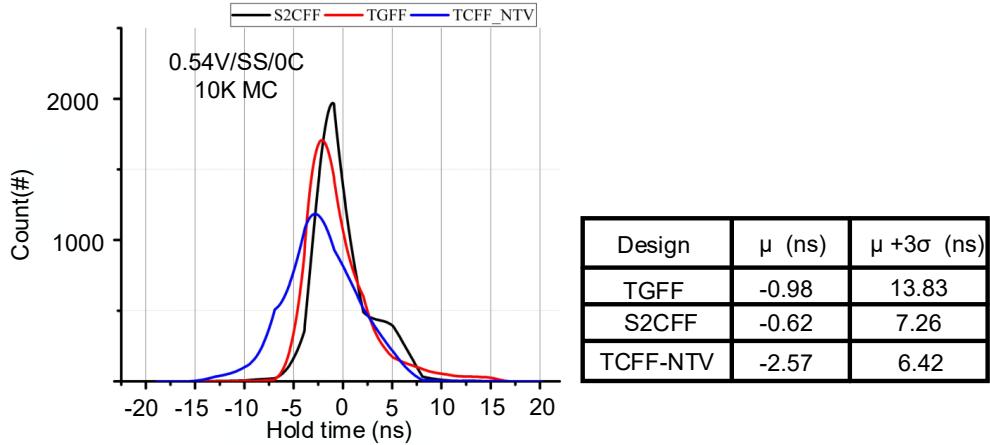

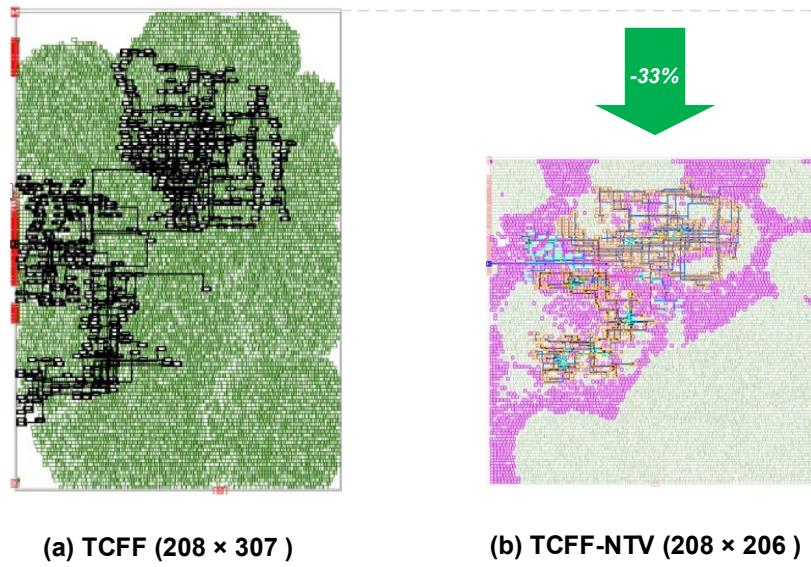

The first contribution of this thesis is the analysis of prominent types of state-of-the-art Single-Phase Clocked (SPC) FFs and analyses their suitability for NTV operation from transistor level to system level. The yield and the design limitation issue in previously published design, TCFF, is highlighted and addressed by proposing a new circuit topology, named TCFF-NTV. The proposed TCFF-NTV improved the yield of the original TCFF by 95% and 65% power reduction compared to TCFF-based design in system level. The second contribution of the thesis is proposing the 18TSPC, a new topology of fully-static contention-free Single-Phase Clocked (SPC) Flip-Flop (FF) with only 18 transistors, the lowest number reported for this type. It achieves 20% cell area reduction compared to the conventional TGFF. Chip experimental measurements at 0.6V, 25°C show that, compared to TGFF, the proposed 18TSPC achieves reductions of 68% and 73% in overall and clock dynamic power, respectively, and 27% lower leakage. Besides the 18TSPC, 3 more ULP SPC FFs are proposed based on the 18TSPC for providing various solutions for designers to target different ULP design requirements at NTV. The third thesis is the development of a novel Single Event Upset(SEU)-resilient Double Master-Latch Transmission Gate FF (DMTGFF), which is capable of self-detection and self-correction of circuit-level SEU errors. And it can operate in SEU error-free with 0.5V supply voltage (NTV level). The result shows that, compared to the widely used Triple Modular Redundant (TMR) technique, the proposed DMTGFF achieves 15% performance improvement and 25% power reduction.

# Contents

|                                                                      |             |

|----------------------------------------------------------------------|-------------|

| <b>Acknowledgements</b>                                              | <b>xvii</b> |

| <b>Nomenclature</b>                                                  | <b>xix</b>  |

| <b>1 Introduction</b>                                                | <b>1</b>    |

| 1.1 Research Justification . . . . .                                 | 4           |

| 1.2 Research Questions . . . . .                                     | 5           |

| 1.3 Research Contributions . . . . .                                 | 6           |

| 1.4 Publications . . . . .                                           | 8           |

| <b>2 Literature Review</b>                                           | <b>9</b>    |

| 2.1 Near-Threshold Voltage Computing . . . . .                       | 9           |

| 2.1.1 Power/Energy Consumption and Dynamic Voltage Scaling . . . . . | 9           |

| 2.1.2 Technique Definitions . . . . .                                | 13          |

| 2.1.3 NTV Design Challenges . . . . .                                | 14          |

| 2.1.4 State-of-the-Art Circuit Level NTV Techniques . . . . .        | 17          |

| 2.2 Sequential Logic Circuits . . . . .                              | 19          |

| 2.2.1 Clocked Memory Logic Elements . . . . .                        | 20          |

| 2.2.2 Flip Flop Timing Characteristics . . . . .                     | 23          |

| 2.2.3 State-of-the-Art Flip-Flops Design . . . . .                   | 23          |

| 2.3 Process Variation and Radiation-Induced Errors . . . . .         | 27          |

| 2.3.1 Process Variation . . . . .                                    | 27          |

| 2.3.2 Radiation Induced Errors in Electronic Devices . . . . .       | 29          |

| 2.3.3 The Error Tolerant Circuits . . . . .                          | 33          |

| 2.4 Concluding Remarks . . . . .                                     | 39          |

| <b>3 Analysis and Development of SPC FFs for NTV applications</b>    | <b>43</b>   |

| 3.1 Analysis of State-of-the-Art SPC FFs . . . . .                   | 45          |

| 3.2 Evaluation of State-of-the-Art SPC FFs Implementation . . . . .  | 47          |

| 3.2.1 Multiple Datapaths and Retention Loops . . . . .               | 48          |

| 3.2.2 Master-Slave Interface . . . . .                               | 50          |

| 3.2.3 Transistor Stacks in datapath . . . . .                        | 52          |

| 3.3 Considerations For System Synthesis . . . . .                    | 54          |

| 3.3.1 Power, Performance, Area . . . . .                             | 56          |

| 3.3.2 Yield Analysis . . . . .                                       | 57          |

| 3.4 Design Requirement of the NTV SPC FF . . . . .                   | 58          |

| 3.5 A modified TCFF circuit for NTV operation . . . . .              | 58          |

| 3.5.1 Proposed TCFF-NTV design for NTV operation . . . . .           | 59          |

---

|          |                                                                         |            |

|----------|-------------------------------------------------------------------------|------------|

| 3.5.2    | Comparative analysis of the proposed TCFF-NTV                           | 61         |

| 3.5.3    | Variability and yield analysis                                          | 62         |

| 3.5.4    | System Synthesis Level Analysis                                         | 65         |

| 3.6      | Concluding Remarks                                                      | 65         |

| <b>4</b> | <b>Ultra-Low Power Single Phase Clocked Flip-Flops Design</b>           | <b>69</b>  |

| 4.1      | Proposed Single-Phase Clocked FF                                        | 71         |

| 4.1.1    | SPC FF design approach                                                  | 71         |

| 4.1.2    | SPC FF circuitry reduction                                              | 72         |

| 4.1.3    | 18TSPC operation and timing path analysis                               | 74         |

| 4.2      | Simulation Results and Analysis                                         | 76         |

| 4.3      | Experimental Validation                                                 | 84         |

| 4.4      | Discussion of 18TSPC                                                    | 89         |

| 4.5      | Extending SPC FFs design based on 18TSPC                                | 91         |

| 4.5.1    | The 20-Transistors SPC FF Design                                        | 91         |

| 4.5.2    | The 19 and 21-Transistor SPC FF Design                                  | 93         |

| 4.6      | Concluding Remarks                                                      | 102        |

| <b>5</b> | <b>Flip Flop Soft Error Estimation and SEU resilient Design for NTV</b> | <b>105</b> |

| 5.1      | Critical Charge and Soft Error Rate Estimation                          | 106        |

| 5.2      | The Proposed Error-Aware Flip Flop Design                               | 110        |

| 5.2.1    | Simulation Results of the proposed EAFF                                 | 111        |

| 5.3      | The Proposed Soft Error Resilient Flip Flop Design                      | 113        |

| 5.3.1    | Analysis of the $Q_{critical}$ Level of the TGFF                        | 114        |

| 5.3.2    | Design of the Dual-Master Latch Transmission Gate Flip-Flop             | 116        |

| 5.3.3    | Simulation Results and Analysis                                         | 123        |

| 5.4      | Concluding Remarks                                                      | 127        |

| <b>6</b> | <b>Conclusion and Future Work</b>                                       | <b>129</b> |

| 6.1      | Summary of the work                                                     | 129        |

| 6.2      | Future Work Direction                                                   | 131        |

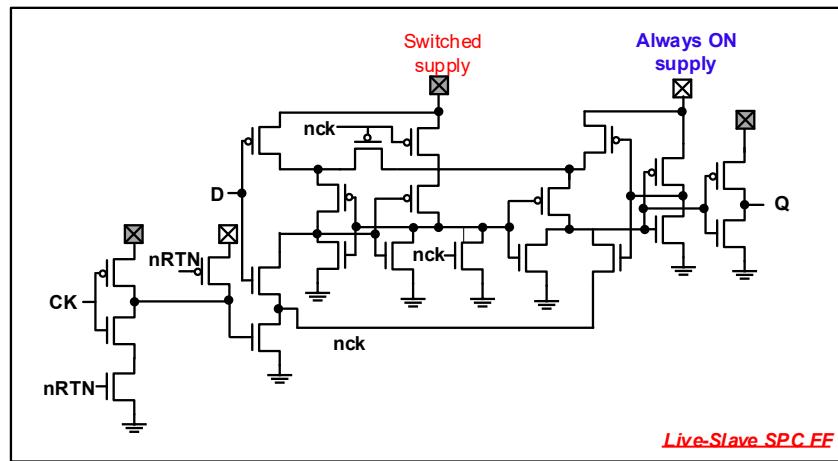

| 6.2.1    | Live-Slave Flip Flop for Further Power Reduction                        | 131        |

| 6.2.2    | Reliability Enhancement for SPC FFs                                     | 132        |

| <b>A</b> | <b>Appendix: Shift Register Verilog Model</b>                           | <b>133</b> |

| <b>B</b> | <b>Appendix: Test Board Information</b>                                 | <b>137</b> |

| B.1      | Address assignment                                                      | 137        |

| <b>C</b> | <b>Appendix: Chip Measurement Programming</b>                           | <b>141</b> |

| C.1      | Shift register general functionality test                               | 141        |

| C.2      | Shift register $V_{min}$ measurement                                    | 143        |

| C.3      | 18TSPC Shift Register Power VS VDD measurement                          | 146        |

| C.4      | Reference TGFF Shift Register Power VS VDD measurement                  | 148        |

| C.5      | 18TSPC CK Power VS VDD measurement                                      | 151        |

| C.6      | Ref TGFF CK Power VS VDD measurement                                    | 153        |

| C.7      | 18TSPC Shift Register power VS activity rate measurement                | 154        |

| C.8      | Ref TGFF Shift Register power vs. activity rate measurement             | 157        |

|                                                      |            |

|------------------------------------------------------|------------|

| C.9 AES scanin/out at different VDD . . . . .        | 159        |

| C.10 AES LBIST based $F_{max}$ measurement . . . . . | 161        |

| C.11 AES LBIST based $V_{min}$ measurement . . . . . | 163        |

| C.12 AES Leakage power VS VDD measurement . . . . .  | 164        |

| <b>References</b>                                    | <b>167</b> |

# List of Figures

|      |                                                                                                                                                                                                                                           |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

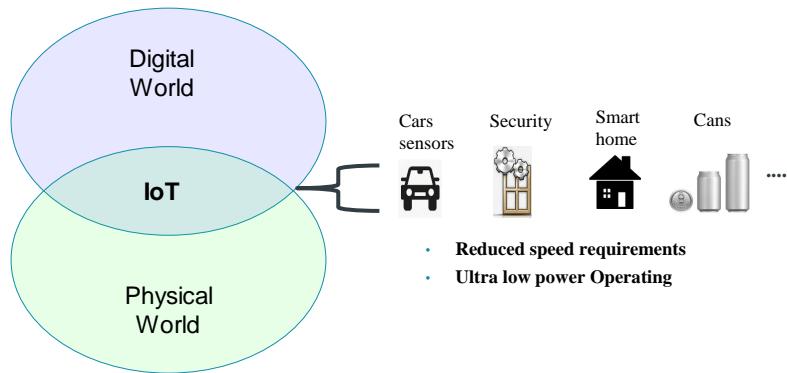

| 1.1  | Internet-of-Things (IoT) is the extention of the digital world into the physical world [6].                                                                                                                                               | 1  |

| 1.2  | The world's smallest ARM-based microcontroller: Kinetis KL03 by Freescale(reproduced from [7]).                                                                                                                                           | 2  |

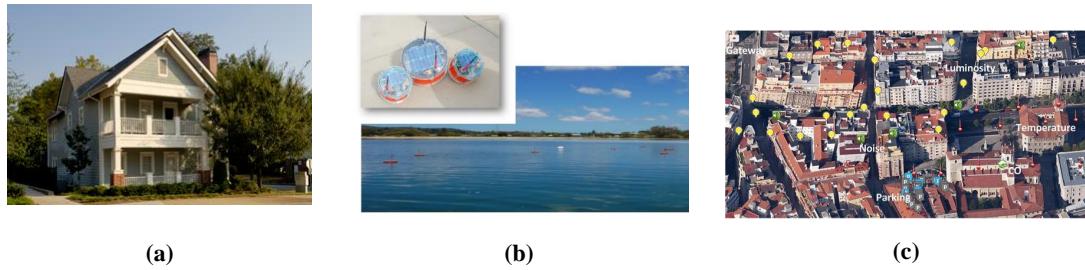

| 1.3  | Some existing IoT platforms, (a) a small sized network, smart home/of-<br>fice project, Aware Home [11], (b) a large sized network, smart water project: SEMAT[12], (c) a medium sized network, smart city project:<br>Smart Santande[13] | 2  |

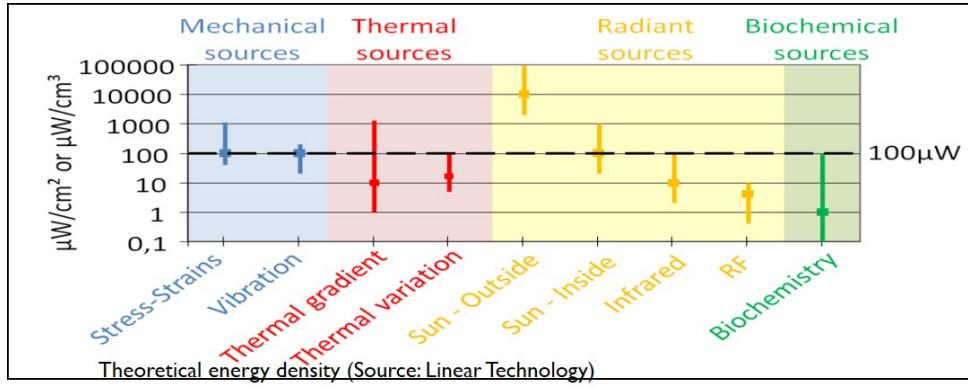

| 1.4  | The power delivered from the state-of-the-art energy harvest technique is in order of $100 \mu W/cm^2$ [6][15].                                                                                                                           | 3  |

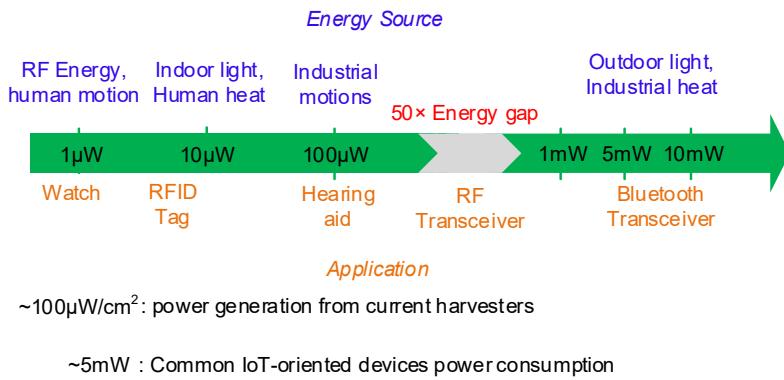

| 1.5  | The energy source and power consumption of devices map [16].                                                                                                                                                                              | 3  |

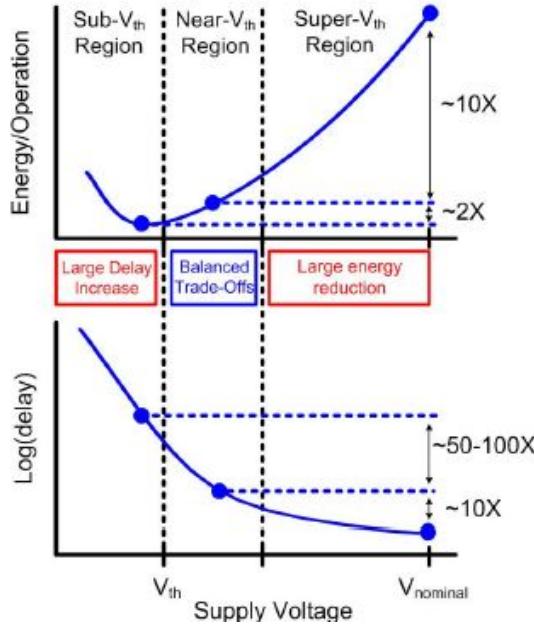

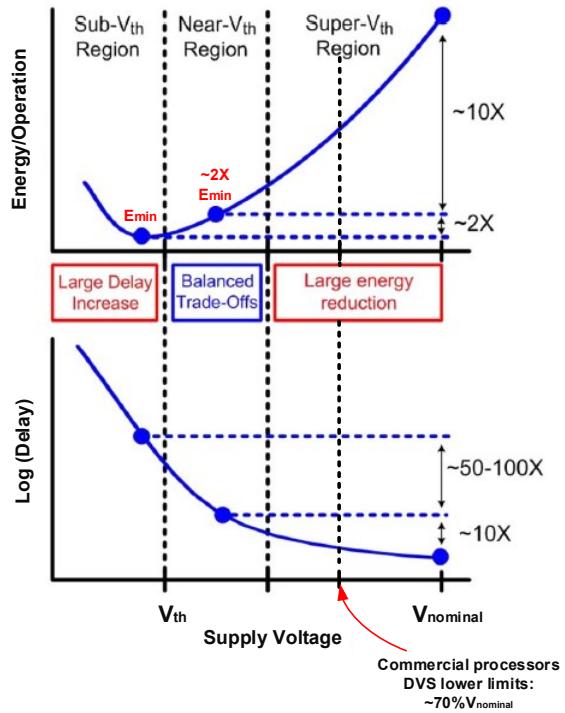

| 1.6  | Energy consumption and delay in different supply voltage [18].                                                                                                                                                                            | 4  |

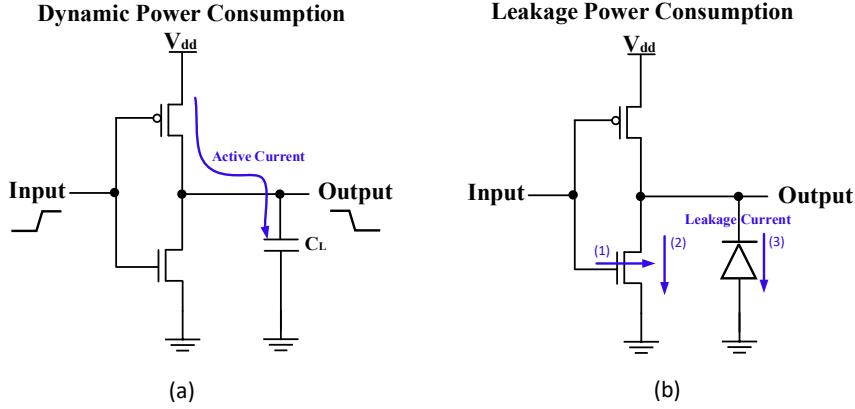

| 2.1  | Power consumption in CMOS digital circuit, sample circuit: INV Gate.<br>(a) Dynamic power consumption. (b) Leakage power consumption.                                                                                                     | 10 |

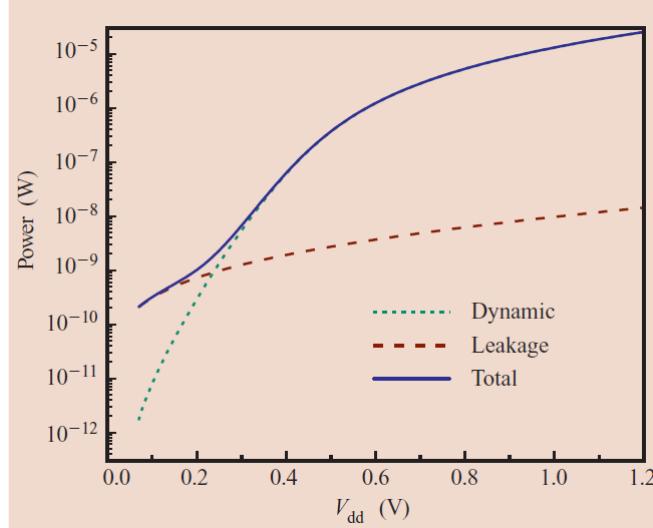

| 2.2  | Power consumption against the supply voltage $V_{dd}$ [45].                                                                                                                                                                               | 11 |

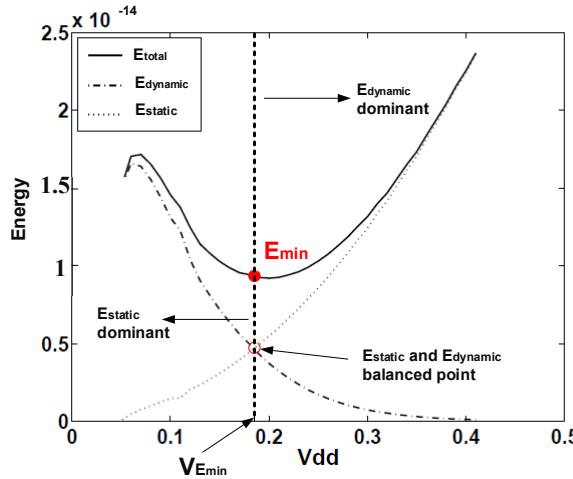

| 2.3  | Energy consumption against the supply voltage $V_{dd}$ [49].                                                                                                                                                                              | 12 |

| 2.4  | The Near-threshold computing operation region [18].                                                                                                                                                                                       | 13 |

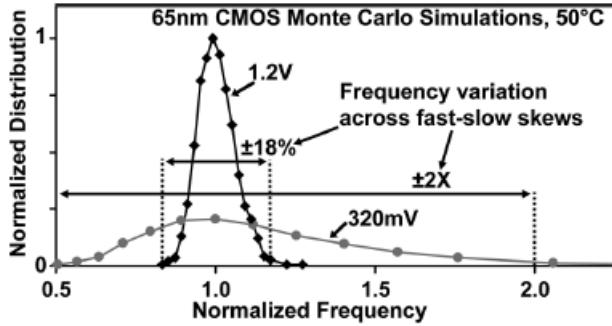

| 2.5  | The frequency distribution in typical process at nominal supply voltage (1.2V) and the frequency distribution in fast-slow die at NTV (320mV) [58].                                                                                       | 15 |

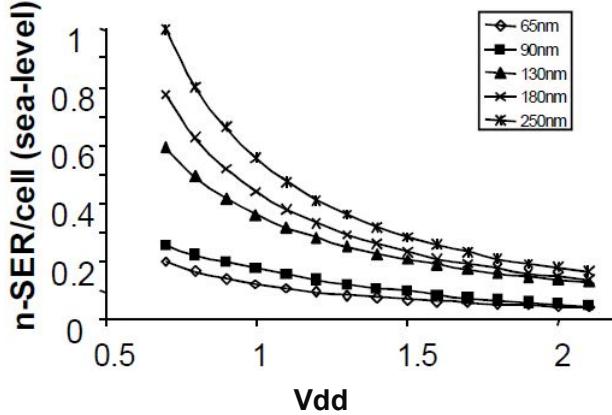

| 2.6  | The correlation between supply voltage and soft error rate in different technology nodes [30].                                                                                                                                            | 16 |

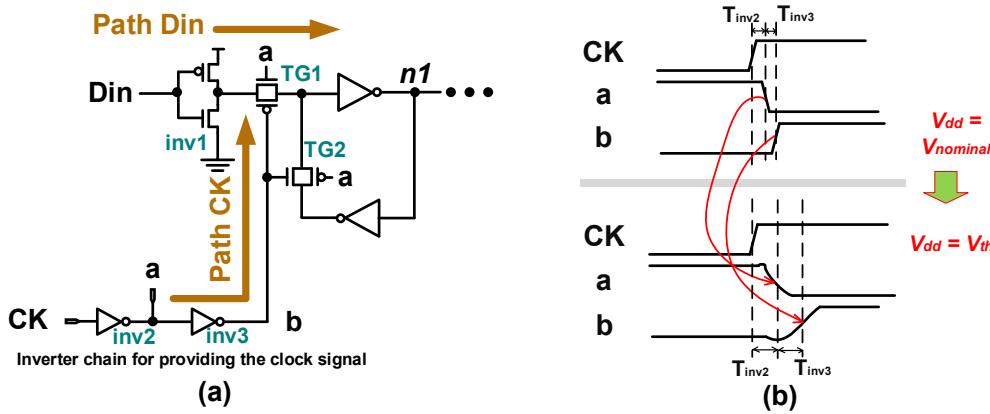

| 2.7  | (a) Hold Time ( $T_{hold}$ ) path analysis of the TGFF [65]. (b) The waveform of the internal clock signal inverter chain with $V_{dd} = V_{nominal}$ and $V_{dd} = V_{th}$ .                                                             | 16 |

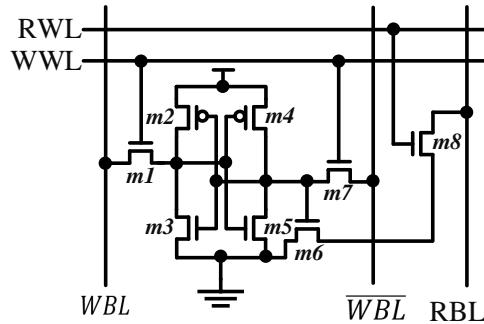

| 2.8  | The schematic diagram of the 8T SRAM [67].                                                                                                                                                                                                | 17 |

| 2.9  | The schematic diagram of the SEFF [69].                                                                                                                                                                                                   | 18 |

| 2.10 | The schematic diagram of the Static Contention-free Single-phase-Clocked Flip Flop (S2CFF) [65].                                                                                                                                          | 19 |

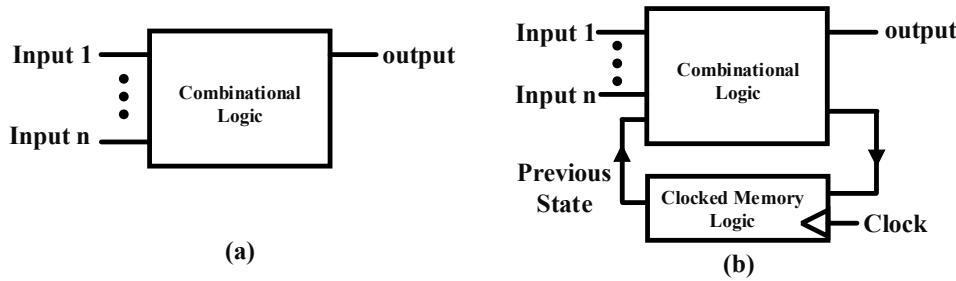

| 2.11 | Abstract of (a) a pure combinational logic circuit. (b) Sequential logic circuit example: state machine.                                                                                                                                  | 20 |

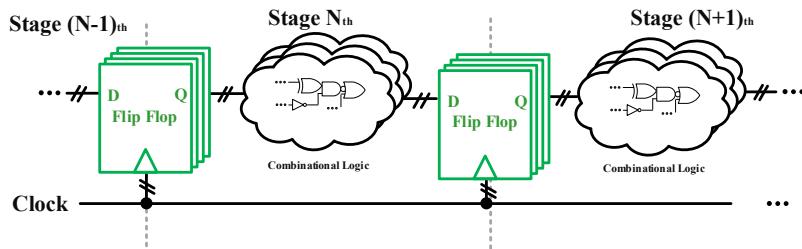

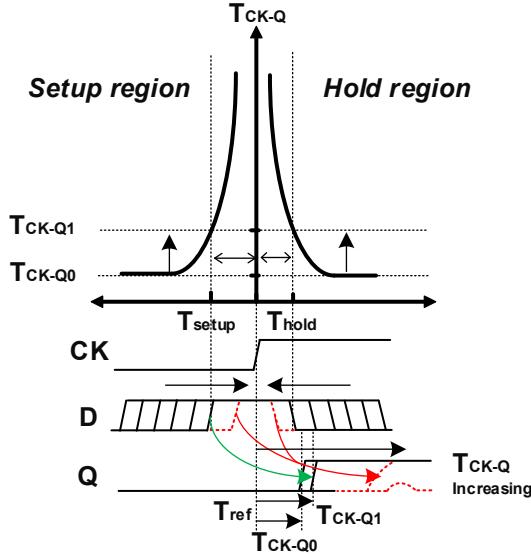

| 2.12 | Diagram showing a pipeline structure system.                                                                                                                                                                                              | 20 |

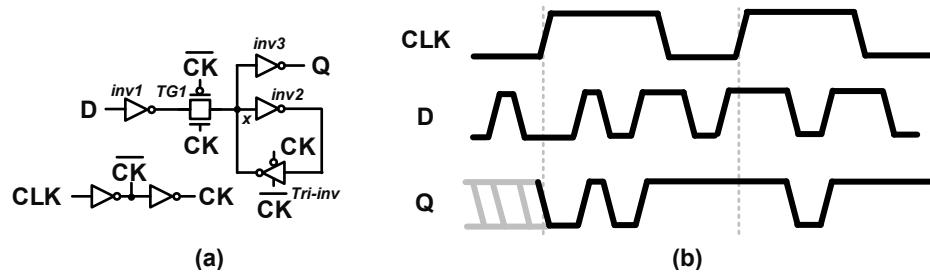

| 2.13 | (a) Schematic diagram of a typical D Latch [20]. (b) Operation waveform of the D Latch                                                                                                                                                    | 21 |

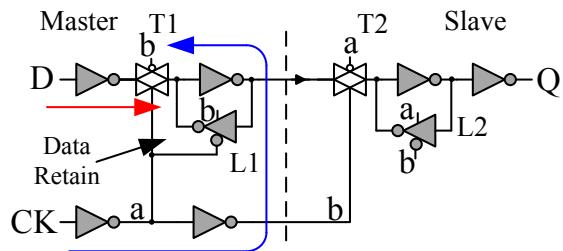

| 2.14 | (a) Transistor level schematic diagram of Transmission Gate Flip Flop (TGFF) [76][78]. (b) Internal nodes waveform of TGFF.                                                                                                               | 22 |

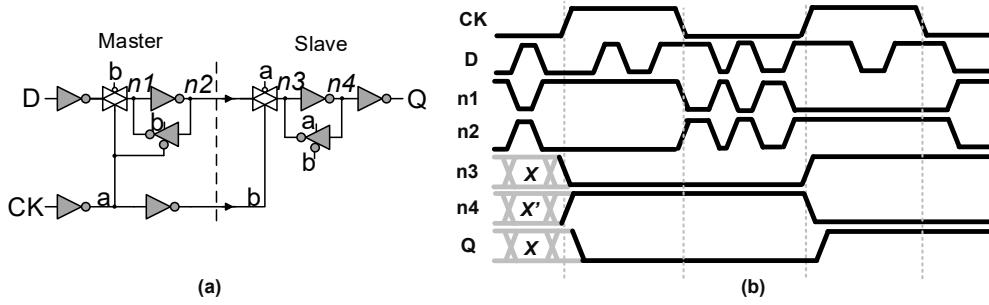

| 2.15 | FF timing characteristics diagram [85].                                                                                                                                                                                                   | 23 |

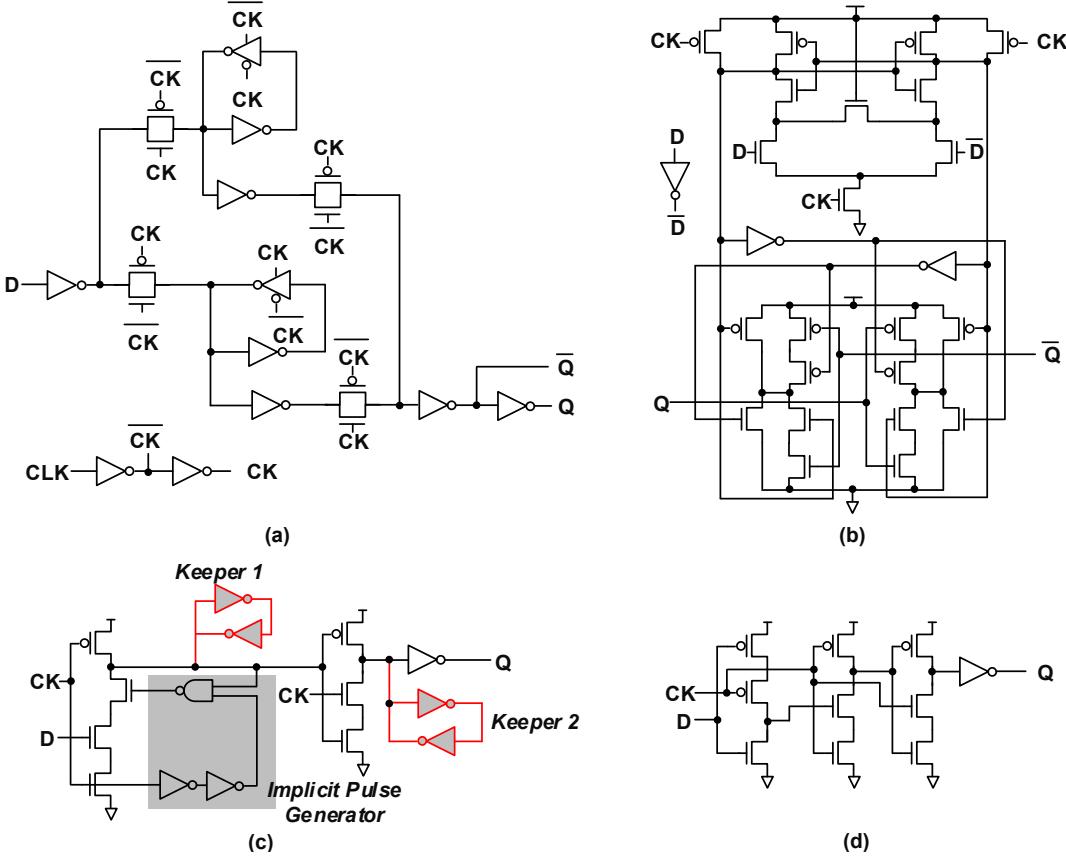

| 2.16 | Other classes of FFs structures and its representative designs: (a)DET-TGLM [86]. (b)MSAFF [87]. (c)SDFF [88]. (d)TSPC (TSPC) [89].                                                                                                       | 24 |

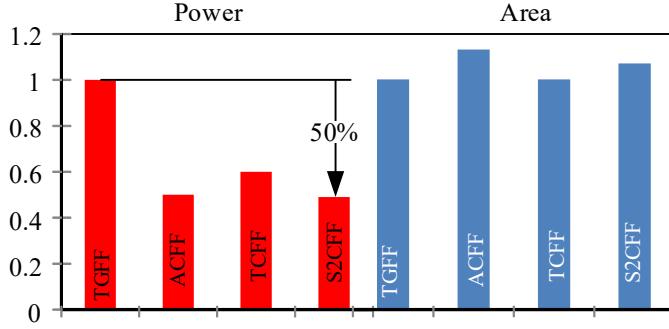

| 2.17 | Claimed benefits of SoA Single Phase Flip-Flops.[65, 108–110]                                                                                                                                                                             | 26 |

|                                                                                                                                                                                                                                                                                                               |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

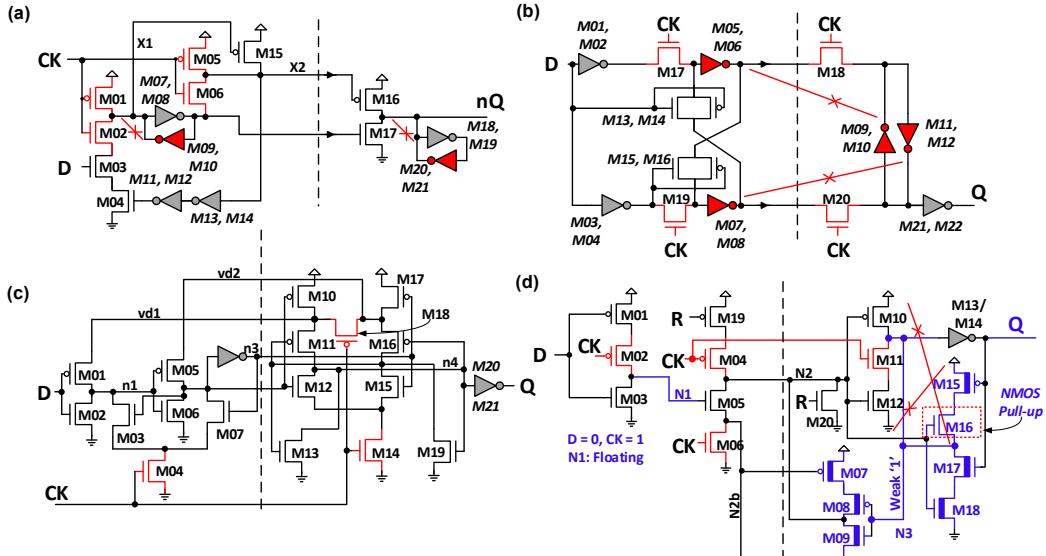

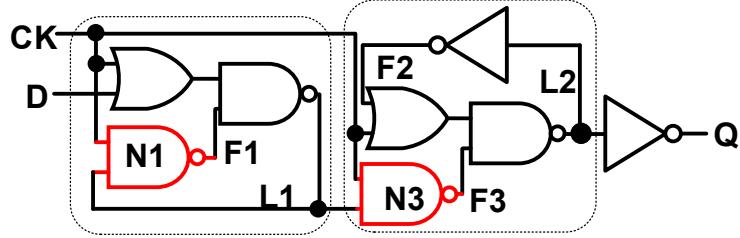

| 2.18 Schematic of SoA SPC FFs, highlighting master-slave isolation, contention paths and clock transistors. (a) Cross Charge-Control FF (XCFF) [108], (b) Adaptive-Coupling FF (ACFF) [109], (c) Topologically-Compressed FF (TCFF) [110]. (d) True-Single-Phase-Clock 18T FF (20T with Reset) [111]. . . . . | 26 |

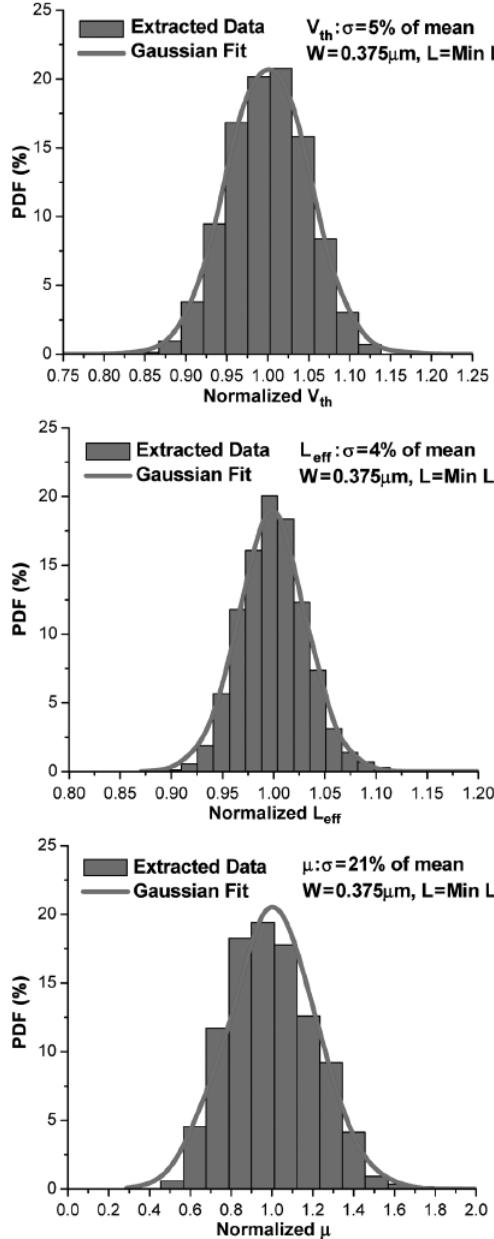

| 2.19 Process variation induced parameter variation in Threshold Voltage ( $V_{th}$ ), Channel Length ( $L_{eff}$ ) and the carrier mobility ( $\mu$ ) in 65nm technology node test chip with standard deviation ( $\sigma$ ) of 5%, 4% and 21% [112]. . . . .                                                 | 28 |

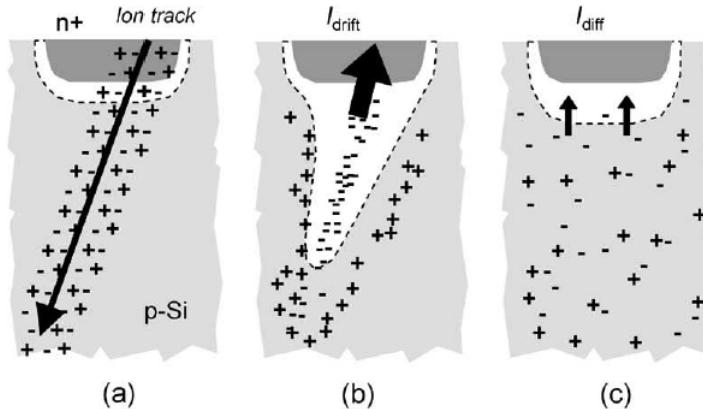

| 2.20 (a) Onset of the heavy ion hitting the silicon substrate; (b) Drift collection process/prompt charge collection. (c) Ion diffusion process [124]. . . . .                                                                                                                                                | 31 |

| 2.21 The transient current pulse is generated due to the ion strikes [124]. . . . .                                                                                                                                                                                                                           | 31 |

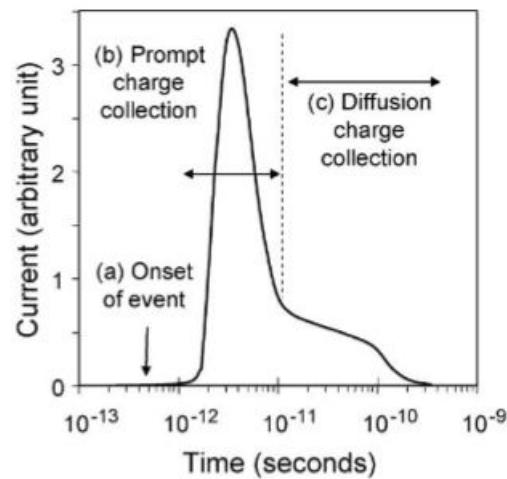

| 2.22 (a)The block diagram of the TMR architecture [116]. (b) The gate level schematic of the TMR Voting Block. . . . .                                                                                                                                                                                        | 34 |

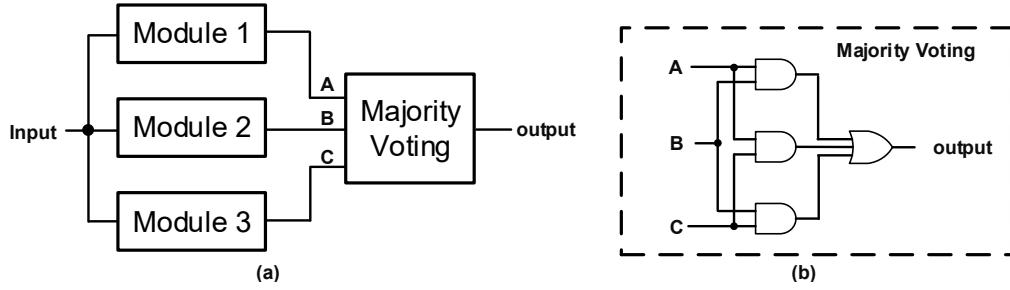

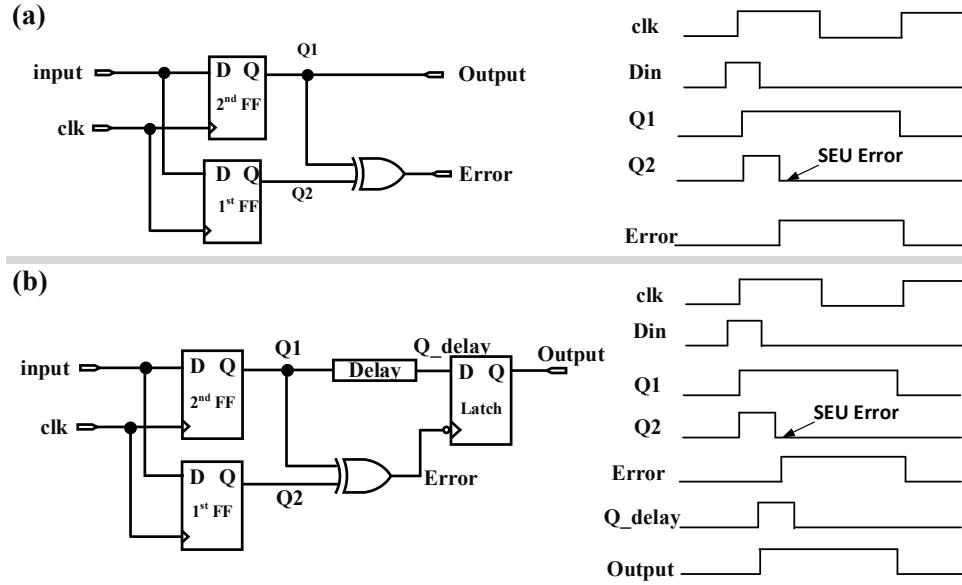

| 2.23 (a) Gate level schematic of the Dual Modular Redundancy (DMR) Architecture and the Timing diagram of the DMR circuit [135]. (b) The DMR circuit with an error recovery function and the Timing diagram of the DMR circuit with an error recovery function [135]. . . . .                                 | 35 |

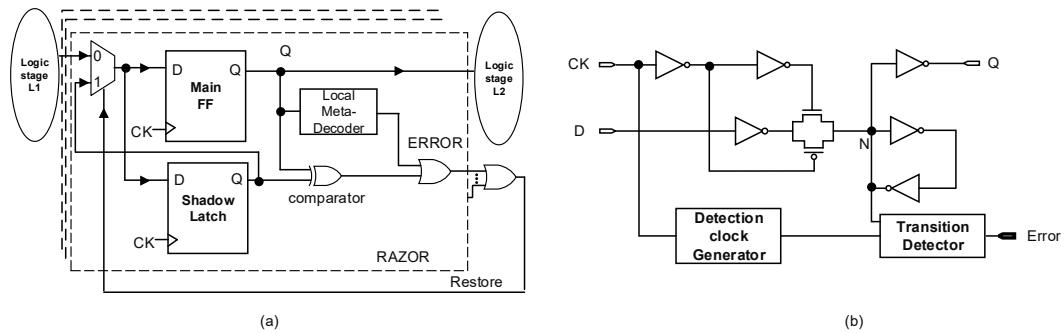

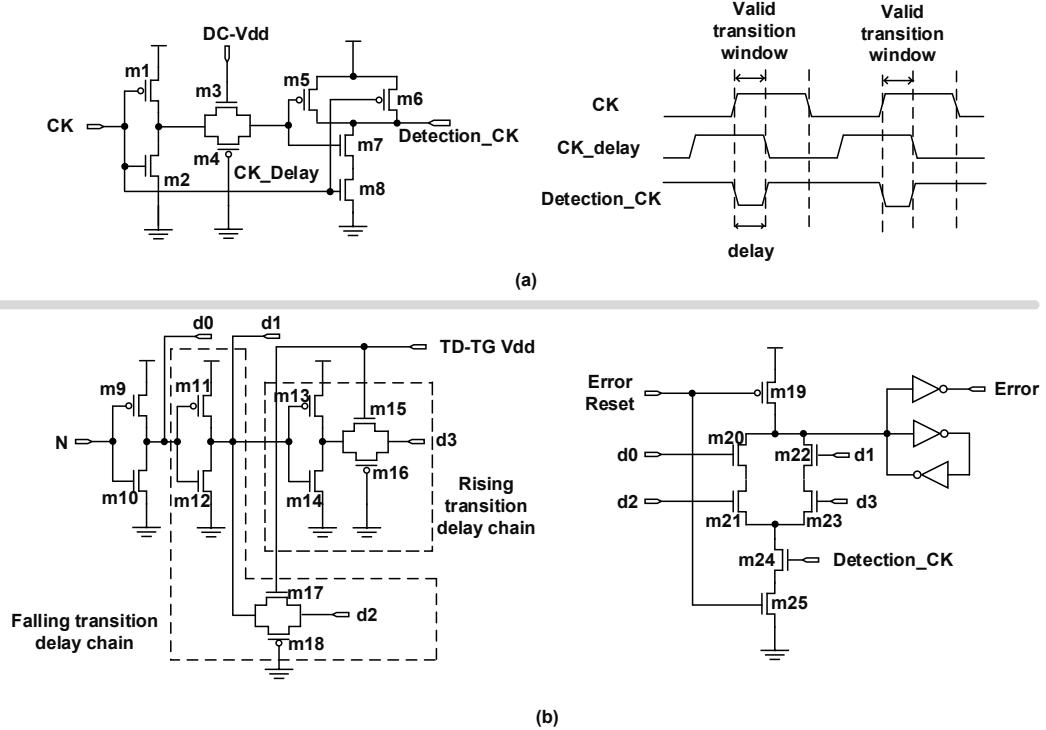

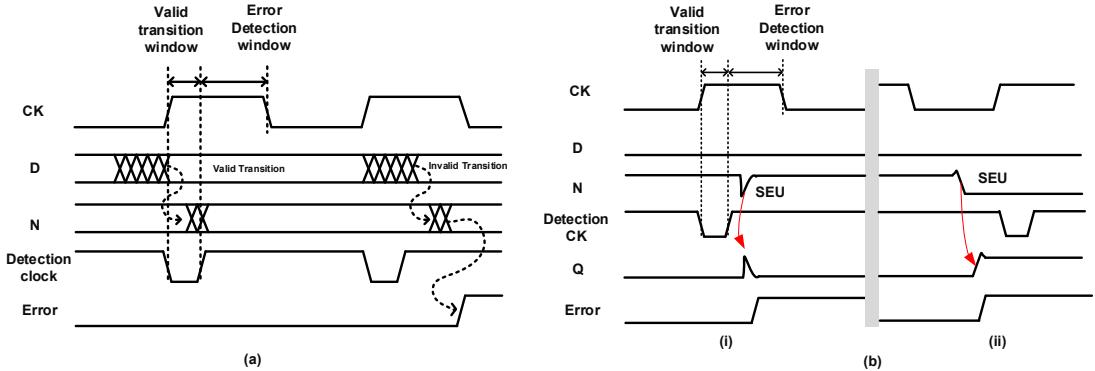

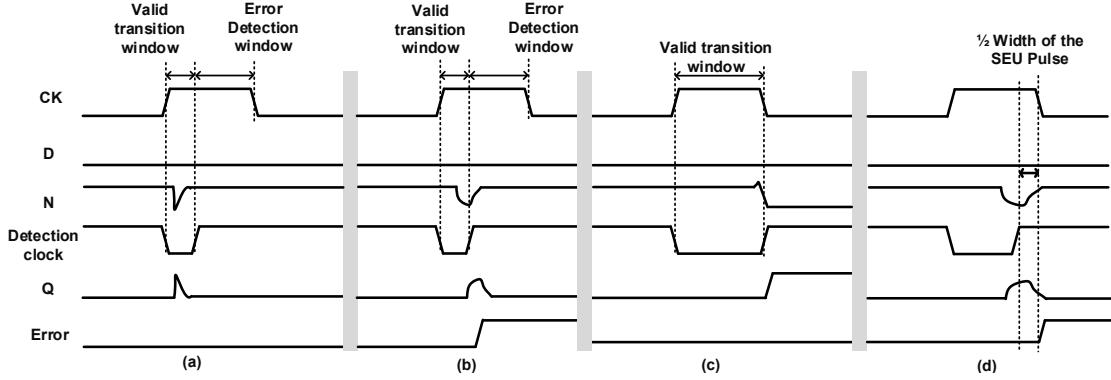

| 2.24 The structure of the (a) Razor FF [137], (b) RazorII FF [138]. . . . .                                                                                                                                                                                                                                   | 35 |

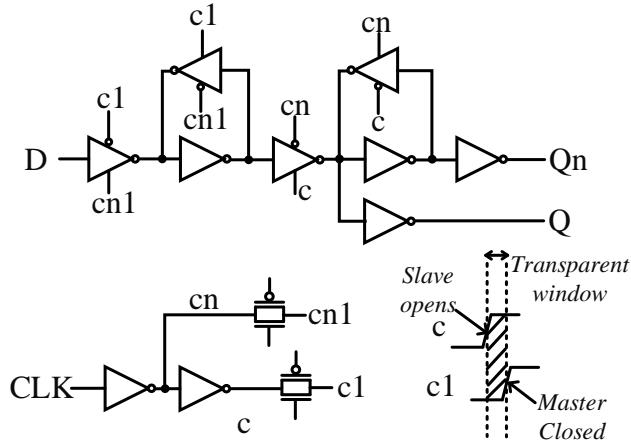

| 2.25 (a) Razor II detection $CK$ generator and waveform (b) Transition Detector [138][141] . . . . .                                                                                                                                                                                                          | 37 |

| 2.26 (a)Razor II error detection waveform. (b) Two scenarios of RazorII detect the SEU error [138, 141] . . . . .                                                                                                                                                                                             | 37 |

| 2.27 Four possible situations where the SEU error occurs during the negative phase of the detection $CK$ [138]. . . . .                                                                                                                                                                                       | 38 |

| 3.1 The widely used TGFF, 24 total transistors, 2 internal inverters included. The TGFF has relatively simple datapath and retention scheme. . . . .                                                                                                                                                          | 43 |

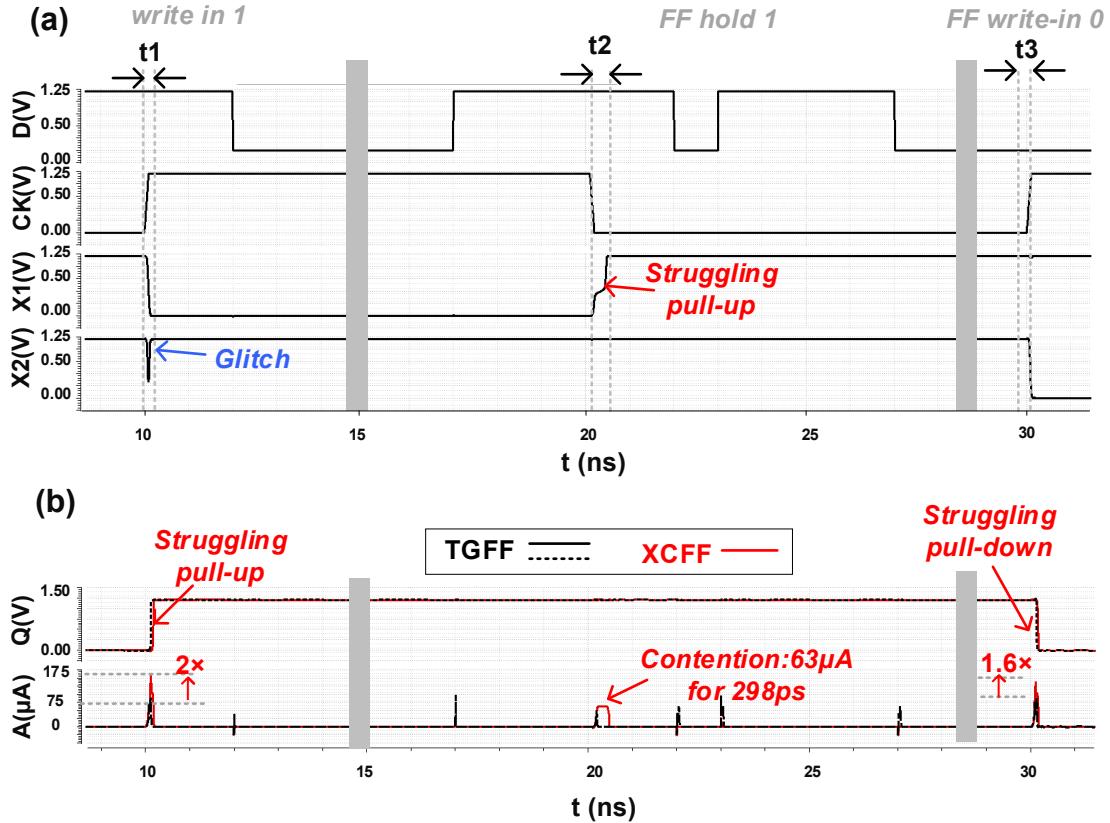

| 3.2 SPICE simulation results of the XCFF, illustrating the contention issue in XCFF. (a) operation waveform of the XCFF internal nodes. (b) Output and Current waveform of the XCFF and TGFF. . . . .                                                                                                         | 46 |

| 3.3 Data dependent setup/hold path and retention loops in S2CFF . . . . .                                                                                                                                                                                                                                     | 48 |

| 3.4 Data dependent setup/hold path and retention loops in TCFF . . . . .                                                                                                                                                                                                                                      | 49 |

| 3.5 Failure mechanism in TCFF at NTV(0.6V) . . . . .                                                                                                                                                                                                                                                          | 50 |

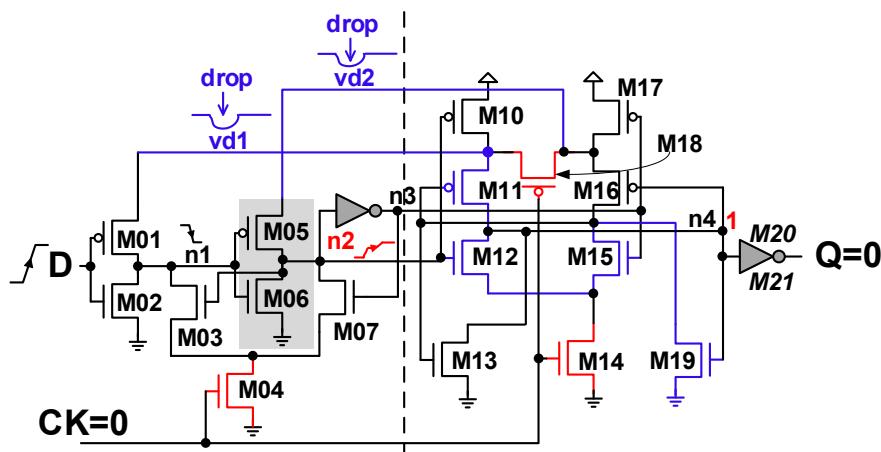

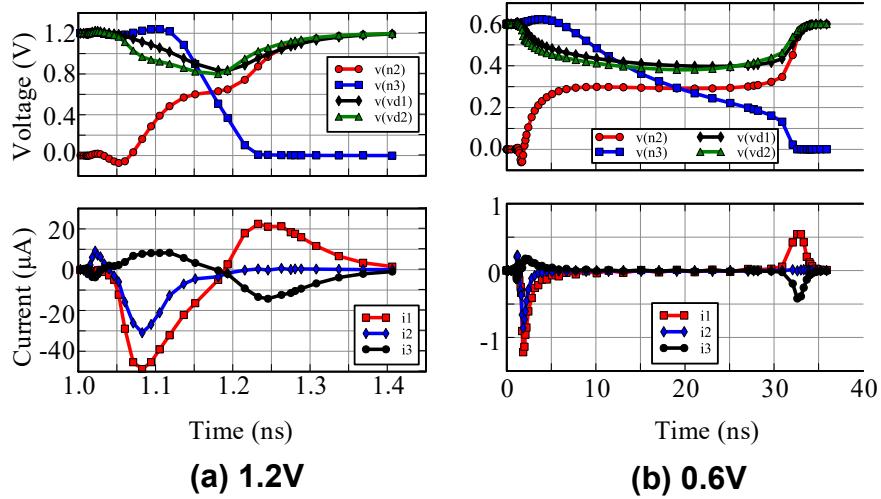

| 3.6 Simulation results show TCFF internal node voltages at (a) $V_{dd} = 1.2V$ ,(b) $V_{dd} = 0.6V$ when $D$ rising at $CK = 0$ . . . . .                                                                                                                                                                     | 51 |

| 3.7 A hypothetical solution for TCFF failure. . . . .                                                                                                                                                                                                                                                         | 52 |

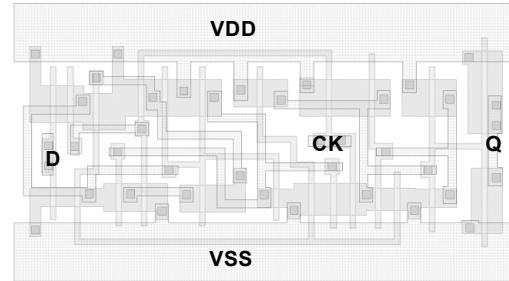

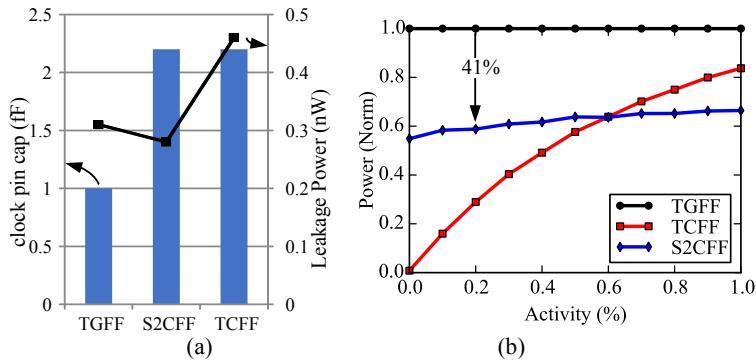

| 3.8 Standard-cell layout of (a) TCFF (b) S2CFF . . . . .                                                                                                                                                                                                                                                      | 53 |

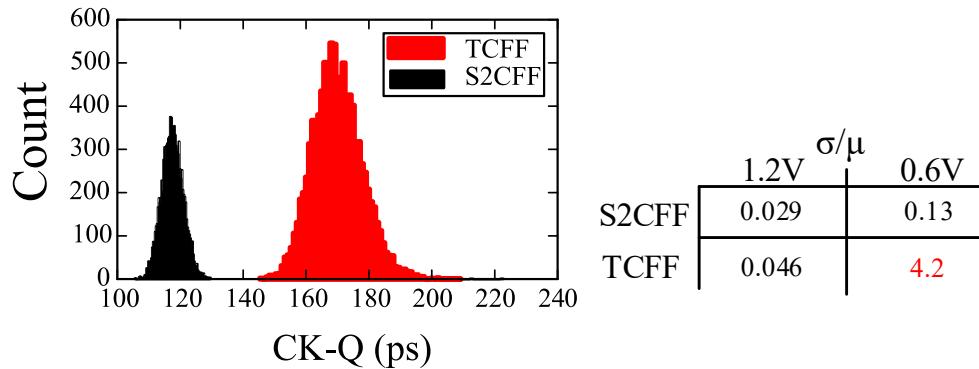

| 3.9 Analysis of Variability at different supply voltage. . . . .                                                                                                                                                                                                                                              | 53 |

| 3.10 Analysis of Variability sensitivity of S2CFF and TCFF. . . . .                                                                                                                                                                                                                                           | 54 |

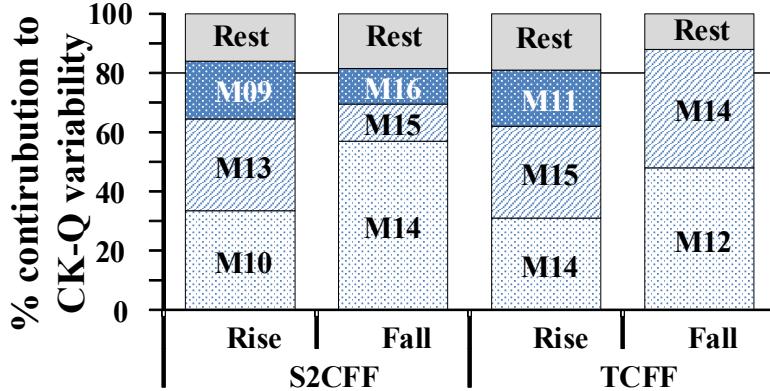

| 3.11 Std-cell design summary, (a) leakage and clock capacitance and (b) power vs activity. . . . .                                                                                                                                                                                                            | 54 |

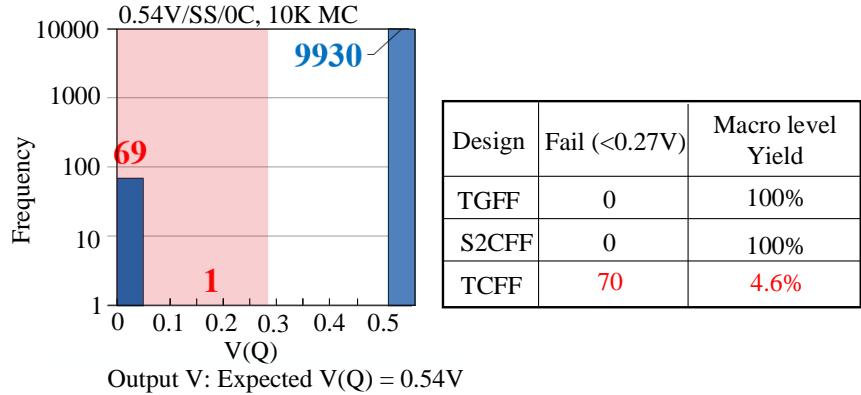

| 3.12 TCFF functionality yield estimation with 10K Monte-Carlo simulation at 0.54V. . . . .                                                                                                                                                                                                                    | 55 |

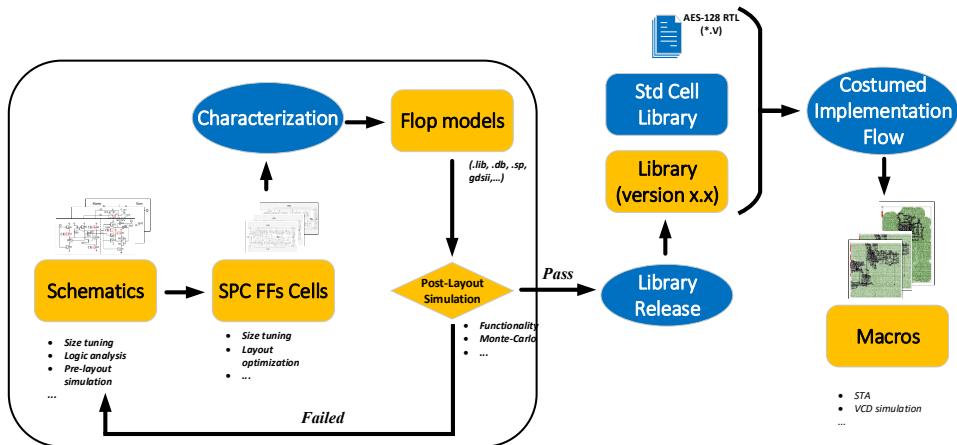

| 3.13 Macro implementation flow: From schematic configuration to macro implementation. . . . .                                                                                                                                                                                                                 | 55 |

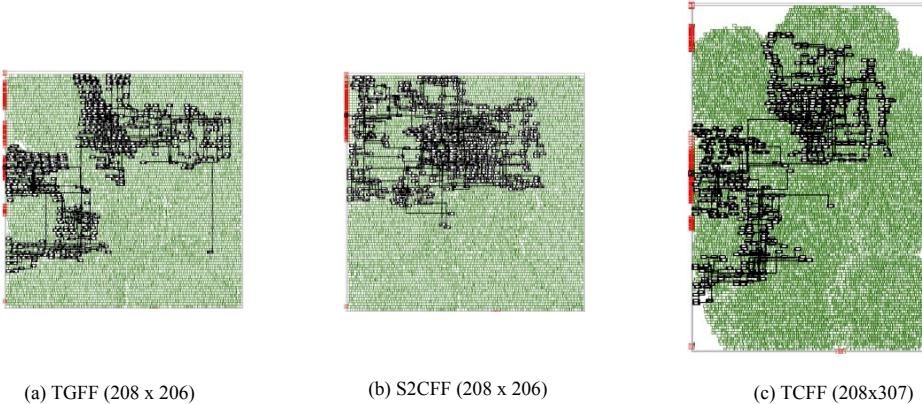

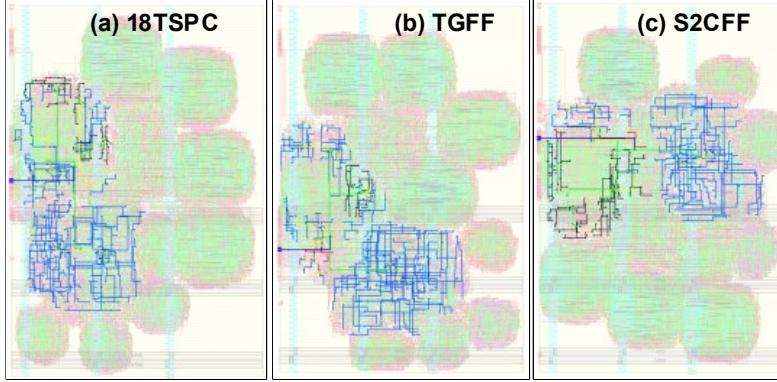

| 3.14 AES-128 implementation floorplan for (a) TGFF (b) S2CFF and (c) TCFF highlighting clock tree, clock buffers and FFs . . . . .                                                                                                                                                                            | 56 |

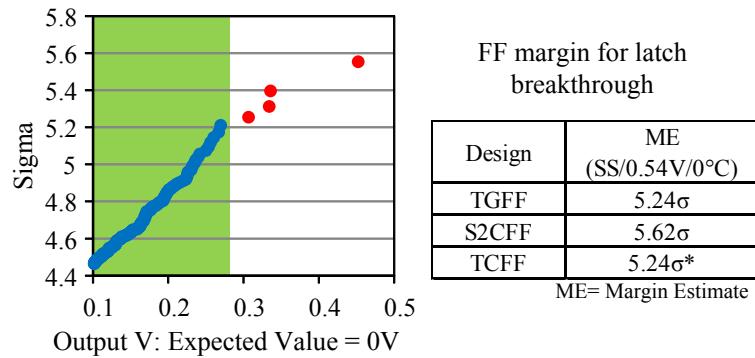

| 3.15 Yield analysis for NTV operation . . . . .                                                                                                                                                                                                                                                               | 57 |

|      |                                                                                                                                                                                            |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

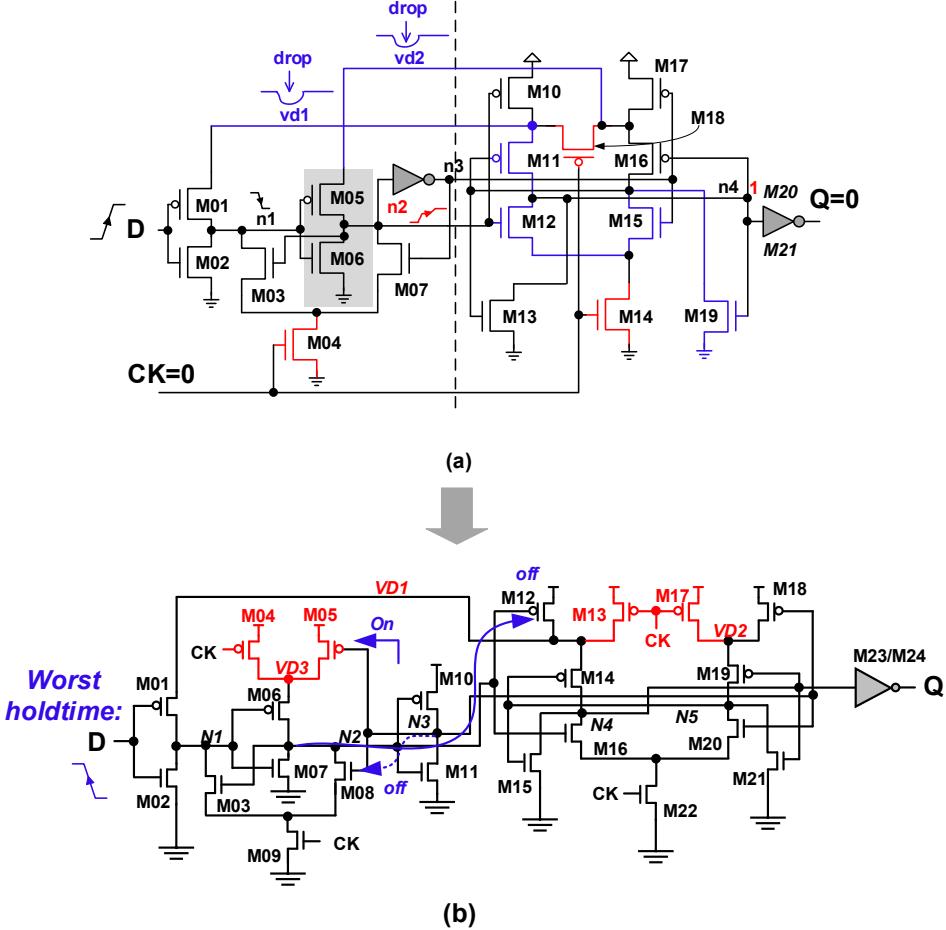

| 3.16 | Proposed TCFF optimization strategy (a) Original TCFF schematics,(b) The Proposed TCFF-NTV schematic, the worst case hold time paths are highlighted. . . . .                              | 59 |

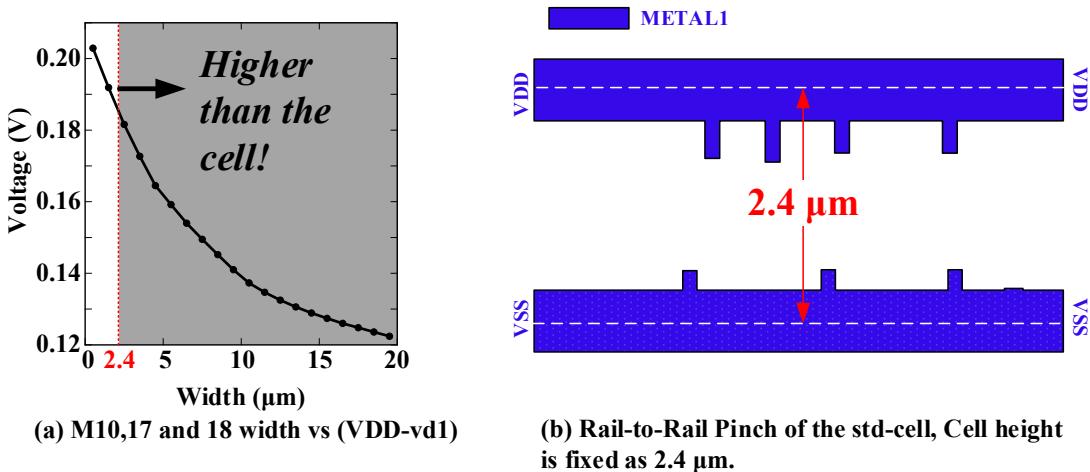

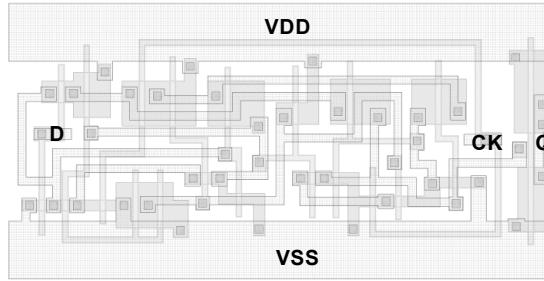

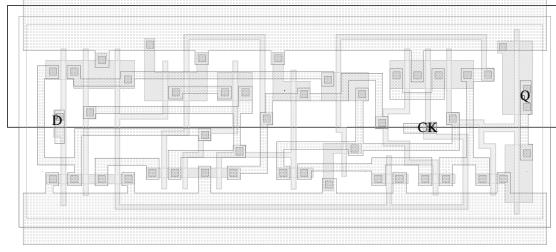

| 3.17 | Standard-cell layout of TCFF-NTV( $2.4 \times 6.4$ ). . . . .                                                                                                                              | 60 |

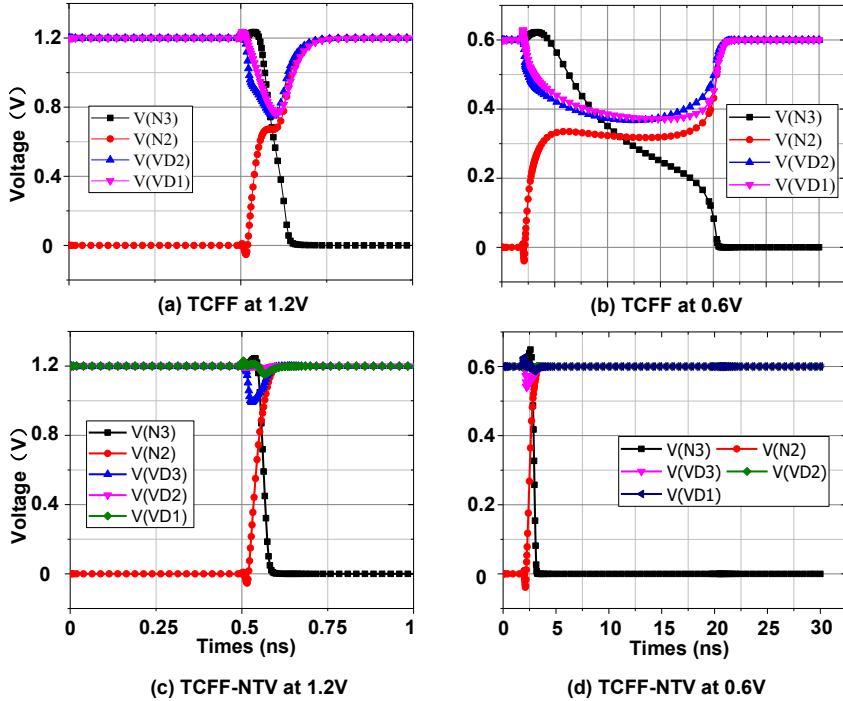

| 3.18 | Operation waveform of TCFF and the proposed TCFF-NTV at (a)(c) 1.2V and (b)(d) 0.6V. . . . .                                                                                               | 60 |

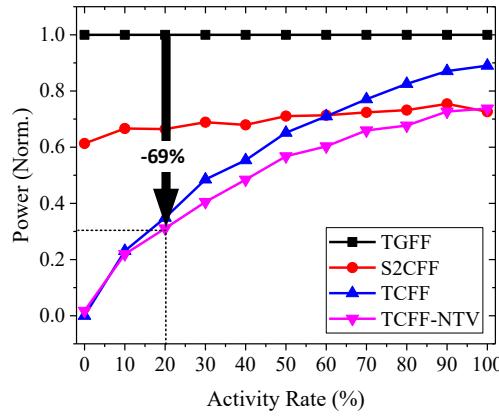

| 3.19 | Normalized power consumption against different activity. . . . .                                                                                                                           | 62 |

| 3.20 | TCFF-NTV functionality yield estimation at 0.54V, SS, 0°C. . . . .                                                                                                                         | 62 |

| 3.21 | Flip-Flop Hold time variation distribution at 0.54V, SS, 0°C. . . . .                                                                                                                      | 63 |

| 3.22 | AES-128 implementation floorplan for (a) TCFF and (b) TCFF-NTV. TCFF-NTV achieves a 33% reduction in block area compared to TCFF based design. . . . .                                     | 64 |

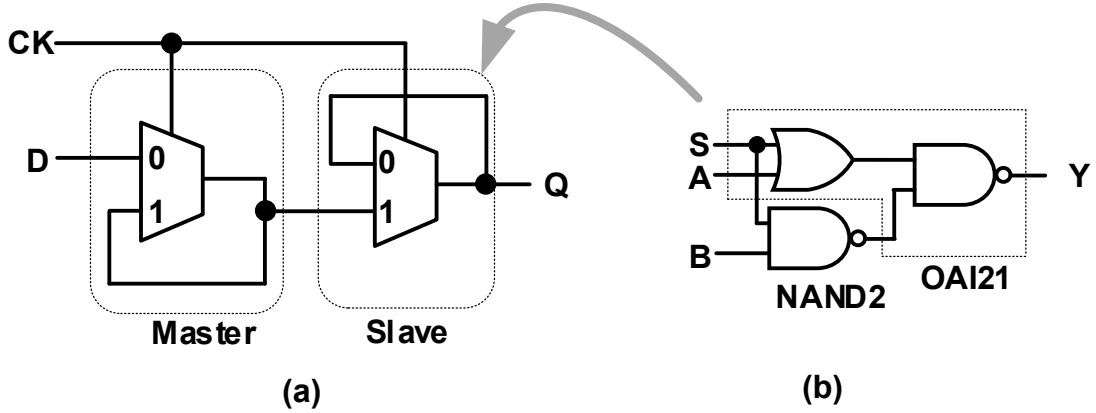

| 4.1  | (a) The 2-to-1 Multiplexer (MUX2) based MS FF[149]. (b) Gate level of the MUX2 without inverters. . . . .                                                                                  | 71 |

| 4.2  | The gate level schematic of the proposed SPC FF. . . . .                                                                                                                                   | 72 |

| 4.3  | Boolean function list of gate level SPC FF at different scenario. . . . .                                                                                                                  | 72 |

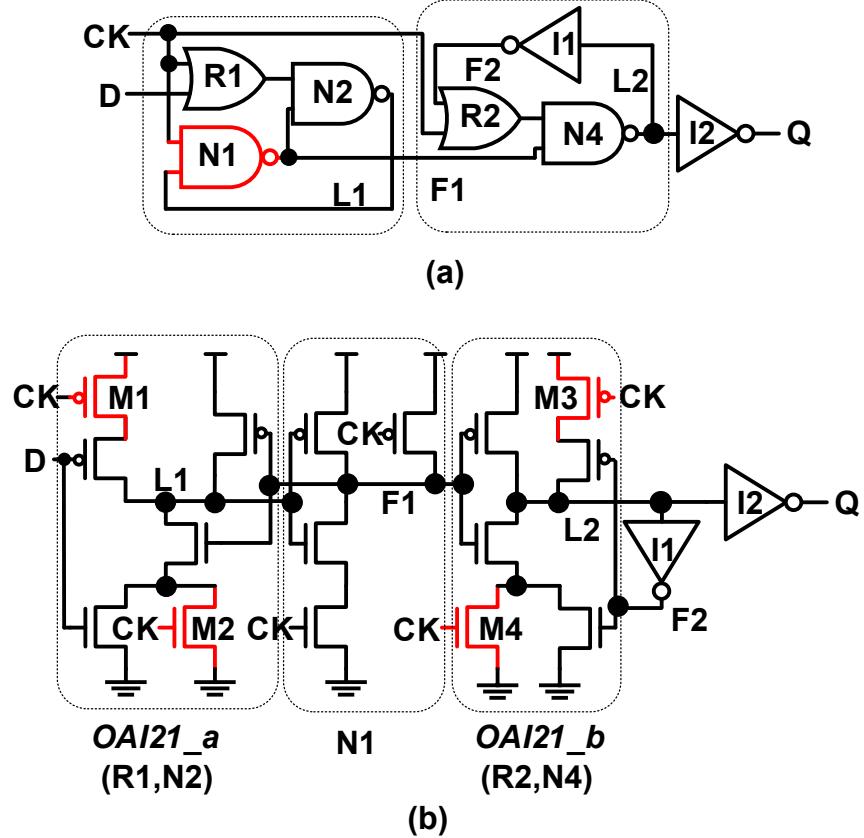

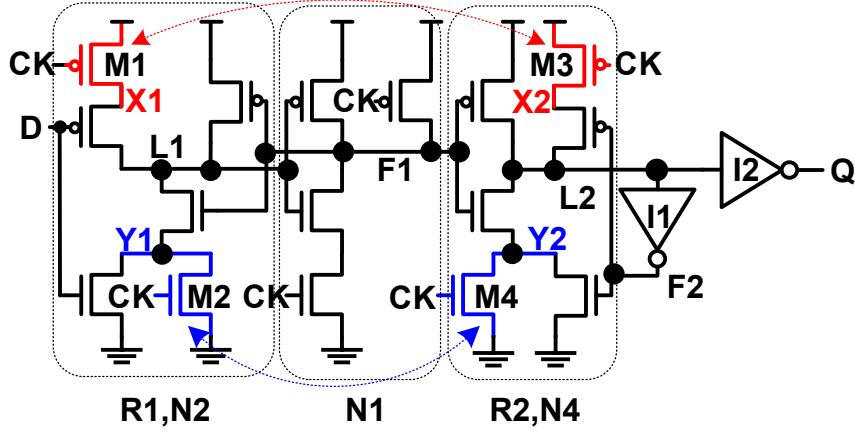

| 4.4  | (a) The gate level schematic of the proposed SPC FF (redundant NAND gate eliminated). (b) Transistor level schematic diagram of the (a). . . . .                                           | 73 |

| 4.5  | The SPC FF with 20 transistors in total. The transistor merging process can be applied to the highlighted transistors. . . . .                                                             | 74 |

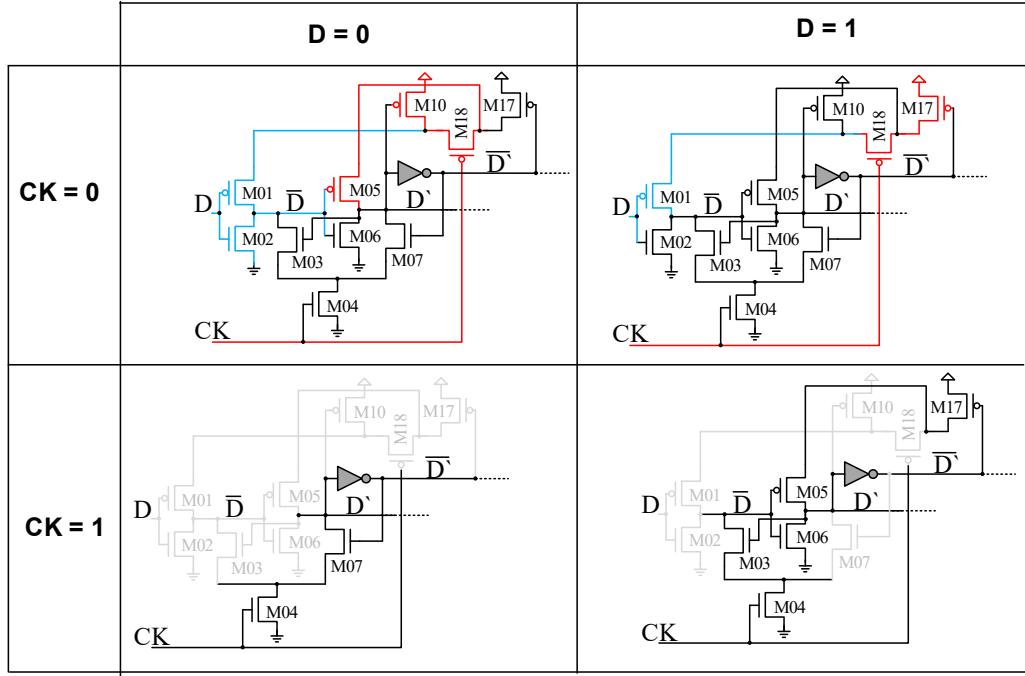

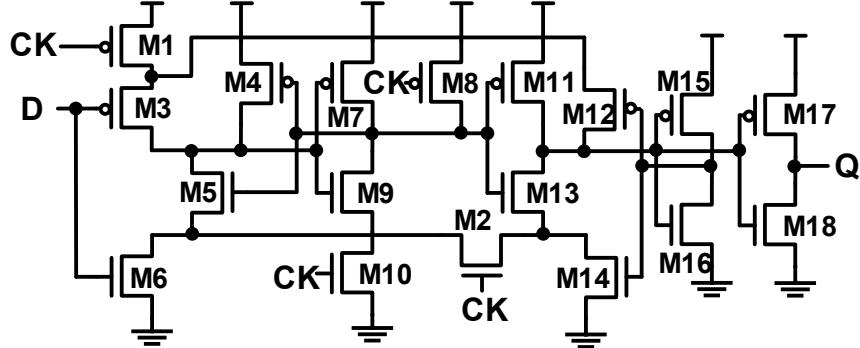

| 4.6  | The schematic diagram of the proposed 18 transistors fully static Flip Flop (18TSPC). . . . .                                                                                              | 74 |

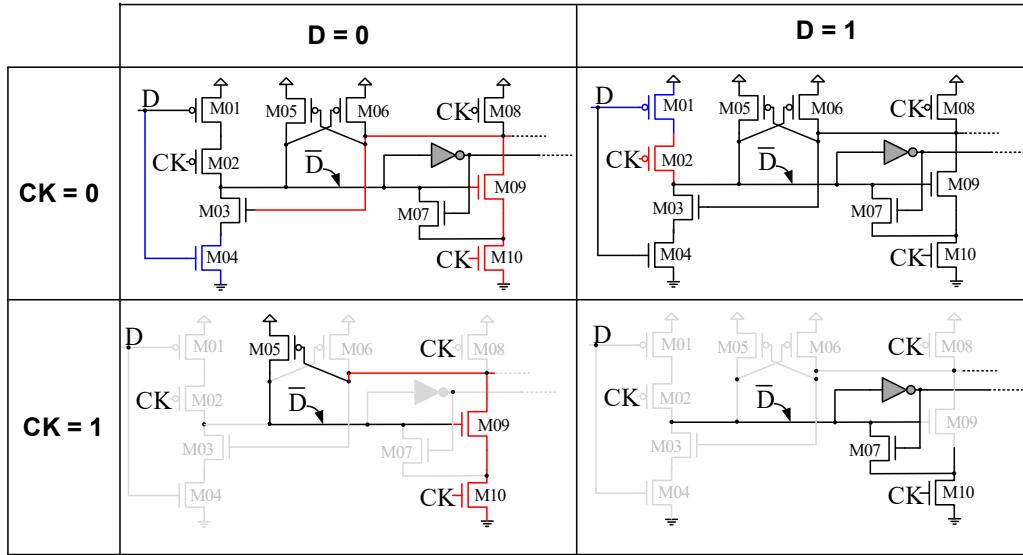

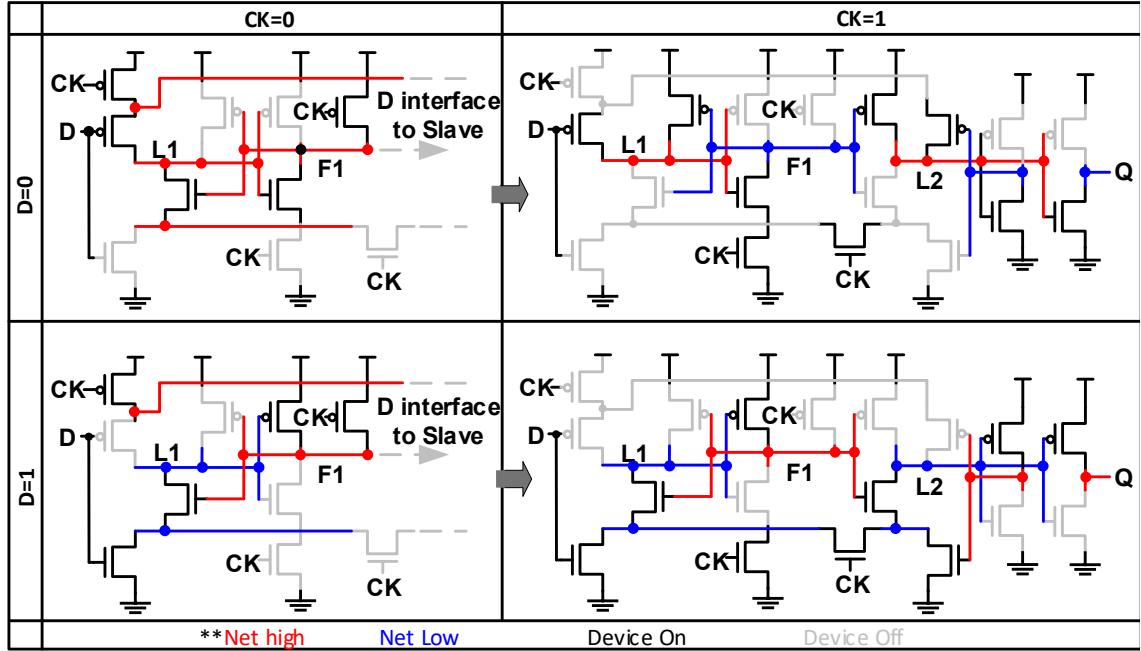

| 4.7  | 18TSPC operation diagram at different $CK$ and $D$ states, highlighting the active devices, logic high nets and logic low nets. . . . .                                                    | 75 |

| 4.8  | Operation Waveform of the internal nodes of 18TSPC. . . . .                                                                                                                                | 75 |

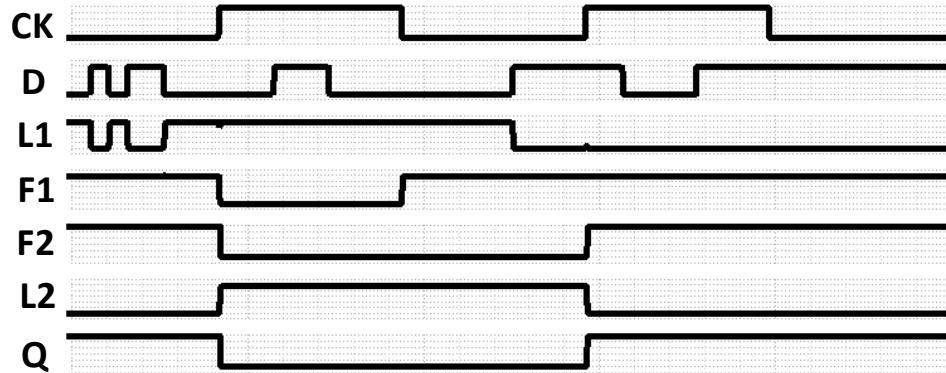

| 4.9  | (a) Worst-case Hold time path analyse of the 18TSPC. (b) SPICE simulation results, waveform of 18TSPC with correct operation and hold violation at worst-case hold time condition. . . . . | 76 |

| 4.10 | $T_{CQ}$ path analysis of the 18TSPC. (a) Q rising at CK edge. (b) Q falling at CK edge. . . . .                                                                                           | 77 |

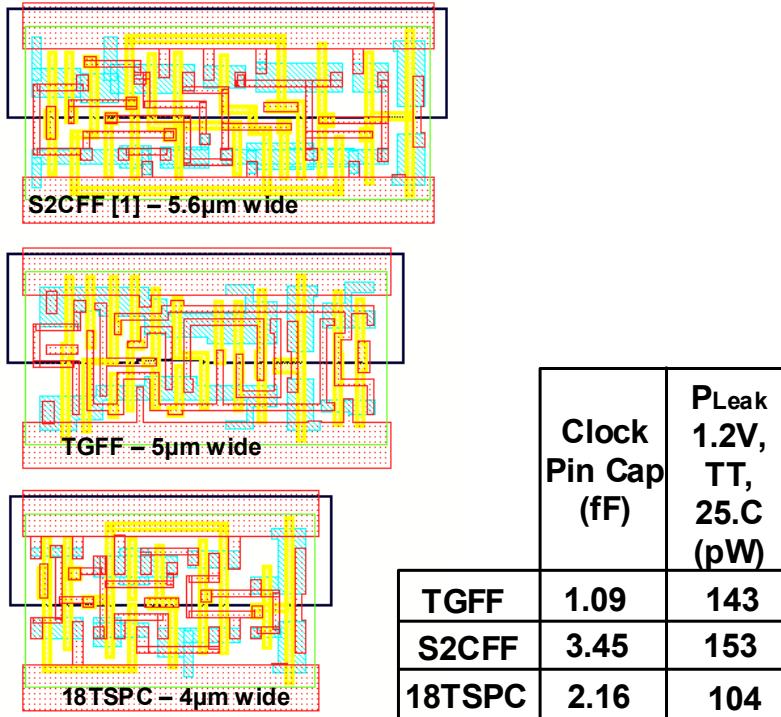

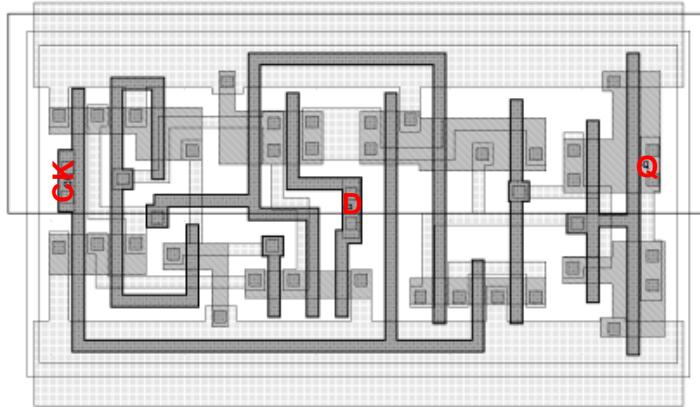

| 4.11 | Layout of the S2CFF, TGFF and the proposed 18TSPC. . . . .                                                                                                                                 | 78 |

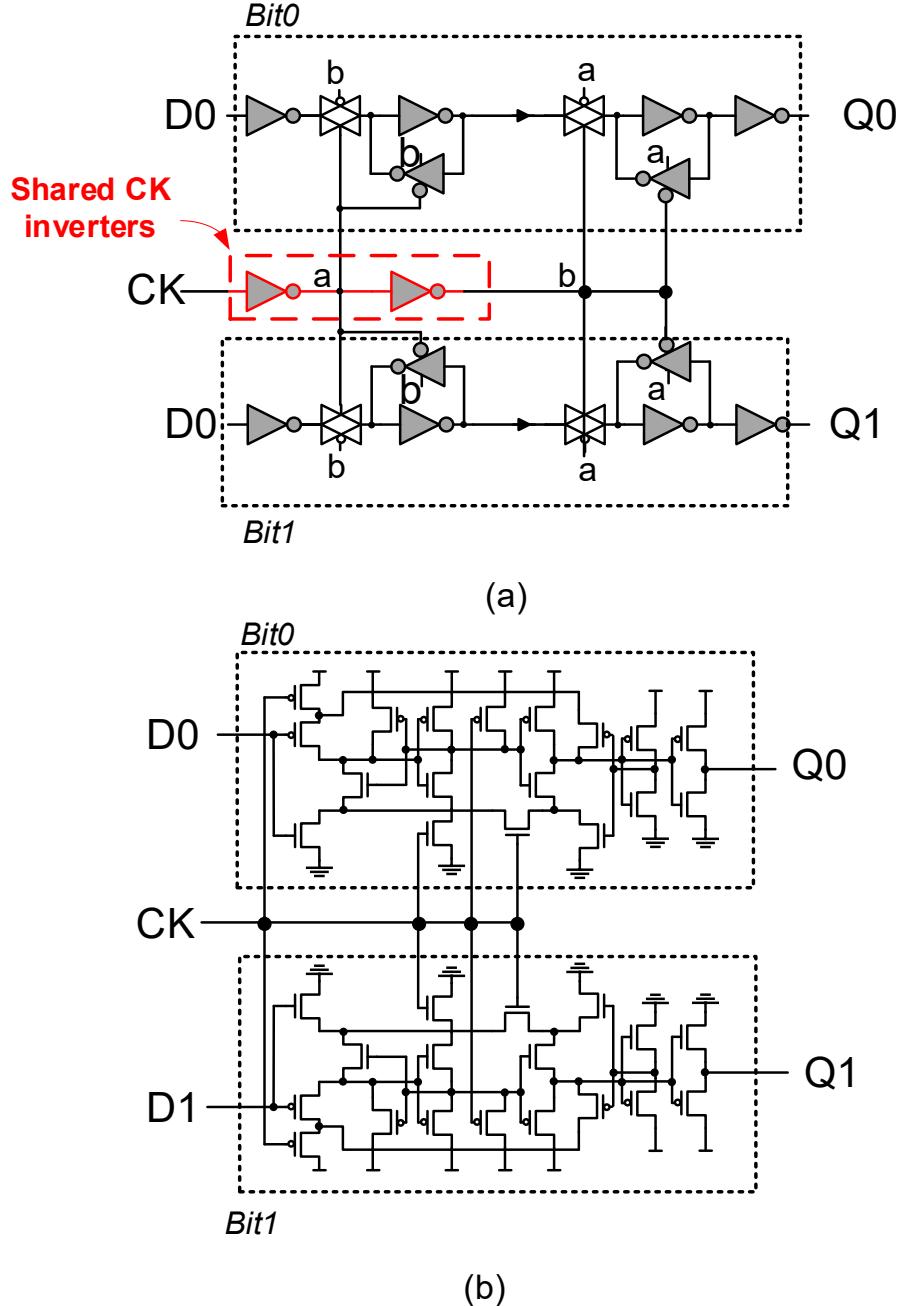

| 4.12 | Schematic diagram of (a) TGFF-based and (b)18TSPC-based 2-bit MBFF . . . . .                                                                                                               | 79 |

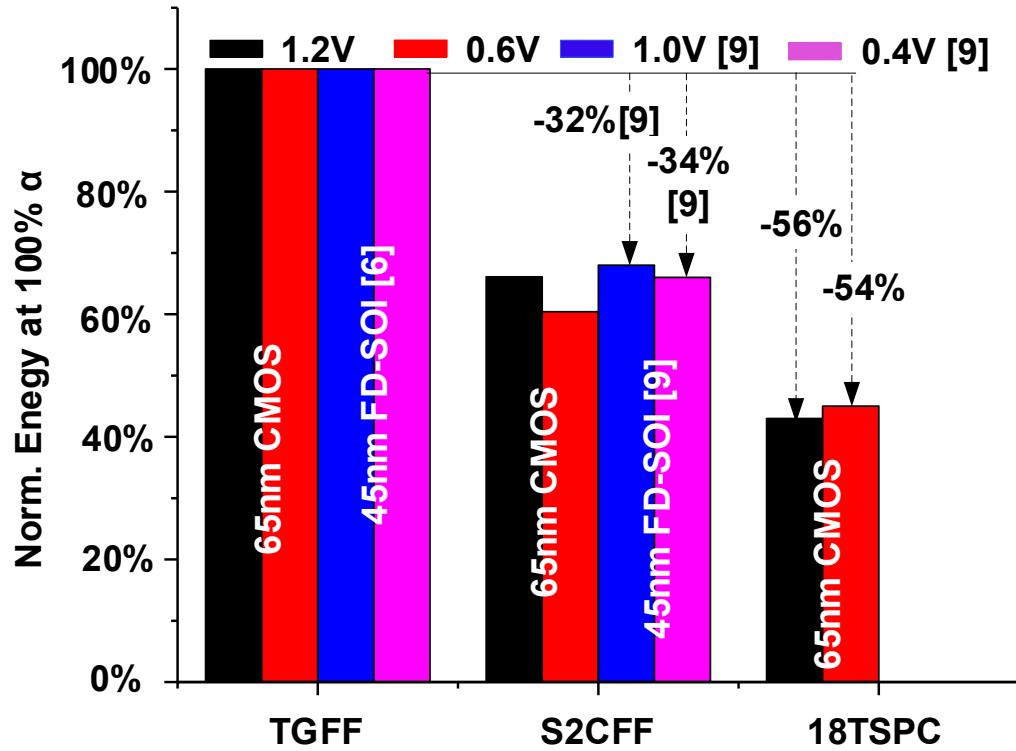

| 4.13 | Normalized Energy/cycle with $\alpha = 100\%$ at nominal supply voltage (1.2V for 65nm CMOS, 1.0V for 45nm FDSOI [65]) and NTV (0.6V for 65nm CMOS, 0.4V for 45nm FDSOI [65]). . . . .     | 80 |

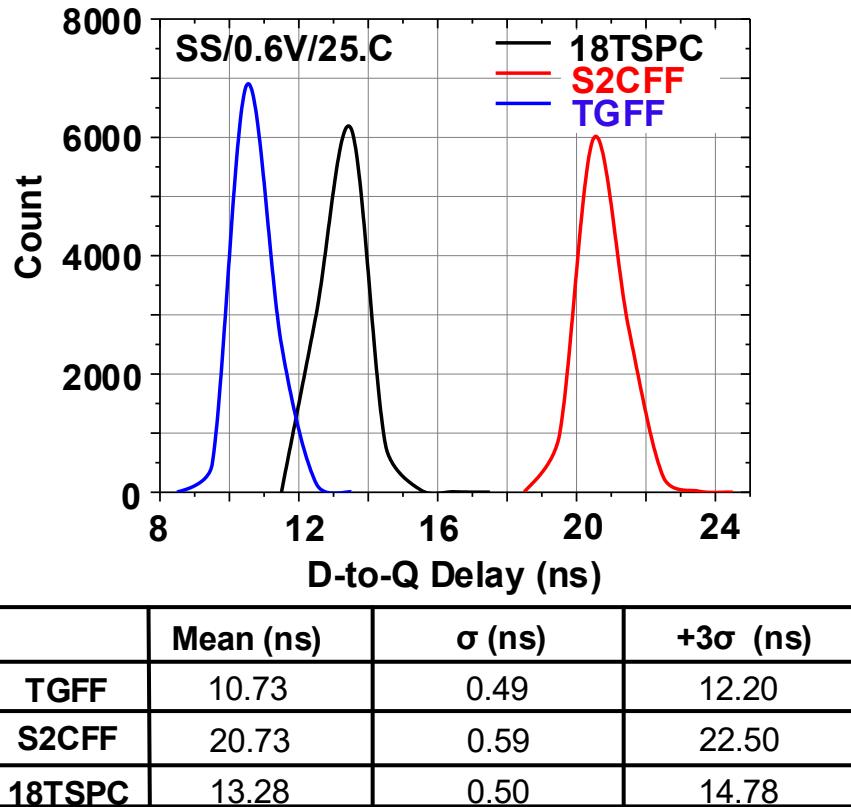

| 4.14 | 10K Monte-Carlo simulation results of D-to-Q Delay. . . . .                                                                                                                                | 81 |

| 4.15 | AES 128 floorplan of (a) 18TSPC, (b) TGFF and (c) S2CFF, the clock tree is highlighted. . . . .                                                                                            | 82 |

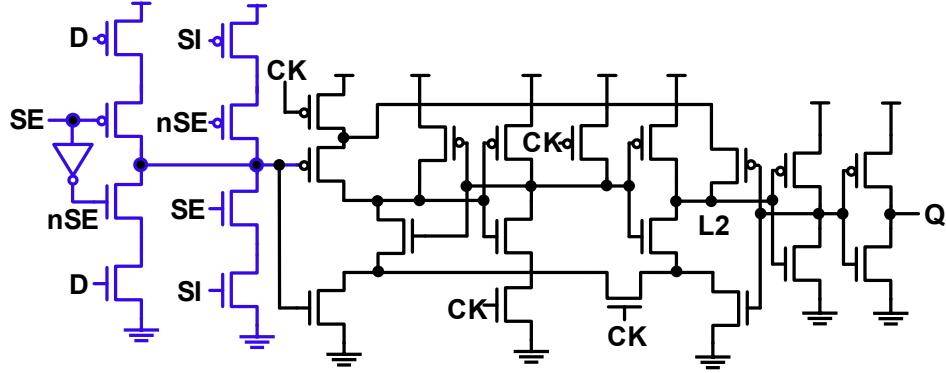

| 4.16 | Schematic diagram of the Scan-18TSPC. Added transistors to the original 18TSPC is highlighted. . . . .                                                                                     | 83 |

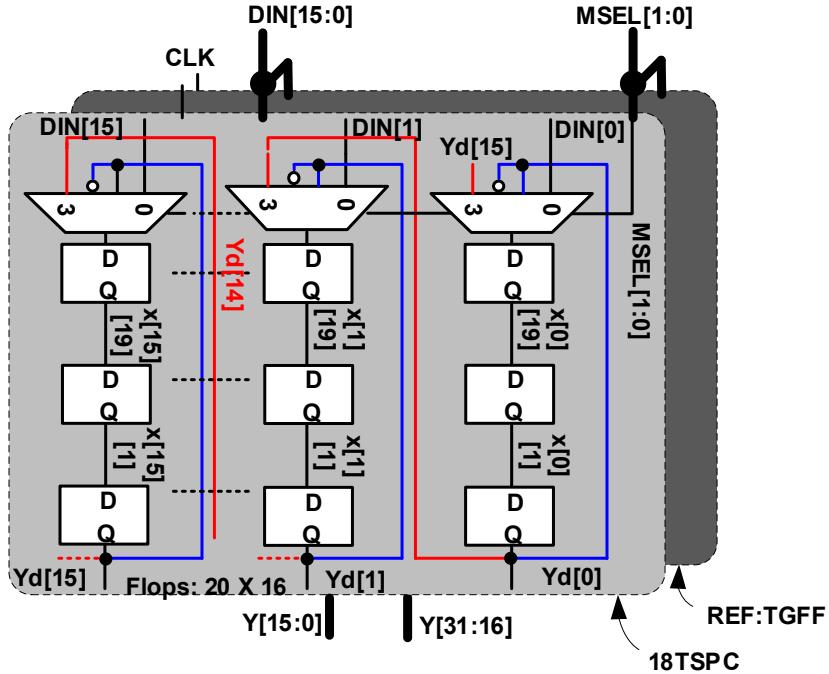

| 4.17 | Block Diagram of the 320-bit Shift-Reg. . . . .                                                                                                                                            | 84 |

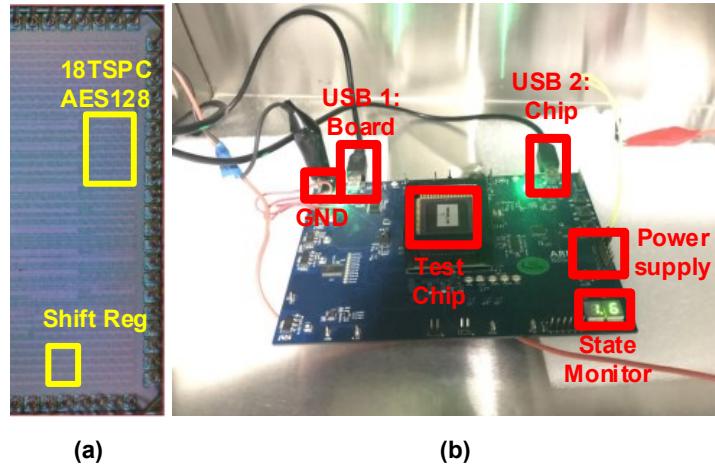

| 4.18 | (a) Die micrograph: two blocks are built in the test chip, the AES-128 and the Shift Register (Shift-Reg). (b) Test Board. . . . .                                                         | 85 |

| 4.19 | (a) model of random element of '20×16 matrix' (b) The functionality test pattern of the shift register . . . . .                                                                           | 85 |

| 4.20 | Shift register power measurement pattern ( $\alpha = 0\text{-}100\%$ ). . . . .                                                                                                            | 86 |

|      |                                                                                                                                                                                                      |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.21 | Measured power of 320-bit Shift-Reg against $\alpha$ at (a) 1.2V (with $0^{\circ}C$ , $25^{\circ}C$ and $85^{\circ}C$ ) (b) 0.6V with $25^{\circ}C$ . . . . .                                        | 87  |

| 4.22 | Measured total power of 320-bit Shift-Reg with (a) $\alpha = 100\%$ (b) $\alpha = 0\%$ with fixed clock frequency ( $F_{Board\_MAX} = 66$ MHz) at different supply voltage. . . . .                  | 88  |

| 4.23 | Measured results of the 18TSPC AES-128 block (Typical Die). . . . .                                                                                                                                  | 89  |

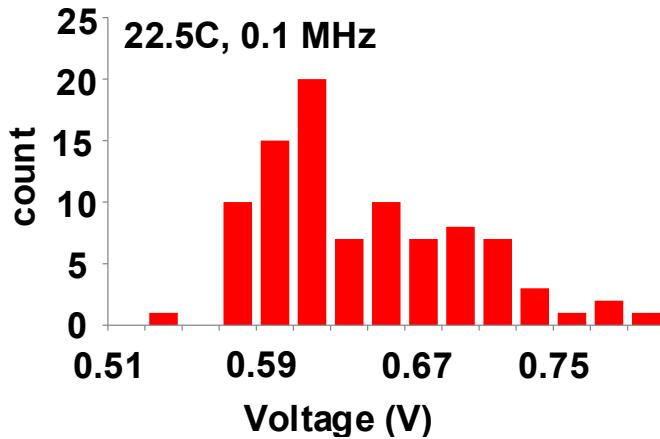

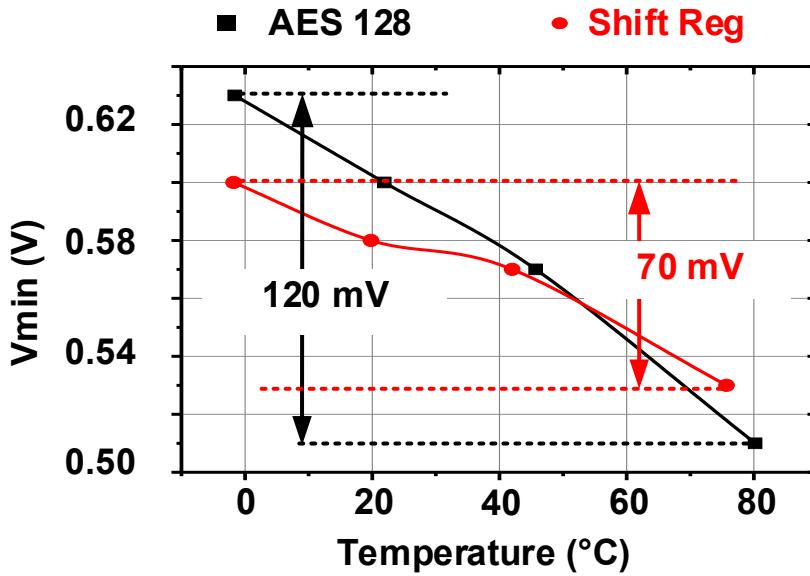

| 4.24 | $V_{min}$ distribution of Shift-Reg over 92 test chips. . . . .                                                                                                                                      | 89  |

| 4.25 | Functional $V_{min}$ of AES-128 block and Shift-Reg with 0.1 MHz clock frequency at different temperature condition. . . . .                                                                         | 90  |

| 4.26 | (a) Gate level schematic diagram (b) The Transistor level schematic diagram of the proposed 20TSPC FF. . . . .                                                                                       | 92  |

| 4.27 | The layout of the proposed 20TSPC; Clock pin capacitance: 1.45 fF; $P_{Leak}$ at 1.2V/TT/ $25^{\circ}C$ : 122 pW; Area: $2.4 \times 4.6 \mu m^2$ . . . . .                                           | 93  |

| 4.28 | 3 stacks pull down path exists in 18TSPC. . . . .                                                                                                                                                    | 94  |

| 4.29 | The transistor level schematic diagram of the 19 Transistor (19T) SPC FF, maximum stack is optimised to 2. . . . .                                                                                   | 95  |

| 4.30 | The layout diagram of the 19TSPC. Clock pin capacitance: 2.99 fF; $P_{Leak}$ at 1.2V/TT/ $25^{\circ}C$ : 113 pW; Area: $2.4 \times 4.2 \mu m^2$ . . . . .                                            | 95  |

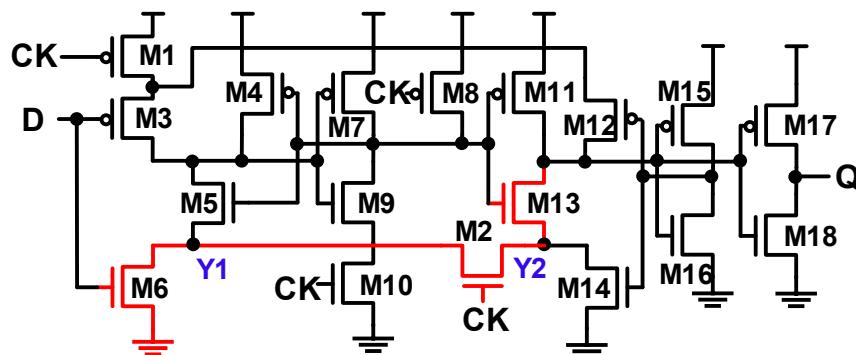

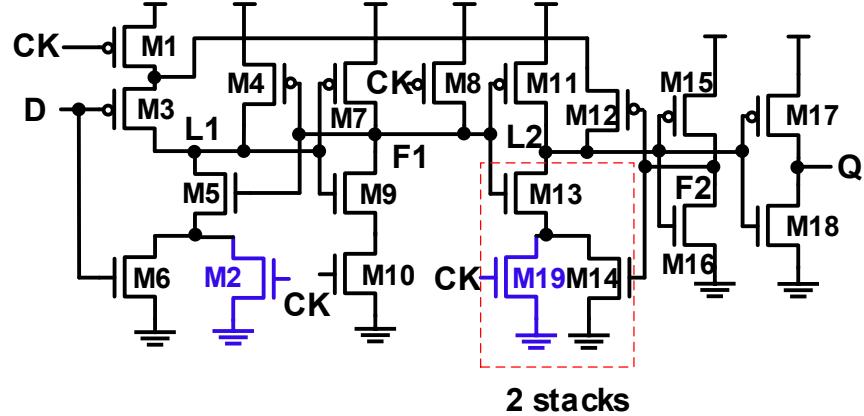

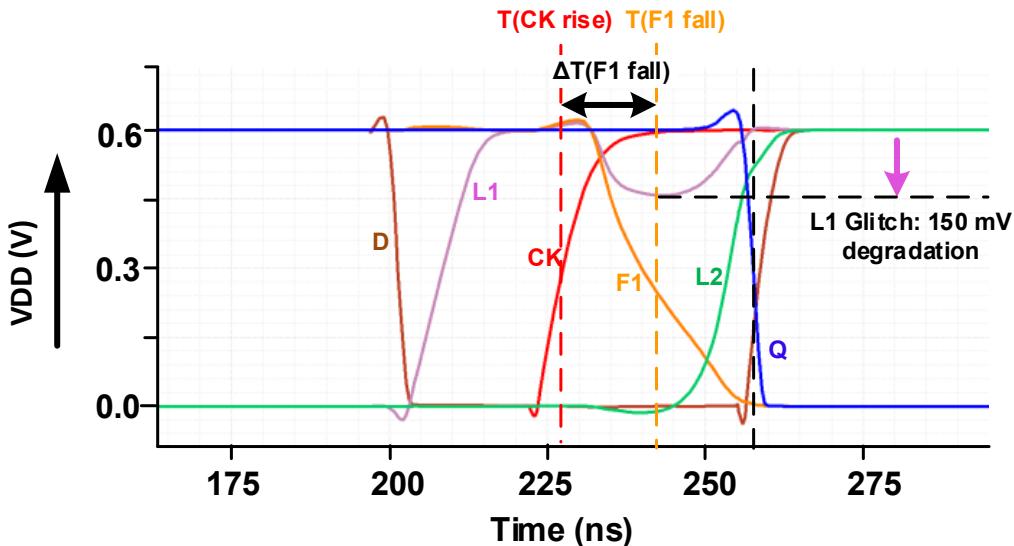

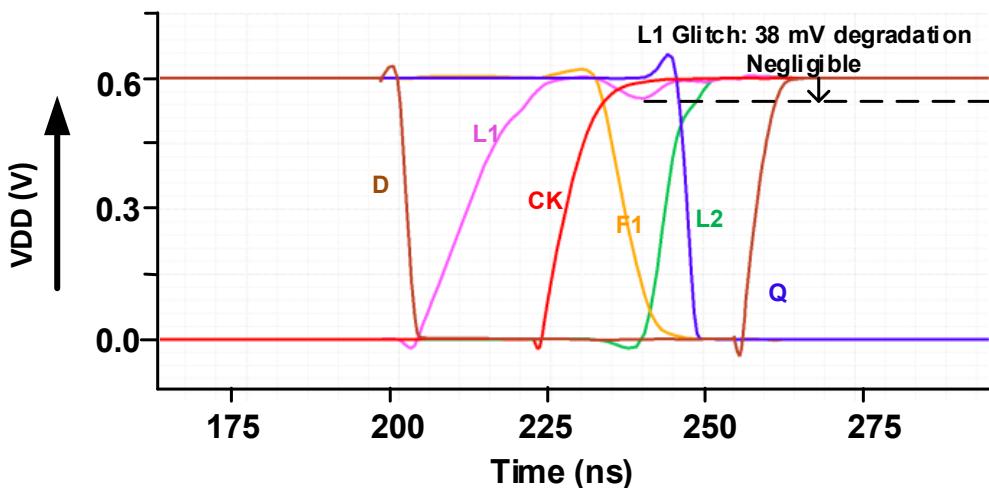

| 4.31 | Operation waveform of 19TSPC at 0.6V/SS/ $0^{\circ}C$ , an non-negligible glitch is observed in 19TSPC internal node L1 (see Figure 4.29). . . . .                                                   | 96  |

| 4.32 | 19TSPC master latch operation path analysis. . . . .                                                                                                                                                 | 97  |

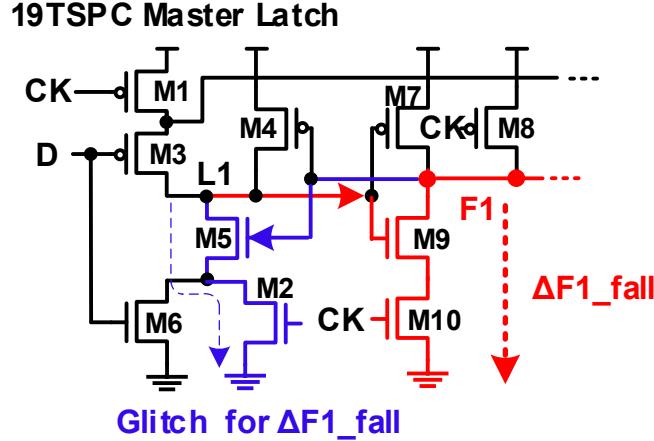

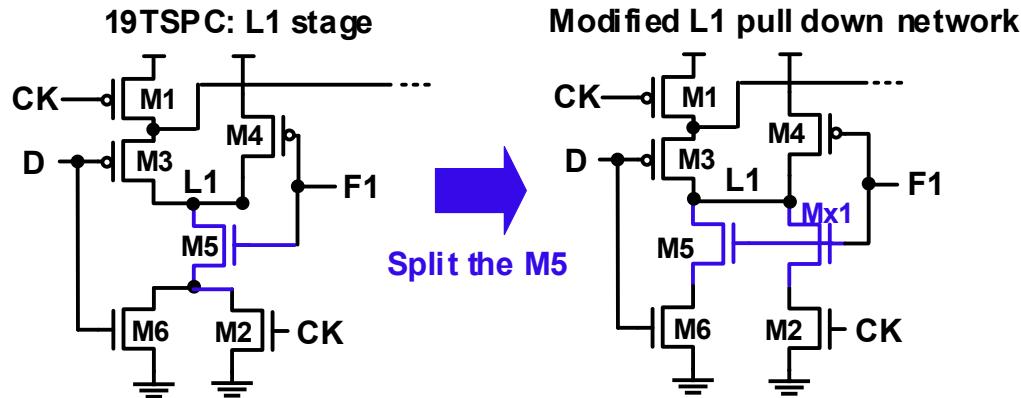

| 4.33 | L1 node pull-down network re-built. . . . .                                                                                                                                                          | 98  |

| 4.34 | Master latch of the 22-Transistors SPC FF. . . . .                                                                                                                                                   | 98  |

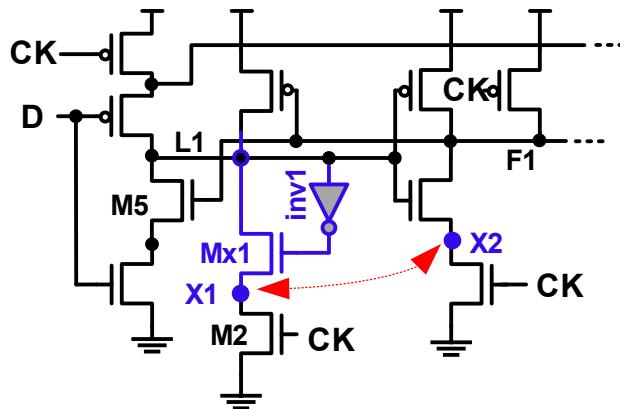

| 4.35 | The Transistor level schematic diagram of the proposed 21TSPC FF. . . . .                                                                                                                            | 99  |

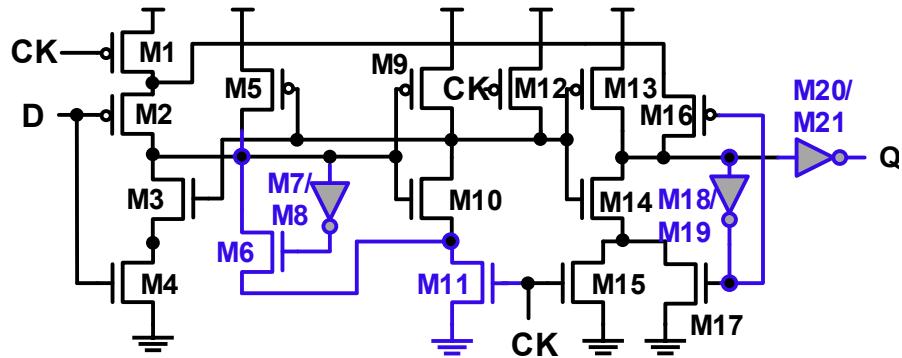

| 4.36 | Layout diagram of the 21TSPC FF. Clock pin capacitance: 2.68 fF; $P_{Leak}$ at 1.2V/TT/ $25^{\circ}C$ : 116 pW; Area: $2.4 \times 4.8 \mu m^2$ . . . . .                                             | 100 |

| 4.37 | Operation waveform of the 21TSPC FF at 0.6V/SS/ $0^{\circ}C$ , the glitch in 19TSPC internal node L1 is negligible . . . . .                                                                         | 100 |

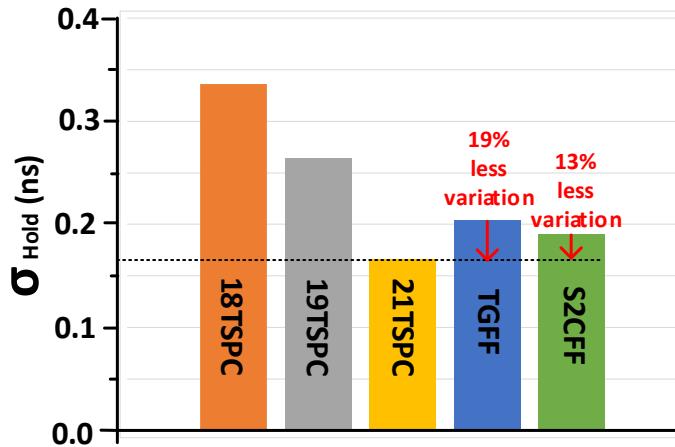

| 4.38 | Hold time standard deviation ( $\sigma_{Hold}$ ) comparison at 0.54V/SS/ $0^{\circ}C$ . . . . .                                                                                                      | 101 |

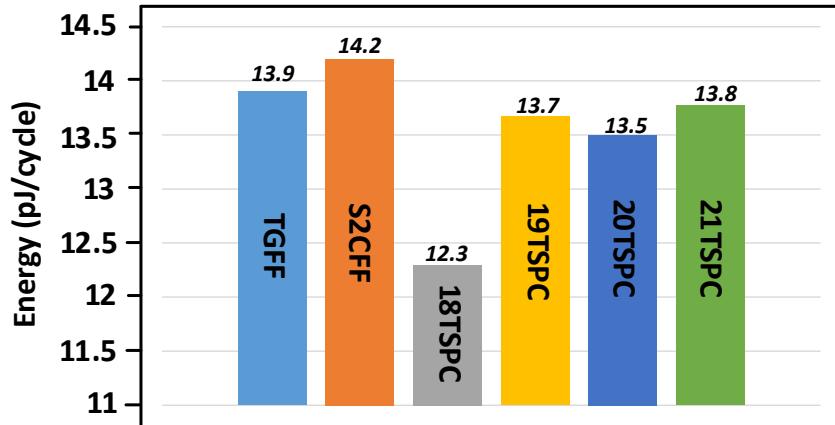

| 4.39 | Energy per cycle of AES-128 block based on different FF at 0.6V/TT/ $25^{\circ}C$ . . . . .                                                                                                          | 101 |

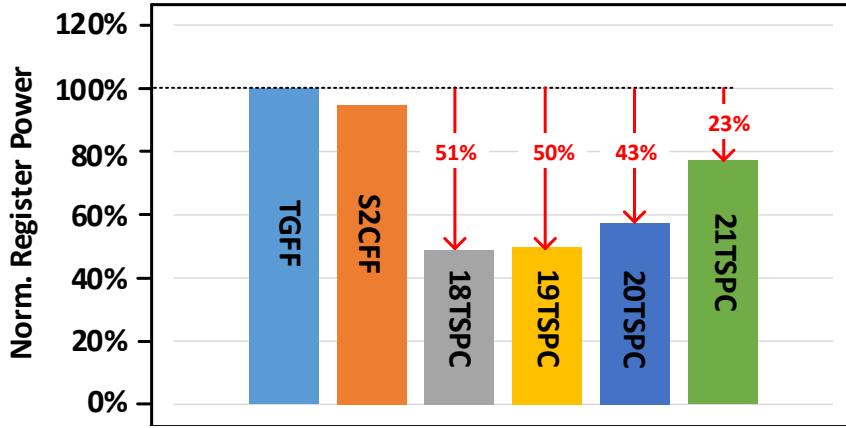

| 4.40 | Parallel comparison of normalized AES register power consumption. . . . .                                                                                                                            | 102 |

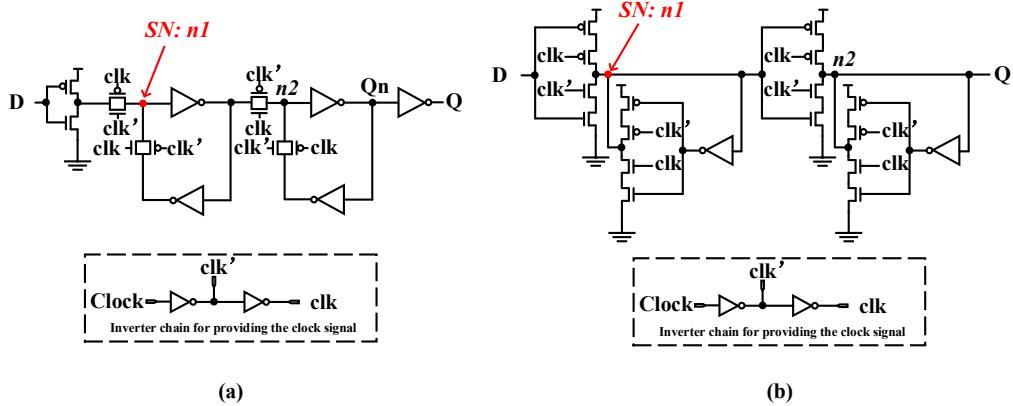

| 5.1  | The SN are the error injection point. (a) The schematic of TGFF and the sensitive node (SN): n1.(b)The schematic of C2MOS FF and the SN: n1. . . . .                                                 | 106 |

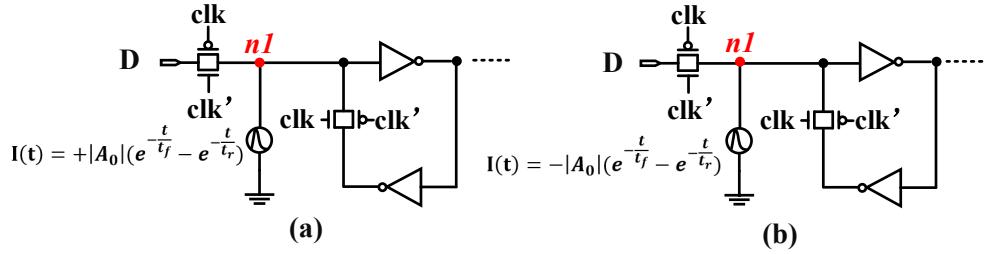

| 5.2  | SEU error injection to the sensitivity node of the TGFF, the figure shows the master latch of the TGFF. (a) The 0 to 1 SEU error injection. (b) The 1 to 0 SEU error injection. . . . .              | 107 |

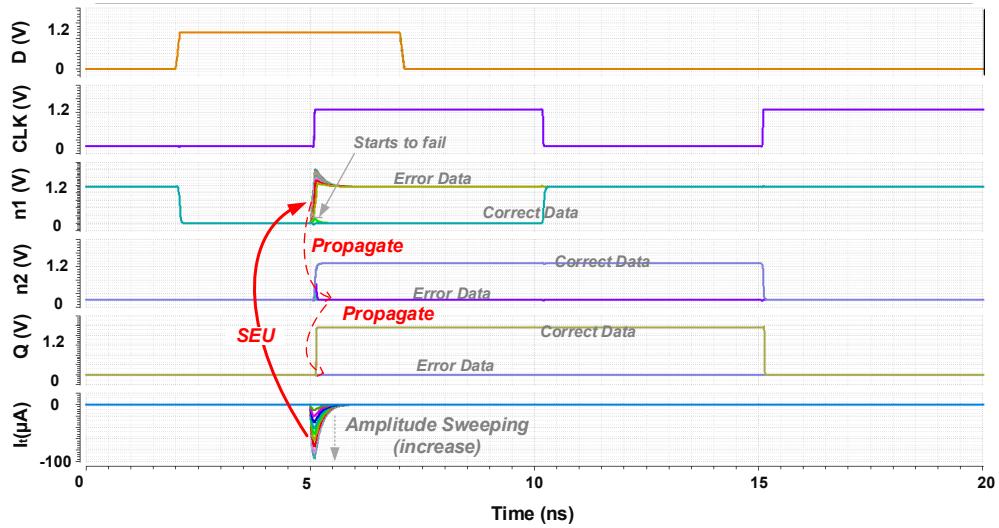

| 5.3  | Simulation results of the $1 \rightarrow 0$ SEU error injection (TGFF). . . . .                                                                                                                      | 107 |

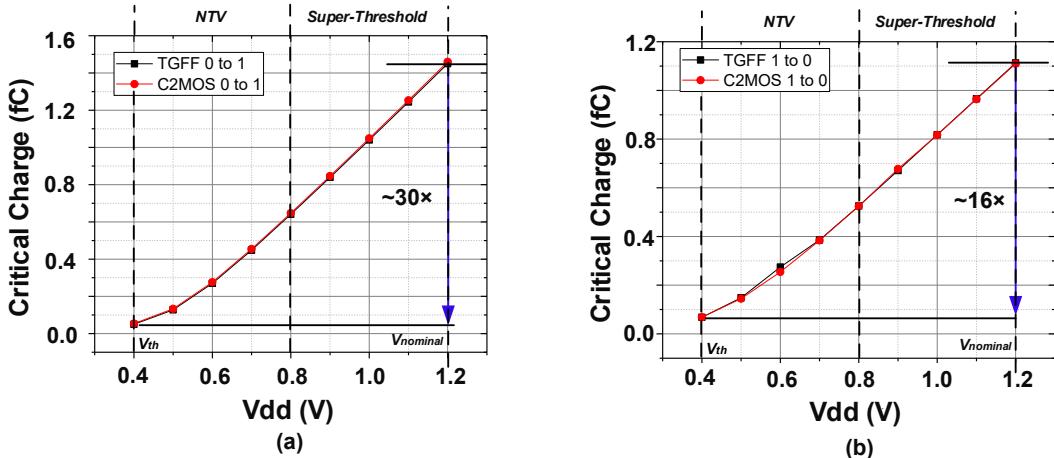

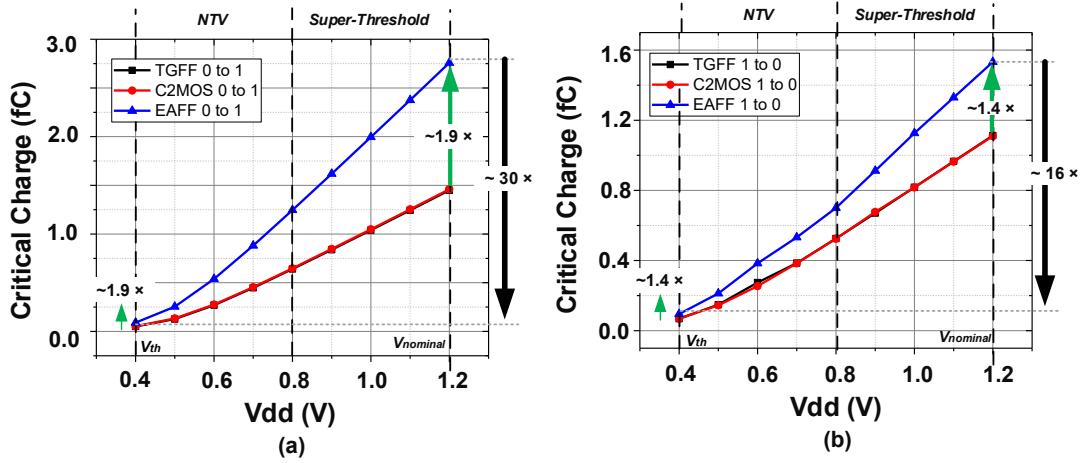

| 5.4  | The Critical Charge ( $fC$ ) of NMOS/PMOS particle strikes on TGFF and C2MOS against the $V_{dd}$ (V), (a) Critical charges of 0 to 1 SEU errors (b) Critical charges of 0 to 1 SEU errors . . . . . | 108 |

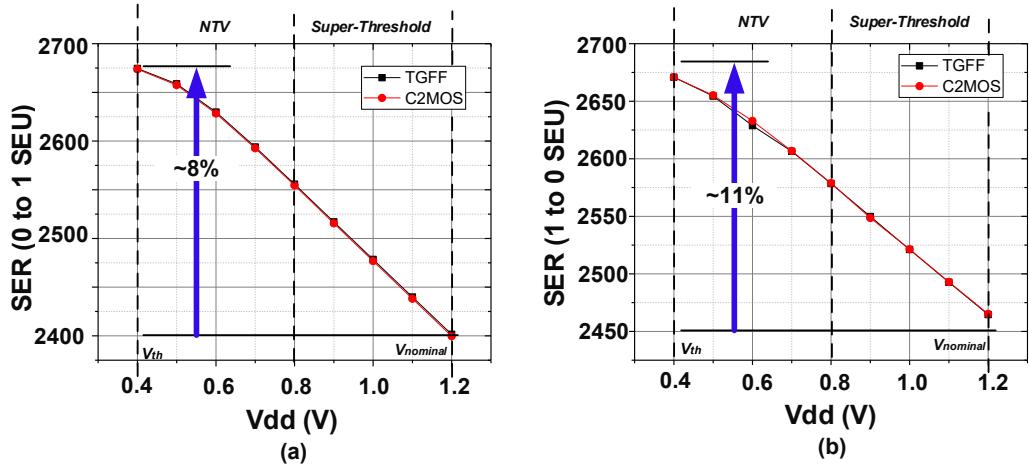

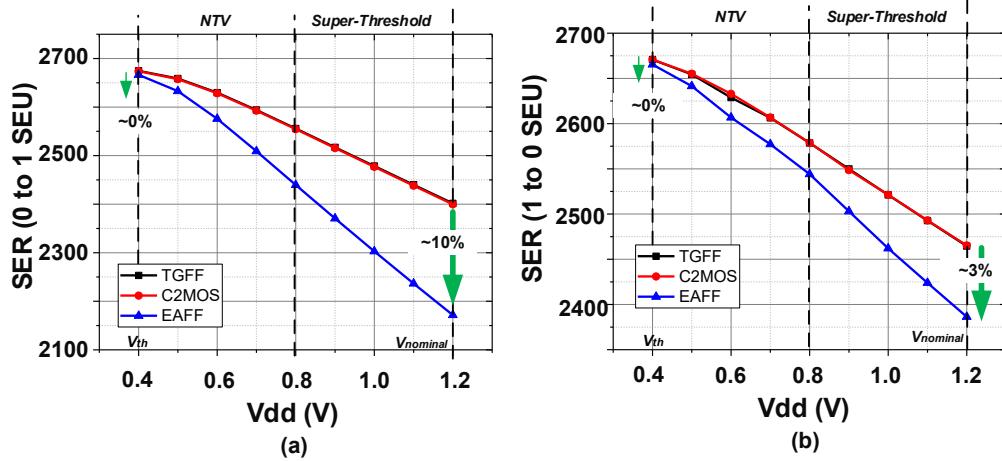

| 5.5  | SER (FIT) of NMOS/PMOS particle strikes on TGFF and C2MOS against the $V_{dd}$ , (a) $0 \rightarrow 1$ SEU SER of both FFs, (b) $1 \rightarrow 0$ SEU SER of both FFs .                              | 109 |

| 5.6  | Circuit schematic of the proposed Error-Aware FF. . . . .                                                                                                                                            | 110 |

| 5.7  | Operation waveform of the EAFF without SEU error injection. . . . .                                                                                                                                  | 110 |

| 5.8  | Operation waveform of the EAFF with $1 \rightarrow 0$ SEU error injection. . . . .                                                                                                                   | 111 |

|      |                                                                                                                                                                                                                                                                                             |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.9  | The Critical Charge (fC) of NMOS/PMOS particle strikes on the proposed FF EAFF, TGFF and C2MOS against the $V_{dd}$ , (a) The $0 \rightarrow 1$ SEU critical charge. (b) The $1 \rightarrow 0$ SEU critical charge. . . . .                                                                 | 112 |

| 5.10 | SER (FIT) of NMOS/PMOS particle strikes on the proposed EAFF, TGFF and C2MOS vs. $V_{dd}$ . (a) The $0 \rightarrow 1$ SEU SER of three FFs. (b) The $1 \rightarrow 0$ SEU SER of three FFs. . . . .                                                                                         | 112 |

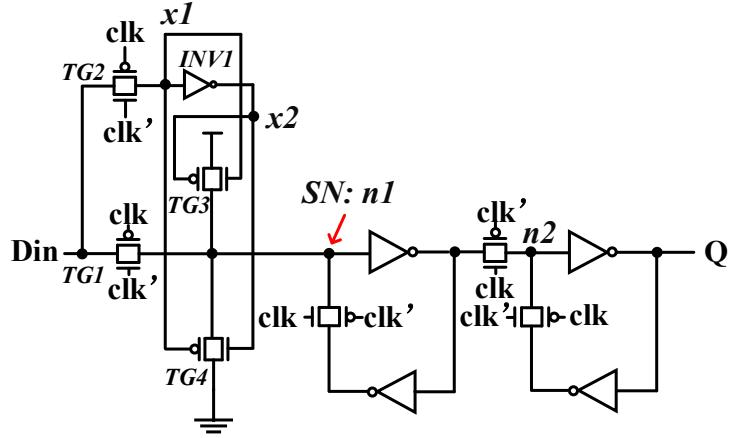

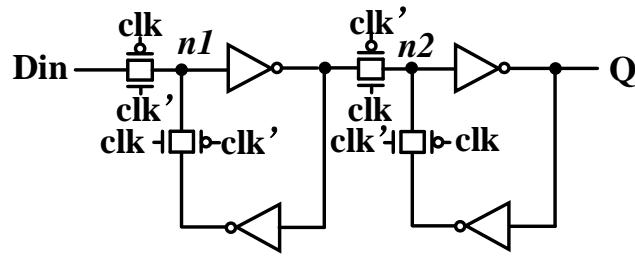

| 5.11 | Transistor schematic of Transmission Gate FF, soft error is injected to the node $n1$ or $n2$ . . . . .                                                                                                                                                                                     | 114 |

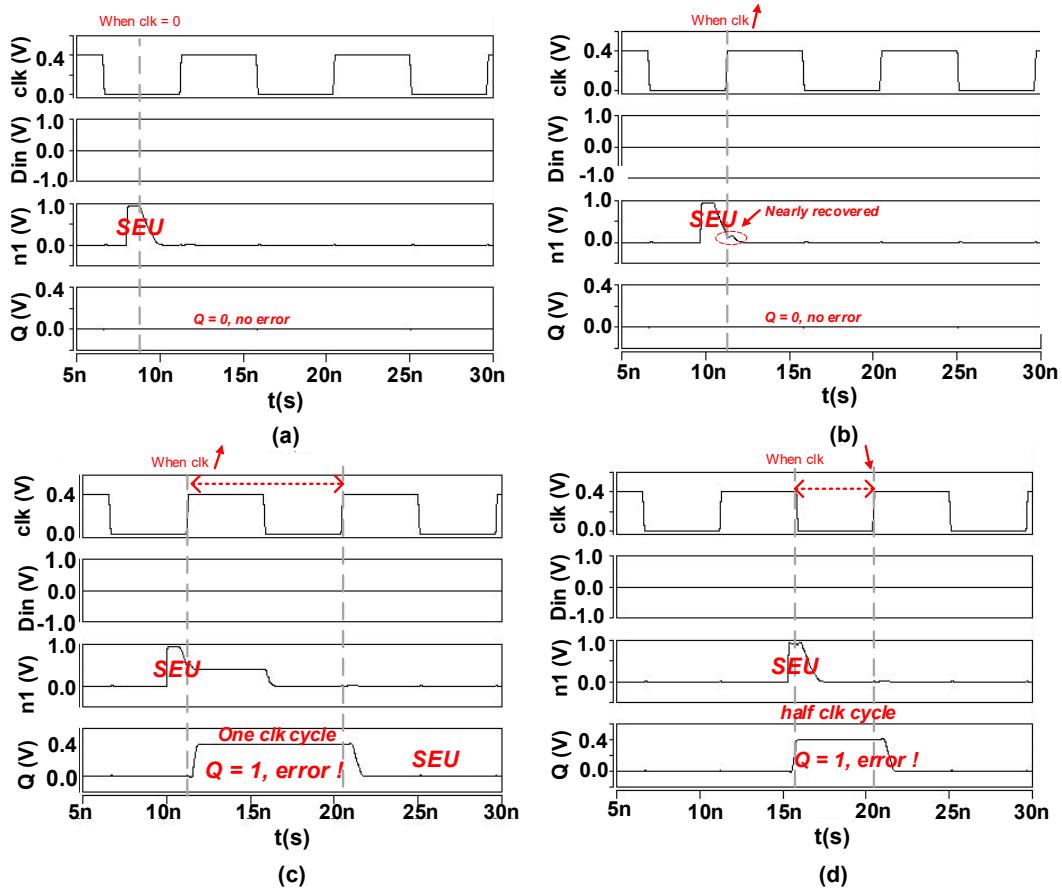

| 5.12 | 4 scenarios showing SEU events in TGFF.(a)SEU event is injected during the negative clock phase. (b)Injection point just before the rising edge of the clock. (c)Injection point is at the rising edge of the clock. (d)Injection point is at the falling edge of the clock. . . . .        | 114 |

| 5.13 | Critical Charge of internal node in master (n1) and slave (n2) latch at 0.4V. . . . .                                                                                                                                                                                                       | 115 |

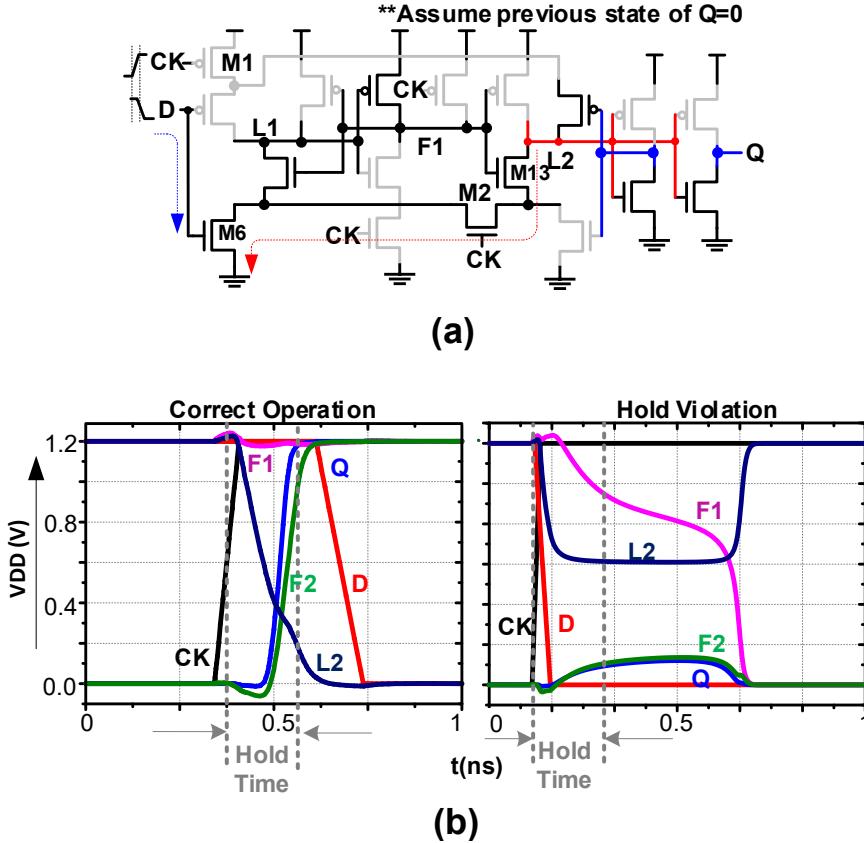

| 5.14 | Gate Level abstract of the proposed SEU resilient FF deisng, Dual-Master Latch Transmission Gate FF (DMTGFF). . . . .                                                                                                                                                                       | 116 |

| 5.15 | The decision block operation diagram for two SEU scenarios in DMTGFF. In both cases, the SEU is assumed to occur at a positive edge of the clock. Case 1: ML1 data is flipped from 0 to 1; Case 2: ML1 data is flipped from 1 to 0. . . . .                                                 | 117 |

| 5.16 | XOR gate implementations (a) a 12 transistors conventional XOR gate. (b) a 6 transistors transmission gate based XOR gate [158]. . . . .                                                                                                                                                    | 118 |

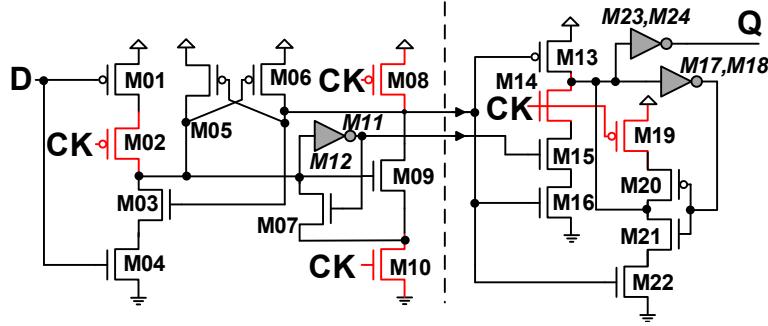

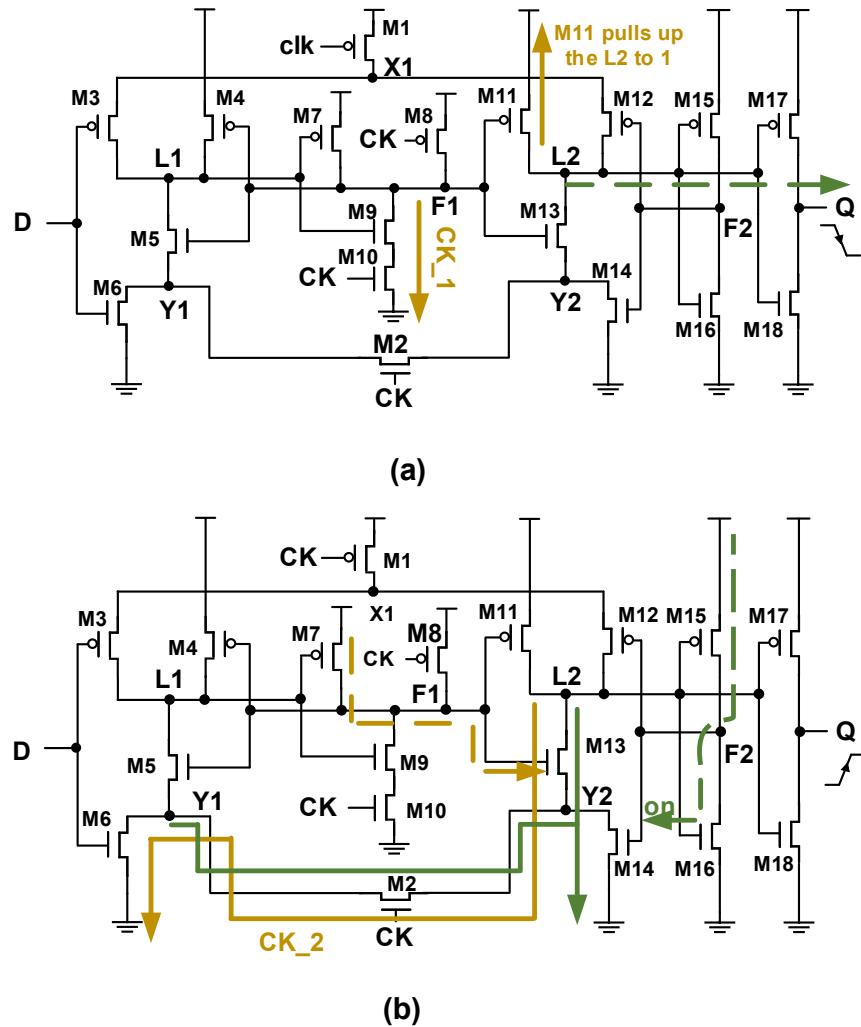

| 5.17 | Transistor level schematics of the decision block . . . . .                                                                                                                                                                                                                                 | 119 |

| 5.18 | Decision Block SPICE simulation results. . . . .                                                                                                                                                                                                                                            | 119 |

| 5.19 | Critical path of the Decision Block, the mechanics of delay mismatching. . . . .                                                                                                                                                                                                            | 120 |

| 5.20 | Delay Elements are inserted between (a) L1 (b) L2 and MUX2 inputs. . . . .                                                                                                                                                                                                                  | 121 |

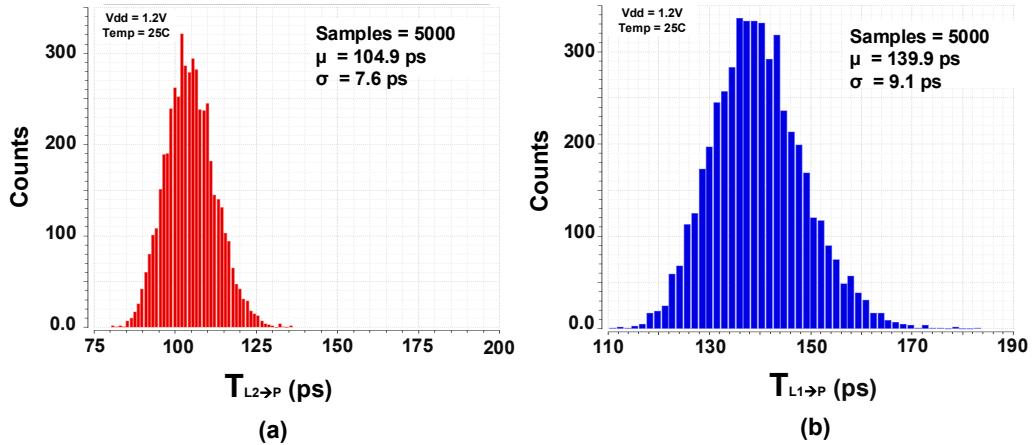

| 5.21 | (a) $T_{L2 \rightarrow P}$ and (b) $T_{L1 \rightarrow P}$ and Monte Carlo simulation at 1.2V. . . . .                                                                                                                                                                                       | 121 |

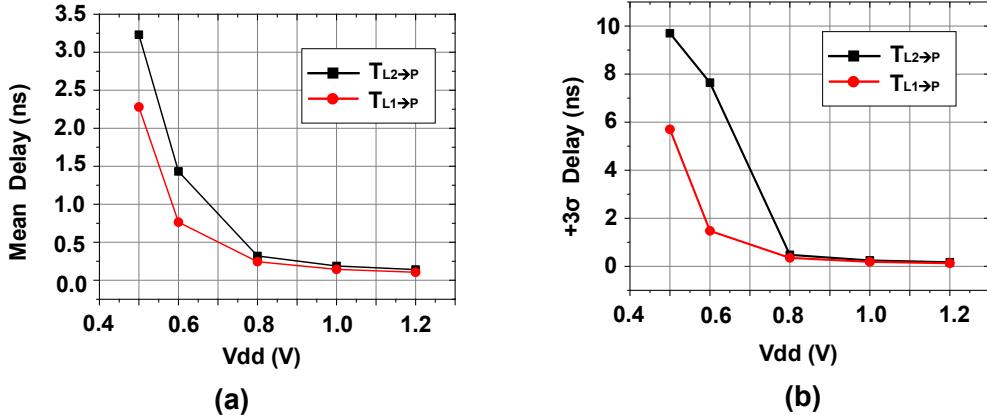

| 5.22 | The mean (a) and worst case scenario (b) $T_{L1 \rightarrow P}$ and $T_{L2 \rightarrow P}$ at different $V_{dd}$ (1.2 - 0.5). . . . .                                                                                                                                                       | 122 |

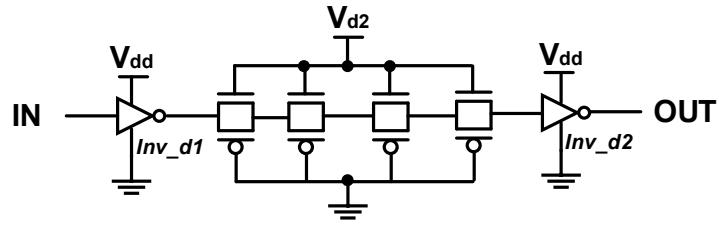

| 5.23 | Schematic of the Delay Element(DE). . . . .                                                                                                                                                                                                                                                 | 123 |

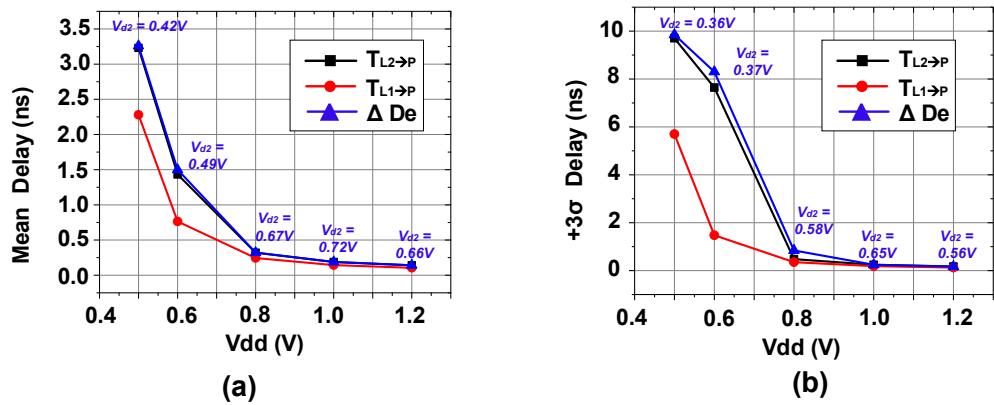

| 5.24 | The propagation delay of the DE at different $V_{dd}$ and corresponded tuning voltage $V_{d2}$ to balance the $T_{L1 \rightarrow P}$ and $T_{L2 \rightarrow P}$ . (a) Mean( $\mu$ ) delay balancing. (b) Worst-case ( $\mu + 3\sigma$ ) delay balancing. . . . .                            | 123 |

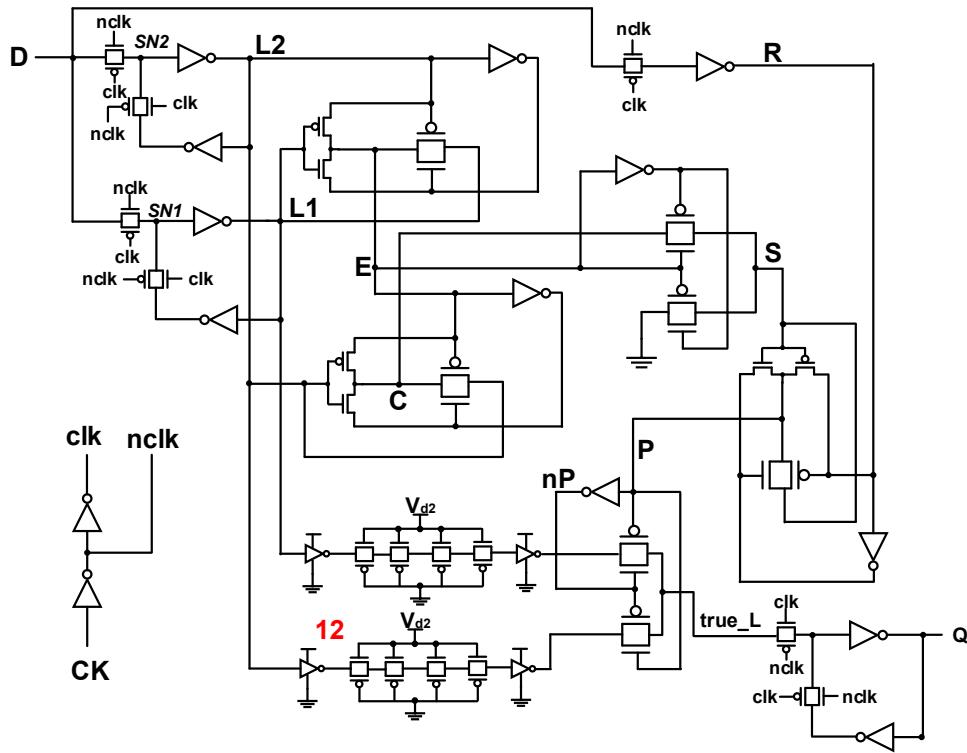

| 5.25 | A full transistor schematic diagram of the proposed DMTGFF. . . . .                                                                                                                                                                                                                         | 124 |

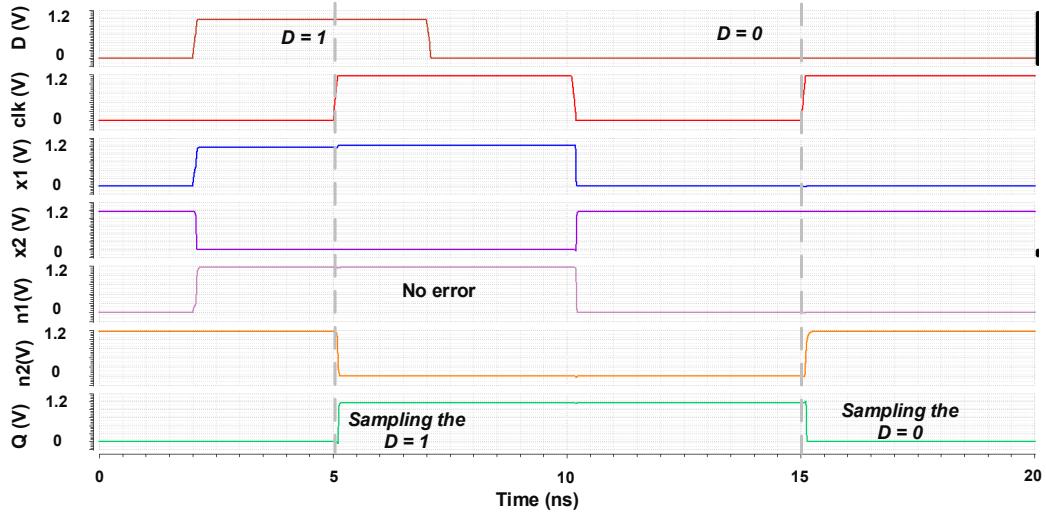

| 5.26 | Functionality tests results at different $V_{dd}$ (1.2V - 0.5V), without error injection. . . . .                                                                                                                                                                                           | 124 |

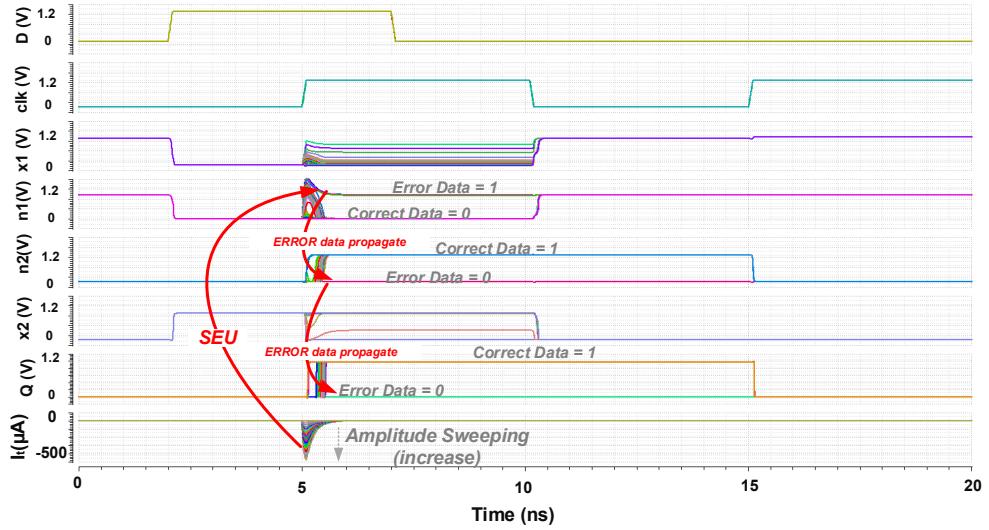

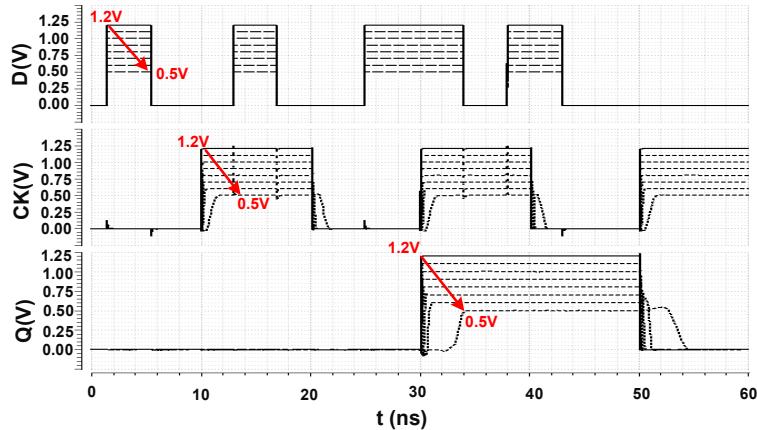

| 5.27 | (a) DMTGFF output recovered from (a) $1 \rightarrow 0$ SEU error which happens in ML1. (b) $1 \rightarrow 0$ SEU error which happens in ML2. (c) $0 \rightarrow 1$ SEU error which happens in ML1. (d) $0 \rightarrow 1$ SEU error which happens in ML2 at NTV ( $V_{dd} = 0.5V$ ). . . . . | 125 |

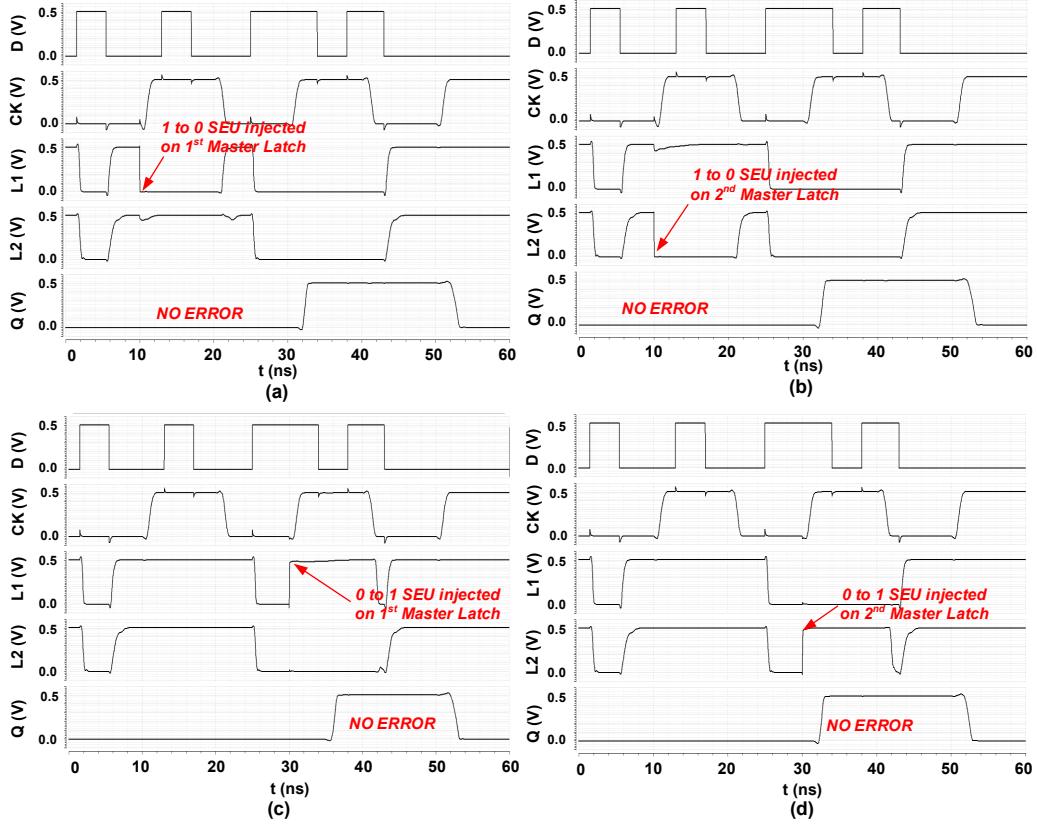

| 5.28 | (a) CK-Q delay of DMTGFF, DMR(with error correction) and TMR at different $V_{dd}$ (0.5V - 1.2V) (b)Power consumption of the proposed DMTGFF, DMR (with error correction) and TMR against the activity rate at $V_{dd} = 0.5V$ . . . . .                                                    | 126 |

| 6.1  | Initial design of Live-Slave Retention FF based on 20TSPC. . . . .                                                                                                                                                                                                                          | 131 |

| B.1  | Test chip address assignment. (continue...) . . . . .                                                                                                                                                                                                                                       | 138 |

| B.2  | Test chip address assignment. . . . .                                                                                                                                                                                                                                                       | 139 |

# List of Tables

|     |                                                                                                |     |

|-----|------------------------------------------------------------------------------------------------|-----|

| 3.1 | Comparison of state-of-the-art SPC FFs . . . . .                                               | 48  |

| 3.2 | Comparison of AES-128 macro for each SPC FF . . . . .                                          | 56  |

| 3.3 | A comparison of each SPC FF . . . . .                                                          | 61  |

| 3.4 | Comparison of AES-128 macro for FFs . . . . .                                                  | 64  |

| 4.1 | Net states at $Y_1$ and $Y_2$ at different $D$ , $D_{SL}^{previous}$ and $CK$ states . . . . . | 73  |

| 4.2 | Dynamic Power Comparison, Energy/cycle and Energy-Delay Product (ED) Comparison . . . . .      | 80  |

| 4.3 | AES-128 Synthesis Results Comparison . . . . .                                                 | 82  |

| 4.4 | Scan FFs Implementation results . . . . .                                                      | 83  |

| 4.5 | summary of Comparison with prior-works . . . . .                                               | 91  |

| 4.6 | Comparison of SPC FFs in terms of power and timing characteristics (I) .                       | 93  |

| 4.7 | Comparison of SPC FFs in terms of power and timing characteristics (II) .                      | 96  |

| 4.8 | Net states at $X_1$ and $X_2$ at different $D$ and $CK$ states . . . . .                       | 99  |

| 4.9 | Comparison of SPC FFs in terms of power and timing characteristics (III) .                     | 101 |

| 5.1 | Truth table of signals in decision block . . . . .                                             | 118 |

| 5.2 | Comparison of Error-tolerant Device Performance . . . . .                                      | 126 |

## Acknowledgements

I would like to use this opportunity to give my thanks to my supervisor Dr. Tom J. Kazmierski and Dr. Alex Weddell for their technical supervision and guidance throughout my PhD. Thank them for their concentration and valuable time during my thesis writing. Much appreciate with their suggestions on this thesis and encourage during the thesis writing. Without their kindness support and encouragement, it is not possible for me to carry on my research successfully.

My special thanks go to Anand Savanth, Pranay Prabhat, James Myers from ARM for their insightful discussions and technical support of the research. It was an enjoyable research experience. My thanks also go to Dr. Ke Li, Dr. Fanfan Meng for their generous advice. I also would like to give my thanks to my colleagues for their invaluable support and the experience sharing. These people include, but is not limited to Prof. David Flynn, Graham Knight, Dr. Sheng Yang, Rohan Gaddh, Yichi Zhang, Kueh Si Mon, Dr. Domenico Balsamo, Prof. Alex Yakovlev.

Finally, I would like to give my warmest thanks to my parents for supporting me with their continuous love, patience, and understanding.

# Nomenclature

|                        |                                                                                |

|------------------------|--------------------------------------------------------------------------------|

| $A_0$                  | Amplitude of the radiation induced transient current.                          |

| $ACFF$                 | Adaptive-Coupling Flip Flop.                                                   |

| $C_L$                  | Load Capacitance                                                               |

| $CPU$                  | Central Processing Unit                                                        |

| $C_{ox}$               | Oxide Capacitance                                                              |

| $CMOS$                 | Complementary Metal-Oxide-Semiconductor                                        |

| $C2MOS$                | Clocked-CMOS flip flop                                                         |

| $CMLE$                 | Clocked Memory Logic Element                                                   |

| $CK$                   | the clock signal.                                                              |

| $DET$                  | Dual-Edge-Triggered                                                            |

| $DET - TGLM$           | Transmission-Gate Latch-MUX                                                    |

| $DCV$                  | Duty Cycle Variation                                                           |

| $DVFS$                 | Dynamic Voltage and Frequency Scaling                                          |

| $DMTGFF$               | Double Master Latch Transmission Gate Flip Flop                                |

| $DIBL$                 | Drain-induced barrier                                                          |

| $DRAM$                 | Dynamic Random Access Memory                                                   |

| $DFT$                  | Discrete Fourier Transform                                                     |

| $DVFS$                 | Dynamic Voltage and Frequency Scaling                                          |

| $DVS$                  | Dynamic Voltage Scaling                                                        |

| $DMR$                  | Dual Modular Redundancy                                                        |

| $DC$                   | Detection Clock                                                                |

| $Din$                  | The Input of the flip flop.                                                    |

| $DATA_{ML}^{present}$  | The present data in Master-Latch.                                              |

| $DATA_{ML}^{previous}$ | The latched data from the input port $Din$ during $CK$ equalled 1.             |

| $DATA_{SL}^{present}$  | The present data in the Slave-Latch.                                           |

| $DATA_{SL}^{previous}$ | The latched data from the output of the ML during $CK$ equalled to 1 in $SL$ . |

| $DTA$                  | Dynamic Timing Analysis.                                                       |

| $E_{min}$              | Minimum Energy                                                                 |

| $E_{switch}$           | Switching probability of the input data                                        |

| $E_{static}$           | static energy consumption                                                      |

| $E_{static}$           | dynamic energy consumption                                                     |

| $E_{total}$            | total energy consumption                                                       |

---

|                |                                                                                |

|----------------|--------------------------------------------------------------------------------|

| <i>EDA</i>     | Electronic Design Automation                                                   |

| <i>EAFF</i>    | Error-Aware Flip Flop                                                          |

| <i>FF</i>      | Flip-Flop                                                                      |

| <i>FCK</i>     | Clock frequency                                                                |

| <i>FO4</i>     | Fan-out-4                                                                      |

| <i>FPGA</i>    | Field Programmable Gate Array                                                  |

| <i>FIT</i>     | Failure in Time.                                                               |

| <i>GDSBD</i>   | The gate-dielectric soft breakdown                                             |

| <i>IoT</i>     | Internet-Of-Things                                                             |

| <i>IoE</i>     | Internet-Of-Everything                                                         |

| $I_{total}$    | Integration if the current over the given time.                                |

| $I_{leakage}$  | Leakage Current                                                                |

| $I_S$          | Source Current                                                                 |

| $IC$           | Inversion Coefficient                                                          |

| $k$            | Boltzmann Constant                                                             |

| $k_{fit}$      | Model fitting parameter                                                        |

| $K_{DIBL}$     | Constants of proportionality capturing the impact of DIBL on threshold voltage |

| $K_T$          | Constants of proportionality capturing the impact of T on threshold voltage    |

| $L_{eff}$      | Efficient channel length                                                       |

| <i>MC</i>      | Monte-Carlo Simulation                                                         |

| <i>MCU</i>     | Micro-controller                                                               |

| <i>ML</i>      | Master Latch                                                                   |

| <i>MS</i>      | Master-Slave Structure                                                         |

| <i>MSFF</i>    | Master-Slave Flip Flop.                                                        |

| <i>MSAFF</i>   | Modified Sense Amplifier Flip Flop                                             |

| <i>MUX2</i>    | 2-to-1 Multiplexer.                                                            |

| <i>NTV</i>     | Near-Threshold Voltage                                                         |

| <i>NMOS</i>    | N-type metal-oxide-semiconductor.                                              |

| $n$            | The Sub-threshold slope parameter                                              |

| <i>NIMUX2</i>  | Non-Inverted Selecting Pin 2-to-1 Multiplexer.                                 |

| <i>OAI21</i>   | OR-AND-INVERTER gate.                                                          |

| <i>PMOS</i>    | P-type metal-oxide-semiconductor.                                              |

| $P_{total}$    | Total power                                                                    |

| $P_{dynamic}$  | Dynamic power consumption                                                      |

| $P_{leakage}$  | Leakage power consumption                                                      |

| <i>PVT</i>     | Process, Voltage and Temperature                                               |

| $q$            | Electron Charge                                                                |

| $Q_{total}$    | Total charge of the radiation induced transient current.                       |

| $Q_{critical}$ | Critical Charge.                                                               |

| <i>RTL</i>     | Register-Transfer Level                                                        |

| <i>SoA</i>     | State-of-the-Art                                                               |

---

|                                    |                                                        |

|------------------------------------|--------------------------------------------------------|

| <i>STV</i>                         | Sub-Threshold Voltage                                  |

| <i>SEU</i>                         | Single-Event Upset                                     |

| <i>SRAM</i>                        | Static Random Access Memory                            |

| <i>SDFF</i>                        | Semi-Dynamic Flip Flop                                 |

| <i>SPC</i>                         | Single Phase Clocked                                   |

| <i>S2CFF</i>                       | Static contention free single phased clocked Flip Flop |

| <i>SEL</i>                         | Single-Event Latch-up                                  |

| <i>SEB</i>                         | Single-Event Burnout                                   |

| <i>SEGR</i>                        | Single-Event Gate Rupture                              |

| <i>SESB</i>                        | Single-Event Snapback                                  |

| <i>SEFF</i>                        | Soft Edge Flip Flop                                    |

| <i>SET</i>                         | Single-Event Transient                                 |

| <i>SEU</i>                         | Single-Event Upset                                     |

| <i>SER</i>                         | Soft Error Rate.                                       |

| <i>SN</i>                          | Sensitive Node.                                        |

| <i>STA</i>                         | Static Timing Analysis.                                |

| <i>SRLatch</i>                     | Set-Reset Latch.                                       |

| <i>SL</i>                          | the Slave-Latch.                                       |

| <i>T</i>                           | Room Temperature                                       |

| <i>TGFF</i>                        | Transmission Gate Flip Flop                            |

| <i>TCFF</i>                        | Topologically-Compressed flip flop                     |

| <i>TSPC</i>                        | True Single-Phase Clock Flip Flop.                     |

| <i>T<sub>CK-Q</sub></i>            | Clock-to-Q delay                                       |

| <i>TG</i>                          | Transmission Gate                                      |

| <i>T<sub>hold</sub></i>            | Data hold time                                         |

| <i>T<sub>setup</sub></i>           | Data setup time                                        |

| <i>t<sub>g</sub></i>               | Gate Delay                                             |

| <i>T<sub>0</sub></i>               | Nominal value of the room temperature                  |

| <i>TMR</i>                         | Triple Modular Redundancy                              |

| <i>tri-inv</i>                     | Tristate inverter                                      |

| <i>ULP</i>                         | Ultra-Low-Power                                        |

| <i>UDSM</i>                        | Ultra-Deep-Sub-Micron                                  |

| <i>V<sub>cc</sub></i>              | Core Supply Voltage                                    |

| <i>V<sub>nominal</sub></i>         | nominal supply voltage                                 |

| <i>V<sub>GS</sub></i>              | Gate-to-Source Voltage                                 |

| <i>V<sub>th</sub></i>              | Threshold Voltage                                      |

| <i>V<sub>dd</sub></i>              | Power Supply Voltage                                   |

| <i>V<sub>dd0</sub></i>             | Nominal Supply Voltage                                 |

| <i>V<sub>th0</sub></i>             | Nominal threshold voltage                              |

| <i>V<sub>th</sub></i>              | Threshold voltage                                      |

| <i>V<sub>E<sub>min</sub></sub></i> | Voltage for minimum energy operation.                  |

|                 |                                                                           |

|-----------------|---------------------------------------------------------------------------|

| <i>VHDL</i>     | VHSIC Hardware Description Language                                       |

| <i>WOV</i>      | Window of Vulnerability.                                                  |

| <i>WNS</i>      | Wireless Sensor Network.                                                  |

| $\mu$           | Mobility, or mean value                                                   |

| $\Phi_t$        | Thermal Voltage                                                           |

| $\sigma_{DIBL}$ | DIBL Factor                                                               |

| $\sigma$        | standard deviation                                                        |

| $\mu$           | Mean value                                                                |

| $\tau_f$        | The time constant for fitting the charge collection process of the MOSFET |

| $\tau_r$        | The time constant for fitting the deposition process of the MOSFET        |

| $\lambda$       | the rail-to-rail pitch of the cell.                                       |

| $\delta$        | the minimum width of the TGFF.                                            |

| $18TSPC$        | 18-Transistor Single-Phase Clock Flip Flop.                               |

| $19TSPC$        | 19-Transistor Single-Phase Clock Flip Flop.                               |

| $20TSPC$        | 20-Transistor Single-Phase Clock Flip Flop.                               |

| $21TSPC$        | 21-Transistor Single-Phase Clock Flip Flop.                               |

# Chapter 1

## Introduction

With the development of Wireless Sensor Network (WSN), energy harvesting, battery and related technologies, the concept of Internet-of-Things(IoT), has been considered as one of the most attractive topics in academic and industrial. The IoT concept refers to the networked interconnection of physical objects via the embedded systems [1], different from the interaction between human and digital devices, IoT enables the interaction of smart objects [2]. Moreover, the key of the IoT network is the IoT leaf nodes devices. Leaf nodes should have the characteristics of sensing, communication, low power (long battery life), low cost and secured. These devices collect the physical data signals and transfer to the cloud for further signal processing. The existed IoT devices, as the interface between the physical world and digital world (see Figure 1.1), have been used in a wide range of applications, i.e. in healthcare, smart environments, and transportation [3][4] etc., and the range of scenarios is still increasing. Market analysis by ARM Ltd., estimates that there will be over one trillion IoT devices produced over the next 20 years [5].

Figure 1.1: Internet-of-Things (IoT) is the extension of the digital world into the physical world [6].

Figure 1.2: The world's smallest ARM-based microcontroller: Kinetis KL03 by Freescale(reproduced from [7]).

(a)

(b)

(c)

Figure 1.3: Some existing IoT platforms, (a) a small sized network, smart home/office project, Aware Home [11], (b) a large sized network, smart water project: SEMAT[12], (c) a medium sized network, smart city project: Smart Santande[13]

To meet the requirements of the applications they are employed in, IoT devices need to be small, low cost and (the most important criteria for such applications) have extremely low energy consumption. In contrast to speed critical applications, IoT devices are designed for long-term use which is not need to operate at high speed. Figure 1.2 shows an example of an IoT device, called Kinetis KL03 microcontroller (MCU), produced by Freescale. It has been revealed as the world's smallest ARM-based MCU [7]. The minimum Kinetis KL03 MCU (16-pin) is only  $9 \text{ mm}^2$ . In the Very-Low-Power-Run (VLPR) mode, the power consumption is as low as  $50 \mu\text{A}/\text{MHz} \cdot V_{cc}$  ( $V_{cc}$ : 1.71 - 3.6 V) [8]. Besides the Freescale's smallest MCU, some other low power MCUs with the bigger areas can also be found on the market. Such as the MSP430FR5733 Mixed-Signal MCU which is produced by Texas Instruments. It is  $36 \text{ mm}^2$  and the active power in low power mode is  $91.7 \mu\text{A}/\text{MHz} \cdot V_{cc}$  ( $V_{cc}$ : 2 - 3.6 V) [9]. The STM32L431CB from STMicroelectronics has a slightly bigger package size of  $49 \text{ mm}^2$  and the active power is  $80 \mu\text{A}/\text{MHz} \cdot V_{cc}$  ( $V_{cc}$ : 1.71 - 3.6 V) [10].

For the large number of incoming IoT leaf node, the power/energy budget is limited. Figure 1.3 shows various existing IoT platforms. The Energy sources of these platforms are either from rechargeable batteries or energy harvesting technologies [2][14]. Although rechargeable battery power is acceptable for current small or medium sized IoT networks

Figure 1.4: The power delivered from the state-of-the-art energy harvest technique is in order of  $100 \mu\text{W}/\text{cm}^2$  [6][15].

Figure 1.5: The energy source and power consumption of IoT devices map [16].

[11][13], it might not be the optimal solution for future IoT devices. With the trend in the development of WSNs, even the small sized IoT networks, such as the smart home/office, will see the number of devices increase. Also, the large sized IoT networks, such as smart water and smart transportation, suggest that the scale of the projects where these devices are employed is foreseeably larger. When the battery runs out after long-term sensing and monitoring operations, the process of recharging/replacing the batteries is predictably difficult. At the same time, applying energy harvesting techniques to IoT devices is also facing challenges. The latest research shows that the power delivered from the SoA energy harvesting technique is in the order of  $100 \mu\text{W}/\text{cm}^2$  (shown in Figure 1.4) [6][15]. Figure 1.5 shows the energy source and the power consumption of the IoT devices. It can be seen that the autonomous sensor nodes and the common IoT-oriented devices consumption would be higher than 5mW. The energy consumption of these common devices is 50× higher than the SoA energy harvest solution which lead to the issue of energy gap [16]. The amount of power budget provided by energy harvesting techniques is quite limited for powering IoT devices.

This means that, for digital circuit and system designers, with limited power/energy reservations, the most critical aim is to further minimize the power/energy consumption of the IoT devices. In order to meet the requirement of long-term operation, the demand

Figure 1.6: Energy consumption and delay in different supply voltage [18].

for implementing applications with Ultra Low Power (ULP) capabilities is becoming obvious.

Indeed, the low power use is not only a requirement for the duty cycled devices, but is also necessary for high performance computing devices. The excessive power density results in a rapid increase in temperature, which limits the yield and reliability of the system. And this roadblock in the semiconductor industry is known as the "power wall" [17]. For all applications, either the limited power budget IoT leaf node devices or the speed-critical devices, the demand for low power is critical.

Driven by the demand for a further reduction in the power/energy consumption of IoT leaf nodes devices with a limited power budgets and the further development of semiconductor technology, research into power reduction and ULP techniques is essential.

## 1.1 Research Justification

The total power/energy consumption of the circuit is proportional to the supply voltage. The dynamic power/energy consumption, as the subcategory of the total power, is both linear function of the supply voltage and operating frequency [19, 20]. In conventional low power/energy design technique, Dynamic Voltage and Frequency Scaling (DVFS) is widely used in today's low power products [21]. It introduced that slightly scales down the supply voltage  $V_{dd}$  from the nominal supply voltage ( $V_{nominal}$ ) (according to the given technology. For 65nm CMOS,  $V_{nominal} = 1.2$  V) and adjusting the clock frequency according to the demand for computing speed. The technique can usually

provide a 20% to 40% reduction in energy consumption [22, 23]. The operation voltage region is introduced as the super-threshold region which is around 70% - 100%  $V_{nominal}$ .

A more aggressive approach, the sub-threshold voltage technique (STV), was introduced to approach the minimum energy ( $E_{min}$ ) operating point (shown in Figure 1.6 in the STV region (Sub- $V_{th}$  Region), which can provide a  $12\times$  improvement in energy efficiency compared to a  $V_{nominal}$  operation, by scaling  $V_{dd}$  below the threshold voltage ( $V_{th}$ ) of the transistors [24–26]. However, the large performance degradation and process variation penalty mean that the STV technique can only be used for some specific custom designed devices [18].

Unlike the STV techniques, the recently introduced Near-Threshold Voltage (NTV) approach promises to scale well with a decreasing supply voltage while yields a higher robustness and reliability in comparison to STV techniques [18], which is likely to be more adaptable for future ULP devices.

NTV techniques, a potential solution for implementing ULP applications in power critical designs, have been shown to reduce energy consumption significantly by decreasing the supply voltage to approach the  $V_{th}$  (shown in Figure 1.6), while preserving favorable variability, energy efficiency ( $2E_{min}$ ) and performance characteristics ( 50-100 $\times$  better) when compared to the STV operations, as a result the NTV technique may be considered as a balanced trade-offs low power technique [27–31].

However, there are some primary challenges in the applications of NTV operations. The first well-known issue which needs to be addressed is the performance loss [30, 32, 33]. Also, there is a pronounced the impact of process variations to circuits is more serve in NTV region than in the Super-Threshold Voltage region [34–36]. What is more, it has been pointed out that circuits working at NTV are more vulnerable to radiation-induced soft errors [30].

## 1.2 Research Questions

Driven by the opportunities and challenges which exist in NTV techniques, this research aims to investigate the method of achieving the power/energy reduction through adopting the NTV technique, while maintaining the robustness of logic circuits, tolerate process variation and being resilient against errors with the minimum performance penalty and area overhead. Based on this, the research carried out aims to solve following questions.

(b) How is the State-of-the-Art (SoA) sequential circuit design fitting with the NTV technique?

- (c) How to propose a novel circuit topology to further reduce the power/energy consumption with (or without) the minimum the yield, performance and area cost penalty.

- (d) How to enhance the reliability of the NTV operating circuits?

### 1.3 Research Contributions

For answering the research questions, the basic concept of power consumption in the digital circuit and the concept of NTV design are reviewed in Chapter 2. Also, the design challenges and the SoA of NTV techniques are introduced in details and concept of sequential logic circuits. What is more, the literature surveyed the concept of the process variation and radiation-induced errors. The SoA error tolerant circuits are reviewed. Based on the background research, the research of this thesis led the following contributions:

1. ULP Flip-Flops evaluation and analysis and design for NTV operation

- Prominent types of SoA Single-Phased Clock (SPC) flip-flop(FF)s are reviewed and their suitability is analysed for NTV operation in Chapter 3. Five SPC FFs are reviewed and based on a preliminary analysis, two designs, which meet all NTV circuit design requirements are further investigated. These SPC FFs are designed for NTV operation in TSMC 65LP and compared against the classic transmission gate FF (TGFF). Cell level design issues and variation are explored in the context of a 5000 gate AES encryption macro. The Key design issues are identified in previously published Topologically Compressed Flip Flop (TCFF), which erode the claimed benefits of TCFF when implemented as part of a larger design for NTV applications. Based on the research, it can be realized that aggressive reduction in FF clock loading offers benefits but can lead to functional failures when OCV is considered, especially at NTV. Given the theoretical benefits of SPC FFs for enabling IoT, the need for further work on SPC FF designs is highlighted.

- Based on the research in evaluation and analysis of SPC FFs at NTV operation, a modified Topologically Compressed Flip Flop is proposed to enable the low voltage (NTV region) operations for addressing the design issues in TCFF, named TCFF-NTV in Chapter 3. The simulation results show the TCFF-NTV improved the yield of original TCFF by 95% and the proposed design brings 54% less hold time variation compare to the conventional TGFF at NTV. Cell-level design issues and variation are explored in the context of a 5000 gate AES encryption macro. The system synthesis results show the TCFF-NTV achieves 65% less activity register power than the TGFF based chip, with 4% area overhead and no performance penalty.

However, from the the evaluation, it can be seen that the area overhead of the new flip-flop design, TCFF-NTV, need always to be considered. This lead for the research on proposing the SPC FFs to meet all ULP FFs design requirements.

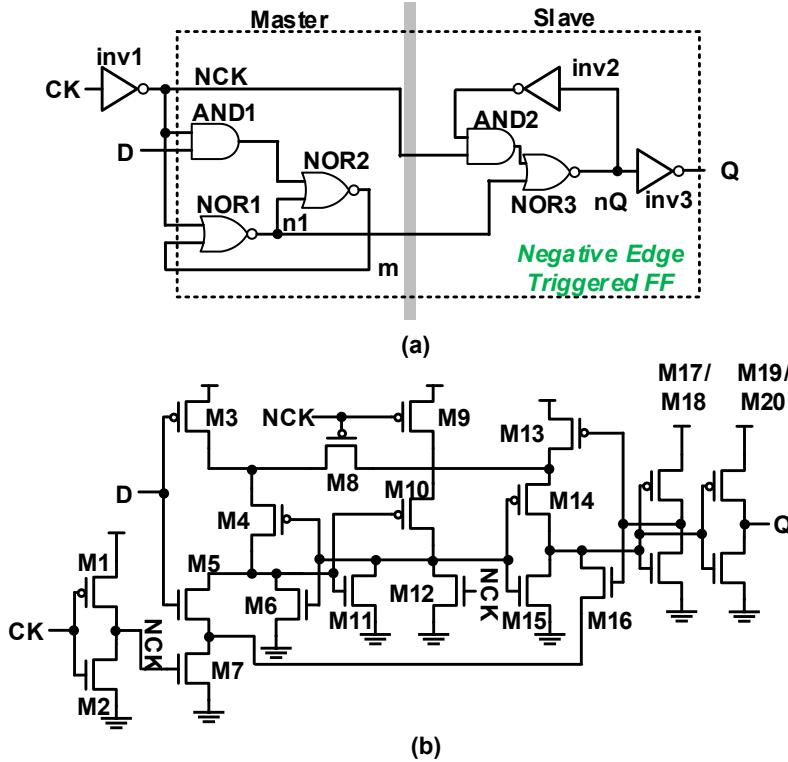

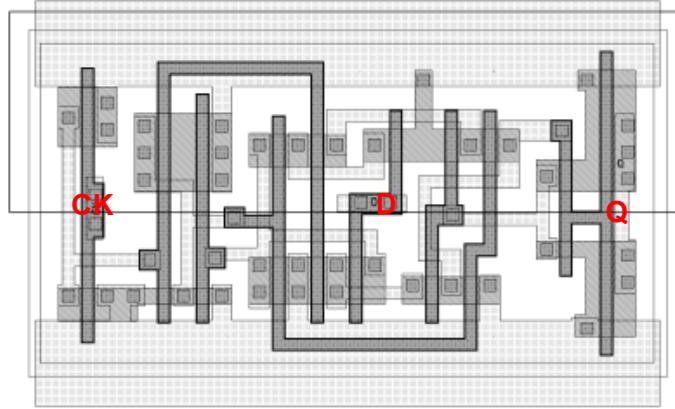

- 18TSPC, a novel master-slave topology SPC FF with only 18 transistors (the lowest reported for a fully-static contention-free SPC FF) is proposed in Chapter 4. With a simplified topology, it delivers a 20% reduction in cell area compared to TGFF. Unlike SoA designs, 18TSPC meets all ultra-low power FF design requirements. Although the performance penalty is observed, thanks to the low power characteristic of the proposed design, 18TSPC achieves about 2 times better ED product. It has been implemented in 65nm CMOS along with a TGFF in 320-bit shift-register and AES-128 encryption engine design. This proves EDA compatibility and demonstrates circuit and system-level benefits. The design was first simulated then experimentally validated, at various Data Activity Rate, showing that the proposed 18TSPC achieves reductions of 68% and 73% in overall and clock dynamic power, respectively, and 27% lower leakage compared to TGFF. Furthermore, unlike TCFF, the measurements indicate superior 18TSPC performance at NTV. Besides the 18TSPC, three extending SPC FFs are proposed for further developing. The details of these designs are also proposed in this chapter. All of these variants meet the design requirement of the ULP FFs design requirements and shows the superior power efficiency compare to the conventional TGFF and SoA designs.

## 2. Soft Error analysis and improvement of digital sequential circuits at NTV.

- The Critical Charge ( $Q_{critical}$ ) and Soft Error Rate (SER) of some typical sequential logic cells, Transmission Gate Flip-Flop (TGFF) and Clocked CMOS Flip-Flop (C2MOS), were estimated at the different supply voltage (0.4V-1.2V) and the simulation results are presented in Chapter 5. The simulation results quantified the increased soft error sensitivity of different devices in the NTV region, The level of increased SER in the NTV Region are also presented. Simulation results show the evidence of devices are more vulnerable to the soft error at NTV while a comparison to the nominal supply voltage operations is provided.

- Based on the research on the soft error in FFs at NTV. Two FF designs are presented in Chapter 5 for achieving the error resilient by increasing the local Critical Charge ( $Q_{critical}$ ) of the FF and adding redundant module blocks to the FF circuit, named Error-Aware Transmission Gate FF (EAFF) and Double Master Transmission Gate FF (DMTGFF). The simulation result shows that the EAFF increased  $Q_{critical}$  of the conventional FFs by  $1.9\times$  at different  $V_{dd}$ . Consequently, the SER decreased at different levels (0.3%-3%) as well.

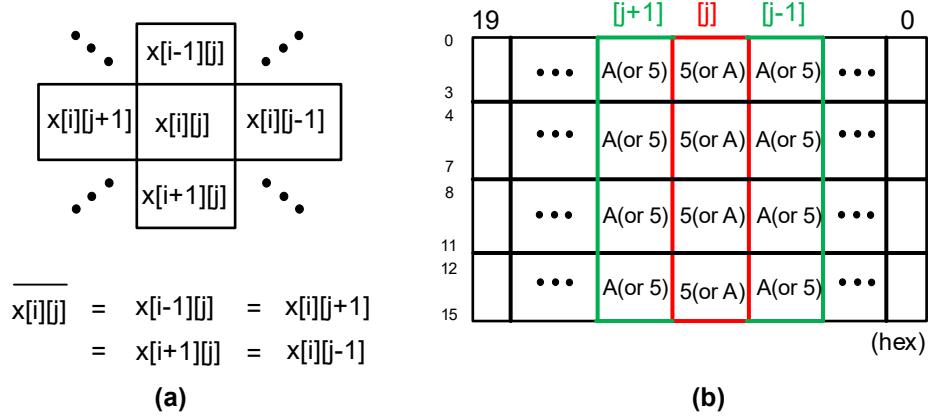

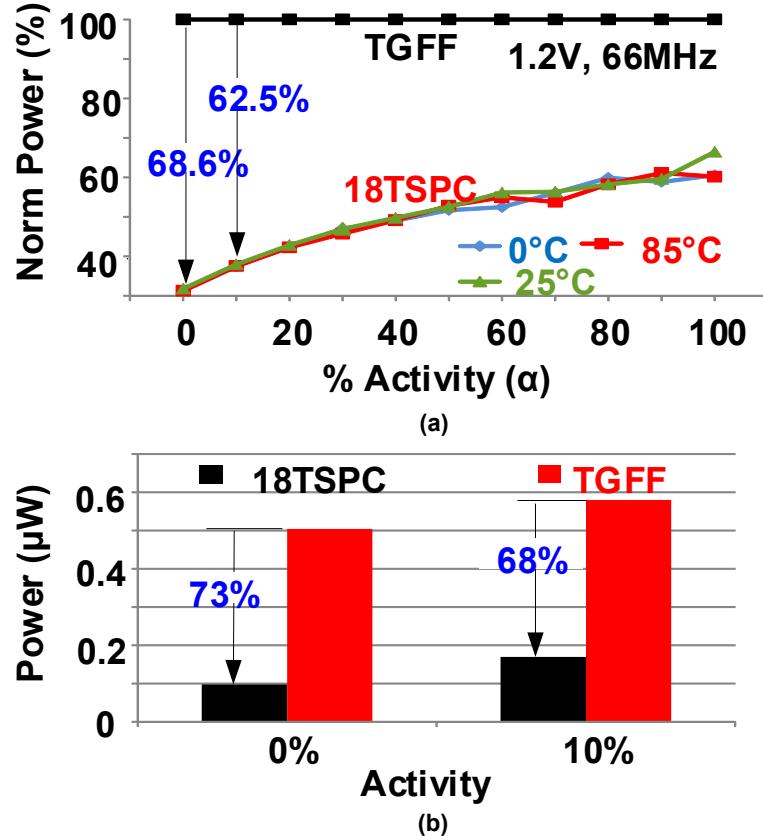

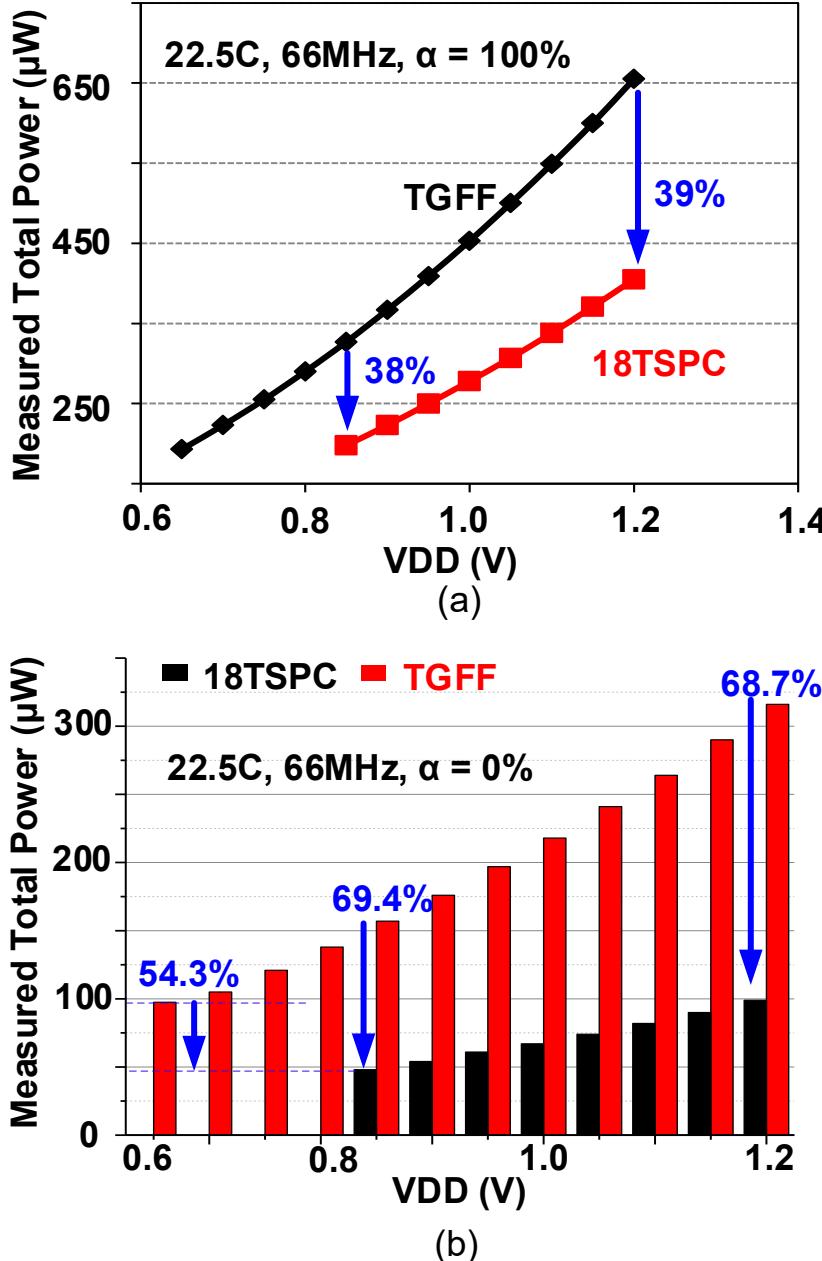

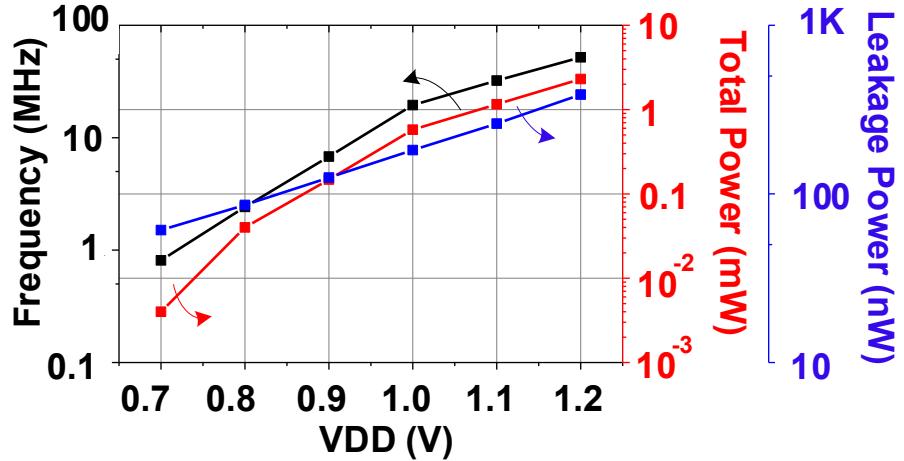

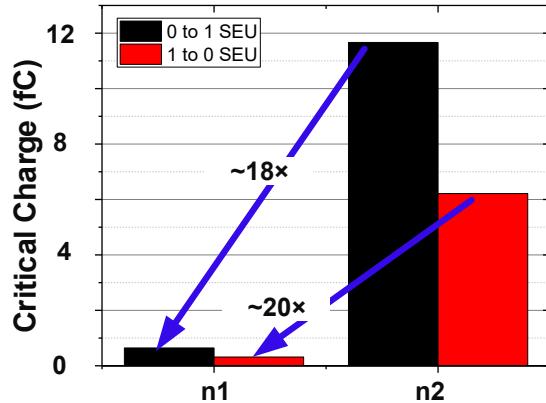

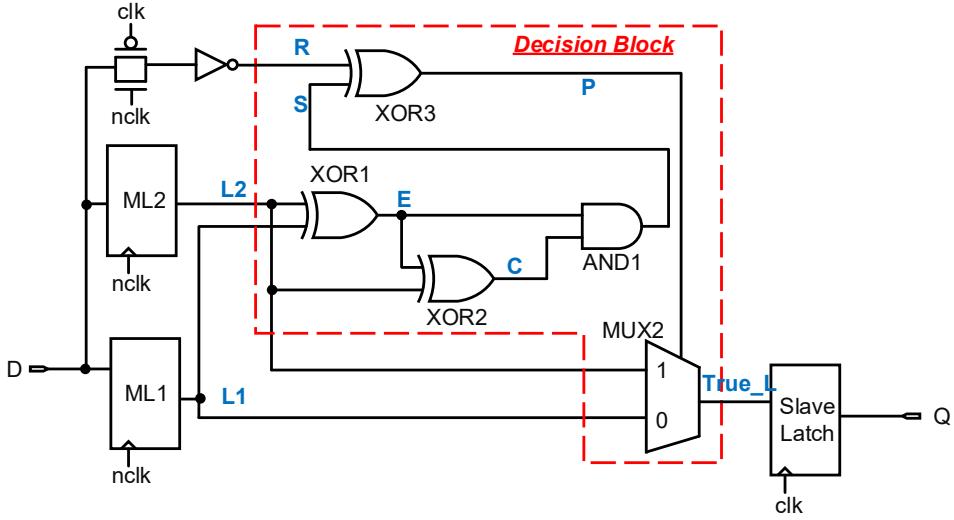

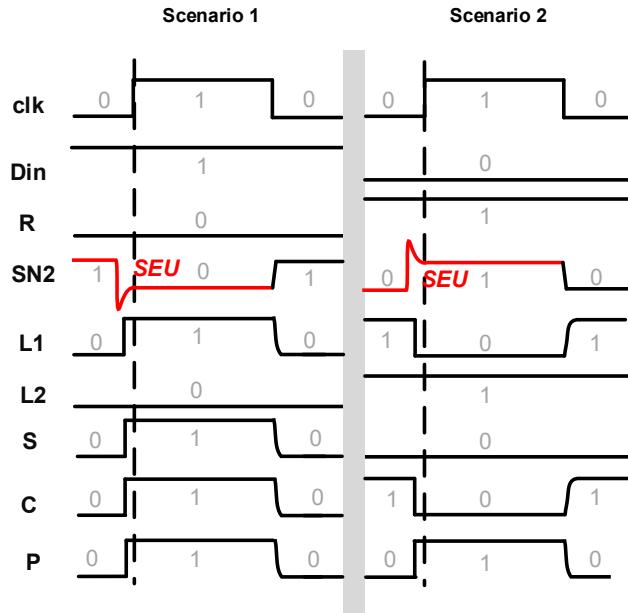

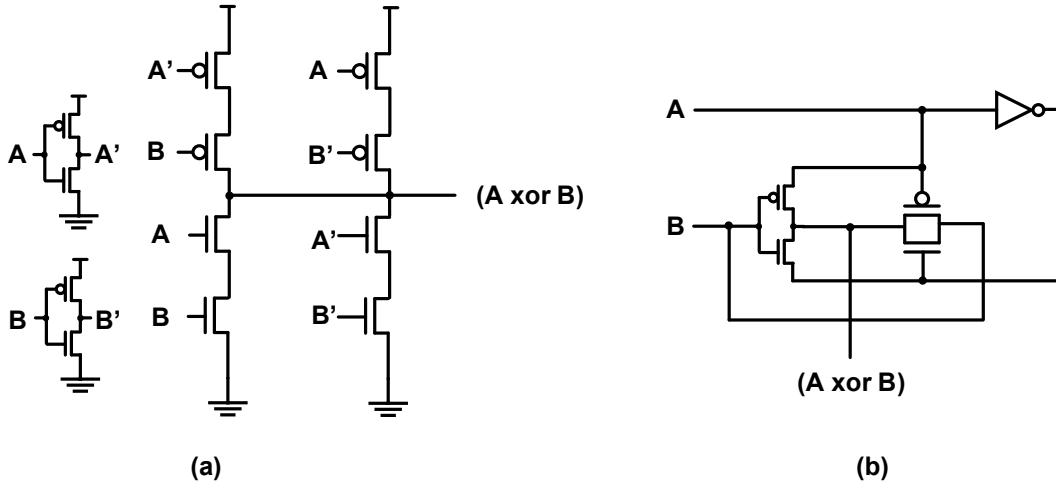

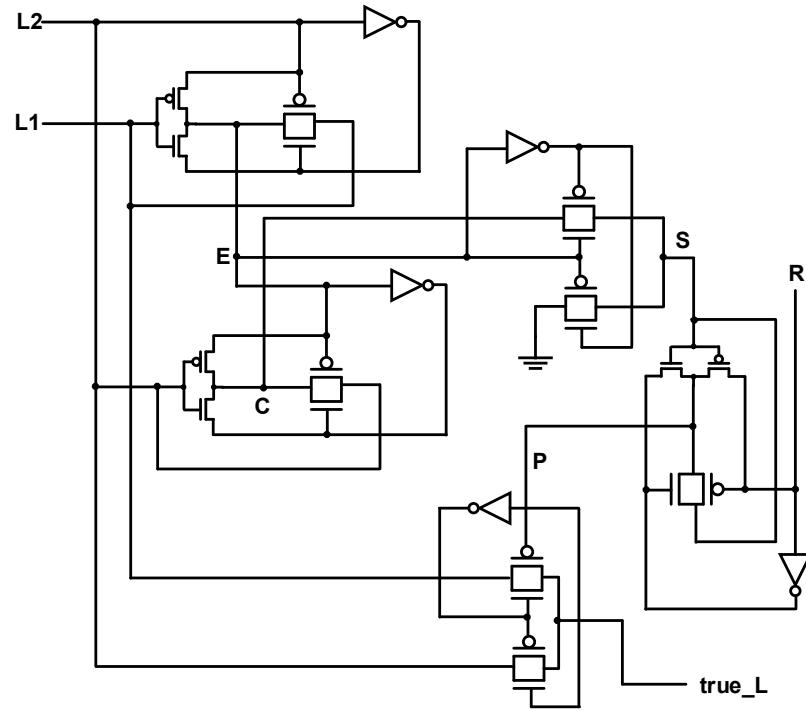

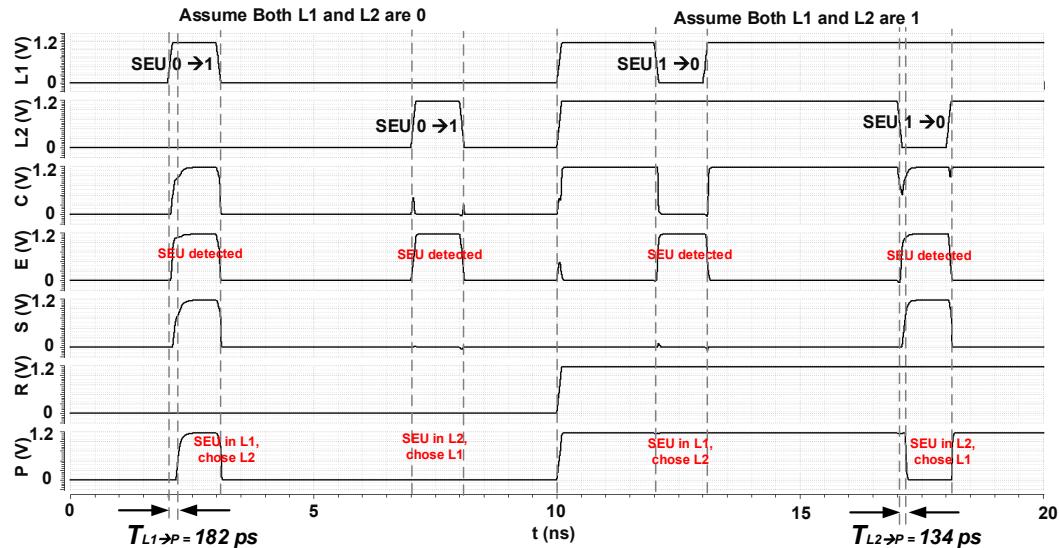

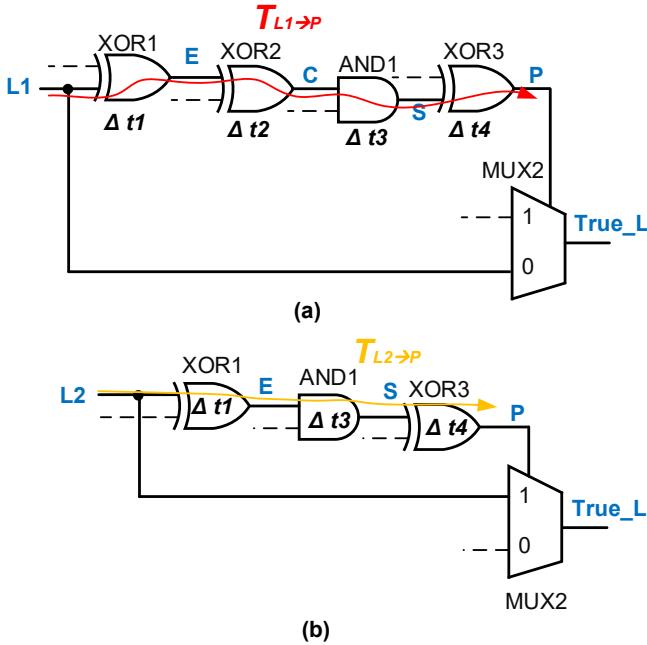

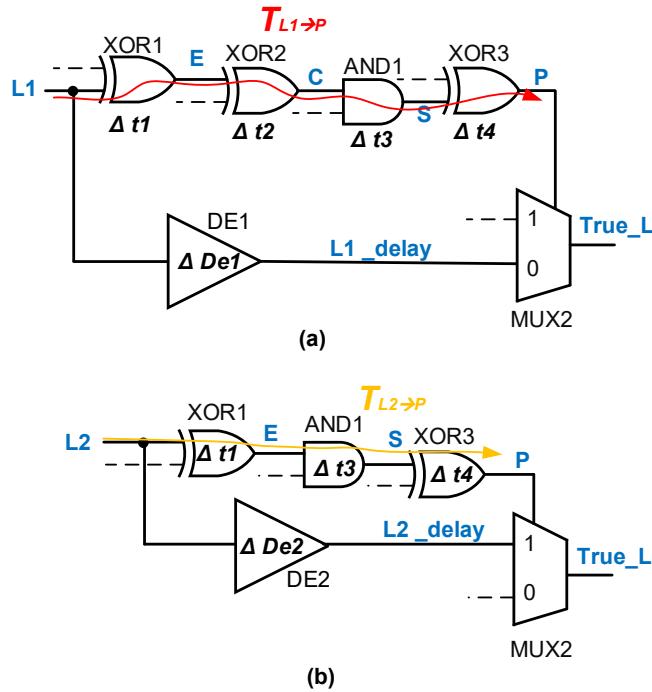

From the simulation results, it can be concluded that the method of increasing soft error tolerance capability by increasing  $Q_{critical}$  is not efficient for NTV operation. So that, the proposed EAFF, aiming to decrease the SER by increasing the  $Q_{critical}$  becomes less effective as the circuits operate at NTV.