#### UNIVERSITY OF SOUTHAMPTON

#### FACULTY OF ENGINEERING AND PHYSICAL SCIENCES Electronics and Computer Science

## Runtime Energy Management of Concurrent Applications for Multi-core Platforms

by

Karunakar Reddy Basireddy

Thesis submitted for the degree of Doctor of Philosophy

April 2019

## UNIVERSITY OF SOUTHAMPTON ABSTRACT

#### FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

Electronics and Computer Science

Doctor of Philosophy

## RUNTIME ENERGY MANAGEMENT OF CONCURRENT APPLICATIONS FOR MULTI-CORE PLATFORMS

by Karunakar Reddy Basireddy

Multi-core platforms are employing a greater number of heterogeneous cores and resource configurations to achieve energy-efficiency and high performance. These platforms often execute applications with different performance constraints concurrently, which contend for resources simultaneously, thereby generating varying workload and resources demands over time. There is a little reported work on runtime energy management of concurrent execution, focusing mostly on homogeneous multi-cores and limited application scenarios. This thesis considers both homogeneous and heterogeneous multi-cores and broadens application scenarios. The following contributions are made in this thesis.

Firstly, this thesis presents online Dynamic Voltage and Frequency Scaling (DVFS) techniques for concurrent execution of single-threaded and multi-threaded applications on homogeneous multi-cores. This includes an experimental analysis and deriving metrics for efficient online workload classification. The DVFS level is proactively set through predicted workload, measured through Memory Reads Per Instruction. The analysis also considers thread synchronisation overheads, and underlying memory and DVFS architectures. Average energy savings of up to 60% are observed when evaluated on three different hardware platforms (Odroid-XU3, Intel Xeon E5-2630, and Xeon Phi 7620P).

Next, an energy efficient static mapping and DVFS approach is proposed for heterogeneous multi-core CPUs. This approach simultaneously exploits different types of cores for each application in a concurrent execution scenario. It first selects performance meeting mapping (no. of cores and type) for each application having minimum energy consumption using offline results. Then online DVFS is applied to adapt to workload and performance variations. Compared to recent techniques, the proposed approach has an average of 33% lower energy consumption when validated on the Odroid-XU3.

To eliminate dependency on the offline application profiling and to adapt to dynamic application arrival/completion, an adaptive mapping approach coupled with DVFS is presented. This is achieved through an accurate performance model, and an energy efficient resource selection technique and a resource manager. Experimental evaluation on the Odroid-XU3 shows an improvement of up to 28% in energy efficiency and 7.9% better prediction accuracy by performance models.

### Contents

| A | bbre  | viation | ns                                                      |   |       | XV    |

|---|-------|---------|---------------------------------------------------------|---|-------|-------|

| N | omen  | ıclatur | re                                                      |   |       | xxi   |

| D | eclar | ation o | of Authorship                                           |   |       | xxiii |

| A | cknov | wledge  | ements                                                  |   |       | xxv   |

| 1 | Intr  | oducti  | ion                                                     |   |       | 1     |

|   | 1.1   | Runtir  | me Energy Management                                    |   |       | . 3   |

|   | 1.2   | Resear  | rch Justification                                       |   |       | . 3   |

|   | 1.3   | Resear  | rch Questions                                           |   |       | . 5   |

|   | 1.4   | Resear  | rch Contributions                                       |   |       | . 5   |

|   | 1.5   | Softwa  | are Contributions                                       |   |       | . 7   |

|   | 1.6   | Public  | cations                                                 |   |       | . 7   |

|   | 1.7   | Thesis  | s Organization                                          | • |       | . 8   |

| 2 | Lite  | rature  | e Review of Runtime Energy Management                   |   |       | 11    |

|   | 2.1   | DVFS    | and Thread-to-Core Mapping                              |   |       | . 12  |

|   |       | 2.1.1   | DVFS                                                    |   |       | . 13  |

|   |       | 2.1.2   | Thread-to-Core Mapping                                  |   |       | . 15  |

|   | 2.2   | Multi-  | -Processor System-on-Chips                              |   |       | . 17  |

|   |       | 2.2.1   | Number of Processing Cores                              |   |       | . 17  |

|   |       | 2.2.2   | Heterogeneity in Processing Cores                       |   |       | . 18  |

|   |       | 2.2.3   | Types of Multi-core Architecture                        |   |       | . 19  |

|   |       |         | 2.2.3.1 Homogeneous Multi-core Architectures            |   |       | . 20  |

|   |       |         | 2.2.3.2 Heterogeneous Multi-core Architectures          |   |       | . 21  |

|   | 2.3   | Appro   | paches to Runtime Energy Management                     |   |       | . 24  |

|   |       | 2.3.1   | Linux Power Governors                                   |   |       |       |

|   |       | 2.3.2   | RTM of Homogeneous Multi-cores                          |   |       | . 26  |

|   |       | 2.3.3   | RTM of Heterogeneous Multi-cores                        |   |       | . 30  |

|   | 2.4   | Experi  | imental Platforms, Applications and Tools               |   |       | . 35  |

|   |       | 2.4.1   | Experimental Platforms                                  |   | <br>• | . 35  |

|   |       |         | 2.4.1.1 Odroid-XU3                                      |   |       | . 36  |

|   |       |         | 2.4.1.2 Intel Xeon E5-2630V2                            |   |       |       |

|   |       |         | 2.4.1.3 Intel Xeon Phi 7120P                            |   |       |       |

|   |       | 2.4.2   | Applications                                            |   |       |       |

|   |       | 2/3     | Tools for Monitoring and Analysis of Porformance Events |   |       | 41    |

vi CONTENTS

|   | 2.5  | Discus                                                                | ssion    |                                                         | 42                   |  |  |

|---|------|-----------------------------------------------------------------------|----------|---------------------------------------------------------|----------------------|--|--|

| 3 | Rur  |                                                                       | _        | ment of DVFS for Homogeneous Multi-cores                | 45                   |  |  |

|   | 3.1  | Workl                                                                 |          | sification                                              |                      |  |  |

|   |      | 3.1.1                                                                 |          | $\operatorname{ology}$                                  |                      |  |  |

|   |      | 3.1.2                                                                 | Results  | and Discussion                                          |                      |  |  |

|   |      |                                                                       | 3.1.2.1  | Execution Time Based Workload Classification            | 49                   |  |  |

|   |      |                                                                       | 3.1.2.2  | PMC Data Based Workload Classification                  | 51                   |  |  |

|   | 3.2  | Runtii                                                                | me Manag | gement of DVFS for Concurrent Execution of Single-threa | $\operatorname{ded}$ |  |  |

|   |      | Applie                                                                | cations. |                                                         | 55                   |  |  |

|   |      | 3.2.1                                                                 | Runtime  | e Management of DVFS                                    | 57                   |  |  |

|   |      |                                                                       | 3.2.1.1  | Workload Selection and Prediction                       | 58                   |  |  |

|   |      |                                                                       | 3.2.1.2  | Workload Selection                                      | 59                   |  |  |

|   |      |                                                                       | 3.2.1.3  | Workload Prediction                                     | 59                   |  |  |

|   |      |                                                                       | 3.2.1.4  | Workload Classification and Frequency Selection         | 61                   |  |  |

|   |      |                                                                       | 3.2.1.5  | Adaptive Sampling                                       | 62                   |  |  |

|   |      |                                                                       | 3.2.1.6  | Performance Evaluation and Compensation                 | 62                   |  |  |

|   |      | 3.2.2                                                                 | Experin  | nental Results                                          | 63                   |  |  |

|   |      |                                                                       | 3.2.2.1  | Workload Prediction and Adaptive Sampling               | 63                   |  |  |

|   |      |                                                                       | 3.2.2.2  | Energy Savings                                          | 64                   |  |  |

|   |      |                                                                       | 3.2.2.3  | Application Performance                                 | 66                   |  |  |

|   |      |                                                                       | 3.2.2.4  | Runtime Overheads                                       | 66                   |  |  |

|   |      | 3.2.3                                                                 | Summa    | ry                                                      | 67                   |  |  |

|   | 3.3  | Runtime Management of DVFS for Concurrent Execution of Multi-Threaded |          |                                                         |                      |  |  |

|   |      | Applications                                                          |          |                                                         |                      |  |  |

|   |      | 3.3.1                                                                 | Runtime  | e DVFS Approach                                         | 69                   |  |  |

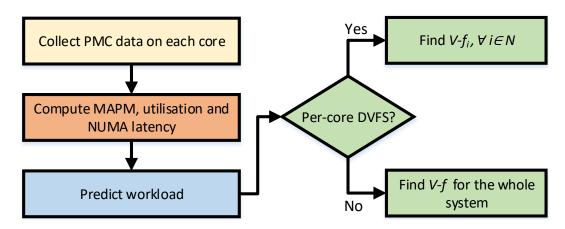

|   |      |                                                                       | 3.3.1.1  | PMC data collection                                     | 70                   |  |  |

|   |      |                                                                       | 3.3.1.2  | Computing MAPM, utilization and NUMA latency .          | 70                   |  |  |

|   |      |                                                                       | 3.3.1.3  | Workload prediction                                     | 71                   |  |  |

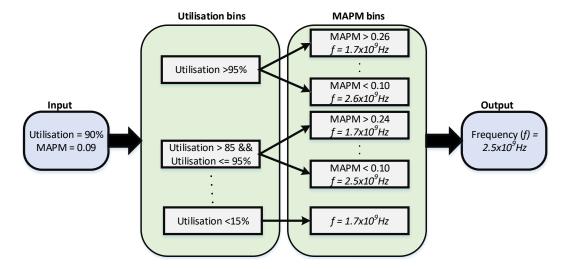

|   |      |                                                                       | 3.3.1.4  | Identification of $V$ - $f$ setting                     | 72                   |  |  |

|   |      | 3.3.2                                                                 |          | nental Results                                          |                      |  |  |

|   |      |                                                                       | 3.3.2.1  | Evaluation on 24-core Xeon E5-2630                      | 75                   |  |  |

|   |      |                                                                       | 3.3.2.2  | Evaluation on 61-core Xeon Phi                          | 78                   |  |  |

|   |      |                                                                       | 3.3.2.3  | Runtime Overheads                                       | 79                   |  |  |

|   | 3.4  | Discus                                                                | ssion    |                                                         | 80                   |  |  |

| 4 | Stat | tic Ma                                                                | pping at | nd DVFS for Heterogeneous Multi-cores                   | 83                   |  |  |

| _ | 4.1  |                                                                       |          | llation                                                 |                      |  |  |

|   | 4.2  |                                                                       |          | co-Core Mapping and DVFS Approach                       |                      |  |  |

|   |      | 4.2.1                                                                 |          | to-Core Mapping                                         |                      |  |  |

|   |      |                                                                       | 4.2.1.1  | Offline Analysis                                        |                      |  |  |

|   |      |                                                                       | 4.2.1.2  | Runtime Mapping Selection                               |                      |  |  |

|   |      | 4.2.2                                                                 |          | Approach                                                |                      |  |  |

|   |      |                                                                       | 4.2.2.1  | Workload Selection and Prediction                       |                      |  |  |

|   |      |                                                                       | 4.2.2.2  | Workload Classification and Frequency Selection         |                      |  |  |

|   |      |                                                                       | 4.2.2.3  | Performance Observation and Compensation                |                      |  |  |

|   | 4.3  | Exper                                                                 |          | Validation                                              |                      |  |  |

CONTENTS vii

|    |       | 4.3.1  | Energy Savings and Performance Comparison         | 98  |

|----|-------|--------|---------------------------------------------------|-----|

|    |       |        | 4.3.1.1 Energy Savings                            | 98  |

|    |       |        | 4.3.1.2 Breakdown of Energy Savings               | 102 |

|    |       |        | 4.3.1.3 Performance                               | 103 |

|    |       | 4.3.2  | Workload Prediction                               | 105 |

|    |       | 4.3.3  | Overheads of the Proposed Approach                |     |

|    |       |        | 4.3.3.1 Runtime Overhead                          |     |

|    |       |        | 4.3.3.2 Offline Analysis Overhead                 | 106 |

|    | 4.4   | Discus | ssion                                             | 106 |

| 5  | Ada   | ptive  | Mapping and DVFS for Heterogeneous Multi-cores    | 109 |

|    | 5.1   | Proble | em Formulation                                    | 113 |

|    | 5.2   | Adapt  | ive Thread-to-Core Mapping and DVFS               | 113 |

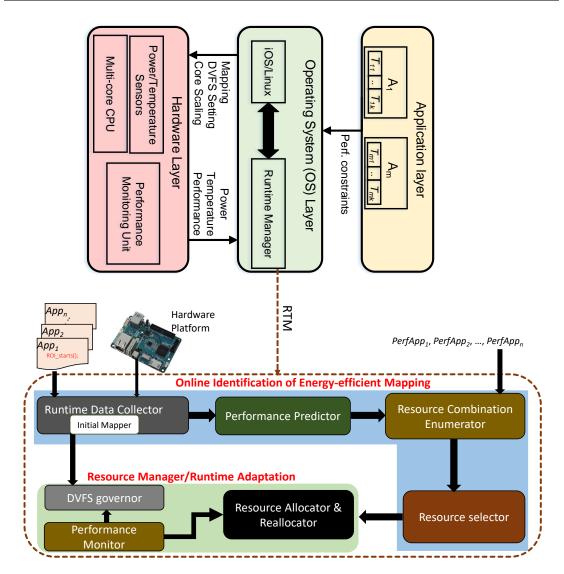

|    |       | 5.2.1  | Online Identification of Energy-efficient Mapping | 115 |

|    |       |        | 5.2.1.1 Runtime Data Collector                    | 115 |

|    |       | 5.2.2  | Performance Predictor                             | 116 |

|    |       | 5.2.3  | Resource Combination Enumerator                   | 119 |

|    |       | 5.2.4  | Resource Selector                                 | 120 |

|    |       | 5.2.5  | Resource Manager/Runtime Adaptation               | 121 |

|    |       |        | 5.2.5.1 Resource Allocator/Reallocator            | 121 |

|    |       |        | 5.2.5.2 Performance Monitor                       | 123 |

|    |       |        | 5.2.5.3 DVFS Governor                             | 124 |

|    | 5.3   | Exper  | imental Results                                   | 125 |

|    |       | 5.3.1  | Experimental Setup and Implementation             | 125 |

|    |       | 5.3.2  | Evaluation of Performance Predictor               | 127 |

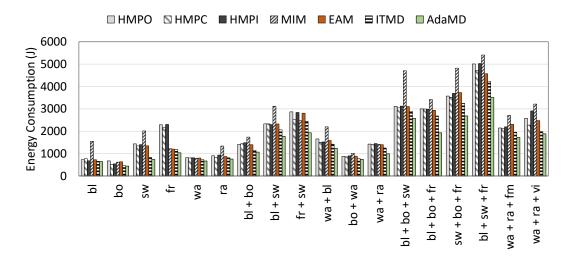

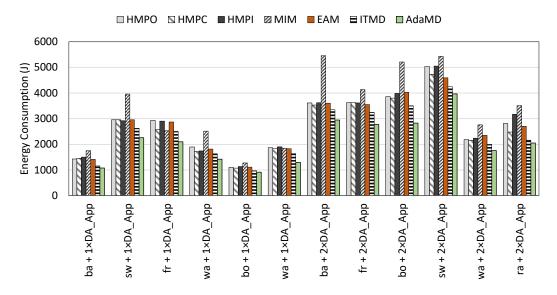

|    |       | 5.3.3  | Comparison of Energy Consumption                  | 129 |

|    |       | 5.3.4  | Performance                                       | 130 |

|    |       | 5.3.5  | Runtime Overheads                                 |     |

|    | 5.4   | Discus | ssion                                             | 132 |

| 6  |       |        | ns and Future Work                                | 133 |

|    | 6.1   |        | usions                                            |     |

|    | 6.2   | Future | e Work                                            | 136 |

| Aı | pen   | dix A  | Application Offline Analysis Results              | 139 |

| Aı | pen   | dix B  | Experimental Data Used in Classification Bins     | 145 |

| A  | pen   | dix C  | Sample Code for Data Collection and Processing    | 149 |

| Re | efere | nces   |                                                   | 161 |

# List of Figures

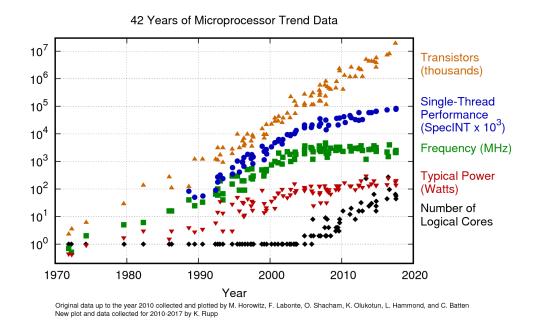

| 1.1  | Historical trends in CPU performance, reprinted from [1]                                                                                               | 1   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

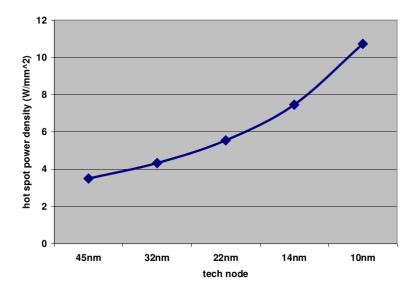

| 1.2  | Hot spot power density scaling with feature size. Reprinted from [2]                                                                                   | 2   |

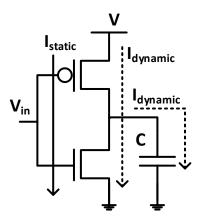

| 2.1  | Illustration of static and dynamic current through an inverter gate                                                                                    | 12  |

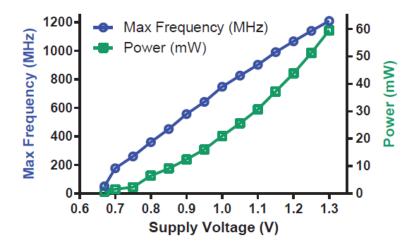

| 2.2  | Relation between maximum frequency and dynamic power versus supply                                                                                     |     |

|      | voltage. Reprinted from [3]                                                                                                                            | 14  |

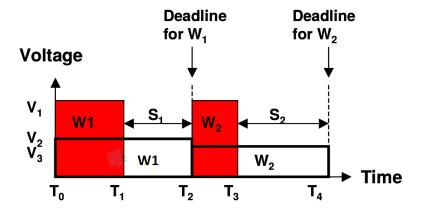

| 2.3  | An illustration of the DVFS technique. Reprinted from [4]                                                                                              | 14  |

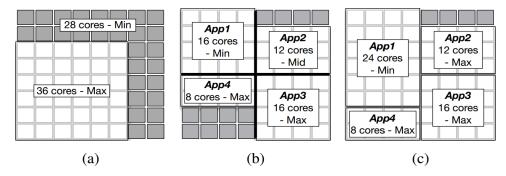

| 2.4  | Illustration of thread-to-core mapping under a power cap. (a) Executing a multithreaded program. (b) and (c) Executing four multithreaded              |     |

|      | applications concurrently. Reprinted from [5]                                                                                                          | 16  |

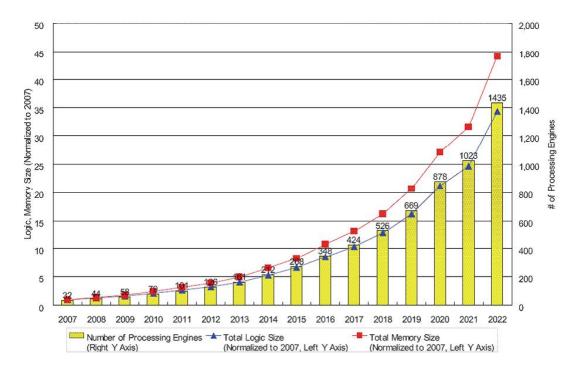

| 2.5  | Evolution of the number of cores in embedded platforms. Extracted from [6].                                                                            | 18  |

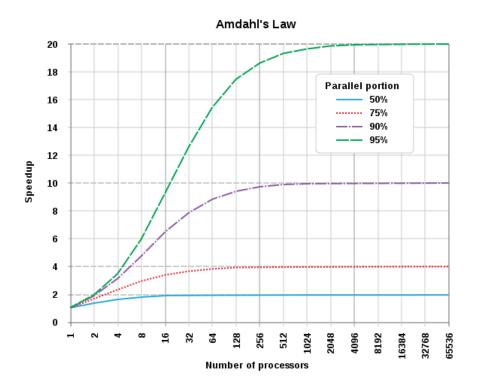

| 2.6  | Speedup vs. number of processors for different portions of parallel code                                                                               |     |

|      | in an application, using Amdahl's law [7]                                                                                                              | 19  |

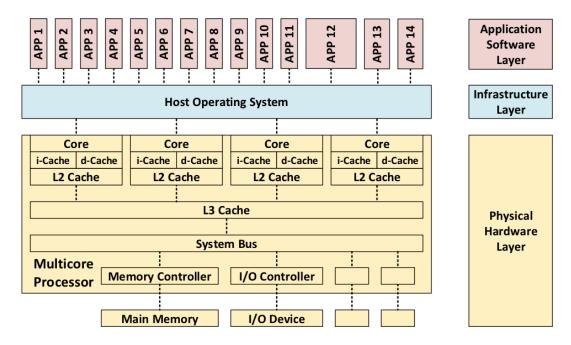

| 2.7  | Homogeneous multi-core architecture of a system in which 14 software applications are allocated by a single host operating system to the cores,        |     |

|      | reprinted from [8]                                                                                                                                     | 20  |

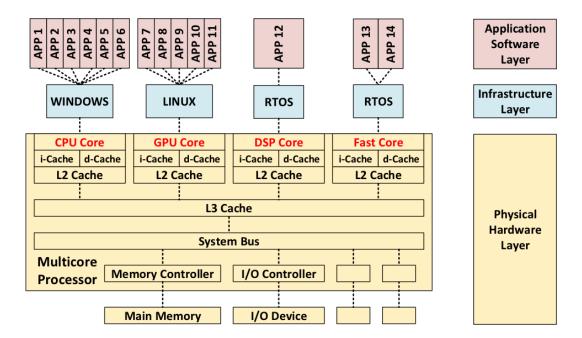

| 2.8  | A heterogeneous multi-core architecture, running four different operating                                                                              |     |

|      | systems and 14 applications, reprinted from [8]                                                                                                        | 22  |

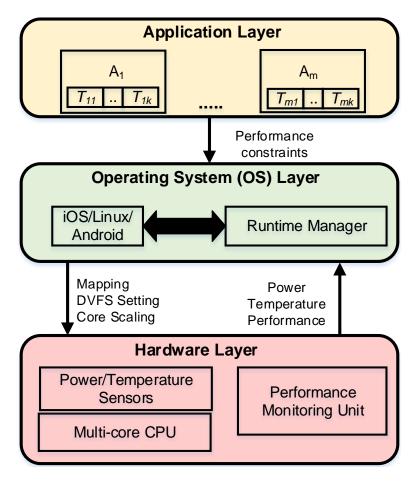

| 2.9  | Representing an embedded systems as three stacked layers: application,                                                                                 |     |

|      | operating system and the hardware                                                                                                                      | 23  |

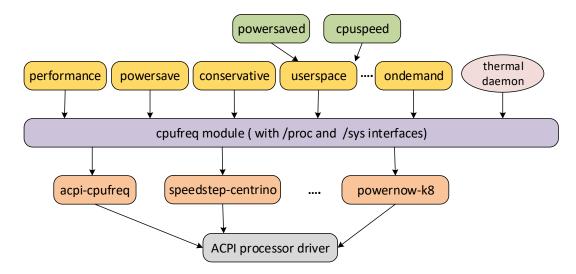

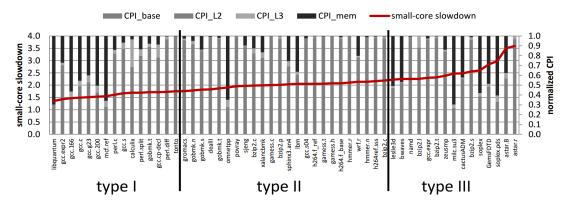

|      | cpufreq infrastructure, a subsystem of the Linux kernel. Extracted from [9]. Normalized big-core CPI stacks (right axis) and small-core slowdown (left | 25  |

|      | axis). Benchmarks are sorted by their small-versus-big core slowdown.                                                                                  |     |

|      | Reprinted from [10]                                                                                                                                    | 30  |

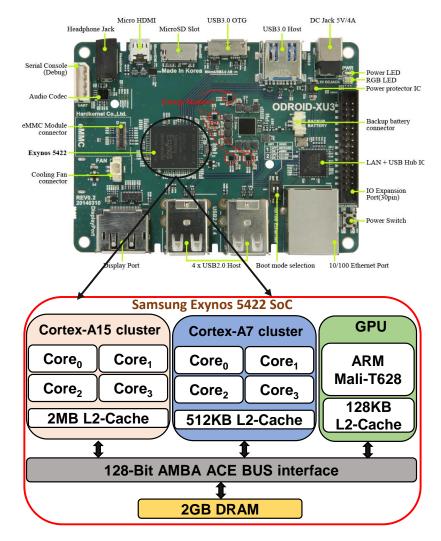

| 2.12 | Odroid-XU3 board (top) containing Samsung Exynos 5422 heterogeneous                                                                                    |     |

|      | MPSoC (bottom). Adapted from [11]                                                                                                                      | 37  |

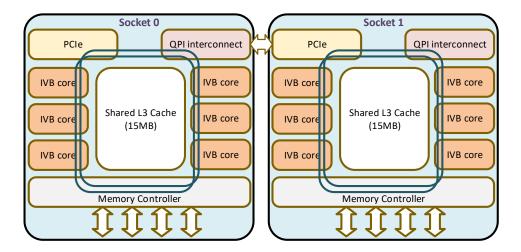

|      | The block diagram of the Intel Xeon E5-2630V2. Redrawn from [12]                                                                                       | 38  |

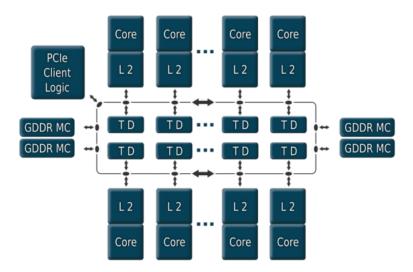

| 2.14 | The Intel Xeon Phi chip architecture layout with ring-based interconnect.                                                                              | 0.6 |

| 0.15 | Taken from [13]                                                                                                                                        | 38  |

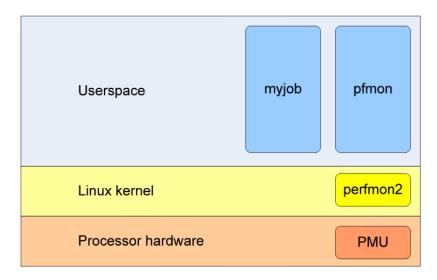

| 2.15 | Perfmon2 and pfmon, sitting in Kernel and Userpsace level, respectively.                                                                               | 41  |

|      | Reprinted from [14]                                                                                                                                    | 41  |

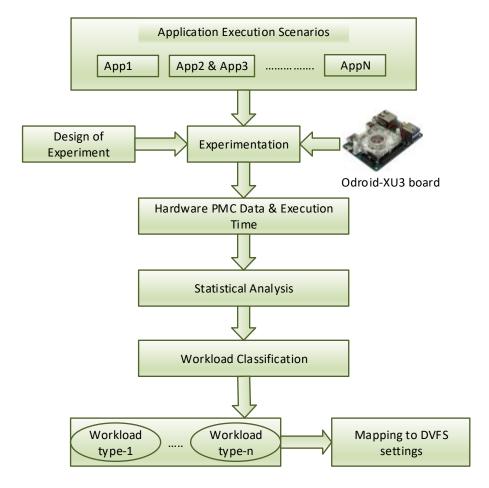

| 3.1  | Experimental methodology used for workload classification                                                                                              | 47  |

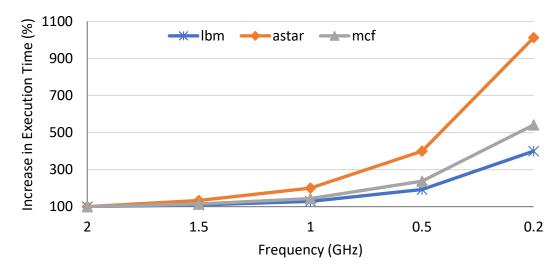

| 3.2  | Variation in execution time with frequency for 1bm, astar and mcf appli-                                                                               |     |

|      | cations running on the Cortex-A15 core                                                                                                                 | 49  |

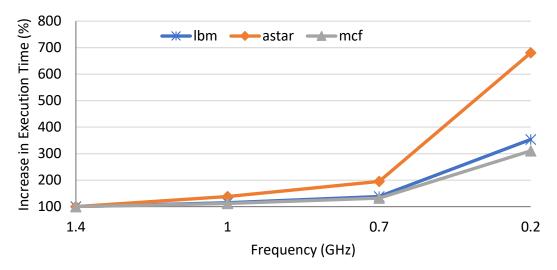

| 3.3  | Variation in execution time with frequency for 1bm, astar and mcf appli-                                                                               |     |

|      | cations running on Cortex-A7 core                                                                                                                      | 49  |

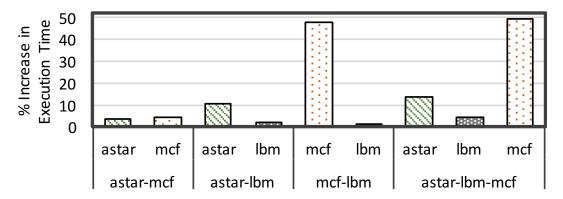

| 3.4  | Effect of concurrent execution on application execution time                                                                                           | 50  |

x LIST OF FIGURES

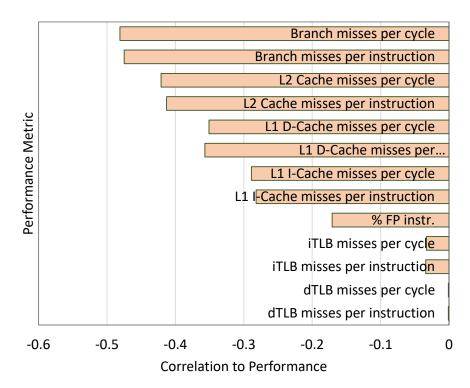

| 3  | Correlation between different performance metrics and application performance, measured in IPC.                                                                         |        | 51       |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|

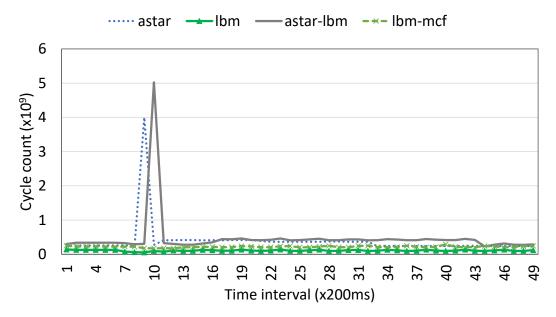

| 3  | Cycle count for sequential and concurrent execution of astar, 1bm and mcf. Samples are collected for every 200 ms                                                       |        | 52       |

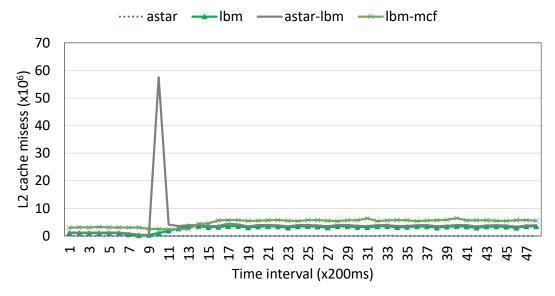

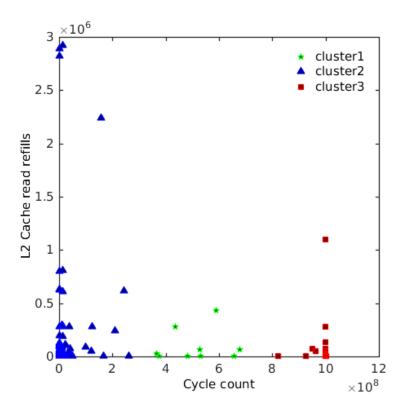

| 3. | L2 cache misses for individual and concurrent execution of astar, 1bm and mcf. Samples are collected for every 200 ms                                                   |        | 52       |

| 3. | K-means clustering of workloads for concurrent execution of astar and lbm                                                                                               |        | 53       |

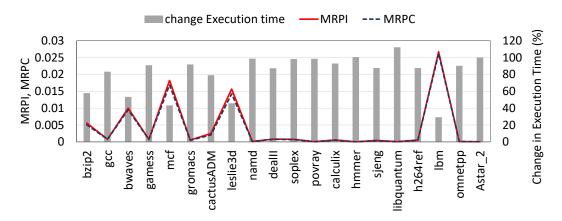

| 3  | MRPI and MRPC of various applications, computed by executing each application to completion. The change in execution time when frequency is scaled from 2 GHz to 1 GHz. |        | 54       |

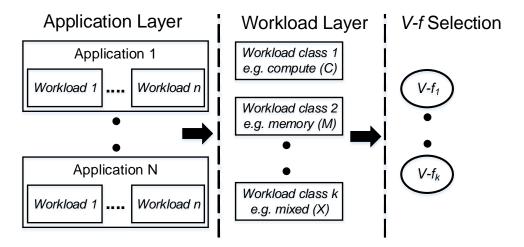

| 3  | O Conceptual overview: Concurrent applications with associated workload classes and the need for optimal <i>V-f</i> selection                                           |        | 55       |

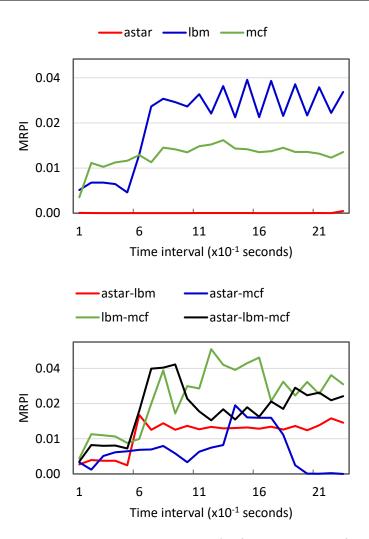

| 3  | 11 Variation in MRPI for individual (top) and concurrent (bottom) execution of applications.                                                                            | L      | 56       |

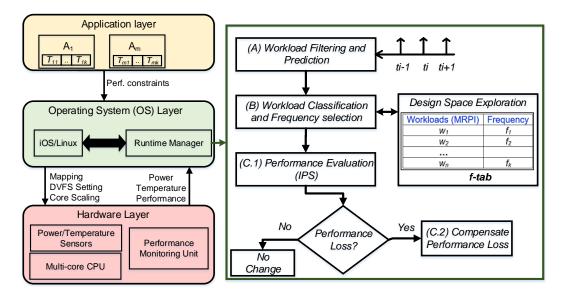

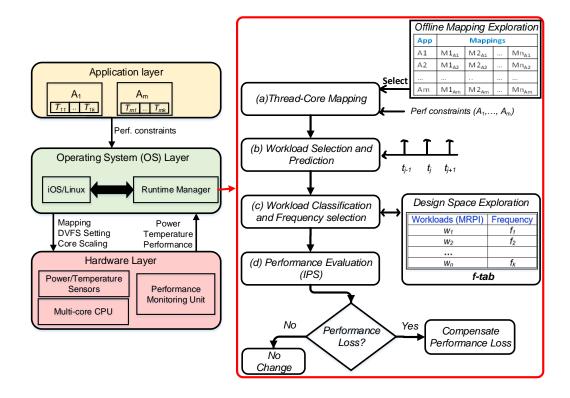

| 3  | 2 Representing a multi-core system as three stacked layers: application operating system and hardware (left), and overview of the proposed online                       | )<br>) |          |

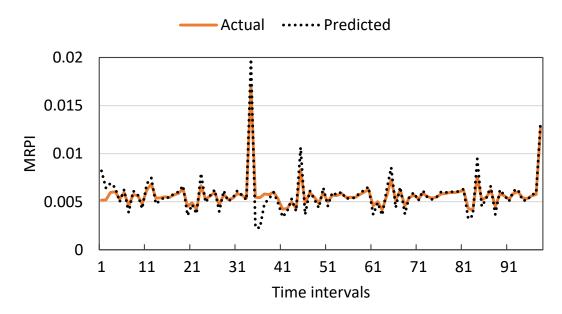

| 2  | energy minimization technique (right)                                                                                                                                   |        | 58<br>63 |

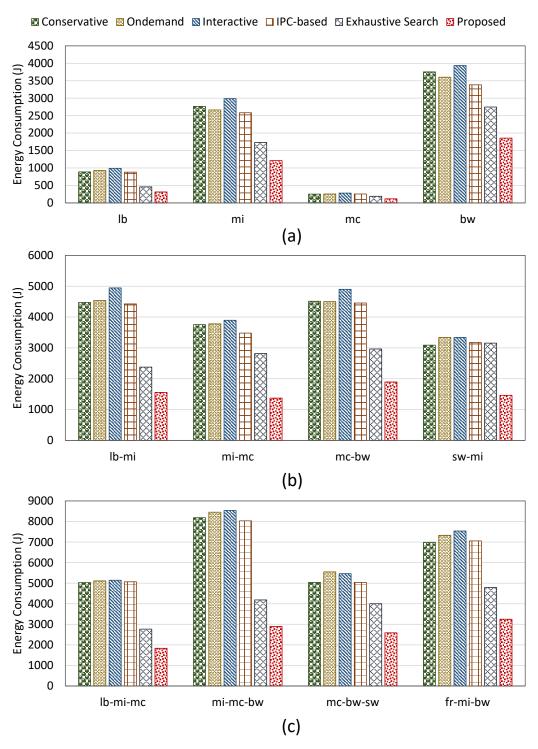

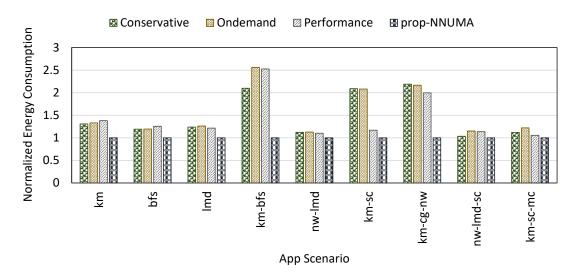

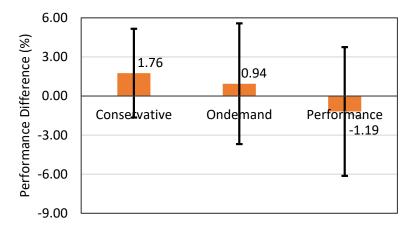

|    | 4 Comparison of proposed approach in terms of energy consumption with                                                                                                   |        | 00       |

| 0. | the existing approaches for different execution scenarios—a) single-application                                                                                         |        | n,       |

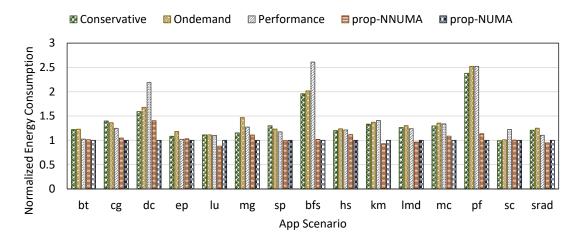

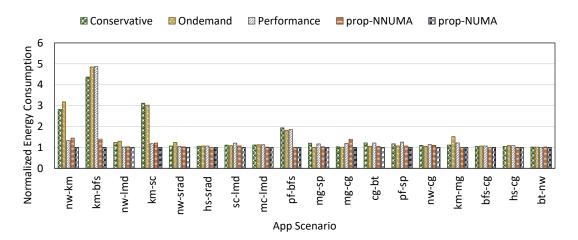

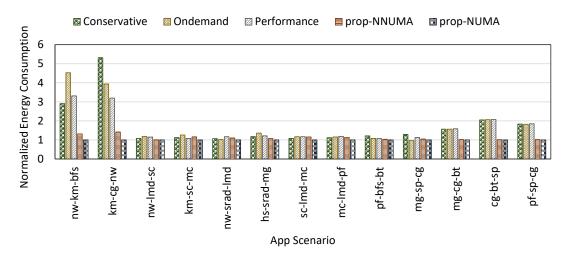

|    | b) double-application, and c) triple-application                                                                                                                        |        | 65       |

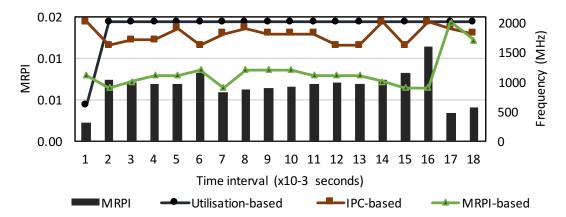

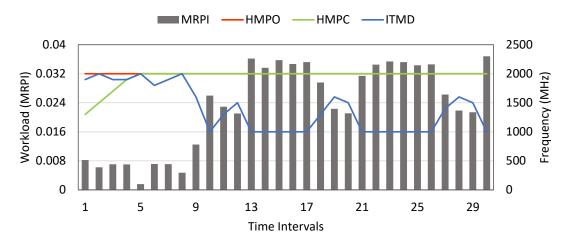

| 3. | 5 MRPI and frequency at different time intervals of the application scenario <i>lb-mi</i> execution for various approaches.                                             |        | 66       |

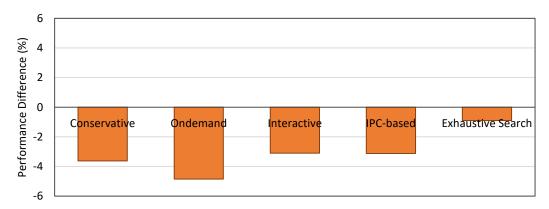

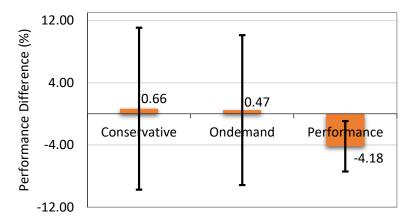

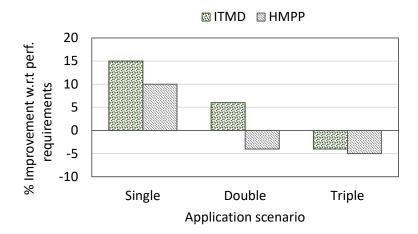

| 3. | Average performance difference between proposed approach and other reported approaches                                                                                  |        | 66       |

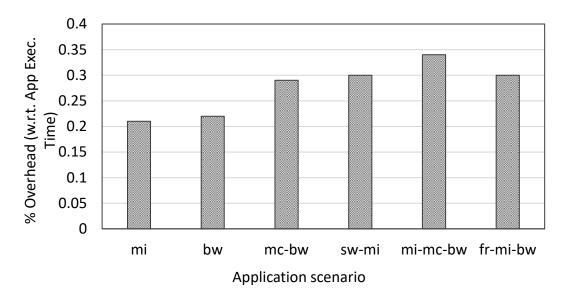

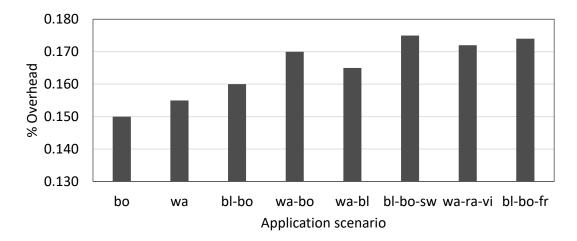

| 3  | 7 Runtime overhead of the proposed approach                                                                                                                             |        | 67       |

| 3  | 8 Illustration of various steps in the proposed approach for runtime energy                                                                                             | 7      |          |

|    | management                                                                                                                                                              |        | 69       |

|    | 19 An example of $V-f$ setting selection using binning based approach                                                                                                   |        | 72       |

| 3. | 20 Comparison of the proposed technique with reported approaches for single                                                                                             |        |          |

|    | application scenario in terms of normalized energy consumption, executing on the Xeon E5-2630.                                                                          |        | 75       |

| 3  | 21 Normalized energy consumption of various approaches for double appli-                                                                                                |        | 10       |

| 0. | cation scenario, executing on the Xeon E5-2630                                                                                                                          |        | 76       |

| 3. | 22 Comparison of the proposed approach with reported approaches for triple                                                                                              |        |          |

|    | application scenario in terms of normalized energy consumption (evaluated on the Xeon E5-2630)                                                                          |        | 76       |

| 3  | 23 Mean performance difference between <i>prop-NUMA</i> and other approaches with standard deviation error bars (evaluated on the Xeon E5-2630)                         | ,      | 77       |

| 3  | 24 Comparison of proposed approach (prop-NNUMA) with reported approach                                                                                                  |        |          |

|    | in terms of normalized energy consumption for various application sce-                                                                                                  |        |          |

|    | narios, executing on the Xeon Phi.                                                                                                                                      |        | 78       |

| 3. | Mean performance difference between <i>prop-NUMA</i> and other approaches with standard deviation error bars (evaluated on the Xeon Phi).                               | ,      | 79       |

LIST OF FIGURES xi

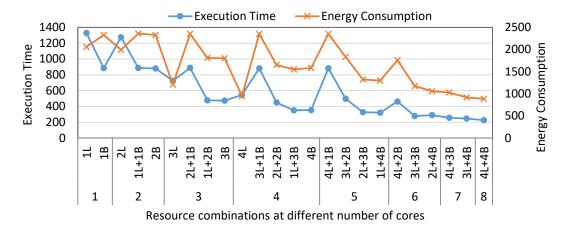

| 4.1  | Execution time (seconds) and energy consumption (J) values by executing<br>the Blackscholes application (from PARSEC benchmark [15]) with var-                                                                                                                                                                                                                     |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | ious core combinations, including inter-cluster, on ARM's big.LITTLE architecture containing 4 big (B) and 4 LITTLE (L) cores                                                                                                                                                                                                                                      | 84  |

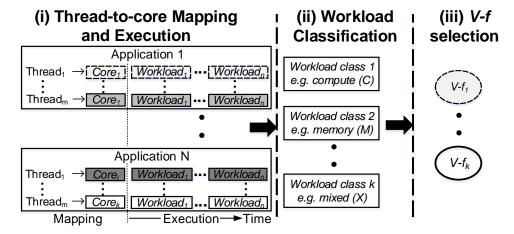

| 4.2  | Key steps in runtime management of concurrent execution of multi-threaded applications on a heterogeneous multi-core architecture.                                                                                                                                                                                                                                 |     |

| 4.3  | Overview of a three-layer representation of a multi-core system (left) and proposed runtime manager (right)                                                                                                                                                                                                                                                        | 88  |

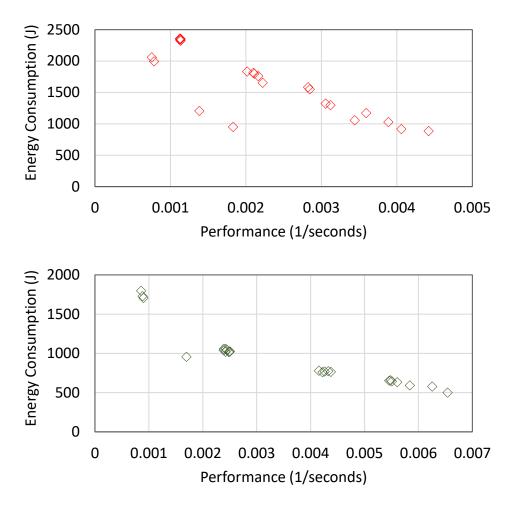

| 4.4  | Design points representing performance and energy trade-off points for Blackscholes (top) and Bodytrack (bottom) applications                                                                                                                                                                                                                                      | 90  |

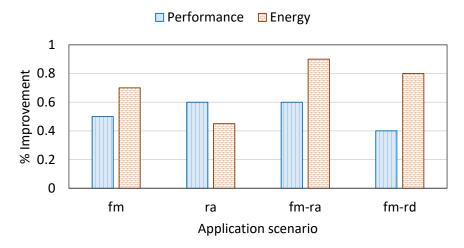

| 4.5  | Effect of adaptive sampling on energy and performance for various application scenarios.                                                                                                                                                                                                                                                                           | 96  |

| 4.6  | Comparison of ITMD approach with reported approaches for single active application.                                                                                                                                                                                                                                                                                | 100 |

| 4.7  | MRPI and frequency at different time intervals of the application $fr$ execution for various approaches                                                                                                                                                                                                                                                            | 100 |

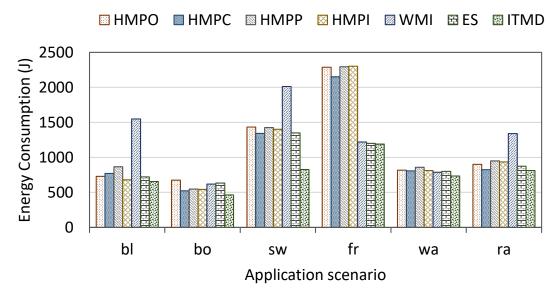

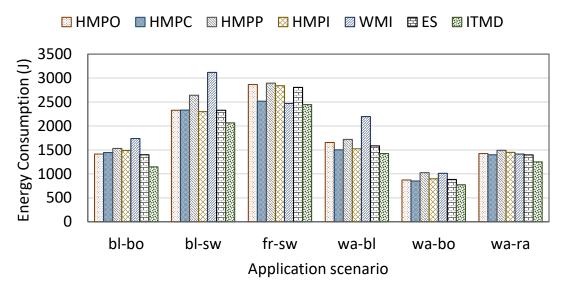

| 4.8  | Comparison of ITMD approach with reported approaches for two active applications                                                                                                                                                                                                                                                                                   |     |

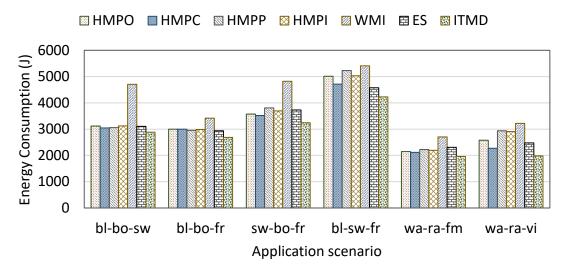

| 4.9  | Comparison of ITMD approach with reported approaches for three active applications.                                                                                                                                                                                                                                                                                |     |

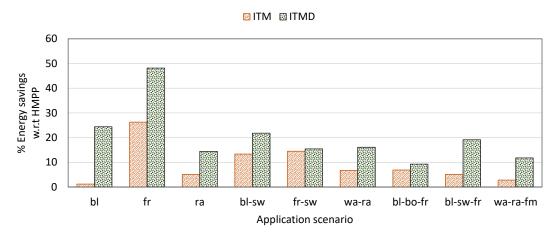

| 4.10 | Percentage of energy savings achieved by proposed <i>ITM</i> and <i>ITMD</i> respectively                                                                                                                                                                                                                                                                          |     |

| 4.11 | Performance improvement/degradation of the adopted approach and HMPH                                                                                                                                                                                                                                                                                               |     |

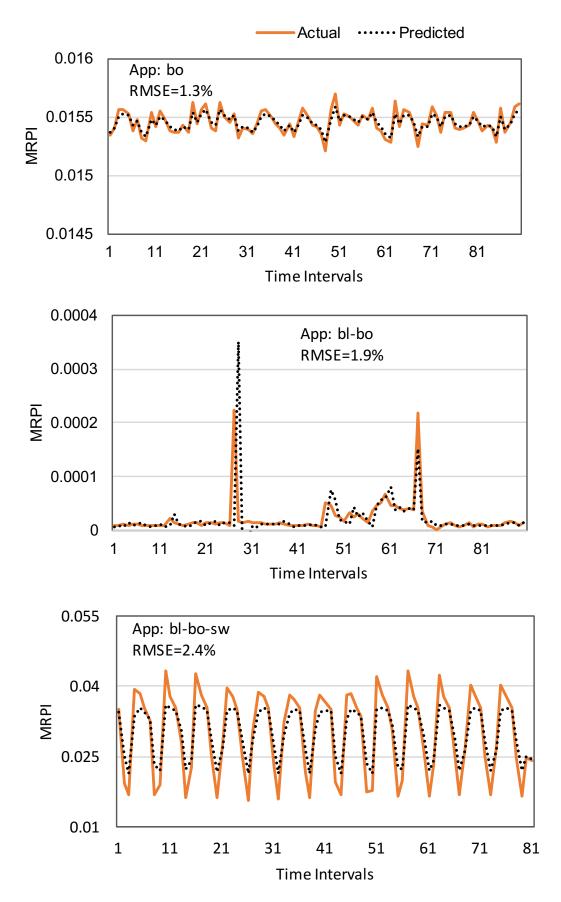

| 4.12 | Workload prediction using EWMA for three different application scenar-                                                                                                                                                                                                                                                                                             | 104 |

| 4.13 | ios - one, two and three active applications (top to bottom)                                                                                                                                                                                                                                                                                                       |     |

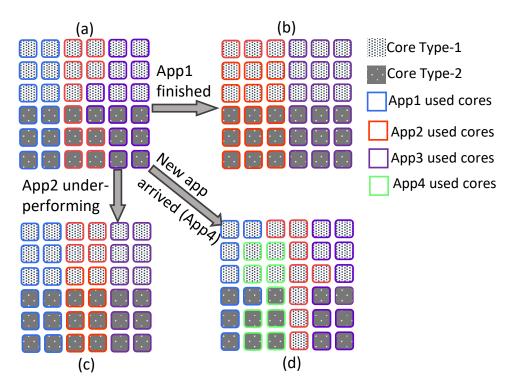

| 5.1  | A motivational example showing three possible runtime execution scenarios (b, c & d) when a system, having two types of cores - Type-1 and Type-2, starts with executing three performance-constrained applications (a). Cores running the same application are encircled with a line of the                                                                       |     |

| 5.2  | same color. App1, App2, App3, and App4 represent user applications Illustration of various steps in the proposed adaptive thread-to-core mapping and DVFS approach (bottom) and showing its placement in the                                                                                                                                                       | 111 |

| 5.3  | three-layer representation of a multi-core platform (top) Energy and execution time at different resource combinations of big (B) and LITTLE (L) for the application Blackscholes (top) Bodytrack (bot-                                                                                                                                                            | 114 |

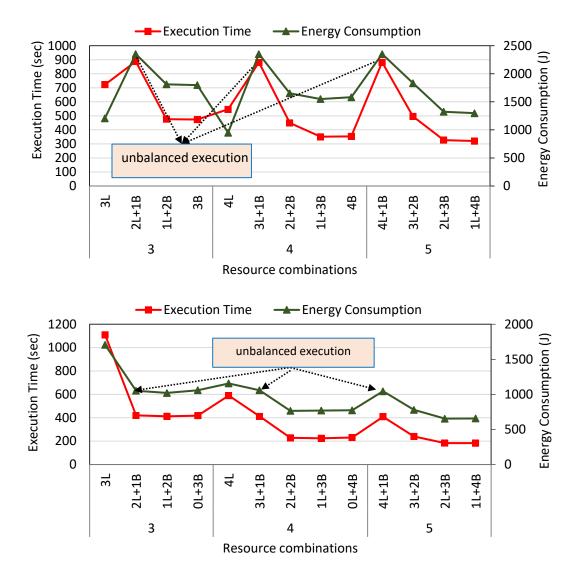

|      | tom) and from PARSEC [15], executing on the Odroid-XU3                                                                                                                                                                                                                                                                                                             | 122 |

| 5.4  | Box plot of absolute percentage error in IPC prediction by proposed performance model for different number of decision stumps used in the additive regression, showing the median, lower quartile, upper quartile and outliers – (a) Estimating the performance of LITTLE given the information about the big core (b) Estimating the performance of big given the |     |

| 5.5  | information about the LITTLE core                                                                                                                                                                                                                                                                                                                                  | 126 |

| 5.6  | of energy consumption for single and concurrent applications                                                                                                                                                                                                                                                                                                       | 128 |

| 2.0  | added dynamically to the system while an application is executing                                                                                                                                                                                                                                                                                                  | 128 |

xii LIST OF FIGURES

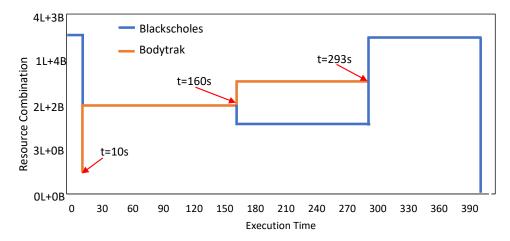

| 5.7 | Resource combination (number of big (B) and LITTLE (L) cores) al-        |

|-----|--------------------------------------------------------------------------|

|     | located to Blackscholes and Bodytrack by the proposed approach to        |

|     | adapt to application arrival/completion and performance variation 129    |

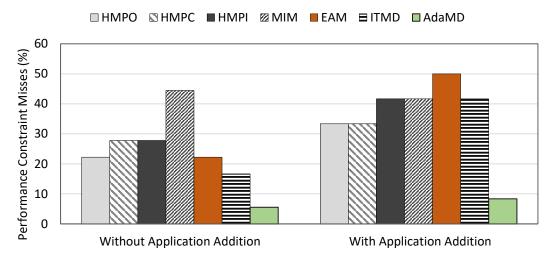

| 5.8 | Evaluation of various approaches in meeting application performance con- |

|     | straints                                                                 |

### List of Tables

| 2.1        | Comparison of various run-time management approaches for homogeneous (homo.) and heterogeneous (heter.) multi-core architectures 33 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 3.1        | Selected applications from Rodinia [16] and NPB [17] and their abbreviations                                                        |

| 4.1        | Design time analysis of workload classes (MRPI range) and corresponding                                                             |

|            | frequencies                                                                                                                         |

| 4.2        | Selected applications from PARSEC [15] and SPLASH [18] benchmarks $$ . 96                                                           |

| 4.3        | Approaches considered for comparison                                                                                                |

| 4.4        | Resource combination achieved by proposed mapping approach at run-<br>time for different application scenarios                      |

| 5.1        | Parameters used in the proposed approach                                                                                            |

| A.1        | Offline profiling results for <b>Blackscholes</b> , executing on the Odroid-XU3 . 139                                               |

| <b>A.2</b> | Offline profiling results for <b>Bodytrack</b> , executing on the Odroid-XU3 140                                                    |

| A.3        | Offline profiling results for <b>Swaptions</b> , executing on the Odroid-XU3 140                                                    |

| A.4        | Offline profiling results for <b>Freqmine</b> , executing on the Odroid-XU3 141                                                     |

| A.5        | Offline profiling results for <b>Streamcluster</b> , executing on the Odroid-XU3 141                                                |

| A.6        | Offline profiling results for Vips, executing on the Odroid-XU3 142                                                                 |

| A.7        | Offline profiling results for Water_Spatial, executing on the Odroid-XU3142                                                         |

| A.8        | Offline profiling results for Raytrace, executing on the Odroid-XU3 143                                                             |

| A.9        | Offline profiling results for <b>Fmm</b> , executing on the Odroid-XU3 143                                                          |

| B.1        | The classification bins, namely - utilisation and MRPI, and corresponding                                                           |

|            | frequencies for odroid-XU3                                                                                                          |

| B.2        | Classifications bins data continued from Table B.1                                                                                  |

| B.3        | The classification bins, namely - utilisation and MRPI, and corresponding                                                           |

|            | frequencies for Intel Xeon E5-2630                                                                                                  |

# List of Algorithms

| 1 | Online energy minimization approach      |

|---|------------------------------------------|

| 2 | Runtime thread-to-core mapping selection |

| 3 | Adaptive DVFS approach                   |

| 4 | Proposed Dynamic Thread-to-core Mapping  |

| 5 | DVFS governor (DVFS())                   |

### Abbreviations

| ACPI | Advanced Configuration and Power Interface          |

|------|-----------------------------------------------------|

| AsAP | Asynchronous Array of Simple Processors             |

| BIOS | Basic Input/Output System                           |

| CFA  | Continuous Frequency Adjustment                     |

| CFD  | Computational Fluid Dynamics                        |

| CP   | Combination Point                                   |

| CPI  | Cycles Per Instruction                              |

| CPU  | Central Processing Unit                             |

| DLP  | Data-Level Parallelism                              |

| DP   | Design Point                                        |

| DRAM | Dynamic Random Access Memory                        |

| DSE  | Design Space Exploration                            |

| DSP  | Digital Signal Processors                           |

| DVFS | Dynamic Voltage and Frequency Scaling               |

| DVS  | Dynamic Voltage Scaling                             |

| DyPO | Dynamic Pareto-Optimal                              |

| ES   | Exhaustive Search                                   |

| EWMA | Exponential Weighted Moving Average                 |

| FPGA | Field-Programmable Gate Array                       |

| GPP  | General Purpose Processors                          |

| GPU  | Graphics Processing Unit                            |

| HMP  | Heterogeneous Multi-Processing                      |

| HIBI | Heterogeneous IP Block Interconnection              |

| ILP  | Instruction-Level Parallelism                       |

| I/O  | Input/Output                                        |

| IP   | Intellectual Property                               |

| IPC  | Instructions Per Cycle                              |

| IPS  | Instructions Per Second                             |

| ISA  | Instruction-Set Architecture                        |

| ITMD | Inter-cluster Thread-to-core Mapping and DVFS       |

| ITRS | International Technology Roadmap for Semiconductors |

| IVP  | Initial Value Problem                               |

| LLC  | Last Level Cache                                    |

xviii ABBREVIATIONS

MAEMean Absolute Error MAPCMemory Accesses Per Cycle MAPEMean Absolute Percentage Error MAPIMemory Accesses Per Instruction MAPMMemory Accesses Per Micro-operation MDEMulticore Development Environment MICIntel Many Integrated Core MIPSMicroprocessor without Interlocked Pipelined Stages MLPMemory-Level Parallelism MLRMultinomial Linear Regression MPSoCMulti-Processor System-on-Chip MPSSManycore Platform Software Stack MSRModel Specific Register MRPCMemory Reads Per Cycle MRPIMemory Reads Per Instruction NPNon-deterministic Polynomial time NUMANon-Uniform Memory Access OoOOut-of-Order PCPersonal Computers PCAPrinciple Component Analysis PCIePeripheral Component Interconnect express PDAPersonal Digital Assistant PEProcessing Element PIDProportional-Integral-Derivative PIEPerformance Impact Estimation PMCPerformance Monitoring Counter PMUPerformance Monitoring Unit PPWPerformance Per Watt QoSQuality of Service QPIQuick Path Interconnect RAWRaw Architecture Workstation RISCReduced Instruction Set Computer RLReinforcement Learning RMSRecognition, Mining, and Synthesis ROIRegion Of Interest RTEMRuntime Energy Management RTLRegister Transfer Level RTMRuntime Manager SMTSimultaneous Multi-threading SoCSystem-on-Chip SPECStandard Performance Evaluation Corporation

ABBREVIATIONS xix

| TRIPS | Tera-op, Reliable, Intelligently adaptive Processing System |

|-------|-------------------------------------------------------------|

| VFS   | Voltage and Frequency Scaling                               |

| WED   | Weighted Euclidean Distance                                 |

| WEKA  | Waikato Environment for Knowledge Analysis                  |

| WMI   | Workload Memory-Intensity                                   |

### Nomenclature

$a_i$  Actual workload

$Apps_{prfr}$  Performance requirements of applications

$CA_{Apps}$  Concurrently active applications

$C_{i\_cores_m}$  Used  $C_i$  type cores for an application m

$C_L$  Load capacitance [F]

$D_{A_m}$  Design points of an application

$\delta, \zeta$  Effect of memory contention on performance (latency)

$E_i$  Cluster with cores of type  $C_i$

$Energy_m$  Energy consumption of an application m [J]

$E_o$  Energy overhead [J]

$E_T$  Total energy consumption [J]

$\eta$  Speedup

f Operating frequency [Hz]

$f_{max}$  Maximum operating frequency [Hz]

$\gamma$  Smoothing factor  $\lambda$  Performance loss

$l_i$  Number of cores of type  $C_i$

$\mu$ -ops Micro-operations retired

$M_i$  MAPM of processing core  $m_l$  Accesses to local memory

$m_T$  Accesses to remote memory

NrCApps Number of active applications

$n_L$  Number of LITTLE cores

$n_b$  Number of big cores

$P_{dynamic}$  Dynamic power consumption [W]

$p_i$  Predicted workload

$PMC_o$  PMC data collection overhead [s]

$P_{static}$  Static power consumption [W]

xxii NOMENCLATURE

$P_T$  Total power consumption [W]

r Number of times adaptation is paused

R Number of threads of an application

$TC_{map}$  Number of thread-to-core mappings

$TC_{map\_VF}$  Total number of resource combinations

$t_e$  Execution time [s]

$\theta$  Measure of latency associated with the remote memory access

$T_{map}$  Thread-to-core-mapping overhead [s]

$T_o$  Total overhead [s]  $T_{sample}$  Time interval [s]

$T_{V-f}$  Overhead associated with V-f pair selection [s]

V Supply voltage [V]

$VfS_o$  V-f switching overhead [s]

W Workload

$W_{E_i}$  Workload on a cluster  $E_i$

#### Declaration of Authorship

- I, Karunakar Reddy Basireddy, declare that the thesis entitled *Runtime Energy Management of Concurrent Applications for Multi-core Platforms* and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University;

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- Where I have consulted the published work of others, this is always clearly attributed;

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- Parts of this work that have been published are listed under the Research Contributions.

| Signed:  | <br> | <br> |  |

|----------|------|------|--|

| <u> </u> |      |      |  |

|          |      |      |  |

| Date:    |      |      |  |

#### Acknowledgements

I would like to take this opportunity to extend my thanks to many people who directly and indirectly supported me during my PhD. First of all, my heartfelt gratitude goes to my supervisors; Dr. Geoff V. Merrett for his invaluable guidance, support, and suggestions throughout my PhD and Prof. Bashir M. Al-Hashimi for his direction and advice at many times, and for providing me with an opportunity to undertake this research. In spite of being busy with many responsibilities, they have always found time for regular discussions with me. I would also like to express my thanks to Dr. Amit Kumar Singh for his insightful and stimulating discussions and suggestions. Without their continuous support, this thesis would not have been in its present form.

Many thanks also go to the Engineering and Physical Sciences Research Council (EP-SRC) funded PRiME Project for financially supporting me throughout the PhD. I also extend my thanks to the School of Electronics and Computer Science, the University of Southampton for providing state-of-the-art research facilities. Being part of the PRiME project, I had the opportunity to work with a unique group of colleagues: Dr. Dwaipayan Biswas, Dr. Domenico Balsamo, Dr. Eduardo Wachter, Matt Walker, Charles Leech, and Dr. Graeme Bragg to name a few. Thanks to all of them for creating a vibrant research environment for thought-provoking discussions and knowledge sharing. Thanks to Kath Kerr for her kind administrative and logistics support. I would also like to thank Dr. Amit Acharyya for always providing me with career guidance and support.

Further, my sincere thanks to all my friends who have always been there to help and for making my stay in Southampton a pleasant memory. In this regard, I would like to mention a few notable names who are part of our regular discussions at tea breaks/gym sessions: Charan, Satya, Rakshith, Ashwini, Amin, Alberto, Oktay, Cai, Sadegh and many more.

Finally, greatest thanks go to my family (Vengamma, Srinivasulu Reddy, Archana and Duggaiah) and Shri Krishna for their infinite love, believing in me and making me into what I am today.

### Chapter 1

### Introduction

Computing systems have emerged in many fields (e.g., medical and business) and the demand for higher performance is ever increasing. Performance is usually defined as the execution time of an application, instructions per second, or instructions per cycle [10, 19, 20]. In the '80s and '90s, frequency scaling helped in meeting the increasing demands for performance. Shortening the critical path and exploiting instruction level parallelism allowed the CPU to run at higher clock speeds to improve throughput [21]. Consequently, processor manufacturers were able to double single-threaded performance approximately every 18 months [22], which has added an increased amount of complex logic to the processor core. For a long time, new process technologies allowed for smaller and less energy consuming transistors. Furthermore, techniques such as pipelining, superscalarity and Out-of-Order (OoO) execution were proposed to improve performance

FIGURE 1.1: Historical trends in CPU performance, reprinted from [1]

FIGURE 1.2: Hot spot power density scaling with feature size. Reprinted from [2]

[23]. However, as Dennard scaling [24,25] came to an end, increasing gate count on a die and scaling the frequency up to meet the performance demands is no longer a favorable way as heat generation became a serious problem.

As a result, the rapid increase in single-threaded performance during the last few decades seems to have come to an end. Fig. 1.1 shows how Moore's law has been continuing over time [21,22]. As can be seen from the figure, the transistor count on a die is still increasing exponentially. As Dennard scaling [24,25] came to an end, power density became a problem as more transistors are crammed together. The increased power on a tiny area leads to higher heat generation than conventional cooling solutions can dissipate. To address this issue, researchers have been working towards achieving higher performance without a further increase in power density. Fig. 1.2 shows the hot spot (heavily used parts of the cores) power density at each technology node. The figure shows that hot spot power density can increase by up to  $3 \times$  from 45nm to 10nm.

While improving performance, one must take care not to exceed the physical limitation of power dissipation. Thus, energy efficiency is key to achieve additional performance gain. Moreover, processors targeting laptops, smartphones and other battery operated mobile devices have always been energy-constrained. In such cases, improved energy efficiency would allow for longer battery life. More recently, mobile processors have become increasingly popular in alternative domains, such as high performance computing due to their low energy budget [26, 27]. Building data centers from low-cost embedded processors is believed to have a huge potential and could change the landscape of supercomputing in the future [27].

#### 1.1 Runtime Energy Management

Traditionally, software applications have been written for serial computation that are executed on a single-core processor. To improve the performance of such applications, techniques such as Instruction-Level Parallelism (ILP), simultaneous execution of multiple instructions with no data dependency; and Memory-Level Parallelism (MLP), servicing multiple outstanding memory accesses at a time), have been used. However, due to the limited ILP and MLP, the single core processors are not effective in improving the performance [2]. Prior art showed that parallelism inherent to an application, including thread-/task-level parallelism (TLP) and data-level parallelism (DLP), is a power-efficient way of achieving high performance than frequency scaling under power limitations. Considering these factors and increased power density, the modern embedded systems [28–30] are employing multi-core processors to utilize the billions of transistors efficiently. Moreover, the energy efficiency has been a primary design objective in embedded systems [31]. These multi/many-core (expected to have 1000+ cores on a single chip [32]) architectures have been demonstrated as a promising solution for energy-efficient computing [33, 34].

Fundamental to improving energy efficiency is managing the operation of the processor in an intelligent way. Modern processors employ various power-saving techniques, such as Dynamic Voltage and Frequency Scaling (DVFS), clock gating, power gating and multiple asymmetric cores (e.g., ARM's big.LITTLE<sup>TM</sup>architecture [4]). DVFS is one of the promising solutions for energy minimization under performance constraints and workload variations. It has been proved that runtime energy management software can make significant energy improvements by controlling these power-saving techniques to smartly manage the energy-performance trade-off while taking other factors into account (e.g., performance requirements and workload variations) [20, 35]. DVFS is usually controlled by such software, e.g., Linux's power governors and ARM's Voltage and Frequency Scaling (VFS) firmware [36]. The basic principle of DVFS is to reduce the operating voltage-frequency (V-f) dynamically at runtime, resulting in a cubic decrease in power consumption [37–39]. A runtime manager can also manage the allocation of processing cores to an application by taking performance constraints, available resources, and optimization goal into account. This is usually called task mapping or thread-to-core mapping, which defines the number of cores and their type allocated to each application. Previous studies [19, 40] showed that efficient thread-to-core mapping leads to energy savings and better performance.

#### 1.2 Research Justification

The existing approaches for runtime energy management for multi-core platforms are generally of three types: 1) offline optimization, 2) online optimization, 3) hybrid (online

optimization is supported by offline profiling). The existing offline optimization based approaches employ DVFS and/or task mapping to find performance-energy trade-off points [4,41–46]. However, these works have several drawbacks, such as they consider a single application at a time [41–45], and most of them are not evaluated on real hardware platforms [42,45,46].

Online optimization has also been considered to cater for dynamic workload scenarios to optimize energy consumption while respecting timing constraints [20, 35, 47–49]. In [47–49], the online algorithm uses hardware performance monitoring counters (PMCs) to achieve energy savings without recompiling the applications. In [20, 35], an online reinforcement learning based DVFS is proposed. These approaches can handle unknown applications, but lead to inefficient results as optimization decisions need to be taken quickly, and offline analysis results are not used. Further, they are agnostic of workload variations of concurrently executing applications. Note that, in this thesis, concurrent execution refers to simultaneous execution of multiple applications that may support various types of parallel computation such as ILP, MLP, DLP, and TLP.

There has also been a focus on online optimization facilitated by offline analysis results [5,10,19,40,50-52]. Such approaches lead to better performance results than only online optimizations as they take advantage from both offline and online computations. In [40], thread-to-core mapping and DVFS is performed based on power constraint. Similarly, in [5], first thread-to-core mapping is obtained based on utilization, and then DVFS is applied depending upon the surplus power. However, the approaches of [5,40] have several drawbacks, such as they target homogeneous multi-core architectures, and do not take the workload variations into account while setting the V-f.

For heterogeneous multi-cores, whose processing cores have distinct micro-architecture with the same (ARM's big.LITTLE architecture) or different instruction-set architecture (ARM's big.LITTLE CPU + Mali GPU), recent works have considered multi-threaded applications [10, 19, 50–52]. However, at a given moment of time, most of these approaches map application threads completely onto one type of core situated within a cluster [10, 19, 51, 52]. This reduces the thread-to-core mapping complexity, but misses to benefit from the distribution of thread of an application to multiple types of cores. Unlike [10] and [51], the approaches of [19, 50] exploit DVFS, but they have several drawbacks. For example, in [19], each single-threaded application is mapped onto only one type of core at a time. In [50], application threads are mapped onto more than one type of cores, but it heavily depends on offline regression analysis and DVFS level is not adjusted during execution. Moreover, the above approaches do not perform adaptations (changing DVFS setting and/or thread-to-core mappings) upon an application arrival or completion. As demonstrated in this thesis, it leads to lower resource utilisation, increased energy consumption and frequent violation of performance constraints.

Multi-core systems usually execute multiple applications with distinct performance constraints concurrently. The interference between applications due to shared resources, workload variations, and limited and dynamic resource availability make runtime energy management a challenging task. As existing approaches are not effective for concurrent execution of multiple applications, there is a need for efficient runtime energy minimization approaches to address the above problems, which is the aim of this thesis.

#### 1.3 Research Questions

The above discussion motivates us to answer the following research questions related runtime energy management:

- 1. Can the application workload be classified efficiently at runtime? Subsequently, how can workload classification be applied to concurrent execution of applications on homogeneous multi-cores to achieve energy efficiency with negligible performance loss?

- 2. For concurrently executing multi-threaded applications on a heterogeneous multicore system, how can available heterogeneity and the DVFS potential of cores be efficiently exploited to minimize energy consumption while satisfying performance and resource constraints?

- 3. How can the dependency of runtime decisions on application offline profiling be removed to facilitate energy-efficient management of unknown applications and adaptation to runtime execution scenarios (e.g., application arrival/completion, performance violations, etc.)?

#### 1.4 Research Contributions

To address the above research questions, the contributions that have been made during the course of this research are summarized as follows:

1. A runtime energy minimization approach through concurrent workload classification on homogeneous multi-cores. To select appropriate DVFS settings as per the workload, an online workload classification is proposed by taking concurrent execution and contention on shared resources into account. The DVFS settings are decided proactively through workload prediction, thereby adapting to workload variations efficiently and reducing power consumption. The online concurrent workload classification is done using a metric called memory reads per instruction (MRPI), derived through extensive statistical analysis of PMC data and

identifying appropriate PMCs that can capture workload variations at runtime. Further, this approach has been extended to utilise the thread synchronisation overheads, non-uniform memory access latencies and underlying DVFS architecture to improve energy efficiency for multi-threaded applications. It proposes a binning based approach for efficiently determining the DVFS setting as per the predicted workload. Validation on three hardware platforms (Odroid-XU3, Intel Xeon E5-2630, and Xeon Phi 7620P) approach achieves an average improvement in energy efficiency of up to 60% compared to existing approaches. Above contribution addresses Research Question 1, and has been published at IEEE/ACM DATE-2018 [53], AMAS Workshop-2018 [54] and IEEE OPTIM-2018 [55].

- 2. An RTM approach for minimizing energy consumption of concurrently executing multi-threaded applications on a heterogeneous multi-core. This approach first selects thread-to-core mapping based on the performance requirements and resource availability. Unlike, existing approaches, the thread-to-core mapping simultaneously exploits different types of cores for each performance-constrained application in a concurrent execution scenario, thereby improving energy efficiency and performance. Then, it applies online adaptation by adjusting the V-f levels of each cluster through concurrent workload classification to achieve energy optimization, without trading-off application performance. Here, the DVFS approach proposed for homogeneous multi-cores in Contribution 1 is extended to take core heterogeneity into account. The experimental results show that the proposed approach achieves an average improvement of up to 33% in energy efficiency compared to existing approaches while meeting the performance requirements. This contribution addresses Research Question 2, and has been published in IEEE/ACM DATE-2017 [56] and IEEE TMSCS-2017 [57].

- 3. An energy-efficient adaptive mapping and DVFS approach. The key feature of the proposed approach is the elimination of dependency on offline profiled results while making runtime decisions. This is achieved through a performance prediction model having a maximum error of 7.9% lower than the previously reported model and an energy-efficient mapping approach that allocates processing cores to applications while respecting performance constraints. Furthermore, this approach adapts to runtime execution scenarios efficiently by monitoring the application status, and performance/workload variations to adjust the previous DVFS settings and thread-to-core mappings. The proposed approach is experimentally validated on the Odroid-XU3, with various combinations of diverse multi-threaded applications from PARSEC and SPLASH benchmarks. Results show an improvement of up to 28% in energy efficiency compared to the recently proposed approach while meeting performance constraints. This contribution addresses Research Question 3, and has been submitted for publication in IEEE TCAD-2019 [58].

In the co-authored publications below, that have resulted from the research work presented in this thesis, my contributions include developing the ideas, implementation and validation of the approach, and writing most of the papers. The remaining co-authors have been primarily involved in discussions on how best to carry out the experimental validations and place the research contributions in the context of relevant previous work and/or providing feedback to improve the presentation of the paper.

#### 1.5 Software Contributions

Intelligent Runtime Management Algorithms: The RTM algorithms presented in Chapter 3 have been implemented as userspace applications for experimental validation. The source codes are available at the addresses: <a href="https://github.com/PRiME-project/rtm-Xeon">https://github.com/PRiME-project/rtm-Xeon</a> (Xeon platforms) and <a href="https://github.com/PRiME-project/RTM\_Concurrent">https://github.com/PRiME-project/RTM\_Concurrent</a> (Odroid-XU3). This RTM has been further integrated into the cross-layer framework, the PRiME Framework (<a href="https://github.com/PRiME-project/PRiME\_Framework">https://github.com/PRiME-project/PRiME\_Framework</a>), for experimental validation.

Furthermore, the runtime energy management approaches presented in Chapter 4 and 5 are also implemented as userspace applications, whose source code is made available at the address: https://github.com/PRiME-project/RTM\_Concurrent and https://github.com/PRiME-project/rtm-dtcm, respectively.

#### 1.6 Publications

The following publications have no PhD student as a co-authors and therefore, they have not been reported in anyone else's thesis.

- K. R. Basireddy, A. K. Singh, G. V. Merrett, and B. M. Al-Hashimi, "AdaMD: Adaptive Mapping and DVFS on Heterogeneous Multi-cores," *submitted* to IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2019 [submitted].

- 2. K. R. Basireddy, A. K. Singh, G. V. Merrett, B. M. Al-Hashimi, "Online concurrent workload classification for multi-core energy management," Design, Automation and Test in Europe (DATE), 2018. [53]

- 3. **K. R. Basireddy**, E. W. Wachter, G. V. Merrett and B. M. Al-Hashimi, "Workload-Aware Runtime Energy Management for HPC Systems," in IEEE International Workshop on Optimization of Energy Efficient HPC & Distributed Systems (OP-TIM), 2018. [55]

- 4. **K. R. Basireddy**, E. W. Wachter, B. M. Al-Hashimi and G. V. Merrett, "Memory-and thread synchronization contention-aware DVFS for HPC systems," Adaptive Many-Core Architectures and Systems workshop, 2018. [54]

- 5. **K. R. Basireddy**, A. K. Singh, G. V. Merrett, and B. M. Al-Hashimi, "ITMD: Run-time Management of Concurrent Mulit-threaded applications on Heterogeneous Multi-cores," Design, Automation and Test in Europe (DATE), pp. 1, 2017. [56]

- K. R. Basireddy, A. K. Singh, Dwaipayan Biswas, G. V. Merrett, and B. M. Al-Hashimi, "Inter-cluster Thread-to-core Mapping and DVFS on Heterogeneous Multi-cores," IEEE Transaction on Multi-Scale Computing Systems (TMSCS), 2017. [57]

As part of the EPSRC funded PRiME project, the following publications were also made through collaboration, which are not reported as contributions in this thesis:

- 1. A. K. Singh, **K. R. Basireddy**, A. Prakash, G. V. Merrett, and B. M. Al-Hashimi, "Energy-Efficient Collaborative Adaptation in Heterogeneous Mobile SoCs," IEEE Transactions on Computers (TC), 2018 [59] (under review).

- 2. E. W. Wachter, C. d. Bellefroid, **K. R. Basireddy**, A. K. Singh, B. M. Al-Hashimi, and G. V. Merrett, "Predictive Thermal Management for Energy-efficient Execution of Concurrent Applications on Heterogeneous Multi-cores," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2019 [60].

- 3. A. K. Singh, A. Prakash, **K. R. Basireddy**, G. V. Merrett, and B. M. Al-Hashimi, "Energy-efficient run-time mapping and thread partitioning of concurrent OpenCL applications on CPU-GPU MPSoCs," ACM Transactions on Embedded Computing Systems (TECS), 2017. [61]

- 4. A. K. Singh, C. Leech, **K. R. Basireddy**, B. M. Al-Hashimi, and G. V. Merrett, "Learning-based run-time power and energy management of multi/many-core systems: current and future trends," Journal of Low Power Electronics (JOLPE), 2017. [62]

- 5. **K. R. Basireddy**, M. J. Walker, D. Balsamo, S. Diestelhorst, B. M. Al-Hashimi, and G. V. Merrett, "Empirical CPU power modelling and estimation in the gem5 simulator,âĂİ in IEEE International Conference on Power and Timing Optimization and Simulation (PATMOS), 2017. [63]

#### 1.7 Thesis Organization

The remainder of the thesis is organized as follows.

Chapter 2 first presents an introduction to energy consumption, DVFS and thread-to-core mapping. It then reviews the existing runtime energy management systems and identifies the drawbacks in those approaches.

Chapter 3 presents the investigation on workload classification using execution time and hardware PMC data. Further, it discusses the proposed energy minimization approach for concurrently executing single-threaded applications, specifically on a homogeneous multi-core system supporting cluster-wide DVFS (cores in a cluster are set to the same DVFS level). It also presents the runtime classification of concurrent workloads and selection of appropriate DVFS level based on the predicted workload.

Chapter 4 extends the online DVFS technique proposed in Chapter 3 to a cluster-based heterogeneous multi-core architecture. It also proposes inter-cluster thread-to-core mapping to efficiently manage multi-threaded applications to improve energy efficiency while meeting their performance and system resource constraints.

Chapter 5 presents an energy efficient adaptive mapping approach coupled with DVFS for performance-constrained applications, executing on heterogeneous multi-cores. It starts with an introduction and gives a motivational example to show the importance of the proposed approach. Then, a detailed discussion on problem formulation and various steps in the proposed approach are given. Finally, experimentally evaluation of performance models and the runtime management approach are carried out to show the benefits in comparison to the existing approaches.

Chapter 6 concludes this work, providing a summary of the key contributions found throughout this thesis. Additionally, potential future directions as an extension are detailed.

# Chapter 2

# Literature Review of Runtime Energy Management

This chapter presents a necessary background and a thorough review of existing approaches to runtime energy management. Embedded systems, which are mainly referred to as a fixed or programmable system for executing a specific function, have crossed the boundaries of embedded computing by supporting general purpose computing with sophisticated system software. For example, mobile phones used to be part of a cellular network, but they now serve various purposes such as audio/video player, video games, voice calling, etc. Similarly, real-time embedded systems that exist in self-driving cars have sophisticated computing infrastructure to handle various aspects (e.g., constructing internal maps, processing input and plotting the path, etc.) As a result, these systems have been employing multi-core processors for meeting the ever-rising performance and power demands of modern complex embedded applications and for improving the energy efficiency. Multi-core platforms containing several homogeneous and/or heterogeneous processing cores are becoming ubiquitous in embedded processing [64]. These platforms can provide better performance-energy tradeoffs by executing parallel threads of applications on different types of processing cores simultaneously. In addition to that, in some cases, each processing core could operate at a different Dynamic Voltage and Frequency Scaling (DVFS) level, possibly at a lower frequency unlike at a very high frequency in single-core processors and thus fulfilling the energy consumption constraint.

In this context, runtime energy management is required to adapt to diverse resource and performance requirements of applications and to achieve energy savings. There are several approaches proposed for homogeneous and heterogeneous multi-core embedded platforms to improve energy efficiency. These approaches usually consider DVFS and/or thread-to-core mapping techniques for efficiently managing the available system resources. For a better understanding of the existing and proposed runtime energy management approaches, DVFS and thread-to-core mapping concepts are briefly explained

FIGURE 2.1: Illustration of static and dynamic current through an inverter gate

in Section 2.1. The recent architectural innovations to improve performance and energy efficiency are given in Section 2.2. Then, a critical review of existing runtime energy management approaches is presented in Section 2.3. This section mainly covers runtime energy management approaches for homogeneous and single-Instruction Set Architecture (ISA) heterogeneous architectures, as these are the focus of this thesis. Finally, the contents of this chapter are summarized in Section 2.5.

## 2.1 DVFS and Thread-to-Core Mapping

The two components that determine total energy consumption in a system are static and dynamic/switching energy consumption. Static energy consumption is caused by a small current continuously leaking through the transistors, while dynamic is due to charging and discharging of output capacitance [65]. The total energy consumption  $(E_T)$  can be represented as a product of total power consumption  $(P_T)$  and execution time  $(t_e)$  as follows:

$$E_T = P_T * t_e \tag{2.1}$$

where  $P_T$  is computed as below:

$$P_T = P_{dynamic} + P_{static} (2.2)$$

Figure 2.1 shows how current flows through an inverter gate at the transistor level. The solid arrow indicates where static leakage occurs, and the two dotted arrows show where charges escape during switching. Static power consumption origins from transistor size and layout, while dynamic power consumption depends on the amount of transistor switching.

Energy consumption of large-scale and embedded computing systems has been increasing by over 15% per year [66]. Furthermore, due to the growing need for high performance yet energy-efficient computing systems, energy management has central importance almost in every current and future computing domain [67]. As a consequence, modern embedded systems are equipped with various low power techniques such as power gating, clock gating, and DVFS. To achieve energy efficiency, the aforementioned techniques need to be managed in an intelligent way during the system operation. Clock gating and power gating are two widely used techniques to reduce dynamic/leakage power by shutting off the unused components and cores from clock tree and power supply. For runtime adaptation and achieving energy efficiency, DVFS helps to scale the Voltage-frequency (V-f) during application execution. Moreover, thread-to-core mapping helps in allocating the system resources (number of cores and their type) to each application to minimize energy consumption while meeting performance and resource constraints.

#### 2.1.1 DVFS

DVFS is a commonly-used technique to save dynamic power, under the workload and/or performance variations, on a wide range of computing systems, from embedded, laptop and desktop computing systems to high-performance server-class systems [68]. DVFS has been used as a means to improve power efficiency by lowering the CPU frequency and voltage when cycles are being wasted, stalled on memory resources, or under low performance requirements. It is based on the following relation between frequency, voltage, and power:

$$P_{dynamic} \propto C * f * V^2 \tag{2.3}$$