# University of Southampton Research Repository

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Lorenzo Mastronardi (2019) " GeSi Franz-Keldysh Modulator for Silicon Photonic Integrated Circuits", University of Southampton, Faculty of Engineering ans Physical Sciences, Optoelectronics Research Centre, PhD Thesis, pagination.

Data: Lorenzo Mastronardi (2019), GeSi Franz-Keldysh Modulator for Silicon Photonic Integrated Circuits. https://doi.org/10.5258/SOTON/D1094

# **University of Southampton**

Faculty of Engineering and Physical Sciences

Optoelectronics Research Centre

GeSi Franz-Keldysh Modulator for Silicon Photonic Integrated Circuits

by

Lorenzo Mastronardi

Thesis for the degree of **Doctor of Philosophy**

October 2019

## **University of Southampton**

### **Abstract**

Faculty of Engineering and Physical Sciences

**Optoelectronics Research Centre**

Thesis for the degree of **Doctor of Philosophy**

#### GeSi Franz-Keldysh Modulator for Silicon Photonic Integrated Circuits

by

#### Lorenzo Mastronardi

The growing of Internet has driven recent development of Silicon Photonics in the attempt of coping with the unceasing demand of bandwidth at cheap cost; datacentres with large footprint and enormous computational performances are deployed every year with a rate that, by 2021, will represent the 53% of the total count of installed servers. An ambitious yet necessary objective is envisioned by 2030, link speed above 1 Tb/s allowing sophisticated web-services to grow and reach users worldwide. Offering a fast, power efficient and easy to produce, integrated optic modulator working in the C and L band of the communication spectrum for datacentre applications, this thesis presents an innovative Franz-Keldysh based modulator, integrated in a rib waveguide on the 800 nm platform and fully CMOS compatible. The novelties of this design are found in the thick platform, which permits better optical confinement, and the wrap-around junction design that enables definition of wide rib while keeping strong electric field distribution in the active portion of the rib.

Starting from a blank canvas, this project benefited from simulation study, process development and fabrication run. A simulation platform was, in fact, built to estimate electro-optic performances of design variations and define process recipes; the design reference was, then, translated in a set of masks used in the fabrication run. As a result, a

device with cutting edge performances was realised, measuring dynamic extinction ratio of 5.2 dB at 56 Gbps with 3dB bandwidth of 56 GHz. Scattering parameters measurements also permitted to evaluate a power consumption of 44 fJ/bit, confirming the exceptional electro-optical efficiency of the design. A side study investigating material engineering by means of rapid thermal annealing to tune the device absorption spectrum, that together with the possibility of customising the device design, permits to expand the operation bandwidth while supporting either the transverse electric or transverse magnetic polarisation, is also presented.

# **Table of Contents**

| Academic           | Thesis: Declaration Of Authorship            | VI    |  |

|--------------------|----------------------------------------------|-------|--|

| Acknowledgements D |                                              |       |  |

| Definitions        | Definitions and Abbreviations                |       |  |

| Chemicals          |                                              | XIV   |  |

| List of Fig        | ures                                         | XVI   |  |

| List of Tab        | oles                                         | XXXIV |  |

| Chapter 1          | Introduction                                 | 1     |  |

| 1.1 Th             | nesis outline                                | 6     |  |

| Chapter 2          | Theoretical Backgrounds                      | 9     |  |

| 2.1 Ge             | ermanium, Silicon and GeSi                   | 10    |  |

| 2.2 O <sub>I</sub> | otic communication link                      | 15    |  |

| 2.2.1              | Transceiver                                  | 16    |  |

| 2.2.2              | Optic Channel                                | 21    |  |

| 2.3 M              | odulation Strategies in the Silicon Platform | 24    |  |

| 2.3.1              | Plasma Dispersion Effect                     | 24    |  |

| 2.3.2              | Franz-Keldysh Effect                         | 25    |  |

| 2.3.3              | Quantum Confined Stark Effect                | 27    |  |

| 2.3.4              | Other Non-Linear Effects                     | 29    |  |

| 2.4 Co             | ommon Structures                             | 30    |  |

| 2.4.1              | Interferometer                               | 30    |  |

| 2.4.2              | Resonant Device                              | 32    |  |

| 2.4.3              | PIN Diode                                    | 33    |  |

| 2.5 Su             | mmary                                        | 34    |  |

| Chapter 3          | Group IV Modulators                          | 37    |  |

| 3.1 Standard    | Metrics                                            | 37 |

|-----------------|----------------------------------------------------|----|

| 3.1.1 Modu      | ulation Efficiency $L_{\pi}V_{\pi}$                | 37 |

| 3.1.2 Inser     | tion Loss and Extinction Ratio                     | 38 |

| 3.1.3 Dark      | Current                                            | 38 |

| 3.1.4 Dyna      | mic Extinction Ratio                               | 39 |

| 3.1.5 Powe      | er consumption and 3dB bandwidth                   | 40 |

| 3.2 Literature  | e Review                                           | 41 |

| 3.2.1 Plasn     | na Dispersion Effect Modulators                    | 42 |

| 3.2.2 QCS       | E Modulators                                       | 43 |

| 3.2.3 Bulk      | Electro Absorption Modulators                      | 43 |

| 3.3 Summary     | y                                                  | 44 |

| Chapter 4 Meth  | ods                                                | 45 |

| 4.1 Design T    | ools                                               | 45 |

| 4.1.1 Device    | ce Process and Electric Simulation in Silvaco TCAD | 46 |

| 4.1.1.1         | Deposition method                                  | 46 |

| 4.1.1.2         | Etch model                                         | 46 |

| 4.1.1.3         | Implant method                                     | 47 |

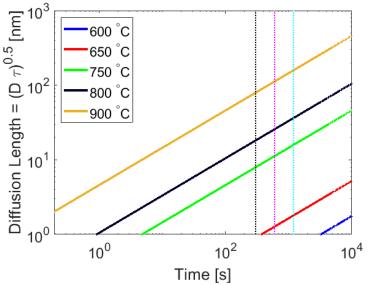

| 4.1.1.4         | Diffusion model                                    | 47 |

| 4.1.1.5         | Bandgap Narrowing Model                            | 48 |

| 4.1.1.6         | Carrier Generation-Recombination Models            | 48 |

| 4.1.1.7         | Mobility models                                    | 49 |

| 4.1.1.8         | Impact Ionization Model                            | 49 |

| 4.1.1.9         | Newton method                                      | 49 |

| 4.1.2 Optic     | cal Solver                                         | 50 |

| 4.1.2.1         | Matlab function                                    | 50 |

| 4.1.2.2         | Lumerical MODE Solutions                           | 50 |

| 4.1.2.3         | Lumerical FDTD Solutions                           | 53 |

| 4.1.3 Mask      | Design Tool                                        | 55 |

| 4.2 Fabrication | on                                                 | 56 |

| 4.2.1 Wafe      | er conditioning                                    | 56 |

| 4.2.2     | Material Deposition                                    | 57         |

|-----------|--------------------------------------------------------|------------|

| 4         | 4.2.2.1 Plasma Enhanced Chemical Vapour Deposition (PE | CVD)57     |

| 4         | 4.2.2.2 Selective Reduced Pressure Chemical Vapour     | Deposition |

|           | (RPCVD)                                                | 58         |

| 4         | 4.2.2.3 Chemical Mechanical Polishing (CMP)            | 62         |

| 4         | 4.2.2.4 Metal Evaporator                               | 64         |

| 4.2.3     | Lithography                                            | 65         |

| 4         | 4.2.3.1 E-beam Lithography                             | 65         |

| 4         | 4.2.3.2 Photolithography                               | 67         |

| 4.2.4     | Inductively Coupled Plasma Etching (ICP)               | 68         |

| 4.2.5     | Metal Lift-off                                         | 70         |

| 4.2.6     | Ion Implant Doping                                     | 72         |

| 4.2.7     | Rapid Thermal Annealing (RTA)                          | 74         |

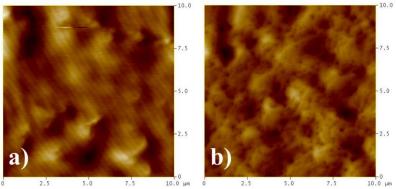

| 4.3 M     | aterial Characterisation                               | 74         |

| 4.3.1     | Atomic Force Microscope (AFM)                          | 75         |

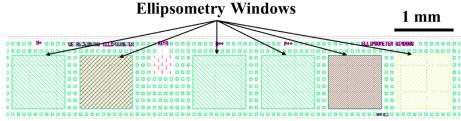

| 4.3.2     | Ellipsometry                                           | 75         |

| 4.3.3     | Scanning Electron Microscopy (SEM)                     | 77         |

| 4.3.4     | Secondary-Ion Mass Spectrometry (SIMS)                 | 77         |

| 4.3.5     | Other methods                                          | 78         |

| 4.4 De    | evice Characterisation                                 | 78         |

| 4.4.1     | DC Experimental Setup                                  | 79         |

| 4.4.2     | High-speed Experimental Setup                          | 82         |

| 4.5 Su    | ımmary                                                 | 83         |

| Chapter 5 | Modelling and Designing                                | 85         |

| 5.1 M     | athematical Model                                      | 86         |

| 5.1.1     | Analysis Parameters                                    | 87         |

| 5.1.2     | Model Validation                                       |            |

| 5.2 Si    | mulation Platform                                      | 91         |

| 5.2.1     | Simulation Platform Validation                         | 95         |

| 5.3 De    | evice Simulations                                      | 97         |

|           |                                                        |            |

| 5.3    | 3.1  | Doping Simulations                            | 98  |

|--------|------|-----------------------------------------------|-----|

| 5.3    | 3.2  | Implantation Recipe Simulations               | 102 |

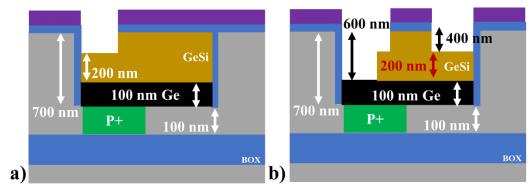

| 5.3    | 3.3  | Layout Simulations                            | 108 |

| 5.3    | 3.4  | Ge buffer layer                               | 112 |

| 5.4    | Siı  | mulations of Passive Structures               | 113 |

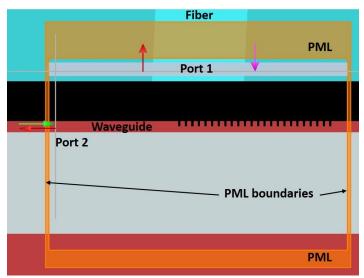

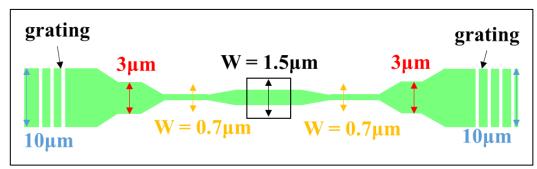

| 5.4    | 4.1  | Grating Coupler and Taper Design              | 113 |

| 5.4    | 4.2  | Mode overlap Simulations                      | 117 |

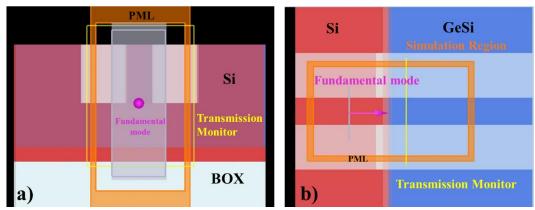

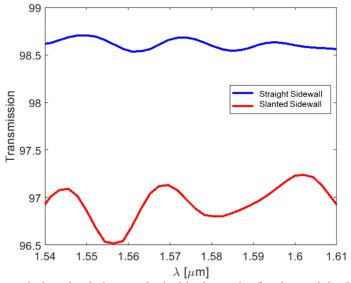

| 5.4    | 4.3  | Transmission Simulations of Angled Interfaces | 118 |

| 5.5    | Ma   | ask layout                                    | 120 |

| 5.5    | 5.1  | Alignment Marks                               | 120 |

| 5.5    | 5.2  | Testing Structures                            | 122 |

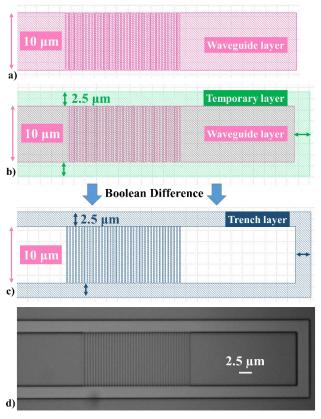

| 5.5    | 5.3  | Waveguide layout                              | 123 |

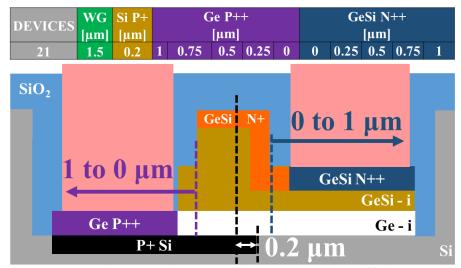

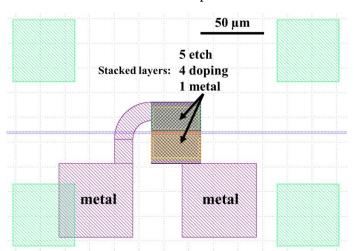

| 5.5    | 5.4  | Device layout                                 | 125 |

| 5.6    | Su   | mmary                                         | 126 |

| Chapte | er 6 | Material Tailoring                            | 129 |

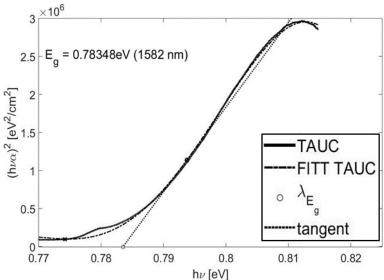

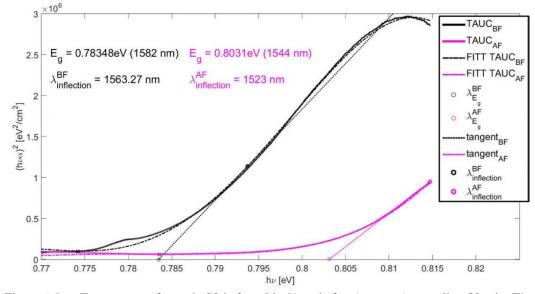

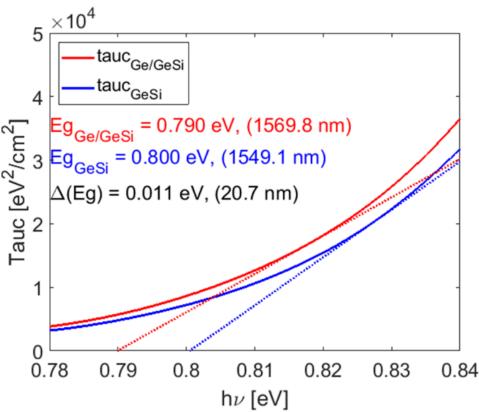

| 6.1    | Di   | rect Bandgap Estimation                       | 130 |

| 6.2    | Fa   | brication Process                             | 131 |

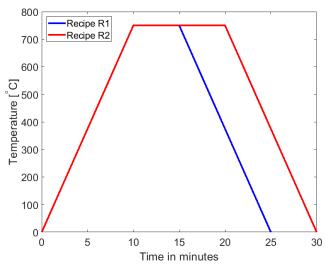

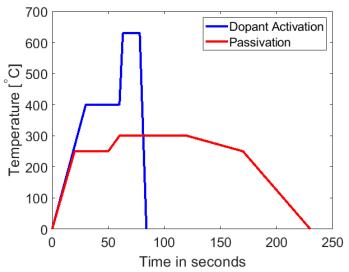

| 6.3    | RT   | ΓA recipe                                     | 132 |

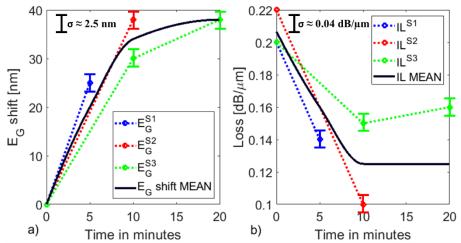

| 6.4    | Me   | easurement analysis                           | 133 |

| 6.5    | Ch   | naracterization                               | 136 |

| 6.6    | Su   | mmary                                         | 141 |

| Chapte | er 7 | GeSi Photonic Modulator                       | 143 |

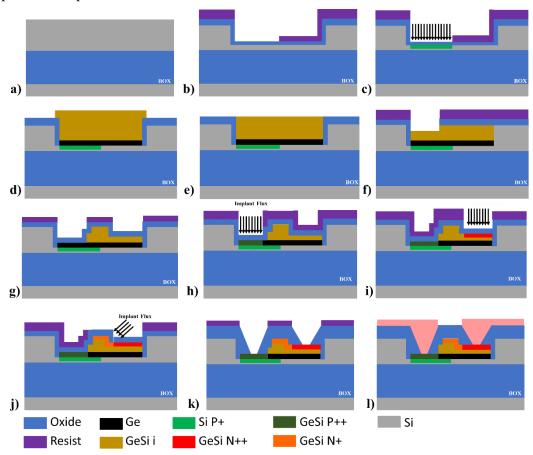

| 7.1    | De   | evice Fabrication Process                     | 144 |

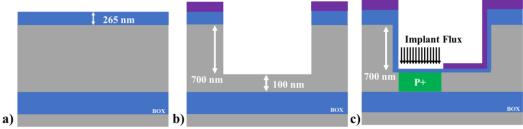

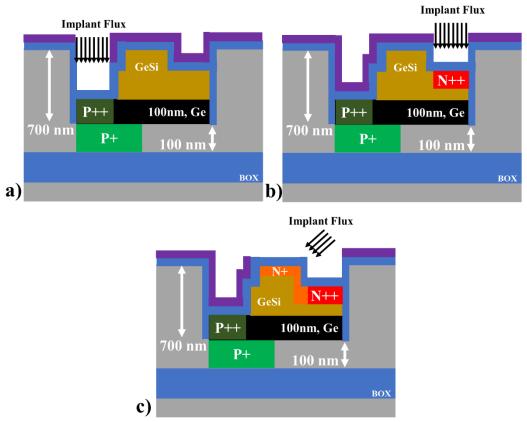

| 7.     | 1.1  | Cavity definition and Si doping               | 145 |

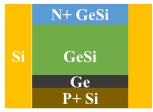

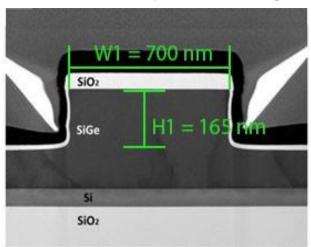

| 7.     | 1.2  | GeSi growth                                   | 146 |

| 7.     | 1.3  | Waveguide and Grating Definition              | 148 |

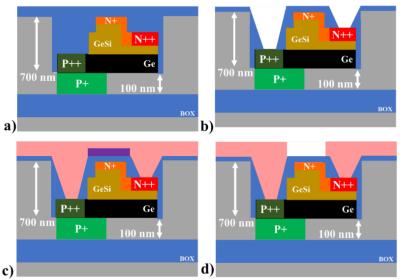

| 7.     | 1.4  | Ge and GeSi doping                            | 149 |

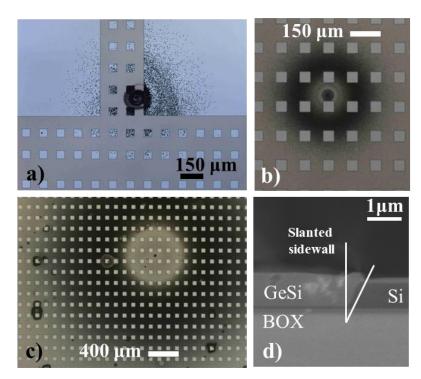

| 7.     | 1.5  | VIAs etch and Metal deposition                | 150 |

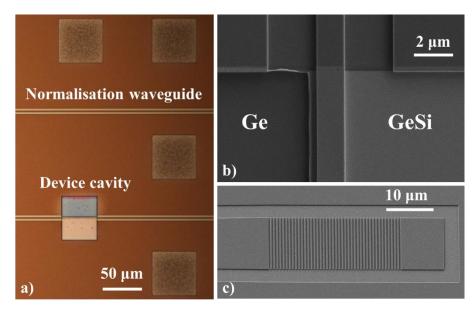

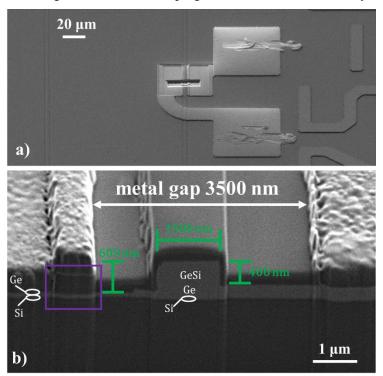

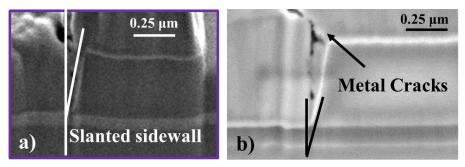

| 7.     | 1.6  | Device Top-View and Cross-Section             | 152 |

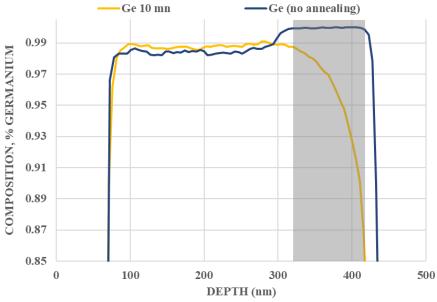

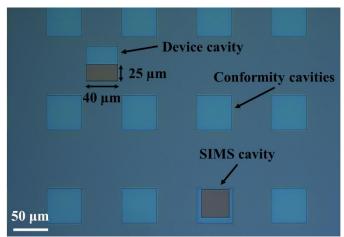

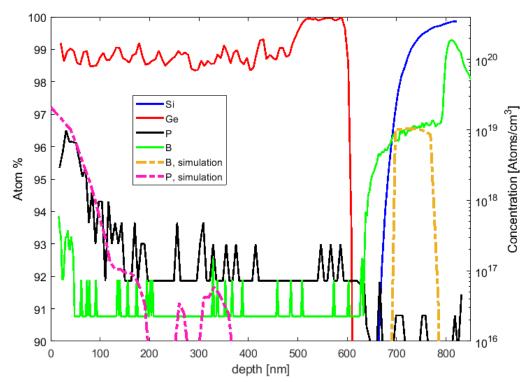

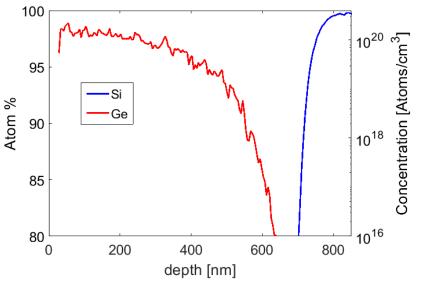

| 7.2    | SI   | MS after Fabrication                          | 153 |

| 1 RTA test on the 800 nm Platform | 154                                                                                                                                                                                                                        |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

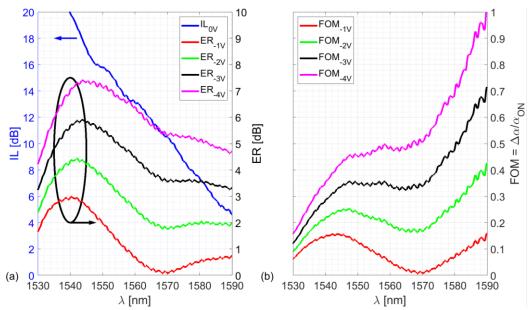

| Electro-optic Measurements        | 155                                                                                                                                                                                                                        |

| 1 IV characterisation             | 156                                                                                                                                                                                                                        |

| 2 DC Characterisation             | 157                                                                                                                                                                                                                        |

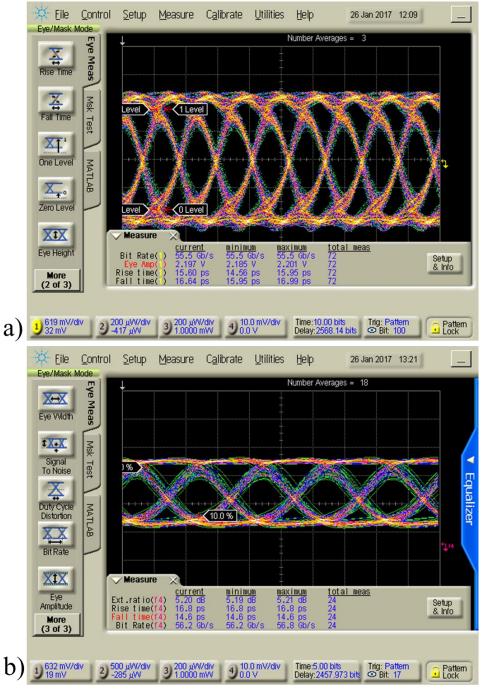

| 3 High-speed Characterisation     | 161                                                                                                                                                                                                                        |

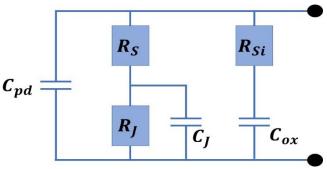

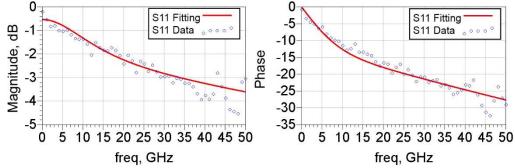

| 4 RF Electric Characterisation    | 163                                                                                                                                                                                                                        |

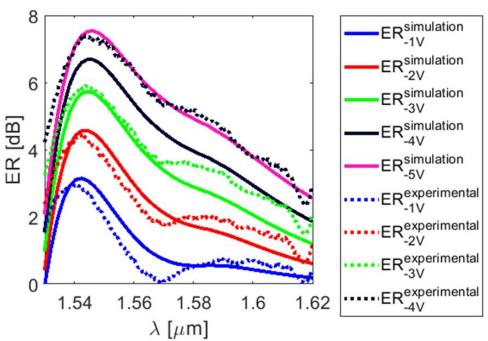

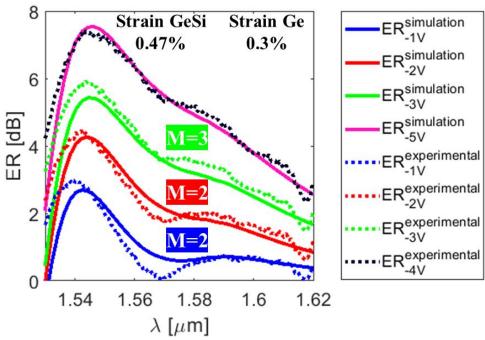

| Comparison with simulation        | 163                                                                                                                                                                                                                        |

| Summary                           | 165                                                                                                                                                                                                                        |

| 8 Conclusions                     | 167                                                                                                                                                                                                                        |

| Findings                          | 170                                                                                                                                                                                                                        |

| Limitations                       | 171                                                                                                                                                                                                                        |

| Perspectives                      | 172                                                                                                                                                                                                                        |

| aphy                              | 173                                                                                                                                                                                                                        |

|                                   | Electro-optic Measurements  I IV characterisation  DC Characterisation  High-speed Characterisation  RF Electric Characterisation  Comparison with simulation  Summary  8 Conclusions  Findings  Limitations  Perspectives |

## **Academic Thesis: Declaration Of Authorship**

#### I, Lorenzo Mastronardi

declare that this thesis and the work presented in it are my own and has been generated by me as the result of my own original research.

GeSi Franz-Keldysh Modulator for Silicon Photonic Integrated Circuits

I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University;

- 2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- 3. Where I have consulted the published work of others, this is always clearly attributed;

- 4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- 5. I have acknowledged all main sources of help;

- 6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- 7. Parts of this work have been published as:

#### First Author Journal Paper

L. Mastronardi, M. Banakar, A.Z. Khokhar, N. Hattasan, T. Rutirawut, T. Domínguez Bucio, K. M. Grabska, C. Littlejohns, A. Bazin, G. Mashanovich, and F.Y. Gardes, "High-speed Si/GeSi hetero-structure Electro Absorption Modulator," Opt. Express 26, 6663-6673 (2018).

#### **Co-author Journal Paper**

K. Debnath, D. J. Thomson, W. Zhang, A. Z. Khokhar, C. Littlejohns, J. Byers, L. Mastronardi, M. K. Husain, K. Ibukuro, F. Y. Gardes, G. T. Reed, and S. Saito, "All-silicon carrier accumulation modulator based on a lateral metal-oxide-semiconductor capacitor," Photon. Res. 6, 373-379 (2018).

#### Recognition

"The Optical Society, CLEO-PR Best Student Paper Award 2018," CLEO Pacific Rim 2018.

### **Conference Paper**

- L. Mastronardi, M. Banakar, A.Z. Khokhar, N. Hattasan, T. Rutirawut, T. Domínguez Bucio, K. M. Grabska, C. Littlejohns, A. Bazin, G. Mashanovich, and F.Y. Gardes, "56 Gbps Si/GeSi integrated EAM," (invited paper) SPIE/COS Photonics Asia, 10823-12 (2018).

- L. Mastronardi, M. Banakar, A.Z. Khokhar, N. Hattasan, T. Rutirawut, T. Domínguez Bucio, K. M. Grabska, C. Littlejohns, A. Bazin, G. Mashanovich, and F.Y. Gardes, "56 Gb/s Si/GeSi Optical Modulator," in CLEO Pacific Rim Conference 2018, OSA Technical Digest (Optical Society of America, 2018), paper Th3C.2.

- L. Mastronardi, M. Banakar, A.Z. Khokhar, N. Hattasan, T. Rutirawut, T. Domínguez Bucio, K. M. Grabska, C. Littlejohns, A. Bazin, G. Mashanovich, and F.Y. Gardes, "56 Gbps GeSi Franz-Keldysh modulator for silicon photonic transceivers," in Proceedings D-Photon (2018).

- L. Mastronardi, M. Banakar, A. Z. Khokhar, T. Dominguez Bucio, C. G. Littlejohns, N. Bernier, E. Robin, J-L. Rouvire, H. Dansas, N. Gambacorti, G Z Mashanovich, and F Y Gardes, "SiGe bandgap tuning for high speed eam," in transactions of 231st ECS Meeting, 77(6), 59-63, (2017).

- K. Debnath, D. J. Thomson, W. Zhang, A. Z. Khokhar, C. Littlejohns, J. Byers, L. Mastronardi, M. K. Husain, F. Y. Gardes, G. T. Reed, and S. Saito, "20Gbps silicon lateral MOS-Capacitor electro-optic modulator," in Conference on Lasers and Electro-Optics, OSA Technical Digest (online) (Optical Society of America, 2018), paper SM3B.5.

- F. Gardes, T. Dominguez Bucio, L. Mastronardi, M. Banakar, A. Bazin, A. Z. Khokhar, C. Lacava, P. Petropoulos, C. Littlejohns, K. Debnath, "Group IV

- Compounds Modulators and Mid Index Waveguides for Enhanced CMOS Photonics," 2018 IEEE Photonics Conference (IPC), Reston, VA, 1-2 (2018).

- D. J. Thomson, K. Debnath, W. Zhang, K. Li, S. Liu, F. Meng, A. Z. Khokhar, C. Littlejohns, J. Byers, L. Mastronardi, M. K. Husain, F. Y. Gardes, S. Saito, X. Chen, M. M. Milosevic, Y. Franz, A. F. J. Runge, S. Mailis, A. C. Peacock, P. Wilson, G. T. Reed, "Towards High Speed and Low Power Silicon Photonic Data Links," 2018 20th International Conference on Transparent Optical Networks (ICTON), Bucharest, 1-4 (2018).

#### Previous Publication un-related to this Work

- C. E. Campanella, L. Mastronardi, F. De Leonardis, P. Malara, G. Gagliardi, and

V. M. N. Passaro, "Investigation of refractive index sensing based on Fano resonance in fiber Bragg grating ring resonators," Opt. Express 23, 14301-14313 (2015).

- P. Malara, L. Mastronardi, C. E. Campanella, A. Giorgini, S. Avino, V. M. N. Passaro, and G. Gagliardi, "Split-mode fiber Bragg grating sensor for high-resolution static strain measurements," Opt. Lett. 39, 6899-6902 (2014).

- C. E. Campanella, L. Mastronardi, F. De Leonardis, P. Malara, G. Gagliardi, and

V. M. N. Passaro, "Investigation of fiber Bragg grating based mode-splitting resonant sensors," Opt. Express 22, 25371-25384 (2014).

- C. E. Campanella, L. Mastronardi, F. De Leonardis, V. M.N. Passaro, "π shifted fiber Bragg grating ring resonators as splitting mode resonant sensors," 20th IMEKO TC4 International Symposium, 414-419 (2014).

| Sign | ned: |      |           |      |       |      |      |  |

|------|------|------|-----------|------|-------|------|------|--|

|      |      | <br> | <br>••••• | <br> | ••••• | <br> | <br> |  |

| Dat  | e:   |      |           |      |       |      |      |  |

|      |      | <br> | <br>      | <br> |       | <br> | <br> |  |

## Acknowledgements

Firstly, I would like to express my sincere gratitude to my supervisors Prof. Frederic Y. Gardes and Prof. Goran Z. Mashanovic for the continuous support during my Ph.D study, for their immense knowledge, motivation and patience. Their guidance helped me in all the time of research and writing of this thesis. No better advisors and mentors for my Ph.D study, I could ever imagined.

My sincere acknowledgment goes to Rockley Photonics Inc. for funding the project; I am grateful to Prof. Andrew Rickman Founder, Chairman and CEO, Rockley Photonics Inc.; Dr. Aaron Zilkie Co-founder and VP R&D Silicon Photonics at Rockley Photonics Inc.; Mr. Guomin Yu Director of High-Speed Devices at Rockley Photonics Inc. for their support and help.

My thanks also go to Dr. Mehdi Banakar, Dr. Ali Khokhar, Dr. Nannicha Hattasan, Dr. Thalia Dominguez Bucio, Dr. Alex Bazin, Dr. David J. Thompson, Dr. Callum G. Littlejohns, Dr. Milos Nedeljković without their precious support the outcome of this project would not be possible. I thank my fellow groupmates for the stimulating discussions, and help.

I am grateful to the group leader Prof. Graham T. Reed for allowing everyone in the group to conduct cutting-edge research in a positive work environment.

Last but not the least, I would like to thank my parents Annalisa and Mimmo, my wife Anna, my brothers Gianpaolo and Mattia, my sister-in-law Ingrid and my nephew Damiano for supporting me spiritually during this long, exciting, sometimes exhausting journey.

### **Definitions and Abbreviations**

- AC Alternate Current

- AFM Atomic Force Microscope

- ASK Amplitude-Shift-Key

- BER Bit Error Rate

- BH Bottom Half

- BOX Buried Oxide

- CAGR Compound Annual Growth Rate

- CB Conduction Band

- CDR Clock and Data Recovery

- CEI Common Electrical (I/O)

- CG Grating Coupler

- CMOS Complementary Metal Oxide Semiconductor

- CMP Chemical Mechanical Polishing

- CW Continuous Wave

- CWDM Coarse Wavelength Division Multiplexing

- DC Direct Current

- DCA Digital Communication Analyser

- DPSK Differential- Phase-Shift-Key

- DUT Device Under Test

- E Electric Field

- EAM Electro Absorption Modulator

- EOM Electro-Optic Modulator

- ER Extinction Ratio

- ER-Dyn Dynamic ER

- FDM Finite Difference Method

- FDTD Finite Difference Time Domain method

- FIB Focused Ion Beam

- FKE Franz-Keldysh Effect

- FOM Figure Of Merit

- FSK Frequency-Shift-Key

- GB Giga Byte

- Gbps Giga bit per second

- GC Grating Coupler

- GDP Gross Domestic Product

- GS Ground Signal

- H Magnetic Field

- HAADF High Angle Annular Dark Field

- IC Layout Integrated Circuit layout

- ICP Inductively Coupled Plasma

- IL Insertion Loss

- IPA IsoPropyl Alcohol

- IR Infrared

- IV Current Voltage

- KE Kerr Effect

- LASER Light Amplification by Stimulated Emission Of Radiation

- LED Light Emitting Diode

- MBE Molecular Beam Epitaxy

- MCSMF Multi Core Single Mode optic Fibres

- MMF Multi Mode optic Fibres

- MMI Multi Mode Interference coupler

- MOS Metal Oxide Semiconductor

- MZI Mach-Zehnder Interferometer

- M-QAM M-Quadrature Amplitude Modulation

- NCUS Nanofabrication Centre of the University of Southampton

- NRZ Non-Return to Zero

- OEIC Opto-Electronic Integrated Circuit

- OIF Optical Internetworking Forum

- OOK On Off Key

- PAM-x Pulse Amplitude Modulation-x

- PDE Plasma Dispersion Effect

- PE Pockels Effect

- PEDT Precession Electron Diffraction Technique

- PECVD Plasma Enhanced Vapour Deposition

- PML Perfectly matched layer

- PoE photoelectric effect

- PIN Acceptor Intrinsic Donor

- PM-SMF Polarisation maintaining Single Mode optic Fibre

- PRBS Pseudo Random Binary Sequence

- PSK Phase Shift Key

- QC Quantum Confinement

- QCSE Quantum Confined Stark Effect

- QPSK Quadrature Phase Shift Key

- QW Quantum Well

- RF Radio Frequency

- RMS Root Mean Square

- RPCVD Reduced Pressure Chemical Vapour Deposition

- RSA Rack Scale Architecture

- RTA Rapid Thermal Annealing

- SC-x Standard Clean-x

- SDM Spatial Division Multiplexing

- SEM Scanning Electron Microscopy

- SER SerDes (Serialiser)

- SHR Shockley Hall Read recombination

- SIMS Secondary Ion Mass Spectrometry

- SMF Single Mode optic Fibre

- SOI Silicon On Insulator

- STEM Scanning Transmission Electron Microscopy

- TCAD Technology Computer-Aided Design

- TDD Threading Dislocation Density

- TE Transverse Electric

- TH Top Half

- TIA Trans Impedance amplifier

- TIR Total Internal Reflection

- TM Transverse Magnetic

- TOR Top of Rack

- TPA Two-Photons Absorption

- UV Ultra Violet light

- UHVCVD Ultra High Vacuum CVD

- VIA Vertical Interconnect Access

- VB Valence Band

- VCSEL Vertical Cavity Surface Emitting Laser

- WDM wavelength Division Multiplexing

### **Chemicals**

- As Arsenic

- Ar Argon

- B Boron

- AsH<sub>3</sub> Arsine

- B<sub>2</sub>H<sub>6</sub> Diborane

- BF<sub>2</sub> Difluoroboryl

- CF<sub>4</sub> Tetrafluoroethane

- C<sub>2</sub>F<sub>6</sub> Hexafluoroethane

- C<sub>4</sub>F<sub>8</sub> Octafluorocyclobutane, or Perfluorocyclobutane

- CHF<sub>3</sub> Fluoroform

- HCl Hydrochloric acid

- HF Hydrofluoric acid

- H<sub>2</sub>O<sub>2</sub> Hydrogen peroxide

- IBGe Iso-Butyl Germane

- N<sub>2</sub> Nitrogen gas

- N<sub>2</sub>O Nitrogen Oxide

- NH<sub>3</sub> Ammonia

- Ge Germanium

- GeCl<sub>4</sub> Germanium Chloride

- GeH<sub>4</sub> Germane

- GeO<sub>2</sub> Germanium Oxide

- GeNi Germanide

- GeSi Germanium Silicon

- SF<sub>6</sub> Sulfur Hexafluoride

- Si Silicon

- SiH<sub>4</sub> Silane

- SiO<sub>2</sub> Silicon dioxide

- SiOH Silanol

- O<sub>2</sub> Oxygen

- P Phosphorus

- PH<sub>3</sub> Phosphine

- TiN Nitinol

# **List of Figures**

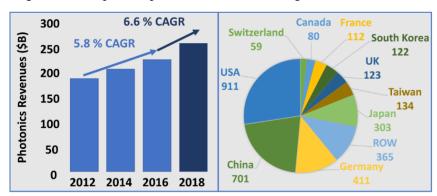

| Figure 1-1 | (left) Photonics revenue CAGR%, (right) Photonics company count by country [1]                                                                                                                                                                                                                       |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

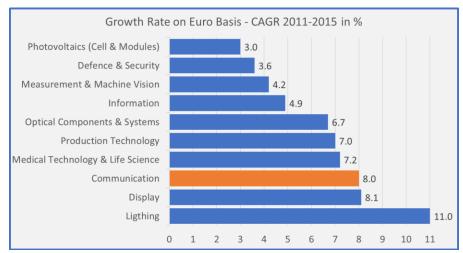

| Figure 1-2 | Photonics market Global growth rate in Euro, CAGR% [2] divided in ten areas. In orange the Communication sector growth, mostly affected by datacentre development.                                                                                                                                   |

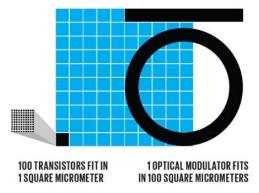

| Figure 1-3 | Footprint comparison between transistors and optic ring resonator modulator, demonstrating that in-chip optic transmission is not practical with current technologies, reproduction from reference [6]                                                                                               |

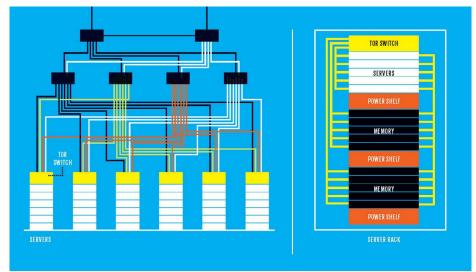

| Figure 1-4 | Standard datacentre topology, from the internet link (top), data is routed via optic fibres to the servers (yellow-white). On the right the Rack Scale Architecture provides distributed server architecture by optically connecting computers to memory, reproduction from reference [6] 3          |

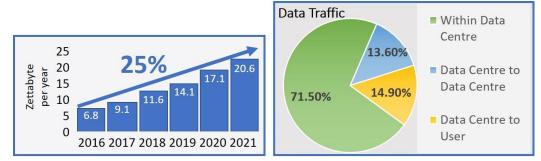

| Figure 1-5 | Cisco Global Datacentre IP growth Prediction (left) and Data traffic ratios (right) [9]                                                                                                                                                                                                              |

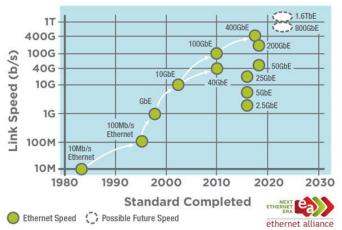

| Figure 1-6 | Ethernet Alliance's roadmap for the Terabit Ethernet, reproduction from reference [10]                                                                                                                                                                                                               |

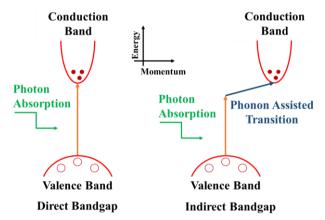

| Figure 2-1 | Direct (left) and Indirect (right) Bandgap Semiconductor. In the first case an e-h pair is created with same momentum by absorbing a photon, in the second case the e-h can be created if a phonon (blue arrow) is absorbed/emitted to change the electron momentum                                  |

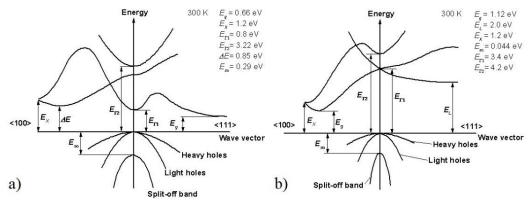

| Figure 2-2 | Band structure of Bulk Ge (a) and Si (b) [40]. Although classified as indirect bandgap semiconductors, both Si and Ge have a direct bandgap. For Ge the corresponding wavelength is about 1550 nm, hence this material can be used for active devices that interacts with light in the near infrared |

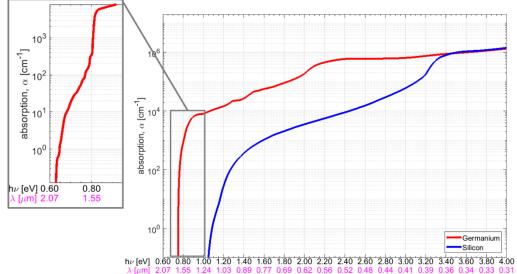

| Figure 2-3  | Absorption spectra of Si (blue) [41] and Ge (red) [42]. In the inset, a zoom for the Ge absorption coefficient around 0.8 eV [43]                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

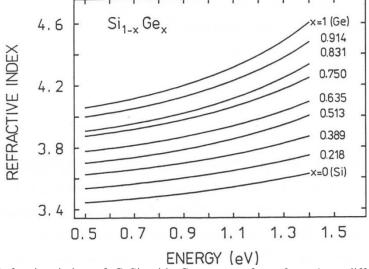

| Figure 2-4  | Refractive index of GeSi with Ge content from 0 to 1 at different energies, reproduction from reference [50]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

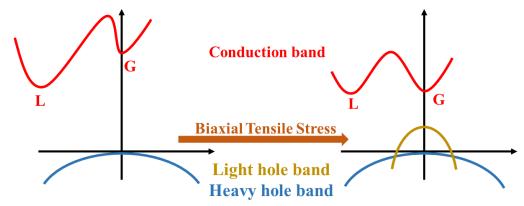

| Figure 2-5  | Effect of the Biaxial Tensile Strain on the Conduction and Valence Bands. The strain reduces the bandgap between the $\Gamma$ (CB) and the light hole VB, thus red-shifting the material band-edge                                                                                                                                                                                                                                                                                                                                                                                          |

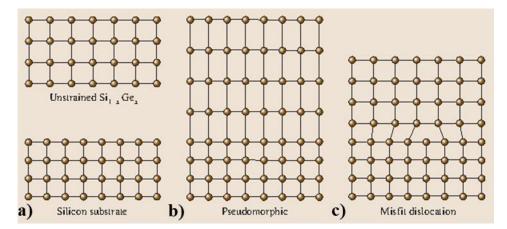

| Figure 2-6  | (a) Atomic drawing of unstrained Ge <sub>x</sub> Si <sub>1-x</sub> (1 <x<0) (b)="" and="" bottom.="" ge<sub="" growth="" of="" on="" pseudomorphic="" silicon="" the="" top="" unstrained="">xSi<sub>1-x</sub> on Si, the lattice mismatch is compensated by elastic strain. (c) Unstrained growth of Ge<sub>x</sub>Si<sub>1-x</sub> on Si with formation of misfit dislocations, misfit dislocations are formed if the critical thickness is overcome in a pseudomorphic growth. Image reproduced from reference [53]</x<0)>                                                               |

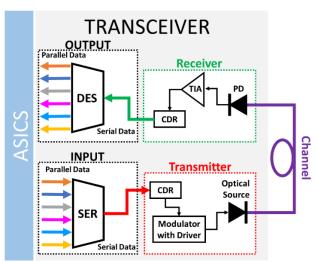

| Figure 2-7  | Representation of a high-speed optical link. Parallel data from the ASICs are serialised with a SerDes (SER) unit. After Clock and Data Recovery (CDR), the electrical input is converted in a pulsed optic signal by modulating a Laser (Optical Source) with a Modulator with Driver. After propagation through the optic fibre (Channel, in purple), the signal is converted into electric with a Photodiode (PD), the photocurrent is then translated in a usable voltage with a Trans Impedance Amplifier (TIA). A CDR stage precedes data parallel conversion with a SerDes (DES). 15 |

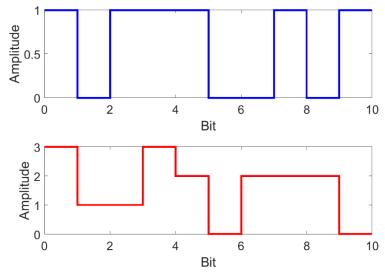

| Figure 2-8  | (top) NRZ encoding, only two logic levels are available, representing the single bit-0 and bit-1. (bottom) PAM-4 encoding, the four levels from 0 to 3 represent symbols of two bits each using the Grey coding (00, 10, 11, 01)                                                                                                                                                                                                                                                                                                                                                            |

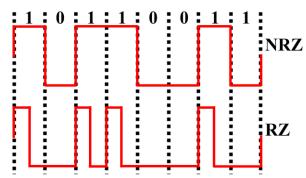

| Figure 2-9  | In NRZ (top) the logic level occupies the whole timeslot Tb, whereas in RZ encoding the logic level return always to the low level                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

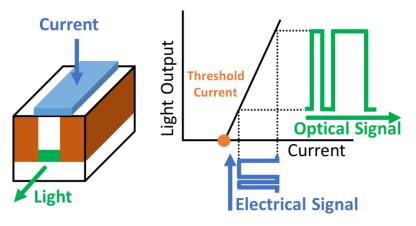

| Figure 2-10 | (left) Laser diode drawing, if the injected current is higher than the Threshold, the device emits light, (right) by modulating the current an optical replica of the electrical signal is obtained                                                                                                                                                                                                                                                                                                                                                                                         |

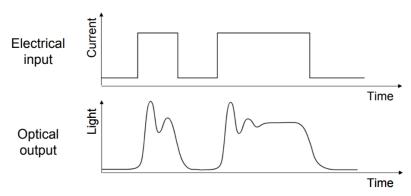

| Figure 2-11 | Electric signal and modulated optical signals with overshooting caused by relaxed oscillations in the direct modulated laser. Reproduction from reference [80].                                                                                                                                                                                                                                                                                                                                                                                                                             |

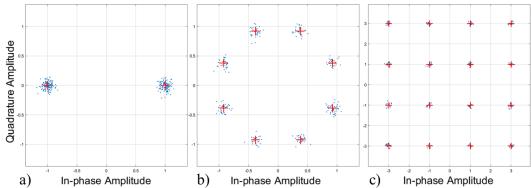

| Figure 2-12 Simulation with Matlab® of PSK (also antipodal ASK), 8-QPSK and 16 QAM modulation. Each symbol is represented by points on the constellation plot (red cross). The received samples (blue) are affected be noise and surround the constellation points; the symbol distance depend on M, while M increases, the distance reduces and with that the robustness of the link to errors and noise                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

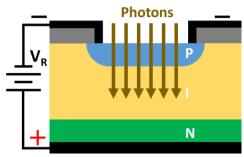

| Figure 2-13 PIN Photodiode schematics reverse biased. Photons are absorbed in the intrinsic layer allowing electrons to go to the conduction band. E-h pair are accelerated by the electric field due to $V_R$ , generating the photocurrent                                                                                                                                                                                                  |

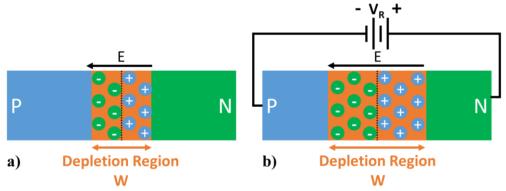

| Figure 2-14 PN diode at equilibrium (a) and under reverse bias (b). W is the depletion region width (orange), E the electric field with its direction and $V_R$ the reverse bias. (a) Without bias, an electric field is generated at the interface by attraction of majority carriers to opposite doping and a zone with minority carriers only is formed (W), with a reverse bias (b) more carried are pulled and the width of W increases. |

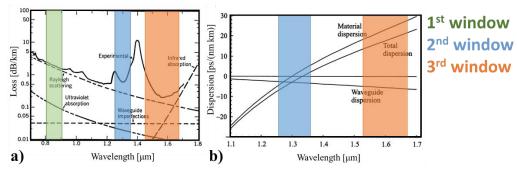

| Figure 2-15 Propagation loss [88] (a) and dispersion (b) of the single mode silica optifibre [74]. (a) The optimum windows are highlighted, the 1 <sup>st</sup> window is green, the 2 <sup>nd</sup> in blue and the 3 <sup>rd</sup> in orange; (b) the dispersion for the 2 <sup>nd</sup> and 3 <sup>rd</sup> windows are highlighted in blue and the in orange, respectively                                                                |

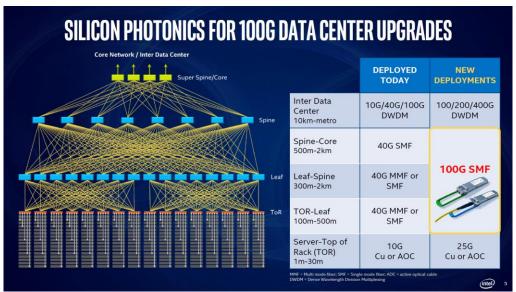

| Figure 2-16 Intel® prediction on datacentre upgrades for the >100 Gbps, reproduction from reference [93].                                                                                                                                                                                                                                                                                                                                     |

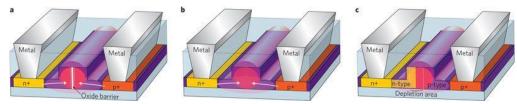

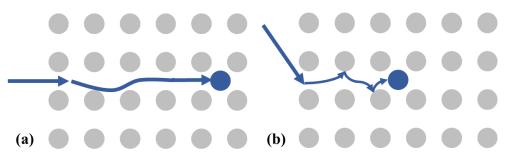

| Figure 2-17 PDE modulation with <b>a</b> Carrier accumulation (capacitor), <b>b</b> Carrier injection (PIN junction in forward bias), <b>c</b> Carrier depletion (PN junction in reverse bias), reproduction from reference [95]                                                                                                                                                                                                              |

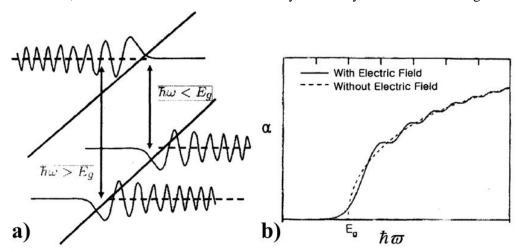

| Figure 2-18 (a) The electric field tilts the Band Edges (Franz-Keldysh Effect allowing photon with lower energy to be absorbed. (b) the Absorption Coefficient curve increases near <i>EG</i> , for photon energies higher than Edges (Franz-Keldysh oscillations (FKO) due to wave-function interference appear. Reproduction from reference [102]                                                                                           |

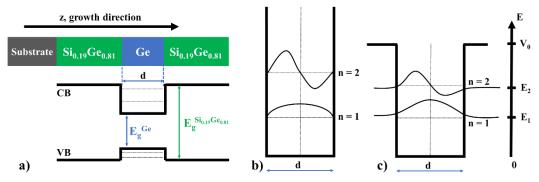

| Figure 2-19 (a) Diagram of the quantum well realised using Si <sub>0.19</sub> Ge <sub>0.81</sub> barriers an Ge thin layer [108], the resulting band diagram is sketched below. The                                                                                                                                                                                                                                                           |

|             | discrete energy levels are shown in dashed lines. (b) Infinite well and (c) finite well with barriers of height $V_0$ showing the wave equation for electrons and holes found at discrete energy levels (n=1, 2)                                                                                                                                                                                                                                                                        |

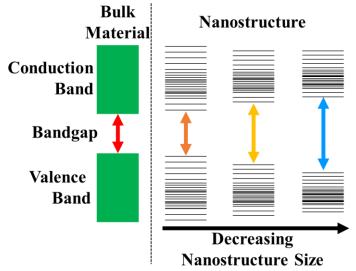

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-20 | Bandgap energy for bulk and nanostructure materials, QC increases the bandgap if the size of the nanostructure reduces                                                                                                                                                                                                                                                                                                                                                                  |

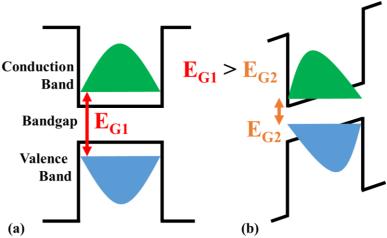

| Figure 2-21 | QCSE, the reverse bias tilts the discrete energy levels allowing photons with lower energy to be absorbed, similarly to FKE                                                                                                                                                                                                                                                                                                                                                             |

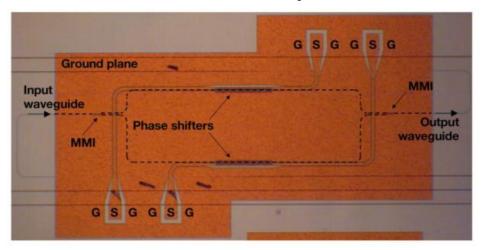

| Figure 2-22 | PDE MZI top view modulator, reproduction from reference [120]. The area is mostly occupied by the interferometer arms and travelling wave metal pads. The phase shifters, the active area, are about 250 µm long.                                                                                                                                                                                                                                                                       |

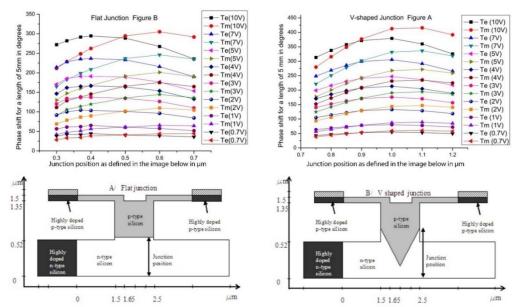

| Figure 2-23 | Phase shift vs junction position for TE and TM modes for the flat projunction (left) and the V-shape pn junction (right), reproduction from reference [122]. By engineering the PN junction a similar phase shit vs bias is obtained for both TE and TM                                                                                                                                                                                                                                 |

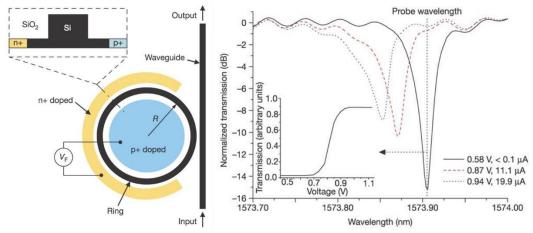

| Figure 2-24 | (Left) Cross-section and top view of a PDE Ring Resonator Modulator, reproduction from reference [123]. In the region with small gap between the ring and the straight waveguide, evanescence coupling is generated, inside the ring the light builds up if constructive interreference is met, the same port allows part of the light to escape and interfere with the incoming light. As a result, (Right) a Notch Filter response is achieved, the notch is then shifted with a bias |

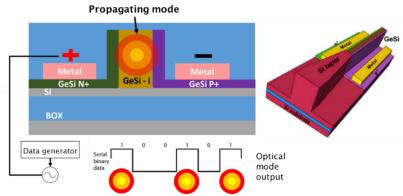

| Figure 2-25 | PIN FKE modulator cross-section and perspective view, reproduction from reference [30]. The encoded electric signal (bit-1/bit-0) is translated in optic by changing the material absorption with the PIN diode integrated in the waveguide and controlled through the metal pads. The amplitude modulation is obtained directly from the bitstream signal 33                                                                                                                           |

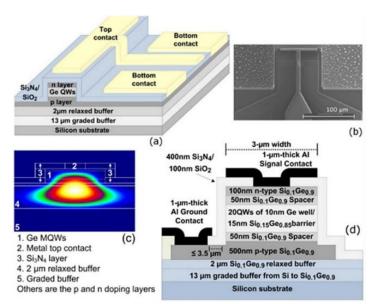

| Figure 2-26 | (Left) Cross-section and electric field distribution, reproduction from reference [127]. The PIN diode is formed with the vertical QW stack. 34                                                                                                                                                                                                                                                                                                                                         |

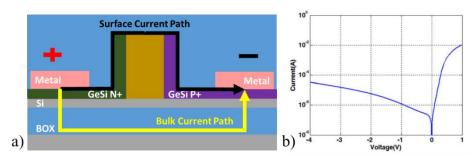

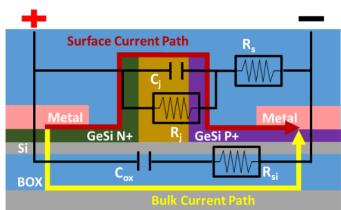

| Figure 3-1  | (a) Cross-section of the device in reference [30] showing the dark current, mainly due to crystal defects and surface roughness, generates from bulk (vellow) and surface (black) current paths. (b) The IV curve.                                                                                                                                                                                                                                                                      |

|            | reproduction from reference [30], is measured from the diode by slowly sweeping the bias                                                                                                                                                                                                                                                  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

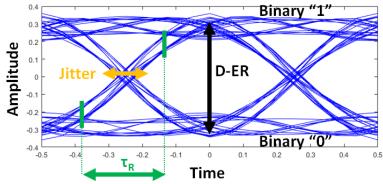

| Figure 3-2 | Transmission Eye generated with Matlab®. The Eye diagram results from the overlapping of the received signals sampled with same clock as the transmitter, Jitter, ER and Rise Time are defined graphically 39                                                                                                                             |

| Figure 3-3 | Example of small signal equivalent circuit from reference [30], the device is approximated with lumped linear elements to characterise the electric behaviour in frequency, the red and the yellow arrows represent the surface current and the bulk current path, respectively                                                           |

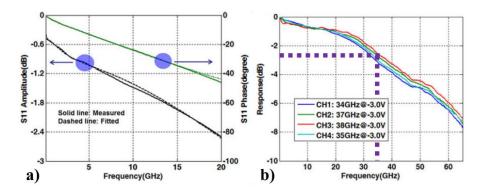

| Figure 3-4 | (a) S11 measurement reproduced from reference [30]. By fitting the S11 curves using the equivalent small signal cirtuit, the power consumption of the modulator can be estimated. (b) S21 measurement from reference [30], the frequency at which the response is reduced by 3dB defines the highest operating speed in Ghz of the device |

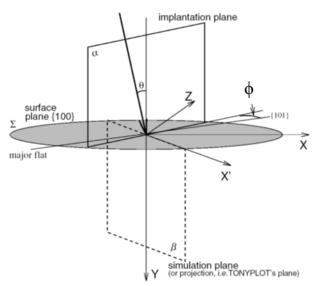

| Figure 4-1 | Implantation geometry, reproduction from reference [163]                                                                                                                                                                                                                                                                                  |

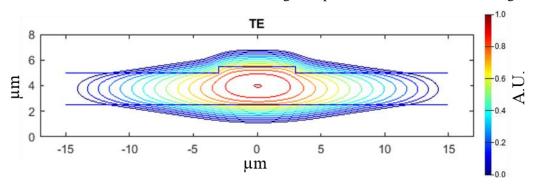

| Figure 4-2 | TE mode solution calculated with wgmodes [185] in a polymeric waveguide                                                                                                                                                                                                                                                                   |

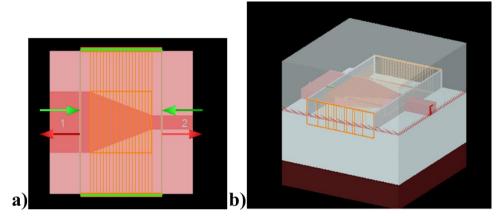

| Figure 4-3 | Taper simulated in MODE Solutions with EME solver, (a) top-view, (b) perspective view                                                                                                                                                                                                                                                     |

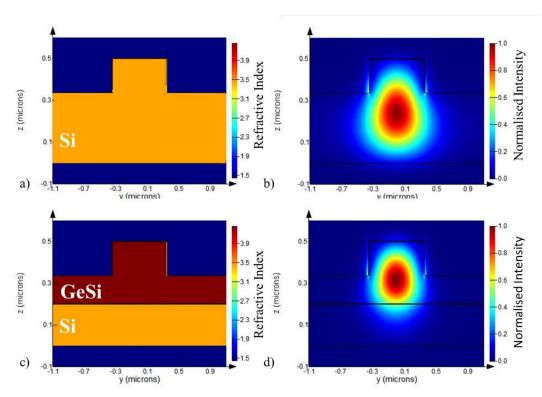

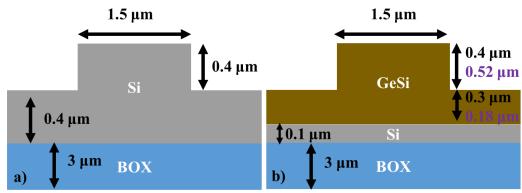

| Figure 4-4 | Structure definition and TE mode distribution for a Si waveguide (a, b) and a multi-layered waveguide (c, d)                                                                                                                                                                                                                              |

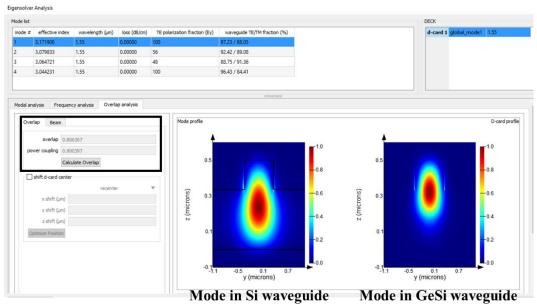

| Figure 4-5 | Mode overlap calculated in Lumerical Mode Solutions, the mode distribution is found in waveguide sections made in Ge and Si, then by calculating the mode overlap, the coupling loss between the two sections, is estimated                                                                                                               |

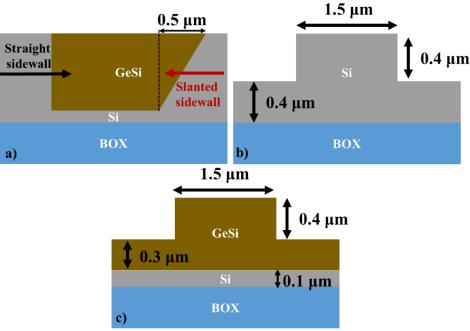

| Figure 4-6 | Cross-section (a) and top-view (b) of the butt-coupled Si-to-GeSi waveguide.                                                                                                                                                                                                                                                              |

| Figure 4-7 | Grating coupler lateral view, reproduction from reference [194]54                                                                                                                                                                                                                                                                         |

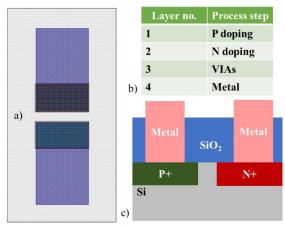

| Figure 4-8 | PIN diode top-view mask (a) defined with 4 layers (b), the device cross-section is depicted in (c).                                                                                                                                                                                                                                       |

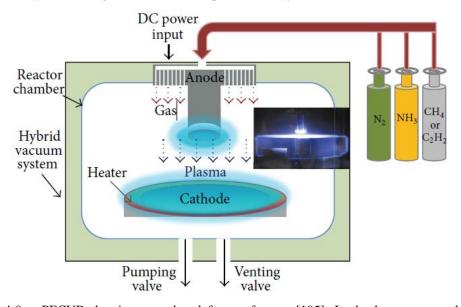

| Figure 4-9  | PECVD drawing reproduced from reference [195]. In the low-pressure                |

|-------------|-----------------------------------------------------------------------------------|

|             | chamber gasses are ionised with an RF current. The plasma reacts with             |

|             | the substrates and material is deposited                                          |

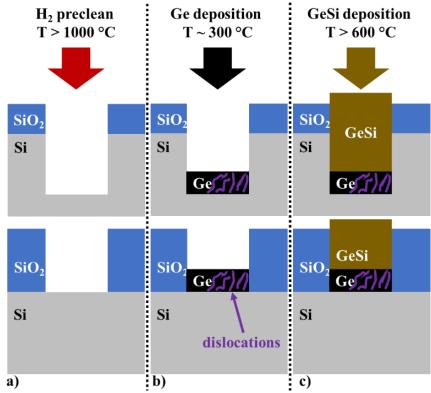

| Figure 4-10 | Selective RPCVD in trenches etched in Si overlay (up) or realised by              |

|             | depositing thick patterned oxide (down), the growth procedure is the              |

|             | same. Wafers are cleaned in H2 to remove contaminant and native oxide             |

|             | on the exposed Si areas (a), then Ge is deposited at low temperature (~300        |

|             | °C) in the trenches only, by tuning the deposition recipe (b). 3D islands         |

|             | are avoided, and a relaxed layer is obtained with dislocations (purple lines      |

|             | in the black Ge box). Finally, temperature is raised >600 °C and GeSi is          |

|             | deposited with lower TDD (c)59                                                    |

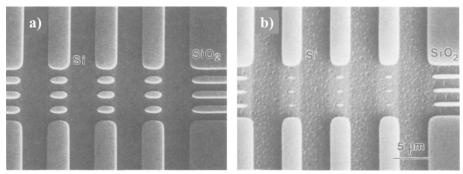

| Figure 4-11 | Precleaning process executed on Si wafer containing SiO <sub>2</sub> feature. (a) |

|             | Before thermal cleaning surface is smooth and sidewalls sharp, (b) after          |

|             | 60 s precleaning at 1000 °C and 1.5E-4 Torr, surface damage and                   |

|             | sidewall consumption are visible, reproduction from reference [200]. 60           |

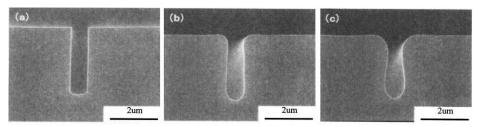

| Figure 4-12 | SEM of trench before (a) and after H <sub>2</sub> annealing with 40 Torr pressure |

|             | for 3 min at 1000 °C (b) and 1100 °C (c), reproduction from reference             |

|             | [201]                                                                             |

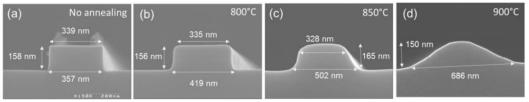

| Figure 4-13 | (a) Rib waveguide before H <sub>2</sub> annealing, (b)-(d) waveguide after        |

|             | annealing at 800 °C (b), 850 °C (c), 900 °C (d), at pressure of 20 Torn           |

|             | for 1 min. Reproduction from reference [202]                                      |

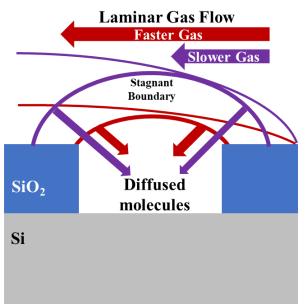

| Figure 4-14 | Classical boundary layer theory, the gas flows laminarly above the wafer          |

|             | (red and purple arrows), a stagnant boundary region is formed on top of           |

|             | the trench depending on gas velocity (purple and red semicircles). If gas         |

|             | flows slowly (purple) the boundary region (purple semicircle) is bigger           |

|             | therefore more molecules can diffuse through the boundary increasing              |

|             | the growth. If the gas velocity is high, the stagnant boundary is small (red      |

|             | semicircle) reducing the number of molecules available for deposition             |

|             | reducing the growth                                                               |

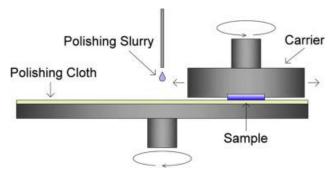

| Figure 4-15 | CMP schematics reproduced from reference [212], a planetary movement              |

|             | of the sample is obtained with the carrier and plate rotation. Polishing          |

|             | slurry is poured while the tool operates 63                                       |

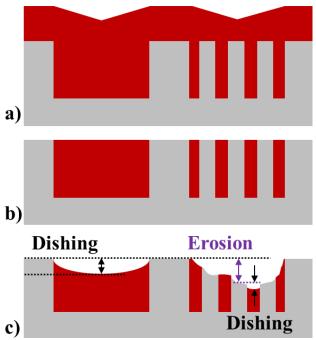

| Figure 4-16 | (a) wafer before CMP, (b) wafer after CMP in ideal conditions, (c)                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | dishing and erosion in real CMP process                                                                                                                                                                                                                                                                                                                                                                                                                                           |

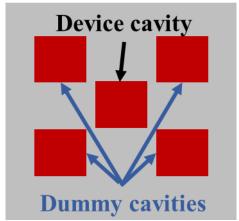

| Figure 4-17 | Top-view of the wafer with dummy cavities surrounding the device cavity                                                                                                                                                                                                                                                                                                                                                                                                           |

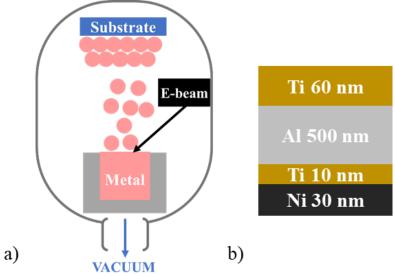

| Figure 4-18 | (a) Evaporator drawing, the metal is heated up until evaporation through an e-beam gun, metal particles then travel upward where the substrate is located. With pressure below 10 <sup>-5</sup> mBar and smooth substrate surface, are even thin metal film can be deposited. (b) Metal stack deposited in this project, Ni was deposited to form GeNi to reduce contact resistance, Ti was used to avoid metal diffusion and as capping layer, Al was used to reach the surface. |

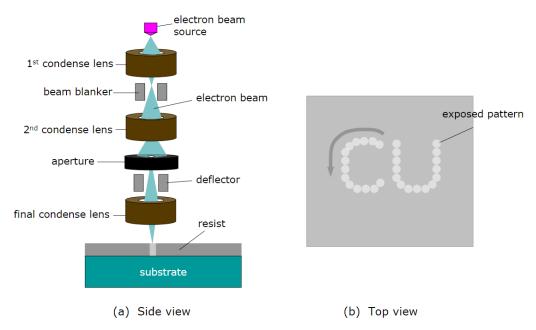

| Figure 4-19 | E-beam drawing reproduced from reference [220], in (a) the e-beam chamber is depicted showing the beam source, the lenses, the aperture and the deflectors; (b) the exposed patterns is dissolved after development bath in ZEDN50.                                                                                                                                                                                                                                               |

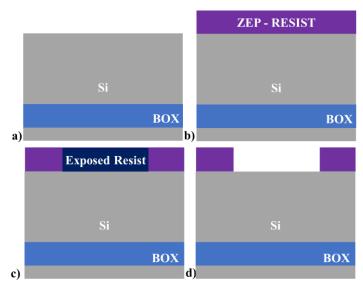

| Figure 4-20 | E-beam process, (a) dehydration, (b) ZEP spin and bake, (c) e-beam writing, (d) resist developing                                                                                                                                                                                                                                                                                                                                                                                 |

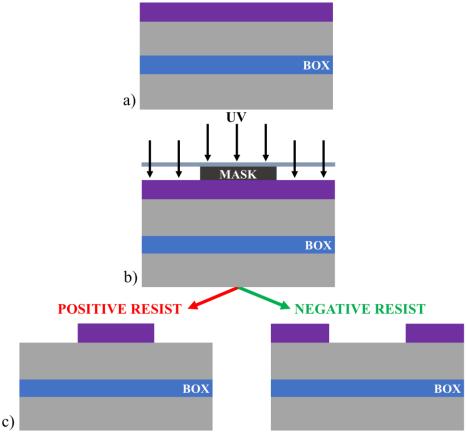

| Figure 4-21 | Photolithography, (a) the photoresist is spin coated and soft baked on the wafer; (b) after aligning the mask with the wafer, an UV lamp shines the whole wafer modifying the chemical composition of the exposed areas (c) whether positive (red) or negative (green) resist is adopted, the exposed or the protected areas are finally removed with the developer                                                                                                               |

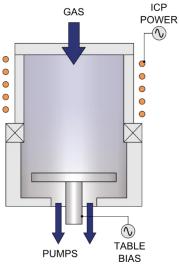

| Figure 4-22 | Drawing of ICP etch tool reproduced from reference [227]                                                                                                                                                                                                                                                                                                                                                                                                                          |

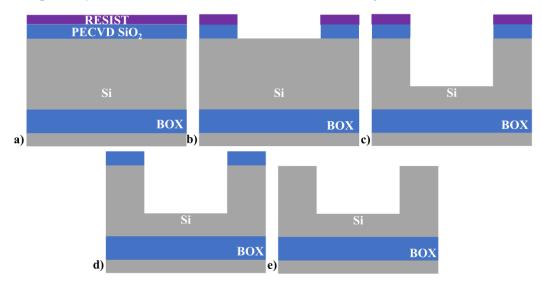

| Figure 4-23 | ICP subprocess etch: first (a) PECVD oxide is deposited with standard recipe, then resist is spun. Following, (b) lithography (e-beam or UV lithography) and oxide etch (ICP-SiO <sub>2</sub> or ICPS-SiO <sub>2</sub> ) are performed, thus silicon is etched with ICP-Si (c). The last steps are resist strip (d) and oxide etch (e)                                                                                                                                            |

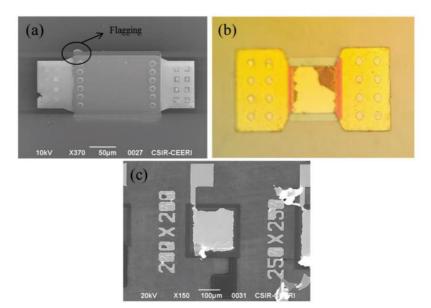

| Figure 4-24 | (a) flagging of material after lift-off, (b)-(c) retention of metal reproduction from reference [229]71                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 4-25 | SEM picture of a Pt ear protruding from the wafer surface, reproduction from reference [230]                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

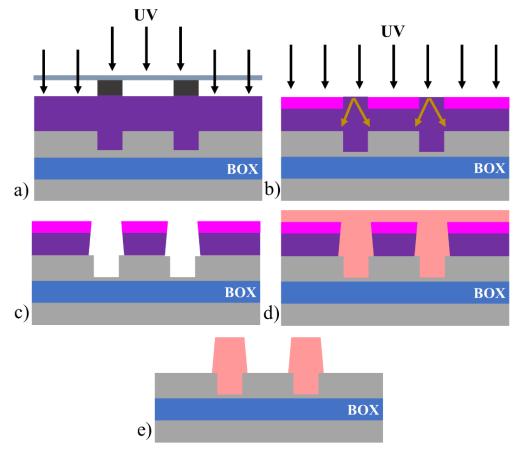

| Figure 4-26 | Lift-off process. (a) Photoresist (AZ5214 in purple) is deposited on the wafer, a double UV exposure is used to open the features, first a short time exposure to transfer the layout from the mask to the resist as shown in (b) in light purple; the arrow in gold refer to the lift-off profile etch. Then as second longer exposure to open the VIAs using AZ400 developer, as shown in (c). (d) Metal is evaporated filling the apertures (VIAs) and covering the resist. Finally, (e) the resist is dissolved, and the unwanted metal removed |

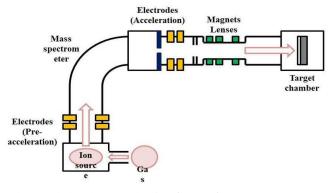

| Figure 4-27 | Ion implant tool sketch, reproduction from reference [232]. Ions, produced by heating up gases, are accelerated with a series of electrodes and magnets. Ions impinge on the sample penetrating it until the kinetic energy is lost due to collisions with the substrate, electrons and nuclei.                                                                                                                                                                                                                                                     |

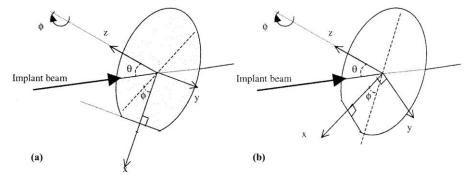

| Figure 4-28 | (a) the wafer is tilt to an angle $\theta$ defined by the wafer normal and the implant beam incident direction. (b) The rotation angle $\phi$ is defined between the plane containing the wafer normal and the plane perpendicular to the primary flat (x). Image reproduced from reference [233]                                                                                                                                                                                                                                                   |

| Figure 4-29 | Channelling effect, (a) if the incident implantation beam lies close to major crystal directions, ions are suffer a small-angle scattering and penetrate more in the crystal; (b) otherwise, large-scale scattering reduces the dopant penetration                                                                                                                                                                                                                                                                                                  |

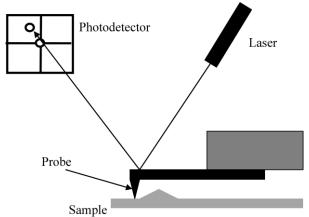

| Figure 4-30 | AFM working principle, reproduction from reference [239]. A nanometric probe is held on a cantilever which scans the wafer. Forces between the probe and the surface cause the probe to bend. The translation is recorded by using an optic system that shines the cantilever and records the reflected beam with a photodetector. The ray deflection information is then translated in normal displacement                                                                                                                                         |

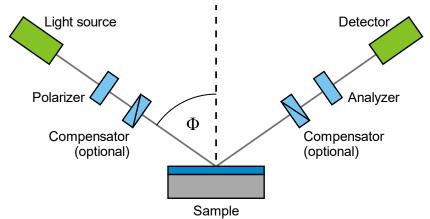

| Figure 4-31 | Ellipsometry working principle, reproduction from reference [240] 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

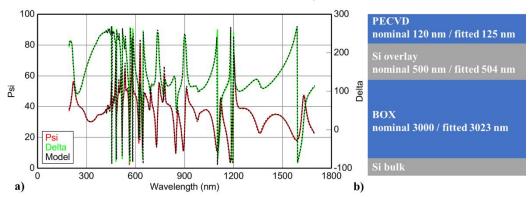

| Figure 4-32 | (a) Ellipsometry measurement fitting with CompleteEASE, Psi in green and Delta in red represent the amplitude change and phase change                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | In dashed lines, the fitting results using the provided SOI model. (b) layer stack with nominal and fitted thicknesses                                                                                                                                                       |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

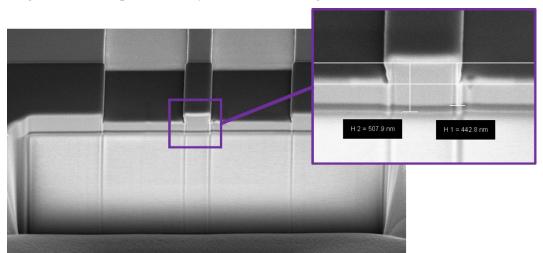

| Figure 4-33 | FIB-SEM image of a waveguide test etch on 500 nm SOI wafer. FIB is used to cut a cross-section visible as a rectangular hole; in the inset, the closup of the rib with relevant dimensions, different speciemen are distinguishable with grey tones                          |

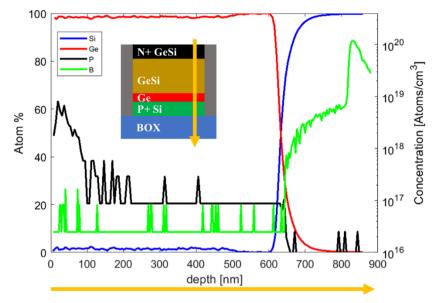

| Figure 4-34 | SIMS analysis of a testing sample, depicted in the inset, along the depth.                                                                                                                                                                                                   |

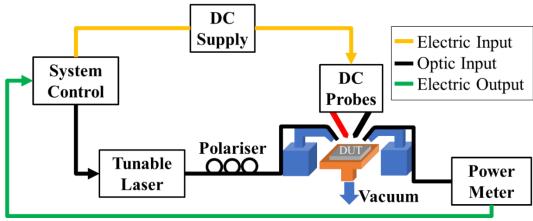

| Figure 4-35 | DC measurement setup                                                                                                                                                                                                                                                         |

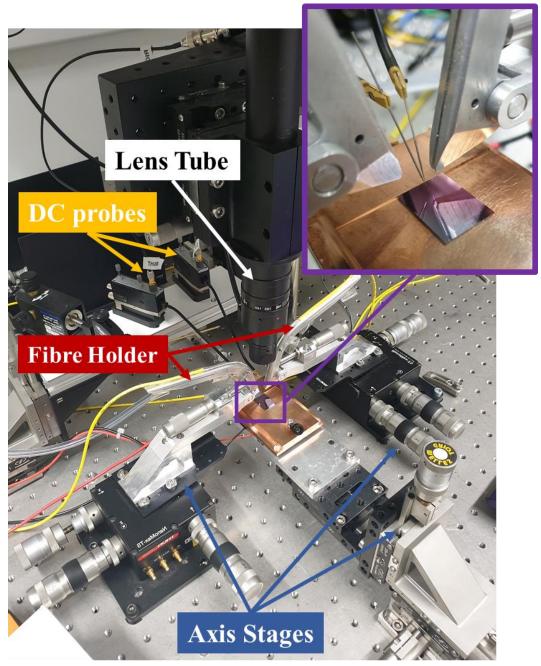

| Figure 4-36 | Experimental setup, in the inset a chip on the copper stage is characterised in DC with optic fibres coming out from the angled fibre holders and titanium needles attached to the Cascade Microtech DC probes. The high-speed stage setup differs only for the RF probes 80 |

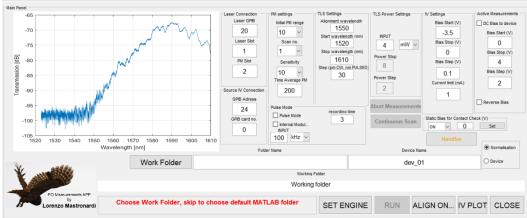

| Figure 4-37 | Graphical interface of the system control app written in Matlab® 81                                                                                                                                                                                                          |

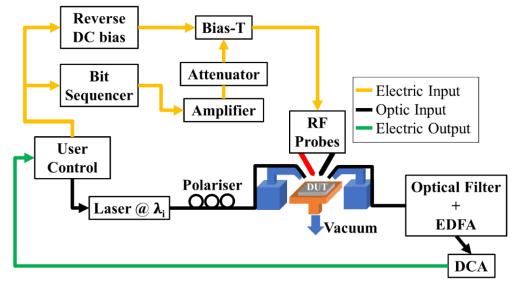

| Figure 4-38 | High-speed measurement setup. 82                                                                                                                                                                                                                                             |

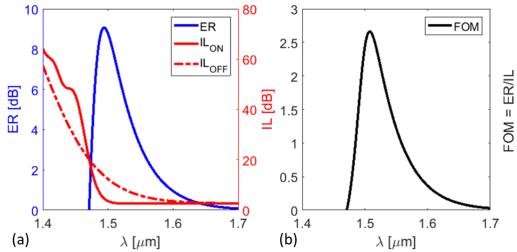

| Figure 5-1  | Example of (a) IL $_{ON}$ , IL $_{OFF}$ , ER and (b) FOM calculated using the model presented in 5.1 for a 50 $\mu$ m long GeSi alloy with 1.5% Si and electric field of 10 kV/cm and 100 kV/cm for the ON and OFF state, respectively                                       |

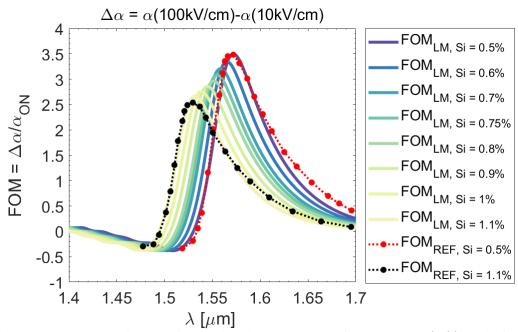

| Figure 5-2  | FOM vs Si content for wavelength range 1.4 μm to 1.7 μm compared with results from reference [102] (dashed lines) by importing the curves with Si=0.5% (red dot) and Si=1.1% (black dot)                                                                                     |

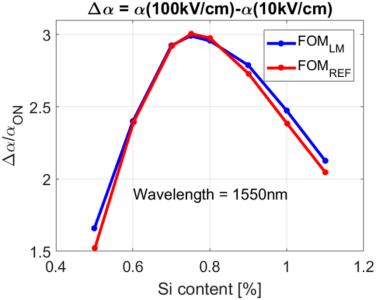

| Figure 5-3  | FOM peak vs Si content for a fixed wavelength, the script curve (blue) is compared with results from reference [102] shown in red90                                                                                                                                          |

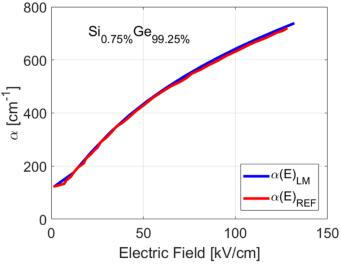

| Figure 5-4  | Absorption coefficient at 1.55 µm vs electric field, the script curve (blue) is compared with the same simulation from reference [102] (red curve)                                                                                                                           |

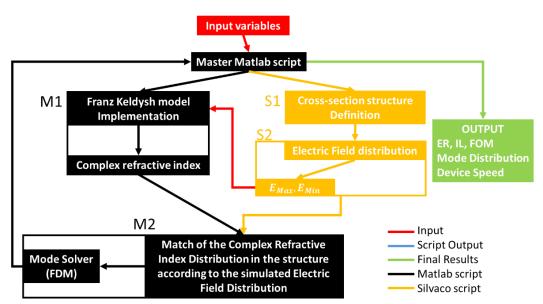

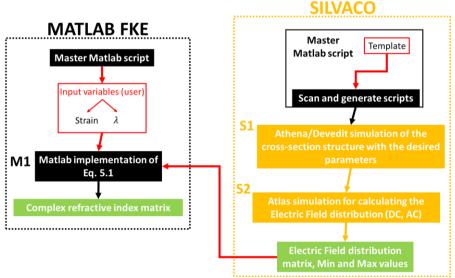

| Figure 5-5  | Simulation Platform Flow chart. Input are passed to the first Matlab® script to generate the design code and run electro-optic calculations (M1).  In vellow the Silvaco code, that builds the device mesh with blocks or                                                    |

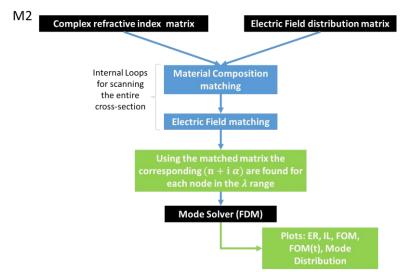

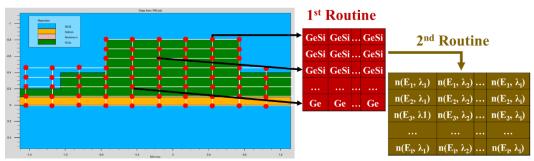

|             | simulating the fabrication process (S1) and evaluates the electric field distribution (S2). Output from M1 and S2 are used in M2 to solve the optical mode under DC bias and/or transient time electric signal 92                                                                                                                                 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5-6  | Flowchart detail of the structure development section. S1 builds the device cross-section and S2 calculates the electric field distribution with DC and transient electric signals. In black the flowchart detail of M1 the part of the code that implements the FKE                                                                              |

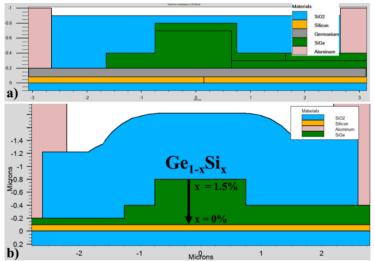

| Figure 5-7  | Device cross-section (a) built with Devedit <sup>™</sup> presents sharp layer boundaries, making the simulation routine faster. (b) The device cross-section is built using the process approach (Athena), the Ge and GeSi layer are defined together by varying the silicon concertation with depth (arrow).                                     |

| Figure 5-8  | M2, Mode solver script Flow chart. The complex refractive map from M1 and the electric field distribution from S1 are interpolated and fed to the mode solver that calculates the modes dependent from wavelength, material composition, device design and applied bias                                                                           |

| Figure 5-9  | M2 routines, for each node the corresponding refractive index is found. The mesh in white is not to scale and is shown as coarse to demonstrate the principle. The routine reads in each node composition (red table) and calculates the complex refractive index for each wavelength and bias (gold table), the result is fed to the mode solver |

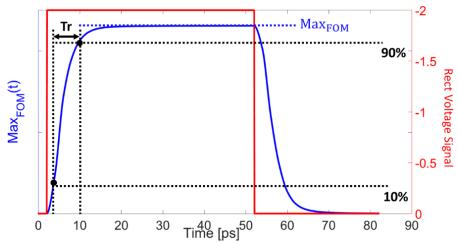

| Figure 5-10 | In red the transient electric signal applied at the device contacts, in blue the resulting time dependant optical efficiency (FOM against time) 95                                                                                                                                                                                                |

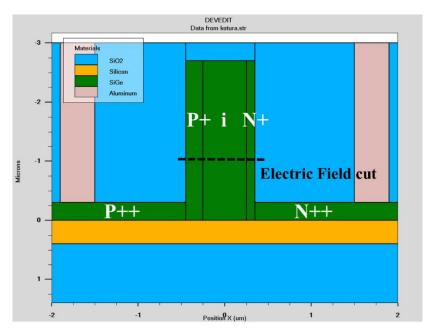

| Figure 5-11 | Device cross-section simulated in Devedit™ of the device found in reference [30]                                                                                                                                                                                                                                                                  |

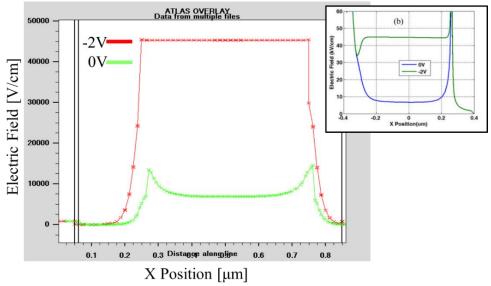

| Figure 5-12 | electric field cut along the dashed line of Figure 5-11 for 0 V (green curve) and -2 V (red curve) bias, in the inset result reproduced from reference [30]                                                                                                                                                                                       |

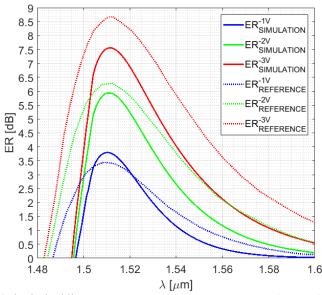

| Figure 5-13 | ER( $\lambda$ ), in dashed lines the experimental results imported from reference [30] with full lines the simulated device. In this case the silicon content is 0.85% but the strain is reduced to 0.05%, if 0.2% of strain is used the plots are redshifted of about 10 nm.                                                                     |

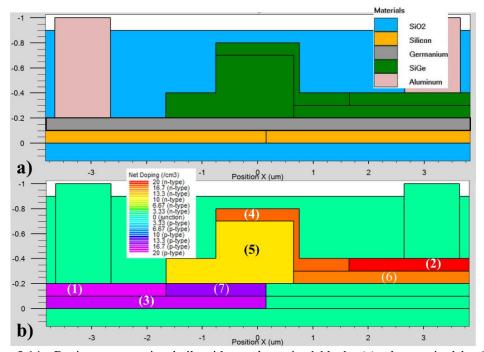

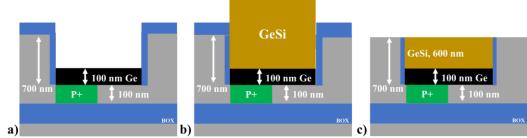

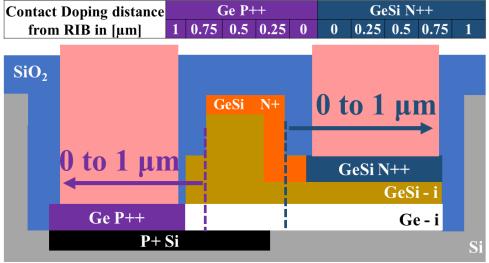

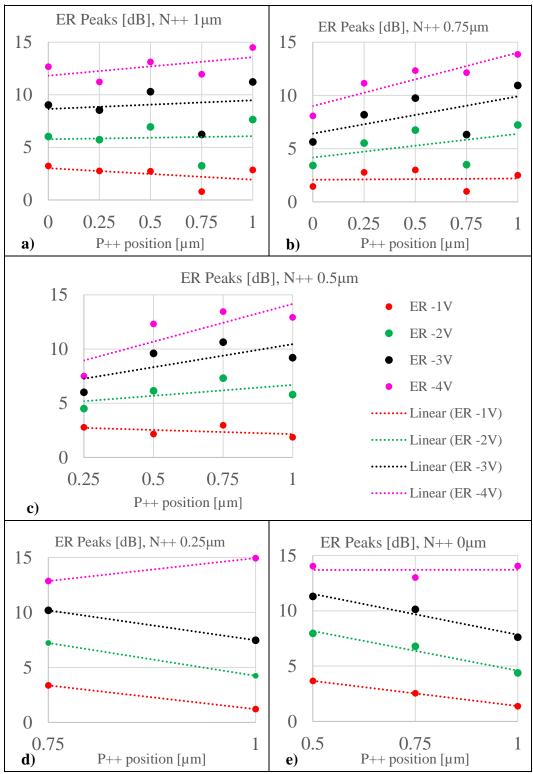

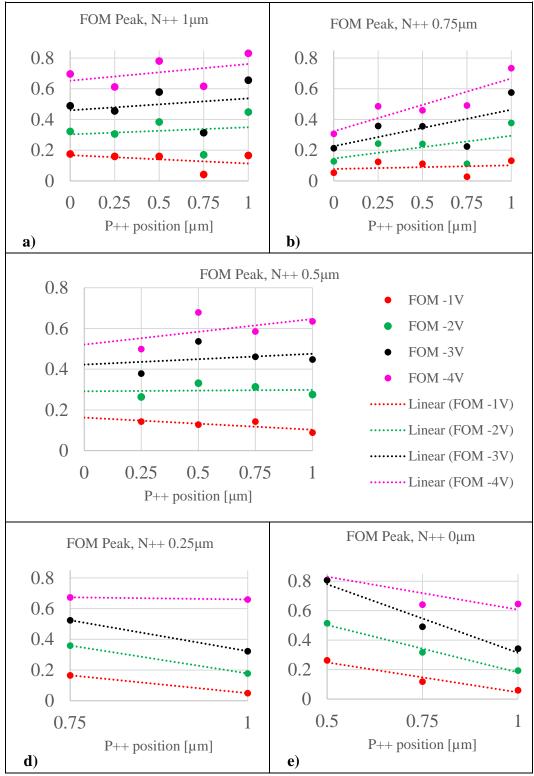

| Figure 5-14 | Device cross-section built with pre-determined blocks (a), characterised by fixed doping concentration (b). In the doping simulations, doping concentrations in (3) and (4) are varied. (dimensions not in scale) 98                                                                                                                                                                                                                                      |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

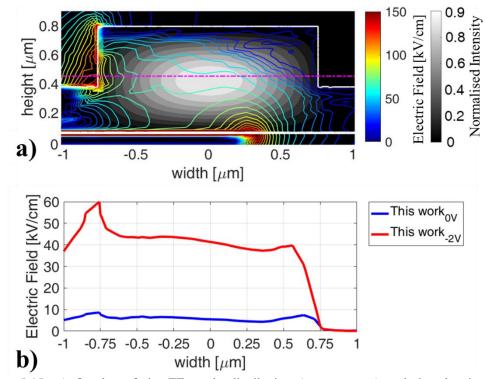

| Figure 5-15 | a) Overlay of the TE mode distribution (grey contour) and the electric field distribution (coloured contour) at -2 V. (b) The extrapolated electric field along the dashed line.                                                                                                                                                                                                                                                                          |

| Figure 5-16 | ER and FOM for simulated devices, a) ER plots show a double bell shape slightly dependants from the junction doping level; the first peak associated with the GeSi layer, centred at 1.54 μm, ranges between 4.3 dB to 4.7 dB. The second peak (1.5 – 2 dB) is centred at 1.58 μm. In b) the FOM is more affected by the Ge buffer layer, the second peak is comparable to the principal one, extending the operation window of this design to the L-band |

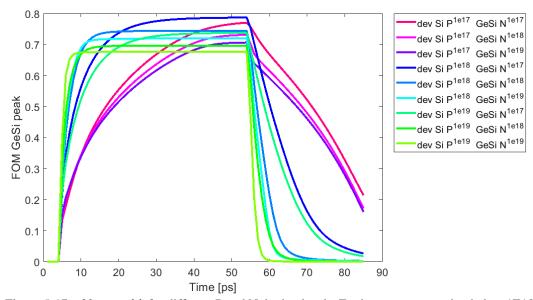

| Figure 5-17 | <i>MaxFOM(t)</i> for different P and N doping levels. For boron concentration below 1E18 cm <sup>-3</sup> (plots in pink shades), the asymptotic FOM value is not fully reached meaning that the device RC constant is too big for high-speed operation. Higher doping concentrations ensure faster speed at cost of reduced FOM peak (plots from blue to green). 101                                                                                     |

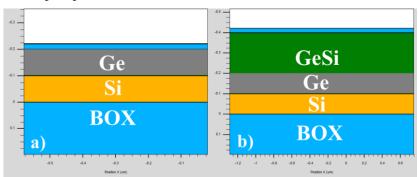

| Figure 5-18 | Bulk structure used in (a) Ge P++ and (b) GeSi N++ doping implant simulations. In green the target material thickness is 100 nm for Ge and 300 nm for Ge/GeSi, to reflect the targeted thickness in the device 102                                                                                                                                                                                                                                        |

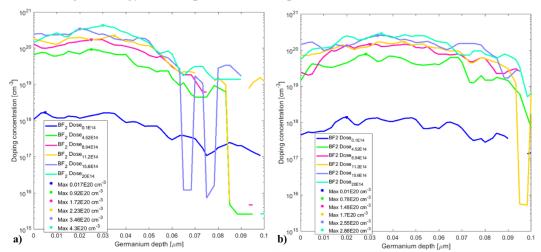

| Figure 5-19 | BF <sub>2</sub> doping simulation SIMS in Ge, kinetic energy is 45 keV (a) and 70 keV (b) while the dose is varied between 1e13 to 20 e14 ions/cm <sup>2</sup> , the doping peak is highlighted with dots                                                                                                                                                                                                                                                 |

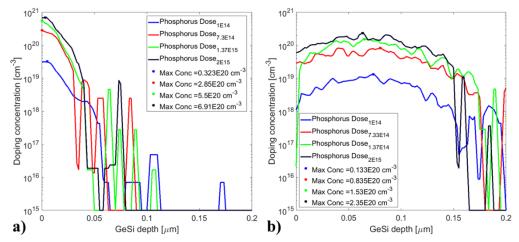

| Figure 5-20 | Phosphorus doping simulation SIMS in GeSi, (a) kinetic energy is 15 keV, (b) kinetic energy is 60 keV. In both simulations, the dose is varied between 1E14 to 2E15 ions/cm <sup>2</sup> ; the doping peak is highlighted with dot                                                                                                                                                                                                                        |

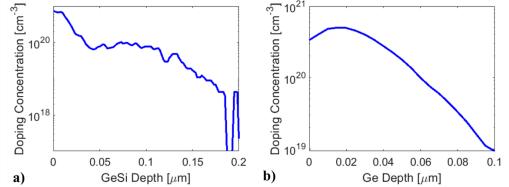

| Figure 5-21 | Simulation of the dual step implant recipe used in fabrication for N++ (a) and P++ (b)                                                                                                                                                                                                                                                                                                                                                                    |

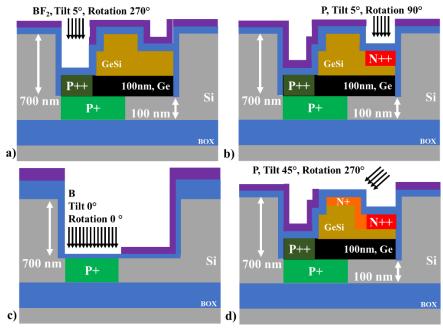

| Figure 5-22 | Doping implant simulation schematics, (a) BF <sub>2</sub> P++ doping in the Gelayer to form the contact doping and (b) P for the N++ doping in GeSi, in both cases 5° tilt and rotation of 270° and 90° respectively. (c) Si doped                                                                                                                                                                                                                        |

|             | P+ with tilt and rotation angles of 0° to ensure doping confinement in the cavity flat surface. (d) GeSi N+ angled implant with tilt angle of 45° and wafer rotation of 270° to form the wrap-around doping shape                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

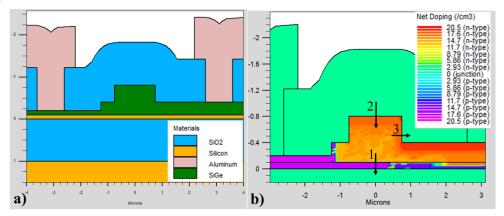

| Figure 5-23 | Device cross-section used for implant simulations, b) active dopant concentration, in red/orange is phosphorus, in blue/purple boron; intrinsic level is cyan. Arrows show the direction of SIMS analysed in the simulations.                                                                                                                                                                    |

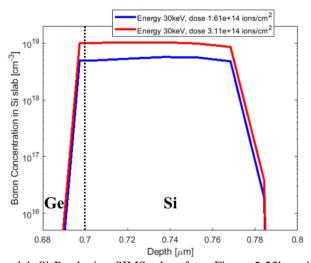

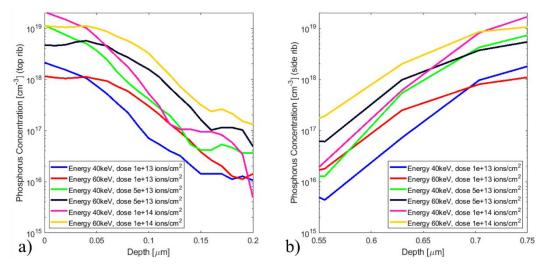

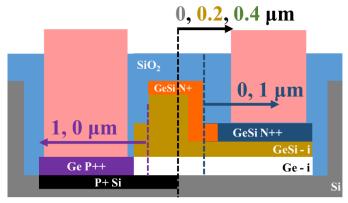

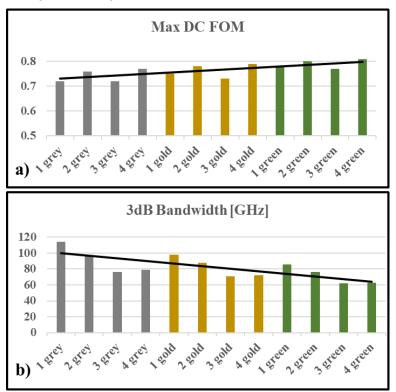

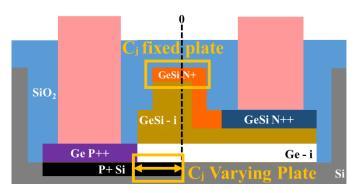

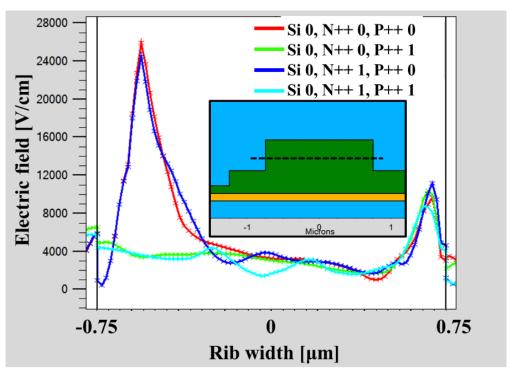

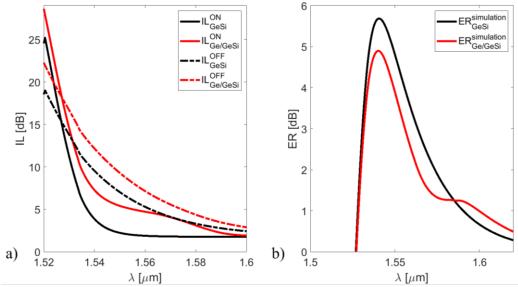

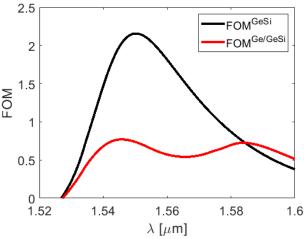

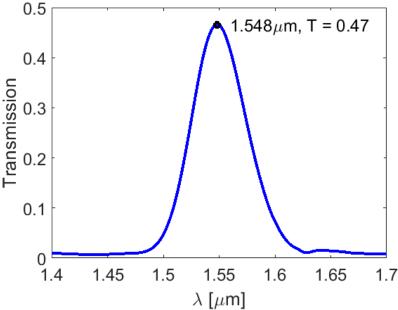

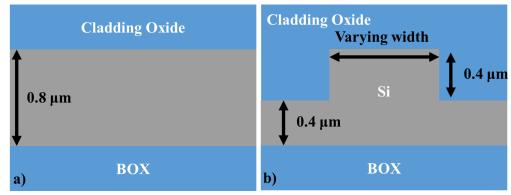

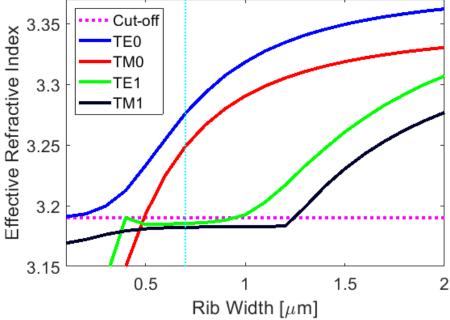

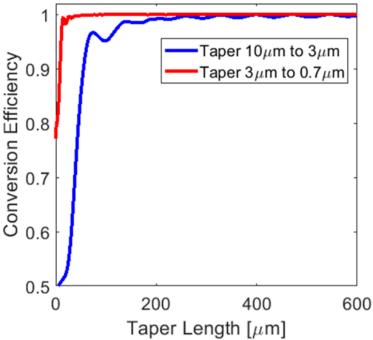

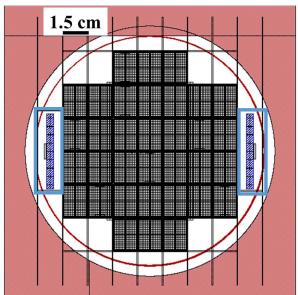

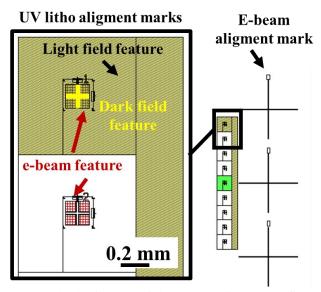

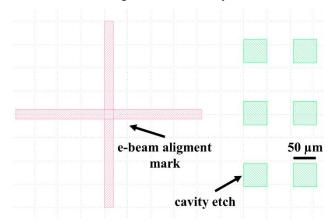

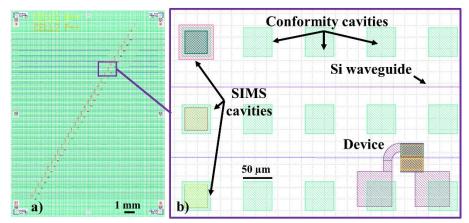

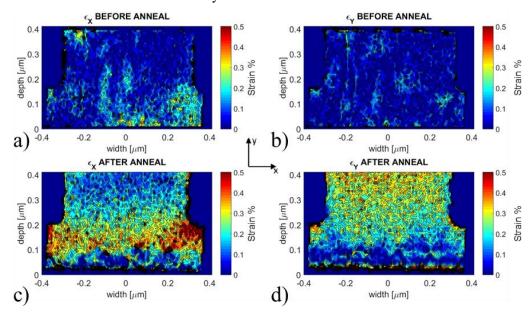

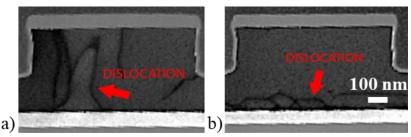

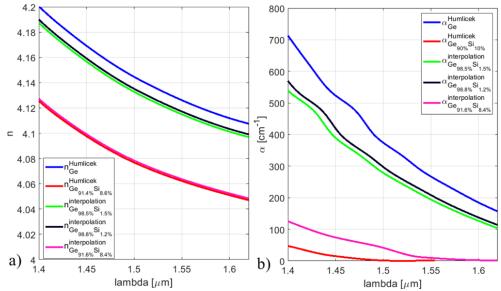

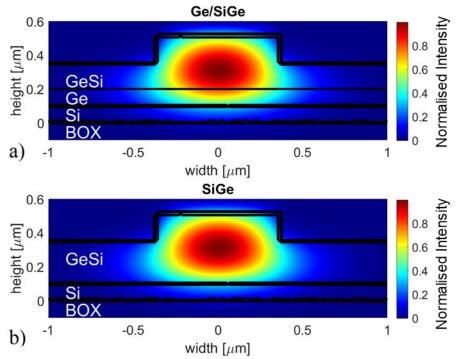

| Figure 5-24 | Bottom slab Si P+ doping SIMS taken from Figure 5-23b region number 1, in this case only the dose was varied between 1.61E14 ions/cm <sup>2</sup> and 3.11E14 ions/cm <sup>2</sup>                                                                                                                                                                                                               |