#### University of Southampton Thesis Licence

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Paolo L. Mennea (2018) "UV-written Waveguide Circuits for Integrated Quantum Optics", University of Southampton, Optoelectronics Research Centre, PhD Thesis, pagination.

Data: Paolo L. Mennea (2018) Title. URI [dataset]

## UNIVERSITY OF SOUTHAMPTON

## FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

Optoelectronics Research Centre

UV-written Waveguide Circuits for Integrated Quantum Optics

by

Paolo L. Mennea

Thesis for the degree of Doctor of Philosophy

March 2018

### UNIVERSITY OF SOUTHAMPTON

#### ABSTRACT

# FACULTY OF ENGINEERING AND PHYSICAL SCIENCES Optoelectronics Research Centre

## Doctor of Philosophy

# UV-WRITTEN WAVEGUIDE CIRCUITS FOR INTEGRATED QUANTUM OPTICS by Paolo L. Mennea

Direct UV-written silica-on-silicon provides an attractive platform for quantum optics, offering the key benefits of low propagation losses and excellent optical fibre compatibility. This work has aimed to develop the necessary techniques and components for completely integrated quantum optics experiments to be carried out using this platform, on a larger scale than previously possible. Arrays of matched on-chip photon sources based on birefringence-matched spontaneous four-wave mixing (FWM) are demonstrated, both at 800 nm and in the telecommunications C-band, along with progress towards further integration of these sources. Thermo-optic phase shifters, for use in room temperature quantum circuits, have been optimised via modelling, and a range of alternative modulator technologies have been explored. Further work has been concerned with the development of a modular system for quantum optics, comprising a set of duplicate reconfigurable modules and the necessary drive electronics and software, with the intent of simplifying the task of identifying and quantifying manufacturing imperfections in large integrated experiments. Efforts have also been made to improve the detection efficiency of on-chip transition edge sensor (TES) single photon detectors, including the use of longer absorbers and high reflectors for multiple absorption passes; this has resulted in the demonstration of a photon-number-resolving detector with a Bragg grating enhanced quantum efficiency of 87%. Approaches for further increasing the detection efficiency are considered and a device for on-chip Hong-Ou-Mandel and photon subtraction experiments using these detectors is reported.

## Declaration of Authorship

I, Paolo L. Mennea, declare that the thesis entitled *UV-written Waveguide Circuits for Integrated Quantum Optics* and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research. I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as: See appendix A

| Signed: | <br> | <br> | <br> |  |

|---------|------|------|------|--|

| 0       |      |      |      |  |

|         |      |      |      |  |

|         |      |      |      |  |

| Date:   | <br> | <br> | <br> |  |

## Acknowledgements

Thanks go to my supervisors James and Peter, without whom this thesis wouldn't exist. My many collaborators; Sae Woo Nam's group at NIST for their work on the detectors, particularly Thomas Gerrits, Adriana Lita and Brice Calkins. Ian Walmsleys group at the University Oxford, especially Ben Metcalf and William Clements for their experiments with the modular chips, and Justin Spring, Thomas Hiemstra, and Adrian Manssen for testing the waveguide sources. Thanks also to my colleagues, Matthew Posner for continuing with the source development, and Rex Bannerman for producing an invaluable mode measuring system. The oft overlooked technical staff also deserve a mention here, for their efforts in keeping the cleanroom facilities running smoothly, most of the time.

To M.D.M

## Contents

| D | eclar                  | ation of Authorship                            | v  |

|---|------------------------|------------------------------------------------|----|

| A | cknov                  | wledgements                                    | vi |

| 1 | Intr                   | roduction                                      | 1  |

|   | 1.1                    | Harnessing Quantum Phenomena                   | 1  |

|   |                        | 1.1.1 Quantum Cryptography                     | 1  |

|   |                        | 1.1.2 Quantum Computing                        | 2  |

|   | 1.2                    | Universal Quantum Computation                  | 2  |

|   |                        | 1.2.1 Scalability and Error Correction         | 2  |

|   |                        | 1.2.2 Surface Code                             | 3  |

|   | 1.3                    | Optical Quantum Computing                      | 4  |

|   |                        | 1.3.1 Encoding Approaches                      | 4  |

|   |                        | 1.3.2 Knill-Laflamme-Milburn (KLM) Scheme      | 4  |

|   |                        | 1.3.3 Boson Sampling                           | 5  |

|   |                        | 1.3.4 A Hybrid approach                        | 6  |

|   | 1.4                    | An Engineering Challenge                       | 6  |

|   |                        | 1.4.1 Components of a Photonic Quantum Machine | 6  |

|   |                        | 1.4.2 Integrated Quantum Optics                |    |

|   |                        | 1.4.3 Material platforms                       | 7  |

|   |                        | 1.4.4 Operating wavelengths                    |    |

|   | 1.5                    | Building Large Quantum States Project          |    |

|   | 1.6                    | Chapter Layout                                 | 11 |

|   | Refe                   | erences                                        | 11 |

| 2 | $\mathbf{U}\mathbf{V}$ | Writing and Integrated Planar Waveguides       | 17 |

|   | 2.1                    | Introduction                                   | 17 |

|   | 2.2                    | Planar Waveguides                              | 17 |

|   |                        | 2.2.1 Waveguide Geometries                     | 17 |

|   | 2.3                    | Modelling of Planar Waveguides                 | 18 |

|   |                        | 2.3.1 Mode Solving                             | 18 |

|   | 2.4                    | Silica-on-silicon                              |    |

|   |                        | 2.4.1 Flame Hydrolysis Deposition              | 19 |

|   |                        | 2.4.2 Layer Metrology                          |    |

|   |                        | 2.4.3 Sample Preparation                       | 22 |

|   | 2.5                    | Direct UV Writing                              |    |

|   |                        | 2.5.1 Photosensitivity Mechanisms              |    |

xii CONTENTS

|   |      | 2.5.2    | Fluence                                | 23 |

|---|------|----------|----------------------------------------|----|

|   | 2.6  | Integra  | ated Bragg Gratings                    |    |

|   |      | 2.6.1    | Planar Bragg Grating Theory            | 24 |

|   |      | 2.6.2    | Bragg Grating Inscription              | 25 |

|   | 2.7  | Spectra  | al Characterisation of Waveguides      | 27 |

|   |      | 2.7.1    | Loss Measurement                       | 27 |

|   |      | 2.7.2    | Layer Birefringence                    | 28 |

|   |      | 2.7.3    | Dispersion Measurement                 | 28 |

|   | 2.8  | Coupli   | ng and Pigtailing                      | 29 |

|   |      | 2.8.1    | Butt coupling                          | 29 |

|   |      | 2.8.2    | Facet Polishing                        | 29 |

|   | 2.9  | Conclu   | sion                                   | 31 |

|   | Refe | rences . |                                        | 31 |

| 3 | Sing | gle Pho  | oton Sources 3                         | 33 |

|   | 3.1  | Introdu  | action                                 | 33 |

|   |      | 3.1.1    | Single-photon Source Metrics           | 33 |

|   |      | 3.1.2    | Coherent light                         | 34 |

|   |      | 3.1.3    | Single-emitter Sources                 | 35 |

|   |      | 3.1.4    | Parametric Photon Sources              | 35 |

|   |      | 3.1.5    | Source Scaling                         | 36 |

|   |      | 3.1.6    | Identical Sources                      | 37 |

|   | 3.2  | Birefrii | ngence Matched FWM Sources             | 37 |

|   |      | 3.2.1    | Four-wave Mixing in Silica             | 38 |

|   | 3.3  | FWM      | ·                                      | 40 |

|   |      | 3.3.1    | Nonclassical Interference Measurements | 41 |

|   |      | 3.3.2    | Birefringence tuning                   | 12 |

|   |      | 3.3.3    | Telecom-band FWM Source                | 13 |

|   | 3.4  | Multi-o  | chip FWM sources                       | 14 |

|   | 3.5  | Quasi-l  | Phase Matching                         | 16 |

|   | 3.6  | Poling   | of Silica                              | 16 |

|   | 3.7  | Poled 1  | UV Writing of Silica                   | 46 |

|   | 3.8  | Toward   | ds Quasi Phase Matched Sources         | 47 |

|   | 3.9  | Conclu   | sion                                   | 48 |

|   | Refe | rences . |                                        | 18 |

| 4 | Pha  |          |                                        | 51 |

|   | 4.1  | Introdu  | action                                 | 51 |

|   |      | 4.1.1    |                                        | 51 |

|   | 4.2  | Amplit   | sude Modulators                        | 52 |

|   |      | 4.2.1    | Cross couplers                         | 52 |

|   | 4.3  |          | •                                      | 53 |

|   |      | 4.3.1    | Thermo-optic Effects in Silica         | 53 |

|   |      | 4.3.2    | Device Modelling                       | 54 |

|   |      | 4.3.3    | Fabrication                            | 56 |

|   |      | 4.3.4    | Device Testing                         | 57 |

|   | 44   | Low-To   | emperature Phase Shifters              | 57 |

CONTENTS xiii

|   | 4.5  | Electr  | o-optic Phase Shifters                             |

|---|------|---------|----------------------------------------------------|

|   |      | 4.5.1   | Device Geometries                                  |

|   |      | 4.5.2   | Choice of materials                                |

|   | 4.6  | Piezoe  | electric Phase Shifters                            |

|   |      | 4.6.1   | Ridge Strain-optic Enhancement                     |

|   | 4.7  | Concl   | usion                                              |

|   | Refe |         |                                                    |

| 5 | Mo   | dular ( | Quantum Circuits 63                                |

|   | 5.1  | Introd  | luction                                            |

|   |      | 5.1.1   | Motivation                                         |

|   |      | 5.1.2   | Viability of a Modular Approach                    |

|   | 5.2  | Syster  | m Design                                           |

|   | 5.3  | Fabric  | eation Approach                                    |

|   |      | 5.3.1   | UV Writing                                         |

|   |      | 5.3.2   | Heater Element Fabrication                         |

|   |      | 5.3.3   | Under-bump Metallisation Layer                     |

|   |      | 5.3.4   | Facet Polishing                                    |

|   |      | 5.3.5   | Module Assembly                                    |

|   | 5.4  | Contr   | ol Electronics                                     |

|   |      | 5.4.1   | Requirements                                       |

|   |      | 5.4.2   | Implementation                                     |

|   | 5.5  | Syster  | n operation                                        |

|   |      | 5.5.1   | Switching Speed Limitations                        |

|   |      | 5.5.2   | Optical alignment and Assembly Procedure           |

|   |      | 5.5.3   | Module testing                                     |

|   |      | 5.5.4   | Built-in self-test                                 |

|   |      | 5.5.5   | Three-module Demonstration                         |

|   | 5.6  | Migra   | tion to Telecommunications Wavelengths             |

|   | 5.7  | Concl   | usion                                              |

|   | Refe | erences |                                                    |

| 6 | Inte | egrated | l Single Photon Detectors 88                       |

|   | 6.1  | Introd  | luction                                            |

|   | 6.2  | Single  | Photon Detectors                                   |

|   |      | 6.2.1   | Telecom-band Single Photon Detection               |

|   |      | 6.2.2   | Superconducting Nanowire Single Photon Detectors 8 |

|   |      | 6.2.3   | Transition Edge Sensors                            |

|   |      | 6.2.4   | Benefits of single photon resolution               |

|   | 6.3  | Uncla   | d UV-written Waveguides                            |

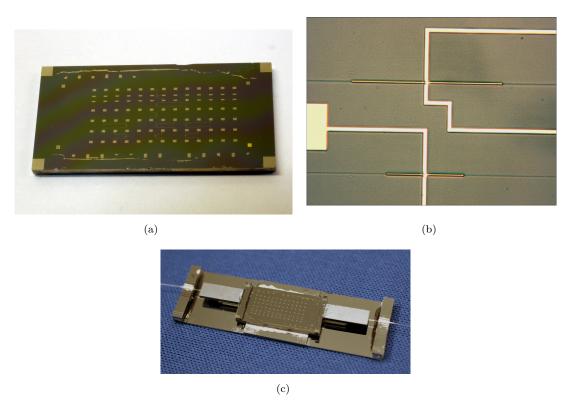

|   | 6.4  | Integr  | ated TES Detectors                                 |

|   |      | 6.4.1   | Alignment Approach                                 |

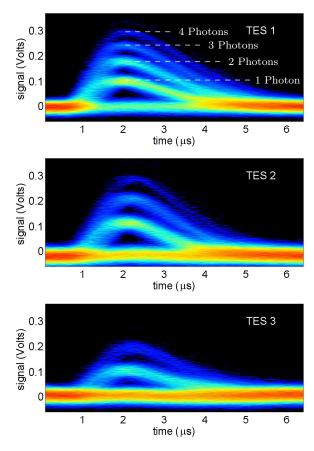

|   |      | 6.4.2   | High Aspect Ratio Devices                          |

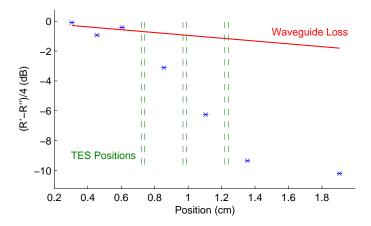

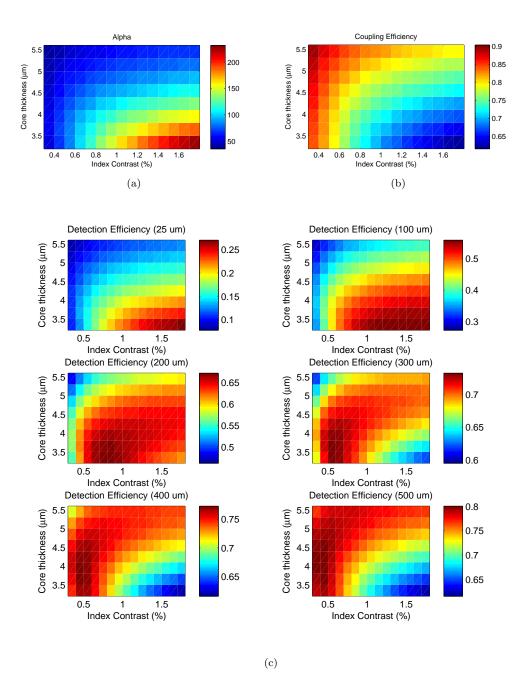

|   |      | 6.4.3   | Grating Based Absorption Measurements 94           |

|   |      | 6.4.4   | Quantum Efficiency Measurements                    |

|   | 6.5  | Device  | e Mounting and Coupling                            |

|   | 6.6  | FHD     | Parameter Optimisation                             |

xiv CONTENTS

|              | 6.7  | Overcladding layer                       | 8 |

|--------------|------|------------------------------------------|---|

|              | 6.8  | Hong-Ou-Mandel Interference Device       | 9 |

|              | 6.9  | Conclusion                               | 0 |

|              | Refe | rences                                   | 1 |

| 7            | Con  | clusions and Outlook 10                  | 3 |

|              | 7.1  | Sources                                  | 3 |

|              | 7.2  | Modulators                               | 4 |

|              | 7.3  | Circuits                                 | 4 |

|              | 7.4  | Detectors                                | 5 |

|              | 7.5  | Areas for further investigation          | 5 |

| $\mathbf{A}$ | ppen | dix A Publication List 10                | 7 |

| $\mathbf{A}$ | ppen | dix B Coupling Ratio Derivation 11       | 1 |

| $\mathbf{A}$ | ppen | dix C Wafer Parameters 11                | 5 |

| $\mathbf{A}$ | ppen | dix D Modular Unit Fabrication Guide 11  | 7 |

|              | D.1  | Sample Preparation                       | 8 |

|              | D.2  | UV Writing                               | 8 |

|              | D.3  | Lift-off Processes                       | 8 |

|              | D.4  | Facet Polishing                          | 0 |

|              | D.5  | Mounting and Electrical Connection       | 1 |

| $\mathbf{A}$ | ppen | dix E Modular System Operating Manual 12 | 3 |

|              | E.1  | System Components                        | 4 |

|              | E.2  | Operating Guidelines                     | 5 |

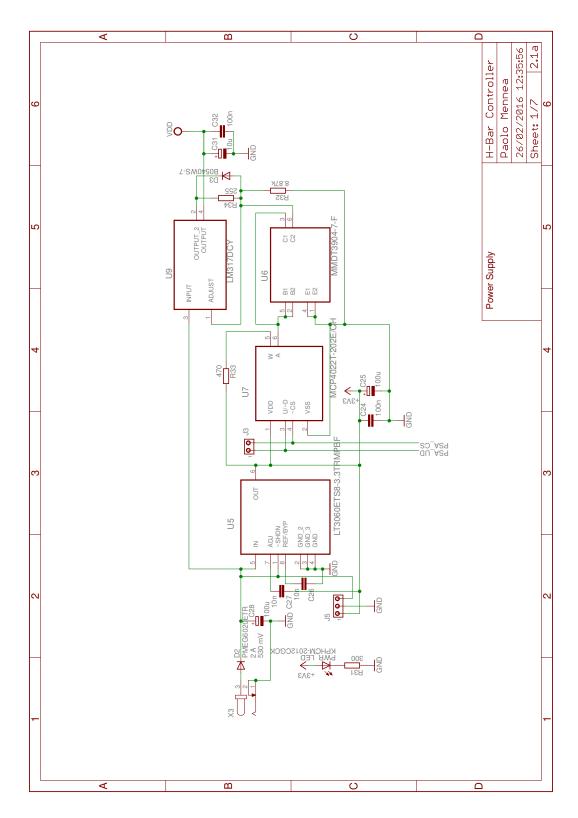

|              |      | E.2.1 Power Supply Adjust                | 5 |

|              | E.3  | Mapping Configuration                    | 6 |

|              | E.4  | Firmware Updating                        | 7 |

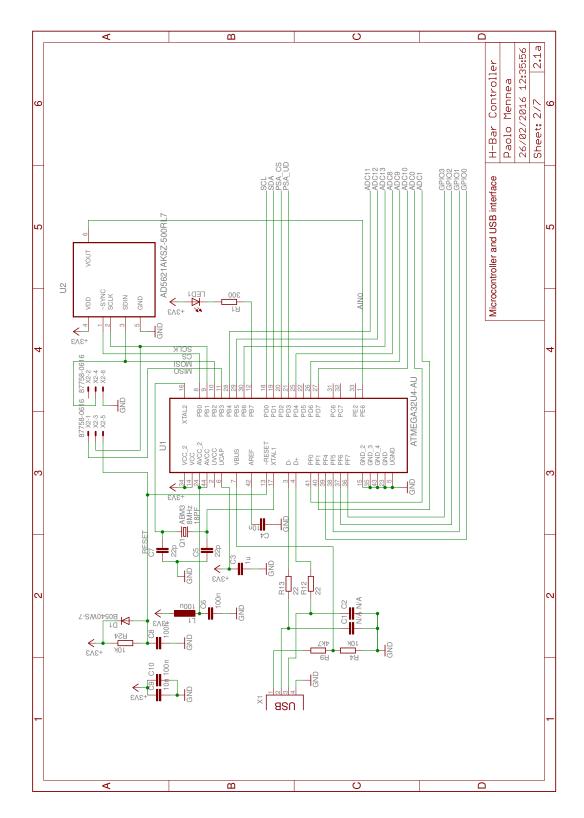

|              |      | E.4.1 Microcontroller                    | 7 |

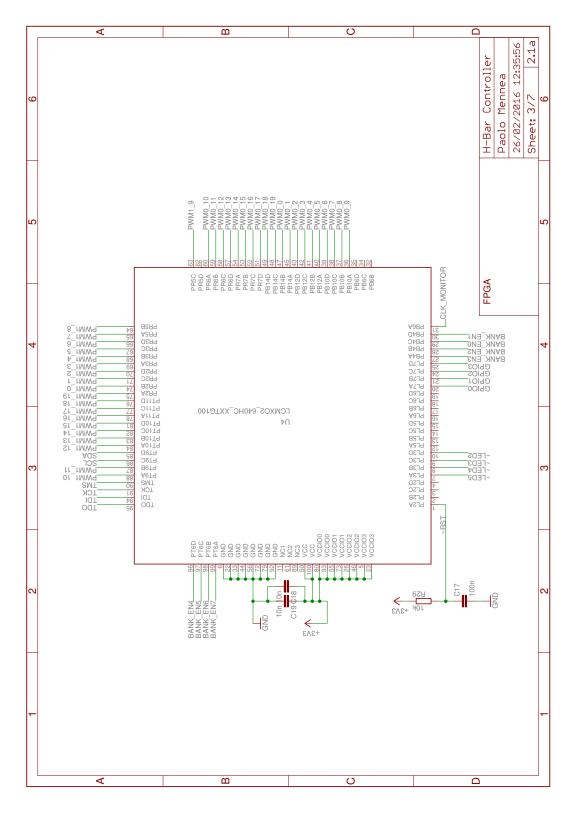

|              |      | E.4.2 FPGA                               | 7 |

|              | E.5  | Bank-bypass Jumpers                      | 9 |

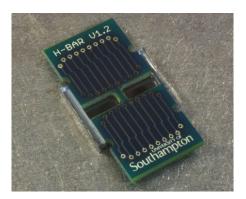

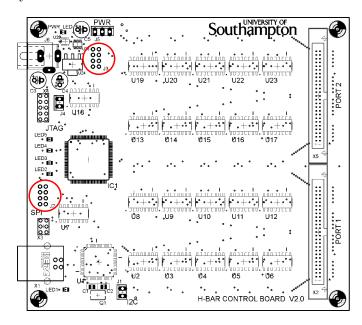

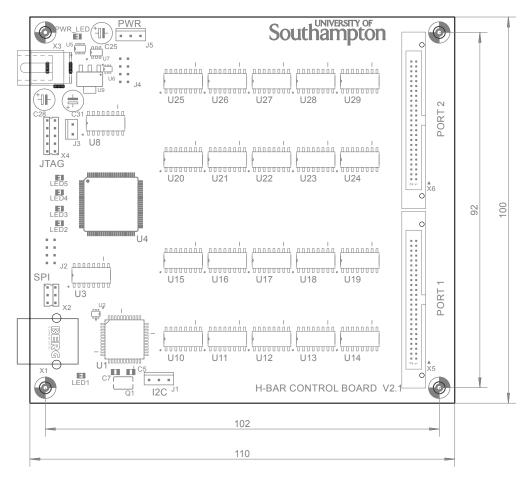

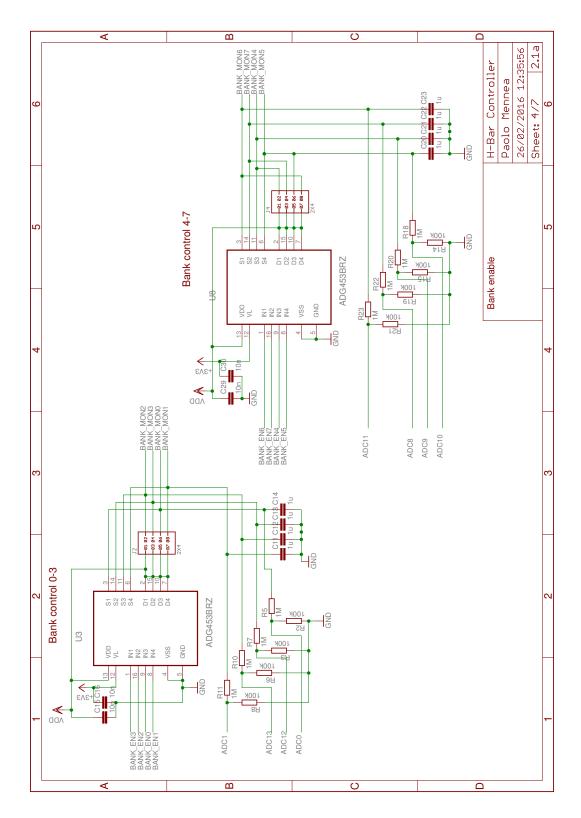

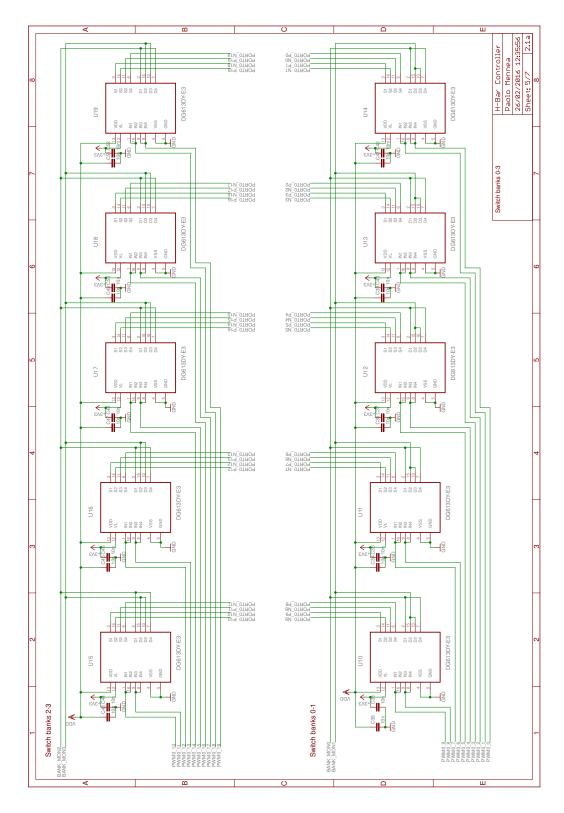

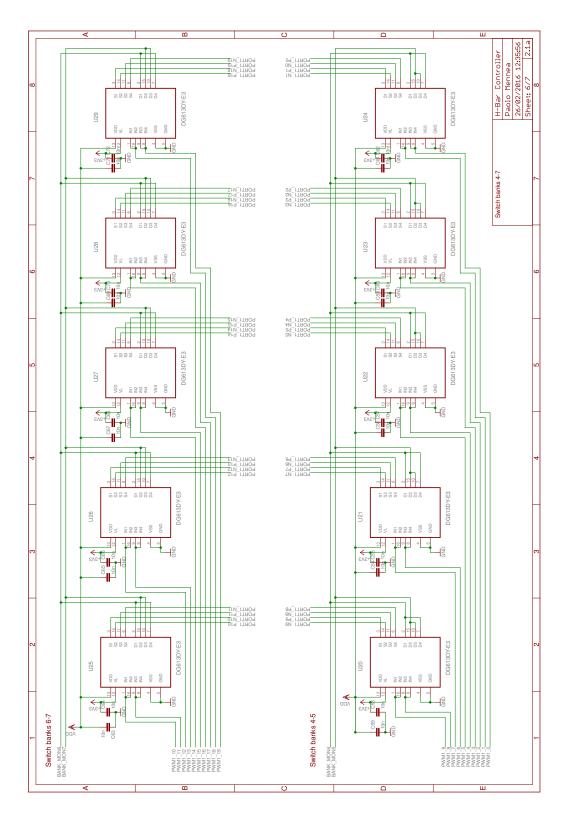

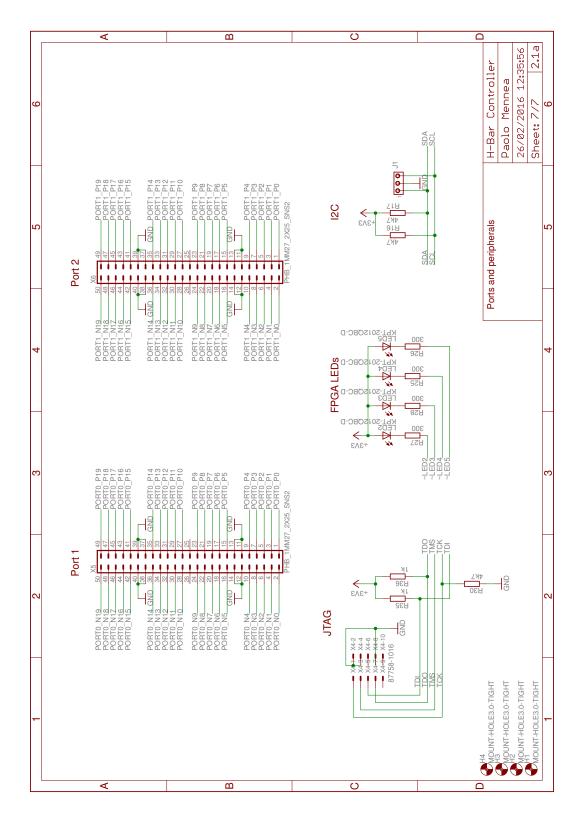

|              | E.6  | H-Bar PCB                                | 0 |

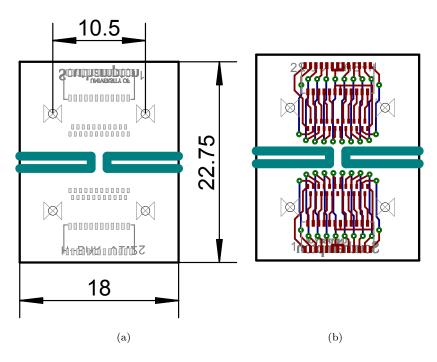

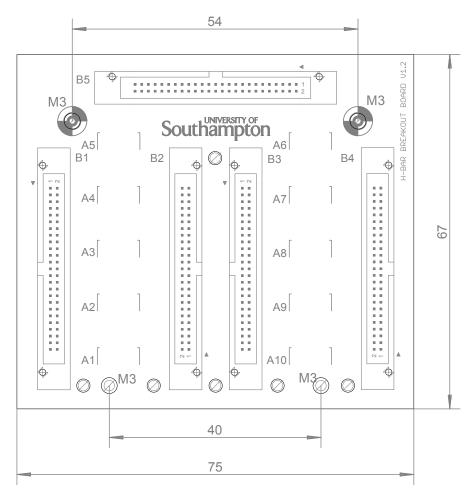

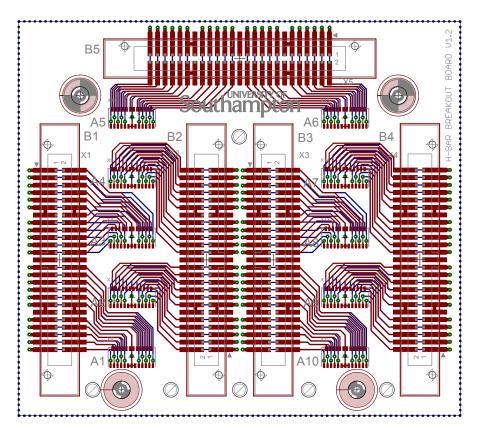

|              | E.7  | Breakout PCB                             | 1 |

|              | E 8  | Controller PCB 13                        | 3 |

# List of Figures

| 1.1  | BLoQS Project outreach chip                                                                    | 11 |

|------|------------------------------------------------------------------------------------------------|----|

| 2.1  | Illustration of planar waveguide structures                                                    | 18 |

| 2.2  | Illustration of planar waveguide modes                                                         | 19 |

| 2.3  | Diagram and image of the FHD system                                                            | 19 |

| 2.4  | Example Metricon prism coupling scan                                                           | 21 |

| 2.5  | Diagram of the two beam UV writing arrangement                                                 | 24 |

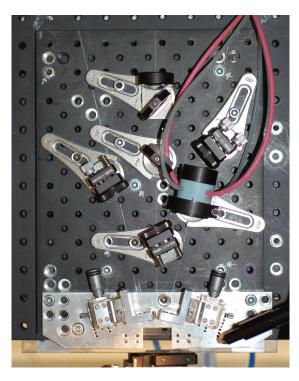

| 2.6  | Image of the UV writing interferometer                                                         | 26 |

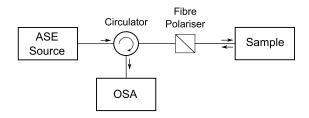

| 2.7  | Reflection characterisation setup                                                              | 27 |

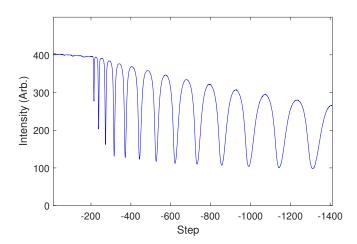

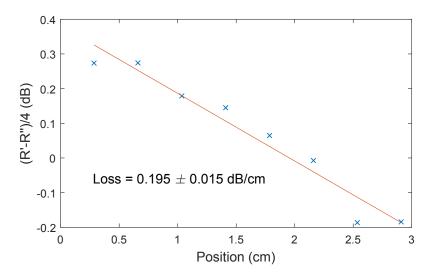

| 2.8  | Example loss-measurement plot                                                                  | 28 |

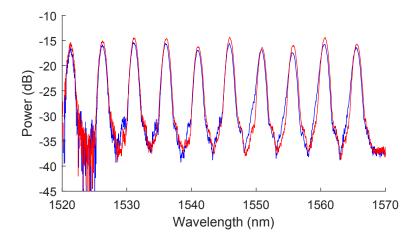

| 2.9  | Example reflection spectra for two polarisations                                               | 29 |

| 2.10 | Sequence of steps used to attach strengthening bars above the chip end                         |    |

|      | facets                                                                                         | 30 |

| 2.11 | OptiPrep polishing system                                                                      | 31 |

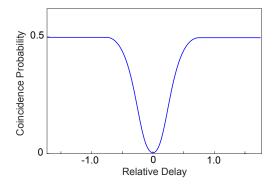

| 3.1  | HOM interference dip as a test of photon source quality                                        | 34 |

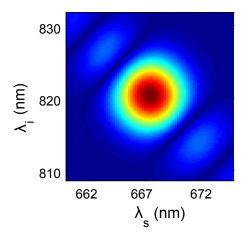

| 3.2  | Joint spectra of a four-wave mixing (FWM) source in silica                                     | 36 |

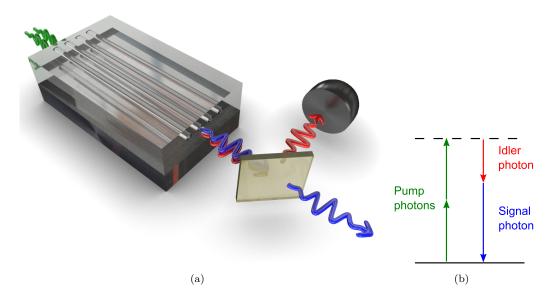

| 3.3  | Four-wave mixing in silica                                                                     | 38 |

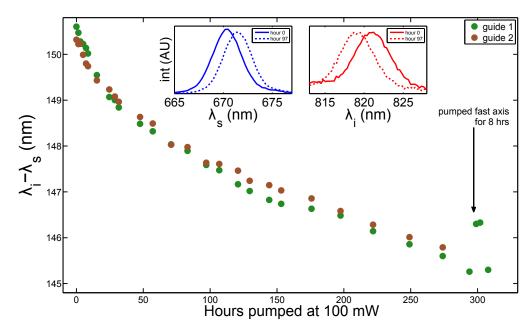

| 3.4  | Signal and idler drift with time                                                               | 40 |

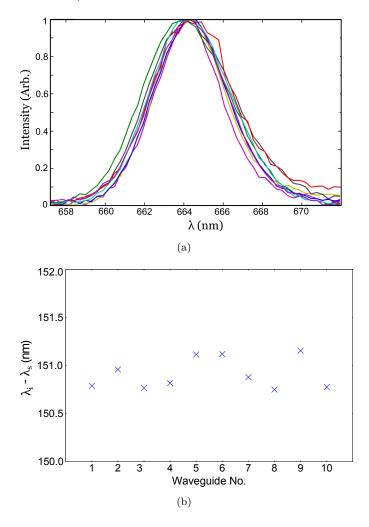

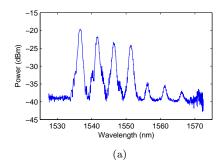

| 3.5  | Idler spectra and signal-idler separation for an array of 10 FWM sources.                      | 41 |

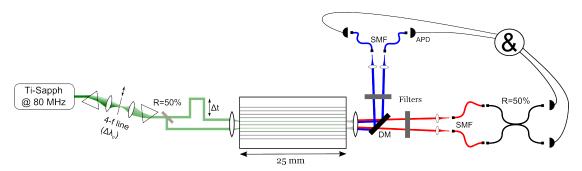

| 3.6  | Experimental setup for nonclassical interference measurements                                  | 42 |

| 3.7  | Nonclassical interference measurements with pairs of sources from the array.                   | 43 |

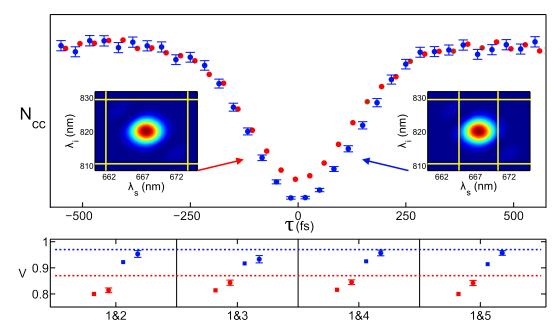

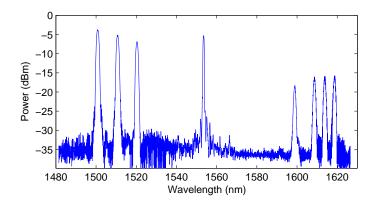

| 3.8  | Telecom-band FWM idler spectrum                                                                | 44 |

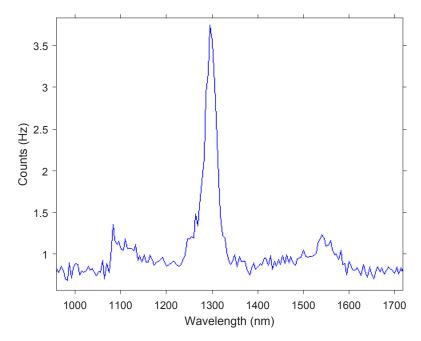

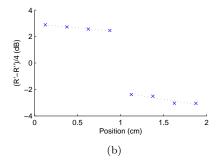

| 3.9  | Schematic of a multi-chip integrated source array                                              | 44 |

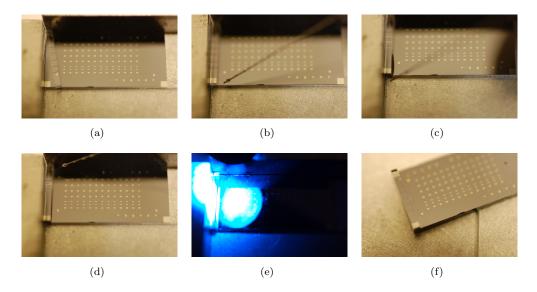

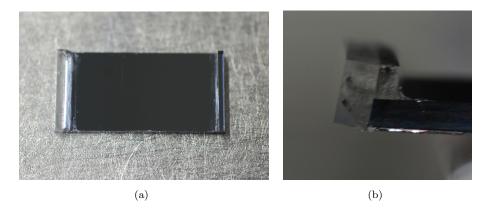

| 3.10 | Glue damage-threshold test chip                                                                | 45 |

| 3.11 | Diagram of the poled UV writing approach                                                       | 47 |

| 3.12 | Image of the insulating chuck produced for poled UV-writing                                    | 47 |

| 4.1  | Diagram of a Mach-Zehnder amplitude modulator based on a thermal                               |    |

|      | phase shifter                                                                                  |    |

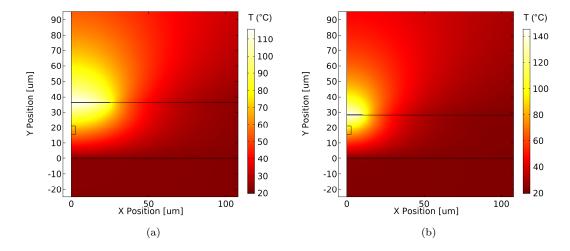

| 4.2  | Modelled temperature profiles for heater elements                                              | 55 |

| 4.3  | Modelled average core temperatures as a function of overcladding thickness for heater elements | 55 |

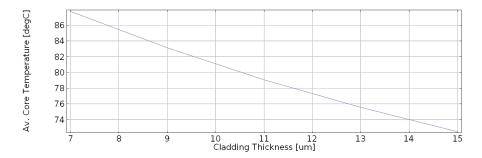

| 4.4  | Diagram of the stages in a lift-off process.                                                   |    |

| 4.5  | Piezoelectric stress based MZI modulator chip                                                  |    |

|      | •                                                                                              |    |

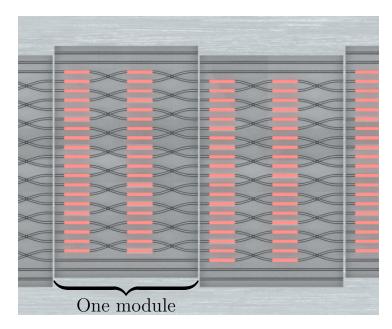

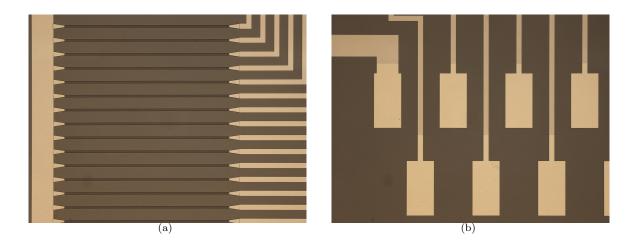

| 5.1  | Layout of the modular devices                                                                  | 66 |

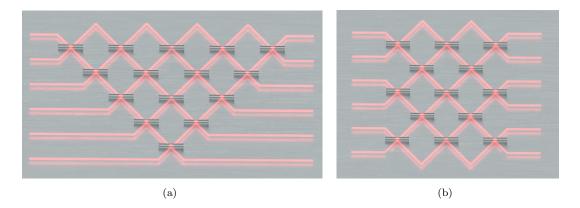

| 5.2  | Diagram of circuit decomposition schemes                                                       |    |

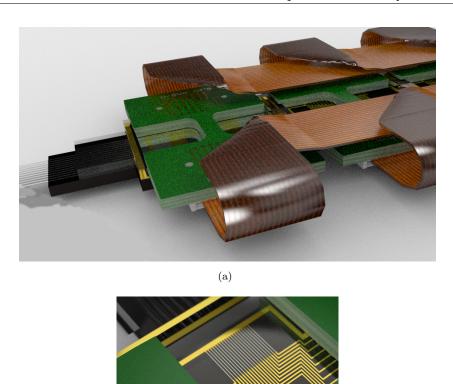

| 5.3  | Concept render of the modular reconfigurable system                                            | 68 |

$ext{xvi}$   $ext{LIST OF FIGURES}$

| 5.4  | Schematic of a 12 mm Mach Zehnder module                                  | . 69  |

|------|---------------------------------------------------------------------------|-------|

| 5.5  | Microscope images of fabricated heater elements                           | . 70  |

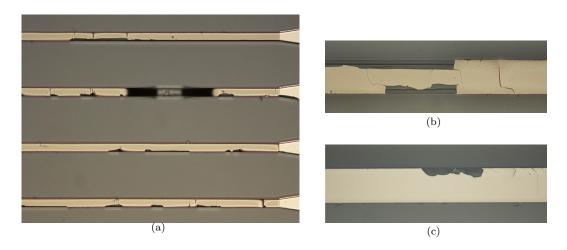

| 5.6  | Images of cracking in the FHD layers following edges of NiCr patterned    |       |

|      | regions                                                                   |       |

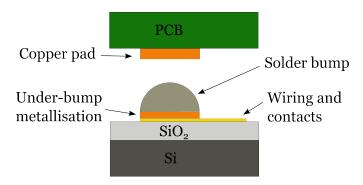

| 5.7  | Diagram of the solder bump bonding approach                               |       |

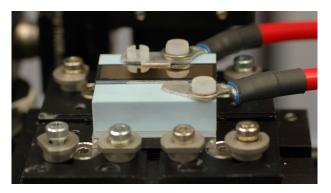

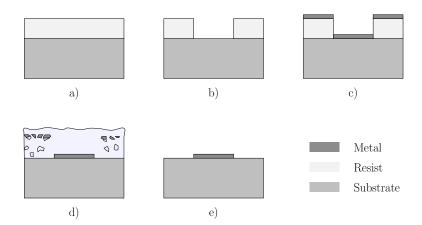

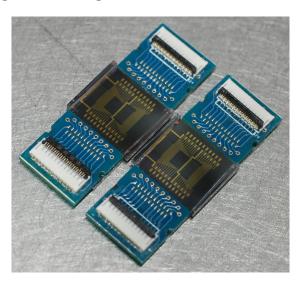

| 5.8  | Pair of completed MZI modules                                             |       |

| 5.9  | Solder-bump assembled module prototype                                    |       |

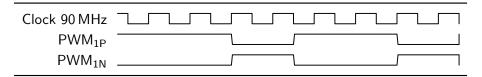

|      | Example PWM control patterns                                              |       |

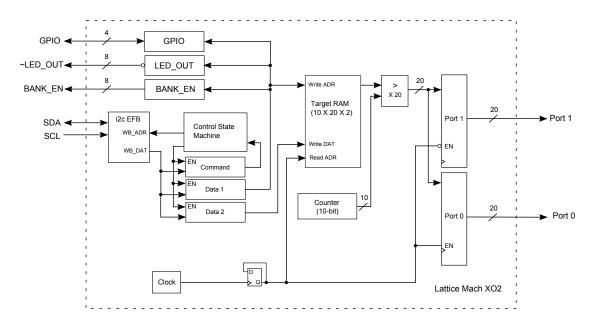

|      | FPGA firmware block diagram                                               |       |

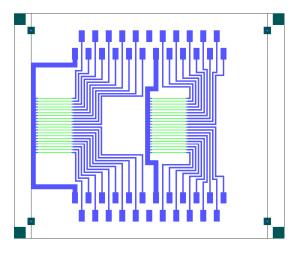

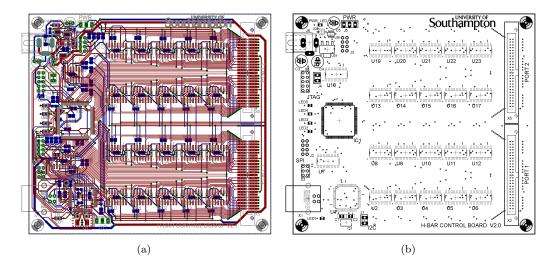

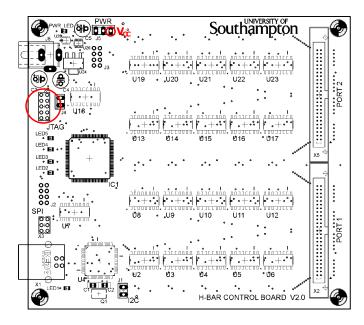

|      | PCB layout of the control board                                           |       |

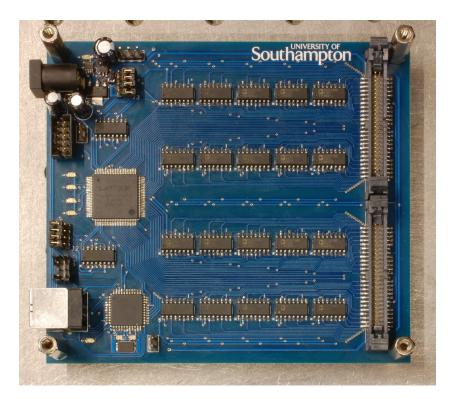

|      | Assembled control board PCB v2.0                                          |       |

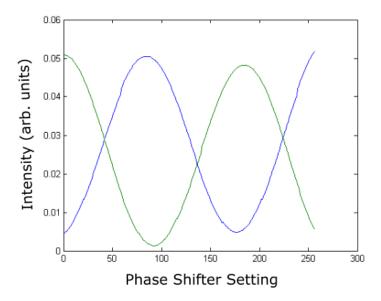

|      | Optical output from a set of four MZIs on a module                        |       |

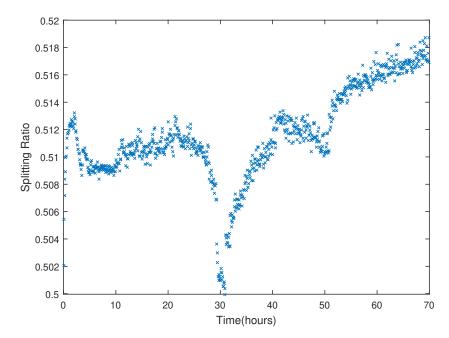

|      | Measurement of stability                                                  |       |

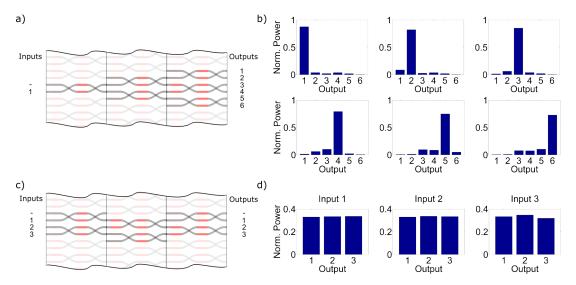

| 5.16 | Measured outputs of a three-module setup in two different configurations. | 81    |

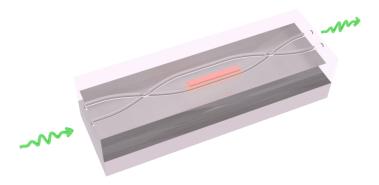

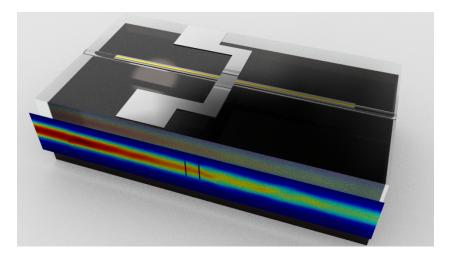

| 6.1  | Integrated TES detector concept                                           |       |

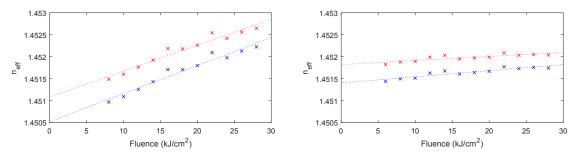

| 6.2  | Measured fluence dependence of $n_{\rm eff}$                              |       |

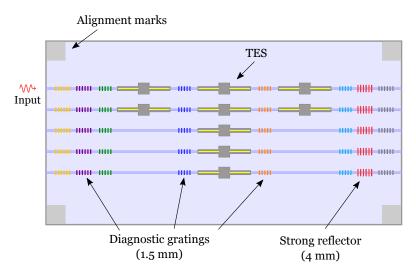

| 6.3  | Final layout of the high aspect ratio device test chip                    | . 92  |

| 6.4  | Normalised reflection spectrum of a waveguide from the high aspect ratio  |       |

|      | device test chip                                                          |       |

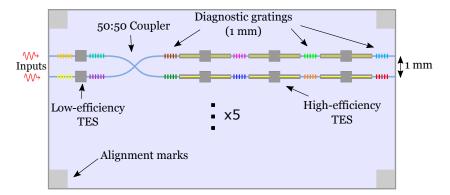

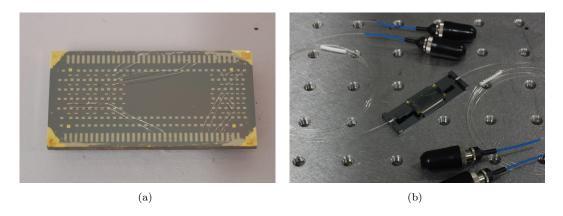

| 6.5  | Fabricated high aspect ratio TES test chip                                |       |

| 6.6  | Relative power profile showing the absorption in each TES region          |       |

| 6.7  | Measured output pulses from each of three series on-chip detectors        | . 95  |

| 6.8  | Modelled modal absorption and fibre coupling efficiency for a range of    | 0.5   |

| 6.0  | waveguide parameters                                                      | . 97  |

| 6.9  | Spectrum and absorption profile of an absorption measurement waveguide    | ne    |

| 6 10 | with a 4.2 µm core and tungsten over-layer                                |       |

|      | Photon subtraction test chip layout                                       |       |

| 0.11 | raphicated HOM clip with TES detectors                                    | . 100 |

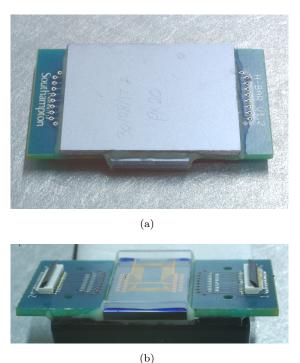

| D.1  | Assembled modular chip bottom and end views                               | . 121 |

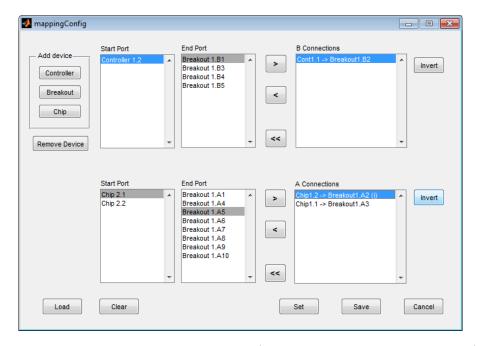

| E.1  | Mapping configuration GUI                                                 | . 127 |

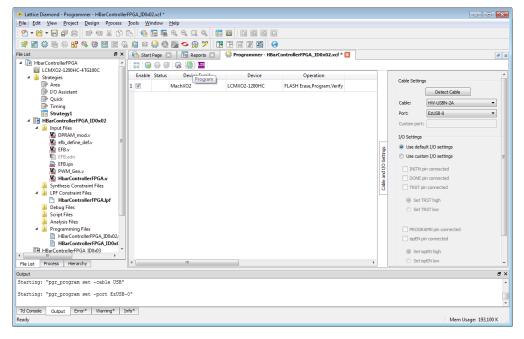

| E.3  | FPGA programming in Lattice Diamond                                       | . 128 |

| E.5  | PCB layout of the H-Bar board.                                            | . 130 |

| E.6  | Breakout PCB Dimensions                                                   | . 131 |

| E.7  | Breakout PCB Layout                                                       | . 132 |

| E.8  | Controller PCB v2.1 dimensions                                            | . 133 |

| E.9  | Controller schematic: Power Supply                                        | . 134 |

| E.10 | Controller schematic: Microcontroller                                     | . 135 |

| E.11 | Controller schematic: FPGA                                                | . 136 |

| E.12 | Controller schematic: Bank enable switches                                | . 137 |

| E.13 | 3 Controller schematic: Switch banks 0–3                                  | . 138 |

| E.14 | Controller schematic: Switch banks 4–7                                    | . 139 |

| E.15 | Controller schematic: Ports and peripherals                               | . 140 |

LIST OF FIGURES xvii

## Acronyms

ADC analogue-to-digital converter.

ADR adiabatic demagnetization refrigerator.

AOM acousto-optic modulator. APD avalanche photodiode.

ASE amplified spontaneous emission.

BPMbeam propagation method.

CAR coincidence to accidental ratio.

controlled-NOT. CNOT

DAC digital-to-analogue converter.

DGWdirect grating writing.

erbium doped fibre amplifier. EDFA

EO electro-optic.

EOM electro-optic modulator.

**FBG** fibre bragg grating.

FFC flat flexible cable.

FFTfast Fourier transform.

FHD flame hydrolysis deposition. FPGA

field-programmable gate array.

FWMfour-wave mixing.

HBTHanbury Brown and Twiss.

HOMHong-Ou-Mandel. ITO indium-tin oxide.

KLM Knill-Laflamme-Milburn.

MMImulti-mode interference.

MZIMach-Zehnder interferometer.

National Institute of Standards and Technol-NIST

ogy.

NQIT Networked Quantum Information Technolo-

gies.

NVnitrogen vacancy.

OBR optical backscatter reflectometer.

ODC oxygen deficiency centre. xx Acronyms

OSA optical spectrum analyser. OVD outside vapour deposition. PCF photonic crystal fibre. PLC planar lightwave circuit. PMpolarisation maintaining. PMT photo-multiplier tube. PNR photon number resolution. PSO position synchronised output. PWMpulse-width modulation.

QIP quantum information processing.

QKD quantum key distribution.

RIE reactive ion etching. RTA rapid thermal annealer.

SLED superluminous light-emitting diode.

SNSPD superconducting nanowire single photon de-

tector.

SPDC spontaneous parametric down conversion. SSPD superconducting single photon detector.

TE transverse electric.

TES transition edge sensor.

TM transverse magnetic.

## Chapter 1

## Introduction

Since the discovery of the 'quantum strangeness' lying at the heart of fundamental interactions at the smallest scales, many a physicist has dreamed of harnessing such effects for useful purposes, both in furthering our understanding of the universe and in performing real work. Great lengths have been taken to make this a reality and significant progress has already been made; and though there is still much to be done, this dream is perhaps at last within our reach.

In selecting a particular entity with which to study this strangeness we have numerous options, from electron spins to whole atoms; here we are concerned solely with photons — their generation, manipulation and detection. If we wish to do this on a large scale (while retaining our sanity), we must look toward integration to simplify matters. In this work, elements of a planar integrated platform are developed for linear quantum optics experiments, with the aim of ultimately forming a complete platform, capable of scaling to support larger experiments than are currently practical.

## 1.1 Harnessing Quantum Phenomena

Quantum information processing (QIP) is a topic of particular current interest, having captured both the public eye and significant industrial interest of late. QIP may broadly be divided into two areas; the first of these, quantum computing, promises an exponential reduction in algorithmic complexity for a variety of problems, while quantum communication offers truly secure communications channels.

#### 1.1.1 Quantum Cryptography

Quantum cryptography is concerned with the application of physical phenomena to the provision of absolute information security. The fundamental security of such methods

stems from the impossibility of duplicating the state of an arbitrary qubit without modifying it, as stated by the quantum no cloning theorem [1].

Typically this takes the form of a lower bandwidth quantum communication channel used in tandem with a traditional classical channel. This quantum channel need not provide a great deal of bandwidth, it may be used purely to distribute secure keys for use in classical encryption algorithms on conventional channels; this is known as quantum key distribution (QKD). A number of commercial implementations of QKD have already been developed, and point-to-point fibre links have been operated over distances in excess of 300 km [2]. The main downfalls of current systems are the incompatibility of these channels with existing optical fibre networks, and the lack of quantum repeaters limiting the achievable link lengths, or equivalently key rates, due to loss.

## 1.1.2 Quantum Computing

The immense parallelism of quantum state evolution leads to the exciting prospect of performing computation in a way entirely different to classical methods. A handful of such algorithms have thusfar been developed, most notably Shor's algorithm for factoring integers [3] and Grover's search algorithm [4]. Both of these algorithms provide an exponential speed-up over the best known classical counterparts given equivalent resources, making their implementation highly desirable. The search for further algorithms offering quantum supremacy is still an active research topic, and indeed the nonexistence of equally fast classical algorithms is as yet unproven.

## 1.2 Universal Quantum Computation

A range of schemes have been proposed as potential platforms for quantum computation, including trapped ions, flux states in superconductors, and photon path states. It is the latter of these which is of relevance in this work. The exceedingly weak coupling of photons to sources of decoherence provides a clear advantage for QIP implementations, while the difficulty of creating and manipulating entanglement between photons poses a significant challenge.

#### 1.2.1 Scalability and Error Correction

In any physical implementation, errors will occur during the course of a computation. In an optical system these predominantly consist of photon losses, though this is exacerbated by the probabilistic nature of the linear optical approach discussed shortly. These errors are introduced to some degree by every component of the system, thus as the system scales and more complex operations are attempted the likelihood of an error

occurring somewhere throughout the course of the computation increases. In order for a computer to be of any practical use clearly it must successfully complete an operation at least some proportion of the time. Thus, either the error probability must be small enough to permit this or the machine must be capable of recovering should an error occur, such a machine is termed fault tolerant.

In a classical computer an operation could simply be repeated until successful, operating on copies of the input; unfortunately, however, the no-cloning theorem mentioned previously prevents us from proceeding in this manner. A solution to these difficulties was proposed by Shor in a scheme in which each logical qubit is encoded within a multiphoton state formed from a set of entangled physical qubits, which can be much more robust to photon loss; operations are carried out on this cluster state and the single qubit result extracted from it for measurement at the end. The additional circuitry to form and operate on this larger state does of course introduce its own source of potential errors.

More recently the use of cluster states for fault tolerant computation has shown great promise, and garnered much interest. In such a state the loss of one qubit, or its measurement as the result of a failed entangling operation, does not collapse the rest of the state; an invaluable property when constructing larger states.

#### 1.2.2 Surface Code

If a 2D array of cluster states is constructed, each formed by entangling a physical qubit with its four nearest neighbours, the resulting structure encodes a set of logical qubits in a surface code. This has a number of beneficial properties for fault-tolerant computation; by monitoring the parity of rows and columns one may detect and locate single bit flip errors within the surface, which may then be corrected by a suitable single-qubit operation [5]. Moreover, a range of multi-qubit errors have no adverse impact on the action of the network provided they form a closed loop of sites, preserving parity.

In this architecture operations are carried out by performing single qubit operations and making measurements on specific logical qubits in a particular order, selectively collapsing the entanglement; this is termed measurement based quantum computing. Since single qubit operations cannot introduce new entanglement the initial surface of cluster states provides the entire entanglement resource for any universal operation.

## 1.3 Optical Quantum Computing

## 1.3.1 Encoding Approaches

A single photon has a number of degrees of freedom which may be exploited for encoding quantum information, with varying degrees of difficulty, these are polarisation, path, frequency, and time-bin.

Polarisation The efficient manipulation of polarisation with free space wave-

plates and beamcubes makes this an ideal encoding scheme for free space experiments. Polarisation is much more difficult to manipulate in an integrated format, though active materials such as

LiNiO<sub>3</sub> and InP have been used for this purpose.

Path encoding is commonly implemented in a dual rail scheme in

which one path represents 0 and another 1. Gates can then readily be formed from beamsplitters and interferometers, which readily

supports an integrated format.

Time-bin/Frequency Time-bin encoding lends itself well to an optical fibre implementa-

tion, where sufficiently long delays may be achieved with relatively little loss. Frequency encoding has seen little use to date due to

the difficulty of switching between frequency bins.

#### 1.3.2 KLM Scheme

The linear optical approach to quantum computing was first proposed by Knill et al. in 2001 [6]. Until this point it was believed that quantum computation required a sufficiently strong non-linearity for high efficiency interactions between single photons to occur, which has not yet been accomplished [7]. The approach makes use of path encoded qubits, and in the simplest case requires single photon sources, beam splitters, phase shifters and high efficiency single photon detectors. Its primary drawback is that it is non-deterministic, that is to say the correct result will only be produced in a proportion of executions [6]. The success of an execution can however be determined through the use of additional 'ancilla' inputs [8], and a success probability arbitrarily close to unity may be obtained through more advanced schemes using additional ancillary resources [8].

This work was closely followed by myriad implementations based on the scheme using bulk optics [9, 10, 11], however, the scaling of these circuits is limited by their physical size [12]. This problem may be solved through integration of the circuit elements, providing a practical option for photonic quantum computing [12]; the monolithic nature of such devices also permits far greater stability than in bulk experiments. In a fully

integrated solution, suitable devices must be found to fulfill each of the roles outlined above.

Fault tolerance may be incorporated into this design by distributing a state of interest amongst several photons; partial measurements on these photons may then be used to determine whether a fault has occurred and to correct it via feed-forward. This permits error free computation to be carried out despite imperfect components, but does however carry the penalty of requiring significant overhead.

The chief difficulty with KLM based computational schemes is their inherently low success probability; this, compounded with material losses leads to impracticable resource requirements for fault-tolerant universal quantum computation based on a surface code architecture, with current best approaches requiring in excess of 10<sup>5</sup> detectors per qubit [13]. High-fidelity quantum memories would drastically improve matters, however based on current progress these are not likely to be available for some time, especially not in a suitably compact format to be used in number.

Even in the eventuality that *universal* all-optical quantum computation does not become feasible in the near future, there still exist a number of more specialised computational tasks to be explored, of which the most notable is boson sampling.

## 1.3.3 Boson Sampling

Whilst a truly universal linear optical quantum computer capable of outperforming classical systems does not appear to be feasible in the short term, principally due to the presence of significant loss and lack of probabilistic nature of linear optical operations, there are areas for which relatively small optical systems can indeed exceed current capabilities; in particular the area of boson sampling.

It has been demonstrated that sampling from the outputs of a linear optical network is equivalent to the calculation of a quantity related to the permanent of the systems' transfer function, and furthermore that this quantity is #P-hard in the computational complexity sense [14]. This means that the problem falls into a class for which, it is believed, no polynomial-time algorithm exists. The consequence of this is that the demonstration of such a computation, that of operating such a network and measuring its outputs, would either invalidate the extended Church-Turing theses or collapse the complexity polynomial hierarchy, both of which are strongly regarded in their respective fields. The former of these states that any algorithm may be efficiently simulated on a non-deterministic Universal Turing machine.

Following this development came a number of small scale demonstrations of such an experiment in integrated networks [15, 16, 17, 18], with no more than three photons. More recently Wang *et al.* showed sampling with up to five bosons [19]. In order for

current classical computers to be outperformed it has been calculated that a network in the region of of 100 modes with 35 photons is required. While challenging, this is within the realms of current capabilities given that, via the scatter-shot approach, simultaneous counts of all input photons are not necessary [20].

#### 1.3.4 A Hybrid approach

Arguably the most promising approach to fault-tolerant computation is a hybrid approach consisting of modules of qubits with high-fidelity state preparation, implemented with trapped ions for example, linked via a photonic interconnect permitting entanglement between modules; it is exactly this scheme that the Networked Quantum Information Technologies (NQIT) project is exploring.

## 1.4 An Engineering Challenge

## 1.4.1 Components of a Photonic Quantum Machine

With the set of one qubit operations and a single two-qubit operation, forming a universal set, it is possible to implement any quantum computational algorithm.

**Photon Sources** To begin with we must first have a source of photons, suitably pure and indistinguishable in order to permit high-quality quantum interference.

**Single-photon Operations** There are three single photon operations, corresponding to the Pauli rotations on the Bloch sphere.

**Two-photon Gates** A circuit performing a two-photon operation such as the controlled-NOT (CNOT) gate; any one type of two-photon gate is sufficient to produce arbitrary circuits. The unitary nature of quantum circuits requires that they have an equal number of inputs and outputs, two in this case.

Photon Detection The outputs of our quantum machine are extracted through detection of photons, of which there are a range of options depending on the encoding scheme. The 'click' type detectors include photo-multiplier tubes (PMTs), avalanche photodiodes (APDs) and superconducting nanowire single photon detectors (SNSPDs), while number-resolving detectors are implemented with transition edge sensors (TESs) or multiplexed click detectors. Detection is not solely a form of readout, in the KLM scheme measurement forms an integral part of the machine's operation.

## 1.4.2 Integrated Quantum Optics

A number of platforms are currently being explored for integrated optical QIP; these include silica-on-silicon, lithium niobate, GaAs and silicon [21]. To date, silica is perhaps the most developed of these for QIP applications, with much of the early experiments being done using this platform. Initial experiments began with the analysis of quantum and classical interference by Politi et al. [22], for which an etched silica-on-silicon directional coupler was used as an integrated equivalent of a beamsplitter. The first integrated, two-qubit path encoded quantum gate, a CNOT gate, was also demonstrated [22]; although full characterisation of this device was not possible at the time due to the additional circuitry required. A CNOT gate has also been produced for polarisation qubits [23].

In 2009, on-chip thermo-optic phase shifters were used in conjunction with Mach-Zehnder interferometers (MZIs) to provide a configurable quantum circuit element using this technology for the first time [24], operating at 800 nm. This was followed by the implementation of a somewhat contrived compiled version of Shor's algorithm, capable of factoring the input 15, and demonstrating entanglement of four photons [25]. In 2011, a fully configurable two qubit gate was produced by Shadbolt et al., this again utilised the combination of thermo-optic phase shifters and MZIs to form variable beam splitters [26]. More recently, this field has seen a great deal of interest, with experiments using up to five photons having been demonstrated.

Silica has also been used extensively in QKD experiments; for example, in 2004 it was utilised to provide the critical MZI component in a QKD system operating at 1550 nm [27]. The excellent fibre coupling possible with silica planar lightwave circuits (PLCs) along with their low waveguide loss of < 0.1 dB/cm makes silica an ideal choice for this type of application [28].

Recently, there has been significant progress in on-chip single photon detection, with two groups developing integrated SNSPDs on GaAs ridge waveguides [29, 30]. Compared with the integrated TES based detector [31], which forms the basis for part of this project, higher detection efficiencies have been reported for SNSPDs, although with significantly lower fibre coupling efficiencies. Additionally, these detectors are not number resolving and photon number resolution has not as yet clearly been demonstrated with superconducting nanowire detectors.

#### 1.4.3 Material platforms

The various material platforms under investigation for QIP each have relative merits; the parameters of most interest being their material loss, achievable coupling loss, and device density. Silica offers the lowest material and fibre coupling losses, while the high-index materials offer improved device densities. Also of importance are the types of

active elements permitted by each material, III-V semiconductors allow for quantumdot based single-photon sources, while lithium niobate and other electro-optic materials offer efficient on-chip modulators. Some important parameters for consideration are collected in table 1.1.

Femtosecond-written silica offers the freedom to define waveguide structures in three dimensions, this has been used to produce 2D-waveguide arrays for quantum-walk simulations. It is also possible to manipulate the waveguide cross section along its length both vertically and horizontally, which has been used to produce mode converters between source and circuit chips of different materials. Historically this fabrication technique suffered from high induced material losses and poor uniformity, however, this technology has improved greatly and is now comparable in device performance to other silica fabrication approaches.

Silicon photonics has seen a great deal of interest of late for quantum applications, principally due to the high device densities possible. The enormous research activity in silicon photonics for electronic device interconnects, among other applications, has led to drastic reductions in both the material and coupling losses of this platform and this trend is likely to continue for some time. Furthermore, commercial photonics foundries have made well-developed processes available to quantum optics researchers. Practical coupling efficiencies are still relatively high however, which has hindered quantum experiments with these devices. Ideally all elements of an experiment, from photon-sources to detectors, would be integrated on a single chip which would make coupling efficiency irrelevant; however, combining cryogenic photon detectors in particular with most modulator and source technologies will be very difficult to achieve due to the limited cooling power of refrigerators – this challenge is discussed in more detail in chapter 6.

Recently, there has been interest in heterogeneous integration [32], combining the advantages of different materials and techniques at the cost of additional fabrication complexity. III–V Quantum dot sources have been integrated with silicon nitride waveguides for example [33], and diamond nitrogen vacancy (NV) centres transferred to fibre tapers [34]. Detectors too have been integrated in this way, Najafi et al. having combined SNSPDs with silicon waveguides via a surprisingly high-yield transfer approach [35].

For each platform the inherent material losses place restrictions on the range of operating wavelengths, which have consequences for the other elements in the system, thereby limiting the types of sources and detectors that may be used and compatibility with memories. In the next section we shall discuss this issue of operating wavelengths specifically.

## 1.4.4 Operating wavelengths

The telecommunication C-band centered at 1550 nm offers a number of important advantages for photonic quantum circuits, principally this is the minimum loss window for silica, itself the lowest loss optical material available for the near infrared [36]. This wavelength also offers compatibility with existing telecommunications components. It is also informative to note that optical fibre is one of only two mediums, along with free space, for which quantum communication is currently believed to be practical [8]. Traditionally, the primary disadvantage of 1550 nm has been the absence of readily available high-efficiency single-photon detectors, as well as the lack of suitable atomic resonances within this band for the production of quantum memories. It is for this reason that the majority of integrated quantum circuits to-date have operated in the 800 nm region. As a result, while moving entirely to 1550 nm would be desirable within this project, work was conducted at both of these wavelengths with a gradual shift to the telecommunications band throughout its course.

Table 1.1: A comparison of common material platforms in use for integrated quantum optics experiments. Free space is included for reference.

| Material                | Operating wavelength <sup>3</sup> | $n^1$ | Propagation <sup>2</sup> loss (dB/cm) | Fibre coupling loss (dB) | Source<br>schemes | Detectors  | Entanglement record |

|-------------------------|-----------------------------------|-------|---------------------------------------|--------------------------|-------------------|------------|---------------------|

| Silica                  | 800 nm                            | 1.4   | 0.3                                   | 0.2                      | FWM               | TES, SNSPD | 4 [37]              |

| Silica                  | 1.5 μm                            | 1.4   | 0.05                                  | 0.1                      | FWM               | TES, SNSPD | 2                   |

| Silicon                 | 1.5 μm                            | 3.5   | 2.0                                   | 5                        | FWM               | SNSPD [35] | 2 [35]              |

| $\mathrm{Si_3N_4}$ $^4$ | 1.5 μm                            | 2.0   | < 0.2                                 | $1^5$                    | FWM [38]          | SNSPD      | 2 [39]              |

| ${\rm LiNiO_3}$         | 1.5 μm                            | 2.4   |                                       |                          |                   | SNSPD [40] | 2                   |

| Diamond                 | 700 nm                            | 2.4   |                                       |                          | Colour centres    | SNSPD      |                     |

| GaAs                    | 920 nm                            | 3.7   | $66~\mathrm{dB/cm}$                   |                          | InGaAs QD [41]    | SNSPD [41] | 2 [42]              |

| Free space              | N/A                               | 1     | 0                                     | N/A                      | SPDC, PPLN        | TES, SNSPD | 8 [43]              |

$<sup>^{1}</sup>$  At operating wavelength.  $^{2}$  Minimum reported for a waveguide in a quantum experiment.  $^{3}$  Typical operating wavelengths for quantum optics experiments.  $^{4}$  TriPlex  $^{5}$  With spot-size conversion [39]

## 1.5 Building Large Quantum States Project

It should be noted that the work detailed herein has a close relationship with the EPSRC funded programme grant, Building Large Quantum States out of light (BLoQS), led by the University of Oxford in collaboration with the University of Southampton and Imperial College London.

Figure 1.1: An outreach chip for the Building Large Quantum States out of light (BLoQS) project, designed and fabricated by the author.

## 1.6 Chapter Layout

The aim of this project is broadly that of further developing the silica-on-silicon platform for integrated quantum optics, including work on on-chip single photon sources, modulators and detectors. In much of this work the Direct UV Writing process is used to pattern waveguiding structures in a photosensitive silica-on-silicon planar structure. In the next chapter the fabrication of this substrate and the UV writing process are detailed, along with other fabrication techniques used throughout the work. Chapter 3 is concerned with work on on-chip single photon sources. Chapter 4 deals with modulators for quantum networks, which is followed by the development of a system of modular circuits in chapter 5. Chapter 6 covers integration of single photon detectors with waveguides. Finally, in Chapter 7 conclusions are drawn and areas for further development highlighted. All work detailed was carried out by the author, and where this is not the case it has been stated explicitly in the relevant section.

### References

[1] B. W. Kok, Pieter; Lovett, Introduction to Optical Quantum Information Processing. New York: Cambridge University Press, 2010.

[2] B. Korzh, C. C. W. Lim, R. Houlmann, N. Gisin, M. J. Li, D. Nolan, B. Sanguinetti, R. Thew, and H. Zbinden, "Provably secure and practical quantum key distribution over 307 km of optical fibre," *Nature Photonics*, vol. 9, no. 3, pp. 163–168, Feb 2015.

- [3] P. W. Shor, "Algorithms for quantum computation: discrete logarithms and factoring," in *Proceedings 35th Annual Symposium on Foundations of Computer Science*, Nov 1994, pp. 124–134.

- [4] L. K. Grover, "A fast quantum mechanical algorithm for database search," in *Proceedings of the Twenty-eighth Annual ACM Symposium on Theory of Computing*, ser. STOC '96. New York, NY, USA: ACM, 1996, pp. 212–219.

- [5] R. Raussendorf and J. Harrington, "Fault-tolerant quantum computation with high threshold in two dimensions," *Phys. Rev. Lett.*, vol. 98, p. 190504, May 2007.

- [6] E. Knill, R. Laflamme, and G. J. Milburn, "A scheme for efficient quantum computation with linear optics." *Nature*, vol. 409, no. 6816, pp. 46–52, Jan 2001.

- [7] S. Tanzilli, A. Martin, F. Kaiser, M. De Micheli, O. Alibart, and D. Ostrowsky, "On the genesis and evolution of Integrated Quantum Optics," *Laser & Photonics Reviews*, vol. 6, no. 1, pp. 115–143, Jan 2012.

- [8] P. Kok, K. Nemoto, T. C. Ralph, J. P. Dowling, and G. J. Milburn, "Linear optical quantum computing with photonic qubits," *Reviews of Modern Physics*, vol. 79, no. 1, pp. 135–174, Jan 2007.

- [9] J. L. O'Brien, G. J. Pryde, A. G. White, T. C. Ralph, and D. Branning, "Demonstration of an all-optical quantum controlled-NOT gate." *Nature*, vol. 426, no. 6964, pp. 264–7, Nov 2003.

- [10] P. Kok, H. Lee, and J. Dowling, "Single-photon quantum-nondemolition detectors constructed with linear optics and projective measurements," *Physical Review A*, vol. 66, no. 6, pp. 1–9, Dec 2002.

- [11] R. Okamoto, J. L. O'Brien, H. F. Hofmann, and S. Takeuchi, "Realization of a Knill-Laflamme-Milburn controlled-NOT photonic quantum circuit combining effective optical nonlinearities." *Proceedings of the National Academy of Sciences of the United States of America*, vol. 108, no. 25, pp. 10067–71, jun 2011.

- [12] A. Politi, J. Matthews, M. Thompson, and J. O'Brien, "Integrated Quantum Photonics," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 15, no. 6, pp. 1673–1684, 2009.

- [13] Y. Li, P. C. Humphreys, G. J. Mendoza, and S. C. Benjamin, "Resource costs for fault-tolerant linear optical quantum computing," *Physical Review X*, vol. 5, no. 4, pp. 1–15, 2015.

[14] S. Aaronson, "A linear-optical proof that the permanent is #p-hard," Proceedings of the Royal Society A: Mathematical, Physical and Engineering Sciences, vol. 467, no. 2136, pp. 3393–3405, Jul 2011.

- [15] J. Spring, B. Metcalf, and P. Humphreys, "Boson sampling on a photonic chip," *Science*, vol. 050502, no. 2008, 2013.

- [16] M. A. Broome, A. Fedrizzi, S. Rahimi-Keshari, J. Dove, S. Aaronson, T. C. Ralph, and A. G. White, "Photonic boson sampling in a tunable circuit," *Science*, vol. 339, no. 6121, pp. 794–798, Dec 2012.

- [17] M. Tillmann, B. Dakić, R. Heilmann, S. Nolte, A. Szameit, and P. Walther, "Experimental boson sampling," *Nature Photonics*, vol. 7, no. 7, pp. 540–544, May 2013.

- [18] A. Crespi, R. Osellame, R. Ramponi, D. J. Brod, E. F. Galvão, N. Spagnolo, C. Vitelli, E. Maiorino, P. Mataloni, and F. Sciarrino, "Integrated multimode interferometers with arbitrary designs for photonic boson sampling," *Nature Photonics*, vol. 7, no. 7, pp. 545–549, May 2013.

- [19] H. Wang, Y. He, Y.-H. Li, Z.-E. Su, B. Li, H.-L. Huang, X. Ding, M.-C. Chen, C. Liu, J. Qin, J.-P. Li, Y.-M. He, C. Schneider, M. Kamp, C.-Z. Peng, S. Höfling, C.-Y. Lu, and J.-W. Pan, "High-efficiency multiphoton boson sampling," *Nature Photonics*, vol. 11, no. 6, pp. 361–365, May 2017.

- [20] M. Bentivegna, N. Spagnolo, C. Vitelli, F. Flamini, N. Viggianiello, L. Latmiral, P. Mataloni, D. J. Brod, E. F. Galvao, A. Crespi, R. Ramponi, R. Osellame, and F. Sciarrino, "Experimental scattershot boson sampling," *Science Advances*, vol. 1, no. 3, Apr 2015.

- [21] M. Thompson, A. Politi, J. Matthews, and J. O'Brien, "Integrated waveguide circuits for optical quantum computing," *IET Circuits, Devices & Systems*, vol. 5, no. 2, p. 94, 2011.

- [22] A. Politi, M. J. Cryan, J. G. Rarity, S. Yu, and J. L. O'Brien, "Silica-on-silicon waveguide quantum circuits." Science (New York, N.Y.), vol. 320, no. 5876, pp. 646–9, may 2008.

- [23] A. Crespi, R. Ramponi, R. Osellame, L. Sansoni, I. Bongioanni, F. Sciarrino, G. Vallone, and P. Mataloni, "Integrated photonic quantum gates for polarization qubits," *Nature communications*, vol. 2, p. 566, Jan 2011.

- [24] B. J. Smith, D. Kundys, N. Thomas-peter, and I. A. Walmsley, "Phase-controlled integrated photonic quantum circuits," *Optics Express*, vol. 17, no. 16, pp. 264–267, Jul 2009.

[25] A. Politi, J. C. F. Matthews, and J. L. O. Brien, "Shor's Quantum Factoring Algorithm on a Photonic Chip," *Quantum Information Processing*, vol. 325, no. 5945, p. 1221, Sep 2009.

- [26] P. J. Shadbolt, M. R. Verde, A. Peruzzo, A. Politi, A. Laing, M. Lobino, J. C. F. Matthews, and J. L. O'Brien, "Generating, manipulating and measuring entanglement and mixture with a reconfigurable photonic circuit," *Nature Photonics*, vol. 6, no. 1, p. 6, Dec 2011.

- [27] Y. Nambu, T. Hatanaka, and K. Nakamura, "BB84 Quantum Key Distribution System Based on Silica-Based Planar Lightwave Circuits," *Japanese Journal of Applied Physics*, vol. 43, no. No. 8B, pp. L1109–L1110, Jul 2004.

- [28] G. P. Agrawal, Lightwave Technology Components and Devices, 2nd ed. Hoboken, New Jersey: John Wiley & Sons, 2004.

- [29] J. P. Sprengers, A. Gaggero, D. Sahin, S. Jahanmirinejad, G. Frucci, F. Mattioli, R. Leoni, J. Beetz, M. Lermer, M. Kamp, S. Hofling, R. Sanjines, and A. Fiore, "Waveguide superconducting single-photon detectors for integrated quantum photonic circuits," *Applied Physics Letters*, vol. 99, no. 18, p. 181110, Nov 2011.

- [30] W. Pernice, C. Schuck, O. Minaeva, M. Li, G. Goltsman, A. Sergienko, and H. Tang, "High-speed and high-efficiency travelling wave single-photon detectors embedded in nanophotonic circuits," *Nature Communications*, vol. 3, no. 1, Jan 2012.

- [31] T. Gerrits, N. Thomas-Peter, J. Gates, A. Lita, B. Metcalf, B. Calkins, N. Tomlin, A. Fox, A. Linares, J. Spring, N. Langford, R. Mirin, P. G. Smith, I. Walmsley, and S. W. Nam, "On-chip, photon-number-resolving, telecommunication-band detectors for scalable photonic information processing," *Physical Review A*, vol. 84, no. 6, pp. 1–4, Dec 2011.

- [32] S. Bogdanov, M. Y. Shalaginov, A. Boltasseva, and V. M. Shalaev, "Material platforms for integrated quantum photonics," *Optical Materials Express*, vol. 7, no. 1, pp. 111–132, Jan 2017.

- [33] M. Davanco, J. Liu, L. Sapienza, C.-Z. Zhang, J. V. D. M. Cardoso, V. Verma, R. Mirin, S. W. Nam, L. Liu, and K. Srinivasan, "Heterogeneous integration for on-chip quantum photonic circuits with single quantum dot devices," *Nature Communications*, vol. 8, no. 1, Oct 2017.

- [34] R. N. Patel, T. Schröder, N. Wan, L. Li, S. L. Mouradian, E. H. Chen, and D. R. Englund, "Efficient photon coupling from a diamond nitrogen vacancy center by integration with silica fiber," *Light: Science & Applications*, vol. 5, p. e16032, Feb 2016.

REFERENCES 15

[35] F. Najafi, J. Mower, N. C. Harris, F. Bellei, A. Dane, C. Lee, X. Hu, P. Kharel, F. Marsili, S. Assefa, K. K. Berggren, and D. Englund, "On-chip detection of non-classical light by scalable integration of single-photon detectors," *Nature Communications*, vol. 6, no. 1, Jan 2015.

- [36] A. Ghatak and K. Thyagarajan, *Introduction to Fiber Optics*. Cambridge University Press, 2000.

- [37] J. Carolan, C. Harrold, C. Sparrow, E. Martin-Lopez, N. J. Russell, J. W. Silverstone, P. J. Shadbolt, N. Matsuda, M. Oguma, M. Itoh, G. D. Marshall, M. G. Thompson, J. C. F. Matthews, T. Hashimoto, J. L. O'Brien, and A. Laing, "Universal linear optics," *Science*, vol. 349, no. 6249, pp. 711–716, Aug 2015.

- [38] X. Zhang, Y. Zhang, C. Xiong, and B. J. Eggleton, "Correlated photon pair generation in low-loss double-stripe silicon nitride waveguides," *Journal of Optics*, vol. 18, no. 7, p. 074016, Jun 2016.

- [39] C. Xiong, X. Zhang, A. Mahendra, J. He, D.-Y. Choi, C. J. Chae, D. Marpaung, A. Leinse, R. G. Heideman, M. Hoekman, C. G. H. Roeloffzen, R. M. Oldenbeuving, P. W. L. van Dijk, C. Taddei, P. H. W. Leong, and B. J. Eggleton, "Compact and reconfigurable silicon nitride time-bin entanglement circuit," Optica, vol. 2, no. 8, pp. 724–727, Aug 2015.

- [40] M. G. Tanner, L. S. E. Alvarez, W. Jiang, R. J. Warburton, Z. H. Barber, and R. H. Hadfield, "A superconducting nanowire single photon detector on lithium niobate," *Nanotechnology*, vol. 23, no. 50, p. 505201, Nov 2012.

- [41] G. Reithmaier, M. Kaniber, F. Flassig, S. Lichtmannecker, K. Mller, A. Andrejew, J. Vukovi, R. Gross, and J. J. Finley, "On-chip generation, routing, and detection of resonance fluorescence," *Nano Letters*, vol. 15, no. 8, pp. 5208–5213, 2015.

- [42] J. Wang, A. Santamato, P. Jiang, D. Bonneau, E. Engin, J. W. Silverstone, M. Lermer, J. Beetz, M. Kamp, S. Höfling, M. G. Tanner, C. M. Natarajan, R. H. Hadfield, S. N. Dorenbos, V. Zwiller, J. L. O'Brien, and M. G. Thompson, "Gallium arsenide (GaAs) quantum photonic waveguide circuits," Optics Communications, vol. 327, pp. 49–55, Sep 2014.

- [43] X.-C. Yao, T.-X. Wang, P. Xu, H. Lu, G.-S. Pan, X.-H. Bao, C.-Z. Peng, C.-Y. Lu, Y.-A. Chen, and J.-W. Pan, "Observation of eight-photon entanglement," *Nature Photonics*, vol. 6, no. 4, pp. 225–228, Feb 2012.

# Chapter 2

# UV Writing and Integrated Planar Waveguides

## 2.1 Introduction

In this chapter we will begin with the fundamental concepts of planar waveguides, as well as the various fabrication techniques used throughout the following chapters in producing UV-written waveguides.

# 2.2 Planar Waveguides

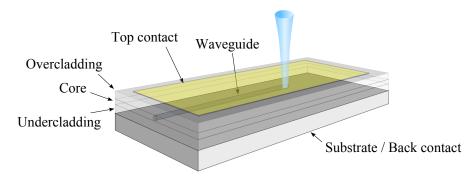

This work makes use of UV written waveguides composed of a fixed slab structure, defining the vertical extent of the waveguide, which is modified through an absorption induced refractive index increase to provide lateral confinement. Typically this structure is composed of undercladding, core, and overcladding layers, while in the integrated detector work of Chapter 6 it is necessary that waveguides without an overcladding are used.

Due to the limited space available a full review of the relevant planar waveguide theory is not possible here, the reader is instead directed to other sources [1, 2] for a more complete treatment.

#### 2.2.1 Waveguide Geometries

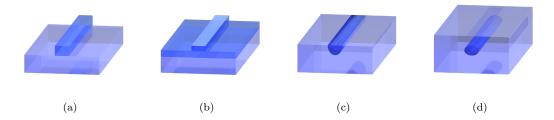

There are several types of planar waveguide geometry, as illustrated in figure 2.1; the first of these is the ridge waveguide, in which the waveguide sits proud of the substrate, the most common form for semiconductor waveguides; this ridge may also only be partially

etched, resulting in a rib waveguide. Next we have the channel waveguide, where the core is in line with the surface of the structure, which is typical of devices formed by ion diffusion. Finally we have the buried channel waveguide in which the core is completely embedded in the cladding, which is typical of laser-written waveguides such as those of this work.

Figure 2.1: An illustration of the types of planar waveguiding structures; (a) ridge, (b) rib, (c) channel and (d) buried channel.

# 2.3 Modelling of Planar Waveguides

Several different techniques were adopted during this project for modelling the behaviour of planar waveguides; these are outlined in the following sections.

#### 2.3.1 Mode Solving

A commercial 2D mode-solving package, FIMMWAVE, was used throughout this work to identify the supported modes in a given waveguide geometry. FIMMWAVE provides mode solvers for a variety of waveguide types; in particular, graded-index structures suitable for representing UV-written waveguides may be analysed with the use of its MWG interface and numerical solvers. Importantly, this software is capable of the complex-mode solving necessary for modelling devices with absorbing metal layers, such as the integrated single-photon detectors of Chapter 4.

Modelling of this type of waveguide is complicated somewhat compared with the step refractive index profiles of etched devices. The photosensitive inscription process results in a lateral profile following the intensity profile of the writing beam. In the vertical dimension the device is typically modelled with a step profile.

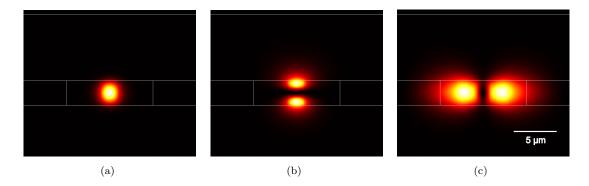

Figure 2.2 presents FIMMWAVE modelling of the typical UV-written waveguiding structure used throughout the following chapters, displayed are profiles of the fundamental mode and first two higher-order modes in the TM polarisation, based on a wafer designed for 780 nm operation (NB215). In the following section the UV-writing process used in fabricating these structures is discussed.

Figure 2.2: (a)  $TM_{00}$  fundamental guided mode and (b)  $TM_{01}$  (c)  $TM_{10}$  higher-order modes of a UV-written waveguide (operating at 780 nm) modelled in FIMMWAVE.

# 2.4 Silica-on-silicon

In this section the fabrication process for the silica-on-silicon waveguides used throughout this work is outlined. The waveguides themselves are either etched or, as is exclusively used here, UV written. UV writing is carried out on individual chips diced from a silicon wafer, on which is deposited a series of glass layers through flame hydrolysis deposition (FHD); it is with this process that we shall commence.

#### 2.4.1 Flame Hydrolysis Deposition

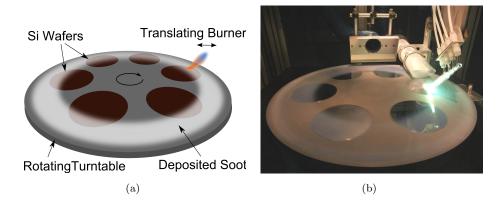

The layered slab waveguide structure used in this work was fabricated via FHD, a process in which doped silica is deposited upon a substrate through hydrolysis and oxidisation of halide precursors in a similar fashion to outside vapour deposition (OVD), which is used to produce optical fibre preforms. A rotating turntable is utilised in combination with a translating torch to deposit a uniform soot layer over a wafer. This soot layer is then consolidated in a furnace at a temperature of  $\sim 1200^{\circ}\mathrm{C}$  to form a glass.

Figure 2.3: (a) Diagram and (b) image of the FHD system (Norberta) in use throughout this work.

#### 2.4.1.1 Substrates for FHD

A silicon wafer is used as the substrate, with a thermally grown native oxide layer commonly forming the undercladding. Silicon provides a low-cost substrate option with the advantage of permitting growth of a thermal oxide. The key parameters restricting the type of substrate that may be used are the thermal expansion coefficient and any layer reactivity.

#### 2.4.1.2 Deposition Process

Core and overcladding layers are then deposited via FHD with a consolidation step for each. Crucially, the precursor composition fed to the flame permits doping of the glass to affect its optical properties and consolidation temperature. Three different dopants are used, germanium, boron, and phosphorus; each having different effects on the properties of the resulting glass matrix. The addition of any of these dopants will tend to reduce the melting point of the glass; each layer should have a lower melting point than that preceding it to prevent re-melting of these layers during subsequent consolidation steps, thus the cladding must be more heavily doped than the core. Germanium doping increases the refractive index of the layer, while also providing the defects that lead to the photosensitivity utilised during UV writing as described in section 2.5.1; it is thus only present in the core layer. Boron reduces the refractive index and is used in combination with the germanium to provide the required index contrast in the core layer, as well as promoting photosensitivity. Phosphorus increases the refractive index without providing photosensitivity, it is used in combination with boron to reduce the melting point of cladding layers while maintaining a refractive index matched to thermal oxide.

The precursors used as the source for these dopants and the silica matrix are halides, SiCl<sub>4</sub>, GeCl<sub>4</sub>, PCl<sub>3</sub> and BCl<sub>3</sub>. With the exception of BCl<sub>3</sub> these precursor gasses are provided via a nitrogen bubbler system; a heated oil bath houses liquid precursors, through which a flow of nitrogen is passed that draws with it a small quantity of the precursor in vapour form. The quantity of precursor is determined by the nitrogen flow rate, controlled via mass-flow controllers. This system has the advantage of purifying the precursors at point of use; in particular transition metal halides have a much lower vapour pressure than do the precursors of interest, thus the system minimises transition metal contamination of the resulting glass. This approach cannot be used for BCl<sub>3</sub> since it is not found in liquid form at atmospheric pressure, it is instead fed directly to the torch in gaseous form. The precursors are fed to a hydrogen oxygen flame with an argon sheath flow. The ratio of these torch gasses controls the shape and temperature of the flame, which in turn affects the properties of the deposited soot particles.

#### 2.4.1.3 Layer Consolidation

Consolidation of the deposited soot to form a glass layer is carried out in a vertical tube furnace; the temperature is ramped from 500°C to the soak temperature of 1360°C for a core layer, 1260°C for a cladding, over a period of two hours. It is held at this temperature for 2-5 hours, during which the layer is above its glass-transition temperature, before a controlled ramp down to 600°C at 7°C ·min<sup>-1</sup>; as the wafer cools it undergoes significant thermal contraction which places the core layer under compressive stress due to the differing expansion coefficients of the FHD layers and silicon substrate. The consolidation process can induce defects in the final glass matrix, typically caused by particulates from the furnace settling on the soot layer. Often, several defects will be induced per layer for a 6-inch wafer.

#### 2.4.2 Layer Metrology

Typically a separate test wafer is included in each layer deposition run, from which the layer thickness and refractive index are determined via a prism coupling technique with knowledge of the substrate refractive index, using a Metricon prism-coupling system. The key parameters of an FHD layer are its thickness and index contrast with respect to the thermal oxide cladding (n = 1.4449 at 1550 nm). The overcladding is commonly index matched to the thermal oxide to make the waveguide symmetrical; the core is often also of small contrast (zero-delta) to improve matching with an optical fibre mode.

Figure 2.4: An example scan from the Metricon prism coupling system for thin film metrology, fitting to the dip positions yields layer refractive index and thickness.

In the prism coupling approach a laser is incident on the layer to be measured via a prism of calibrated refractive index which is held in contact. The reflected beam power

is monitored as the assembly is rotated, adjusting the incident angle; for some angles light is coupled into a guided planar mode of the layer and reflection is suppressed, leading to a plot like that of figure 2.4. The angles at which these couplings occur are related to the effective indices of the guided modes, from which the refractive index and thickness of the layer may be computed.

#### 2.4.3 Sample Preparation

After fabrication, the wafer is diced into individual chips of the desired size, usually 10 mm wide and between 10 mm and 60 mm long depending on the application, with the use of a dicing saw. Careful choice of blades and suitable blade dressing procedures enables optical-quality facets to be produced through dicing alone [3]; in most cases however this is unnecessary since butt-coupling is used, making the effects of top-surface chipping and facet imperfections less significant. For the majority of wafer dicing in this work, 1200 grit diamond embedded resin blades were used at 20,000 rpm with a feed rate of 0.4 mm·s<sup>-1</sup>.

# 2.5 Direct UV Writing

Direct UV Writing is a technique to produce channel waveguides in photosensitive glass layers, commonly produced via FHD. It is a versatile technique capable of producing a range of waveguiding structures rapidly without the need for photolithographic processing or cleanroom conditions. A focussed 244 nm UV laser beam is translated over the surface using a 4-axis air-bearing stage system under software control. Absorption in exposed regions leads to a localised refractive index increase in the visible to near infrared via the Kramers-Kronig relationship, allowing wave-guiding structures to be produced. Refractive index contrasts of the order of  $10^{-3}$  are typically achieved through this process; this makes it suitable for devices with mode sizes matched to that of optical fibre ( $\approx 8~\mu m$  at 1550 nm), permitting high coupling efficiencies to be achieved between the two [4]. Waveguides have been produced using this technique with propagation losses as low as 0.05 dB/cm [5]; the relatively low index contrasts do, however, place restrictions on the achievable device dimensions, thus limiting the packing density in more complex devices.

#### 2.5.1 Photosensitivity Mechanisms

Photosensitivity is induced in the core layer through the addition of germanium and boron in the glass matrix. This leads to the formation of a variety of lattice defects known as oxygen deficiency centres (ODCs), which absorb in the UV. It is believed that the majority of the observed UV induced index change is due to the breaking of bonds associated with these defects [6], although thermal effects and densification likely also contribute to the change [7].

#### 2.5.1.1 Hydrogen Loading

Hydrogenation of the samples, achieved by storing them in a high pressure hydrogen cell for  $\sim 1$  week, is used to enhance the photosensitivity. This increase in photosensitivity is due both to the formation of OH groups, which leave additional ODCs, and its action as a photobleaching catalyst [6].

This hydrogen does out-diffuse over time at room temperature. After hydrogenation, the samples are thus stored in liquid nitrogen to greatly slow this process until UV writing is carried out.

#### 2.5.2 Fluence

The magnitude of this index increase is dependent on the total exposure, or writing fluence, used. This relationship is approximately linear but saturates at higher fluence values. The writing fluence also affects the lateral dimension of the waveguide; although this is largely determined by the spot size, the Gaussian beam profile will be reflected in the induced index profile, hence the increasing peak index with fluence will also cause broadening of the waveguide.

# 2.6 Integrated Bragg Gratings

One particular advantage of the direct UV writing approach is that Bragg gratings may readily be incorporated within the defined waveguides. This is achieved through the use of a pair of overlapping beams, providing an interference pattern with a period defined by the wavelength and crossing angle of the beams.

The grating period is not limited to that of the interference pattern however. Selectively exposing areas as the spot is translated allows other periods to be built up; this may be accomplished by either amplitude modulating the beam, or by shifting the interference pattern via a phase shift. This will result in a reduced modulation depth for periods with increasing detuning from the interference pattern period, though this effect is small and periods corresponding to wavelengths between 1400 nm and 1700 nm are achievable in the current system due to the small number of fringes present within the spot size.

Bragg gratings have proven to be an invaluable tool, both out-of-band for characterisation of waveguide arrangements, and in-band, particularly in the work of section 6.4.3.

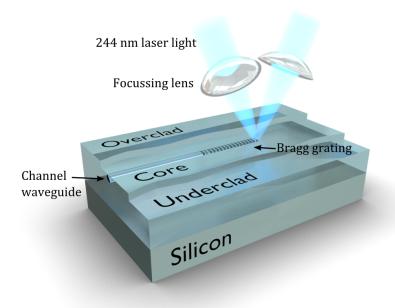

Figure 2.5: The two-beam UV writing arrangement – laser beams at 244 nm are focussed and overlapped in the core of a photosensitive sample, the resulting interference pattern is used to inscribe both waveguides and gratings as the sample is translated relative to the writing spot.

Gaussian apodised gratings are primarily used here since their suppressed sidebands permit closer spectral spacing of gratings without significant interference between adjacent peaks [8].

#### 2.6.1 Planar Bragg Grating Theory

A Bragg grating is a periodic variation in refractive index that coherently scatters forward propagating light into a backwards propagating mode; this occurs for a range of wavelengths with centre, or Bragg wavelength  $\lambda_{\rm B}$ , set by the period  $\Lambda$  of the grating via the Bragg equation (Eq.2.1), where  $n_{\rm eff}$  is the effective index of the guided mode.

$$\Lambda = \frac{\lambda_{\rm B}}{2 \cdot n_{\rm eff}} \tag{2.1}$$