## University of Southampton Research Repository

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Author (Year of Submission) "Full thesis title", University of Southampton, name of the University Faculty or School or Department, PhD Thesis, pagination.

UNIVERSITY OF SOUTHAMPTON

# **Cost-efficient Delay-Fault Sensors for Ageing Prediction**

by

Gaole Sai

A thesis submitted for the

degree of Doctor of Philosophy

in the

Faculty of Physical Science and Engineering

School of Electronics and Computer Science

November 2018

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF PHYSICAL SCIENCE AND ENGINEERING

SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

by **Gaole Sai**

Aggressive technology scaling has accelerated the ageing of CMOS devices. Ageing refers to a slow progressive degradation in the performance of MOS transistors. Consequently, the speed of a chip can significantly degrade over time; this results in delay faults. Dynamic reliability management schemes have been proposed to assure an IC's lifetime reliability. Such schemes are typically based on the use of ageing sensors to predict a circuit's failure before the actual errors appear. Existing ageing sensors are usually placed on the circuit's longest delay paths, which are deemed to be the most vulnerable to delay faults. Such an approach is very costly and may be infeasible in today's complex designs that typically have a large number of long delay paths that need to be monitored. Existing ageing models are proposed to estimate the lifetime of an IC before it's fabrication. However, The result is inaccurate without considering the actual operating conditions of the circuit. Various ageing mitigation technique has been proposed to extend the lifetime of an IC. A trade-off between lifetime and performance usually achieves such approaches. Such sacrifices are reluctant.

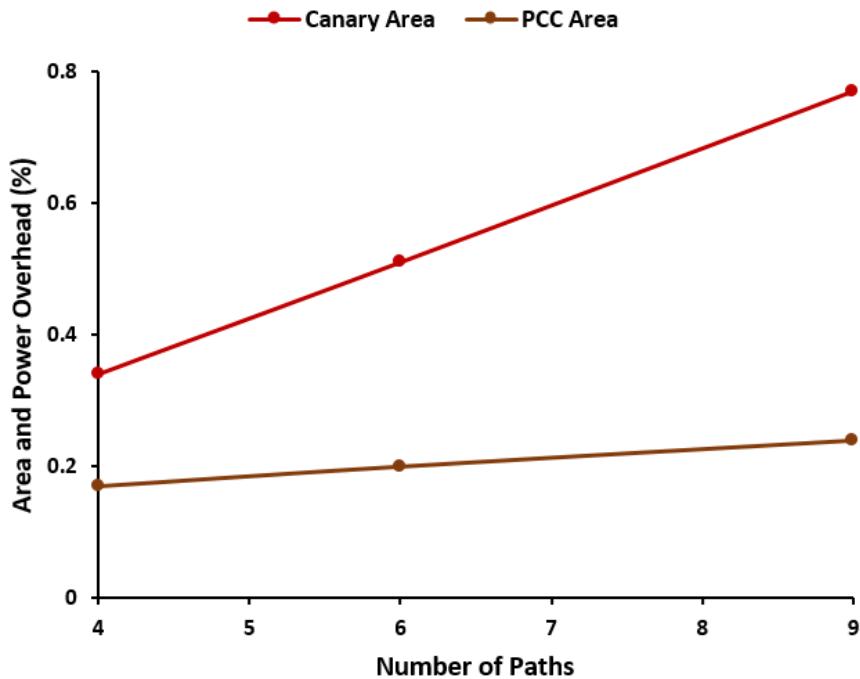

We propose two sensors, Parity Check Circuit (PCC) and Differential Multiple Error Detection Sensor (DMEDS), for cost-efficient delay fault monitoring. Both of those two sensors can monitor multiple paths simultaneously, which reduces the number of sensors significantly. The PCC has been designed and verified in a 65nm technology. Our results indicate that using the proposed sensor for delay fault monitoring in a 32-bit MIPS can lead to a significant saving in the area and power overheads, compared to the use of canary flip-flops [40]: by two-thirds and one-third, respectively. The DMEDS has been designed at transistor level in a 32 nm and 90 nm CMOS technology and verified at the system level. Our results indicate that the use of the proposed sensor for delay fault monitoring across ten paths can lead to a significant saving in area overhead compared to Razor [29], and Canary [40]: 87.59%, 77.67%, respectively. We also propose an idea of lifetime prediction system, and it compares the data with reference to analysis the ageing of the device. Our results indicate that the use of the proposed system for lifetime prediction system can accurately estimate the lifetime of the IC compared with the data from the ageing model. The error is controlled within 5% with limited reference data.

# Contents

|                         |                                                                       |           |

|-------------------------|-----------------------------------------------------------------------|-----------|

| <b>Acknowledgements</b> | <b>xv</b>                                                             |           |

| <b>1</b>                | <b>Introduction</b>                                                   | <b>1</b>  |

| 1.1                     | Motivations For Research . . . . .                                    | 1         |

| 1.2                     | Delay Fault Monitoring and PVTA Variations . . . . .                  | 2         |

| 1.2.1                   | Delay Fault Monitoring Techniques . . . . .                           | 2         |

| 1.2.2                   | PVT Variations . . . . .                                              | 3         |

| 1.2.3                   | Ageing Variation . . . . .                                            | 3         |

| 1.2.4                   | The limitation of state-of-the-art techniques . . . . .               | 4         |

| 1.3                     | Objectives . . . . .                                                  | 4         |

| 1.4                     | Contributions . . . . .                                               | 5         |

| 1.5                     | Thesis Structure . . . . .                                            | 5         |

| 1.6                     | Publications . . . . .                                                | 6         |

| <b>2</b>                | <b>Background</b>                                                     | <b>7</b>  |

| 2.0.1                   | Static Timing Analysis and Delay Fault . . . . .                      | 7         |

| 2.1                     | Process, Voltage and Temperature Variations . . . . .                 | 8         |

| 2.1.1                   | Process Variations . . . . .                                          | 10        |

| 2.1.2                   | Voltage Variations . . . . .                                          | 10        |

| 2.1.3                   | Temperature Variation . . . . .                                       | 12        |

| 2.1.4                   | Discussion . . . . .                                                  | 12        |

| 2.2                     | Negative-Bias Temperature Instability and Ageing Mechanisms . . . . . | 13        |

| 2.2.1                   | Negative-Bias Temperature Instability . . . . .                       | 14        |

| 2.2.2                   | Influence Factors of NBTI . . . . .                                   | 17        |

| 2.2.3                   | HCI and PBTI . . . . .                                                | 22        |

| 2.3                     | Ageing Mitigation and Lifetime Prediction Techniques . . . . .        | 23        |

| 2.3.1                   | Ageing Mitigation . . . . .                                           | 23        |

| 2.3.2                   | Lifetime Prediction . . . . .                                         | 27        |

| 2.4                     | Ageing Sensors . . . . .                                              | 28        |

| 2.4.1                   | Razor FF . . . . .                                                    | 28        |

| 2.4.2                   | Razor II . . . . .                                                    | 31        |

| 2.4.3                   | Canary FF . . . . .                                                   | 32        |

| 2.4.4                   | TDS FF . . . . .                                                      | 32        |

| 2.5                     | Concluding Remarks . . . . .                                          | 35        |

| <b>3</b>                | <b>Parity Check Circuitry</b>                                         | <b>37</b> |

| 3.1                     | Introduction . . . . .                                                | 37        |

---

|          |                                                                           |            |

|----------|---------------------------------------------------------------------------|------------|

| 3.2      | PCC Design Principles . . . . .                                           | 38         |

| 3.3      | Path Selection for PCC . . . . .                                          | 43         |

| 3.3.1    | Path Selection . . . . .                                                  | 43         |

| 3.3.2    | Potential Critical Path Identification . . . . .                          | 45         |

| 3.4      | PCC Implementation . . . . .                                              | 48         |

| 3.5      | Verification and Comparative Analysis . . . . .                           | 51         |

| 3.5.1    | System level Simulation Results . . . . .                                 | 51         |

| 3.5.2    | Area and Power Overheads Comparison . . . . .                             | 53         |

| 3.6      | Concluding Remarks . . . . .                                              | 55         |

| <b>4</b> | <b>Differential Multiple Error Detection Sensor</b>                       | <b>57</b>  |

| 4.1      | Introduction . . . . .                                                    | 57         |

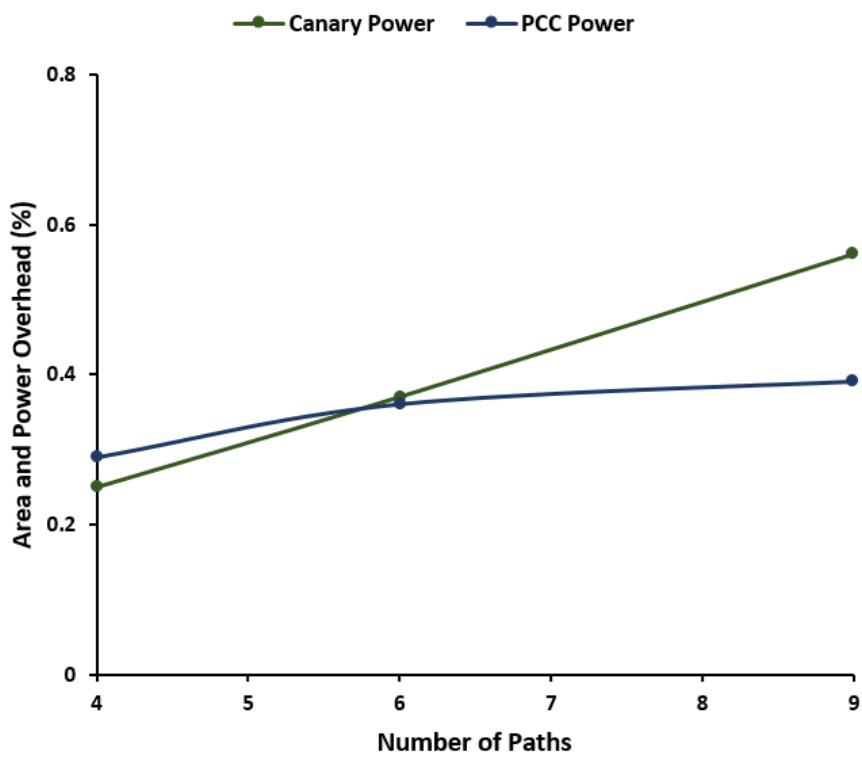

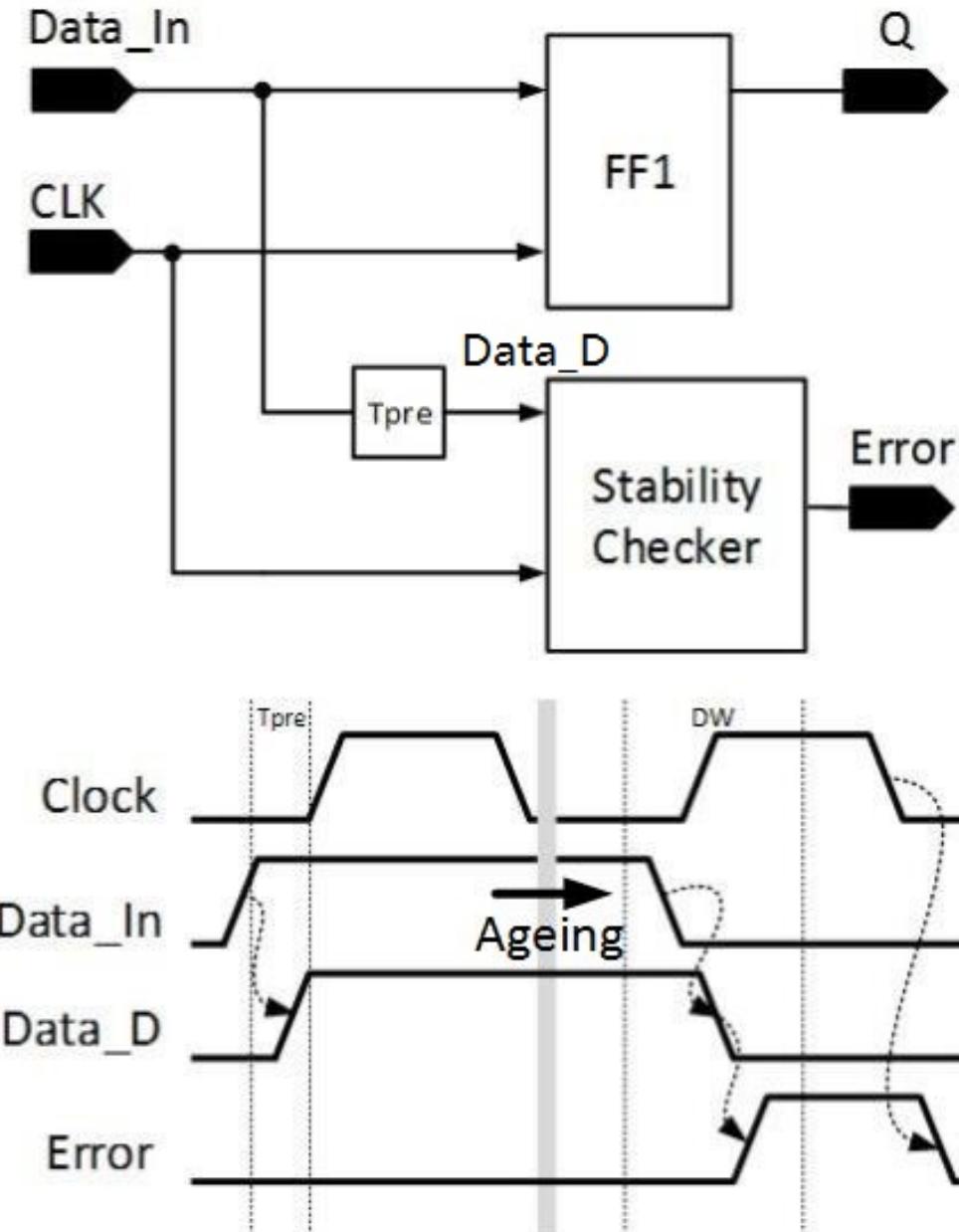

| 4.2      | DMEDS Design Principles . . . . .                                         | 58         |

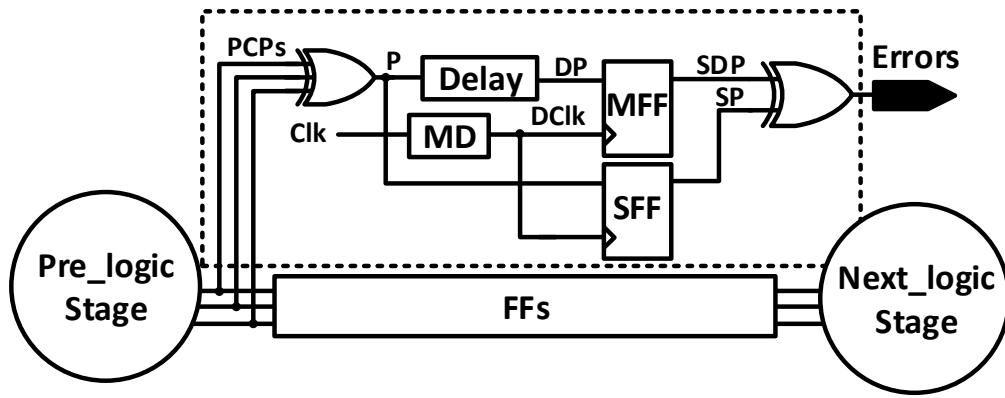

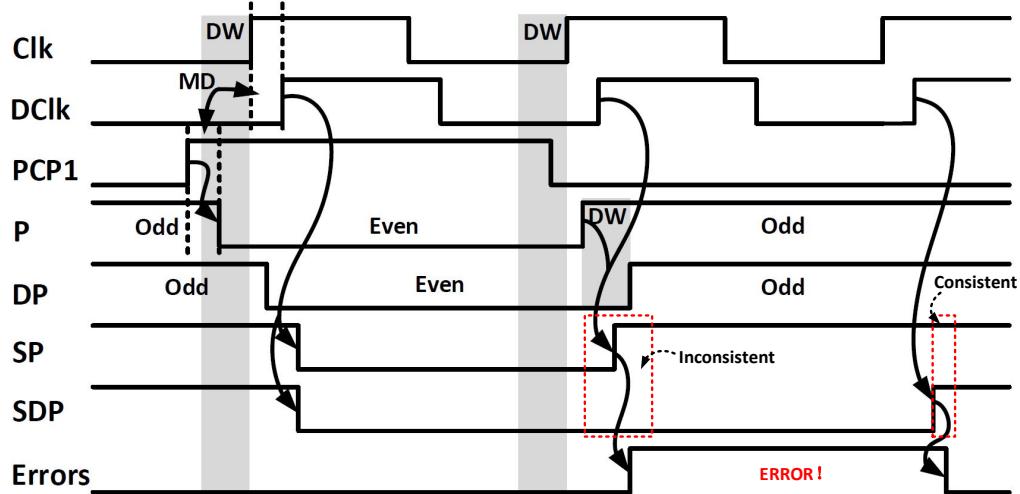

| 4.3      | Operating Principles of SEDS . . . . .                                    | 59         |

| 4.4      | Operating Principles of DMEDS . . . . .                                   | 59         |

| 4.5      | Transistor Level Design of DMEDS . . . . .                                | 63         |

| 4.6      | Gate Level Design of DMEDS . . . . .                                      | 66         |

| 4.7      | DMEDS Implementation . . . . .                                            | 67         |

| 4.8      | Verification and Comparative Analysis . . . . .                           | 68         |

| 4.8.1    | Transistor Level Verification and Analysis in 90 nm . . . . .             | 69         |

| 4.8.1.1  | Transistor Level Simulation Results in 90 nm . . . . .                    | 69         |

| 4.8.1.2  | Transistor Level Cost Comparison in 90 nm . . . . .                       | 72         |

| 4.8.2    | System Level Verification and Analysis in 90 nm . . . . .                 | 73         |

| 4.8.2.1  | DMEDS Synthesis and Simulation . . . . .                                  | 73         |

| 4.8.2.2  | Comparison of Power and Area Overhead . . . . .                           | 75         |

| 4.8.3    | Transistor Level verification and cost Comparison in 32 nm . . . . .      | 77         |

| 4.8.3.1  | Transistor Level verification in 32 nm . . . . .                          | 77         |

| 4.8.3.2  | Cost Comparison in 32 nm . . . . .                                        | 78         |

| 4.8.4    | System Level verification in 32 nm . . . . .                              | 79         |

| 4.9      | Concluding Remarks . . . . .                                              | 79         |

| <b>5</b> | <b>DVS for Ageing Prediction</b>                                          | <b>83</b>  |

| 5.1      | Introduction . . . . .                                                    | 83         |

| 5.2      | Ageing Prediction System Design Principle . . . . .                       | 85         |

| 5.3      | Reference Circuit Estimation . . . . .                                    | 91         |

| 5.3.1    | Define the Margin . . . . .                                               | 92         |

| 5.3.2    | Define the Characteristic of DVS . . . . .                                | 97         |

| 5.3.3    | Circuit Ageing Delay Estimation . . . . .                                 | 98         |

| 5.3.4    | Reference Circuit Ageing Behaviour Estimation . . . . .                   | 101        |

| 5.3.5    | Discussion . . . . .                                                      | 107        |

| 5.4      | Verification and Analysis . . . . .                                       | 107        |

| 5.4.1    | Lifetime Estimation and Comparison in Details . . . . .                   | 107        |

| 5.4.2    | Lifetime Estimation and Comparison with More than One Reference . . . . . | 111        |

| 5.5      | Concluding Remarks . . . . .                                              | 111        |

| <b>6</b> | <b>Conclusions</b>                                                        | <b>113</b> |

|                   |             |            |

|-------------------|-------------|------------|

| 6.1               | Conclusions | 113        |

| 6.2               | Future work | 114        |

| <b>References</b> |             | <b>117</b> |

# List of Figures

|      |                                                                                                                            |    |

|------|----------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | The Architecture of a Pipelined MIPS, Reproduced from [48] . . . . .                                                       | 8  |

| 2.2  | Margins, Reproduced from [57] . . . . .                                                                                    | 8  |

| 2.3  | Technology node of the CPUs from Intel, Reproduced from [45, 61] . . . . .                                                 | 9  |

| 2.4  | $V_{th}$ Shift Random Due to the Process Variations, Reproduced from [52] . .                                              | 10 |

| 2.5  | Relation Between Supply Voltage and Logic Delay of a Multiplier Circuit in 65nm Technology, Reproduced from [85] . . . . . | 11 |

| 2.6  | Within Die Temperature Variation, Reproduced from [14] . . . . .                                                           | 12 |

| 2.7  | NBTI: Hydrogen Atoms Diffusion, Reproduced from [77] . . . . .                                                             | 14 |

| 2.8  | Static NBTI, Reproduced from [10] . . . . .                                                                                | 15 |

| 2.9  | Dynamic NBTI, Reproduced from [4] . . . . .                                                                                | 16 |

| 2.10 | Dynamic NBTI for a minimum sized PMOS transistor of 90nm technology, Reproduced from [10] . . . . .                        | 17 |

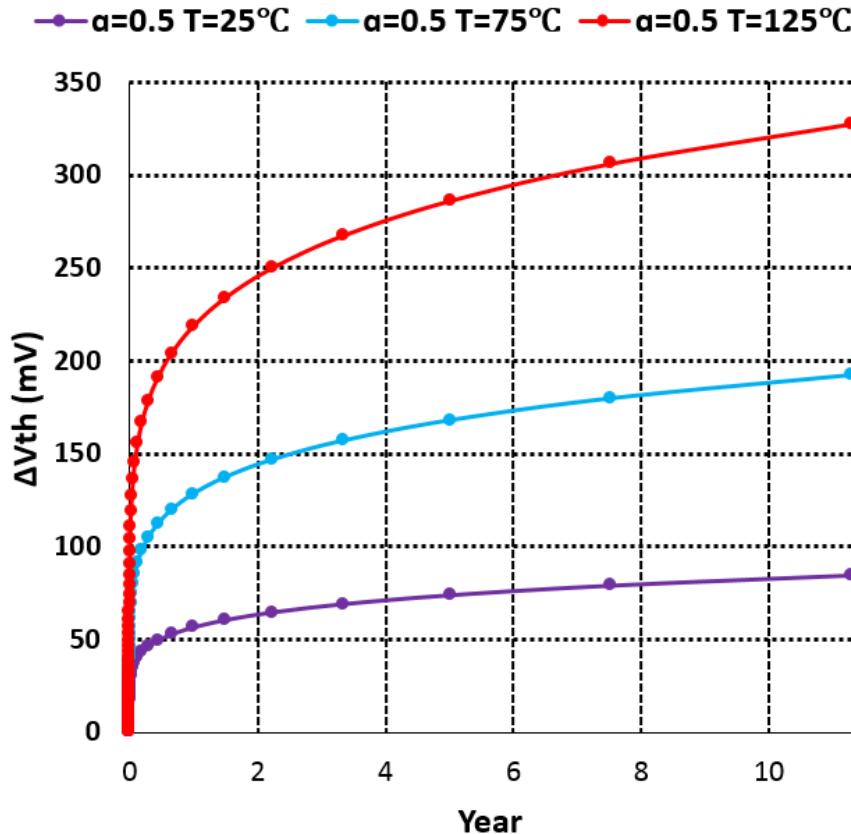

| 2.11 | Long Term Dynamic NBTI with Different Duty Cycle . . . . .                                                                 | 18 |

| 2.12 | Long Term Dynamic NBTI with Difference Temperature, Reproduced from [3] . . . . .                                          | 19 |

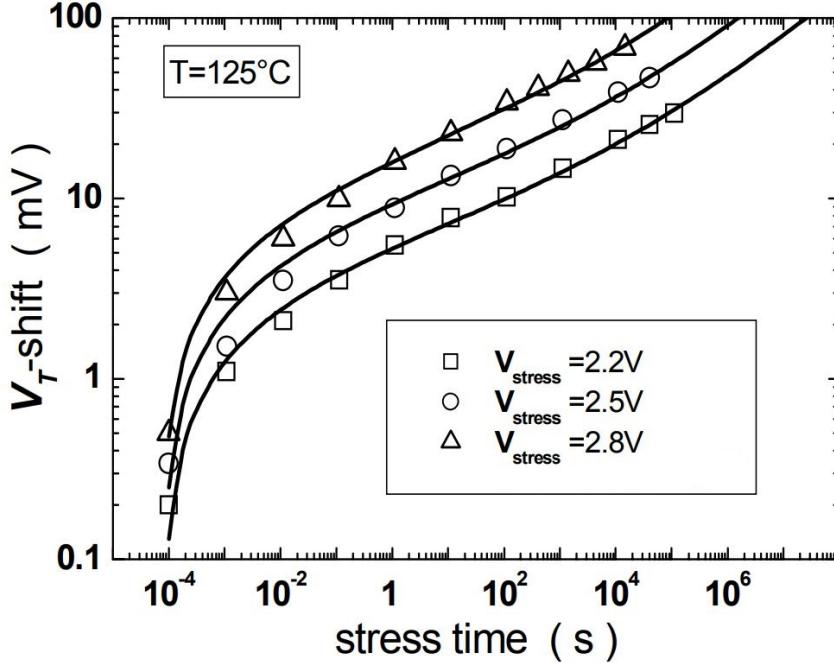

| 2.13 | Long Term Dynamic NBTI with Different $V_{gs}$ , Reproduced from [62] . . .                                                | 20 |

| 2.14 | Relationship between Duty Cycle, VDD and $\Delta V_{th}$ , Reproduced from [10] .                                          | 21 |

| 2.15 | NBTI: Hydrogen Atoms Diffusion, Reproduced from [77] . . . . .                                                             | 22 |

| 2.16 | Ageing Mechanisms, Reproduced from [25, 90] . . . . .                                                                      | 23 |

| 2.17 | NBTI-aware Power Gating, Reproduced from [27] . . . . .                                                                    | 24 |

| 2.18 | The Frequency f vs. Supply Voltage VDD Shmoo Plot of the Traditional DVS Technique, Reproduced from [44] . . . . .         | 25 |

| 2.19 | Ageing mitigation by using DVS, Reproduced from [24] . . . . .                                                             | 26 |

| 2.20 | Supply Voltage Scaling Flowchart, Reproduced from [17] . . . . .                                                           | 27 |

| 2.21 | Lifetime Prediction Flow Chart, Reproduced from [22, 34] . . . . .                                                         | 29 |

| 2.22 | The Razor FF and Timing Diagram, Reproduced from [35] . . . . .                                                            | 30 |

| 2.23 | Razor II and Timing Diagram, Reproduced from [30] . . . . .                                                                | 31 |

| 2.24 | The Canary FF and Timing Diagram, Reproduced from [40] . . . . .                                                           | 33 |

| 2.25 | TDS FF, Reproduced from [71] . . . . .                                                                                     | 34 |

| 2.26 | TDS FF Timing Diagram, Reproduced from [71] . . . . .                                                                      | 34 |

| 3.1  | Architecture of The Proposed Circuitry . . . . .                                                                           | 39 |

| 3.2  | Odd Number of Transitions . . . . .                                                                                        | 40 |

| 3.3  | Even Number of Transitions . . . . .                                                                                       | 40 |

| 3.4  | Unpredictable Error . . . . .                                                                                              | 41 |

| 3.5  | PCC Implementation Process . . . . .                                                                                       | 42 |

| 3.6  | Percentage of Transitions . . . . .                                                                                        | 44 |

| 3.7  | Determining the Width of Detection Window . . . . .                                                                        | 45 |

|      |                                                                                |    |

|------|--------------------------------------------------------------------------------|----|

| 3.8  | Potential BTI Critical Paths Estimation Process                                | 47 |

| 3.9  | Synthesised 4-bit signed full adder with a loose timing constraint             | 48 |

| 3.10 | Synthesised 4-bit signed full adder with a tight timing constraint             | 48 |

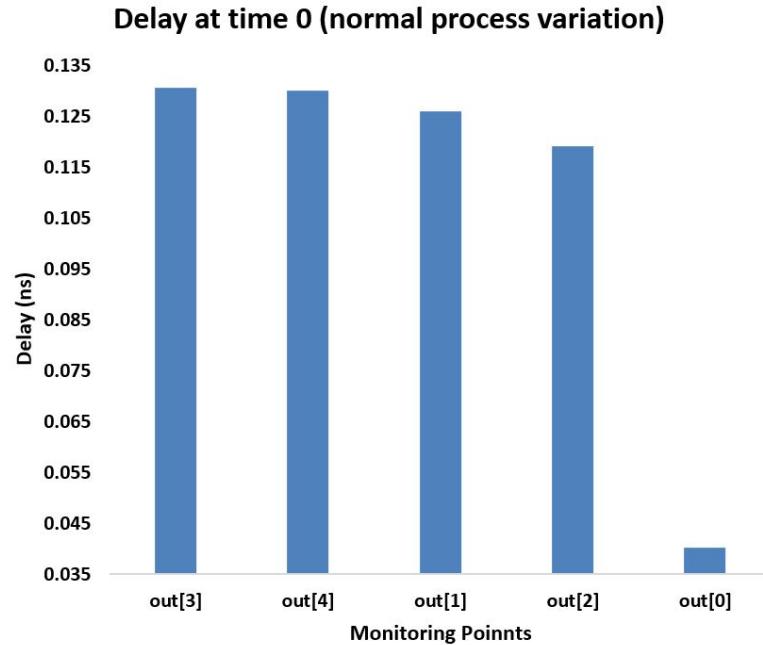

| 3.11 | Delay at Time Zero (Normal Process Variation)                                  | 49 |

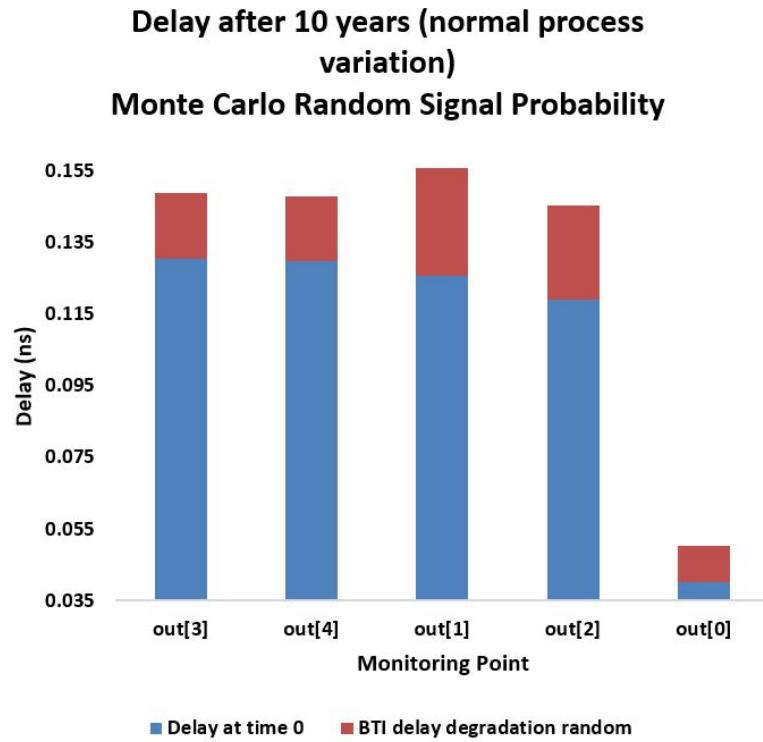

| 3.12 | Delay After 10 Years (Normal Process Variation) Random Signal Probability      | 49 |

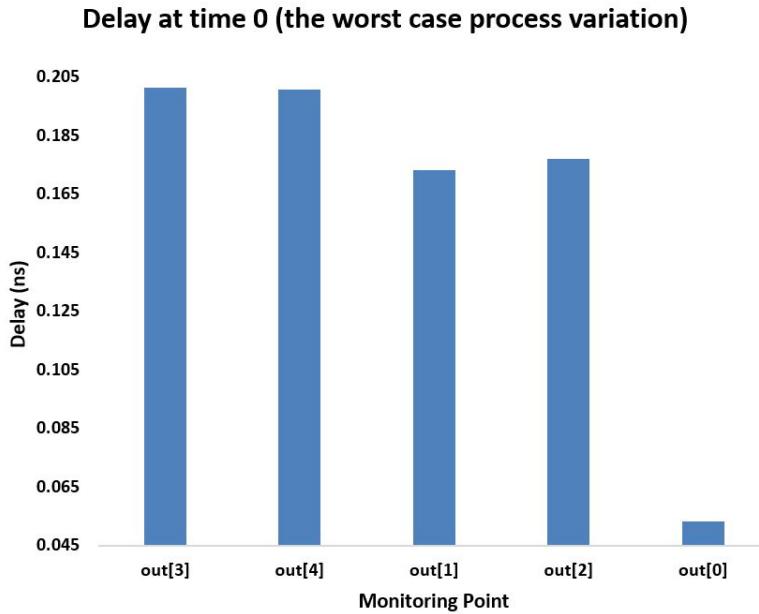

| 3.13 | Delay at Time Zero (The Worst Process Variation)                               | 50 |

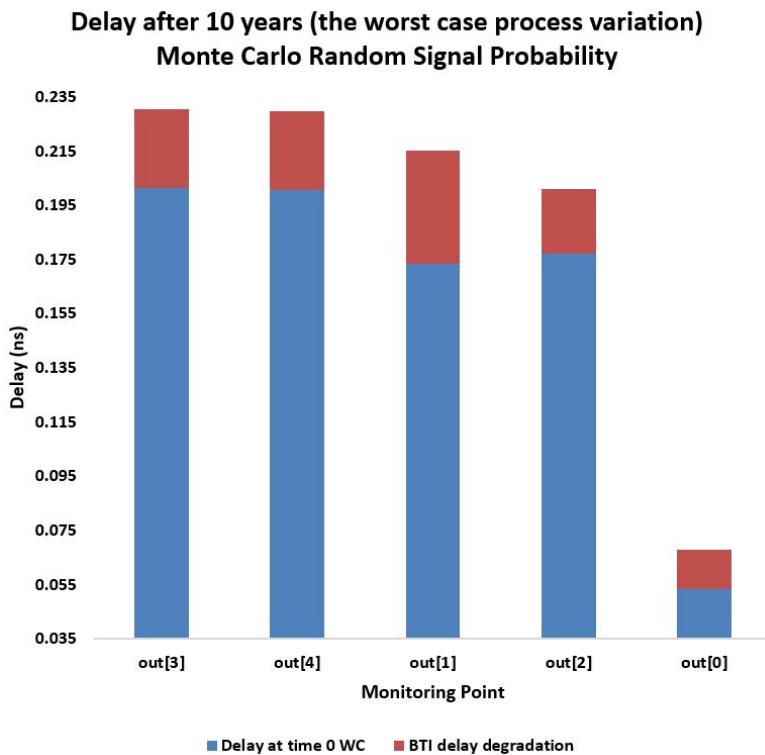

| 3.14 | Delay After 10 Years (The Worst Process Variation)                             | 50 |

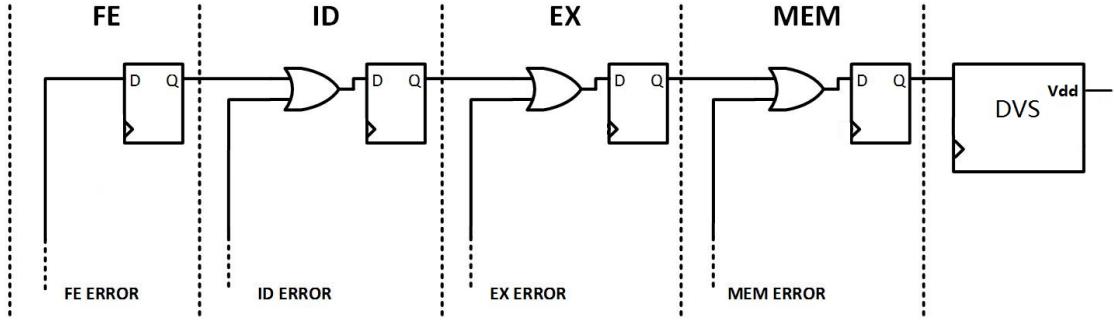

| 3.15 | DVS in a MIPS microprocessor with a pipeline                                   | 51 |

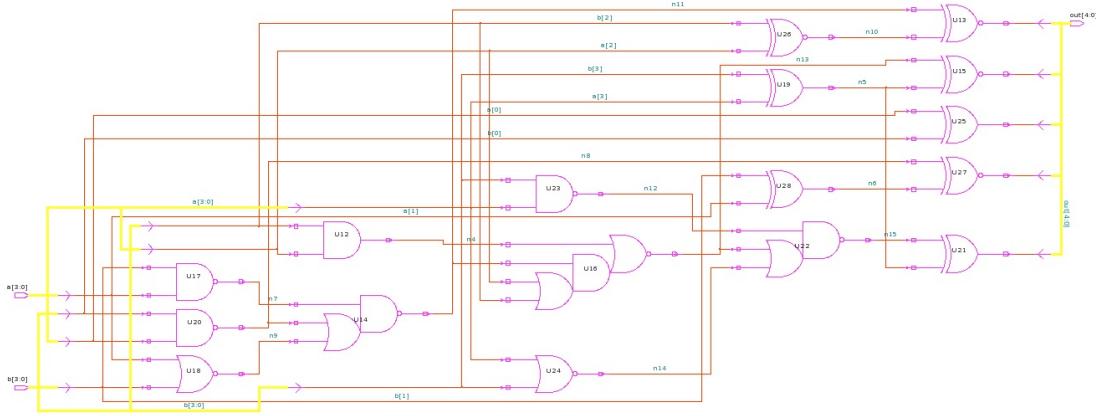

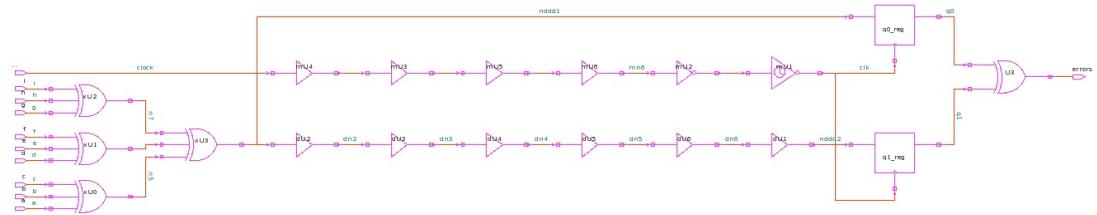

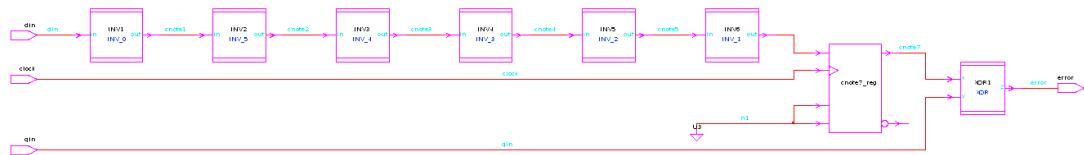

| 3.16 | 9 Input PCC Block Diagram after Synthesis                                      | 51 |

| 3.17 | 4-input PCC functional verification in a 32-bit MIPS                           | 52 |

| 3.18 | 9 Input Canary FF Block Diagram after Synthesis                                | 53 |

| 3.19 | Area Overhead                                                                  | 54 |

| 3.20 | Power Overhead                                                                 | 54 |

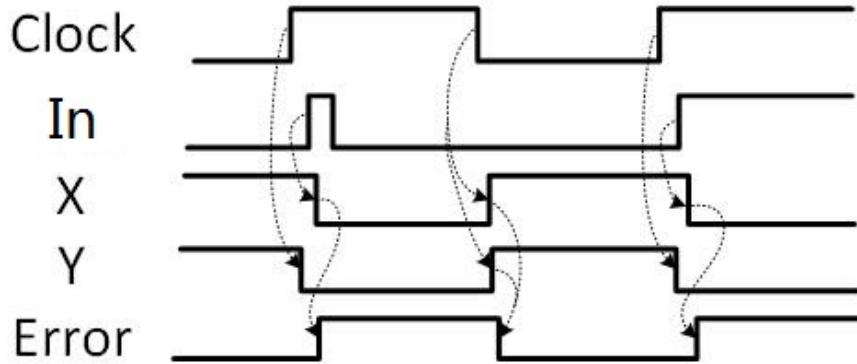

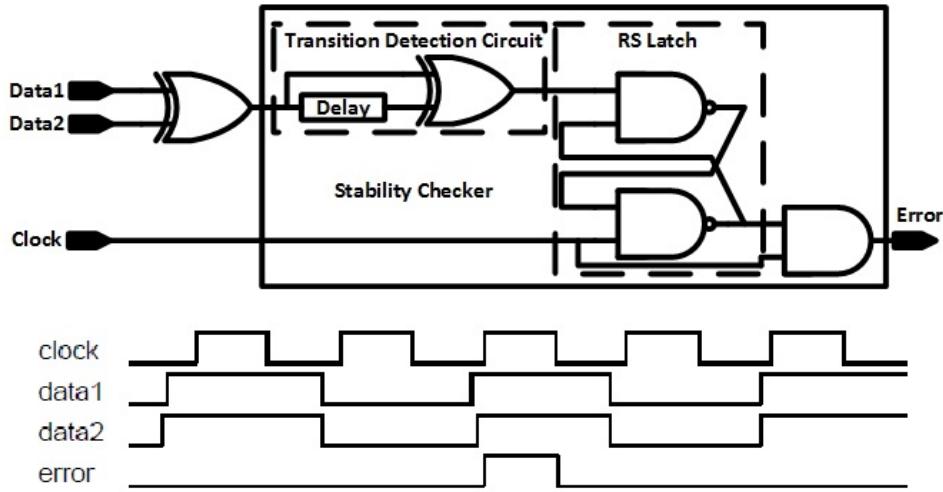

| 4.1  | The Architecture and timing diagram of SEDS                                    | 60 |

| 4.2  | The Architecture of DMEDS                                                      | 61 |

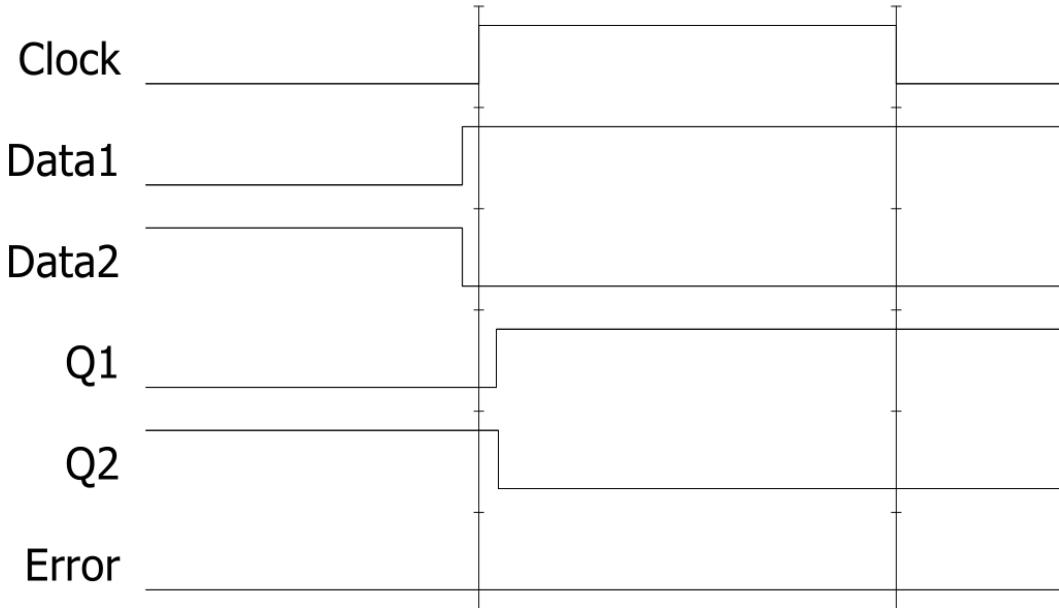

| 4.3  | MDU Timing Diagram                                                             | 61 |

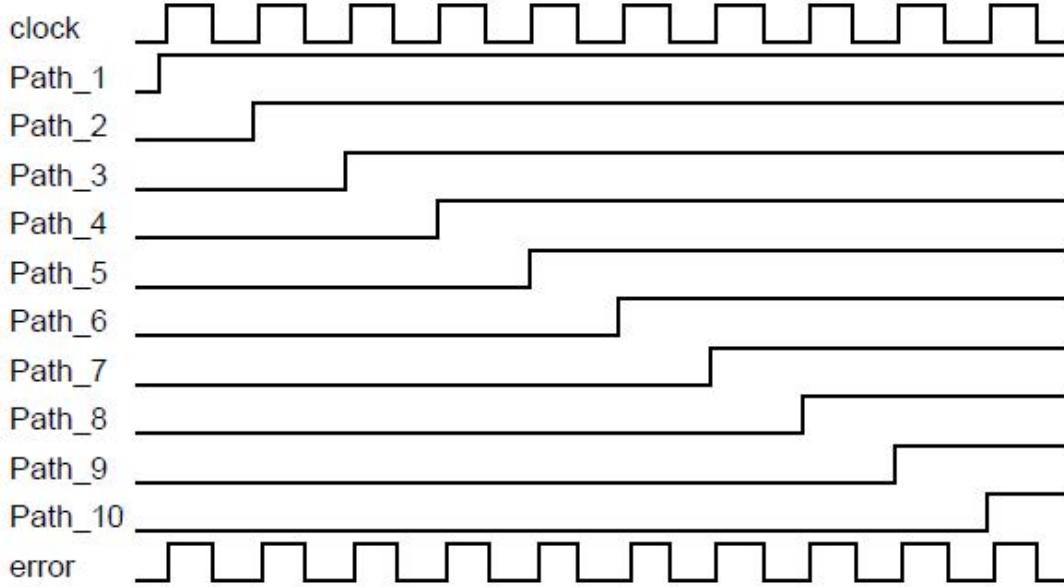

| 4.4  | DMEDS Timing Diagram                                                           | 62 |

| 4.5  | The Adjustable Delay Element                                                   | 64 |

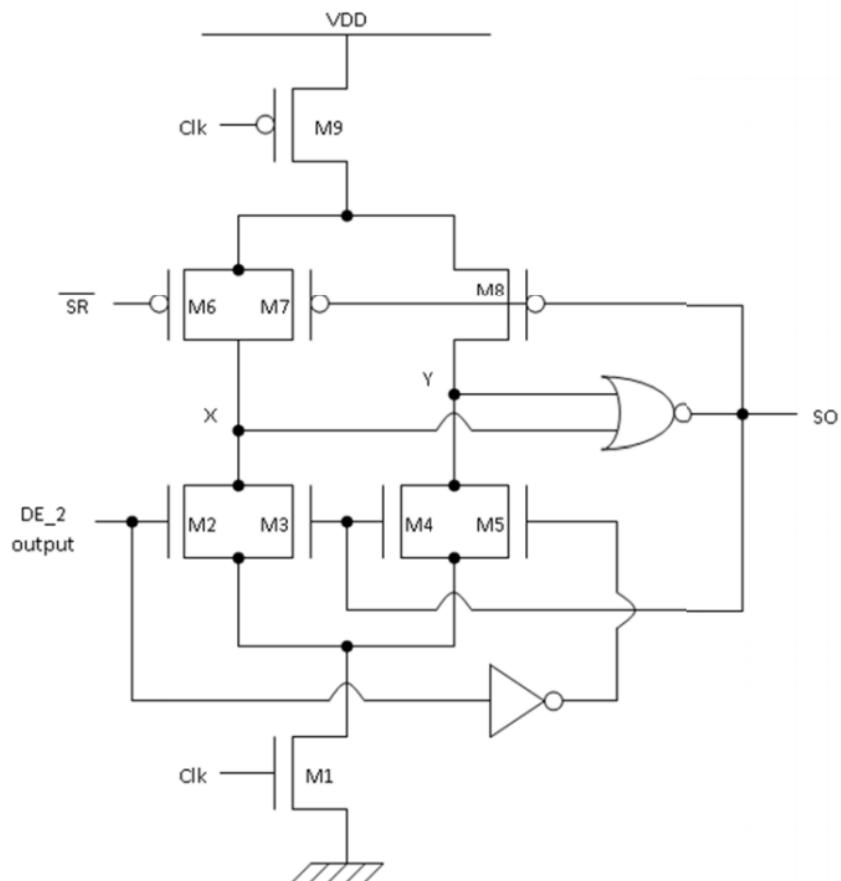

| 4.6  | The Stability Checker                                                          | 64 |

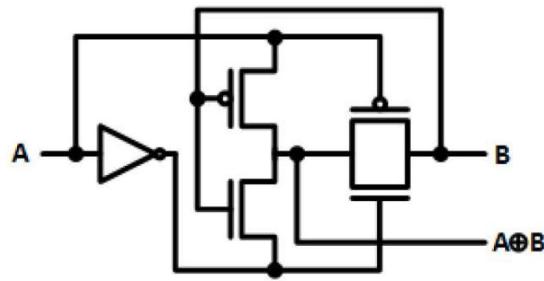

| 4.7  | 6 Transistor XOR Gate                                                          | 65 |

| 4.8  | Previously Design of Stability Checker[66]                                     | 65 |

| 4.9  | Stability Checker Timing Diagram                                               | 66 |

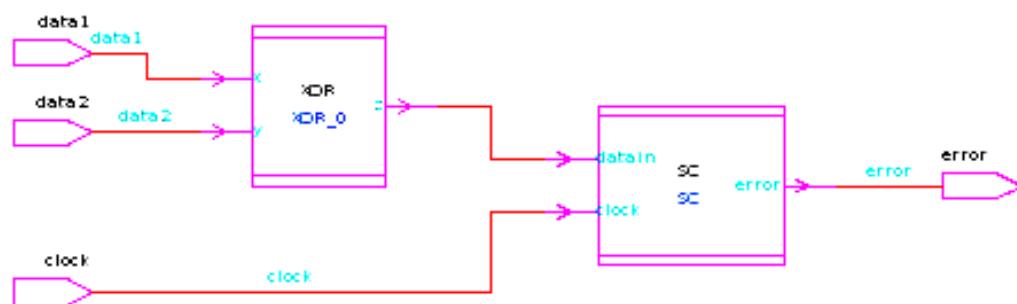

| 4.10 | Gate Level DMEDS                                                               | 66 |

| 4.11 | Gate Level Transition Detection Timing Diagram                                 | 67 |

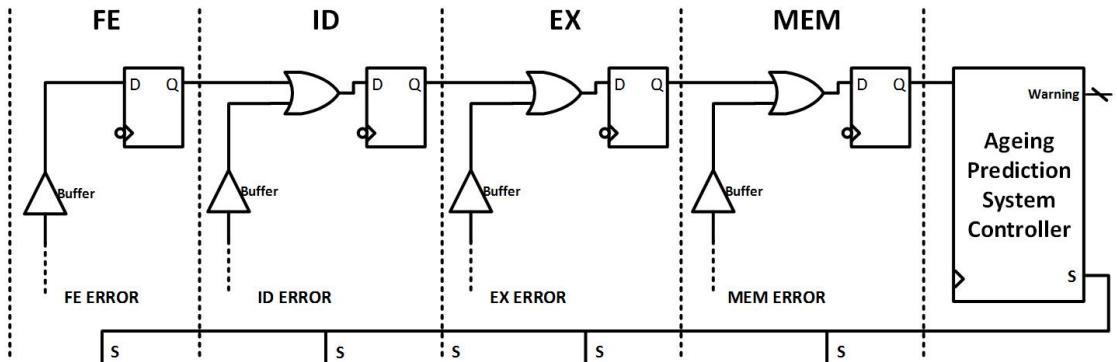

| 4.12 | Ageing Prediction System in a MIPS microprocessor with a pipeline              | 67 |

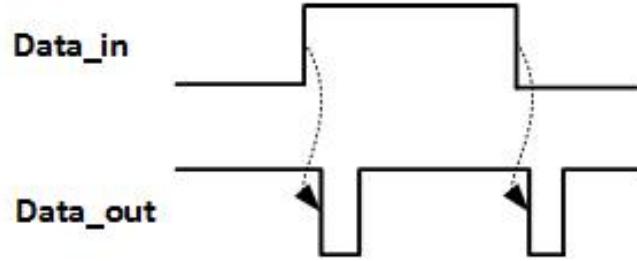

| 4.13 | Timing Diagram of Buffer                                                       | 68 |

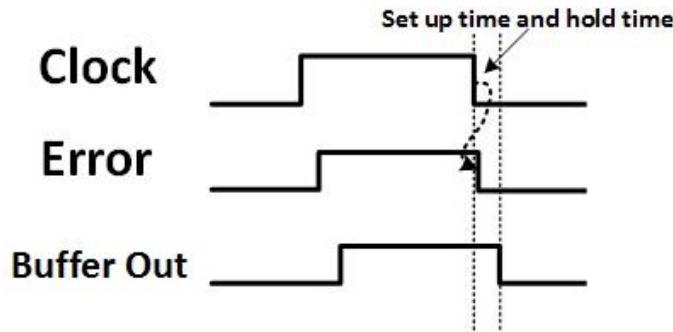

| 4.14 | Metastability Resistance Simulation result in Spice                            | 69 |

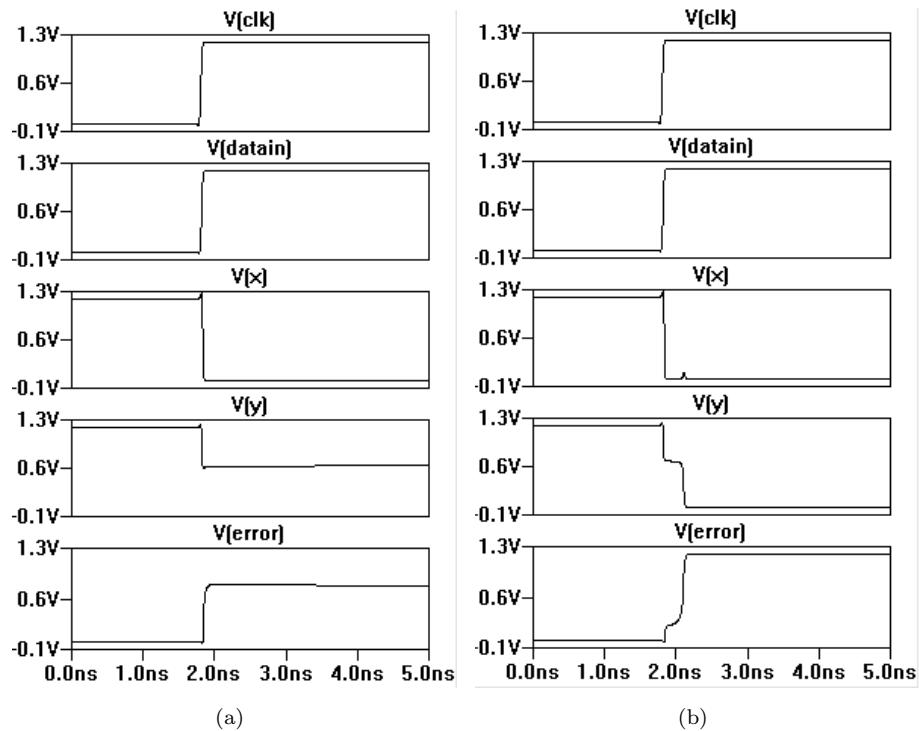

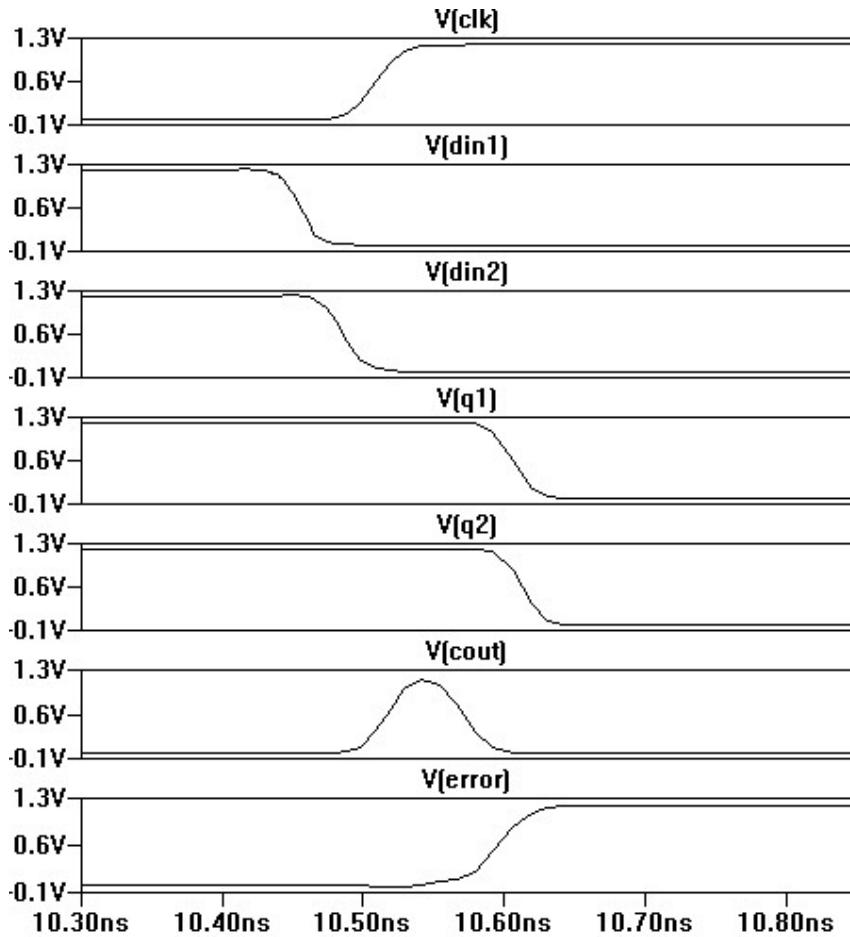

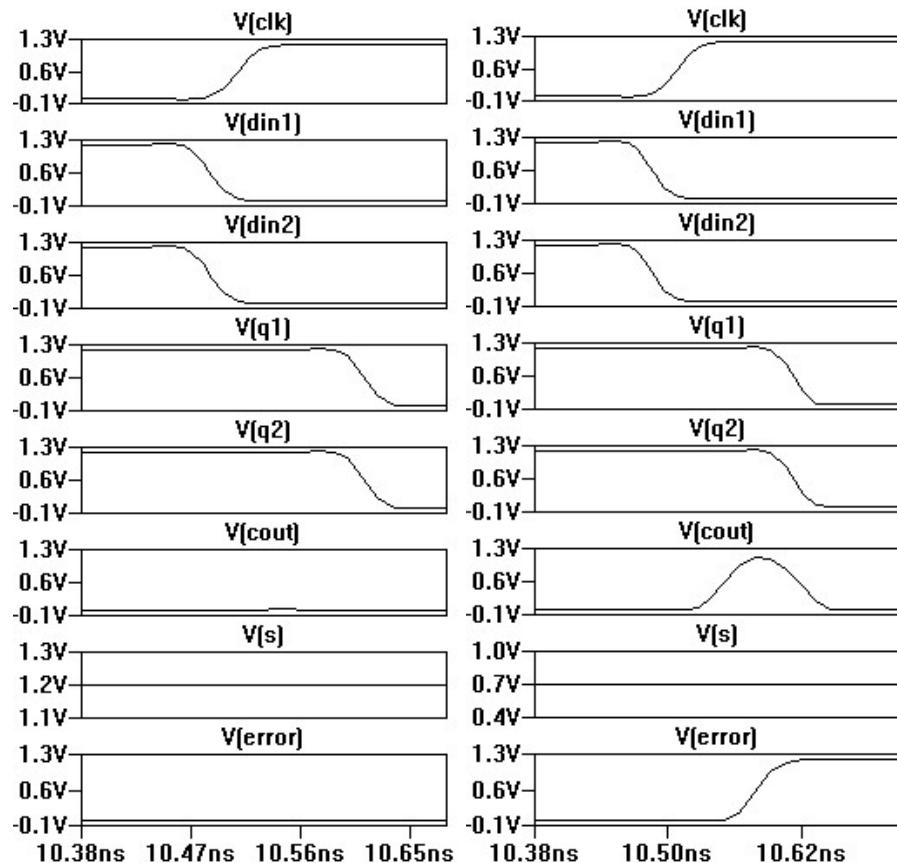

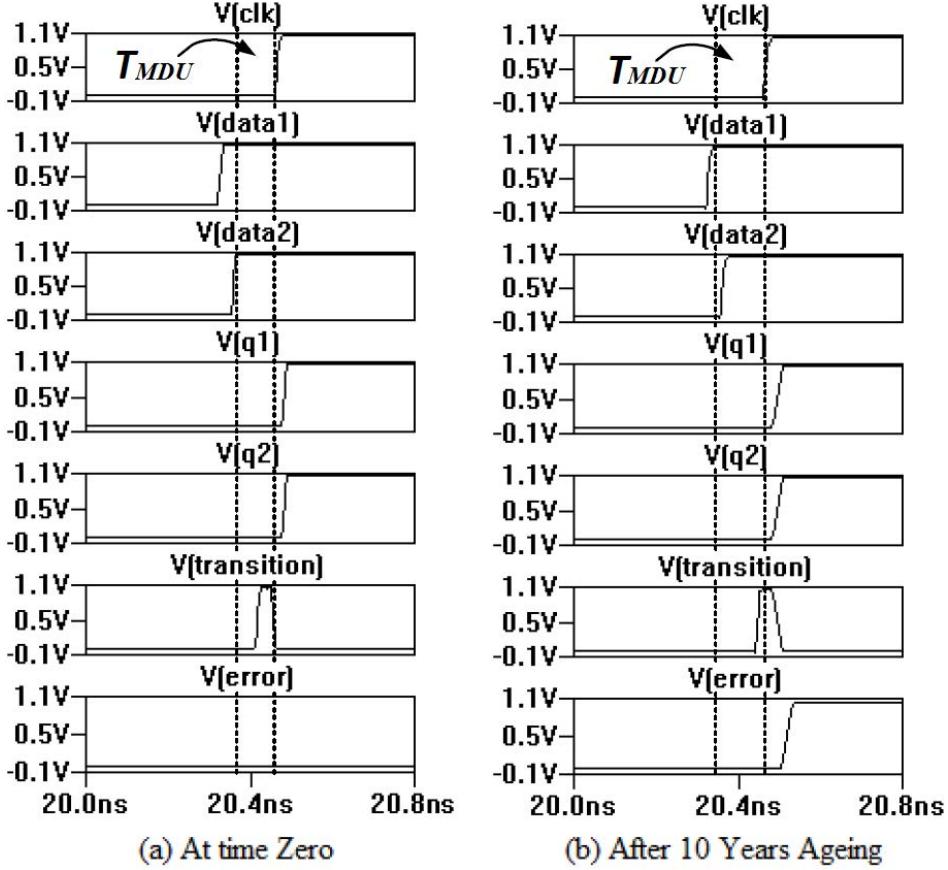

| 4.15 | Transistor Level Multiple Timing Error Detection Simulation result in Spice    | 70 |

| 4.16 | Transistor Level Worst Case Timing Error Prediction Simulation result in Spice | 71 |

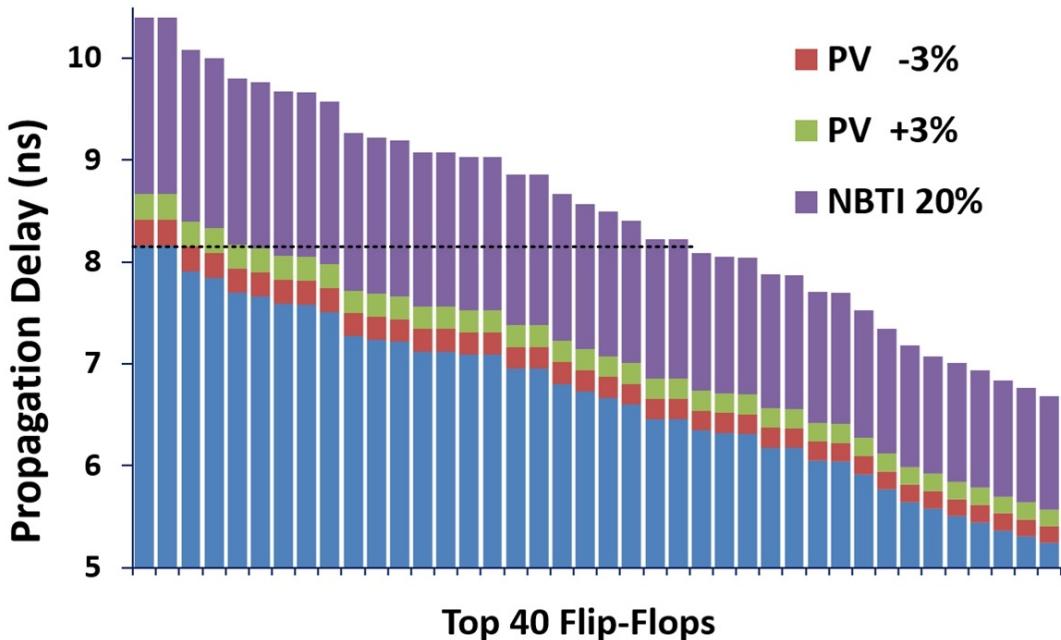

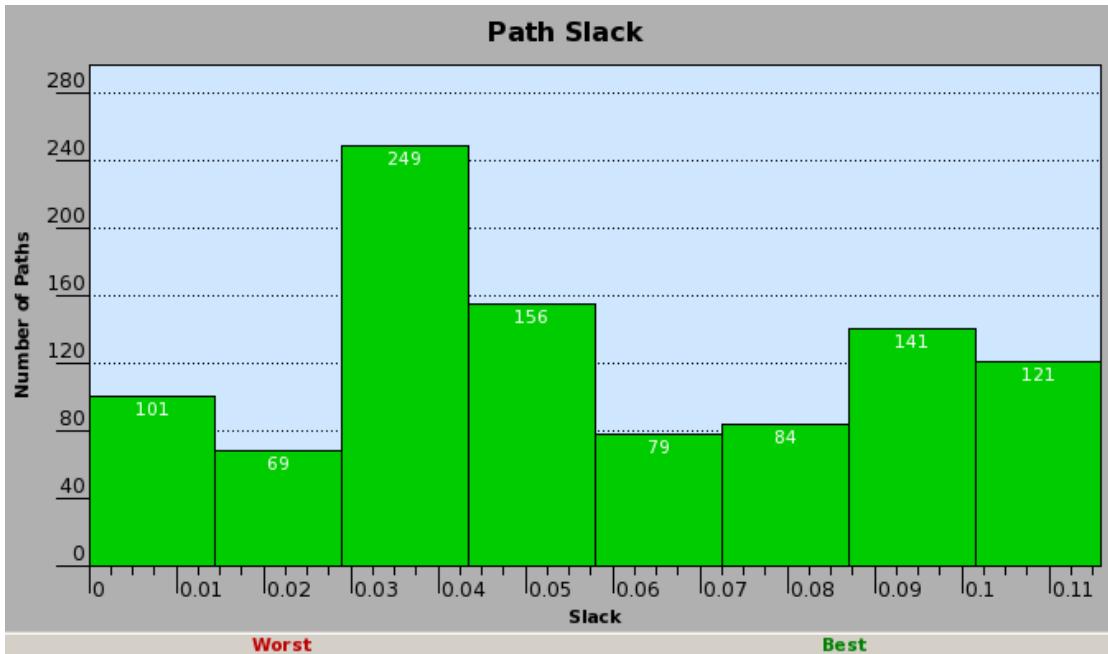

| 4.17 | Timing Report of the EX Stage in a 32-bit Pipelined MIPS                       | 72 |

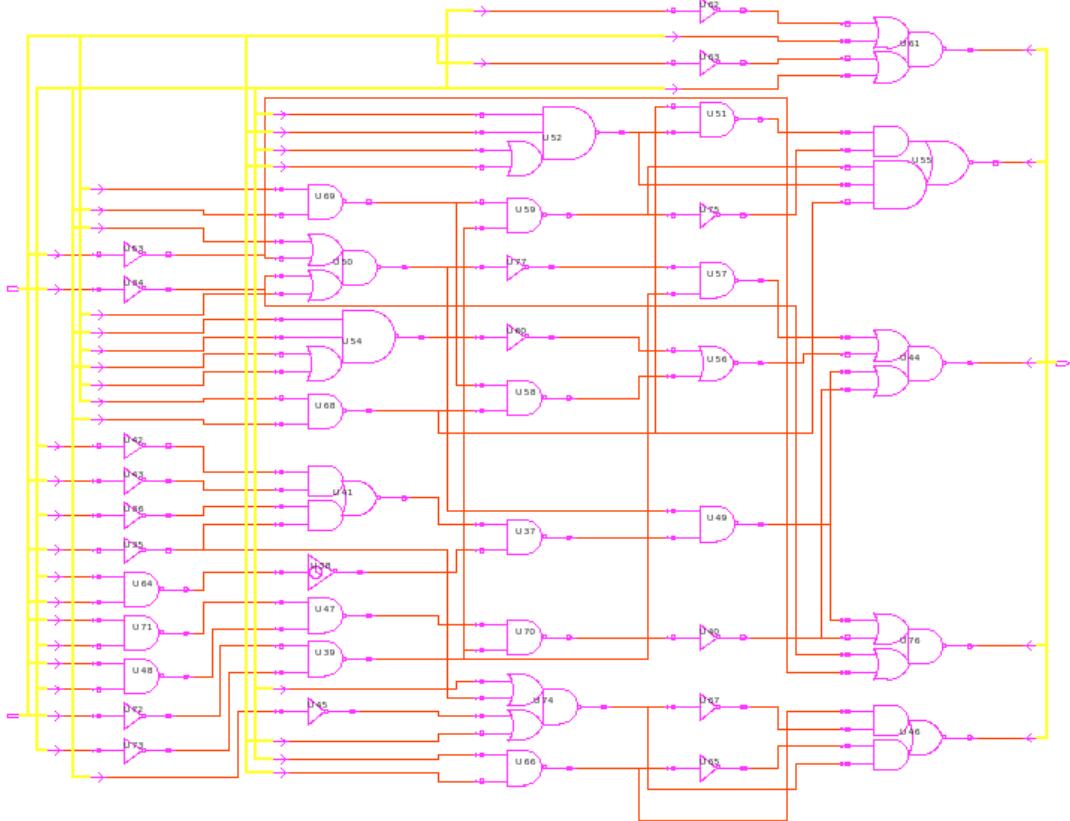

| 4.18 | DMEDS Block Diagram after Synthesis                                            | 73 |

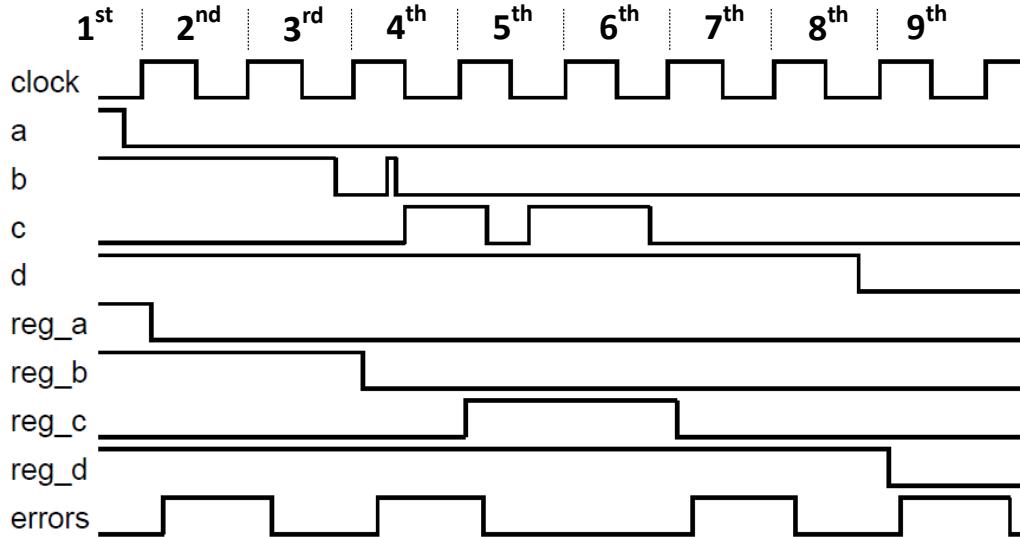

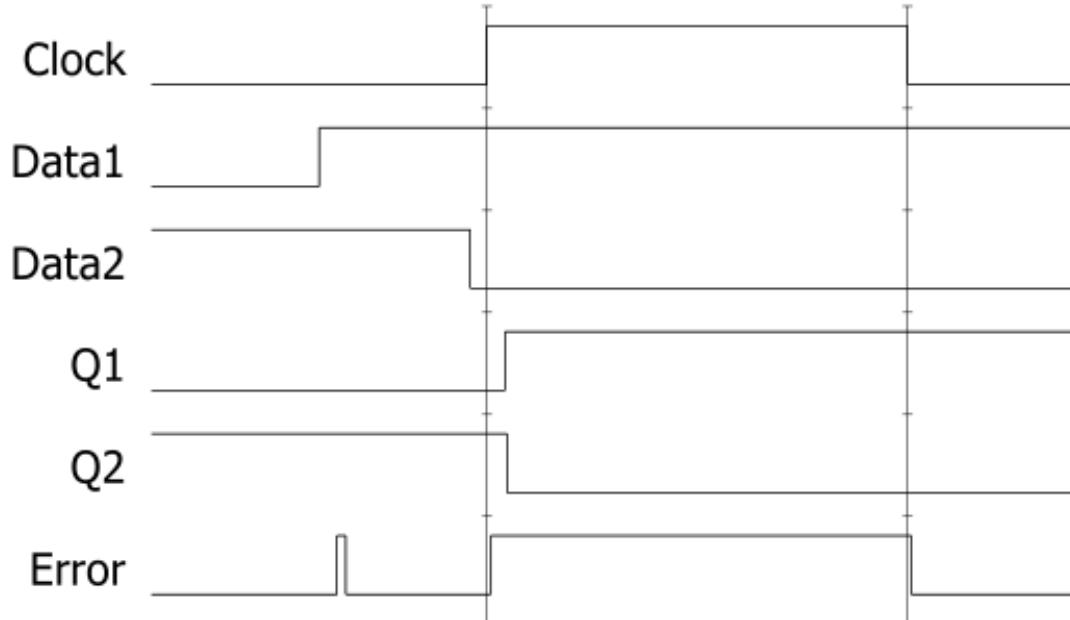

| 4.19 | Verilog Simulation Result of Timing Error Prediction in Modelsim               | 74 |

| 4.20 | Verilog Simulation Result of Worst Case Timing Error Prediction in Modelsim    | 75 |

| 4.21 | Canary FF Block Diagram after Synthesis                                        | 75 |

| 4.22 | Timing Report of the 32 bit MIPS                                               | 77 |

| 4.23 | Multiple Timing Error Detection                                                | 78 |

| 4.24 | Equivalent Model of DMEDS and Simulation Result                                | 80 |

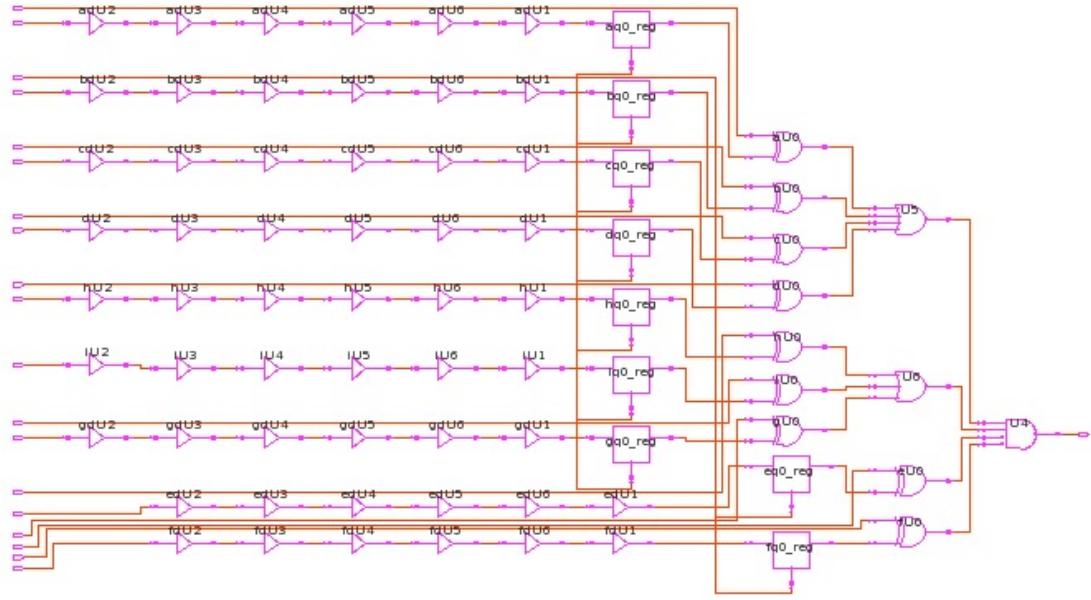

| 4.25 | 10-input DMEDS functionality verification in a 32-bit MIPS                     | 80 |

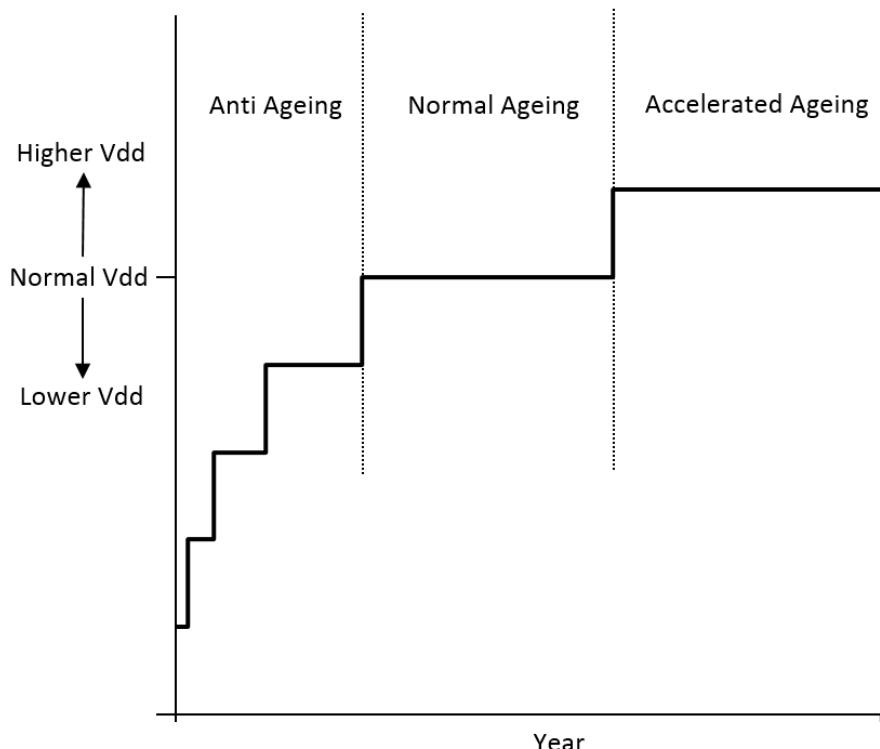

| 5.1  | The Average Supply Voltage of a Circuit with DVS Over the Years                | 85 |

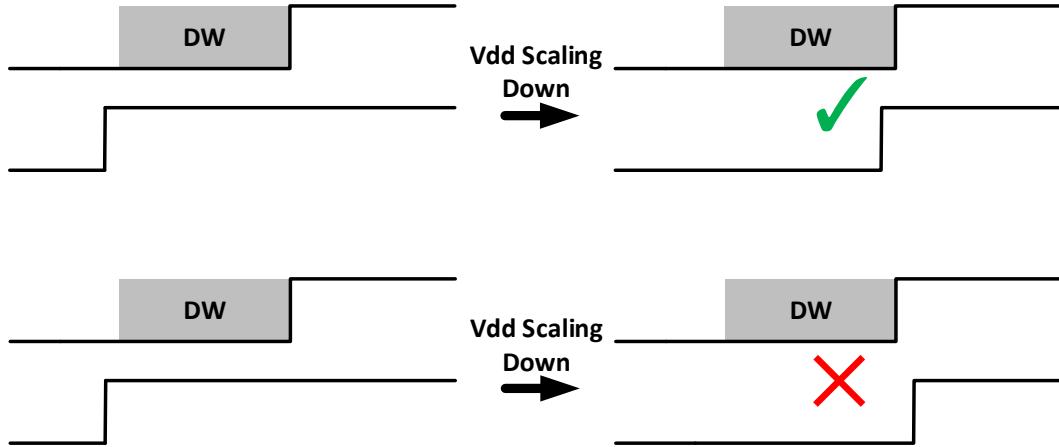

| 5.2  | Voltage Scaling                                                                | 86 |

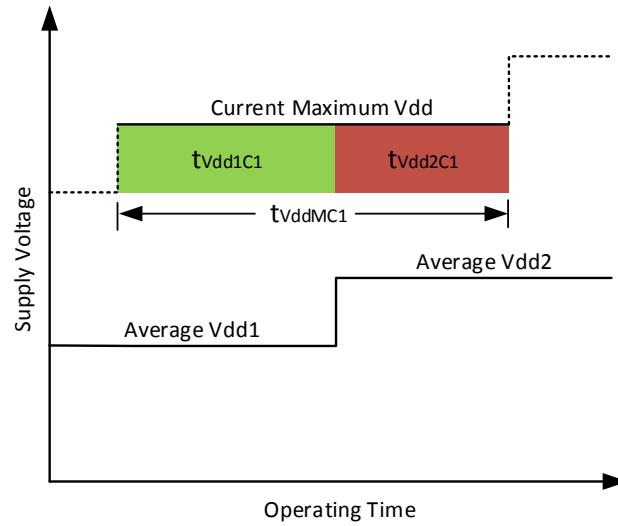

| 5.3  | Relationship Between Circuit's Operating Time and Supply Voltage               | 90 |

| 5.4  | Lifetime Estimation Flow Chart                                                 | 91 |

|      |                                                                                                         |     |

|------|---------------------------------------------------------------------------------------------------------|-----|

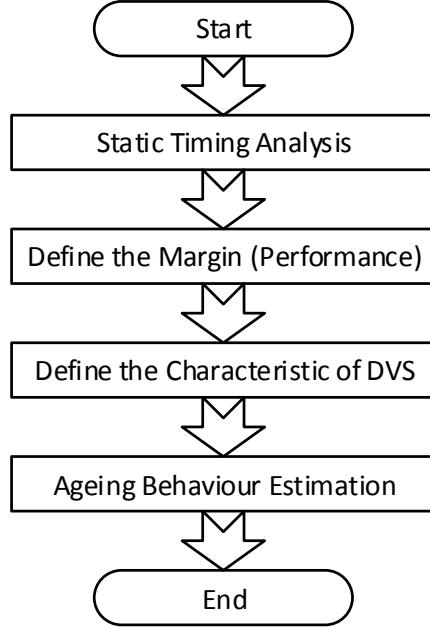

| 5.5  | Reference Circuit Estimation Flow Chart                                                                 | 92  |

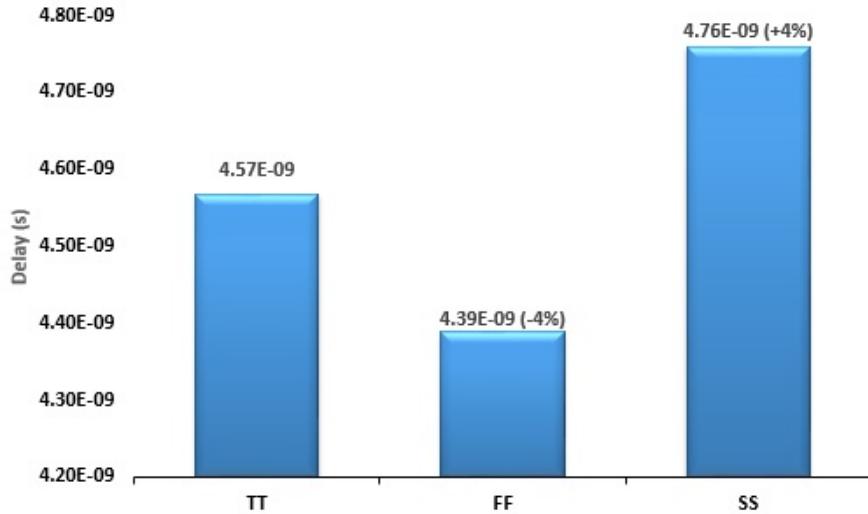

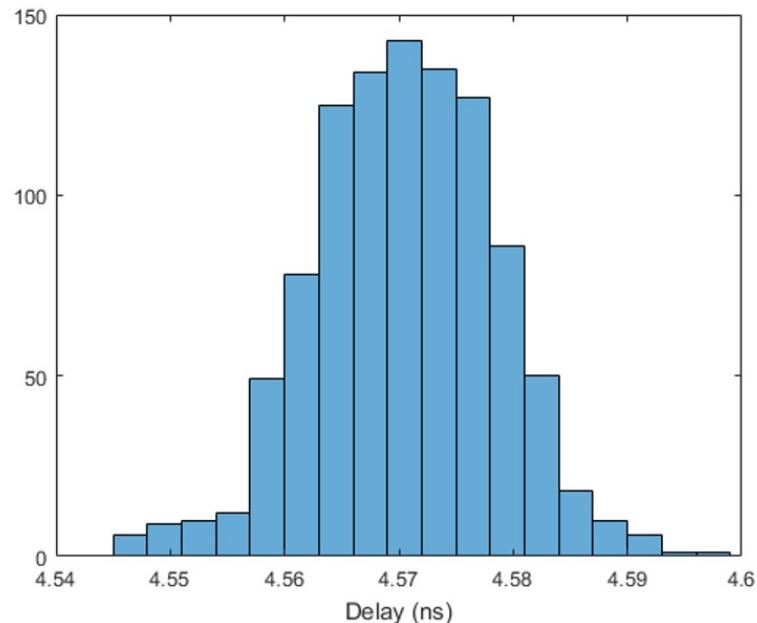

| 5.6  | The worst and best case process variations of an inverter chain of 90 nm technology                     | 93  |

| 5.7  | The random process variations distribution for an inverter chain of 90 nm technology sample size (1000) | 93  |

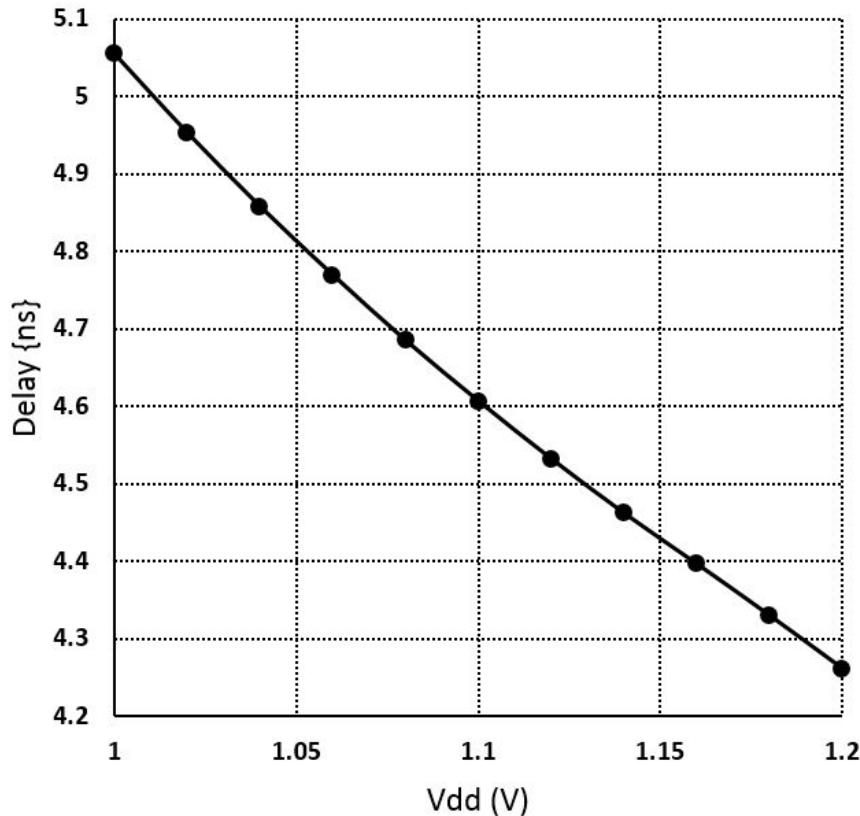

| 5.8  | The Relation Between Supply Voltage and Delay                                                           | 94  |

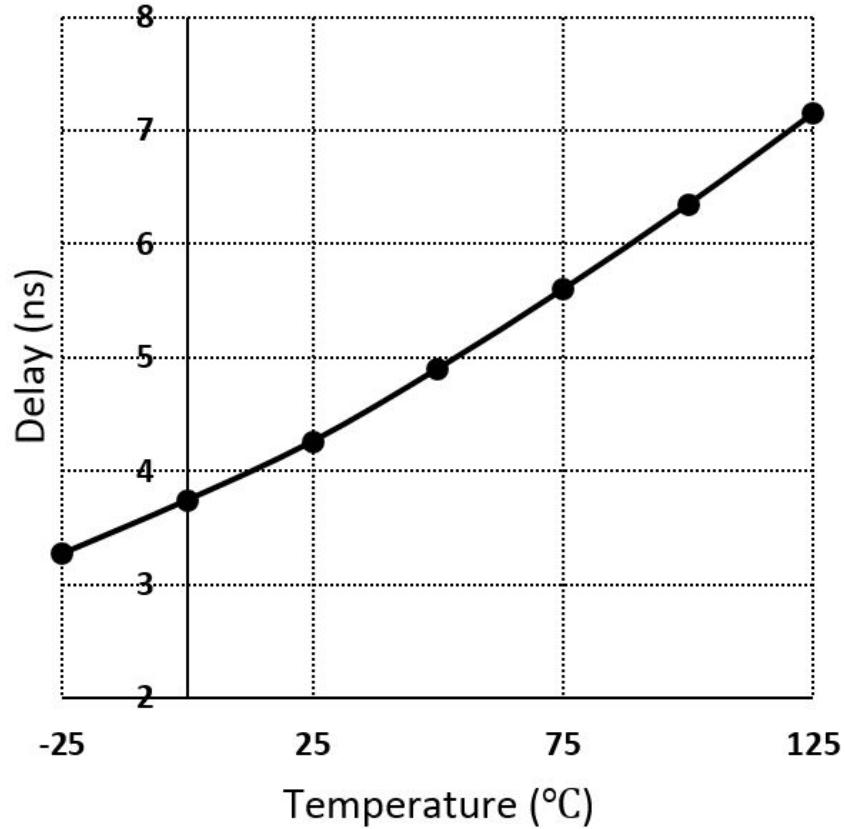

| 5.9  | The Relation Between Temperature and Delay                                                              | 95  |

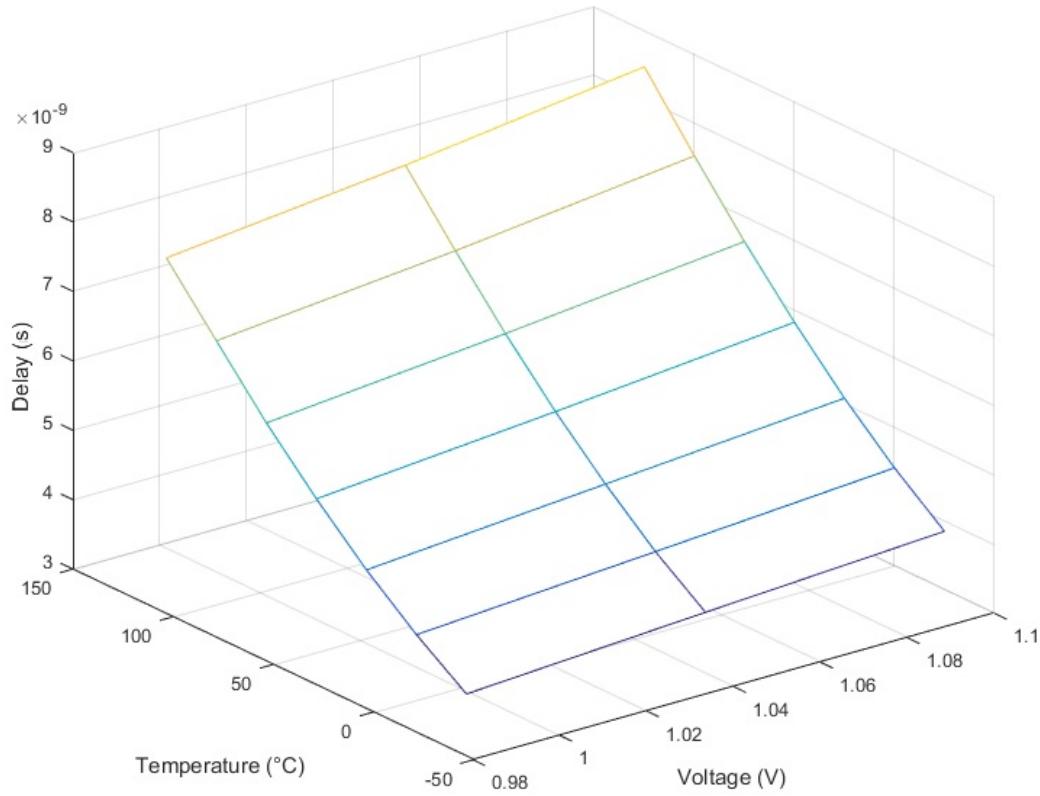

| 5.10 | The Relationship between Temperature Variation, Voltage Variation and Delay Degradation at time zero    | 96  |

| 5.11 | The margin for inverter Chain                                                                           | 97  |

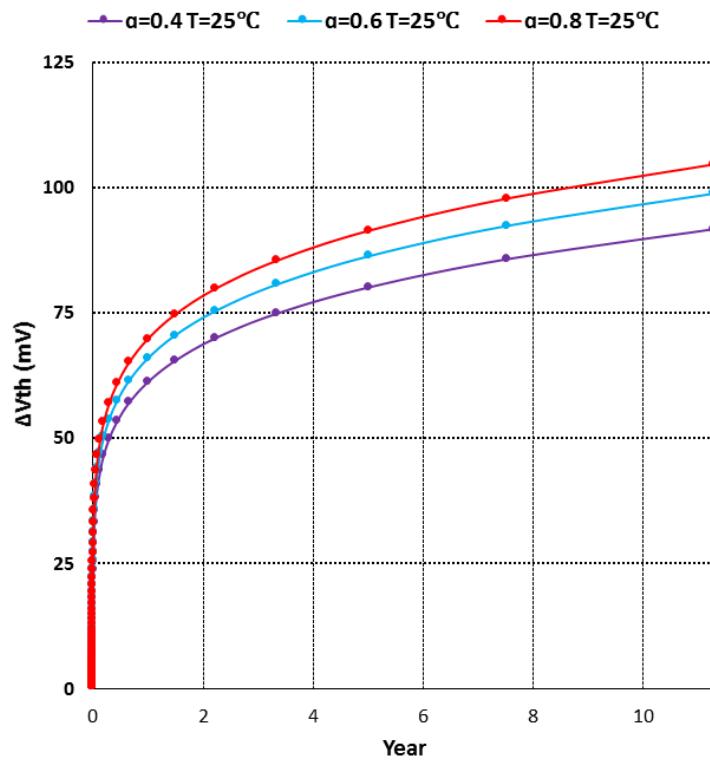

| 5.12 | Long Term Dynamic NBTI with Different Duty Cycle                                                        | 99  |

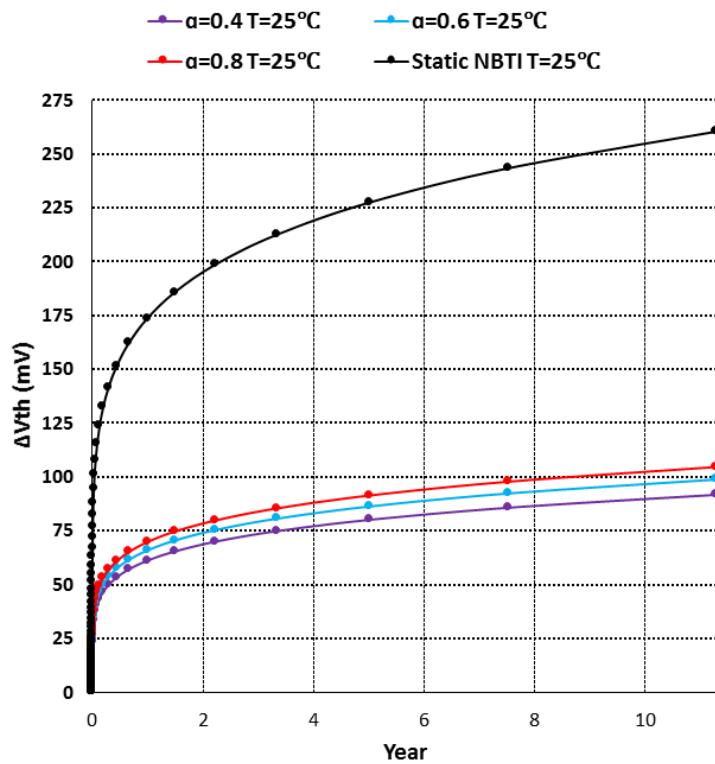

| 5.13 | Long Term Dynamic NBTI with Different Temperature                                                       | 100 |

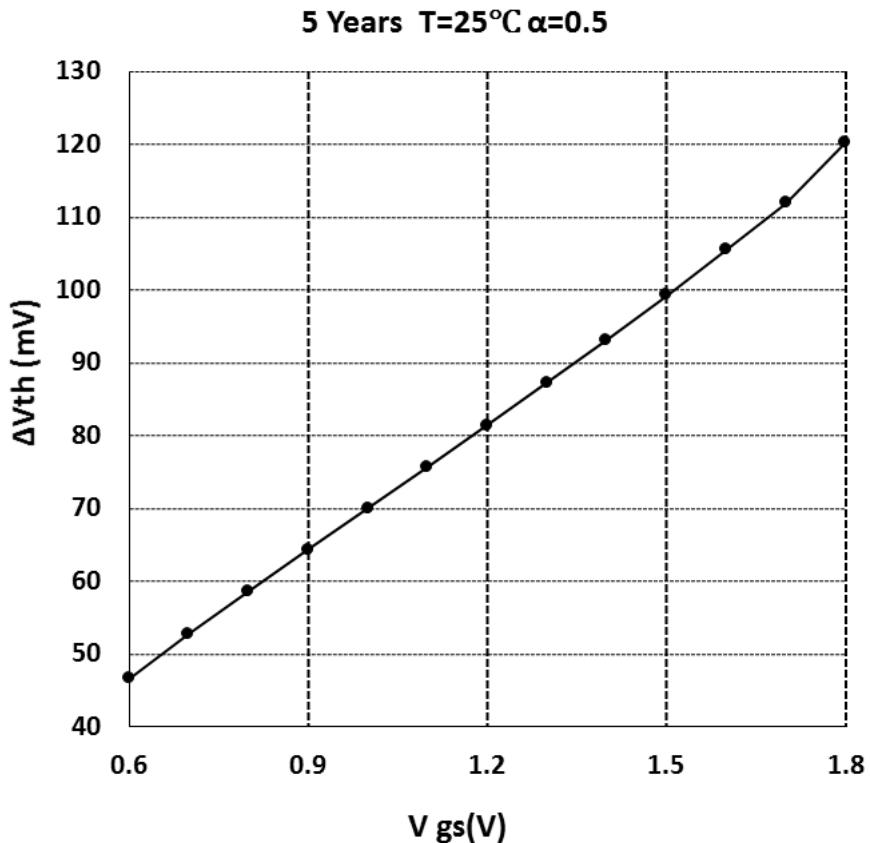

| 5.14 | Long Term Dynamic NBTI with Different Vgs                                                               | 101 |

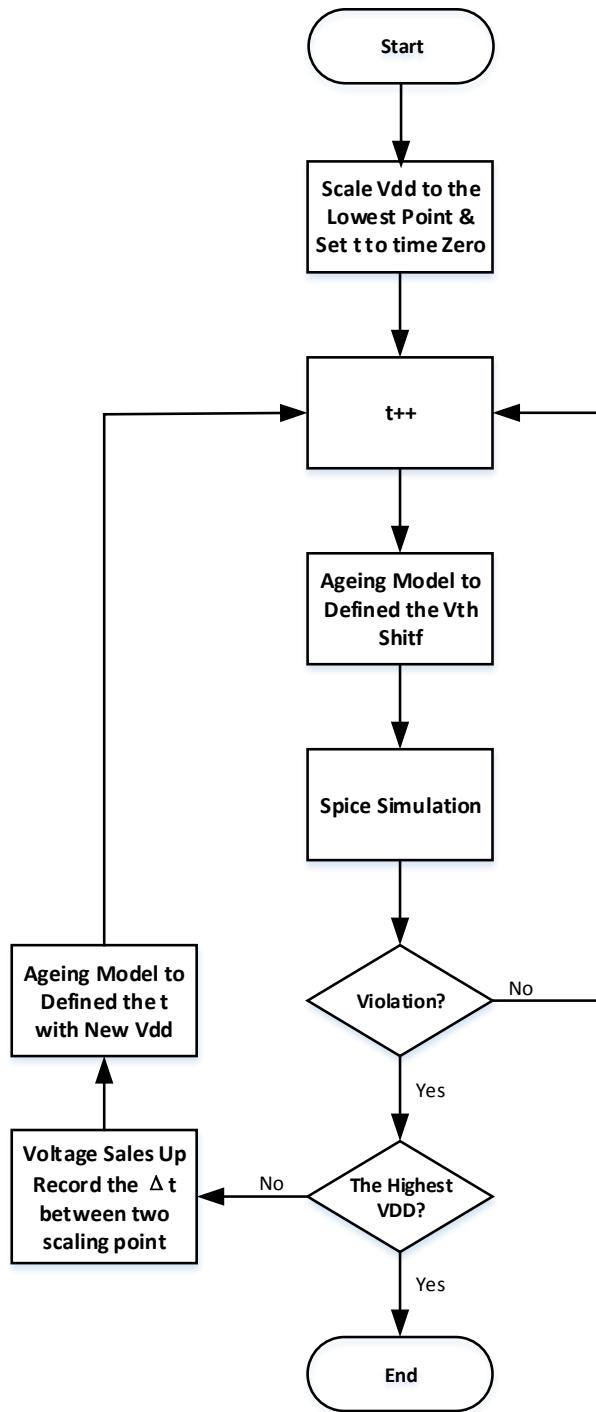

| 5.15 | Circuit Ageing Behaviour Estimation Flow Chart                                                          | 102 |

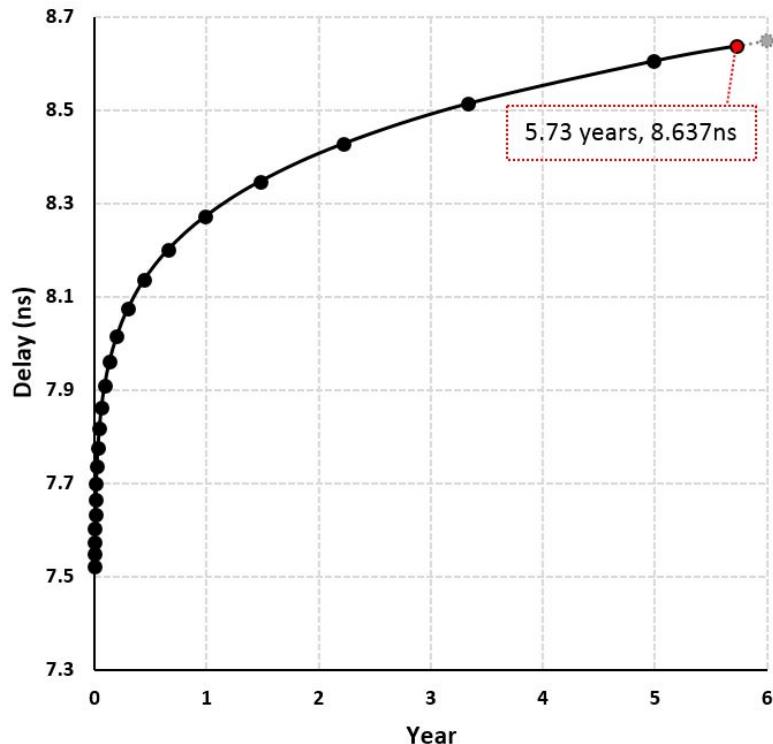

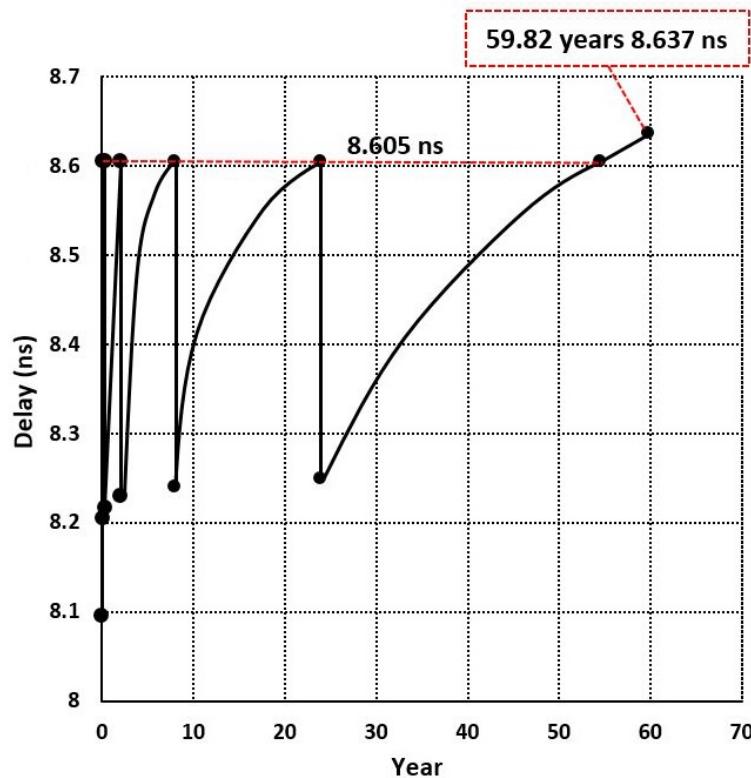

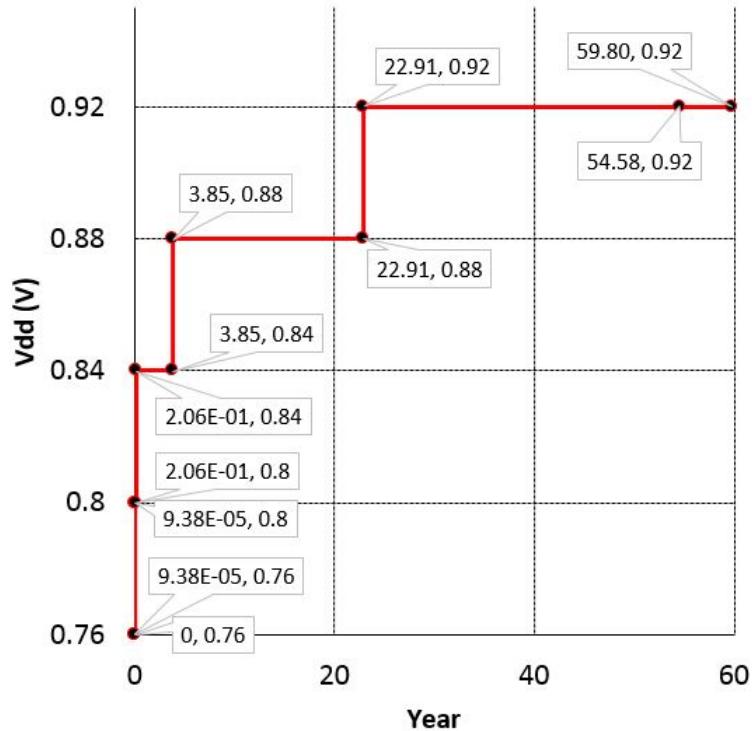

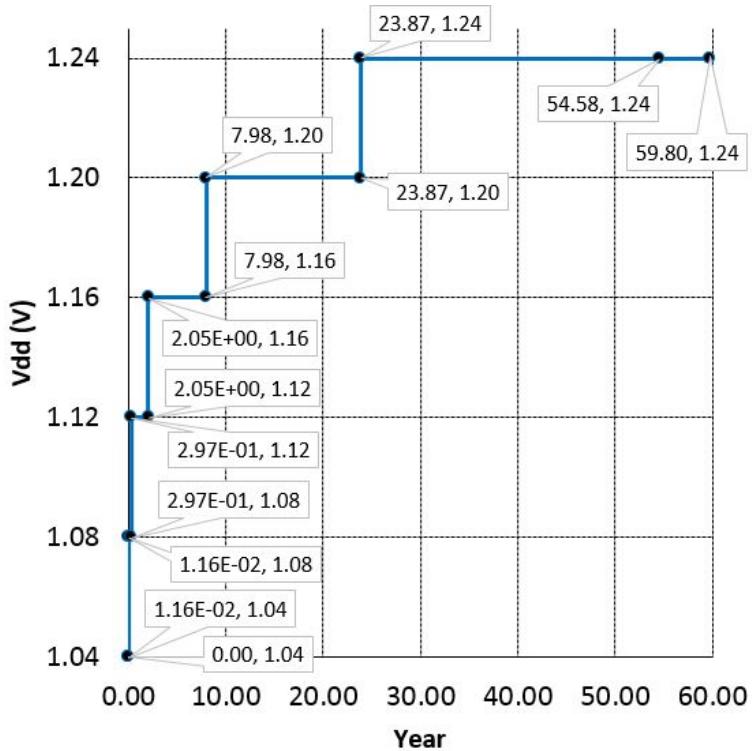

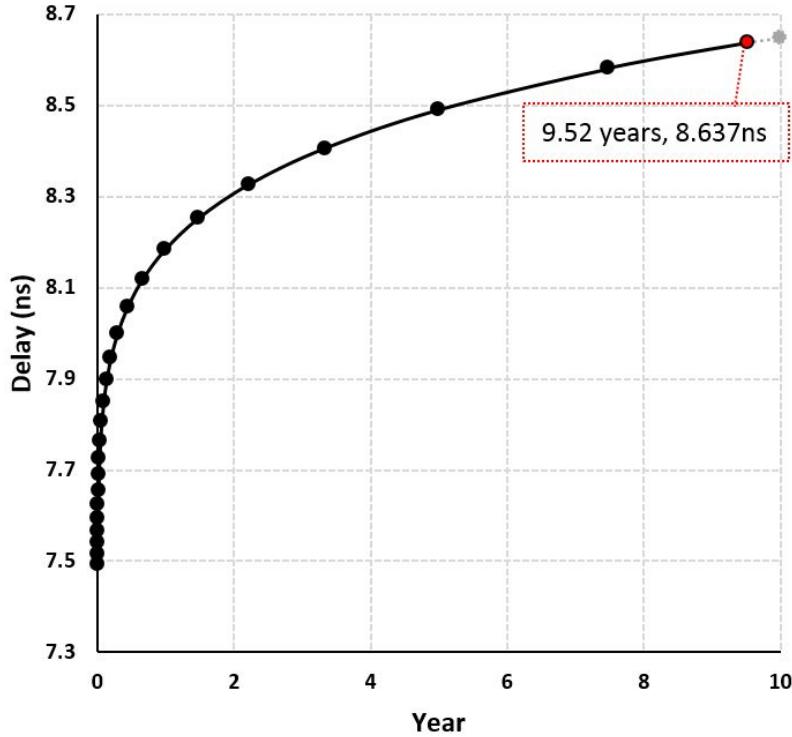

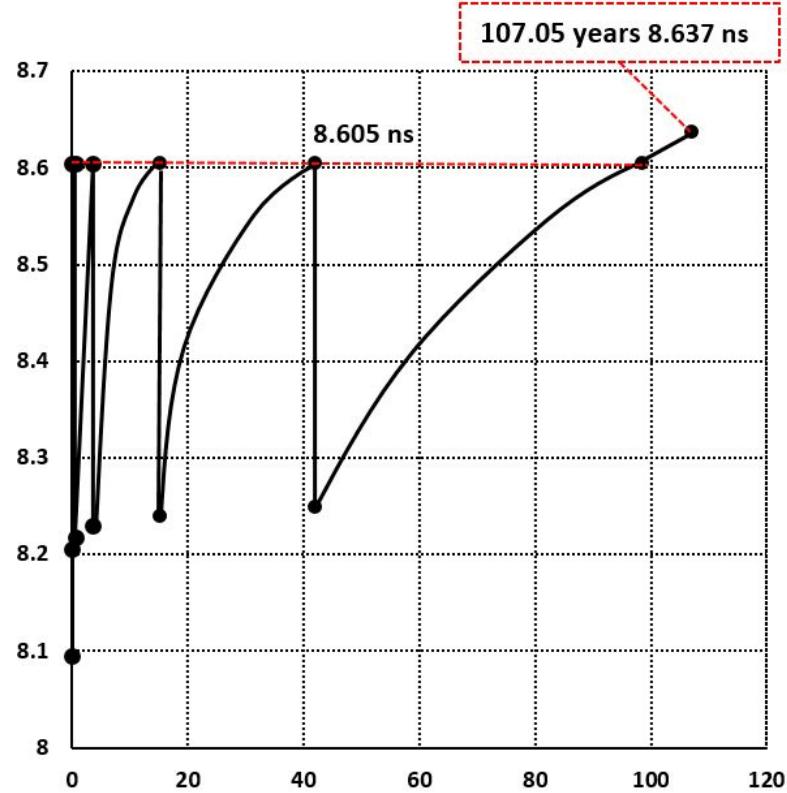

| 5.16 | Circuit Lifetime Estimation When $T=50^{\circ}\text{C}$                                                 | 103 |

| 5.17 | Lifetime Estimation of a Circuit With DVS When $T=50^{\circ}\text{C}$                                   | 104 |

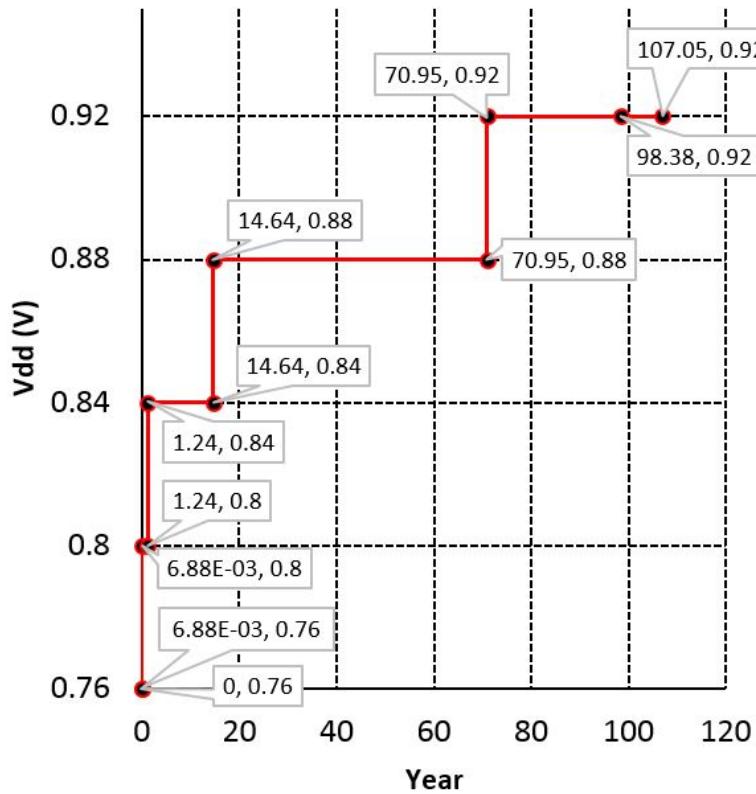

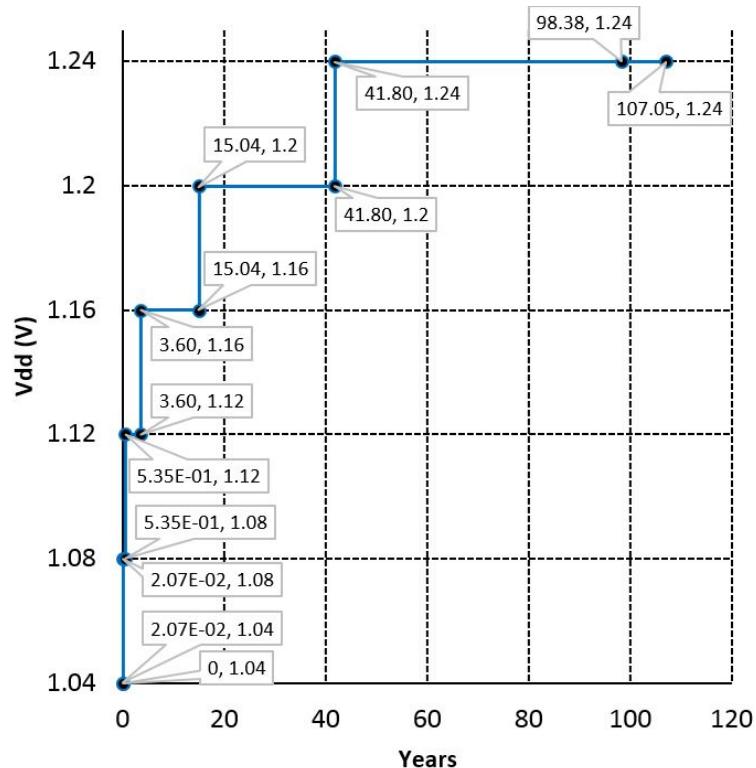

| 5.18 | Average Vdd During the Circuit's Lifetime When $T=50^{\circ}\text{C}$                                   | 105 |

| 5.19 | Maximum Vdd During the Circuit's Lifetime When $T=50^{\circ}\text{C}$                                   | 106 |

| 5.20 | Circuit Lifetime Estimation when $T=45^{\circ}\text{C}$                                                 | 108 |

| 5.21 | Lifetime Estimation of a Circuit with DVS when $T=45^{\circ}\text{C}$                                   | 109 |

| 5.22 | Average Vdd During the Circuit's Lifetime When $T=45^{\circ}\text{C}$                                   | 110 |

| 5.23 | Maximum Vdd During the Circuit's Lifetime When $T=45^{\circ}\text{C}$                                   | 110 |

# List of Tables

|      |                                                                            |     |

|------|----------------------------------------------------------------------------|-----|

| 2.1  | NBTI Vth Degradation Comparison in Different Operating Temperatures        | 19  |

| 2.2  | Estimated Threshold Voltage and Delay Degradation of an Inverter . . . . . | 21  |

| 3.1  | Percentage of Transitions from 4 paths . . . . .                           | 39  |

| 4.1  | Truth Table of the RS Latch . . . . .                                      | 66  |

| 4.2  | Comparison with Razor and Canary FF . . . . .                              | 73  |

| 4.3  | Comparison with Canary FF . . . . .                                        | 76  |

| 4.4  | Comparison with Canary FF in a 32 bit MIPS . . . . .                       | 76  |

| 4.5  | Comparison with other designs . . . . .                                    | 79  |

| 5.1  | Delay Degradation Comparison in Different Temperatures . . . . .           | 95  |

| 5.2  | The Best and Worst Intrinsic Delay Degradation of a Long Delay Path . .    | 96  |

| 5.3  | Intrinsic Delay with Different Vdd Under the Worst PVT variations . . .    | 97  |

| 5.4  | NBTI Vth Degradation Comparison in Different Operating Temperatures        | 100 |

| 5.5  | Weighted Average of Power Saving When Average T = 50°C . . . . .           | 106 |

| 5.6  | The Ratio of Average VDD $T_{avg} = 50^\circ\text{C}$ . . . . .            | 107 |

| 5.7  | Weighted Average of Power Saving When Average T = 45°C . . . . .           | 108 |

| 5.8  | Lifetime Estimation When T=45°C . . . . .                                  | 109 |

| 5.9  | Reference Data When T= 55°C and 50°C . . . . .                             | 111 |

| 5.10 | Target Data When T= 51°C - 54°C . . . . .                                  | 112 |

## Research Thesis: Declaration of Authorship

|             |           |

|-------------|-----------|

| Print name: | Gaole Sai |

|-------------|-----------|

|                  |                                                          |

|------------------|----------------------------------------------------------|

| Title of thesis: | Cost-efficient Delay-Fault Sensors for Ageing Prediction |

|------------------|----------------------------------------------------------|

I declare that this thesis and the work presented in it are my own and has been generated by me as the result of my own original research.

I confirm that:

1. This work was done wholly or mainly while in candidature for a research degree at this University;

2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

3. Where I have consulted the published work of others, this is always clearly attributed;

4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

5. I have acknowledged all main sources of help;

6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

7. Parts of this work have been published as:

Sai G, Halak B, Zwolinski M. A cost-efficient delay-fault monitor[C]/Circuits and Systems (ISCAS), 2017 IEEE International Symposium on. IEEE, 2017: 1-4.

Sai G, Halak B, Zwolinski M. Multi-Path Aging Sensor for Cost-Efficient Delay Fault Prediction [J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2018, 65(4): 491-495.

|            |  |       |  |

|------------|--|-------|--|

| Signature: |  | Date: |  |

|------------|--|-------|--|

## **Acknowledgements**

I would like to thank my supervisor, Professor Mark Zwolinski, for his continuous support and guidance in This work. It has been an honour to be his PhD student. His patient and vision in approaching a problem is a great thing that I have learnt during my PhD. I am grateful all this contribution of ideas and time to make my PhD experience fruitful and inspiring.

I would like to acknowledge my co-supervisor, Dr Basel Halak, for his advice and valuable reviews on this research. I immensely appreciate that I had a chance to work with him.

I would also like to take this opportunity to thank my parents and my partner for their continuous support and encouragement over the years.

Finally, I would like to thank all my colleagues who have helped me during my PhD.

# Chapter 1

## Introduction

### 1.1 Motivations For Research

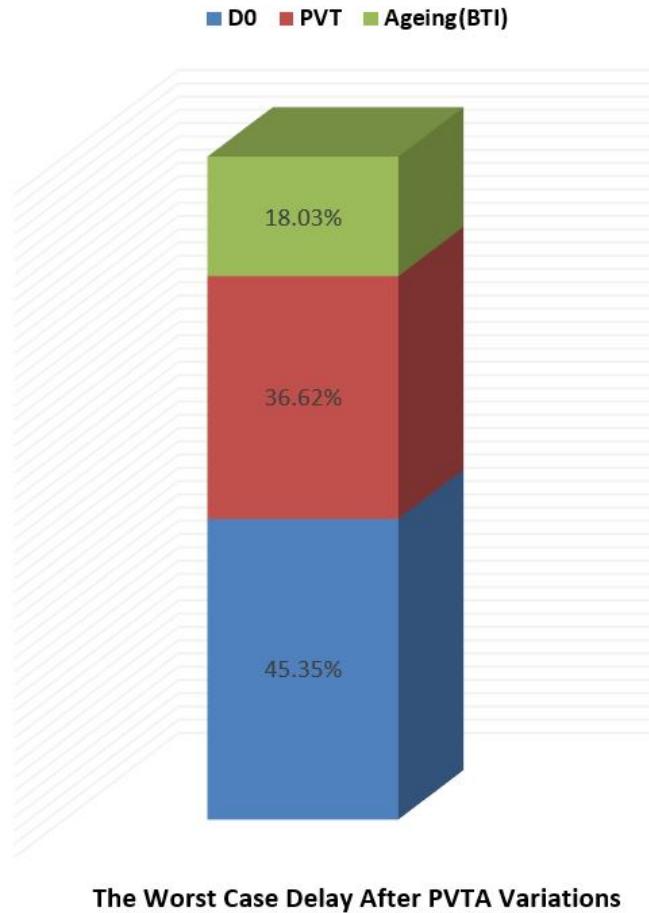

This research is motivated by the challenges arising from the reliability issues in modern technology node. The feature size of the technology node has been shrunk by more than 700 times, in the last five decades. The technology scaling results in a significant achievement regarding performance, power-efficiency and device density of the semiconductor devices. However, the side effect leads to the increasing of reliability issues. The Process, Voltage, Temperature variations and Ageing-induced (PVTA) device degradation are becoming major reliability concerns in modern semiconductor technologies. Those phenomena lead to performance degradation, and hence a timing error. To avoid delay fault induced failures, the integrated circuits are typically designed with large safety margins. This generally means a circuit is designed for worst-case operating conditions. Such an approach may limit system performance and lead to an increase in power consumption.

Dynamic reliability management schemes have been proposed to assure an IC's lifetime reliability. Such schemes are typically based on the use of sensors to predict circuit failures before the actual errors appear. The system can then adaptively scale its operating frequency and supply voltage according to the actual operating conditions to compensate for performance degradation. Various in-situ delay monitoring sensors have been proposed. These include delay fault detection and prediction techniques. Existing delay fault sensors are usually placed on the circuit's longest delay paths. However, the increasing complexity of ICs has led to a significant rise in the number of long paths and potential ageing-critical paths that may be vulnerable to timing errors. This means the cost of in-situ delay monitoring may be prohibitive.

Many research groups have been working on ageing models for years to estimate the lifetime of an IC before it's fabrication. However, the performance and lifetime degradation

from ageing effect is depending on the circuit's operating temperature, supply voltage and stress workload. Each chip might be running in different workload and environment. Therefore the environment and workload of an IC are unpredictable in the design stage of the CMOS circuits. The lifetime prediction of each chip is when it is predicted by using such models. On the other hand, the intrinsic delay of each chip is different due to the process variations delay degradation. This means the ageing prediction approaches are becoming unattainable. On the other hand, various ageing mitigation technique has been proposed to extend the lifetime of an IC. A trade-off between lifetime and performance usually achieves such approaches. A faster operation speed always the pursuit of people. Therefore, performance is one of the primary concern of the IC design nowadays. The performance is the one of primary concern of the IC design nowadays. Such sacrifices are reluctant.

## 1.2 Delay Fault Monitoring and PVT Variations

This Chapter briefly introduces the preliminary about delay fault monitoring and PVT variations, and Section 1.2.1 introduces the delay fault monitoring techniques, Section 1.2.2 outlines PVT variations, Section 1.2.3 explains the PVT variations and 1.2.4 summarises the limitation of state-of-the-art techniques.

### 1.2.1 Delay Fault Monitoring Techniques

Delay fault occurs when a late signal arrives and crossed timing constraint in a sequential logic circuit. This may result in the failure of the circuit. Various in-situ delay monitoring sensors have been proposed. These include delay fault detection and prediction techniques. The delay fault detection sensors check data consistency after the rising clock edge and delay prediction sensors check data consistency after the rising clock edge. The in-situ delay monitoring sensors usually work with the Dynamic Voltage and Frequency Scaling (DVFS) system. The sensor triggers an error signal when a late arriving signal is captured. It then sends the error signal to the DVFS system. Then the DVFS will decide to scale up the supply voltage or scale down the operating frequency. However, existing sensors usually detect/predicts the delay fault from one path, with the increasing complexity of ICs has led to a significant rise in the number of long paths and potential ageing-critical paths, cost of in-situ delay monitoring has become prohibitive. Moreover, existing sensors usually replace the flip-flop of the original design; therefore it is hard to implement, and it influences the functionality of the original design. Moreover, flip-flop type sensors are usually suffering from the metastability issue which affects the reliability and power dissipation of the digital circuit.

### 1.2.2 PVT Variations

The process, voltage, and temperature (PVT) variations have negative impacts on the performance of a manufactured chip. The effect of PVT variations has been increased due to aggressive fabrication technology scaling. Process variations are occurred due to the variations in channel length or doping concentration which causes the threshold voltage shift at time zero it, therefore, affects the performance of the CMOS devices. Voltage variations are considered as there are unexpected voltage drops in the power supply networks and also the variations in the supply voltage itself. Temperature variations are raised due to temperature fluctuations of the CMOS circuits and the environmental impacts. The PVT-induced leads to delay variations which affect the propagation delays the synchronous circuits it, therefore, cause the timing errors. The PVT variations affect both clock signals and data paths. Hence the longest delay paths may fail to deliver its output data within a given clock period.

### 1.2.3 Ageing Variation

Negative Bias Temperature Instability (NBTI) is considered one of the most critical ageing reliability issues in PMOS transistors. NBTI occurs because interface traps at the gate oxide interface are generated when a negative gate bias – a negative potential difference between gate and source, is applied. It manifests itself as an increase in the threshold voltage ( $V_{th}$ ) and a decrease in the drain current, thereby degrading timing. NBTI can cause more than 20% timing degradation in the worst-case operating conditions, which reduces the lifetime of an IC.

Positive BTI (PBTI) is an ageing reliability issue in NMOS transistors. The threshold voltage shift of PBTI has become significant in High-K Metal Gate technologies. The double effect of NBTI and PBTI exacerbates the timing degradation of ICs.

Hot-Carrier Injection (HCI) is a critical ageing issue in NMOS. HCI phenomenon occurs because the interface traps are generated at the drain end gate oxide interface when the current flow between the source and drain during the switching time. It manifests as the degradation of the switching characteristics, threshold voltage, drain-current and noise margin. Even worse, the HCI effect is unrecoverable. Therefore, although the HCI effect will not cause significant delay degradation like the NBTI effect, however, it accelerates the degradation of the device lifetime directly.

Existing ageing models estimate the lifetime of an IC before its fabrication without considering the actual operating conditions. The estimation result will be a range of lifetime which is not accurate.

### 1.2.4 The limitation of state-of-the-art techniques

The shortage of excising state-of-the-art techniques are summarised as follows:

1. Technology scaling arises the reliability issues of IC by the PVTA variations.

2. The cost of existing sensors implementation is very high, and the implementation usually replaces the original Flip Flop of the design as a sensor, which brings more reliability issues of ICs. The sensors are suffering from the metastability, and usually not suitable for ageing prediction.

3. Existing lifetime prediction techniques are either unreliable or not cost-efficient, and the state-of-the-art ageing mitigation techniques are usually sacrifices the performance of an IC.

The objectives of this research are raised by the limitation of state-of-the-art techniques, shown in the next Section.

## 1.3 Objectives

There are several research questions which are summarised by state-of-the-art techniques introduced in Section 1.2.

1. How do the PVTA variations impact the CMOS circuits, and what the PVTA variations arise reliability issues?

2. Is there a solution for cost-efficient delay-fault monitoring without replacing the original Flip Flop of the design, resistance to the metastability, and suitable for ageing prediction?

3. Can we propose a reliable lifetime prediction algorithm with the consideration of real operating conditions and also suitable for ageing mitigation without sacrifice the performance?

The first question is answered by the background study for this research shown in Chapter 2. The second question is answered in Chapter 3 and 4. Two cost-efficient sensors are proposed for delay-fault monitoring, Parity Check Circuit (PCC) and Differential Multiple Error Detection Sensor (DMEDS). Both sensors can monitor two or more paths synchronously and monitor the delay fault without replacing the original Flip Flop of the Design. Furthermore, the DMEDS is resistance to the metastability. The last question is answered in Chapter 5. An ageing prediction algorithm is proposed for real-time lifetime

prediction. The ageing prediction algorithm predicts the lifetime of an IC by using the limited information which is provided by the sensors (PCC or DMEDS). Together with the Dynamic Voltage Scaling (DVS), the system can predict and extend the lifetime simultaneously. The contributions of this research are shown in the next Section.

## 1.4 Contributions

In Chapter 3.1, we propose a cost-efficient Parity Check Circuit (PCC) for delay fault prediction to mitigate the cost of in situ delay monitoring. PCC can monitor multiple paths simultaneously, which significantly reduces the number of sensors. The proposed sensor has been designed and verified in a 65nm technology. Our results indicate that using the proposed sensor for delay fault monitoring in a 32-bit MIPS can lead to a significant saving in the area and power overheads, compared to the use of canary flip-flops [40]: by two-thirds and one-third, respectively.

In Chapter 4, we propose a new Differential Multiple Error Detection Sensor (DMEDS) for timing errors. DMEDS can monitor multiple paths simultaneously, which significantly reduces the number of sensors needed to monitor ageing-induced delay faults. DMEDS has been designed at transistor level in a 32nm 90 nm CMOS technology and verified at the system level. Our results indicate that the use of the proposed sensor for delay fault monitoring across 10 paths can lead to a significant saving in area overhead compared to Razor [29], and Canary [40]: 87.59%, 77.67%, respectively.

At the end of this thesis, we propose an idea of lifetime prediction system, and the ageing prediction controller receives the error signal from the ageing prediction sensors such as DMEDS and PCC, it then compares the data with reference to analysis the ageing of the device. The ageing data of the reference comes from the existing ageing model. Our results indicate that the use of the proposed system for lifetime prediction system can accurately estimate the lifetime of the IC compared with the data from the ageing model. The error is controlled within 5% with limited reference data.

## 1.5 Thesis Structure

The rest of the thesis is organized as follows. Chapter 2 briefly describes related work, the Dynamic Voltage Scaling (DVS) system; ageing mechanisms; and existing sensors. Chapter 3 outlines the design of new ageing predicting sensor PCC. Chapter 4 outlines the design of new ageing predicting sensor DMEDS. A new lifetime predicting model is outlined in chapter 5. Finally, conclusions and future works are drawn in chapter 6.

## 1.6 Publications

The contributions presented in this thesis have been published in the flowing papers:

1. Sai, Gaole, Basel Halak, and Mark Zwolinski. "A cost-efficient delay-fault monitor." *Circuits and Systems (ISCAS), 2017 IEEE International Symposium on*. IEEE, 2017.

2. Sai, Gaole, Basel Halak, and Mark Zwolinski. "Multi-Path Aging Sensor for Cost-Efficient Delay Fault Prediction." *IEEE Transactions on Circuits and Systems II: Express Briefs* 65.4 (2018): 491-495.

# Chapter 2

## Background

This chapter gives an extensive overview of state-of-the-art existing technologies which are related to the research of this thesis. It introduces the relevant background of Chapter 3, 4 and 5 respectively.

### 2.0.1 Static Timing Analysis and Delay Fault

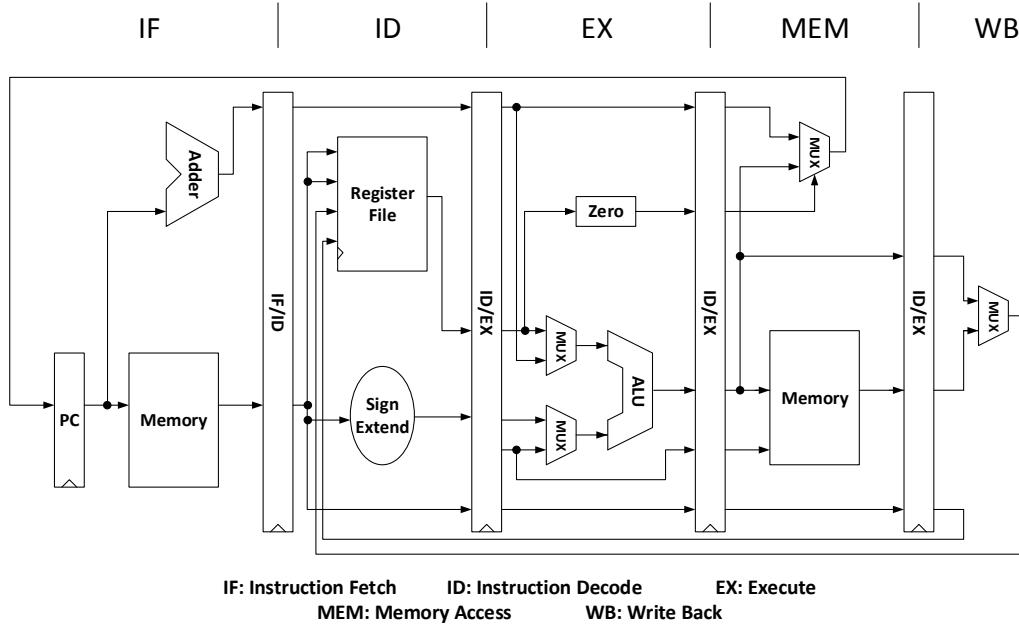

Static timing analysis (STA) is used to predict performance (the clock speed) of a fabricated digital circuit. It is widely used in high-performance circuit design, [51]. The critical path (the longest delay path) is defined as the path between an input and an output with the maximum delay after STA. Figure 2.1 shows the architecture of a basic pipelined MIPS. The pipelined divides the processor to several to improve the performance of the processor. The traditional processor runs the instructions one by one, and it usually takes a few clock cycles to run each instruction. The pipelined design is able to run more than one instruction simultaneously. The MIPS, as shown in 2.1, for example, is able to run 5 instruction at the same clock cycle. The delay fault occurs when a late signal arrives and crossed timing constraint in a sequential logic circuit. This may result in the failure of the circuit, [38, 70] .

The critical path of the design, as shown in Figure 2.1 is the longest delay path from those state, IF, ID EX MEM and WB after. The minimum clock cycle should be higher than the delay from the critical path; otherwise, it may result in a delay fault. The technology scaling results in a significant achievement regarding performance, power-efficiency and device density of the semiconductor devices. However, the side effect leads to the increasing of reliability issues. The Process, Voltage, Temperature variations and Aging-induced (PVTA) device degradation are becoming major reliability concerns in modern semiconductor technologies. Those phenomena lead to performance degradation, and hence a timing error. To avoid failures caused by delay fault, the integrated circuits are

FIGURE 2.1: The Architecture of a Pipelined MIPS, Reproduced from [48]

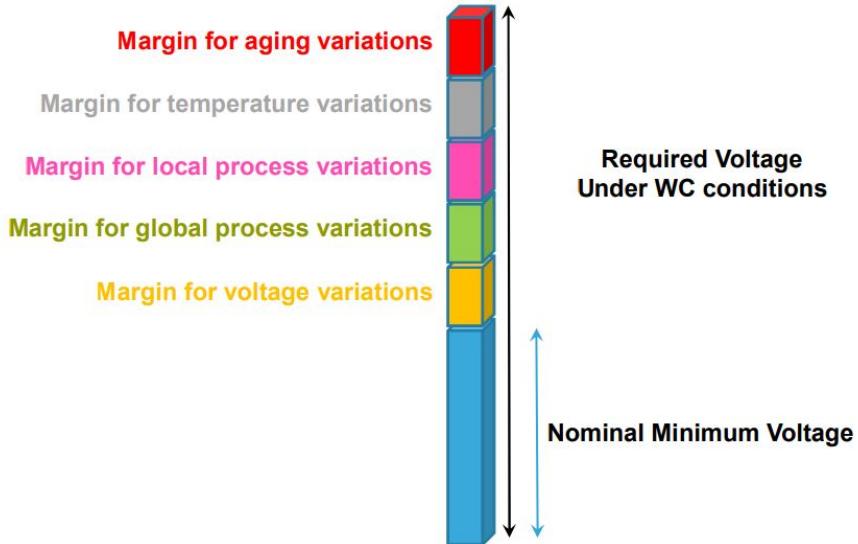

typically designed with large safety margins. This generally means a circuit is designed for worst-case operating conditions, as shown in Figure 2.2.

FIGURE 2.2: Margins, Reproduced from [57]

## 2.1 Process, Voltage and Temperature Variations

The process, voltage, and temperature (PVT) variations have negative impacts on the performance of a manufactured chip. The effect of PVT variations has been increased

due to aggressive fabrication technology scaling. Figure 2.3 shows the technology node of the CPUs from Intel over the last 46 years. As the Figure shows, the technology has been shrunk 714 times over the years.

FIGURE 2.3: Technology node of the CPUs from Intel, Reproduced from [45, 61]

Process variations are occurred due to the variations in channel length or doping concentration which cause the threshold voltage shift at time zero it, therefore, degrades the performance of the CMOS devices. Voltage variations are considered as there are unexpected voltage drops in the power supply networks and also the variations in the supply voltage itself. Temperature variations are raised due to temperature fluctuations of the CMOS circuits and the environmental impacts. The PVT variations lead to the delay degradation which affect the propagation delays the synchronous circuits it, therefore, cause the timing errors. The PVT variations affect both clock signals and data paths. Hence the longest delay paths may fail to deliver its output data within a given clock period. Section 2.1.1, 2.1.2 and 2.1.3 describes the process, voltage and temperature variations respectively. Section 2.1.4 concludes performance degradation due to the PVT variations.

### 2.1.1 Process Variations

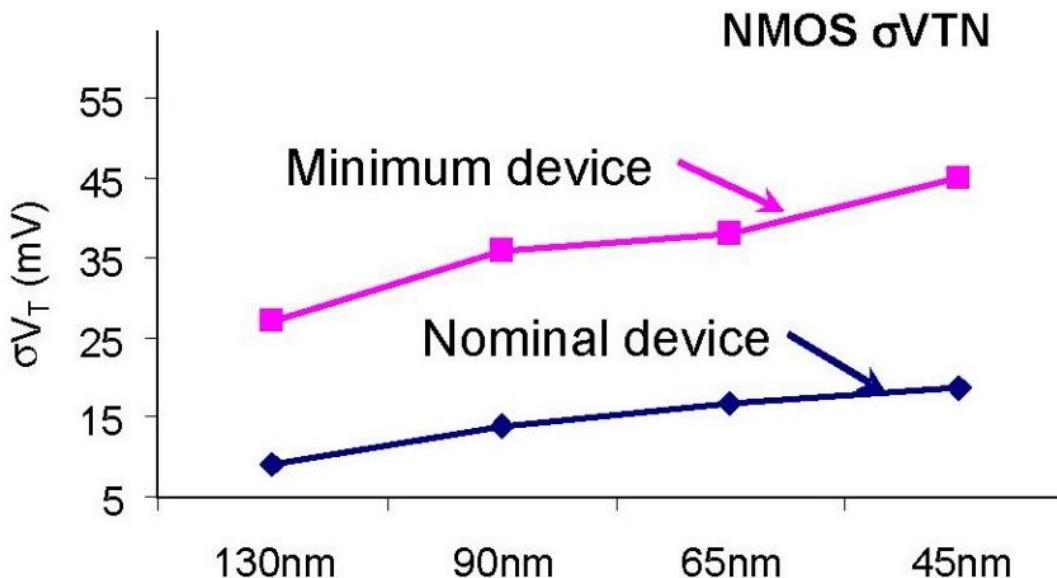

Process variation is a naturally occurring variation in the semiconductor circuit. It is embodied in the variations in length, widths, oxide thickness of transistors during the circuits fabrication. The technology scale saves the area significantly. However, the process variations have become more significant due to the aggressive fabrication technology scaling with the percentage of the variations in length, widths, oxide thickness.

FIGURE 2.4:  $V_{th}$  Shift Random Due to the Process Variations, Reproduced from [52]

Same as other critical areas in the semiconductor processing, meeting Moores law scaling with variation challenges require the combining of innovations to improve the strategies, [13]. Figure 2.4 shows the  $V_{th}$  shift of NMOS transistor due to process variations over the technology generation. As the Figure shows, the  $V_{th}$  shift at 45nm technology node has almost doubled compared with the  $V_{th}$  shift at 130nm technology, and the percentage of  $V_{th}$  shift is even worst. The value of  $V_{th}$  decreases over the technology generation, from 0.34V to 0.29V. This means the technologies scaling has increased the uncertainty of the intrinsic delay after fabrication. The process variation has become a new challenge associated with advanced CMOS technologies for the IC, industry, [13, 53].

### 2.1.2 Voltage Variations

Voltage variations are mainly occurred by the IR drop and  $di/dt$  noise. Both effects will not only decrease the supply voltage but also increase the supply voltage in an IC. The IR drop is caused by current flow over the parasitic resistance of the integrated circuit supply rail. The parasitic inductance, resistance and capacitance of the integrated circuit supply rail and the package causes the  $di/dt$  noise, [85]. Therefore, the voltage variations

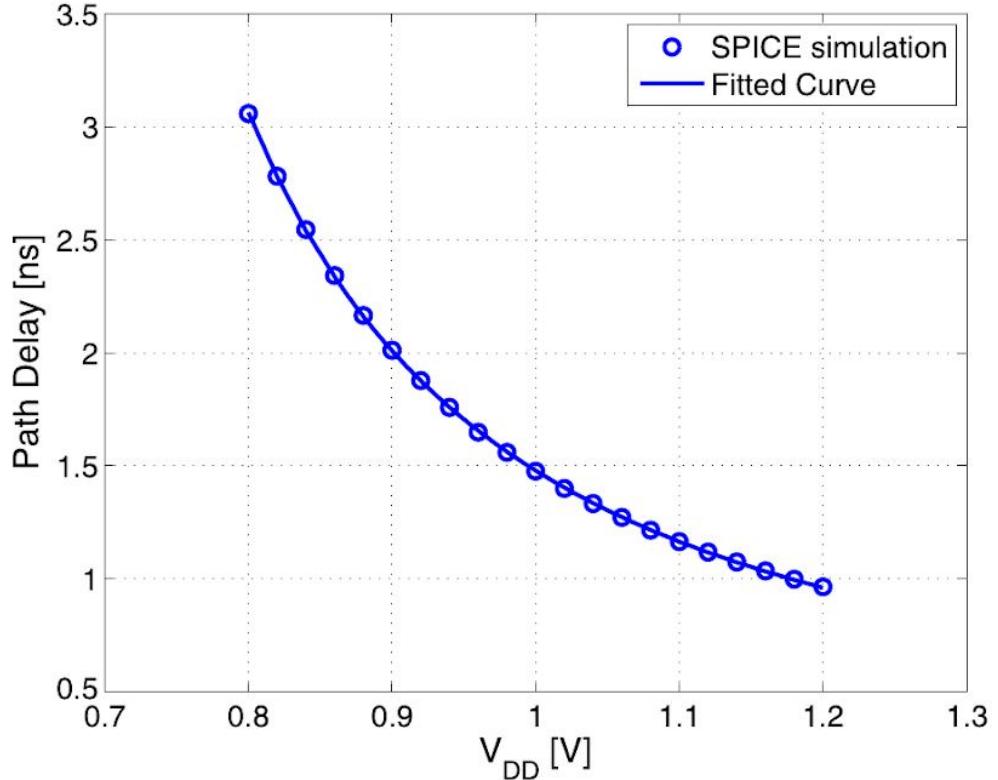

FIGURE 2.5: Relation Between Supply Voltage and Logic Delay of a Multiplier Circuit in 65nm Technology, Reproduced from [85]

follow the Ohm's Law and the Inductance Effect, as shown in equation (2.1) and (2.2). With the aggressive technology scaling of CMOS circuits well into the nanometer regime and the increasing demand for the ultra-low power/low voltage systems, the reliability due to voltage variations become more and more impotent in CMOS circuits and systems, [23, 88].

$$\Delta V_{IR\_Drop} = IR_{parasitic} \quad (2.1)$$

$$\Delta V_{di/dt} = L_{parasitic} \frac{di}{dt} \quad (2.1)$$

$$T_{pd} = \frac{V_{DD}}{b(V_{DD} - V_{th})^a} \quad [85] \quad (2.3)$$

Figure 2.5 shows the relation between the supply voltage and logic delay of a multiplier circuit in 65nm Technology. The simulation result is accurately matched with equation (2.1), where  $V_{DD}$  is the supply voltage,  $V_{th}$  is the threshold voltage,  $a$  and  $b$  are the specific gate fitting parameters, [85]. As the figure shows, the correlation between the

FIGURE 2.6: Within Die Temperature Variation, Reproduced from [14]

supply voltage and propagation delay are negative. Hence, means the performance of a digital circuit decreases when the voltage goes down.

### 2.1.3 Temperature Variation

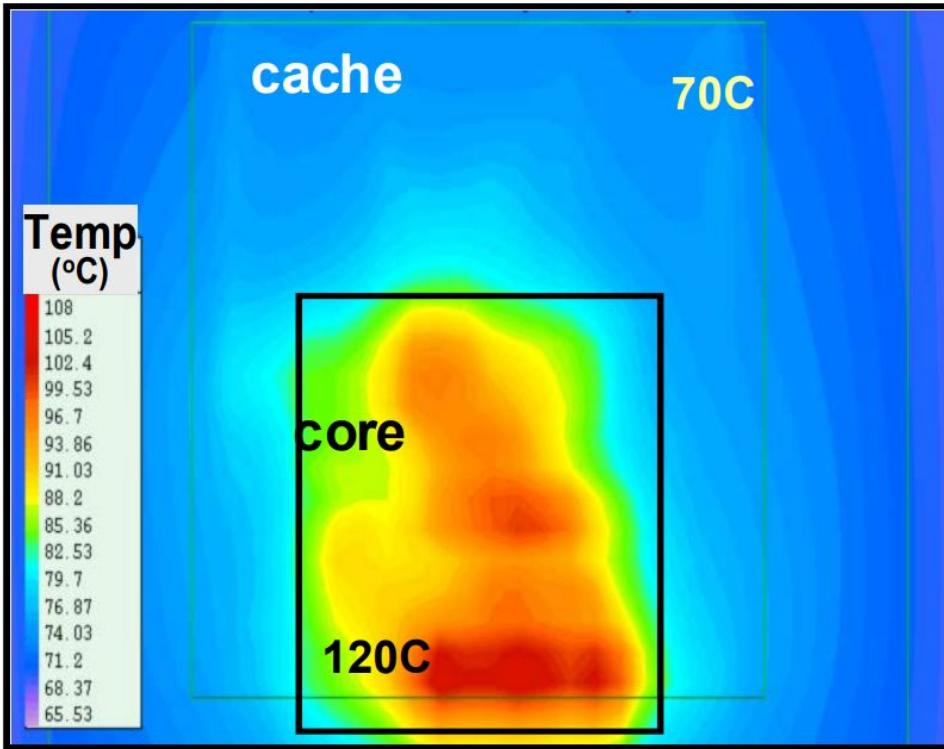

Temperature changes the mobility of transistors. The mobility goes down when the temperature increases, and this causes a decrease in the drain current[9]. It, therefore, increases the propagation delay of the CMOS circuits. Temperature variation has become more and more critical as the increase of power density due to technology scaling, [86]. Figure 2.6 shows the thermal image of a microprocessor. Within-die temperature fluctuations have become a significant performance and packaging challenge for many years. The High temperature causes performance degradation. Moreover, the temperature variation may cause the performance mismatches, therefore, resulting in failures of a system, [14]. As the Figure shows, the internal temperature of a chip can be higher than 100°C.

### 2.1.4 Discussion

As section 2.1.1, 2.1.2 and 2.1.3 shows, the PVT variations not only reduces the propagation delay but also enhances the propagation delay of a digital circuit. The increase

of propagation delay leads to significant performance degradation, especially in the synchronous circuit system. The temperature variation causes the most reduction of the performance compared with others. Furthermore, ageing variations are becoming significant due to the technology shirking, see the next Section.

## 2.2 Negative-Bias Temperature Instability and Ageing Mechanisms

With aggressive scaling down of the feature size of the IC, the ageing effect has become one of the most important critical issues of MOS devices. Especially in many timing-dependent wear-out mechanisms such as BTI, HCI and TDDB refer to a slow progressive degradation in the performance of MOS transistors. Consequently, the speed of a chip can significantly degrade over time; this results in delay faults.

Many research groups and companies have carried out extensive research on the ageing of MOS devices:

1. The Electronic Systems and Devices research group at the University of Southampton is focusing on the reliability of memory and PUF, ageing monitoring and ageing modelling, [1, 33, 59, 60, 63, 67, 80].

2. The Nano-scale Integration and Modelling research group at the Arizona State University is focusing on the NBTI and HCI modelling, [10, 58, 77].

3. The Device Modelling screech Group research group in the University of Glasgow is focusing on reliability problems of SRAM due to device wear out and process variation, [6, 31].

4. A research group from the University of Algarve is focusing on delay-faults prediction Ageing sensors, [56, 66].

5. A research group from the University of Athens is focusing on delay-faults detection Ageing sensors, [71, 72, 73].

6. Cisco systems ltd and IBM Technology and Qualification are focusing on the lifetime of DRAM under HCI effect, [7, 8, 15, 84].

7. The U.S. Patent and Trademark Office on 11<sup>th</sup> March 2014 issued Apple a patent describing a method of monitoring the ageing of a device's electronics, [39].

This section describes the specific detail of the NBTI effect and the Reaction-Diffusion (RD) model, which is the most prevalent NBTI model. It then states the main influence

factors of NBTI and NBTI mitigation. A brief overview of PBTI and HCI effect due to ageing is stated at the end of this chapter.

Section 2.1.1, 2.1.2 and 2.1.3 describes the process, voltage and temperature variations respectively. Section 2.1.4 concludes performance degradation due to the PVT variations.

### 2.2.1 Negative-Bias Temperature Instability

Negative-Bias Temperature Instability (NBTI) was discovered in 1966, [65]. However, It is considered as one of the most important reliability issues in integrated circuits during late few years, as a result of technology scaling and the increase of device operating temperature. NBTI is an ageing reliability issue in P-channel Metal-Oxide-Semiconductor field-effect (PMOS) transistors, [11, 20]. NBTI occurs because interface traps at the gate oxide interface are generated when a negative gate bias, a negative potential difference between gate and source ( $V_{gs}$ ), is applied, [60]. It manifests itself as an increase in the threshold voltage ( $V_{th}$ ) and a decrease in the drain current. The  $V_{th}$  is the minimum voltage to conducting the path between the source and drain of a transistor. Thereby, the shift of the  $V_{th}$  produces delay degradation of CMOS circuits. NBTI can produce more than 20% timing degradation in the worst-case operating conditions[58], which means the performance degradation especially of the synchronous circuit system is becoming more intense.

#### ReactionDiffusion Model

To estimate the behaviour of an IC due to NBTI effects, many NBTI models have been proposed. The Reaction-Diffusion (R-D) model is the most widely used NBTI model to estimate the  $V_{th}$  degradation due to NBTI, [10, 77].

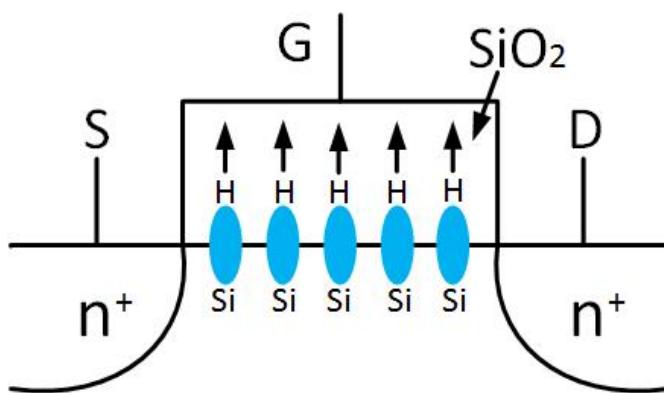

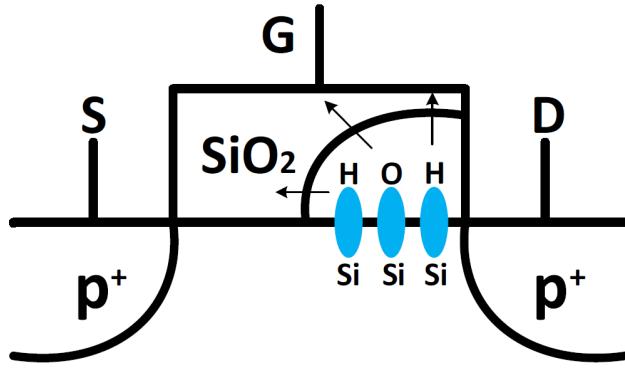

FIGURE 2.7: NBTI: Hydrogen Atoms Diffusion, Reproduced from [77]

As shown in Figure 2.7, the Si-H bonds at the oxide gate interface will be broken when a PMOS transistor is under electrical stress (the reaction phase) by creating positive holes at the gate oxide interface. The hydrogen atoms which are generated by the reaction then diffuse away from the interface to the gate (diffusion). The NBTI effect generates the interface traps uniformly in the channel, [77]. Models for threshold voltage degradation ( $\Delta V_{th}$ ) due to NBTI have been proposed for different levels of abstraction, [10, 33, 77]. The behaviour of a CMOS circuit can be predicted by integrating the  $\Delta V_{th}$  estimation result into circuit simulation tools such as Spice. There are two types of NBTI effect: static NBTI and Dynamic NBTI, shown as follows:

### Static and Dynamic NBTI

In this section, The R-D model from one of those research groups is applied to estimate the NBTI effect as shown in Figure 2.10 and Figure 2.8, [10, 58, 77].

#### A. Static NBTI

Static NBTI is a situation when a PMOS transistor is always under stress (a constant logic 0 input). In this case, the PMOS transistor suffers from the most serious wear out due to the NBTI effect.

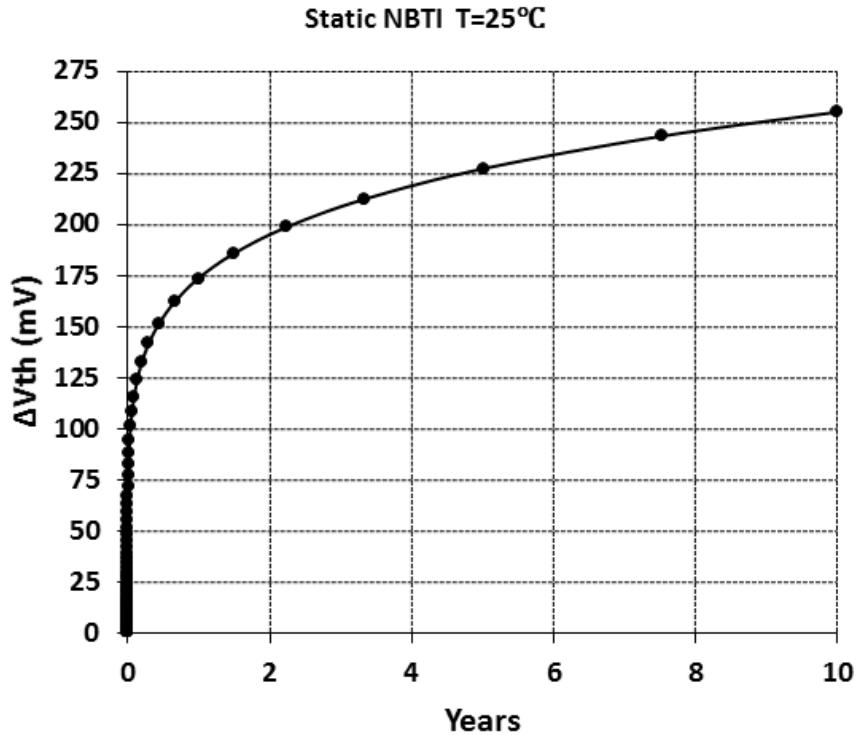

FIGURE 2.8: Static NBTI, Reproduced from [10]

Figure 2.8 shows the threshold voltage degradation of static NBTI for a minimum sized PMOS transistor of 90nm ( $V_{th}$  at time zero 0.276V) technology in 25 °C and  $V_{gs}=1.2V$

over ten years. As the figure shows, The threshold voltage degradation is increased 255mV after ten years, which is 92.4% threshold voltage shift compared with time zero. This threshold voltage shift leads to significant performance degradation of a circuit. The static become an issue if the when a logic gate has a constant logic 0 input. Such as the data stored in memory.

### B. Dynamic NBTI

FIGURE 2.9: Dynamic NBTI, Reproduced from [4]

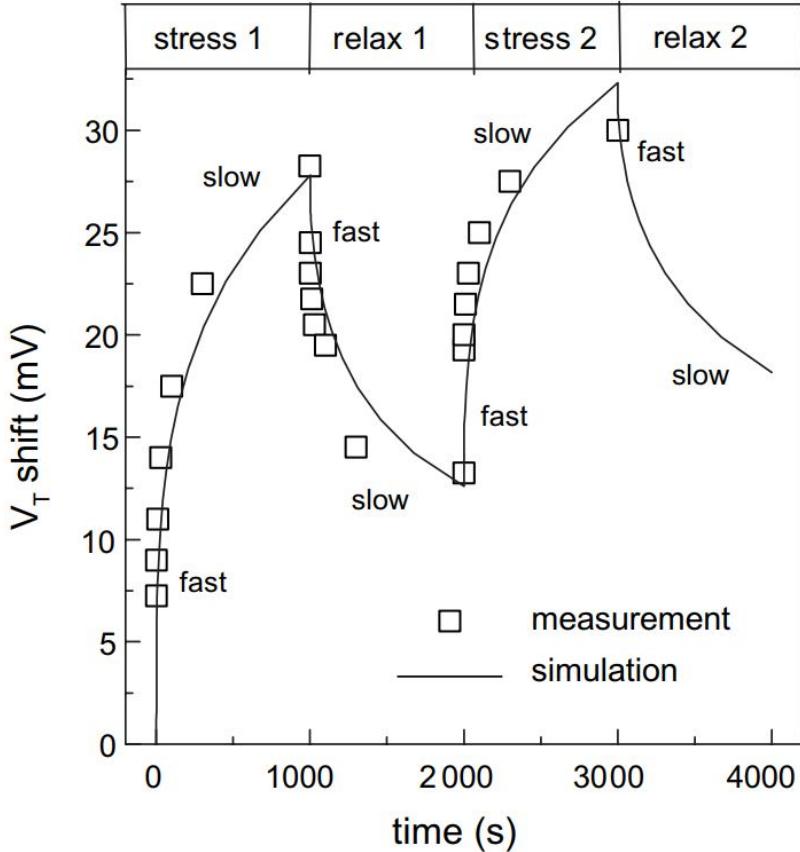

Unlike the static NBTI, the PMOS transistor will not have a constant input over time in the case of dynamic NBTI. The input of PMOS transistor circulates between stress period (a logic 0 input) and recovery period (a logic 1 input). As the name suggests,  $V_{th}$  increases during the stress period, and it decreases during the recovery period over time. Figure 2.9 shows the threshold voltage degradation during two stress and recovery process. As the threshold voltage shift during the stress time cannot be fully recovered during the relax time,  $\Delta V_{th}$  increases after each stress and relax period. Therefore, it causes the threshold voltage degradation over a long period.

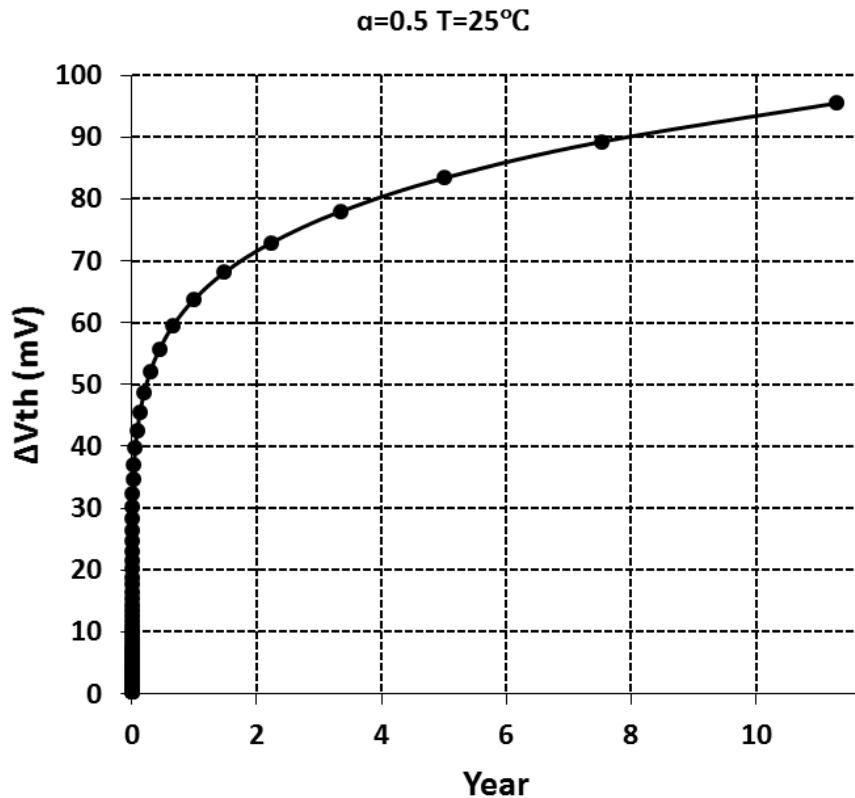

Figure 2.10 shows the threshold voltage degradation of dynamic NBTI for a minimum sized PMOS transistor of 90nm technology at 0.5 stress duty cycle, 100MHz switching activity, 125 °C and 1.2V V<sub>gs</sub> over the years. As the figure shows, the threshold voltage

is slowly accumulating during its operating. The  $V_{th}$  shifts about one-third compared with time zero over ten years. In spite of that, the  $V_{th}$  degradation of dynamic NBTI is not as substantial as the  $V_{th}$  degradation of static NBTI; however, it leads to significant performance degradation of a long delay path in complex circuitry (see the delay degradation over time in Chapter 5).

FIGURE 2.10: Dynamic NBTI for a minimum sized PMOS transistor of 90nm technology, Reproduced from [10]

### 2.2.2 Influence Factors of NBTI

Research groups have been working on the R-D model of NBTI for years. NBTI effect is operation time, temperature, stress duty cycle and  $V_{gs}$  dependent, [10, 77, 82, 83].

#### Duty cycle Dependence

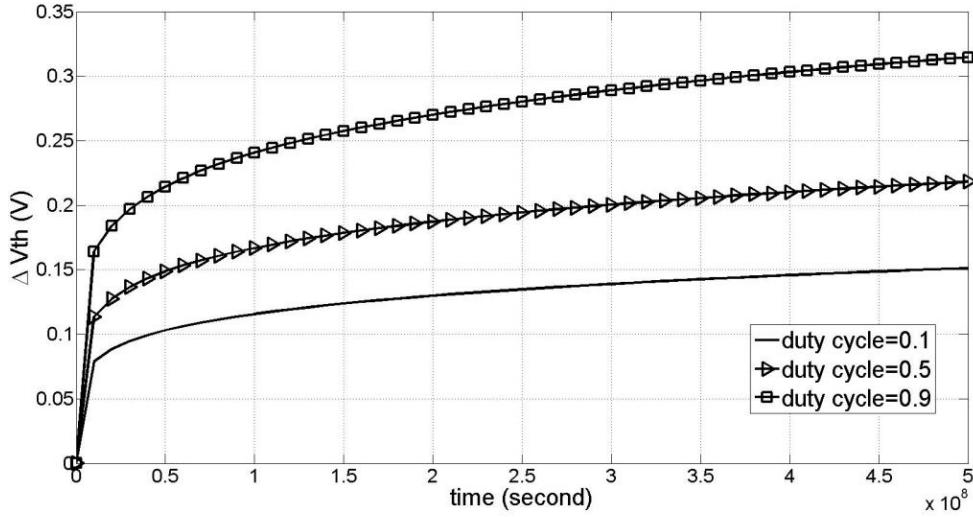

The threshold voltage degradation from dynamic NBTI of a PMOS transistor depends on the duty cycle of the input signal. Figure 2.11 shows the threshold voltage degradation of static NBTI and dynamic NBTI over the time. As Figure 2.11 (a) shows, the  $V_{th}$  degradation is stronger with higher duty cycle. As the results show in Figure 2.11 (b),  $\Delta V_{th}$  grows over time, and the  $V_{th}$  degradation of static NBTI is much stronger than dynamic NBTI. Because the recovery of  $\Delta V_{th}$  is rapid during the beginning of

(a) NBTI with Different Duty Cycle, Reproduced from [32]

(b) Compared with The Static NBTI, Reproduced from [79]

FIGURE 2.11: Long Term Dynamic NBTI with Different Duty Cycle

recovery time, as shown in Figure 2.9. Compare to static NBTI,  $\Delta V_{th}$  of dynamic NBTI is decreased significantly even though the duty cycle is close to one. Because of the correlation between duty cycle and  $\Delta V_{th}$  are positive, the input vector control can mitigate the performance degradation from NBTI, as shown in [83].

## Temperature Dependence

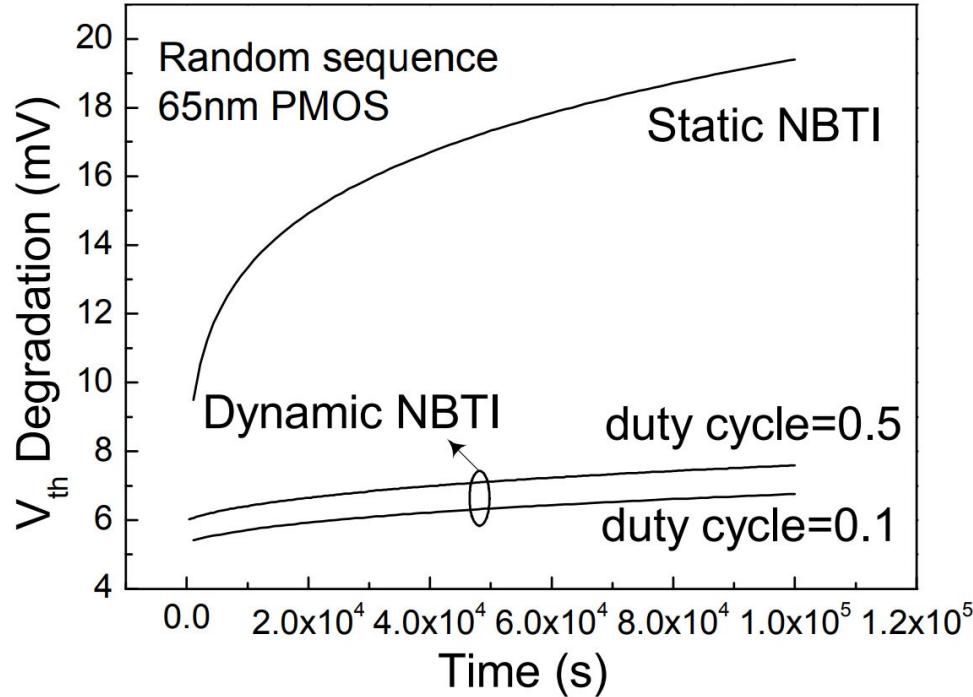

The threshold voltage degradation from dynamic NBTI of a PMOS transistor depends on the operating temperature. Figure 2.12 shows the threshold voltage degradation due to dynamic NBTI in temperature over time. As the estimate  $\Delta V_{th}$ , as shown in Figure 2.12, the correlation between temperature and  $\Delta V_{th}$  are positive. As the temperature increases, the degradation of the  $V_{th}$  increases sharply.

FIGURE 2.12: Long Term Dynamic NBTI with Difference Temperature, Reproduced from [3]

| Temperature( °C ) | Delay (ns) | Delay degradation |

|-------------------|------------|-------------------|

| 25                | 82.99      | 30.00%            |

| 30                | 91.58      | 33.18%            |

| 35                | 100.65     | 36.47%            |

| 40                | 110.19     | 39.93%            |

| 45                | 120.19     | 43.55%            |

| 50                | 130.63     | 47.32%            |

TABLE 2.1: NBTI  $V_{th}$  Degradation Comparison in Different Operating Temperatures

The  $V_{th}$  degradations are estimated and compared with relatively smaller temperature difference, shown in Table 2.1, to show the influences from the temperature in detail. According to the estimation results, shown in the Table, each 5-degree increase in the temperature leads to a 3% degradation of  $V_{th}$ . The internal temperature of a chip increases rapidly when the system is running at the high performing stage. Combined

with the results, as shown in Section 2.1.3, a good cooling system will not only let the IC circuit running at higher performance but also extends the lifetime of the IC circuit.

### V<sub>gs</sub> Dependence

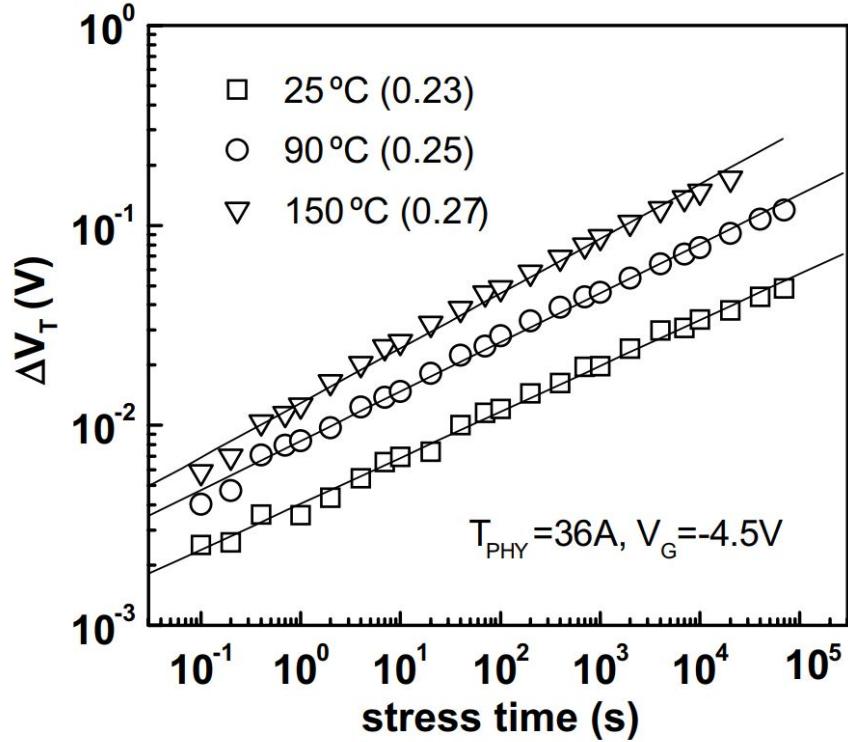

FIGURE 2.13: Long Term Dynamic NBTI with Different V<sub>gs</sub>, Reproduced from [62]

Figure 2.13 shows the threshold voltage degradation of dynamic NBTI V<sub>gs</sub> after time. As the estimated results shown, the correlation between V<sub>gs</sub> and  $\Delta V_{th}$  is positive.

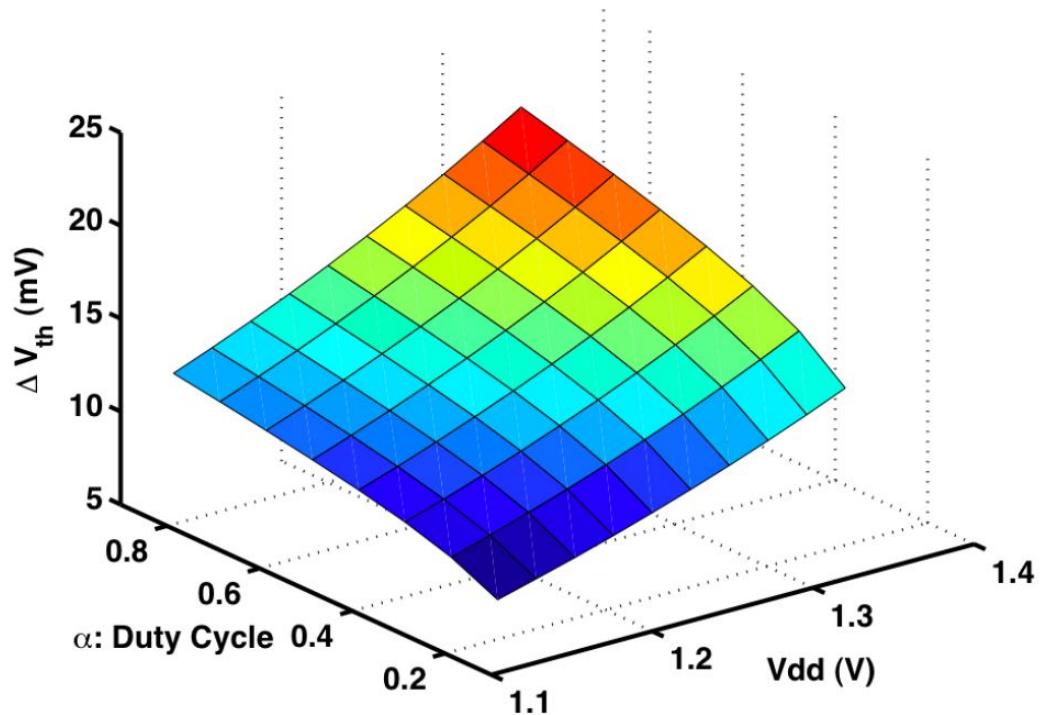

### Discussion

As stated above, the NBTI effect is dependent on time, temperature, and stress duty cycle and V<sub>gs</sub>. Figure 2.14 shows the relationship between Duty Cycle, VDD and  $\Delta V_{th}$ . Previous research groups have also stated that the relationship between  $\Delta V_{th}$  and operating frequency (switching activity) is de-correlated or  $\Delta V_{th}$  weak frequency dependent at high-frequency,[3, 10, 77]. However, this discounts the relationship between switching activity and temperature. The Power dissipation of a CMOS is consists of static power dissipation, dynamic power dissipation and short-circuit power dissipation, [43, 75]. Dynamic power dissipation and short-circuit power dissipation are depended on switching activity, and  $\Delta T = T_0 + \theta P$  [69] , where  $\theta$  is the thermal resistance. Therefore, the temperature is switching activity dependent. Hence, the NBTI effect is non-frequency dependent if and only if there is a cooling system which keeps the temperature of the device to be constant.

FIGURE 2.14: Relationship between Duty Cycle, VDD and  $\Delta V_{th}$ , Reproduced from [10]

Once the threshold voltage degradation ( $\Delta V_{th}$ ) is estimated, the NBTI effect can be integrated into the circuit simulation tools such as Spice. The threshold voltage and delay degradation are estimated by using the R-D model at the 90nm technique is shown in table 2.2. As the table shows, the delay degradation changes in different time, duty cycle, temperature and Vgs.

| Years | Duty Cycle | Vgs(V) | Temperature °C | $\Delta V_{th}$ (mV) | Delay(ps) | $\Delta t$ |

|-------|------------|--------|----------------|----------------------|-----------|------------|

| 0     | 0.5        | 2.0    | 50             | 0                    | 16.40     | 0%         |

| 1     | 0.5        | 2.0    | 50             | 112.15               | 18.14     | 10.61%     |

| 5     | 0.5        | 2.0    | 50             | 146.65               | 18.73     | 14.21%     |

| 5     | 0.9        | 2.0    | 50             | 167.77               | 19.09     | 16.40%     |

| 5     | 0.5        | 2.0    | 75             | 212.39               | 19.91     | 21.40%     |

| 5     | 0.5        | 2.5    | 50             | 162.25               | 19.00     | 15.85%     |

TABLE 2.2: Estimated Threshold Voltage and Delay Degradation of an Inverter

### 2.2.3 HCl and PBTI

#### Hot-Carrier Injection

Hot-Carrier Injection (HCl) is a critical ageing issue in n-channel Metal-Oxide-Semiconductor field-effect transistor (NMOS), [28, 42, 49, 87]. HCl phenomenon occurs because the interface traps are generated at the drain end gate oxide interface when the current flow between the source and drain during the switching time. It manifests as the degradation of the switching characteristics, threshold voltage, drain-current and noise margin. Even worse, the HCl effect is unrecoverable, [77, 81]. Therefore, although the HCl effect will not cause significant delay degradation like the NBTI effect[77], however, it accelerates the degradation of the device lifetime directly.

FIGURE 2.15: NBTI: Hydrogen Atoms Diffusion, Reproduced from [77]

The R-D model can describe the HCl effect. The Si-H or Si-O bonds at the drain end of gate oxide interface might be broken (reaction) when the PMOS transistor is switching, and this generates the interface traps at the drain end gate oxide interface permanently. Those hydrogen atoms generated by reaction then diffuse away from the interface to the gate (diffusion), [64, 77, 81].

#### Positive-Bias Temperature Instability

Positive BTI (PBTI) is an ageing reliability issue in N-channel MOS (NMOS) transistors. Unlike the NBTI, PBTI occurs when a positive gate bias, a positive potential difference between gate and source ( $V_{gs}$ ), is applied, [74]. It has been considered negligible because the degradation due to PBTI was inconsequential compared with other ageing phenomena; however, the threshold voltage shift of PBTI has become significant in High-K Metal Gate technologies, [74]. The double effect of NBTI and PBTI exacerbates the timing degradation of ICs.

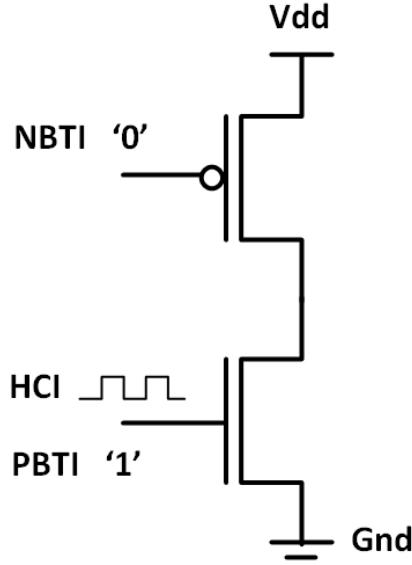

In this section, we introduced three ageing mechanisms, NBTI, HCl and PBTI, shown in Figure 2.16. Those three mechanisms lead to the lifetime degradation of CMOS circuits.

The ranking of critical paths might change due to those wear out mechanisms.  $V_{th}$  degradation can be estimated by using the existing ageing model. The  $\Delta V_{th}$  can be incorporated into the simulation tools to estimate the propagation delay after ageing of the design. A method of potential NBTI critical path identification is introduced in Section 3.3.

FIGURE 2.16: Ageing Mechanisms, Reproduced from [25, 90]

## 2.3 Ageing Mitigation and Lifetime Prediction Techniques

### 2.3.1 Ageing Mitigation

As Section 2.2.1 shows, the ageing of an IC degrades the IC's performance and reduces the IC's lifetime significantly over time. Research groups proposed many ageing mitigation techniques. Such as Input Vector control [1, 37, 83], Ageing-Aware synthesis[33, 67], Dynamic Voltage Scaling [58], and Power Gating [18, 27]. This Section introduces two efficient ageing mitigation techniques for NBTI effect mitigation.

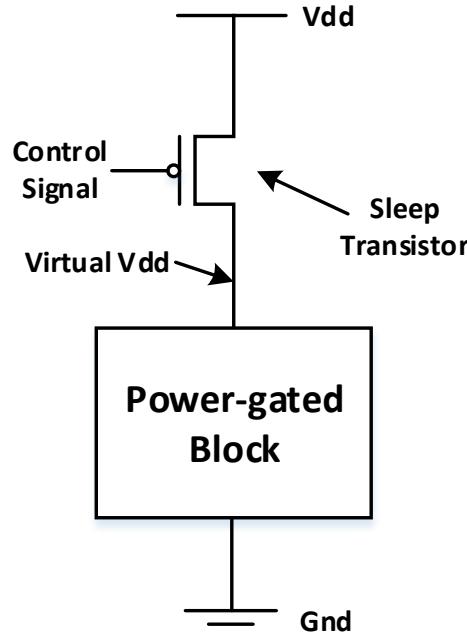

#### Power Gating

Power Gating is widely used to reduce the leakage power when a digital IC is at the idle periods, as the percentage of leakage power has increased significantly due to the technology node scaling, [24, 27]. The power gating techniques can also be used for the NBTI mitigation. Figure 2.17 shows the structure of a header-based power gating sleep transistor. As the figure shows, a High- $V_{th}$  PMOS transistor is inserted between the power rail and the logic gates as a sleep transistor. The virtual  $V_{dd}$  replaces the  $V_{dd}$

of the original circuit. The size of the transistors is usually carefully designed to reduce the leakage current and mitigate the NBTI simultaneously, [24].

FIGURE 2.17: NBTI-aware Power Gating, Reproduced from [27]

The power gating technique causes the delay, area and wake-up time overhead as the insertion of the PMOS transistor. According to the result stated in Section 2.2.2, the NBTI is  $V_{gs}$  dependent. The 'Control signal', as shown in Figure 2.17, is set as a log '1' while the IC is at the idle period. The virtual  $V_{dd}$  is tending to the ground gradually as the leakage current of the Power-gated Block is relatively higher than the sleep transistor. It, therefore, reduced the stress of the PMOS transistors in the Power-gated Block. The power gating technique can extend the lifetime effectively, [18, 24]. However, it causes the reduction of performance and additional area overhead simultaneously, which are the primarily concerned of the IC design nowadays.

### Dynamic Voltage Scaling

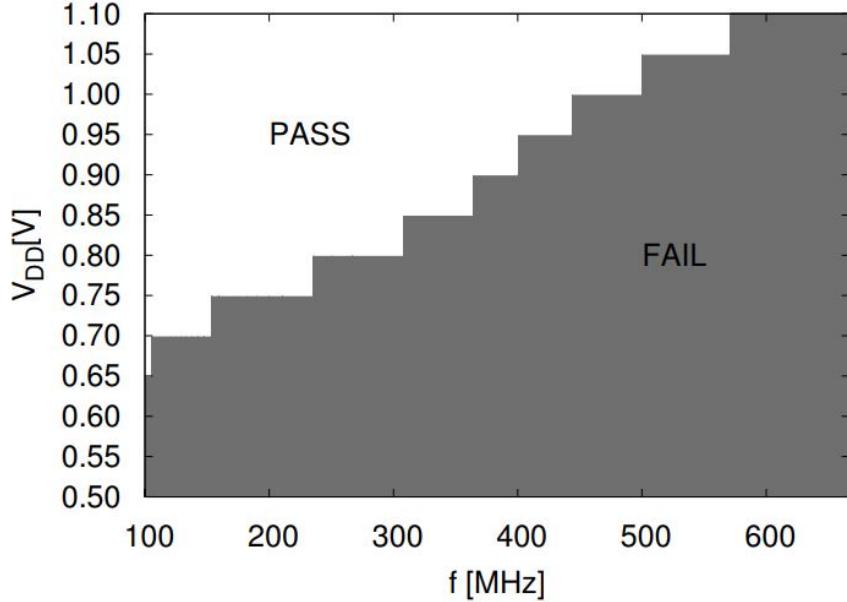

Dynamic Voltage Scaling (DVS) techniques are a widely used technique to reduce power consumption. There are two types of DVS techniques, Traditional DVS and On-line DVS.

The traditional DVS scales the supply voltage and the operating frequency simultaneously. Figure 2.18 shows the frequency  $f$  vs. supply voltage  $V_{DD}$  shmoo plot

of the ARM M4F combined with the traditional DVS technique. As the figure shows, the system is running under a specific operating frequency with a corresponding supply voltage, because of the propagation delay of a CMOS device decreases with the lower supply voltage.

FIGURE 2.18: The Frequency  $f$  vs. Supply Voltage  $VDD$  Shmoo Plot of the Traditional DVS Technique, Reproduced from [44]

The On-line DVS widely used technique to reduce power consumption and compensate for PVTA variations. Process variations and ageing-induced device degradation are becoming major reliability concerns in modern semiconductor technologies. Both phenomena lead to performance degradation, and hence timing errors. The integrated circuits are typically designed with large safety margins to avoid delay fault induced failures, [2]. This generally means a circuit is designed for worst-case operating conditions. Such an approach may limit system performance and lead to an increase in power consumption, [58]. The on-line DVS has been proposed to assure an IC's lifetime reliability. Such schemes are typically based on the use of sensors to predict circuit failures before actual errors appear. The system can then adaptively scale its operating frequency and supply voltage according to the actual operating conditions to compensate for performance degradation, [2]. Unlike the traditional DVS, the on-line DVS removes the large safety margin for PVTA variations to reduce power consumption further and improve the performance of an IC.

Various in situ delay monitoring sensors have been proposed. These include delay fault detection and prediction techniques, [29, 40]. Existing delay fault sensors are usually placed on the circuit's longest delay paths. However, the increasing complexity of ICs has led to a significant rise in the number of long paths and potential ageing-critical

paths that may be vulnerable to timing errors, [19, 33, 67], and this means the cost of in situ delay monitoring may be prohibitive.

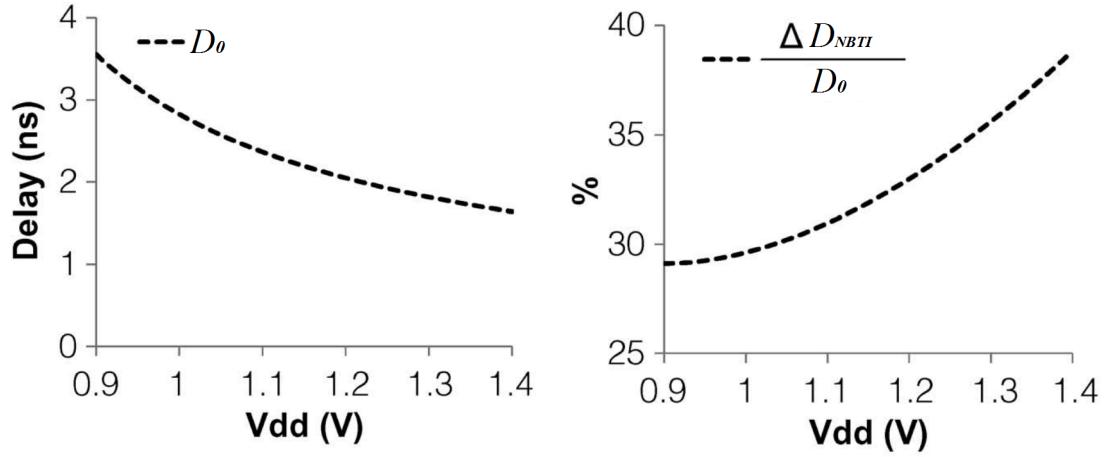

(a) The relationship between intrinsic delay and supply voltage (b) The relationship between percentage intrinsic delay degradation and supply voltage

FIGURE 2.19: Ageing mitigation by using DVS, Reproduced from [24]

Figure 2.19 (a) shows the relationship between intrinsic delay and supply voltage. As the Figure shows, the intrinsic delay decreases with the increase of the supply voltage. Figure 2.19 (b) shows the relationship between intrinsic delay degradation and supply voltage. As the Figure shows, the intrinsic delay degradation increases with the decrease of the supply voltage.

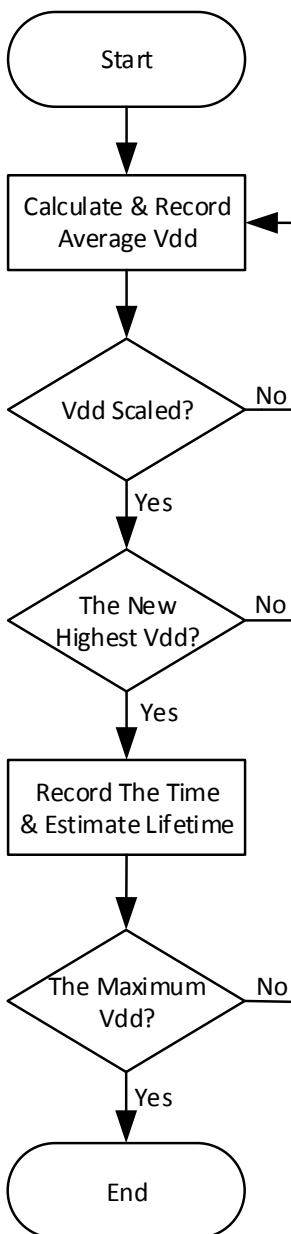

DVS is the adjustment of power and speed settings on a computing devices various processors, controller chips and peripheral devices to optimise resource allotment for tasks and maximise power saving when those resources are not needed. DVS allows devices to perform needed tasks with the minimum amount of required power. The technology is used in almost all modern computer hardware to maximise power savings, battery life and longevity of devices while still maintaining ready compute performance availability. Figure 2.20 shows the supply voltage scaling flowchart. Where  $N_{loop}$  is the number of the clock cycles that the circuit has been monitored in one voltage scaling period,  $N_{set}$  defines the voltage scaling period,  $n$  is the number of error that occurred in voltage scaling period,  $n_{set}$  is the threshold for voltage scaling .

The DVS system costs more area overhead due to the sensors insertion, however, it reduces the power and extends the lifetime without sacrifice the performance of ICs, which is an advantage over the power gating techniques.

As Figure 2.20 shows, the principle of the DVS system is to keep the supply voltage at the lower state while the number of error is tolerable. Compared with leaving a safety margin for timing degradation from the Process, Voltage, Temperature and Ageing (PVTA) variations, implementing a DVS system for the devices not only saves power

FIGURE 2.20: Supply Voltage Scaling Flowchart, Reproduced from [17]

during the lifetime but also slows down the power supply voltage dependent wear out mechanisms.

### 2.3.2 Lifetime Prediction

The RD model can predict the behaviour of an IC, [33, 67], therefore predicts the lifetime of ICs before its fabrication. Equation (2.4) shows a simplified NBTI model, [33].

$$\Delta D_{nbt} = K \cdot D_0 \cdot \alpha^{0.16} \cdot t^{0.16} \quad (2.4)$$

Where  $\Delta D_{nbt}$  is the delay degradation for a given set of operating time and stress duty cycles.  $K$  is a fitting parameter dependent on the operating temperature, supply voltage and the technology node;  $\alpha$  is the stress duty cycle;  $t$  is the operational time of the circuit. As the equation shows, the delay degradation is depending on stress duty cycle during the circuits operating time. In another word, the workload affects the lifetime of a circuit. The Equation can also be derived as follows:

$$t = \sqrt[0.16]{\frac{\Delta D_{nbt}}{K \cdot D_0 \cdot \alpha^{0.16}}} \quad (2.5)$$

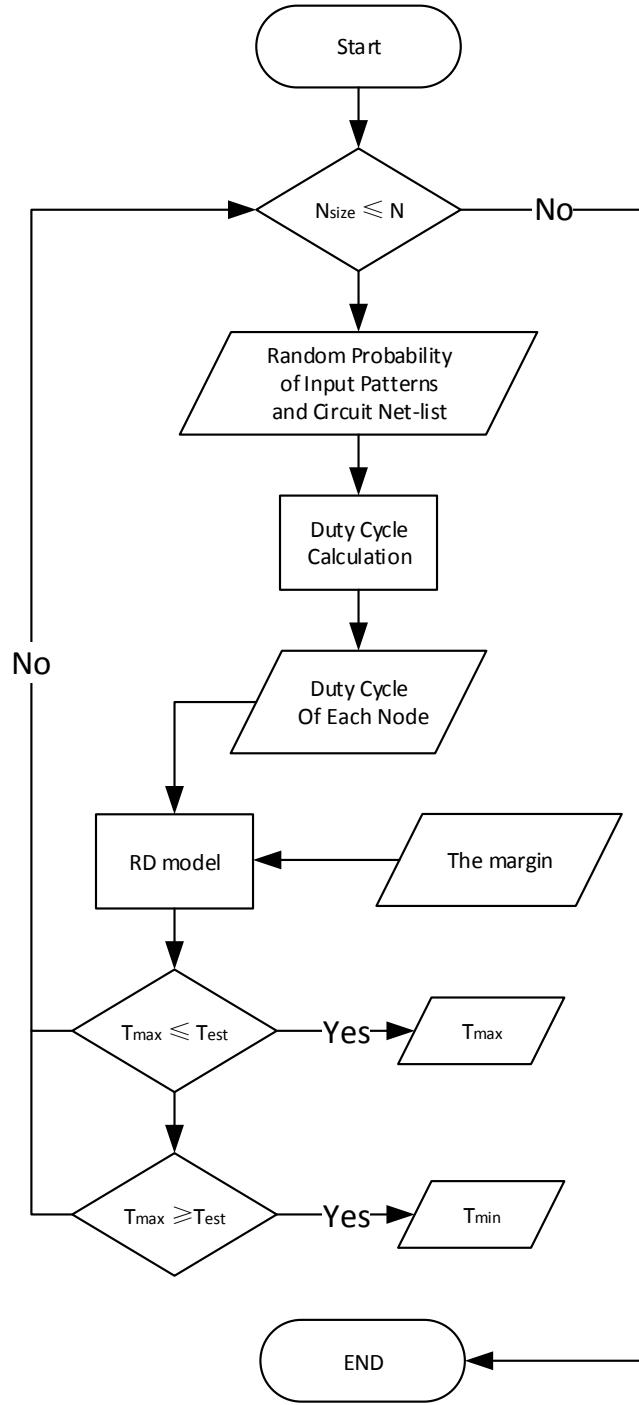

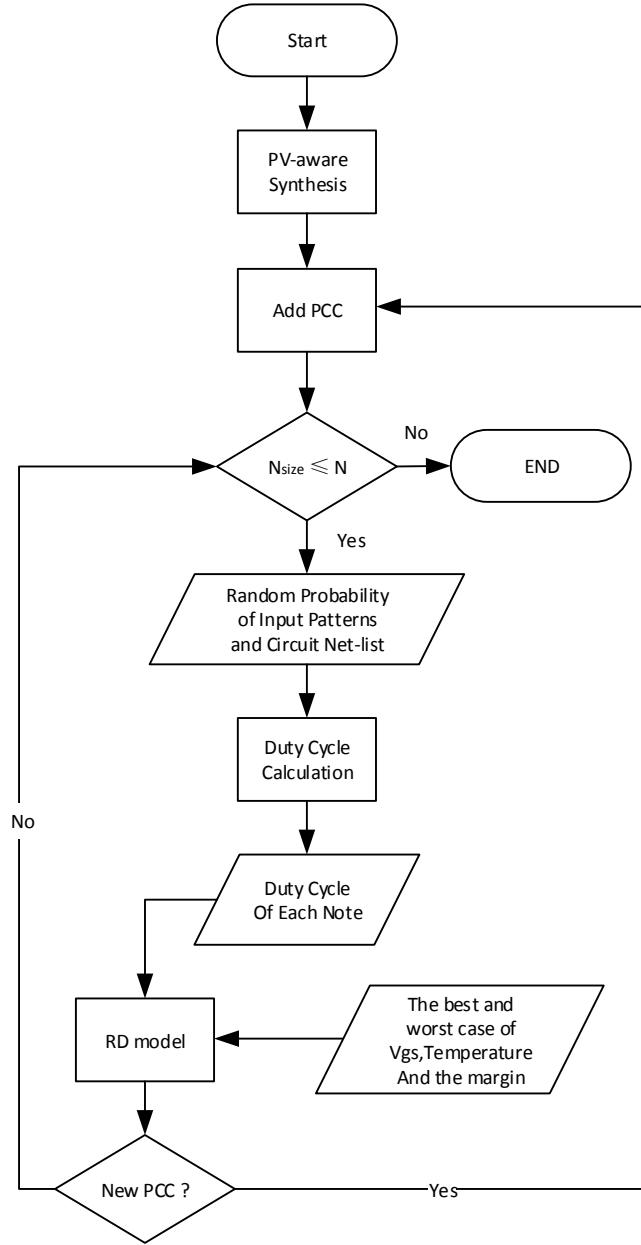

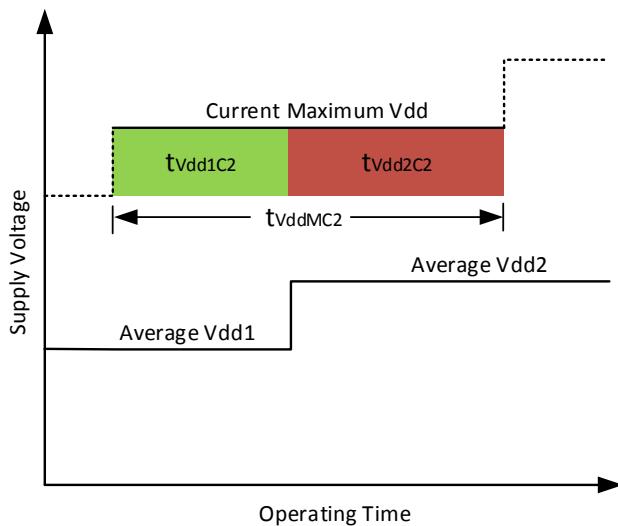

In modern IC design, a timing margin is inserted for the ageing variation. The lifetime of an IC can be estimated by substitute the timing margin into the equation as  $D_{nbt}$ . Figure 2.21 shows the lifetime prediction flowchart. Where  $N$  is the current number of cycles,  $N_{size}$  is the sample size of input pattern random probability,  $T_{est}$  is the lifetime estimation result from a single calculation,  $T_{max}$  and  $T_{min}$  are the maximum and the minimum lifetime estimation which was calculated so far.

As Figure 2.21 shows, the first step in lifetime prediction is to estimate the signal probability (duty cycle), from input patterns and logic circuit net-list. Then estimate lifetime ( $T_{est}$ ) by using the RD model (equation(2.5)) and the timing margin. Finally, the  $T_{est}$  will be compared with the maximum and the minimum lifetime estimation ( $T_{max}$  and  $T_{min}$ ).  $T_{max}$  will be saved as  $T_{est}$  if  $T_{est}$  is greater than or equal to  $T_{max}$  and  $T_{min}$  will be saved as  $T_{est}$  if  $T_{est}$  is less than or equal to  $T_{max}$ . The loop will end until  $N$  is greater than or equal to  $N_{size}$ . The lifetime in specific operating temperature, supply voltage can be predicted precisely if the sample size is large enough.

HSPICE MOSRA is a model for transistor-level ageing behaviour estimation , [46]. Unlike the RD model, as shown in equation 2.4, MOSRA is more suitable for small circuitries. It invokes ageing mechanisms such as HCI and BTI to estimate the behaviour of a circuit after ageing. Ageing mechanisms depend on the workload, the circuit's operating conditions, the circuit's operating time, technology node and the structure of circuitry. MOSRA combines those parameters and predicts circuit's behaviour after ageing. Therefore, the HSPICE MOSRA is useful in the design phase of a small circuit when the circuit's ageing is taking into account.

## 2.4 Ageing Sensors

### 2.4.1 Razor FF

Razor FF [35, 50] is a delay-fault detection sensor, which is a flip-flop-type sensor using the double sampling technique. It detects the consistency of the output signal from

FIGURE 2.21: Lifetime Prediction Flow Chart, Reproduced from [22, 34]

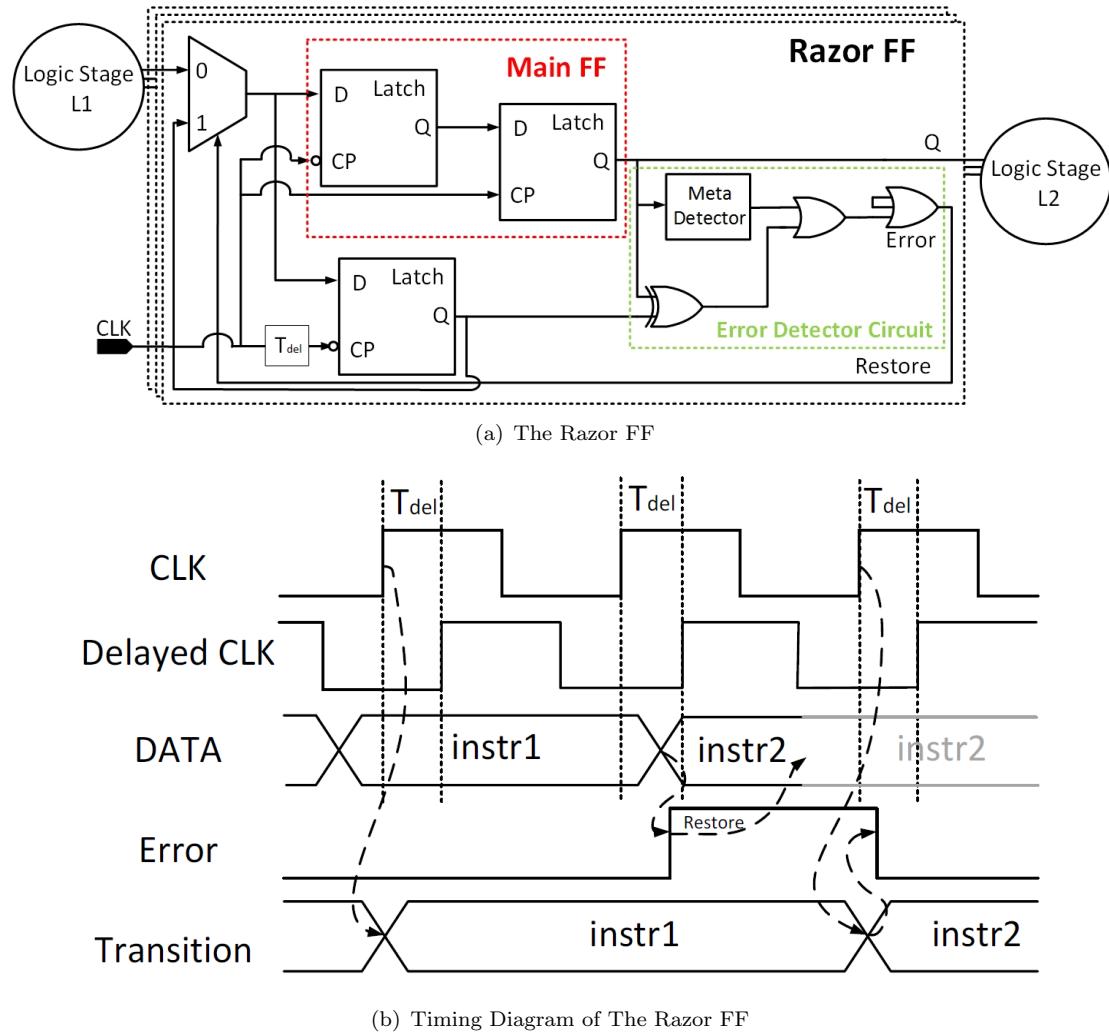

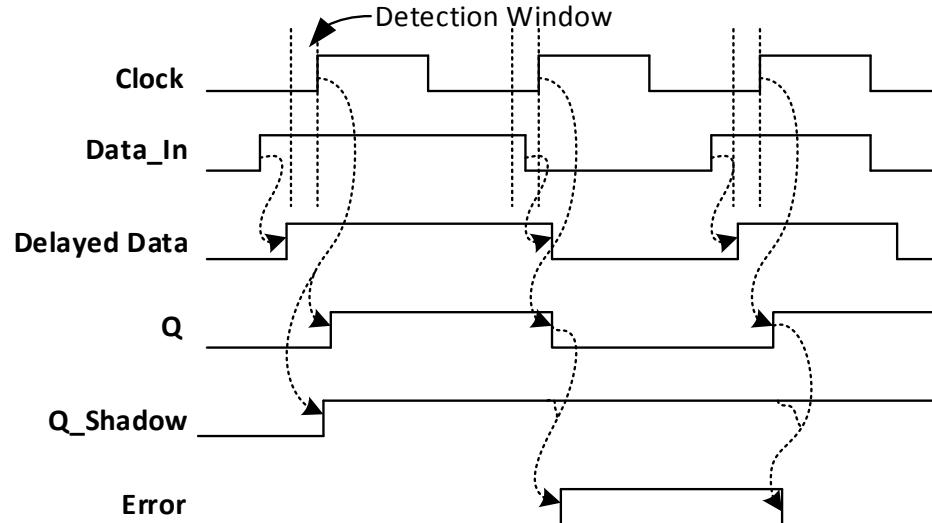

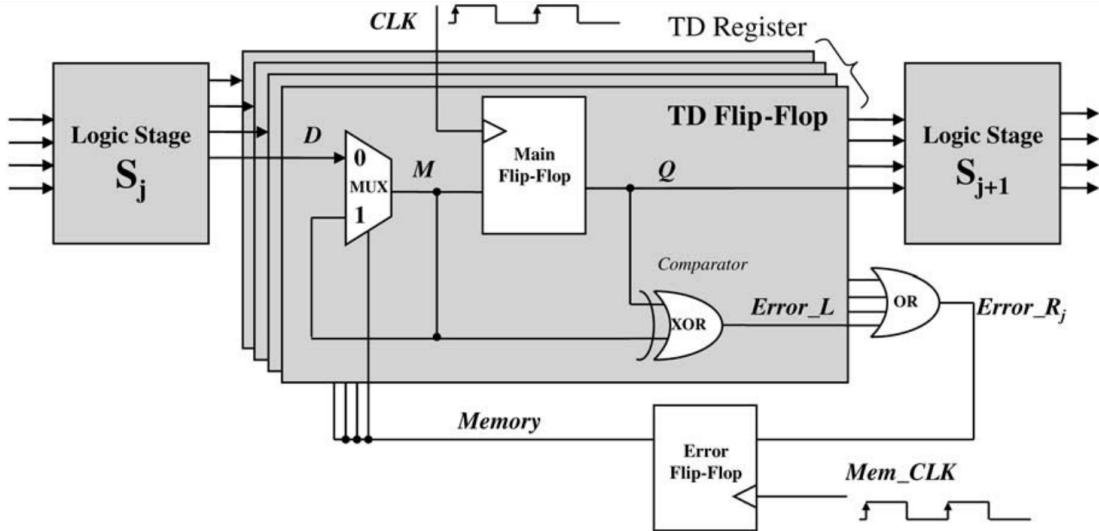

a near critical path after the rising clock edge. As Figure 2.22 (a) shows, Razor FF consists of a main Flip-Flop, a shadow latch, a multiplexer, one delay element and an Error Detector Circuit. The shadow latch receives data as a reference which is sampled after clock rising edge to help the detection circuit detecting the delay-faults. The error

signal is generated by comparing the data between the main FF and shadow latch. Razor FF is a fault tolerant sensor which can restore the data when the sample is missed. The delay element generates a detection window,  $T_{del}$ , shown in Figure 2.22 (b). Transitions in this detection window,  $T_{del}$ , causes the shadow latch to sample a different signal with the main FF, therefore, triggers the error signal as the inconsistency between the samples from the main FF and the shadow latch. Usually, there are two methods to correct this error: Suspend the process for one clock cycle then restore the data in the shadow latch via the multiplexer in the next clock cycle shown in Figure 2.22 (b) or replay the instruction at the system level, [40].

FIGURE 2.22: The Razor FF and Timing Diagram, Reproduced from [35]

Razor FFs are typically implemented on the critical paths of logic designs, but it only detects a timing error after it occurs. Therefore they cannot be used for predicting ageing-induced delay-faults unless the design is modified accordingly, which would further increase its area overheads. Razor FF can only detect the delay-faults in one path, and the area cost for multi-path monitoring using Razor can be prohibitive. The timing degradation of paths increases with circuit ageing, the slack between the rising clock edge

and the transition of the input signal decreases. Hence, the input signal first violates the setup time of the main FF. Meta-stability occurs in the main FF when the clock and input change about the same time. Therefore, the checking circuitry is required to detect meta-stability in the main FF, as shown in Figure 2.22 (a). Moreover, as a delay fault detection sensor, Razor is not suitable for ageing prediction. Because of the upcoming timing error is unpredictable in this case.

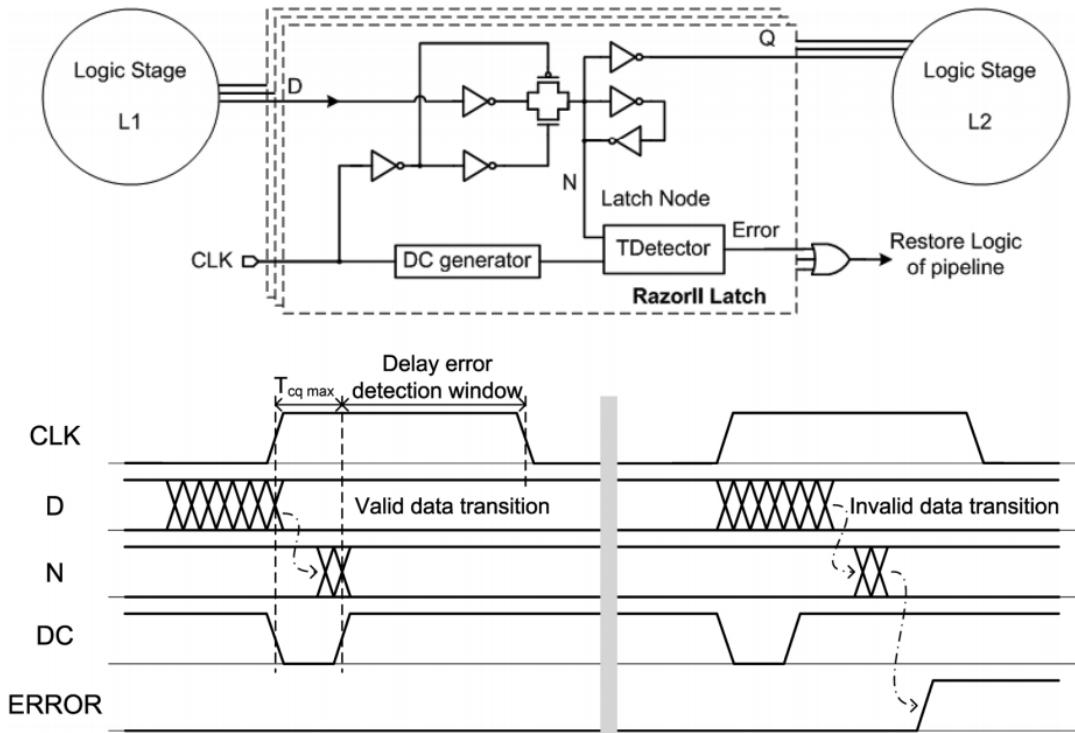

#### 2.4.2 Razor II

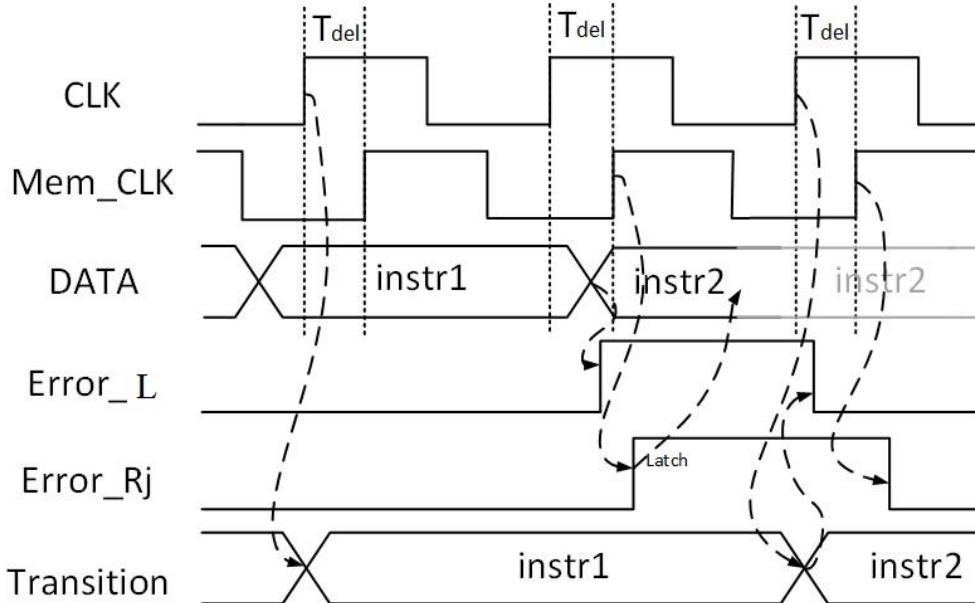

A number of latch-type delay fault monitoring sensors have been proposed in recent years, [16, 89]. These replace the main FF with a latch to solve the metastability issue and to decrease the transition time from D to Q. Razor II was proposed as a latch-type version of Razor FF, which can address the timing issues more effectively. It replaces the Flip-Flop by a single latch, which decreased transition time from D to Q.

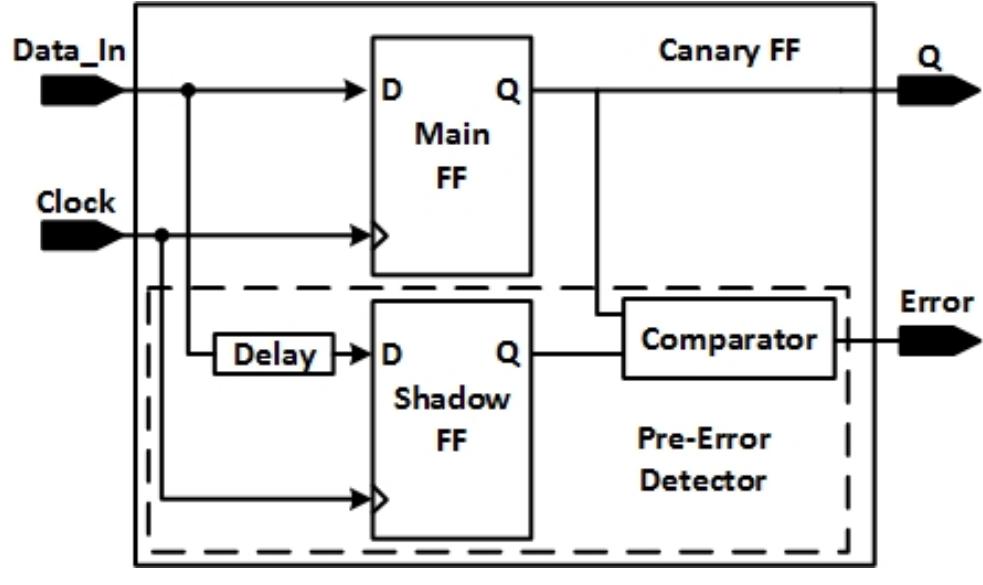

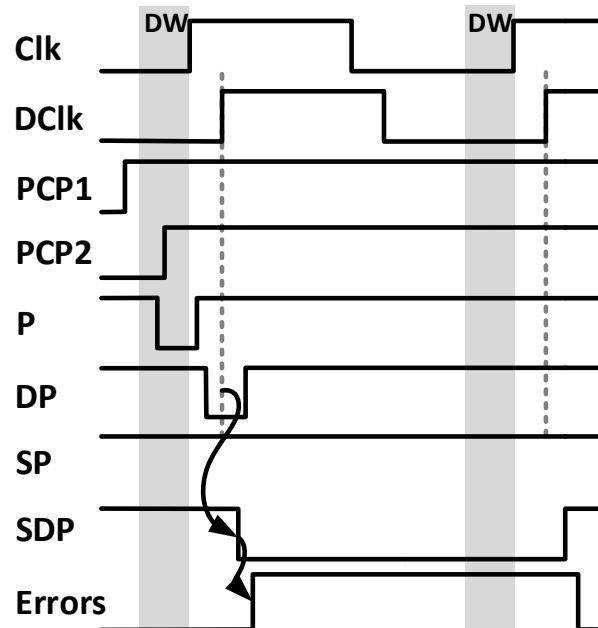

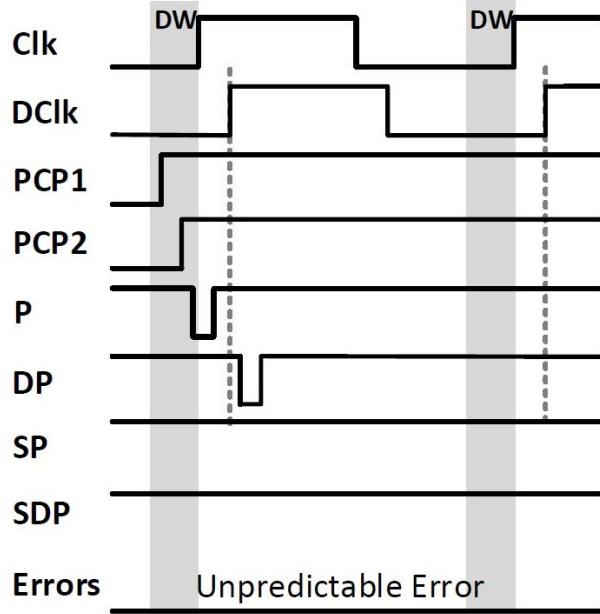

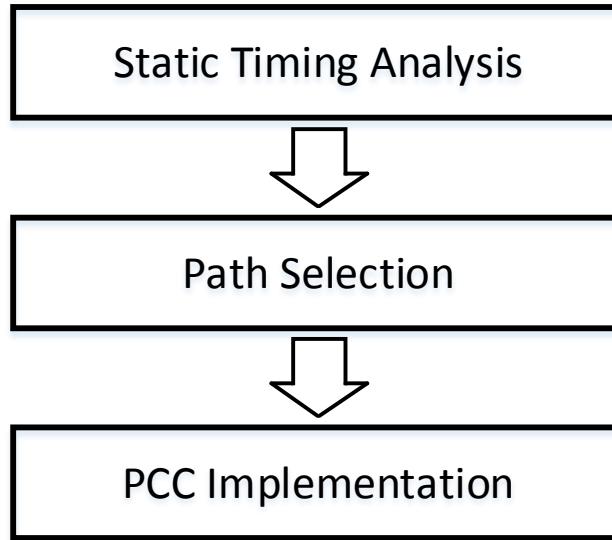

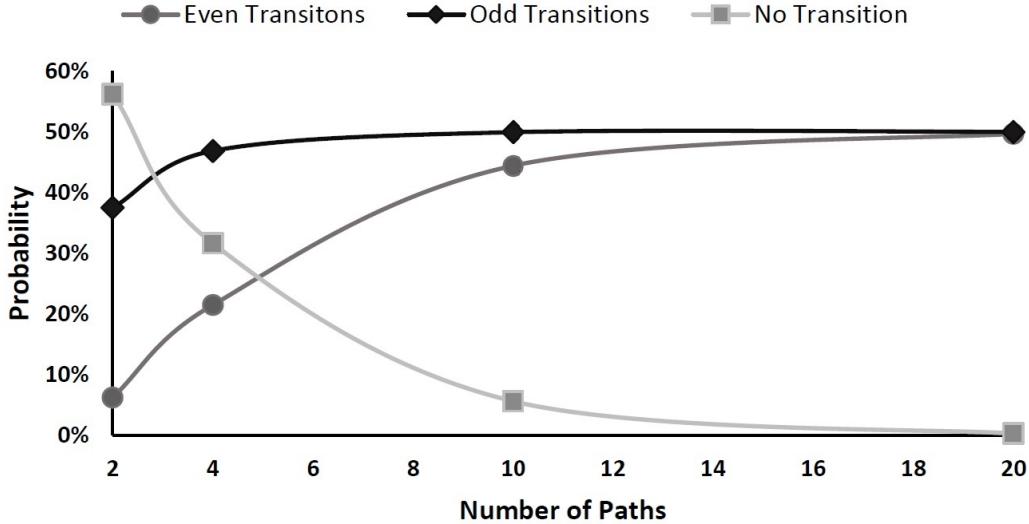

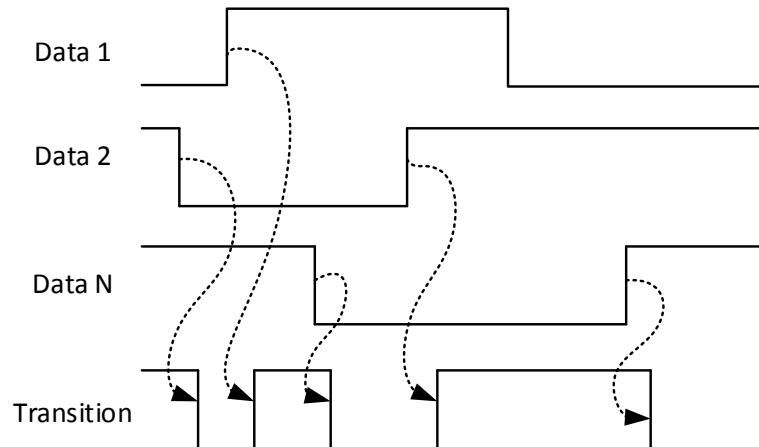

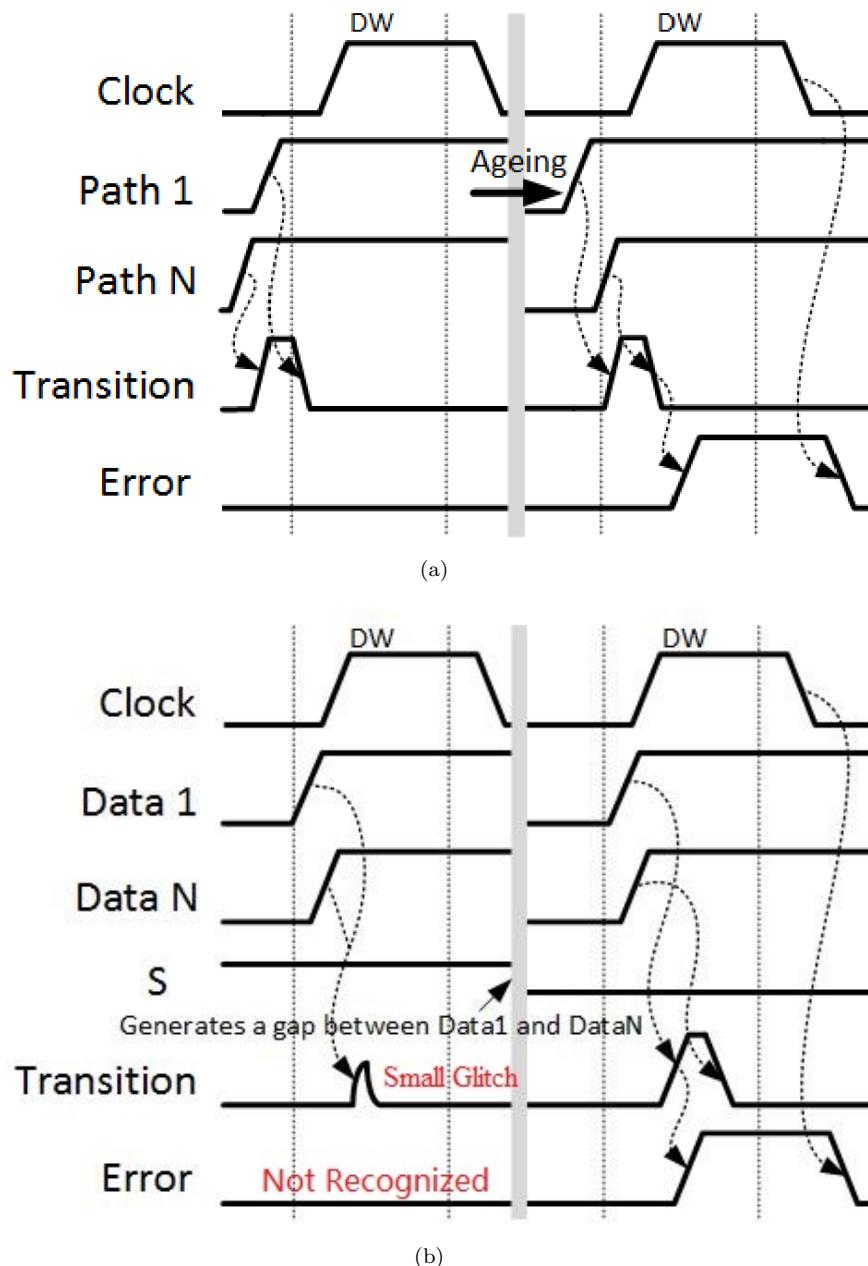

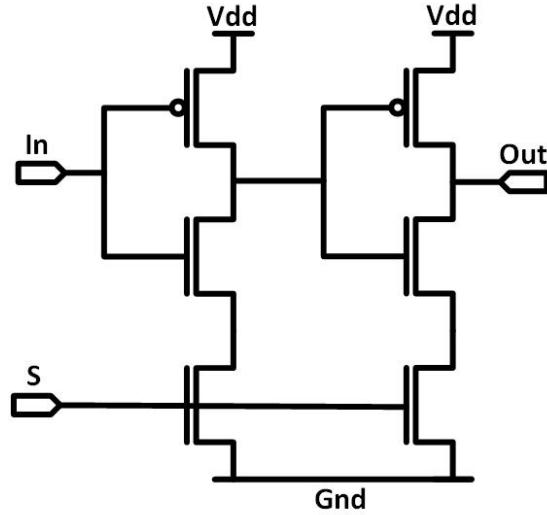

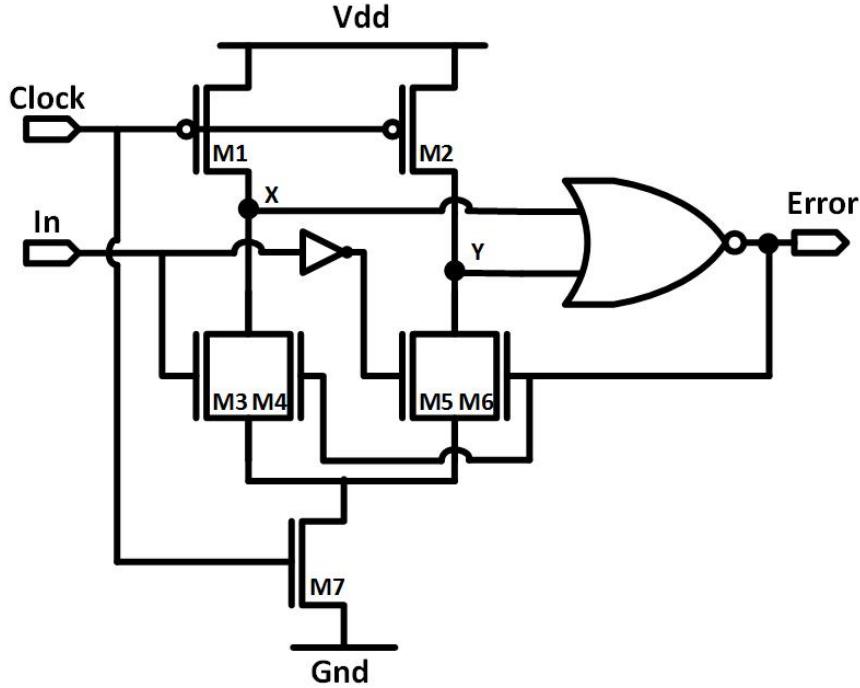

FIGURE 2.23: Razor II and Timing Diagram, Reproduced from [30]