#### UNIVERSITY OF SOUTHAMPTON

### Neural signal processing with metal-oxide RRAM devices

by

Isha Gupta

A thesis submitted in partial fulfillment for the degree of Doctor of Philosophy

in the Faculty of Physical Sciences Engineering School of Electronics and Computer Science

September 2018

# Academic Thesis: Declaration of Authorship

I, Isha Gupta declare that this thesis and the work presented in it are my own and has been generated by me as the result of my own original research.

Neural Signal Processing with metal-oxide RRAM devices

I confirm that:

This work was done wholly or mainly while in candidature for a research degree at this University;

Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

Where I have consulted the published work of others, this is always clearly attributed;

Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

I have acknowledged all main sources of help;

Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

Parts of this work have been published as:

Gupta, I., Serb, A., Berdan, R., Khiat, A., Regoutz, A. and Prodromakis, T., 2015. 'A cell classifier for RRAM process development'. *IEEE Transactions on Circuits and Systems II:* Express Briefs, 62(7), pp.676-680.

Gupta, I., Serb, A., Khiat, A., Zeitler, R., Vassanelli, S. and Prodromakis, T., 2016. 'Real-time encoding and compression of neuronal spikes by metal-oxide memristors'. *Nature communications*, 7.

Gupta, I., Serb, A., Khiat, A. and Prodromakis, T., 2016, May. 'Practical operation considerations for memristive integrating sensors'. *IEEE International Symposium on Circuits and Systems (ISCAS)*, 2016 (pp. 2322-2325).

Gupta, I., Serb, A., Khiat, A. and Prodromakis, T., 2017. 'Improving Detection Accuracy of Memristor-Based Bio-Signal Sensing Platform'. *IEEE Transactions on Biomedical Circuits and Systems*, 11(1), pp.203-211.

Gupta, I., Serb, A., Khiat, A. and Prodromakis, T., 2016. 'Towards a memristor-based spike-sorting platform'. *IEEE Biomedical Circuits and Systems*, pp.1-4.

Gupta, I., Serb, A., Berdan, R., Khiat, A. and Prodromakis, T., 2017. 'Volatility Characterization for RRAM Devices'. *IEEE Electron Device Letters*, 38(1), pp.28-31.

Gupta, I., Serb, A., Khiat, A., Zeitler, R., Vassanelli, S. and Prodromakis, T., 2018. 'Sub 100nW volatile nano-metal-oxide memristor as synaptic-like encoder of neuronal spikes.' *IEEE Transactions on Biomedical Circuits and Systems*.

Gupta, I., Serb, A., Khiat, A., and Prodromakis, T., 'Mitigating noise effects in volatile nano-metal oxide devices, *IEEE International Symposium on Circuits and Systems (ISCAS)*, 2017.

Gupta, I., Serb, A., Khiat, A., and Prodromakis, T., 'Spike Sorting using non-volatile metal-oxide devices, *Nature Scientific Reports, Under Review*.

Trapatseli, M., Carta, D., Regoutz, A., Khiat, A., Serb, A., Gupta, I. and Prodromakis, T., 2015. 'Conductive atomic force microscopy investigation of switching thresholds in titanium dioxide thin films'. *The Journal of Physical Chemistry C*, 119(21), pp.11958-11964.

Regoutz, A., Gupta, I., Serb, A., Khiat, A., Borgatti, F., Lee, T.L., Schlueter, C., Torelli, P., Gobaut, B., Light, M. and Carta, D., 2016. 'Role and Optimization of the Active Oxide Layer in  $TiO_2$  based RRAM'. Advanced Functional Materials, 26(4), pp.507-513.

Carta, D., Hitchcock, A.P., Guttmann, P., Regoutz, A., Khiat, A., Serb, A., Gupta, I. and Prodromakis, T., 2016. 'Spatially resolved  $TiO_x$  phases in switched RRAM devices using soft X-ray spectromicroscopy'. Scientific reports, 6.

Carta, D., Guttmann, P., Regoutz, A., Khiat, A., Serb, A., Gupta, I., Mehonic, A., Buckwell, M., Hudziak, S., Kenyon, A.J. and Prodromakis, T., 2016. 'X-ray spectromicroscopy investigation of soft and hard breakdown in RRAM devices'. *Nanotechnology*, 27(34), p.345705.

Messaris, I., Nikolaidis, S., Serb, A., Stathopoulos, S., Gupta, I., Khiat, A., & Prodromakis, T. (2017, May), A TiO<sub>2</sub> ReRAM parameter extraction method, 2017 IEEE International Symposium on circuits and Systems (ISCAS) (pp. 1-4).

Messaris, I., Nikolaidis, S., Serb, A., Stathopoulos, S., Gupta, I., Khiat, A., & Prodromakis, T. (2017, May), *Live demonstartion: A TiO*<sub>2</sub> *ReRAM parameter extraction method*, 2017 IEEE International Symposium on circuits and Systems (ISCAS) (pp. 1-4).

Signature: Isha Gupta (March 2018)

### Copyright Declaration

The copyright of this thesis rests with the author and is made available under a Creative Commons Attribution Non-Commercial No Derivatives licence. Researchers are free to copy, distribute or transmit the thesis on the condition that they attribute it, that they do not use it for commercial purposes and that they do not alter, transform or build upon it. For any reuse or redistribution, researchers must make clear to others the licence terms of this work.

#### UNIVERSITY OF SOUTHAMPTON

#### ABSTRACT

## FACULTY OF PHYSICAL SCIENCES AND ENGINEERING SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

#### Doctor of Philosophy

by Isha Gupta

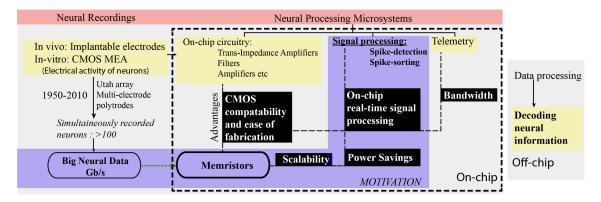

This thesis delves in the issue of processing huge volume of neural data recorded using *invitro* monitoring technologies. The real-time processing of neuronal signals imposes excessive strain on bandwidth, energy and computation capacity prohibiting scaling of present neural interfaces. This work offers a unique solution to the challenge of encoding electrophysiological neural bio-signal information in a power efficient way thus capable of impacting the field of neuroprosthetic applications or for instance, the emerging area of bio-electronic medicines.

The thesis mainly focussed on exploiting the intrinsic properties of nanoscale metal-oxide-metal devices commonly known as 'memristors' for demonstrating **spike detection** and **spike sorting** at the proof-of-concept level. Memristive devices were fed with extracellular neuronal activity and the thresholded integrating property of both **non-volatile** and **volatile** devices was used to differentiate between high-amplitude spiking events and low-amplitude background noise that forms the majority of the neuronal signals samples. The spiking events of supra-threshold strength are detected as memory state transitions thus compressing information on neuronal spikes in real-time. These experiments show a substantial improvement in the bandwidth required per sensing site ( $\approx 200:1$ ), while concurrently offering more energy efficient paradigm, estimated at  $\approx 100$ nW per channel as compared to the present state-of-the-art spike detection techniques. For all the experiments, for quantification of the obtained results, the spike detection performance was benchmarked against state-of-the-art template matching.

Importantly, the experimental work carried for demonstrating this application also involved developing electrical characterisation modules for carrying out en-masse testing of the fabricated devices and ensure process development. Furthermore, the same concept was used to demonstrate a much more computationally intensive task i.e. 'spike-sorting'. It is a procedure of identifying the activity of individual neurons from the data collected through electrophysiological experiments. The experiments performed show how the intrinsic analogue programmability of memristive devices can be used to perform the task of spike sorting. This idea can thus potentially open new avenues for performing spike-detection and sorting both on-chip using miniaturised chips at minimal power costs, demonstrating the technology's potential to build scalable, yet energy efficient on-node processors for brain-chip interfaces.

### Contents

| D | eclar | ration                                                                           | iii  |

|---|-------|----------------------------------------------------------------------------------|------|

| D | eclar | ration                                                                           | vii  |

| A | bstra | act                                                                              | viii |

| A | ckno  | wledgements                                                                      | xxix |

| 1 | Inti  | roduction                                                                        | 1    |

|   | 1.1   | Motivation                                                                       | 1    |

|   | 1.2   | Research Objectives                                                              |      |

|   | 1.3   | Thesis Organisation                                                              | 4    |

| 2 | Net   | ıral Signals: Acquisition and Processing                                         | 7    |

|   | 2.1   | Biology, Neural Signals and Recordings                                           | . 8  |

|   |       | 2.1.1 Action potentials: source, nature and importance                           |      |

|   |       | 2.1.2 Approaches to monitor the electrical activity of cells                     |      |

|   |       | 2.1.3 Perspective: Growth of neural data                                         |      |

|   | 2.2   | Advances in Microelectrode technology                                            |      |

|   | 2.3   | Front-end electronic circuitry                                                   |      |

|   | 2.4   | Neural Signal Processing                                                         |      |

|   |       | 2.4.1 Spike Detection Techniques: A Review                                       |      |

|   |       | 2.4.2 Spike Sorting Techniques: A Review                                         |      |

|   |       | 2.4.3 To sort, or not to sort?                                                   |      |

|   | ~ ~   | 2.4.4 Limitations and Challenges in Spike Detection and Spike Sorting            |      |

|   | 2.5   | Summary                                                                          | 20   |

| 3 | Me    | tal-Oxide RRAM                                                                   | 23   |

|   | 3.1   | RRAM: Background                                                                 |      |

|   | 3.2   | History and Science of Memristor                                                 |      |

|   | 3.3   | Memristive materials                                                             |      |

|   | 3.4   | Resistive switching behaviour, electrical characteristics and mechanisms         |      |

|   | 3.5   | Potential Applications and Performance Parameters                                | 31   |

|   | 3.6   | $TiO_x$ RRAM Devices, Electrical Characterisation and Automated Characterisation |      |

|   | 0.7   | isation Protocols                                                                |      |

|   | 3.7   | Characterisation Protocols                                                       |      |

|   |       | 3.7.1 Characterisation Protocol I                                                |      |

|   |       | 3.7.1.1 Algorithm Description                                                    | . 34 |

X CONTENTS

|   |      | 3.7.1.2 Implementation and Testing                                        | 35         |

|---|------|---------------------------------------------------------------------------|------------|

|   |      | 3.7.1.3 Results and Discussion                                            | 38         |

|   |      | 3.7.2 Characterisation Protocol II                                        | 10         |

|   |      | 3.7.2.1 Volatility Characterisation Protocol                              | 11         |

|   |      | 3.7.2.2 Algorithm Description and Implementation                          | 11         |

|   |      |                                                                           | 13         |

|   | 3.8  |                                                                           | 16         |

| 4 | Spil | ke detection using metal-oxide devices in non-volatile regime 4           | <b>!</b> 7 |

|   | 4.1  | Introduction                                                              | 17         |

|   | 4.2  | Memristive Integrating Sensors (MIS)                                      | 18         |

|   | 4.3  | Memristors as encoders of neuronal spikes                                 | 50         |

|   |      | 4.3.1 Neural spiking compression with memristors                          | 51         |

|   |      | 4.3.2 Signal-conditioning methodology                                     | 52         |

|   |      | 4.3.3 Spike detected in MIS-based platform                                | 53         |

|   | 4.4  |                                                                           | 56         |

|   | 4.5  |                                                                           | 30         |

|   |      |                                                                           | 30         |

|   |      |                                                                           | 31         |

|   | 4.6  |                                                                           | 33         |

|   |      |                                                                           | 34         |

|   |      | •                                                                         | 66         |

|   |      |                                                                           | 37         |

|   |      |                                                                           | 38         |

|   |      | 4.6.5 Data Analysis: Noise band settings comparison                       | 70         |

|   |      |                                                                           | 70         |

|   |      |                                                                           | 71         |

|   |      | 4.6.6 Frequent resets strategy with optimised gain, offset and noise band |            |

|   |      | settings                                                                  | 72         |

|   |      | 4.6.7 Discussion                                                          | 75         |

|   | 4.7  | Power estimations                                                         | 76         |

|   | 4.8  | Summary                                                                   | 77         |

| 5 | Spil | ke detection using metal-oxide devices in volatile regime 7               | <b>'</b> 9 |

|   | 5.1  | Introduction                                                              | 79         |

|   | 5.2  | Operation of memristive devices as volatile cells                         | 30         |

|   | 5.3  | Memristive devices as volatile spike-detectors                            | 34         |

|   | 5.4  | Nanoscale-metal oxide devices as volatile spike encoders                  | 39         |

|   | 5.5  | Optimising operation parameters for volatile devices                      | 90         |

|   | 5.6  | Mitigating Noise-effects in volatile metal-oxide devices                  | 90         |

|   |      | * *                                                                       | )1         |

|   |      | 5.6.2 Effect of sub-threshold events                                      | )4         |

|   |      | 1                                                                         | 95         |

|   | 5.7  | Discussion                                                                | 96         |

|   | 5.8  | Summary                                                                   | 97         |

| 6 | Spil | ke Sorting using metal-oxide devices in non-volatile regime               | 9          |

CONTENTS xi

|              | 6.1   | Introduction                                                               | 99  |

|--------------|-------|----------------------------------------------------------------------------|-----|

|              | 6.2   | Spike sorting using non-volatile metal oxide devices                       | 100 |

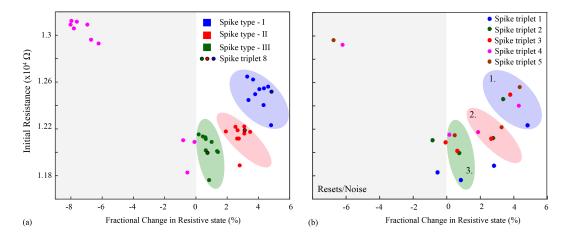

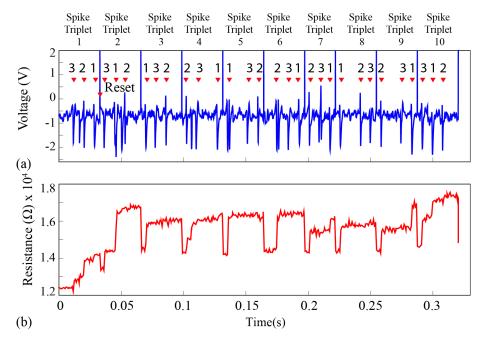

|              |       | 6.2.1 Proof-of-concept/Initial Results                                     | 100 |

|              | 6.3   | Memristor-based spike sorting platform                                     | 105 |

|              |       | 6.3.1 Repeatability                                                        | 105 |

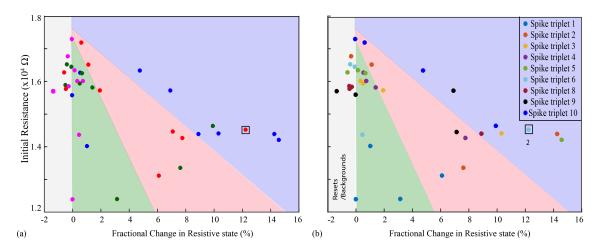

|              |       | 6.3.2 Randomised instances                                                 | 108 |

|              | 6.4   | Discussion and Summary                                                     | 110 |

| 7            | Con   | iclusions and Future Work                                                  | 111 |

|              | 7.1   | Conclusions/Summary                                                        | 111 |

|              | 7.2   | Author's viewpoint: Recommendations for future work                        | 112 |

| A            | Fab   | rication of Solid-state Metal-Oxide Devices                                | 115 |

| В            | Cha   | racterisation Tool for RRAM devices: ArC Instruments                       | 117 |

| $\mathbf{C}$ | Neu   | ral Data Acquisition System                                                | 119 |

| D            | Pow   | ver Estimations                                                            | 121 |

|              | D.1   | Estimation of power dissipated per channel using manual frequent resetting |     |

|              |       | method (Non-volatile region)                                               | 121 |

|              | D.2   | Estimation of power dissipated per channel in volatile MIS platform        | 122 |

| E            | Neu   | ral Data for Spike sorting                                                 | 125 |

| $\mathbf{F}$ | Con   | tributions                                                                 | 129 |

|              | F.1   | Research publications specific to the proposed thesis                      | 129 |

|              | F.2   | Contributions to group's research                                          | 130 |

|              | F.3   | Innovations                                                                | 130 |

| Bi           | bliog | graphy                                                                     | 133 |

# List of Figures

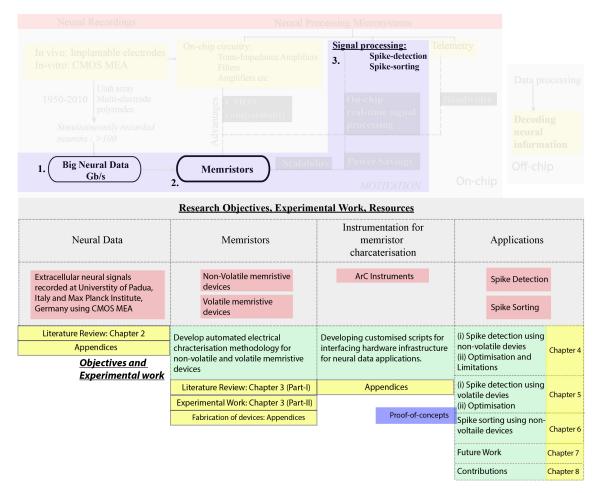

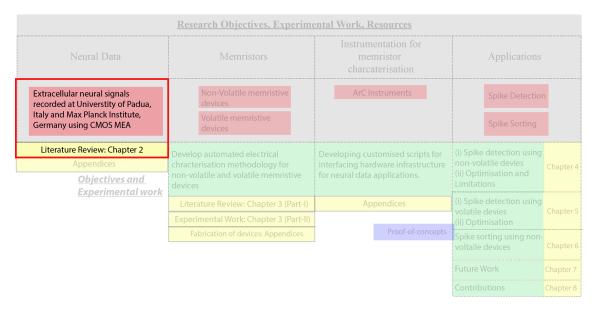

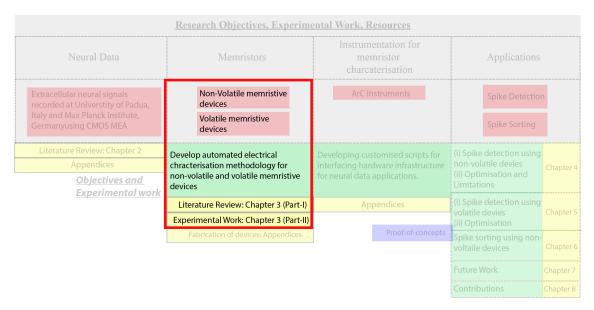

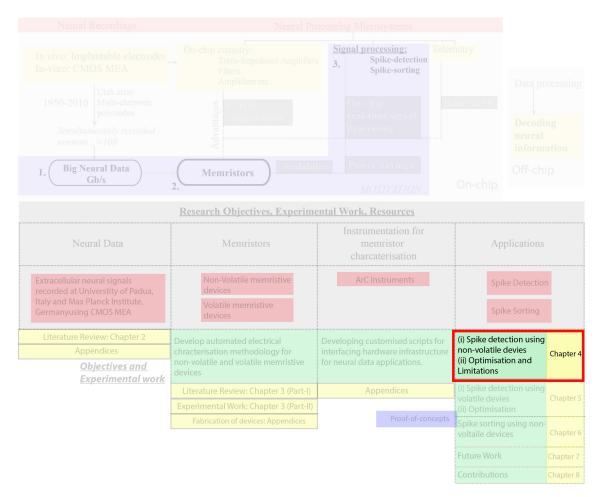

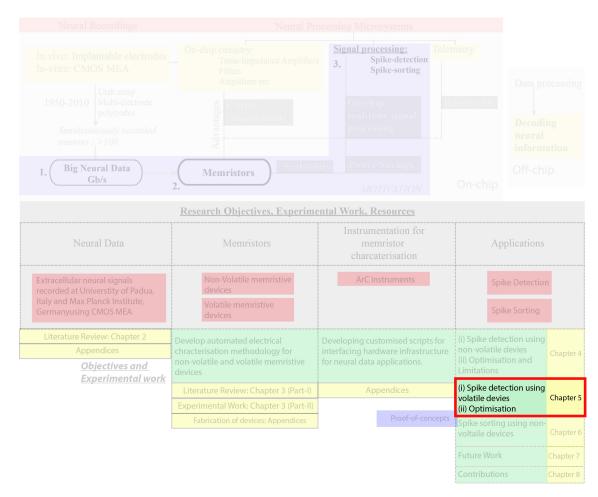

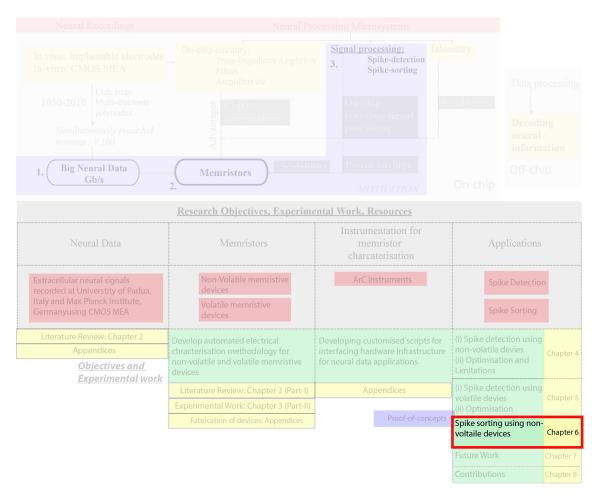

| 1.1        | scope of the experimental work.  Research Objectives, Experimental work, Resources and Thesis Organisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $\frac{1}{2}$ |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 1.2        | research Objectives, Experimental work, resources and Thesis Organisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |

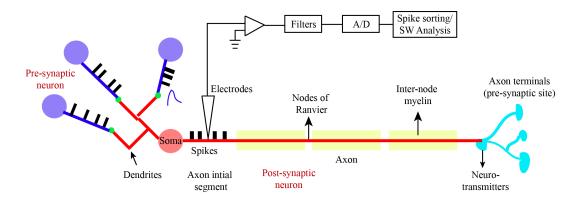

| 2.1<br>2.2 | The research objective of this chapter.  A neuron comprises of dendrites and axon branching out of soma. Axon is covered with a lipid myelin sheath which isolates it from the surrounding neurons and intermittently consists of small-gaps termed as 'Nodes of Ranvier'. The initial segment of the axon and uncovered small-gaps consists of ion-channels which helps in propagating the action potentials along the axon [35]. Axon and dendrites communicate via synapses (green). Neural activity can be acquired by placing microelectode in the region of interest. | 8             |

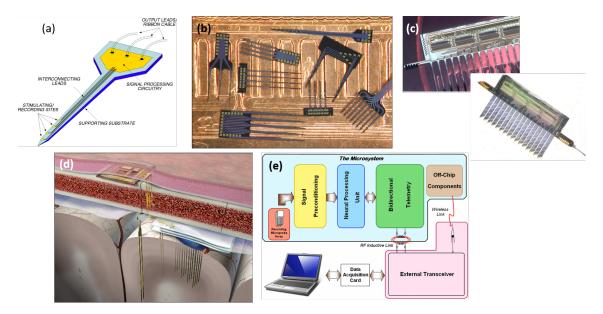

| 2.3<br>2.4 | The numbers of neurons simultaneously recorded over the years In-vivo interfacing. All figures replicated from [20]: (a) Early neural probes, b) several neural probe designs on the back of US penny, c) A 64-site eight-channel stimulating probes with sites on $400  \mu \mathrm{m}$ centres with CMOS electronics for stimulus generation and recording, (d) and (e) A wireless implantable                                                                                                                                                                            | 10            |

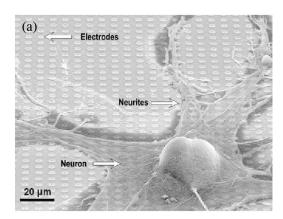

| 2.5        | micro system and block diagram respectively.  (a) Neurons on chip [47].(b) Image of measurement setup used to acquire neural recordings ([48]) and the inset shows he multi-transistor array neurochip fabricated on the basis of CMOS [39].                                                                                                                                                                                                                                                                                                                                | 11<br>13      |

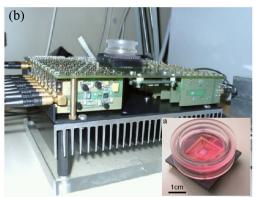

| 2.6        | Conceptual diagram for spike detection and sorting. The single-unit activity i.e. activity of few neurons effectively in the vicinity of $\approx 50\mu\mathrm{m}$ from the recording electrode can be distinguished in individual components. The raw data is filtered to obtain local field potentials (LFP) and spike trains. Spike trains are then broken down in individual spike shapes by spike detection fol-                                                                                                                                                       |               |

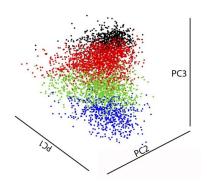

| 2.7        | lowed by feature extraction and clustering (triangles in grey represent neurons). Concept: Feature extraction and clustering. PC: Principal Component                                                                                                                                                                                                                                                                                                                                                                                                                       | 14<br>18      |

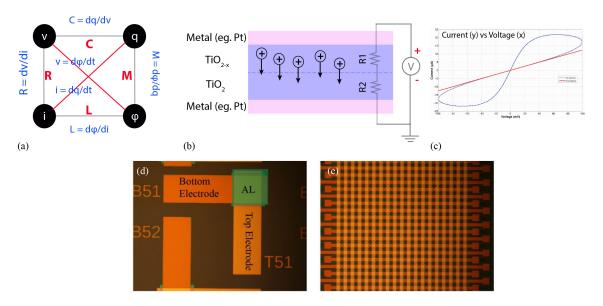

| 3.1<br>3.2 | The research objective of this chapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23            |

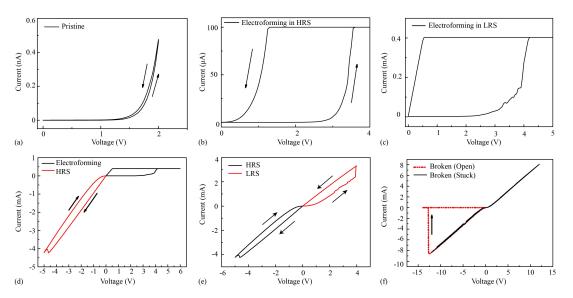

| 3.3        | voltage [78]. (d) Single devices, and (e) cross-bar architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 24            |

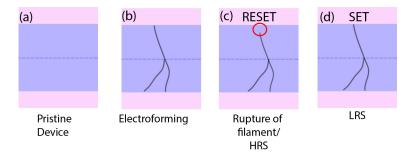

| 3.4        | Device switched in LRS, (f) Broken device (Open and Stuck) Filamentary switching mechanism. (a) Pristine Device, (b) Electroforming                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26            |

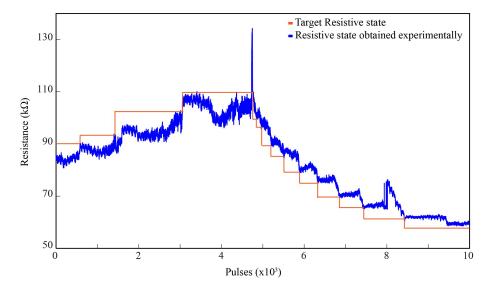

| 3.5        | procedure, (c) Rupture of filament (HRS), and (d) SET process, LRS Capability of the device to switch to multi-resistive state                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27<br>28      |

xiv LIST OF FIGURES

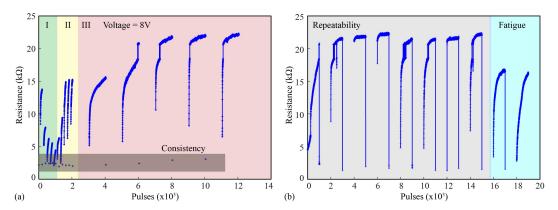

| 3.6     | Biasing of packaged single devices using the hardware infrastructure (see Appendix. B). The applied pulse voltage is 8 V.(a) Resistive change in the state of DUT under pulse width 1ms (I), 10 ms (II) for 100 pulses, 10 ms for 1000 pulses.(b) Testing the repeatability of the same device which eventually tends to fatigue. The device switches to low resistive state with 8 V (10ms) and high                                                                               |                 |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|         | resistive state with -5 V (1ms)                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29              |

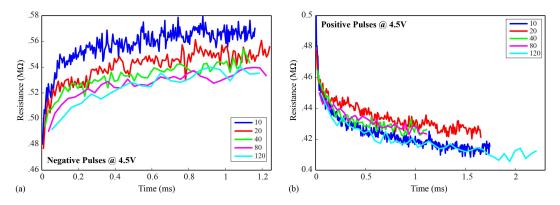

| 3.7     | Resistive behaviour of the device with pulse width of $10\mu s$ (blue), $20\mu s$ (red), $40\mu s$ (green), $80\mu s$ (pink) and $120\mu s$ (cyan) for pulse amplitude (a) -4.5 V and (b) +4.5 V                                                                                                                                                                                                                                                                                    | 29              |

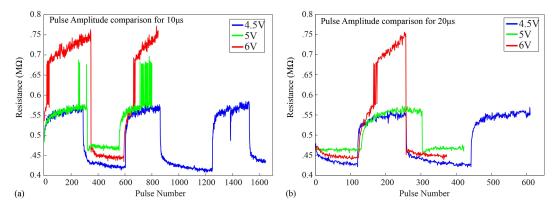

| 3.8     | Resistive behaviour of the device with pulse amplitude of 4.5,5 and 6 V with pulse width of (a) $10\mu$ s and (b) $20\mu$ s                                                                                                                                                                                                                                                                                                                                                         | 29              |

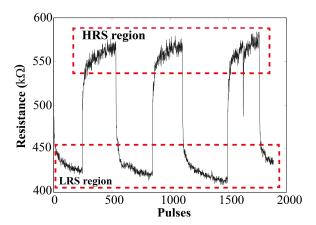

| 3.9     | Resistive switching in $TiO_x$ RRAM devices. A bipolar biasing protocol was used to introduce transitions between High Resistive State (HRS) and Low Resistive State (LRS)                                                                                                                                                                                                                                                                                                          | 34              |

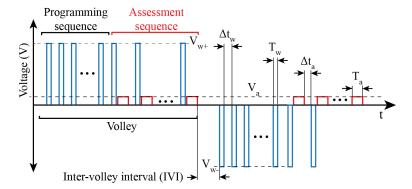

| 3.10    | Typical biasing scheme applied to devices under test. Only two out of the four volleys are shown. The first volley toggles functioning devices into LRS whereas the second into HRS. Each assessment pulse results in an estimate of                                                                                                                                                                                                                                                |                 |

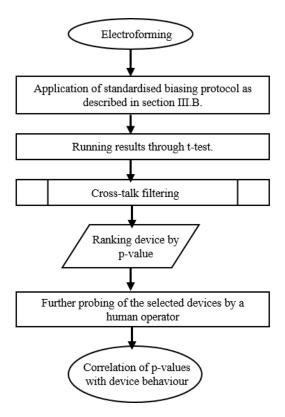

| 3 11    | resistive state after the application of the 'write' pulse train                                                                                                                                                                                                                                                                                                                                                                                                                    | $\frac{35}{37}$ |

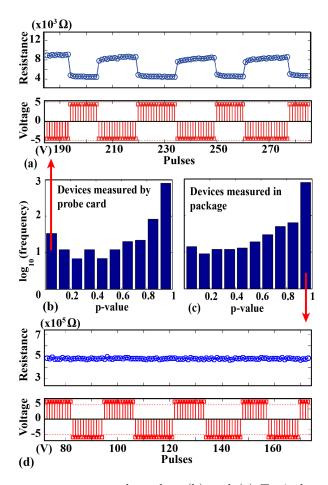

|         | First measurement round results: (b) and (c) Typical examples of histograms showing number of devices versus p-value taken from probe-card-accessed and packaged crossbar arrays, respectively. Typical behaviour of devices that                                                                                                                                                                                                                                                   | 51              |

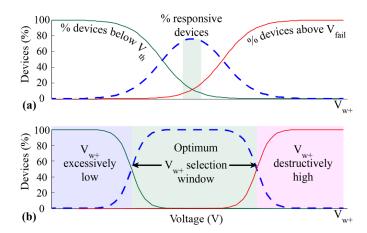

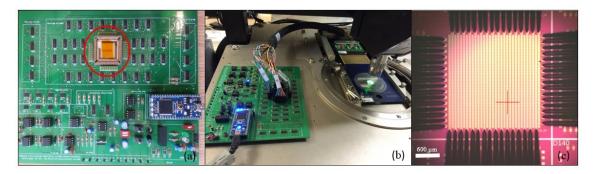

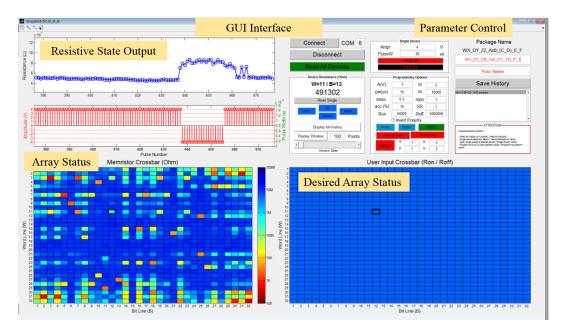

| 3.13    | scored (a) low p-values and (d) high p-values                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39              |

|         | which switching parameters can be set freely.                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39              |

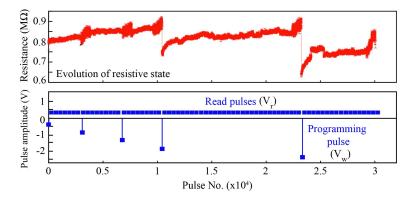

| 3.14    | Typical volatile characteristics of the solid-state $TiO_x$ RRAM devices. Programming pulse and read pulse is denoted by $V_w$ and $V_r$ respectively                                                                                                                                                                                                                                                                                                                               | 41              |

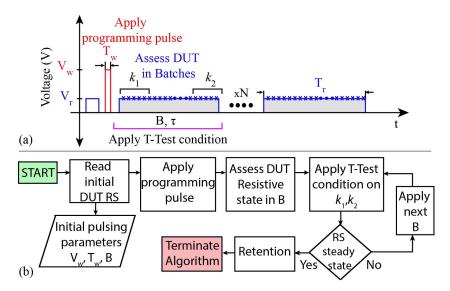

| 3.15    | Volatility module. (a) Schematic for the volatility module. The red and blue color illustrates the programming pulse and read pulses respectively. Grey color indicates one batch of read pulses. (b) Flow chart for the volatility algorithm implementing standard t-test condition                                                                                                                                                                                                | 42              |

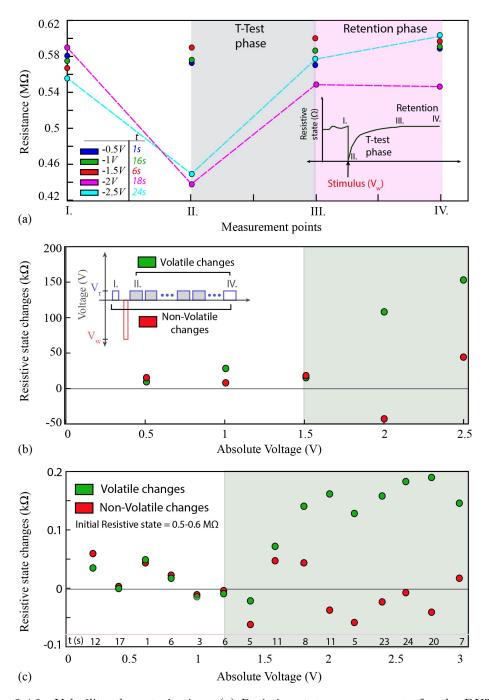

| 3.16    | Volatility characterisation. (a) Resistive state measurements for the DUT. The grey and pink band indicates the t-test and retention phase respectively. The presented time (t) in the inset is the duration the DUT takes to exit the t-test phase. (b) Volatile (green colour) and non-volatile (red colour) resistive state changes for the same DUT as in (a). (c) Same as (b) for a $200  nm^2$ memristive device. Grey band in (b) and (c) indicates the threshold of the DUT | 44              |

| / 1     | The research objective of this experimental chapter                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17              |

| 4.1 4.2 | The research objective of this experimental chapter                                                                                                                                                                                                                                                                                                                                                                                                                                 | 47              |

|         | the device would cause a change in resistive state of the device                                                                                                                                                                                                                                                                                                                                                                                                                    | 48              |

LIST OF FIGURES xv

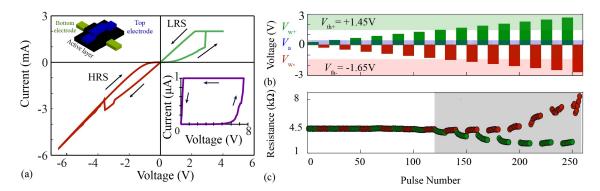

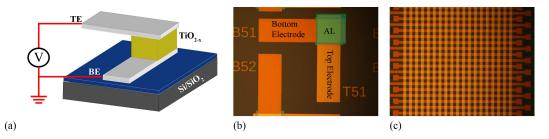

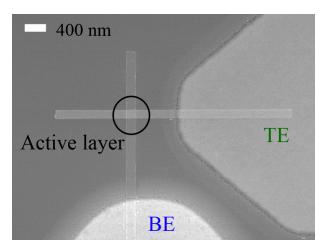

| 4.3 | Device architecture and electrical characterisation of solid-state $TiO_x$ RRAM devices.(a) Inset in the first quadrant represents a schematic illustration of a $TiO_x$ RRAM memristor. The inset in the fourth quadrant shows the 'electro- |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | forming step' where the device forms to 'ON' state under positive bias, shown in purple colour. After electroforming, the device exhibits bipolar switching                                                                                   |    |

|     | with low resistive state (LRS, illustrated in green) to high resistive state (HRS, illustrated in red) transitions at $\approx \pm 3$ V. RESET occurs under negative bias                                                                     |    |

|     | whilst the complementary SET transitions occur under positive bias. (b,c)                                                                                                                                                                     |    |

|     | Pulse based characterisation of the DUT. Resistive state changes (bottom trace) in response to the input pulses above threshold, $V_{w+}$ and $V_{w-}$ indicated                                                                              |    |

|     | in green and red circles respectively. Read pulses of amplitude $V_a$ are indicated in blue. In bipolar devices two inherent thresholds exist, one for each voltage                                                                           |    |

|     | polarity. For this device, we obtained $V_{th+} = +1.45 \mathrm{V}$ and $V_{th-} = -1.65 \mathrm{V}$ as indicated by the green and pink shadowed areas of the plot respectively                                                               | 49 |

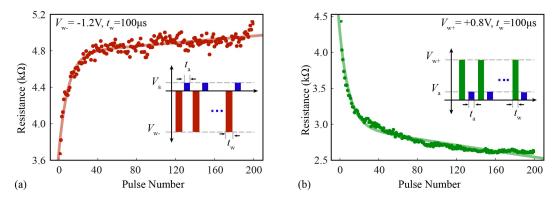

| 4.4 | (a), (b) Gradual resistive switching under a pulse train stimulation (200 pulses per train) as illustrated in the respective insets. The DUT response is fitted                                                                               |    |

|     | with a second order exponential function (continuous line). Typical biasing                                                                                                                                                                   |    |

|     | scheme parameters (insets): negative write pulse voltage $V_{w-} = -1.2 \text{ V}$ , positive write pulse voltage $V_{w+} = +0.8 \text{ V}$ , read pulse voltage $V_a = 0.5 \text{ V}$ , write                                                |    |

|     | pulse width $t_w = 100 \mu s$ and read pulse width $t_a$ automatically determined by                                                                                                                                                          |    |

|     | the measurement system.                                                                                                                                                                                                                       | 51 |

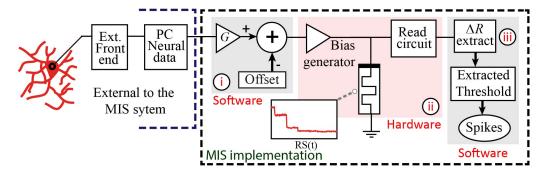

| 4.5 | Memristive Integrating Sensors (MIS) concept and operation. Block diagram of the signal processing in the proposed spike-detection system. An external                                                                                        |    |

|     | front-end (a CMOS Multi-Electrode-Array (MEA) system) located 'externally' to the MIS platform records extracellular neuronal signals and ampli-                                                                                              |    |

|     | fies them. The pre-amplified, acquired neural recordings are then fed into the characterisation instrument, suitably gain-boosted (G) and offset $(V_{off})$ to render them compatible with the memristors voltage operating regimes (i).     |    |

|     | The conditioned waveform is fed into a memristor and its resistive state is then periodically assessed (ii). Changes in resistive state caused by spiking                                                                                     |    |

| 1 C | events are extracted offline (iii)                                                                                                                                                                                                            | 51 |

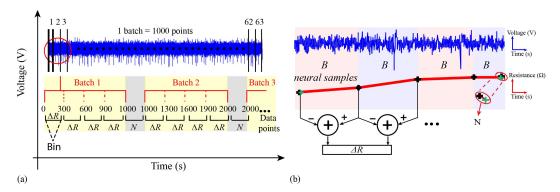

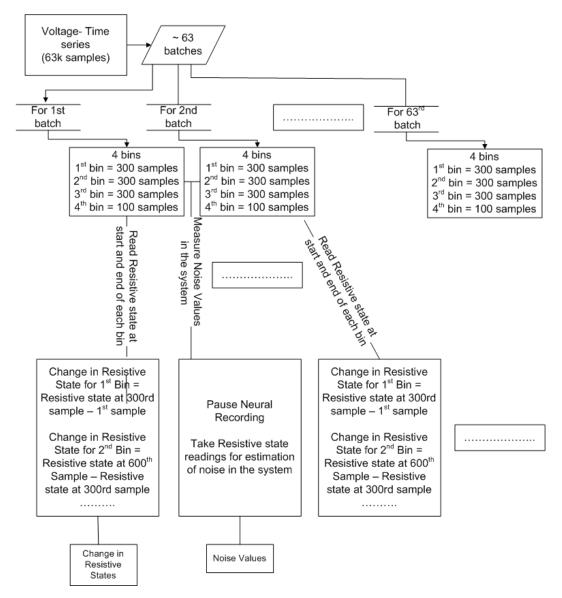

| 4.6 | Standard read-out scheme for evaluating the time evolution of the resistive state of test devices subjected to input neuronal signal. (a) A single neural recording (blue trace) contains exactly 63016 data-points. Input data is fed to     |    |

|     | the devices in batches of 1000 data points with resistive state of the device be-                                                                                                                                                             |    |

|     | ing assessed at the beginning of each batch, then every 300 samples (termed as                                                                                                                                                                |    |

|     | bin, B) and finally at the end of each batch. A single neural recording consists                                                                                                                                                              |    |

|     | of 63 batches. Changes in resistive state ( $\Delta R$ ) are extracted from consecutive                                                                                                                                                       |    |

|     | resistive state assessments. Resistive state changes occurring between the last measurement of each batch and the first measurement of the next batch, i.e.                                                                                   |    |

|     | with no interceding pulse biasing, (N) can be used to determine the 'noise                                                                                                                                                                    |    |

|     | band'. (b) Conceptual read-out scheme for evaluating the time evolution of                                                                                                                                                                    |    |

|     | the resistive state of test devices subjected to input stimulation for one batch.                                                                                                                                                             |    |

|     | Assessment points are marked by crosses                                                                                                                                                                                                       | 53 |

| 4.7 | Flow chart for signal processing methodology                                                                                                                                                                                                  | 54 |

xvi LIST OF FIGURES

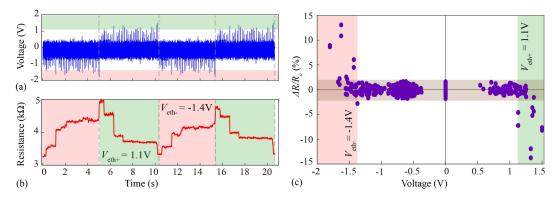

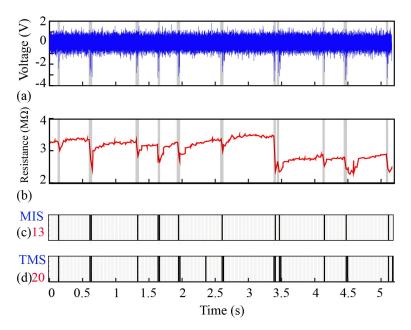

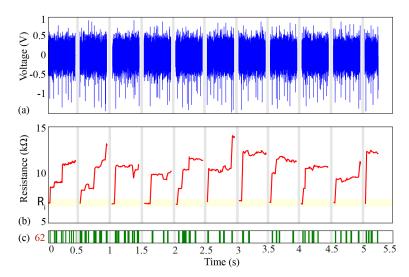

| 4.8  | (a),(b) (Upper Trace) An arbitrary input waveform consisting of four concatenated copies of the same retinal cell neural recording and artificially inverted to produce spike trains with alternating polarities is used. (Bottom Trace) The response of DUT in response to the waveform shown in (a). The collated recording copies in (a) have been subjected to appropriate scaling and offsetting in order to accommodate the devices asymmetric threshold voltages, resulting in balanced resistive state SET and RESET. (c) Fractional resistive state modulation ( $\Delta R/R_o$ ) extrapolated from (b) showcasing significant resistive state modulation occurring only above $V_{eth+}$ and below $V_{eth-}$ while intermediate bias values (noise, N) leads to no significant change. The extracted threshold voltages are identified here as, $V_{eth+}=1.1\mathrm{V}$ and $V_{eth-}=-1.4\mathrm{V}$ represented in the green and pink band respectively                                                                       | 55 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

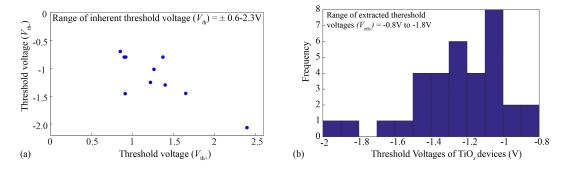

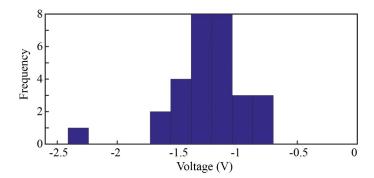

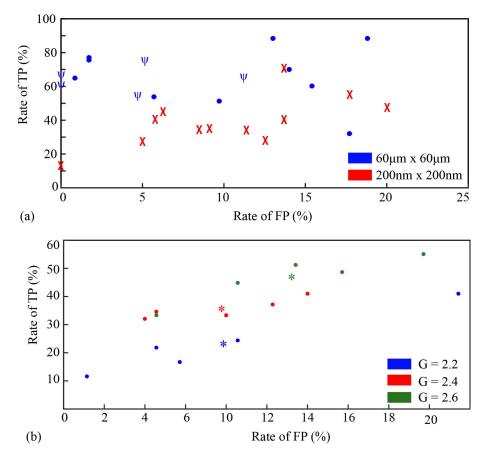

| 4.9  | Inherent and effective threshold of the memristive devices. (a) Range of the 'inherent threshold voltage $(V_{th-}/V_{th+})$ is approximately $\pm 0.6$ -2.3V. (b) Distribution of effective threshold voltage $(V_{eth-}/V_{eth+})$ of the TiOx devices used. Range of the effective threshold voltages used for the experiment is -0.8V to -1.8V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55 |

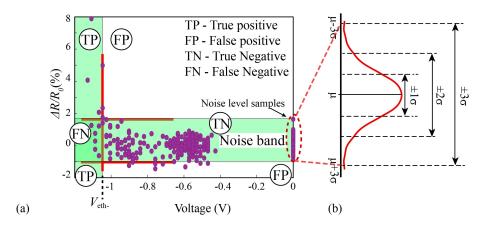

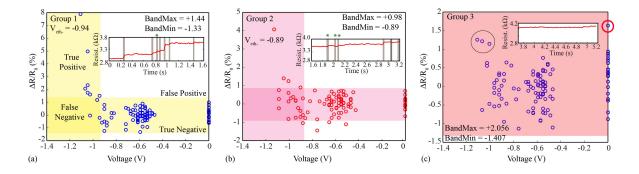

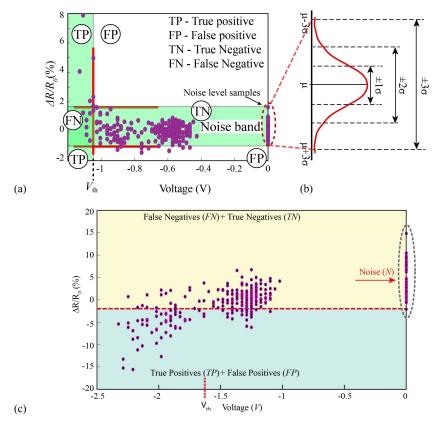

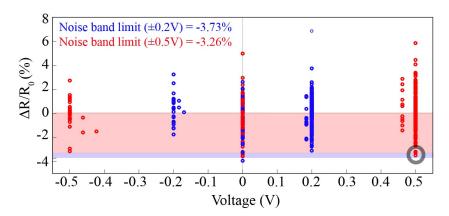

| 4.10 | Concept of estimation of effective threshold voltage $(V_{eth-})$ and quantification of data obtained from the MIS platform. (a) Normalised plot of resistive state changes $(\Delta R/R_o)$ values in each bin is plotted as a function of maximum voltage magnitude of interceding events. (b) Illustration of 6 sigma method used for the setting of the 'noise band limits'. Quantification parameters: True Positive (TP), False Positive (FP), True Negative (TN) and False Negative (FN).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56 |

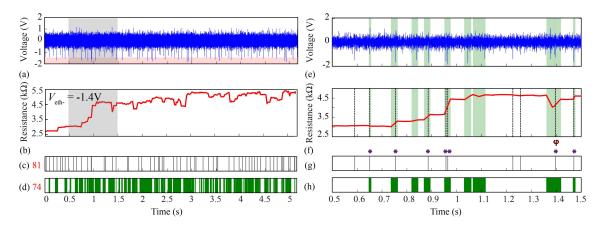

| 4.11 | Benchmarking memristor-based system against state-of-art template matching system. (a) A pre-conditioned neural recording trace with gain and offset value of 2.8 and 0 respectively, causes the resistive state time evolution shown in (b). (c) 81 spikes were detected by the template matching system, with grey lines indicating spike positions. (d) Green shading indicates time intervals within which one or more spikes were detected through the MIS; total of 74. (e) and (f) are close-ups of the neural recording and resistive state evolution shaded grey in (a) and (b) respectively. Time intervals where the MIS detects spikes are shaded green whilst the locations of spikes detected by the template matching system are indicated by grey vertical dashed lines. (g) and (h) Comparison of the detection of spikes by the two systems. The asterisk mark (*) indicates agreement between the two systems and the $\phi$ symbol indicates the resistive state drop associated to the occurrence of a large-amplitude |    |

| 4.12 | positive event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 57 |

|      | experiments, signal conditioning parameters, that is software added gain and offset remained fixed at $G = 2.2$ , $V_{off} = 0$ respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58 |

LIST OF FIGURES xvii

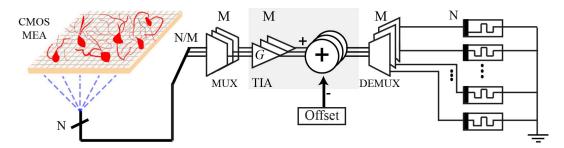

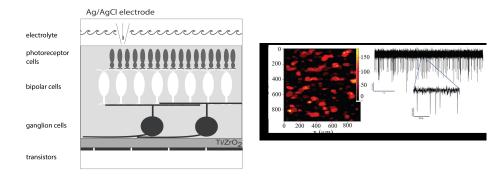

| 4.13        | Towards array level integration. (a) Conceptual diagram indicating conditioning of data from N pixels through multiple gain and offset cascade (M). CMOS MEA: Multi-transistor Array Block, manufactured in standard, commercially available CMOS technology. TIA: Trans-impedance amplifier converting cur-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

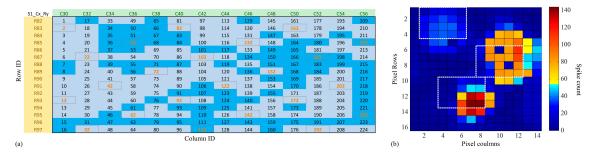

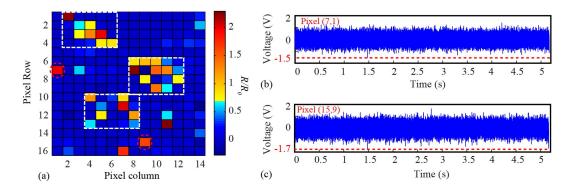

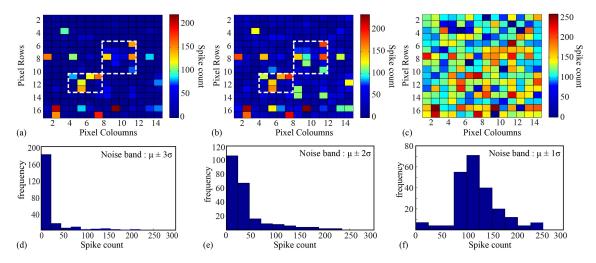

| 4.14        | rent to voltage with appropriate amplification. (a) Overview of the MEA 16x14 sub-array recordings. Green cells: MEA column coordinates of recordings employed. Yellow cells: MEA row coordinates of recordings employed. Blue cells: unique pixel identifier numbers. Dark blue cells indicate recordings that contain at least 1 data sample with magnitude above $0.5\mathrm{V}$ ; this includes a number of recordings that barely pass the $0.5\mathrm{V}$ mark. The map therefore represents the presence of spikes as benchmarked by simple threshold method. The 23 recordings illustrated in orange colour were chosen as a representative sample of the entire array and were then used to estimate gain (G) and offset values $(V_{off})$ for the main experiments. (b) Spike count pixel map yielded by the conventional template matching system | 60 |

| 4.15        | for the MEA sub-array recordings used to obtain 4.11 (c). Three major regions of activity can be clearly seen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 61 |

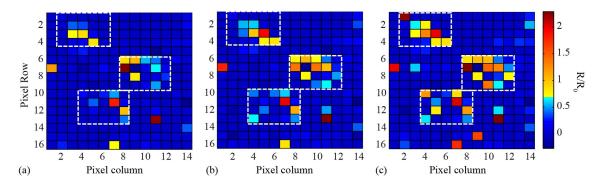

| <i>1</i> 16 | the three main regions of activity detected by the template matching system (marked by white, dashed lines) in 4.14(b). Colour bar mapping has been chosen to correspond to the one employed in Fig. 4.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 62 |

| 4.10        | sensor as shown in 4.15 (c). (a) Memristive device array final state pixel map. It shows the DUT final/initial resistive state ratio. The three main regions of activity are enclosed in white, dashed line boxes, as are two of the four 'stray' pixels circled in red that show remarkable change in state without belonging to any of the three main clusters. (b) and (c) Investigation of the neural recordings corresponding to these stray pixels and it was found that they all contain lone, remarkably high amplitude events i.e1.5V for the former and                                                                                                                                                                                                                                                                                             | 40 |

| 4.17        | -1.7V for the latter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 63 |

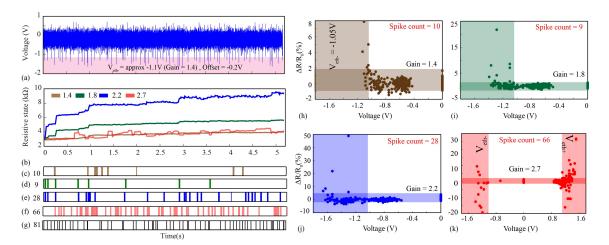

|             | Normalised changes in resistive state for each bin plotted as a function of maximum voltage magnitude within bin for gain 1.4, 1.8, 2.2 and 2.7, respectively. Time axis in (g) applies to entire column.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 64 |

xviii LIST OF FIGURES

| 4.18 | Comparison of MIS data for different sampling rates. (a) The response of the DUT when subjected to neural waveform shown in Fig. 4.17 (a) with gain and offset value of 1.4 and -0.2, respectively. The device was biased thrice and evaluated for three sampling rates (read after every 300, 200 and 100 data points - blue, red and green traces respectively). Corresponding time bin raster plots also shown (inset). (b) and (c) Normalised changes in the resistive state of the device for sampling periods of 300 and 100 pts. plotted as a function of max. bin voltage including noise band estimation | 66 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.19 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 00 |

| 4.20 | corresponding voltage sensitivity plots                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 67 |

| 4.21 | potential significant $\Delta R$ changes respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 68 |

| 4.22 | (b), (e) $\mu \pm 2\sigma$ and (c), (f) $\mu \pm 1\sigma$ , respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 70 |

|      | by the MIS system. The total number of bin columns are 252                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 72 |

LIST OF FIGURES xix

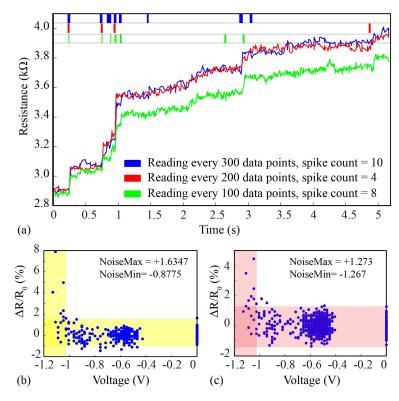

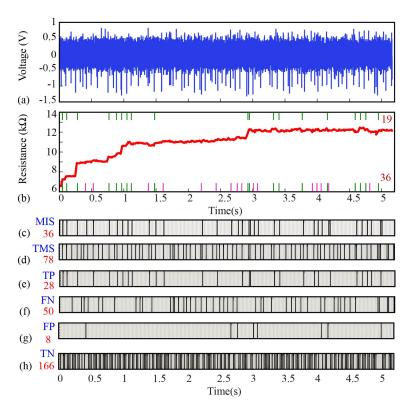

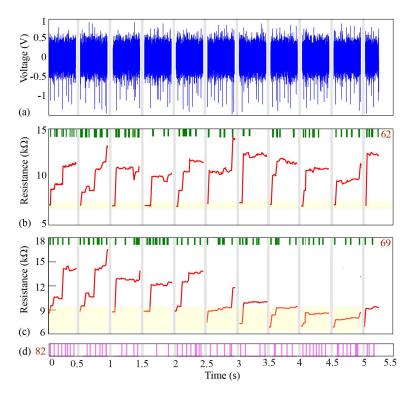

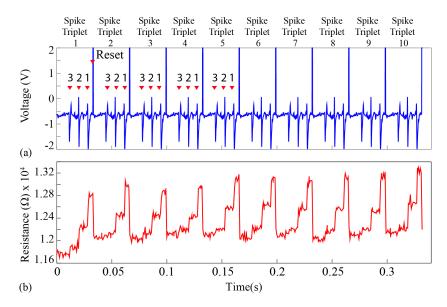

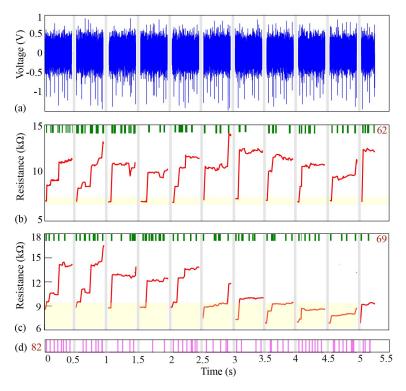

| 4.23       | Frequent resetting of the memristive device in order to improve the spike count of the system. (a) Slicing of the neural recording used in Fig. 4.22 in eleven parts each lasting for $0.5\mathrm{s}$ separated by grey bands. The device is manually reset to its initial state after each run (yellow bands in (b) and (c)). $R_{on}$ is approx. equal to 6-8 k $\Omega$ . (b) and (c) Output of the device when biased with neural recording in (a) with $G = 2.2, V_{off} = 0$ and $G = 2, V_{off} = -0.2$ . Green bands indicates the bins in which neural activity is detected by the MIS system when the noise band is calculated using $\mu \pm 2\sigma$ method. (d) Spikes indicated by the TMS, which is equal to 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 73 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

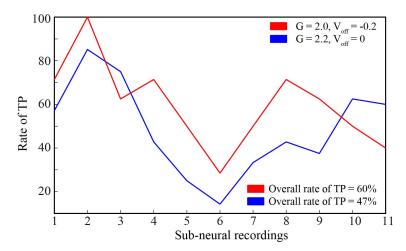

| 4.24       | Rate of True positives detected for two cases illustrated in Fig. 4.23 b and c with different gain and offset settings for the same device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 74 |

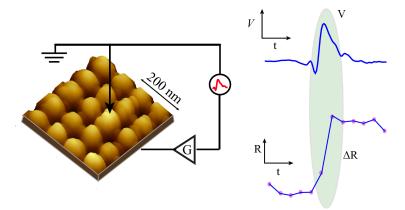

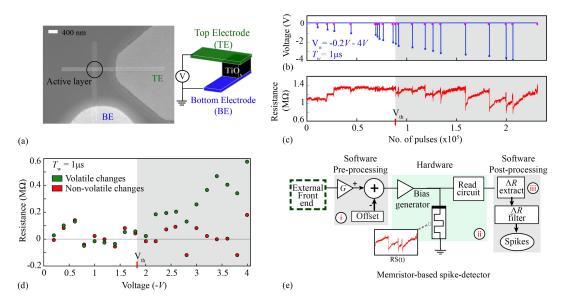

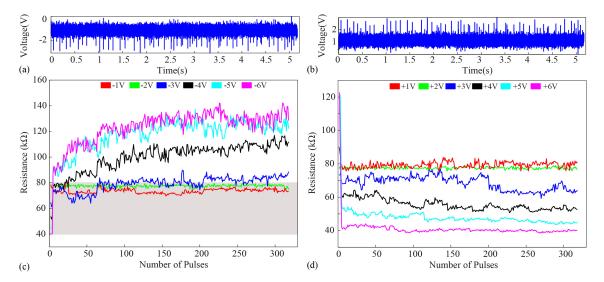

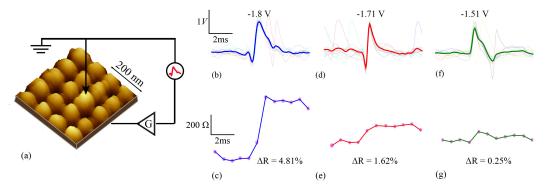

| 5.1<br>5.2 | The research objective of this experimental chapter. Device architecture and electrical characterisation of nano-scale $TiO_x$ memristive devices in the volatile region. (a) Schematic (right) and Scanning Electron Microscopic (SEM) image (left) of the employed 200 nm x 200 nm memristive device. (b,c) Electrical characterisation of memristive device exhibiting volatility using an automatic volatility characterisation module [133] and the resistive state evolution of the DUT in response to the applied stimuli is illustrated in (c). The device operates in the $600\mathrm{k}\Omega$ - $1.3\mathrm{M}\Omega$ range. After a first electroforming stage, the algorithm applies a series of progressively increasing input pulses (blue bars) of amplitude $(V_w)$ and width $(T_w)$ to the target device, following which its resistive state is monitored. In the example, the write pulses $(V_w)$ were applied in the range of -0.2 V to -4 V in steps of $0.2\mathrm{V}$ . $T_w$ was $1\mu\mathrm{s}$ . The module operates on a standard statistical two mean t-test condition and terminates when the device reaches a steady state. Thus, equilibrium retention is verified by repeated readings over $60\mathrm{s}$ (marked as pink rectangles), following which a new stimulus is delivered. (d) Determination of the operating voltage range of the DUT in volatile region. For every step of input stimulus applied, volatile (green circles) and residual non-volatile (red circles) resistive state changes were measured. The grey band indicates the voltage region for ensuring operation of the DUT in volatile conditions, with approximately -1.8 V being the inherent threshold voltage of the DUT $(V_{th})$ . (e) Schematic for the implementation of memristor-based spike-detection platform [118] | 79 |

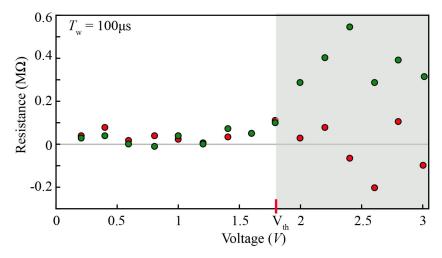

| 5.3        | Volatility characterisation of the $TiO_x$ nano-devices (200 nm x 200 nm). Input stimulus was applied to the DUT in range of 0 to -3 V in steps of 0.2 V. The pulse width, $T_W$ , of the applied voltage was fixed, in this case, to 100 $\mu$ s. Red and green circles indicate the non-volatile and volatile changes respectively. For the DUT the threshold of the device was found to be approximately -1.8 V. The grey band indicates the region where the device can be operated in the volatile region.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 83 |

| 5.4        | Range of inherent threshold voltages $(V_{th-})$ for the memristive devices in volatile region as extracted from 29 different devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 83 |

XX LIST OF FIGURES

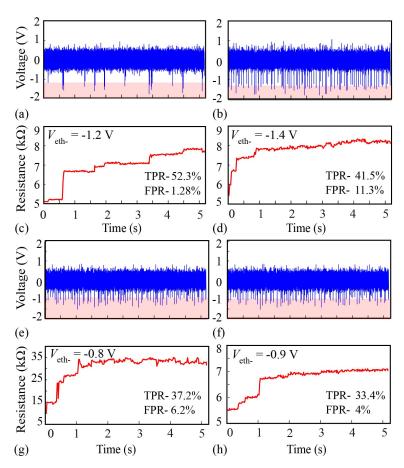

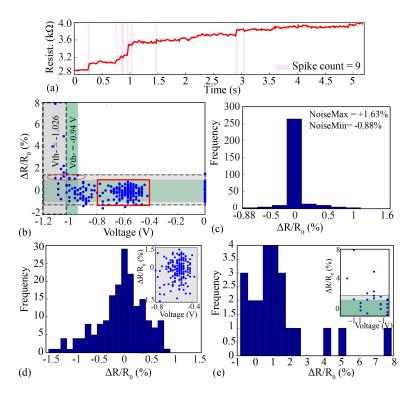

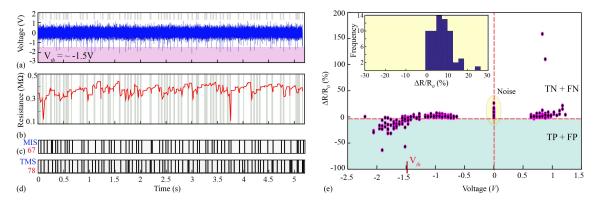

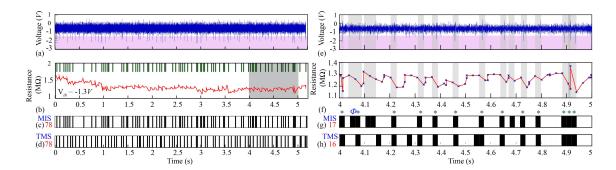

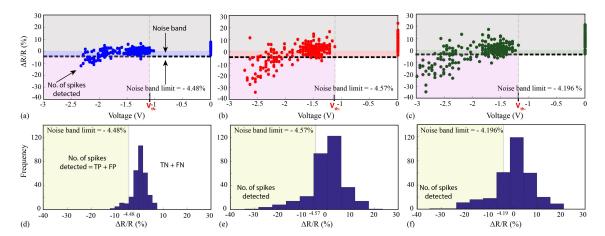

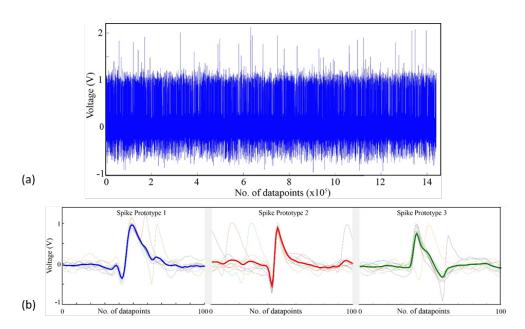

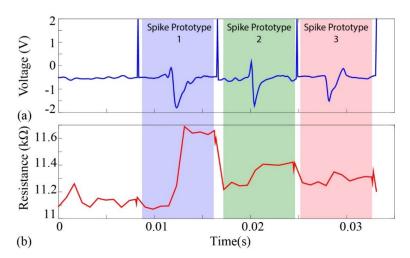

| 5.5 | Spike-detection via volatile metal-oxide memristive device and benchmarking of the results against the TMS. (a) Neural recording used for biasing the DUT. Gain (G) and offset $(V_{off})$ values in this experiment were fixed at 3.2 and 0, respectively. The pink band indicates the inherent threshold voltage of the DUT $(V_{th})$ which is approximately equal to -1.5 V. (b) Resistive state evolution of the DUT with time in response to the neural recording in (a). Time intervals where our spike-detector identifies events are indicated in grey. (c) total number of spikes detected by volatile spike detector and (d) via the TMS. (e) Normalised changes in the resistive state of the device $(\Delta R/R_0)$ in each bin are plotted as a function of highest voltage magnitude in each bin. The resistive state measurements in the yellow eclipse represents the noise measurements made at the end of each batch and beginning of the next batch with no neural feed. The inset represents the histogram for the noise measurements. The red dashed line on the horizontal axis represents the boundaries of the noise band estimated using the $4\sigma$ method that is $\mu \pm 2\sigma$ whilst the green band indicates the significant resistive state changes detected. TP: True Positives, FP: False Positives, TN: True Negatives and FN: False   | 8.4 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.6 | Negatives.  Biasing of $60 \mu\mathrm{m} \times 60 \mu\mathrm{m}  TiO_x$ devices using a neural recording in the volatile region. Close-up of the neural recording employed in Fig. 5.5(a) and the resistive state evolution in (b) for time window 2.5s - 3.5s, respectively. (c) and (d) Spikes detected by the volatile spike detection platform and the TMS system, respectively. In the close-up window the two systems agree for majority of instances except the point marked by *. The grey band indicates the bins with significant resistive state changes estimated as spikes. The quantification parameters for this specific recording are as follows: TP, FP, TN and FN are 58, 9, 166 and 20 respectively. The rate of TP (TPR) and FP (FPR) for this specific recording is estimated to be 74.3 and 5.14 respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 84  |

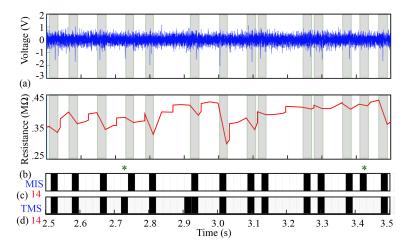

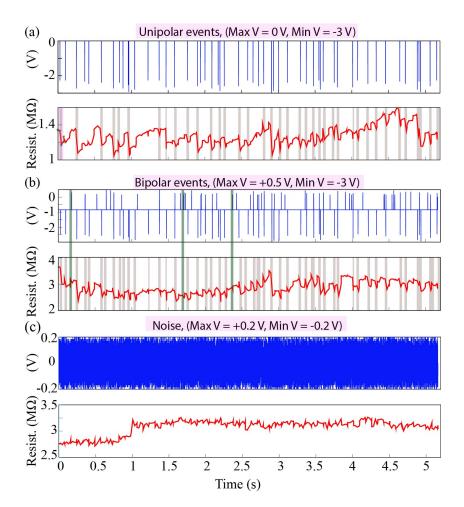

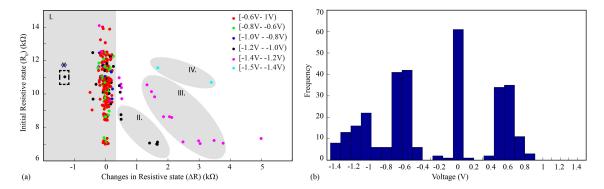

| 5.7 | Comparison of the Noise band diagrams in the <b>volatile</b> and <b>non-volatile</b> region of operation [129]. (a) Noise-band diagram settings in the <b>non-volatile</b> region. Normalised plot of resistive state changes $(\Delta R/R_0)$ in each bin is plotted as a function of maximum voltage magnitude in each bin. The noise-band (horizontal band marked in green colour) is estimated using the noise band measurements made at the end of each batch and the beginning of next batch with no interceding neural data points. (b) Assuming Gaussian distribution, mean and the standard deviation are estimated. 6 sigma method is chosen to set the boundaries of the noise-band. (c) Noise-band diagram in the <b>volatile region</b> . For the experiments with neural recordings in the volatile region most of the significant spikes are present in the negative polarity. Noise measurements are marked using a grey dashed eclipse indicating the spread of measurements which notably is inclined in the positive polarity. For the noise band boundary settings in the volatile region, the noise band measurements in the negative polarity are used. The boundary is set using the 4-sigma method which is indicated by the horizontal red dashed line dividing the resistive state changes in two quadrants i.e. TP + FP (spikes detected) and FN + TN | 86  |

|     | in two quadrants i.e. $TP + FP$ (spikes detected) and $FN + TN$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 86  |

LIST OF FIGURES xxi