#### UNIVERSITY OF SOUTHAMPTON

Faculty of Engineering and Physical Sciences School of Electronics and Computer Science

# Narrow Slot Fully-Crystalline Accumulation Modulator for Low-Power Optoelectronic Interconnection

by

James Byers

A thesis submitted for the degree of Doctor of Philosophy

July 2020

#### UNIVERSITY OF SOUTHAMPTON

#### ABSTRACT

# FACULTY OF ENGINEERING AND PHYSICAL SCIENCES SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

#### Doctor of Philosophy

#### Narrow Slot Fully-Crystalline Accumulation Modulator for Low-Power Optoelectronic Interconnection

by James Byers

The information and telecommunication industry relies heavily on the opto-electronic (OE) modulator link between electronic computation and optical data transmission. As global data consumption has increased, the bandwidth, efficiency and cost demands placed upon OE modulators (in data centres for example) has also increased. OE modulators based on a silicon photonic platform have the potential to meet these bandwidth and efficiency demands, whilst remaining cost effective and industrially scalable due to their compatibility with conventional complementary metal-oxide semiconductor (CMOS) fabrication processes.

The goal of this PhD project was to design and demonstrate a new type of energy efficiency, high-speed, fully-crystalline-Si (c-Si) modulator that could potentially answer the industry needs. To this end, in this thesis I present two new c-Si accumulation plasma dispersion effect (PDE) modulator designs. The critical OE component of these designs is, on the one hand, a bi-planar, horizontal-slot fin-waveguide on a double-silicon-on-insulator (SOI) platform, and on the other hand, a planar, partially recrystallised, vertical-slot rib-waveguide.

The key contributions I have made are (1) the development of a unique fabrication process involving anisotropic wet etching of mirrored Si crystal planes to realise the low-loss  $(0.85 \mathrm{dB/mm})$  bi-planar, horizontal-slot fin-waveguide for use in an OE modulator, and (2) the fabrication of an efficient, fully-c-Si accumulation modulator with switching speed of  $25\mathrm{Gb/s}$  and modulation efficiency of  $1.53\mathrm{V}\cdot\pi$ . This modulator is the first demonstration of a uniquely designed modulator architecture which, with optimization, has the potential the genuinely address the industry demand for an energy-efficient, high-speed CMOS compatible OE modulator.

# Contents

| Li           | st of | Figur                  | es                                                                        | vii   |

|--------------|-------|------------------------|---------------------------------------------------------------------------|-------|

| Li           | st of | Table                  | s                                                                         | xi    |

| $\mathbf{G}$ | lossa | $\mathbf{r}\mathbf{y}$ |                                                                           | xiii  |

| Ъ            | aalam | ation .                | of Authorabia                                                             | :     |

| יט           | eciar | ation (                | of Authorship                                                             | xxi   |

| A            | ckno  | wledge                 | ements                                                                    | xxiii |

| 1            | Intr  | roduct                 | ion                                                                       | 1     |

| 2            | The   | •                      | nd Literature Review                                                      | 7     |

|              | 2.1   | Wave                   | $\operatorname{guides}$                                                   | 7     |

|              |       | 2.1.1                  | Electromagnetic Propagation in 2-Dimensional Waveguides: Maxwel           |       |

|              |       |                        | equations                                                                 |       |

|              |       | 2.1.2                  | Optical Loss Mechanisms                                                   |       |

|              | 2.2   |                        | lators                                                                    |       |

|              |       | 2.2.1                  | Si and Non-Si Optoelectronic Modulators                                   |       |

|              |       | 2.2.2                  | Plasma Dispersion Effect                                                  | 13    |

|              |       | 2.2.3                  | Injection, Depletion and Accumulation Plasma Dispersion Effect Modulation | 15    |

|              |       | 2.2.4                  | Review of Injection, Depletion and Accumulation Modulator De-             | 10    |

|              |       | 2.2.4                  | vices in Literature                                                       | 17    |

|              |       | 2.2.5                  | Plasma Dispersion Effect Accumulation Mach-Zehnder Interferom-            |       |

|              |       | 2.2.0                  | eter Modulators                                                           | 19    |

|              | 2.3   | Fabrio                 | cation                                                                    |       |

|              |       | 2.3.1                  | Direct Bonding                                                            |       |

|              |       | 2.3.2                  | Tetramethylammonium Hydroxide Etching                                     |       |

| 3            | Des   | ign an                 | ad Methodology                                                            | 29    |

|              | 3.1   | Horizo                 | ontal-Slot Fin-Waveguide Accumulation Modulator                           | 30    |

|              |       | 3.1.1                  | Design                                                                    | 30    |

|              |       | 3.1.2                  | Simulation                                                                |       |

|              |       | 3.1.3                  | Fabrication Process Flow                                                  | 33    |

|              | 3.2   | Vertic                 | al-Slot Rib-Waveguide Accumulation Modulator                              | 34    |

|              |       | 3.2.1                  | Design                                                                    | 34    |

|              |       | 3.2.2                  | Simulation                                                                | 36    |

|              |       | 3 2 3                  | Fabrication Process Flow                                                  | 37    |

vi CONTENTS

|    | 3.3   | Fabrication Techniques                                     |     |

|----|-------|------------------------------------------------------------|-----|

|    |       | 3.3.1 Electron-beam Lithography: Pattering and Development |     |

|    |       | 3.3.2 Inductictively Coupled Plasma Etching                |     |

|    |       | 3.3.3 Plasma Enhanced Chemical Vapour Deposition           |     |

|    |       | 3.3.4 Chemical Mechanical Polishing                        |     |

|    |       | 3.3.5 $\operatorname{SiO}_2/\operatorname{SiO}_2$ Bonding  |     |

|    |       | 3.3.6 Local Oxidation of Silicon                           | 46  |

| 4  | Bor   | nded Double-SOI and Horizontal-Slot Strip-Waveguide        | 47  |

|    | 4.1   | Bonded MOScap                                              | 47  |

|    |       | 4.1.1 Fabrication                                          | 47  |

|    |       | 4.1.2 Interface Quality Characterisation                   | 50  |

|    | 4.2   | Horizontal-Slot Strip-Waveguide                            | 53  |

|    |       | 4.2.1 Fabrication                                          | 53  |

|    |       | 4.2.2 Optical Characterisation                             | 62  |

|    | 4.3   | Conclusion                                                 | 63  |

| 5  | Fin   | Waveguides and Passive Mach-Zehnder Interferometer         | 65  |

|    | 5.1   | Fabrication                                                | 65  |

|    | 5.2   | Optical Characterisation                                   | 68  |

|    | 5.3   | Conclusion                                                 | 76  |

| 6  | Ver   | tical-slot Waveguide and Accumulation Modulator            | 81  |

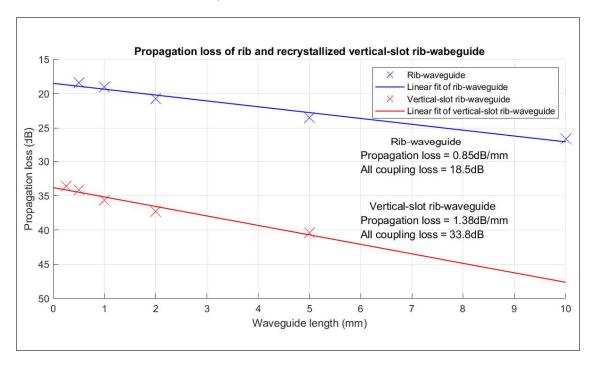

|    | 6.1   | Vertical-Slot Rib-Waveguide Characterisation               | 81  |

|    |       | 6.1.1 Fabrication                                          | 82  |

|    |       | 6.1.2 Transmission Characterisation                        | 85  |

|    | 6.2   | Vertical-Slot Accumulation Modulator Characterisation      | 87  |

|    | 6.3   | Conclusion                                                 | 93  |

| 7  | Cor   | nclusions                                                  | 95  |

|    | 7.1   | Thesis Summary                                             | 95  |

|    | 7.2   | Future Work                                                | 97  |

|    |       | 7.2.1 Horizontal-Slot Fin-Waveguide Accumulation Modulator | 97  |

|    |       | 7.2.2 Vertical-Slot Rib-Waveguide Accumulation Modulator   | 98  |

| A  | Pul   | olications and Conferences                                 | 101 |

| Aj | ppen  | adix                                                       | 100 |

| Bi | bliog | graphy                                                     | 103 |

# List of Figures

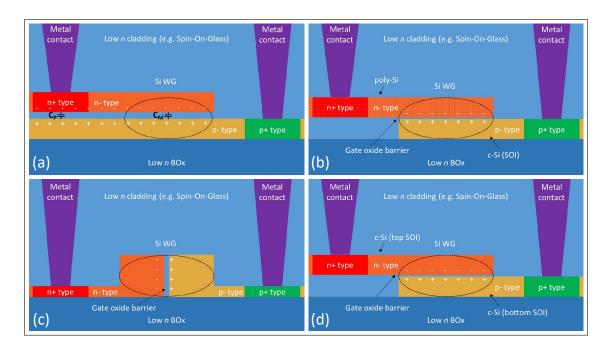

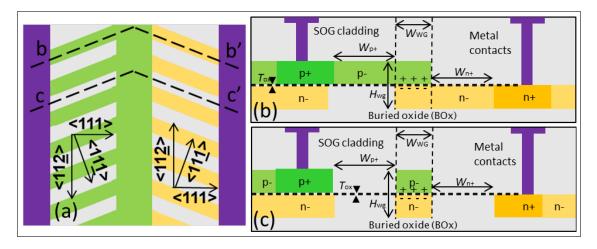

| 1.1  | Conventional accumulation modulator designs, demonstrating their inherent weaknesses, and two proposed solutions to these weaknesses | 5    |

|------|--------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1  | Schematic and transverse electric mode profile of conventional strip-waveguid                                                        | e 10 |

| 2.2  | Real and imaginary refractive index change in Si with applied electric field and photon energy respectively                          | 13   |

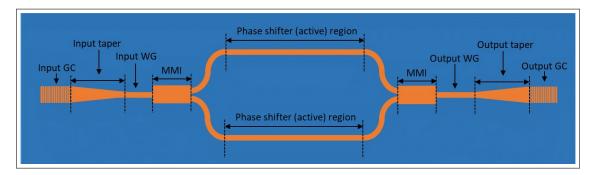

| 2.3  | Schematic of typical Mach-Zehdner interferometer modulator design                                                                    | 14   |

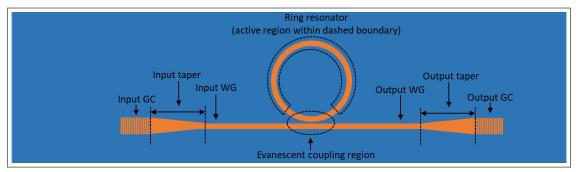

| 2.4  | Schematic of typical ring resonator modulator design                                                                                 | 14   |

| 2.5  | Schematic of accumulation, injection and depletion plasma dispersion ef-                                                             | 11   |

|      | fect modulators                                                                                                                      | 16   |

| 2.6  | Schematic of poly-Si SISCAP accumulation modulator                                                                                   | 20   |

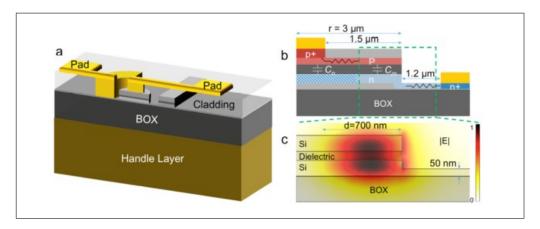

| 2.7  | Schematic of c-Si accumulation microdisc resonator                                                                                   | 20   |

| 2.8  | Schematic of direct wafer bonding and thinning down process                                                                          | 21   |

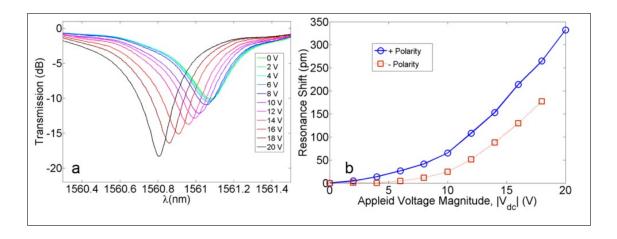

| 2.9  | Transmission and resonance shift as a function of wavelength and applied                                                             |      |

|      | voltage respectively, for a microdisc resonator modulator                                                                            | 23   |

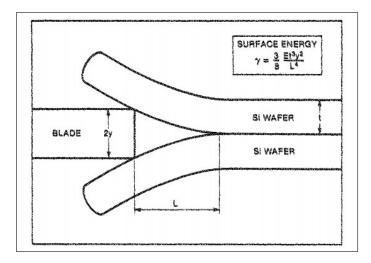

| 2.10 | Schematic of crack opening method                                                                                                    | 24   |

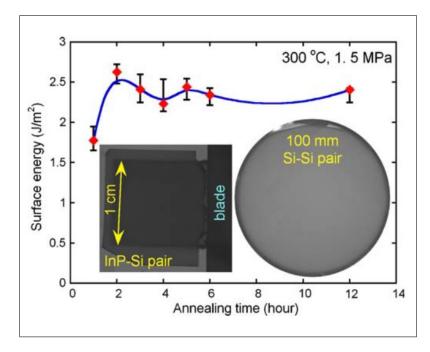

| 2.11 | 7                                                                                                                                    | 25   |

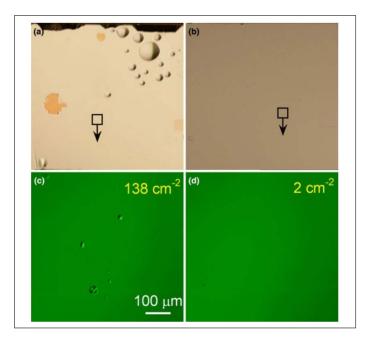

| 2.12 | Images of void density on bonded samples having undergone different $O_2$                                                            | 2.0  |

| 0.10 | plasma treatment                                                                                                                     | 26   |

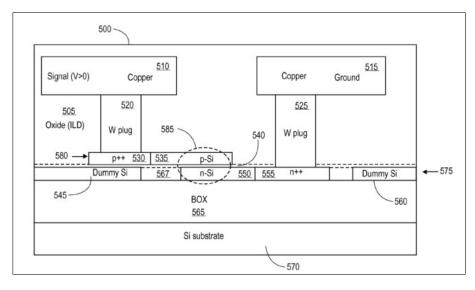

|      | Schematic of patented optical modulator                                                                                              | 26   |

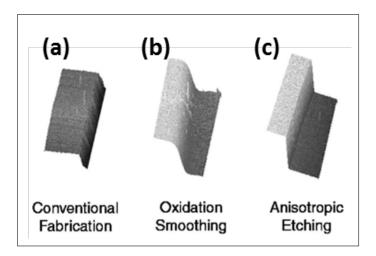

| 2.14 | Atomic force microscope (AFM) images of waveguides having undergone various sidewall smoothening processes                           | 28   |

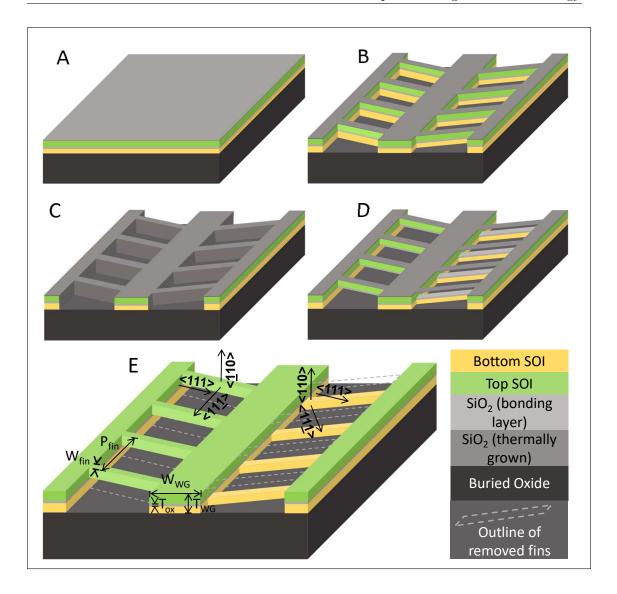

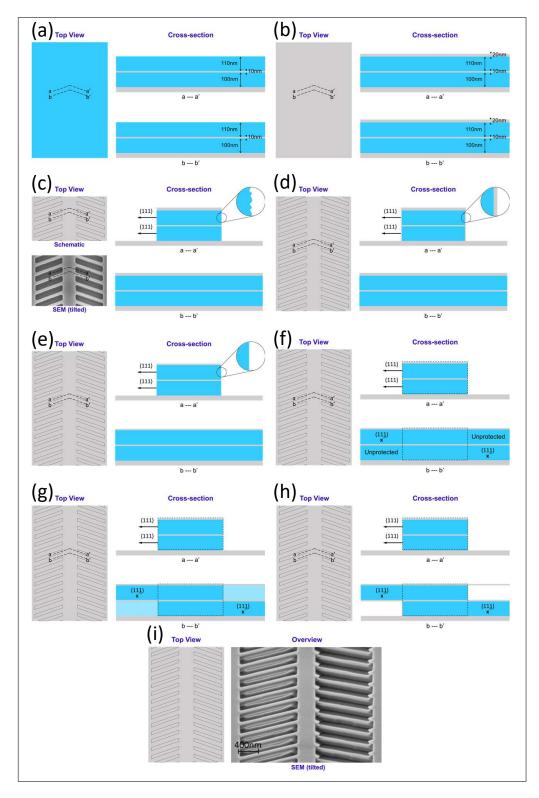

| 3.1  | Schematic of 3-dimensional fin waveguide design                                                                                      | 30   |

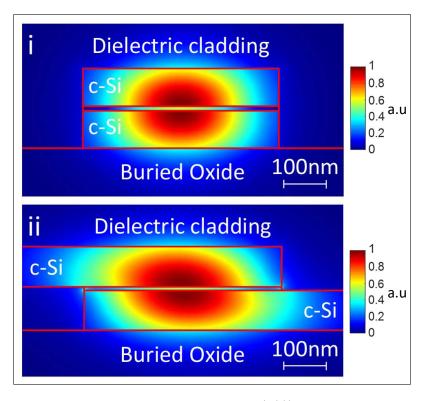

| 3.2  | Simulated transverse electric optical mode profile of strip-waveguide                                                                | 31   |

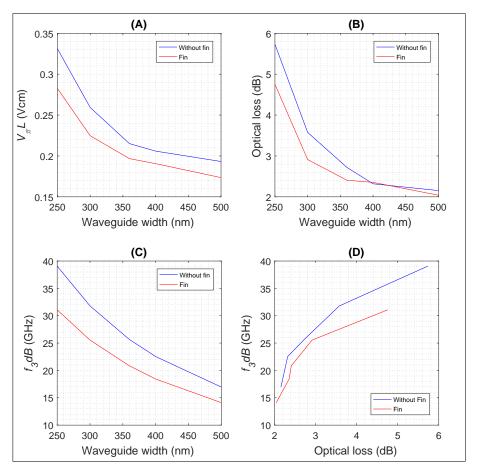

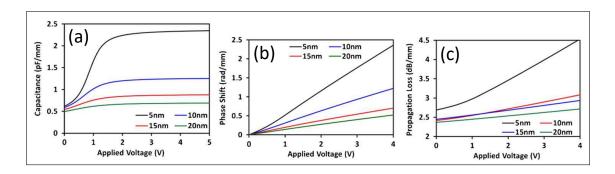

| 3.3  | Horizontal-slot fin-waveguide accumulation modulator simulated performance characteristiscs                                          | 32   |

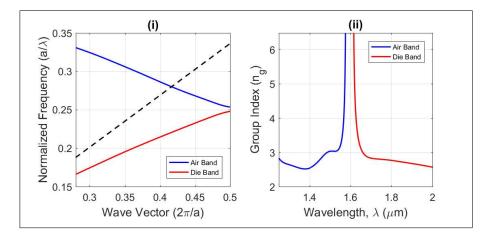

| 3.4  | Dispersion relation of pseudo-1D PhC fin-waveguide design exhibiting pho-                                                            | 02   |

| 0.1  | tonic bandgap                                                                                                                        | 33   |

| 3.5  | Horizontal-slot fully-crystalline fin-waveguide fabrication process flow (from                                                       |      |

|      | bonded double-SOI)                                                                                                                   | 34   |

| 3.6  | Vertical-slot rib-waveguide cross-section                                                                                            | 35   |

| 3.7  | Active MZI section of vertical-slot rib-waveguide accumulation modulator,                                                            |      |

|      | 3D schematic                                                                                                                         | 35   |

| 3.8  | Carrier concentration, TE mode profile and rib-waveguide to rib-slot-                                                                |      |

| 0.0  | waveguide coupling simulations                                                                                                       | 36   |

| 3.9  | Vertical-slot rib-waveguide accumulation modulator: Capacitance, phase                                                               |      |

|      | shift and propagation loss simulation results for gate $SiO_2$ thickness = $5nm.20nm$                                                | 37   |

viii LIST OF FIGURES

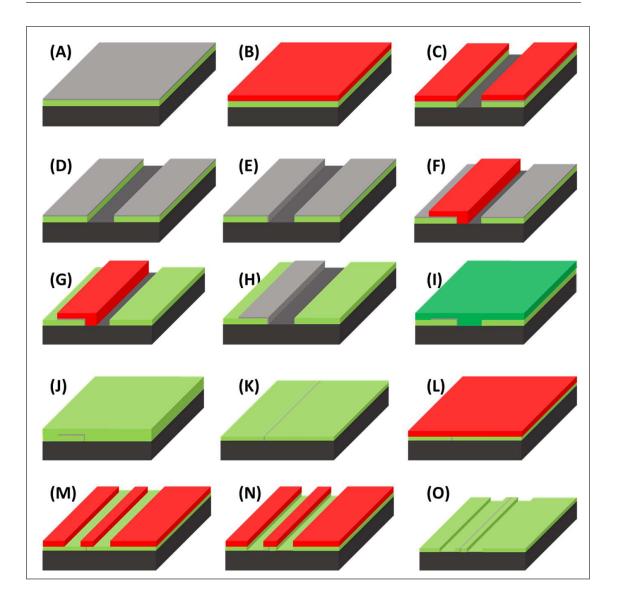

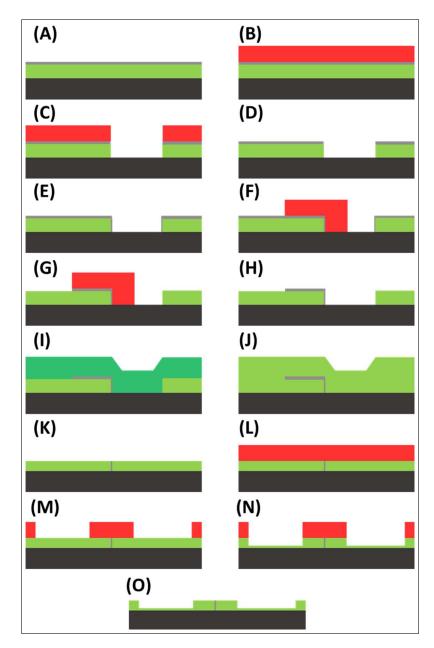

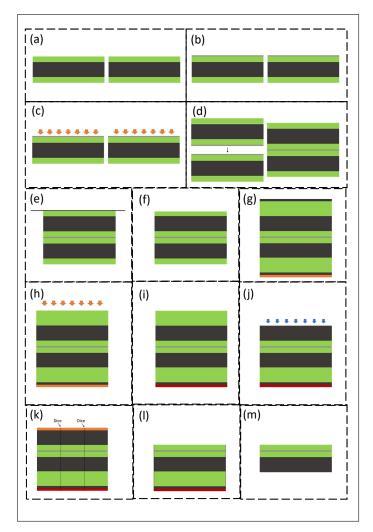

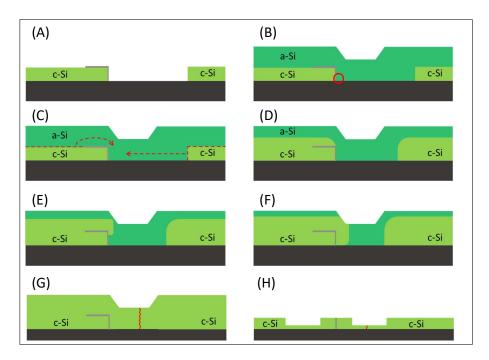

| 3.10 | Fabrication of passive vertical-slot fin-waveguide process flow schematic (3D)                   | 38         |

|------|--------------------------------------------------------------------------------------------------|------------|

| 3 11 | Fabrication of passive vertical-slot fin-waveguide process flow schematic                        | <b>3</b> 0 |

| 0.11 | (2D cross-section)                                                                               | 39         |

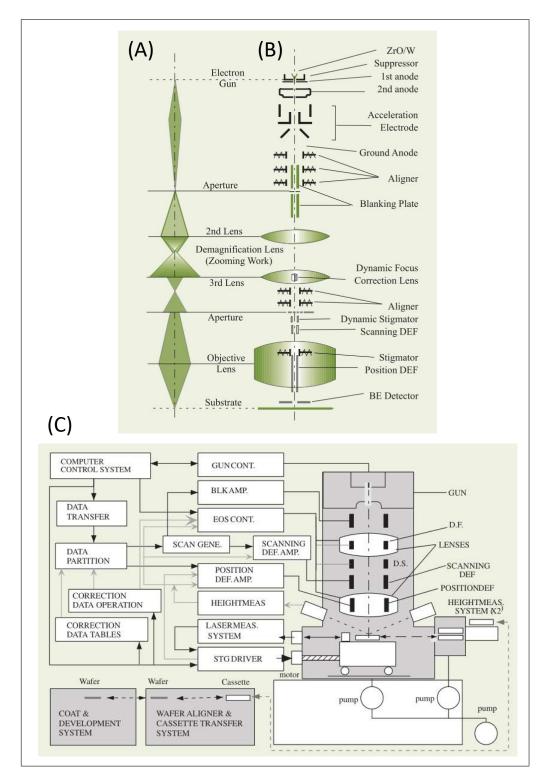

| 3 12 | Electron-beam lithography schematic                                                              | 41         |

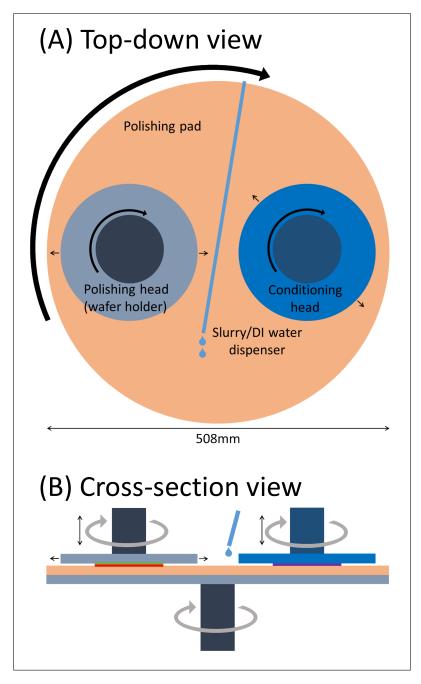

|      | Schematic of CMP tool                                                                            | 44         |

|      | CMP tool image                                                                                   | 45         |

|      |                                                                                                  |            |

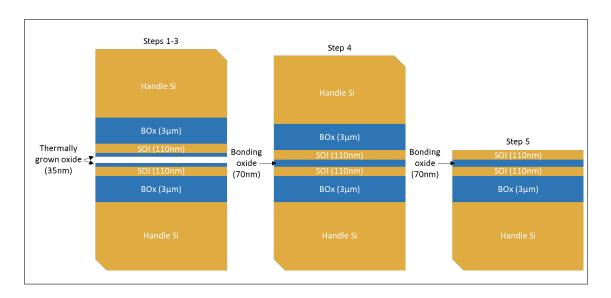

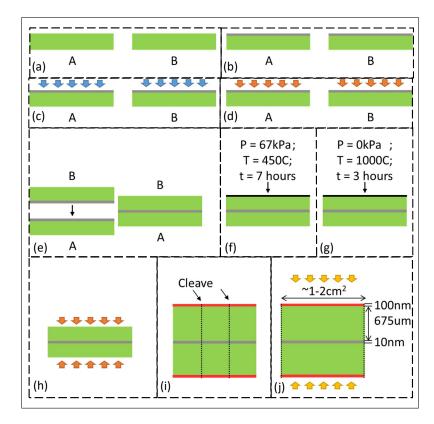

| 4.1  | Process flow for $SiO_2/SiO_2$ bonding                                                           | 49         |

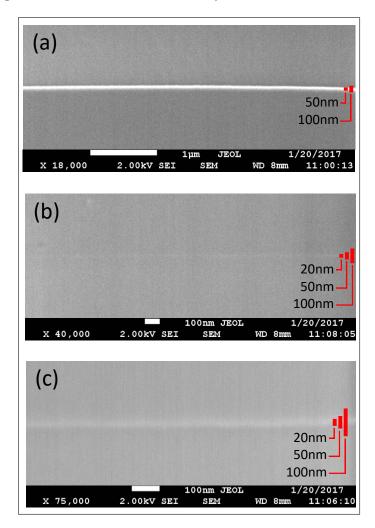

| 4.2  | Scanning electron microscope images of bonded c-Si/SiO $_2$ /c-Si interface .                    | 50         |

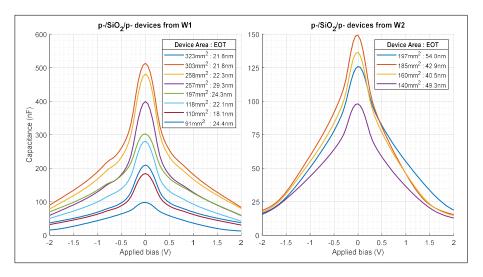

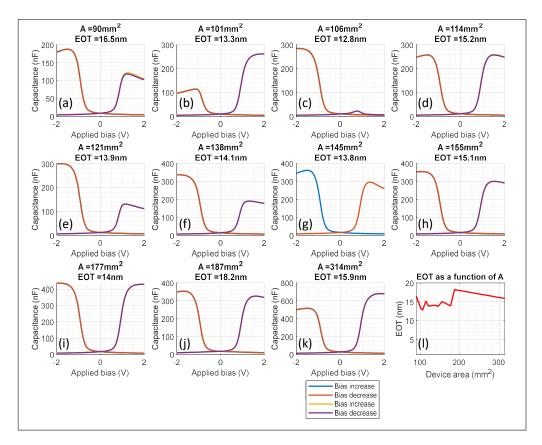

| 4.3  | CV measurements for bonded p-/SiO $_2$ /p- devices                                               | 51         |

| 4.4  | CV measurements for bonded p-/SiO $_2$ /n- devices                                               | 52         |

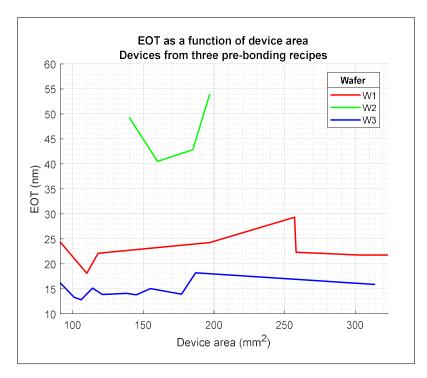

| 4.5  | Measured equivalent oxide thickness as a function of device area from                            |            |

|      | bonded wafer utilizing different pre-bonding recipes                                             | 53         |

| 4.6  | Process flow showing double-SOI substrate fabrication                                            | 54         |

| 4.7  | Schematic showing KOH wafer edge etching                                                         | 55         |

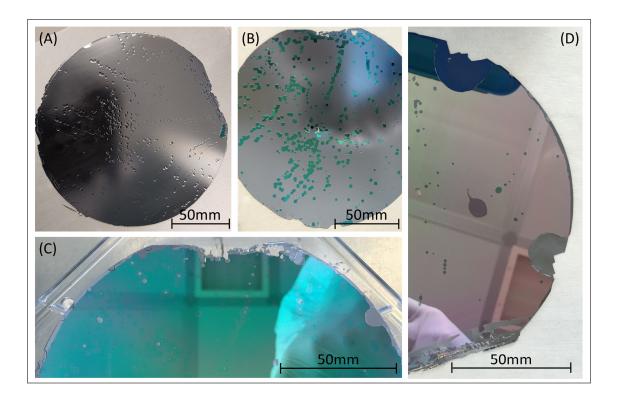

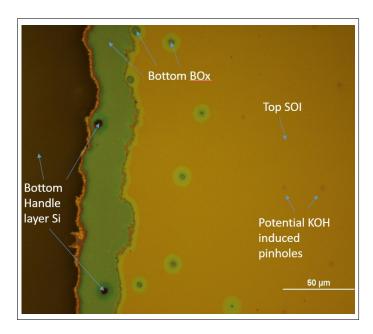

| 4.8  | Images of bonded double-SOI wafers thinned by KOH                                                | 56         |

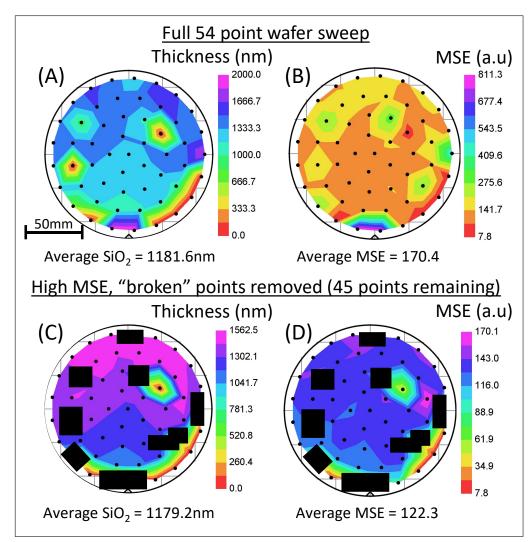

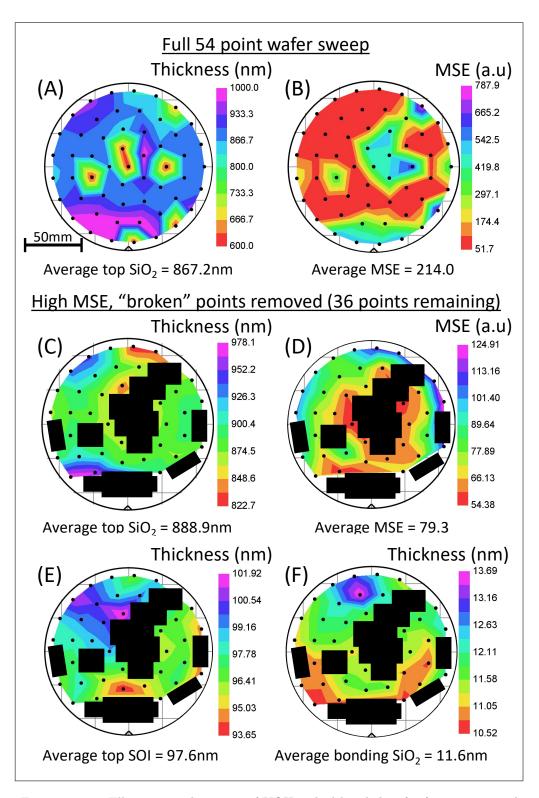

| 4.9  | Ellipsometry data map of KOH etched bonded wafer (906 minute etch time)                          | 57         |

| 4.10 | Ellipsometry data map of KOH etched bonded wafer (840 minute etch time)                          | 58         |

| 4.11 |                                                                                                  | CO         |

| 4.10 | on bonded double-SOI                                                                             | 60         |

|      | Optical image of surface blemishes on KOH thinned double-SOI                                     | 60         |

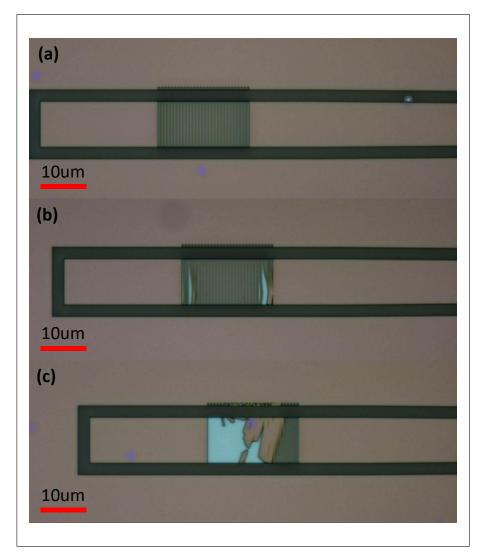

|      | Optical images of grating couplers fabricated on double-SOI                                      | 61         |

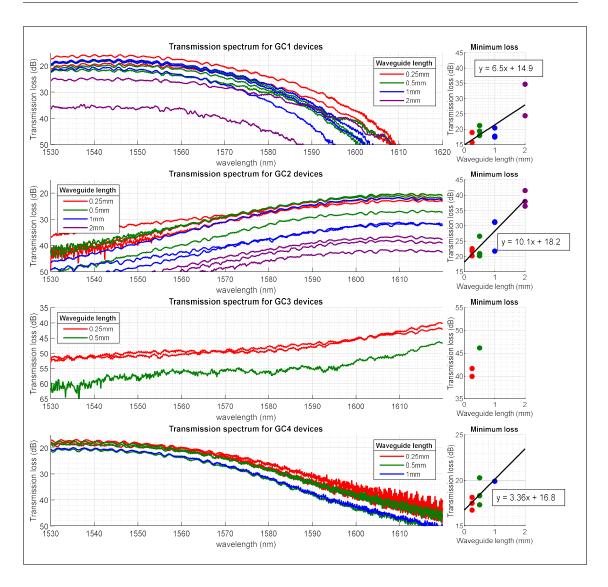

| 4.14 | Horizontal-slot strip-waveguide fabricated on KOH thinned double-SOI transmission spectrum       | 63         |

|      | transmission spectrum                                                                            | 00         |

| 5.1  | Process flow showing fabrication of horizontal-slot fin-waveguide from bonded                    |            |

|      | double-SOI                                                                                       | 67         |

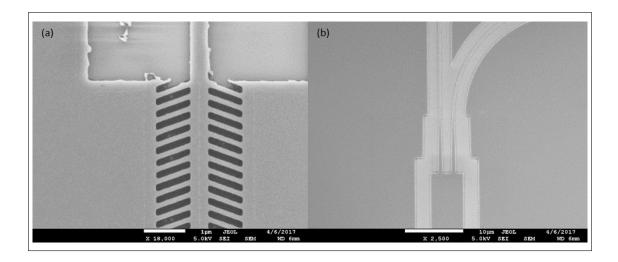

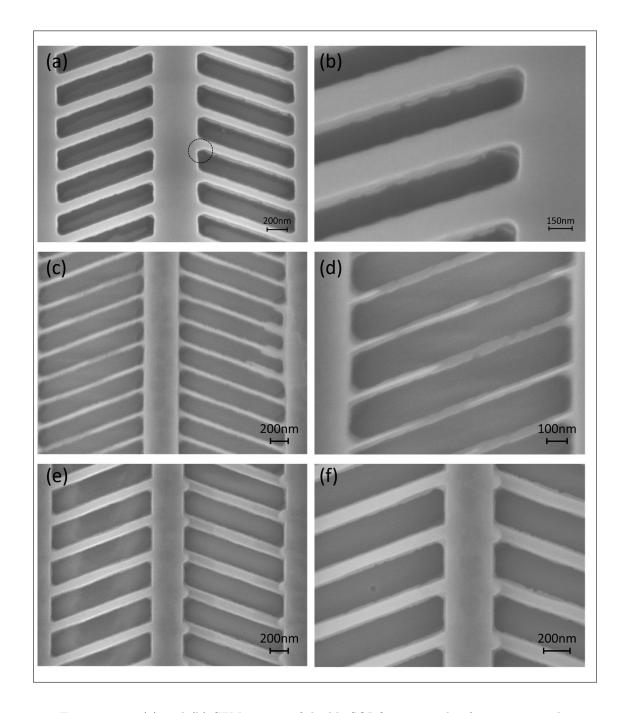

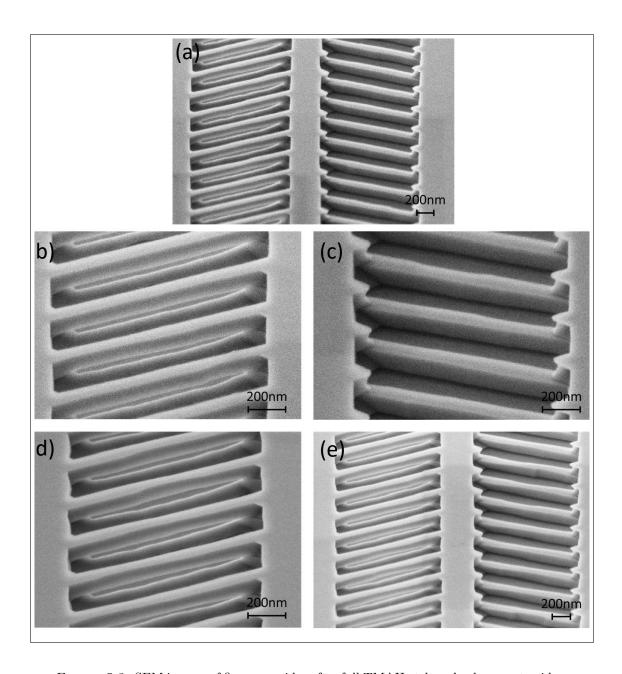

| 5.2  | SEM images of TMAH-etched fin-waveguides                                                         | 69         |

| 5.3  | SEM images of fin-waveguide on double-SOI after 105min TMAH etching                              |            |

|      | and oxide removal                                                                                | 70         |

| 5.4  | SEM images of partially etched grating couplers, broken fin-waveguide                            |            |

|      | and strip-waveguide/fin-waveguide transition                                                     | 71         |

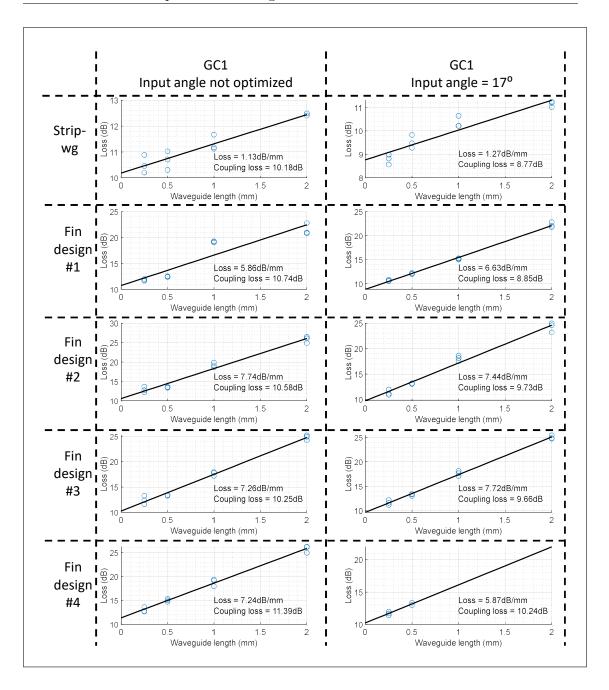

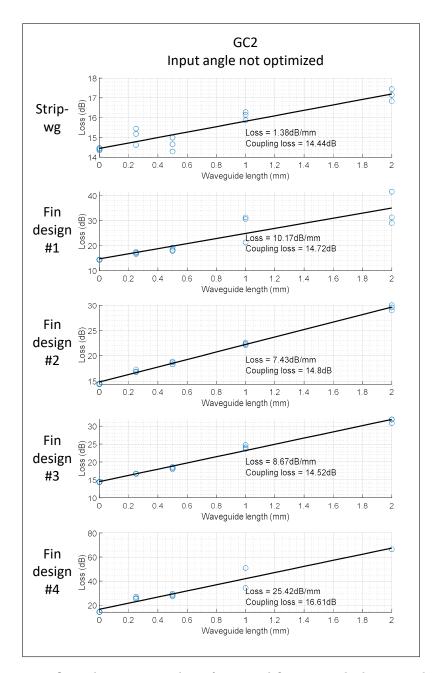

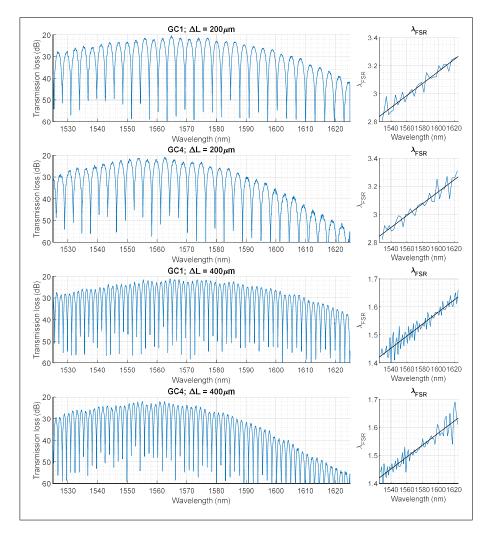

| 5.5  | Optical transmission loss of strip and fin-waveguide devices with GC#1 .                         | 72         |

| 5.6  | Optical transmission loss of strip and fin-waveguide devices with GC#2                           | 73         |

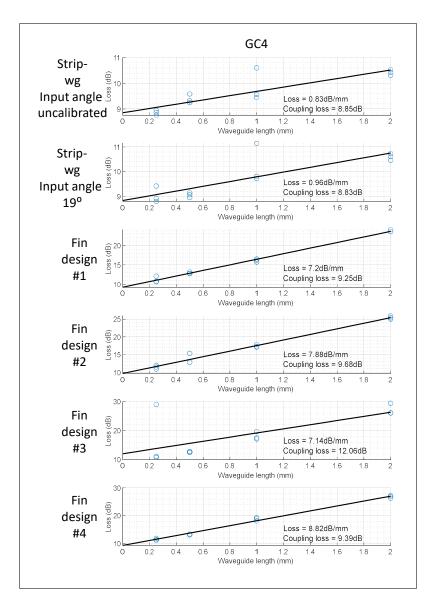

| 5.7  | Optical transmission loss of strip and fin-waveguide devices with GC#4 .                         | 74         |

| 5.8  | Coupling loss for GC#4 as a function of fibre input angle                                        | 75<br>     |

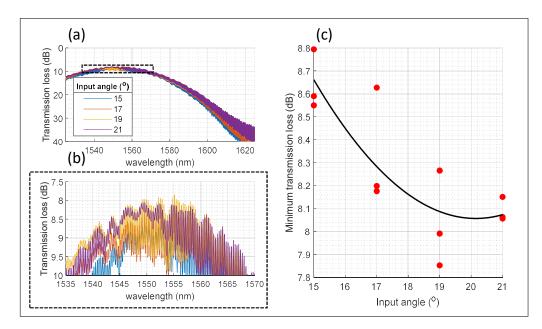

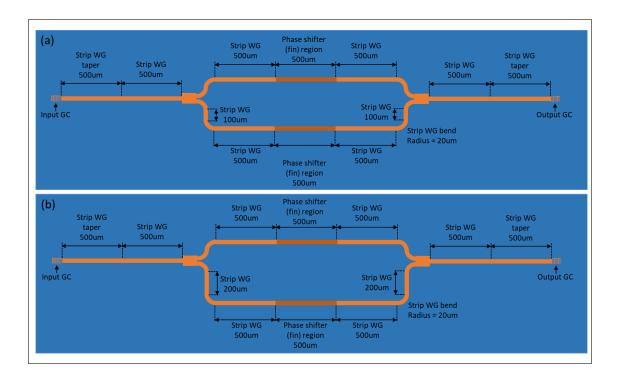

| 5.9  | Design schematic of fabricated passive MZI                                                       | 75<br>76   |

| 5.10 | Design of MMI used in fabricated passive MZI                                                     | 76         |

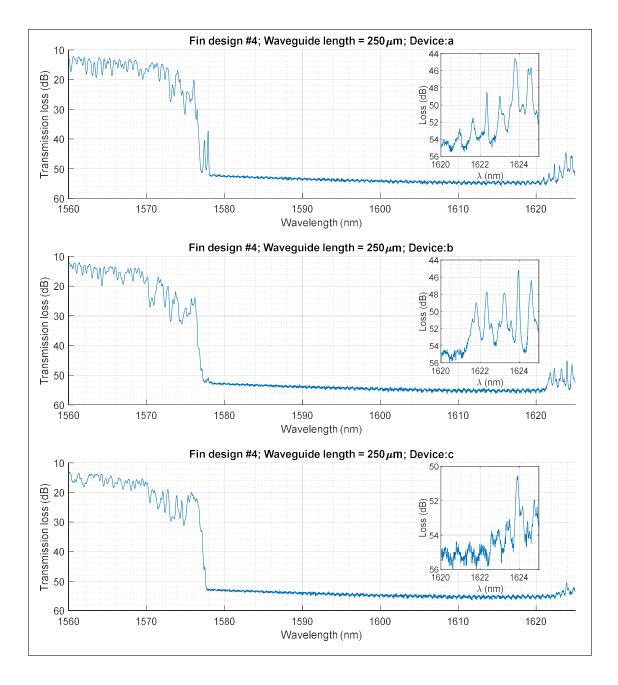

|      | Passive MZI transmission spectrum                                                                | 77         |

| 5.12 | Transmission spectrum of fin-waveguide on double-SOI showing designed                            | 70         |

|      | photonic bandgap                                                                                 | 78         |

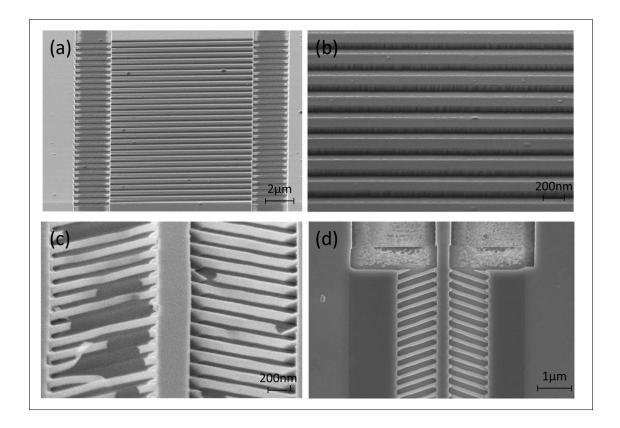

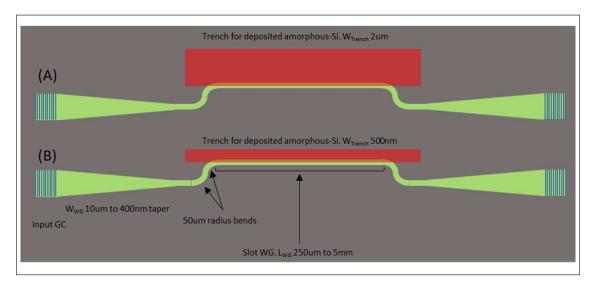

| 6.1  |                                                                                                  |            |

|      | Passive vertical-slot rib-waveguide device schematic showing trench posi-                        |            |

|      | Passive vertical-slot rib-waveguide device schematic showing trench position for a-Si deposition | 82         |

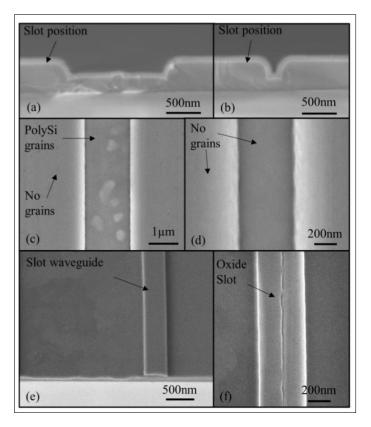

| 6.2  |                                                                                                  | 82         |

LIST OF FIGURES ix

| 6.3 |                                                                                                                                                         |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | windows for vertical-SiO <sub>2</sub> slot                                                                                                              | 84 |

| 6.4 | Transmission loss results for vertical-slot rib-waveguide and no-slot waveguide as reference                                                            | 86 |

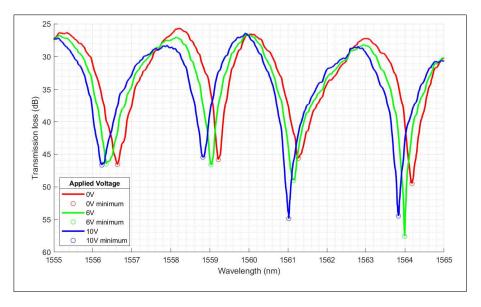

| 6.5 | Transmission loss results for active modulator device at various applied                                                                                |    |

|     | DC bias                                                                                                                                                 | 87 |

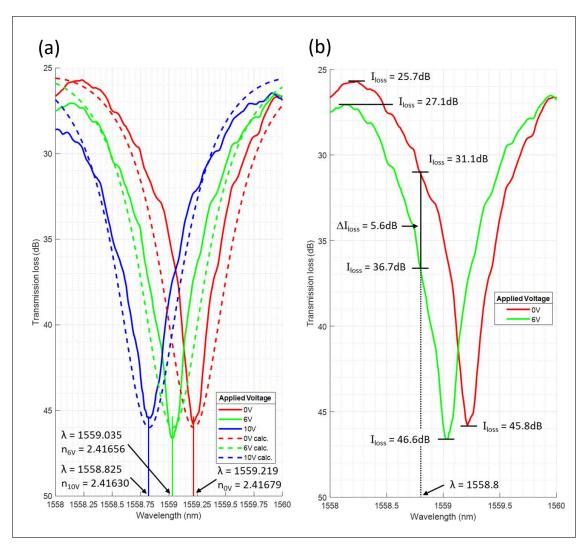

| 6.6 | Transmission spectrum of vertical-slot rib-waveguide modulator at applied DC bias $0V$ , $6V$ , $10V$ , with overlaid calculated spectrum at varied $n$ | 90 |

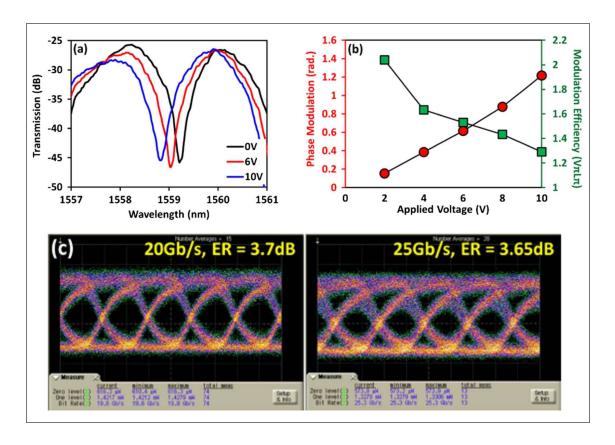

| 6.7 | Characterisation results for active vertical-slot rib-waveguide accumulation modulator                                                                  | 92 |

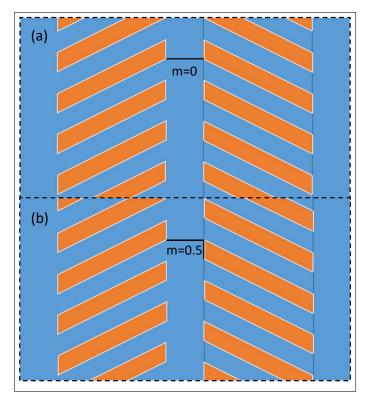

| 7.1 | Top-down schematic of horizontal-slot fin-waveguide with and withouth                                                                                   | 98 |

# List of Tables

| 3.1 | Four different fin designs (with different fin widths and fin periods) | 33 |

|-----|------------------------------------------------------------------------|----|

| 3.2 | ICP etch recipes                                                       | 42 |

| 3.3 | PECVD recipes                                                          | 43 |

| 4.1 | Summary of $SiO_2/SiO_2$ pre-bonding recipe parameters                 | 48 |

| 4.2 | Grating coupler designs and target peak coupling efficiency $\lambda$  | 62 |

| 5.1 | Summary of coupling efficiency for different waveguide designs         | 77 |

| 5.2 | Summary of transmission loss for strip and fin-waveguides              | 79 |

Acronyms xiii

#### Acronyms

**1D** 1-dimensional

**2D** 2-dimensional

**3D** 3-dimensional

**a-Si** amorphous-Si

**AFM** atomic force microscope

ALD atomic layer deposition

**BOx** buried oxide

**c-Si** crystalline-Si

CMOS complemetary metal-oxide semiconductor

CMP chemical mechanical polishing

${f CV}$  capacitance/voltage

**CW** continuous-wave

**DC** direct current

DCA digital communication analyzer

**DI** deionized

**EDFA** erbium doped fibre amplifier

**EM** electromagnetic

**EO** electro-optic

**EOT** equivalent oxide thickness

**ER** extinction ratio

FCA free carrier absorption

**FDTD** finite difference time domain

**FSR** free-spectral-range

GC grating coupler

xiv Acronyms

**GSG** ground-signal-ground

I/O input/output

IC integrated circuit

ICP inductively coupled plasma

LOCOS local oxidation of silicon

MMI multimode interferometer

MOScap metal-oxide-semiconductor capacitor

MSE mean squared error

MZI Mach-Zehnder interferometer

**n-type** negatively doped Si

**OE** opto-electronic

**OEIC** optoelectronic integrated circuit

**p-type** positively doped Si

PBG photonic bandgap

PDE plasma dispersion effect

PECVD plasma enhanced chemical vapour deposition

PhC photonic crystal

poly-Si polycrystalline-Si

PRBS pseudo-random bit sequence

**Q-factor** quality factor

RCA clean

RF radio frequency

RIE reactive ion etching

rms root mean squared

RTA rapid temperature annealing

**SEM** scanning electron microscope

SISCap semiconductor-insulator-semiconductor capacitor

**SMF** single mode fibre

**SOI** silicon-on-insulator

TE transverse electric

TIR total internal reflection

TM transverse magnetic

WDDeM wavelength devision demultiplexer

WDM wavelength division multiplexer

WGM whispering gallery mode

#### Symbols and Nomenclature

$C_m$  functional capacitance

$C_p$  parasitic capacitance

$C_{junction}$  junction capacitance

$E_{mod}$  modulus of elasticity

$H_{wq}$  waveguide height

$I_{loss}$  transmission loss

$I_{max}$  maximum transmission intensity

$I_{min}$  minimum transmission intensity

$I_t$  transmission intensity

L wafer crack length

$L_{

m shifter}$  phase shifter arm length

$N_{eff}$  mode effective refractive index

$R_{loss}$  loss coefficient

$W_{fin}$  fin width

$W_{trench}$  trench width

$W_{wg}$  waveguide width

$\Delta \alpha$  apsorption coefficient change

$\Delta n$  refractive index change

$\Delta L_{arm}$  arm length difference

$\Delta N_e$  change in free electron concentration

$\Delta N_h$  change in free hole concentration

$\Delta \alpha_h$   $\Delta \alpha$  attributed to free hole concentration change

$\Delta \alpha_e$   $\Delta \alpha$  attributed to free electron concentration change

$\Delta n_e$   $\Delta e$  attributed to free electron concentration change

$\Delta n_h$   $\Delta e$  attributed to free hole concentration change

$\Lambda_{fin}$  fin period

$\alpha$  absorption coefficient

$\beta$  propagation constant

$\delta$  phase change

$\delta_{\Delta L}$  asymmetric section phase

$\delta_{active}$  active arm phase

$\delta_{reference}$  reference arm phase

$\epsilon_0$  electric permittivity of free space

$\epsilon_r$  relative electric permittivity of dielectric

$\lambda_{FSR}$  free spectral range

$V_{\pi}L$   $V \cdot cm$  required to induce  $\pi$  phase shift

$\mu$  magnetic permeability

$\mu_0$  magnetic permeability of free space

$\omega$  angular frequency

$\rho$  charge density

$\sigma$  conductivity

v specific surface energy

$f_{3dB}$  3dB bandwidth

$k_0$  wavevector

n refractive index

$r_3$  Pockels electro-optic tensor

$t_{\rm carrier}$  free carrier lifetime

$t_{ox}$  oxide thickness

$t_{relax}$  electrical circuit relaxation time

y wafer crack separation distance/2

B magnetic induction

D electric displacement

E electric field

H magnetic field

C total capacitance

N doping concentration

$s_3$  Kerr coefficient

t time

A area

J current density

R resistance

$\mathbf{t}_{\mathrm{w}}$  wafer thickness

$\mathbf{V}_{\mathrm{eff}}$  effective volume

$\mathbf{V}_{dc}$  direct current voltage

### Chemicals and Reagents

ACE acetone

Al aluminium

Ar argon

$\mathbf{CHF}_3$  fluoroform

**Espacer** thin-film conductive polymer

F fluoride

FOx16 flowable oxide from Dow Corning

GaAs gallium arsenide

$\mathbf{H}_2\mathbf{SO}_4$  sulfuric acid

**HF** hydrofluoric acid

**HMDS** hexamethyldisilazane

InP indium phosphide

IPA isopropanol

KOH potassium hydroxide

$LiNbO_3$  lithium niobate

MIBK Methyl isobutyl ketone

$N_2$  nitrogen

$NH_2$  amino group

$\mathbf{NH_4OH}$  ammonium hydroxide

NMP N-methyl-2-pyrrolidone

$\mathbf{O}_2$  oxygen

**PMMA** poly(methyl methacrylate)

S1813 protective photo lithography resist

$\mathbf{SF}_6$  sulfur hexafluoride

Si silicon

$\mathbf{Si}_{3}\mathbf{N}_{4}$  silicon nitride

$Si(OH)_4$  orthosicilic acid

$SiO_2$  silicon dioxide

Ti titanium

TiN titanium nitride

$\mathbf{TMAH} \qquad \text{tetramethylammonium hydroxide}$

${f UVN ext{-}30}$  negative electron-beam lithography resist

$\mathbf{ZED} \ \mathbf{N50} \quad \text{ n-Amyl Acetate}$

${\bf ZEP520A} \quad \hbox{positive electron-beam lithography resist}$

#### Declaration of Authorship

I, James Joseph Byers, declare that the thesis entitled *Narrow Slot Fully-Crystalline Accumulation Modulator for Low-Power Optoelectronic Interconnection*, and the work presented in the thesis are both my own, and have been generated by me as a result of my own original research.

#### I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as: [1], [2], [3], [4], [5], and [6].

| signea: | <br>• • • • • • • • • • • • • • • • • • • • | <br>• • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • • | • • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • • |

|---------|---------------------------------------------|-----------------------------|-----------------------------------------|-------------------------|-----------------------------------------|

|         |                                             |                             |                                         |                         |                                         |

|         |                                             |                             |                                         |                         |                                         |

|         |                                             |                             |                                         |                         |                                         |

| Date:   |                                             | <br>                        |                                         |                         |                                         |

#### Acknowledgements

I would like to thank my supervisor Professor Shinichi Saito for his guidance during my PhD, as well as my secondary supervisor Dr Kapil Debnath, both of whom have provided invaluable support technically, as well as in terms of my general understanding as a student. I would also like to thank Dr Khaled Husain for his invaluable support with fabrication, Moise Sotto for his help with some simulations, and Dr Hideo Arimoto for providing the initial horizontal-slot fin-waveguide designs. I would like to thank the rest of my research group generally, as well as the technical staff at the Southampton Nanofabrication Centre.

I want to thank my friends in Southampton for looking after me and keeping me on the (mostly) straight and narrow, particularly Daniel Burt, Rafa Gutierrez, Kevin Alabarta and Cesar Angeles. I would also like to thank my family for their support and encouragement throughout, particularly my parents Richard Byers and Ann Wilson. And lastly I would like to thank my girlfriend Iris, who believed in me even when I didn't believe in myself.

For Iris

## Chapter 1

## Introduction

For over 40 years optical interconnects have been developed to replace, first, long range electronic communication (erbium doped fibre amplifier (EDFA) enabled optical fibres replacing copper coaxial cables for long-distance (1km-10,000km) telecommunication), then medium range electronic communication (fibre optics replacing copper cables for 1m-1km distances), and now they are set to replace electrical short-range (<1m) communication. Whenever shorter range interconnects have transitioned from electronic to optical communication, it has required the development not only of the new fibre optic cables themselves, but also the light source, amplifier, detector, wavelength division multiplexer (WDM) and wavelength devision demultiplexer (WDDeM) components, and importantly, the opto-electronic (OE) modulator to convert the electronic signal into an optical signal.

Silicon (Si) based devices have long been chosen for passive optical components due to the refractive index (n) difference  $(\Delta n)^8$  of Si with its native oxide silicon dioxide (SiO<sub>2</sub>), low optical loss<sup>9</sup>, high mode confinement <sup>10</sup> (effective volume (V<sub>eff</sub>)), high bandwidth <sup>11</sup> (sustaining multiple wavelengths simultaneously for multi-channel operation), transparency at telecommunication wavelengths, and ease of production. However, owing to the fact that unstrained Si exhibits no 1<sup>st</sup> order electro-optic (EO) effect <sup>12</sup> (due to its centrosymmetric crystal structure <sup>13</sup>), only a very weak 2<sup>nd</sup> order EO effect, and lacks a direct energy bandgap, III-V semiconductor materials have traditionally dominated active optoelectronic components such as lasers <sup>14,15</sup>, detectors <sup>16</sup> and modulators <sup>17</sup>. Despite these challenges, the desire for fully integrated on-chip optoelectronic integrated circuits (OE-ICs) with fully integrated optical emission, amplification, modulation and detection has driven active OE component innovation in the direction of Si photonics, which benefits from over 50 years of Si integrated circuit (IC) development and investment.

The rapid growth in the amount of data traffic in modern data centres from 4.7ZB per year in 2015 to a projected 15.3ZB per year for 2020 (27% annual compound growth

rate) 18 is pushing the electronic and OE performance metrics of device density, modulation speed, thermal output and energy consumption per bit etc. to the limit of what is possible with current technology. On-chip transistor density and computation speed continues to increase, but as parallel computation increases and bandwidth required for input/output (I/O) increases, the industry is now encountering the "bottleneck" interconnect problem, whereby increased computation is now limited by the speed at which information can be communicated between chips and servers <sup>19,20</sup>. Along with a Si laser/photodiode and small-scale photodetector, a critical technology required to solve this bottleneck problem of data transfer is an on-chip OE modulator. This device could in the long-run bridge the gap between separate components within a chip, and in the near term will allow better high-speed communication with off-chip systems. Traditionally, on-chip and off-chip interconnects have been metal (with IC being completely electronic), but industry is moving towards OE modulators to help solve the bottleneck problem of low power<sup>21,22</sup>, high speed<sup>23</sup>, cheap interconnects. Si photonics is also a logical approach to this problem because it is already compatible with complemetary metal-oxide semiconductor (CMOS) standard fabrication processes. Optical interconnects experience no crosstalk<sup>24,25</sup>, have higher density with WDM fibres exhibiting 96 separate channels<sup>26</sup> commercially (more channels demonstrated academically) with a wavelength separation of 0.4 nm (50GHz) etc.

OE modulators come in a variety of forms, using different modulation mechanisms, for example the  $1^{\rm st}$  order nonlinear EO Pockel's effect (which lithium niobate crystal exhibits) or the  $2^{\rm nd}$  order nonlinear EO Kerr effect which have traditionally been used in non-Si photonic devices. These effects can be used to change the n of the waveguide material as a function of input voltage (driven by an electronic signal), and therefore change the n of the propagating light. The electronic signal modulates at a certain speed, which modulates the input voltage of the device, which modulates the refractive index of the light. In an interference design device architecture, this very small refractive index change can be converted into a phase change between two beams of light, which results in either constructive or destructive interference, modulating the output light intensity. If the device architecture incorporates a resonant structure, this very small refractive index will cause the light to couple or decouple to the resonant structure, also modulating the output light intensity.

The main problem for Si based OE modulators is that due to its centrosymmetric crystal structure  $^{27}$ , it does not exhibit Pockel's effect  $^{28}$ , and it exhibits the Kerr effect very weakly  $^{28}$ . The bias V required to induce  $\Delta n$  in Si sufficient for phase change modulation using an Mach-Zehnder interferometer (MZI) or resonant structure exceeds the break down voltage of Si (Si becomes conductive at this point). The Franz-Keldysh effect is also very weak in Si at telecommunication wavelengths. Together, these three effects are the dominant operating mechanisms of III-V material semiconductor modulators. The solution to this problem is to use either the plasma dispersion effect (PDE) or the

thermo-optic effect. As the thermo-optic effect is limited to switching speeds on the order of MHz, it is too slow for GHz+ modulation speed required for telecommunication interconnects, which can only be produced in silicon based devices using PDE.

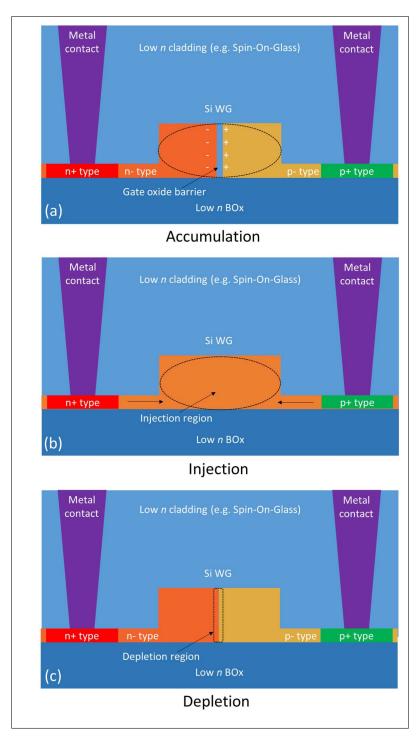

The PDE operates by changing the concentration of electrons and/or holes in a Si waveguide, which can change the n of the propagating light, which can then be converted into a change in output intensity (using an interference or resonance device). The concentration of free electrons and holes can be changed using one of three device architectures and corresponding mechanisms. One, carriers can be injected into the centre of a p-i-n diode structure. Two, carriers can be depleted from a depletion region at the centre of a p-n diode structure. Three, carriers can be accumulated either side of a narrow gate oxide slot in the middle of a metal-oxide-semiconductor capacitor (MOScap) structure.

The development of PDE Si OE modulators began with the development of very-low-speed(<MHz) carrier injection devices  $^{29-31}$  due to the fact that fabrication of p-i-n diode structures within the waveguide was considerably less demanding than the fabrication of p-n diode structures or MOScap structures within the waveguide. Despite the fact that the first Si photonic OE switch was demonstrated in 1987<sup>32</sup> (which utilized carrier injection into the intrinsic region of a p-i-n diode waveguide as the mechanism to manipulate waveguide n), it took 13 years before the demonstration of a modulator with an operational speed >10MHz<sup>33</sup>, and a further 4 years before the demonstration of the first a modulator with an operational speed >1GHz<sup>34</sup> (which was rapidly improved the following year when an operational speed of 10Gbit<sup>-1</sup> was demonstrated<sup>35</sup>).

Despite the initial high-speed breakthrough occurring using a MOScap accumulation based device <sup>34,35</sup>, due to fabrication concerns and a desire to increase operational speed, many high-speed, low-efficiency depletion based devices were subsequently demonstrated <sup>36–42</sup>, with several exhibiting operational speed of 50Gbit<sup>-143-46</sup>. The current record for operational-speed in literature is 90Gbits<sup>-147</sup>, which was achieved in a depletion device. High-speed depletion devices come at the cost of decreased energy efficiency compared to injection devices (which correspondingly suffer from lower speed limits, but with higher energy-efficiency). The important figure-of-merit used to determine modulation energy efficiency is  $V_{\pi}L$ , which is the required voltage applied of 1cm of the device to induce  $\pi$ phase-shift in the propagating light. The 50Gbits<sup>-1</sup> devices demonstrated by Tu et al. <sup>46</sup> and Thomson et al<sup>43</sup> have  $V_{\pi}L$  energy efficiencies of 26.7Vcm and 2.8Vcm, respectively, for example. The modulation speed is certainly one of the most important operating parameters, and there is niche industry demand for very-high-speed modulation at the cost of efficiency, however, because energy and cooling costs are such a large and growing concern for large data-centres, the primary industry demand is for medium-speed, high-energy-efficiency modulation.

Several medium-speed accumulation modulators have been demonstrated with high energy efficiency <sup>48–52</sup>. Fujikawa et al. demonstrated an operational speed of 25Gbits<sup>-1</sup> with

a  $V_{\pi}L$  of  $0.28 \text{Vcm}^{50}$ , Webster et al. demonstrated an operational speed of  $28 \text{Gbits}^{-1}$  with a  $V_{\pi}L$  of  $0.2 \text{Vcm}^{52}$ . These devices demonstrate the principle that accumulation based modulators can target the industry need for "middle-ground" OE interconnects between high-speed, low-efficiency depletion devices (which currently dominate the market, but present scaling problems due to high energy inefficiency), and low-speed, high-efficiency injection devices (which cannot support the high speeds necessary to satisfy most OE interconnect requirements). Because of the industry need for "middle-ground" OE interconnect devices, and the fact that fabrication methods have improved significantly over the last 20 years such that previously very challenging MOScap embedded waveguide designs can now be fabricated and tested in an academic environment, it is now a very promising time to pursue novel accumulation modulator designs to address this industry need.

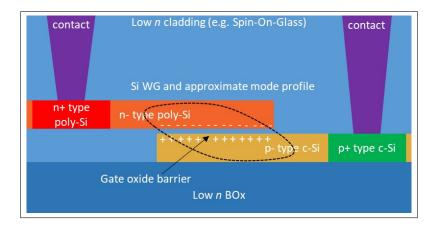

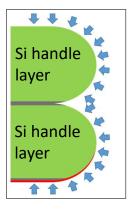

Conventional accumulation OE modulators utilize a vertically stacked Si/SiO<sub>2</sub>/Si MOScap structure built into a rib-waveguide. This structure relies on either high-optical-loss, deposited, partially amorphous-Si (a-Si) or polycrystalline-Si (poly-Si)<sup>34,48,49</sup>, or bonded double-crystalline horizontal-slot waveguide structures which introduces parasitic capacitance which increases energy consumption and limits switching speed<sup>51</sup>. Schematic representations of a conventional accumulation modulator utilizing poly-Si, and one using a bonded double-crystalline substrate are shown in 1.1 (a) and (b) respectively. A key challenge that must be solved is the design and fabrication of a fully-crystalline-Si (c-Si) slot-waveguide structure without any intrinsic parasitic capacitance. This thesis will explore two proposed solutions to this challenge.

The first possible solution that is explored is a design based on a horizontal-slot, finwaveguide on bonded double-silicon-on-insulator (SOI)<sup>1</sup>, which allows one to take advantage of the inherent c-Si/SiO<sub>2</sub>/c-Si structure easily<sup>53</sup>. A schematic of this design is presented in 1.1 (d). Fabrication of high quality OE devices on double-SOI is also a prerequisite to the further development of multi-layer optoelectronic devices or multi-layer integrated optoelectronic and microelectronic devices on the same double-SOI substrate. A challenge associated with using a horizontal-slot double-SOI is how to pattern the bottom SOI layer using lithography of the top SOI layer, since the double-SOI wafers must be bonded prior to patterning so as to ensure excellent interface quality. I will demonstrate the use of anisotropic wet-etching of mirror-aligned top and bottom SOI layers to solve this challenge, and and thereby establishing a unique fabrication process to fabricate horizontal-slot strip/fin-waveguides consisting of two c-Si SOI layers separated by a 10nm gate oxide  $SiO_2$  layer, with multiple fin-gratings for use as electrode connections. In the future this design will also enable optical communication to be overlaid directly above microelectronic computation, which will lead to a whole new architecture of fully integrated (as well as vertically integrated) optoelectronic integrated circuits (OEIC). This structure also has the secondary benefit that it allows for easy ion implantation/doping of the SiO<sub>2</sub> slot (for example in the case of an erbium doped slot-waveguide

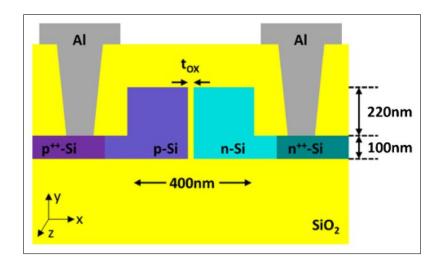

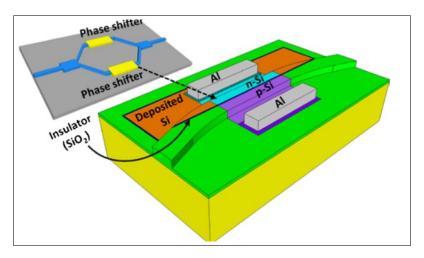

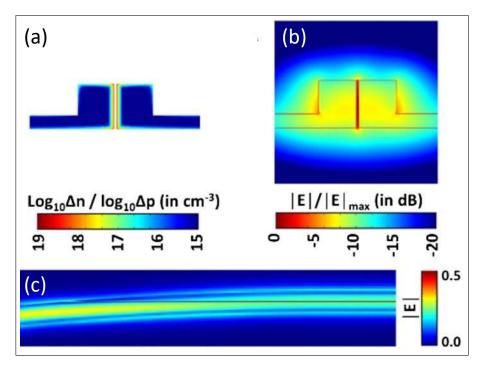

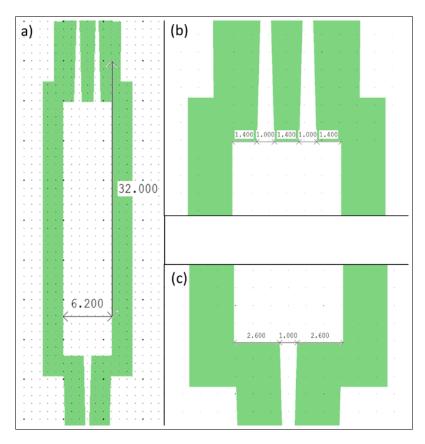

FIGURE 1.1: Schematic representations of conventional accumulation modulator designs ((a) and (b)), demonstrating their inherent weaknesses, and two proposed solutions to these weaknesses ((c) and (d)). Cross-section through active region of waveguide. Black dotted oval represent approximate region of propagating mode. (a) Doublec-Si design formed by bonding two (100) orientation SOI wafers. Total capacitance across the gate oxide is made up of two components,  $C_m$  and  $C_p$ , only the  $C_m$ . Utilizing this platform there is currently no way to remove the bottom-left SOI, thus removing  $C_p$ . The propagating mode is maintained in the position that it is (at the edge of the top SOI) as a WGM at the edge of a microdisk resonator. (b) Deposited a-Si can only be partially recrystallized to high-optical loss poly-Si. (c) Proposed solution design #1: Vertical-slot oxide grown on the side of exposed Si wall using LOCOS process, then a-Si is deposited and recrystallized, before patterning waveguide with vertical slot in the centre. (d) Proposed solution design #2: Double-c-Si design formed by bonding two (110) orientation SOI wafers. Anisotropic tetramethylammonium hydroxide (TMAH) wet etching can be used to suspend the top SOI, thus removing  $C_p$ .

optical amplifier), a process that is difficult to achieve for high aspect ratio vertical-slot designs.

The second possible solution that is explored is the use of a fully-c-Si vertical-slot rib-waveguide <sup>3,54</sup> accumulation modulator. A schematic of this design is presented in 1.1 (c). This device is fabricated using a process involving sidewall local oxidation of silicon (LOCOS) to grow the vertical gate-oxide layer, deposition of a-Si which is then fully recrystallised using the SOI layer as a crystallization seed, chemical mechanical polishing (CMP) planarization, waveguide patterning and etching. Subsequently, electrically active components (doping, metal contacts etc.) are fabricated to complete the electrically active design. This design is planar, and is therefore compatible with established Si photonics devices on the same chip, which has advantages in terms of on-chip integration. This solution will be shown to satisfy the key aim of the PhD which is to fabricate

and characterise a low-power-consumption fully-c-Si OE modulator that overcomes the challenges listed above.

The key aims of this thesis are:

- 1. Propose two new possible fully-c-Si slot-waveguide design architectures that do not include intrinsic parasitic capacitance, for use in an energy-efficient, high-speed accumulation modulator.

- 2. Demonstrate the feasibility of fabricating these two fully-c-Si slot-waveguide designs.

- 3. Utilize one of the new designs to fabricate an optoelectronically active, high-efficiency, high-speed accumulation modulator, and demonstrate such performance.

#### The thesis is organized as follows:

Chapter 2 will give an overview of the theory and relevant literature relating to three areas. Firstly electromagnetic (EM) wave propagation (for strip and slot waveguides, grating couplers (GCs), multimode interferometers (MMIs), Mach-Zehnder interferometers (MZI) and photonic crystal (PhC) bandgap guided propagation (relevant for one of the fin-waveguide designs)) will be discussed. Secondly, the active use of OE modulators, focusing on accumulation modulators, will be presented. And thirdly, some key Si photonics fabrication techniques (wafer bonding and thinning, and anisotropic wet etching using tetramethylammonium hydroxide (TMAH) etc.) will be discussed.

Chapter 3 will present the two distinct designs (horizontal-slot fin-waveguide accumulation modulator and vertical-slot rib-waveguide accumulation modulator) that make up the two proposed solutions in this thesis. These will be presented with relevant computational simulations. The fabrication process flow for each of these designs will also be presented in detail here.

Chapter 4 will present the fabrication characterisation and the post-fabrication characterisation and analysis of the passive horizontal-slot strip-waveguides. This chapter will also present the characterisation of MOScap devices fabricated on the bonded double-SOI demonstrating the quality of the bonding-oxide and its suitability for use in an active modulator.

Chapter 5 will present the analysis of the fin-waveguides themselves, and the their use in passive MZI devices.

Chapter 6 will present the fabrication characterisation and the post-fabrication characterisation and analysis of the passive vertical-slot rib-waveguides, and will then go on to present the analysis and operational characteristics of the active accumulation modulator based on the vertical-slot rib-waveguide.

Finally, Chapter 7 will provide a summary of the thesis, highlighting the key conclusions (two new silicon photonics architectures proposed and developed, and a new architecture accumulation modulator demonstrated), and propose some possible future work.

## Chapter 2

## Theory And Literature Review

#### 2.1 Waveguides

EM waves with  $\lambda$  smaller than the cross-section of the waveguide through which they are guided can often be described using total internal reflection (TIR) and Snell's law. However, when the cross-sectional dimensions of the waveguide approach or are smaller than the  $\lambda$  of the propagating EM wave, the wave nature of light needs to be taken into consideration and Maxwell's equations need to be utilized.

# 2.1.1 Electromagnetic Propagation in 2-Dimensional Waveguides: Maxwell's equations

The wave equation can be derived from Maxwell's equations. Maxwell's four differential equations relate the electric field (**E**) and electric displacement (**D**) to the magnetic field (**H**) and magnetic induction (**B**), as well as the charge density ( $\rho$ ) and the current density (J) as follows (for the specific case of a charge free ( $\rho = 0$ , J = 0), nonmagnetic (magnetic permeability ( $\mu$ ) = magnetic permeability of free space ( $\mu$ <sub>0</sub>)) dielectric (conductivity ( $\sigma$ )= 0) medium):

$$\nabla \cdot \mathbf{E} = 0 \tag{2.1}$$

$$\nabla \cdot \mathbf{H} = 0 \tag{2.2}$$

$$\nabla \times \mathbf{E} = -\frac{\partial \mathbf{H}}{\partial t} \tag{2.3}$$

$$\nabla \times \mathbf{H} = \mu_0 \epsilon_0 \frac{\partial \mathbf{E}}{\partial t} \tag{2.4}$$

$\mu_0$  = magnetic permeability of free space (H/m) =  $4\pi \times 10^{-7}$  H/m  $\epsilon_0$  = electric permittivity of free space (F/m) t = time (s)

These four equations can be used to derive the wave equations for magnetic (2.5) and electric fields (2.6) in an inhomogeneous medium  $(n(\mathbf{r}) = \mathbf{r})$ .

$$\nabla^2 \mathbf{H} = \mu_0 \epsilon_0 n^2 \frac{\partial^2 \mathbf{H}}{\partial t^2} \tag{2.5}$$

$$\nabla^2 \mathbf{E} = \mu_0 \epsilon_0 n^2 \frac{\partial^2 \mathbf{E}}{\partial t^2} \tag{2.6}$$

A propagating EM wave can be split into x, y and z component parts,  $E_x$ ,  $E_y$ ,  $E_z$ ,  $H_x$ ,  $H_y$ ,  $H_z$ . For an EM wave propagating in the z-direction, it can be polarized in two ways that must be considered for waveguide design. These are transverse electric (TE) polarization or transverse magnetic (TM) polarization, which are defined as follows:

TE polarization:

$$\mathbf{E} = \mathbf{E}_x$$

;  $\mathbf{E}_y = \mathbf{E}_z = 0$ ;  $\mathbf{H}_x = 0$

TM polarization:

$$\mathbf{H} = \mathbf{H}_x$$

;  $\mathbf{H}_y = \mathbf{H}_z = 0$ ;  $\mathbf{E}_x = 0$

The TM wave equation (2.7) and TE wave equation (2.8) describe a polarized EM wave propagating in the z-direction in a homogeneous medium, and incorporate the mode defining parameter, the propagation constant  $(\beta)$ .

$$\frac{\partial H_x(y)}{\partial t^2} = [k_0^2 n^2(y) - \beta^2] H_x \tag{2.7}$$

$$\frac{\partial \mathcal{E}_x(y)}{\partial t^2} = [k_0^2 n^2(y) - \beta^2] \mathcal{E}_x \tag{2.8}$$

$H_x(y)$  indicates that the magnetic field in the x-direction is a function of y.

$k_0 = \text{wavevector} = (\frac{2\pi}{\lambda_0})^2 = \mu_0 \epsilon_0 \omega^2$

$\lambda_0 = \text{wavelength in vacuum (nm)}$

$\omega = \text{angular frequency (rad/s)}$

n = refractive index (constant in this case)

$\beta = k_0 N_{eff}$

$N_{eff} = \text{mode}$  effective refractive index

$\beta$  defines a unique EM field distribution, which is a unique mode of propagation.  $\beta$  can be determined from the transcendental equations (which are specific to the waveguide geometry) for TE and TM polarization separately. If a single solution to either of these equations exist, a single propagating mode exists; the waveguide is single-mode. If multiple solutions exist, multiple propagation modes exist; the waveguide is multi-mode, however, the first "fundamental" mode carries most of the energy. Only a finite number of discrete propagation modes can exist. If no solution exists, no propagation mode exists and only unguided radiation modes exist, which will leak out into the surrounding material. The horizontal-slot, strip and fin-waveguides, as well as the vertical-slot rib waveguide, on which the accumulation modulators proposed in this thesis are based, are designed to contain one fundamental propagating TE mode for the energy spectrum of

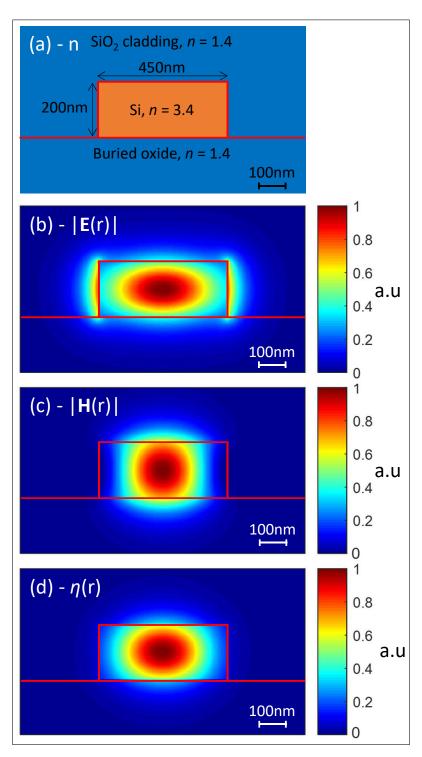

interest ( $\lambda \sim 1500\text{-}1600\text{nm}$ ). A schematic and finite difference eigenmode simulation of a TE mode, conventional Si on buried oxide (BOx) strip-waveguide with SiO<sub>2</sub> cladding (performed using *Lumerical Solutions MODE*: Waveguide Simulator, version 2017a<sup>55</sup>) is presented in Figure 2.1.

The conventional TE mode presented in Figure 2.1 is the fundamental spacial profile solution to discretized Maxwell's equations, across a 2-dimensional (2D) cross-sectional area, for this particular geometry. The electric field intensity, |E(r)| (Figure 2.1(a)), and magnetic field intensity, |H(r)| (Figure 2.1(b)), at each point, r, are functions of their x, y, z components, and are defined in 2.9 and 2.10 respectively:

$$|E(r)| = |E_x(r)|^2 + |E_y(r)|^2 + |E_z(r)|^2$$

(2.9)

$$|H(r)| = |H_x(r)|^2 + |H_y(r)|^2 + |H_z(r)|^2$$

(2.10)

The energy density,  $\eta(r)$ , at each point, r, is a function of |E(r)|, |H(r)| and  $\epsilon(r)$ , and is defined in 2.11:

$$\eta(r) = \frac{1}{2} (\epsilon(r)|E(r)| + \mu_0|H(r)|)$$

(2.11)

where  $\epsilon(r) = \epsilon_0 n(r)^2$ .  $\epsilon(r)$  is not dependent on changeable  $\mu(r)$  as neither Si nor SiO<sub>2</sub> are magnetic, and therefore  $\mu(r) = \mu_0$  for all values of r. Despite the fact that there is an obvious |E(r)| peak either side of the waveguide, within the low n cladding, as evidenced in Figure 2.1(b), this only has a minor effect on the  $\eta(r)$  in this region (Figure 2.1(c)). Each peak accounts for 9% of the total  $\int |E(r)| dxdy$  across the entire simulation region (56% of total  $\int |E(r)| dxdy$  is within the Si waveguide), but <1% of the total  $\int \eta(r) dxdy$  across the entire simulation region (73% of total  $\int \eta(r) dxdy$  is within the Si waveguide). This is for two reasons: (1) |H(r)| contributes negligibly to  $\eta(r)$  in this region, and (2),  $\frac{\epsilon(Si)}{\epsilon(SiO_2)} = 5.5$ , and therefore the same |E(r)| contributes to higher  $\eta(r)$  in the Si waveguide region.

#### 2.1.2 Optical Loss Mechanisms

In an ideal single mode waveguide, the propagating mode is perfectly confined in two dimensions and is subject to 0% optical transmission loss. However, in reality, there are several important loss mechanisms that must be taken into account, and are outlined herein (in order of increasing importance for nm scale strip and slot-waveguide designs):

#### • Inter-band absorption

A photon excites a valance band electron across the bandgap into the conduction band, which then relaxes in Si's case usually with the emission of a phonon. This effect is negligible at  $\lambda=1.55~\mu\mathrm{m}$ , as the incident photons do not have the required energy to excite electrons across the bandgap.

FIGURE 2.1: (a) Cross-section schematic of simple Si strip-waveguide on BOx with typical design parameters; waveguide width = 450nm and waveguide height= 200nm.  $n_{\rm Si}$ =3.4;  $n_{\rm BOx}$ =1.4;  $n_{\rm clad}$  = 1.4. Normalized electric field intensity ( $|\mathbf{E}(\mathbf{r})|$ ), normalized magnetic field intensity ( $|\mathbf{E}(\mathbf{r})|$ ), and normalized energy density ( $\eta(\mathbf{r})$ ), for the fundamental TE mode of structure (a) is shown in (b), (c) and (d) respectively. The majority of dominating components are strongly confined to the high n Si strip-waveguide. Normalized profile and arbitrary units used as absolute values depend on arbitrary input power.

# • Volumetric inhomogeneity scattering

Any internal discontinuity in  $n_{x,y}(z)$  (for a 2D waveguide propagating in the z-direction) causes a change in the mode profile. This mode-mismatch causes scattering of the electromagnetic wave into the cladding. It is for this reason that it is crucial to maintain a uniform oxide layer through excellent bonding quality (no voids) when fabricating strip-waveguides with on bonded double-SOI with nm scale bonding oxide.

# • Free Carrier Absorption (FCA)

Photons are absorbed by free electrons or holes present in the material. This is particularly important when considering positively doped Si (p-type) and negatively doped Si (n-type) regions for active devices such as OE modulators. It is also a necessary side effect of increasing the free carrier density to manipulate the material n. This effect is described by the Drude-Lorenz equation, and is explained in more detail in Section 2.2.2. As a rough estimate, a free carrier concentration of  $10^{18}/\text{cm}^3$  is responsible for an additional FCA propagation loss of approximately 10dB/cm.

# • Surface roughness scattering

Waveguide surface roughness can be modelled as a random variation in waveguide width, with changes in local n along the sidewall surface. This random change of refractive index is a "pseudo-grating" (as opposed to a normal grating which has a periodic change in refractive index), which can couple light into the surrounding cladding <sup>56</sup>. As waveguide width decreases, the sidewall/interface region makes up a larger proportion of the waveguide area, and therefore (in a conventional device) there is a greater mode concentration at the sidewall and the pseudo-grating has a larger effect on the mode. Surface roughness scattering is proportional to  $\Delta n^{357}$ . This is the dominant loss mechanism for passive single-mode waveguides (dry etching incurs significant roughness) with widths  $< 1\mu$ m, and must therefore be minimised if possible by wet etching techniques.

# 2.2 Modulators

# 2.2.1 Si and Non-Si Optoelectronic Modulators

Si was initially not an obvious material on which to build active OE components. It exhibits no 1<sup>st</sup> order EO effect (Pockels effect) due to its centrosymmetric crystal structure, and only a very weak 2<sup>nd</sup> order EO effect (Kerr effect) with which to directly modulate a change in the real refractive index change ( $\Delta n$ ) or the imaginary refractive index (apsorption coefficient change ( $\Delta \alpha$ )) in the material. Traditionally, non-centrosymmetric materials that demonstrate one of these effects, such as lithium niobate (LiNbO<sub>3</sub>), which

possesses ferroelectric properties (local internal electric polarization which can be manipulated by an applied electric field) or III-V material gallium arsenide (GaAs) (which has the added benefit of having a direct energy bandgap and can be used to make near-infrared laser diodes<sup>58</sup>) have been used to modulate light directly.

Optical modulation requires the change of output optical intensity, either by directly modulating changes in absorption or by modulating changes in the refractive index (which can be used in a device such as an interferometer to shift the phase of a propagating wave, or in a resonator to couple light from the main (access) waveguide into a secondary resonant structure, which then indirectly effects the output intensity). The refractive index of a material is made up of a real and an imaginary component, the refractive index (n) and the absorption coefficient  $(\alpha)$  respectively.

$\Delta n$  - refractive index change

$\Delta \alpha$  - apsorption coefficient change

An electrical signal can induce a change in **E** in the material which then causes a  $\Delta n$  and  $\Delta \alpha$  in the material, which modulates the light propagating through that material, thus converting the electrical signal into an optical signal. The primary mechanisms traditionally used by non-Si modulators to effect material  $\Delta n$  and  $\Delta \alpha$  are the following:

# Pockels effect (not present in Si)

The 1<sup>st</sup> order (linear) electro-optic effect changes n proportional to the applied electric field,  $\mathbf{E}$ , by changing the materials birefringence (a material property whereby the refractive index of the material is dependent on the light polarization and propagation direction) according to the following equation  $2.12^{59}$  (when the direction of the applied  $\mathbf{E}$  field is aligned with the direction of the principle crystal axis):

$$\Delta n = r_3 n_3 \frac{\mathbf{E}_3}{2} \tag{2.12}$$

Where:

$r_3$  = Pockels electro-optic tensor (material and crystallographic orientation dependent, hence the subscript "3" denoting the alignment in the three relevant crystal planes)

$n_3$  = refractive index in the direction of the applied field, **E**.

$\mathbf{E} = \text{applied electric field}$

# Kerr effect (weakly present in Si)

The 2<sup>nd</sup> order (quadratic) EO effect.  $\Delta n$  is proportional to  $\mathbf{E}^2$  according to the following equation 2.13:

$$\Delta n = s_3 n_0 \frac{\mathbf{E}^2}{2} \tag{2.13}$$

Where:

$s_3 = \text{Kerr coefficient}$

$n_0 = \text{refractive index whe n } \mathbf{E} = 0$

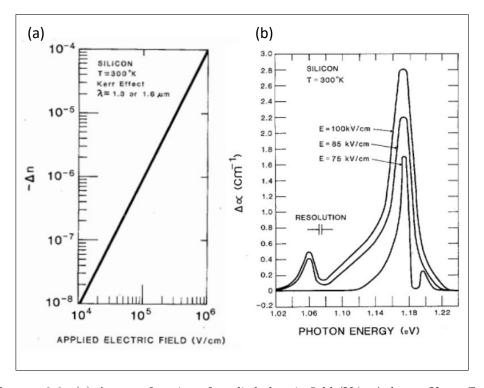

$\Delta n$  is independent of **E** direction relative to crystal axis. Applied **E** required for  $\Delta n$  sufficient for phase change modulation in Si occurs at an applied  $\mathbf{E} \sim 100 \mathrm{V}/\mu\mathrm{m}$  at  $\lambda = 1.33\mu\mathrm{m}$  (theoretically calculated by Soref and Bennet<sup>12</sup>) which is above the breakdown voltage of Si. The change in  $\Delta n$  as a function of applied electric field for  $\lambda = 1.3$ - $1.6\mu\mathrm{m}$  is plotted in Figure 2.2 (a) (from Soref and Bennet<sup>12</sup>). Figure 2.2 (b) (from Soref and Bennet<sup>12</sup>, original data from Wendland and Chester<sup>60</sup>, and also reproduced in Reed, Chapter 4, Figure 4.4<sup>59</sup>) shows the change in the  $\Delta \alpha$  of Si as a function of photon energy at various applied electric fields. At photon energy < 1.02eV (i.e. at  $\lambda > 1033\mathrm{nm}$ ) the Franz-Keldysh effect contributes negligibly to total absorption coefficient ( $\alpha$ ) compared to other loss mechanisms such as volumetric scattering, free carrier absorption (FCA) or surface roughness scattering<sup>59</sup>.

FIGURE 2.2: (a)  $\Delta n$  as a function of applied electric field (V/cm) due to Kerr effect. Reproduced from Soref and Bennet <sup>12</sup>. (b)  $\Delta \alpha$  as a function of photon energy at applied **E** fields 75 kV/cm, 85 kV/cm, and 100 kV/cm, due to the Franz-Keldysh effect. Reproduced from Wendland and Chester <sup>60</sup>.

# 2.2.2 Plasma Dispersion Effect

The only available mechanism to modulate light at high speed in Si is the PDE. This is the phenomenon whereby the n and  $\alpha$  change independently as a function of concentration of free carriers (either electrons or holes), according to the following analytic equations

produced by Soref and Bennet<sup>9</sup> (at wavelength  $1.55\mu m$ ):

$$\Delta n = \Delta n_e + \Delta n_h = -[8.8 \times 10^{-22} \times \Delta N_e + 8.5 \times 10^{-18} \times (\Delta N_h)^{0.8}]$$

(2.14)

$$\Delta \alpha = \Delta \alpha_e + \Delta \alpha_h = [8.5 \times 10^{-18} \times \Delta N_e + 6.0 \times 10^{-18} \times (\Delta N_h)^{0.8}]$$

(2.15)

Where:

$\Delta n_e$  = refractive index change attributed to change in free electron concentration

$\Delta n_h$  = refractive index change attributed to change in free hole concentration

$\Delta \alpha_e$  = absorption coefficient change attributed to change in free electron concentration

$\Delta \alpha_h$  = absorption coefficient change attributed to change in free hole concentration

$\Delta N_e$  = change in free electron concentration

$\Delta N_h$  = change in free hole concentration

FIGURE 2.3: Typical MZI modulator design

FIGURE 2.4: Typical ring resonator modulator design

Using equation 2.14 we can determine that carrier density change of  $5 \times 10^{17}$  cm<sup>-3</sup> results in a  $\Delta n = 1.66 \times 10^{-3}$ . This can be used in certain architectures to realise a significant output intensity change. In a typical MZI design (Figure 2.3), light is coupled from the input fibre into a waveguide and split into two parallel waveguides that make up the phase shifter section of the device. If  $\Delta n$  is induced in one waveguide and not the other, the group velocity of the light propagating in that waveguide is decreased. If  $\Delta n$  and phase shifter arm length ( $L_{\rm shifter}$ ) are sufficient, when the two waves are recombined they will destructively interfere and the output intensity will be 0 (in an ideal case). The V · cm required to induce  $\pi$  phase shift ( $V_{\pi}L$ ) (V·cm) of a device is a critical figure of

merit for MZI devices that defines the V·cm required to achieve one full  $\pi$  phase shift, for maximum destructive interference. In typical resonant ring/disk modulators (2.4) a  $\Delta n$  induced in the waveguide making up the ring/disk changes the resonant frequency of the ring/disk and light from the adjacent waveguide couples evanescently into the resonating ring/disk structure. At requisite  $\Delta n$  caused by biased induced  $\mathbf{E}$  in the active region, all light couples into the ring/disk and output light intensity at the end of the waveguide decreases to 0.

# 2.2.3 Injection, Depletion and Accumulation Plasma Dispersion Effect Modulation

Three different PDE operating mechanisms can be used to modulate free carrier dispersion in the waveguide section of a device. These are carrier accumulation, depletion or carrier injection (Figure 2.5). In a carrier accumulation semiconductor-insulator-semiconductor capacitor (SISCap) device  $^{34}$ , a gate dielectric layer (usually SiO<sub>2</sub>) is sandwiched between lightly doped Si strips that make up the waveguide. When a bias V is applied across the capacitor, free carriers of opposite charge accumulate on either side of the dielectric layer, changing their concentration where the mode concentration is highest, inducing  $\Delta n$ . This approach has the potential to achieve the highest switching speed (i.e. high-speed, high data throughput) because it is not limited by high free carrier lifetime ( $t_{\text{carrier}}$ ), before recombination, associated with the other mechanisms. However, there are a few fabrication challenges associated with this design such as dielectric-semiconductor interface quality, and the reliance on a-Si or poly-Si for one-half of the waveguide.

Carrier depletion modulators have a waveguide made up of a p-type and n-type regions so that they form a p-n diode, and operate in reverse-bias. When V is applied across the diode, carriers are attracted away from the centre p-n interface region, forming a depletion layer at the centre of the waveguide. In carrier injection modulators the waveguide is formed of three separately doped regions, p-type, intrinsic and n-type, forming a p-i-n diode. When V is applied across the p-i-n diode in forward bias, free carriers are injected from the doped regions into the intrinsic central region. Injection type modulators have lower switching speeds compared to depletion type modulators due to high free carrier lifetime,  $t_{\text{carrier}}$ , before recombination.

The "figures of merit" that define the performance quality of optoelectronic modulators are the following:

# • Modulation 3dB bandwidth $(f_{3dB})$

The frequency over which transmission is at least 50% of maximum transmission value. Resonant structure modulators (ring/disk) are "narrowband" devices with much lower bandwidths available for modulation (on the order of 100s pm <sup>61</sup>).

FIGURE 2.5: Schematic of (a) accumulation based PDE Si strip modulator with horizontal gate oxide barrier, (b) injection based PDE Si strip modulator and (c) depletion based PDE Si strip modulator.

Narrowband devices also suffer from very low fabrication tolerance (e.g. resonant wavelength of a ring/disk can change by as much as 0.25nm, double modulation bandwidth, for a 1nm increase in ring width <sup>62</sup>), and have higher temperature sensitivity than MZI devices <sup>63,64</sup>. MZI devices have much larger available bandwidths (10s of nm's) and are said to be "wideband" devices.

## • Modulation depth

Ratio of maximum transmission intensity ( $I_{max}$ ) to modulated minimum transmission intensity ( $I_{min}$ ) in dB. The required modulation depth depends on the intended application, 4-5dB is often sufficient <sup>11</sup>, however, if minimizing device footprint and power consumption are a priority, a lower modulation depth may be tolerable.

## • Modulation speed

Speed at which light can be reliably modulated. Under high-speed operation the output "eye diagram" must remain open for reliable modulation.

# • Optical loss

"Passive" and "active" loss as explained in 2.1.2. As waveguide cross-sections have been decreased to reduce device footprint and increase light-matter interaction <sup>65</sup>, increase speed and decrease power consumption, passive optical loss has increased.

## • Device footprint

Reducing device footprint increases device density and decreases cost per device, however, this is often at the expense of other performance metrics, such as a significantly reduced bandwidth and high thermal sensitivity (with incumbent additional power required to maintain device temperature) when comparing small device footprint resonator devices to large device footprint MZI devices.

• Power consumption (or power consumption per bit)

Energy required per modulated bit. Lightwire's accumulation modulator operating at 10Gbit s-1 has an energy consumption of 5pJ bit<sup>7,11</sup>.

# 2.2.4 Review of Injection, Depletion and Accumulation Modulator Devices in Literature

The three modulation mechanisms (injection, depletion and accumulation) and the two device architectures (MZI and ring resonator) each have pros and cons. This subsection will review the development of these three mechanisms in the literature, highlighting which mechanisms/architectures are suitable for which applications. Injection mechanism modulators are the easiest to fabricate, as the p-type and n-type doped regions are separated by the intrinsic region, so doping layer alignment and controlling the dopant diffusion pattern is less critical than with depletion devices, and the waveguide doesn't need to be built around a precise oxide capacitor layer, as with accumulation devices. The ease of fabrication is exemplified by the fact that injection mechanism switches were the first to be developed from 1987<sup>29</sup> which utilized "x-switch" splitter architecture <sup>29,66</sup>, MZI freespace architecture <sup>31</sup>, and MZI on-chip architecture <sup>33,67</sup>, prior to achieving high-speed modulation in 2004<sup>68</sup> which utilized a microdisk resonator architecture. Since then many medium-speed, high efficiency injection devices have been demonstrated <sup>45,69–75</sup>. Exceptionally low energy consumption per bit has been achieved with injection devices.

Preston, K. et al. demonstrated 86fJ/bit energy consumption at 3Gbit/s operation  $^{73}$  using a micro-ring resonator architecture, and Debnath, K. et al. demonstrated 1.6fJ/bit energy consumption at 0.5Gbit/s operation  $^{74}$  using a cascaded WDM PhC resonator architecture. The majority of injection mechanism modulators demonstrate operational speed < 20Gbit/s, and because of the long minority carrier lifetime ( $t_{\text{carrier}}$ ) in Si they will be restricted to lower operational speeds at <2V drive voltage (IC compatible drive voltage). This speed limitation can be circumvented to an extent by utilizing resonant structures  $^{45}$  but these devices are narrow-bandwidth compared to MZI architecture devices, and require thermal heaters to tune the devices, which increases energy/bit massively, generally offsetting the efficiency of injection mechanism devices.

Depletion mechanism modulators are more challenging to fabricate due to the need to carefully control the placement of the p-type and n-type doped regions and dopant diffusion pattern. The first deletion mechanism modulator was proposed in  $2005^{76}$ , and realised in  $2007^{36,37}$ . Since then many medium/high-speed depletion devices with various designs have been realised  $^{19,39,44,77-83}$ , with some demonstrating operational speeds up to  $90\text{Gbit/s}^{47}$ . Despite the plethora of medium/high-speed depletion devices demonstrated, they all have corresponding high energy consumption, with most reported devices (and most cited in this paragraph) having  $V_{\pi}L > 2 \text{ V·cm}$ , with Zeilbell, M. et al. reporting 3.5V·cm for 40Gbit/s operational speed  $^{84}$ , and Thomson, D. J. et al. reporting 2.8V·cm for 50Gbit/s operational speed  $^{43}$  as representative examples.

As previously mentioned, the accumulation mechanism modulator was the first to demonstrate  $> 1 {\rm Gbit/s^{34}}$  and then  $> 10 {\rm Gbit/s^{35}}$  performance. It was understood that accumulation mechanism modulators could outperform injection mechanism modulators as they are not limited by long minority carrier lifetimes, but instead are limited by device resistance and capacitance  $^{11}$ , which can be optimized with appropriate fabrication methods. However, despite the recognised potential, accumulation modulator development was slow due to inherent fabrication challenges. As fabrication methods improved, several MZI accumulation modulators with operational speed  $> 20 {\rm Gbit/s}$  and  ${\rm V_{\pi}L} < 0.3 {\rm V \cdot cm}$  have been demonstrated  $^{48-50,52}$ , as well as low energy-per-bit operation micro-disk resonator structures  $^{51}$ . Accumulation modulator operational speeds are slightly (  $20 {\rm Gbit/s}$ ) lower than that demonstrated by depletion modulators, but their  ${\rm V_{\pi}L}$  efficiency is almost an entire order of magnitude that that demonstrated by depletion modulators.

As can be seen, different modulation mechanisms are suitable for different purposes, with injection mechanism modulators suitable for applications where ultra-high speed is not necessary but that require ultra-high efficiency, depletion mechanism modulators suitable for ultra-high-speed applications at lower efficiency, and accumulation mechanism modulators suitable for middle-ground applications that require both high-speed and high-efficiency. The goal of this project is to realise an efficiency (low $V_{\pi}L$ ), low optical loss, high bandwidth, high speed modulator for short range OE interconnects. This application area is particularly important because of the growing energy concerns

within the telecommunications/OE of data-centres industry. The most promising mechanism to achieve this middle-ground of high-speed and high-efficiency is the accumulation mechanism.

# 2.2.5 Plasma Dispersion Effect Accumulation Mach-Zehnder Interferometer Modulators

The first GHz Si OE modulator was based on carrier injection into a p-i-n diode waveguide, demonstrated in 2004 with a speed of 5GHz<sup>85</sup>. The switching speed of this type of device was limited by the long  $t_{\rm carrier}$ . In 2004 Intel demonstrated a Si accumulation modulator with an operating speed exceeding 1GHz<sup>34</sup> (1Gbit/s pseudo-random bit sequence (PRBS) successfully modulated). This was improved in 2009 when Lightwire demonstrated an accumulation modulator with 10Gbits<sup>-1</sup> operation, with a modulation depth of 9dB<sup>11</sup>. In 2013 Cisco demonstrated another MOScap accumulation Si modulator with 28Gbits<sup>-1</sup> and 9dB modulation depth (40Gbits<sup>-1</sup> for 8dB modulation depth) <sup>48</sup>. The goal of this thesis is to modify and improve upon this design.