# Southampton

# University of Southampton Research Repository

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Author (Year of Submission) "Full thesis title", University of Southampton, name of the University Faculty or School or Department, PhD Thesis, pagination.

Data: Author (Year) Title. URI [dataset]

i

## **University of Southampton**

Faculty of Physical Science and Engineering

School of Electronics and Computer Science

# Manipulation of the Random telegraph signals for quantum random number generation

Ву

Fayong Liu

Thesis for the degree of Doctor of Philosophy

September 2019

## **University of Southampton**

#### <u>Abstract</u>

Faculty of Physical Science and Engineering School of Electronics and Computer Science Thesis for the degree of Doctor of Philosophy

Manipulation of the Random telegraph signals for quantum random number generation

Ву

Fayong Liu

The random telegraph signals (RTSs) has become a serious reliability issue during the scaling of the CMOS technology. From the fundamental physics point of view, the RTS is generated by the defects at the Si/SiO<sub>2</sub> interface or in the gate oxide layer, they can not be eliminated completely. The study on RTSs topic has led a paradigm shift from eliminating the RTSs to utilizing the RTSs. The RTSs phenomenon provides two contrasting states by the quantum effect. It also has shown that the capture and emission time are related to the bias conditions. Principally, the RTSs can be a promising candidate for the new QRNG source. However, the RTSs are usually generated by randomly distributed traps, it prevents the people to have a certain RTSs source. In this case, there is a high demand to develop a certain and stable RTSs source.

In this PhD project, we successfully fabricated the RTSs source with the artificial quantum dot in the multi-gate silicon nanowire transistors. The RTSs generated from the artificial quantum dot could be manipulated by the bias condition of the multi-gate. The probability of the two states in the typical RTSs could be balanced equally by the voltage control. In addition, the RTSs phenomenon in conventional MOSFETs was investigated at different temperatures. The quantum confinement in our silicon nanowires was characterized.

# **Table of Contents**

| Tabl | e of Co  | ontents                                                      | v    |

|------|----------|--------------------------------------------------------------|------|

| Tabl | e of Ta  | ables                                                        | ix   |

| Tabl | e of Fig | gures                                                        | xi   |

| Rese | earch T  | hesis: Declaration of Authorshipx                            | xiii |

| Ackr | nowled   | lgements                                                     | κxv  |

| Chap | oter 1   | Introduction                                                 | 1    |

| 1.1  | Mot      | tivation                                                     | 1    |

| 1.2  | Aim      | ۱                                                            | 3    |

| 1.3  | Out      | line of the thesis                                           | 3    |

| Chap | oter 2   | Background and literature review                             | 5    |

| 2.1  | Ran      | ndom telegraph signal phenomenology                          | 5    |

|      | 2.1.1    | The SRH framework                                            | 5    |

|      | 2.1.2    | Tunneling transitions of the RTSs at different temperatures. | 6    |

|      | 2.1.3    | The RTS amplitude                                            | 7    |

|      | 2.1.4    | RTSs in the gate leakage current                             | 8    |

|      | 2.1.5    | 1/f noise and RTS                                            | 8    |

| 2.2  | Qua      | antum random number generators                               | 9    |

|      | 2.2.1    | QRNGs based on the radioactive decay                         | 9    |

|      | 2.2.2    | QRNGs based on the noise                                     | 10   |

|      | 2.2.3    | QRNG based on photon                                         | 10   |

| 2.3  | RTS      | s in the silicon devices using as QRNGs source               | 12   |

| 2.4  | Su     | mmary                                                              | 14 |

|------|--------|--------------------------------------------------------------------|----|

| Chap | oter 3 | Random telegraph signals in MOSFET at low temperature              | 15 |

| 3.1  | M      | ethods                                                             | 15 |

| 3.2  | Lo     | w-temperature measurement system and sample packaging              | 20 |

| 3.3  | RT     | Ss in a wide-channel MOSFET (W/L=10um/75nm)                        | 25 |

|      | 3.3.1  | Measurement                                                        | 25 |

|      | 3.3.2  | Discussion                                                         | 35 |

| 3.4  | RT     | N in a narrow-channel MOSFET (W/L=60nm/60nm)                       | 45 |

|      | 3.4.1  | Measurement system upgrade                                         | 45 |

|      | 3.4.2  | Measurements and discussion                                        | 49 |

| 3.5  | Est    | ablish the relationship between the Coulomb diamond, RTSs and QRNG | 60 |

| 3.6  | su     | mmary                                                              | 61 |

| Chap | oter 4 | Fabrication of the multi-gate silicon nanowire transistor devices  | 62 |

| 4.1  | Int    | roduction                                                          | 62 |

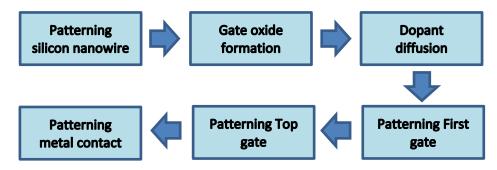

| 4.2  | Fa     | brication process flow                                             | 62 |

|      | 4.2.1  | Patterning silicon nanowire                                        | 62 |

|      | 4.2.2  | Gate oxide formation                                               | 65 |

|      | 4.2.3  | Dopant diffusion                                                   | 66 |

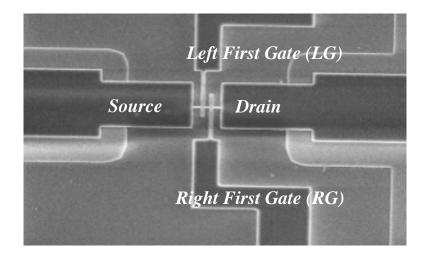

|      | 4.2.4  | Patterning the First gate                                          | 67 |

|      | 4.2.5  | Patterning Top gate                                                | 68 |

|      | 4.2.6  | Patterning metal contact                                           | 69 |

| 4.3  | Qı     | antum confinement in the silicon nanowires                         | 71 |

|                                                | 4.3.1                               | Measurement and discussion7                                           | 2                |

|------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------|------------------|

| 4.4                                            | Sum                                 | mary                                                                  | 1                |

| Chap                                           | ter 5                               | Manipulate the RTSs in the artificial quantum dot with the multi-gate |                  |

|                                                |                                     | silicon nanowire transistor8                                          | 3                |

| 5.1                                            | Intro                               | oduction                                                              | 3                |

| 5.2                                            | Dev                                 | ce structure                                                          | 3                |

| 5.3                                            | Mea                                 | surement and results                                                  | 4                |

| 5.4                                            | Sum                                 | mary9                                                                 | 3                |

|                                                |                                     |                                                                       |                  |

| Chap                                           | oter 6                              | Application of the RTSs for QRNG source9                              | 4                |

| <b>Chap</b><br>6.1                             |                                     | Application of the RTSs for QRNG source                               |                  |

| •                                              | Intro                               |                                                                       | 4                |

| 6.1                                            | Intro<br>Devi                       | oduction                                                              | 4<br>4           |

| 6.1<br>6.2                                     | Intro<br>Devi<br>Mea                | oduction                                                              | 4<br>4<br>5      |

| 6.1<br>6.2<br>6.3                              | Intro<br>Devi<br>Mea<br>Rano        | oduction                                                              | 4<br>5<br>7      |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5                | Intro<br>Devi<br>Mea<br>Rano<br>Sum | oduction                                                              | 4<br>4<br>7<br>9 |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br><b>Chap</b> | Intro<br>Devi<br>Mea<br>Rano<br>Sum | oduction                                                              | 4<br>5<br>7<br>9 |

## **Table of Tables**

| Table 1 | The comparison of the features between this work and the existing optical |   |

|---------|---------------------------------------------------------------------------|---|

|         | QRNGs.                                                                    | 4 |

# **Table of Figures**

| Figure 2.1 The str  | ucture of the triple gates silicon nanowire transistor13                                  |

|---------------------|-------------------------------------------------------------------------------------------|

| Figure 3.1 Device   | layout in the optical microscope. The core of the device was located in the               |

| 1                   | niddle with 4 metal pads connected. From left to right, they were Gate, Source,           |

| i                   | Drain and Bulk electrodes15                                                               |

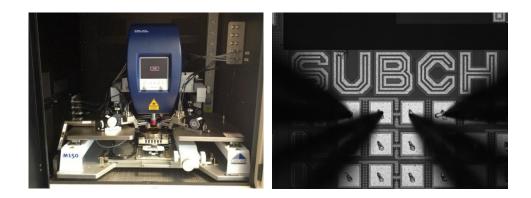

| Figure 3.2 (Left) N | MEMS prober station with all high-quality triaxial cables feedthrough setting.            |

| (                   | (Right) Cascade highly reliable probe connecting with device16                            |

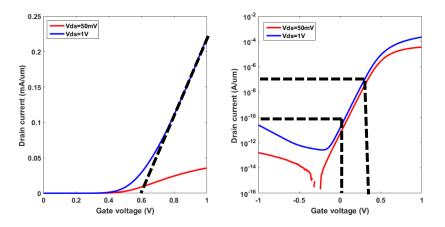

| Figure 3.3 Drain o  | current with gate voltage dependence, drain voltage (Vds) was set to 50mV and             |

| -                   | <i>IV: (Left) Linear scale to investigate the threshold voltage. (Right) Log scale to</i> |

| 1                   | investigate the subthreshold slope16                                                      |

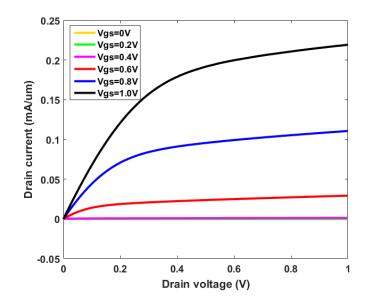

| Figure 3.4 Drain    | current with drain voltage dependence. Gate voltage (Vgs) was set to 0V, 0.2V,            |

| (                   | 0.4V, 0.6V, 0.8V and 1V17                                                                 |

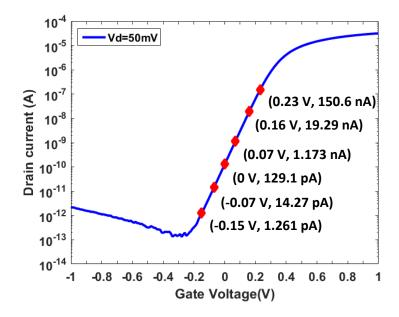

| Figure 3.5 Drain    | current with gate voltage dependence. Drain voltage $(V_D)$ was set to 50mV. The          |

|                     | Sex selected points were marked as red diamonds, which represented the $I_D$ in 1         |

| l                   | pA, 10 pA, 100 pA, 1 nA, 10 nA, and 100 nA levels                                         |

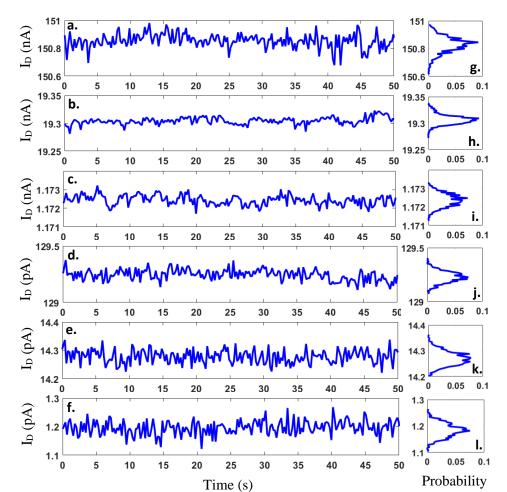

| Figure 3.6 Drain o  | current with gate voltage dependence. Drain voltage $(V_D)$ was set to 50mV. The          |

| 2                   | Sex selected points were marked as red diamonds, which represented the $I_D$ in           |

|                     | l pA, 10 pA, 100 pA, 1 nA, 10 nA and 100 nA levels. (a-f)The time domain                  |

| 1                   | neasurement results with the first 50s. (g-l)The probability distribution of the $I_D$ .  |

|                     |                                                                                           |

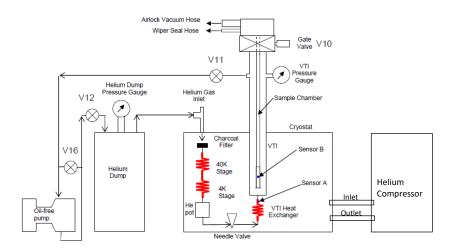

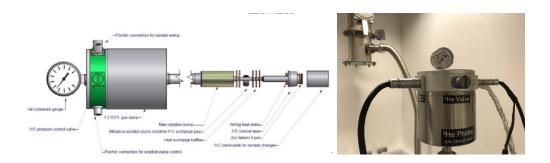

| Figure 3.7 The cry  | vogen-free high field measurement system20                                                |

| Figure 3.8 The scl  | nematic structure of the cryogen-free high field measurement system21                     |

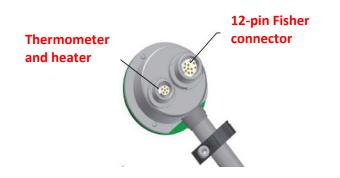

| Figure 3.9 (Left) The schematic structure of the He-3 insert. (Right) He-3 insert with electrical        |

|----------------------------------------------------------------------------------------------------------|

| connections                                                                                              |

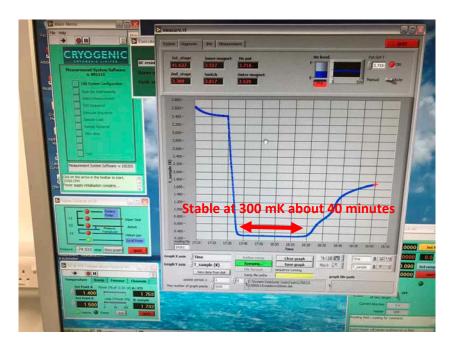

| Figure 3.10 The performance of the He-3 insert. The lowest temperature was 298 mK. It can be             |

| stable around 40 minutes from 17:37 to 18:18                                                             |

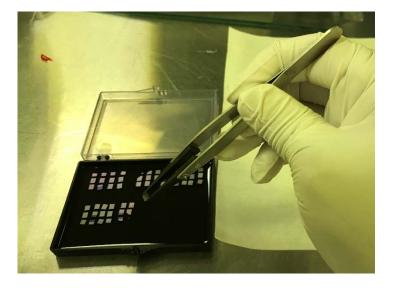

| Figure 3.11 Maximum 3mm* 5mm small chips after dicing. The cleaned samples were stored in a              |

| jelly sample box23                                                                                       |

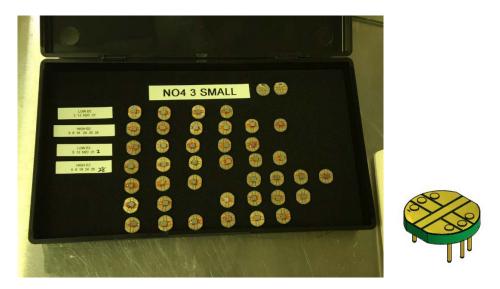

| Figure 3.12 The MOSFETs samples mounted to a 6-pin chip carrier with a yellow no-conductive              |

| <i>epoxy</i>                                                                                             |

| Figure 3.13 The optical microscope view of the sample which was mounted and successfully                 |

| bonded to a 6-pin chip carrier with 4 gold wires24                                                       |

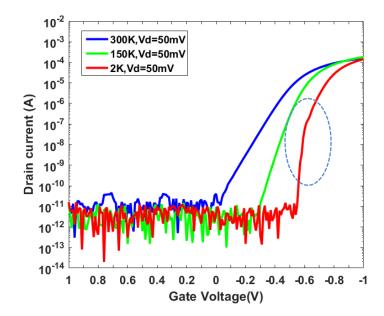

| Figure 3.14 Drain current with gate voltage dependence for the pMOSFET (10 $\mu$ m long and 75 nm        |

| wide). $V_D$ was set to 50mV to make a stable measurement temperature 25                                 |

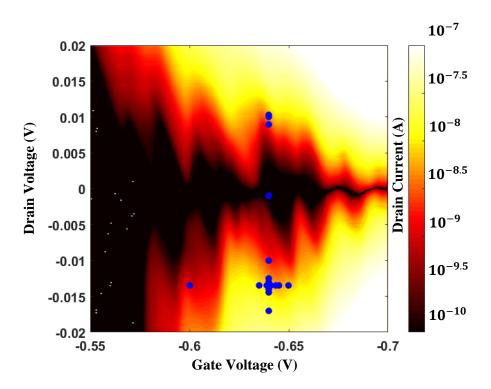

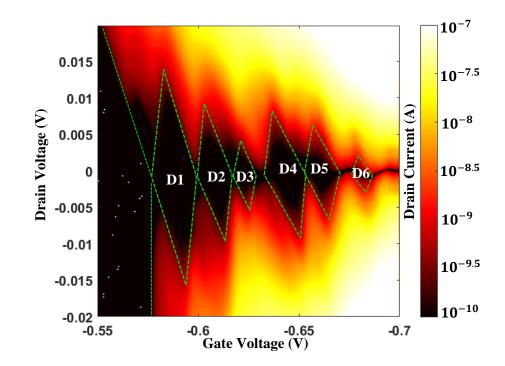

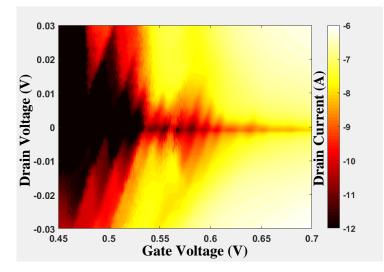

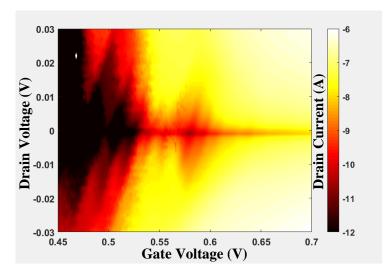

| Figure 3.15 The contour plot for drain current versus gate voltage and drain voltage of the              |

| pMOSFET at 2K. The bluepoints were selected conditions to extract the gate                               |

| voltage and drain voltage. Then the RTSs time-domain measurement was carried                             |

| on the voltage conditions of these points. The results were shown in Figure 3.18-                        |

| <i>3.20 and 3.22-3.24</i> <b>26</b>                                                                      |

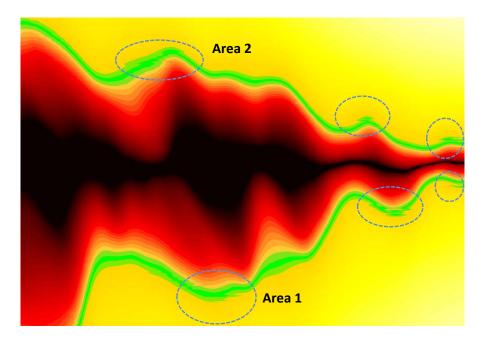

| Figure 3.16 Horizontal peaks happened at the edges of the Coulomb diamond areas27                        |

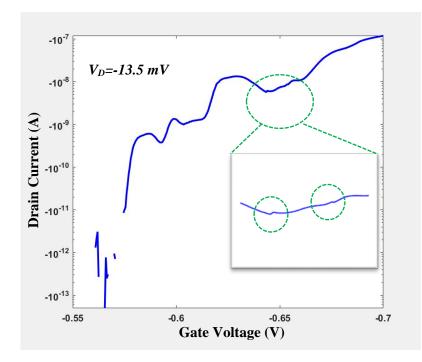

| Figure 3.17 One $I_DV_G$ curve ( $V_D$ =-13.5 mV) extracted from Figure 3.15. The step changes of the    |

| current can be found around $V_G$ =-0.65 V (In the Area 1 of Figure 3.16)27                              |

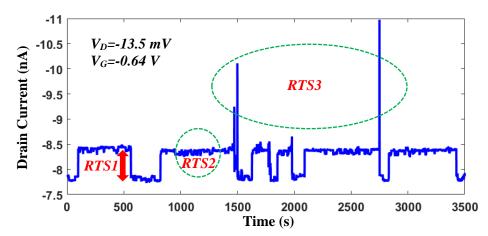

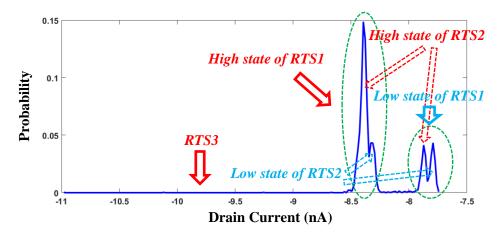

| Figure 3.18 The time-domain measurement of $I_D$ with the bias condition of $V_D$ =-13.5 mV and $V_G$ =- |

| 0.64 V. Three types of RTSs were found                                                                   |

xii

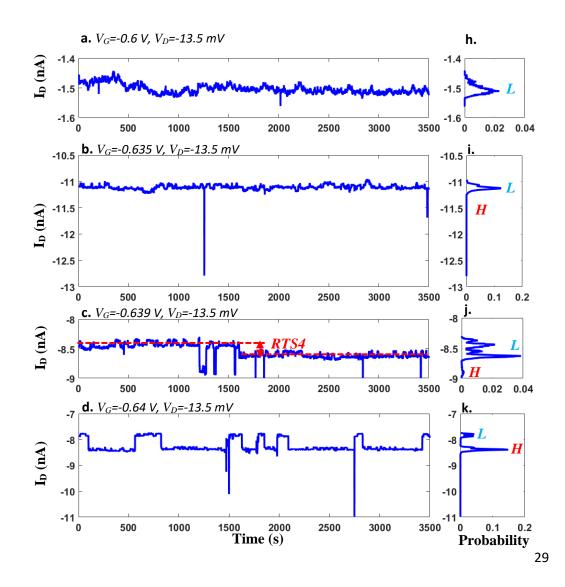

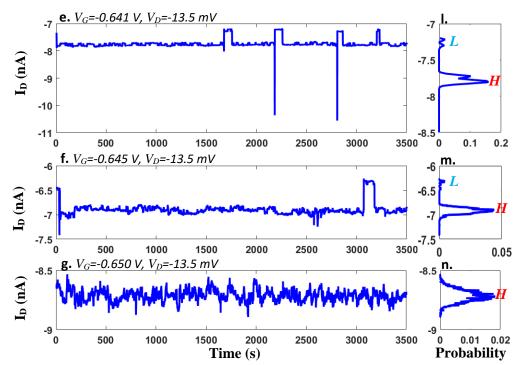

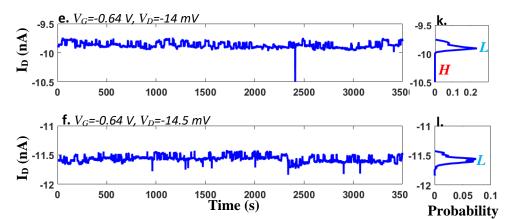

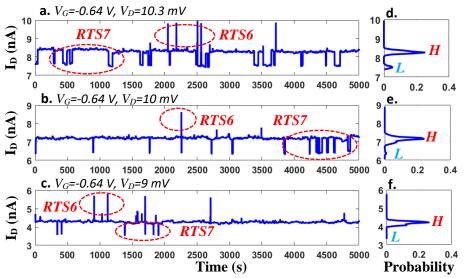

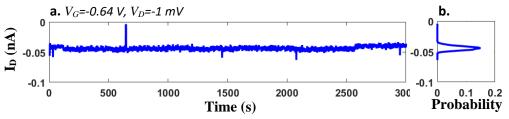

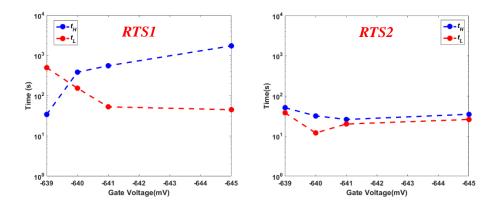

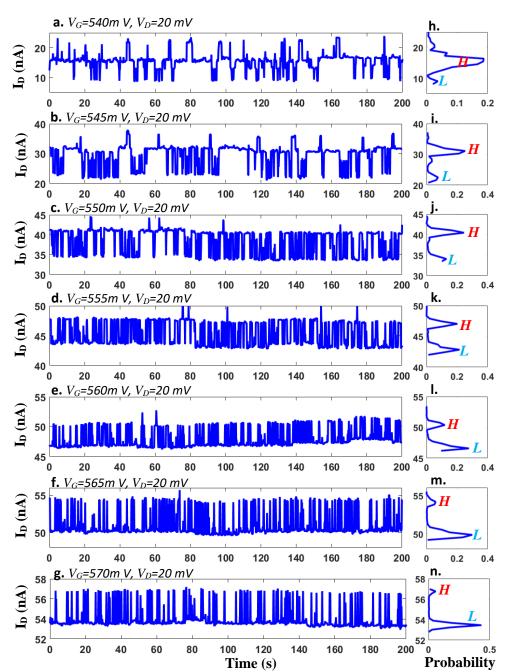

- Figure 3.19 (a-g) The time-domain measurement results of the V<sub>G</sub> dependence for the RTSs. (h-n) The probability distribution of the current versus its valve. The high state of RTS1 was marked as red "H"; the low state of RTS1 was marked as blue "L". .....30

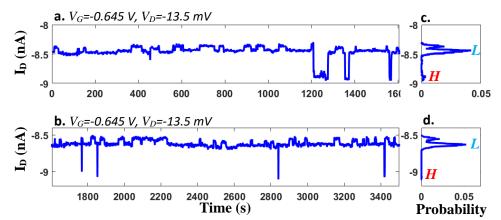

- Figure 3.20 The time-domain measurement results in Figure 3.19 (c) were divided into (a) (from 0 to 1605s) and (b) (from 1605s to 3500s).of the V<sub>G</sub> dependence for the RTSs. (c,d)

The probability distribution of the current versus its valve. The high state of RTS1 was marked as red "H"; the low state of RTS1 was marked as blue "L". .....31

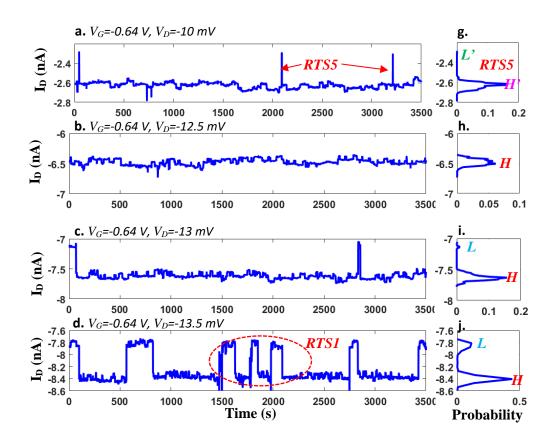

- Figure 3.22 (b-f) The time-domain measurement results of the V<sub>D</sub> dependence for the RTSs. (h-l)

The probability distribution of the current versus its valve. The high state of RTS1 was marked as red "H"; the low state of RTS1 was marked as blue "L". (a,g)

The RTS5 appeared. The high state of the RTS5 was marked as red "H'"; the low state of the RTS5 was marked as red "H". 33

- Figure 3.25 The contour plot for drain current versus gate voltage and drain voltage of the pMOSFET at 2K......35

- *Figure 3.26 The equivalent circuit model for the single hole transistor.......*36

- Figure 3.27 (a) The schematic diagram for the structure model of the device. The quantum dot was formed by the remote Poly-Si grains. (b) The band structure diagram in the

| channel. The $E_f$ was the Fermi energy level. The $E_{VB}$ was the valence band energ                      |

|-------------------------------------------------------------------------------------------------------------|

| level                                                                                                       |

| Figure 3.28 The schematic diagram for the structure model of the device. Many different quantum             |

| dots were formed by the randomly distributed Poly-Si grains                                                 |

| Figure 3.29 The average high-state current ( $\tau H$ ) and the average low-state current ( $\tau L$ ) as a |

| function of gate voltage for the RTS1 and RTS2                                                              |

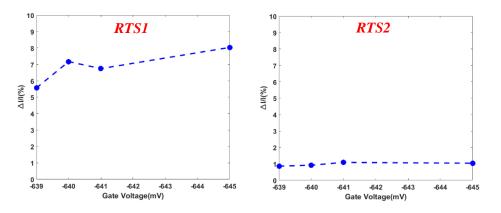

| Figure 3.30 The $\Delta I/I$ as a function of gate voltage for the RTS1 and RTS2                            |

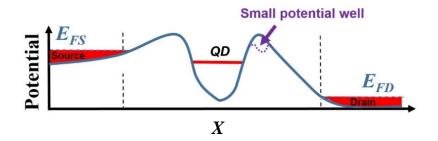

| Figure 3.31 The physical model to explain the original source to form the RTS1 and RTS2 40                  |

| Figure 3.32 The schematic diagram of the potential in the channel cross-section from source to              |

| <i>drain</i>                                                                                                |

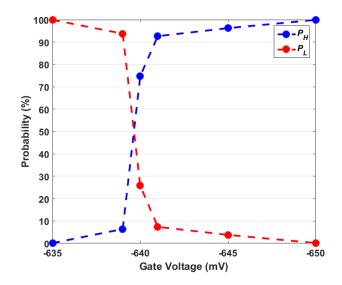

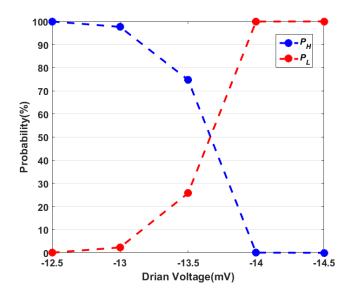

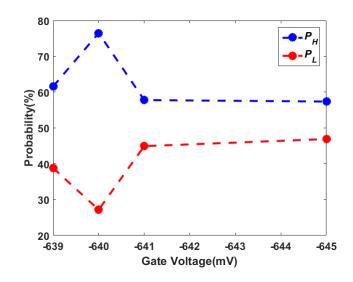

| Figure 3.33 The $V_G$ dependence of $P_H$ and $P_L$ in RTS1. $V_D$ bias was -13.5 mV                        |

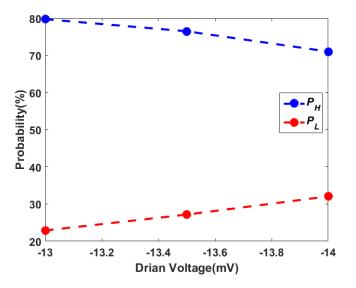

| Figure 3.34 The $V_D$ dependence of $P_H$ and $P_L$ in RTS1. $V_G$ bias was -640 mV                         |

| Figure 3.35 The potential diagram with the hole trapping and de-trapping from the oxide layer to            |

| the gate electrode                                                                                          |

| Figure 3.36 The $V_G$ dependence of $P_H$ and $P_L$ in RTS2. $V_D$ bias was -13.5 mV                        |

| Figure 3.37 The $V_D$ dependence of $P_H$ and $P_L$ in RTS2. $V_G$ bias was -640 mV                         |

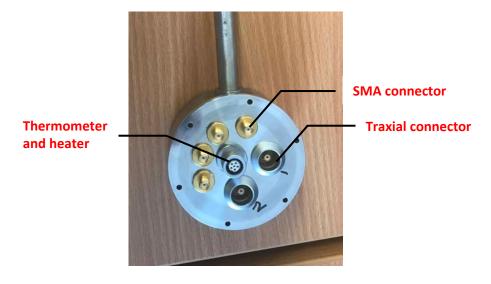

| Figure 3.38 New "Break-out" box with full metal shield                                                      |

| Figure 3.39 The original connection panel layout with all singles mixed in one 12-pin Fisher connector[134] |

| Figure 3.40 The modified connection panel layout with 4-SMA connectors and 2-triaxial                       |

connectors to separate the singles by independent guarding and shielding...47

| Figure 3.41 (Left) T | The original chip o | carrier mo | unted tube | , which  | could moi | ınt 2 chip | carriers a | <i>it the</i> |

|----------------------|---------------------|------------|------------|----------|-----------|------------|------------|---------------|

| sa                   | me time. (Right)    | The re-des | igned chip | carrier  | mounted   | tube, whic | ch only ha | d 2           |

| ch                   | nip carrier positio | n, but low | noise leve | <i>l</i> |           |            | 4          | 17            |

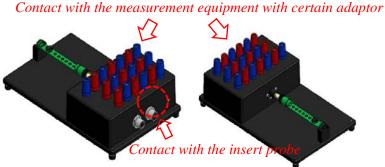

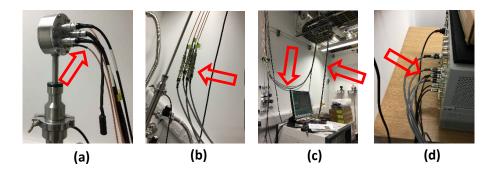

| Figure 3.42 (a) 4 | SMA cables and 2 triaxial cables making the electrical connection between the    |

|-------------------|----------------------------------------------------------------------------------|

|                   | insert probe and outside equipment. (b) SMA cables connecting to triaxial cables |

|                   | by guard disconnected adaptors. (c) The long triaxial cables through the ceiling |

|                   | to reach the Agilent B1500. (d) Triaxial cables connecting with Agilent B1500    |

|                   | SMU ports                                                                        |

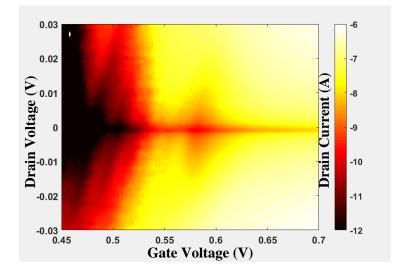

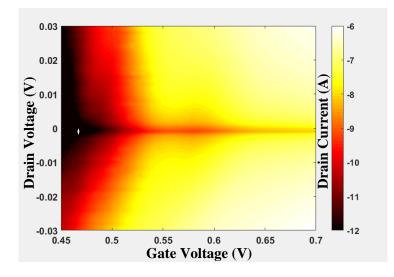

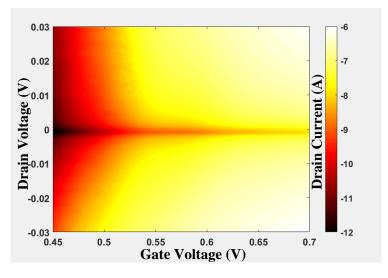

| Figure 3.44 The contour plot for $I_D$ versus $V_G$ and $T$ | $V_D$ of the nMOS at 10K49 |

|-------------------------------------------------------------|----------------------------|

|-------------------------------------------------------------|----------------------------|

| Figure 3.45 The contour plot for $I_D$ versus $V_G$ and $V_D$ of the nMOS at 20K | 50 |

|----------------------------------------------------------------------------------|----|

Figure 3.47 The contour plot for  $I_D$  versus  $V_G$  and  $V_D$  of the nMOS at 60K......50

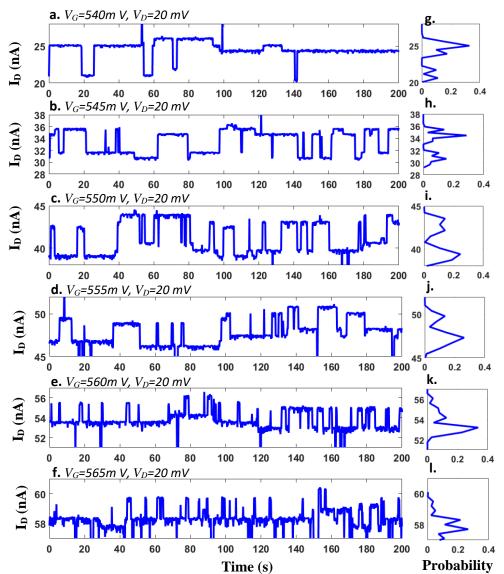

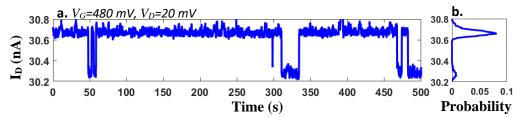

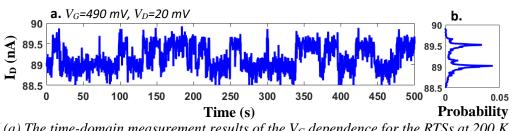

Figure 3.48 (a-g) The time-domain measurement results of the V<sub>G</sub> dependence for the RTSs at 10

K. (h-n) The probability distribution of the current versus its valve. The high state of RTS was marked as red "H"; the low state of RTS was marked as blue "L".52

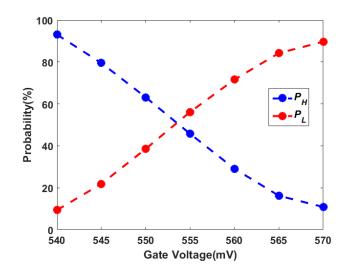

| Figure 3.49 The $V_G$ dependence of $P_H$ and $P_L$ in RTSs. $V_D$ bias was 20 mV                   |

|-----------------------------------------------------------------------------------------------------|

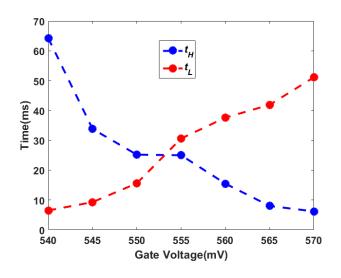

| Figure 3.50 The $\tau$ H and the $\tau$ L as a function of gate voltage for the RTS54               |

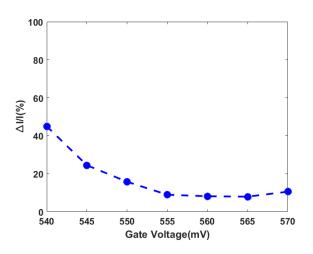

| Figure 3.51 The $\Delta I/I$ as a function of gate voltage for the RTS                              |

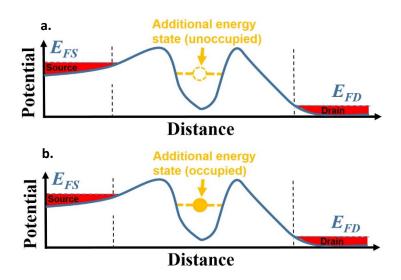

| Figure 3.52 The physical model of the RTS. (a) The unoccupied state of the additional energy state. |

- Figure 3.53 (a-f) The time-domain measurement results of the V<sub>G</sub> dependence for the RTSs at 40 K.

(g-l) The probability distribution of the current versus its valve. The high state of RTS was marked as red "H"; the low state of RTS was marked as blue "L".56

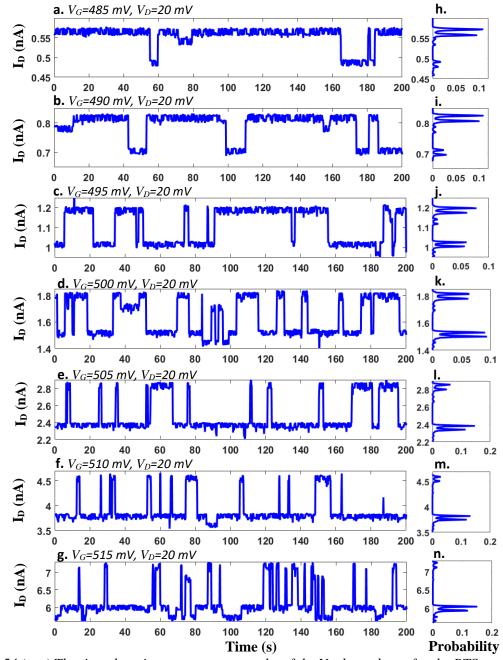

- Figure 3.54 (a-g) The time-domain measurement results of the V<sub>G</sub> dependence for the RTSs at 60

K. (h-n) The probability distribution of the current versus its valve. The high state of RTS was marked as red "H"; the low state of RTS was marked as blue "L".57

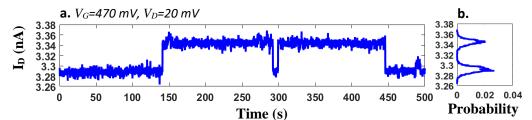

- Figure 3.55 (a) The time-domain measurement results of the V<sub>G</sub> dependence for the RTSs at 100 K.

(b) The probability distribution of the current versus its valve. The high state of RTS was marked as red "H"; the low state of RTS was marked as blue "L".58

- Figure 3.56 (a) The time-domain measurement results of the V<sub>G</sub> dependence for the RTSs at 150 K.

(b) The probability distribution of the current versus its valve. The high state of RTS was marked as red "H"; the low state of RTS was marked as blue "L".58

- Figure 3.57 (a) The time-domain measurement results of the V<sub>G</sub> dependence for the RTSs at 200 K.

(b) The probability distribution of the current versus its valve. The high state of RTS was marked as red "H"; the low state of RTS was marked as blue "L".59

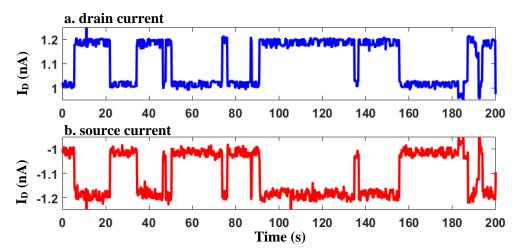

| Figure 3.58 The comparison of the $I_D$ and $I_S$ of the RTS at the same time scale. (a) The $I_D$ time- |

|----------------------------------------------------------------------------------------------------------|

| domain measurement results of the $V_G$ dependence for the RTS (b) The $I_S$ time-                       |

| domain measurement results of the $V_G$ dependence for the RTS59                                         |

| Figure 4.1 The fabrication process flow chart62                                                          |

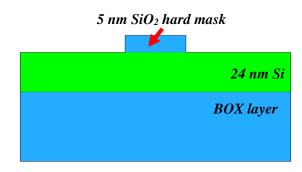

| Figure 4.2 Schematic diagram after E-beam lithography63                                                  |

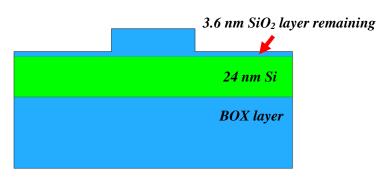

| Figure 4.3 Schematic diagram after RIE63                                                                 |

| Figure 4.4 Schematic diagram after HF etching63                                                          |

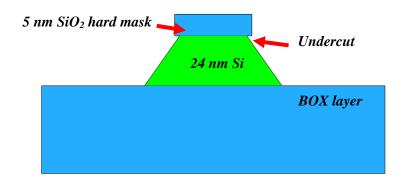

| Figure 4.5 Schematic diagram after TMAH etching and undercut part                                        |

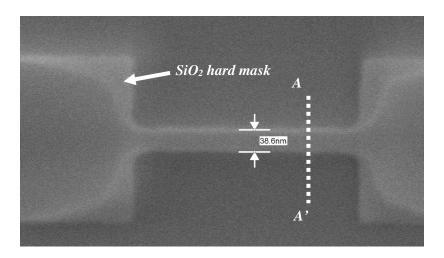

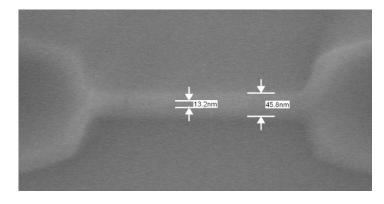

| Figure 4.6 SEM view of the nanowire after TMAH etching64                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.7 SEM view of the nanowire after removing the hard mask65                                                                                                          |

| Figure 4.8 The nanowire dimensions from the TCAD simulation (HSQ mask: 30 nm)65                                                                                             |

| Figure 4.9 The nanowire dimensions from the TCAD simulation (HSQ mask: 50 nm)65                                                                                             |

| Figure 4.10 The nanowire dimensions from the TCAD simulation (HSQ mask: 75 nm)66                                                                                            |

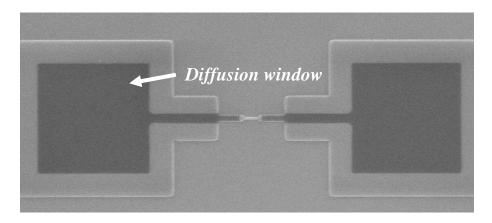

| Figure 4.11 SEM image for the diffusion windows location66                                                                                                                  |

| Figure 4.12 Schematic diagram after depositing the Poly-Si layer67                                                                                                          |

| Figure 4.13 Schematic diagram after ICP etching67                                                                                                                           |

| Figure 4.14 SEM image after ICP etching68                                                                                                                                   |

| Figure 4.15 Schematic diagram after patterning the Top gate68                                                                                                               |

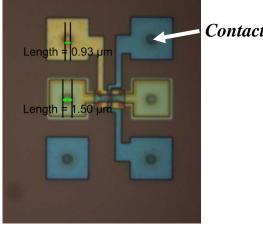

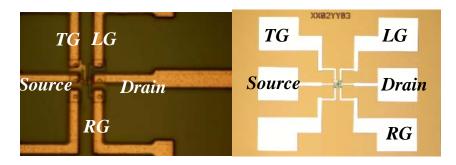

| Figure 4.16 Optical image after patterning the Top gate69                                                                                                                   |

| Figure 4.17 Optical image for the contact windows                                                                                                                           |

| Figure 4.18 (Left) Optical image for the metal contact. (Right) Optical image for one device70                                                                              |

| Figure 4.19 Optical image for the damaged metal layer70                                                                                                                     |

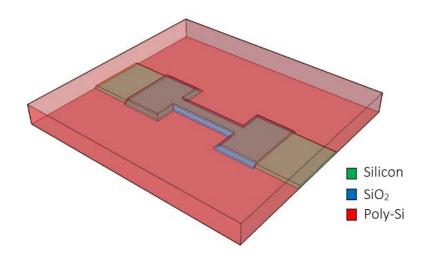

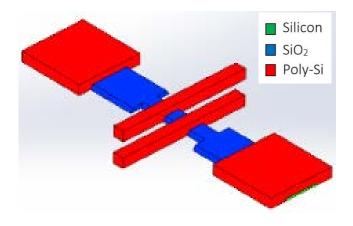

| Figure 4.20 The schematic diagram of the silicon nanowire transistor and the layer structure.71                                                                             |

| Figure 4.21 The optical image of the silicon nanowire transistor71                                                                                                          |

| Figure 4.22 (a) The planar view of the device region. (b) The planar view of nanowire region. (c)<br>The energy spectrum in $AA*$ direction (blue dash line) (d) The energy |

| The cross-sectional view in AA* direction (blue dash line). (d) The cross-                                                                                                  |

| sectional view in BB* direction (yellow dash line)                                                                                                                          |

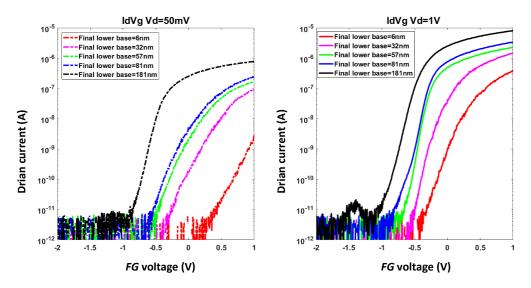

| Figure 4.23 Drain current versus First gate voltage characteristics on drain voltage at 50mV and                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1V with different channel width73                                                                                                                                                                                             |

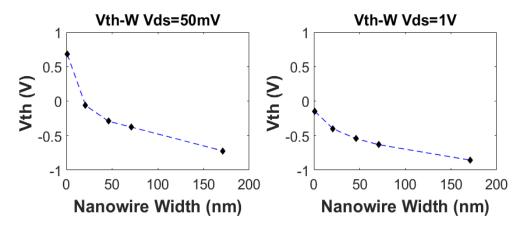

| Figure 4.24 Threshold voltage of the silicon nanowire transistors with different width73                                                                                                                                      |

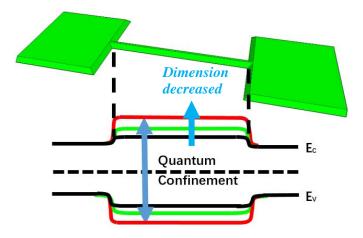

| Figure 4.25 Quantum confinement in the smaller dimensional silicon devices                                                                                                                                                    |

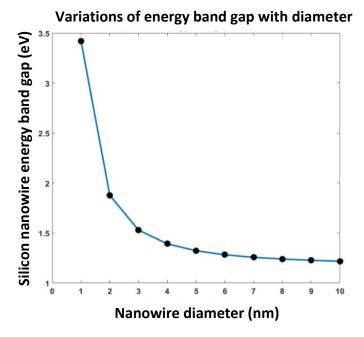

| Figure 4.26 The diameter dependence of the energy bandgap in a silicon nanowire by fitting the results from the literature                                                                                                    |

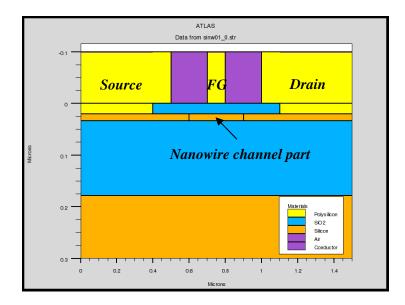

| Figure 4.27 2D transistor model in TCAD77                                                                                                                                                                                     |

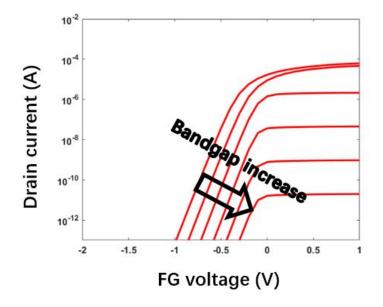

| Figure 4.28 $I_D$ versus $V_{FG}$ characteristics on $V_D=50$ mV with different bandgaps and affinity78                                                                                                                       |

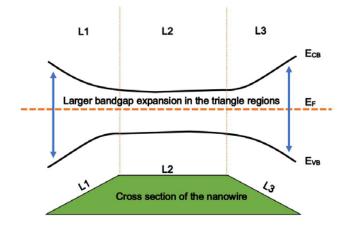

| Figure 4.29 The schematic diagram to show the bandgap expansion in different part of the nanowire channel from the cross section of view                                                                                      |

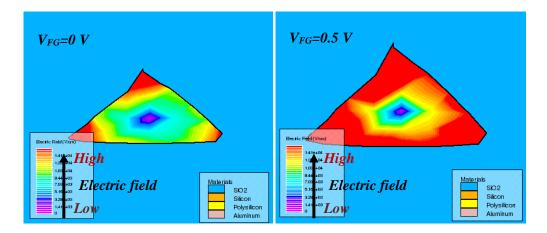

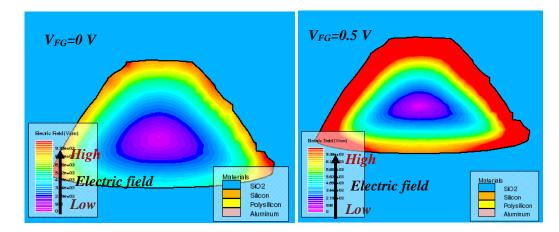

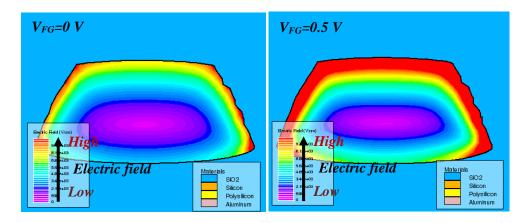

| Figure 4.30 The electric field distribution in the cross section of the nanowire from the TCAD simulation (HSQ mask: 30 nm). In the left, $V_{FG}=0$ V. In the right, $V_{FG}=0.5$ V79                                        |

| Figure 4.31 The electric field distribution in the cross section of the nanowire from the TCAD simulation (HSQ mask: 50 nm). In the left, $V_{FG}=0$ V. In the right, $V_{FG}=0.5$ V79                                        |

| Figure 4.32 The electric field distribution in the cross-section of the nanowire from the TCAD simulation (HSQ mask: 75 nm). In the left, $V_{FG}=0$ V. In the right, $V_{FG}=0.5$ V80                                        |

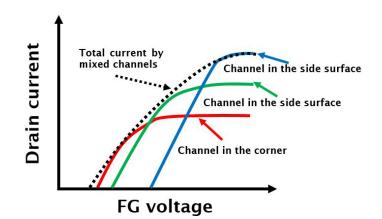

| Figure 4.33 The multi-channel transport model to explain the SS degradation                                                                                                                                                   |

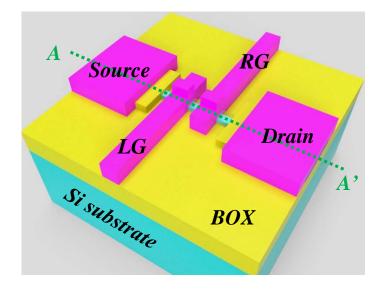

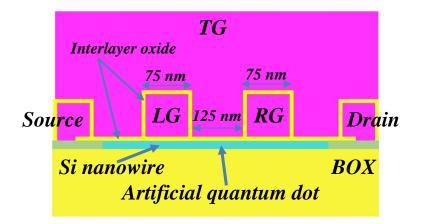

| Figure 5.1 The 3D schematic structure of the device. TG was not shown [142]                                                                                                                                                   |

| Figure 5.2 The cross section of view from AA' direction in Figure 5.1[142]84                                                                                                                                                  |

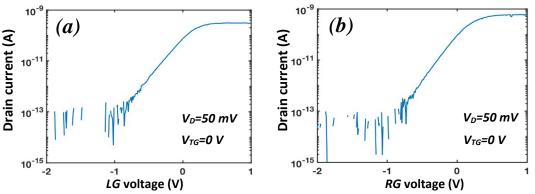

| Figure 5.3 (a)The $I_D$ versus $V_{LG}$ characteristics with $V_{TG}=0$ V and $V_{RG}$ floating at $V_D=50$ mV. (b)<br>The $I_D$ versus $V_{RG}$ characteristics with $V_{TG}=0$ V and $V_{LG}$ floating at $V_D=50$ mV [142] |

xviii

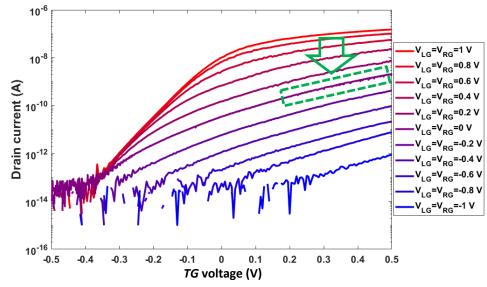

| Figure 5.4 (a) The $I_D$ versus | $V_{TG}$ characteristics with different | ent $V_{LG} = V_{RG}$ at $V_D = 3$ | 50 mV in log scale |

|---------------------------------|-----------------------------------------|------------------------------------|--------------------|

| [142]                           |                                         |                                    | 85                 |

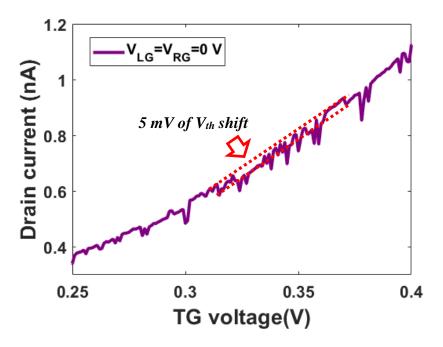

Figure 5.5 The marked area in Figure 5.4 where the RTSs could be observed [142]......86

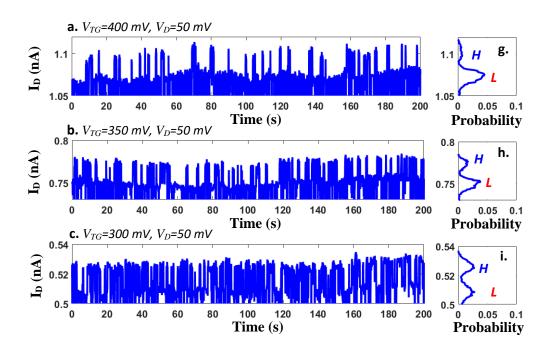

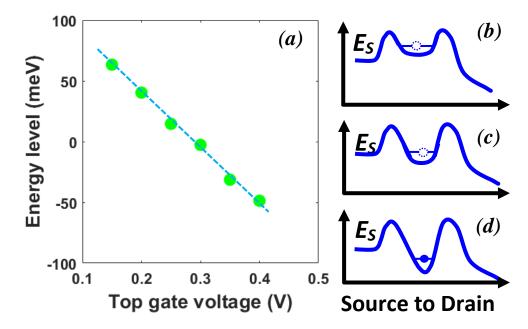

Figure 5.6 (a-f) The time-domain measurements on  $V_{TG}$  dependence with  $V_{LG}=V_{RG}=0$  V and  $V_D=50$  mV. (g-l) The corresponding probability distribution of the  $I_D$  [142]......87

Figure 5.8 (a) The  $\tau$ H and  $\tau$ L with the  $V_{TG}$  dependence. (b) The ratio of the  $\tau$ H $\tau$ L with the  $V_{TG}$  dependence in the log scale by a linear fitting [142]......88

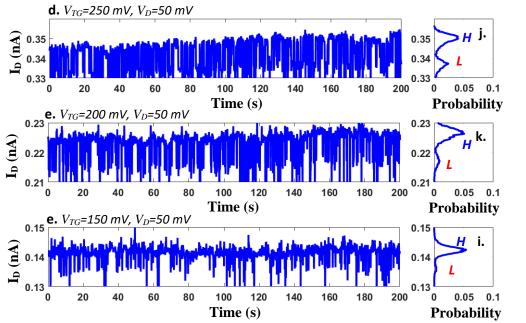

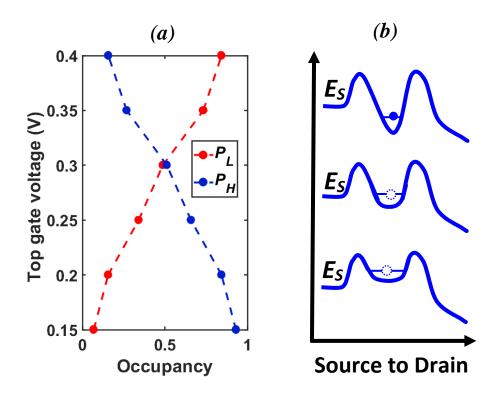

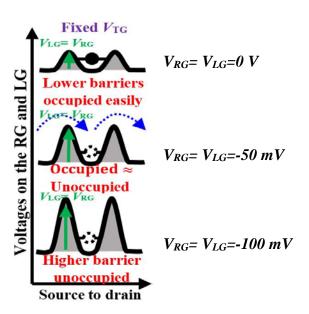

Figure 5.9 (a) The energy level of the quantum dot on the V<sub>TG</sub>. The dash line was the linear fitting for the extracted points from the measurement results. (b-d) The schematic diagram of the energy level in the quantum with different V<sub>TG</sub> bias [142].....89

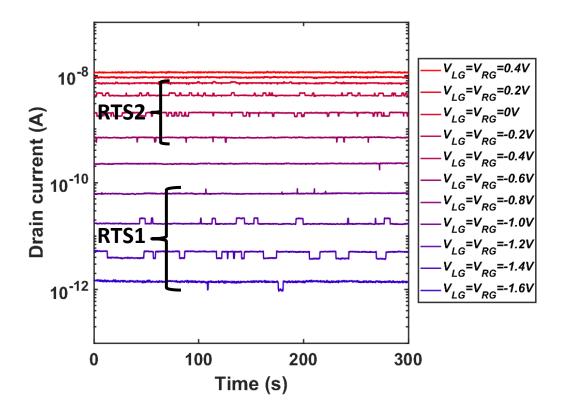

Figure 5.10 The time-domain measurement results on  $V_{LG}=V_{RG}$  dependence with  $V_{TG}=50$  mV and  $V_D=50$  mV [142].....90

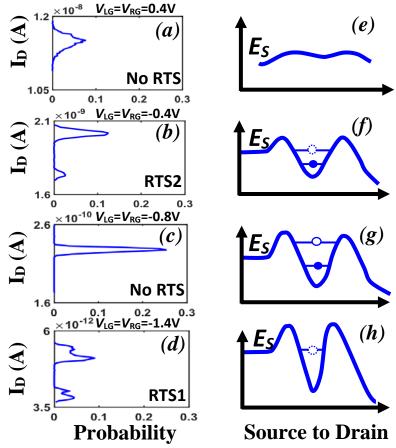

Figure 5.11 (a-d) The typical probability distribution of the  $I_D$  in the selected  $V_{LG}=V_{RG}$  bias condition. (e-f) The schematic diagram of the different energy levels in the quantum dot corresponding to (a-d) [142]......91

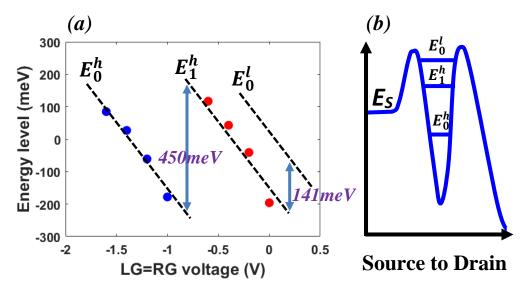

Figure 5.13 (a) The energy level of the quantum dot with different First gates voltage. The filled circles and squares were extracted from the measurement data for RTS1 and RTS2 respectively. The lines were the linear fitting for the different energy level (E0h, E1h and E0l) by the effective mass approximation [142]......92

| Figure 6.1 The structure of the triple gates silicon nanowire transistor with the atomically flat                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| interface (a) The artificial quantum dot created by TG, LG and RG bias. (b) The                                                                                                       |

| schematic diagram of the device                                                                                                                                                       |

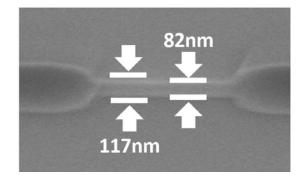

| Figure 6.2 Dimension confirmation for the nanowire after TMAH in SEM image                                                                                                            |

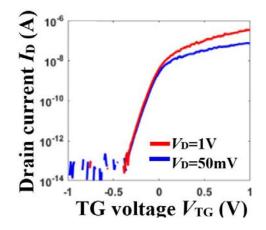

| Figure 6.3 $I_D$ - $V_{TG}$ characteristics with $V_{LG} = V_{RG} = 0V$ at $V_D = 50$ mV and 1 V                                                                                      |

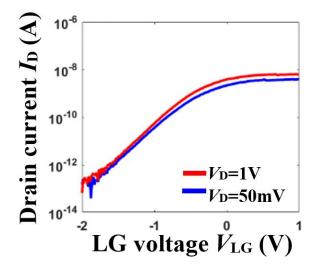

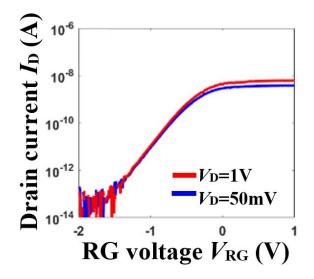

| Figure 6.4 $I_D$ - $V_{LG}$ characteristics with $V_{TG}=0$ V and $V_{RG}$ floating at $V_D=50$ mV and 1 V                                                                            |

| Figure 6.5 $I_D$ - $V_{RG}$ characteristics with $V_{TG}=0$ V and $V_{LG}$ floating at $V_D=50$ mV and 1 V                                                                            |

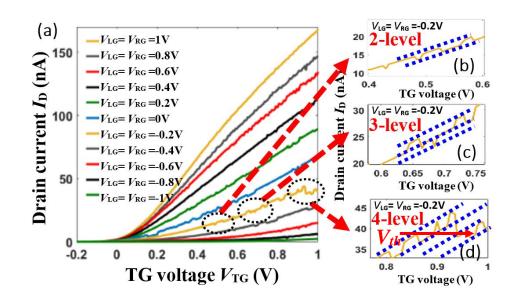

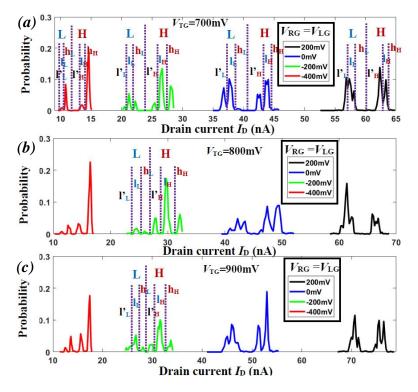

| Figure 6.6 The Multi-level RTSs observed in low, medium, and high $V_{TG}$ region and clearly shift the Vth in the linear region                                                      |

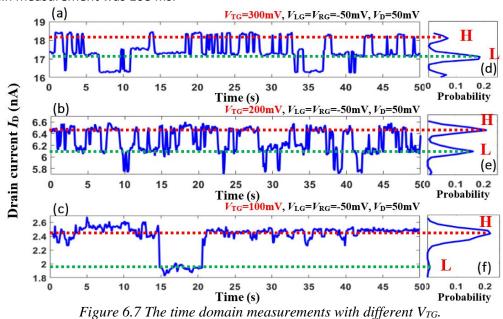

| Figure 6.7 The time domain measurements with different $V_{TG}$                                                                                                                       |

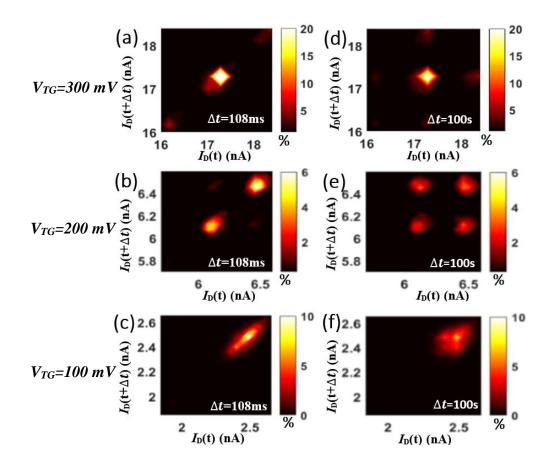

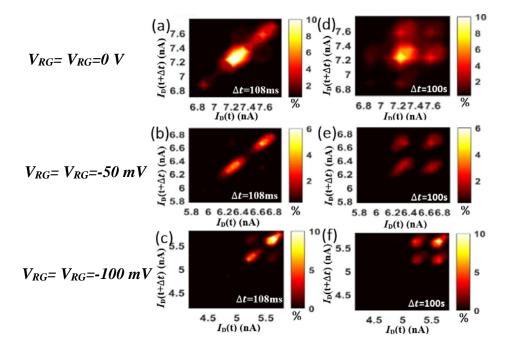

| Figure 6.8 The lag plots with time lag ( $\Delta t$ ) at 108 ms and 100 s to show the local correlation of the $I_D$ with different $V_{TG}$ bias                                     |

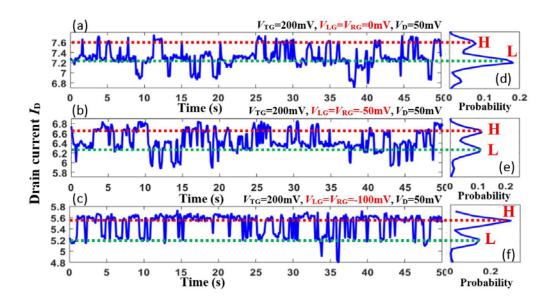

| Figure 6.9 The time domain measurements with different $V_{RG}=V_{LG}$                                                                                                                |

| Figure 6.10 The schematic diagram of the energy level in the quantum dot100                                                                                                           |

| Figure 6.11 The lag plots with time lag ( $\Delta t$ ) at 108 ms and 100 s to show the local correlation of<br>the $I_D$ with different $V_{RG}=V_{LG}$ bias                          |

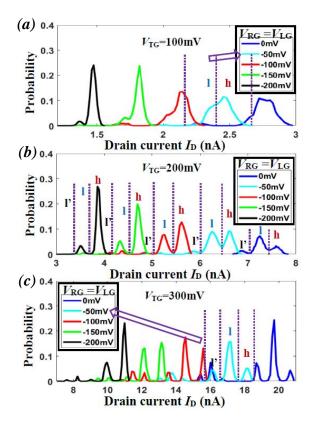

| Figure 6.12 The variation tendency of probability distribution of $I_D$ in "high (h)" and "low (l)"<br>states with $V_{LG} = V_{RG}$ from 50 mV to -200 mV in the low $V_{TG}$ region |

| Figure 6.13 The variation tendency of the probability distribution of $I_D$ in "High (H)" and "Low                                                                                    |

(L)" states with  $V_{LG} = V_{RG}$  from 200 mV to -400 mV in the high  $V_{TG}$  region. 102

| Figure 6.14 (a) The occupation rate of the three states on $V_{RG}=V_{LG}$ dependence with $V_{TG}=200$ mV.<br>(b)The occupation rate of the three states on $V_{TG}$ dependence with $V_{RG}=V_{LG}=-100$ mV                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

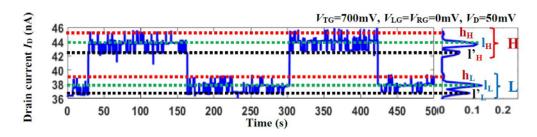

| Figure 6.15 The time-domain measurement at $V_{TG}$ =700 mV, $V_{RG}$ = $V_{LG}$ =0 V and $V_D$ =50 mV. The RTS2 was marked as "H" and "L". The RTS1 was marked as "h", "l" and "l".<br>104                                         |

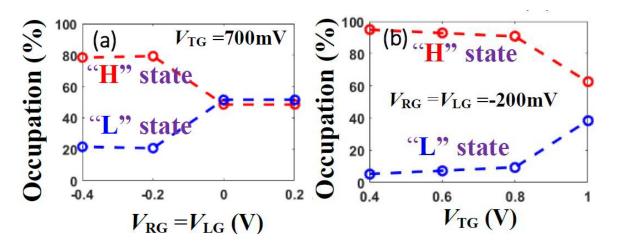

| Figure 6.16 The occupation rate of the "HIGH" (H) and "LOW" (L) state in RTS2 (a) on $V_{RG}=V_{LG}$<br>dependence with $V_{TG}=700$ mV and (b) on $V_{TG}$ dependence with $V_{RG}=V_{LG}=-200$<br>mV                              |

| Figure 6.17 The occupation rate of the "high" (h), "low" (l) and "low2" (l') states of RTS1 (a) in<br>the "HIGH" (H) state of RTS2 and (b) in the "LOW" (L) state of RTS2 on $V_{TG}$<br>dependence with $V_{RG}=V_{LG}=-200$ mV105 |

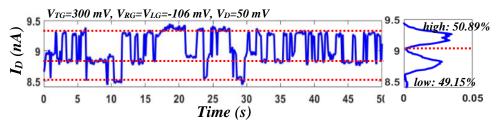

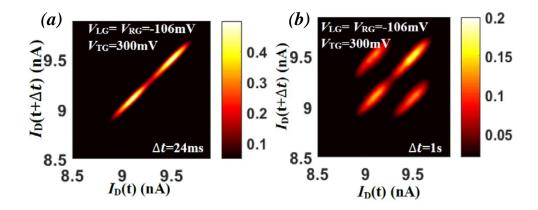

| Figure 6.18 The time-domain measurement on $V_{TG}$ =300 mV, $V_{RG}$ = $V_{LG}$ =-106 mV and $V_D$ =50 mV.<br>                                                                                                                     |

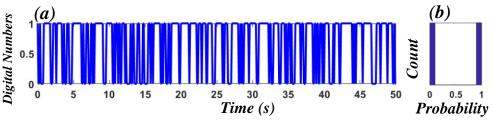

| Figure 6.19 The lag plots with time lag ( $\Delta t$ ) at (a) 24 ms and (b) 1 s to show the local correlation of the $I_D$ with a certain voltage bias                                                                              |

| Figure 6.20 (a) The 0 and 1 digital numbers extracted from the re-sampling data. (b) The number count of 0 and 1                                                                                                                    |

| Figure 6.21 (a) Self-correlation plots for 8-bit random numbers generated by our device. (b) Self-<br>correlation plots for 8-bit random numbers generated by MATLAB108                                                             |

## **Research Thesis: Declaration of Authorship**

Print name: Fayong Liu

Title of thesis: Manipulation of the Random telegraph signals for quantum random number generation

I declare that this thesis and the work presented in it are my own and have been generated by me as the result of my own original research.

I confirm that:

1. This work is based on a research project by a candidate in collaboration with researchers in the University of Southampton;

2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

3. Where I have consulted the published work of others, this is always clearly attributed;

4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

5. I have acknowledged all main sources of help;

6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

7. Parts of this work have been published as:

References [142],[143], and [154].

Signature:

Date:

xxiii

xxiv

## Acknowledgements

I would like to express my gratitude to my parents, Dr. Shaoqing Liu and Xiuping Shen, for their great financial and moral support. It was solid backing during my PhD life.

I would like to sincerely thank my supervisor, Prof. Shinichi Saito, for his great support in finance and excellent supervision both in my MSc and PhD courses. His rigorous academic attitude highly affected my self-improvement. He is not only an academic supervisor but also my career mentor.

I also would like to sincerely thank my second supervisor, Dr. Yoshishige Tsuchiya, for his full support in the experimental activities. His valuable experience helped me establish the standard methodology in the high-quality measurement in Nanoelectronics.

I also would like to sincerely thank Prof. Harvey Rutt, Dr. Jonathan Fletcher, Dr. Stephen Giblin and Dr. Masaya Kataoka for their creative support to help me establish the low-temperature and high-frequency measurement systems.

I also would like to sincerely thank Mr. Mark R. Long and Mr. James C. Chalk for their full support in the Mechanical Workshop.

I also would like to sincerely thank Dr. Muhammad K. Husain and Dr. Zuo Li for their hard work and help in the device fabrication.

I also would like to sincerely thank all the members of the Sustainable Electronics and Technology group for their help and advice, and all the technicians in the Southampton Nanofabrication Centre for their help and training.

I would like to appreciate all other colleagues, Dr. Abdelrahman Z. R. Al-Attili, Dr. Kapil Debnath, Dr. Yichi Zhang, Dr. Moise Sotto, Dr. Daniel Burt, Mr. Kouta Ibukuro, Mr. James Byers, Mr. Joseph W. Hillier to build a family-like working environment to help each other and learn from each other.

### Chapter 1 Introduction

#### 1.1 Motivation

The semiconductor industry development had been guided by Moore's law in the past 50 years [1] which has promoted the continuous technological progress in computing power. Nowadays, computer-based modern communications, designs, data analysis, healthcare, and artificial intelligence (AI) computing have been used as an essential part of everyone's life. The core in a personal electronic device even has similar computing power to one of the modern supercomputer cores. After Apple iPhone XS was launched in September 2018 and AMD Radeon VII graphics card was released in January 2019, both the mobile device and the desktop computer had been announced to step into 7 nm node generation. During the time while people are enjoying the latest technology and expecting the next amazing product, designing a reliable electrical system has become increasingly difficult. With aggressively scaling the Complementary Metal-Oxide-Semiconductor (CMOS) transistors, the reliability issues have become a nightmare for semiconductor engineers. In recent researches, random telegraph signals (RTSs) had attracted so much attention from the fundamental physics researchers as well as the device engineers. When the device size was approaching the level of atoms, RTS had emerged as a source of a series of reliability and variability issues which caused the failure of device [2,3,4]. The detailed reason was that the number of activated traps at the Si/SiO2 interface or in the dielectrics was reduced to a countable number during the scaling of the Metal-Oxide-Semiconductor-Field-Effect Transistor (MOSFET) area. In this condition, the carrier transport in the scaled transistors would be influenced just by one or a few activated defects. If one or a few traps randomly influenced the current in nearly 100% amplitude, the device would lose the function as a logic element [5].

RTS was first demonstrated by Ralls *et al.* in MOSFETs with 1 um channel length and 100nm channel width in 1984 [6]. It was simply illustrated as the drain current  $I_D$  or the drain voltage  $V_D$  which was randomly switched between two levels, "high" and "low" [7]. Researchers described the current which temporally switched between two levels as the high state "high" and the low state "low". The variation between high-level and low-level currents was characterized by the switching amplitude  $\Delta I_D$ .

The fundamental physical properties of the RTS were usually interpreted as a single electron or hole captured and emitted by a trap, which fluctuated the current characteristics in orders of magnitude. In MOSFETs, these traps were usually located at the Si/SiO<sub>2</sub> interface or in the gate oxide layer [5,7], which were generated in the fabrication processes. Engineers had tried some strategies to suppress

#### Chapter 1

the effect of the RTSs both in the process-level and in the circuit-level. For example, by changing the dielectric materials in the fabrication process, the oxide interface trap density for the nonnitrided transistors was one order of magnitude lower than the nitrided devices [8]. In the circuit level, by using the correlated multiple sampling differential averaging (CSMDA) technique, the RTS and thermal noise could be effectively reduced [9]. However, the CSMDA technique was not so effective for the multi-level RTSs. Actually, the charged trap could never be eliminated completely from the view of fundamental physics. Then it led a paradigm shift from fighting with the RTSs to utilizing the RTSs phenomenon.

The discrete nature of RTS provided a unique way to investigate the single-electron phenomenon caused by activated traps in the semiconductor devices. Researchers can not only extract the properties of the traps such as the energy level and capture cross-section [5], but also derive their physical position such as the trap depth and lateral position in the channel [5]. From the application perspective, the "high and "low" states of the RTSs provided the essential element for a quantum random number generator (QRNG) source, in which the switching behavior was dominated by the pure quantum mechanics. From the previous study of the RTSs [10,11,12], it had been shown that the capture and emission time had a strong dependence on the voltage bias, which gave a way to make an unbiased "high" and "low" states. In principle, the RTSs could be a promising candidate as a QRNG source.

The QRNGs produced random numbers with pure quantum mechanical effects [13]. A random number should be unpredictable and cannot be reproduced. Random numbers were the foundational element for information security and they built the blocks of encryption, key wrapping, signing, one-time codes, authentication, and other cryptographic applications [14]. Random numbers were also essential elements for computer assistant modeling and modern digital gaming or lottery. There is no doubt that the quality of the random numbers had a fatal impact on modern security. Attackers do not usually attempt to crack encryption, they simply steal or guess keys. The digital keys generated by the poor quality random numbers would be much easier to be cracked by the attackers. Comparing with the classical random number generators [15-18], the QRNGs delivered the higher quality random number due to their intrinsic randomness from the quantum physical processes.

Some commercial QRNGs products had been available in the market [19-24] and most of them were based on optical quantum phenomena. Today's technology had provided a broad range of choices for both the light source and the precise detectors [25-27]. However, as long as the QRNGs were based on the optical quantum effects, the common issues such as unbalanced detectors [28], detector dead time [28-30], time precision [29], photon resolving capability [30], source instability [31] and so on, could not be avoided. In addition, it increased the difficulty of integrating the QRNGs into the VLSI circuit while the light source was needed. According to most of the commercial QRNGs outputting random numbers by the USB link as an independent component, the discrete QRNG devices from the motherboard or central processing unit (CPU) would increase the risk that the attackers might modify the random numbers in the software level.

The QRNGs based on the RTSs would avoid the common issues of the optical QRNGs without using any light source and detectors. As the RTSs could be generated by the standard MOSFETs, it could be easily integrated into the VLSI design to form a private communication environment between the QRNGs and the logical units which provided a new way to enhance the security level at the hardware layer. However, there were few proposals for QRNG based on the RTSs demonstrated in the past decade years. The main reason was that the traps were randomly generated in the devices and the standard statistical investigation was quite time-consuming [32-37]. A certain RTSs source was highly demanded to develop toward the application of QRNGs.

#### 1.2 Aim

The aim of this PhD project was to develop a RTS source with an artificial quantum dot in multi-gate silicon nanowire transistors. To achieve the final aim, the standard MOSFETs needed to be measured at different temperatures to investigate the fundamental physics of the RTS phenomenon and establish the characterization method to identify the RTSs. Based on the established method, the multi-gate silicon nanowire transistors needed to be designed and fabricated by collaborating with the senior researchers. Then the RTSs from the artificial quantum dot needed to be evaluated whether it could be a candidate as a QRNG source or not from the perspective of the fundamental physics.

#### **1.3** Outline of the thesis

In chapter 2, the development of the QRNGs and the research progress in the RTS phenomenology were reviewed. Based on the different kinds of quantum effect phenomena, the advantages and challenges of the existing QRNGs were summarised. Then the design concept of the QRNG based on the RTSs was pointed out.

In chapter 3, the RTSs in the conventional MOSFETs were measured at different temperatures with a cryostat system. In order to get the high-resolution measurement results, the cryostat was redesigned to decrease the noise level. Two types of RTSs in both of the wide-channel MOSFETs and

#### Chapter 1

narrow-channel MOSFETs were observed and investigated. The study established the theoretical basis to manipulate the RTSs in multi-gate transistor devices.

In chapter 4, the fabrication processes for the multi-gate the silicon nanowire devices were demonstrated in detail. After successfully finishing the fabrication of the devices, the transport properties of the silicon nanowires were investigated with a single gate. The quantum confinement in the special type of silicon nanowires was discussed.

In chapter 5, the main devices with the artificial quantum dot were characterized at room temperature. Not only the typical RTSs were observed in a certain bias condition, but also the probability of the "high" and "low" states could be manipulated by the multi-gate voltages. The functionalities of the top gate and the first gates were identified.

In chapter 6, the main devices were measured in different bias combinations to investigate the quality of the RTSs to be as a QRNG source. The way to find a better quality of RTSs generated by the artificial quantum dot was established. The challenges for our design to be a practical QRNG source were discussed based on the measurement results.

Chapter 7 concluded my PhD studies. The main features of the QRNG in this work was shown in the table below comparing to the existing optical QRNGs.

|                     | This work                                  | Optical RNG                          |

|---------------------|--------------------------------------------|--------------------------------------|

| Qubit               | Single-electron                            | Single-photon                        |

| Speed               | 1bps (Potentially<br>10Gbps )              | Mbps<br>Gbps                         |

| Working Temperature | Room temperature                           | Room temperature                     |

| Size                | Transistor scale                           | Equipment scale                      |

| Integration         | CMOS compatible                            | No                                   |

| Calibration         | Gate bias calibration<br>in hardware level | Mainly software level<br>calibration |

Table 1 The comparison of the features between this work and the existing optical QRNGs.

### Chapter 2 Background and literature review

#### 2.1 Random telegraph signal phenomenology

Since the report of the random telegraph signals (RTSs) was published in 1984 [6], most of the research on the RTSs were based on the MOSFETs structure [5]. The typical RTS phenomenon was that the drain current or drain voltage was temporally switched between two levels [7]. The RTS characterization mainly included three elements: the time in high state, the time in low state and the switching amplitude. Usually, the RTS phenomenon was explained according to the frame of the Shockley-Read-Hall (SRH) theory [6, 37]. The RTSs were driven by thermal energy at room temperature [38-41]. At low temperatures, while the thermal energy was decreased, the RTS was mainly characterized by the different tunneling transitions [42, 43]. In addition, the RTS amplitude could be extracted from the measurement results even without the statistical distribution, but it was quite difficult to derive a universal model to describe the RTS amplitude [5]. It was reported that the RTS amplitude could be related to the carrier number fluctuation in the channel [44], the change of the channel mobility [45-48], the gate voltage and drain voltage [49, 50], the impact of the device scaling [51-54] and so on. Moreover, the RTSs in the gate current was observed in the thin oxide layer devices [55]. It should be carefully distinguished with the channel RTS. The details were discussed in the following parts.

#### 2.1.1 The SRH framework

The SRH theory could be used to describe the capture ( $\tau_c$ ) and emission ( $\tau_e$ ) time for the charge trap. By assuming that the charged trap was allocated in the interface between the channel and gate oxide layer in the n-channel devices, the average capture time for an electron from the inversion layer could be described as [6, 37],

$$\tau_c = \frac{1}{n\sigma_n \nu_{thn}} \tag{2.1}$$

The *n* was the volume concentration, which was proportional to the drain current. The  $v_{thn}$  was the thermal velocity for the electrons. The precondition to use this equation was that the inversion layer quantization could be neglected [37]. The ratio of the capture and emission time constant also could be described as [6],

$$\frac{\tau_c}{\tau_e} = g \, exp\left(\frac{E_T - E_F}{kT}\right) = \frac{1 - f_T}{f_T} \tag{2.2}$$

#### Chapter 2

The  $E_F$  was the Fermi level in the surface. The  $E_T$  was the energy level of the charge trap. The k was the Boltzmann constant. The  $f_T$  was the occupancy of the charge trap by an electron. The g was the trap degeneracy, which was usually assumed to 1. By considering [7],

$$n = N_C \exp\left(\frac{E_C - E_F}{kT}\right)$$

(2.3)

Where  $N_C$  was the density of the states and  $E_C$  was the bottom of the conduction band, the  $\tau_e$  could be derived as,

$$\tau_e = \frac{1}{N_C \sigma_n \nu_{thn}} \exp\left(\frac{E_T - E_F}{kT}\right)$$

(2.4)

In the p-channel devices, we could replace the  $\sigma_n$  by  $\sigma_p$ , the  $\nu_{thn}$  by  $\nu_{thp}$  (the thermal velocity for holes) and  $E_C - E_F$  by  $E_T - E_V$ . The  $E_V$  was the top of the valance band.

In the SRH theory, it also demonstrated the way to identify the low state and high state with either the capture or the emission behaviors. As an example, for the acceptor charge trap in an nMOS, the charge state was switched from more positive to more negative by trapping an electron. By changing the local potential in the channel, the capture of an electron was corresponding to the low current state, while the emission of the electron was corresponding to the high current state [10]. By obtaining the  $\tau_c$  and  $\tau_e$  parameters, the feature of the charge trap such as energy level, barrier height and location could be derived by the SRH approaching method [37, 46, 56-59].

However, some results had shown that the RTSs that were influenced by the Coulomb blockade effects were exceeded of the validity range of the SRH theory [60, 61]. The Coulomb blockade happened on the way where the electron transfer from the semiconductor to the charged trap. It formed a single electron transistor system, which should be taken into account while calculating the  $\tau_c$  and  $\tau_e$  parameters [61]. Especially at the cryogenic temperature, while the thermal energy was quite small, the electron or hole might be bound to the charge trap in a bi-stable configuration [62, 63]. In this case, the typical RTSs could not be observed because no carrier was exchanged between the semiconductor and the charge trap.

#### 2.1.2 Tunneling transitions of the RTSs at different temperatures.

At room temperature, the typical RTSs behavior was recognized as being thermally activated [6-7, 37]. It implied that the elastic tunneling effect was smaller enough to be negligible at the energy level around  $E_F$  [65]. By decreasing the temperature, it was observed that the thermally activated transitions were gradually changed to the temperature-independent tunneling transitions [43]. The temperature-independent tunneling transitions were considered between the localized state and

the two-dimensional electron gas (2DEG) in the channel, which dictated by the Fermi's golden rule [42]. While the temperature was decreased to the liquid helium temperatures, the tunneling twostate system was identified at the Si/SiO<sub>2</sub> interfaces due to the degeneration of the 2DEG [12, 66]. It was suggested that the two-level system was only caused by the energy exchange between the charged trap and the 2DEG without carriers exchange [66]. That induced the change for the inversion layer electrons in the scattering cross-section, which led the channel resistance changing. It also observed that the energy separation between the two-level states could be controlled by the gate voltage [67]. At the milli-kelvin temperature, the tunneling transitions between the single defect state to the 2DEG showed the finite temperature counterpart of the Fermi-edge singularity [67]. A peak of the tunneling rate could be observed while the energy level of the defect was aligned to the Fermi level of the channel, which was consistent with the Fermi-edge singularity theory at the finite temperature [67].

## 2.1.3 The RTS amplitude

The RTS amplitude was usually normalized to  $\Delta I/I_D$  [5]. By assuming that the channel was uniform, the first model to describe the RTS amplitude was demonstrated that the local resistivity (*R*) was enhanced by the trap capturing an electron [44]. That resulted,

$$\frac{\Delta R}{R} = \frac{1}{WL} \frac{q\beta}{(C_{OX} + C_D - \beta Q_n)}$$

(2.5)

The  $\beta$  was equal to q/kT. The W was the width of the channel. The L was the length of the channel. The  $C_{OX}$  was the oxide capacitance per unit of area. The  $C_D$  was the depletion capacitance per unit of area. The  $Q_n$  was the channel charge density in  $/cm^2$ . It implied that the normalized RTS amplitude was affected by the total number of the carriers (N) in the channel, due to [44, 49]

$$\frac{1}{N} = \frac{q}{WLQ_n} \tag{2.6}$$

Although the model could explain the gate voltage dependence of the RTS amplitude, it could explain the large RTS amplitude, especially in the weak inversion due to the image charge screening effect [68-70].

It was also demonstrated that normalized RTS amplitude was related to the change of the channel mobility ( $\Delta\mu$ ) [45,47]. After the oxide trap captured a carrier, the local electrical potential would be changed. This induced the scattering increase in the local cross-section, and then changed the channel mobility. If assuming the channel was uniform and the change was uniform, the relationship between the normalized RTS amplitude and the mobility could be [45, 47],

$$\frac{\Delta I}{I} = \frac{\Delta n_S}{n_S} + \frac{\Delta \mu}{\mu} \tag{2.7}$$

The  $n_S$  was the surface carrier density. There was evidence to show that the  $\Delta n_S$  was dominated by the  $\Delta \mu$  [46, 48].

In addition, it was indicated that the RTS amplitude was not only dependent on the gate voltage but also dependent on the drain voltage [46, 49-50, 71-72]. By exchanging the role of the source and drain, the asymmetry RTS amplitudes were usually observed, which could be used to extract the lateral trap position [49,71] and to be as a local probe for the surface potential in the channel [72].

Moreover, it was confirmed that the RTS amplitude was increased significantly during device scaling [51-54]. In the ultra-narrow transistors, the charged trap could be just located in the strategic position to block the channel current by changing the surface potential. However, in the thin gate oxide devices, the screening of the metal gate influenced the RTS amplitude drastically [5]. It had been confirmed that the image charge effect from the gate electrode decreased the RTS amplitude significantly [73].

## 2.1.4 RTSs in the gate leakage current

Since the thin gate oxide layer was widely implemented in the advance CMOS technology, the RTS in the gate leakage current attracted more attention both from the researchers and from the engineers [55, 74-81]. Even in the high- $\kappa$  material transistors, the RTSs in the gate current was also observed [82-85]. It was pointed out that the gate leakage current in high state was corresponding to the charge trap capturing the electron, which was opposite to the channel RTS [55]. The reason was suggested as the trapped electron in the oxide layer increased the transmission probability to cross the dielectric layer by the image force reduction [5]. In this case, while the RTSs were observed in the drain current, the source, drain and gate leakage should be all plotted out. It should be clearly distinguished between the RTS in the gate leakage current and the RTS in the channel current.

## 2.1.5 1/f noise and RTS

The 1/f noise was a noise signal with the functionalized behavior in frequency spectrum that the power spectral density was proportional to frequency inversely, shown as:

$$S(f) \propto \frac{1}{f^{\alpha}}$$

Where S is the power spectral density, f is the noise frequency and  $0 < \alpha < 2$ . The 1/f noise was an intermediate between the white noise and Brownian motion noise, which was neither correlation in time nor correlation between increments. In this case, the 1/f noise can not be generated by integration or differentiation from the common signals. And there were no simple formulas to generate the 1/f signals. Enormous experimental data had exhibited that the 1/f noise was commonly observed in both electronic and optical devices [145,146]. However, as the 1/f noise was defined from the observed features, the physical mechanism has not been clarified. In the nanoscale electronic devices, the RTS has been proposed to be the possible origin for the 1/f noise in the microscopic view [147]. From another point of view, the 1/f noise could be the macroscopic feature of the summation of many RTSs in the large scale devices.

# 2.2 Quantum random number generators

In the 1980s, the pioneers including Paul Benioff, Yuri Manin, Richard Feynman and David Deutsch initially established the quantum computing research field [86-88], which theoretically gave the hope to have the computing capability to against the exponential growth of Hilbert space with increasing the number of particles. Quantum computing was based on quantum effect phenomena including superposition, entanglement and so on [89]. After nearly 40 years' developing, the experimental achievements in quantum technology areas in the last decades had shown that quantum physics could offer some new ways in computation, security, and cryptography. One important, emerging and more closed to daily life quantum technology was quantum random number generation. Quantum random number generators (QRNGs) were devices that used quantum mechanical effects to produce random numbers and applied to the simulation or cryptography. Comparing with classical physics, quantum physics was fundamentally random. Its intrinsic randomness became the overwhelming superiority in random number generator design. The main types of QRNGs were summarized in the following parts with their fundamental physics, strength, and limitation.

## 2.2.1 QRNGs based on the radioactive decay

The first QRNGs was designed based on the radioactive decay [90-91]. The core of this kind of QRNGs mainly included the radioactive samples and the Geiger-Muller (GM) tubes [92]. In the GM tube, the ionization event was produced by a single particle and was amplified in the Townsend avalanche. The device could generate the pulse for each detected particle. The probability for the numbers of the atom to decay in a certain time interval would be an exponential random number, which followed the Poisson distribution. In addition, the time intervals between different detected pulses would be also an exponential random number. That time intervals would not be affected by

the previous results [93]. By replacing the GM detectors to the semiconductor detectors in the modern proposals [94-97], the QRNG based on the radioactive decay was still a convenient method to generate high-quality random numbers. However, there were obvious limitations in the practical using of the QRNG based on the radioactive decay. The first one was due to the radioactive source. In order to improve the speed of the random generation, the highly radioactive source like Nickel-63 [97], Americium-241 [96], Cesium-137 [98], Strontium-90 [99], Cobalt-60 [90] were introduced. Meanwhile, these radioactive substances required strict health and safety measures. This problem prevented the device to be commonly used and made it quite difficult to integrate into the computer circuit. The second one was that the bit generation rate was limited by the dead time from the detector recovery. The ions generated in the GM tube would stop the further avalanches which amplified each count until they recovered to the normal state [92]. So that the dead time was the essential time interval for the GM tube recovering to the full capability, which would be around microseconds level [90, 96-99]. Even in the semiconductor detectors, they also needed a microseconds time interval to the carriers replenishing after each detection [94-97]. The last but most one was that the detector could be degraded by the radiation. Especially in the semiconductor detectors, the radiation would damage the device surfaces and change the electrical properties [94-95].

## 2.2.2 QRNGs based on the noise

Most of the noise-based random number generators belong to classical physical random number generators, like thermal noise [15], avalanche noise [16], dark noise [17] and so on. Besides, the shot noise-based devices [100-103] could be considered as QRNGs. The shot noise was generated by the discrete carriers passing through the potential barrier, which showed the quantum fluctuations. However, the thermal noise was generated by the thermal fluctuation of the carrier, which had the temperature dependence. Practically, these two kinds of noise were difficult to separate and mixed together [104]. So that the QRNGs based on the shot noise would be affected by many environmental fluctuations. It implied that the quantum effects were not well controlled and isolated in the QRNGs based on shot noise. Due to the simple electrical circuits, some commercial QRNGs based on the shot noise had been available in the market [101].

## 2.2.3 QRNG based on photon

The optical QRNGs had the largest family in the latest research. The light provided the quantum states in many aspects with inherent randomness to be used as a QRNG source. The quantum states were usually described by the fock states and the coherent states [105-106]. The fock states contained numbers of photons sharing the same mode such as frequency, polarization, common

path, temporal profile and so on. The coherent states could be considered as the superposition of number states, which shared the properties with the classical light. The representative examples of the optical QRNGs were classified by the physical principles in the following parts.

#### a) Beam splitting

The beam splitting method was based on the single photon arriving at the beam splitter and passing with either of two different channels [107]. The beam splitter had equal transmissivity and reflectivity to provide equal probabilities for the two different paths. Two detectors were allocated in the two paths. By clicking the detectors with the arriving photon, the two detectors generated the "0" or "1" random number sequence. One problem for the optical path branching QRNGs was the same as the radioactive decay ones. The detectors needed a certain time to recover the sensitivity to the single phonon. It limited the maximum speed of the QRNGs in the Mbps level [108]. The other one was that the real beam splitter and detectors would cause a certain bias due to the different efficiency of the detector and the coupling ratios [12].

## b) Photon counting

A large number of optical QRNGs was based on the photon counting in a certain time interval. The number of total photons that arrived at the detection in a fixed interval was an exponential random variable, which obeyed the Poisson distribution [109]. In order to assign the "0" and "1" bit, the post-processes were required to adjust the mean photon level of the source. In this case, the random number was not directly generated by the quantum effects. It was generated from the post-processes by setting a certain mean photon level to make sure the probability of "0" and "1" bit were almost equal [110]. Then the limitation for the QRNGs based on the photon counting was that it highly relied on the post-processes to get the equal probability of "0" and "1" bit. The detection rate was also limited by the dead time.

## c) Time of photon arrival

The method for the QRNGs based on the time of photon arrival was similar to the radioactive decay generators. The detector would receive an average number of the photons from the LED incoherent light source and from the coherent laser source in a short time period respectively in one measurement cycle. Both of the arrival times followed the exponential distributions. The difference between the two arrival times was also an exponential random number. By comparing two of the time difference  $t_1$  and  $t_2$  in two measurement cycles, we could assign  $t_1 > t_2$  as "1" bit, and  $t_1 < t_2$  as "0" bit [111-112]. It could be found that the precise time tagging was highly recommended. The clock speed to digitizing the time arrivals could limit the precision of the measurement. As the photon detectors were utilized, the dead time could not be ignored.

## d) Vaccum fluctuations

The QRNGs based on the quantum vacuum fluctuations was designed with the homodyne detection techniques [113]. The homodyne detector mixed the reference laser with the vacuum state in a balanced beam splitter. Two detectors were allocated in the output of the beam splitter. By subtracting and processing the results from two detectors, the final current output could be digitized to the random numbers. Although the rate of this kind of QRNGs could exceed the Mbps rate of photon detection method and could reach Gbps [114], the main measurement would be dominated by the shot-noise. Then the performance would be affected by the classical thermal noise. In addition, complex post-processes were required to digitize the current out to random numbers.

# 2.3 RTSs in the silicon devices using as QRNGs source

From the fundamental physics of view, the RTSs fluctuations in the MOSFETs were generated from the single electron or hole trapped or de-trapped by a trap in the oxide layer or at the  $Si/SiO_2$ interfaces [5]. The observed the "high" and "low" state were truly random events, which were dominated by the quantum effects. Principally, if we could adjust the probability of the "high" and "low" states to be equal, and assigned the "high" state to "1" bit, the "low" state to "0" bit, the devices could be a promising QRNG source. Comparing with most popular optical QRNGs, the QRNGs based on RTSs do not need the high power light source and the photon detectors. It avoided the dead time as a common issue for most of the optical QRNGs [12]. In addition, the RTSs could be manipulated by the gate bias to achieve equal probabilities for each state [5]. So that it reserved the methods for calibration and maintenance from the original quantum process. Comparing to the QRNGs based on the photon counting, once the emission source was fabricated, the emission processes could not be controlled. The random numbers could only be generated from the complex post-processes. In this case, all the calibration and maintenance could only be implemented in the post-processes, not in the quantum processes. Moreover, the QRNGs source based on the RTSs was just transistor size. Without any light source and radioactive source, the transistor size device could be convenient to integrate to the electrical circuits, or even into the CPU directly. Comparing to the QRNGs based on the shot noise which suffering from the thermal noise, the QRNGs based on the RTSs could use the voltage bias to restrain the effect from the temperature. At different temperatures, the voltage bias could always manipulate the probability distribution of the "high" and "low" states.

It looks like the RTSs should be a perfect candidate as a QRNG source. However, it was rear to find papers to discuss the QRNGs using the RTS phenomenon. The typical one was proposed 17 years

ago in the International Electron Devices Meeting [115]. It was based on the single-electron transistor with back gate. Although recently researchers also proposed to use the RTS to generate random numbers [116, 148-150], they still based on the conventional one gate CMOS structure. And no commercial products were made based on the RTS till now. The main reason was that the original source of the RTSs was the defect, and the defects were randomly formed in the transistor devices during the fabrication processes. In this case, people need to measure thousands of devices to find the RTSs with the statistical investigation. From the engineering point of view, that means the stabilized RTSs source was not available now. Even the radiation could be utilized to introduce the interface-trap to the transistor devices, the energy level of the traps could not be controlled. In order to use the RTSs as a QRNG source, the RTSs source of certainty was highly demanded.

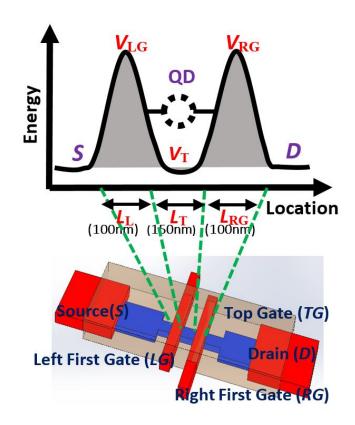

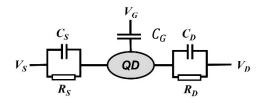

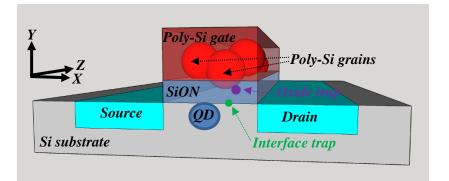

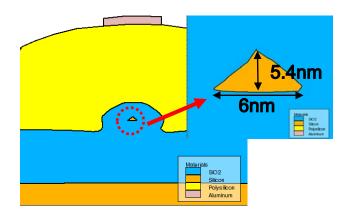

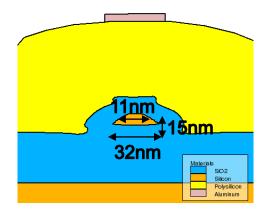

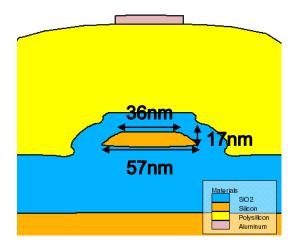

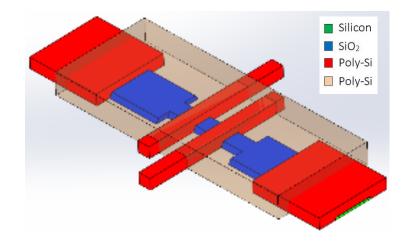

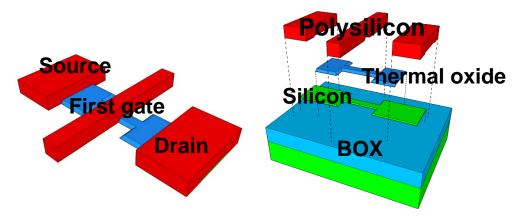

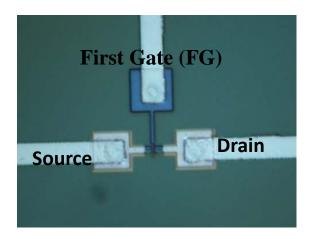

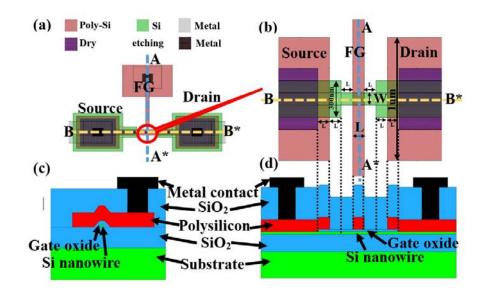

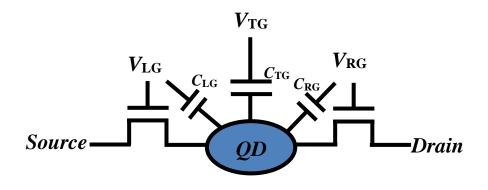

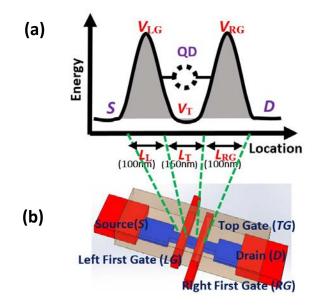

Based on the basic physical model of the RTSs, we proposed the multi-gate transistor design to form an artificial quantum dot in the channel, shown in Figure 2.2. The artificial quantum dot would work as a defect to trap and de-trap the electron and generate the RTSs. By manipulating the voltage bias of the multi-gate, we could control both the energy level in the quantum dot and the potential barriers of the quantum dot. In this case, the occupation and un-occupation of the electron were highly tunable. The drain current switching between two states could be a source of certainty for the quantum random number generation.

Figure 2.1 The structure of the triple gates silicon nanowire transistor

# 2.4 Summary

In summary, the phenomenology of the RTS in the MOSFETs was reviewed. We clarified the characterizing method to describe the feature of the RTS. The RTSs in the gate leakage current and in the channel current from source to drain should be distinguished. By reviewing the existing QRNGs, the disadvantages from these devices provided the way to propose the new QRNGs. Based on the standard single-electron transistor model, we proposed our multi-gate transistor design for a QRNG source.

# Chapter 3 Random telegraph signals in MOSFET at low temperature

This chapter summarized the experimental RTS behavior in the conventional metal-on-silicon fieldeffect-transistors (MOSFET) in sub-100nm scale. For the wide-channel device, a pMOS with 10  $\mu$ m channel width and 75 nm channel length was characterized. For the narrow-channel device, a nMOS with 60  $\mu$ m channel width and 60 nm channel length was characterized. The key physics and fabrication processes of silicon quantum random number generation devices are based on the conventional MOSFET. The industrial-level MOSFETs were measured using a low noise cryostat to get a better understanding of RTS behavior and investigate the RTS characterization methodology before we fabricated the devices at the University of Southampton.

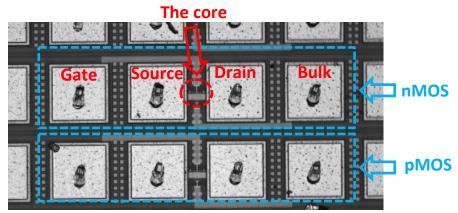

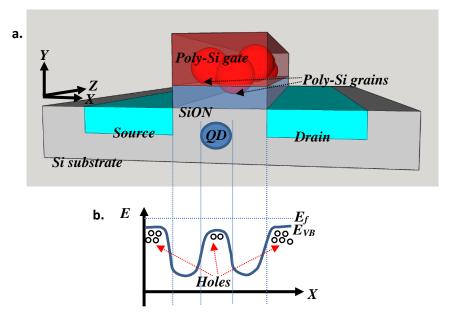

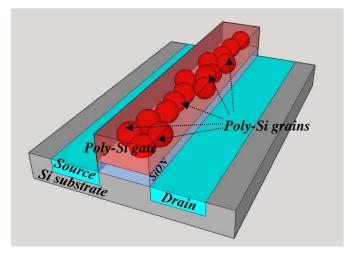

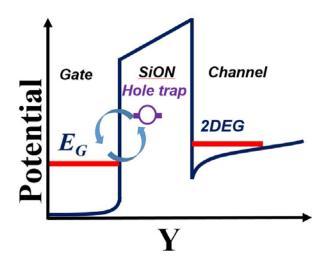

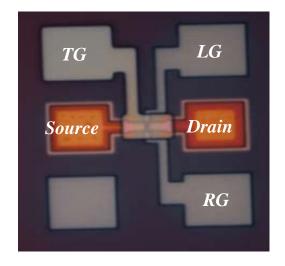

# 3.1 Methods

The samples were planar bulk silicon n-type and p-type MOSFET fabricated using 65nm technology by industrial collaborators, which is shown in Figure 3.1. The material of the gate electrode was high-doped polycrystalline silicon (Poly-Si). The gate insulator was made of silicon oxynitride (SiON), in which the equivalent oxide thickness was 2.4nm. The source, drain, gate and bulk electrodes of each transistor were connected with 4 metal pads, which dimension was 100  $\mu$ m long and 100  $\mu$ m wide. The pMOS and nMOS which have the same channel dimensions were located up and down next to each other.

Figure 3.1 Device layout in the optical microscope. The core of the device was located in the middle with 4 metal pads connected. From left to right, they were Gate, Source, Drain and Bulk electrodes.