UNIVERSITY OF SOUTHAMPTON

**High Performance CMOS modulator

drivers for Silicon Photonics

Mach-Zehnder Modulator**

by

Shenghao LIU

A thesis submitted in partial fulfillment for the

degree of Doctor of Philosophy

in the

Faculty of Physical Sciences and Engineering

Optoelectronics Research Centre

September 2019

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF PHYSICAL SCIENCES AND ENGINEERING

DEPARTMENT OF OPTOELECTRONICS RESEARCH CENTRE

Doctor of Philosophy

by **Shenghao LIU**

The modulator driver is a crucial electrical module within the optical transceiver. All the data to be conveyed optically must pass through this device, which typically requires it to operate at the highest operation speed of any electrical modules among the whole communication system. In addition, due to the weakness of the electro-optical effects of these high-speed modulators, the driver must produce relatively large voltage swing, which not only exceeds the nominal breakdown voltage of these ultra-deep-submicron CMOS technologies, but also leads to the concerns about the power efficiency and thermal reliability.

To address all these challenges, this work commenced from the design and implementation of a new driver circuit at 40nm CMOS technology. Silicon proven results demonstrated this new circuit could operate properly up to 40Gb/s. Thanks to the experience and knowledge base of the Silicon Photonics team that author is embedded into, a holistic solution has been proposed as a synergistic design approach between the CMOS driver and the depletion type Si MZM. The proposed solution has been illustrated from circuit-level design to real chip tape-out at 28nm process node, which not only features with the outstanding power efficiency (1.6 pJ/bit) and operation speed(40Gb/s), but also enabled the compact integration among optical and electrical component. In addition, target on the thermal reliability issue, a CMOS driver circuit has been proposed and demonstrated with relatively stable performance over the temperature range 27°C to 110°C.

The endless effort has been made and will continuously be devoted to speed enhancement and the optimization of power efficiency on each generation of the optoelectrical transceiver. It is hoped some of the research outcome recorded in this work will become as a step-stone for future research, where the driver and modulator will be co-designed as a complex function for the future communication system.

# Contents

|                                                                                  |             |

|----------------------------------------------------------------------------------|-------------|

| <b>Acknowledgements</b>                                                          | <b>xv</b>   |

| <b>Nomenclature</b>                                                              | <b>xvii</b> |

| <b>1 Introduction</b>                                                            | <b>1</b>    |

| 1.1 Interconnect bottleneck and silicon photonics . . . . .                      | 1           |

| 1.2 Motivation and objectives . . . . .                                          | 3           |

| 1.3 Thesis Organization and Contributions . . . . .                              | 6           |

| <b>2 States of the Art</b>                                                       | <b>9</b>    |

| 2.1 Introduction . . . . .                                                       | 9           |

| 2.2 The top Level circuit of optical transceivers . . . . .                      | 10          |

| 2.3 Common optical devices and circuits . . . . .                                | 12          |

| 2.4 Integration . . . . .                                                        | 16          |

| 2.5 High speed limiting amplifiers . . . . .                                     | 21          |

| 2.5.1 Inductive peaking amplifier . . . . .                                      | 22          |

| 2.5.2 Cherry Hooper amplifier . . . . .                                          | 24          |

| 2.5.3 Capacitive Degeneration amplifier . . . . .                                | 26          |

| 2.5.4 Active feedback amplifier . . . . .                                        | 28          |

| 2.6 Output Stage of Modulator Driver . . . . .                                   | 30          |

| 2.6.1 Push pull on output stage . . . . .                                        | 32          |

| 2.6.2 Current mode logic on output stage . . . . .                               | 32          |

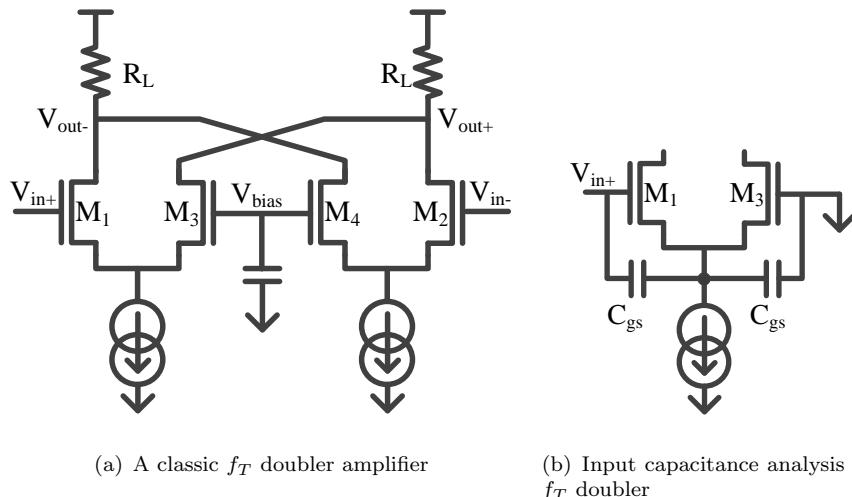

| 2.6.3 $f_T$ doubler on output stage . . . . .                                    | 34          |

| 2.6.4 Open drain on output stage . . . . .                                       | 35          |

| 2.6.5 Distribute amplifier . . . . .                                             | 36          |

| 2.7 Optical transmitter with complex modulations . . . . .                       | 39          |

| 2.7.1 Wavelength-division multiplexing . . . . .                                 | 39          |

| 2.7.2 Optical pulse amplitude modulation . . . . .                               | 40          |

| 2.7.3 Coherent optical transmitters . . . . .                                    | 42          |

| 2.7.4 Optical Discrete multi-tone modulation . . . . .                           | 44          |

| 2.8 Summary . . . . .                                                            | 46          |

| <b>3 Theoretical Analysis of<br/>N Over N Cascode Push Pull Modulator Driver</b> | <b>47</b>   |

| 3.1 Introduction . . . . .                                                       | 47          |

| 3.2 Functionality of proposed circuit . . . . .                                  | 48          |

| 3.3 Mid-band performance analysis . . . . .                                      | 49          |

| 3.4 Frequency response analysis . . . . .                                        | 51          |

---

|          |                                                                   |            |

|----------|-------------------------------------------------------------------|------------|

| 3.5      | Comparison of multiple circuit topologies . . . . .               | 57         |

| 3.6      | Improved proposed circuit with inductive peaking . . . . .        | 61         |

| 3.7      | Proposed circuit with a CML pre-stage . . . . .                   | 66         |

| 3.8      | Summary . . . . .                                                 | 67         |

| <b>4</b> | <b>Implementation of</b>                                          |            |

|          | <b>N over N cascode push pull modulator driver</b>                | <b>69</b>  |

| 4.1      | Introduction . . . . .                                            | 69         |

| 4.2      | Implementation I                                                  |            |

|          | A basic N-over-N cascode modulator driver . . . . .               | 70         |

|          | 4.2.1 Top level schematic of optical transmitter . . . . .        | 70         |

|          | 4.2.2 Pre-driver system . . . . .                                 | 70         |

|          | 4.2.3 Output stage of modulator driver . . . . .                  | 73         |

|          | 4.2.4 Modulator driver layout . . . . .                           | 75         |

|          | 4.2.5 Simulation result . . . . .                                 | 75         |

|          | 4.2.6 Testing result . . . . .                                    | 78         |

| 4.3      | Implementation II                                                 |            |

|          | N over N cascode modulator driver with inductor peaking . . . . . | 81         |

|          | 4.3.1 Top-level schematic of optical transmitter . . . . .        | 82         |

|          | 4.3.2 Pre-driver of modulator driver . . . . .                    | 82         |

|          | 4.3.3 Output stage of modulator driver . . . . .                  | 84         |

|          | 4.3.4 Modulator driver layout . . . . .                           | 85         |

|          | 4.3.5 Simulation result . . . . .                                 | 85         |

|          | 4.3.6 Testing result . . . . .                                    | 88         |

| 4.4      | Implementation III                                                |            |

|          | N over N cascode modulator driver with CML pre stage . . . . .    | 93         |

|          | 4.4.1 Top level schematic of optical transmitter . . . . .        | 93         |

|          | 4.4.2 Pre-driver of modulator driver . . . . .                    | 94         |

|          | 4.4.3 Output stage with CML pre-stage . . . . .                   | 94         |

|          | 4.4.4 Modulator driver layout . . . . .                           | 95         |

|          | 4.4.5 Simulation result . . . . .                                 | 96         |

|          | 4.4.6 Testing result . . . . .                                    | 99         |

| 4.5      | Analysis . . . . .                                                | 101        |

| 4.6      | Summary . . . . .                                                 | 103        |

| <b>5</b> | <b>Design methodology of</b>                                      |            |

|          | <b>a synergistic designed optical transmitter</b>                 | <b>105</b> |

| 5.1      | Introduction . . . . .                                            | 105        |

| 5.2      | Synergistic design . . . . .                                      | 106        |

| 5.3      | An efficient optical transmitter design . . . . .                 | 106        |

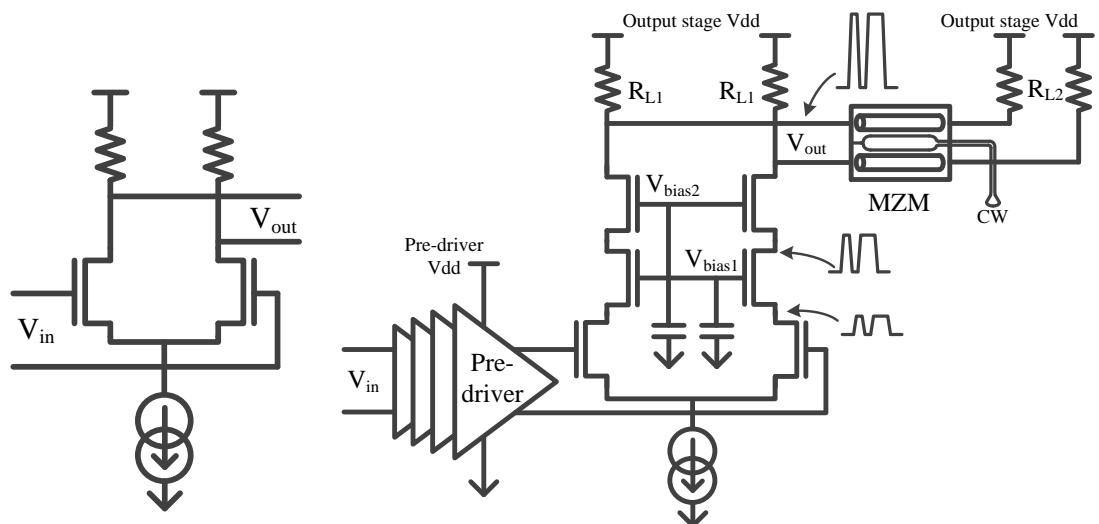

|          | 5.3.1 Open drain modulator driver . . . . .                       | 107        |

|          | 5.3.2 U-shape MZM and on CMOS chip termination . . . . .          | 109        |

| 5.4      | PAM4 optical transmitter . . . . .                                | 110        |

|          | 5.4.1 An efficient PAM4 optical transmitter . . . . .             | 112        |

|          | 5.4.2 Linearity adjustment of optical PAM4 . . . . .              | 113        |

| 5.5      | Summary . . . . .                                                 | 115        |

| <b>6</b> | <b>Implementation of</b>                                          |            |

---

|                                                                                   |            |

|-----------------------------------------------------------------------------------|------------|

| <b>a synergistic designed optical transmitter</b>                                 | <b>117</b> |

| 6.1 Introduction . . . . .                                                        | 117        |

| 6.2 Optical transmitter . . . . .                                                 | 118        |

| 6.3 Simulation result . . . . .                                                   | 119        |

| 6.4 Package the optical transmitter . . . . .                                     | 122        |

| 6.5 Testing result . . . . .                                                      | 123        |

| 6.5.1 NRZ transmitter testing . . . . .                                           | 124        |

| 6.5.2 BER testing . . . . .                                                       | 127        |

| 6.5.3 PAM4 testing . . . . .                                                      | 129        |

| 6.6 Analysis . . . . .                                                            | 131        |

| 6.7 Summary . . . . .                                                             | 131        |

| <b>7 Theoretical Analysis of Temperature Variation Tolerance Modulator Driver</b> | <b>133</b> |

| 7.1 Introduction . . . . .                                                        | 133        |

| 7.2 Temperature analysis of device and circuit . . . . .                          | 134        |

| 7.2.1 Temperature analysis of CMOS transistors . . . . .                          | 135        |

| 7.2.2 Temperature analysis of limiting amplifiers . . . . .                       | 136        |

| 7.3 Temperature variation tolerance limiting amplifier . . . . .                  | 138        |

| 7.4 Temperature variation tolerance output stage . . . . .                        | 140        |

| 7.5 Summary . . . . .                                                             | 142        |

| <b>8 Implementation of Temperature Variation Tolerance Modulator Driver</b>       | <b>143</b> |

| 8.1 Introduction . . . . .                                                        | 143        |

| 8.1.1 Top level design . . . . .                                                  | 143        |

| 8.1.2 Modulator driver . . . . .                                                  | 145        |

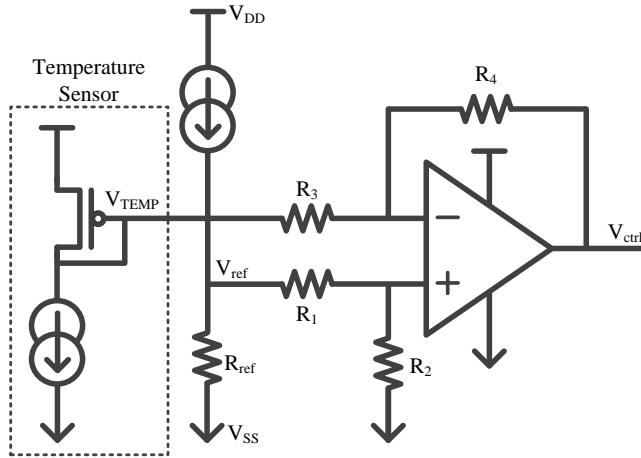

| 8.1.3 Temperature variation sensor and voltage control . . . . .                  | 147        |

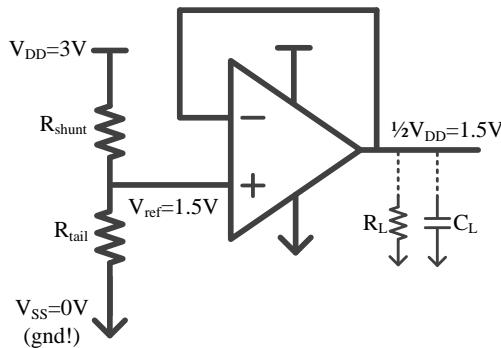

| 8.1.4 Half $V_{DD}$ generator . . . . .                                           | 148        |

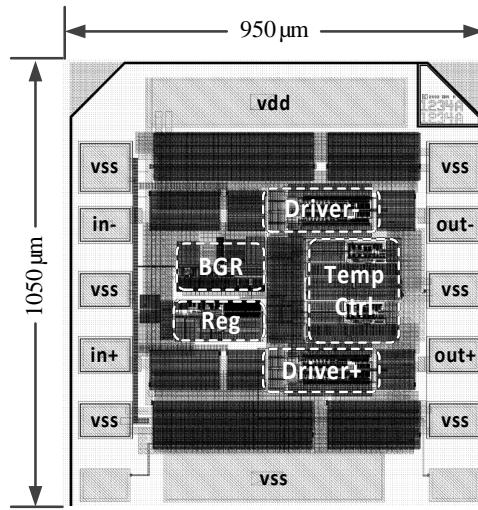

| 8.1.5 Modulator driver layout . . . . .                                           | 149        |

| 8.2 Simulation result . . . . .                                                   | 149        |

| 8.3 Testing result . . . . .                                                      | 151        |

| 8.4 Analysis . . . . .                                                            | 153        |

| 8.5 Summary . . . . .                                                             | 155        |

| <b>9 Conclusions and future work</b>                                              | <b>157</b> |

| 9.1 Conclusions . . . . .                                                         | 157        |

| 9.2 Future work . . . . .                                                         | 159        |

| <b>A General circuit design process</b>                                           | <b>161</b> |

| <b>Bibliography</b>                                                               | <b>167</b> |

# List of Figures

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Gate and Interconnection Delay feature versed Technology Generation [81]                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2  |

| 2.1  | Abstract view of an example optical data link (edited from [12])                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10 |

| 2.2  | Abstract view of an example brief optical data link                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11 |

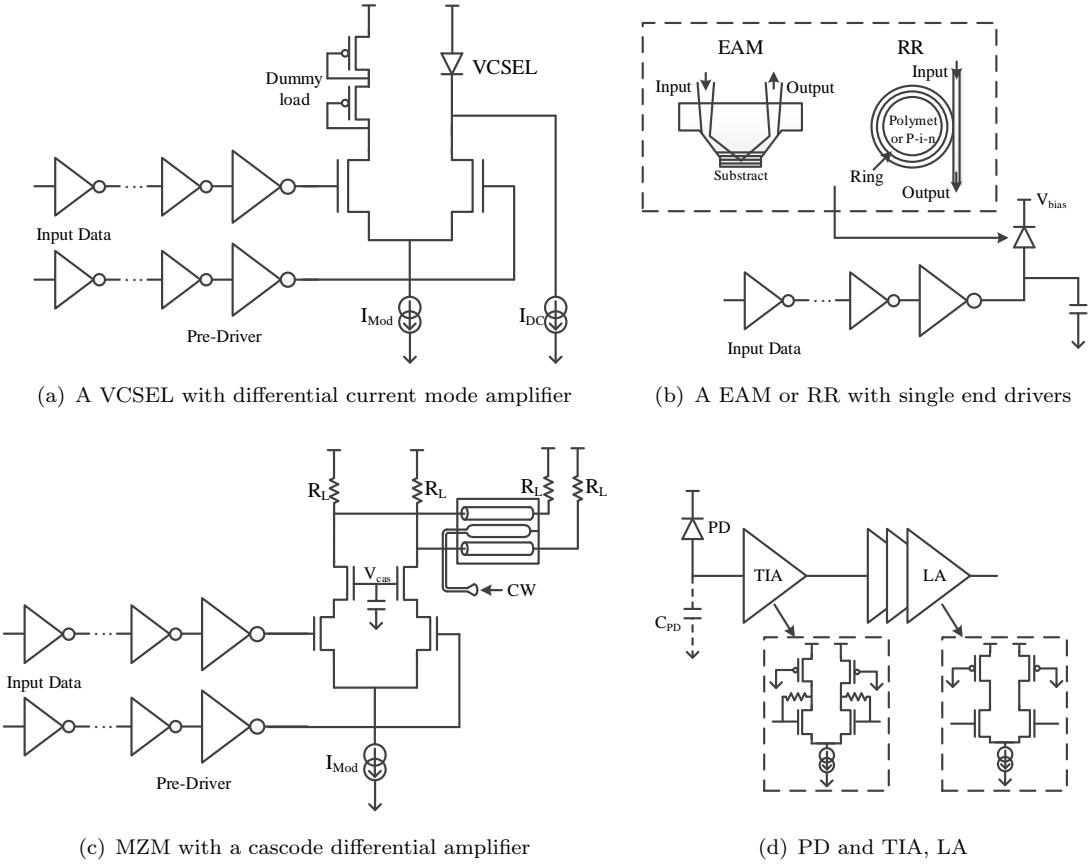

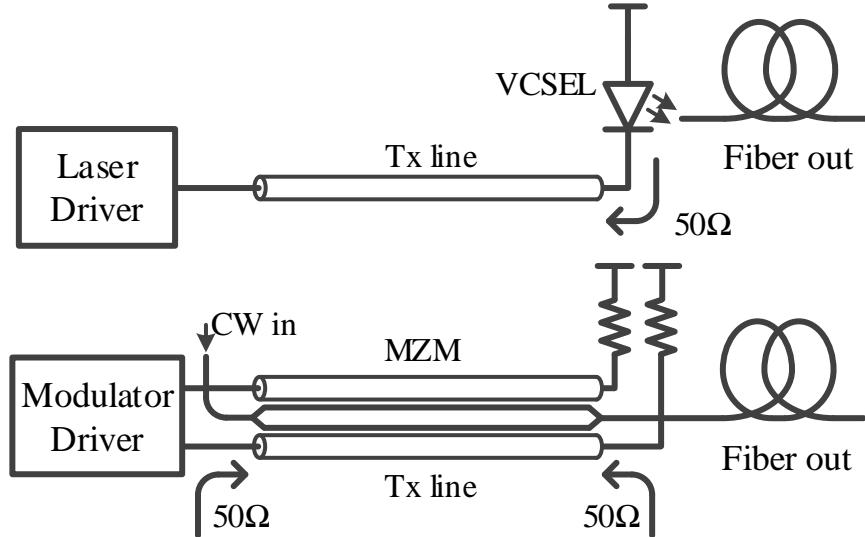

| 2.3  | Schematic of (a) VCSEL (b) EAM and RR (c) MZM with common driving circuit (d)PD & TIA receiving system                                                                                                                                                                                                                                                                                                                                                                                                                | 12 |

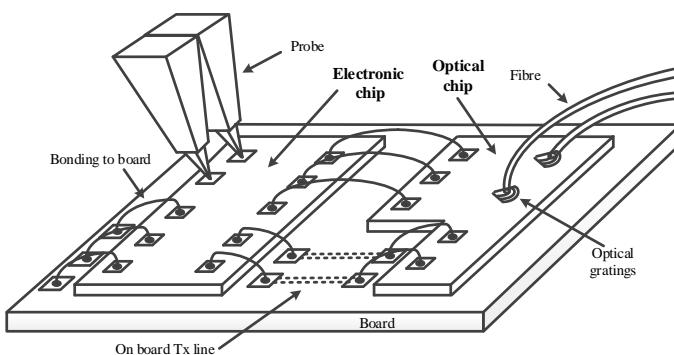

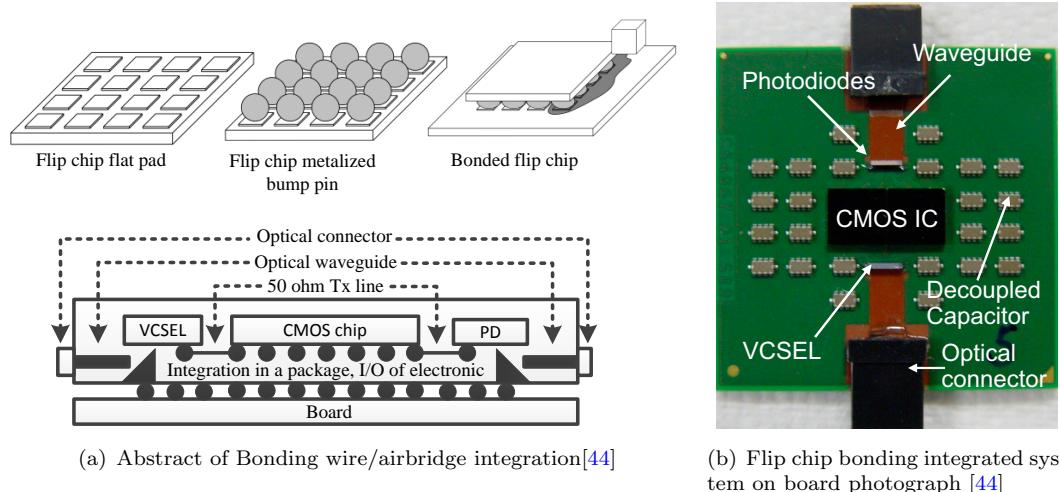

| 2.4  | Wire bonding integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16 |

| 2.5  | Flip chip bonding integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17 |

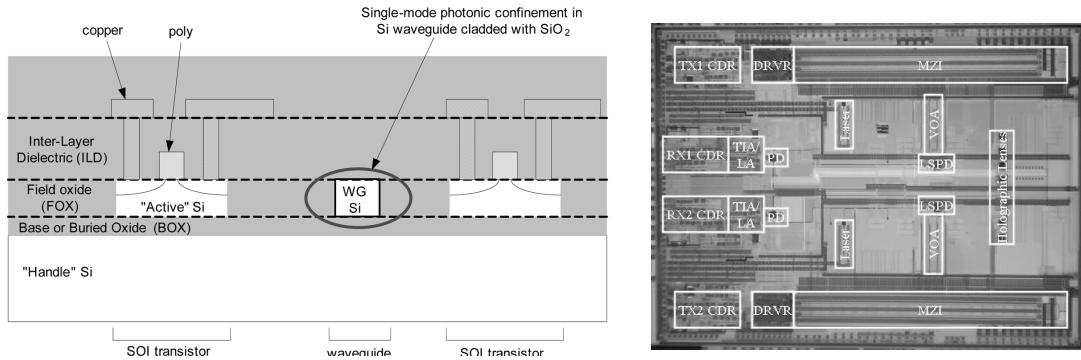

| 2.6  | Monolithic photonics platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18 |

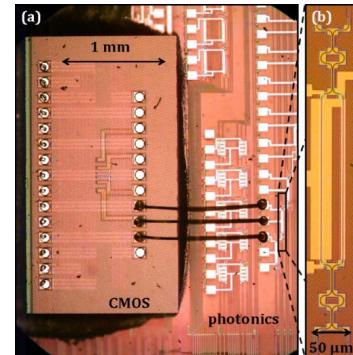

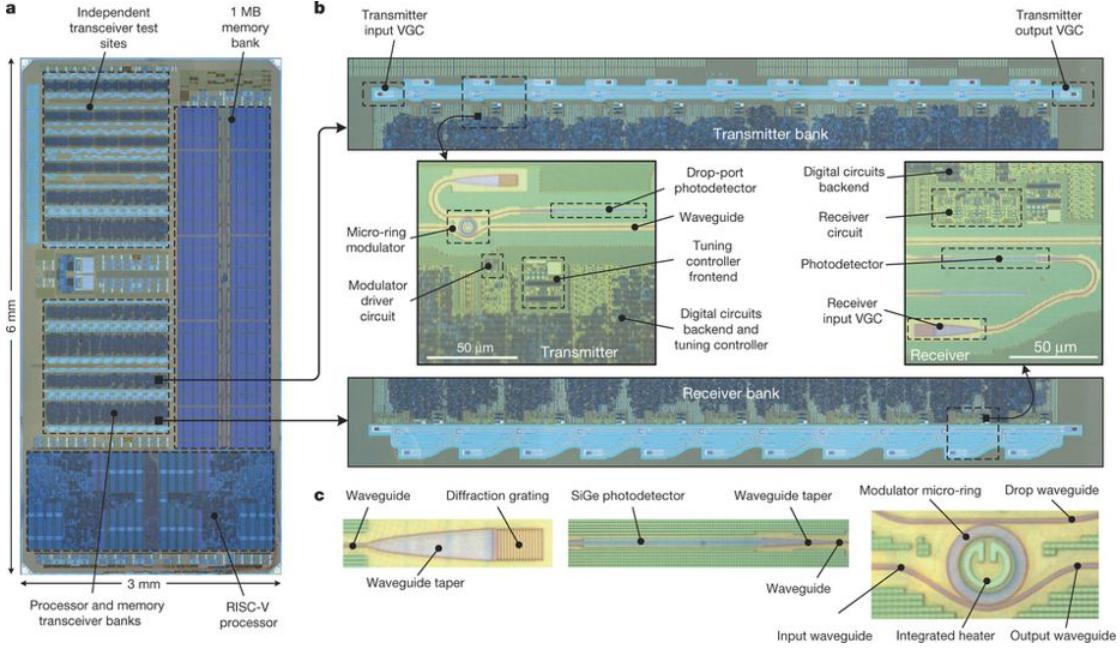

| 2.7  | Single-chip microprocessor that communicates directly using light (a, Die photo of the $3mm \times 6mm$ chip showing the locations and relative sizes of the processor, memory, and transceiver banks, imaged from the backside of the chip. b, The processor transmitter and receiver banks (the memory transmitter and receiver banks are identical) with close-ups of individual transmitters and receivers sites. c, Micrographs of the grating coupler, photodetector, and resonant micro-ring modulators.)[109] | 20 |

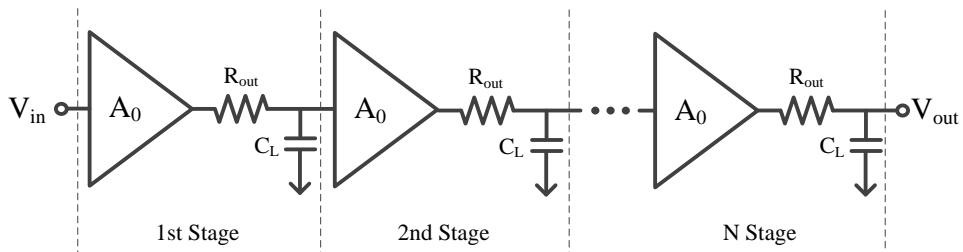

| 2.8  | Cascade gain multiple stage amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21 |

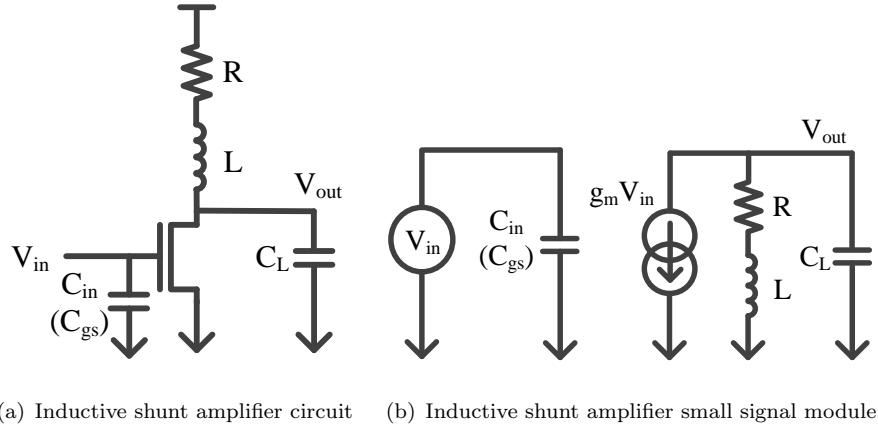

| 2.9  | Broadband amplifier with a shunt inductive peaking[114]                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23 |

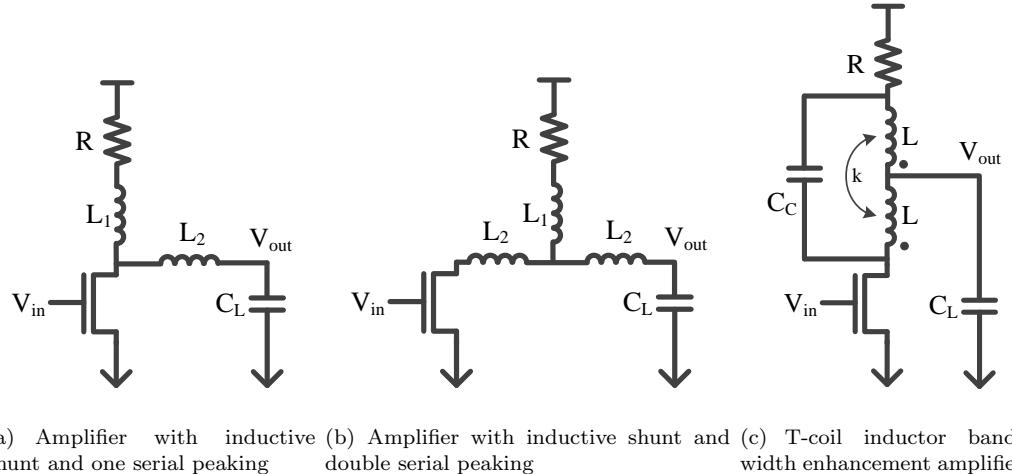

| 2.10 | Three optimized topology with more inductive peaking[114]                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23 |

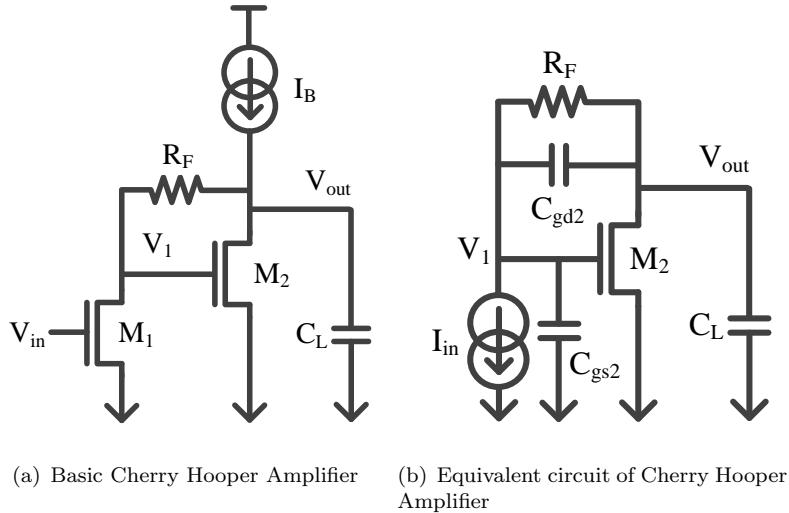

| 2.11 | Cherry Hooper Amplifier topology analysis[12]                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 24 |

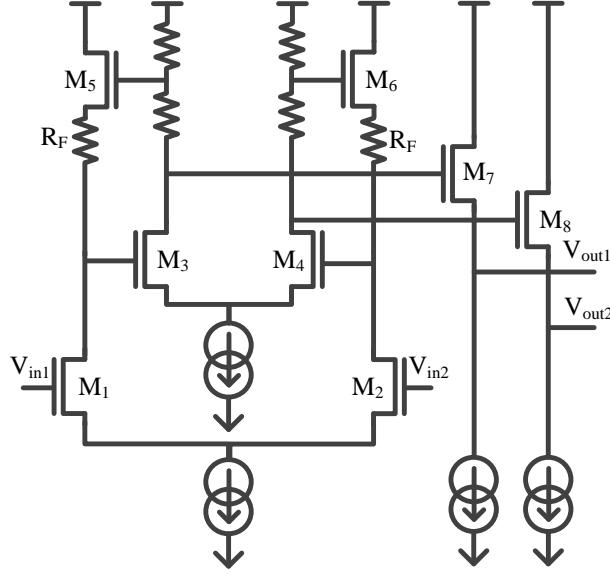

| 2.12 | Modified CMOS Cherry Hooper differential amplifier with DC bias reset for limiting amplifier application[15]                                                                                                                                                                                                                                                                                                                                                                                                          | 26 |

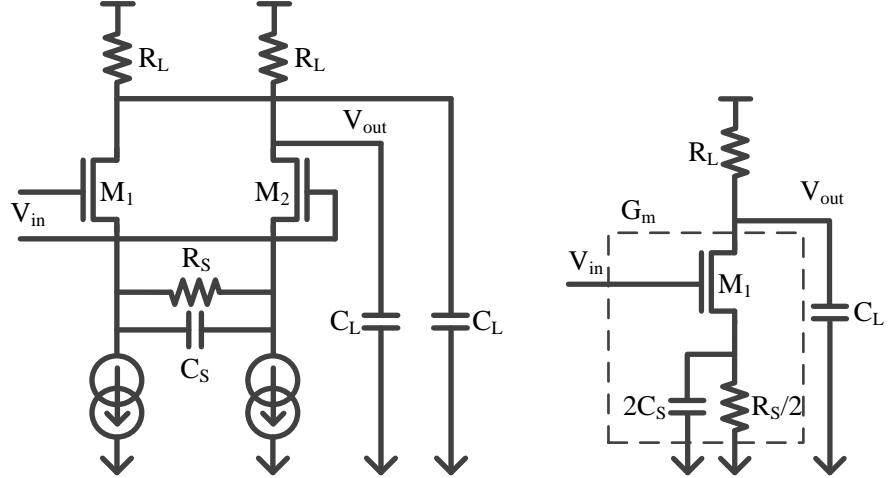

| 2.13 | Capacitance degeneration analysis[12]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27 |

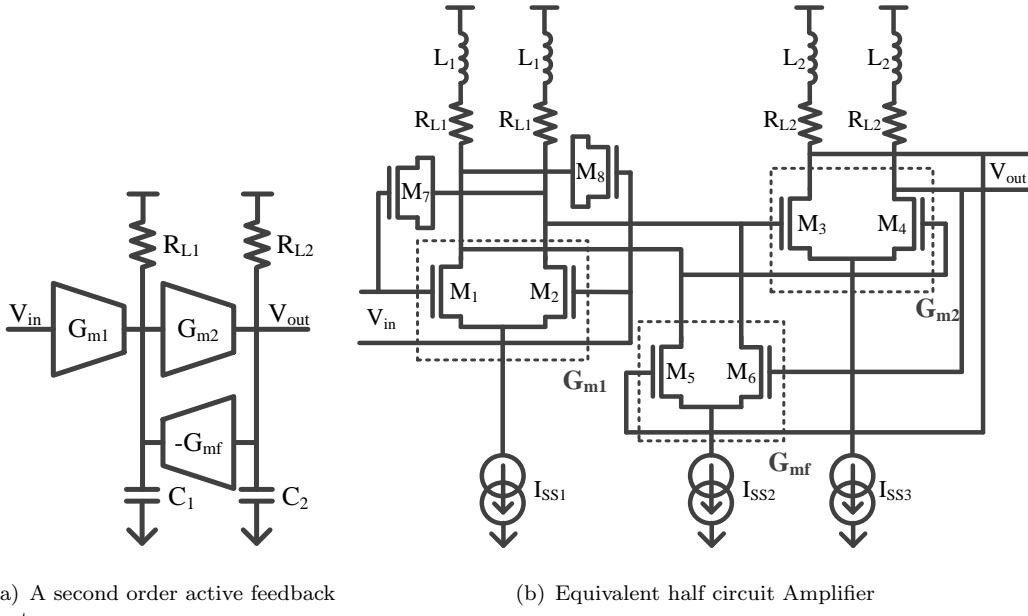

| 2.14 | Active feedback amplifier topology analysis[12; 32]                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28 |

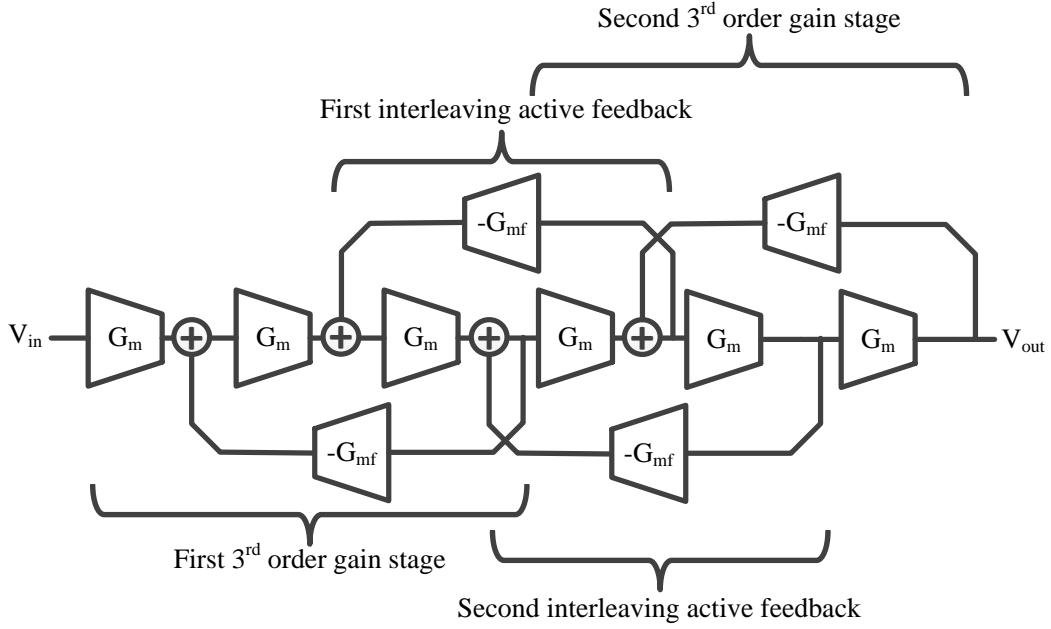

| 2.15 | Third order interleaving active feedback cascade gain amplifier topology [41]                                                                                                                                                                                                                                                                                                                                                                                                                                         | 30 |

| 2.16 | Laser driver output impedance matching with a optical modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31 |

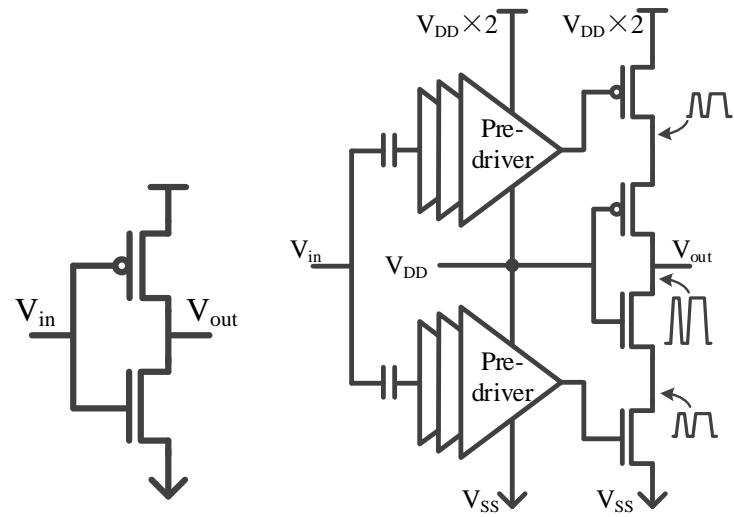

| 2.17 | Push pull output stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33 |

| 2.18 | Current mode logic output stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33 |

| 2.19 | $f_T$ doubler output stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34 |

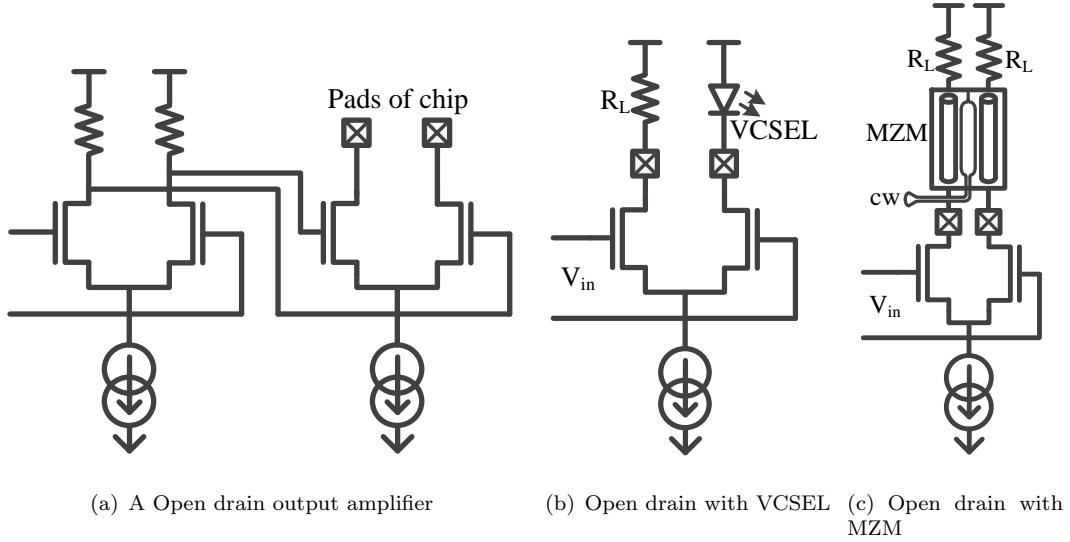

| 2.20 | Open drain topology analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36 |

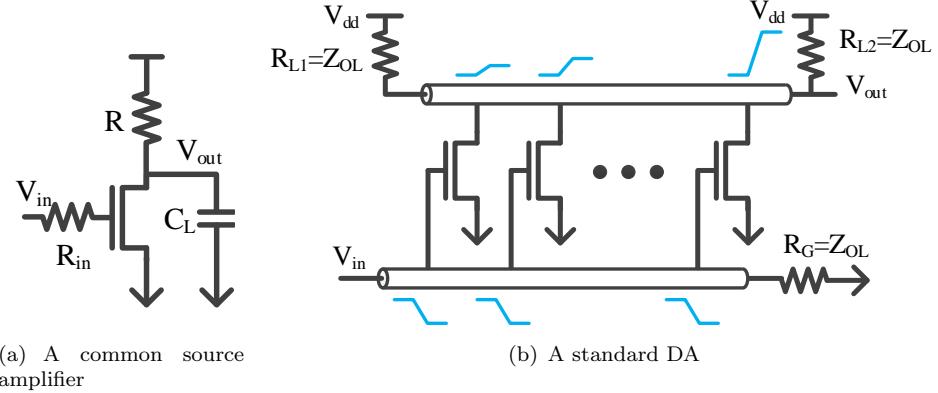

| 2.21 | DA analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 37 |

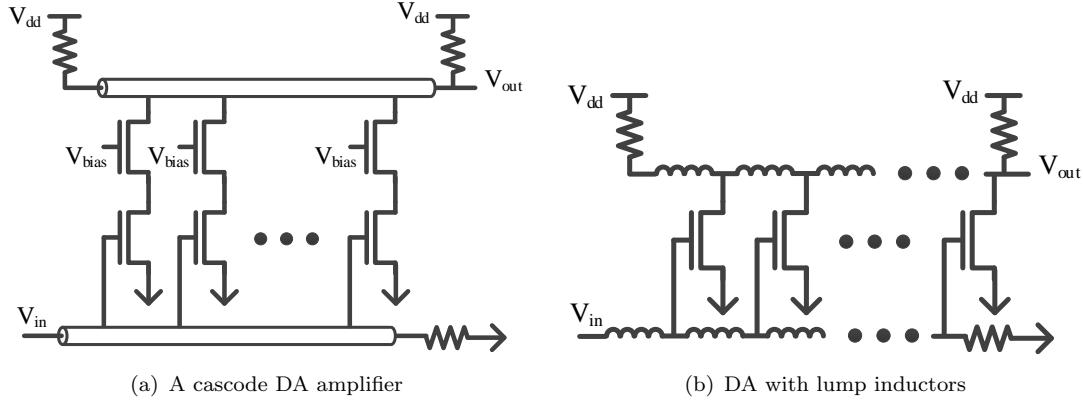

| 2.22 | Two optimization on conventional DA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 38 |

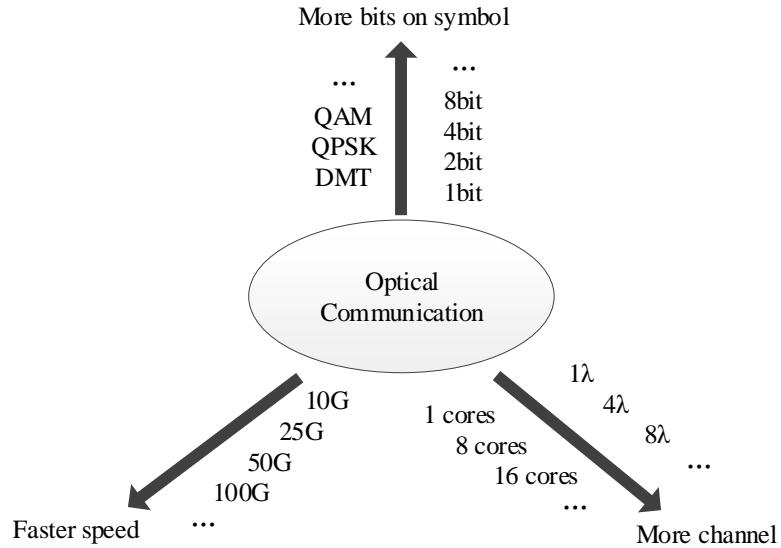

| 2.23 | Transmission capability development of optical communication                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39 |

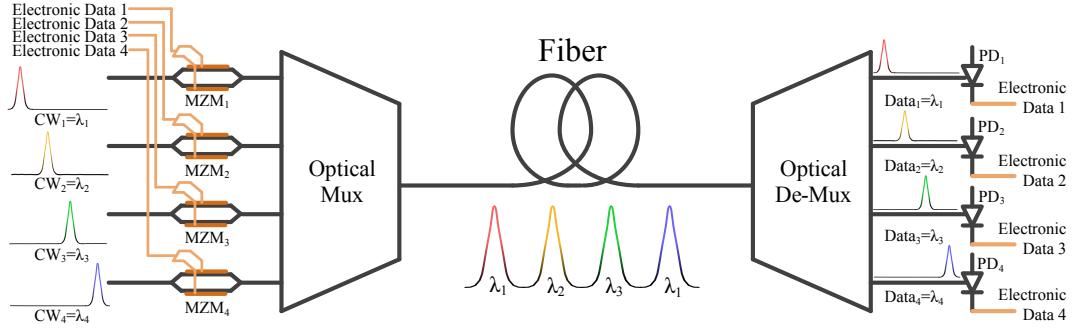

| 2.24 | Optical connection with multiple channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40 |

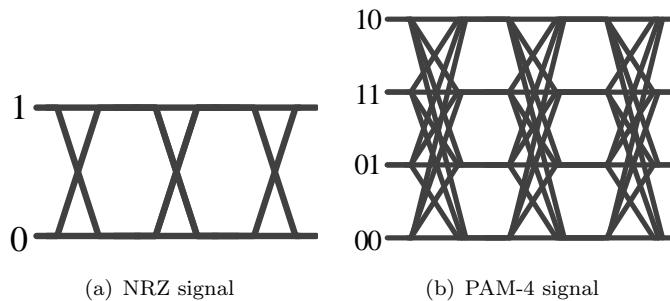

| 2.25 | A NRZ data and a PAM4 data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40 |

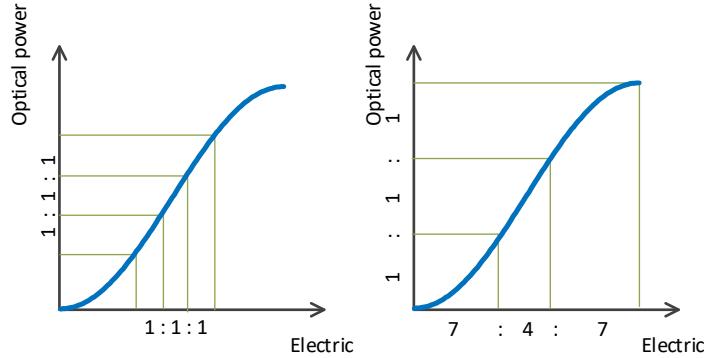

| 2.26 | Optical PAM linearity problem example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41 |

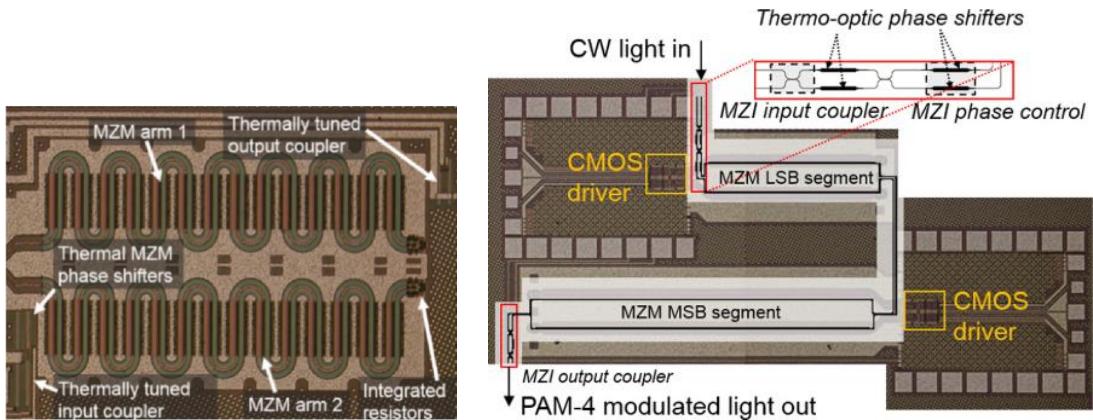

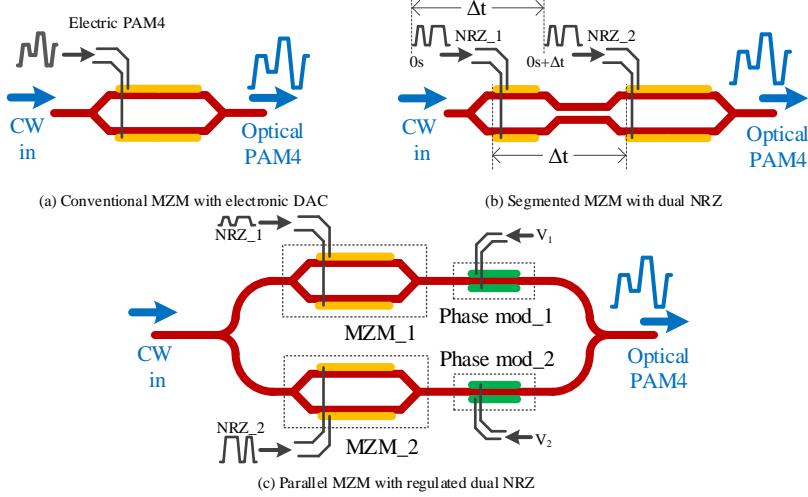

| 2.27 | Optical PAM example with PAM4 on MZM[99]                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42 |

|      |                                                                                                                    |    |

|------|--------------------------------------------------------------------------------------------------------------------|----|

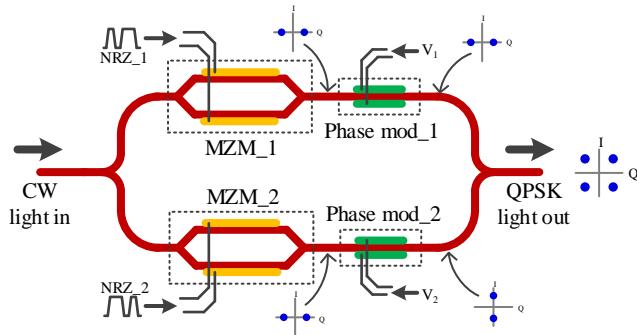

| 2.28 | Optical QPSK with two MZM, edited from[74] . . . . .                                                               | 43 |

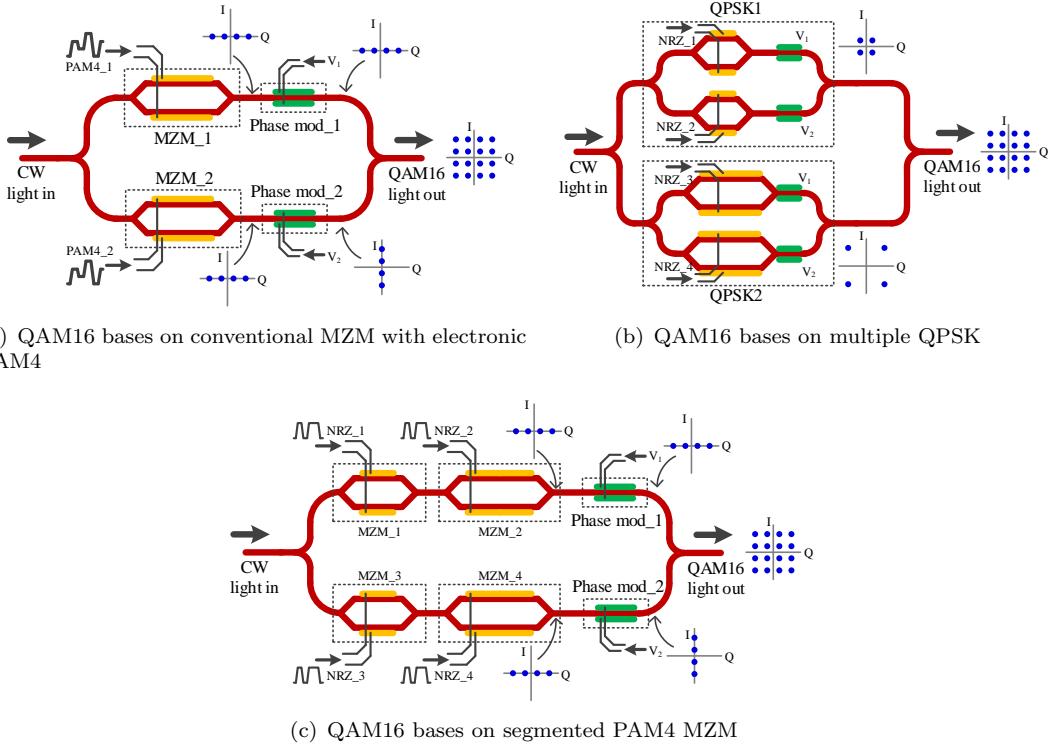

| 2.29 | Three architectures of QAM16 optical transmitter . . . . .                                                         | 44 |

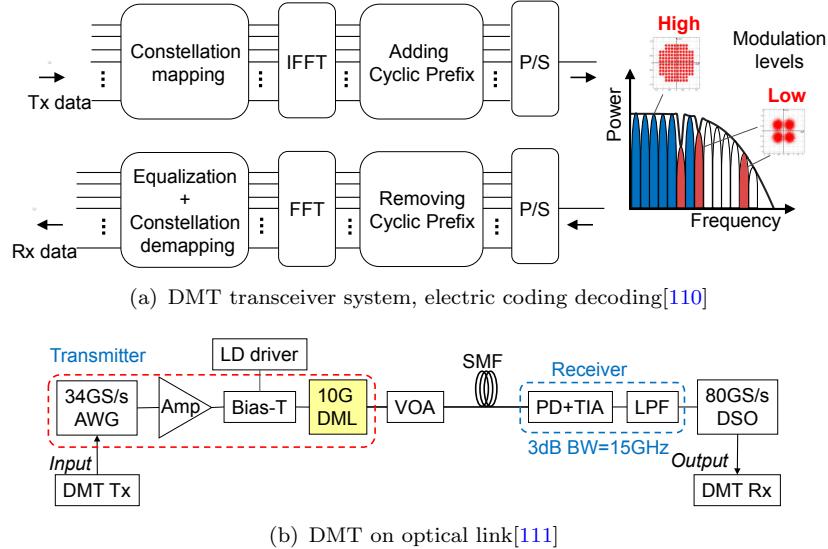

| 2.30 | Optical DMT full link system . . . . .                                                                             | 45 |

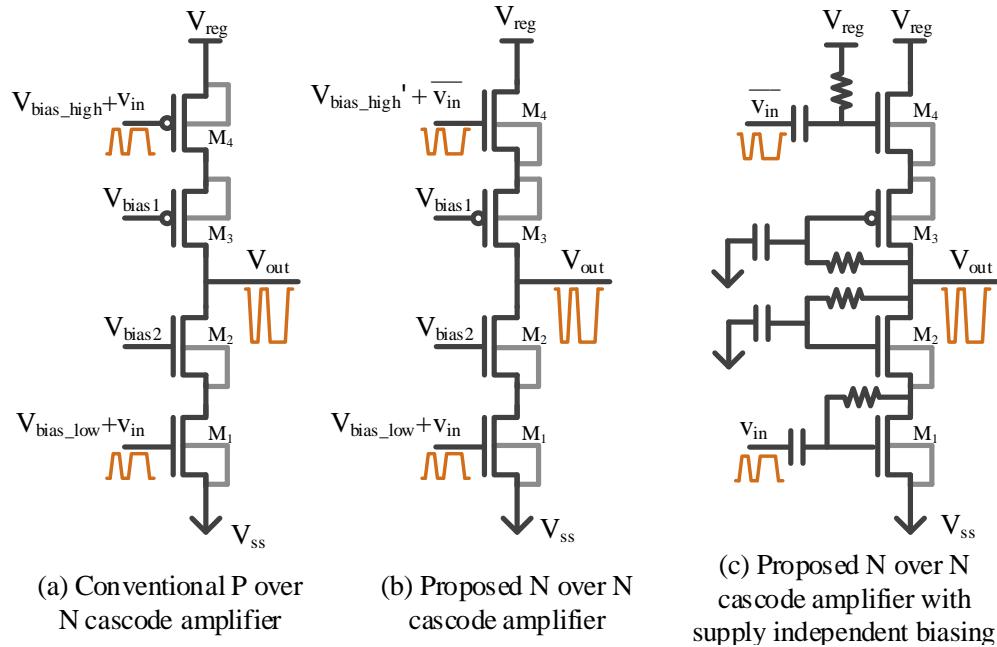

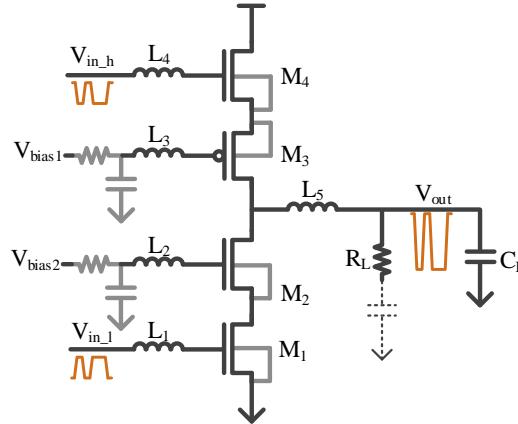

| 3.1  | Circuit topology of N over N cascode push pull amplifier . . . . .                                                 | 48 |

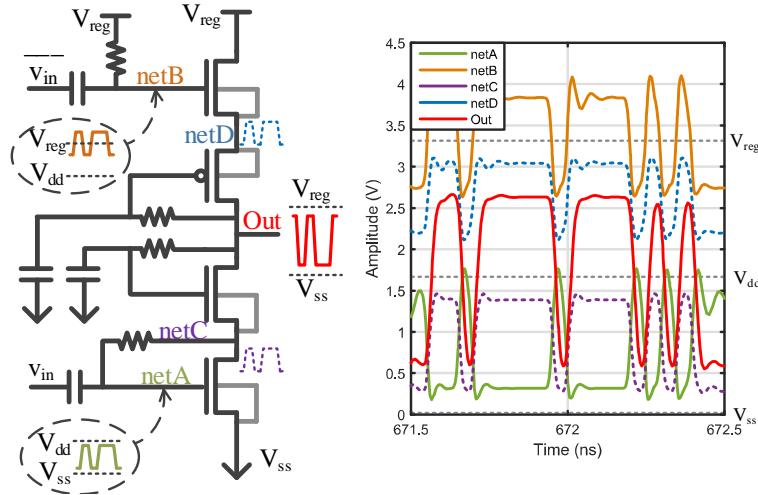

| 3.2  | Functionality of N over N cascode amplifier . . . . .                                                              | 49 |

| 3.3  | Mid-band small signal model of N over N cascode amplifier . . . . .                                                | 50 |

| 3.4  | Simplified equivalent mid-band small signal model of N over N cascode amplifier . . . . .                          | 50 |

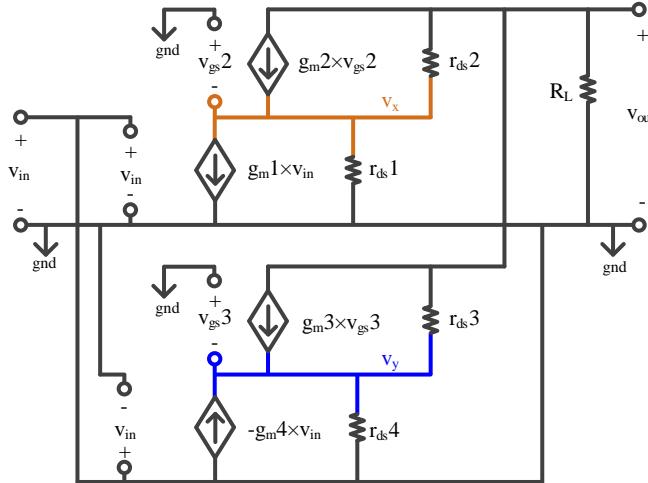

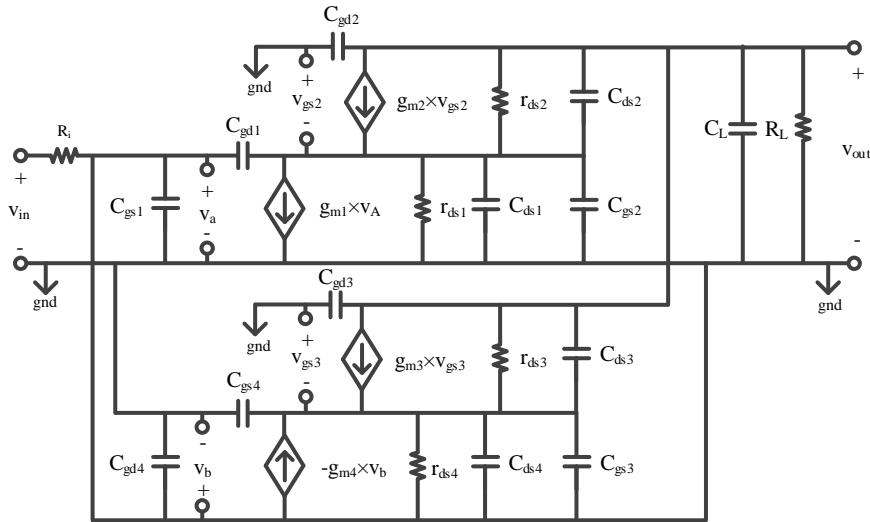

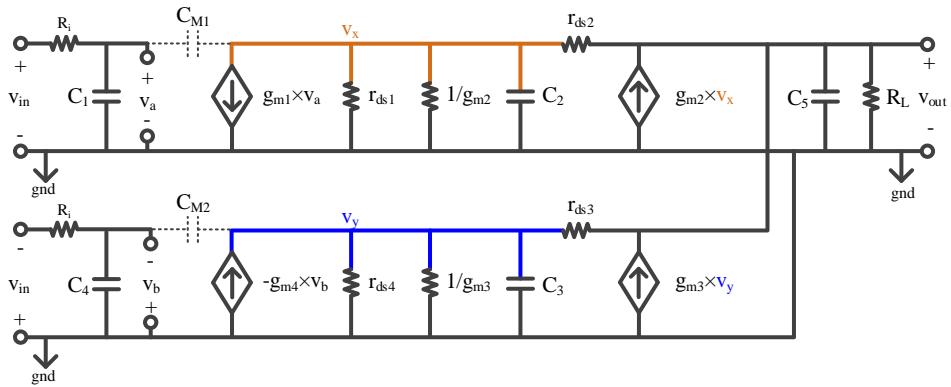

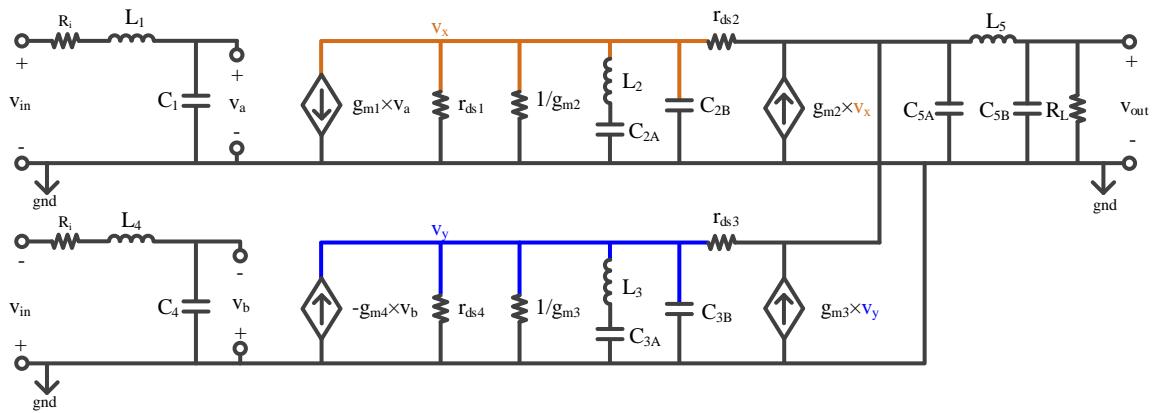

| 3.5  | Small signal model of N over N cascode amplifier . . . . .                                                         | 52 |

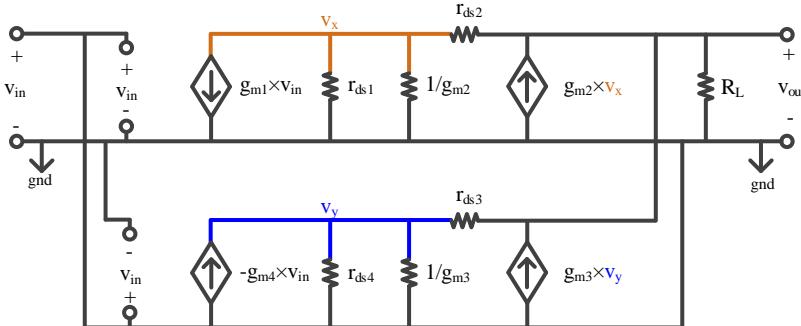

| 3.6  | Simplified equivalent small signal model of N over N cascode amplifier . .                                         | 52 |

| 3.7  | A comparison of small signal model analysis and Spectre simulation on example N over N cascode amplifier . . . . . | 56 |

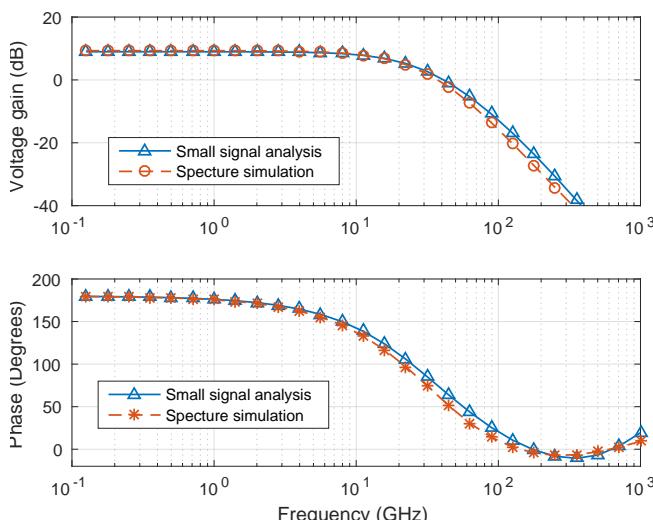

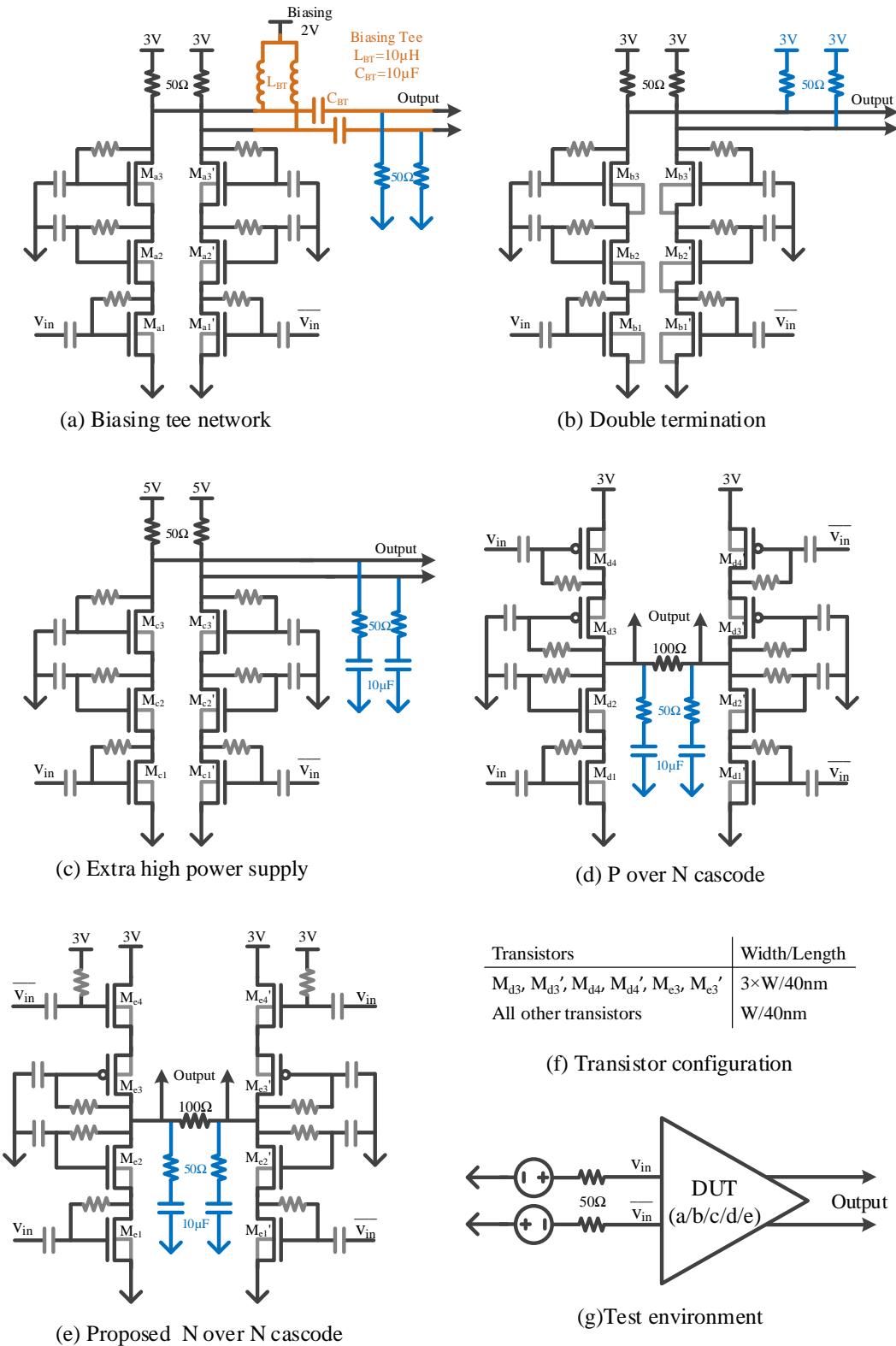

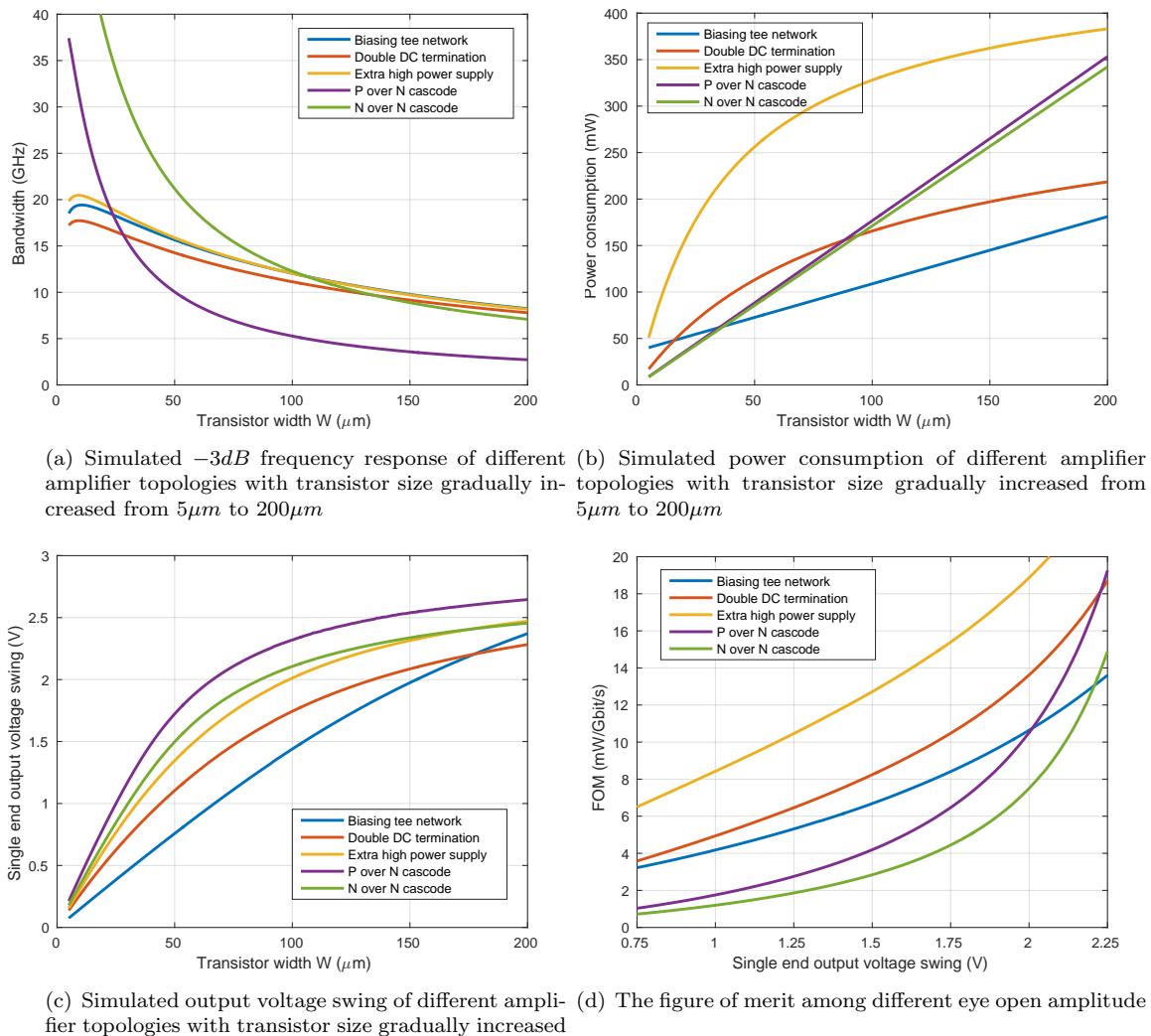

| 3.8  | Five different output stage of modulator driver circuit topologies and the testing environment . . . . .           | 58 |

| 3.9  | Simulation comparison result of five different modulator driver (amplifier) circuit topologies . . . . .           | 60 |

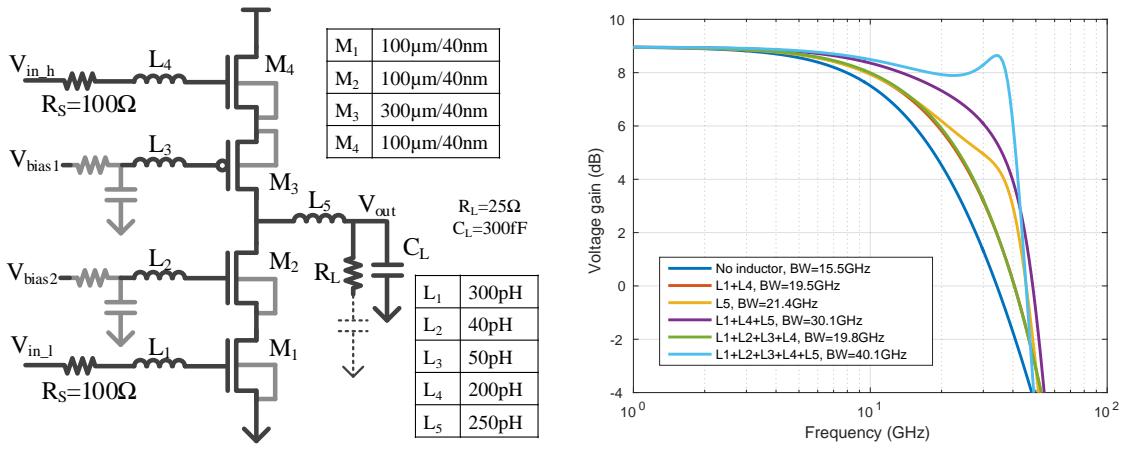

| 3.10 | N over N cascode amplifier with inductor peaking bandwidth enhancement                                             | 62 |

| 3.11 | Small signal model of N over N cascode amplifier with inductive peaking .                                          | 62 |

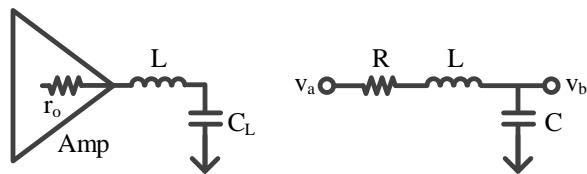

| 3.12 | Bandwidth enhancement based on serial inductive peaking on loading capacitance . . . . .                           | 63 |

| 3.13 | Bandwidth enhancement based on serial inductive peaking on loading capacitance . . . . .                           | 64 |

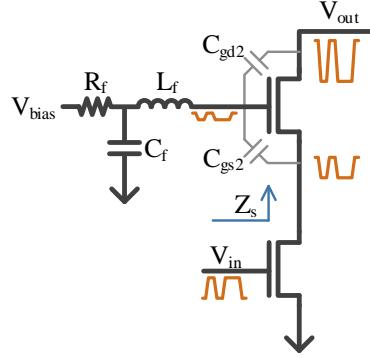

| 3.14 | Cascode transistor is biased by reference voltage through a RCL network                                            | 65 |

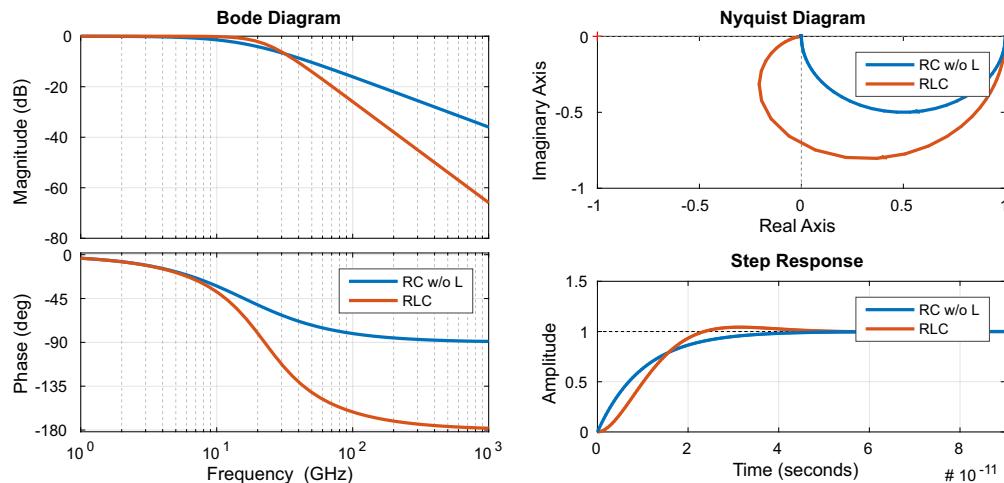

| 3.15 | An example of inductive peaking bandwidth enhancement on N over N cascode amplifier . . . . .                      | 66 |

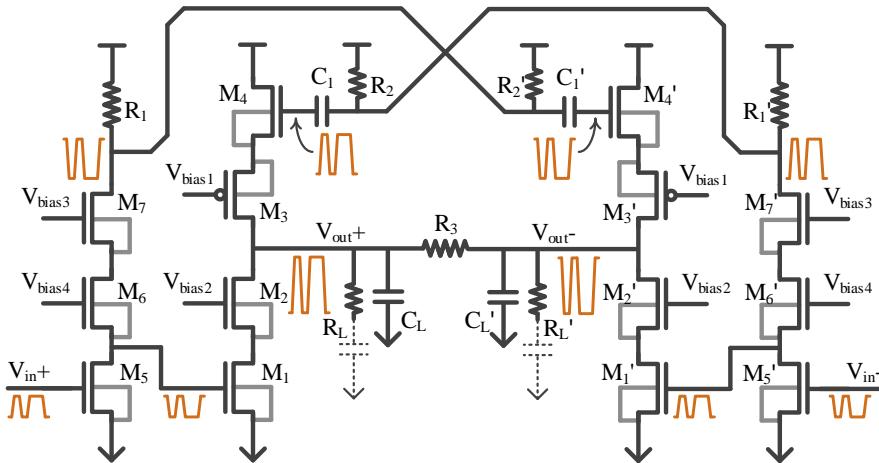

| 3.16 | N over N cascode amplifier with a CML pre-stage . . . . .                                                          | 66 |

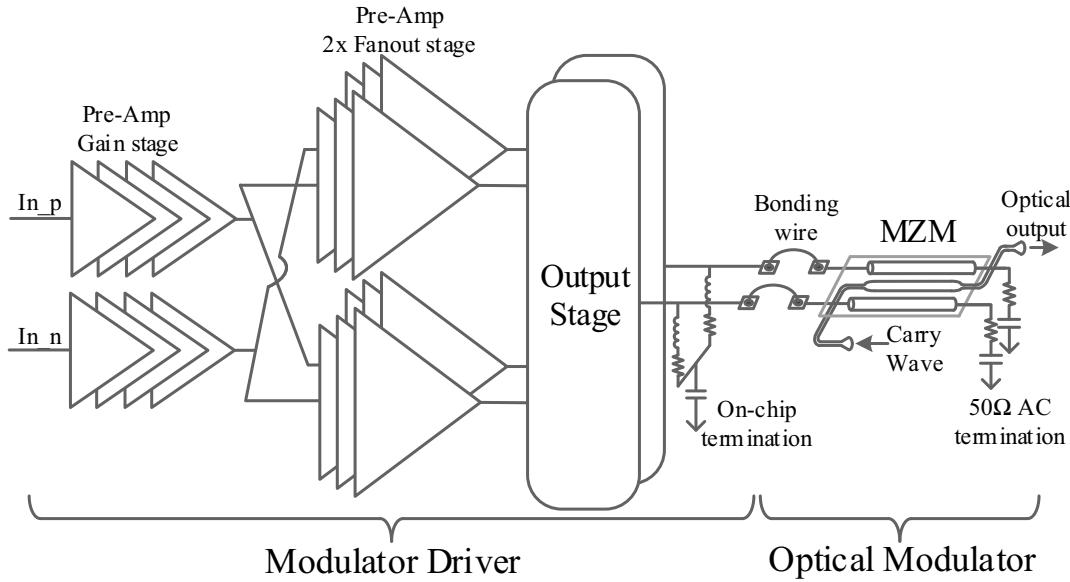

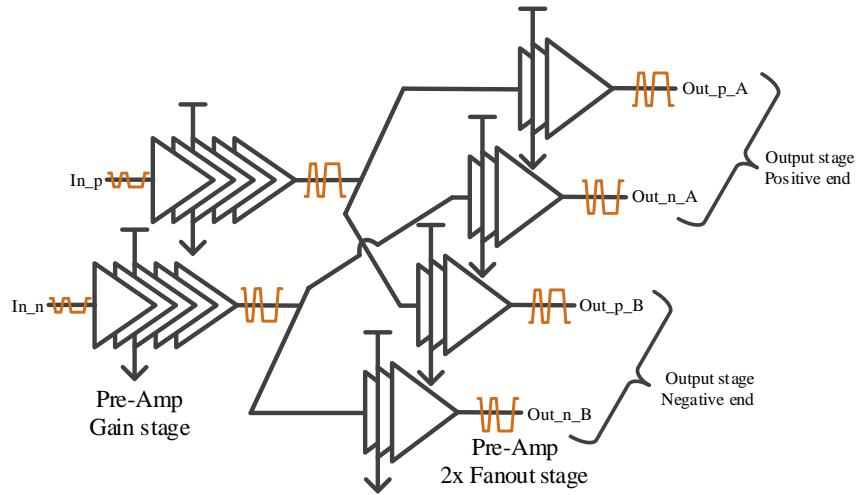

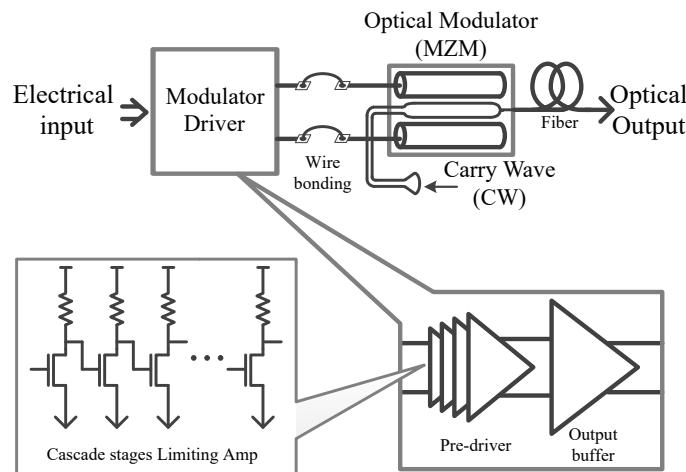

| 4.1  | Top level schematic of optical transmitter . . . . .                                                               | 71 |

| 4.2  | Pre-driver of modulator driver . . . . .                                                                           | 71 |

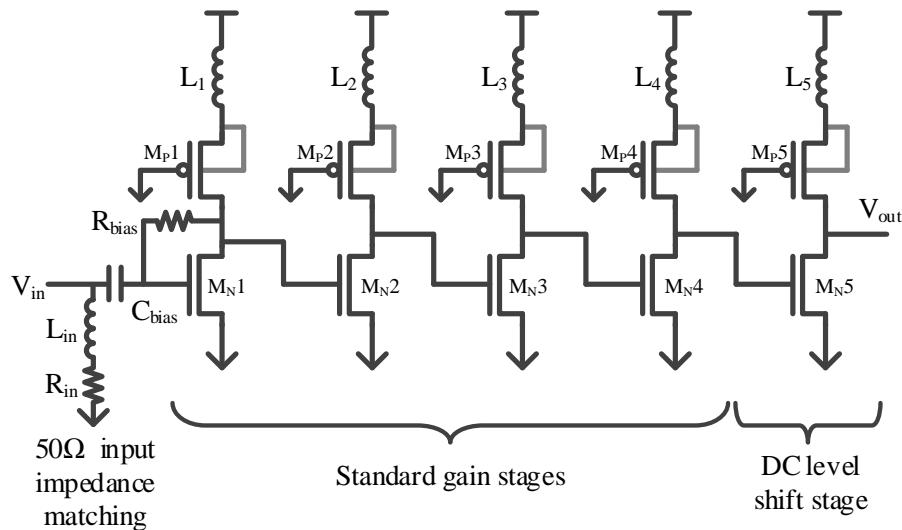

| 4.3  | Schematic of pre-driver gain stage . . . . .                                                                       | 72 |

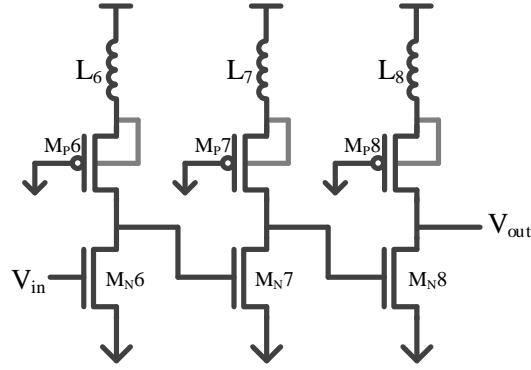

| 4.4  | Schematic of pre-driver double fan-out stage . . . . .                                                             | 73 |

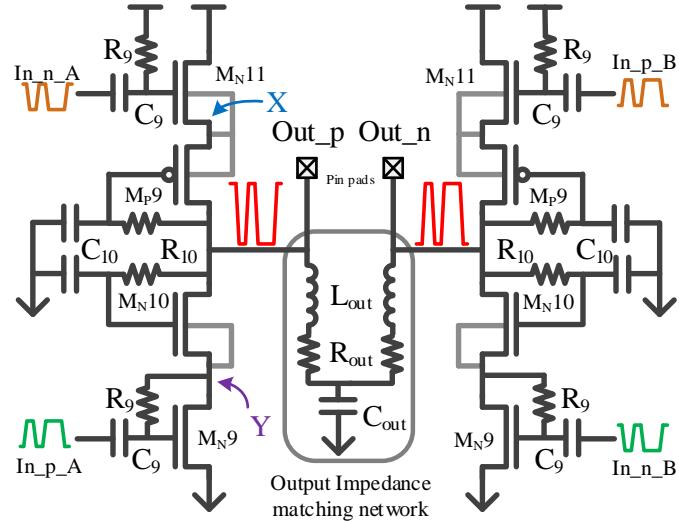

| 4.5  | Schematic of Output stage of modulator driver . . . . .                                                            | 73 |

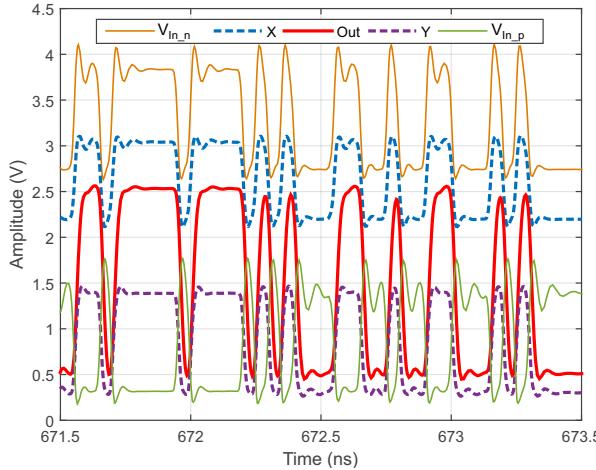

| 4.6  | Transient signal on different nets in output stage . . . . .                                                       | 74 |

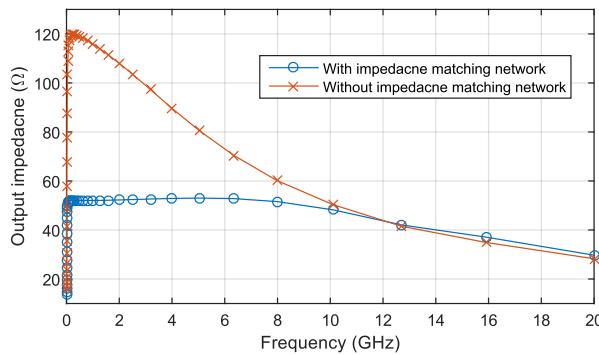

| 4.7  | Output stage impedance matching network . . . . .                                                                  | 74 |

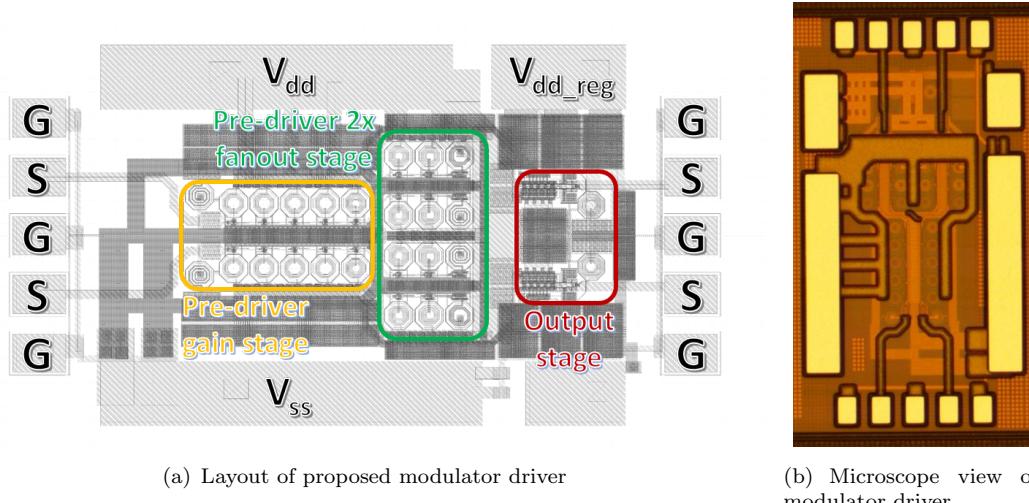

| 4.8  | Layout and microscope view of modulator driver design . . . . .                                                    | 75 |

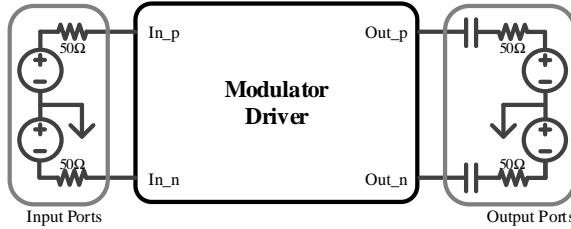

| 4.9  | Modulator driver S-parameter test bench . . . . .                                                                  | 76 |

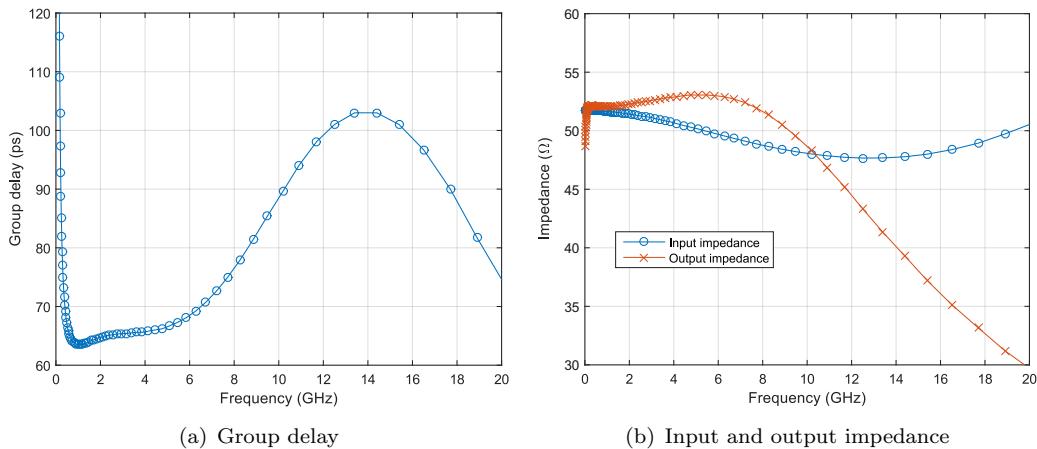

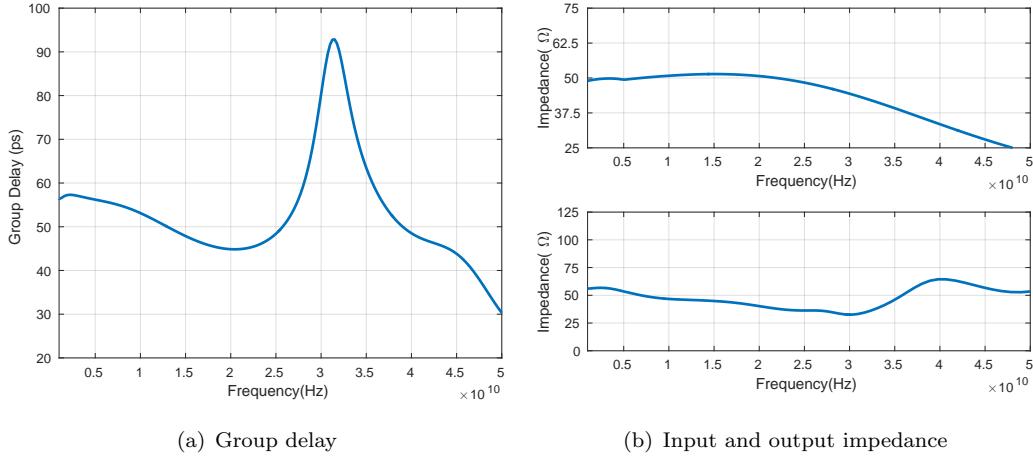

| 4.10 | Group delay and impedance characteristic of modulator driver . . . . .                                             | 76 |

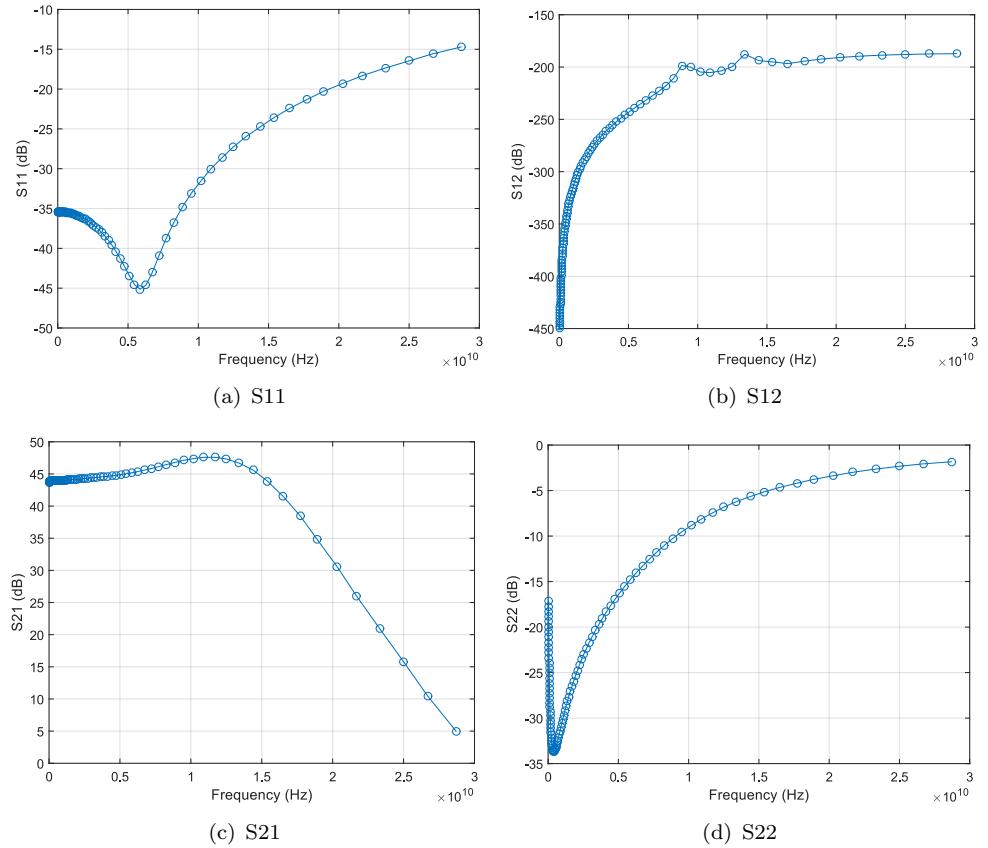

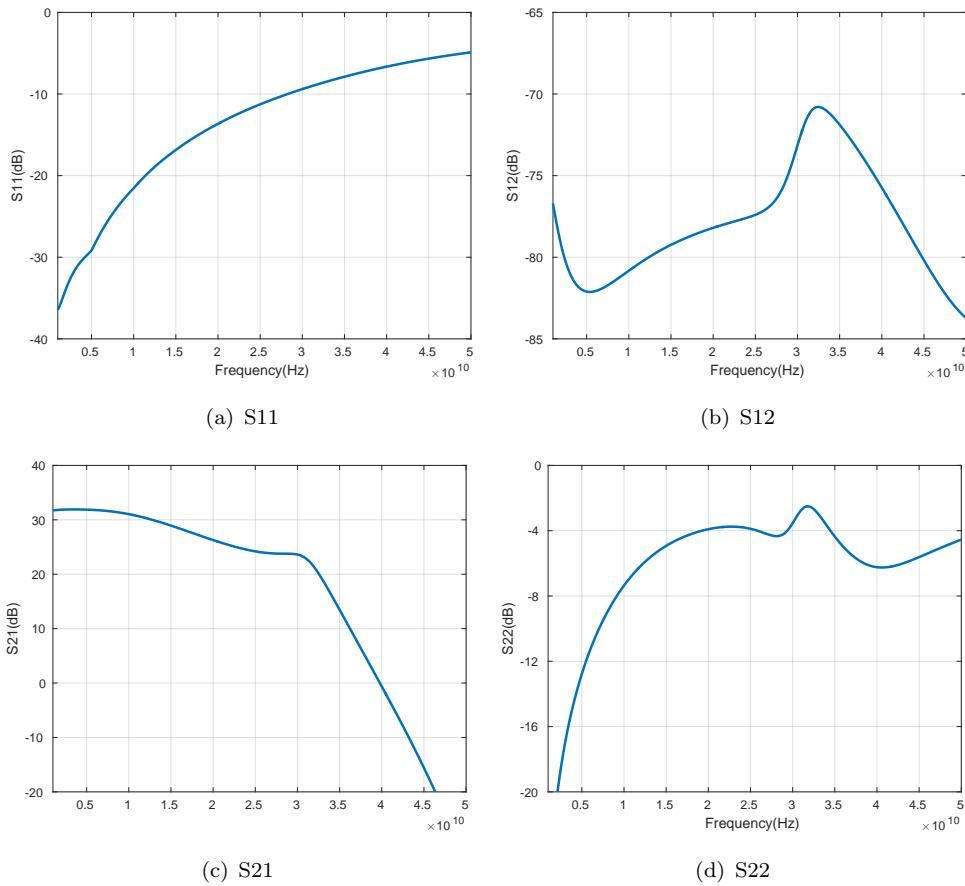

| 4.11 | S-parameter result of modulator driver . . . . .                                                                   | 77 |

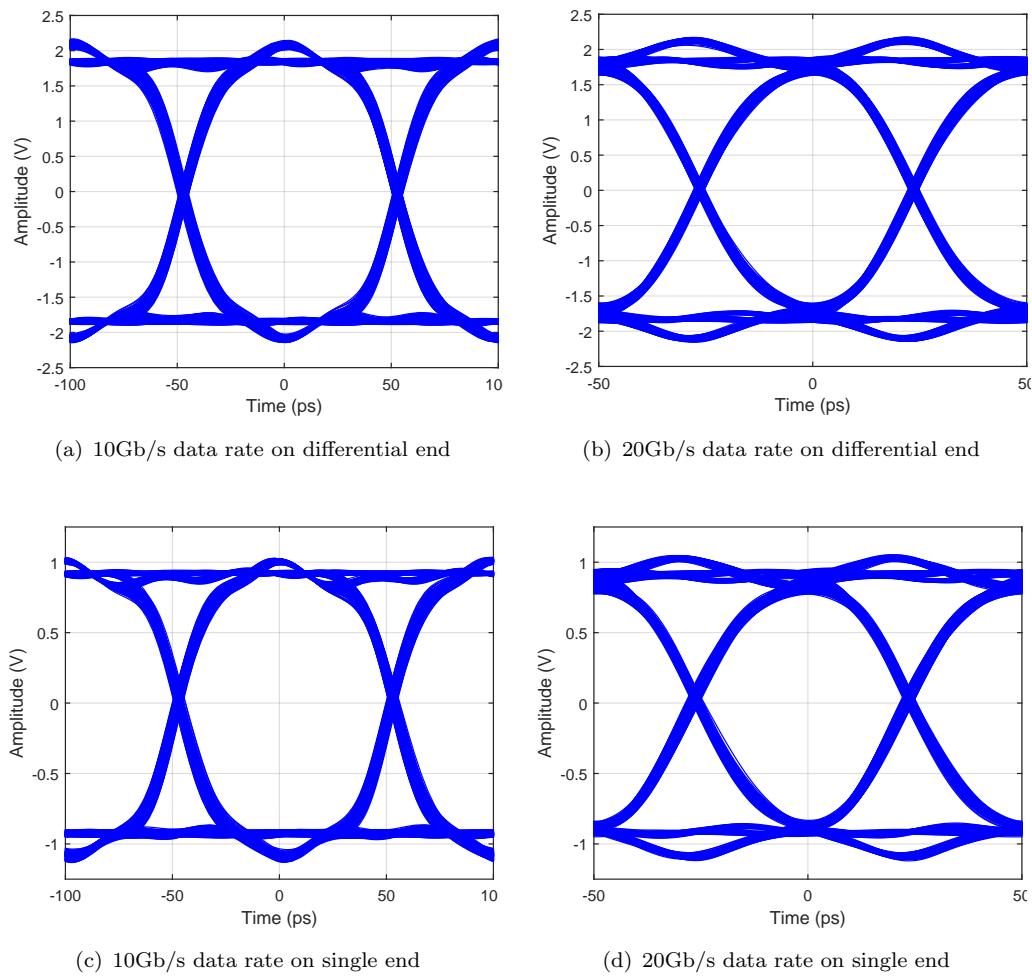

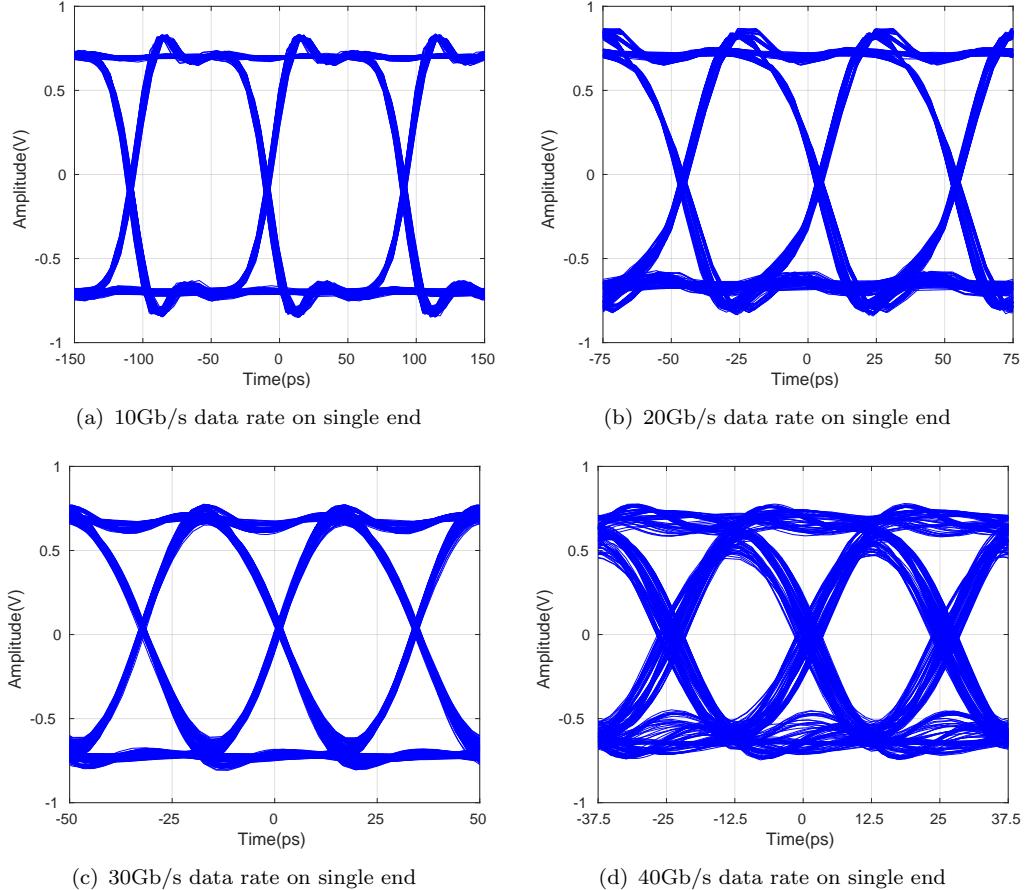

| 4.12 | Transient simulation result of modulator driver . . . . .                                                          | 78 |

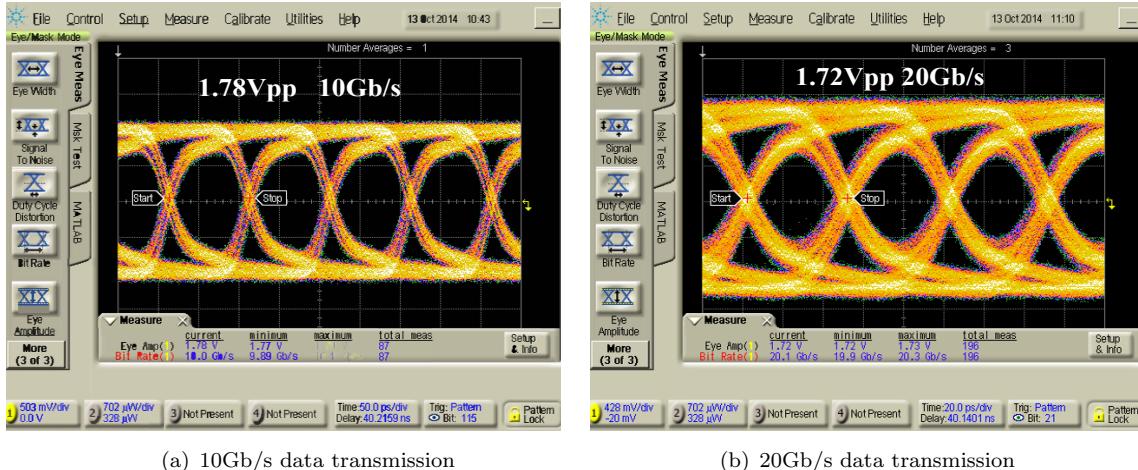

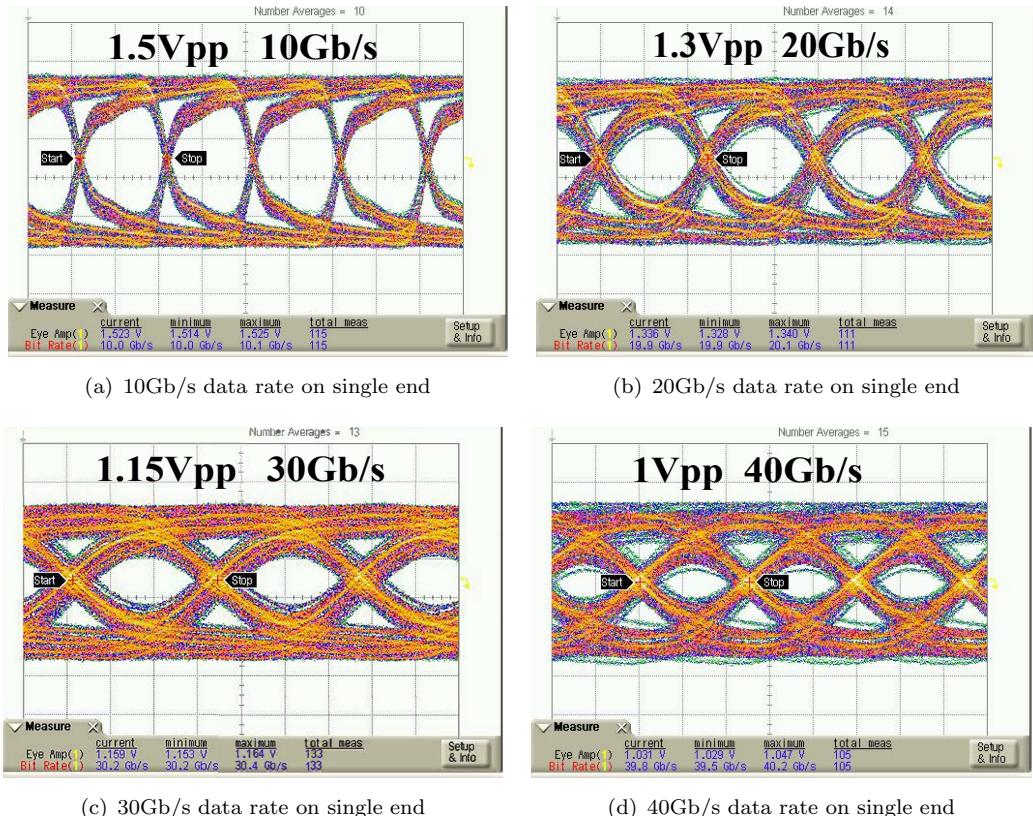

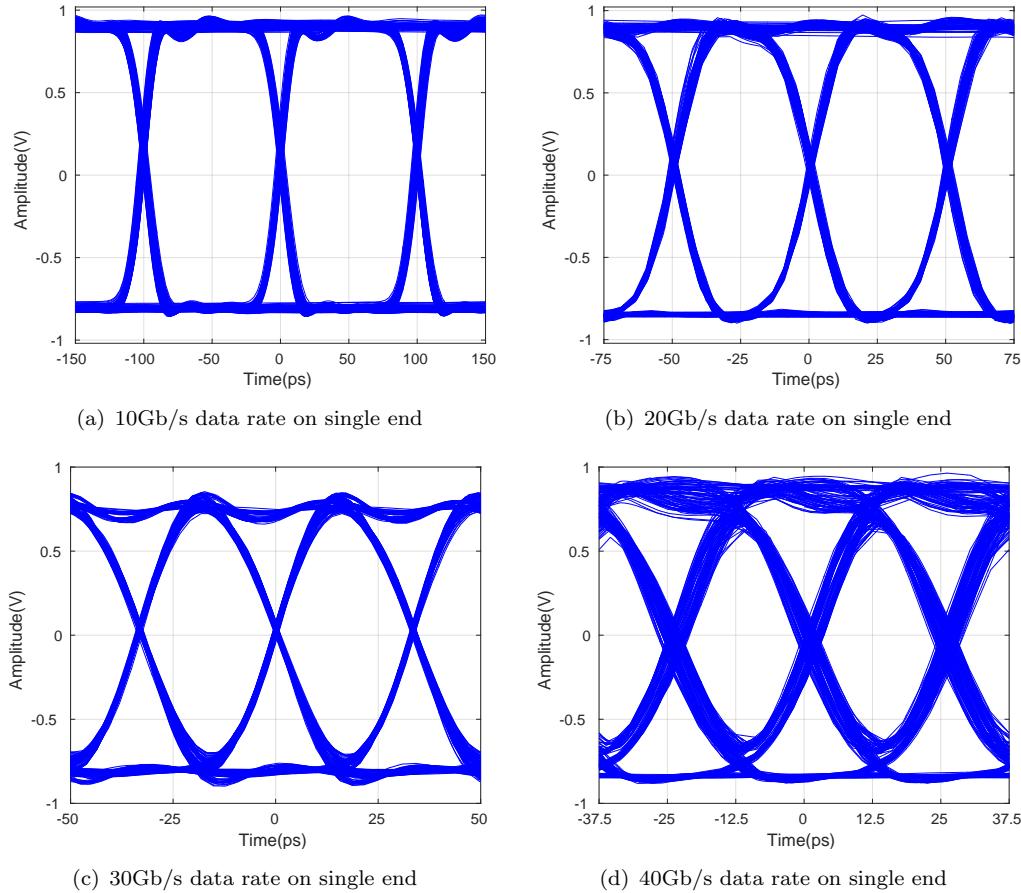

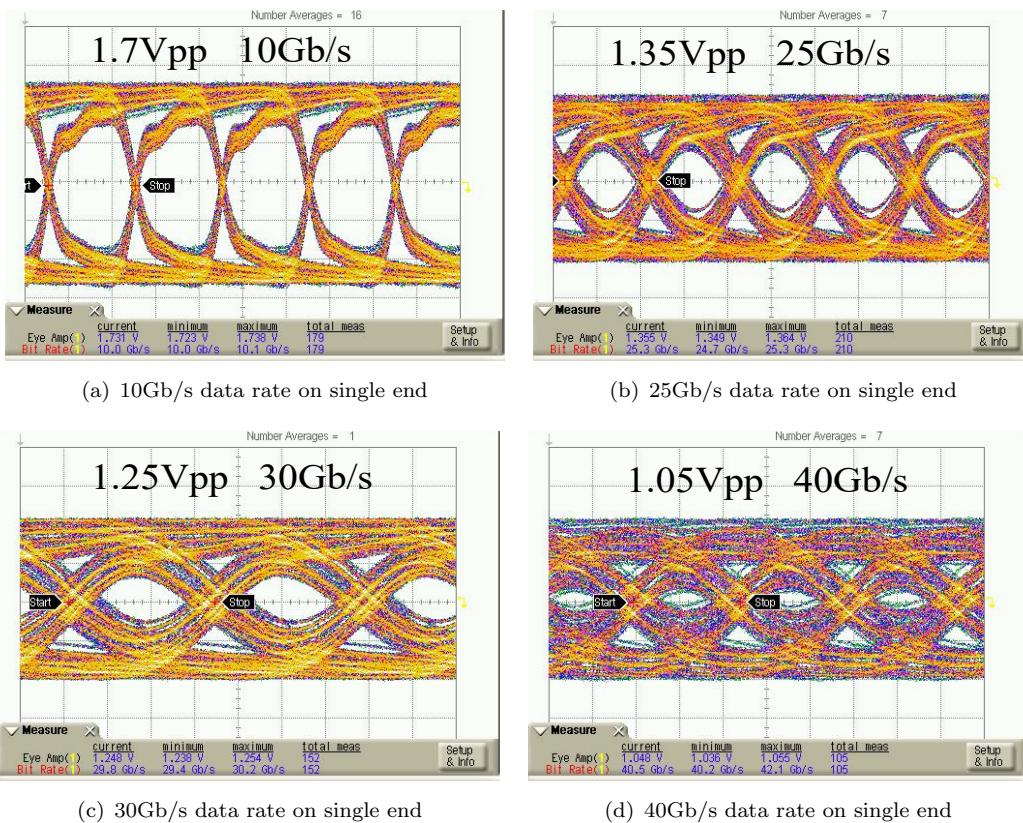

| 4.13 | Modulator driver electric measurement result with $2^{15-1}$ PRBS . . . . .                                        | 79 |

| 4.14 | The optical transmitter . . . . .                                                                                  | 80 |

| 4.15 | Testing hierarchy of the integrated optical modulator . . . . .                                                    | 80 |

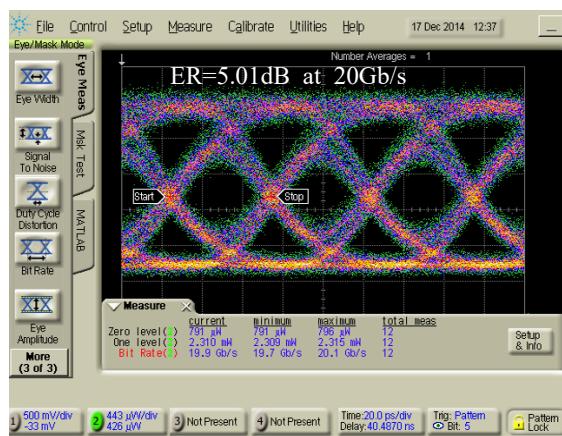

| 4.16 | Optical measurement of optical modulator with $2^{15-1}$ PRBS at 20Gb/s .                                          | 81 |

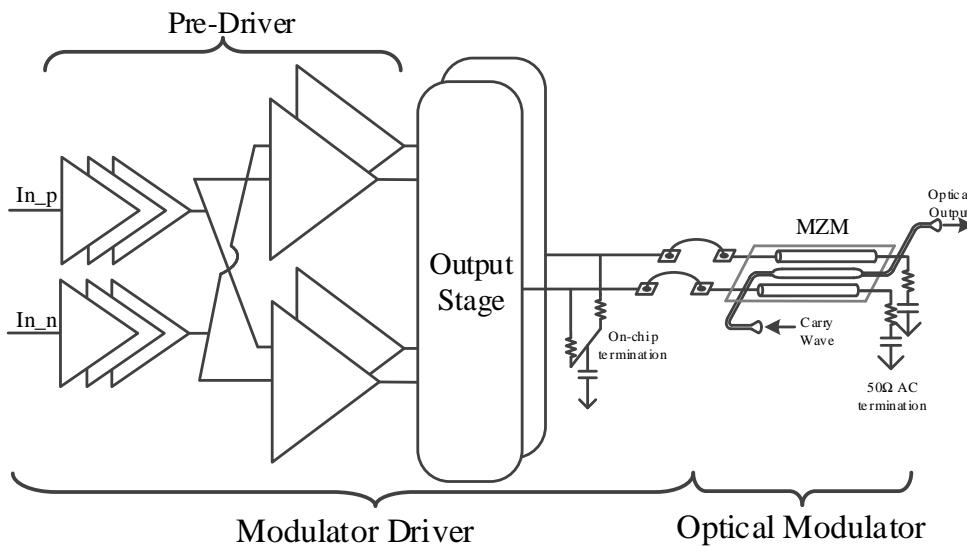

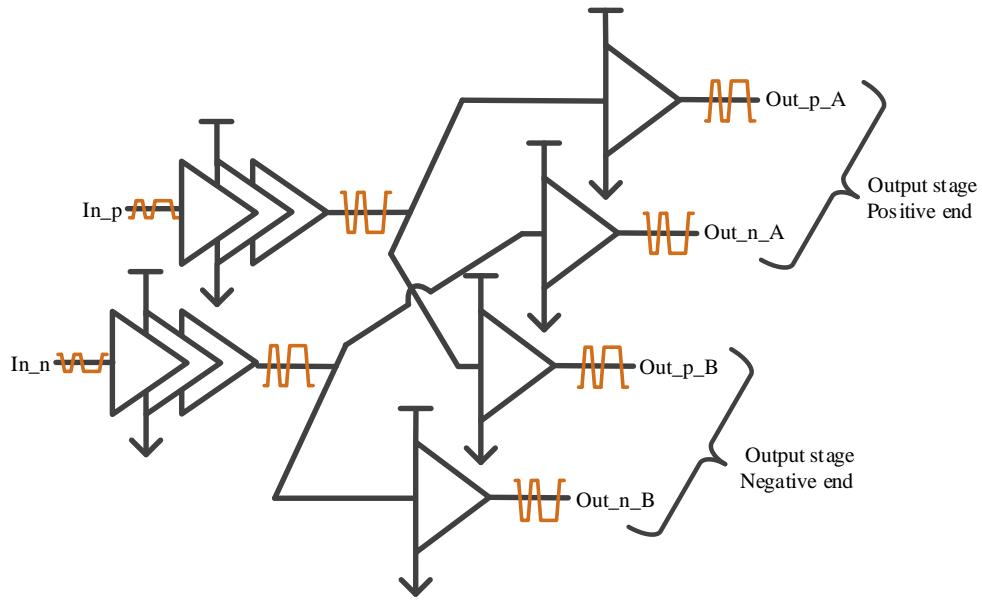

| 4.17 | Top level schematic of optical transmitter . . . . .                                                               | 82 |

| 4.18 | Abstract of pre-driver in modulator driver . . . . .                                                               | 83 |

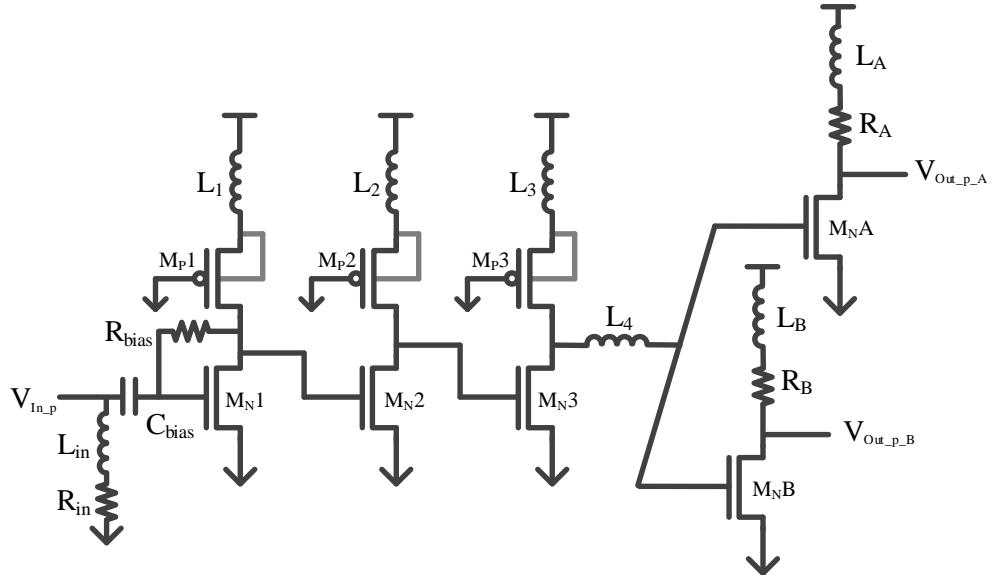

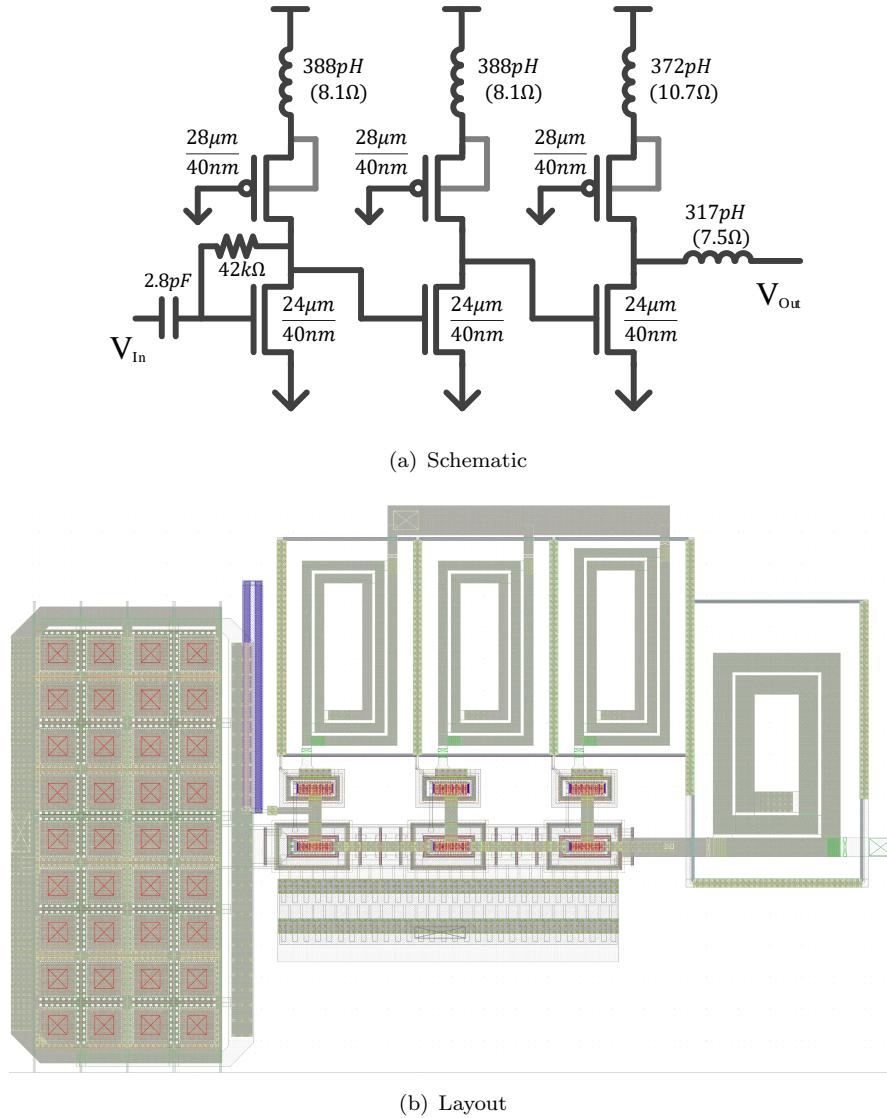

| 4.19 | Schematic of pre-driver in modulator driver . . . . .                                                              | 83 |

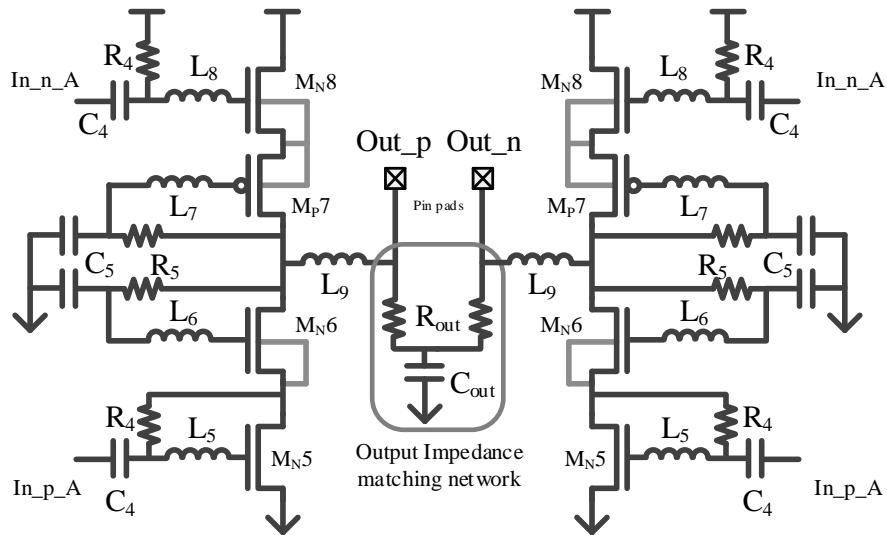

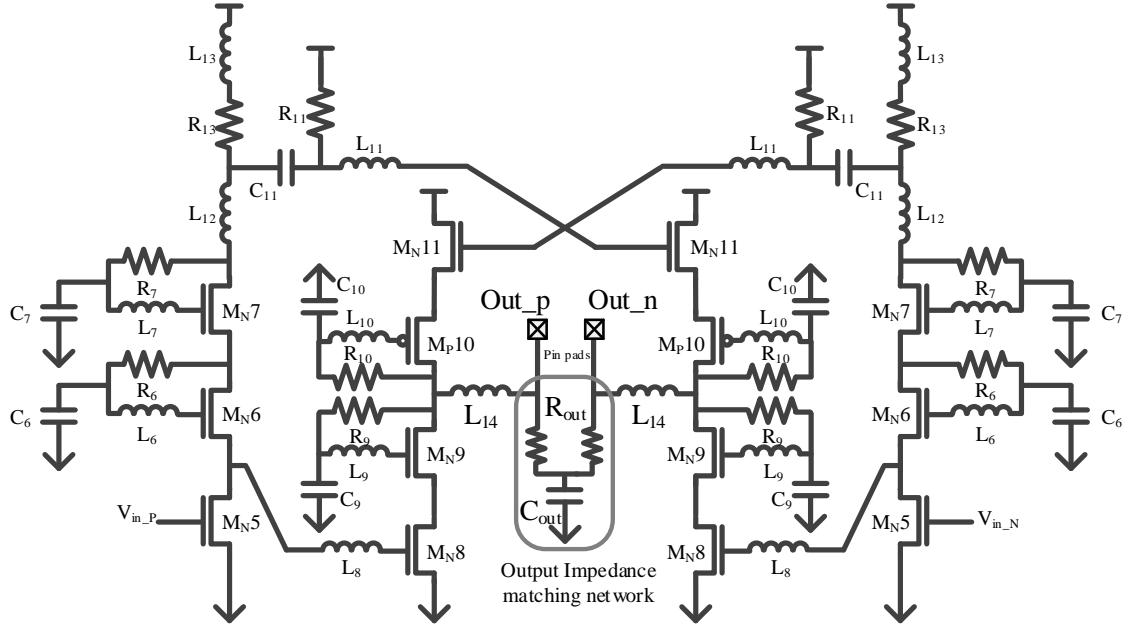

| 4.20 | Schematic of output stage in modulator driver . . . . .                                                            | 84 |

|      |                                                                                                                |     |

|------|----------------------------------------------------------------------------------------------------------------|-----|

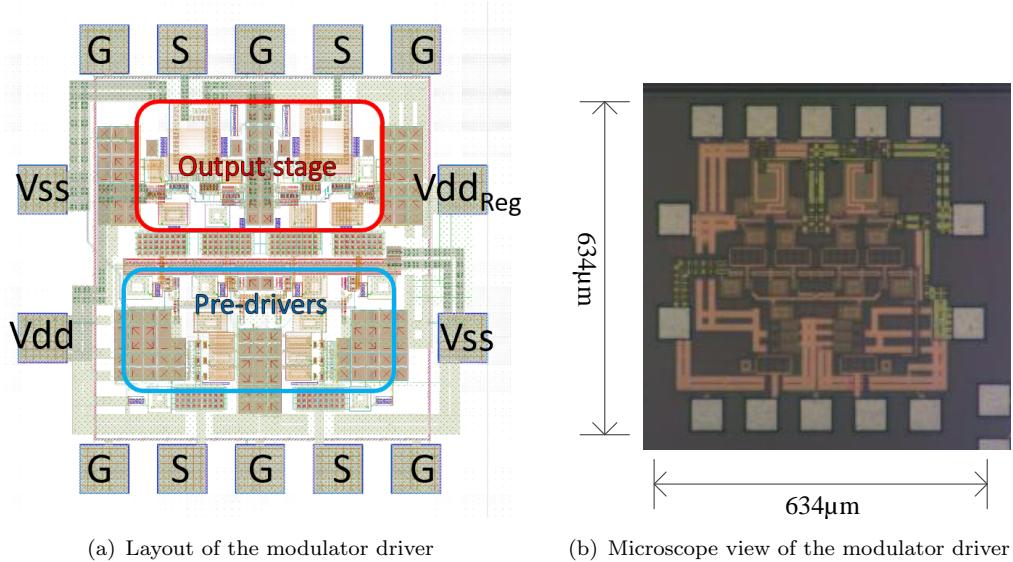

| 4.21 | Layout and microscope view of the modulator driver . . . . .                                                   | 85  |

| 4.22 | Group delay and impedance characteristic of modulator driver . . . . .                                         | 86  |

| 4.23 | Schematic of conventional cascode push pull amplifiers . . . . .                                               | 86  |

| 4.24 | Transient simulation result of modulator driver . . . . .                                                      | 87  |

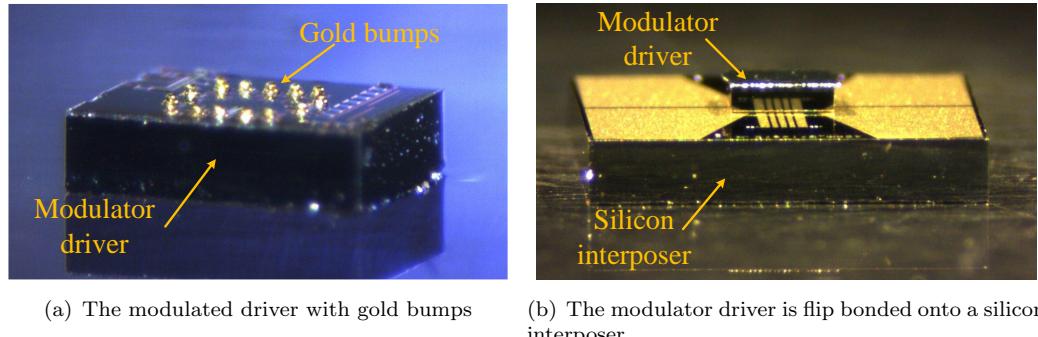

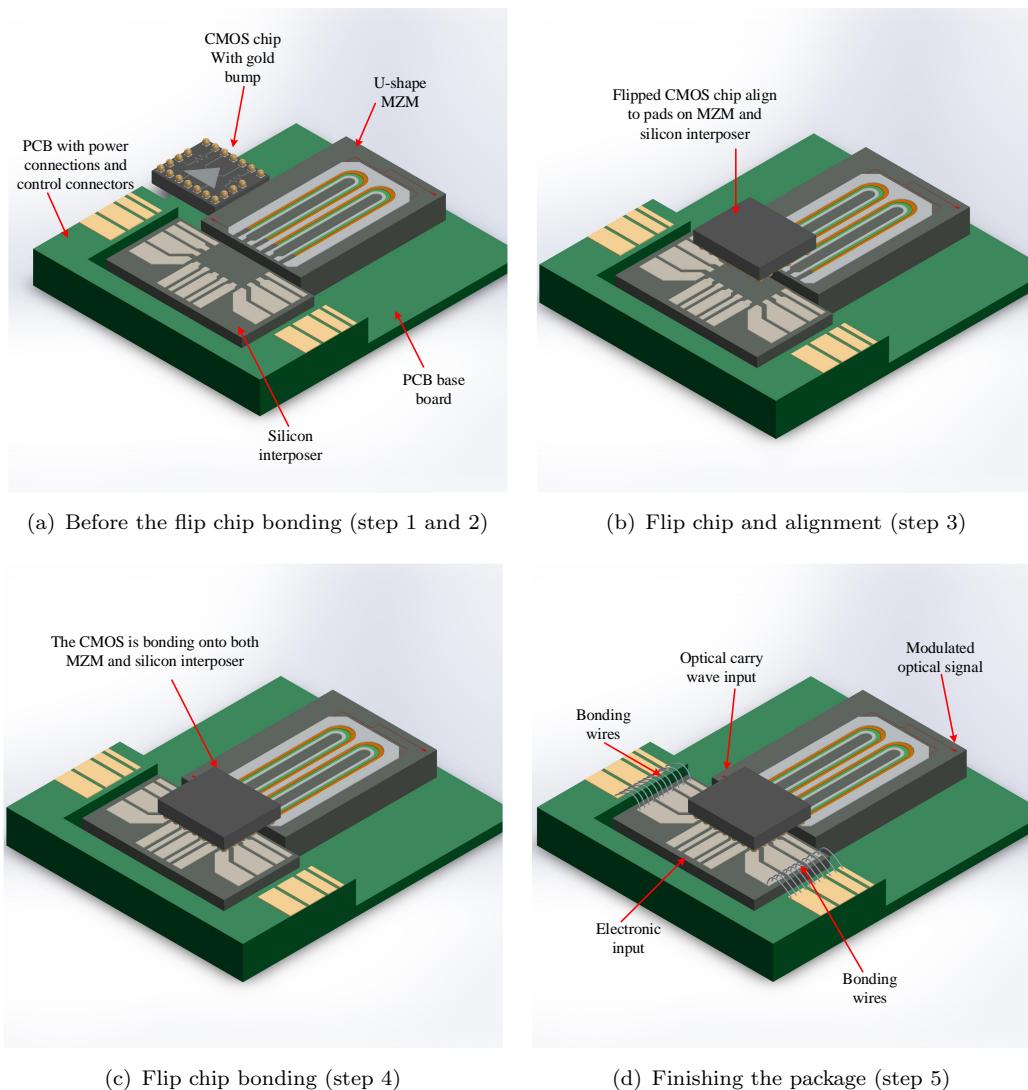

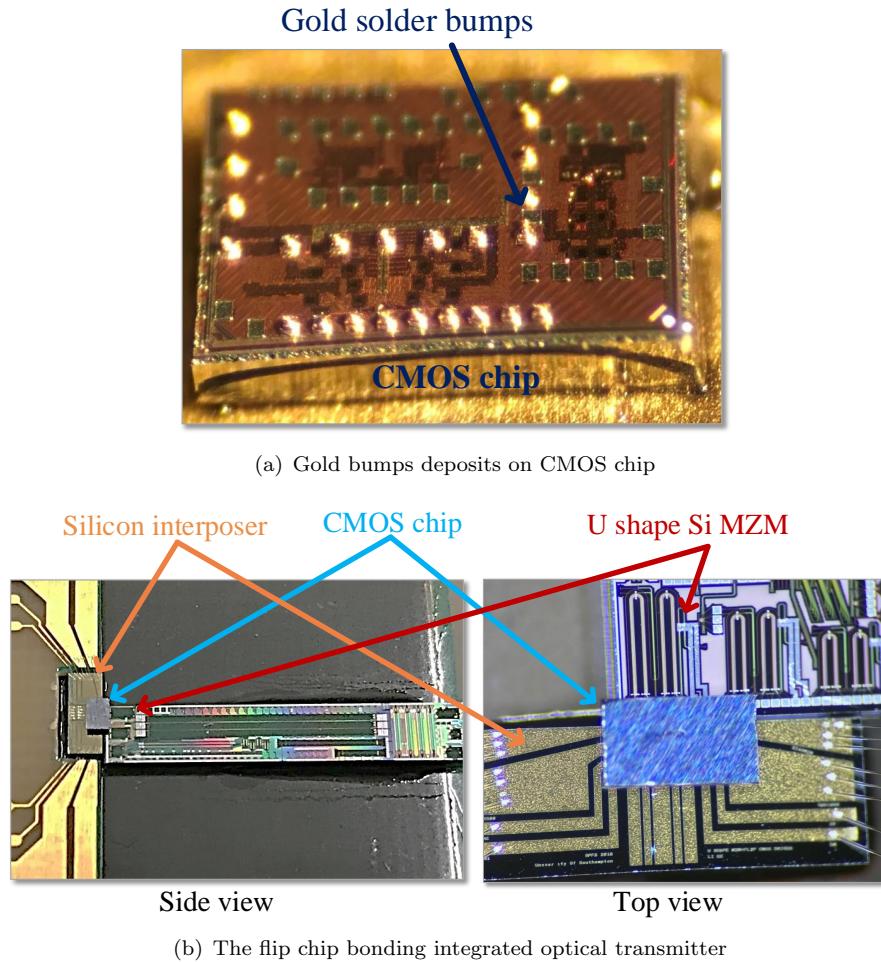

| 4.25 | The modulator driver flip chip bonding onto silicon interposer . . . . .                                       | 89  |

| 4.26 | Electric testing result of modulator driver . . . . .                                                          | 89  |

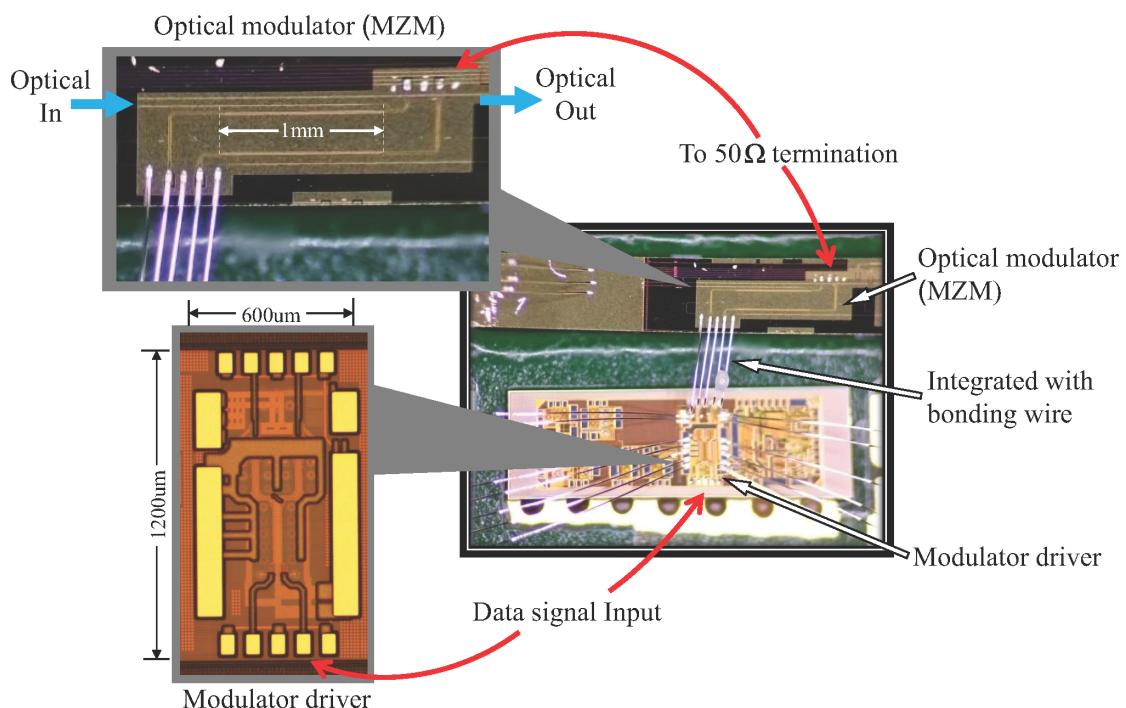

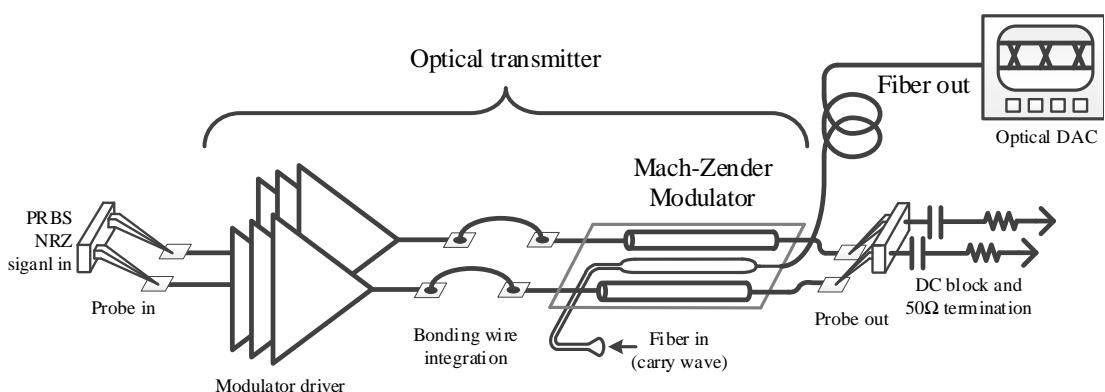

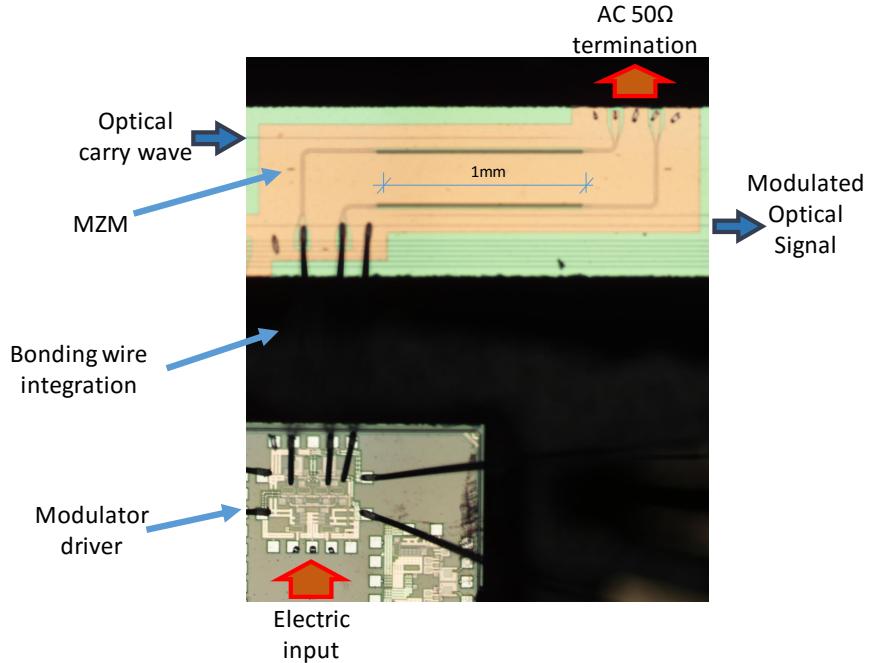

| 4.27 | Modulator driver integrated with MZM from [116] . . . . .                                                      | 91  |

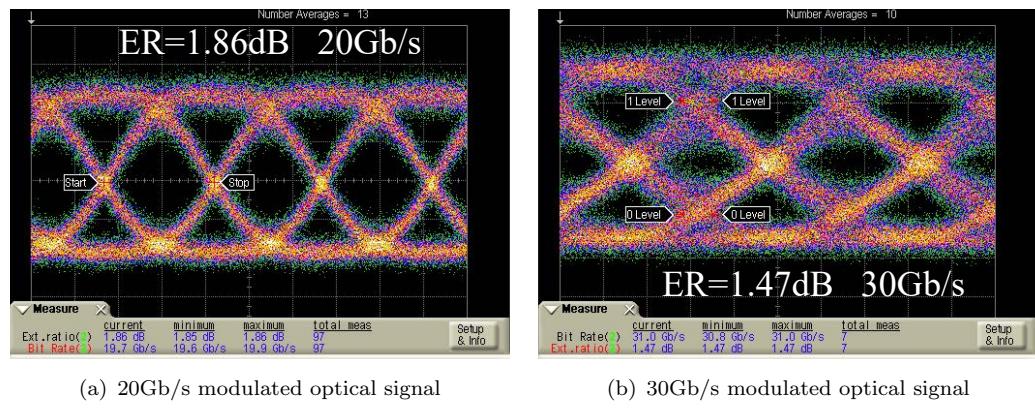

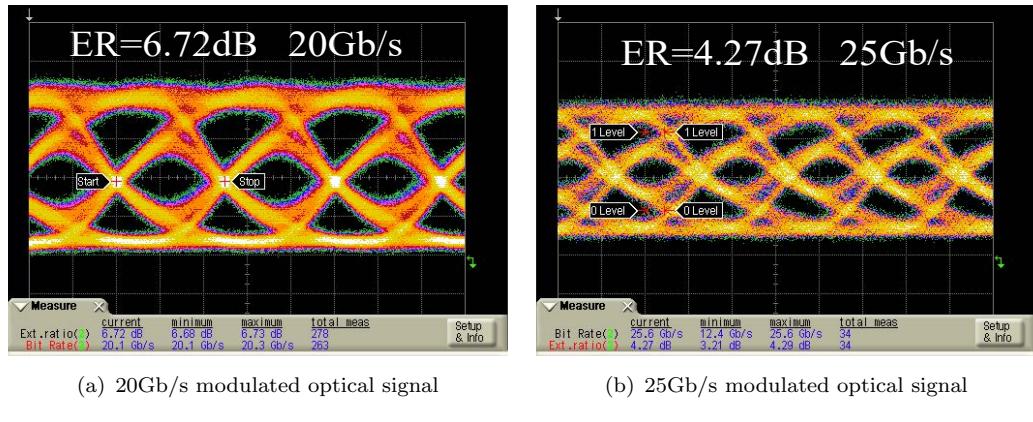

| 4.28 | The modulated optical signals from optical transmitter based on modulator driver and MZM from [116] . . . . .  | 91  |

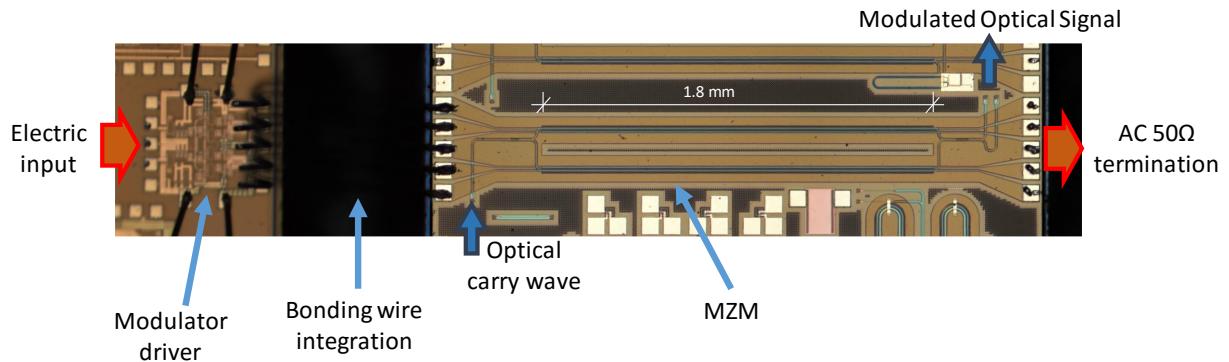

| 4.29 | Modulator driver integrated with MZM2 . . . . .                                                                | 92  |

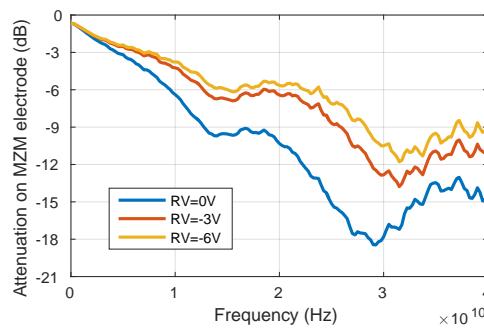

| 4.30 | Attenuation of electrodes on MZM at different reverse bias[55] . . . . .                                       | 92  |

| 4.31 | Electric testing result of modulator driver . . . . .                                                          | 93  |

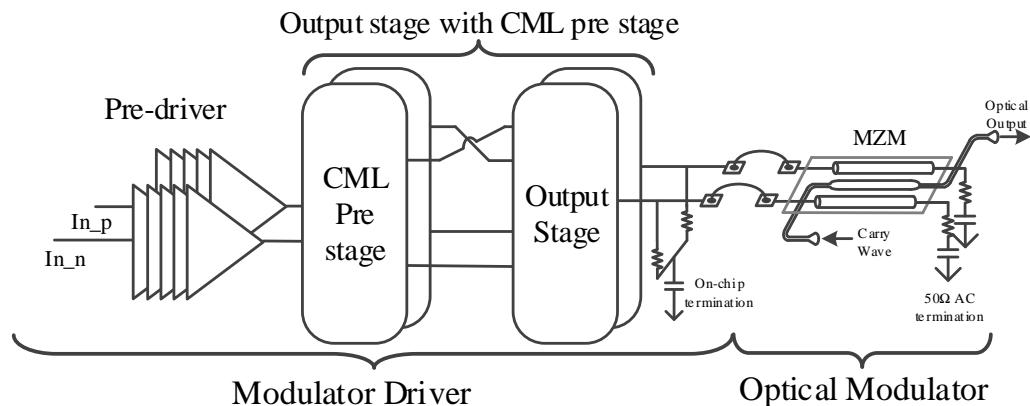

| 4.32 | Top level schematic of the optical transmitter . . . . .                                                       | 93  |

| 4.33 | Schematic of pre-driver in modulator driver . . . . .                                                          | 94  |

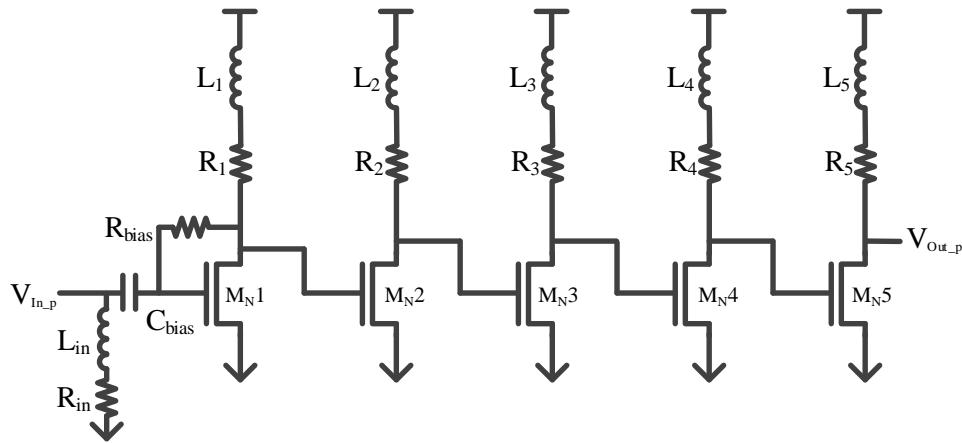

| 4.34 | Schematic of output stage with CML pre-stage in modulator driver . . . . .                                     | 95  |

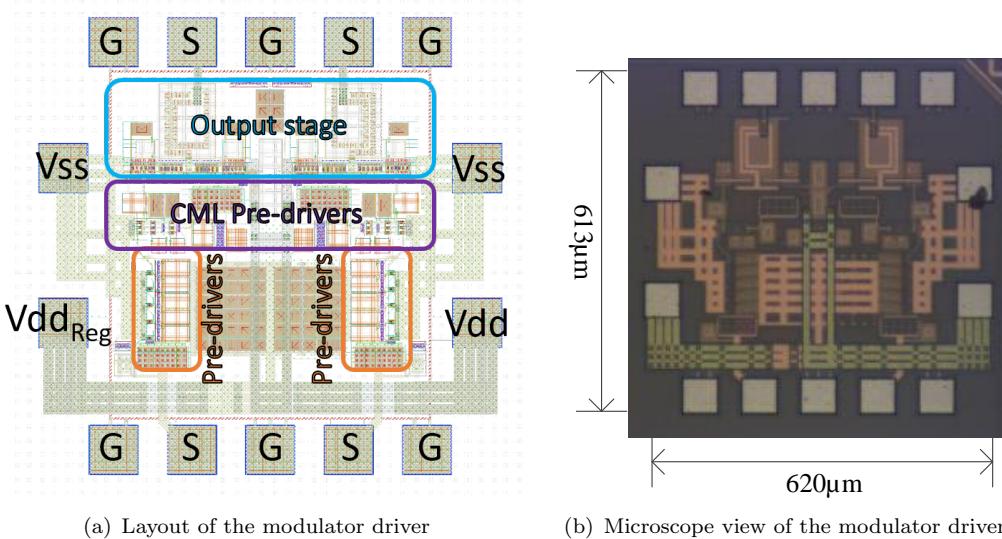

| 4.35 | Layout and photograph of modulator driver . . . . .                                                            | 96  |

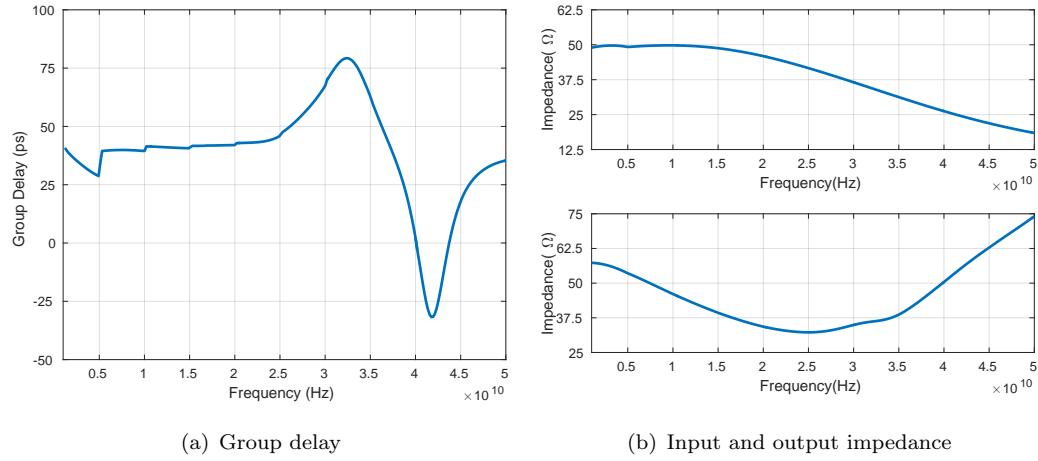

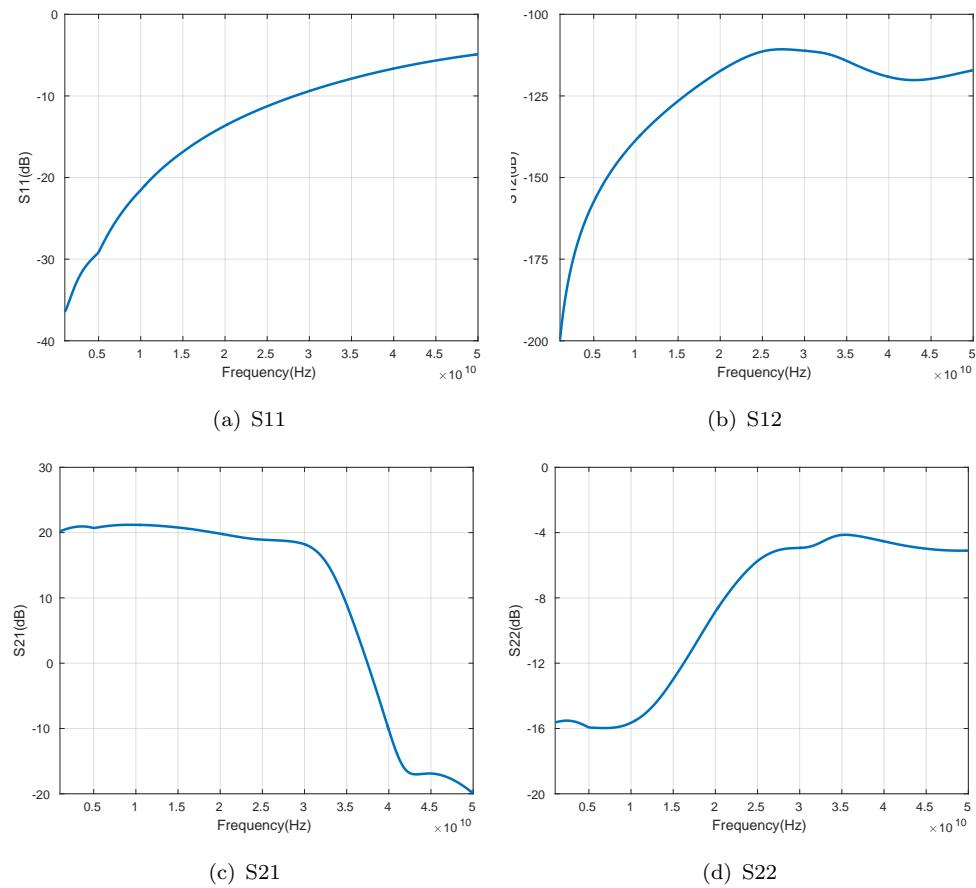

| 4.36 | Group delay and impedance characteristic of modulator driver . . . . .                                         | 97  |

| 4.37 | Schematic of conventional cascode push pull amplifiers . . . . .                                               | 97  |

| 4.38 | Transient simulation result of modulator driver . . . . .                                                      | 98  |

| 4.39 | Electric testing result of modulator driver . . . . .                                                          | 100 |

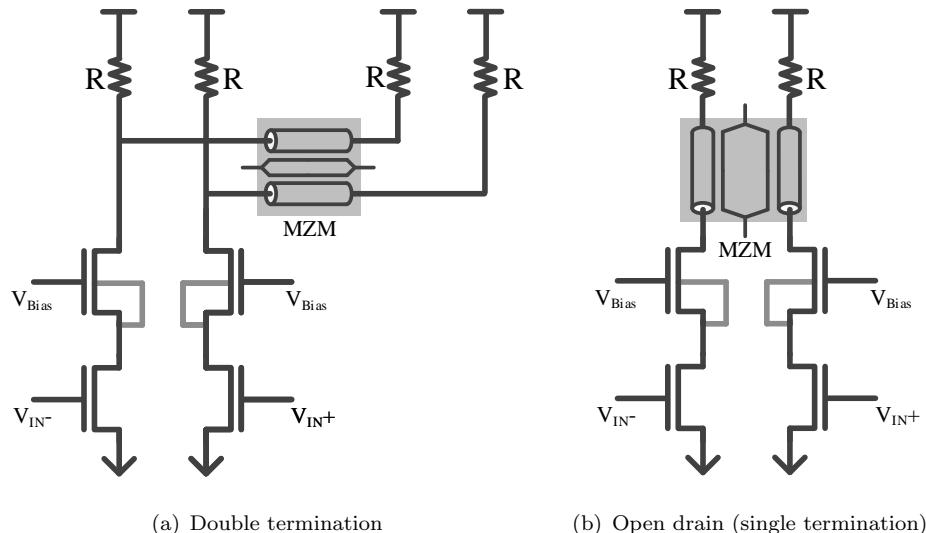

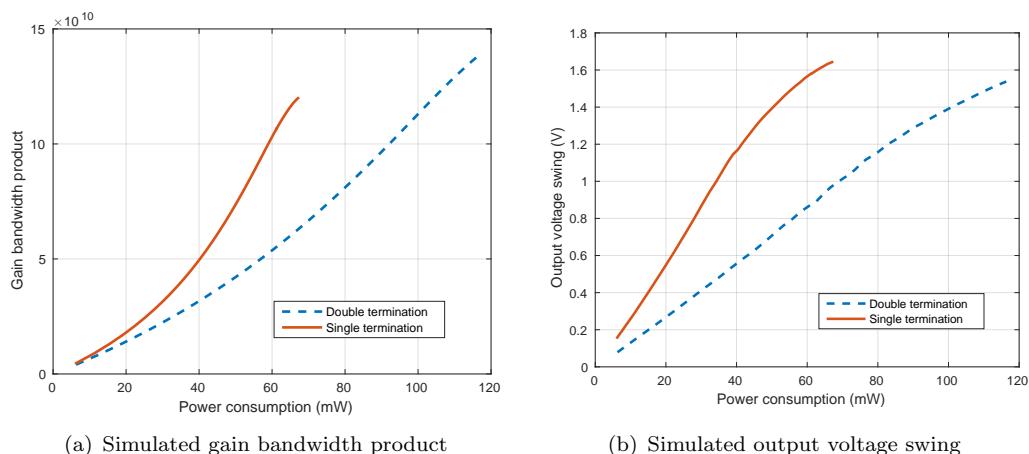

| 5.1  | A modulator driver with two termination configurations . . . . .                                               | 107 |

| 5.2  | Two typical modulator driver topologies integrates with a nominal $50\Omega$ MZM . . . . .                     | 108 |

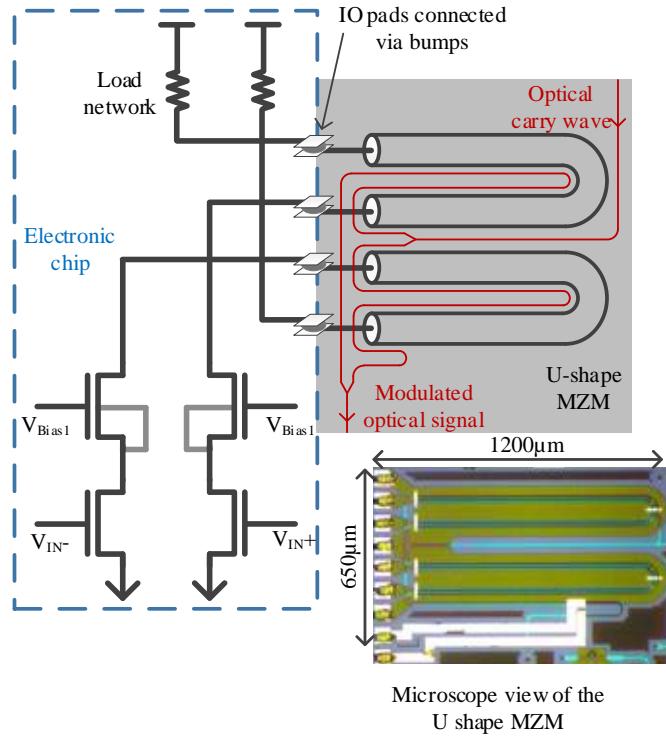

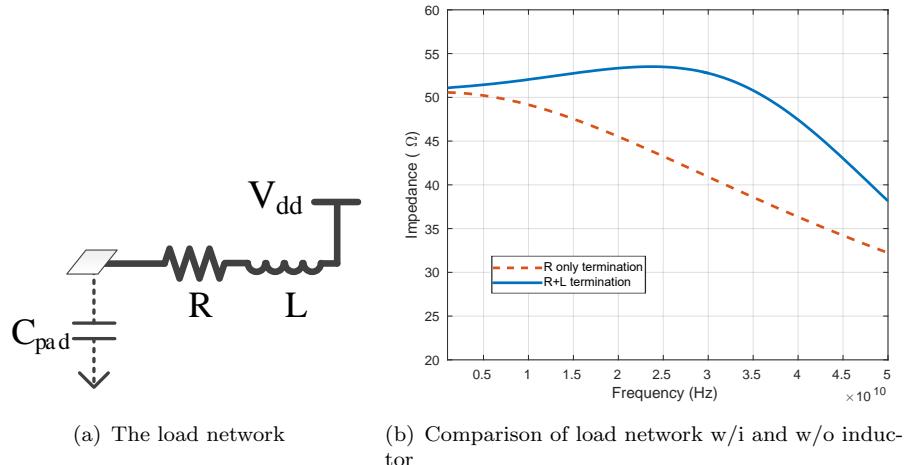

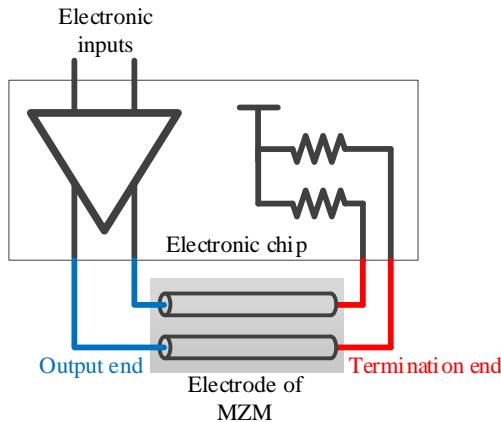

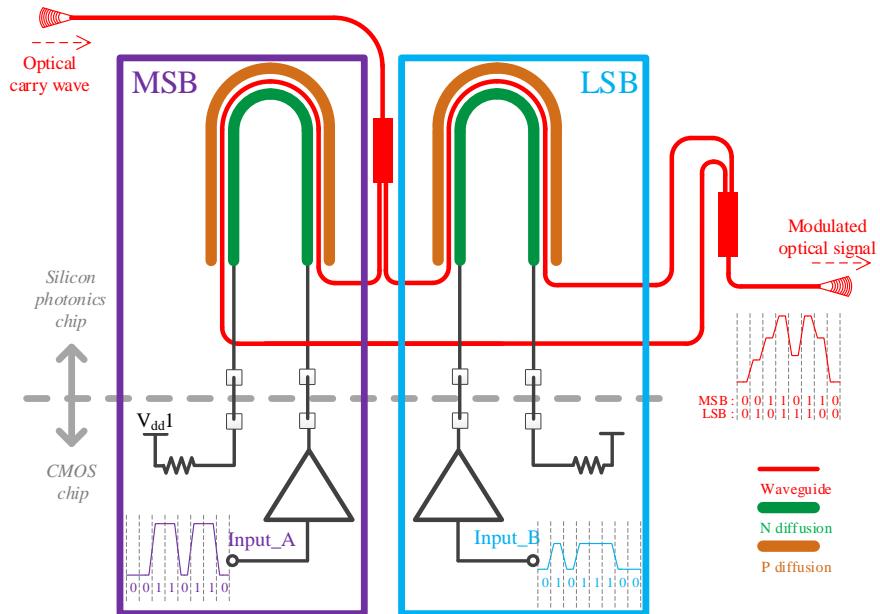

| 5.3  | Abstract view of modulator driver integrated with U-shape MZM and microscope view of the U-shape MZM . . . . . | 110 |

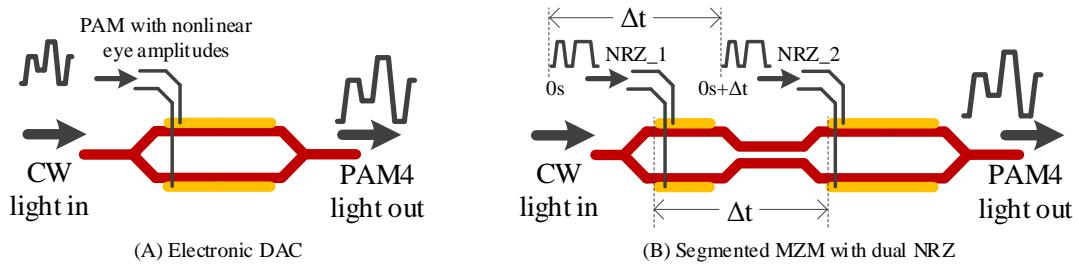

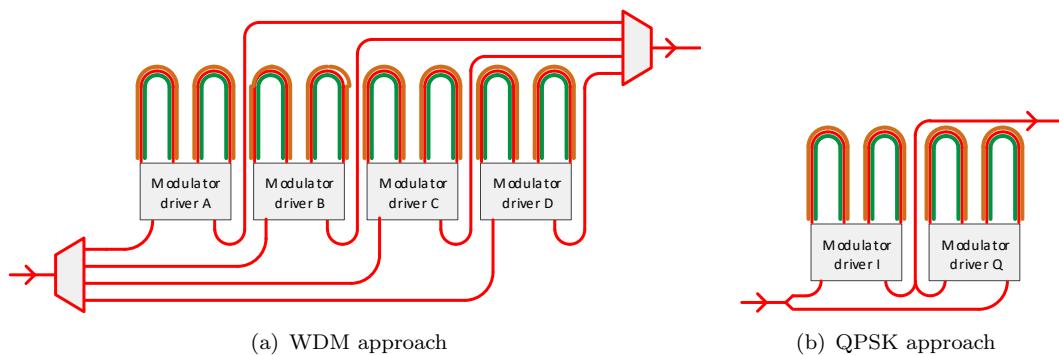

| 5.4  | Two typical modulator driver topologies integrates with a nominal $50\Omega$ MZM . . . . .                     | 111 |

| 5.5  | Conventional PAM4 optical transmitter . . . . .                                                                | 111 |

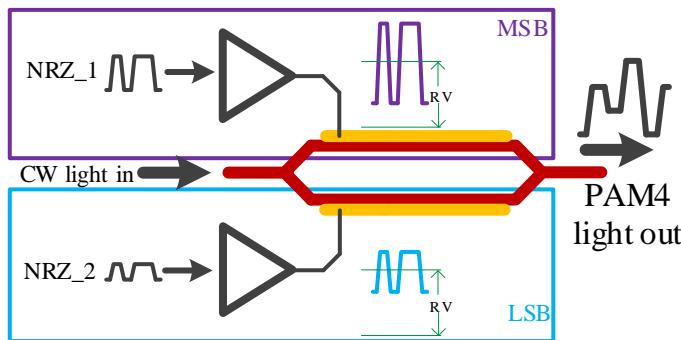

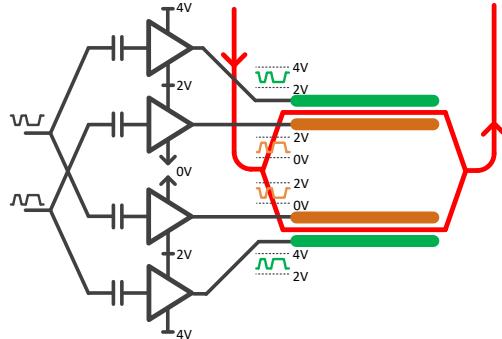

| 5.6  | Low cost PAM4 optical transmitter . . . . .                                                                    | 112 |

| 5.7  | Linearity of PAM4 optical signal . . . . .                                                                     | 113 |

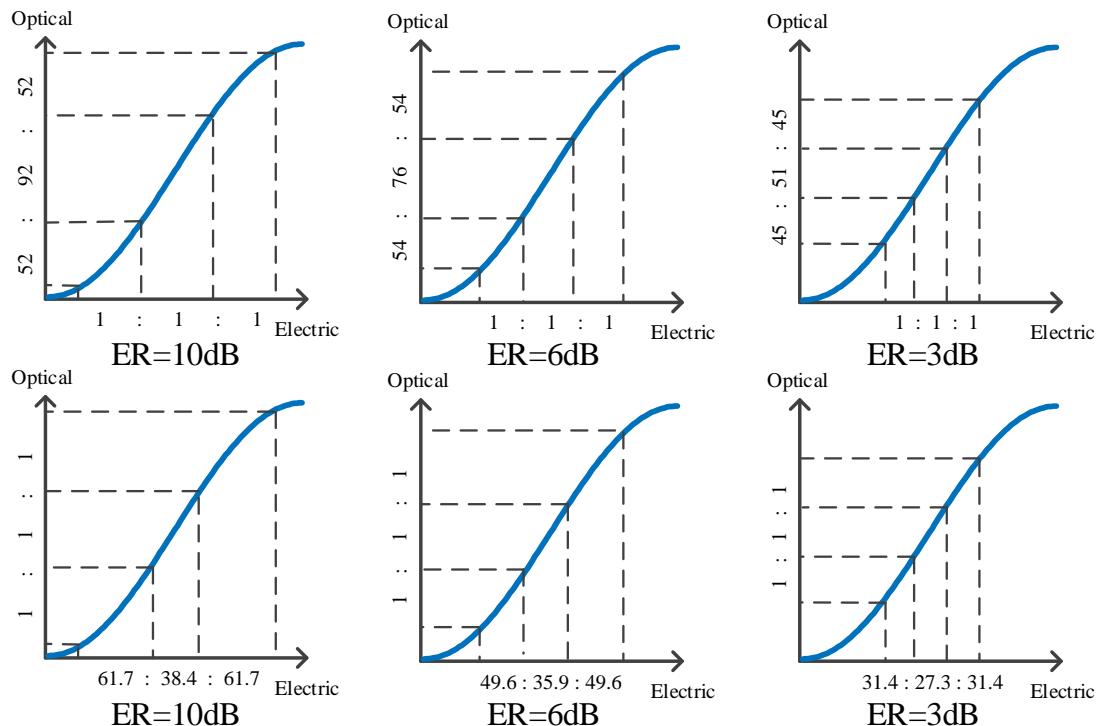

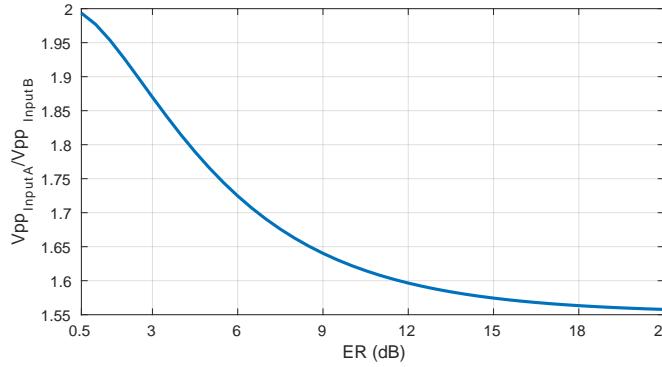

| 5.8  | Input $V_{pp}$ ratio to targeting ER . . . . .                                                                 | 114 |

| 5.9  | Input $V_{pp}$ ratio on different targeting ER . . . . .                                                       | 114 |

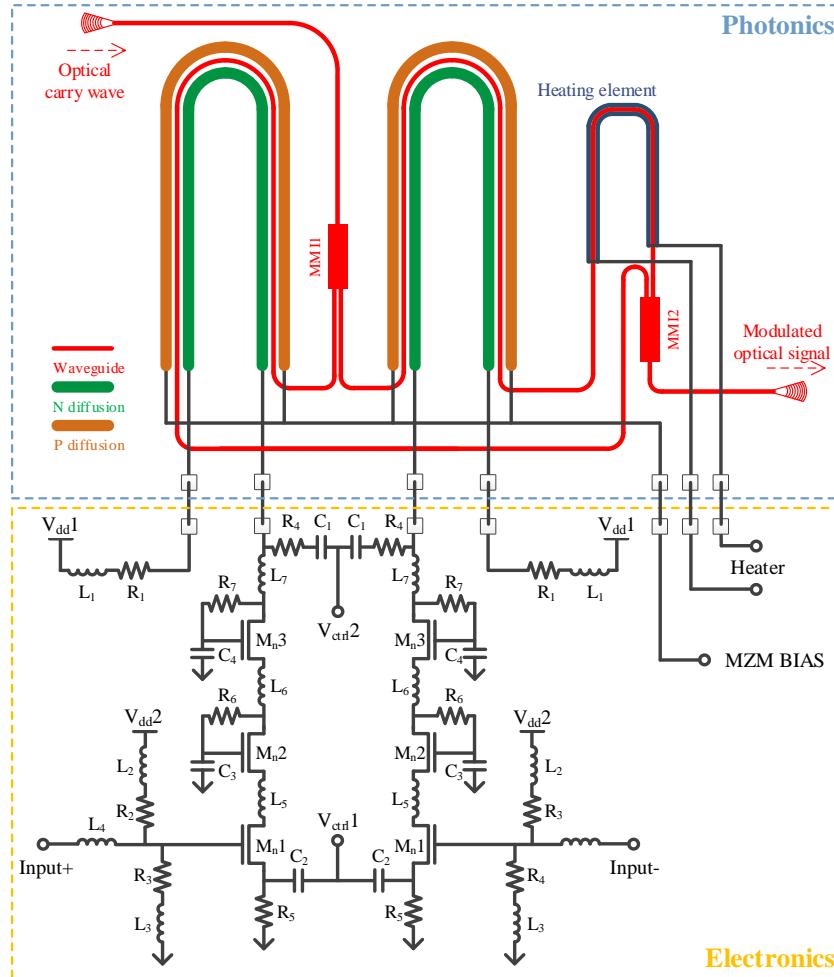

| 6.1  | Schematic of optical transmitter . . . . .                                                                     | 118 |

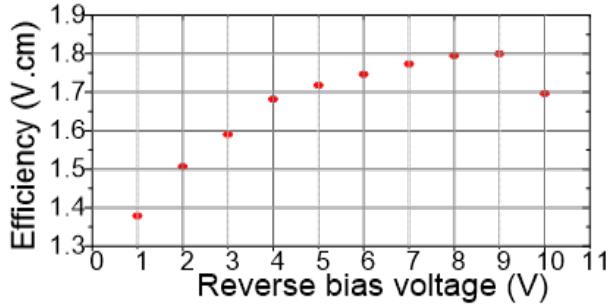

| 6.2  | Measured modulation efficiency under different reverse bias voltage. . . . .                                   | 119 |

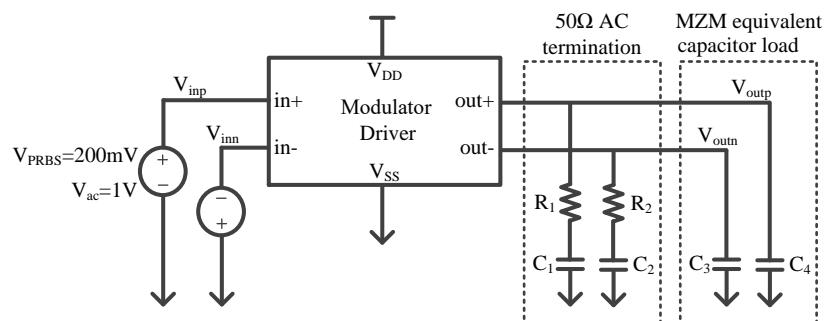

| 6.3  | Electric simulation environment . . . . .                                                                      | 120 |

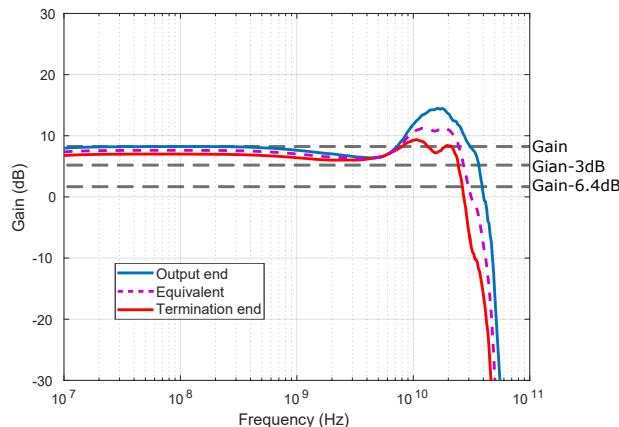

| 6.4  | AC simulation result of U-shape optical transmitter (schematic level) . . . . .                                | 120 |

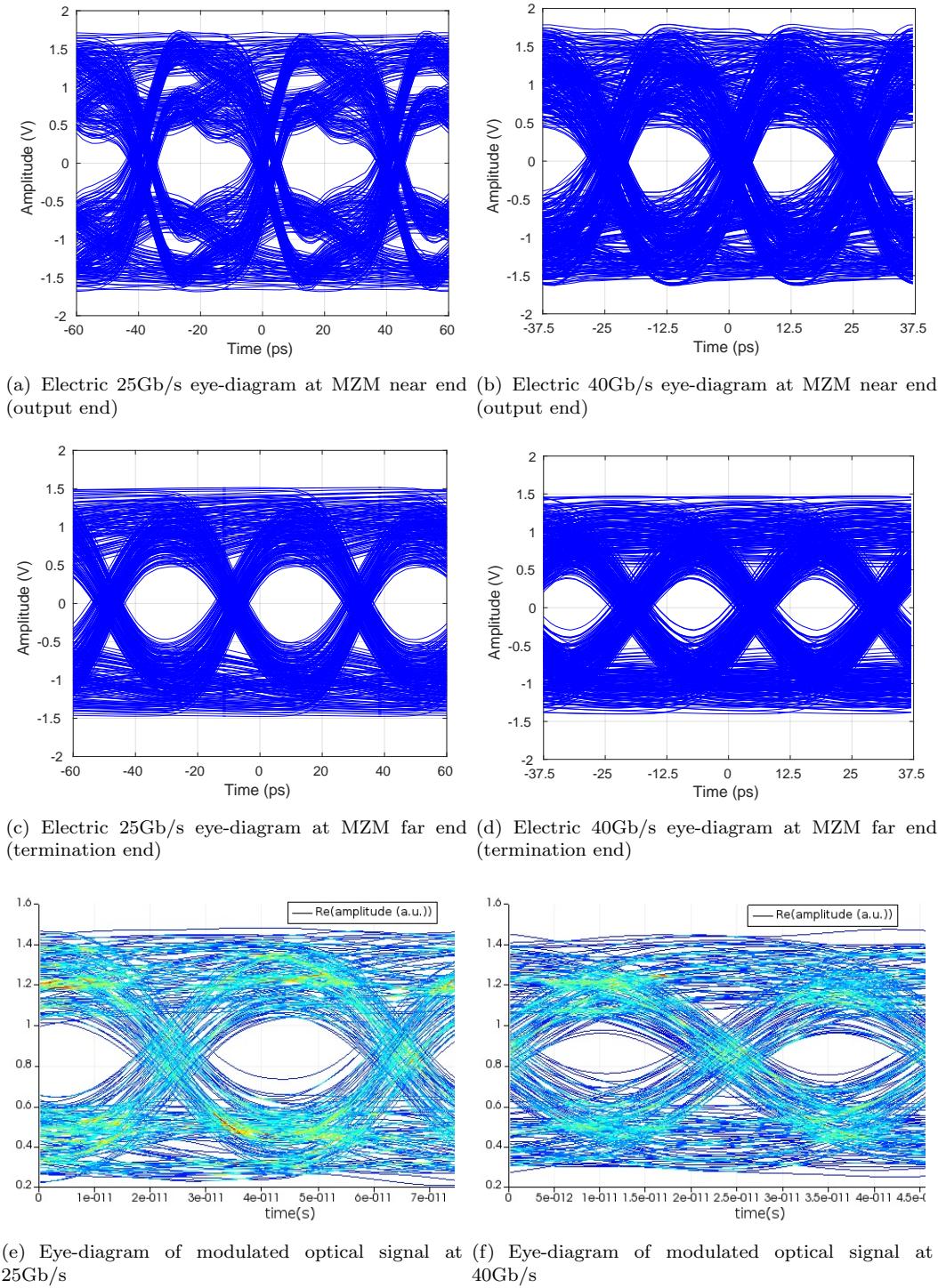

| 6.5  | Transient simulation result of U-shape optical transmitter . . . . .                                           | 121 |

| 6.6  | Combinational integration of the optical transmitter . . . . .                                                 | 123 |

| 6.7  | Transient simulation result of U-shape optical transmitter . . . . .                                           | 124 |

| 6.8  | Transient simulation result of modulator driver . . . . .                                                      | 125 |

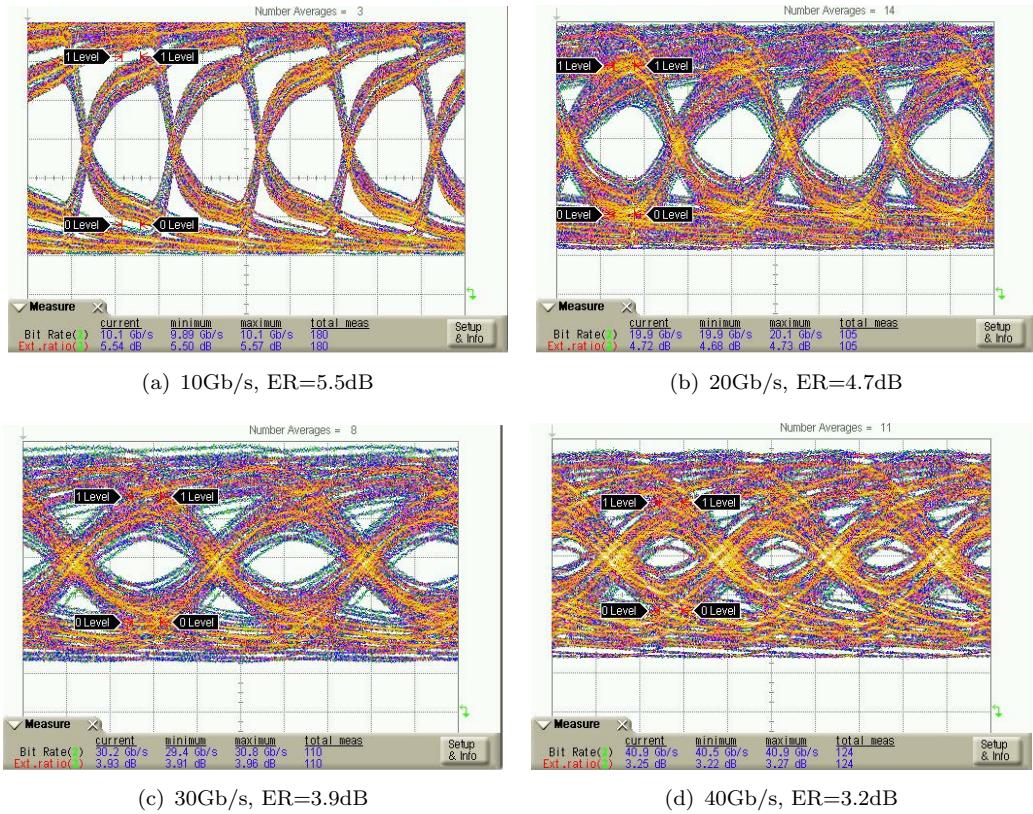

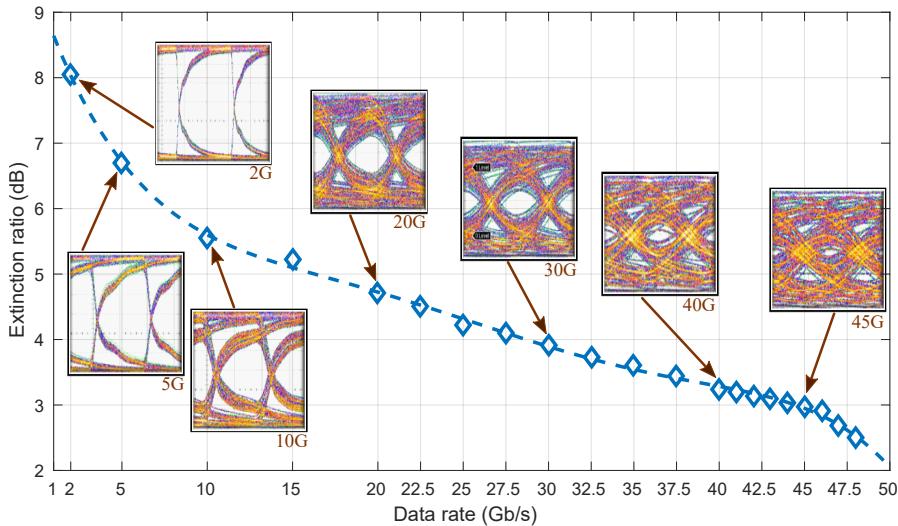

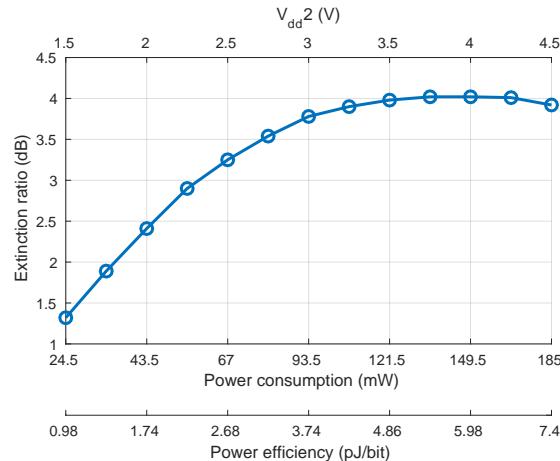

| 6.9  | ER of optical transmitter under different operating data rate . . . . .                                        | 126 |

| 6.10 | ER at 25Gb/s with $V_{dd2}$ gradually increase from 1.5V to 4.5V . . . . .                                     | 126 |

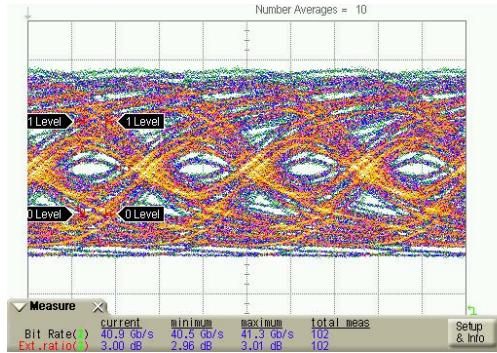

| 6.11 | Optical transmitter outputs 40Gb/s with 1.6pJ/bit . . . . .                                                    | 127 |

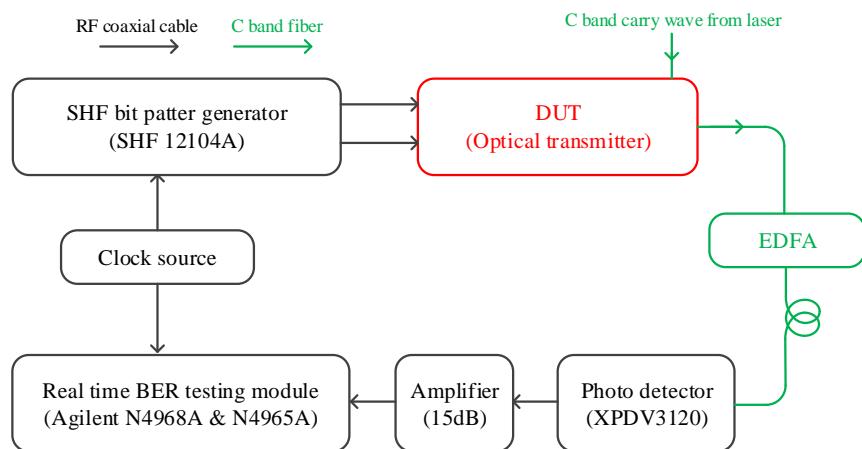

| 6.12 | The BER testing setup . . . . .                                                                                | 127 |

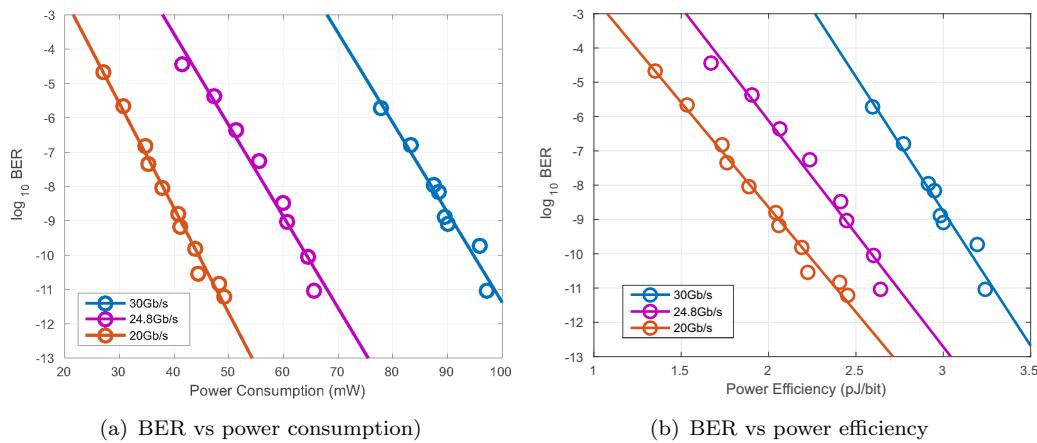

| 6.13 | BER result of the optical transmitter . . . . .                                                                | 128 |

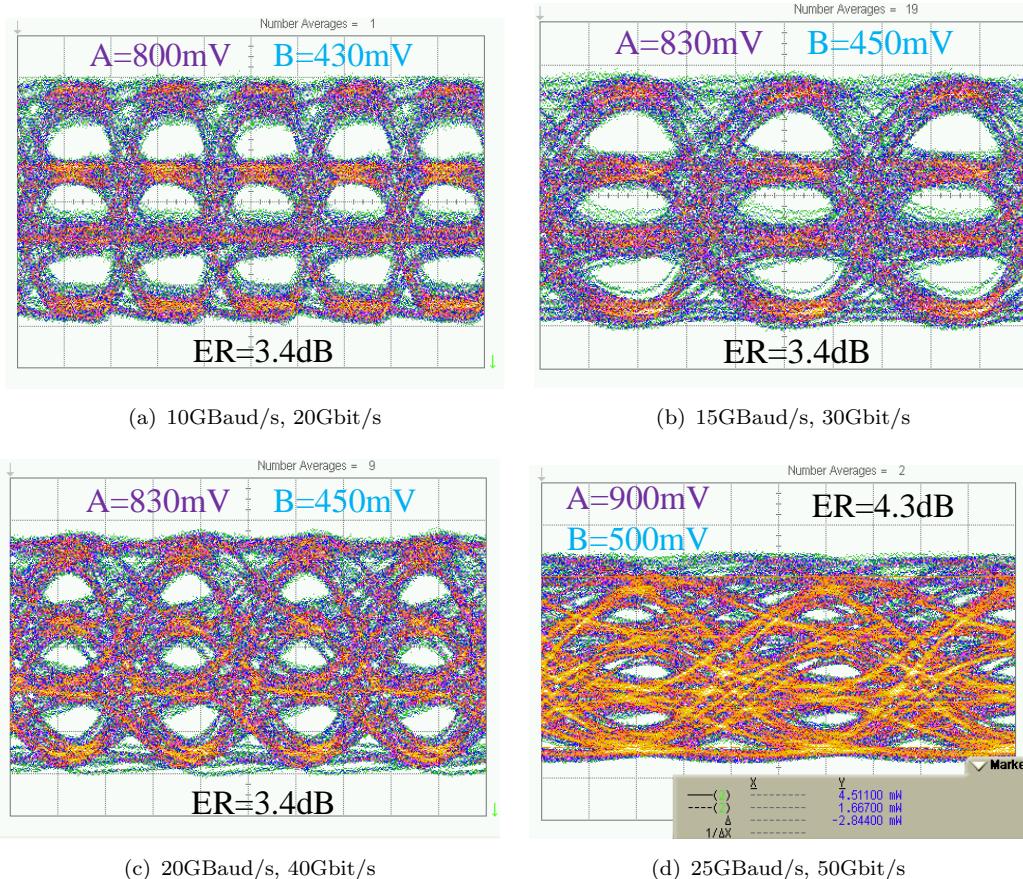

| 6.14 | The PAM4 transmission on the synergistic designed optical transmitter .                                        | 129 |

|      |                                                                                                                         |     |

|------|-------------------------------------------------------------------------------------------------------------------------|-----|

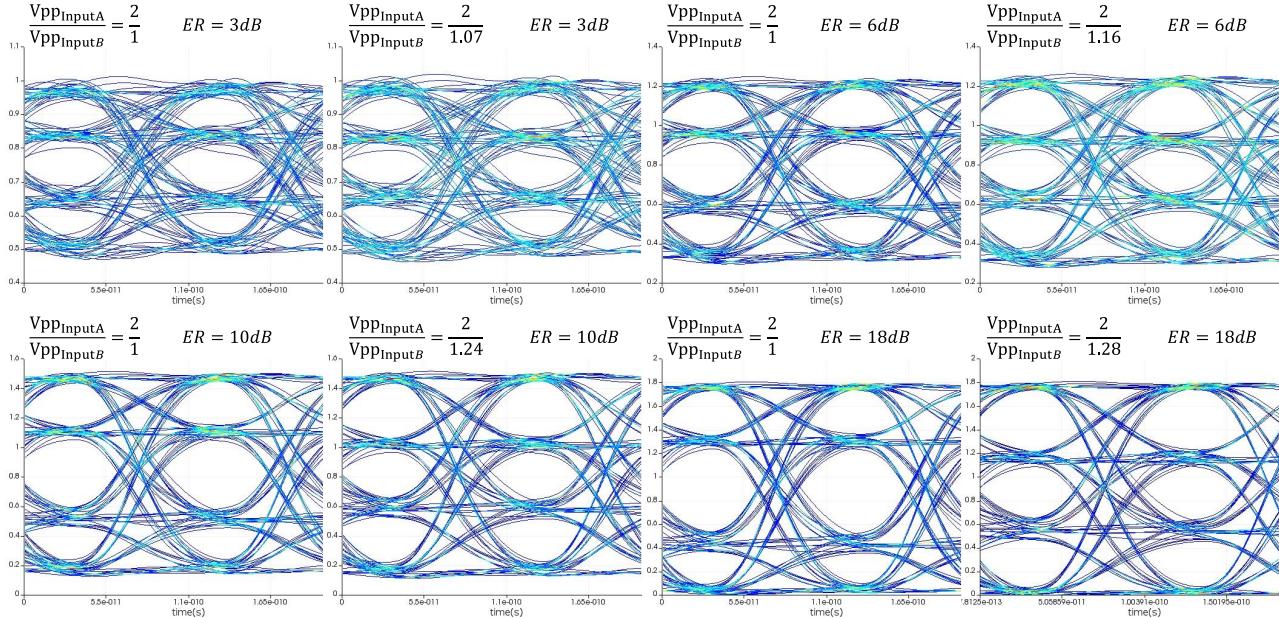

| 6.15 | PAM4 result of the optical transmitter . . . . .                                                                        | 130 |

| 7.1  | Modulator driver integrated with optical modulator . . . . .                                                            | 134 |

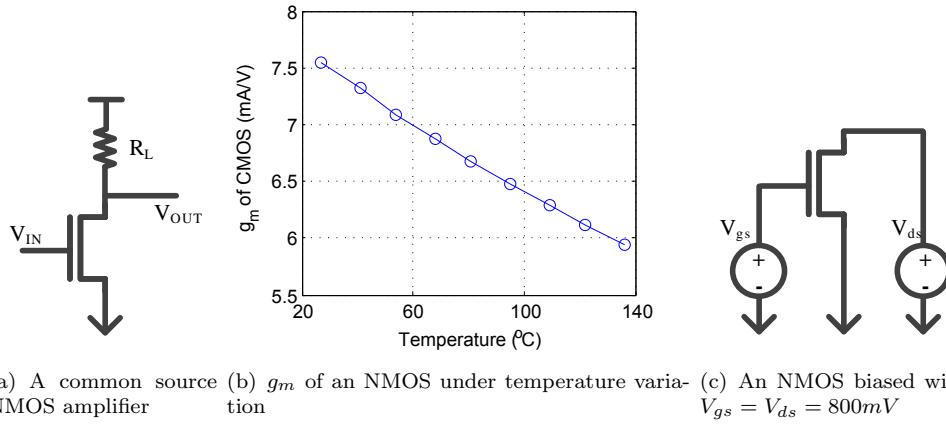

| 7.2  | Schematic of two individual stage of example limiting amplifiers . . . . .                                              | 135 |

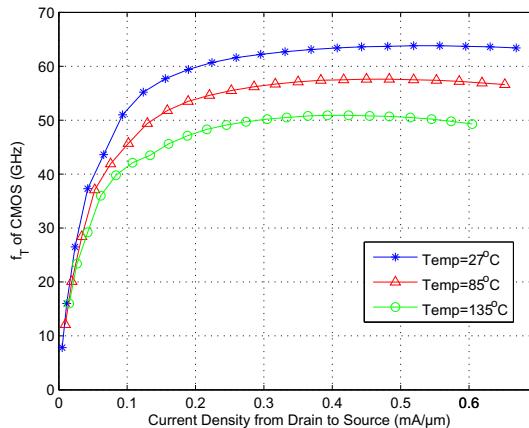

| 7.3  | $f_T$ of a NMOS in temperature variation . . . . .                                                                      | 136 |

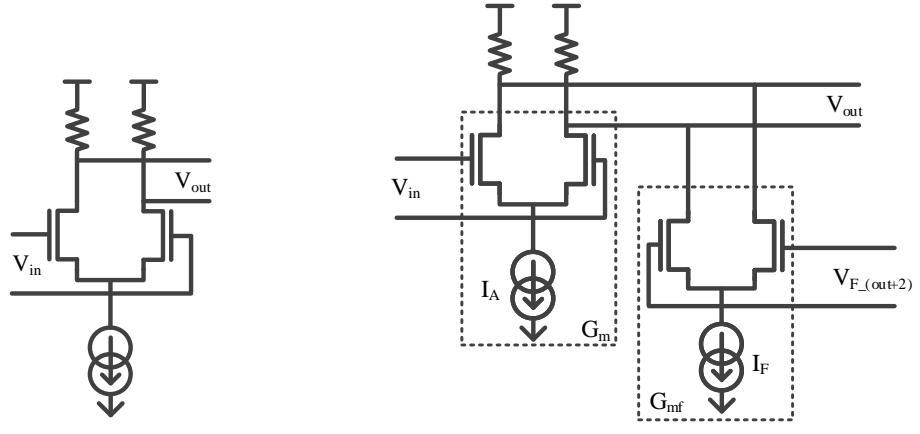

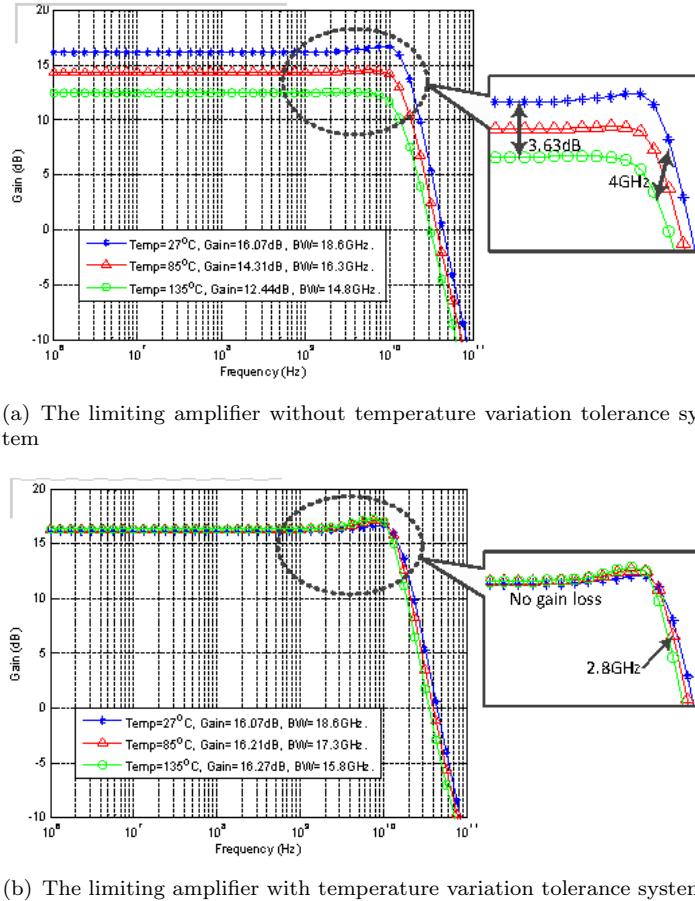

| 7.4  | Schematic of two individual stage of example limiting amplifiers . . . . .                                              | 137 |

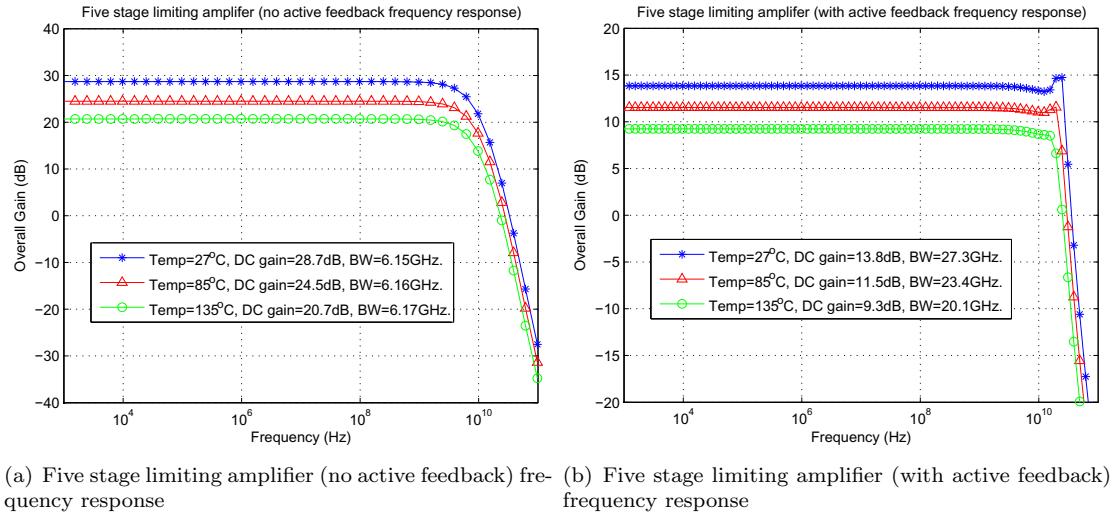

| 7.5  | Frequency response plot of example limiting amplifiers . . . . .                                                        | 138 |

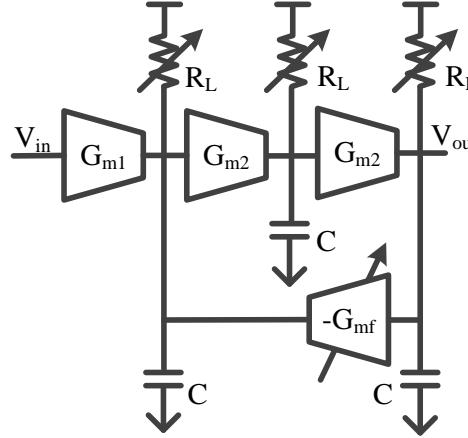

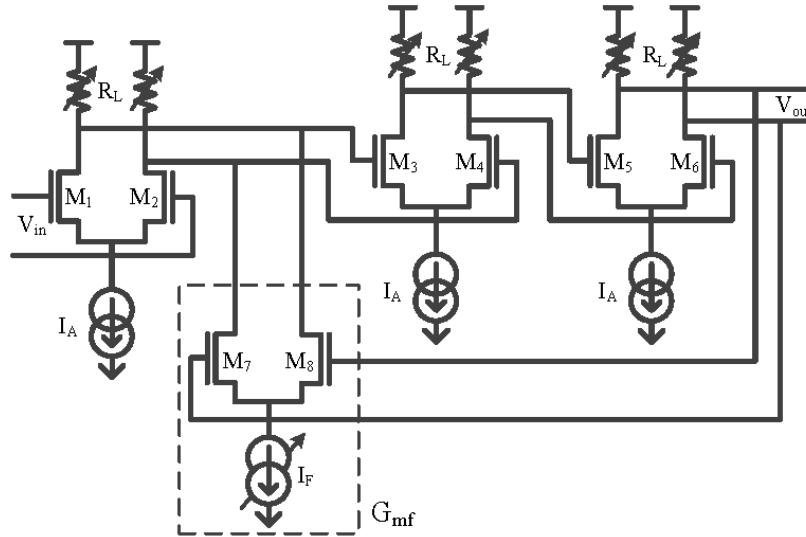

| 7.6  | Topology level analysis of temperature variation tolerance system on a second order active feedback amplifier . . . . . | 138 |

| 7.7  | Temperature variation tolerance system on second order limiting amplifier                                               | 139 |

| 7.8  | Frequency response of limiting amplifier with and without temperature variation tolerance adjustment . . . . .          | 141 |

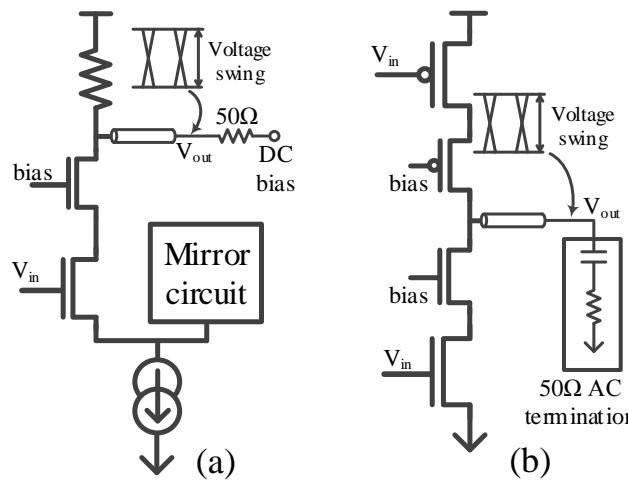

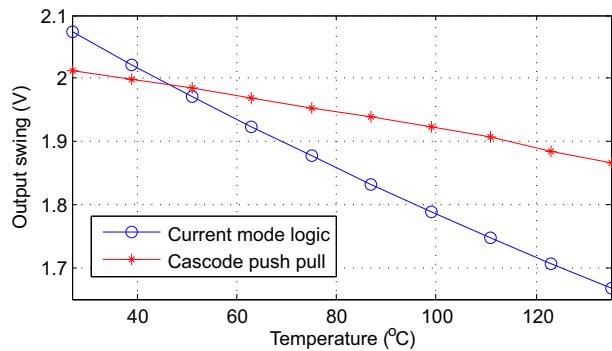

| 7.9  | Output stage of (a) current mode logic and (b) cascode push pull . . . . .                                              | 142 |

| 7.10 | Voltage swing of output stage . . . . .                                                                                 | 142 |

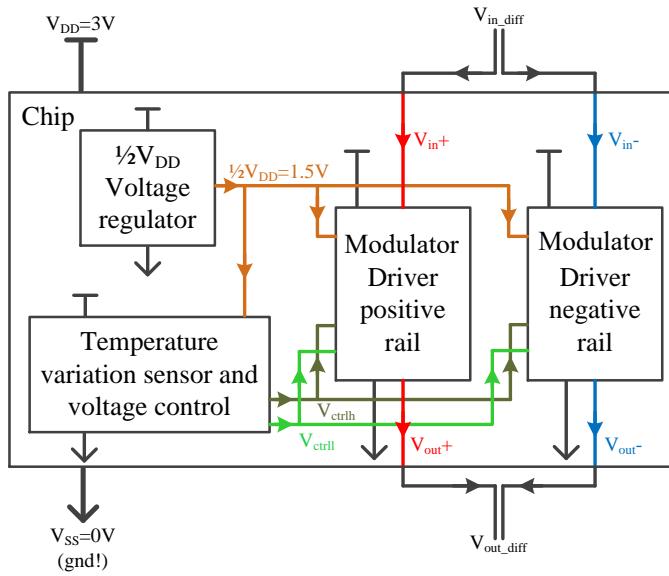

| 8.1  | Top level of temperature variation tolerance modulator driver system . . . . .                                          | 144 |

| 8.2  | Modulator driver . . . . .                                                                                              | 145 |

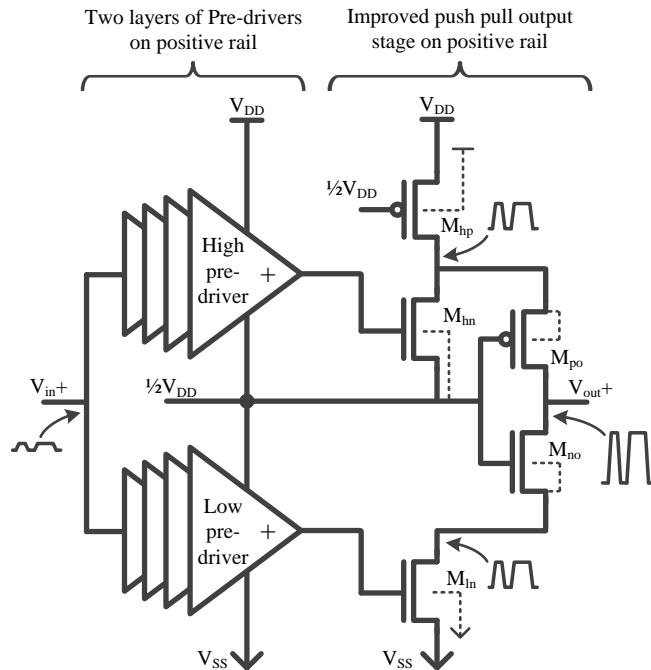

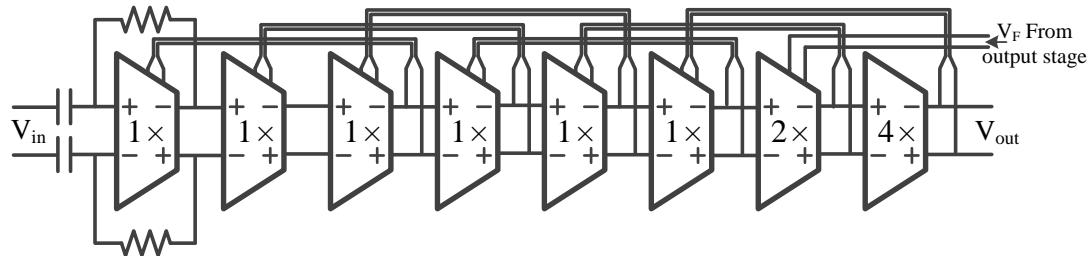

| 8.3  | Temperature variation tolerance limiting amplifier . . . . .                                                            | 146 |

| 8.4  | Temperature variation tolerance limiting amplifier cell . . . . .                                                       | 146 |

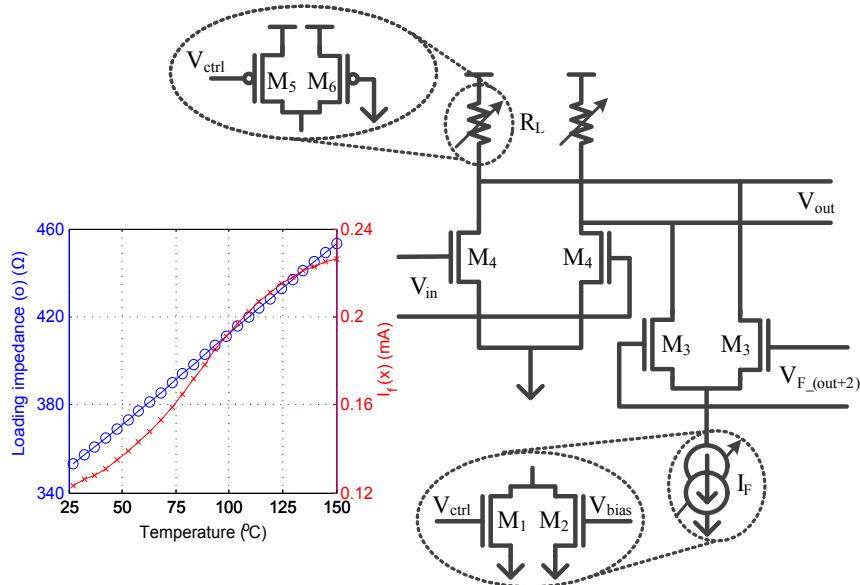

| 8.5  | Temperature variation sensor and voltage control . . . . .                                                              | 147 |

| 8.6  | $1/2V_{DD}$ regulator . . . . .                                                                                         | 148 |

| 8.7  | Layout of temperature tolerance modulator driver . . . . .                                                              | 149 |

| 8.8  | Testing environment of temperature variation tolerance modulator driver                                                 | 149 |

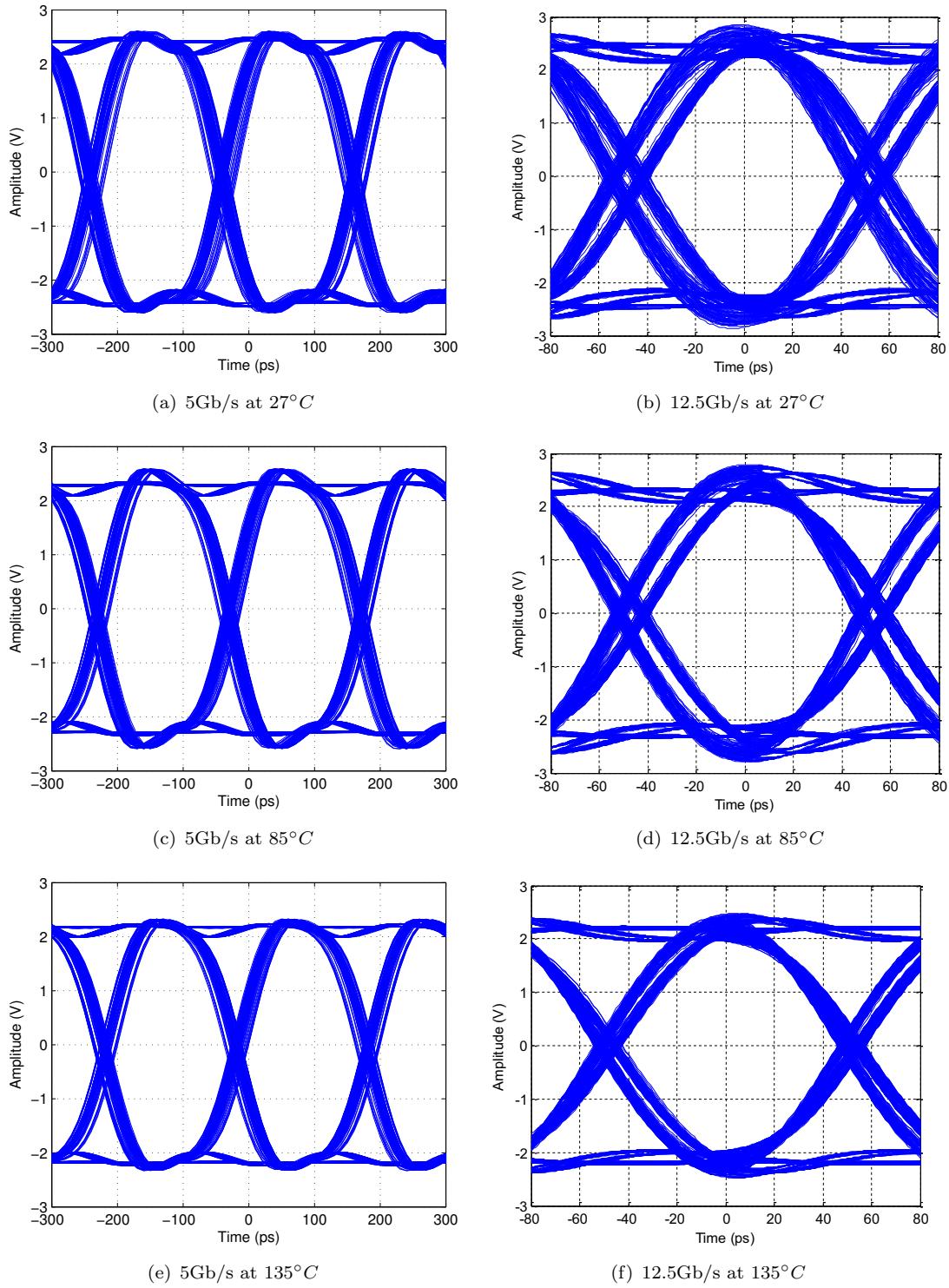

| 8.9  | Modulator driver outputs under temperature variation . . . . .                                                          | 150 |

| 8.10 | AC response of modulator driver under temperature variation . . . . .                                                   | 151 |

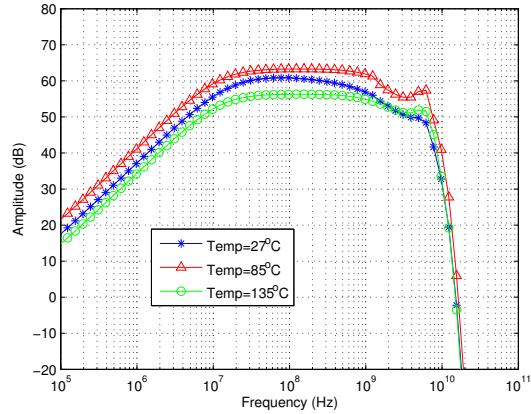

| 8.11 | Microscope view of the modulator driver . . . . .                                                                       | 152 |

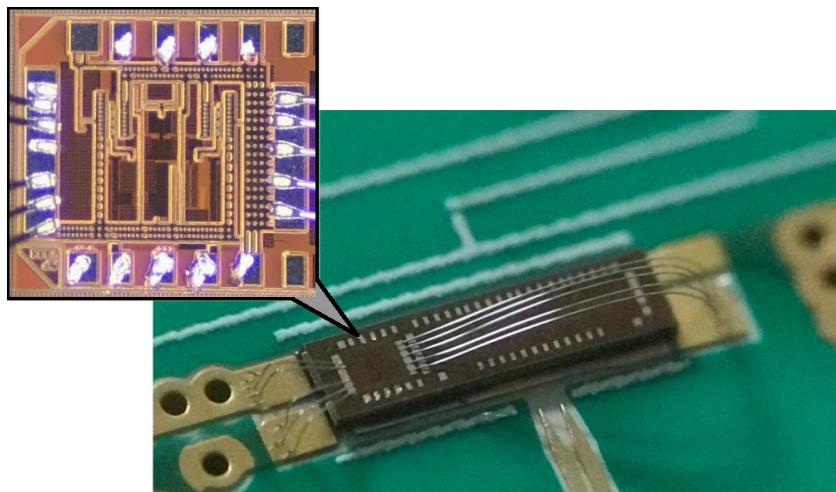

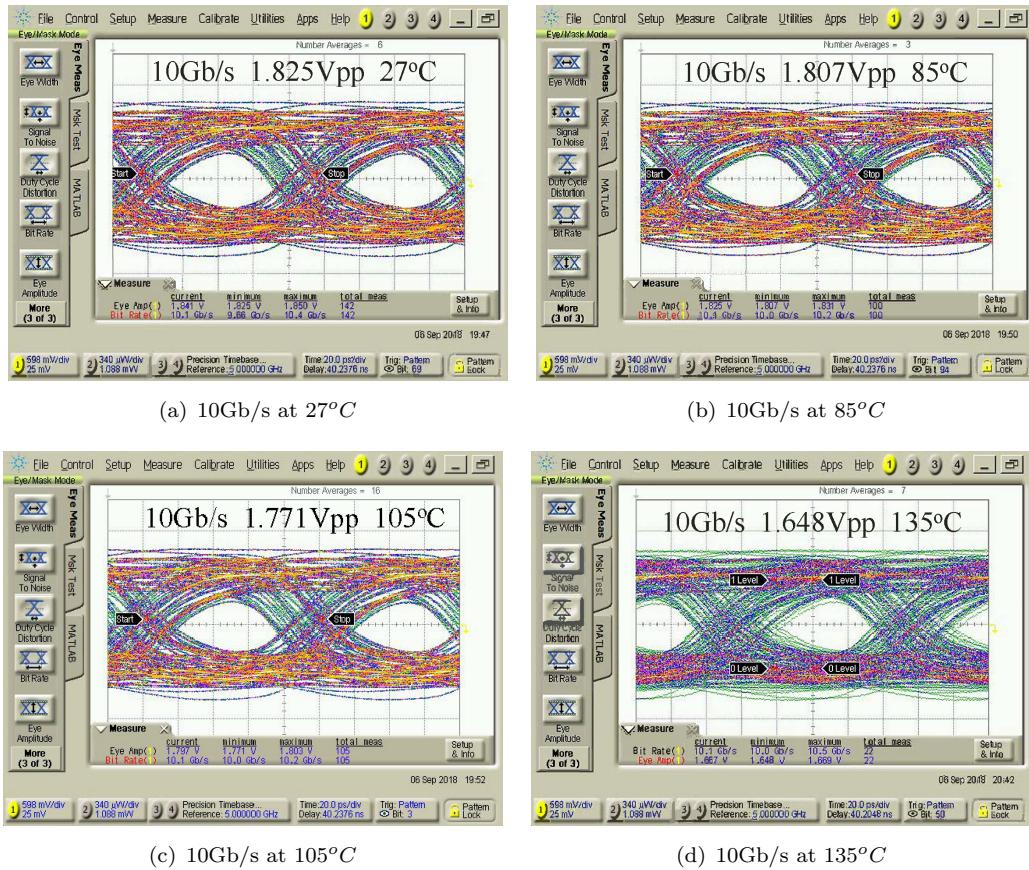

| 8.12 | Measurement of modulator driver at room temperature . . . . .                                                           | 153 |

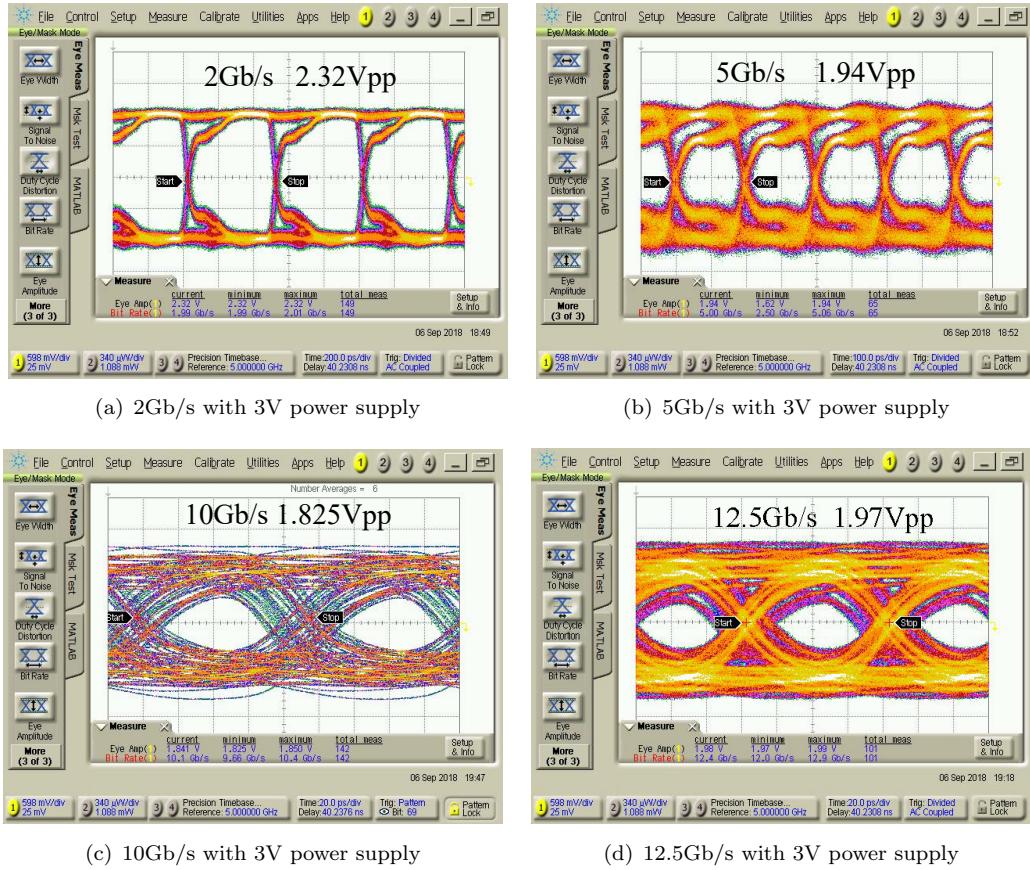

| 8.13 | Measurement of modulator driver in thermal environment . . . . .                                                        | 154 |

| 9.1  | Optional caption for list of figures . . . . .                                                                          | 159 |

| 9.2  | Optical transmitter consists of 4 modulator drivers and bifilar MZM . . . . .                                           | 160 |

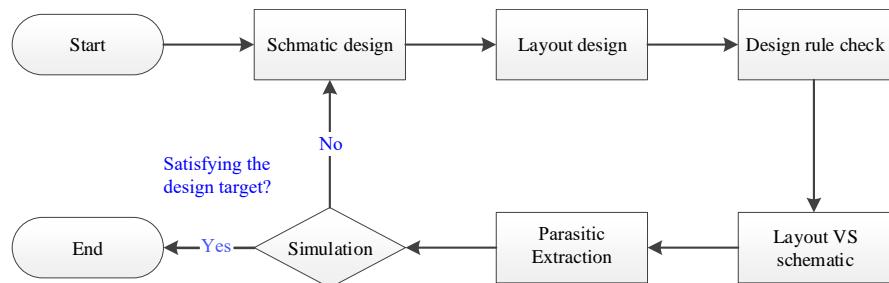

| A.1  | General design process . . . . .                                                                                        | 161 |

| A.2  | The example limiting amplifier . . . . .                                                                                | 162 |

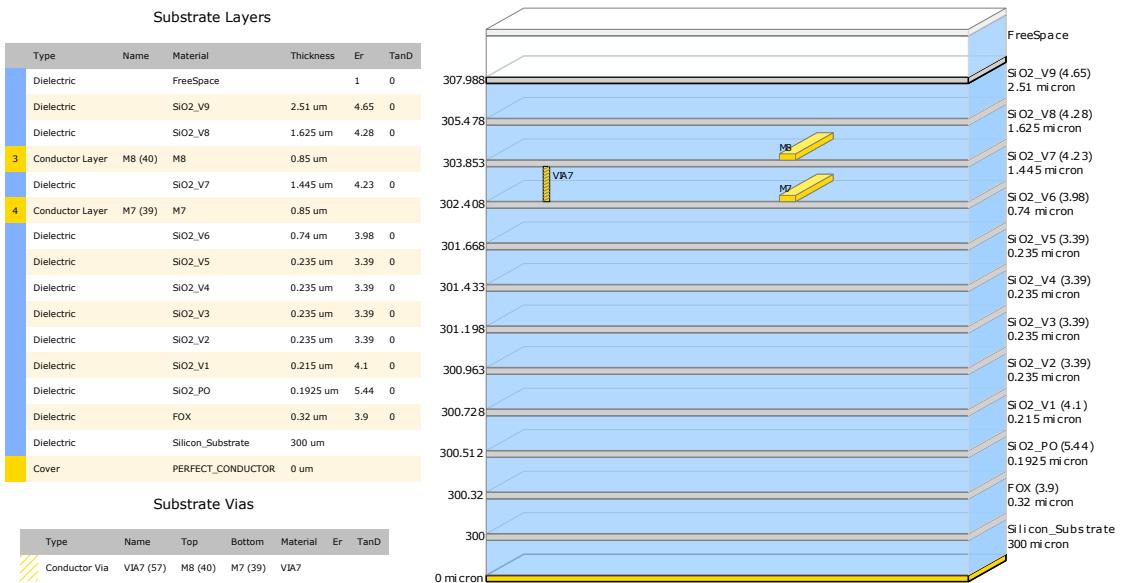

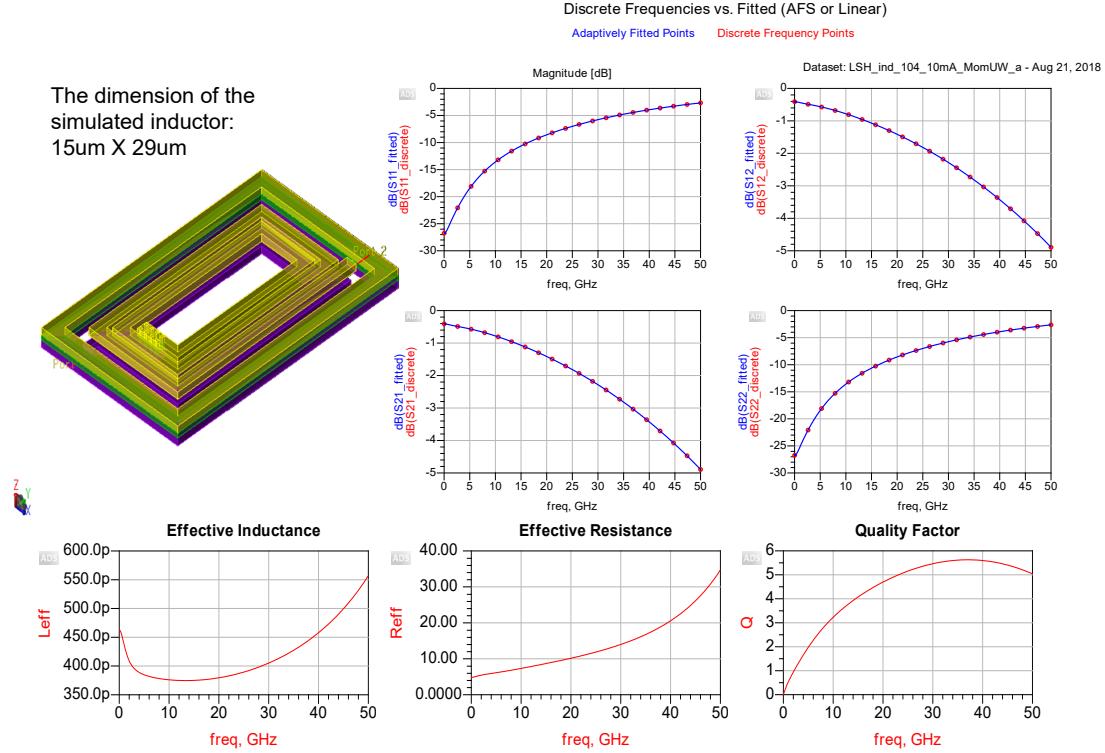

| A.3  | Substrate data utilized in ADS for example custom inducor . . . . .                                                     | 163 |

| A.4  | Modeling the custom inductor in ADS . . . . .                                                                           | 164 |

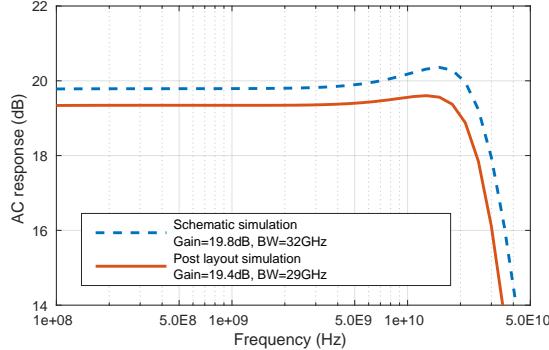

| A.5  | Comparison of simulated AC response on schematic and extracted layout                                                   | 164 |

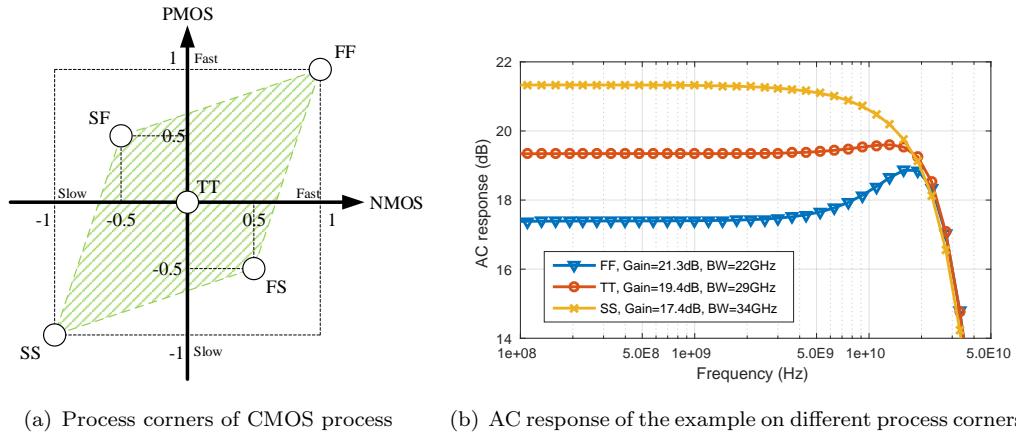

| A.6  | Process corners of CMOS process and the AC response of example circuit on different process corners . . . . .           | 165 |

# List of Tables

|     |                                                                          |     |

|-----|--------------------------------------------------------------------------|-----|

| 1.1 | Evolution of optical interconnects (Courtesy of M. Taubenblatt [112])    | 3   |

| 2.1 | Modulator comparison[Rakowski]                                           | 16  |

| 2.2 | Output stage amplifier comparison                                        | 38  |

| 3.1 | Performance comparison of multiple amplifier output stage circuits       | 61  |

| 4.1 | Parameters of major components in gain stage of pre-driver               | 72  |

| 4.2 | Parameters of major components in double fan-out stage                   | 72  |

| 4.3 | Parameters of major components in output stage                           | 74  |

| 4.4 | Parameter of major components in pre-driver                              | 84  |

| 4.5 | Parameter of major components in output stage                            | 84  |

| 4.6 | Design detail of output stage                                            | 90  |

| 4.7 | Parameter of major components in pre-driver                              | 94  |

| 4.8 | Parameter of major components in output stage with CML pre-stage         | 95  |

| 4.9 | Performance compaction of related works                                  | 102 |

| 6.1 | Parameters of major electric components in optical transmitter           | 118 |

| 6.2 | Power efficiency increase leads BER improve                              | 129 |

| 7.1 | Detail of temperature variation tolerance system example                 | 140 |

| 8.1 | Parameters of major components in the improved push pull output stage    | 145 |

| 8.2 | Design detail of temperature variation tolerance limiting amplifier cell | 147 |

| A.1 | DRC, LVS and parasitic extraction for different processes                | 162 |

## Acknowledgements

I am deeply grateful to my advisees, Dr Ke Li, Dr Dave Thomson, Prof Peter Wilson and Prof Graham T. Reed, who has always supported and guided my researches. In particular, I have to reaffirm the thankful to Dr Ke Li. Since I was working at the earliest stage as MSc student at Southampton University, he has helped and taught me unselfishly throughout the PhD period. I would also like to express my gratitude to my internal examiner Dr Frederic Gardes. I also really appreciate the rest of the colleagues in our group, for their support and their warm friendship.

No word can express my gratitude to my parents, for their unbounded support and best wishes. It was never possible to do PhD without the warmly supporting from them.

In the end, I must give my special thanks to Dr Wei Xu, Dr Zhihong Zhang and the rest of healthcare staffs from Jiangsu Province Hospital. During the author's lymphatic cancer, these doctors, nurses and other staffs have given the author extra warm cares while he was being treated. It was their efforts that enabled me to return to research as soon as possible after I was remission.

# Nomenclature

|                          |                                                    |

|--------------------------|----------------------------------------------------|

| <i>NTRS</i>              | National Road-map for Semiconductors               |

| <i>CMOS</i>              | Complementary metal-oxide-semiconductor            |

| <i>Txline</i>            | transmission line                                  |

| <i>InP</i>               | Indium phosphide                                   |

| <i>GaAs</i>              | Gallium arsenide                                   |

| <i>LiNbO<sub>3</sub></i> | Lithium niobate                                    |

| <i>MZM</i>               | Mach-Zehnder modulator                             |

| <i>Si</i> or <i>si</i>   | Silicon                                            |

| <i>RRM</i>               | Ring resonator modulator                           |

| <i>RF</i>                | Radio frequency                                    |

| <i>UKSP</i>              | UK Silicon Photonics                               |

| <i>SPFS</i>              | Silicon Photonics for Future Systems               |

| <i>EPSRC</i>             | Engineering and Physical Sciences Research Council |

| <i>NRZ</i>               | None return zero                                   |

| <i>PLL</i>               | Phase lock loop                                    |

| <i>PD</i>                | Photo detector                                     |

| <i>LA</i>                | Limiting amplifier                                 |

| <i>TIA</i>               | Trans-impedance amplifier                          |

| <i>CDR</i>               | Clock and data recovery                            |

| <i>SerDes</i>            | Serializer and de-serializer                       |

| <i>S2D</i>               | Single to differential converter                   |

| <i>EAM</i>               | Electrodeposition modulator                        |

| <i>MZI</i>               | Mach-Zehnder interferometer                        |

| <i>MSM</i>               | Metal-semiconductor-metal                          |

| <i>SOI</i>               | Silicon on insulator                               |

| <i>CML</i>               | Current mode logic                                 |

| <i>DA</i>                | Distribute amplifier                               |

| <i>WDM</i>               | Wavelength-division multiplexing                   |

| <i>PAM</i>               | Pulse amplitude modulation                         |

| <i>OMA</i>               | Optical modulating amplitude                       |

| <i>ER</i>                | Extinction ratio                                   |

| <i>MSB</i>               | Most significant bit                               |

|             |                                         |

|-------------|-----------------------------------------|

| <i>LSB</i>  | Least significant bit                   |

| <i>QPSK</i> | Quadrature Phase-Shift Keying           |

| <i>PDM</i>  | Polarization-division-multiplex         |

| <i>QAM</i>  | Indium phosphide                        |

| <i>TM</i>   | Transverse electric                     |

| <i>TE</i>   | Transverse magnetic                     |

| <i>DMT</i>  | Discrete multi-tone                     |

| <i>FFT</i>  | Fast Fourier transform                  |

| <i>IFFT</i> | Inverse fast Fourier transform          |

| <i>DML</i>  | Directly modulated laser                |

| <i>AWG</i>  | Arbitrary waveform generator            |

| <i>DSO</i>  | Digital storage oscilloscope            |

| <i>OFDM</i> | Orthogonal frequency-division multiplex |

| <i>PRBS</i> | Pseudo random binary sequence           |

| <i>FOM</i>  | Figure of merit                         |

| <i>EDFA</i> | Erbium-Doped Fiber Amplifier            |

| <i>BER</i>  | Bit error ratio                         |

| <i>DUT</i>  | Design under test                       |

| <i>BGR</i>  | Band gap reference                      |

| <i>ADS</i>  | Advanced Design System                  |

| <i>DRC</i>  | Design Rule Check                       |

| <i>LVS</i>  | Layout VS Schematic                     |

# Chapter 1

## Introduction

### 1.1 Interconnect bottleneck and silicon photonics

It is an understatement to remark that the modern world is becoming reliant on a computing technology that depends on silicon technology. Almost all industries are now driven by advanced technology based on integrated electronic circuits which are fabricated on silicon wafers. Along with the demand for large quantities of high performance and powerful computing components in all industries, the development of silicon-based manufacturing has evolved rapidly. In 1965, the famous Gordon Moore's law, which states that development progress is similar to an economic project plan,

- The complexity for minimum component costs has increased at a rate of approximately a factor of two per year.[78]

The complexity may be understood as either the number of transistors or the computing performance of the smallest component. Depending on the development of the manufacturing process, the transistor size is both gradually reduced and its speed becomes faster. Therefore, in the past few decades, the electronics manufacturing industry though has been recently slowed down, has been following Moore's Law.

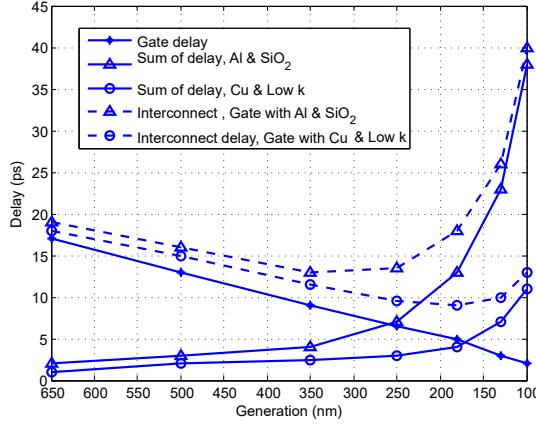

However, a serious problem challenging Moore's Law has been noticed and summarized in a report by the National Road-map for Semiconductors (NTRS), which states that, along with the progress of semiconductor manufacturing technology, although the transistor size and speed have been optimized, the interconnection has become a bottleneck. Fig.1.1 is extracted from the NTRS 1997 reports and it clearly describes the problem that is after the 200nm gate feature size, the interconnection delay is dominating the overall delay. No matter on which conductor and dielectric metrical, the interconnection metal is thinner and narrower while the process development. The RC capacitive charging and discharging delay dominates the overall performance of integrated circuits. A modern

electronic chip contains over  $1\text{km}$  length of metal wires on  $1\text{cm}^2$  chip area, therefore the interconnection delay is the inhibition of chip performance.[\[45\]](#) The exposure problem is often referred to as the interconnect bottleneck.

FIGURE 1.1: Gate and Interconnection Delay feature versed Technology Generation [\[81\]](#)

An interconnect bottleneck not only directly affects the continuity of Moore's Law, but it is also an indicator that the limits of electrical transmission progress are approaching. Not only the on-chip interconnections, but all the electrical connections between chips, and between chips and devices, will also be affected, because, as transmission rates increase, the attenuation of the high frequency signal in the transmission line (Tx line) also increases significantly. Current solutions for interconnect bottlenecks could be summarized as increasing the pin counts of chips (more parallel signals), optimizing the low-k dielectrics or limiting the distance of interconnections. However, according to updates of the ITRS report relating to interconnects and packaging[\[46\]](#), these traditional electrical interconnect optimizations may difficult to satisfy future performance requirements.

The interconnect bottleneck, which is difficult to solve by traditional electrical methods may be resolved by optical technology. Many expect photonics to provide a solution that relieves the interconnect bottleneck in the long term.[\[28; 36; 75; 78\]](#) The potential benefits of optical interconnections include delay reductions, crosstalk removal, and power consumption reduction. Traditional optical devices made from III-V-based compounds such as indium phosphide (*InP*), gallium arsenide (*GaAs*) or the electro-optic crystal lithium niobate (*LiNbO<sub>3</sub>*) could be used to replace traditional electrical connections between chips or modules. But these solutions come at either higher manufacturing and materials costs, or they will require a large layout area. In addition, they are often custom-made and are assembled from discrete components which are hand-assembled and require very little automation.[\[36\]](#) More importantly, they are too difficult to be integrated into the CMOS computing chips and replaces the on-chip interconnections. Aside of these traditional optical devices, another obvious solution is the silicon photonics.

Firstly, silicon gains the manufacturing experience which has been the mainstay of the

TABLE 1.1: Evolution of optical interconnects (Courtesy of M. Taubenblatt [112])

|                 |  |  |  |  |                              |

|-----------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------|

|                 | <b>LAN</b><br>Rack level                                                          | <b>System</b><br>Card level                                                        | <b>Board</b><br>On Card                                                             | <b>Module</b><br>Chip level                                                         | <b>Sub module</b><br>On-chip |

| Distance        | 30+m                                                                              | Less 1m                                                                            | 0.1-0.3m                                                                            | 5-100mm                                                                             | 0.1-10mm                     |

| Number of lines | ~ 100                                                                             | ~ 100 – 1000                                                                       | ~ 1000                                                                              | ~ 10'000                                                                            | ~ 100'000                    |

electronics industry for more than 40 years. The feature sizes needed for processing these silicon waveguides are on the order of  $0.5 - 1\mu m$ . Therefore, even with 90-nm CMOS lithography, it is still sufficient to fabricate the optical device on the silicon wafer.[36] Silicon is also used for fabricating electrons and holes that are also required in silicon active optic devices to modulate the optical signals.

Secondly, silicon photonics provides an important compatible possibility with existing CMOS fabrications. Only if implementing the optical device and the state of the art CMOS computing device in the same silicon die (monolithic photonics platform), the on-chip interconnection could be replaced as an optical connection.[109]

Thirdly, unlike the traditional optical devices, the size and scale of silicon photonics devices could be closer to the state of the art CMOS devices, since these minimal sized silicon photonics modulators and detectors only occupy tens of square microns layout areas.[28; 109] These small size designs are similar to the nanometer scale CMOS devices.

Finally, the advantages of silicon-based manufacturing in terms of materials and lower costs are significant, since clearly, in interconnection, which has an extremely wide range of application, high-cost technology is unlikely to be widely implemented.

Table 1.1 demonstrates the evolution of optical interconnects, it covers the rack level communication which mainly serves the data centers to on-chip communications. As research has progressed, the transmission distance has gradually decreased, while the number of lines has rapidly increased dramatically. Especially in the module and sub module stages, based on existing computing components in silicon-based manufacturing, almost only silicon photonics can be an effective solution.

## 1.2 Motivation and objectives

Although silicon photonics have their advantages, the modulation (or generation) and detection of optical signals is highly challenging. Especially in the si modulators, limited by the properties of silicon-based materials, both the reliability and efficiency of the device need to be concerned. The depletion-type si Mach-Zehnder modulator (MZM)

is well researched in the silicon photonics. Though the MZM is always devalued for its relatively inferior power efficiency and large footprint, the fact is that depletion-type si MZM is almost always preferred because of its practical benefits. In comparison to carrier injection modulators and the Ring Resonator Modulators (RRM), depletion-type si Mach-Zehnder modulator has its advantages in the speed modulation reliability and environmental tolerance.[37]

According to a recent publications, the si MZM has already attained over 90Gb/s NRZ optical modulation.[128] However this result, like most other MZM transmission experiments, is based on the testing setup using all commercial modulator drivers. In the testing and research phase, testing using commercial equipment is faultless, however, a reality reveals is that a significant gap has already appeared between these commercial devices and future applications of silicon photonics. Commercial modulator drivers are usually a broadband radio frequency (RF) amplifier, which is quite difficult to integrate to the MZMs due to its huge volume. Simultaneously, the power consumption of these amplifiers is now more than 1W, which suggests that optical transmitter efficiency of the optical transmitter has now moved beyond the practical stage. Additionally, most commercial devices are not built on the CMOS technology. In future, silicon photonics, no matter how monolithic their photonics platform level integration or other integrations with CMOS based computing units are, such commercial devices are almost impossible integrate efficiently into the systems.

The optical transmitter should not only be an electric-optical transforming device, but a combinational circuit or system, which, most importantly, should include the electrical devices available to directly integrate with the state of the art CMOS computing units. Therefore, it is essential to build modulator drivers that rely only on CMOS technology. A proper modulator driver needs to demonstrate not only enough bandwidth performance but that it is also sufficiently efficient for it to be integrated into the MZM.

In 2011, the state of the art silicon photonics research shows the si depletion MZM [116] is functional up to 40Gb/s. But this result is based on commercial driver devices in the testing lab. For future silicon photonics circuit and related applications, it is difficult to broadly use commercial driver due to the size (at least several  $mm^2$  per driver) and power consumption (could be over Watt). To optimize the opto-electronic circuit from the discrete devices level to the compacted packaged level, and to provide a driver that has a low area cost and low power consumption, CMOS based optical modulator driver design is one of several options. The cost of the CMOS process is much lower than III/V material ones and even lower than a BiCMOS process. A further advantage of the CMOS process creates a possibility to build drivers as IO of the processing unit including computing elements, DSP units and/or SerDes systems, which is also using standard CMOS process. Although the BiCMOS process is compatible with both Bipolar and CMOS transistors, the CMOS used in the BiCMOS process is much slower than the current method which is not appropriate for processing units.

In order to provide a proper CMOS modulator driver, this PhD project aims to establish optical transmitter, based on si MZM with a CMOS circuit at, or over, 40Gb/s data transmission that meets the si MZM, which has been presented in 2012. Even in latter phase of this project, the current Si photonics modulator has reached 90Gb/s[128], while most industrial optical interconnect level applications is still at or lower than 40Gbaud/s per electric IO[21; 22]. Therefore, the 40Gb/s opto-electronic transmitter which includes a CMOS modulator driver, is an alternative in terms of this project's research target. The reliability, efficiency and integration methods of CMOS modulator driver should be researched in this project. The MZM samples which integrates with the modulator driver should be provided by the co-operative optical designer in the same research project.

Between 2012 and 2018, while the author has been working on this PhD, silicon photonics technology has undergone six years of rapid development. During the period, most state of the art CMOS based modulator drivers for MZM amounted only to approximately 10Gb/s and it required a high power consumption. Today's MZM, however, is functional upto 90Gb/s with the commercial testing devices, and the CMOS circuit which integrates with MZM, operates to a level higher than 40Gb/s.

At the beginning of the PhD project, MZM temperature reliability was well understood, however, the modulator driver, which provides performance independent of temperature was too expensive. In addition, the author lacked high-speed CMOS circuit design experience; therefore, it was the first time the author has been involved with the opto-electronic design. The topic then become high speed low power design as it relates to temperature reliability, whereas the first CMOS design, which was the project's original subject, related to circuit research and design.

Following the first design, during the second year of this project, I proposed a novel structure which optimized the conventional push pull modulator driver to enable it to attain a higher operating speed alongside a lower power consumption. During the next two years, the modulator driver was modified and optimized in two tape outs within two different CMOS processes. The final result enables the modulator driver to operate at 40Gb/s transmission with relatively low power consumption.

In late 2015, together with colleagues, author devised a novel plan that consisted of a U-shape MZM and an efficient modulator driver. The electric chip design I was working on for the optical device unfortunately had to be abandoned, for 20 months as I contracted lymphoma. Although the author contributed to the research, the electronic circuit design was completed by a colleague. In late 2017, after the lymphoma was in complete remission, I continued with integrating and testing for the optical transmitter, in late 2018, the project came to an end.

The author's PhD is a sub-topics of two continued research projects in University of Southampton. These two research projects are on the order of UK Silicon Photonics

(UKSP) and Silicon Photonics for Future Systems (SPFS) which are both funded by Engineering and Physical Sciences Research Council (EPSRC).

### 1.3 Thesis Organization and Contributions

This thesis is structured as follow:

The state of the art is reviewed in the Chapter 2. The chapter is divided into six sections which review the general optical transceivers, optical devices and related electronic circuits, integration methods of silicon photonics, high speed amplifier design methodologies, the output stage structures and the complex modulation on silicon photonics.

Chapter 3 provides a novel N-over-N cascode amplifier structure to optimize the state of the art CMOS modulator drivers. The chapter theoretical analysis the proposed amplifier structure, compared the circuit with conventional circuit topologies, and provide two parts of optimizations on the proposed circuit.

Chapter 4 includes three implementations bases on the proposed circuit in Chapter 3. These three implementations on the order to demonstrate the functionality of N-over-N cascode amplifier and two optimizations. Each implementation is independent designed and analyzed. Both the simulation and experimental testing result are also included in the chapter.

Chapter 5 provides a efficient optical transmitter design which includes the CMOS driver. This design is a synergistic design which contributes by both of the optical and electric designers in the research projects. Rely on the synergistic design technology, the MZM is embedded into the electronic circuit design. Apart of the theoretical analysis which focuses on the electronic circuit design and the top-level topologies and integration is presented in the chapter. In addition, to use the optical transmitter to demonstrate an efficiency PAM4 optical transmitting, an analysis PAM4 modulating on si MZM is followed in the chapter.

Chapter 6 includes the implementations result of the synergistic designed optical transmitter which is analyzed in Chapter 5. The experimental result demonstrates the NRZ transmission, bit error ratio test and the PAM4 transmission of the design.

Chapter 7 provides a optimized temperature variation tolerance modulator driver design methodology. The proposed circuit demonstrates high reliability in unstable thermal environment. The modulator driver could be used for MZM which avoids the electric signal integrity loss in high temperature.

Chapter 8 demonstrates the implemented circuit which bases on the analysis in chapter 7. With a on-chip control loop, the modulator driver provides almost no damaged signal up to 12.5Gb/s in a wide temperature range.

Chapter 9 concludes this thesis with a summary of the research outcome in this project. Several potential research ideas have been discussed as continuously work for this PhD project.

Finally, it is necessary to point out that this thesis has covered a wide range of technical topics, include the design and fabrication of optical devices, the packaging and integration of photonics and electronic devices, the design and simulation of high-speed CMOS circuit, the functional verification and performance characterization of the optical transmitter. Apparently, all these works require team-work among many research colleagues. It is therefore necessary to clarify the contribution made by the author.

- Firstly, the author mainly focuses on the design and characterization of CMOS circuit whereas the design and fabrication of these optical devices are finished by the colleagues in the Silicon Photonics Group.

- Secondly, the beginning of this PhD project commenced from the design and modelling of the temperature behavior of high-speed CMOS amplifier. A self-sustained temperature tolerant CMOS amplifier is proposed by the author with its functionality verified by a series testing results.

- Thirdly, the idea of N-over-N cascode amplifier is proposed by the author and the concept is demonstrated and characterized by the electrical tape-out at TSMC 40nm CMOS process node.

- Finally, the last contribution of this PhD project is the synergistic designed optical transmitter which consists of a U-shaped MZM and 28nm CMOS driver. It is an honor that the author has deeply involved with the invention and discussion of this idea at the beginning of it. It is a regret that author missed the circuit design and fabrication stage due the severe illness. It is so lucky that after 20 months of medical treatment, the author recovered from the illness and caught up with the integration and testing stage of this work.

8 publications have arisen from this work in the author's PhD period. The published articles are 2 journal papers and 6 conference papers. The publishes are listed below:

- Liu Shenghao, Li Ke and Wilson Peter R. (2015) **A temperature independent driver for Mach-Zehnder modulators.** ISCAS 2015: IEEE International Symposium on Circuits and Systems, Portugal. 24 - 27 May 2015.

- Li Ke, Thomson D., Wilson Peter R., Liu Shenghao and Reed Graham T. (2015) **A 30 Gb/s CMOS driver integrated with silicon photonics MZM.** RFIC 2015: 2015 IEEE Radio Frequency Integrated Circuits Symposium, RFIC2015/Microwave Week 2015, United States. 17 - 19 May 2015.

- Reed G.T., Li K., Thomson D.J., Liu S., Wilson P.R., Hu Y., Gardes F.Y., and Mashanovich G.Z., **Devices for an integrated Silicon Photonics platform**, International Photonics and Optoelectronics Meetings (POEM), Wuhan, China, 13-20 Jun. 2015 (Invited)

- Liu Shenghao, Thomson D., Li K., Wilson Peter and Reed Graham T. (2015) **N-over-N cascode push-pull modulator driver in 130nm CMOS enabling 20Gb/s optical interconnection with Mach-Zehnder modulator.** Electronics Letters, 51 (23), 1900-1902.

- Cao Wei, Hagan David, Thomson David J., Nedeljkovic Milos, Littlejohns Callum G., Knights Andy, Alam Shaif Ul, Wang Junjia, Gardes Frederic, Zhang Weiwei, Liu Shenghao, Li Ke, Rouifed Mohamed Said, Xin Guo, Wang Wanjun, Wang Hong, Reed Graham T. and Mashanovich Goran Z. (2018) **High-speed silicon modulators for the 2 m wavelength band.** Optica, 5 (9), 1055-1062.

- Thomson David, Gardes Frederic, Debnath Kapil, Zhang Weiwei, Li Ke, Liu Shenghao, Meng Fanfan, Khokhar Ali, Littlejohns Callum, Byers James, Mastronardi Lorenzo, Husain Muhammad, Saito Shinichi, Chen Xia, Miloevic Milan, Franz Yohann, Runge Antoine F.J., Mailis Sakellaris, Peacock Anna, Wilson Peter and Reed Graham (2018) **Towards high speed and low power silicon photonic data links.** ICTON 2018 - International Conference on Transparent Optical Networks, Bucharest. 01 - 05 Jul 2018.

- Liu Shenghao , Thomson Dave J., Li Ke, Wilson Peter and Reed Graham T. (2018) **A 40Gb/s low power CMOS driver for MZM.** European Optical Society Biennial Meeting (EOSAM) Delft, Netherlands, Oct. 2018

- Li Ke, Thomson David, Liu Shenghao, Meng Fanfan, Shakoor Abdul, Khokhar Ali, Cao Wei, Zhang Weiwei, Wilson P. and Reed G.T. (2018) **Co-design of electronics and photonics components for Silicon Photonics transmitters.** In 44th European Conference on Optical Communication. OSA.

# Chapter 2

## States of the Art

In the past years, the research on Silicon Photonics gains a significant amount of momentum. In both interconnection and long-haul communication applications, some of the commercial transceivers on silicon photonics has been produced. A growing number of silicon photonics research is not limited to the devices, but to the silicon photonics circuit and system. Silicon photonics has the integration advantages with CMOS chips; therefore the electronic chip technology associated with silicon photons is also evolved. Many electrical chip studies have been continuously improved from traditional circuits to specifically serve silicon photonics circuits and achieving better integration and overall performance results.

This chapter is a literature review covers from a conventional optical transceiver's architecture to a optical transmitter with complex modulating. Since the PhD project is aiming to develop the CMOS circuit for silicon photonics modulators, the states of the art have been focused on the electronic circuits in related area, not just silicon photonics.

### 2.1 Introduction

Hereinafter in this chapter, six sections gradually review the silicon photonics and its related electronic circuit.

Firstly, a conventional optical transceiver has been reviewed and the importance of a modulator drive which acts as the electric-optical interface has been pointing out. Secondly, in order to relate the silicon photonics device to electronic circuits, an introduction covers types of optical devices. After that, a review illustrates three integration method for electronic and optical devices. Then, there are two sections on the order reviewing the high speed amplifier and output stage circuit for optical modulators. Lastly, as the most common silicon photonics circuit, the complex modulating optical transmitter is also reviewed.

Due to the target of the author's project, the states of the art chapter has focused on the modulator driver and its related content as the electrical circuit that directly serves the silicon photonics device.

## 2.2 The top Level circuit of optical transceivers

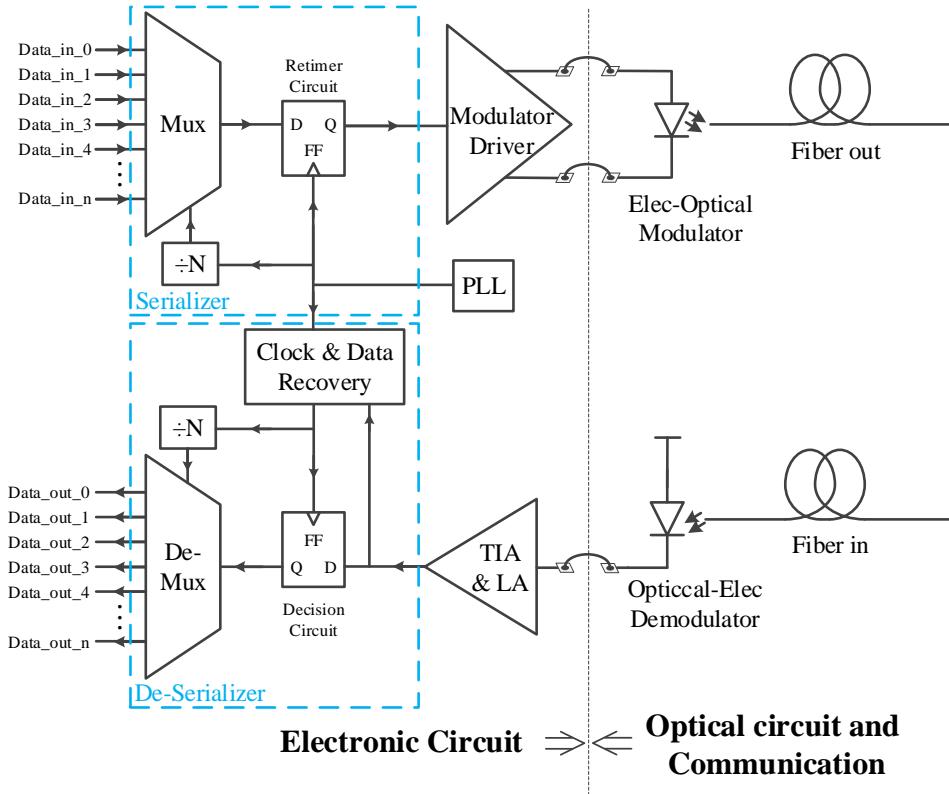

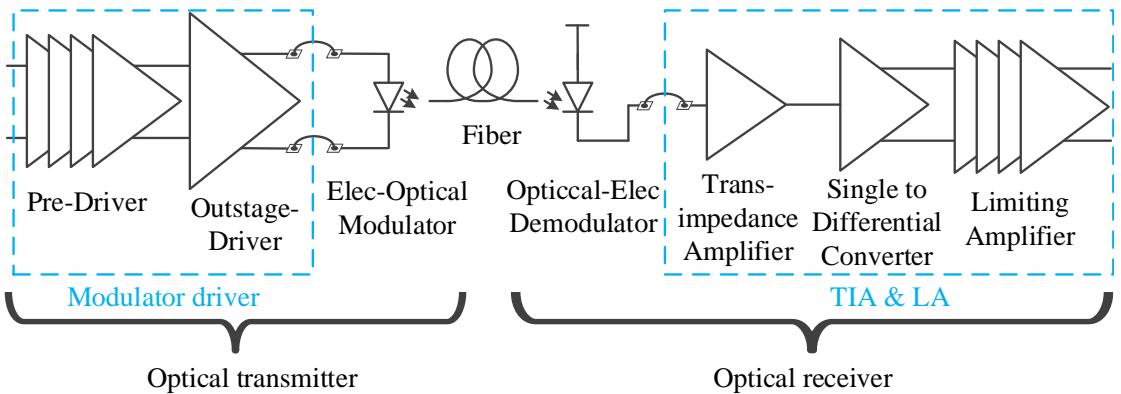

The primary function of the general optical link is to transfer data between the transmitter and receiver via fiber or other optical channels. In Fig.2.1, there is a system level transceiver of the optical data link. In order to focus on the full structure of transceiver, it is not intended for a particular type of modulator or laser as an electro-optic modulator. In this transceiver, the transmission data is assumed as none return zero (NRZ) data with the single wavelength of optical carry wave, and more complex optical modulations are presented in Sec.2.7.

FIGURE 2.1: Abstract view of an example optical data link (edited from [12])