# University of Southampton Research Repository

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Author (Year of Submission) "Full thesis title", University of Southampton, name of the University Faculty or School or Department, PhD Thesis, pagination.

Data: Author (Year) Title. URI [dataset]

## **University of Southampton**

Faculty of Physical Sciences and Engineering Electronics and Computer Science

# Cost-Effective 3D-IC Design using Near-Field Inter-Tier Wireless Communication

by

Benjamin Fletcher

A thesis submitted for the degree of Doctor of Philosophy

November, 2020

#### **UNIVERSITY OF SOUTHAMPTON**

### **ABSTRACT**

# FACULTY OF ENGINEERING AND PHYSICAL SCIENCES ELECTRONICS AND COMPUTER SCIENCE

Thesis for the degree of Doctor of Philosophy

# COST-EFFECTIVE 3D-IC DESIGN USING NEAR-FIELD INTER-TIER WIRELESS COMMUNICATION

by Benjamin Fletcher

Modern Internet of Things (IoT) devices are becoming increasingly complex, often incorporating a range of different components (sensors/processing/memory/logic) fabricated using a variety of process technologies. To integrate these disparate elements in a low-cost, small and power-efficient way, research has looked to '3D integration' where several tiers are stacked and interconnected vertically within a single chip. Most research into 3D integration assumes the use of Through Silicon Vias (TSVs) to interconnect stacked tiers; however, TSVs are presently expensive to manufacture and only available in leading-edge process nodes, making them poorly suited to cost-sensitive IoT applications.

In this thesis, wireless Inductive Coupling Links (ICLs) are investigated as an alternative to TSVs for vertical communication (and power delivery) within a 3D-IC. The motivation for focusing on wireless links is primarily cost-driven, as ICLs do not require 3D-specific fabrication processes and can facilitate simple pick-and-place assembly using only adhesive. Specifically, this work explores the design challenges associated with such ICLs, aiming to establish a standard interface that can be used for IoT-style 3D stacking applications. The key novel contributions include: (i) A low-energy ICL transceiver that uses timedomain encoding to reduce the number of transmit pulses, and hence overall energy, by over 13% when compared to existing solutions. (ii) A CAD tool for automated ICL inductor optimisation that significantly reduces the design time (by over 6 orders-of-magnitude) when compared with finite element tools, whilst maintaining an average accuracy within 7.8%. (iii) A near-field wireless clock link for many-tier clock synchronisation that achieves low-skew clock distribution across a wide range of frequencies (results show less than 61ps of clock skew across five tiers when operating between 50MHz and 2.3GHz). (iv) A hybrid ICL transceiver for concurrent wireless data and power transmission. The proposed transceiver can achieve wireless power transfer of up-to 2.0mW/link whilst simultaneously transferring 1.4Gbps of data using a BPSK scheme.

These four contributions are also validated through two 3D-stacked silicon test-chip demonstrators, the first fabricated in 0.35 µm CMOS technology (showcasing the low-energy ICL transceiver), and the second fabricated in 65nm CMOS technology (showcasing wireless data, power and clock transmission as part of a 3D stacked Arm Cortex M0 SoC). Overall, this work represents an exciting step towards a new era in VLSI where IC designers can 'pick-and-mix' the functional circuit blocks and technologies within a given chip (in the form of separate semiconductor dies) and stack them together in a low-cost way using ICLs.

# **Table of Contents**

| Al | ostra  | ct                                                       | iii  |

|----|--------|----------------------------------------------------------|------|

| De | eclara | ation of Authorship                                      | ix   |

| A  | cknov  | wledgements                                              | xi   |

| A  | crony  | ms/Abbreviations                                         | xiii |

| No | omen   | nclature                                                 | xvii |

| 1  | Intro  | oduction                                                 | 1    |

|    | 1.1    | 3D Integration Approaches                                | 2    |

|    |        | 1.1.1 Through Silicon Vias                               | 3    |

|    |        | 1.1.2 3D SiPs using Wire Bonding                         | 4    |

|    |        | 1.1.3 Monolithic 3D Integration                          | 5    |

|    | 1.2    | Wireless 3D Integration                                  | 6    |

|    | 1.3    | Research Justification                                   | 8    |

|    | 1.4    | Research Context                                         | 10   |

|    | 1.5    | Research Questions                                       | 12   |

|    | 1.6    | Research Contributions                                   | 13   |

|    | 1.7    | Publications and Patents                                 | 14   |

|    |        | 1.7.1 Peer-Reviewed Publications                         | 14   |

|    |        | 1.7.2 Patents                                            | 16   |

|    |        | 1.7.3 Other Research Engagement Activities               | 16   |

|    | 1.8    | Thesis Outline                                           | 16   |

| 2  | Wir    | eless Three-Dimensional (3D) Integrated Circuits         | 19   |

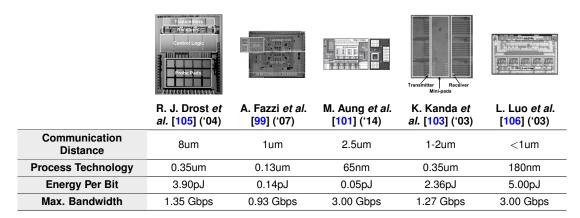

|    | 2.1    | Capacitive Coupling Links                                | 19   |

|    | 2.2    | Inductive Coupling Links                                 | 23   |

|    |        | 2.2.1 Data Encoding Schemes                              | 25   |

|    |        | 2.2.2 Transceiver Designs                                | 28   |

|    |        | 2.2.3 Inductor Layout for ICLs                           | 32   |

|    | 2.3    | Clock Delivery in Wireless 3D-ICs                        | 33   |

|    |        | 2.3.1 Wireless Clock Delivery                            | 34   |

|    | 2.4    | Power Delivery in Wireless 3D-ICs                        | 35   |

|    |        | 2.4.1 Wireless Power Transfer                            | 36   |

|    | 2.5    | Summary                                                  | 39   |

| 3  | Low    | v-Energy Transceiver Design using Spike-Latency Encoding | 41   |

| •  |        | Background and Related Work                              | 42   |

|   | 3.2 | Proposed Spike-Latency Encoding Modulation Scheme         |

|---|-----|-----------------------------------------------------------|

|   |     | 3.2.1 Mathematical Modelling                              |

|   | 3.3 | Architecture Design and Hardware Implementation           |

|   |     | 3.3.1 Encoding/Decoding Logic                             |

|   |     | 3.3.2 Tuneable Current Driver                             |

|   |     | 3.3.3 Inductive Channel                                   |

|   |     | 3.3.4 Sense Amplifier                                     |

|   |     | 3.3.5 Clock Synchronisation                               |

|   | 3.4 | Experimental Validation and Results                       |

|   | 0.1 | 3.4.1 ICL Layout Parameter Selection                      |

|   |     | 3.4.2 Validation using Mathematical Models                |

|   |     | 3.4.3 Experimental Validation using SPICE                 |

|   | 2 = |                                                           |

|   | 3.5 |                                                           |

|   |     | 3.5.1 Tuneable Current Driver Evaluation                  |

|   |     | 3.5.2 Timing Margin Evaluation                            |

|   |     | 3.5.3 Energy-per-Bit Evaluation                           |

|   | 3.6 | Discussion                                                |

|   | 3.7 | Summary                                                   |

| 4 | Doc | ign and Optimisation of Inductive Coupling Channels       |

| 4 | 4.1 | Background and Related Work                               |

|   | 4.1 | Modelling and Analysis of ICLs                            |

|   | 4.2 |                                                           |

|   |     |                                                           |

|   |     | 4.2.2 Inductive Coupling Power Links                      |

|   |     | 4.2.3 Objective Functions                                 |

|   | 4.0 | 4.2.4 Planar Spiral Inductors                             |

|   | 4.3 | ICL Layout Optimisation (COIL-3D)                         |

|   |     | 4.3.1 Scalable Inductor Model                             |

|   |     | 4.3.2 Parameter Evaluation                                |

|   |     | 4.3.3 Optimisation Approach                               |

|   |     | 4.3.4 Software Implementation                             |

|   | 4.4 | Experimental Results and Evaluation                       |

|   |     | 4.4.1 Inductor Topology Evaluation                        |

|   |     | 4.4.2 Lumped Model Accuracy Evaluation                    |

|   |     | 4.4.3 Empirical Expression Evaluation                     |

|   |     | 4.4.4 Optimisation Flow Evaluation                        |

|   |     | 4.4.5 Overhead Evaluation                                 |

|   | 4.5 | COIL-3D Example Usage Application                         |

|   | 4.6 | Summary                                                   |

|   |     |                                                           |

| 5 |     | eless Inter-Tier Clock Distribution Using Inductive Links |

|   | 5.1 | Background and Related Work                               |

|   | 5.2 | WiSync Design and Implementation                          |

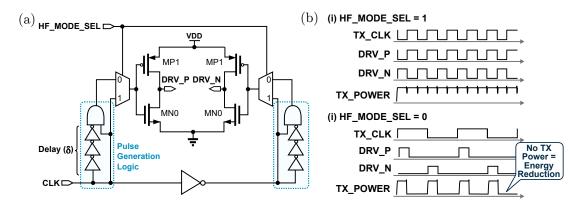

|   |     | 5.2.1 Dual-Mode Transmitter Design                        |

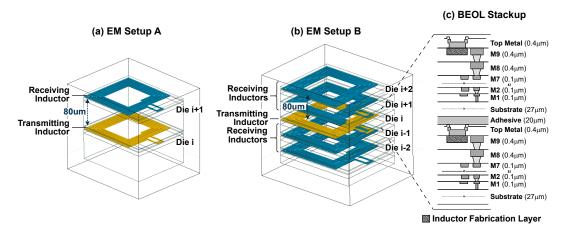

|   |     | 5.2.2 Inductor Layout Selection                           |

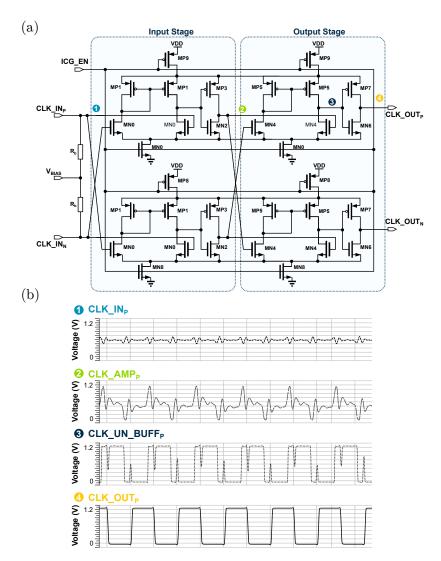

|   |     | 5.2.3 Receiver Design                                     |

|   | 5.3 | Experimental Validation and Results                       |

|   |     | 5.3.1 Device Sizing and Area Evaluation                   |

|          |              | 5.3.2 Energy per Cycle Evaluation                                | 108         |

|----------|--------------|------------------------------------------------------------------|-------------|

|          |              | 5.3.3 Cycle Error Rate (CER) and Maximum Stack Height Evaluation | 109         |

|          |              | 5.3.4 Clock Skew Evaluation                                      | 11          |

|          | 5.4          | Test-Chip Validation                                             | 11:         |

|          |              | 5.4.1 Parameter Tuning                                           | 114         |

|          |              | 5.4.2 Energy Measurement                                         | 114         |

|          |              | 5.4.3 Jitter Measurement                                         | 116         |

|          |              | 5.4.4 Tolerance to Misalignment                                  | 116         |

|          |              | 5.4.5 Discussion                                                 | 118         |

|          | 5.5          | Summary                                                          | 119         |

| 6        | Con          | Source Wireless Date and Dower Transmission                      | 101         |

| O        |              |                                                                  | 121<br>122  |

|          | $6.1 \\ 6.2$ |                                                                  |             |

|          | 0.2          | Concurrent Power and Data Delivery Architecture                  | 123         |

|          |              | 6.2.1 Bi-Phase Transmitter Design                                | 124         |

|          |              | 6.2.2 Inductive Channel and Tuning Circuit Design                | 126         |

|          |              | 6.2.3 Rectifier and Low Drop-Out Regulator Design                | 128         |

|          |              | 6.2.4 Bi-Phase Demodulator Design                                | 129         |

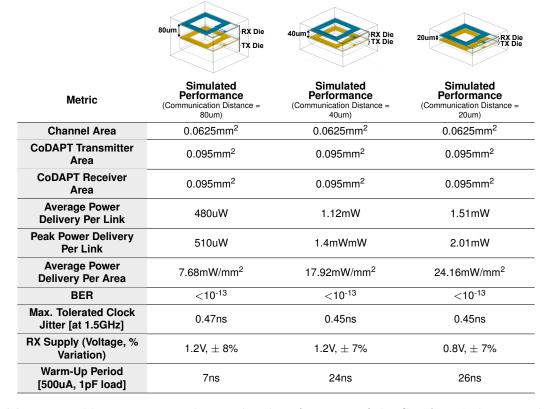

|          | 6.3          | Results and Evaluation                                           | 130         |

|          |              | 6.3.1 Channel Inductor Optimisation                              | 13          |

|          |              | 6.3.2 Area Evaluation                                            | 132         |

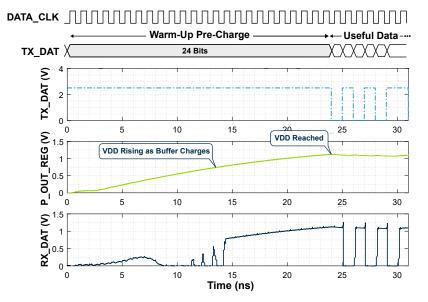

|          |              | 6.3.3 Start-Up and Transient Performance                         | 133         |

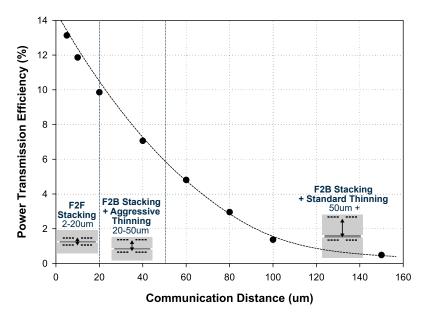

|          |              | 6.3.4 Power Delivery Performance                                 | 134         |

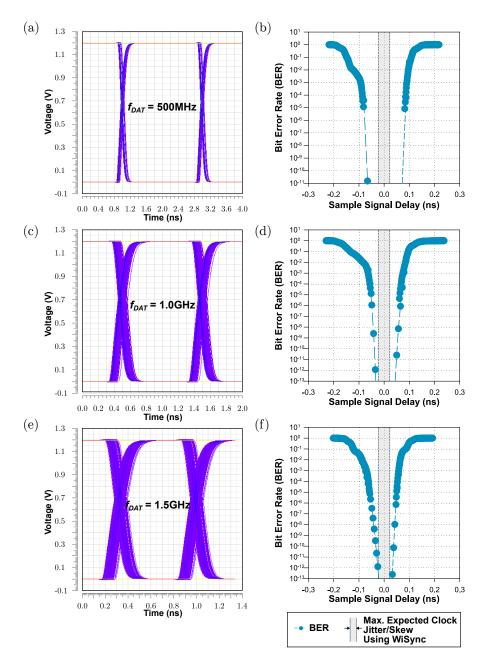

|          |              | 6.3.5 Data Delivery Performance                                  | 136         |

|          | 6.4          | Case Study: A 3D stacked Arm Cortex M0 SoC (Silicon Evaluation)  | 137         |

|          |              | 6.4.1 ICL AHB-Lite Bus Integration                               | 139         |

|          |              | 6.4.2 System Design                                              | 142         |

|          |              | 6.4.3 Experimental Results                                       | 143         |

|          | 6.5          | Summary                                                          | 149         |

| 7        | Con          | clusions and Future Work                                         | <b>15</b> 1 |

|          | 7.1          | Research Questions                                               | 153         |

|          | 7.2          | Future Work                                                      | 156         |

|          |              | 7.2.1 Security for ICL-based 3D-ICs                              | 156         |

|          |              | 7.2.2 Thermal Management for ICL-based 3D-ICs                    | 158         |

|          |              | 7.2.3 Interference and PVT Variation Effects in ICLs             | 159         |

|          |              | 7.2.4 Interposed Silicon Usage in ICL Channels                   | 160         |

|          | App          | pendix                                                           | vi          |

| <b>A</b> |              |                                                                  | 101         |

| A        | ISO-<br>A.1  |                                                                  | 165<br>166  |

|          |              | Interface using Inductive Coupling Links                         | 168         |

|          | A.2          |                                                                  |             |

|          | A.3          | Comparison Results                                               | 171         |

|          | A.4          | Discussion                                                       | 173         |

| В        |              | •                                                                | 175         |

|          | D 1          | Overvious                                                        | 17          |

|              | B.2   | Mathematical Modelling                |     |

|--------------|-------|---------------------------------------|-----|

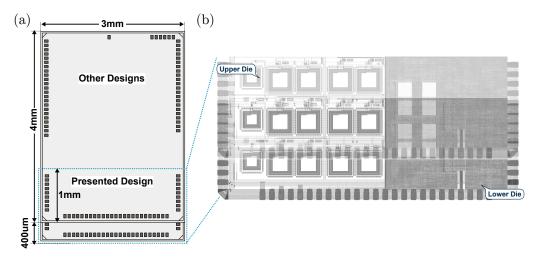

| $\mathbf{C}$ | Test  | Chip 1 Fabrication & Assembly Details | 179 |

|              | C.1   | Layout and Floorplan                  | 179 |

|              | C.2   | Thinning and Stacking                 | 181 |

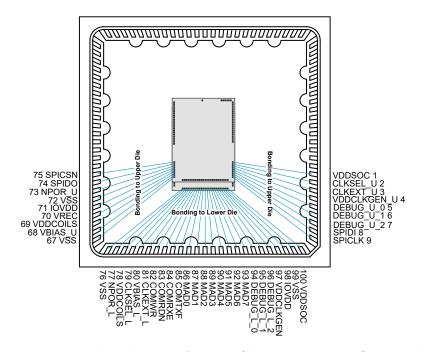

|              | C.3   | Bonding and Packaging                 | 181 |

| D            | Test  | Chip 2 Fabrication & Assembly Details | 183 |

|              | D.1   | Layout and Floorplan                  | 183 |

|              | D.2   | Thinning and Stacking                 | 184 |

|              | D.3   | Bonding and Packaging                 | 185 |

| Re           | ferer | nces                                  | 187 |

## **Declaration of Authorship**

I, Benjamin Fletcher, declare that this thesis entitled *Cost-Effective 3D-IC Design using Near-Field Inter-Tier Wireless Communication* and the work presented in it are my own and have been generated by me as the result of my own original research.

#### I confirm that:

- 1. This work was done wholly or mainly while in candidature for a research degree at this University;

- 2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- 3. Where I have consulted the published work of others, this is always clearly attributed;

- 4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- 5. I have acknowledged all main sources of help;

- 6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- 7. Parts of this work have been published as:

Publications reported directly as contributions (listed in reverse chronological order):

- B. J. Fletcher, S. Das, T. Mak, "A Spike-Latency Transceiver with Tuneable Pulse Control for Low-Energy Wireless 3D Integration", IEEE Journal on Solid State Circuits (JSSC) 55(9) pp. 2414-28 (2020).

- B. J. Fletcher, T. Mak and S. Das, "A 3D-Stacked Cortex-M0 SoC with 20.3Gbps/mm<sup>2</sup> 7.1mW/mm<sup>2</sup> Simultaneous Wireless Inter-Tier Data and Power Transfer," *IEEE Symposium on VLSI Circuits*, Honolulu, Hawaii, 2020 pp. 1-2.

- B. J. Fletcher, S. Das and T. Mak, "A 10.8pJ/bit Pulse-Position Inductive Transceiver for Low-Energy Wireless 3D Integration," *IEEE European Solid State Circuits Conference* (ESSCIRC), Cracow, Poland, 2019, pp. 121-4.

- B. J. Fletcher, S. Das, T. Mak, "A Low-Energy Inductive Transceiver using Spike-Latency Encoding for Wireless 3D Integration," *IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED)*, Lausanne, Switzerland, 2019, pp. 1-6.

- B. J. Fletcher, S. Das and T. Mak, "Design and Optimization of Inductive-Coupling Links for 3-D-ICs," *IEEE Transactions on Transactions on Very Large Scale Integration (VLSI)* Systems 27(3) pp. 711-23 (2019).

- B. J. Fletcher, S. Das, T. Mak, "CoDAPT: a concurrent data and power transceiver for fully wireless 3D-ICs,", *Design, Automation & Test in Europe Conference & Exhibition* (DATE), Florence, Italy, 2019, pp. 1343-48.

- B. J. Fletcher, S. Das, T. Mak, "Cost-effective 3D integration using inductive coupling links: Can we make stacking silicon as easy as stacking Lego?", *Arm Research Summit 2018*, Cambridge, United Kingdom. 17 19 Sep 2018.

- B. J. Fletcher, S. Das, T. Mak, "A High-Speed Design Methodology for Inductive Coupling Links in 3D-ICs", *Design, Automation & Test in Europe Conference & Exhibition (DATE)*, Dresden, Germany, 2018, pp. 497-502.

- B. J. Fletcher, S. Das, T. Mak, "Low-Power 3D Integration using Inductive Coupling Links for Neurotechnology Applications,", *Design, Automation & Test in Europe Conference & Exhibition (DATE)*, Dresden, Germany, 2018, pp. 497-502.

Patents directly reported as contributions:

- B. J. Fletcher, J. Myers, S. Das and T. Mak, "A Pseudo System-on-Chip Architecture Incorporating Wirelessly Connected Bus Slaves.", U.S. Patent 16/685,090, Nov 2019 (pending).

- S. Gamage, B. Fletcher, and S. Das, "Adaptive Coding for Wireless Communication.", U.S. Patent 16/656,937, Oct 2019 (pending).

Other publications completed during my PhD candidature:

- D. Balsamo, B. J. Fletcher, A. J. Weddell, G. Karatziolas, B. Al-Hashimi and G. V. Merrett, "Power neutral performance scaling with intrinsic MPPT for energy harvesting computing systems," ACM Transactions on Embedded Computing Systems, 17(6), pp. 1-25 (2019).

- B. J. Fletcher, D. Balsamo and G. V. Merrett, "Power-neutral performance scaling for self-powered multicore computing systems,", Adaptive Many-Core Architectures and Systems Workshop, York, United Kingdom, 13 Jun 2018.

- Q. Ding, B. J. Fletcher, T. Mak, "Globally Wireless Locally Wired: A Clock Distribution Network for Many-Core Systems," *IEEE International Symposium on Circuits and Systems (ISCAS)*, Florence, Italy, 2018, pp. 1-5.

- B. J. Fletcher, D. Balsamo and G. V. Merrett, "Power neutral performance scaling for energy harvesting MP-SoCs,", Design, Automation & Test in Europe Conference & Exhibition (DATE), 2017, Lausanne, Switzerland, 2017, pp. 1516-21.

| Signed: |  |  |

|---------|--|--|

| Date:   |  |  |

# **Acknowledgements**

The work presented in this thesis would not have been possible without the wonderful people that I have had the fortune of working with over the past four years, and so I must take this opportunity to extend my thanks to them.

First and foremost, I would like to express my sincere thanks and appreciation to my academic supervisor, Terrence Mak. I am very grateful to Terrence for his constant encouragement, enthusiasm and incredible creativity, which inspired me to pursue such an exciting and novel research topic. Your positivity has been contagious and has made the PhD experience truly enjoyable. I am also sincerely thankful to Shidhartha Das, my industrial supervisor at Arm Research. Sid's support and friendship have been invaluable, and I have thoroughly enjoyed working under his guidance; it has been a great privilege learn from someone with such broad technical ability.

My special thanks also go to James Myers and the rest of the Devices Circuits and Systems (DCS) group at Arm Research (including, but not limited to, Fernando, Prannay, Benoit, Sahan, Philex, Andy and Graham) for hosting and mentoring me. It has been fantastic to have the opportunity to work with, and learn from, such a talented group of researchers and our discussions have inspired much of the work presented in this thesis. I must also thank my colleagues from the University of Southampton's Cyber Physical Systems research group, including my secondary academic supervisor Geoff Merrett, as well as Qian and Domenico. It has been a joy to work with you all and our collaborations have been a great support over the past four years.

I also wish to thank Arm Research, the Engineering and Physical Sciences Research Council (EPSRC), and the University of Southampton for their financial support with tuition fees, conference attendances and chip tape-outs, without whom this work would not have been possible.

Finally, I must also take the opportunity to thank my family, particularly my parents and my wife Heather for her continued love, support and encouragement throughout the process.

# Acronyms/Abbreviations

**APR** Automatic Place and Route

**ASK** Amplitude Shift Keying

**BEOL** Back End Of Line

**BER** Bit Error Rate

**BPM** Bi-Phase Modulation

**BPSK** Bi-Phase Shift Keying

**CCL** Capacitive Coupling Link

**CDN** Clock Distribution Network

**CER** Cycle Error Rate

**CMOS** Complementary Metal Oxide Semiconductor

**CMP** Chemical-Mechanical Polishing

**CoDAPT** Concurrent Data and Power Transfer

**DLL** Delay Locked Loop

**DMA** Direct Memory Access

**DoS** Denial of Service

**DP** Dynamic Programming

**DRC** Design Rule Check

**ECC** Error Correction Code

**EDA** Electronic Design Automation

**EH** Energy Harvesting

**EM** Electro-Magnetic

F2B Face-to-Back

**F2F** Face-to-Face

**FDM** Frequency-Division Multiplexing

**FEM** Finite Element Method

FIFO First-In-First-Out

**FLL** Frequency Locked Loop

**FPGA** Field Programmable Gate Array

**HDSV** Highly-Doped Silicon Via

HF High FrequencyIC Integrated Circuit

ICL Inductive Coupling Link

Internet of Things

IP Intellectual Property

**LDO** Low Drop Out

LNA Low-Noise Amplifier

LSB Least Significant Bit

M3D Monolithic 3D Integration

MCM Multi-Chip Module

MDLL Multiplying Delay Locked Loop

MEMS Micro-Electromechanical Systems

MI Mutual Inductance

MIV Metal Insulator Metal

Monolithic Inter-tier Via

MSO Mixed Signal Oscilloscope

MUX Multiplexor

NF Near Field

**NFC** Near-Field Communication

NRZ Non-Return to Zero

NVM Non-Volatile Memory

**PAM** Pulse Amplitude Modulation

PCB Printed Circuit Board

**PCM** Phase Change Memory

PLL Phase Locked Loop

**PPM** Pulse Position Modulation

PRBS Pseudo-Random Binary sequence

**PVT** Process Voltage Temperature

QFN Quad Flat No-leads

QFP Quad Flat Package

RC Resistor-Capacitor

RF Radio Frequency

**RFID** Radio-Frequency Identification

RIE Reactive Ion Etching

**RO** Ring Oscillator

**RRAM** Resistive Random Access Memory

**RX** Receiver

SA Sense Amplifier

**SAFF** Sense Amplifier Flip Flop

SET Spike-latency Encoding Transceiver

SMU System in Package

SMU Source Meter Unit

**SoC** System-on-Chip

**SPM** Single-Phase Modulation

SR Set-Reset

**STT-RAM** Spin-Transfer-Torque Random Access Memory

TSV Through Silicon Via

TX Transmitter

**VLSI** Very Large Scale Integration

WBI Wireless Bus Interface

**WPT** Wireless Power Transfer

# **Nomenclature**

$\chi_s$  Track spacing graduation coefficient

$\chi_w$  Track width graduation coefficient

$C_{i,j,k}$  Capacitance of segment k, of turn j, of inductor i [F]

$t_c$  Inductor metal thickness [m]

X Communication distance [m]

*k* Magnetic coupling coefficient

$\delta$  TX pulse duration [s]

d Inner diameter of inductor [m]

D Outer diameter of inductor [m]

Length of an inductor coil segment [m]

$E_{pb}$  Energy per bit [J]

$\eta_{dat}$  Efficiency of data ICL

$\eta_{pow}$  Efficiency of power ICL

$f_{

m COUNT}$  Counter frequency [Hz]

$f_{clk}$  Clock frequency [Hz]

$f_{\mathrm{DAT}}$  Data frequency [Hz]

$f_{hf}$  BPSK carrier Signal Frequency [Hz]

$\phi$  Inductor fill-factor

f Link operating frequency [Hz]

$f_{

m sr}$  Self-resonant frequency [Hz]

g Minimum technology grid unit [m]

$L_{i,j,k}$  Inductance of segment k, of turn j, of inductor i [H]

$R_L$  Load resistance  $[\Omega]$

Mutual inductance [H]

$\omega$  Angular frequency [rad/s]

N Number of bits per TX pulse

$I_p$  TX pulse amplitude [A]

$R_{i,j,k}$  Resistance of segment k, of turn j, of inductor i [ $\Omega$ ]

$I_{\mathrm{RX}}$  Receiver current [A]

$L_{

m RX}$  Inductance of RX inductor [H]

$V_{\mathrm{RX}}$  Received voltage [V]

s Spacing between inductor tracks [m]

$V_{\mathrm{DD}}$  Supply voltage [V]

$I_{\rm SL}$  Current of transceiver supporting logic [A]

$I_{\mathrm{TX}}$  Transmitter current [A]

$L_{

m TX}$  Inductance of TX inductor [H]

$V_{

m TX}$  Transmit voltage [V]

$\lambda$  TX Signal wavelength [m]

## **Chapter 1**

# Introduction

For over 40 years Moore's Law has accurately predicted, and underpinned, the biennial doubling of device density within Integrated Circuits (ICs) [1]. However, as conventional channel length scaling progresses beyond the 10nm technology node, power and performance returns of traditional scaling are becoming incommensurate. Smaller gates require denser finer-pitch interconnect, and hence global Resistor-Capacitor (RC) interconnect delay has become the limiting factor for the performance of Complementary Metal Oxide Semiconductor (CMOS) ICs [2]. To overcome these obstacles, the semiconductor industry has explored a diversity of more-than-Moore technologies, each of which augment the performance of conventional ICs, to prolong the yearly incremental performance improvements expected by consumers. One such more-than-Moore technology is three-dimensional (3D) integration [3]. In 3D integrated circuits, active devices are not restricted to a single plane, moreover multiple planes (or tiers) of semiconductor dies are stacked and interconnected vertically. This has the effect of increasing transistor density and reducing long global interconnect traces to shorter vertical hops, improving performance [4].

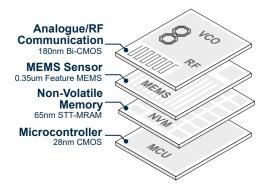

Another, often overlooked, benefit of 3D integration is the facility that it offers for combining multiple different process technologies within a single heterogeneous IC. Heterogeneous 3D integration has the potential to unlock a new era in Very Large Scale Integration (VLSI) where designers can merge Micro-Electromechanical Systems (MEMS), low power CMOS, Radio Frequency (RF) Bi-CMOS and novel Non-Volatile Memory (NVM) technologies (such as Phase Change Memory (PCM), Spin-Transfer-Torque Random Access Memory (STT-RAM), and Resistive Random Access Memory (RRAM)) together within a single IC. This makes it a promising enabling platform for Internet of Things (IoT) devices which must often bring together these disparate elements within strict power and size budgets [5].

Unfortunately, however, the ideal of using 3D integration to construct highly-integrated heterogeneous IoT chips (illustrated by Figure 1.1) has not yet been realised. The commercial use of 3D integration is presently limited to homogeneous memory stacking applications (for example stacked DRAM [6–8] or Flash [9]) and examples of technologically heterogeneous 3D-ICs are sparse, even within the research community. Whilst this is in-part due to

**Figure 1.1:** Conceptual illustration of a heterogeneous stacked 3D-IC suited for IoT sensing and compute-at-the-edge applications.

the novelty of the 3D integration concept (in addition to the lack of EDA support for designing 3D chips), when considering IoT applications (where minimising manufacturing costs is of paramount importance), it is primarily due to the high costs of designing and fabricating 3D-ICs, in addition to the limited number of TSV-enabled process nodes enabled by foundries<sup>1</sup>.

To address this challenge, this thesis explores a low-cost alternative to existing 3D integration methodologies, achievable at any process technology node: using wireless vertical links to communicate data and power between tiers. The use of wireless communication means that an existing 2D fabrication processes can be used, without any alteration, making development straightforward, and possible across all technologies. In addition to this, the use of wireless communication means that the lateral placement tolerance (between stacked dies) is significantly relaxed, facilitating low-cost pick-and-place 3D assembly. Considering these benefits, the main appeal of Inductive Coupling Link (ICL)-based 3D integration is in applications that require low cost, heterogeneous stacking such as the IoT applications discussed above.

## 1.1 3D Integration Approaches

Broadly, three dimensional integrated circuits are defined as: "Integrated circuits containing multiples layers of interconnected active devices" [11]. Whilst stacking multiple tiers of active devices is a relatively straightforward task, establishing a method of connecting these vertically integrated tiers poses a more significant challenge. Early research in the field of 3D integration proposed innovative and controversial approaches to interconnect silicon dies, with some of the very first publications suggesting vertical communication between using "photonic light beams passing through the silicon wafer" (1987 [12]) or using "mechanical spring clips" (1990 [13]). However, as time has progressed, the research community has

<sup>&</sup>lt;sup>1</sup>For example, TSMC's 'Memory Cube', their only *true* 3D fabrication process (using TSVs to stack several tiers) is only available at nodes <28nm [10].

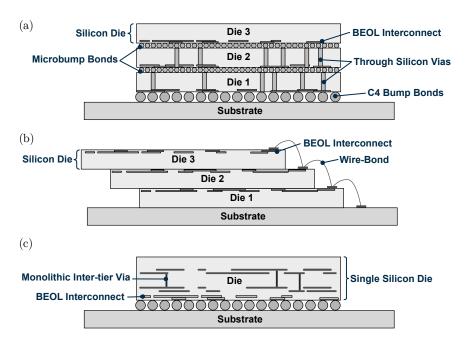

**Figure 1.2:** Conceptual illustration of existing 3D integration approaches including (a) a 3-tier 3D-IC assembled using TSVs to provide vertical connectivity between dies, (b) a 3 tier 3D stacked SiP using wire-bonds to interconnect stacked tiers, and (c) a monolithic 3D-IC with three sequentially fabricated active silicon tiers.

become increasingly focussed on a limited number of 3D assembly approaches which are outlined in the following sub-sections.

### 1.1.1 Through Silicon Vias

Over recent years, Through Silicon Vias (TSVs) have become synonymous with 3D integration. Within the context of 3D-IC design, the number of TSV-related publication eclipse those of competing approaches with approximately three-quarters of published works assuming TSV-based stacking. TSVs are electrical connections that pass entirely through the silicon substrate from front to back [14], allowing several dies to be stacked using microbumping in a fashion reminiscent of multi-layer Printed Circuit Boards (PCBs). Figure 1.2 (a) illustrates conceptually a 3D-IC assembled using through silicon vias to interconnect the Back End Of Line (BEOL) layers of each stacked die. TSVs can be fabricated in a number of ways including via-first (before Front End Of Line (FEOL) processing [15]), via-middle (after FEOL processing, but before BEOL processing [16]), or via-last (after BEOL processing [17]), however broadly, incorporating Through Silicon Vias (TSVs) necessitates deep Reactive Ion Etching (RIE) of the substrate, deposition and plating (of the conductive via material, typically polysilicon, copper, or tungsten), and aggressive Chemical-Mechanical Polishing (CMP) for thinning the wafer [18]. Compared to other vertical interconnect technologies, TSVs are a popular choice as they provide high density, high bandwidth connectivity between, potentially tens of stacked dies [19].

One drawback when using TSVs, however, is that they are presently only available at the latest foundry nodes, and are difficult to retrospectively include (using via-last fabrication) due to the high temperatures required for the annealing process [20]. This limits the facility for building the heterogeneous 3D-ICs discussed above. TSV-based 3D-ICs are also often also reported to suffer from yield and reliability challenges [21], arising from TSV/micro-bump deformation if precise alignment is not achieved between layers of the stack [22, 23].

Another significant drawback, particularly when considering IoT devices (which are highly cost-sensitive), is the high cost of TSV-enabled manufacturing processes [24]. Due to the additional fabrication and assembly stages associated with TSV-based 3D integration, it is estimated that, presently, the fabrication of a TSV-based 3D-IC will cost  $1.4-2\times$  that of a comparable system in 2D [24].

#### 1.1.2 3D SiPs using Wire Bonding

To address this, and facilitate 3D integration with low-cost (even at non-TSV-supporting process nodes), some researchers are exploring 3D assembly using wire-bonds between tiers [25]. One notable example where this is well applied in the IoT domain is the Michigan Micromote project [25–27], where multiple heterogeneous silicon tiers are stacked and integrated together for IoT sensing applications [28, 29]. Figure 1.2 (b) illustrates a stacked 3D-SiP assembled using wire-bonding. Here, each tier is placed upon the previous with a small lateral offset to allow access to the pads placed at the edge of the die. Wire-bonds are then used to interconnect the dies in the same way as the chip-to-package bonding process as illustrated in Figure 1.2 (b). This is, by far, the most mature (and hence cost-effective) technologies when considering 3D integration [30], but typically classed as three-dimensional System in Package solution. The distinction between 3D packaging (3D System in Package (SiP)) and 3D Integrated Circuits (3D-ICs) is widely debated however generally, 3D SiPs consist of multiple dies packaged together with only sparse package-level interconnect between them [19].

Whilst 3D-SiP assembly using wire-bonding can enable highly heterogeneous integration, the complexity of the required stacking arrangements, and the physical limits of wire-bonding (including loop-height, pitch, etc.) mean that assembling dies in this way quickly reaches practical limits. The ICs fabricated for the Micromote project ([25–29], discussed above) require custom, manual wire-bonding in an assembly process that cannot be scaled to mass production. Further to this, interconnects in wire-bonded SiPs must be placed on the periphery of each die, meaning that the achievable integration bandwidth is low and, due to their length, interconnect parasitics (capacitance and inductance) are high when using wire-bonds, limiting the die-to-die signalling speed [19].

Another 3D packaging approach which addresses some of these issues is flip-chip bonding, whereby fine pitch solder bumps are used to bond adjacent layers. When using flip-chip

bonding, landing pads are created on the surface of the recipient wafer or die which are then deposited with solder paste. The donor chip (which is to be bonded) is flipped and aligned with the recipient, before being heated to re-melt the solder bumps, resulting in an electrical bond between the two die. Whilst flip-chip bonding is an alternative SiP solution that can scale well in mass production (and can offer relatively high inter-tier interconnect bandwidths with achievable pitches between 50 µm and 200 µm [31]), one significant drawback of flip-chip bonding is that support is limited to only two tiers as dies are bonded in a face-to-face fashion [31].

### 1.1.3 Monolithic 3D Integration

Another approach to 3D integration involves sequentially fabricating multiple silicon layers, one after another, known as Monolithic 3D Integration (M3D). Of all the 3D integration approaches, M3D is the closest to the conceptual ideal of seamless 3D integration. In M3D, transistors are fabricated in sequential layers which are interconnected using fine-pitched Monolithic Inter-tier Vias (MIVs) [32]. Compared to other 3D-IC approaches which bring together each of the layers post-fabrication, the sequential M3D approach facilitates much higher connection density, allowing even for gate level vertical connectivity [33]. This is illustrated in Figure 1.2 (c).

The ability to fabricate several layers of active devices within an IC is clearly desirable. However presently, M3D is in very early stages of development, and is not a viable option for commercial fabrication. As an indication of the progress in this area, some of the leading research into monolithic 3D integration at the time of writing is being performed by the Taiwan Semiconductor Research Institute (TSRI). Their work, however, has only successfully managed to fabricate a handful of transistors (< 10) in the upper layer [34].

The biggest challenges facing M3D are the thermal budget constraints for sequential fabrication. Presently, it is not possible to utilise high processing temperatures (> 400-500°C) after forming the copper BEOL interconnect of the 'lower' die [32, 35], however, such temperatures are essential for silicon epitaxy and reliable low-resistance gate formation [36]. One of the leading device-based research groups seeking to overcome this challenge is CAE-Leti, as part of their CoolCube<sup>TM</sup> technology. Recent published work by CAE-Leti demonstrates the very first SRAM bit cells formed at low-temperatures (<500°C), in addition to a functional 81 stage ring oscillator fabricated end-to-end using process temperatures not exceeding 500°C [37]. This is achieved by: (1) performing in-situ dopant activation using an excimer laser (to lower gate resistance), and (2) replacing the traditional epitaxial pre-bake stage (HF-Last cleaning and 650°C bake) with an in-situ Siconi NH<sub>3</sub>/NF<sub>3</sub> remote plasma process that can be followed by a 500°C H<sub>2</sub> bake [38].

Whilst these recent breakthroughs have not been demonstrated as part of a monolithic 3D chip, the ability to fabricate functional and yielding devices within the temperature budgets

imposed by M3D represents a significant milestone, meaning that is only a matter of time before two-layer M3D is possible [39]. It is, however, important to note that M3D is a long way from being commercially viable at scale (due to the challenges related to yield). Further to this, because all processing stages in a monolithic 3D-IC must be agreeable with previous layers (including temperature, materials and mechanical stresses), it is unlikely that M3D will ever be an enabling technology for the truly *heterogeneous* 3D integration discussed above (to combine several different technologies in the same chip).

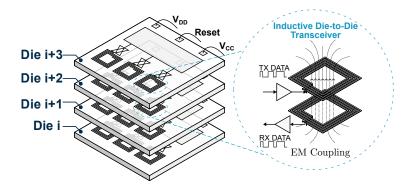

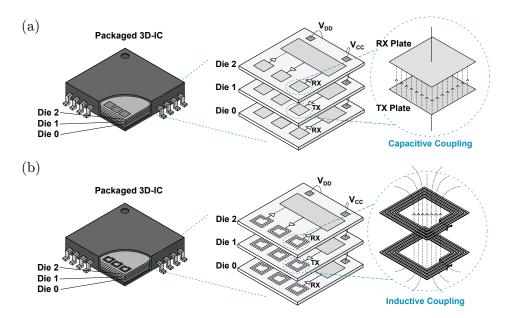

## 1.2 Wireless 3D Integration

One final 3D integration approach (which forms the focus of this thesis) is using wireless inter-tier links. Here, instead of physically connecting the dies within the 3D stack, data to be communicated between layers is encoded as an Electro-Magnetic (EM) field to allow contactless communication, in a way similar to Near-Field Communication (NFC)/Radio-Frequency Identification (RFID) tags used in contactless smart cards.

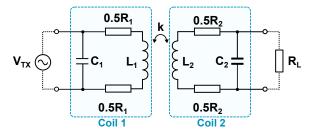

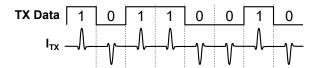

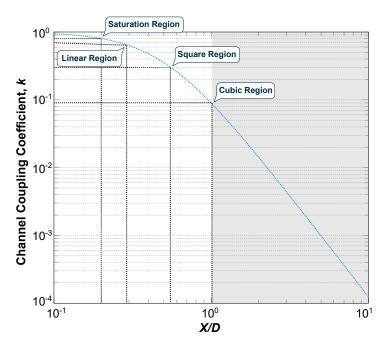

To achieve reasonable power efficiency wireless inter-tier links typically operate in the nearfield region of the electromagnetic (EM) spectrum [40] (where communication occurs across a distance less than the Fraunhofer distance, given by  $2D^2/\lambda$ , where  $\lambda$  is the wavelength of the communicated signal and D is the diameter of the antenna [41]). Approaches to wireless 3D integration in this near-field region can broadly be sub-divided into two main categories: communication through inductive coupling (which relies upon the modulation of a magnetic, H-Field) and communication through capacitive coupling (which relies upon the modulation of an electric, **E**-Field). As capacitive coupling is voltage driven (meaning that the communication distance increases proportionally to the drive voltage,  $V_{\rm RX} \propto C dV_{\rm TX}/dt$ ) and inductive coupling is current driven (meaning that the communication distance increases proportionally to the drive current,  $V_{\rm RX} \propto L dI_{\rm TX}/dt$ ), ICLs are usually favoured. This is because it is much easier to increase the drive current on-chip (simply by increasing the channel width (or number) of driver transistors), than it is to increase the drive voltage beyond VDD (which requires complex structures such as charge pumps etc. [42])<sup>2</sup>. This means that ICLs can offer significantly enhanced communication distances when compared with Capacitive Coupling Links (CCLs) which are typically limited to Face-to-Face (F2F) stacking arrangements.

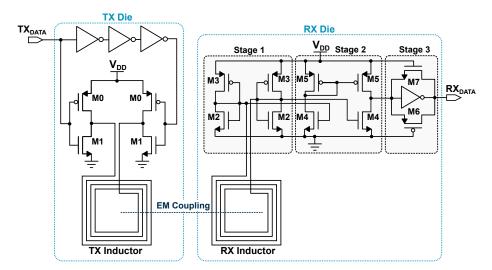

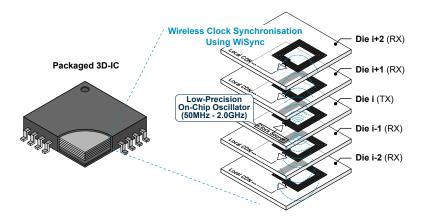

When performing contactless 3D integration using ICLs, data is transmitted via electromagnetic (EM) coupling between transmit (TX) and receive (RX) coils fabricated in the upper BEOL interconnect layers of each die as illustrated in Figure 1.3. Typically, to maximise  $dI_{\rm TX}/dt$ , whilst minimising energy dissipation, pulse-based modulation schemes are used, where the data is encoded into a series of short, discrete current bursts. As these current

<sup>&</sup>lt;sup>2</sup>A more complete comparison of each of these approaches (wireless 3D integration using capacitive coupling and wireless 3D integration using inductive coupling) is provided in Chapter 2.

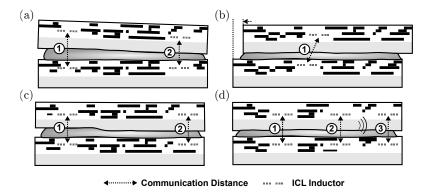

**Figure 1.3:** Illustration of a multi-tier wireless 3D-IC vertical inter-die implemented using near-field inductive coupling links (ICLs).

pulses flow through the Transmitter (TX) coil, a magnetic field is formed [43]. Provided that the Receiver (RX) coil intersects this magnetic field, a corresponding current (and hence voltage) will be induced, according to Faraday's law [44]. This induced voltage can be detected and decoded in the recipient die to recover the transmitted data. This process allows communication between several Face-to-Back (F2B) stacked dies [45] without the need for 3D-specific nanotechnology, or precise alignment between stacked tiers.

When compared to the use of TSVs, this *wireless* approach to 3D integration promises several potential benefits, one of which being significantly reduced fabrication costs. The inductors required for ICLs can easily be fabricated in the BEOL interconnect layers of existing CMOS processes with no alteration. These standard processes are highly refined, and hence fabrication using this method is much less expensive.

The economic benefits of using ICLs are also evident at the assembly/packaging stage. Whilst 3D-ICs assembled using TSVs require sub-micron pick and place accuracy to ensure reliable operation [22] (in addition to wafer bumping and then micro-bump bonding to interconnect layers), 3D-ICs assembled using ICLs can simply be picked and attached using adhesive, with a relatively relaxed placement tolerance (in the order of 10's of micro meters [24]). This means that, overall, manufacturing is significantly cheaper. ICLs can also be integrated at almost any process technology (unlike TSVs which are presently only available at the most advanced foundry nodes, as discussed previously). The ability to go off-menu with respect to foundry process technologies, thereby allowing each separate functional element in the 3D system to be fabricated in the most cost-effective way, makes ICLs well suited for low-cost heterogeneous integration applications such as the IoT stack illustrated conceptually in Figure 1.1 [46].

Another benefit of performing 3D integration using ICLs, particularly when considering IoT-style applications is the fact that they offer a high level of customisability. For example, disparate sensor/processing/memory/logic dies (each of which manufactured by different vendors), could be designed to communicate using the same wireless ICL interface (even

offering the possibility of intrinsic wireless voltage level conversion between dies operating at different supply voltages [46]), thereby allowing system-level designers to 'pick-and-mix' the circuit blocks that they require. These blocks could then be stacked in a customised 3D-IC, tailored for a specific application, with minimal cost and effort. This is presently not possible using TSVs as the physical specifications of via placement/pitch/diameter etc. very between vendors.

One final benefit of using ICLs is that design cycle times (which is another significant concern for IoT devices) can be significantly reduced compared with TSVs, due to the fact that ICLs can be designed and signed off using existing planar (2D) Electronic Design Automation (EDA) tools. Designing with TSVs introduces a whole range of new requirements for partitioning, Automatic Place and Route (APR) and Design Rule Checks (DRCs), etc all of which are immature at the moment.

For these reasons, wireless 3D integration using inductive coupling links (ICLs) has been identified as a compelling alternative to TSVs, to enable the heterogeneous computing ideals discussed above, with little additional cost when compared to standard planar ICs.

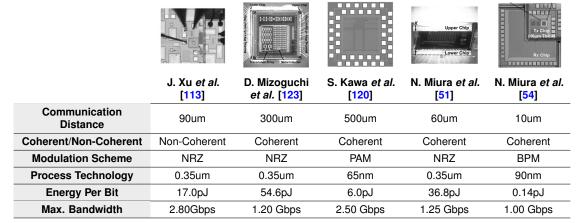

#### 1.3 Research Justification

Despite these potential benefits, wireless 3D integration does have several drawbacks. One of the biggest criticisms of wireless 3D integration is its inferior power efficiency when compared with traditional contact-based approaches [47]. For markets like the IoT (where devices typically operate from limited battery, or Energy Harvesting (EH) sources), maintaining low power consumption is essential [48]. Because of this, the use of wireless 3D integration has not yet been considered, despite its potential economic benefits. Most works presenting ICL transceivers prioritise performance (in terms of link-bandwidth) above energy-efficiency [43, 49, 50]. One focus of this thesis, therefore, will be exploring energy-efficient ICL transceiver design in order to reduce the energy consumption of existing ICL transceivers to an acceptable level for Internet of Things devices.

Extending this further, when considering the sources of power consumption within an ICL transceiver, by far the most energy inefficient component is the inductive channel itself [51], with a significant proportion of the energy used to form the H-Field often being wasted [52]. To maximise the energy efficiency, therefore, it is essential that the layout/geometry of the inductors used to form the ICL channel (for example shape, track-width, track-spacing, number of turns etc.) is optimised [51]. Presently, this involves using Finite Element Method (FEM) tools for EM analysis, and then converting the system's EM characteristics into equivalent circuit models that can be handled by electrical simulators (e.g. SPICE) [52]. The layout can then be manually adjusted, and the process repeated until a satisfactory solution is found. Solvers using FEM, however, often take several hours to converge, even whilst

analysing a single geometry [53]. Due to this, determining coil pairs with optimised geometries (which typically necessitates analysing thousands of layouts) is extremely computationally expensive, if not impossible. Another focus of the research in this thesis will, therefore, be the ICL inductor design process, with the target of achieving rapid inductor layout optimisation to maximise power efficiency.

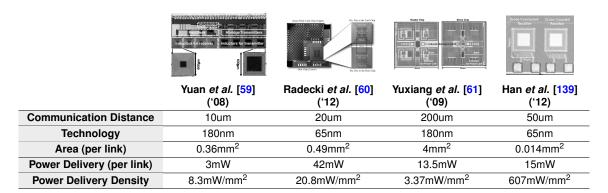

Whilst there are a range of prior works exploring the use of wireless data communication between tiers of a 3D stack [43, 49, 50, 54–56], to make the stacking process truly wireless (and avoid the need for, and hence cost of, die-to-die wire bonding completely) it is also necessary to perform wireless power delivery between tiers. Presently, most 3D-ICs using ICLs rely on wire-bonded power and ground connections to supply power to each die in the stack [43, 55, 57, 58]. Whilst this is an adequate solution that circumvents the use of TSVs, the addition of wire-bonds to each tier of the 3D stack undermines many of the benefits associated with wireless 3D integration and inflates the assembly cost and complexity. Because of this, a handful of works also explore using Wireless Power Transfer (WPT) within the chip [59–61]. All of these works, however, separate wireless power transfer and data communication across two inductive channels, meaning that a minimum of four inductors are required for a given system [59–61]. One often-faced criticism of using ICLs for 3D integration is their high silicon area usage (due to the relatively large footprint of the on-chip inductors) [62]. Doubling the number of channels (to perform power and data transfer) exacerbates this problem, especially considering that WPT links typically require larger channels (in some cases consuming up to as much as 4mm<sup>2</sup> of silicon area [61]). To address this issue, the third research theme of this thesis is to explore new approaches for wireless power delivery in contactless 3D-ICs, with a focus on area efficiency.

In a similar vein, to achieve fully wireless 3D integration, especially when implementing a coherent data transceiver, it is necessary to achieve precise clock synchronisation between the transmitting and receiving dies. In many prior works, clock delivery is performed externally using wire-bonding [19]. Although this is an adequate solution, the addition of wire-bonds suffers from the same issues discussed above and is incompatible with fully-wireless 3D integration. Further to this, the parasitic overheads of the pad drivers (and RLC parasitics of each bond-wire) mean that the clock frequency that can be achieved is limited. The use of coupled resonators has been proposed to address this issue, delivering the clock wirelessly between tiers [43, 63–65]. Here, LC tanks with a resonant frequency corresponding to the clock frequency are used, where the inductive (L) component is part of a coupled inductive link [63]. The use of coupled resonators is a promising solution that allows the clock to be wirelessly transmitted between dies with low jitter and skew (due to the natural harmonics of the link), however such links must either be very high-frequency or very large in terms of area (as the resonant LC decreases with diameter, D, of the inductor, L). To achieve clock distribution at frequencies in the order of 100's of Mega Hertz using this approach

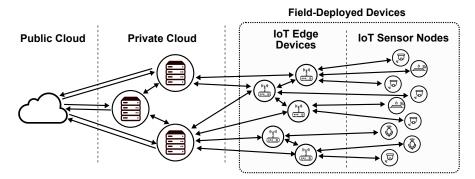

Figure 1.4: A typical Internet of Things (IoT) fog network (reproduced from [67]).

(which is typical for IoT applications) often requires inductors with diameter  $> 300 \,\mu\text{m}$  [64]. Motivated by this, the fourth theme of this research will be clock distribution in wireless inductive 3D-ICs, again focusing on area efficiency.

Finally, although there are already several impressive works demonstrating many-tier vertical interconnection using ICLs, the number of publications demonstrating such links as part of a fully-functional system are limited [51] and even when full system integration is performed (for example [66]), custom non-standard communication protocols are used. For IoT applications, short time-to-market is essential and hence it is desirable to integrate functional blocks in a standardised way. The final research focus of this thesis, therefore, will be developing a standardised ICL interface to enable 'pick-and-mix' stacking of different circuit blocks (in the form of separate semiconductor dies) with short design times and low-cost.

#### 1.4 Research Context

In addition to outlining the *justification* for this research, it is also important to discuss the *context* of the research and the Power, Performance and Area (PPA) constraints for Integrated Circuits (ICs) used in low-cost Internet of Things (IoT) devices. Figure 1.4 (reproduced from [67]) illustrates the topology of a typical IoT fog network [68]. As shown, a hierarchy of devices exists, with data initially being collected by small embedded systems or sensors, collated by larger field-deployed edge devices and then being processed on cloud-based servers [67, 68]. It is estimated that, by 2030, there will be 24.1 billion field-deployed IoT devices and so establishing ways of manufacturing the ICs in these devices, with low-cost, is of paramount importance [69] (hence forming the motivation for this work).

As shown in Figure 1.4, field-deployed IoT devices can broadly be categorised in two main classes:

• Wireless Sensor Nodes - Small sensor devices that gather data about their surroundings and communicate it through the network (e.g. body-worn sensors for healthcare applications [70], traffic sensors for city-management [71], or asset tracking devices

1.4. Research Context 11

|                                             | IoT Sensors                      |                                                                                                       |                                                                                                                                                                                                                                 |  |  |

|---------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Metric                                      | Importance Typical Specification |                                                                                                       | Comments                                                                                                                                                                                                                        |  |  |

| IC Die Size                                 | High                             | 0.5-5mm <sup>2</sup> [25, 27, 74]                                                                     | IC size is important for IoT sensors which are often deployed constrained locations (such as labels [72], implanted devices [75] or other in-situ sensing/monitoring devices [76]).                                             |  |  |

| IC Power<br>Consumption                     | Very High                        | <50mW [25, 27, 74, 75]                                                                                | Due to the volume constraints of IoT sensors, energy storage is typically limited. This means that minimising power consumption is of very high importance, to avoid the need for frequent battery replacement/recharging [77]. |  |  |

| IC Clock<br>Frequency                       | Low                              | <10MHz [25, 27, 74, 78]                                                                               | Most data is processed away from the sensor, so high-frequency processing is not required within IoT sensor ICs [75].                                                                                                           |  |  |

| Heterogeneity<br>/ Functional<br>Components | High                             | MEMS, Wireless<br>Communications,<br>Non-Volatile Memory,<br>Energy Storage, Energy<br>Harvesters [5] | loT sensors typically require a high level of heterogeneous integration to combine sensing dies (e.g. using MEMS), memory and power management/storage circuits [5].                                                            |  |  |

|                                             | IoT Edge Devices                 |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                 |  |

|---------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Metric                                      | Importance Typical Specification |                                                                                                                                                                                                                            | Comments                                                                                                                                                                                                                                                        |  |

| IC Die Size                                 | Medium                           | 5-20mm <sup>2</sup> [79–81]                                                                                                                                                                                                | Edge devices must be low-cost and remotely deployable which means that typical IC die sizes are limited (when compared with, for example, desktop or server-scale compute dies) [67].                                                                           |  |

| IC Power<br>Consumption                     | High                             | 50-200mW [79–81]                                                                                                                                                                                                           | These devices are typically battery powered (often with energy harvesting top-ups), meaning that power efficiency is of high importance. However, as edge devices are slightly larger than typical sensors, their power budgets are usually more generous [77]. |  |

| IC Clock<br>Frequency                       | 1 0w   200-800MHz   79-811       | IC Clock frequencies for edge devices must be sufficient to perform useful local data processing and networking However, typical frequencies are much lower than most consumer electronic devices to conserve energy [79]. |                                                                                                                                                                                                                                                                 |  |

| Heterogeneity<br>/ Functional<br>Components | Medium                           | CPU, DRAM,<br>Networking, Wireless<br>Communications                                                                                                                                                                       | Edge devices require integration of networking, processing and memory components which may each be fabricated in different technologies to reduce the overall device cost and/or energy consumption [82].                                                       |  |

**Table 1.1:** Tabular outline of the typical PPA constraints for Integrated Circuits (ICs) used in (i) IoT *edge* device ICs and (ii) IoT *sensor* device ICs.

[<del>72</del>]).

• Edge Devices - Field deployed hubs to collate and process data from several sensors before forwarding it to web-servers in the cloud [67, 68, 73].

The typical requirements of the ICs used in these two classes of IoT device are discussed in the paragraphs below, with a concluding tabular summary presented in Table 1.1.

Wireless sensor nodes must often adhere to very strict size/volume constraints, particularly when integrated within small objects (e.g. in labels used for asset tracking [72]) or when deployed in confined spaces (e.g. in healthcare applications, where devices must be implanted into the human body [70]). Such ICs must often also combine a range of different heterogeneous elements and process technologies such as MEMS (for performing sensing), NVM (for

storing sensor data), and wireless networking. As discussed above, this makes 3D integration a highly promising enabling technology for constructing wireless sensor node ICs [5]. Due their stringent volume constraints however, energy storage, and hence power budgets for these devices are typically very limited, meaning that minimising energy consumption is often of paramount importance. State-of-the-art battery technologies can provide power densities between 670mWh/cm³ (Li coin cell/alkaline battery [77]) and 760mWh/cm³ (Li-ion 18650 battery [77]) which means that, as an example, a small ~5cm³ sensor which operates intermittently for a total of 2 hours per day is limited to a power budget of around 5mW (assuming it must last for at least one year without battery replacement). As wireless sensor nodes do not typically perform any processing of the gathered data, operating frequency is a low priority for these ICs. Existing implementations of 3D stacked IoT sensors operate with very low clock frequencies (73kHz [27] - 500kHz [78]), sometimes with short high-frequency bursts to handle wireless communication via protocols like Zigbee or Bluetooth [71].

In contrast with this, IoT edge devices (which do perform data processing) typically operate with clock frequencies in the order of 100's of Mega Hertz [79–81]. Although not bound by the same stringent volume constraints as many IoT sensors, IoT edge devices are typically battery powered and often supplement their charge using energy harvesting. This results in slightly larger power budgets than discussed previously for IoT sensor nodes (in the region of 50-200mW across previously published works [79–81]), but still means that energy efficiency is a very important design factor. Although edge devices do not need to incorporate sensor dies, they can still benefit from heterogeneous 3D integration for bringing together wireless communication, non-volatile memory, and digital processing elements with high energy efficiency and low cost.

Table 1.1 provides a summary of these requirements (for both IoT sensor and edge devices). Overall, it is clear that alongside manufacturing cost, energy consumption is the most important constraint when considering integrated circuit design for IoT devices. Low-energy ICL implementation will therefore form a key focus of the research presented in this thesis. Secondary to cost and energy efficiency, silicon area is also a significant factor, particularly in IoT sensor devices which are deployed in constrained environments. Therefore, ways of improving area-efficiency when designing inductive coupling links will also be explored as part of this work.

#### 1.5 Research Questions

The above discussion motivates the following six research questions which will be answered in this thesis:

1. How is it possible to reduce the energy consumption of existing ICL transceivers for use in IoT devices?

- 2. How can the search process for finding optimised inductor geometries for inductive coupling link applications be automated? Subsequently, what techniques can be used to evaluate a given inductor geometry faster than using finite element modelling?

- 3. Is it practical to design an ICL transceiver for use in 3D stacked ICs that performs both wireless data transfer and wireless power transfer?

- 4. How should clock distribution be performed in a many-tier, wirelessly stacked 3D-IC?

- 5. What is the sensitivity of inductive coupling links to die-to-die stacking misalignment during the packaging process?

- 6. For the IoT, customisability is important. Is it practical to design ICLs in a standard way to allow interchangeable stacking with a range of different memory/sensor/logic dies?

#### 1.6 Research Contributions

Towards addressing these research questions, the major contributions of this thesis include:

### A Low-Energy Inductive Transceiver Using Spike-Latency Encoding

The first contribution of this thesis, to address Research Question 1 is a novel, lowenergy inductive transceiver that uses a time-domain encoding technique to represent frames of data in terms of the *latency* between sequential pulses. This reduces the number of transmit pulses required to send given bit stream, hence reducing the overall system energy consumption. The presented transceiver also includes a tuneable pulse-based transmitter which allows the transmit current to be precisely adjusted, postfabrication, to compensate for stacking assembly defects (such as uneven die-thinning, or stacking misalignment), also addressing Research Question 5.

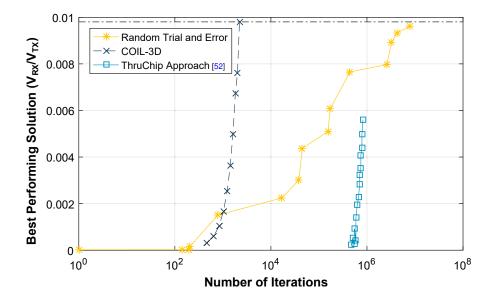

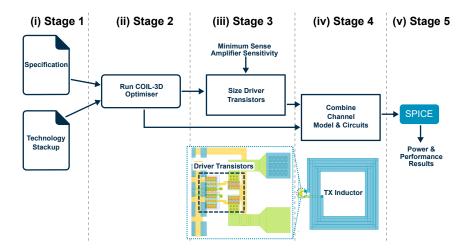

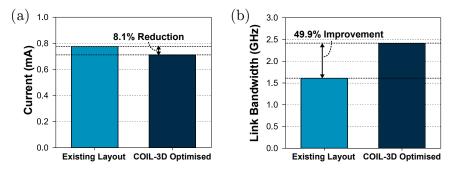

#### COIL-3D

The second contribution of this thesis is COIL-3D, A CAD tool for the Optimisation of Inductive Links in 3D ICs. For power efficient design of inductive coupling links, it is essential that the layouts of the coupled inductors (forming the EM channel) are optimised. COIL-3D is a software tool<sup>3</sup> that utilises a rapid solver based upon semi-empirical expressions to quickly and accurately characterise a given link, in conjunction with a high-speed refined optimisation flow (also developed as part of this work) to find optimal inductor geometries to maximise efficiency in ICL channels. COIL-3D is developed to address Research Question 2, related to optimisation of ICL channels.

#### CoDAPT

<sup>&</sup>lt;sup>3</sup>Available for open-source download at https://github.com/bjf1g13/coil-3d.

The third contribution presented in this thesis, is a novel ICL transceiver for Concurrent wireless Data And Power Transfer (CoDAPT). To address Research Question 3, the CoDAPT transceiver is designed to perform simultaneous wireless data and power transmission, through a single inductive channel, using a Bi-Phase Shift Keying (BPSK) scheme. WPT is achieved using the high-frequency BPSK carrier signal, whilst data is encoded by modulating and sampling the phase. Combining wireless power and data delivery in a single inductive channel results in significant area savings when compared with prior works that use separate links for data and power transmission.

In addition to this, to address Research Question 6 (focussed on maintaining a high level of customisability), the CoDAPT link is implemented as part of a standard AHB-lite bus to realise a pseudo-System-on-Chip (SoC) architecture<sup>4</sup>. This allows, for example, a range of different standard AHB sensor/memory/processor Intellectual Property (IP) blocks to be vertically interconnected in a standardised way, with the CoDAPT ICL forming the main system bus.

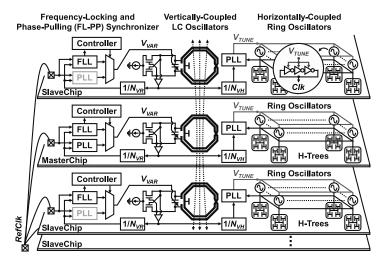

### WiSync

The final contribution of this thesis is WiSync, a low-area, inductive link for Wireless clock Synchronisation in many-tier 3D-ICs. The WiSync transceiver directly addresses Research Question 4, facilitating low-skew clock distribution across several stacked silicon tiers. The practical implementation of the WiSync transceiver is also used for a study exploring the effects of die-to-die stacking alignment on link performance, thereby also addressing Research Question 5 which is focussed on quantifying the sensitivity of ICLs to errors/variations during the packaging process.

#### 1.7 Publications and Patents

Some of the research presented in this thesis has also published and patented, as outlined in the following sub-sections. The first part of Section 1.7.1 lists the peer-reviewed (conference and journal) publications completed during my PhD candidature that are directly reported as contributions in this thesis, whilst the second half of the list outlined peer-reviewed publications that were completed during my PhD candidature, but are not directly reported as contributions in this thesis. Section 1.7.2 outlines the patents submitted as a direct result of this work and finally, Section 1.7.3 list other academic engagement activities stemming from the research presented in this thesis such as awards.

#### 1.7.1 Peer-Reviewed Publications

B. J. Fletcher, S. Das, T. Mak, "A Spike-Latency Transceiver with Tuneable Pulse Control for Low-Energy Wireless 3D Integration", IEEE Journal on Solid State Circuits (JSSC) 55(9) pp.

<sup>&</sup>lt;sup>4</sup>The 'pseudo'-SoC refers to the fact that, architecturally, the components form a standard System-on-Chip, but physically, the SoC elements exist in separate wirelessly connected dies.

- 2414-28 (2020). [83]

- B. J. Fletcher, T. Mak and S. Das, "A 3D-Stacked Cortex-M0 SoC with 20.3Gbps/mm<sup>2</sup> 7.1mW/mm<sup>2</sup> Simultaneous Wireless Inter-Tier Data and Power Transfer," *IEEE Symposium on VLSI Circuits*, Honolulu, Hawaii, 2020 pp. 1-2. [84]

- 3. B. J. Fletcher, S. Das and T. Mak, "A 10.8pJ/bit Pulse-Position Inductive Transceiver for Low-Energy Wireless 3D Integration," *IEEE European Solid State Circuits Conference (ESSCIRC)*, Cracow, Poland, 2019, pp. 121-4. [85]

- B. J. Fletcher, S. Das, T. Mak, "A Low-Energy Inductive Transceiver using Spike-Latency Encoding for Wireless 3D Integration," *IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED)*, Lausanne, Switzerland, 2019, pp. 1-6. [86] (Best-Paper Award Winner)

- B. J. Fletcher, S. Das and T. Mak, "Design and Optimization of Inductive-Coupling Links for 3-D-ICs," *IEEE Transactions on Transactions on Very Large Scale Integration (VLSI) Systems* 27(3) pp. 711-23 (2019). [87]

- 6. B. J. Fletcher, S. Das, T. Mak, "CoDAPT: a concurrent data and power transceiver for fully wireless 3D-ICs,", *Design, Automation & Test in Europe Conference & Exhibition (DATE)*, Florence, Italy, 2019, pp. 1343-48. [88] (Best-Paper Award Nominee)

- 7. B. J. Fletcher, S. Das, T. Mak, "Cost-effective 3D integration using inductive coupling links: Can we make stacking silicon as easy as stacking Lego?", *Arm Research Summit 2018*, Cambridge, United Kingdom. 17 19 Sep 2018. [89]

- 8. B. J. Fletcher, S. Das, T. Mak, "A High-Speed Design Methodology for Inductive Coupling Links in 3D-ICs", *Design, Automation & Test in Europe Conference & Exhibition (DATE)*, Dresden, Germany, 2018, pp. 497-502. [90]

- 9. B. J. Fletcher, S. Das, T. Mak, "Low-Power 3D Integration using Inductive Coupling Links for Neurotechnology Applications,", *Design, Automation & Test in Europe Conference & Exhibition (DATE)*, Dresden, Germany, 2018, pp. 497-502. [91]

During the time of my PhD candidature, I have also authored the following peer-reviewed papers, however these are not reported as contributions within this thesis:

- 11. D. Balsamo, B. J. Fletcher, A. J. Weddell, G. Karatziolas, B. Al-Hashimi and G. V. Merrett, "Power neutral performance scaling with intrinsic MPPT for energy harvesting computing systems," *ACM Transactions on Embedded Computing Systems*, 17(6), 1-25 (2019). [92]

- B. J. Fletcher, D. Balsamo and G. V. Merrett, "Power-neutral performance scaling for self-powered multicore computing systems,", Adaptive Many-Core Architectures and Systems Workshop, York, United Kingdom, 13-15 Jun 2018. [93]

- Q. Ding, B. J. Fletcher, T. Mak, "Globally Wireless Locally Wired: A Clock Distribution Network for Many-Core Systems," *IEEE International Symposium on Circuits and Systems (ISCAS)*, Florence, Italy, 2018, pp. 1-5. [94]

- B. J. Fletcher, D. Balsamo and G. V. Merrett, "Power neutral performance scaling for energy harvesting MP-SoCs,", Design, Automation & Test in Europe Conference & Exhibition (DATE), 2017, Lausanne, Switzerland, 2017, pp. 1516-21. [95]

#### 1.7.2 Patents

In addition to the publications listed below, the work presented in this thesis has also led to the filling of two patents:

- B. J. Fletcher, J. Myers, S. Das and T. Mak, "A Pseudo System-on-Chip Architecture Incorporating Wirelessly Connected Bus Slaves.", U.S. Patent 16/685,090, Nov 2019 (pending).

[96]

- S. Gamage, B. Fletcher, and S. Das, "Adaptive Coding for Wireless Communication.", U.S. Patent 16/656,937, Oct 2019 (pending). [97]

#### 1.7.3 Other Research Engagement Activities

Finally, the work presented in this thesis has directly resulted in the following awards.

- B. J. Fletcher, S. Das, and T. Mak "3D Integration Using Wireless Inductive Links," Science Technology and Mathematics for Britain Exhibition, London, Mar. 2020. (IEEE ComSoc Award Winner)

- 18. B. J. Fletcher, "Can we make stacking silicon as easy as stacking Lego?," The Institution of Engineering and Technology (IET) Postgraduate Prize, 2018. (Winner)

#### 1.8 Thesis Outline

The remaining content of this thesis is organised as follows. Chapter 2 first provides background information on near-field wireless 3D integration, summarising the prior art using capacitive coupling transceivers (Section 2.1) and inductive coupling transceivers (Section 2.2). Chapter 2 also discusses ICL channel layout optimisation (Section 2.2.3), wireless power transfer in 3D-ICs (Section 2.4) and near-field clock delivery (Section 2.3).

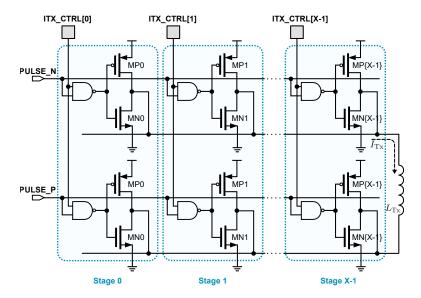

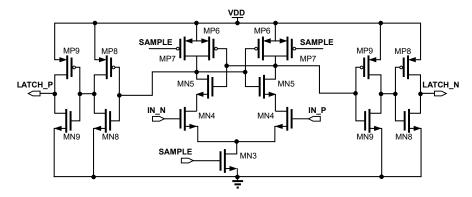

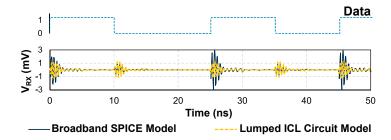

Following this, Chapter 3 focusses on low-energy transceiver design, presenting a time-domain modulation scheme (spike-latency encoding) to facilitate low-energy data consumption in wireless 3D-ICs. This is the first instance of time-domain coding in the context of die-to-die communication, resulting in significant energy savings when the approach is evaluated (Section 3.4). A tuneable pulse driver circuit is also presented in Chapter 3, which allows the transmit pulse energy to be tuned to an absolute minimum (post-assembly), accounting for any variations in the manufacturing or stacking process.

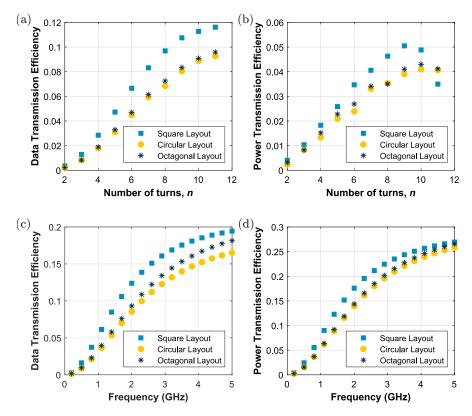

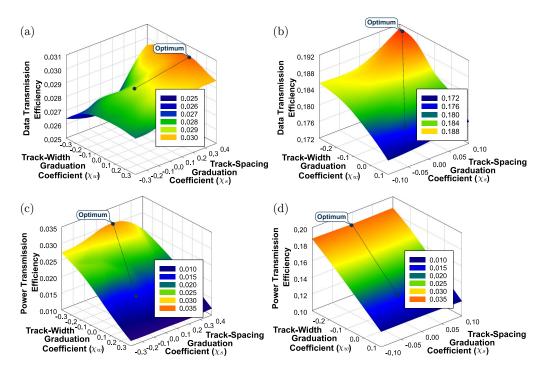

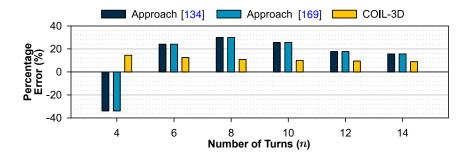

Having explored the energy optimisation in the transceiver circuits in Chapter 3, Chapter 4 then focuses on energy optimisation of the inductive channel itself. A set of strictly solvable mathematical expressions are presented for evaluating a link's performance directly from its layout parameters, alongside a refined optimisation flow (Section 4.3.2) as a high-speed alternative to manual geometry optimisation using FEM. Comparison of different inductor

1.8. Thesis Outline

shapes (square, circle, octagon) in terms of bandwidth and energy efficiency is also presented in this chapter.

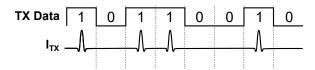

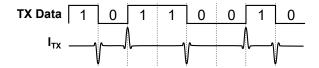

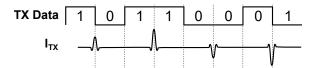

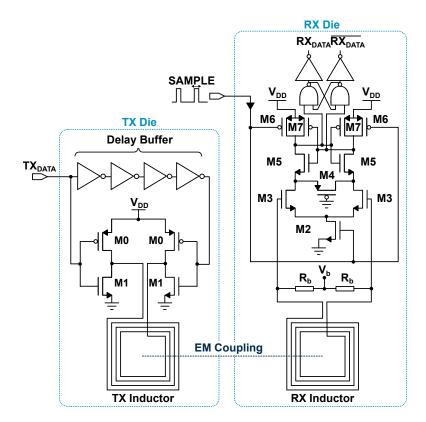

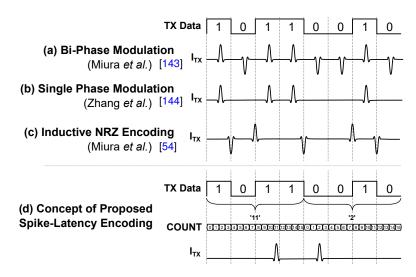

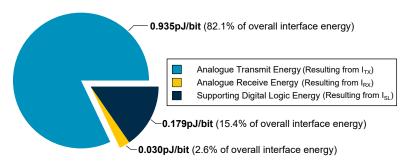

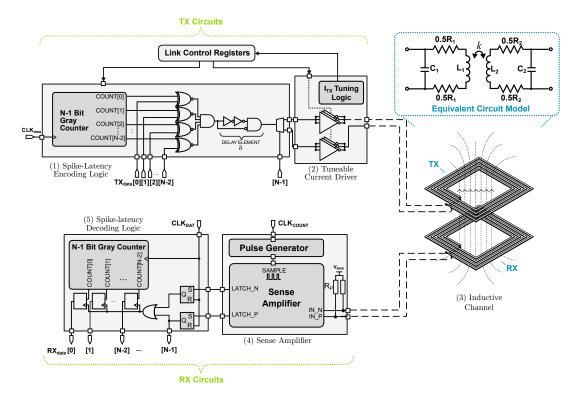

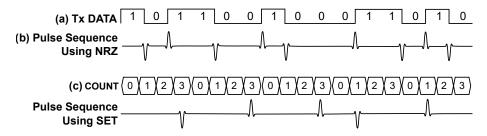

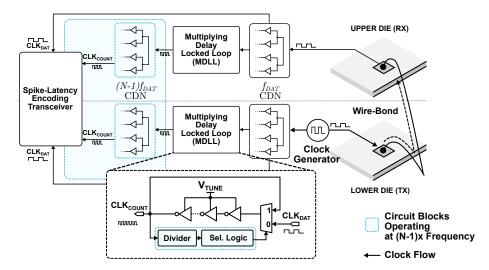

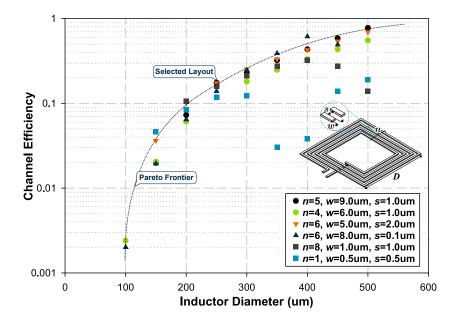

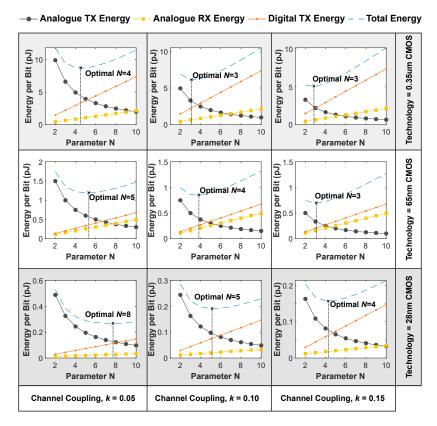

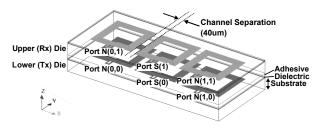

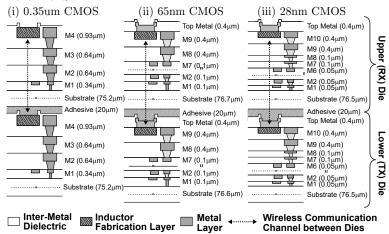

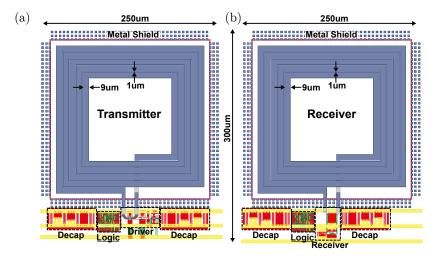

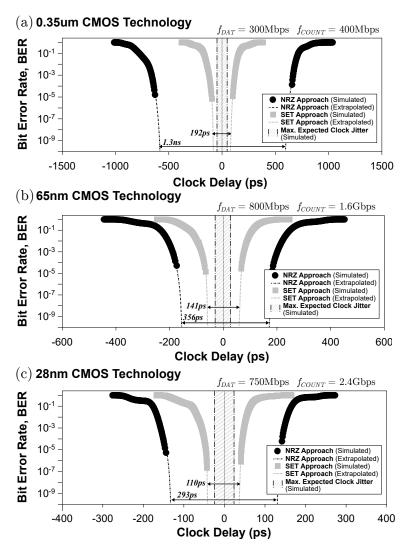

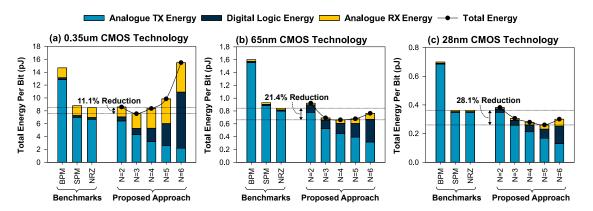

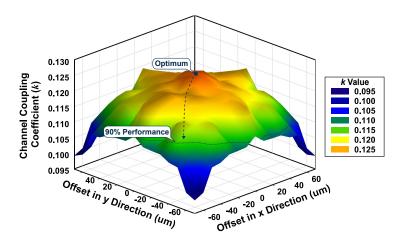

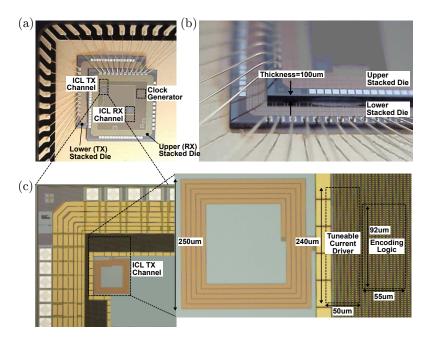

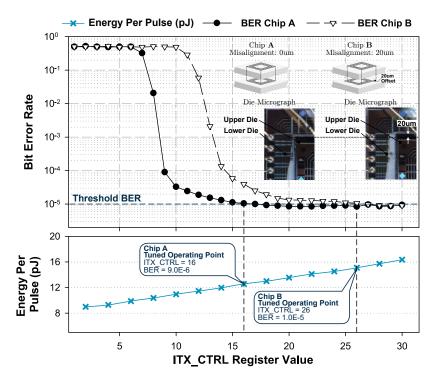

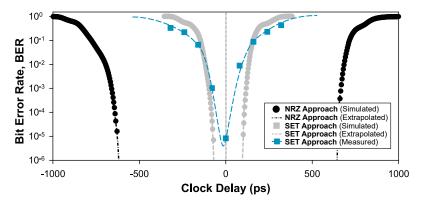

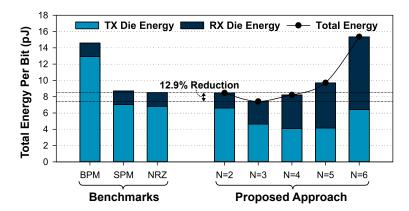

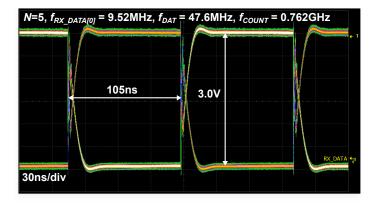

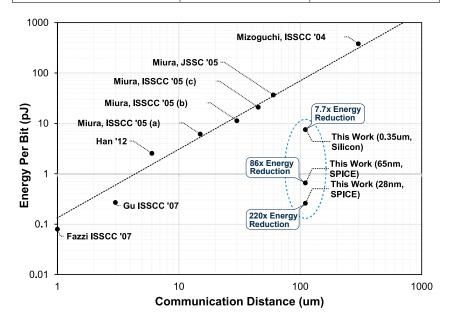

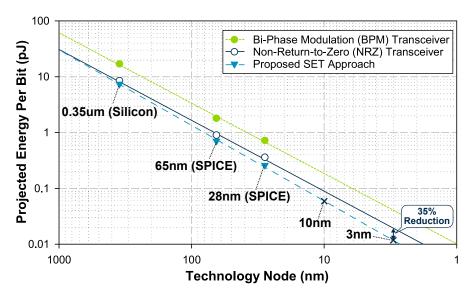

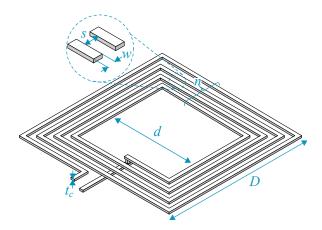

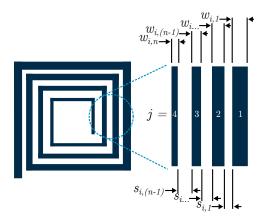

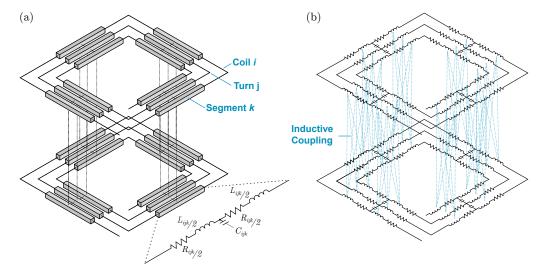

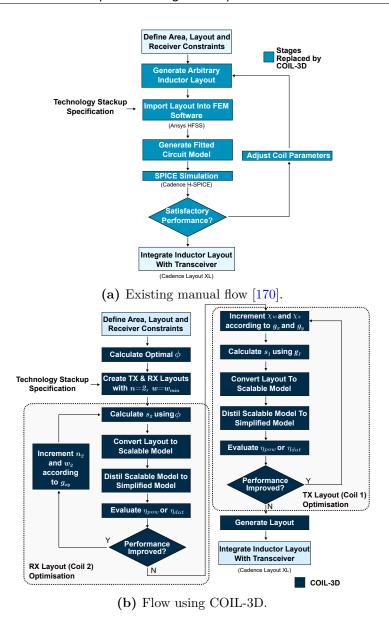

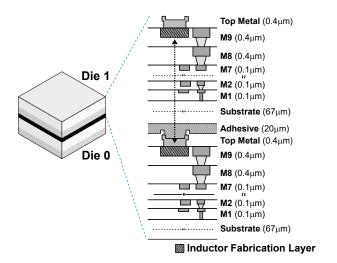

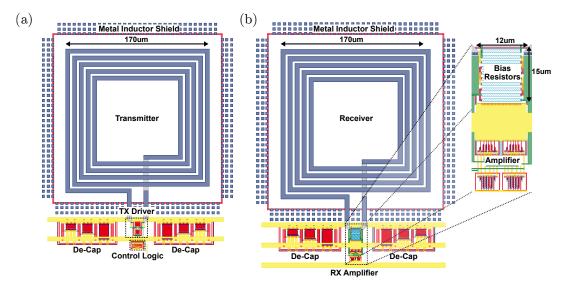

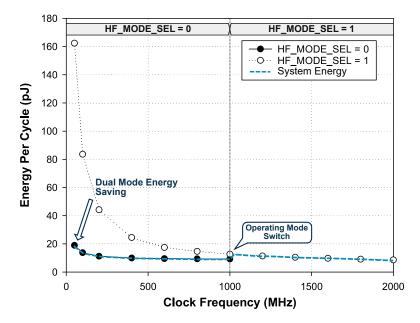

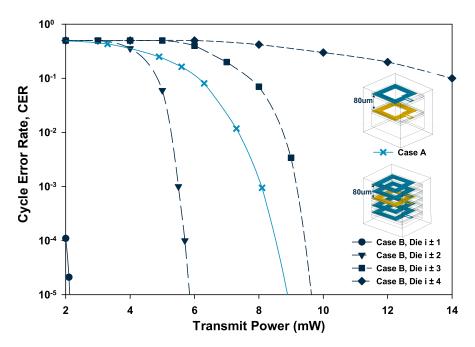

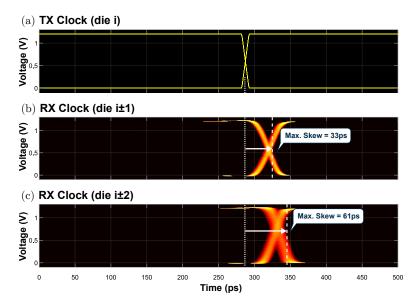

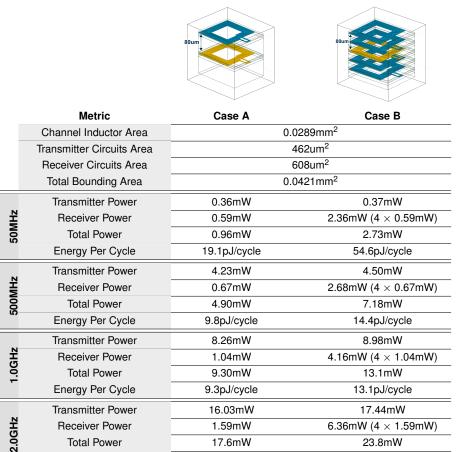

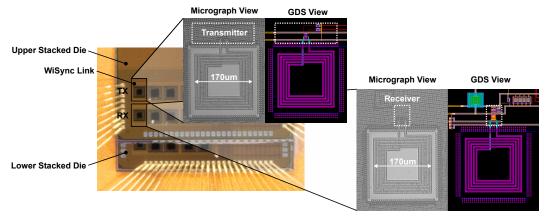

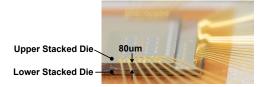

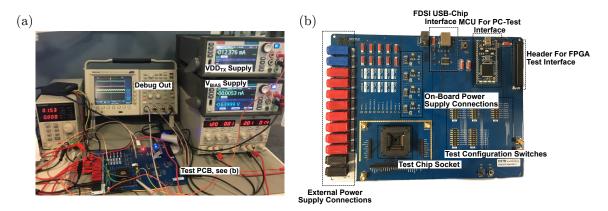

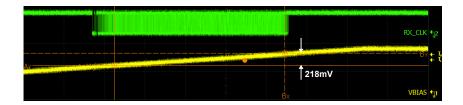

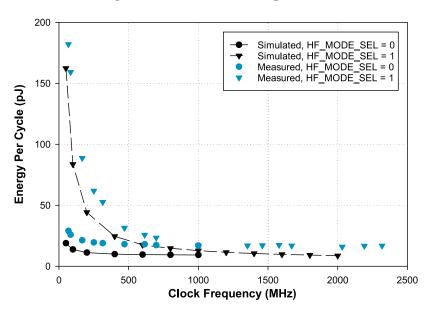

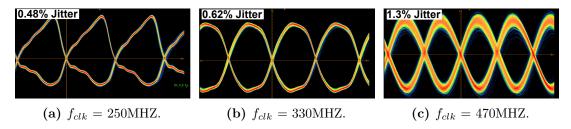

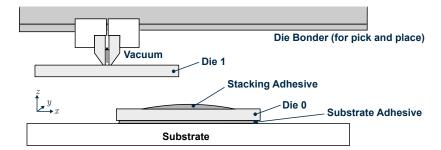

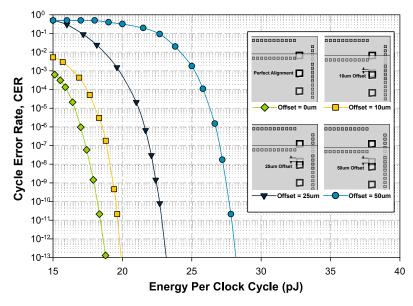

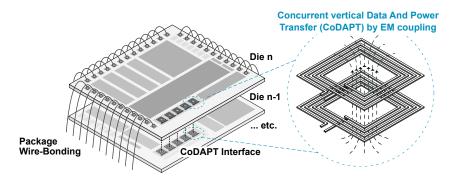

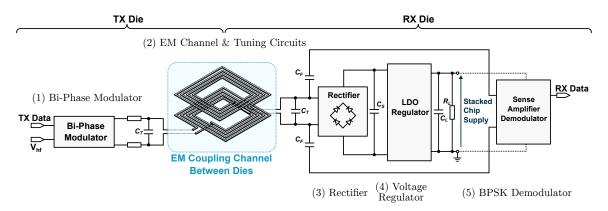

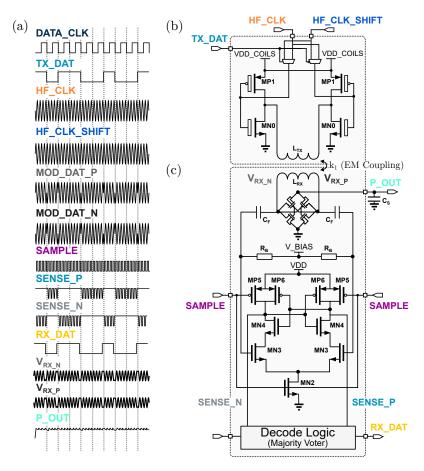

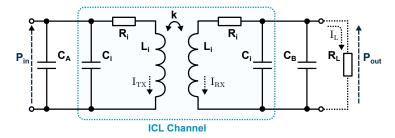

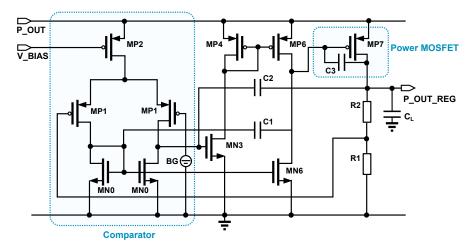

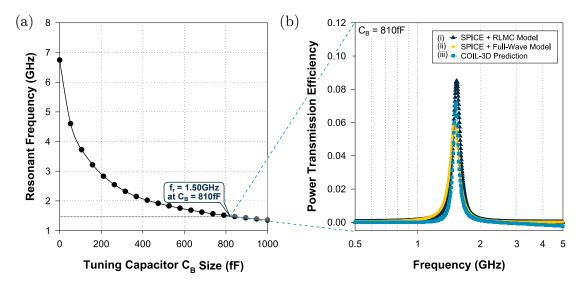

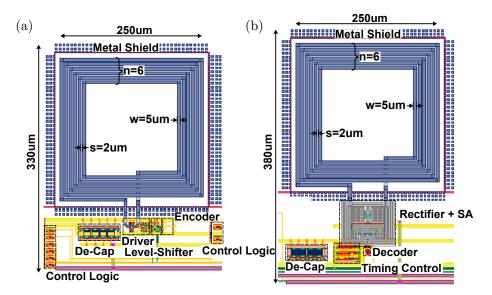

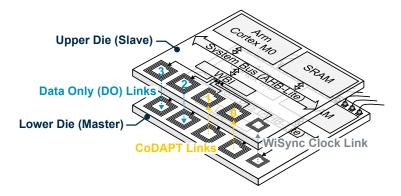

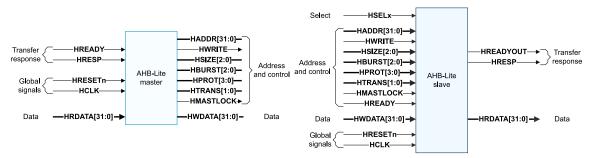

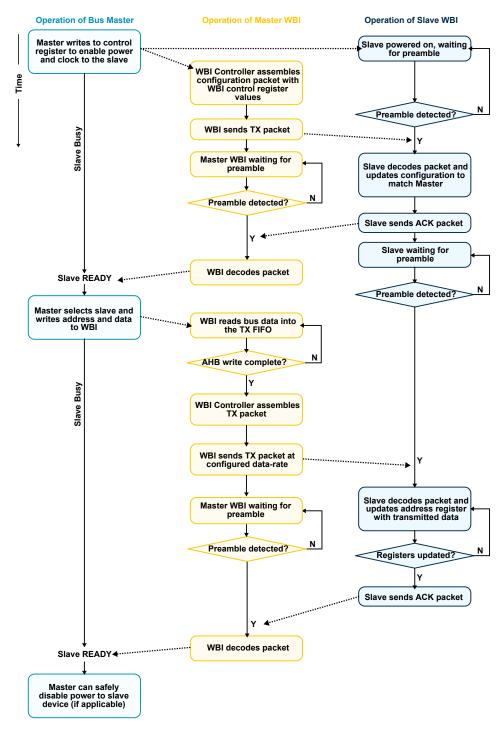

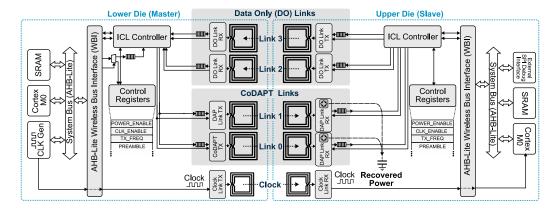

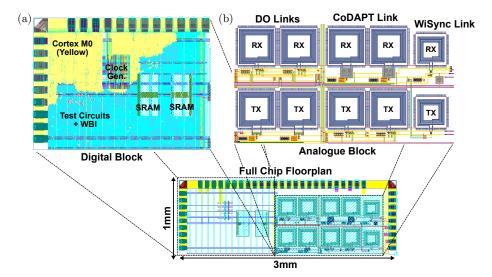

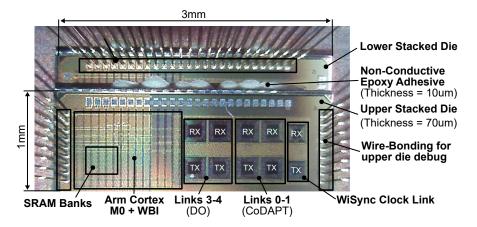

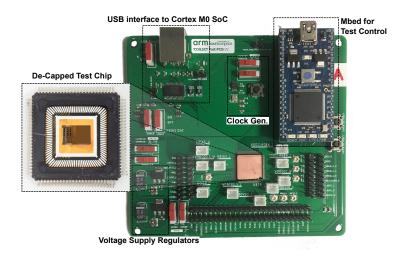

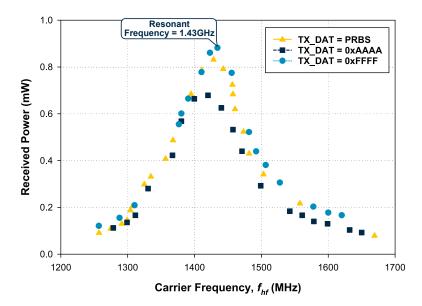

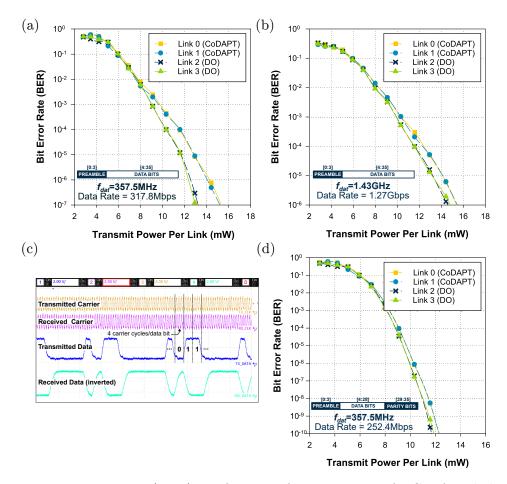

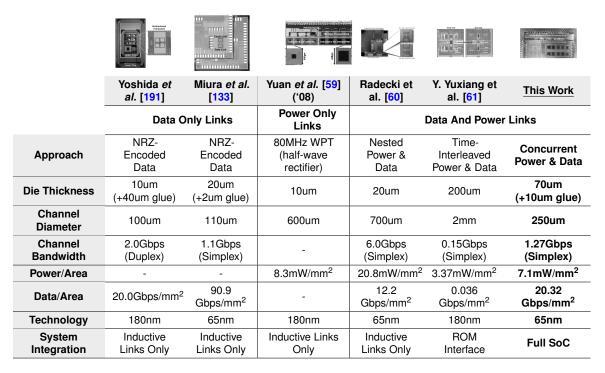

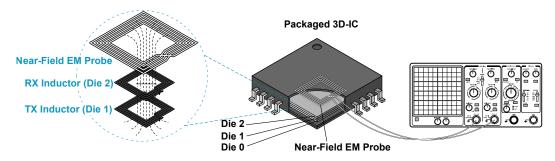

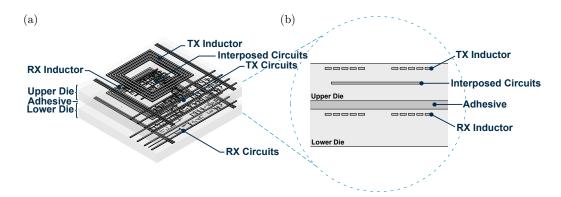

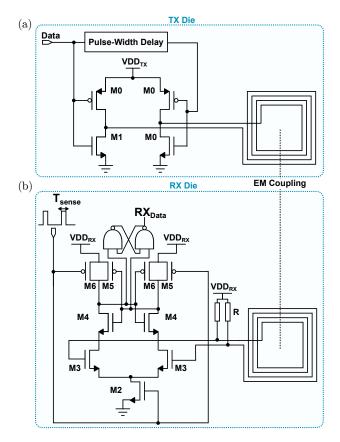

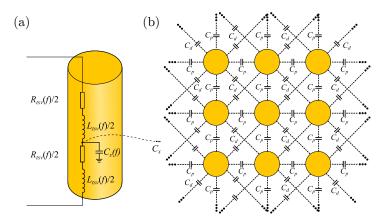

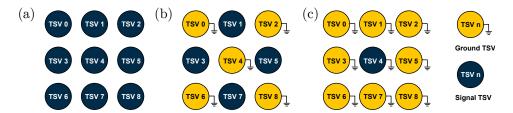

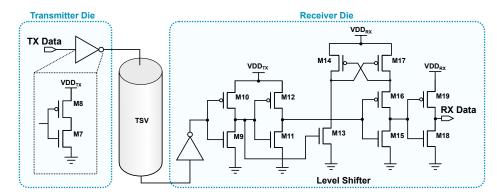

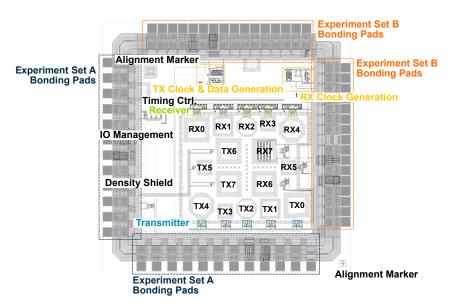

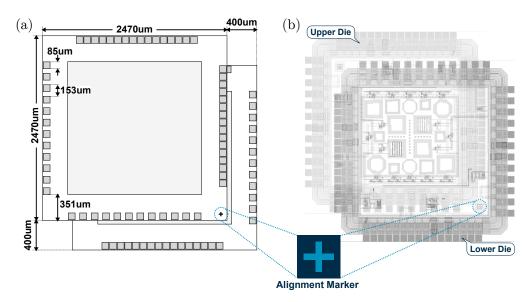

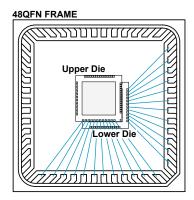

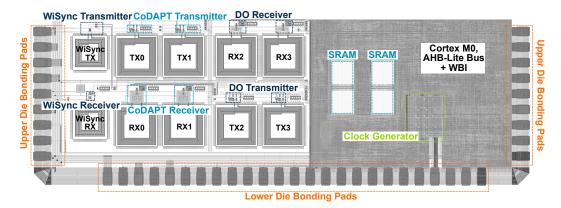

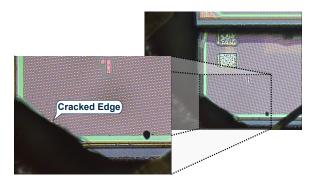

Chapters 5 and 6 focus on enabling fully wireless 3D integration, exploring wireless clock distribution and power delivery respectively. The wireless many-tier clock link presented in Chapter 5 uses a dual-mode transmitter to conserve energy, whilst operating in the non-resonant portion of the link's frequency spectrum. As a result of this, the design can operate across a wide range of frequencies (making it suitable for use with a variety of different coherent data ICL designs, such as the spike-latency encoding transceiver from Chapter 3 and the CoDAPT transceiver in Chapter 6). Operating away from resonance also means that the silicon area can be significantly reduced, and as such the design presented in Chapter 5 achieves the lowest silicon area overhead ever reported for an inductive clock link. Section 5.4.4 of Chapter 3 also presents a practical study of die-to-die misalignment on the link's performance.