UNIVERSITY OF SOUTHAMPTON

**A Globally Wireless Locally Wired

Hybrid Clock Distribution Network for

Many-core Systems**

by

Qian Ding

A thesis submitted in partial fulfillment for the

degree of Doctor of Philosophy

in the

Faculty of Engineering and Physical Science

School of Electronics and Computer Science

February 2021

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

**A Globally Wireless Locally Wired Hybrid Clock Distribution Network for

Many-core Systems**

by Qian Ding

Modern ICs are now facing critical issues on generating power-efficient and globally interconnected clock networks, as the clock distribution network might contribute to more than 50% of the overall power consumption. Besides, due to the increasing wire delay caused by shrinking interconnect dimensions, synchronous many-core systems are now facing challenges such as to propagate high-frequency clock signals across the chip with limited power budget. Delivering a clock with low uncertainties across active dies with large chip density has also become one of the major tasks using conventional metallic interconnects.

This thesis presents a novel architecture and comprehensive evaluations for a power-efficient and extremely low-delay approach using hybrid wire-wireless clock distribution network (CDN). The proposed hybrid CDN adopts wireless on-chip clock transmitters and receivers for broadcasting the clock signal globally. It then incorporates with conventional metal-based clock tree or mesh for local clock distribution. Comparisons between the proposed approach and two baseline architectures, namely a full fan-out tree and a global tree local mesh (TLM) structure, have been presented. Also, an accurate mathematical model with interconnect RLC parameters for the local clock distribution is employed.

The hybrid CDN has shown its superiority in terms of low clock delay, low clock skew and high energy efficiency compared with conventional solutions, which is evaluated via an industrial standard Arm Mali G77 GPU case study. Experimental results indicate that the proposed clock distribution network can achieve a significant global delay reduction of up to 28.8%. Also, on average, an up to 62.8% and 42.7% reduction in clock skew and power consumption, are identified, respectively, in our proposed test bench. Hence, our proposed approach offers a promising solution to clock distribution in future many-core integrated circuits, especially for high-performance systems.

# Contents

|                                                                             |             |

|-----------------------------------------------------------------------------|-------------|

| <b>Nomenclature</b>                                                         | <b>xv</b>   |

| <b>Acknowledgements</b>                                                     | <b>xvii</b> |

| <b>1 Introduction</b>                                                       | <b>1</b>    |

| 1.1 Challenges of the Conventional Interconnect . . . . .                   | 1           |

| 1.2 Motivations for the Proposed Hybrid Clock Distribution Scheme . . . . . | 6           |

| 1.2.1 The Impact of Wire Delay . . . . .                                    | 6           |

| 1.2.2 Synchronisation in Modern Many-Core Systems . . . . .                 | 8           |

| 1.3 Thesis Contributions and Structures . . . . .                           | 11          |

| <b>2 Literature Review</b>                                                  | <b>15</b>   |

| 2.1 Reviewing of the Emerging Interconnect Techniques . . . . .             | 15          |

| 2.1.1 Wireless Interconnect . . . . .                                       | 15          |

| 2.1.2 Other Radio-frequency Based Interconnects . . . . .                   | 17          |

| 2.1.3 Optical Interconnect . . . . .                                        | 19          |

| 2.2 Conventional CDN with Broadcast Architecture . . . . .                  | 20          |

| 2.2.1 Combination of Binary-tree, H-tree, X-tree and Clock Grid . . . . .   | 21          |

| 2.2.2 Challenges of Existing Metallic Wire-based CDN . . . . .              | 24          |

| 2.3 Optical CDN with Broadcast Architecture . . . . .                       | 26          |

| 2.3.1 Guided and Free-space Optical CDN . . . . .                           | 26          |

| 2.3.2 Challenges of Existing Optical CDN . . . . .                          | 28          |

| 2.4 Wireless CDN with Broadcast Architecture . . . . .                      | 28          |

| 2.4.1 Wireless CDN with VCO and Frequency Divider . . . . .                 | 29          |

| 2.4.2 Wireless CDN with Digital Modulation Techniques . . . . .             | 30          |

| 2.4.3 Challenges of Existing Wireless CDN . . . . .                         | 32          |

| 2.5 Summary . . . . .                                                       | 33          |

| <b>3 Proposed Models and Algorithms for Local Wired CDN</b>                 | <b>35</b>   |

| 3.1 Delay Models of Conventional CDN . . . . .                              | 35          |

| 3.2 Model of the Tree-based CDN . . . . .                                   | 41          |

| 3.2.1 Balanced Bi-partitioning Algorithm for Clock Tree Synthesis . . . . . | 44          |

| 3.2.2 K-means Bi-partitioning (KBP) Algorithm for Clock Tree Synthesis      | 47          |

| 3.2.3 Merging Tree Generation . . . . .                                     | 51          |

| 3.2.4 Buffer Insertion with Inverted Slew-estimation . . . . .              | 53          |

| 3.3 Model of the Mesh-based CDN . . . . .                                   | 55          |

| 3.3.1 Isolated Mesh Model . . . . .                                         | 55          |

| 3.3.2 Coupled Mesh Model . . . . .                                          | 57          |

|          |                                                                        |            |

|----------|------------------------------------------------------------------------|------------|

| 3.3.3    | Clock Receiver Planning . . . . .                                      | 59         |

| 3.3.4    | Local Mesh Design . . . . .                                            | 60         |

| 3.4      | Model of the Proposed Hybrid Wireless-Wired CDN . . . . .              | 62         |

| 3.5      | Summary . . . . .                                                      | 66         |

| <b>4</b> | <b>Proposed Clock Transmitter and Receiver for Global Wireless CDN</b> | <b>67</b>  |

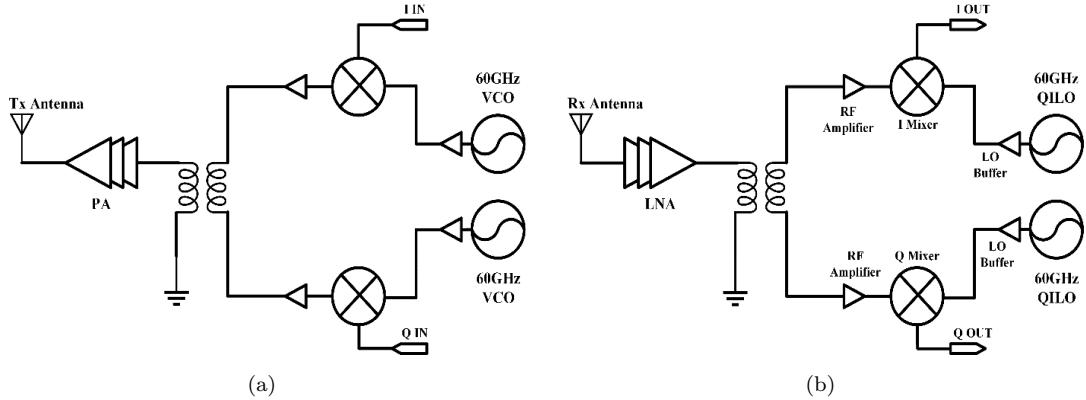

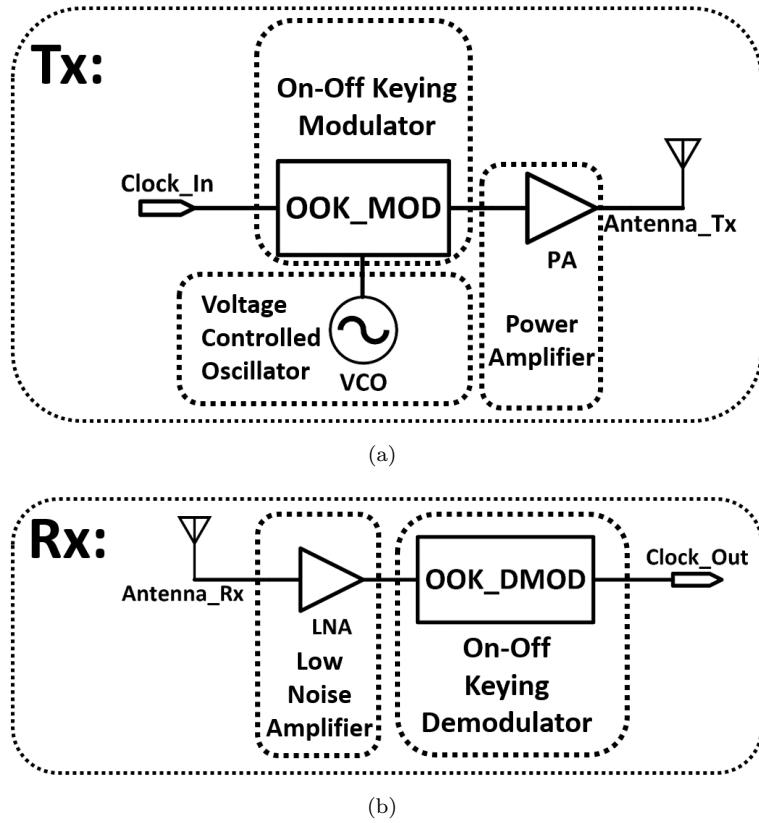

| 4.1      | Clock Transmitter Design . . . . .                                     | 69         |

| 4.1.1    | Voltage-Controlled Oscillator Design . . . . .                         | 69         |

| 4.1.2    | On-Off Keying Modulator Design . . . . .                               | 71         |

| 4.2      | Clock Receiver Design . . . . .                                        | 75         |

| 4.2.1    | Low Noise Amplifier Design . . . . .                                   | 75         |

| 4.2.2    | On-Off Keying Demodulator Design . . . . .                             | 78         |

| 4.3      | On-chip Antenna Design . . . . .                                       | 80         |

| 4.4      | Summary . . . . .                                                      | 83         |

| <b>5</b> | <b>Experimental Setup and Evaluations of the Proposed Hybrid CDN</b>   | <b>85</b>  |

| 5.1      | Results of the Proposed Antenna for Hybrid CDN . . . . .               | 86         |

| 5.2      | Results of the Proposed Clock Transmitter . . . . .                    | 92         |

| 5.3      | Results of the Proposed Clock Receiver . . . . .                       | 95         |

| 5.4      | Impacts of the Local Parameters on Global CDN Performance . . . . .    | 100        |

| 5.5      | Summary . . . . .                                                      | 108        |

| <b>6</b> | <b>Case Study: the Proposed CDN Verified by Testbench Circuits</b>     | <b>111</b> |

| 6.1      | Architectures of the Proposed Test Case . . . . .                      | 111        |

| 6.2      | Test Case Circuit Generations and Experimental Setup . . . . .         | 114        |

| 6.3      | Test Case Results and Analysis . . . . .                               | 116        |

| 6.4      | Summary . . . . .                                                      | 118        |

| <b>7</b> | <b>Conclusions and Future Works</b>                                    | <b>121</b> |

| 7.1      | Conclusions and Contributions of the Thesis . . . . .                  | 121        |

| 7.2      | Challenges of the Thesis . . . . .                                     | 123        |

| 7.3      | Potential Future Works . . . . .                                       | 124        |

| 7.3.1    | Short Term Future Works . . . . .                                      | 124        |

| 7.3.2    | Long Term Future Works . . . . .                                       | 125        |

|          | <b>Bibliography</b>                                                    | <b>127</b> |

# List of Figures

|      |                                                                                                                                                                                                                                                 |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

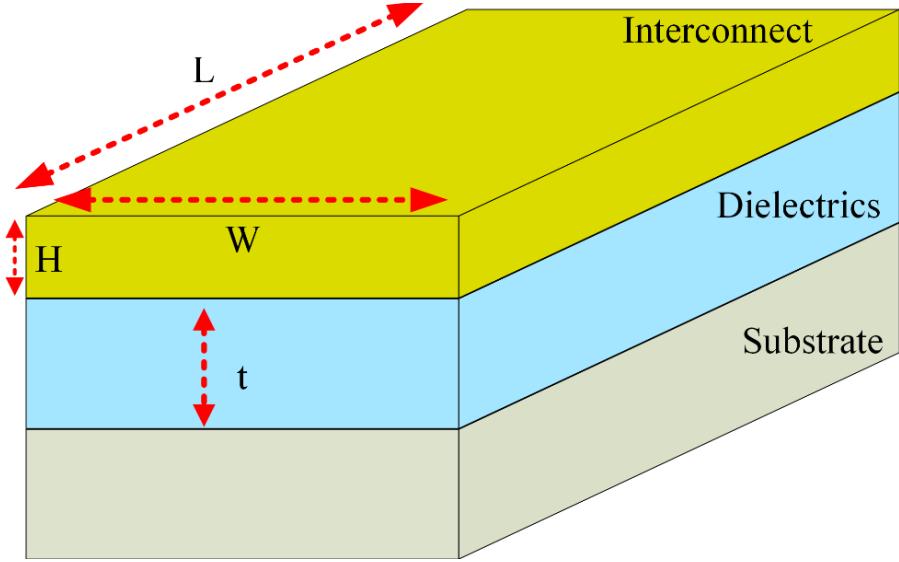

| 1.1  | Simplified interconnect structure. . . . .                                                                                                                                                                                                      | 3  |

| 1.2  | Simplified interconnect structures with wiring capacitance. . . . .                                                                                                                                                                             | 4  |

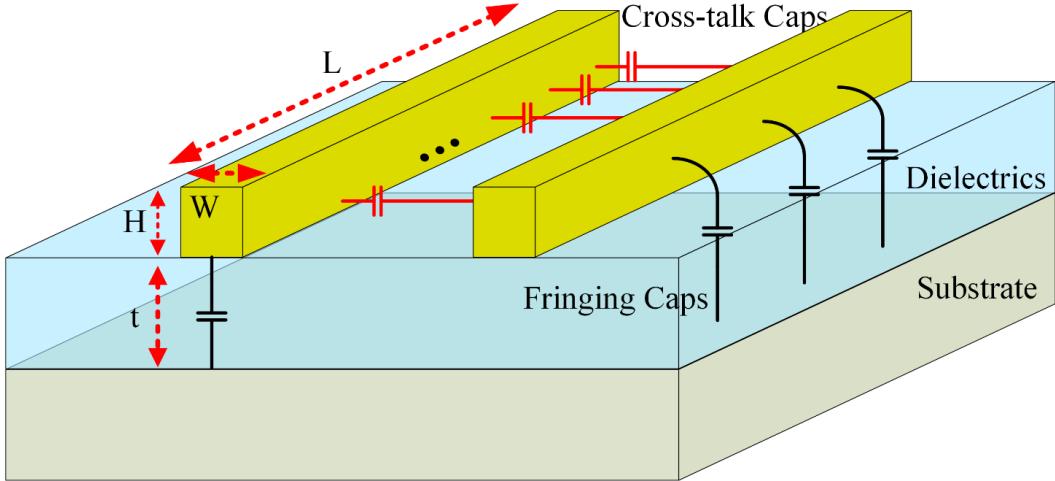

| 1.3  | The propagation delay vs shrinking technology node for transistor gate delay, local communication delay and global communication delay, respectively, according to [1]. . . . .                                                                 | 5  |

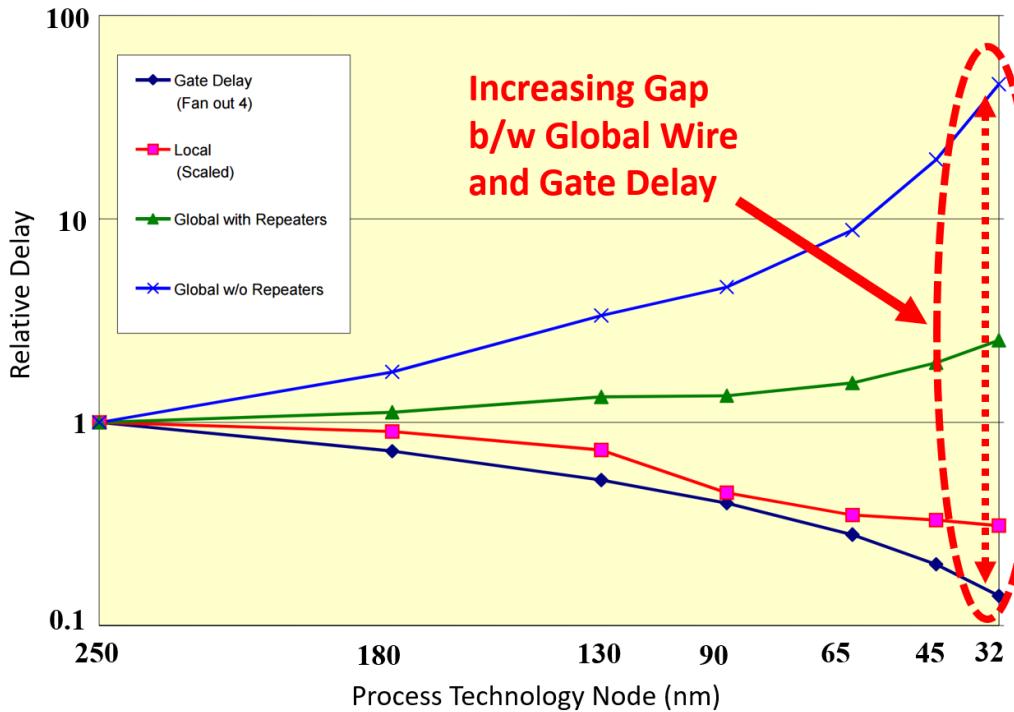

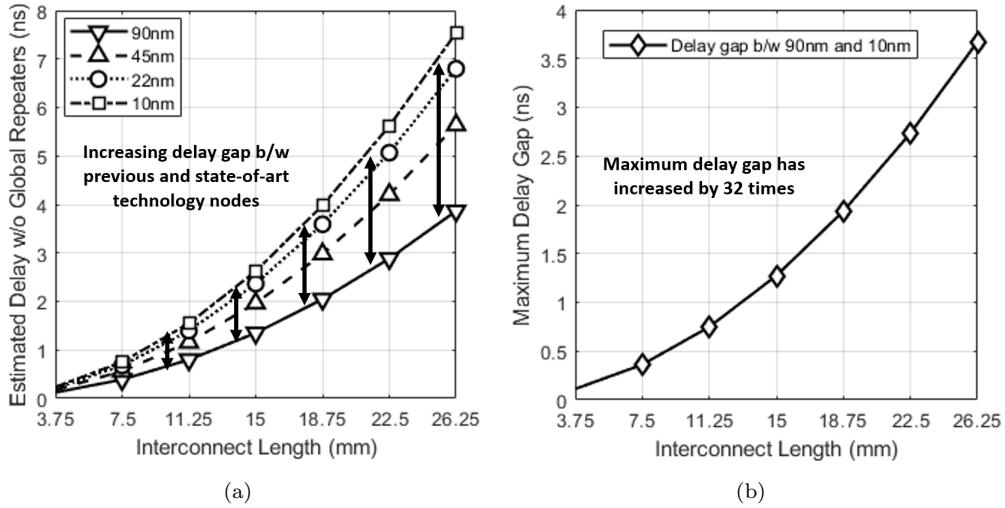

| 1.4  | Increasing interconnect delay within a specific 4-level H-tree network with (a) interconnect delay under different technology nodes using the same geometry, and (b) Increasing delay gap between 90 nm and 10 nm process. ©2021 IEEE . . . . . | 6  |

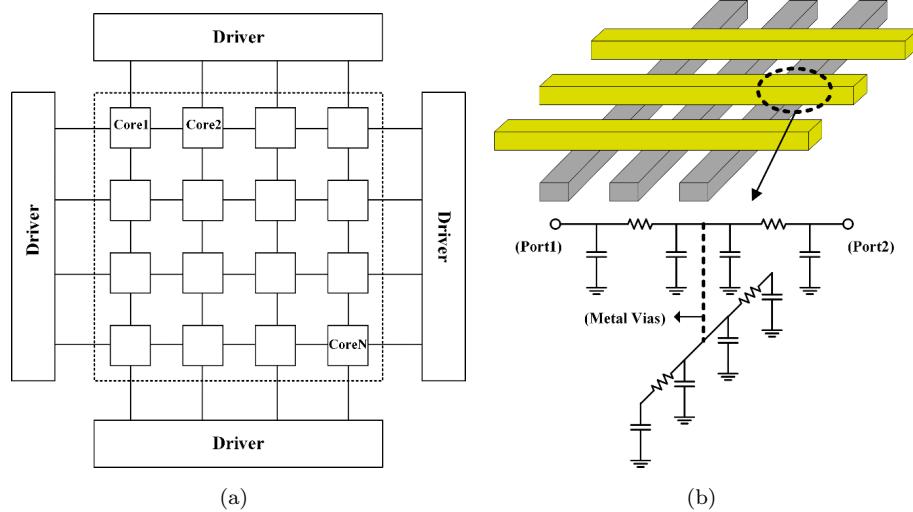

| 1.5  | A typical structure of (a) plan view of a conventional mesh-based CDN and (b) $\pi$ -model of the mesh wires. . . . .                                                                                                                           | 7  |

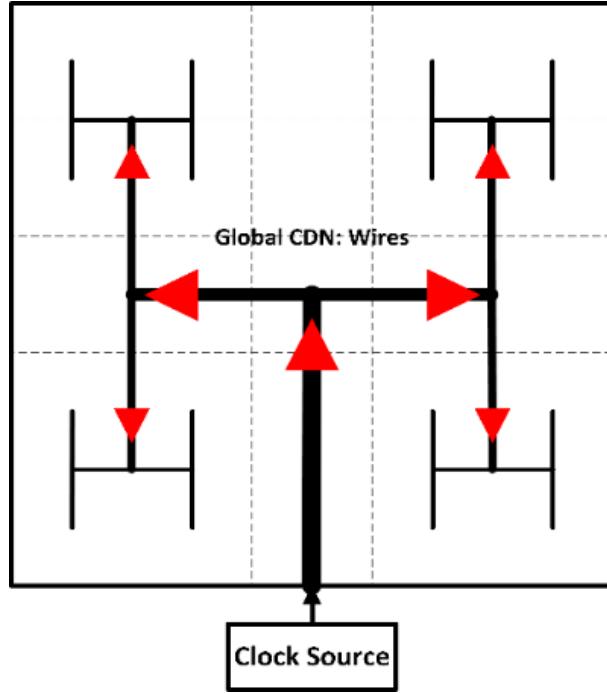

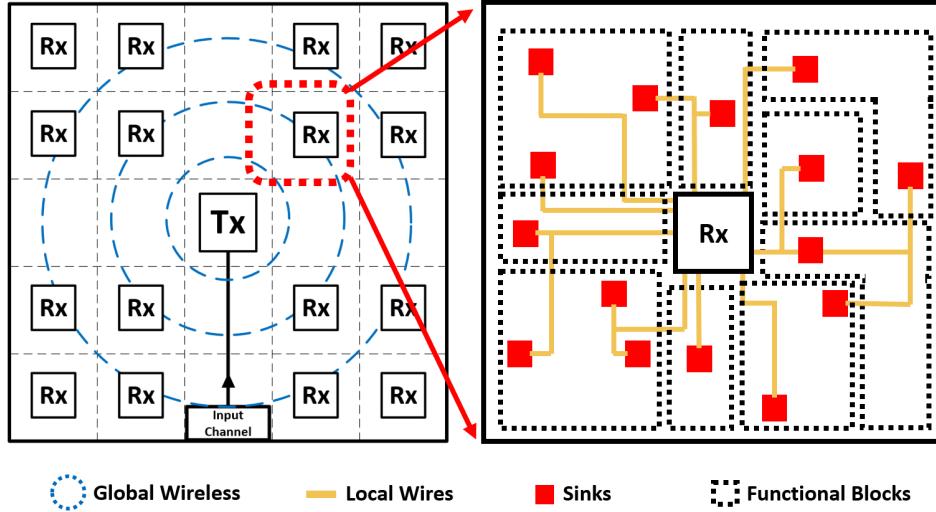

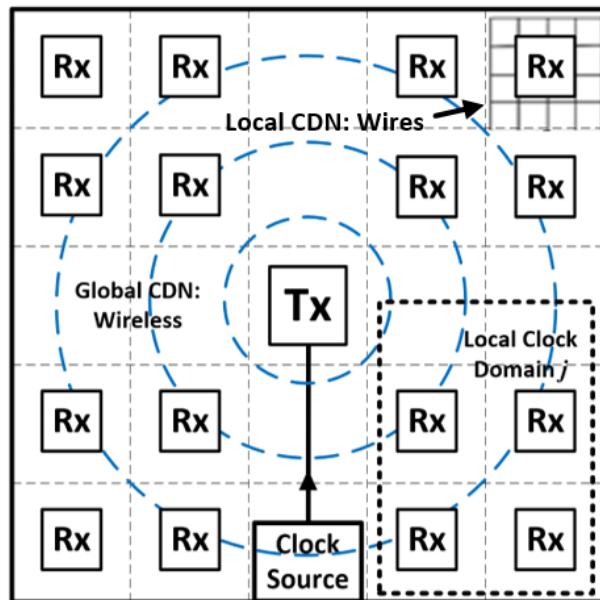

| 1.6  | The proposed hybrid clock distribution network which combines both global wireless interconnect and local metallic wires. . . . .                                                                                                               | 10 |

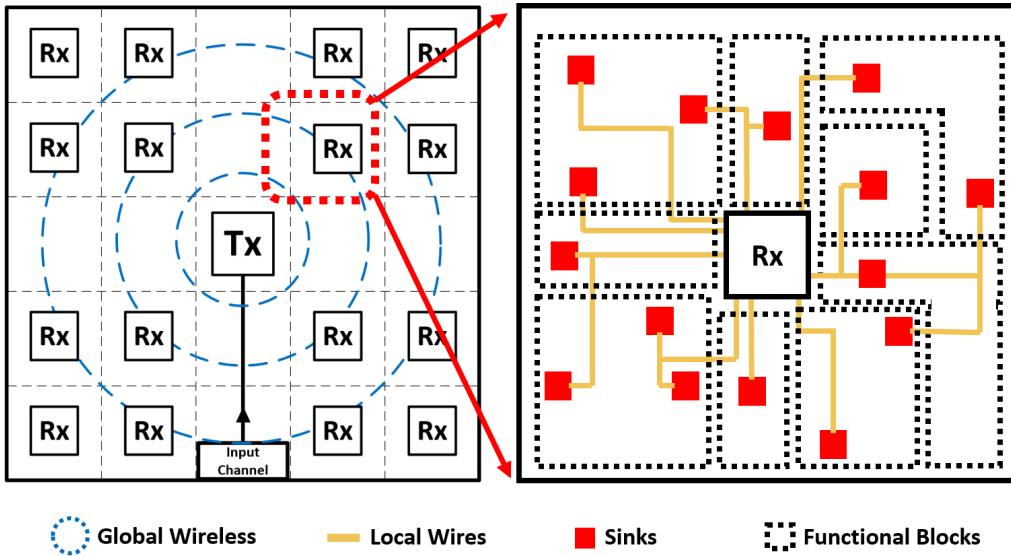

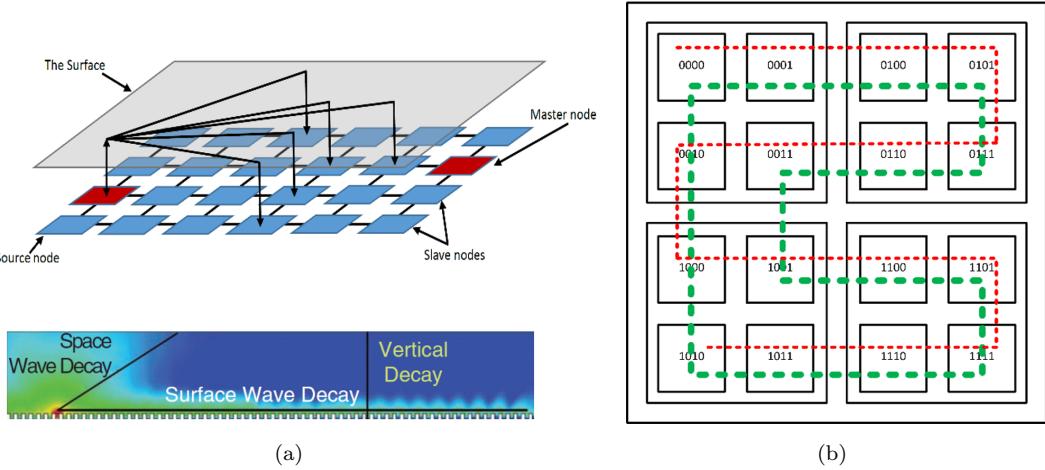

| 2.1  | Wireless interconnect with WCube as application [2]. Wireless interconnect serves as the global communication channel. . . . .                                                                                                                  | 16 |

| 2.2  | A typical structure of (a) surface-wave interconnect (SWI) and (b) transmission line interconnect (Tx-line) for global communication. . . . .                                                                                                   | 18 |

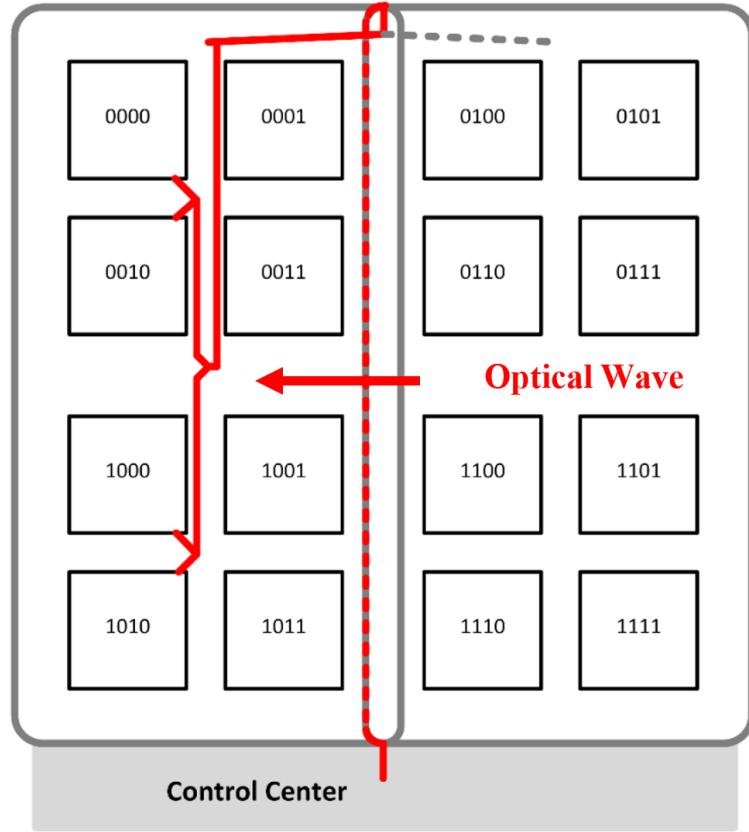

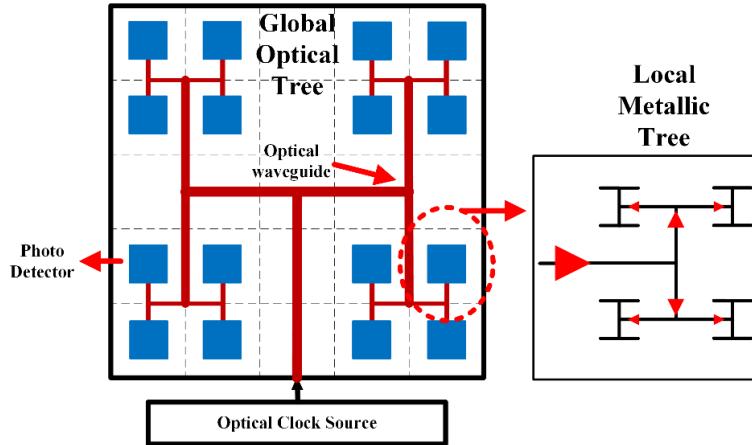

| 2.3  | An global H-tree constructed using optical interconnect to distribute clock signals. . . . .                                                                                                                                                    | 19 |

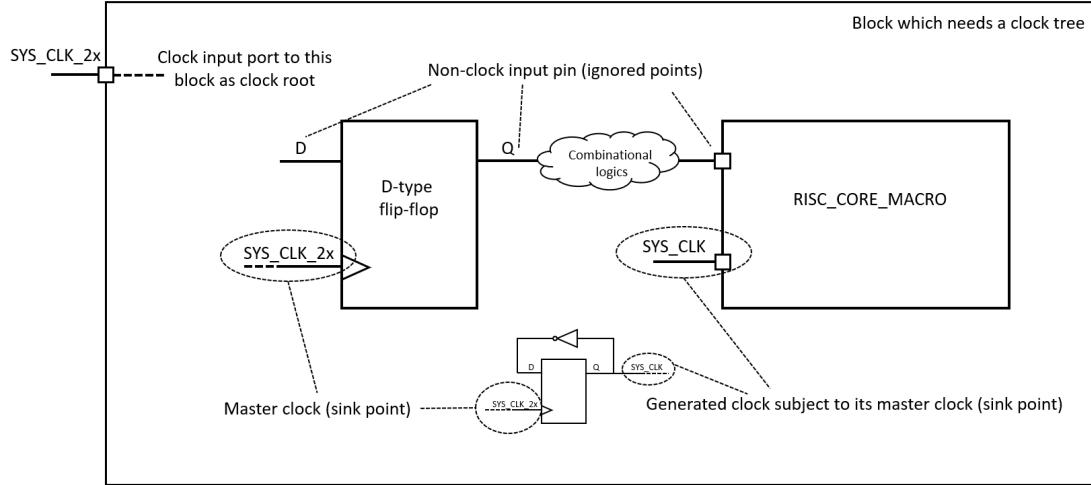

| 2.4  | Identifying the start and the endpoints of a typical clock tree in a design. . . . .                                                                                                                                                            | 21 |

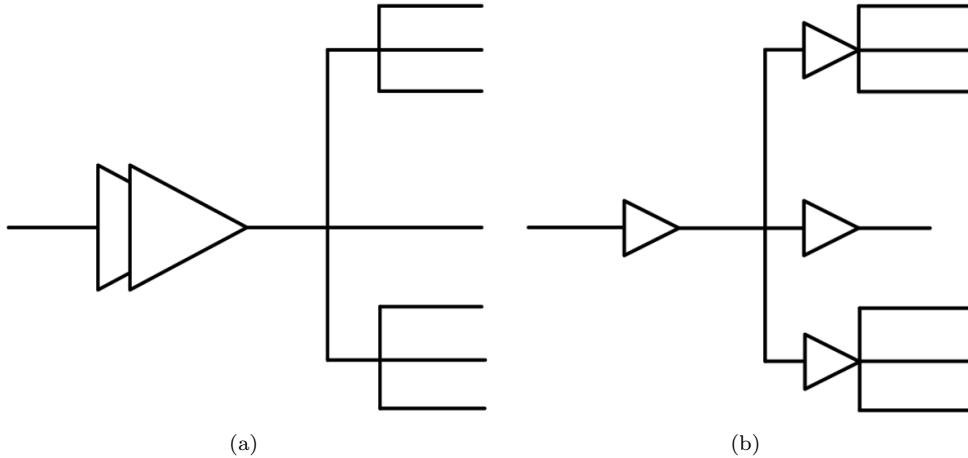

| 2.5  | A typical structure of (a) single and big buffer/driver insertion strategy in a CDN and (b) the distributed and small buffer/driver insertion strategy in a CDN. . . . .                                                                        | 22 |

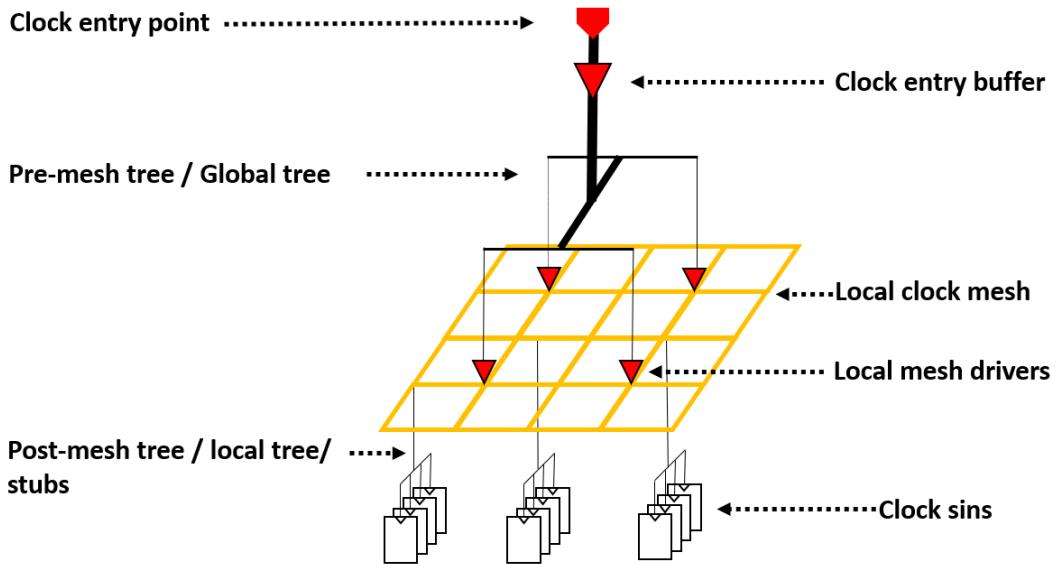

| 2.6  | Buffered-tree with local clock grid for DEC Alpha 21064 clock distribution structure. . . . .                                                                                                                                                   | 23 |

| 2.7  | A typical structure of global tree and local mesh (TLM) clock distribution scheme. . . . .                                                                                                                                                      | 23 |

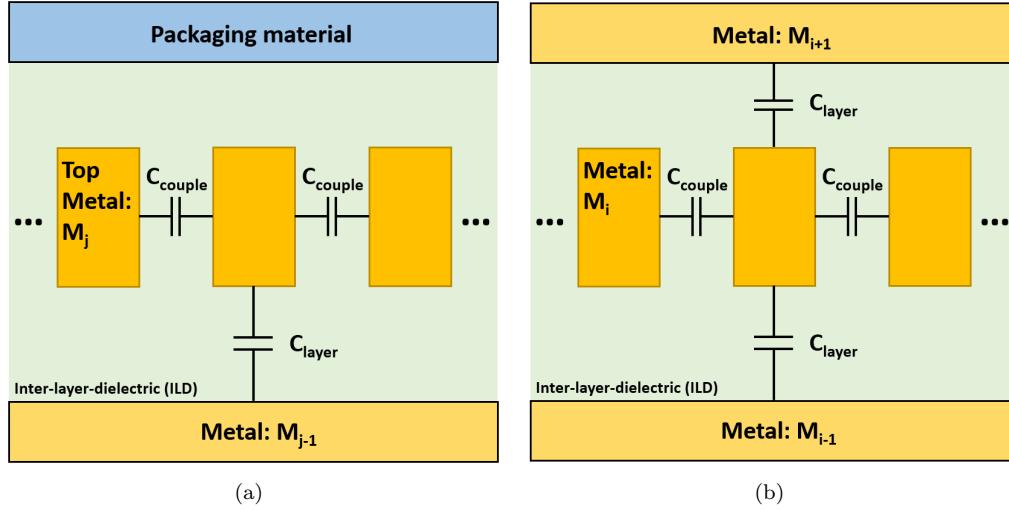

| 2.8  | A typical structure of interconnect model from PTM with (a) global and (b) local wiring structure [3]. . . . .                                                                                                                                  | 25 |

| 2.9  | CDN architecture for global optical guided interconnect and local metallic H-tree. . . . .                                                                                                                                                      | 26 |

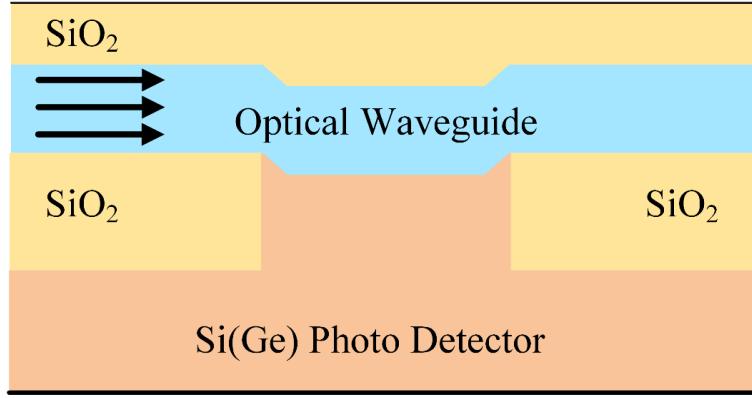

| 2.10 | Stack-up schematic of the optical CDN proposed in [4]. . . . .                                                                                                                                                                                  | 26 |

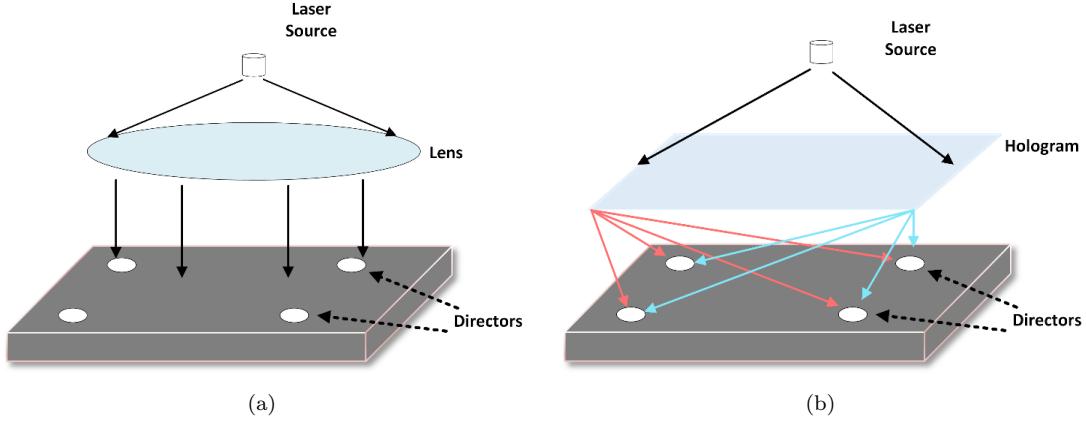

| 2.11 | Free-space optical interconnect with (a) unfocused and (b) focused clock broadcast architecture [5]. . . . .                                                                                                                                    | 27 |

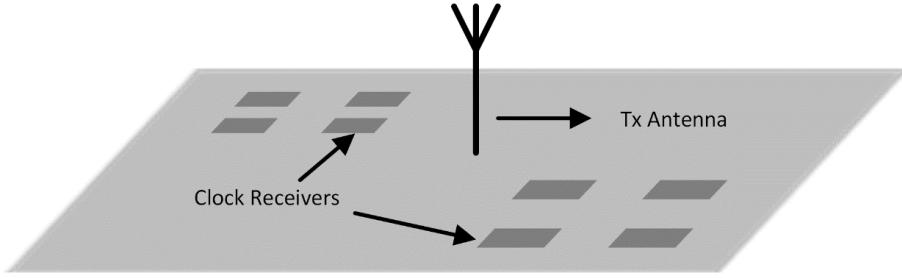

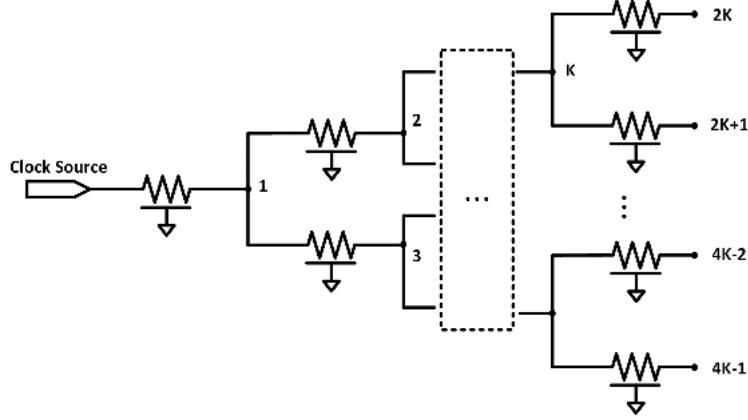

| 2.12 | General architecture of a wireless CDN with integrated wireless clock transmitter and receivers. . . . .                                                                                                                                        | 29 |

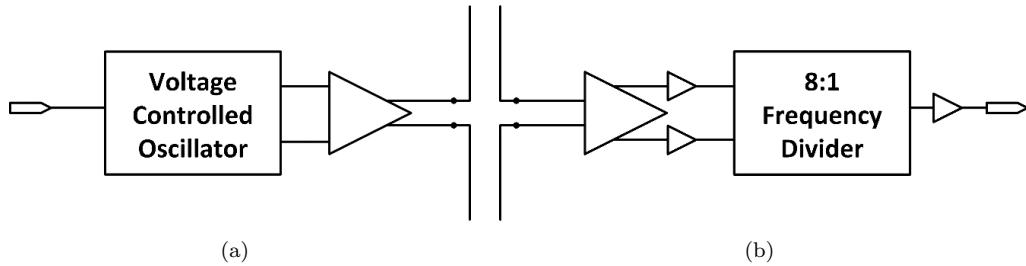

| 2.13 | Block diagrams of wireless CDN [6] with (a) clock transmitter and (b) clock receiver. . . . .                                                                                                                                                   | 30 |

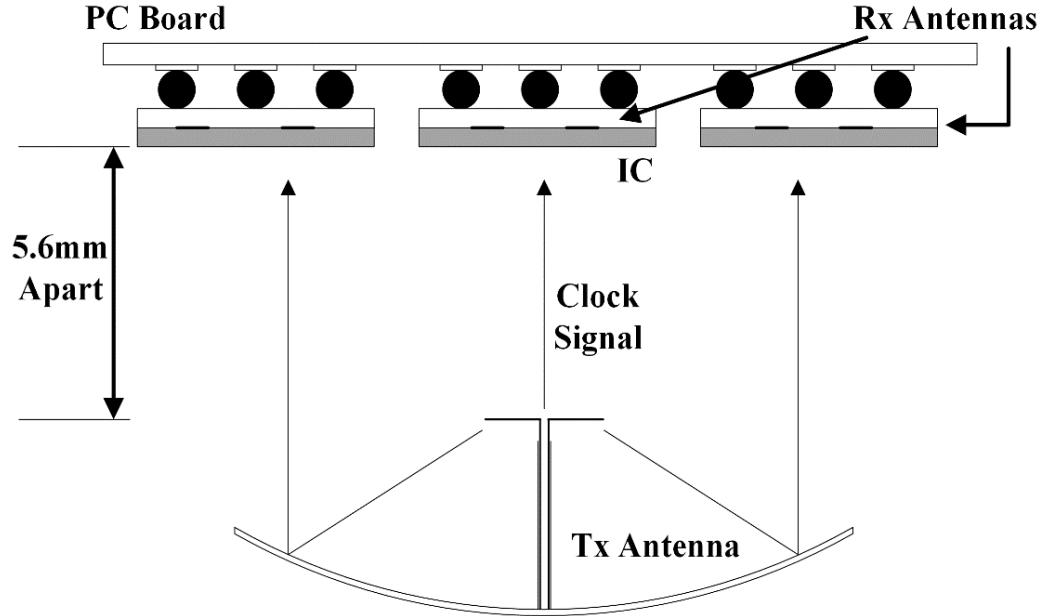

|      |                                                                                                                                                                                                                                                                                                                                                                         |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.14 | Wireless CDN transceiver architecture in [7] with 5.6mm propagation distance. . . . .                                                                                                                                                                                                                                                                                   | 31 |

| 2.15 | Simplified 64-QAM wireless interconnect architecture [8] with (a) transmitter and (b) receiver. . . . .                                                                                                                                                                                                                                                                 | 32 |

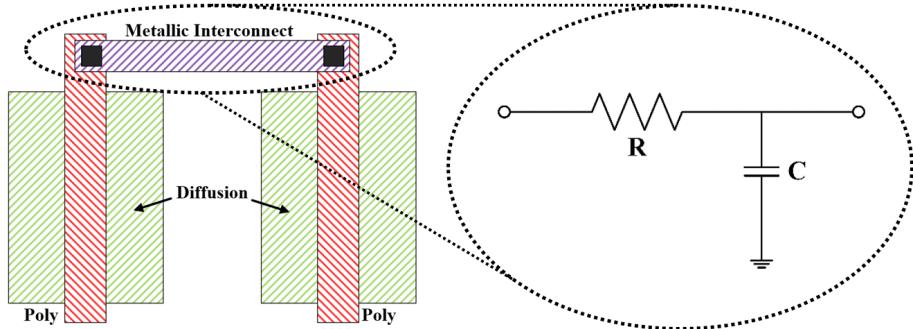

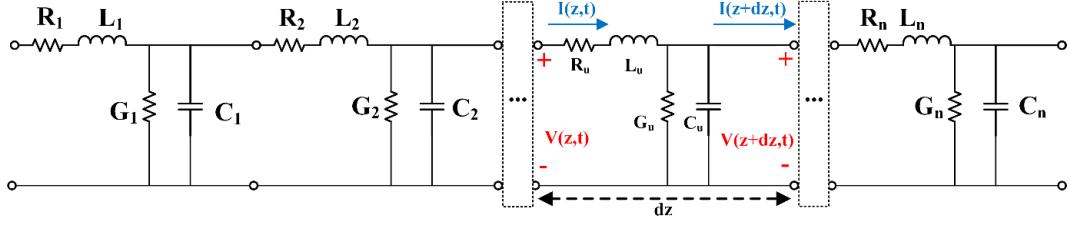

| 3.1  | Conventional metallic interconnect structure and its lumped RC model. . . . .                                                                                                                                                                                                                                                                                           | 36 |

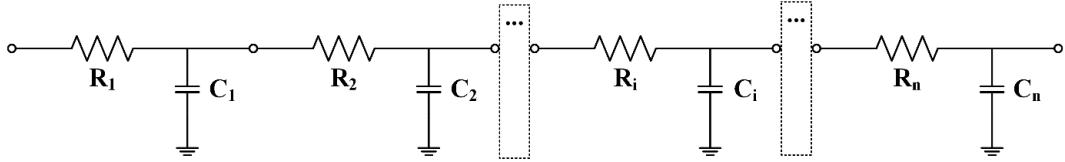

| 3.2  | Distributed lumped circuit structure for improved accuracy of interconnect model. . . . .                                                                                                                                                                                                                                                                               | 37 |

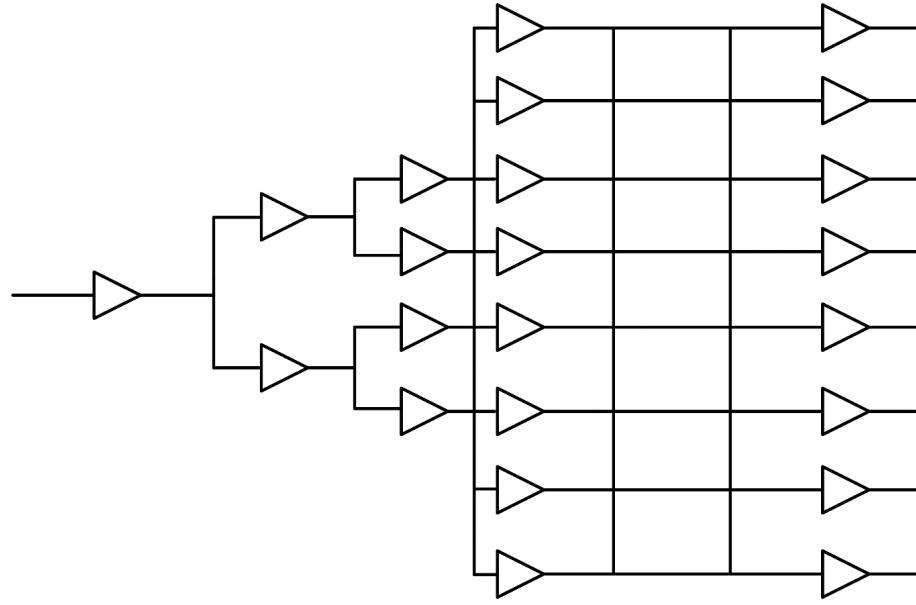

| 3.3  | Conventional tapered H-tree network as baseline architecture with 16 fan-out nodes. . . . .                                                                                                                                                                                                                                                                             | 39 |

| 3.4  | A $k$ -level H-tree modelled as a folded binary RC tree with $k^2$ fan-out. . . . .                                                                                                                                                                                                                                                                                     | 40 |

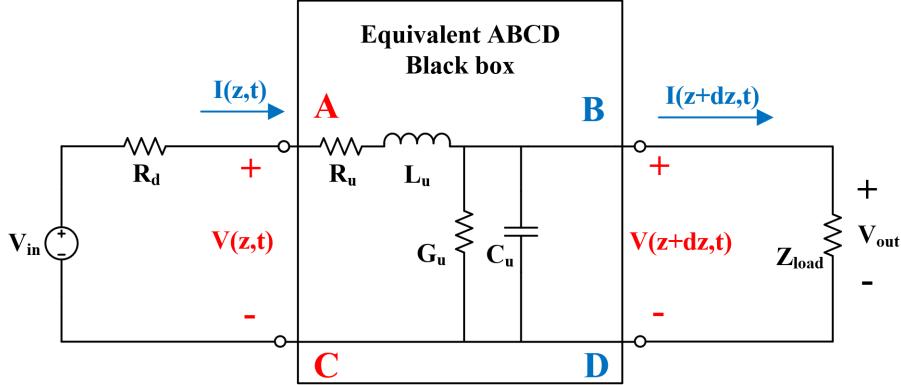

| 3.5  | Transmission line model with distributed elements $R_u$ , $L_u$ , $G_u$ , and $C_u$ , respectively. . . . .                                                                                                                                                                                                                                                             | 41 |

| 3.6  | Equivalent ABCD representation of an interconnect in transmission line model. . . . .                                                                                                                                                                                                                                                                                   | 42 |

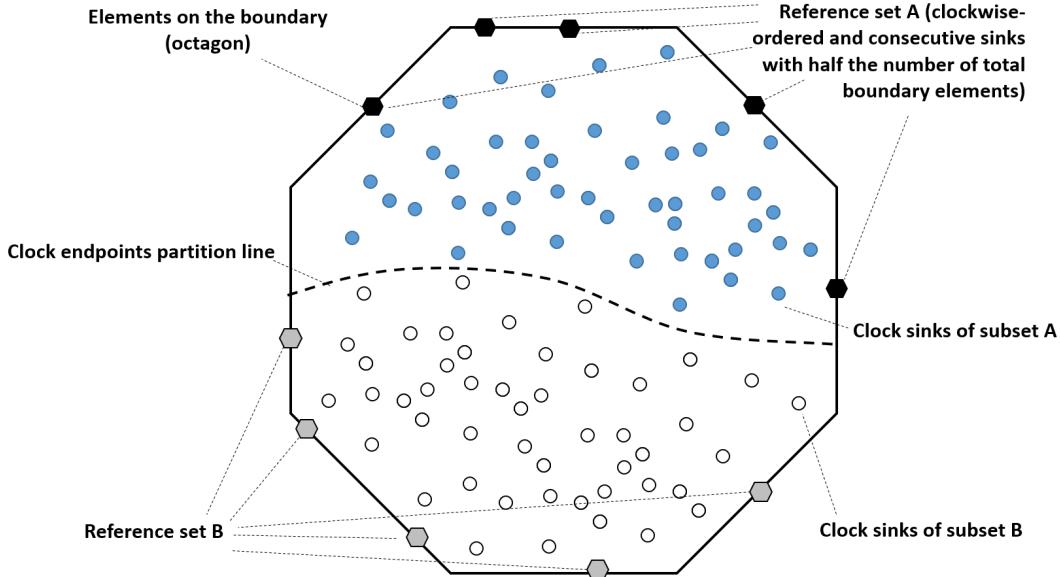

| 3.7  | Top view of the Balanced Bi-partitioning (BB) Algorithm with half of the sinks on the boundary as a reference set. The clock sinks within the octagon that are closer to the reference set A are partitioned into subset A, the rest are grouped into subset B. Also, the summation of the capacitance of clock sinks are minimised. . . . .                            | 45 |

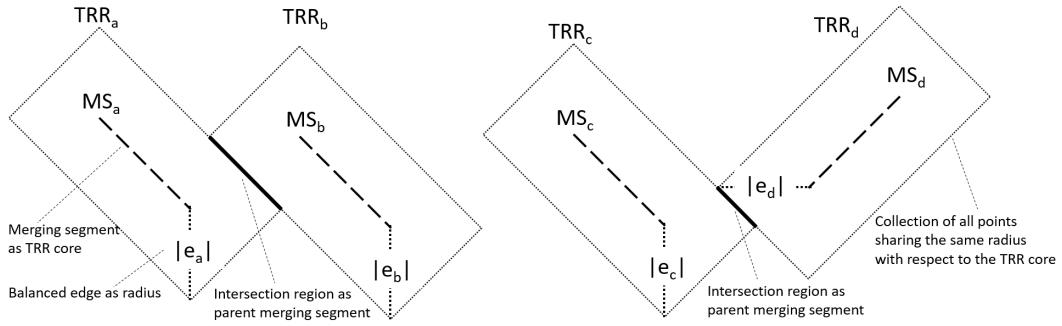

| 3.8  | Example of the merging segment generation, with $MS_a$ , $MS_b$ as a tuple element and $MS_c$ , $MS_d$ as a tuple element, respectively. The generated parent merging segments are the intersection region of the two TRRs with the respective child merging segments as cores and calculated/balanced edges as radius. . . . .                                         | 46 |

| 3.9  | Example of the topology tree generation with a sink set containing 8 clock endpoints. The layer 1 MS are constructed in iteration 1 with tuple 1 (8 sinks) as input, the layer 2 MS are constructed in iteration 2 with tuple 2 (layer 1 MS) as input. The iterations are executed from a bottom-up fashion, until the root merging segment has been generated. . . . . | 46 |

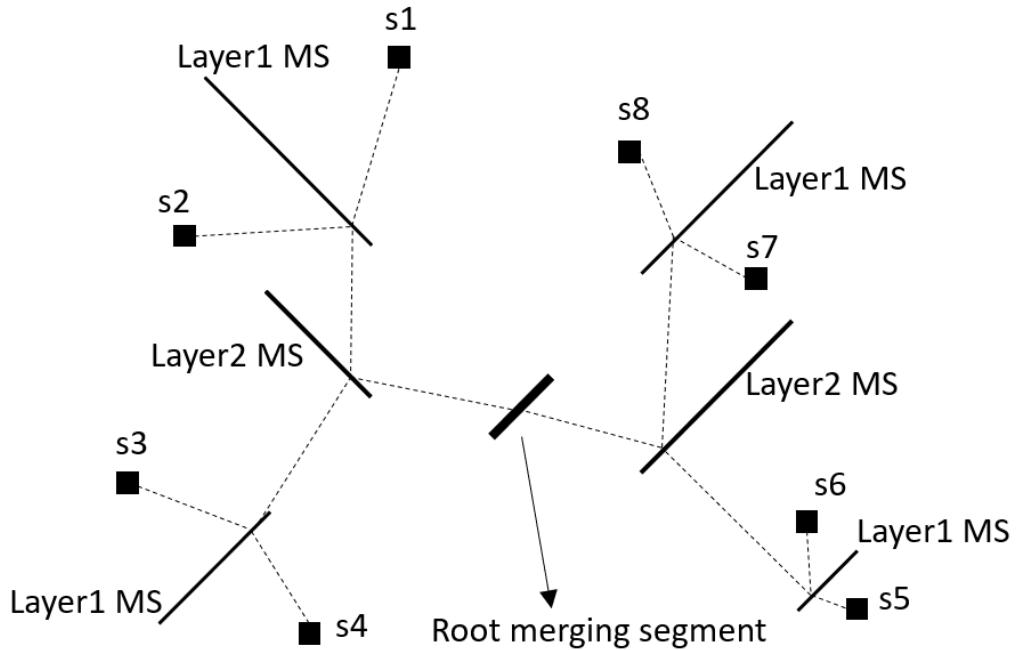

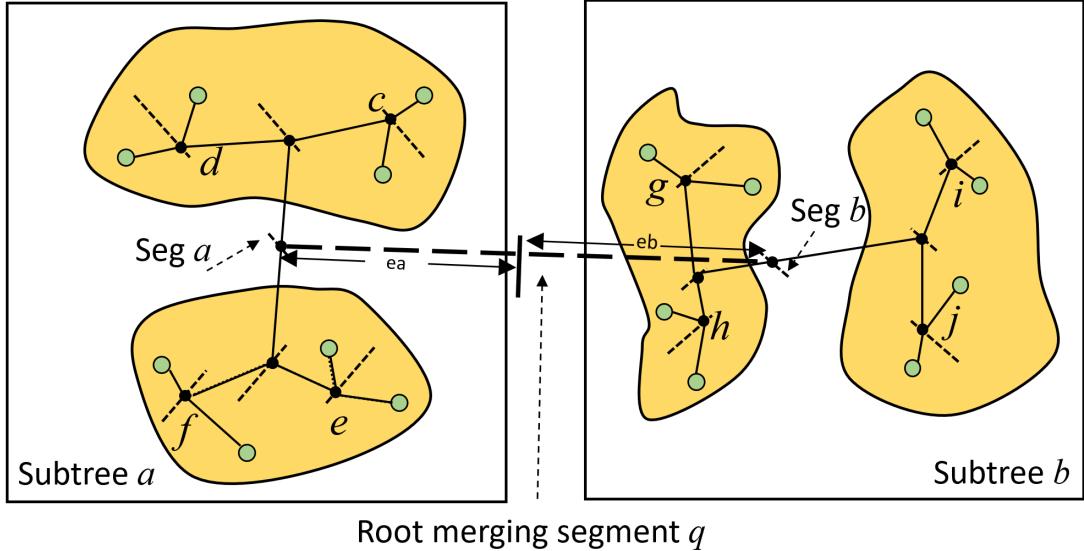

| 3.10 | Illustration of the xy-cut, using (a) a conventional balanced bi-partition in [9], and (b) our proposed xy-cut algorithm for minimum wire usage. The total wire reduction between the proposed method and the conventional method is around 15.1% in this example, thus improving energy efficiency. . . . .                                                            | 49 |

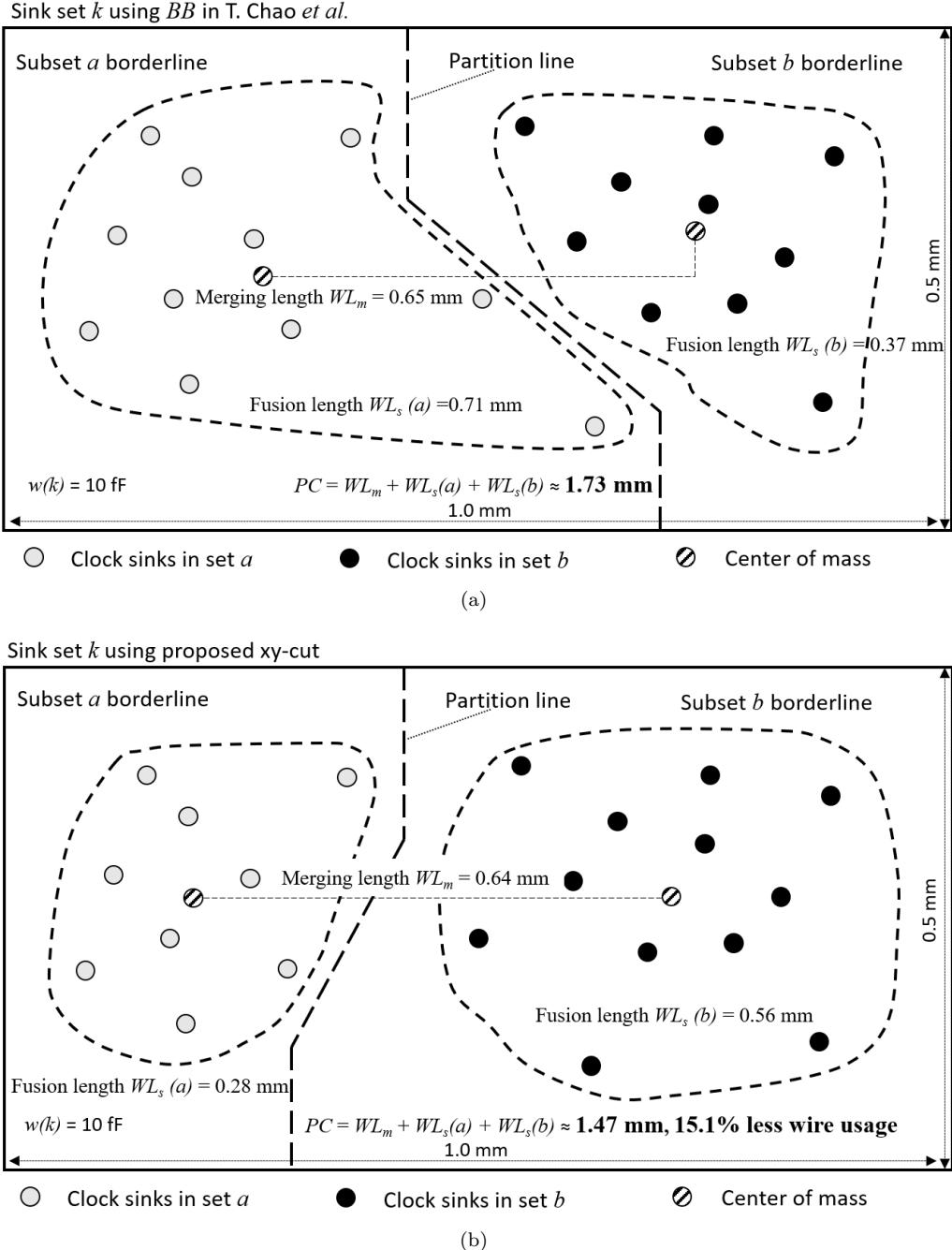

| 3.11 | Example of the merging tree generation with two sink sets, each of which contains 8 clock endpoints (not to scale). The two subtrees are merged with root segment $q$ . . . . .                                                                                                                                                                                         | 51 |

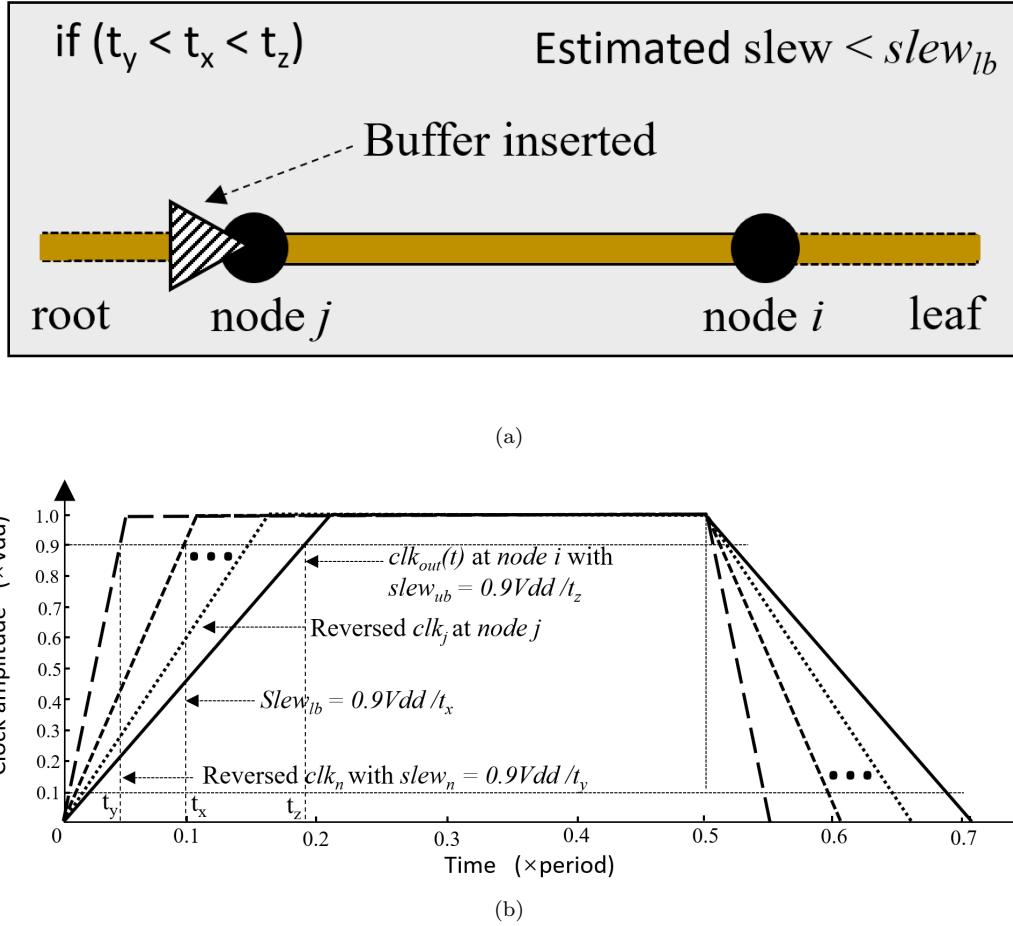

| 3.12 | Illustration of the (a) proposed buffer insertion method with inverted slew-estimation and (b) its time-domain behavior when the estimated slew is smaller than the slew lower bound of the driver. Without a clock driver, the child clock end point might violate the slew constraint. . . . .                                                                        | 54 |

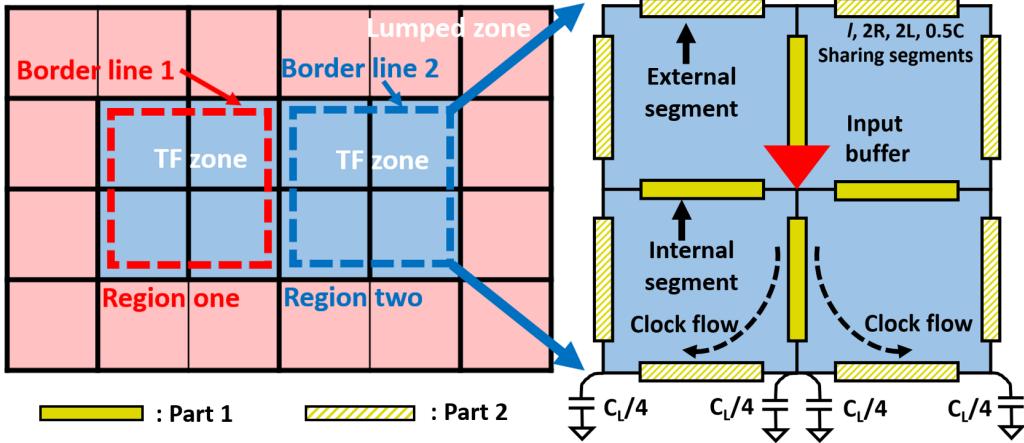

| 3.13 | Partial top views of the proposed isolated model, including transfer function zone (TF zone) and lumped zone. Unit cells are considered independent of each other. ©2021 IEEE . . . . .                                                                                                                                                                                 | 56 |

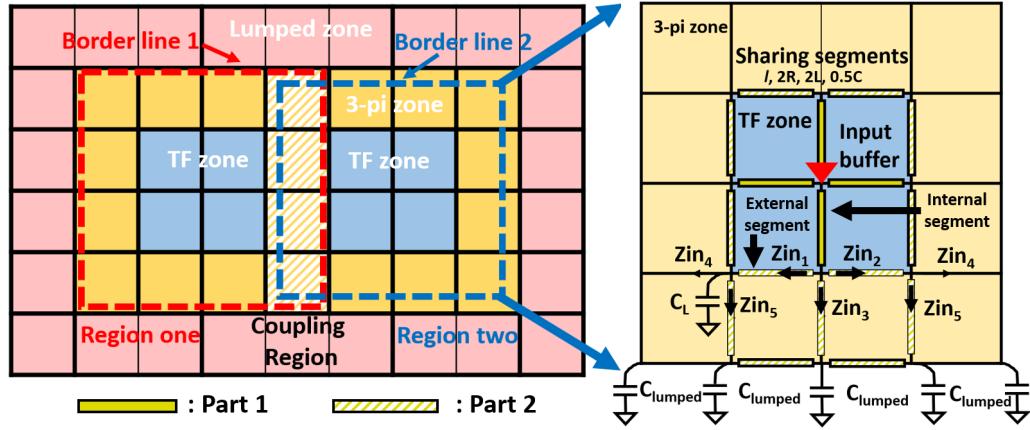

| 3.14 | Partial top views of the proposed coupled model (not to scale), including transfer function zone (TF zone), 3- $\pi$ zone and lumped zone. Unit cells are considered coupled to each other shown in the overlapped region. ©2021 IEEE . . . . .                                                                                                                         | 57 |

|      |                                                                                                                                                                                                                                                                         |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

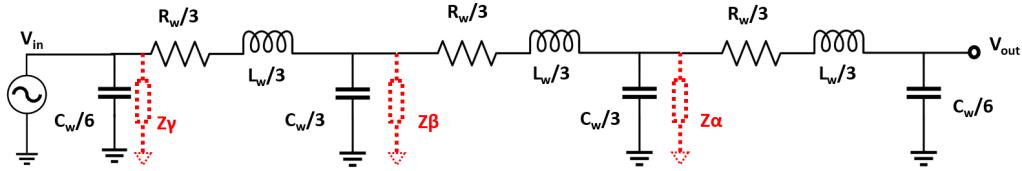

| 3.15 | Typical structure of an RLC 3- $\pi$ model [10] which has been used in our proposed model for representing interconnect segments longer than 100 $\mu\text{m}$ inside 3- $\pi$ region. . . . .                                                                          | 59 |

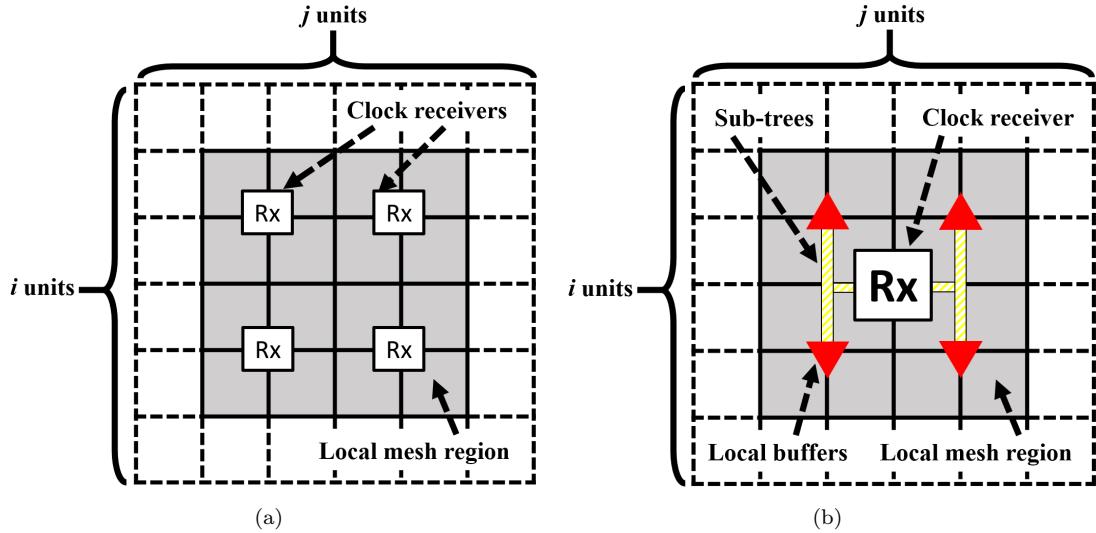

| 3.16 | Top view of (a) distributed planning and (b) concentrated planning in an arbitrary $i \times j$ local mesh network. . . . .                                                                                                                                             | 59 |

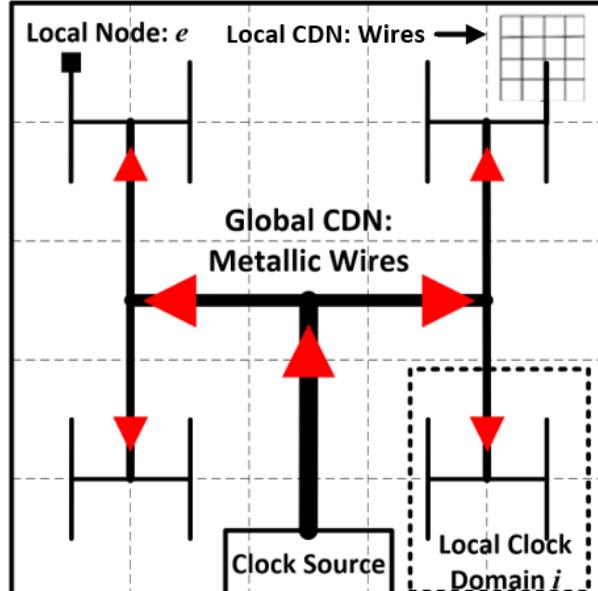

| 3.17 | The proposed hybrid clock distribution network which combines both global RF-I and local metallic wires. . . . .                                                                                                                                                        | 63 |

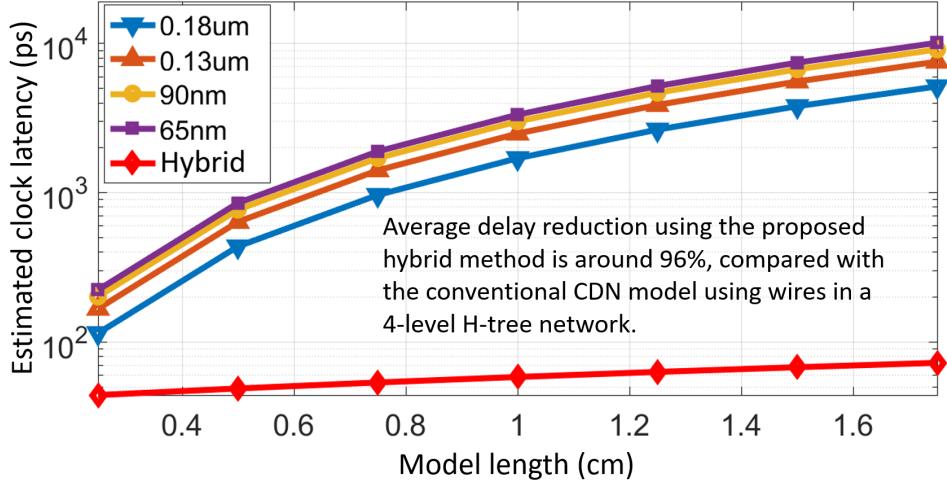

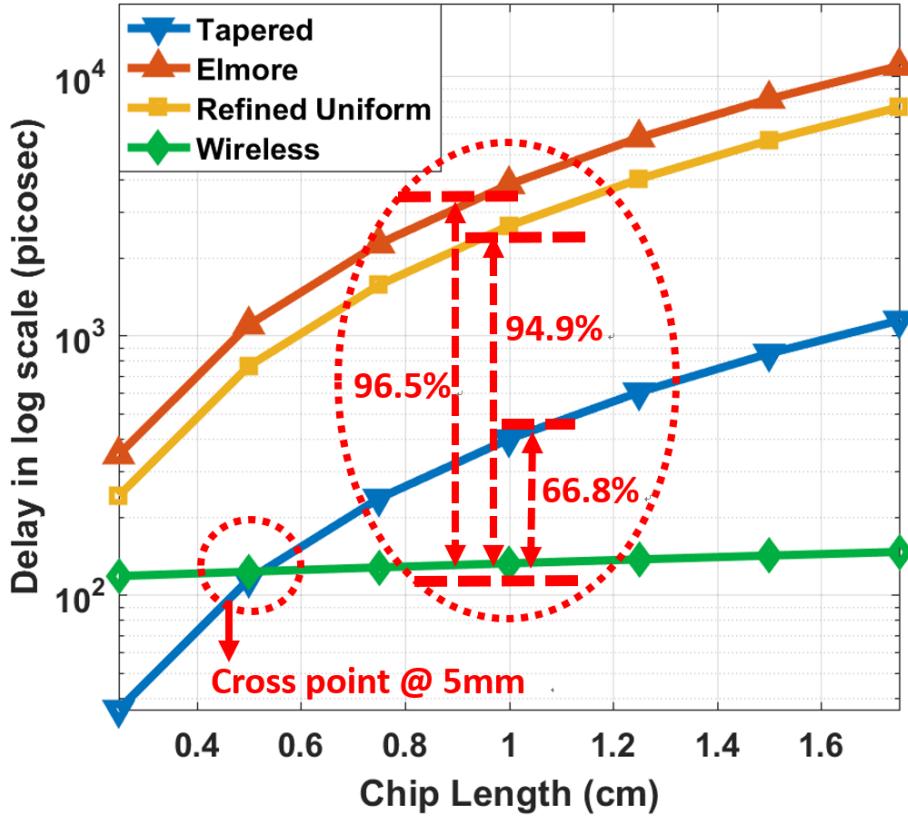

| 3.18 | Estimated results using the proposed hybrid model and a conventional H-tree CDN with 96% average delay reduction. . . . .                                                                                                                                               | 65 |

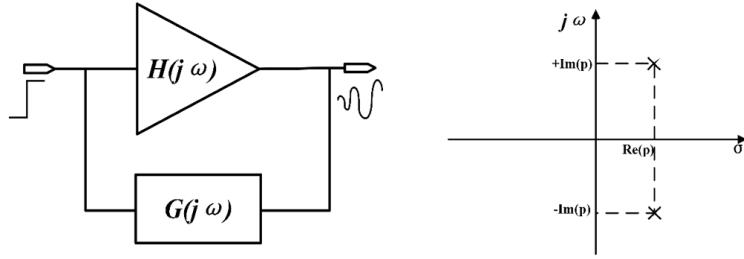

| 4.1  | Block diagrams of the proposed (a) clock transmitter and (b) clock receiver. . . . .                                                                                                                                                                                    | 68 |

| 4.2  | General oscillatory condition of feedback system. . . . .                                                                                                                                                                                                               | 69 |

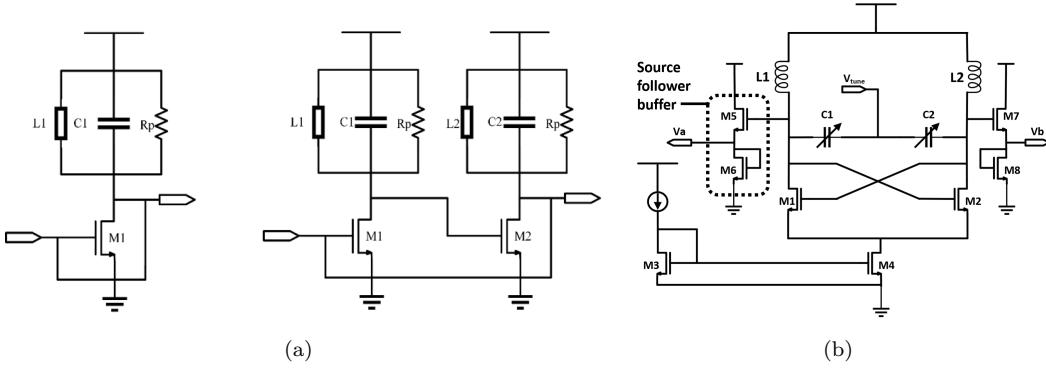

| 4.3  | Circuit schematics of the proposed (a) tuned stage and (b) the proposed balanced VCO with cross-coupled NMOS pair and source follower buffers. . . . .                                                                                                                  | 70 |

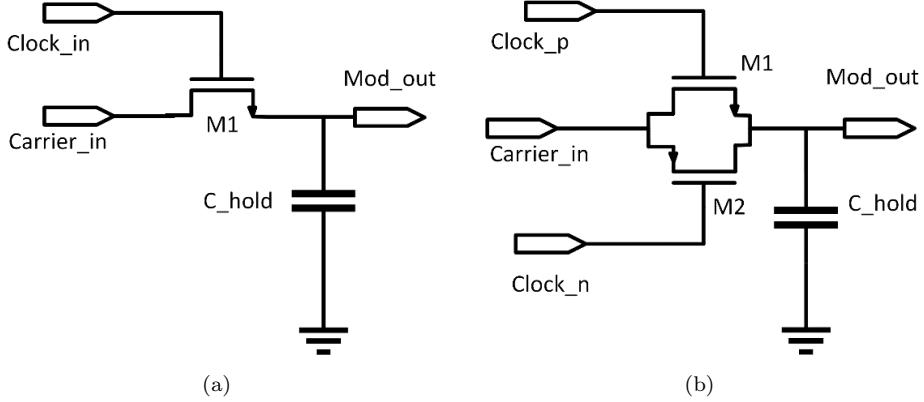

| 4.4  | Typical structure of the (a) single and (b) complementary implementation of a MOS switch. . . . .                                                                                                                                                                       | 72 |

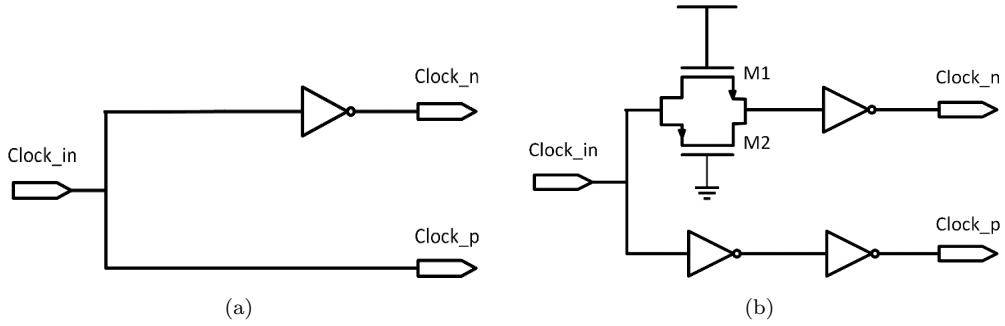

| 4.5  | 1-to-2 Clock buffer with (a) unbalanced propagation delay and (b) balanced propagation delay. . . . .                                                                                                                                                                   | 72 |

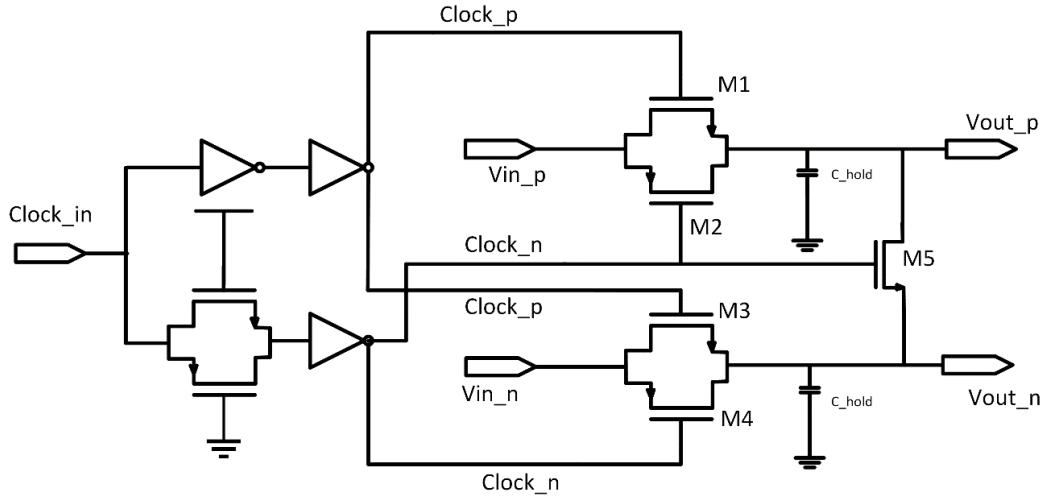

| 4.6  | The schematic of MOS switch-based OOK modulator with differential signaling. . . . .                                                                                                                                                                                    | 73 |

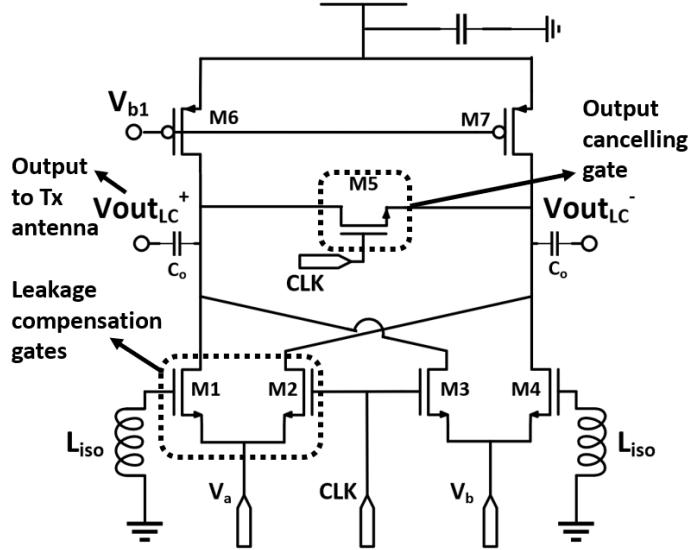

| 4.7  | Schematic of the proposed OOK modulator with differential signaling and leakage compensation cross-coupling NMOS pairs. . . . .                                                                                                                                         | 74 |

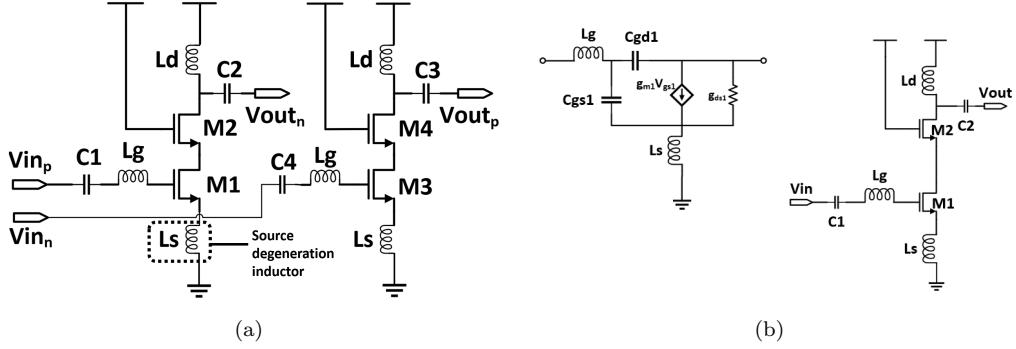

| 4.8  | Schematics of the proposed (a) pseudo-differential Inductive degeneration LNA and (b) its high frequency single-stage small signal model. . . . .                                                                                                                       | 75 |

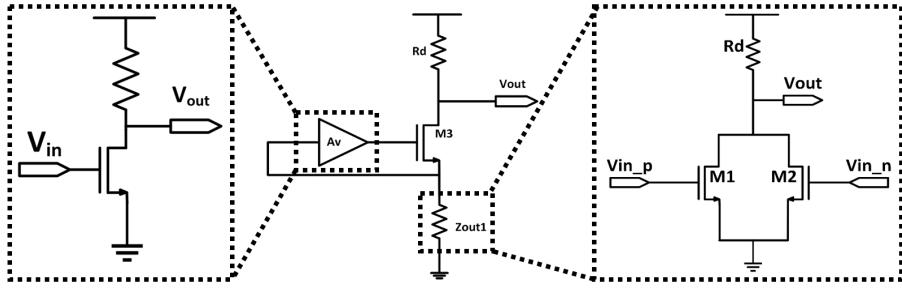

| 4.9  | Schematic of the proposed gain-boosting load, with a conventional NMOS rectifier to rectify the input radio frequency signals. . . . .                                                                                                                                  | 78 |

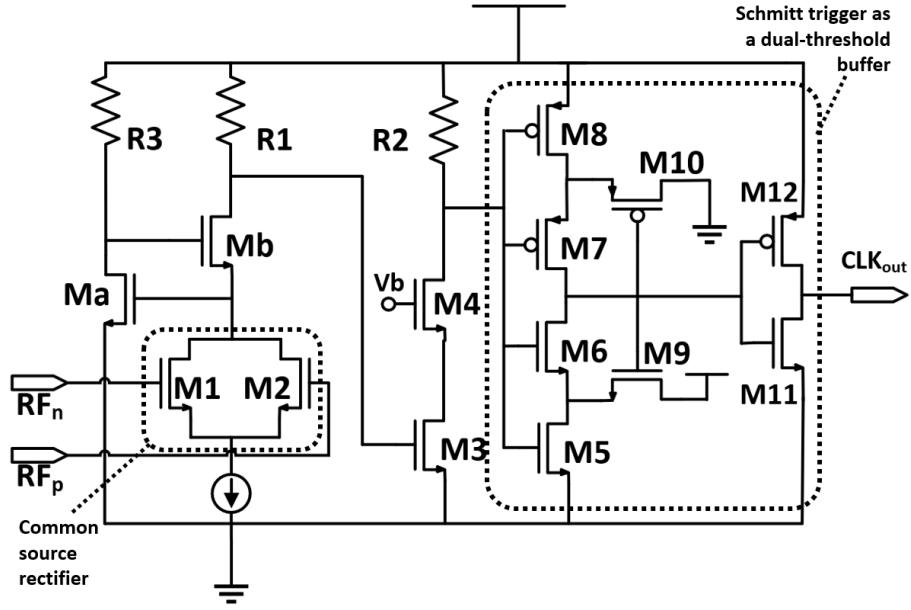

| 4.10 | Schematic of the proposed Proposed OOK demodulator with gain-boosting technique and noise-compensation output buffer. . . . .                                                                                                                                           | 79 |

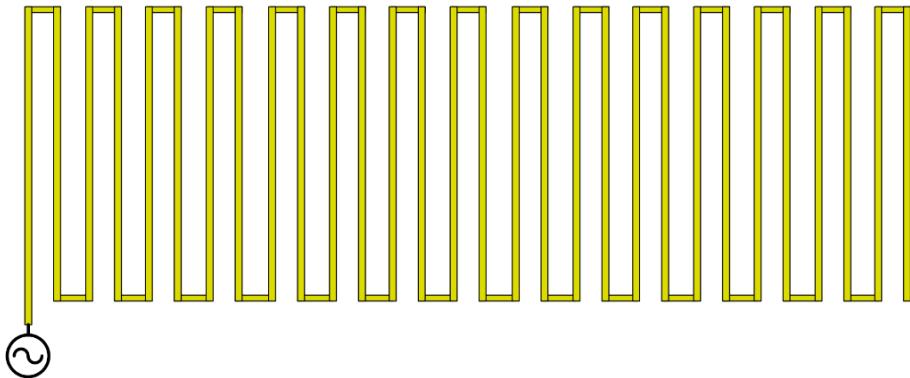

| 4.11 | Top view of the proposed meander monopole antenna (MMA) structure with top copper layer. . . . .                                                                                                                                                                        | 81 |

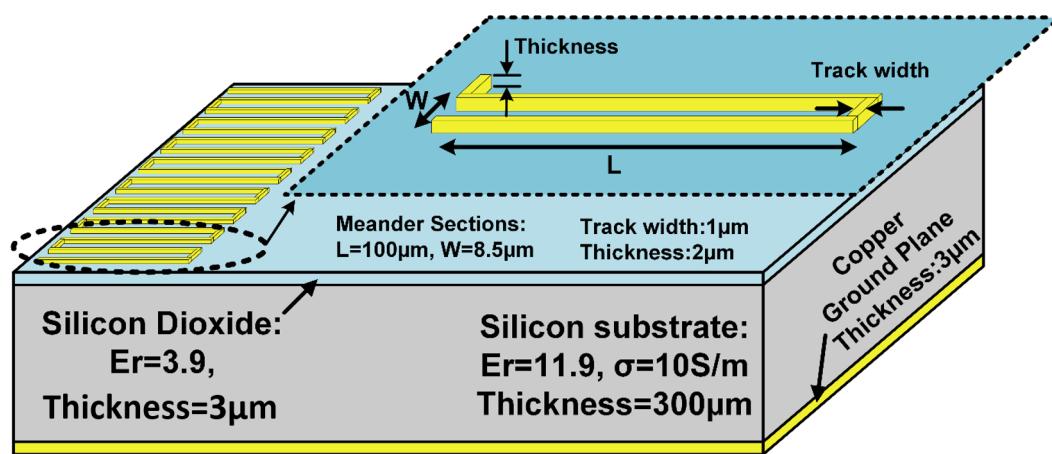

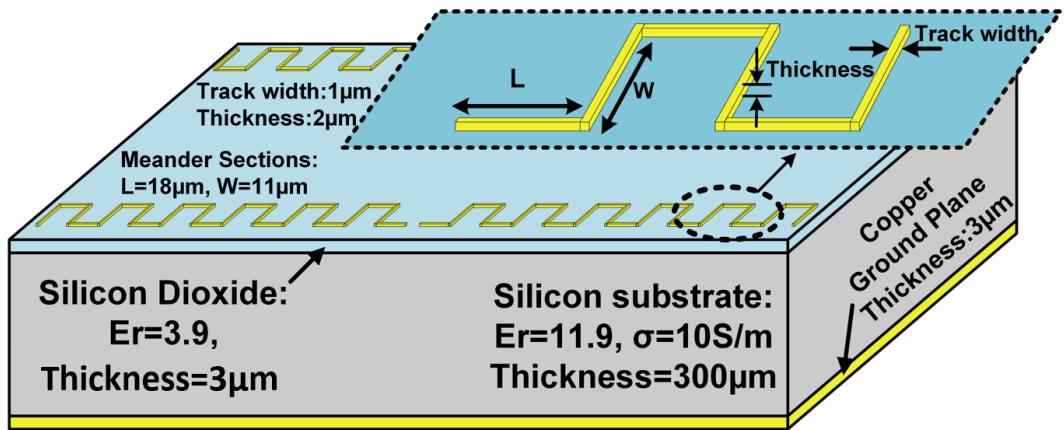

| 4.12 | Proposed meandering monopole antenna (MMA) structure with EM simulation model setup (not to scale). . . . .                                                                                                                                                             | 81 |

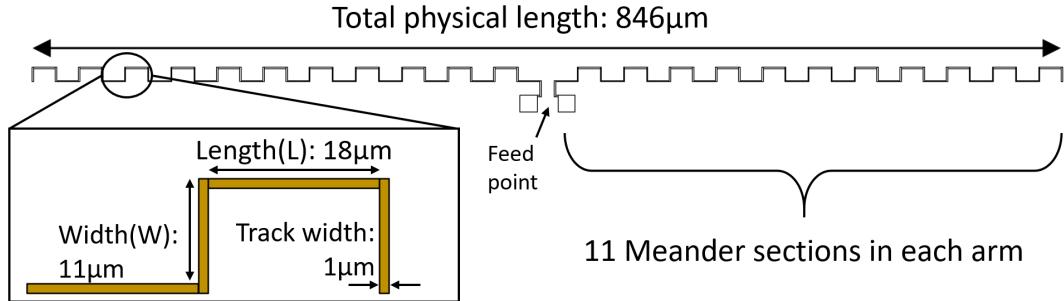

| 4.13 | Top view of the proposed meander dipole antenna (MDA) structure with top copper layer. . . . .                                                                                                                                                                          | 82 |

| 4.14 | Proposed meandering dipole antenna (MDA) structure with EM simulation model setup (not to scale). ©2021 IEEE . . . . .                                                                                                                                                  | 82 |

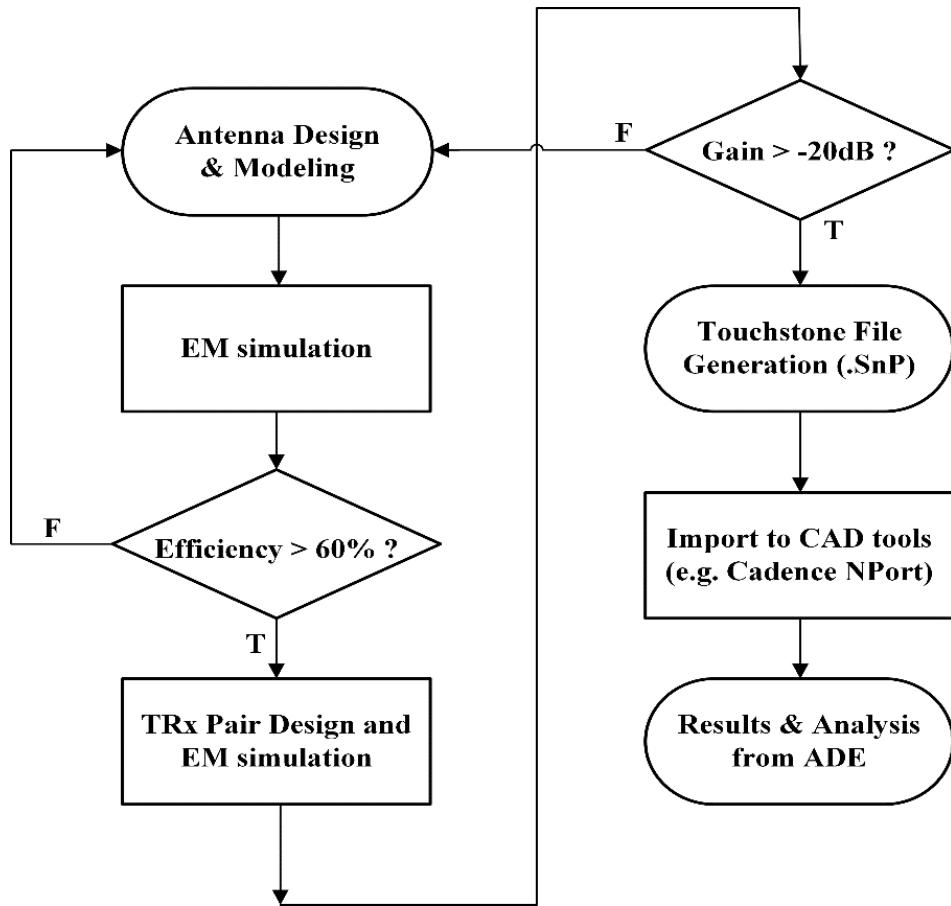

| 5.1  | Complete antenna-circuits co-simulation flow diagram for global wireless CDN verification. . . . .                                                                                                                                                                      | 87 |

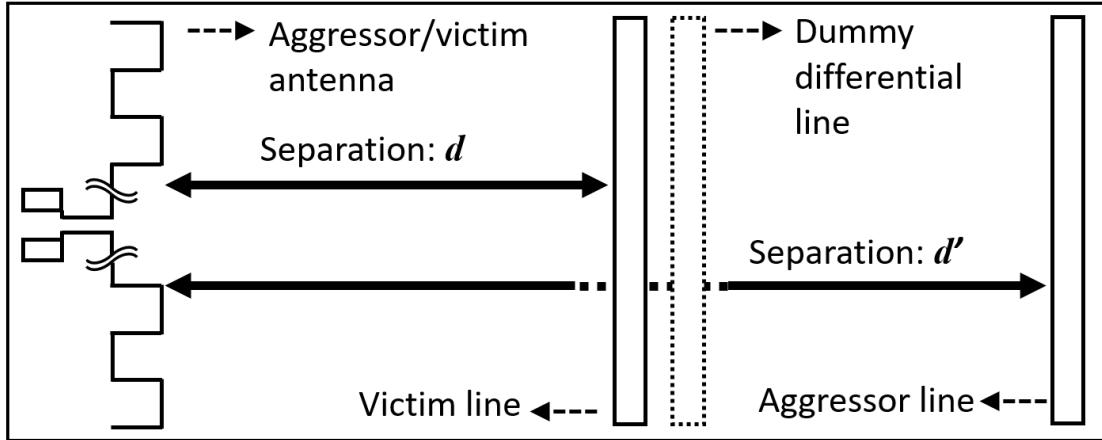

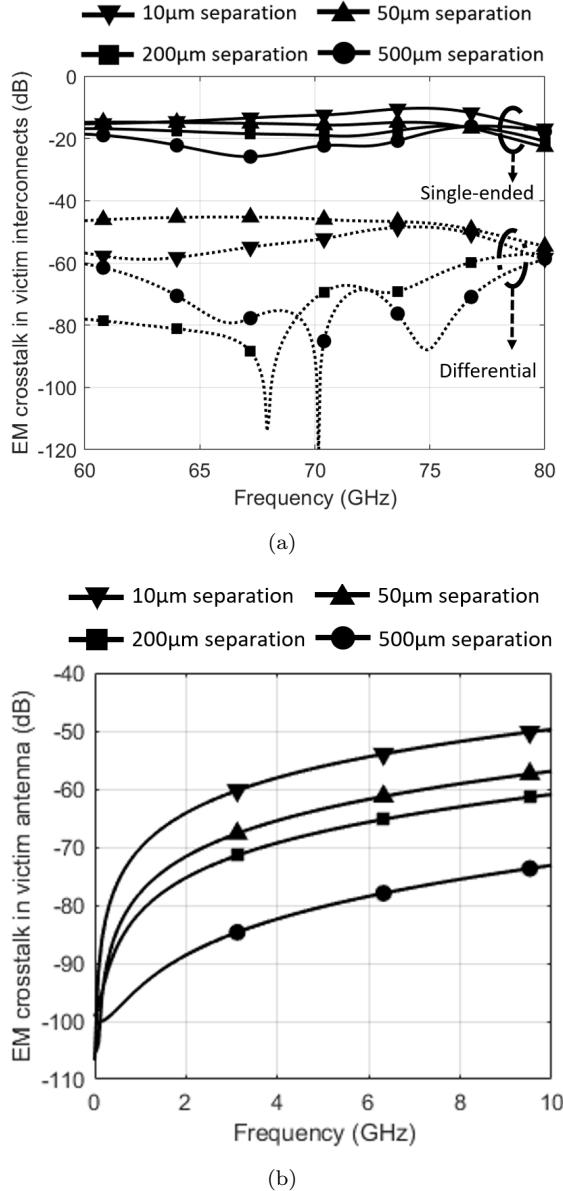

| 5.2  | Top view of the test structure for the study of EM crosstalk between TRx antenna and the nearby interconnects with different separation distance. The antenna and nearby lines act as the victim of the crosstalk in the experiment, respectively. ©2021 IEEE . . . . . | 88 |

| 5.3  | EM crosstalks versus the frequency of interest in (a) victim interconnects and (b) victim antenna, measured in $S_{21}$ . The differential signaling can reduce the common-mode noise by 35 dB averagely, in the victim lines. . . . .                                  | 89 |

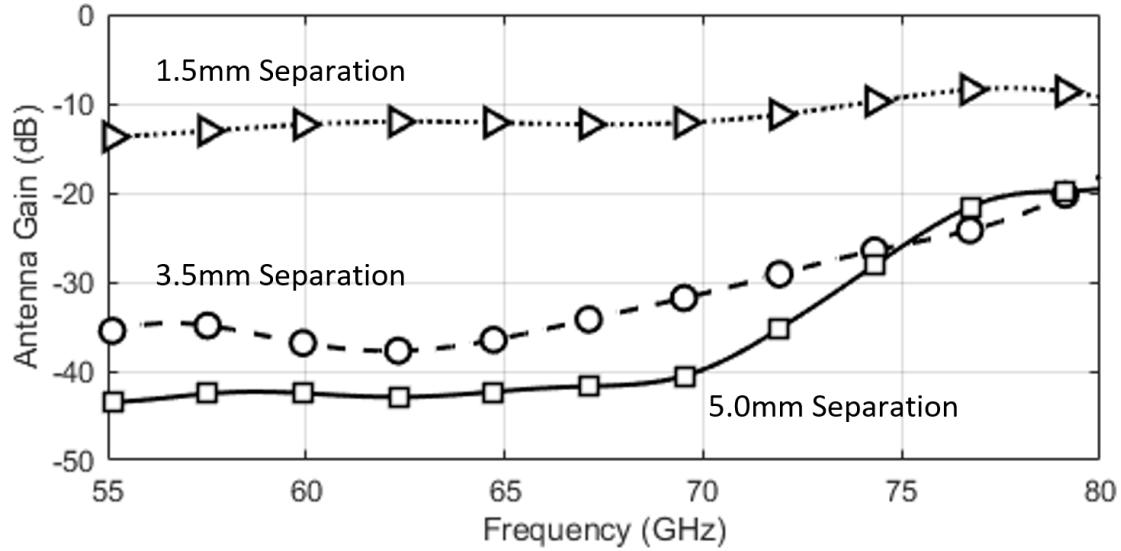

| 5.4  | Antenna gain under matched condition with 3 separation distances ranging from 1.5 mm to 5 mm, which shows it's suitable for the proposed hybrid CDN. ©2021 IEEE . . . . .                                                                                               | 90 |

|      |                                                                                                                                                                                                                                                                                                                          |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

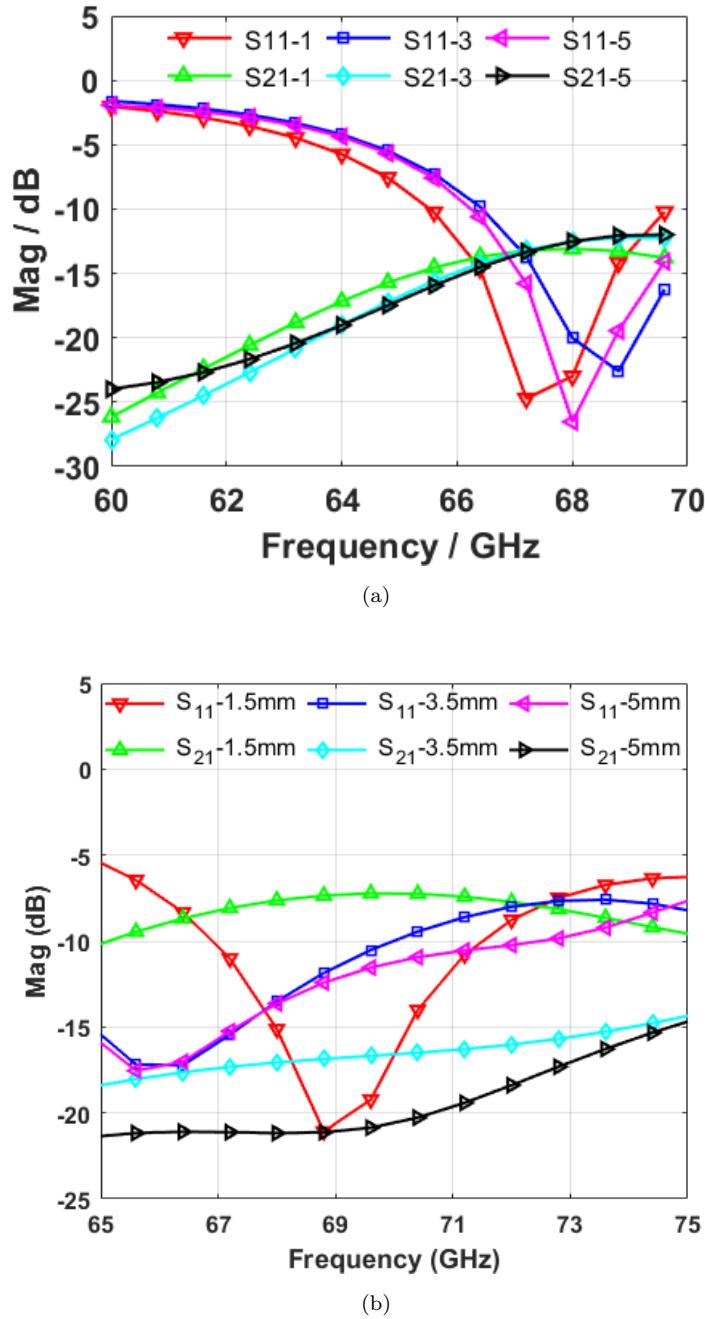

| 5.5  | EM simulation in terms of S-parameter results for (a) the proposed meander monopole antenna (MMA) antenna and (b) the proposed meander dipole antenna (MDA) antenna, with 3 separation distances ranging from 1.5 mm to 5 mm. . . . .                                                                                    | 91  |

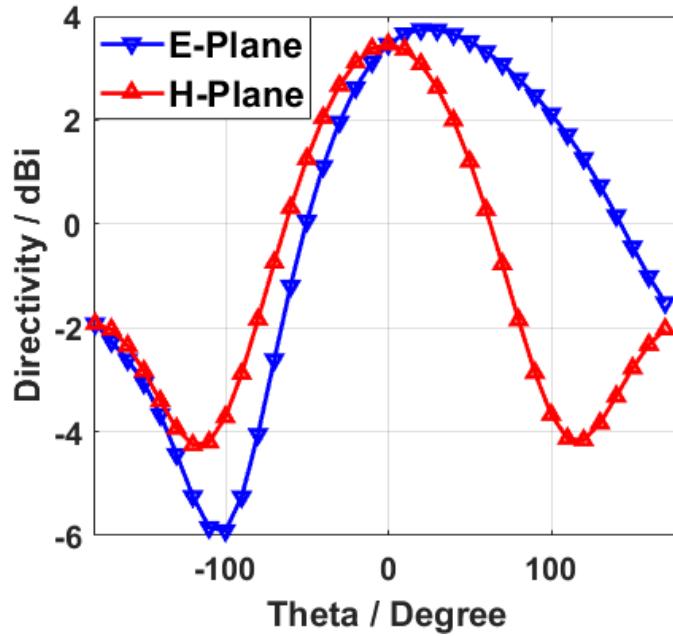

| 5.6  | Directivity of the proposed meander dipole antenna (MDA) with 1.5 mm Tx and Rx separation, which shows it's suitable for our proposed hybrid CDN. . . . .                                                                                                                                                                | 92  |

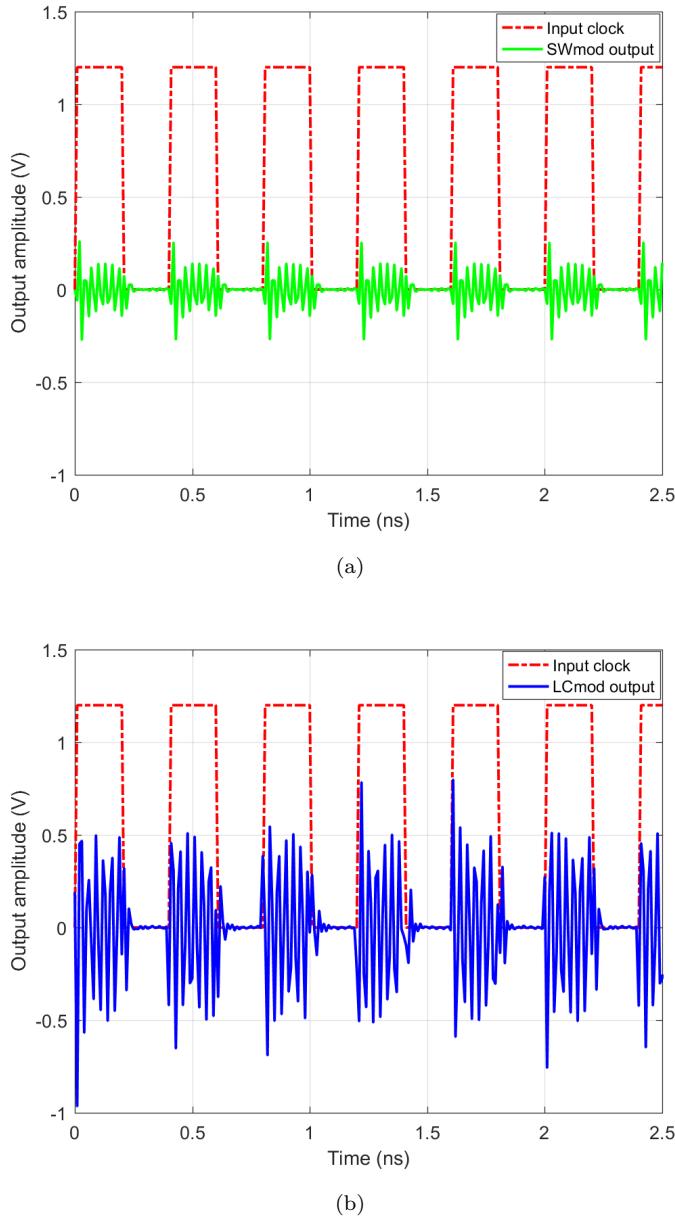

| 5.7  | Output clock signal with an input 2.5 GHz nominal clock for the proposed (a) switch-based modulator (SWM) and (b) leakage-compensation modulator (LCM). . . . .                                                                                                                                                          | 93  |

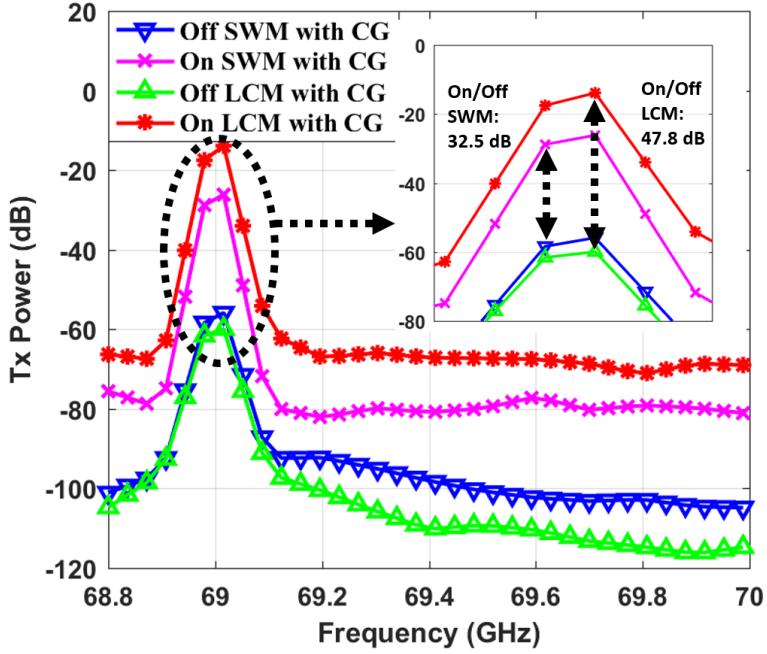

| 5.8  | 65 nm leakage compensation modulator (LCM) and switching modulator (SWM) output in frequency domain with the proposed cancelling gate M5 and M6. . . . .                                                                                                                                                                 | 94  |

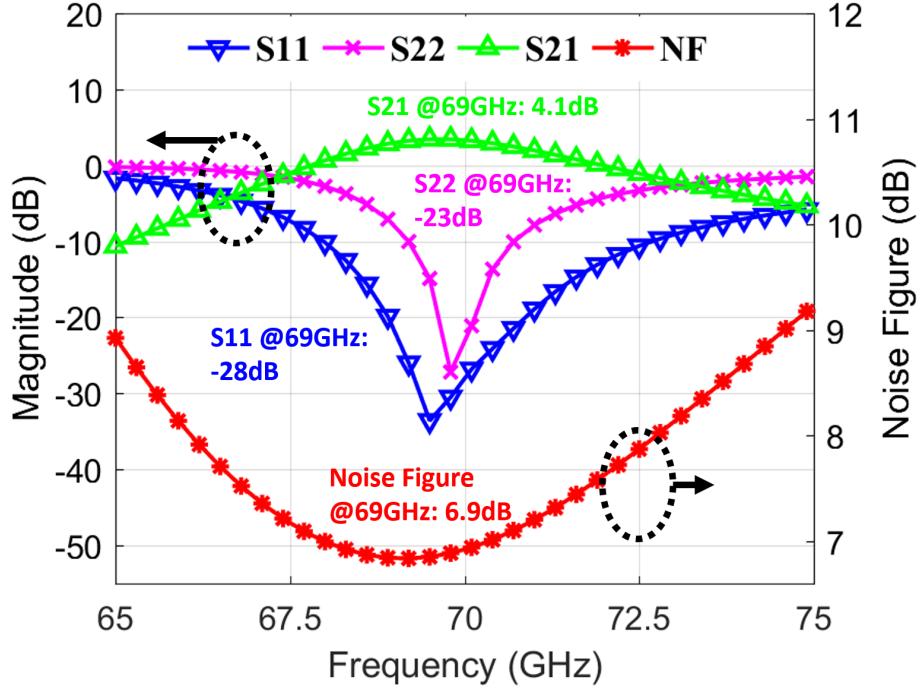

| 5.9  | Rx front-end results in terms of the S-parameters of the proposed pseudo-differential low-noise amplifier (lna) and noise figure at 69 GHz. . . . .                                                                                                                                                                      | 95  |

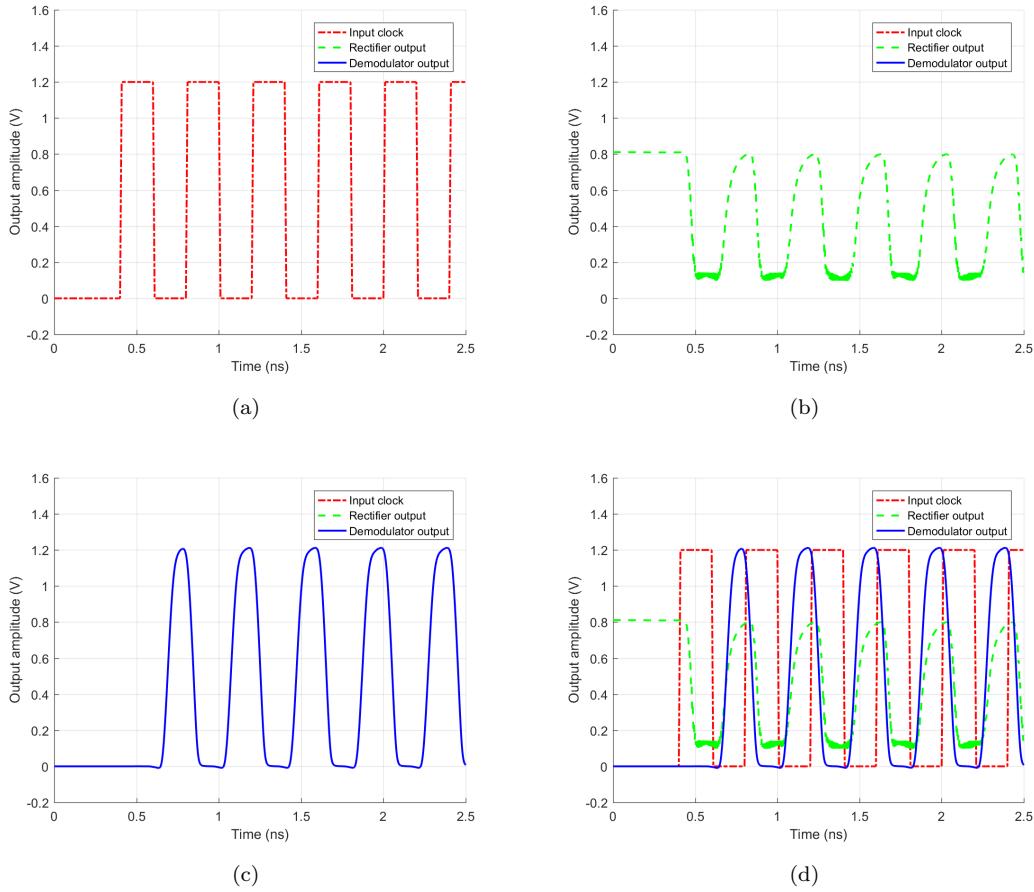

| 5.10 | Waveform of the (a) input 2.5 GHz nominal clock signal, (b) rectifier output with inverted signal polarization, (c) the full-swing demodulator output signal at 1.2 V and (d) effective signal stack-up. . . . .                                                                                                         | 96  |

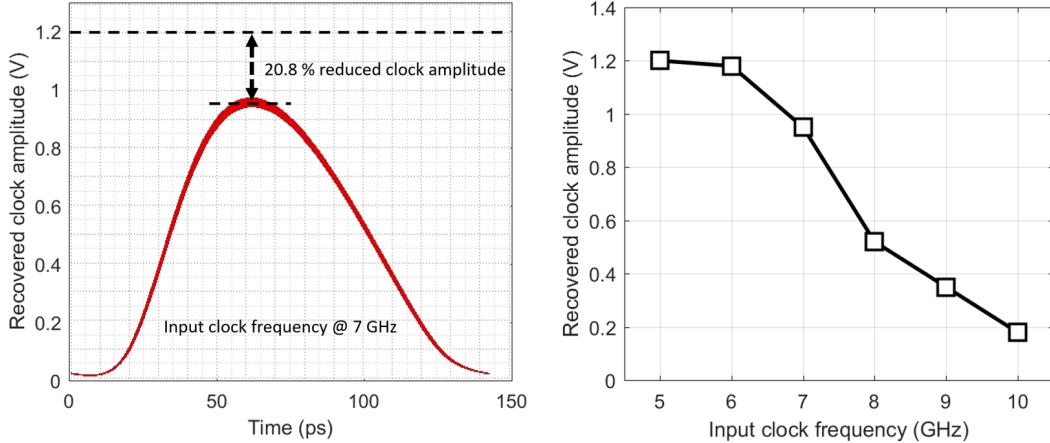

| 5.11 | Example of 7 GHz recovered clock signal with 20.8% reduced signal swing. Clock amplitude will keep degrading with the increase of input clock frequency, transistors in clock Rx circuit cannot switch on/off completely in a reducing clock cycle, hence generating attenuated recovered clocks. . . . .                | 97  |

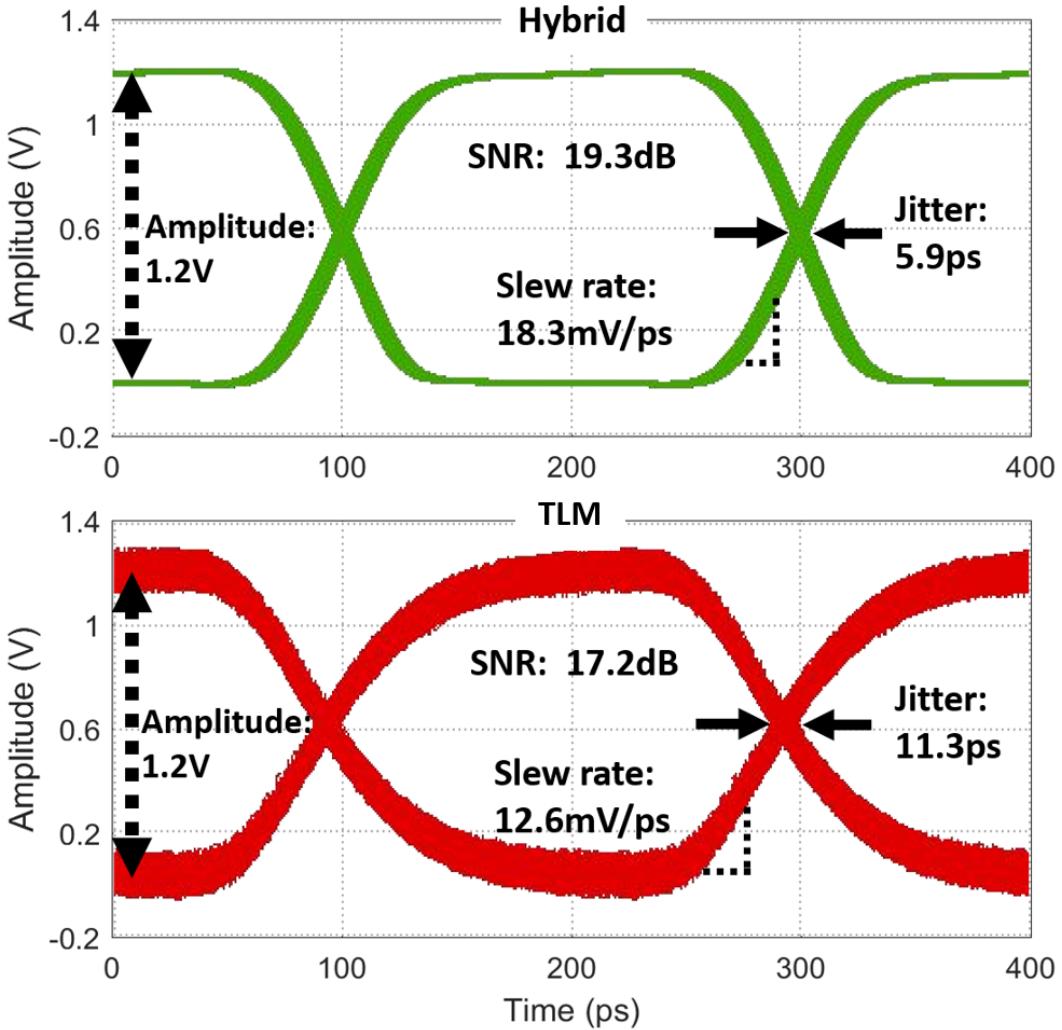

| 5.12 | Comparisons between the measured eye diagrams of the recovered clock signal from conventional wired global tree local mesh (TLM) CDN and our proposed wireless global CDN at 2.5 GHz, with robust eye height/clock amplitude around 1.2 V with 50 mV additive noise at the output of clock buffers. ©2021 IEEE . . . . . | 98  |

| 5.13 | Clock skew with a pseudo-mesh based topology at 2.5 GHz using 65 nm Technology. (a) An overall 16 fan-out architecture is adopted with an average skew reduction of 45.5% under random unbalanced load ranging from 10 fF to 500 fF, and (b) unbalanced load allocation (NBFS) for skew minimisation. . . . .            | 99  |

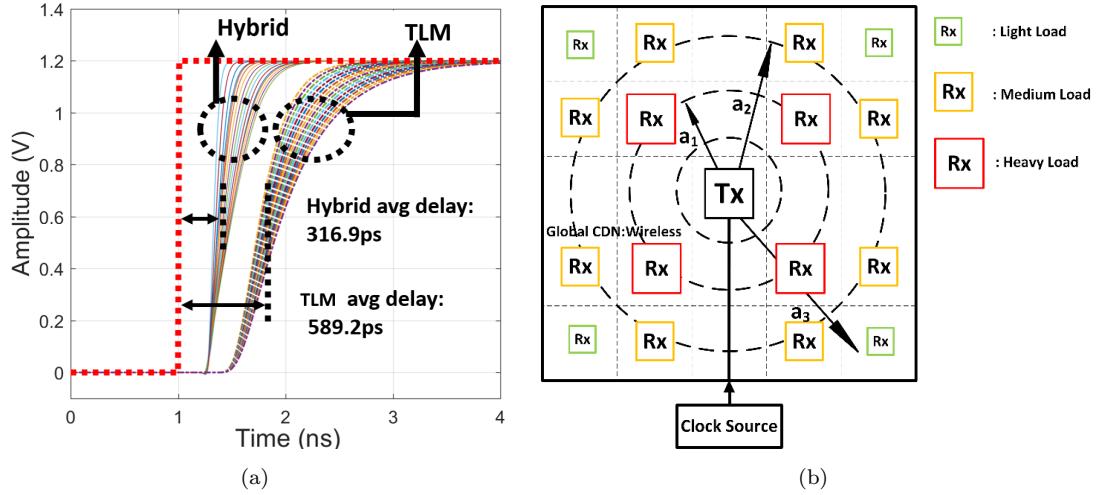

| 5.14 | Propagation delay comparison between H-tree and proposed wireless CDN. ©2021 IET . . . . .                                                                                                                                                                                                                               | 100 |

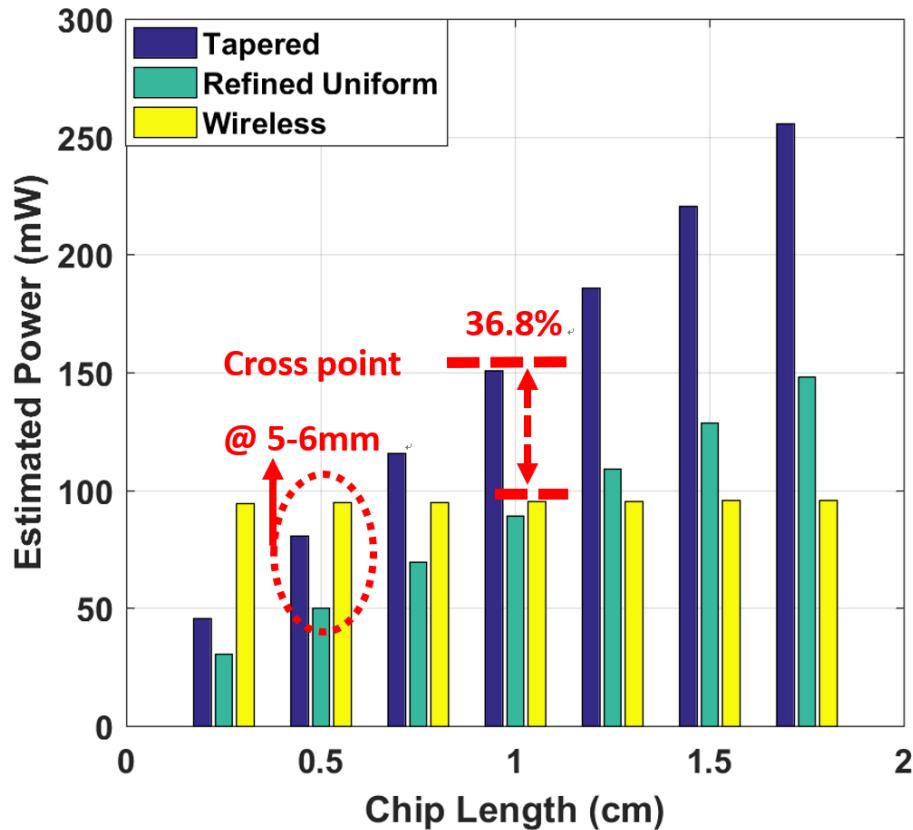

| 5.15 | Power comparison between global H-tree and proposed global wireless CDN. ©2021 IET . . . . .                                                                                                                                                                                                                             | 101 |

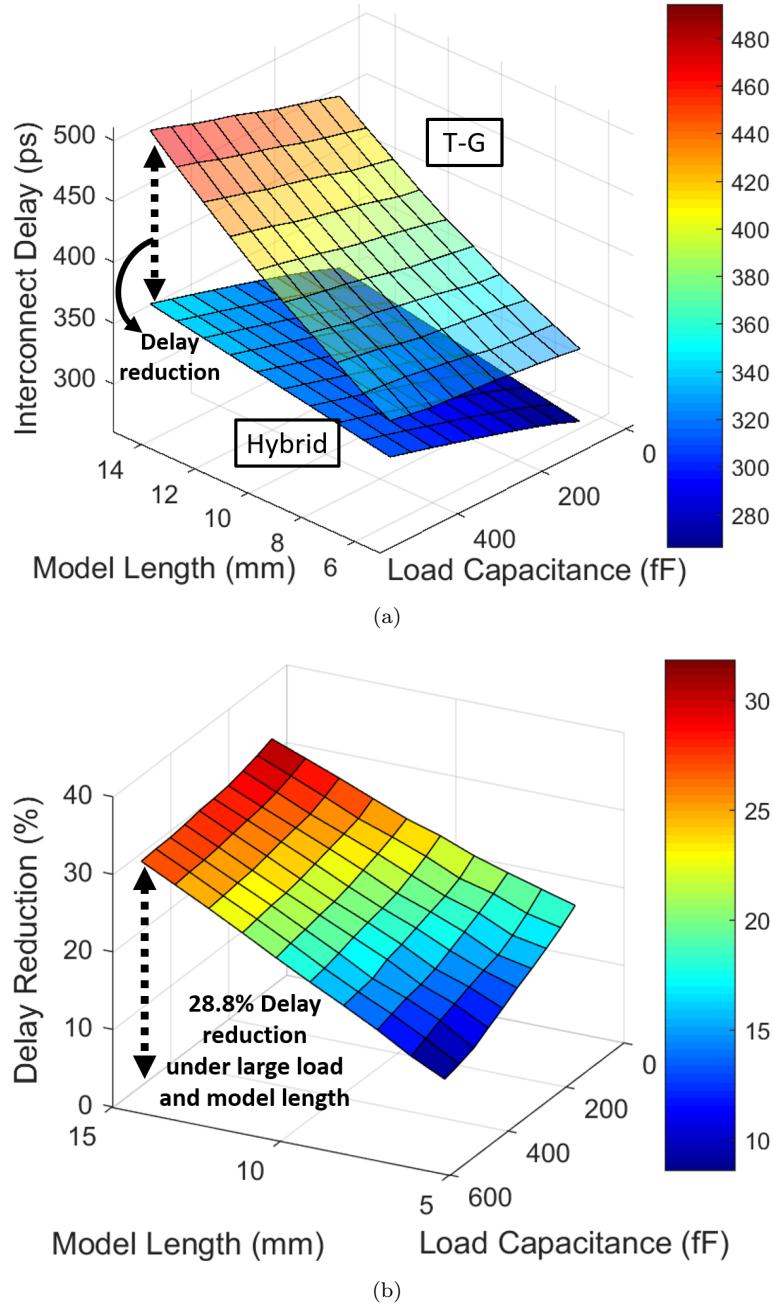

| 5.16 | Comparison between the TLM approach and the proposed hybrid architecture of (a) interconnect delay and (b) normalised delay reduction according to size and load variation with a maximum 28.8% decrease under a large model scale. ©2021 IEEE . . . . .                                                                 | 103 |

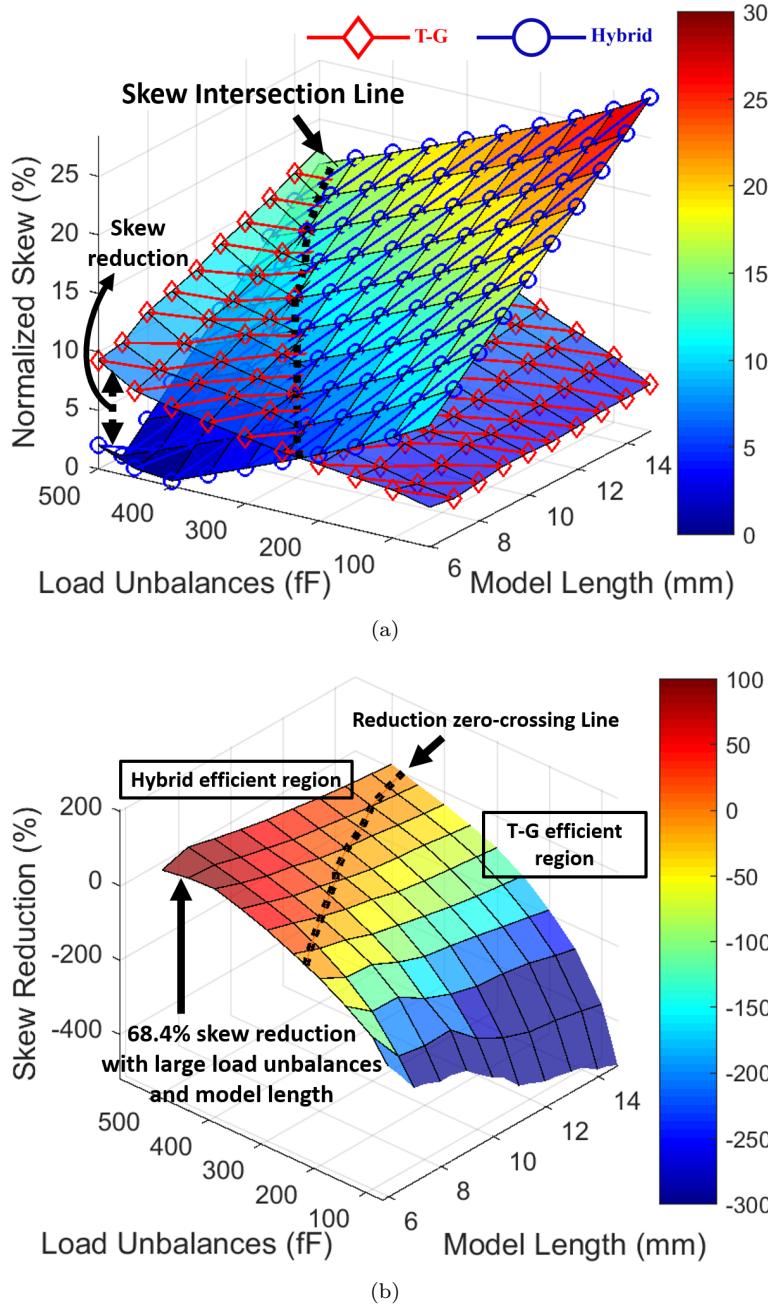

| 5.17 | Comparison between the TLM and the proposed hybrid architecture of (a) global clock skew and (b) normalised skew reduction according to size and load variation with a maximum 68.1% decrease under large load unbalance, within one clock domain. ©2021 IEEE . . . . .                                                  | 104 |

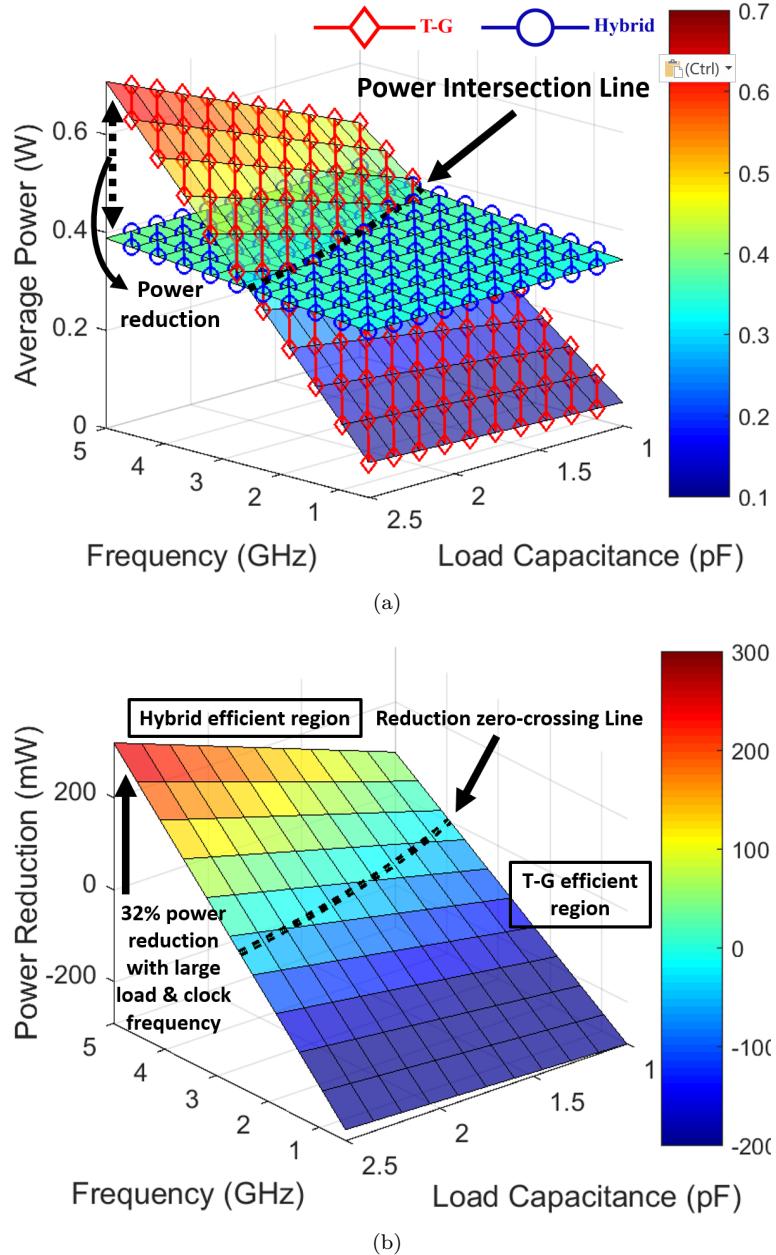

| 5.18 | Comparisons between the TLM approach and the proposed hybrid architecture of (a) overall power consumption, (b) power reduction according to local clock frequency and load variation with a maximum 32% decrease under large local clock frequency. ©2021 IEEE . . . . .                                                | 105 |

---

|      |                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

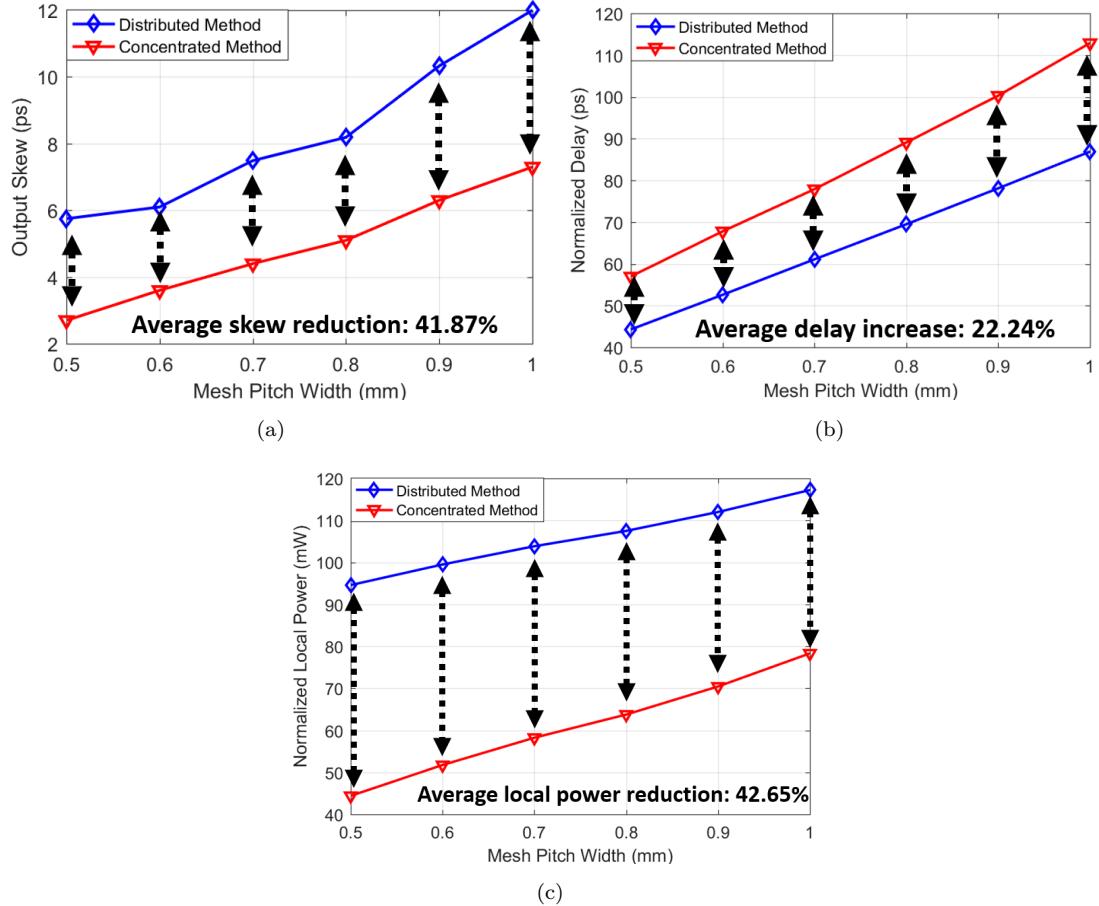

| 5.19 | Different parameters in terms of (a) output skew, (b) clock latency and (c) power consumption in the test case for both distributed and concentrated planning. Concentrated planning trade higher propagation delay with better skew and power performance using coupled model. . . . .                                                                                                                           | 106 |

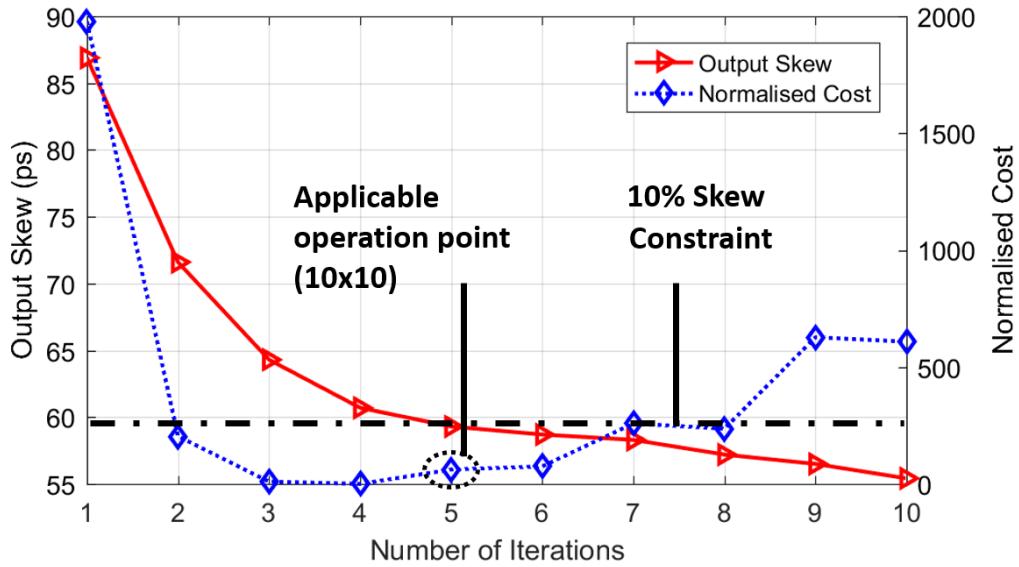

| 5.20 | Total skew and normalised cost in the local region with increasing iterations. ©2021 IEEE . . . . .                                                                                                                                                                                                                                                                                                               | 107 |

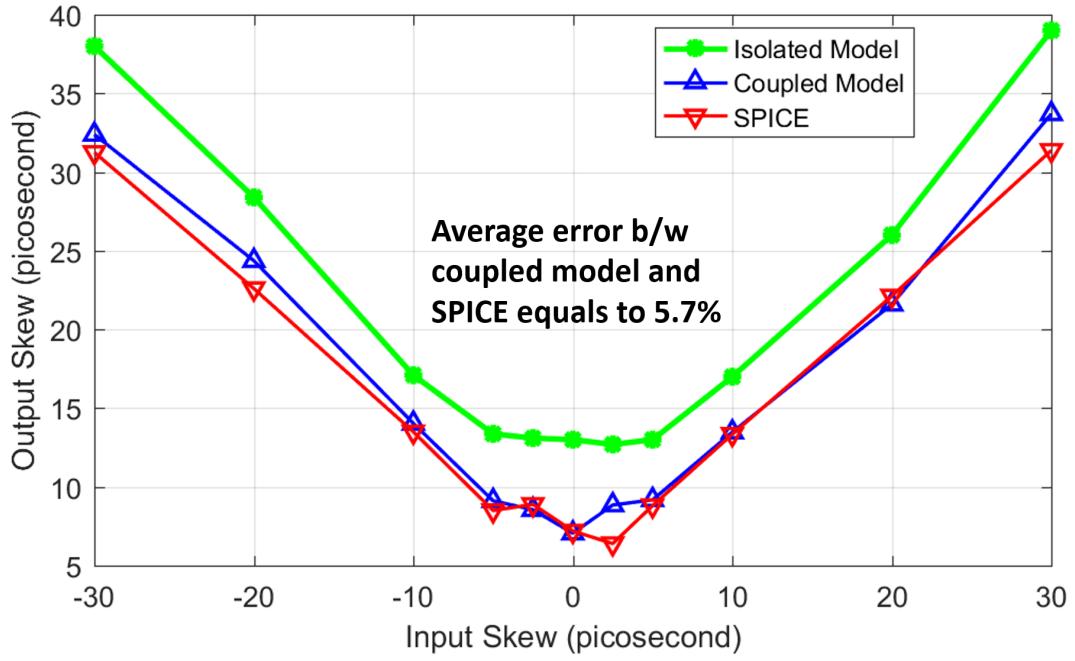

| 5.21 | Output skew in local CDN under different input global skew caused by different communication distance or buffer mismatch. The coupled model shows an average 5.7% error comparing to SPICE simulation. ©2021 IEEE                                                                                                                                                                                                 | 108 |

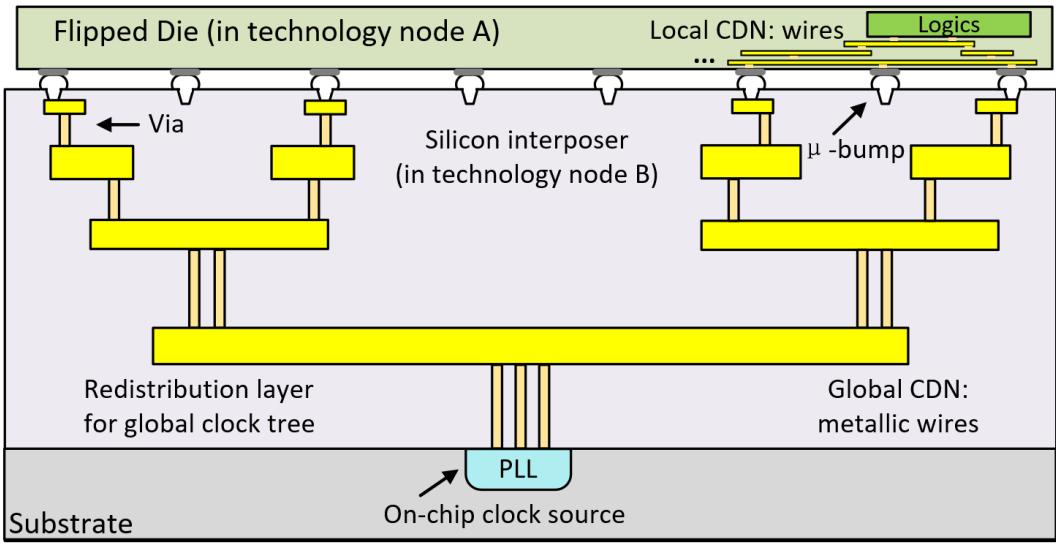

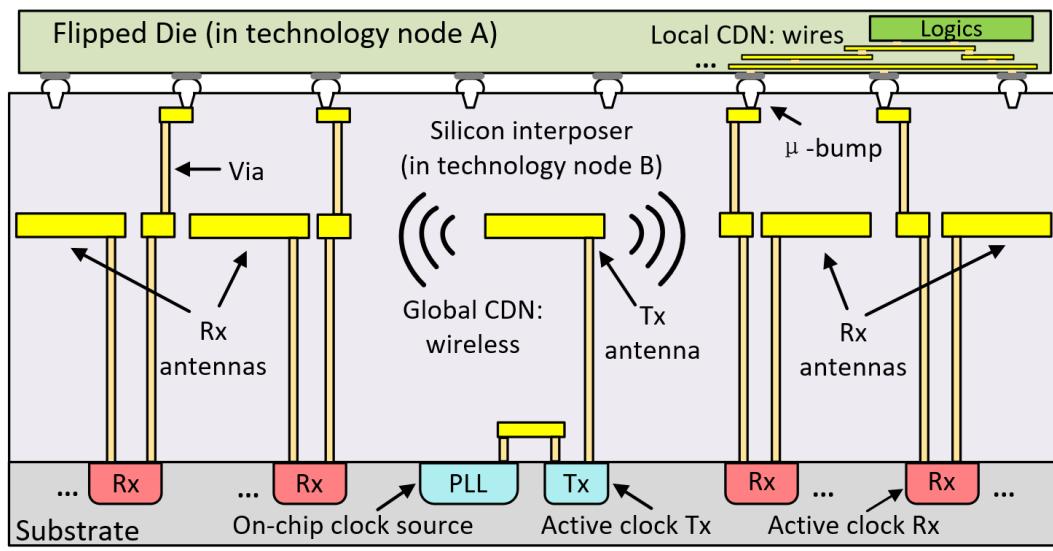

| 6.1  | Models of a typical conventional global-tree local-mesh structure with (a) top view, (b) cross-sectional view, which consumes a large amount of metal. The flipped die could use a different technology node than the active silicon interposer, e.g. the flipped die is in 7 nm process and the interposer is in 65 nm process, which provides flexibility to the integration of different technologies. . . . . | 112 |

| 6.2  | Models of our proposed hybrid clock distribution network, with (a) top view and (b) cross-sectional view, respectively. The flipped die could use a different technology node than the active silicon interposer, e.g. the flipped die is in 7 nm process and the interposer is in 65 nm process, which provides flexibility to the integration of different technologies. . . . .                                | 113 |

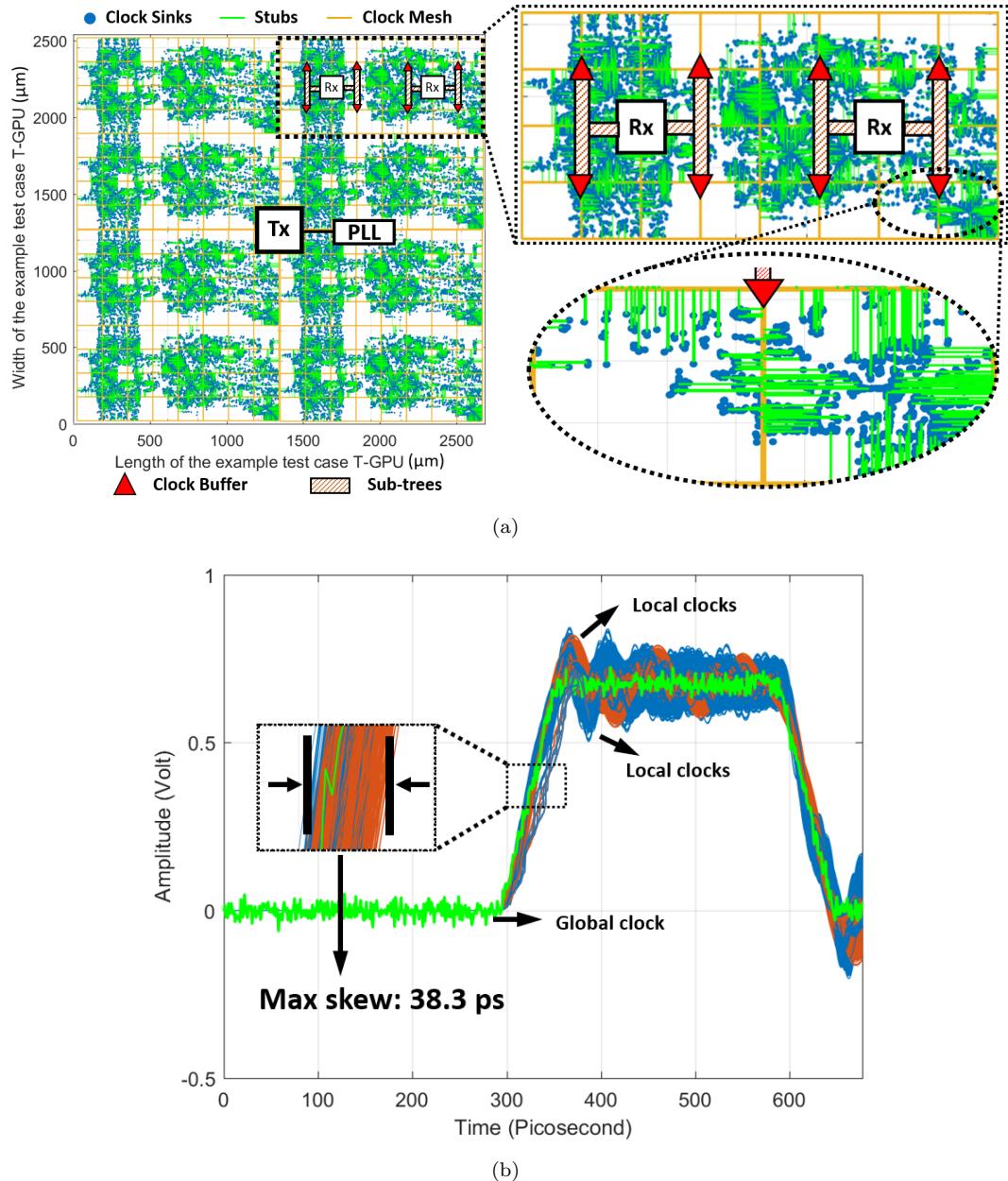

| 6.3  | Unevenly distributed test case $T_{GPU}$ extracted from Arm Mali-G77 GPU with (a) an example top view and (b) time-domain responses for $T_{GPU}$ with 1.7 GHz recovered global clock input in an 8-core system. ©2021 IEEE                                                                                                                                                                                       | 115 |

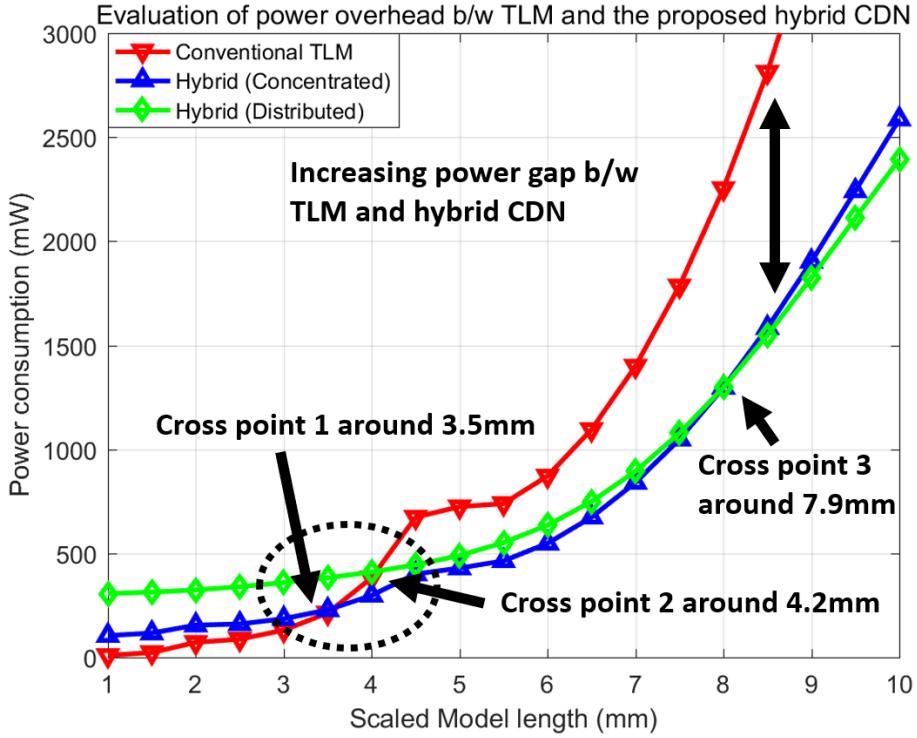

| 6.4  | Power output in local region with incremental iterations in the proposed test case $T_{GPU}$ , with an wireless/wire crossing point near 3.5 mm. . . . .                                                                                                                                                                                                                                                          | 118 |

# List of Tables

|     |                                                                                                                                                      |     |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Interconnect parameters for global and local wires from 180 nm process to 7 nm process in terms of both resistance and capacitance per unit length.  | 25  |

| 2.2 | Qualitative analysis of the CDN using the conventional and emerging interconnect techniques. . . . .                                                 | 34  |

| 5.1 | Comparisons between different implementation of the wireless transmitter in related researches and our proposed LCM-based clock transmitter. . . . . | 94  |

| 5.2 | Comparisons between different implementation of global CDNs using wire and wireless approaches . . . . .                                             | 99  |

| 6.1 | Overall CDN Performance Comparison for Test Case $T_{GPU}$ using Concentrated Receiver Planning . . . . .                                            | 117 |

| 6.2 | Overall CDN Performance Comparison for Test Case $T_{GPU}$ using Distributed Receiver Planning . . . . .                                             | 117 |

# Nomenclature

|                           |                                                                                                      |

|---------------------------|------------------------------------------------------------------------------------------------------|

| $A_k$                     | Amplitude of the $k$ th-order harmonic of a Fourier series representation of the local clock signal. |

| $\alpha$                  | Coefficient for horizontal interconnect segment.                                                     |

| $\beta$                   | Coefficient for vertical interconnect segment.                                                       |

| $cent_a$                  | Centroid vector of sink set $a$ .                                                                    |

| $cent_b$                  | Centroid vector of sink set $b$ .                                                                    |

| $C_{\alpha,\beta,\gamma}$ | Cost coefficients for power, area and skew, respectively.                                            |

| $C_i$                     | Capacitance per unit length for interconnect segment $i$ .                                           |

| $C_L$                     | Lumped capacitive loading of local clock sinks.                                                      |

| $C_t$                     | Number of all clock endpoints within current TF zone.                                                |

| $D(i, j)$                 | 50% logic transition delay from point $i$ to point $j$ .                                             |

| $d_{m,n}$                 | An arbitrary clock sink in a $m \times n$ local mesh network.                                        |

| $e_a$                     | Edge length connecting set $a$ to its parent set.                                                    |

| $e_b$                     | Edge length connecting set $b$ to its parent set.                                                    |

| $G_i$                     | Admittance per unit length for interconnect segment $i$ .                                            |

| $H_i(s)$                  | Transfer function of the interconnect segment $i$ .                                                  |

| $Horz(i)$                 | Horizontal segment condition for the $i$ -th layer in a CDN.                                         |

| $I$                       | Iteration count to increment mesh cells in Algorithm 3.                                              |

| $I_{max}$                 | Max iteration count to avoid deadlock in Algorithm 3.                                                |

| $l_i$                     | Physical length of the interconnect segment $i$ .                                                    |

| $l_{ub}$                  | Overall interconnect length upper bound of a design.                                                 |

| $i_{max}$                 | Max iteration count to avoid deadlock in Algorithm 1.                                                |

| $index_a$                 | Index vector of sink set $a$ .                                                                       |

| $index_b$                 | Index vector of sink set $b$ .                                                                       |

| $L_i$                     | Inductance per unit length for interconnect segment $i$ .                                            |

| $N_0$                     | Root node of the given CDN.                                                                          |

| $n_b$                     | Number of neighbor meshes of an arbitrary mesh cell.                                                 |

| $num_x$                   | Number of single mesh segments in x direction.                                                       |

| $num_y$                   | Number of single mesh segments in y direction.                                                       |

| $PC_k$                    | Power cost evaluated by wire length for sink set $k$ .                                               |

| $P_i$                     | Power consumption of a single interconnect segment.                                                  |

| $P_{sum}$                 | Overall power consumption of a local network.                                                        |

---

|                             |                                                               |

|-----------------------------|---------------------------------------------------------------|

| $P_{ub}$                    | Overall power upper bound of a design.                        |

| $P$                         | Probability vector in $xy$ -cut procedures.                   |

| $P_x$                       | Probability interval vector in $xy$ -cut procedures.          |

| $R_d$                       | Output resistance of an arbitrary local clock buffer.         |

| $Re(Z_{in})$                | Real part of the complex input impedance.                     |

| $R_i$                       | Resistance per unit length for interconnect segment $i$ .     |

| $s_{m,n}$                   | An arbitrary clock source in a $m \times n$ local mesh.       |

| $sk_{ub}$                   | Overall skew upper bound of a design.                         |

| $T$                         | Period of the clock signal.                                   |

| $Vert(i)$                   | Vertical segment condition for the $i$ -th layer in a CDN.    |

| $v$                         | Velocity of the electromagnetic wave.                         |

| $WL_m(a, b)$                | Merging length of the sink set $m$ with subset $a$ and $b$ .  |

| $WL_s(m)$                   | Fusion length of the sink set $m$ .                           |

| $Z_{\alpha, \beta, \gamma}$ | Effective impedance for 3- $\pi$ interconnect model.          |

| $Z_d$                       | Effective output impedance of local buffer.                   |

| $Z_{in}$                    | Input impedance seen at an arbitrary local clock buffer.      |

| $Z_{load_i}$                | Effective load impedance at the end of interconnect $i$ .     |

| $Z_{o_i}$                   | Characteristic impedance of interconnect segment $i$ .        |

| $\delta$                    | Convergence coefficient for topology tree generation.         |

| $\gamma_i$                  | Propagation constant of interconnect segment $i$ .            |

| $\theta_{m,n}$              | Set of all unit mesh regions for a $m \times n$ mesh network. |

| $\tau$                      | Logic transition time of the clock signal.                    |

## **Acknowledgements**

I would like to thank my supervisor and friend, Dr Terrence Mak, for his support and invaluable guidance as well as our friendship through my PhD period. I have been extremely fortunate to have such supervisor who cared so much about my work and responded to my questions so promptly.

Also, I would like to offer my thanks to the staffs and students in CPS group, for their kind help and advice, which can always encourage me when needed. Finally, my wife and my parents have always been my strongest supporters. I am greatly thankful for their love, and I would like to dedicate this work to them.

*To my family and friends who always support me during these

meaningful and exciting years.*

# Chapter 1

## Introduction

Clock signal is the heartbeat of a chip. It is one of the most commonly adopted global signals in a synchronous system, served as a timing reference to control the timing behaviour of all sequential logic on a silicon die. To deliver the clock signal across the entire core area, a unique routing network is used, namely clock distribution network (CDN). Conventional CDNs adopt a tree or mesh-based topology to evenly deliver a global clock signal along the designated wires inside CDN to each of the local logic which requires a clock signal. Previously, the design of a CDN is less of an overall concern during the VLSI design stages, however, with the shrinking of the CMOS fabrication process, it now becomes one of the major challenges for very large scale integrated circuits (VLSI) designers.

With the fast development of technology, modern ICs have already beyond billion transistors scale. As the process technology scaling down, it becomes more and more sophisticated for chip designers to make trade-offs between power and system performance. In the state-of-art technology nodes such as 7nm or 5nm, dimensions of conventional metallic wires are getting smaller and raised a lot of new physical challenges. As the signal propagation delay has already exceeded circuitry gate delay, according to [1] and [11], the performance of interconnects inside an IC becomes the dominant factor which limits the performance of a chip. Hence, it is essential to consider the interconnect delay when designing a combination or sequential logic if there's any potential global signal, such as the clock signal input to this logic.

### 1.1 Challenges of the Conventional Interconnect

Different researchers such as [12] and [13], have suggested that the increasing RC characteristic of the interconnect has become the major constraint for clock distribution in synchronous VLSI systems, as the clock distribution network will consume more than

half of the overall power budget. Furthermore, another challenge is that the different arrival time of the clock signal (clock skew) significantly affects the timing performance of a synchronous system, especially for the logic cells which are correlated on the data path. Fixing timing convergence issues caused by clock skew via inserting clock buffers and delay elements in one region will result in new timing violations in other regions, thus producing design iterations and extra works. Major reasons for the time convergence challenge can be elaborated as follows:

1. The increasing propagation delay of the interconnect wires becomes the major delay contribution of the overall delay elements inside the chip, because of the increasing product of unit length resistance and capacitance. Since wiring density keeps increasing with the shrinking technology, space between interconnects is getting smaller, which will in turn, increases the coupling capacitance and cross-talk noise between wires. Besides, since the resistance per unit length of a conductor is inversely proportional to the cross-sectional area of an interconnect segment, the electron scattering effect [14], [15] of the thinner wires also leads to an increasing overall wiring resistance. Hence, for the first order approximation of the propagation delay of an interconnect segment, the delay constant  $\tau$  [14] essentially becomes bigger, thus limiting overall clock period between two subsequent sequential elements.

2. CMOS process variations are becoming unpredictable and difficult to control, as the physical size of the fabricated chips is approaching to their physical limit. For example, in the state-of-art 7nm process, the minimum interconnect pitch width is around  $0.03 \mu\text{m}$ . A slight fabrication variation near 2 nm will cause a  $\pm 7\%$  variation compared to the standard wire dimension, thus cause unnecessary signal distortion in this specific interconnect segment. In addition, the thickness of the gate oxide of a typical transistor is almost near the width of a few atoms. Even a slight change of one atom in width can cause different switching speed among all transistors, thus producing unpredictable circuit delays.

3. The ever-increasing clock frequency and design complexity, especially for high-performance systems, makes it difficult to get a positive slack during static timing analysis (STA) stage. Thus, designers need to spend more time on iteratively checking the timing constraints and the design itself.

From the above points, to provide an accurate timing reference for system timing convergence, it becomes one of the top challenges when designing a clock distribution network using the conventional interconnects. The basic structure of a conventional wire model is given as follows shown in Figure 1.1. As interconnect unit length resistance is inversely proportional to the cross-section area of a metallic conductor according to Equation 1.1, the shrinking wires essentially lead to a situation with increasing wire RC characteristics.

Figure 1.1: Simplified interconnect structure.

Wire delay, especially global interconnect suffers from this phenomenon significantly. Although there are several solutions trying to tackle out this problem, such as adopting new interconnect materials or inserting global repeaters to reduce the total length of the global wires, the overall delay gap between gate and wire delay is still increasing.

For normalised wire resistance according to 1.1, is can be given that:

$$R = \rho \cdot \frac{L}{A} = \rho \cdot \frac{L}{W \cdot H} \quad (1.1)$$

where  $\rho$  is the resistivity of a metallic conductor,  $L$  represent the total length of this wire and  $A$  denotes the cross-section area of the wire with the dimension of  $W$  as wire width and  $H$  as wire height. Hence, we could naturally get:

$$r_{wire} = \frac{\rho}{A} \quad (1.2)$$

where  $r_{wire}$  is the unit length resistance of the wire of interest.

Besides, to model the interconnect capacitance, it could be first simplified as a parallel plate capacitor model with dielectric material filled in between the two conductors according to Figure 1.2:

$$C_{wire} = W \cdot L \cdot \frac{\epsilon}{t} \quad (1.3)$$

where  $\epsilon$  is the dielectric constant of the dielectric material usually as  $SiO_2$ , and  $t$  is the spacing between the interconnect and the silicon substrate. With the CMOS technology node keeps shrinking, the wire capacitance should decrease as the width  $W$  decreases so that this could somehow reduce the interconnect capacitance so as to compensate the total wire delay caused by RC product. However, as the dimensions of the wire

Figure 1.2: Simplified interconnect structures with wiring capacitance.

are getting smaller with the increasing wire density, the  $W/H$  ratio has already dropped below unity as shown in Figure 1.2. Under such circumstances, the original parallel plate capacitor is no longer accurate to model the interconnect capacitance. As Figure 1.2 shown below, this situation will lead to a sidewall effect which the side of any interconnect conductor will generate a fringing capacitance and this value will contribute to the overall wire capacitance. For the system working on high frequencies, those parasitic may severely reduce system performance in terms of signal integrity, propagation delay, etc. Cross-talks between interconnects will also be a troublesome problem because the sidewall area of a wire is essentially larger than the bottom or top surface area and hence producing the dominant contribution to wire capacitance, therefore generating interference and noise thus lead to erroneous signal transfer. The total normalised signal propagation delay within a conductor could then be modelled as:

$$T_{pd} = \tau r_{wire} (L c_{wire} + C_{load}) = \tau^2 \frac{\rho}{H \cdot W} (c_{cross} + c_{fringing} + \frac{C_{load}}{L}) \quad (1.4)$$

where  $\tau$  is a conductor geometry-dependent constant,  $L$  is the total wire length,  $r_{wire}$  is the wire resistance per unit length,  $C_{load}$  is the load capacitance,  $c_{wire}$  is the total capacitance per unit length which consists of cross-talking capacitance  $c_{cross}$  and sidewall fringing capacitance  $c_{fringing}$  respectively. Using the above equation, we could consequently get the fact that the overall global signal propagation delay inside a metallic global interconnect keep increasing pseudo-exponentially as the geometry of the wire getting smaller. The above elaboration of the delay constant essentially presents the major reason for the increasing delay gap shown in Figure 1.3.

Besides, the increasing wire delay and chip density can also lead to larger global communication delay with the scaling up broadcast/multicast demands. The techniques utilised by modern many-core systems, such as cache-coherence protocol, will need to

Figure 1.3: The propagation delay vs shrinking technology node for transistor gate delay, local communication delay and global communication delay, respectively, according to [1].

send calculated or updated data to the remaining nodes and cores to maintain the coherence of data in all cores. Therefore, this situation generates an increasing hop count which leads to large data traversal time/delay and power consumption if a conventional duplicated unicast scheme is still adopted.

To sum up the above existing problems, conventional interconnects seem to have reached their bottleneck in some particular applications, because of the reduced size and the increasing new communication requirements. To optimise this limitation, novel interconnect techniques are now emerging to meet the needs of new design targets and tackle out the existing drawbacks. In order to better incorporate with the existing CMOS process, most of these newly developed interconnects are mostly CMOS compatible which means they could be directly fabricated via standard CMOS developing procedures. Other novel interconnect techniques require extra on-chip components such as wave guides, forking points, etc. Further details related to the emerging interconnects and their application as a component of the CDN will be given in Chapter 2.

Figure 1.4: Increasing interconnect delay within a specific 4-level H-tree network with (a) interconnect delay under different technology nodes using the same geometry, and (b) Increasing delay gap between 90 nm and 10 nm process. ©2021 IEEE

## 1.2 Motivations for the Proposed Hybrid Clock Distribution Scheme

### 1.2.1 The Impact of Wire Delay

A balanced clock distribution network (CDN) is one of the most essential applications of interconnects to propagate clock signals with equally wire delay inside a sequential system. Conventional CDN incorporates metal base wires with different topologies to achieve the highest clock frequency as well as the smallest clock uncertainty including clock skew and clock jitter. Typical CDNs such as X-tree or H-tree network which is similar to a folded binary tree, which fanout to two new branches with similar length, at each end of a tree segment.

For an ideal H-tree network, each route from the clock source to the sink is equal in length, therefore generating minimal clock skew [16], [17]. However, as the load on a realistic chip would not be spread evenly, there could be difference in terms of route length and capacitive loadings among the root and sink pairs, hence generating different propagation delay and subsequently, clock skew. In order to avoid any setup or hold violation leading towards metastability, a synchronous system need to select the worst-case propagation delay as the clock period. The clock skew will possibly limit overall system performance, as it affects the system setup/hold margin.

As a global signal, clock tree should use clock buffers to improve driven strength and compensate different route delay and signal decay. A large number of clock buffers will be added onto the clock route to meet the user-specified design target during clock tree synthesis, thereby increasing power consumption and area occupation.

Figure 1.5: A typical structure of (a) plan view of a conventional mesh-based CDN and (b)  $\pi$ -model of the mesh wires.

Clock latency is another issue to be considered about, as the delay from clock root to an arbitrary clock sink is also a target to minimise during clock tree synthesis (CTS) stage. Clock routes with longer length lead to higher performance degradation caused by on-chip variation (OCV). Also, the clock uncertainties are proportional to the overall clock delay. Hence to design a CDN with reasonable performance, modern EDA tools are treating the clock latency as one of the most important goals during CTS stage. As an example, the global clock distribution delay has almost doubled its value when distributing a unit step signal in a designated H-tree network in 10 nm process compared with the same geometry using 90 nm process, which is presented in Figure 1.4. Therefore, the conventional interconnect seems to be reaching its limit for high-frequency global communication requirements such as broadcasting clock signals, because of the increasing delay.

As shown in Figure 1.4 from [18], a comprehensive clock delay comparison is given by using Elmore delay on a 4-level 16-fanout H-tree topology with its terminals tied to several 10 ff capacitive loadings. This model has a wirelength of the clock tree ranging from 3.75 to 26.25 mm and clock buffers allocated at the branching point of each level. Under the assumptions that this H-tree is implemented using top metals to maintain relatively small clock latency, based on the data from Predictive Technology Model (PTM), the RC product for global communication in 90 nm node has almost doubled its value in the more advanced technology node in 10 nm [18]. Since the Elmore delay of an interconnect segment is proportional to the product of the unit length resistance and capacitance, the clock latency from the clock source to an arbitrary clock tree fanout will also increase to twice of its original value. Besides, an increasing delay gap between 90 nm implementation and the 10 nm implementation can be found with the increase of

the CDN wirelength, hence request a fine-grain design of the CDN for applications with tight latency constraint.

Clock mesh/grid is another solution which produces less clock uncertainty for a high-performance system. Shown in Figure 1.5, as a simple but efficient topology, clock grid is easy for designers to use and generate as a mesh-based interconnect work is implemented for global clock transmission typically using the top two metal layers. However, because of the wiring requirements, the characteristic of a clock grid will lead to a high power and area consumption when compared with H-tree or X-tree when the same synchronisation area requested. The requirement of clock straps will also increase the demand for routing resources. Spine-based CDN is the balance between binary trees and clock grid. As the global clock CDN is in the form of a spine, local CDN still need to be customised with either comb or tree structures.

### 1.2.2 Synchronisation in Modern Many-Core Systems

Modern many-core systems adopt GALS structure to provide a solution to clocking and synchronisation problems. Based on the key techniques used, GALS system can be identified into 3 different categories, namely pausable clock, asynchronous interface and loosely synchronous.

First of all, pausable clock exists among asynchronous blocks with uncertain clock relationships. It performs certain types of handshaking and simply delays or pauses the sampling clock edge in a clock domain after the arrival of valid data signals from another clock domain, thus mitigating metastability [19]. Some challenges in designing a pausable clock GALS system are related to the design of a ring oscillator with robust and promising performance [20], [21]. As the clock signal and clock generators are delayed and restarted subject to clock domain crossing requirements, the varying cycle-to-cycle clock jitter generated by the ring oscillator will be accumulated and propagated along the down stream clock network and further impact the timing margin. Therefore, the pausable clock technique remains to be a niche technique.

A fully-asynchronous system means the blocks belong to different clock domains with irrelevant clock frequency and phase information. This kind of GALS system requires synchronisation circuits (synchronisers, asynchronous bridges) to mitigate the impact of clock domain crossing. One of the major concerns of using an asynchronous interface is related to the modelling, validation and delay analysis of synchronisation circuits. [19] indicates a rule of thumb design standard that at least 40 gates delay should be reserved for a valid and stable CDC signal. Based on this rule, asynchronous GALS style can be used in applications that can tolerate extra synchronisation delay, or that have low clock frequencies, which is not the first choice for high-performance GALS design.

Another GALS type contains loosely synchronous interfaces. This type of the CDC interface can offer a better performance because of the reduction of handshaking circuits, thus providing improved delay [19], [22]. The loosely synchronised GALS itself can be divided into three groups, namely *mesochronous*, *plesiochronous*, and *heterochronous* [23], based on different frequency and phase relations between each block in the same system.

*Mesochronous* yields same operation frequency and unknown phase information among blocks. *Plesiochronous* offers the same nominal operation frequency for all blocks with minor random frequency variation, thus creating and accumulating phase drift. *Heterochronous* operates at different nominal frequencies with periodic phase relationships between each block, which is similar to generated clock in a synchronous design.

To sum up, GALS based many-core system offers flexibility of synchronisation at the cost of extra interfaces between blocks, especially for pausable clock and asynchronous GALS, which lead to inevitable delay and impact system throughput. Loosely synchronous can benefit from the reduce of synchronisation circuits thus providing better performance, but still, it will require a global clock (with arbitrary clock latency and without tight skew constraint) or multiple PLLs under the same operation frequency. With the scale of the GALS system keeps growing, the wiring delay of conventional interconnects will eventually generate more challenges, which will impact system performance and power.

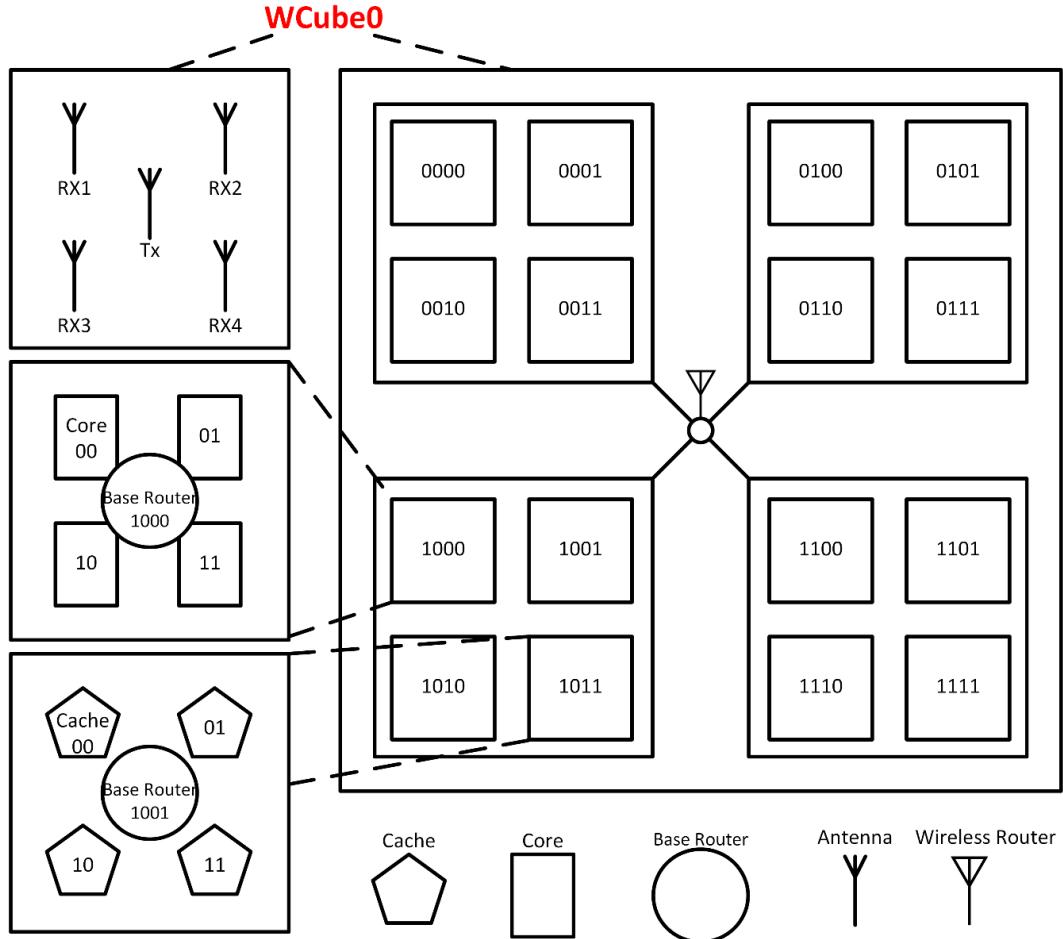

Alternatively, utilising the emerging interconnects as global distribution route of the CDN becomes available in recent decades. For instance, using optical or wireless interconnect including transmitter and receiver could effectively improve the performance and power consumption of CDN. As the radiated EM wave just need one hop from the source to the sink, overall signal propagation delay would be reduced rapidly. Moreover, taking advantage of the multicast feature, a wireless CDN becomes highly competitive comparing to conventional high-performance CDN with a much lower global power and global delay with moderate complexity overhead. However, similar to the spine or mesh-based CDN, the local network of wireless CDN also need to be customised manually. Further details of the novel interconnect and different clock distribution network would be given in Chapter 2.

Newly emerged interconnects in recent decades have significantly enlarged the area of application. Most of the developing interconnects are targeted at reducing multicast delay and enhancing fan-out architecture, which provides a positive potential to future many-core architecture that requires high speed and high-quality global communication. Hence, as shown in Figure 1.6, the proposed hybrid clock distribution network incorporates both a global-broadcasting-based interconnect with an integrated antenna inside the clock transmitter and receiver, and the conventional wire-based local network, such that the global delay and power can be potentially reduced significantly at the cost of moderate area and complexity overhead. This type of clock distribution can not only

Figure 1.6: The proposed hybrid clock distribution network which combines both global wireless interconnect and local metallic wires.

be applied to fully-synchronous systems but also a GALS structure with mesochronous clocking. It provides a global clock signal with significant reduced delay and improved energy efficiency, which can benefit the synchronisation of a many-core system.

Under the assumption that the radio-frequency signal can propagate through the antenna following a omnidirectional radiation pattern, the latency of the wireless transmission is proportional to the distance between the receiver(Rx) and transmitter(Tx). Hence, wireless TRx pairs need to be allocated well such that the difference in communication distances can be minimised.

For general applications such as only part of the chip needs to be synchronised, or the synchronisation area has a non-nominal shape, the location of the Tx can then be adjusted accordingly to maintain the relatively balanced feature. Locations such as the centre of mass of a 2D shape or even place the clock Tx off-chip can be used, to satisfy certain DRC or design specifications. An off-chip wireless clock can benefit from the power reduction of the wireless clock Tx. Also, since the area overhead for the clock Tx is no longer to be a limitation, the design of the wireless Tx and antenna can be refined to have better SNR performance, therefore increase the frequency of the propagated baseband clock signal. One penalty of this implementation is that the distances between the Tx and Rx array are not identical/symmetrical, therefore the global clock skew will increase due to unbalanced structure. Other Tx allocations such as above die allocation (in a 3-D IC) exhibits different attributes. Although the Tx can be allocated in a different tier to provide more flexibility and to satisfy certain design specifications such as balanced latency, this implementation will bring challenges that the RF signal needs to penetrate the silicon substrate and the bounding bumps. Partial

RF energy will be wasted, absorbed or reflected by the metallic material, therefore mitigating overall wireless clock SNR [24].

This thesis will focus on the clock distribution in a nominal synchronisation area. For a simplified experimental model with a square topology as shown in Figure 1.6, in order to have a balanced structure for similar transmission latency, the Tx is located at the centre of the chip and hence the delay can then be quantified using the radius of the global wireless EM signals to the Tx.

As an essential attribute of a CDN, for a fully-synchronous system, ideally the clock skew should be reduced to the minimum level where possible, to mitigate the negative impact of clock uncertainties on timing closure. Based on certain CTS algorithms, its possible to generate a zero-skew CDN. However, this comes with the cost of unnecessary resource waste such as excessive CDN wirelength, thereby occupying large chip area and generating large CDN capacitance. Taking advantage of the CAD support such as useful skew and concurrent clock and data optimisation (CCD) [25], [26], the constraint on clock skew has been relaxed in the recent decade. For high-performance VLSI design with high clock frequency, the global clock skew is set up to 10% of the overall system cycle time [27]. Hence, in this thesis, various implementations of the CDN are compared with a 10% skew upper bound, to observe the synchronicity of different solutions.

In conclusion, CDN using a novel interconnect instead of metal-based wires shows a promising prospect in terms of system performance improvement and power reduction. This research will investigate a hybrid wireless-wire architecture, which will adopt wireless interconnect during global clock distribution stage instead of wires.

### 1.3 Thesis Contributions and Structures

This thesis has proposed a low-delay and power efficient CDN design methodology, major contributions of which include:

1. A novel globally wireless CDN using wireless interconnect with efficient On-Off Keying (OOK) modulation with the advantage of efficiency and performance was proposed and it provides significant power reduction of up to 32%.

2. A novel local CDN wired CDN design algorithm which provides low-local skew and wiring usage.

3. An improved circuit for the leakage-canceling modulator with 47.1% improvement in on-off isolation and a non-coherent noise-compensated demodulator were proposed.

4. Reductions of up to 23.9%, 28.8% and 11.4%, for power, delay and skew, respectively using mathematical modelling with MATLAB and Cadence co-simulations, were identified in our proposed novel industrial test case with Arm Mali-G77 GPU.

The basic structure of this thesis will show a throughout study of the proposed hybrid clock distribution schemes. Details of each chapter is given by:

Exploring the conventional and newly emerged interconnects for CDN design, reviewing the existing literature about clock networks using high-speed wireless and optical CDN will be given in Chapter 2.

Design of the proposed system architecture, mathematical model construction for local wired CDN will be shown in Chapter 3.

Design of the proposed system in circuit-level components for transmitter and receiver respectively, as well as the design of proposed two on-chip meandering antennas with structure and Electromagnetic simulation model setup, will be given in Chapter 4).

Experimental results and evaluation of the overall system performance of distributing clock signal will be shown in Chapter 5.

A comprehensive test case is then presented to give a full evaluation of the proposed hybrid CDN, and to test whether it can work on realistic scenarios. These materials will be given in Chapter 6.

Lastly, Chapter 7 will conclude this thesis towards the completion milestone and the potential future works to further explore and optimise the proposed design.

In addition, published and the on-going works would be included, for the purpose of academic evaluation. Walking towards the completion milestone, progress to-date includes:

1. “On High-speed Clock Distribution Network Using Hybrid Wire-Wireless Interconnects”, Proceedings of Oxford Circuits and System Conference (OXCAS) 2017.

2. “Globally wireless locally wired (glowilow): A clock distribution network for many-core systems,” in IEEE International Symposium on Circuits and Systems (IS-CAS), pp. 1-5, May 2018.

3. “Hybrid interconnect network for on-chip low-power clock distribution,” IET Electronics Letters, vol. 55, no. 5, pp. 244-246, May 2019.

4. “An Active Silicon Interposer with Low-Power Hybrid Wireless-Wired Clock Distribution Network for Many-Core Systems”, in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 28, no. 9, pp. 2042-2054, September 2020.

5. “Energy-Efficient and Low-Skew 3D-KBP Algorithm for Clock Distribution Network Design in Many-Core 3-D Stacking Systems”, in IEEE Transactions on Computers, Special Issue on Communications for Many-Core Processors and Accelerators, October, 2020 (Major revision).

# Chapter 2

## Literature Review

This chapter will discuss and explore different types of clock distribution network (CDN) utilizing both conventional interconnect as well as newly emerged interconnects. These solutions will be compared through a qualitative analysis and the state-of-art interconnects will be used as the components of our proposed design.

The developing interconnect techniques have received great attention for the past few decades from researchers and engineers. For the consideration of high clock frequency and low clock uncertainty, various types of CDN using different topology have been developed. For conventional metal-based CDN, interference caused by crosstalk due to the scaling down technology, will consequently affect the quality of clock distribution, hence lead to unnecessary extra power and area dissipation. Thereby the mutual target for various newly emerged techniques is to reduce overall CDN power and area consumption caused by wiring issues [28], [29] and simultaneously remain rather low clock latency and uncertainties. These techniques are introduced as follows.

### 2.1 Reviewing of the Emerging Interconnect Techniques

First of all, various emerging interconnect techniques will be reviewed. The advantages and the drawbacks of these novel interconnects are then summarised to observe their potential of being used for on-chip global communication.

#### 2.1.1 Wireless Interconnect

Wireless interconnect is considered to be one of the most promising solutions to solve the above existing challenges for its developed background and CMOS compatibility. Under the help of matured RF technique applied to communication area as well as smaller CMOS technology nodes, chip designers could now design and implement a compact

Figure 2.1: Wireless interconnect with WCube as application [2]. Wireless interconnect serves as the global communication channel.

on-chip wireless system with competitive performance when compared with conventional metallic interconnects. This cost-effective alternative aims to integrate on-chip transceivers with antennas so as to propagate electromagnetic radiation in between silicon substrate and bottom ground plane with a rather high speed. The surrounding nodes could therefore retrieve the decayed EM wave and then do the amplification/demodulation so that the originally transmitted data could be recovered accordingly. The inherent fan-out feature of the EM wave propagation significantly enhances the broadcast performance because the idealised propagation without considering any nearby interference could be regarded as a 360-degree circular pattern, hence generating less delay for higher data transmission rate. Receiving nodes could be arranged in a form of any geometry depends on the system performance requirements and load capacitance.

Ideally, wireless interconnect has the potential to take the place of conventional metallic interconnect in some particular areas, especially under the circumstances of large multicast demands or global signal transmission, however, the on-chip antenna integration currently becomes the bottleneck of this technique. Some on-chip antennas suffer from relatively low efficiency because of their dimension such that part of the power would not

be radiated out into substrate. This phenomenon will need extra energy to compensate the power loss in order to maintain adequate signal power level.

Another issue is the lossy silicon substrate. Radiated energy would essentially be dissipated for some amount because of the material property of the silicon [8]. Hence similarly, extra energy is required to mitigate this power decay, such as using power amplifiers at the transmitter front-end.

Apart from power loss, nearby electromagnetic interference (EMI) is another important issue that needed to be carefully considered. Analog signals are considered to be more "fragile" than common digital signals with only two logic levels. Since most of the wireless interconnects incorporate analogue techniques to local digital IPs, any signal distortion, for instance, spikes, would essentially cause severe error thereby generating erroneous data bits to downstream logic cells. The nearby flopping signal edge would affect analogue signals because of cross-talk existing between the analogue trace and digital components. Therefore, robustness is of paramount importance when considering adopting wireless interconnect for on-chip communications.