## University of Southampton Research Repository

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given,

e.g.

Thesis: Author (Year of Submission) "Full thesis title", University of Southampton, name of the University Faculty or School or Department, PhD Thesis, pagination.

Data: Author (Year) Title. URI [dataset]

UNIVERSITY OF SOUTHAMPTON

FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

School of Electronics & Computer Science

# Silicon-based Ultrathin Layers for Hole-Selective Contacts in Silicon Solar Cells

by

Edris Khorani

Thesis for the degree of Doctor of Philosophy

December 2020

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

Electronics and Computer Science

Doctor of Philosophy

SILICON-BASED ULTRATHIN LAYERS FOR HOLE-SELECTIVE CONTACTS IN

SILICON SOLAR CELLS

by Edris Khorani

This thesis presents a collection of work investigating the optoelectronic properties of atomic layer deposited silicon nitride nanolayers as a hole-selective tunnelling layer in passivating contacts for silicon solar cells. We also look at forming p-type polycrystalline silicon as charge modulation layers for such contacts via hot wire chemical vapour deposition. Carrier-selective passivating contacts are currently the state-of-the-art in terms of exceeding current power conversion efficiency barriers in high performance solar cell architectures. To date, less success has been achieved with hole-selective contacts than with electron-selective contacts. In this thesis, we first study the growth quality of polycrystalline silicon films using a hot wire process. We optimise the morphological characteristics towards creating more uniform films that require minimal post-deposition heat-treatment. Following this, we investigate using ultrathin silicon nitride as a tunnelling layer that can both reduce parasitic losses associated with charge carrier recombination and promote hole transport. For the first time in literature, we present an experimental report on the band alignments at the SiN-Si heterojunction interface, showing favourability towards hole transport. We then look at contact formation using various metal electrodes on our heterojunction, studying the specific contact resistivity. Finally, we show the prospects of a poly-Si/SiN/Si heterocontact via Sentaurus TCAD, with direct comparisons of carrier tunnelling probability and tunnelling current in a tunnelling oxide passivating contact counterpart. For SiN and SiO<sub>2</sub> films of equivalent thickness, hole current densities are predicted to be at least ten times higher in SiN. This work takes important steps towards forming high-performance carrier-selective contacts that can be utilized in multiples avenues of photovoltaics research.

# Contents

|                                                                              |           |

|------------------------------------------------------------------------------|-----------|

| <b>List of Figures.....</b>                                                  | <b>9</b>  |

| <b>List of Tables .....</b>                                                  | <b>13</b> |

| <b>Publications .....</b>                                                    | <b>14</b> |

| <b>Declaration of Authorship.....</b>                                        | <b>15</b> |

| <b>Acknowledgements .....</b>                                                | <b>16</b> |

| <b>Introduction.....</b>                                                     | <b>18</b> |

| <b>1.1    Motivation for Photovoltaics.....</b>                              | <b>18</b> |

| <b>1.2    Thesis outline.....</b>                                            | <b>22</b> |

| <b>Photovoltaic device characteristics &amp; typical Si solar cells.....</b> | <b>25</b> |

| <b>2.1    Fundamentals of solar cell operation .....</b>                     | <b>25</b> |

| 2.1.1    Silicon Semiconductor Properties.....                               | 25        |

| 2.1.2    P-N Junction Silicon Diodes and Charge Extraction.....              | 28        |

| 2.1.3    The Photovoltaic Effect and Solar Cell Operation .....              | 31        |

| 2.1.4    The Theoretical Power Conversion Efficiency Limit.....              | 35        |

| 2.1.5    Silicon Passivation .....                                           | 37        |

| <b>2.2    Silicon Photovoltaics – Past, Present &amp; Future .....</b>       | <b>40</b> |

| 2.2.1    Screen-printed and Al-BSF Solar Cells .....                         | 40        |

| 2.2.2    Passivated emitter rear-contact solar cell.....                     | 42        |

| 2.2.3    Heterojunction and Buried contact solar cells .....                 | 43        |

| 2.2.4    Interdigitated back-contact solar cell .....                        | 44        |

| 2.2.5    Progress & future of Si solar cells .....                           | 46        |

| <b>Carrier-selective contacts .....</b>                                      | <b>49</b> |

| <b>3.1    Quantifying Carrier-selectivity.....</b>                           | <b>49</b> |

| <b>3.2    Carrier-selectivity via Heterocontacts.....</b>                    | <b>51</b> |

| <b>3.3    TOPCon and POLO .....</b>                                          | <b>54</b> |

| <b>3.4    Potential for SiN hole-selective contacts .....</b>                | <b>57</b> |

| <b>3.5    CVD processes for conductive layer formation.....</b>              | <b>59</b> |

| 3.5.1    PECVD .....                                                         | 59        |

| 3.5.2    HWCVD .....                                                         | 60        |

| <b>Experimental Methods .....</b>                                            | <b>62</b> |

| <b>4.1    Nanofabrication and processing methods.....</b>                    | <b>62</b> |

| 4.1.1    Hot wire chemical vapour deposition .....                           | 62        |

| 4.1.2    Plasma-enhanced atomic layer deposition .....                       | 63        |

| 4.1.3    Electron-beam evaporation .....                                     | 64        |

|                                                                      |                                                                               |            |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------|------------|

| 4.1.4                                                                | Rapid thermal annealing .....                                                 | 65         |

| 4.1.5                                                                | Wafer cleaning and wet chemical etching .....                                 | 66         |

| 4.1.6                                                                | Photolithography.....                                                         | 66         |

| <b>4.2</b>                                                           | <b>Optoelectronic and morphological characterisation techniques .....</b>     | <b>67</b>  |

| 4.2.1                                                                | Raman spectroscopy .....                                                      | 67         |

| 4.2.2                                                                | Scanning electron microscopy and X-ray diffraction .....                      | 68         |

| 4.2.3                                                                | Atomic force microscopy .....                                                 | 69         |

| 4.2.4                                                                | Transmission electron microscopy and selective-area electron diffraction..... | 69         |

| 4.2.5                                                                | X-ray photoelectron spectroscopy .....                                        | 70         |

| 4.2.6                                                                | Secondary ion mass spectrometry.....                                          | 71         |

| 4.2.7                                                                | Spectroscopic ellipsometry .....                                              | 72         |

| 4.2.8                                                                | Photoconductance lifetime.....                                                | 73         |

| 4.2.9                                                                | Current-voltage measurements .....                                            | 73         |

| <b>4.3</b>                                                           | <b>Device simulation methods.....</b>                                         | <b>74</b>  |

| 4.3.1                                                                | Quokka 2 .....                                                                | 74         |

| 4.3.2                                                                | EDNA 2 .....                                                                  | 75         |

| 4.3.3                                                                | TCAD.....                                                                     | 75         |

| <b>P-type Polycrystalline Silicon formation via HWCVD.....</b>       |                                                                               | <b>76</b>  |

| <b>5.1</b>                                                           | <b>Introduction.....</b>                                                      | <b>76</b>  |

| <b>5.2</b>                                                           | <b>HWCVD deposition temperature configuration .....</b>                       | <b>76</b>  |

| 5.2.1                                                                | Tungsten filament configuration.....                                          | 77         |

| 5.2.2                                                                | Deposition temperature monitoring .....                                       | 78         |

| <b>5.3</b>                                                           | <b>Boron-doped silicon formation .....</b>                                    | <b>80</b>  |

| 5.3.1                                                                | HWCVD growth recipe .....                                                     | 80         |

| 5.3.2                                                                | Growth rate and thickness uniformity.....                                     | 81         |

| 5.3.3                                                                | Crystallinity of as-deposited films via Raman spectroscopy .....              | 82         |

| <b>5.4</b>                                                           | <b>Optimisation of post-deposition anneal process.....</b>                    | <b>84</b>  |

| 5.4.1                                                                | Re-crystallisation .....                                                      | 84         |

| 5.4.2                                                                | Topographical characterisation .....                                          | 86         |

| 5.4.3                                                                | Transmission electron microscopy imaging .....                                | 87         |

| 5.4.4                                                                | Selective area electron diffraction .....                                     | 89         |

| <b>5.5</b>                                                           | <b>P<sup>+</sup> doping evaluation .....</b>                                  | <b>90</b>  |

| 5.5.1                                                                | Dopant levels and diffusion .....                                             | 90         |

| 5.5.2                                                                | Saturation current and collection efficiency .....                            | 91         |

| 5.5.3                                                                | Emitter implications on cell performance .....                                | 93         |

| <b>5.6</b>                                                           | <b>Surface passivation .....</b>                                              | <b>97</b>  |

| 5.6.1                                                                | Passivation of p-type and n-type silicon using AlOx.....                      | 97         |

| 5.6.2                                                                | De-activation of intrinsic defects in FZ substrates .....                     | 99         |

| 5.6.3                                                                | Passivation of HWCVD junction.....                                            | 100        |

| <b>5.7</b>                                                           | <b>Dark current-voltage characteristics .....</b>                             | <b>101</b> |

| 5.7.1                                                                | Al metallization for current-voltage extraction.....                          | 102        |

| 5.7.2                                                                | 2-diode model fitting.....                                                    | 102        |

| <b>5.8</b>                                                           | <b>Conclusions.....</b>                                                       | <b>103</b> |

| <b>5.9</b>                                                           | <b>Contributions.....</b>                                                     | <b>104</b> |

| <b>SiN as Hole-Selective Nanolayers in Passivating Contacts.....</b> |                                                                               | <b>105</b> |

| <b>6.1</b>                                                           | <b>Introduction.....</b>                                                      | <b>105</b> |

|                                                                             |            |

|-----------------------------------------------------------------------------|------------|

| <b>6.2 ALD silicon nitride growth.....</b>                                  | <b>105</b> |

| 6.2.1 Cyclic SiN <sub>x</sub> ALD recipe.....                               | 106        |

| 6.2.2 BTBAS dosing time.....                                                | 107        |

| 6.2.3 Growth rate of ALD SiN <sub>x</sub> .....                             | 108        |

| 6.2.4 Thickness uniformity .....                                            | 109        |

| <b>6.3 Ultrathin ALD nitride properties .....</b>                           | <b>110</b> |

| 6.3.1 Refractive index .....                                                | 110        |

| 6.3.2 Atomic concentration ratio .....                                      | 111        |

| 6.3.3 Optical transmission & band gap .....                                 | 113        |

| <b>6.4 SiN<sub>x</sub>/Si band offset determination.....</b>                | <b>115</b> |

| 6.4.1 Krauts method for band offset determination .....                     | 115        |

| 6.4.2 Electron core level energy and valence band maxima determination..... | 117        |

| 6.4.3 SiN-Si band offsets .....                                             | 119        |

| <b>6.5 Understanding nanolayer degradation .....</b>                        | <b>120</b> |

| 6.5.1 Thickness alteration .....                                            | 120        |

| 6.5.2 Degraded SiN/Si band offsets .....                                    | 121        |

| 6.5.3 Chemical compositional ratio .....                                    | 123        |

| <b>6.6 Conclusions.....</b>                                                 | <b>124</b> |

| <b>6.7 Contributions.....</b>                                               | <b>124</b> |

| <b>Contact formation using SiN nanolayers .....</b>                         | <b>125</b> |

| <b>7.1 Introduction.....</b>                                                | <b>125</b> |

| <b>7.2 Contact resistivity .....</b>                                        | <b>125</b> |

| 7.2.1 Expanded Cox and Stack method .....                                   | 126        |

| 7.2.2 Al/p-Si contact resistivity .....                                     | 128        |

| 7.2.3 Al/SiN/p-Si contact resistivity .....                                 | 131        |

| 7.2.4 Limitations of Al for hole contacts .....                             | 135        |

| <b>7.3 Contact resistivity using Au .....</b>                               | <b>137</b> |

| 7.3.1 Au/p-Si contact resistivity.....                                      | 137        |

| 7.3.2 Au/SiN/p-Si contact resistivity .....                                 | 138        |

| <b>7.4 Silicon nitride nanolayers as hole selective contacts .....</b>      | <b>140</b> |

| 7.4.1 SiN electron hole tunnelling probability.....                         | 140        |

| 7.4.2 Tunnelling current via Sentaurus TCAD .....                           | 141        |

| <b>7.5 Conclusion .....</b>                                                 | <b>143</b> |

| <b>7.6 Contributions.....</b>                                               | <b>144</b> |

| <b>Conclusion and Outlook .....</b>                                         | <b>145</b> |

| <b>8.1 Key findings.....</b>                                                | <b>145</b> |

| <b>8.2 Research Outlook.....</b>                                            | <b>147</b> |

| 8.2.1 Silicon surface passivation using SiN nanolayers .....                | 147        |

| 8.2.2 IBC silicon solar cell with SiN hole-selective contacts .....         | 150        |

| <b>References.....</b>                                                      | <b>152</b> |

| <b>Appendix.....</b>                                                        | <b>165</b> |

| <b>9.1 Quokka (MATLAB) solar cell models .....</b>                          | <b>165</b> |

| 9.1.1 IBC silicon solar cell.....                                           | 165        |

| 9.1.2 HTJ silicon solar cell .....                                          | 167        |

# List of Figures

|                                                                                                                                                                                                                                                                           |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>Figure 1:</b> Illustration of valence and conduction bands in insulator, semiconductor and conductor materials.....                                                                                                                                                    | 26 |

| <b>Figure 2:</b> Energy band dispersion difference between direct and indirect band gap semiconductors.                                                                                                                                                                   | 27 |

| <b>Figure 3:</b> Schematic diagram of an intrinsic, n-type and p-type silicon crystal lattice.....                                                                                                                                                                        | 28 |

| <b>Figure 4:</b> (a) P-N junction at thermal equilibrium and (b) schematic band diagram of P-N junction under illumination at steady-state.....                                                                                                                           | 29 |

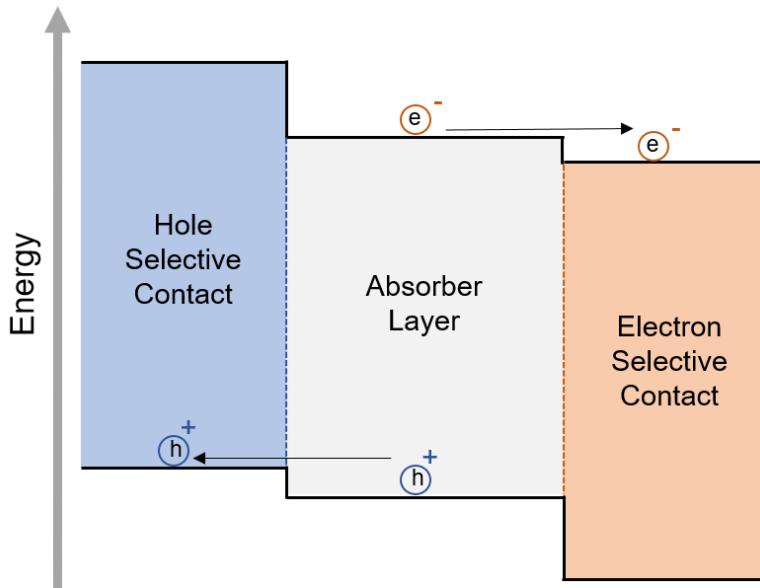

| <b>Figure 5:</b> Simplified band diagram of solar cell with hole-selective and electron-selective contacts.                                                                                                                                                               | 31 |

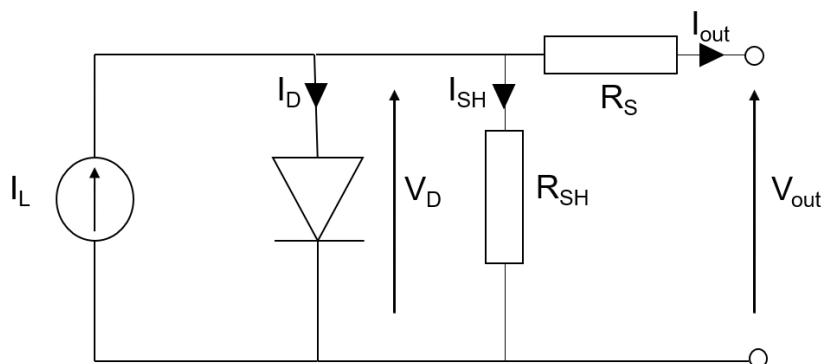

| <b>Figure 6:</b> Equivalent electrical circuit for solar cells.....                                                                                                                                                                                                       | 32 |

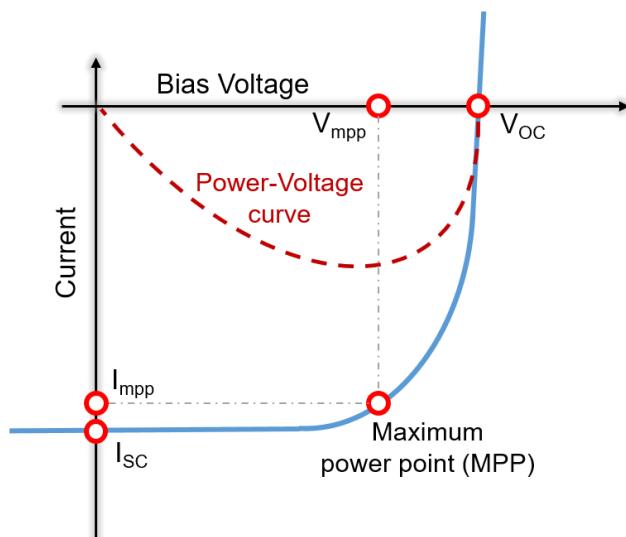

| <b>Figure 7:</b> Typical I-V characteristics of illuminated solar cell. Key characteristics identified – $V_{OC}$ is the open-circuit voltage, $I_{SC}$ is the short-circuit current, and $V_{mpp}$ and $I_{mpp}$ are the voltage and current at the maximum power point. | 34 |

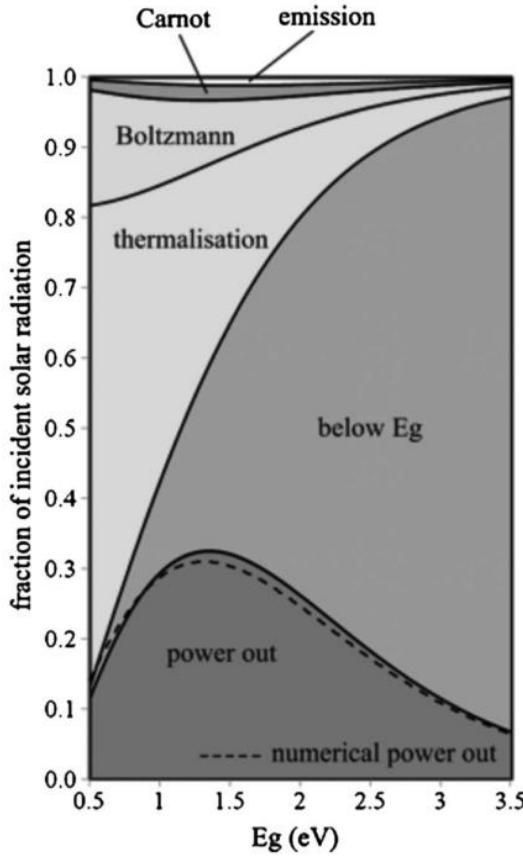

| <b>Figure 8:</b> Intrinsic losses of single junction solar cells, based on the Shockley-Queisser limit, taken from [18].                                                                                                                                                  | 36 |

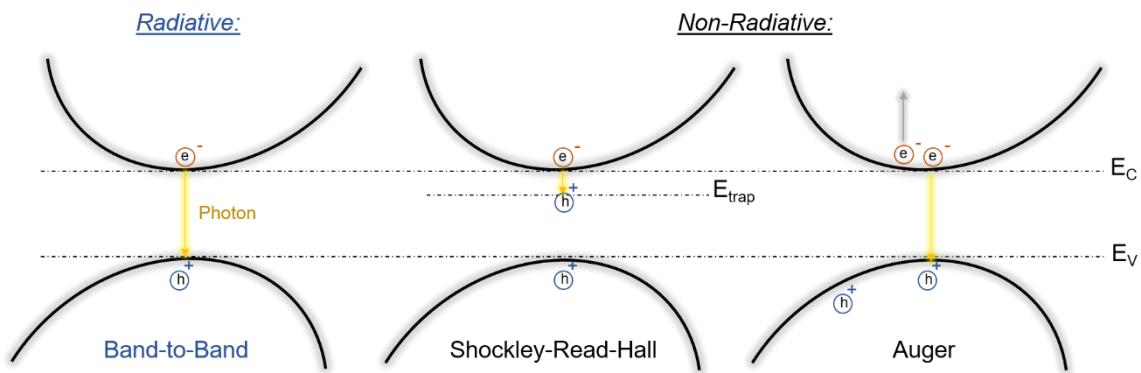

| <b>Figure 9:</b> Carrier energy band transition in (a) band-to-band recombination, (b) Shockley-Read-Hall recombination and (c) Auger recombination.                                                                                                                      | 37 |

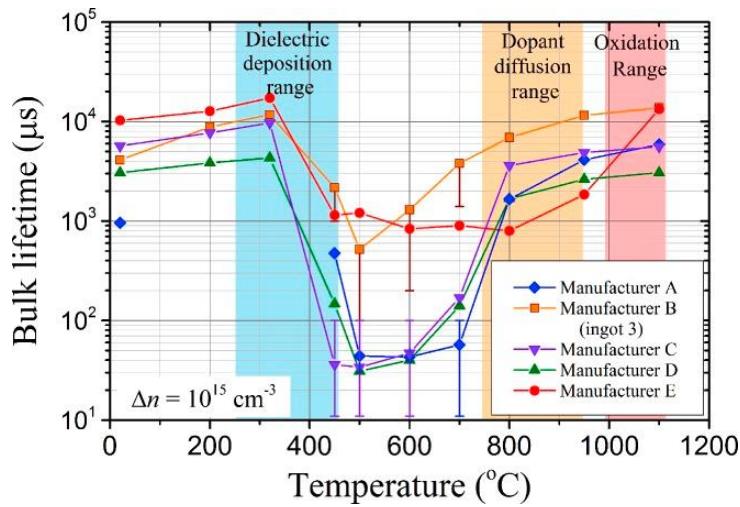

| <b>Figure 10:</b> Bulk carrier lifetime versus annealing temperature for five different FZ silicon ingots [44].                                                                                                                                                           | 39 |

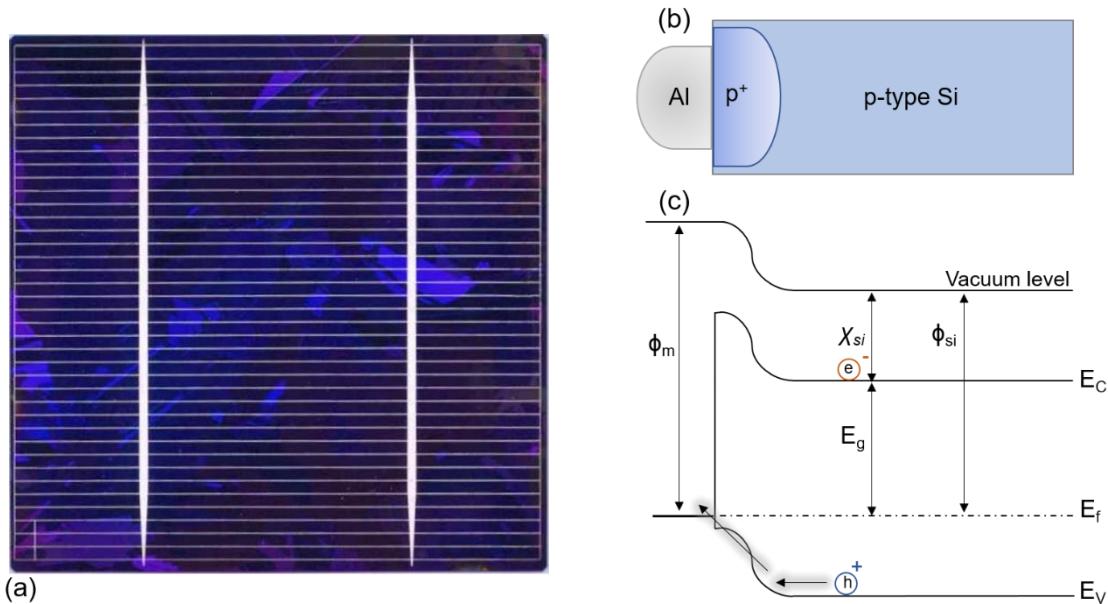

| <b>Figure 11:</b> (a) top-down photograph of screen-printed solar cell, (b) schematic of heavily-doped p-type contact and (c) electronic band diagram of contact.....                                                                                                     | 41 |

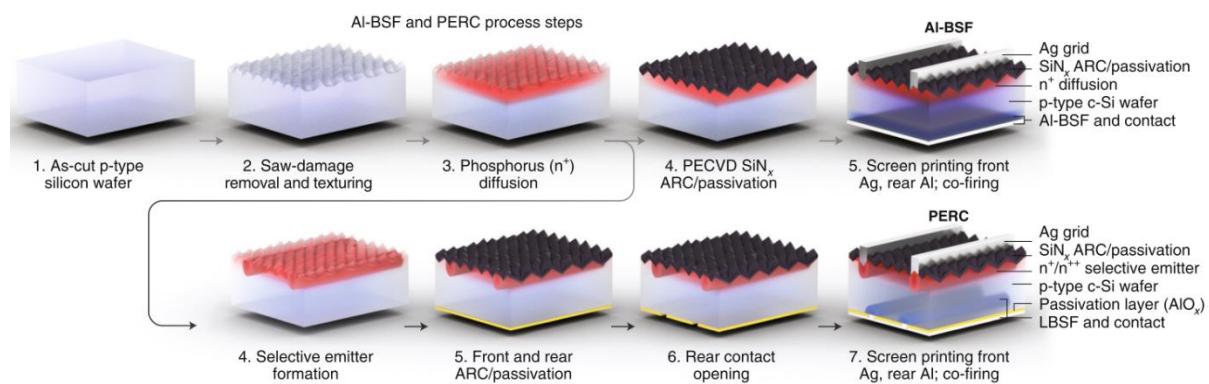

| <b>Figure 12:</b> Fabrication of Al-BSF and PERC cells [16].                                                                                                                                                                                                              | 42 |

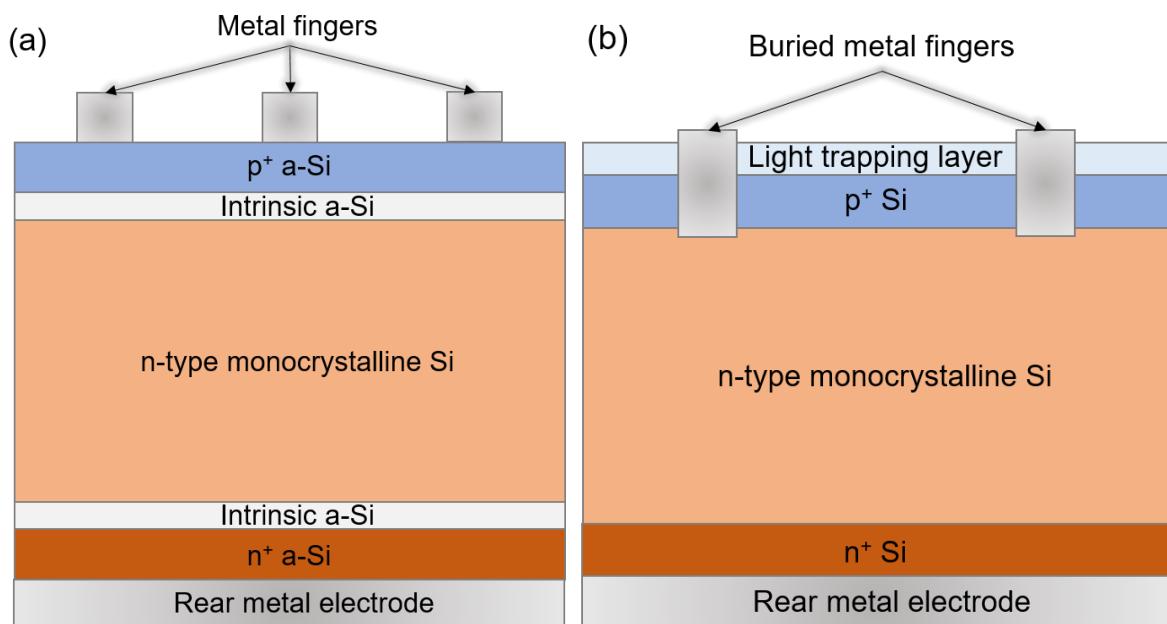

| <b>Figure 13:</b> Cross-section schematic of conventional (a) heterojunction with intrinsic layer and (b) buried contact silicon solar cells.                                                                                                                             | 43 |

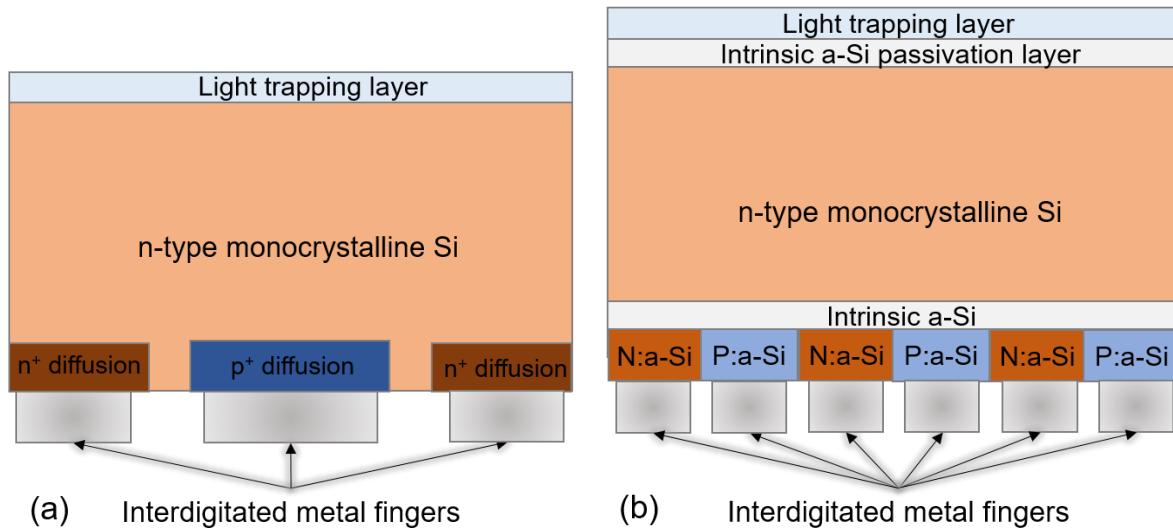

| <b>Figure 14:</b> (a) Generic diffused junction IBC and (b) SHJ-IBC solar cell.....                                                                                                                                                                                       | 45 |

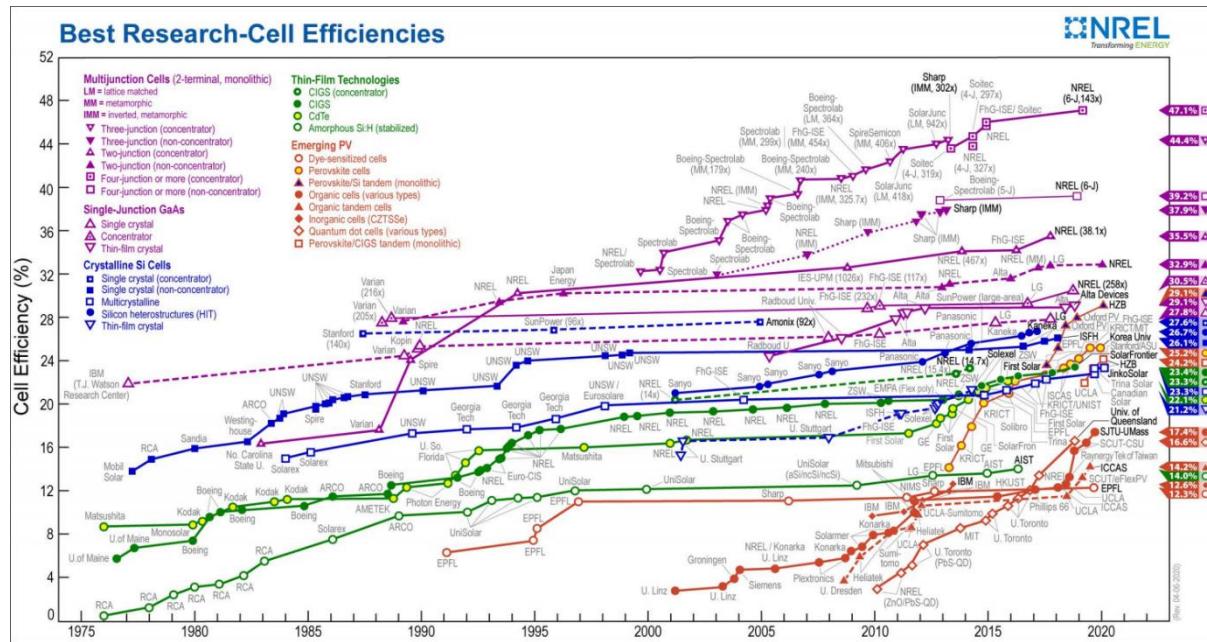

| <b>Figure 15:</b> Research-scale progress in power conversion efficiency of PV devices between 1976 and 2020 [10].                                                                                                                                                        | 47 |

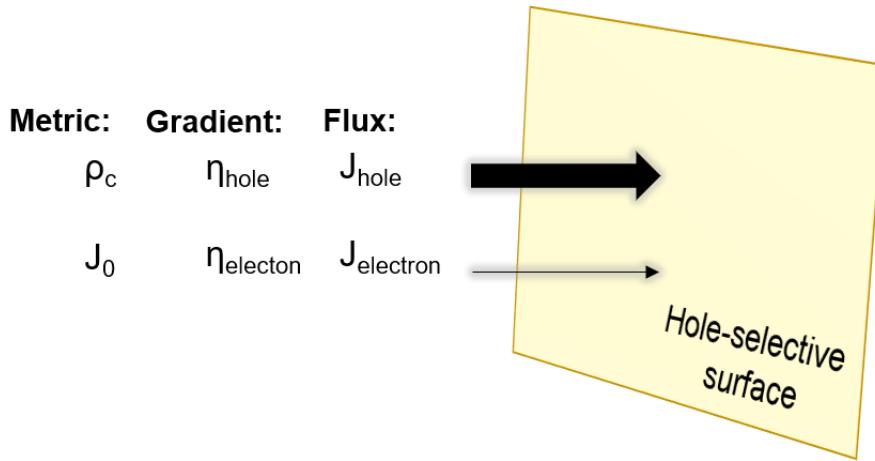

| <b>Figure 16:</b> Schematic representation of a hole-selective virtual surface.....                                                                                                                                                                                       | 50 |

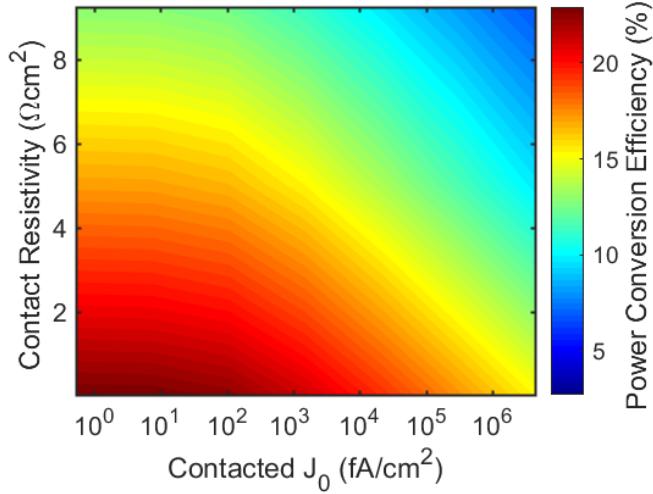

| <b>Figure 17:</b> Quokka simulation showing the impact of $J_0$ and $\rho_c$ on efficiency of an HTJ cell.....                                                                                                                                                            | 51 |

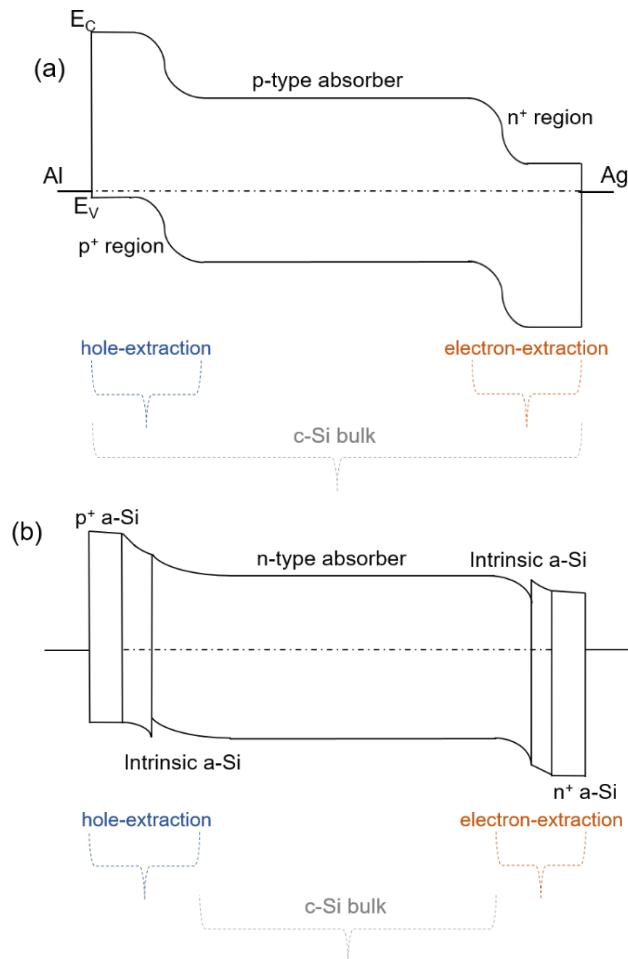

| <b>Figure 18:</b> Energy band diagram of conventional (a) p-type dopant diffused and (b) silicon heterojunction solar cell at thermal equilibrium.                                                                                                                        | 52 |

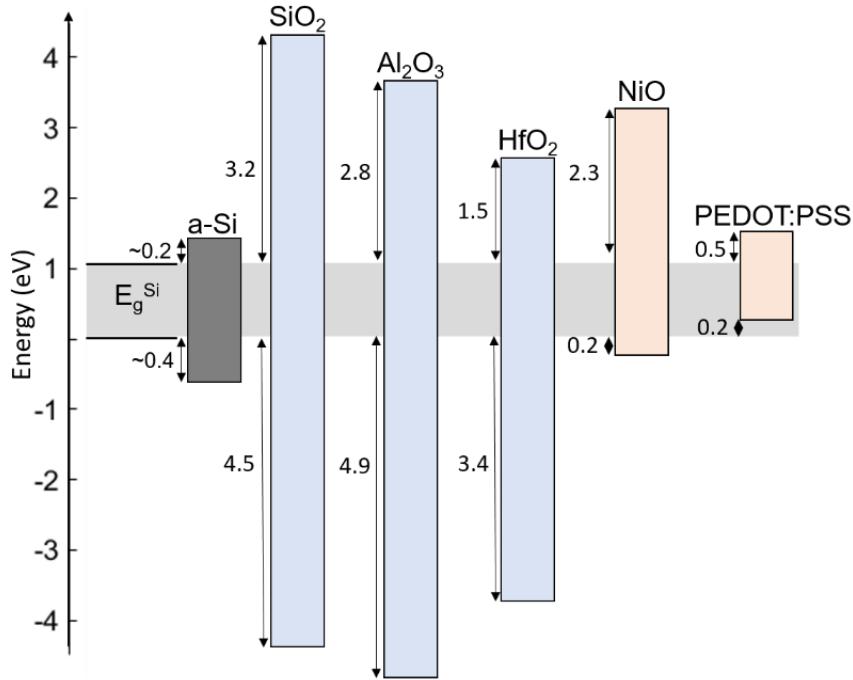

| <b>Figure 19:</b> Valence and conduction band offsets of various thin film materials with respect to c-Si [72]–[78].                                                                                                                                                      | 54 |

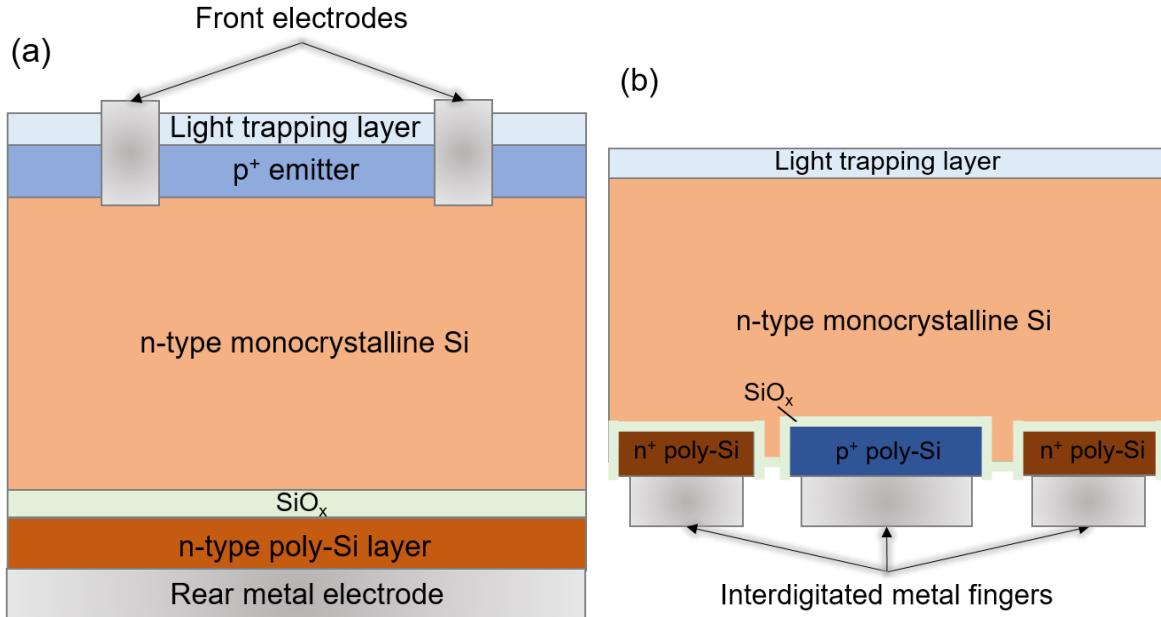

| <b>Figure 20:</b> Cross-sectional schematic of (a) typical TOPCon and (b) POLO-IBC solar cell.                                                                                                                                                                            | 56 |

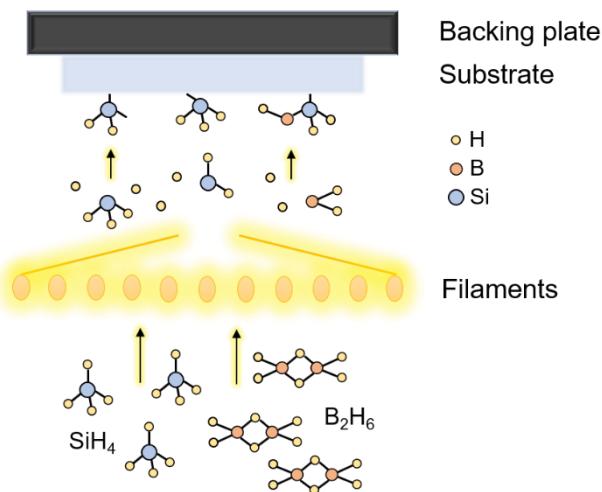

| <b>Figure 21:</b> Schematic diagram of catalytic dissociation of precursor molecules in HWCVD chamber.                                                                                                                                                                    | 63 |

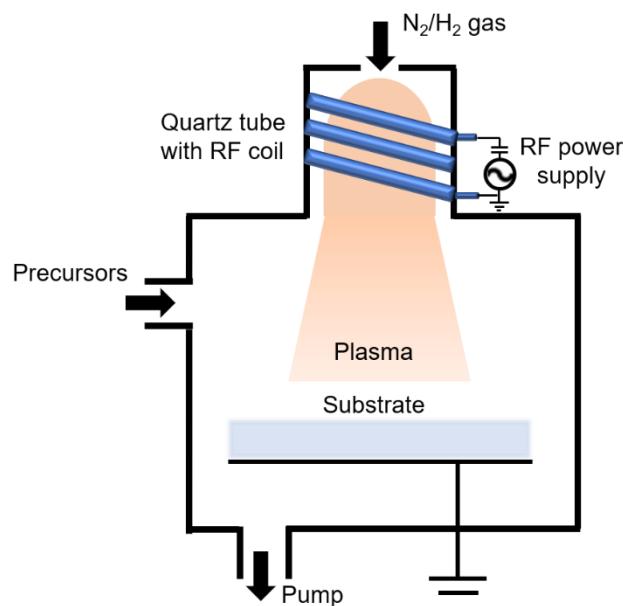

| <b>Figure 22:</b> Schematic diagram of plasma-enhanced atomic layer deposition chamber.                                                                                                                                                                                   | 64 |

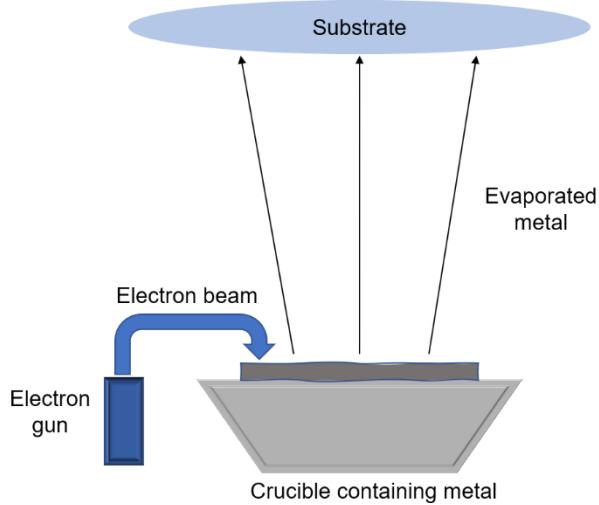

| <b>Figure 23:</b> Simplified illustration of E-beam evaporation process.                                                                                                                                                                                                  | 65 |

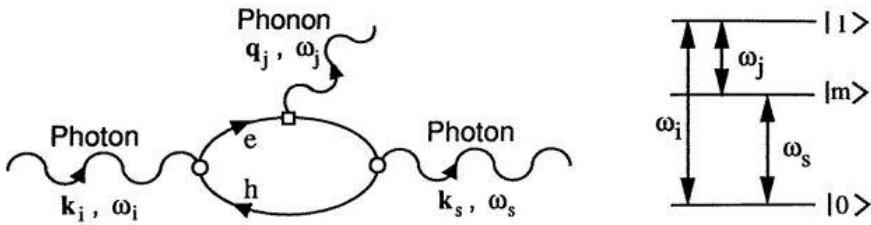

| <b>Figure 24:</b> Feynman diagram and energy levels for a first-order Stokes scattering process [108].                                                                                                                                                                    | 68 |

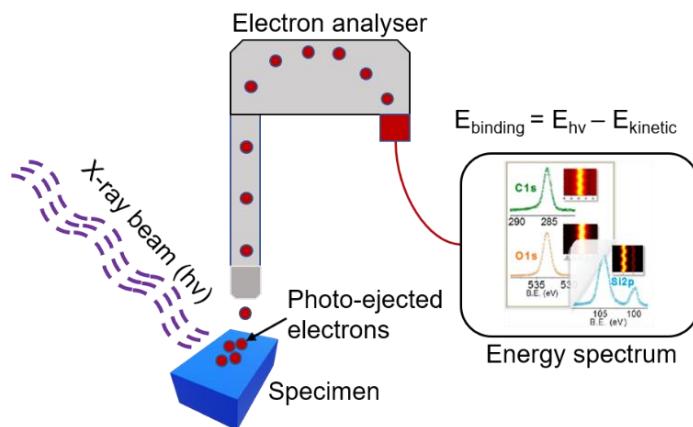

| <b>Figure 25:</b> Simplified illustration of X-ray photoelectron spectroscopy process.                                                                                                                                                                                    | 71 |

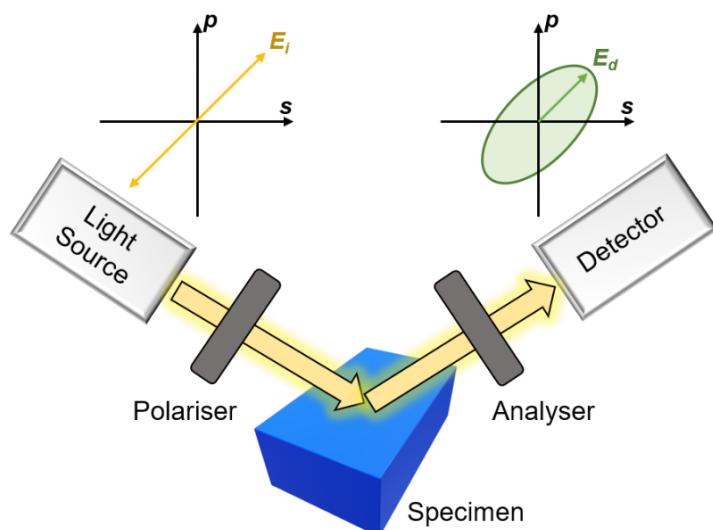

| <b>Figure 26:</b> Simplified schematic diagram of the operation of spectroscopic ellipsometry, showing the linear and circular polarisation of light at the light source and the detector ends respectively.                                                              | 72 |

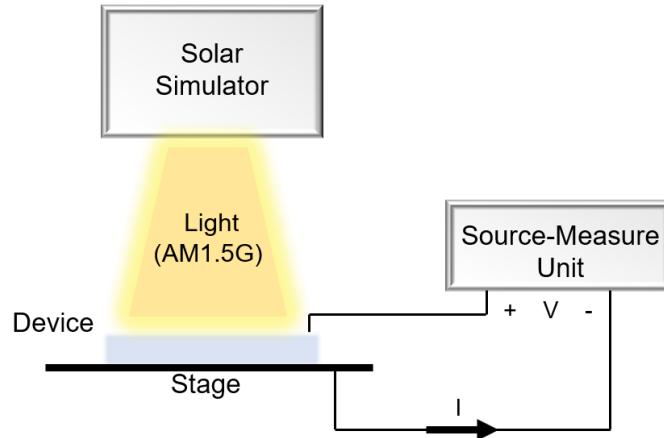

| <b>Figure 27:</b> Illustration of solar simulator set-up used for current-voltage extraction from PV devices.                                                                                                                                                             | 74 |

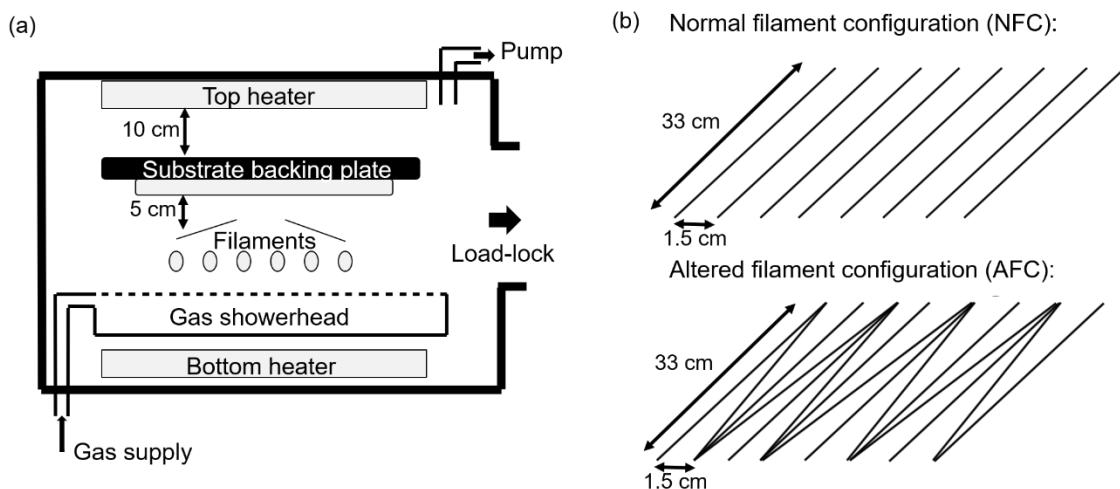

| <b>Figure 28:</b> (a) Schematic diagram of HWCVD chamber and (b) NFC and AFC Tungsten filament configurations.                                                                                                                                                            | 77 |

|                                                                                                                                                                                                                                                                                             |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

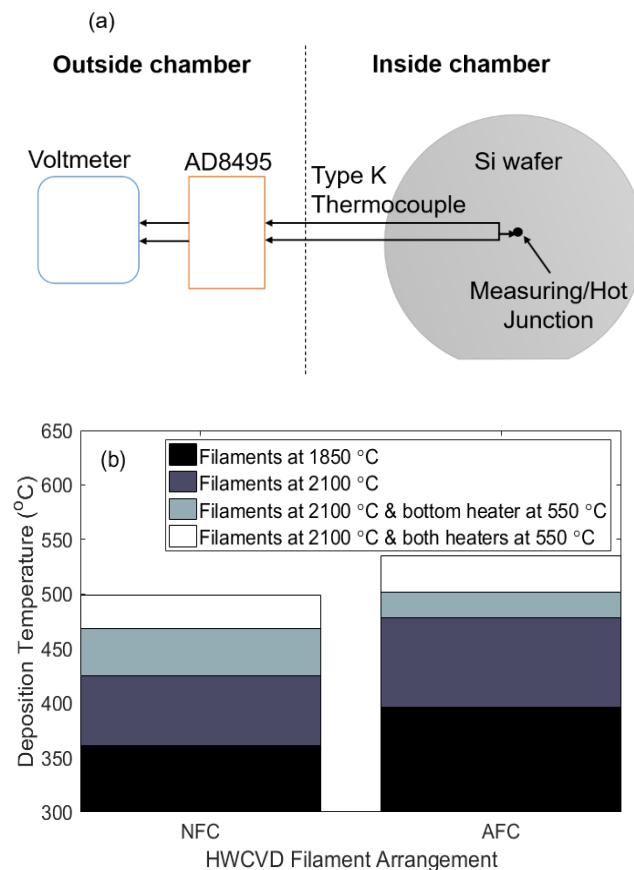

| <b>Figure 29:</b> (a) Diagram of deposition temperature measurement set-up and (b) measured deposition temperatures under NFC and AFC.....                                                                                                                                                  | 78  |

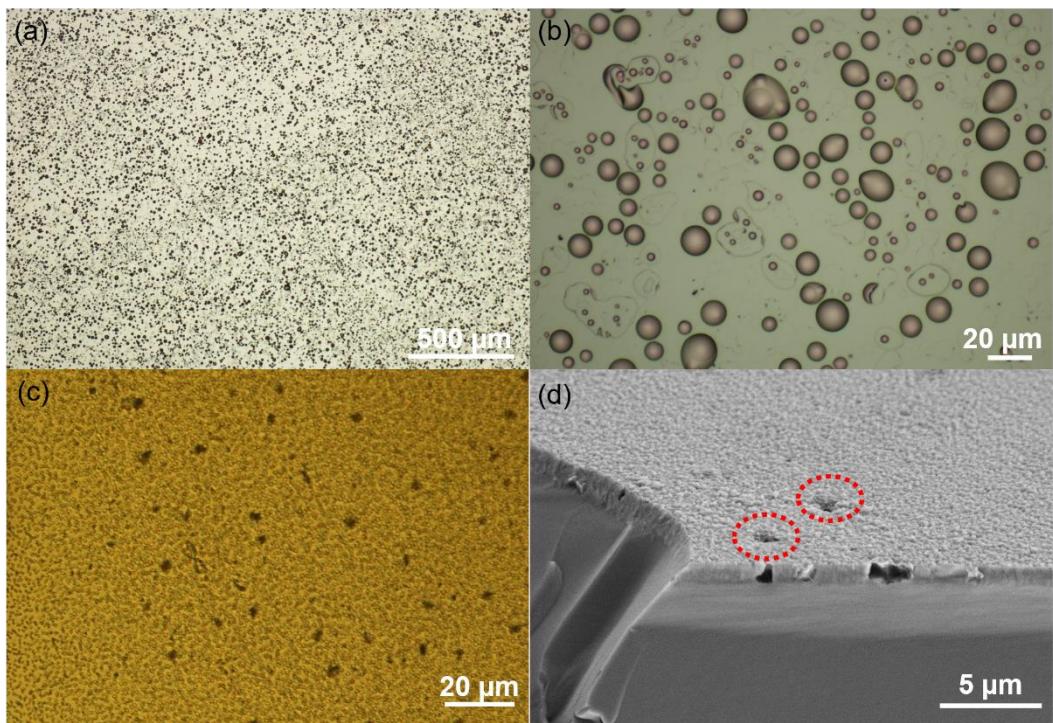

| <b>Figure 30:</b> (a)-(c) Top-down microscope images taken from Si films grown using 5/5 and 20/20 sccm gas flow ratios and (d) cross-sectional SEM image of 20/20 sccm grown film.....                                                                                                     | 81  |

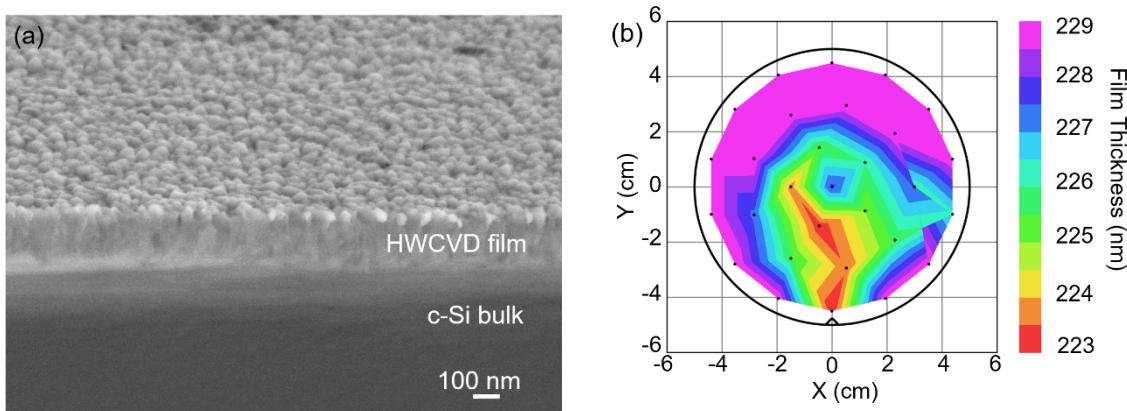

| <b>Figure 31:</b> (a) Cross-sectional SEM image taken from boron-doped silicon film grown using 10/10 sccm gas flow ratio and (b) spatial thickness map taken from optical ellipsometry.....                                                                                                | 81  |

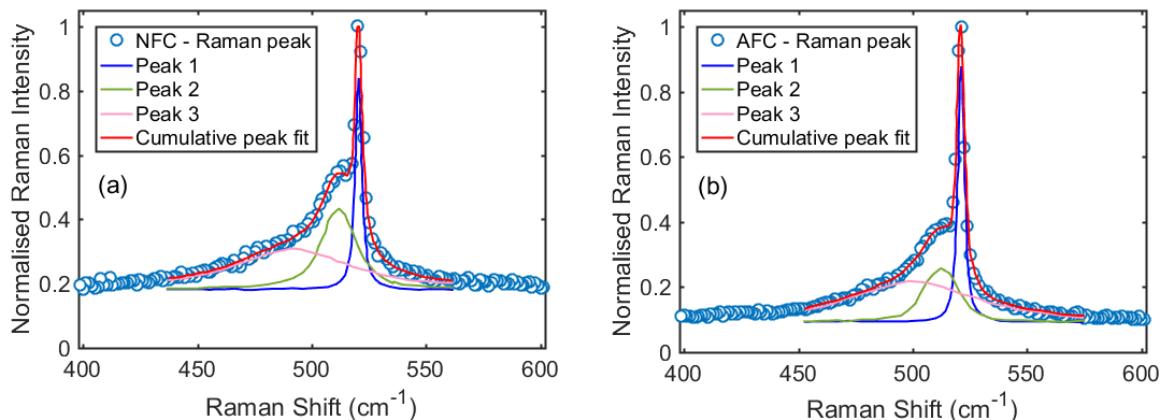

| <b>Figure 32:</b> Stokes Raman spectra for as-deposited boron-doped Si films via (a) NFC and (b) AFC..                                                                                                                                                                                      | 82  |

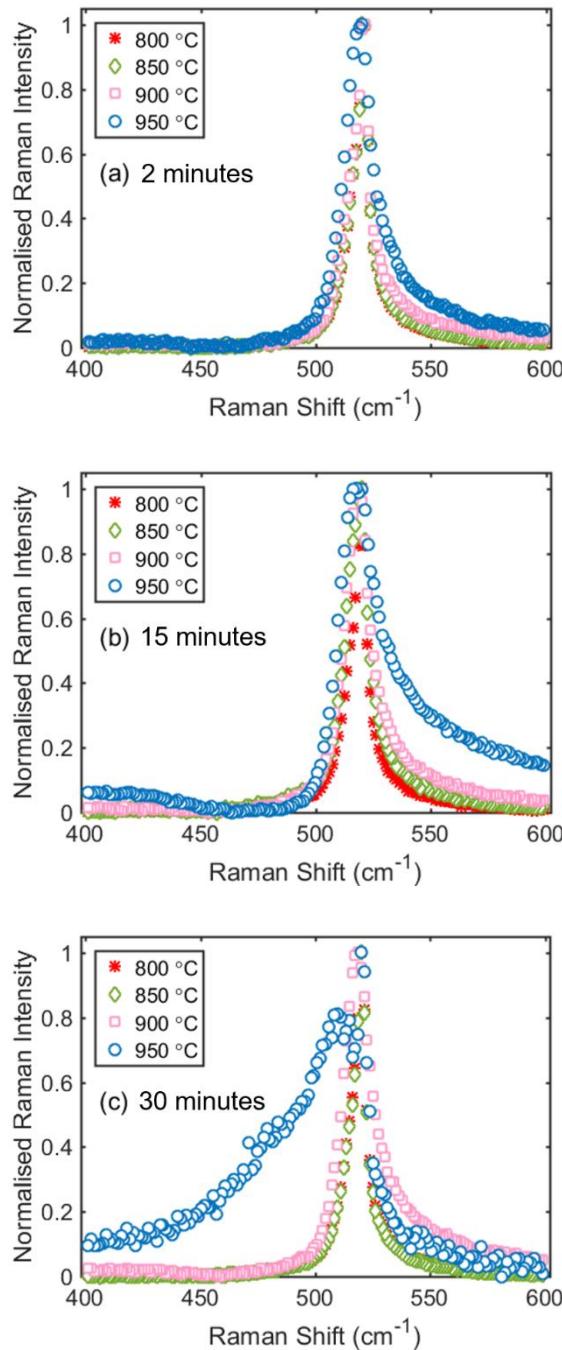

| <b>Figure 33:</b> Raman spectra taken from boron-doped Si films after annealing at 800-950 °C for (a) 2 minutes, (b) 15 minutes and (c) 30 minutes.....                                                                                                                                     | 85  |

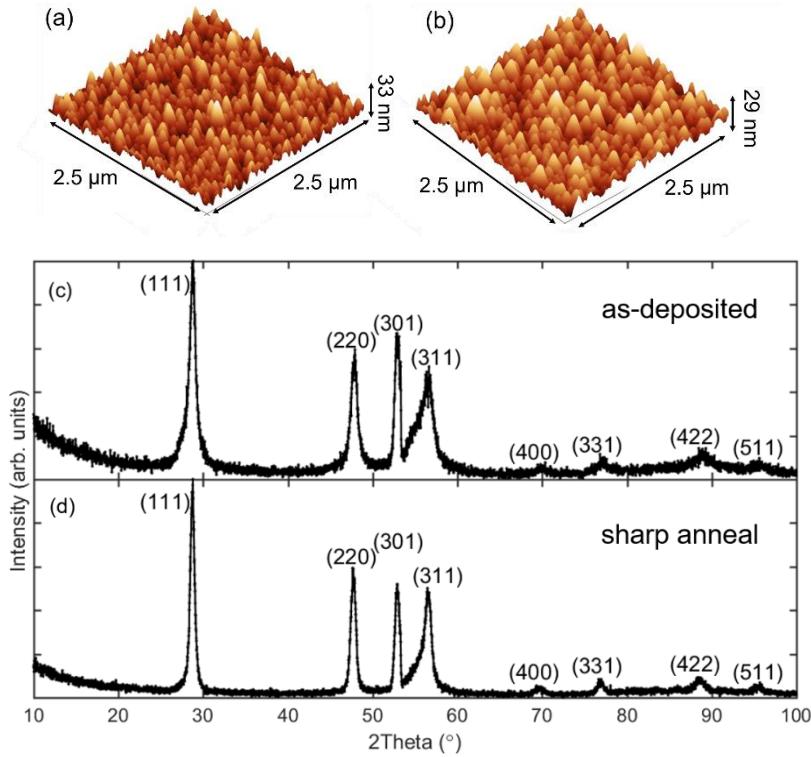

| <b>Figure 34:</b> 3D-formatted AFM scan of (a) as-deposited and (b) heat-treated HWCVD films. (c) XRD spectra for as-deposited and heat-treated Si films.....                                                                                                                               | 87  |

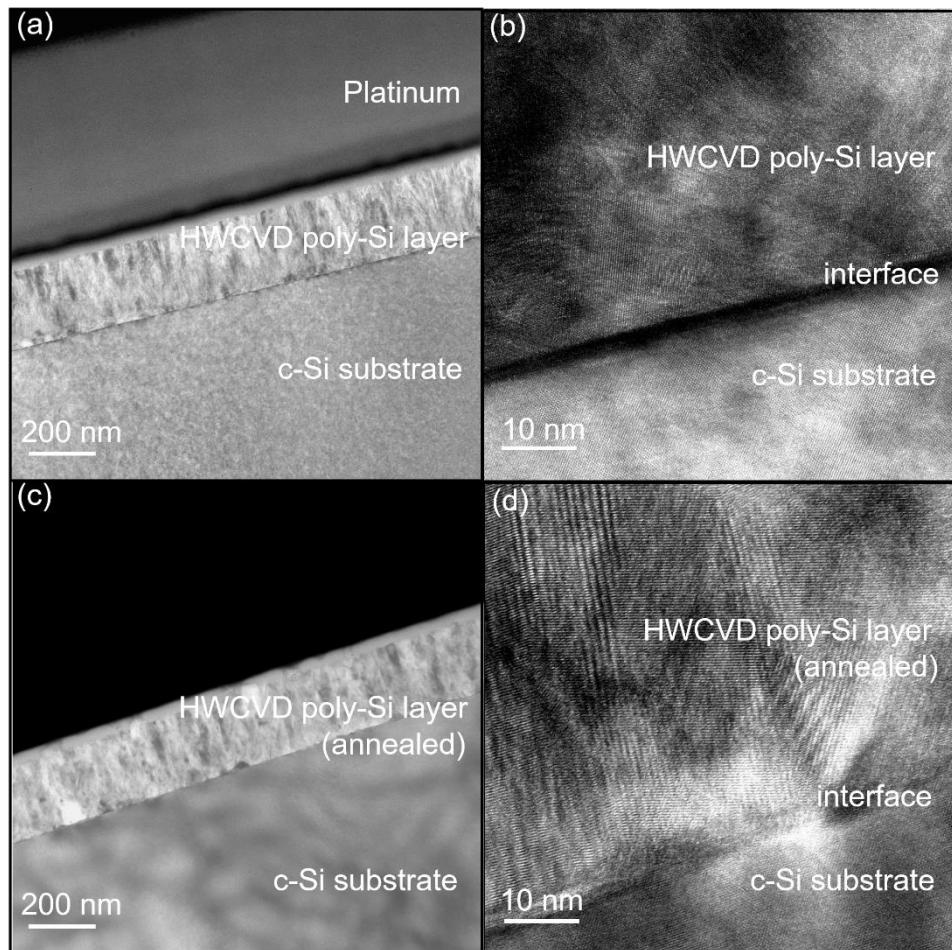

| <b>Figure 35:</b> TEM images of (a)-(b) as-deposited and (c)-(d) heat-treated HWCVD boron-doped Si films.....                                                                                                                                                                               | 88  |

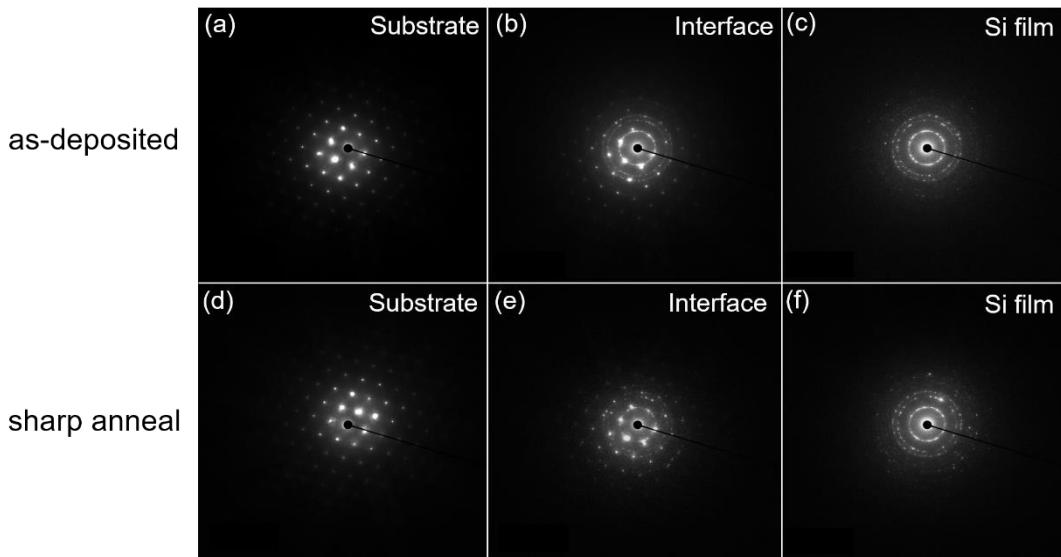

| <b>Figure 36:</b> SAED diffraction pattern for as-deposited HWCVD samples taken at (a) c-Si substrate, (b) interface and (c) grown film. SAED pattern for heat-treated HWCVD samples taken at (d) c-Si substrate, (e) interface and (f) heat-treated film.....                              | 89  |

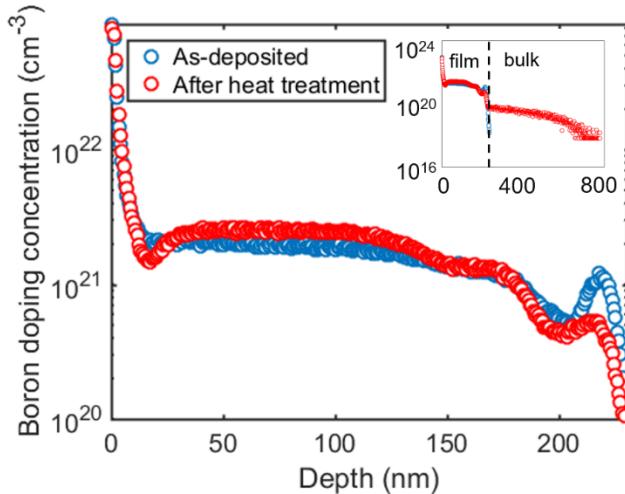

| <b>Figure 37:</b> Boron doping as a function of depth for as-deposited and heat-treated films taken from secondary ion-mass spectrometry.....                                                                                                                                               | 91  |

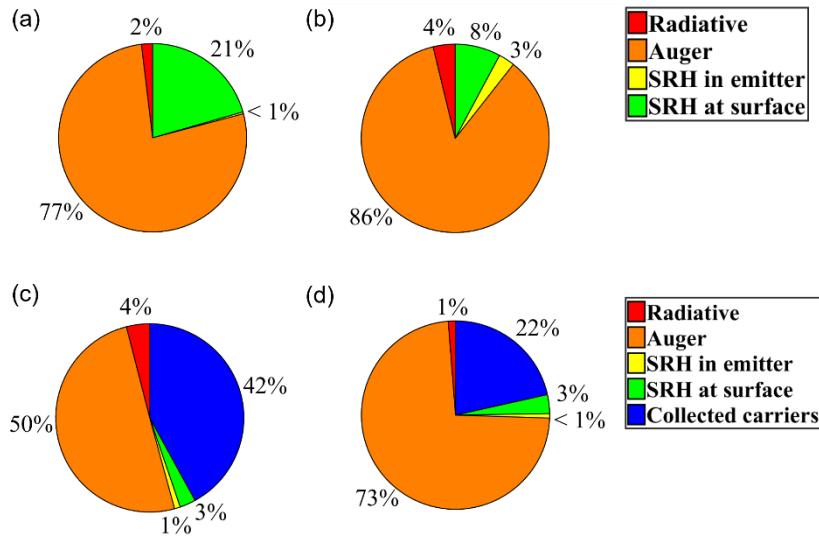

| <b>Figure 38:</b> A breakdown of the contributing recombination mechanisms to $J_{0E}$ for (a) as-deposited and (b) annealed HWCVD Si emitters. Similar breakdown for limitations to $IQE_E$ for (c) as-deposited and (d) heat-treated emitters. Taken from EDNA 2 simulation results. .... | 93  |

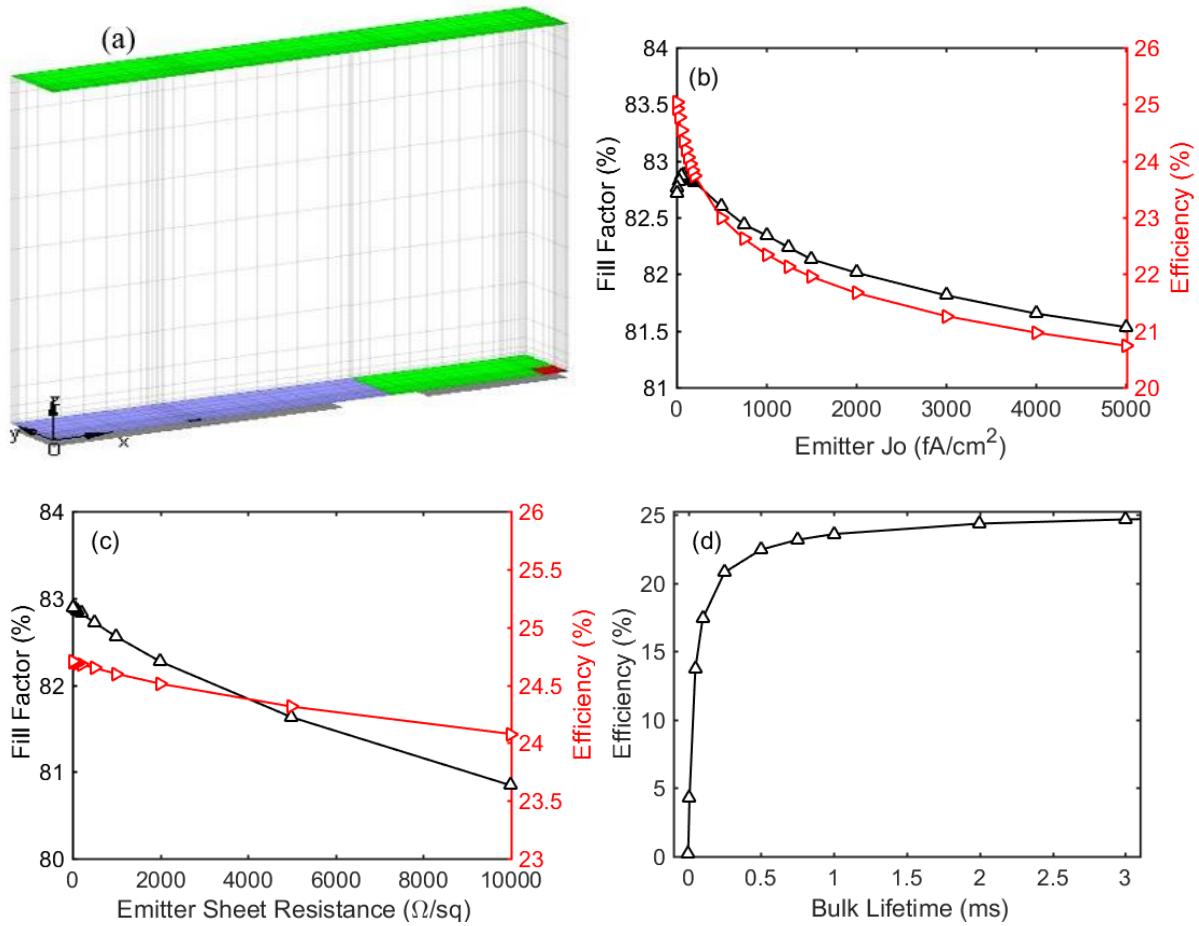

| <b>Figure 39:</b> (a) IBC unit cell from Quokka model, with Quokka IBC simulation results used for quantitative analysis of (b) emitter $J_0$ , (c) emitter sheet resistance and (d) bulk lifetime on IBC performance ..                                                                    | 95  |

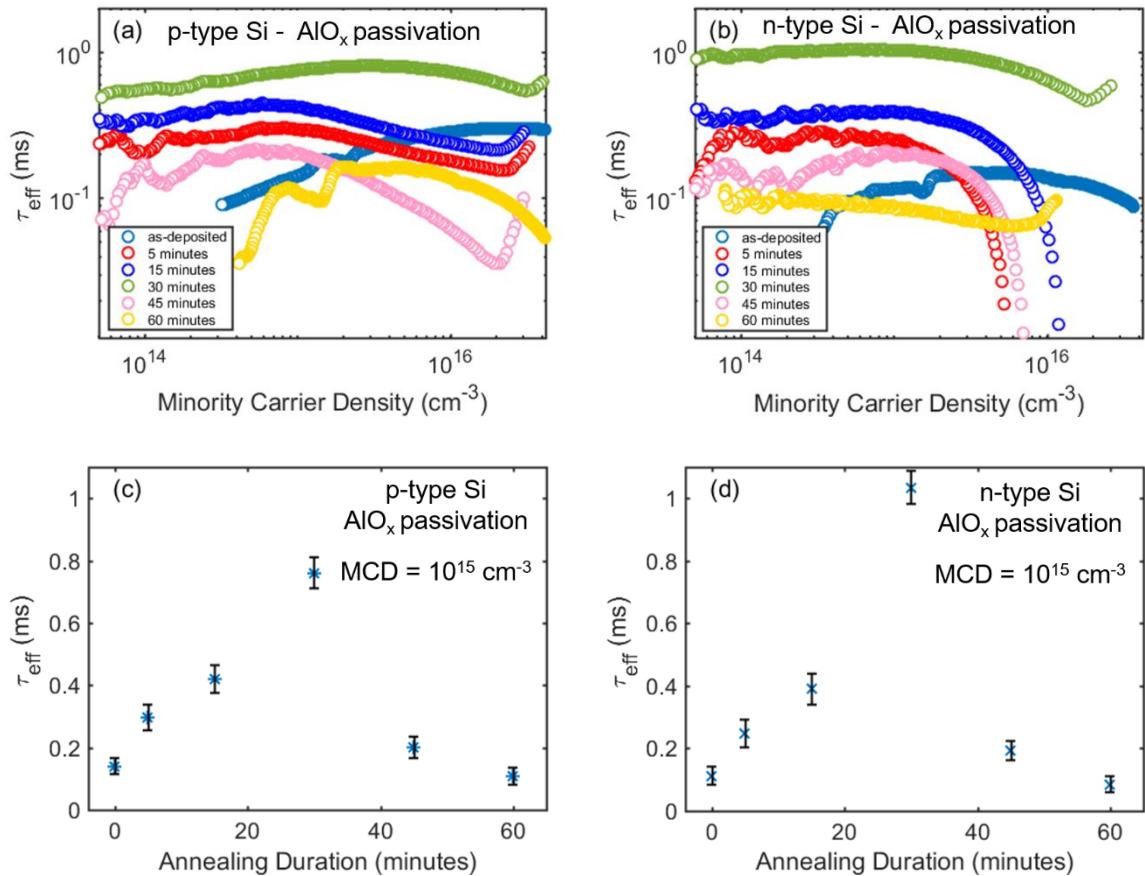

| <b>Figure 40:</b> Effective minority carrier lifetime vs. carrier density measured for $\text{AlO}_x$ passivated (a) p-type Si and (b) n-type Si, and effective minority carrier lifetime vs. annealing duration for (c) p-type Si and (d) n-type Si. ....                                  | 98  |

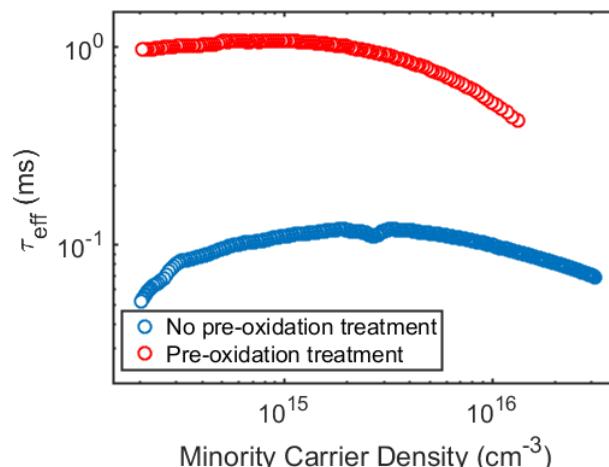

| <b>Figure 41:</b> Minority carrier lifetime vs carrier density measured with and without pre-oxidation treatment of $\text{AlO}_x$ passivated n-type FZ Si wafer. ....                                                                                                                      | 99  |

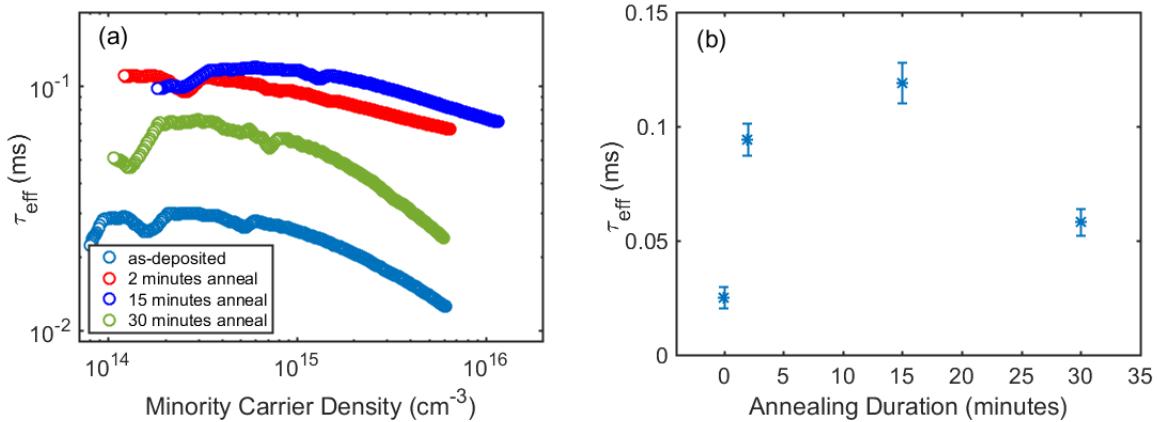

| <b>Figure 42:</b> (a) Minority carrier lifetime vs carrier density and (b) minority carrier lifetime vs annealing duration for $\text{AlO}_x$ passivated HWCVD emitters. ....                                                                                                               | 101 |

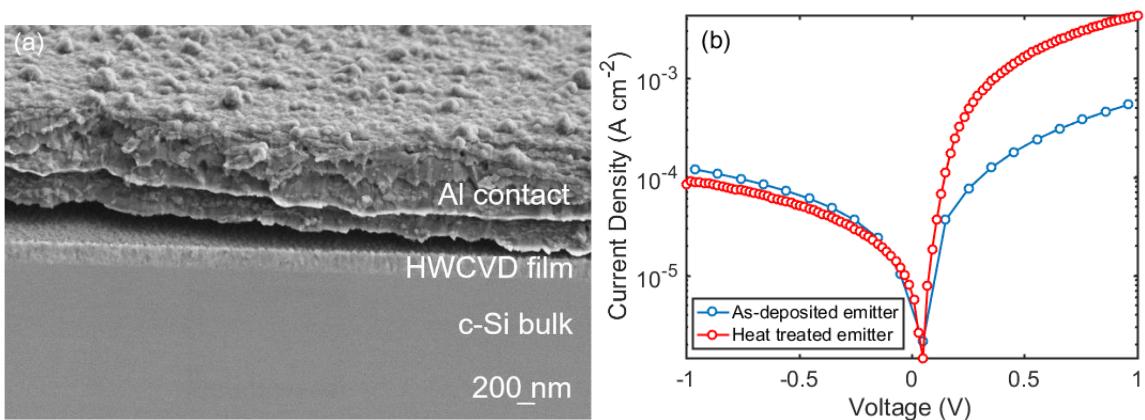

| <b>Figure 43:</b> (a) Cross-sectional SEM image of metallized HWCVD junction and (b) current density vs. voltage for as-deposited and heat-treated HWCVD emitters.....                                                                                                                      | 102 |

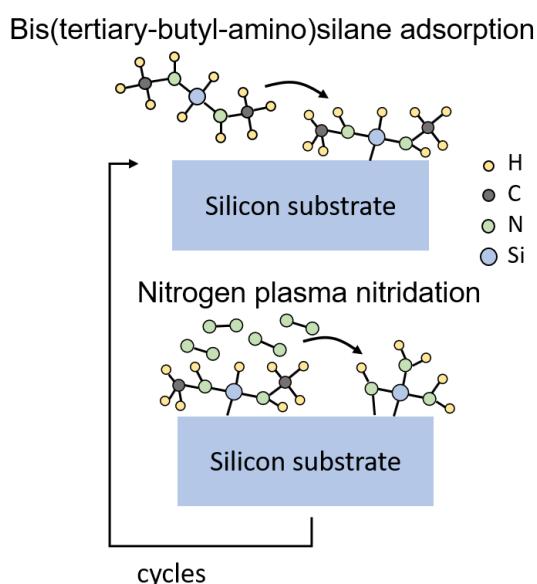

| <b>Figure 44:</b> Schematic diagram illustrating the cyclic growth of $\text{SiN}_x$ via atomic layer deposition. ..                                                                                                                                                                        | 106 |

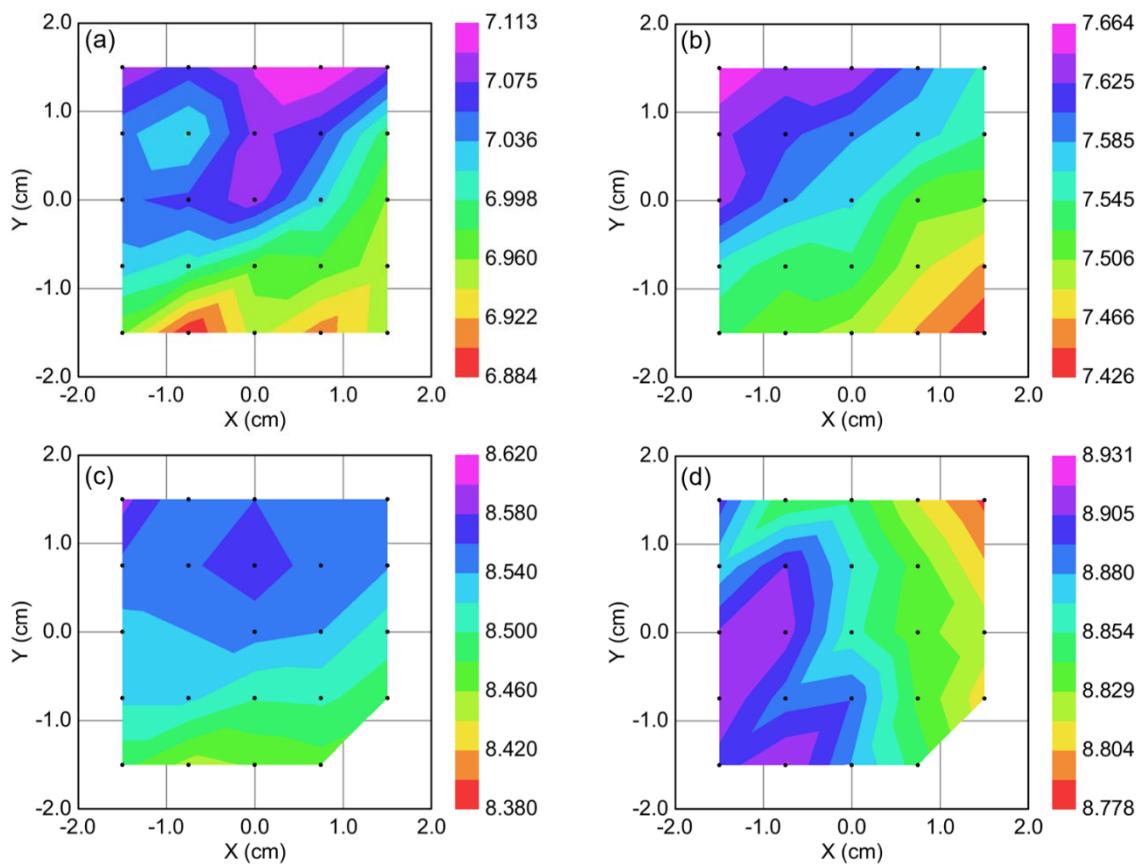

| <b>Figure 45:</b> Spatial thickness maps from spectroscopic ellipsometry measurements taken from $\text{SiN}_x$ films grown for 625 cycles at (a) 25 ms (b) 75 ms (c) 175 ms and (d) 225 ms BTBAS dosing times. The colour bar axis is measured in nm. ....                                 | 107 |

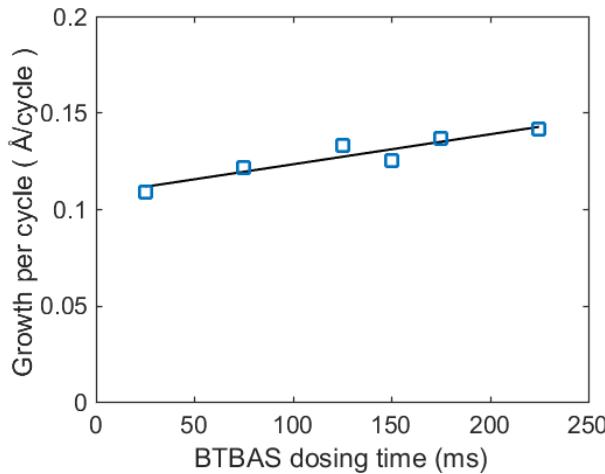

| <b>Figure 46:</b> Growth of $\text{SiN}_x$ per ALD cycle as a function of BTBAS dosing time. ....                                                                                                                                                                                           | 108 |

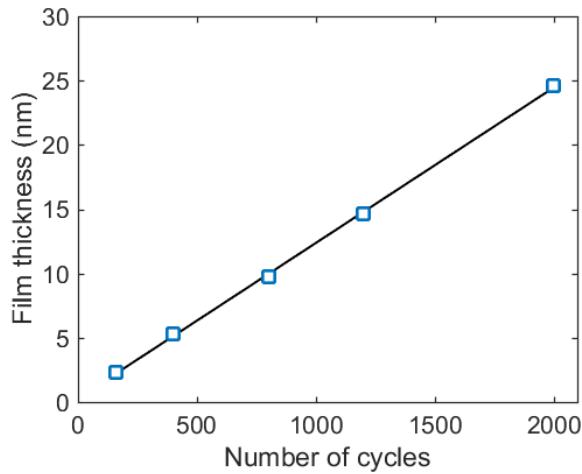

| <b>Figure 47:</b> $\text{SiN}_x$ film thickness as a function of number of ALD cycles grown at a fixed BTBAS dosing time of 150 ms. ....                                                                                                                                                    | 109 |

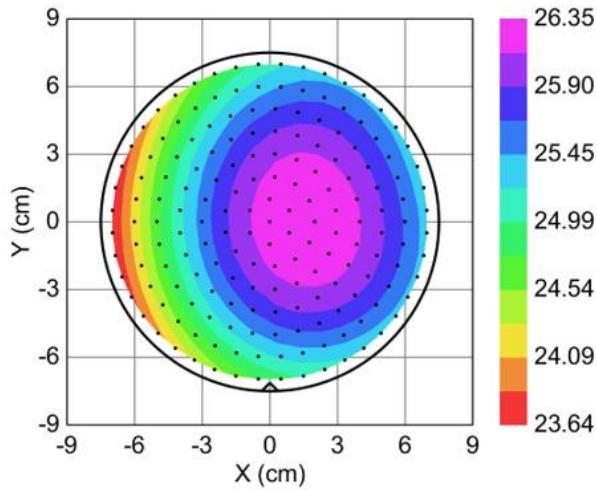

| <b>Figure 48:</b> Spatial thickness map taken from spectroscopic ellipsometry measurements taken from $\text{SiN}_x$ films grown from 2000 ALD cycles at a fixed BTBAS dosing time of 150 ms. The colour bar axis is measured in nm. ....                                                   | 110 |

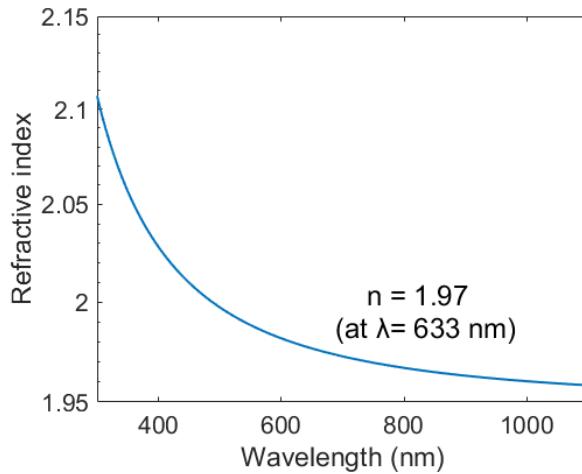

| <b>Figure 49:</b> Refractive index of ALD $\text{SiN}_x$ taken from variable angle spectroscopic ellipsometry. K data is negligible beyond 235 nm. ....                                                                                                                                     | 111 |

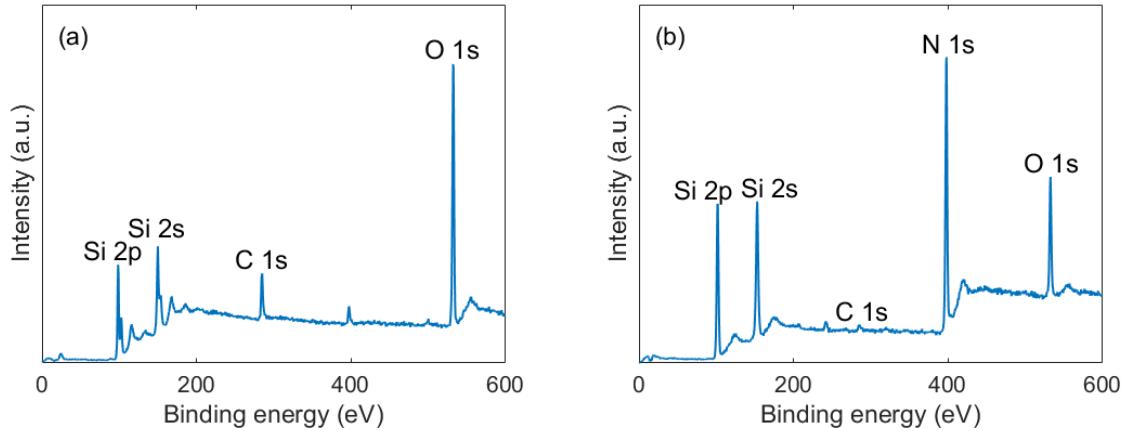

| <b>Figure 50:</b> X-ray photoelectron spectroscopy spectra taken from (a) p-Si substrate and (b) 25 nm $\text{SiN}_x$ film grown on p-Si substrate.....                                                                                                                                     | 112 |

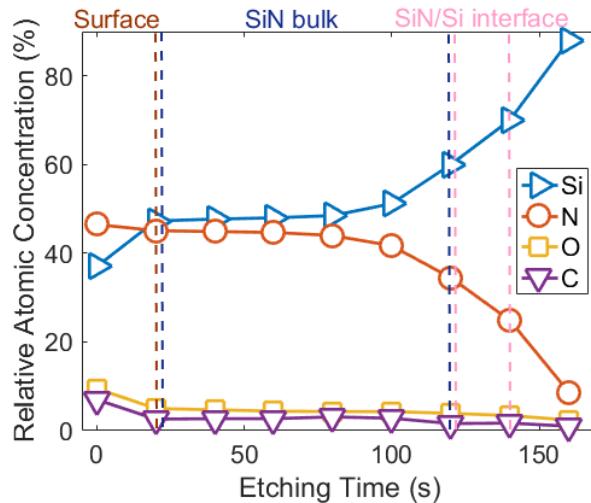

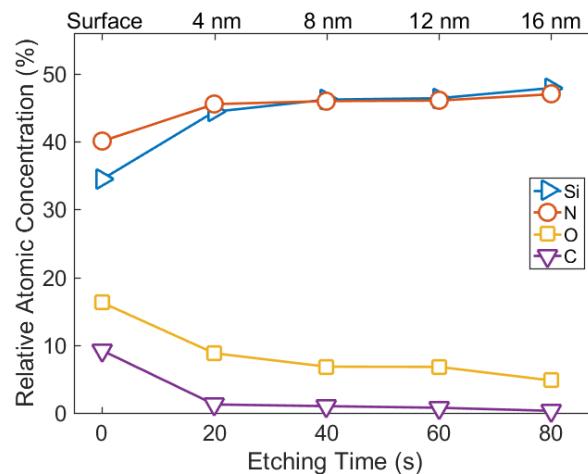

| <b>Figure 51:</b> Relative atomic concentration of Si, N, O and C as a function of etching time in as-deposited 25 nm $\text{SiN}_x$ film. ....                                                                                                                                             | 113 |

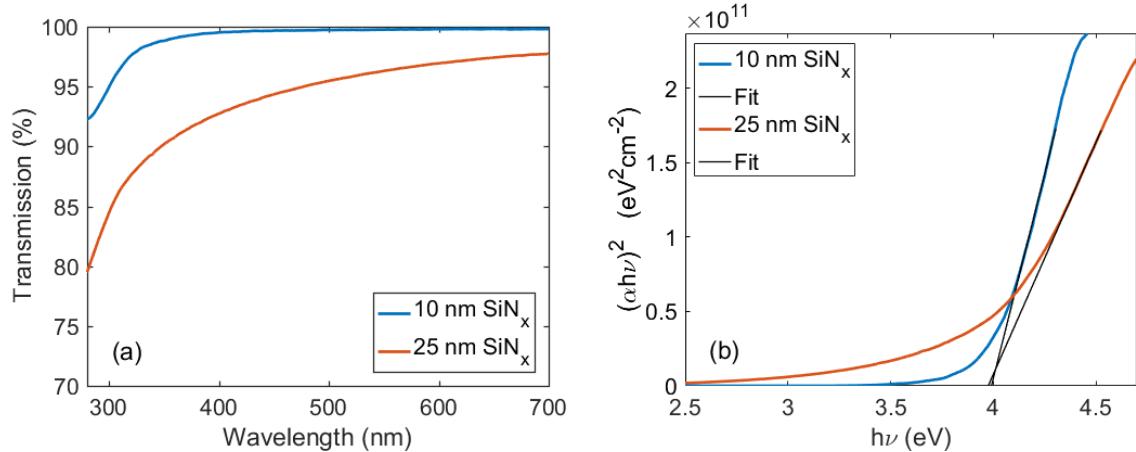

| <b>Figure 52:</b> (a) Transmission spectra and (b) Tauc $((\alpha h\nu)^2$ vs $h\nu$ ) plot for 10 nm and 25 nm $\text{SiN}_x$ film. ....                                                                                                                                                   | 114 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

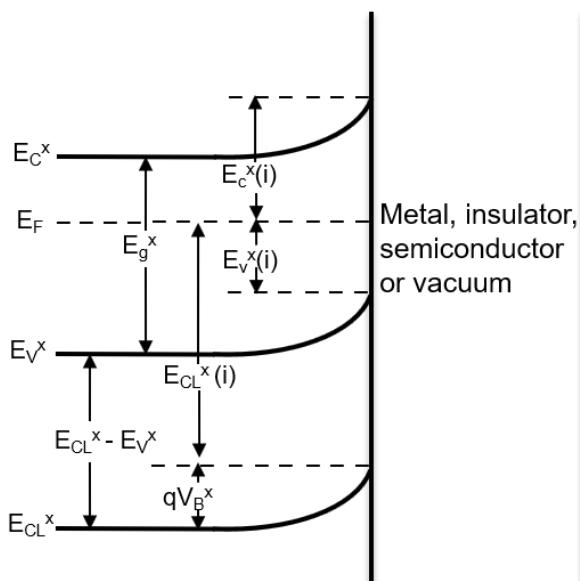

| <b>Figure 53:</b> Generalised energy band diagram at an abrupt interface between a semiconductor and metal, insulator, different semiconductor, or vacuum. Inspired from [145]. ..                                                                                                                                                                                                                                                                                                                                                                                                                 | 115 |

| <b>Figure 54:</b> Schematic diagram of band offsets at the SiN/Si interface. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 117 |

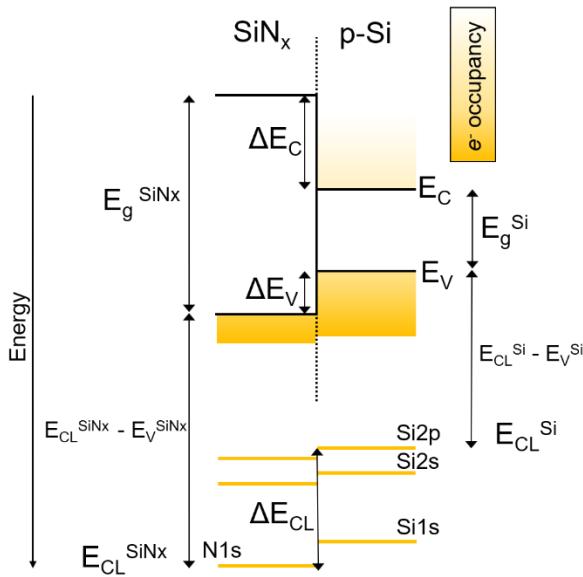

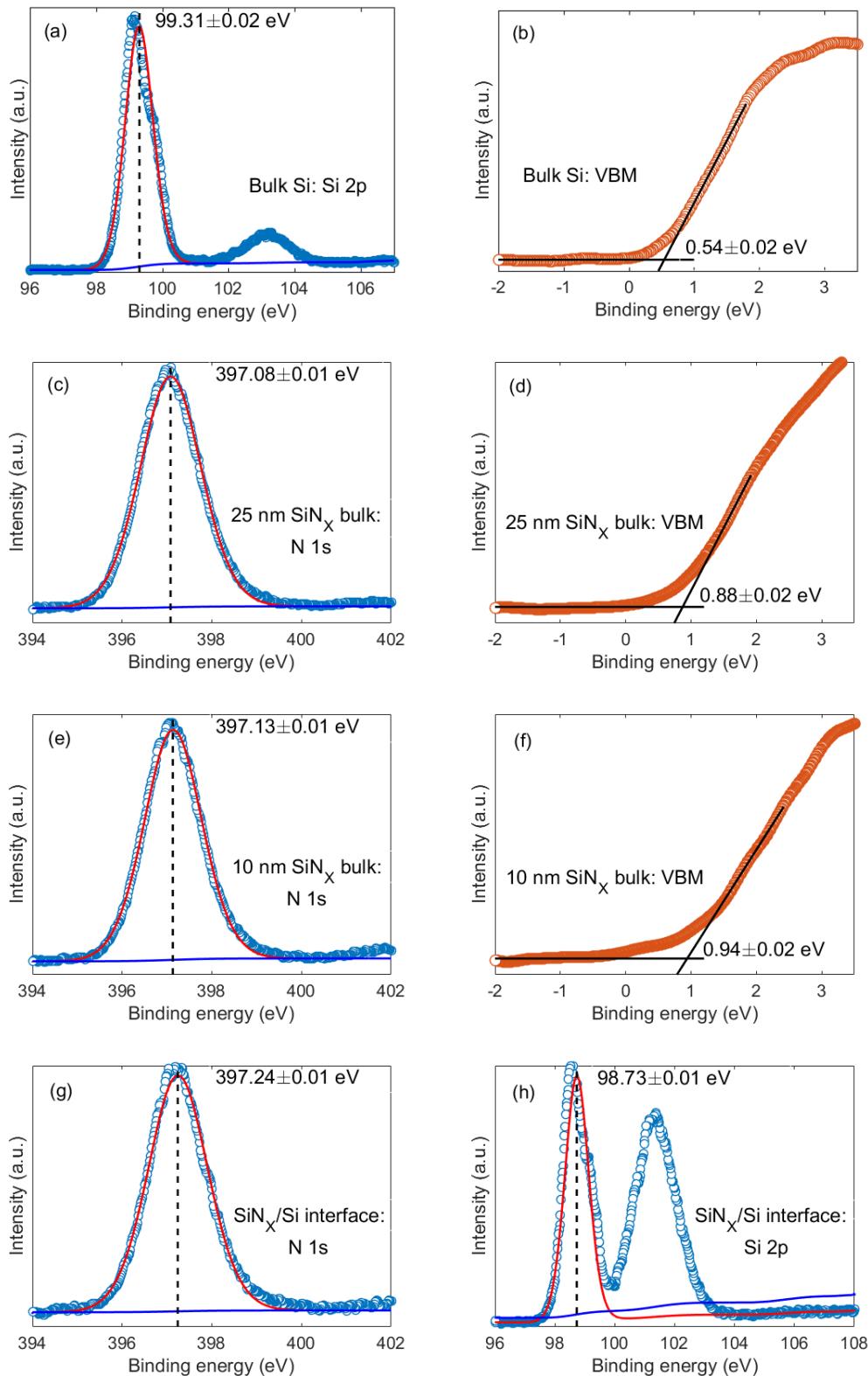

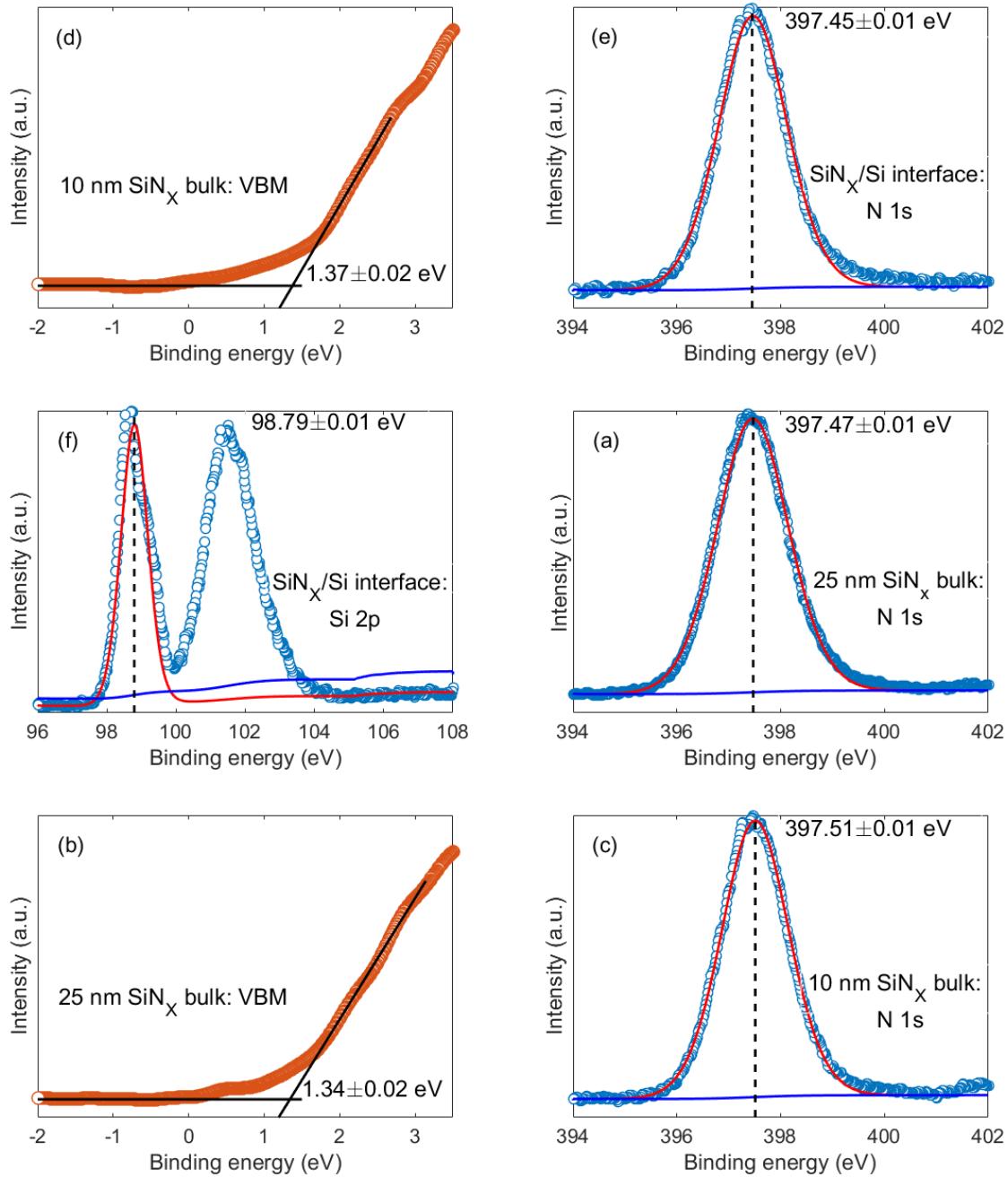

| <b>Figure 55:</b> XPS spectra showing (a) Si 2p CL and (b) valence band edge from bulk p-type Si, (c) N 1s CL and (d) valence band edge from 25 nm (bulk) SiN <sub>x</sub> , (e) N 1s CL and (f) valence band edge from 10 nm (bulk) SiN <sub>x</sub> and (g) N 1s CL and (h) Si 2p CL from 3 nm (interface) SiN <sub>x</sub> on p-type Si. Solid red lines show Voigt fits, solid blue lines show the Shirley background, dashed black lines show the CL centroid positions (in a, c, e, g and h) and the solid black lines show the extrapolations to determine the VB edge (in b, d and f)..... | 118 |

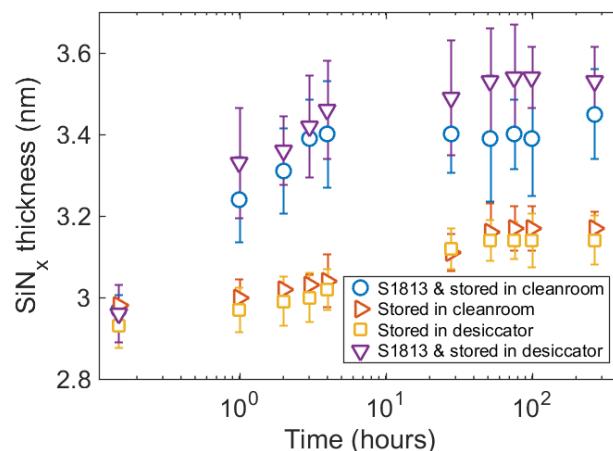

| <b>Figure 56:</b> SiN thickness measured over two weeks when stored in a cleanroom and desiccator, with and without S1813 photoresist protection layer.....                                                                                                                                                                                                                                                                                                                                                                                                                                        | 120 |

| <b>Figure 57:</b> XPS spectra of aged films, showing (a) N 1s CL and (b) valence band edge from 25nm SiN <sub>x</sub> , (c) N 1s CL and (d) valence band edge from 10nm SiN <sub>x</sub> and (e) N 1s CL and (f) Si 2p CL from 3nm SiN <sub>x</sub> on p-Si. Solid red lines show Voigt fits, solid blue lines show the Shirley background, dashed black lines show the CL centroid positions (in a, c, e and f) and the solid black lines show the extrapolations to determine the VB edge (in b and d). .....                                                                                    | 122 |

| <b>Figure 58:</b> Relative atomic concentration ratio of Si, N, O and C as a function of etching time (corresponding to depth into the film) in aged SiN bulk (25 nm thick film). .....                                                                                                                                                                                                                                                                                                                                                                                                            | 123 |

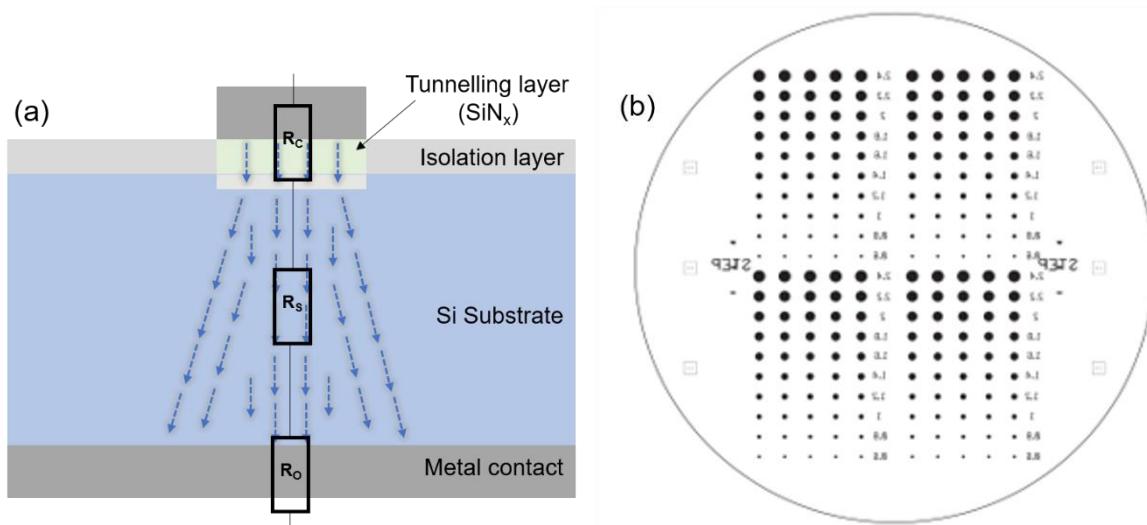

| <b>Figure 59:</b> (a) Cross-sectional current flow in carrier-selective contact device structures using the Cox and Strack method and (b) an example from the lithography masks made for conducting the Cox and Strack technique for extracting $\rho_c$ . .....                                                                                                                                                                                                                                                                                                                                   | 127 |

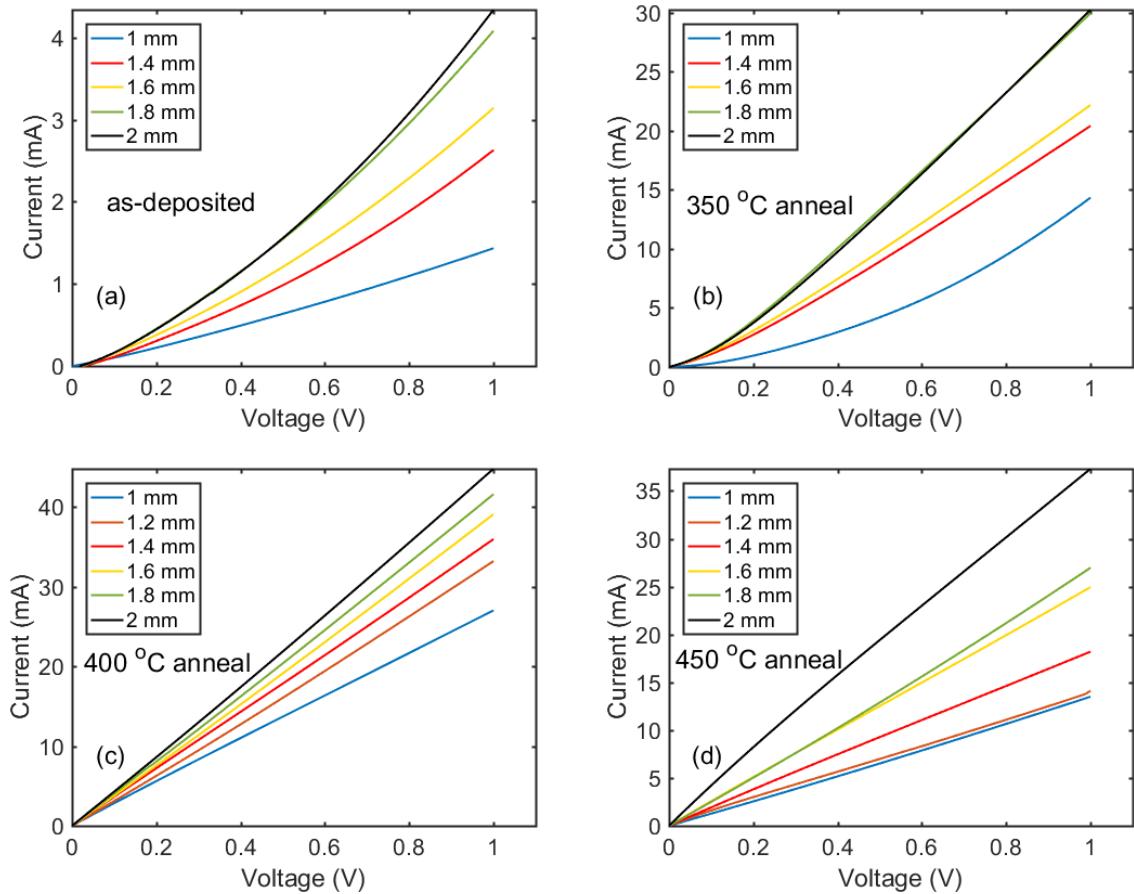

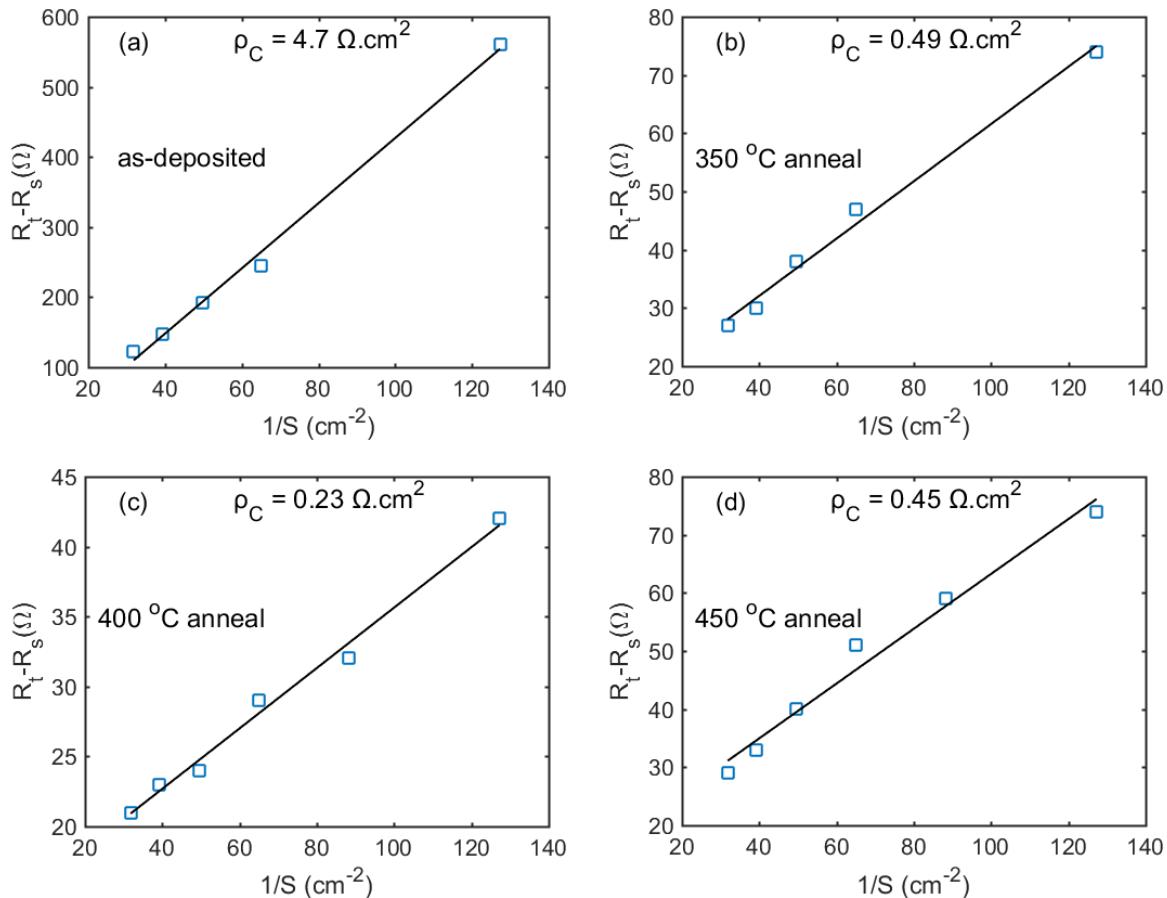

| <b>Figure 60:</b> Current-voltage characteristics taken from Al/Si/Al structures (a) as-deposited, annealed at (b) 350 °C, (c) 400 °C and (d) 450 °C. ....                                                                                                                                                                                                                                                                                                                                                                                                                                         | 129 |

| <b>Figure 61:</b> $R_T - R_S$ versus 1/S plots and the corresponding linear fits for extracting $\rho_c$ from Al/Si/Al structures. (a) as-deposited, annealed at (b) 350 °C, (c) 400 °C and (d) 450 °C. ....                                                                                                                                                                                                                                                                                                                                                                                       | 130 |

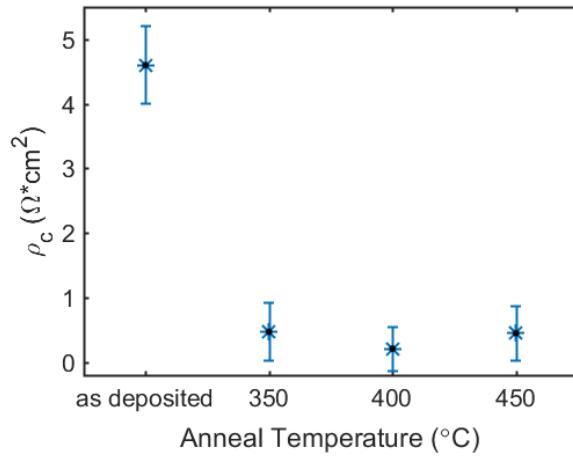

| <b>Figure 62:</b> Dependance of $\rho_c$ of the Al-Si contacts on the post-deposition annealing temperature... ..                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 131 |

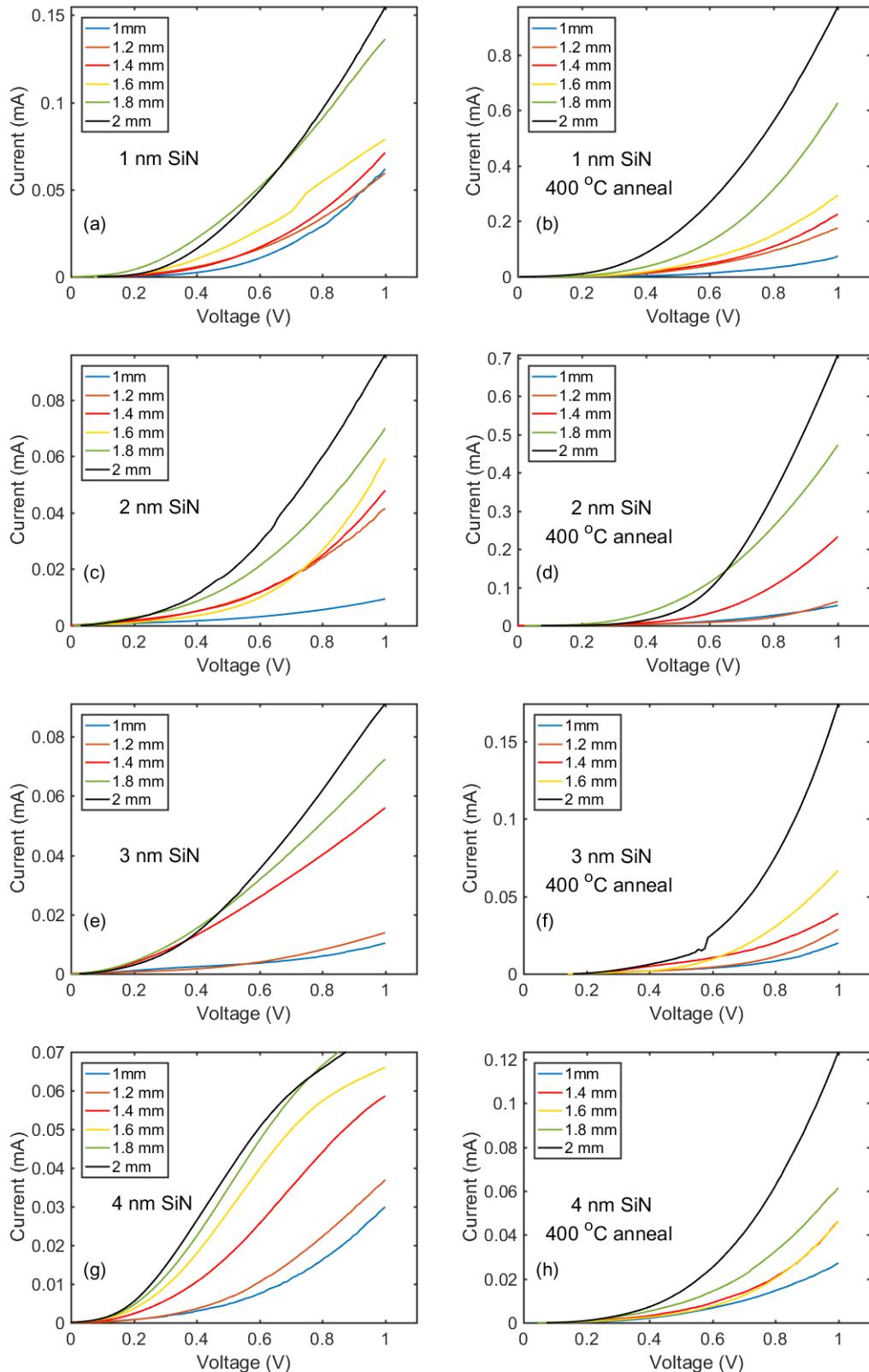

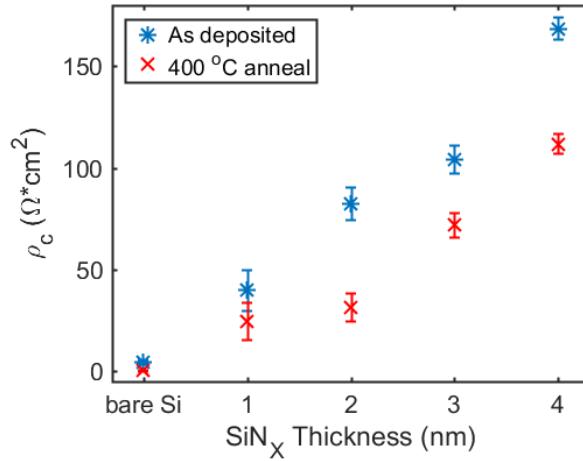

| <b>Figure 63:</b> Current-voltage characteristics taken from Al/SiN/Si/Al structures. As deposited: (a) 1 nm SiN, (c) 2 nm SiN, (e) 3 nm SiN and (g) 4 nm SiN. Annealed at 400 °C for 1 minute: (b) 1 nm SiN, (d) 2 nm SiN, (f) 3 nm SiN and (h) 4 nm SiN.....                                                                                                                                                                                                                                                                                                                                     | 132 |

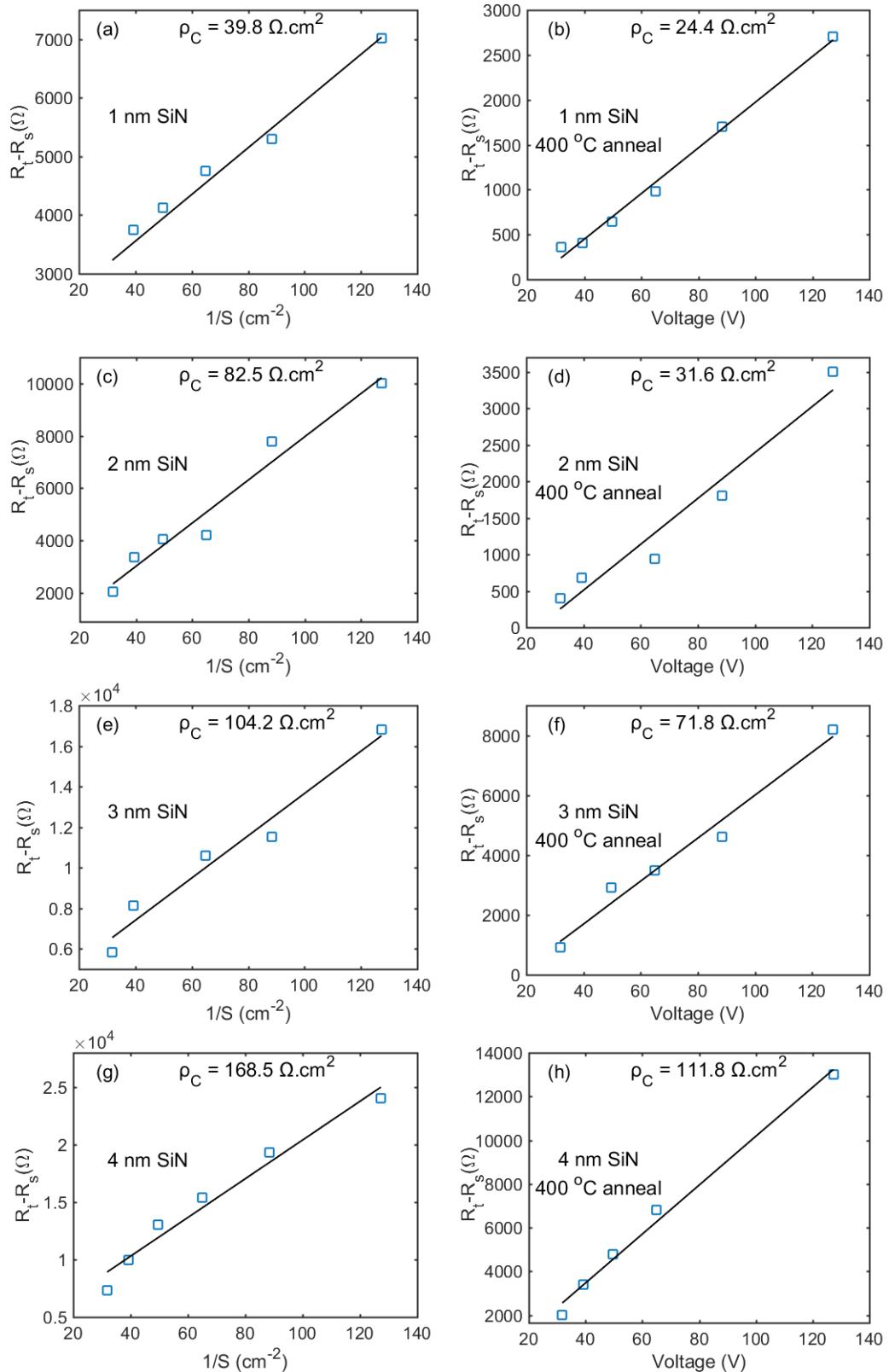

| <b>Figure 64:</b> $R_T - R_S$ versus 1/S plots and the corresponding linear fits for extracting $\rho_c$ from Al/SiN/Si/Al structures. As deposited: (a) 1 nm SiN, (c) 2 nm SiN, (e) 3 nm SiN and (g) 4 nm SiN. Annealed at 400 °C for 1 minute: (b) 1 nm SiN, (d) 2 nm SiN, (f) 3 nm SiN and (h) 4 nm SiN.....                                                                                                                                                                                                                                                                                    | 134 |

| <b>Figure 65:</b> Dependence of $\rho_c$ of the Al-SiN-Si contacts on the thickness of the SiN tunnelling layer for thicknesses between 1 nm – 4 nm. ....                                                                                                                                                                                                                                                                                                                                                                                                                                          | 135 |

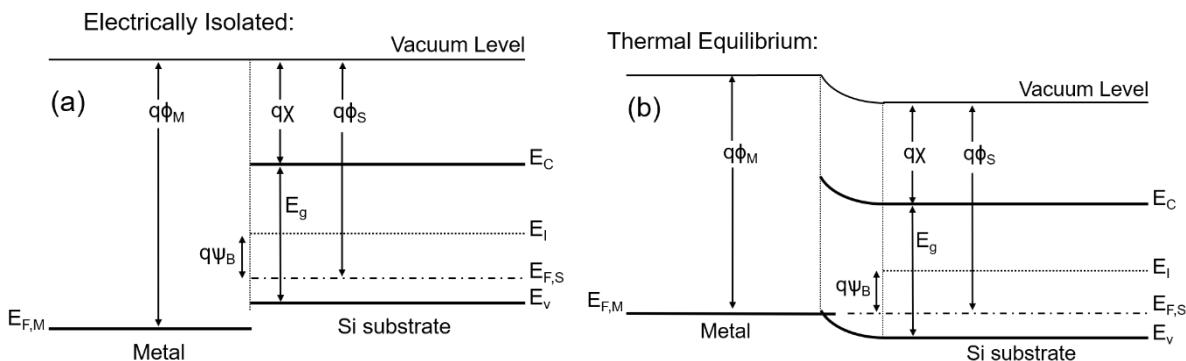

| <b>Figure 66:</b> Energy band diagrams for metal-Si interface under (a) electrical isolation and (b) thermal equilibrium.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 135 |

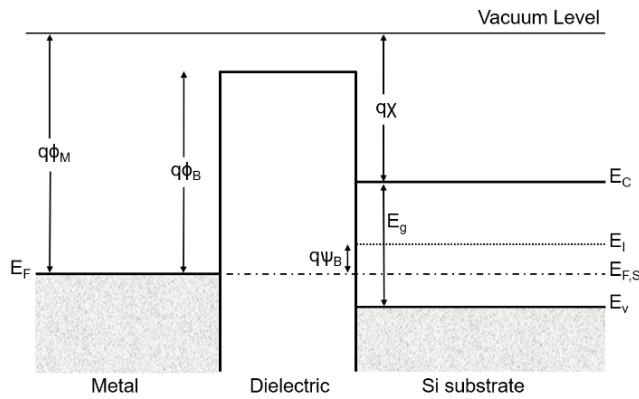

| <b>Figure 67:</b> Energy band diagram for metal-dielectric-silicon interface at flatband condition. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 137 |

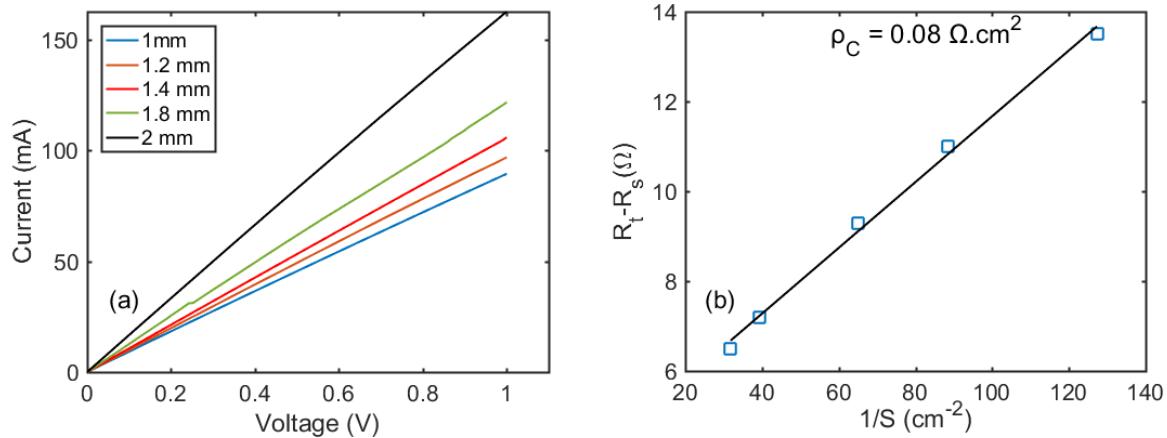

| <b>Figure 68:</b> (a) Current-voltage characteristics taken from Au/Si/Au structures, and (b) $R_T - R_S$ versus 1/S and the corresponding linear fit for extracting $\rho_c$ . .....                                                                                                                                                                                                                                                                                                                                                                                                              | 138 |

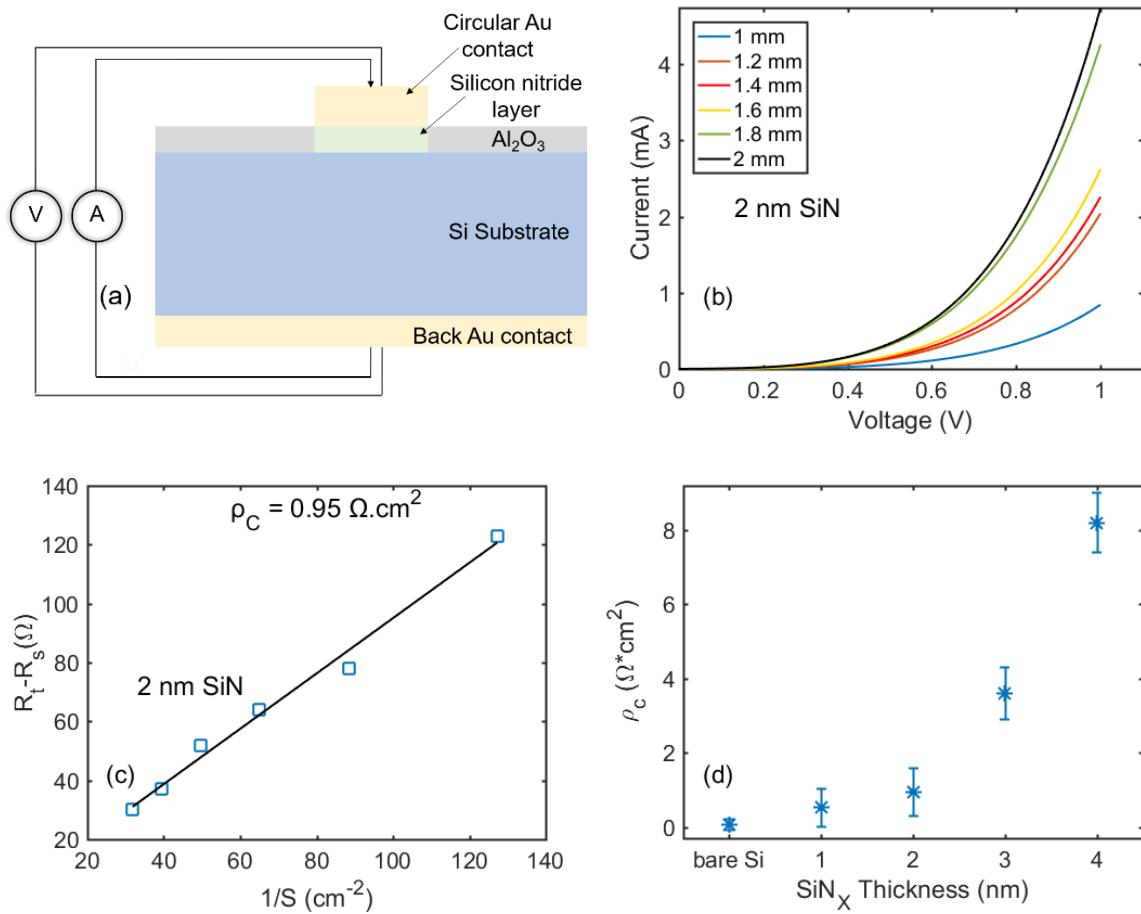

| <b>Figure 69:</b> (a) Cross-sectional diagram of fabricated Au/SiN/Si/Au for CSM measurements, (b) current-voltage characteristics from 2 nm SiN thickness structure, (c) $R_T - R_S$ vs 1/s from 2 nm SiN thickness CSM structure and (d) dependency of $\rho_c$ on SiN thickness.....                                                                                                                                                                                                                                                                                                            | 139 |

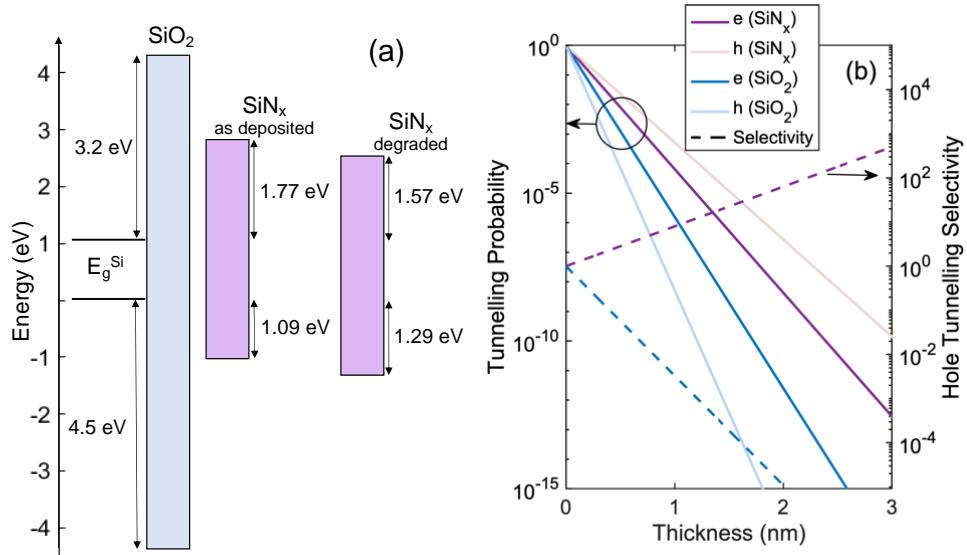

| <b>Figure 70:</b> (a) Measured $\Delta E_C$ and $\Delta E_V$ of ALD SiN compared to that for SiO <sub>2</sub> , and (b) tunnelling probability and tunnelling selectivity of ALD SiN and SiO <sub>2</sub> .....                                                                                                                                                                                                                                                                                                                                                                                    | 141 |

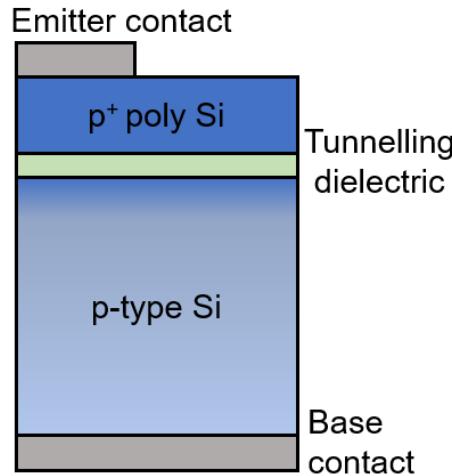

| <b>Figure 71:</b> Schematic of structure used for tunnelling current simulations via Sentaurus TCAD. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 142 |

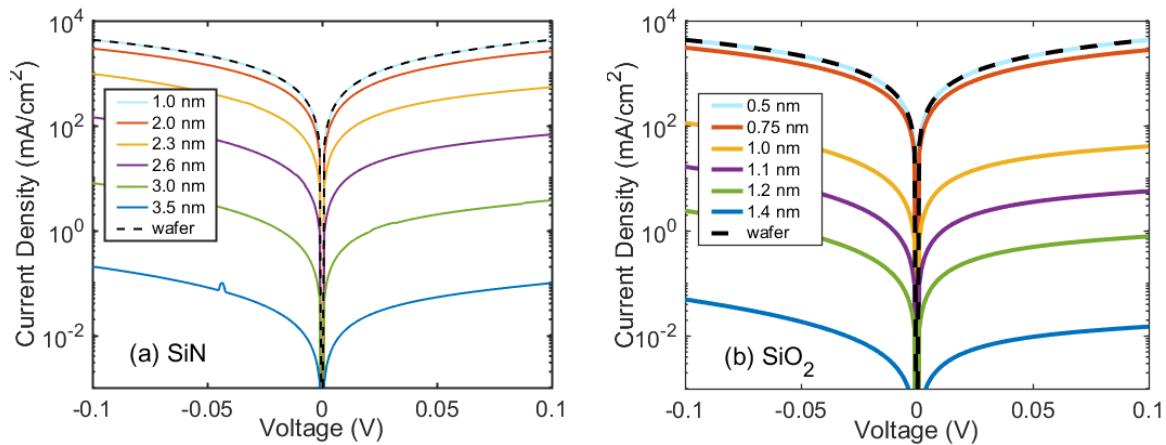

| <b>Figure 72:</b> Tunnelling current of (a) ALD SiN and (b) SiO <sub>2</sub> . .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 143 |

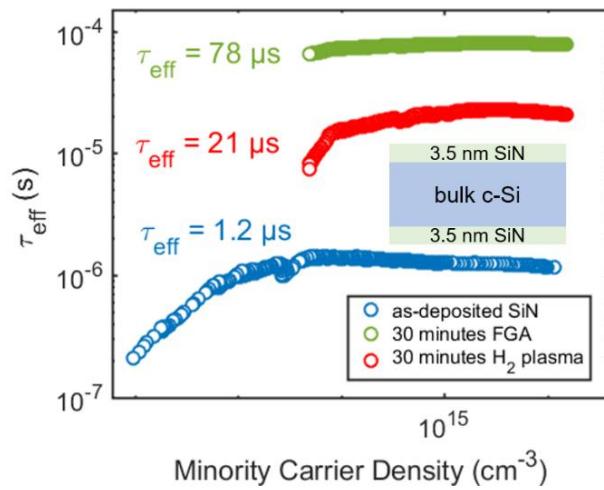

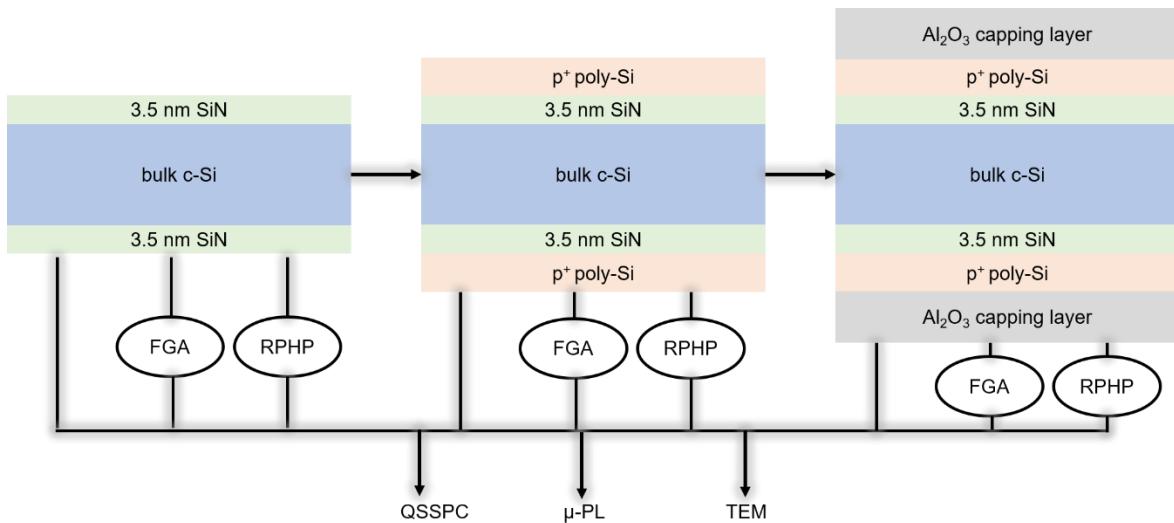

| <b>Figure 73:</b> Minority carrier density as a function of effective carrier lifetime from SiN/Si/SiN structures, measured as deposited, after rapid plasma hydrogen passivation and forming gas annealing. ....                                                                                                                                                                                                                                                                                                                                                                                  | 148 |

**Figure 74:** Schematic diagram showing various passivation stacks to promote hydrogenation in SiN nanolayer and possible measurements identified to determine performance in a passivating contact configuration..... 149

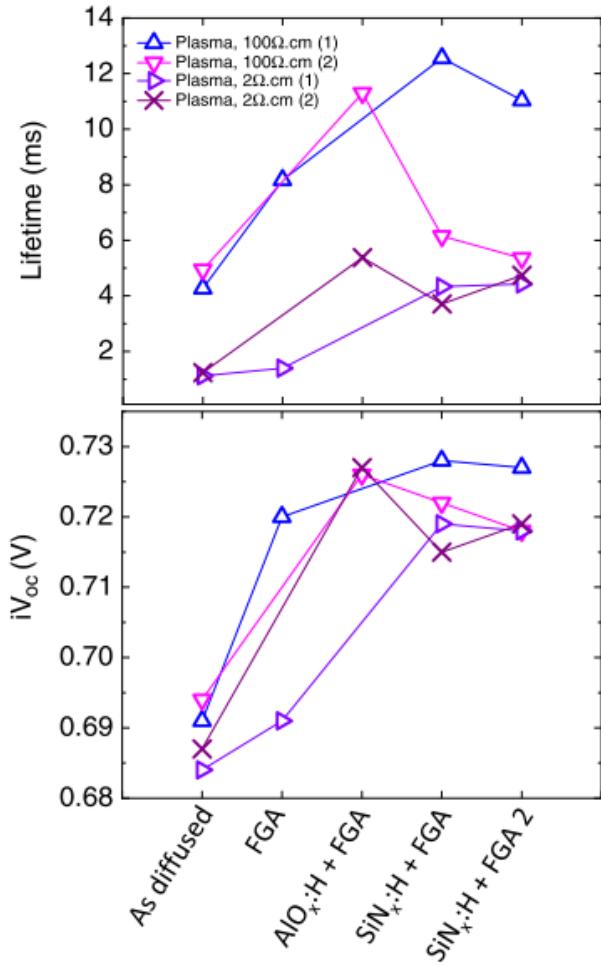

**Figure 75:** Implied open-circuit voltage and minority carrier lifetime from samples before and after FGA and capping layer formation taken from plasma-assisted ALD deposition from [175]..... 150

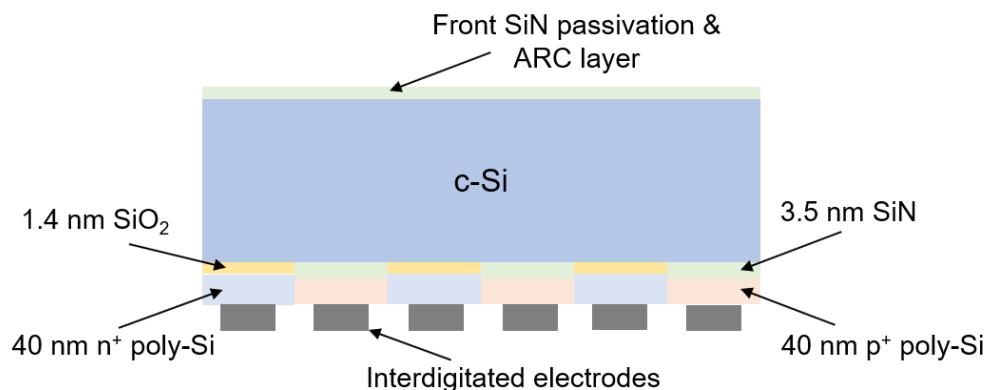

**Figure 76:** Cross-sectional schematic diagram of IBC solar cell with SiN hole tunnelling contacts. 151

# List of Tables

|                                                                                                                                                                    |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>Table 1:</b> The performance of various contact architectures in photovoltaics [16], [24], [71].....                                                            | 51  |

| <b>Table 2:</b> Optoelectronic properties of PECVD Si <sub>3</sub> N <sub>4</sub> [78], [90], [91]. .....                                                          | 57  |

| <b>Table 3:</b> Measured HWCVD deposition parameters.....                                                                                                          | 79  |

| <b>Table 4:</b> Fitted Voigt function parameters for Raman spectra taken from HWCVD NFC and AFC grown films.....                                                   | 83  |

| <b>Table 5:</b> HWCVD silicon emitter electrical properties taken from EDNA 2 simulation results using p <sup>+</sup> doping profiles. .....                       | 92  |

| <b>Table 6:</b> Input parameters for IBC model in Quokka, taken from IBC cell in [33]. .....                                                                       | 93  |

| <b>Table 7:</b> Simulated and measured IBC solar cell results using Quokka, comparing to Fell et al and ANU IBC [33], [71].....                                    | 94  |

| <b>Table 8:</b> 2-diode model fitting results from current density vs. voltage characteristics taken from HWCVD grown emitters. .....                              | 103 |

| <b>Table 9:</b> XPS data required for determining the band offsets at the SiN/Si interface using the Krauts method, taken from the measured data in Figure 55..... | 120 |

# Publications

## Journals

1. **Khorani, E**, McNab, S, Scheul, T.S., Rahman, T, Bonilla, R.S., Boden, S.A. and Wilshaw, P.R. (2020). Optoelectronic properties of ultrathin ALD silicon nitride and its potential as a hole-selective nanolayer for high efficiency solar cells, *APL Materials*, 8, 111106.

2. **Khorani, E**, Scheul, T.E., Tarazona, A, Nutter, J, Rahman, T and Boden, S.A. (2020). P+ polycrystalline silicon growth via Hot wire chemical vapour deposition for silicon solar cells, *Thin Solid Films*, 705, 137978.

3. Scheul, T.E., **Khorani, E**, Rahman, T, Charlton, M.D.B. and Boden, S.B. (2020) Wavelength and angle resolved reflectance of pyramidal textures for crystalline silicon photovoltaics, *Progress in Photovoltaics*, 1-10.

4. Scheul, T.E., **Khorani, E**, Rahman, T, Charlton, M.D.B. and Boden, S.B. (2020) Light scattering from black silicon surfaces and its benefits for encapsulated solar cells, *Progress in Photovoltaics*, under review.

5. Mercier, T.M, Krishnan, C, Rahman, T, **Khorani, E**, Shaw, P.J, Pollard, M.E, Boden, S.A, Lagoudakis, P.V, Charlton, M.D.B. (2020), High symmetry nano-photonic quasi-crystals providing novel light management in silicon solar cells, *Nano Energy*, under review.

## Conferences

1. Scheul, T.E., **Khorani, E**, Rahman, T and Boden, S.A. Characterization of atomic layer deposition alumina thin films on black silicon textures using helium ion microscopy. 9th International Conference on Silicon Photovoltaics, Leuven, Belgium, 8 – 10 April 2019.

2. **Khorani, E**, Scheul, T, E, Tarazona, A, Rahman, T and Boden, S.A. Boron-doped silicon growth via Hotwire CVD towards emitter formation for interdigitated back-contact silicon solar cells, PV-SAT 15, Warwick, United Kingdom. 10 – 12 April 2019.

3. Scheul, T.E., **Khorani, E**, Rahman, T and Boden, S.A. Wavelength and angle-resolved scattering measurements of textured silicon solar cells, PV-SAT 15, Warwick, United Kingdom. 10 – 12 April 2019.

4. **Khorani, E**, Scheul, T.E., Tarazona, A, Rahman, T and Boden, S.A. Optimisation of ex-situ annealing process for epitaxial silicon emitters via hot wire CVD, PV-SAT 14, London, United Kingdom. 18 - 20 Apr 2018.

5. Scheul, T.E., **Khorani, E**, Rahman, T and Boden, S.A. Metal-assisted chemically etched black silicon for crystalline silicon solar cells, PV-SAT 14, London, United Kingdom. 18 - 20 Apr 2018.

## Declaration of Authorship

I, Edris Khorani, declare that the thesis entitled silicon-based ultrathin layers for hole-selective contacts in silicon solar cells and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University;

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- Where I have consulted the published work of others, this is always clearly attributed;

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

Signed:.....

Date:.....

# Acknowledgements

Firstly, I'm extremely grateful for all the support and encouragement from the Sustainable Electronic Technologies group and the Zepler Nanofabrication centre in Southampton. I'd like to thank my supervisors Stuart Boden and Tasmiat Rahman for their guidance and support throughout the project. Through regular meetings and correspondence, they provided their full backing to the research and regularly contributed with their wisdom and expertise. I'd also like to thank colleagues and collaborators including Tudor Scheul, Jack Tyson, Thomas Mercier, Chris Bailey, Omesh Kapur, Peter Shaw, Shona McNab, and Sebastian Bonilla. Everyone contributed substantially in either the research or my sanity throughout the project.

I am thankful for the Engineering and Physical Sciences Research Council (EPSRC) for funding this project as part of the Centre for Doctoral Training in Photovoltaics (CDT-PV). Thanks to everyone in CDT-PV, especially cohort 3 for a highly enjoyable and productive first year of the PhD. I'd also like to thank the Henry Royce institute for funding the transmission electron microscopy study at the University of Sheffield, as well as collaborators in the Department of Materials at the University of Oxford and Imperial College London.

I'd like to also thank my friends for their kind support throughout my time as a student. They contributed to this project by keeping my spirits up and always provided enthusiasm.

Most importantly, I'd like to thank my parents for their backing from the very beginning. I dedicate this thesis to you.

Thank you all.

# Chapter 1

## Introduction

### 1.1 Motivation for Photovoltaics

Our ever-increasing global energy demands have rapidly escalated the pressure put on our natural fossil fuel reserves, as well as amplifying the environmental detriment from using these non-renewable energy sources. The total share of global electricity production using fossil fuels has consistently remained above 60 % since 1990, with the current consumption reported at 65 % [1], [2]. This is the equivalent of almost 11 billion tonnes of oil in fossil fuels every year, equating to over 35 billion tonnes of annual CO<sub>2</sub> emissions [3]. At this rate of consumption, a maximum period of only a few hundred years' supply of fossil fuels is predicted. Furthermore, the increasing CO<sub>2</sub> emissions intensify the greenhouse effect, which in-turn traps the solar radiation within the earth's atmosphere and results in global warming. In fact, out of the 17 warmest years ever recorded to date, 16 have occurred since 2001 and a global temperature increase between 2 - 5 °C is forecasted by the year 2100 [4]. Further studies on this matter have shown that the severity of damaging human-induced change depends not only on the magnitude of the change but also the potential of irreversibility, where 1,000 years of irreversibility is predicted from our current activities [5]. Clearly, the world must find alternative energy sources to supply such high demands and to decelerate the current deterioration of non-renewable sources. Inevitably, renewable energy provides the most viable and sustainable solution to this problem, with the type of which typically dependent on geographical prospects and technological progress. Currently, a total share of only 10.4 % of electricity generation and 5.0 % of total energy generation is globally sustained through renewables [6].

Amongst all renewable energy sources, solar energy is considered key towards a completely 'green' future. Photovoltaic (PV) technologies offer great promise due to the high abundance of solar energy, the versatility and scalability of the technology, and the relative ease in development and installation in both domestic and commercial applications. In 2016, PV became the fastest growing source of net electricity generation capacity, with one-third of all

new electricity generation capacity installed globally in 2017 being in the form of PV [6], [7]. Furthermore, the continuous expansion of PV deployment is expected to result in this technology having the largest renewable electricity generation capacity by 2022, exceeding wind energy [8]. One of the main reasons for this transition is the continuous drop in the initial fixed cost of PV systems. To put this into perspective, the cost of typical PV panels has dropped from \$76 to under \$0.28 per peak watt from 1977 to 2019 [9]. In addition, the process of converting light energy to electrical energy using this technology has seen considerable improvements over the years. For example, single crystal silicon PV, which is currently the predominant commercial PV technology, has seen power conversion efficiency (PCE) improvements from 13 % to over 26 % from 1977 to date in research laboratories [10]. In turn, these improvements have allowed the levelized cost of energy of PV technologies to become increasingly competitive, promoting its global implementation. Despite these merits, further efforts must be made towards the expansion of PV deployment as currently only 2 % of global energy demands are being supplied by solar energy [6]. In other words, the levelized cost of this source of energy must be reduced further to extend the financial value of this technology to the consumer market and hence aid its further deployment.

Since the emergence of the first solar cell from Bell Labs in 1954 [11], PV technologies have been primarily fabricated using the semiconductor silicon (Si) as the light absorbing layer. This material is not only the second most abundant element in the earth's crust, but the technological evolution of PV using Si since its emergence has built a robust platform for its current widespread use in commercial and domestic applications. Currently, PV technologies using silicon comprise roughly 95 % of the commercial PV market and have consistently dominated with over 70 % of the market share since 1980 [12]. Inherently, silicon wafers are usually doped with either boron or phosphorus to create p-type or n-type doping respectively. This is to increase the amount of de-localised charge during photo-generation in this material for PV applications. Historically, p-type cells were preferred due to the greater resistance to irradiation damage that was crucial for space applications [13]. However, the industry is now focusing more on n-type cells due to the inherent boron-oxygen related defects that arise in p-type wafers which cause cell degradation [14]. This type of technology is conventionally grouped into categories, namely mono-crystalline and multi-crystalline silicon PV. The term crystallinity here refers to the degree of structural order to the atoms or molecules in a solid. Hence, in this case, a mono-crystalline silicon solar cell refers to an absorber layer with one periodic orientation or order of silicon atoms, and multi-crystalline meaning of many orientations or

orders. Typically, multi-crystalline silicon solar cells suffer from electrical losses due to the crystallographic dislocations and defects from the structural imperfections in the absorber layer. This results in a lower PCE being achieved when using multi-crystalline silicon instead of mono-crystalline. The popularity of multi-crystalline silicon over the years has mainly been due to the cheaper fabrication cost of this material and ease in processing. However, a sudden drop in the cost of mono-crystalline wafers in 2016 resulted in a large popularity shift towards mono-crystalline silicon PV. This is exemplified by the increase in the total market share of single crystal silicon PV from just under 25 % to over 65 % from 2016 to date [12].

As briefly mentioned, monocrystalline (or single crystal) silicon PV technologies have already reached a record PCE of 26.7 % [10], [15]. However, this is still at research level and the commercial market remains dominated by silicon technologies that have PCE's between 18 – 24 % [8], [16]. Further information regarding these specific types of silicon solar cells is provided in the next chapter. What is important for our discussion here is that the most predominant feature that currents limits the PCE of the majority of the silicon PV industry is the direct application of the metal electrode onto the silicon absorber layer [16], [17]. Traditionally, solar cells consisted of a p-type silicon wafer, with an n-type emitter layer (for charge separation), silver paste contacts and a silicon nitride anti-reflective coating. These types of cell architectures suffer from high electrical losses at the metal-Si interface, limiting these technologies to PCEs considerably lower (~20 %) than the single absorber solar cell theoretical limit of 29.4 % [16], [18]. This limitation occurs due to the high density of electronically active states that arise at the metal-Si interface. These active states are defective or trap regions that limit the flow of photo-generated charge carriers from the absorber to the external circuit, through a mechanism known as Shockley-Read-Hall (SRH) recombination [19]. In other words, the resistance to current flow is heightened by incorporating metal-Si interfaces in these devices. Attempts to mitigate this loss using highly doped regions under the contacts causes the excess energy of the photo-generated charge carriers to be lost, through a different mechanism called Auger recombination, which further limits the overall performance. Further attempts to reduce these losses involved reducing the contacted region area, but this does not eradicate the root of the problem and introduces further fabrication complexities.

Currently, industrial Si PV fabrication lines are based on the passivated emitter rear-contact (PERC) cell (more information on the functionality of this cell is provided in the next chapter) [8]. This architecture limits the recombination losses discussed to some extent by passivating the non-contacted regions of the cell. In simple terms, silicon passivation involves reducing the

surface states (“dangling bonds”) at these interfaces by introducing a dielectric medium [20]. Despite these benefits, the PERC cell is still limited to PCEs of up to 24 %, which is still considerably lower than the theoretical power conversion limit [18], [21]. Regardless of the cell architecture, the pathway to achieving higher performance silicon solar cells is to passivate the contacted regions of the device [16], [22], [23]. To passivate a contact, recombination must be prevented, but not at the expense of the contact conductance. As dielectrics are usually used for surface passivation, and these materials possess high resistance to current flow, the introduction of additional contact resistance with this method is unavoidable. Therefore, these dielectrics must not only be made thin enough to minimise resistance in these contacts, but a mechanism for promoting or demoting charge carrier transport through these contacts is also required, namely charge-carrier selectivity. In PV, the electron and electron-hole (or just hole) are considered as the negative and positive charges respectively, where a hole is the absence of an electron in the atomic structure. These types of contacts that can simultaneously provide charge carrier selectivity and suppress recombination are known as carrier-selective passivating contacts [16], [24].

Ideally, a good carrier-selective passivating contact suppresses the electrical losses at the interface whilst maintaining a low resistivity [16], [25]. Silicon PV devices require passivation of both electron and hole contacts in order to reach PCEs exceeding 25 % [16]. In emerging cell architectures, silicon dioxide ( $\text{SiO}_2$ ) or phosphorous-doped hydrogenated amorphous silicon (a-Si:H) are used as electron-selective passivating contacts. The inherent silicon surface passivation ability and the favourable interfacial band alignments on crystalline silicon make these materials highly suitable. To further promote charge carrier-selectivity, the surface charge carrier concentration of these contacts is modulated using a material with a high fixed charge density, which is generally n-type polycrystalline silicon for electron contacts [24]. However,  $\text{SiO}_2$  is not as effective for hole contacts as electron contacts [17], [26], [27]. In addition, the high temperature ex-situ (after-growth) doping process for the polycrystalline silicon conduction layer used for these types of contacts remains a fabrication barrier. Typically, using thermal diffusion to dope this layer in these contacts involves both forming relatively non-uniform doping profiles as well as fabrication methods that involve processing in temperatures exceeding 1000 °C for multiple hours [28], [29]. Work into alternative structures for hole contacts is currently an important area of research [30], [31]. To date, the most promising material candidates have been p-type amorphous silicon and silicon-rich silicon carbide, but compatibility with conventional high temperature Ag screen printing in industry still remains

an issue [15], [26]. Furthermore, a better method for growing polycrystalline silicon layers, with an in-situ p-type doping process, that can produce relatively uniform films at a lower thermal budget is also of importance. If successful, this growth method could also be implemented towards forming the emitter layer in conventional silicon solar cells, as the same issue with thermal diffusion of dopants (with ex-situ doping) still exists [29], [32], [33].

## 1.2 Thesis outline

The project discussed in this thesis is primarily focused on the formation of hole-selective passivating contacts for silicon solar cells. In summary, the three main objectives for the project outlined are:

1. Produce a novel chemical vapour deposition (CVD) process for growing polycrystalline silicon films with a highly uniform fixed positive charge density through in-situ doping.

2. Develop a highly controllable growth process for a dielectric material that can simultaneously enhance silicon surface passivation and promote hole tunnelling.

3. Form a hole-selective passivating contact for silicon solar cells. Analyse and compare electrical performance with counterparts.

This thesis is comprised of eight chapters in total, with three of these covering the experimental research carried out during this project. Each results chapter begins with a brief introduction, then several sections that essentially comprise the results and discussion, and ends with conclusive remarks and a note on contributions.

**Chapter 2** discusses the fundamental properties of solar cells, which includes the general characteristics of semiconductors and PV devices and defines the key performance metrics of interest. In addition, the technological evolution in design, fabrication, and performance of silicon solar cells to date is discussed.

**Chapter 3** follows on by reviewing the literature on relevant carrier-selective passivating contact architectures for PV applications. This is a built up towards our proposed hole contact architecture in this project, which involves using hot wire chemical vapour deposition (HWCVD) for conductive layer formation and atomic layer deposition (ALD) for dielectric nano-layer formation. This chapter is aimed at giving the reader a good understanding of both the topic of interest and how we propose to achieve a high-performance hole-selective passivating contact.

**Chapter 4** encompasses the experimental and analytical techniques used in the subsequent results chapters. A brief description of the technique or apparatus, background principles and how these are intended to be used for our research is mentioned. This covers the fabrication procedures, characterisation methods and PV device modelling techniques that are a pivotal part of this project.

**Chapter 5** is the first of the three results chapters in this thesis. This chapter is focused on the development of a HWCVD growth process for forming p<sup>+</sup> polycrystalline silicon films. At first, the growth capabilities of the HWCVD tool are analysed and the tungsten filaments are re-configured to increase the deposition temperature. We analyse the boron-doped films grown using this method, studying the morphological and electrical properties. In addition, the in-situ doped silicon growth process is optimized using a sharp post-deposition annealing process that improves film quality.

**Chapter 6** studies the formation of a hole-selective silicon nitride nanolayer. This follows on from chapter 5 where we find the requirement for an interfacial layer to be essential for mitigating carrier recombination and to promote hole tunnelling. Hence, ALD-grown SiN is studied and a highly-controllable growth process is achieved. Using a photoemission-based method, the band alignments at the SiN/Si interface are studied to analyse the potential for hole-selectivity of this nanolayer. The work here provides important information relating to the band structure at this interface and the potential applications of this material.

**Chapter 7**, the final results chapter, looks at carrier-selective contact formation using the work from the two preceding results chapters. At first, the specific contact resistivity of ALD-grown SiN nanolayers are studied. We present findings on the effect of dielectric thickness and metal electrode work function on hole contact performance. Furthermore, we study the hole tunnelling probability and current in our contacts, and make direct comparisons with the SiO<sub>2</sub> counterpart provided.

**Chapter 8** concludes the thesis, summarising the work and providing an outlook on the research carried out.

# Chapter 2

## Photovoltaic device characteristics & typical Si solar cells

### 2.1 Fundamentals of solar cell operation

#### 2.1.1 Silicon Semiconductor Properties

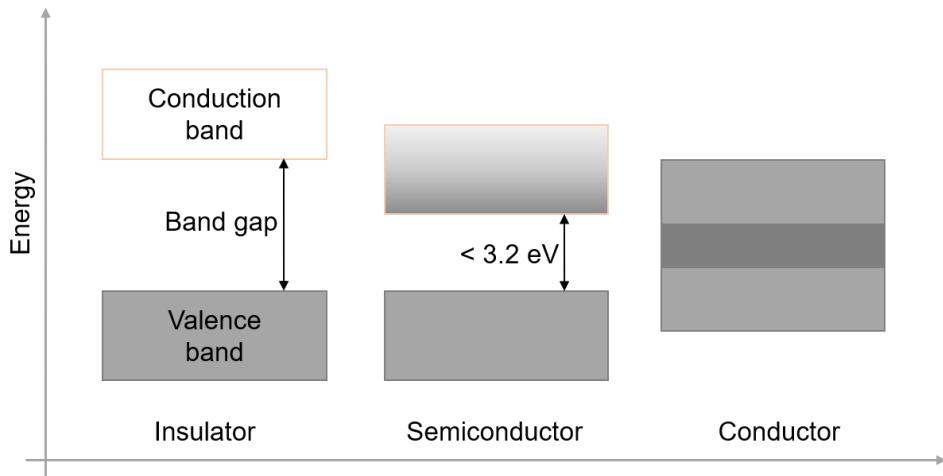

A semiconductor is a material typically comprised from elements either in group IV of the periodic table, or from a combination of group III and V, or group II and VI. These materials possess an electrical conductivity range that lies between that of an insulator and a conductor, which is advantageous in optoelectronics. Simply put, this means that these materials can become conductive once sufficient optical or thermal energy is applied, where the amount of energy required is much lower than that would be required for an insulating material (typically less than 3.2 eV) [11]. This energy, namely the band gap energy, is equivalent to the energy gap between the highest filled electron energy level and the lowest unfilled energy level in the semiconducting material. The notion of energy levels here originates from the Bohr model, where each atom is defined as a small nucleus surrounded by orbiting electrons. Each of these orbiting electrons are at a unique energy level that is defined by the electrostatic force from the nucleus. When these atoms are bonded together in a material, so many electrons and hence energy levels co-exist that it becomes much simpler to define these as continuous bands. In semiconductors, the highest filled and lowest unfilled electron bands are known as the valence and conduction band, respectively. An illustration showing these bands and the difference in band gap between insulators, semiconductors and conductors is presented in Figure 1. As depicted, the valence and conduction bands in a conductor overlap, which is why materials like common metals are electrically conductive without requiring any external energy.

**Figure 1:** Illustration of valence and conduction bands in insulator, semiconductor and conductor materials.

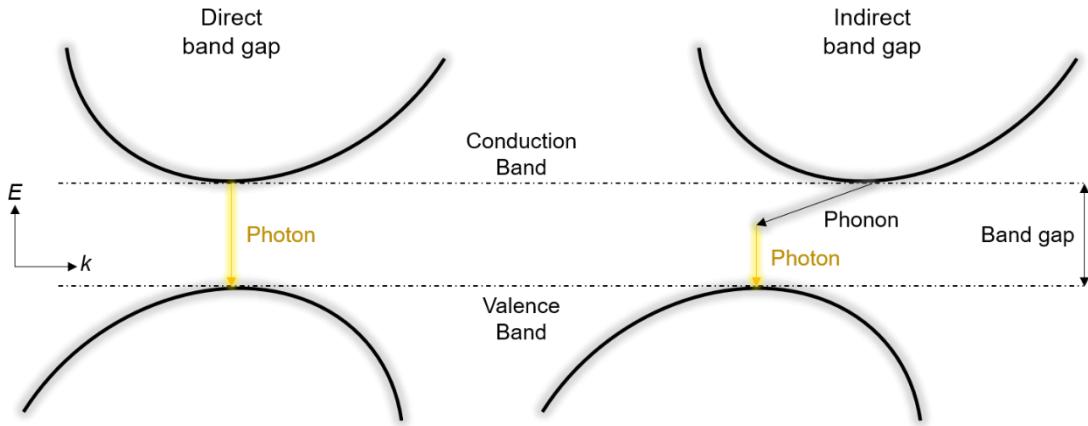

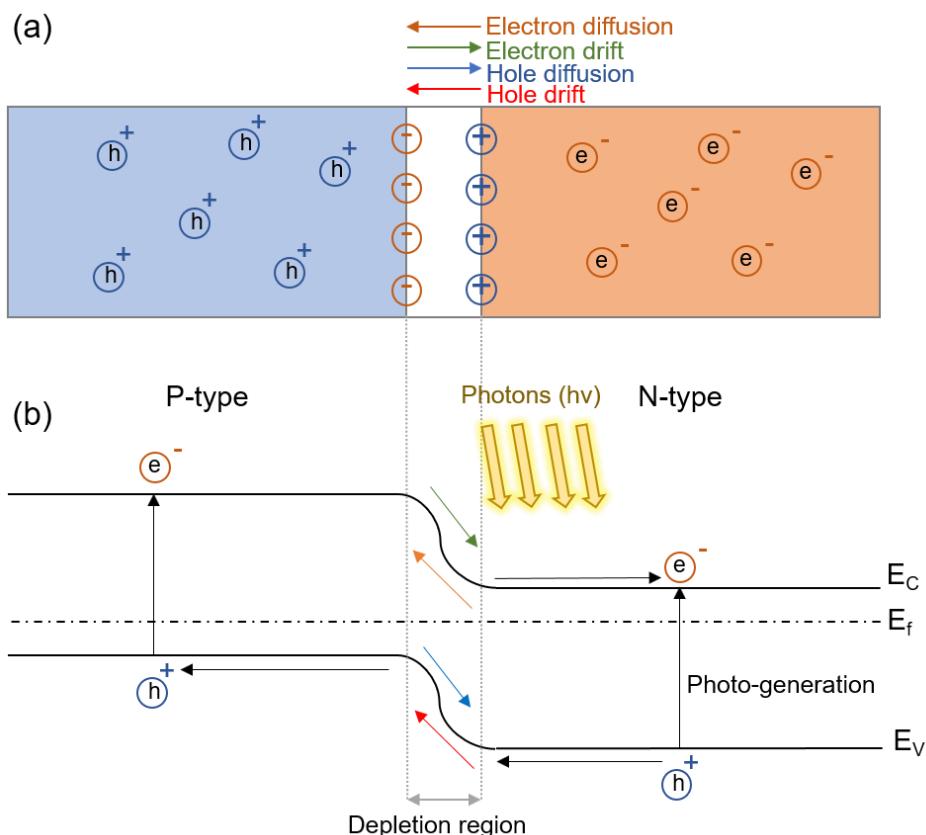

The band gap energy is the minimum energy required to promote an electron from the valence band to the conduction band, which causes de-localisation of charge in a semiconductor material. When this occurs, free carriers have now been created in both energy bands – an electron in conduction and a hole (or electron absence) in the valence band. Hence, we consider two currents in semiconductor physics – electron and hole current. However, the simplified illustration of the energy bands in Figure 1 cannot depict the true transition of carriers between these bands. Typically, depending on the position of the minimum energy state in the conduction band and the maximum energy state in the valence band, semiconductor materials are classed as either direct or indirect band gap materials. These states are each defined by a certain momentum,  $k$ , in the Brillouin zone [34], where if the  $k$ -vectors are identical, the energy gap is considered to be a direct transition. On the other hand, if the  $k$ -vectors are different, an indirect band gap is considered. This phenomenon arises from the shape of the energy bands, where these are most often parabolic near the maximum and minimum points. An illustration of these energy bands showing the difference between a direct and indirect band gap material is shown in Figure 2. Silicon in crystalline form is considered to have an indirect band gap. This means that for the transfer of electrons between these bands, an intermediate state is required for momentum transfer, as depicted in Figure 2. Hence, when an electron recombines with a hole by relaxing to the valence band from the conduction band in such materials, a photon is rarely emitted, and this is considered as non-radiative recombination. For an indirect band gap material to undergo radiative recombination (as in Figure 2), the photon, phonon and electron-hole pair required in this process must occur at the same time and this is virtually impossible in the physical world. In most cases, the free carriers in indirect band gap materials

non-radiatively recombine via Shockley-Reed-Hall or Auger recombination (more information on these phenomena provided later in this chapter). Non-radiative recombination is disadvantageous for PV device performance as the recombination energy is dissipated through lattice vibrations, namely phonons, rather than optical energy that could be re-harnessed in the absorber layer.

**Figure 2:** Energy band dispersion difference between direct and indirect band gap semiconductors.

Typically, a semiconductor material like silicon, which has not had impurities added to it to alter the concentration of carriers (or localised electrons/holes), is called an intrinsic semiconductor. In effect, the number of free electrons in the conduction band or holes in the valence band of such materials is called the intrinsic carrier concentration,  $n_i$ . This is typically defined as a function of temperature,  $T$ , by [35]:

$$n_i = 5.29 \times 10^{19} \left(\frac{T}{300}\right)^{2.54} e^{-6726/T} \quad (1)$$

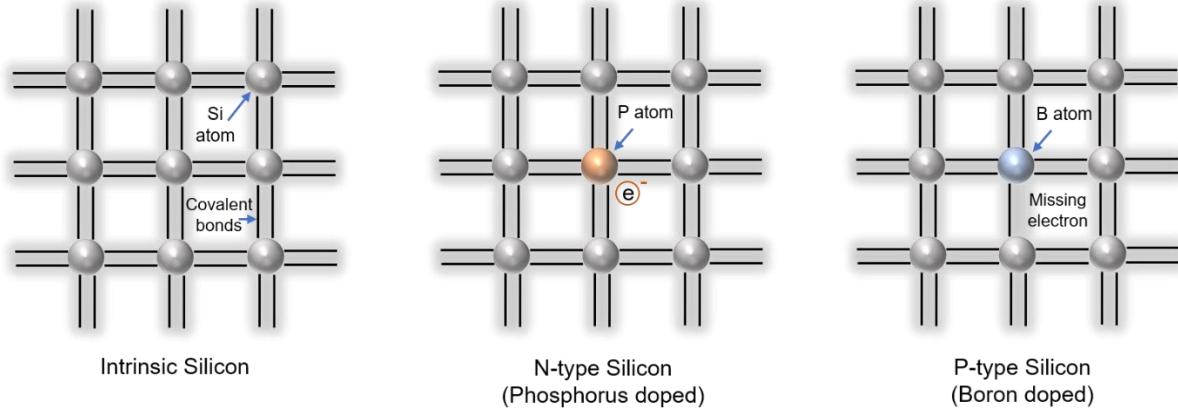

For crystalline silicon,  $n_i$  is typically measured at  $9.65 \times 10^9 \text{ cm}^{-3}$  at room temperature (300 K) [36]. To vary this concentration, silicon is usually doped with electron-rich (group VI) or electron-deficient (group IV) elements to increase the number of de-localised electrons or holes respectively. The notion of electron (n-type) and hole (p-type) doping in a silicon crystal lattice is depicted in the schematic diagram in Figure 3. When doped, namely extrinsic, the semiconductor now possesses a higher concentration of either electrons or holes, which are called the majority carrier in this medium. The other carrier type is named the minority carrier. Typically for photovoltaic applications, silicon substrates that are used as the absorber layer are doped at an extrinsic carrier concentration of between  $10^{14} - 10^{15} \text{ cm}^{-3}$ . At equilibrium, the product of the majority and minority carrier concentration is expressed by the Law of Mass Action and is defined as:

$$n_0 p_0 = n_i^2 \quad (2)$$