# Low-Power Electronic Technologies in Harsh Radiation Environments

J. Prinzie<sup>1</sup>, F. Simanjuntak<sup>2</sup>, P. Leroux<sup>1</sup>, and T. Prodromakis<sup>2</sup>

<sup>1</sup>Department of Electrical Engineering, KU Leuven, Belgium <sup>2</sup>Centre for Electronics Frontiers, University of Southampton, UK

October 26, 2020

1 Abstract

10

11

12

13

14

15

16

17

Over the past decades, electronic technologies have evolved to serve a wide range of applications, with some necessitating their reliable operation in harsh radiation environments. This perspective article reviews the current landscape in rad-hard electronics, covering the scope of radiation environments, the application needs, the underlying phenomena that impose functional constraints as well as established design methodologies, relying on commercially available technologies (CMOS) for mitigating effects that lead to failure. We further examine the potential of emerging memristive technologies in this field and their properties that render these rad-hard. We also review a variety of rad-hard device designs, rad-mitigation techniques, and experimental procedures for validating the performance of the most promising solutions. Finally, we conclude this article by presenting a roadmap on new concepts and application opportunities enabled by the introduction of novel technologies and designs that can reliably operate under such extreme conditions.

### 1 Introduction

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

32

33

34

35

36

37

38

39

Modern electronic technologies have progressed to the level that they can nowadays be deployed almost everywhere – enabling the IoT era and deep learning AI. Significant benefits, however, can be realized by deploying electronics into harsh and inaccessible environments that require operating under high pressure, temperature, concentrations of toxic/corrosive gases, and radiation. Whilst efforts on developing appropriate packaging schemes can render electronics operation practical under most of these conditions, exposure to radiation often leads to an invasive process that causes irreversible damage to the packaged semiconductor devices due to ionization and collision phenomena generated by high-energy photons and particles. Packaging and shielding are often ineffective and may even exacerbate the impact of radiation owing to nuclear reactions induced in the packaging materials.

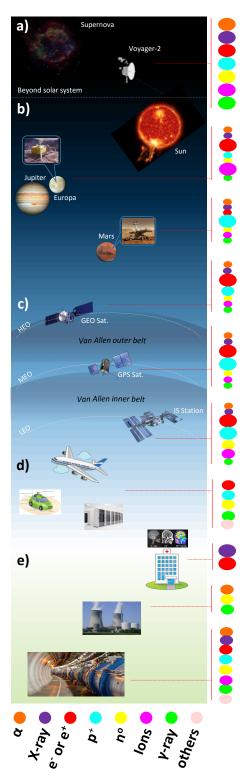

The sources of these high-energy photons and particles are either natural (extraterrestrial and terrestrial) or generated artificially in facilities like nuclear power plants or particle accelerators (Fig. 1). The impact of radiation on electronics depends on the mission or the location where the electronics are being deployed and thus on the characteristics of the radiation environment. The Curiosity probe, sent to the surface of Mars, should have high resilience towards cosmic radiation, especially p<sup>+</sup> radiation from solar activities, since Mars has a low-density atmosphere and no global magnetic field to shield its surface. One of the future destination for interplanetary exploration missions would be Europa, one of Jupiter's moons, where Clipper and Lander probes will face even more extreme radiation of  $\beta$ , p<sup>+</sup>, as well as energetic oxygen and sulfur ions originated from Europa's plasma condition and the strong magnetosphere of Jupiter.<sup>2</sup> Some long-term mission probes may encounter different radiation conditions; the Voyager-2 probe swingby several planets (Jupiter, Saturn, Uranus, and Neptune) along its way to interstellar space. The orbital infrastructures located near the Van Allen belts, such as GEO and GPS satellites and the International Space Station (ISS) (at high, medium and low earth orbits, respectively), are irradiated by the trapped  $\beta$  and p<sup>+</sup> that could damage their electronic systems.<sup>3-5</sup> Maintenance and replacement in such radiative and inaccessible environments entail high cost and risk. Sending a replacement unit to the ISS at the low earth orbit alone costs US\$ 10.000,- for each pound of payload.<sup>6</sup> Henceforth, radhard technologies have a crucial role in space exploration and long-distance communications.

Radiation induced electronic failure has also become an increasing concern in avionics and even ground systems. The  $n^0$  and  $p^+$  particles coming from the atmosphere are found to be responsible for the occurrence of au-

topilot upsets that occur on average once in every 200 flight hours, notwithstanding, electrical upsets in automotive electronics and data centers. $^{3,7}$  In addition, the solar flares' intense particles and X-rays ionize and increase the density of the low layers of ionosphere, respectively, and interact with the electromagnetic waves resulting into disturbances in the high-frequency radio communication system by fading of the HF signal.<sup>3</sup> These problems eventually affect the stability of the flight system, and traffic operations and navigations both in airspace and on the ground, where safety assurance is of primary importance. Similarly, the operation of nuclear facilities in a safety critical manner is of paramount importance and rad-hard technologies are 10 commonly employed to enhance the overall safety margins.<sup>8</sup> Moreover, radiation effects raise a concern in medical and industrial equipment where 12 X-ray and  $\beta$  are used for therapy and diagnostic purposes while in high-13 energy physics facilities, various particles and photons are generated by the 14 collisions in particle accelerators which pose a severe challenge for the ac-15 celerator instrumentation and the radiation detection, data acquisition and 16 communication in the embarked experiments.<sup>9</sup> 17

Nevertheless, rad-hard integrated circuit technologies often require additional processing and more complex configurations than the standard fabrication flow that makes the rad-hard electronics, particularly low-power electronic technologies, difficult to keep up with the International Technology Roadmap for Semiconductors (ITRS) guide. This article examines the latest logic and memory design techniques for radiation effect mitigation and presents future trends for rad-hard technologies.

18

19

20

21

22

Figure 1: Energetic radiation environment. (a) Cosmic galactic radiation is the result of galactic events, such as supernova explosions and pulsars that emit  $\gamma$ -ray and high energy particles (83.3% p<sup>+</sup>, 13.72%  $\alpha$ , 2%  $\beta$ , 0.98% heavy ions). (b) Another source at deep space is the cosmic solar radiation where it emits  $p^+$ ,  $\beta$ , X-ray, and  $\gamma$ -ray; the concentration and energy of these components vary depending on the solar activities (solar wind, solar flare, and coronal mass ejections) that occur randomly.(c) The earth's magnetic field and atmosphere play a significant role in limiting some of these particles reaching the surface of the earth where they are trapped inside the Van Allen outer magnetic belt (it consists mainly of  $\beta$ ), whereas the other cosmic particles interact with atmospheric particles producing  $\beta$ , p<sup>+</sup>, and a small portion of heavy ions and trapped inside the inner belt. Thus, the Van Allen belts can be classified as a radiation environment located at the earth's orbital region. (d) Nevertheless, some of the cosmic radiation can still pass through these belts and react with the earth's atmospheric molecules (such as oxygen and nitrogen) producing  $n^0$ ,  $p^+$ , and pions  $(\pi)$ ; the  $\pi$  eventually produces  $\beta$  pairs (e<sup>-</sup>-e<sup>+</sup>)and neutrinos. In addition to these particles,  $\gamma$ -rays are also emitted from the atmosphere during thunderstorms. (e) Radioactive materials, such as uranium, thorium, and their derivatives, are another terrestrial radiation source which emit  $\alpha$ ,  $\beta$ , and  $\gamma$ -ray. Radiation can also be intentionally generated using radiation generators for medical and industrial purposes (X-ray and  $\beta$ ) or particle accelerators (various photons and particles) and some are unwanted by products of nuclear reaction  $(\alpha, \beta, n^0,$ and  $\gamma$ -ray) that are produced by power plant facilities. The contribution of each type of radiation varies depending on the location where the electronic is deployed as depicted in each zone, see supplementary Tables 1 and 2 for details.  $\beta$ represents e or e particles

# 2 Physics of radiation-induced electronic failures

2

13

14

15

16

17

18

19

20

21

22

23

24

25

27

28

29

30

31

34

35

36

37

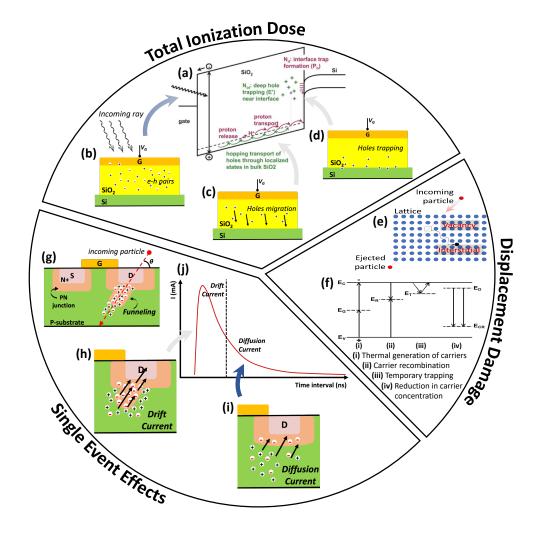

High-energy photons (X-ray, and  $\gamma$ -ray) and particles (n°, $\beta$ , p<sup>+</sup>,  $\alpha$ , and heavy ions) interact with their environment and may deposit energy into material along their path. This energy deposition may result in temporary or permanent effects in this material. The severity depends on the impact of the radiation on the physical or chemical properties of the material. For semiconductor devices, the impact predominantly occurs in the semiconductor and insulator materials, rather than in the metals. Radiation can result in both temporary and permanent damages which are classified into three classes: total ionization dose (TID), displacement damage (DD), and single event effects (SEEs), as depicted in Fig. 2.

Both photons and particles can ionize materials in semiconductor devices. The cumulative dose is quantified by the amount of absorbed ionizing energy per mass, having an SI unit of Gray (Gy; 1 Gy = 1 J/kg = 100 rad). 11 Current semiconductor circuits and systems suffer electrical degradation after several tens of Gy up to several tens of kGy for space certified components. A limited number of custom radiation-hardened components can sustain up to hundreds of kGy. 12 Fig. 2(a) shows a band diagram of a Metal-Oxide Semiconductor (MOS) device and the schematic of the TID degradation mechanism due to trapped charges in the surrounding oxide layers. The mechanism is started with the ionization of atoms resulting in electron-hole (e-h) pairs in the SiO<sub>2</sub> material (Fig. 2(b)); this process occurs in a few femtoseconds and requires approximately 17 eV per e-h pair. 11 Since the electron mobility is higher than the hole mobility, the electrons can easily escape the oxide material through the positively biased gate within a few picoseconds. A fraction of electrons recombines with the holes (Fig. 2(c)). Note that high-energy photons have a high charge yield and may generate a higher number of un-recombined holes compared to high-energy particles.<sup>13</sup> Hereafter, the holes drift toward the interface through localized states in the bulk Silicon where they may release protons (H<sup>+</sup>) which are embedded as impurities in the crystal. The holes can be trapped in bulk defects or at the Si-SiO<sub>2</sub> interface (Fig. 2(d). The H<sup>+</sup>, that also migrate to the interface, are known to cause depassivation of the Si-H bonds at the interface thus forming additional interface traps. The trapped charges are responsible for a degraded current gain and an increased recombination rate in bipolar transistors, reduced mobility, threshold voltage shifts, an increase of 1/f noise, mismatch and leakage current in MOS transistors. 11,12,14 From a circuit perspective, device TID effects deteriorate circuit behaviour and may lead to a reduced performance to even complete failure in CMOS circuits and systems.

DD is a non-ionizing mechanism that is initiated by the collision of parti-2 cles with the atoms of the semiconductor and may result in physical damage in the lattice. Photons can indirectly induce DD by producing secondary electrons having high kinetic energy. 11 The affected atoms may be displaced from their initial position, creating vacancy and interstitial defects in the lattice which may interact further to form cluster defects (Fig. 2(e)). The concentration of these defects may become significant upon continuous or repeated radiation exposure. The severity of the damage not only depends on the total radiation exposure time but also on the type of particles. A 1 10 MeV no can induce multiple collisions in the lattice (damage cascade) from 11 a single incidence while a high atomic mass incident ion, such as 15 keV As 12 (74.9 Da), may locally deposit a considerable amount of energy and melt the 13 material forming amorphous clusters; the cluster size can be up to 5 nm.<sup>15</sup> 14 These defects create deep-level traps within the bandgap and are responsible 15 for the increase of recombination rates and the reduction of charge carrier 16 lifetime (Fig. 2(f)). As a result, DD increases the saturation voltage and 17 a reduction of the current gain in a bipolar transistor. <sup>14</sup> Bipolar transistors start to degrade typically at neutron fluxes of 10<sup>10</sup>-10<sup>11</sup> while MOSFETs do 19 not tend to degrade till 10<sup>15</sup> n°/cm<sup>2</sup>; this indicates that bipolar transistor are 20 more sensitive to DD than MOSFETs (CMOS) since the latter are surface de-21 vices which suffer less impact from bulk defects. 14 Also photovoltaic devices 22 tend to degrade due to DD, which is a problematic issue in space where they 23 are being used as the primary power source. <sup>15</sup> In addition, opto-electronic 24 devices such as photodiodes used for instance in optical communication, but 25 also in camera chips, degrade from the reduced charge carrier life-time as 26  $well.^{16}$ 27

A one-time ionization event from an energetic particle hitting a semiconductor device can also induce severe temporary or permanent electronic failures. The mechanism of the SEE starts with the creation of e<sup>-</sup>h pairs along the track of the impinging particle in the semiconductor material (Si), known as a charge funnel. The incidence angle, mass, and energy of the particle determine the density of the e<sup>-</sup>h pairs in the funneling region (Fig. 2(g)).<sup>17</sup> The excess e<sup>-</sup>h pairs will either recombine or be transported through drift or diffusion.<sup>11</sup> The actual SEEs are predominantly caused by the charges generated in the vicinity of the doped regions like the source and drain junctions of a MOS device. There, self-recombination cannot be the dominant response when the device is under bias and electric fields are present and most carriers will be transported. The transport of electrons follows a two-step process. A high number of electrons drift to the opposite polarity bias due to a strong electric field near the device's source and drain junctions (Fig. 2(h)), fol-

28

29

30

31

33

34

35

36

lowed by the diffusion of the remaining scattered electrons (Fig. 2(i)). This results in a parasitic current pulse in nanoseconds interval (Fig. 2(j)) with a steep edge (fast drift) followed by a long tail (slow diffusion). This charge spike may induce temporary (non-destructive) soft-errors (such as upsets and transients) or permanent destructive errors (such as latch-up, burnt-out, gate rupture, and snap-back) in the circuit.

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

33

The concurrent effect of TID and SEEs in CMOS devices has changed over time with technology scaling. Threshold voltage degradation in MOS devices is proportional with the square of the gate-oxide thickness  $t_{ox}^{2.18}$ Therefore, scaled devices are generally more resilient to long term degradation induced by trapped charges in the gate-oxide. However, the present deep sub-micrometer technologies have very thin gate oxides which cause minimal impact and the remaining effects are mostly dominated by trapped charges and interface traps in the surrounding oxides like STI and SiN spacers or fin oxides<sup>19</sup> and are far from negligible, especially at MGy dose levels. The actual TID impact on the devices can be very different between technologies and even between foundries and are highly dependent on sizing, bias conditions and even temperature. For SEEs the general tendency is opposite meaning that they become worse in deep sub-micron devices due to shrinking node capacitances and reduced supply voltages. The amount of radiation induced charges becomes larger relative to the functional charge in the devices increasing the amplitude of the transients and the amount of upsets. The smaller device sizes also result in a higher probability of single particle strikes affecting multiple devices increasing the number of multi-bit upsets.

The radiation levels on earth are considerably lower than those in space and it would take many decades for TID or DD to become an issue. However, even at a very low dose rate, every single energetic particle (especially  $\alpha$  and  $\rm n^o$ ) can potentially induce an SEE in high-altitude and on-ground systems. <sup>11</sup> Therefore, SEE is the most challenging issue in the terrestrial environment. Radiation hardening techniques are commonly used to mitigate upsets and latch-up in memory cells and logic devices, respectively. <sup>11</sup> Notwithstanding, TID may still be a concern for medical and industrial electronics where highenergy photons and particles are often used for therapy, sterilization, and inspection and definitely for instrumentation in nuclear energy facilities and high-energy physics experiments where dose levels can go up to several MGy.

Figure 2: The routes of radiation damage in electronics. Total ionization dose (TID), displacement damage (DD), and single event effects (SEE) could lead to damages in semiconductor devices. (a) TID is a cumulative charge incidence phenomenon contributed by (b) e-h pairs generated in the oxide, (c) low mobility holes that slowly migrate through localized states and (d) holes trapped at the interface region. (e) DD is a cumulative collision phenomenon where particles alter the position of atoms in the semiconductor lattice affecting (f) carrier recombination, trapping, and concentration. (g) SEE is a single charge incidence phenomenon induced by particles hitting the device creating e-h pairs along its trajectory and generates (h) drift and (i) diffusion currents, (j) despite the current spike occurs in a few nanoseconds it can lead to either temporary or permanent failure. The schematics are adopted from 13, 15, 17

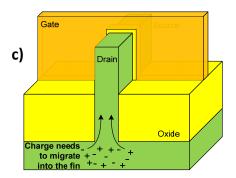

## 3 Radiation Hardening by Design

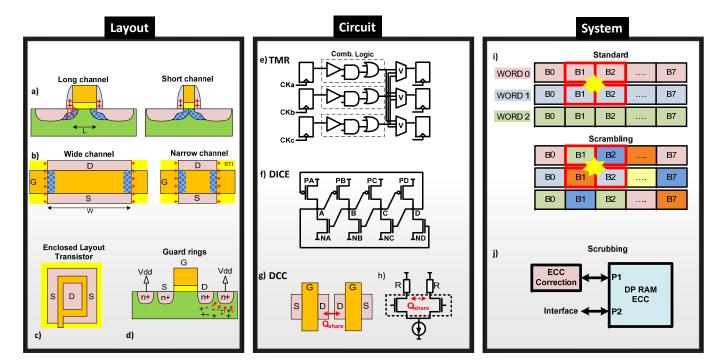

Integrated circuits and systems can be protected from radiation effects using a variety of techniques across distinct design levels, taking into account:

(i) Layout, (ii) Circuit techniques and (iii) System level mitigation techniques. Since SEEs and TID effects differ in terms of timescale and device impact, their mitigation methods are different too. Layout techniques are more generic and can be applied broadly. Circuit and system level mitigation approaches are, however, more specific and generally distinct strategies exist for digital and analog circuits, with an exception at layout level. Fig. 3 shows various radiation hardening techniques for CMOS implementations. Note that radiation hardened processes are an alternative strategy but they come with significantly higher development cost and often a lower performance.

Long term radiation exposure may result in positive trapped oxide charges. Following Moore's scaling trend, the gate oxide thickness has shrunk dramatically and secondary oxides, mainly SiN spacers and Shallow Trench Isolation (STI) became primary hotspots. <sup>19</sup> Trapped charges in the SiN spacers influence the local potential in lightly doped LDD (Local Drain Diffusion) regions (Fig. 3(a)). <sup>22</sup> For PMOS transistors, p-doped LDDs become highly resistive, rendering an overall increase of the channel resistance. For NMOS transistors, n-doped LDDs become more negative making LDD less effective for hot carrier degradation; the reason why LDD is used. For long channels, the effect is relatively less dominant than short channels due to an unaffected central region. Charges trapped in the STI regions affect the local threshold voltage in the channel edge, as is shown on Fig. 3(b), similarly to trapped charges in the gate oxide. <sup>23,24</sup> This results in an increased leakage current for NMOS devices. <sup>25</sup> Since trapped STI charges only affect the channel edge, wide devices suffer relatively less than narrow devices.

A generally effective technique for mitigating long term degradation in deep-submicron technologies is using long and wide devices. Large widths are often unfavorable due to power consumption and area constraints. To overcome STI edge effects, an edgeless transistor can efficiently mitigate these effects, as shown on Fig. 3(c). The Enclosed Layout Transistor (ELT) has its drain in the middle, enclosed by the channel and no STI touching the channel. However, design rule compliance and matching becomes more challenging. Mitigating SEEs at layout level can also be done by adding reverse biased guard rings nearby sensitive nodes, as depicted on Fig. 3(d). Large reverse bias voltages and depletion regions enhance charge collection capabilities so electron-hole pairs in the substrate are diverted towards the guard rings. Alternative structures like dummy junctions are often used to

save area.<sup>29</sup> These techniques can be applied for different circuits, which makes layout techniques the preferred option for rad-hardening.

At circuit level, many mitigation methods exist for different circuits. The most popular technique for SEE mitigation is employing the concept of Triple Modular Redundancy (TMR), shown on Fig. 3(e). Digital logic, consisting of sequential and combinational logic, is implemented thrice such that single logical errors can be corrected. Voters select the majority of the inputs and implement single error correction. In nanoscale technologies, single particle strikes can affect multiple gates simultaneously, hence gate spacing becomes mandatory to prevent multi-cell upsets. Unfortunately, TMR results in a more than 3x power, area and speed penalty due to the voters and long interconnects. To alleviate these drawbacks, several alternatives are possible 33,34

Instead of logic level triplication, these individual gates can be hardened by design too. The DICE (Dual Interlocked Cell) latch, shown on Fig. 3(f),<sup>35</sup> is an example of a radiation hardened latch. Instead of using two storage nodes, an additional pair is added. The latching positive feedback runs in both directions in the circuit but if an SEE occurs at any node A-D, the SEE can never propagate through the entire loop and will be blocked by an inactive device.

For analog circuits, SEE mitigation is less trivial. Redundancy can be used here, for instance in current mirrors, where each gate finger of the input device is connected to each individual finger of the output device resulting in a reduction of a single finger transient by the amount of fingers used. This requires higher bias currents and thus comes at the expense of the overall area and power needed. Another commonly used technique is to increase the sensitive node capacitance to reduce voltage disturbances. This however comes at the cost of speed or power. However, for DC circuits like bandgaps and biasing circuitry, capacitive decoupling, capacitive negative feedback or intermediate low pass filtering are simple and efficient. For fast signaling, Differential Charge Cancellation (DCC) mitigates SEEs in analog differential circuits. Two closely spaced junctions can share the charge of a particle strike, as shown on Fig. 3(g). If those drain junctions operate differentially, as shown on Fig 3(h), the shared charge acts as a common mode signal to the circuit and can thus be easily suppressed.

At system level less generic and more specific mitigation is used. For instance, processors can use software level mitigation like signatures or tightly coupled cores, executing the same program.<sup>39</sup> For memories, several generic techniques exists, like error correcting codes (ECC),<sup>40</sup> data scrambling<sup>41,42</sup> and memory scrubbing.<sup>41,43</sup> ECC uses coding schemes with redundant bits for error correction. Depending on the ECC, single or even multiple errors

can be detected and corrected. Hamming codes are frequently used with single bit correcting capability although multiple errors in a single word are non-correctable unless more complex codes are used. As shown on Fig. 3(i), standard physical word placement can be susceptible to multi-bit upsets in adjacent cells. Data scrambling is an effective technique to distribute same word bits physically such that multi-cell upset clusters do not affect multiple bits in a word. 41,42 Hence, each affected bit is correctable. If bits become corrupted in the memory, they remain faulty until corrected. A methodology for on-line Error Detection and Correction (EDAC) is shown in Fig. 3(j). A dual port memory has both a memory scrubbing interface to continuously 10 scan through the memory to correct erroneous words and an application interface. Memory scrubbing should be fast enough to prevent 2 different 12 particles hitting the same word between ECC checks. 41,43 13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

33

34

35

36

37

38

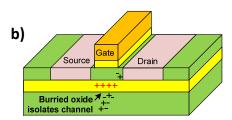

As previously noted, the CMOS process itself has an important impact on the radiation hardness. Aside from bespoke radiation hardened technologies, a variety of alternative, commercially available, CMOS technologies exist: bulk CMOS, Silicon-on-Insulator (SOI) and FinFets with varying radiation responses. 44-46 The above mentioned effects apply specifically to conventional planar CMOS devices on a bulk Si substrate, shown in Fig. 4(a). SOI transistors, alike the ones shown in Fig. 4(b), are intrinsically less susceptibility to SEEs due to the buried oxide (BOX) layer that isolates the channel from the substrate.<sup>47</sup> In a similar fashion to bulk-CMOS, particles create an ionization track deep in the substrate, yet, deep substrate charges cannot migrate towards the junctions since they are isolated by the BOX. Hence, only a fraction of the total generated charge is collected. However, the additional BOX layer comes at the cost of a thick oxide facing the entire channel area where charges can be trapped, similarly to the gate oxide, resulting in threshold voltage shifts. 44 State-of-the-art ultra-thin SOI processes employ BOX thicknesses in the range of 7-15 nm<sup>48</sup> and their TID radiation hardness compares to 0.35  $\mu m$  - 1  $\mu m$  bulk CMOS technologies. The improved SEE sensitivity and moderate TID degradation explains the success of SOI technology for many space applications, where the total doses are rather limited. As BOX thicknesses have shrunk over time, they have become useful as secondary gates to adjust the threshold voltage of the devices offering the ability to cancel threshold voltage shifts.<sup>49</sup>

In contrast to planar CMOS technologies, FinFets are 3D structures with surface conductivity at different edges of the fin. As illustrated in Fig. 4(c), thick oxides are not in direct contact with the active regions and improved TID sensitivity is therefore expected. However, since the devices have become extremely small in terms of volume, trapped charges in surrounding oxides can indirectly impact the channel region.<sup>50</sup> For SEEs, if particles

Figure 3: Radiation Hardening by Design (a) Short channel effects from trapped charges in the SiN spacers. (b) Narrow channel effects from trapped charges in the STI. (c) Enclosed layout transistor (ELT) layout to avoid STI contact with the channel. (d) Reverse biased guard rings near the sensitive nodes to divert charges. (e) Triple Modular Redundancy (TMR): Logic cells are triplicated. Both sequential cells and combinational cells can be redundant. Voters are inserted for single error correction. (f) Dual Interlocked Cell (DICE): Radiation hardened latch with an additional storage pair and interlocked connectivity. (g) Differential charge cancellation (DCC): Charge sharing by closely spacing differential nodes to convert disturbances to a common mode signal. (i) Multi-Bit Upsets (MBUs) in memories can be mitigated by distributing common bits spatially such that a single particle cannot affect multiple bits of the same word. (j) Continuous read and correction of a memory to correct for single accumulated errors.

Figure 4: Radiation effects in advanced

CMOS devices (a) In Bulk CMOS, charges

- 1 hit the fin directly, these charges can be captured by the junctions. This

- 2 probability is however relatively low and due to the limited volume, a small

- 3 amount of charge can be generated in the fin. The remainder of the charge

- 4 is typically deposited in the substrate and overall charge diffusion into the

- fin is limited.<sup>51,52</sup>

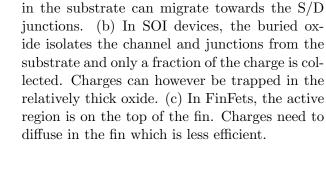

# 4 Radiation Effects in Integrated Memories

Memories are often tailored to achieve high density (bits/area) with specific device structures, each having radiation assurance concerns. Different memory technologies like SRAM, DRAM, flash, MRAM and ReRAM have different performance trade-offs such as volatility, access time, power consumption and compatibility with CMOS platforms.<sup>53</sup> Bi-stable Static Random Access Memories (SRAM; Fig. 5(a)) are widely used as local on-chip memories due to their fast operation and integration with CMOS processes. Information is retained on two complementary circuit nodes through positive feedback, however, SEEs can result in a bit flip if sufficient charge is injected. This charge is known as the critical charge, Q<sub>crit</sub>, which depends on the node 11 capacitance, device strength (or feedback) and supply voltage. 54,55 Reduc-12 ing any of these parameters reduces the radiation resilience, which explains 13 why nanoscale technologies have become more sensitive to SEEs.<sup>55</sup> Circuit 14 hardening techniques like capacitive and resistive decoupling  $^{56-59}$  and sys-15 tem level mitigation, discussed in Section 3, improve robustness significantly. 16 Dynamic Random Access Memories (DRAMs) rely on charges stored on ca-17 pacitors (Fig. 5(b)). SEEs result from charge deposition on the storage 18 capacitor, corrupting the stored (multi-level) information, although errors in 19 surrounding logic contribute too.<sup>60,61</sup> Smaller capacitances and multi-level 20 schemes make DRAMs more sensitive to upsets.<sup>62</sup> 21

Flash memories are non-volatile elements with charges stored on a floating gate, shown in Fig. 5(c). The device is read by measuring the threshold voltage of the MOS structure which depends on the floating gate charge. Similarly to DRAMs, multi-level flash memories are used today. Due to TID, positive charges may accumulate in both oxides and will neutralize electrons in the floating gate resulting in a threshold voltage shift over time. Therefore, memory cells will become corrupted as the ionizing dose increases and in contrast to general CMOS scaling, the tunneling oxide thickness of floating gate devices is not shrinking significantly beyond 7 nm<sup>64</sup>. Multi-bit storage makes flash memories more susceptible due to smaller margins. Since the floating gate is isolated from active regions, SEEs cannot corrupt information directly but can occur due to configuration upsets or readout errors.

22

24

25

26

27

28

29

31

32

33

34

35

36

37

38

DRAM, SRAM, and flash technologies are all suffering from scaling issues and struggle to keep up with Moore's Law.<sup>10</sup> Various emerging non-volatile memory technologies are being proposed to replace them, such as ferroelectric-RAM (FeRAM), phase change-RAM (PCRAM), magnetic-RAM (MRAM), and Resistive-RAM (ReRAM). Here we ruled out FeRAM and PCRAM due to several challenges that hinder their potential as future rad-

hard memory. Specifically FeRAM is sensitive to contamination during the back-end-process integration, while PCRAM is temperature-sensitive which makes it ill-suited for space and nuclear applications.<sup>67</sup> MRAM and ReRAM are considered as the forerunners due to their excellent performance, CMOS compatibility, and radiation tolerance.

The discovery of room temperature-giant magnetoresistance in 1988 had led to the rapid development of spintronic devices, particularly MRAM.<sup>68</sup> The MRAM device structure is based on metal/magnetic material/insulator/magnetic material/metal stack (Fig. 5(d)) and the tunneling conductance between this stack is controlled by the magnetization of the two magnetic materials, de-10 noted as tunneling magnetoresistance (T-MR). The polarization of one of the magnetic materials is fixed (reference layer) while the other's polarization can 12 be flipped (free layer) by a spin-polarized current inducing spin torque effect, 13 and the device can be turned On and Off when the magnetic polarization of 14 both materials are in anti-parallel and parallel, respectively.<sup>68</sup> In principle, 15 the overall size of an MRAM cell can be miniaturized down to single nanome-16 tre scale, demonstrating MRAM's excellent scalability prospects. Moreover, 17 the underlying mechanism relies on the current density rather than the ab-18 solute current which scales with the cell size.<sup>68</sup> In practice, however, scaling 19 such technologies can be limited by the thermal stability factor  $(\Delta)$  where 20 decreasing the anisotropy of the magnetic material decreases  $\Delta$ .  $\Delta$  lower 21 than 60 may result in an unstable magnetic moment and thus lead into poor 22 memory retention at elevated temperatures.<sup>69</sup> SEEs can potentially induce 23 bit flip soft-errors in the MRAM cell. Nevertheless, the occurrence probability is significantly lower compared to charge-based memories.<sup>70</sup> DD, however, can cause an issue when scaling down the MRAM cell, where the interfacial 26 quality between the ultra-thin multilayers is difficult to maintain.<sup>68</sup> The 27 energetic particles damage the interfacial structures forming an intermixing 28 phase in the insulator degrading the T-MR effect.<sup>68</sup> 29

The ReRAM, that is part of memristor (memory-resistor) technologies, has a simple metal/insulator (storage layer)/metal sandwich device structure (Fig. 5(e)). Various materials can serve as the insulator (oxide, chalcogenide, nitride, or polymer), and it can be designed in such a way as to exhibit digital or analog behaviour.<sup>71</sup> The switching mechanism of such memristor cells is controlled by the movement of anions and cations under an electric field. This ionic movement induces the formation and rupture of a conducting filament/region (consisting of donor defects (valence-change type), or metallic ions (electrochemical type)) that controls the electron flows in the cell. This phenomenon can be traced back to 1962,<sup>72</sup> and yet it had not gained enough attention until the HP Labs showcased its potential for the next-generation high-density data storage in 2008.<sup>73</sup> The memristor shows the potential of

30

31

33

34

35

36

scalability towards 10 nm node<sup>74</sup> and the insulator can be thinning down to sub-10 nm. 75,76 Such a thin insulator will only absorb very little energy from the radiation, which makes memristor an intrinsically rad-hard element.<sup>77</sup> Memristor cells are sufficiently high resistant to SEEs (bit flips only occur due to the transient photocurrent effect originating from the nearest neighbor transistors not from the memristor cell itself)<sup>78,79</sup> and a very high fluence (above 10<sup>18</sup> 1-MeV-equivalent-neutrons/cm<sup>2</sup>)<sup>80</sup> or dose (tens to hundreds of kGy)<sup>81,82</sup> is required to show noticeable effects on the cells due to DD and TID, respectively. Such a high dose is above the minimum requirement for space electronics.<sup>83</sup> The radiation could induce defects generation<sup>84,85</sup> and, 10 in some cases, phase transformation in chalcogenide<sup>86</sup> and oxide<sup>81</sup> materials. There is, however, still a limited number of comparison studies between the 12 switching mechanism of valence-change and electrochemical types performing 13 in radiation rich environments. Any of these radiation-induced defect/phase 14 changes may lead to an increase in leakage current, a decrease of the memory 15 window and switching instability, and overall variation of switching parame-16 ters. Nevertheless, this form of degradation does not significantly affect any 17 digital functionality.<sup>87,88</sup> The defects generation could become a problematic issue when it degrades the synaptic functions<sup>79,89</sup> (such as dynamic range 19 and linearity properties, (Fig. 5(e)) of the analog memristors where these 20 metrics are particularly crucial for the realization of in-memory computing 21 and bio-inspired computing applications.<sup>90</sup> 22

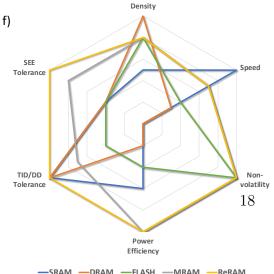

SRAM, DRAM, and flash are commercially available memory technologies in the market. SRAM and DRAM serve as the primary (system) storage since they can perform high-speed switching and robust endurance while flash serves as the secondary storage due to its non-volatility characteristic. MRAM and ReRAM are non-volatile memories and their performance is much better than flash and almost as good as SRAM and DRAM.<sup>53</sup> Henceforth, these two emerging technologies could serve as universal memories for both primary and secondary data storage (Fig. 5(f)). The use of non-volatile memories as the primary storage is beneficial for achieving disaster-resilient computing where the system can retain the computation result after a sudden loss of power, which can be caused by cosmic radiation.<sup>3,70</sup> MRAM, however, still can suffer from SEE and DD while ReRAM appears to be susceptible to DD. Whilst both technologies appear to be appealing for rad-hard electronics applications, additional efforts are needed for benchmarking their resilience to DD and SEE. Nevertheless, MRAM cells are used in series with a transistor as the selector element in an array configuration (1T1MTJ).<sup>53</sup> Hence, the array is prone to the three types of radiation damage. Meanwhile, for ReRAM, the transistor can be replaced with a Zener diode (1D1R). The Zener diode has the same sandwich architecture as ReRAM which could have

23

24

26

27

28

29

30

31

33

34

35

36

- 1 high resiliency in highly radiative environments as ReRAM does. Moreover,

- $_{2}$  this diode's architecture is advantageous to retain the maximum achievable

- 3 scalability in the array configuration. This makes ReRAM more appealing

- <sup>4</sup> for rad-hard electronics than MRAM.

Figure 5: Radiation effects in memory technologies. (a) SRAM devices store information on two complementary nodes. An SEE on each node can flip the state of the cell. With sufficient charge and due to positive feedback, the other node will also flip. (b) DRAM devices can store multiple bits on a single capacitor. SEEs on the switch transistor inject charges on the storage capacitor and the resulting voltage error can result in erroneous information. (c) Flash memories are non-volatile devices that rely on fixed charges in a floating gate which are measured through threshold voltage shifts. Long term TID effects result in trapped charges in both oxides shifting the threshold voltage which results in faulty bits accumulated over time. (d) MRAM uses magnetization direction to store information through an ultra-thin barrier layer sandwiched between two magnetic layers. Radiation results in the formation of an intermixing phase in the barrier layer and deteriorates the tunneling magnetoresistance effect. (e) ReRAM is based on ionic movement and the defects concentration inside the switching layer controls this movement. Radiation induced defects generation can occur after a huge dose of radiation and increases the leakage current. (f) Performance comparison of the different memory technologies.

### 5 Future prospects

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

32

33

34

35

36

37

38

39

For the past few decades, CMOS technology scaling has enabled a massive increase in system complexity and performance. Logic gate delays have shrunk to less than 10 ps enabling multi-GHz operation with up to a billion transistors on a single chip. In addition, the overall memory capacity and bandwidth has increased in modern systems. These improvements have fueled a series of disruptive developments in areas such as Machine Learning, Artificial Intelligence, Computer Vision and Autonomous Decision making. Cyber-physical systems, where computer intelligence is integrated inside the application, are nowadays offered as standard.

Total dose and displacement resilience generally improves with device scaling, intrinsically allowing circuits to survive higher radiation doses. New CMOS platforms will more easily find their way in avionic, space and nuclear applications. This might enable a drastic increase in autonomous decision making and broad context Artificial Intelligence in space, consumer electronics in cubesat missions, Intelligent computer vision algorithms in nuclear fusion and fission reactors and self-exploring unmanned vehicles for nuclear accident intervention and dismantling. Improved radiation hardening techniques can enhance the systems' lifetimes in these environments and will find additional uses in high-dose applications like particle accelerator and detector instrumentation. On the other hand, as small technological nodes become more sensitive to SEEs, even safety critical transport applications like airplane autopilot systems, railway systems and the emerging field of autonomous cars that strongly relies on advanced signal processing and AI, require fault mitigation strategies either at circuit, system or software level to fulfill their highly challenging MTTF (Mean Time To Failure) requirements. Resilient implementation of next-generation electronic technologies with little overhead (performance, power, cost) is thus the key to unlock these future applications.

Along these lines, MRAM and ReRAM technologies show great prospects for replacing SRAM and DRAM as primary storage due to their non-volatility that can support a variety of fault mitigation strategies and allow to implement more easily disaster-resilient computing. The trend of NewSpace commercial space flights necessitates the development and use of reliable and compact electronics that can also contribute in reducing the launch and maintenance costs. MRAM and ReRAM technologies are a good fit to this requirement due to their excellent rad-hard performance, low-power consumption, high density and independence to auxiliary components, unlike SRAM and DRAM, that should respectively be backed by battery and capacitor cells.

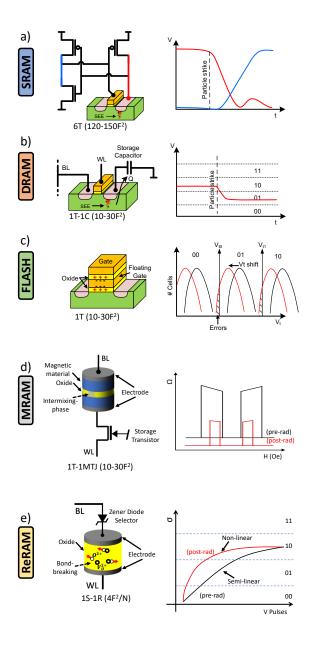

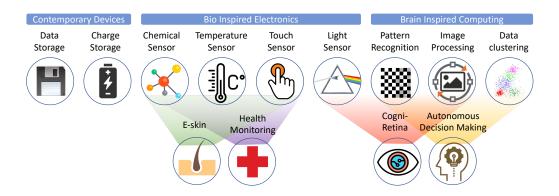

The role of emerging non-volatile memories becomes even more significant 1 in applications that rely on novel functions (beyond storage), as shown in Fig. 2 6, to eventually find their way towards mission and safety critical applications. ReRAM, as an adjustable resistor, can replace the conventional resistor in passive circuits to make them tuneable and, likewise, it may minimize the use of tuning transistor active circuits; this technique could reduce the power dissipation and increase the density of the circuits owing to its non-volatility and small feature size, respectively, that benefit lowering down the cost of deployment. ReRAM offers the flexibility to implement programmable logic. Flash-based FPGAs can benefit from the radiation hardness of ReRAM, 10 making them a suitable alternative to implement configuration memory for non-volatile FPGAs. It could also be exploited for non-volatile circuit ap-12 plications, such as physical unclonable functions (PUFs). PUFs are unique, 13 uncontrollable and unpredictable fingerprints that are widely used in crypto-14 graphic challenge-response authentication where they rely on semiconductor 15 variability in oxides, which tends to be sensitive to radiation. To resolve this 16 issue, PUFs can be implemented by exploiting the analogous variability of 17 ReRAM providing alternative architectures with increased robustness. 18

Recently, ReRAMs are also being explored for various sensors due to its capability to respond towards external stimuli, which can expand the deployment of ReRAMs for anywhere sensory on things. SRAM memories have started to be implemented also as a radiation detector where the number of bit errors gives an estimation on the radiation intensity. The sensitivity of the cells is adjustable by altering their supply voltage. Recent works on SRAMs have proposed to use both single-bit and multi-bit upset data to even estimate energy levels of the environment. A similar methodology can be applied to ReRAM too. Such developments put radiation hardening in perspective.

19

20

21

22

23

24

25

26

27

28

29

30

31

33

34

35

36

37

The emerging memory technologies have been considered for brain-inspired (neuromorphic) computing to overcome the bottleneck of von Neumann's computer architecture by making in-memory computation possible. Although MRAM has superior performance than other emerging memory technologies, it requires complex circuit designs due to its small dynamic range. Thus, it makes ReRAM the most feasible choice for enabling AI machines in space and nuclear environments that will play a significant role in designing self-configuration electronic system for mitigating radiation damages, radiation safety measures, and cyber-physical system for on-satellite real-time data analysis. Eventually, this could reduce the cost and risk of maintenance and replacement in such inaccessible environments.

Figure 6: Prospective rad-had applications of emerging memory technologies. Memristor technologies are based on electrochemical phenomena which offer broad applications beyond data storage. A non-zero-crossing I-V characteristic was observed in memristor cells due to the excess concentrations of charged species, inducing electromotive force in the cells that indicate nanobattery behavior. 93 The I-V characteristics can also be modulated by external stimuli such as chemical (liquid and gas), 94,95 temperature, 96 touch, 97 and light 98 which shows the potential for sensory applications. The integration of these sensors could make up artificial skins<sup>99</sup> useful for health monitoring systems.<sup>100</sup> Furthermore, the electrochemical process in memristors can mimic the synaptic plasticity of the biological synapses. This neuromorphic capability opens the potential for in-memory computing and could revolutionize the traditional von Neumann's computer architecture. 101 Several neuromorphic computing applications have been explored, such as pattern recognition, 90 image processing, 102 and data clustering 103 where these functions push the computation capability in more complex machines, for example, cogni-retina for bionics/robotics, <sup>104</sup> and autonomous machines. <sup>90</sup>

### References

- [1] Dallas E. Evans, David E. Pitts, G. L. K. Venus and Mars Nominal Natural Environment for Advanced Manned Planetary Mission Programs (NASA SP-3016). Tech. Rep. (1965).

- [2] Bagenal, F. et al. Plasma conditions at Europa's orbit. *Icarus* **261**, 1–13 (2015).

- [3] Cannon, P. Extreme space weather: impacts on engineered systems and infrastructures (2013). URL http://www.raeng.org.uk/news/publications/list/reports/Space\_Weather\_Full\_Re

- [4] Bourdarie, S., Friedel, R. H. W., Fennell, J., Kanekal, S. & Cayton, T. E. Radiation belt representation of the energetic electron environment: Model and data synthesis using the Salammbô radiation belt transport code and Los Alamos geosynchronous and GPS energetic particle data. Space Weather 3, n/a-n/a (2005).

- [5] Morley, S. K. et al. Energetic Particle Data From the Global Positioning System Constellation. Space Weather 15, 283–289 (2017).

- [6] Pettegrew, R., Easton, J., Struk, P. & Anderson, E. In-Flight Manual Electronics Repair for Deep-Space Missions. In 2007 IEEE Aerospace Conference, 1-16 (IEEE, 2007). URL http://ieeexplore.ieee.org/document/4161574/.

- [7] Michalak, S. E. et al. Assessment of the Impact of Cosmic-Ray-Induced Neutrons on Hardware in the Roadrunner Supercomputer. IEEE Transactions on Device and Materials Reliability 12, 445-454 (2012). URL http://ieeexplore.ieee.org/document/6193419/.

- [8] Nidhin, T., Bhattacharyya, A., Behera, R., Jayanthi, T. & Velusamy, K. Understanding radiation effects in SRAM-based field programmable gate arrays for implementing instrumentation and control systems of nuclear power plants. Nuclear Engineering and Technology 49, 1589–1599 (2017). URL https://doi.org/10.1016/j.net.2017.09.002 https://linkinghub.elsevier.com/retrieve/pii/S1738573317302723.

- [9] Brugger, M. Radiation damage to electronics at the LHC. In *IPAC* 2012 International Particle Accelerator Conference 2012, 3734–3736 (2012).

- [10] ITRS. International Technology Roadmap for Semiconductors 2.0: Executive Report. Tech. Rep. (2015).

- [11] Baumann, R. & Kruckmeyer, K. Radiation handbook for electronics (2019).

- [12] Chatzikyriakou, E., Morgan, K. & de Groot, C. H. K. To-Hardened Mitigation Strategies Ionizing Dose and in Submicrometer CMOS Beyond. IEEETransand onElectron*Devices* **65**, 808-819 (2018).URL http://ieeexplore.ieee.org/document/8272514/.

- [13] Schwank, J. R. et al. Radiation Effects in MOS Oxides. *IEEE Transactions on Nuclear Science* 55, 1833–1853 (2008). URL http://ieeexplore.ieee.org/document/4636929/.

- [14] Khanna, V. K. Radiation effects on electronics. In Extreme-Temperature and Harsh-Environment Electronics Physics, technology and applications, 0-14 (IOP Publishing, 2017). URL http://iopscience.iop.org/book/978-0-7503-1155-7/chapter/bk978-0-7503-1155-

- [15] Srour, J. R. & Palko, J. W. Displacement damage effects in irradiated semiconductor devices. *IEEE Transactions on Nuclear Science* 60, 1740–1766 (2013).

- [16] Monteiro, W. A. (ed.) Radiation Effects in Materials (InTech, 2016). URL http://www.intechopen.com/books/radiation-effects-in-materials.

- [17] Raphael, R. N. S. et al. Overview About Radiation-Matter Interaction Mechanisms and Mitigation Techniques. In Proceedings of the 3rd Brazilian Technology Symposium, vol. 1, 223–238 (Springer International Publishing, Cham, 2019). URL http://link.springer.com/10.1007/978-3-319-93112-8-23.

- [18] Lacoe, R. C. Improving integrated circuit performance through the application of hardness-by-design methodology. *IEEE transactions on Nuclear Science* **55**, 1903–1925 (2008).

- [19] Faccio, F., Michelis, S., Cornale, D., Paccagnella, A. & Gerardin, S. Radiation-induced short channel (risce) and narrow channel (rince) effects in 65 and 130 nm mosfets. *IEEE Transactions on Nuclear Science* **62**, 2933–2940 (2015).

- [20] Gambles, J. W., Maki, G. & Whitaker, S. Radiation hardening by design. *International journal of electronics* **95**, 11–26 (2008).

- [21] Holman, W. Radiation-tolerant design for high performance mixed-signal circuits. *International journal of high speed electronics and systems* **14**, 353–366 (2004).

- [22] Faccio, F. et al. Influence of ldd spacers and h+ transport on the total-ionizing-dose response of 65-nm mosfets irradiated to ultrahigh doses. *IEEE Transactions on Nuclear Science* **65**, 164–174 (2017).

- [23] Faccio, F. & Cervelli, G. Radiation-induced edge effects in deep submicron cmos transistors. *IEEE Transactions on Nuclear Science* **52**, 2413–2420 (2005).

- [24] Baoping, H., Zhibin, Y., Zujun, W. & Shaoyan, H. Irradiation and anneal response of shallow trench isolation oxides in 0.18 [mu] m cmos technology. *Scientific Journal of Microelectronics* 4, 5 (2014).

- [25] Gonella, L. et al. Total ionizing dose effects in 130-nm commercial cmos technologies for hep experiments. Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment 582, 750–754 (2007).

- [26] Bucher, M. et al. Total ionizing dose effects on analog performance of 65 nm bulk cmos with enclosed-gate and standard layout. In 2018 IEEE International Conference on Microelectronic Test Structures (ICMTS), 166–170 (IEEE, 2018).

- [27] Giraldo, A., Paccagnella, A. & Minzoni, A. Aspect ratio calculation in n-channel mosfets with a gate-enclosed layout. *Solid-State Electronics* 44, 981–989 (2000).

- [28] Narasimham, B., Gambles, J. W., Shuler, R. L., Bhuva, B. L. & Massengill, L. W. Quantifying the effect of guard rings and guard drains in mitigating charge collection and charge spread. *IEEE Transactions on Nuclear Science* **55**, 3456–3460 (2008).

- [29] Chen, R. et al. Single-event multiple transients in conventional and guard-ring hardened inverter chains under pulsed laser and heavy-ion irradiation. *IEEE Transactions on Nuclear Science* **64**, 2511–2518 (2017).

- [30] Ruano, O., Reviriego, P. & Maestro, J. Automatic insertion of selective tmr for seu mitigation. In 2008 European Conference on Radiation and Its Effects on Components and Systems, 284–287 (IEEE, 2008).

- [31] Hasanbegović, A. & Aunet, S. Heavy ion characterization of temporal-, dual-and triple redundant flip-flops across a wide supply voltage range in a 65 nm bulk cmos process. *IEEE Transactions on Nuclear Science* **63**, 2962–2970 (2016).

- [32] Bhuva, B. et al. Multi-cell soft errors at advanced technology nodes. *IEEE Transactions on Nuclear Science* **62**, 2585–2591 (2015).

- [33] Toro, D. G., Arzel, M., Seguin, F. & Jézéquel, M. Soft error detection and correction technique for radiation hardening based on c-element and bics. *IEEE Transactions on Circuits and Systems II: Express Briefs* **61**, 952–956 (2014).

- [34] Schmidt, R., García-Ortiz, A. & Fey, G. Temporal redundancy latch-based architecture for soft error mitigation. In 2017 IEEE 23rd International Symposium on On-Line Testing and Robust System Design (IOLTS), 240–243 (IEEE, 2017).

- [35] Calin, T., Nicolaidis, M. & Velazco, R. Upset hardened memory design for submicron cmos technology. *IEEE Transactions on Nuclear Science* 43, 2874–2878 (1996).

- [36] Zanchi, A., Buchner, S., Hafer, C., Hisano, S. & Kerwin, D. B. Investigation and mitigation of analog set on a bandgap reference in triple-well cmos using pulsed laser techniques. *IEEE Transactions on Nuclear Science* **58**, 2570–2577 (2011).

- [37] Uemura, T., Tanabe, R., Tosaka, Y. & Satoh, S. Using low pass filters in mitigation techniques against single-event transients in 45nm technology lsis. In 2008 14th IEEE International On-Line Testing Symposium, 117–122 (IEEE, 2008).

- [38] Kelly, A. T. *et al.* Differential analog layout for improved aset tolerance. *IEEE Transactions on Nuclear Science* **54**, 2053–2059 (2007).

- [39] Oh, N., Shirvani, P. P. & McCluskey, E. J. Control-flow checking by software signatures. *IEEE transactions on Reliability* **51**, 111–122 (2002).

- [40] Zhang, Y. et al. Design and verification of sram self-detection repair based on ecc and bisr circuit. In 2019 IEEE 26th International Symposium on Physical and Failure Analysis of Integrated Circuits (IPFA), 1–5 (IEEE, 2019).

- [41] Mavis, D. et al. Multiple bit upsets and error mitigation in ultra-deep submicron srams. *IEEE Transactions on Nuclear Science* **55**, 3288–3294 (2008).

- [42] Gasiot, G., Giot, D. & Roche, P. Multiple cell upsets as the key contribution to the total ser of 65 nm cmos srams and its dependence on well engineering. *IEEE Transactions on Nuclear Science* **54**, 2468–2473 (2007).

- [43] Rezgui, S. et al. Complex upset mitigation applied to a re-configurable embedded processor. *IEEE transactions on nuclear science* **52**, 2468–2474 (2005).

- [44] Hughes, H. et al. Total ionizing dose radiation effects on 14 nm finfet and soi utbb technologies. In 2015 IEEE Radiation Effects Data Workshop (REDW), 1–6 (IEEE, 2015).

- [45] Simoen, E. et al. Radiation effects in advanced multiple gate and silicon-on-insulator transistors. *IEEE Transactions on Nuclear Science* **60**, 1970–1991 (2013).

- [46] Put, S. et al. Influence of back-gate bias and process conditions on the gamma degradation of the transconductance of mugfets. *IEEE Transactions on Nuclear Science* 57, 1771–1776 (2010).

- [47] Liu, R. et al. Single event transient and tid study in 28 nm utbb fdsoi technology. *IEEE Transactions on Nuclear Science* **64**, 113–118 (2016).

- [48] Gaillardin, M. et al. Impact of soi substrate on the radiation response of ultrathin transistors down to the 20 nm node. *IEEE Transactions on Nuclear Science* **60**, 2583–2589 (2013).

- [49] Gaillardin, M. et al. Total ionizing dose effects mitigation strategy for nanoscaled fdsoi technologies. IEEE Transactions on Nuclear Science 61, 3023–3029 (2014).

- [50] King, M. P. *et al.* Analysis of tid process, geometry, and bias condition dependence in 14-nm finfets and implications for rf and sram performance. *IEEE Transactions on Nuclear Science* **64**, 285–292 (2016).

- [51] Nsengiyumva, P. et al. A comparison of the seu response of planar and finfet d flip-flops at advanced technology nodes. *IEEE Transactions on Nuclear Science* **63**, 266–272 (2016).

- [52] Seifert, N. et al. Soft error susceptibilities of 22 nm tri-gate devices. *IEEE Transactions on Nuclear Science* **59**, 2666–2673 (2012).

- [53] Salahuddin, S., Ni, K. & Datta, S. The era of hyper-scaling in electronics. *Nature Electronics* (2018).

- [54] Guertin, S. M., Yang-Scharlotta, J., Blaisdell-Pijuan, P. & Some, R. Options for radiation tolerant high-performance memory. In 2017 17th European Conference on Radiation and Its Effects on Components and Systems (RADECS), 1–7 (IEEE, 2017).

- [55] Raine, M., Gaillardin, M., Lagutere, T., Duhamel, O. & Paillet, P. Estimation of the single-event upset sensitivity of advanced soi srams. *IEEE Transactions on Nuclear Science* **65**, 339–345 (2018).

- [56] Shiyanovskii, Y., Wolff, F. & Papachristou, C. Sram cell design protected from seu upsets. In 2008 14th IEEE International On-Line Testing Symposium, 169–170 (IEEE, 2008).

- [57] Geppert, L. A static ram says goodbye to data errors [radiation induced soft errors]. *IEEE Spectrum* **41**, 16–17 (2004).

- [58] Roche, P., Jacquet, F., Caillat, C. & Schoellkopf, J.-P. An alpha immune and ultra low neutron ser high density sram. In 2004 IEEE International Reliability Physics Symposium. Proceedings, 671–672 (IEEE, 2004).

- [59] Diehl, S., Ochoa, A., Dressendorfer, P., Koga, R. & Kolasinski, W. Error analysis and prevention of cosmic ion-induced soft errors in static emos rams. *IEEE transactions on nuclear science* **29**, 2032–2039 (1982).

- [60] Takai, M. et al. Soft error susceptibility and immune structures in dynamic random access memories (drams) investigated by nuclear microprobes. IEEE Transactions on Nuclear Science 43, 696–704 (1996).

- [61] Bougerol, A. et al. Use of laser to explain heavy ion induced sefis in sdrams. *IEEE Transactions on Nuclear Science* **57**, 272–278 (2010).

- [62] Borucki, L., Schindlbeck, G. & Slayman, C. Impact of dram process technology on neutron-induced soft errors. In 2007 IEEE International Integrated Reliability Workshop Final Report, 143–146 (2007).

- [63] Chen, D. et al. Heavy ion and proton-induced single event upset characteristics of a 3-d nand flash memory. *IEEE Transactions on Nuclear Science* **65**, 19–26 (2018).

- [64] Zhao, C., Zhao, C. Z., Taylor, S. & Chalker, P. R. Review on non-volatile memory with high-k dielectrics: Flash for generation beyond 32 nm. *Materials* 7, 5117–5145 (2014).

- [65] Bagatin, M. et al. Effects of heavy-ion irradiation on vertical 3-d nand flash memories. *IEEE Transactions on Nuclear Science* **65**, 318–325 (2018).

- [66] Oldham, T. R. et al. See and tid characterization of an advanced commercial 2gbit nand flash nonvolatile memory. *IEEE Transactions on Nuclear Science* **53**, 3217–3222 (2006).

- [67] Baldi, L., Bez, R. & Sandhu, G. Emerging memories. Solid-State Electronics 102, 2-11 (2014). URL http://dx.doi.org/10.1016/j.sse.2014.06.009.

- [68] Lu, J. et al. Radiation effects on the magnetism and the spin dependent transport in magnetic materials and nanostructures for spintronic applications. *Journal of Materials Research* **30**, 1430–1439 (2015).

- [69] Bhatti, S. et al. Spintronics based random access memory: a review. Materials Today 20, 530-548 (2017). URL https://linkinghub.elsevier.com/retrieve/pii/S1369702117304285.

- [70] Hirose, K., Kobayashi, D., Ito, T. & Endoh, T. Memory reliability of spintronic materials and devices for disaster-resilient computing against radiation-induced bit flips on the ground. *Japanese Journal of Applied Physics* 56 (2017).

- [71] Stathopoulos, S. et al. Multibit memory operation of metal-oxide bi-layer memristors. Scientific Reports 7, 17532 (2017). URL http://www.nature.com/articles/s41598-017-17785-1.

- [72] Hickmott, T. W. Low-Frequency Negative Resistance in Thin Anodic Oxide Films. *Journal of Applied Physics* 33, 2669 (1962). URL http://scitation.aip.org/content/aip/journal/jap/33/9/10.1063/1.1702530.

- [73] Yang, J. J. et al. Memristive switching mechanism for metal/oxide/metal nanodevices. Nature Nanotechnology 3, 429–433 (2008).

- [74] Zuloaga, S., Liu, R., Chen, P.-Y. & Yu, S. Scaling 2-layer RRAM cross-point array towards 10 nm node: A device-circuit codesign. In 2015 IEEE International Symposium on Circuits and Systems (ISCAS), vol. 2015-July, 193-196 (IEEE, 2015). URL http://ieeexplore.ieee.org/document/7168603/.

- [75] Zhang, Z., Wu, Y., Wong, H.-S. P. & Wong, S. S. Nanometer-Scale HfOx RRAM. *IEEE Electron Device Letters* **34**, 1005-1007 (2013). URL https://ieeexplore.ieee.org/document/6553186/.

- [76] Khiat, A., Ayliffe, P. & Prodromakis, T. High Density Crossbar Arrays with Sub-15 nm Single Cells via Liftoff Process only. *Scientific Reports* **6**, 1–8 (2016).

- [77] Zhang, L. et al. Total Ionizing Dose (TID) Effects on TaOx -Based Resistance Change Memory. IEEE Transactions on Electron Devices 58, 2800-2804 (2011). URL http://ieeexplore.ieee.org/document/5779725/.

- [78] Liu, R., Mahalanabis, D., Barnaby, H. J. & Yu, S. Investigation of Single-Bit and Multiple-Bit Upsets in Oxide RRAM-Based 1T1R and Crossbar Memory Arrays. *IEEE Transactions on Nuclear Science* **62**, 2294–2301 (2015). URL http://ieeexplore.ieee.org/document/7274484/.

- [79] Ye, Z., Liu, R., Taggart, J. L., Barnaby, H. J. & Yu, S. Evaluation of Radiation Effects in RRAM-Based Neuromorphic Computing System for Inference. *IEEE Transactions on Nuclear Science* 66, 97–103 (2019). URL https://ieeexplore.ieee.org/document/8576612/.

- [80] DeIonno, E., Looper, M. D., Osborn, J. V., Barnaby, H. J. & Tong, W. M. Radiation effects studies on thin film TiO¡inf¿2¡/inf¿ memristor devices. In 2013 IEEE Aerospace Conference, 1-8 (IEEE, 2013). URL http://ieeexplore.ieee.org/document/6497378/.

- [81] Agashe, K. et al. Effect of gamma irradiation on resistive switching of Al/TiO 2 /n + Si ReRAM. Nuclear Instruments and Methods in Physics Research Section B: Beam Interactions with Materials and Atoms 403, 38-44 (2017). URL https://linkinghub.elsevier.com/retrieve/pii/S0168583X17305499.

- [82] Dandamudi, P., Kozicki, M. N., Barnaby, H. J., Gonzalez-Velo, Y. & Holbert, K. E. Total ionizing dose tolerance of Ag Ge40S60 based programmable metallization cells. *IEEE Transactions on Nuclear Science* **61**, 1726–1731 (2014).

- [83] Shaneyfelt, M. et al. Hardness variability in commercial technologies. IEEE Transactions on Nuclear Science 41, 2536-2543 (1994). URL http://ieeexplore.ieee.org/document/340613/.

- [84] Fang, R. et al. Total ionizing dose effect of γ-ray radiation on the switching characteristics and filament stability of HfOx resistive random access memory. Applied Physics Letters 104 (2014). URL http://dx.doi.org/10.1063/1.4875748.

- [85] Hughart, D. R. etal.Radiation-induced resistance changes in TaOx and TiO2 memristors. In 2014 IEEE Aerospace Conference, 1 - 11URL (IEEE, 2014). http://ieeexplore.ieee.org/document/6836465/.

- [86] Gonzalez-Velo, Y., Barnaby, H. J. & Kozicki, M. N. Review of radiation effects on ReRAM devices and technology. *Semiconductor Science and Technology* **32** (2017).

- [87] Barnaby, H. J. et al. Impact of Alpha Particles on the Electrical Characteristics of TiO<sub>2</sub> Memristors. *IEEE Transactions on Nuclear Science* **58**, 2838–2844 (2011). URL http://ieeexplore.ieee.org/document/6061922/.

- [88] Yuan, F. et al. Total ionizing dose (TID) effects of  $\gamma$  ray radiation on switching behaviors of Ag/AlOx/Pt RRAM device. Nanoscale Research Letters 9, 1–6 (2014).

- [89] Wang, J. et al. A radiation-hardening Ta/Ta2O5-x/Al2O3/InGaZnO4 memristor for harsh electronics. Applied Physics Letters 113, 2–6 (2018).

- [90] Xia, Q. & Yang, J. J. Memristive crossbar arrays for brain-inspired computing. *Nature Materials* 18, 309–323 (2019). URL http://dx.doi.org/10.1038/s41563-019-0291-x.

- [91] Prinzie, J. et al. An sram-based radiation monitor with dynamic voltage control in 0.18-μm cmos technology. *IEEE Transactions on Nuclear Science* **66**, 282–289 (2018).

- [92] Grollier, J. et al. Neuromorphic spintronics. Nature Electronics 3, 360-370 (2020). URL http://www.nature.com/articles/s41928-019-0360-9.

- [93] Valov, I. et al. Nanobatteries in redox-based resistive switches require extension of memristor theory. Nature Communications 4, 1771 (2013). URL http://www.nature.com/articles/ncomms2784.

- [94] Tzouvadaki, I. et al. Label-Free Ultrasensitive Memristive Aptasensor. Nano Letters 16, 4472-4476 (2016). URL https://pubs.acs.org/doi/10.1021/acs.nanolett.6b01648.

- [95] Vidiš, M. et al. Gasistor: A memristor based gas-triggered switch and gas sensor with memory. Applied Physics Letters 115, 093504 (2019). URL http://aip.scitation.org/doi/10.1063/1.5099685.

- [96] Nguyen, T.-N. & Shin, D. Statistical Memristor-Based Temperature Sensors without Analog-to-Digital Conversion. In 2018 IEEE 7th Non-Volatile Memory Systems and Applications Symposium (NVMSA), 99-104 (IEEE, 2018). URL https://ieeexplore.ieee.org/document/8537702/.

- [97] Zhang, C. et al. Bioinspired Artificial Sensory Nerve Based on Nafion Memristor. Advanced Functional Materials 29, 1–10 (2019).

- [98] Bera, etal.Α Versatile Light-Switchable Nanorod Memory: Wurtzite ZnO Perovskite SrTiO Adon **23**. URL vanced Functional Materials 4977–4984 (2013). http://doi.wiley.com/10.1002/adfm.201300509.

- [99] Soni, M. & Dahiya, R. Soft eSkin: distributed touch sensing with harmonized energy and computing. *Philosophical Transactions of the Royal Society A: Mathematical, Physical and Engineering Sciences* 378, 20190156 (2020). URL https://royalsocietypublishing.org/doi/10.1098/rsta.2019.0156.

- [100] Gao, Y., Yu, L., Yeo, J. C. & Lim, C. T. Flexible Hybrid Sensors for Health Monitoring: Materials and Mechanisms to Render Wearability. *Advanced Materials* **32**, 1–31 (2020).

- [101] Serb, et al.Unsupervised learning in probabilistic neural networks with multi-state metal-oxide memristive Nature Communications 7, 12611 (2016).URL http://www.nature.com/articles/ncomms12611.

- [102] Li, C. et al. Analogue signal and image processing with large memristor crossbars. Nature Electronics 1, 52–59 (2018).

- [103] Jeong, Y. J., Lee, J., Moon, J., Shin, J. H. & Lu, W. D. K-means Data Clustering with Memristor Networks. Nano Letters 18, 4447– 4453 (2018).

- [104] Berco, D. & Shenp Ang, D. Recent Progress in Synaptic Devices Paving the Way toward an Artificial Cogni-Retina for Bionic and Machine Vision. *Advanced Intelligent Systems* 1, 1900003 (2019).