This is the author's version of the work. It is posted here for personal use, not for redistribution. The final version was published in IEEEExplore and IEEE owns the copyright.

# A Compact, Low-Power Analog Front-End with Event-Driven Input Biasing for High-Density Neural Recording in 22-nm FDSOI

Xiaohua Huang, *Student Member, IEEE*, Marco Ballini, *Member, IEEE*, Shiwei Wang, Beatrice Miccoli, Chris Van Hoof, Georges Gielen, *Fellow, IEEE*, Jan Craninckx, *Fellow, IEEE*, Nick Van Helleputte, *Member, IEEE*, and Carolina Mora Lopez, *Senior Member, IEEE*

**Abstract**—An ultra-small-area, low-power analog front-end (AFE) for high-density neural recording is presented in this paper. It features an 11-bit incremental delta-sigma analog-to-digital converter ( $\Delta\Sigma$  ADC) enhanced with an offset-rejecting event-driven input biasing network. This network avoids saturation of the ADC input caused by leakage of the input-coupling capacitor implemented in an advanced technology node. Combining AC-coupling with direct data conversion, the proposed AFE can tolerate a rail-to-rail electrode offset and achieves a good trade-off between power, noise, bandwidth, input impedance, and area. Fabricated in a 22-nm fully-depleted silicon on insulator (FDSOI) process, the design occupies an active area of  $<0.001$  mm $^2$ , the smallest obtained to this date for a neural AFE, and consumes  $<3$   $\mu$ W from a 0.8-V supply. It achieves an input-referred noise of 11.3  $\mu$ V<sub>rms</sub> in the action potential band (300 Hz – 10 kHz) and 10  $\mu$ V<sub>rms</sub> in the local field potential band (1 Hz – 300 Hz).

**Index Terms**— Small area, low power, AFE, multi-channel neural recording, reset alignment, event driven, incremental,  $\Delta\Sigma$  ADC, AC-coupling, direct data conversion, reconstruction.

## I. INTRODUCTION

Multi-channel, high-density extracellular neural recordings of low-frequency local field potentials (LFPs) and high-frequency action potentials (APs) [1] have contributed substantially to neuroscience research. Knowledge gained from those studies greatly enables the understanding of neurological disorders and their underlying mechanisms. However, as the maximum number of simultaneously recorded neurons to this date is many orders of magnitude smaller than the total number of neurons in the brain, there is a strong need for a much higher number of parallel readout channels in electrophysiology tools. This could be achieved by significantly reducing the area of the readout channel, while still maintaining low-power operation and high signal fidelity, in combination with high-density arrays of small electrodes (a few tens of  $\mu$ m diameter or less).

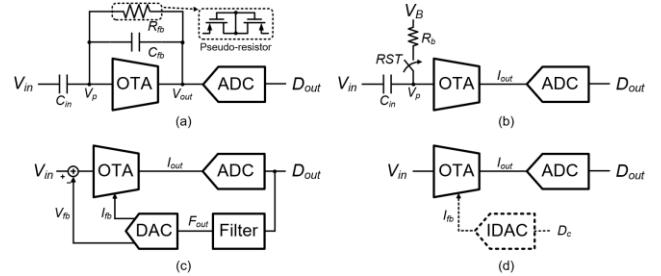

As shown in Fig. 1, the past two decades have witnessed the emergence of several novel neural readout architectures that try

Fig. 1. State-of-the-art neural AFEs: (a) AC-coupling with pseudo-resistor, (b) AC-coupling with duty-cycled resistor, (c) DC-coupling with mixed-signal feedback, and (d) DC-coupling with direct data conversion.

to achieve the requirements mentioned above. Since its first introduction in [2], AC-coupled amplification with pseudo-resistor biasing (Fig. 1(a)) has been used widely [3]–[5]. However, pseudo-resistors are highly sensitive to process variations and light, nonlinear, and very prone to large offsets caused by leakage currents. Duty-cycled resistors (Fig. 1(b)) with single- and multi-rate control [6], [7] have been proposed to address some of those issues. Nonetheless, the maximum achievable resistance (~tens of G $\Omega$ ) is limited by the parasitic capacitors, and large passives are still needed to achieve a sub-Hz high-pass corner frequency. DC-coupled solutions have been explored as well. A mixed-signal feedback (Fig. 1(c)) was implemented in [8]–[10] to reject electrode DC offsets and low-frequency disturbances. In this case, the corner frequency is tuned in the digital domain. The main drawback of such approach is the limited offset rejection, which requires large power or area for the low noise and wide dynamic range (DR) feedback digital-to-analog converters (DACs). By removing the feedback path or adding a coarse DAC for offset rejection (Fig. 1(d)), a significant area reduction is achieved in [11], [12]. With the help of a global reference control, those designs work well using a floating measurement setup. While for grounded *in vivo* applications, they may bring the OTA out of its input common-mode range. A wide DR for offset and artifact

Manuscript received August 3, 2021.

X. Huang, C. Van Hoof, and G. Gielen are with the Department of Electrical Engineering (ESAT)-MICAS, KU Leuven, Leuven, Belgium and imec, Leuven, Belgium (e-mail: xiaohua.huang@imec.be).

M. Ballini was with imec, Leuven, Belgium and is now with TDK InvenSense, Milan, Italy.

J. Craninckx, N. Van Helleputte, and C. M. Lopez are with imec, Leuven, Belgium.

S. Wang was with imec, Leuven, Belgium and is now with the University of Southampton, Southampton, United Kingdom.

B. Miccoli was with imec, Leuven, Belgium and is now with Chameleon Communications International, London, United Kingdom.

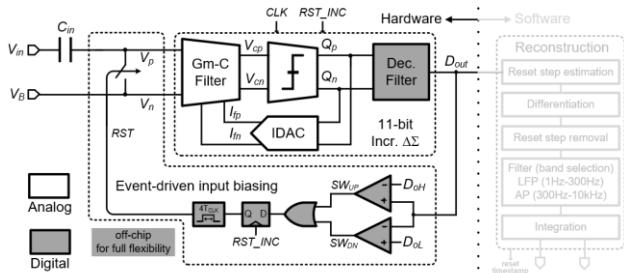

Fig. 2. Proposed hybrid AFE based on the hardware and software co-design.

tolerance has also been implemented in [13]-[16]. However, since the large unwanted electrode offset is also digitized together with the small neural signals, this approach achieves poor power efficiency. It is worth mentioning that direct time division multiplexing at the electrode is another promising method to achieve area reduction [17], [18]. However, it works well only for the large mm-scale electrodes used for ECoG [18], while the low input impedance and noise folding induced by the multiplexing operation pose big concerns for small  $\mu\text{m}$ -scale electrodes [17].

This paper presents an ultra-small-area low-power analog front-end (AFE) that tackles these offset-rejection problems by introducing a direct data conversion architecture with an event-driven input-biasing solution. The incremental operation, combined with reset timing control and signal reconstruction, prevents data-sample corruption in the occurrence of an input biasing reset event.

## II. NEURAL AFE WITH EVENT-DRIVEN INPUT BIASING

Fig. 2 shows the simplified block diagram of the proposed hybrid AFE architecture. It consists of an input capacitor  $C_{in}$ , an 11-bit incremental  $\Delta\Sigma$  ADC, an event-driven input-biasing network and a reconstruction block for signal post-processing. The decimation filter and the event-driven logic are implemented off-chip for full flexibility in the fabricated test chip. The signal reconstruction, which is outside the critical closed-loop control of the AFE, is done in software and could easily be merged with other external signal processing units, e.g., spike detection and sorting algorithms. The different components of this architecture are explained in the following subsections.

### A. Event-driven Input Biasing

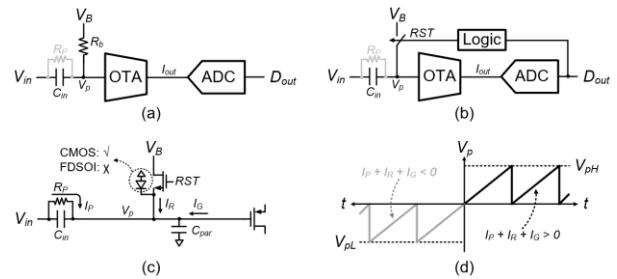

The area efficiency of direct data conversion using oversampled ADCs without pre-amplification has already been demonstrated in [11], [12], [19]. However, the asynchronous control in [19] makes the serialization of the multi-channel outputs difficult to implement in a power-efficient manner, and the area and power consumption of the digital logic in [11], [12] are significant due to the relatively old process used (180 nm). Hence, an architecture that combines AC-coupling with direct data conversion implemented in a scaled technology node would address all the above-mentioned limitations and enable the implementation of high-channel-count neural interfaces. Such a scheme is shown in Fig. 3(a) and it consists of a passive high-pass filter for electrode-offset rejection and a  $\Delta\Sigma$  modulator with Gm-C technique to achieve sufficiently low

Fig. 3. Direct data conversion with (a) AC-coupling with pseudo-resistor, (b) event-driven input biasing; (c) Circuit schematic showing the main leakage paths and (d) illustration of time-domain waveform at node  $V_p$  with event-driven input biasing.

quantization noise and distortion. In our design, we use a 22-nm fully-depleted silicon-on-insulator (FDSOI) technology to benefit from the power and area scaling in the digital circuits. However, the high-density metal-oxide-metal (MOM) capacitors in this scaled technology node suffer from significant leakage. As illustrated in Fig. 3(a), the parasitic resistor  $R_p$  that models the leakage of the AC-coupling capacitor  $C_{in}$  forms a voltage divider with the pseudo-resistor  $R_b$ . Therefore, only finite attenuation is achieved at DC, which causes a residual offset voltage at node  $V_p$ . This residual offset can saturate the AFE when large input DC offsets are present at the electrode interface. This problem can be tackled by removing the pseudo-resistor  $R_b$  and pre-charging the node  $V_p$  to a biasing voltage  $V_B$  before recording. However, the leakage currents will cause this node to drift up or down until it saturates the AFE. To avoid this, the node  $V_p$  can be pulled back to  $V_B$  when it comes close to the limit input range of the modulator. This concept is shown in Fig. 3(b), where  $V_p$  is dynamically biased via an event-driven reset switch. Fig. 3(c) illustrates the main leakage current paths at node  $V_p$ . In order to limit the occurrence of the reset event to only once every few seconds, the leakage at node  $V_p$  has been minimized and maintained within the fA range. In this way, the reset will have a negligible impact on the overall signal quality. The gate leakage  $I_G$  generated by the input differential pair of the Gm-C filter can be minimized by using thick-oxide transistors. The leakage from the reset transistor  $I_R$  is made negligible by sizing it to achieve large OFF resistance. Moreover, the source-to-bulk leakage path is not present in the used FDSOI technology.

A high-density ( $4.5 \text{ fF}/\mu\text{m}^2$ ) alternate-polarity MOM (APMOM) capacitor is chosen for the input capacitance and stacked above the active circuits to minimize area. Simulations show that the capacitor leakage  $I_p$  dominates when a large electrode offset ( $V_{in}$ ) and a bias voltage ( $V_B$ ) of 0 V are applied. The time-domain waveform at node  $V_p$  when event-driven biasing is applied is illustrated in Fig. 3(d). The reset switch is turned ON whenever the node  $V_p$  crosses the low-limit ( $V_{pL}$ ) or high-limit ( $V_{pH}$ ) thresholds of the linear input range. A sampling kT/C noise of  $40.5 \mu\text{V}_{\text{rms}}$  is introduced at the instant of a reset event. However, this noise gets averaged and becomes negligible due to the very infrequent reset operation. While large motion or stimulation artifacts could potentially trigger the input reset more frequently and temporarily increase the kT/C noise, such artifacts do not occur often and are limited to short periods.

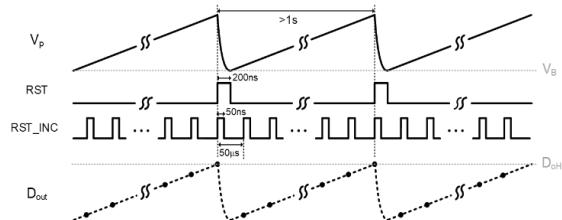

Fig. 4. Timing diagram of input reset ( $RST$ ) and incremental  $\Delta\Sigma$  reset ( $RST\_INC$ ).

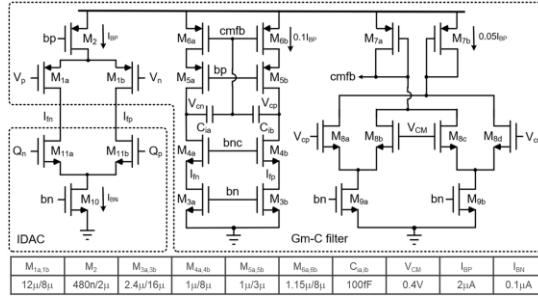

Fig. 5. Circuit schematics of Gm-C filter and IDAC.

Note that the proposed input-biasing scheme is similar to the signal folding technique reported in [20], where a reset is applied to extend the limited AFE input range ( $\sim 0.2$  mV<sub>pp</sub>) and enable the recording of large LFP signals. Due to the small input range, large signals would trigger the reset very frequently, significantly degrading the noise. In contrast, the input range of our AFE is designed large enough ( $>10$  mV<sub>pp</sub>) to accommodate both LFP and AP signals and make sure that the sporadic resets would have only negligible impact on the overall noise.

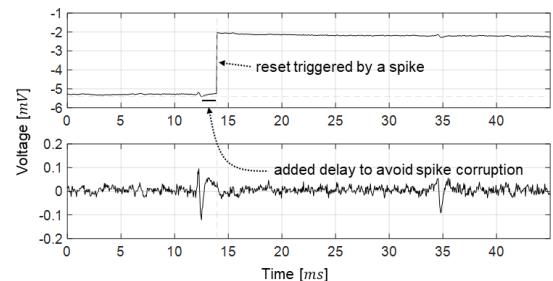

### B. Incremental Operation with Reset Alignment

The approach of event-driven input biasing achieves a large offset rejection with negligible area and power overhead. However, at every reset event, the node  $V_p$  is quickly pulled back to the initial DC biasing point, which is essentially a large step of half the linear input range. Due to the finite-bandwidth response of the decimation filter following a classical  $\Delta\Sigma$  modulator, this large step would result in signal distortion (glitches with long recovery time). This can be avoided by operating the modulator in incremental mode. Since the steps are caused by input resets, we know very accurately when they occur. This knowledge is leveraged to properly align the input reset  $RST$  and the incremental reset  $RST\_INC$ , as shown in Fig. 4. This technique guarantees that only one data sample in the digital output  $D_{out}$  gets “corrupted” at every reset event. Since only 4 clock cycles (200 ns) are sufficient to reset the input and the incremental integration period (50  $\mu$ s) consists of 1000 clock cycles, the Nyquist-rate sample following the reset event can be converted with  $\leq 0.4\%$  error.

### C. Signal Reconstruction

The slow drift caused by leakage current and the large reset steps are removed by post-processing the output signals in the digital domain. The reconstruction algorithm estimates the reset step and filters the data within the signal band of interest. The residual error at the time of a reset may affect the shape of an AP signal occurring concurrently. Therefore, the reset events are time-stamped to enable further data processing by other

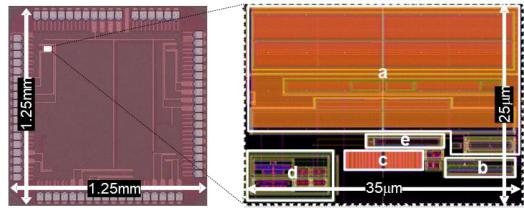

Fig. 6. Chip micrograph and AFE layout, (a) OTA and  $C_{in}$ , (b) common-mode feedback, (c) integration capacitors, (d) comparator, (e) feedback IDAC.

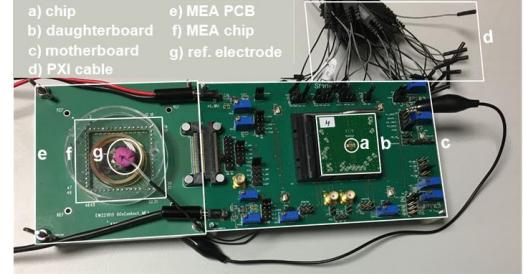

Fig. 7. Setup for electrical characterization and *in vitro* measurements.

external software algorithms. Due to the very slow drift caused by the fA-level leakage current, an AP event could trigger the biasing reset when the baseline is near the thresholds. To prevent this, the reset activation is delayed with respect to the threshold crossing by a few samples. This delay allows the acquisition of the AP waveform without any residual error, reducing further the chance of distorted spikes that could be mis-classified by a spike sorter.

## III. CIRCUIT IMPLEMENTATION

As shown in Fig. 2, the input capacitor  $C_{in}$  decouples the OTA input common-mode voltage from the electrode offset. It is a 2.5 pF APMOM capacitor from metal 5 to metal 8, and has an area of 35  $\mu$ m x 16  $\mu$ m. This capacitor value leads to a signal attenuation of <10% and a negligible modulator distortion due to the non-linear parasitic capacitance  $C_{par}$  at node  $V_p$ . A ground-shielding layer is placed below the input capacitor to avoid any coupling from the active circuit. Fig. 5 shows the circuit schematics of the Gm-C integrator and the feedback current DAC (IDAC). A fully-differential folded-cascode architecture is employed for the Gm stage to obtain a large output impedance. The common-mode feedback amplifier sets the DC common-mode output level. The auxiliary high-frequency capacitive-feedback path (from the common node of the integration capacitors to node  $cmfb$ ) enhances the phase margin of the common-mode feedback loop. For minimal area, the IDAC is implemented using current sinks only. Simulations show that the asymmetrical current feedback has a negligible impact on the overall distortion performance. This is because the ripple at the oversampling frequency is attenuated by the output common-mode rejection of the Gm-C filter.

A StrongARM dynamic comparator quantizes the filter output to a bitstream running at the system clock  $CLK$ . The 11-bit digital output signal can be obtained by a 10-bit ripple counter, which is extended with 1 bit by extracting the sign information of the comparator input at the end of each conversion [11]. The calculated quantization noise is 1.6  $\mu$ V<sub>rms</sub> for a full-scale input range of 11.5 mV<sub>pp</sub>. Due to the frequency-

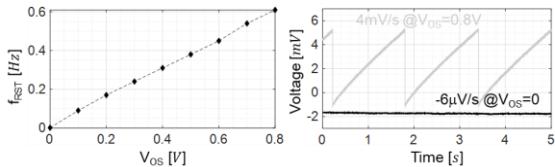

Fig. 8. Measured reset frequency  $f_{RST}$  as a function of electrode offset  $V_{OS}$  (left) and leakage of node  $V_p$  with an offset of 0 V and 0.8 V (right).

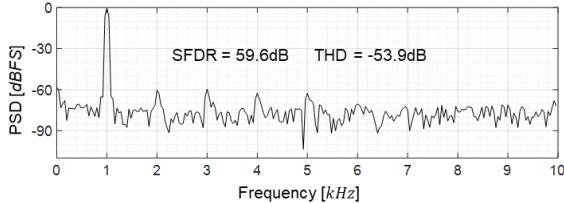

Fig. 9. Linearity measurement with a 1 kHz full-scale input.

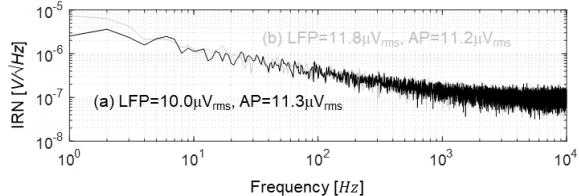

Fig. 10. Input-referred noise (IRN) measurements with (a) a zero offset and (b) periodic reset at 1 Hz.

resolution limitation of the instrument used for testing, a 20-MHz system clock was used for simplicity, resulting in an over-sampling ratio of 1000 (instead of 1024). The slightly degraded quantization noise has a negligible impact on the overall output signal fidelity. This is because the quantization noise is a bit over-designed compared to the circuit intrinsic noise (thermal and flicker), with little power overhead. An input biasing-reset pulse is generated when the decimated output  $D_{out}$  reaches the upper limit  $D_{oH}$  or the lower limit  $D_{oL}$  of the linear output range, which is then time-aligned to  $RST\_INC$  to perform the reset. The pulse width is tuned to be 4 clock cycles to achieve the proper input resetting, as discussed above.

#### IV. MEASUREMENT RESULTS

A single-channel prototype of the proposed AFE architecture has been implemented in a 22-nm FDSOI process to prove the concept. Fig. 6 shows the chip micrograph and zoomed-in channel layout with an active area of only  $875\text{ }\mu\text{m}^2$  ( $35 \times 25\text{ }\mu\text{m}^2$ ). The power consumption is  $2.5\text{ }\mu\text{W}$  from a  $0.8\text{-V}$  supply. In this prototype, the digital part (decimation filter and event-driven logic) is implemented off-chip for full flexibility. Its power and area are estimated to be around  $0.3\text{ }\mu\text{W}$  and  $100\text{ }\mu\text{m}^2$  for an on-chip implementation, resulting in only  $\sim 10\%$  overheads. The signal reconstruction is done in software, and can easily be merged with other signal-processing algorithms such as spike-sorting analysis.

Fig. 7 shows the setup used for the electrical characterization and *in vitro* measurements described below. The measured input-biasing reset frequency and leakage at node  $V_p$  are presented in Fig. 8. The drift is only  $-6\text{ }\mu\text{V/s}$  with an offset of 0 V and  $4\text{ mV/s}$  with a worst-case offset of 0.8 V. This results in a maximum reset frequency of only 0.6 Hz. The worst-case offset is limited by the standard IO ESD protection, but it is

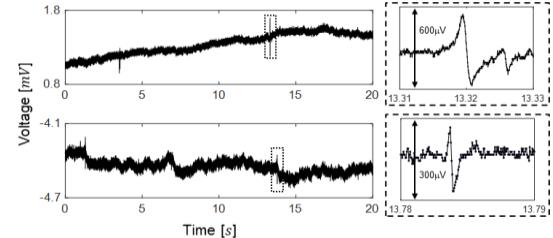

Fig. 11. *In vitro* measurement of neuronal action potentials, before (top) and after reconstruction (bottom).

Fig. 12. *In vitro* measurements (raw data without filtering) of cardiac cells (top) and neuronal cells (bottom).

sufficient to accomodate the electrode offsets and artifacts normally observed in our setups. The thresholds at which a biasing reset is triggered are made programmable and set to  $\pm 5.4\text{ mV}$ . This means that, before reaching the saturation limits of  $\pm 5.75\text{ mV}$ , the system still has a headroom of  $0.35\text{ mV}$  for any ongoing AP signal. Shown in Fig. 9, the measured spurious-free dynamic range (SFDR) and total harmonic distortion (THD) are  $59.6\text{ dB}$  and  $-53.9\text{ dB}$  when applying a 1-kHz full-scale sine wave directly at node  $V_p$ . In this measurement, the input capacitor  $C_{in}$  is bypassed to avoid any offset-induced drift at node  $V_p$  and ensure full control of the input signal amplitude. Fig. 10 shows the noise measurements for two different conditions: (a)  $V_{in}$  shorted to ground and node  $V_p$  controlled by the automatic reset mechanism (i.e. no offset and minimum reset frequency), and (b) node  $V_p$  periodically forced to reset at 1 Hz (approximately representing the worst-case offset scenario). The noise is analyzed after reconstruction, and the spectrum indicates the effect of the residual reconstruction error on the noise in the LFP and AP bands. These measurements confirm that, even with worst-case resetting, the input-bias reset results in only  $\sim 10\%$  noise increase in the LFP band, which is well within the acceptable range for the application.

In order to test the functionality of the proposed AFE and validate the effectiveness of the reconstruction algorithm in a real application, we have done *in vitro* recordings with neuronal and cardiac cells grown on top of multi-electrode array (MEA) chips. The MEA consisted of TiN electrodes of different sizes ( $20\text{-}121\text{ }\mu\text{m}^2$ ), while the reference electrode was an external Pt wire. All the experiments involving primary cell cultures were executed according to the guidelines approved by the KU Leuven animal ethics committee and compliant with the European Communities Council Directive of November 24, 1986 (86/609/EEC). Fig. 11 shows *in vitro* measurements of neuronal AP signals before and after reconstruction. In this recording, a reset event was triggered by a spike. A delay of around 20 Nyquist samples (1 ms) is added to avoid spike

TABLE I. PERFORMANCE SUMMARY AND COMPARISON

|                                | Huang[10]<br>SSCL'18        | Leene[19]<br>JSSC'18        | De Dorigo[11]<br>JSSC'18       | Uehlin[18]<br>TBCAS'20                  | Wendler[12]<br>ISSCC'21       | This<br>Work                               |

|--------------------------------|-----------------------------|-----------------------------|--------------------------------|-----------------------------------------|-------------------------------|--------------------------------------------|

| Technology                     | 65nm                        | 65nm                        | 180nm                          | 65nm                                    | 180nm                         | 22nm                                       |

| Supply [V]                     | 0.6                         | 0.5                         | 1.8                            | 0.5/2.5                                 | 1.8                           | 0.8                                        |

| Power [ $\mu$ W]               | 3.2                         | 1.275                       | 39.14/43.32/46.29 <sup>a</sup> | 2.98                                    | 8.59                          | 2.5 <sup>b</sup>                           |

| Bandwidth [Hz]                 | 0.1-500                     | 10-11k                      | 0-10k                          | 1-1k <sup>b</sup>                       | 0-10k                         | 10k <sup>c</sup>                           |

| IRN [ $\mu$ V <sub>rms</sub> ] | 2.2<br>(1-500Hz)            | 3.8<br>(10-10kHz)           | 10.46/13.04/20.19 <sup>d</sup> | 1.66<br>(1-1kHz)                        | 4.37 <sup>d</sup>             | 11.3 <sup>d</sup>                          |

| THD                            | --                          | 0.21%<br>@2mV <sub>pp</sub> | 0.22%<br>@10mV <sub>pp</sub>   | 1% <sup>e</sup><br>@0.6mV <sub>pp</sub> | 0.078%<br>@10mV <sub>pp</sub> | 0.2% <sup>f</sup><br>@11.5mV <sub>pp</sub> |

| Input<br>impedance             | >500M $\Omega$<br>(in band) | --                          | --                             | 92M $\Omega$<br>@2kHz                   | 398M $\Omega$ <sup>g</sup>    | --<br>@1kHz                                |

| Offset tolerance               | 100mV <sub>pp</sub>         | rail-to-rail                | sum:                           | sum:                                    | 120mV <sub>pp</sub>           | rail-to-rail                               |

| Input range                    | $\geq$ 2mV <sub>pp</sub>    | 4mV <sub>pp</sub>           | 22.5/45/90mV <sub>pp</sub>     | 110mV <sub>pp</sub>                     | 14mV <sub>pp</sub>            | 11.5mV <sub>pp</sub>                       |

| Area [mm <sup>2</sup> ]        | 0.01                        | 0.006                       | 0.0049                         | 0.0023                                  | 0.00462                       | 0.000875 <sup>h</sup>                      |

<sup>a</sup> Power for data transfer on the probe shank included. <sup>b</sup> 10Hz high-pass corner during CMS. <sup>c</sup> High-pass corner determined by the input capacitor and leakage resistor (measured around 3mHz). <sup>d</sup> For AP band of 300Hz-10kHz. <sup>e</sup> For LFP band of 1Hz-300Hz. <sup>f</sup> For LFP band of 0.5Hz-1kHz. <sup>g</sup> Frequency dependent for  $\Delta$  modulator, estimated from measurement for frequencies above 200Hz. <sup>h</sup> Decimation filter and event-driven logic not included, estimated power 0.3 $\mu$ W and area 0.0001mm<sup>2</sup>. <sup>i</sup> Input capacitor bypassed. <sup>j</sup> From post-layout simulation. <sup>NA</sup> Not allowed. <sup>NA</sup> Not reported.

distortion due to the reset operation. Additional *in vitro* measurements of cardiac cells and neuronal cells are shown in Fig. 12. Here, spikes with larger amplitudes and longer durations are recorded from cardiac cells. Low-frequency components, mostly coming from the electrode noise and voltage drift, are also observed in this recording. No reset was required over more than one minute of acquisition due to the low leakage (only 20 seconds are shown).

The performance summary of the designed prototype and a comparison with state-of-the-art readout circuits (i.e. those achieving very small silicon area) are shown in Table I. With an active area occupation of  $<0.001$  mm<sup>2</sup>, our design is over 4x smaller than the non-multiplexed AFE in [12] and over 2x smaller than the highly multiplexed design in [18]. With respect to [12], a rail-to-rail electrode offset can be tolerated in this work without having to bias the OTA input or cell culture to an arbitrary voltage. A much smaller recording bandwidth of 1 kHz is covered in [18], which makes that design unsuitable for AP-signal recording. The input-referred noise in our design could be improved by using chopping, but at the cost of a degraded input impedance. Finally, a preliminary design analysis suggests that the event-driven logic and decimation filter could be implemented on-chip with  $\sim$ 10% area and power overhead in this technology node. This means that the proposed AFE could be easily scaled to a multi-channel implementation.

## V. CONCLUSION

An ultra-compact, low-power AFE for multi-channel high-density neural recording applications is presented. It features an offset-rejecting event-driven input biasing scheme with direct data conversion. Co-design across the hardware and software dimensions greatly improved the area- and power-efficiency of the readout circuit. Compared to the state-of-the-art, the smallest channel-area to this date has been achieved while comparable electrical performance is still maintained.

## ACKNOWLEDGEMENTS

The authors would like to thank D. G. Salinas and other team colleagues for the valuable discussions, O. Krylychkina for the preparation of *in vitro* cell cultures, and A. Carton, B. Delrongo and E. Roskin for their support on PCB design.

## REFERENCES

- [1] J. J. Jun *et al.*, “Fully integrated silicon probes for high-density recording of neural activity,” *Nature*, vol. 551, no. 7679, pp. 232-236, Nov. 2017.

- [2] R. R. Harrison and C. Charles, “A low-power low-noise CMOS amplifier for neural recording applications,” *IEEE J. Solid-State Circuits*, vol. 38, no. 6, pp. 958-965, Jun. 2003.

- [3] J. Dragas *et al.*, “*In vitro* multi-functional microelectrode array featuring 59760 electrodes, 2048 electrophysiology channels, stimulation, impedance measurement, and neurotransmitter detection channels,” *IEEE J. Solid-State Circuits*, vol. 52, no. 6, pp. 1576-1590, Jun. 2017.

- [4] C. M. Lopez *et al.*, “A multimodal CMOS MEA for high-throughput intracellular action potential measurements and impedance spectroscopy in drug-screening applications,” *IEEE J. Solid-State Circuits*, vol. 53, no. 11, pp. 3076-3086, Nov. 2018.

- [5] S. Wang *et al.*, “A compact quad-shank CMOS neural probe with 5,120 addressable recording sites and 384 fully differential parallel channels,” *IEEE Trans. Biomed. Circuits Syst.*, vol. 13, no. 6, pp. 1625-1634, Dec. 2019.

- [6] W. Jiang *et al.*, “A  $\pm 50$ -mV linear-input-range VCO-based neural-recording front-end with digital nonlinearity correction,” *IEEE J. Solid-State Circuits*, vol. 52, no. 1, pp. 173-184, Jan. 2017.

- [7] H. Chandrakumar and D. Marković, “An 80-mV<sub>pp</sub> linear-input range, 1.6-G $\Omega$  input impedance, low-power chopper amplifier for closed-loop neural recording that is tolerant to 650-mV<sub>pp</sub> common-mode interference,” *IEEE J. Solid-State Circuits*, vol. 52, no. 11, pp. 2811-2828, Nov. 2017.

- [8] R. Muller, S. Gambini, and J. M. Rabaey, “A 0.013 mm<sup>2</sup>, 5  $\mu$ W, DC-coupled neural signal acquisition IC with 0.5 V supply,” *IEEE J. Solid-State Circuits*, vol. 47, no. 1, pp. 232-243, Jan. 2012.

- [9] R. Muller *et al.*, “A minimally invasive 64-channel wireless  $\mu$ ECoG implant,” *IEEE J. Solid-State Circuits*, vol. 50, no. 1, pp. 344-359, Jan. 2015.

- [10] J. Huang *et al.*, “A 0.01-mm<sup>2</sup> mostly digital capacitor-less AFE for distributed autonomous neural sensor nodes,” *IEEE Solid-State Circuits Lett.*, vol. 1, no. 7, pp. 162-165, July 2018.

- [11] D. D. Dorigo *et al.*, “Fully immersible subcortical neural probes with modular architecture and a delta-sigma ADC integrated under each electrode for parallel readout of 144 recording sites,” *IEEE J. Solid-State Circuits*, vol. 53, no. 11, pp. 3111-3125, Nov. 2018.

- [12] D. Wendler *et al.*, “A 0.00378mm<sup>2</sup> scalable neural recording front-end for fully immersible neural probes based on a two-step incremental delta-sigma converter with extended counting and hardware reuse,” in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, 2021, pp. 398-400.

- [13] B. C. Johnson *et al.*, “An implantable 700 $\mu$ W 64-channel neuromodulation IC for simultaneous recording and stimulation with rapid artifact recovery,” in *Proc. Symp. VLSI Circuits*, 2017, pp. C48-C49.

- [14] J. S. Bang *et al.*, “A 6.5 $\mu$ W 92.3dB-DR biopotential-recording front-end with 360mV<sub>pp</sub> linear input range,” in *Proc. Symp. VLSI Circuits*, 2018, pp. 239-240.

- [15] H. Jeon *et al.*, “A high DR, DC-coupled, time-based neural-recording IC with degeneration R-DAC for bidirectional neural interface,” *IEEE J. Solid-State Circuits*, vol. 54, no. 10, pp. 2658-2670, Oct. 2019.

- [16] C. Lee *et al.*, “A 6.5- $\mu$ W 10-kHz BW 80.4-dB SNDR G<sub>m</sub>-C-based CT  $\Delta$  $\Sigma$  modulator with a feedback-assisted G<sub>m</sub> linearization for artifact-tolerant neural recording,” *IEEE J. Solid-State Circuits*, vol. 55, no. 11, pp. 2889-2901, Nov. 2020.

- [17] M. Sharma *et al.*, “Acquisition of neural action potentials using rapid multiplexing directly at the electrodes,” *Micromachines*, vol. 9, no. 10, Sep. 2018, Art. No. 477.

- [18] J. P. Uehlin *et al.*, “A 0.0023 mm<sup>2</sup>/ch. delta-encoded, time-division multiplexed mixed-signal ECoG recording architecture with stimulus artifact suppression,” *IEEE Trans. Biomed. Circuits Syst.*, vol. 14, no. 2, pp. 319-331, Apr. 2020.

- [19] L. B. Leene and T. Constantiniou, “A 0.006 mm<sup>2</sup> 1.2  $\mu$ W analog-to-time converter for asynchronous bio-sensors,” *IEEE J. Solid-State Circuits*, vol. 53, no. 9, pp. 2604-2613, Sep. 2018.

- [20] Y. Chen *et al.*, “A digitally assisted, signal folding neural recording amplifier,” *IEEE Trans. Biomed. Circuits Syst.*, vol. 8, no. 4, pp. 528-542, Aug. 2014.