1

# Thermal Effects on Initial Volatile Response and Relaxation Dynamics of Resistive RAM Devices

Thomas Abbey\*, Christos Giotis\*, Alex Serb, Spyros Stathopoulos, Themis Prodromakis

Abstract—Resistive RAM (RRAM) or memristors are a class of electronic device whose resistance depends on voltage history. The changes in resistance can be divided into two categories, volatile and non-volatile. To date, the characteristics of non-volatile switching have been explored extensively with volatile switching behaviour still remaining more obscure. Here we investigate the temperature effects on TiOx based memristor volatility, and integrate these observations into a previously developed model for volatile switching. We show how device temperature affects the magnitude of the volatile resistive state in response to input stimulation, as well as the corresponding relaxation time constant. Importantly, these effects are polarity dependent. This work is part of an effort towards building a more comprehensive model of RRAM behaviour covering volatile and non-volatile phenomena as well as various environmental effects on them.

${\it Index\ Terms} {\it --} Memristors,\ RRAM,\ Thermal\ Volatility,\ Modelling.$

#### I. Introduction

A memristor's switching behaviour can be divided into two components: volatile and non-volatile [1], [2]. Non-volatile switching was shown to support long-term-stable and finely tuneable set-up of the device's resistive state [3] and underpins the well-established function of memristors as memory elements. The volatile, time variant component, on the other hand, manifesting itself as a drift back towards its initial resistance value after programming, can be used for the emulation of short-term effects in advanced memristive synapses [4], [5].

The majority of research undertaken on memristors thus far has had a strong focus on their non-volatile memory characteristics. While this is garnering the highest level of interest, due to the development of high density memory arrays [6], [7], volatile memory characteristics open the way for more complex memory systems integrating temporal dynamics at different scales [8], [9]. In this work, we show how temperature affects the volatile behaviour of our metal-oxide-based memristive devices. The significance of the temperature parameter is twofold. First, it aims to improve the accuracy by which volatility is accounted for when circuit-integrated RRAM systems undergo expected heat cycles in real environment operations. Also, temperature can be used explicitly as an application input parameter [10]. We use data captured using our ArC ONE memory characterisation platform [11] from

This work has been supported by the EPSRC EP/R024642/1 programme grant.

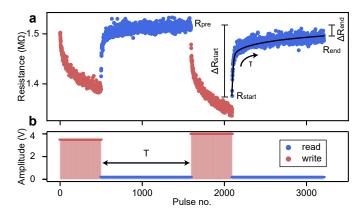

Fig. 1: (a) Stimulation and relaxation of a device under progressively more invasive programming cycles. The resistance measured during write and read phases is colour-coded and follows the stimulation profile shown in (b). Key volatility variables are noted.

several devices to build upon previously developed RRAM volatility modelling parameters [12], namely the magnitude of the *volatile jump* in resistive state after stimulation and the volatile effect's retention time constant. Compared to existing physical models such as [13] and [14], the presented model is data-driven and focuses on the volatile effects observed when displacing the device from its HRS.

#### II. METHODOLOGY

For the purposes of this work, volatility is defined as the transient change in the resistance R(t) of a device under test (DUT) within a predefined time window  $t_w$ , after DUT is subjected to an invasive stimulation protocol as illustrated in Fig. 1. Stimulation is achieved via a series of invasive write pulses and R(t) is monitored continuously using noninvasive read pulses (Fig. 1b). We define  $R_{\text{start}} = R(0)$  and  $R_{\rm end} = R(t_w)$ . Assuming a pre-stimulation resistive state of  $R_{\rm pre}$ , the initial volatile change, or *jump* experienced by DUT is defined as  $\Delta R_{\rm start}=R_{\rm start}-R_{\rm pre}$ . Any lasting change in R beyond  $t_w$ , i.e.  $\Delta R_{\rm end}=R_{\rm end}-R_{\rm pre}$  is considered a non-volatile residue. R(t) can be modelled accurately using a stretched exponential function (see Eq. 1) [12], [15]. Accordingly, volatile relaxation is described by  $\tau$  which is the exponential relaxation time constant.  $\alpha$ ,  $\beta$  and  $\gamma$  are fitting parameters representing initial displacement from the projected non-volatile saturation point, the exponential stretch factor and the saturation point respectively.

T. Abbey, C. Giotis, A. Serb, S. Stathopoulos, and T. Prodromakis are with the Centre for Electronics Frontiers, Department of Electronics and Computer Science, University of Southampton, SO17 1BJ, Southampton, UK (e-mail: ta5g14@ecs.soton.ac.uk, c.giotis@soton.ac.uk, a.serb@soton.ac.uk, s.stathopoulos@soton.ac.uk, t.prodromakis@soton.ac.uk).

<sup>\*</sup> Authors have contributed equally and are shared first authors.

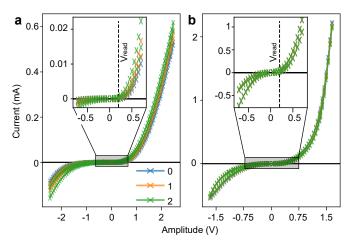

Fig. 2: I-V measurements on a (a) pristine and (b) electroformed DUT. The data reveals a non-Ohmic relationship at 3 distinct measurement cycles. Our chosen reading voltage  $V_{read}$  is marked in the insets, these also show the difference in high/low ratio between pristine and formed devices.

$$R(t) = a \cdot e^{-\left(\frac{t}{\tau}\right)^{\beta}} + \gamma \tag{1}$$

Here, we investigate how the volatile signatures of TiO<sub>2</sub> memristors (Au/TiO<sub>2</sub>/Pt - electrode<sub>bottom</sub>/active oxide/electrode<sub>top</sub> - with 20nm active oxide thickness) depend on the bipolar amplitude of stimulation  $V_P$  and temperature. Specifically, we focus how these variables affect  $\Delta R_{start}$ , as measured from raw data and the relaxation time constant  $\tau$ , extracted using Eq. 1. Since this model is comprised of purely fitting parameters, this paper does not consider the evolution of  $\alpha$ ,  $\beta$  and  $\gamma$ , although their dependence on stimulation characteristics is thoroughly discussed in [12]. In order to ensure that the changes in resistance is purely that of the volatile characteristics, these devices are purposely left to operate in their pristine (non-electroformed) state. The corresponding switching (I-V) characteristics can be seen in Fig. 2. The pristine state of the devices results in a relatively low high/low ratio compared to formed examples, seen in the insets. This stems from the absence of permanent electrochemical effects induced by electroforming.

A range of  $V_P \in \pm [1.5, 5.0]$  V write pulses is examined under temperatures T =  $\{22, 40, 55, 70\}^{\circ}$ C, with the temperature being controlled via a thermal control chuck, ensuring close thermal contact with the wafer, while other stimulation parameters are kept constant. Specifically, each stimulation run consists of N = 500 identical 100  $\mu$ s pulses, evenly spaced every 1 ms. Our chosen value for  $t_w$  is 1 minute and resistance was measured using non-invasive read pulses at 0.2 V. Temperature sweeping order was randomised (different T readings were equally spaced by 10 minutes apart) and repeated a minimum of three times to rule out history dependency as a factor affecting the measured data. Between each repeat of the switching measurements, each device was left for 1 hour during which time it would return to its original, pre-stimulation resistance. Moreover, relative

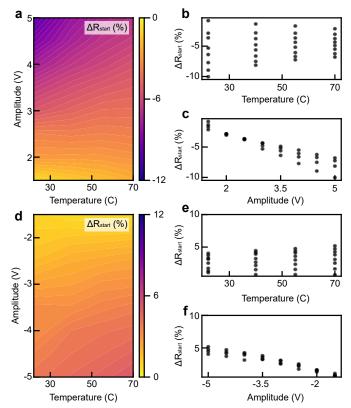

Fig. 3: (a) Volatile jump  $\Delta R_{\rm start}$  for positive stimulation, and its relationship with temperature and pulse amplitude. (b) Projection of the jump-temperature relationship. (c) Projection of the jump-amplitude relationship. Respective results for negative stimulation are shown in (d-f). Resistance changes are normalised with respect to  $R_{\rm pre}$ .

$\Delta R_{\rm start}$  values with respect to  $R_{pre}$  have been considered to normalise across baseline changes in R due to temperature. Hence,  $\Delta R_{\rm start}(\%) = \frac{\Delta R_{\rm start} - R_{pre}}{R_{pre}} \times 100\%$ . Three devices have been examined, while we present the mean average across measurements.

## III. RESULTS AND DISCUSSION

## A. Volatile resistive change

From the projections of Fig. 3 a, (b and c), the magnitude of the volatile jumps increases linearly with voltage but shows increased variability as stimulation amplitude increases towards 5V. Conversely, temperature decreases the variance of these jumps with its effects on jump magnitude depending on stimulation voltage (higher T enhances switching at low voltages, but inhibits it at higher).

In the case of negative amplitude pulses, Fig. 3d-f, greater voltages lead to greater volatile jumps, linearly but with saturation with increasing voltage. In this case, temperature increases the variability of these jumps with low-voltage stimulation remaining relatively insensitive and higher voltages experiencing inhibition of switching.

Fig. 4: (a) Relaxation time constant  $\tau$  and its relationship to temperature and pulse amplitude for positive stimulation. (b) Projection of the time constant-temperature relationship. (c) Projection of the time constant-amplitude relationship. Respective results for negative stimulation are shown in (d-f). Resistance changes are normalised with respect to  $R_{\rm pre}$ .

## B. Retention time constant

The projections displayed in Fig. 4 c, f show that a larger pulse voltage, and thus a larger initial displacement will result in a longer time constant. Similar to Fig, 3 this parameter is linearly increasing with  $|V_p|$  for positive bias and increasing with saturation for negative. For positive stimulation there is little evidence of a temperature effect on the  $\tau$  whilst for negative stimulation the time constant seems to simultaneously drop (at least for higher bias voltages) and become increasingly voltage-insensitive for higher temperatures.

## IV. DISCUSSION AND CONCLUSION

Comparing the results from Figs. 3 and 4 we notice a dissimilarity between qualitative behaviour for different signal polarities. We note that the inhibition/enhancement effects of temperature on the magnitude of the volatile jump are opposite for the two polarities: not only does temperature inhibit switching at positive polarity and enhance it at negative polarity for high bias voltage magnitudes, but at low bias magnitudes we have enhancement for positive polarity and inhibition for negative. This precludes a scenario where we could conceivably map a mirror image of Fig. 3(d) to a subset or superset of corresponding panel (a) even after 'stretching' panel (d) along the voltage or temperature axes. It is unclear

what electrochemical mechanisms give rise to this fundamental, qualitative difference in behaviour across polarities, but hints towards a distinct balance of mechanisms at play during volatile behaviour for the positive and negative polarity cases. Investigating each polarity separately and noticing how the these effects reverse with bias also raises the question of multiple mechanisms at play for each polarity.

The picture for time-constants is even more complex, exhibiting a dissimilarity in the range of t for each polarity and clear difference in the temperature-sensitivity of the t for each polarity. Moreover, even for negative polarity we can distinguish at least two regimes: at low voltage magnitudes we see no, or weak temperature-dependence, in contrast to the high magnitude case. This complete decorrelation across polarities and the qualitatively different behaviour observed vs. bias voltage magnitude for negative polarities reinforces the suspicions of multiple volatility-causing mechanisms interacting with each other and the distinct balances between them for each polarity. Finally, we observe a relatively narrow band of bias voltages in both polarities for which temperature-sensitivity for both volatile jump and relaxation time-constant is approximately zero. This occurs at slightly over  $\pm 2V$ .

The above observations suggest some interesting implications for practical circuit design using volatility: a) It seems possible to operate volatility (approximately) independent of temperature. b) By choosing the orientation of the RRAM component within the circuit and independently setting the voltages for positive/negative stimulation we may determine the sign of the temperature coefficient of the volatile jump. c) There is more freedom in setting the actual value of the temperature coefficient in one direction than the other (it's easier to inhibit volatile jump for positive stimulation than to enhance it). d) There seems to be an opportunity to choose operation in temperature-sensitive or temperature-insensitive time-constant modes simply by selecting the bias polarity.

Scrutinising our results can yield even more insight, thought it is clear that volatility offers a complex, but also potentially rewarding design space if voltage levels and polarities can be tailored to match the desired device response. To achieve high yield in performance accuracy one may be required to decipher the dependence of all volatility modelling parameters on the operational environment conditions if keeping these conditions fixed becomes a challenge. We also note that extending this investigation towards memristors employing different active materials is imperative, since it is still unknown whether such alteration would result into relative changes in volatile behaviours or different phenomena altogether.

In conclusion, this study has shown that our RRAM devices show asymmetric and non-monotonic behaviour effects as a function of bias voltage and temperature. This covers both the magnitude of the volatile jump and the relaxation time constant. The interplay between qualitatively different behavioural regimes created for both variables in the voltage-temperature plane create a challenging, but also promising design space for practical use of volatility in circuit design. It is the intent of this work to provide the fundamental data for modelling this design space and unlocking the operation of RRAM devices in volatile mode to the circuit design community.

#### REFERENCES

- C. Giotis, A. Serb, S. Stathopoulos, L. Michalas, A. Khiat, and T. Prodromakis, "Bidirectional Volatile Signatures of Metal–Oxide Memristors—Part I: Characterization," *IEEE Transactions on Electron Devices*, vol. 67, no. 11, pp. 5158–5165, 2020.

- [2] Z. Wu, X. Zhang, T. Shi, Y. Wang, R. Wang, J. Lu, J. Wei, P. Zhang, and Q. Liu, "Convertible Volatile and non-Volatile Resistive Switching in a Self-Rectifying Pt/TiOx/Ti Memristor," in 2021 5th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), 2021, pp. 1–3.

- [3] S. Stathopoulos, A. Khiat, M. Trapatseli, S. Cortese, A. Serb, I. Valov, and T. Prodromakis, "Multibit memory operation of metal-oxide Bi-layer memristors," *Scientific Reports*, vol. 7, no. 1, 2017.

- [4] M. Shahsavari, P. Falez, and P. Boulet, "Combining a volatile and nonvolatile memristor in artificial synapse to improve learning in Spiking Neural Networks," in 2016 IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH), 2016, pp. 67–72.

- [5] E. Covi, Y. H. Lin, W. Wang, T. Stecconi, V. Milo, A. Bricalli, E. Ambrosi, G. Pedretti, T. Y. Tseng, and D. Ielmini, "A Volatile RRAM Synapse for Neuromorphic Computing," in 2019 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS), 2019, pp. 903–906.

- [6] S. Pi, C. Li, H. Jiang, W. Xia, H. Xin, J. J. Yang, and Q. Xia, "Memristor crossbar arrays with 6-nm half-pitch and 2-nm critical dimension," *Nature Nanotechnology*, vol. 14, no. 1, pp. 35–39, 2019. [Online]. Available: https://doi.org/10.1038/s41565-018-0302-0

- [7] K.-H. Kim, S. Gaba, D. Wheeler, J. M. Cruz-Albrecht, T. Hussain, N. Srinivasa, and W. Lu, "A Functional Hybrid Memristor Crossbar-Array/CMOS System for Data Storage and Neuromorphic Applications," Nano Letters, vol. 12, no. 1, pp. 389–395, jan 2012. [Online]. Available: https://doi.org/10.1021/nl203687n

- [8] C. Li, Z. Wang, M. Rao, D. Belkin, W. Song, H. Jiang, P. Yan, Y. Li, P. Lin, M. Hu, N. Ge, J. P. Strachan, M. Barnell, Q. Wu, R. S. Williams, J. J. Yang, and Q. Xia, "Long short-term memory networks in memristor crossbar arrays," *Nature Machine Intelligence*, vol. 1, no. 1, pp. 49–57, 2019. [Online]. Available: https://doi.org/10.1038/s42256-018-0001-4

- [9] H.-J. Tsai, C.-C. Chen, K.-H. Yang, T.-C. Yang, L.-Y. Huang, C.-H. Chung, M.-F. Chang, and T.-F. Chen, "Leveraging data lifetime for energy-aware last level non-volatile SRAM caches using redundant store elimination," in 2014 51st ACM/EDAC/IEEE Design Automation Conference (DAC), 2014, pp. 1–6.

- [10] T. Abbey, A. Serb, S. Stathopoulos, L. Michalas and T. Prodromakis, "Emulating homoeostatic effects with metal-oxide memristors Tdependence" arXiv, 2110.04102, 2021. [Online]. Available: https://arxiv.org/abs/2110.04102

- [11] A. Serb, R. Berdan, A. Khiat, C. Papavassiliou, and T. Prodromakis, "Live demonstration: A versatile, low-cost platform for testing large ReRAM cross-bar arrays," in 2014 IEEE International Symposium on Circuits and Systems (ISCAS), 2014, p. 441.

- [12] C. Giotis, A. Serb, S. Stathopoulos, and T. Prodromakis, "Bidirectional Volatile Signatures of Metal-Oxide Memristors—Part II: Modeling," *IEEE Transactions on Electron Devices*, vol. 67, pp. 5166–5173, nov 2020

- [13] Y. Zhuo, R. Midya, W. Song, Z. Wang, S. Asapu, M. Rao, P. Lin, H. Jiang, Q. Xia, R.S. Williams, and J. Yang, "A Dynamical Compact Model of Diffusive and Drift Memristors for Neuromorphic Computing," Advanced Electronic Materials, 2100696, oct 2021. [Online]. Available: https://doi.org/10.1002/aelm.202100696

- [14] Z. Wang, S. Joshi, S. Savel'ev, H. Jiang, R. Midya, P. Lin, M. Hu, N. Ge, JP. Strachan, Z. Li, Q. Wu, M. Barnell, GL. Li, H. Xin, R.S. Williams, Q. Xia, J. Yang, "Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing," *Nature Materials*, vol. 16, pp.101–108, 2017. [Online]. Available: https://doi.org/10.1038/nmat4756

- [15] T. Chang, S. H. Jo, and W. Lu, "Short-term memory to long-term memory transition in a nanoscale memristor," ACS Nano, vol. 5, no. 9, pp. 7669–7676, 2011. [Online]. Available: www.acsnano.org