# University of Southampton Research Repository

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Author (Year of Submission) "Full thesis title", University of Southampton, name of the University Faculty or School or Department, PhD Thesis, pagination.

Data: Author (Year) Title. URI [dataset]

## University of Southampton

Faculty of Engineering and Physical Sciences Zepler Institute for Photonics and Nanoelectronics

# Experimental Demonstration of RRAM-based Computational Cells for Reconfigurable Mixed-Signal Neuro-Inspired Circuits and Systems

DOI: TBA

by

## Georgios Papandroulidakis

MEng, MSc

ORCiD: 0000-0002-9203-2557

A thesis for the degree of Doctor of Philosophy

November 2021

#### University of Southampton

#### **Abstract**

Faculty of Engineering and Physical Sciences Zepler Institute for Photonics and Nanoelectronics

### Doctor of Philosophy

# **Experimental Demonstration of RRAM-based Computational Cells for Reconfigurable Mixed-Signal Neuro-Inspired Circuits and Systems**

by Georgios Papandroulidakis

Modern electronics drive a shift from distributed, cloud and/or mainframe computing towards the 'edge'. To realise this vision, we need access to hardware technologies that are both energy and scale efficient. During the last decade, the introduction of Resistive Random Access Memory (RRAM), also known as memristors, has fuelled interest in extending conventional circuits' capabilities. Specifically, their capacity to act as scalable, non-volatile, finely tuneable, electrically programmable resistive elements render them promising candidates for future computer architectures. RRAM technologies have been considered by many as a promising candidate for implementing reconfigurable neuro-inspired circuits and systems capable of processing data in both digital and analogue formats. Presently, there is no extensive study of the behaviour of such circuits when realised physically with real RRAM devices. Hence, there are ample opportunities for developing novel electronic circuits for reconfigurable mixed-signal data processors in silico.

This thesis explores the design, implementation and testing of in-silico data processors capable of mapping data from one information domain to another and enabling a mixed-signal data processing. Through this research, I am introducing RRAM-based circuit designs operationally validated through simulations with state-of-art RRAM device model and then practically implemented proof-of-concept designs of these hybrid RRAM-CMOS circuits on hardware. The hardware implementation and testing of low-complexity primitive RRAM-based circuits that can process information in the analogue domain due to the introduction of programmable RRAM devices is the main contributions through this project. In this work, findings are presented regarding the implementation and testing in hardware of a RRAM-based primitive Multiply-Accumulate circuit, RRAM-enhanced Threshold Logic Gate design and as well as larger circuits on these primitive circuits that are easily integrated into RRAM-based In-Memory Computing (IMC) and Near-Memory Computing (NMC) architectures.

# **Contents**

| Li | st of 1 | Figures                                                       | vii   |

|----|---------|---------------------------------------------------------------|-------|

| Li | st of   | Tables                                                        | xix   |

| Li | sting   | s                                                             | xxi   |

| D  | eclara  | ation of Authorship                                           | xxi   |

| A  | cknov   | wledgements                                                   | xxiii |

| D  | efinit  | ions and Abbreviations                                        | xxvii |

| 1  | Intr    | oduction                                                      | 1     |

|    | 1.1     | Motivation                                                    | 1     |

|    | 1.2     | Research Aims                                                 | 4     |

|    | 1.3     | Objectives                                                    | 5     |

|    | 1.4     | Contributions of this work                                    | 7     |

| 2  | Mer     | mory and logic co-location circuits for in silico classifiers | 9     |

|    | 2.1     | Circuits and Systems for Data Processing                      | 9     |

|    | 2.2     | Computer logic inspired by biological neural processing       | 11    |

|    | 2.3     | In-memory computing                                           | 15    |

|    | 2.4     | Threshold Logic Computing Circuit Design                      | 20    |

|    | 2.5     | Associative Memories and Data Conversion                      | 29    |

|    | 2.6     | Metal Oxide Resistive Memory Technology                       | 30    |

|    | 2.7     | RRAM-based Logic Circuits                                     | 35    |

|    | 2.8     | Conclusions                                                   | 42    |

| 3  | RRA     | AM-Based Reconfigurable MAC Circuit for IMC systems           | 45    |

|    | 3.1     | Multiply and Accumulate Circuits Design Methodology           | 46    |

|    | 3.2     | 1T1R-based Circuits Configuration Map for In-Memory Computing | 48    |

|    | 3.3     | MAC Circuit Design                                            | 51    |

|    | 3.4     | MAC Circuit Operation and Experimental Measurements           | 53    |

|    | 3.5     | MAC Circuit employment in Winner-Take-All System              | 59    |

|    | 3.6     | Comparison of WTA case study with state-of-art                | 66    |

|    | 3.7     | Conclusions                                                   | 69    |

| 4  | Mer     | mristively-Enhanced Threshold Logic Gate                      | 73    |

|    | 4.1     | RRAM-Enabled TLGs Design Methodology                          | 74    |

vi CONTENTS

|    | 4.2                             | Overview of RRAM Devices Characterisation            | 76  |

|----|---------------------------------|------------------------------------------------------|-----|

|    | 4.3                             | Design and Operation                                 | 81  |

|    | 4.4                             | Experimental Setup and Measurement Methods           | 84  |

|    | 4.5                             | Measurements and Logic Operation Validation          | 85  |

|    | 4.6                             | Comparison of proposed TLG design with state-of-art  | 93  |

|    | 4.7                             | Conclusions                                          | 98  |

| 5  | Com                             | posite application for mixed-signal data classifiers | 101 |

|    | 5.1                             | Combined circuit for MAC and TL operations           | 102 |

|    | 5.2                             | RRAM-based Wake-Up-Circuit Design                    | 109 |

|    | 5.3                             | WUC Simulation and Results                           | 114 |

|    | 5.4                             | Conclusions                                          | 119 |

| 6  | Con                             | clusions and Discussion                              | 121 |

| Αŗ | Appendix A List of publications |                                                      |     |

| Re | References 1                    |                                                      |     |

# **List of Figures**

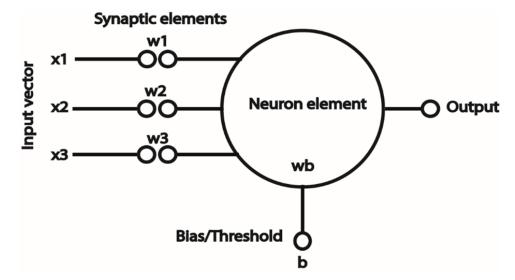

| 2.1  | Schematic of the fundamentals of an artificial neurons design. Synap-     |     |

|------|---------------------------------------------------------------------------|-----|

|      | tic connections are mapping the input space into an appropriate for-      |     |

|      | mat through the use of synaptic weights. The synapse-dependent trans-     |     |

|      | formed signals are then used as inputs for the neuron which decides       |     |

|      | whether to fire or not depending on the total effect of the input signals |     |

|      | compared against a biasing signal                                         | 21  |

| 2.2  | Schematic of LCTL design proposed by Strandberg and Yuan (2000).          |     |

|      | Schematic adapted from Strandberg and Yuan (2000)                         | 25  |

| 2.3  | Schematic of CIAL design proposed by Hidalgo-Lopez et al. (1995). Schema  | tic |

|      | adapted from Hidalgo-Lopez et al. (1995)                                  | 26  |

| 2.4  | Schematic of CIAL-TL design proposed by Leshner et al. (2010). Schematic  |     |

|      | adapted from Leshner et al. (2010)                                        | 27  |

| 2.5  | Schematic of ECMTLG proposed by Bobba and Hajj (2000). Schematic          |     |

|      | adapted from Bobba and Hajj (2000)                                        | 28  |

| 2.6  | Schematic of the DCMTLG proposed by Bobba and Hajj (2000). Schematic      |     |

|      | adapted from Bobba and Hajj (2000)                                        | 28  |

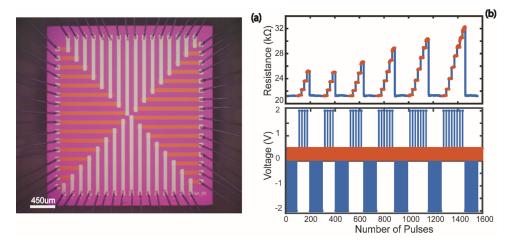

| 2.7  | Die photo of RRAM devices developed by Stathopoulos et al. (2017) and     |     |

|      | example behaviour of multi-state programming of the devices (details of   |     |

|      | the experiment and detailed device response are exhibited by Stathopou-   |     |

|      | los et al. (2017))                                                        | 33  |

| 2.8  | Schematic of a 1-transistor-1-RRAM (1T1R) array that is employed for      |     |

|      | building active RRAM-based memory arrays. The use of accompany-           |     |

|      | ing MOSFET devices as selector devices enable the better control of the   |     |

|      | access of the RRAM devices and eliminates issues such as the parasitic    |     |

|      | sneak-path problem that occurs in passive arrays Vourkas et al. (2016).   | 37  |

| 2.9  | Schematic of a RRAM-based passive array that can implement IMPLY          |     |

|      | logic.                                                                    | 38  |

| 2.10 | Schematic of Memristor-based Threshold Logic (MTL) design proposed        |     |

|      | by Rajendran et al. (2010)                                                | 41  |

viii LIST OF FIGURES

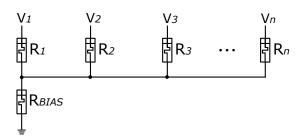

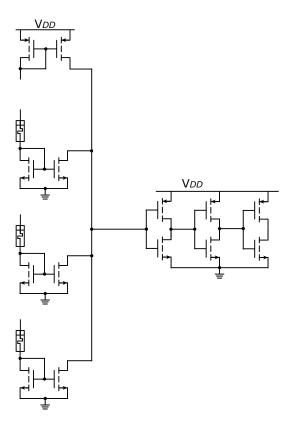

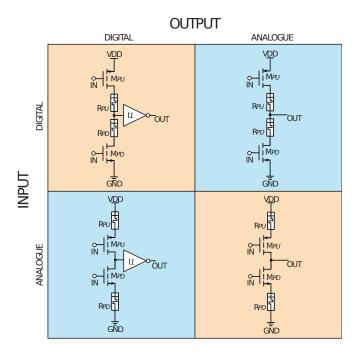

Map of different primitive RRAM-based circuit configurations of elements introducing a hard switch/selection (i.e. MOSFET devices) and elements introducing a continuous value of contributions (i.e. RRAM devices). Additional hard-threshold circuits (such as CMOS-based inverters and latching elements) can be used to binarise an output signal generated by the hybrid RRAM-MOSFET circuits. By enabling small differences in the circuit configuration and circuit control scheme a variety of reconfigurable circuits can be designed that will be fitted towards receiving inputs and emitting outputs in our choice of analogue or digital format. Given the analogue nature of RRAM devices operation and behaviour, the main computation (i.e. MAC operations) is always performed in the analogue domain. The implementation that connects the same signal domain is considered as non-Converting Logic (non-CL), while the circuits that bridge different signal domains are considered as Converting Logic (CL) gates. In the map, the non-CL circuits are denoted with orange while the CL circuits with blue. This map of primitive hybrid RRAM-CMOS circuits showcase the computationally flexibility of such circuits and exhibit their capability in being employed into novel implementations of analogue or mixed-signal associative memory sys-

51

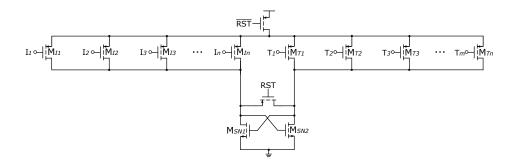

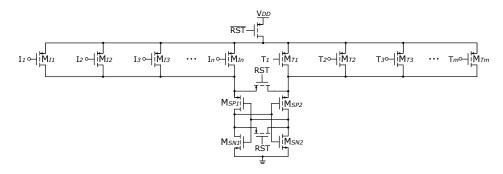

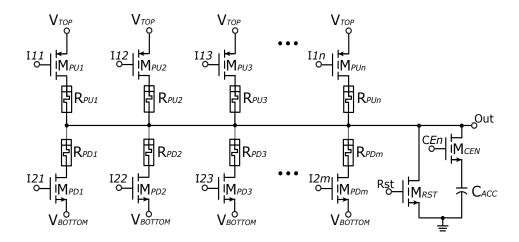

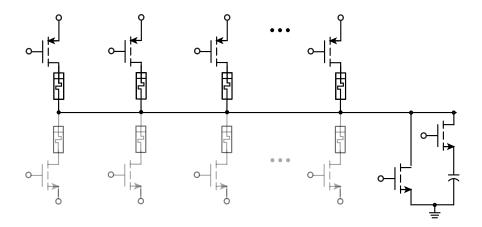

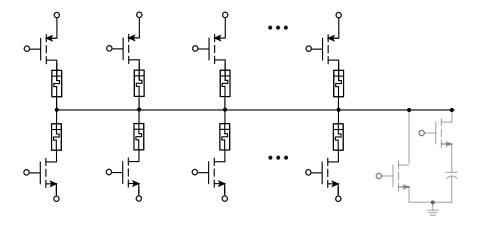

Schematic of the RRAM-based Multiply-Accumulate (MAC) circuit implementation of this work. The multiplication operation performed per each 1T1R composite element depends on the RRAM memory contents while the accumulation of all the active 1T1R element contributions is performed naturally in current form through the common output node. The circuit can be employed as a form of simplified heteroassociative memory system used to map a digital memory word to an analogue output value. The input digital word can be considered as a train of digital spikes send as stimulus to the hybrid RRAM-CMOS associative memory thus further enhancing the concept of neuro-inspired design in such circuits. The output being could be stored in a integrating capacitor to retain the information-rich analogue signal. The heteroassociative memory mapping capabilities can be easily expanded by increasing the size of the 1T1R memory arrays, thus the number of 1T1R component for the pull-up and/or the pull-down network. Furthermore, this circuit can be easily integrated as part of a crossbar memory array (i.e. the pull-up and pull-down 1T1R-based networks can be easily integrated within a RRAM-based crossbar memory topology), thus it can easily be incorpo-

LIST OF FIGURES ix

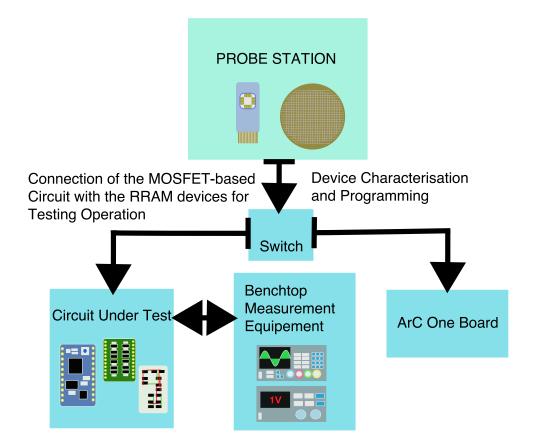

| 3.3 | Block diagram of the setup for the hardware experimental measurements. The hardware experiments consist of programming appropriately a spe-             |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | cific number of RRAM devices. The RRAM devices are accessed through                                                                                     |    |

|     | a probe station and programmed through the use of the ArC One instru-                                                                                   |    |

|     | mentation board (ArC Instruments, UK). When the device preparation                                                                                      |    |

|     | phase is finished, the RRAM devices (still accessed through the probe                                                                                   |    |

|     | station are disconnected from the ArC One board and connected to the                                                                                    |    |

|     | appropriate hardware prototype that includes the other part of the hy-                                                                                  |    |

|     | brid RRAM-CMOS circuit under test, thus the MOS components. Along-                                                                                      |    |

|     | side the circuit under test other smaller accompanying boards (e.g. volt-                                                                               |    |

|     | age dividers for lowering the voltage levels), micro-controller or single                                                                               |    |

|     | board PCs (e.g. RPi for sending appropriate control signals) are em-                                                                                    |    |

|     | ployed. Additional bench-top measurement equipment (e.g. voltage                                                                                        |    |

|     | sources, oscilloscopes, etc.) is also used to test the circuit and measure                                                                              |    |

|     | its response                                                                                                                                            | 54 |

| 3.4 | Schematic of the RRAM-based MAC circuit focusing on the integrator                                                                                      |    |

|     | mode of operation. In this mode the pull-up 1T1R network is used to                                                                                     |    |

|     | charge the accumulating capacitor and store the weighted sum in an                                                                                      |    |

|     | analogue format. This mode is essentially performing a current mode                                                                                     |    |

|     | dot-product operation                                                                                                                                   | 55 |

| 3.5 | Schematic of the RRAM-based MAC circuit focusing on the combinato-                                                                                      |    |

|     | rial mode of operation. In this mode, the output accumulating capacitor                                                                                 |    |

|     | is disconnected since for the specific operation mode a fast voltage di-                                                                                |    |

|     | vider -based operation of the RRAM-based network is required. The                                                                                       |    |

|     | pull-down 1T1R network is connected and act as a biasing network that                                                                                   | EE |

| 2.6 | subtracts from the pull-up signal                                                                                                                       | 55 |

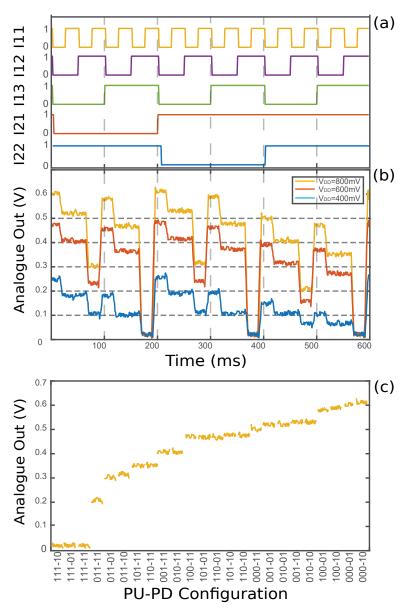

| 3.6 | Measured results of the first hardware experiment. In this first case                                                                                   |    |

|     | study, a 3 1T1R pull-up array (PU: $5.5k\Omega$ , $11k\Omega$ , $11.5k\Omega$ ) with a 2 1T1R                                                           |    |

|     | pull-down array (PD: $7.3k\Omega$ , $6k\Omega$ ) was implemented and experimentally measured. The MAC circuit was realised by using $Pt/TiO_x/AlO_x/Pt$ |    |

|     | RRAM devices, as shown by Stathopoulos et al. (2017). In Fig. 3.6a                                                                                      |    |

|     | the digital input vectors controlling the transistors of the 1T1R array are                                                                             |    |

|     | shown with the $I_{11}$ , $I_{12}$ , $I_{13}$ the control signals for the pull-up components                                                            |    |

|     | and $I_{21}$ , $I_{22}$ for the pull-down components. The pull-up 1T1R network is                                                                       |    |

|     | using pMOS devices, thus the high logic '1' and low logic '0' denotes a                                                                                 |    |

|     | non-conductive and conductive transistor states, respectively, 1T1R. In                                                                                 |    |

|     | Fig 3.6b, the circuit response ( $V_{AnalogueOut}$ ) for all the different configu-                                                                     |    |

|     | ration vectors of the control signals ( $I_{11}$ , $I_{12}$ , $I_{13}$ , $I_{21}$ and $I_{22}$ ) are shown                                              |    |

|     | under 400mV, 600mV and 800mV power supply voltages. In Fig 3.6c, the                                                                                    |    |

|     | response for 800mV power supply is rearranged into an analogue volt-                                                                                    |    |

|     | age output ( $V_{AnalogueOut}$ ) versus digital vector input map (signals $I_{11}$ $I_{12}$                                                             |    |

|     | $I_{13}$ - $I_{21}$ $I_{22}$ are encoded into a digital control word displayed along the                                                                |    |

|     | x-axis). Multiple output levels can be discerned                                                                                                        | 57 |

x LIST OF FIGURES

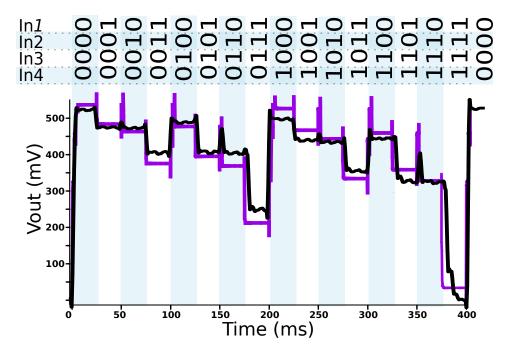

| 3.7 | Graph exhibiting the results from the second experiment. In this case study, a hardware MAC circuit of 4 pull-up 1T1R components (PU: $461k\Omega$ , $508k\Omega$ , $534k\Omega$ , $539k\Omega$ ) and 1 pull-down biasing component (PD: $330k\Omega$ ) using $Pt/TiO_x/AlO_x/Pt$ devices, as exhibited by Stathopoulos et al. (2017), was implemented and measured. The same configuration is used for the simulation of the circuit in Cadence Virtuoso Spectre environment towards comparing the response of the circuit using real devices and simulated device models. For the MOSFET models, I used a commercially available 65nm technology node library. The RRAM device models are based on the Messaris et al. (2018) and the RRAM model instances are fitted based on the same devices used for the practical circuit implementation. The black trace is the experimentally measured response while the purple line is the simulated circuit response. The comparison highlights that the simulated circuit follows the response of the real hardware implementation. These preliminary results suggest the circuit robustness against transistors variations (in one case large discrete components and in the other case (55nm CMOS). | 50 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.8 | components and in the other case 65nm CMOS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 58 |

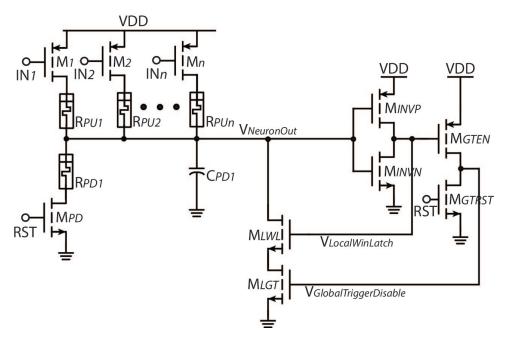

| 3.9 | multiple neuron to be performed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62 |

|     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

LIST OF FIGURES xi

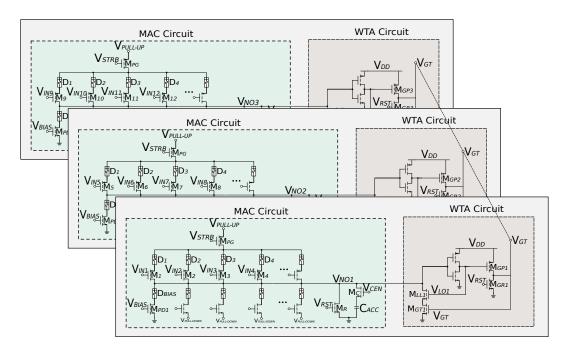

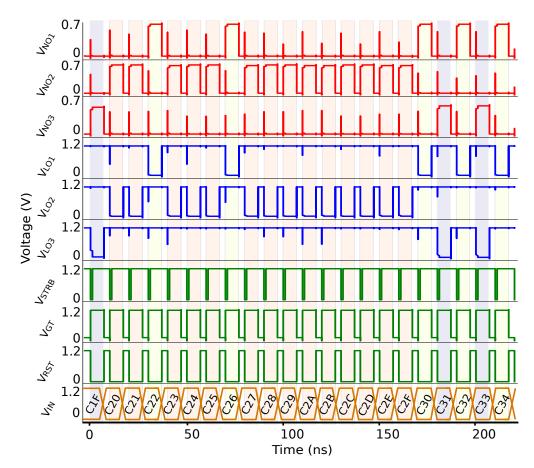

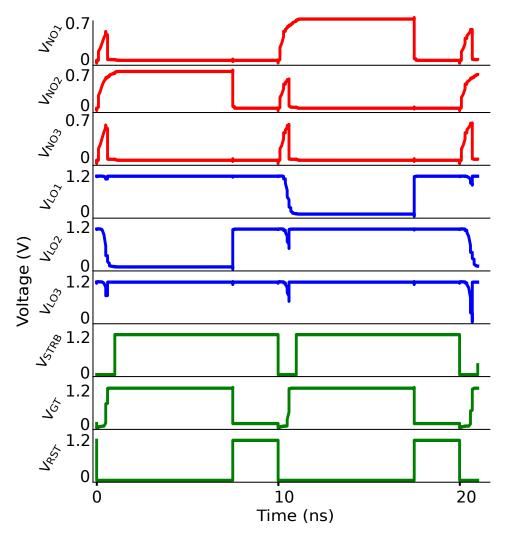

3.10 The results of the Winner-Take-All (WTA) network are showcased in this figure. The results are based on the example 3-neuron circuits presented in Fig. 3.9. The waveforms for the latch outputs ( $V_{LO1}$ ,  $V_{LO2}$  and  $V_{LO2}$ ), that comprise the classification word encoding of the WTA lateral network state, the neuron output  $(V_{NO1}, V_{NO2})$  and  $V_{NO3}$  that feeds into the WTA classification system during the evaluation phase, as well as the control signals that enable the cycles of operation for the presented network ( $V_{STRB}$ ,  $V_{GT}$ ,  $V_{IN}$ ). The  $V_{IN}$  is encoded into a hexadecimal value representing the input vector  $V_{in1-12}$  controlling the pull-up 1T1R network used for this example. The connectivity of the  $V_{IN}$  vector is shown in Fig. 3.9. The artificial neurons (see Fig. 3.9) were based on multiple instances of the extracted RRAM models as described in Section III.A (see Table 3.1). The simulation was performed in Cadence's Virtuoso Spectre using a commercially available 65nm technology node for the transistor devices. It can be clearly shown that when a winning node is evaluated by the WTA by observing the  $V_{GT}$  signal. Distinct coloured shading has been added to highlight when one neuron is winning over the rest. . . .

63

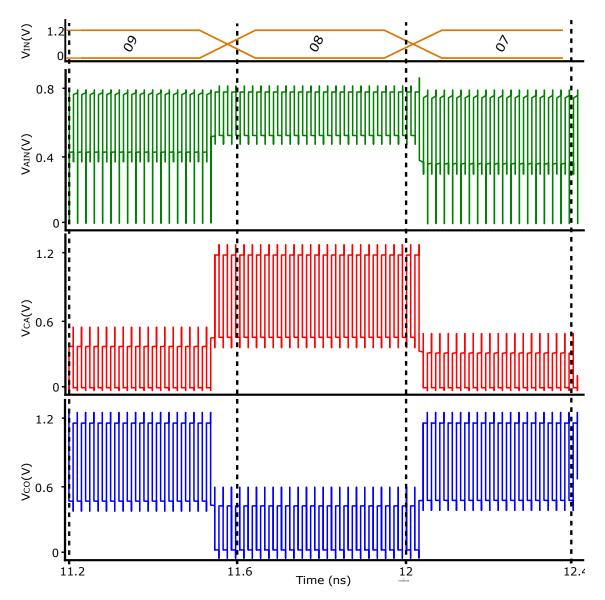

3.11 In this figure, a focused analysis of the WTA operation cycle is show-cased. The red traces ( $V_{NO1}$ ,  $V_{NO2}$  and  $V_{NO3}$ ) showcase the outputs of the 3 artificial neurons while the blue traces ( $V_{LO1}$ ,  $V_{LO2}$  and  $V_{LO3}$ ) showcase the latches output (winning node is the node with latch output at logic '0'). The green traces are the signals controlling the operation cycle of the WTA. The  $V_{RST}$  initialise the system when set to high (logic '1') and the  $V_{STRB}$  is the signal controlling the power gates of the artificial neuron. The  $V_{GT}$  is low when the WTA is initialised/evaluating and high when the winning neurons has been evaluated. A single period of operation (defined by  $V_{RST}$ ) is 10ns from this proof-of-concept example and the classification operation requires  $t_{op}$ = 1ns. The voltage racing operation of the circuit can be highlighted from the artificial neurons outputs that before the winning neuron is found all the traces are racing to the top but the fastest one is locking the latches to an one-hot encoded digital word.

64

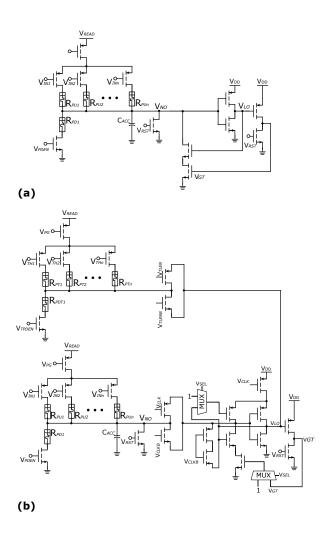

3.12 Schematic of the proposed Winner-Take-All (WTA) circuit in (a) and its adaptation (b) for enabling the implementation of a programmable classification circuit. In (a), the MAC circuit is connected through the  $V_{NOut}$ node to a half-latch-based circuit that is based on the implementation presented by Wu et al. (2017) as shown in Fig. 3.8 and Fig. 3.9. In (b), the WTA part of the neuron model can be implemented by connecting/disconnecting appropriate pMOS and nMOS MOSFET devices of a CMOS full latch, similar to the main sensor component used in differential TLG designs, as discussed in Chapter 2, as shown by Papandroulidakis et al. (2018); Dara et al. (2017); Mozaffari and Tragoudas (2018). Thus, the design employed here shows compatibility with some RRAM-based TLG implementations that can be used to efficiently implement a novel seaof-gates reconfigurable computer, as shown by Beiu et al. (2003b). The configurable CMOS-based classifier can be used as periphery circuitry to a RRAM crossbar array where multiple 1T1M arrays that can be used to create a configurable neuro-inspired system capable of easily reconfigur-

xii LIST OF FIGURES

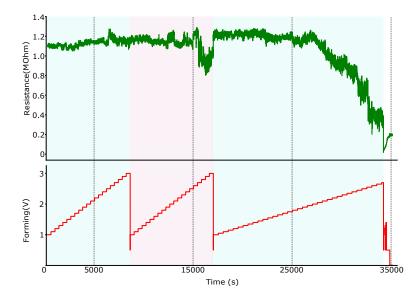

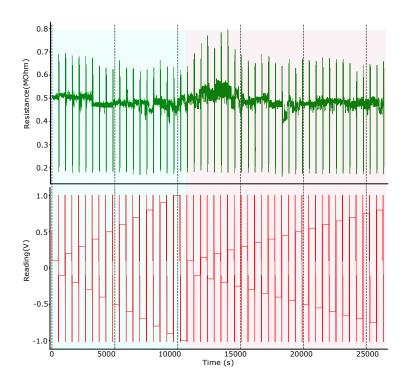

4.1 Example of the forming process applied to pristine RRAM devices. The Forming (V) signal is the stimulus to the RRAM device and the Resistance (MOhm) signal is the resistance progression read of the device under test. A staircase-like train of pulse of increasing voltage amplitude is applied to the RRAM device. In this example, three phases of programming staircase-like pulses from 1V to 3V are applied. At the end of the third phase the resistance of the RRAM device under test has been set to approximate  $200k\Omega$ . This process is theorised that changes the geometry of the RRAM devices towards enabling it to form conduction paths that are necessary for the correct operation of the RRAM which includes the programming to different states. The details of the RRAM mechanics and chemistry is out of scope of this thesis and more information can be found in the work of Stathopoulos et al. (2017); Michalas et al. (2017). . . 4.2 Automated programming testing can also be employed to map the RRAM

77

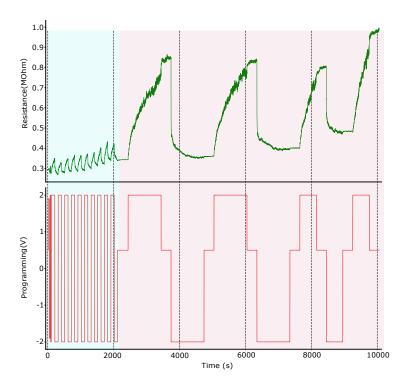

programming behaviour between resistance states. The Programming(V)signal is the stimulus to the RRAM device and the *Resistance*(*MOhm*) signal is the resistance progression read of the device under test. This process can test the endurance and stability of the switching operation between two or more resistive states and how reproducible is the switching before a large enough state drift occurs that requires correction. Programming voltage pulses of different amplitude and duration are applied to the device towards setting the device to an appropriate resistance level as dictated by requirements of the experiment. Reading pulses are also applied usually in low amplitude range of 200-500mV (Reading(V)), Reading signal) towards avoiding unwanted programming during the reading operation. Through the reading pulsed I am performing the appropriate testing the programmed resistance value. More information regarding the process of setting up an automated process for programming and testing a RRAM device are showcased by Serb et al. (2014,

LIST OF FIGURES xiii

Example of detailed RRAM device response mapping for a specific range of input stimulus. The Reading(V) signal is the stimulus to the RRAM device and the *Resistance*(*MOhm*) signal is the resistance progression read of the device under test. This process is followed during the parameter extraction of the devices that is used in order to create unique instances of the Verilog-A RRAM model, as discussed by Messaris et al. (2018). The process includes the continued pulsing of the RRAM device under test with a specific voltage amplitude thus testing the endurance of the device to retain the specific resistive state under the stress of the stimulus (state drift test). Afterwards, a full current-voltage characteristic graph is created for a specific range of voltages to test the nonlinearity of the device under test. The process is sequentially repeated for a predefined set of voltage amplitudes similarly to what is shown in this example. The detailed process is discussed by Messaris et al. (2018). Since the experiments and simulations performed in this thesis are focused around the program-once-read-many operation, the devices at this stage of the characterisation process are tested for the non-switching part of their response. This is usually found in the range of 0V to approximately 1V. Hence, for this range of voltage stimulus the devices under test do not exhibit any unwanted resistive state alteration and instead keep relatively stable the state in which they were programmed to in previous steps of the characterisation and preparation for employment

79

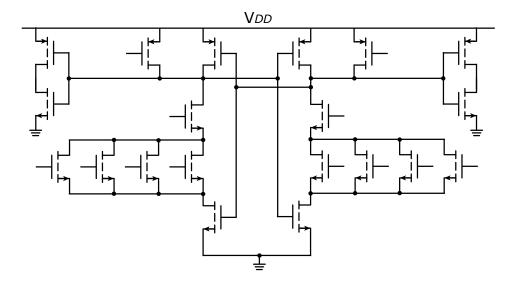

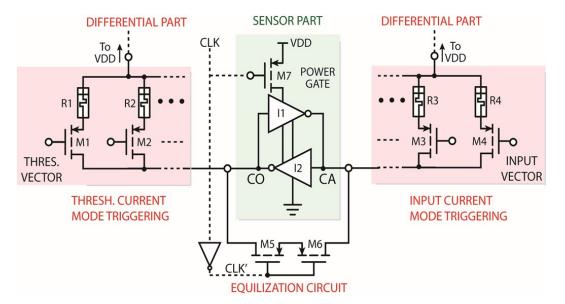

Schematic of a RRAM-based differential current mode TLG design. The specific design implemented and tested in this chapter is also referred to as RRAM-based Current Mode Threshold Logic Gate (MCMTLG). The two basic parts of design are the RRAM-based 1T1R array performing a dot-product multiplication between the RRAM memory contents (resistive memory state also referred to as memristance, i.e. memory resistance) and the binary input vector controlling the accompanying pMOS MOSFET device, and the sensor determining which 1T1R array outputs greater current. Further details for the differential TLG design can be found in Chapter 2. The canonical (CA) and complementary (CO) circuit nodes are the output nodes during the evaluation phase while they are connected to the differential 1T1R arrays (thus the output of the MAC operations are used as input to the sense amplifier). The outputs are available during the evaluation phase when the differential current flows have been compared and a final stable state of the sensor part has been obtained. The clock signal (CLK) and the complementary clock signal (CLK') are controlling the sensor's power gate and the equalisation circuit, respectively. Hence, the CLK signal defines the transition between the two TLG operation phases, equalisation (reset) and evaluation (set).

xiv LIST OF FIGURES

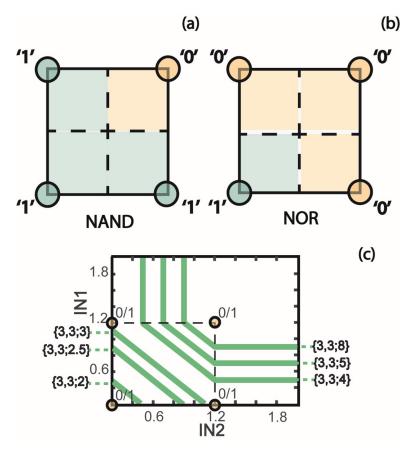

| 4.5 | Concept-level figures highlighting the space separation performed by TLGs and the programming capability of the threshold. (a), (b) Indicative 2D input space splitting performed by the 2-input RRAM-based TLG design, for the NAND case (a) and the NOR case (b) respectively. (c) LT-Spice simulation of this TLG design shown in Fig. 4.4 using resistors instead of RRAM devices. Changing the threshold weight alters the decision boundary of the classification operation performed in the TLG. Each weight configurations denoted on the side of each case, in the form of a, b: c, in units of M $\Omega$ , where a, b are the weights mapped in the input array and c is the threshold/bias resistive weight which defines the classification boundary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 87 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

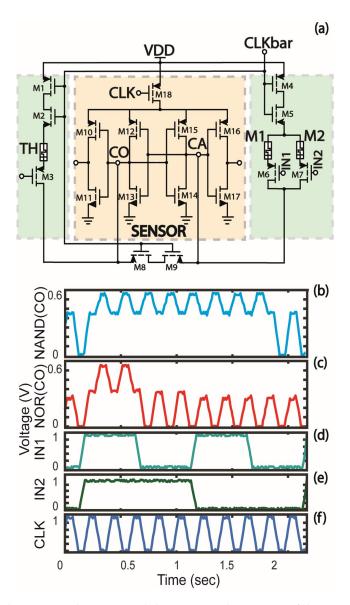

| 4.6 | The circuit schematic and the measured response of the practically implemented 2-input RRAM-based TLG configuration. (a) Circuit schematic of the practically implemented RRAM-based TLG design showcased here (also referred to as RRAM-based Current Mode Threshold Logic Gate (MCMTLG)). (b) Measurements taken from an experimental implementation of a RRAM-based TLG configuration showcasing NAND functionality, thus an appropriate RRAM-based weight configuration used for mapping AND/NAND logic function. (c) Similarly to the previous case a different RRAM-based weight configuration showcase a NOR functionality as measured from the CO output of the RRAM-based TLG configured to map OR/NOR logic function. (d, e) The 2-input digital input vector signals are showcased. (f) The clock signal controlling the equalisation/evaluation phases. Regarding the RRAM weight configurations, I employed the following sets in the experimental hardware implementation:M1, M2; TH = $60.5 \text{k}\Omega$ , $60 \text{k}\Omega$ 33k $\Omega$ 33k $\Omega$ , 18.3k $\Omega$ 41.7k $\Omega$ for the AND/NAND function and OR/NOR function, respectively. Due to the use of pMOS devices as the accompanying MOSFET device for the 1T1R differential arrays, the HIGH and LOW voltage level, of the input vector, corresponds to non-conductive and conductive MOSFET device, respectively. | 88 |

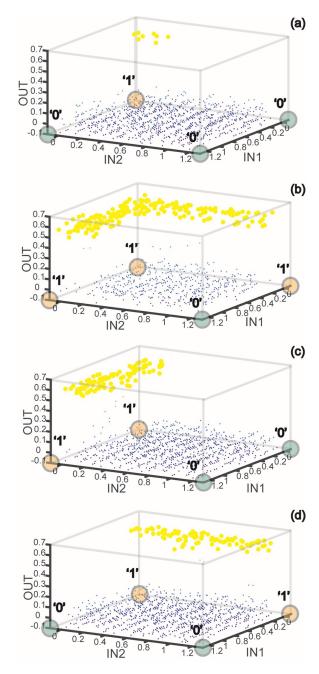

| 4.7 | Experimental measurement of the RRAM-based TLG under test. In this example, the TLG configuration classifies a 2-input vector, thus 2 1T1R composite components are employed from the input array. By using analogue inputs (ramps from 0V to 1.2V per input) a clearer map of the circuit response is created. Four different cases are presented in this experiment, mapping every possible TL Boolean function. (a) AND TLG (M1, M2 $\stackrel{.}{_{\downarrow}}$ TH and M1—M2 $\stackrel{.}{_{\downarrow}}$ TH), (b) OR (M1, M2 $\stackrel{.}{_{\downarrow}}$ TH), (c) OUT = IN1 (M1 $\stackrel{.}{_{\downarrow}}$ TH, M2 $\stackrel{.}{_{\downarrow}}$ TH) and (d) OUT = IN2 (M1 $\stackrel{.}{_{\downarrow}}$ TH, M2 $\stackrel{.}{_{\downarrow}}$ TH). The memory configurations for each case of the experiment is set as follows: AND 109.1k $\Omega$ , 105.7k $\Omega$ ; 86.7k $\Omega$ , OR 83.6k $\Omega$ , 85.9k $\Omega$ 262.5k $\Omega$ , IN1 78.4k $\Omega$ , 233.2k $\Omega$ ; 109.1k $\Omega$ and IN2 253.5k $\Omega$ , 82.8k $\Omega$ 39.2k $\Omega$ . The input/output mapping on the quantised, binary space is also included. An input activates (deactivates) a specific RRAM device branch of the 1T1R array by getting LOW (HIGH), due to the use of pMOS as the transistors in 1T1R                                                                                             | 00 |

|     | computing arrays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 89 |

LIST OF FIGURES xv

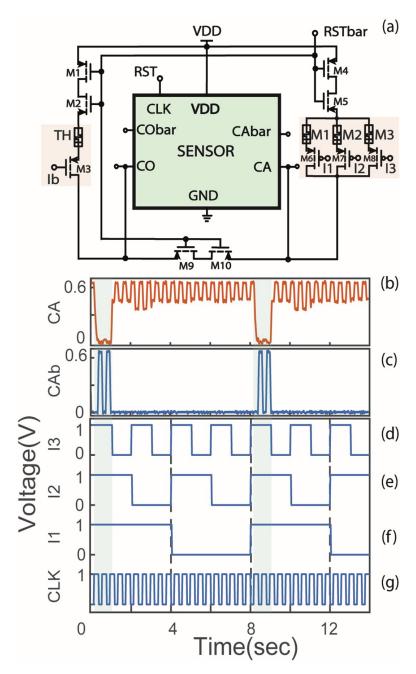

| 4.8 | Practical implementation of 3-input RRAM-based TLG experiment. (a) Schematic of 3-input MCMTLG, where the sensor component now includes the CMOS latching element plus two additional restoration inverters per output. An example of how a 3D input space is split by the TLG. (b) Canonical (CA) output and (c) and the complementary (CAb) output as buffered by a CMOS inverter gate to isolate the sense amplifier's output nodes from the following circuit cascade. As can be seen in Fig. 4.8(c) the CAb output does not include the full voltage information of the CA but instead "selects to transmit only the final output state available during the evaluation phase. (d-g) control signals (3-input vector I1, I2, I3 plus clock). The clock signal is the same as the RST signal in this schematic since the resetting/initialisation operation (performed during the equalisation phase) is controlled CLK. The weight configuration for                                                                                                              |          |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

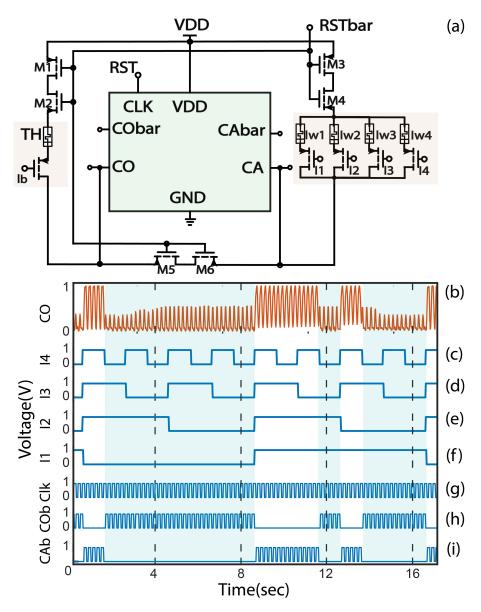

| 4.9 | the OR3/NOR3 is M1, M2, M3; TH=31.5k $\Omega$ , 30k $\Omega$ , 28.2k $\Omega$ 68.2k $\Omega$ Practical implementation of 4-input MCMTLG. (a) Schematic of the 4-input MCMTLG. (b) Circuit response measured at the complementary output (CO). (c-f) The signals for the digital 4-bit input vector (I1, I2, I3, I4). (g) The clock signal controlling the circuit. The clock signal is the same as the RST signal in this schematic since the resetting/initialisation operation (performed during the equalisation phase) is controlled CLK. Additionally, to the analogous measured CO output of the sensor, the threshold-based processed responses from the isolation inverters are also shown (h,i). The memristive weight configuration is M1, M2, M3, M4; TH = 30k $\Omega$ , 21.6k $\Omega$ , 31.2k $\Omega$ , 25.2k $\Omega$ 19.1k $\Omega$ . This configuration of the MCMTLG performs the following Boolean function: F= MAJ2(I1,I2,I3,I4), thus needing at least two conductive inputs for the total input current to be larger than the threshold current | 90<br>92 |

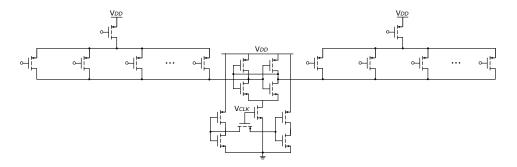

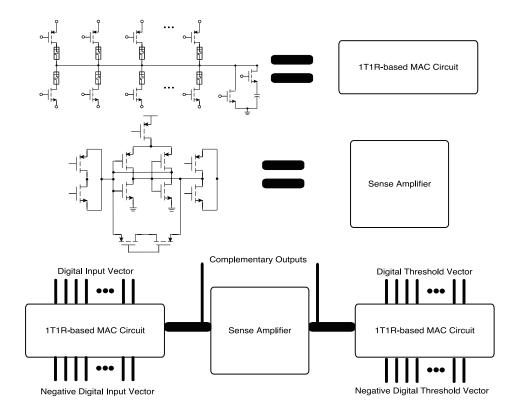

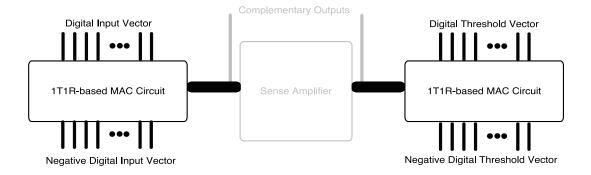

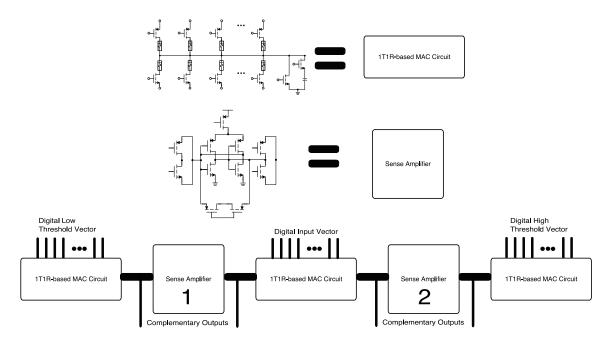

| 5.1 | Schematic of a combined near-memory primitive circuit for MAC operations and TL computing. The circuit is based on the employment of two 1T1R computing arrays and a single sense amplifier. The circuits can be reconfigured to either the MAC circuit (shown in Chapters 3) or the RRAM-based TLG (shown in Chapters 4). The additional capacitor at the output of the MAC Circuit can provide analogue integration and storage capabilities and is also available for the combined computational circuit. The positive digital input/threshold vector is controlling the pull-up 1T1R array while the negative digital input/threshold vector is controlling the pull-down 1T1R array                                                                                                                                                                                                                                                                                                                                                                               | 103      |

| 5.2 | Schematic of a combined near-memory primitive circuit configured to perform MAC operations. The sense amplifier that can perform the TL operation (current-mode comparison between the two arrays) is deactivated. Thus, each 1T1R array is capable of performing a separate MAC computation in parallel. The negative digital vectors are active and a simultaneous mapping of input and/or threshold biasing (per array) can be performed. Hence, negative input-weight and negative threshold-weight combinations are available for the MAC operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 105      |

xvi LIST OF FIGURES

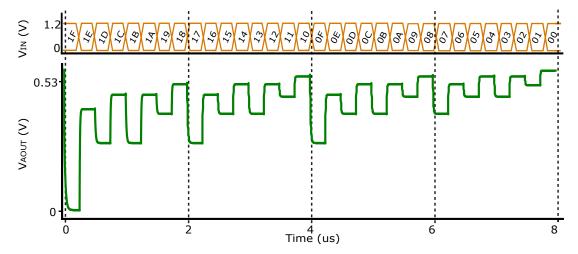

| 5.3 | Simulated waveform when the combined primitive circuit has been configured to perform analogue MAC operations. The $V_{IN}$ is shown in a hexadecimal format as $MSB$ - $(000V_{IN5})$ ( $V_{IN4}$ $V_{IN3}$ $V_{IN2}$ $V_{IN1}$ )- $LSB$ . A pull-down resistive weight of $900$ k $\Omega$ is also used for the combinatorial MAC mode. The integrating capacitor is disconnected from the circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 105 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

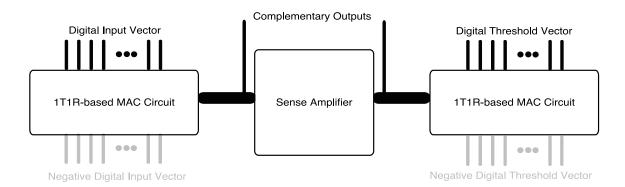

| 5.4 | Schematic of a combined near-memory primitive circuit configured to perform TL operations. The negative digital input and threshold vectors and thus the pull-down 1T1R arrays are deactivated. The two 1T1R arrays form a differential pair for mapping input and threshold analogue weights. The two adversarial currents generated by the reading operation of the two 1T1R arrays are compared through the sense amplifier circuit. Due to the design of the sense amplifier as a SRAM-based latching element complementary outputs can be obtained as the result of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 103 |

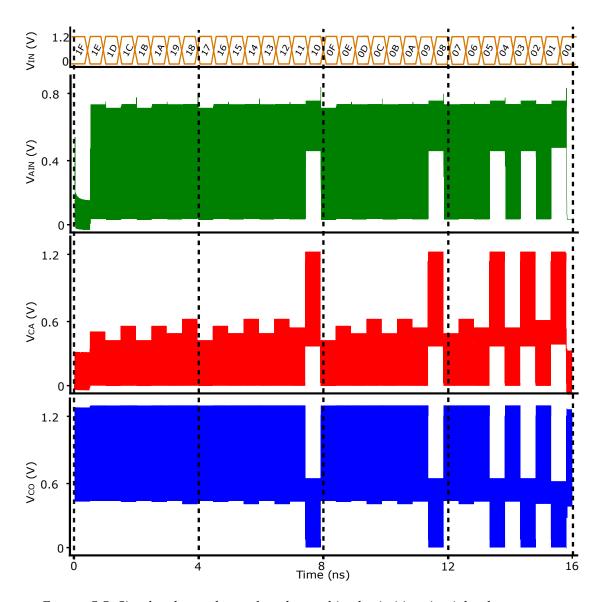

| 5.5 | comparison process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 106 |

|     | format as $MSB$ - $(000V_{IN5})$ ( $V_{IN4}$ $V_{IN3}$ $V_{IN2}$ $V_{IN1}$ )- $LSB$ . The TLG weights are configured as $\{212k\Omega, 408k\Omega, 403k\Omega, 415k\Omega, 417k\Omega;; 97k\Omega\}$ . The $V_{AIN}$ is the voltage of the analogue output of the input-dependent 1T1R-based array. The $V_{CA}$ and $V_{CO}$ are the complementary outputs of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 5.6 | sense amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 107 |

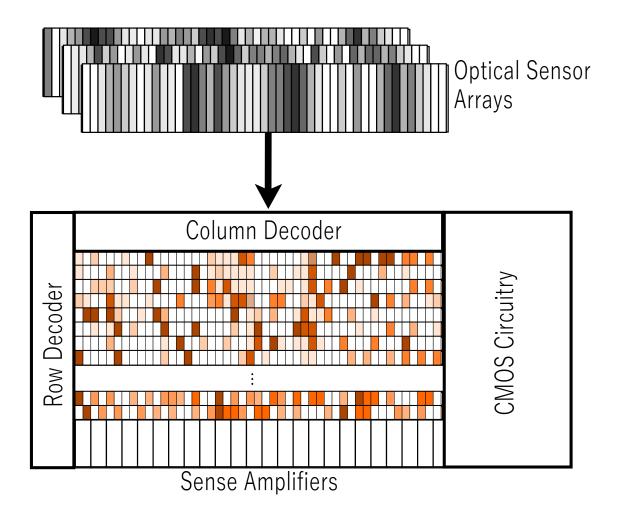

| 5.7 | In this figure, a general block diagram description of the main components of the RRAM-based Wake-Up System is showcased. The optical sensor is an example considered for this concept and other types of sensing systems could be employed to convert an environmental (with regards to the computer) observation to an appropriate set of electrical signals. The output of the sensor send the input stimulus to the IMC system with the different coloured cells representing different RRAM-based weights. I assume a DRAM-like crossbar-based structure for the IMC system. the main memory and computing unit is found in the form of the 1T1R array. The main WUC operation are performed inside the memory array (through the 1T1R arrays and the sense amplifiers) with some additional peripheral circuitry necessary for the whole pattern detection system to be complete, thus making this system a Near-Memory Computing (NMC) architecture. If a pattern is matched then a wake-up signal (pattern match flag signal) is generated to enable a high-performance system towards processing the environmental stimulus further. The actual high-performance computer is out of scope for the WUC design of this section. Similar system configurations that incorporate a event-detecting systems' duty-cycling is considered important especially for applications at the edge where the continuous operation of bright performance continuous operation of this bright performance. | 108 |

|     | high-performance systems can be hard to implement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 112 |

LIST OF FIGURES xvii

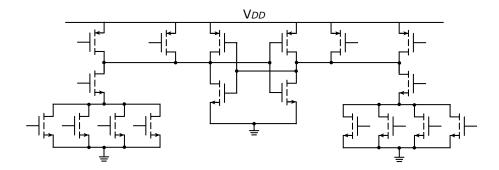

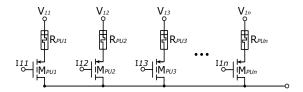

| 5.8  | Schematic of the circuit-level system representation is showcased. The          |     |

|------|---------------------------------------------------------------------------------|-----|

|      | main computing circuits are the memory array itself used as a minia-            |     |

|      | turised associative memory to map information of a vector of analogue           |     |

|      | voltages into a single analogue value. In order to complete the com-            |     |

|      | putation additional circuitry is necessary thus categorising the specific       |     |

|      | RRAM-based WUC design under the near-memory computing (NMC)                     |     |

|      | techniques. It is worth noting that the main computing circuits where           |     |

|      | the data mapping is performed such as the 1T1R arrays and the sense             |     |

|      | amplifiers are traditionally fundamental parts of a typical memory ar-          |     |

|      | chitecture, such as DRAM. Hence, essentially the overhead is of the shift       |     |

|      | registers, counters and additional Boolean logic gates used to enable the       |     |

|      | tracking of the signal and the generation of appropriate enabling/dis-          |     |

|      | abling signals in case of a pattern match/mismatch. In the block diagram        |     |

|      | of the system, the digital input vector is controlling the input 1T1R array     |     |

|      | while the digital low and high threshold vector is controlling the low          |     |

|      | and high thresholds, respectively. For this specific case study the nega-       |     |

|      | tive vectors (controlling the pull-down network of the MAC circuit) are         |     |

|      | not active. The first and second sense amplifier performs the comparison        |     |

|      | of the input against the low and high threshold, respectively                   | 114 |

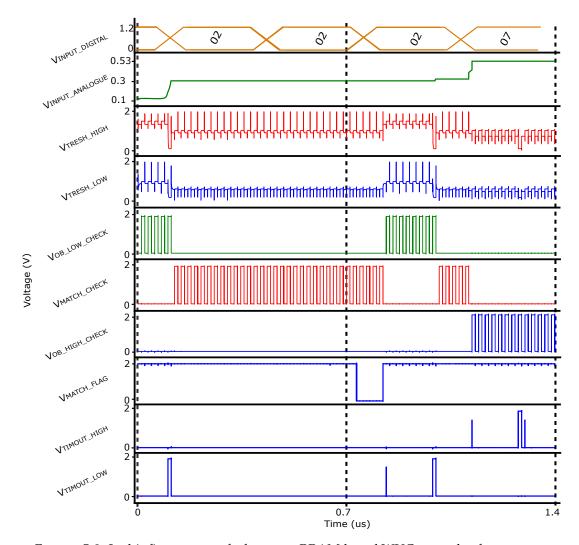

| 5.9  | In this figure, a proof-of-concept RRAM-based WUC example of a pat-             |     |

|      | tern mismatch is exhibited. After confirming a match for the first phase        |     |

|      | of this two-phase pattern ( $V_{MATCH_FLAG}$ goes LOW), the signal generated    |     |

|      | by the input 1T1R array is outbound for the second phase of the pattern.        |     |

|      | This result in the firing of the signal $V_{OB_LOW_CHECK}$ and the generation   |     |

|      | of a total pattern match reset with the $V_{TIMOUT_LOW}$ signal. It is possible |     |

|      | to configure the timing constraints by increasing the size of the CMOS          |     |

|      | DFF-based counters                                                              | 115 |

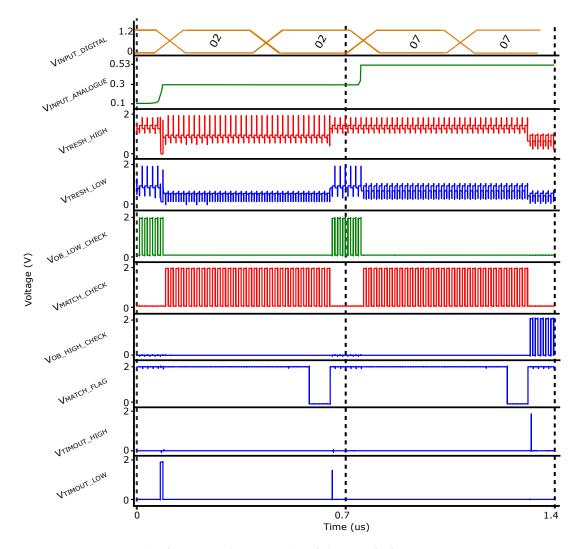

| 5.10 | In this figure another example of the proof-of-concept WUC operation is         |     |

|      | showcased. In this simulation results a two-phase pattern match is con-         |     |

|      | firmed. The $V_{MATCH_FLAG}$ signal is confirming both phases of the example    |     |

|      | two-phase pattern. Thus, with additional circuitry (i.e. a counter or shift     |     |

|      | register) the appropriate wake-up signal, enabling the high-performance         |     |

|      | and high-precision computer, can be generated                                   | 116 |

|      |                                                                                 |     |

# **List of Tables**

| 3.1 | Fitting Parameters from Extracted Models                      | 59 |

|-----|---------------------------------------------------------------|----|

| 3.2 | Performance of Previous State-of-Art WTA systems              | 68 |

| 3.3 | Comparison between Proposed Hybrid RRAM-CMOS and State-of-Art |    |

|     | Fully CMOS-based Racing Voltage WTA                           | 69 |

| 4.1 | Overview of State-of-Art RRAM-based TLG Designs Performance   | 96 |

| 4.2 | Comparison of Proposed RRAM-based MCMTLG for Different Fan-In |    |

|     | Cases                                                         | 97 |

## **Declaration of Authorship**

I declare that this thesis and the work presented in it is my own and has been generated by me as the result of my own original research.

#### I confirm that:

- 1. This work was done wholly or mainly while in candidature for a research degree at this University;

- 2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- 3. Where I have consulted the published work of others, this is always clearly attributed;

- 4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- 5. I have acknowledged all main sources of help;

- 6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- 7. Parts of this work have been published as: Papandroulidakis et al. (2018) Papandroulidakis et al. (2019b) Papandroulidakis et al. (2019a)

| Signed: | Date: |

|---------|-------|

| Signed  | Date  |

## Acknowledgements

Thanks to my family and friends for their support throughout my studies. Special thanks to my father Vasileios Papandroulidakis for his tireless support and trust in me which was very valuable and encouraging to me every time I needed it the most during my journey. I would also like to thank my wife Aleksandra Nazeraj for her crucial support without which I wouldn't be able to complete my PhD program. Furthermore, many thanks to my supervisors and colleagues for their tremendous help during my PhD. I would like to thank Prof. Themis Prodromakis, Prof. Geoff V. Merrett and Dr. Alexander Serb for their continuous support and helpful supervision throughout my doctoral studies. Additionally, many thanks to my PhD viva examiners, Dr. Basel Halak and Dr. Hadi Heidari, whose feedback was important and helpful.

To my wife Aleksandra

xxvii

## **Definitions and Abbreviations**

MIM Metal-Insulator-Metal device topology

MOSFET Metal-Oxide-Semiconductor Field Effect Transistor

pMOSp-type Metal-Oxide-Semiconductor (Field Effect Transistor)nMOSn-type Metal-Oxide-Semiconductor (Field Effect Transistor)

TLG Threshold Logic GateIMC In-Memory ComputingMAC Multiply and Accumulate

WTA Winner Take AllWUC Wake Up Circuit

RRAM Resistive Random Access MemoryDRAM Dynamic Random Access MemorySRAM Static Random Access Memory

*NVM* Non-Volatile Memory

CMOS Complementary Metal Oxide Semiconductor

CiM Compute in Memory

LiM Logic in Memory

NMC Near-Memory ComputingPCM Phase Change MemoryCwM Compute with Memory

DCCMLDual Clocked Current Mode Threshold Logic GateMCMTLGMemristor-based Current Mode Threshold Logic Gate

CIAL Coupled Inverters with Asymmetrical Loads

GND Ground node connection in circuits and systems

# Chapter 1

## Introduction

#### 1.1 Motivation

In recent years, hardware technologies are moving away from older methods of computing, such as mainframe computing, and instead are focusing on the new era of highly distributed computing, also known as edge computing. Towards materialising the added requirements for edge computing new design methodologies need to be found, methodologies that are both energy and scale-efficient. At the same time, in order to accommodate system designs capable of performing a variety of data processing applications efficiently, modern electronic systems are often required to be reconfigurable. Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) and Complementary Metal-Oxide Semiconductor (CMOS) technologies cannot alone deal with the increasing computing needs of modern systems and thus potential solutions are sought in hybrid systems incorporating emerging technologies in computer architecture design, as discussed by Hamdioui et al. (2016). Towards accelerating computing, a few important operations have been selected as the main computationally primitive computing operations that complex algorithms and applications can be "disintegrated" into, as discussed by Serb et al. (2018a). The observation that most computingdemanding algorithms can be decomposed into a large number of fundamental operations, such as multiplication, accumulation, comparison etc., drove the need to design specialised hardware towards accelerating these specific operations, with examples shown by Huang et al. (2016); Carlson et al. (2014); Shafiee et al. (2016), which resulted in the acceleration of larger systems and computer architectures that base their operation in these fundamental computing tasks. Through accumulated research effort, findings suggest that computational concepts from the biological neural networks can be adapted into artificial neuro-inspired circuits with positive results in the acceleration of fundamental computer arithmetic and logic operations, as showcased by Ielmini and Wong (2018). Many such neuro-inspired computing circuits and systems showcased

that massively parallel computing structures and networks of simple computing components can be an important design paradigm for approaching accelerator designs as suggested by many researchers including the work by Furber (2016); Indiveri and Liu (2015).

Most of the neuro-inspired circuits and systems suggested over the years are based on conventional MOSFET and CMOS technologies that defined computers for more than 40 years. One of the earliest examples that showcases a simplified Artificial Neural Networks (ANNs) fitted for computer logic can be found in the work of McCulloch and Pitts (1943) where the concepts of the primitive perceptron circuit and perceptron-based networks were introduced. More recent implementations suggest artificial synapseneuron circuits (the basic computing node of ANNs) with analogue output with some relevant examples including the results showcased by Anderson et al. (1992); Mead and Allen (1991); Douglas et al. (1995); Indiveri (2001); Indiveri et al. (2006). One family of primitive circuits for MAC, the neuro-inspired artificial neuron category of circuits, has been evolved over the last few decades to become one of the most important hardware solutions to perform massively parallel digital or analogue Multiply-Accumulate (MAC) operations, a cornerstone arithmetic operation highlighted by Indiveri et al. (2011); Indiveri and Liu (2015); Payvand et al. (2018); Dara et al. (2013); Bobba and Hajj (2000); Papandroulidakis et al. (2018).

Towards building better hardware accelerators for edge computing, that can process data in a massively parallel manner, new computing methodologies have been developed, i.e. the design concepts showcased by Kang and Shanbhag (2016); Zhu et al. (2013); Zhang et al. (2020b); Gallo et al. (2017). In recent years, the development of novel big data hardware accelerators has been extensively studied, e.g. by Santoro et al. (2019); Jeloka et al. (2016); Gonugondla et al. (2018), and led to the rise of the modern post-von Neumann design paradigm known as In-Memory Computing (IMC). IMC is based on the use of memory systems that can simultaneously be employed as processing units (for processing data in place). In such systems, specific logic functions can be performed with the data stored inside the same memory enabling a logic and memory co-location computing concept to be realised. The fundamental concept of IMC is based on the memory and logic co-location circuits, another neuro-inspired technique discussed by many researchers including Seshadri et al. (2017); Li et al. (2017); Kim et al. (2018); Yin and Jiang (2020).

Recent breakthroughs indicate that some emerging technologies can be used along-side conventional MOSFET/CMOS-based circuits towards providing new capabilities in computing systems, e.g. as suggested by Serb et al. (2017); Bayat et al. (2018); Danial et al. (2018, 2019). More specifically, advances in emerging memory technologies introduce a new component for future computer circuit design. Memristor (abbreviation from memory-resistor) devices, also known as Resistive Random Access Memory (RRAM), are two-terminal, tuneable, non-volatile, nanoscale resistive memory devices.

1.1. Motivation 3

RRAM has many traits over conventional memory, such as the capability to store multibit information per single device, e.g. as shown by Stathopoulos et al. (2017); Sebastian et al. (2018, 2020). Additionally, as highlighted by Sebastian et al. (2020); Zhang et al. (2020b) and other researchers, RRAM can be integrated to implement computationally-capable memory-based systems with low power consumption, an important advantage for large MAC-based ANN systems implemented as edge computing solutions.

Given the numerous advantages of RRAM device technologies, much effort has been dedicated to the design of novel post von Neumann computer systems, with some examples shown by Dastanova et al. (2018); Kvatinsky et al. (2012); Papandroulidakis et al. (2017, 2018). The usage of memory-centric topologies (such as crossbar arrays), as suggested by Zha and Li (2017); Chakrabarti et al. (2017), can provide a very efficient topological organisation of memristor devices and thus memristor circuits that can be employed to accelerate MAC operations. Towards covering all the requirements for a new generation of accelerators for big data processing and solve the limitations conventional technologies impose, highlighted by Mutlu et al. (2015), hardware solutions that employ memristors/RRAM devices have been used to develop novel IMC systems. As shown by Zha and Li (2017), hybrid RRAM-enhanced IMC systems can be employed to better capture the basic principles of biological neural-systems for in silico implementations that are capable of performing low-power logic operations inside a memory architecture. This can result in novel systems that showcase competitive traits against conventional accelerator designs. The advent of emerging memory technologies, such as memristor/RRAM, provided new opportunities to develop nanoelectronic programmable logic fabric that is power and area efficient, with similar hybrid IMC-based concepts being tested, for example, by Hu et al. (2016b); Kumar Maan et al. (2016); Zha and Li (2017); Chakrabarti et al. (2017).

Naturally, as presented by Ielmini and Wong (2018); Serb et al. (2018b), with the advent of RRAM devices there has been a great interest in novel circuits designs that attempt to introduce solutions inspired by biological neural networks, i.e. using RRAM devices to emulate biological synapses in hardware ANNs. To that end, emerging memory technologies, including RRAM, is considered a catalyst for implementing analogue programmable inference engines by efficiently emulating synaptic weights as well as initiating a next generation of analogue and mixed-signal computer architectures at the nano-scale, for example, novel computing systems such as the one showcased by Gallo et al. (2017). Hence, it is envisioned that RRAM-based (also mentioned as memristive) inference engines can be used for performing analogue or mixed-signal reconfigurable classification operations in silico. This can in principle be achieved via arbitrarily shaping the classification decision boundary of perceptron units through tuning individual memristive states, as shown by Serb et al. (2018a). Logic-wise, this means that it is possible to design circuit concepts that are applicable for dealing with both analogue and digital signal processing modes. Presently, there is no extensive study of the behaviour

of classification circuits realised physically with state-of-art memristor devices, providing ample opportunities for a PhD programme in this area that can contribute to the aforementioned needs of modern electronics.

## 1.2 Research Aims

The aim of this PhD is to build a RRAM-enhanced reconfigurable computing system capable of performing neuro-inspired primitive classification operations. For this purpose, I am following the main principles of IMC design paradigms towards being capable of integrating the RRAM and CMOS technologies into novel IMC circuits and system that are still compatible with the general existing accelerator design methodology. The main concept studied, explored and then materialised through hardware experimental proof-of-concept implementations and additional simulations in this thesis is the design of primitive circuits capable of fundamental computer operations such as multiplication, comparison, classification etc. aimed for integration into IMC architectures. The systems employ the naturally analogue RRAM technology, as discussed and presented by Stathopoulos et al. (2017); Sebastian et al. (2020); Ielmini and Wong (2018), to increase the benefits of IMC-related circuit in performing reconfigurable mixedsignal logic operations, with the main part of the computing being performed in the analogue domain and the inputs and/or outputs being digital. The bigger picture is the implementation of a reconfigurable sea-of-gates system, centred around a RRAMbased memory system, where each memory-based gate is based on the aforementioned functionality of programmable converting logic, an important step towards future field programmable mixed-signal arrays.

The main concept investigated in this work is the neuro-inspired concept of memory and logic co-location computing which is the baseline concept for the area of inmemory computing (IMC). The main objective is to physically implement and test reconfigurable RRAM-based hybrid primitive circuits that base their operation in low-complexity but powerful computing operation. The main goal of this thesis is the introduction of novel IMC circuits and systems for implementing low-complexity fundamental logic operations, such as multiply and accumulate (MAC) and analogue comparison operations. I am testing the functionality of the proposed designs through the practical implementations of the circuits using real RRAM devices alongside discrete conventional electronic devices and circuits. Through these implementations I am showcasing the capabilities of the specific RRAM technology under test in primitive neuro-inspired circuits, thus extrapolating the computational capabilities of building larger systems that employ such primitive hybrid circuits.

1.3. Objectives 5