## University of Southampton Research Repository

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Author (Year of Submission) "Full thesis title", University of Southampton, name of the University Faculty or School or Department, PhD Thesis, pagination.

Data: Author (Year) Title. URI [dataset]

#### University of Southampton

Faculty of Engineering and Physical Sciences Electronics and Computer Science

# Real-time hardware architecture for characterising functional brain connectivity from mobile electroencephalogram

by

Rafael Angel Gutierrez Nuno

ORCiD: 0000-0002-8226-4725

A thesis for the degree of Doctor of Philosophy

November 2021

#### University of Southampton

#### **Abstract**

Faculty of Engineering and Physical Sciences

Electronics and Computer Science

#### Doctor of Philosophy

# Real-time hardware architecture for characterising functional brain connectivity from mobile electroencephalogram

by Rafael Angel Gutierrez Nuno

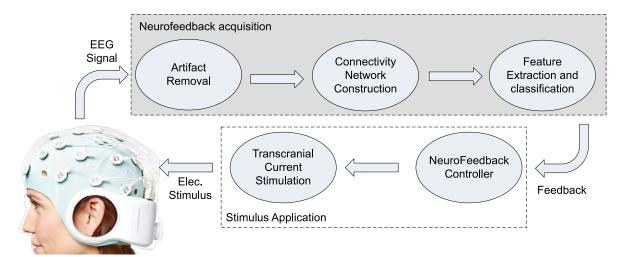

The usage of transcranial current stimulation has recently gained attention due to its potential as an alternative treatment to mental and neurological disorders, but its usage remains questionable due to the lack of protocols in its implementation. Different studies suggest that functional brain connectivity (FC) can be used to guide the stimulus and provide more accurate treatment. This, combined with wearable electroencephalogram (EEG) systems, opens the possibility for a new treatment where the patient is continuously monitored and the stimulus is correctly applied when needed. However, this approach would require real-time EEG signal processing to characterise the FC, which have only been done in computer software, thus limiting the scope of this treatment.

To address this, a new real-time hardware architecture for characterising FC from mobile EEG is proposed in this work. This architecture performs the characterisation in real-time and can be implemented on a field-programmable gate array (FPGA) as a wearable device instead of a computer. To achieve this performance, every process involved in the calculation was analysed and optimised using different design approaches to select the most efficient implementation to decrease the computational complexity, allowing real-time processing and low energy consumption.

The architecture was synthesised in an FPGA as a proof-of-concept, and it was able to calculate the FC and its characterisation in a total time of 273.10  $\mu$ s with a power consumption of 51.84 mW, meeting the timing and energy requirements established for this project. Furthermore, a seizure classifier was created to evaluate the impact in performance using the proposed hardware architecture against its software equivalent. The result showed a maximum difference of 0.15% in the classifier performance, demonstrating that the proposed architecture can be used for the real-time calculation and characterisation of the FC with minimal impact in the final performance.

## **Contents**

| Li         | st of 1                  | Figures                  | 3                                        |                                                                    | xi                   |

|------------|--------------------------|--------------------------|------------------------------------------|--------------------------------------------------------------------|----------------------|

| Li         | st of                    | Tables                   |                                          |                                                                    | xiii                 |

| D          | eclara                   | ition of                 | Authors                                  | hip                                                                | xv                   |

| A          | cknov                    | vledge                   | ments                                    |                                                                    | xvii                 |

| <b>A</b> l | bbrev                    | iations                  | 3                                        |                                                                    | xix                  |

| 1          | 1.1<br>1.2<br>1.3<br>1.4 | Aims<br>Contr            | ation<br>and Obje<br>ibutions            | ctives                                                             | . 4<br>. 5           |

| 2          |                          | _                        |                                          | erature Review: Electroencephalography, Artifact Remo<br>nectivity | val<br>9             |

|            | 2.1                      | The p. 2.1.1 2.1.2 2.1.3 | Brain ac<br>Generat                      | of the brain and electroencephalography                            | . 9<br>. 11          |

|            |                          |                          | 2.1.3.1<br>2.1.3.2<br>2.1.3.3<br>2.1.3.4 | Electroencephalography (EEG)                                       | . 14<br>. 14         |

|            |                          | 2.1.4                    |                                          | functional Near-Infrared Spectroscopy (fNIRS) Comparison           | . 15<br>. 16<br>. 18 |

|            | 2.2                      | Artifa<br>2.2.1          |                                          | neir treatment in EEG signals                                      | . 19<br>. 19<br>. 19 |

|            |                          | 2.2.2                    | Artifact 2.2.2.1 2.2.2.2 2.2.2.3 2.2.4   | removal algorithms                                                 | . 20<br>. 21         |

vi CONTENTS

|   |       |                         | 2.2.2.5 Empirical Mode Decomposition (EMD)                                                                                                                                                                                                                                           | 24                                                       |

|---|-------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|   |       | 2.2.3                   | Comparison of the algorithms                                                                                                                                                                                                                                                         | 24                                                       |

|   |       | 2.2.4                   | Challenges of artifact separation in wearable EEG                                                                                                                                                                                                                                    | 26                                                       |

|   | 2.3   | Brain                   | Connectivity Networks                                                                                                                                                                                                                                                                | 26                                                       |

|   |       | 2.3.1                   | Effective connectivity (EC)                                                                                                                                                                                                                                                          | 27                                                       |

|   |       | 2.3.2                   | Functional connectivity (FC)                                                                                                                                                                                                                                                         | 27                                                       |

|   |       |                         | 2.3.2.1 General Synchronization Index (GSI)                                                                                                                                                                                                                                          | 28                                                       |

|   |       |                         | 2.3.2.2 Phase locking value (PLV)                                                                                                                                                                                                                                                    | 29                                                       |

|   |       |                         | 2.3.2.3 Phase lag index (PLI)                                                                                                                                                                                                                                                        | 30                                                       |

|   | 2.4   | Chara                   | cterisation of Brain connectivity networks                                                                                                                                                                                                                                           | 31                                                       |

|   | 2.5   |                         | cations of Brain connectivity networks in different disease pheno-                                                                                                                                                                                                                   |                                                          |

|   |       |                         |                                                                                                                                                                                                                                                                                      | 32                                                       |

| _ |       |                         |                                                                                                                                                                                                                                                                                      | 22                                                       |

| 3 | -     | _                       | ecification and design approach                                                                                                                                                                                                                                                      | <b>33</b> 33                                             |

|   | 3.1   | •                       | n specification                                                                                                                                                                                                                                                                      | 33                                                       |

|   |       | 3.1.1                   | Timing specification                                                                                                                                                                                                                                                                 | 33                                                       |

|   |       | 3.1.2                   | Power specification                                                                                                                                                                                                                                                                  |                                                          |

|   | 2.2   | 3.1.3                   | Summary of the system specifications                                                                                                                                                                                                                                                 | 36                                                       |

|   | 3.2   |                         | esign approach                                                                                                                                                                                                                                                                       | 36<br>37                                                 |

|   |       | 3.2.1<br>3.2.2          | Algorithmic reformulation of computational intensive modules . Design flow                                                                                                                                                                                                           | 38                                                       |

|   |       | 3.2.2                   | Design now                                                                                                                                                                                                                                                                           | 30                                                       |

| 4 | Rea   | l-time                  | artifact removal hardware based on hybrid WPT-EMD algorithm                                                                                                                                                                                                                          |                                                          |

|   | for 1 | multich                 | nannel wearable wireless EEG system                                                                                                                                                                                                                                                  | 41                                                       |

|   | 4.1   | Introd                  | luction                                                                                                                                                                                                                                                                              | 41                                                       |

|   | 4.2   | Backg                   | round                                                                                                                                                                                                                                                                                | 42                                                       |

|   |       | 4.2.1                   | State of the art artifact removal algorithms                                                                                                                                                                                                                                         | 42                                                       |

|   |       | 4.2.2                   | Hybrid WPT-EMD Artifact Removal Algorithm                                                                                                                                                                                                                                            | 44                                                       |

|   |       |                         | 4.2.2.1 Wavelet Packet Decomposition (WPT)                                                                                                                                                                                                                                           | 44                                                       |

|   |       |                         | 4.2.2.2 Empirical Mode Decomposition (EMD)                                                                                                                                                                                                                                           | 45                                                       |

|   |       | 4.2.3                   | Performance parameters                                                                                                                                                                                                                                                               | 46                                                       |

|   |       | 4.2.4                   | Algorithm shortcomings                                                                                                                                                                                                                                                               | 46                                                       |

|   | 4.3   | 0                       |                                                                                                                                                                                                                                                                                      |                                                          |

|   |       | ware i                  | ithmic Formulation and parameter determination for real-time hard-                                                                                                                                                                                                                   |                                                          |

|   |       |                         | implementation                                                                                                                                                                                                                                                                       | 47                                                       |

|   |       | 4.3.1                   | implementation                                                                                                                                                                                                                                                                       | 48                                                       |

|   |       |                         | implementation                                                                                                                                                                                                                                                                       | 48<br>48                                                 |

|   |       | 4.3.1                   | Implementation                                                                                                                                                                                                                                                                       | 48<br>48<br>48                                           |

|   |       | 4.3.1<br>4.3.2          | Experimental data                                                                                                                                                                                                                                                                    | 48<br>48<br>48<br>50                                     |

|   |       | 4.3.1                   | Experimental data WPT 4.3.2.1 Window size and Mother Wavelet 4.3.2.2 Node removal selection EMD                                                                                                                                                                                      | 48<br>48<br>48<br>50<br>50                               |

|   |       | 4.3.1<br>4.3.2          | Experimental data WPT 4.3.2.1 Window size and Mother Wavelet 4.3.2.2 Node removal selection EMD 4.3.3.1 Window size                                                                                                                                                                  | 48<br>48<br>48<br>50<br>50                               |

|   |       | 4.3.1<br>4.3.2          | Experimental data WPT 4.3.2.1 Window size and Mother Wavelet 4.3.2.2 Node removal selection EMD 4.3.3.1 Window size 4.3.3.2 Interpolation method                                                                                                                                     | 48<br>48<br>48<br>50<br>50<br>50                         |

|   |       | 4.3.1<br>4.3.2          | implementation                                                                                                                                                                                                                                                                       | 48<br>48<br>50<br>50<br>50<br>51<br>52                   |

|   |       | 4.3.1<br>4.3.2          | implementation                                                                                                                                                                                                                                                                       | 48<br>48<br>50<br>50<br>50<br>51<br>52<br>53             |

|   |       | 4.3.1<br>4.3.2<br>4.3.3 | implementation  Experimental data  WPT  4.3.2.1 Window size and Mother Wavelet  4.3.2.2 Node removal selection  EMD  4.3.3.1 Window size  4.3.3.2 Interpolation method  4.3.3.3 Sifting Iterations  4.3.3.4 Maximum Number of IMF  4.3.3.5 IMF removal selection                     | 48<br>48<br>50<br>50<br>50<br>51<br>52<br>53<br>54       |

|   |       | 4.3.1<br>4.3.2<br>4.3.3 | implementation  Experimental data  WPT  4.3.2.1 Window size and Mother Wavelet  4.3.2.2 Node removal selection  EMD  4.3.3.1 Window size  4.3.3.2 Interpolation method  4.3.3.3 Sifting Iterations  4.3.3.4 Maximum Number of IMF  4.3.3.5 IMF removal selection  Rejection Criteria | 48<br>48<br>48<br>50<br>50<br>51<br>52<br>53<br>54<br>54 |

|   | 4.4   | 4.3.1<br>4.3.2<br>4.3.3 | implementation  Experimental data  WPT  4.3.2.1 Window size and Mother Wavelet  4.3.2.2 Node removal selection  EMD  4.3.3.1 Window size  4.3.3.2 Interpolation method  4.3.3.3 Sifting Iterations  4.3.3.4 Maximum Number of IMF  4.3.3.5 IMF removal selection                     | 48<br>48<br>50<br>50<br>50<br>51<br>52<br>53<br>54       |

*CONTENTS* vii

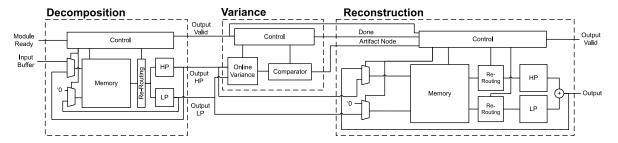

|   |              | 4.4.1.1 WPT Decomposition Module                                         | 5 |

|---|--------------|--------------------------------------------------------------------------|---|

|   |              | 4.4.1.2 Variance Module                                                  | 7 |

|   |              | 4.4.1.3 WPT Reconstruction Module                                        | 7 |

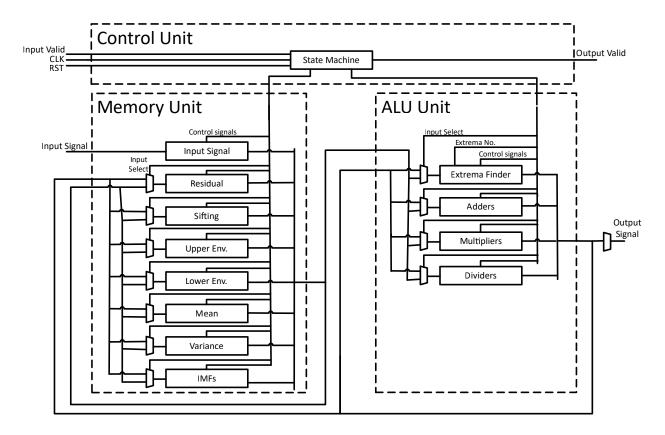

|   |              | 4.4.2 EMD architecture                                                   | 8 |

|   |              | 4.4.2.1 Memory Unit                                                      | 3 |

|   |              | 4.4.2.2 Arithmetic Logic Unit (ALU)                                      | 9 |

|   | 4.5          | Results                                                                  | O |

|   |              | 4.5.1 Validation using a simulated artifact                              | O |

|   |              | 4.5.2 Validation using real artifacts                                    | 3 |

|   |              | 4.5.3 Hardware Resources                                                 |   |

|   |              | 4.5.4 Architectural Complexity                                           |   |

|   |              | 4.5.5 Power Analysis                                                     |   |

|   |              | 4.5.6 Comparison                                                         |   |

|   | 4.6          | Conclusion                                                               |   |

|   |              |                                                                          |   |

| 5 |              | se Lag Index hardware implementation for real-time network connectivity  |   |

|   |              | rulation 71                                                              | _ |

|   | 5.1          | Introduction                                                             |   |

|   | 5.2          | Background                                                               |   |

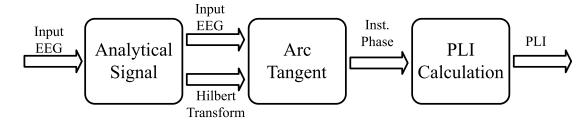

|   |              | 5.2.1 The Computational flow of PLI calculation                          |   |

|   | 5.3          | Algorithm complexity and accuracy analysis of PLI components             |   |

|   |              | 5.3.1 Implementation of the Hilbert transform                            |   |

|   |              | 5.3.1.1 Hilbert transform using Fourier transform                        |   |

|   |              | 5.3.1.2 Hilbert transformer Filter                                       |   |

|   |              | 5.3.1.3 Comparison                                                       |   |

|   |              | 5.3.2 Instantaneous Phase Calculation                                    |   |

|   |              | 5.3.2.1 LUT                                                              |   |

|   |              | 5.3.2.2 Coordinate rotation digital computer (CORDIC) 77                 |   |

|   |              | 5.3.2.3 Comparison                                                       |   |

|   |              | 5.3.3 PLI calculation                                                    |   |

|   | 5.4          | Hardware Implementation                                                  |   |

|   |              | 5.4.1 The analytic signal                                                |   |

|   |              | 5.4.2 The phase calculation                                              |   |

|   |              | 5.4.3 The PLI Calculation                                                |   |

|   |              | 5.4.4 PLI module integration                                             |   |

|   | 5.5          | Results                                                                  |   |

|   |              | 5.5.1 Validation                                                         |   |

|   |              | 5.5.2 Comparison                                                         |   |

|   | 5.6          | Conclusion                                                               | 5 |

| 6 | Har          | Iware architecture for real-time EEG-based functional brain connectivity |   |

| U |              | meter extraction                                                         | 7 |

|   | 6.1          | Introduction                                                             |   |

|   | 6.2          | Background                                                               |   |

|   | ~ · <b>-</b> | 6.2.1 Network integration parameters                                     |   |

|   |              | 6.2.1.1 Degree and Weighted Degree                                       |   |

|   |              | 6.2.1.2 Density                                                          |   |

|   |              |                                                                          |   |

viii CONTENTS

|   |            |            | 6.2.1.3 Characteristic Path Length                                 |

|---|------------|------------|--------------------------------------------------------------------|

|   |            |            | 6.2.1.4 Eccentricity, Radius and Diameter                          |

|   |            | 6.2.2      | Network segregation parameters                                     |

|   |            |            | 6.2.2.1 Clustering Coefficient                                     |

|   |            |            | 6.2.2.2 Transitivity                                               |

|   | 6.3        | Algor      | thmic optimisation of the computational burden of the parameters 9 |

|   |            | 6.3.1      | Clustering Coefficient Optimisation                                |

|   |            | 6.3.2      | Transitivity                                                       |

|   |            | 6.3.3      | Density                                                            |

|   | 6.4        | Hardy      | vare Architecture                                                  |

|   |            | 6.4.1      | PLI Architecture                                                   |

|   |            | 6.4.2      | Clustering Coefficient                                             |

|   |            | 6.4.3      | Degree and Weighted degree                                         |

|   |            | 6.4.4      | Density                                                            |

|   |            | 6.4.5      | Transitivity                                                       |

|   |            | 6.4.6      | Characteristic Path Length                                         |

|   |            | 6.4.7      | Eccentricity, Radius, and Diameter                                 |

|   | 6.5        | Valida     | tion and Results                                                   |

|   |            | 6.5.1      | Validation data                                                    |

|   |            | 6.5.2      | Functional Validation                                              |

|   |            |            | 6.5.2.1 Error calculation                                          |

|   |            |            | 6.5.2.2 Time calculation                                           |

|   |            | 6.5.3      | Hardware savings                                                   |

|   |            | 6.5.4      | Synthesis Results                                                  |

|   |            | 6.5.5      | Power Consumption                                                  |

|   |            | 6.5.6      | Comparison                                                         |

|   | 6.6        | Concl      | asions                                                             |

|   |            |            |                                                                    |

| 7 |            |            | Validation of a Seizure Classifier 10                              |

|   | 7.1        |            | uction                                                             |

|   | 7.2        |            | als and methods                                                    |

|   |            | 7.2.1      | Data and pre-processing                                            |

|   |            | 7.2.2      | Classification algorithms                                          |

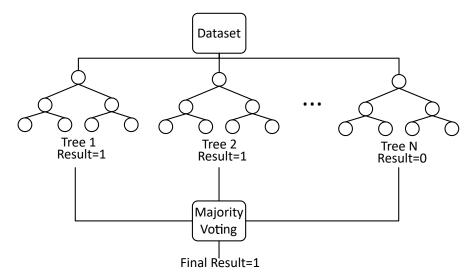

|   |            |            | 7.2.2.1 Random Forest                                              |

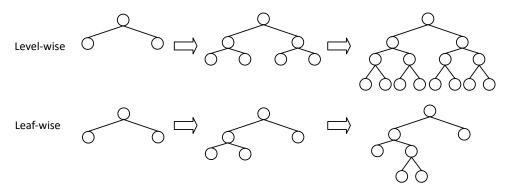

|   |            |            | 7.2.2.2 LightGBM                                                   |

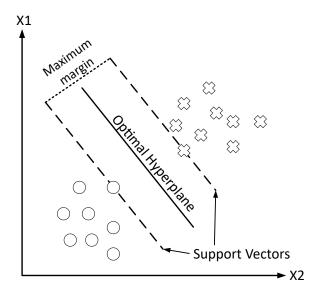

|   |            | =          | 7.2.2.3 SVM                                                        |

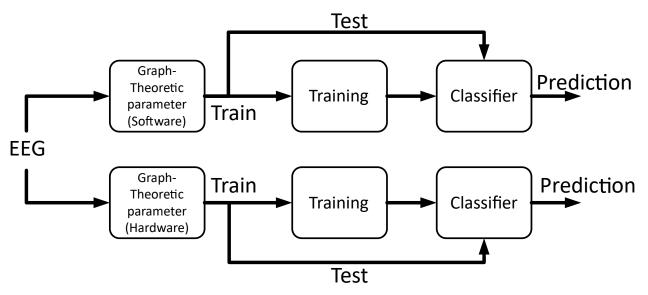

|   |            | 7.2.3      | Methodology                                                        |

|   |            |            | 7.2.3.1 Feature calculation                                        |

|   | = 0        | -          | 7.2.3.2 Data split for training and testing                        |

|   | 7.3        |            | mental Results                                                     |

|   |            | 7.3.1      | Performance metrics                                                |

|   |            |            | 7.3.1.1 Random Forest                                              |

|   |            |            | 7.3.1.2 LightGBM                                                   |

|   |            | <b>722</b> | 7.3.1.3 SVM                                                        |

|   | <b>-</b> . | 7.3.2      | Comparison                                                         |

|   | 7.4        | Concl      | asions                                                             |

| CONTENTS | ix |

|----------|----|

|          |    |

|    | 8.1    | Future Works |     |

|----|--------|--------------|-----|

| Re | eferei | nces         | 125 |

# **List of Figures**

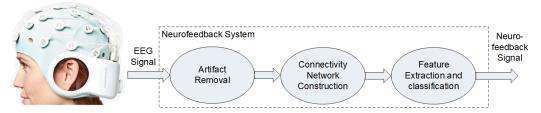

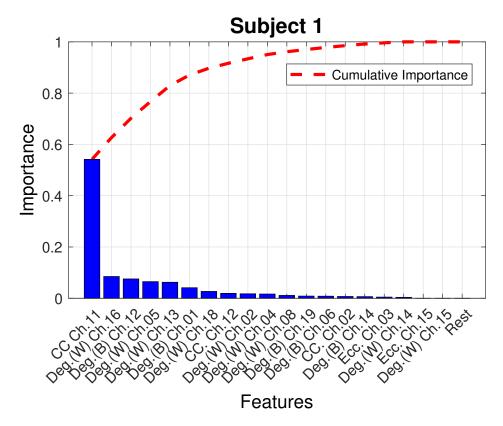

| 1.1  | Overall schematic of the proposed neurofeedback wearable system                 | 3  |

|------|---------------------------------------------------------------------------------|----|

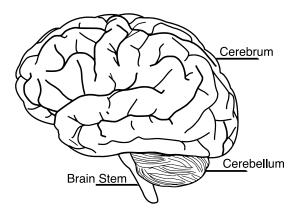

| 2.1  | The general structure of the brain.                                             | 10 |

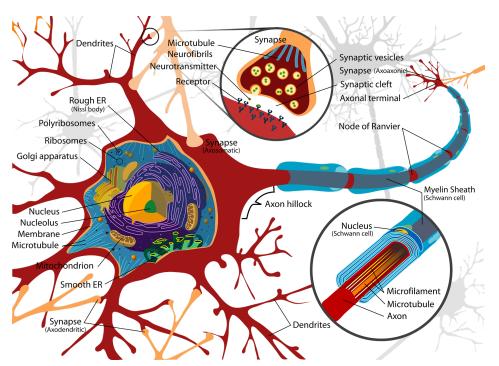

| 2.2  | Diagram of the neuron structure and its synapse junction                        | 10 |

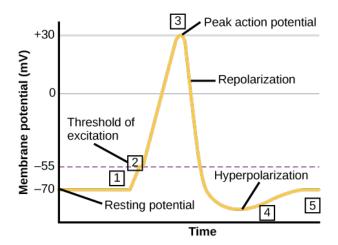

| 2.3  | Refractory period for a neuron activation                                       | 12 |

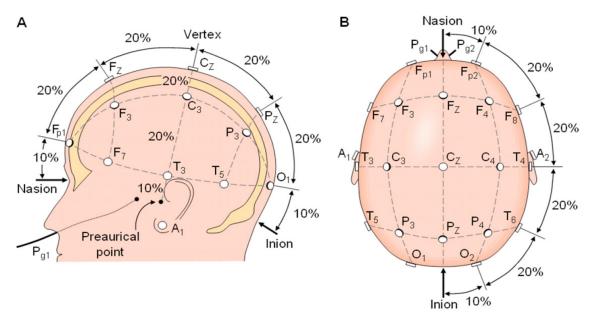

| 2.4  | Electrode placement based on the 10-20 system                                   | 13 |

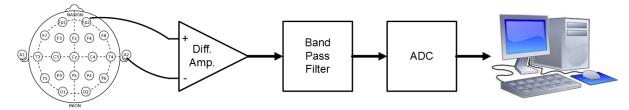

| 2.5  | Block diagram of the EEG acquisition                                            | 14 |

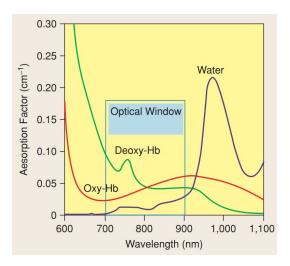

| 2.6  | Absorption spectrum in near-infrared (NIR) window                               | 16 |

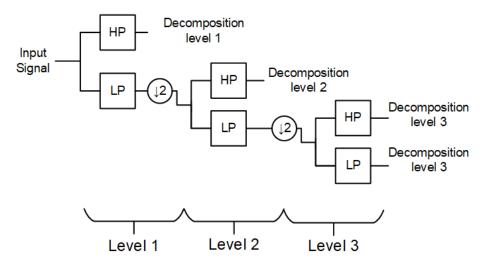

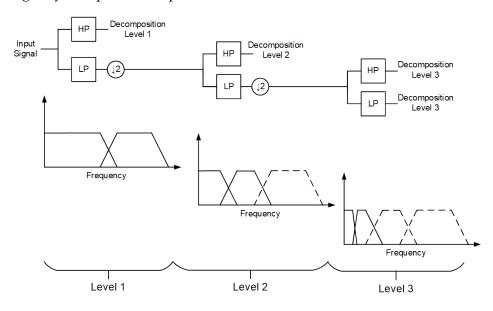

| 2.7  | Example of a DWT using a level 3 decomposition                                  | 22 |

| 2.8  | DWT frequency spectrum sub-band splitting                                       | 23 |

| 2.9  | Signal reconstruction using the IDWT for a level 3 decomposition                | 23 |

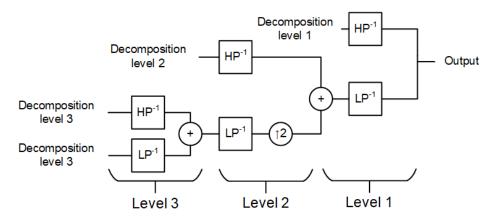

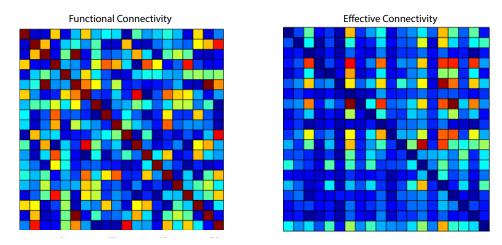

| 2.10 | Flowchart of the EMD algorithm                                                  | 25 |

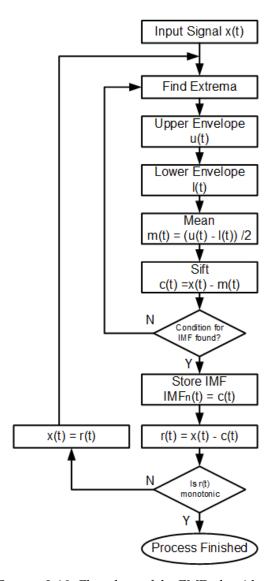

| 2.11 | Functional and Effective connectivity matrix                                    | 27 |

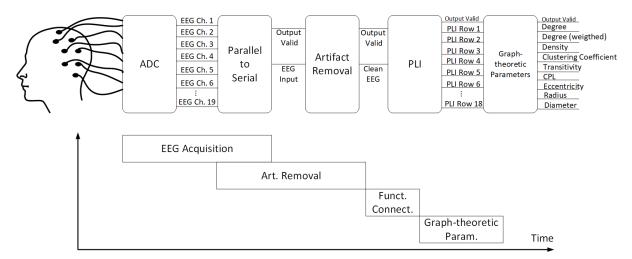

| 3.1  | Block diagram of the complete neurofeedback system                              | 37 |

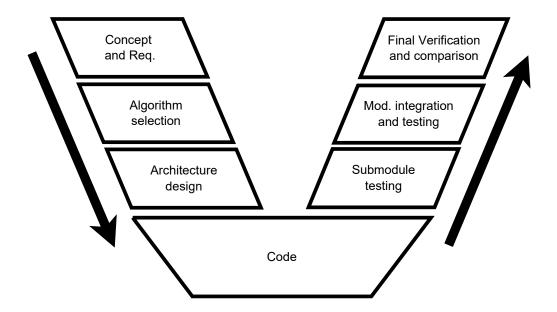

| 3.2  | Design flow followed in this work, based on the V-model used in agile           |    |

|      | software development                                                            | 39 |

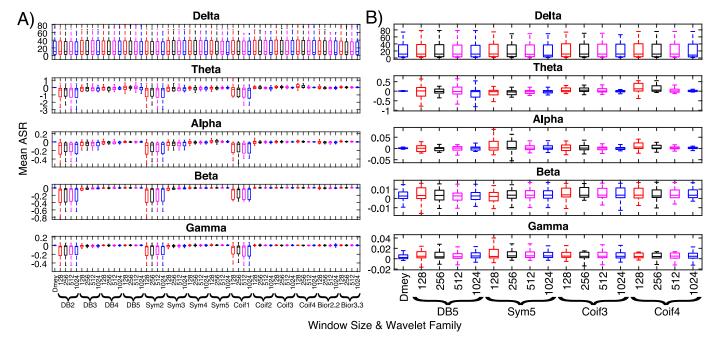

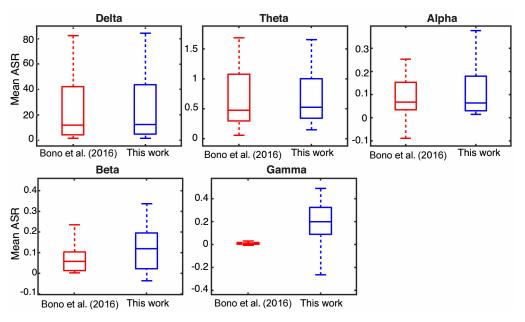

| 4.1  | Mean ASR comparison using the Dmey wavelet against using different              |    |

|      | wavelet functions                                                               | 49 |

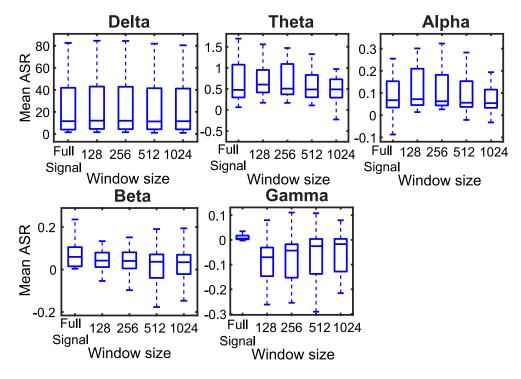

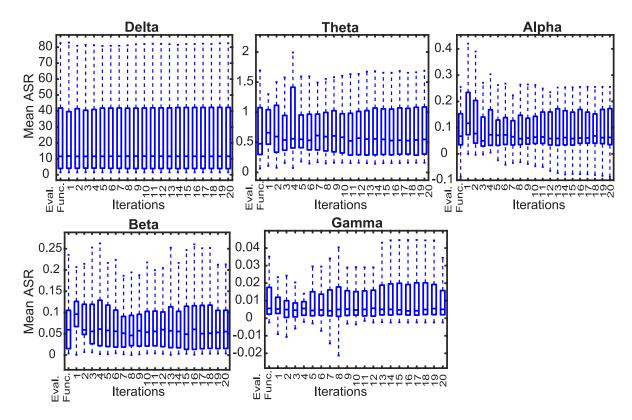

| 4.2  | Mean ASR Comparison for the EMD using different windows sizes                   | 52 |

| 4.3  | Comparison of the mean ASR performance using different number of                |    |

|      | iterations for the sifting process                                              | 53 |

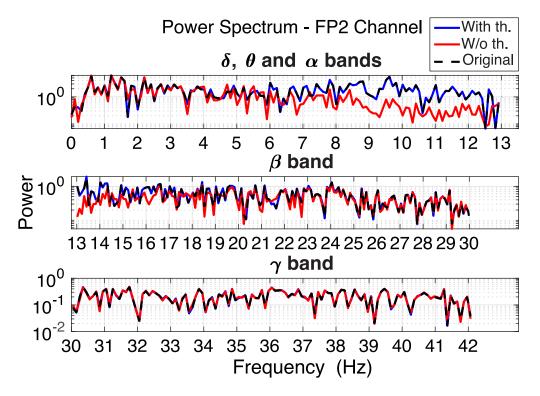

| 4.4  | Power spectrum comparison using the proposed rejection criteria                 | 55 |

| 4.5  | Architecture of the WPT module composed of the decomposition and                | _  |

| 1.0  | reconstruction modules                                                          | 56 |

| 4.6  | General architecture of the EMD module                                          | 59 |

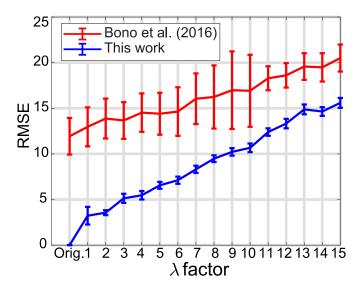

| 4.7  | Comparison of the RMSE after cleaning the simulated eye blink artifact.         | 61 |

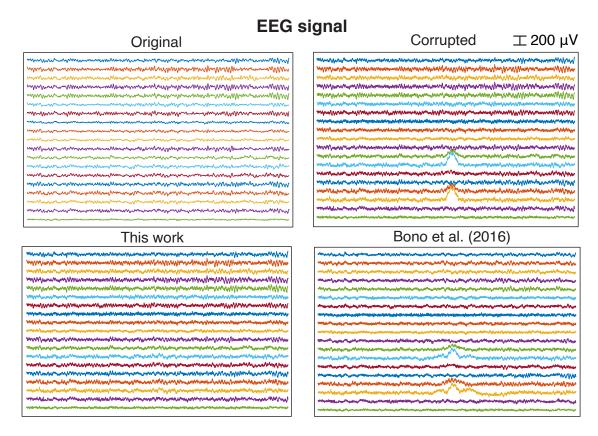

| 4.8  | Comparison between the original and corrupted signal against the cleaned signal | 62 |

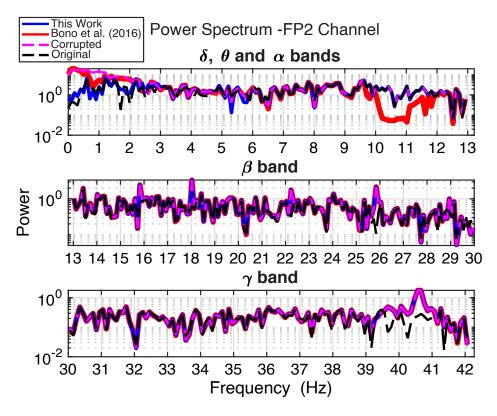

| 4.9  | Comparison in the power spectrum between the signals                            | 63 |

| 4.10 | Visual comparison between a corrupted signal (muscle artifacts) and the         |    |

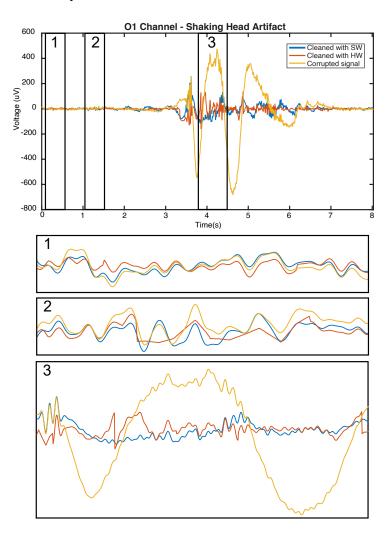

|      | processed output signal using the algorithm in software                         | 64 |

| 4.11 | Comparison of the performance achieved using the algorithm from Bono            |    |

|      | et al. (2016) against the modified algorithm presented in this work             | 65 |

| 5.1  | Diagram of the computational flow used for the calculation of the PLI           |    |

|      | index                                                                           | 73 |

xii LIST OF FIGURES

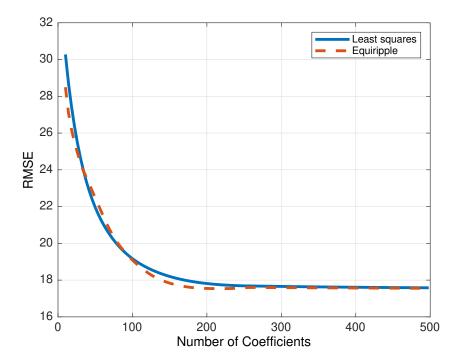

| 5.2 | Mean RMSE across all patients for the Hilbert transform calculated with the Fourier transform and the Hilbert transformer filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 75  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.3 | RMSE of the Hilbert transform calculated with the Fourier transform and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13  |

| J.J | the Hilbert transformer filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76  |

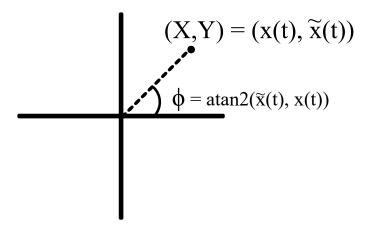

| 5.4 | The Atan2 calculation is used to calculate the angle $\phi$ of a given point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | , 0 |

| 0.1 | (X,Y) in the Cartesian plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 76  |

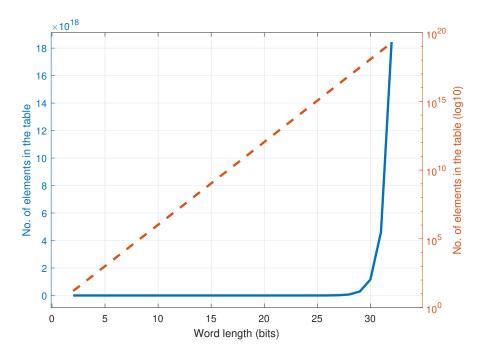

| 5.5 | Estimation of the number of elements required for the lookup table based on the equation Equation 5.5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 78  |

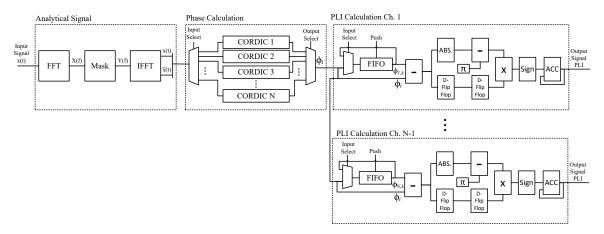

| 5.6 | Block diagram of the hardware architecture proposed for the PLI calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 79  |

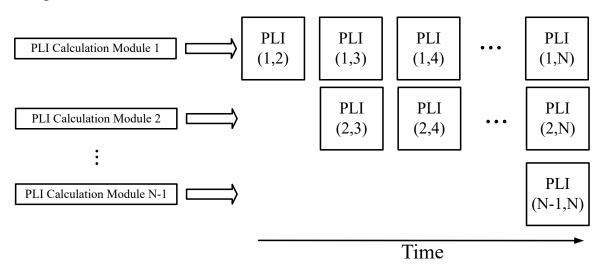

| 5.7 | Block diagram of the output from the PLI calculation modules. The output from these modules is used to create the final PLI matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 82  |

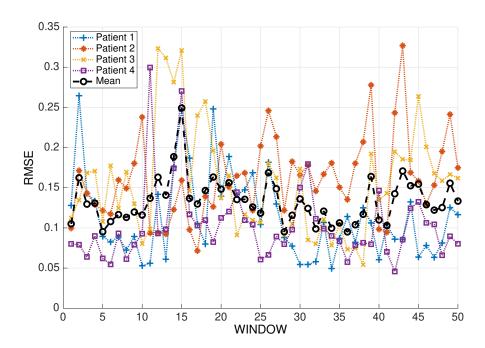

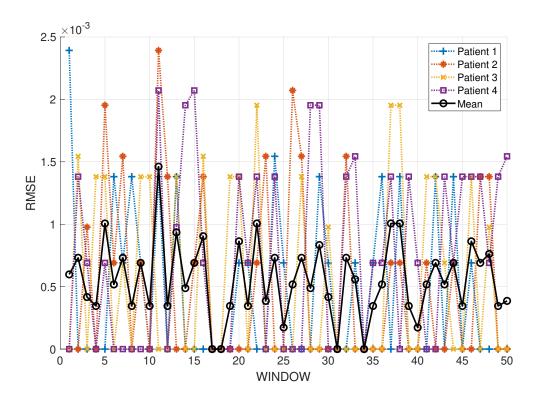

| 5.8 | RMSE comparison between the four patients and 50 windows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 83  |

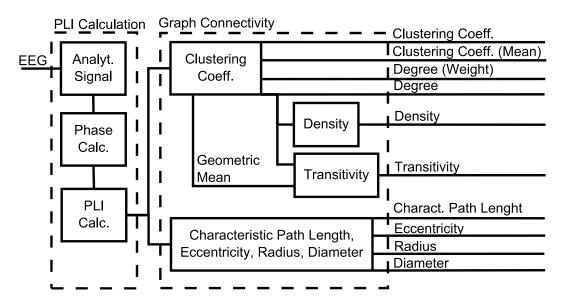

| 6.1 | Block diagram of the general architecture for the PLI and the graph-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 02  |

| 6.2 | theoretic measurements calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 92  |

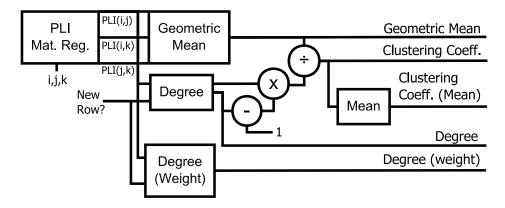

| 6.2 | coefficient                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 95  |

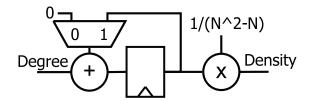

| 6.3 | Block diagram of the hardware architecture proposed for the Density                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 96  |

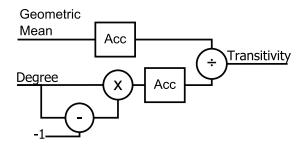

| 6.4 | Block diagram of the hardware architecture proposed for the Transitivity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 96  |

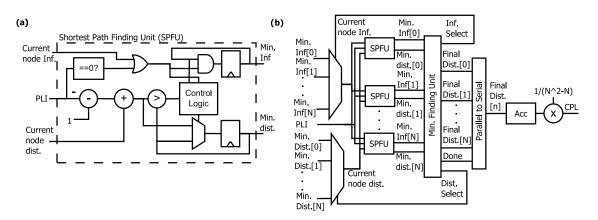

| 6.5 | Block diagram of the hardware architecture proposed for the characteristic path length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 97  |

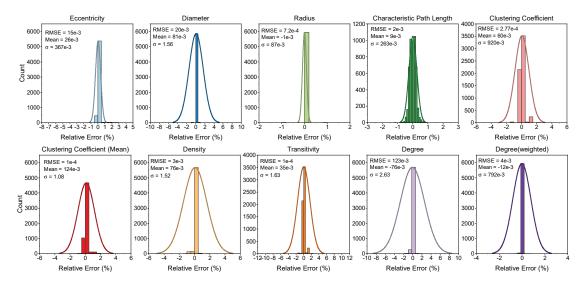

| 6.6 | Histogram with the relative error results from the functional validation for every graph-theoretic parameter calculated for the 600 windows and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|     | the 10 subjects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 99  |

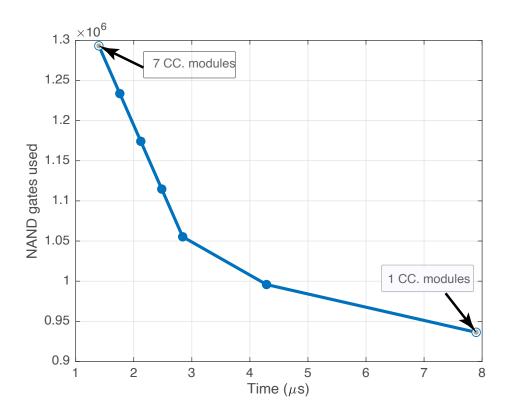

| 6.7 | Calculation time and the number of NAND gates required for the design with multiple clustering coefficient modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 105 |

| 7.1 | Diagram of a random decision forest.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 109 |