**University of Southampton**

Faculty of Physical and Applied Sciences

Electronics and Computer Science

**Bit-serial Artificial Neural Networks for Epilepsy Seizure Detection**

by

**Si Mon Kueh**

Thesis for the degree of Doctor of Philosophy

May 2021

UNIVERSITY OF SOUTHAMPTON

FACULTY OF PHYSICAL AND APPLIED SCIENCES

Electronics and Computer Science

ABSTRACT

Thesis for the degree of Doctor of Philosophy

BIT-SERIAL ARTIFICIAL NEURAL NETWORKS FOR EPILEPSY SEIZURE

DETECTION

by Si Mon Kueh

Fifty million of the world's population are afflicted with epilepsy and 80% of these epileptic patients live in developing countries. It is crucial to develop a low cost, power saving and reliable home-based seizure detection system for those disabled individuals who have insufficient access to seizure detection equipment.

This research presents three contributions. The first demonstrates that simple bit-serial architecture can be used when designing extremely low-power and low-cost neural network processors to detect epileptic seizures. The proposed design is tailored to be cost effective by employing variable bit precision to allow for compromise between the detection accuracy and the hardware cost.

The second contribution highlights extensive studies of epileptic seizure detection by DPU arrays, using bit-serial neural networks (BSNN) where the control module consists of only simple finite state machines. It has been demonstrated that epilepsy detection through such low-cost and low-energy dedicated neural network is feasible and there is potential for massively parallel network configuration. Different network configurations with variable numbers of network nodes and layers were designed and tested on FPGAs. The best performing version of the complete system has been implemented on an ALTERA Cyclone V FPGA which uses 3931 ALMs with an average recognition rate of 89%.

The third contribution illustrates the development of a dedicated feature extraction component to be used as part of the proposed epilepsy detection system. Two different dedicated feature extraction hardware systems have been designed to provide inputs to the neural network in order to facilitate the classification of EEG waveforms. The EEG features extracted in this research are the slope and mean energy in EEG waveforms. Through multiple experiments, it was found that using a combination of both features as input to the proposed BSNN provides a detection accuracy of 90%.

Results of this research have been published in three conference papers and also in the IEEE Journal on Translational Engineering in Health and Medicine.

# Contents

|                                                                                                                                  |           |

|----------------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>Abbreviations and Parameters</b>                                                                                              | <b>xv</b> |

| <b>1 Introduction</b>                                                                                                            | <b>1</b>  |

| 1.1 Background Information . . . . .                                                                                             | 1         |

| 1.2 Specification and Approach . . . . .                                                                                         | 2         |

| 1.2.1 Why a bit-serial neural processor design? . . . . .                                                                        | 2         |

| 1.2.2 Why an artificial neural network? . . . . .                                                                                | 3         |

| 1.2.3 Specification of our design . . . . .                                                                                      | 3         |

| 1.2.4 Hardware and software used for simulation and hardware testing .                                                           | 4         |

| 1.3 Aims and Contributions . . . . .                                                                                             | 4         |

| 1.4 Thesis Organization . . . . .                                                                                                | 6         |

| <b>2 Background Research</b>                                                                                                     | <b>7</b>  |

| 2.1 EEG Research in Epilepsy Detection . . . . .                                                                                 | 8         |

| 2.1.1 EEG Waveform Analysis Methodology . . . . .                                                                                | 8         |

| 2.2 Conventional Classification Methods for Epilepsy Detection . . . . .                                                         | 11        |

| 2.3 Parallel Learning System . . . . .                                                                                           | 16        |

| 2.4 Epilepsy Detection Using Software . . . . .                                                                                  | 18        |

| 2.5 Deep Learning Neural Networks . . . . .                                                                                      | 24        |

| 2.6 Neural Network Processors . . . . .                                                                                          | 26        |

| 2.6.1 Radial Basis Function Network . . . . .                                                                                    | 26        |

| 2.6.2 Stochastic Neural Networks . . . . .                                                                                       | 27        |

| 2.6.3 Parallel FDFM Processor Core for Neural Networks . . . . .                                                                 | 28        |

| 2.6.4 Restricted Boltzmann Machine (RBM) . . . . .                                                                               | 29        |

| 2.6.5 FPGA-based co-processors . . . . .                                                                                         | 31        |

| 2.6.6 SNN based Auto-associative based memory . . . . .                                                                          | 32        |

| 2.6.7 Synchronous and Self-timed neuroprocessor . . . . .                                                                        | 33        |

| 2.6.8 Block-based Neural Networks . . . . .                                                                                      | 34        |

| 2.7 Prediction Application Using Different Forms of NN . . . . .                                                                 | 35        |

| 2.7.1 Neural Models Assisted Hardware Implementation Using FPGAs .                                                               | 35        |

| 2.7.2 SpiNNaker: A Massive-Parallel Chip Multiprocessor . . . . .                                                                | 36        |

| 2.7.3 Condition Monitoring Using Different Forms of ANN . . . . .                                                                | 37        |

| 2.8 Real Time Hardware Based Epilepsy Detection and Prediction Research .                                                        | 39        |

| 2.8.1 Wearable Embedded Seizure Detection Devices . . . . .                                                                      | 39        |

| 2.8.2 PennBMBI: A General Purpose Wireless BMBI Interface System Design and Developed further for Unrestrained Animals . . . . . | 40        |

| 2.9 Bit-Serial Architecture with Relation to Neural Network Processors . . . . .                                                 | 41        |

---

|          |                                                                                             |           |

|----------|---------------------------------------------------------------------------------------------|-----------|

| 2.9.1    | Basics of Bit-Serial Architecture and Advantages over State of the Art Technology . . . . . | 41        |

| 2.9.2    | COLUMNUS & Bit-serial CORDIC . . . . .                                                      | 41        |

| 2.9.3    | Bit-Serial Architecture For Neural Network and Various Applications . . . . .               | 41        |

| 2.9.4    | Bit-Serial Multiplier Architecture . . . . .                                                | 42        |

| 2.10     | Support Vector Machine Contribution to Epilepsy Detection . . . . .                         | 44        |

| 2.10.1   | Support Vector Machine Used in Medical Technologies . . . . .                               | 44        |

| 2.10.2   | Vapnik's Statistical Learning Theory . . . . .                                              | 44        |

| 2.11     | Other Related Work . . . . .                                                                | 45        |

| 2.11.1   | Energy Efficient VLSI Neural Network Design . . . . .                                       | 45        |

| 2.11.2   | Dedicated Neural Hardware for Medical Technologies . . . . .                                | 46        |

| 2.12     | Critical Analysis . . . . .                                                                 | 46        |

| 2.12.1   | Why not deep learning neural networks in this research? . . . . .                           | 48        |

| 2.12.2   | Why FPGA for prototyping? . . . . .                                                         | 48        |

| 2.12.3   | Why not SVM? . . . . .                                                                      | 49        |

| 2.12.4   | Why bit-serial architecture? . . . . .                                                      | 49        |

| 2.13     | Conclusion . . . . .                                                                        | 50        |

| <b>3</b> | <b>Bit-serial Dedicated Neural Data Processing Unit (DPU)</b>                               | <b>53</b> |

| 3.1      | Neural Processor Model . . . . .                                                            | 53        |

| 3.2      | Bit-Serial DPU Design . . . . .                                                             | 54        |

| 3.2.1    | Hardware Counters for Neural Operation . . . . .                                            | 56        |

| 3.2.2    | Layer Finite State Machine (FSM) . . . . .                                                  | 57        |

| 3.3      | DPU Verification . . . . .                                                                  | 59        |

| 3.3.1    | Simple Classification with BSNN . . . . .                                                   | 59        |

| 3.3.2    | Peak Detection Using the Proposed Vector Processor Design . . . . .                         | 61        |

| 3.3.3    | Bit-Serial DPU FPGA Synthesis . . . . .                                                     | 63        |

| 3.4      | Discussion and Comparison . . . . .                                                         | 68        |

| 3.5      | Conclusive Remarks . . . . .                                                                | 73        |

| <b>4</b> | <b>Bit-serial Based Hardware Neural Network for Epilepsy Detection</b>                      | <b>75</b> |

| 4.1      | A Neural Network Model for Hardware . . . . .                                               | 75        |

| 4.2      | Proposed Approach: Novel Hardware Neural Network Implementation Design . . . . .            | 77        |

| 4.2.1    | Central Control FSM . . . . .                                                               | 77        |

| 4.2.2    | BSNN Data Path . . . . .                                                                    | 78        |

| 4.3      | Case Study: Training and Testing of BSNN For Epilepsy Detection . . . . .                   | 80        |

| 4.3.1    | Epileptic seizure detection in EEG Waveform . . . . .                                       | 80        |

| 4.3.2    | Network Architecture Development . . . . .                                                  | 81        |

| 4.3.3    | Neural Network Design Validation and Testing . . . . .                                      | 83        |

| 4.3.3.1  | Network Validation . . . . .                                                                | 83        |

| 4.3.3.2  | Network Testing . . . . .                                                                   | 92        |

| 4.4      | Discussion and Comparison . . . . .                                                         | 97        |

| 4.4.1    | Evaluation of MATLAB Results . . . . .                                                      | 97        |

| 4.4.2    | Evaluation and discussion of hardware results . . . . .                                     | 98        |

| 4.5      | Conclusive Remarks . . . . .                                                                | 101       |

|                                                                       |            |

|-----------------------------------------------------------------------|------------|

| <b>5 EEG Feature Analysis for Complete Epilepsy Prediction System</b> | <b>103</b> |

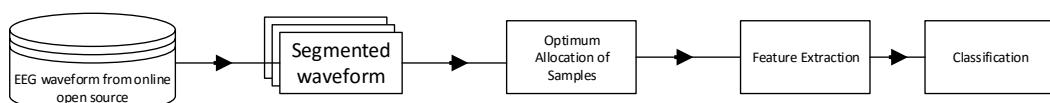

| 5.1 Optimal Allocation Sampling of EEG Signals . . . . .              | 103        |

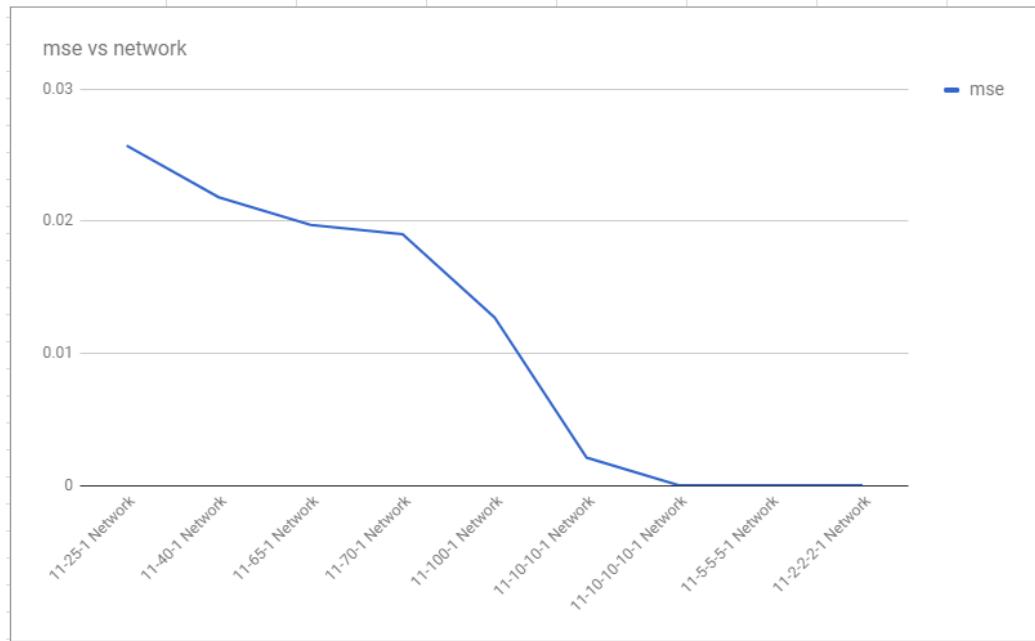

| 5.1.1 Optimal BSNN Configuration for Epilepsy Detection . . . . .     | 106        |

| 5.1.2 Hardware Network Validation and Testing . . . . .               | 106        |

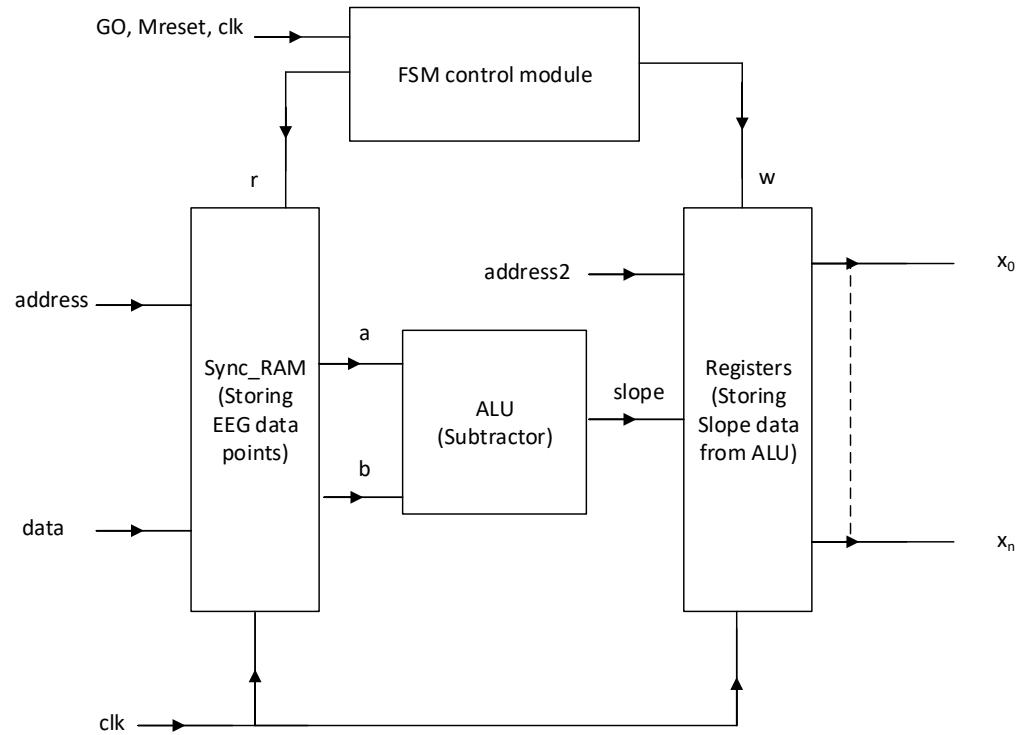

| 5.2 Proposed Feature Extraction Hardware . . . . .                    | 108        |

| 5.2.1 Slope calculator . . . . .                                      | 108        |

| 5.2.2 EEG waveform slope Used as Feature Vector . . . . .             | 108        |

| 5.2.3 Experiments with Mean Energy . . . . .                          | 110        |

| 5.3 Proposed System: Feature Extraction + BSNN . . . . .              | 112        |

| 5.3.1 Improved System . . . . .                                       | 112        |

| 5.3.2 Potential for Massively Parallel BSNN System . . . . .          | 114        |

| 5.4 Comparison with Related Work . . . . .                            | 115        |

| 5.5 Conclusive Remarks . . . . .                                      | 120        |

| <b>6 Conclusion</b>                                                   | <b>123</b> |

| 6.1 Further Work . . . . .                                            | 125        |

| <b>7 Publications</b>                                                 | <b>127</b> |

| <b>References</b>                                                     | <b>129</b> |

# List of Figures

|      |                                                                                                                                            |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

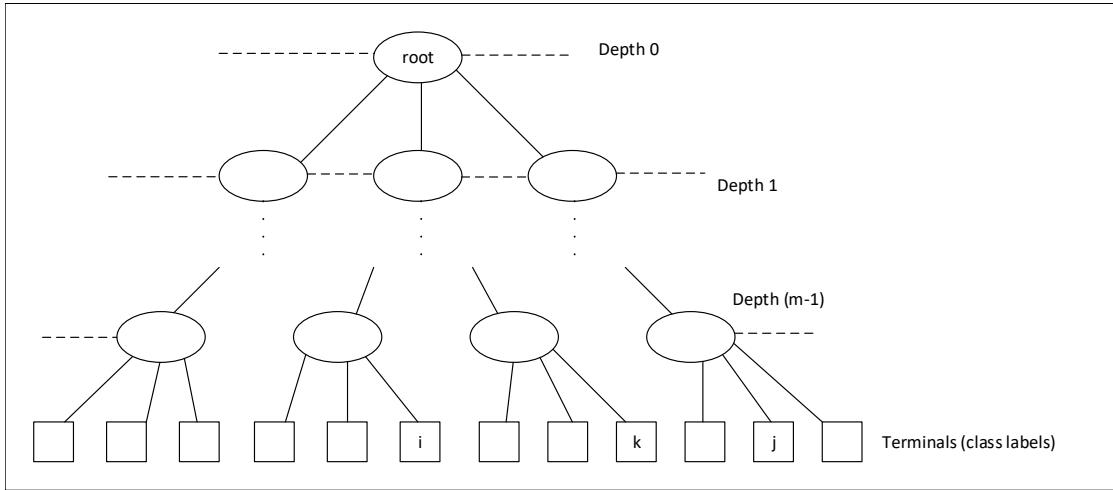

| 2.1  | General Design of a Decision Tree (Reproduced from paper [37]). . . . .                                                                    | 14 |

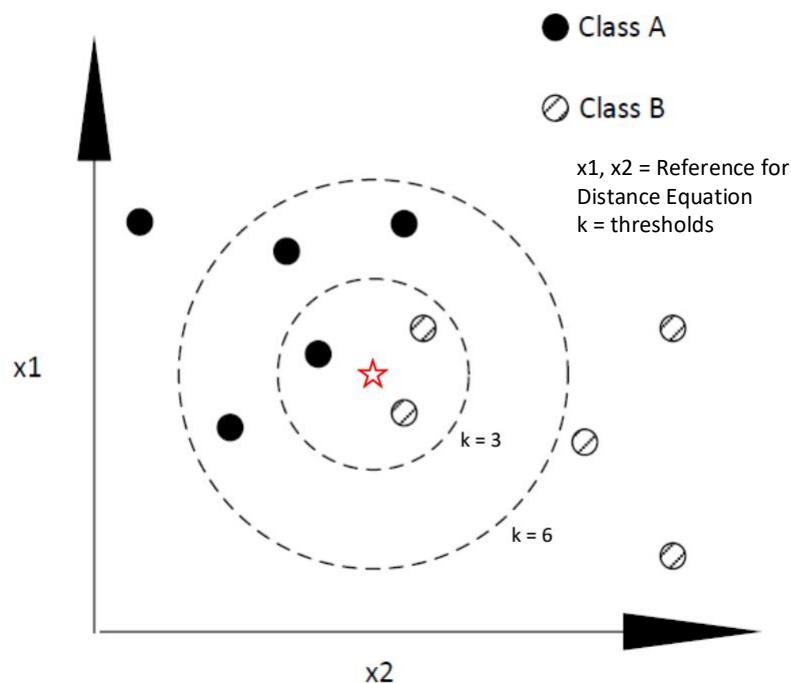

| 2.2  | General Idea of a k-NN classifier (reproduced from [40]). . . . .                                                                          | 15 |

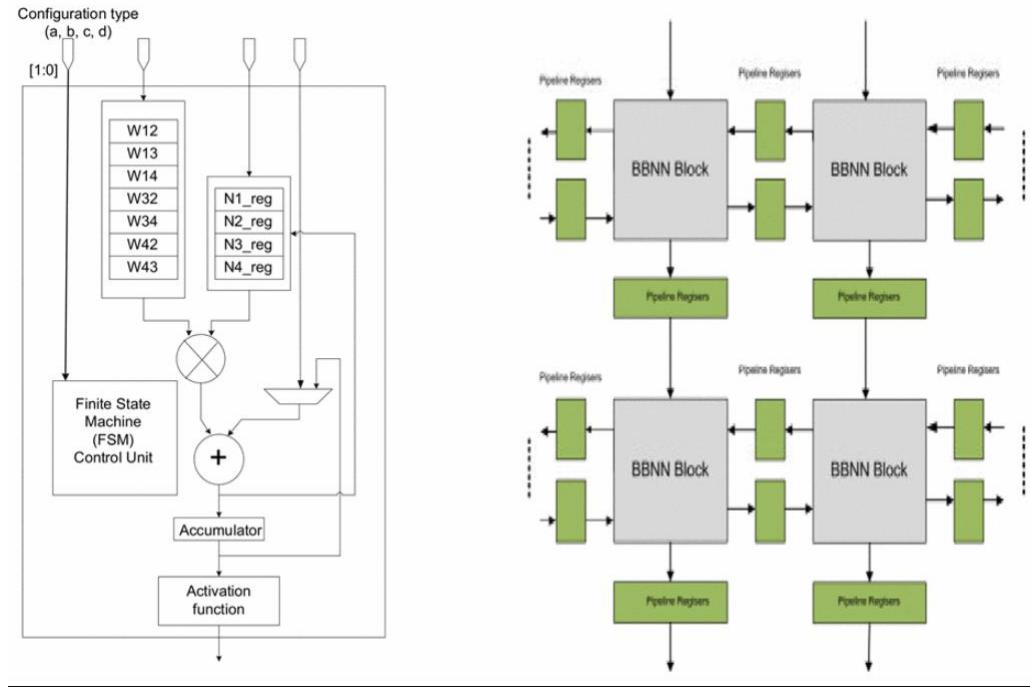

| 2.3  | The Block Based Neural Network (BBNN) design block diagram (extracted from paper [42]). . . . .                                            | 17 |

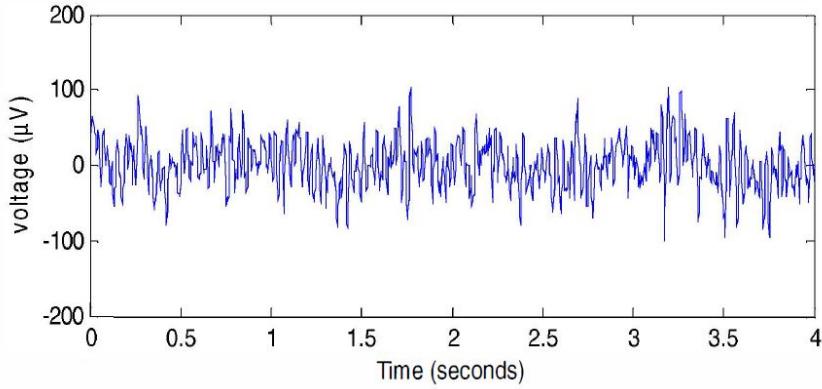

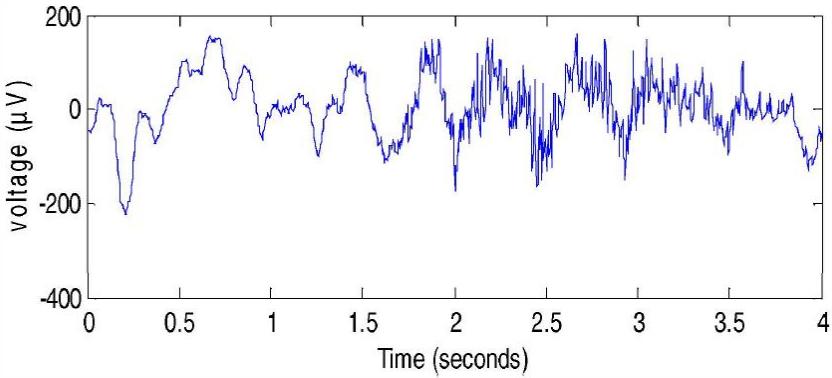

| 2.4  | Sample of normal EEG signal. . . . .                                                                                                       | 18 |

| 2.5  | Sample of a Seizure EEG signal. . . . .                                                                                                    | 18 |

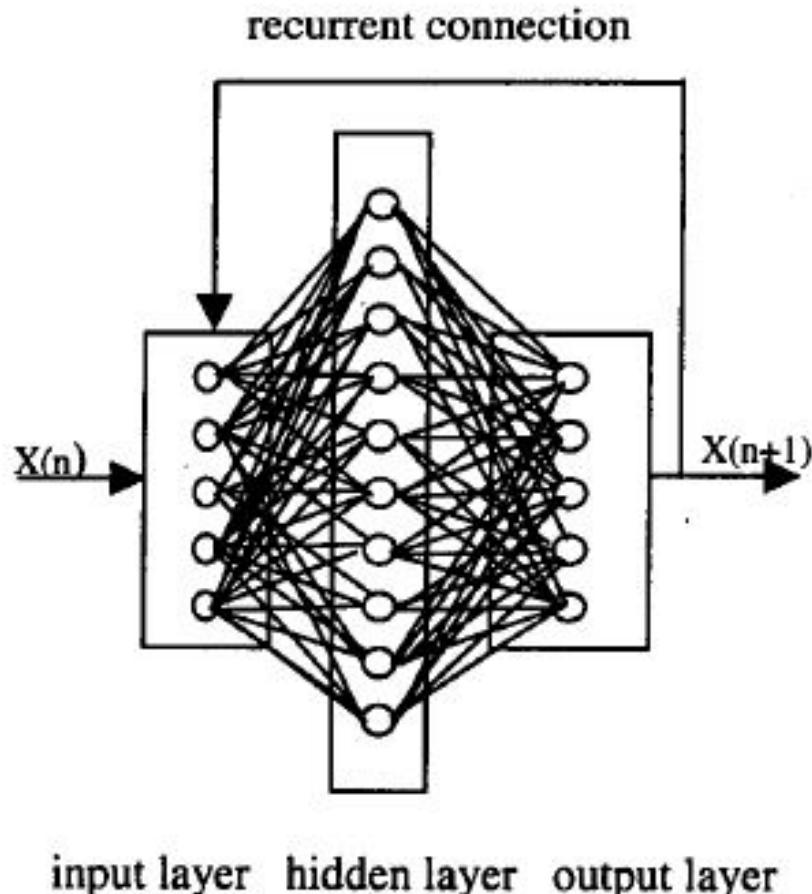

| 2.6  | Network Structure of recurrent BPN Design (extracted from paper Kiranmayi <i>et al.</i> 's work [8]) . . . . .                             | 19 |

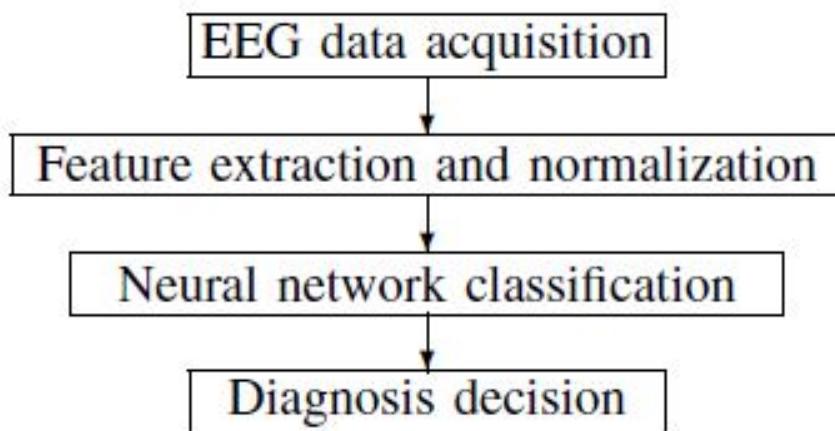

| 2.7  | Flow diagram of EEG classification scheme incorporating ANN (reproduced from work [51]) . . . . .                                          | 20 |

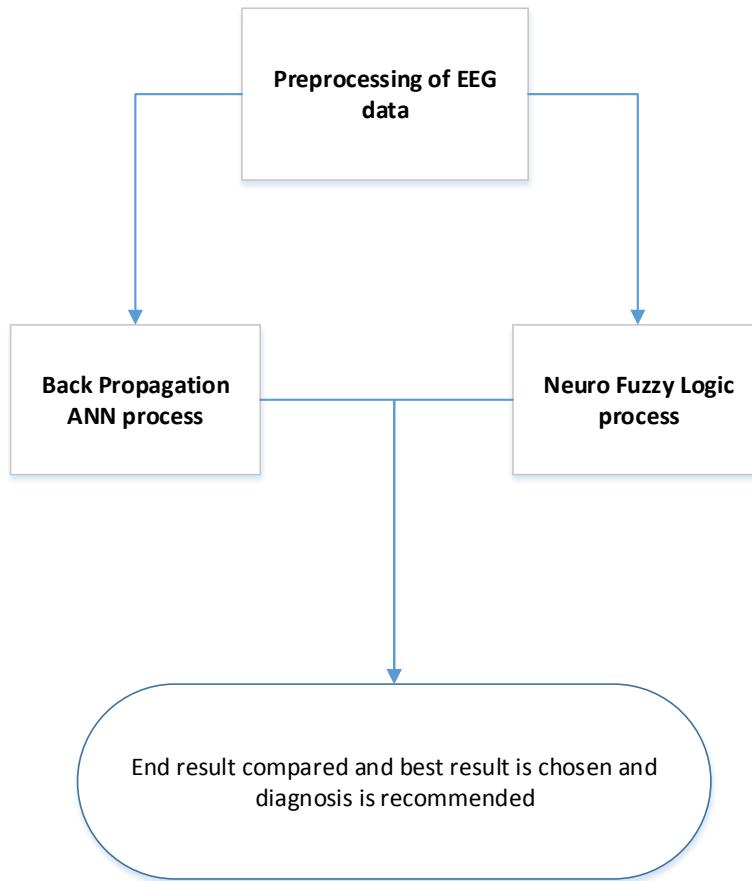

| 2.8  | Block diagram showing a whole system comparing BPN and a fuzzy logic system [51]. . . . .                                                  | 21 |

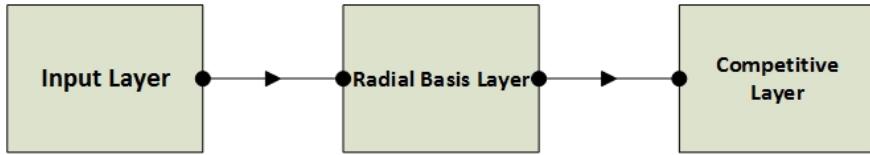

| 2.9  | Network Structure of PNN Design [51]. . . . .                                                                                              | 22 |

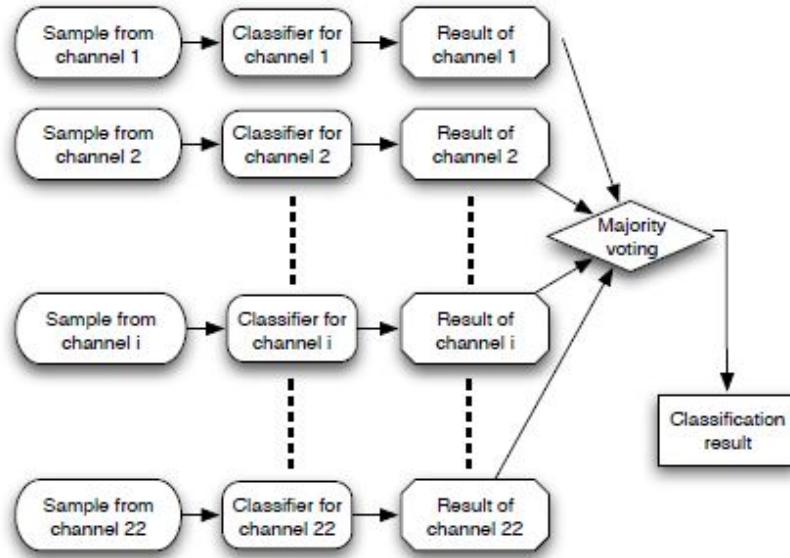

| 2.10 | Voting scheme used in the classification process [57], . . . . .                                                                           | 23 |

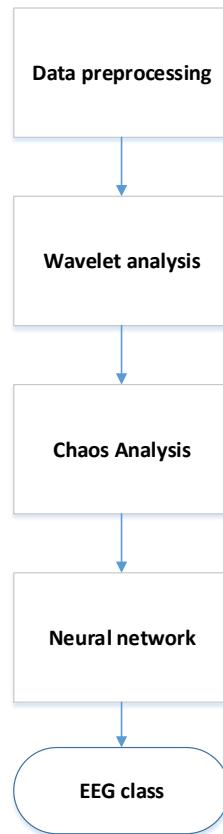

| 2.11 | The different processes leading to the neural network in classification problem [21], . . . . .                                            | 25 |

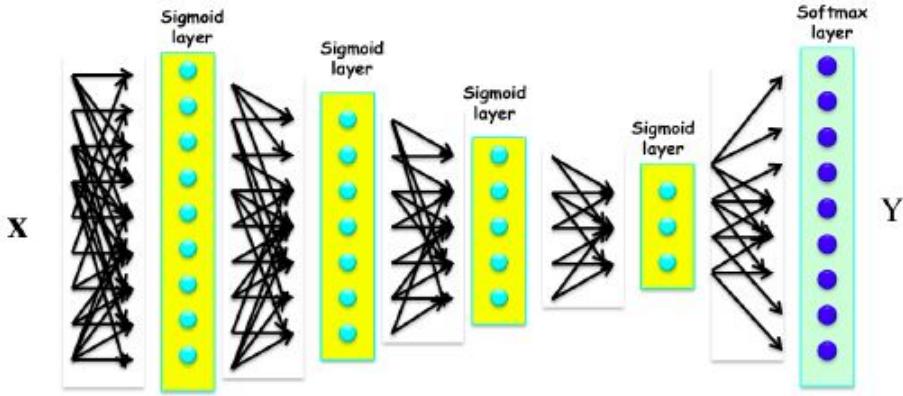

| 2.12 | A DNN with four hidden layers [68], . . . . .                                                                                              | 26 |

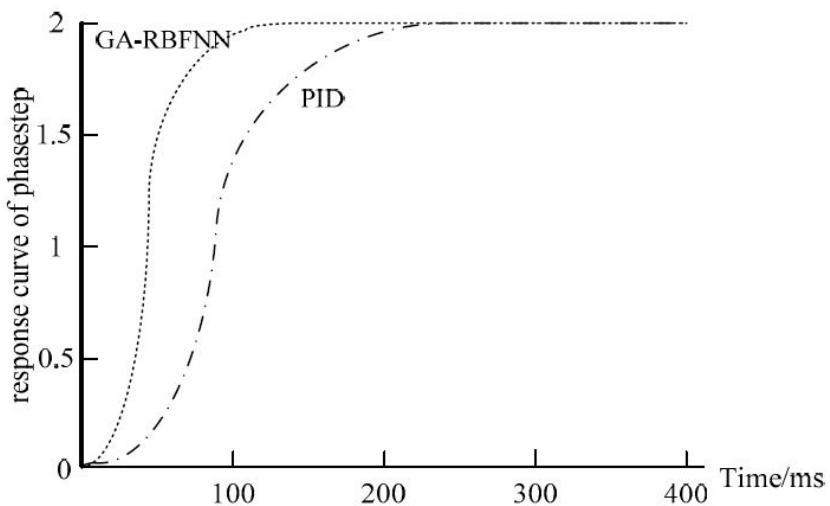

| 2.13 | The response curve of the phasestep between two different approaches [71], . . . . .                                                       | 27 |

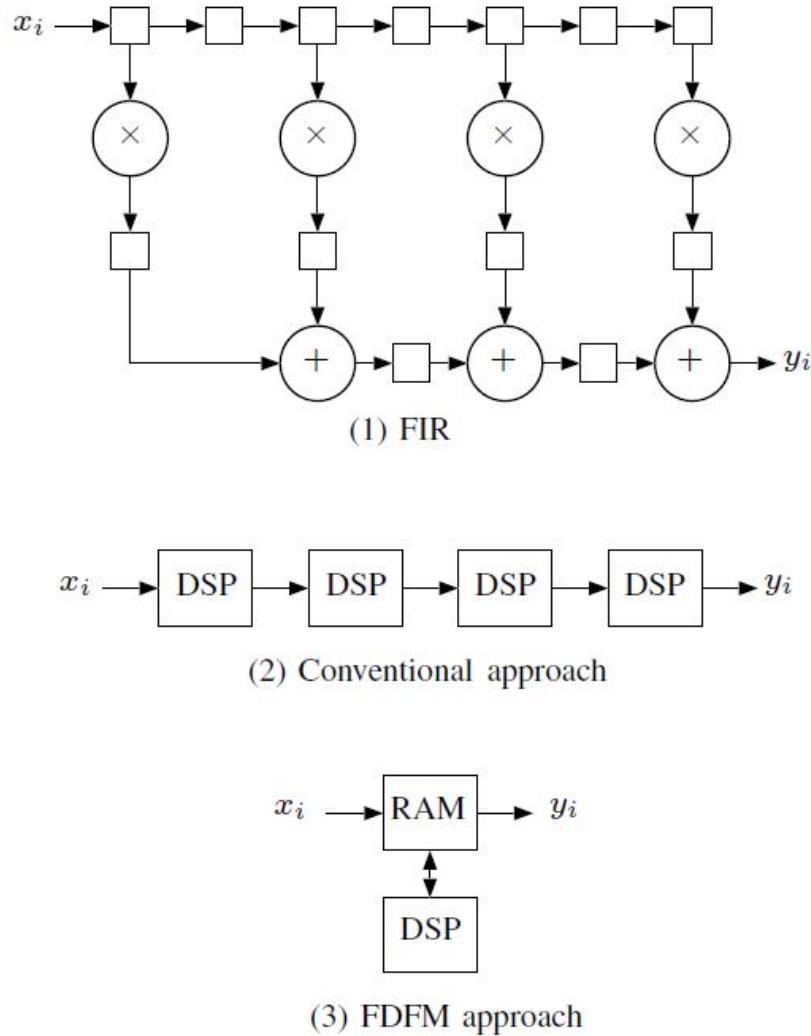

| 2.14 | The different Processor Core approach [73] . . . . .                                                                                       | 29 |

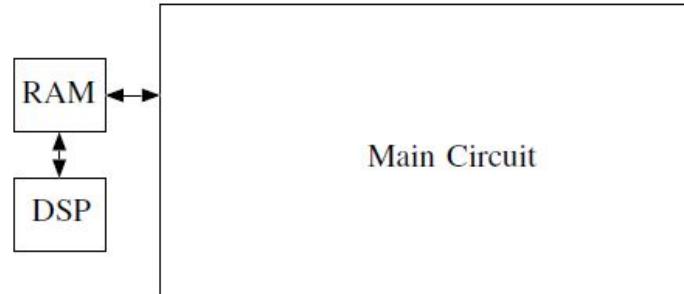

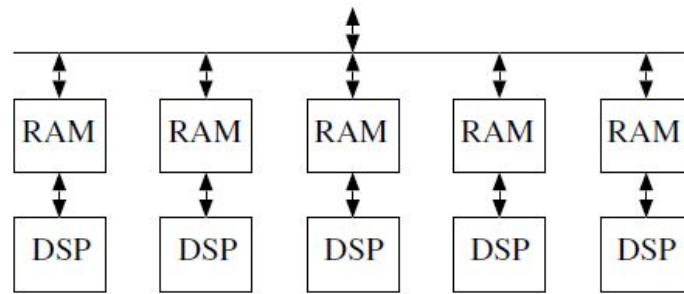

| 2.15 | The Advantage of FDFM Processor Core approach [73]. . . . .                                                                                | 30 |

| 2.16 | 3 Layer MLP Design [73]. . . . .                                                                                                           | 30 |

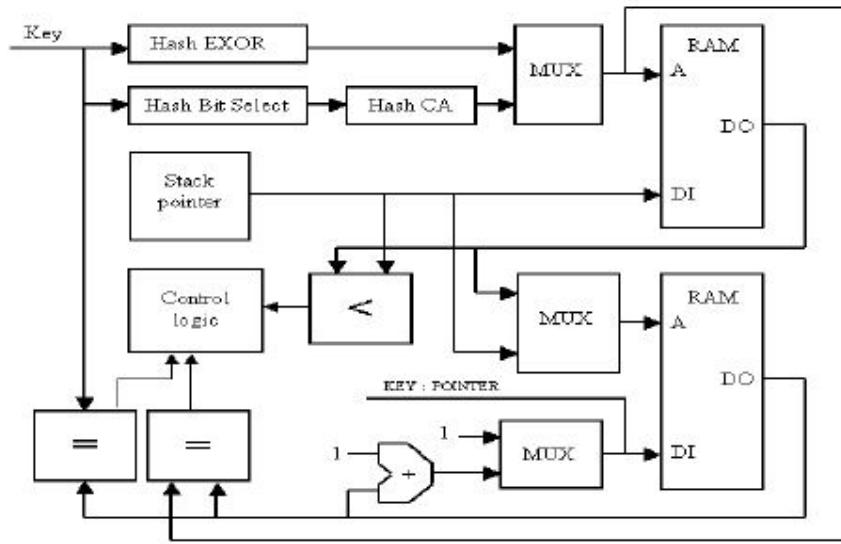

| 2.17 | The Hardware Hashing Memory [76]. . . . .                                                                                                  | 32 |

| 2.18 | The ITS functional unit [76]. . . . .                                                                                                      | 32 |

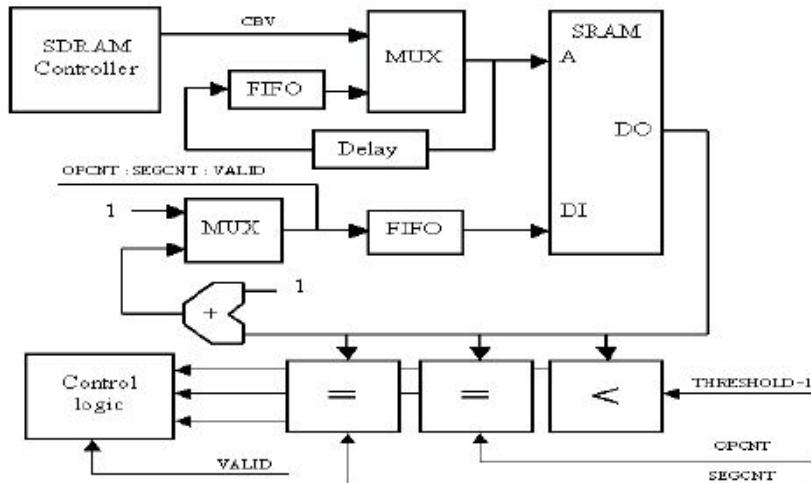

| 2.19 | The SNN auto-associative memory general functionality [78]. . . . .                                                                        | 33 |

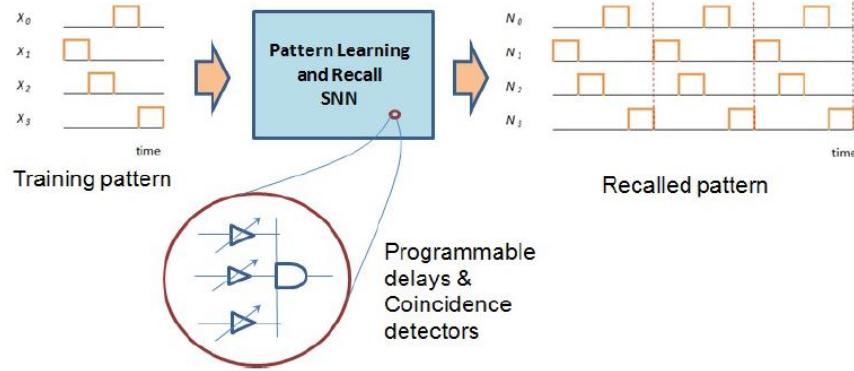

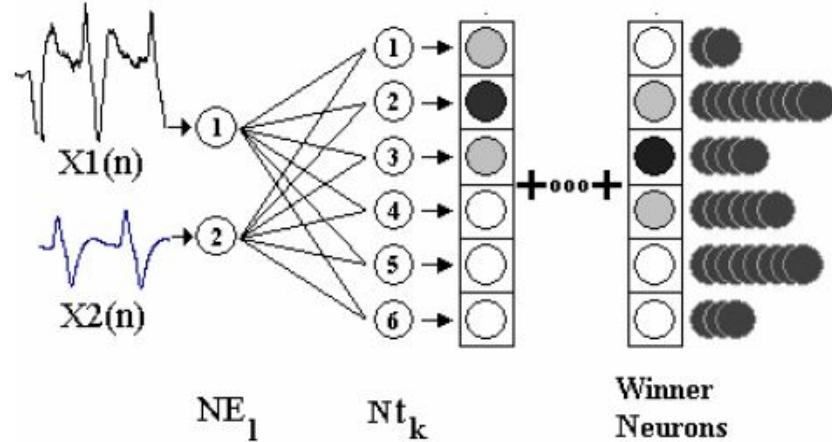

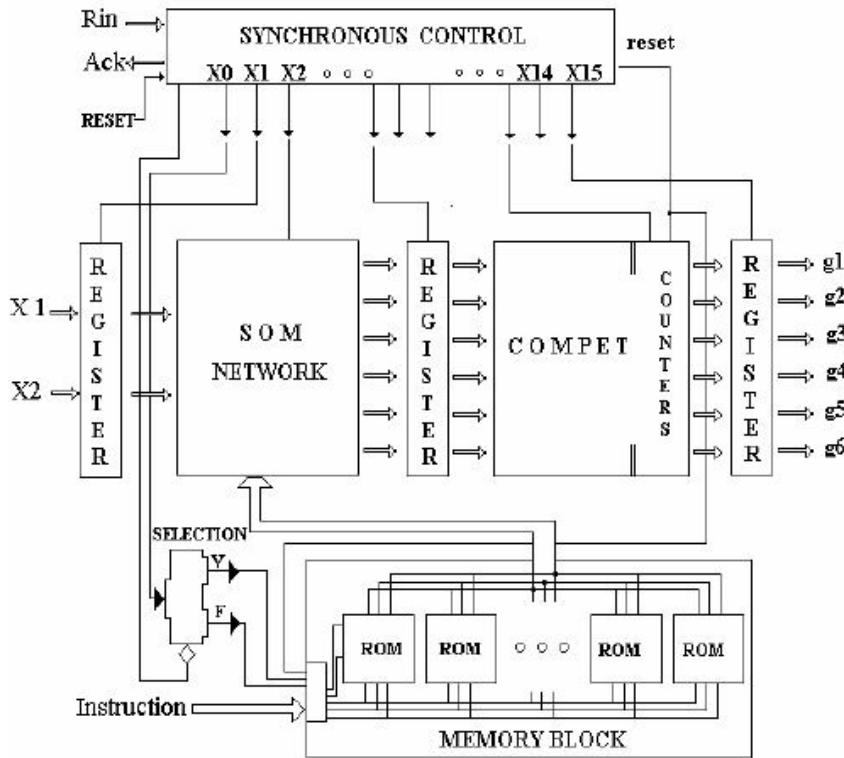

| 2.20 | The SOM architecture [10]. . . . .                                                                                                         | 33 |

| 2.21 | The SOM neural network extracted from the source. [10]. . . . .                                                                            | 34 |

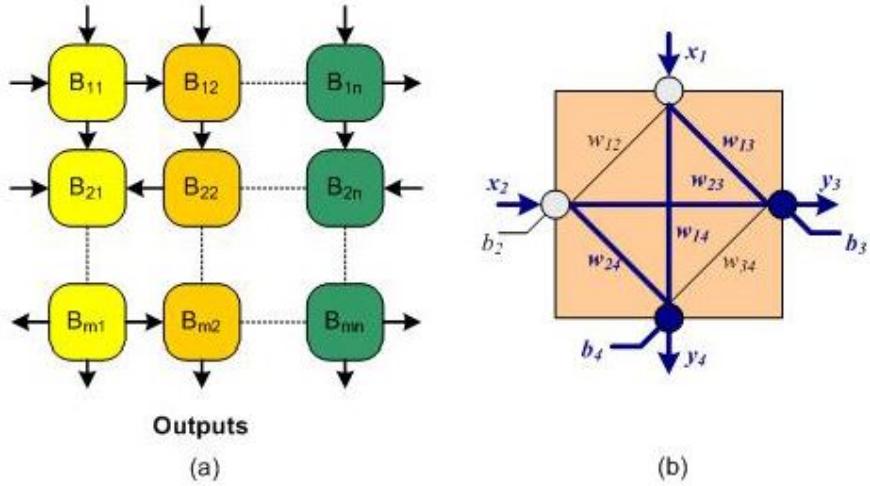

| 2.22 | (a) The BBNN consisting of basic blocks. (b) A 2/2 internal configuration of the network [80]. . . . .                                     | 35 |

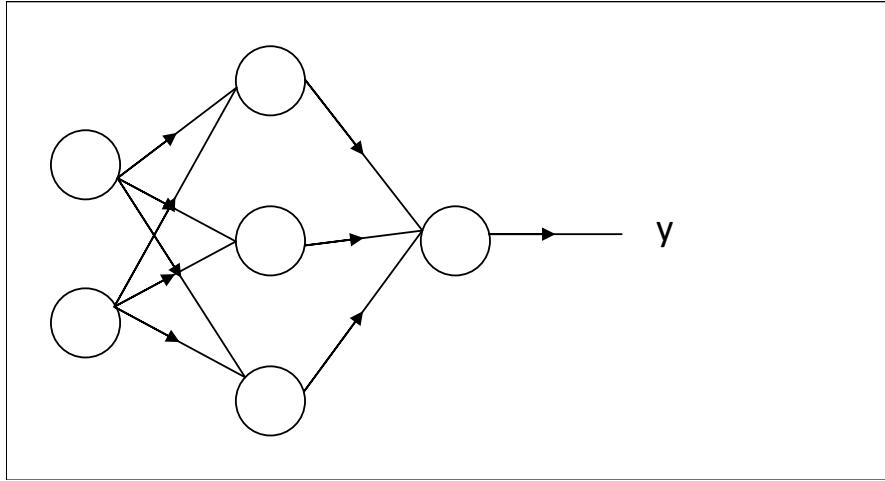

| 2.23 | General Back Propagation Neural Network (BPN) (Reproduced from paper [8]). . . . .                                                         | 38 |

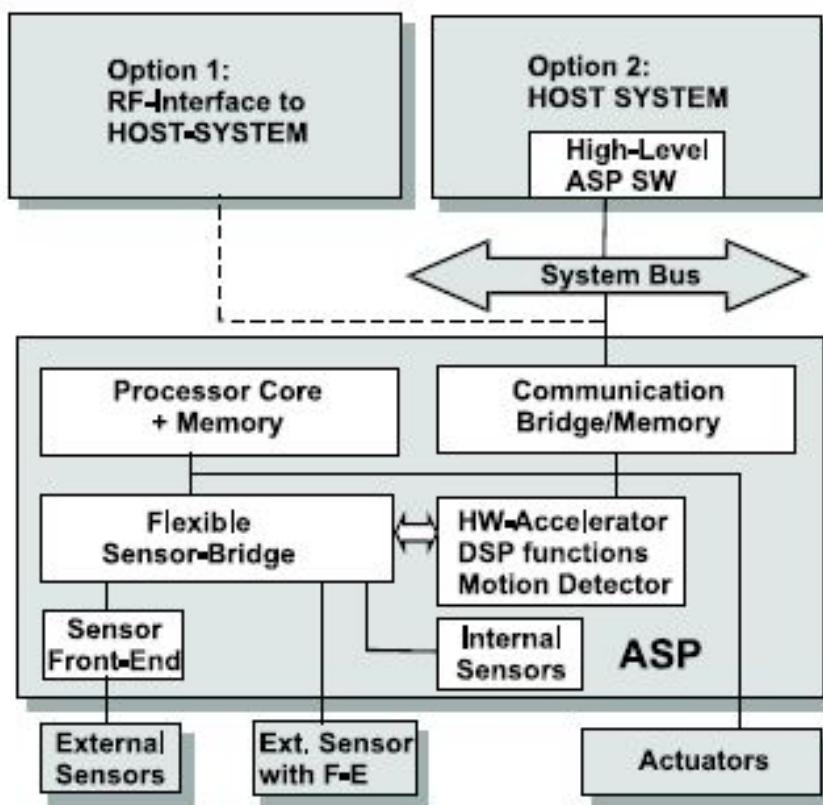

| 2.24 | The ASP architecture allows two different option of interfacing with the application processor [98]. . . . .                               | 40 |

| 2.25 | A Comparative Analysis Table Extracted From The Literature [23] Detailing Different Algorithms Using Support Vector Machine (SVM). . . . . | 45 |

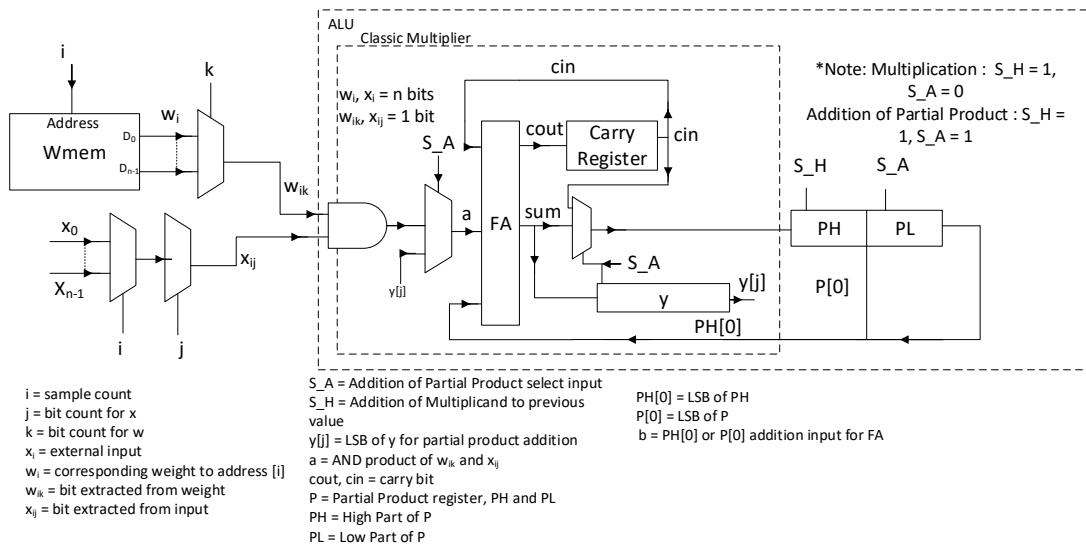

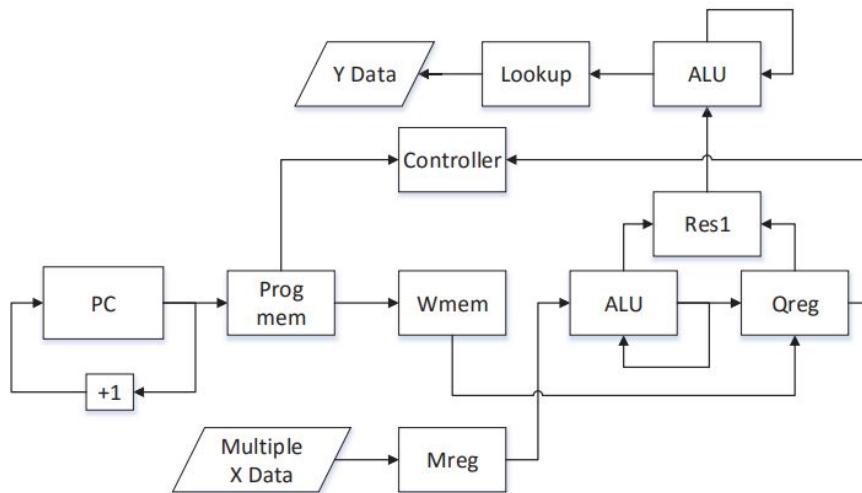

| 3.1  | Proposed DPU Design. . . . .                                                                                                               | 55 |

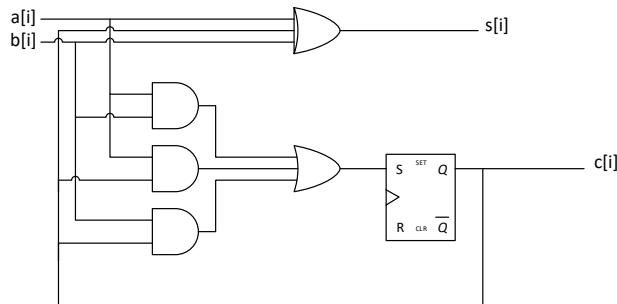

| 3.2  | Single Bit-adder Circuit in the proposed Bit-Serial Processor. . . . .                                                                     | 55 |

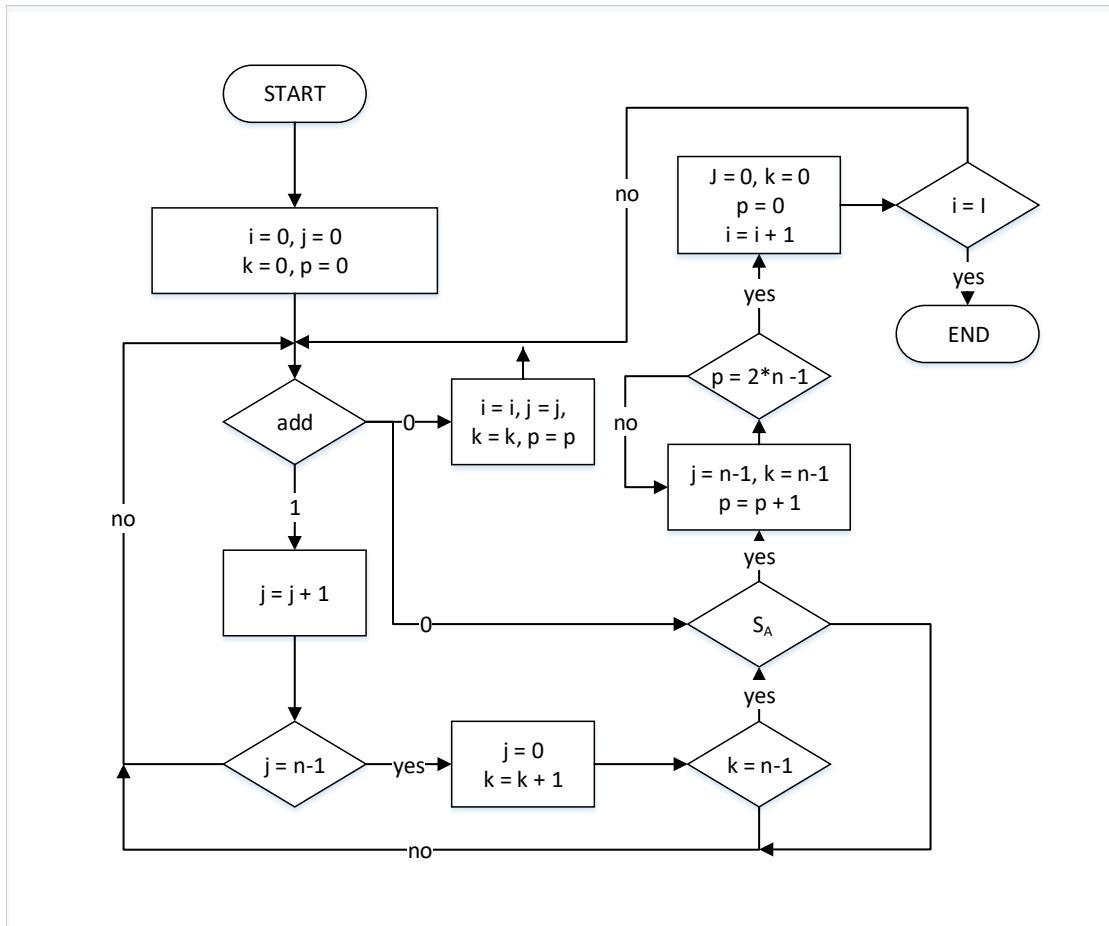

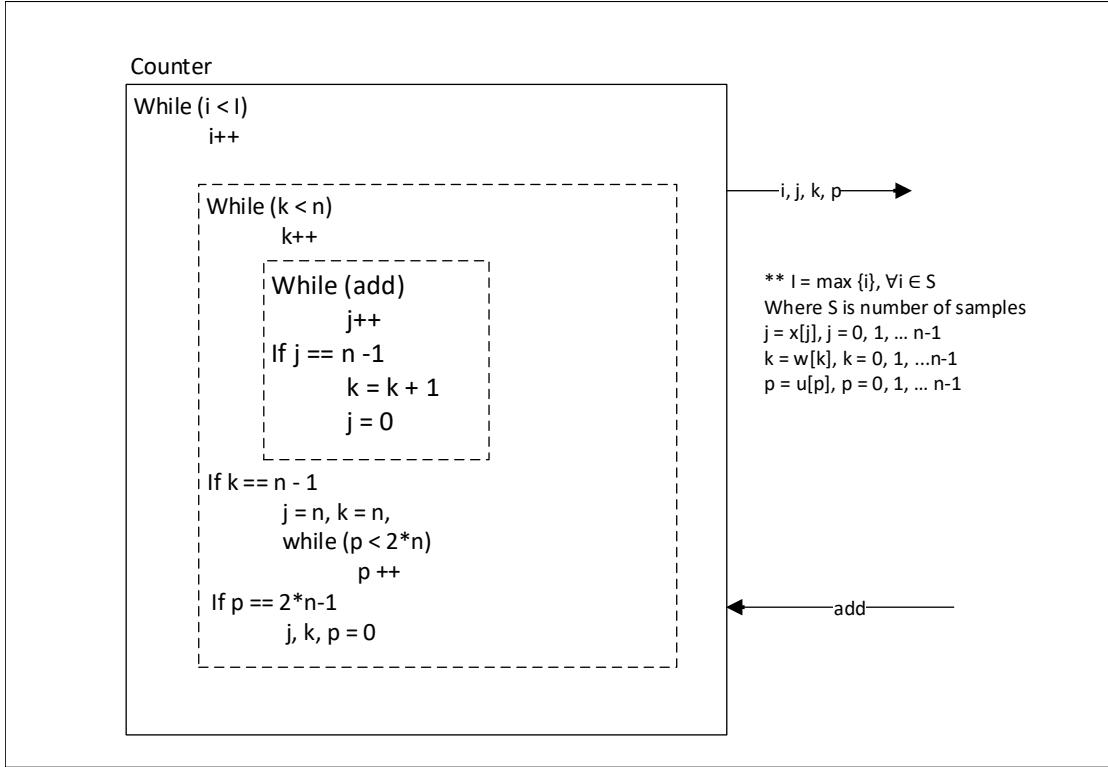

| 3.3  | Counters algorithm for the hardware neural network . . . . .                                                                               | 58 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.4  | Multiple counters diagram for the hardware neural network . . . . .                                                                                                                                                                                                                                                                                                                            | 59 |

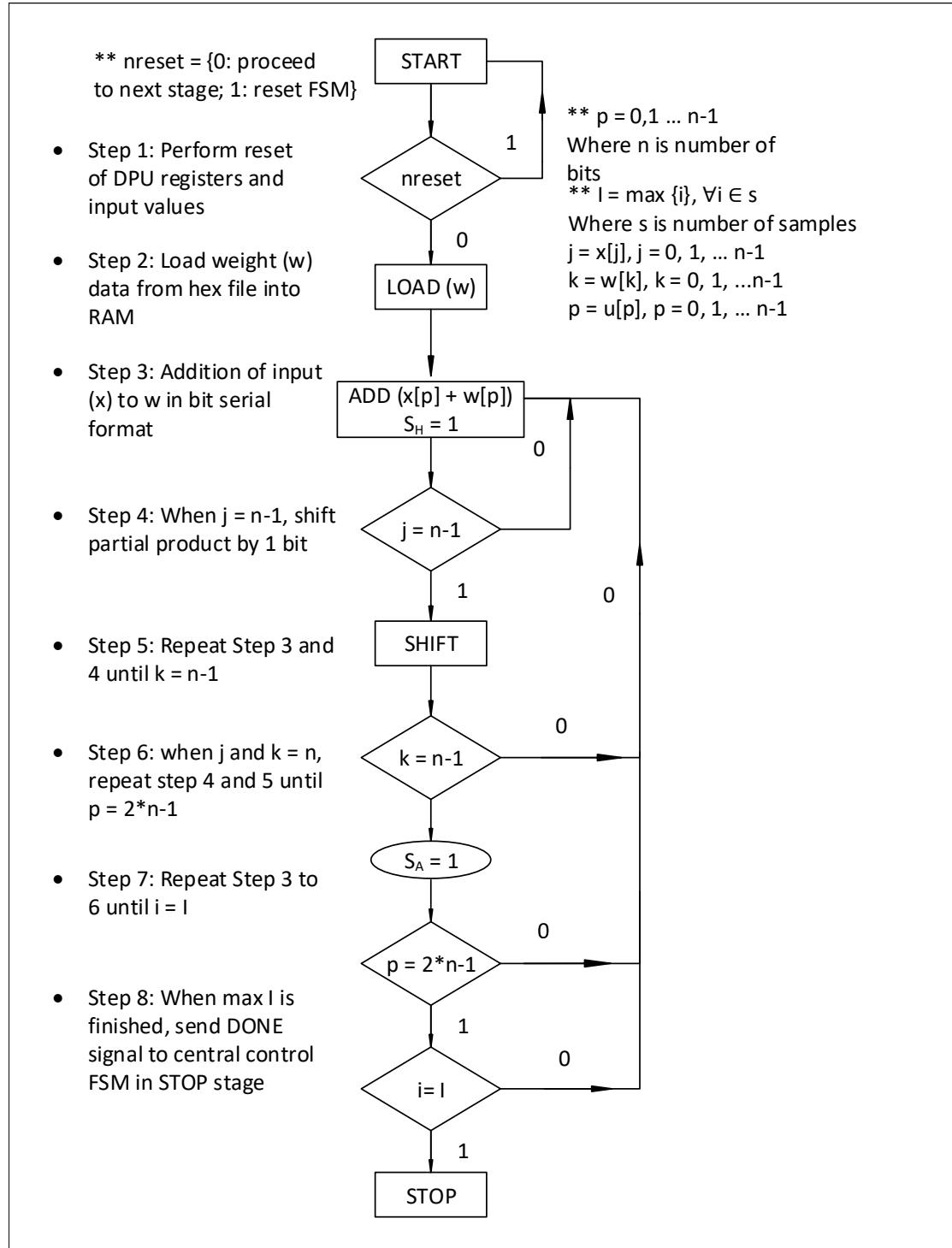

| 3.5  | A finite state machine for the Layer FSM . . . . .                                                                                                                                                                                                                                                                                                                                             | 60 |

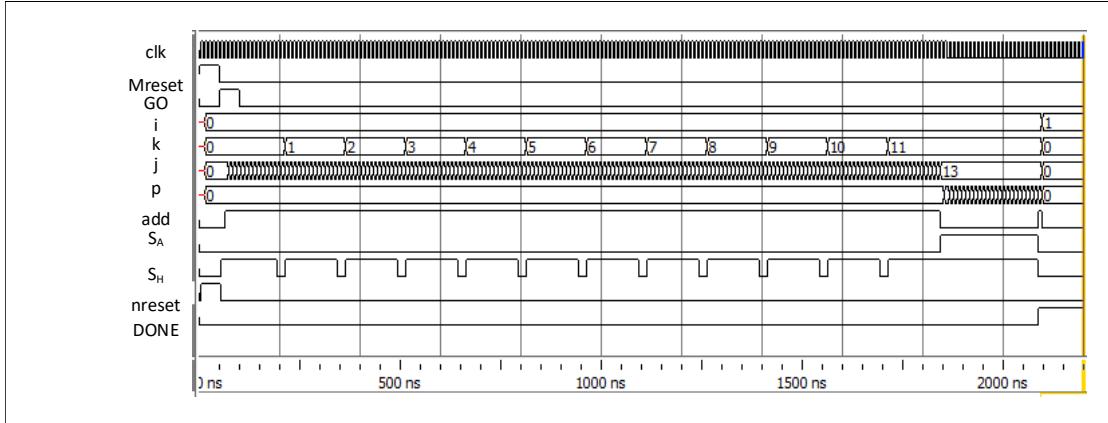

| 3.6  | Timing diagram of a single sample neural operation (clk = global clock, Mreset = Master reset signal, i = sample number, k = bit in weight, j = bit in input x, p = accumulated product, u, add = add signal, $S_H$ , $S_A$ = signal from the FSM to perform shift and add algorithm, nreset = nreset signal, DONE = signal in every layer of the neural network to stop operation ) . . . . . | 61 |

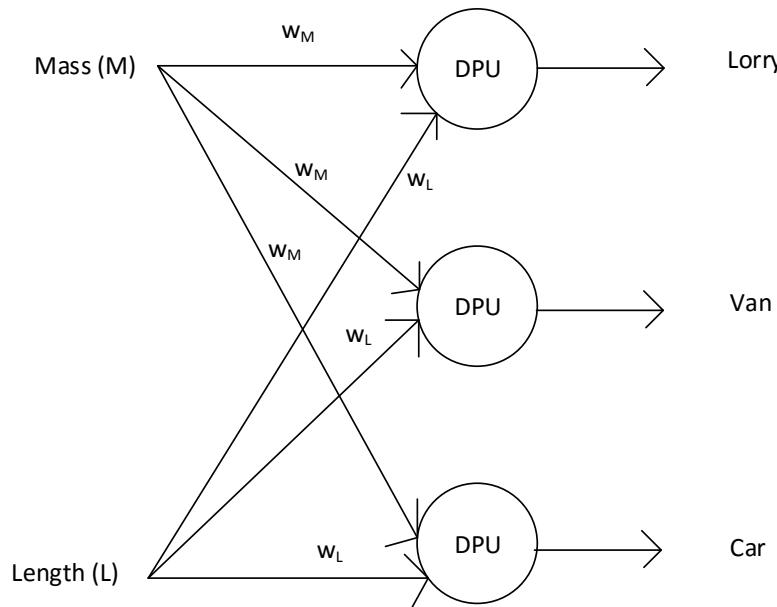

| 3.7  | Simple Single Layer Neural Network (Mass (M), Length (L) as inputs and $w_i$ = weights) . . . . .                                                                                                                                                                                                                                                                                              | 61 |

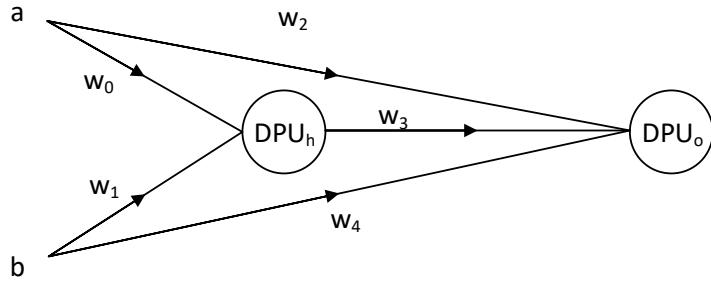

| 3.8  | XOR gate double Layer Neural Network (a and b as inputs and $w_i$ = weights) . . . . .                                                                                                                                                                                                                                                                                                         | 62 |

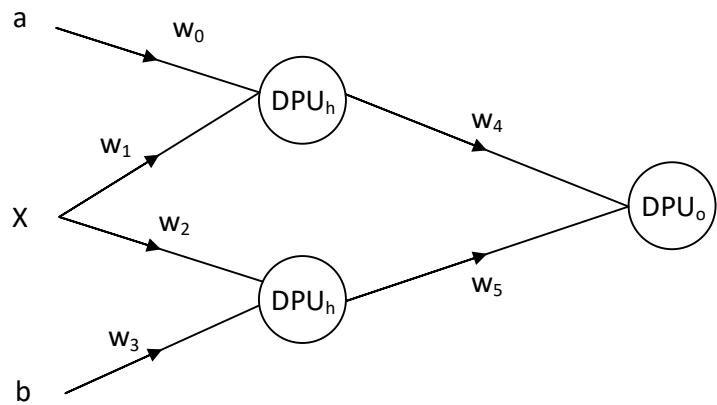

| 3.9  | Simple Multi Layer Neural Network for ECG Plot Peak Detection (a, X, b as inputs and $w_i$ = weights) . . . . .                                                                                                                                                                                                                                                                                | 62 |

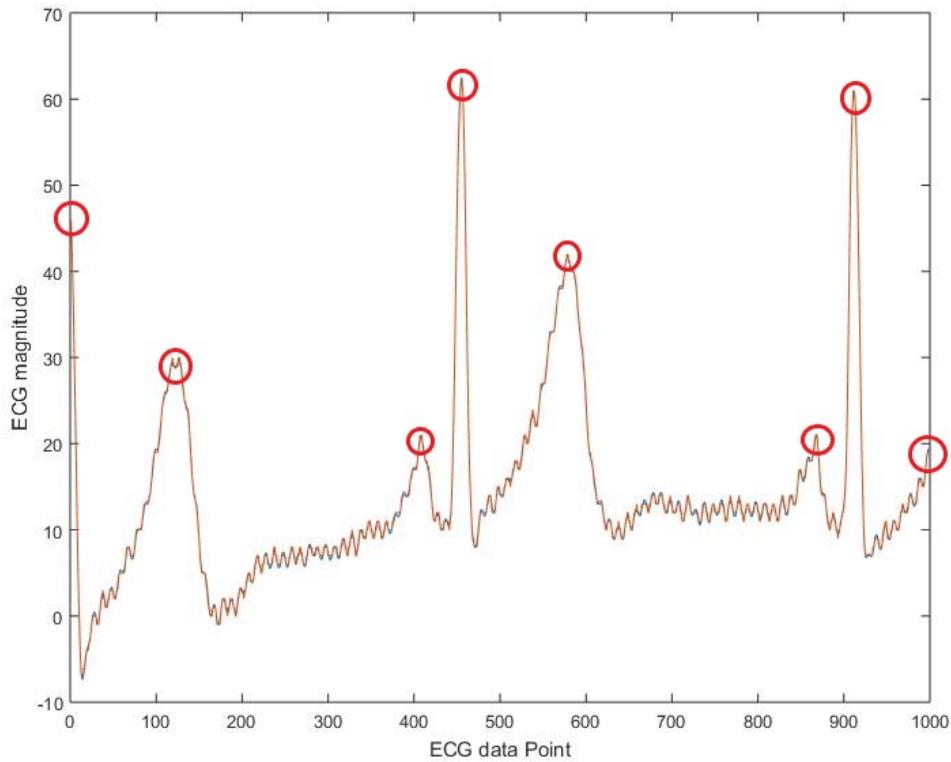

| 3.10 | ECG Plot For Simple Peak Detection . . . . .                                                                                                                                                                                                                                                                                                                                                   | 63 |

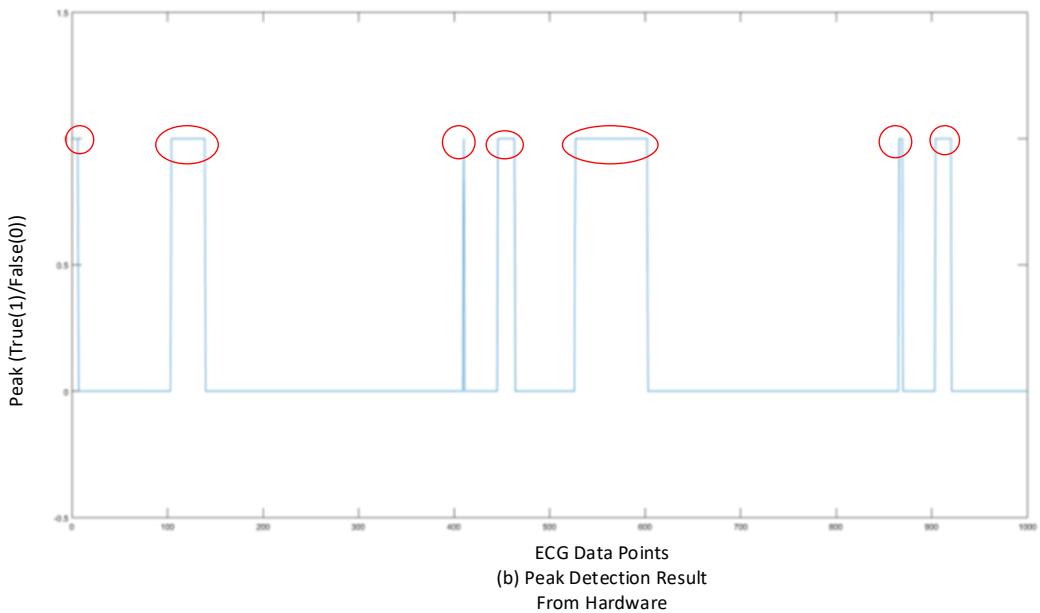

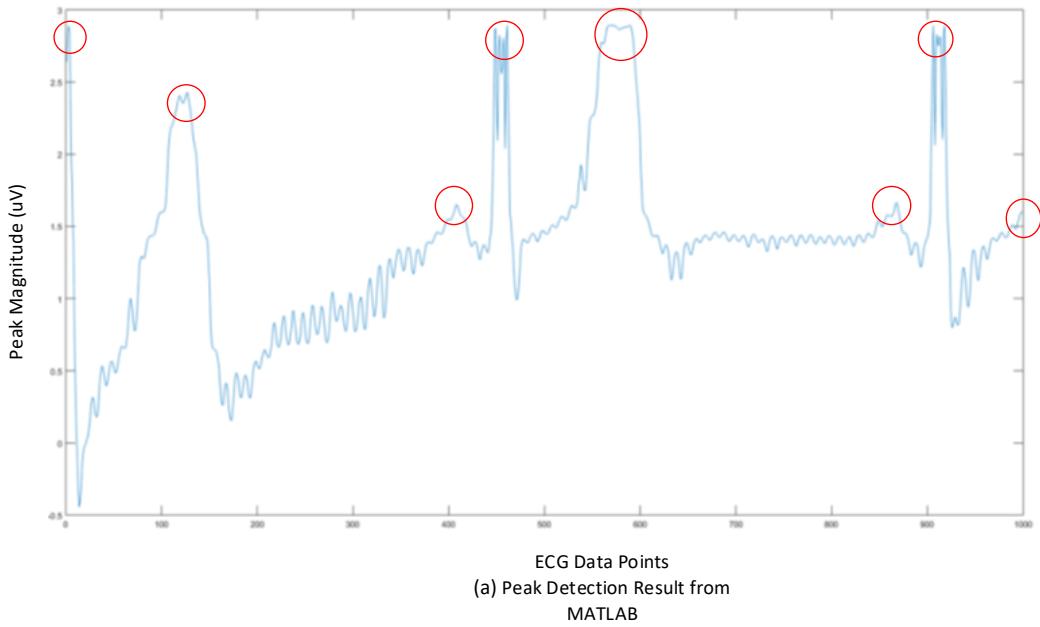

| 3.11 | Peak Result obtained from (a) MATLAB & (b) Hardware to be compared against Figure 3.10 . . . . .                                                                                                                                                                                                                                                                                               | 64 |

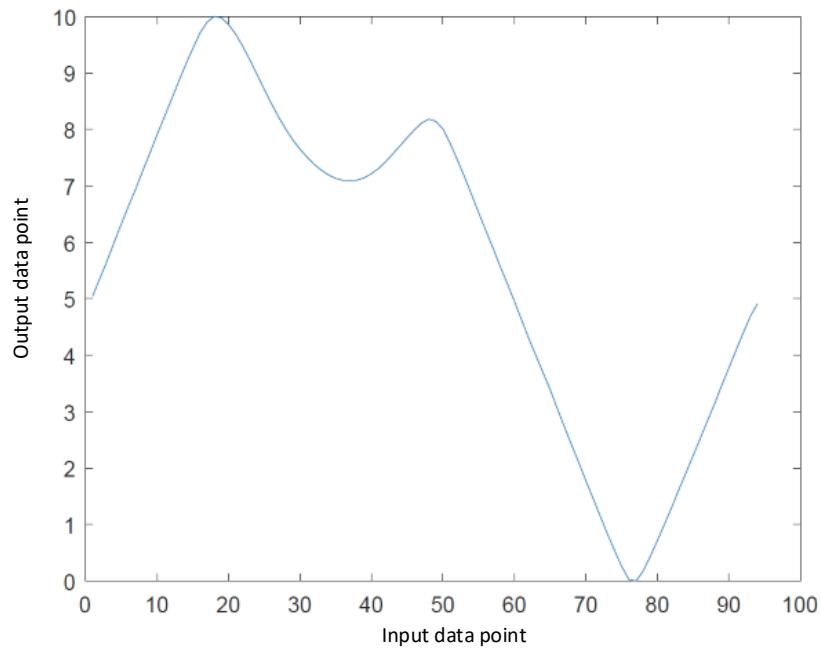

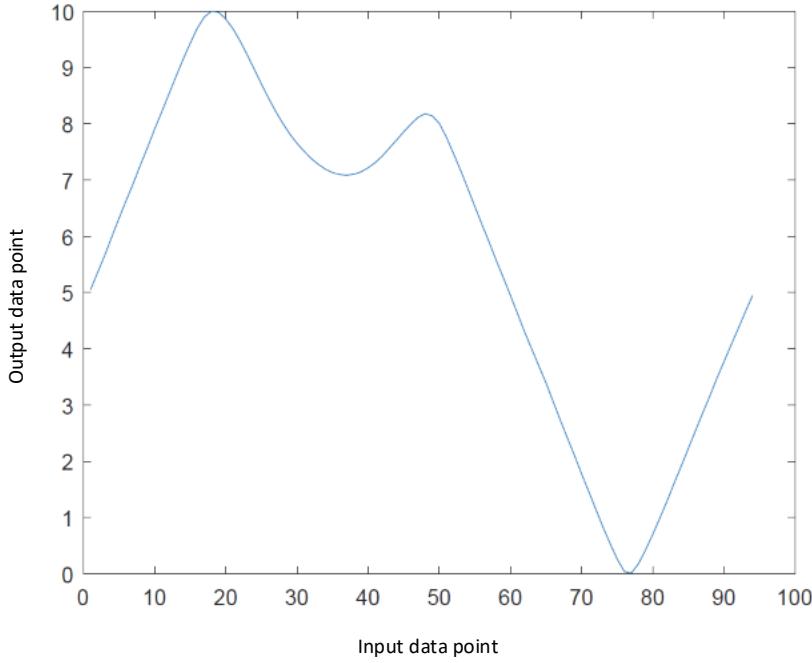

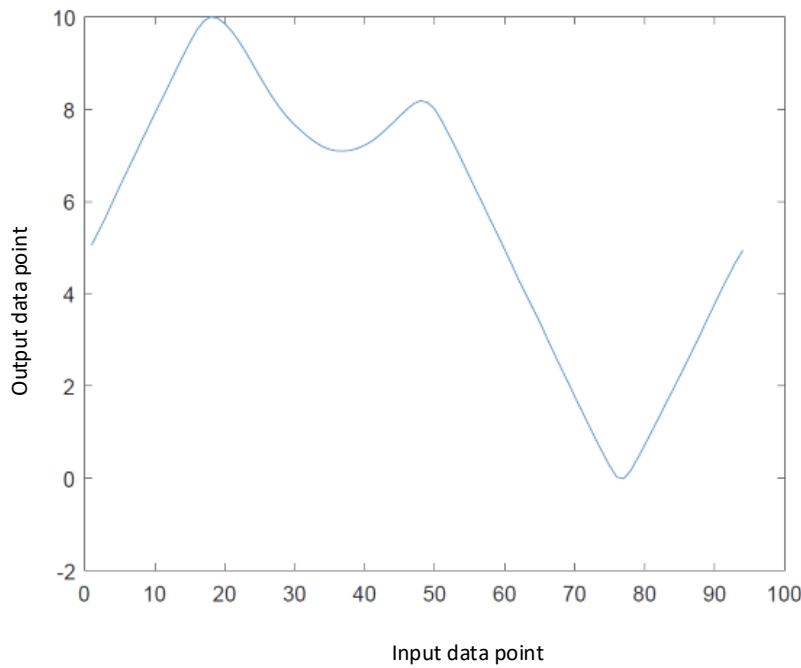

| 3.12 | Target output waveform to be matched by hardware . . . . .                                                                                                                                                                                                                                                                                                                                     | 65 |

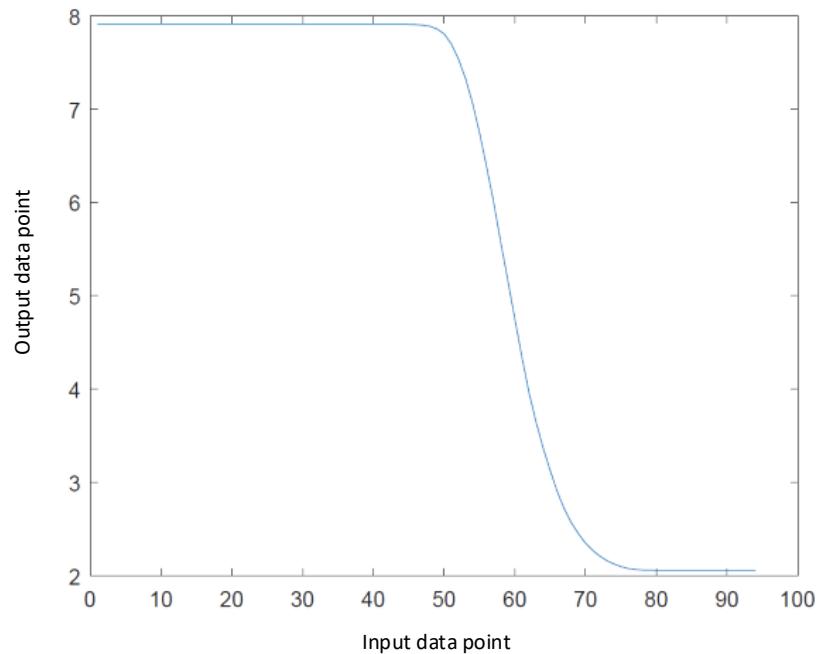

| 3.13 | Output Waveform obtained from using 6-bit precision 1-8-1 hardware . .                                                                                                                                                                                                                                                                                                                         | 65 |

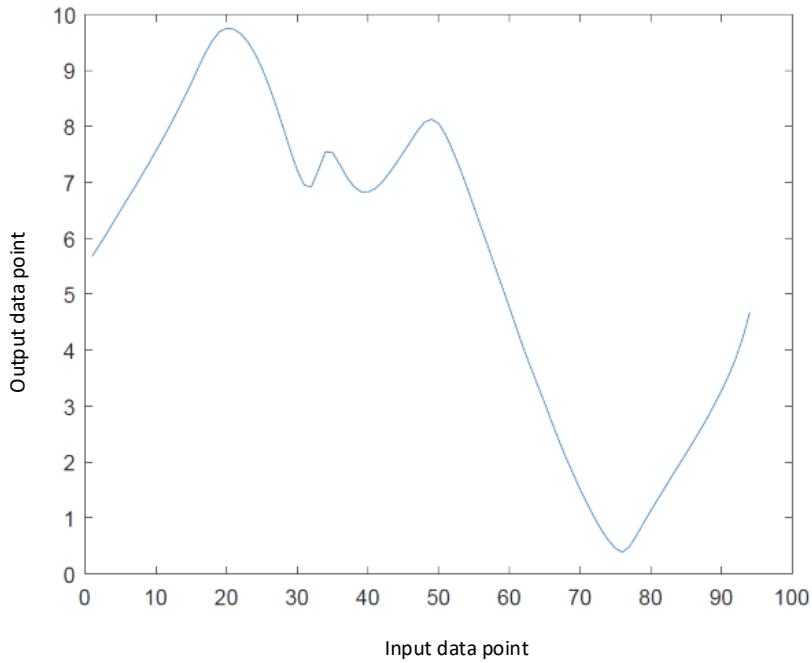

| 3.14 | Output Waveform obtained from using 8-bit precision 1-8-1 hardware . .                                                                                                                                                                                                                                                                                                                         | 66 |

| 3.15 | SOuput Waveform obtained from using 12-bit precision 1-8-1 hardware . .                                                                                                                                                                                                                                                                                                                        | 66 |

| 3.16 | Output Waveform obtained from using 16-bit precision 1-8-1 hardware . .                                                                                                                                                                                                                                                                                                                        | 67 |

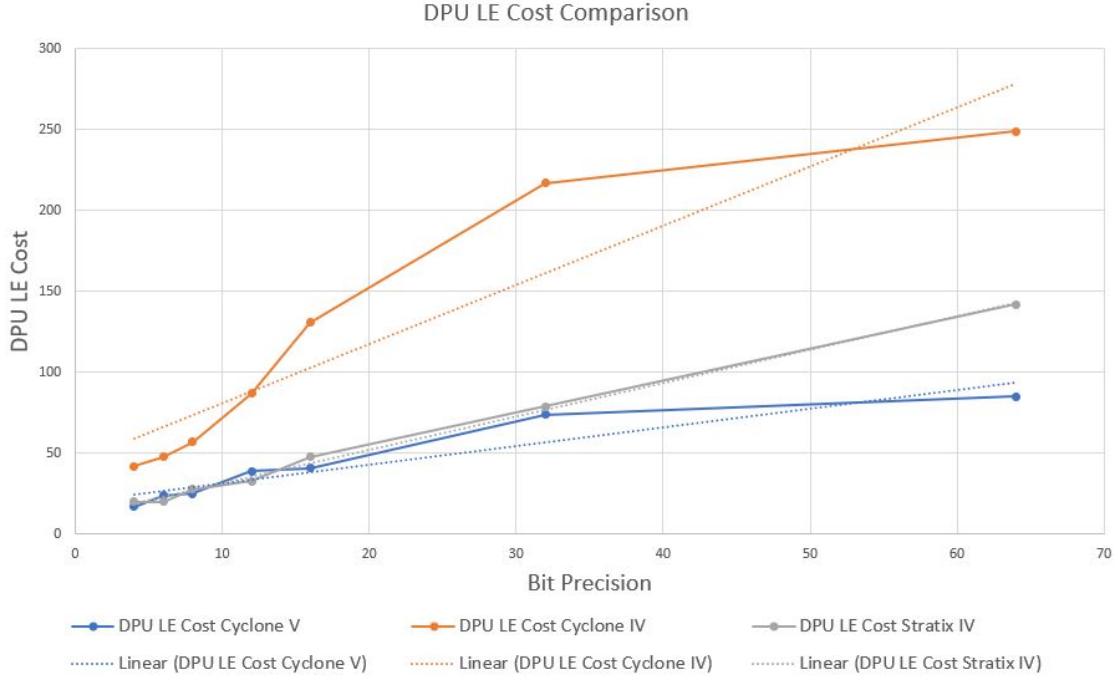

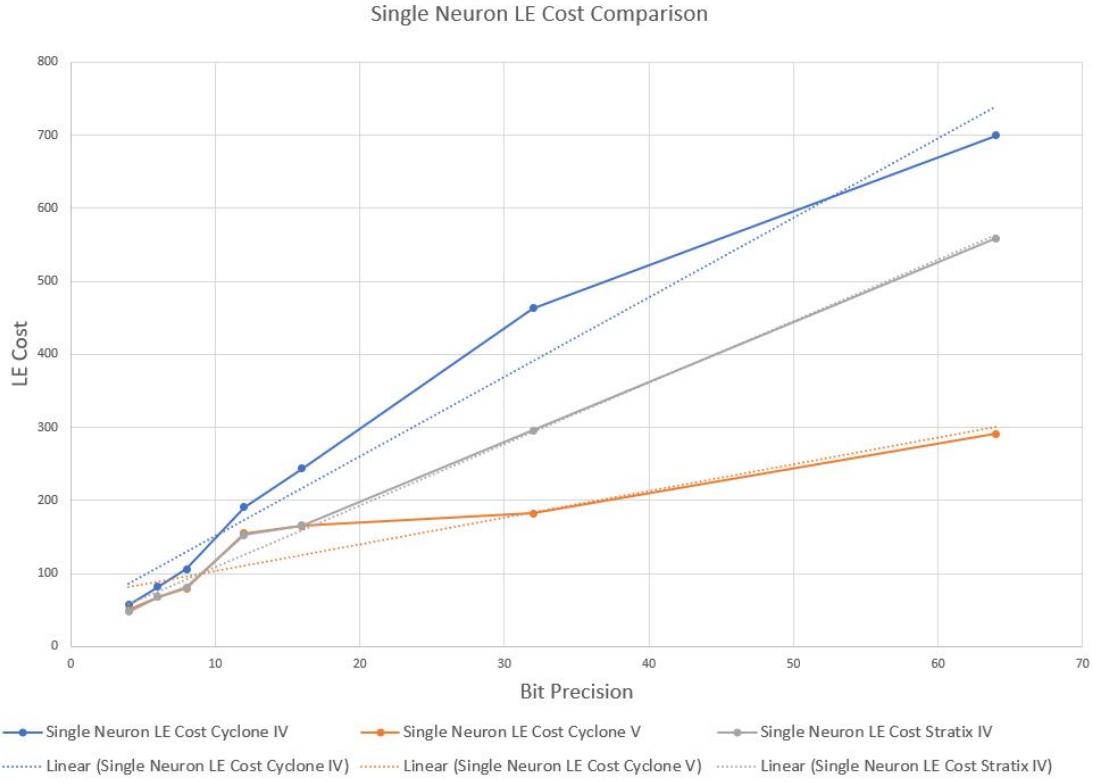

| 3.17 | DPU LE Cost Comparison Between Cyclone IV, Cyclone V and Stratix IV                                                                                                                                                                                                                                                                                                                            | 69 |

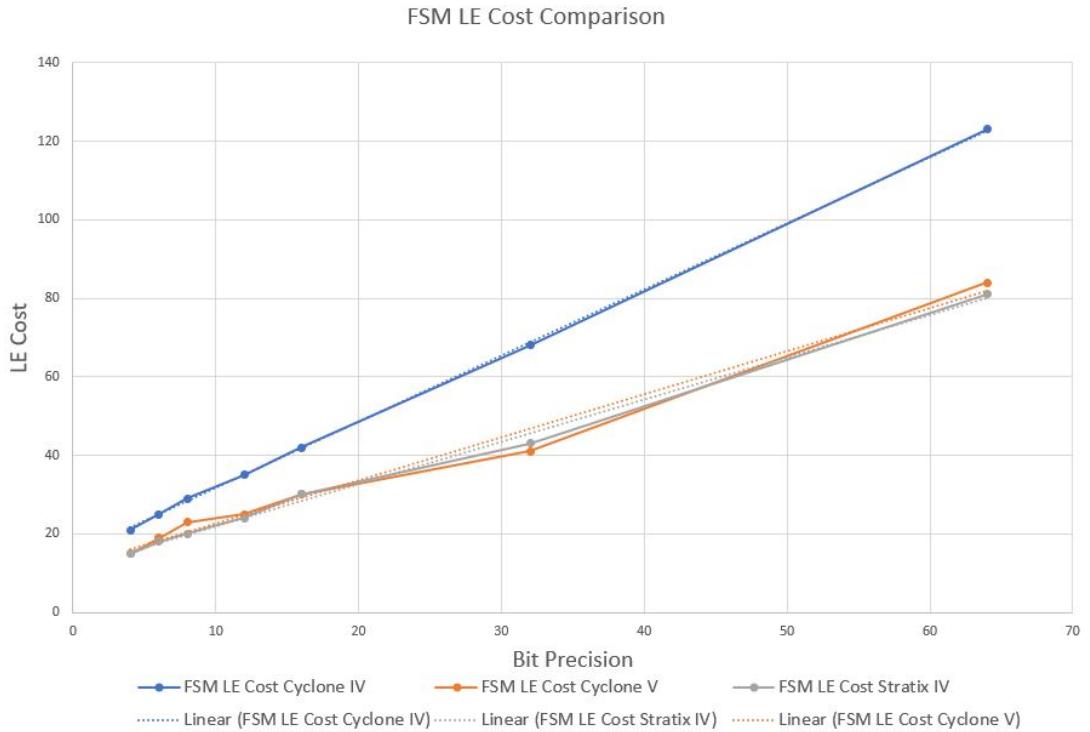

| 3.18 | FSM LE Cost Comparison Between Cyclone IV, Cyclone V and Stratix IV                                                                                                                                                                                                                                                                                                                            | 69 |

| 3.19 | Single Layer LE Cost Comparison Between Cyclone IV, Cyclone V and Stratix IV . . . . .                                                                                                                                                                                                                                                                                                         | 70 |

| 3.20 | First DPU Design Published in WASET Paper [128] . . . . .                                                                                                                                                                                                                                                                                                                                      | 71 |

| 3.21 | Table for logic cell comparison (Extracted from datasheet [131] . . . . .                                                                                                                                                                                                                                                                                                                      | 72 |

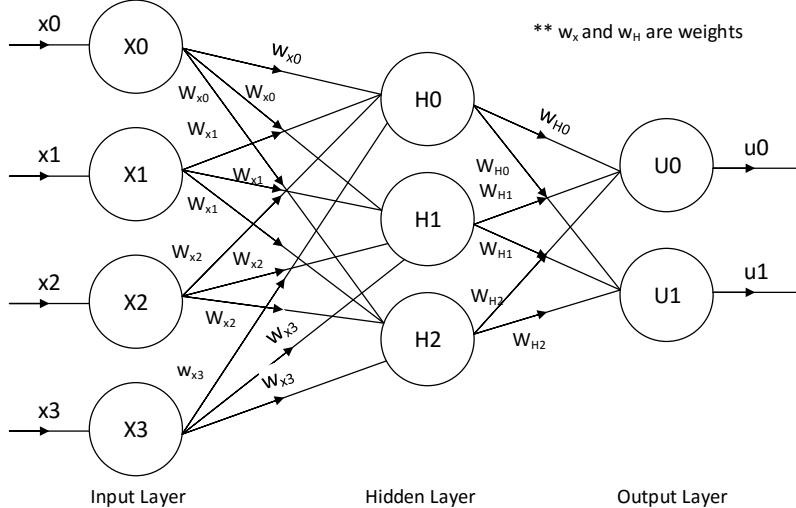

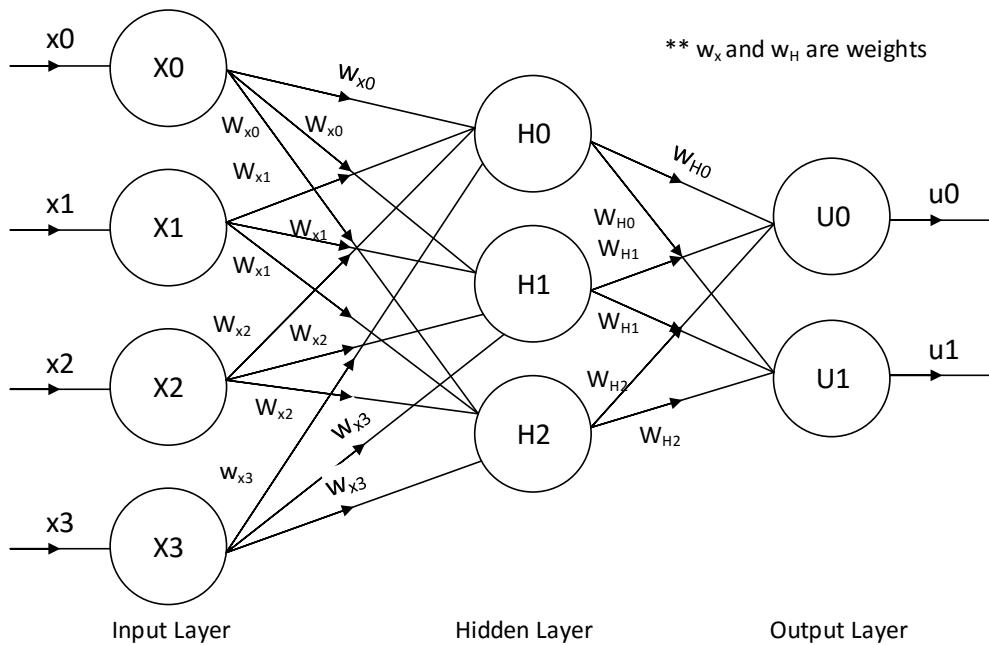

| 4.1  | 4-3-2 Network Topology . . . . .                                                                                                                                                                                                                                                                                                                                                               | 76 |

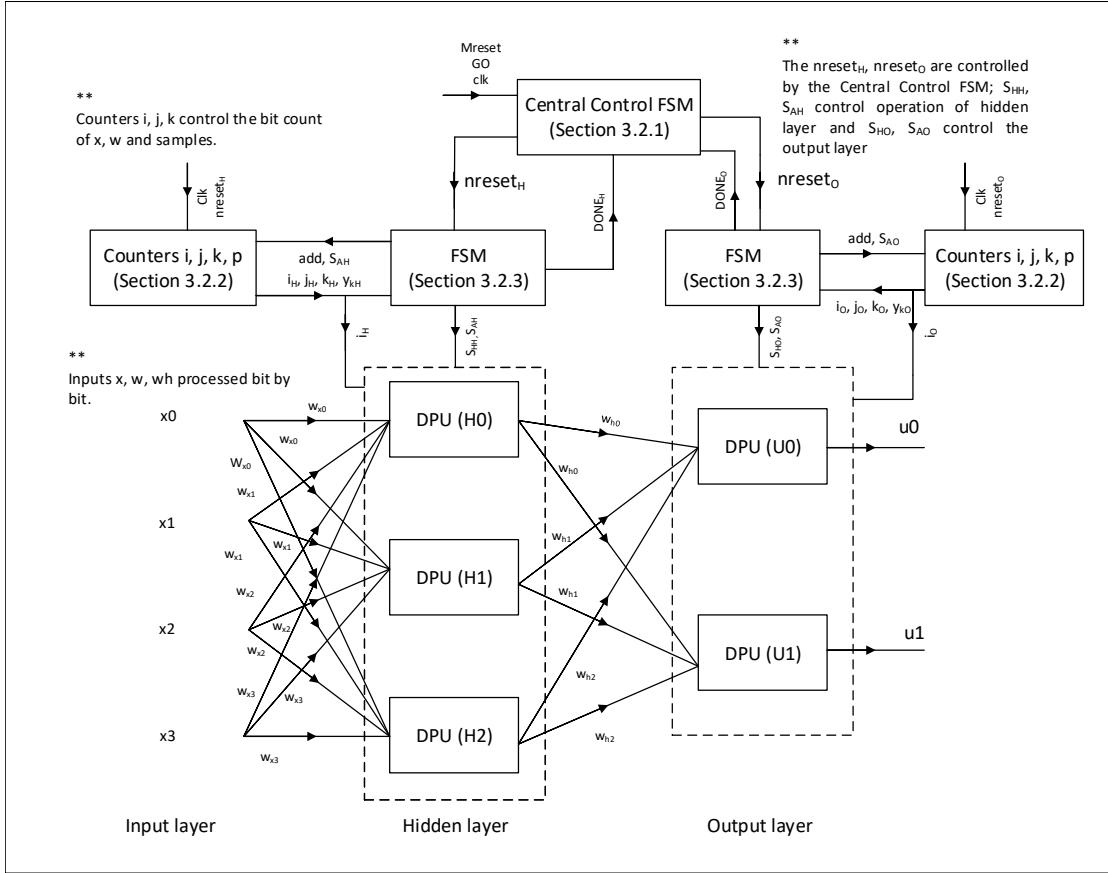

| 4.2  | 4-3-2 Network Topology in hardware . . . . .                                                                                                                                                                                                                                                                                                                                                   | 77 |

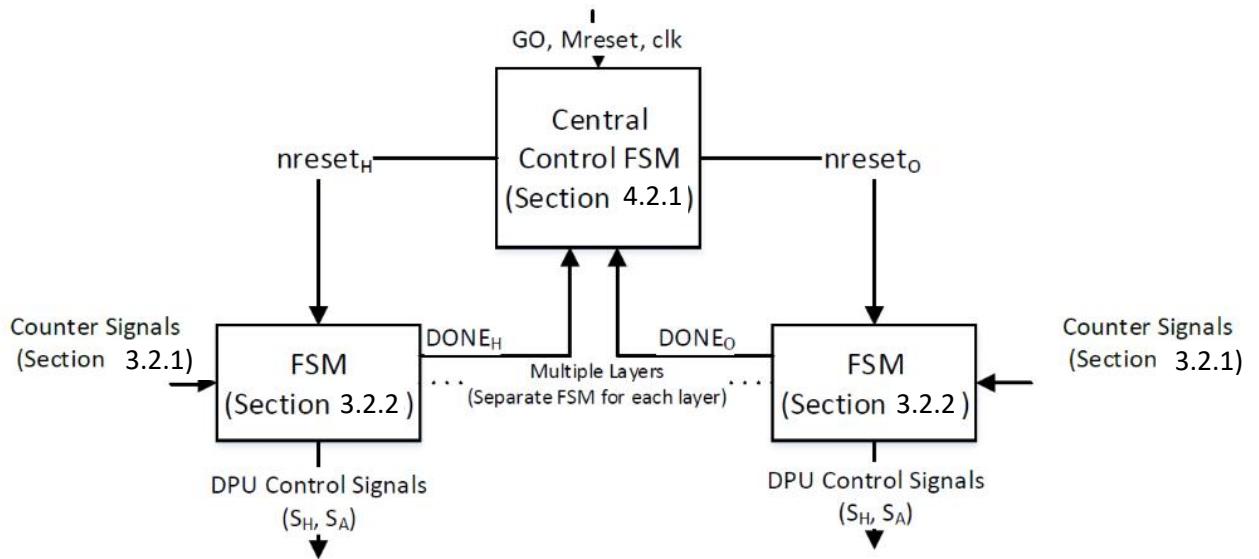

| 4.3  | Control Path for Vector Processor. . . . .                                                                                                                                                                                                                                                                                                                                                     | 78 |

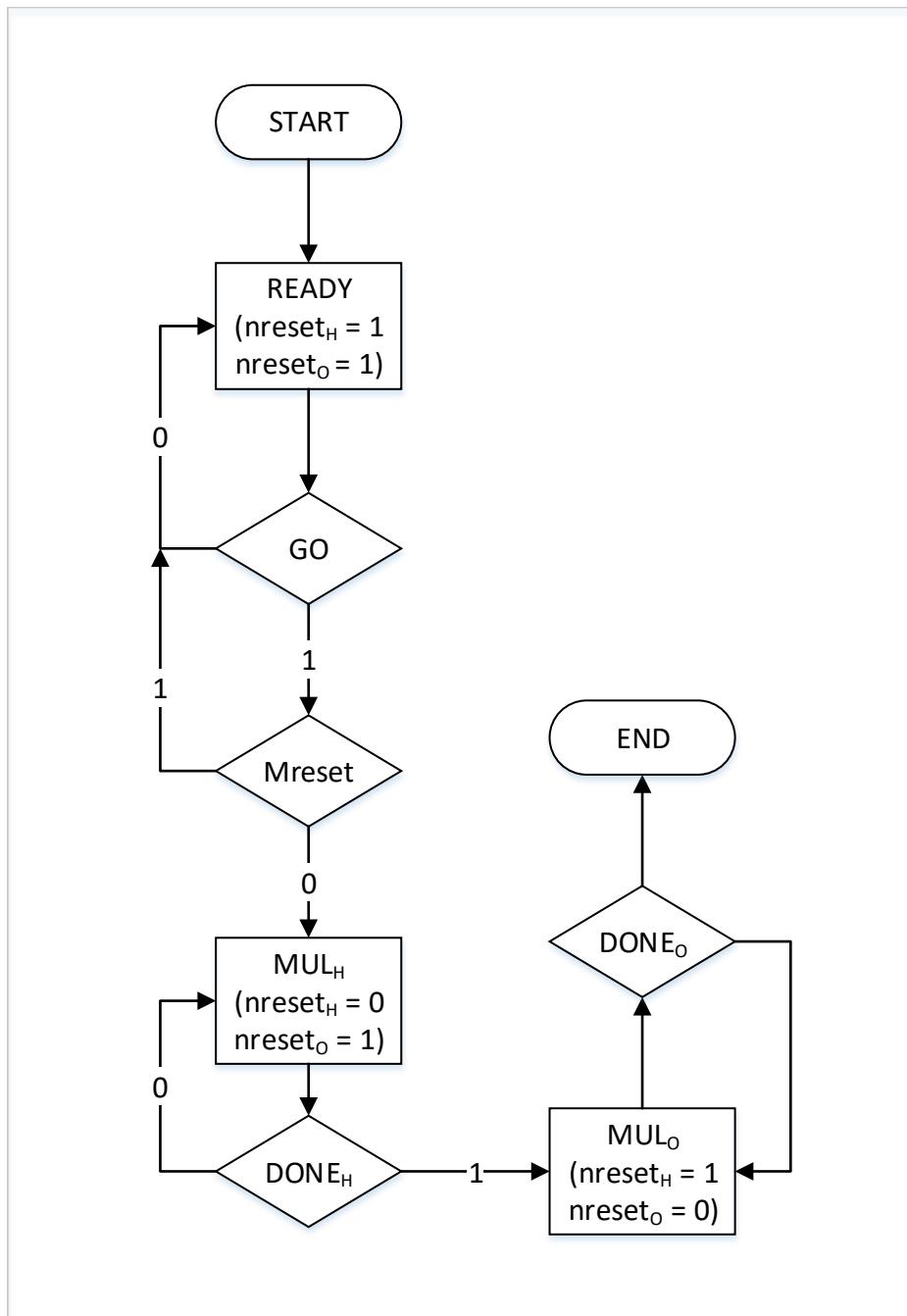

| 4.4  | Flow chart for the central control FSM . . . . .                                                                                                                                                                                                                                                                                                                                               | 79 |

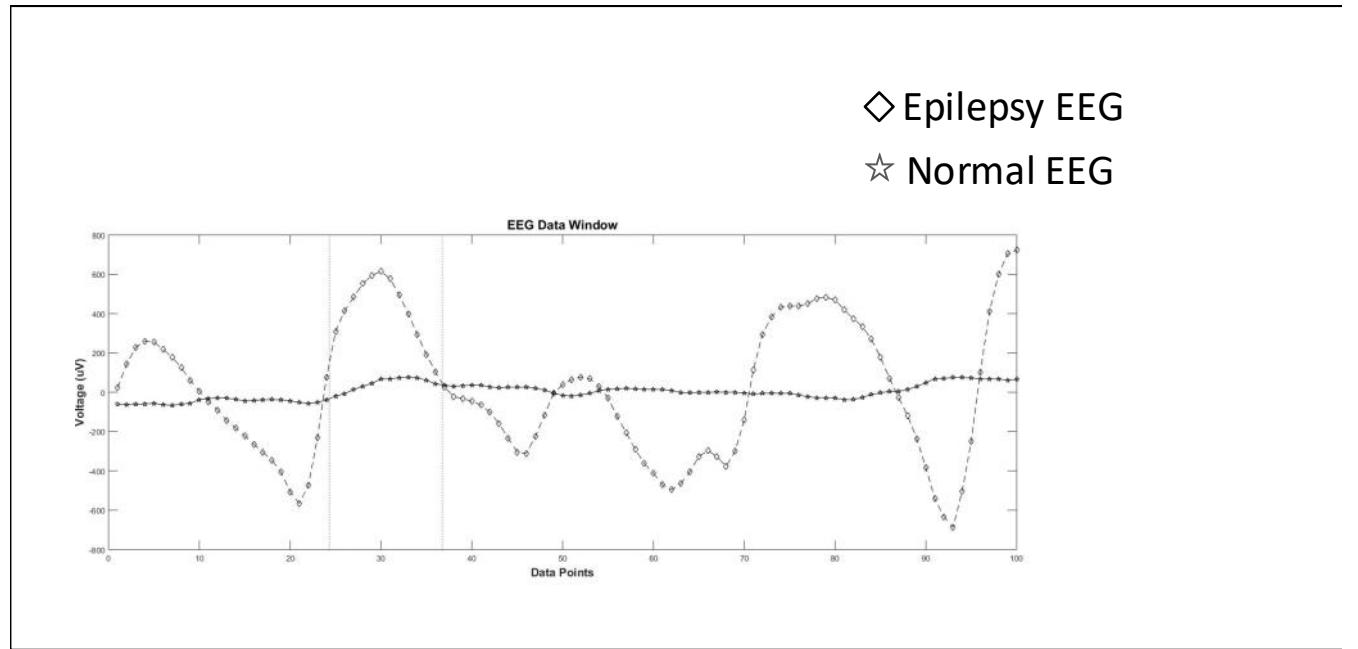

| 4.5  | EEG data window . . . . .                                                                                                                                                                                                                                                                                                                                                                      | 80 |

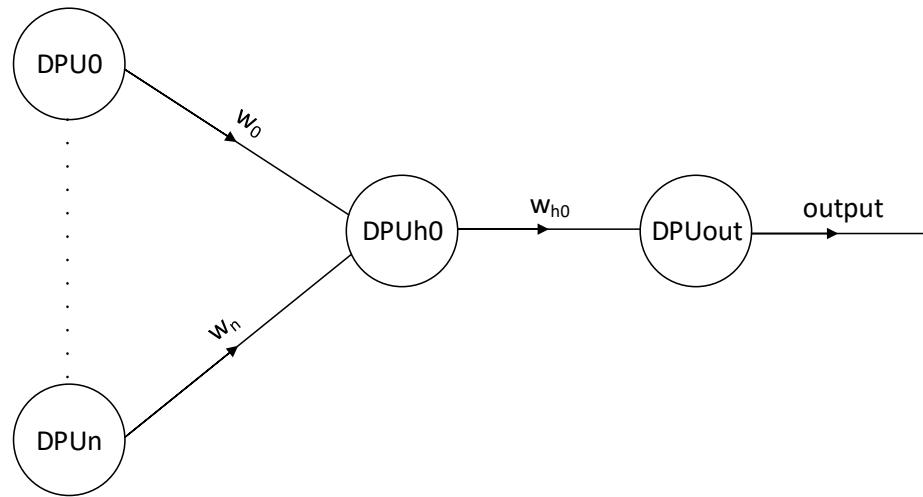

| 4.6  | Simple Neural Network Testing (e.g. n-1-1) . . . . .                                                                                                                                                                                                                                                                                                                                           | 81 |

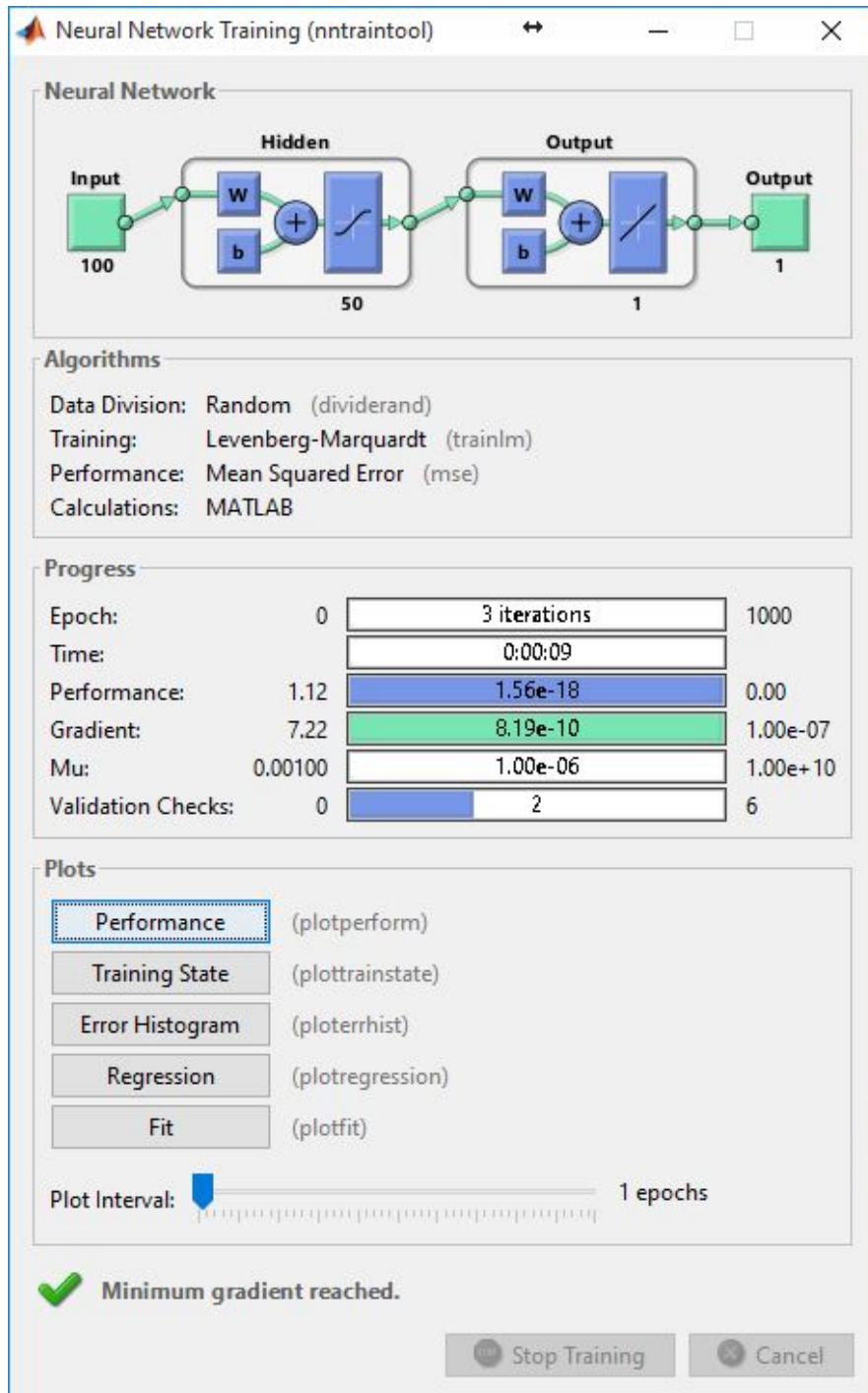

| 4.7  | The training of the neural network provided in MATLAB . . . . .                                                                                                                                                                                                                                                                                                                                | 82 |

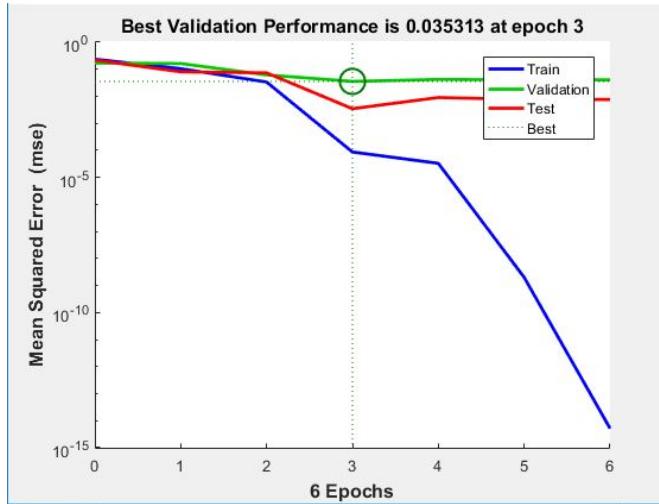

| 4.8  | (a) training process in MATLAB (Levenberg-Marquardt algorithm) . . . .                                                                                                                                                                                                                                                                                                                         | 84 |

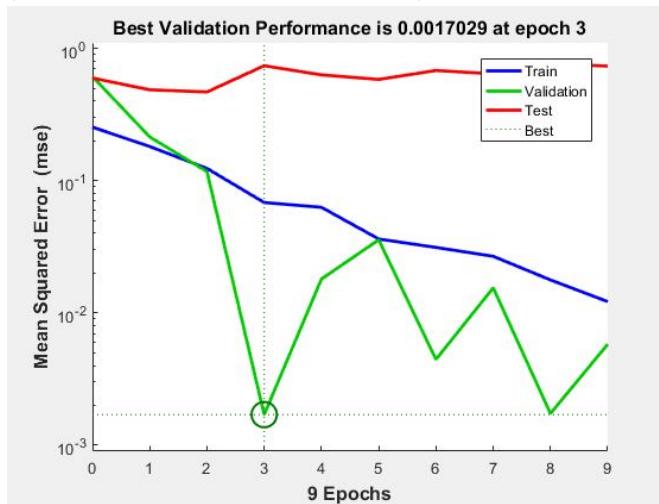

| 4.9  | (b) training process in MATLAB (BFGS Quasi-Newton algorithm) . . . .                                                                                                                                                                                                                                                                                                                           | 84 |

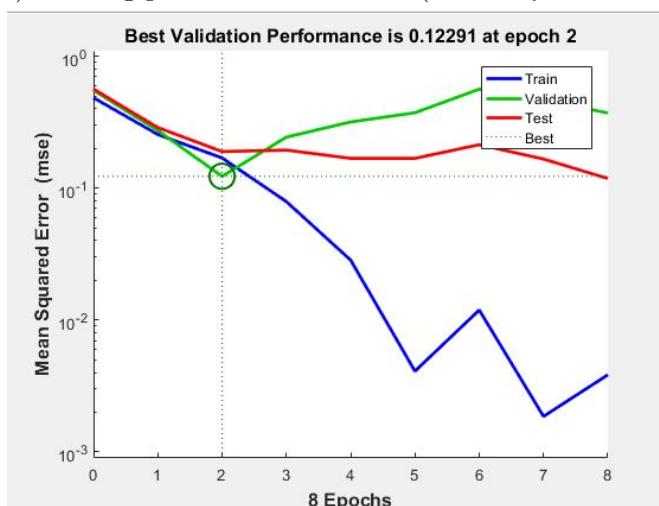

| 4.10 | (c) training process in MATLAB (Resilient Backpropagation algorithm) .                                                                                                                                                                                                                                                                                                                         | 84 |

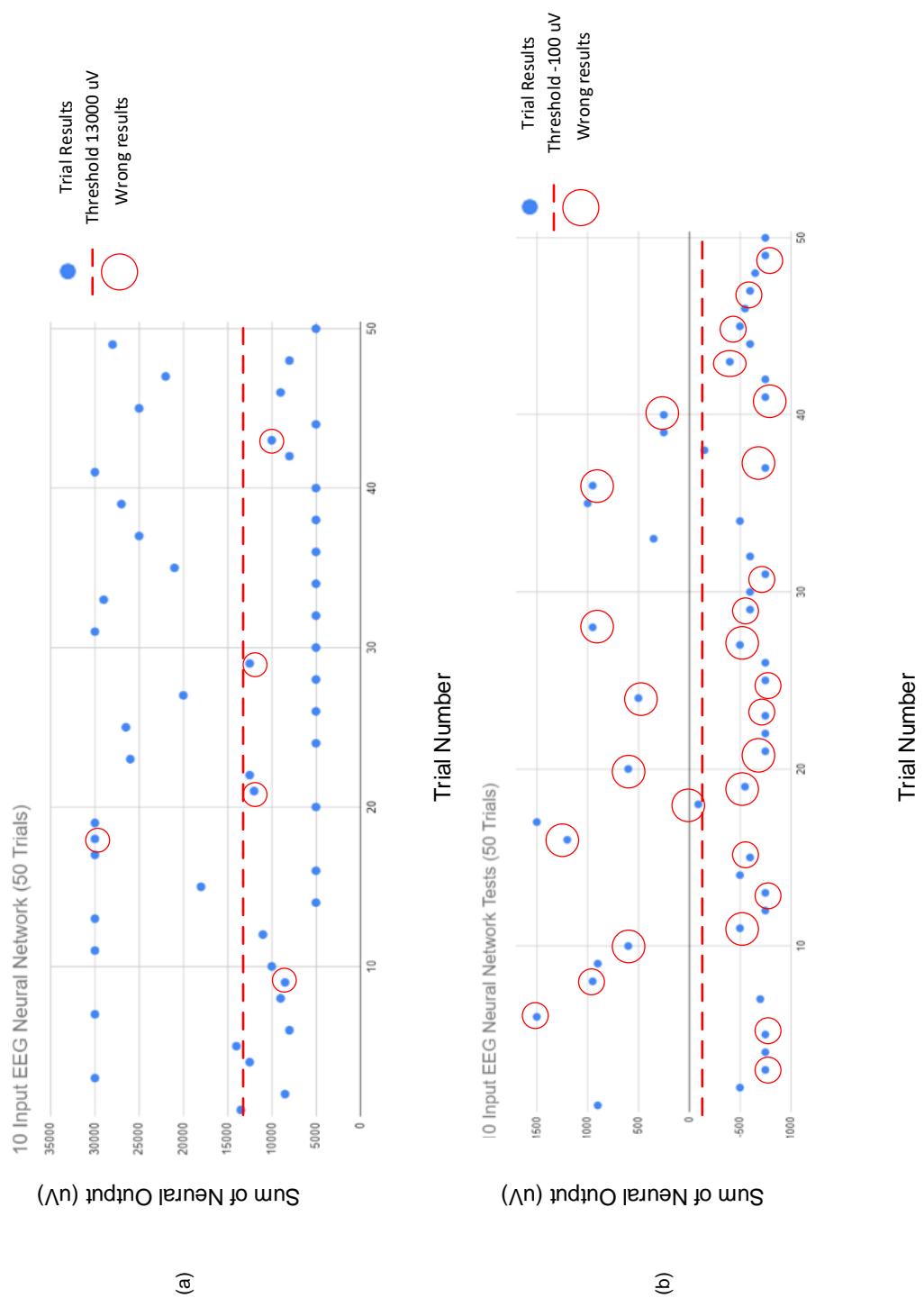

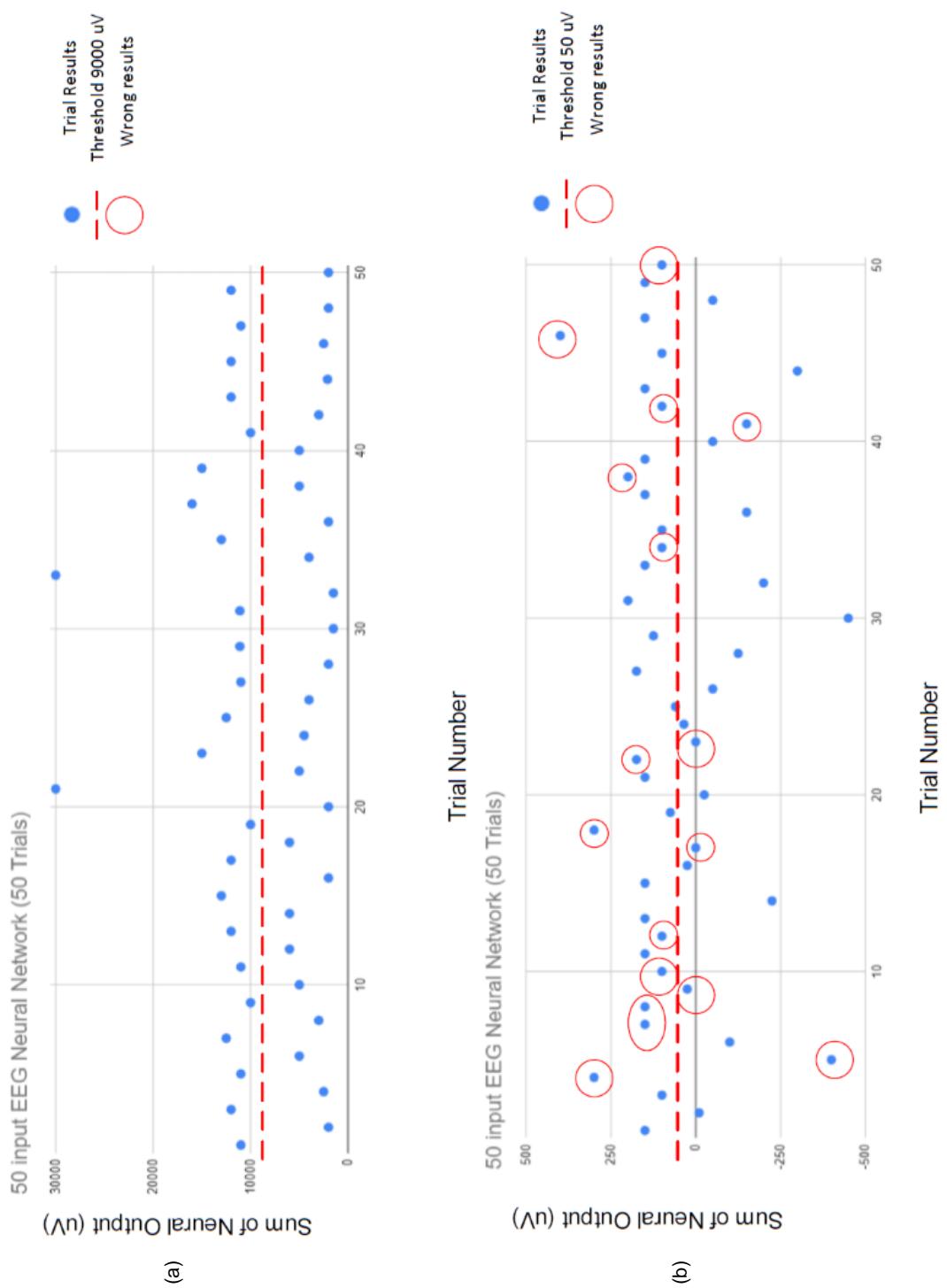

| 4.11 | 10 Input EEG Neural Network Test ((a) 12 bit representation, (b) 6 bit representation) . . . . .                                                                                                                                                                                                                                                                                               | 86 |

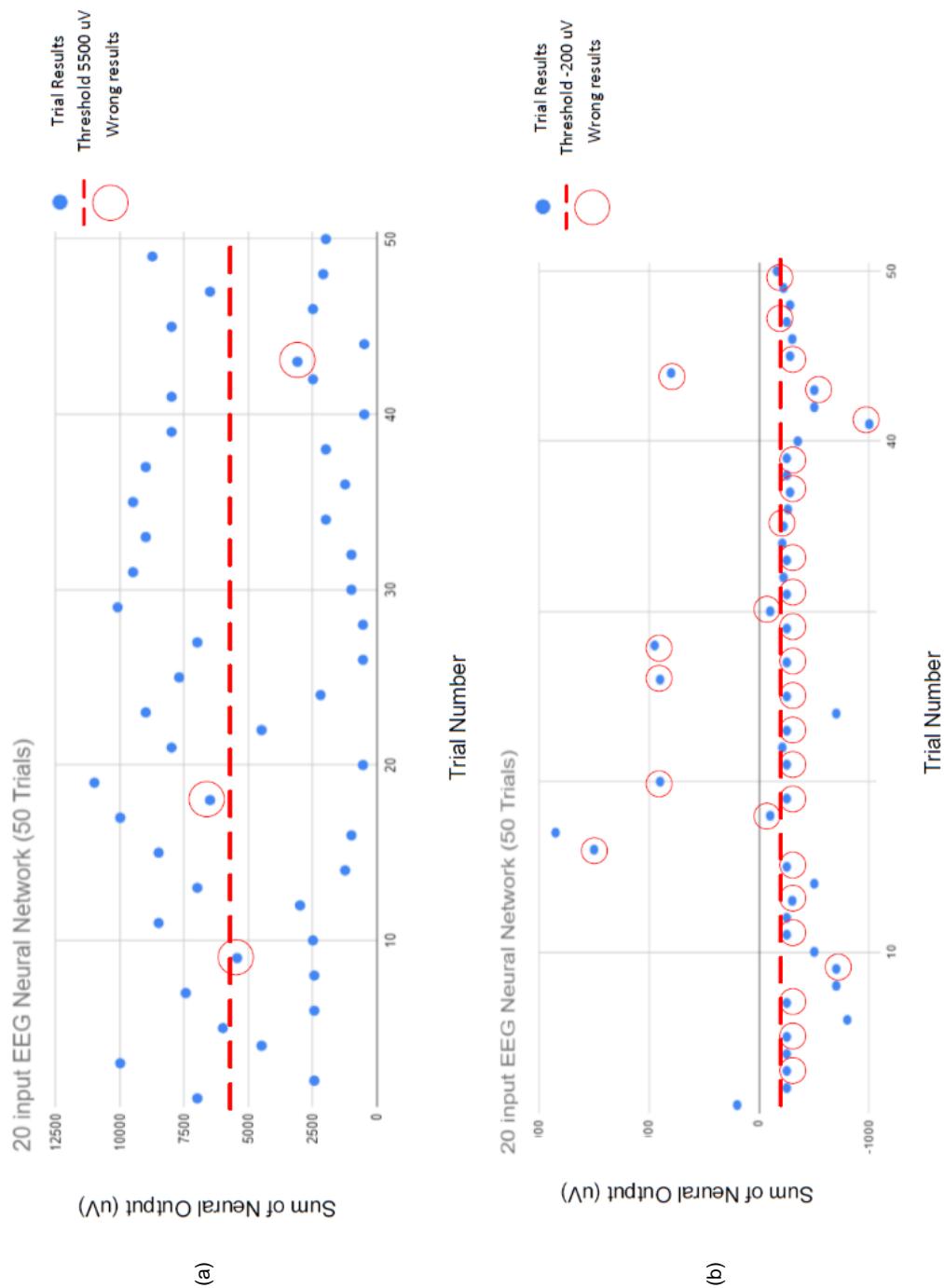

| 4.12 | 20 Input EEG Neural Network Test ((a) 12 bit representation, (b) 6 bit representation) . . . . .                                                                                                                                                                                                                                                                                               | 87 |

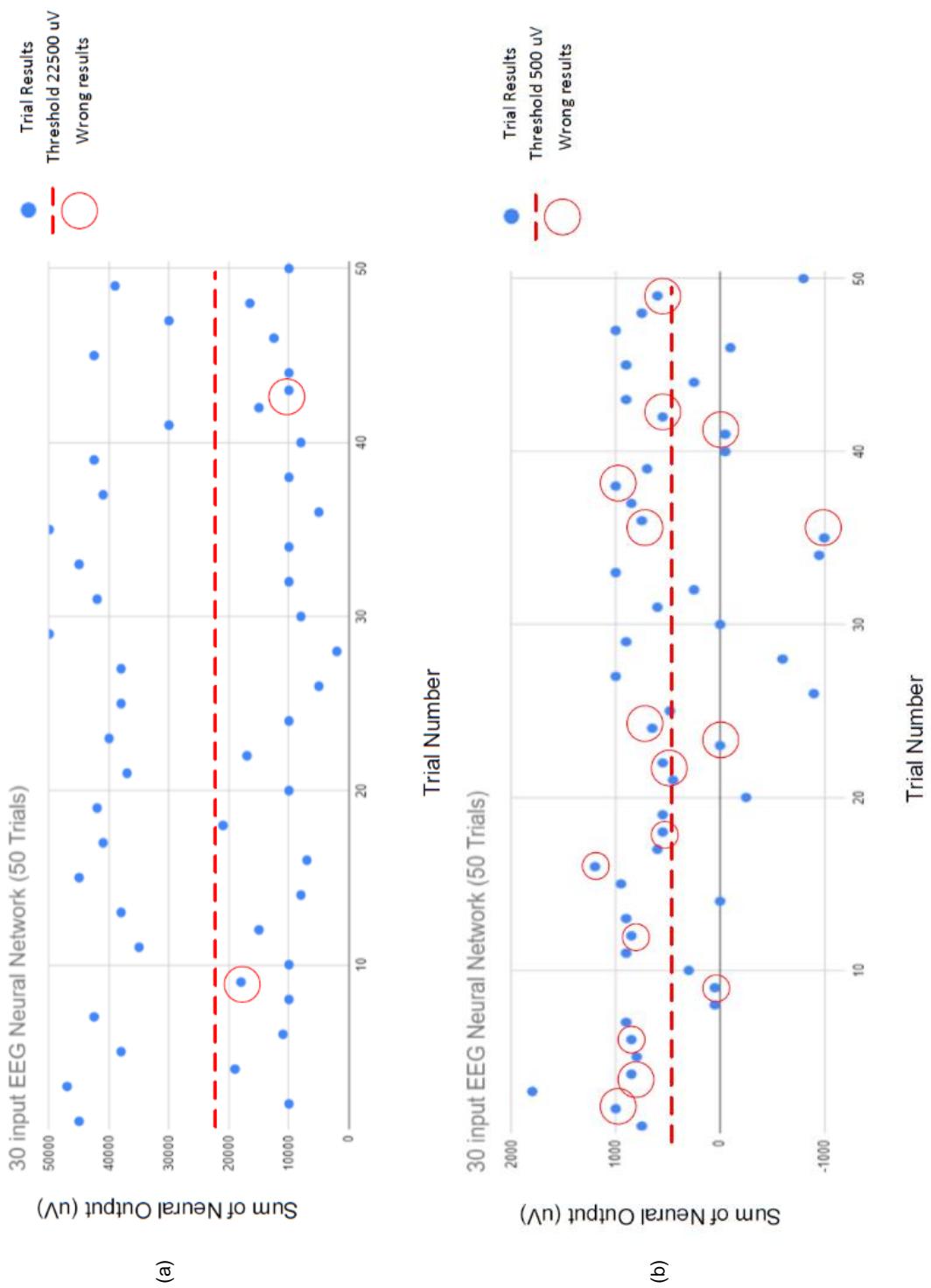

| 4.13 | 30 Input EEG Neural Network Test ((a) 12 bit representation, (b) 6 bit representation) . . . . .                                                                                                                                                                                                                                                                                               | 88 |

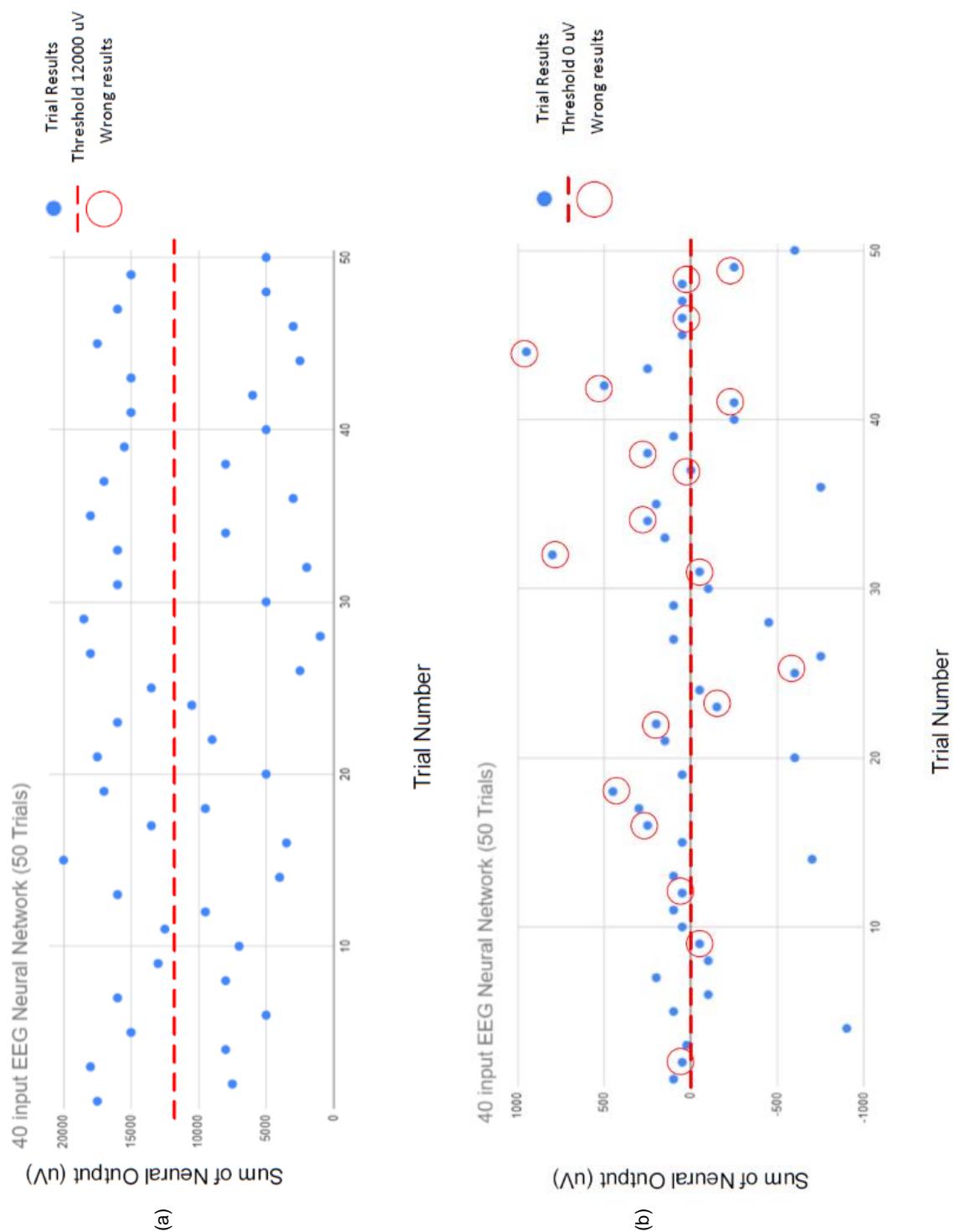

| 4.14 | 40 Input EEG Neural Network Test ((a) 12 bit representation, (b) 6 bit representation) . . . . .                                                                                                                                                                                                                                                                                               | 89 |

|                                                                                                       |     |

|-------------------------------------------------------------------------------------------------------|-----|

| 4.15 50 Input EEG Neural Network Test ((a) 12 bit representation, (b) 6 bit representation) . . . . . | 90  |

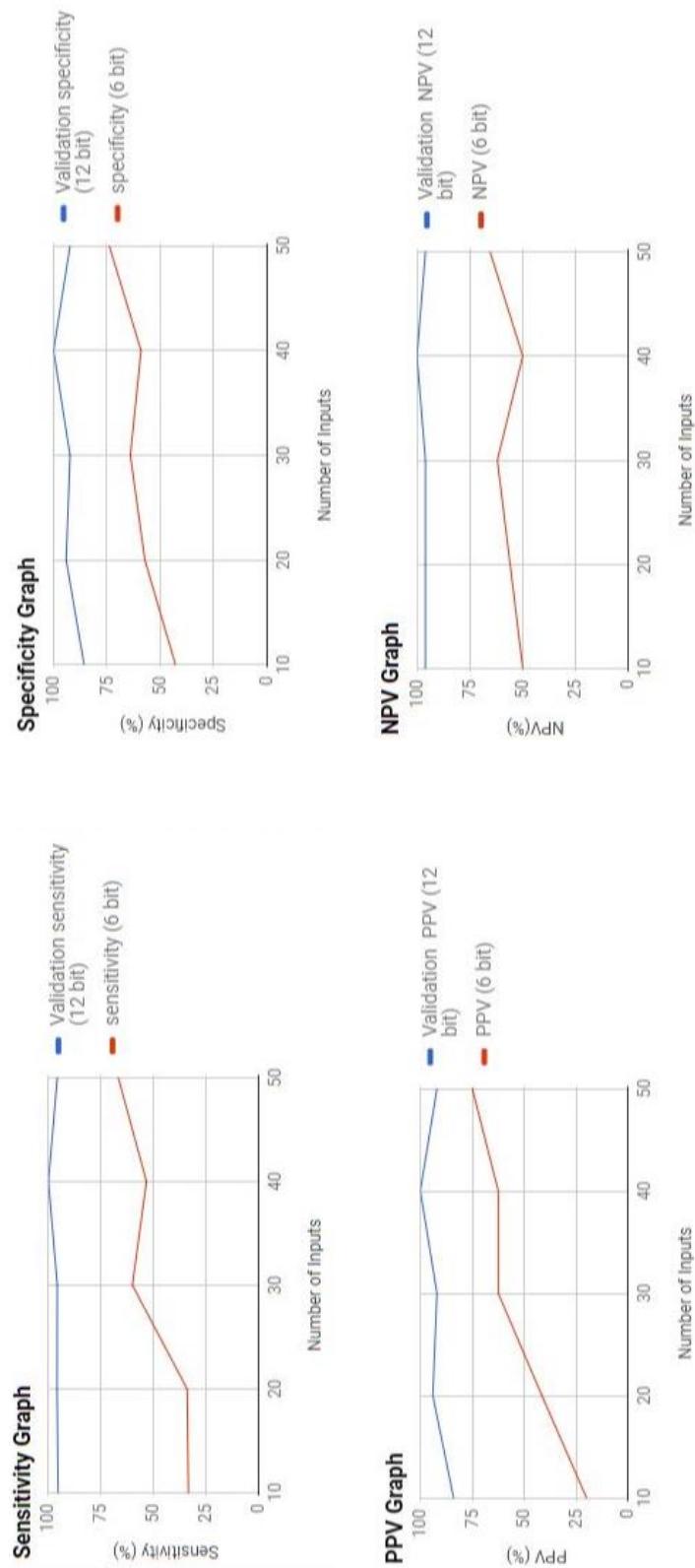

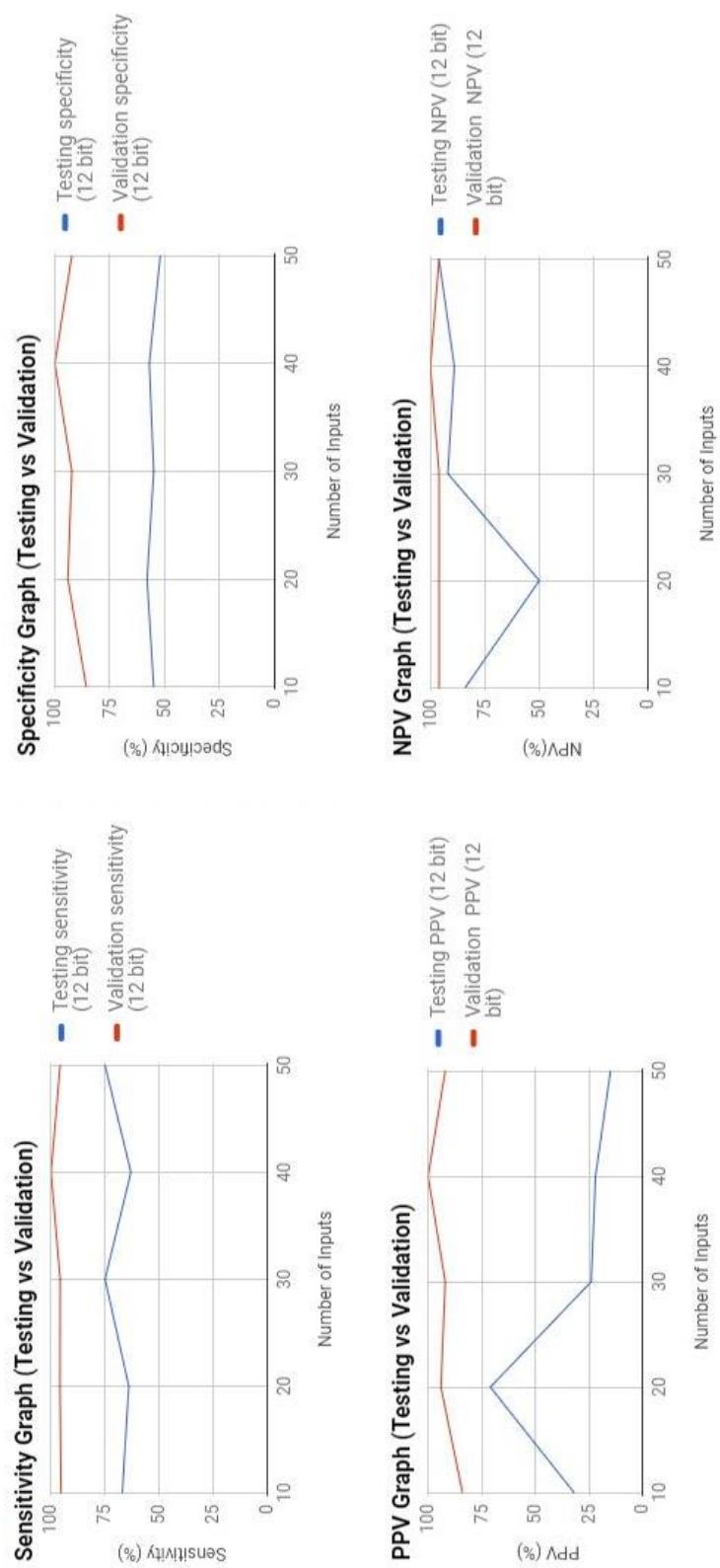

| 4.16 Various Evaluation Metrics . . . . .                                                             | 93  |

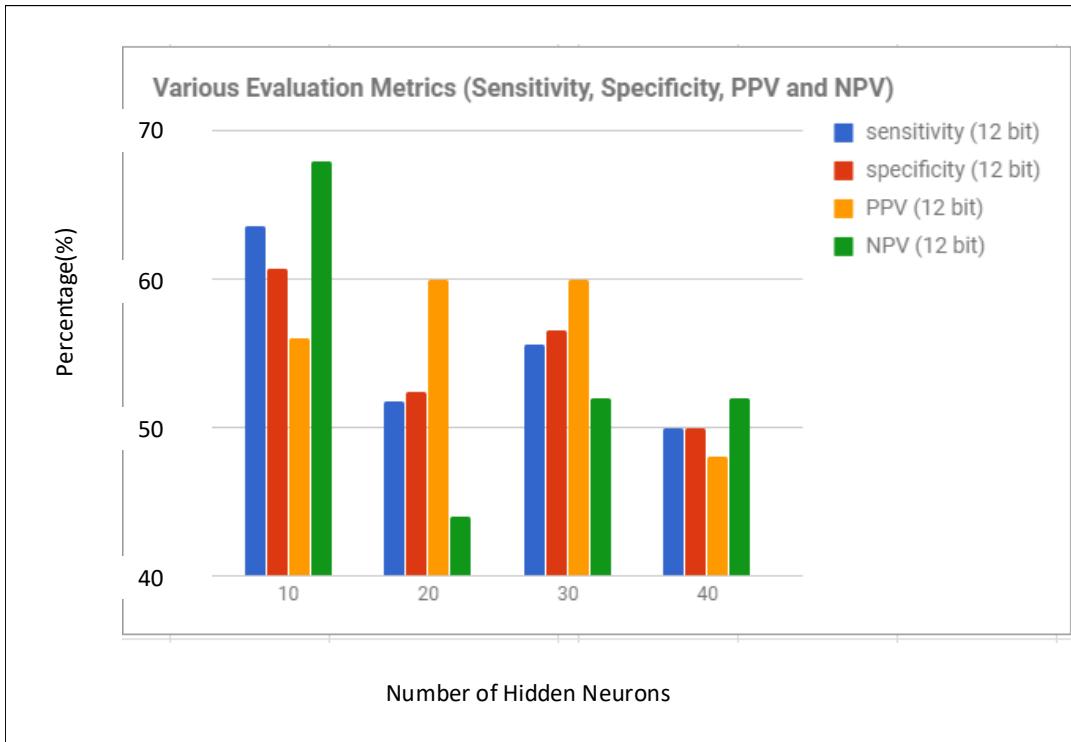

| 4.17 Various Evaluation Metrics . . . . .                                                             | 94  |

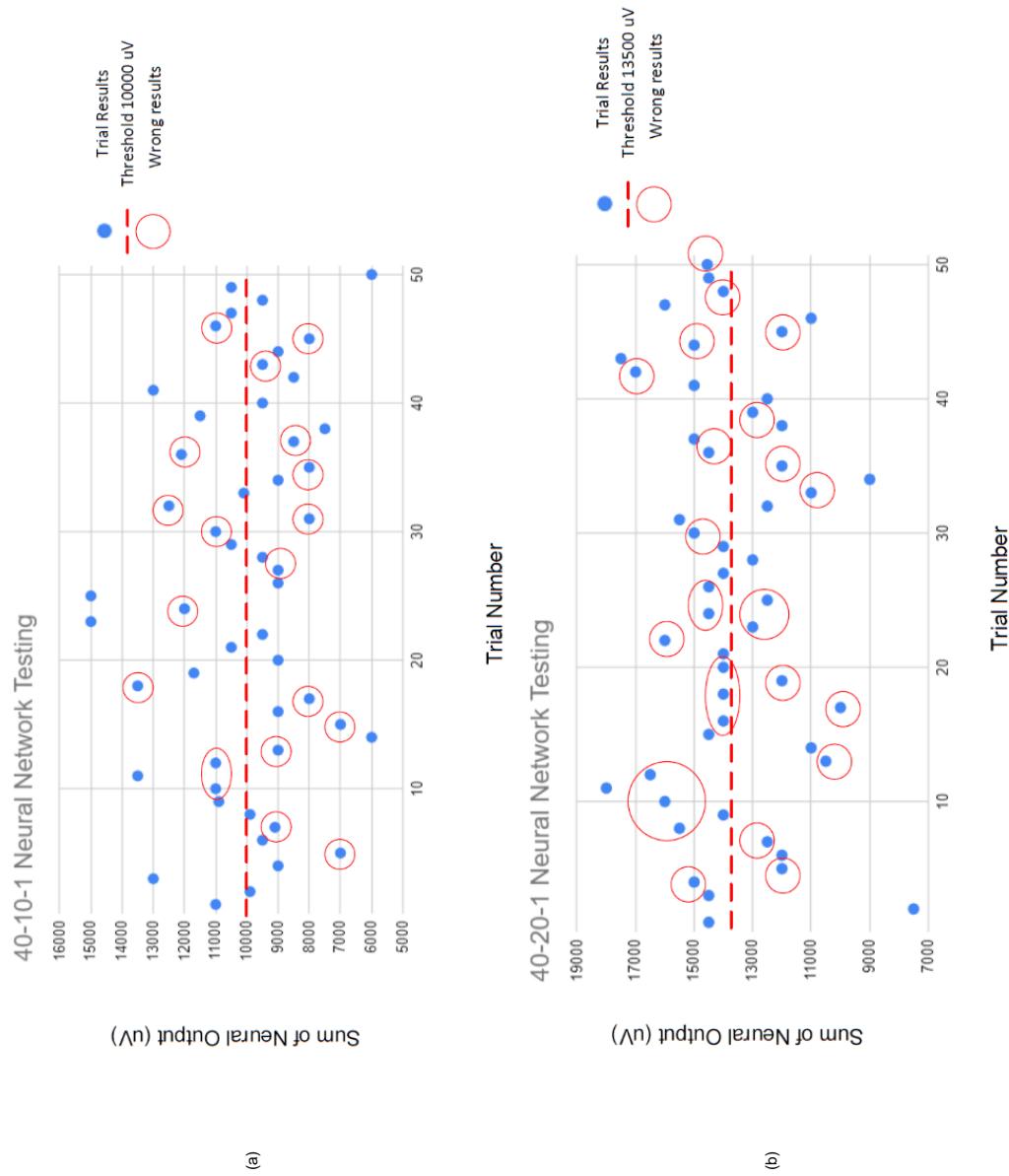

| 4.18 (a) 40-10-1 network configuration (b) 40-20-1 network configuration . . . . .                    | 95  |

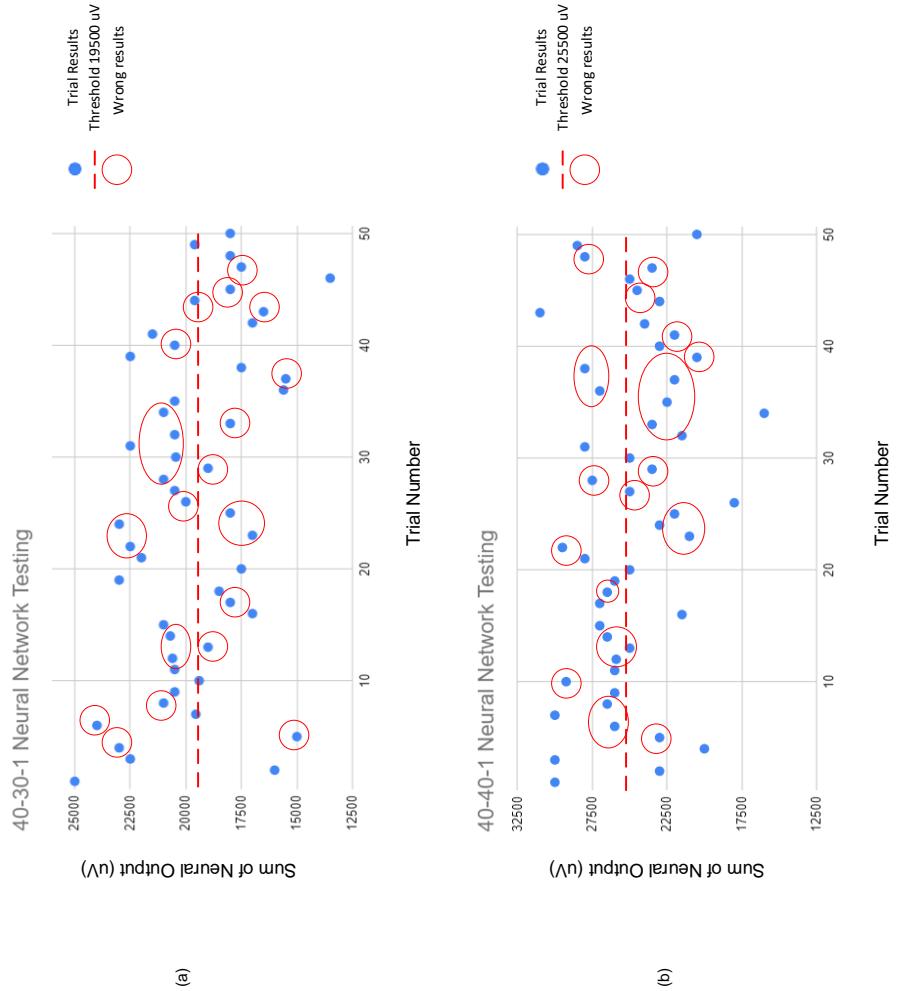

| 4.19 (a) 40-30-1 network configuration (b) 40-40-1 network configuration . . . . .                    | 96  |

| 4.20 Evaluation Metrics . . . . .                                                                     | 97  |

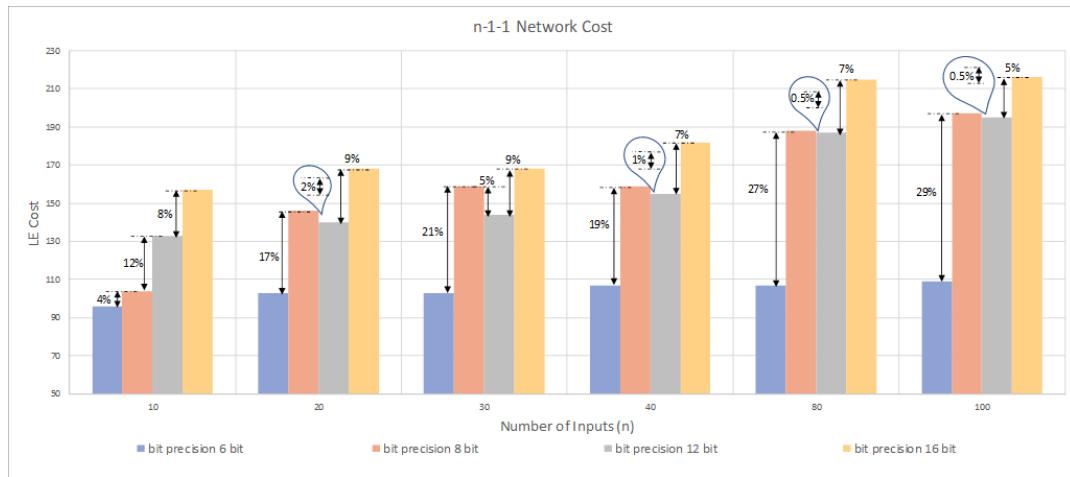

| 4.21 n-1-1 Network Cost Comparison . . . . .                                                          | 99  |

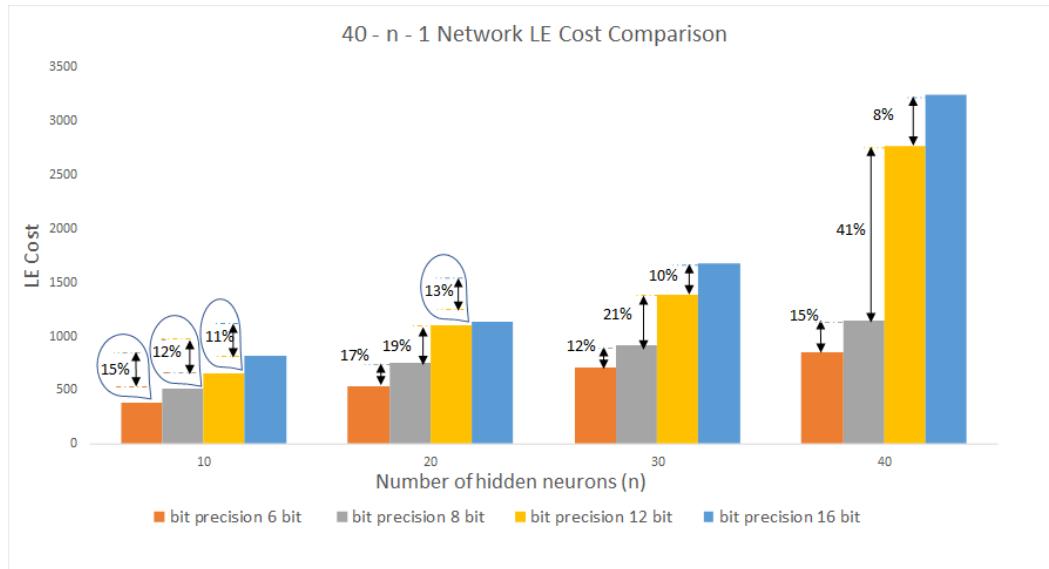

| 4.22 40-n-1 Network Cost Comparison . . . . .                                                         | 101 |

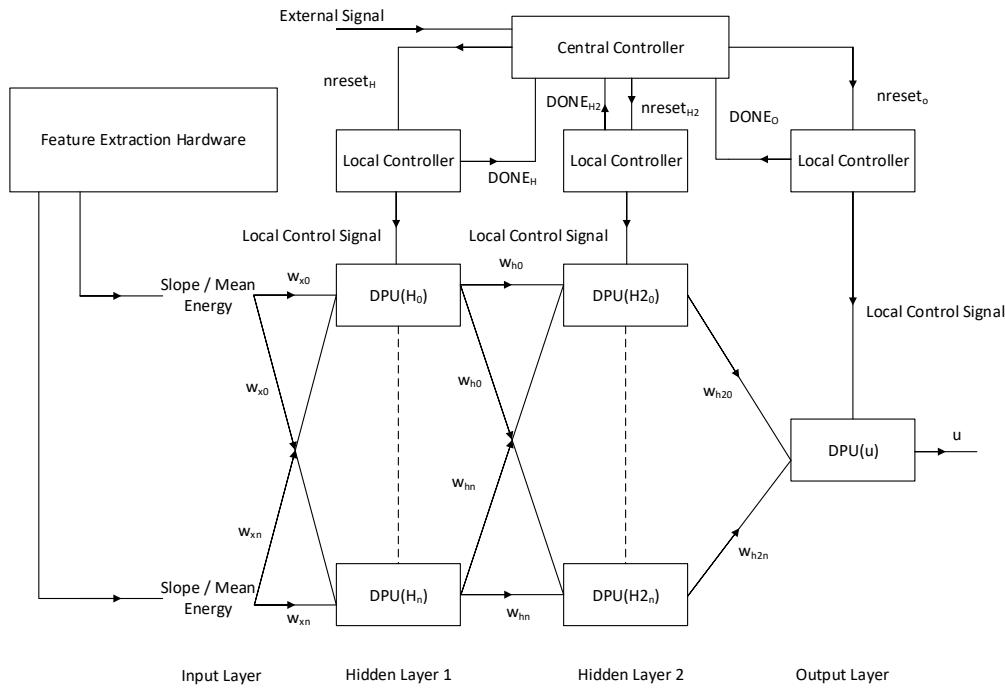

| 5.1 Proposed System Design . . . . .                                                                  | 104 |

| 5.2 Work Flow of Epilepsy Detection with Optimum Allocation . . . . .                                 | 105 |

| 5.3 Performance (MSE) of different ANN configuration . . . . .                                        | 107 |

| 5.4 Feature Extraction Hardware (Slope Feature) . . . . .                                             | 109 |

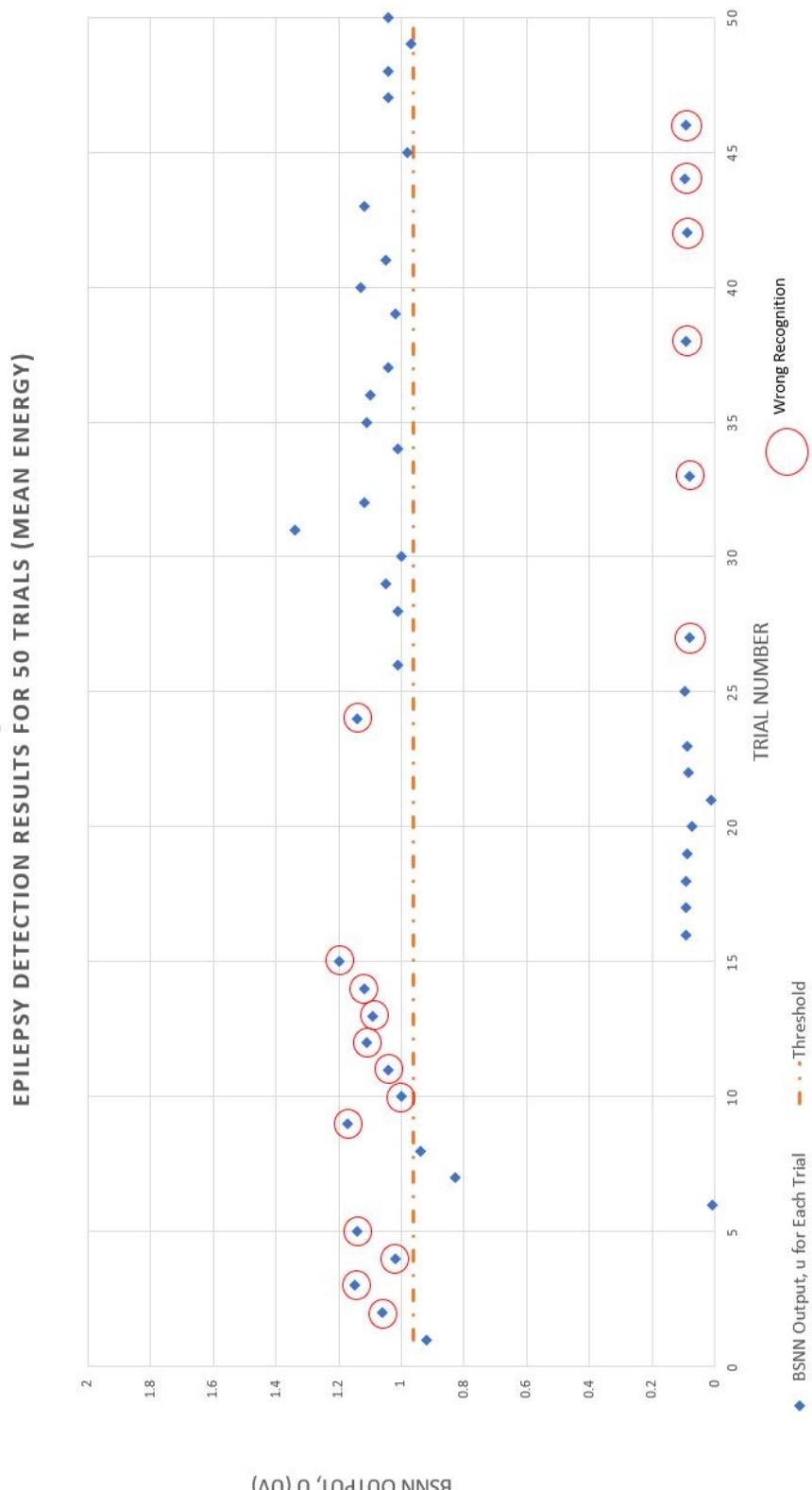

| 5.5 Mean Energy System Experiment Output . . . . .                                                    | 111 |

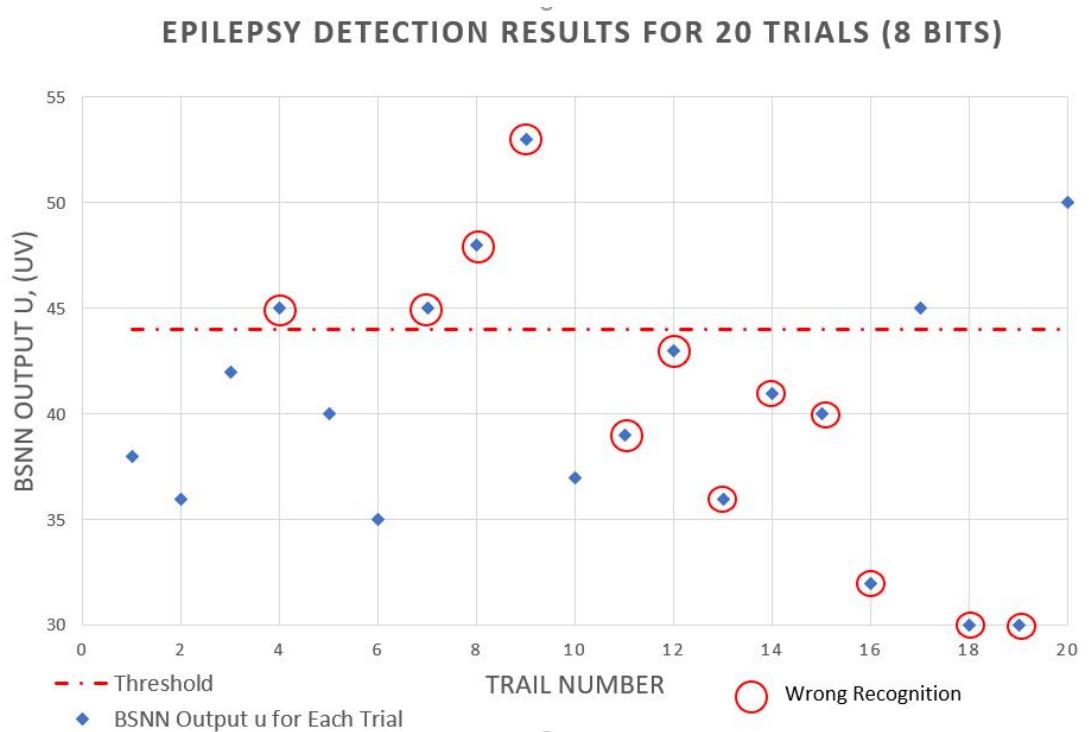

| 5.6 Output of Improved System Using 8 bit Architecture . . . . .                                      | 113 |

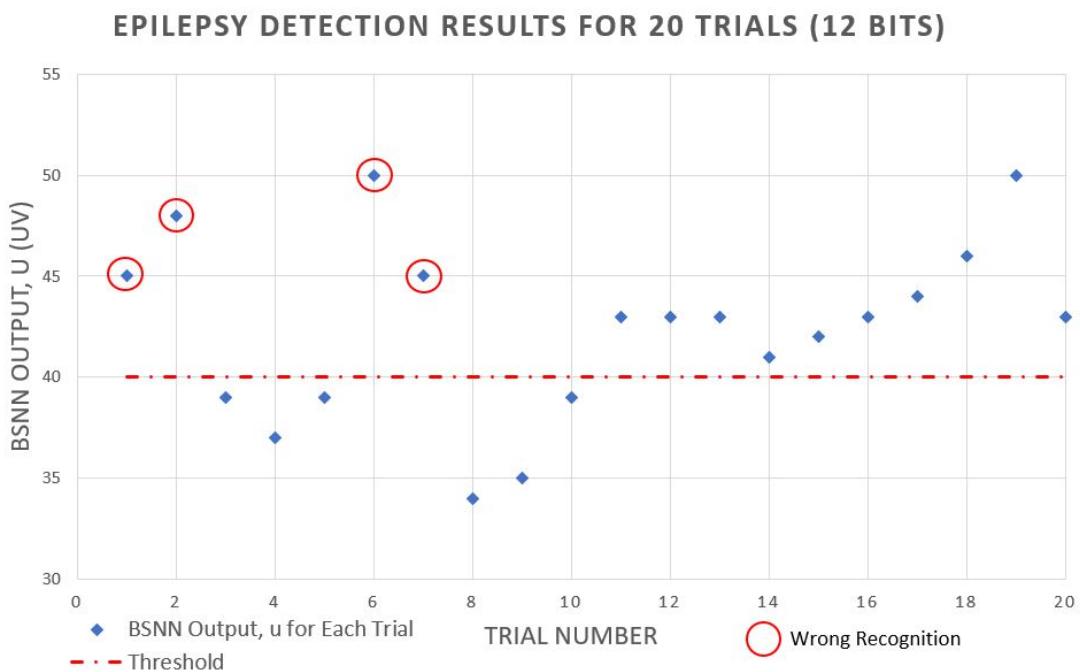

| 5.7 Output of Improved System Using 12 bit Architecture . . . . .                                     | 113 |

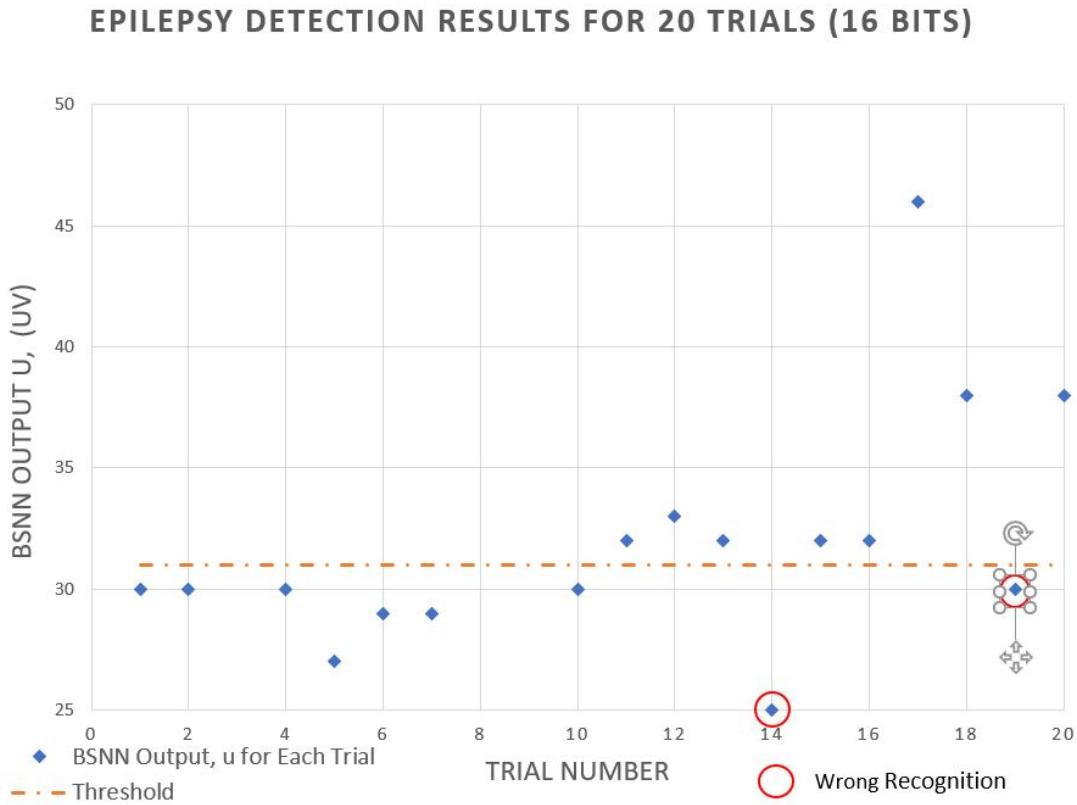

| 5.8 Output of Improved System Using 16 bit Architecture . . . . .                                     | 114 |

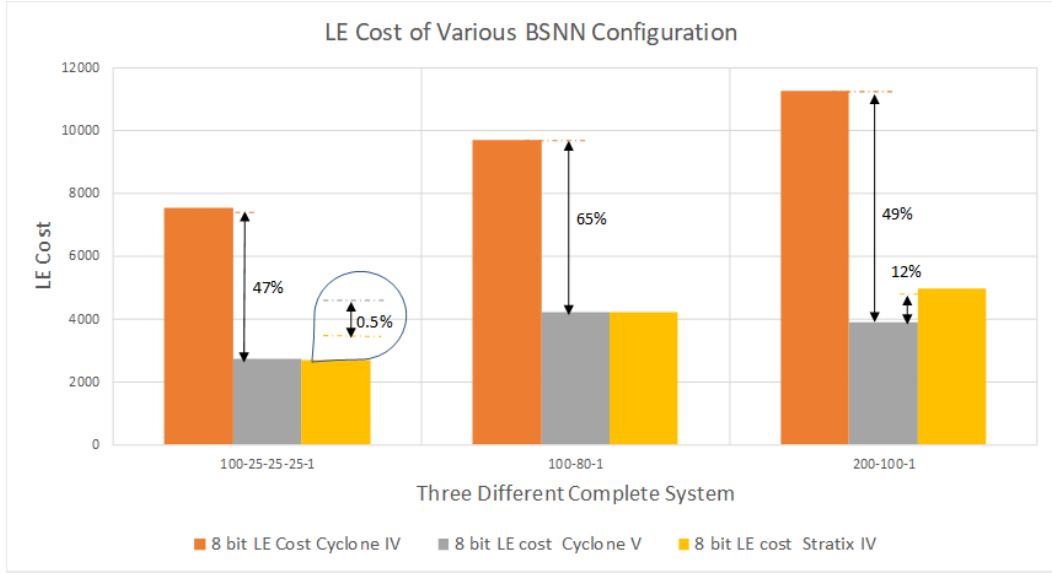

| 5.9 LE Cost of Three Different Systems Using 8 Bit Precision . . . . .                                | 116 |

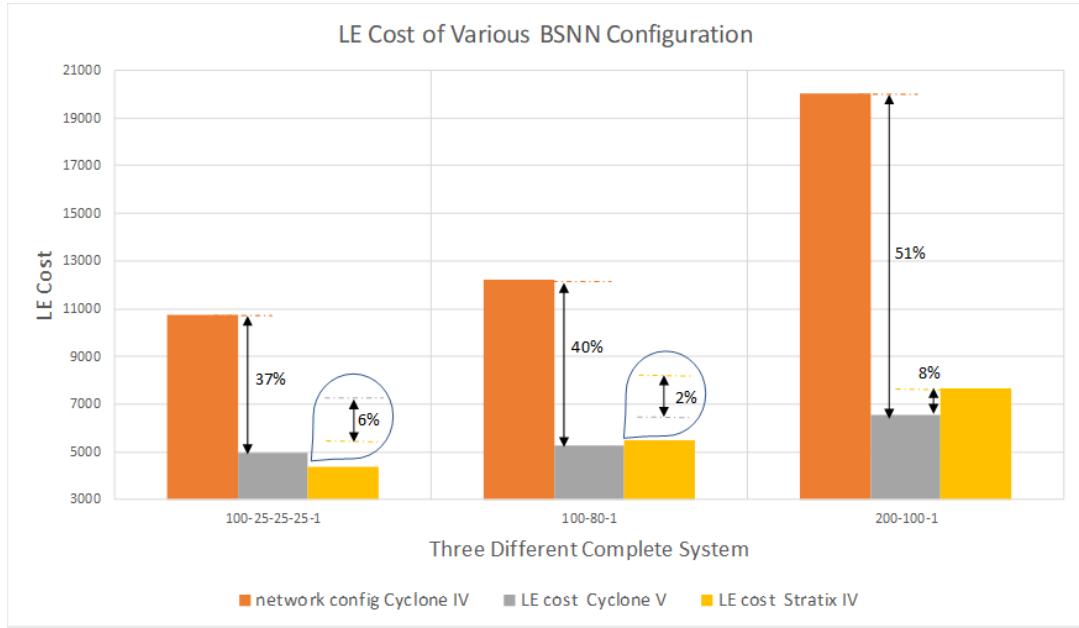

| 5.10 LE Cost of Three Different Systems Using 12 Bit Precision . . . . .                              | 116 |

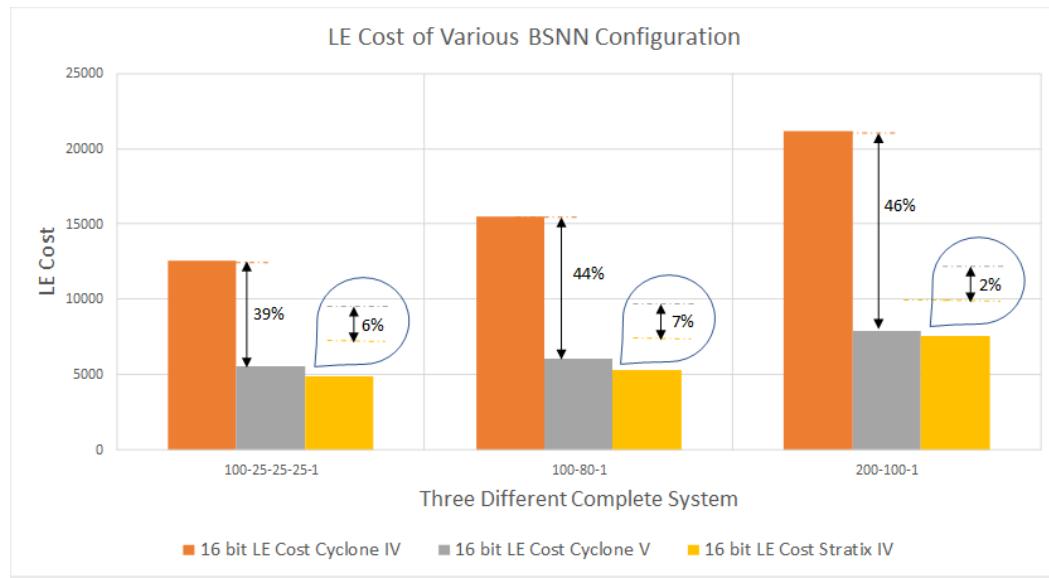

| 5.11 LE Cost of Three Different Systems Using 16 Bit Precision . . . . .                              | 117 |

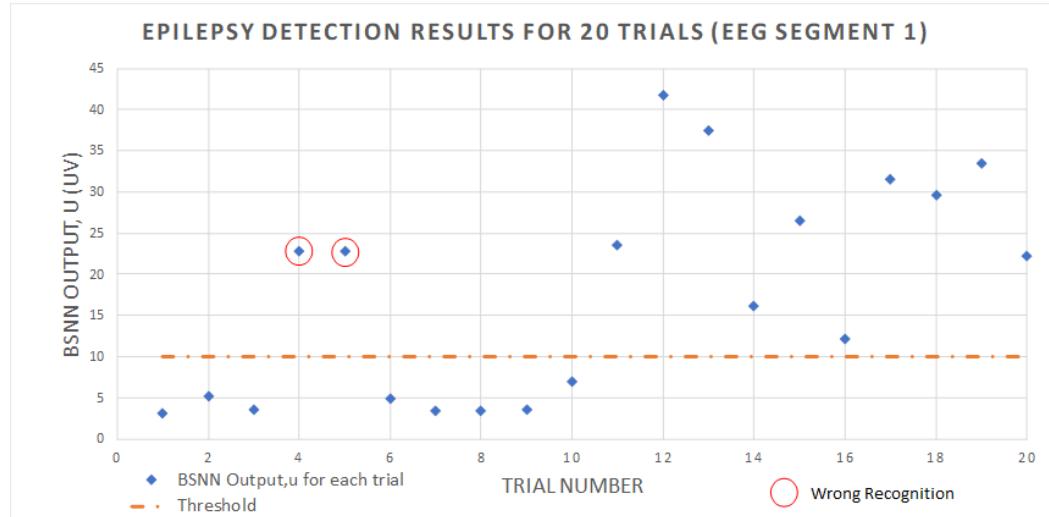

| 5.12 Segment 1 Output Using Slope Feature . . . . .                                                   | 117 |

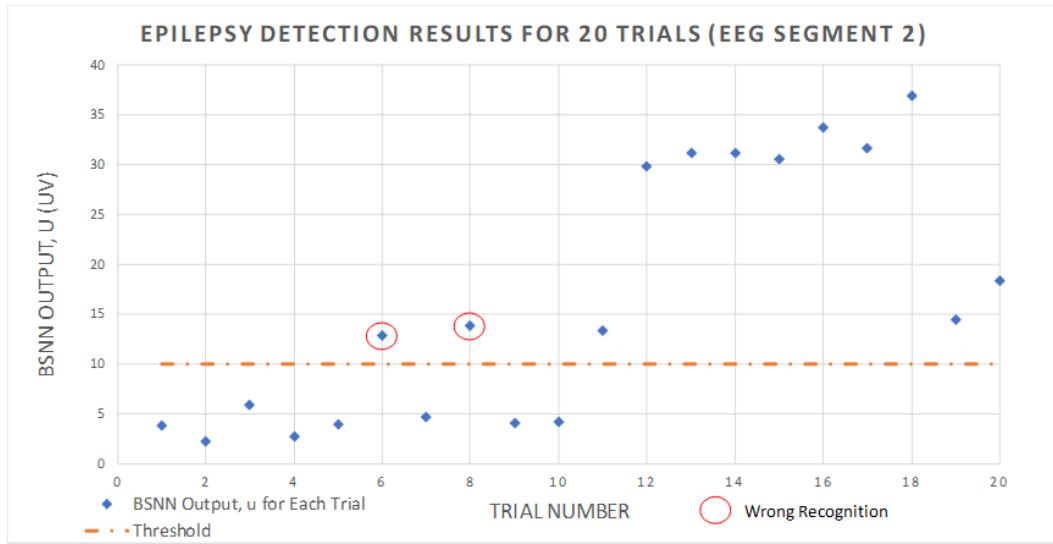

| 5.13 Segment 2 Output Using Slope Feature . . . . .                                                   | 118 |

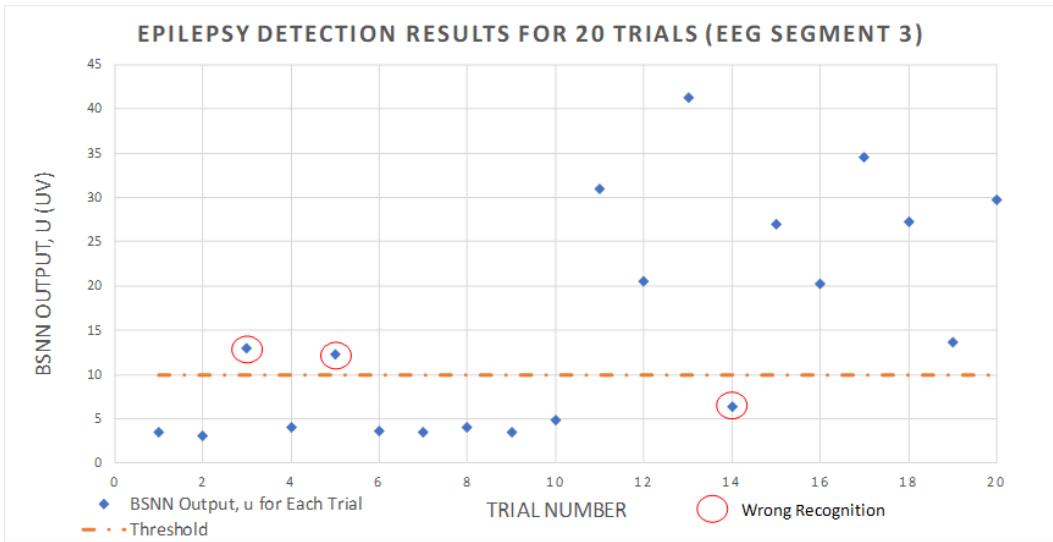

| 5.14 Segment 3 Output Using Slope Feature . . . . .                                                   | 118 |

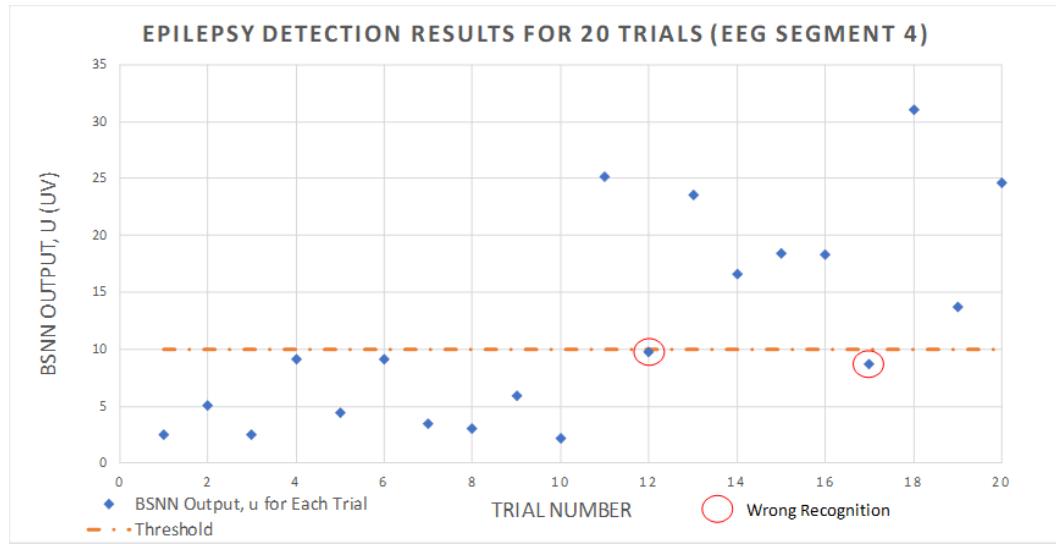

| 5.15 Segment 4 Output Using Slope Feature . . . . .                                                   | 119 |

# List of Tables

|     |                                                                                                                                                                             |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | EEG sample data related to thesis research using NB classifier [36] . . . . .                                                                                               | 12 |

| 2.2 | Table displaying a simple example of using NB classifier in the context of epilepsy detection . . . . .                                                                     | 12 |

| 2.3 | Advantages and Disadvantages of the reviewed EEG research technologies [124, 125] . . . . .                                                                                 | 47 |

| 2.4 | Advantages and Disadvantages of different conventional epilepsy detection classification methods . . . . .                                                                  | 47 |

| 2.5 | Advantages and Disadvantages of different bit-serial architecture ANN . .                                                                                                   | 48 |

| 2.6 | Advantages and Disadvantages of different type of processors . . . . .                                                                                                      | 48 |

| 2.7 | Advantages and Disadvantages of different bit-serial architecture ANN . .                                                                                                   | 49 |

| 3.1 | Table: Example of the bit-serial operation performed using the proposed DPU using 3 bit precision. ( $P = [PH + PL]$ , $w1 = 2$ , $x1 = 1$ , $w2 = 1$ , $x2 = 1$ ). . . . . | 57 |

| 3.2 | Logic elements needed for DPU tested with three different FPGA technologies . . . . .                                                                                       | 67 |

| 3.3 | Logic elements needed for FSM tested with three different FPGA technologies . . . . .                                                                                       | 68 |

| 3.4 | Logic elements needed for a single neuron tested with three different FPGA technologies . . . . .                                                                           | 68 |

| 3.5 | Cost comparison between three different processors. . . . .                                                                                                                 | 72 |

| 4.1 | Correct Recognition of different inputs for Bit-Serial Vector Processor Using Mean (n-1-1 network, 12 bit precision)) . . . . .                                             | 85 |

| 4.2 | Correct Recognition of different inputs for Bit-Serial Vector Processor Using Median (n-1-1 network, 12 bit precision) . . . . .                                            | 85 |

| 4.3 | Correct Recognition of different inputs for Bit-Serial Vector Processor Using Mean(n-1-1 network, 6 bit precision) . . . . .                                                | 85 |

| 4.4 | Correct Recognition of different inputs for Bit-Serial Vector Processor Using Median(n-1-1 network, 6 bit precision) . . . . .                                              | 85 |

| 4.5 | Evaluation of different number input for single neuron design with 12 bit architecture . . . . .                                                                            | 92 |

| 4.6 | Evaluation of different number input for single neuron design with 6 bit architecture . . . . .                                                                             | 92 |

| 4.7 | Correct Recognition of different inputs for Bit-Serial Vector Processor Using Mean(40-n-1 network, 12 bit precision) . . . . .                                              | 92 |

| 4.8 | Evaluation of different number of hidden neuron network design (40 inputs, 12 bit precision) . . . . .                                                                      | 96 |

|      |                                                                                                                                                                                                              |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.9  | Logic elements needed for a single neuron with different number of inputs<br>(6 bit precision) . . . . .                                                                                                     | 98  |

| 4.10 | Logic elements needed for a single neuron with different number of inputs<br>(8 bit precision) . . . . .                                                                                                     | 98  |

| 4.11 | Logic elements needed for a single neuron with different number of inputs<br>(12 bit precision) . . . . .                                                                                                    | 99  |

| 4.12 | Logic elements needed for a single neuron with different number of inputs<br>(16 bit precision) . . . . .                                                                                                    | 99  |

| 4.13 | Logic elements needed for a 40-10-1 network with different bit architecture                                                                                                                                  | 100 |

| 4.14 | Logic elements needed for a 40-20-1 network with different bit architecture                                                                                                                                  | 100 |

| 4.15 | Logic elements needed for a 40-30-1 network with different bit architecture                                                                                                                                  | 100 |

| 4.16 | Logic elements needed for a 40-40-1 network with different bit architecture                                                                                                                                  | 100 |

| 5.1  | Sample Number Determined using OAT for Each Segment . . . . .                                                                                                                                                | 105 |

| 5.2  | Correct Recognition of different hardware ANN configuration . . . . .                                                                                                                                        | 107 |

| 5.3  | Correct Recognition of different hardware ANN configuration using EEG<br>waveform slope . . . . .                                                                                                            | 109 |

| 5.4  | Statistic for Network Configuration Evaluation (Against Training Data) .                                                                                                                                     | 110 |

| 5.5  | Statistic for Network Configuration Evaluation (Against Additional Data)                                                                                                                                     | 110 |

| 5.6  | Network Configuration with a different number of inputs . . . . .                                                                                                                                            | 112 |

| 5.7  | Improved system statistics using 100-40-40-1 network configuration . . .                                                                                                                                     | 114 |

| 5.8  | Hardware Cost (LE) Implemented on Cyclone IV FPGA . . . . .                                                                                                                                                  | 115 |

| 5.9  | Hardware Cost Implemented on Cyclone V FPGA . . . . .                                                                                                                                                        | 115 |

| 5.10 | Hardware Cost Implemented on Stratix IV FPGA . . . . .                                                                                                                                                       | 115 |

| 5.11 | Results Obtained when tested with different EEG Segments . . . . .                                                                                                                                           | 117 |

| 5.12 | Results Obtained when tested with different Classifiers (S = Slope Fea-<br>ture, E = Mean Energy Feature) . . . . .                                                                                          | 119 |

| 5.13 | Results Obtained when tested with different Hardware Classifiers (S =<br>Slope Feature, E = Mean Energy Feature , Cost = in terms of total<br>hardware resources provided by the development chip) . . . . . | 119 |

| 5.14 | Comparison between three different proposed systems . . . . .                                                                                                                                                | 120 |

# Abbreviations and Parameters

|               |                                                          |

|---------------|----------------------------------------------------------|

| $a$           | amplitude values of EEG signal spikes                    |

| <i>ADL</i>    | Activities of Daily Living                               |

| <i>AED</i>    | Anti-Epileptic Drugs                                     |

| <i>ANN</i>    | Artificial Neural Network                                |

| <i>ANFIS</i>  | Adaptive neuro fuzzy inference system                    |

| <i>ATPG</i>   | Automatic Test Pattern Generation                        |

| <i>ApEn</i>   | approximate entropy                                      |

| <i>AR</i>     | Autoregressive                                           |

| <i>ASP</i>    | Advanced Sensor Processor                                |

| <i>ASIC</i>   | Application Specific Integrated Circuit                  |

| <i>ASLAN</i>  | Automatic methodology for Sequential Logic ApproximatioN |

| <i>AURA</i>   | Advanced Uncertain Reasoning Architecture                |

| $b_k$         | bias value                                               |

| <i>BBNN</i>   | Block-based Neural Network                               |

| <i>BFGS</i>   | BroydenFletcherGoldfarbShanno algorithm                  |

| <i>BIC</i>    | Bayesian Information Criterion                           |

| <i>BMBI</i>   | Brain Machine Brain Interface                            |

| <i>BPN</i>    | Back Propagation Network                                 |

| <i>BSNN</i>   | Bit Serial Neural Network                                |

| $c_i$         | centre of the $i$ -th basis function                     |

| $c_j$         | real number for respective hidden node                   |

| <i>CBV</i>    | Compact Bit Vector                                       |

| <i>CA</i>     | Cellular Automata                                        |

| <i>CMAC</i>   | Cerebellar model articulation controller                 |

| $C - RBM$     | Convolutional Restricted Boltzmann Machine               |

| <i>CDNN</i>   | Convolutional Deep Neural Network                        |

| <i>CETs</i>   | Candidate for epileptiform transients                    |

| <i>CGB</i>    | Conjugate Gradient with Powell/Beale Restarts            |

| <i>CMM</i>    | Core Correlation Matrix Memory                           |

| <i>CNN</i>    | Convolutional Neural Network                             |

| <i>CPLD</i>   | Complex Programmable Logic Device                        |

| <i>CORDIC</i> | COordinate Rotation DIgital Computer                     |

---

|                   |                                                                             |

|-------------------|-----------------------------------------------------------------------------|

| <i>CV</i>         | cross validation                                                            |

| <i>CWT</i>        | Continuous Wavelet Transform                                                |

| <i>DaDN</i>       | DaDianNao                                                                   |

| <i>DMA</i>        | Direct Memory Access                                                        |

| <i>DNN</i>        | Deep Neural Network                                                         |

| <i>DPU</i>        | Data Processing Unit                                                        |

| <i>DWT</i>        | Discrete Wavelet Transform                                                  |

| <i>DSP</i>        | Digital Signal Processor                                                    |

| <i>DTC</i>        | Decision Tree Classifier                                                    |

| <i>d</i>          | error margin for desired 99% confidence level                               |

| $d(x_j, x_k)$     | distance between point $x_j$ and $x_k$                                      |

| $E(v, h; \theta)$ | joint energy of visible and hidden units                                    |

| <i>EA</i>         | Evolutionary Algorithm                                                      |

| <i>ECG</i>        | Electrocardiogram                                                           |

| <i>ED</i>         | Epileptiform Discharges                                                     |

| <i>EEG</i>        | electroencephalogram                                                        |

| <i>EN</i>         | Elman Network                                                               |

| <i>EMG</i>        | Electromyography                                                            |

| <i>EPSRC</i>      | Engineering and Physical Sciences Research Council                          |

| <i>FA</i>         | Full Adder                                                                  |

| <i>FD</i>         | fractal dimensions                                                          |

| <i>FDFM</i>       | Few DSP slices and Few block RAMs                                           |

| <i>FFT</i>        | Fast Fourier Transform                                                      |

| <i>FFBP</i>       | Feed Forward Back Propagation                                               |

| <i>FIR</i>        | Finite Impulse Response                                                     |

| <i>FNN</i>        | Forward Neural Network                                                      |

| <i>FN</i>         | False Negative                                                              |

| <i>FP</i>         | False Positive                                                              |

| <i>FPGA</i>       | Field Programmable Gate Array                                               |

| <i>FSM</i>        | Finite State Machine                                                        |

| <i>g</i>          | equivalent to an activation function                                        |

| <i>GA</i>         | Genetic Algorithm                                                           |

| <i>GB</i>         | GigaByte                                                                    |

| <i>GHA</i>        | General Hebbian Algorithm                                                   |

| <i>GP</i>         | Genetic Programming                                                         |

| <i>h</i>          | hidden variable                                                             |

| $h'_j$            | target output range                                                         |

| <i>HDMEA</i>      | high density multiple-electrode arrays                                      |

| <i>HI – POCT</i>  | Healthcare Innovations and Point of Care Technologies                       |

| <i>HRQOL</i>      | Health Related Quality of Life                                              |

| <i>ICANNML</i>    | International Conference on Artificial Neural Networks and Machine Learning |

---

|                           |                                                             |

|---------------------------|-------------------------------------------------------------|

| <i>JTEHM</i>              | Journal of Translational Engineering in Health and Medicine |

| <i>I</i>                  | Query Input Pattern                                         |

| <i>ICD</i>                | Implantable Cardioverter Defibrillators                     |

| <i>LE</i>                 | Logic Element                                               |

| <i>LLE</i>                | Largest Lyapunov Exponent                                   |

| <i>LM</i>                 | Levenberg-Marquardt                                         |

| <i>LNA</i>                | low noise amplifier                                         |

| <i>LOOCV</i>              | Leave-One-Out Cross-Validation                              |

| <i>MEA</i>                | Multiple Electrode Array                                    |

| <i>MLP</i>                | Multiple Layer Perceptron                                   |

| <i>mse</i>                | mean square error                                           |

| <i>MVML</i>               | Multi-Views Multi-Learners                                  |

| <i>MVSL</i>               | Multi-Views Single-Learners                                 |

| <i>N</i>                  | Negative sample: Normal Patient EEG                         |

| <i>NCDP</i>               | total number of correctly detected patterns                 |

| <i>NAPP</i>               | total number of applied patterns                            |

| <i>N<sub>x</sub></i>      | number of input layer nodes                                 |

| <i>N<sub>h</sub></i>      | number of hidden layer nodes                                |

| <i>N<sub>o</sub></i>      | number of output layer nodes                                |

| <i>NB</i>                 | Naive Bayes                                                 |

| <i>NLG</i>                | Neural Logic Gate                                           |

| <i>NPV</i>                | Negative Predictive Value                                   |

| <i>NRMSE</i>              | normalized root mean square error                           |

| <i>O</i>                  | Output Pattern                                              |

| <i>OA</i>                 | Overall Performance                                         |

| <i>OAT</i>                | Optimal Allocation Technique                                |

| <i>P</i>                  | Positive Sample: Epileptic Patient EEG                      |

| <i>P(C<sub>i</sub> Y)</i> | posterior probability                                       |

| <i>P(C<sub>i</sub>)</i>   | prior probabilities                                         |

| <i>P(Y C<sub>j</sub>)</i> | posterior probability of Y                                  |

| <i>P(c x)</i>             | posterior probability of a target given specific attribute  |

| <i>P(c)</i>               | prior probability of the target                             |

| <i>PEMS</i>               | Predictive emission monitoring systems                      |

| <i>PID</i>                | Proportional-Integral-Derivative                            |

| <i>POMS</i>               | Profile of Mood State                                       |

| <i>PNN</i>                | Probabilistic Neural Network                                |

| <i>PPV</i>                | Positive Predictive Value                                   |

| $\psi$                    | optimal wavelet basis function                              |

| <i>P(x)</i>               | prior probability of an attribute                           |

| <i>P(x c)</i>             | probability of an attribute given the target                |

| <i>P(Y)</i>               | prior probability of (Y)                                    |

---

|                   |                                                      |

|-------------------|------------------------------------------------------|

| <i>QOLIE</i> – 89 | Quality of Life of Epilepsy questionnaire            |

| <i>RAM</i>        | Random Access Memory                                 |

| <i>RBF</i>        | Radial Basis Function Network                        |

| <i>RBM</i>        | Restricted Boltzmann Machine                         |

| <i>ROM</i>        | Read Only Memory                                     |

| <i>RR</i>         | recognition rate                                     |

| <i>RTL</i>        | Register Transfer Level                              |

| <i>s</i>          | scale                                                |

| <i>SDNN</i>       | Space Displacement Neural Network                    |

| <i>SNN</i>        | Spiking Neural Network                               |

| <i>SOM</i>        | Self-Organizing Map                                  |

| <i>SSSS</i>       | Small System Simulation Symposium 2018               |

| <i>STFT</i>       | Short Time Fourier Transform                         |

| <i>STR</i>        | Stripes                                              |

| $\tau$            | shift                                                |

| <i>TE</i>         | Tenesse Eastman                                      |

| <i>TN</i>         | True Negative                                        |

| <i>TP</i>         | True Positive                                        |

| <i>th</i>         | threshold value                                      |

| <i>TLE</i>        | Temporal Lobe Epilepsy                               |

| <i>TPR</i>        | True Positive Rate / Sensitivity                     |

| <i>TNR</i>        | True Negative Rate / Specificity                     |

| <i>u</i>          | sum of products of the BSNN                          |

| <i>v</i>          | visible variable                                     |

| $v_{i,j}$         | weight of each connection                            |

| <i>VLSI</i>       | Very Large Scale Integration                         |

| <i>VNS</i>        | vagus nerve stimulation                              |

| $w_n$             | weight for number, n neuron                          |

| <i>WASET</i>      | World Academy of Science, Engineering and Technology |

| <i>WHO</i>        | World Health Organisation                            |

| <i>WSNs</i>       | wireless sensor networks                             |

| <i>X</i>          | real number                                          |

| $X_{Mean}$        | mean                                                 |

| $X_{Median}$      | median                                               |

| $X_{Mode}$        | mode                                                 |

| $X_{StdDev}$      | standard deviation                                   |

| $X_{Q1}$          | first quartile                                       |

| $X_{Q3}$          | third quartile                                       |

| $X_{IQR}$         | inter-quartile range                                 |

| $X_{skew}$        | skewness                                             |

| $X_{kurtosis}$    | kurtosis                                             |

|             |                                                    |

|-------------|----------------------------------------------------|

| $X_{Min}$   | minimum                                            |

| $X_{Max}$   | maximum                                            |

| $x_n$       | input x for number, n neuron                       |

| $\xi(t)$    | Seizure Spike Representation                       |

| $y$         | output from activation function / output           |

| $Z(\theta)$ | normalisation constant                             |

| $z$         | value used to achieve desired 99% confidence level |

# Chapter 1

## Introduction

### 1.1 Background Information

In 2018, the World Health Organization (WHO) statistics revealed that 50 million of the world's population is affected by epilepsy [1]. Approximately 80% of the reported epileptic cases are found in developing countries. These countries may not have readily available treatment facilities and medications. Many epileptic cases are not reported especially in developing countries because epileptic patients and their families are afraid of being stigmatised and discriminated upon. This research addresses the problem of detecting epileptic seizures that affects these individuals around the world. Epilepsy is caused by abnormal impulses generated in the brain, the most complex part of the human body. It is well known that only 10% of the  $10^{13}$  cells are involved in the information processing and communicating part of the brain [1]. The cells that make up the most integral part of the human body are neurons. The brain itself is enclosed in a skull, and protected by a dura matter which is the dense protective fibre like layer. The brain consist of three main parts: cerebrum; cerebellum; brain stem.

Currently, epilepsy treatments are usually provided in the form of anti-epileptic drugs (AEDs) [2]. In the 1920s, the ketogenic diet was popularised as an alternative form of treatment for epilepsy. This diet was popular among children with epilepsy as it had a success rate of 30% to 50% which was good in those days. Another popular form of treatment was the vagus nerve stimulation (VNS) technique which was used to treat problematic seizures. In 1997, this device was approved by the U.S Food and Drug Administration unfortunately it is less effective than AEDs as only 50 percent of the 40% of patients treated respond to the treatment [3]. In 1970, the development of seizure prediction research was started by Viglione and colleagues. Seizure prediction analyses have several different categories: time-domain analysis; frequency-domain analysis; non-linear dynamics [4]. Most of the previous work will be explained in more

detail in Chapter 2. Unfortunately, nowadays there is still no home-based seizure detection system that can specifically differentiate between epileptic and non-epileptic seizure electroencephalogram (EEG) patterns.

To address the problem of epilepsy seizure detection, this thesis has reviewed different state of the art seizure detection methods. These methods are categorized as linear methods and non-linear methods. Linear methods have the advantage of simplicity and versatility compared with non-linear methods that are more capable of addressing the non-stationary nature of the EEG signals. It was decided to use one of the linear methodology to develop the epilepsy detection system which requires lower computational power [5]. The Artificial Neural Network (ANN) is a form of classifier that works in conjunction with feature extraction for epilepsy detection. ANN provides a more reliable seizure prediction with a range of error from 89 to 100%, verified with the datasets tested in this research. Thus, ANN have been chosen as the basis of the classifier designed in this thesis to overcome the problem of epilepsy detection.

Furthermore, the research project known as Ambient Assisted Living (AAL) have been of interest internationally in recent years [6],[7]. Through technological advancement which contributes to various smart objects with the capability of identifying, locating, sensing and connecting and thus leading to new forms of communication between people and things. Ambient Assisted Living (AAL) involves the use of various technical systems to support elderly people in their daily routine to allow an independent and safe lifestyle as long as possible. Personal communication between elderly people, their environment and relevant groups of care givers is an important aspect in AAL. Therefore, it is possible that epileptic patients also can benefit from the use of AAL in their daily lives. In order to accomplish such a feat, there is the need of identifying the best architecture may it be hardware plus software or just software for this seizure detection system. The thesis hopes to incorporate a viable seizure detection system into the AAL ecosystem and possibly future smart homes.

## 1.2 Specification and Approach

This section provides the approach and specification of this research. It should be noted that other literature have used the assumption that EEG is generated by a highly complex linear system [8]. This assumption is also being used in our research.

### 1.2.1 Why a bit-serial neural processor design?

In order to develop a wearable, home-based seizure detection system, the size and energy efficiency issue of the system will need to be addressed. The bit-serial architecture was chosen as the basis of this design because this method is generally perceived and

recognised as a method of choice for producing low cost and low power processors. When compared with the alternative which is the bit-parallel approach which prioritize speed over cost, the bit-serial architecture methodology is preferred for developing a neural processor for this research as a wearable system needs to prioritize cost over speed.

### **1.2.2 Why an artificial neural network?**

A neural processor would be the ideal design to simulate a biological neuron as it is also commonly used in brain modelling [9]. As part of the epilepsy detection system, the performance and speed of the system can be compromised to obtain a minimum hardware cost. It is expected that the small design developed in this research would be more energy efficient than a general processor and therefore used for this particular application. In this research, the developed system is mainly implemented on a Field Programmable Gate Array (FPGA) board. It is anticipated that in the near future, it will be necessary to completely design and fabricate an ASIC model of this neural hardware. It will then be fully tested to gauge its energy efficiency and feasibility to be used by epilepsy patients during their daily activities.

### **1.2.3 Specification of our design**

At present, there is still no standard specifications for good epileptic seizure detection. Therefore, this research has set specifications based on reference literatures i.e. the paper by Painkras et al. [9] which is closely related to this area of studies. The design proposed in this research have met certain specifications required for epileptic seizure detection. As the design decision involves a wearable system, the size of the proposed system should be less than 20% of the provided hardware resources of an FPGA chipset. In this research, comparisons have been made using three different chipsets, including Cyclone IV, Cyclone V and Stratix IV. As the research is still a proof of concept, evaluation of the results mainly focus on correct recognition rate of EEG patterns and hardware cost. Estimation of power and latency have also been included. However, the author strongly advised that these are estimated values which can be further optimised.

In order to compete with designs shown in other literature, the average accuracy of the proposed system must be over 80% as to convince experts world wide that this device can successfully detect epileptic seizure patterns. This specification is reinforced in a paper presented by Raygoza-Panduro et al. [10] which have an accuracy of 80%. The paper has been accepted and published by IEEE.

### 1.2.4 Hardware and software used for simulation and hardware testing

Software simulation have been proven to be faster and more accurate for ANN testing. However, software simulation requires the use of a laptop with an i5 processor, 8 GB RAM and a 64-bit operating system which is both bulky and cumbersome. In contrast, the proposed hardware is portable and can be used without the need of a connected laptop. In this research, an FPGA board have been used for hardware implementation. Synthesis for this design was conducted suing an Altera Quartus II software.

## 1.3 Aims and Contributions

In this section, the author wishes to address the research aims and objectives that led to the completion of this thesis. This research was started on the premise that it is vital for an epileptic patient to have a early seizure detection device that will prevent any unnecessary injuries or accidents. This objective then led to the various questions of developing a wearable seizure detection system. In order to complete this task, the author have established a few research aims that were addressed in this thesis. Firstly, the wearable seizure detection system aims to be developed using simple hardware as to minimize the hardware cost and power consumption. Secondly, this device must also run on an algorithm that provides an acceptable compromise between speed and accuracy (recognition rate). Finally, the research aims to be a proof of concept for future research such as smart homes and ambient assisted living.

Over the course of this research, three different contributions were made and published [11, 12, 13]. The completed system designs are tested and synthesised on FPGAs. The complete epilepsy detection system is illustrated in the Healthcare Innovations and Point of Care Technologies (HI-POCT) revised journal paper.

### 1. Proposal of a low-cost and low-energy data processing unit (DPU) [11]

At the beginning of this research, a detailed literature review was done in order to fully comprehend the state of the art epilepsy detection systems as well as the basic principles of their application. This literature review is included in Chapter 2 of this thesis. It was found that most epilepsy detection systems analyses EEG signals using software implementation techniques which consumes high computational power and therefore is not desirable for use in a portable, home-based epilepsy detection device. Thus, the research proposed a prototype low-cost and low-energy portable epilepsy detection system using bit serial ANN.

The data processing unit (DPU)was proposed to fully implement the functionality of a biological neuron. This proposed DPU found in Chapter 3 is based on a bit-serial architecture which has the capability of minimizing the hardware cost

in terms of logic elements (LE) needed for the dedicated neural hardware when compared with other bit-serial architecture processors. The advantages and disadvantages of these proposed bit serial techniques and hardware is analysed in the critical analysis section, section 2.12.

## 2. Development and testing of dedicated hardware ANNs [11, 12]

The research progressed further to develop a fully functional ANN using the proposed dedicated DPU [11] in Chapter 4 . The various ANN configurations developed in this research are based on bit-serial architecture. The first set of experiments involves the implementation of a single neuron accurately. The developed ANNs is known as the bit-serial neural network (BSNN). The BSNN uses identical DPU as each network nodes. Each layer of the network will have a number of the DPUs aligned in a vector arrangement and controlled easily using simple finite state machines (FSM). Next, the BSNN have a central controller FSM. This removes the need of complex program and further reduces the necessary hardware cost.

As part of the verification process of testing the functionality of the DPU, various forms of simple ANNs have been designed and experiments were conducted. In these tests, EEG input have also been used to test the BSNN. First, the tests used to detect epilepsy involve a single neuron with multiple inputs. Furthermore, multiple hidden neurons were used to further improve the accuracy of the network. Multiple experiments were also conducted using a number of hidden layers to find the best network configuration.

The proposed hardware neural network was synthesised on different FGPAs as a form of comparison and to find the best development chip for our design. The hardware cost of each system are shown in section 4.4. Different bit-precision were also used as a method of choosing the best trade off between performance and size. The tests are then evaluated with different metrics such as sensitivity (TPR), specificity (TNR), positive predictive value (PPV) and negative predictive value (NPV). Further details of these experiments can be found in Chapter 4.

## 3. EEG feature analysis and implementation of the optimal BSNN design [11]; [12]; [13]

In order to fully implement the epilepsy prediction system, a feature extraction component was designed to provide the inputs to the BSNN. Two different feature extraction hardware were designed and multiple experiments have been conducted to test for an optimal feature extraction component. The first component is a simple slope calculator. The other component calculates the mean energy value of a single EEG window.

Experiments conducted using the slope calculator have an accuracy over 85% while the mean energy system have a 62% accuracy. Chapter 5 discuss the reason behind

such a low accuracy for the mean energy system. A combination of both feature extraction hardware has a 90% accuracy which only accord a 2% improvement when compared with the slope calculator system. With this in mind, the slope calculator system was preferred.

The network configurations used in our experiments were closely based on a recent work that used ANNs in their classification process [14]. The results were then closely compared with a suitable EEG benchmark in section 5.4. In order to keep human error to a minimum when writing the hardware codes, this research provides an automated method to complete the hardware codes for a massive parallel neural network with simple Python scripts. Section 6.1 presents some further work which would be to improve and implement this wearable epilepsy detection system physically for an epilepsy patient. This involves synthesis of the physical layout of the DPU and the full system using an ASIC technology. This will help in estimating the area and power needed for the dedicated neural hardware system.

## 1.4 Thesis Organization

This thesis is broken down into several chapters. Chapter 1 introduces the problem and the reason for conducting this research, the different challenges, a brief explanation of any previous work and address the contributions achieved in this research. Chapter 2 is the literature review which discusses research conducted by various groups over the past decades. It gives details of the state of the art seizure detection technology, neural processors, different forms of neural networks and other useful information. Chapter 3 then proposes a novel approach with a new bit-serial data processing unit (DPU) design along with various tests that were conducted to test the functionality of the processor. Chapter 4 presents a novel bit-serial neural network (BSNN) using the DPU proposed in Chapter 3 for a simple and wearable epilepsy detection system. Multiple experiments were also conducted to find out the feasibility and efficiency of the BSNN. The cost of various BSNN configurations is also discussed. Chapter 5 includes EEG feature analysis and BSNN optimization. This chapter presents two dedicated extraction hardware that is incorporated into the complete epilepsy detection system. Chapter 6 concludes the thesis, explains associated limitations of this research and presents future possibilities of this research.

## Chapter 2

# Background Research