## University of Southampton Research Repository

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Author (Year of Submission) "Full thesis title", University of Southampton, name of the University Faculty or School or Department, PhD Thesis, pagination.

Data: Author (Year) Title. URI [dataset]

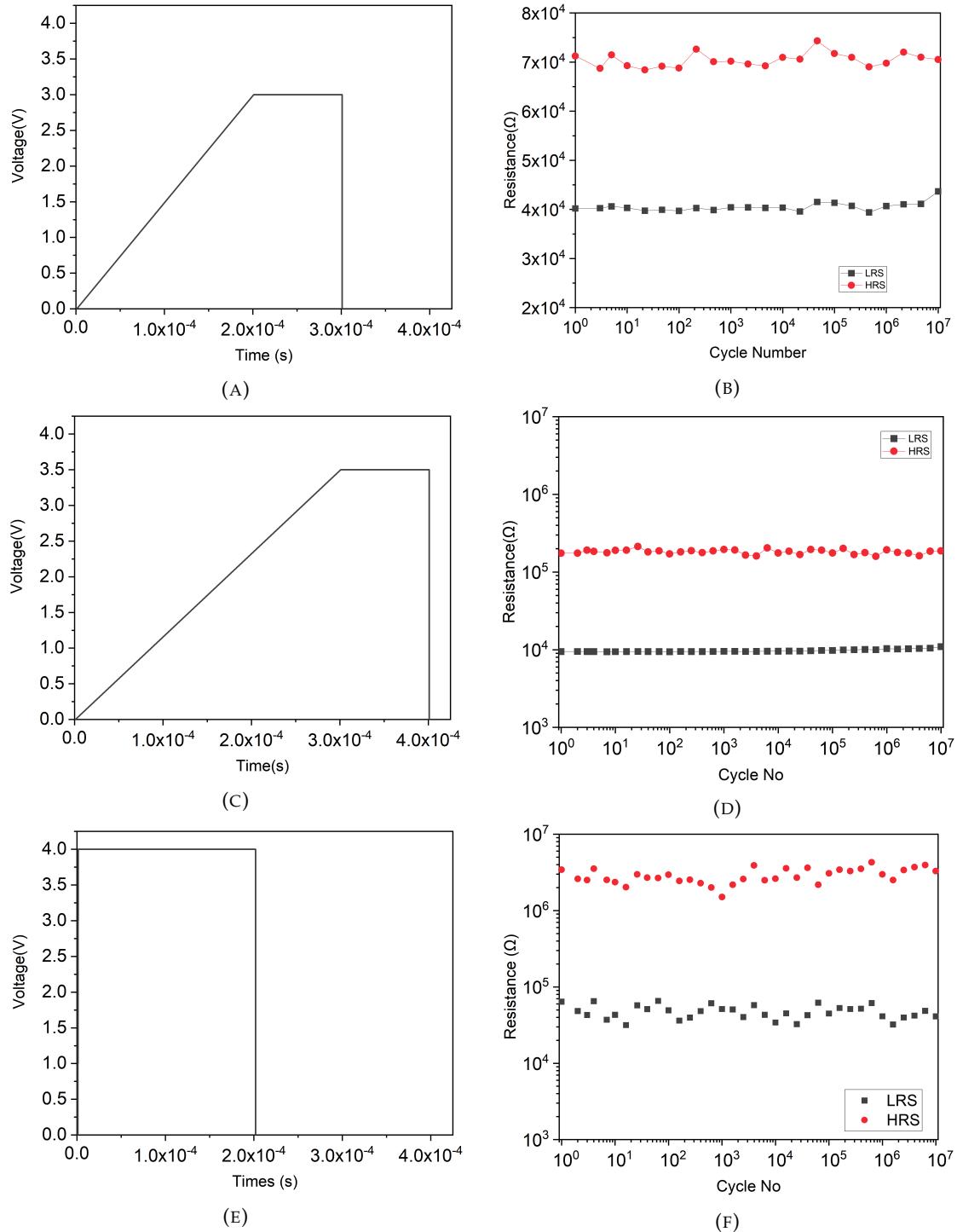

**UNIVERSITY OF SOUTHAMPTON**

Faculty of Engineering and Physical Sciences

School of Electronics and Computer Science

**Plasma Enhanced Chemical Vapour

Deposited Silicon Carbide For

Back-End-Of-Line Resistive Memory**

*by*

**Omesh Radhev Kapur**

MEng

*A thesis for the degree of

Doctor of Philosophy*

April 2022

University of Southampton

Abstract

Faculty of Engineering and Physical Sciences

School of Electronics and Computer Science

Doctor of Philosophy

**Plasma Enhanced Chemical Vapour Deposited Silicon Carbide For

Back-End-Of-Line Resistive Memory**

by Omesh Radhev Kapur

Resistive random-access memory (RRAM) are one of the most promising candidates for the next generation of memory technologies. Silicon Carbide-based memories are investigated in this thesis due to its heavy use as a back-end-of-the-line (BEOL) dielectric. This means that such devices could be fabricated directly on top of transistors, reducing the interconnect delay, and would be compatible with current commercial fabrication processes. This makes integration easier and cost effective. Our group has previously shown that Silicon Carbide-based RRAM show zero degradation up to 2MRad of  $\gamma$  irradiation. However, the fabrication process used yields devices with a low cyclability of around 10 switching cycles. Therefore, this thesis focuses on developing a new fabrication process that increases the performance and reliability of such memory cells. This is so that we can be assured that any measured failures in future life-time testing is due to the applied ion bombardment, instead of the inherent failures in the electronic properties of such a device.

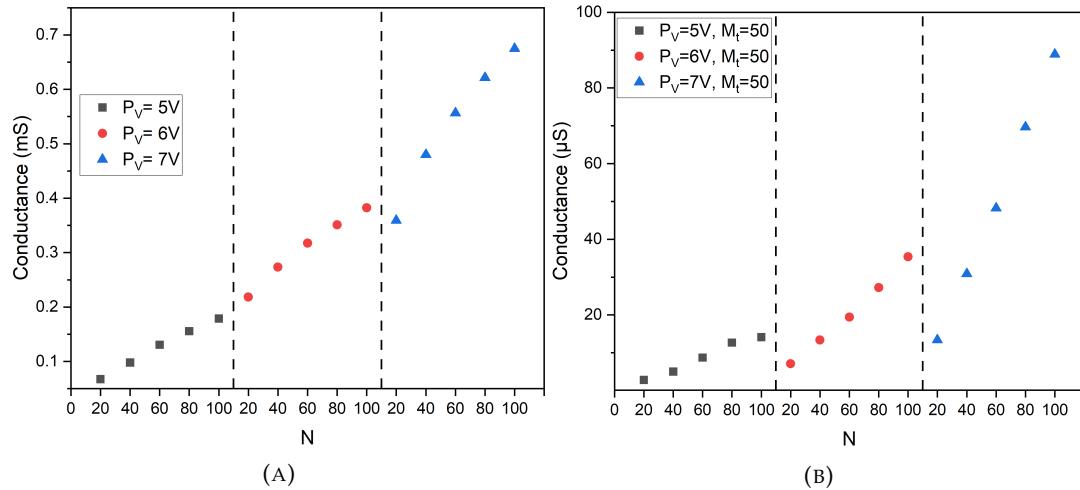

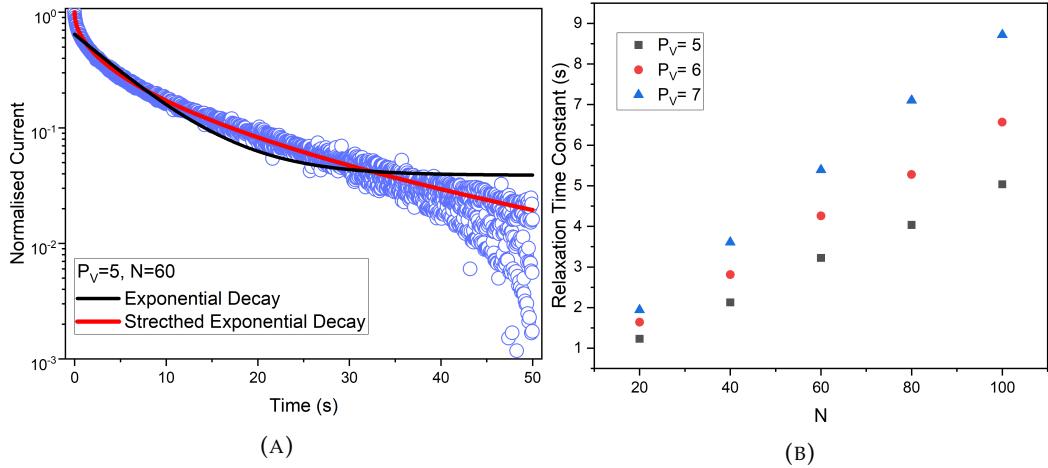

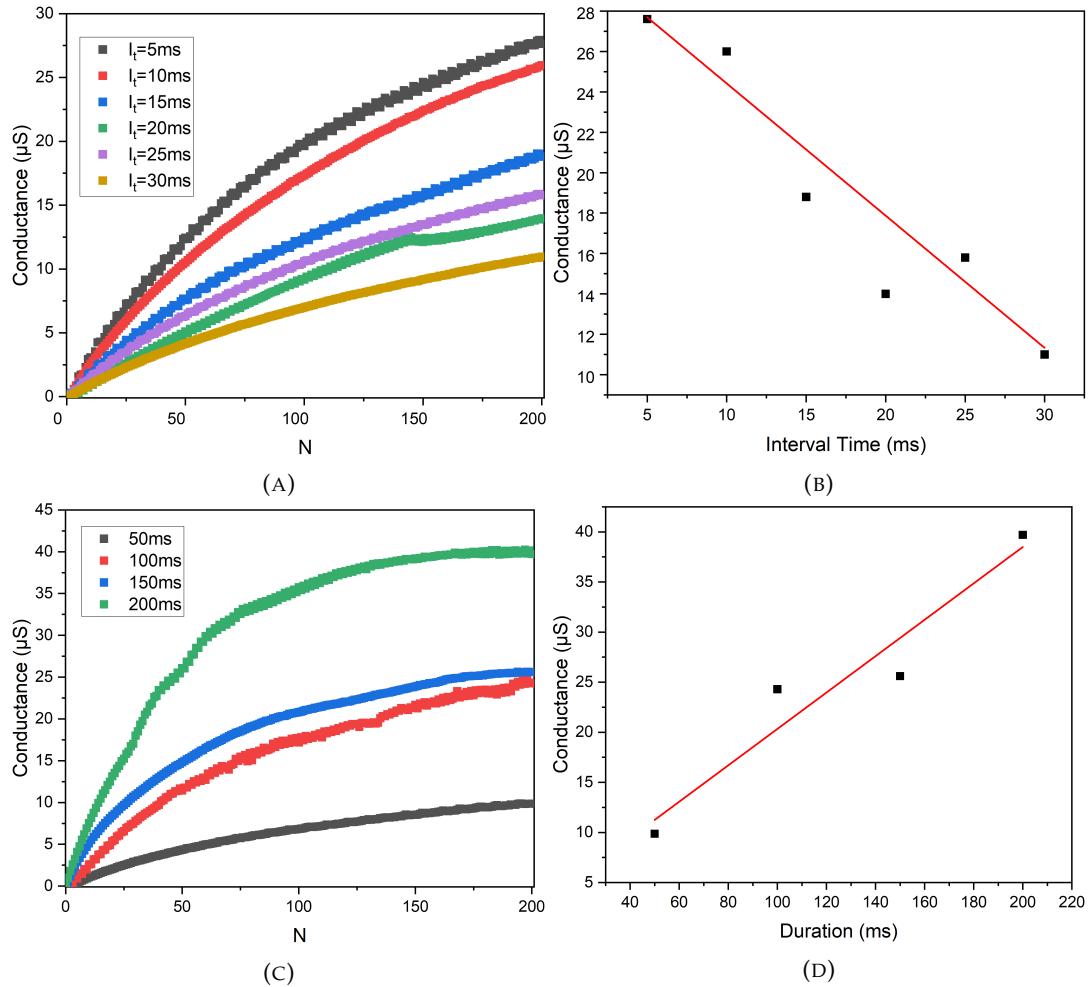

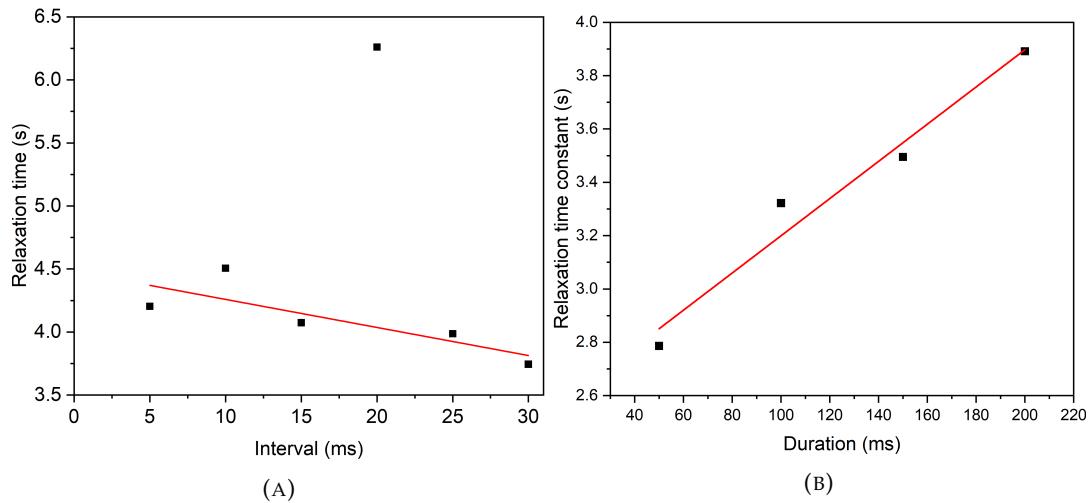

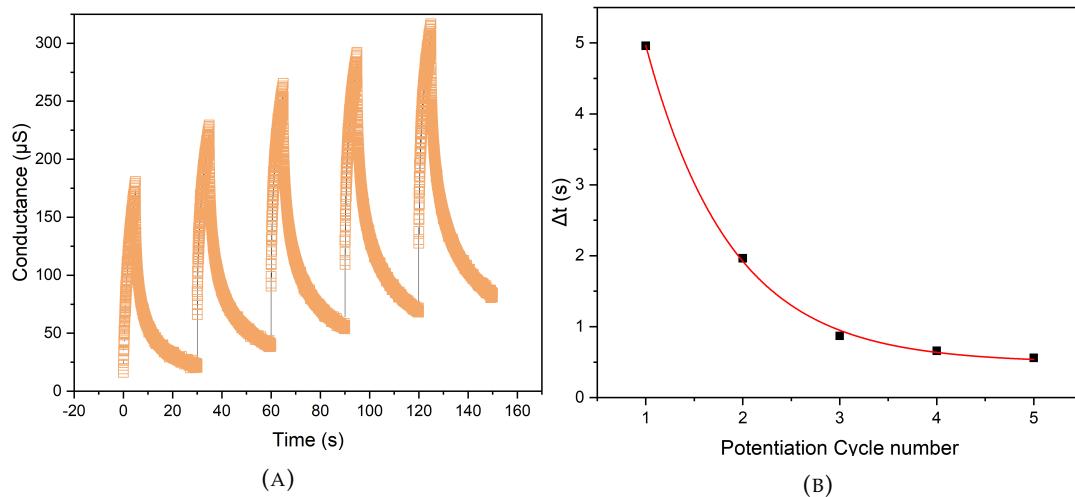

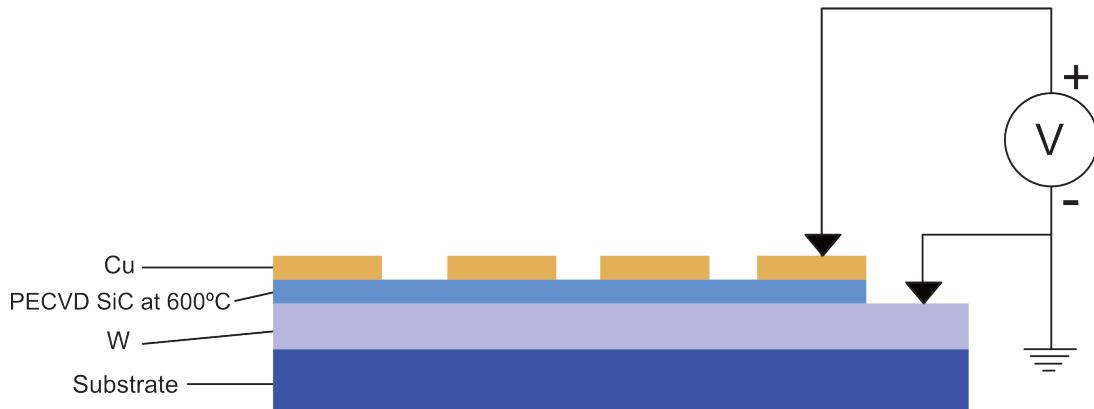

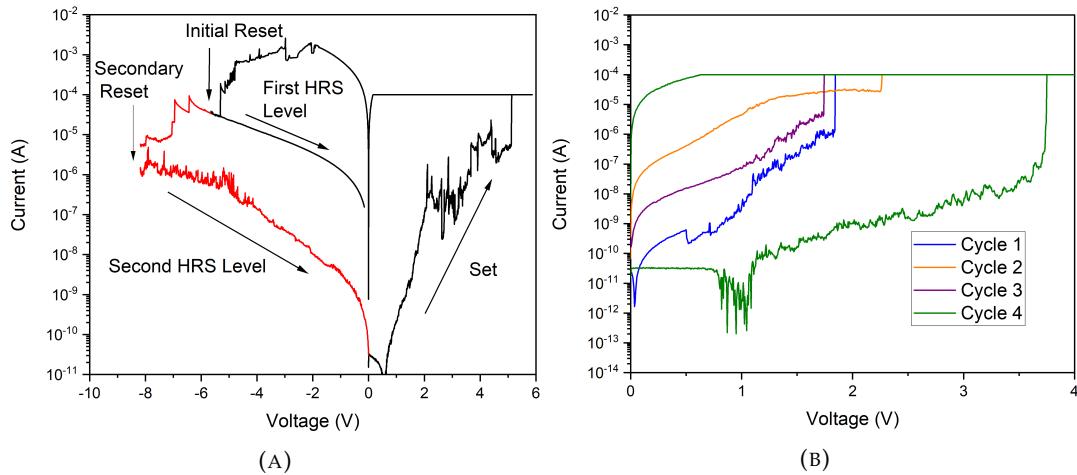

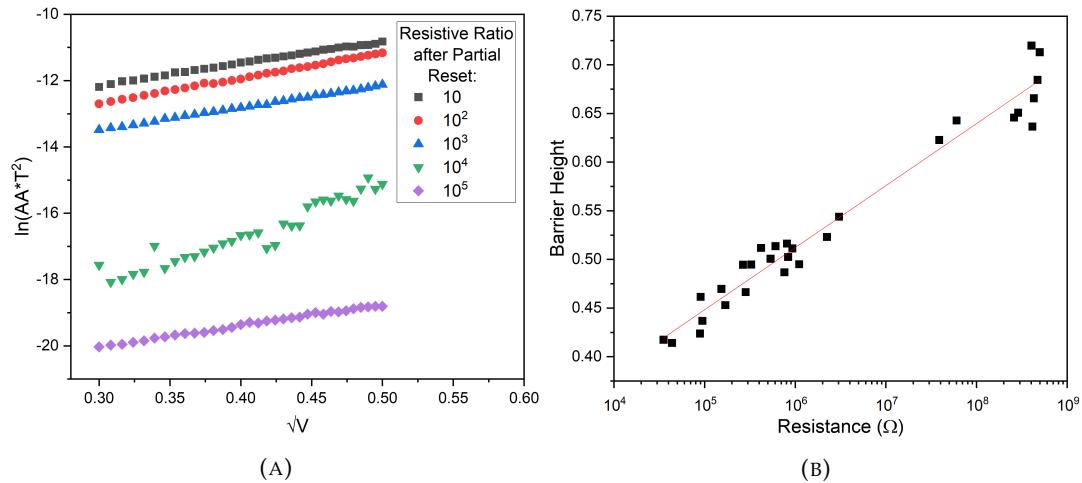

In this work I have developed a plasma enhanced chemical vapour deposition (PECVD) based SiC resistive memory which shows both volatile and non-volatile switching. The resistive memory devices showed reproducible and reliable switching across an entire 4-inch wafer. Both the On and Off state of the W/SiC/Cu devices were found to be dominated by Schottky emission with a change in the barrier height, which can be controlled with the applied voltage and number of sweeps. The volatile behaviour was characterised using varying pulse parameters and analyses of the change in conductance and the On state decay with time. The measured characteristics show emulation of short-term potentiation (STP) which takes place between the synapse of neurons. This work is the first to have a detailed analysis of STP in SiC-based RRAM memory cell. STP is understood to be key in information processing in the brain and this emulation can be used for brain-inspired computing. By varying the interval between 5ms and 30ms, we can further tune the peak conductance of our resistive memory cell and

show that our decay between the input stimuli is in the order of milliseconds. The control in the conductance state is thought to be due to the ion migration caused by the applied pulses and the spontaneous diffusion of the conductive filament. It was also found that applying multiple STP potentiation and decay cycles showed that the overall peak conductance increased with cycle number. Therefore, taking a single conductance point of  $181\mu\text{S}$  it was found that this specified conductance state could be re-learned exponentially quicker with each cycle, which has been seen in other neuromorphic based devices. The simple BEOL-compatible fabrication process and their ability to emulate STP functions in the brain make these memory cells a perfect candidate for embedded neuromorphic computing.

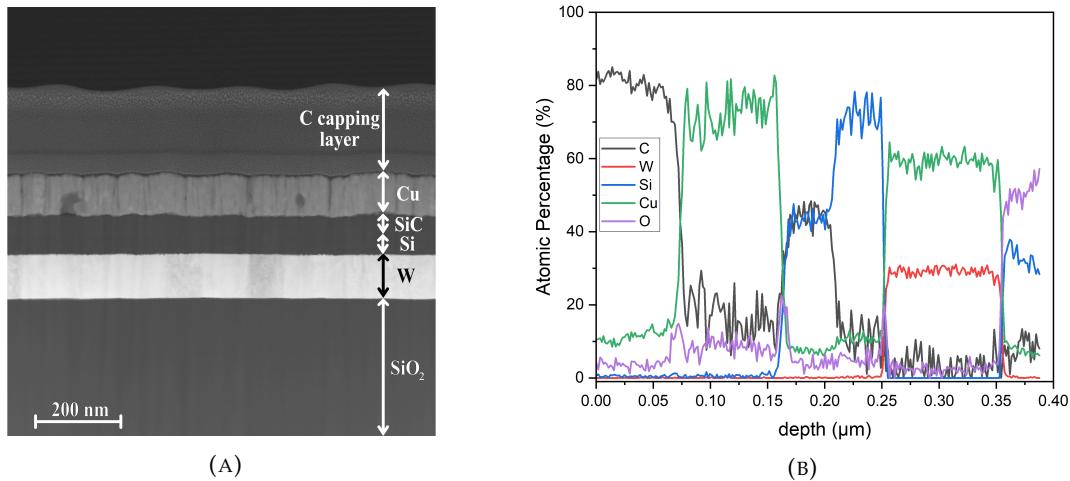

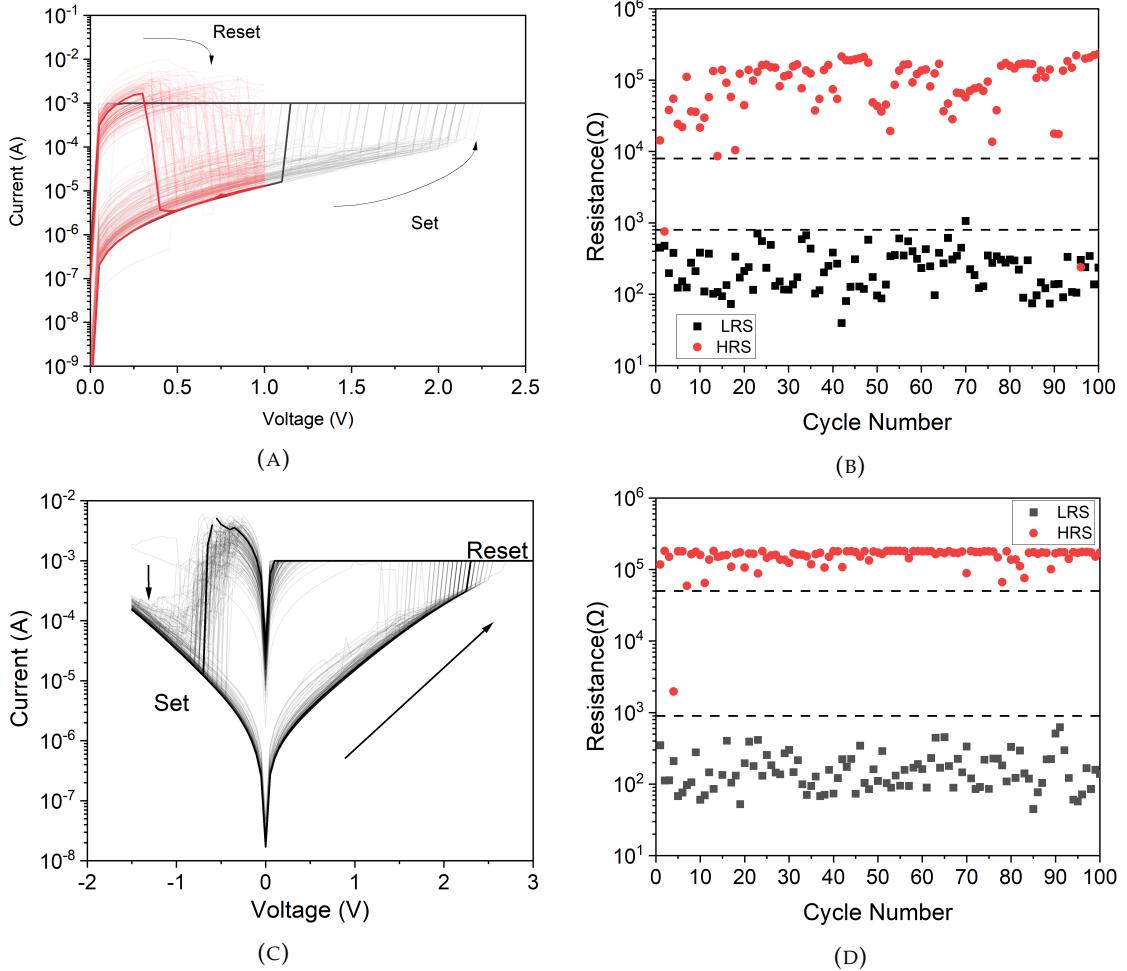

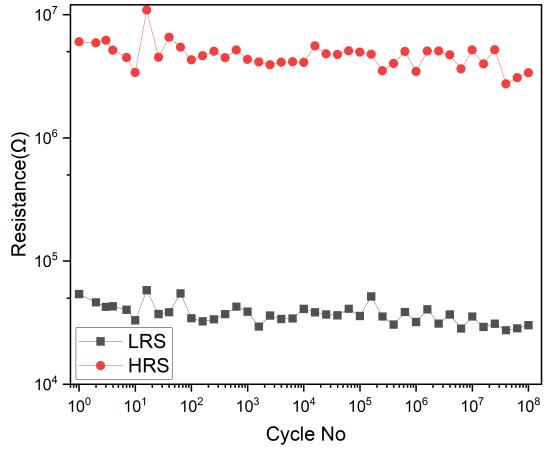

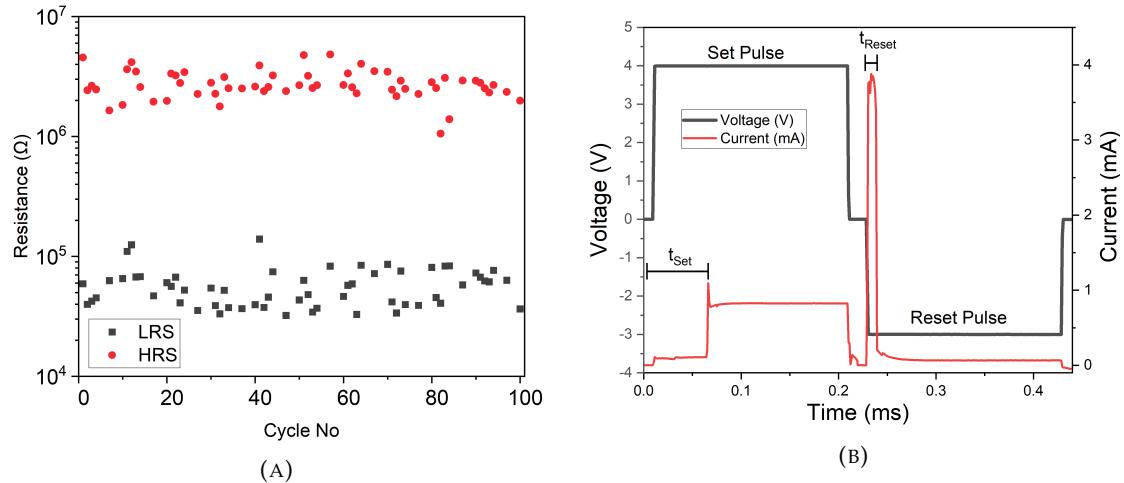

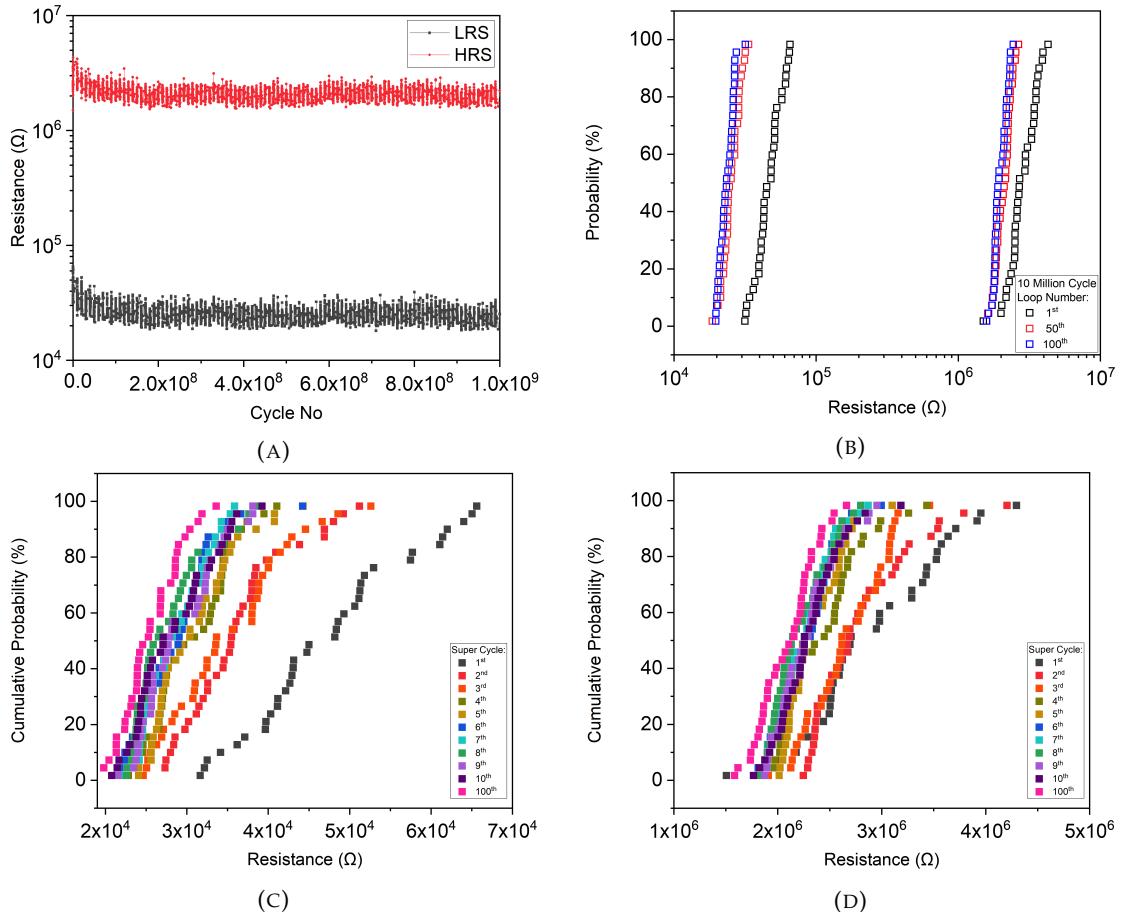

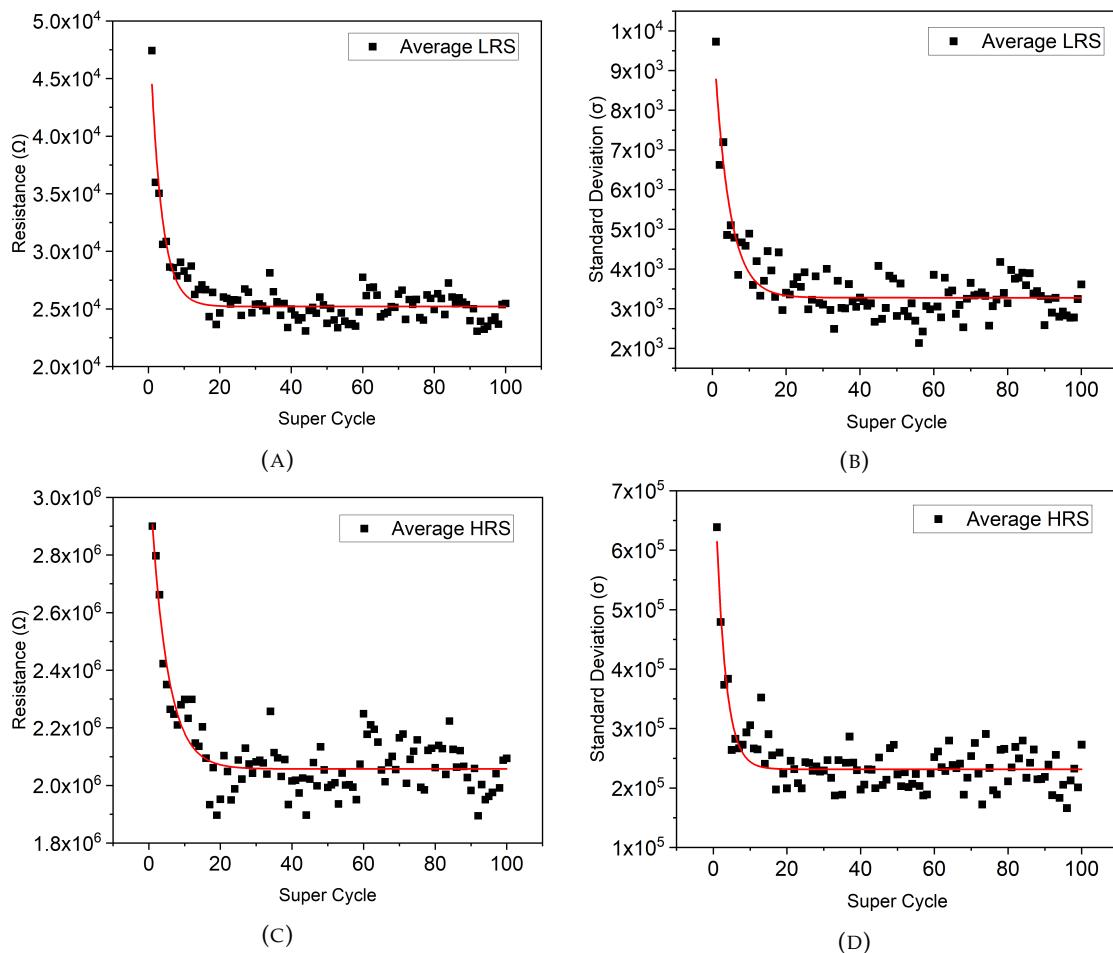

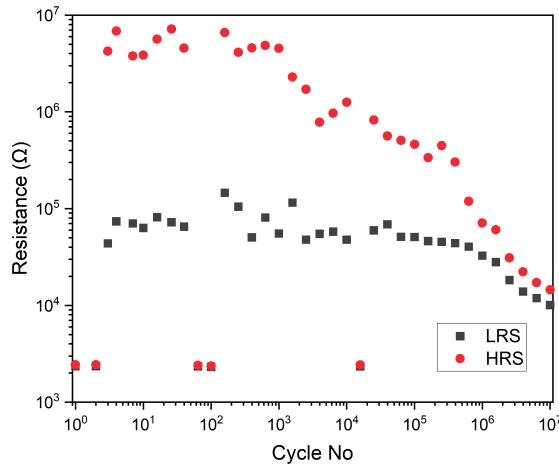

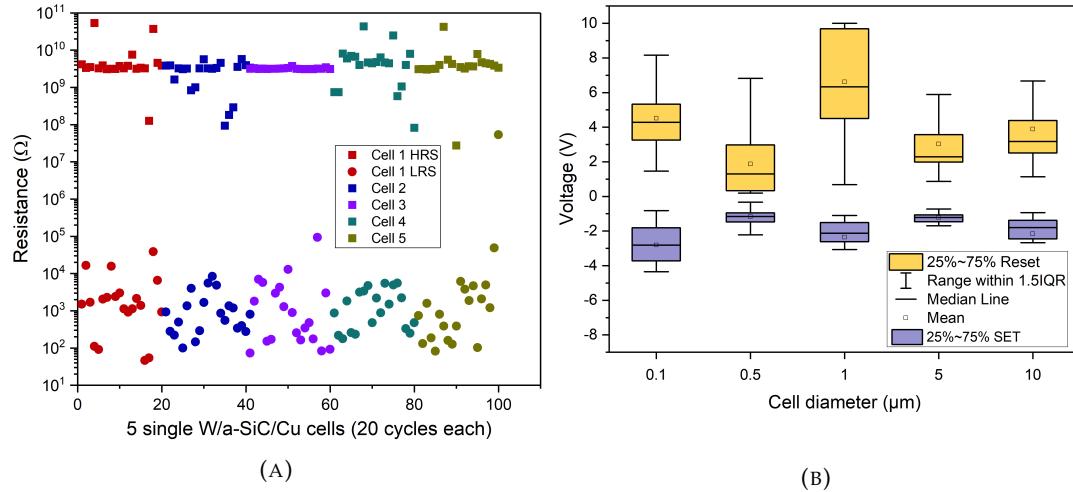

I developed Si/SiC bilayer memory cells deposited by PECVD with 50nm of amorphous-Si layer followed by a silicon rich 50nm of amorphous-SiC. These W/Si/SiC/Cu devices showed a similar switching mechanism to previously reported sputtered SiC-based dielectrics with the off state dominated by Schottky emission and the On state by Ohmic conduction. The Set and Reset voltages were measured to be around 2.1V and -0.8V respectively, with an average resistive ratio of  $10^3$  across 100 cycles. Using an external compliance current circuit, a pulsed measurement scheme was implemented to analyse the long-term endurance capabilities. Using a  $200\mu\text{s}$  pulse, it is possible to Set and Reset the memory cells at 4V and -3V over a billion times. Analysing the average resistance and deviation across this billion cycle range, it was found that the memory cells showed no degradation and instead improved with cycle number. The endurance and stability is one of the highest recorded endurance for conductive bridge based resistive memory (CBRAM) and outperforms current commercially available RRAM devices targeted specifically for radiation hardened applications. These samples were also re-fabricated to determine if the devices were reproducible. These devices showed near identical inherent characteristics, displaying the reproducible fabrication process that was developed. This work presents the potential for a scalable and BEOL compatible embedded memory solution.

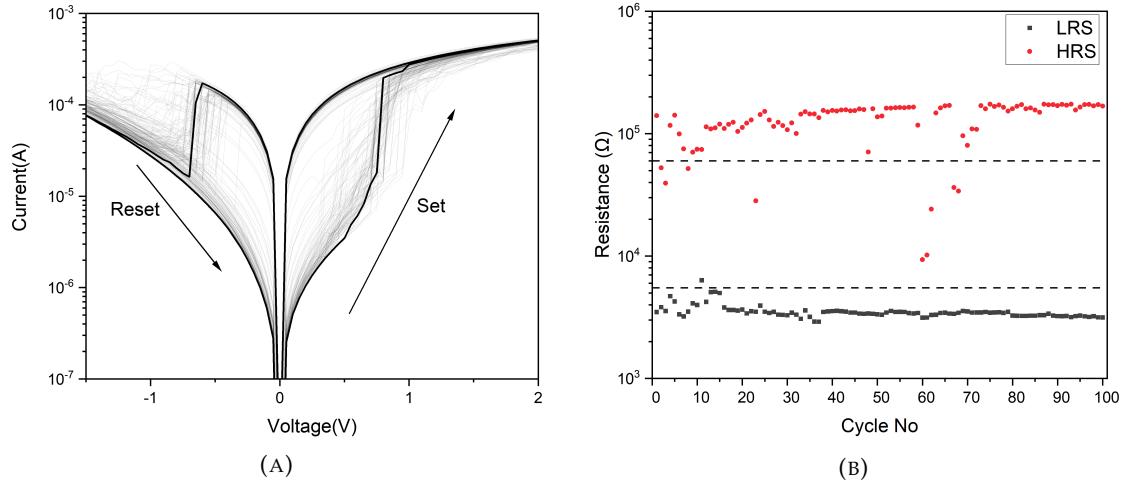

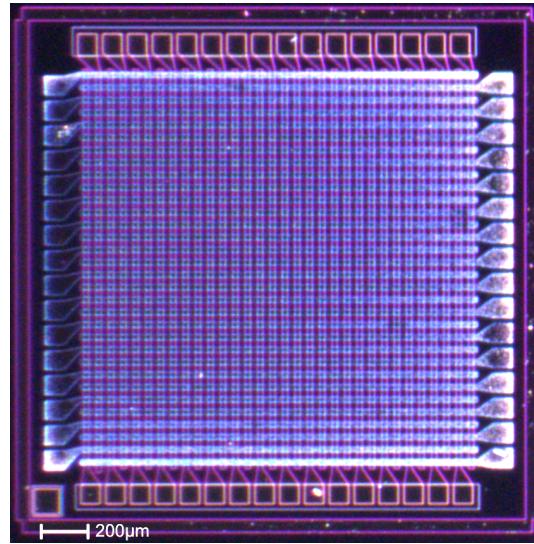

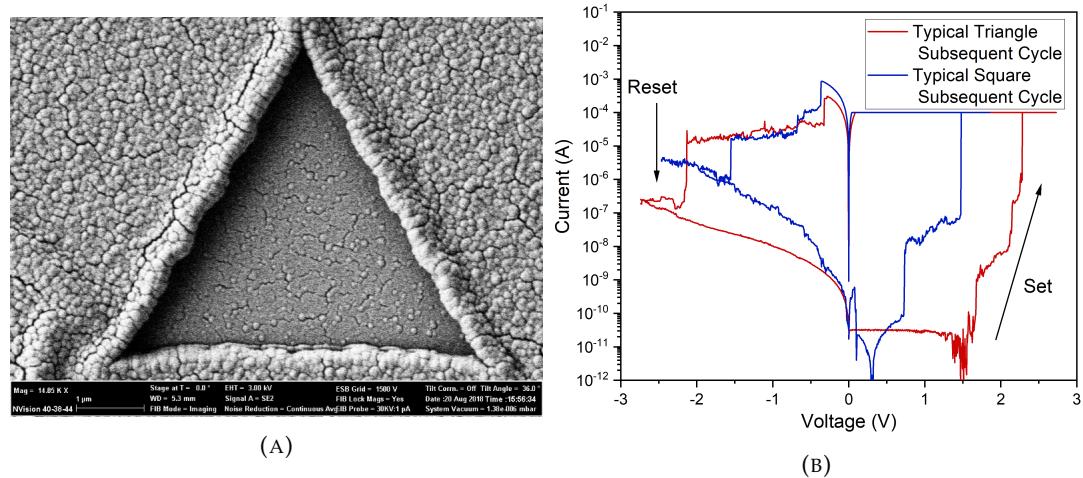

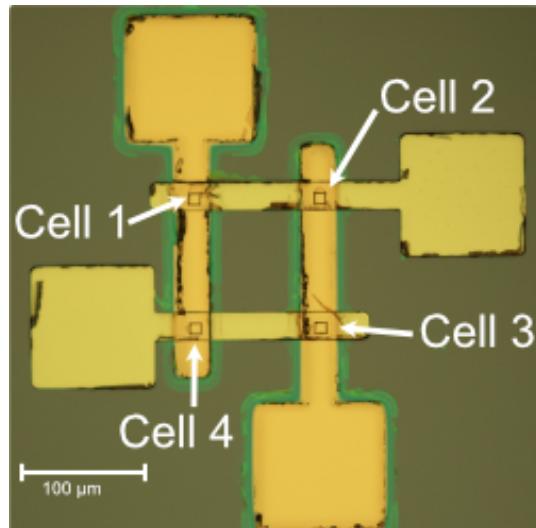

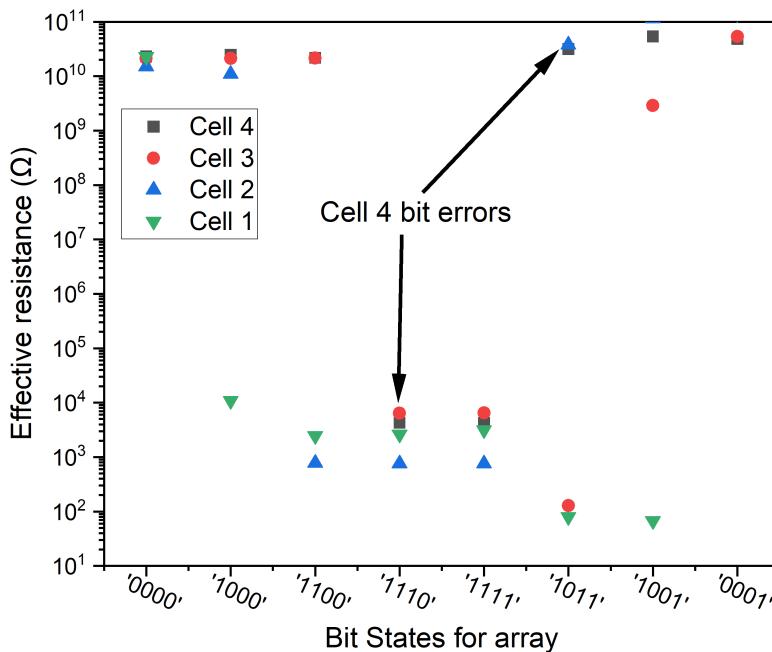

Typically, high performance memory is fabricated in a Crosspoint array. In this work I have investigated the fabrication process flow for Crosspoint structures for the optimum device characteristics. I have also fabricated the first recorded SiC-based Crosspoint structure. By embedding cells using e-beam lithography and a  $\text{SiO}_2$  isolation layer, the endurance of the cells increased from 12 to over 100 cycles. Both devices exhibited high resistive ratio of around  $10^6$ , in keeping with previous SiC-based resistive memory. By analysing the read and write schemes across a 2x2 array, the sneakpath was investigated which showed the potential issues that can arise in the form of bit errors. This demonstrates how the high endurance memory cells that are developed require the use of a selector device when combined into a Crosspoint structure.

# Contents

|                                                                   |            |

|-------------------------------------------------------------------|------------|

| <b>Declaration of Authorship</b>                                  | <b>vii</b> |

| <b>Acknowledgements</b>                                           | <b>ix</b>  |

| <b>1 Introduction</b>                                             | <b>3</b>   |

| <b>2 Resistive Memory Background and Literature Review</b>        | <b>5</b>   |

| 2.1 Resistive Random Access Memory . . . . .                      | 5          |

| 2.2 SiC-based Resistive Memory Performance . . . . .              | 10         |

| 2.3 Bilayer Resistive Memory . . . . .                            | 17         |

| 2.4 Theory of Neuromorphic Computing . . . . .                    | 21         |

| 2.5 System Architecture . . . . .                                 | 27         |

| 2.6 Resistive Memory and Radiation Harsh Environments . . . . .   | 31         |

| 2.6.1 Types of Radiation Effects . . . . .                        | 31         |

| 2.6.2 Theory of Radiation Interaction . . . . .                   | 35         |

| 2.6.3 A Review Of Radiation Effects In Resistive Memory . . . . . | 38         |

| 2.7 Conclusions . . . . .                                         | 43         |

| <b>3 Fabrication of PECVD SiC-based Resistive Memory</b>          | <b>45</b>  |

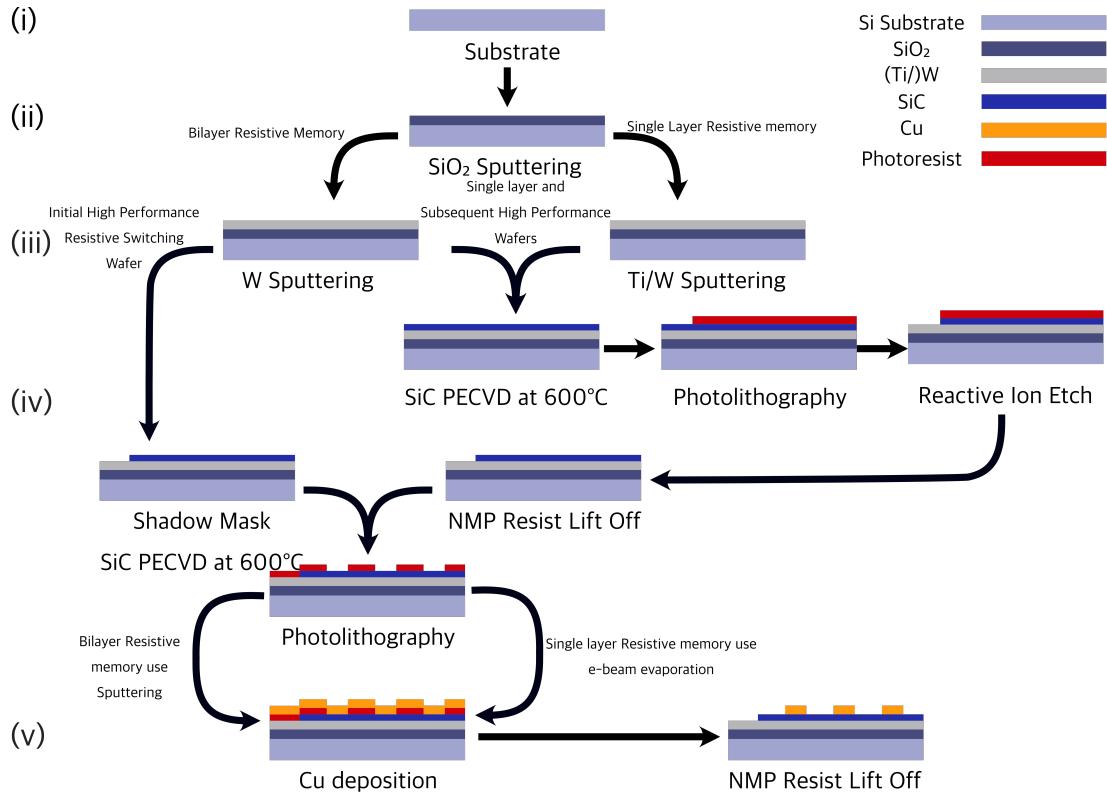

| 3.1 Silicon Substrate and Silicon Dioxide Insulation . . . . .    | 46         |

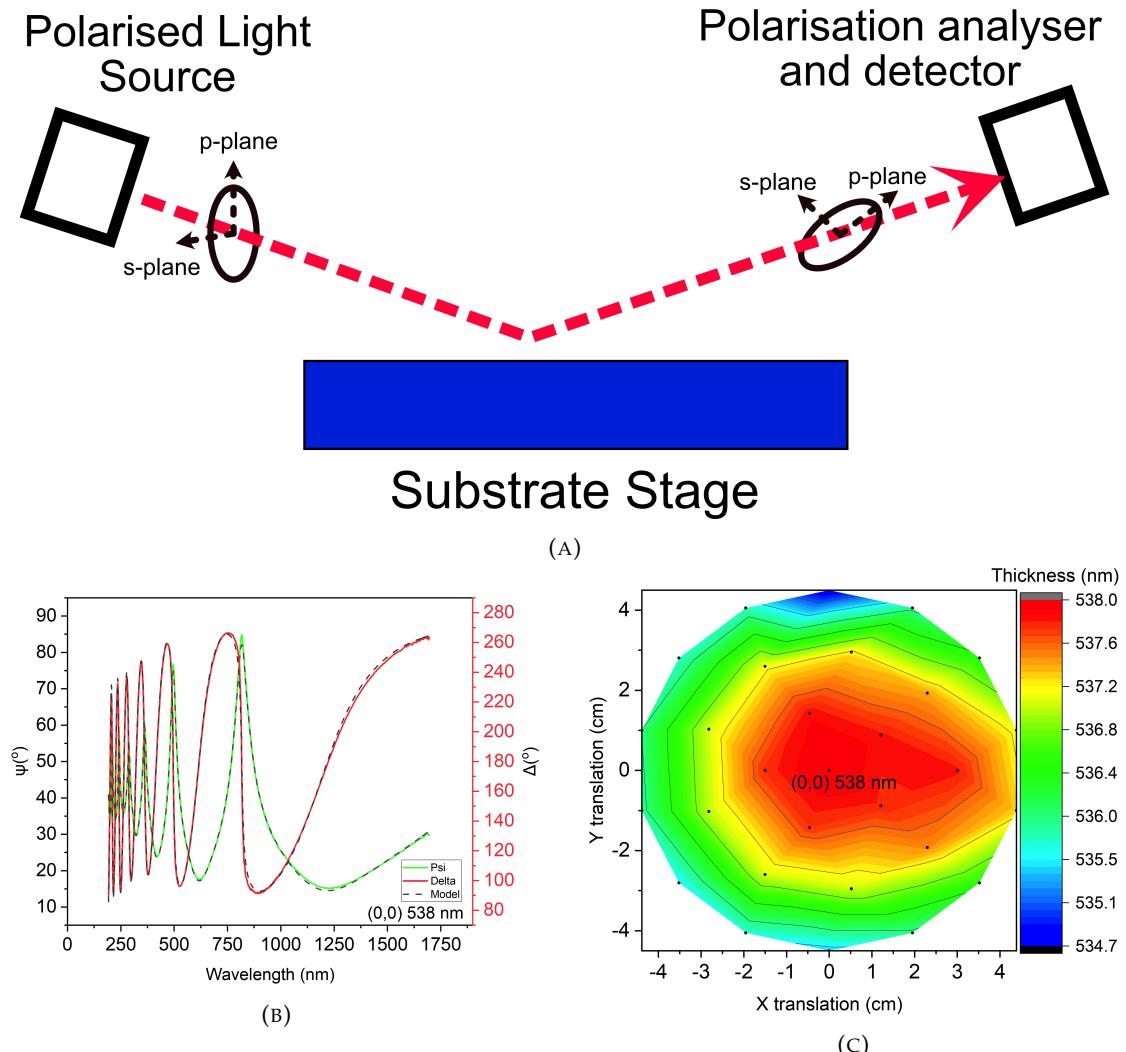

| 3.1.1 Ellipsometry Measurements . . . . .                         | 47         |

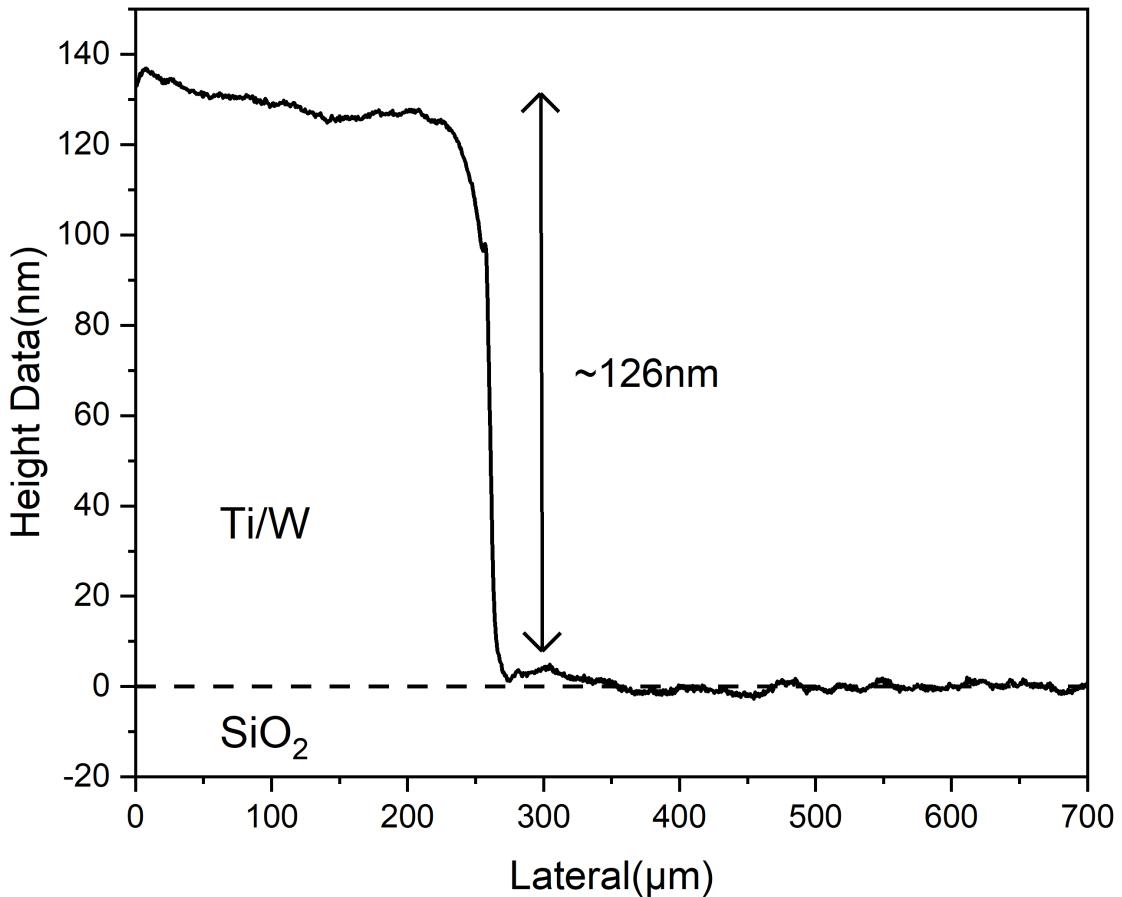

| 3.2 W Bottom electrode with and without Ti adhesion . . . . .     | 48         |

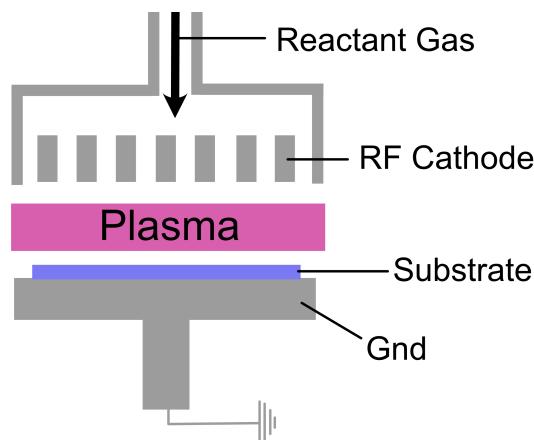

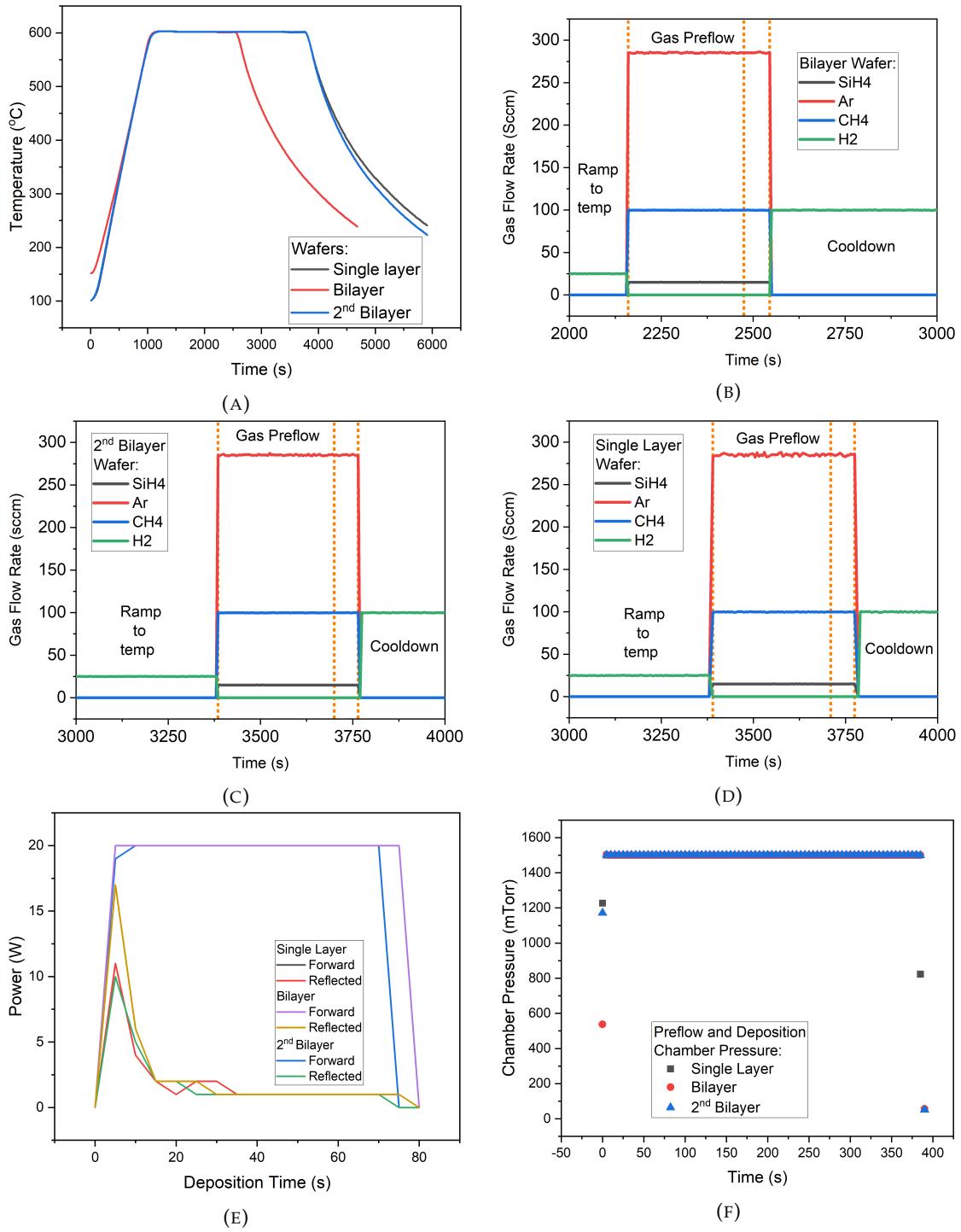

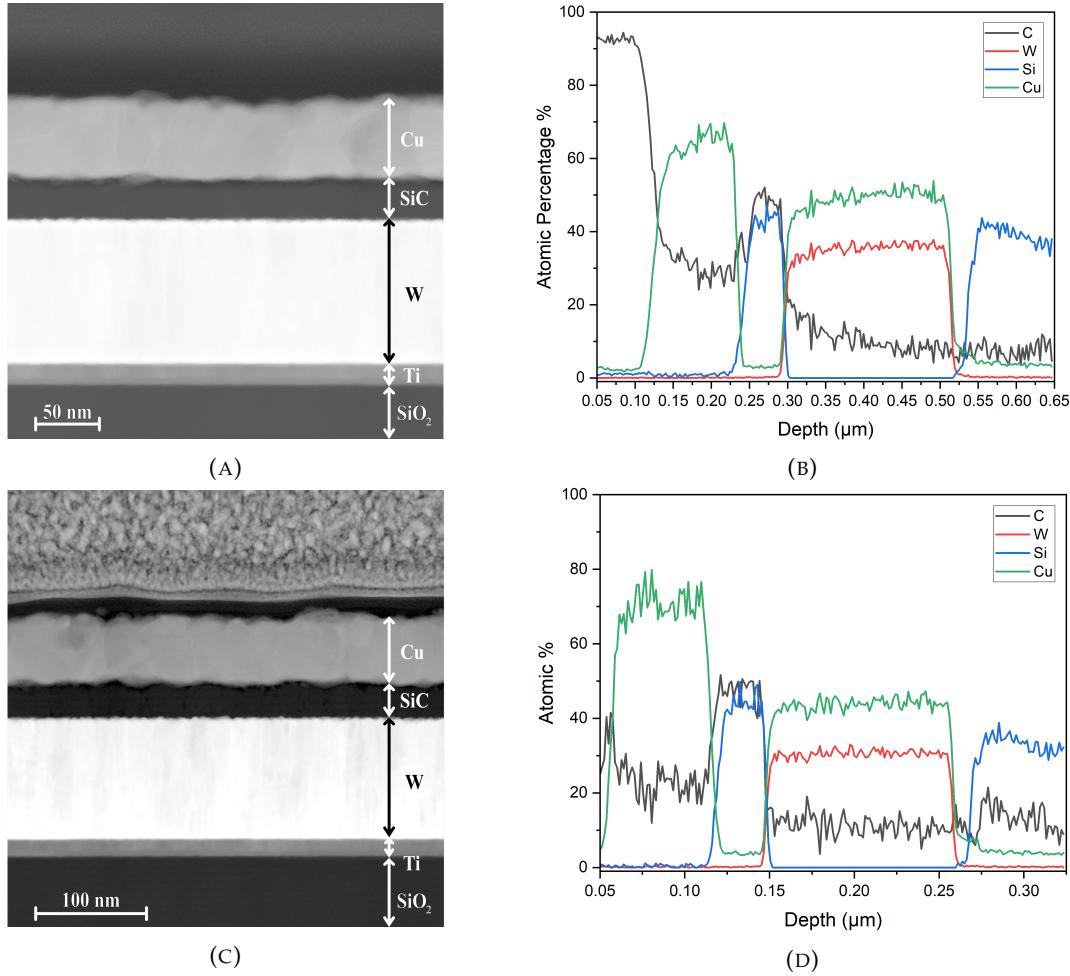

| 3.3 Amorphous Si/SiC deposition . . . . .                         | 52         |

| 3.3.1 Plasma Enhanced Chemical Vapour Deposition . . . . .        | 52         |

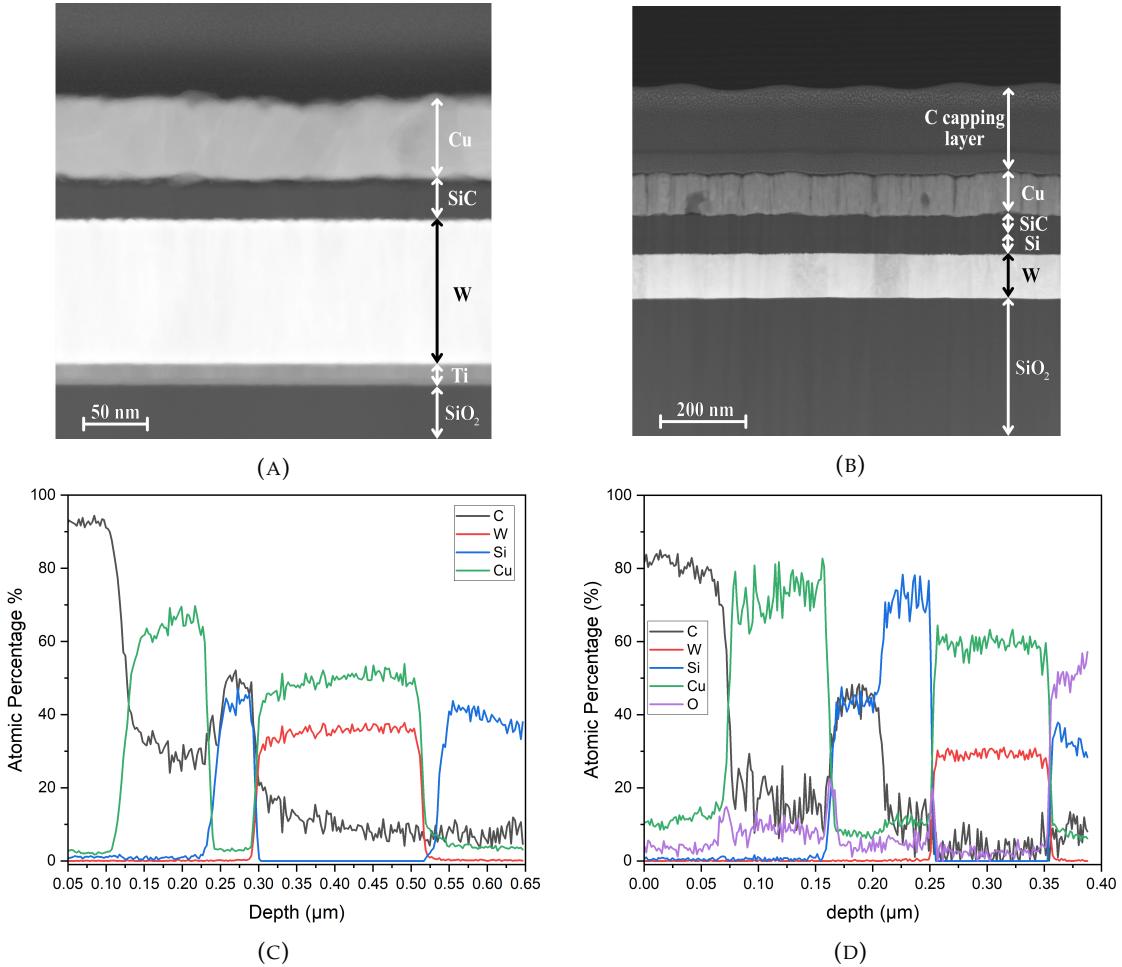

| 3.3.2 Material Characterisation . . . . .                         | 55         |

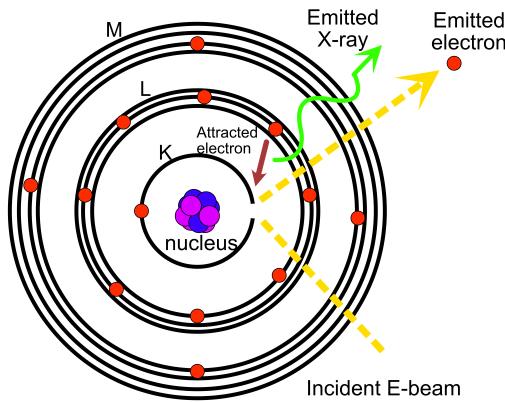

| 3.3.2.1 Energy Dispersive X-ray . . . . .                         | 55         |

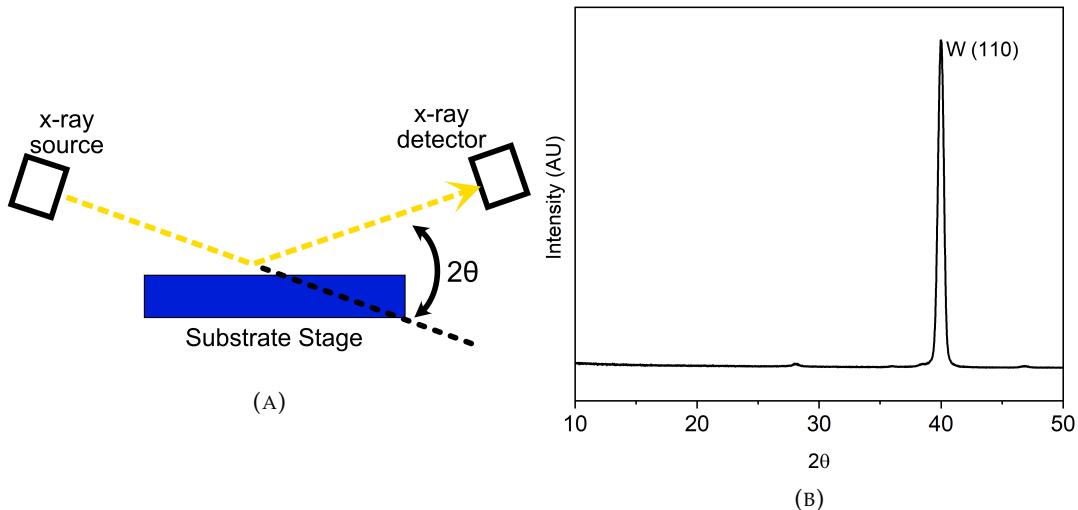

| 3.3.2.2 X-ray Diffraction . . . . .                               | 57         |

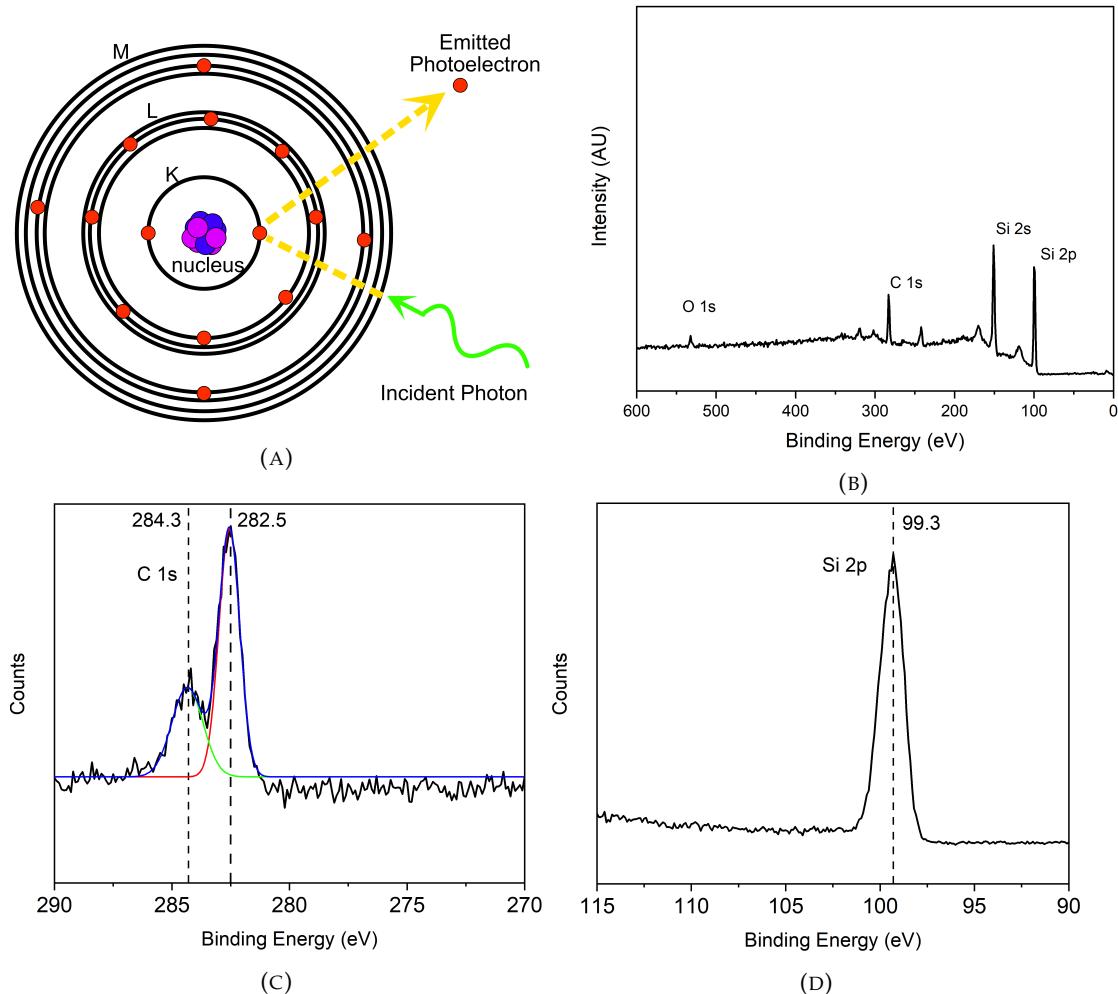

| 3.3.2.3 X-ray Photoelectron Spectroscopy . . . . .                | 59         |

| 3.3.2.4 Raman Spectroscopy . . . . .                              | 61         |

| 3.3.3 Patterning Bottom Electrode Windows . . . . .               | 63         |

| 3.4 Cu top electrode . . . . .                                    | 65         |

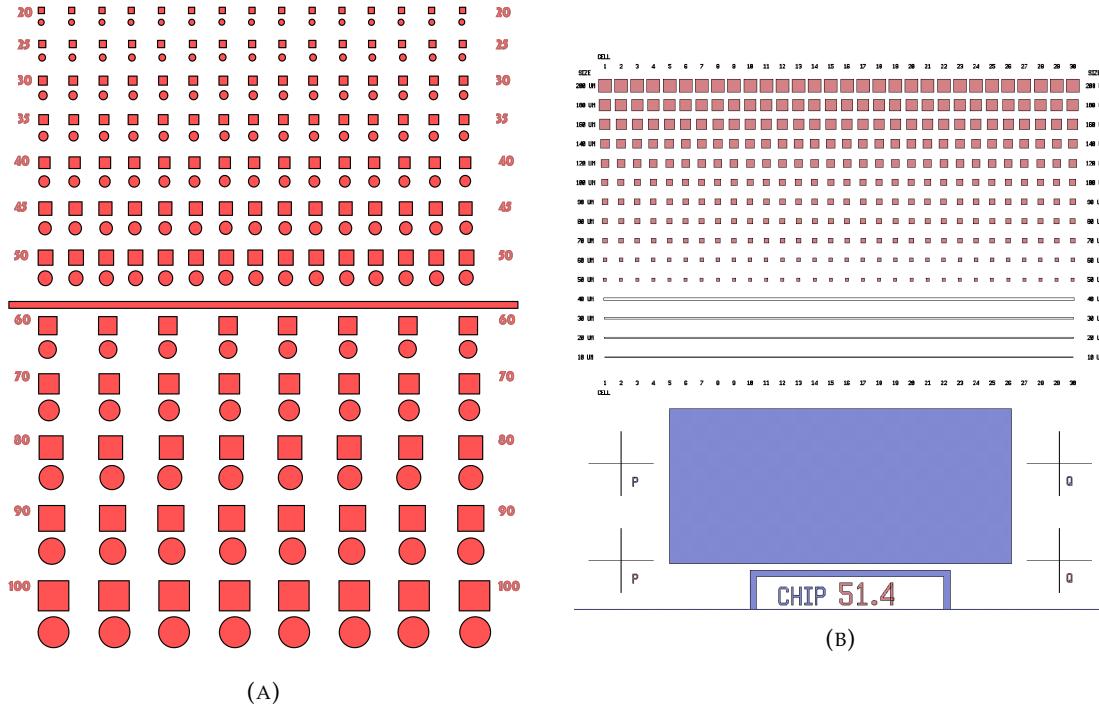

| 3.4.1 Photolithography layout . . . . .                           | 65         |

| 3.4.2 Physical vapour deposition of Cu . . . . .                  | 68         |

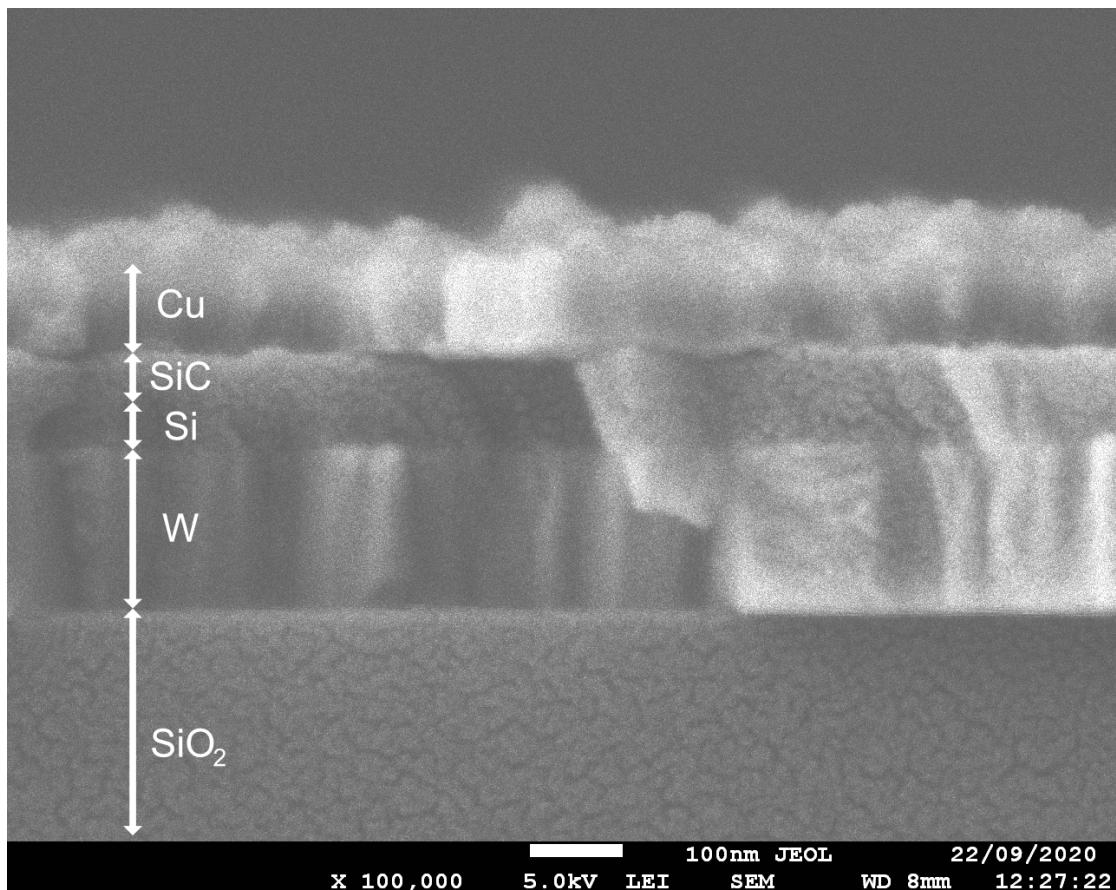

| 3.5 Final memory cell structure . . . . .                         | 69         |

| <b>4 SiC Resistive Memory and Short-term Potentiation</b>         | <b>71</b>  |

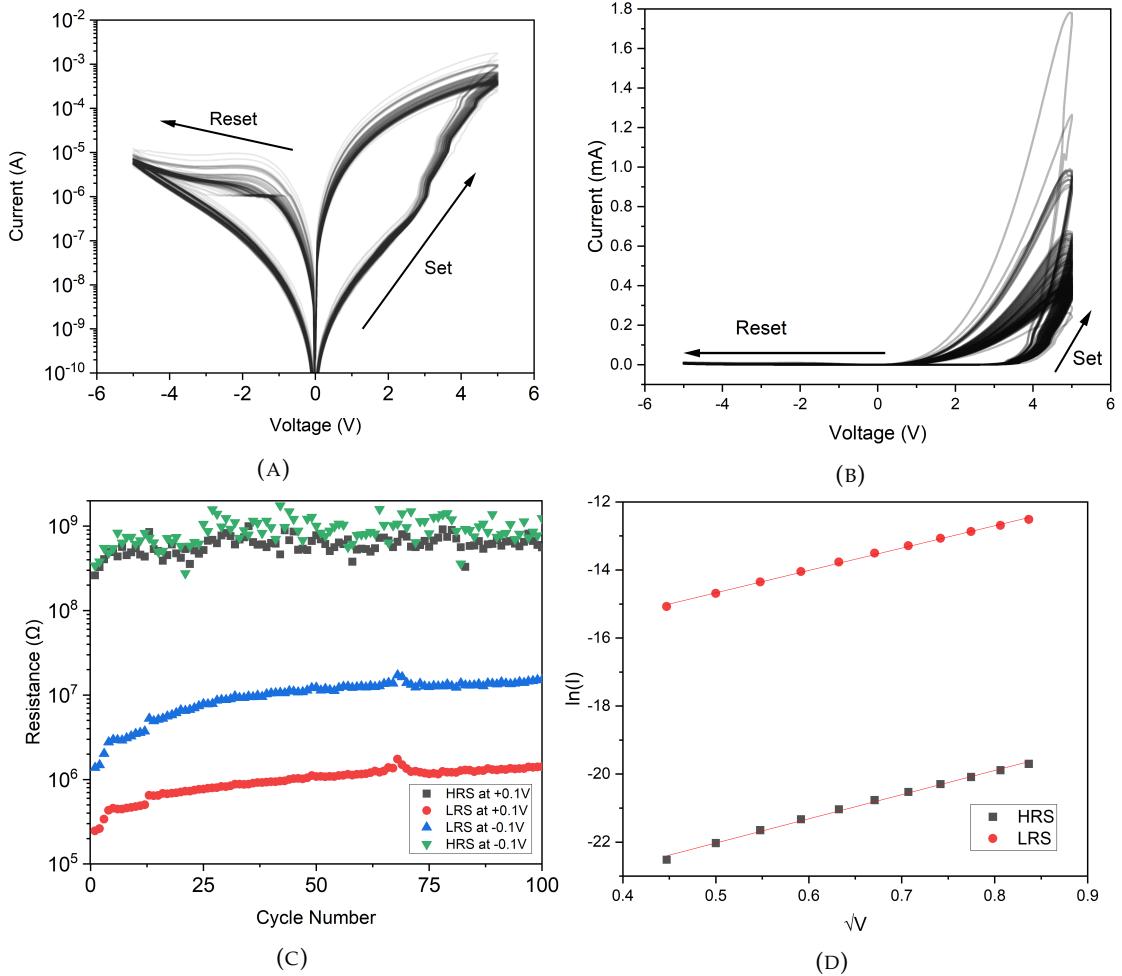

| 4.1 Electrical Measurement Setup and DC Behaviour . . . . .       | 71         |

| 4.2 Short Term Potentiation Characteristics . . . . .             | 76         |

|                                                                           |            |

|---------------------------------------------------------------------------|------------|

| 4.3 Conclusion . . . . .                                                  | 82         |

| <b>5 High Performance Bilayer SiC Resistive Memory</b>                    | <b>83</b>  |

| 5.1 Electrical Measurement Setup and Current Compliance Investigation . . | 83         |

| 5.2 DC Switching Results . . . . .                                        | 88         |

| 5.3 Pulsed Switching Results . . . . .                                    | 92         |

| 5.4 Wafer Reproducibility . . . . .                                       | 99         |

| 5.5 Future Radiation Experiments . . . . .                                | 104        |

| 5.6 Conclusion . . . . .                                                  | 105        |

| <b>6 Crosspoint Structures and Investigation of Sneakpath</b>             | <b>107</b> |

| 6.1 E-beam Device Design and Fabrication . . . . .                        | 107        |

| 6.2 Crosspoint Memory Electrical Characteristics . . . . .                | 113        |

| 6.2.1 Single Device Characterisation . . . . .                            | 113        |

| 6.2.2 Sneak Path Analysis . . . . .                                       | 119        |

| 6.3 Conclusion . . . . .                                                  | 120        |

| <b>7 Conclusion and Future Work</b>                                       | <b>123</b> |

| 7.1 Conclusion . . . . .                                                  | 123        |

| 7.2 Future work . . . . .                                                 | 125        |

| <b>References</b>                                                         | <b>127</b> |

## **Declaration of Authorship**

I declare that this thesis and the work presented in it is my own and has been generated by me as the result of my own original research.

I confirm that:

1. This work was done wholly or mainly while in candidature for a research degree at this University;

2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

3. Where I have consulted the published work of others, this is always clearly attributed;

4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

5. I have acknowledged all main sources of help;

6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

7. None of this work has been published before submission

Signed:.....

Date:.....

## Acknowledgements

I would like to thank my supervisors Professor Kees de Groot and Professor Liudi Jiang for your support, guidance and help throughout my PhD. I have learnt so much and I am extremely grateful to have been able to work on this project with you. I would also like to thank Dr Ruomeng Huang, who has also given me a huge amount of support and guidance and I have felt so fortunate to be able work alongside you.

I would also like to thank the Engineering and Physical Sciences Research Council (EPSRC) and Atomic Weapons Establishment (AWE) who have funded my project and made my PhD possible. I would especially like to thank Chris Shaw who has provided me with many opportunities to share my research with AWE.

I would also like to thank Junqing Fan for his help and support at the start of my PhD. I would also like to thank Dongkai Guo who has helped with electrical characterisation.

Thank you also to Jamie Reynolds and Anushka Gangnaik who has provided me with invaluable guidance and support throughout my PhD and also made sure I laughed along the way. A special thank you to Ella Hill as well, who has supported and cheered me on so much, I couldn't have done it without you.

I would also like to thank Rafidha Petra, Swe Oo, Ben Rowlinson, Katarina Cicvaric, Joshua Akrofi, Joe Hillier and many more who have made this journey an enjoyable one. A special thank you to Daniel Newbrook who has been an amazing friend throughout my time at Southampton.

I would also like to thank everyone who works in the cleanroom, especially the staff who have always taken time to help me with even minor queries. This PhD would not have been possible without you and a special thanks to Owain Clark, Kathleen leblanc, Liam Boodhoo, Xiangjun Wang and Kian Kiang.

Finally, I would like to thank my family, friends and especially my parents who have supported me throughout my time in academia and always pushed me forward when I needed it the most.

# List of Publications

## Peer reviewed journal publications

J.Fan, **O.Kapur**, R. Huang, S. W. King, C. H. de Groot, L. Jiang (2018) "*Back-End-Of-The-Line  $a\text{-SiO}_x\text{C}_y$  Dielectrics for Resistive Memory*", American Institute of Physics Advances, 8(9), 095215

**O.Kapur**, J.Fan, J.Reynolds, Yisong Han, Richard Beanland, Ruomeng Huang, Liudi Jiang, C.H. Kees de Groot "*High endurance amorphous SiC resistive memory by chemical vapour deposition*" (submitted to IEEE Transactions on Electron Devices)

**O.Kapur**, Dongkai Guo, Jamie Reynolds, Yisong Han, Richard Beanland, Ruomeng Huang, Liudi Jiang, C.H. Kees de Groot "*Analysis of Short-Term Potentiation in Schottky Barrier-Switching Cu/SiC/W*" (in preparation)

## Conference Attendance

**O.Kapur**, J. Fan, L. Jiang, C.H. de Groot (2018) "*Passive Resistive Random Access Memory Matrices Using Amorphous Silicon Carbide*", Micro and Nano Engineering (MNE) Copenhagen, Denmark.

**O.Kapur**, J. Fan, L. Jiang, C.H. de Groot (2018) "*Passive Amorphous Silicon Carbide Resistive Random Access Memory Arrays*", Non-Volatile Memory Symposium (NVMTS) Sendai, Japan.

**O.Kapur**, J. Fan, L. Jiang, C.H. de Groot (2018) "*Passive Resistive Random Access Memory Matrices Using Amorphous Silicon Carbide*" Defence and Security Doctoral Symposium (DSDS) Swindon, UK.

# Chapter 1

## Introduction

Non-volatile memory can retain bit states when power to the system is taken away. Such technologies like FLASH has seen widespread adoption due to their continuously increasing capacity and low cost [1]. However, current FLASH devices cannot be reliably used in radiation harsh environments with data loss showing to occur around 10krad to 100krad of exposure [2]. Reliable radiation-hardened memory cells are important for a wide range of applications, for example, defence and space exploration.

There are several candidates that can be used for the next generation of non-volatile memory [3]. The most promising of these candidates are Resistive Random-Access Memory (RRAM) cells. This is because resistive memory can be fabricated using back-end of the line (BEOL) materials. This means that such memory could be fabricated directly on top of transistors, reducing the interconnect delay, and would be compatible with current commercial fabrication processes. Our group has previously shown that silicon carbide-based resistive random access memory (ReRAM) cells have shown large resistive ratios of up to  $10^{10}$  and successful data retention at radiation doses up to 2MRad [4, 5]. However, these radiation tolerant devices suffer from poor performance with an extremely low cyclability, being able to switch on/off 10 times. For reliable and secure data storage in harsh environments, data must be able to be written and stored continuously without the fear of any loss of information. The improvement in switching performance is the focus of this thesis. This work will look at the fabrication of PECVD memory cells which have the ability to be written and read continuously without fear of losing information. The endurance and stability of resistive memory will be analysed in depth.

Furthermore, will also discuss the use of a single thin film, that can exhibit both volatile and non-volatile behaviour. Such behaviour is useful for Neuromorphic computing, which is inspired by the highly efficient parallel processing of the brain. By using resistive memory to emulate synapse functions it is possible to create highly dense neural

networks. This thesis focuses on the analysis of Short-term potentiation (STP). Understanding STP with a given dielectric is key aspect in creating a neuromorphic computing system and is the first in-depth analysis for SiC-based devices.

The final part of this project will look at the fabrication of Crosspoint structures. Crosspoint structures are the method in which multiple bits of non-volatile memory are connected together, to produce highly dense arrays. These Crosspoint structures suffer from parasitic currents, known as sneakpath, which reduce the possible size of the arrays. This work looks at the optimum fabrication process and the effects of different Crosspoint structures on the electrical characteristics of RRAM memory cells. There is also a detailed analysis of sneakpath to To do this there needs to be a fabrication process that would allow for 100nm Crosspoint structures and an analysis of the current sneakpath problem.

The entire objectives of this project are broken down in the section below.

## Objectives

- Development and characterisation of Silicon Carbide based resistive memory.

- Develop a fabrication process that will enable the emulation of synapse functions

- Characterise analogue switching resistive measurements using DC switching

- Characterise synapse functions using precise pulsing for both the strengthening and weakening of connections between neurons.

- Development and characterisation of Bilayer Silicon Carbide based resistive memory.

- Develop a fabrication process flow that can produce devices with reliable switching characteristics.

- A detailed comparison of IV characteristics using both DC and pulsed switching

- Fabrication and Characterisation of the first SiC based Crosspoint Structure.

- Fabricate Crosspoint structures with 100nm devices

- Analyse Sneakpath in a Crosspoint structure

- Fabricate a 1kb SiC based Crosspoint chip

## Chapter 2

# Resistive Memory Background and Literature Review

This chapter will present the general operation of resistive memory. This is followed by an in-depth literature review of Silicon Carbide (SiC) based resistive memory. After this details on the operation of bilayer memory, neuromorphic computing and the effects of radiation harsh environments on resistive memory will be presented.

## 2.1 Resistive Random Access Memory

There are several candidates that can be used for the next generation of non-volatile memory [3]. Phase Change Memory (PCM) utilise the change in resistivity that occurs when transitioning between an amorphous and crystalline phase [6]. Ferroelectric tunnelling junction (FTJ) and Spin-Transfer Torque Magnetic RAM (STT-MRAM) have also been investigated and utilise the change in the tunnelling current depending on the direction of the ferroelectric or the spin polarisation, which can be changed through an applied voltage [7,8]. However, the most promising of these candidates are Resistive Random-Access Memory (ReRAM) cells. This is because resistive memory can be fabricated using back-end of the line (BEOL) materials. This means that such memory could be fabricated directly on top of transistors, reducing the interconnect delay, and would be compatible with current commercial fabrication processes. This makes integration easier and cost effective. This is in contrast to memories such as phase-change, which require rare-earth elements such as tellurium. Resistive memory have also been shown to be a good candidate for radiation hard memory [9]. Its radiation hardness can be attributed to the use of a ruptured/formed conductive bridge to store information compared to charges in a floating gate that is currently employed in commercially available non-volatile memory technologies [10].

Resistive switching is the characteristic that enables a device with certain materials to change its electrical resistance when exposed to a voltage stress [11]. Studies on this phenomenon have been reported as far back as the early 1960s [12]. The differing resistances can be used to represent logic states, making these devices useful for information storage and computation. A device in the High Resistance State (HRS) usually represents a bit 0. To store a bit 1 the device must be in a Low Resistance State (LRS). Some materials have been found to achieve multiple resistances states, which could be used for processing applications [13–18].

These resistive switching devices possess a similar metal-insulator-metal (MIM) structure to a capacitor. This design allows for the use of simple fabrication techniques to create highly dense memory arrays that can achieve  $4F^2/n$  effective area, where  $F$  is the feature size and  $n$  is the number of stacking layers [19,20]. This high density allows for it to be a good competitor against current commercially available alternatives.

Many different electrode and dielectric materials have been investigated, which can significantly alter the resistive switching mechanisms and I-V characteristics. The most common electrodes that have been investigated include Pt, Ag, Cu, TiN and W [11,18, 21–24]. These metals can be split in terms of their use as an active or inert electrode [25]. An inert metal acts as a standard electrode while an active electrode allows the diffusion or drift of ions to the dielectric which alters the resistance state.

A large range of dielectric materials has also been investigated including chalcogenides, perovskites and 2D materials [26,27]. Research has focused on tuning these materials to achieve a highly efficient performance. Some devices even utilise multiple stacked layers between the electrodes to achieve their desired characteristics [28,29]. The most promising combination of materials are based on a  $TaO_x$  bilayer dielectrics with Pt electrodes. These devices have shown unmatched performance with 10ns switching times, greater than  $10^{12}$  endurance and retention of 10 years at 85°C [30]. This will be further discussed in Chapter 5.

Depending upon the materials chosen for both the electrodes and the dielectric the resistive switching mechanism can be classed into either an interfacial or filamentary device. The latter has a single filament in its On state. The former is attributed to the change in the Schottky barrier height, caused by the accumulation and depletion of carriers at the interface between the electrode and the dielectric [31–33].

A filamentary device, also known as Conductive Bridge Resistive Random Access Memory (CBRAM), utilises the formation and rupture of a conductive bridge through the movement of ions. The device has two resistance states depending upon whether the top and bottom electrodes are connected or disconnected by this filament. This means that the resistance of the cell is not dependent upon the area of the capacitor, but instead, the area of the filament [34]. This filament formation is separated by either cation or anion migration. Anion based CBRAM is referred to as Valence Change Memory

(VCM) and it involves the migration of oxygen ions to create a conductive pathway. Cation migration utilises the migration of ions donated from the top electrode and is known as Electrochemical Metallisation (ECM) [35]. This donation of ions requires the use of an active electrode, described above, and a bottom inert electrode. On the other hand, VCM devices require the use of inert electrodes as the anions are donated from the dielectric material.

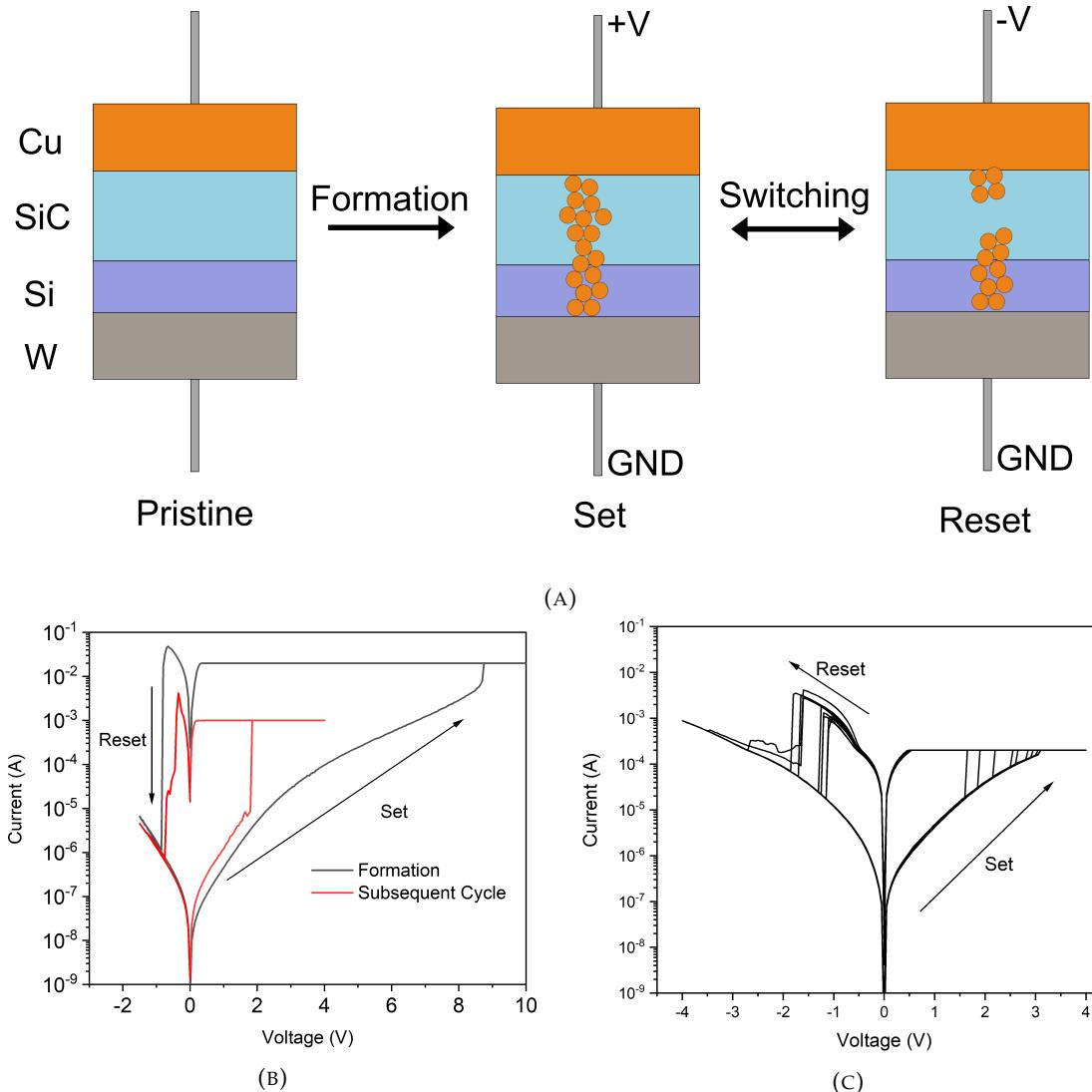

To understand the movement of ions in a CBRAM device we will consider an ECM mechanism with Cu as an active electrode. In its initial state, ECM cells are in the HRS and are usually referred to as being in a Pristine state, as the conductive bridge requires forming. This formation utilises the ion migration described above and requires a voltage bias across the cell. This voltage causes the active electrode to undergo oxidation resulting in mobile cations that can be used to form the conductive bridge. This oxidation is presented in equation 2.1.

Through the presence of a high electric field, due to the applied voltage bias, the cations drift through the solid electrolyte forming a bridge towards the inert electrode [36]. Through electro-crystallisation the Cu ions are reduced on the surface of the inert electrode as shown by equation 2.2.

Once the two metal plates have been connected together the resistance of the cell is reduced and now is dominated by Ohmic conduction. This is known as the Formation of a cell and often requires a higher voltage than is used for subsequent cycles. The lower voltage in the subsequent cycles is due to the conductive bridge being only partially ruptured when moving from the Formation to the HRS. Therefore the conductive bridge requires less overall energy to reform the bridge. This process is also known as a partial dielectric breakdown due to its reversible nature and use of a programming current ( $I_{prog}$ ).  $I_{prog}$  is used to prevent a hard dielectric breakdown which makes the subsequent rupture of the filament impossible. This hard dielectric breakdown is a permanent change.

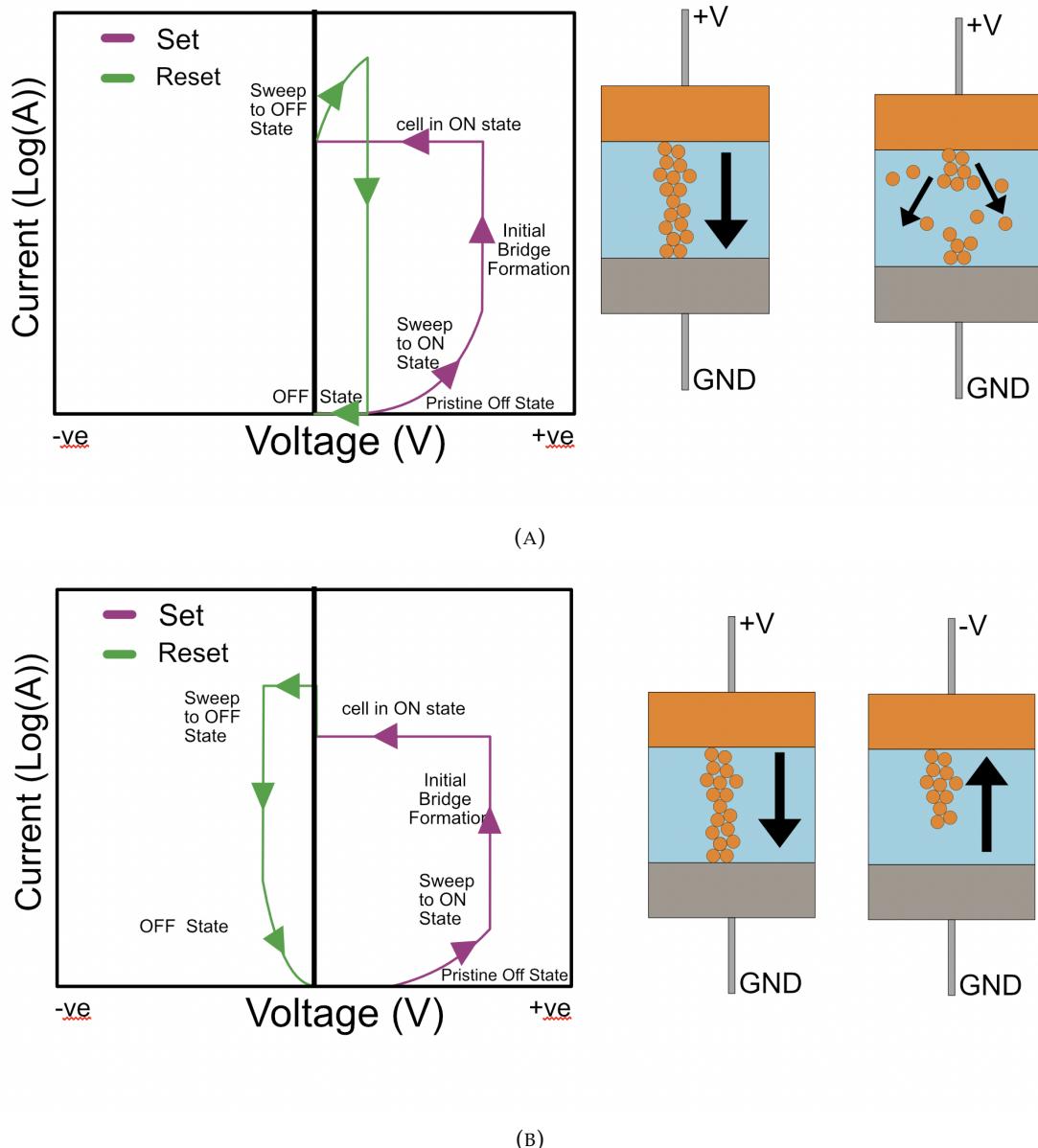

ReRAM devices can also have two operating modes known, depending on the polarity used to reset the device, known as Unipolar and Bipolar switching. Each mode is defined by the method in which the conductive bridge is partially ruptured causing a change in resistance from a LRS to a HRS, as shown in figure 2.1. Operating in a Unipolar mode, the Reset and Set voltages are dependent on the current applied to the cell and not on the voltage polarity [34,37]. Let us consider a device that is currently in

the HRS. If we were to form the conductive bridge, described above, using a positive voltage bias the state of the cell would alter from a HRS to a LRS. The reset for unipolar switching is dominated by a thermal chemical mechanism (TCM). To rupture the filament, a voltage with the same polarity is applied without  $I_{prog}$ . As the current passes the original  $I_{prog}$ , the conductive bridge increases in temperature, due to Joule heating. This rise in temperature within the conductive bridge allows for a thermally-activated Reset though the partial breakdown of the conductive bridge. This breakdown is said to occur in a diffuse manner, as unlike the formation process the ions do not electromigrate [38]. This diffusive rupture of the filament forces the memory cell back into a HRS. Even though this process does not require an  $I_{prog}$ , it is self-limiting due to the rupture of the filament.

The diffusive rupture of the filament is not completely destroyed during this reset process. This is because the whole conductive bridge does not need to be ruptured to switch the cell into a HRS. This means that any subsequent Set voltages applied to the cell would be lower than the initial formation voltage, keeping the overall power consumption lower.

The Bipolar switching mechanism differs from Unipolar in that it is dependent upon the applied polarity between the Set and Reset voltages [39]. Rupturing of the conductive bridge occurs from the electro-migration of ions away from the inert metal plate instead of thermal diffusion. In this method, the opposite voltage polarity is needed to reverse the ion migration that initially formed the conductive bridge. Therefore, if we were to initially use a positive voltage to form the conductive bridge a negative voltage would be required to rupture the filament in a Bipolar switch, to switch the device from a LRS to a HRS. This method enables a lower power operation than Unipolar switching. This method also maintains the partial rupture of the filament meaning that Set voltages after the initial formation are kept lower.

With both of these switching mechanisms in mind, it must be mentioned that a material can exhibit both Unipolar and Bipolar switching. This is known as nonpolar switching and enables the cell to diversify its use in terms of its peripheral circuits [40, 41].

Operating these devices using a DC voltage is extremely slow and requires a large amount of energy when cycling through states. This also provides a large amount of stress to the device which can cause premature failure [42]. Alternatively, short pulses can provide a fast and low-stress method of measuring resistive switching properties. This can also help measure large cycle numbers with devices with high endurance and using this method is also closer to real-world applications. Therefore, investigations in the scalability of these devices can be conducted by reviewing the optimum characteristics of a memory device. These requirements can be broken down into 4 separate categories [37].

FIGURE 2.1: Representation of the two operating modes of resistive switching device

(A) Unipolar switching (i) I-V graph showing the same voltage polarity used without an  $I_{prog}$  (ii) Thermally activated diffusive movement of ions which ruptures the filament between the metal electrodes. (B) Bipolar switching (i) I-V graph showing the same voltage polarity being used for the Set and Reset process. (ii) Drift movement through electro-migration of ions which ruptures the filament.

- The voltages required for the read and write operation. The voltage required to turn the device On/Off should be lower than 5V and allow for overall low power consumption.

- The resistive ratio, which describes the difference in the On/Off current. A large resistive ratio is preferable as it increases the sense margin which makes the potential for reading errors lower.

- The endurance of a memory device is the estimated number of On/Off cycles that can be achieved before a breakdown occurs and the memory can no longer change state. This failure mechanism can be estimated with cycle number by looking at the change in the resistive ratio over cycle number. As the device starts to fail this ratio should reduce. This endurance should be more than  $10^7$  cycles to compete with Flash.

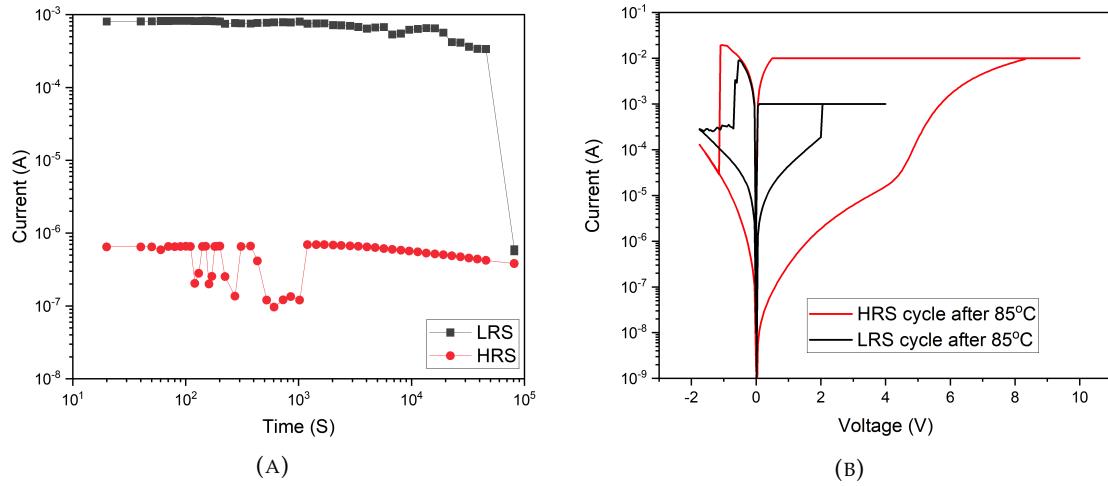

- Retention of the device measures the stability of a device to hold its bit state. The requirement for a non-volatile memory device is the ability to hold its state for 10 years at  $85^\circ\text{C}$ .

These requirements will be investigated in this thesis to accurately determine the potential of the operation of the device for use as a next-generation technology. Notable resistive memories that achieve these requirements are presented in table 2.1. The  $\text{Ta}_2\text{O}_5/\text{TaO}_2$  has shown the highest ever endurance for resistive memory.  $\text{SiO}_2$  is a valence change memory that shows a large resistive ratio between its on and off state, with a much lower endurance.  $\text{HfO}_x$  shows a stable resistive memory with its ability to withstand  $150^\circ\text{C}$  for 10 years. The sputtered SiC shows the largest endurance recorded for SiC (other than this this thesis). The PECVD Si(O)C is a electro-chemical metallization memory that shows one of the highest resistive ratios recorded.

TABLE 2.1: Varying dielectrics that have been investigated for resistive switching devices and their associated ratio, endurance and retention characteristics

| Dielectric                                | Resistance Ratio | Endurance | Retention                       |

|-------------------------------------------|------------------|-----------|---------------------------------|

| $\text{Ta}_2\text{O}_5/\text{TaO}_2$ [30] | $\sim 10$        | $10^{12}$ | 10 years at $85^\circ\text{C}$  |

| $\text{SiO}_2$ [43]                       | $10^7$           | $10^5$    | 6.8 years at RT                 |

| $\text{HfO}_x$ [44]                       | $\sim 10$        | $10^6$    | 10 years at $150^\circ\text{C}$ |

| Sputtered SiC [45]                        | $10^2$           | $10^5$    | 10 years at $85^\circ\text{C}$  |

| PECVD Si(O)C [4]                          | $10^{10}$        | 5         | $10^5$ at RT                    |

## 2.2 SiC-based Resistive Memory Performance

Silicon carbide (SiC) is a material with a low dielectric constant that has been widely investigated for different semiconductor applications, due to its wide bandgap, high

operational temperatures, as well as its mechanical strength, higher chemical and radiation resistance compared to Silicon [46]. SiC is also a promising candidate for Resistive Random Access Memory, due to it already being used in the back-end-of-the-line (BEOL) processes as an interconnect dielectric because it acts as a high diffusive barrier to  $Cu^+$  ions [47]. Utilising BEOL materials such as SiC mean that the fabrication of these cells would be simple and cost-effective, but would also mean the potential for ReRAM to be fabricated directly on top of transistors, reducing the interconnect delay. Therefore, a significant research into BEOL resistive switching materials have been conducted [48–50]. Below is a discussion on the different SiC-based resistive memory devices that have been investigated and are separated in terms of their deposition techniques.

### **Sputtered Amorphous SiC**

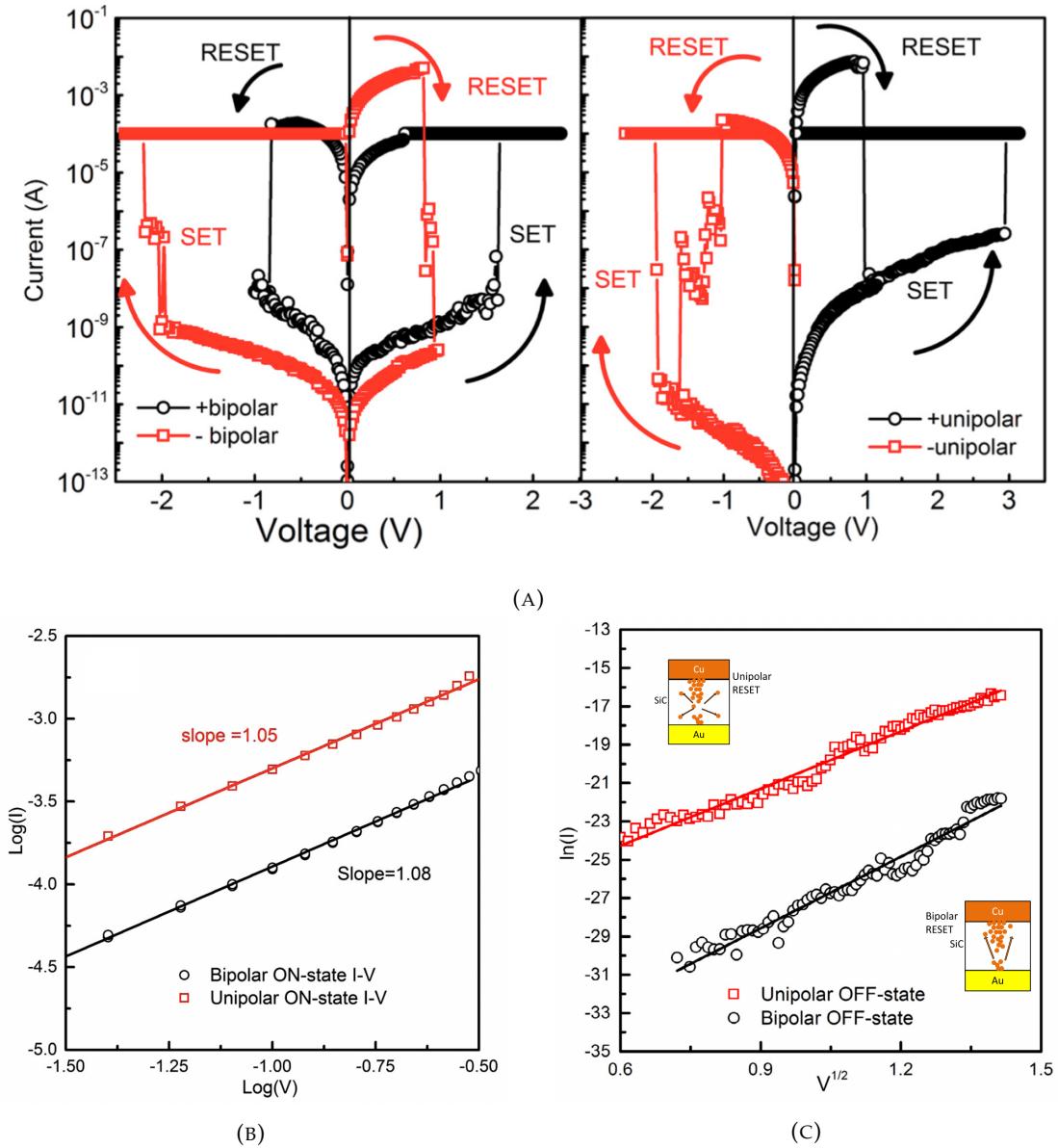

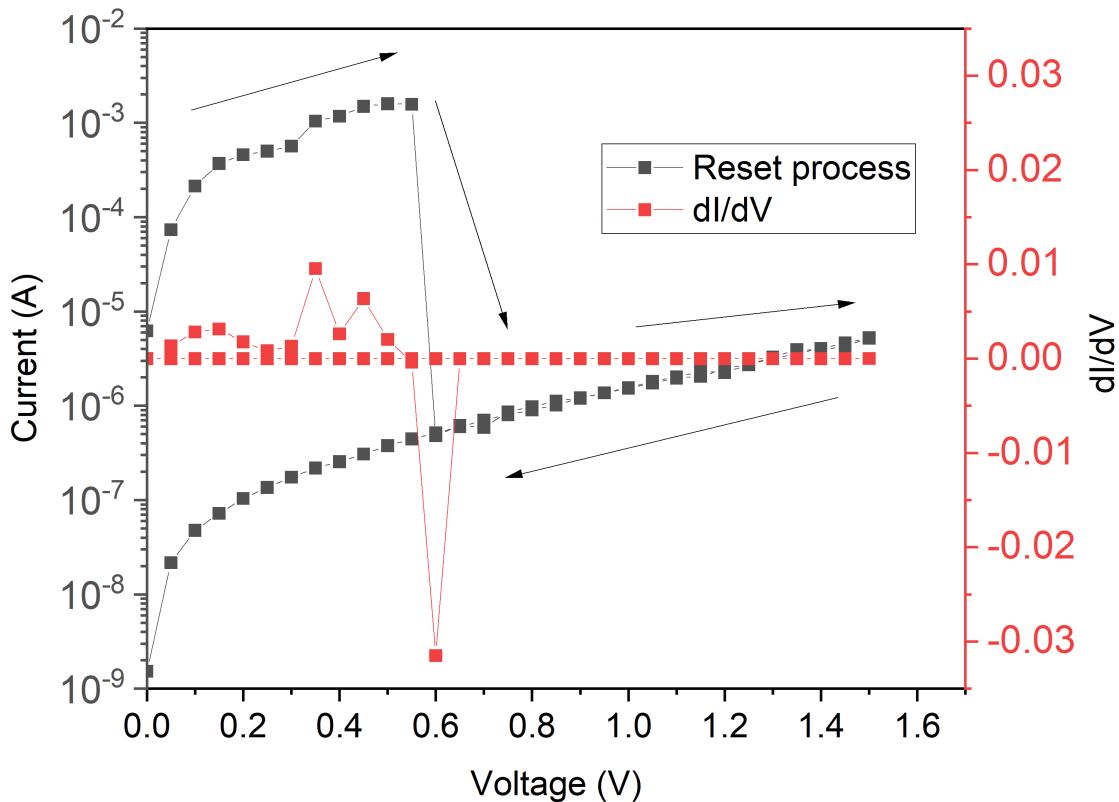

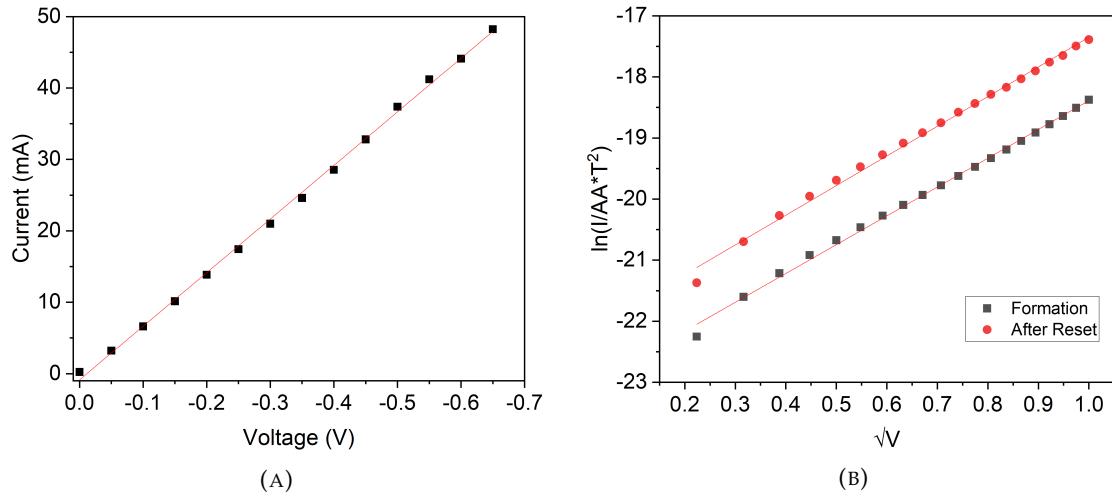

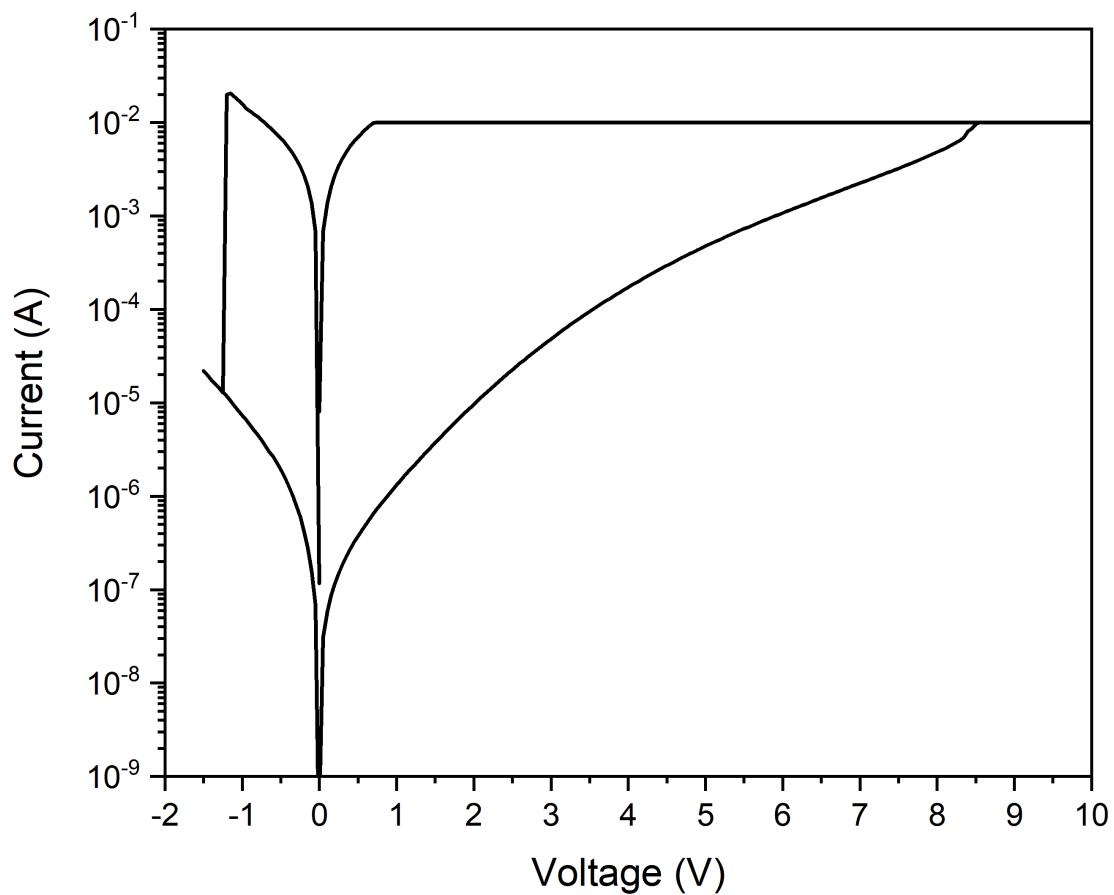

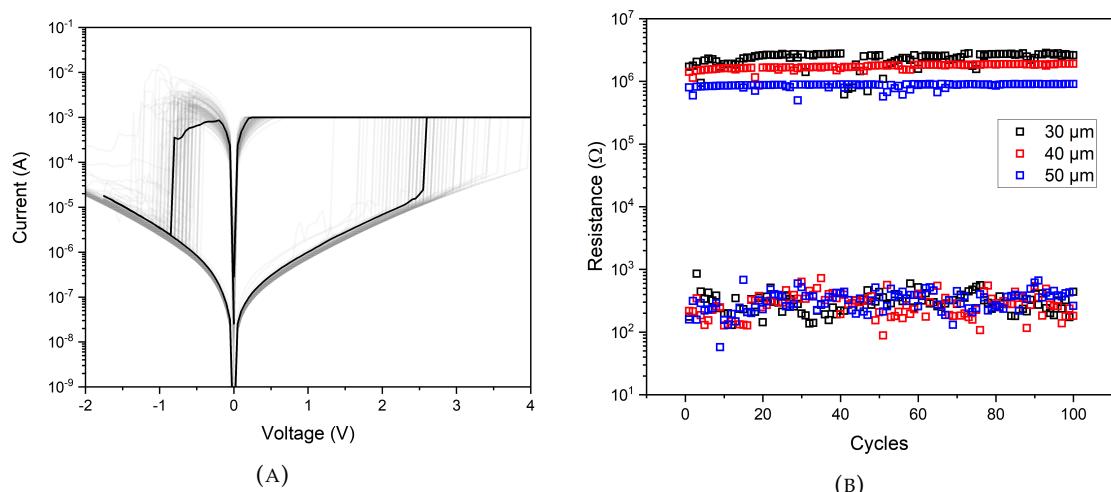

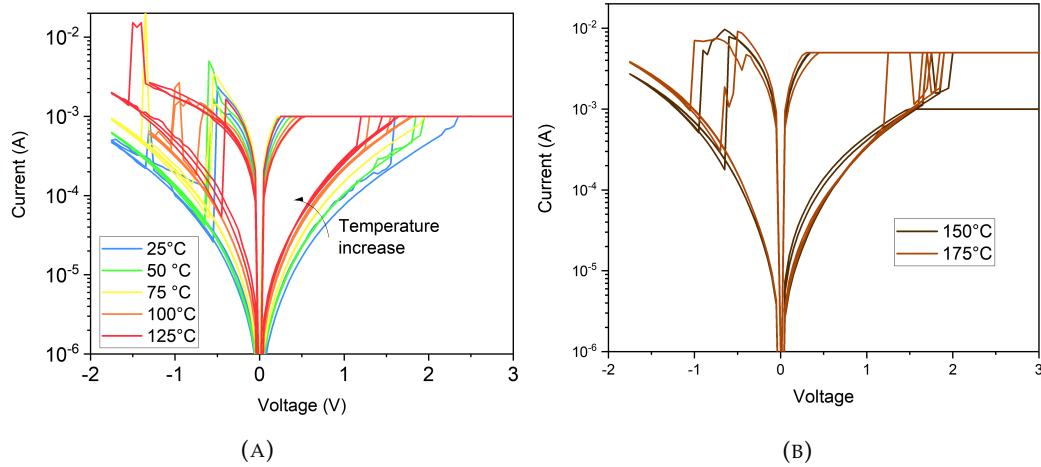

Initial investigations within our group were conducted on Cu/SiC/Au ReRAM devices. This work shows that 40nm SiC-based memory can achieve nonpolar characteristics, as shown in figure 2.2 [41]. This means that the device exhibit both unipolar and bipolar switching. Bipolar switching is controlled through the reversal of electromigration be changing the applied polarity of the voltage bias. Unipolar switching is achieved by increasing the applied current compliance and allowing for the thermal rupture of the filament to take place. It was shown that switching was possible with both a positive or a negative Set for either mechanism. This due to the ion migration of both the Cu and Au, depending upon polarity. This was confirmed through extracting the temperature coefficient of the filaments for both mechanisms. These devices were estimated to able to retain their bit state for over 10 years at  $85^\circ C$  with no loss to information at a resistive ratio of  $10^7$ . Further investigation also showed that these devices could achieve some of the highest resistive ratios known to ReRAM, at  $10^9$  between the on and off state [51]. These extremely high resistive ratios are advantageous as it reduces the chances of reading errors and is thought to originate from the presence of a Schottky barrier between the Cu and SiC layers.

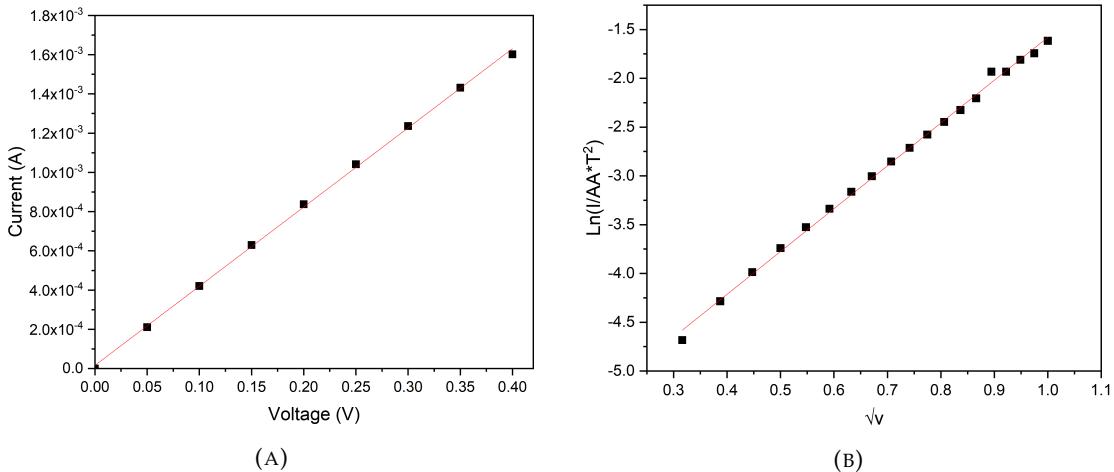

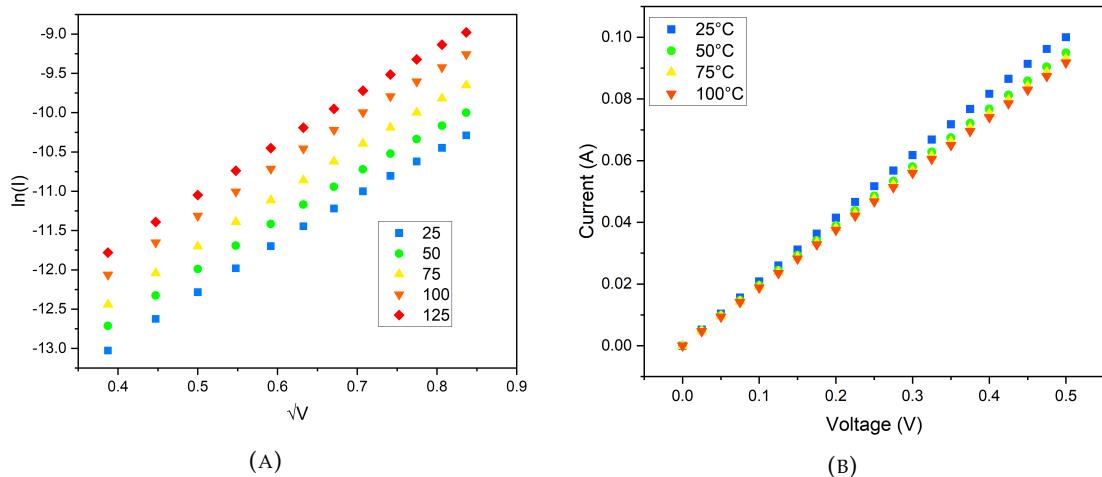

The conduction mechanisms of the On and Off state was analysed, with the former dominated by Ohmic conduction, due to its linear I-V nature. The latter is dominated by Schottky emission and its relationship was found through the Schottky emission equation which can be shown by equation 2.3, where  $I$  is the current,  $A$  is the area,  $T$  is the temperature,  $A^*$  is the Richardson's constant,  $q$  is the charge of one electron,  $k$  is the Boltzmann constant,  $E$  is the electric field,  $\epsilon_I$  is the permittivity and  $\phi_B$  is the energy barrier height.  $A^*$  is equal to  $4\pi mek^2/h^3$ , where  $m$  is the mass of electron,  $e$  is elementary charge, and  $h$  is Plank's constant. It should be noted that this constant is multiplied by a correction factor which depends on the material.

FIGURE 2.2: Characteristics of sputtered SiC resistive memory (A) nonpolar resistive switching characteristics, with the device being able to Reset using both the same and opposite voltage polarity [41]. (B)  $\log(I)$ - $\log(V)$  graph showing that Ohmic conduction is the dominant mechanism in the LRS [51] (C)  $\ln(I)$ - $\sqrt{V}$  graph showing that Schottky emission is the dominant mechanism in the HRS [51]

$$I = AA^*T^2 \exp\left[q\left(\phi_B - \frac{\sqrt{\frac{qE_I}{4\pi\epsilon_I}}}{kT}\right)\right] \quad (2.3)$$

The above equation can be rearranged to form equation 2.4, where V is the voltage and d is the distance between the top and bottom electrode in the pristine state, or the distance between the filament and the bottom electrode at the subsequent state. This equation can be used to see if the off-state fits a linear curve when plotting  $\ln(I/AA^*T^2) - \sqrt{V}$  graph. This is expected as the SiC dielectric in the device is also widely used for Schottky diode applications [52].

$$\ln\left(\frac{I}{AA^*T^2}\right) = \frac{q\sqrt{\frac{q}{4\pi\epsilon_Id}}}{kT}\sqrt{V} - \frac{q\phi_B}{kT} \quad (2.4)$$

Characteristics of these devices were also investigated with an alteration of the inert electrode. By using W instead of Au it was found that the Off state resistance could be further increased [18]. This is thought to be due to a possible Oxide barrier that could have formed on the W/a-SiC surface, due to its high affinity to  $O_2$  than Au. This not only produces ultra-high ratios but can also enable low power use.

Both the Au and W electrodes devices were also shown to have multi-level states that were controlled by the  $I_{prog}$  in the Set operation [53]. By varying the applied current compliance during the Set process, the LRS can be controlled between  $10M\Omega$  and  $1K\Omega$ . The diameter of the filament was extracted to be around 1nm for the W and 4nm for the Au electrode. The lack of area dependency in the On state confirmed the filamentary nature of these devices.

Further analysis of the Cu/a-SiC/Au device show extreme radiation-hardened characteristics, with no changes to the resistive ratio and conduction mechanisms against up to 2MRad of  $\gamma$ -radiation [5]. It indicates that this form of memory is well suited for such extreme environments and that the radiation-sensitive areas within such a memory system would be the peripheral circuitry.

Looking at the varying thicknesses of sputtered SiC dielectrics, between 50 and 100nm, it has been shown that an increase in the thickness increases the formation voltage [54]. This is due to the increase in the distance required, for the initial formation of the conductive bridge. Pt, W and Ag were investigated as top electrodes, with the bottom electrode being Au, however, these devices suffered from extremely low endurance of fewer than 60 cycles.

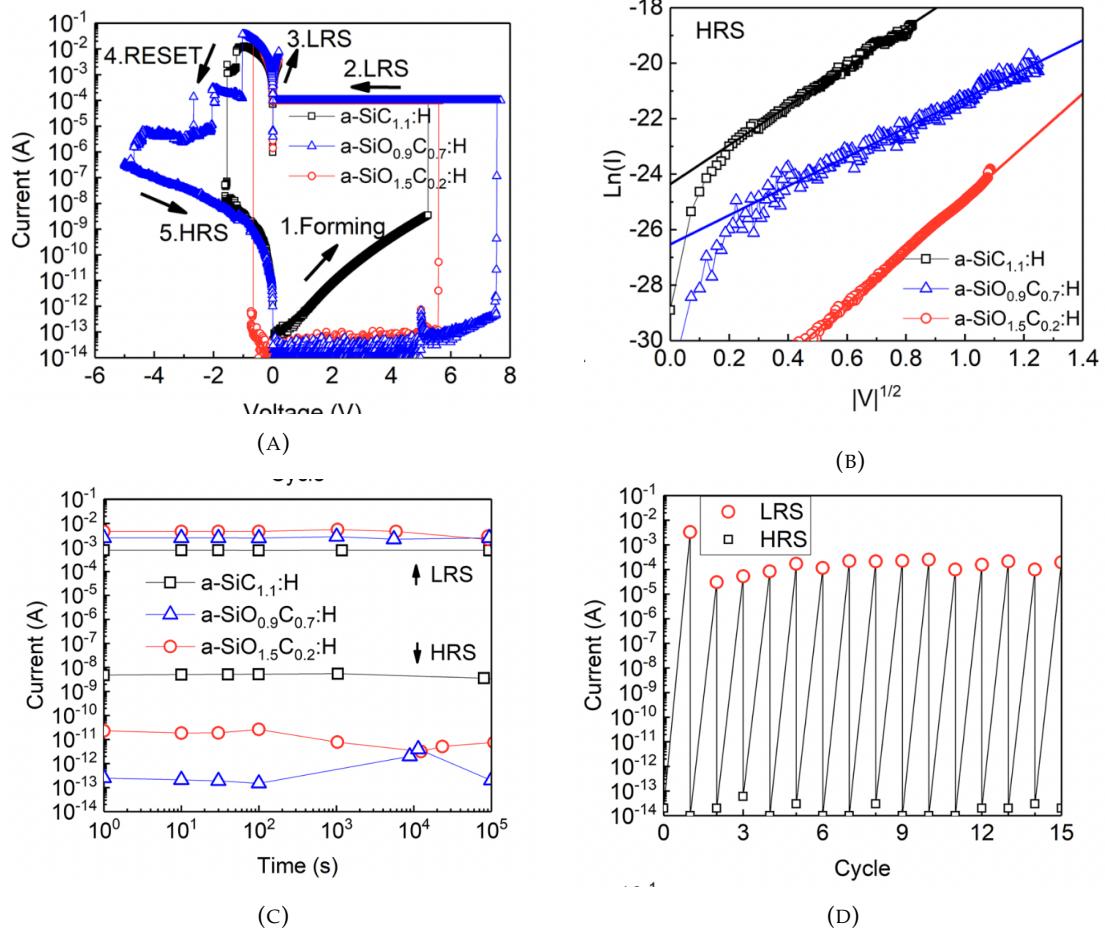

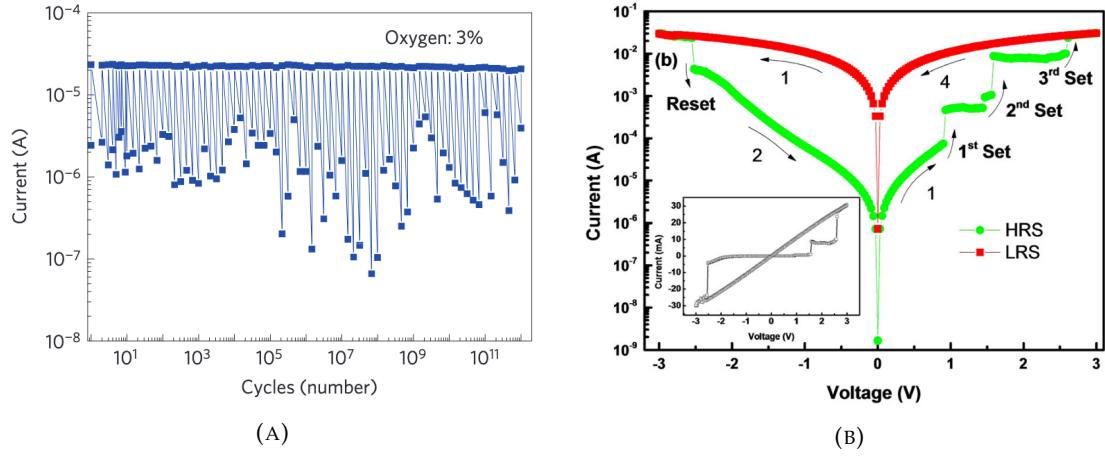

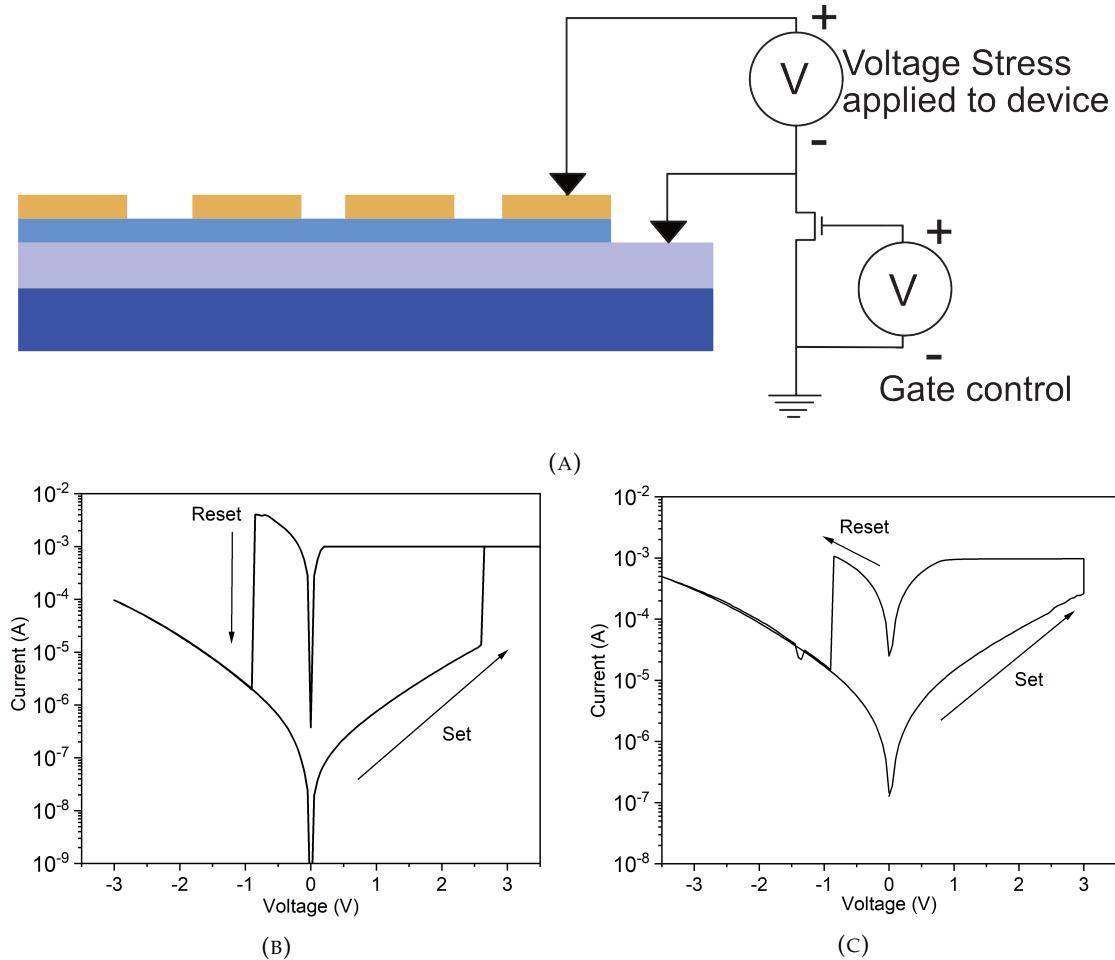

Currently the most promising sputtered SiC-based ReRAM in literature is based on 40nm of sputtered SiC with an active Cu and an inert Pt electrode, as shown in Figure 2.3a. These devices on their own have shown  $10^5$  switching cycles with two orders of

FIGURE 2.3: (A) Largest endurance measured of SiC-based resistive memory [45] (B) I-V graph showing the increase in resistive ratio and reduction in the switching voltages by adding a  $Ge_2Sb_2Te_5$  thermal barrier [55]

magnitude On/Off ratio [45]. By adding a  $Ge_2Sb_2Te_5$  thermal barrier layer the switching voltages were decreased, as shown in figure 2.3b. These devices also showed reduced switching times from 10 $\mu$ s to 500ns [55]. As SiC is usually seen as a slow form of memory for ReRAM devices, this opens the possibility to be able to significantly reduce the switching times.

### Chemical Vapour deposition of SiC, SiOC and SiCN

Other deposition method have been investigated for SiCN using both PECVD and ALD. 10nm of SiCN sandwiched between Indium Tin Oxide (ITO) and AZO has shown switching characteristics with resistive ratios larger than  $10^3$  for  $10^6$  cycles [56]. These devices exhibited ion migration as its switching control mechanism, with confirmation from TEM images. A similar dielectric with Cu/Ta as the top electrode show resistive switching, however, with an extremely poor endurance with DC switching failing before 200 cycles [57]. With the addition of an  $Al_2O_3$  thin film in between the dielectric, the endurance is enhanced and the cell is able to switch up to  $1.6 \times 10^4$  times.

15nm of  $SiC_xN_y$  deposited through plasma-enhanced atomic layer deposition (PEALD) at 30W provided resistive switching characteristics with a ratio of 2 orders of magnitude for 30 cycles [58]. Depositing the same thin film at 50W, however, provided volatile threshold switching. This type of switching can be used for a device known as a selector. Selectors will be discussed in depth in chapter 6, but it is important to note that SiC-based devices can exhibit both volatile and non-volatile behaviour.

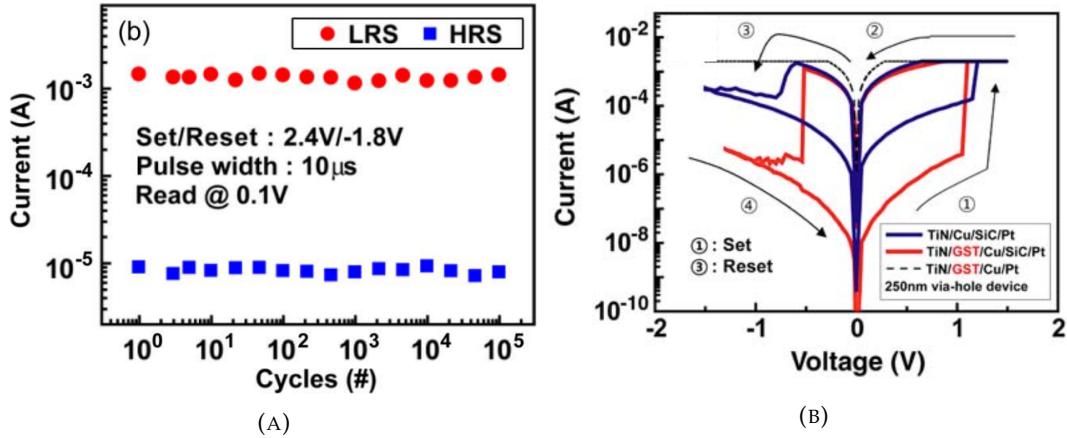

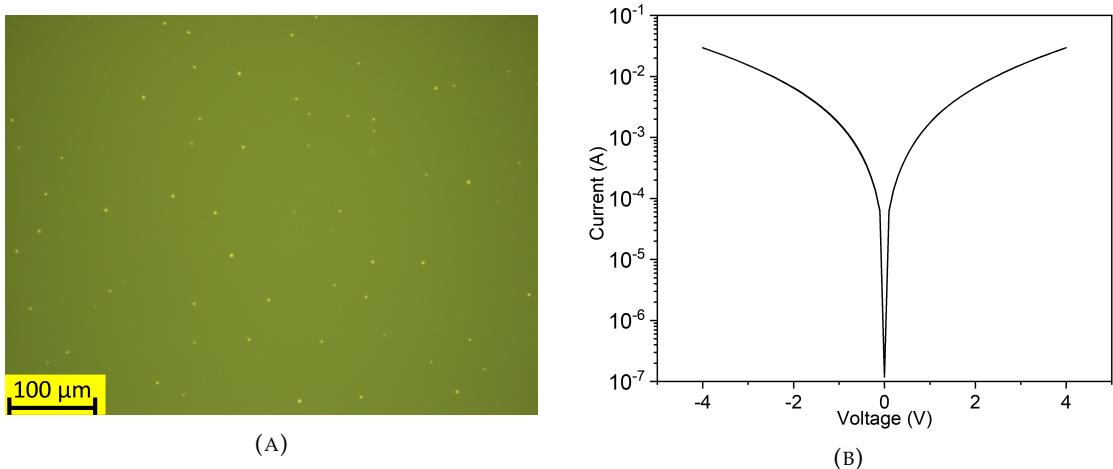

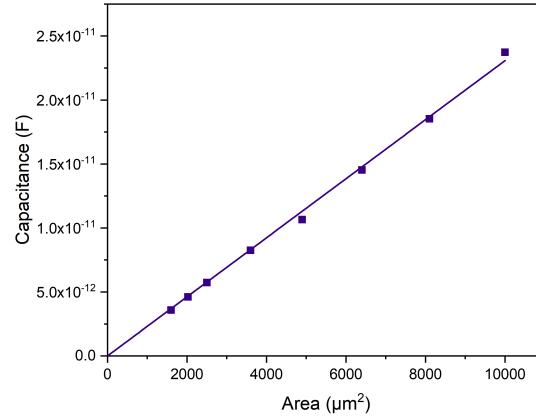

Previous work has been conducted in our group, in collaboration with Intel [4]. PECVD  $SiO_xC_y$  films were provided by Intel and the top electrodes were patterned and deposited in Southampton. I contributed to the measurement of the resistive switching

FIGURE 2.4: Resistive switching devices with dielectrics of varying oxygen content. (A) Formation of each device (B)  $\ln(I) - \sqrt{V}$  showing Schottky conduction is the dominant mechanism in the HRS (C) Retention of the LRS and HRS (D) Endurance of 15 cycles. [4]

characteristics of these devices, which have a simple  $Cu/SiO_xC_y/W$  structure that allow for Cu ion migration. Varying levels of oxygen was investigated with x equal to 0, 0.9 and 1.5, and y equal to 1.1, 0.7 and 0.2 respectively.

It was shown that the lowest formation voltage was achieved for devices without oxygen, as shown by the formation graph in figure 2.4a. The Set voltages were also lower for these devices. However, the dielectric with the highest oxygen content had the lowest reset voltages. It was also shown that as we increase the oxygen content the resistive ratio also increases from  $10^6$  up to  $10^{10}$ . This is due to an alteration of the HRS caused by a change in the Schottky barrier, as shown in figure 2.4b.

These devices show promising performances with some of the highest resistive ratios recorded and with retention measured at  $10^5$  seconds. However, these devices show poor cyclability with the largest number measured being 15. Therefore, further improvement to these types of dielectrics need to be made.

## Physical deposition of SiC and derived structures

Other methods of ReRAM based SiC has been investigated using polymeric composites embedding SiC powders, which were fabricated from a tire recycling process [59]. These devices, however, only had a ratio of 1 to 2 orders of magnitude change and endurance of 10 cycles, with extremely large switching voltages around  $\pm 25V$ .

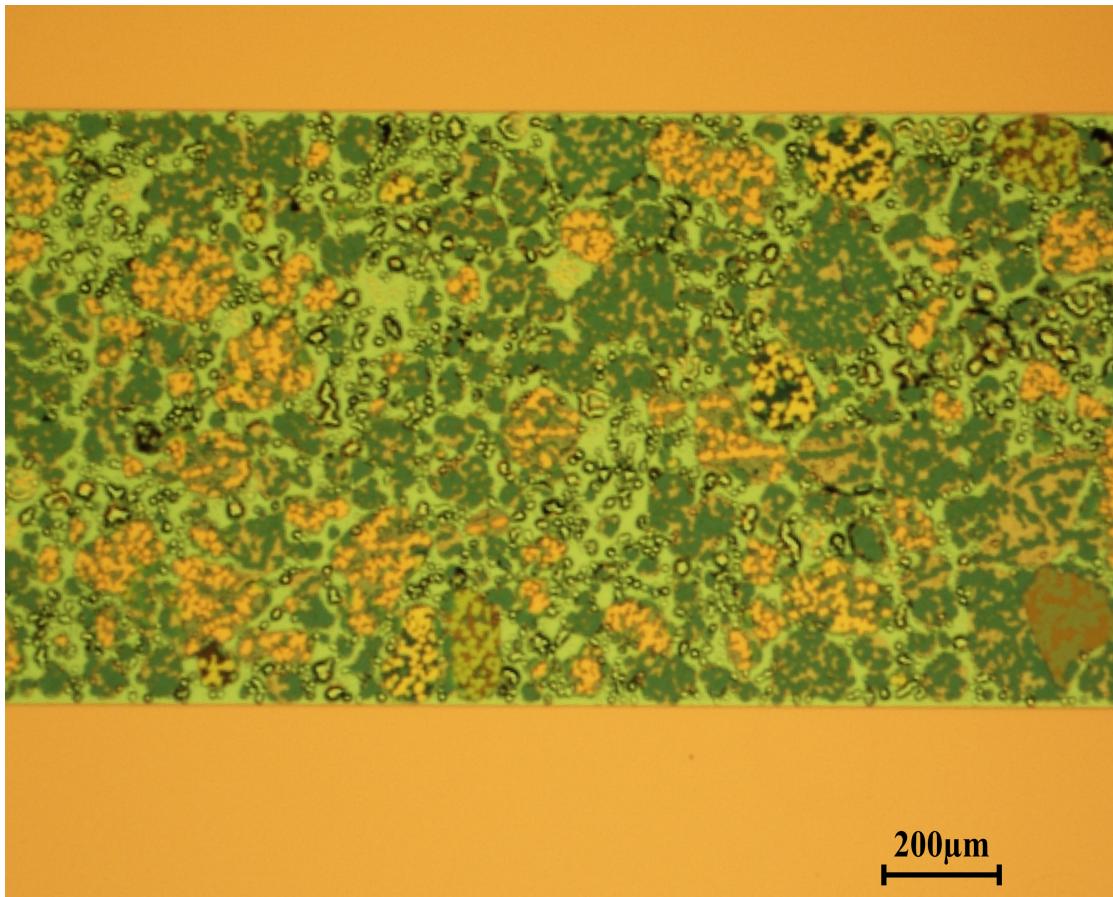

Alternate SiC structures have also been investigated, which shows that there is the potential for increased performance, compared to previously mentioned devices. Cu was co-sputtered with the SiC dielectric to see if there were any effects to the switching mechanisms, depending upon concentration [60, 61]. The percentage of Cu nanoparticles in the thin film was controlled by adjusting the target RF and DC power. It was found that an increase in the concentration provided reduced formation and Set voltages. It was also found that an increase in the concentration also increases the endurance of the devices from 12 to 60 cycles, with a change of 0 – 30% of the nanoparticles.

Silicon oxycarbide (SiOC) has also been investigated using sputtered films [62]. Sputtered SiOC with varying amounts of oxygen increasing 0 to 2% has shown an increase in the resistive ratio by 8 times and all samples were able to reach over 200 DC switching cycles. However, the device structure  $Ag/SiC_xO_y/p^+ - Si/Al$  requires the use of a heavily boron-doped substrate in between the metal electrodes. This can cause scalability issues, especially considering that standard ReRAM structures can be fabricated on any type of substrates.

Similar research has also shown the effects of Boron doping within the SiC based dielectrics in  $Ag/Si_xC_{1-x}/p\text{-Si}$  resistive switching cells [63]. The Boron doped devices show reduced switching voltages with a similar resistive ratio of around  $10^4$ . However, in this case the silicon substrate is being utilised as a back contact, which still provides the same scalability issues.

Tri-layer stacked Al/SiC/Ag/SiC/Al was also investigated to look at an enhanced performance [28, 64]. 10nm of SiC was used for both layers with the Ag thickness varied. It should be noted that these devices were not sputtered but instead utilised a pulsed laser deposition technique. These devices showed electro-free forming characteristics with ratios of  $10^2$  and endurance of over 100 cycles. The HRS is dominated by electron trapping/de-trapping and the switching voltages vary depending upon the concentration of the Ag nanoparticles.

Other methods of altering the SiC dielectric have also be investigated, for example using SiCN [65]. SiCN that was sputtered with a device structure of Cu/SiCN/Pt has shown bipolar switching with an endurance of  $10^5$  cycles at a ratio of  $10^3$  and retention of  $10^4$ s at  $200^\circ C$ . As with the previous dielectrics 40nm was deposited and the LRS was shown to be due to Ohmic conduction, however, detailed analysis of the HRS showed

no Schottky emission and instead space charge limited conduction (SCLC) mechanism. This means that the formation and rupture of the filament would not involve the movement of Cu ions, but instead of electron trapping/de-trapping caused by the Nitrogen ions. This was confirmed with temperature dependent tests.

Further investigations looked at using 30nm of the sputtered SiCN dielectric with W and Ag top electrodes [13]. It was shown that the device using W as the top electrode exhibited similar properties to the previously described measurements, with SCLC dominating in the HRS. The device with Ag as the top electrode, however, exhibited 3 separate resistance states. The first two are attributed to the electron charge trapping and de-trapping, while the third state is attributed to the formation of an Ag filament. This was confirmed through temperature dependent tests and shows the large change in characteristics and mechanisms that can occur with small alterations in the device structure.

A summary of the best SiC-based resistive memory is shown in table 2.2. This table includes memories with the highest reported endurance, ratios and retention for SiC-based devices. We can see that overall the retention properties of SiC is great for all SiC-based memories, due to the stable nature of the conductive filament. The resistive ratios are also greater than or equal to 2 orders of magnitude. However, there is no resistive switching memory with an endurance greater than  $10^6$  cycles. For operational memory we must have an endurance greater than this value, to be able to write continuously without the fear of loss of information. To improve this, bilayer resistive memory can be investigated. The theory of this is presented in the next section.

TABLE 2.2: Summary of the best SiC-based resistive memory from literature and their characteristics

| Structure    | Deposition | Resistive Ratio    | Endurance | Retention               |

|--------------|------------|--------------------|-----------|-------------------------|

| Cu/SiC/Pt    | Sputtered  | 100                | $10^5$    | 150°C for $10^4$ s [45] |

| Cu/SiCN/Pt   | Sputtered  | $10^3$             | $10^5$    | 200°C for $10^5$ s [65] |

| Cu/Si(O)C/W  | PECVD      | $10^6$ - $10^{10}$ | 15        | RT for $10^5$ s [4]     |

| ITO/SICN/AZO | PECVD      | $10^3$             | $10^6$    | 130°C for $10^5$ s [56] |

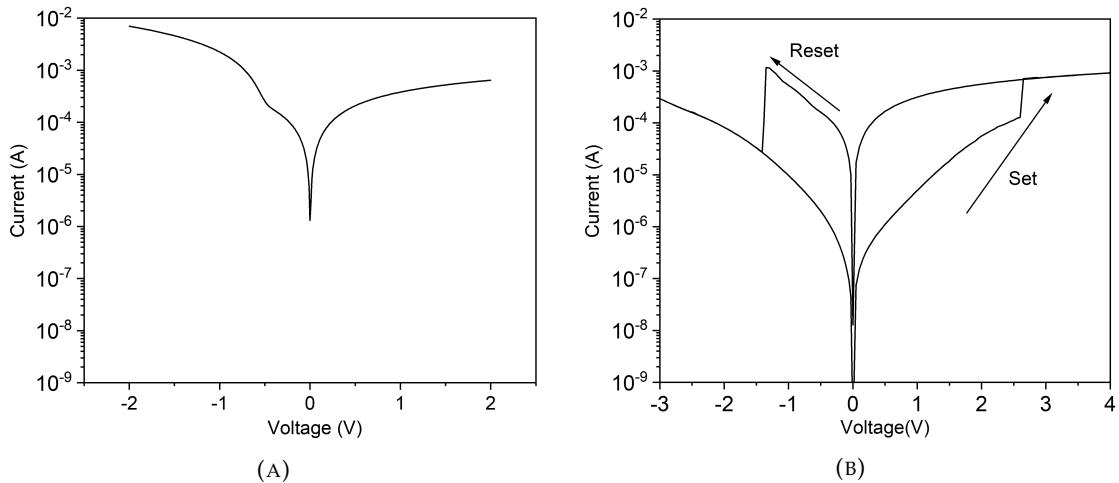

## 2.3 Bilayer Resistive Memory

Depositing multiple dielectrics in between two metal electrodes can provide a variety of performance enhancements to RRAM devices. In the above section we discussed how GST was used as a thermal barrier layer to reduce the switching time from  $\mu$ s to ns, of sputtered SiC based devices [55]. As well as this, a comparison of Ti/SiC/Pt and Ti/ $HfO_x$ /SiC/Pt has also been conducted [66]. These devices utilise 45 nm of SiC, which was deposited by RF magnetron sputtering. The  $HfO_x$  layer was utilised a

FIGURE 2.5: Switching characteristics of Oxide-based Bi-layer RRAM devices (A) Enhanced endurance of  $10^{12}$  cycles using  $\text{Pt}/\text{Ta}_2\text{O}_{5-x}/\text{TaO}_{2-x}/\text{Pt}$  [30] (B) Multi-state switching controlled through the SET operation  $\text{Au}/\text{TiO}_x/\text{TiO}_{2-x}\text{Au}/$  [68]

solution based spin coating technique. Both devices were able to switch over 500 cycles using DC sweeps and the addition of the  $\text{HfO}_x$  layer increased the resistive ratio from 2.78 to 14. The increased in resistive ratio using the bi-layer dielectric is due to the increase in resistance of the HRS, which is inherent to the properties of the dielectrics used. The switching voltages also seem to lower slightly by adding the  $\text{HfO}_x$  layer. However, this change is small with the single and bilayer having an average Set voltage of 1.05 V and 0.92V, and Reset of -0.99V and -0.83V respectively.

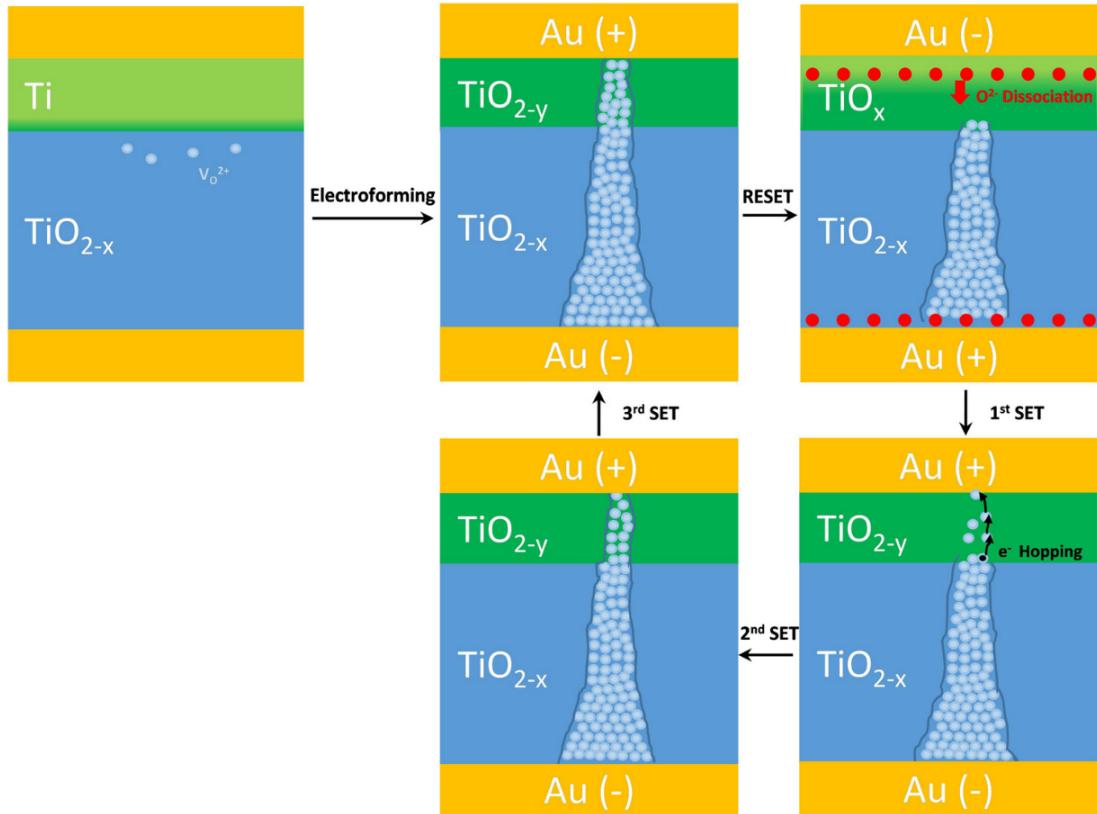

Other uses of bi-layer structures are found heavily in oxide-based RRAM. Utilising an Oxygen rich and poor layer has shown to give an unmatched endurance for resistive switching memory using  $\text{Pt}/\text{Ta}_2\text{O}_{5-x}/\text{TaO}_{2-x}/\text{Pt}$ . This is shown in figure 2.5a which shows the endurance of such a memory which switches on and off  $10^{12}$  times and is currently the world record for resistive memory [30].

This enhancement in performance was analysed using both electrical characterisation and numerical modelling in  $\text{TiN}/\text{Ti}/\text{TiO}_{2-x}/\text{TiO}_{2-y}/\text{Au}$  RRAM devices [67]. Through increasing the oxygen concentration of the top layer and keeping the bottom layer constant, it was possible to tune the resistive switching characteristics, for example altering the resistive ratio. Further investigations into  $\text{Au}/\text{TiO}_x/\text{TiO}_{2-x}/\text{Au}$  devices show that by altering the compliance current, the conductive filament will form multi-level states controlled in the SET process [68,69]. These multi-level switching steps also have a self-compliance behaviour, as seen in figure 2.5b. This figure shows that through increasing the voltage bias in the Set process, we are able to achieve 3 stable states.

These multi-level steps are thought to be the alteration in the number of vacancies in the oxygen poor thin film. This is presented in figure 2.6 and also applies to electro-chemical metallization, but instead of oxygen vacancies it is the movement of metal ions. The first image shows the resistive switching cell to be in the pristine state. By

applying a voltage across the device we are able to form the conductive bridge through the bilayers. Reversing this polarity ruptures the filament in the oxygen poor thin film. This HRS state would be interfacial, as the resistance depends upon the area the entire top thin film. With a small increase in bias we are able to move a small amount of oxygen vacancies back through the top layer. The effective doping reduces the barrier height and we end up with a new multi-state, that is still interfacial. By further increasing this bias we are able to connect the two electrodes with a thin conductive bridge, allowing us to be in a second multi-state. This is no longer interfacial as the conduction is occurring directly through the filament. Increasing the width of this filament, through increasing the bias, provides us with the final multi-state, which is the same as the initial LRS after electroforming. This shows that the bilayer allows for a region in which the ion migration can be manipulated and hence allow for precise control of the resistance state. This control and fine tuning increases the stability of our RRAM memory cell overall, as we see below.

FIGURE 2.6: Representation of the different filament growth from multi-state switching from pristine state to each subsequent multi-level state [68]

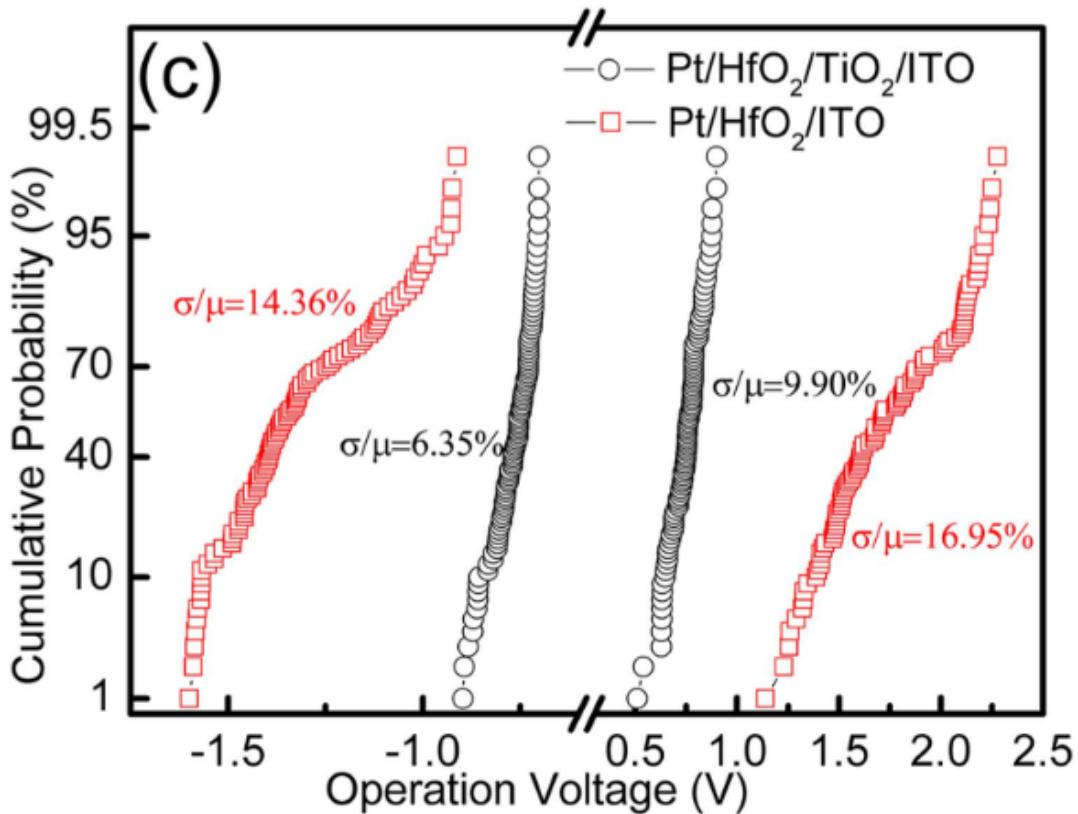

A direct comparison of the a single and bi-layer device was also conducted, using  $\text{Pt}/\text{HfO}_2/\text{TiO}_2/\text{ITO}$  and  $\text{Pt}/\text{HfO}_2/\text{ITO}$  RRAM devices [70]. It was found that the bi-layer reduced the voltages for both the Set operation. As well as this, the cumulative probability plot in figure 2.7 shows that the bilayer causes the gradient of the plot to

become steeper. This means that the standard deviation between the measured switching voltages improves drastically. The uniformity of the resistive switching states was also greatly improved, due to the stabilised filament formation and rupture at the interface of the two dielectrics. TiN/ZrO<sub>2-x</sub>/ZrO<sub>2</sub>/TiN based devices showed the ability

FIGURE 2.7: Increase in uniformity of the resistance states of a bi-layer (Pt/HfO<sub>2</sub>/TiO<sub>2</sub>/ITO) compared to a single thin film RRAM device (Pt/HfO<sub>2</sub>/ITO) [70]

to be switched using both a positive or negative SET polarity, through bipolar switching [71]. The positive polarity provided a greater uniformity in both the switching voltages and the distribution of the resistance states, compared to the negative polarity. As well as this, the negative polarity and a single layer device of the same materials (TiN/ZrO<sub>2</sub>/TiN) showed near identical switching characteristics. This was thought to be due to the possibility of being able to form a stronger filament when connecting a conductive bridge directly to the metal electrode. The depleted Oxygen thin film allows for confinement of the filament size. It was also found that by adjusting the oxygen content of the depleted thin film, the switching characteristics could be tuned. By decreasing x the resistive ratio increased.

Pt/Ga<sub>2</sub>O<sub>3-x</sub>/SiC/Pt has also been investigated and showed that the conduction mechanism still utilised oxygen vacancies [72]. It is thought that these vacancies drift through the SiC layer due to both diffusion and drift. In comparison with a previously reported Pt/GaO<sub>1.3</sub>/Pt device, there is an increase in the resistive ratio from 2 to 10<sup>3</sup> [73]. The

retention of the device also greatly improve, with no degradation observed over  $10^4$  seconds.

There have also been investigations into poly-crystalline SiC bi-layer based RRAM devices. Au/SiO<sub>2</sub>/SiO<sub>x</sub>/3C-SiC/n-Si/Al based devices showed an endurance of  $10^4$  cycles, whilst Au/Al<sub>2</sub>O<sub>3</sub>/3C – SiC/n – Si/Al devices have an endurance of  $10^5$  cycles [74, 75]. Even though these devices exhibit good cyclability, their resistive ratios were less than 10.

Other materials have also been investigated, for example TaN/ZrO<sub>2</sub> / HfO<sub>x</sub>/TiN, which has shown fast switching speeds of 40ns with  $10^7$  cycles, along with the multi-SET process [76]. As well as this, multi-layer devices can also be used to alter I-V characteristics, so that they show a diode-like behaviour [29, 77, 78]. This characteristic is preferable when combining individual bits together into Crosspoint structures. These types of devices will be discussed in depth in Chapter 6.

Investigations into Tri-layers have also shown promising characteristics, with metal nanoparticles being co-deposited with their corresponding dielectrics. A study on SiC/Ag/SiC showed that depositing Ag for 100 and 200 seconds yielded forming free devices highly asymmetrical characteristics suitable for Crosspoint structures [28].

TiN/ZrO<sub>2</sub>/ZrO<sub>2-x</sub>/ZrO<sub>2</sub>/TiN devices also exhibited forming free switching and both interfacial and filamentary switching was observed [31]. The two mechanisms were controlled depending upon the applied voltage bias. The interfacial devices exhibited improved deviation of the resistance states, while also exhibiting lower currents with similar resistive ratios.

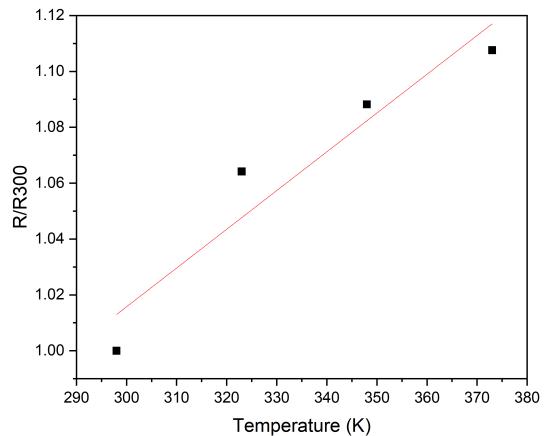

With all this in mind, it can be clearly seen that by utilising bi-layer dielectrics in resistive switching devices, it is possible to both improve and tune varying electrical characteristics. This chapter looks at the use of Si/SiC bi-layers for enhanced endurance, for the use in radiation harsh testing. The next section will look at the characterisation setup that was developed to measure these devices.

## 2.4 Theory of Neuromorphic Computing

Neuromorphic computing is inspired by the highly efficient and unmatched parallel performance of the brain. Current computer architectures separate its memory and processor, therefore, time and energy are spent fetching data, computing the necessary information and writing it back to storage. This constant movement between processor and memory can limit the efficiency and overall computation power of a system. This is known as the Von-Neumann bottleneck [79, 80].

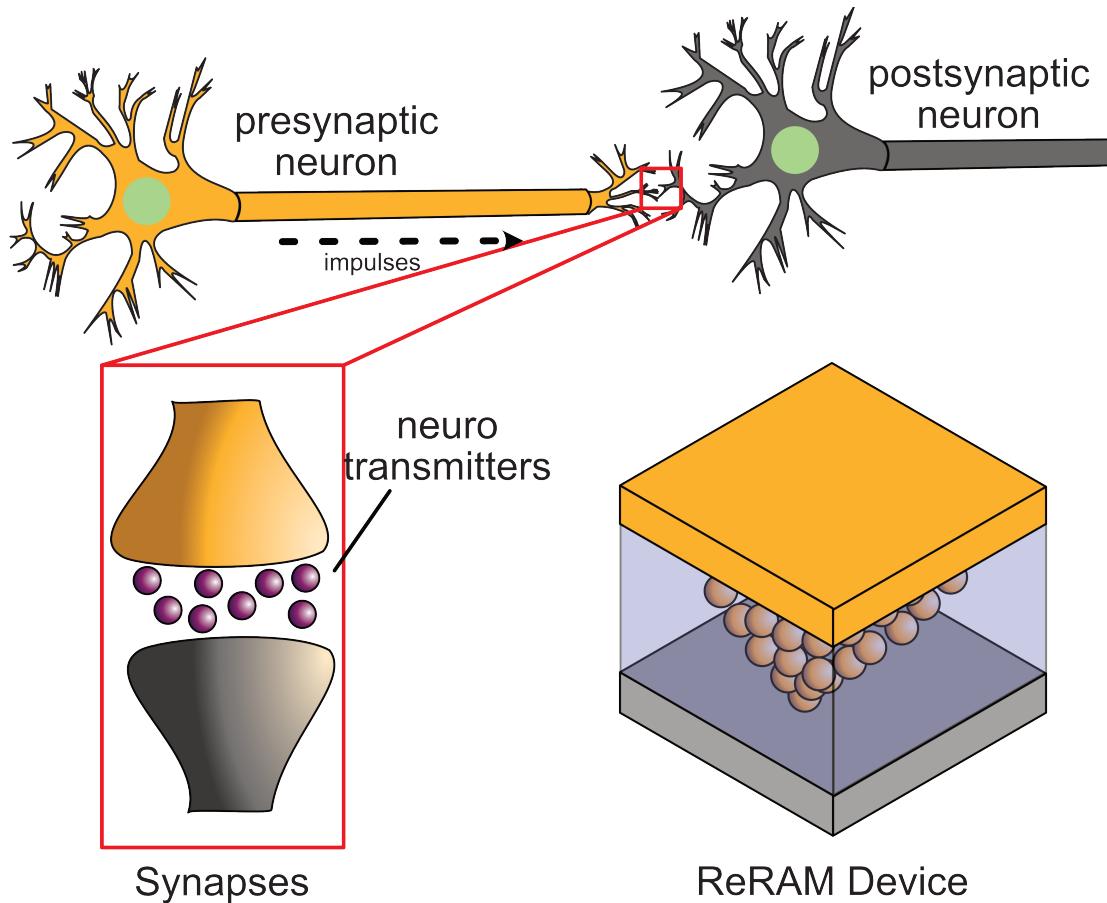

FIGURE 2.8: Illustrations showing the pre and postsynaptic neurons and the direction in which the impulses of the action potentials move across a neuron. The zoomed-in portion shows the synapse connects ion with neuro-transmitters diffusing across to alter the conductance state. Next to this is a RRAM device with Cu ions diffusing to change its conductance state.

The brain manages to store information and compute complex problems, such as language processing, in parallel while only utilising around 20W of energy. For context, the BERT supercomputer is designed as a state of the art neural network for language processing and can train for 80 hours, using around 1000kWh of energy, whilst the brain would use the same amount of energy over 6 years [81]. Therefore, we can see that the future of high-performance computing is to emulate the functions of the brain. This type of system is known as neuromorphic computing and has the potential for highly efficient and fast artificial intelligence (AI) processing [82].

To understand how neuromorphic computing works we first must understand how the brain functions. The brain consists of neurons that are connected by synapses, as shown by figure 2.8. Neurons communicate through electrical signals known as action potentials. These are alterations in the voltage across the membrane due to the movement of potassium and sodium ions. These action potentials reach the synapse which regulates the flow of information in the brain. This is done by the formation of new, discarding redundant or altering the strength of pre-existing synapses. This is done

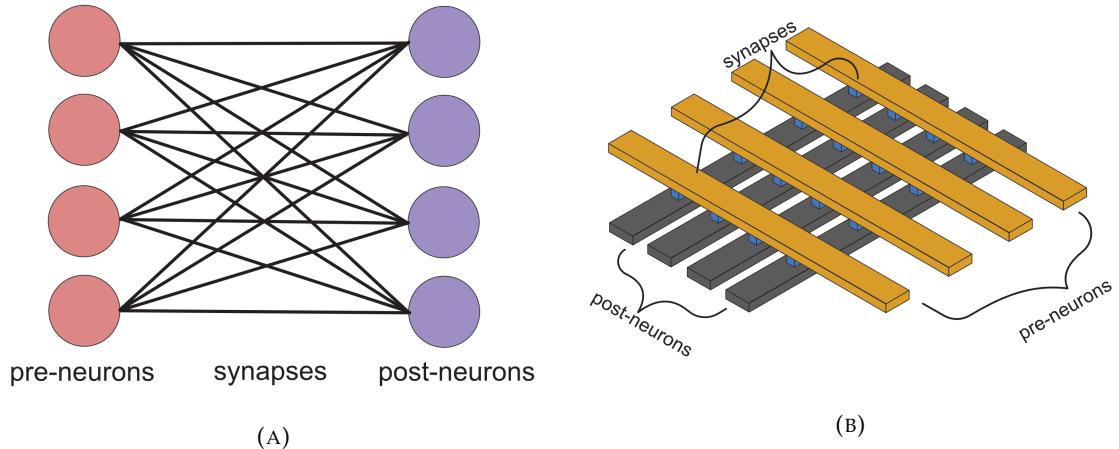

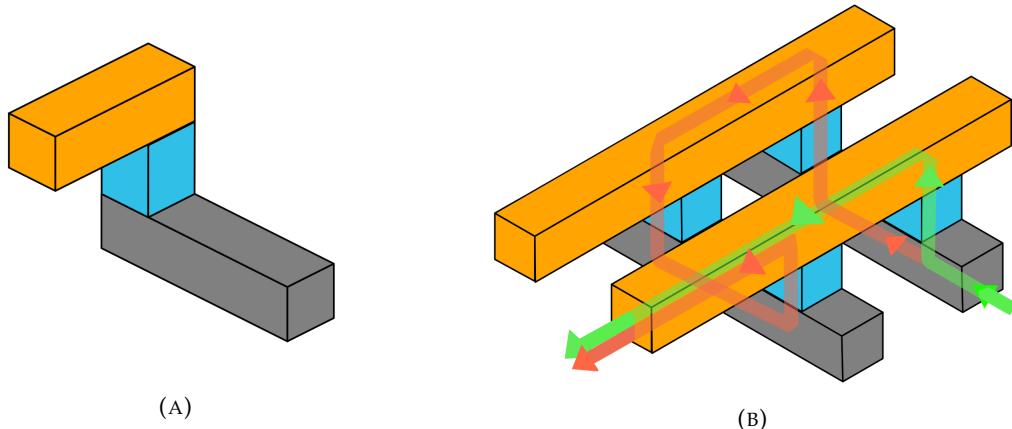

FIGURE 2.9: Representation of neuromorphic computing with neurons and synapses shown in (A) standard model used to describe synapse connections in AI processing (B) Crosspoint structures with the same functionality

through the use of neurotransmitters which are calcium gated channel ions. These calcium ions are also known as neurotransmitters and move between the synapses to alter the strength of their connections. It has been shown that the ion migration used in RRAM devices can emulate the movement of the  $Ca^{2+}$  neurotransmitters to produce artificial synapses [83–88]. By combining these device together we could potentially emulate the brain through neuromorphic computing, through a large number of synapses that are connected to groups of neurons [89]. A Crosspoint structure, as discussed in Chapter 6, can perfectly emulate this with each word/bit line connecting neurons (CMOS connections) and each bit acting as a synapse (RRAM device) figure 2.9 [90].

The strengthening and weakening of synapses between depend upon the levels of activity, this is known as synaptic plasticity [91]. These responses require the application of an appropriate input pulse that can effectively emulate the effects of the action potentials generated from a neuron under a stimulus. By increasing the number (N), duration (D), the interval (I) and the amplitude (A) of the pulses, we can simulate a varying degree of stimulation that reaches the synapse to strengthen or weaken connections by altering the conductance of the device [92].

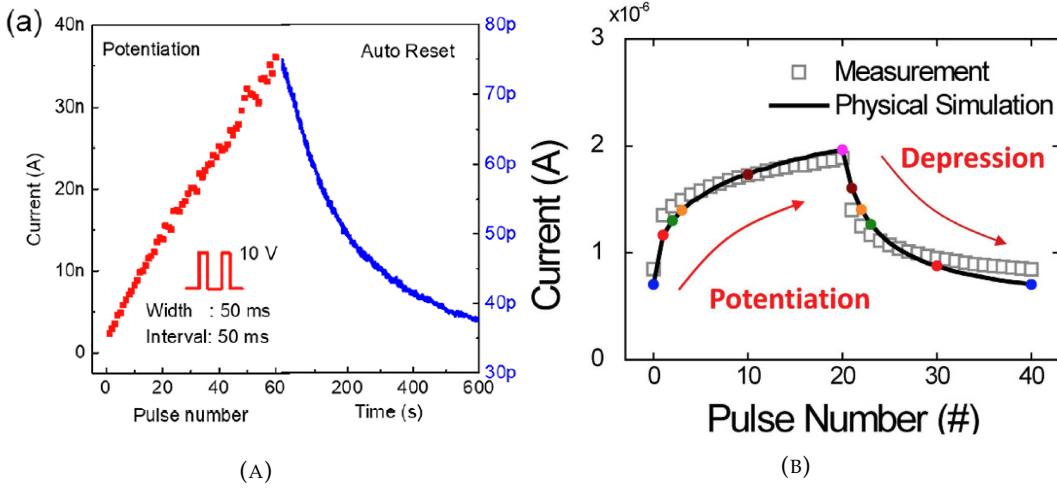

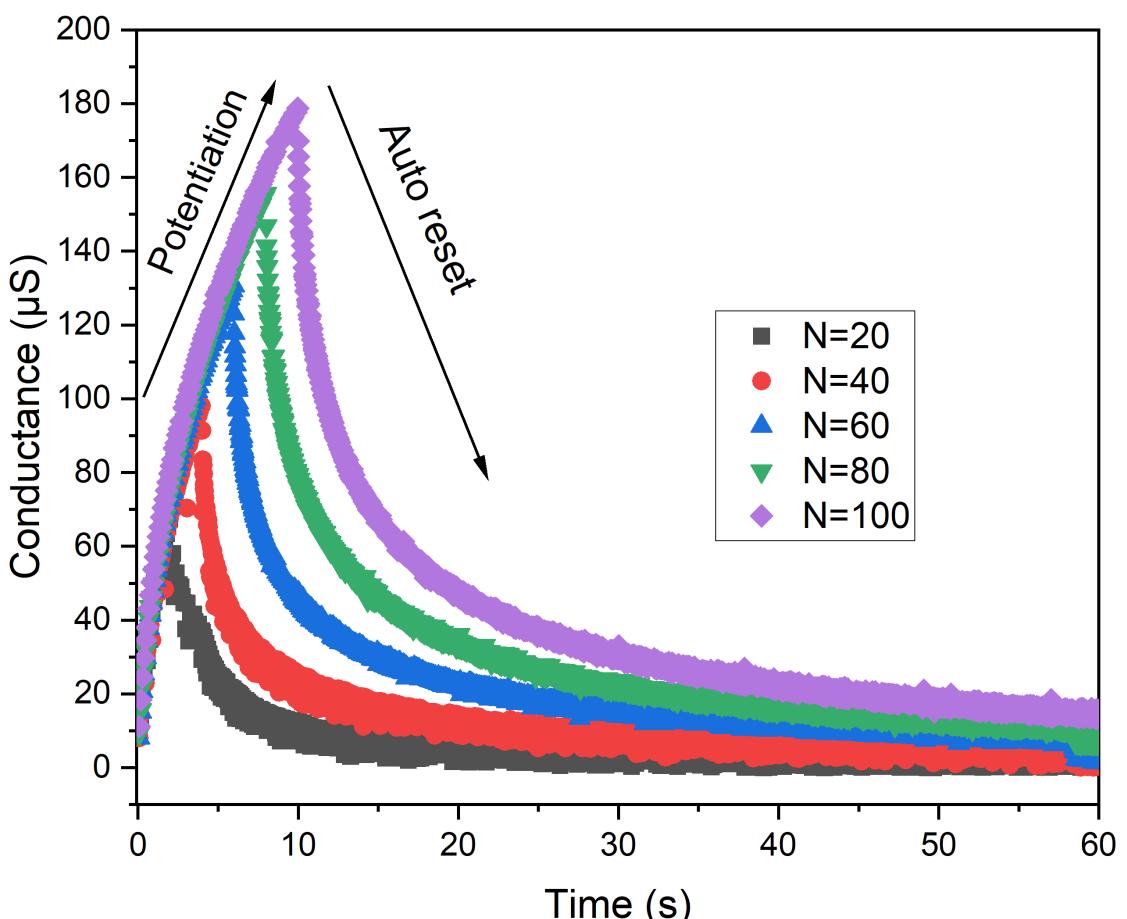

Synaptic plasticity is separated according to the duration in the change in the strength of the synapse [93]. For RRAM devices this change in strength can be associated with the change in resistance, with a strong connection being equivalent to a low resistance state, although in neuromorphic systems it is usual to talk about conductance rather than resistance. When a brief high-frequency train of stimuli is applied to the synapse an increase in the conductance is observed with each input pulse. If the synaptic change in plasticity is short-lasting and eventually falls back to its original conductance state it is known as short-term potentiation (STP). An example of this is shown in figure 2.10a [94], which shows STP with a measured auto reset. Initially, pulse widths and

FIGURE 2.10: Current-pulse graphs showing how alteration in the input stimuli can create (A) Short-term potentiation, in which the input stimuli is not enough to retain the information for long periods [94] (B) Long-term potentiation, in which the synapse remembers its state and must undergo depression to return to its original state [95].

intervals of 50ms are applied to the memory cell and the increase in conductance is observed. Once the pulse train has been taken away the conductance is continually measured, without applying any further input stimuli. The conductance gradually falls back down to its steady state, which can also be considered an observable volatile change in resistance.

If the increase in conductance remains after the input stimuli is taken away, which for RRAM would be a non-volatile change in resistance, we can say that the synapse has undergone long-term potentiation (LTP), figure 2.10b. This is similar to the standard resistive switching process in which a change in the filament has decreased the resistance of the device semi-permanently. Therefore, to weaken the synapse and return it to its original conductance we can employ a similar mechanism to the bipolar switching discussed in chapter 2. Through reversing the polarity and applying another set of pulse trains we can control the dissolution of the conductive bridge and alter the conductance to its original state. This is known as long-term depression (LTD). An example of these plasticity mechanisms is shown in figure 2.10b, which shows LTP and LTD in a resistive switching device [95]. Initially, single pulse trains are applied and there is an increase in the conductance. As the potentiation occurs there is a non-volatile change in the resistance and so the memory cell is able to keep this bit-state when power is taken away. This is the potentiation of the memory cell. Separate input stimuli is then applied, with a reversal in the polarity. This reduces the current with pulse number and causes the depression back to the original conductance. LTP and LTD have been thought to provide the necessary tools for memory and learning, whilst STP can support different types of computation [96].

It should be noted that in a RRAM device, the change in conductance is done through

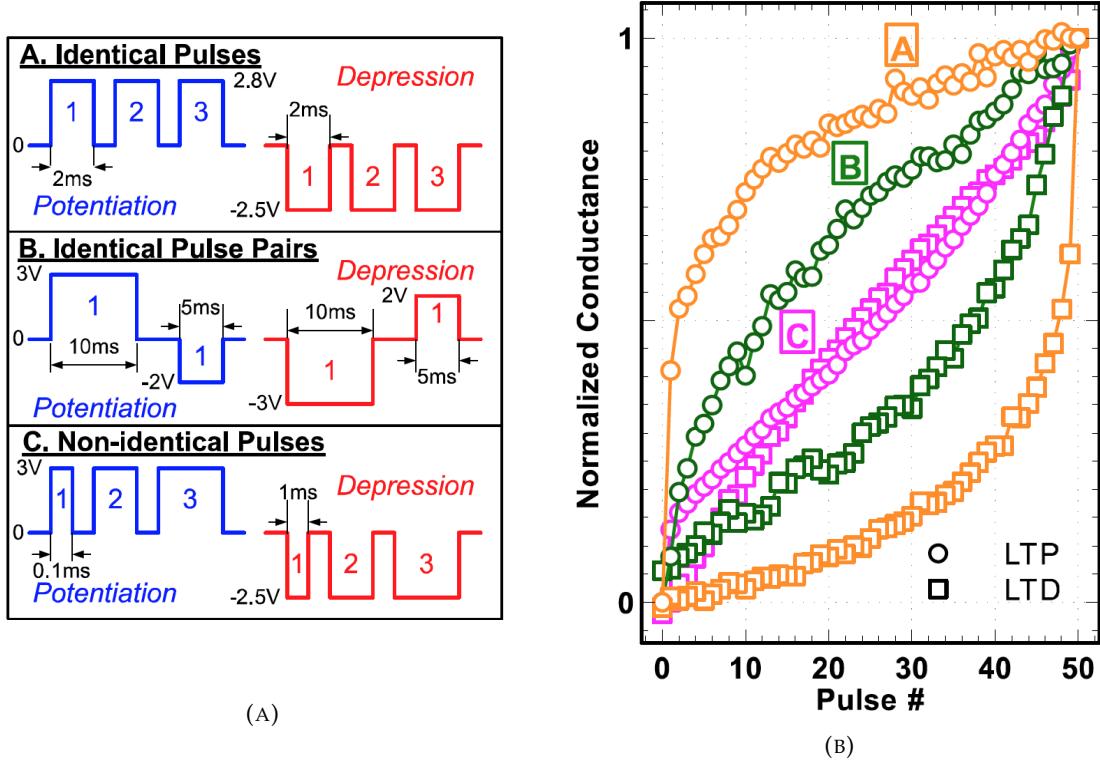

FIGURE 2.11: (A) Voltage-time graphs of different potentiation and depression schemes to improve the linearity of the change in conductance (B) Associated Conductance-pulse number graph showing the change in linearity when altering the parameters of the input pulses [98]

the controlled formation of the conductive bridge. However, due to the nature of this switching mechanism it has been shown that these devices alter their conductance in a non-linear mechanism. To successfully emulate a neuron a linear alteration in its conductance is required. This linear trend is possible through the use of a diffusion limiting layer or by having a dual gated RRAM structure that enables control over the ion migration [27, 97]. A simpler method, however, is to use differing input pulses to force a linear change in the conductance. This can be done by using an identical pair pulse, in which a small pulse is applied with the opposite polarity to force a linear change. Another method is to use non-identical pulses which will allow for a gradual linear change in the potentiation. Both these methods are shown in figure 2.11 showing the pulse input and its respective alteration in the conductance [98].

Finally, both LTP and LTD inputs can be used as pre and post-synaptic weights for spike-timing-dependant plasticity (STDP), which is believed to be the route of learning and information storage in the brain, known as Hebbian learning [99]. If the pre-synaptic signal precedes the post-synaptic one, LTP will be induced and if the signals are reversed LTD will be induced [100]. By also altering the timing between the pre and post-synaptic signals the overall weight on the device will alter. There are four possible types of the Hebbian learning mechanism which depend upon the time between the pre- and post-synaptic signals.

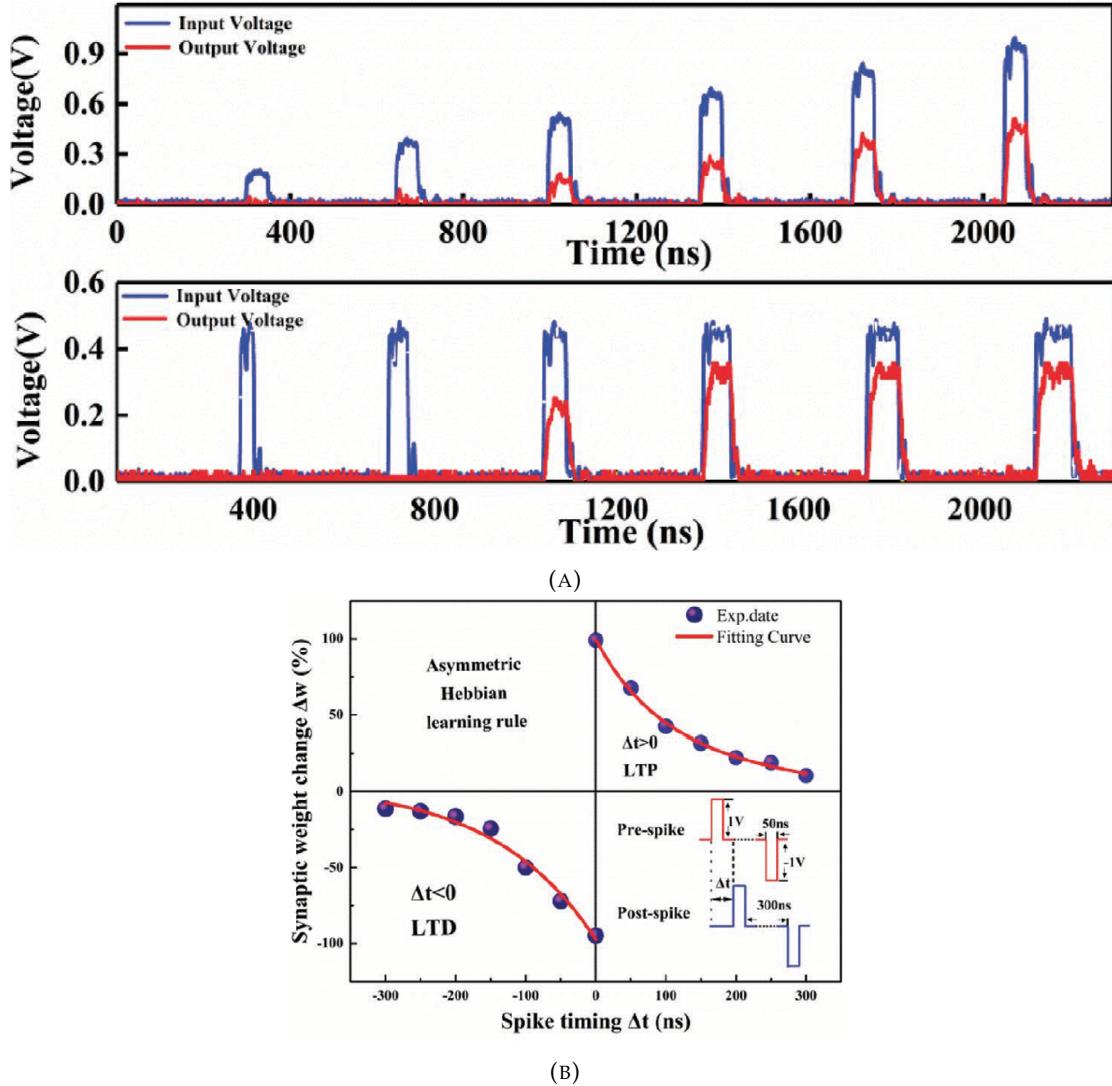

FIGURE 2.12: Neuromorphic behaviour from a sputtered SiC dielectric (A) Effects of varying amplitude and duration of the input pulse (blue) on the device conductance (red) (B) measured Asymmetrical Hebbian Learning behaviour [101]

A 10nm SiC dielectric has been shown to exhibit synaptic behaviour and Hebbian learning, [101]. The memory cells are sputtered using radio frequency magnetron sputtering and shows bipolar resistive switching characteristics below  $\pm 1V$  and switching times below 40ns, using Ag as the top electrode. Figure 2.12a shows that by altering the amplitude of the applied voltage pulse, the measured voltage also increased. By increasing the width of the applied voltage, the measured output voltage also increases until it plateaus. Figure 2.12 shows the Asymmetric Hebbian learning that was measured, which is when the weight of the conductance increases while decreasing the time in between the pre- and post-synaptic signals. There is a sharp alteration between strengthening and weakening connections as the time differences crosses zero. However, these results do not provide a detailed analysis of the effects of input stimuli on the relaxation caused by STP.

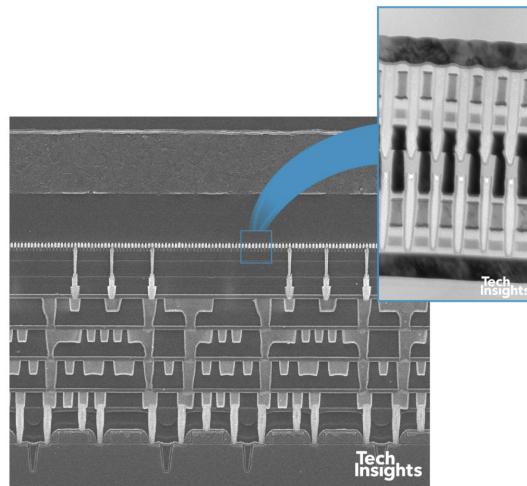

FIGURE 2.13: Cross-section SEM and TEM images taken of Intel's 3D Xpoint memory arrays which show a phase change cells in series with an Ovonic threshold selector. [103]

## 2.5 System Architecture

To achieve a scalable technology, for both consumer and radiation harsh memory, the individual SiC devices must be combined into Crosspoint Structures. These structures position individual bits in arrays that can be independently accessed and such as structure has become commercially available with the release of Optane 3D Xpoint memory from Intel and Micron Technology [102]. However, this type of memory storage is based on phase change memory, which utilises rare materials such as tellurium to achieve its memory performance, shown in figure 2.13 [103]. This is reflected in the commercial price with a 1.5TB Optane P4800x SSD costing over \$5000 [104]. Comparatively, both silicon and carbon are extremely cheap and abundant materials, making them a desirable option for the future of Crosspoint structures.

In a Crosspoint structure, devices are connected through rows and columns which are also known as word and bit lines. By selecting a specific word and bit line individual memory devices can be accessed, as shown by the green arrow in figure 2.14b. The red arrow shows parallel leakage paths through unselected cells which are known as sneakpath [105]. The presence of sneakpath, as well as series, interconnect resistances, can cause limited sizes of the Crosspoint structures and also reduce the sense margins of the resistance states. Therefore, research must be conducted to analyse this phenomenon to counteract its effect.

Sneakpath in a Crosspoint structure with  $N$  number of devices can be simplified into the  $2 \times 2$  array shown in figure 2.14b [106]. Therefore, this structure will be the focus of this chapter, however, as discussed in section 6.1 larger arrays have also been fabricated.

FIGURE 2.14: Representation of Non volatile memory:(A) a single ReRAM cell with a two metal contacts in between a dielectric. (B) a 2x2 Crosspoint structure with the word and bit lines acting as the top and bottom electrodes. The green arrow shows a device being selected and the red arrow shows parasitic leakages through unselected devices.

To counteract sneakpath the individual devices need to be confined from each other by including a selector device. Selectors are separated into two different categories, which are known as active and passive arrays. Active arrays utilise an external selector, for example, a MOSFET to connect the word and bit line. This is often called 1T1R and it can eliminate sneakpath from the Crosspoint structure as the current can only flow through the selected device when the transistor is turned on through the gate. This method, however, increases the overall size of the chip and increases the complexity of the fabrication process.

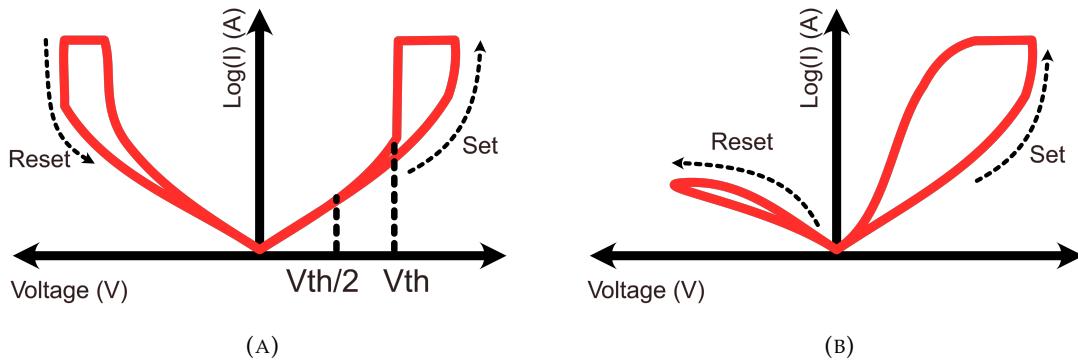

Alternatively, passive arrays utilise selectors built into each memory device. This reduces the fabrication complexity as it only requires the deposition of materials between the top and bottom electrodes of each ReRAM device. This means that extra lithography steps do not have to take place to include these types of selectors. This form of a selector is known as 1S1R and are classified according to their effects on the I-V characteristics when in series with a memory device. The first method requires a threshold voltage ( $V_{th}$ ) for the read/write operation, causing a non-linear I-V characteristic to the ReRAM device, figure 2.15a. When a read or write scheme is applied, at  $V_{th}$ , to a specific device the voltage through the unselected devices is equivalent to  $\frac{V_{th}}{2}$ . This effectively counteracts the problems associated with sneakpath, as the unselected cells cannot reach the  $V_{th}$  during a read/write operation.

The second method is known as a self-rectifying selector. A representation of a self-rectifying Reset is presented in figure 2.15(B). In this method, the I-V characteristics of the Set operation are as expected and the device alters its state. Once the polarity of the applied voltage is reversed, the measured current is suppressed significantly compared to the standard I-V characteristic, however, its resistance state is still altered.

FIGURE 2.15: Representation of I-V characteristics of a selector in series with a ReRAM device providing non-linear switching to counteract sneakpath through (A) threshold switching (B) self-rectifying switching.

This asymmetric non-linear I-V characteristic eliminates sneakpath by counteracting the possibility for the parasitic leakages through the unselected devices.

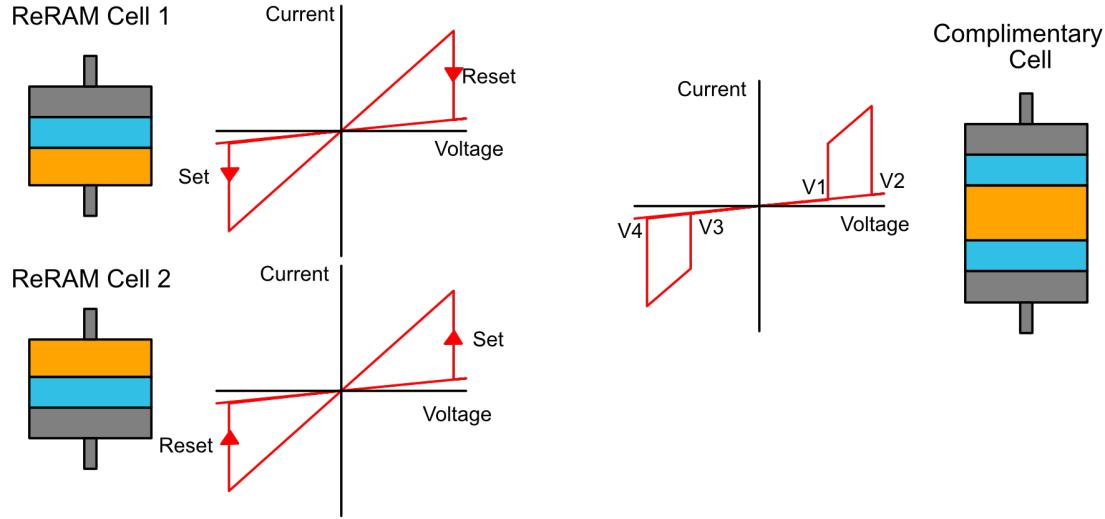

The final method of counteracting sneakpath is known as complementary switching. This utilises two resistive switching cells that are connected anti-serially, as shown by figure 2.16. The simplicity of this structure allows for a similar fabrication process as the passive arrays while giving the ability to stack crossbars on top of each other [107]. These stacked layers operate by superimposing the IV characteristics of both devices. This also assumes that the switching voltages are consistent while using either a positive or negative polarity for the Set operation.

The complimentary devices cannot be read in the same manner as a standard ReRAM device. There are four different states that the complimentary device can be in and are given in table 2.3. The initial OFF state only occurs at the pristine state of the devices, just after fabrication. To switch the complimentary cell into a bit 0 or 1 a voltage is applied that is just above  $V_1$  or below  $V_3$  as shown in figure 2.16. This would switch cell 1 or cell 2, depending on which state is chosen. For this example, if a bit 0 is desired cell 1 would have to be in the HRS and cell 2 in the LRS. As the complimentary device acts as a voltage divider when a standard read voltage is applied, the majority of the voltage drops across the single cell in the HRS, in this case, cell 1. Therefore, whether the complimentary device is in bit 1 or 0 the overall resistance of the stacked layers will appear to be in the HRS. Therefore, the system operates at low power consumption and also halts sneakpath across the Crosspoint structure.

To accurately read the resistance state of the device a destructive reading must take place. Using the previous example of cell 1 being in the HRS and cell 2 in the LRS, if a Set voltage is applied to cell 2, as it is already in the LRS, there is no change to the overall resistance and the complimentary device remains in the HRS. If a Set voltage is applied to cell 1 it would cause the entire complimentary device to now read as being

in the LRS state. This means that we know that cell 1 was previously in the HRS and cell 2 in the LRS, corresponding to bit 0.

The destructive reading of the complimentary devices means that the peripheral circuitry required would be more complex than a standard Crosspoint structure using a 1T1R or 1S1R [108]. As well as this the read endurance would also be equal to the write endurance, while also utilising a higher power consumption [109].

FIGURE 2.16: Representation of the IV characteristics of Complimentary switching. The left shows both the individual bits in its anti-serial configuration. On the Right presents the combined characteristics of two ReRAM cells into a complimentary device.

TABLE 2.3: Bit states of the individual ReRAM devices, cell 1 and cell 2, that make up a complimentary device. Also shown is their corresponding effect on the overall state of the complimentary device.

| Complimentary state   | ReRAM cell 1 | ReRAM cell 2 | Overall Resistance |

|-----------------------|--------------|--------------|--------------------|

| OFF (Pristine cells)  | HRS          | HRS          | HRS                |

| HRS (Bit 0)           | HRS          | LRS          | HRS                |

| LRS (Bit 1)           | LRS          | HRS          | HRS                |

| ON(Only when reading) | LRS          | LRS          | LRS+LRS            |

It should be noted that it is also possible to use inherent non-linear I-V characteristics of ReRAM devices to reduce the impact of sneakpath, without the need for physical selectors. This is done by using an intrinsic self-rectifying ReRAM device, which has been previously shown to be successful, for example, a study using amorphous silicon in a 40 x 40 integrated Crosspoint structure [110]. However, this study had a large error rate, with around 75% of the measured resistance values only reaching 50% of the targeted value and required the device to already have these non-linear characteristics. As the Neuromorphic devices exhibit some non-linear I-V characteristics, it might be possible in the future to fabricate these into Crosspoint structures without the need for any form of selectors.

Other types of selector-less arrays include the use of a differential amplifier, with the effective sneakpath current used as a reference input [111]. However, this utilises a complex peripheral circuitry for the standard operation of the matrix.

To design and fabricate selectors for SiC devices it is important to first understand sneakpath in Crosspoint structures to accurately determine the best possible method to counteract these effects. The next section focuses on the design and fabrication of Crosspoint structures without selectors, so that this sneakpath effect can be analysed.

## 2.6 Resistive Memory and Radiation Harsh Environments

It was the original purpose of this research to study the radiation hardness of resistive memory. Unfortunately, due to COVID-19 the radiation facility was closed and such measurements could not be performed as part of this thesis. However, here we discuss the literature of radiation effects and resistive memory. The planned experiments are included in Chapter 5 and this section should be viewed as context for why reliable information storage is important in harsh environments.

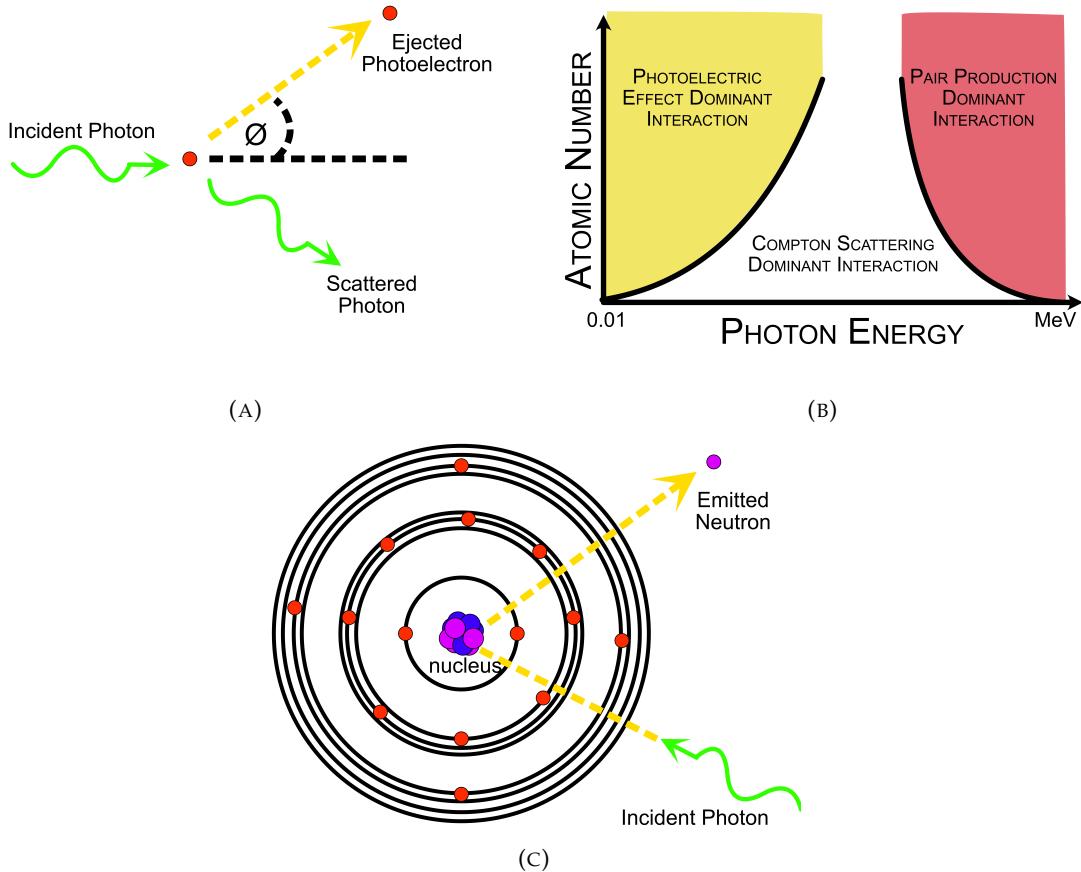

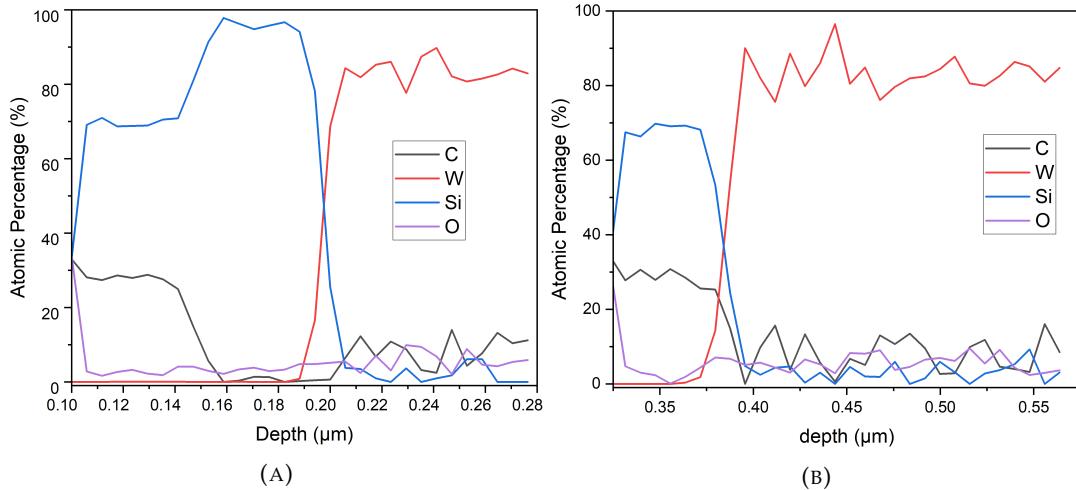

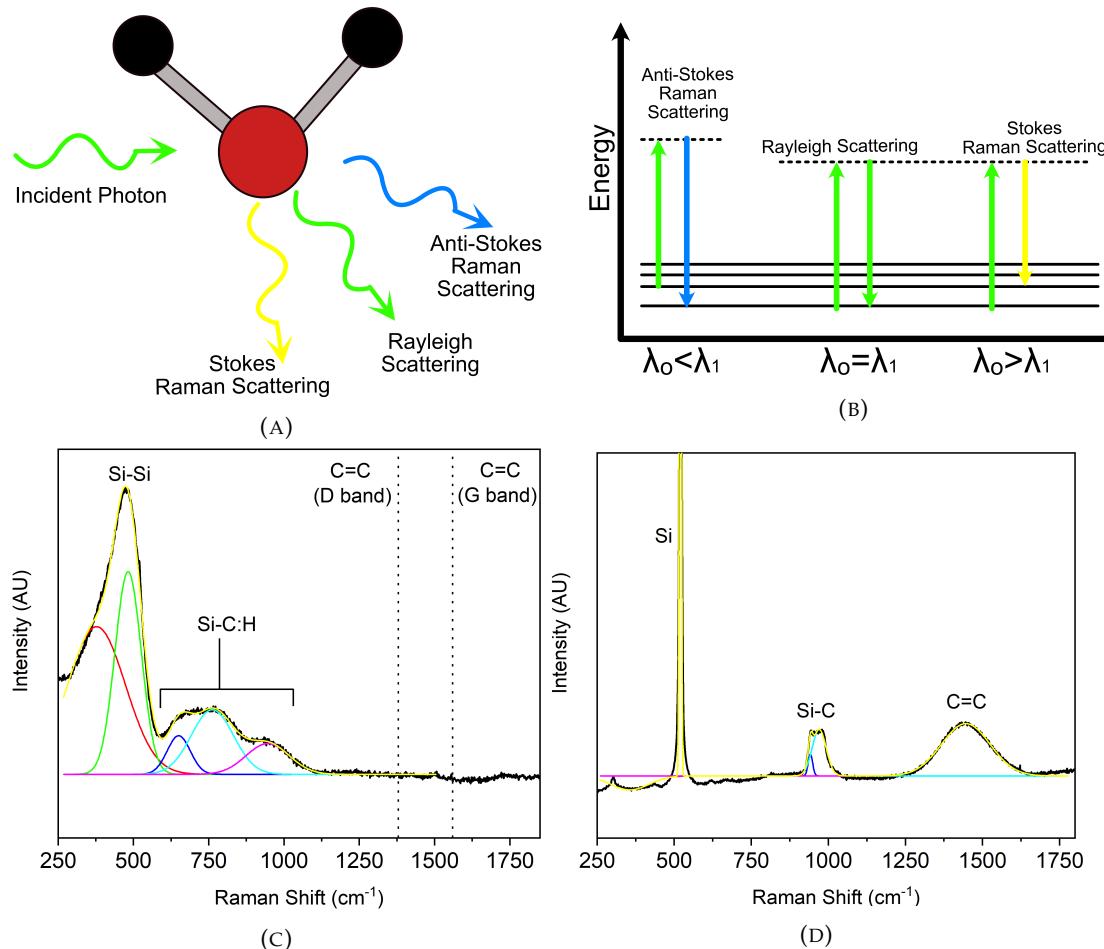

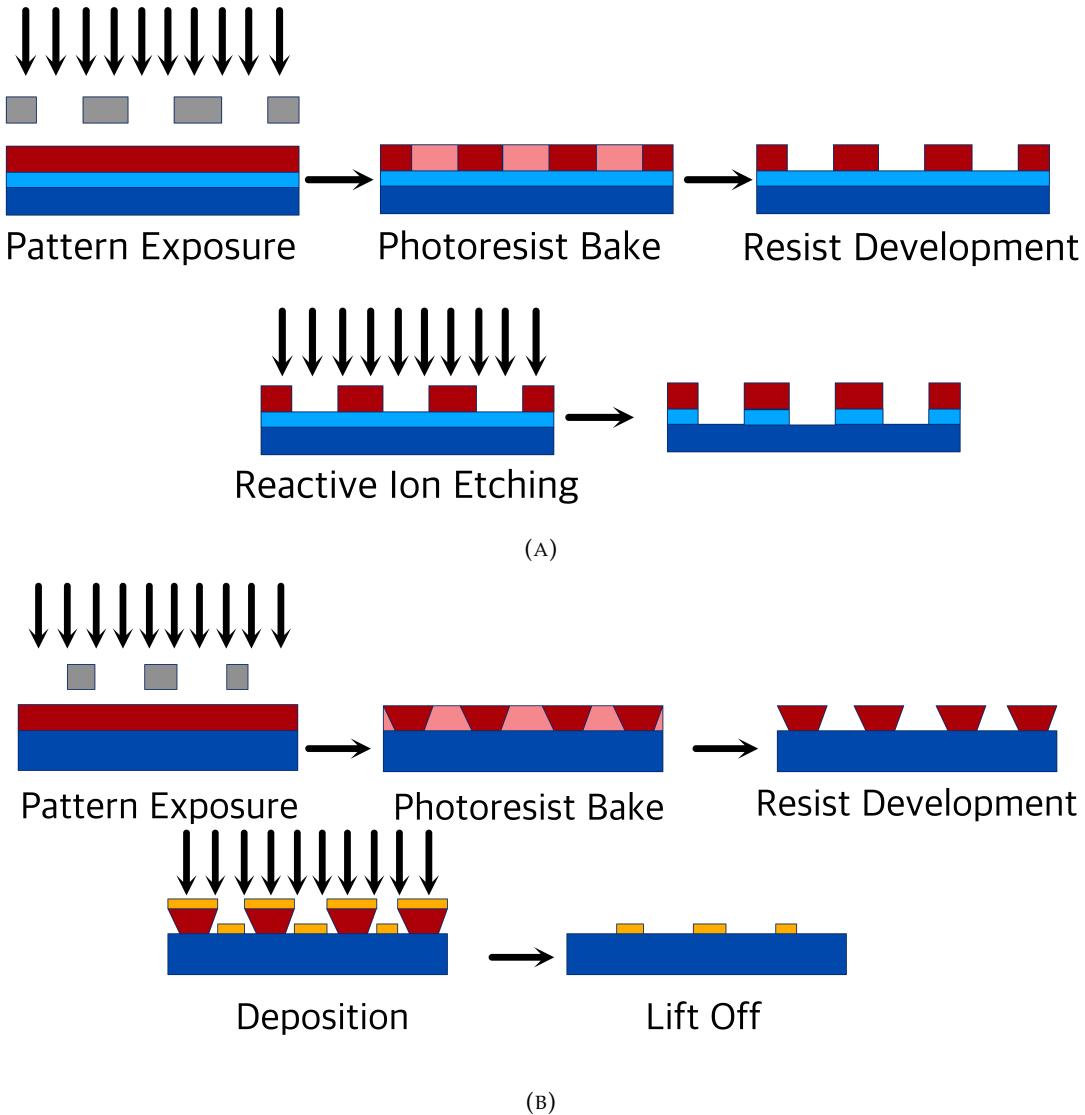

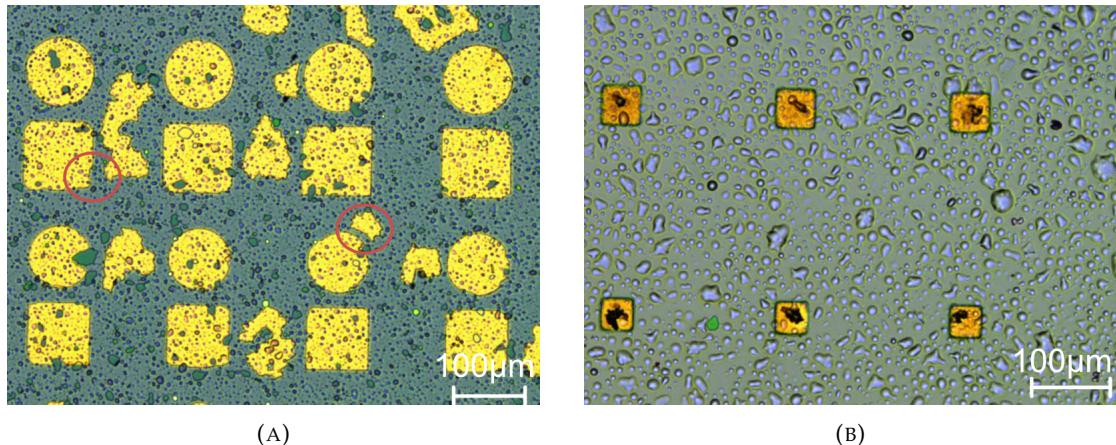

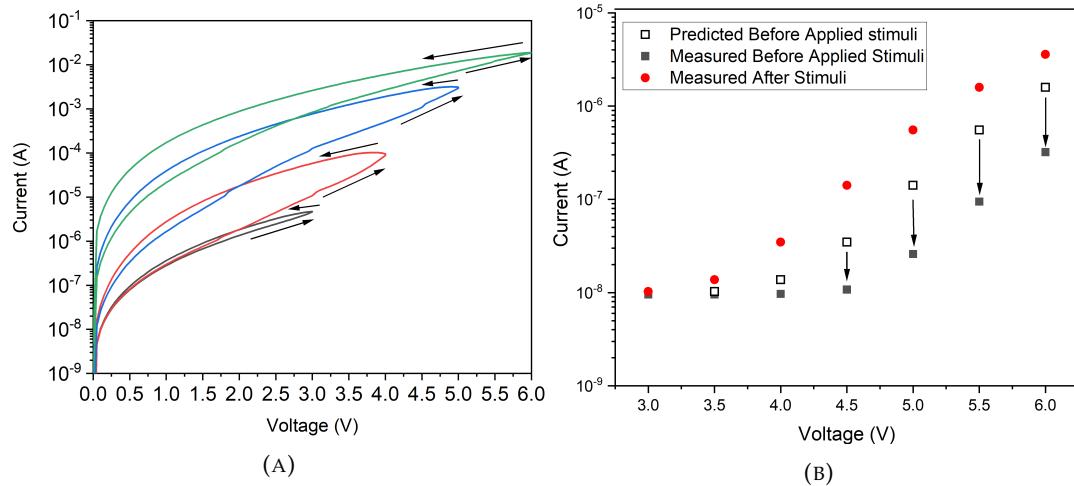

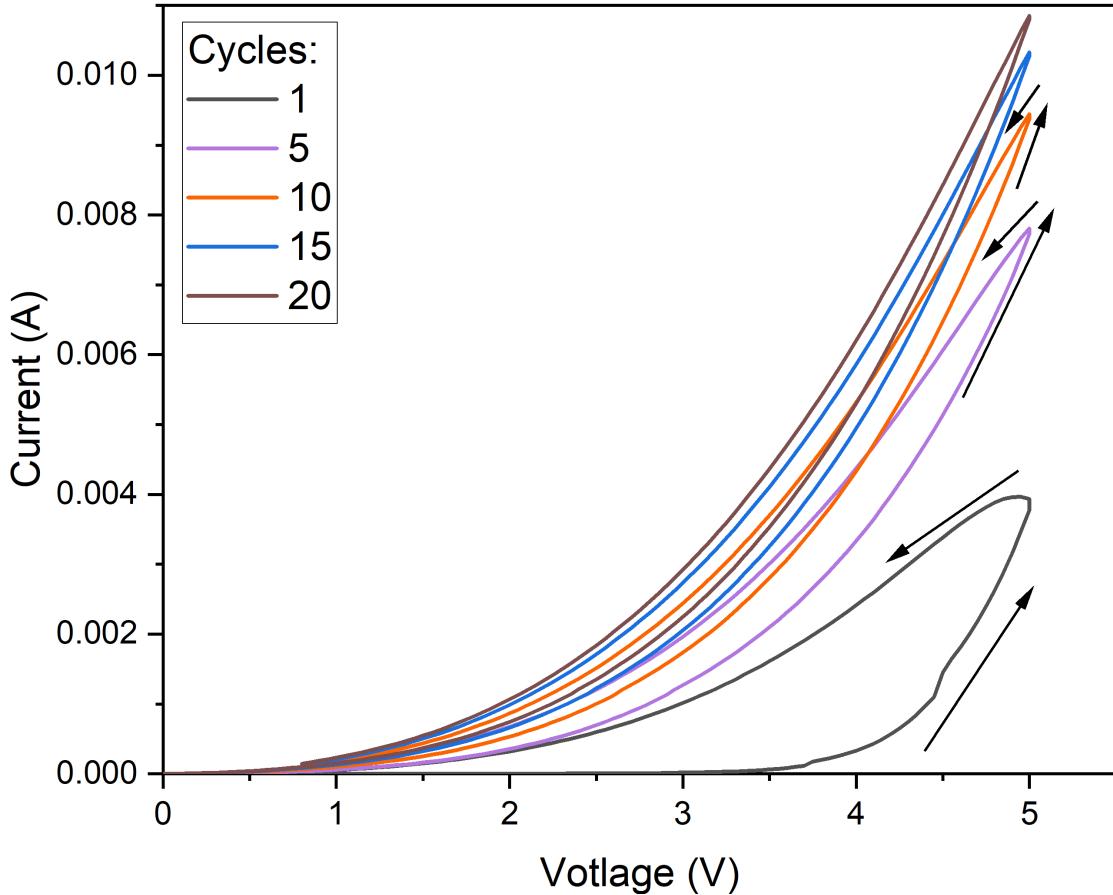

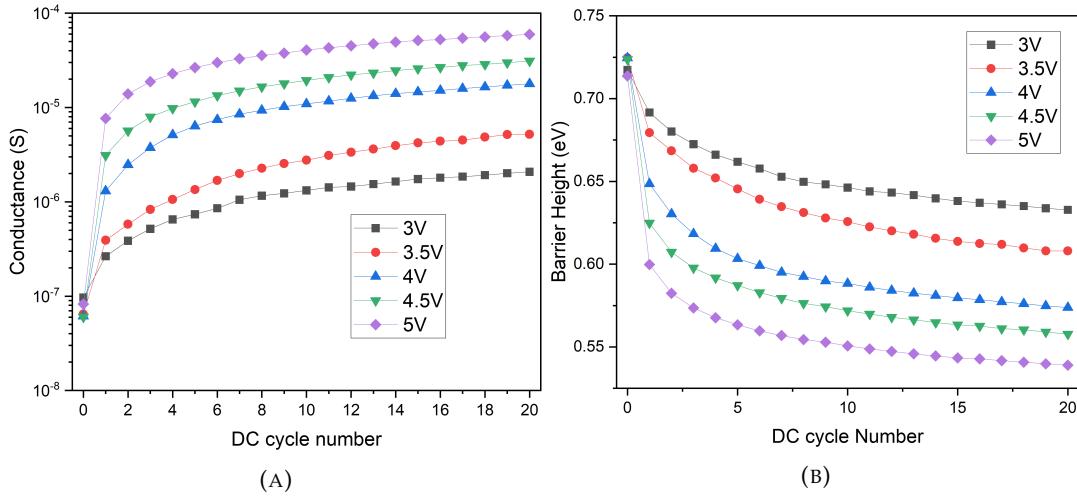

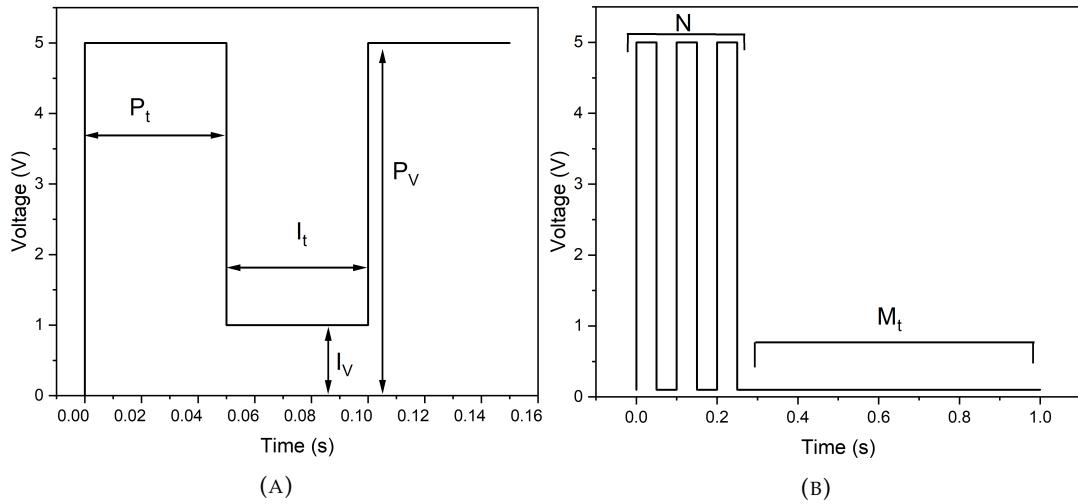

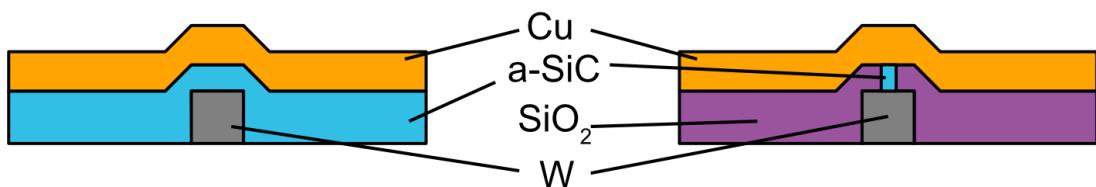

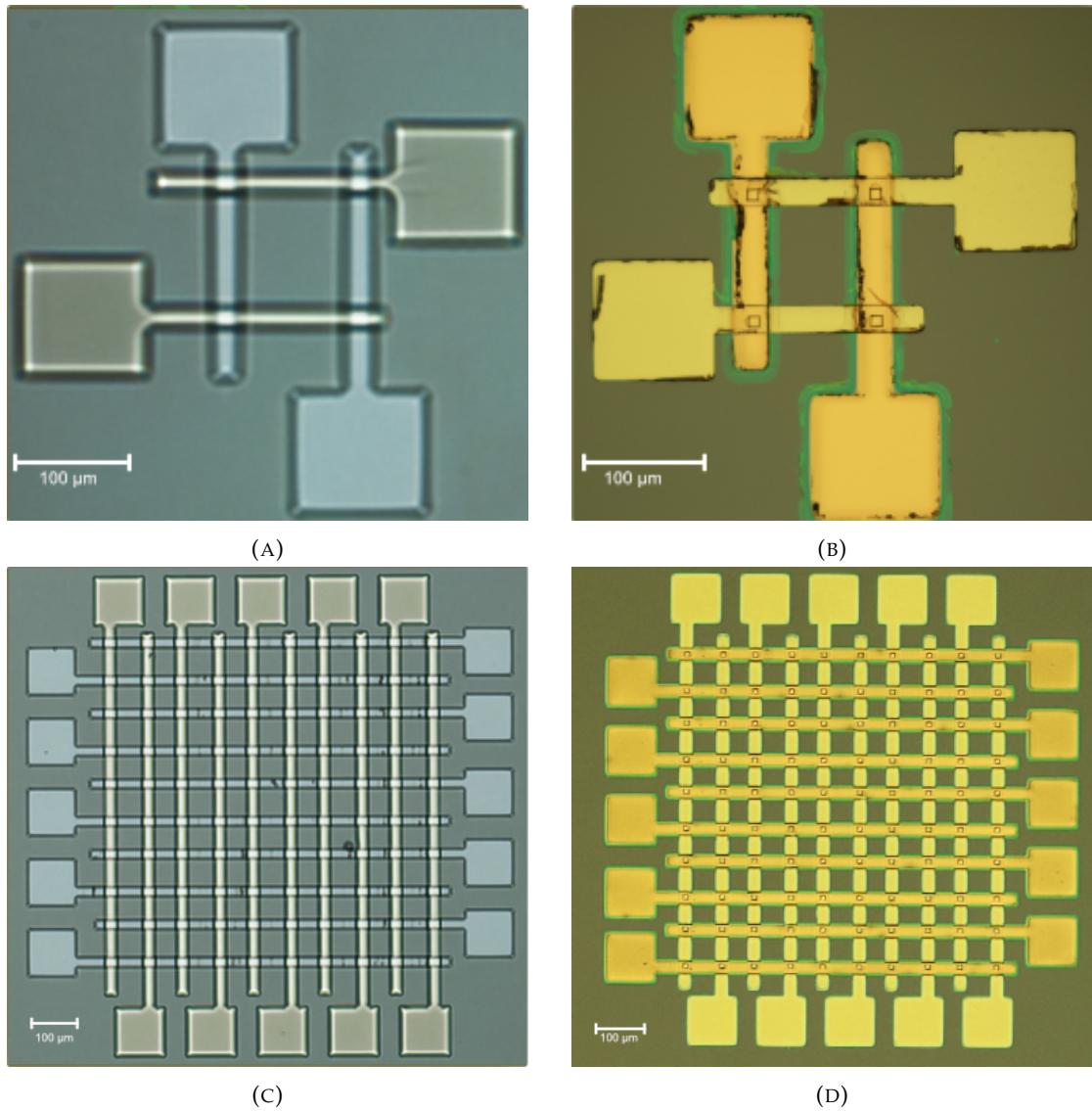

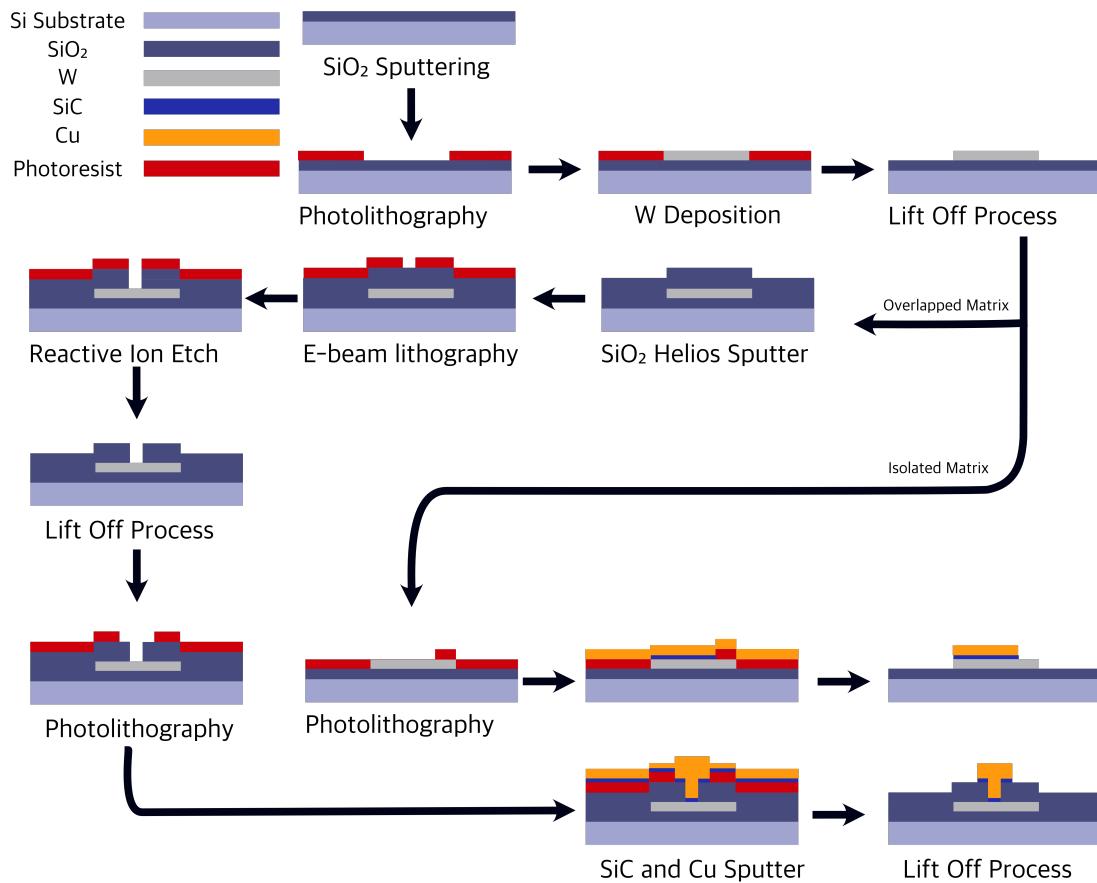

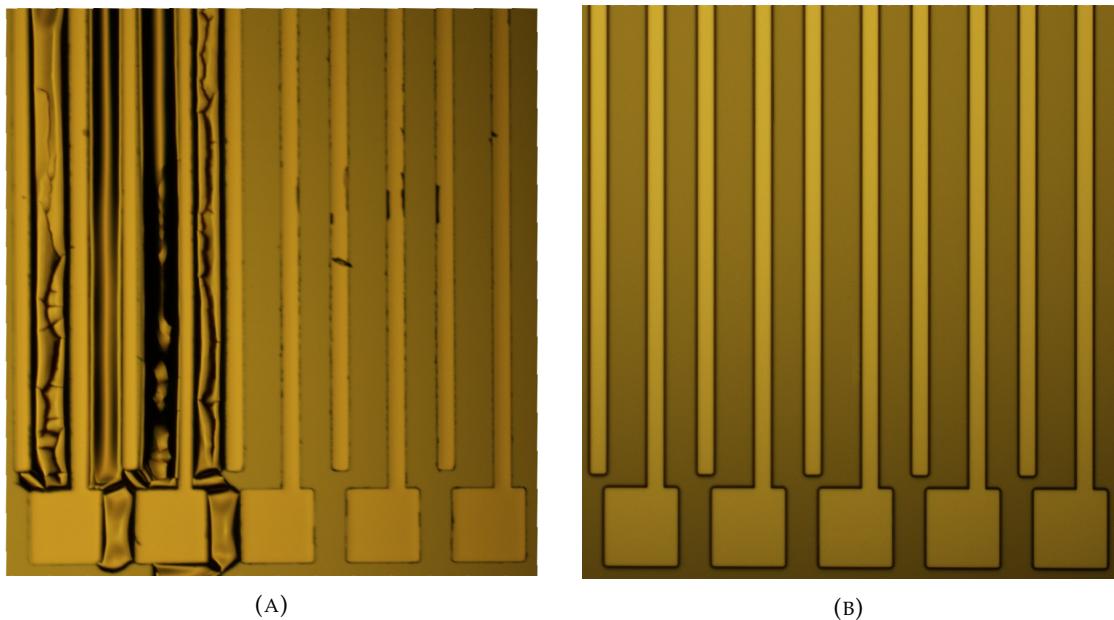

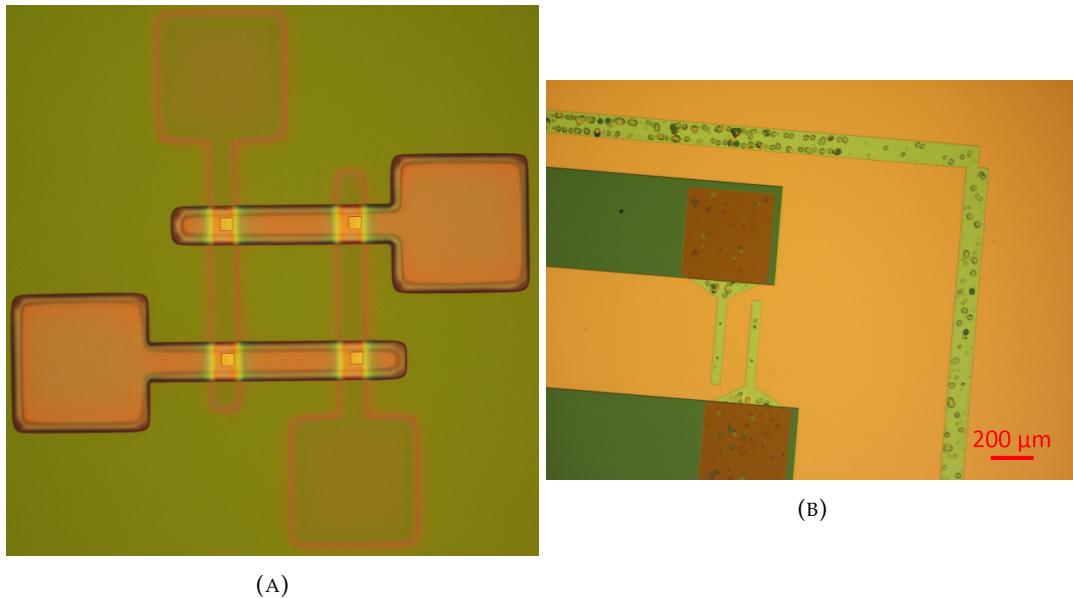

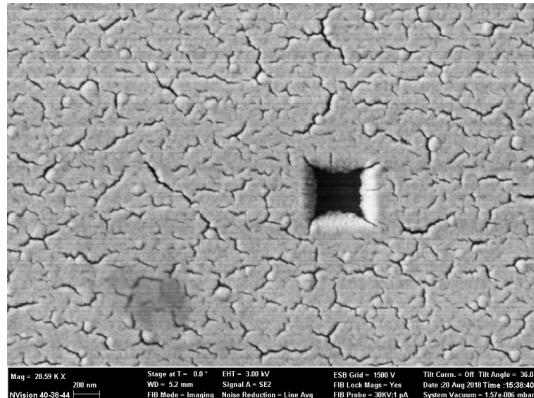

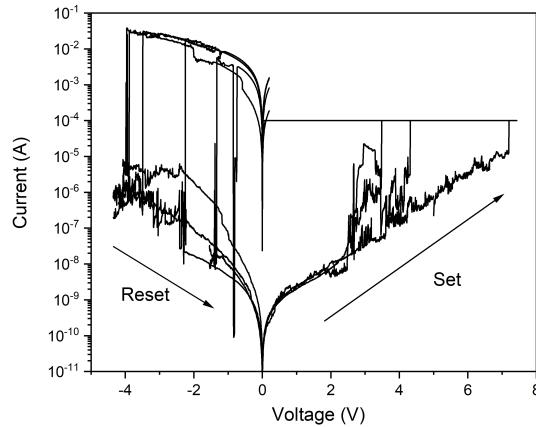

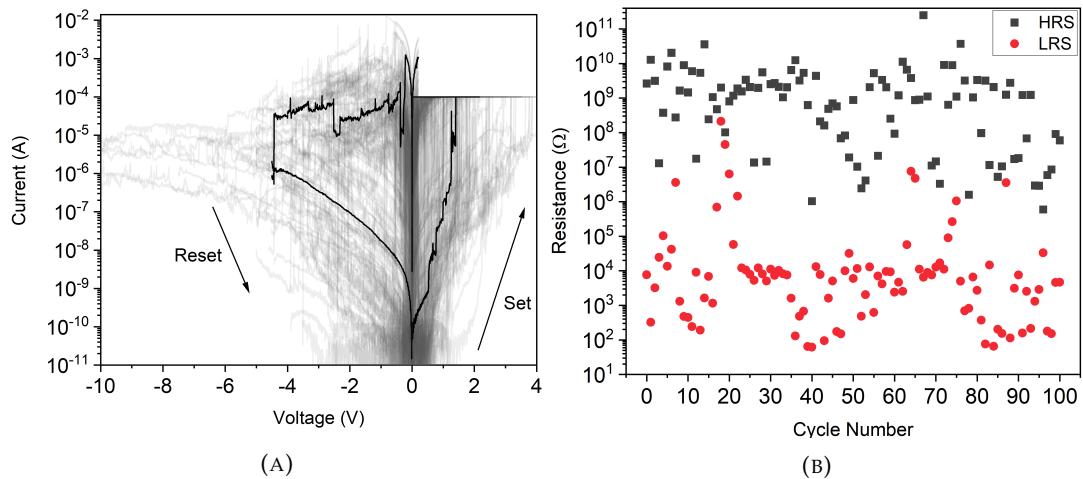

### 2.6.1 Types of Radiation Effects