AN INVESTIGATION OF LEAKAGE CURRENTS

AND CHARGE PUMPING CURRENTS IN Si-DIODES

A Thesis for the degree of

Master of Philosophy

submitted to the

University of Southampton

by

ZAMBIA J. DALIERAKIS

January 1975 - December 1976

#### ACKNOWLEDGEMENTS

The author is very much indebted to the following:

For continuing support and encouragement my supervisor, Dr. D.R. Lamb.

Dr. P.C.T. Roberts for his invaluable advice, enthusiasm and guidance throughout the course of this work.

Mr. J. Smith for his supervision during Dr. Lamb's absence.

Mrs J. Humphrey for processing all the experimental devices used in this work.

The entire staff of Microelectronics Lab. for their help and co-operation.

Miss J. Shaw, for typing from my hand-written manuscript without complaining and with patience.

Finally my husband, whose understanding, patience and continued support in all respects made the task of writing this thesis easier.

## CONTENTS

PAGE:

|                                                                                                                          |    |

|--------------------------------------------------------------------------------------------------------------------------|----|

| 1. INTRODUCTION                                                                                                          |    |

| 1a Leakage Current                                                                                                       | 1  |

| 1b Interface State Measurements                                                                                          | 6  |

| 2. LEAKAGE CURRENT INVESTIGATION                                                                                         |    |

| 2a Theory of Leakage Current                                                                                             | 8  |

| 2b Gated diode fabrication using HCl oxidation                                                                           | 17 |

| 2c Leakage Current Measurements on HCl gated diodes                                                                      | 21 |

| 2d Leakage Current Measurements on CCD's.                                                                                | 37 |

| 3. CHARGE PUMPED CURRENT INVESTIGATION                                                                                   |    |

| 3a Charge Pumping Method                                                                                                 | 43 |

| 3b Theoretical calculation of the Surface State density as a function of Energy from Charge Pumping Current Measurements | 54 |

| 3c Charge Pumping Current Measurements on gated diodes                                                                   | 68 |

| 3d Charge Pumping Current Measurements on CCD's                                                                          | 85 |

| 4. LEAKAGE CURRENT AND CHARGE PUMPING CURRENT MEASUREMENTS ON DEVICES WITH TCE OXIDATION                                 |    |

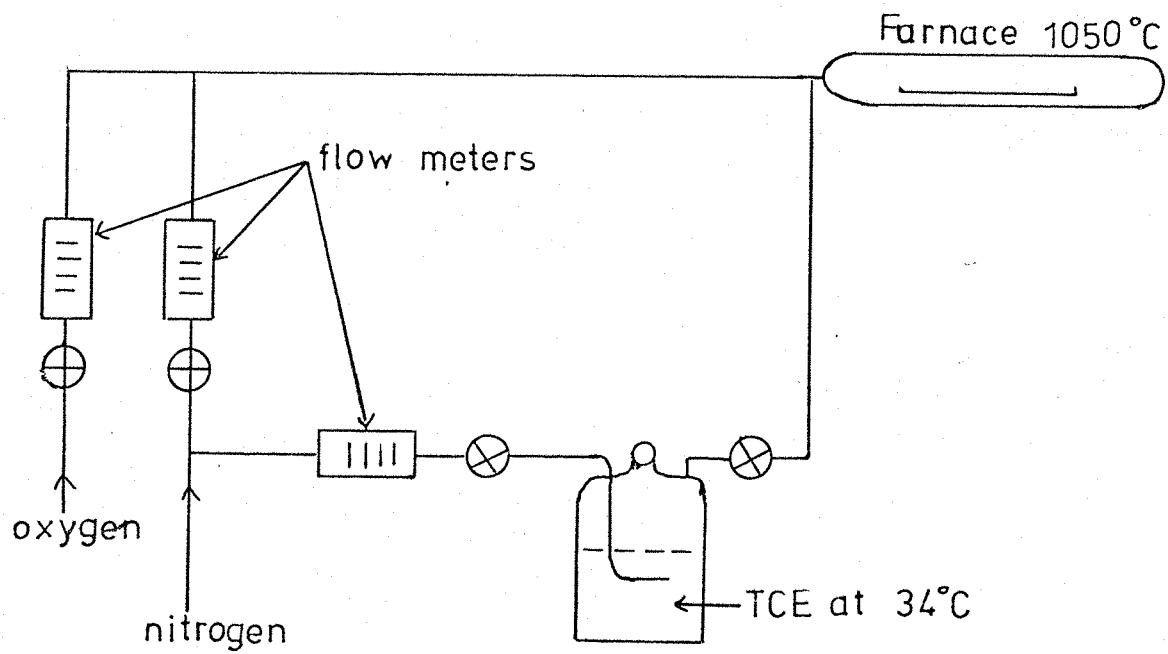

| 4a Gated diode fabrication using TCE oxidation                                                                           | 88 |

| 4b Leakage Current Measurements on TCE gated diodes                                                                      | 88 |

| 4c Charge Pumping Current Measurements on TCE gated diodes                                                               | 93 |

| 4d Comparison of results of 'TCE' devices with results on 'HCl' devices                                                  | 96 |

| 5. CONCLUSIONS                                                                                                           |    |

| 5a Comparison of the effects of different processing schedules.                                                          | 97 |

| 5b Usefulness of the measurement technique as related to packaged CCD's                                                  | 97 |

| REFERENCES                                                                                                               |    |

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF SCIENCE

ELECTRONICS

Master of Philosophy

AN INVESTIGATION OF LEAKAGE CURRENTS

AND CHARGE PUMPING CURRENTS IN Si-DIODES

by Zambia J. Dalierakis

A study of leakage current in silicon p-n gated diodes with HCl gate oxidation and 'TCE' gate oxidation is presented. The investigation was concerned with the relative importance of the different HCl concentration in the process which were used, and the variants of processing of the devices. A study was made using an alternative oxidation technique using Trichloroethylyne performed by G.J. Decklerk of the Katholieke Universiteit Leuven, Belgium. It is concluded that there was an overriding controlling factor in the processing schedules used here, which resulted in the improvements in the values of bulk lifetime and surface recombination velocity.

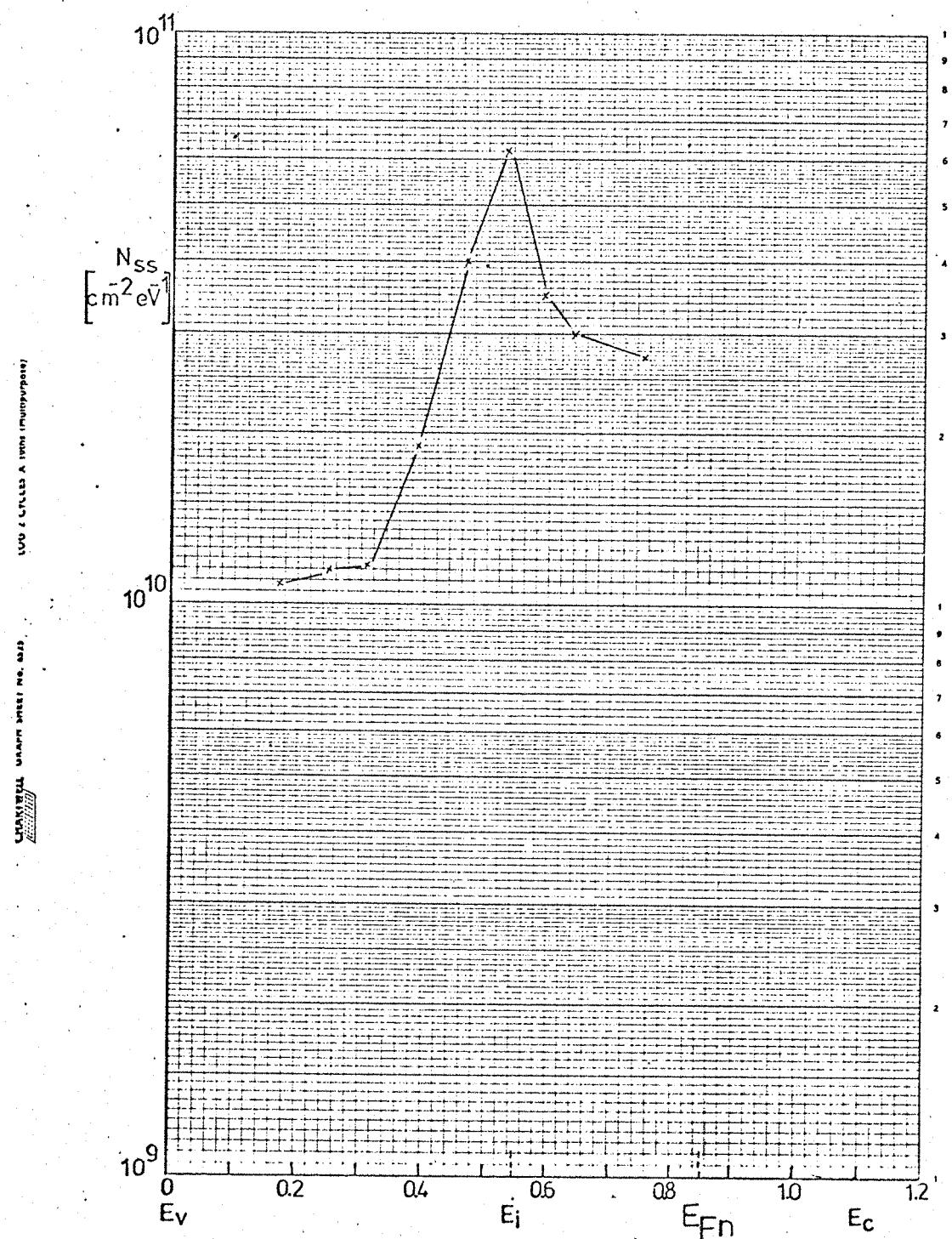

A new method is described for determining the surface state density at the Si-SiO<sub>2</sub> interface in the channel of a p<sup>+</sup>n gated diode from the charge pumped current flowing to the substrate when gate pulses of constant amplitude are applied. A theoretical analysis of this method is described which suggests that from a simple measurement of the pumped current the energy distribution of surface state density may be obtained. Representative results obtained on a set of gated diodes and a CCD show an increase in the surface state density near the middle of the band-gap. However, further work must be done to confirm the reliability of the data in order to apply the technique for general purpose surface state density measurements.

## 1. INTRODUCTION

### 1a Leakage Current

One of the most important requirements of the microelectronics industry is the fabrication of suitable p-n junctions in semi-conducting crystals. Silicon, for many reasons, has evolved as the most suitable material in which to form the devices required for complex electronic systems. Planar processing of silicon has been developed in the last decade into a highly sophisticated method of fabrication since the pioneering work of Shockley in the 1940's (1). Rectifying p-n junctions are manufactured in silicon by doping, through a 'mask', selected regions with elements from group III or V of the Period Table in a silicon substrate which is already lightly doped with group V or III elements respectively. The 'mask' is a thin film of silicon oxide thermally grown on the substrate. The junction thus formed will pass high currents for a forward bias of only about 1 volt and a relatively very small current at reverse biases of many volts (Fig. 1.1). The magnitude of this reverse current is usually called 'leakage current' and is dependent on the physical structure of the junctions as will be shown in Chapter 2.

Usually, the leakage current is insignificant. However, for some applications, extremely low leakage is required, e.g., opto-electronic imagers, charge coupled devices (surface and buried channel), self addressed diode arrays high gain, low current, bipolar transistors.

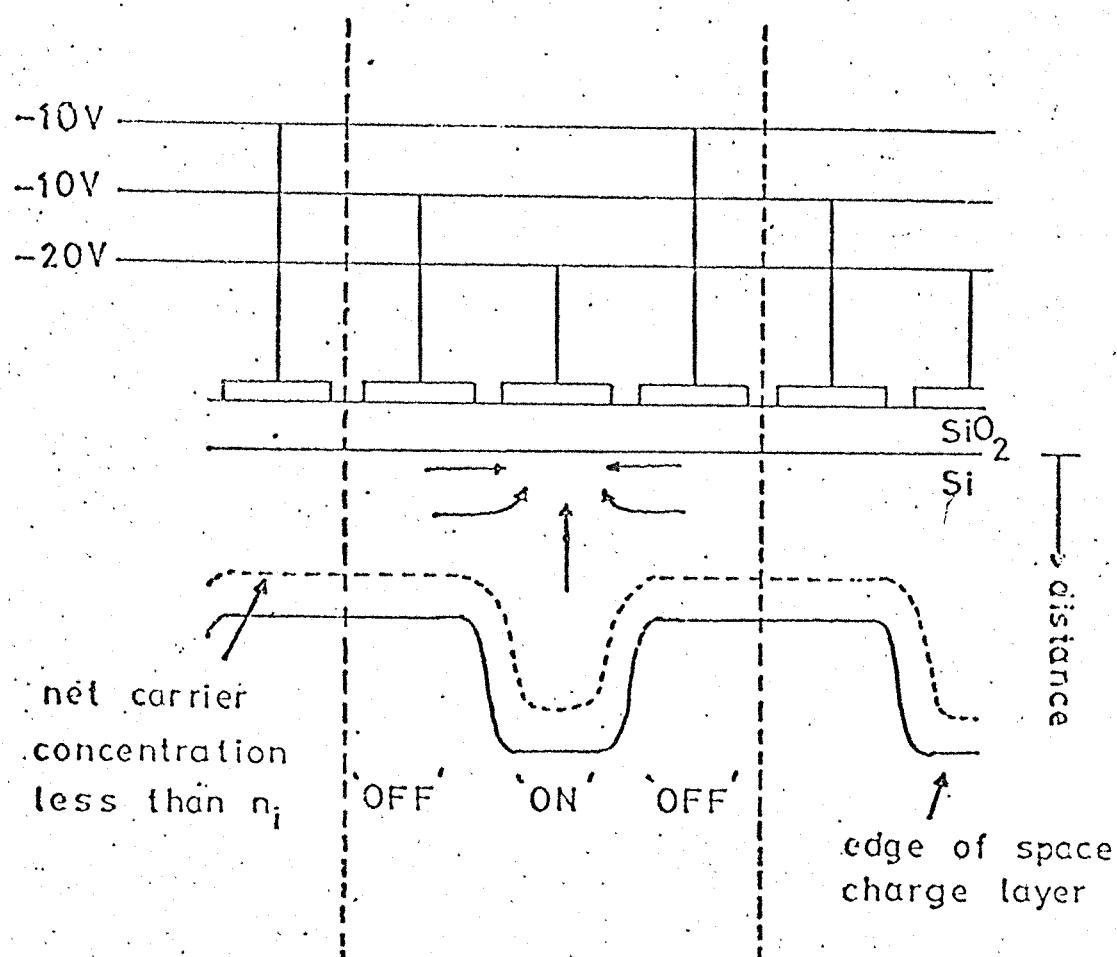

In Chapter 2 and 4 of this thesis we are interested in the leakage current in gated diodes and charge coupled devices. Surface channel charge coupled devices (SCCD) consist of closely spaced MOS capacitors that are pulsed into deep depletion sequentially for times much shorter than that required to form an inversion layer of minority carriers by thermal generation. This causes potential wells to be formed at the Si-SiO<sub>2</sub> interface which are then used to store and transfer minority carriers representing the sampled analogue signal, as shown in Fig. 1.2. In the buried-channel charge coupled device (BCCD) the potential wells are formed at some distance below the oxide-semiconductor interface and are used to store and transfer majority carriers, as shown in Fig. 1.3.

For image sensing purposes, the potential well pattern is held constant for a certain time known as the 'intergration time'

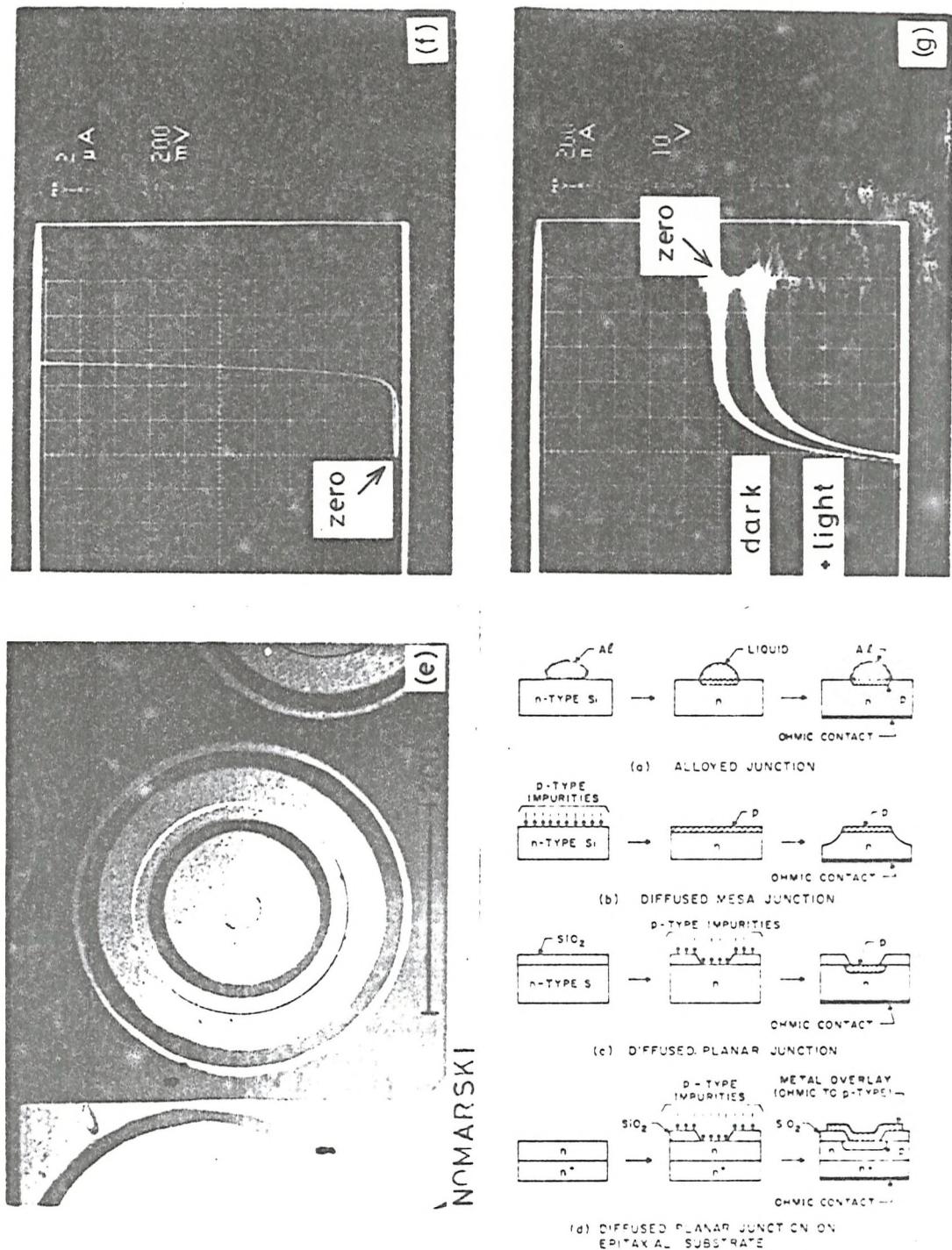

(a) - (d) junction fabrication methods.

(e) planar diode (two metal electrodes on oxide) + one central anode contact

Fig. 1.1

Fig. 1.2 A surface channel CCD

Fig. 1.3 A Buried channel CCD

(typically tens of msecs) whence a spatial distribution of optically generated minority carriers under the CCD elements is obtained representing the image. These charges are then transferred and collected by a quick succession of clock pulses for further processing and display. For low light level imaging applications the integration time needs to be as long as possible but the limit is set by the thermal generation of carriers in the substrate.

In the low frequency operation of the CCD's the same thermal generation again sets the limit. In this case, the potential pattern sweeps all of the gates at a constant rate and hence the contribution of thermally generated carriers to each of the output pulses will be roughly the same. If the generation current under each gate is assumed uniform and equal to  $J$  (in one electrode area  $A_s$ ), and  $t_c$  is the clock period and equal to  $1/f_c$  where  $f_c$  is clock frequency, and if there are  $n$  electrodes in all, then the total contribution of thermally generated carriers to each output pulse will be:

$$Q_\ell = q(n t_c) J A_s = q \left( \frac{n}{f_c} \right) J A_s \quad [C] \quad 1a.1$$

So this noise limits the size of the signal that can be transferred with a reasonable signal to noise ratio.

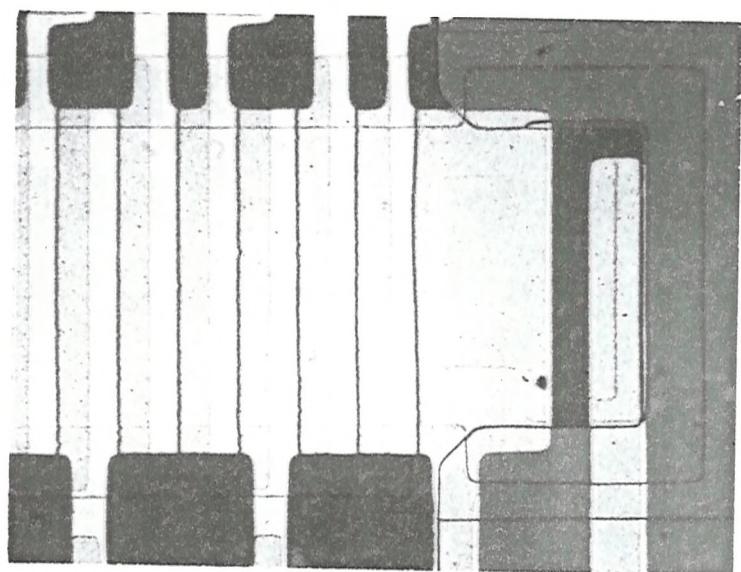

In plate 1 is shown the output voltage pulses from a CCD 134DRLMPS which is an 8 bit three-phase, p-channel, Aluminium-gate device operated in 'Interrupted Clock' integration mode. This device was manufactured in the Microelectronics laboratory of the Department of Electronics at Southampton University using the same process as is used for the devices extensively measured in this work with the addition of an  $n^+$  'guard'-ring diffusion step at the beginning of the process. In plate 2 the complete CCD is shown.

There are three major components of thermal generation current,  $J$ :

- a) Surface generation.

- b) Generation in the depleted space-charge region in the bulk.

- c) Generation in the neutral bulk within a diffusion length of the depletion region.

Usually at room temperature in Silicon the contribution of the last one is negligible compared to that of the first two.

Plate 1. The split time-base display showing the output pulses for an integration time of 30 msec with a clock readout frequency of 5kHz.

Plate 2. The topography of the 134 DRLMPS 3-phase surface channel CCD used to obtain plate 1.

### 1b Interface State Measurements

Another aspect of CCD performance is that of transfer inefficiency. In surface channel devices the two most important charge loss mechanisms which limit the charge transfer efficiency of the device are backward flow loss and interface state loss (2).

However, the backward flow loss is a function of the clock driving voltages and by suitable choice of the clocking, waveforms the backward flow loss can be made significantly less than the interface state loss except at high frequencies. So in practice at all but the highest operating frequencies the charge transfer efficiency of the device is expected to be limited by the interface state trapping mechanism.

This loss occurs by the interface states at the Si-SiO<sub>2</sub> interface trapping some of the signal charge carriers and not re-emitting all of them within the time allowed for the free charge transfer. It was first thought that the use of Fat Zeroes (i.e. the continuous circulation of a non-zero background charge) would tend to keep the interface states filled and dramatically reduce the loss since this loss occurs because of the unsymmetrical filling and emptying of the interface states. However, it has subsequently become apparent that this technique is only partially successful due to the so called "Edge Effect" which is associated with the edge regions of the transfer gases where the interface states are not refilled by the Fat Zero charge (3,4). This then means that the only really effective way of reducing the interface state loss is to reduce the interface state density. This is achieved in practice by using (100) orientation substrates and including in the processing steps both high temperature (1050°C, N<sub>2</sub>) and low temperature (420°C, H<sub>2</sub>/N<sub>2</sub>) annealing treatments. In the best devices to date the value of interface state density is of the order of 10<sup>9</sup>/cm<sup>2</sup>eV and reasonably uniform over the band gap (5). Conventional methods of measuring interface state density are, with the exception of the conductance technique (6), unable to obtain sufficient precision to measure these low values of interface state density.

The conductance technique, though, is a very laborious and time consuming method and it would be highly desirable to develop an alternative, simpler, technique for measuring a finished CCD.

In Chapter 3 an investigation of the technique of 'charge

'pumping' is presented which was first suggested by Brugler and Jespers (7) and subsequently by Elliot (8). This is a measuring technique for low surface state densities in packaged commercial devices. The technique involves only a knowledge of the active area of the gate region, the doping level of the substrate and the oxide thickness in the gate regions together with measurements of current flowing to the substrate in order to calculate the interface state density. The magnitude of the current is of the order of nA depending of the interface state density and the rate of pumping. For very low interface state densities it is merely necessary to increase the rate of pumping charge through the interface states to obtain easily measured currents. The only serious limitation to the method is the presence of gate protection diodes internally connected to the gate to be measured, since it is necessary in some cases to pulse either side of zero volts.

In Chapter 4 the leakage current and charge pumping currents are measured in gated diodes that are fabricated using TCE (trichloroethylene) instead of HCl in the gate oxidation process.

Finally, conclusions and comparisons of the different processing steps are included in the last chapter of this work together with a discussion of the usefulness of the measurement technique.

## 2. LEAKAGE CURRENT INVESTIGATION

### 2a Theory of Leakage Current

It is known that under equilibrium conditions electron holes pairs thermally generated everywhere within a p-n junction diode, on average all recombine and no current flow results in the absence of an applied voltage.

However, if a negative voltage is applied to the p-region of a diode with respect to the n-region (reverse bias) the electron-hole pairs after generation will be separated and their probability of recombination is thereby diminished. Thus the reverse currents observed in p-n junction diodes are due to electron-hole pairs generated some-place in the semiconductor (Shockley-Read-Hall, 9). At room temperature the reverse current of a silicon p-n junction is due to electron-hole pairs generated predominantly (through the action of recombination-generation centres) within the depletion region where the net carrier concentration is below the intrinsic carrier concentration  $n_i$  and is called the generation current. At higher temperatures it is also necessary to consider the current due to electron-hole pairs generated in the neutral regions of the p-n junction which is called the diffusion current. This can be seen from the expressions for diffusion and generation currents. Thus for n-type material and  $|V_R| \gg \frac{kT}{q}$  (Shockley) we have,

$$I_{\text{diff},p} = q \frac{P_{\text{no}}}{\tau_p} L_p A_{\text{MJ}} = q D_p \frac{n_i^2}{N_D L_p} A_{\text{MJ}} \quad 2a.1$$

where  $P_{\text{no}}$  is the minority carrier density in equilibrium

$\tau_p$  is the minority carrier lifetime in the neutral region

$A_{\text{MJ}}$  is the cross-sectional area of the junction

$L_p = \sqrt{D_p \tau_p}$  is the diffusion length of holes in the neutral n-region.

Thus the diffusion current is independent of bias but has a temperature dependence proportional to  $n_i^2$  ( $n_i^2 \propto e^{-Eg/KT}$ ).

The magnitude of the generation current (current due to generation within the depletion region as explained above) is given by: (Grove, 10).

$$I_{\text{gen}} = q|U|WA_{\text{MJ}} = \frac{1}{2}q\frac{n_i}{\tau_o} WA_{\text{MJ}} \quad 2a.2$$

where  $\tau_o$  is the effective lifetime within a reversed bias depletion region and is given by:

$$\tau_o = \frac{\sigma_n e^{-(E_t - E_i)/KT} + \sigma_p e^{-(E_t - E_i)/KT}}{2\sigma_p \sigma_n v_{\text{th}} N} \quad 2a.3$$

$U$  is the rate of generation of electron-hole pairs in the depletion region.

$W$  is the width of depletion region.

For the simple case of  $E_t = E_i$  we can see that the generation current component has the same temperature dependence as  $n_i$  that is

$$I_{\text{gen}} \propto e^{-E_g/2KT}$$

All the experiments that will be described here are done at room temperature so the current that we measure is almost all generation current from the depletion region.

So far we have considered only generation of electron-hole pairs at centres that are distributed uniformly within the semiconductor bulk. However, at the surface of a semiconductor the generation of electron-hole pairs is associated with a possibly different concentration of centres and their spatial distribution is usually not known. In this case a recombination velocity of the surface,  $S_o$ , is defined which is related to the surface generation rate  $U_s$  per unit area as will be shown later and is defined as

$$S_o = \sigma_s v_{\text{th}} N_{\text{st}}$$

where  $\sigma_s$  is the mean cross section for holes and electrons,  $v_{\text{th}}$  is the thermal velocity,

$N_{\text{st}}$  is the density of the centres per unit surface area.

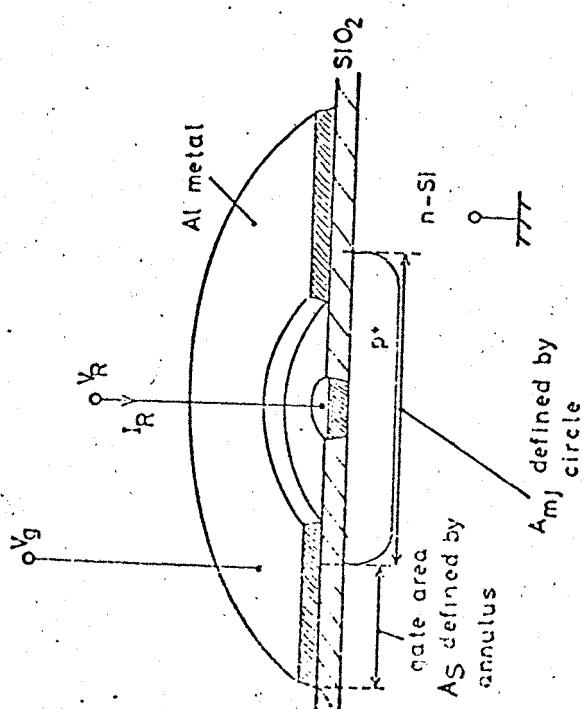

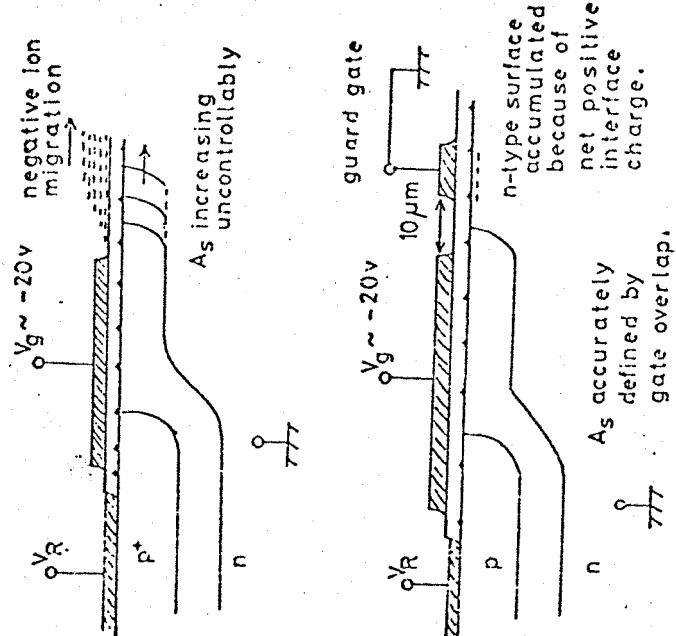

In order to distinguish between the surface generation current and the generation current in the rest of the depletion region a gated diode structure, as was introduced by Grove (10) is used. This structure is shown in Fig. 2.1. The introduction of a gate electrode over the surface as shown, enables the geometry of the depletion region at the surface to be modified in a controlled manner. In particular, this enables us to change the active

Fig. 2.1

Fig. 2.2

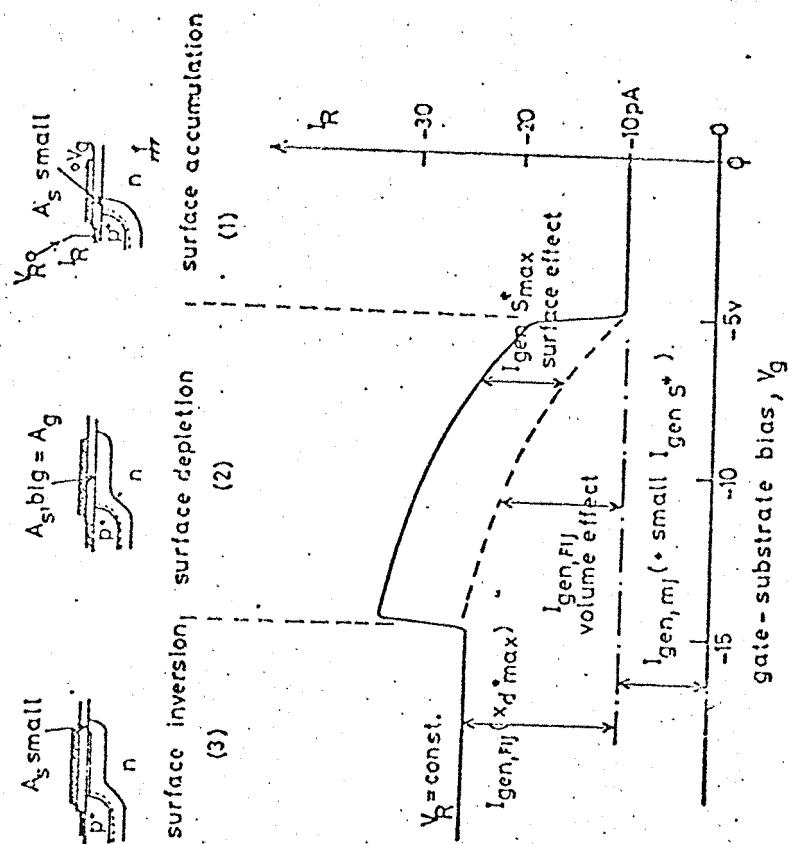

surface area,  $A_s$ , by altering the gate voltage. Thus we are able to measure an increased surface generation component from which we can determine the value of the surface recombination velocity  $S_0$  as will be shown later in this chapter. Let us now consider the reverse current versus gate voltage characteristic at a fixed reverse voltage of a gate controlled  $p^+n$  junction depicted in Fig. 2.2. An analogous characteristic holds for  $n^+p$  with the appropriate changes in sign for voltages and currents. At zero gate voltage it is usually found that (for n-type substrate) the semiconductor surface is in accumulation (11). In this case only those centers which are within the depletion region of the metallurgical junction contribute to the leakage current. This is shown in the case (1) of Fig. 2.2. As the gate is biased more negatively, a voltage is reached at which the surface under the gate changes from being accumulated to being depleted. This is shown in case (2) of Fig. 2.2. At this point we observe an increase in leakage current. This increase is due to the changed surface area of the depletion region and also to the changed surface generation rate,  $U_s$ , which is dependent on the concentration of free carriers at the surface. The gate voltage at which this occurs is such that the surface potential,  $\psi_s$ , is sufficient to deplete the surface of majority carriers  $n_s$ . This surface generation current depends on the product  $A_s U_s$ . But  $U_s$  depends on the surface recombination velocity  $S$  and on the value of the suppression of the carrier concentration at the surface  $\Delta p$ , which for a reverse bias  $|V_R| \gg \frac{KT}{q}$  is usually constant and equal to the minority carriers concentration at equilibrium,  $-p_{no}$ .

So we have

$$U_s = S \Delta p \quad 2a.4$$

Therefore

$$U_{s,max} = -S_{max} p_{no} = -S_0 \frac{n_{no}}{2n_i} p_{no} \quad 2a.5$$

$$\text{since } n_{no} p_{no} = n_i^2, U_{s,max} = -S_0 \frac{n_i}{2} \quad 2a.6$$

Where the conventional approximations

$\sigma_{ns} = \sigma_{ps} = \sigma_s$  and  $E_{ts} = E_{is}$  have been made. Therefore while the surface is depleted, we have a total surface generation component,

$$I_{gen,s} = qU_{s,max} \quad A_s = \frac{1}{2}qn_i S_o A_s \quad 2a.7$$

The surface area  $A_s$ , in this region is defined by the entire area of the gate electrode covering the undiffused substrate as shown in Fig. 2.1. This current is independent of the reverse voltage and remains constant with changes in the gate voltage as long as the surface is in depletion but reduces again when the surface becomes inverted with sufficient carriers to reduce the surface generation rate  $U_s$ .

In the second case as well as the surface current, we have a generation component from the depletion region below the surface, the field induced junction,

$$I_{gen,FIJ} = qUx_d A_s = q\left(\frac{x_d}{2\tau_{oFIJ}}\right) A_s \quad 2a.8$$

This component, however, increases as  $V_G$  is made more negative, because  $x_d$  increases and takes the maximum  $x_{d,max}$  when inversion is reached. It is evident from this equation that  $I_{gen,FIJ}$  depends on the magnitude of reverse bias through  $x_d$ , and in fact increases with  $V_R$  since  $x_d \propto V_R^{\frac{1}{2}}$  for an abrupt one-sided junction. This current reaches a limit at inversion of the interface, as shown in Fig. 2.2(b). At some more negative gate voltage depending on the value of reverse junction bias, the substrate surface becomes inverted. The surface is no longer included in the depletion region and therefore the extra surface generation current is reduced almost to zero leaving only the field induced depletion region below the surface and the metallurgical junction as significant sources of electron-hole pairs. In this case the width of the field induced depletion region reaches its maximum value  $x_{d,max}$ . So during inversion the total current reduces to some value depending on the volume of the Field Induced depletion region and the Metallurgical Junction depletion region and the lifetimes  $\tau_{oFIJ}$ ,  $\tau_{oMJ}$  respectively, and remains at this value for further negatively increased gate voltages as is shown in case (3) of Fig. 2.2. Summarising, for all three cases we have

For accumulation:

$$I_L = I_{gen,MJ} = \frac{1}{2}q \frac{n_i}{\tau_{oMJ}} WA_{MJ} \quad 2a.9$$

For depletion:

$$\begin{aligned}

I_2 &= I_{\text{gen}, \text{MJ}} + I_{\text{gen}, \text{FIJ}} + I_{\text{gen}, s} \\

&= \frac{1}{2}q \frac{n_i}{\tau_{\text{oMJ}}} W A_{\text{MJ}} + \frac{1}{2}q \frac{n_i}{\tau_{\text{oFIJ}}} x_d A_s + \frac{1}{2}q n_i S_o A_s

\end{aligned} \quad 2a.10$$

For inversion:

$$\begin{aligned}

I_3 &= I_{\text{gen}, \text{MJ}} + I_{\text{gen}, \text{FIJ}} \\

&= \frac{1}{2}q \frac{n_i}{\tau_{\text{oMJ}}} W A_{\text{MJ}} + \frac{1}{2}q \frac{n_i}{\tau_{\text{oFIJ}}} x_{\text{dmax}} A_s

\end{aligned} \quad 2a.11$$

The currents  $I_1, I_2, I_3$  are measured experimentally and the difference between  $I_2$  and  $I_3$  gives the surface generation current from which  $S_o$  can be calculated. The difference between  $I_3$  and  $I_1$  gives the field induced junction current from which  $\tau_{\text{oFIJ}}$  can then be calculated.  $A_s$  may be measured by photography and geometric calculations as will be shown later in this chapter while  $x_{\text{dmax}}$  may be calculated from the measured doping concentration using the relationship:

$$x_{\text{dmax}} = \frac{2\epsilon_o K_s \psi_s (\text{inv})}{qN_D} \quad 2a.12$$

as shown by Roberts (15),

where  $\epsilon_o$  = permittivity of free space

$K_s$  = relative permittivity of silicon

$N_D$  = donor concentration.

$\psi_s$  (inv) = surface potential at inversion where  $p_s = N_D$

$$\approx (V_R + 2\psi_B)$$

$V_R$  = reverse bias applied to the diode

$$\psi_B = \frac{KT}{q} \cdot \ln \frac{N_D}{n_i} = \text{bulk Fermi potential}$$

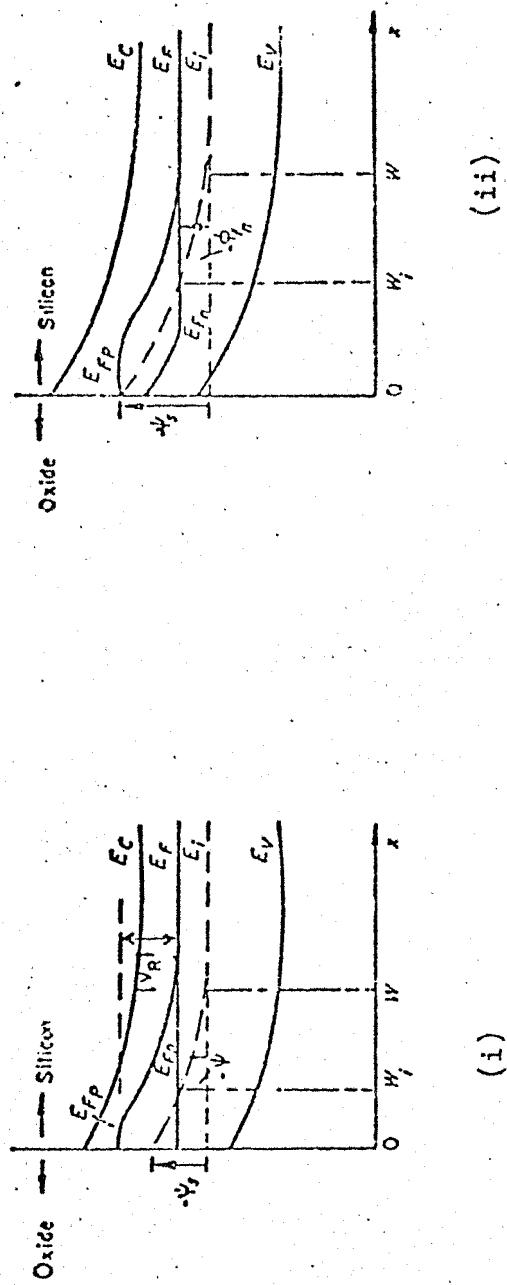

In the above analysis the assumption that the generation rate  $U$  is constant over all the space-charge layer was used, but Calzolari and Graffi (13) suggested that this is not true. They have shown that the active generating volume is the region bounded by the two points where the Quasi-Fermi levels cross the intrinsic Fermi level (Fig. 2.3). Thus  $U$  is only constant over a certain interval  $W_i$  and drops rapidly to negligible values outside this but  $W_i$  is by no means

Fig. 2.3 Energy band diagrams showing active generation width  $W_i$  in relation to the depletion width  $W$  for the two cases,

$$(i) |\psi_s| < |V_R| + |\phi_{fn}| \quad \text{and} \quad (ii) |\psi_s| = |V_R| + |\phi_{fn}|$$

(Roberts and Beynon<sup>14</sup>)

equal to  $W$ . On the contrary, it remains much smaller than  $W$  up to voltages so high that the multiplication current is no longer negligible. Thus the generation current from the metallurgical junction becomes:

$$I_{\text{gen},\text{MJ}} = \frac{1}{2}q \frac{n_i}{\tau_{\text{oMj}}} W_i A_{\text{MJ}} = \frac{1}{2}q \frac{n_i}{\tau_{\text{oMj}}} W \left( \frac{W_i}{W} \right) A_{\text{MJ}} \quad 2a.13$$

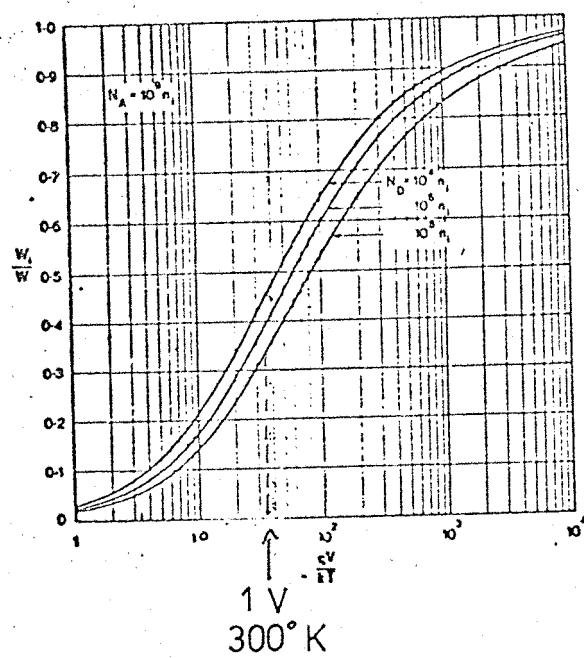

where  $\frac{W_i}{W}$  versus  $\frac{qV_R}{KT}$  is shown in Fig. 2.4 (13).

Roberts and Beynon (14) used the same criterion as Calzolari for the field induced junction depletion region of the gated diode structure. The Field induced space-charge region closely resembles the structure of an abrupt p-n junction when the silicon immediately under the oxide is inverted.

In this case  $U_{\text{FIJ}}$  is constant over a width  $W_i$  that is less than  $x_{\text{dmax}}$  given by (14):

$$\frac{W_i}{x_{\text{dmax}}} = 1 - \frac{\phi_{\text{Fn}}}{\psi_s(\text{inv})} = 1 - \frac{\phi_{\text{Fn}}}{|V_R| + |\phi_{\text{Fn}}|} \quad 2a.14$$

Thus the  $I_{\text{gen},\text{FIJ}}$  at inversion becomes

$$I_{\text{gen},\text{FIJ}} = \frac{1}{2}q \frac{n_i}{\tau_{\text{oFIJ}}} W_i A_s = \frac{1}{2}q \frac{n_i}{\tau_{\text{oFIJ}}} x_{\text{dmax}} \left( \frac{W_i}{x_{\text{dmax}}} \right) A_s \quad 2a.15$$

In the above analysis the non-equilibrium MOS theory was employed in the study of recombination generation processes within the space-charge region of gate controlled p-n junction diodes. In particular it was shown that the surface recombination velocity  $S_o$  and the minority carrier lifetime in the surface space-charge region  $\tau_{\text{oFIJ}}$  of an oxidized silicon surface can be determined by measuring the reverse bias current as a function of gate voltage.

In the next section of this chapter the fabrication of gated diodes using different processing is described, together with the measurement technique.

Fig. 2.4.

2b. Gated diode fabrication using HCl oxidation

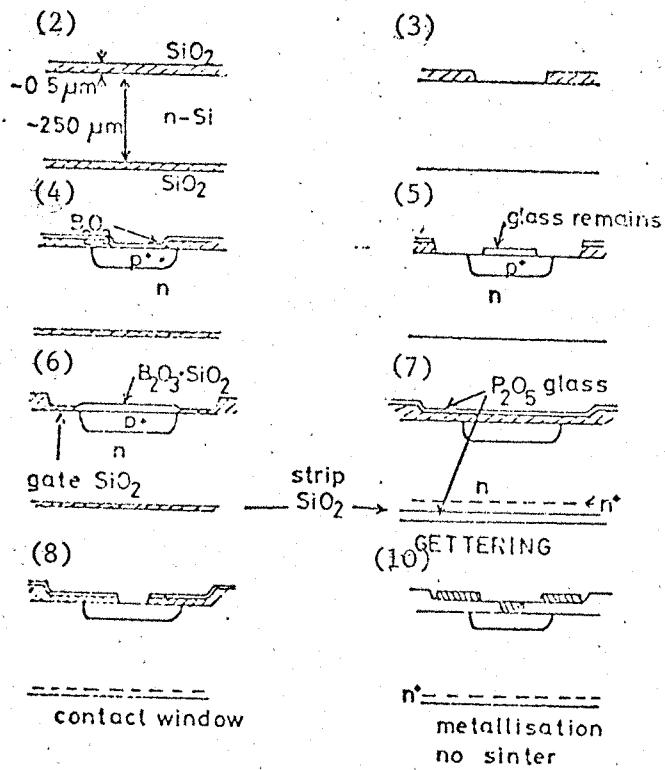

The process for producing gate-controlled  $p^+n$  diodes that was used for the present work was chosen to be the same as the CCD fabrication schedule. The only difference between the gated diode structure and the CCD structure for the p-channel Aluminium-gate shadow-gap devices is the absence of the  $n^+$  diffused guard ring. Three types of gated diodes were manufactured with a variation in the process described below

1. No gettering step apart from the HCl oxidation

2. A gettering step listed as stage 7 below performed before the HCl oxidation for the gate oxide.

3. A gettering step again listed as 7 below, performed without alteration of the complete process.

The complete process is described below with the omission of the  $n^+$  phosphorus guard ring which is not necessary for the gated diode operation. This allowed a more rapid manufacture of the slices thereby permitting quicker evaluation and a large number of repeat processes for estimating the reliability of the data obtained. The material that was used was n-type (111) orientation with  $3-6 \Omega \text{ cm}$  resistivity. The diameter of the whole slice is 2" and they were cut before processing in half since the furnace tubes in use at the time in the laboratory were only  $1\frac{1}{2}$ " diameter.

Gated diode process schedule:

1. Cleaning - The slices are boiled in a quartz beaker with concentrated  $\text{HNO}_3$  (Analar grade) for 5 mins. Then a thorough wash in double distilled water ( $\text{DDH}_2\text{O}$ ) followed by a 20 sec dip each in buffered HF (6:1 of  $\text{NH}_4\text{F:HF}$ ) in a Teflon plastic beaker and again a thorough wash in  $\text{DDH}_2\text{O}$ . This is to degrease the slice and remove any particular residue from the surface. This is followed by another boil in concentrated  $\text{HNO}_3$  for 15 mins in the quartz beaker followed in turn by a thorough wash in  $\text{DDH}_2\text{O}$ . The slices are then spun dry on a PTFE coated plastic spinner. They are then presented to the furnace for the first heat treatment.

2. Initial Oxidation - The slices are put in the initial oxidation furnace at  $1200^\circ\text{C}$  for 50 mins at a flow rate of 1000cc/min in an ambient of oxygen bubbled through distilled  $\text{H}_2\text{O}$  which is maintained at  $80^\circ\text{C}$ . Then the oxygen flow is diverted from the bubbler giving a dry oxidation for a further 5 mins to prepare the slices for the first photomechanical stage.

3. Photomechanical stage - With this stage the diffusion windows are defined. After the photomech the slices are etched in buffered HF at room temperature and washed with  $H_2O$ . Then the resist is stripped off by washing the slices with  $1H_2SO_4:1H_2O_2$  mixture. The slices then are thoroughly washed in  $DDH_2O$  and spun dry to prepare them for the next stage.

4. Boron deposition - The slices are put in the Boron deposition furnace at  $960^{\circ}C$  in a nitrogen ambient for 10 min. The sheet resistance of Boron diffusion was then 100 /D. This produces a shallow diffusion of Boron in the silicon from the doped glass on the surface. The slices are washed in  $DDH_2O$  and spun dry. Then the cleaned slices are put in the Boron drive in furnace at  $1200^{\circ}C$  in an ambient of dry  $O_2$  for 40 min. The slices then are ready to be prepared for the reoxidation.

5. Oxide strip and re-oxidation - The oxide of the gate regions of the slices is stripped off with HF and cleaned. The slices are next put in the gate oxide double walled furnace at  $1150^{\circ}C$  for 30 mins in an ambient of  $O_2$  in which a trace amount of HCl gas was added. Different volume ratios of HCl-gas were used. These ratios used were 0.5%, 1.5%, 3.7% and 6%. After the oxidation period the  $O_2$  is switched off and nitrogen is switched on and the slices are pulled to the mouth of the furnace in the nitrogen ambient. The furnace is cooled down to  $1050^{\circ}C$  then the slices are again pushed into the furnace for 30 min. This is the high temperature annealing treatment in a nitrogen ambient which has been found to produce a minimum in the interface  $N_{ss}$  (Lamb Badcock, 20).

6. The slices are prepared for the gettering process for this resist is spun on the front of the slice, then they are exposed fully to UV, they are then baked for 5 mins at  $150^{\circ}C$  and then the oxide from the back of the slices is etched off. The slices then are cleaned with  $1H_2SO_4:1H_2O_2$  mixture, washed with  $DDH_2O$  and spun dry.

7. Phosphorus gettering - The slices are put in the phosphorus gettering furnace at  $1050^{\circ}C$  for 10 min in an ambient of 1000 cc/min nitrogen plus 10cc/min  $O_2$  and 200cc/min.  $N_2$  bubbled through  $POCl_3$  at melting-ice temperature. After 10 min the oxygen and  $POCl_3$  vapor are switched off and the slices are exposed to a 1000 cc/min nitrogen ambient for a further 30 min at  $1050^{\circ}C$ . During this step the slices are supported on pimples to give an  $n^+$  diffusion in back.

8. Photomechanical stage - With this photomech the contact windows in the slices are defined. Then the slices are etched, washed and spun dry.

9. Low temperature anneal - The slices are then put in the low temperature anneal furnace at  $400^{\circ}\text{C}$  for 40 min in an ambient of 60%  $\text{H}_2$  and 40%  $\text{N}_2$ .

10. Metallization I - The slices then are put in a vacumn chamber which is pumped down to about  $10^{-5}$  torr and Aluminium in a tungsten filament is evaporated onto the front of the slice to about  $0.5\mu\text{m}$  thickness.

11. Photomechanical stage - With this step the gate,  $\text{p}^+\text{n}$  contact and metal guard ring are defined. The rest of the Aluminium is then etched off.

12. Metallization II - This step is the same as no. 9 step except that the Aluminium is deposited on the back of the slice so as to ensure a good ohmic contact to the back of the wafer.

The processing steps are shown schematically in Fig. 2.5. It was mentioned earlier that three types of gated diodes were manufactured. For the first type, gated-diodes without gettering the no. 7 step is omitted from the process described above. For the second type, gated diodes with phosphorus gettering before oxidation, the no. 7 step comes before no. 5 step and no. 6 is omitted. For the last type the processing was as described above without alteration.

The three types of gated diodes are now tested as described in the next section of this chapter.

Fig. 2.5 Stages of process - type 3 with getter after oxidation.

2c. Leakage Current Measurements on HC1 gate diodes.

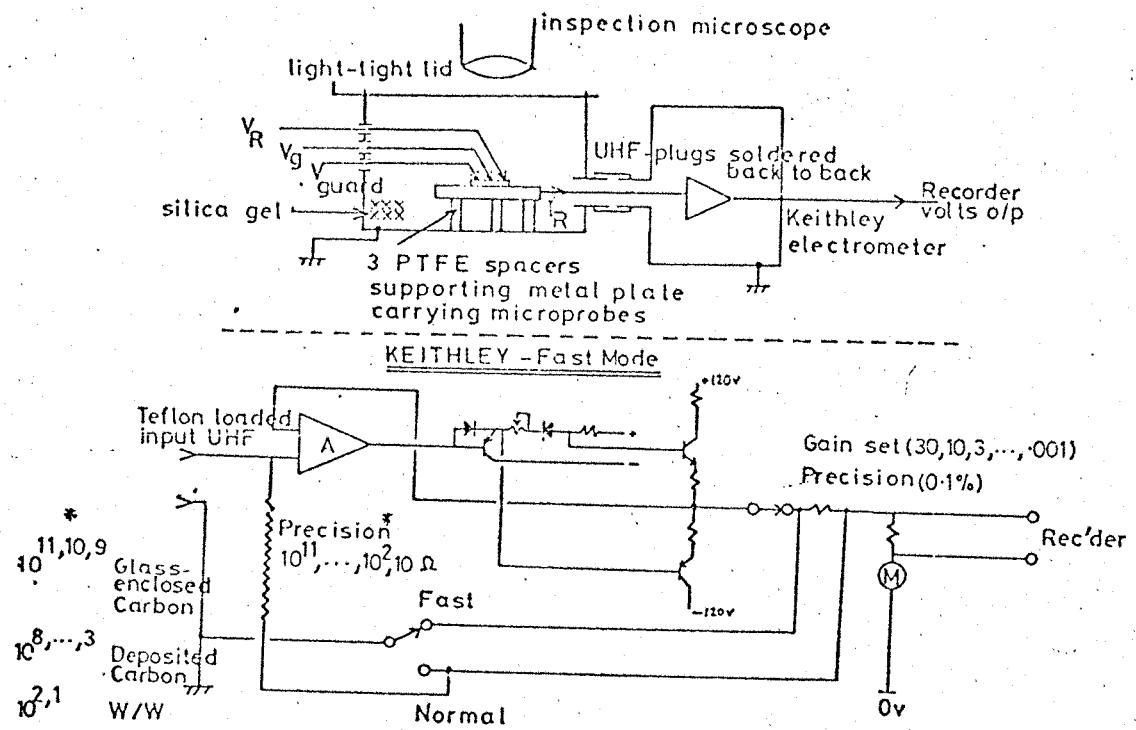

The leakage currents that we have to measure are expected to be as low as  $10^{-13}$  amps at -1V bias. So it is necessary for the environment of the devices to be at least one order of magnitude lower leakage. That is the parallel resistance due to the measuring jig must be in excess of  $10^{14}$   $\Omega$ hms. It is convenient to probe directly on to the diode since defective devices can be quickly detected and there is no need to dice the slice into individual chips with possible damage.

A light tight metal box was therefore constructed with a metal platform supported at three points by PTFE pillars about 1" long and  $\frac{1}{4}$ " diameter. The area of the platform 6" x 8" is large enough to accommodate three PTFE insulated microphone assemblies. This gives a total of four probes with each probe of 5 $\mu$ m tip radius.

Bias inputs to the box internally are via self supporting coiled wires to each of the four probes and from the platform out via a PTFE loaded VHF plug and socket rigidly connected to the electrometer. This arrangement gives a total insulation of  $5 \times 10^{14}$   $\Omega$ hms at D.C. with about 10% to 30% relative humidity. To measure the currents a Kiethley instruments electrometer type 610C was used. This instrument incorporates a feedback loop in the current measuring circuit as shown in Fig. 2.6., which causes the input of the instrument to be a 'virtual earth' at a maximum of 100 $\mu$ V away from earth potential. The accuracy claimed by the manufacturer is 4% of full scale on  $0.001 \times 10^{-11}$  range with an input impedance of  $10^{14} \Omega$  shunted by 22pF without feedback. Drift after one hour warm up is less than 200 V/ $^{\circ}$ C in any hour which implies on the most sensitive current range a drift of less than  $1 \times 10^{-15}$  amps. The input offset of the 610C is  $5 \times 10^{-15}$  amps.

There is a recorder output from the instrument (0-3V, 1k $\Omega$ ) with a noise of less than 3%RMS of full scale at maximum sensitivity.

The output was measured by a Hewlett Packard x-y recorder type 7035B which has a linearity of better than 0.1% of full scale with repeatability of better than 0.2% of full scale. The Kiethley output was displayed in y-axis and the x-axis used as a voltmeter to display gate volts.

The value of the anode volts measured by a Solartron Digital voltmeter type LM1420.2 to  $\pm 1$  part in 9999.0. The lowest leakage devices measured had settle times of the order of a second or so

Fig. 2.6

Fig. 2.7

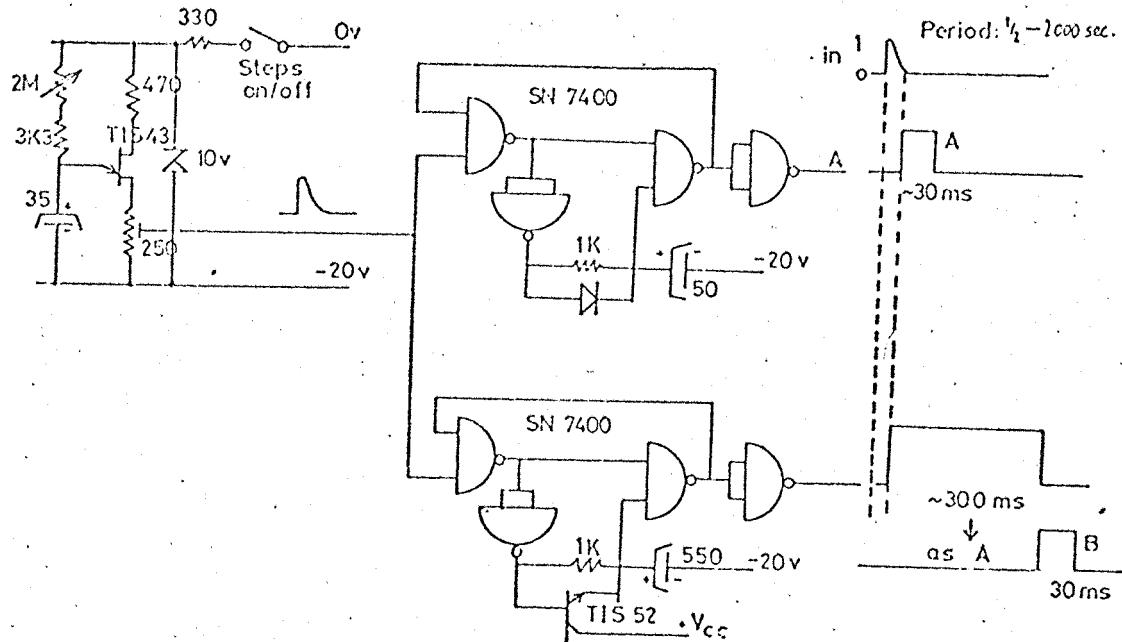

(a) Logic control cct

(b) Data-logging drives

because of the gate capacitance - leakage resistance time constant.

It was found difficult to make measurements by 'hand' and so a semi-automatic control box was used (15) (Fig. 2.8). With this control box the pen of the x-y recorder is brought down only after an interval of say 4 seconds has elapsed since the gate voltage was last stepped. This method enables rapid measurements of transfer characteristics ( $I_R$ ,  $V_G$  at constant  $V_R$ ) without incurring capacitive current component.

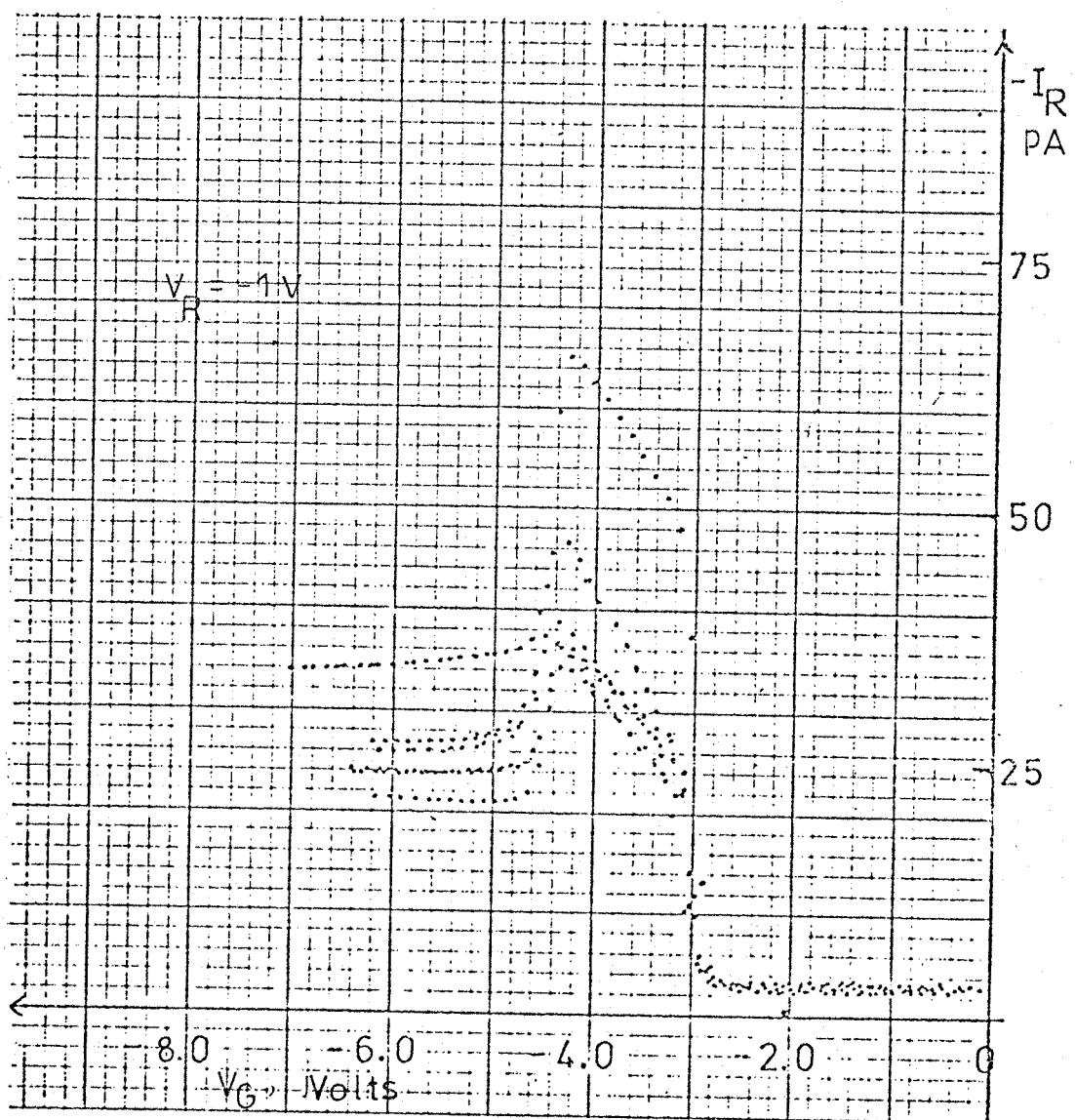

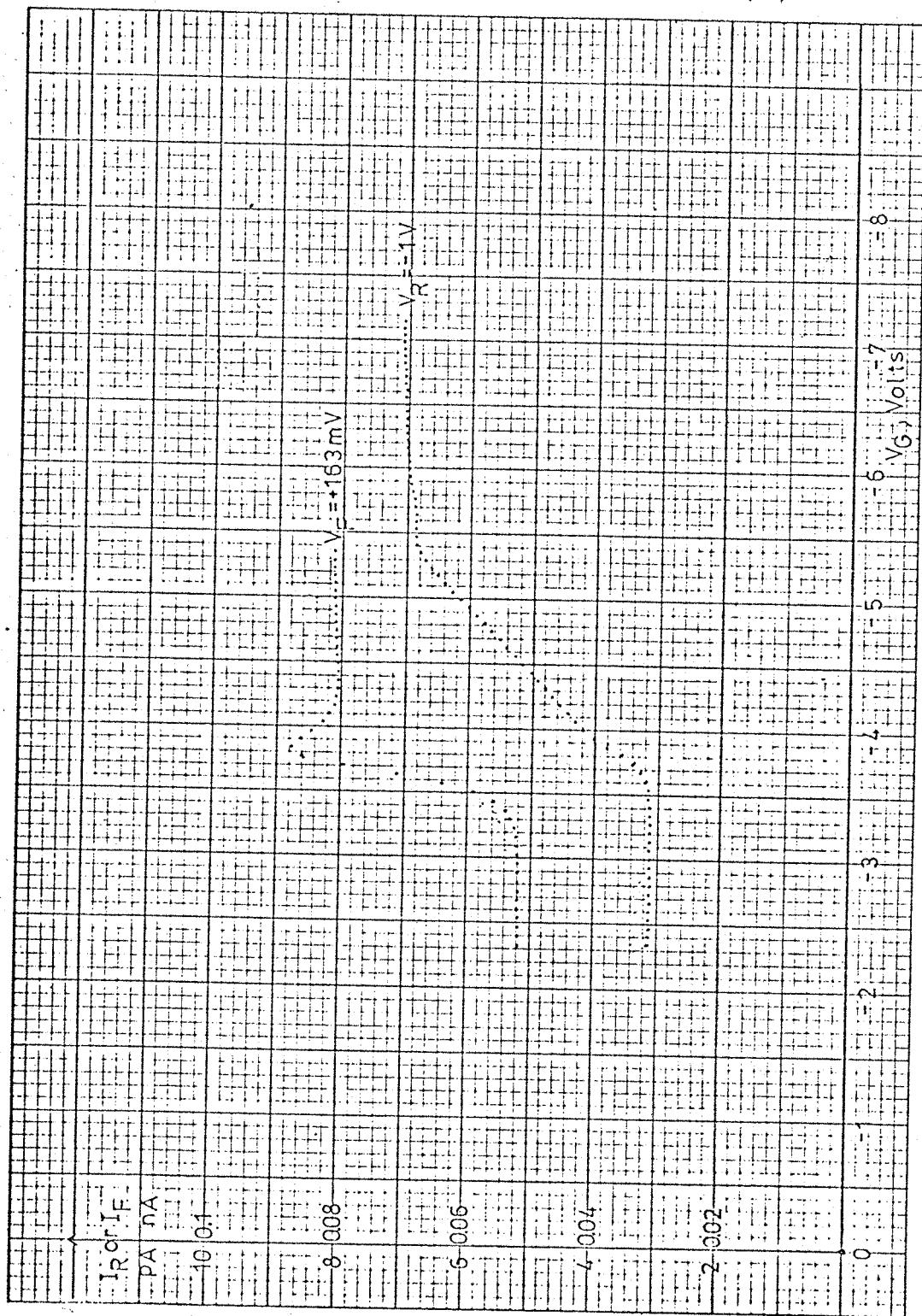

Using the apparatus described above transfer characteristics similar to those shown in Fig. 2.9 were obtained.

In the Fig. 2.9 transfer characteristics of several devices have been plotted on the same axis to enable an estimate of the spread of values of leakage currents in the three regions. The devices were chosen from a single line of the array of the devices selecting only those which did not exhibit gross defects such as leaking gate to substrate poor diffusion leakage or short circuits gate to diffusion. This procedure permitted a reasonable estimate to be made with a minimum of devices measured.

From these transfer characteristics the values for  $I_{MJ}$ ,  $I_{FIJ}$ ,  $I_s$  were obtained. The value of  $I_{MJ}$  current is the leakage current in the accumulation regime which is a direct measurement.

The value of  $I_{FIJ}$  current is the value obtained by subtracting the value  $I_{MJ}$  from the leakage current in the inversion regime. And finally the surface current  $I_s$  is obtained by estimating first of all the value of bulk current in the depletion regime, using a straight line approximation. The straight line joins the leakage current at the up-turn of the transfer characteristic to the leakage current at the bottom part of the down-turn of the transfer characteristic. This value of bulk current is subtracted from the leakage current in the depletion regime of the transfer characteristic to give the value of surface leakage current  $I_s$ . The values thus obtained are averaged and a value of standard deviation was calculated using the formula:

$$S_x = \frac{\sum x^2 - \frac{(\sum x)^2}{n}}{n - 1}$$

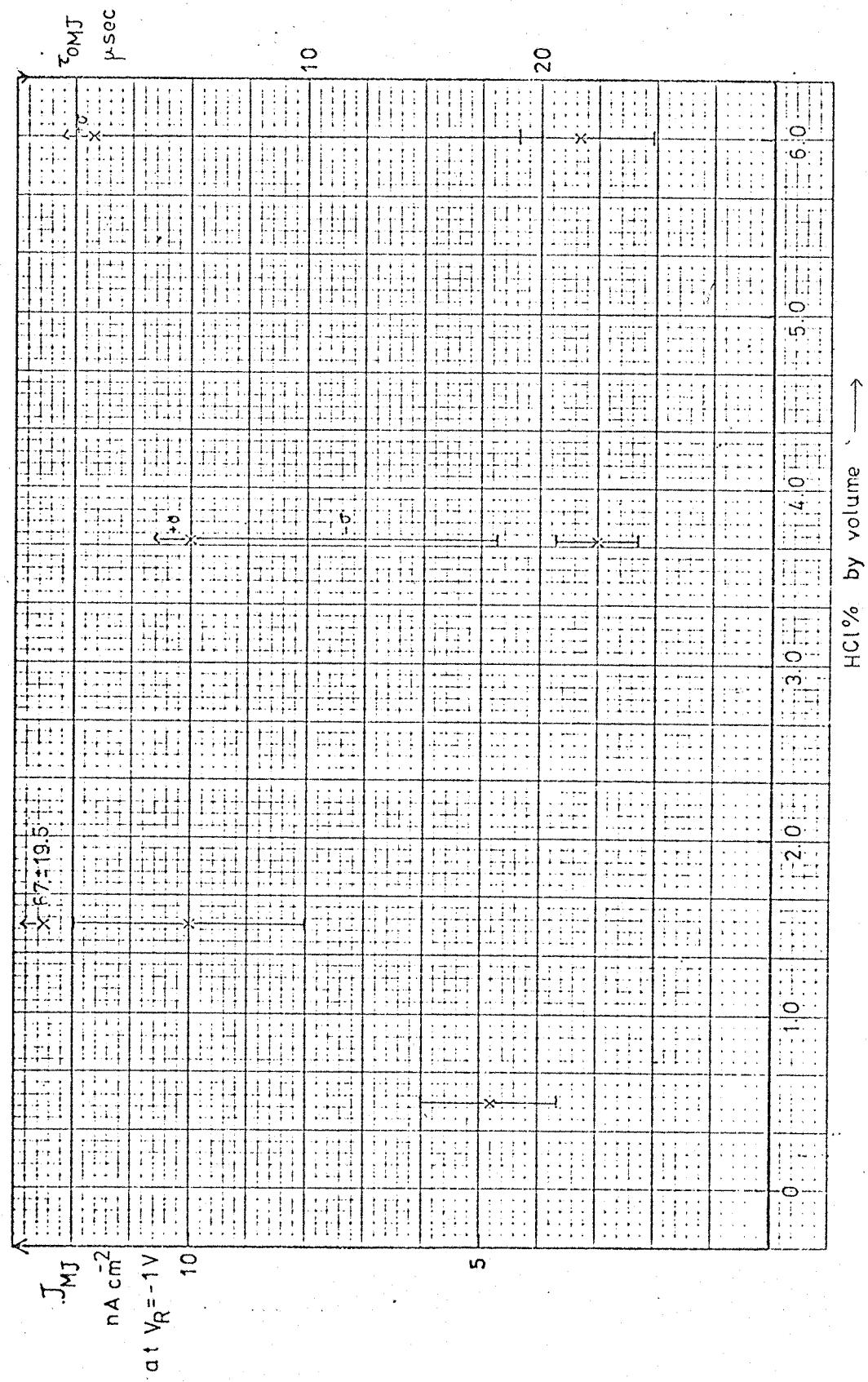

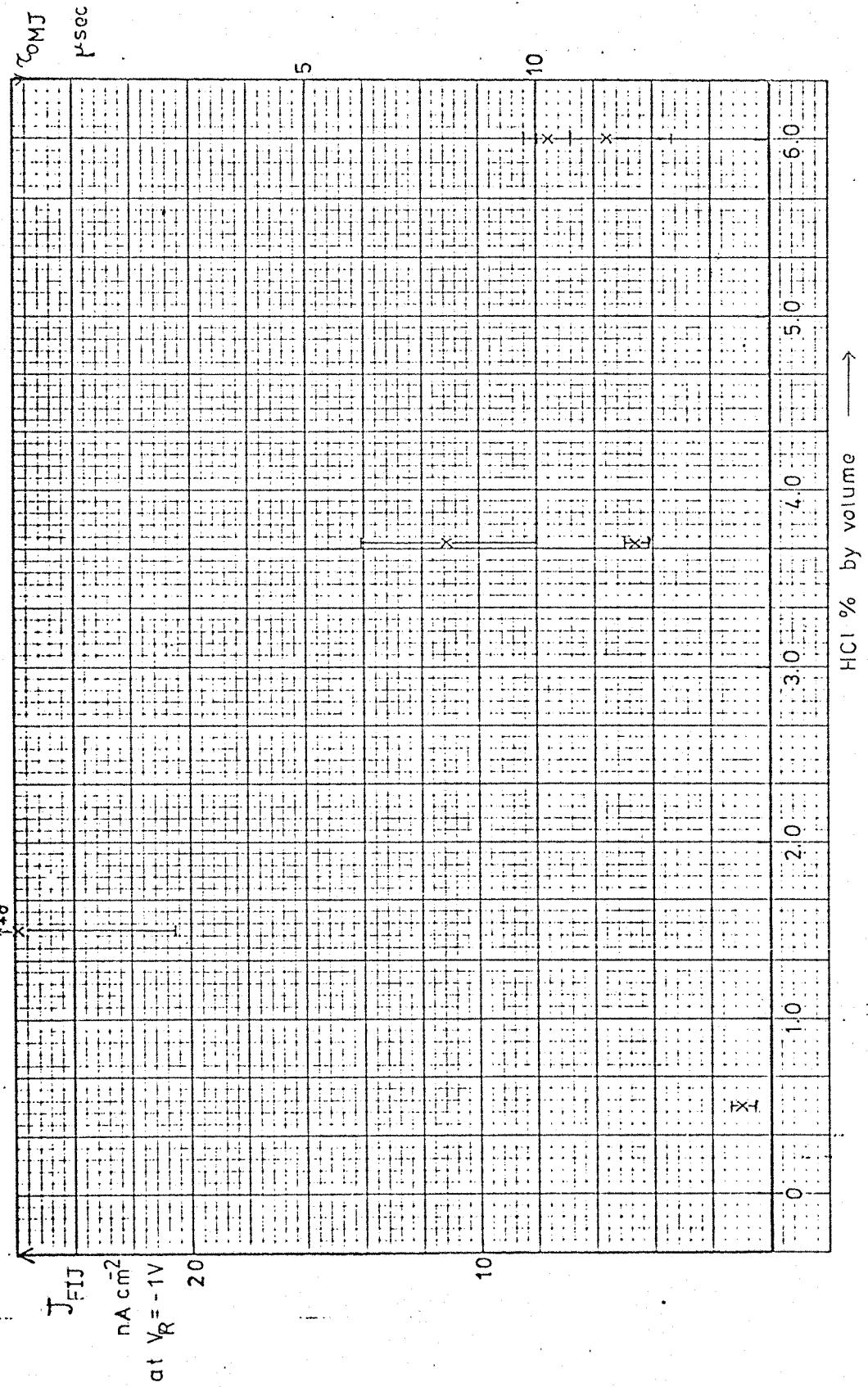

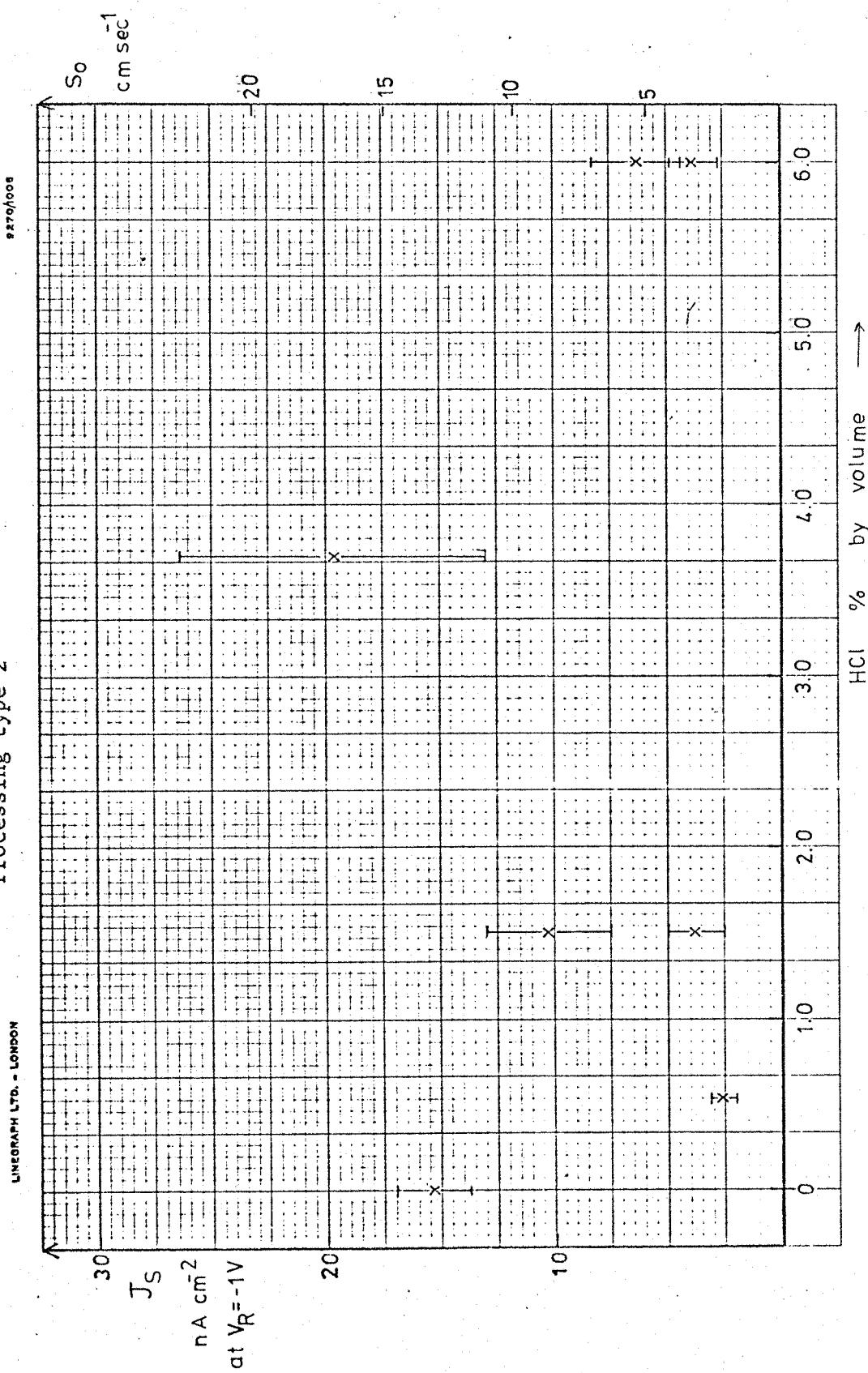

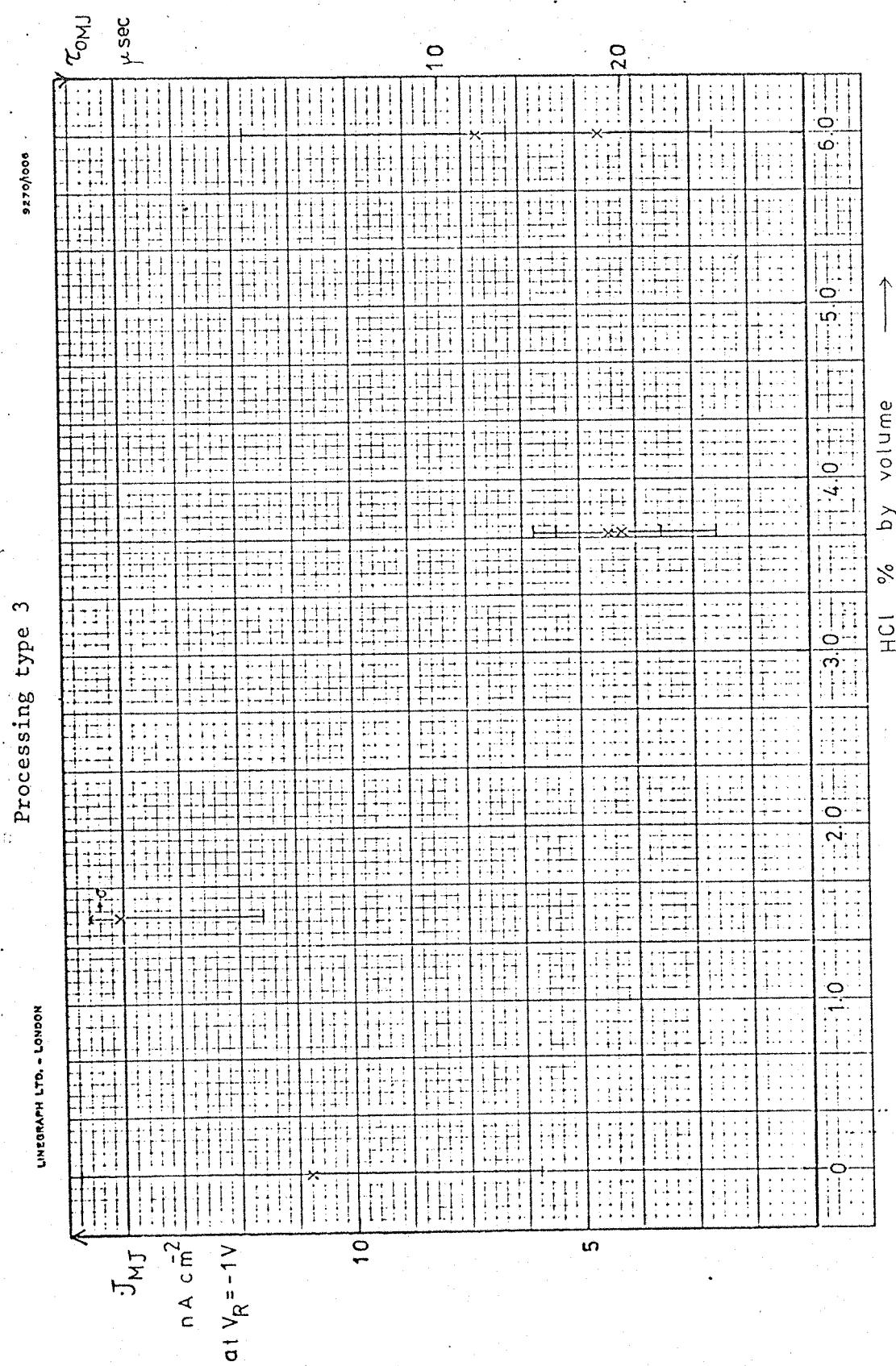

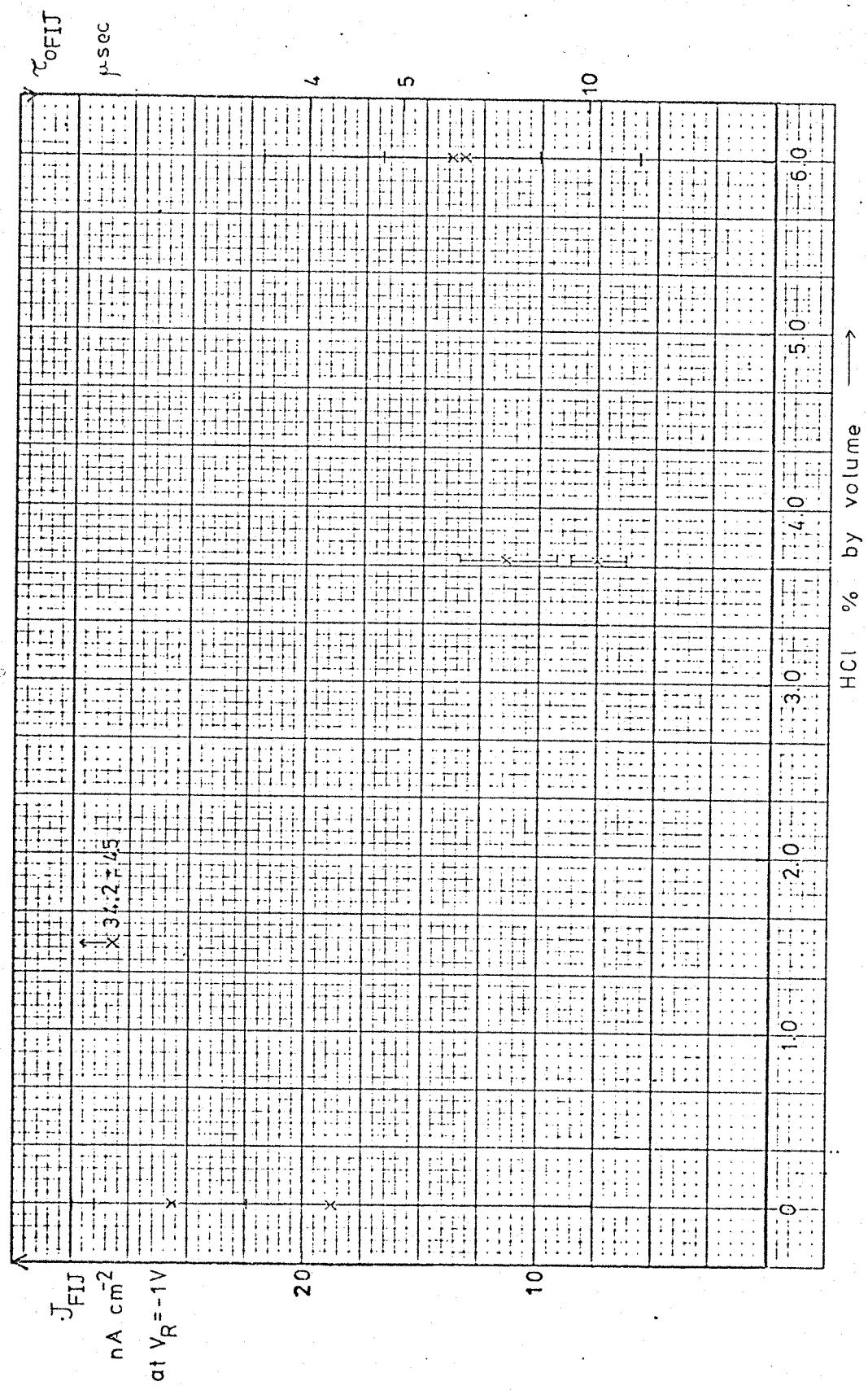

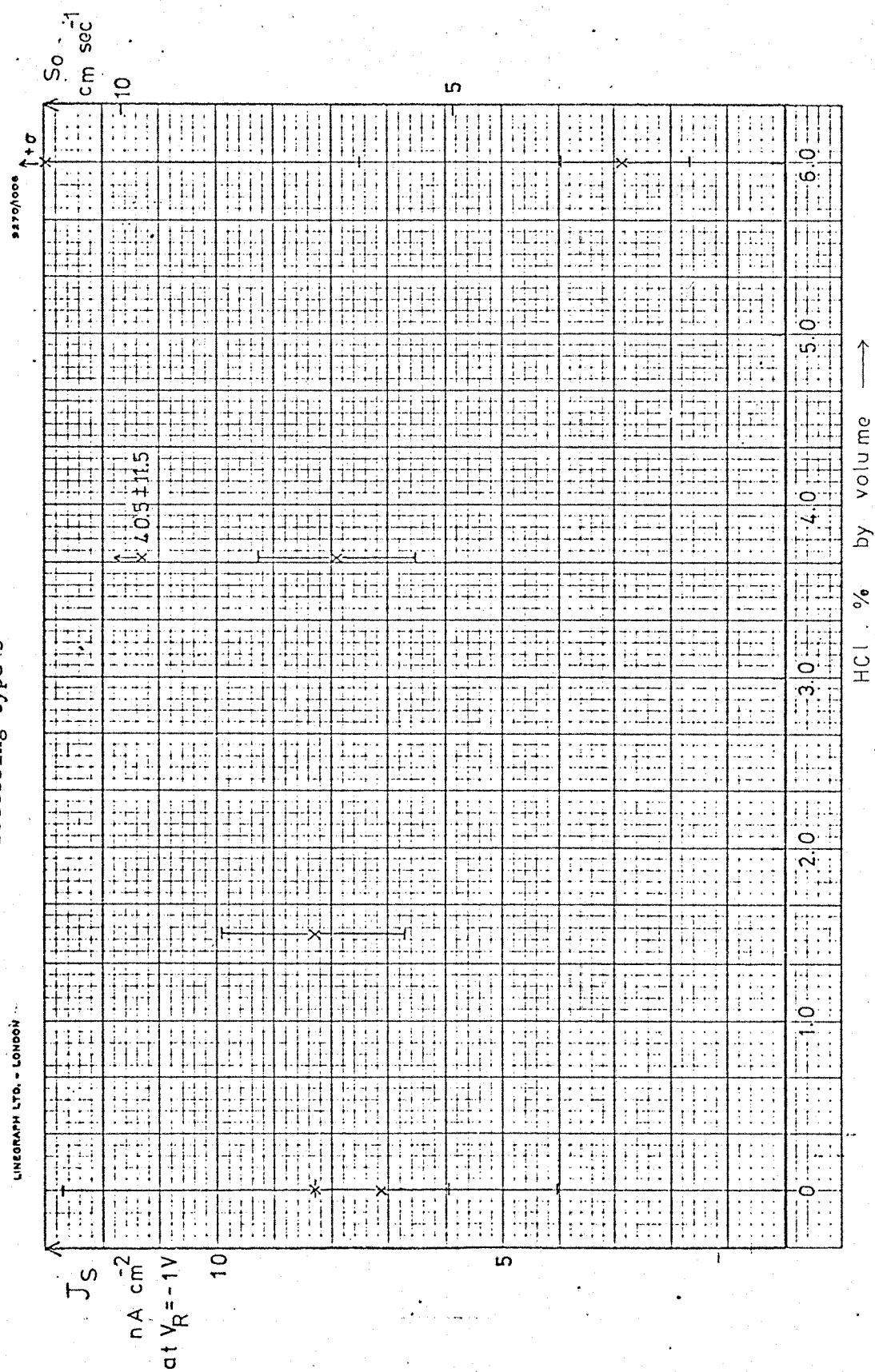

The average values of current densities are shown plotted in Figs. 2.10 through 2.18, with the standard deviation shown by an error bar, as a function of HCl percentage by volume for the three

Fig. 2.9

processing types.

Fig. 2.10 shows  $I_{MJ}$  current density obtained by measuring a 200 $\mu\text{m}$  diffusion diameter diode and dividing the value of the leakage current by the diffusion cross sectional area  $A_{MJ}$  ignoring any side-wall components. The area  $A_{MJ}$  for the devices that we measure here is equal to  $3.0 \times 10^{-4} \text{ cm}^2 \pm 5\%$ . The processing conditions were type 1 where no phosphorous gettering treatment is purposely introduced. No devices of this type were manufactured with 0% HCl since previous work (16) has shown that in general much higher leakage currents are obtained when no gettering is included.

As can be seen from the Fig. 2.10 there is no definite trend of  $I_{MJ}$  with changes in HCl concentration for this process.

The values of lifetime are shown on the same graph and have been calculated using the relationship:

$$\tau_{oMJ} = q \frac{n_i}{2J_{MJ}} W_i \quad 2c.1$$

Where  $q$  is the electronic charge and equal to  $1.6 \times 10^{-19}$  coulomb  $n_i$  the intrinsic concentration and is equal  $1.45 \times 10^{10} \text{ cm}^{-3}$  and  $W_i$  the depletion width which is equal to

$$\left(\frac{W_i}{W}\right) W = (0.45) \times 1.5 \times 10^{-4} \text{ cm} = 0.675 \times 10^{-4} \text{ cm}$$

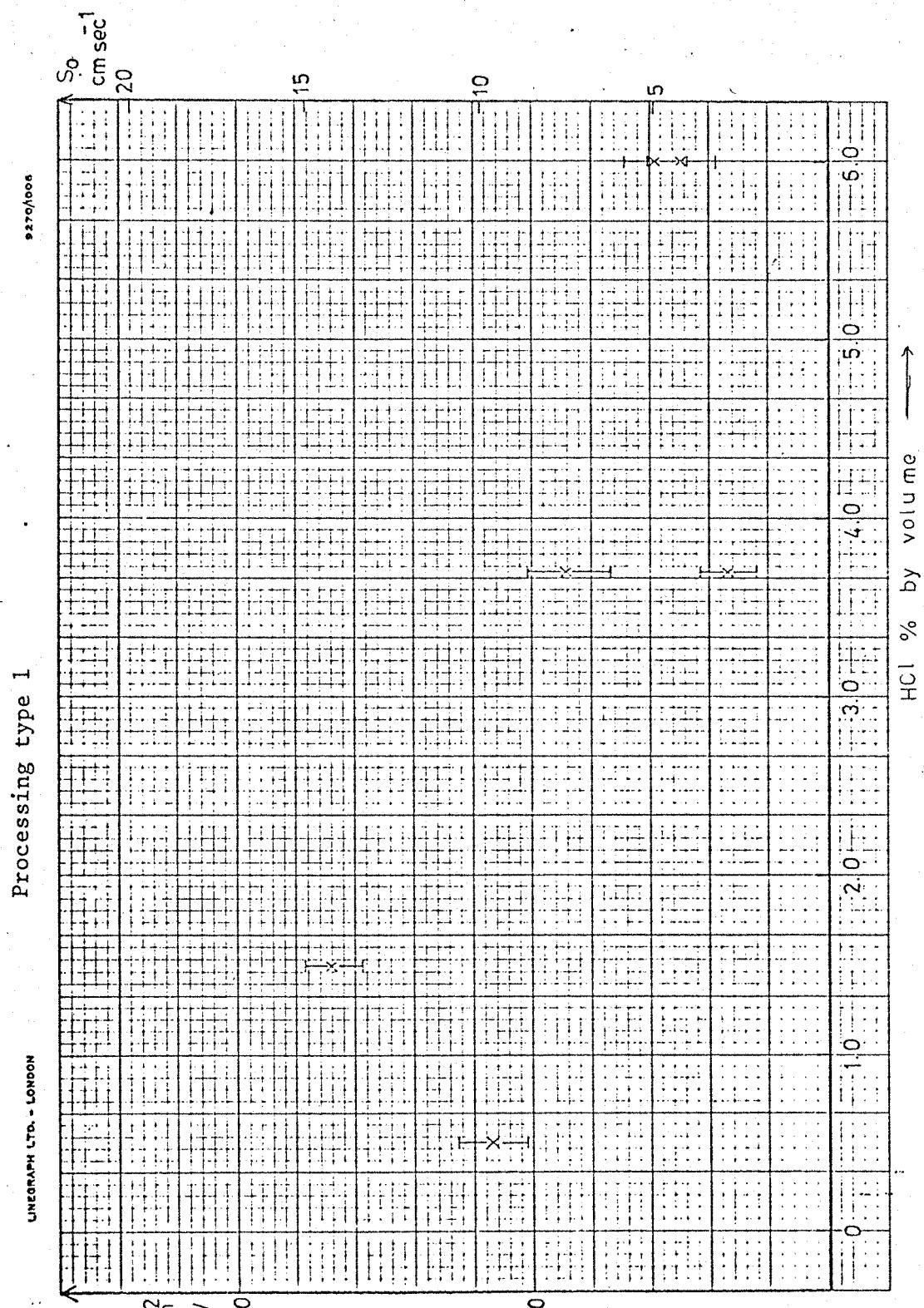

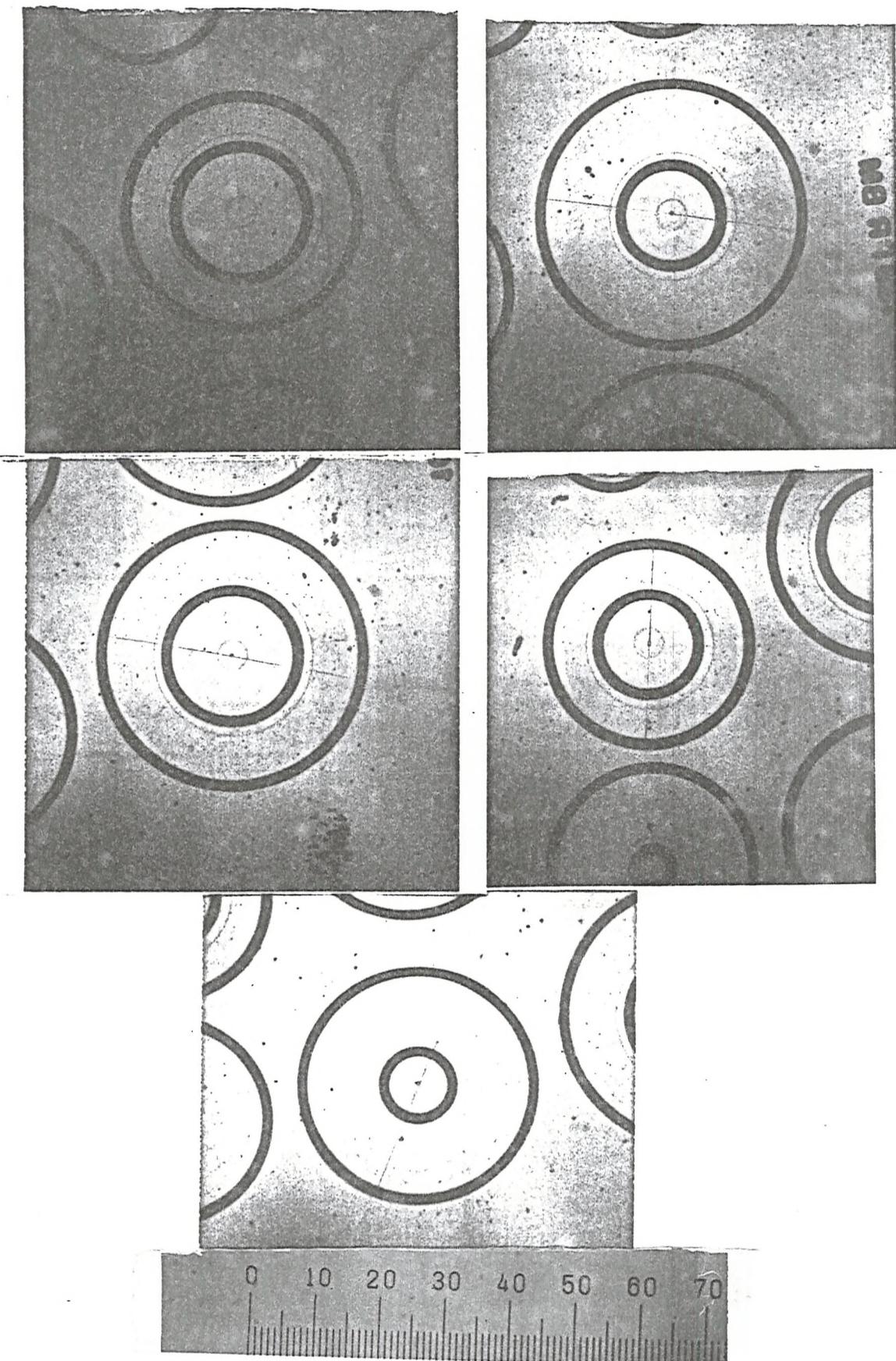

Fig. 2.11 shows the  $J_{FIJ}$  current density obtained by measuring the same 200 $\mu\text{m}$  diffusion diameter diode as before and taking the difference in leakage current as explained above and dividing by the value of the gate area  $A_s$ . In the devices that were used here for the whole work a second 'guard' gate electrode separated by 10 $\mu\text{m}$  from the 'active' gate was incorporated to enable the gate area  $A_s$  to be clearly defined by biasing the 'guard' gate so as to accumulate the semiconductor surface under this electrode as shown in Fig.

2.7. The device is photographed and the area  $A_s$  is calculated by measuring the diameter. It is found that  $A_s$  is

$$\frac{\pi(d_1^2 - d_2^2)}{4} \quad \text{and is equal to } 8.65 \times 10^{-4} \text{ cm}^2 \pm 5\%$$

Again it can be seen that there is no definite trend of  $J_{FIJ}$  with changes in HCl concentration. The values of lifetime  $\tau_{oFIJ}$  are shown in the same graph and have been calculating using the relationship.

$$\tau_{oFIJ} = q \frac{n_i}{2J_{FIJ}} W_i \quad 2c.2$$

where  $W_i$  is equal to  $\left(\frac{W_i}{x_{dmax}}\right) x_{dmax} = (0.51) \times 1.43 \times 10^{-4} \text{ cm} = 0.78 \times 10^{-4} \text{ cm}$

Fig. 2.12 shows the  $J_s$  current density obtained again by measuring the same 200  $\mu\text{m}$  diffusion diode as before and dividing the  $I_s$  leakage current (which is obtained as explained above) by the same gate area  $A_s$  as before. Again it can be seen that there is no definitized trend of  $I_s$  with changes in HCl concentration.

The values of surface recombination velocity are shown in the same graph and have been calculated using the relationship:

$$S_o = \frac{2J_s}{qn_i} \quad 2c.3$$

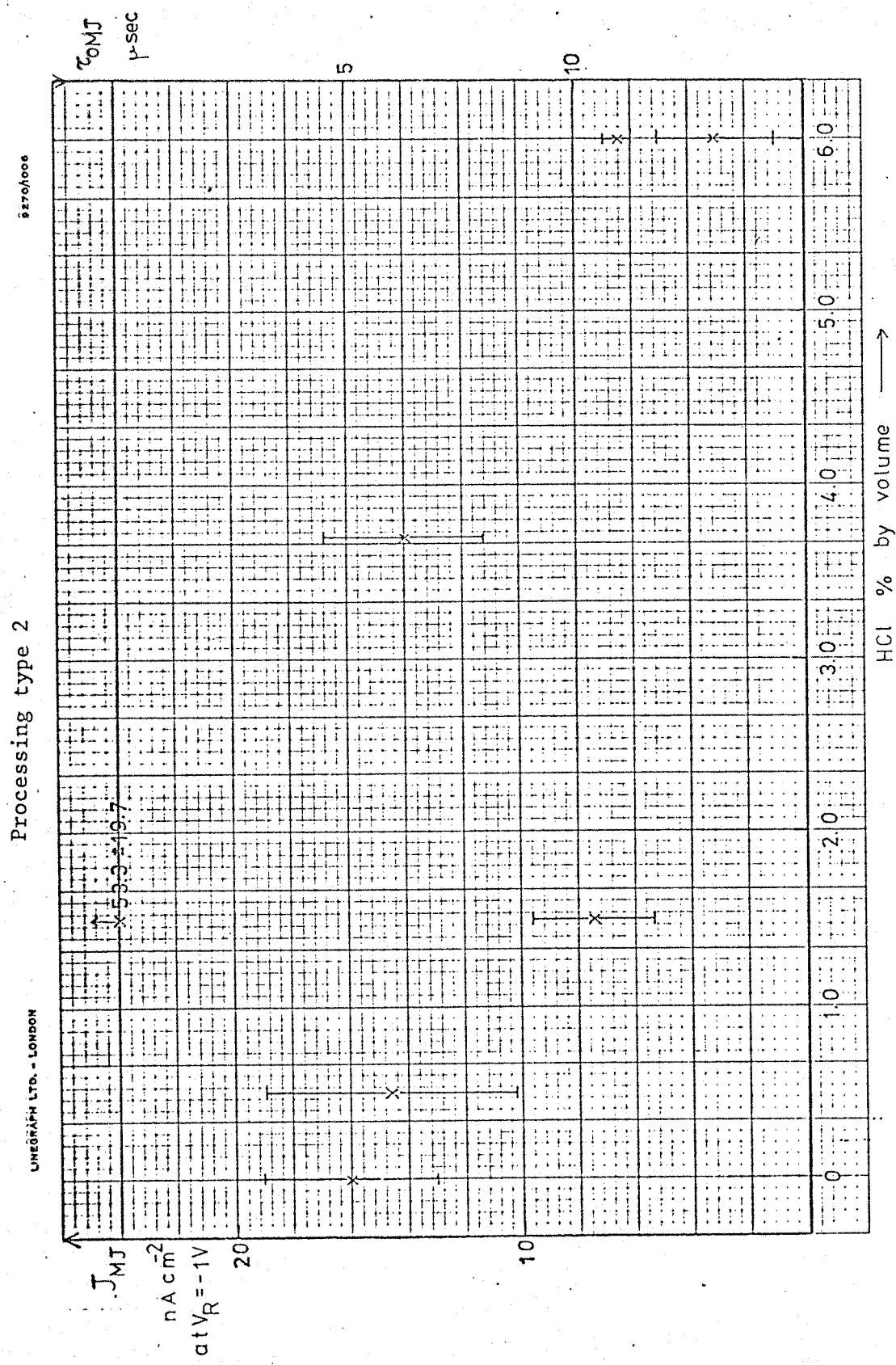

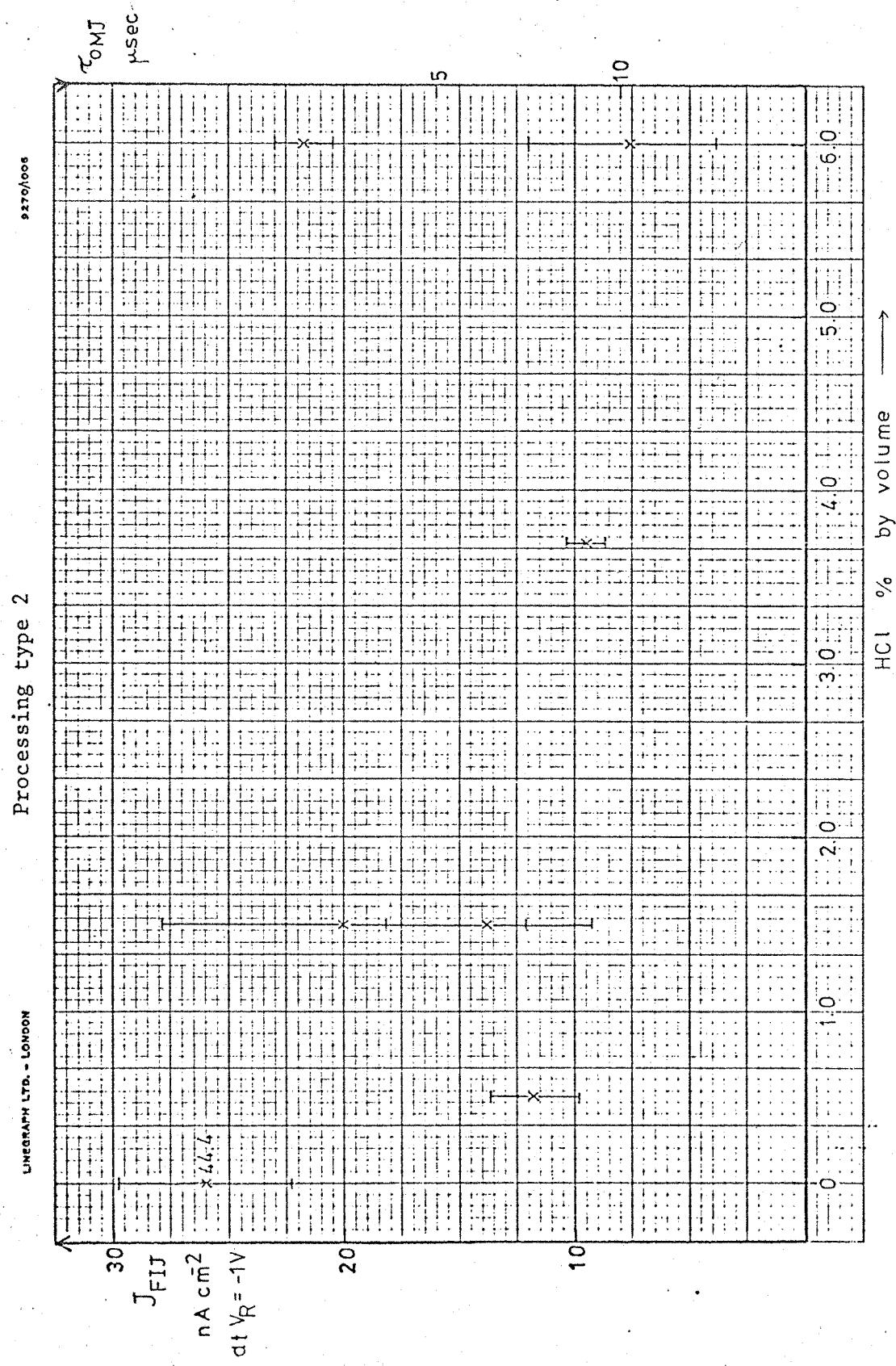

The graphs in the Fig. 2.13, 2.14, 2.15 show the analogous current densities, lifetimes and surface recombination velocities but for devices which were type 2, that is with phosphorous gettering before HCl oxidation. The rest of the graphs in Fig. 2.16, 2.17, 2.18 were obtained from measuring type 3 devices that is with phosphorous gettering after HCl oxidation.

Processing type 1

UNIGRAPH LTD. - LONDON

5270/008

Fig. 2.10

Processing type 1

LINEGRAPH LTD. - LONDON

9.27/1000

Fig. 2.11

Fig. 2.12

Fig. 2.13

Fig. 2.14

Processing type 2

Fig. 2.15

Fig. 2.16

Processing type 3

LINEGRAPH LTD. - LONDON

22704008

Fig. 2.17

### Processing type 3

Fig. 2.18

## 2d Leakage Current Measurements on CCD's

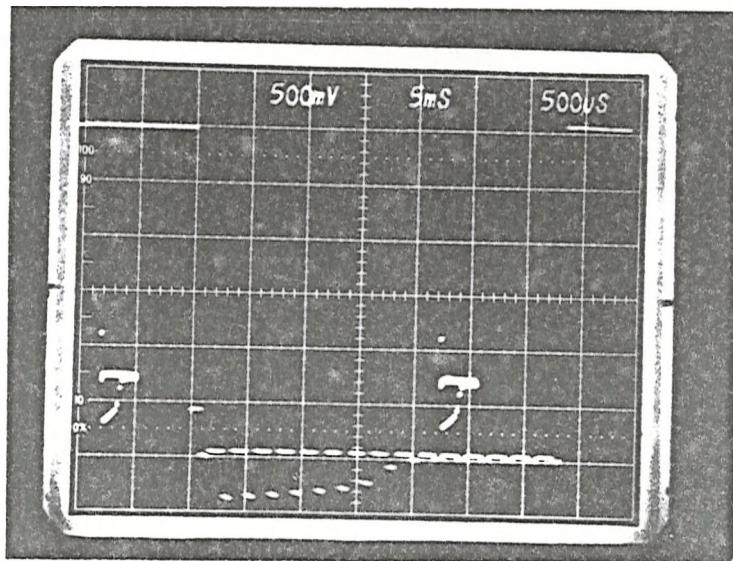

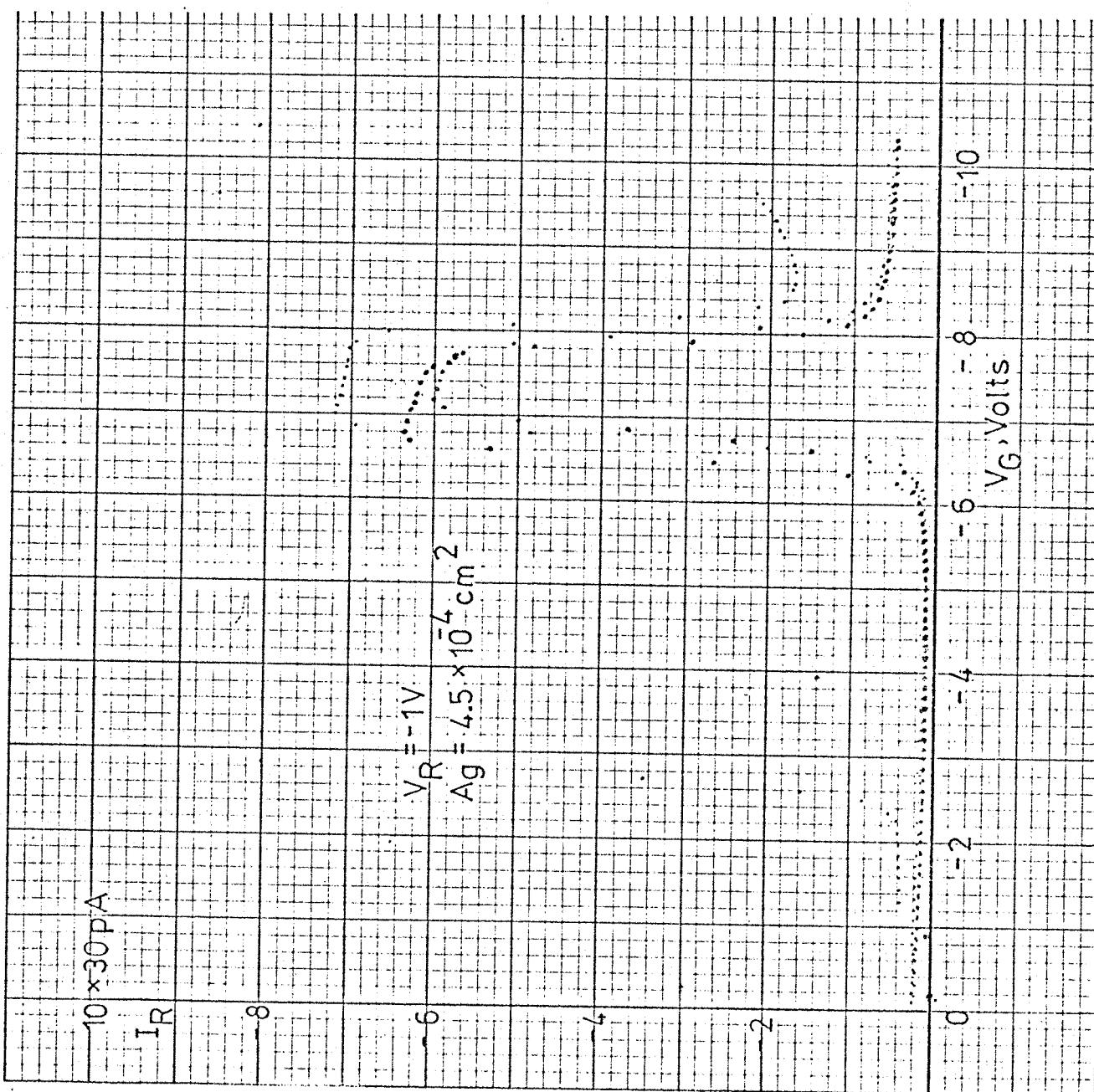

Leakage current measurements were made in a 134,8-bit, three-phase, aluminium gate, CCD (sample 1) fabricated on a (111) orientation substrate, (p-channel) which was manufactured at the Microelectronics Lab. at the University of Southampton. The measurement technique applied was the same as described in section 2c for gated diodes. These measurements were made on the input circuit that is the input diode and input gate of the CCD. The photograph of this CCD is shown in Fig. 2.19. In Fig. 2.20 both the forward bias and reverse bias transfer characteristics are shown. The diffusion area  $A_{MJ}$  was measured from the photograph of the Fig. 2.19 and is equal to  $0.47 \times 10^{-4} \text{ cm}^2$ . The gate area  $A_s$  was also measured and is equal to  $0.18 \times 10^{-4} \text{ cm}^2$ . From the reverse bias transfer characteristic in Fig. 2.20 the metallurgical junction current  $I_{MJ}$  was measured and it was found to be equal to 3.2pA. Also the field induced current  $I_{FIJ}$  and surface generation current  $I_s$  were measured from this curve as was explained in section 2c of this chapter and were found to be 4pA and 0.4pA respectively.

Thus using equation 2a.9 we have for the metallurgical junction a lifetime,

$$\tau_{oMJ} = \frac{1}{2}q \frac{n_i}{I_{MJ}} W_i A_{MJ} \quad 2d.1$$

From this equation for  $n_i = 1.45 \times 10^{10} \text{ cm}^{-3}$ ,  $W_i = 0.675 \times 10^{-4} \text{ cm}$ ,  $A_{MJ} = 0.47 \times 10^{-4} \text{ cm}^2$  and  $I_{MJ} = 3.2 \text{ pA}$  we have a value,

$$\tau_{oMJ} = 1.15 \mu\text{sec}$$

For the field induced junction we have a current,

$$I_{FIJ} = \frac{1}{2}q \frac{n_i}{\tau_{oFIJ}} W_i' A_s ,$$

or a lifetime,

$$\tau_{oFIJ} = \frac{1}{2}q \frac{n_i}{I_{FIJ}} W_i' A_s .$$

For  $W_i' = 0.78 \times 10^{-4} \text{ cm}$ ,  $A_s = 0.18 \times 10^{-4} \text{ cm}^2$  and  $I_{FIJ} = 4 \times 10^{-12} \text{ A}$ , we have a value.

Fig. 2.19 Input structure of a 134 DRL MPS CCD.

The channel width is  $100\mu\text{m}$ , the

phase gate length is  $20\mu\text{m}$ .

LINEGRAPH LTD. - LONDON

9270/1006

Fig. 2.20

$$\tau_{oFIJ} = 380 \times 10^{-9} \text{ sec} = 380 \text{nsec}$$

For the surface area in depletion we have a current,

$$I_s = \frac{1}{2} q n_i S_o A_s$$

or a recombination velocity

$$S_o = \frac{2I_s}{qn_i A_s} = 19 \text{ cm/sec}$$

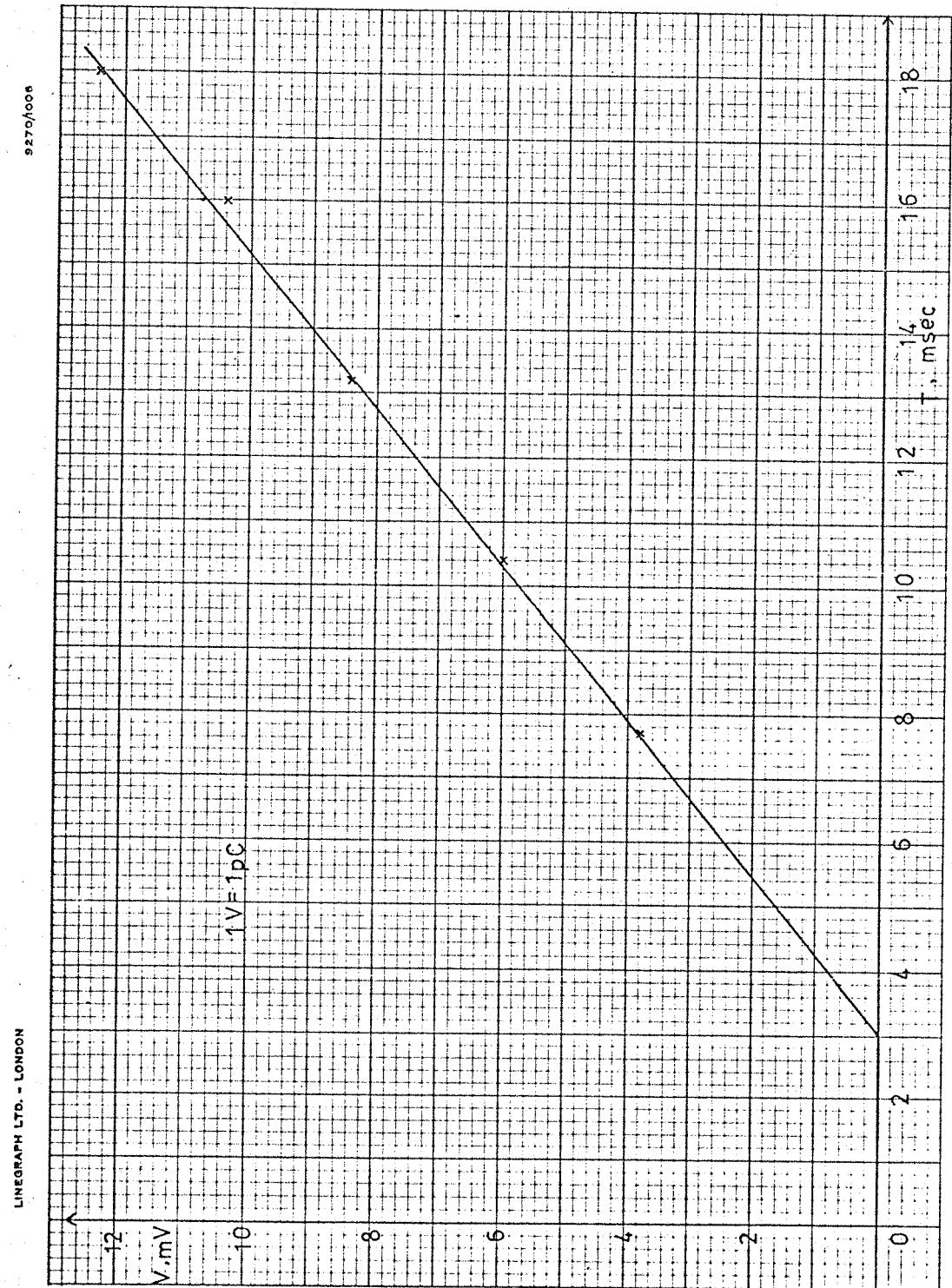

This particular device was also measured in the 'Interrupted Clock' mode using three-level clock voltages (21). The voltages on the gates were  $\phi_1 = -5V$ ,  $\phi_2 = -25V$  and  $\phi_3 = -15V$  for integration times up to 18ms at room temperature. The results over a range of integration times, from about 8msec to 18msec, shows a straight line of collected charge versus integration time as in Fig. 2.21. From the slope of this line the total generation current  $I_{gen}$  can be obtained. Two limiting cases for the partitioning of this current can be assumed. Firstly, it can be assumed that the current is exclusively from the depleted surface under the two phase gates adjacent to the storage gate. With this assumption the value of surface recombination velocity can be obtained using eq. 2a.7 as follows:

$$S_o = \frac{2I_{gen}}{qn_i^2 A_s} = \frac{2 \times 85 \times 10^{-12} \text{ A}}{1.6 \times 10^{-19} \text{ C} \times 1.45 \times 10^{10} \text{ cm}^{-3} \times 0.2 \times 10^{-4} \text{ cm}^2}$$

$$= 1831 \text{ cm/sec}$$

where  $A_s$  is the area of each of the non-storage gates.

Alternatively, it can be assumed that the bulk current dominates the total response and furthermore that the depletion regions do not reduce significantly during the integration period. With an estimated value of  $V_{FB} = -3.5V$  from the input circuit measurements, the surface potential  $\psi_s$  under each gate region can be calculated using eq. 3b.23. From these values of  $\psi_s$  the depletion widths  $x_d$  can be calculated using eq. 2a.12 as well as the fraction of the depletion width  $\frac{w_i}{x_d}$  under the three gates using eq. 2a.14.

The average value of  $\tau_{oFIJ}$  can be calculated as follows:

Fig. 2.21

$$\overline{\tau}_{\text{oFIJ}} = \frac{1}{2} \frac{q n_i}{I_{\text{gen}}} \left[ x_{d1} \left( \frac{W_{i1}'}{x_{d1}} \right) + x_{d2} \left( \frac{W_{i2}'}{x_{d2}} \right) + x_{d3} \left( \frac{W_{i3}'}{x_{d3}} \right) \right] A_s$$

$$= 183 \text{nsec}$$

Comparing this average value of  $\tau_{\text{oFIJ}}$  with the value obtained from the input circuit measurements it can be seen that there is only about a factor of 2 discrepancy. The value from the 'Interrupted Clock' CCD measurements is an average over the whole device where we have assumed a uniform distribution of bulk leakage current and a uniform value of Flat-band voltage. Under these assumptions the comparison is reasonably close.

However, the values of surface recombination velocity  $S_o$  do not agree at all. The conclusion is therefore that the leakage current is bulk current almost exclusively.

Thus it seems reasonable to use the input structure of the CCD for making gated diode measurements and using the values of  $\tau_{\text{oFIJ}}$  and  $S_o$  for the whole structure in small CCD's. This will not be true for CCD's with a large number of bits because of random variations in generation rate in large structures. For these structures we may predict the leakage current to a reasonable degree of precision using the values  $\tau_{\text{oFIJ}}$  and  $S_o$  measured from the input structure.

### 3. CHARGE PUMPED CURRENT INVESTIGATION

#### 3a Charge Pumping Method

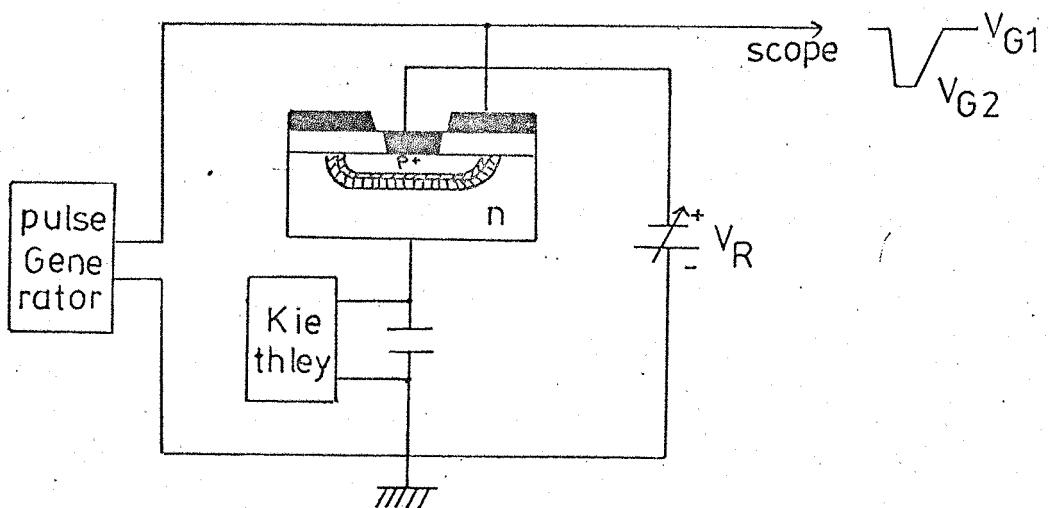

This method was first developed by Brugler and Jespers (7), and it is useful in obtaining a quick estimation of the total surface state density from a complete device. They show that repetitive gate pulses of magnitude sufficient to turn-on, (ie. to change the conductivity type of the surface under the gate), an MOS transistor, can stimulate a net flow of majority carriers from the source and drain to the substrate via the interface states. In the following description of the charge pumping phenomenon a gate-controlled diode as was described earlier is considered, with n-type substrate. The set up is shown schematically in Fig. 3.1. For simplicity the p-type region is assumed to be much more heavily doped than the substrate. The junction is reverse biased with an applied voltage  $V_R$  (non-equilibrium condition). The gate is connected to the pulse generator with respect to the substrate. In the absence of any gate pulse the silicon surface would be in accumulation and the ammeter simply indicates the junction negative reverse leakage current.

If a pulse is applied to the gate such that  $V_G < V_T(V_R)$  where  $V_T(V_R)$  is the turn-on voltage, then the surface is only depleted. In this case the band bending is insufficient to bring the conduction band near enough to the quasi-Fermi level for holes (minority carriers) to cause inversion, and the diode is not switched on so the current that the ammeter registers is very small, being only the leakage current.

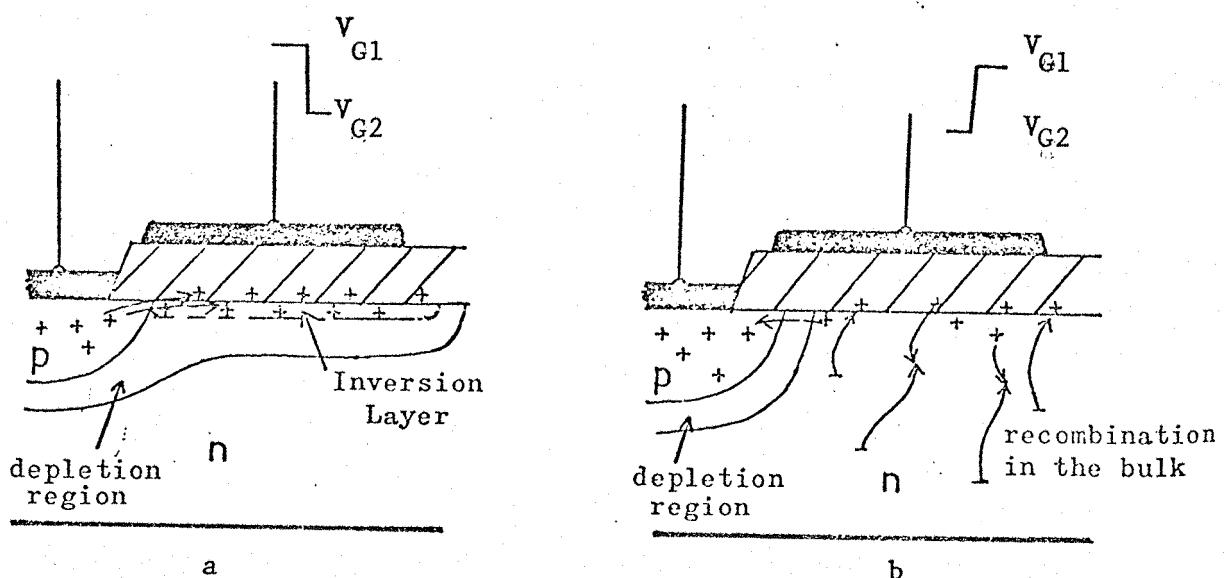

If the pulse applied to the gate is such that  $V_G > V_T$  then the diode is switched on and holes from the  $p^+$  region flow into the n region under the gate. Thus an inversion surface layer is formed as is seen in Fig. 3.2a.

Some of the holes that flow into the n region under the gate are trapped by the surface states and the rest are present as mobile carriers in the inversion layer. When the voltage on the gate is turned off the mobile minority carriers (holes) flow back to the  $p^+$  region under the influence of the reverse bias and leave behind the trapped holes in the interface states as shown in Fig. 3.2b. During the period that the pulse is off, electrons from the n-type substrate recombine with the trapped holes from the surface states thus giving rise to a

Fig. 3.3.1 Block diagram of Charge Pumping measurement circuitry

Fig. 3.2 Physical mechanism for the origin of pumped current

net flow of positive charge into the substrate. A repetitive application of the negative gate pulse results in a unidirectional current of majority carriers from the p+ region to the substrate through the interface states. This current is called 'charge pumping' current. If the gate area is large and the turn-off time of the pulse is too small some of the mobile carriers will not be able to flow back to the p+ region fast enough so they too recombine with the substrate electrons thus contributing to the pumped current. The net pumped charge density per gate pulse may therefore be expressed as follows:

$$Q_T = aQ_p + qN_{st}, \left[ \text{C cm}^{-2} \right] \quad 3a.1$$

where

$a$  = fraction of mobile carriers under the gate that recombine in the bulk ,

$q$  = electronic charge [C] ,

$N_{st}$  = total fast surface-state density contributing to the effect with energy levels which are swept through the Fermi level when the pulse is applied  $\left[ \text{cm}^{-2} \right]$  ,

$Q_p$  = mobile minority charge (holes) density in the inverted n-region  $\left[ \text{C cm}^{-2} \right]$ , which from the MOS theory (18) is:

$$Q_p \approx 0 \quad |V_G| < |V_T|$$

$$Q_p = C_{ox} |(V_G - V_T)| + N_D x_{inv} \quad |V_G| \geq |V_T|$$

Where  $C_{ox}$  is the oxide capacitance per unit area  $\left[ \text{C cm}^{-2} \right]$  and  $x_{inv}$  is the effective inversion layer thickness for a rectangular distribution. The pumped current is simply  $Q_T$  multiplied by the gate area  $A_g$  and gate pulse frequency  $f$ .

So for  $|V_G| \geq |V_T|$  the pumped current is:

$$I_{cp} = A_g f Q_T = A_g f \{ a [C_{ox} (V_G - V_T) + N_D x_{inv}] + qN_{st} \} \quad 3a.2$$

For a small gate length, a sufficiently long turn-off time (i.e.,  $\sim 100 \mu\text{sec}$ ) and a sufficiently large  $V_R$  the term in squarebrackets in the above equation 3a.2 of charge pumping the geometric components can be made negligible so that the charge pumping current will be only due to the surface state density, that is:

$$I_{cp} = A_g f q N_{st} \quad 3a.3$$

Thus a simple way of determining the total density of surface states with energy levels which are swept through by the Fermi level when a gate pulse is applied is to measure the substrate current when a small reverse bias is applied to the junction. One volt is usually adequate to eliminate the 'geometric component' as will be shown later.

Equation (3a.3) due to Brugler (7) gives only a total number of interface states since no value is required for the actual quasi-Fermi level excursion. In CCD operation it is very important to have a low density of interface states throughout the part of the band gap scanned by the quasi-Fermi level.

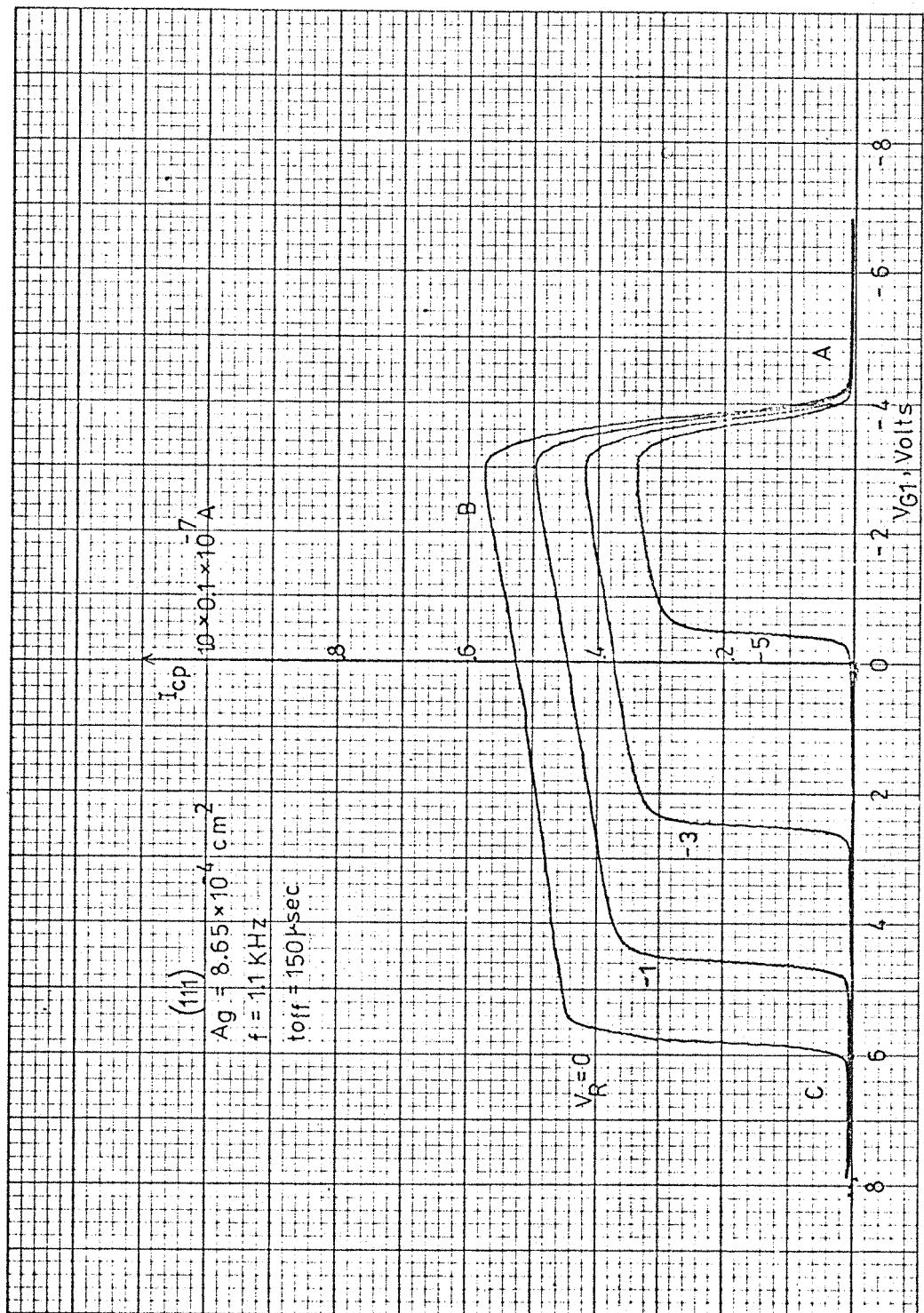

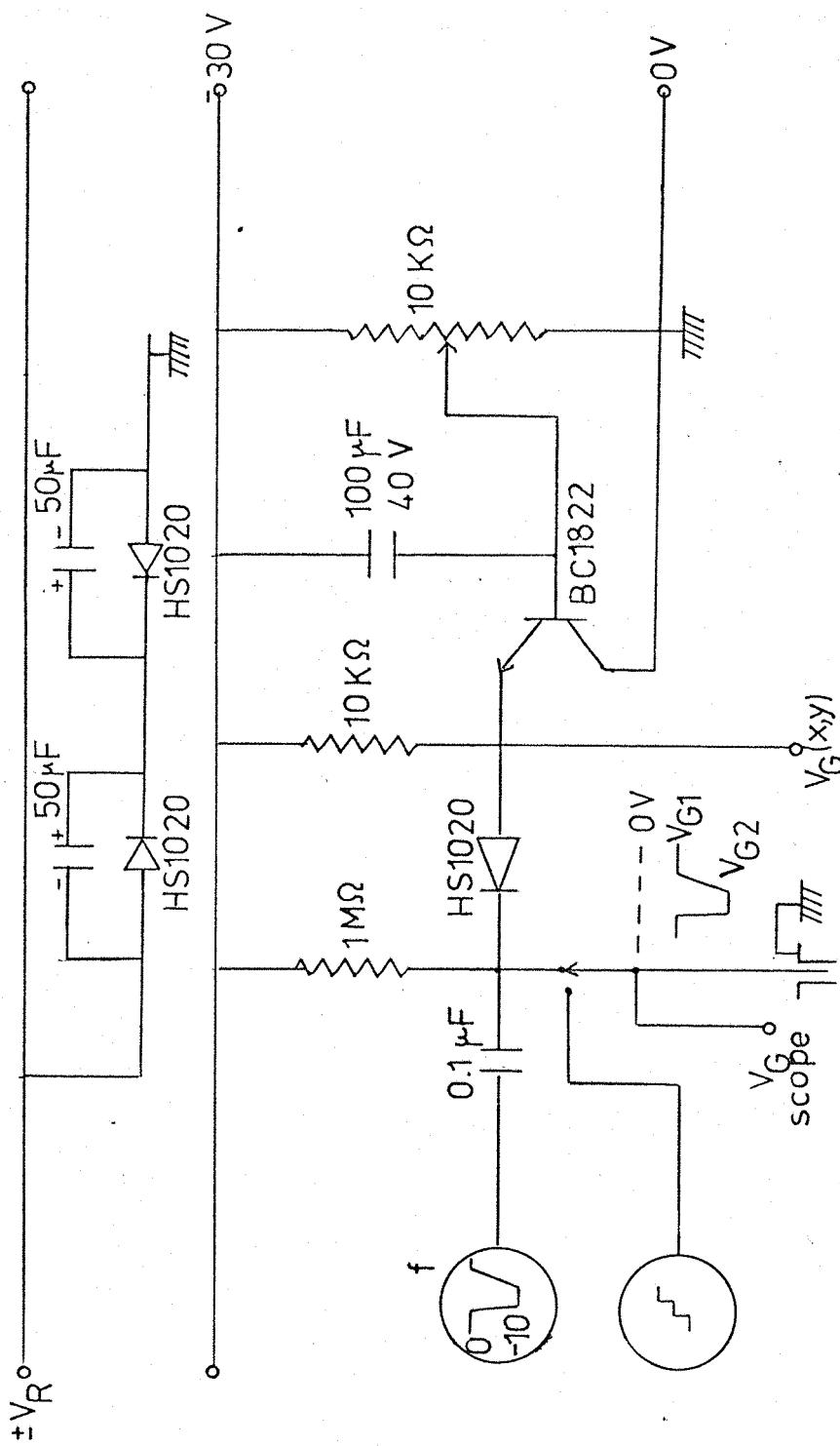

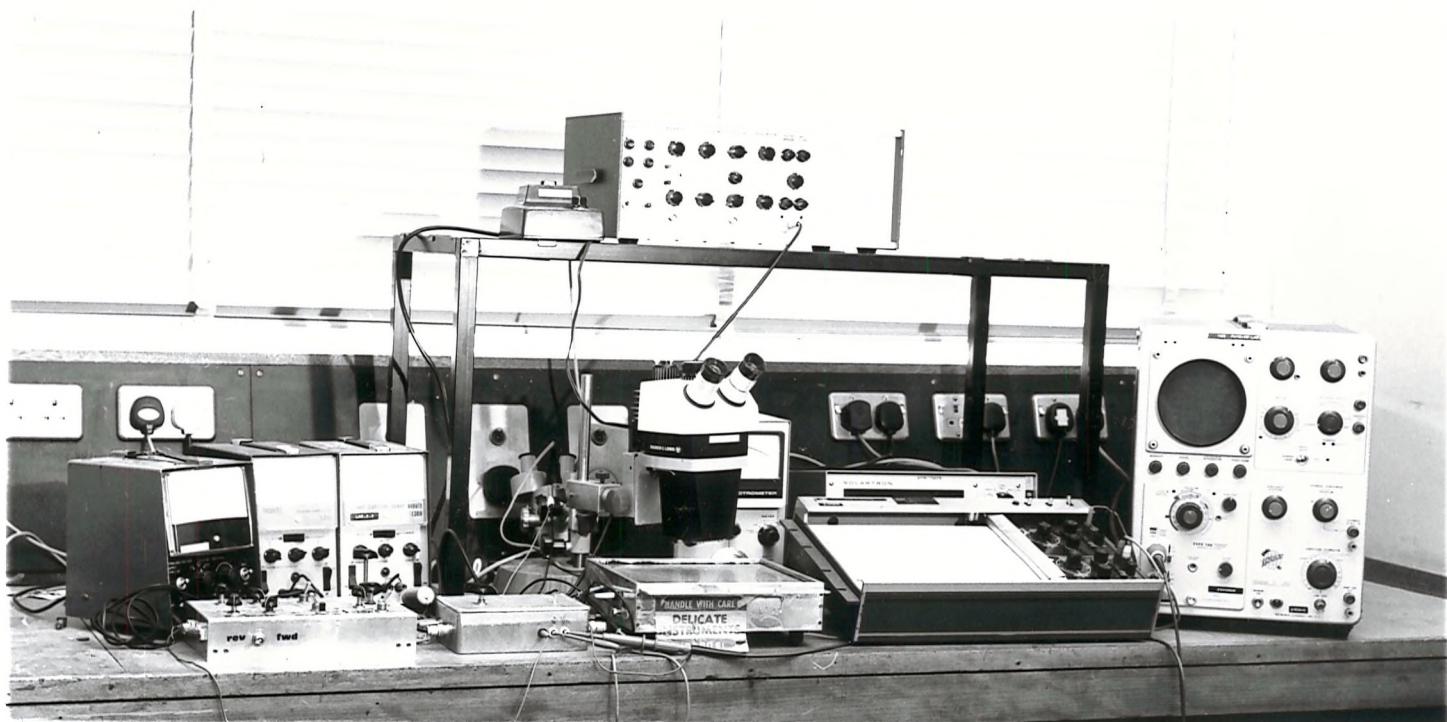

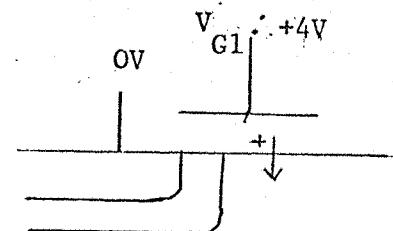

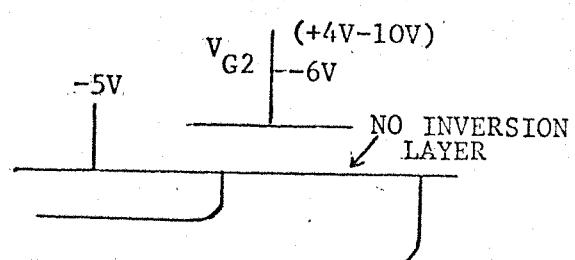

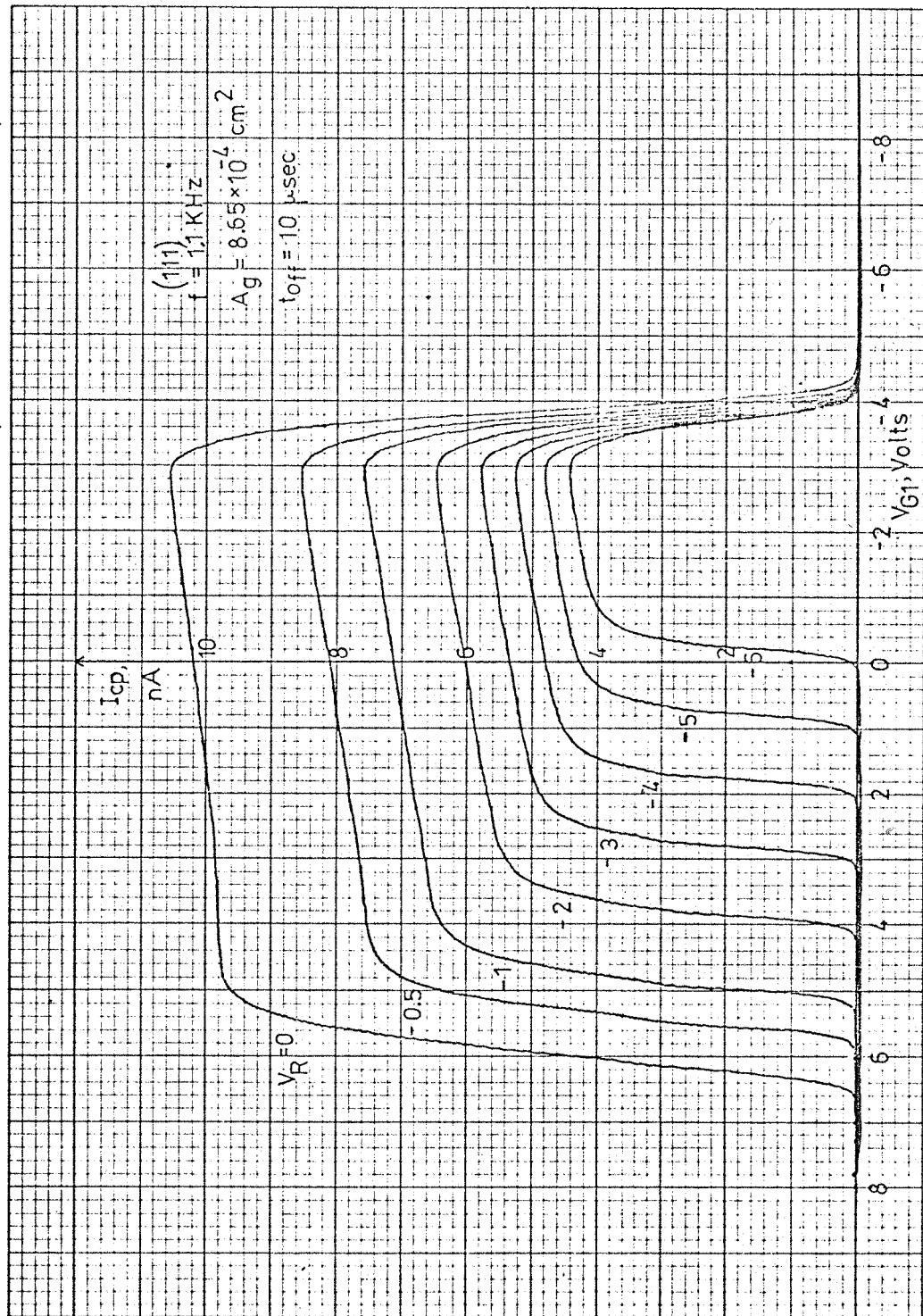

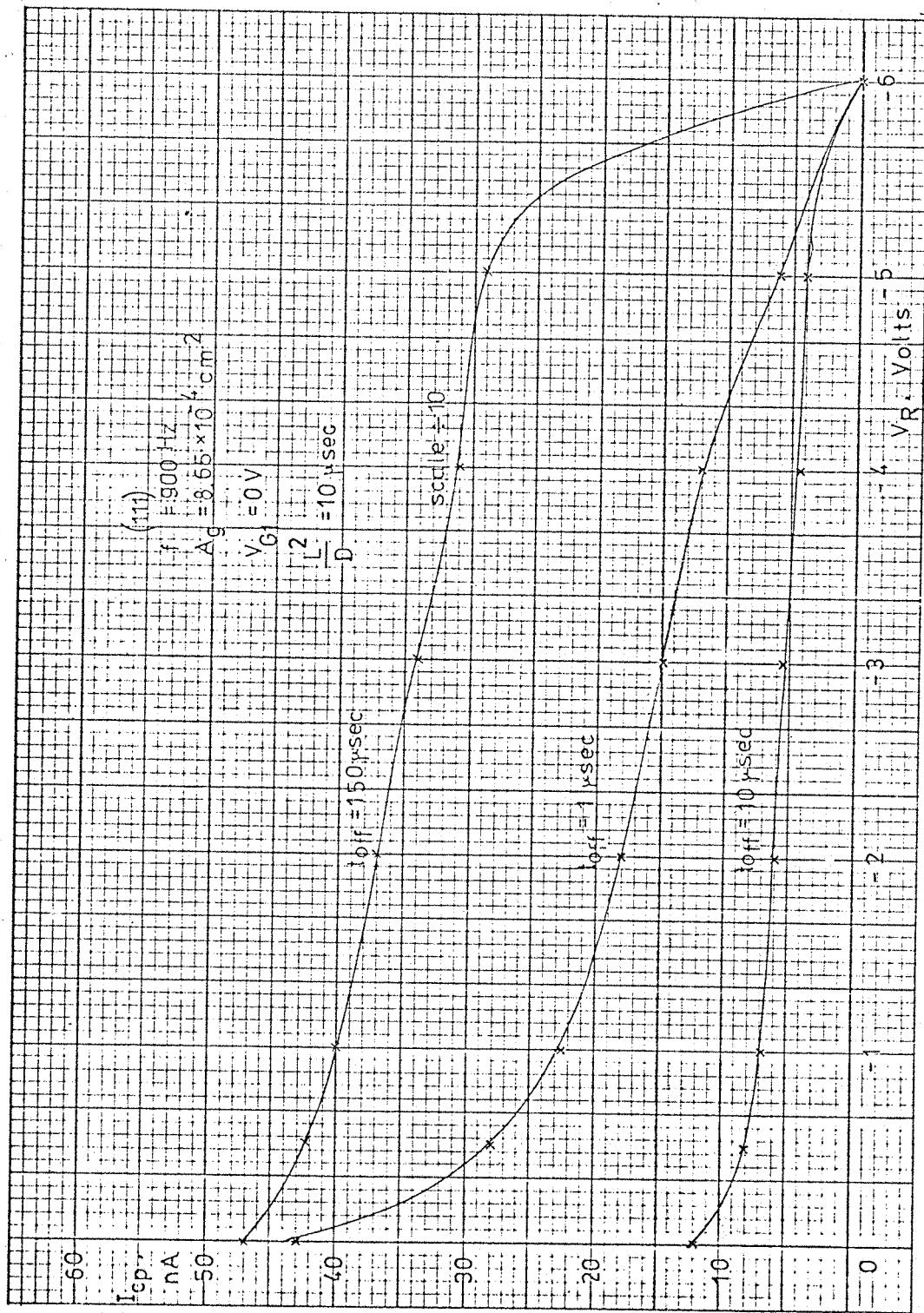

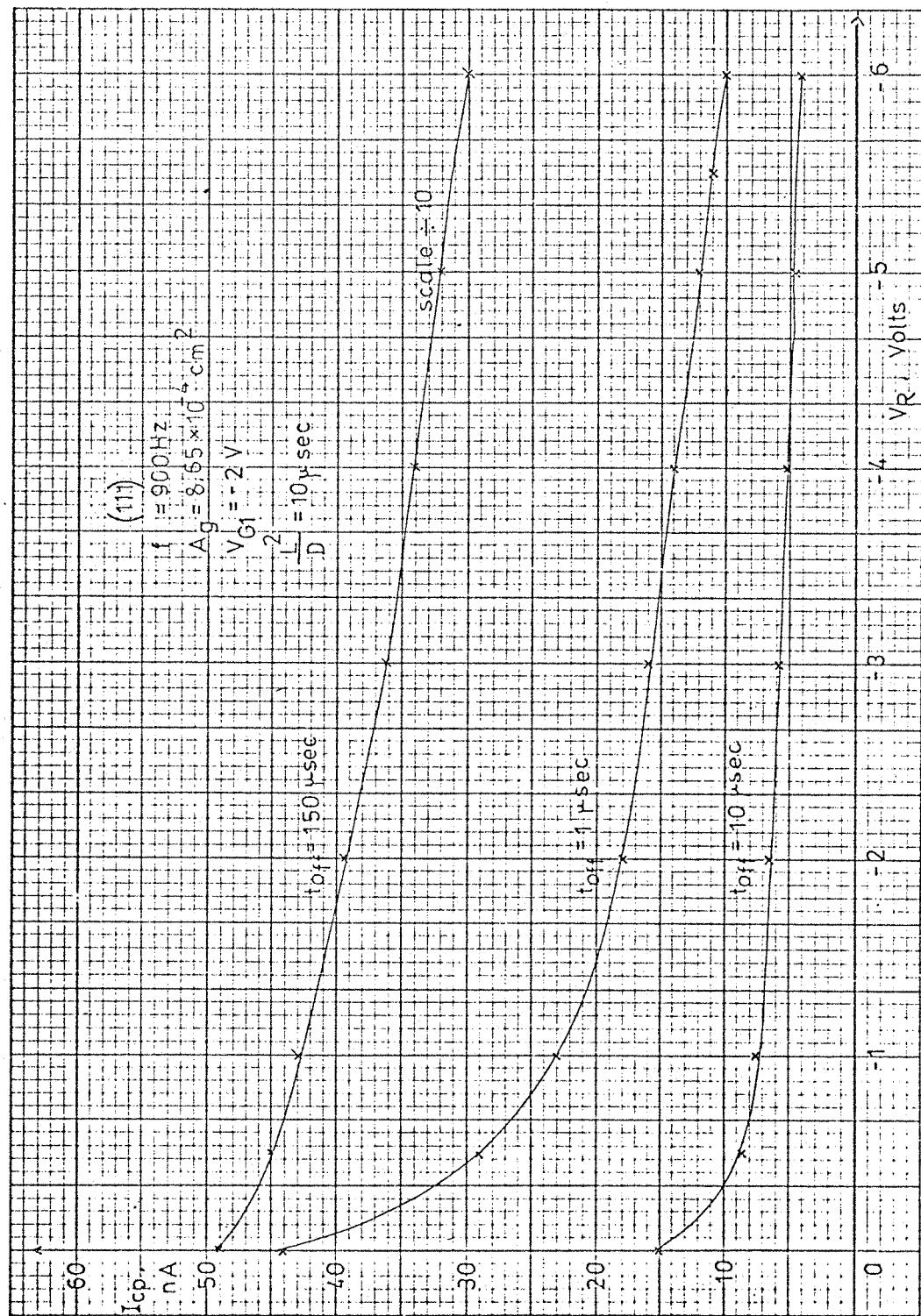

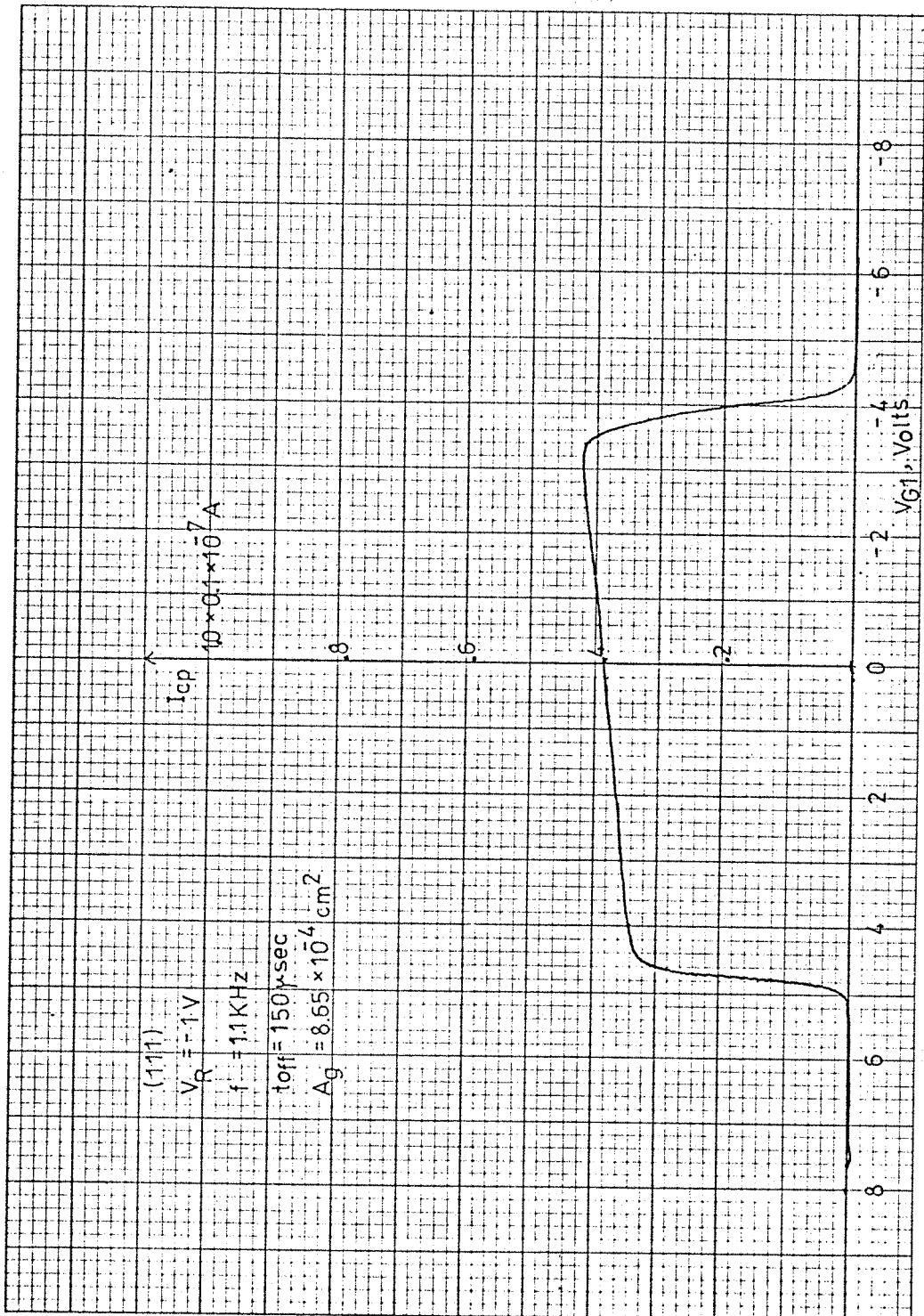

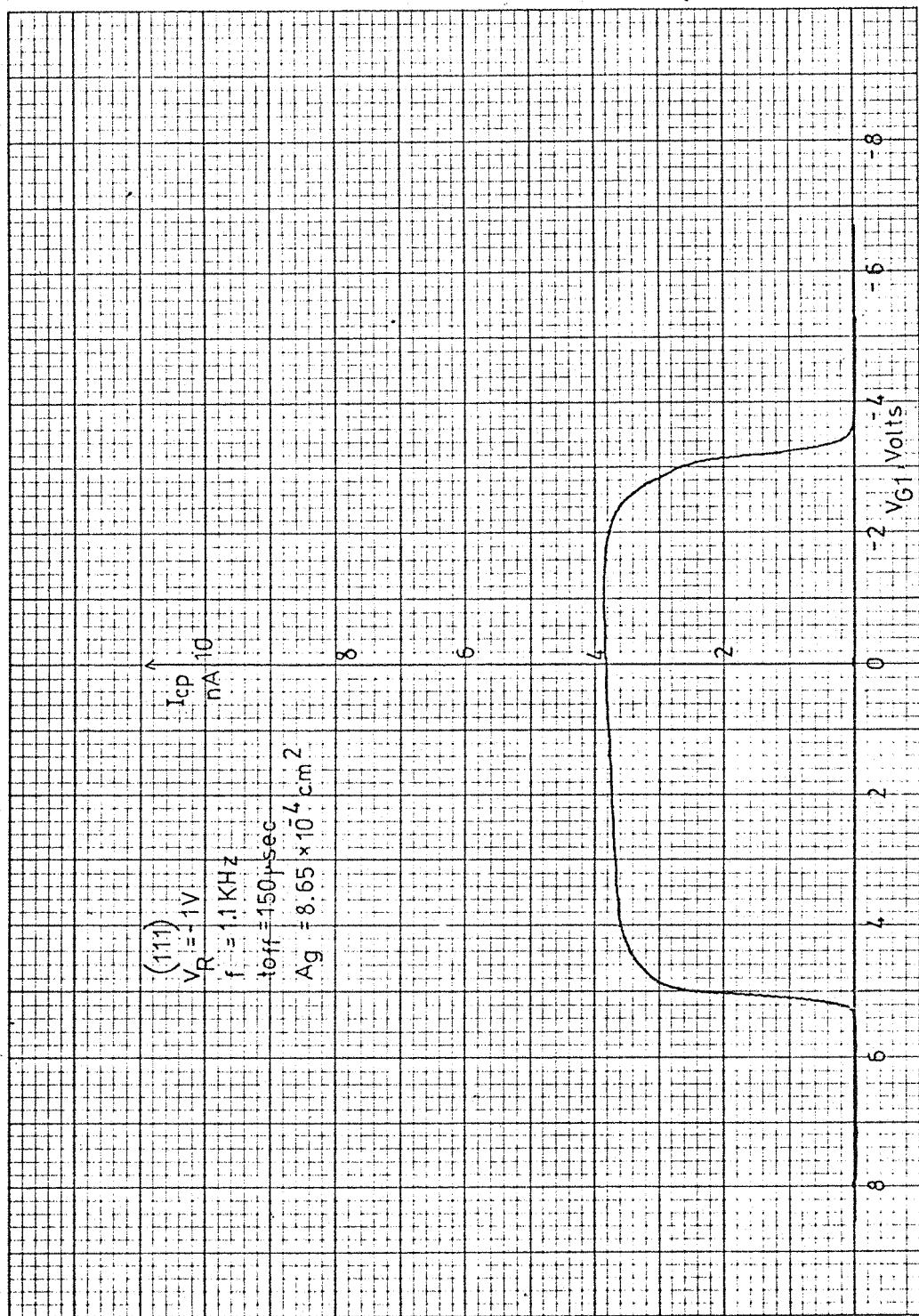

Elliot (8) used an alternative approach which does enable the surface state energy distribution to be examined across most of the forbidden band gap. This is achieved by measuring the charge pumping current as a function of the pulse base level, while keeping the pulse amplitude constant. Characteristics of this type are shown in Fig. 3.3 where a gate pulse of constant amplitude equal to -10V has a base level which is scanned from +8V to -8V. Consider first region A. Here, the gate voltage goes from -6V to -16V. Both these values are above the device turn-on voltage thus the interface states are filled but are never allowed to empty and the pumped current is consequently very small. As the base level is shifted towards zero volts the pumped current increases to a maximum value because the base level is now below the turn-on voltage but the pulse level is above it. This is shown in region B. If the base level is then shifted to positive values, eventually the gate pulse is insufficient to turn the channel on at all. In this case the interface states are never filled with holes and the current is again small in region C. Thus the current level in region B corresponds to the saturation level in Fig. 3.3 and is the value required to obtain the total interface state density  $N_{st}$ . The current is a function of the reverse bias voltage since the turn-on voltage is a function of the reverse bias voltage. These characteristics were taken from a 200 $\mu$ m diffusion diameter gated diode (14/S, 168, 3.7% HCl) fabricated on a (111) orientation substrate. The circuit used to obtain these measurements is shown in Fig. 3.4. In the photograph of the complete test fixture in Fig. 3.5 the central box with the oscilloscope probe attached contains the circuit shown in Fig. 3.4.

Fig. 3.3

Fig. 3.4 Circuit to produce -10V amplitude pulses with +ve or -ve base level.

Fig. 3.5 The complete test fixture showing the centrally placed light-tight low leakage box

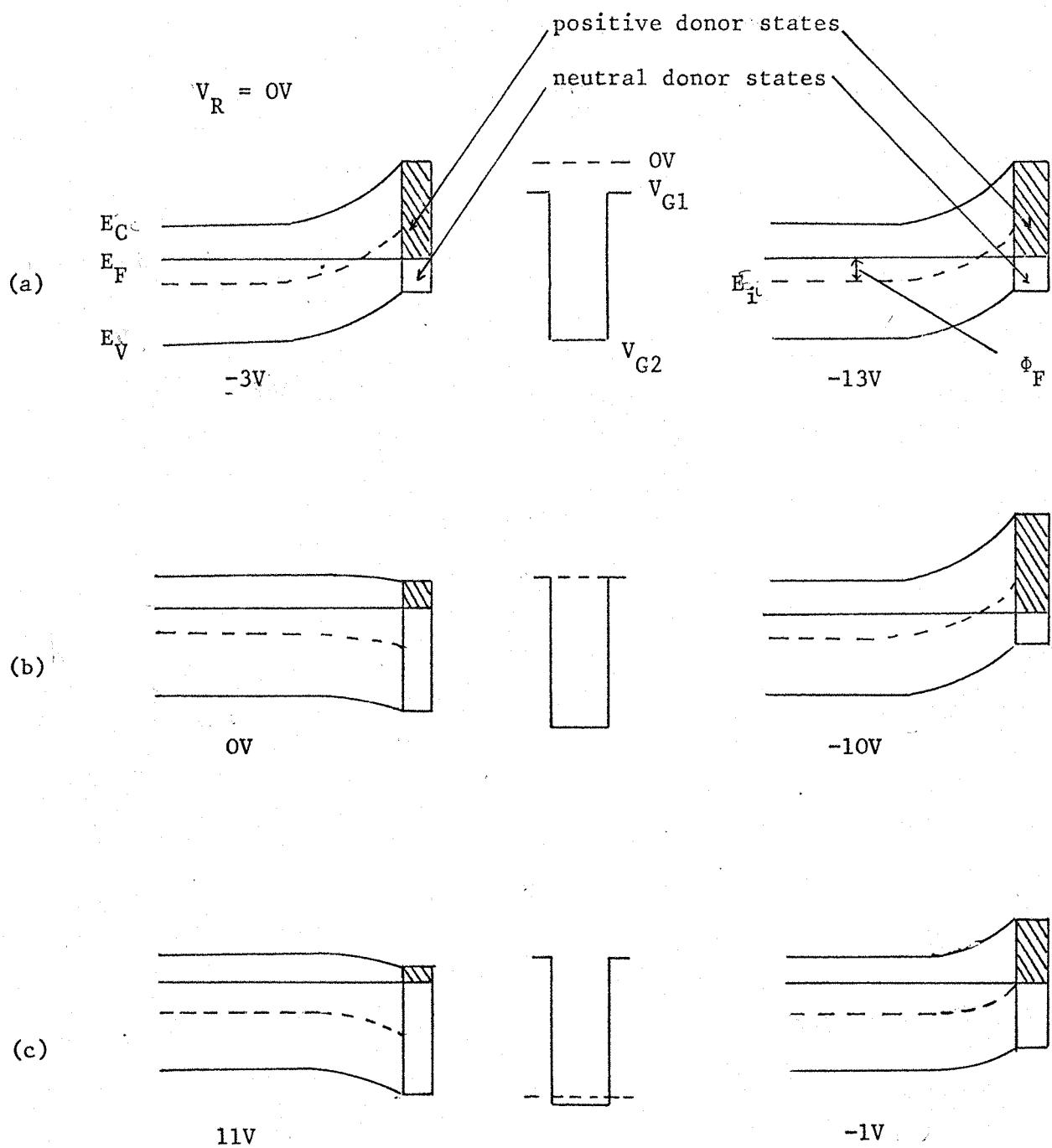

A simple interpretation of how the surface states are able to act as a charge coupling medium can be given by reference to the energy band diagrams in Fig. 3.6 which are drawn for a direction normal to the n-type substrate surface. The equilibrium case is first considered, that is  $V_R = 0V$ , and it is assumed that only donor states are present at the interface but the situation is not significantly different if acceptor states also exist. The energy band diagrams are not intended to be accurate they simply indicate the form of the band bending near the surface in order to simplify the description of the processes which give rise to the zero bias voltage characteristic in Fig. 3.3. In (a) the gate pulse goes from  $-3V$  to  $-13V$  and the surface potential is close to  $2\phi_{Fn}$  level at both values of the gate voltage so there is little change in the occupancy of the surface states and consequently the contribution of surface states to the pumped current is small.

In (b) where the gate pulse goes from  $0$  to  $-10V$  some of the surface donor states which have been filled with holes during the previous pulse are below the Fermi level when the pulse is off and therefore trapped holes will be emitted and recombine subsequently with electrons from the n-type substrate giving rise to a significant charge pumping current.

In (c) where the gate pulse goes from  $+11V$  to  $-1V$  the pulse level becomes more positive and the gate voltage is below the threshold voltage even when the pulse is on and the surface states can no longer be filled by holes from the p+ region. This leads to a rapid decrease of the charge pumping current.

In all the above cases the net injected charge is proportional to the uniform trap density  $N_{ss}$  times the peak-to-peak band bending  $(\psi_{s1} - \psi_{s2})$ . Therefore:

$$Q_T = qN_{ss} (\psi_{s1} - \psi_{s2}) = qN_{ss} \Delta\psi_s = qN_{st} [Ccm^{-2}] \quad 3a.4$$

Thus the current will be:

$$I_{cp} = A_g f q N_{ss} \Delta\psi_s = A_g f q N_{st} \quad 3a.5$$

When a reverse bias is applied to the junction the gate voltage at which an inversion layer forms is changed to a more negative value. This should give only a change in the voltage axis as shown in Fig. 3.3. However, there is a reduction in the overall current

Fig. 3.6 Energy band diagrams in the device channel normal to the surface.

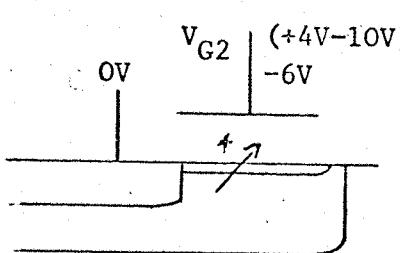

level because the time taken for the gate voltage to change from the new turn-on voltage to the flat band voltage is longer and allows some of the faster interface states to empty their holes which are then re-collected by the p+ region. The gate voltage at which we have the transition from region A to B is not affected by the reverse bias because the base level gate voltage here is insufficient to cause depletion of the surface at any value of reverse bias therefore we always collect those holes which were trapped during the previous turn-on period if any. This is shown schematically in Fig. 3.7 for two values of reverse bias.

The rising edge in Fig. 3.3 from A to B clearly contains information on the energy distribution of surface states and the method used to determine this distribution is explained in the next section.

$V_T = -5V$

CURRENT PUMPED

NO CURRENT PUMPED

Fig. 3.7

3b Theoretical Calculation of the Surface State Density as a Function of Energy from Charge Pumping current measurements

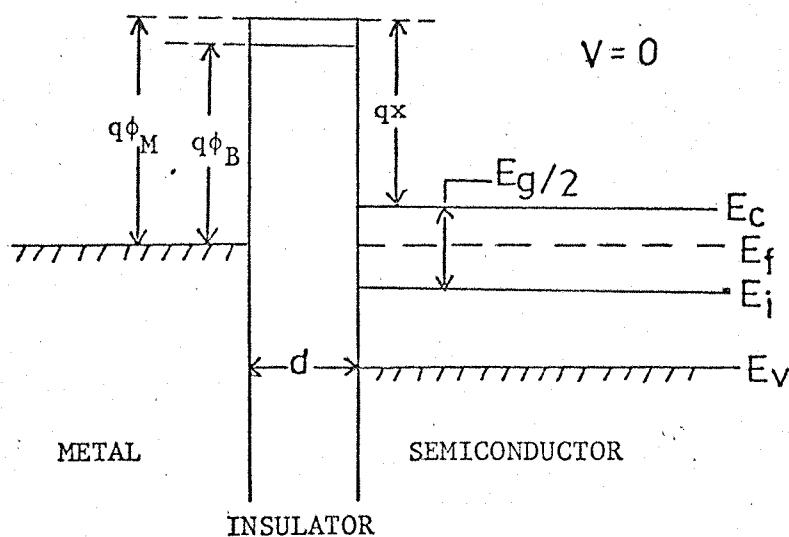

In Section 3a it was shown that the charge pumping current must be proportional to the excursion of surface potential  $\Delta\psi_s$  caused by the gate voltage pulse. From the theory of the gated diode the relation between  $V_G$  and  $\psi_s$  in non-equilibrium case can be obtained (17). From this relation the graph of  $\Delta V_G$  versus  $\Delta\psi_s$  can be calculated. This graph, with the assumption that  $N_{ss}$  is constant as a function of  $\psi_s$ , should have the same shape as the  $I_{cp}$  versus  $V_G$ . We shall see later that in fact the theoretical graph  $\Delta\psi_s$  versus  $V_G$  has almost the same shape as the experimentally measured curves of  $I_{cp}$  versus  $V_G$ , thus the agreement between the theory and experiment seems to be quite good. Let us now consider the case of an ideal gated diode with an n-type substrate in the non-equilibrium condition.

For an ideal gated diode we define the following conditions:

1. At zero applied gate voltage  $V_G$  there is no energy difference between the metal work function  $\phi_m$  and the semiconductor work function  $\phi_s$  is zero as is shown in Fig. 3.8 (17), therefore,

$$\phi_{ms} = \phi_m - (x + \frac{Eg}{2q} - \psi_B) = 0,$$

where  $x$  is the semiconductor electron affinity,

$Eg$  the band gap of the semiconductor and

$\psi_B$  the potential difference between the Fermi level  $E_F$  and intrinsic Fermi level  $E_i$ .

In other words, the bands are flat (Flat-band condition) when there is no applied voltage.

2. The only charges which can exist in the structure under the condition  $V_G \neq 0$  are those in the semiconductor with equal but opposite sign to the change on the metal surface adjacent to the  $\text{SiO}_2$

3. The resistivity of the insulator is infinite.

For non-equilibrium situations the relation between the gate voltage and surface potential  $\psi_s$  in an ideal diode can be derived as follows. The gate voltage  $V_G$  will appear partly across the oxide and partly across the silicon that is,

$$V_G = V_{ox} + \psi_s$$

3b.1

Fig. 3.8. Ideal MIS diode (n-type semiconductor)

Fig. 3.9. Energy diagram near the surface in non-equilibrium for n-type diode.

By Gauss' law the electric displacement must be continuous across the oxide-silicon interface in the absence of charge at the interface. Therefore

$$\epsilon_{ox} \ell_{ox} = \epsilon_{si} \ell_{si} \quad 3b.2$$

Since we deal with ideal diode  $\ell_{ox}$  must be uniform i.e.,

$$\ell_{ox} = - \frac{V_{ox}}{X_{ox}} \quad 3b.3$$

where  $V_{ox}$  is the voltage across the oxide and  $X_{ox}$  the oxide thickness.

At the Si surface by Gauss' theorem we have

$$\ell_{si} = - \frac{Q_s}{\epsilon_{si}} \quad 3b.4$$

where  $Q_s$  is the total charge in the silicon and  $\epsilon_{si}$  the permitivity of the silicon.

Combining 3b.2, 3b.3, 3b.4 we have

$$V_G = - \frac{X_{ox}}{\epsilon_{ox}} Q_s + \psi_s = - \frac{Q_s}{C_{ox}} + \psi_s \quad 3b.5$$

$$\text{where } C_{ox} = \frac{\epsilon_{ox}}{X_{ox}}$$

$Q_s$  is also a function of surface potential and in this case of non-equilibrium, it is a function of the reverse bias-voltage,  $V_R$ .

Thus we write,

$$V_G = - \frac{Q_s(\psi_s, V_R)}{C_{ox}} + \psi_s \quad 3b.6$$

The analytical function of  $Q_s$  can be derived as follows.

The one dimensional Poisson equation for the potential  $\psi$  is:

$$\frac{\partial^2 \psi}{\partial x^2} = - \frac{\rho(x)}{\epsilon_{si}} \quad 3b.7$$

where  $\rho(x)$  is the total space charge density given by:

$$\rho(x) = q(N_D^+ - N_A^- + p_n - n_n) \quad 3b.8$$

where  $N_D^+$ ,  $N_A^-$  are the densities of the ionized donors and

acceptors respectively and  $p_n$ ,  $n_n$  the minority and majority carriers in the space charge region of the diode.

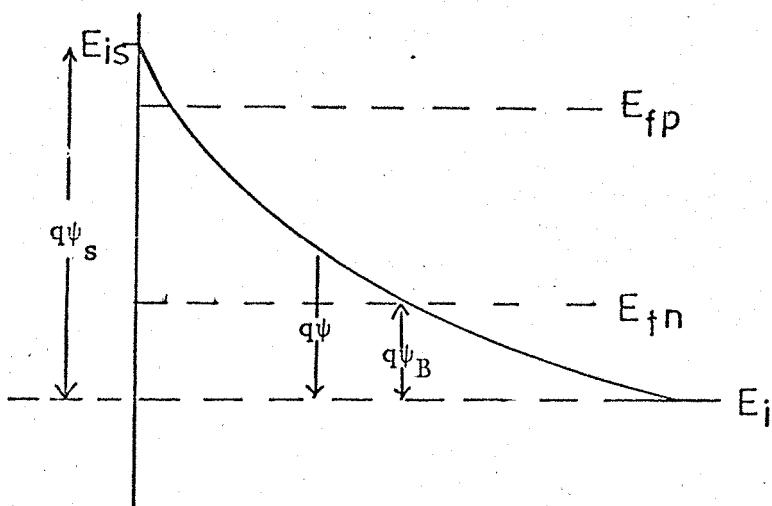

Fig. 3.9 shows the energy diagram near the surface for a n-type gate diode from which the expressions for  $p_n$ ,  $n_n$  can be derived, for non-equilibrium. Therefore,

$$\begin{aligned} n_n &= n_i e^{-(E_{Fn} - E_i + q\psi)/KT} = n_i e^{(E_{Fn} - E_i)/KT} e^{-q\psi/KT} \\ &= n_{no} e^{q\psi/KT} = n_{no} e^{\beta\psi} \end{aligned} \quad 3b.9$$

where  $n_{no}$  is the majority carrier density in the bulk of the semiconductor and  $\beta = q/KT$  ( $K$  = Boltzmann's constant).

For  $p_n$  we have, as seen from the Fig. 3.9.

$$\begin{aligned} p_n &= n_i e^{-(E_{Fp} - E_i + q\psi)/KT} \\ &= n_i e^{-(E_{Fn} - qV_R - E_i + q\psi)/KT} \\ &= n_i e^{-(E_{Fn} - E_i)} e^{(qV_R - q\psi)/KT} \\ &= p_{no} e^{(qV_R - q\psi)/KT} = p_{no} e^{(-\beta\psi + \beta V_R)} \end{aligned} \quad 3b.10$$

where  $p_{no}$  is the equilibrium minority carrier density in the bulk of the semiconductor.

At the surface we have, for  $p_n$ ,  $n_n$ :

$$n_{ns} = n_{no} e^{\beta\psi_s} \quad 3b.11$$

$$p_{ns} = p_{no} e^{(-\beta\psi_s + \beta V_R)} \quad 3b.12$$

Combining equations 3b.7 and 3b.8 we have

$$\frac{\partial^2 \psi}{\partial x^2} = -\frac{q}{\epsilon_{si}} (N_D^+ - N_A^- + p_n - n_n) \quad 3b.13$$

Substituting equations 3b.9 and 3b.10 into 3b.13 we have

$$\frac{\partial^2 \psi}{\partial x^2} = -\frac{q}{\epsilon_{si}} (N_D^+ - N_A^- + p_{no} e^{(-\beta\psi + \beta V_R)} - n_{no} e^{\beta\psi}) \quad 3b.14$$

In the bulk of the semiconductor far from the surface, charge neutrality must exist. Therefore  $\rho(\infty) = 0$  and  $\psi(\infty) = 0$ . Thus in the bulk we have,

$$N_D^+ - N_A^- + p_{no} - n_{no} = 0, \text{ or } N_D^+ - N_A^- = n_{no} - p_{no}$$

The resultant Poisson equation to be solved is therefore:

$$\frac{\partial^2 \psi}{\partial x^2} = -\frac{q}{\epsilon_{si}} (n_{no} - p_{no} + p_{no} e^{(-\beta\psi + \beta V_R)} - n_{no} e^{\beta\psi}) \quad 3b.15$$

or

$$\frac{\partial^2 \psi}{\partial x^2} = -\frac{q}{\epsilon_{si}} (p_{no} (e^{(-\beta\psi + \beta V_R)} - 1) - n_{no} (e^{\beta\psi} - 1)) \quad 3b.16$$

Integration of Equation 3b.16 from the bulk towards the surface (19) gives,

$$\int_0^{\psi} \frac{\partial \psi}{\partial x} d\left(\frac{\partial \psi}{\partial x}\right) = -\frac{q}{\epsilon_{si}} \int_0^{\psi} \left[ p_{no} (e^{(-\beta\psi + \beta V_R)} - 1) - n_{no} (e^{\beta\psi} - 1) \right] d\psi \quad 3b.17$$

which gives the relation between the electric field  $E$

$(E \equiv \frac{\partial \psi}{\partial x})$  and the potential  $\psi$  as

$$E = \left(\frac{2kT}{q}\right)^2 \left(\frac{q n_{no}}{2\epsilon_{si}}\right) \left[ \frac{p_{no}}{n_{no}} (e^{(-\beta\psi + \beta V_R)} + \beta\psi - e^{\beta V_R}) - (\beta\psi - e^{\beta\psi} + 1) \right] \quad 3b.18$$

We shall introduce the following abbreviations:

$$L_D = \sqrt{\frac{2kT\epsilon_s}{n_{no}q^2}} = \sqrt{\frac{2\epsilon_{si}}{2n_{no}} \beta}$$

and

$$F(\beta\psi, V_R, \frac{p_{no}}{n_{no}}) = \left[ \frac{p_{no}}{n_{no}} (e^{(-\beta\psi + \beta V_R)} + \beta\psi - e^{\beta V_R}) - (\beta\psi - e^{\beta\psi} + 1) \right]^{\frac{1}{2}} \geq 0$$

where  $L_D$  is called the extrinsic Debye length for electrons. Thus the electric field becomes

$$E = -\frac{\partial \psi}{\partial x} = \pm \frac{2kT}{qL_D} F(\beta\psi, V_R, \frac{p_{no}}{n_{no}}) \quad 3b.19$$

with the positive sign for  $\psi > 0$  and the negative sign for  $\psi < 0$ . To determine the electric field at the surface, we let  $\psi = \psi_s$ , so that

$$\mathcal{E}_s = \pm \frac{2KT}{qL_D} F(\beta\psi_s, V_R, \frac{p_{no}}{n_{no}}) \quad 3b.20$$

Similarly, by Gauss' law the space charge per unit area required to produce this field is

$$Q_s = -\epsilon_{si} \mathcal{E}_s = \mp \frac{2KT\epsilon_{si}}{qL_D} F(\beta\psi_s, V_R, \frac{p_{no}}{n_{no}})$$

Thus equation 3b.6 becomes:

$$V_G = -\frac{Q_s}{C_{ox}} + \psi_s = \pm \frac{2KT\epsilon_{si}}{qL_D C_{ox}} F(\beta\psi_s, V_R, \frac{p_{no}}{n_{no}}) + \psi_s \quad 3b.21$$

or

$$V_G = \pm \frac{2KTX_{ox}\epsilon_{si}}{qL_D \epsilon_{ox}} \left[ \frac{p_{no}}{n_{no}} (e^{(-\beta\psi_s + \beta V_R)} + \beta\psi_s - e^{\beta V_R}) + (e^{\beta\psi_s} - \beta\psi_s - 1) \right]^{\frac{1}{2}} + \psi_s \quad 3b.22$$

or

$$V_G = \pm \frac{2KTX_{ox}\epsilon_{si}}{qL_D \epsilon_{ox}} \left[ \frac{p_{no}}{n_{no}} e^{\beta V_R} \frac{(-\beta\psi_s)}{(e^{-\beta\psi_s} + \beta\psi_s e^{\beta V_R} - 1)} + (e^{\beta\psi_s} - \beta\psi_s - 1) \right]^{\frac{1}{2}} + \psi_s \quad 3b.23$$

where again the signs are for  $\psi_s > 0$  and  $\psi_s < 0$  respectively.

We are interested here in the values of  $V_G > V_T (V_R)$  that is the case for strong inversion.

$\psi_s$  is then given by,

$$\psi_s \approx V_R + 2\psi_B \quad 3b.24$$

Where  $\psi_B$  the potential in the bulk equal to  $E_i - E_{Fn}$  as shown in Fig. 3.9 and  $V_T$  is the turn-on voltage.

Thus we obtain,

$$V_T = -\frac{Q_s(V_R)}{C_{ox}} + V_R + 2\psi_B \quad 3b.25$$

For  $V_R = -1V$ ,  $X_{ox} = 1.2 \times 10^{-5} \text{ cm}$ ,  $n_{no} = 10^{15} \text{ cm}^{-3}$ ,  $p_{no} = 2.1 \times 10^5 \text{ cm}^{-3}$ .

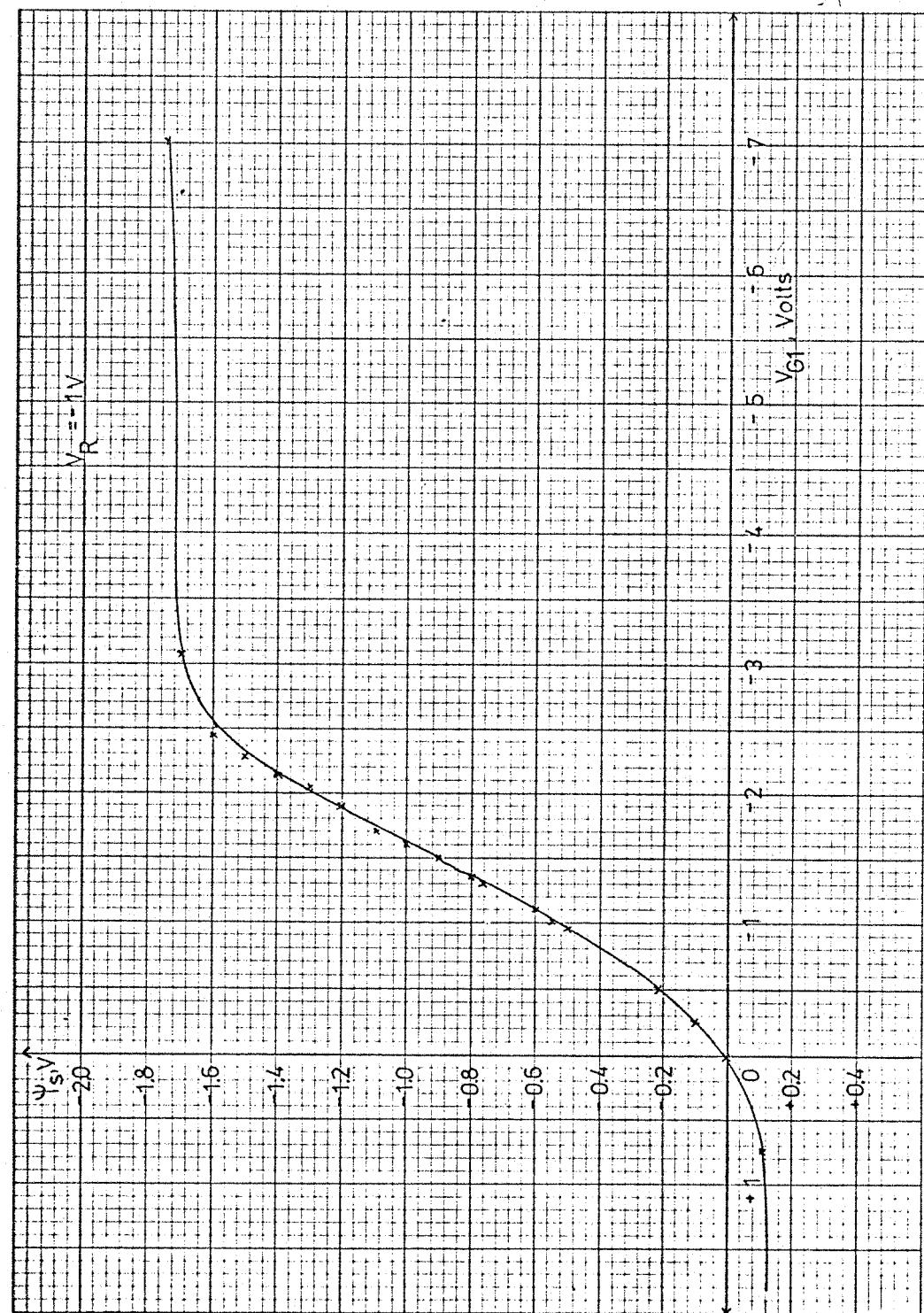

we can get values of  $V_G$  from equ. 3b.23 which shows the changes of  $V_G$  with  $\psi_s$ . These are listed in table 1.

Table 1

| $\psi_s$ | $V_{G1}$  |

|----------|-----------|

| -1.9     | -54.597   |

| -1.8     | - 9.486   |

| -1.7     | - 3.080   |

| -1.6     | - 2.426   |

| -1.5     | - 2.284   |

| -1.4     | - 2.159   |

| -1.3     | - 2.029   |

| -1.2     | - 1.900   |

| -1.1     | - 1.769   |

| -1.0     | - 1.630   |

| -0.9     | - 1.504   |

| -0.8     | - 1.364   |

| -0.5     | - 0.944   |

| -0.1     | - 0.275   |

| 0.0      | 0.000     |

| +0.1     | + 0.776   |

| +0.3     | +34.310   |

| +0.6     | +8239.600 |

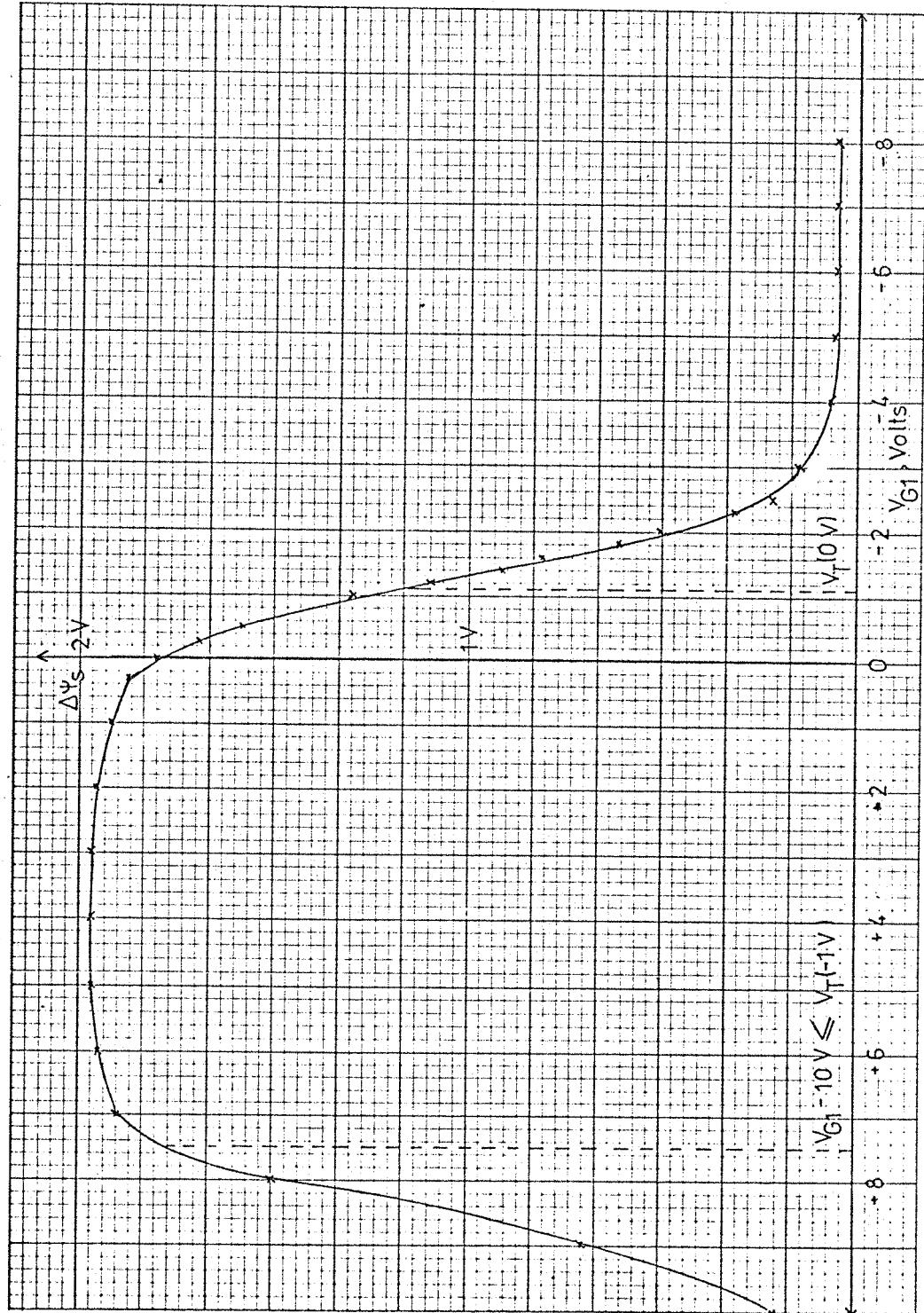

These data are plotted in Fig. 3.10.

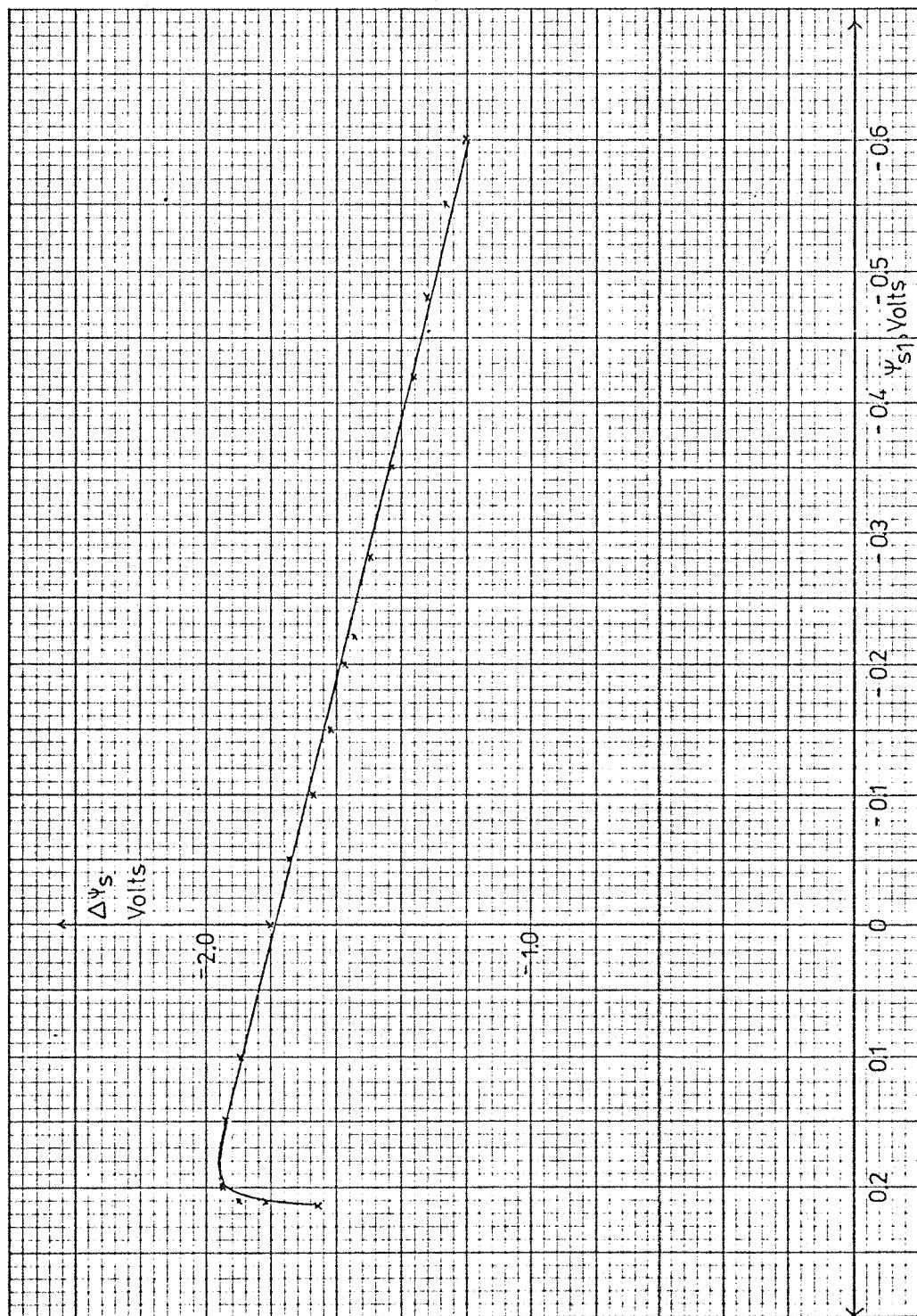

From this graph we can obtain approximate values of  $\Delta\psi_s$  versus  $V_{G1}$ , (where  $V_G$  switches between the two values  $V_{G1}$ , and  $V_{G2}$ ) the difference being 10 volts and the values are shown in table 2 and subsequently plotted in Fig. 3.11.

9270/008

Fig. 3.10

Table 2

| $V_{G1}$ (volts) | $V_{G2}$ (volts) | $\Delta\psi_s$ (volts) |

|------------------|------------------|------------------------|

| -8.0             | -18              | 0.06                   |

| -7.0             | -17              | 0.06                   |

| -6.0             | -16              | 0.07                   |

| -5.0             | -15              | 0.07                   |

| -4.0             | -14              | 0.08                   |

| -3.0             | -13              | 0.15                   |

| -2.5             | -12.5            | 0.22                   |

| -2.3             | -12.3            | 0.32                   |

| -2.0             | -12.0            | 0.52                   |

| -1.8             | -11.8            | 0.63                   |

| -1.6             | -11.6            | 0.82                   |

| -1.4             | -11.4            | 0.92                   |

| -1.2             | -11.2            | 1.11                   |

| -1.0             | -11.0            | 1.30                   |

| -0.5             | -10.5            | 1.59                   |

| -0.3             | -10.3            | 1.70                   |

| 0.0              | -10.0            | 1.81                   |

| +0.3             | -9.7             | 1.89                   |

| +0.5             | -9.5             | 1.90                   |

| +0.8             | -9.8             | 1.91                   |

| +1.0             | -9.0             | 1.93                   |

| +2.0             | -8.0             | 1.96                   |

| +3.0             | -9.0             | 1.97                   |

| +4.0             | -6.0             | 1.97                   |

| +5.0             | -5.0             | 1.97                   |

| +6.0             | -4.0             | 1.95                   |

| +7.0             | -3.0             | 1.90                   |

| +8.0             | -2.0             | 1.50                   |

| +9.0             | -1.0             | 0.70                   |

| +10.0            | 0.0              | 0.20                   |

9270/1006

LINERGRAPH LTD. - LONDON

Fig. 3.11

Indicated on the graph of Fig. 3.11 are the two extremes of  $V_{G1}$  between which an inversion layer is created by the pulse, together with a return of the gate voltage to a value such that the surface is approximately at the Flat-band condition. These two conditions are necessary and sufficient to obtain the charge pumped current.

The charge pumped current is the result of a scan of surface potential between  $\psi_{s1}$  and  $\psi_{s2}$  corresponding to  $V_{G1}$  and  $V_{G2}$ . This leads immediately to the following expression for the pumped current

$$I_{cp} = qfA_g \left[ - \int_{\psi_{s1}}^{\psi_{s2}} N_{ss} d\psi_s \right]. \quad 3b.26$$

In order to obtain a scan of the value of the distribution of  $N_{ss}$ , that is the value of  $N_{ss}$  at each  $\psi_{s1}$  it is necessary to form the derived function of  $I_{cp}$  with respect to  $\psi_{s1}$ .

Therefore, using the calculus method we have:

$$I_{cp} + \delta I_{cp} = qfA_g \left[ - \int_{\psi_{s1} + \delta \psi_{s1}}^{\psi_{s2} + \delta \psi_{s2}} N_{ss} d\psi_s \right] \quad 3b.27$$

or

$$I_{cp} + \delta I_{cp} = qfA_g \left[ - \left( \int_{\psi_{s1}}^{\psi_{s2}} N_{ss} d\psi_s + \int_{\psi_{s2}}^{\psi_{s2} + \delta \psi_{s2}} N_{ss} d\psi_s + \int_{\psi_{s1} + \delta \psi_{s1}}^{\psi_{s1}} N_{ss} d\psi_s \right) \right] \quad 3b.28$$

or

$$I_{cp} + \delta I_{cp} = qfA_g \left[ - \int_{\psi_{s1}}^{\psi_{s2}} N_{ss} d\psi_s \right] - qfA_g \left[ \int_{\psi_{s2}}^{\psi_{s2} + \delta \psi_{s2}} N_{ss} d\psi_s + \int_{\psi_{s1} + \delta \psi_{s1}}^{\psi_{s1}} N_{ss} d\psi_s \right] \quad 3b.29$$

or

$$\delta I_{cp} = -qfA_g \left[ \int_{\psi_{s2}}^{\psi_{s2} + \delta\psi_{s2}} N_{ss} d\psi_s + \int_{\psi_{s1}}^{\psi_{s1} + \delta\psi_{s1}} N_{ss} d\psi_s \right] \quad 3b.30$$

hence (19)

$$\delta I_{cp} = -qfA_g \delta\psi_{s2} N_{ss} (\psi_{s2} + \theta\delta\psi_{s2}) + \delta\psi_{s1} N_{ss} (\psi_{s1} + \beta\delta\psi_{s1}) \quad 3b.31$$

where  $\theta$  and  $\beta$  have some value between 0 and 1.

Dividing equation 3b.31 by  $\delta\psi_{s1}$  we have

$$\frac{\delta I_{cp}}{\delta\psi_{s1}} = -qfA_g \frac{\delta\psi_{s2}}{\delta\psi_{s1}} N_{ss} (\psi_{s2} + \theta\delta\psi_{s2}) + qfA_g N_{ss} (\psi_{s1} + \beta\delta\psi_{s1}) \quad 3b.32$$

On proceeding to the limit  $\delta\psi_{s1} \rightarrow 0$  (also  $\delta\psi_{s2} \rightarrow 0$ ) we have

$$\frac{dI_{cp}}{d\psi_{s1}} = -qfA_g \frac{d\psi_{s2}}{d\psi_{s1}} N_{ss} (\psi_{s2}) + qfA_g N_{ss} (\psi_{s1}) \quad 3b.33$$

or

$$\frac{dI_{cp}}{d\psi_{s1}} = qfA_g N_{ss} (\psi_{s1}) - qfA_g \frac{d\psi_{s2}}{d\psi_{s1}} N_{ss} (\psi_{s2}) \quad 3b.34$$

$$\text{But } \frac{dI_{cp}}{d\psi_{s1}} = \frac{dI_{cp}}{dV_{G1}} \cdot \frac{dV_{G1}}{d\psi_{s1}} \quad 3b.35$$

so we have,

$$\frac{dI_{cp}}{dV_{G1}} \cdot \frac{dV_{G1}}{d\psi_{s1}} = qfA_g N_{ss} (\psi_{s1}) - qfA_g \frac{d\psi_{s2}}{d\psi_{s1}} N_{ss} (\psi_{s2}) \quad 3b.36$$

However,  $\frac{d\psi_{s2}}{d\psi_{s1}}$  can be found from a graphical plot of  $\Delta\psi_s$

versus  $\psi_{s1}$  as shown in Fig. 3.12. The slope of the graph is equal to  $1 - \frac{d\psi_{s2}}{d\psi_{s1}}$  and in the range of interest we find that the

9270/1006

LINEGRAPH LTD. - LONDON

Fig. 3.12

value of  $\frac{d\psi_{s2}}{d\psi_{s1}}$  is  $\ll 1$ . Consequently we may write:

$$\frac{dI_{cp}}{dV_{G1}} \frac{dV_{G1}}{d\psi_{s1}} = qfA_N_{ss}(\psi_{s1}) \quad 3b.37$$

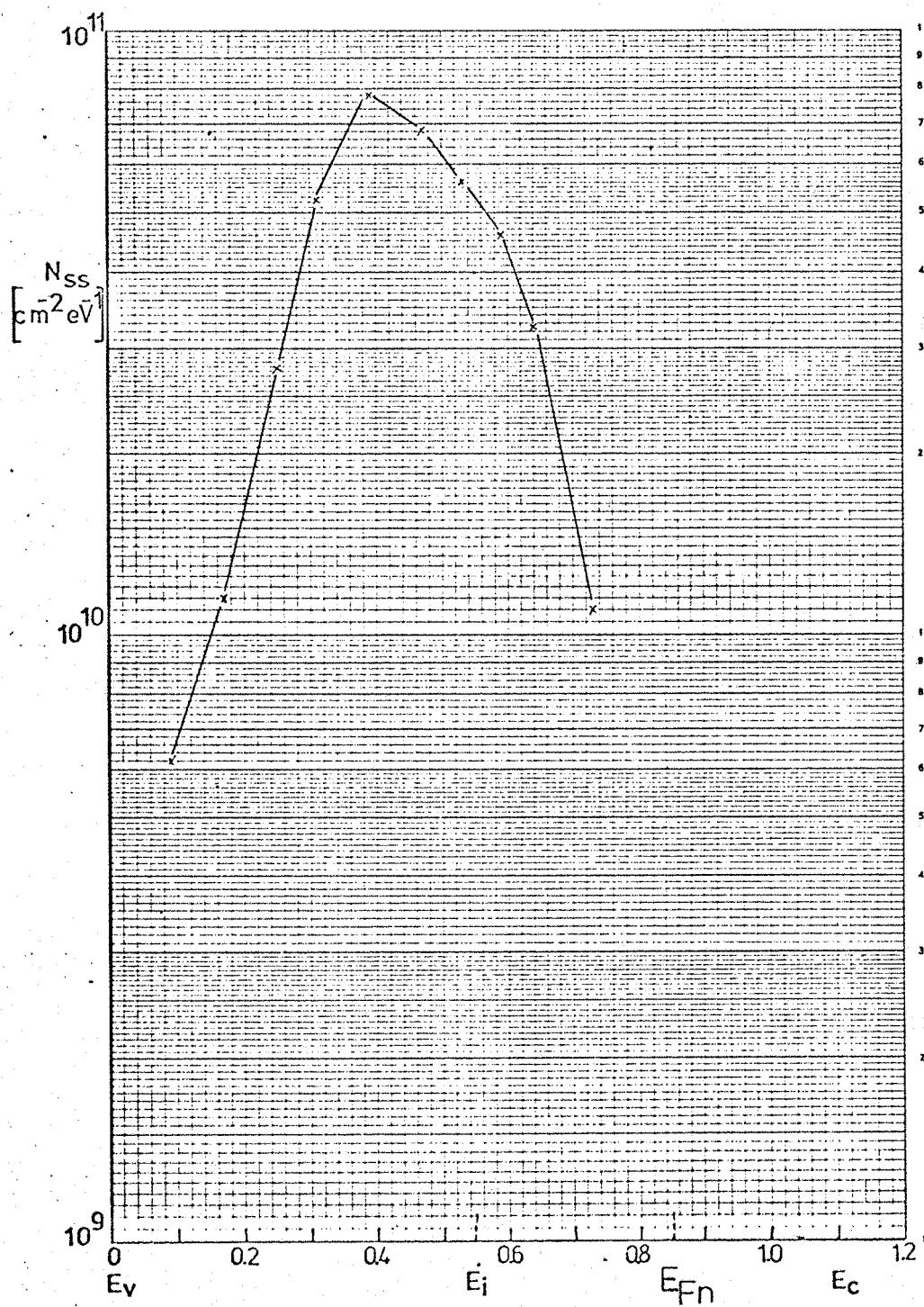

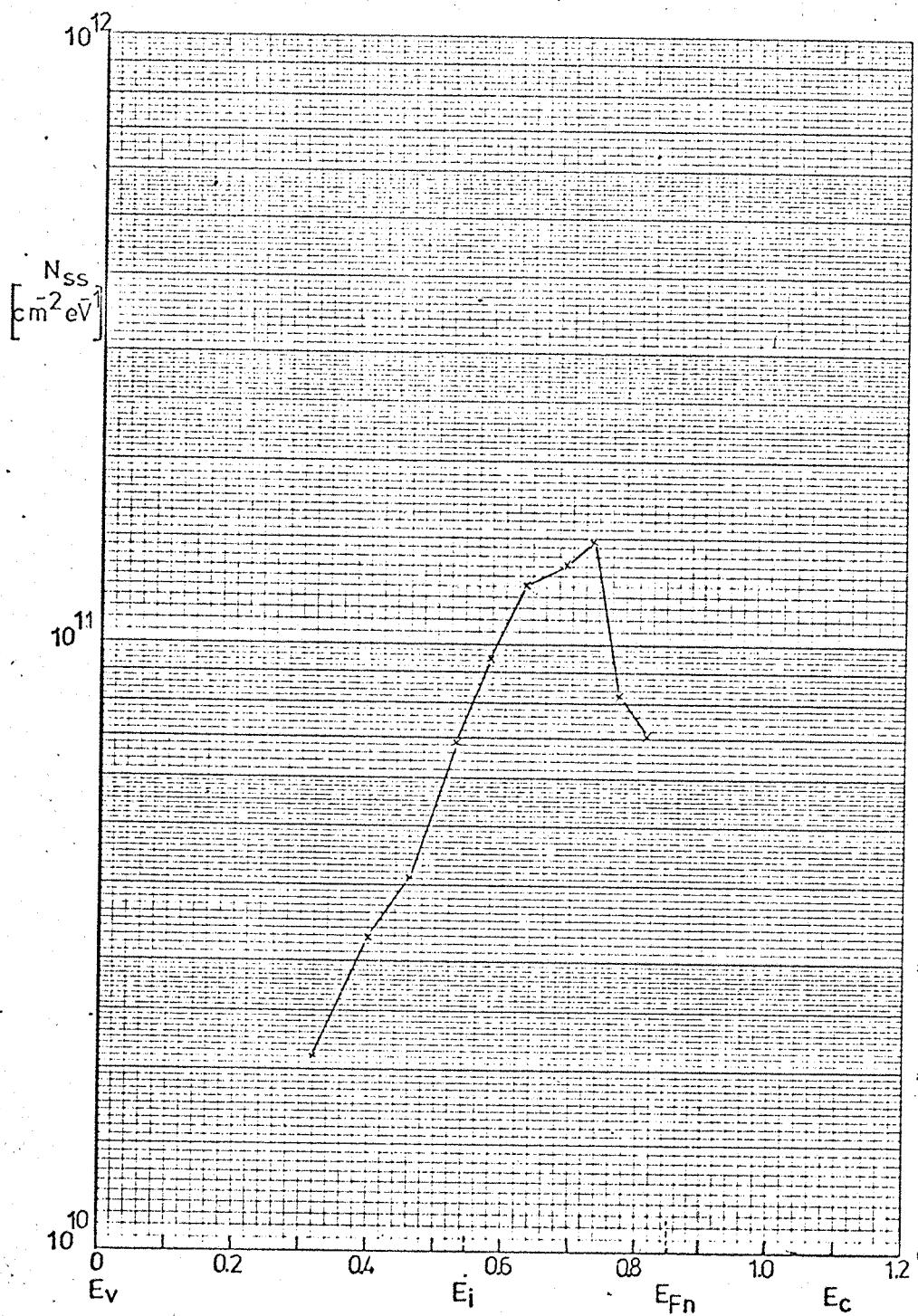

From this equation we can obtain the value of  $N_{ss}$  at each  $\psi_{s1}$  since we have a measurement of  $I_{cp}$  versus  $V_{G1}$  and a calculated graph of  $V_{G1}$  versus  $\psi_{s1}$ , as will be shown in the next section.

### 3c Change Pumping current measurements on gated diodes

In this section, the charge pumping current measurements were made on the gated diodes that were used for the leakage current measurements described in Chapter 2.

In fact all these measurements were made on gated diodes from the same slice with characteristics

14/S 3.7% HCl type 1

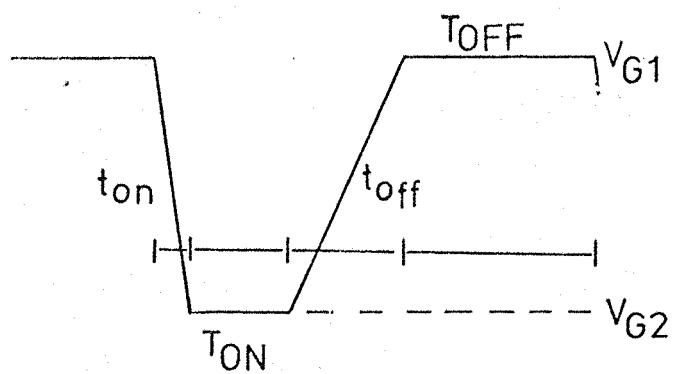

The apparatus used for these measurements was described in section 3a of this present chapter. For all the following measurements the pulse which is applied to the gate has a constant amplitude of 10V and is shown in Fig. 3.13.

The following measurements were made so as to check the validity of equation 35.26.

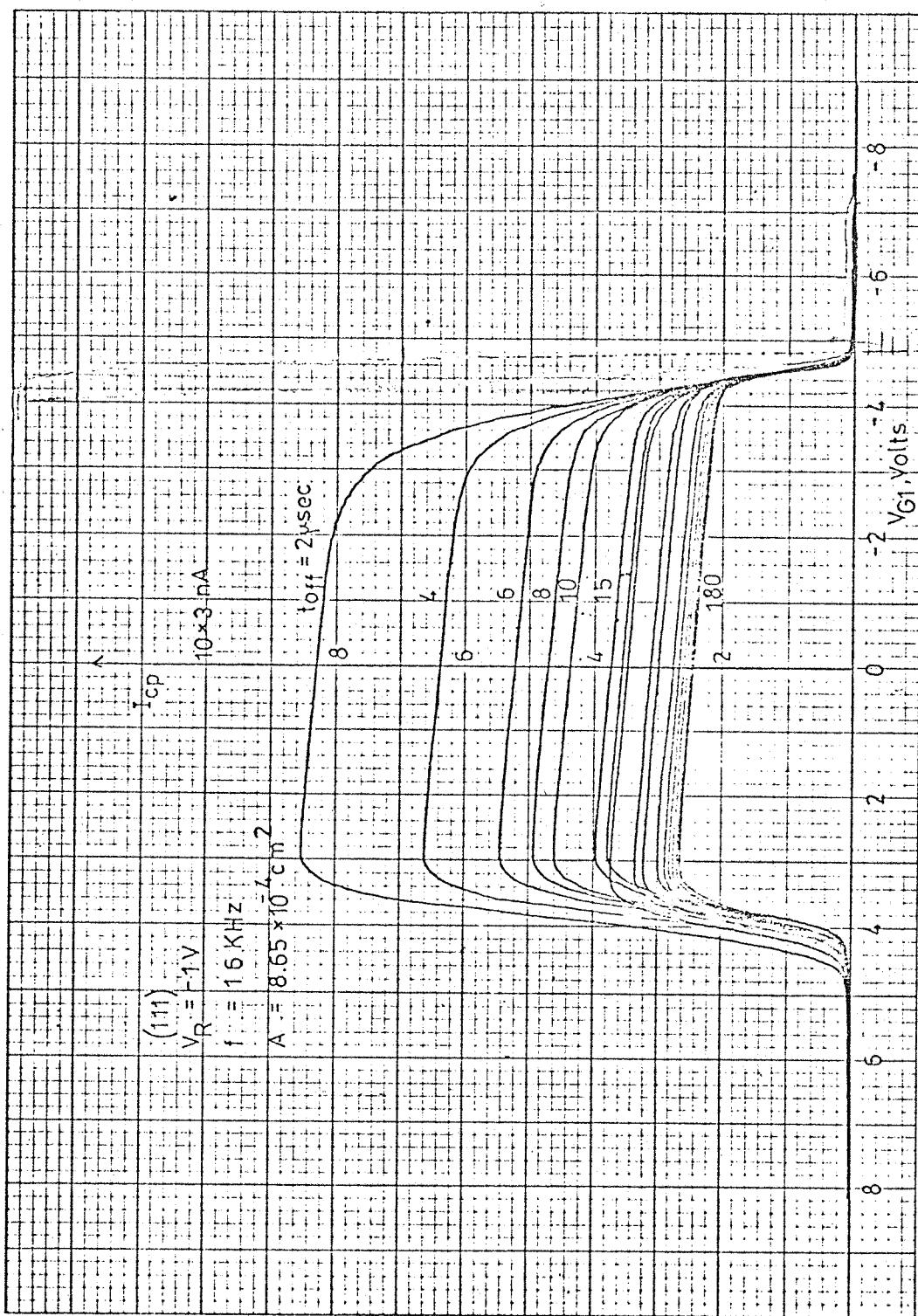

At first we want to find the proper turn-off time,  $t_{off}$ , of the applied pulse for which the 'geometric component' of the charge pumped current is eliminated.

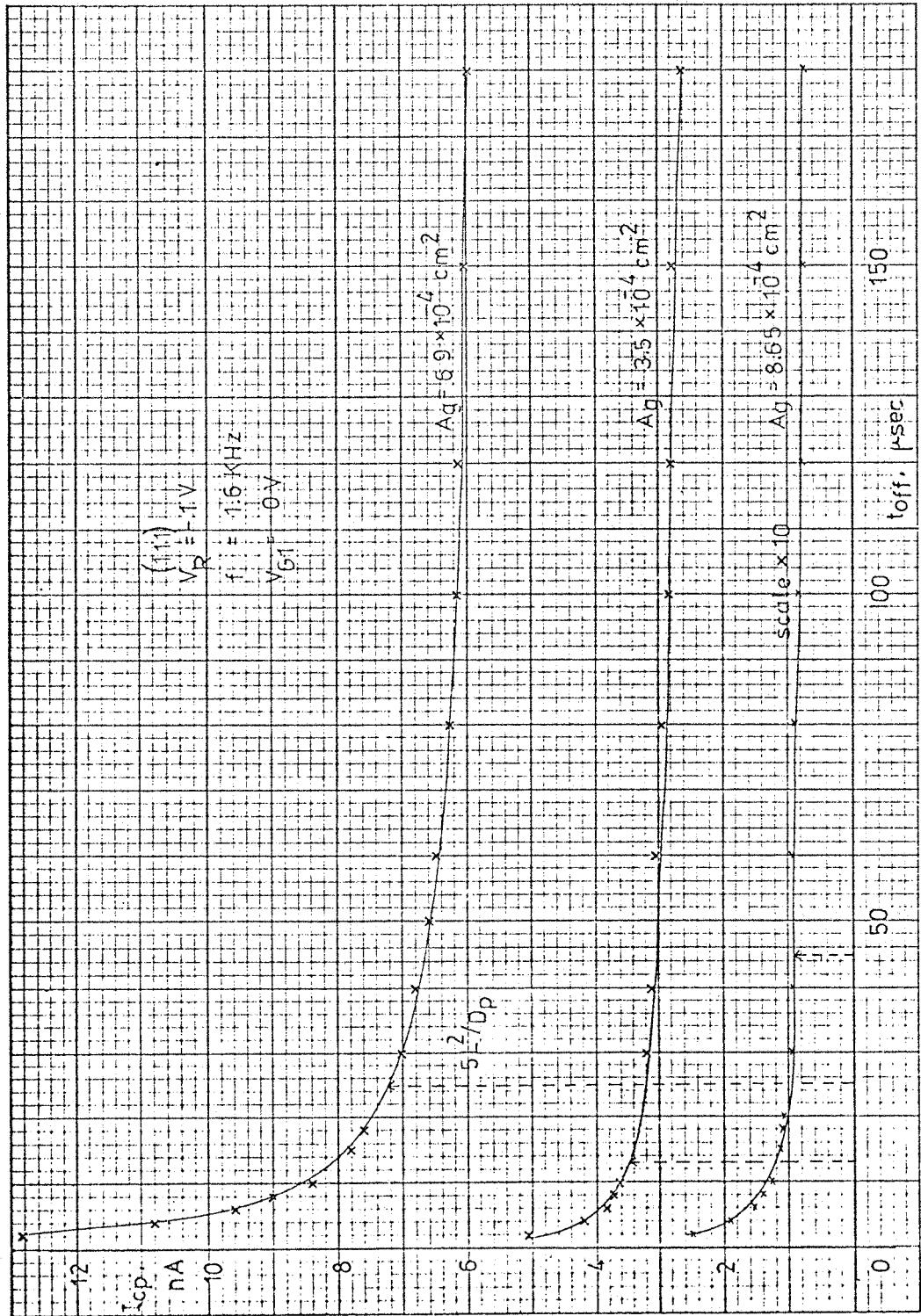

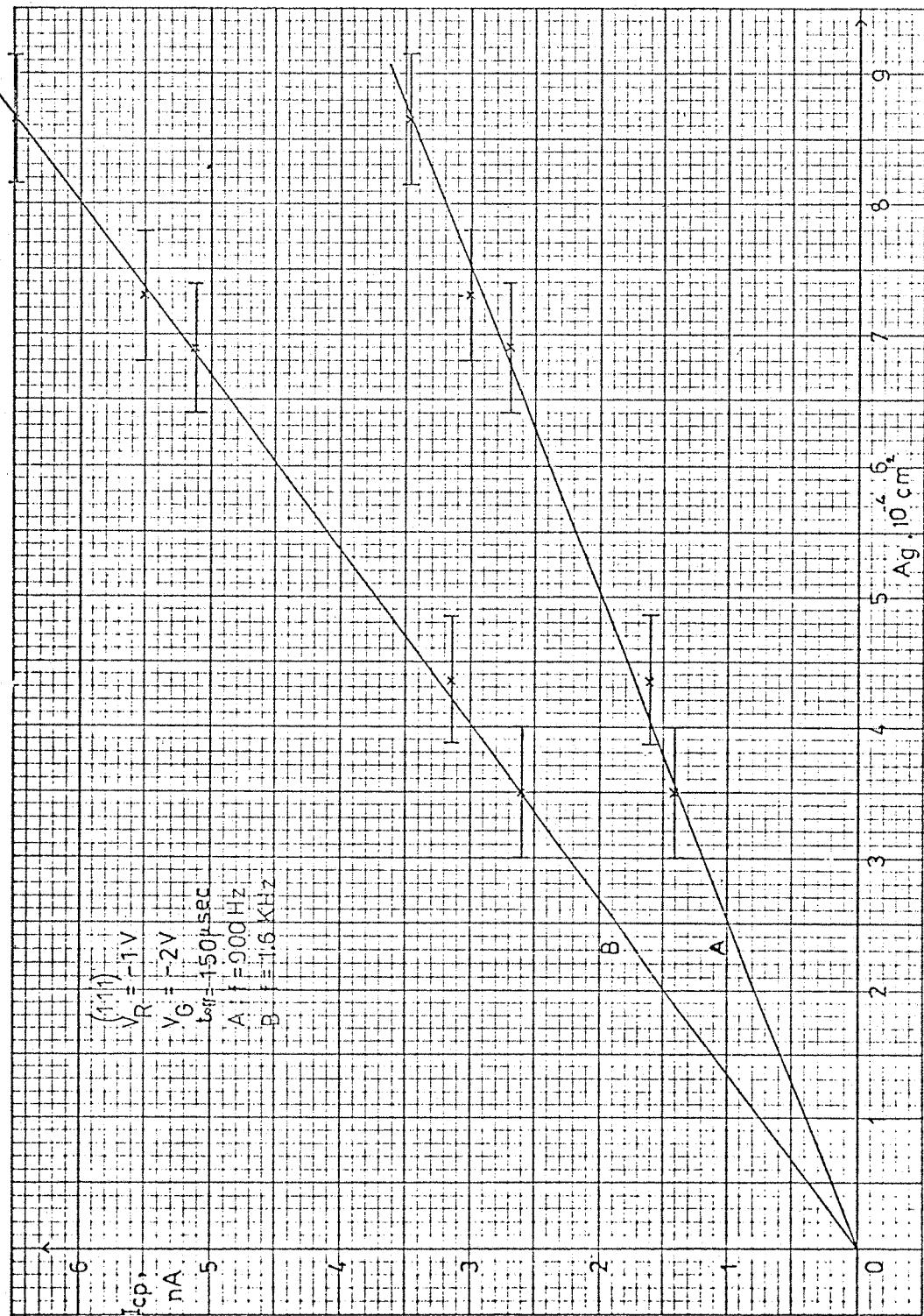

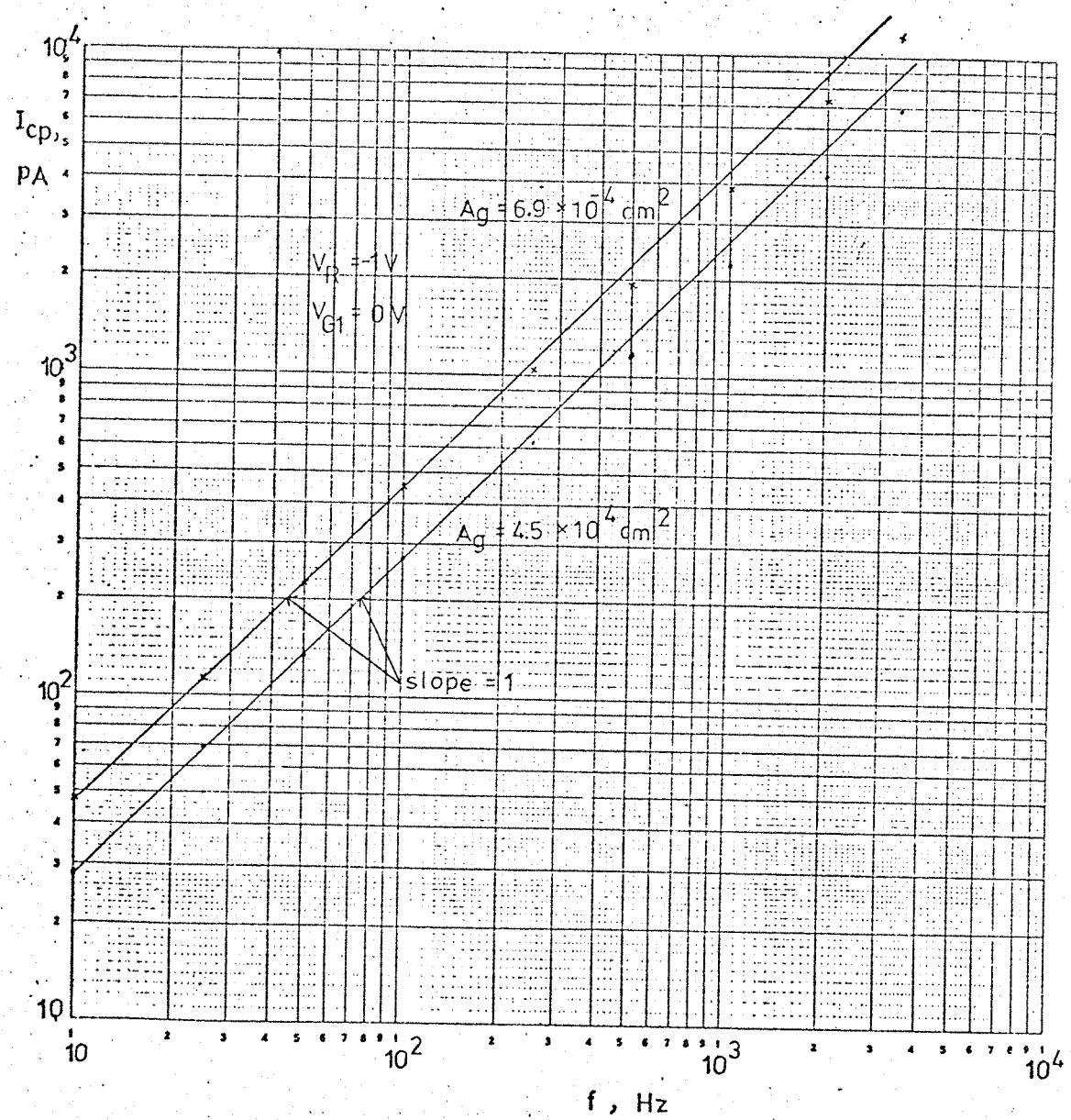

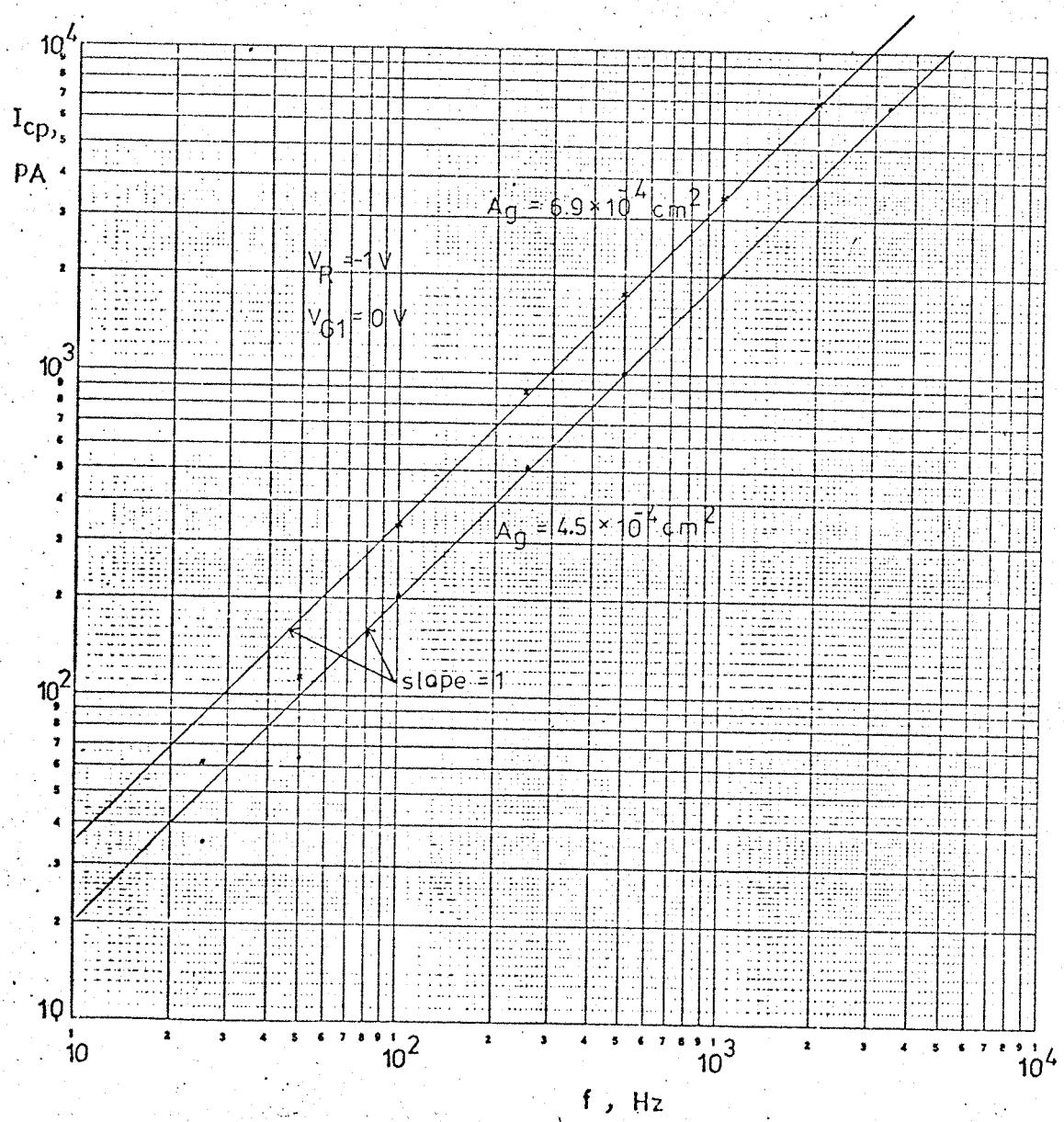

In Fig. 3.14 the charge pumped current versus the gate pulse testing voltage  $V_{G1}$  is shown for a particular gated diode with a gate area of  $8.65 \times 10^{-4} \text{ cm}^2$  and width of gate annulus,  $L$ , equal to  $100\mu\text{m}$ . The pulse applied to the gate had a frequency of about 2kHz, and the resting level,  $V_{G1}$ , of this pulse was scanned from -8 to +8 volt. The diode was reversed biased to a value of  $V_R$  equal to -1V. The turn-off time of the pulse (defined in Fig. 3.13) was different for each scan and the range was from  $2\mu\text{sec}$  to  $180\mu\text{sec}$ .

From these experimental curves the graph of charge pumped current versus  $t_{off}$  of the gate pulse, at a constant  $V_{G1}$  was obtained. This is shown in graph A of Fig. 3.15. The rest of the graphs in this Fig. were taken from repeating the experiment using other diodes with a different gate area as indicated. On each graph the value of the time constant  $\frac{5L^2}{D_p}$  is indicated where  $D_p$  is the diffusion coefficient for

holes in the inversion layer and is taken to be equal to  $10\text{cm}^2 \text{ sec}^{-1}$  (22).

This time constant is the criterion for mobile carriers to escape and not give rise to a 'geometric component' of charge pumped current.

$$V_{G1} - V_{G2} = 10 \text{ V}$$

Fig. 3.13

Fig. 3.14

LINEOGRAPH LTD. - LONDON

9270/1008

Fig. 3.15

Thus for values of  $t_{off}$  larger than  $5L^2/D_p$  the 'geometric component' (explained in section 3a) should be eliminated. This can be seen from the graphs in Fig. 3.14 where for  $t_{off} < 5L^2/D_p$  the  $I_{cp}$  rises rapidly and for  $t \gg 5L^2/D_p$  there is little change since in this range the  $I_{cp}$  is due predominantly to trapped charge pumping.