UNIVERSITY OF SOUTHAMPTON

DEPARTMENT OF ELECTRONICS AND COMPUTER SCIENCE

**High-level Floating-Point Synthesis**

Zaher A. Baidas

July, 2000

A thesis submitted for the title of

Doctor of Philosophy.

UNIVERSITY OF SOUTHAMPTON

# **High Level Floating-Point Synthesis**

by

Zaher Abdulkarim Baidas

A thesis submitted for the degree of

Doctor of Philosophy.

Department of Electronics and Computer Science,

University of Southampton

July, 2000

UNIVERSITY OF SOUTHAMPTON

## **ABSTRACT**

FACULTY OF ENGINEERING AND APPLIED SCIENCE

DEPARTMENT OF ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

# **High Level Floating-Point Synthesis**

by Zaher Abdulkarim Baidas

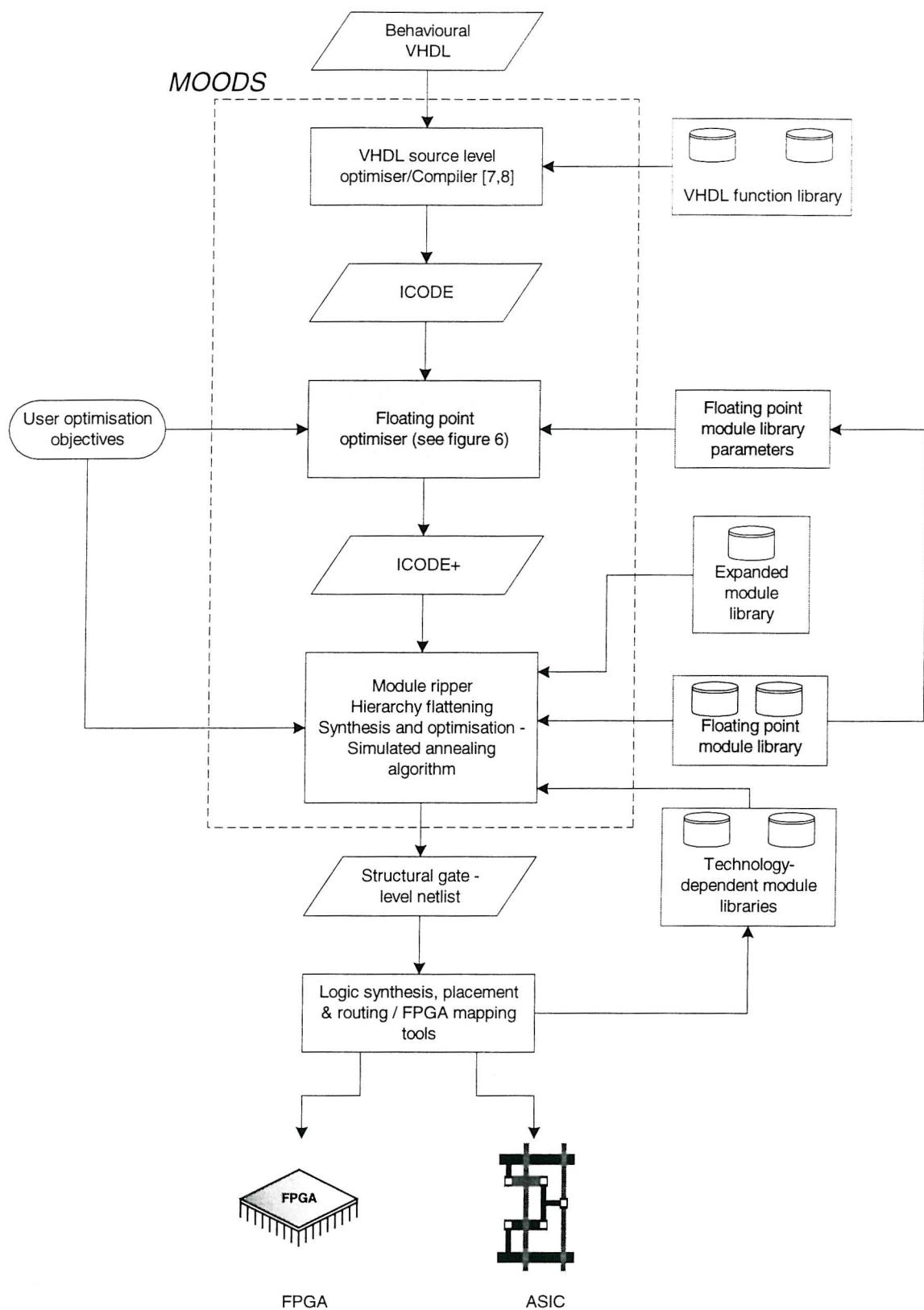

MOODS (Multiple Objective Optimisation in Data and control path Synthesis) is a high-level synthesis system which provides the ability to synthesise a system level behavioural description into a structural representation. The thesis represents an enhancement to the original MOODS system to allow the designer to manipulate floating-point and complex variables on an equal footing with all other data types; the additional complexities arising from floating-point manipulation are completely hidden from the user.

Originally, the data processed by MOODS was fixed (occasionally variable) width integers, and the functional units available were relatively unsophisticated (adders, subtractors, multipliers, multiplexers and so on). The floating-point synthesis system described here provides a library of high-level floating-point functions (trigonometric, transcendental, and complex) to support the synthesis of behavioural designs incorporating floating-point operations.

The floating-point library components themselves are implemented using a number of *base techniques*, namely table lookup, the CORDIC algorithm, and iterative series. Decisions about the mapping of base techniques onto functional units are left to a *floating-point optimiser*, which makes individual binding choices based on global knowledge of the overall design, allowing the internal sub-structures of these units to be shared which results in a dramatic decrease in the overall hardware resources required to implement the design.

Finally, an exemplar is designed and analysed in detail: a cubic equation solver synthesised using the floating-point capability integrated within the MOODS environment.

# Contents

|                                                         |           |

|---------------------------------------------------------|-----------|

| <b>Acknowledgements .....</b>                           | <b>12</b> |

| <b>Chapter 1: Introduction.....</b>                     | <b>13</b> |

| <b>Chapter 2: MOODS and behavioural synthesis .....</b> | <b>16</b> |

| 2.1 VHDL for behavioural synthesis .....                | 16        |

| 2.2 Behavioural synthesis .....                         | 19        |

| 2.3 The design space.....                               | 20        |

| 2.4 Internal representation .....                       | 21        |

| 2.5 Scheduling and allocation.....                      | 25        |

| 2.6 MOODS synthesis system .....                        | 29        |

| 2.6.1 ICODE and internal representation.....            | 31        |

| 2.6.2 Transformations .....                             | 36        |

| 2.6.3 The cost function .....                           | 39        |

| 2.6.4 Simulated annealing optimisation.....             | 39        |

| 2.6.5 Hierarchical module expansion .....               | 42        |

| 2.6.6 Floating-point enhancement .....                  | 43        |

| <b>Chapter 3: Background and related work .....</b>     | <b>45</b> |

| 3.1 Real number representation .....                    | 45        |

| 3.2 Fixed point functional units.....                   | 47        |

| 3.2.1 Modified Booth multiplier .....                   | 48        |

| 3.2.2 Rapid division algorithm .....                    | 50        |

| 3.3 Developing floating-point functional units.....     | 52        |

| 3.4 Floating-point arithmetic on FPGA.....              | 53        |

| 3.5 Automatic floating-point implementation .....       | 56        |

| 3.5.1 Module generators .....                           | 56        |

| 3.5.2 Block diagram tools .....                         | 58        |

|                                                        |            |

|--------------------------------------------------------|------------|

| <b>Chapter 4: Floating-point library design .....</b>  | <b>62</b>  |

| 4.1 Function evaluation .....                          | 62         |

| 4.1.1 Range reduction .....                            | 63         |

| 4.1.2 Table lookup .....                               | 64         |

| 4.1.3 The CORDIC algorithm.....                        | 73         |

| 4.1.4 Iterative series .....                           | 76         |

| 4.1.5 Post evaluation.....                             | 82         |

| 4.2 The status register .....                          | 83         |

| 4.3 Supported functions.....                           | 85         |

| 4.3.1 Algebraic operations .....                       | 87         |

| 4.3.2 Logarithmic and exponential functions .....      | 91         |

| 4.3.3 Trigonometric functions .....                    | 92         |

| 4.3.4 Hyperbolic functions.....                        | 92         |

| 4.3.5 Type conversion functions.....                   | 93         |

| 4.3.5 Complex units.....                               | 94         |

| 4.4 Function implementation.....                       | 96         |

| 4.4.1 Hierarchical unit expansion .....                | 97         |

| 4.4.2 Expanded module formation.....                   | 98         |

| <b>Chapter 5: Floating-point optimisation .....</b>    | <b>101</b> |

| 5.1 Function implementation interactions .....         | 101        |

| 5.2 Numerical interaction .....                        | 105        |

| 5.2.1 Error propagation.....                           | 106        |

| 5.2.2 Accuracy variation effect .....                  | 109        |

| 5.3 Optimisation algorithm.....                        | 111        |

| 5.4 Experimental evaluation .....                      | 126        |

| <b>Chapter 6: Practical synthesis using FPGAs.....</b> | <b>133</b> |

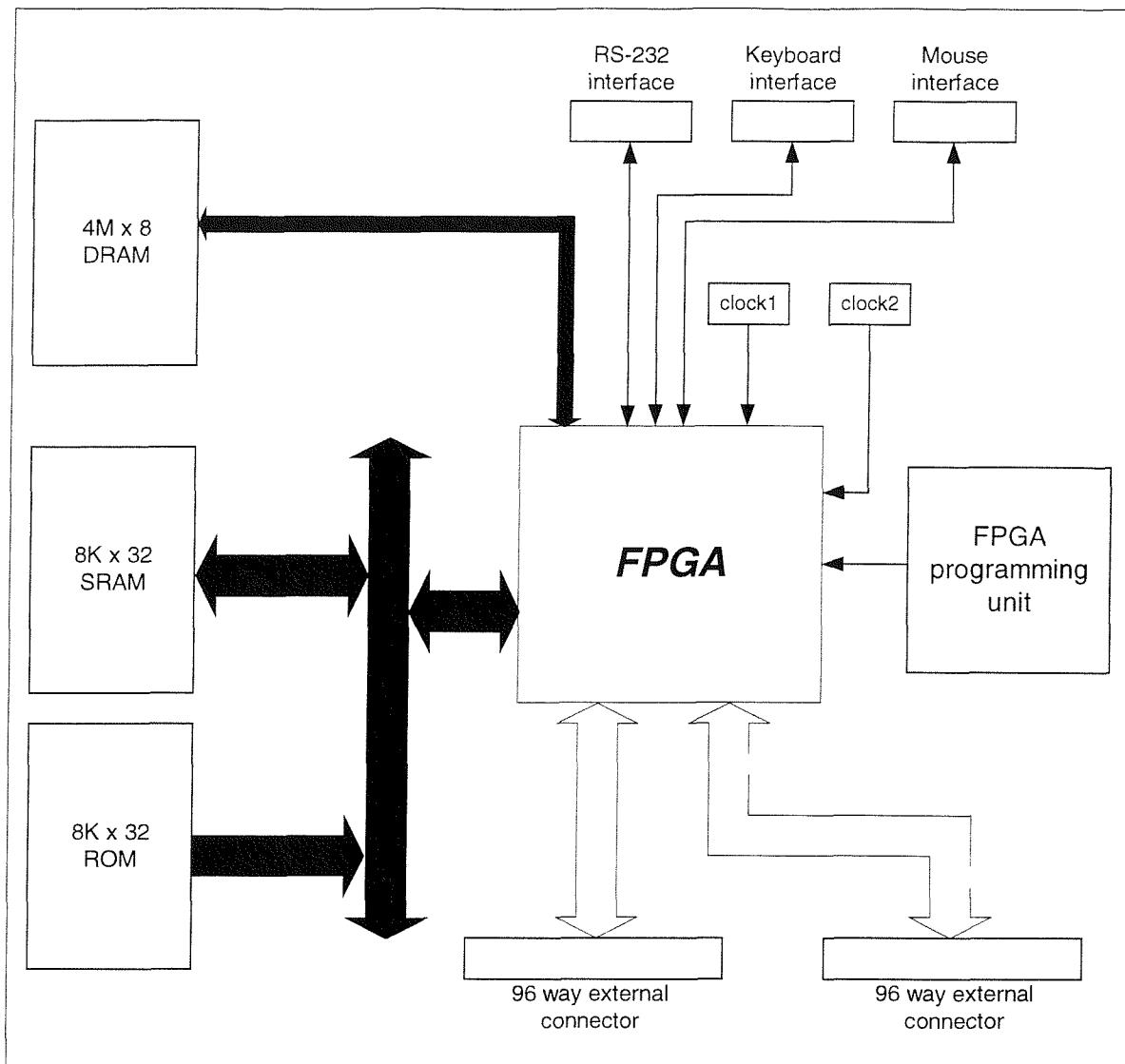

| 6.1 FPGA prototyping board .....                       | 133        |

| 6.2 Algebraic cubic equation solver .....              | 136        |

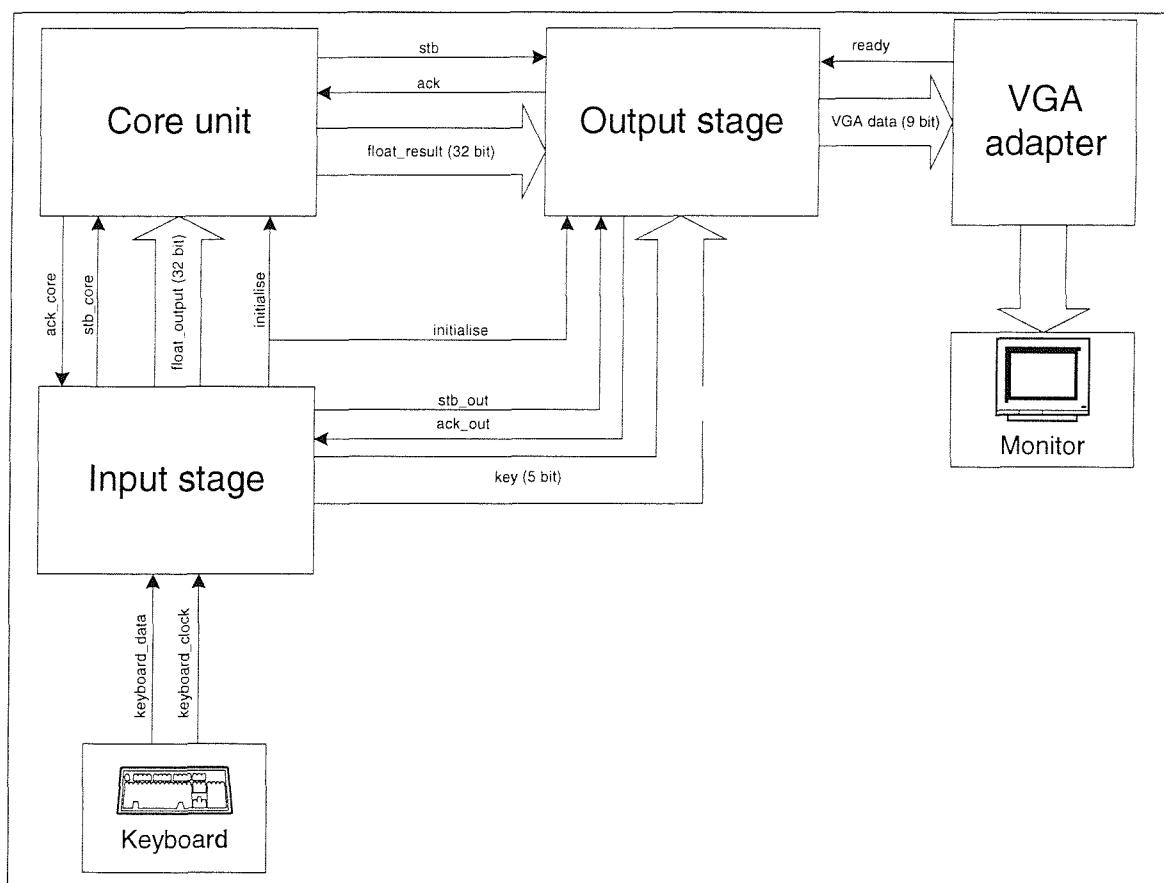

| 6.2.1 Input stage .....                                | 138        |

| 6.2.2 Output stage .....                               | 138        |

| 6.2.3 Core unit .....                                  | 139        |

|                                                                            |            |

|----------------------------------------------------------------------------|------------|

| 6.3 Synthesis issues .....                                                 | 145        |

| 6.3.1 Area reduction.....                                                  | 145        |

| 6.3.2 Meeting timing specifications.....                                   | 148        |

| 6.3.3 Synchronisation and communication.....                               | 150        |

| 6.3.4 Physical implementation issues .....                                 | 152        |

| 6.3.5 Final implementation.....                                            | 153        |

| 6.4 Comparison with microprocessors .....                                  | 156        |

| <b>Chapter 7: Conclusions and further work.....</b>                        | <b>159</b> |

| 7.1 Source level optimisation from a floating-point perspective.....       | 160        |

| 7.2 Variable precision floating-point library .....                        | 160        |

| 7.3 Component library .....                                                | 161        |

| 7.4 Function inversion block .....                                         | 162        |

| 7.5 Multi-operand floating-point units .....                               | 164        |

| <b>Appendix A: IEEE standard for binary floating point arithmetic.....</b> | <b>166</b> |

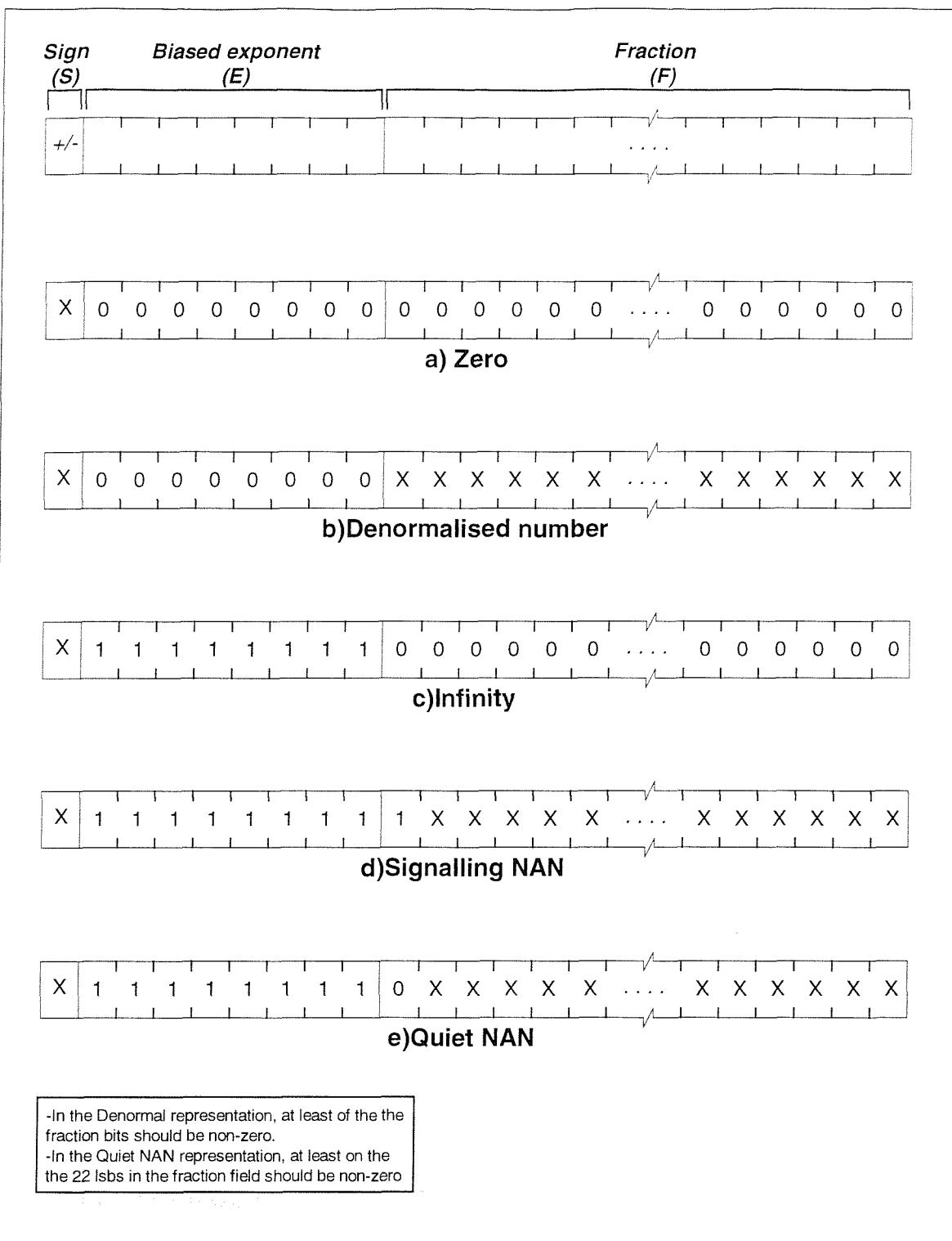

| A.1 Single-precision format evaluation.....                                | 167        |

| A.2 Operations with NAN .....                                              | 170        |

| A.3 Status flags.....                                                      | 171        |

| A.4 Comparison operations .....                                            | 171        |

| A.5 Rounding.....                                                          | 172        |

| <b>Appendix B: The CORDIC algorithm .....</b>                              | <b>175</b> |

| B.1 The original CORDIC algorithm .....                                    | 175        |

| B.2 The enhanced CORDIC algorithm.....                                     | 178        |

| B.3 Computation of inverse sine and inverse cosine using CORDIC .....      | 183        |

| <b>Appendix C: Elementary functions details .....</b>                      | <b>186</b> |

| C.1 Sine and cosine functions.....                                         | 186        |

| C.1.1 Pre-processing stage.....                                            | 186        |

| C.1.2 Function generation unit .....                                       | 189        |

| C.2 Inverse sine and inverse cosine functions .....                        | 195        |

| C.3 Inverse tangent function .....                                         | 199        |

| C.4 Logarithmic functions .....                                            | 206        |

| C.5 Exponential function.....                                              | 212        |

|                                                 |            |

|-------------------------------------------------|------------|

| C.6 Square root function.....                   | 217        |

| C.7 VHDL library .....                          | 221        |

| <b>Appendix D: Implementation details .....</b> | <b>227</b> |

| D.1 File formats .....                          | 227        |

| D.1.1 ICODE instruction database .....          | 227        |

| D.1.2 Floating-point instruction database ..... | 229        |

| D.1.3 Floating-point module library .....       | 230        |

| D.1.4 Floating-point expanded instruction ..... | 232        |

| D.2 The ICODE format .....                      | 234        |

| D.3 ICODE+.....                                 | 236        |

| D.4 Adding a new instruction.....               | 239        |

| <b>Appendix E: Example details .....</b>        | <b>241</b> |

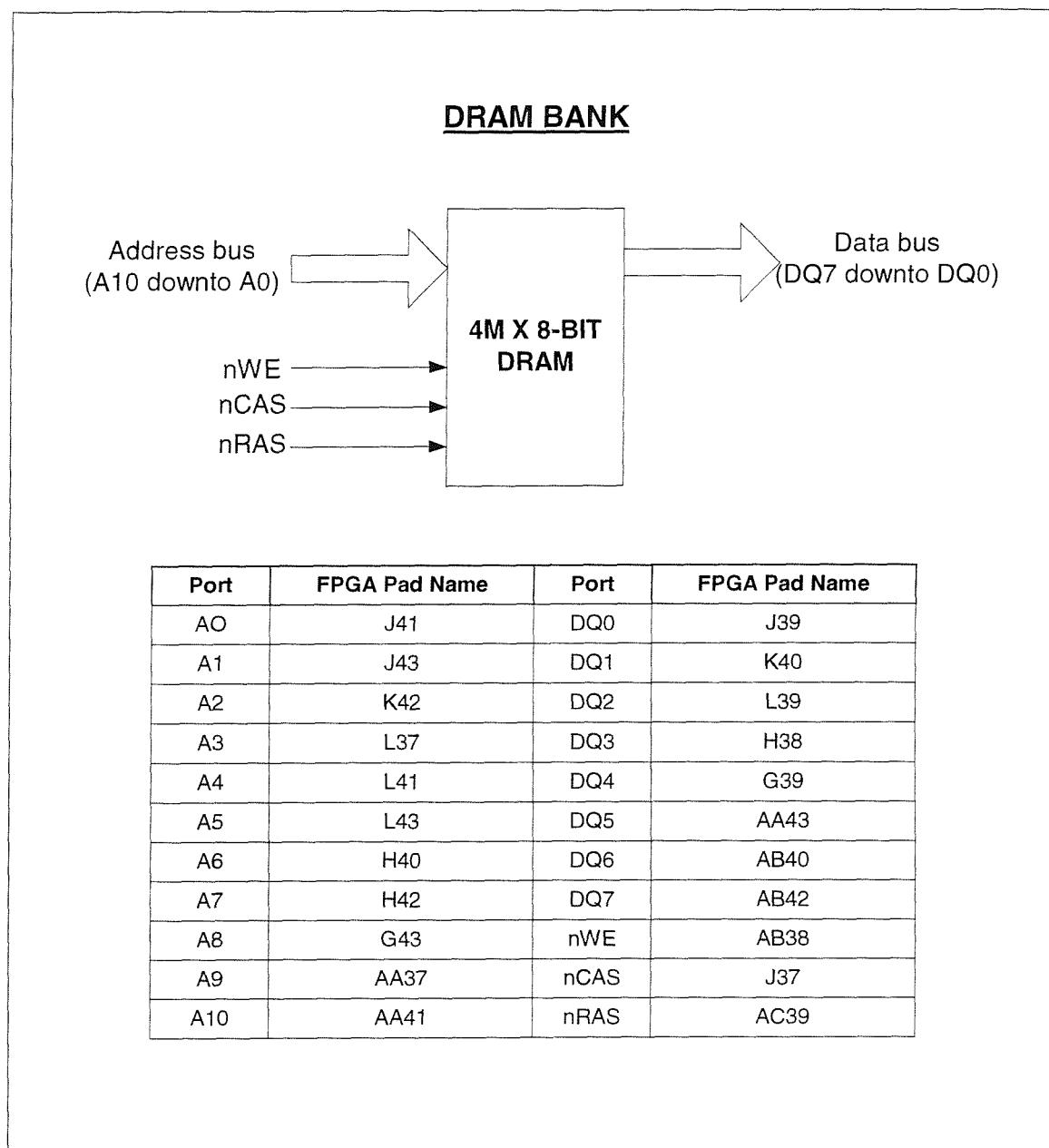

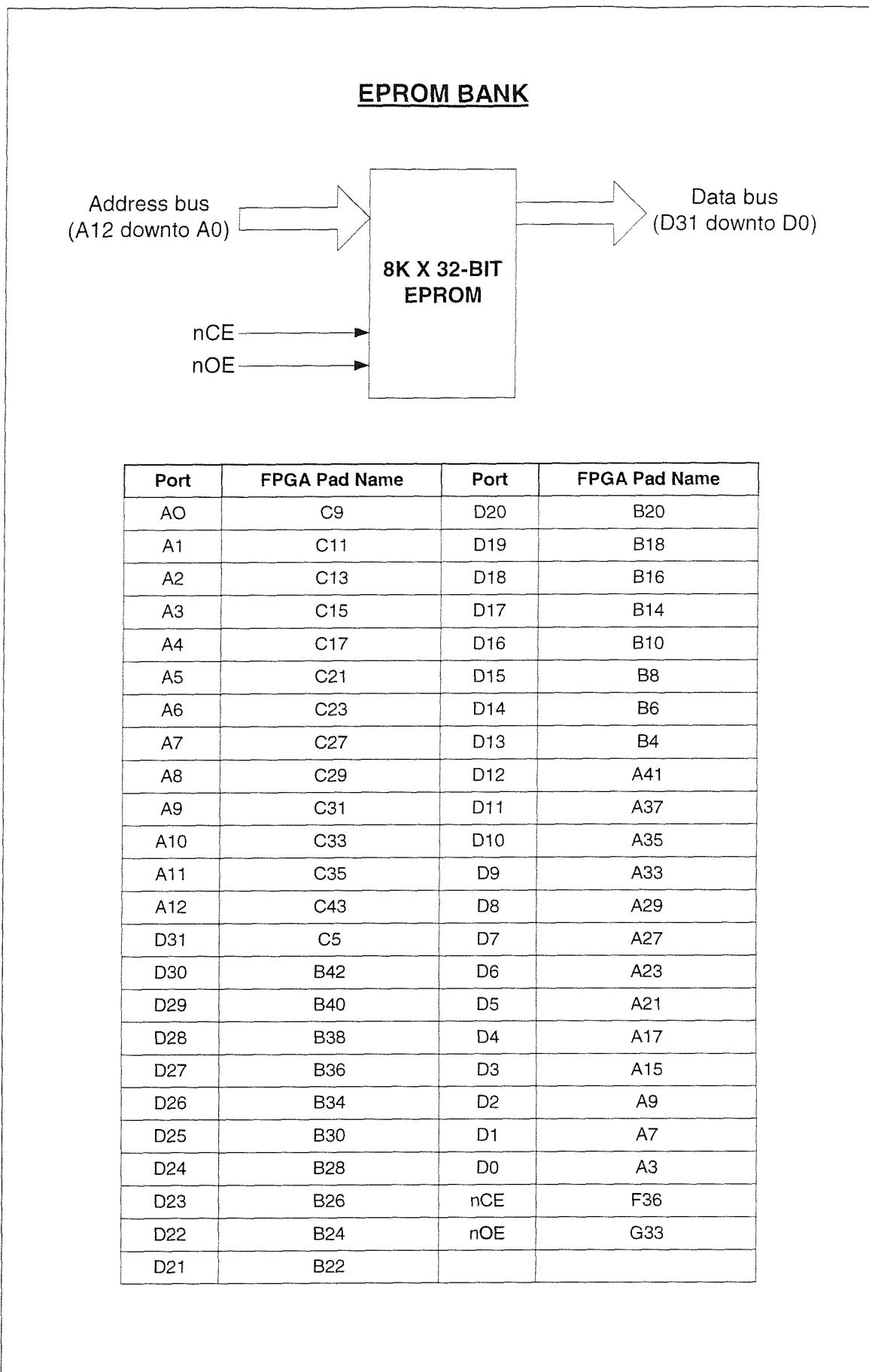

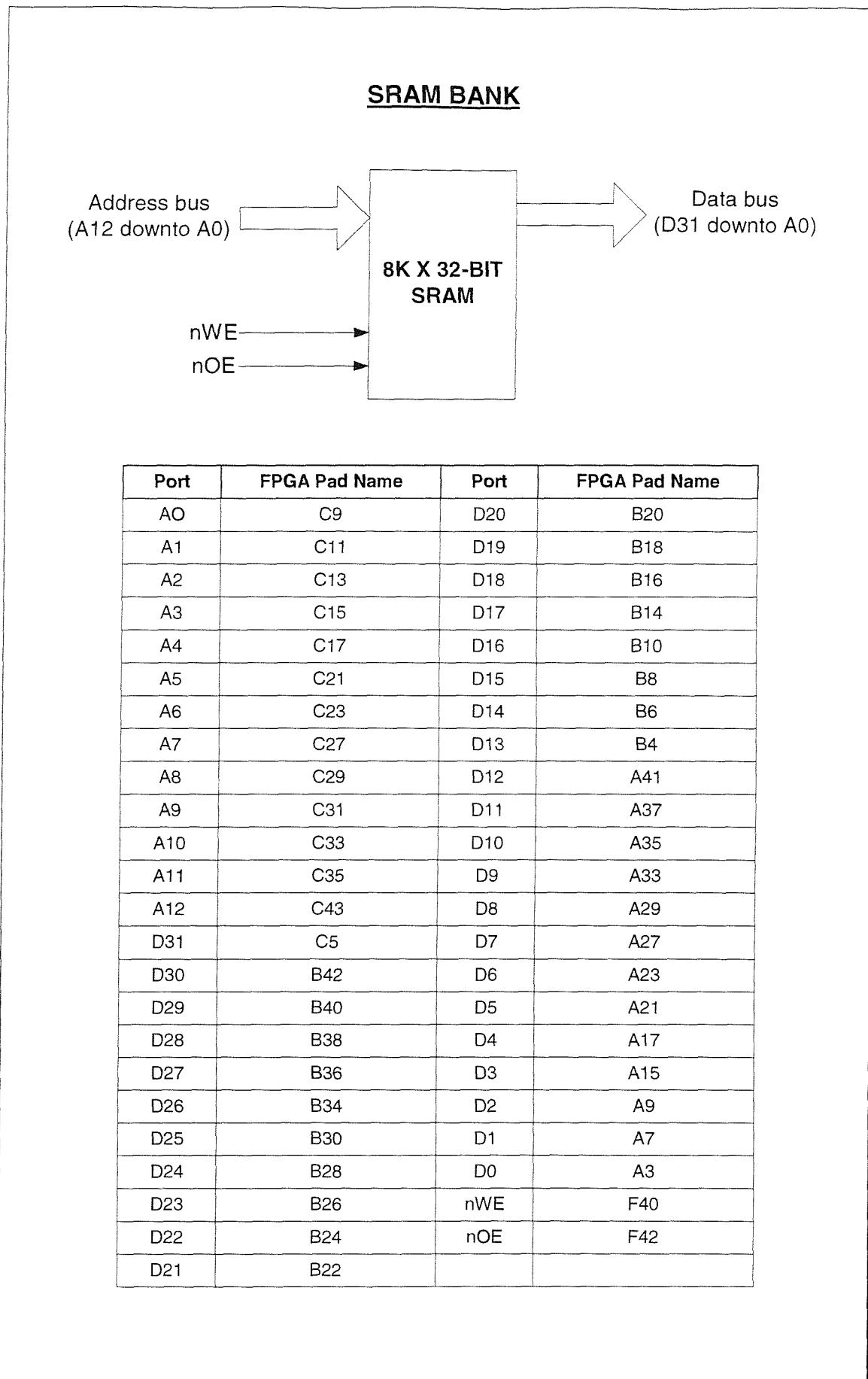

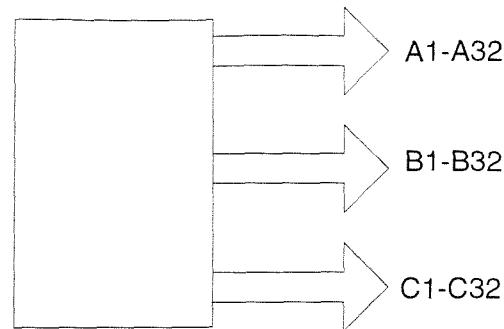

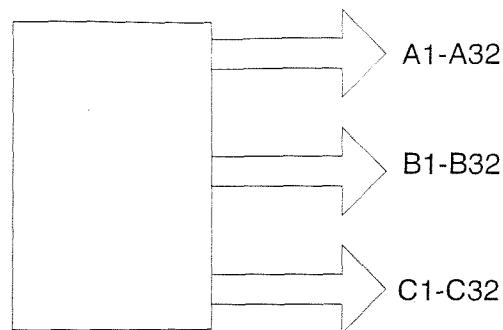

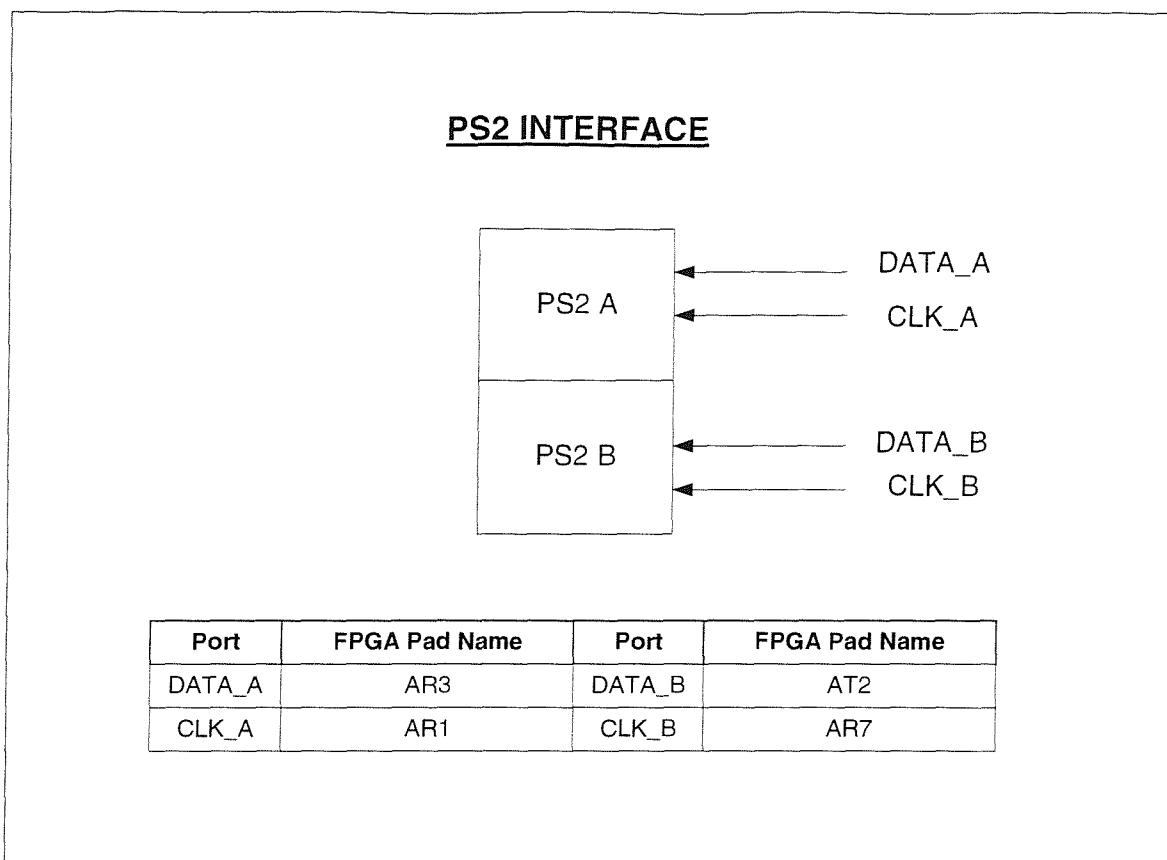

| E.1 FPGA prototyping board data .....           | 241        |

| E.1.1 FPGA pin-out .....                        | 241        |

| E.1.2 Device programming.....                   | 242        |

| E.1.3 Device pin-assignment .....               | 243        |

| E.2 VGA adapter .....                           | 249        |

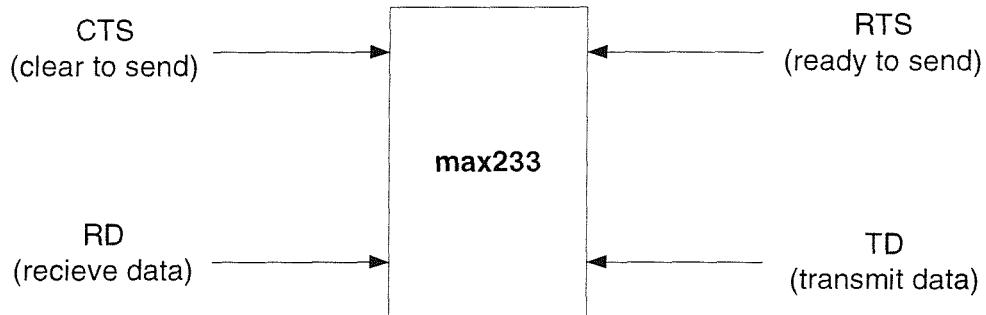

| E.3 IO stage details .....                      | 252        |

| E.3.1 Input stage .....                         | 252        |

| E.3.2 Output stage.....                         | 257        |

| E.4 Source code listings.....                   | 260        |

| <b>Appendix F: Papers .....</b>                 | <b>289</b> |

| <b>References .....</b>                         | <b>320</b> |

# List of Figures

|                                                                             |    |

|-----------------------------------------------------------------------------|----|

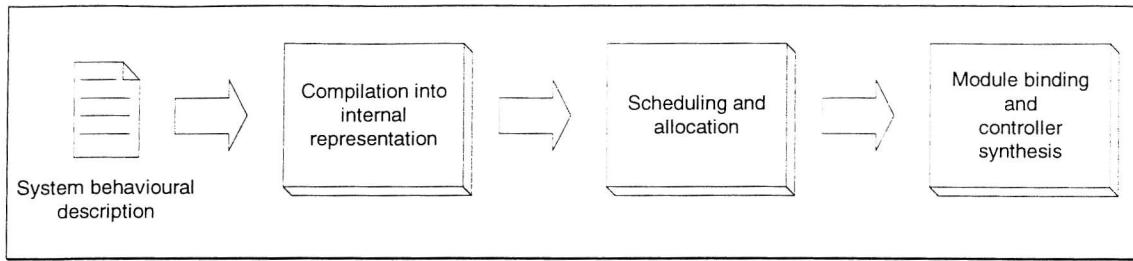

| Figure 2.1 A generic high-level synthesis system.....                       | 20 |

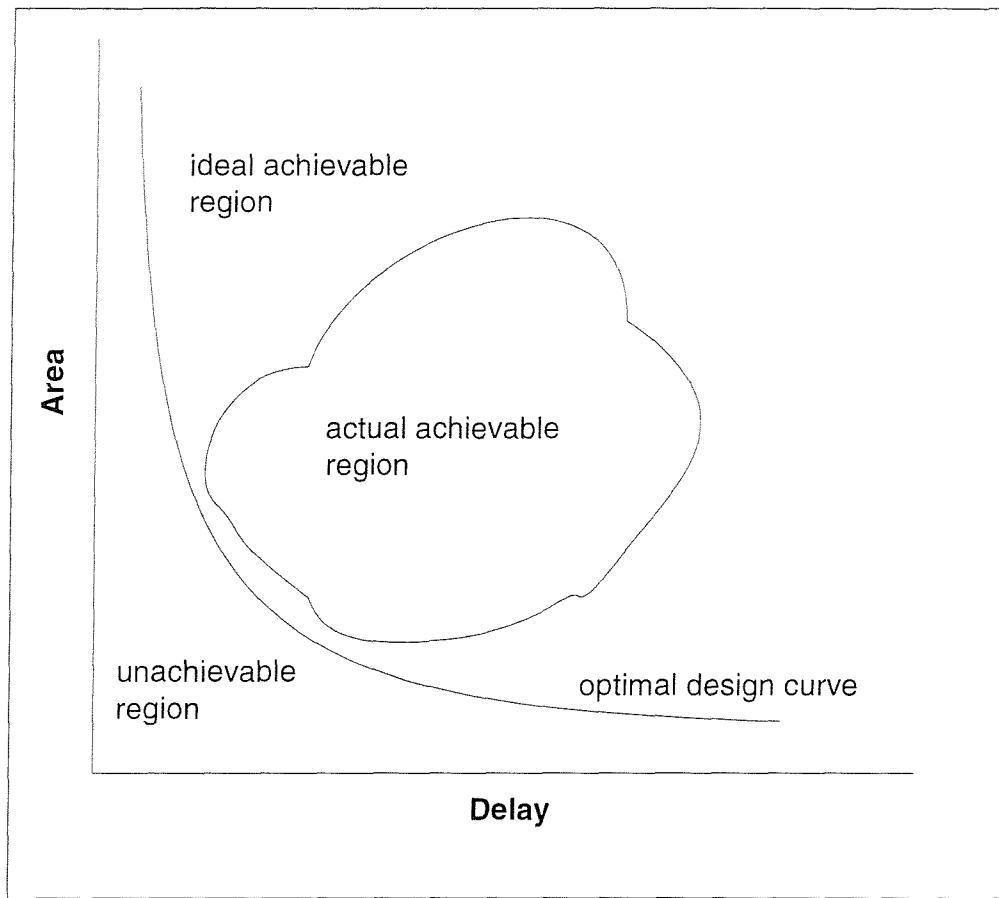

| Figure 2.2 Area versus delay design space .....                             | 21 |

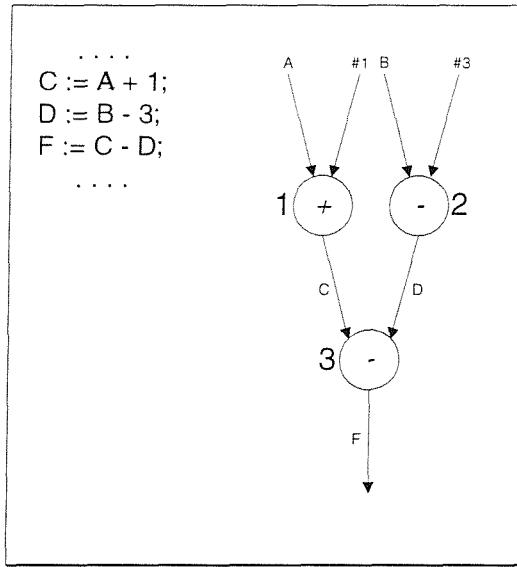

| Figure 2.3 Data flow graph representation .....                             | 22 |

| Figure 2.4 A sample VHDL example .....                                      | 23 |

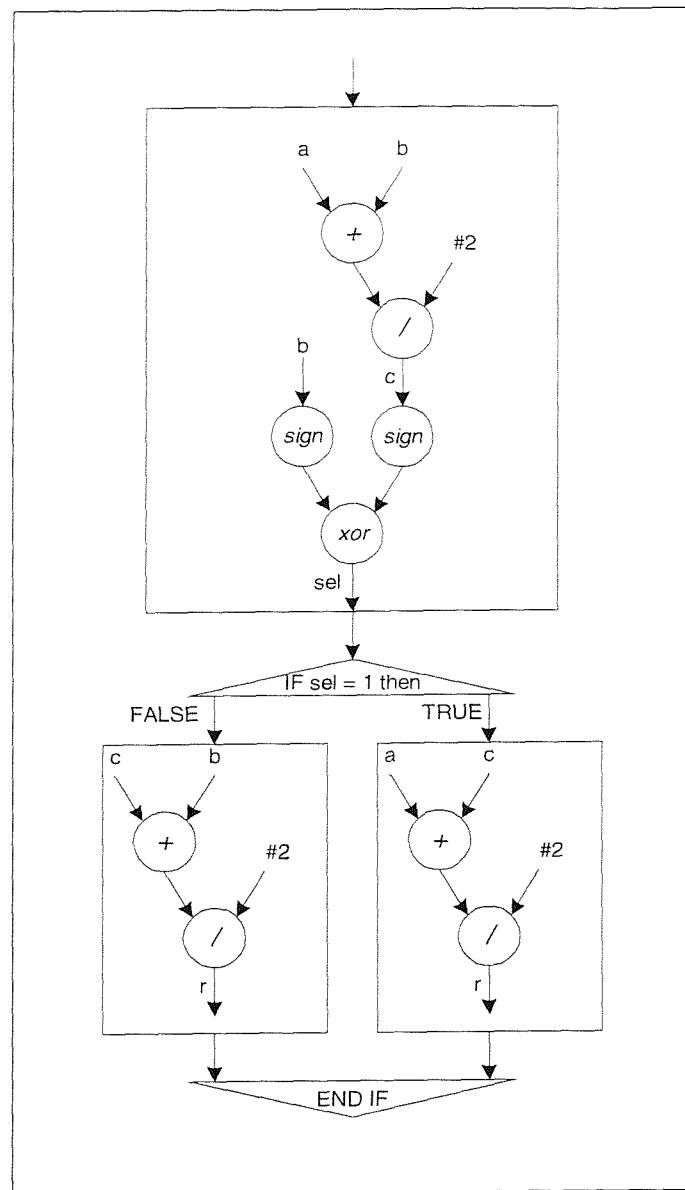

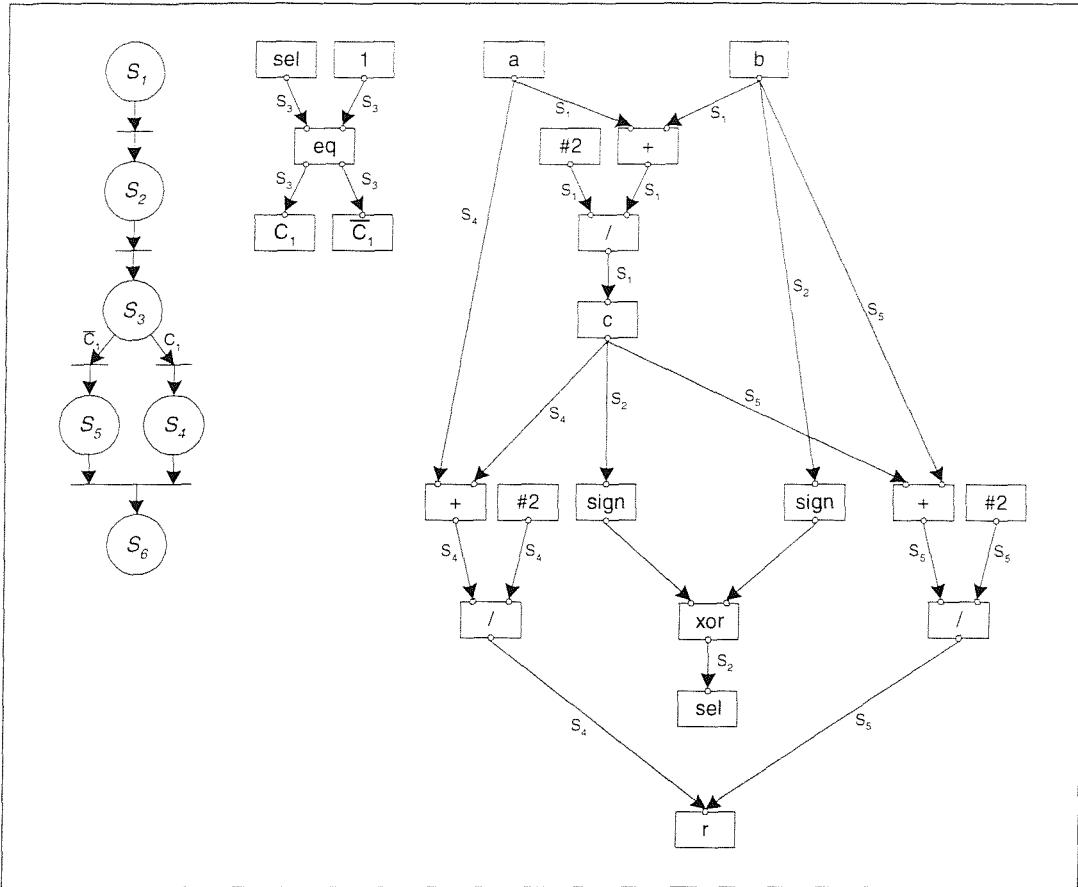

| Figure 2.5 Control dataflow graph.....                                      | 24 |

| Figure 2.6 Extended timed Petri-net .....                                   | 25 |

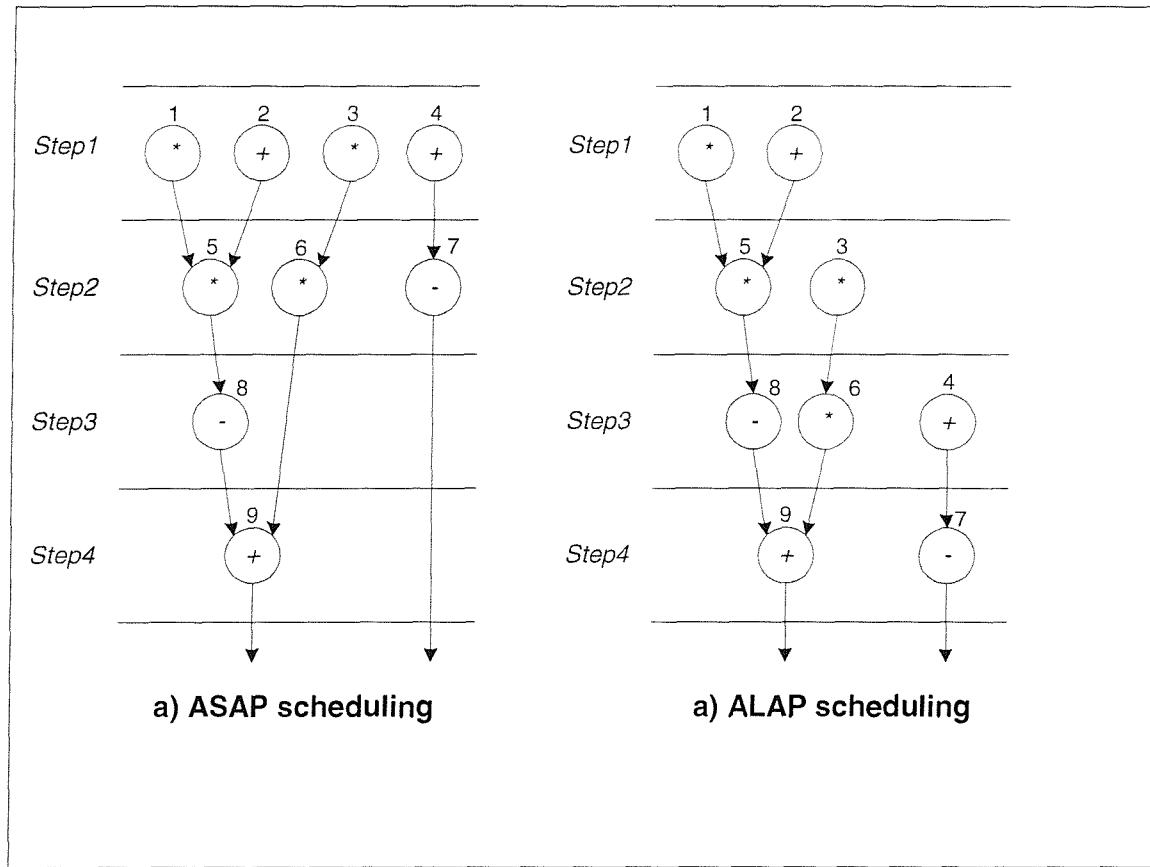

| Figure 2.7 ASAP and ALAP scheduling .....                                   | 27 |

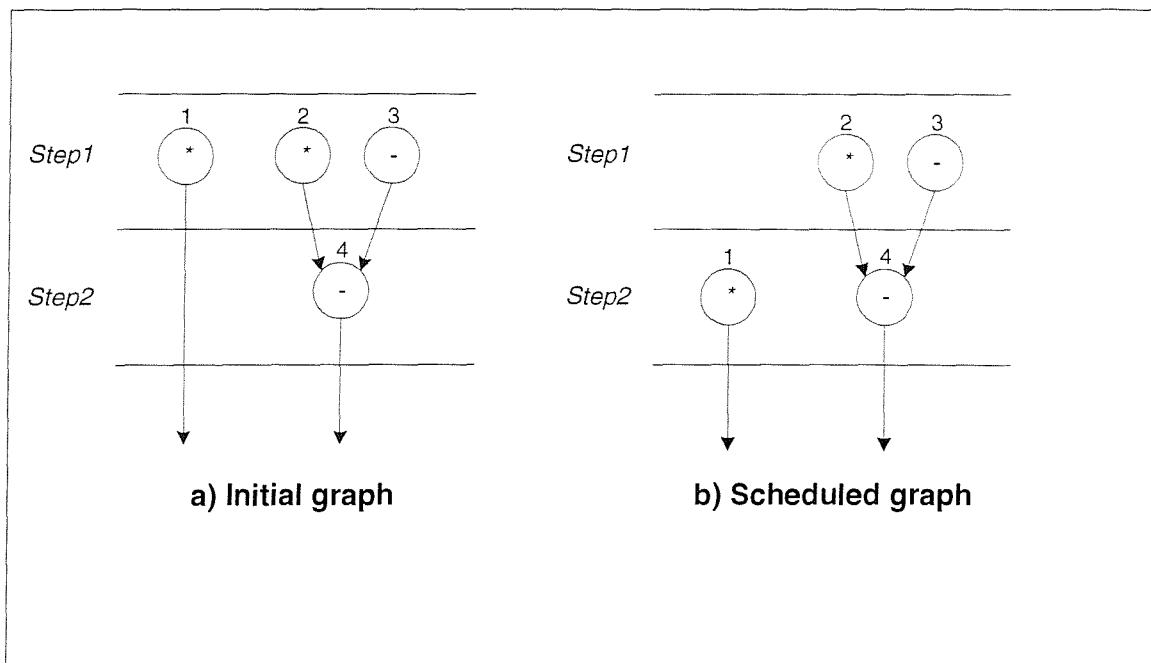

| Figure 2.8 List scheduling.....                                             | 28 |

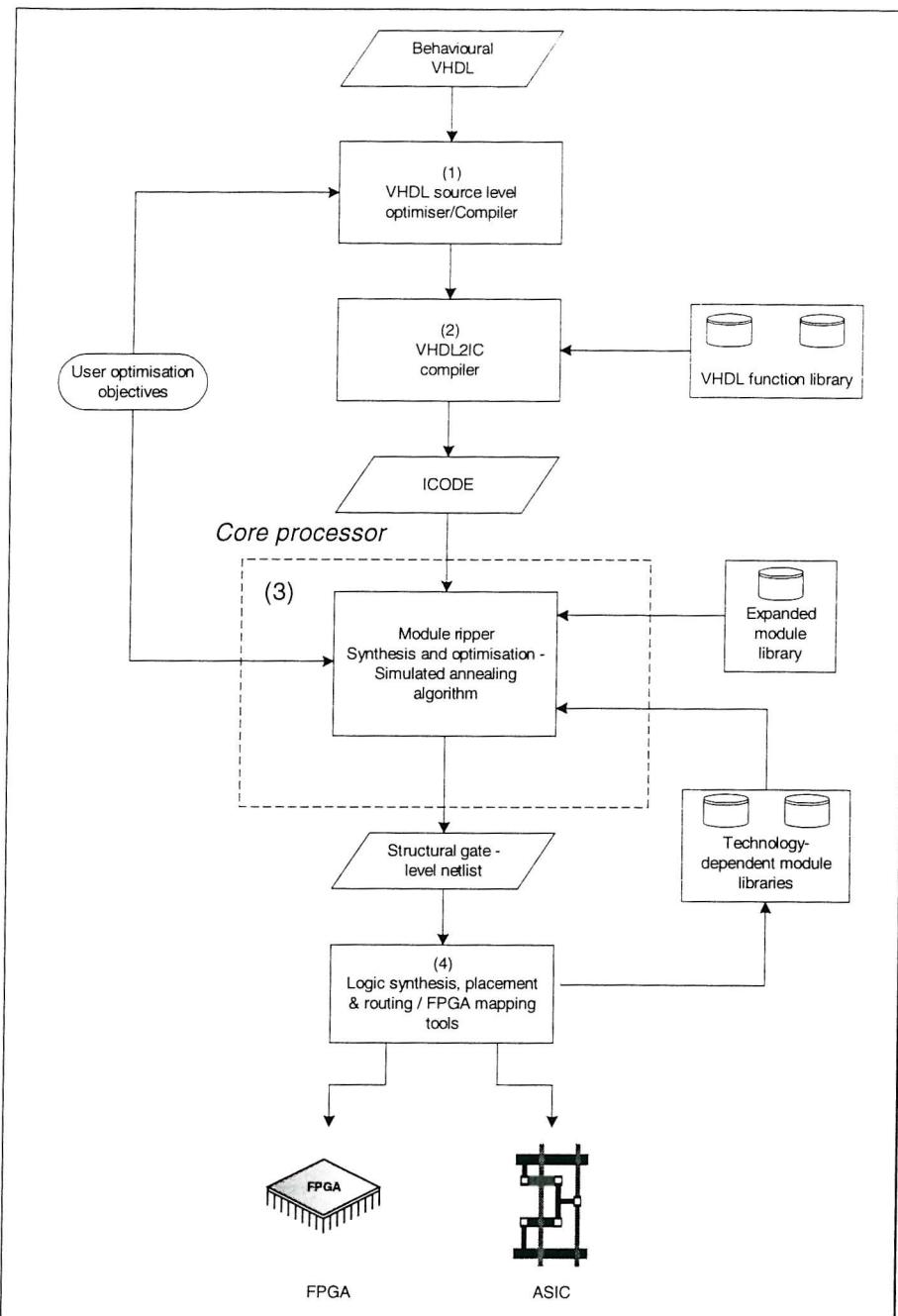

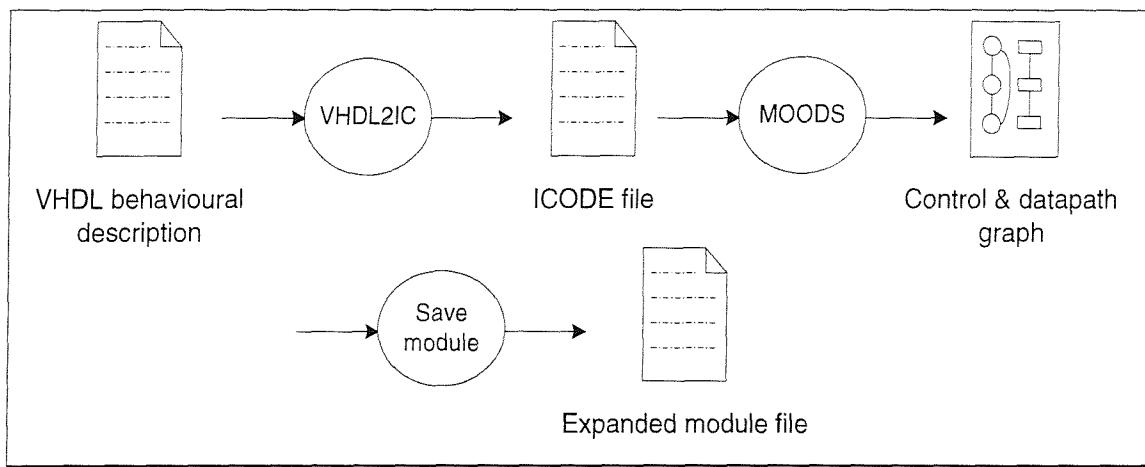

| Figure 2.9 Original MOODS system data flow .....                            | 31 |

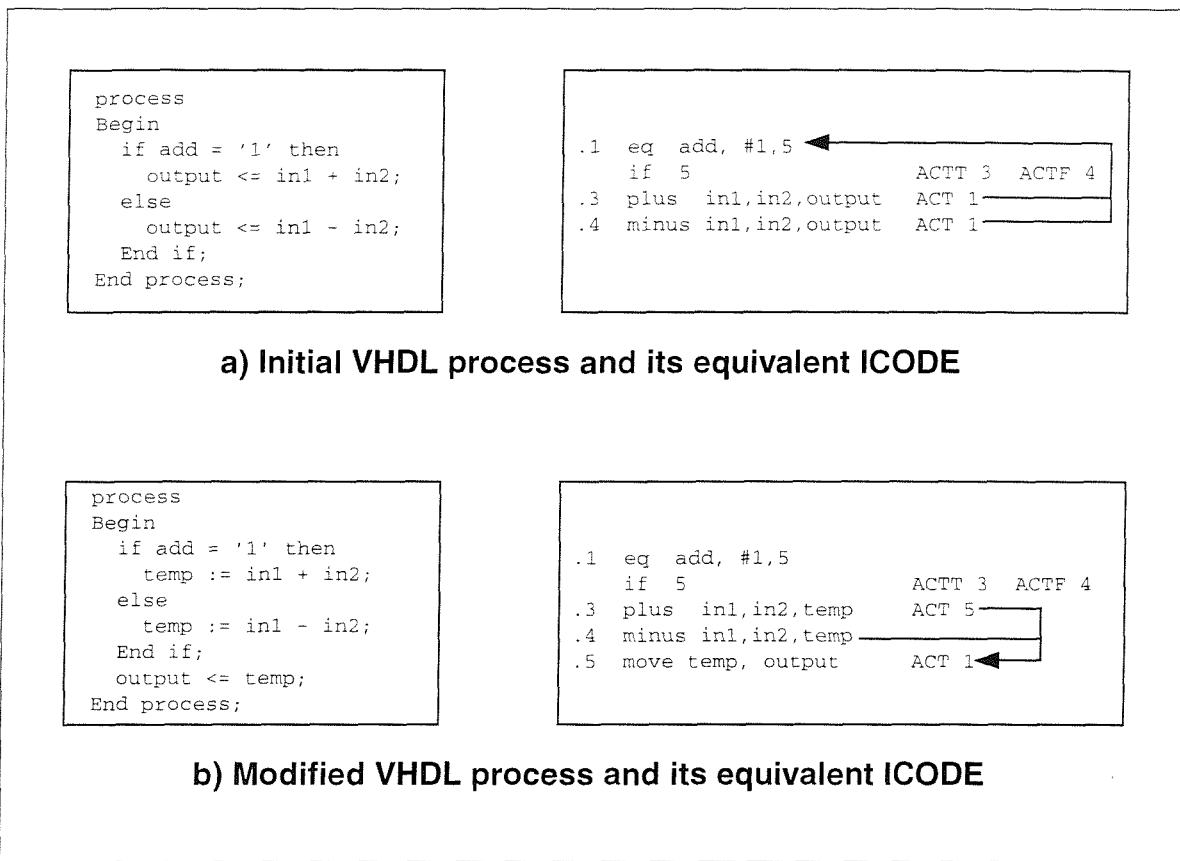

| Figure 2.10 VHDL and the equivalent ICODE example .....                     | 33 |

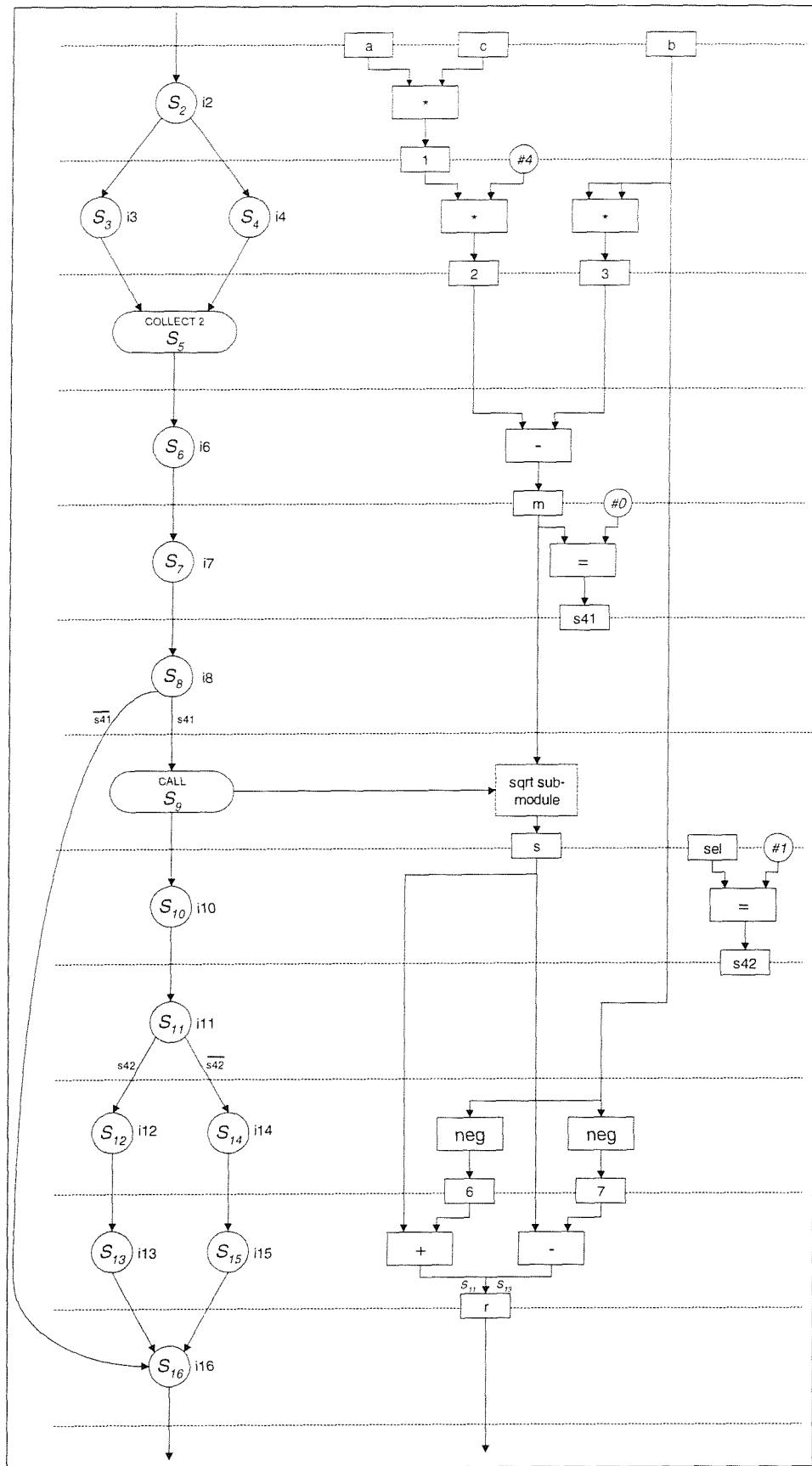

| Figure 2.11 Control and datapath graphs.....                                | 35 |

| Figure 2.12 Transformation application steps .....                          | 37 |

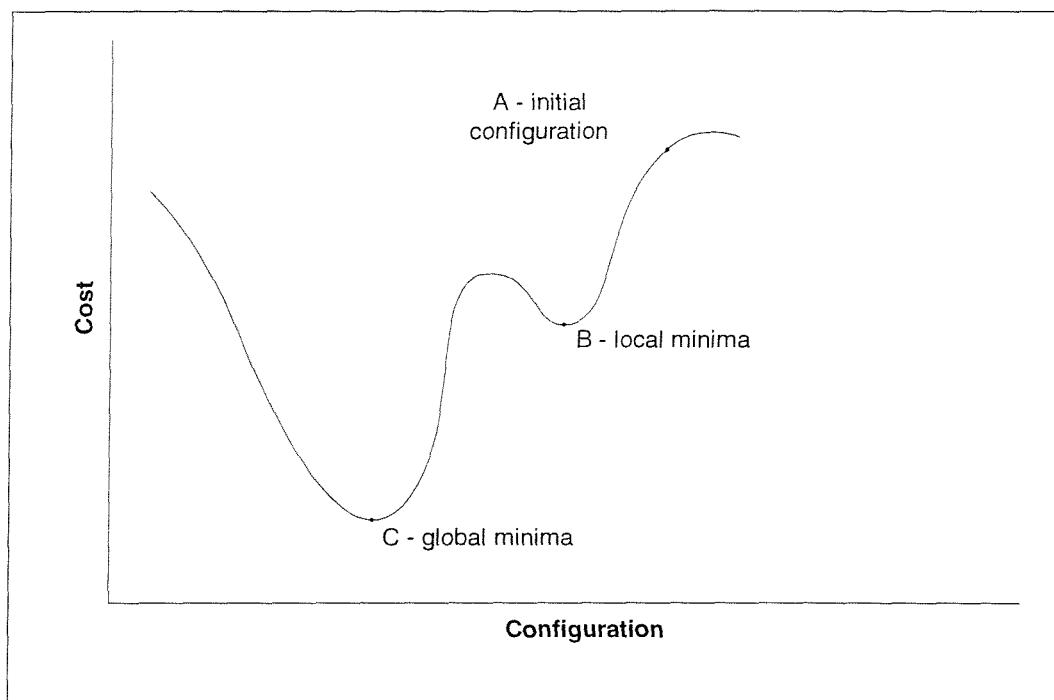

| Figure 2.13 A one-dimensional configuration space .....                     | 40 |

| Figure 2.14 The simulated annealing algorithm .....                         | 41 |

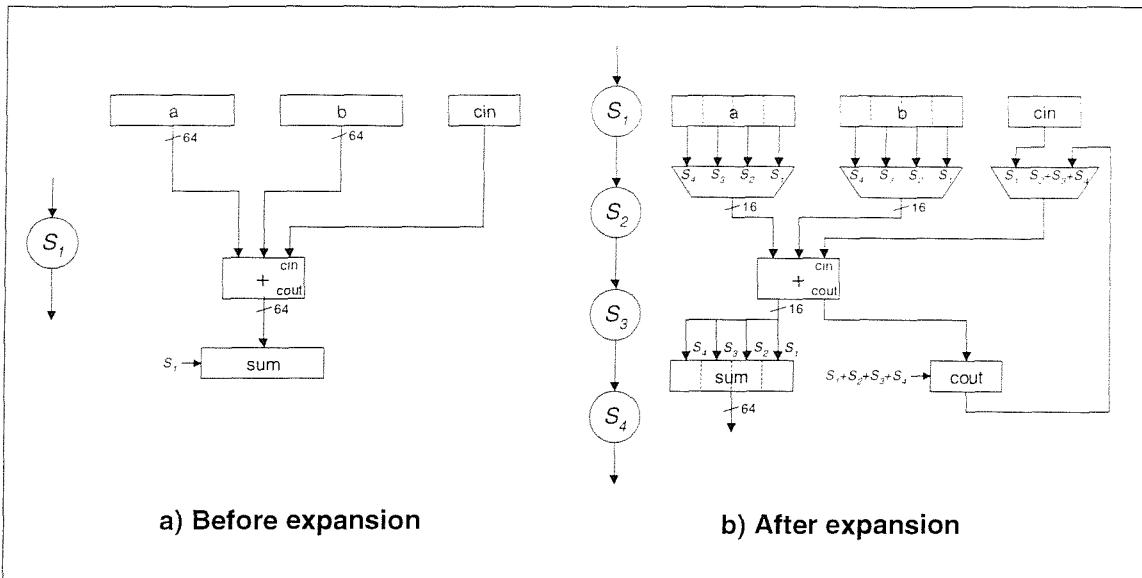

| Figure 2.15 Expansion process .....                                         | 43 |

| Figure 2.16 MOODS synthesis system with the floating-point enhancement..... | 44 |

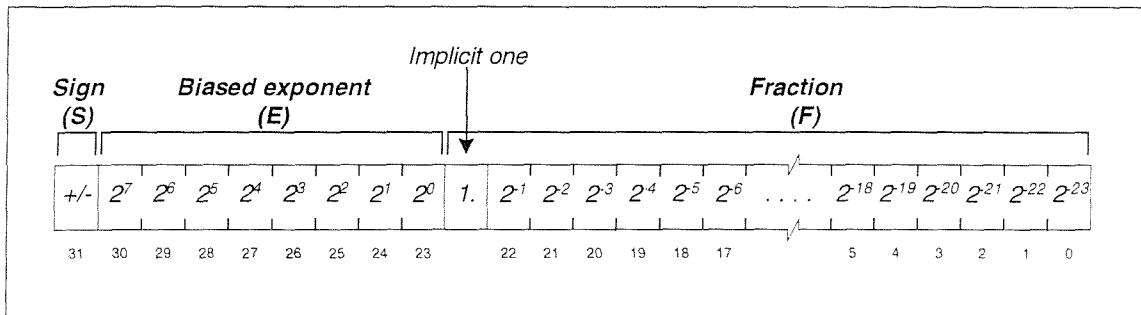

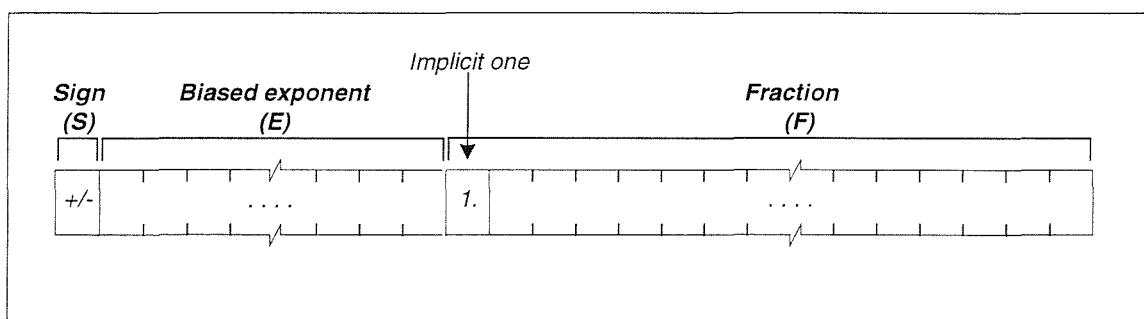

| Figure 3.1 IEEE single-precision floating-point format .....                | 46 |

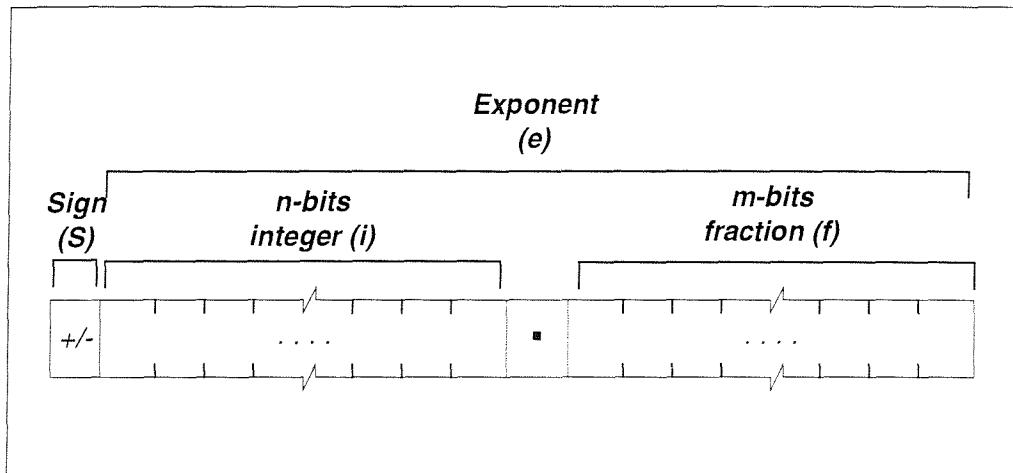

| Figure 3.2 Logarithmic number format .....                                  | 47 |

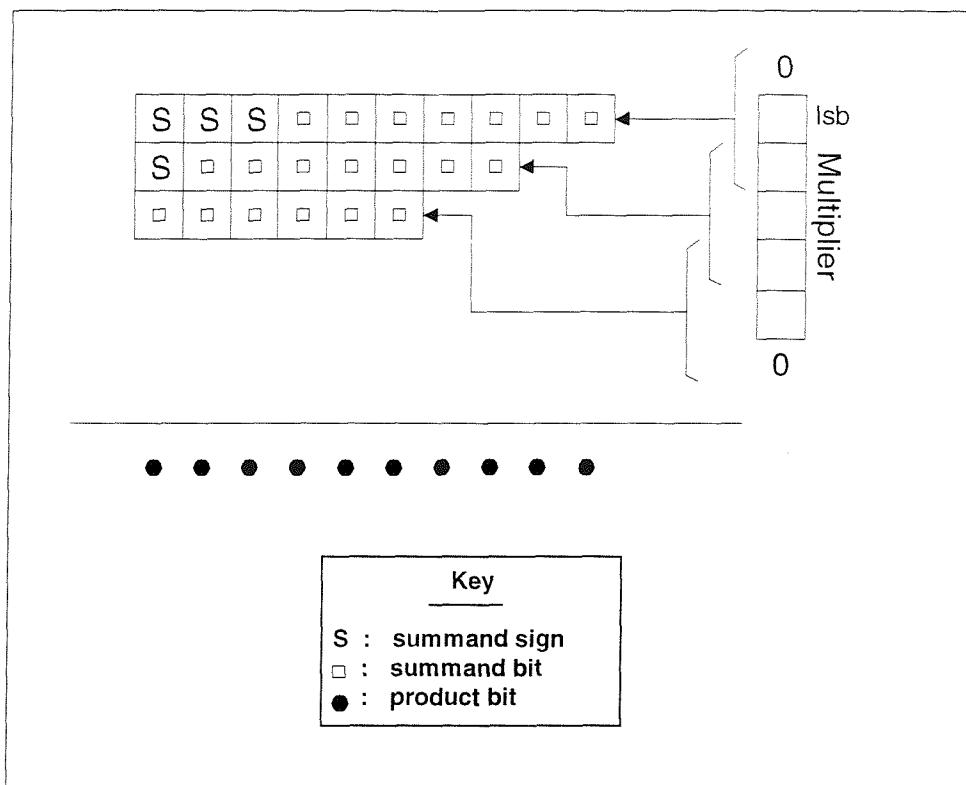

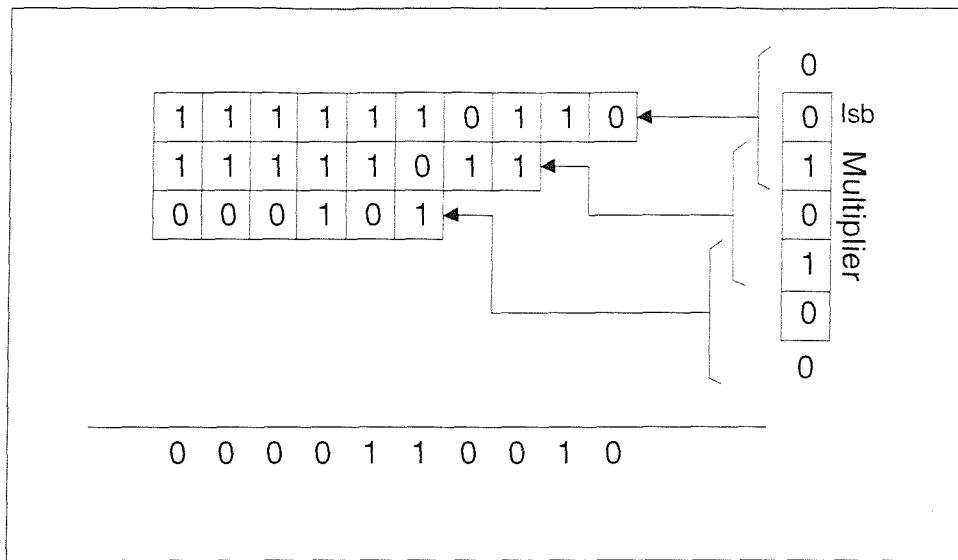

| Figure 3.3 Modified Booth multiplier.....                                   | 49 |

| Figure 3.4 Modified Booth multiplication example .....                      | 50 |

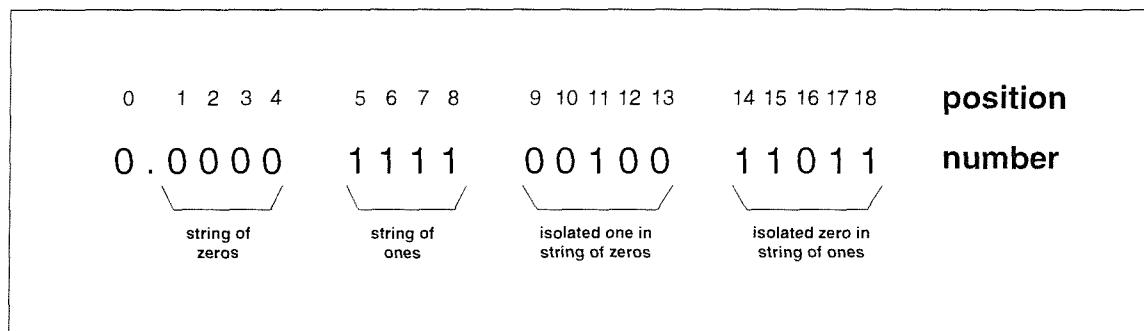

| Figure 3.5 A decomposition of a number into four types of strings .....     | 50 |

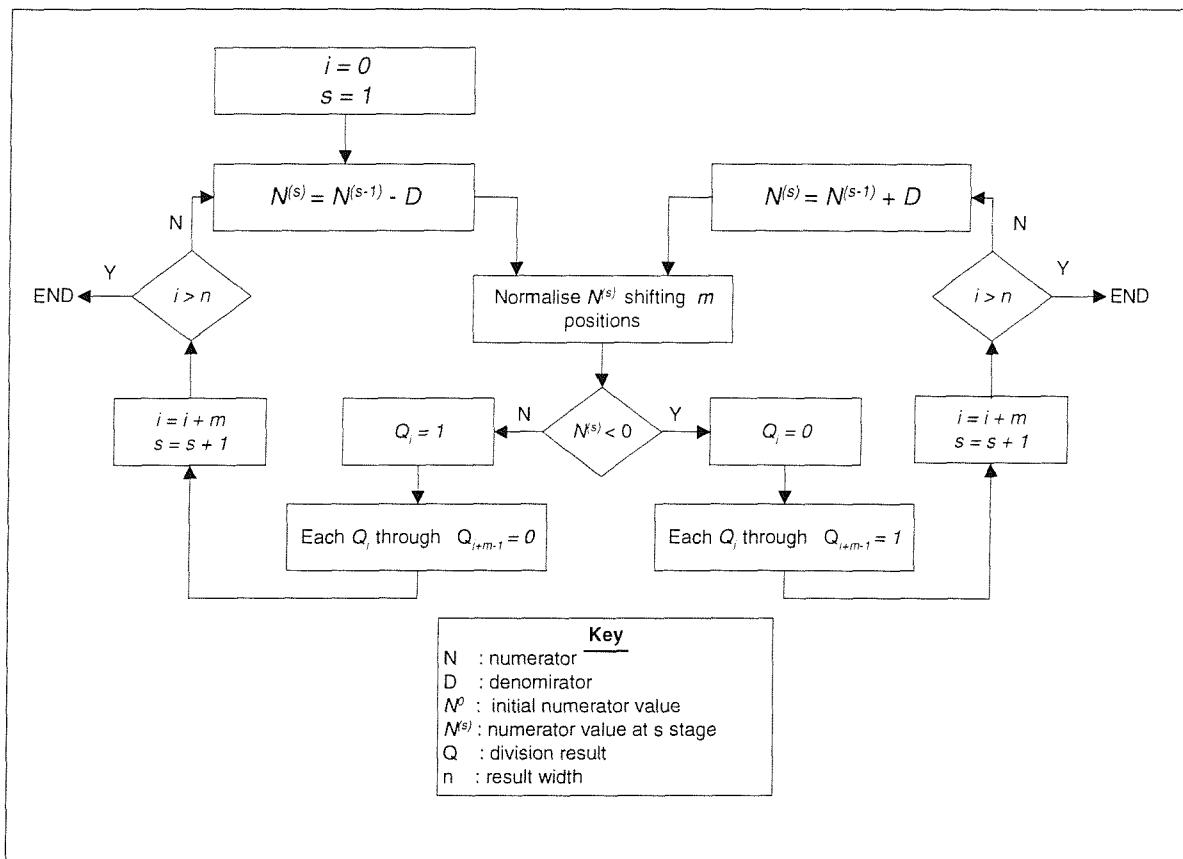

| Figure 3.6 Rapid division algorithm flowchart.....                          | 51 |

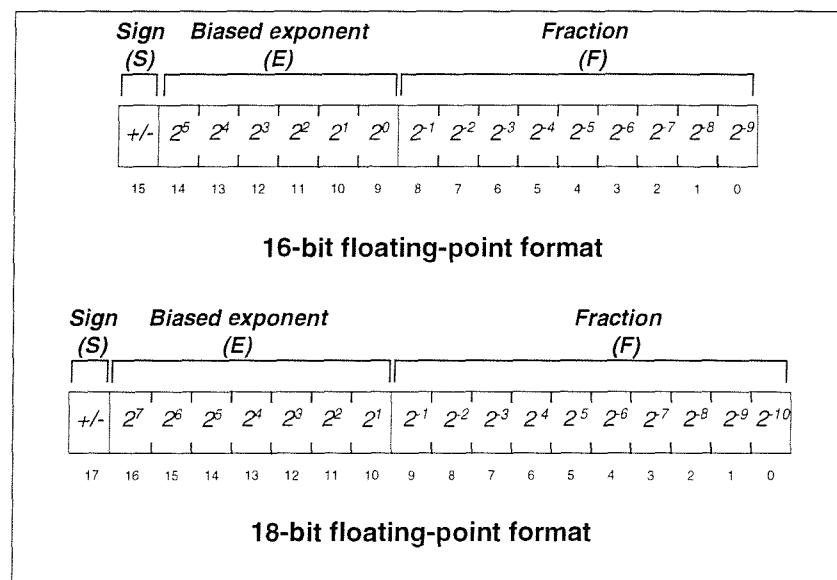

| Figure 3.7 Short floating-point formats .....                               | 54 |

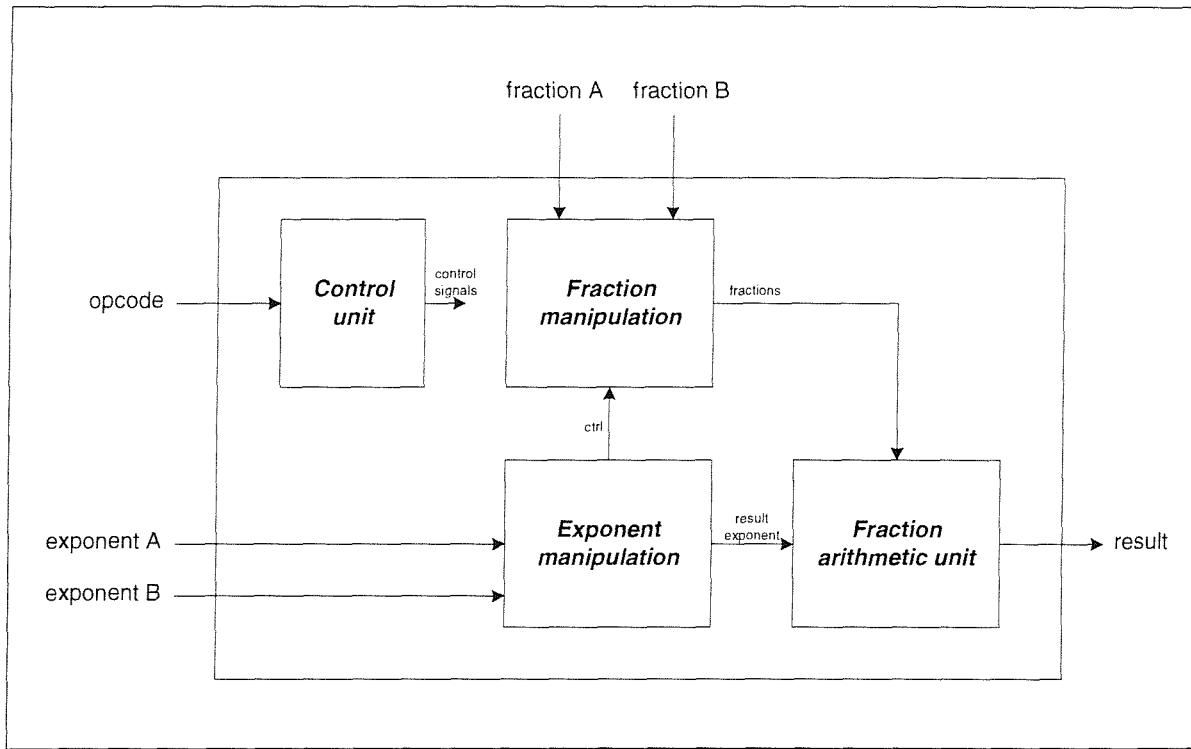

| Figure 3.8 FPGA-based data path block diagram.....                          | 55 |

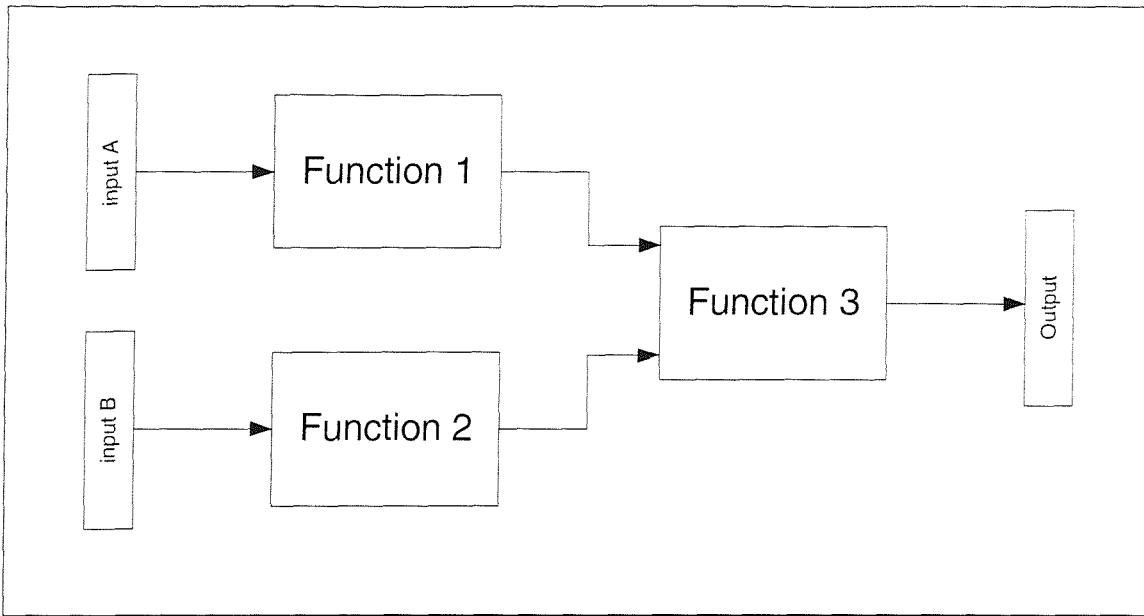

| Figure 3.9 A design represented as a block diagram .....                    | 59 |

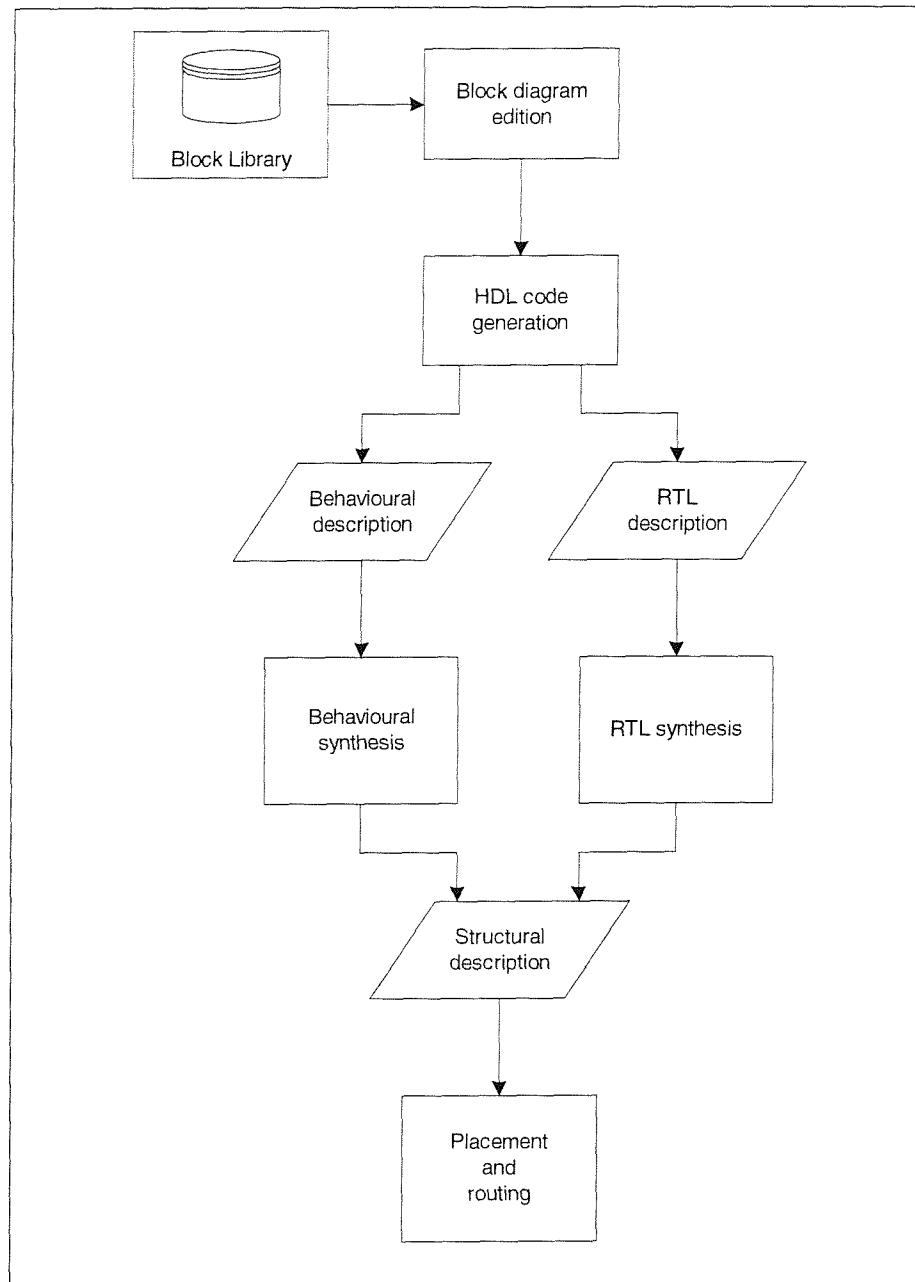

| Figure 3.10 Block diagram oriented tools data flow.....                     | 60 |

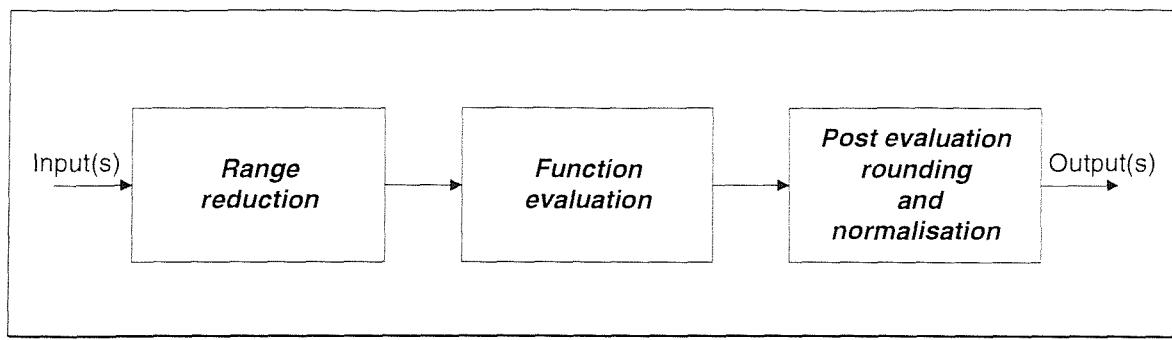

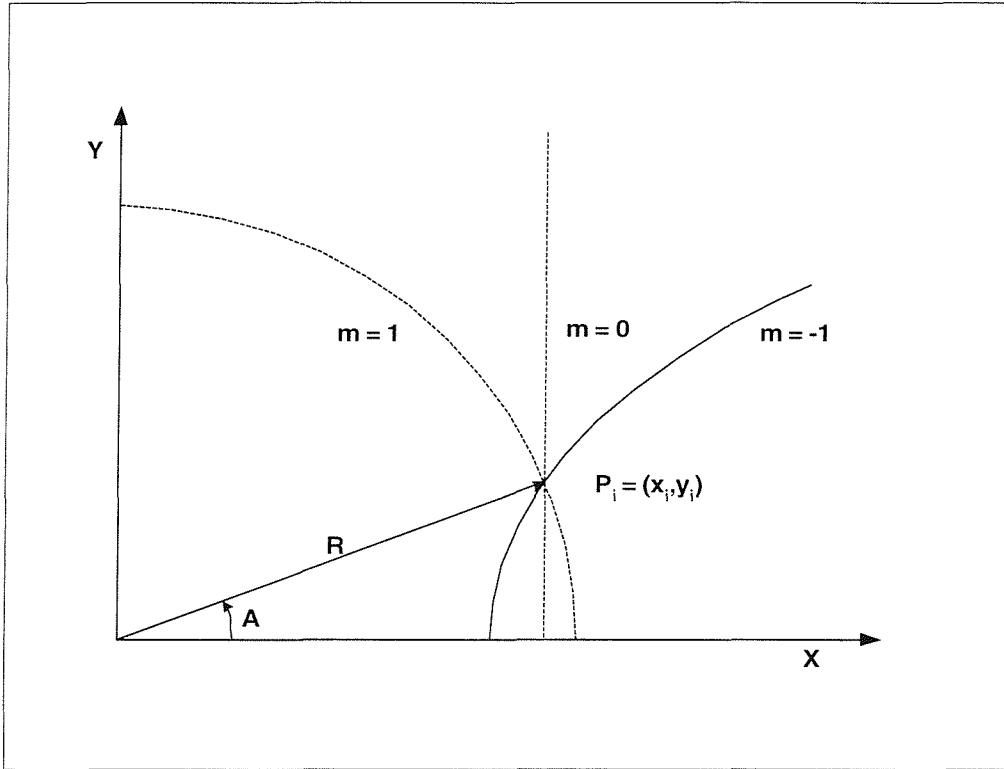

| Figure 4.1 Functional unit building blocks.....                             | 63 |

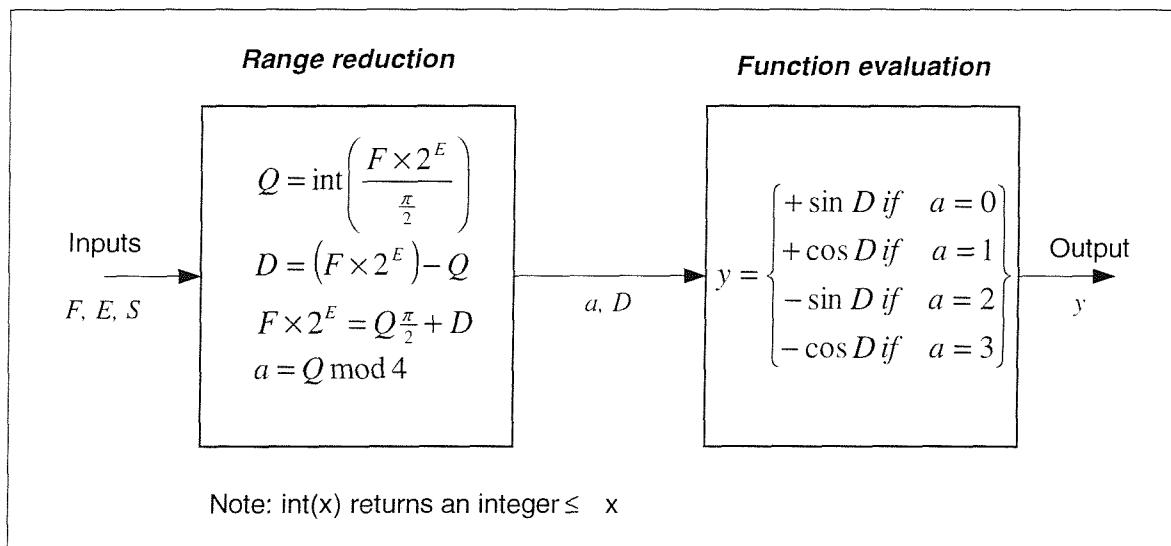

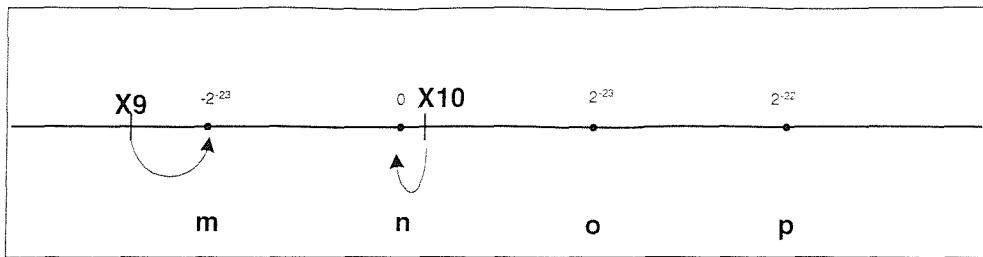

| Figure 4.2 Range reduction example .....                                    | 64 |

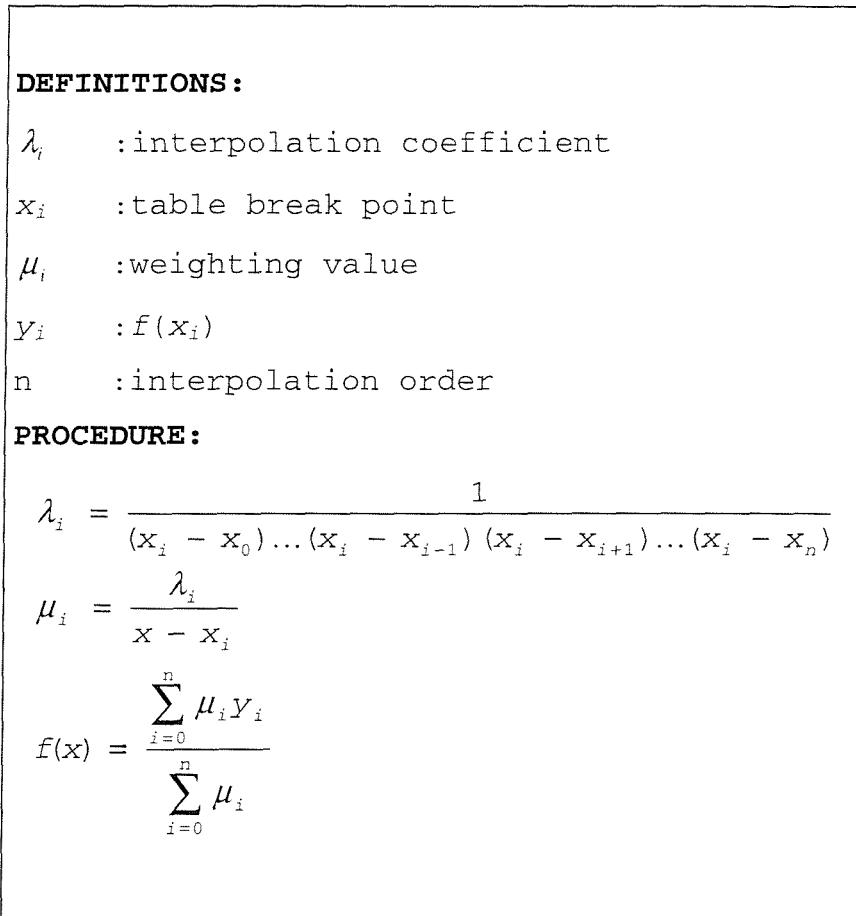

| Figure 4.3 Interpolation procedure .....                                    | 65 |

|                                                                                                                            |     |

|----------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.4 Linear interpolation procedure .....                                                                            | 66  |

| Figure 4.5 Cubic interpolation .....                                                                                       | 67  |

| Figure 4.6 Cubic interpolation procedure .....                                                                             | 67  |

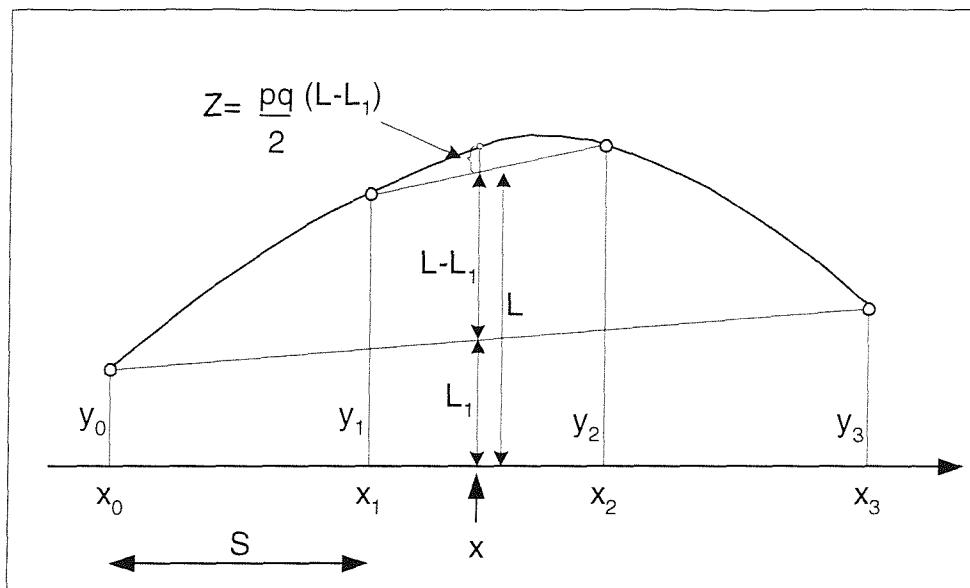

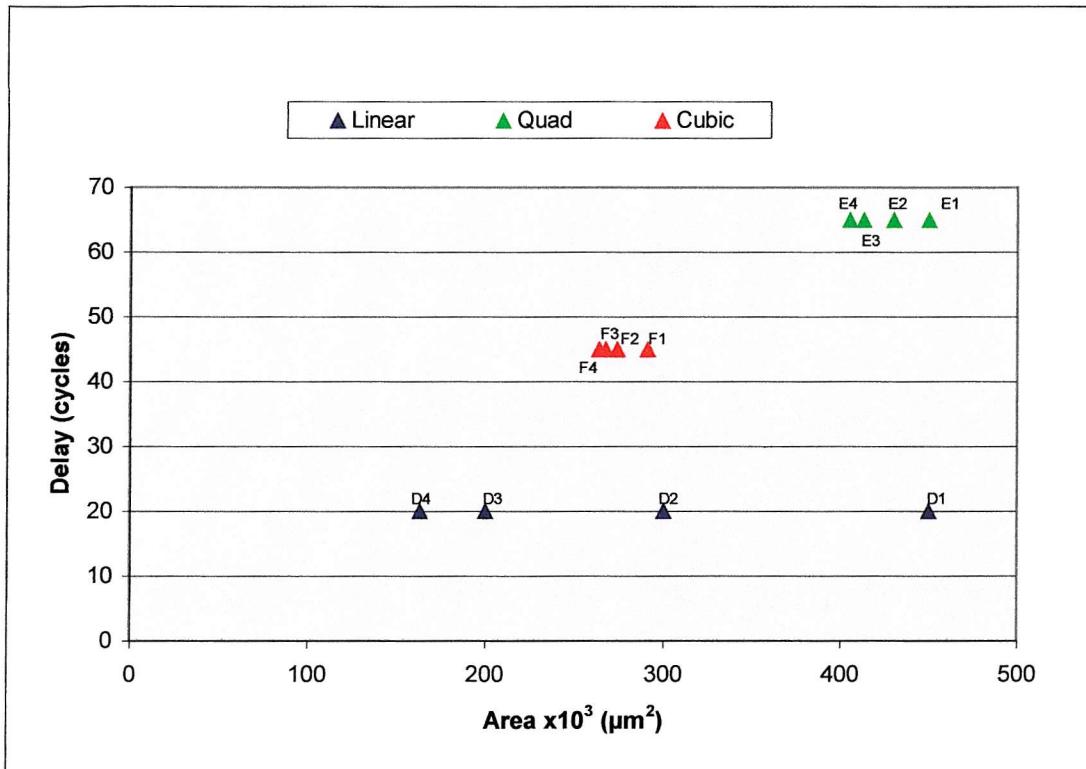

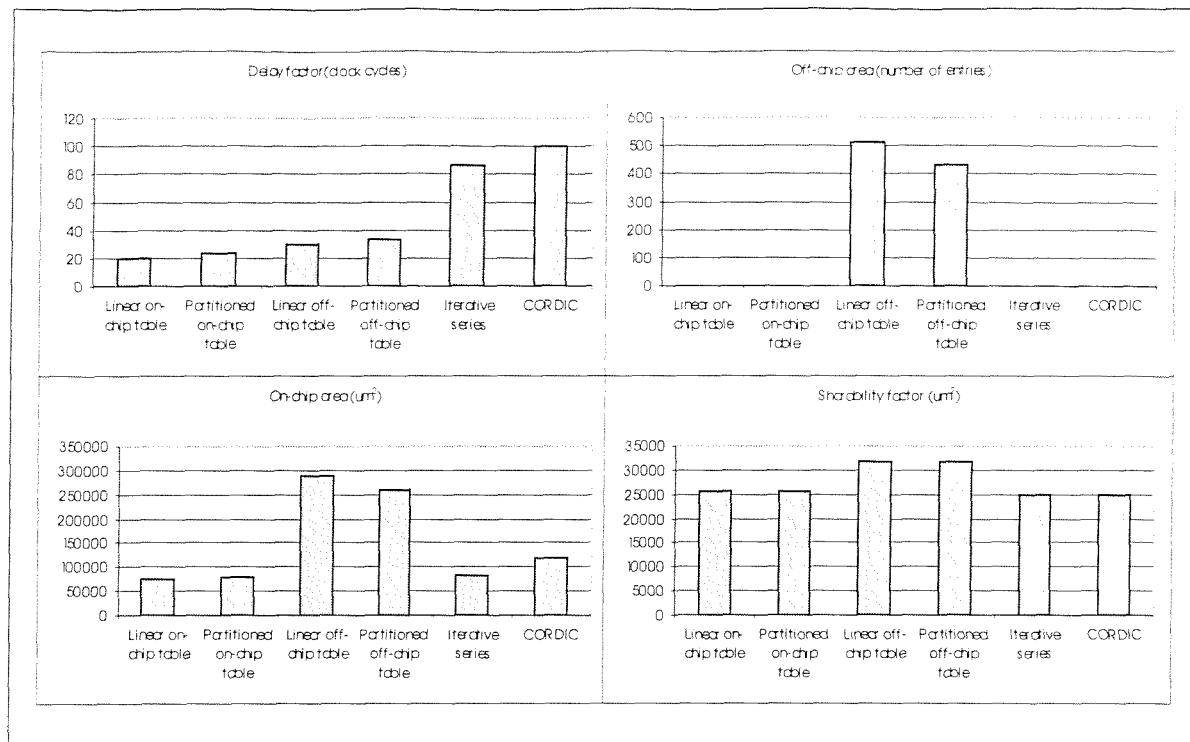

| Figure 4.7 Table entries variation with different interpolation degrees.....                                               | 70  |

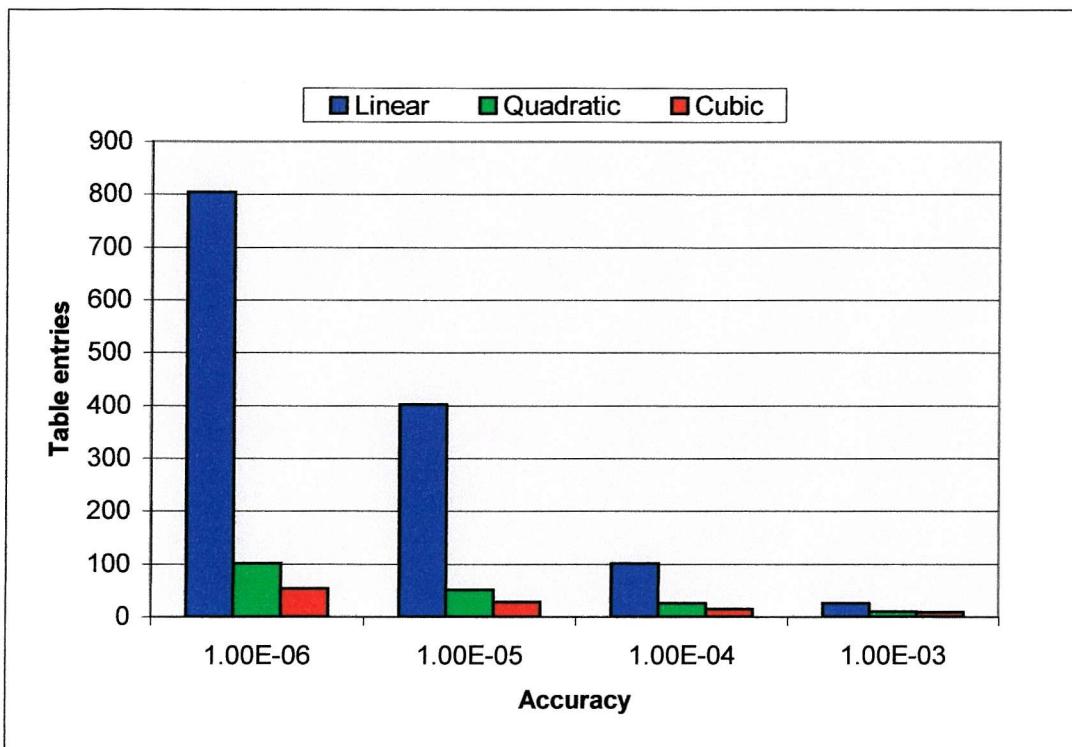

| Figure 4.8 Area/delay costs for different interpolation and infinite external ROM .....                                    | 70  |

| Figure 4.9 Area/delay costs for different interpolation without external ROM.....                                          | 71  |

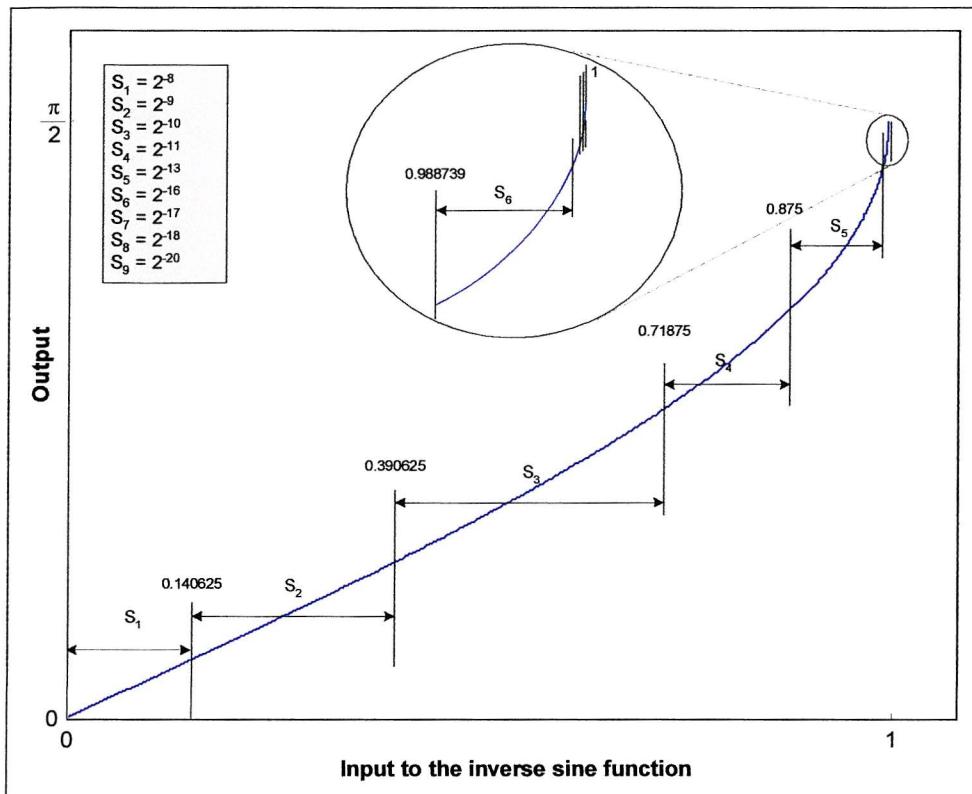

| Figure 4.10 Partitioning the inverse sine function into sub-tables .....                                                   | 72  |

| Figure 4.11 Linear interpolation multiple sub-tables procedure.....                                                        | 73  |

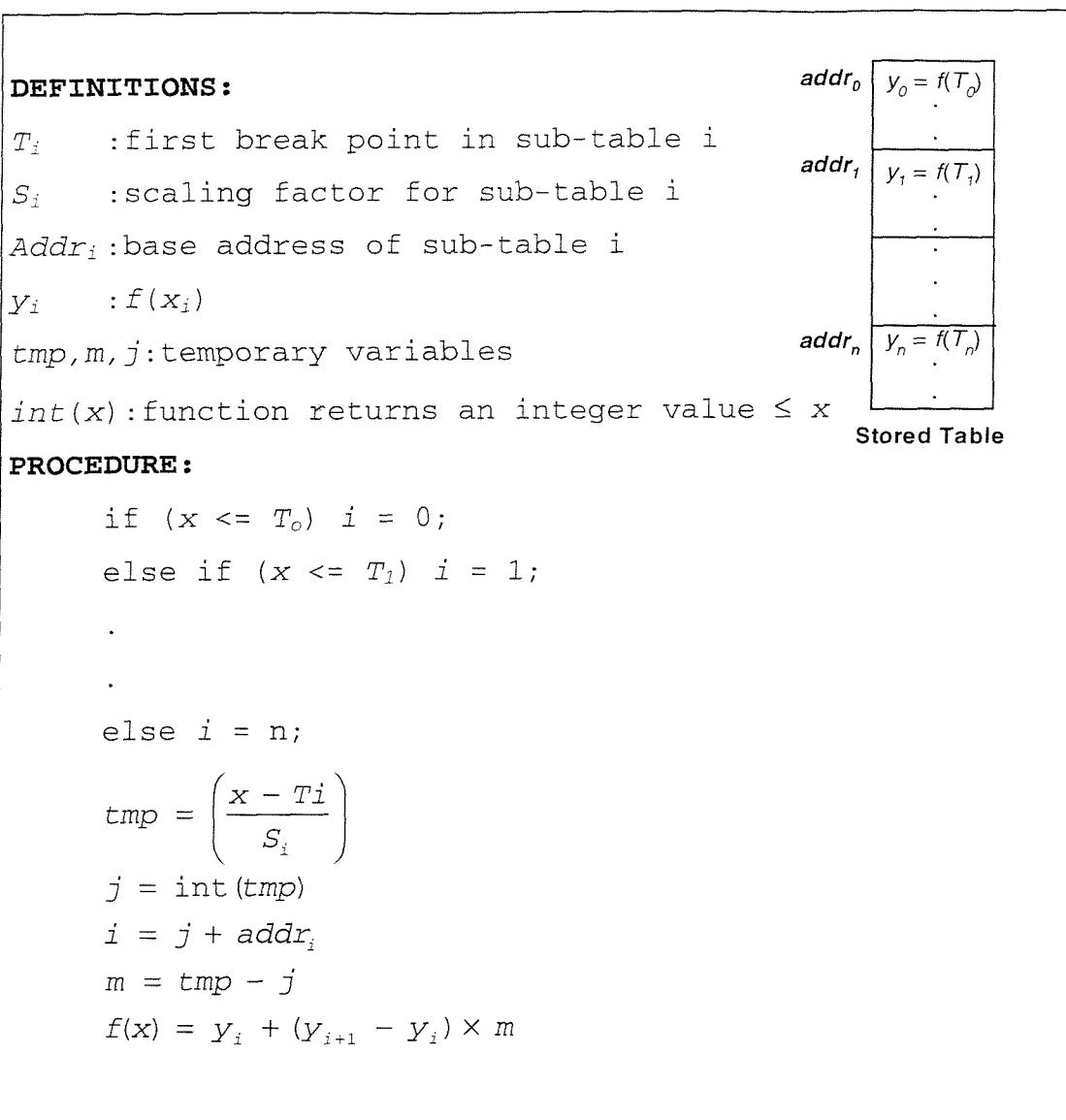

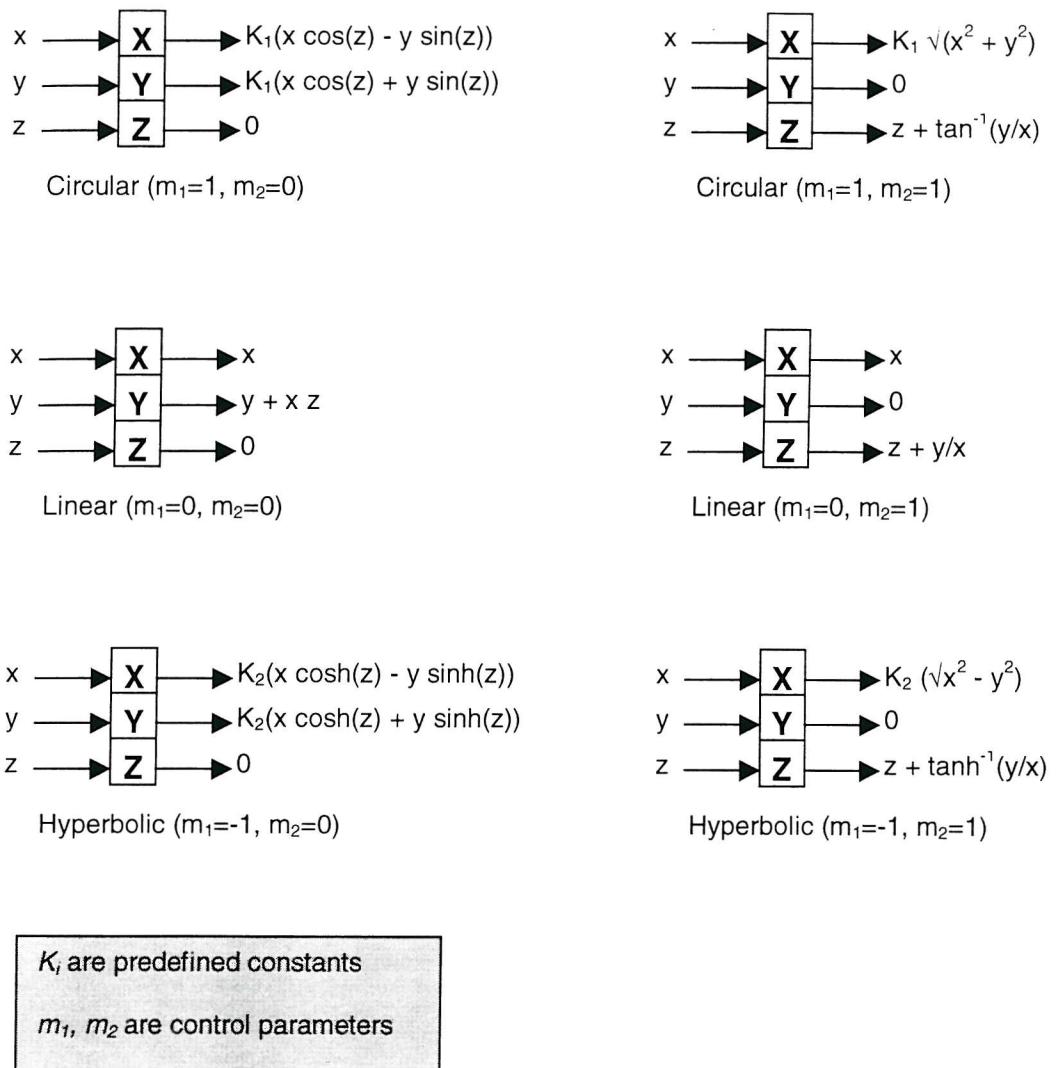

| Figure 4.12 The CORDIC algorithm .....                                                                                     | 74  |

| Figure 4.13 Output functions for CORDIC .....                                                                              | 75  |

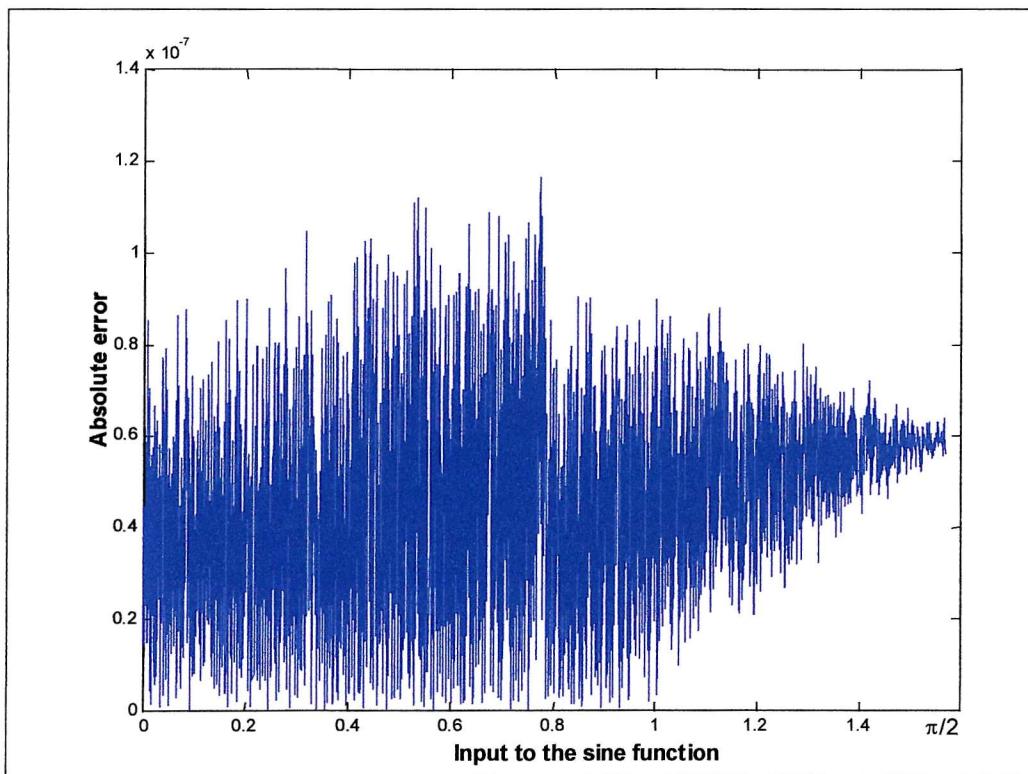

| Figure 4.14 Absolute error in the CORDIC sine generator for 25 iterations.....                                             | 75  |

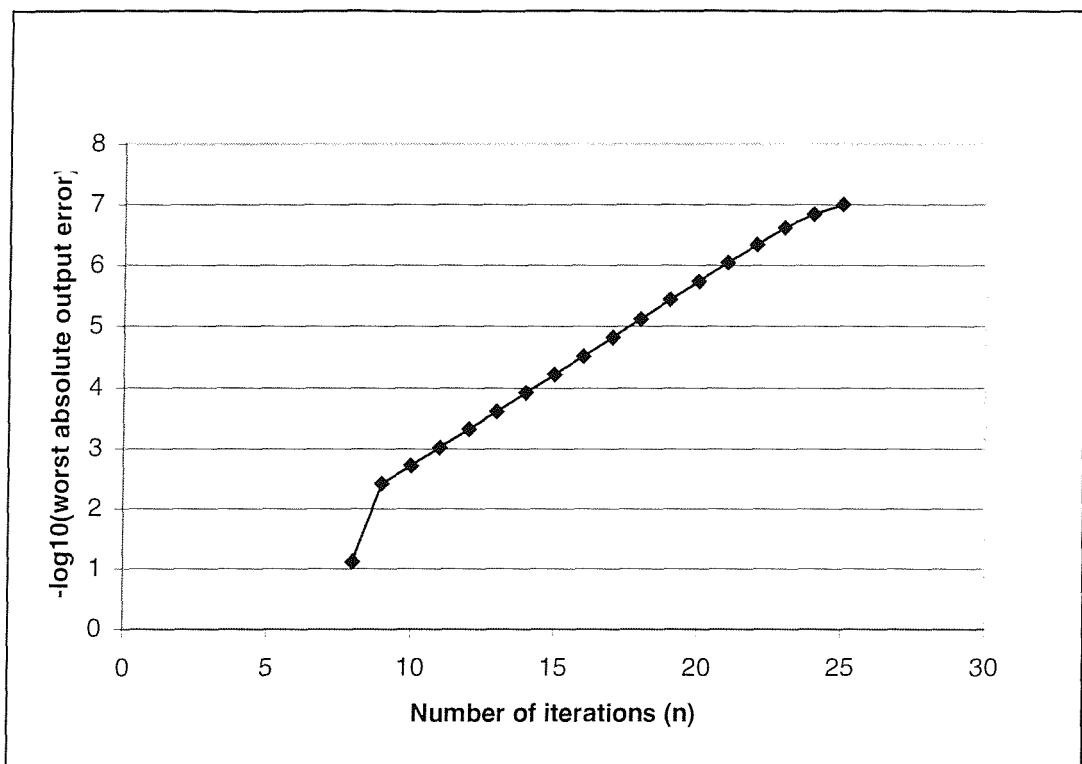

| Figure 4.15 CORDIC error variation with the number of iterations.....                                                      | 76  |

| Figure 4.16 Taylor Theorem .....                                                                                           | 77  |

| Figure 4.17 Minimax approximation base theorems .....                                                                      | 78  |

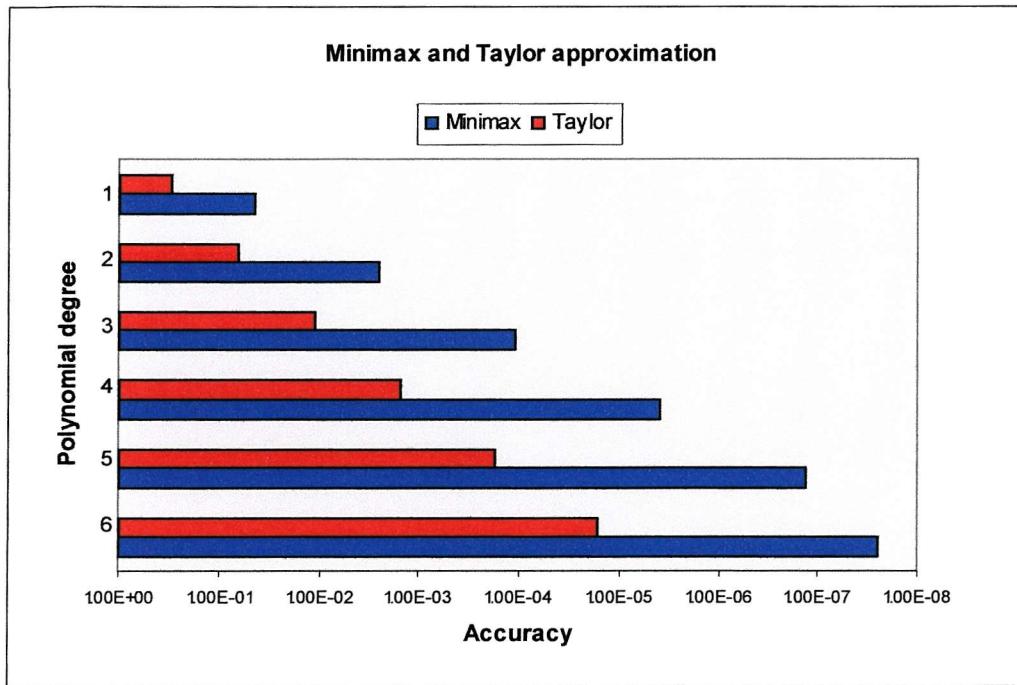

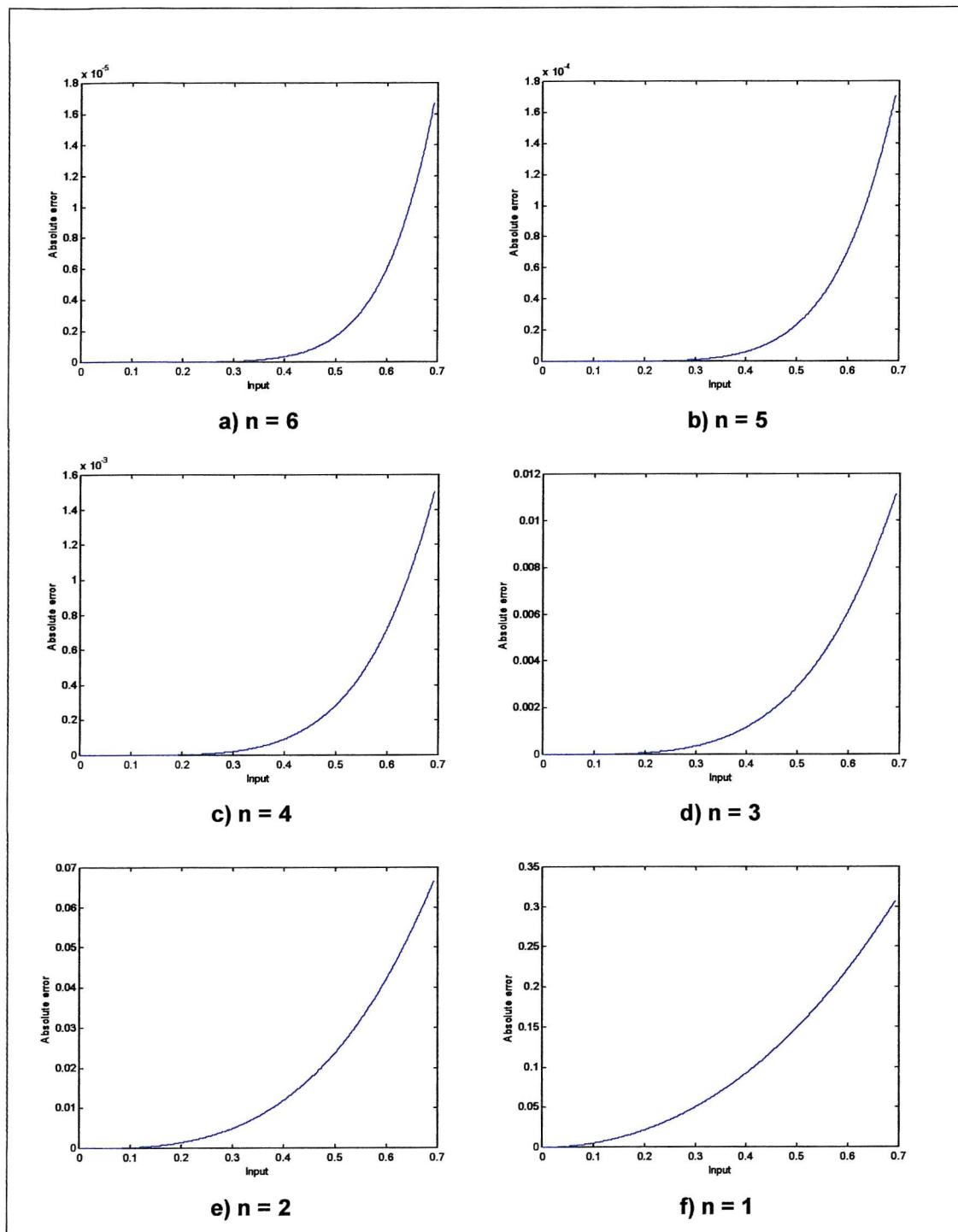

| Figure 4.18 Comparison between minimax and Taylor accuracy for different interpolation degrees .....                       | 79  |

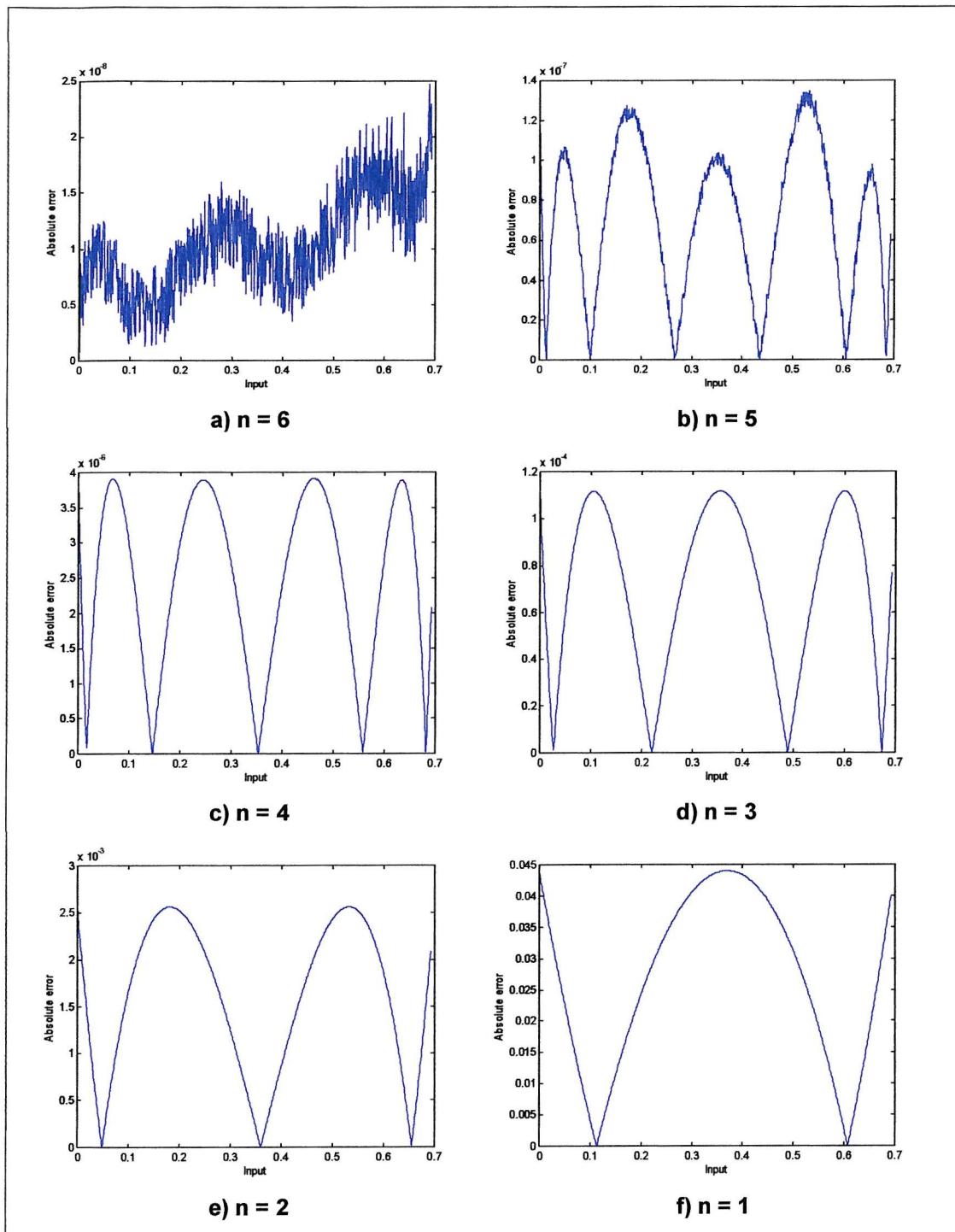

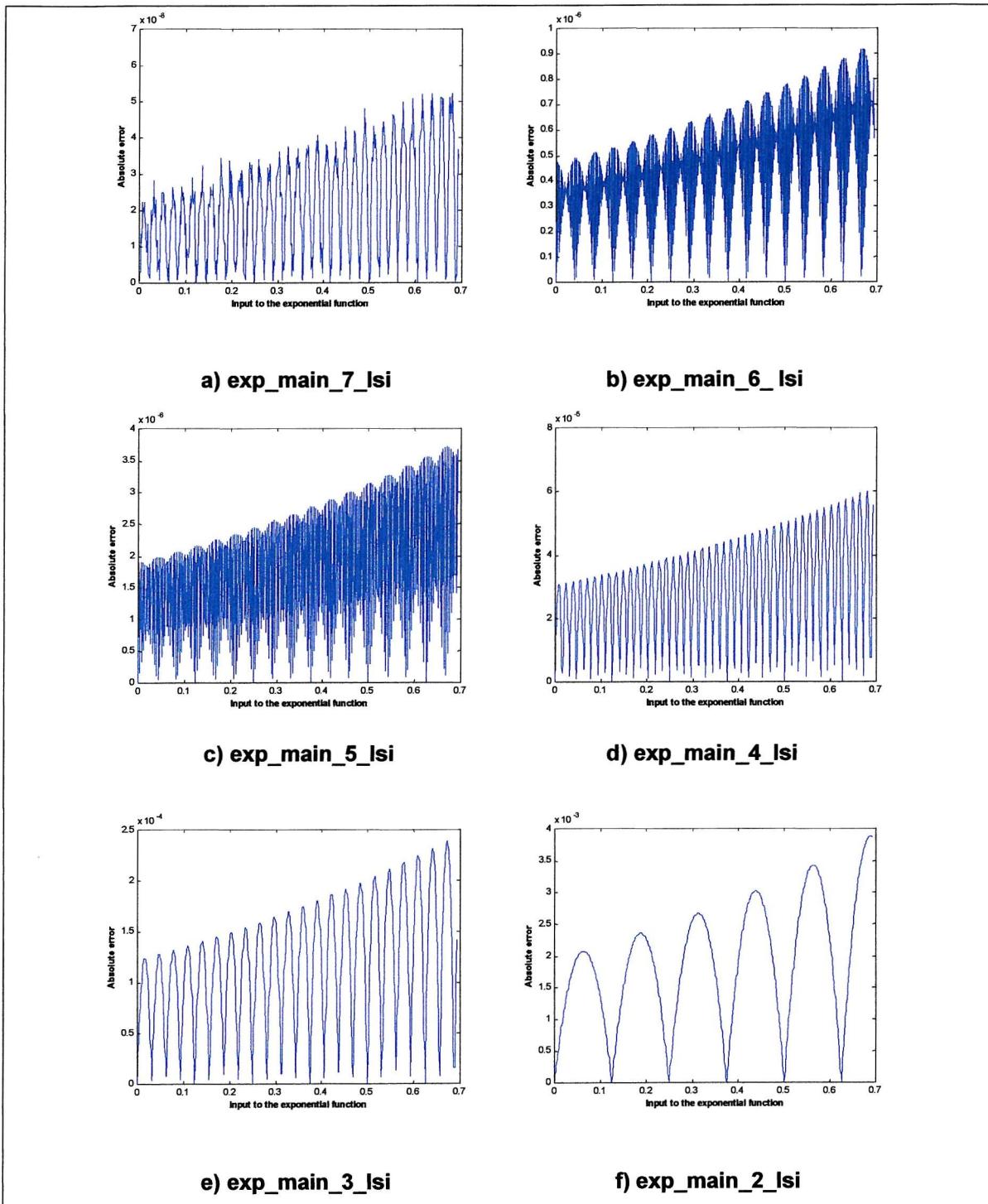

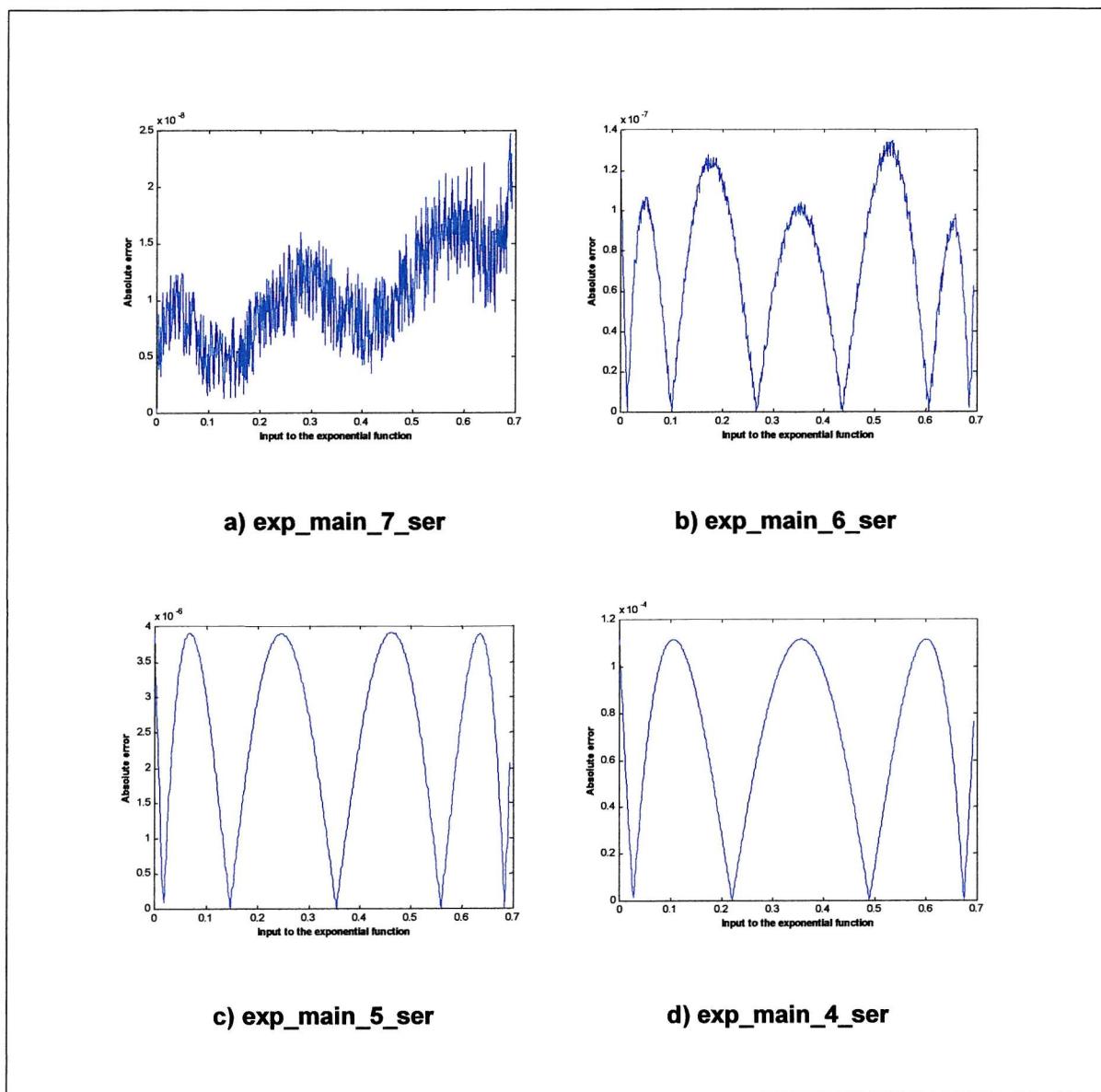

| Figure 4.19 Absolute error in the minimax approximation for the exponential function different approximation degrees ..... | 80  |

| Figure 4.20 Absolute error in the Taylor expansion for the exponential function for different approximation degrees .....  | 81  |

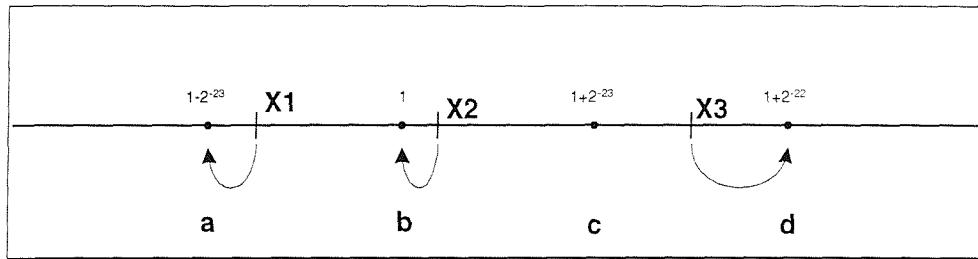

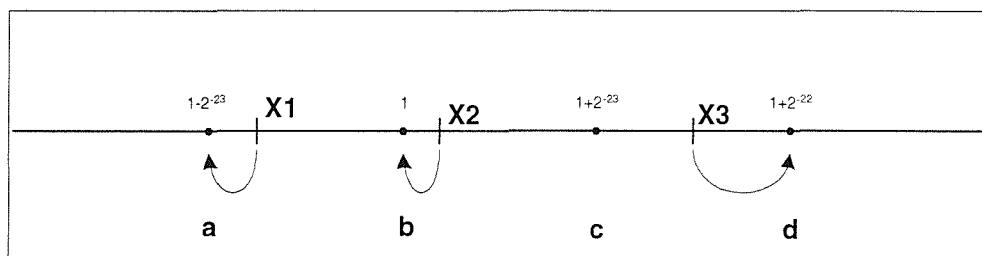

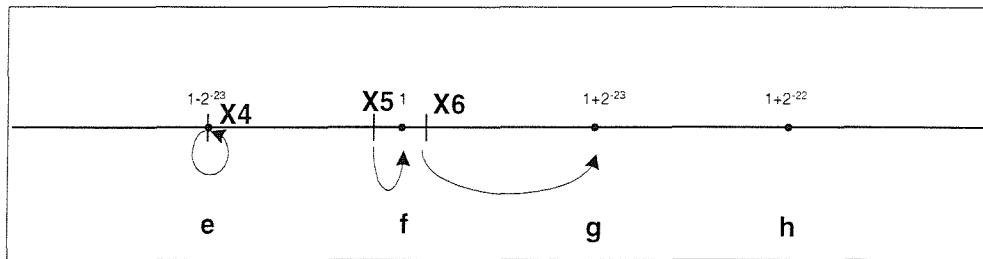

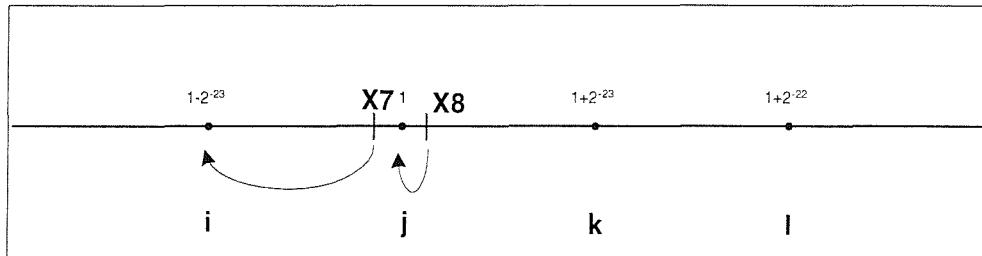

| Figure 4.21 Round to the nearest example .....                                                                             | 83  |

| Figure 4.22 Raising a status flag example .....                                                                            | 85  |

| Figure 4.23 Hyperbolic function evaluation equations.....                                                                  | 93  |

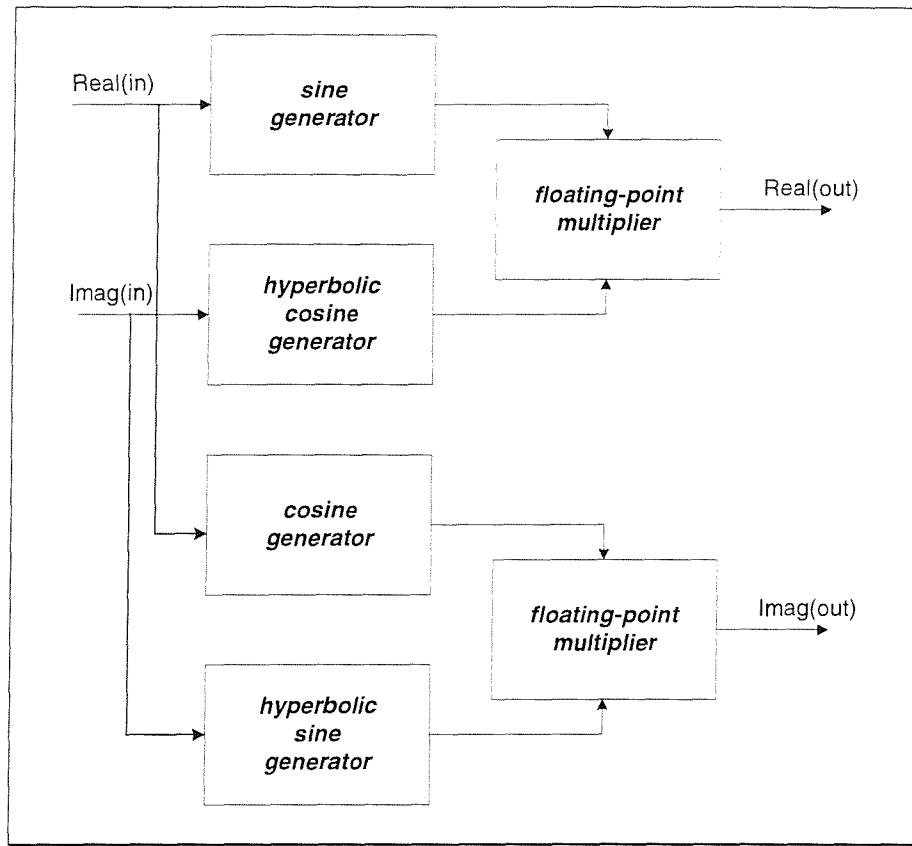

| Figure 4.24 Complex sine function generator building blocks.....                                                           | 95  |

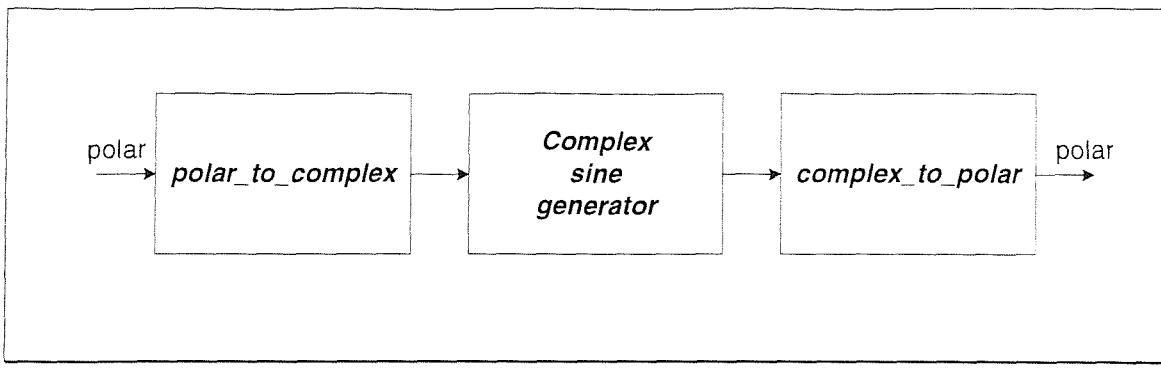

| Figure 4.25 Polar sine function generator building blocks .....                                                            | 96  |

| Figure 4.26 Complex function evaluation equations .....                                                                    | 96  |

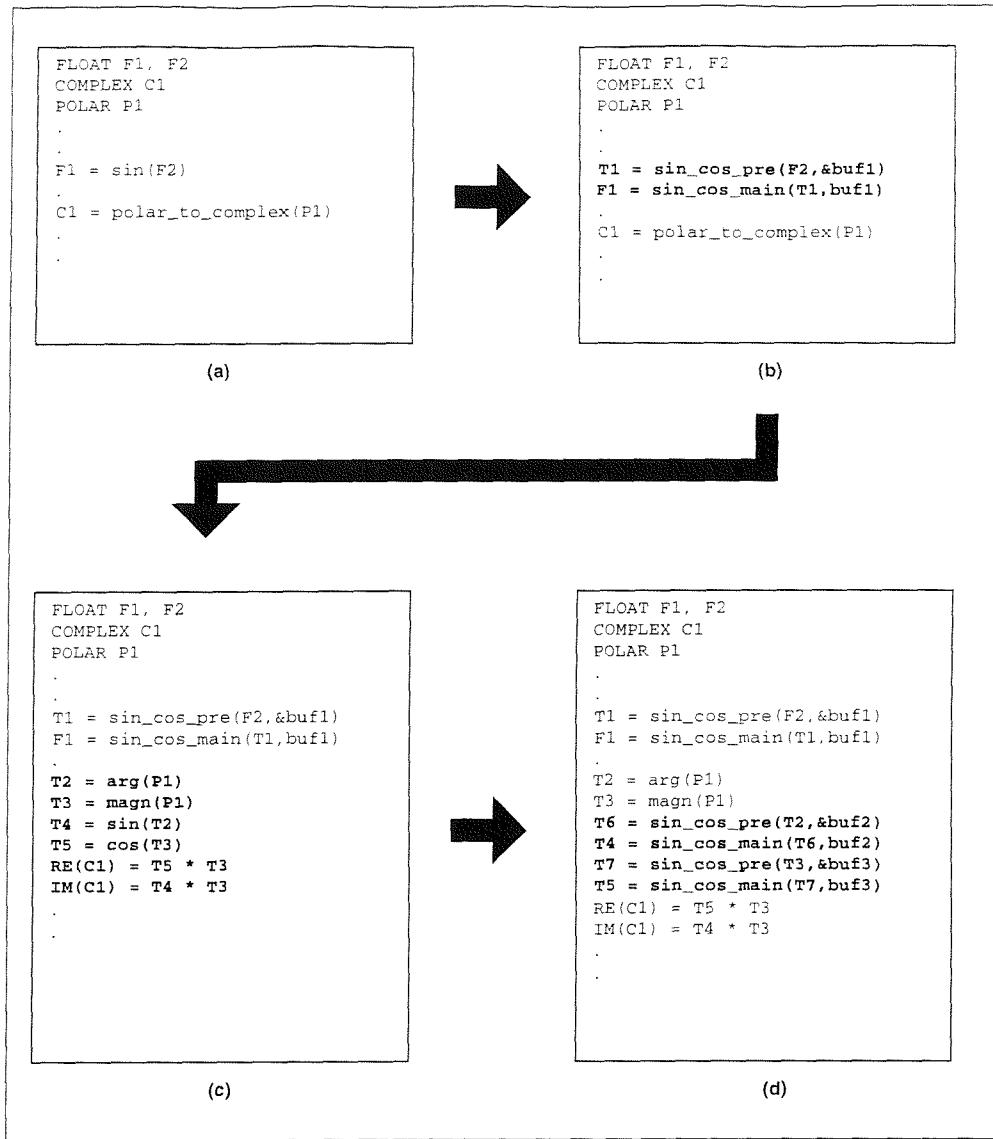

| Figure 4.27 Hierarchical unit expansion example .....                                                                      | 98  |

| Figure 4.28 Expanded module formation .....                                                                                | 99  |

| Figure 4.29 Expanded module development example.....                                                                       | 100 |

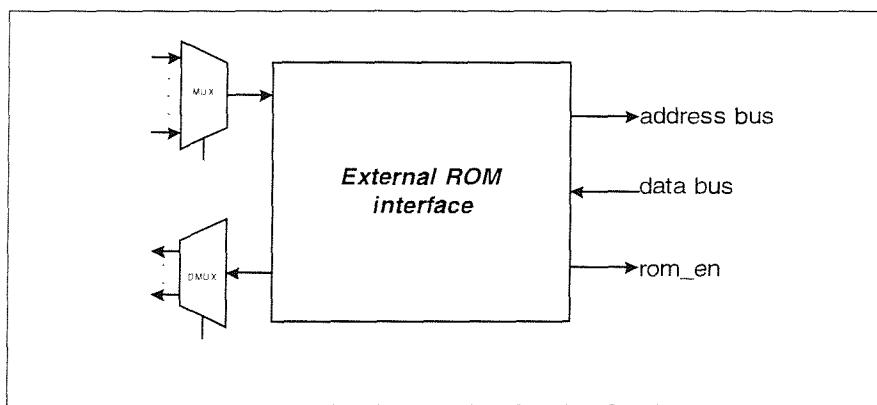

| Figure 5.1 Sharing an external ROM interfacing unit .....                                                                  | 103 |

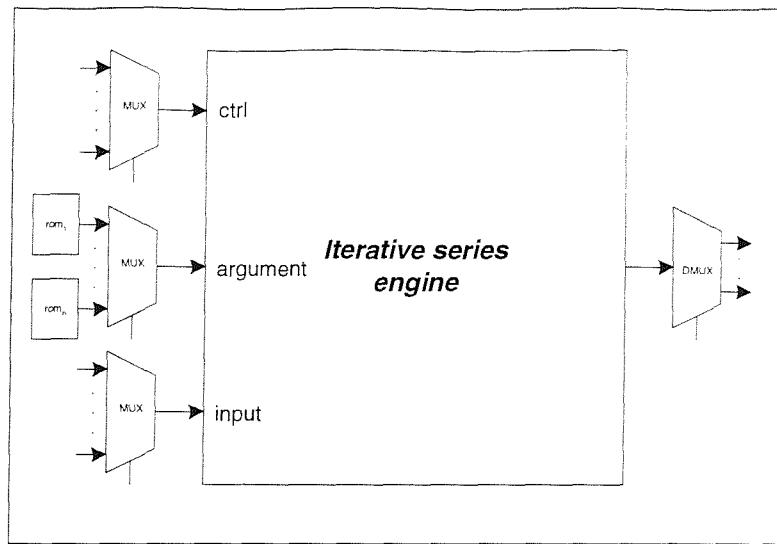

| Figure 5.2 Sharing iterative series engine.....                                                                            | 104 |

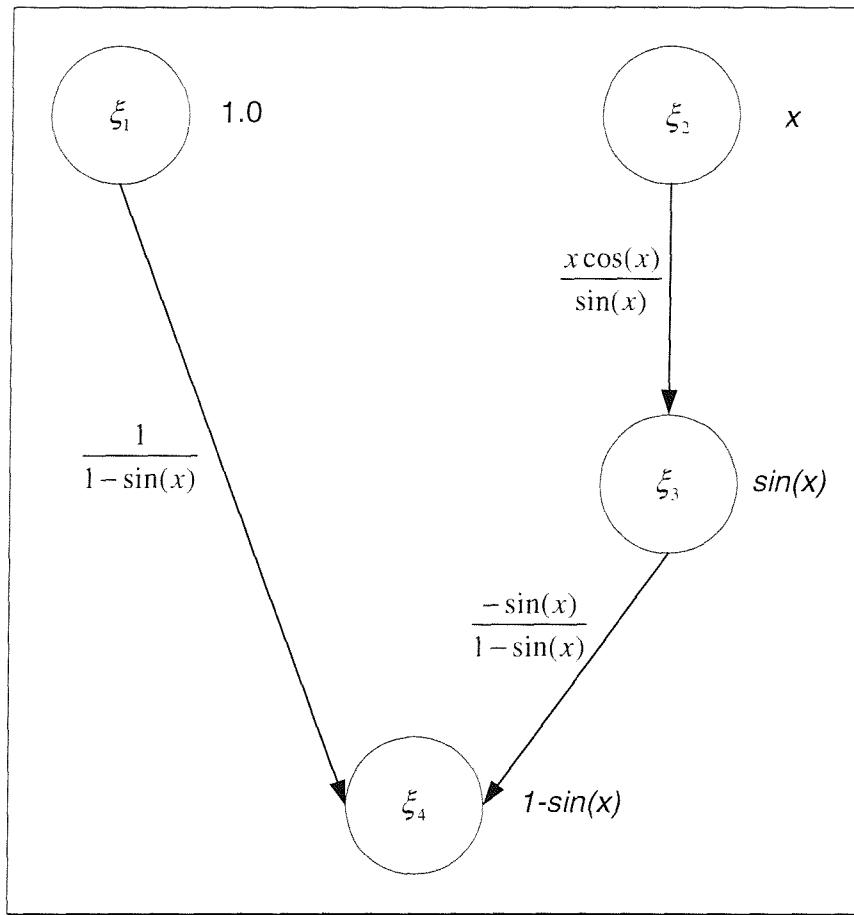

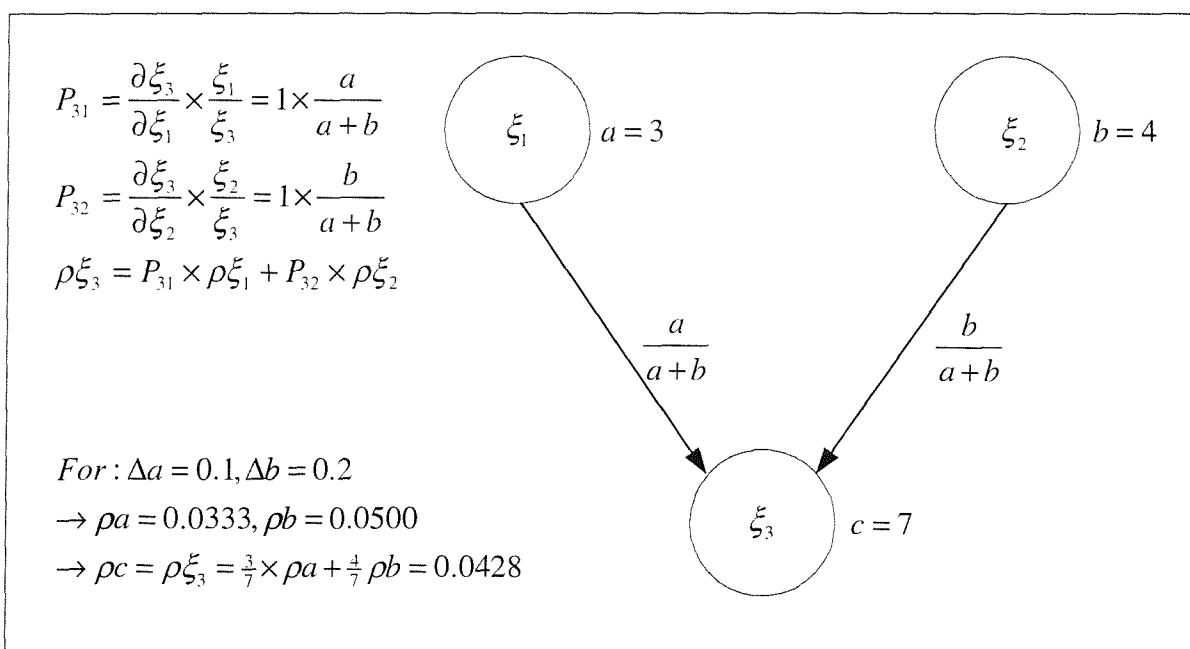

| Figure 5.3 Computational graph example.....                                                                                | 107 |

| Figure 5.4 Error propagation model example .....                                                                           | 108 |

|                                                                                                                                                                                      |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

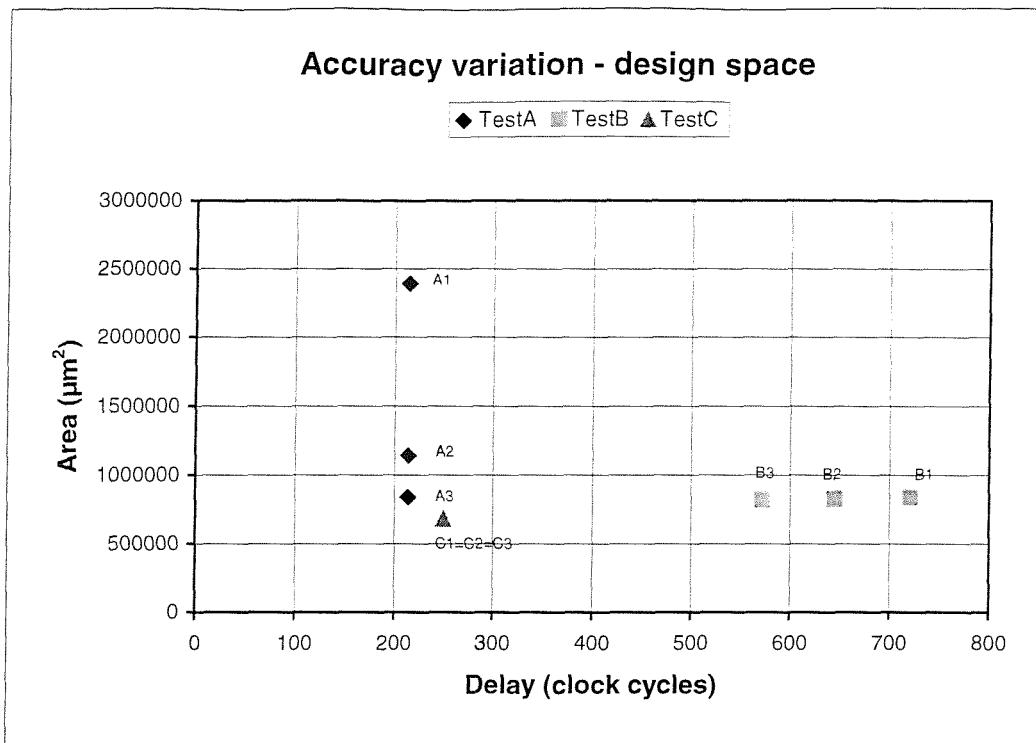

| Figure 5.5 Design space for the three different benchmarks .....                                                                                                                     | 110 |

| Figure 5.6 The inverse tangent function parameters for a target accuracy = $10^{-6}$ .....                                                                                           | 112 |

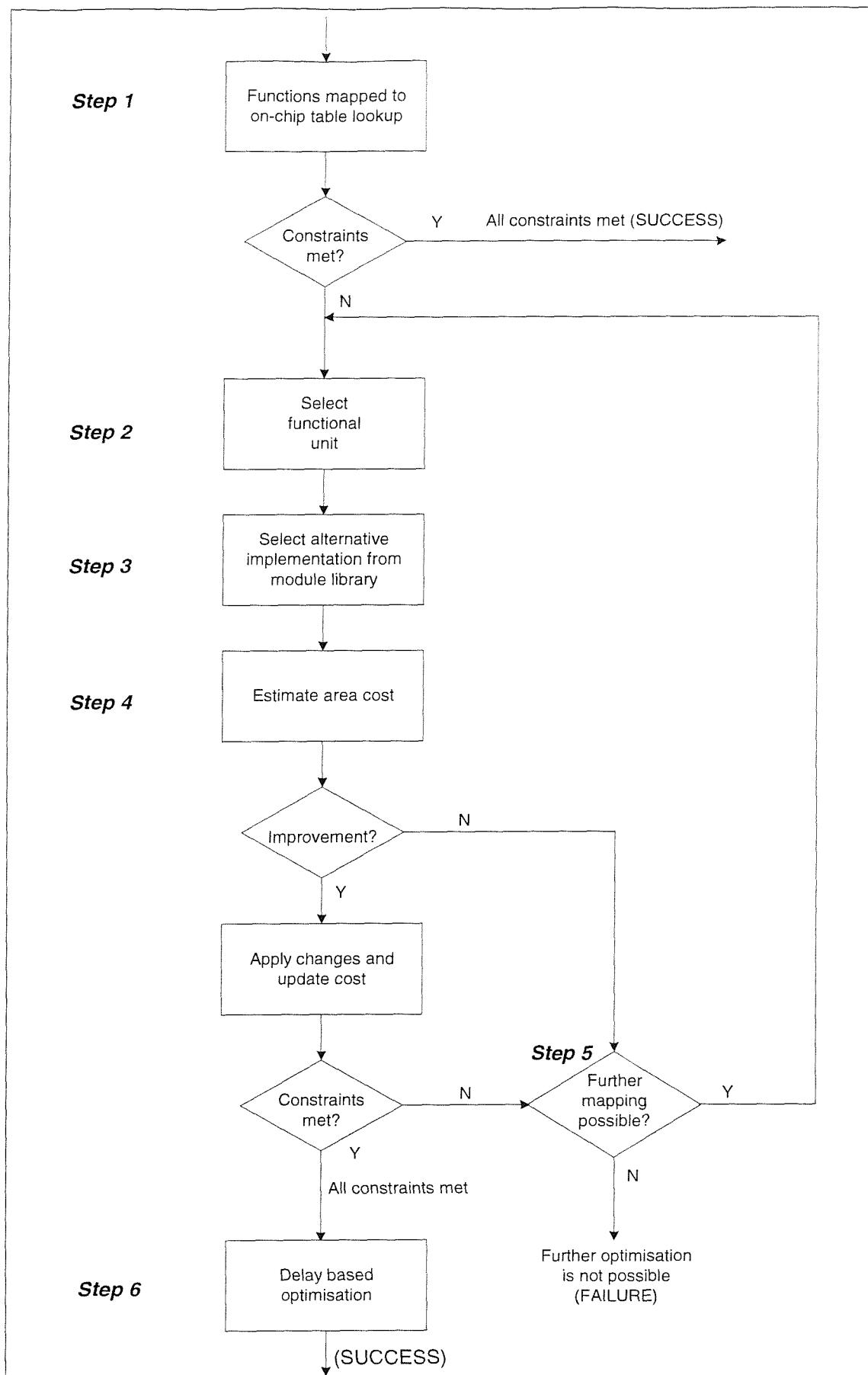

| Figure 5.7 Optimisation algorithm flowchart .....                                                                                                                                    | 114 |

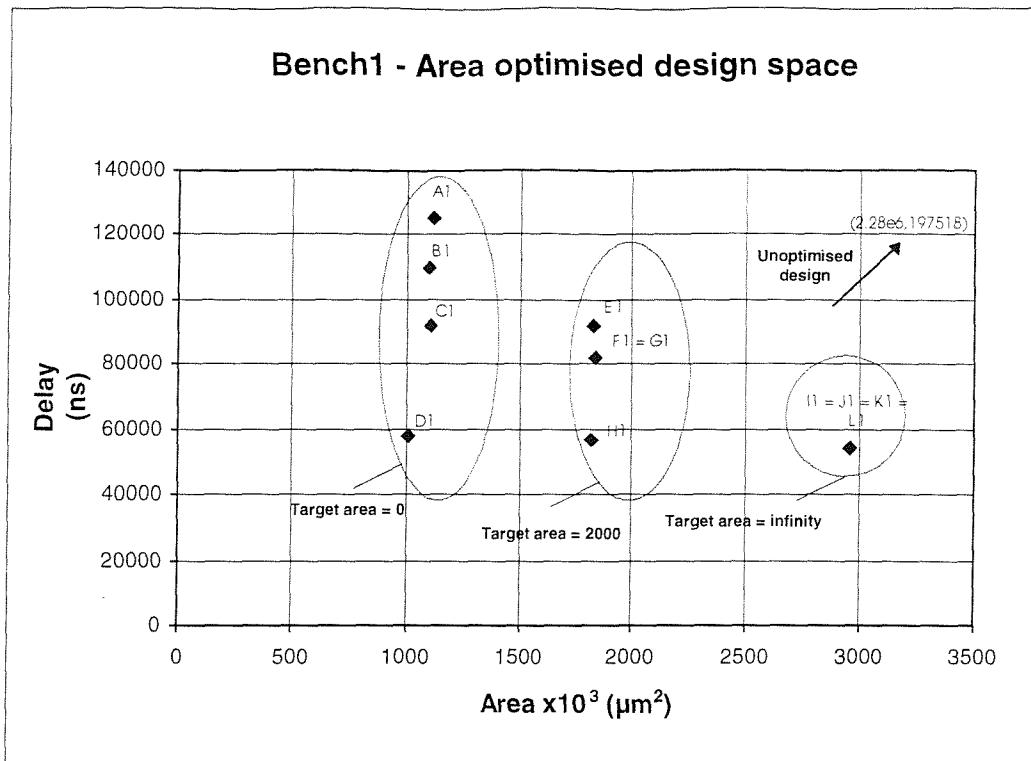

| Figure 5.8 Bench1 design space.....                                                                                                                                                  | 120 |

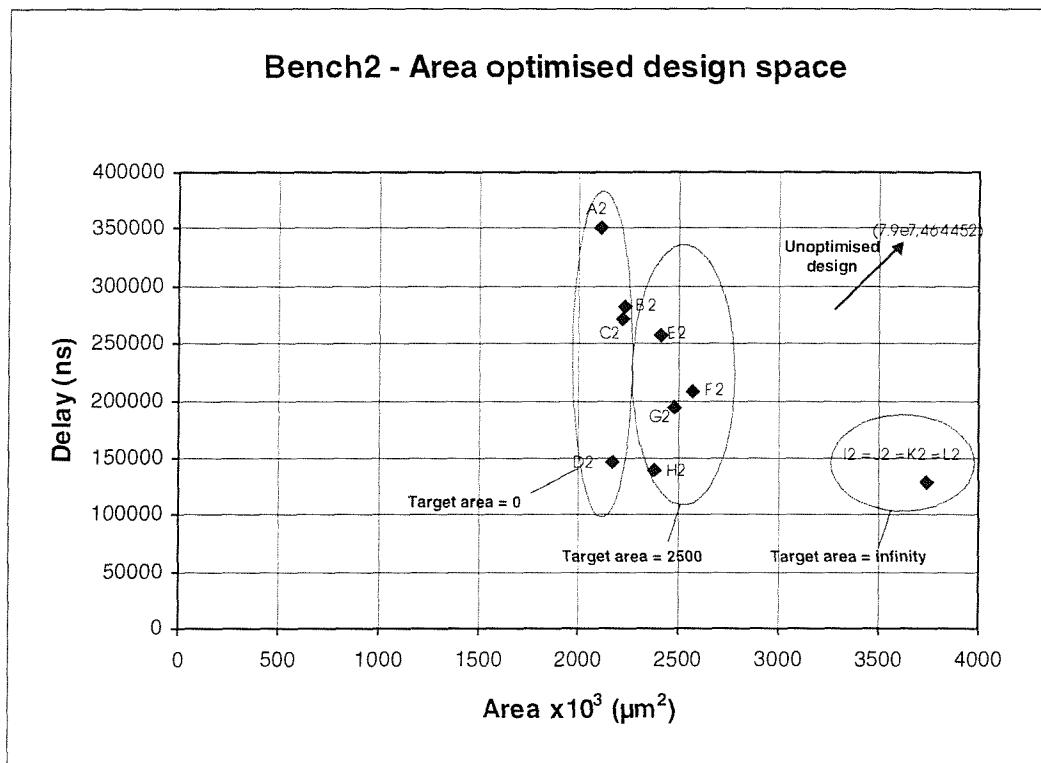

| Figure 5.9 Bench2 design space.....                                                                                                                                                  | 120 |

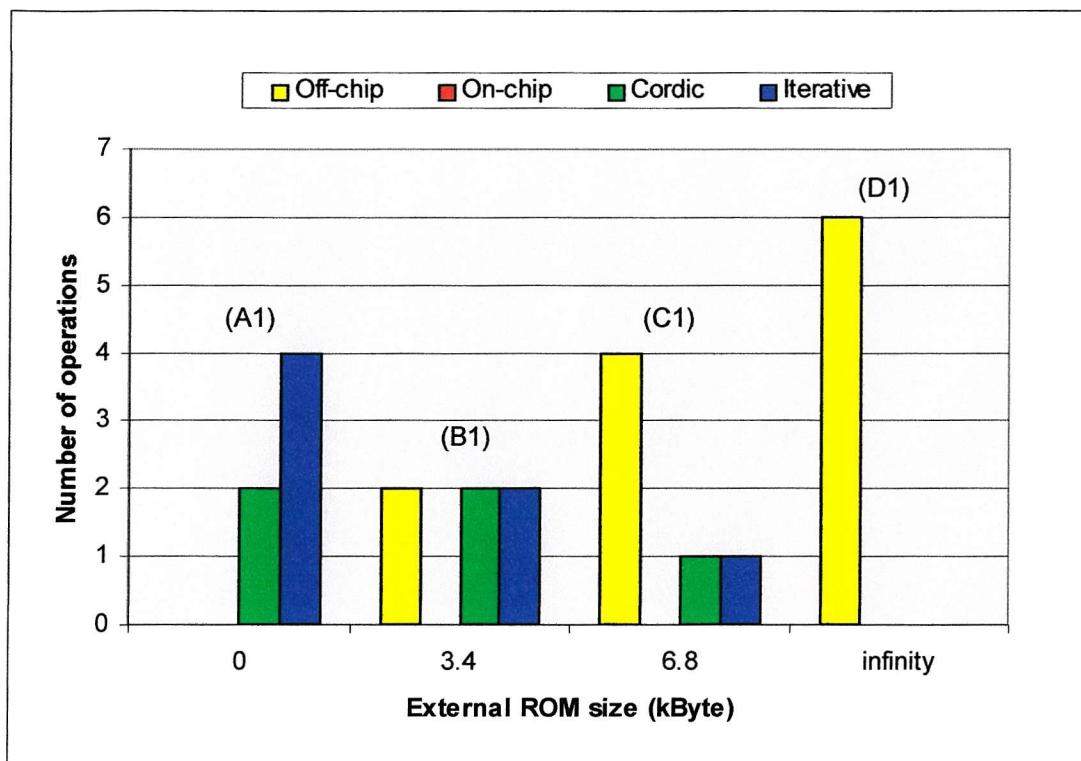

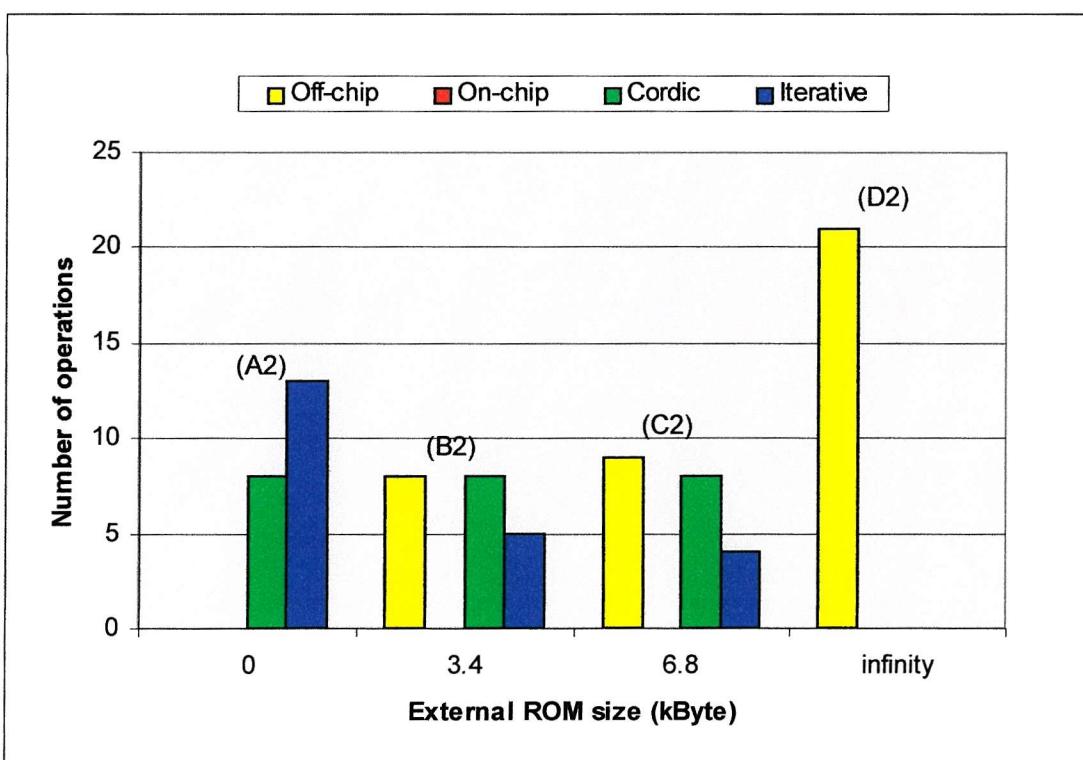

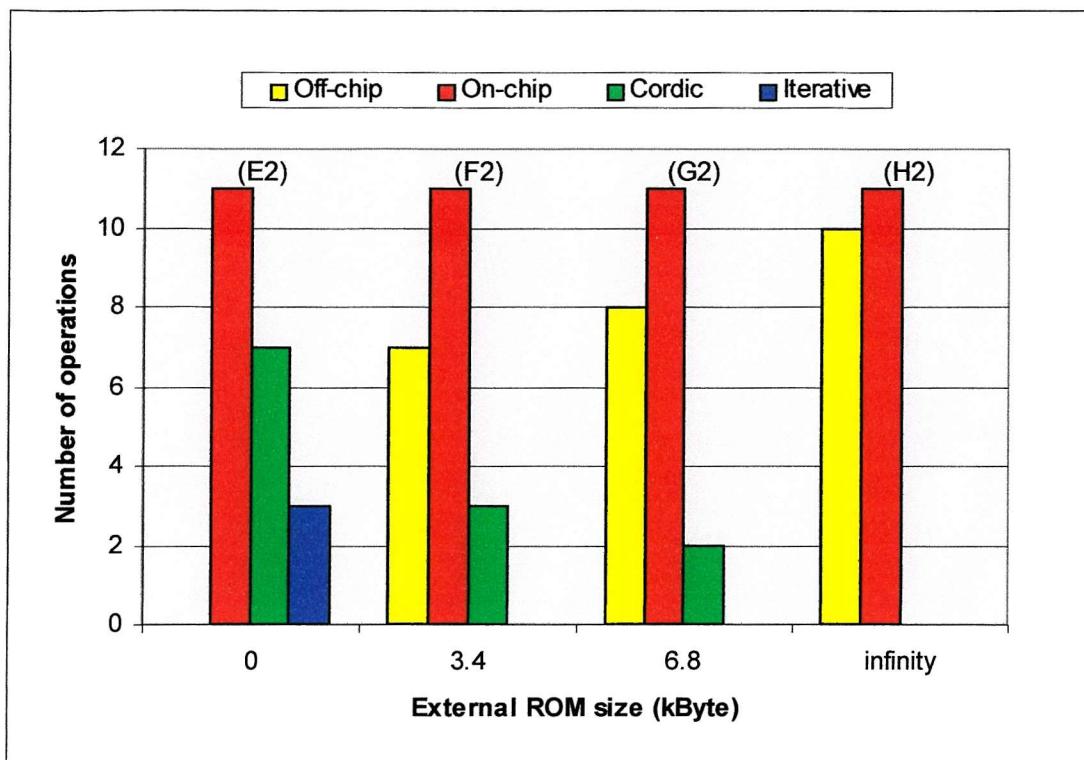

| Figure 5.10 Distribution of functional units between the three base techniques for bench1<br>for target area = $0 \mu\text{m}^2$ as a function of external ROM size .....            | 121 |

| Figure 5.11 Distribution of functional units between the three base techniques for bench1<br>for target area = $2\text{e}6 \mu\text{m}^2$ as a function of external ROM size .....   | 121 |

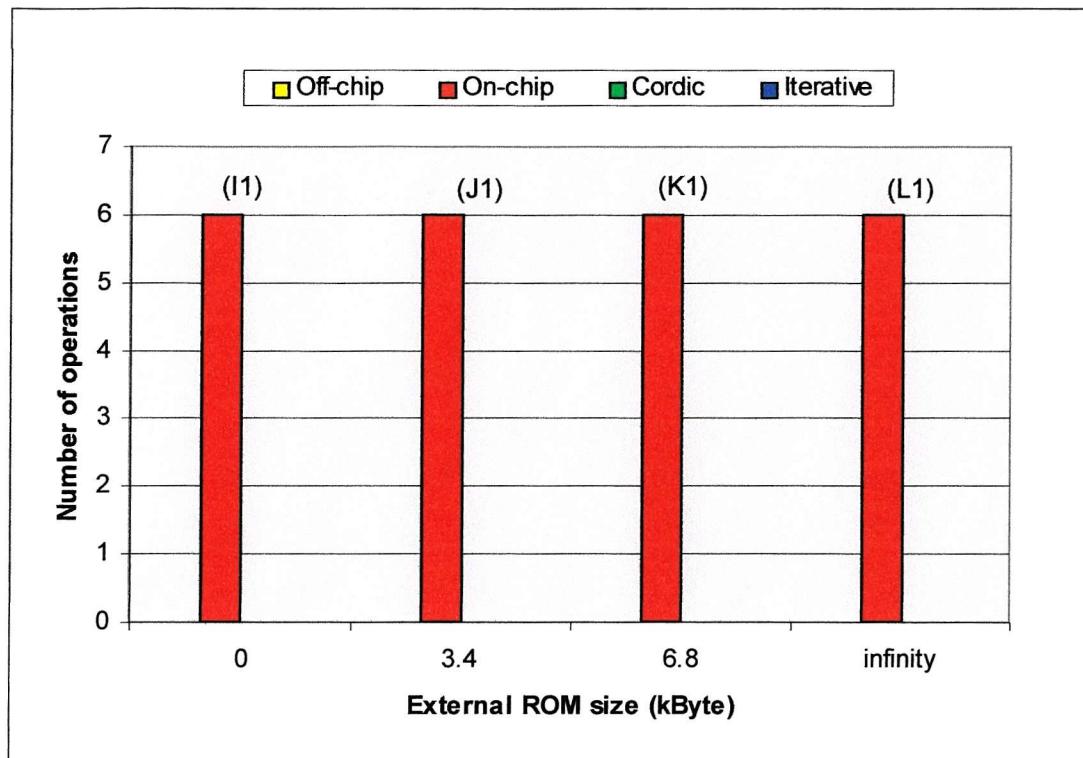

| Figure 5.12 Distribution of functional units between the three base techniques for bench1<br>for target area = infinity $\mu\text{m}^2$ as a function of external ROM size .....     | 122 |

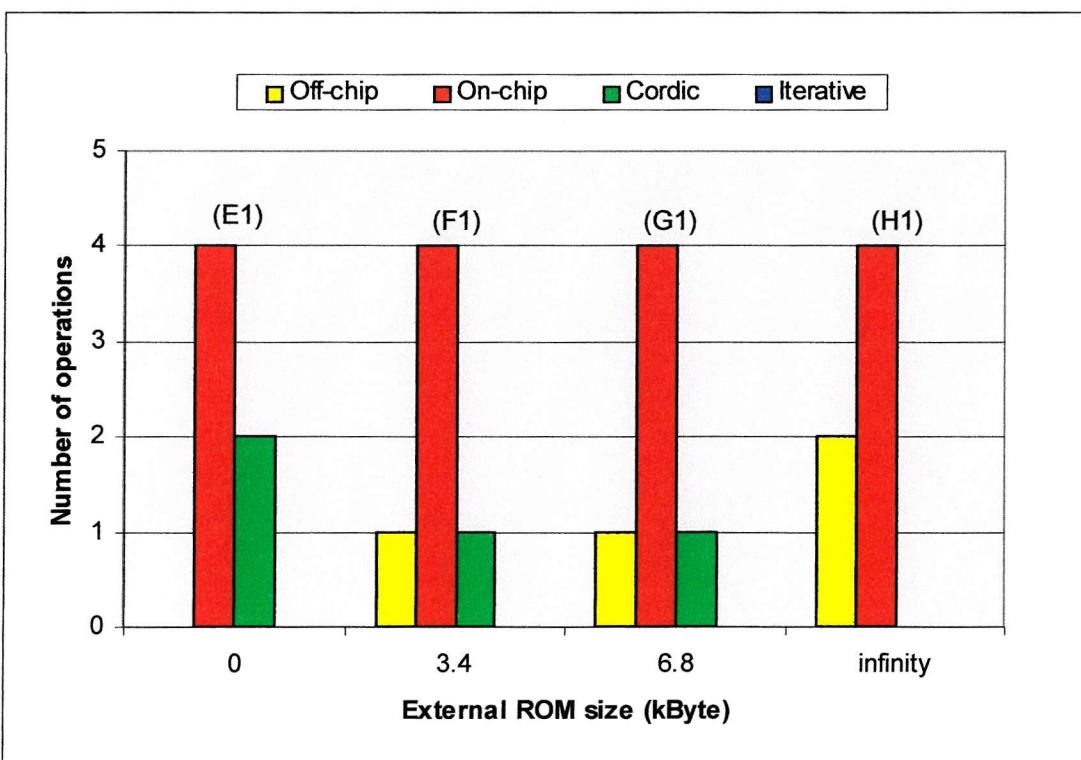

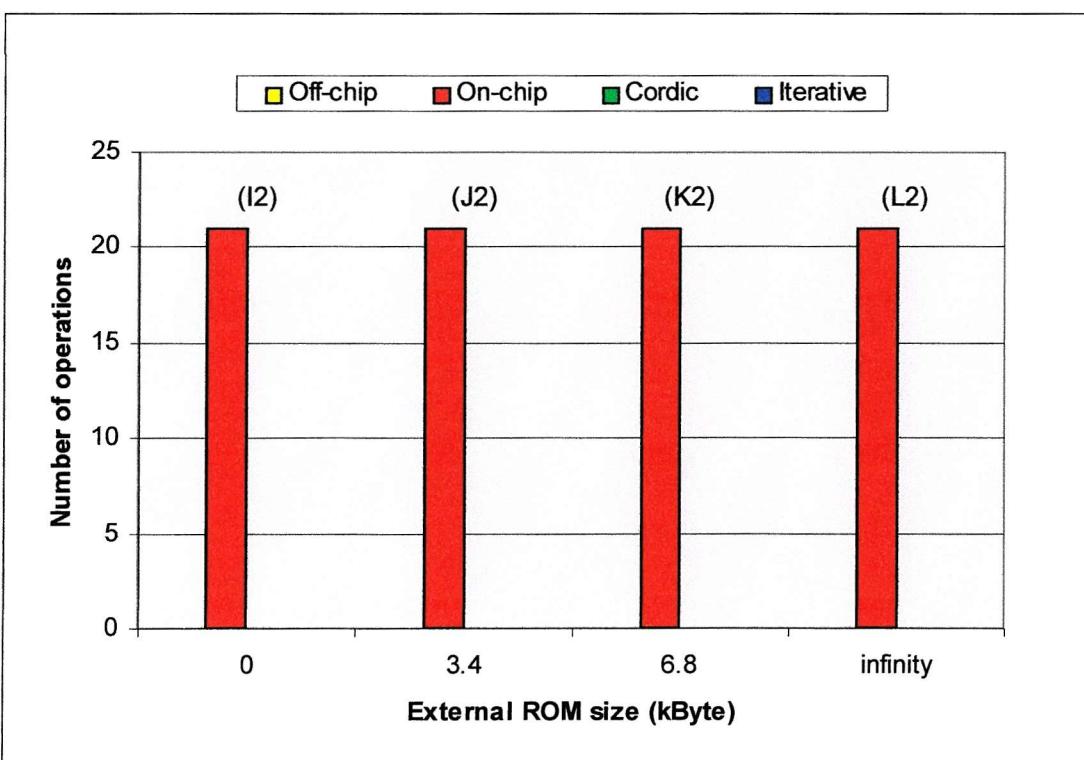

| Figure 5.13 Distribution of functional units between the three base techniques for bench2<br>for target area = $0 \mu\text{m}^2$ as a function of external ROM size .....            | 122 |

| Figure 5.14 Distribution of functional units between the three base techniques for bench2<br>for target area = $2.5\text{e}6 \mu\text{m}^2$ as a function of external ROM size ..... | 123 |

| Figure 5.15 Distribution of functional units between the three base techniques for bench2<br>for target area = infinity $\mu\text{m}^2$ as a function of external ROM size .....     | 123 |

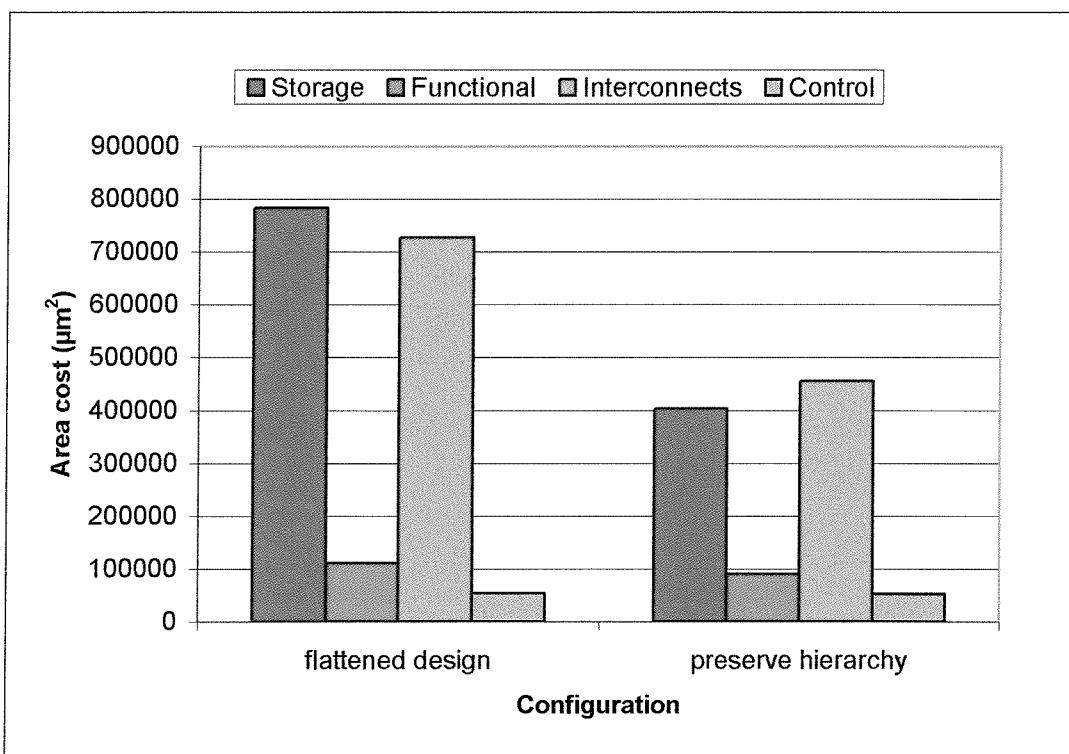

| Figure 5.16 Area breakdown of the two designs based on similar base techniques (on-chip<br>based implementation).....                                                                | 124 |

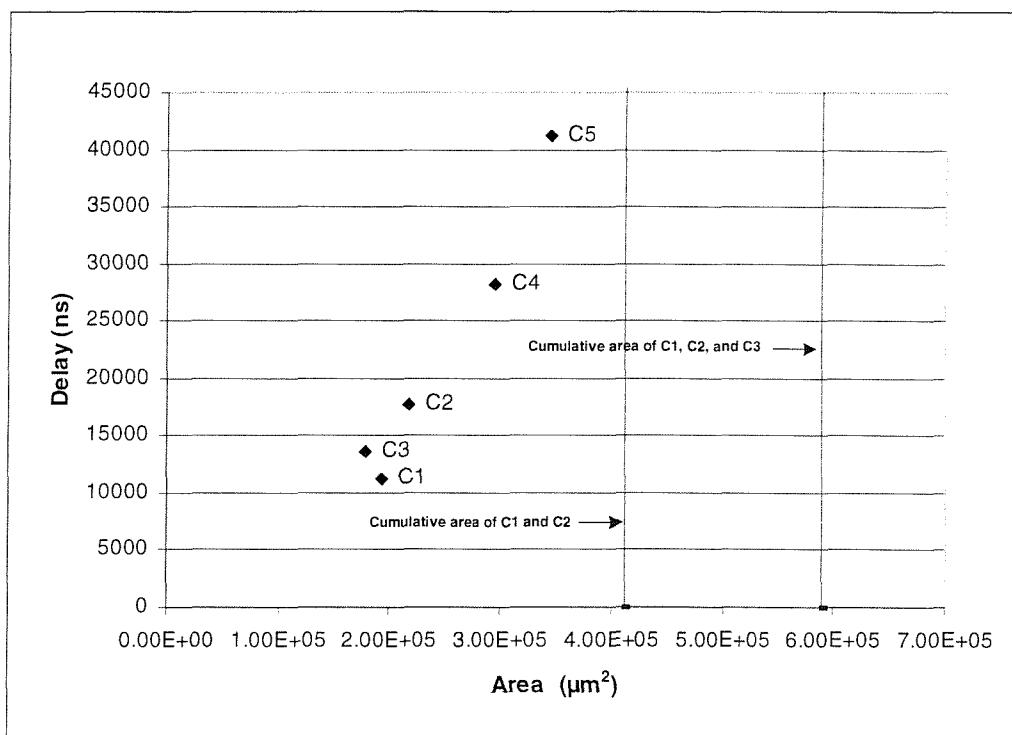

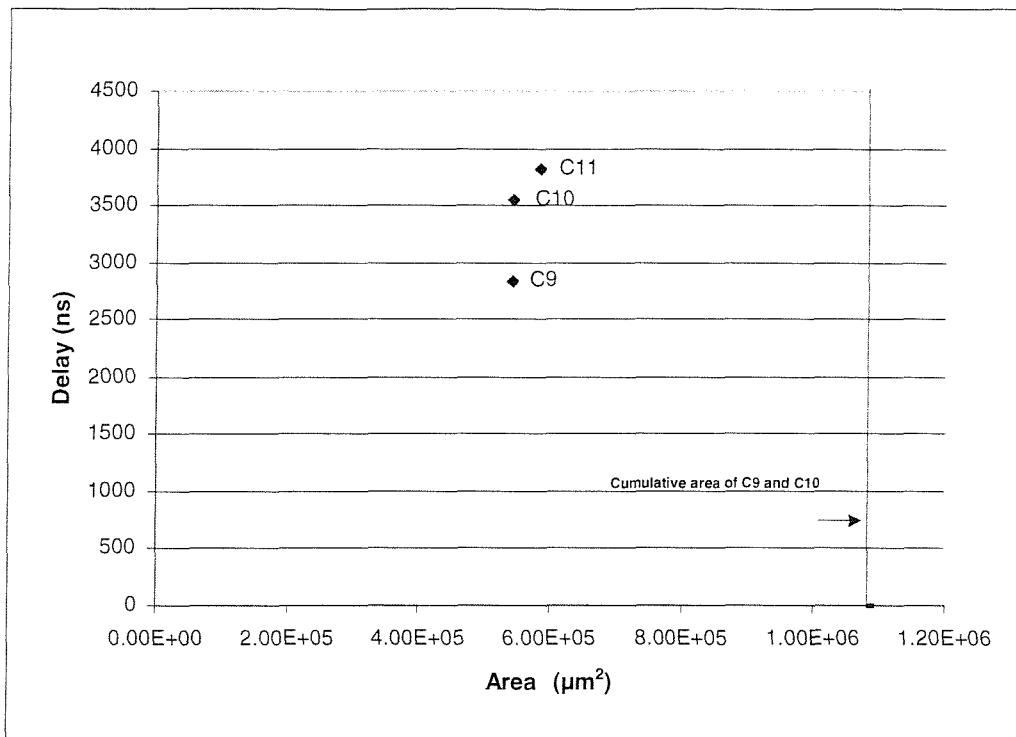

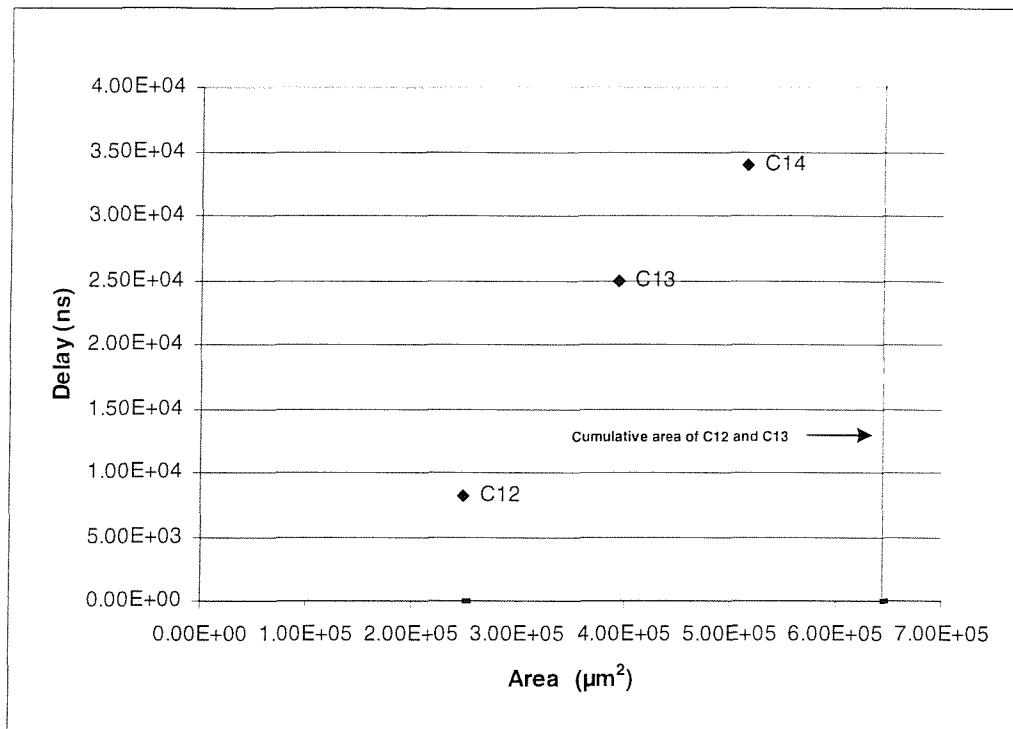

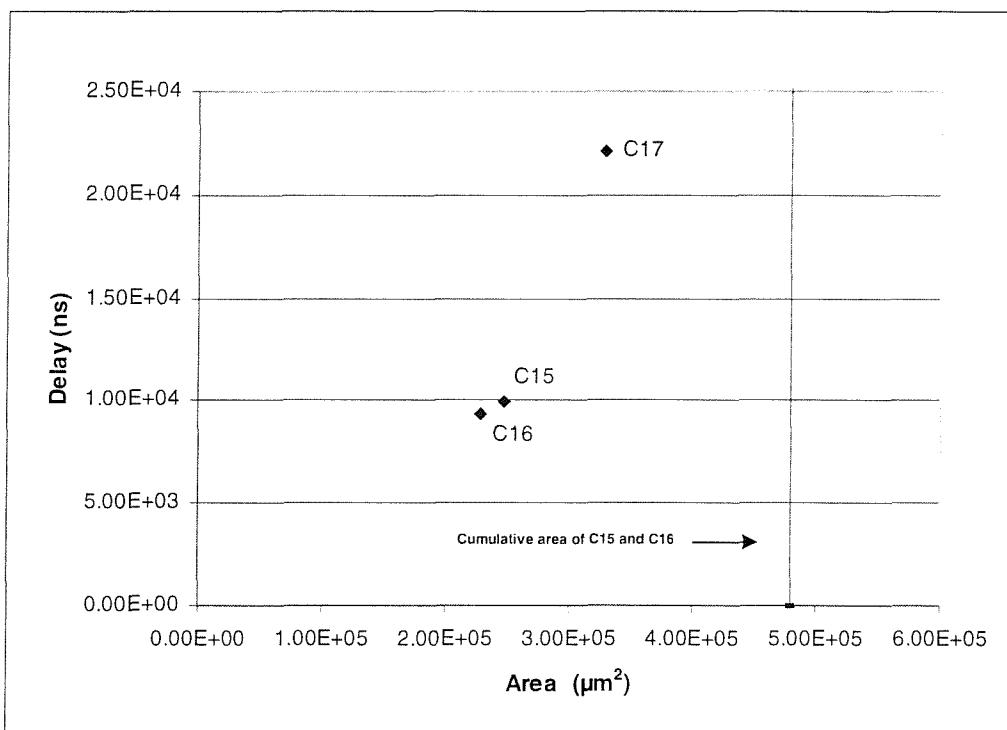

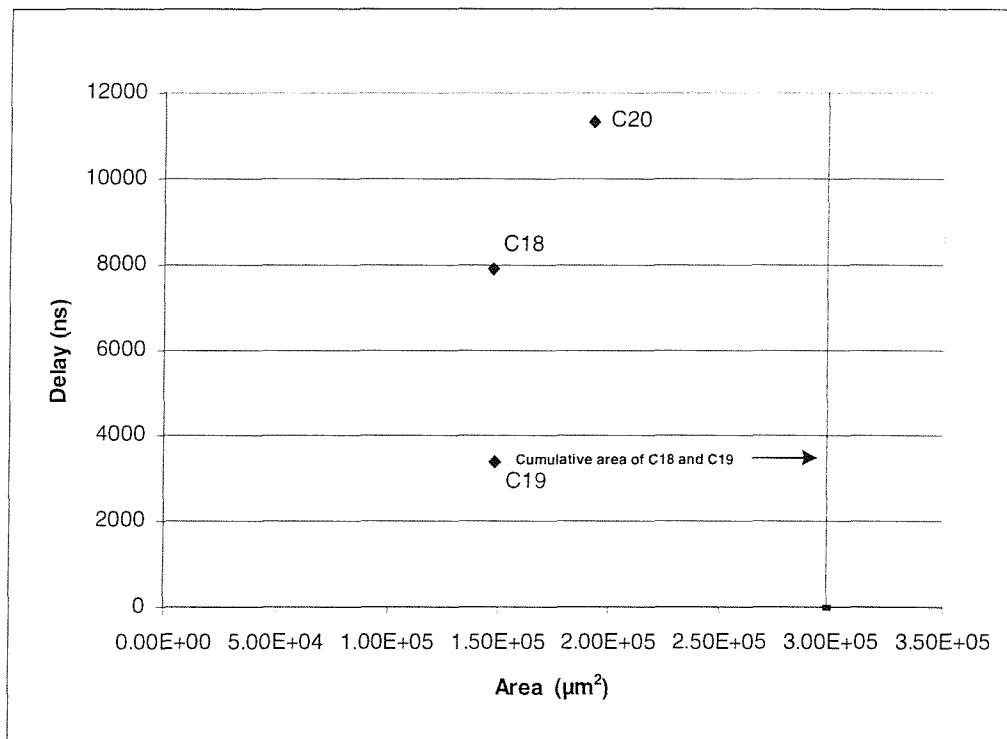

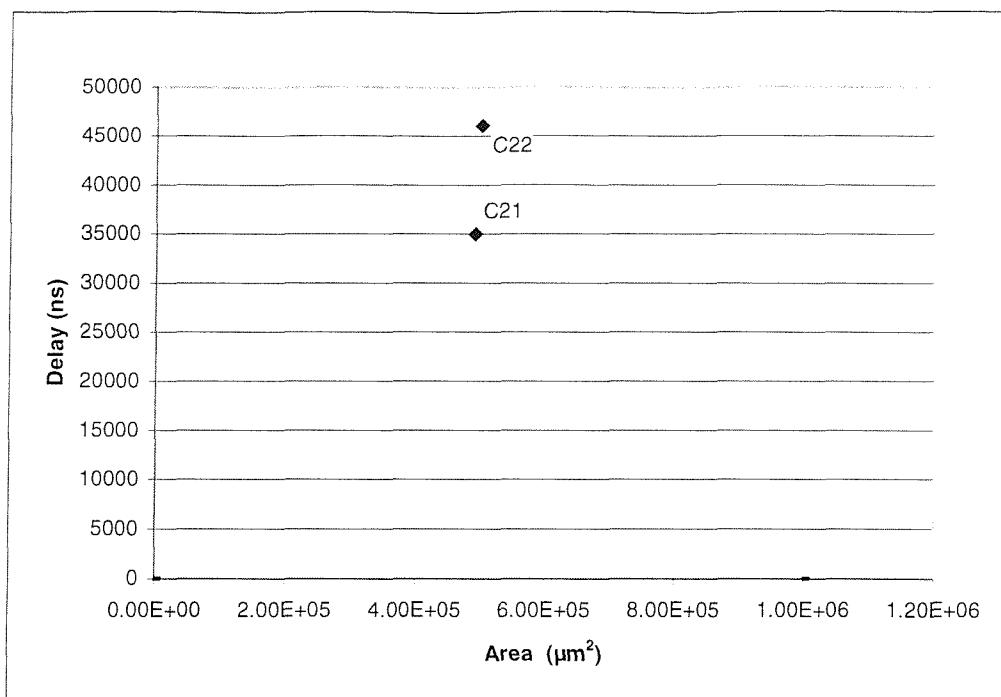

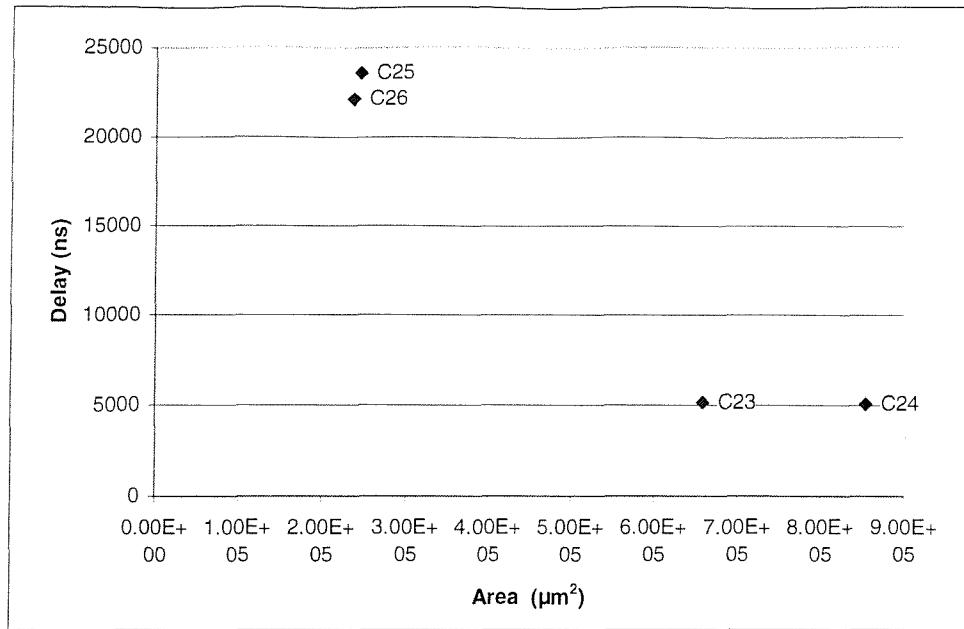

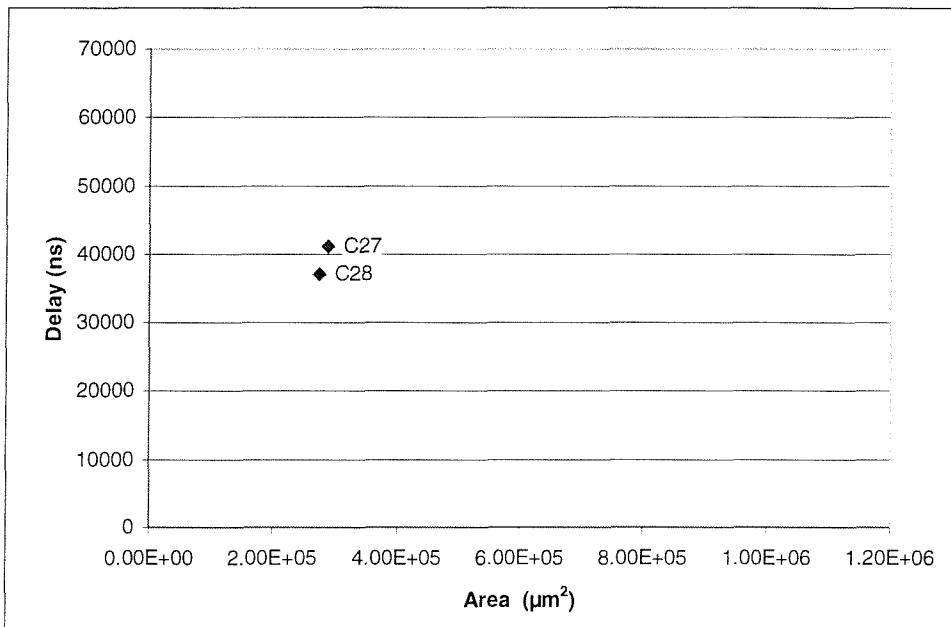

| Figure 5.17 Design space for the first set of designs .....                                                                                                                          | 126 |

| Figure 5.18 Design space for the second set of designs.....                                                                                                                          | 127 |

| Figure 5.19 Design space for the third set of designs .....                                                                                                                          | 128 |

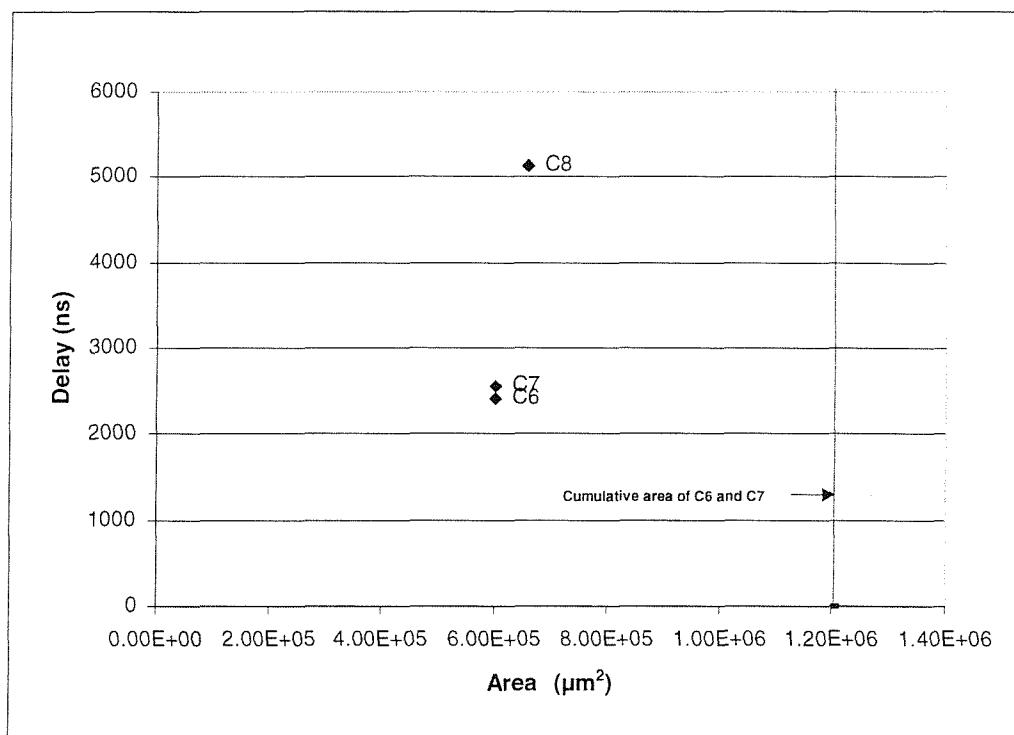

| Figure 5.20 Design space for the fourth set of designs.....                                                                                                                          | 129 |

| Figure 5.21 Design space for the fifth set of designs.....                                                                                                                           | 129 |

| Figure 5.22 Design space for the sixth set of designs.....                                                                                                                           | 130 |

| Figure 5.23 Design space for the seventh set of designs .....                                                                                                                        | 131 |

| Figure 5.24 Design space for the eighth set of designs.....                                                                                                                          | 132 |

| Figure 5.25 Design space for the ninth set of designs .....                                                                                                                          | 132 |

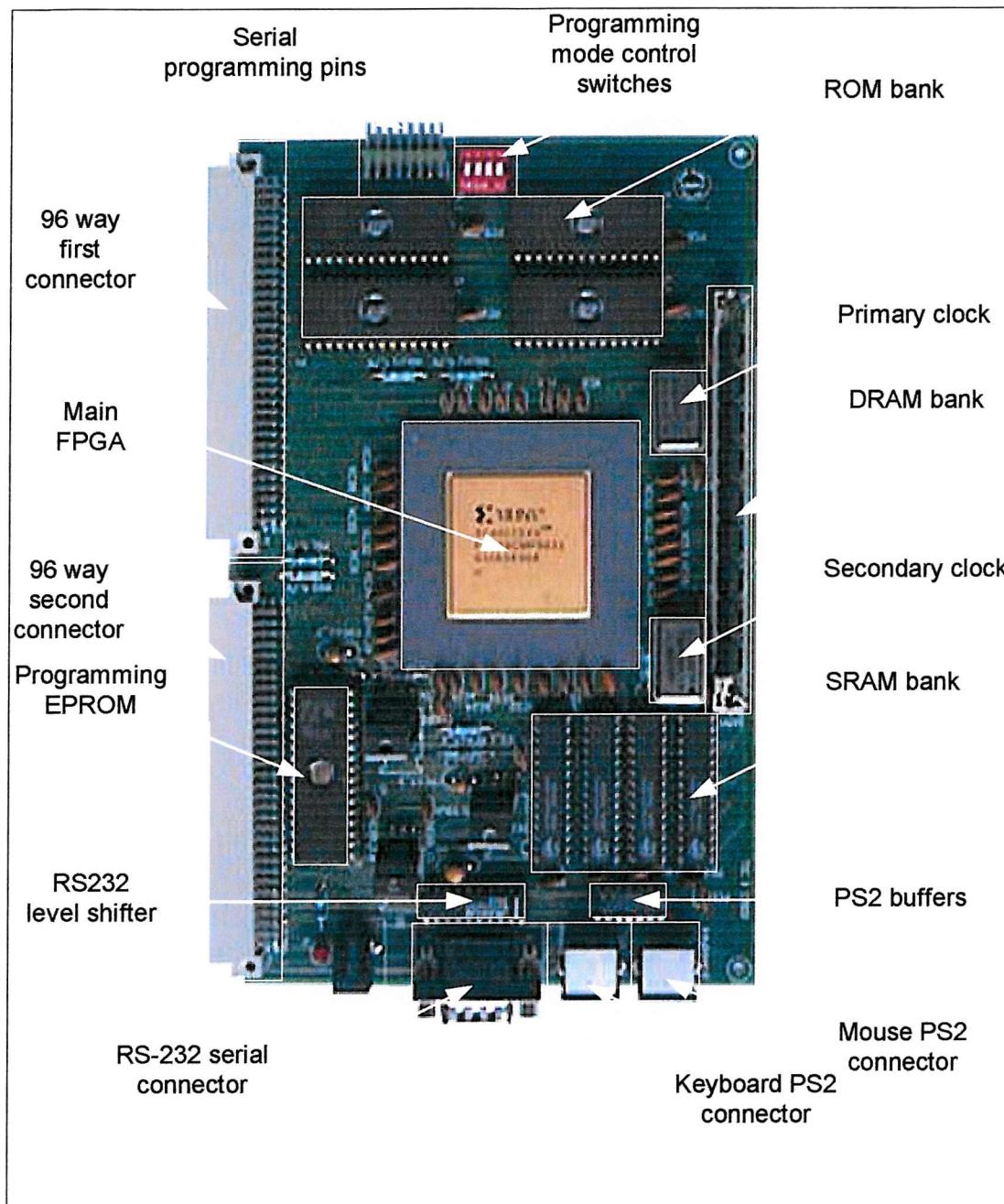

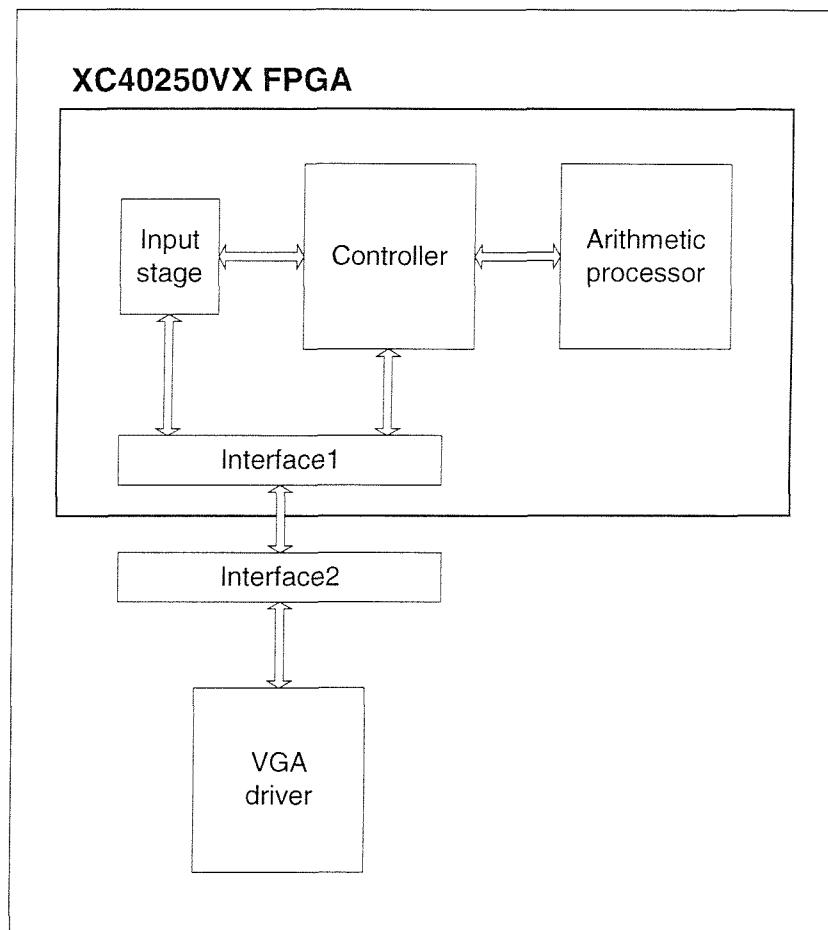

| Figure 6.1 FPGA board block diagram.....                                                                                                                                             | 134 |

| Figure 6.2 FPGA board photograph.....                                                                                                                                                | 136 |

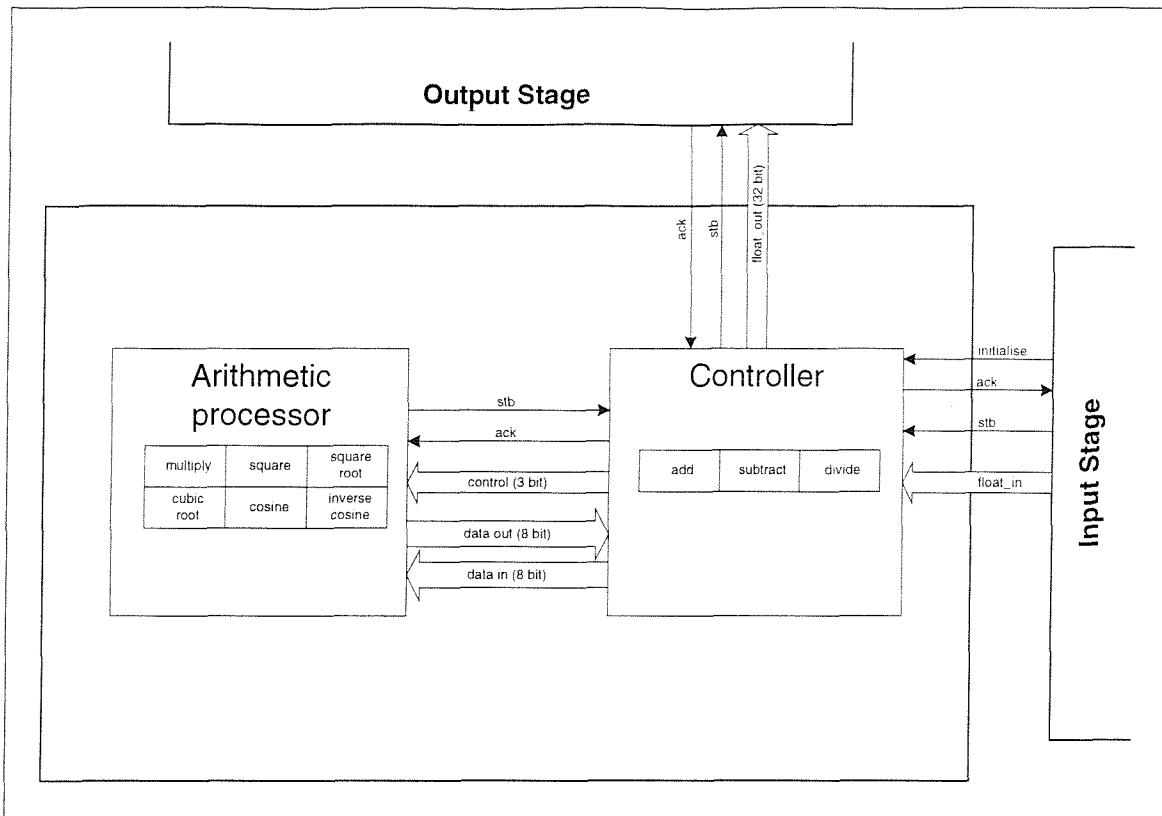

| Figure 6.3 Cubic equation solver block diagram .....                                                                                                                                 | 137 |

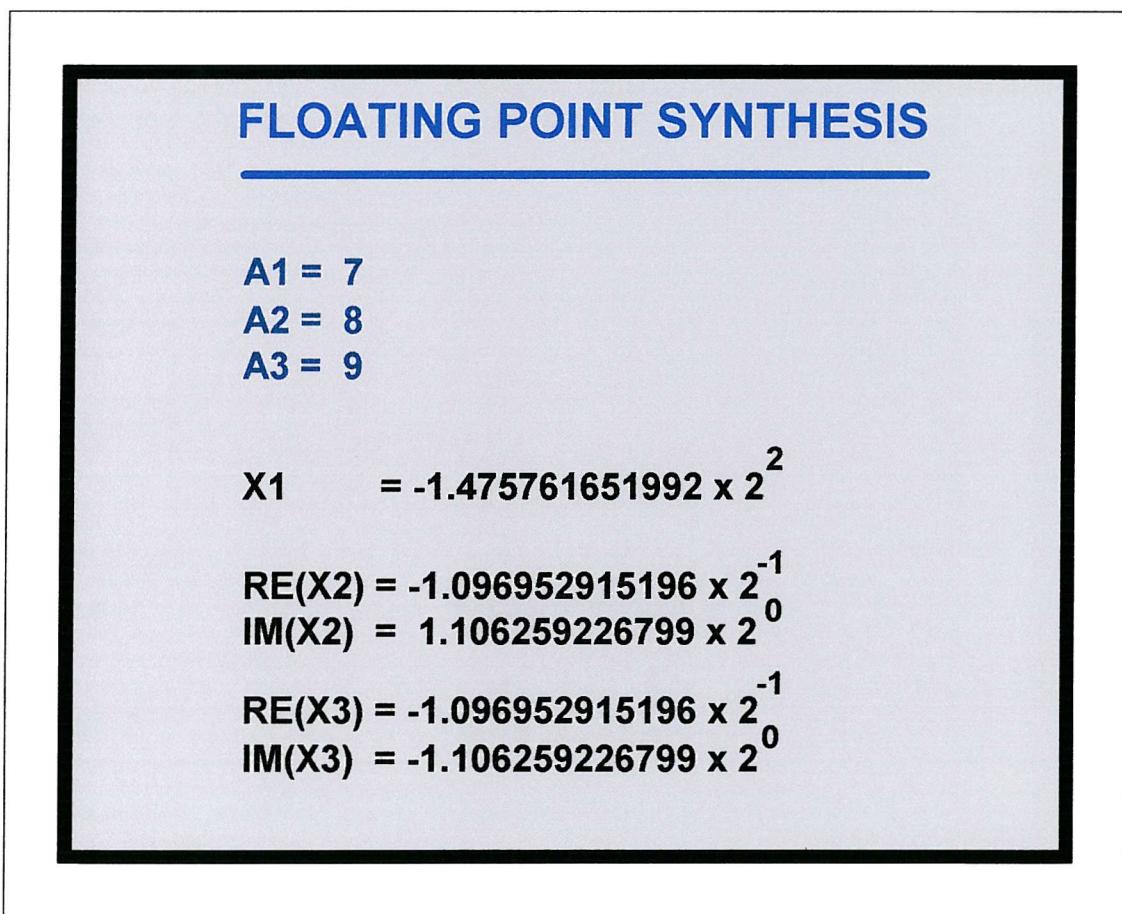

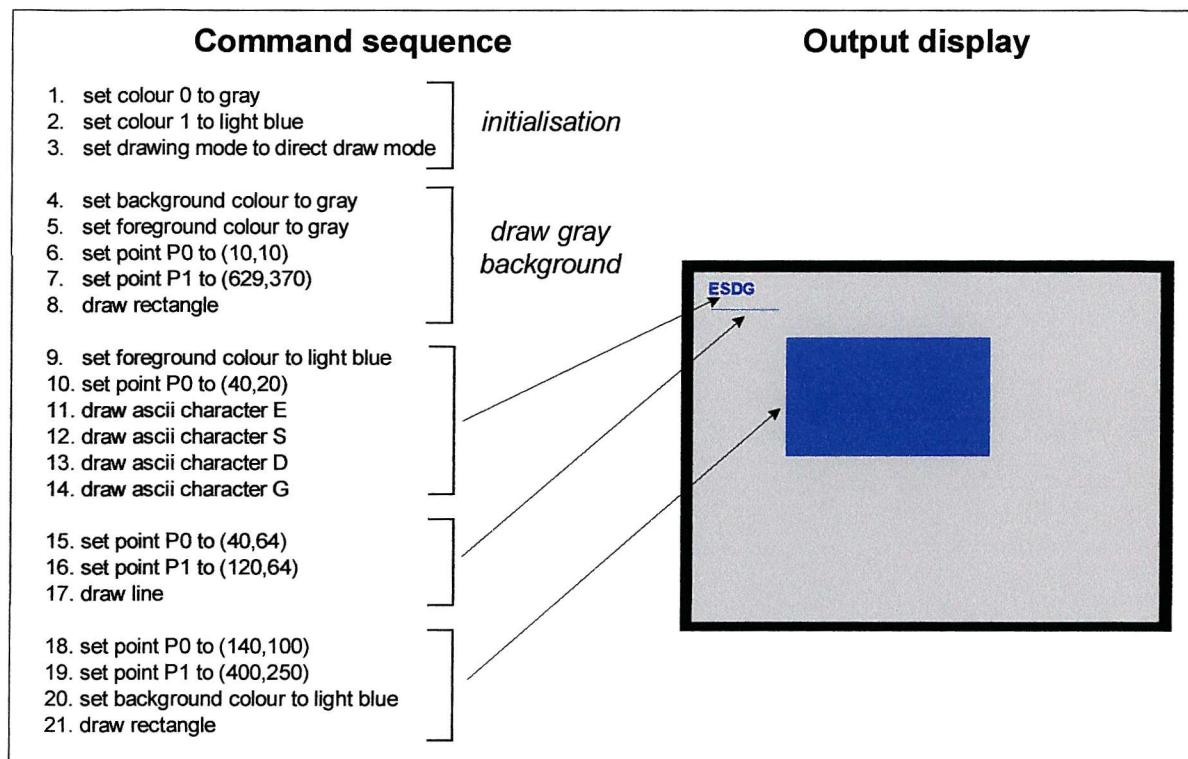

| Figure 6.4 Cubic equation solver display .....                                                                                                                                       | 138 |

| Figure 6.5 Cubic equation solution.....                                                                                                                                              | 139 |

|                                                                                                                                            |     |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6.6 Design1 VHDL behavioural description .....                                                                                      | 140 |

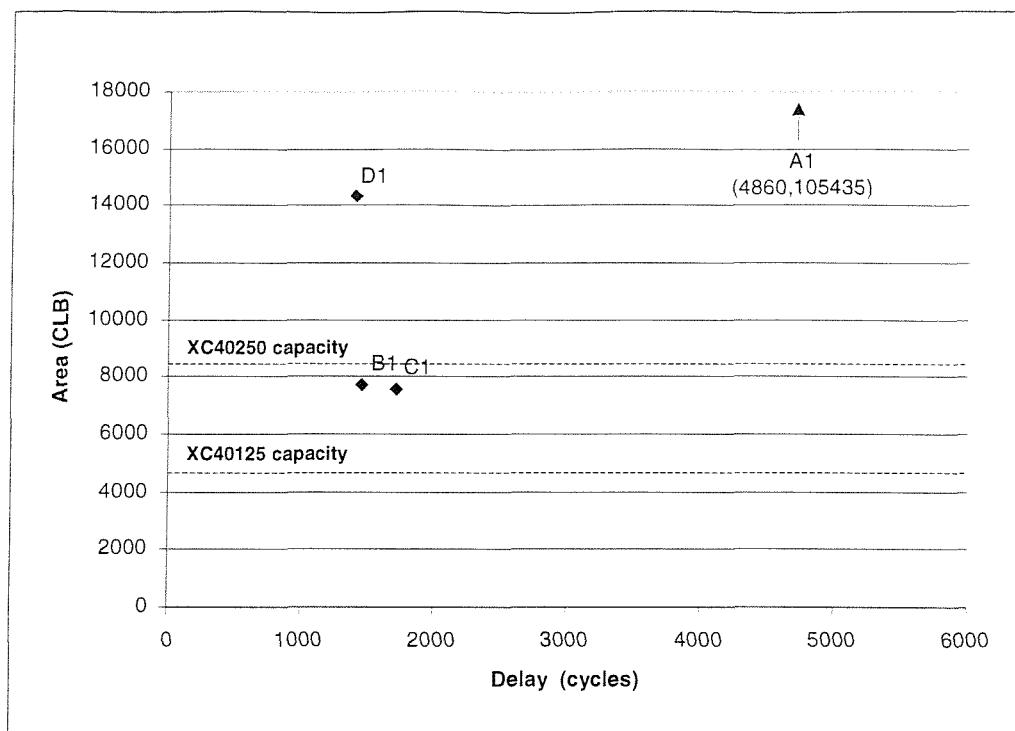

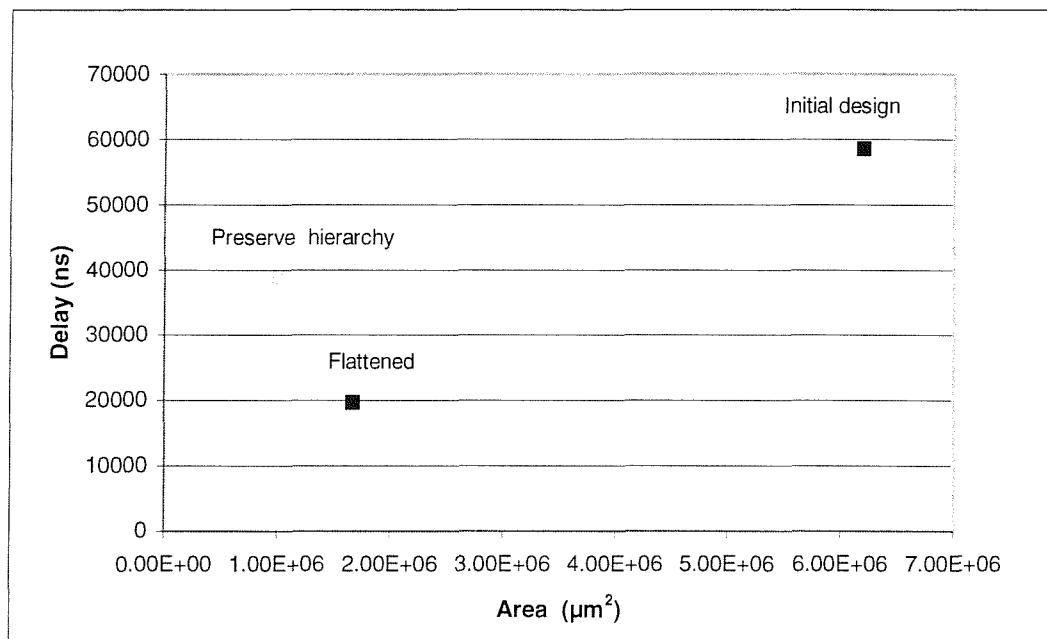

| Figure 6.7 Design space for the original design.....                                                                                       | 141 |

| Figure 6.8 Partitioned core unit block diagram .....                                                                                       | 142 |

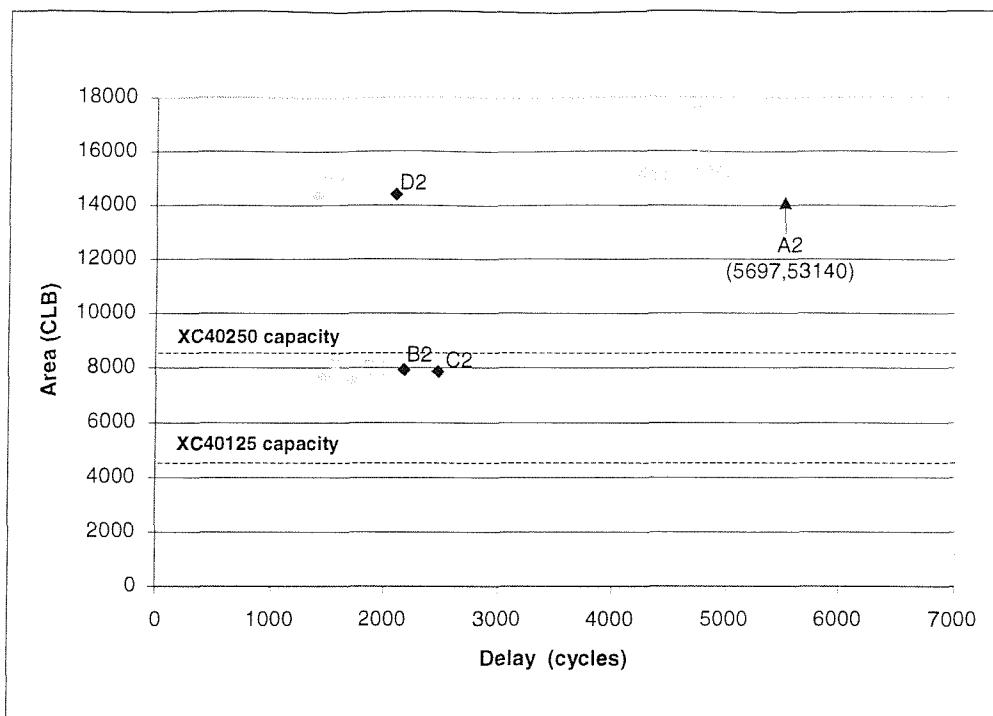

| Figure 6.9 Core unit design space.....                                                                                                     | 143 |

| Figure 6.10 Alternative optimisation strategies .....                                                                                      | 146 |

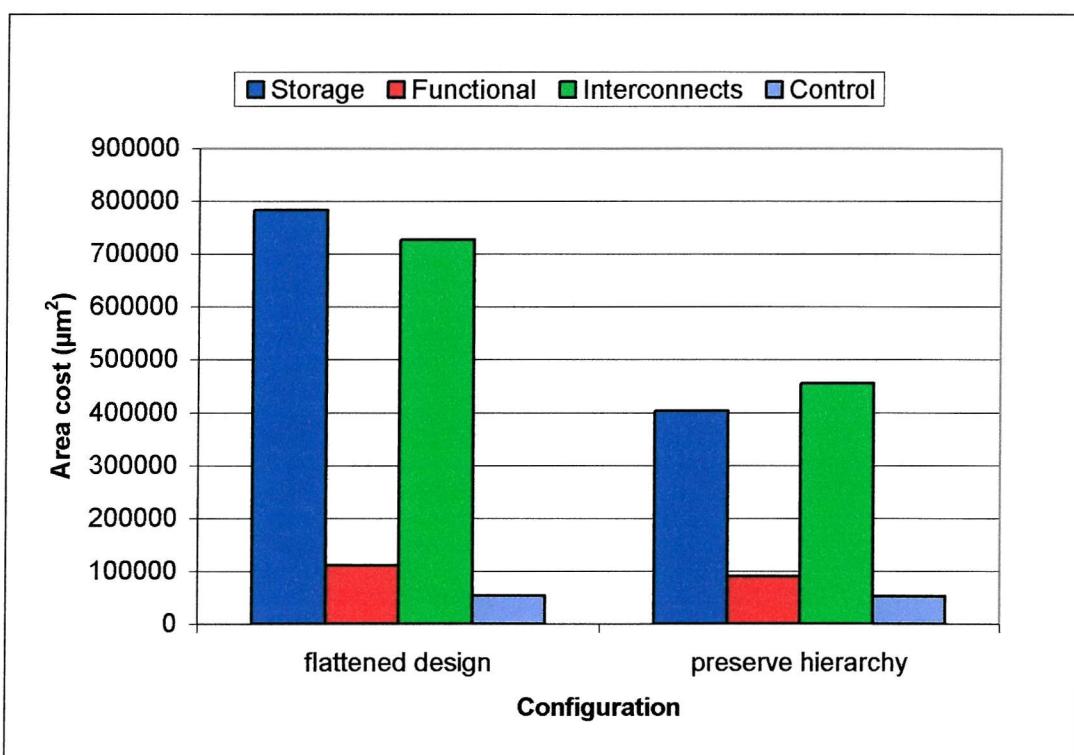

| Figure 6.11 Area breakdown of both designs .....                                                                                           | 147 |

| Figure 6.12 Using the protect instruction .....                                                                                            | 148 |

| Figure 6.13 Macro port example.....                                                                                                        | 149 |

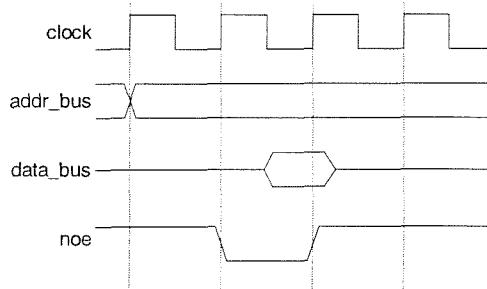

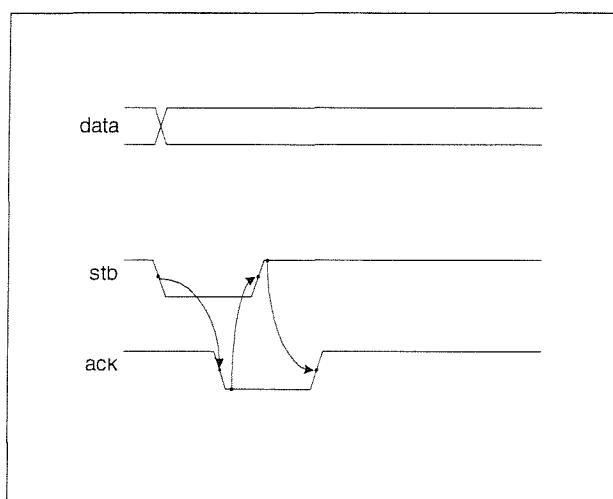

| Figure 6.14 Handshaking signal waveform .....                                                                                              | 150 |

| Figure 6.15 Synchronisation within VHDL.....                                                                                               | 151 |

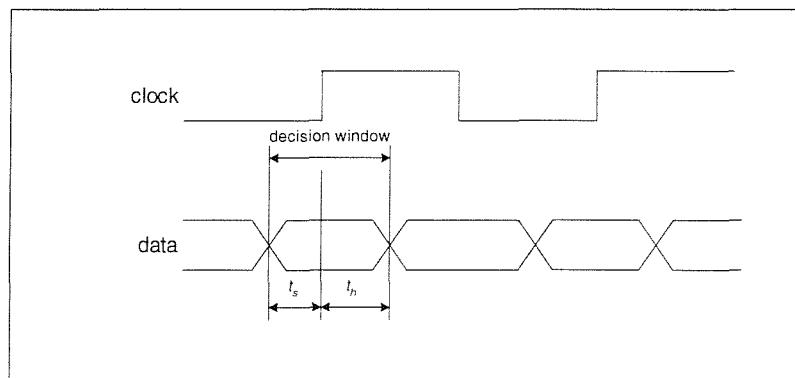

| Figure 6.16 Flip-flop timing parameters.....                                                                                               | 151 |

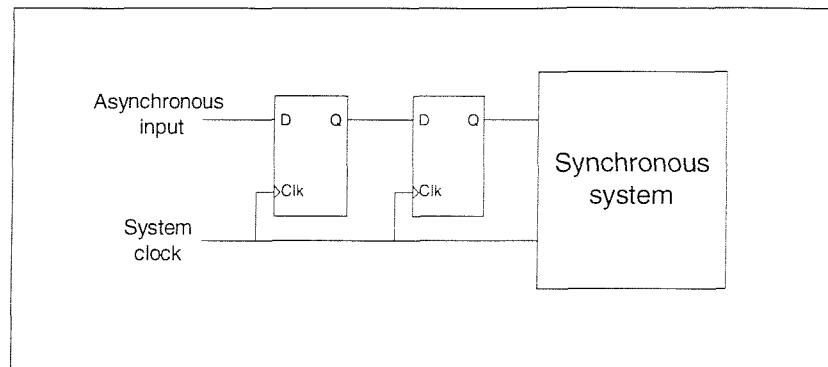

| Figure 6.17 Synchroniser schematic .....                                                                                                   | 152 |

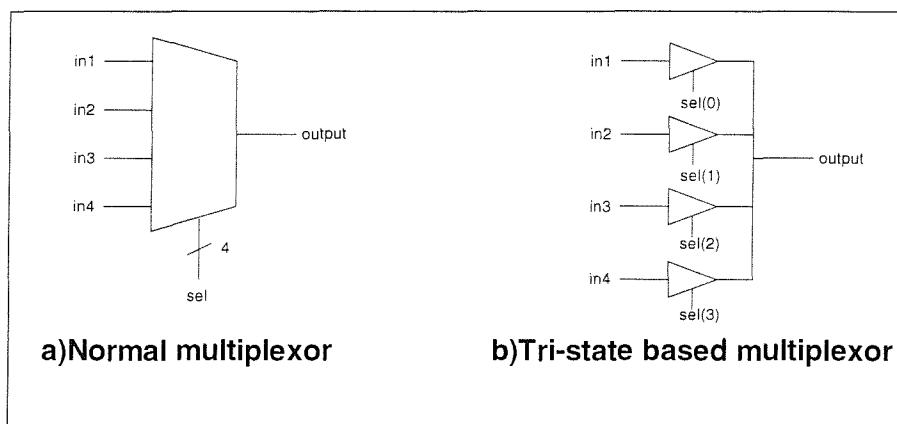

| Figure 6.18 MOODS multiplexors models.....                                                                                                 | 152 |

| Figure 6.19 Final implementation block diagram.....                                                                                        | 155 |

| Figure 6.20 FPGA utilisation figures.....                                                                                                  | 155 |

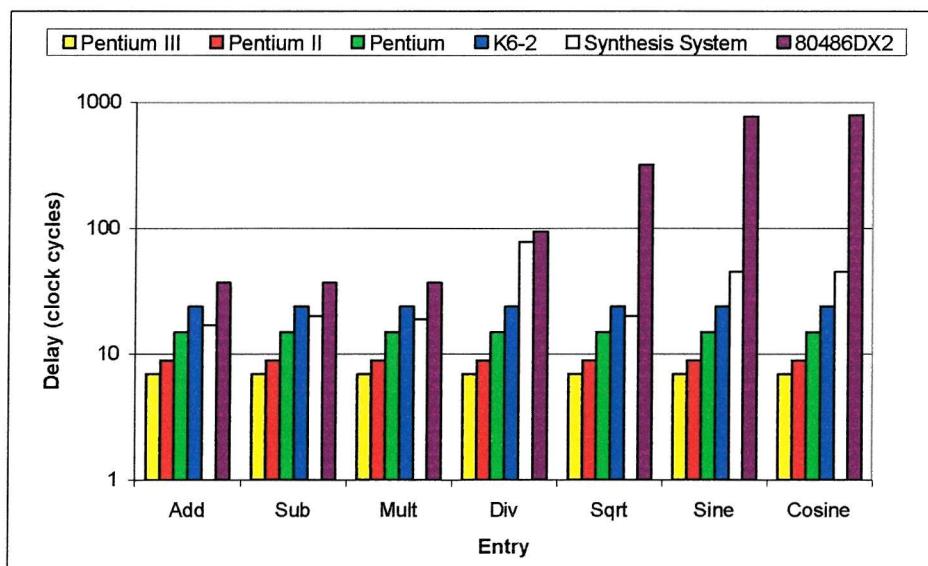

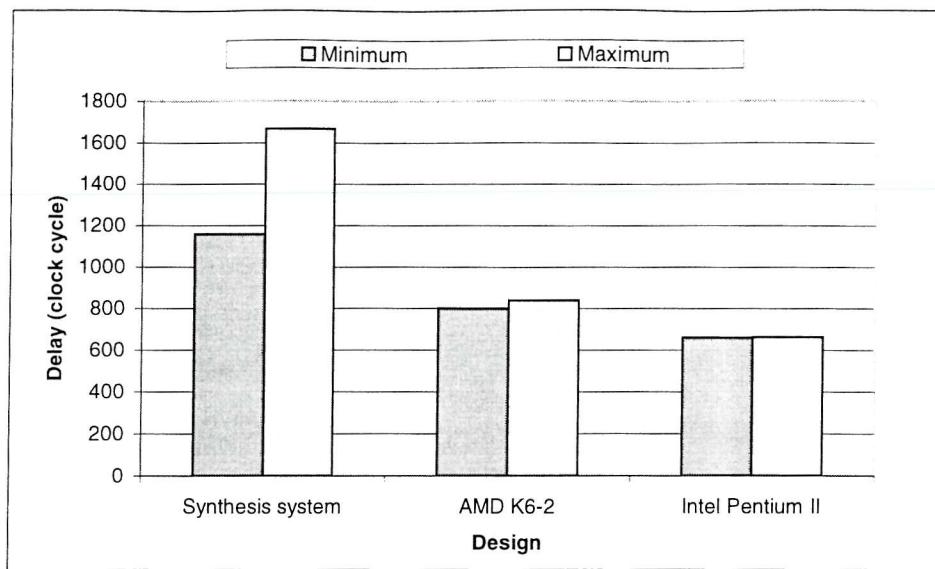

| Figure 6.21 The floating-point performance of different microprocessors compared to the<br>MOODS synthesis system .....                    | 157 |

| Figure 6.22 The cubic equation solver floating-point performance compared to modern<br>microprocessors .....                               | 158 |

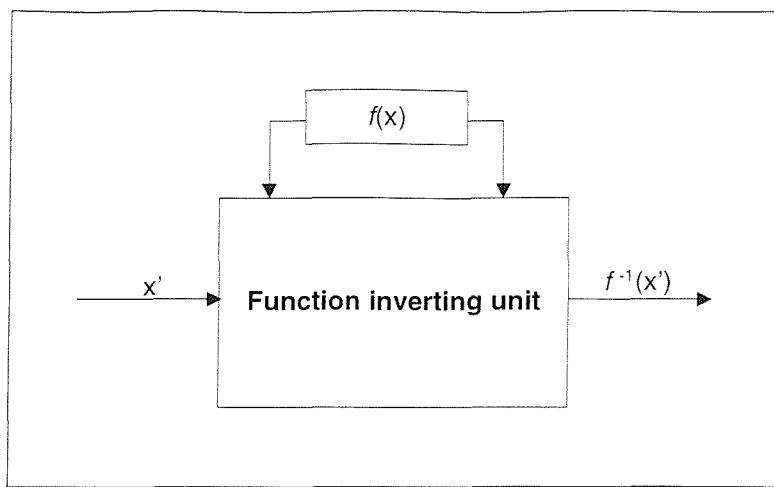

| Figure 7.1 Function inversion block .....                                                                                                  | 163 |

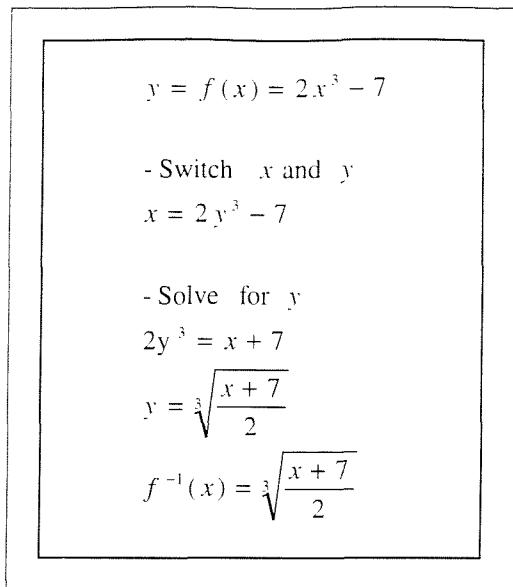

| Figure 7.2 Constructing the inverse function algebraically .....                                                                           | 164 |

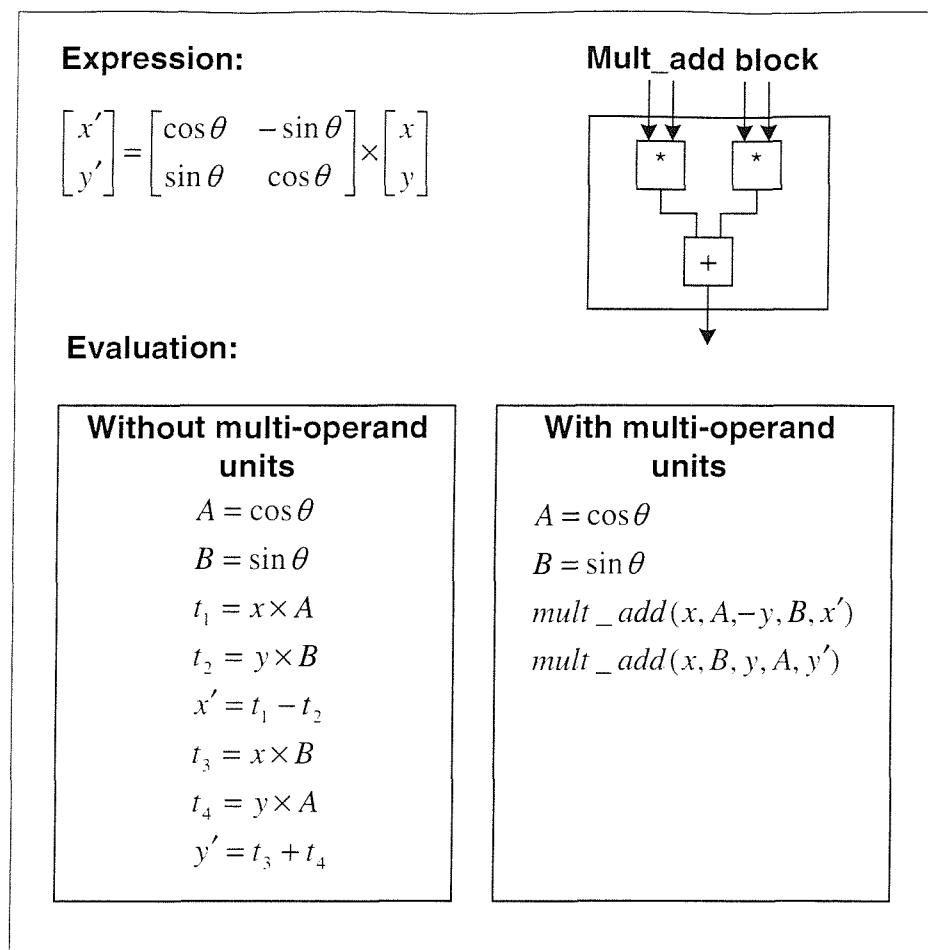

| Figure 7.3 Multi-operand floating-point unit example .....                                                                                 | 165 |

| Figure A.1 Floating-point number representation .....                                                                                      | 166 |

| Figure A.2 Floating-point number bit patterns .....                                                                                        | 169 |

| Figure A.3 "Rounding to the nearest" examples .....                                                                                        | 172 |

| Figure A.4 "Rounding toward +infinity" example .....                                                                                       | 173 |

| Figure A.5 "Rounding toward -infinity" example .....                                                                                       | 173 |

| Figure A.6 "Rounding towards zero" example.....                                                                                            | 174 |

| Figure B.1 A vector in three co-ordinate systems.....                                                                                      | 178 |

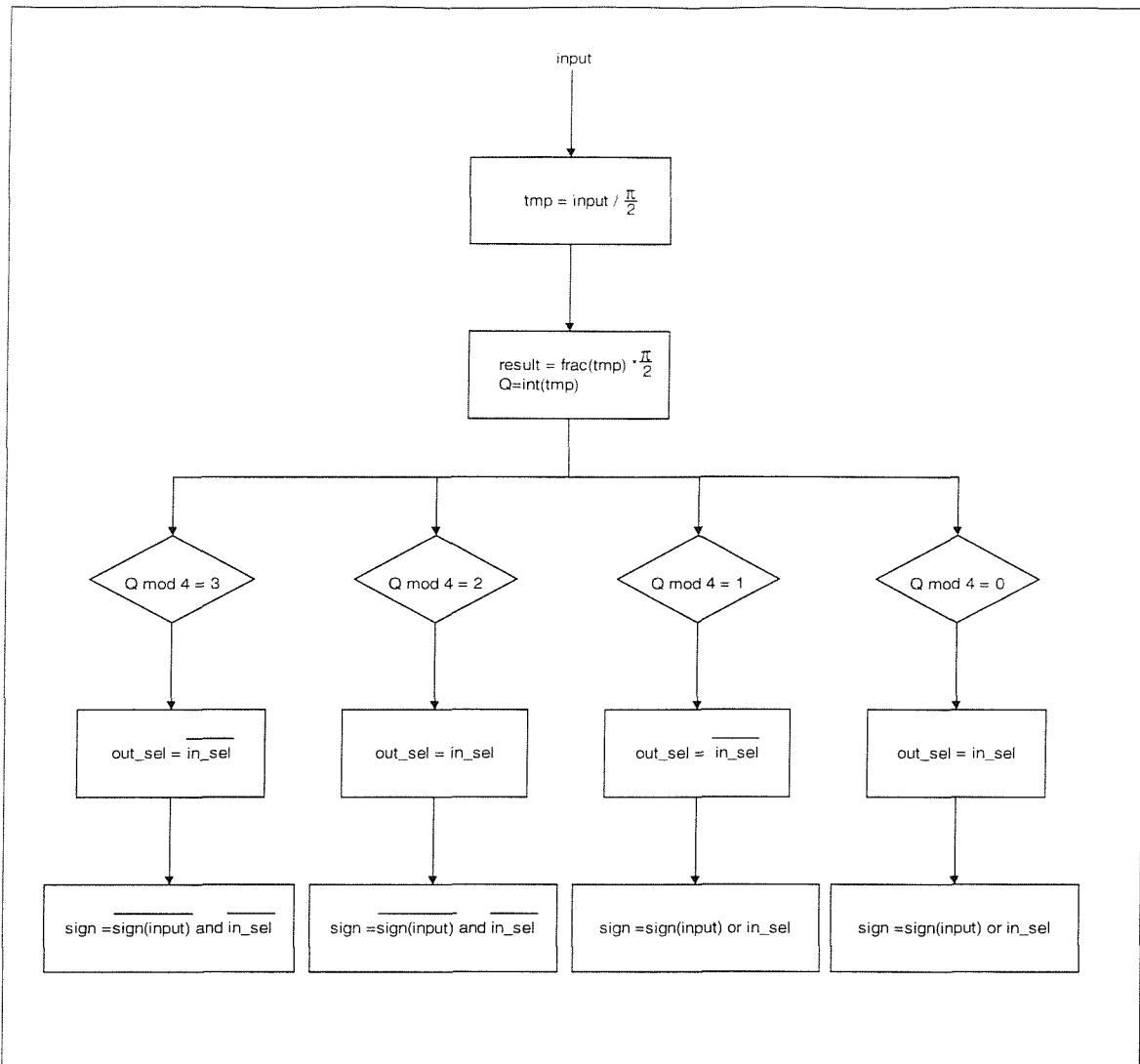

| Figure C.1 Sine/cosine pre-processing stage .....                                                                                          | 187 |

| Figure C.2 Sine/cosine range reduction flow chart.....                                                                                     | 189 |

| Figure C.3 Error in the sine/cosine generator using linear interpolation engine with a<br>single-table and for different table sizes ..... | 191 |

|                                                                                                                                         |     |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

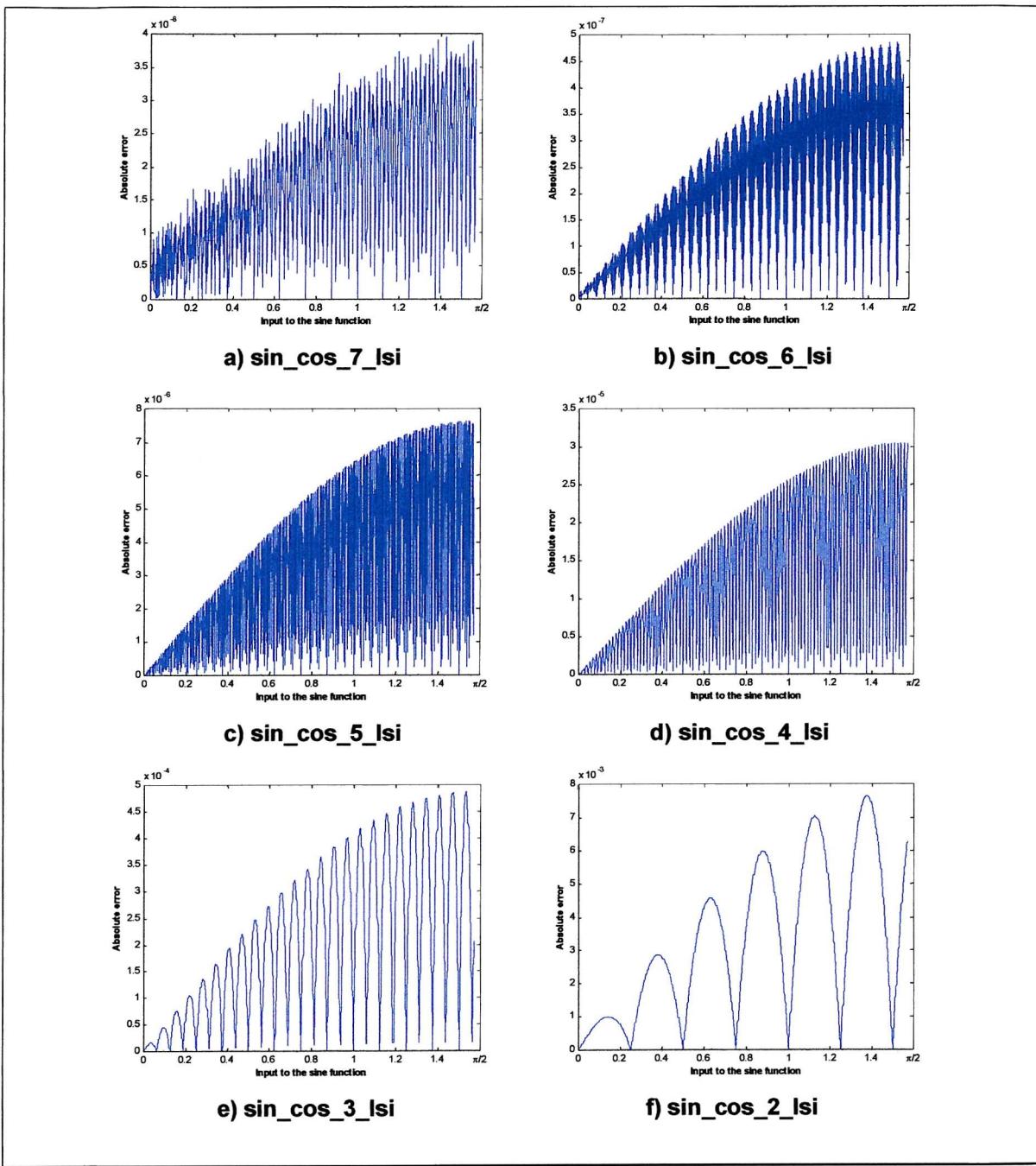

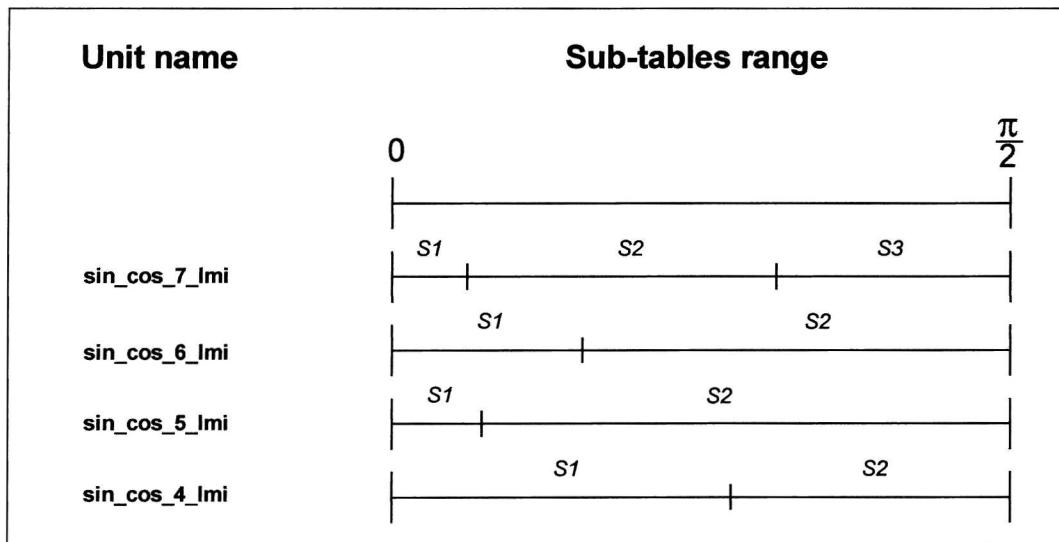

| Figure C.4 Error in the sine/cosine generator using linear interpolation and a partitioned table for different table sizes.....         | 192 |

| Figure C.5 Sub-tables range in the sine/cosine generator using linear interpolation and partitioned table .....                         | 192 |

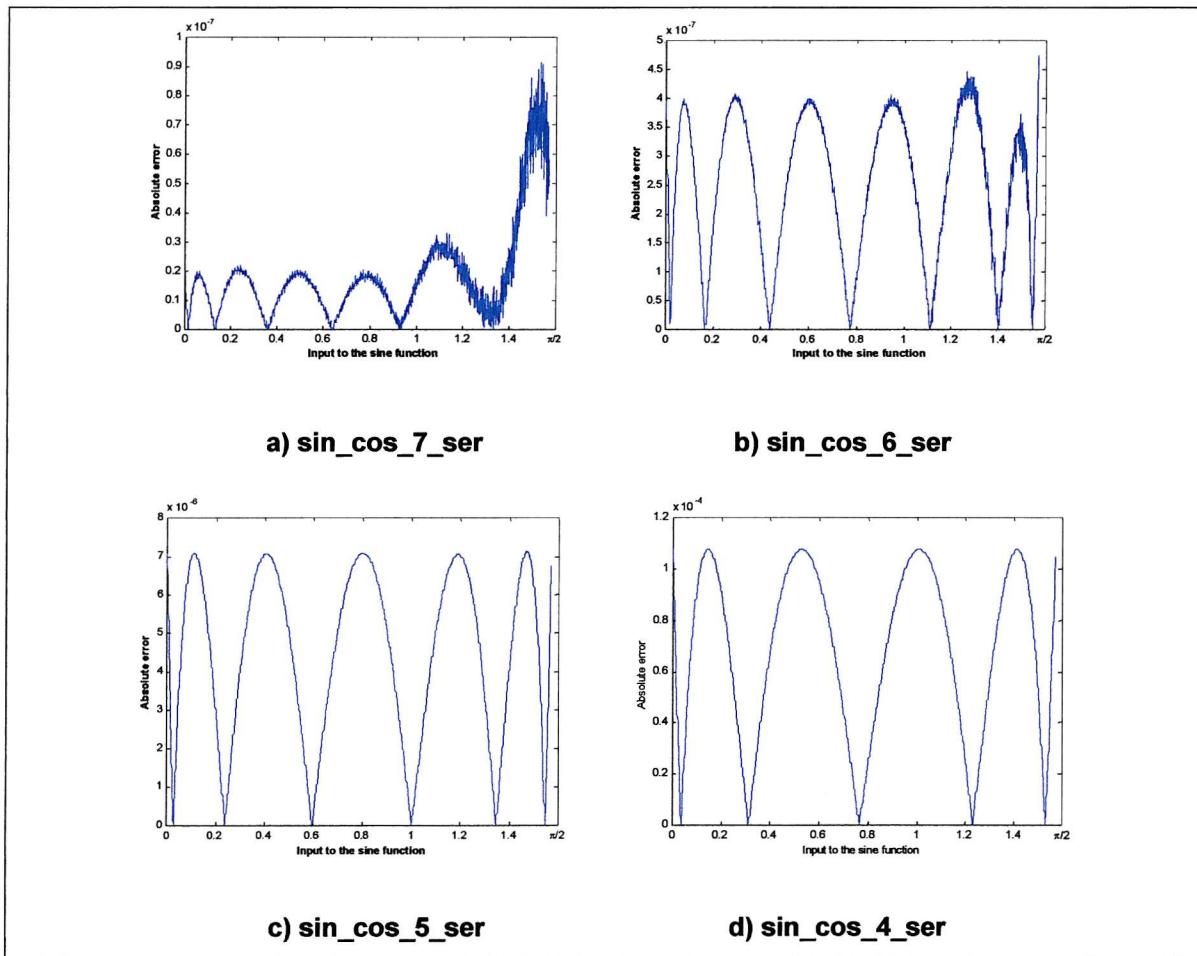

| Figure C.6 Error in the sine/cosine minimax engine for different approximation degrees                                                  | 193 |

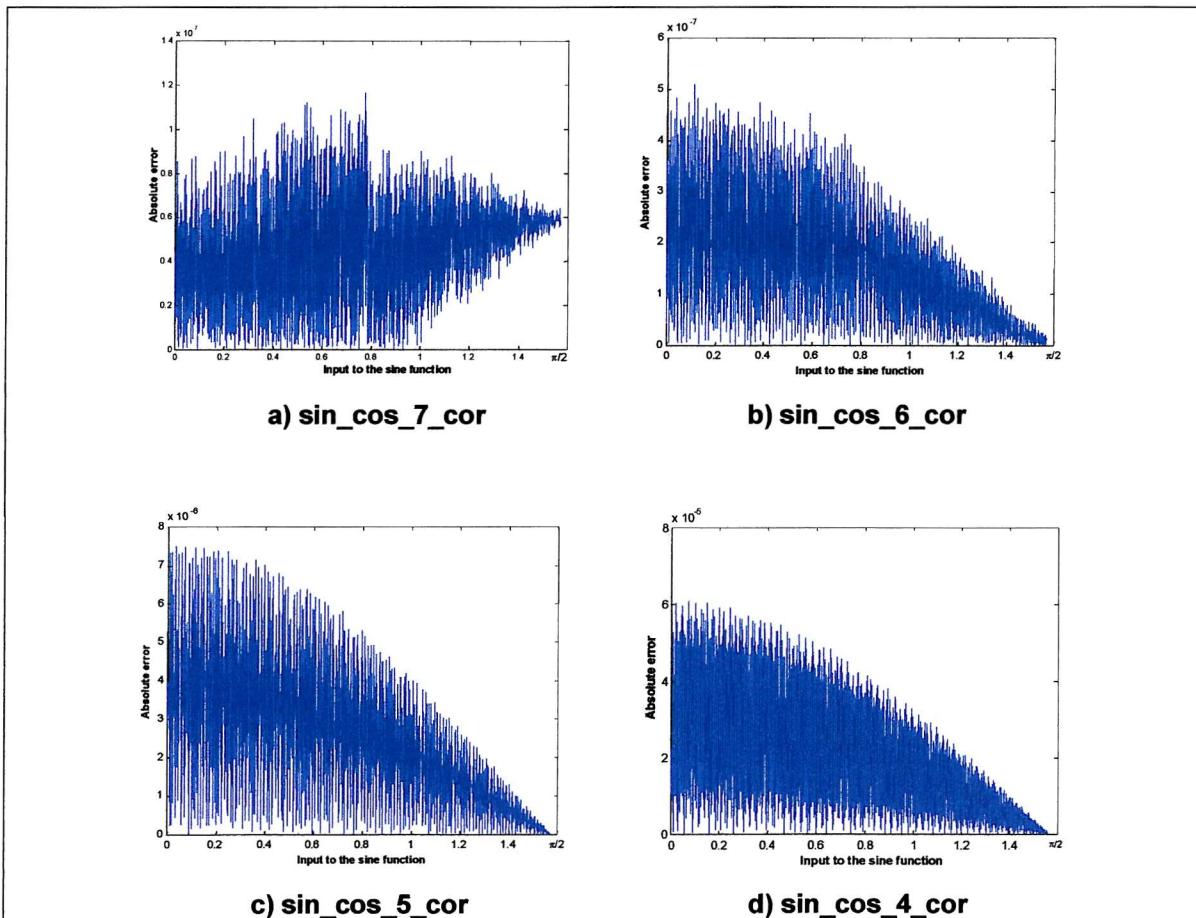

| Figure C.7 Error in the sine/cosine CORDIC unit for different number of iterations .....                                                | 194 |

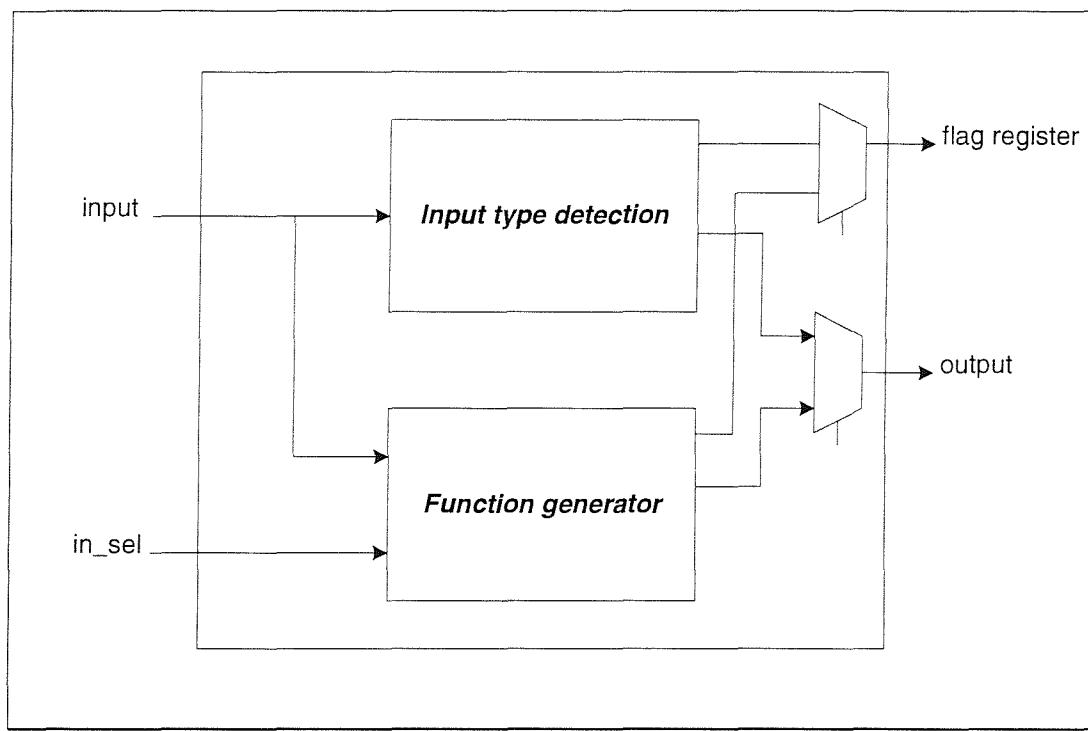

| Figure C.8 inverse sine/inverse cosine generation unit .....                                                                            | 195 |

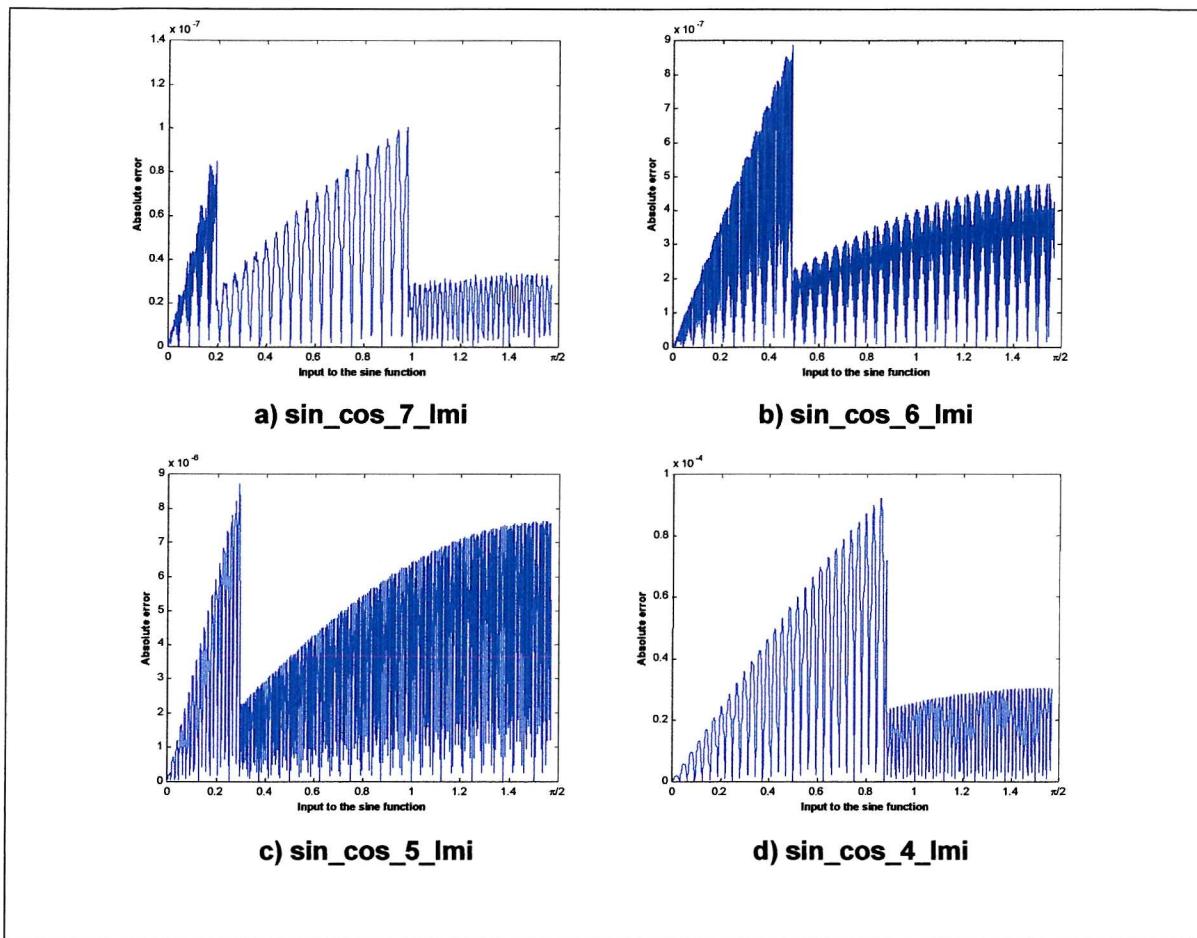

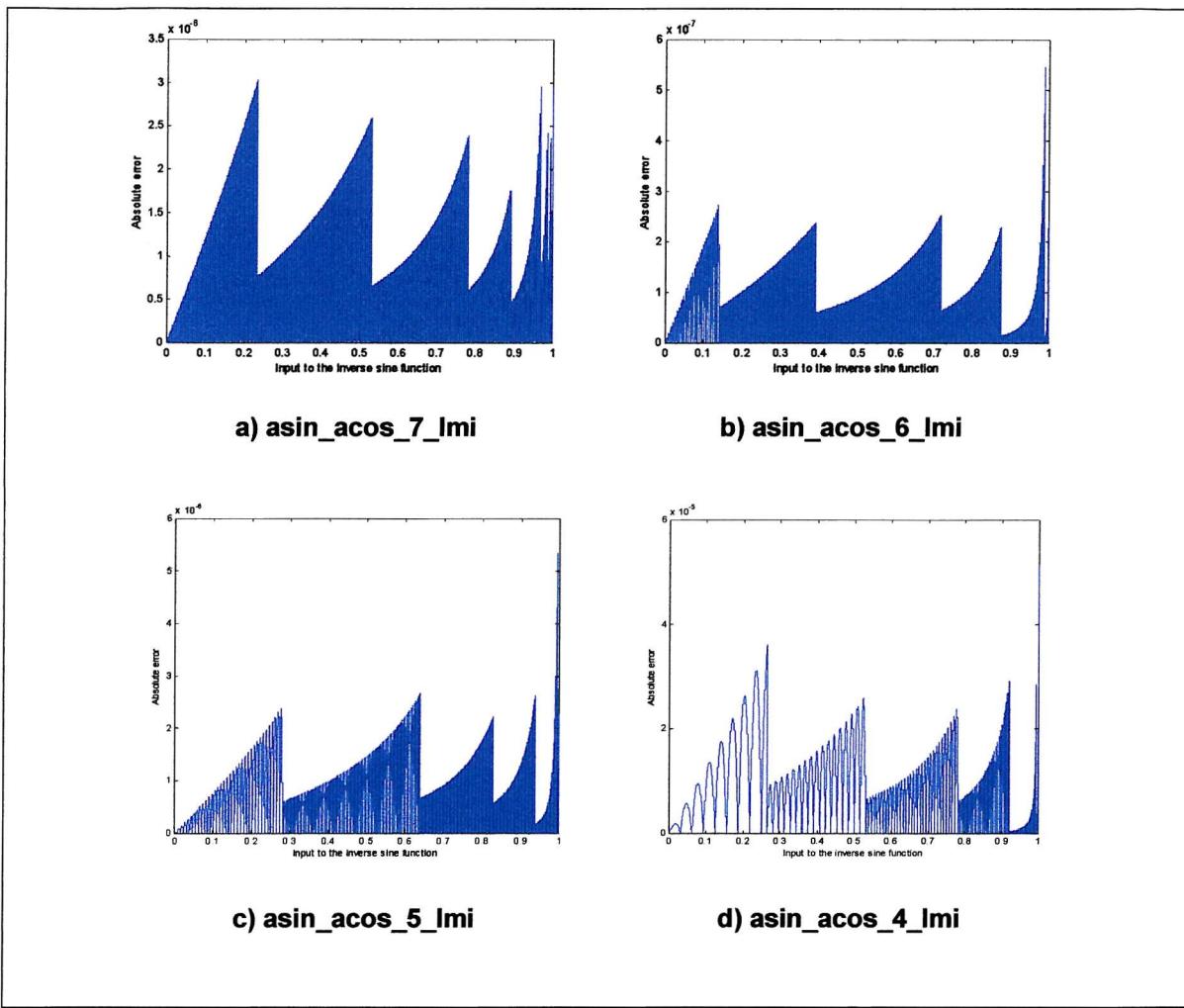

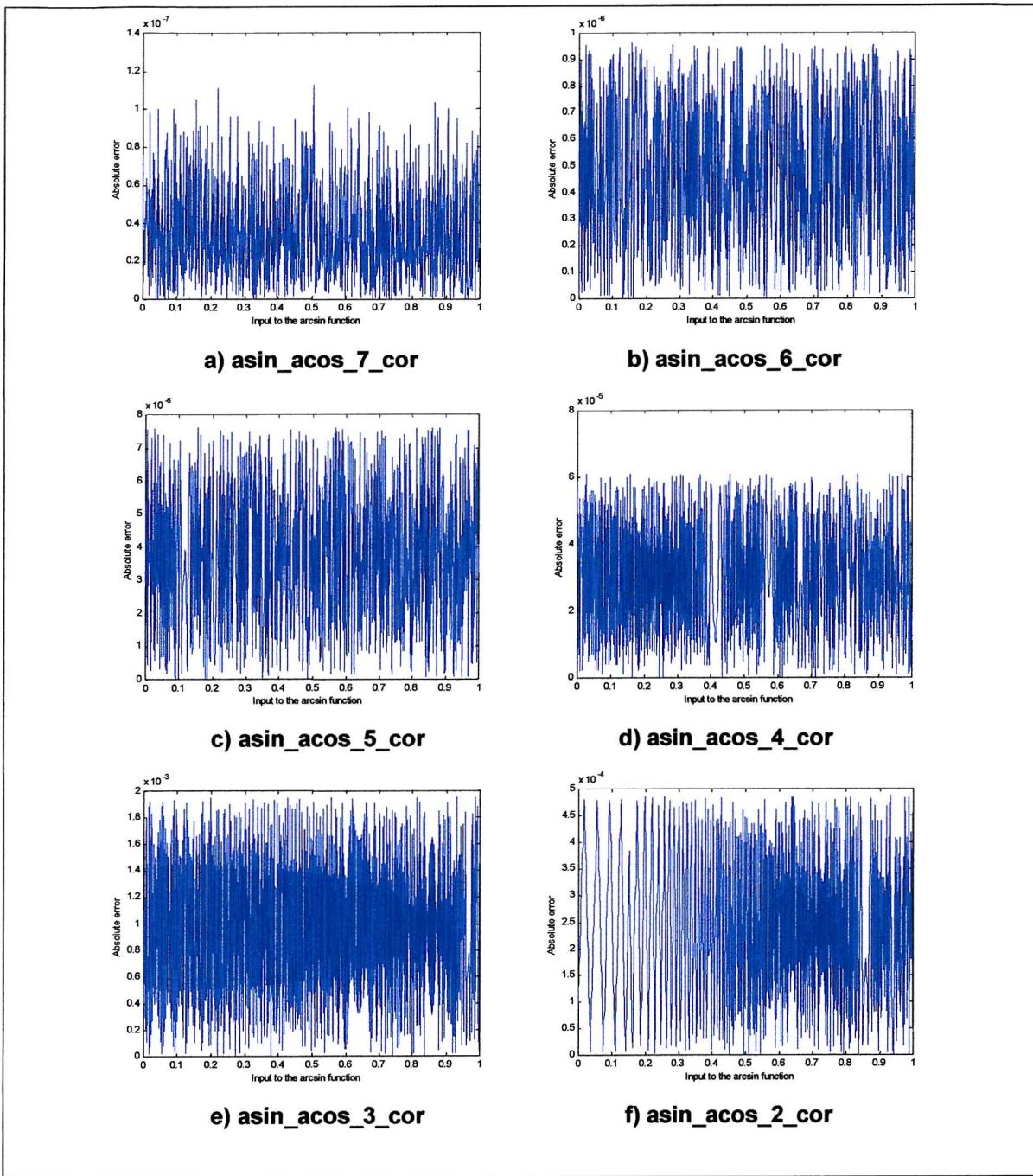

| Figure C.9 Error in the inverse sine/inverse cosine generator using linear interpolation engine with a partitioned table lookup.....    | 198 |

| Figure C.10 Error in the asin/acos generator based on the CORDIC engine for different number of iterations .....                        | 199 |

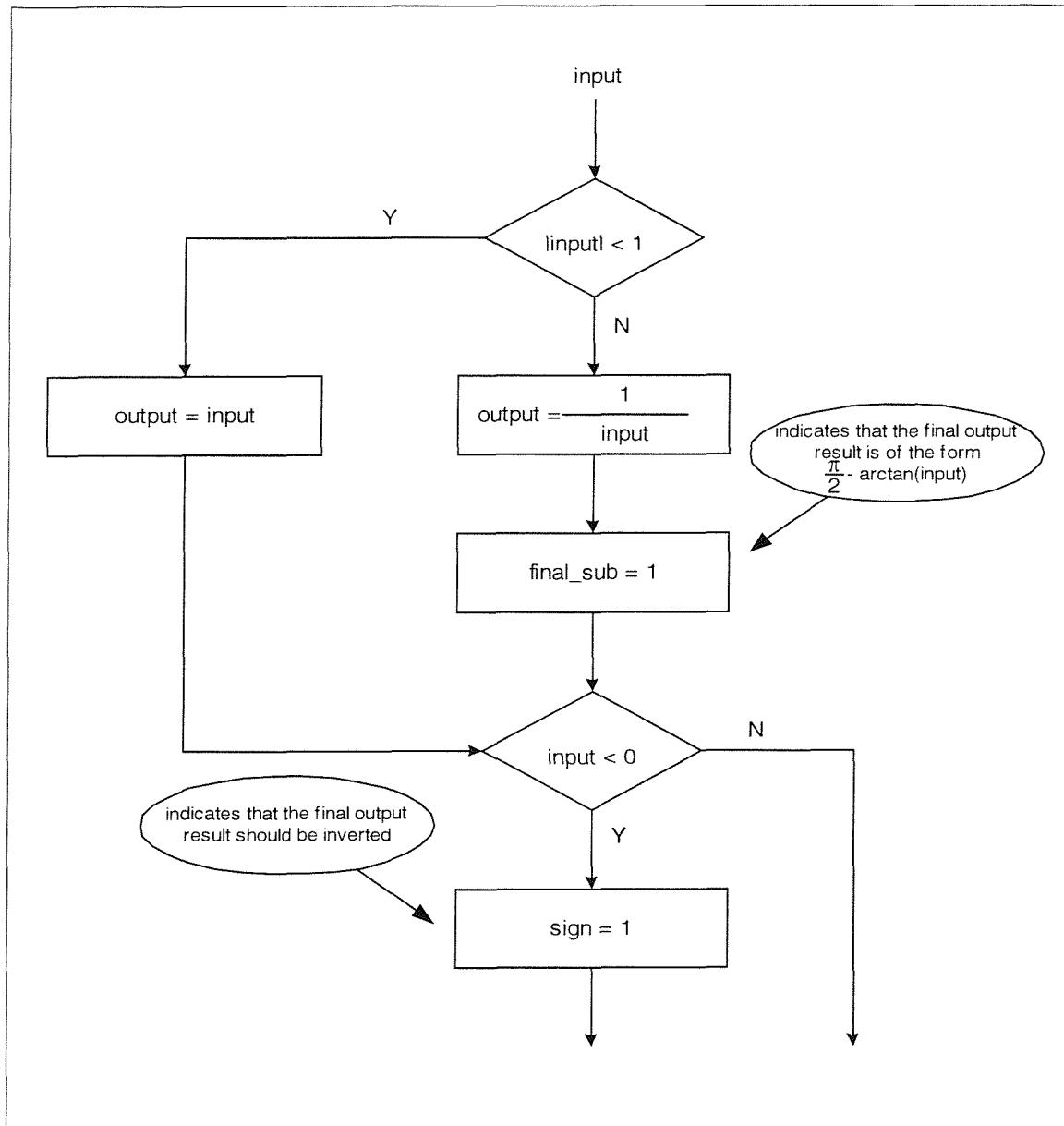

| Figure C.11 Inverse tangent range reduction flow chart.....                                                                             | 201 |

| Figure C.12 Error in the inverse tangent generator using a single table and linear interpolation for different table sizes .....        | 203 |

| Figure C.13 Error in the inverse tangent generator using a partitioned table and linear interpolation for different table sizes .....   | 204 |

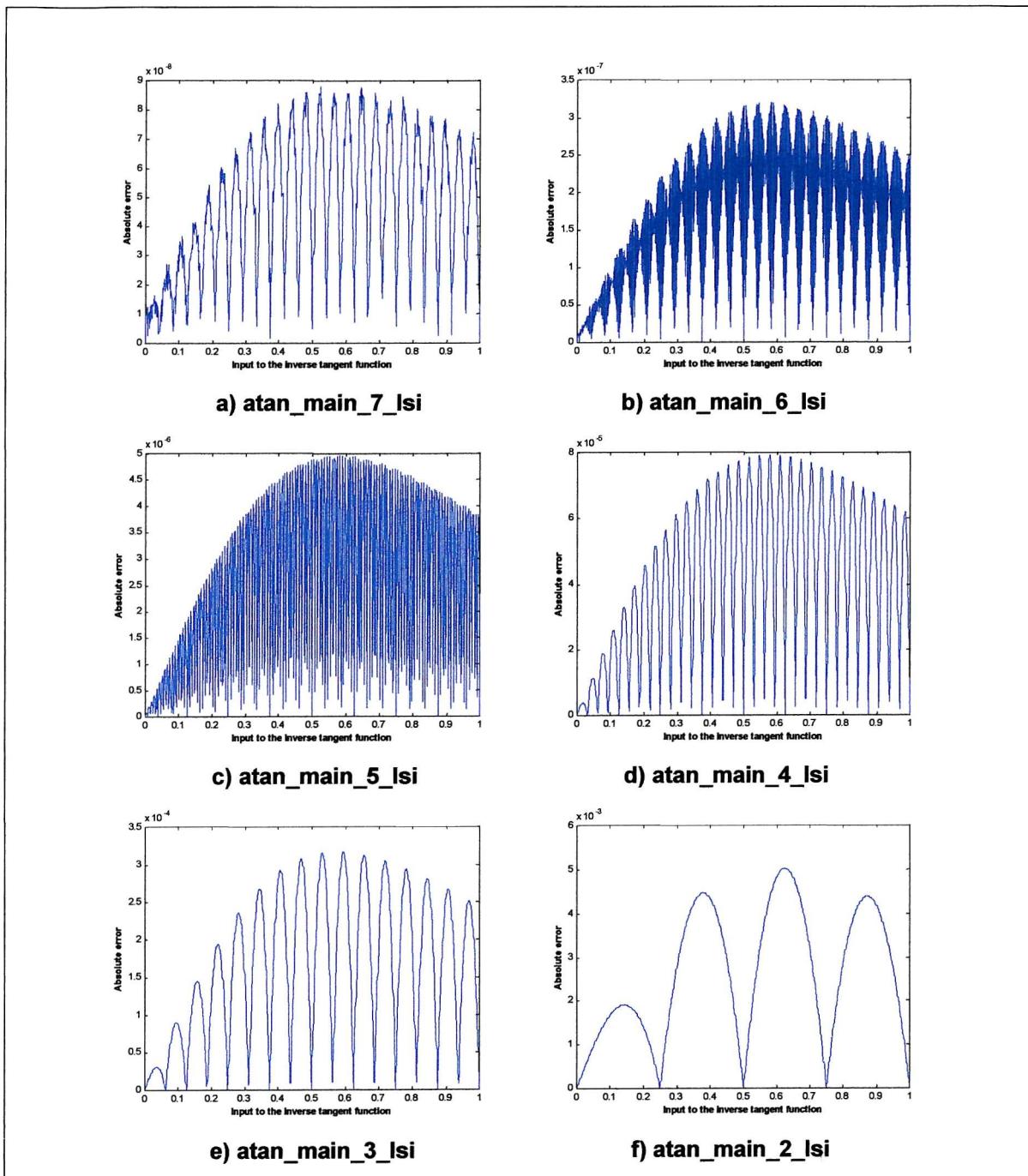

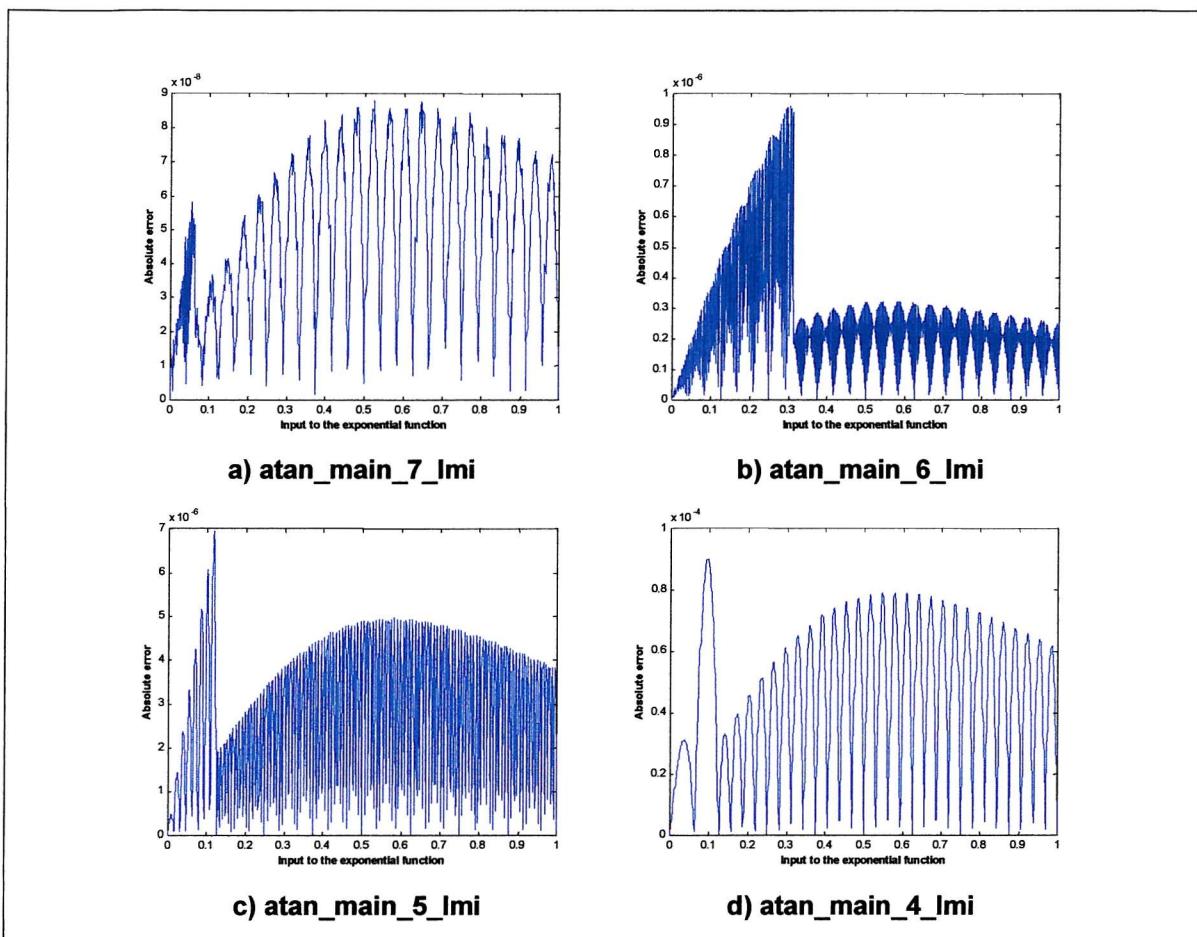

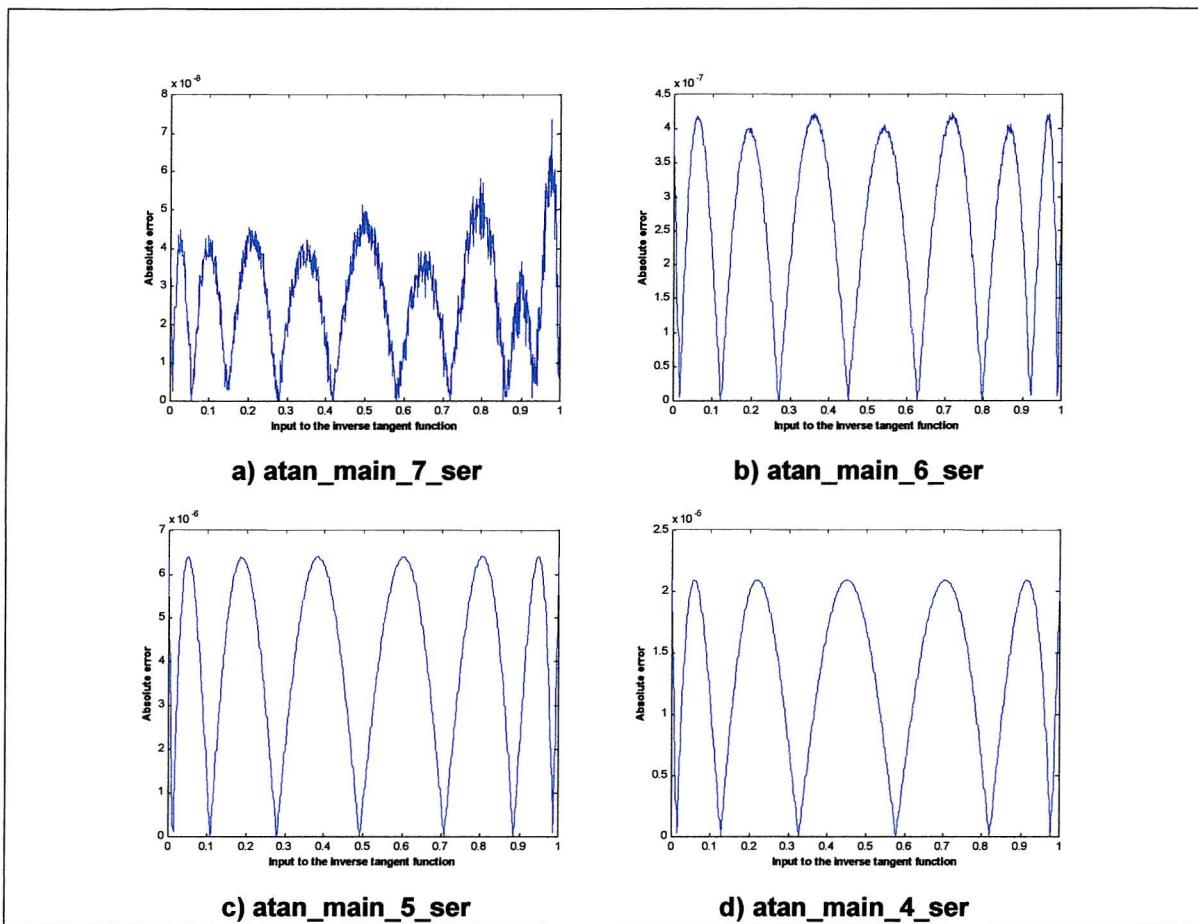

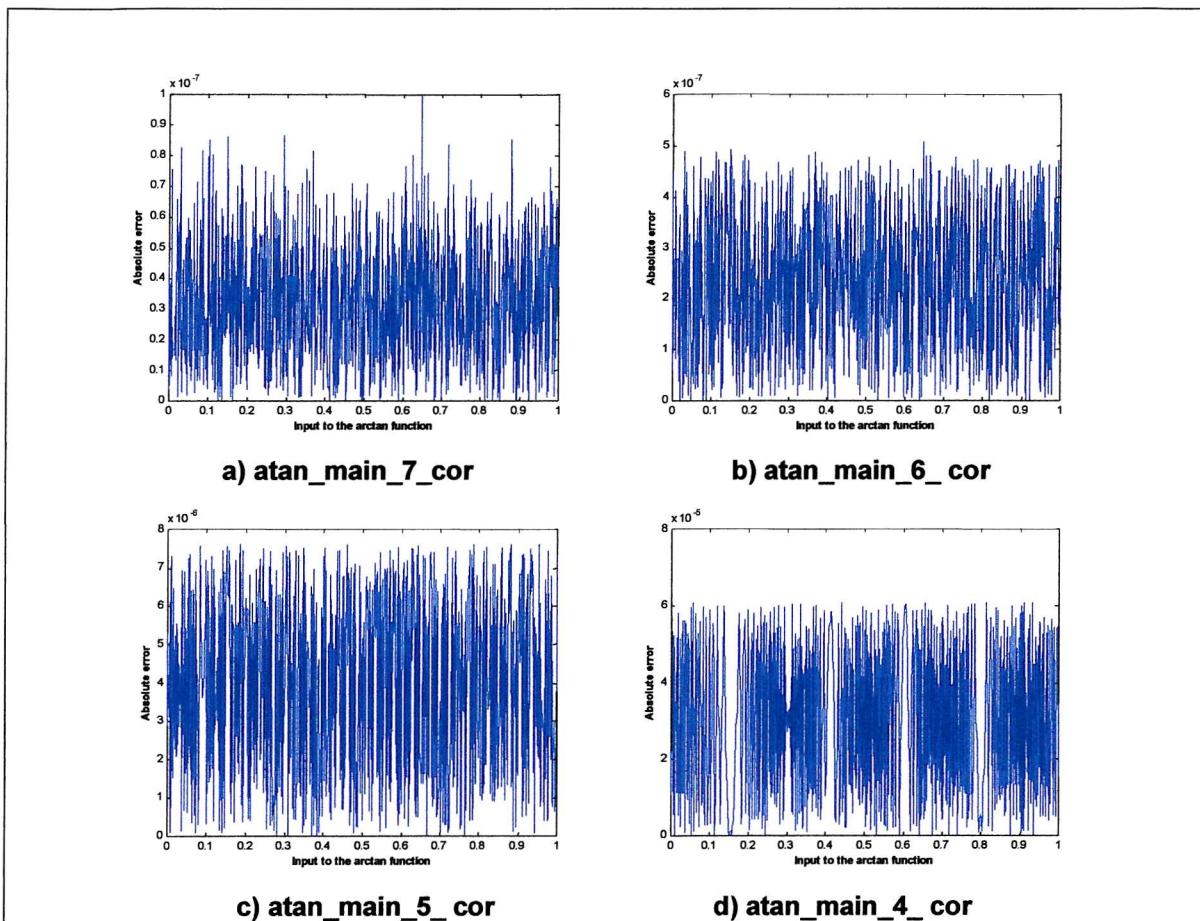

| Figure C.14 Error in the inverse tangent generator using the minimax approximation for different approximation degrees .....            | 205 |

| Figure C.15 Error in the inverse tangent generator using the CORDIC algorithm for different number of iterations .....                  | 206 |

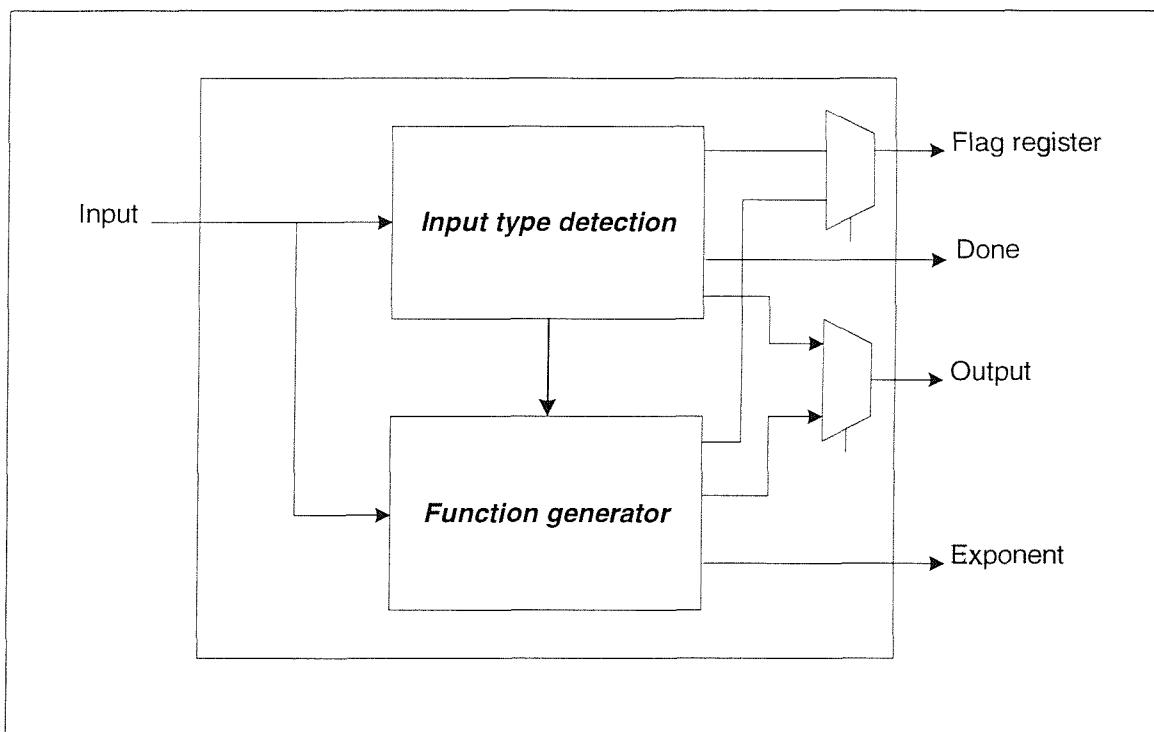

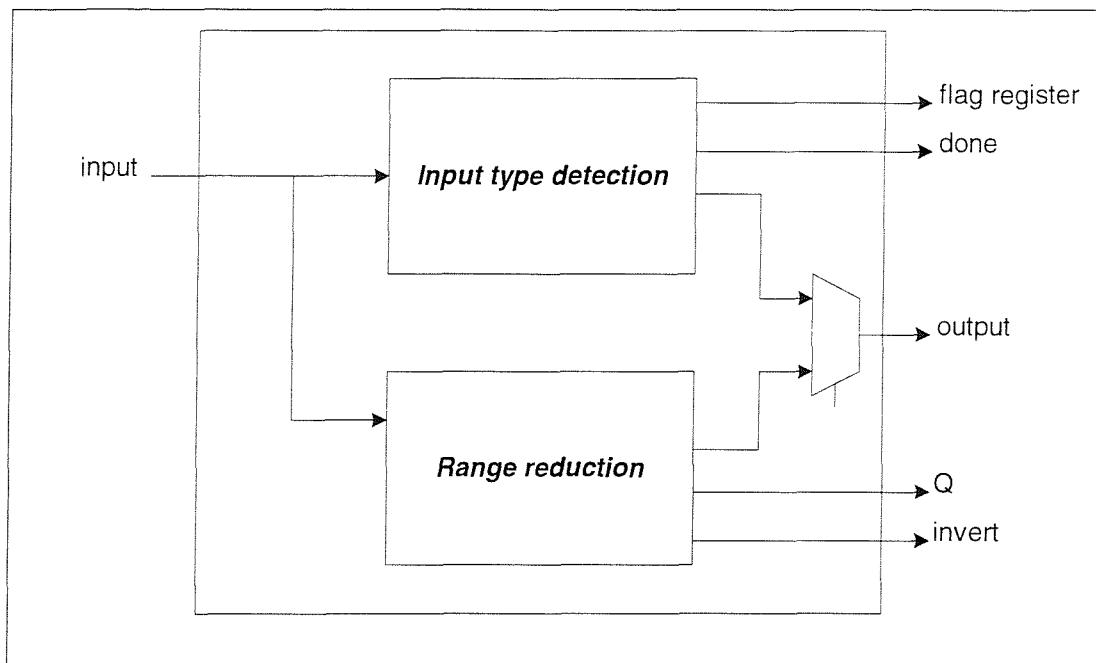

| Figure C.16 Initial unit in the logarithm generator unit.....                                                                           | 207 |

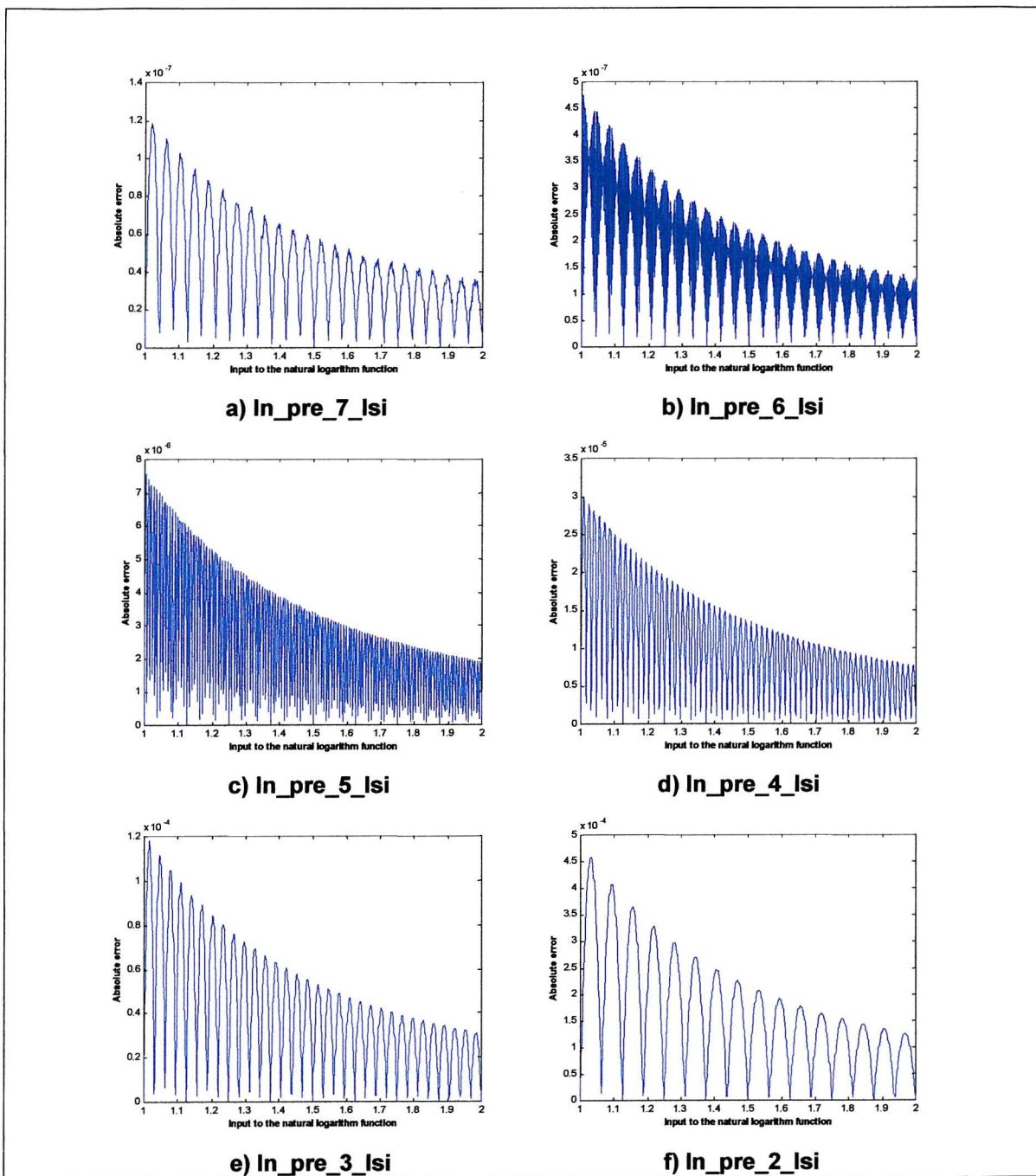

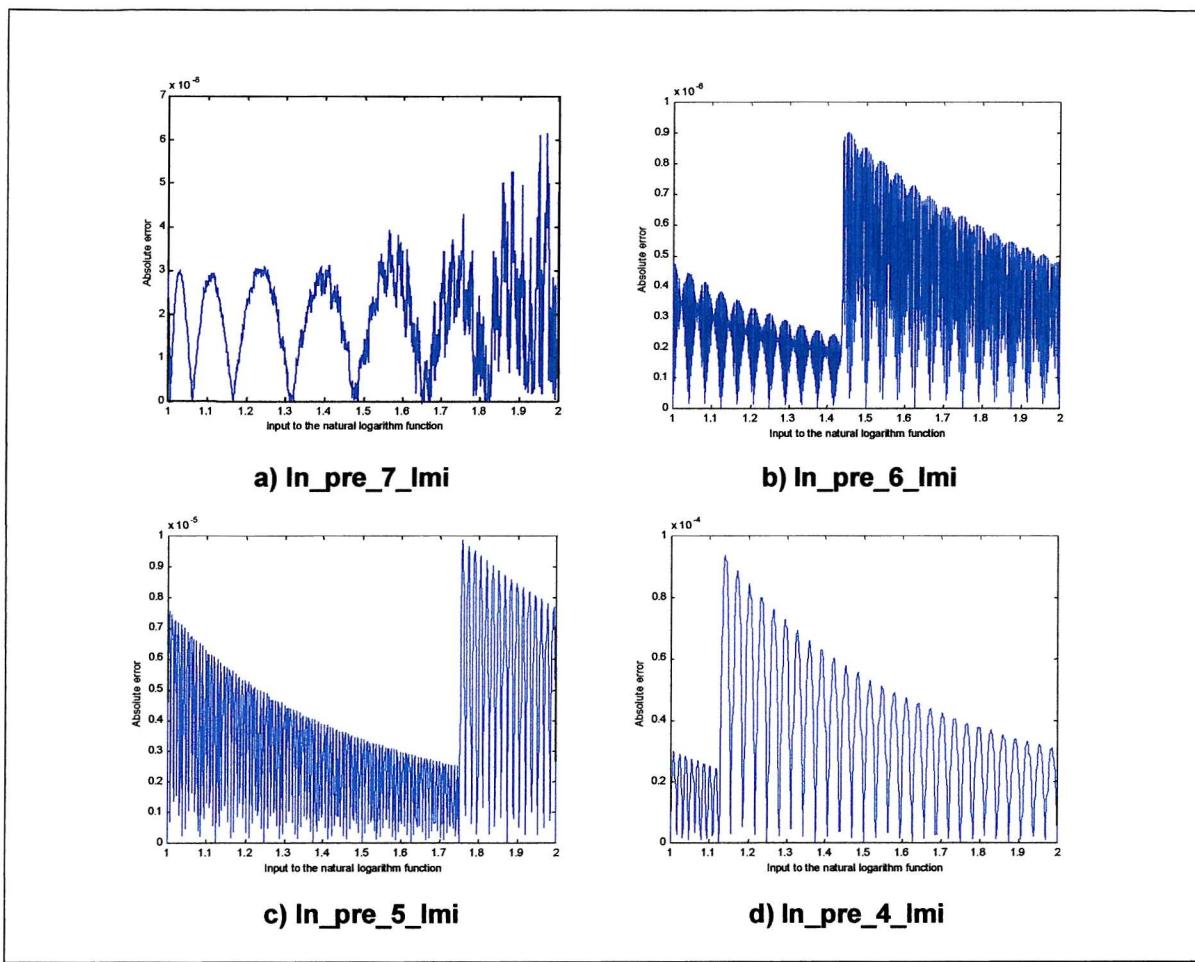

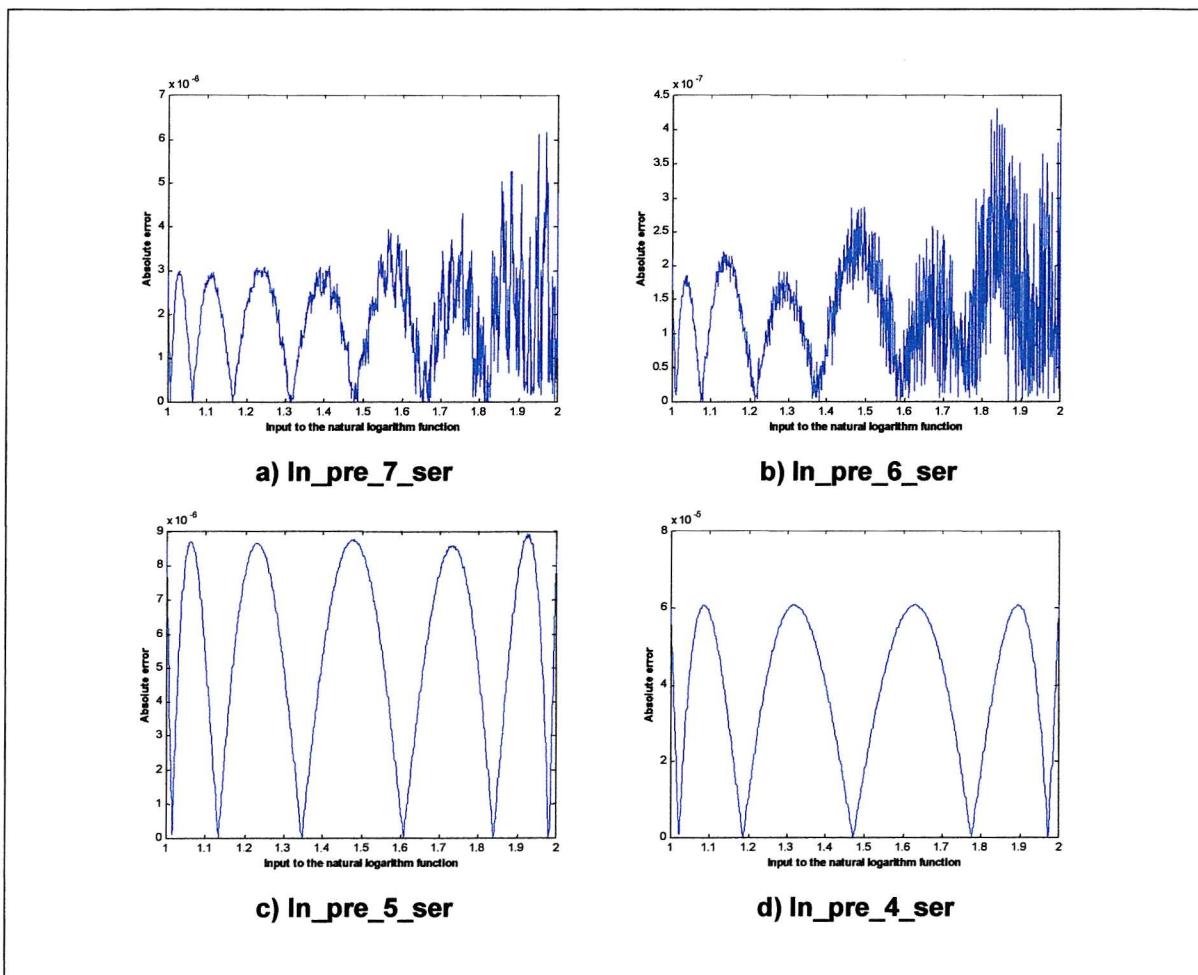

| Figure C.17 Error in the natural logarithm generator using a single table and linear interpolation for different table sizes .....      | 209 |

| Figure C.18 Error in the natural logarithm generator using a partitioned table and linear interpolation for different table sizes ..... | 210 |

| Figure C.19 Error in the natural logarithm generator using the minimax approximation and for different approximation degrees .....      | 211 |

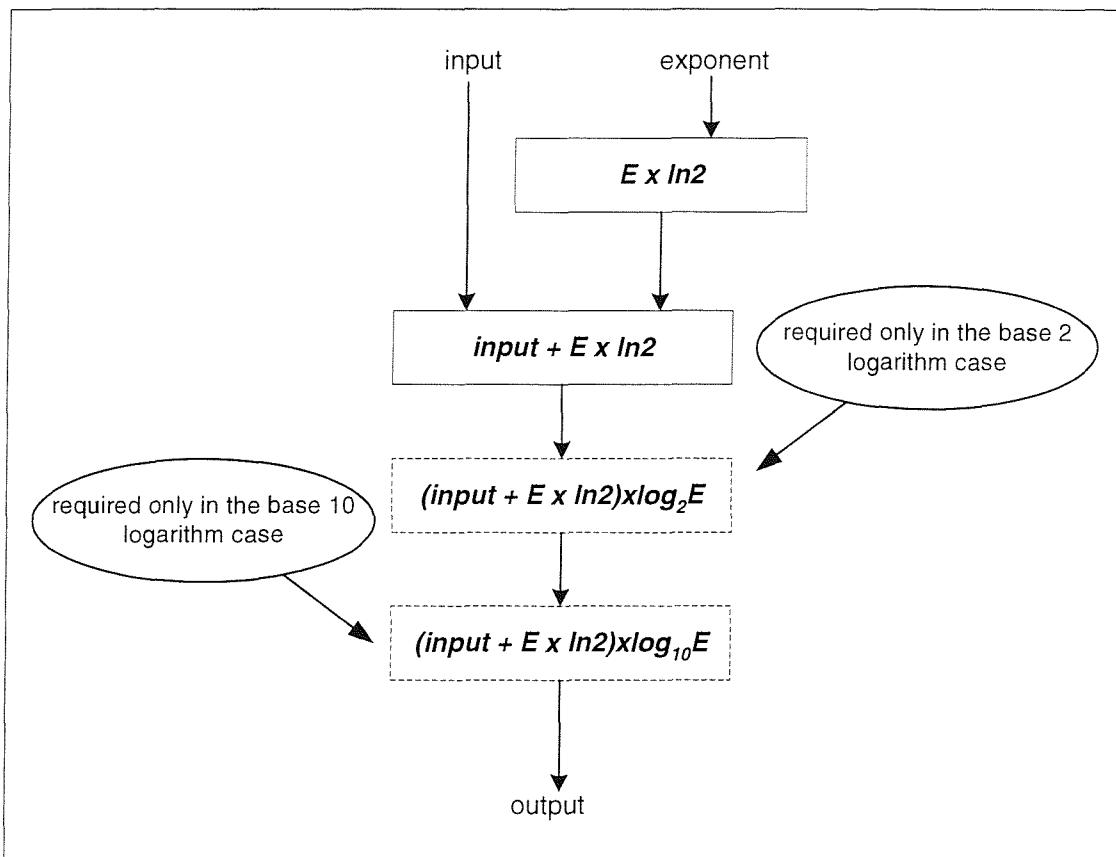

| Figure C.20 Data flow in the logarithm post-processing stage.....                                                                       | 212 |

| Figure C.21 Exponential pre-processing stage .....                                                                                      | 213 |

| Figure C.22 Error in the exponential generator using a single table and linear interpolation for different table sizes .....            | 215 |

| Figure C.23 Error in the exponential generator using the minimax approximation and for different approximation degrees .....            | 216 |

|                                                                                                                                   |     |

|-----------------------------------------------------------------------------------------------------------------------------------|-----|

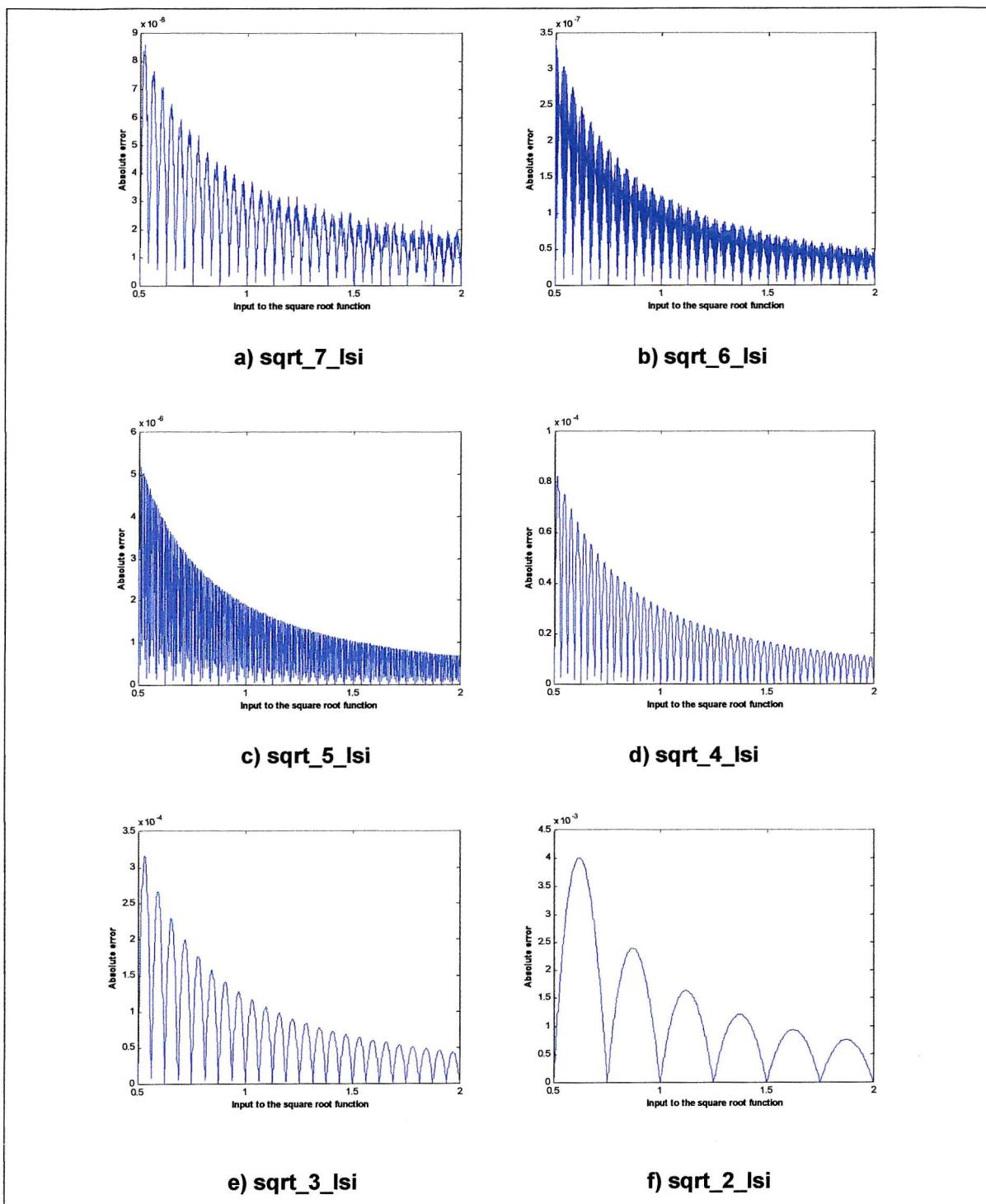

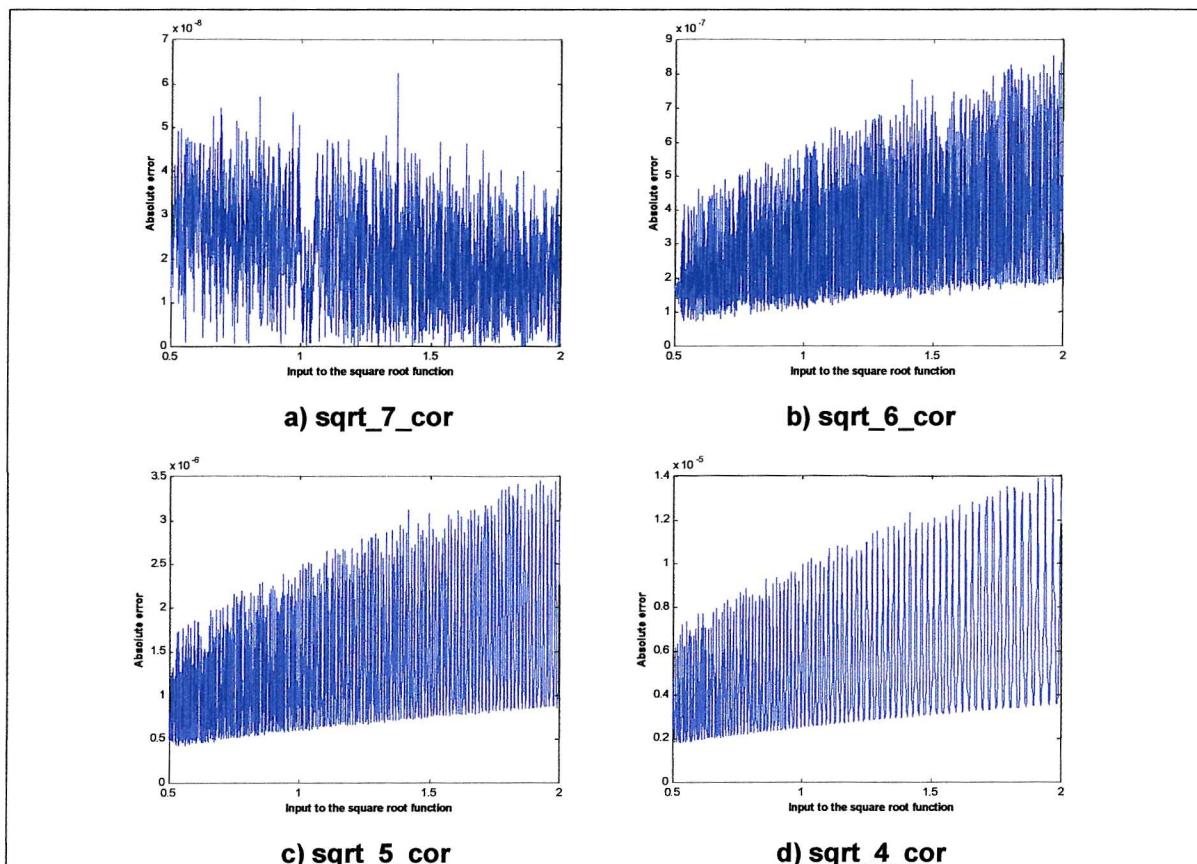

| Figure C.24 Error in the square root generator implemented as a single table lookup unit and for different table sizes.....       | 218 |

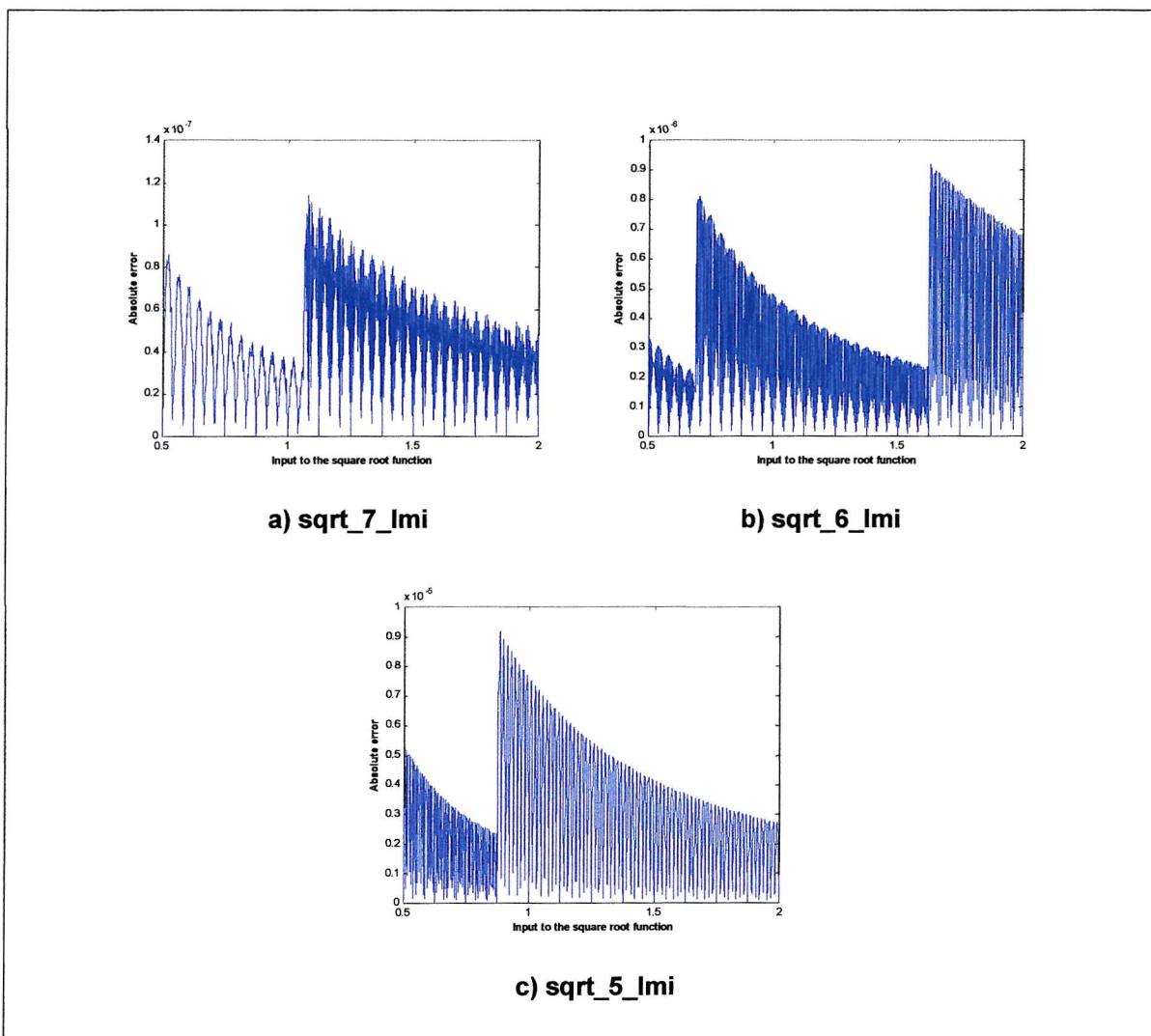

| Figure C.25 Error in the square root generator implemented as a partitioned table lookup unit and for different table sizes ..... | 219 |

| Figure C.26 Error in the square root generator using CORDIC and for different number of iterations .....                          | 220 |

| Figure D.1 ICODE instruction database file.....                                                                                   | 229 |

| Figure D.2 Floating-point instruction database file .....                                                                         | 230 |

| Figure D.3 Floating-point Module library file .....                                                                               | 232 |

| Figure D.4 Expanded ICODE instruction file.....                                                                                   | 233 |

| Figure D.5 Example ICODE file .....                                                                                               | 235 |

| Figure D.6 Example VHDL and ICODE files .....                                                                                     | 237 |

| Figure D.7 Example ICODE+ file .....                                                                                              | 238 |

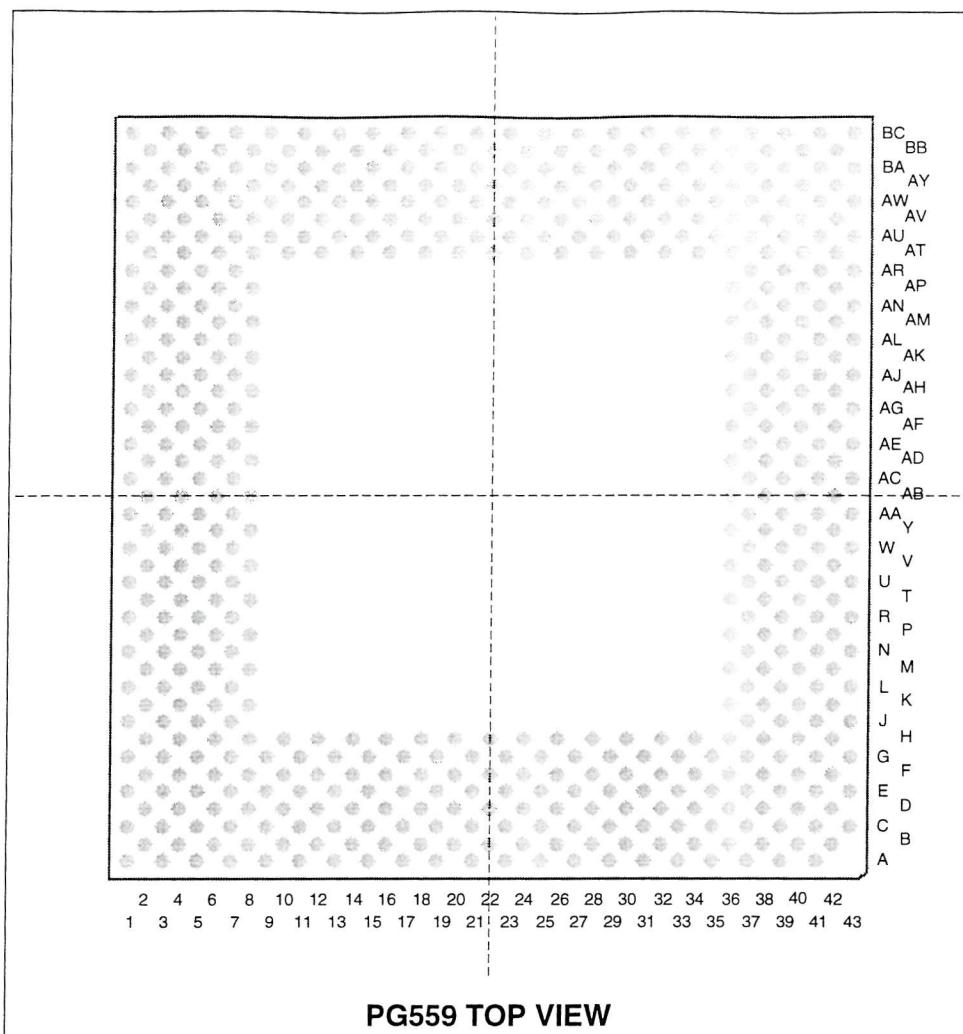

| Figure E.1 FPGA package for the Xilinx FPGA used in the board.....                                                                | 242 |

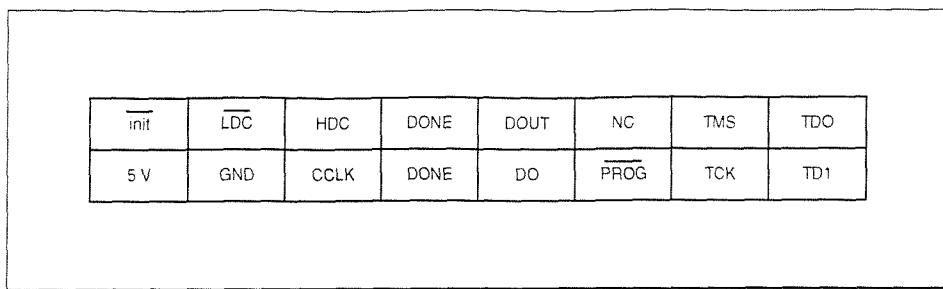

| Figure E.2 Serial programming cable connector .....                                                                               | 243 |

| Figure E.3 VGA adapter example.....                                                                                               | 251 |

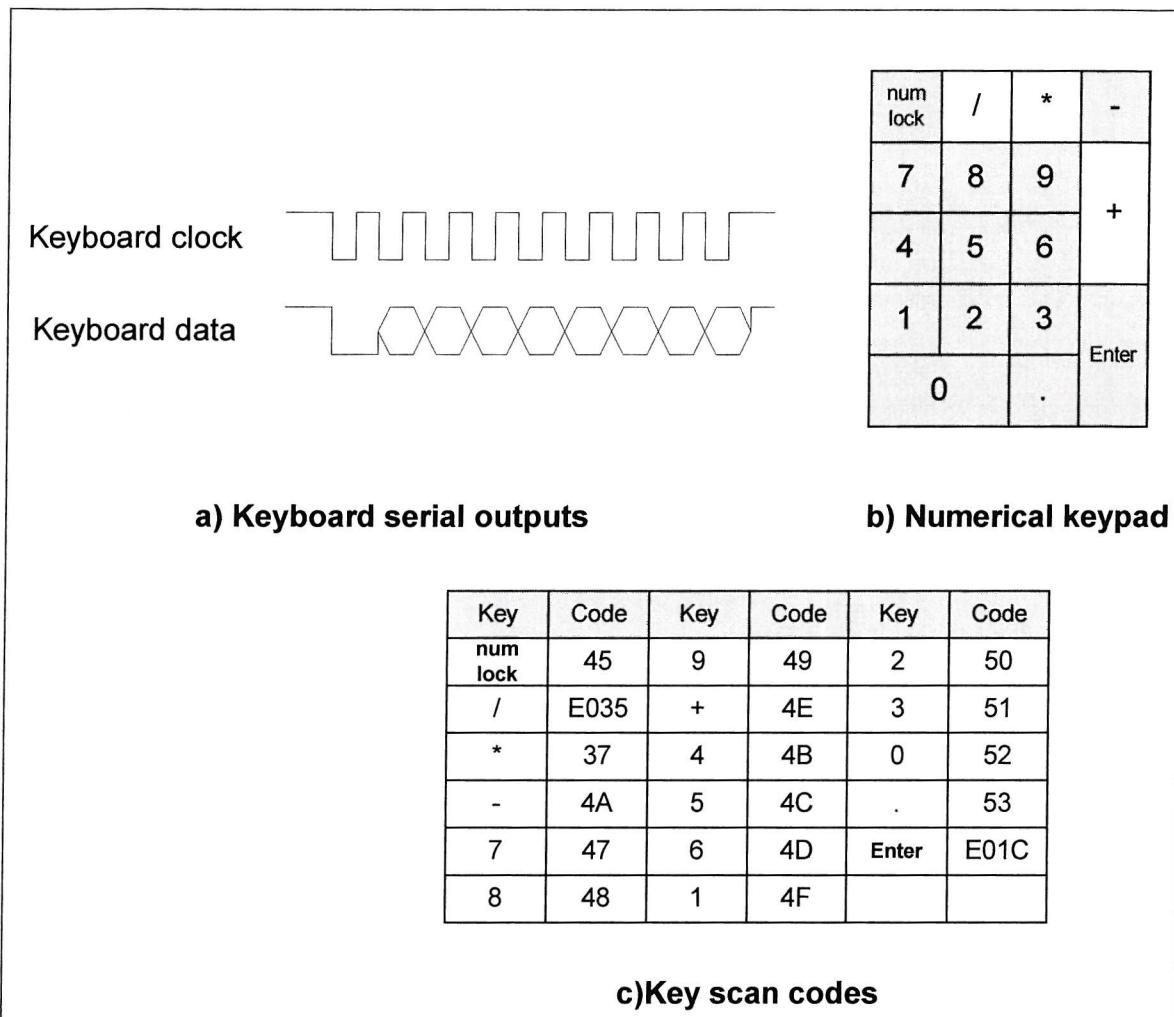

| Figure E.4 Keyboard Information .....                                                                                             | 253 |

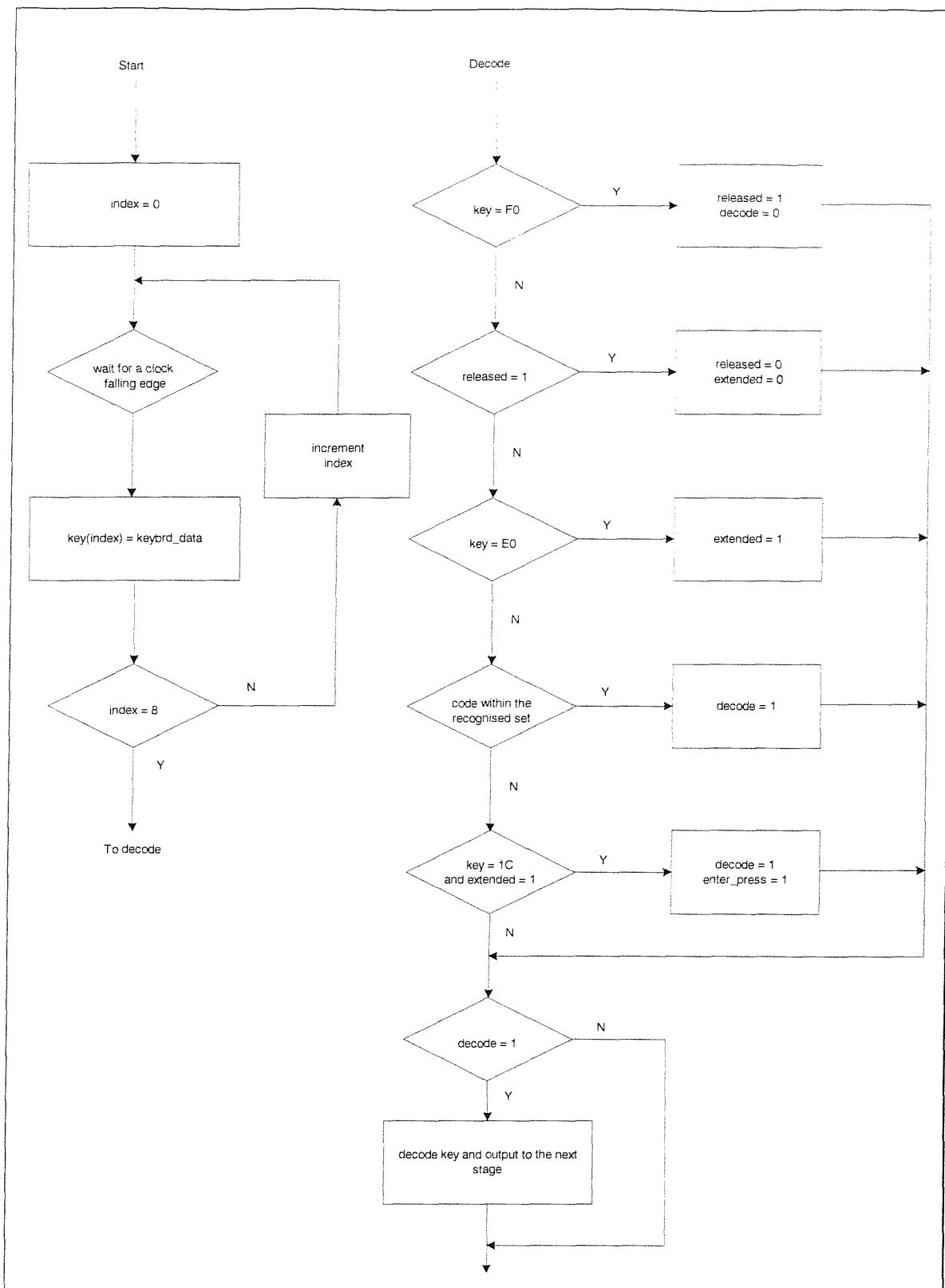

| Figure E.5 Keyboard interface flowchart.....                                                                                      | 254 |

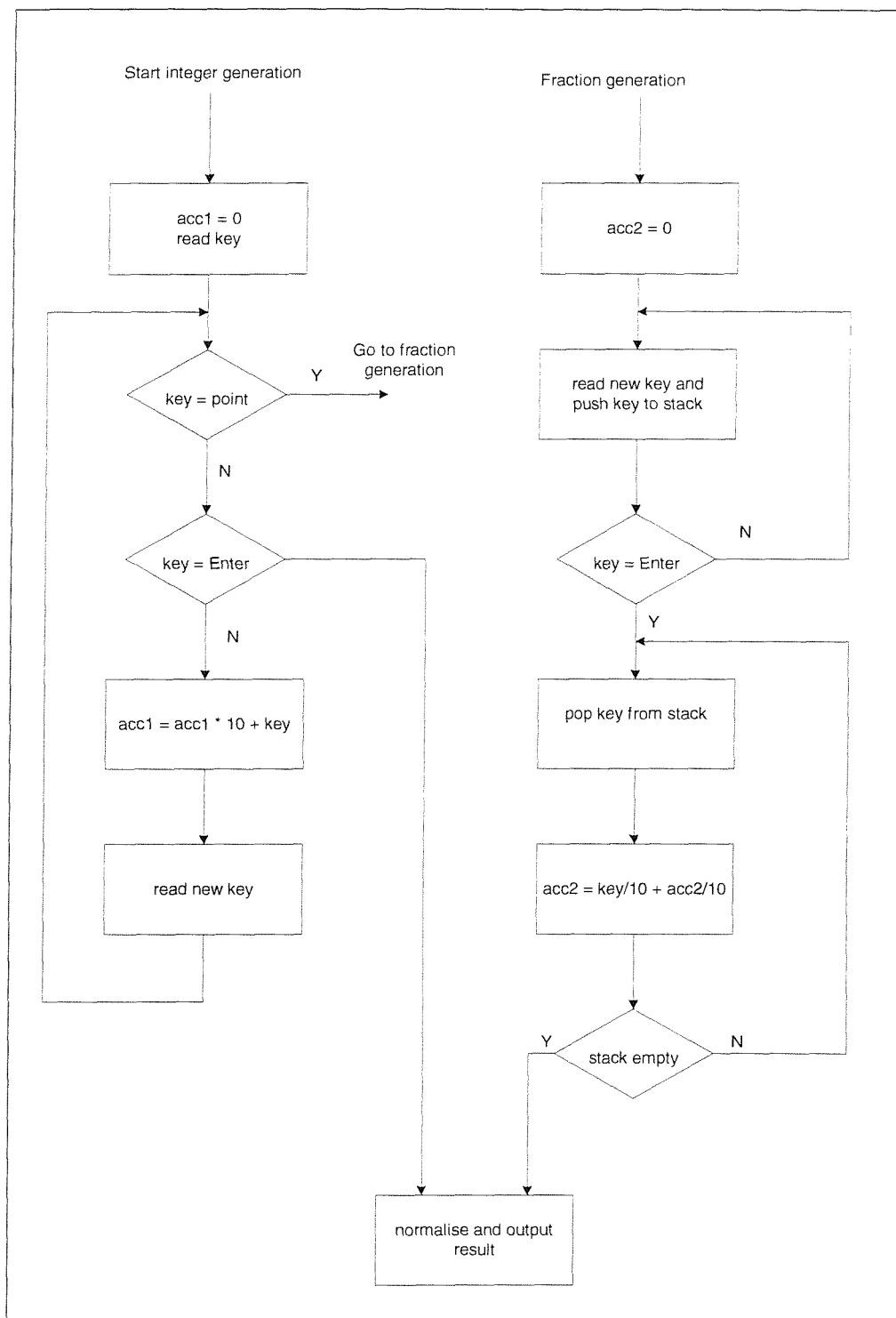

| Figure E.6 Format conversion unit flowchart .....                                                                                 | 256 |

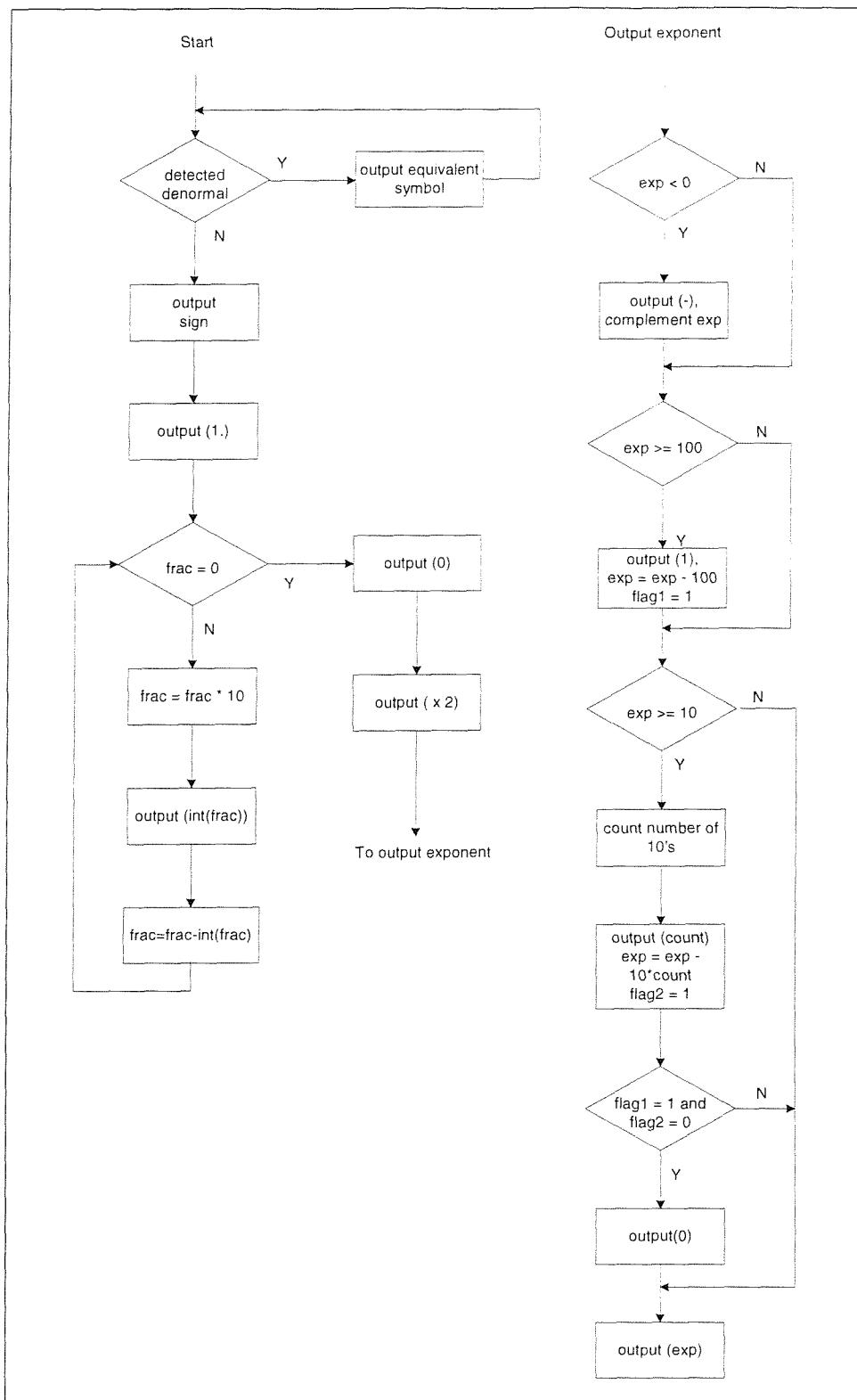

| Figure E.7 Output stage type conversion flowchart.....                                                                            | 259 |

# Acknowledgements

I would like to express my profound thanks to a number of people around me who helped make this project reality.

First I would like to thank my supervisor, Professor Andrew Brown. His constant and consistent guidance, advice, encouragement, and confidence were essential for completion of this thesis, and are highly appreciated

I would also like to thank Dr. Alan Williams for his invaluable help and great patience and diligence in answering my endless requests.

Thanks to all other members of the Electronics Systems Design Group at the University of Southampton, in particular I am grateful to Dr. Mark Zwolinski for his ideas and information and for giving me the chance to join the University as an MSc student at the first place.

Finally, I would like to say a big thanks to my family. They have given their unconditional support, knowing that doing so contributed greatly to my absence in my postgraduate studies, during which we could have been geographically closer.

# Chapter 1

## Introduction

A floating-point number representation can simultaneously provide a large range of values and a high degree of precision. However, their manipulation is considerably more complicated than the corresponding fixed point operations. As a result, a portion of modern microprocessors is often dedicated to hardware for floating-point computation.

In the past, silicon area constraints have limited the opportunity of synthesising floating-point arithmetic units. Advances in integrated circuit fabrication technology have resulted in both smaller feature size and increased die area, which has provided a larger transistor budget. It is now therefore possible to implement floating-point systems on an ASIC or even programmable logic devices. However, the complexity of floating-point units is still a major limitation in realising cost effective, low volume systems. To overcome this limitation, advances in current CAD tools are needed, to make it possible to sensibly implement floating-point systems.

Behavioural synthesis works on a description that specifies the relationship between system inputs and outputs by describing abstract data structures and functions to manipulate them. The physical structure is not described, as the emphasis is on what the design does and not how it does it. In addition, the data flow manipulation aspects for a synthesis system are not generally concerned with the data *type*; the limitations of integer arithmetic are imposed simply by the lack of functional units for more complicated data types.

The MOODS (Multiple Objective Optimisation in Data and control path Synthesis) [1, 2, 3, 4, 5] is a behavioural synthesis system which transforms a VHDL (Very High Speed IC Hardware Description Language) [6] description into a structural netlist. It implements global optimisation of a design data flow and control graph by the repeated application of small, reversible (behaviour preserving) transformations. The system is designed to

support overall optimisation with respect to widely differing objectives: currently these are total area and maximum delay. The manipulation of these objectives form the basis for exploration of the design space, which is defined as the n-dimensional space that contains all possible implementations of a specific design. The exploration is steered by a simulated annealing algorithm that allows the diverse penalty functions from the various optimisation criteria to be compared.

This thesis describes an enhancement to the basic MOODS synthesis system to support the processing of designs containing floating-point (and complex) arithmetic. In particular, the development of a floating-point module library and a floating-point optimiser capable of making strategic decisions about the high level binding of each floating-point operation in a way that meets the user's pre-defined goal.

The thesis is divided into seven chapters. Chapter 2 provides a general introduction to behavioural synthesis and describes the basic MOODS synthesis system together with more detailed examination of the core synthesis sub-tasks. This is followed in chapter 3 by a discussion of some related work and commercial systems.

The design and implementation of the floating-point library is described in chapter 4, along with several additional improvements to make the floating-point library integration more flexible.

Chapter 5 provides an in-depth look at the floating-point optimisation challenges and the way they were handled.

Chapter 6 highlights the development of a general purpose FPGA prototyping board and details the design and synthesis of an exemplar: a cubic equation solver, utilises the floating-point system discussed in the previous chapters.

Finally, chapter 7 concludes by suggesting a number of enhancements to the present system providing areas for further research.

A number of appendices are also included providing additional information on various aspects of the work. In particular, Appendix A outlines the main features of the IEEE 754 floating-point standard. Appendix B contains a detailed discussion of the CORDIC

algorithm. Appendix C provides further details of the floating-point library design and implementation. Appendix D gives implementation details of the software, and Appendix E gives details of the hardware used to support the demonstrator. Finally, Appendix F contains a pre-print of a paper submitted to IEEE-CAD.

# Chapter 2

## MOODS and behavioural synthesis

Digital designs can be distinguished by the level of abstraction required to describe them in three main domains [7, 8]: *Algorithmic* or *behavioural level* views the system as a set of variables and functions to manipulate them. *Register transfer level*, where the system is described as a set of registers and a set of transfer functions specifying the flow of data between these registers [9]. *Logic level* describes the system as a network of logic gates and flip-flops with logic equations specifying the behaviour.

Behavioural or high-level synthesis tools [7, 8, 10, 11, 12] bridge the gap between an abstract behavioural specification of a digital system and a register transfer level structure that realises the given behaviour. It provides an environment that allows the designer to experiment with a wide range of structural alternatives.

Starting with a behavioural description of a design and a set of user specified objectives, behavioural synthesis builds a datapath by allocating hardware elements (functional units, storage units and interconnects) and provides a controller to specify a set of operations to be performed during every control step. It frees the designer from the difficulties of selecting a good implementation, as it does not include design decisions such as timing and parallelism.

### 2.1 VHDL for behavioural synthesis

VHDL [6] is a language for describing digital systems. It arose from the program funded by the US Department of Defense in the late 1970s and early 1980s. In 1986, VHDL was proposed as an IEEE standard, and it was adopted as the IEEE 1076 standard in December 1987. The language is being used for documentation, verification and synthesis of large

digital designs. This is actually one of the key features of VHDL, since the same VHDL code can theoretically achieve all three of these goals.

The description of a digital system using VHDL is achieved with a set of *design units*. Each element in this hierarchy consists (usually) of a pair of design units: an *entity* and an *architecture*. The entity describes the IO ports of the element, and the architecture describes the internal structure and/or the functionality (thus it is possible for an entity to correspond to multiple architectures). This partitioning allows the design of an overall system to be distributed amongst a number of designers; once the entity definitions are established and agreed, the architecture designs can be carried out independently.

Within an architecture, VHDL allows three types of statement to describe the internals:

1. *Component instantiation* allows the use of any entity/architecture pair as a component in the design architecture. Each instantiation has two parts: the *name* and the *port map*. The component name defines the unit to be used, while the port map defines the way the signals in the design connect the component IO ports.

2. *Signal assignment* is used to describe the dataflow through the system. It is divided into two groups: 1) simple signal assignment (`x <= a xor b;`), which simply assigns to the target signal the value of the source expression, and 2) conditional signal assignment (`x <= a xor b when c = '1' else not (a xor b);`), which assigns to the target the value of the first expression when the condition is true or the second if the condition is false.

3. *Processes* provide a method to describe activities that must occur in a sequential order. A process has three main parts: 1) a sensitivity list, 2) declaration part, and 3) statement part. The sensitivity list defines the signals to which the process is sensitive. Any event occurring on one of these signals causes the process to execute once. If the sensitivity list is absent, the process will run forever, unless the user explicitly pauses the execution with a (`wait`) statement. The declaration part of the process allows the declaration of types, variables, functions, and procedures, which are local to the process. Finally, the statement part of the process contains a set of sequential statements executed every time the process is activated.

VHDL was initially designed as a simulation language. This leads to a number of problems when integrating VHDL in a synthesis environment and results in imposing some limitations on the language features. Moreover, the language synthesisable subset interpretation varies according to the level of abstraction at which the synthesis takes place. As far as *behavioural* synthesis is concerned, the set of restrictions applied to semantic interpretation of VHDL [13, 14] are summarised in the following:

- Processes do not execute in zero time, but take a number of clock cycles. Thus there is no implicit assumption about the execution time of a process. In the simulation model, the process executes in zero time unless the user explicitly defines a delay using a `wait` statement.

- Time expressions (`wait for x sec`) are converted into control steps. Therefore, delay specifications (pausing process execution) can only be implemented as multiples of the clock period. A delay of any period can be specified using the same `wait` statement in the simulation model.

- Processes cannot be used to specify combinational logic. In contrast, a process can be used to *model* combinational logic in a simulation and/or RTL environment.

- Structural definitions such as component instantiation and *generate* statements are not allowed.

- Recursion within procedures is excluded, due to the difficulties created.

- *Assert* statements are for verification during simulation. They are ignored during synthesis.

- Statements within a process are executed in a sequential manner governed by an implicit clock signal.

- Sensitivity lists, such as (`wait on input`) will not activate on asynchronous edges.

In the VHDL simulation model, a delay occurs within a process when a `wait` statement appears. Sequential blocks between `wait` statements execute in zero delay. However, when the design is synthesised, these blocks may take a number of clock cycles to execute, dictated by the data dependency between operations and the synthesis objectives. It is

common in a simulation model to employ such processes to describe combinational logic blocks that get activated when a transition occurs on any of the inputs and executes in zero delay (or a delay specified by a wait statement). When synthesised, these blocks will not be mapped to a combinational unit, instead, the system will generate a multi-cycled sequential block with a number of internal registers.

Sensitivity lists are another issue that introduce major differences between a simulation and a synthesis environment. *Wait on* and *wait until* statements originally detect asynchronous edges of the monitored signals. However, in a behavioural synthesis environment, signal edges will be synchronised to the system clock, and transitions will only be effective at clock edges, which might introduce timing mismatches between the behavioural model and the synthesised structural model.

## 2.2 Behavioural synthesis

There are several advantages to high-level synthesis over conventional RTL synthesis systems [9, 10, 15]. First, moving automation to a higher level assures a much shorter design cycle<sup>1</sup>. Second, it allows comparing several designs in a reasonable amount of time. Finally, an automated process may out-perform a human engineer in meeting most design objectives.

The main tasks involved in a behavioural synthesis process are illustrated in Figure 2.1, which shows the flow of data in a generic high-level synthesis system. A behavioural description forms a starting point for a high-level synthesis system. The behavioural description is then compiled into an *internal representation*. This stage may include a compiler-like optimisation phase [16, 17] such as loop unrolling, common sub-expression elimination, dead code elimination and inline expansion of procedures.

---

<sup>1</sup> The increase in productivity of behavioural design versus RTL design is typically quoted as a factor of five [18].

**Figure 2.1** A generic high-level synthesis system

The next two steps form the basis of translating behaviour into structure: *scheduling* and *allocation*. Scheduling assigns operations to control steps (a control step is usually a single clock cycle). Allocation involves assigning operations and variables to functional units, storage hardware and communication paths.

The final step in this process consists of module *binding* and *controller synthesis*. In module binding, the abstract datapath units are mapped to specific hardware implementation provided by a technology dependent module library, while controller synthesis provides the control circuitry responsible for generating the datapath control signals.

## 2.3 The design space

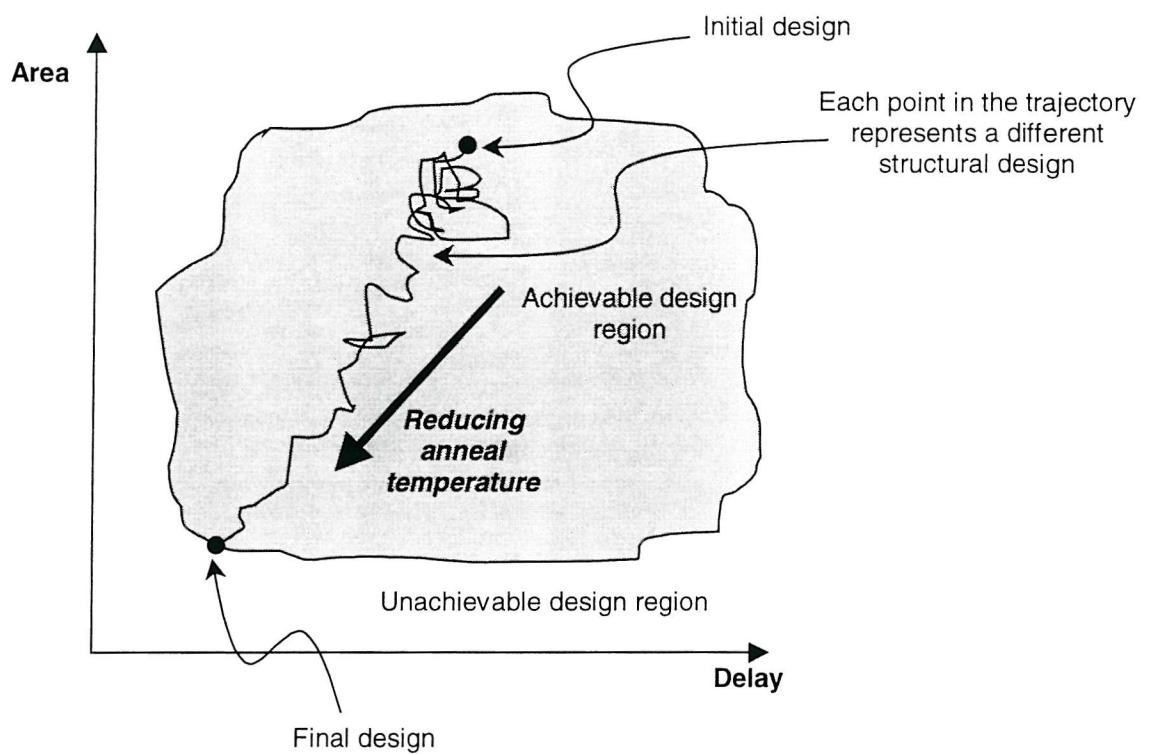

High level synthesis allows the designer to investigate a range of implementations for a particular input description, representing different trade-offs between a set of pre-defined objectives. Each of these implementations forms a single point in what is called the *design space* [4, 7, 19, 20], which is the n-dimensional space describing all possible implementations of a single behavioural description, in terms of n design aspects. Figure 2.2 shows a two-dimensional design space represented by area and delay (processing time). The design space is divided into two regions, containing designs that are either *achievable* or *unachievable*. The two regions are separated by the *optimal design curve*, which consists of a set of discrete points representing the most efficient implementations. For a particular design, only a portion of the achievable region may be obtained as indicated by the *actual achievable region* in Figure 2.2. This limitation in the design space is due to a number of factors such as optimisation algorithms and design space modelling methods [21].

**Figure 2.2** Area versus delay design space

## 2.4 Internal representation

The first step in high-level synthesis is to capture the behaviour of the design in the form of an internal representation. This is essentially a one-to-one translation of the behavioural description into a graph-based representation containing both the data flow and the control flow of the design.

For simple designs, the *data flow graph* (DFG) [11] can be employed to describe the system. The representation consists of a set of nodes, each node representing an operation in the original behavioural description. Data dependency between two nodes is represented by an arc connecting them. Figure 2.3 shows a sample VHDL input with the associated data flow graph. Three nodes are generated representing one addition and two subtraction operations. Node 3's dependency on nodes 1 and 2 is simply indicated by two arcs, the first arc labelled C indicates node 3 dependency on node 1 through the internal variable C, and the arc labelled D represents node 3's dependency on node 2.

**Figure 2.3** Data flow graph representation

The DFG is not sufficient for representing systems in which the execution sequence is based on external conditions (`if-else` and `case` blocks). The reason is that DFG is based on data dependency, while a method of representing the control flow as well as the data dependency is absolutely essential in such systems.

To represent the control and the data flow, some systems choose to combine the control and datapath graphs into one structure, such as the *Control Dataflow Graph* (CDFG) [22]. Other systems maintain separate graphs for data flow and control, with binding indicating the relationship between elements in both graphs. An example of the latter is the *Extended Timed Petri-Net* (ETPN) [14] representation.

To illustrate these representations, a simple example is introduced in Figure 2.4 showing a fragment of VHDL code. The graph representation of the code using CDFG and ETPN is shown in Figure 2.5 and Figure 2.6 respectively.

```

. . .

c := (a + b) / 2;

sel := sign(c) xor sign(b);

IF sel = '1' then

r := (a + c) / 2;

ELSE

r := (b + c) / 2;

END IF;

. . .

```

**Figure 2.4** A sample VHDL example

The CDFG describes the control flow of the system as a directed graph. Each node in this graph is actually a separate DFG representing a block of assignments or a conditional statement. The CDFG in Figure 2.5 comprises three DFGs. The first one represents the two sequential assignments, the second two graphs representing the two conditional assignments.

ETPN represents the datapath as a directed graph [14] with nodes and conditional arcs. The nodes capture both the operators and the variables, while the arcs represent the connections between nodes. These connections are only available if the arc associated control signal ( $S_n$ ) is activated. The control part of the design is described by the passage of *tokens* through a Petri-net, with vertices representing control states. The state transaction is controlled by conditions ( $C_i$ ) generated in the datapath. When a control state receives a token, it activates the associated datapath conditional arc through its ( $S_n$ ) signal

**Figure 2.5** Control dataflow graph

**Figure 2.6** Extended timed Petri-net

## 2.5 Scheduling and allocation

*Scheduling* and *allocation* form the basis of transferring behaviour into structure [10, 15]. These two tasks are closely interconnected and dependent on each other. For example, high performance (speed optimised) designs require allocating more components in each control step, to allow the exploitation of parallel execution of operations. On the other hand, the most area-efficient designs use a minimum number of slow components, which results in a large number of control steps. This dependency gives rise to a major problem: any decision taken by one of the two tasks might reduce the number of possible implementations, hence, reduce the actual achievable region in the design space.

The simplest approach to this problem is to set some resource limit before scheduling; this is usually achieved by imposing a limit on the number of functional units available to implement the design (e.g. one multiplier and two adders). An improved version of this approach allows the process to iterate by re-synthesising with a modified resource limit. In a similar way, the resource limit is imposed, and then scheduling is performed. The result

is then evaluated against the user objectives. According to the evaluation result, the resource limit may be altered and the scheduling is performed again for a possible improved implementation.

Another approach to this problem is to perform allocation before scheduling, trying to produce an area minimised design within the timing constraints given. For example, some systems [23] perform complete datapath synthesis including hardware component mapping. Both global and local optimisations are employed at this stage to minimise the area cost. Once the datapath is implemented, controller synthesis is then performed, optimising the number of states according to the constrained imposed by allocation and the timing constraints given.

The approach employed by the MOODS synthesis system, is to combine scheduling and allocation together as a *general* optimisation problem and introduces an optimisation technique to minimise it.

The techniques that perform scheduling can be classified into two types [24]: *constructive* and *transformational*. Constructive scheduling creates a schedule from scratch by adding operations one at a time until all operations are scheduled. Transformational scheduling, on the other hand, starts with an initial schedule, generally maximally serial or maximally parallel, and attempts to improve it by applying a number of local transformations.

Simple constructive scheduling is possible by scheduling operations ‘as soon as possible’ (ASAP) or ‘as late as possible’ (ALAP) [25]. ASAP schedules operations in the earliest time step allowed by data dependency, while ALAP assigns operations to the latest possible time step. Figure 2.7 illustrates the meaning of ASAP and ALAP. The main disadvantage of both techniques is that all operations are treated equally, with no priority given to the more critical ones. When resource constraints are imposed, operations that are less critical can be scheduled first on a limited resource (e.g. single multiplier). This might block critical operations scheduling and result in an overall performance degradation.

*List scheduling* [25] solves this problem by taking more controlled approach in selecting the operation to be scheduled. At each control step, operations available to be scheduled are kept in a list ordered by some *priority function*; each operation in the list is then scheduled in turn as long as the required resource is available, otherwise, it will be postponed.

to the next scheduling step. Figure 2.8 represents list scheduling of a simple control graph: operation 2 has a higher priority than operation 1, and is therefore scheduled before it, providing an optimal solution in this case.

**Figure 2.7 ASAP and ALAP scheduling**

In contrast with the above algorithms, the *force directed scheduling* [26] attempts to create an optimal schedule based on a more global view. The algorithm attempt to minimise the number of resources required to implement the design within a given time constraint, by distributing sharable operations as evenly as possible between the control steps.

**Figure 2.8** List scheduling

In contrast to constructive scheduling, transformational scheduling is based on an iterative process that applies a set of local transformations to the design initial schedule, moving the design towards the point that meets the user pre-defined objectives in the design space. Early transformational scheduling schemes employed exhaustive search to perform scheduling. The approach tests all possible combinations of transformations and chooses the best result. The method guarantees reaching an optimal solution, since all possible designs are tested. However, it is very expensive in terms of computing time and may not be considered as a viable solution for large designs.

Another approach to scheduling by transformations is to handle scheduling as an optimisation problem, and employ an optimisation algorithm that exploits different transformations to achieve the desired result [7]. At this stage, a heuristic approach may be employed to minimise the problem by selecting and applying transformations according to a pre-defined regime guided by an analysis of the design.

In a similar manner to scheduling, resource allocation can be achieved using different approaches. Allocation involves binding operators to functional units, binding variables to storage units, and providing interconnect between registers and functional units. Algorithms that implement allocation can be divided into two classes [10]: *iterative/constructive* and *global*.

The iterative/constructive algorithms perform allocation by iteratively assigning operations, one at a time. These algorithms are distinguished by the method employed to select both the element to be assigned and the unit to which it will be assigned. The selection methods can be simply implemented to select elements in a fixed order; usually the same order appears in the data flow graph. A more sophisticated approach relies on a global selection, which tries to make the most suitable selection based on some metric: for example, selecting an element that has the least effect on the total system area cost.

Global allocation techniques, on the other hand, deal with the datapath as a whole, and try to allocate all its elements at once. A number of techniques may be used for global allocation. A possible technique is to use a graph-based clique-partitioning algorithm [27], which attempts to build up a graph representing datapath elements by nodes, with arcs joining nodes that can share the same hardware. The problem is then reduced to finding a maximal partitioning of fully interconnected nodes. Since each partition will represent elements that can share the same hardware without conflict, the solution will represent the minimum hardware cost.

Alternatively, branch-and-bound techniques [28] can be employed to perform global allocation. The algorithm performs an exhaustive search by trying all possible allocations of the datapath elements. The approach is very powerful since it checks every possible solution and provides an efficient allocation for small designs. However, the exponential increase in processing time makes it very expensive as the number of elements to be allocated grows. The latter problem can be tackled by imposing bounding heuristics to limit the number of solutions tried, for example, aborting any search that results in a cost increase higher than a certain limit.

## 2.6 MOODS synthesis system

The vehicle used to carry out this synthesis research is called MOODS [1, 2, 3] (Multiple Objective Optimisation of Data and control path Synthesis). The MOODS synthesis system has been developed to compile a behavioural description of a digital circuit into a structural description (VHDL or Verilog structural netlist), which utilises third-party tools to implement the design. Figure 2.9 is the original MOODS system data flow showing the major building blocks. It consists of four different tasks:

1. The VHDL behavioural description passes the source level optimiser [16, 17]. This performs a source level optimisation on the VHDL source code, to reduce the area/delay cost of the final hardware. Compiler-like transformations are applied at this stage, such as algebraic simplification, dead code removal and inline expansion of procedures.

2. The optimiser output is then compiler to an *intermediate code* (ICODE) using a VHDL language compiler. The ICODE represents the behaviour of the design at the register-transfer level.

3. This stage is the actual synthesis process. It takes as input the ICODE file and a set of user objectives, such as the design total area and maximum delay, and performs scheduling, allocation and module binding and outputs a VHDL structural netlist suitable for the target logic synthesis tool.

4. The final stage in this data flow is the low-level logic synthesis and technology mapping, which utilises third-party tools, such as Cadence Synergy [29], LeonardoSpectrum [30], and Xilinx Foundation [31], to transfer the structural netlist into a physical circuit on an ASIC or a programmable logic device.

A detailed description of the MOODS synthesis system may be found in the literature [1, 2, 4, 5, 19, 32]. Outlined in the following sections are three major aspects of the synthesis system which have a particular bearing on the discussion of the floating point subsystem:

- The initial compilation into ICODE and the internal representation.

- Module expansion.

- Global optimisation.

**Figure 2.9** Original MOODS system data flow

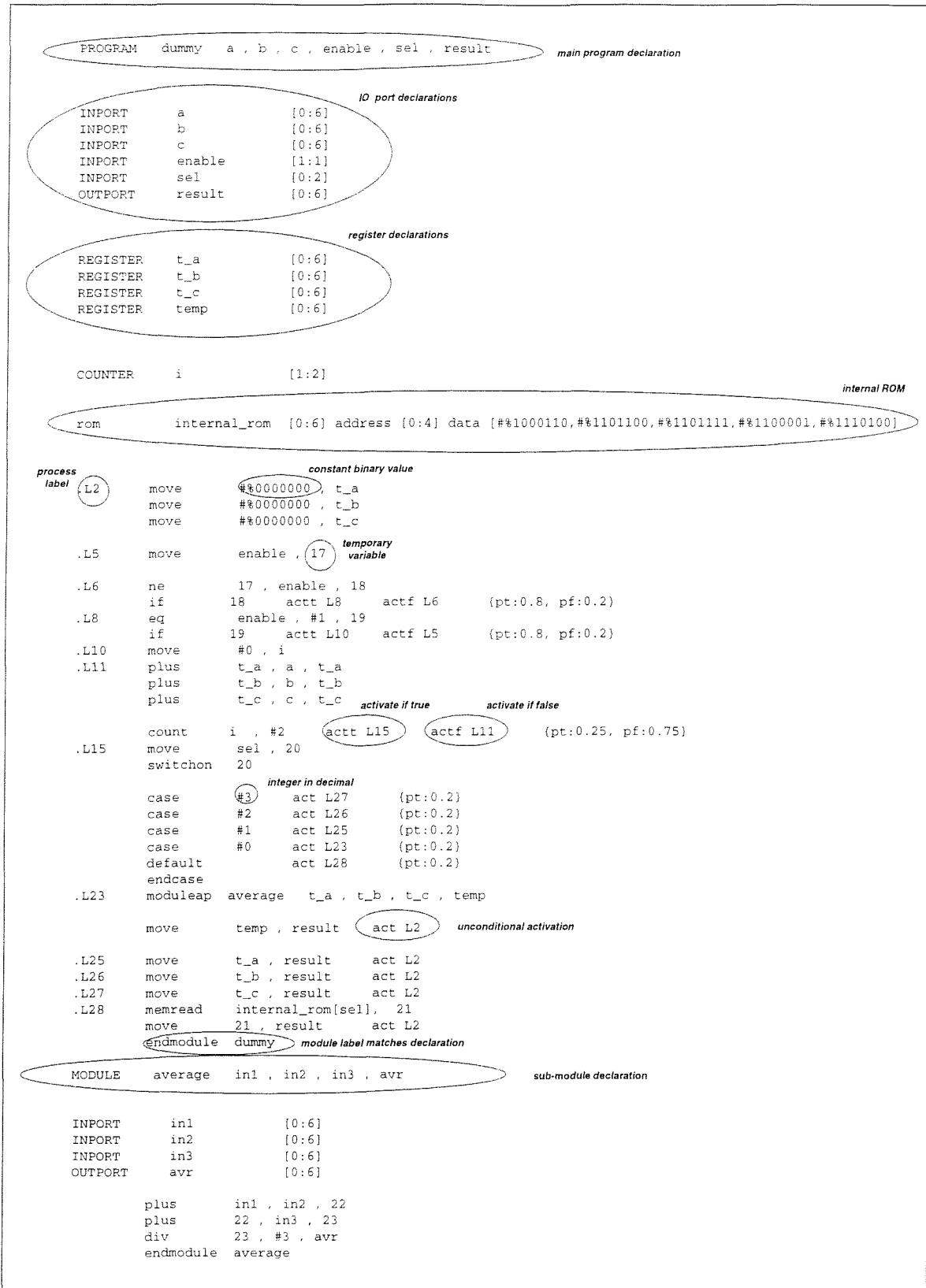

### 2.6.1 ICODE and internal representation

The MOODS synthesis system does not directly read the input behavioural description. It reads an ICODE file. The logic behind this is to have MOODS as a general purpose synthesis system that can handle different input languages simply by changing the ICODE compiler at the front end. The VHDL2IC compiler (Figure 2.9(2)) translates the VHDL description into an ICODE representation. The ICODE is in some way similar to an assembly language, with additional control flow information. A simple example showing a

fragment of VHDL code with its equivalent ICODE is shown in Figure 2.10. It outlines the key features of the ICODE language:

- An ICODE instruction has the general form:

```

OPERATION <inputs> , <outputs> <activation list>

```

- Each ICODE instruction is executed once it has been *activated*. (Excluding the first instruction, which is activated on the system reset.) Upon conclusion of an instruction, all instructions in its *activation list* are activated. If the activation list is missing, the next instruction is activated by default. For example, instruction *i2* activates both *i3* and *i4*. While the absence of an activation list in *i6* results in an automatic activation of *i7*.

- Complex expressions are split down into a number of simple ICODE instructions, with temporary variables identified in the figure as numeric literals. In the figure, the VHDL assignment to the variable *m* is represented by five ICODE instructions (*i2* to *i6*).

- VHDL functions and procedures are implemented as a separate *module*, with a dedicated instruction MODULEAP to transfer the control to them. Instruction *i9*, for example, halts the main execution and passes the control to the *sqrt* module. The module output is returned in the variable *m* before the main execution continues.

- Conditional branches are implemented as an IF instruction with two activation lists. One for the true condition (ACTT) and the other for the false (ACTF). In Figure 2.10, the VHDL conditional statement (IF *sel* = 1 THEN ... ELSE ... END IF) is implemented as two instructions *i10* and *i11*, with instruction *i12* being activated if the condition is true, and *i14* being activated if the condition is false.

A complete definition of the ICODE is provided in Appendix D.

| VHDL                            | ICODE                                                                                                        |

|---------------------------------|--------------------------------------------------------------------------------------------------------------|

| <pre>m := b*b - 4*a*c;</pre>    | <pre>i2 : MULT a,c,1 ACT i3,i4 i3 : MULT 1,#4,2 ACT i5 i4 : MULT b,b,3 i5 : COLLECT 2 i6 : MINUS 3,2,m</pre> |

| <pre>IF m &gt;= 0 then</pre>    | <pre>i7 : GE m,#0,4 i8 : IF 4 ACTT i9 ACTF i16</pre>                                                         |

| <pre>    s := sqrt(m);</pre>    | <pre>i9 : MODULEAP sqrt m,s</pre>                                                                            |

| <pre>    IF sel = 1 THEN</pre>  | <pre>i10 : EQ sel,#1,5 i11: IF 5 ACTT i12 ACTF i14</pre>                                                     |

| <pre>        r := -b + s;</pre> | <pre>i12: NEG b,6 i13: PLUS 6,s,r ACT i16</pre>                                                              |

| <pre>    ELSE</pre>             | <pre>i14: NEG b,7 i15: MINUS 7,s,r</pre>                                                                     |

| <pre>        r := -b - s;</pre> | <pre>i16: . . .</pre>                                                                                        |

| <pre>    END IF;</pre>          | <pre>.</pre>                                                                                                 |

| <pre>END IF;</pre>              | <pre>.</pre>                                                                                                 |

| <pre>.</pre>                    | <pre>.</pre>                                                                                                 |

| <pre>FUNCTION</pre>             | <pre>MODULE sqrt input,output</pre>                                                                          |

| <pre>sqrt(input:integer)</pre>  | <pre>.</pre>                                                                                                 |

| <pre>return integer is</pre>    | <pre>.</pre>                                                                                                 |

| <pre>.</pre>                    | <pre>END MODULE sqrt;</pre>                                                                                  |

| <pre>END;</pre>                 |                                                                                                              |

**Figure 2.10** VHDL and the equivalent ICODE example

In the core processor input stage, the design, in the form of an ICODE file, is transformed into a control and datapath graph [1, 19]. Figure 2.11 shows the initial control and datapath graphs for the ICODE listed in Figure 2.10.

The control graph defines the execution order of the ICODE instructions. Each node in the graph defines a control state. Input and output arcs define a conditional control flow, governed by signals generated on the datapath. For example, the datapath signal  $s41$  decides on the transition from state  $S_8$  to state  $S_9$  or  $S_{16}$ . Each control node has an instruction list, defining the instruction to be executed when this node is activated. A set of acyclic subgraphs divide these instructions into groups of *dependent instructions*. Each group has a unique *group number*. Instructions with different group numbers may be executed concurrently. Instructions with the same group number are dependent on each other and must be executed sequentially within the same control state.

The MOODS control graph is of six types of node (refer to Figure 2.11):

1. *General node* (for example  $S_6$ ): has one input and one output, and can contain any ICODE instructions except COLLECT, MODULEAP, or conditionals.

2. *Fork node* (for example  $S_2$ ): the same as general node except that it has two or more unconditional outputs. This node defines the starting point of a set of parallel execution threads, where all the successors executed independently.

3. *Conditional node* (for example  $S_8$ ): has one input and two or more outputs. The output conditions are controlled by a signal from the datapath. This node is generated from an ICODE conditional instruction such as an IF or CASE statement.

4. *Dot node* (for example  $S_{16}$ ): has two or more inputs, any of which can activate the node. This node is a counterpart to the conditional node; it represents the reconvergence of mutually exclusive control threads.

5. *Call node* (for example  $S_9$ ): the call node results from a module call instruction. When this node is activated, it activates the execution of the required sub module. When the sub module exits, control is returned to the submodule successor.

6. *Collect node* (for example  $S_5$ ): results from an ICODE collect instruction. The node will not activate its descendant node until a fixed number of activations (indicated by its argument) is received, thereby synchronising a set of parallel execution threads. The node is a complement to the fork node, where the concurrent branches are joined into a single node.

The MOODS datapath graph represents the functionality of the ICODE instructions with a set of functional units, storage units, and interconnects. The flow of data through this graph is governed by control signals generated by the appropriate control state in the control graph.

The initial datapath graph is created as a one-to-one mapping of ICODE operations and variables, with each ICODE variable represented as a storage unit (register), each ICODE arithmetic or logical operation represented as a separate functional unit, and each assignment operation represented as a set of registers, interconnects and control signals.

**Figure 2.11** Control and datapath graphs

It is worth mentioning that the initial control and datapath graph represents a valid structural implementation of the design. However, it is almost certainly a highly inefficient implementation in terms of the total execution time and the large area cost. The optimisation phase of MOODS now moves this implementation in the design space towards the point that meets (if possible) the cost objective specified by the user

## 2.6.2 Transformations

MOODS employs an iterative optimisation strategy to perform synthesis. Iterative optimisation is achieved by dividing the synthesis task into a number of local transformations that are applied to different parts of the design using a dedicated optimisation algorithm. This allows simultaneous consideration of synthesis sub-tasks by performing scheduling, allocation and module binding simultaneously.

At present, MOODS has a set of fourteen different transformations. These transformations are *complete*, as a transformation applied to a valid design will result in a valid design. The availability of inverse transformations allows a previous design decision to be reversed at any stage during optimisation, which provides a solution for the problem encountered with premature binding decisions which may result in a design that is not optimal.

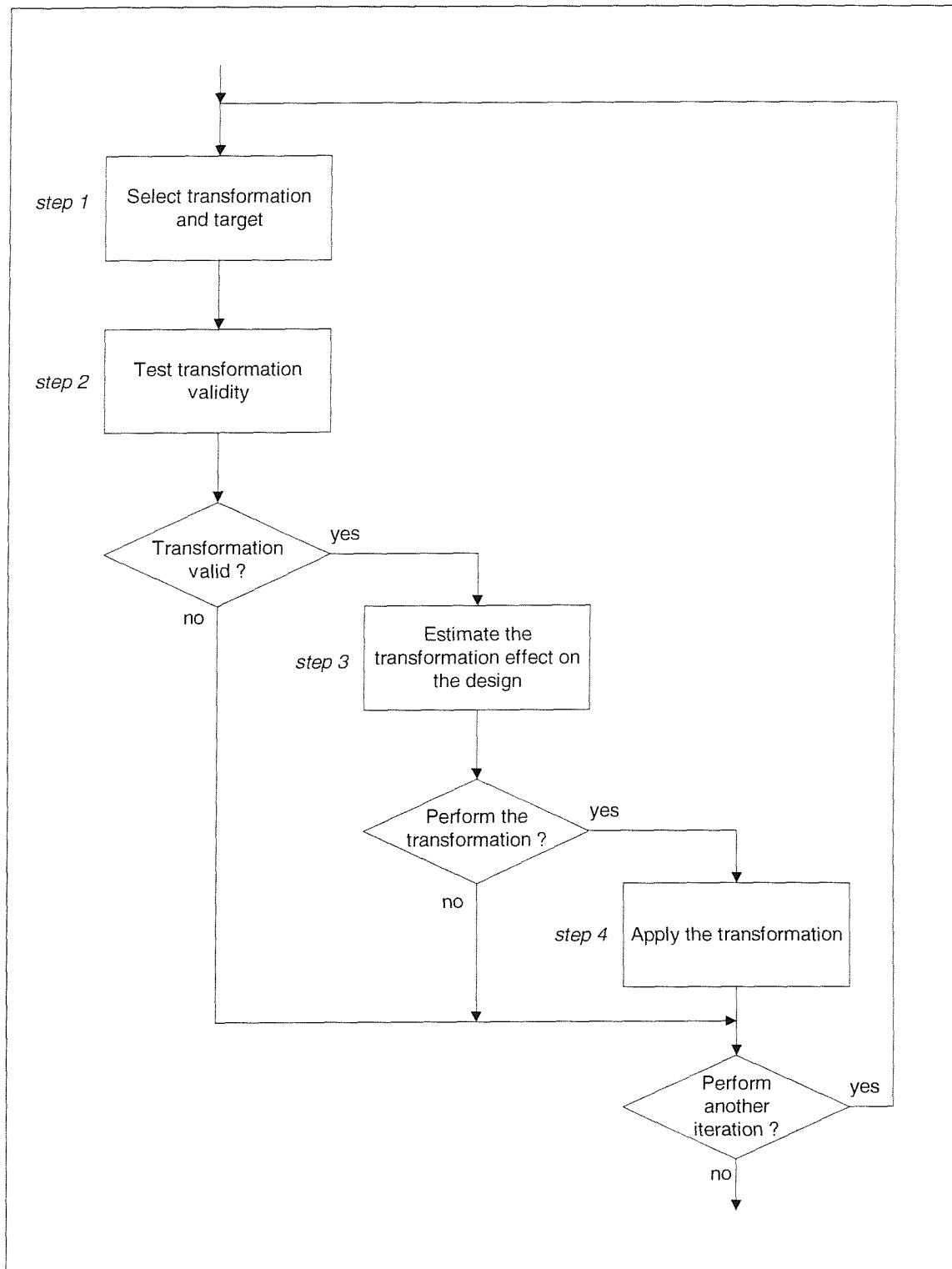

Transformation selection and application consists of four distinct steps, as illustrated in Figure 2.12:

1. *Data selection* involves selecting a transformation and the portion of the design to which it should be applied. The selection varies according to the optimisation algorithm involved and is performed randomly in the *simulated annealing* algorithm (see section 2.6.4).

2. *Testing* involves checking the validity of the transformation and ensuring that it will not modify the design behaviour.

3. *Estimation* predicts the effect of the transformation on the system performance without actually altering the design.

4. *Execution*, applies the transformation to the design.

MOODS transformations are divided into two groups: *scheduling transformations* which apply mainly to the control graph, and *allocation and binding transformations* which modify the design datapath. Scheduling transformations are listed in Table 2.1, while allocation and binding transformations are listed in Table 2.2.

**Figure 2.12** Transformation application steps

| Transformation name                          | Effect                                                                                                                                                                                                                                                                                   |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b><i>sequential merge</i></b>               | Combines two sequential control nodes (i.e. nodes executed sequentially) to form a single control node implementing multiple instructions.                                                                                                                                               |

| <b><i>parallel merge</i></b>                 | Combines several concurrently executing nodes into one control node.                                                                                                                                                                                                                     |

| <b><i>merge fork and successor</i></b>       | Combines a fork node with one of its successors, with the successor instructions becoming conditional instructions executed in the fork node control state.                                                                                                                              |

| <b><i>group instructions on register</i></b> | Tries to bypass datapath registers that have a single input and a single output net (i.e. a register implementing a variable accessed by one read and one write instruction) and moves the instruction group that contains the write instruction into the read instruction control node. |

| <b><i>ungroup node into groups</i></b>       | Moves an instruction group into its own separate control node.                                                                                                                                                                                                                           |

| <b><i>ungroup node into time slices</i></b>  | Divides instructions within a control node into new control nodes, such that no control state has an execution time greater than a specified period.                                                                                                                                     |

| <b><i>clock set / multi-cycling</i></b>      | A global optimisation transformation that employs <i>ungroup node into time slices</i> transformation to meet a clock period constraint set by the user.                                                                                                                                 |

Table 2.1 Scheduling transformations

| Transformation name                             | Effect                                                                                                                                                                                                                                                                   |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

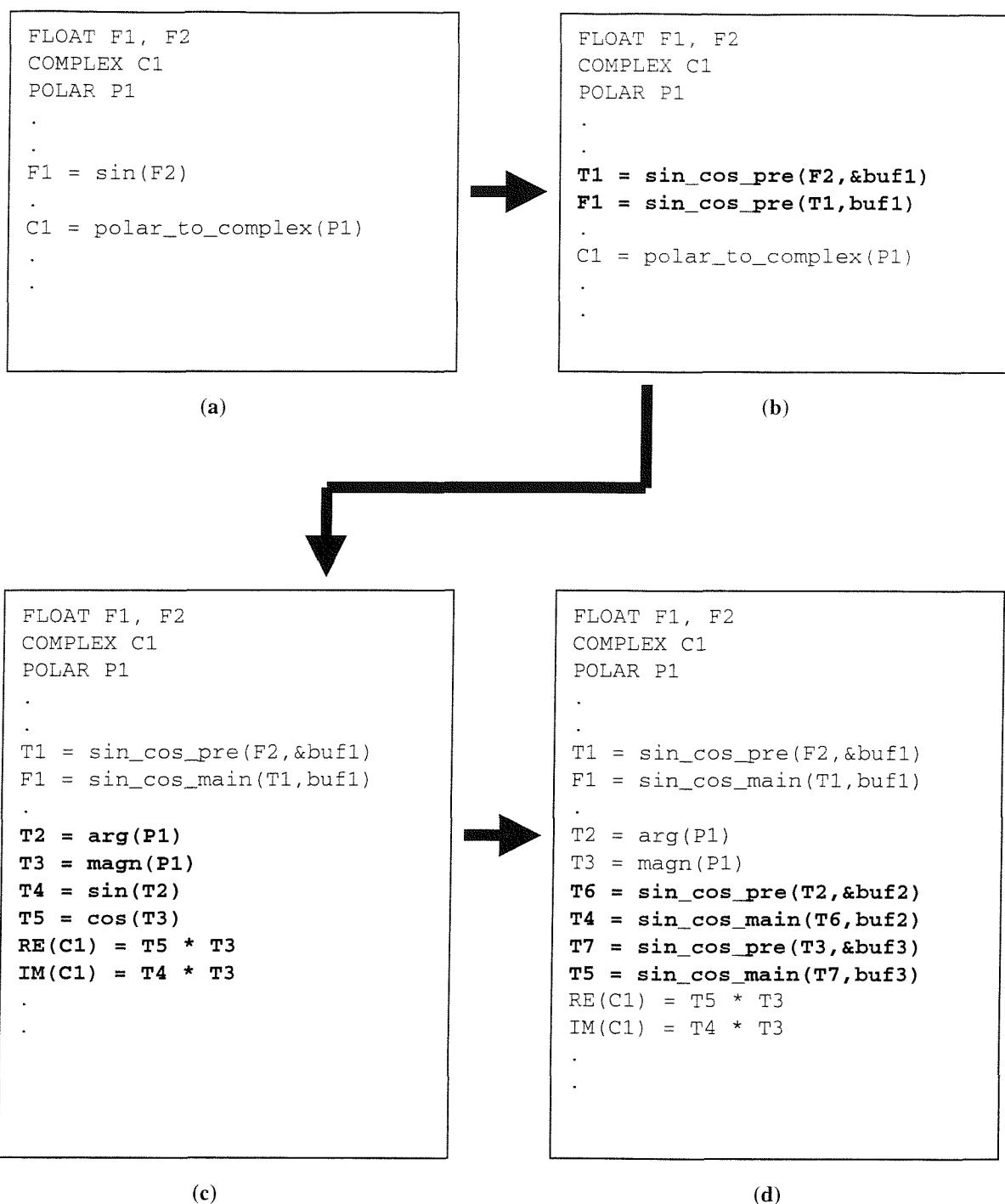

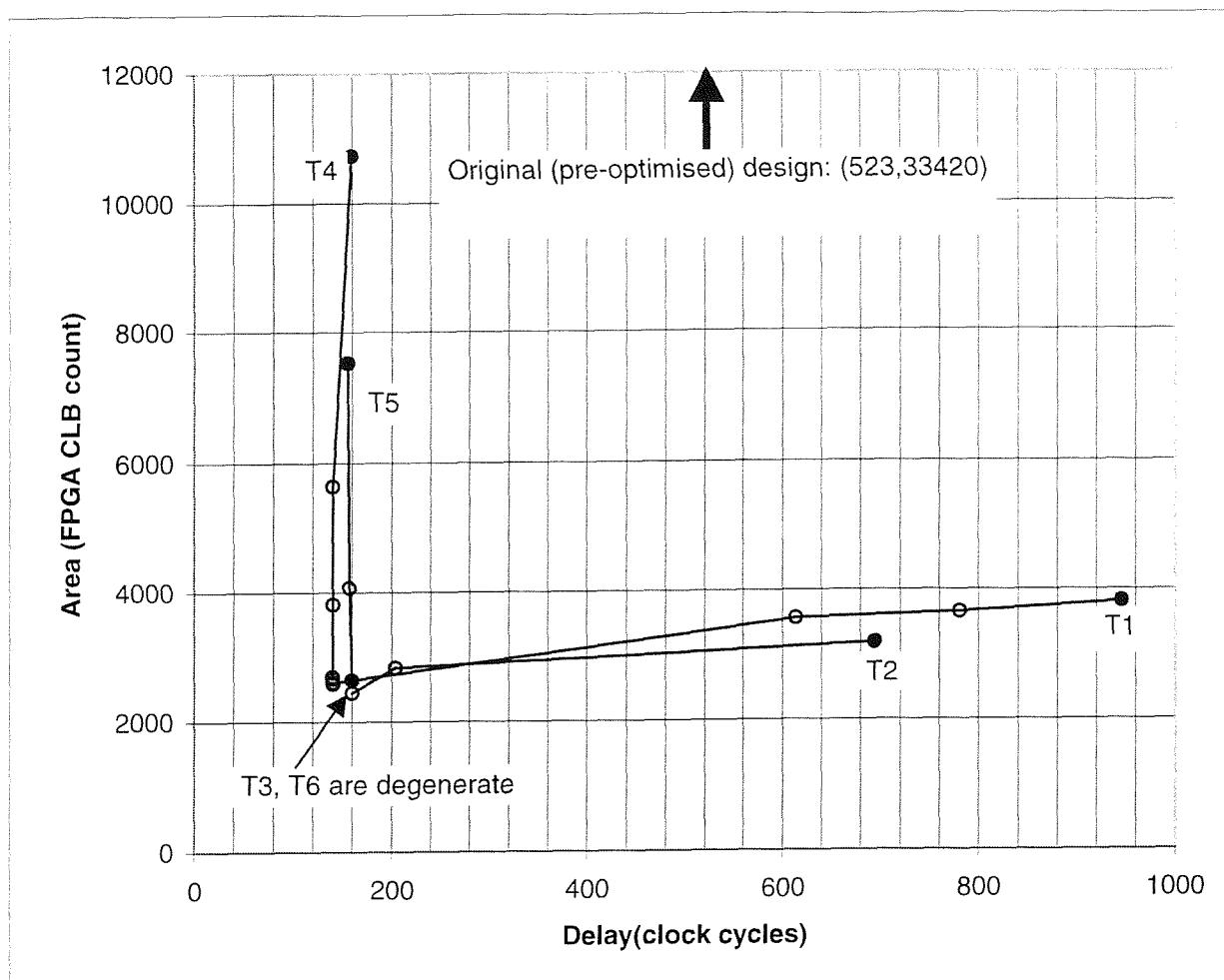

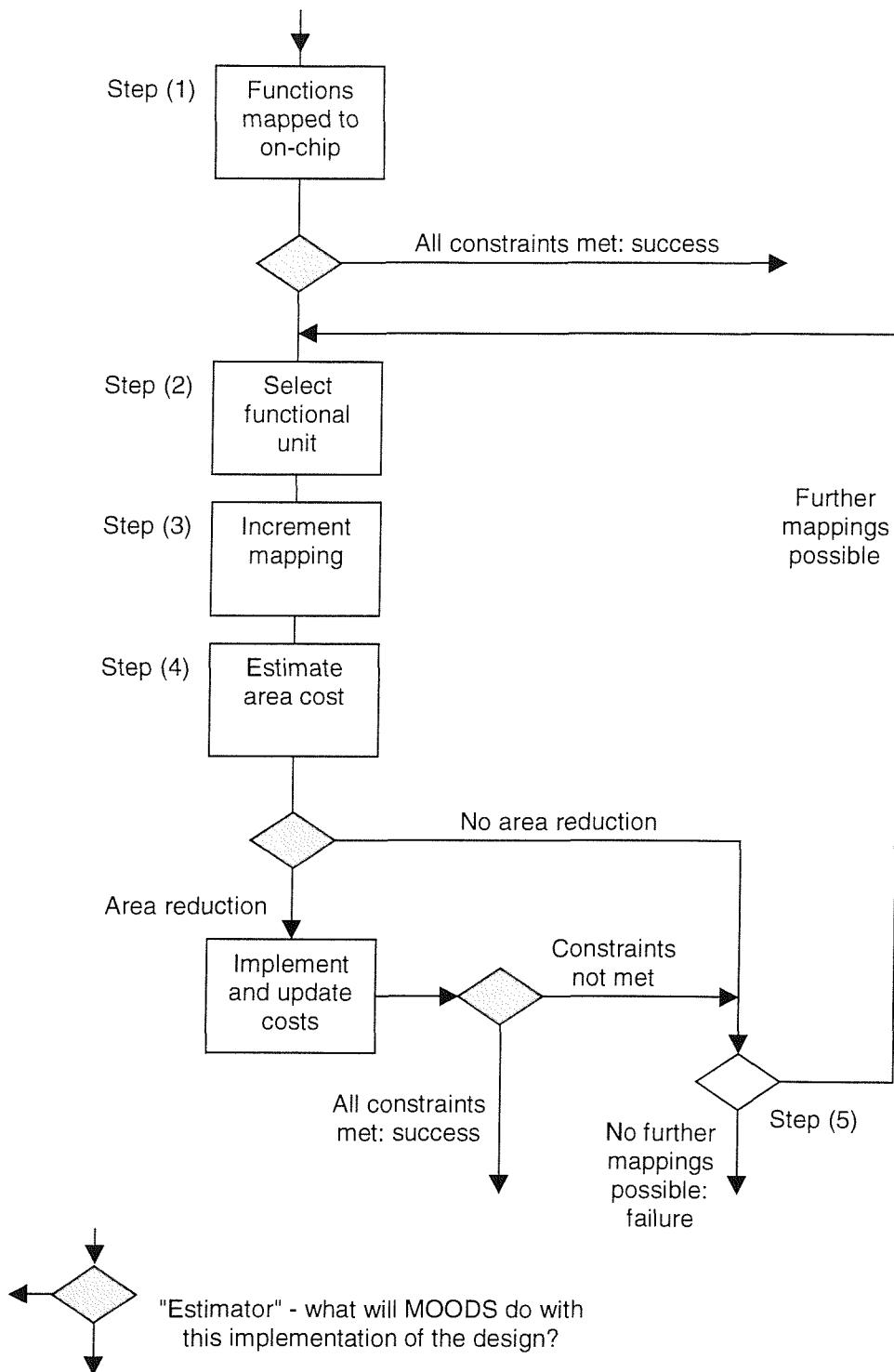

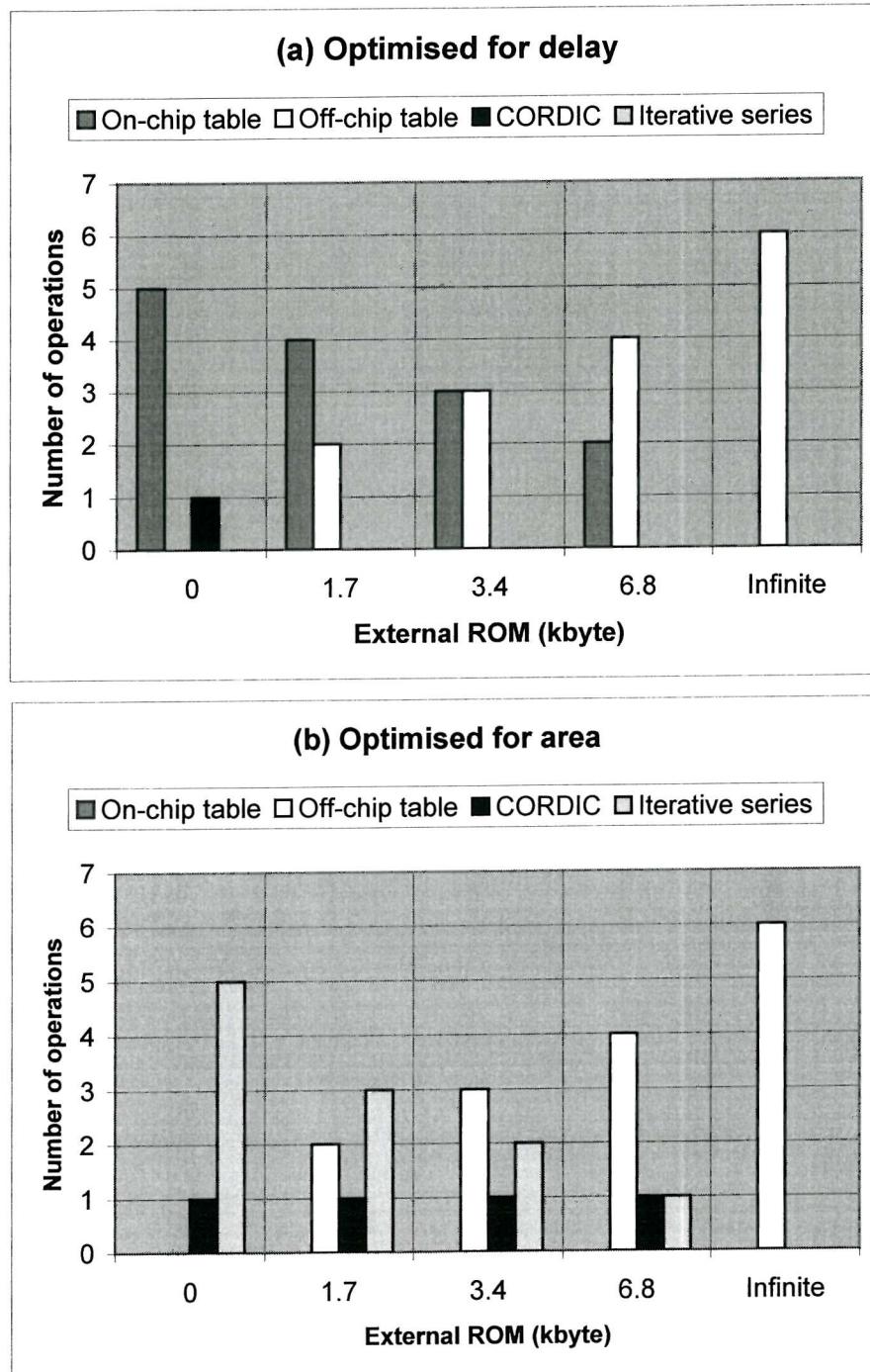

| <b><i>combine functional units</i></b>          | Responsible for joining two functional units into one, time-shared between several operations. For example, combining an add and a subtract unit into a single add/subtract ALU.                                                                                         |