## Modelling and Characterisation of Silicon-On-Insulator Lateral Double Diffused MOSFETs for Analogue Circuit Simulation

by Nele D'Halleweyn

Doctor of Philosophy, January 2002

# UNIVERSITY OF SOUTHAMPTON FACULTY OF ENGINEERING AND APPLIED SCIENCE DEPARTMENT OF ELECTRONICS AND COMPUTER SCIENCE

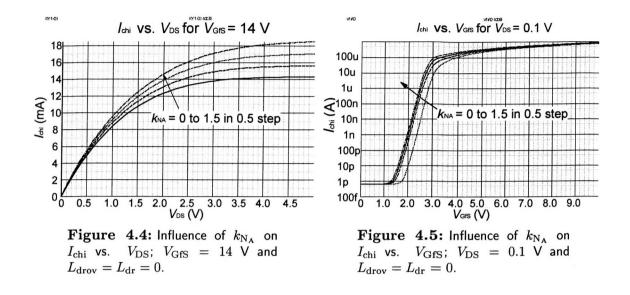

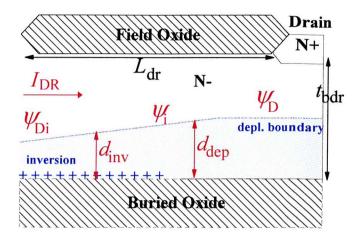

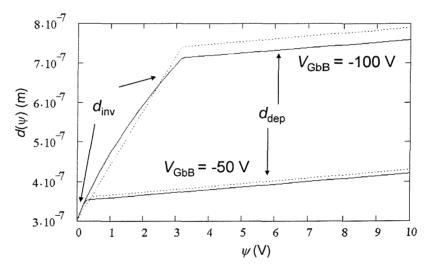

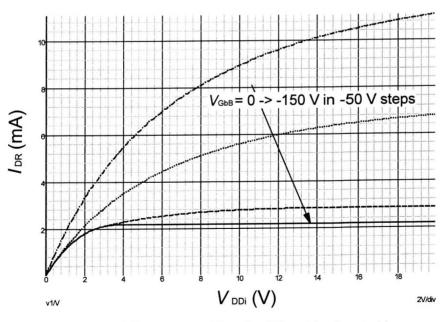

# MODELLING AND CHARACTERISATION OF SILICON-ON-INSULATOR LATERAL DOUBLE DIFFUSED MOSFETS FOR ANALOGUE CIRCUIT SIMULATION

by Nele D'Halleweyn

#### UNIVERSITY OF SOUTHAMPTON

#### ABSTRACT

## FACULTY OF ENGINEERING AND APPLIED SCIENCE DEPARTMENT OF ELECTRONICS AND COMPUTER SCIENCE

### Doctor of Philosophy

# MODELLING AND CHARACTERISATION OF SILICON-ON-INSULATOR LATERAL DOUBLE DIFFUSED MOSFETS FOR ANALOGUE CIRCUIT SIMULATION

by Nele D'Halleweyn

As the scaling down of smart power ICs is gaining in importance, SOI technology is becoming more attractive. The LDMOS transistor is one of the key devices in HV ICs, and a good model is indispensable in order to perform accurate circuit design. Some subcircuit models for bulk and SOI LDMOS devices are available, but, when certain special aspects of device characteristics become critical, they are not always sufficient, and the need for an accurate, robust compact model is apparent. Particular emphasis has been placed on the behaviour and circuit level modelling issues related to high side drive applications, and on the self- and mutual heating. For the N-type LDMOS, high side operation increases the on-resistance and demands specific modelling effort.

In this thesis a circuit simulator model is developed, based on a detailed study of device physics of the LDMOS. First, the subcircuit modelling approach was followed, resulting in a 'quick-fix' LDMOS model. The drawbacks of this modelling approach are the complexity of the circuit, and convergence problems.

To overcome these disadvantages a compact model is presented. The model has only one internal node, situated in the channel at the transition point from thin gate oxide into field oxide. Both currents are carefully derived, to keep the model as physical as possible. The current under the thin gate oxide is described in terms of the surface potentials, whilst taking into account the lateral doping gradient and the overlap of the gate over the  $N^-$  drift region. The impact of the thickness of the depletion layer at the buried oxide on the current under the field oxide is studied rigorously, leading to a good prediction of the unique high-side behaviour. Next, the complete SOI LDMOS charge model is set out, presenting a promising new approach to deal with the unusual charge partitioning in the LDMOS.

DC simulations with the compact model match the measured characteristics well for a wide range of geometries, with self-heating and high-side effects being accounted for. The simulated and measured capacitance characteristics for a range of geometries show excellent qualitative behaviour, and demonstrate the soundness of the new charge model.

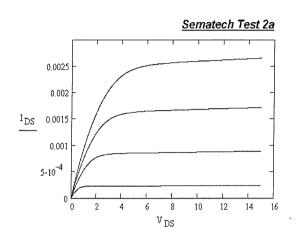

The model has been implemented in the SPICE circuit simulator and careful formulation and coding has led to a very robust SOI LDMOS model, which converges easily without the need for node setting. The model is evaluated thoroughly, using a set of simulations based on the SEMATECH tests. Finally, two special analogue circuits were designed and fabricated to allow circuit level evaluation of the accuracy and robustness of our model. The model predicts the measurement results well for circuits containing LV and MV transistors, and also gives a reasonable prediction of the HV circuits. We can conclude that, with further optimisation, our compact SOI LDMOS model can provide a practical and reliable simulation tool for commercial design use.

## Contents

| bstra                           | act                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | i                                                                               |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| onte                            | nts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ii                                                                              |

| st of                           | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | vii                                                                             |

| st of                           | Symbols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | viii                                                                            |

| st of                           | Acronyms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\mathbf{x}\mathbf{v}$                                                          |

| ckno                            | wledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | xvi                                                                             |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | History of Power Devices Silicon-On-Insulator Technology SOI versus Bulk for High Voltage and Power IC Applications The LDMOS  1.4.1 The Fabrication Process 1.4.2 The LDMOS Characteristics Overview of Power Semiconductor Device Modelling for Circuit Simulation 1.5.1 Introduction 1.5.2 Model Implementation 1.5.3 Parameter Extraction 1.5.4 Existing LDMOS Models Objective of this Work Structure of Thesis Extent of Originality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1<br>1<br>4<br>5<br>6<br>6<br>8<br>14<br>15<br>16<br>17<br>17<br>19<br>20<br>20 |

| LDI                             | MOST in a SOI HV Process: Overview of Device Physics for Models Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . <b>24</b> 24 25                                                               |

|                                 | nterst of st | 1.2 Silicon-On-Insulator Technology                                             |

|   |                   | 2.3.3 Avalanche current                                                    |

|---|-------------------|----------------------------------------------------------------------------|

|   | 2.4               | The High Voltage LDMOS                                                     |

|   |                   | 2.4.1 Breakdown Voltage versus On-Resistance 45                            |

|   | 2.5               | Linear and saturation regions for the LDMOS                                |

|   | 2.6               | Thermal behaviour of the LDMOS                                             |

|   |                   | 2.6.1 Saturation velocity and mobility                                     |

|   |                   | 2.6.2 Threshold voltage                                                    |

|   |                   | 2.6.3 Drain current                                                        |

|   |                   | 2.6.4 Leakage current                                                      |

|   | 2.7               | Switching behaviour                                                        |

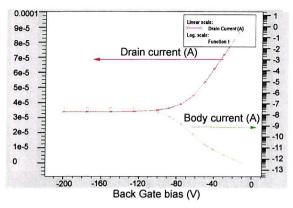

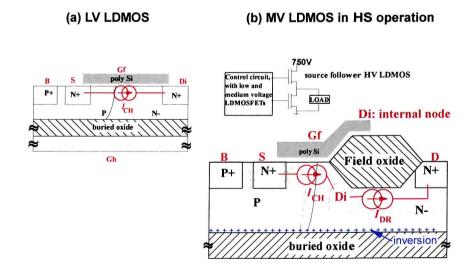

|   | 2.8               | Influence of High Side Behaviour                                           |

|   |                   | 2.8.1 Influence of High Side Behaviour on LDMOST 51                        |

|   |                   | 2.8.2 Influence of High Side Behaviour on SOI CMOS 54                      |

|   | 2.9               | Summary                                                                    |

|   |                   | prences                                                                    |

| 3 | A G               | Subcircuit Model for the LDMOS 59                                          |

| J | 3.1               | Introduction                                                               |

|   | $3.1 \\ 3.2$      | The LV N-LDMOS Model                                                       |

|   | IJ.∠              | 3.2.1 MOS Model 9.02                                                       |

|   |                   | 3.2.2 JUNCAP model                                                         |

|   |                   | 3.2.3 The Depletion Mode MOSFET for the Drift Region Modelling (M30.02) 61 |

|   |                   | 3.2.4 Modelling of the Capacitances                                        |

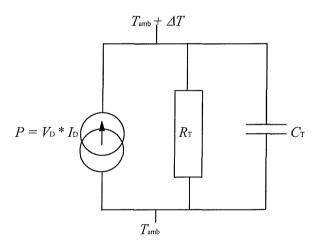

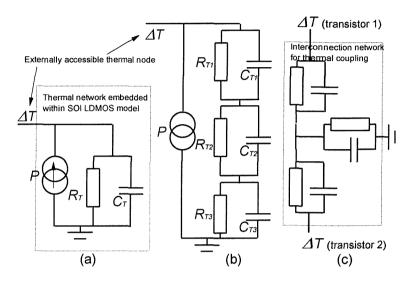

|   |                   | 3.2.5 Self Heating                                                         |

|   |                   | 3.2.6 Model Implementation                                                 |

|   |                   | 3.2.7 Extraction Strategy with ICCAP and Model Validation 67               |

|   | 3.3               | The MV Model                                                               |

|   | 5.5               | 3.3.1 The SOI Depletion Type MOSFET (M40)                                  |

|   |                   | 3.3.2 Model Implementation                                                 |

|   |                   | 3.3.3 Extraction Strategy with ICCAP and Model Validation 74               |

|   | 3.4               | Limitations of the Models and Conclusion                                   |

|   |                   | erences                                                                    |

| 4 | Con               | nnact DC Model 78                                                          |

| 4 | 4.1               | npact DC Model 78 Introduction                                             |

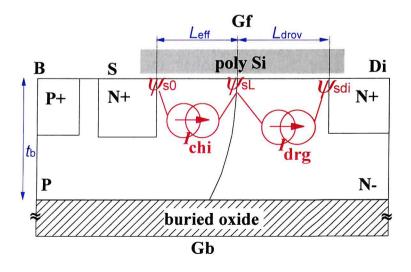

|   | $\frac{4.1}{4.2}$ | Current under Thin Gate Oxide                                              |

|   | 4.4               | 4.2.1 The Inversion Channel Current                                        |

|   |                   | 4.2.2 The Accumulation/Drift Current under Thin Gate Oxide 84              |

|   |                   | 4.2.3 Solving for Surface Potential at the End of the Inversion Channel 85 |

|   |                   | 4.2.4 Inclusion of High Field Effects                                      |

|   |                   | 4.2.5 Calculation of the Saturation Voltage                                |

|   |                   | 4.2.6 The Total Current Expression                                         |

|   |                   | 4.2.7 The Sub-Threshold Current                                            |

|   |                   | 4.2.8 Auxiliary Model                                                      |

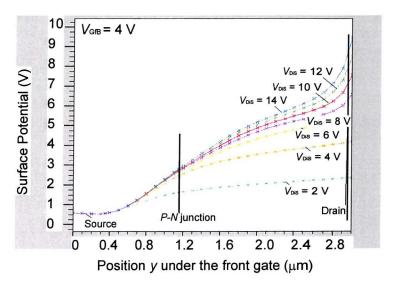

|   | 4.9               | Drift Current under the Field Oxide                                        |

|   | 4.3               | 4.3.1 The Intrinsic Drift Current                                          |

|   |                   | 4.3.2 Saturation by Pinch-off                                              |

|   |                   | 4.3.3 Velocity Saturation                                                  |

|   | 4.4               | Modelling Heating Effects                                                  |

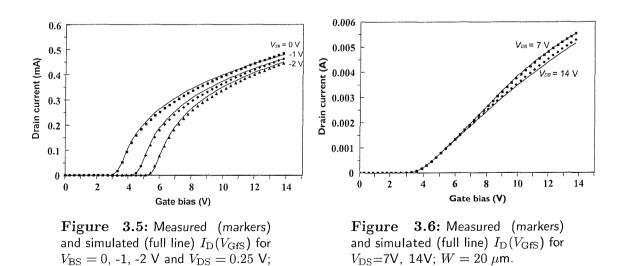

|   | 4.4               | Validation                                                                 |

|   | T. ( )            | _ v(b)(\(\(\)(\)(\)(\)(\)(\)(\)(\)(\)(\)(\)(\                              |

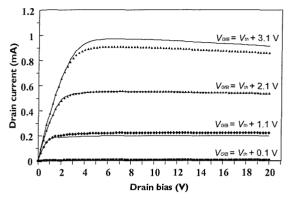

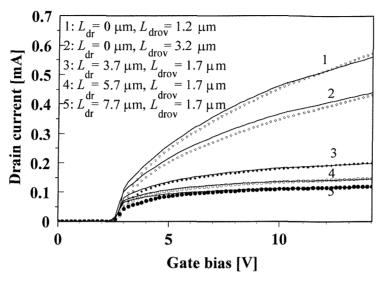

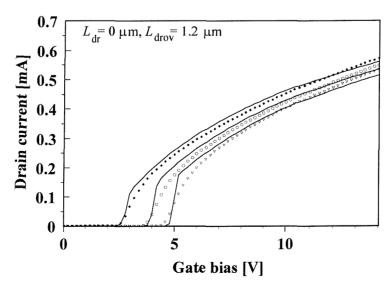

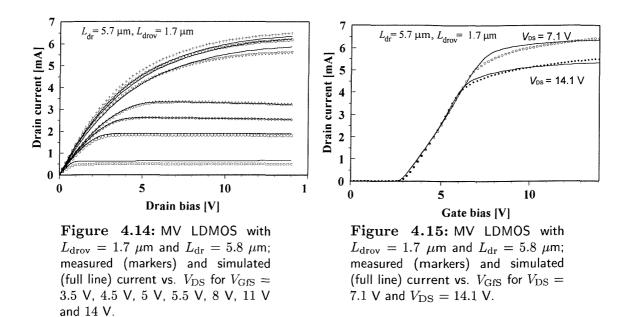

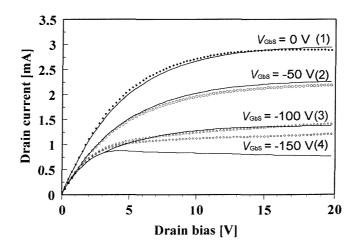

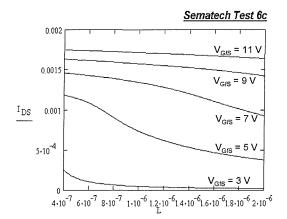

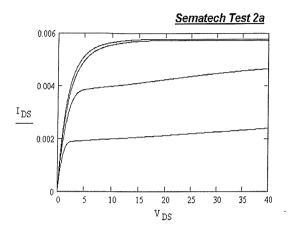

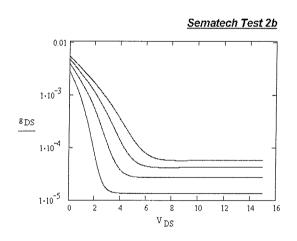

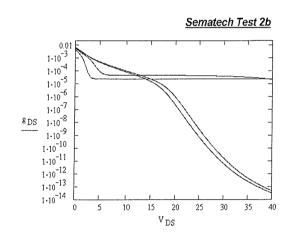

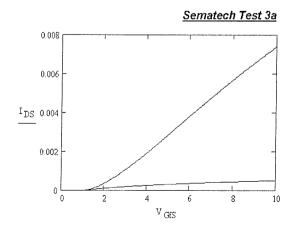

|   |            | 4.5.1 Linear Characteristics                                                      |

|---|------------|-----------------------------------------------------------------------------------|

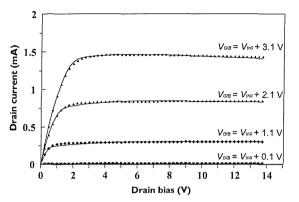

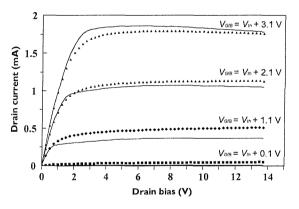

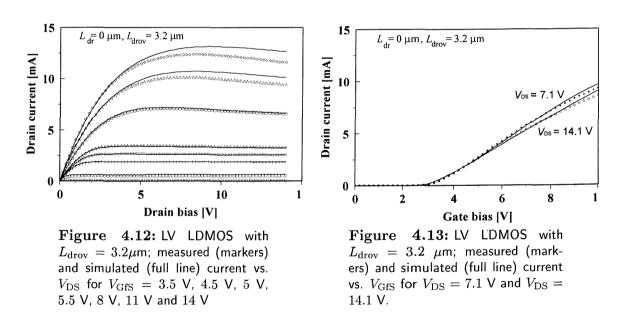

|   |            | 4.5.2 Output Characteristics                                                      |

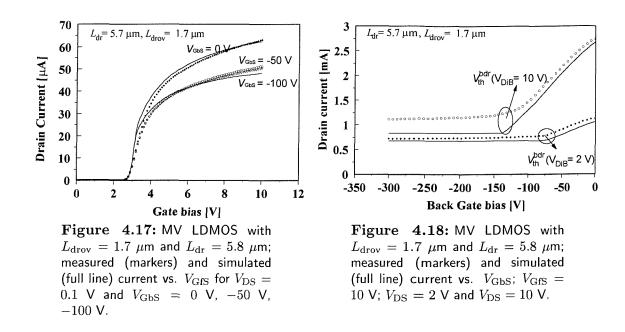

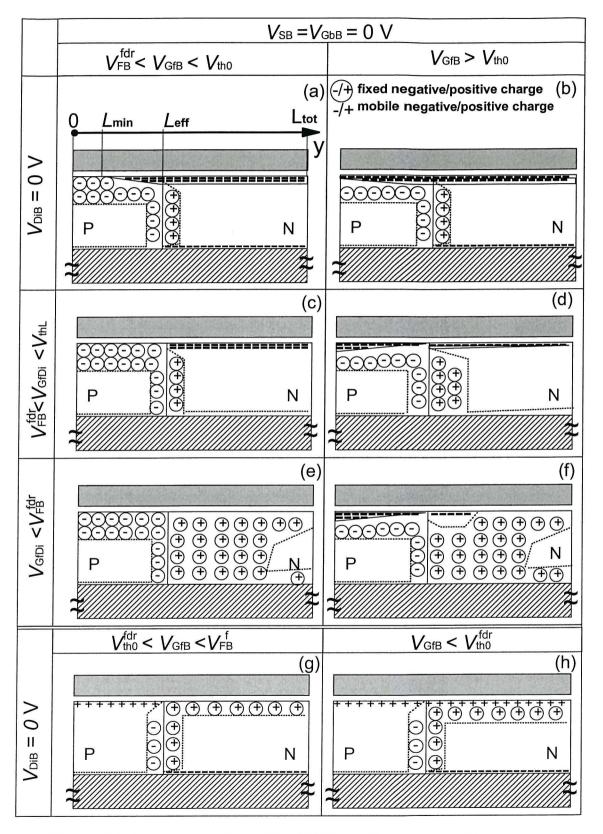

|   |            | 4.5.3 High-Side Behaviour                                                         |

|   | 4.6        | Summary                                                                           |

|   | Refe       | erences                                                                           |

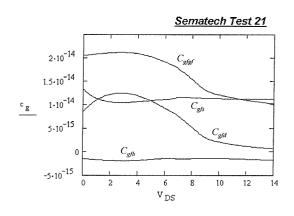

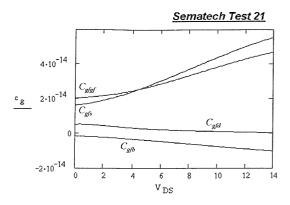

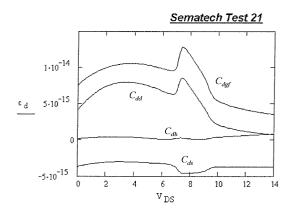

| 5 | Cor        | mpact Charge Model 109                                                            |

| J | 5.1        | Introduction                                                                      |

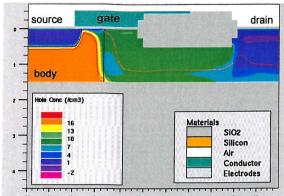

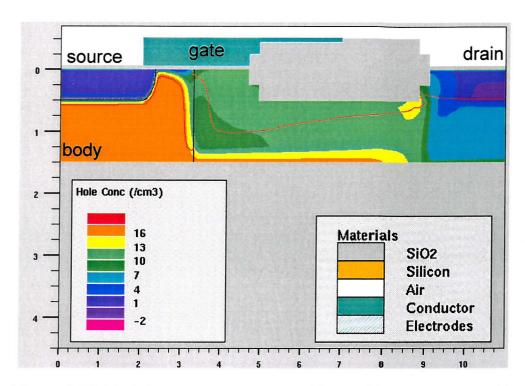

|   | 5.2        | Overview of the Charges in the LV LDMOS                                           |

|   | 0.2        | 5.2.1 Charges in the OFF-state                                                    |

|   |            | 5.2.2 Charges in the ON-state                                                     |

|   |            | 5.2.3 Charges at the Back Oxide Interface                                         |

|   |            | 5.2.4 A Fluid Dynamical Analogue for the Channel Charge 112                       |

|   | 5.3        | Nodal Charges Originating from the Channel Charge                                 |

|   |            | 5.3.1 The Ward and Dutton Partitioning Scheme                                     |

|   |            | 5.3.2 The Modified Ward and Dutton Partitioning Scheme for LDMOST . 117           |

|   |            | 5.3.3 Calculation of $L_{\min}$                                                   |

|   |            | 5.3.4 The Charge Distribution in the Channel                                      |

|   |            | 5.3.5 Final Expression for the Nodal Charges Originating from the Chan-           |

|   |            | nel Charge                                                                        |

|   | 5.4        | Nodal Charge Originating from Depletion under the Front Gate in the $P$ -Body 125 |

|   | 5.5        | Nodal Charges Originating from Accumulation under the Front Gate in the           |

|   |            | <i>P</i> -Body                                                                    |

|   | 5.6        | Capacitances for a MOSFET with Lateral Doping Gradient in the Channel 128         |

|   | 5.7        | Nodal Charges Originating from the Depletion under the Front Gate in the          |

|   |            | Drift Region                                                                      |

|   | 5.8        | Nodal Charges Originating from Inversion under the Front Gate in the Drift        |

|   | <b>-</b> 0 | Region                                                                            |

|   | 5.9        | Total of all Nodal Charges in the intrinsic part of the SOI LDMOS 134             |

|   | 5.10       | The Extrinsic Part                                                                |

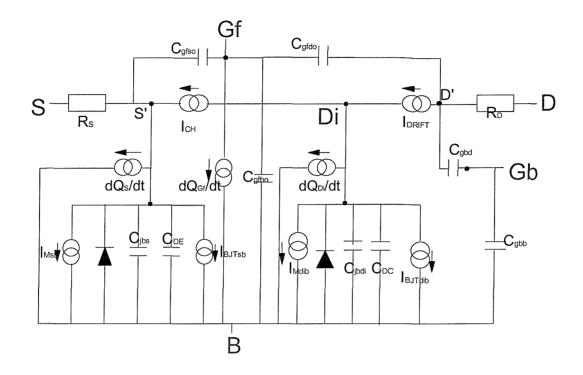

|   |            | The Large and Small Signal Model                                                  |

|   | 0.12       | 5.12.1 Measurement Method and Test Structures                                     |

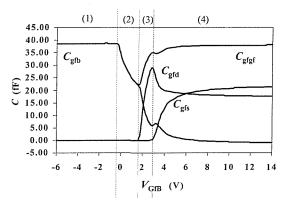

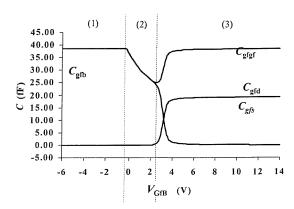

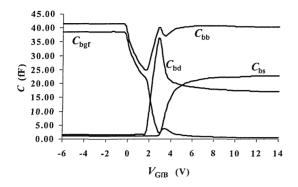

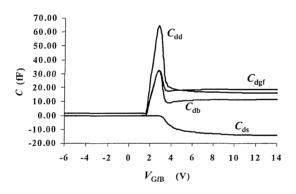

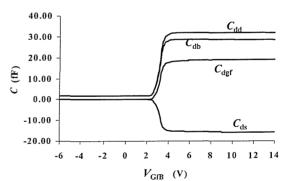

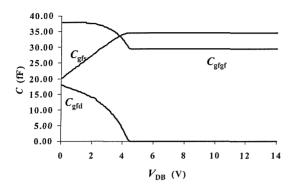

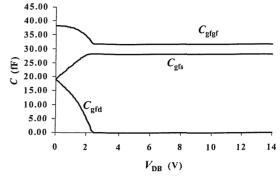

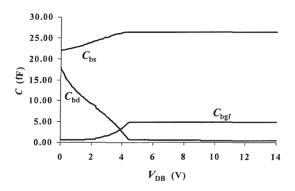

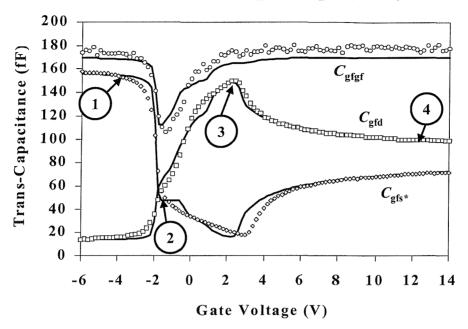

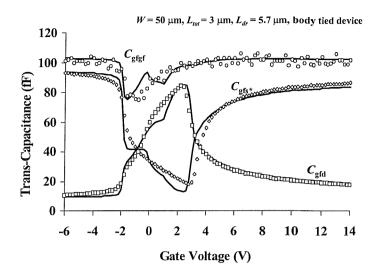

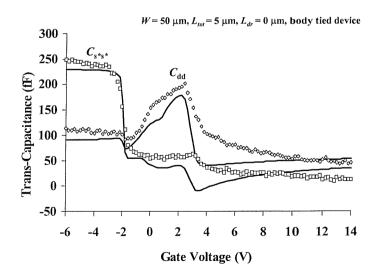

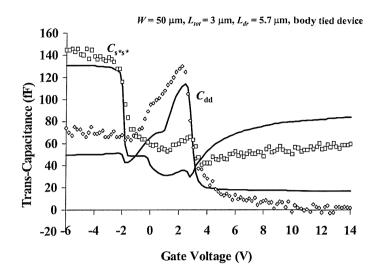

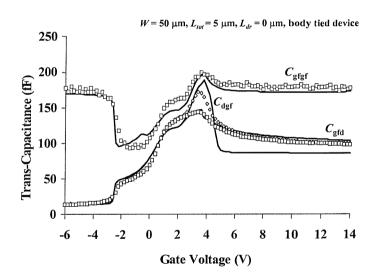

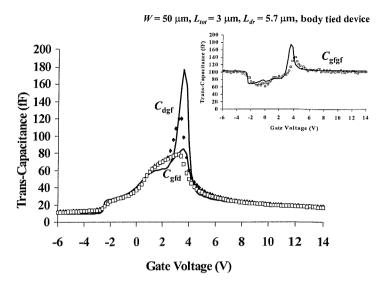

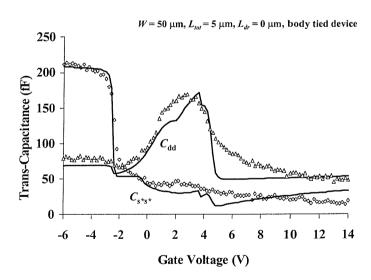

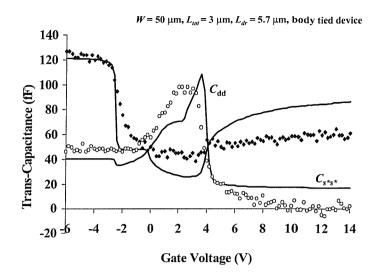

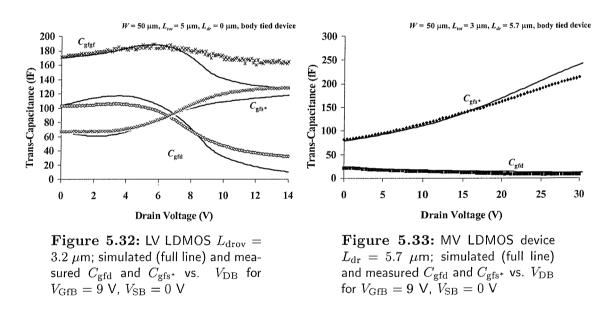

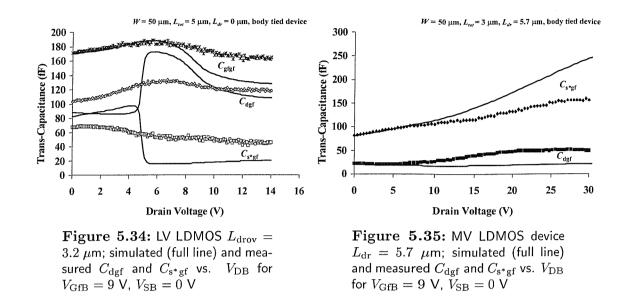

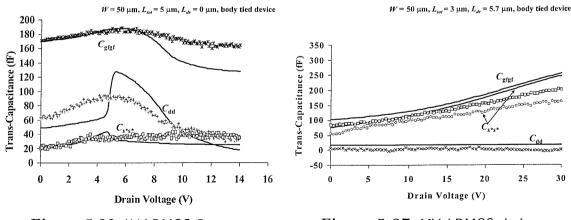

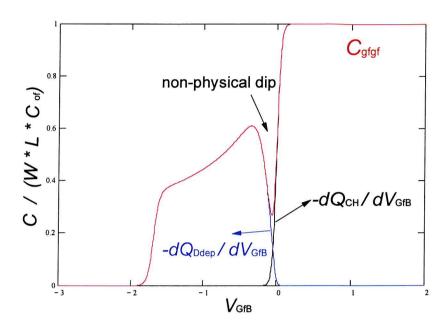

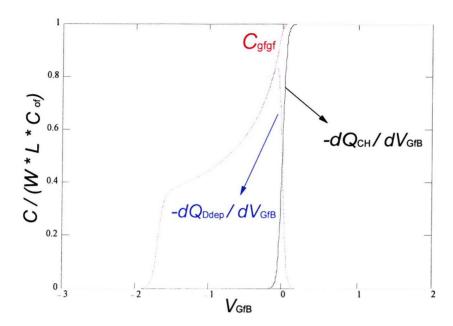

|   |            | 5.12.2 Results                                                                    |

|   | 5 13       | Summary                                                                           |

|   |            | rences                                                                            |

| , |            |                                                                                   |

| 3 | _          | lementation of the Model in Spice3  146                                           |

|   | 6.1        | Introduction                                                                      |

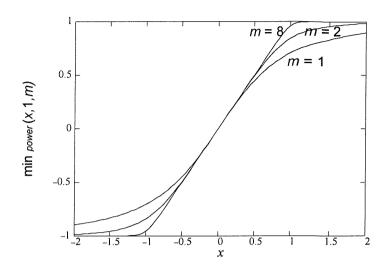

|   | 6.2        | 6.2.1 Overview                                                                    |

|   |            | 6.2.2 Combining Different Smoothing Functions                                     |

|   | 6.3        | Underflow, Overflow and Accuracy Problems                                         |

|   | 6.4        | Voltage Limiting Scheme                                                           |

|   | 6.5        | Summary                                                                           |

|   |            | conces 155                                                                        |

| 7            | $\mathbf{Mo}$ | del Evaluation                                                          | 156   |

|--------------|---------------|-------------------------------------------------------------------------|-------|

|              | 7.1           | Introduction                                                            | . 156 |

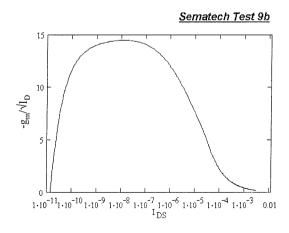

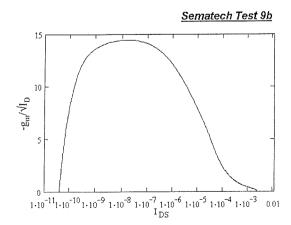

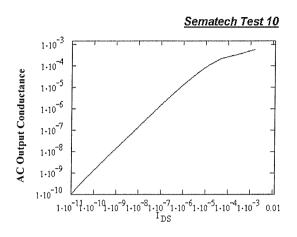

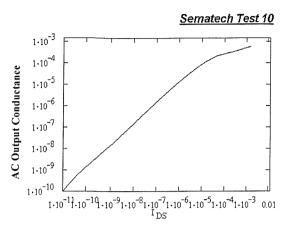

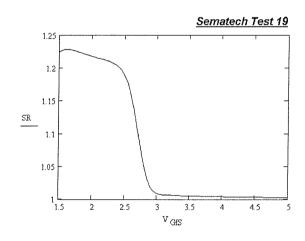

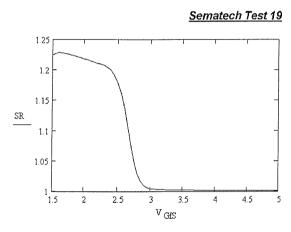

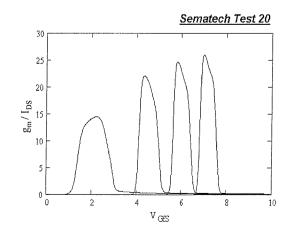

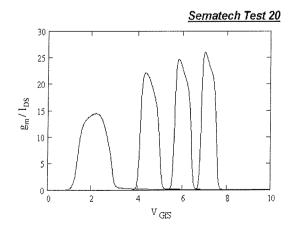

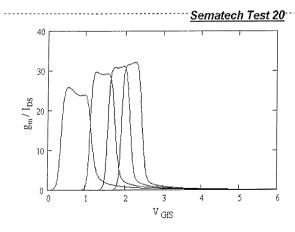

|              | 7.2           | Qualitative Tests                                                       | . 156 |

|              |               | 7.2.1 Introduction                                                      | . 156 |

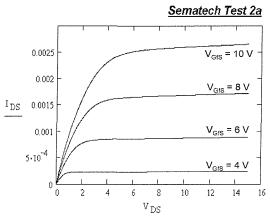

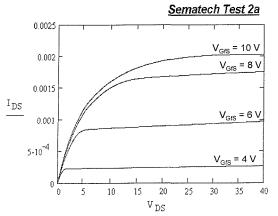

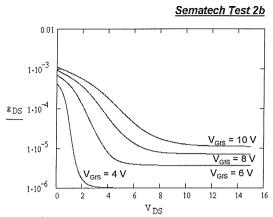

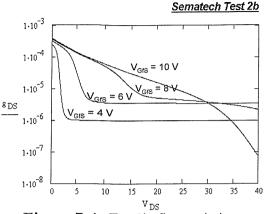

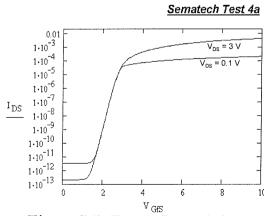

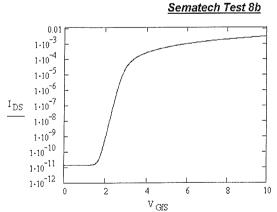

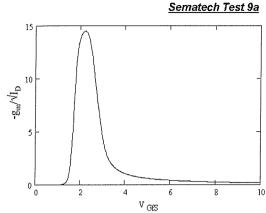

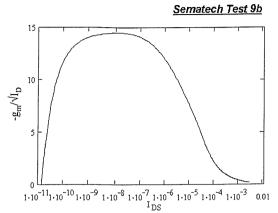

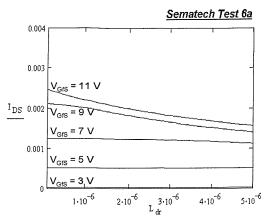

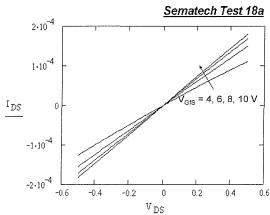

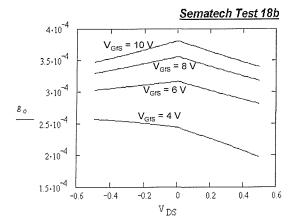

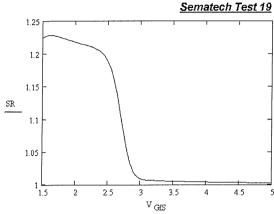

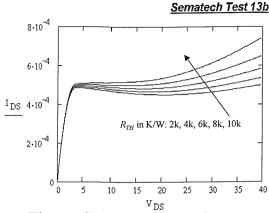

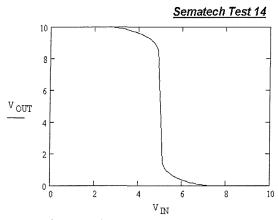

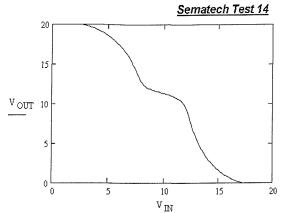

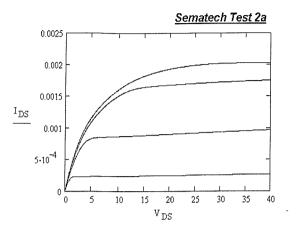

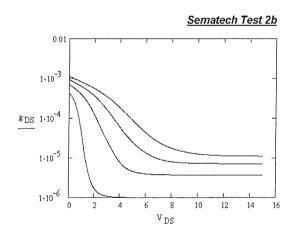

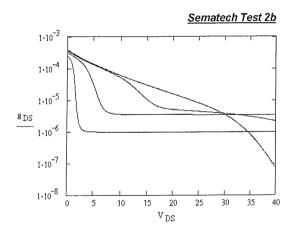

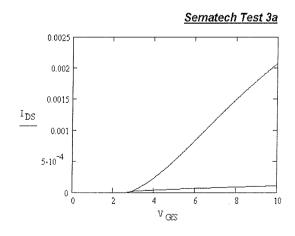

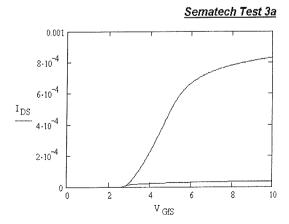

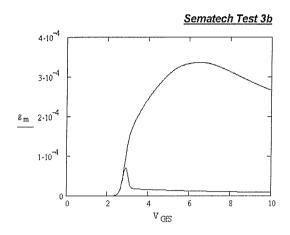

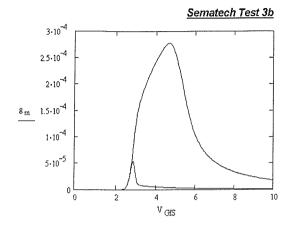

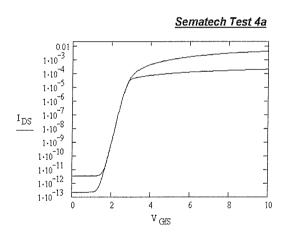

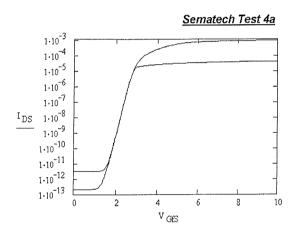

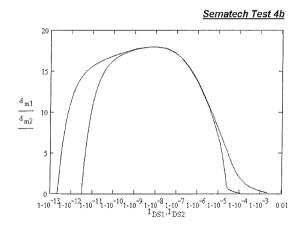

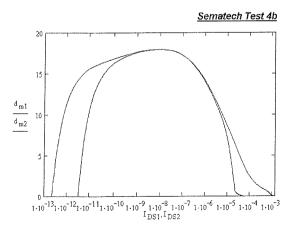

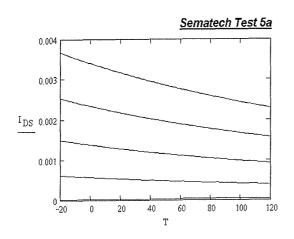

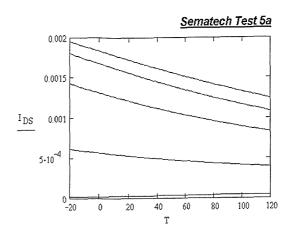

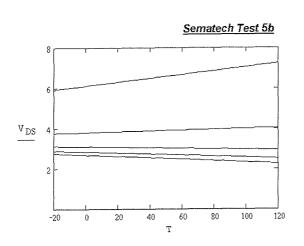

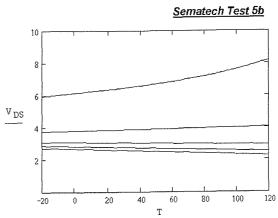

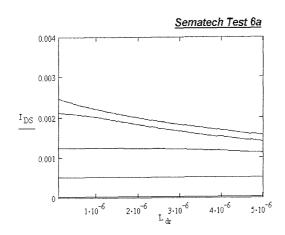

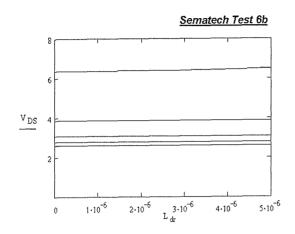

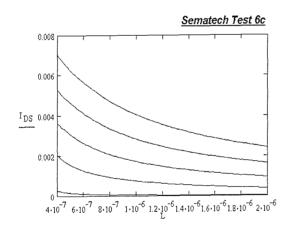

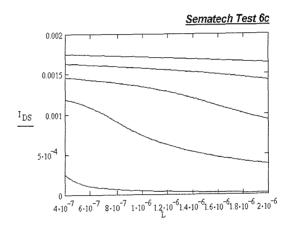

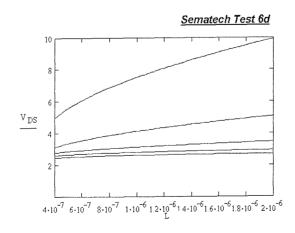

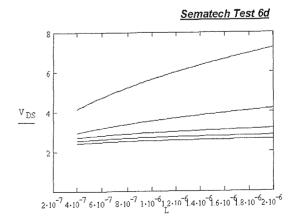

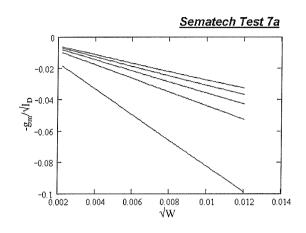

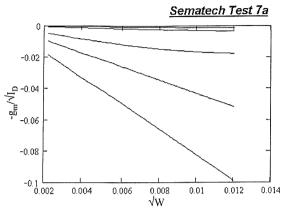

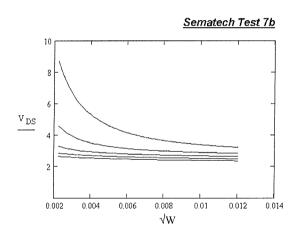

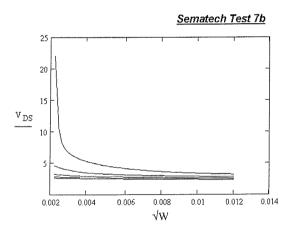

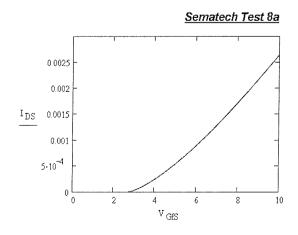

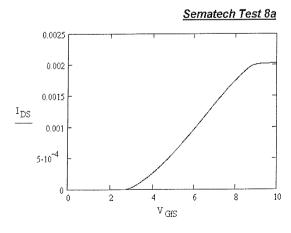

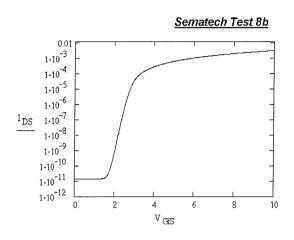

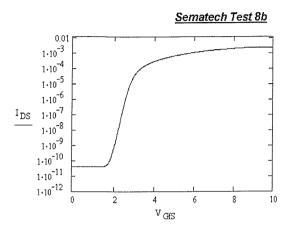

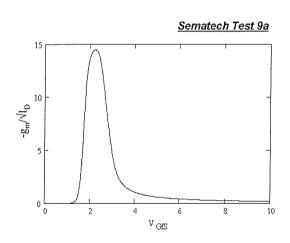

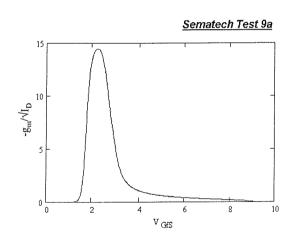

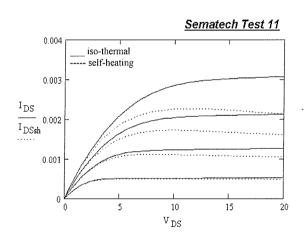

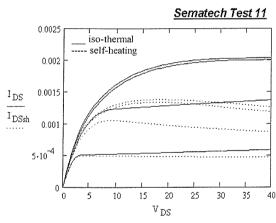

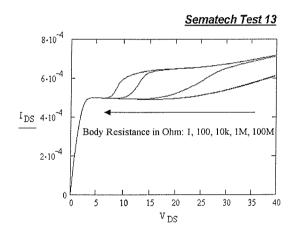

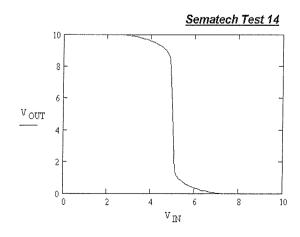

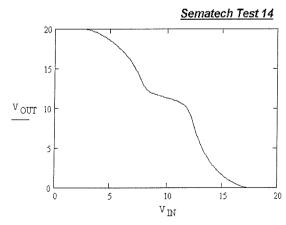

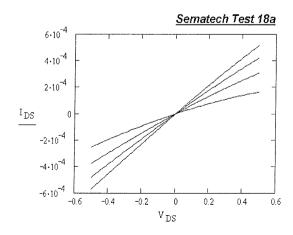

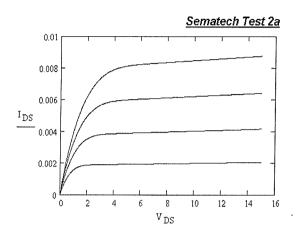

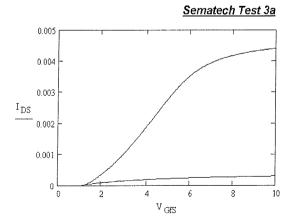

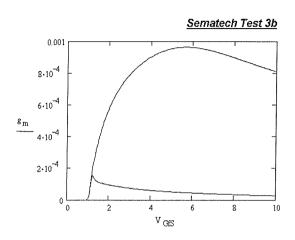

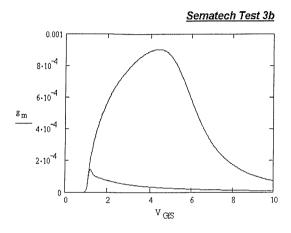

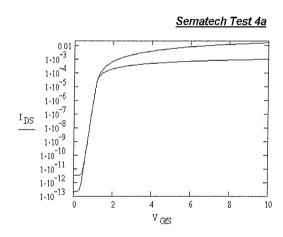

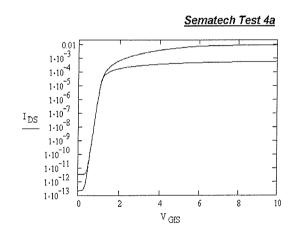

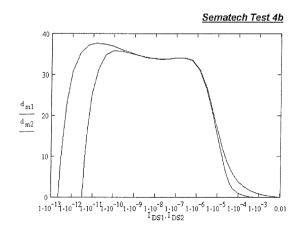

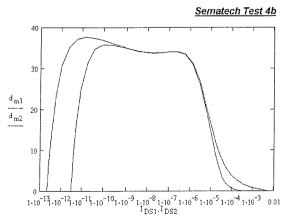

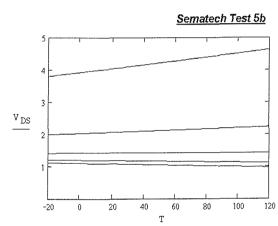

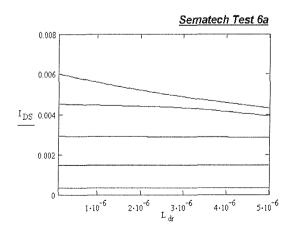

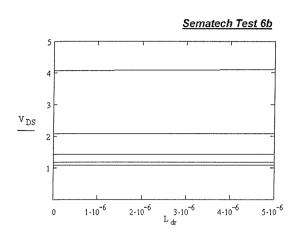

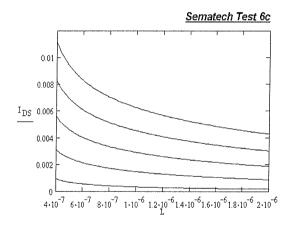

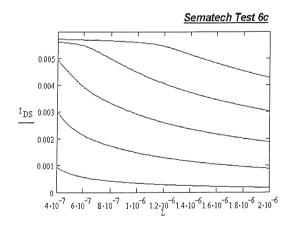

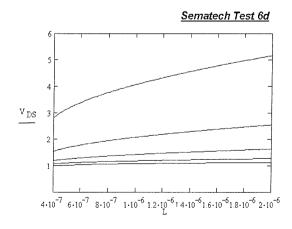

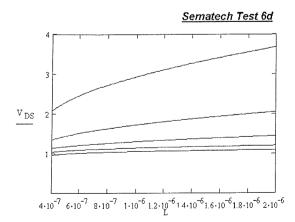

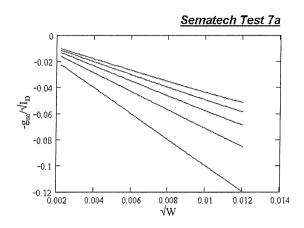

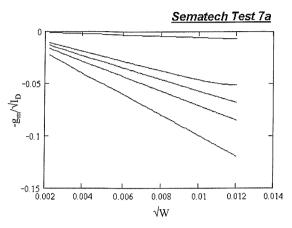

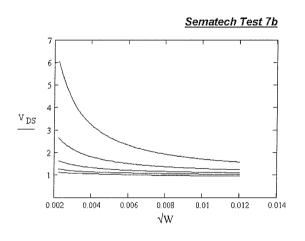

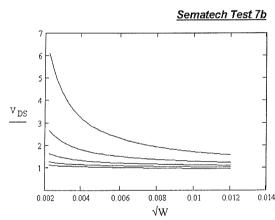

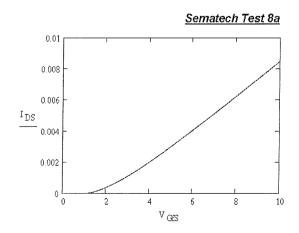

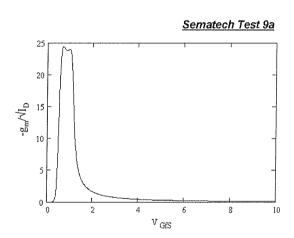

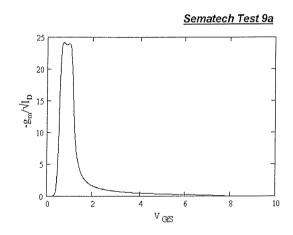

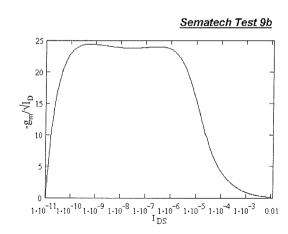

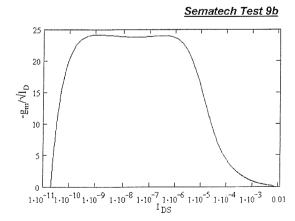

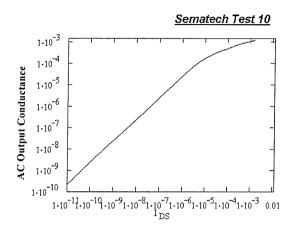

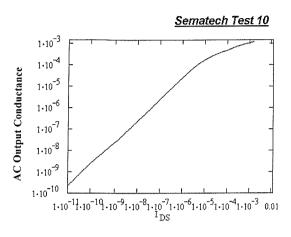

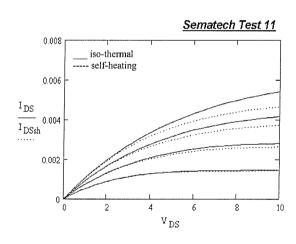

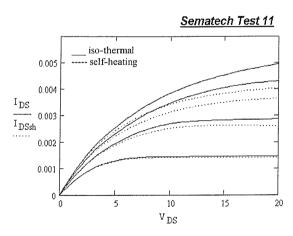

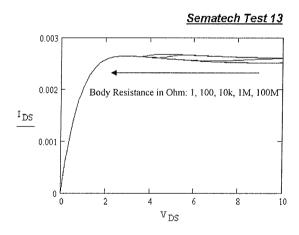

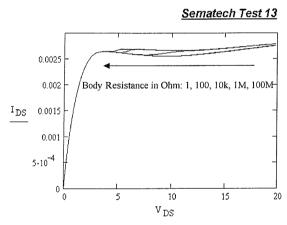

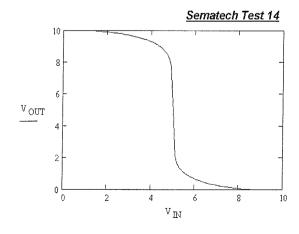

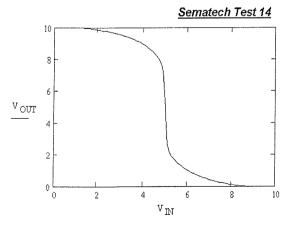

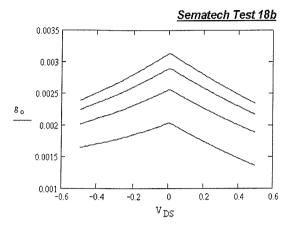

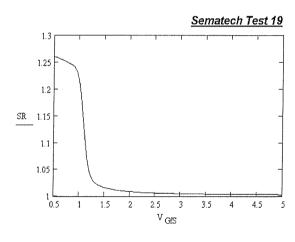

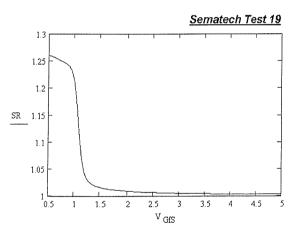

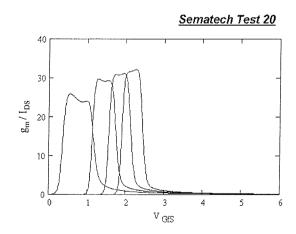

|              |               | 7.2.2 DC tests                                                          | . 157 |

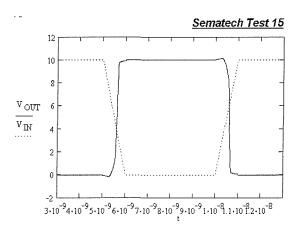

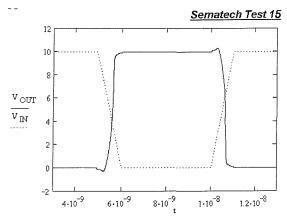

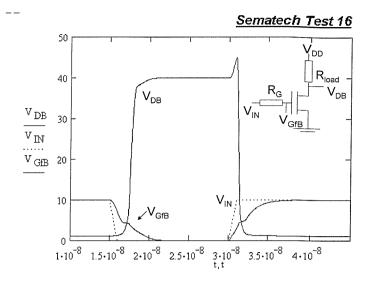

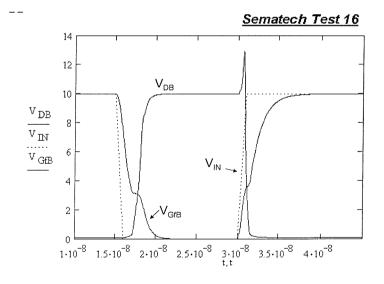

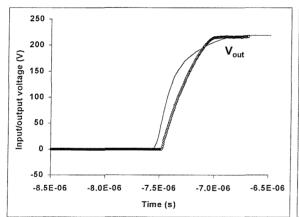

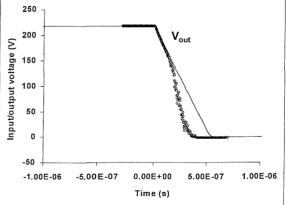

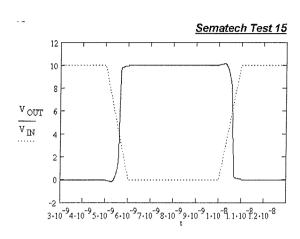

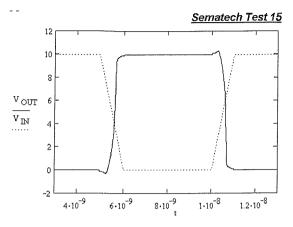

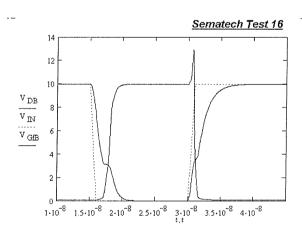

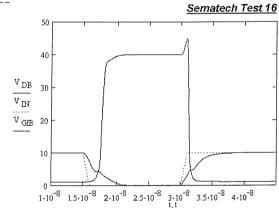

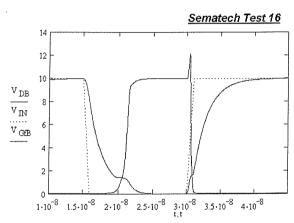

|              |               | 7.2.3 Transient tests                                                   |       |

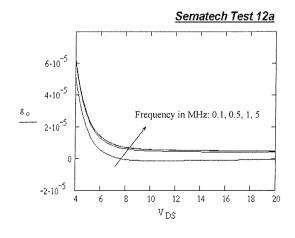

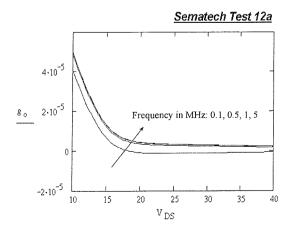

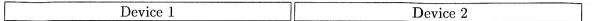

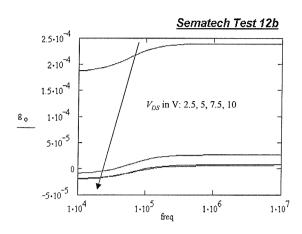

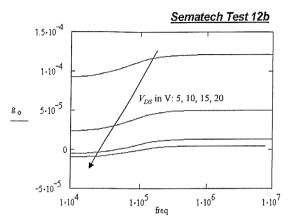

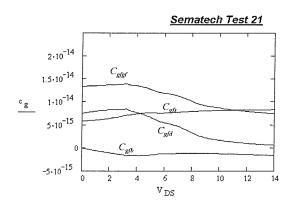

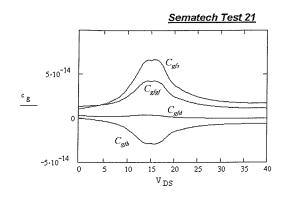

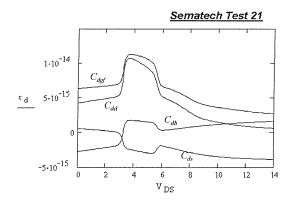

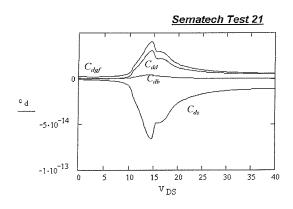

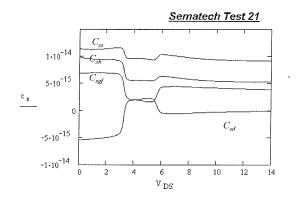

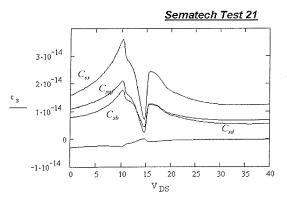

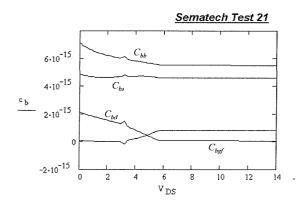

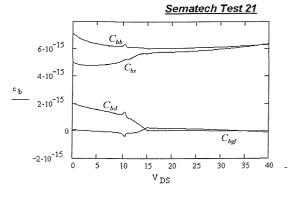

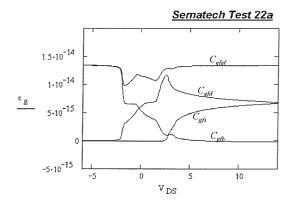

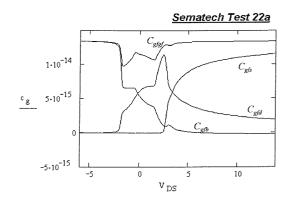

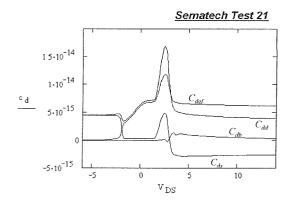

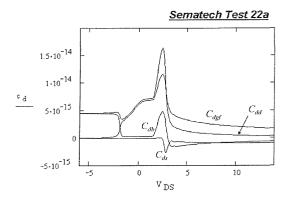

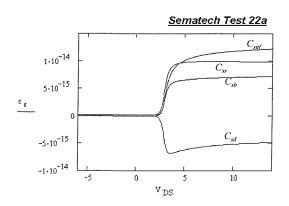

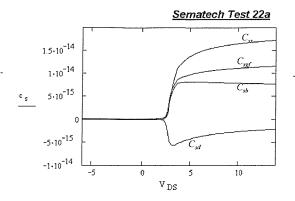

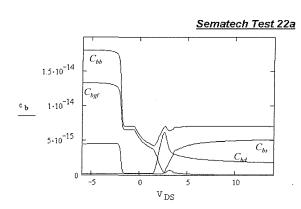

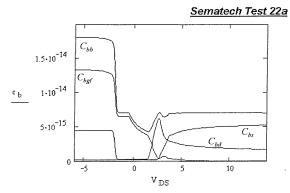

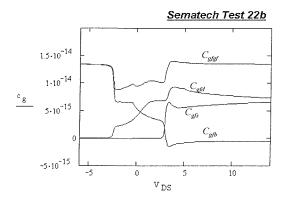

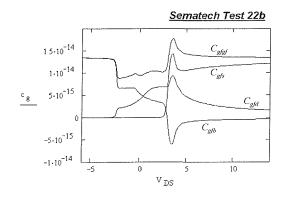

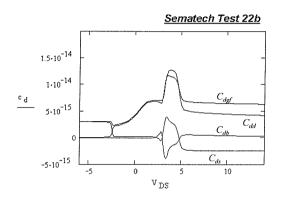

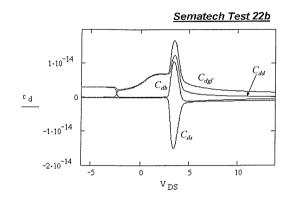

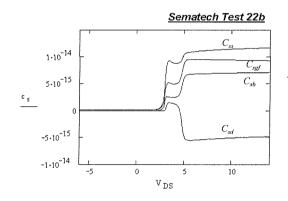

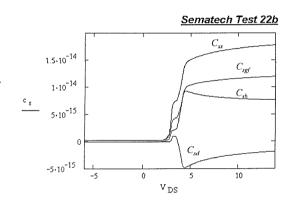

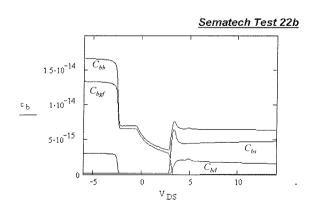

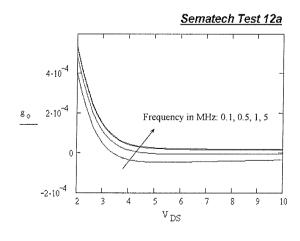

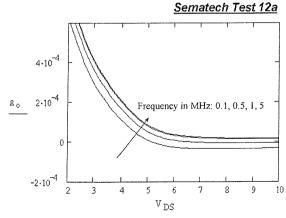

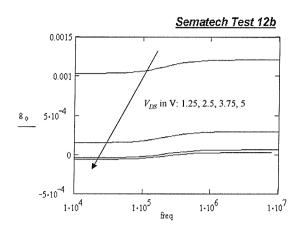

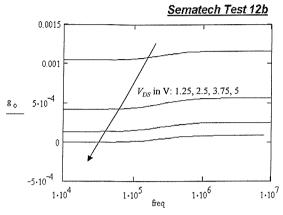

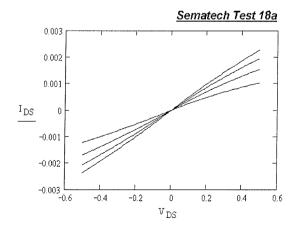

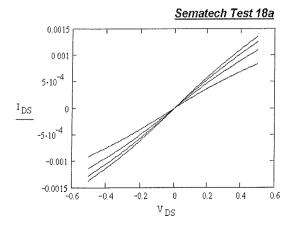

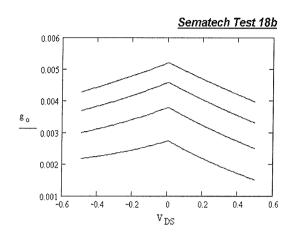

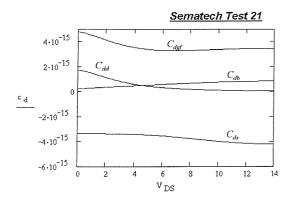

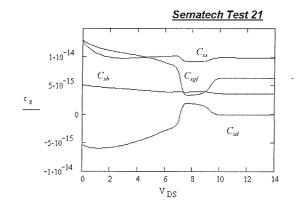

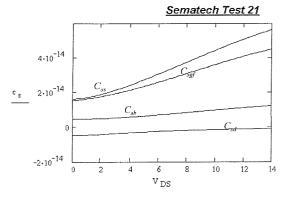

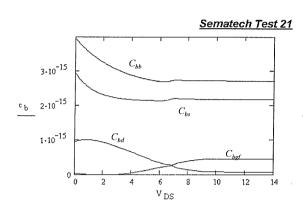

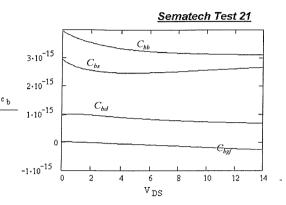

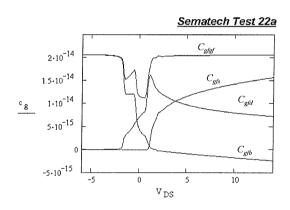

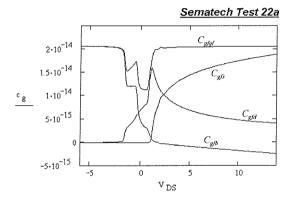

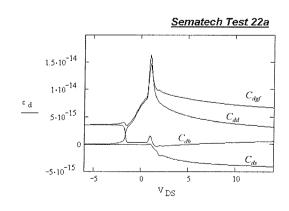

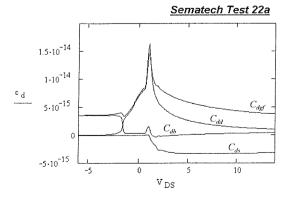

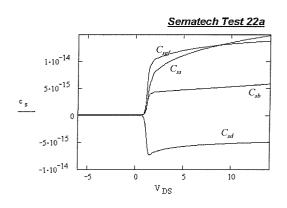

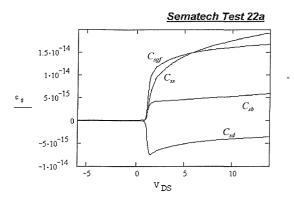

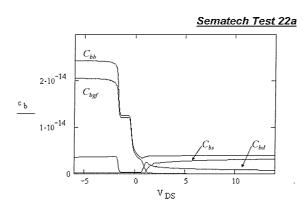

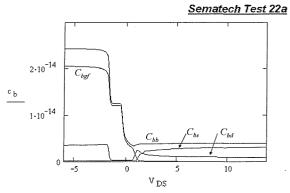

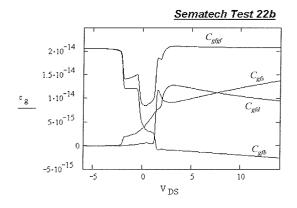

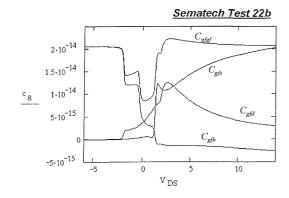

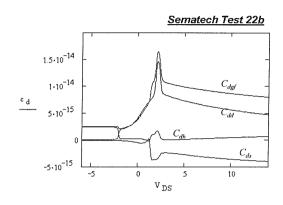

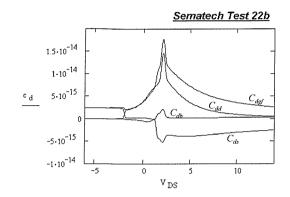

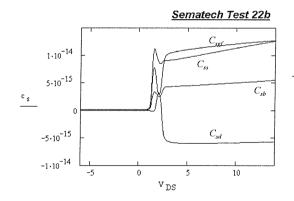

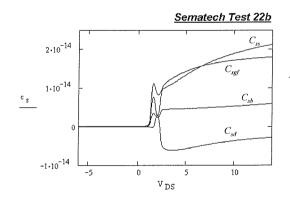

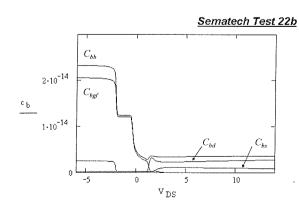

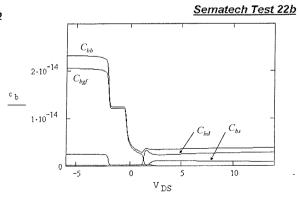

|              |               | 7.2.4 Capacitance Tests                                                 |       |

|              | 7.3           | Circuit Simulation Performance                                          |       |

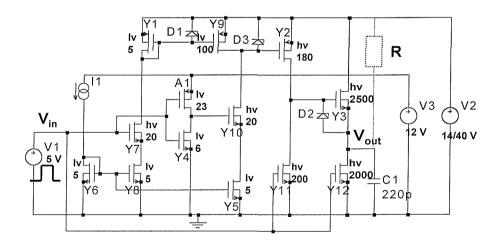

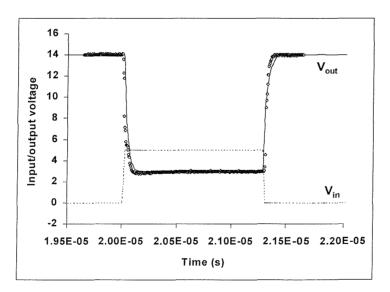

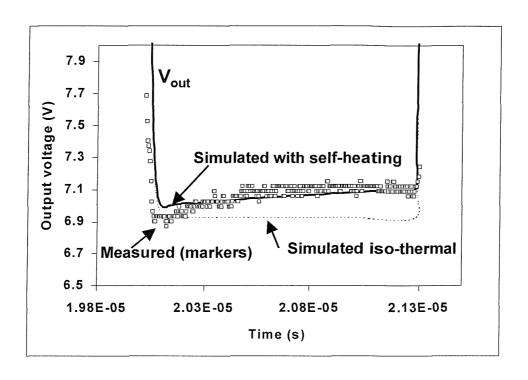

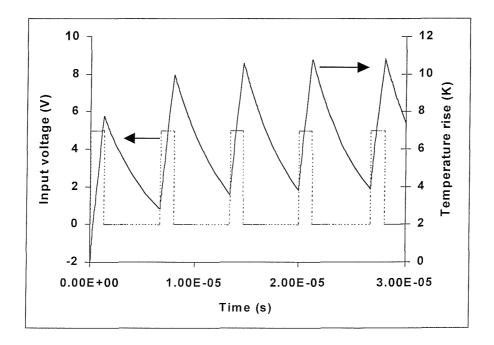

|              |               | 7.3.1 Switching Power Circuit                                           |       |

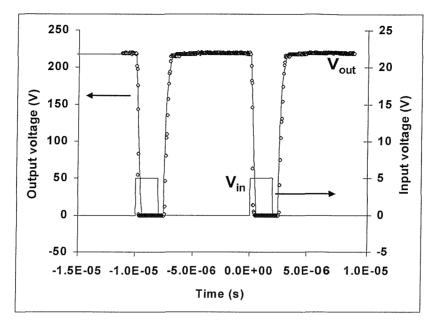

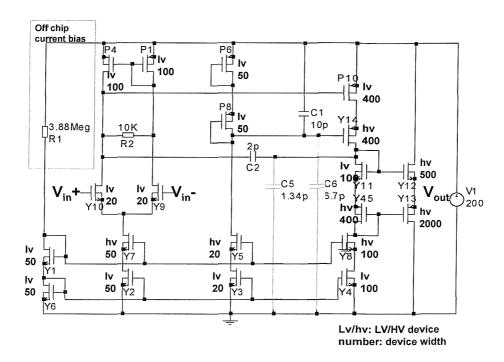

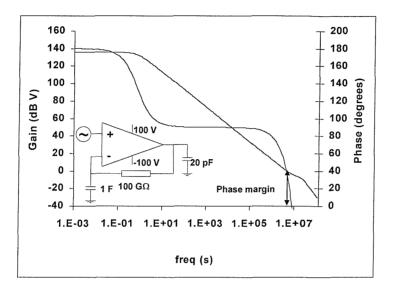

|              |               | 7.3.2 Operational Amplifier Circuit                                     |       |

|              | 7.4           | Summary                                                                 |       |

|              |               | erences                                                                 |       |

|              | rter          | archees                                                                 | . 1.0 |

| 8            | Cor           | nclusions and Further Work                                              | 178   |

|              | 8.1           | Conclusions                                                             |       |

|              | 8.2           | Ideas for Future Work                                                   | . 180 |

|              | Refe          | erences                                                                 | . 181 |

|              | A 500         |                                                                         | 100   |

| А            | AT            | LAS Results for the LDMOS                                               | 182   |

| В            | PH            | ILIPS model parameters for MM902, M30 and M40                           | 184   |

| $\mathbf{C}$ | Mo            | del Description                                                         | 191   |

|              | C.1           | Model Card                                                              | . 191 |

|              | C.2           | Element Card                                                            | . 196 |

|              | C.3           | Electrical Parameter set                                                | . 196 |

|              | C.4           | Conversion from Geometrical to Electrical Parameter Set                 |       |

|              | _             | C.4.1 Calculation of Some Temperature Independent Parameters            |       |

|              |               | C.4.2 Calculation of the Temperature Dependent Parameters at the Nom-   |       |

|              |               | inal Temperature                                                        | 200   |

|              | C.5           | Parameter Preprocessing from electrical parameter set                   |       |

|              | 0.0           | C.5.1 Calculation of the Temperature Dependent Electrical Parameters at |       |

|              |               | the Nominal Temperature                                                 | 201   |

|              |               | C.5.2 Calculation of the Temperature Dependent Electrical Parameters at |       |

|              |               | the Ambient Temperature                                                 | 202   |

|              |               | C.5.3 Inclusion of Self and Coupled Heating for the Major Temperature   | 202   |

|              |               | Dependent Model Parameters                                              | 203   |

|              | $C \in$       | Smoothing Functions                                                     |       |

|              | C.6           | The LV LDMOS Current                                                    |       |

|              | C.7           |                                                                         |       |

|              |               |                                                                         |       |

|              |               | C.7.2 Block 1B                                                          |       |

|              |               | C.7.3 Block 1C                                                          |       |

|              |               | C.7.4 Block 1D                                                          |       |

|              |               | C.7.5 Block 1E                                                          |       |

|              |               | C.7.6 Block 1F                                                          |       |

|              | C.8           | The Drift Region Current Under the Field Oxide                          |       |

|              | C.9           | The Charge Equations                                                    |       |

|              |               | C.9.1 The Body Channel Charge                                           |       |

|              |               | C.9.2 The Body Charge (Block 8)                                         |       |

|              |               | C.9.3 The Body Accumulation Charge (Block 9)                            | 214   |

|   | (      | C.9.4   | The Drain Gate Depletion Charge (Block 10)             |   |  |       |  |  |     |   | 214 |

|---|--------|---------|--------------------------------------------------------|---|--|-------|--|--|-----|---|-----|

|   |        |         | The Drift Accumulation charge (Block 11)               |   |  |       |  |  |     |   |     |

|   | (      | C.9.6   | The Drift Inversion charge                             |   |  | <br>  |  |  |     |   | 216 |

|   | (      | C.9.7   | The Nodal Charges                                      |   |  | <br>  |  |  |     |   | 216 |

|   | C.10 T | The Ex  | strinsic Model (copied from the STAG model)            |   |  | <br>  |  |  |     |   | 217 |

|   | (      | C.10.1  | Series Resistance                                      |   |  |       |  |  |     |   | 217 |

|   | (      | C.10.2  | Impact Ionisation Model                                |   |  | <br>  |  |  |     |   | 217 |

|   | (      | C.10.3  | Diodes and Parasitic Bipolar Transistor $\dots$        |   |  | <br>  |  |  |     |   | 217 |

|   | (      | C.10.4  | Self-Heating Model                                     |   |  |       |  |  |     |   | 218 |

|   | (      | C.10.5  | Noise Models                                           | • |  | <br>• |  |  | . • |   | 218 |

| D | Proof  | f for V | $I_{ m Psat}$ used in $I_{ m DR}$                      |   |  |       |  |  |     | 2 | 219 |

| E | Deriv  | ation   | of $q_{ m Llim}$ , $q_{ m Lacclim}$ and $q_{ m dilim}$ |   |  |       |  |  |     | 2 | 221 |

| F | SEM    | ATEC    | CH Tests                                               |   |  |       |  |  |     | 2 | 223 |

|   | F.1 F  | Parame  | eter Sets of the Evaluated Devices                     |   |  |       |  |  |     |   | 223 |

|   |        |         | FECH Tests                                             |   |  |       |  |  |     |   |     |

| G | Parar  | neter   | Set for the LV, MV and HV LDMOS                        |   |  |       |  |  |     | 2 | 256 |

## List of Tables

| 1.1 | The geometry parameters                                                                             |

|-----|-----------------------------------------------------------------------------------------------------|

| 1.3 | The derived parameters                                                                              |

| 3.1 | The subcircuit model definition as formulated for PSTAR 67                                          |

| 3.2 | Extraction strategy for the LV LDMOS parameters                                                     |

| 3.3 | The MV LDMOS subcircuit model definition as formulated for PSTAR 74                                 |

| 4.1 | Measurement set-ups for parameter extraction                                                        |

| 4.2 | The optimised parameters compared to their initial values                                           |

| 7.1 | Overview of devices evaluated by the SEMATECH tests                                                 |

| В.1 | Description of the MM9.02 electrical model parameters                                               |

| B.2 | Description of the M30.02 model parameters                                                          |

| B.3 | Description of the M40 model parameters                                                             |

| B.4 | Optimised parameter set for the LV LDMOS                                                            |

| B.5 | Optimised parameter set for the MV LDMOS                                                            |

| C.1 | Descriptions and default values of all LDMOS model parameters $\dots 192$                           |

| F.1 | Overview of devices evaluated by the SEMATECH tests                                                 |

| F.2 | Parameter Set 1 and 2; to be continued on the next page                                             |

| F.3 | Adapted SEMATECH Tests for SOI LDMOS; continued on next page 226                                    |

| G.1 | Parameter Set for the LV SOI N-LDMOS, the MV SOI N-LDMOS, the HV SOI N-LDMOS and the HV SOI P-LDMOS |

## List of Symbols

## Symbol Conventions:

| $V_{ m XY}$         | Voltage drop between nodes $X$ and $Y$ [V]                                    |

|---------------------|-------------------------------------------------------------------------------|

| $C_{\mathrm{xy}}$   | (Trans)capacitance of node X with respect to node Y [F]                       |

| $d\mathbf{r}$       | subscript referring to the drift region                                       |

| f                   | subscript referring to the front gate                                         |

| b                   | subscript referring to the back gate                                          |

|                     |                                                                               |

|                     |                                                                               |

| $\alpha$            | Normalised pinch-off region length (second CLM model) [-]                     |

| $lpha_{	heta}$      | Scattering coefficient [cm/V]                                                 |

| $\beta$             | Inversion layer gain factor $[A/V^2]$                                         |

| $eta_{ m acce}$     | Effective drift region accumulation layer gain factor $[{\rm A/V^2}]$         |

| $eta_{ m acc}$      | Drift region accumulation layer gain factor $[A/V^2]$                         |

| $eta_{ m e}$        | Effective inversion layer gain factor $[A/V^2]$                               |

| χ                   | Temperature coefficient for the threshold voltage $[V/K]$                     |

| $\Delta L$          | Threshold roll-off with channel length [m]                                    |

| $\Delta L$          | Threshold roll-up with channel width [m]                                      |

| $\Delta T$          | Device temperature rise [K]                                                   |

| $\epsilon_0$        | Permittivity of vacuum $[8.854 \cdot 10^{-12} \text{F/m}]$                    |

| $\epsilon_{ m ox}$  | Permittivity of silicon-dioxide $[3.9 \cdot 8.854 \cdot 10^{-12} \text{F/m}]$ |

| $\epsilon_{ m si}$  | Permittivity of silicon $[11.7 \cdot 8.854 \cdot 10^{-12} \text{F/m}]$        |

| $\eta_{\mathtt{S}}$ | Fast surface states coefficient [-]                                           |

| $\gamma$            | Local front gate body factor $[\sqrt{V}]$                                     |

| $\gamma^{ m bdr}$   | Back gate body factor in the drift region $[\sqrt{V}]$                        |

| $\gamma^{ m b}$     | Back gate body factor in the body $[\sqrt{V}]$                                |

| $\gamma^{ m fdr}$   | Front gate body factor in the drift region $[\sqrt{V}]$                       |

| $\gamma_0$          | Front gate body factor in the body $[\sqrt{V}]$                               |

| $\gamma_{ m e1}$    | Mean value of $\gamma$ for $L_{\min} < y < L_{\rm i}[\sqrt{\rm V}]$           |

| $\gamma_{ m e2}$    | Mean value of $\gamma$ for $L_{\rm i} < y < L_{\rm eff}[\sqrt{\rm V}]$        |

```

Mean value for the front gate body factor in the body [\sqrt{V}]

\gamma_{

m m}

Electrical drain induced barrier lowering factor [-]

\gamma_{00}

Thermal conductivity of SiO_2 [W/(m·K)]

\kappa_{\rm ox}

Electrical CLM factor [1/V]

λ

CLM factor [m/V]

\lambda_{

m r}

Low field carrier mobility for electrons [cm^2/(V \cdot s)]

\mu_{0n}

Low field carrier mobility for holes [cm^2/(V \cdot s)]

\mu_{0p}

Low field carrier mobility [cm^2/(V \cdot s)]

\mu_0

Zero field accumulation surface mobility [cm^2/(V \cdot s)]

\mu_{\rm acc}

Effective drift region mobility [cm^2/(V \cdot s)]

\mu_{\mathrm{dreff}}

Zero field drift region mobility [cm^2/(V \cdot s)]

\mu_{\mathrm{dr}}

High field effective mobility [cm^2/(V \cdot s)]

\mu_{\mathrm{eff}}

Zero field inversion surface mobility [cm^2/(V \cdot s)]

\mu_{\mathrm{s}}

Effective mobility accounting for vertical mobility degradation [cm<sup>2</sup>/(V·s)]

\mu_{\text{xeff}}

Effective mobility accounting for carrier velocity saturation [cm<sup>2</sup>/(V·s)]

\mu_{\text{veff}}

Built-in potential for the D-B diode [V]

\phi_{

m bid}

Built-in potential for the S-B diode [V]

\phi_{\rm bis}

\phi_{\rm Fdr}

Fermi-potential for the drift region [V]

Fermi-potential for the body region [V]

\phi_{

m F}

Thermal voltage [V]

\phi_{\mathrm{t}}

\psi

Local channel potential [V]

Channel potential at the internal drain [V]

\psi_{\mathrm{Di}}

Channel potential at the drain [V]

\psi_{\mathrm{D}}

Channel potential where inversion at the buried oxide stops [V]

\psi_{\mathsf{i}}

Surface potential at the source end of the channel (y = 0) [V]

\psi_{

m s0}

Surface potential at the drain end of the channel (y = L_{drov} + L_{eff}) [V]

\psi_{\mathrm{sdi}}

Strong inversion surface potential at the source end of the channel (y=0) [V]

\psi_{\rm si0}

Charge model expression for the strong inversion surface potential at the left

\psi_{

m siLinv}

side of the body-drain junction (y = L_{\text{eff}}^-) [V]

Strong inversion surface potential at the body-drain junction (y = L_{\text{eff}}) [V]

\psi_{

m siL}

Strong inversion surface potential in the channel [V]

\psi_{

m si}

\psi_{\rm si}^{\rm dr}

Strong inversion surface potential in the drift region under the front gate [V]

Surface potential at the right side of the body-drain junction (y = L_{\text{eff}}^+) [V]

\psi_{

m sLacc}

Surface potential at y = L_{\min} [V]

\psi_{

m sLmin}

Combined expression for the subthreshold and saturation surface potential [V]

\psi_{\mathrm{sLsatf}}

Saturation surface potential [V]

\psi_{\mathrm{sLsat}}

Surface potential at the body-drain junction (y = L_{\text{eff}}) [V]

\psi_{\mathrm{sL}}

Subthreshold surface potential at the source end of the channel (y = 0) [V]

\psi_{

m ss0}

```

| $\psi_{ m ssL}$        | Subthreshold surface potential at the body-drain junction $(y = L_{\text{eff}})$ [V]                |

|------------------------|-----------------------------------------------------------------------------------------------------|

| $\psi_{ m ss}$         | Subthreshold surface potential in the channel [V]                                                   |

| $\psi_{ m ss}^{ m dr}$ | Subthreshold surface potential in the drift region under the front gate [V]                         |

| $\psi_{ m st0}$        | Surface potential at the source end of the channel, not including high-field effects $[V]$          |

| $\psi_{ m s}$          | Surface potential in the channel [V]                                                                |

| $\psi_{ m s}^{ m dr}$  | Surface potential in the drift region under the front gate [V]                                      |

| $\sigma$               | Drain induced barrier lowering factor [m]                                                           |

| au                     | Carrier life time [s]                                                                               |

| $\theta$               | Vertical field inversion mobility degradation factor $[V^{-1}]$                                     |

| $	heta_{ m 3dr}$       | Velocity saturation drift mobility degradation factor $[V^{-1}]$                                    |

| $	heta_{ m acc}$       | Vertical field accumulation mobility degradation factor $[V^{-1}]$                                  |

| $\xi_{ m c}$           | Critical electric field [V/cm]                                                                      |

| $\xi_{	ext{xeff}}$     | Effective transverse electric field [V/cm]                                                          |

| $\xi_{ m x}$           | Transverse electric field [V/cm]                                                                    |

| $\zeta_{ m x}$         | Empirical parameter used in the formula for $\xi_x$ [-]                                             |

| $C_{ m gbbo}$          | Back gate-body overlap capacitance [F]                                                              |

| $C_{ m gbdo}$          | Back gate-drain overlap capacitance [F]                                                             |

| $C_{ m gbso}$          | Back gate-source overlap capacitance [F]                                                            |

| $C_{ m gfs}$           | Transcapacitance of the front gate node with respect to the body node [F]                           |

| $C_{ m gfbo}$          | Front gate-body overlap capacitance [F]                                                             |

| $C_{ m gfd}$           | Transcapacitance of the front gate node with respect to the drain node [F]                          |

| $C_{ m gfdo}$          | Front gate-drain overlap capacitance [F]                                                            |

| $C_{ m gfgf}$          | Capacitance of the gate [F]                                                                         |

| $C_{ m gfs}$           | Transcapacitance of the front gate node with respect to the source node [F]                         |

| $C_{ m gfs*}$          | Transcapacitance of the front gate node with respect to the source and body nodes tied together [F] |

| $C_{ m gfso}$          | Front gate-source overlap capacitance [F]                                                           |

| $C_{ m dd}$            | Capacitance of the drain node [F]                                                                   |

| $C_{ m dgf}$           | Transcapacitance of the drain node with respect to the front gate node [F]                          |

| $C_{ m ds}$            | Transcapacitance of the drain node with respect to the source node [F]                              |

| $C_{ m ds*}$           | Transcapacitance of the drain node with respect to the source and body nodes tied together [F]      |

| $C_{ m sd}$            | Transcapacitance of the source node with respect to the drain node [F]                              |

| $C_{ m sgf}$           | Transcapacitance of the source node with respect to the front gate node [F]                         |

| $C_{ m ss}$            | Capacitance of the source node [F]                                                                  |

| $C_{\mathrm{s*d}}$     | Transcapacitance of the source and body nodes tied together with respect to the drain node [F]      |

| $C_{ m s*gf}$       | Transcapacitance of the source and body nodes tied together with respect to the front gate node [F] |

|---------------------|-----------------------------------------------------------------------------------------------------|

| $C_{\mathrm{s*s*}}$ | Capacitance of the source and body nodes tied together [F]                                          |

| $C_{ m ij}$         | (Trans)capacitance between nodes i and j [F]                                                        |

| $C_{ m ob}$         | Back gate oxide capacitance per unit area [F/m <sup>2</sup> ]                                       |

| $C_{ m of}$         | Front gate oxide capacitance per unit area [F/m <sup>2</sup> ]                                      |

| $C_{ m T}$          | Thermal capacitance $[J/K]$                                                                         |

| D                   | Diffusion constant [cm <sup>2</sup> /s]                                                             |

| d                   | Local depletion layer thickness extending from the buried oxide in the drift region [m]             |

| $d_{ m dep}$        | Expression for $d$ with inversion at the buried oxide [m]                                           |

| $d_{ m inv}$        | Expression for $d$ without inversion at the buried oxide [m]                                        |

| $D_{ m itb}$        | Back fast surface state density $[cm^{-2}eV^{-1}]$                                                  |

| $D_{ m itf}$        | Front fast surface state density $[cm^{-2}eV^{-1}]$                                                 |

| $E_{ m g}$          | Band gap [eV]                                                                                       |

| $f_{\mathbf{v}}$    | Factor to account for the partially vertical current flow [-]                                       |

| $I_{ m acc}$        | Simplified expression for the current in the accumulation layer under the thin gate oxide [A]       |

| $I_{ m CH0}$        | Current under the thin gate oxide, without CLM and DIBL [A]                                         |

| $I_{ m chi}$        | Current in the inversion layer under the thin gate oxide [A]                                        |

| $I_{ m CHsat}$      | Saturation current under the thin gate oxide [A]                                                    |

| $I_{ m CH}$         | Current under the thin gate oxide [A]                                                               |

| $I_{ m DR0}$        | Drift region current under the field oxide without velocity saturation [A]                          |

| $I_{ m drg}$        | Current in the drift region under the thin gate oxide [A]                                           |

| $I_{ m DR}$         | Drift region current under the field oxide [A]                                                      |

| $I_{ m dr}$         | Simplified expression for the current in the drift region under the field oxide [A]                 |

| $I_{ m DS}$         | Drain-Source Current [A]                                                                            |

| $I_{ m D}$          | Drain Current [A]                                                                                   |

| $I_{ m inv}$        | Simplified expression for the current in the inversion layer under the thin gate oxide [A]          |

| k                   | Temperature exponent for $\mu_{\rm s}$ [-]                                                          |

| $k_{ m acc}$        | Temperature exponent for $\mu_{\rm acc}$ [-]                                                        |

| $k_{ m dr}$         | Temperature exponent for $\mu_{\rm dr}$ [-]                                                         |

| $k_{ m N_A}$        | Doping gradient in the body [-]                                                                     |

| L                   | Under-diffusion of the body-well [m]                                                                |

| $L_{ m drov}$       | Overlap of the front gate over the drift region [m]                                                 |

| $L_{ m dr}$         | Length of the drift region under the field oxide [m]                                                |

| $L_{ m D}$          | Under-diffusion of the source [m]                                                                   |

|                     |                                                                                                     |

```

Reduction in effective channel length due to CLM [m]

l_{\rm d}

Effective channel length [m]

L_{\text{eff}}

Mean value of L_{\min} and L_{\text{eff}} [m]

L_{i}

L_{\min 0}

Expression for L_{\min} when inversion charge is present at the drain end ) [m]

L_{\min L}

Expression for L_{\min} when no inversion charge is present at the drain end [m]

u position for which inversion in the channel starts) [m]

L_{\min}

L_{\rm tot}

Total channel length (= L_{\text{drov}} + L_{\text{eff}}) [m]

Effective pinch-off region length (second CLM model) [m]

l_{\mathbf{x}}

m

Smoothing factor [-]

M_{\rm exp}

Maximum argument allowable in an exponential function [-]

Mobile carrier density [cm^{-3}]

n

Body doping concentration at the drain end [cm^{-3}]

N_{\mathrm{Ad}}

Body doping concentration at the source end [cm^{-3}]

N_{\mathrm{As}}

N_{\rm A}

Body doping concentration [cm^{-3}]

Bottom doping concentration in an SOI PMOS [cm<sup>-3</sup>]

N_{\rm h}

Drift region doping concentration [cm^{-3}]

N_{\rm D}

Intrinsic carrier concentration of silicon [cm<sup>-3</sup>]

n_{i}

Back fixed charge density [cm^{-2}]

N_{

m QFB}

Front fixed charge density [cm^{-2}]

N_{

m QFF}

P

Dissipated device power [W]

Inversion channel charge density at the source end of the channel (y = 0)

q_0

[\mathrm{C/m^2}]

Body depletion charge under front gate oxide [C]

Q_{\mathrm{Bdep}}

Drift region inversion charge under front gate oxide [C]

Q_{\rm Binv}

Q_{\mathrm{B}}

Total body charge [C]

Body depletion charge density under the front gate [C/m^2]

q_{\mathrm{b}}

q_{\rm b}^{\rm dr}

Free bulk charge density in the drift region [C/m<sup>2</sup>]

Expression for limited q_{\text{cacc}} used in Q_{\text{Swdlim}} [C/m<sup>2</sup>]

q_{

m cacclim}

Drift region accumulation channel charge density [C/m<sup>2</sup>]

q_{\rm cacc}

Q_{\mathrm{CHacc}}

Total accumulation channel charge [C]

Total inversion channel charge [C]

Q_{\rm CHinv}

Total channel charge [C]

Q_{\rm CH}

Expression for limited q_{\text{cinv}} used in Q_{\text{Swdlim}} [C/m<sup>2</sup>]

q_{

m cinvlim}

Inversion channel charge density [C/m<sup>2</sup>]

q_{

m cinv}

q_{

m cinv}^{

m dr}

Drift region inversion charge density under the front gate [C/m<sup>2</sup>]

Drift depletion charge under front gate oxide [C]

Q_{\mathrm{Ddep}}

q_{\rm dep}^{\rm dr} at y = L_{\rm tot} [C/m<sup>2</sup>]

q_{

m depdi}^{

m dr}

```

$q_{\rm dep}^{\rm dr}$  at  $y=L_{\rm eff}^+$  [C/m<sup>2</sup>]

$q_{

m depL}^{

m dr}$

$q_{

m dep}^{

m dr}$ Drift depletion charge density under the front gate [C/m<sup>2</sup>]  $Q_{\text{Di}}$  as predicted by the Ward and Dutton partitioning scheme [C]  $Q_{\text{Diwd}}$ Total internal drain charge[C]  $Q_{\mathrm{Di}}$ Accumulation Channel charge density at the internal drain  $(y = L_{\text{tot}})$  [C/m<sup>2</sup>]  $q_{\mathrm{di}}$  $Q_{\mathrm{Dwd}}^{\mathrm{MOS}}$ Drain charge as predicted by the Ward and Dutton partitioning scheme in a MOSFET [C] Total front gate charge [C]  $Q_{\mathrm{Gf}}$ Accumulation Channel charge density at  $y = L_{\text{eff}}^+ [\text{C/m}^2]$  $q_{\mathrm{Lacc}}$ Expression for limited  $q_{\rm L}$  used in  $Q_{\rm Swdlim}$  [C/m<sup>2</sup>]  $q_{

m Llim}$ Inversion Channel charge density at  $y = L_{\min} [C/m^2]$  $q_{

m Lmin}$ Inversion Channel charge density at the body-drain junction  $(y = L_{\text{eff}})$  [C/m<sup>2</sup>]  $q_{

m L}$ Extra charge added to  $Q_{\text{Dwd}}$  ( $Q_{\text{D}} = Q_{\text{Dwd}} + Q_{\text{Swdlim}}$  [C]  $Q_{\text{Swdlim}}$  $Q_{\rm S}$  as predicted by the Ward and Dutton partitioning scheme [C]  $Q_{\mathrm{Swd}}$  $Q_{\mathrm{Swd}}^{\mathrm{MOS}}$ Source charge as predicted by the Ward and Dutton partitioning scheme in a MOSFET [C]  $Q_{\rm S}$ Total source charge [C] Drain series resistance  $[\Omega]$  $R_{\rm D}$ ON resistance in the drift region under the thin gate oxide  $[\Omega/\text{square}]$  $R_{\rm ON}$  $R_{\rm ON}^{

m dr}$ ON resistance in the drift region under the field oxide  $[\Omega/\text{square}]$  $R_{\rm shdr}$ Sheet resistance in the drift region under the field oxide  $[\Omega/\text{square}]$  $R_{\rm S}$ Source series resistance  $[\Omega]$ Thermal resistance [K/W]  $R_{\rm T}$ Ambient temperature [°C]  $T_{\rm amb}$ Silicon film thickness in the drift region (under LOCOS) [m]  $t_{

m bdr}$ Silicon film thickness [m]  $t_{

m b}$  $T_{\text{nom}}$ Parameter measurement temperature [°C]  $t_{

m ob}$ Buried oxide thickness [m] Front gate oxide thickness [m]  $t_{of}$ Body bias with respect to the source [V]  $V_{\mathrm{BS}}$  $V_{\rm b}$ Breakdown voltage [V] Drain bias with respect to the body limited to  $V_{\text{Psat}}$  [V]  $V_{

m DBst}$ Drain bias with respect to the body including pinch-off and velocity saturation  $V_{

m DBs}$ in the drift region [V]  $V_{\rm DB}$ Drain bias with respect to the body [V] Drain bias with respect to the internal drain [V]  $V_{\mathrm{DDi}}$ Internal drain bias with respect to the body limited to  $V_{Psat}$  [V]  $V_{

m DiBs}$  $V_{\rm DiB}$ Internal drain bias with respect to the body [V]

Internal drain bias with respect to the source limited to  $V_{\text{dsat}}$  [V]

$V_{

m DiSn}$

| $V_{ m DiS}$          | Internal drain bias with respect to the source [V]                               |

|-----------------------|----------------------------------------------------------------------------------|

| $V_{ m dsat}$         | Internal drain-source saturation voltage [V]                                     |

| $V_{ m DS}$           | Drain bias with respect to the source [V]                                        |

| $V_{ m FB}^{ m bdr}$  | Flat band voltage between the substrate and the drift region [V]                 |

| $V_{ m FB}^{ m b}$    | Flat band voltage between the substrate and the body [V]                         |

| $V_{ m FB}^{ m fdr}$  | Flat band voltage between the poly silicon gate and the drift region [V]         |

| $V_{ m FB}^{ m f}$    | Flat band voltage between the poly silicon gate and the body [V]                 |

| $V_{ m GbB}$          | Back gate bias with respect to the body [V]                                      |

| $V_{ m GbS}$          | Back gate bias with respect to the source [V]                                    |

| $V_{ m GfB}$          | Front gate bias with respect to the body [V]                                     |

| $V_{ m GfS}$          | Front gate bias with respect to the source [V]                                   |

| $V_{ m Pdep}$         | Drift region pinch-off voltage under zero bias conditions [V]                    |

| $V_{ m Psat}$         | Drift region pinch-off voltage [V]                                               |

| $V_{ m P}$            | Fitting parameter (second CLM model) [V]                                         |

| $V_{ m satdep}$       | Expression for $V_{\mathrm{Psat}}$ without inversion at the buried oxide [V]     |

| $v_{ m satdr}$        | Drift region saturation velocity [cm/s]                                          |

| $V_{ m satinv}$       | Expression for $V_{\mathrm{Psat}}$ with inversion at the buried oxide [V]        |

| $v_{ m sat}$          | Saturation velocity [cm/s]                                                       |

| $V_{ m sat}^*$        | Drain-body saturation voltage due to velocity saturation in the drift region [V] |

| $V_{ m th0}$          | Front gate threshold voltage at the source end of the body [V]                   |

| $V_{ m th0}^{ m bdr}$ | Back gate threshold voltage for the drift region [V]                             |

| $V_{ m th0}^{ m b}$   | Back gate threshold voltage for the body [V]                                     |

| $V_{ m th0}^{ m fdr}$ | Front gate threshold voltage for the drift region [V]                            |

| $V_{ m thL}$          | Front gate threshold voltage at the drain end of the body [V]                    |

| W                     | Transistor width [m]                                                             |

| $W_{ m D}$            | Drain width [m]                                                                  |

| $W_{ m S}$            | Source width [m]                                                                 |

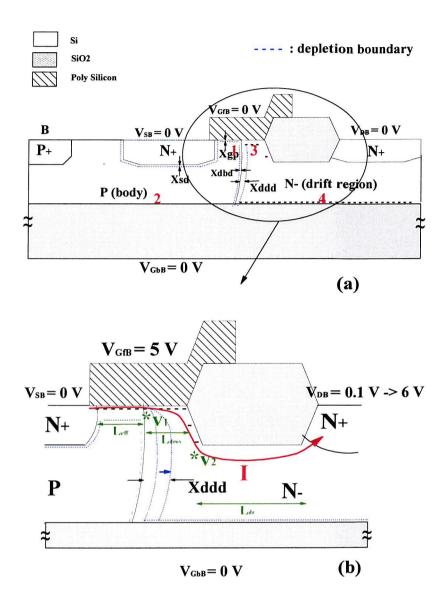

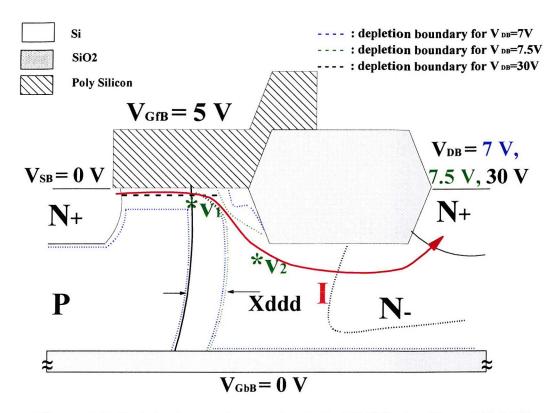

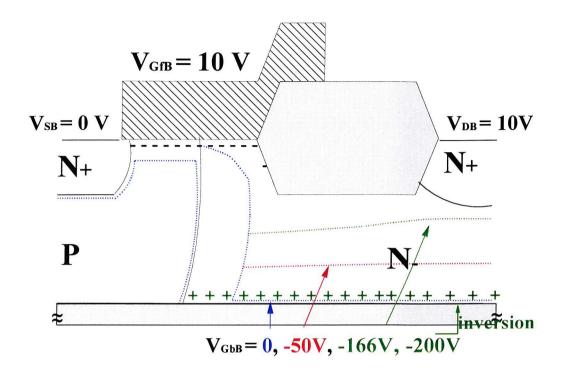

| $X_{ m ddb}$          | Depletion layer width at the body side of the drain-body junction [m]            |

| $X_{ m ddd}$          | Depletion layer width at the drain side of the drain-body junction [m]           |

| $X_{ m gbdr}$         | Depletion layer width at the buried oxide in the drift region [m]                |

| $X_{ m gfb}$          | Depletion layer width under the front gate in the body [m]                       |

| $X_{ m gfdr}$         | Depletion layer width under the front gate in the drift region [m]               |

| $X_{ m sd}$           | Depletion layer width under the source [m]                                       |

## List of Acronyms

BESOI Bond and Etch-back Silicon-On-Insulator

BJT Bipolar Junction Transistor CLM Channel Length Modulation

CMOS Complementary Metal-Oxide-Semiconductor (technology)

COMFET Conductivity Modulated Field Effect Transistor

DIBL Drain Induced Barrier Lowering

DMOS Double Diffused MOS

DUT Device Under Test

FD Fully Depleted

FET Field Effect Transistor

GIDL Gate Induced Drain Leakage

HPIB Hewlett Packard Interface Bus

HV High Voltage IC Integrated Circuit

IGBT Insulated Gate Bipolar Transistor

JFET Junction Field Effect Transistor

JUNCAP PHILIPS junction model

LDMOS Lateral Double Diffused MOS

LOCOS Local Oxidation of Silicon

LPCVD Low Pressure Chemical Vapour Deposition

LV Low Voltage

MCT MOS Controlled Thyristor

M30.02 PHILIPS Depletion mode MOSFET

MM9.02 MOS Model 9.02 (recent Philips MOS model)

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MV Medium Voltage

PD Partially Depleted

PIC Power Integrated Circuit

PSTAR PHILIPS circuit simulator

RESURF REduced SURFace field

SIMOX Separation by Implanted Oxygen

SOI Silicon-On-Insulator SOS Silicon-On-Sapphire

SMU Stimulus-Measurement Unit

STAG Southampton Thermal AnaloGue (SOI MOSFET SPICE model)

TEM Transmission Electron Microscope VDMOS Vertical Double Diffused MOS VLSI Very Large Scale Integration

VMOS V-groove DMOS

## Acknowledgements

This thesis, written in 'tropical' Southampton would not have been possible without the technical and moral support of many people.

First, I would like to thank my supervisor Dr Bill Redman-White, for his continuous guidance and support throughout this project. He has provided valuable insight into analogue circuit design. However he never managed to convince me to go to a pantomime, nor to explain to me the difference between Star Wars and Star Trek.

Many thanks also to Jim Benson, for the interesting modelling and football discussions, and for correcting the many English mistakes in my thesis. One day I will remember the difference between local and international competitions...and one day Belgium will be the best!! Also special thanks to Ketan Mistry, my other office companion, for his patient help with the circuit measurements and wonderful tiramisu.

I am very grateful to PHILIPS Semiconductors Nijmegen, not only for the financial support for this project, but also for the excellent technical collaboration. Many thanks to Huug Van der Vlist, Rene Zingg, Michiel Stoutjesdijk, Maarten Swanenberg (or Mr. Solve All Your Problems), Hans van Zwol (in the end the circuits were fabricated thanks to some Belgian beer, hein?!), Peter Rommers (alias Belgian joke man), Inesz Weijland, Jan-Jaap de Koning, Raymond Van Roijen, Stan Meeuwsen, Paul Eggenkamp, Jan Claes, Hans Brugman, Priscilla Boos, Eelco de Koning and Kees van Velthoven for many inspiring discussions about device physics and HV SOI technology, and for making me appreciate the Dutch Trapisten beer (almost as good as the Belgian beer...). Also special thanks to the circuit designers and in particular Wim-Jan Brummelman and Jan Dikkens for their useful help and and enjoyable discussions (as long as the dents in my car were not mentioned...). Thanks also to the silicon processing staff at PHILIPS Semiconductors for the fabrication of the test chips.

During the development of the compact LDMOS model a lot of help came from the PHILIPS Research in Eindhoven, and I would like to mention in particular Annemarie Aarts, who is at present implementing the compact LDMOS model in PSTAR, and has checked my hard maths thoroughly, Luuk Tiemeijer for his help with the S-parameter measurements, and Dick Klaassen, Willy Kloosterman and Ronald van Langevelde for their useful comments on my papers.

The microelectronics group at Southampton University has provided a very pleasant environment to carry out this work and I would like to thank all lecturers, technicians, secretaries and students who have worked in this group over the past years. A special word of thanks to to Audrey for helping me deal with the financial bureaucratic system, to Jilly for helping me to defend myself in this men's world, to Trevor Niblock for his fatherly (?!) support in bad times and for the very entertaining squash sessions, to Paul Routley who fixes everything, to Dominik Kunz for reminding me how to swear properly, to Mir (alias the Sexy Lieutenant) for making me smile in the corridor, to Michael, to Harold for making English so easy to understand, to Martin, to Kees, to all the volleyball players, and to all the people I forgot to mention.

Many thanks to my dear friends, Stephan Weiss for reading my thesis with great interest and for his wonderful potato salads, Sandrine Morin for reminding me of the French way of life and for her excellent moral support (et pour mon bisou le matin), Lizzie Nicholson for making me dream about Yorkshire, Edward Young for being such an excellent house mate (and gardener), and Shoaib Allam for always being there when a friend is needed.

Finally, I am immensely grateful to Gaetan for his unforgettable surprises, making my life and my research so much more exiting.

## Chapter 1

## Introduction

## 1.1 History of Power Devices

In the late 1940s, research developments made the first steps towards what is today's semiconductor industry [1], [2]. In 1954, the first commercially available silicon bipolar transistors were announced, but it was not until the 1960s that their application to high power devices began. We find the real beginning of the power transistor business with the introduction of the planar process, and the application of photo-lithography to wafer processing [3]. The main advantages of the bipolar technology were the simple manufacturing process (complete double diffusion technology with high yield and low cost) and the low on-resistance due to minority carrier current. The main drawbacks were the low switching speed, the need for a high base current to control the device, and the secondary breakdown [4]. Nowadays bipolar devices with current handling capabilities of several hundred amperes, and blocking voltages of the order of kV's are fabricated.

In the late 1970s, as MOS-IC technology became more mature [5], the first power MOS transistors appeared, and, since then development has accelerated, moving away from the bipolar transistor. The primary feature of the power MOSFET is a high input impedance, which greatly simplifies the gate drive circuitry and reduces the cost of the power electronics. They can withstand the simultaneous application of high voltage and high current without showing any secondary breakdown.

In addition to the new discrete devices, monolithic high voltage ICs (HVIC) which have a high supply voltage but a low output current, and combine power and control circuitry on the same chip, have come onto the scene. This has allowed cost efficiency in the power industry for the first time. Applications have been found in the areas of telecommunications, power supplies, high voltage displays, etc. More recently power ICs (PIC), which use both high voltage and high current circuitry, have been developed.

Smart PICs, where different power device functions are combined with logic functions on the same chip, is a fast growing branch in industry for applications in television, automobiles, aircraft, motors, lighting, audio equipment, switching devices, etc [6]. They offer substantial improvements in performance, and the cost price is lower than the price

of the separate packages connected together.

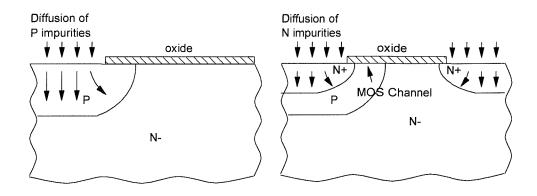

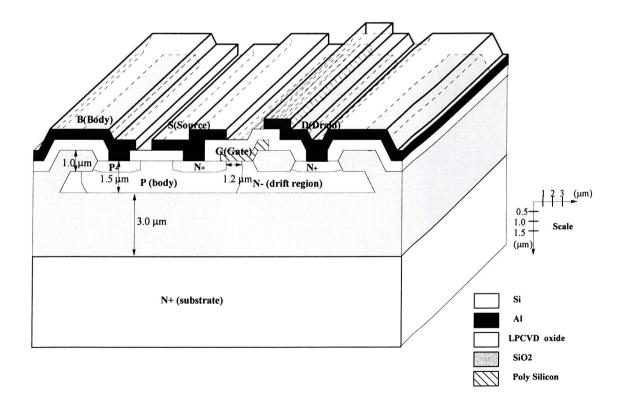

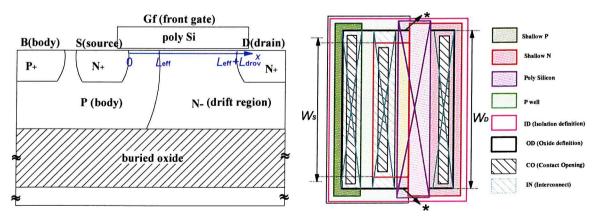

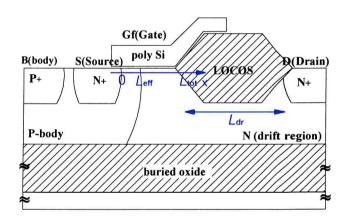

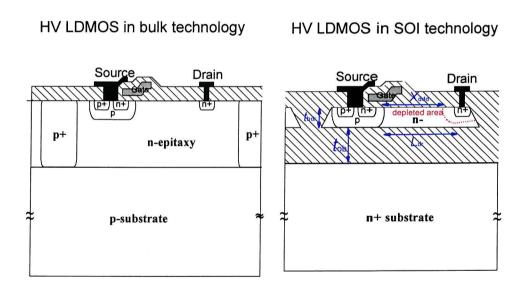

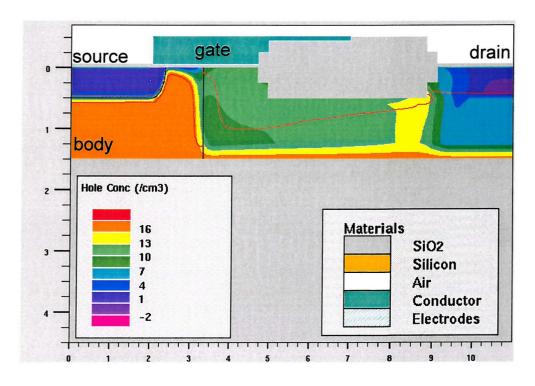

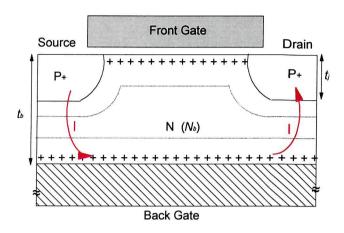

Figure 1.1: The Double Diffused MOS process

The rapid growth of the PIC industry was made possible by the arrival of the DMOS transistor [7–10] (double diffused transistor). The channel of the device is created by the sequential diffusion of two different doping impurities under the gate, as illustrated in Fig. 1.1. The P-base is driven in deeper than the  $N^+$  source, and the difference in the lateral diffusion between the P-base and the  $N^+$  source regions defines the surface channel region. When these double diffusion techniques were developed in the 1970s, they were used to obtain what at the time were very short channel lengths (1-3  $\mu$ m).

A major change compared with the basic MOSFET structure has been the incorporation of a lightly doped drift region between the channel and the heavily doped drain [11]. The main advantages of the DMOS include the absence of secondary breakdown, negligible steady-state input current, and fast switching. The main drawback compared with the bipolar range is the increased on-resistance with increasing blocking capability.

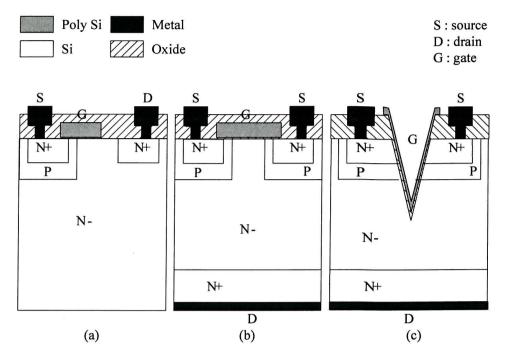

At present, a whole range of different DMOS structures exist, but we can split them into three main categories, which are illustrated in Fig. 1.2: the VDMOS (Vertical DMOS), the LDMOS (Lateral DMOS) and the VMOS (V-groove DMOS).

The VDMOS and the LDMOS depend upon lateral diffusion profiles and sequential diffusions under the same oxide to achieve the channel region, while the channel of the VMOS derives from the vertical diffusion profile. The choice of a < 100 > material for the LDMOS and VDMOS increases the electron inversion layer mobility and scattering-limited velocity, in contrast to the VMOS, which has its channel along an etched < 111 > surface. The initial focus on VMOS transistors was based on the belief that they had a lower resistance than VDMOS devices. However, research pointed out that the existence

Figure 1.2: (a) LDMOS; (b) VDMOS; (c) VMOS.

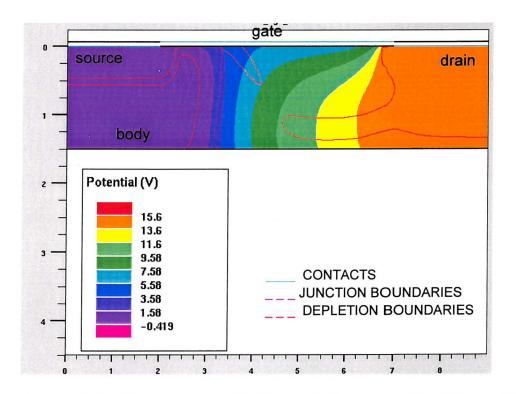

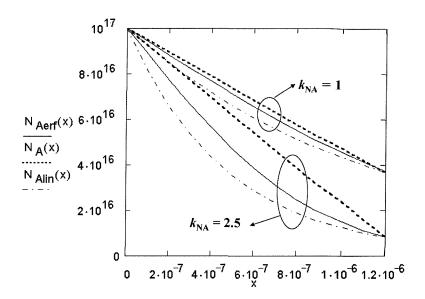

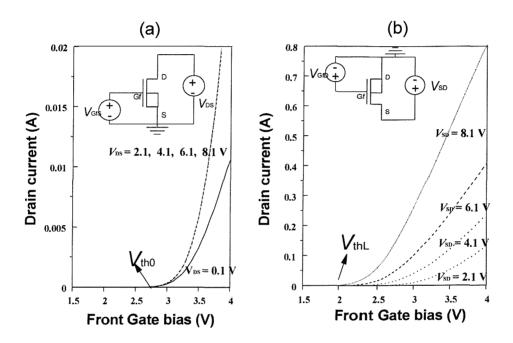

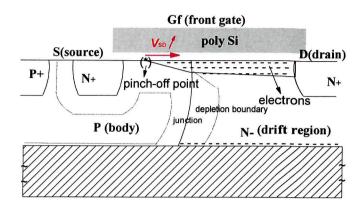

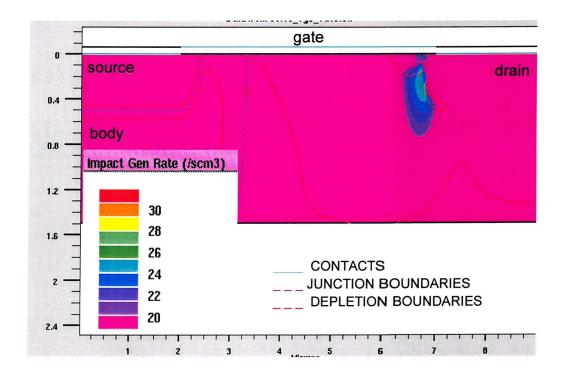

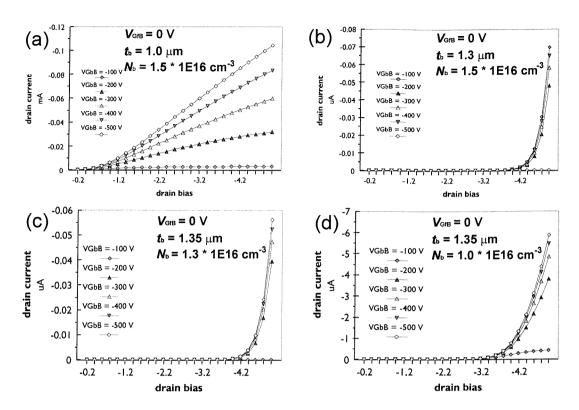

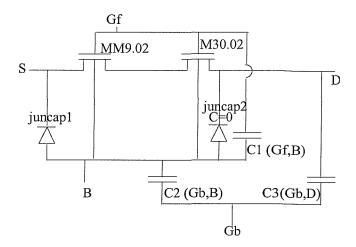

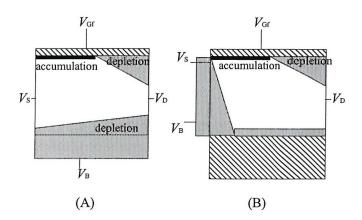

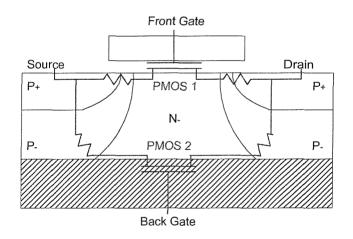

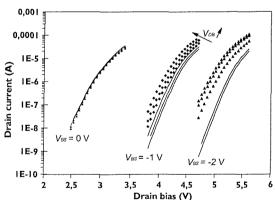

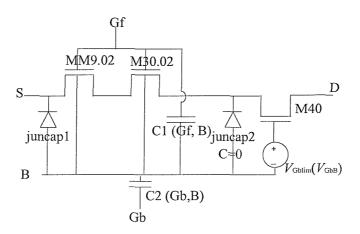

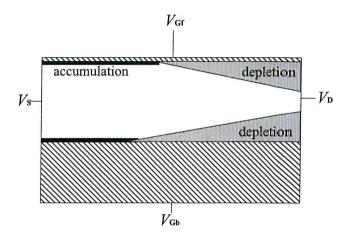

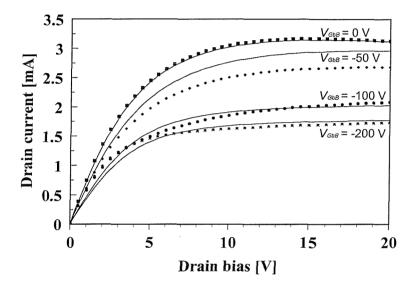

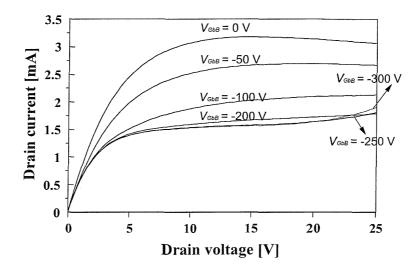

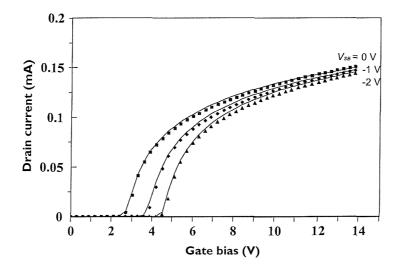

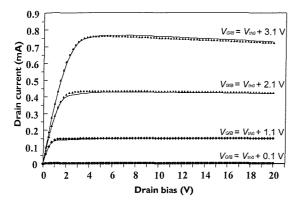

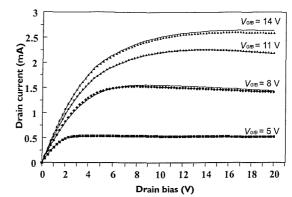

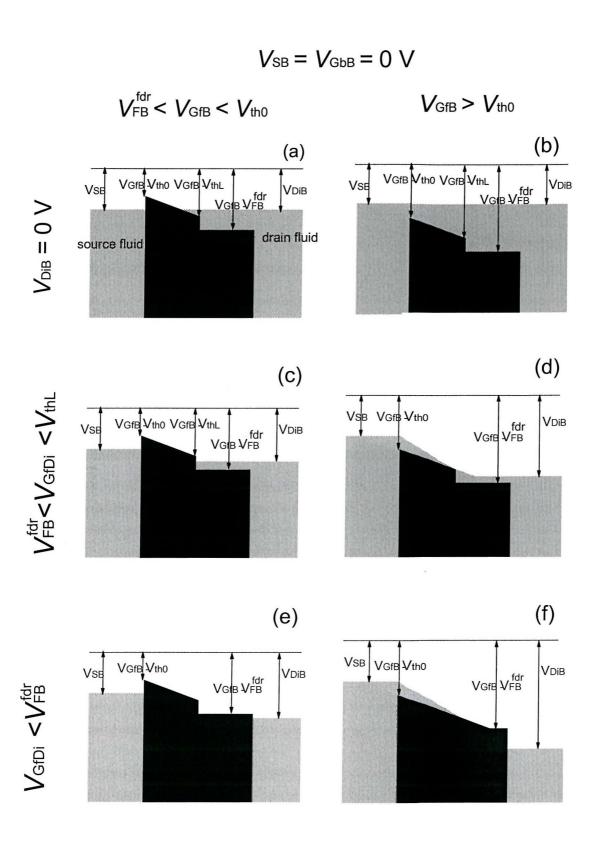

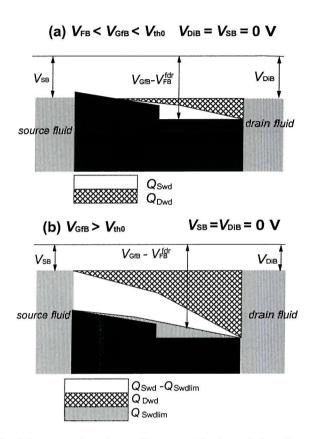

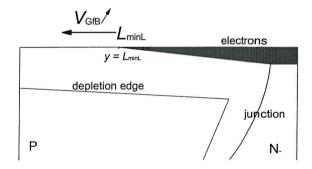

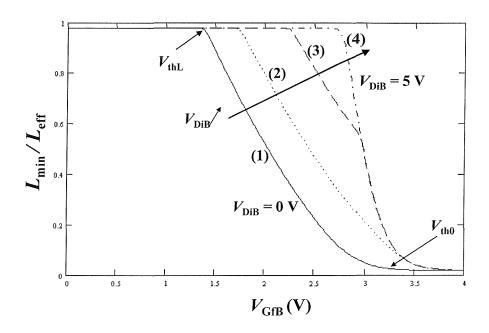

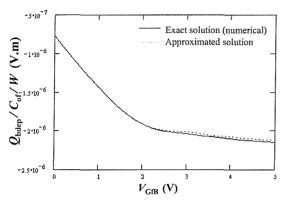

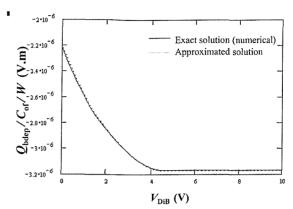

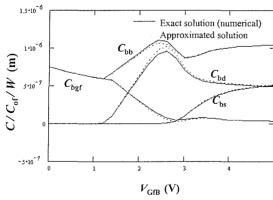

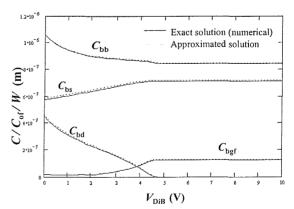

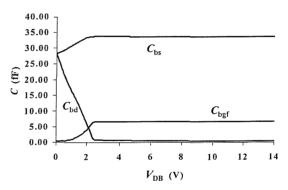

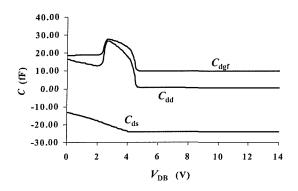

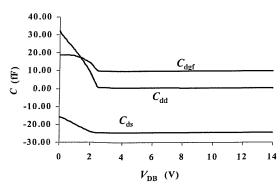

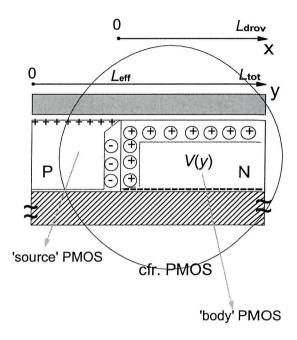

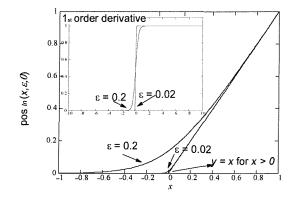

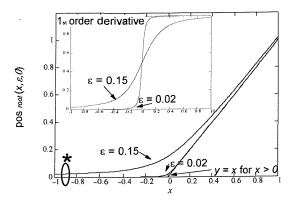

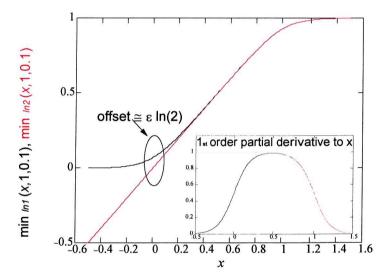

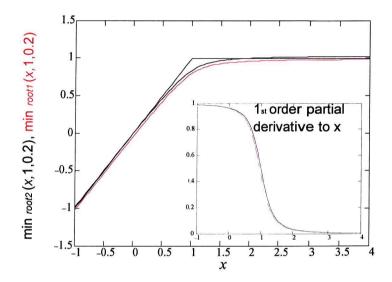

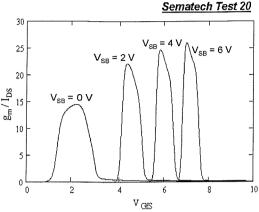

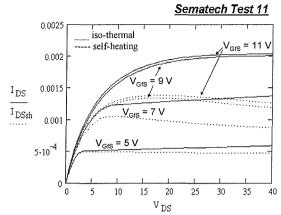

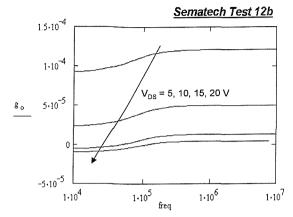

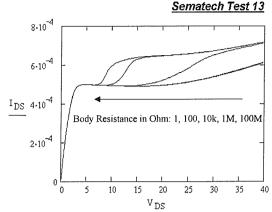

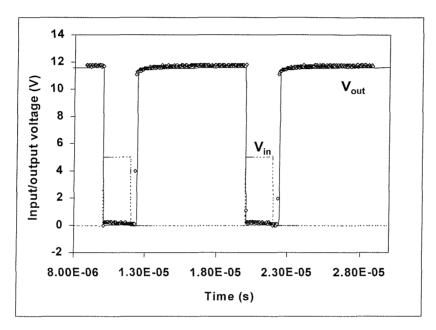

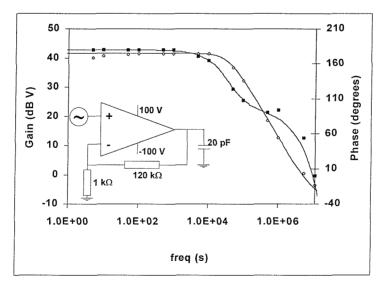

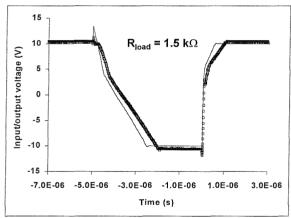

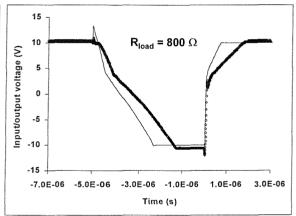

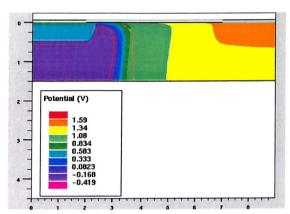

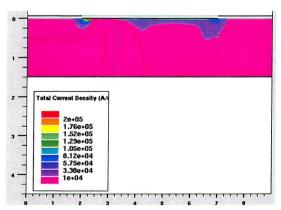

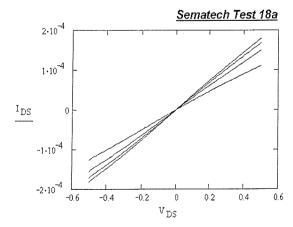

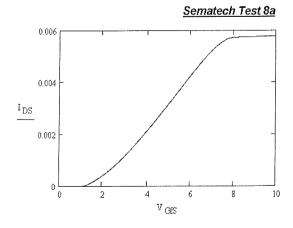

of a high electric field at the bottom of the V-groves results in a significant reduction of the breakdown voltage, and the VMOS idea became less popular.