**DESIGN, FABRICATION AND

CHARACTERISATION OF ADVANCED

SUBSTRATE CROSSTALK SUPPRESSION

STRUCTURES IN SILICON-ON-INSULATOR

SUBSTRATES WITH BURIED GROUND

PLANES (GPSOI)**

By

Stefanos Stefanou

Dipl. Eng., M.Sc.

A thesis submitted for the degree of

Doctor of Philosophy

Department of Electronics and Computer Science,

University of Southampton,

United Kingdom.

July 2002

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF ENGINEERING

ELECTRONICS AND COMPUTER SCIENCE DEPARTMENT

Doctor of Philosophy

**Design, Fabrication and Characterisation of Advanced Substrate

Crosstalk Suppression Structures in Silicon-on-Insulator Substrates

with Buried Ground Planes (GPSOI)**

by Stefanos Stefanou

Substrate crosstalk or coupling has been acknowledged to be a limiting factor in mixed signal RF integration. Although, high levels of integration and high frequencies of operation are desirable for mixed mode RF and microwave circuits, they make substrate crosstalk more pronounced and may lead to circuit performance degradation. High signal isolation is dictated by requirements for low power dissipation, reduced number of components and lower integration costs for feasible system-on-chip (SoC) solutions.

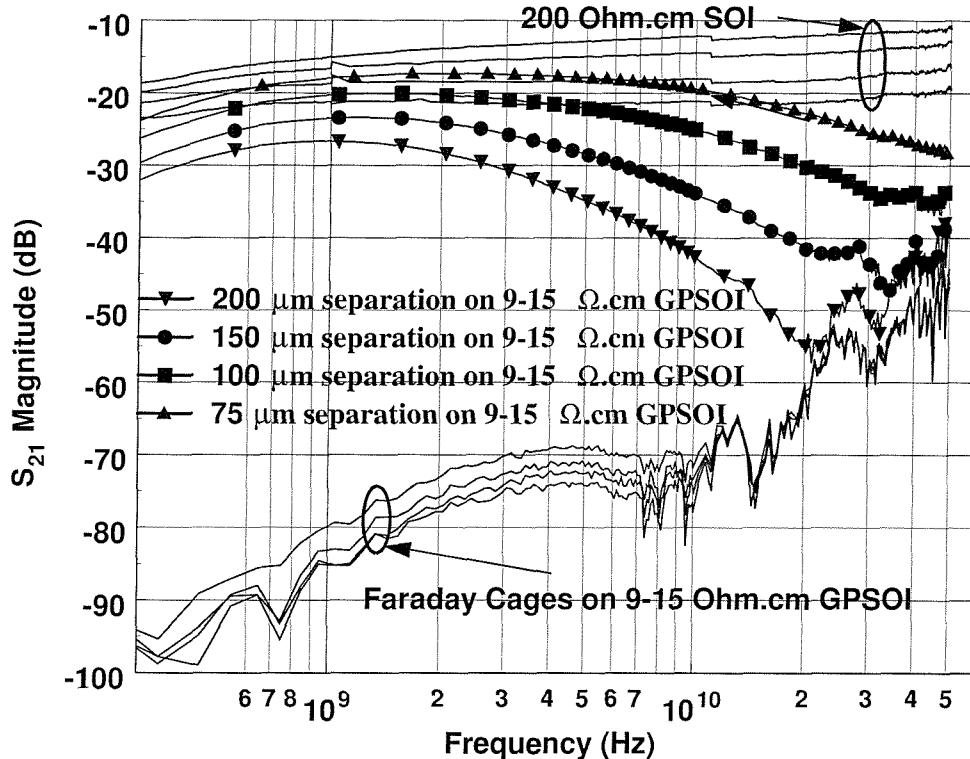

Substrate crosstalk suppression in ground plane silicon-on-insulator (GPSOI) substrates is investigated in this thesis. Test structures are designed and fabricated on SOI substrates with a buried  $WSi_2$  plane that is connected to ground; hence it is called a ground plane. A Faraday cage structure that exhibits very high degrees of signal isolation is presented and compared to other SOI isolation schemes. The Faraday cage structure is shown to achieve 20 dB increased isolation in the frequency range of 0.5-50 GHz compared to published data for high resistivity ( $200 \Omega \cdot cm$ ) thin film SOI substrates with no ground planes, but where capacitive guard rings were used. The measurement results are analysed with the aid of planar electromagnetic simulators and compact lumped element models of all the fabricated test structures are developed. The accuracy of the lumped models is validated against experimental measurements.

# Contents

|                                                                     |       |

|---------------------------------------------------------------------|-------|

| Contents                                                            | ii    |

| List of Figures                                                     | vi    |

| List of Tables                                                      | xiv   |

| Acknowledgements                                                    | xv    |

| List of Symbols                                                     | xvii  |

| List of Acronyms                                                    | xviii |

| Chapter 1 Introduction                                              | 1     |

| Chapter 2 Substrate Crosstalk Theory and Literature Review          | 5     |

| 2.1 Introduction . . . . .                                          | 5     |

| 2.2 Substrate Crosstalk Definition and Metrics . . . . .            | 5     |

| 2.3 Comparison of Crosstalk in Different Technologies . . . . .     | 6     |

| 2.4 Isolation Schemes . . . . .                                     | 8     |

| 2.5 Simulation and Modelling Tools . . . . .                        | 10    |

| 2.6 Conclusion . . . . .                                            | 12    |

| Chapter 3 Substrate Crosstalk Suppression with Buried Ground Planes | 13    |

| 3.1 Introduction . . . . .                                          | 13    |

| 3.2 Buried Ground Plane and GPSOI Substrates . . . . .              | 13    |

| 3.3 Substrate Crosstalk Test Structures and Experiments . . . . .   | 14    |

| 3.4 Measurement Considerations . . . . .                            | 18    |

| 3.5 Measurement Results . . . . .                                   | 20    |

| 3.6 Discussion . . . . .                                            | 22    |

| 3.7 Conclusion . . . . .                                            | 23    |

| Chapter 4 Modelling Substrate Crosstalk on GPSOI Substrates         | 25    |

| 4.1 Introduction . . . . .                                          | 25    |

|                                                                                                                       |                                                                                                  |    |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----|

| 4.2                                                                                                                   | Electromagnetic Modelling . . . . .                                                              | 25 |

| 4.3                                                                                                                   | A Lumped Element Model for GPSOI crosstalk . . . . .                                             | 26 |

| 4.3.1                                                                                                                 | A Thin Film SOI Crosstalk Model . . . . .                                                        | 29 |

| 4.3.2                                                                                                                 | A Crosstalk Model in GPSOI Substrates . . . . .                                                  | 30 |

| 4.3.3                                                                                                                 | Model Analysis - The Capacitive $\pi$ Network . . . . .                                          | 32 |

| 4.3.4                                                                                                                 | Model Analysis - Simplified Substrate Crosstalk Model . . .                                      | 33 |

| 4.3.5                                                                                                                 | Importance of De-embedding - The "AC loading" Effect . .                                         | 34 |

| 4.3.6                                                                                                                 | Predicting the Value of Crosstalk Capacitance . . . . .                                          | 36 |

| 4.4                                                                                                                   | Conclusions . . . . .                                                                            | 42 |

| Chapter 5 Analysis Of Buried Oxide And Ground Plane Resistivity Effects<br>On Pseudo-Ground Plane Substrate Crosstalk |                                                                                                  | 43 |

| 5.1                                                                                                                   | Introduction . . . . .                                                                           | 43 |

| 5.2                                                                                                                   | Pseudo-Ground Plane Test Structures . . . . .                                                    | 43 |

| 5.3                                                                                                                   | Probe-to-Probe Crosstalk - A Noise "Floor" of the Measurement<br>Equipment . . . . .             | 45 |

| 5.4                                                                                                                   | The Effect of Oxide Thickness and Ground Plane Resistivity on Sub-<br>strate Crosstalk . . . . . | 48 |

| 5.5                                                                                                                   | Coupled Microstrip Lines on Pseudo-Buried Ground Plane Substrates                                | 53 |

| 5.5.1                                                                                                                 | Coupled Microstrip Lines on Aluminium ("Perfect") Ground<br>Planes . . . . .                     | 54 |

| 5.5.2                                                                                                                 | Coupled Microstrip Lumped Model Validation . . . . .                                             | 56 |

| 5.5.3                                                                                                                 | Coupled Microstrip Lines on $\text{TiSi}_2$ (lossy) Ground Planes . .                            | 59 |

| 5.6                                                                                                                   | Conclusions . . . . .                                                                            | 62 |

| Chapter 6 A Substrate Crosstalk Analysis Of Silicon-On-Insulator (SOI) Sub-<br>strates                                |                                                                                                  | 63 |

| 6.1                                                                                                                   | Introduction . . . . .                                                                           | 63 |

| 6.2                                                                                                                   | Substrate Coupling in Bulk Silicon Substrates . . . . .                                          | 63 |

| 6.3                                                                                                                   | Substrate Coupling in SOI Substrates . . . . .                                                   | 66 |

| 6.4                                                                                                                   | Parameter Extraction in SOI Substrates . . . . .                                                 | 67 |

| 6.5                                                                                                                   | Model Parameter Prediction . . . . .                                                             | 71 |

| 6.5.1                                                                                                                 | The Symmetrical Double-Strip Coplanar Waveguide Problem                                          | 72 |

| 6.5.2                                                                                                                 | Application to SOI Substrate Crosstalk . . . . .                                                 | 73 |

| 6.5.3                                                                                                                 | Calculation of Conductive Coupling . . . . .                                                     | 75 |

| 6.6                                                                                                                   | Experimental Verification and Model Validation . . . . .                                         | 76 |

| 6.6.1                                                                                                                 | Description of Experiments . . . . .                                                             | 76 |

| 6.6.2                                                                                                                 | Measurements . . . . .                                                                           | 78 |

| 6.7                                                                                                                   | Electromagnetic Modelling and Lumped Model Validation . . . . .                                  | 80 |

| 6.7.1                                                                                                                 | Electromagnetic Modelling . . . . .                                                              | 80 |

|                                                                                                |                                                                                            |     |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----|

| 6.7.2                                                                                          | Lumped Element Model Formulation and Validation . . . . .                                  | 80  |

| 6.7.3                                                                                          | Lumped Model Validation . . . . .                                                          | 83  |

| 6.7.4                                                                                          | Effect of Finite Pad Length . . . . .                                                      | 84  |

| 6.7.5                                                                                          | Effect of Handle Substrate Resistivity . . . . .                                           | 86  |

| 6.8                                                                                            | Conclusions . . . . .                                                                      | 88  |

| Chapter 7 Ground Plane Silicon on Insulator (GPSOI) Substrate Crosstalk Analysis and Modelling |                                                                                            | 90  |

| 7.1                                                                                            | Introduction . . . . .                                                                     | 90  |

| 7.2                                                                                            | The Ground Plane Silicon-On-Insulator (GPSOI) Substrate . . . . .                          | 90  |

| 7.3                                                                                            | Test Structure Description and Fabrication . . . . .                                       | 91  |

| 7.4                                                                                            | GPSOI Substrate Crosstalk Analysis and Modelling . . . . .                                 | 92  |

| 7.5                                                                                            | Electromagnetic Analysis of the Buried Oxide Capacitance in a GP-SOI Substrate. . . . .    | 98  |

| 7.6                                                                                            | Experimental Verification and Model Validation . . . . .                                   | 102 |

| 7.7                                                                                            | Active Layer Thickness and Crosstalk . . . . .                                             | 105 |

| 7.8                                                                                            | Discussion . . . . .                                                                       | 107 |

| 7.9                                                                                            | Conclusions . . . . .                                                                      | 109 |

| Chapter 8 A Novel Faraday Cage Structure For Advanced Substrate Crosstalk Suppression          |                                                                                            | 110 |

| 8.1                                                                                            | Introduction . . . . .                                                                     | 110 |

| 8.2                                                                                            | Faraday Cage Structure Description and Fabrication . . . . .                               | 111 |

| 8.3                                                                                            | Measurement Results . . . . .                                                              | 114 |

| 8.4                                                                                            | Analysis Using EM Simulations and Comparison with Buried Ground Plane Substrates . . . . . | 115 |

| 8.5                                                                                            | Discussion . . . . .                                                                       | 120 |

| 8.6                                                                                            | Conclusions . . . . .                                                                      | 123 |

| Chapter 9 Conclusions and Future Work                                                          |                                                                                            | 125 |

| 9.1                                                                                            | Conclusions . . . . .                                                                      | 125 |

| 9.2                                                                                            | Future Work . . . . .                                                                      | 129 |

| Appendix A List of Publications                                                                |                                                                                            | 131 |

| Appendix B Listing of the Buried Ground Plane Test Structure Fabrication Process               |                                                                                            | 133 |

| Appendix C Listing of the "Pseudo" Buried Ground Plane Test Structure Fabrication Process      |                                                                                            | 135 |

|                                                                                     |     |

|-------------------------------------------------------------------------------------|-----|

| Appendix D Listing of the SOI Test Structure Fabrication Process                    | 138 |

| Appendix E Listing of the GPSOI and Faraday Cage Test Structure Fabrication Process | 140 |

| Bibliography                                                                        | 143 |

# List of Figures

|      |                                                                                                                                                                                                                                                   |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Scattering transmission coefficient definition. . . . .                                                                                                                                                                                           | 6  |

| 2.2  | Bulk CMOS coupling path. . . . .                                                                                                                                                                                                                  | 7  |

| 2.3  | Heavily doped p <sup>+</sup> buried layer coupling path. . . . .                                                                                                                                                                                  | 7  |

| 2.4  | Thin film SOI coupling path [1]. . . . .                                                                                                                                                                                                          | 8  |

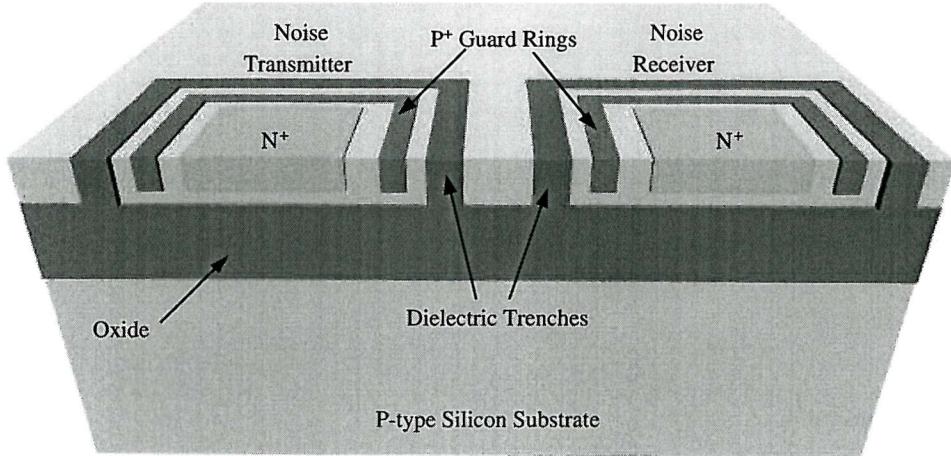

| 2.5  | Combination of guard rings and dielectric trenches in a SOI substrate. . . . .                                                                                                                                                                    | 9  |

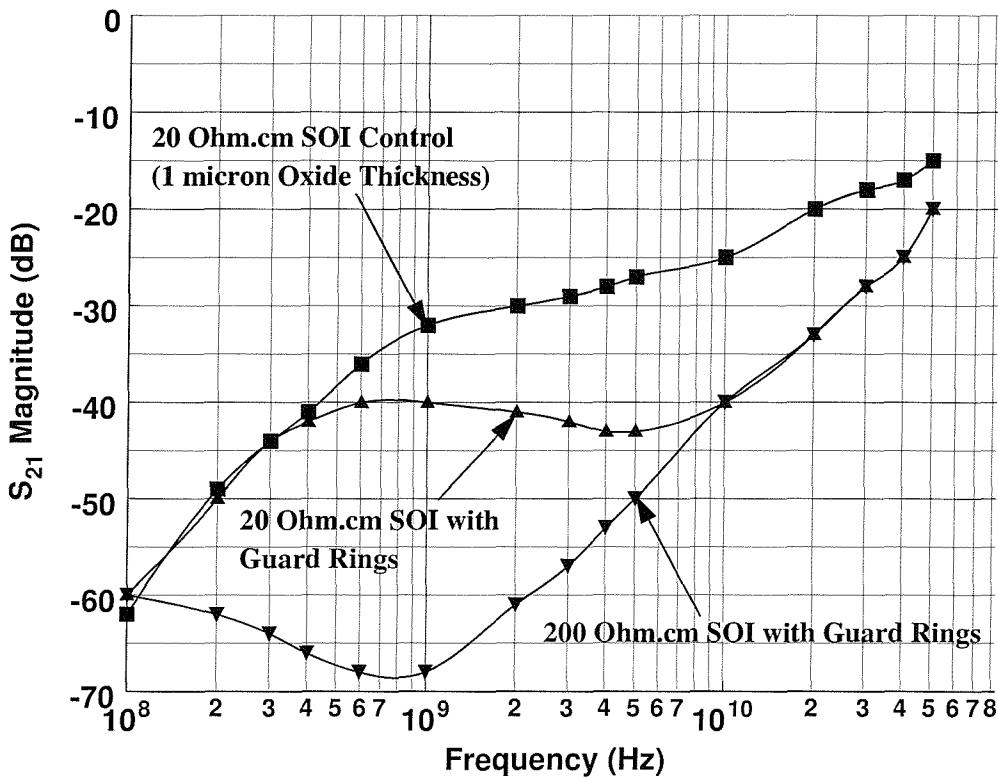

| 2.6  | Comparison of high resistivity thin film SOI substrate with guard rings with standard resistivity SOI with guard rings and bulk. The oxide thickness is 0.4 $\mu\text{m}$ for the SOI cases and 0.95 $\mu\text{m}$ for the bulk case [1]. . . . . | 10 |

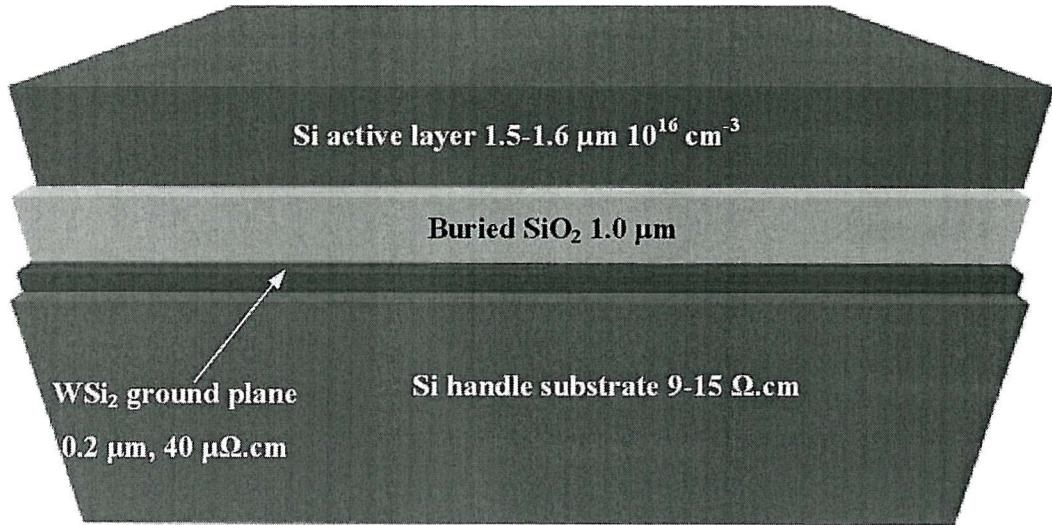

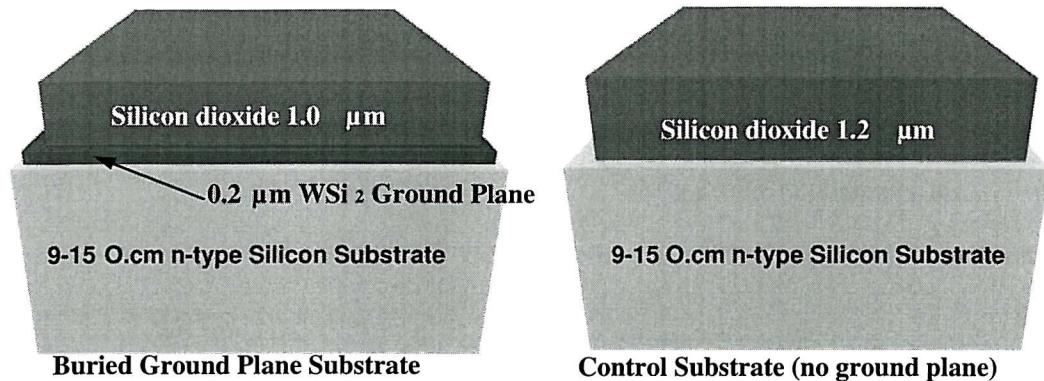

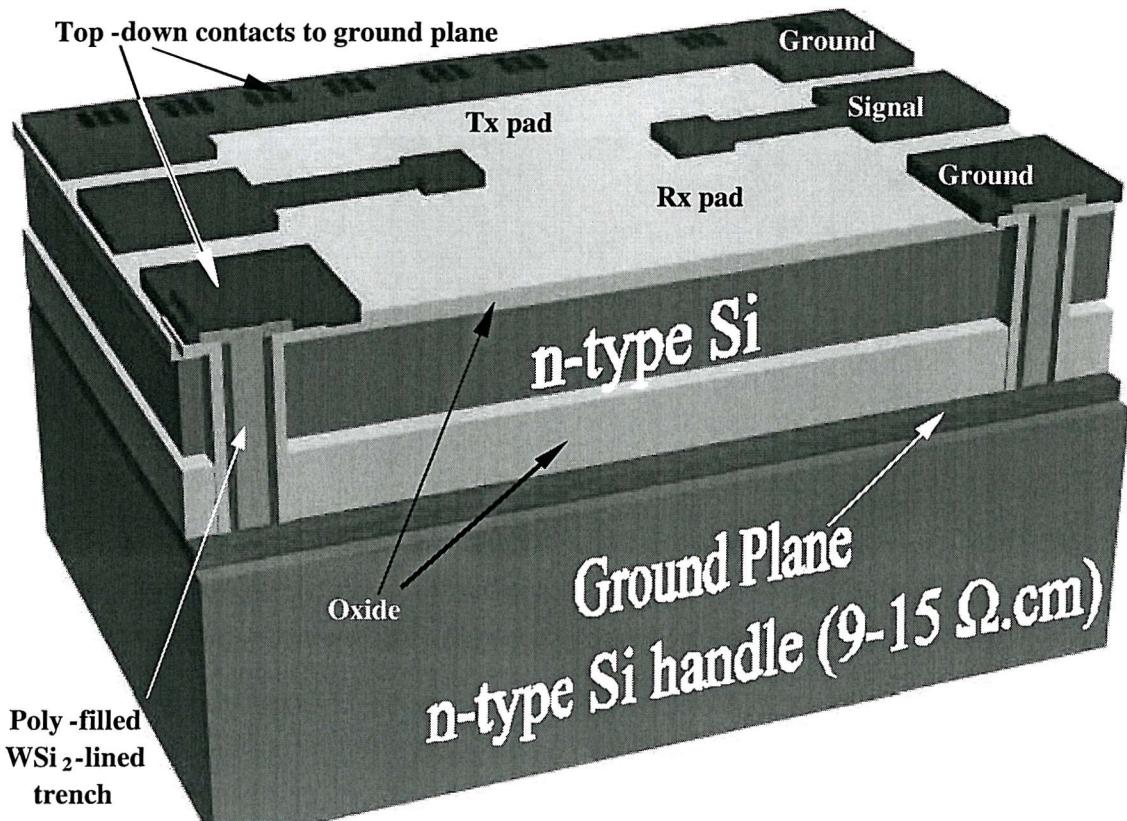

| 3.1  | Cross-sectional view of the GPSOI substrate. . . . .                                                                                                                                                                                              | 14 |

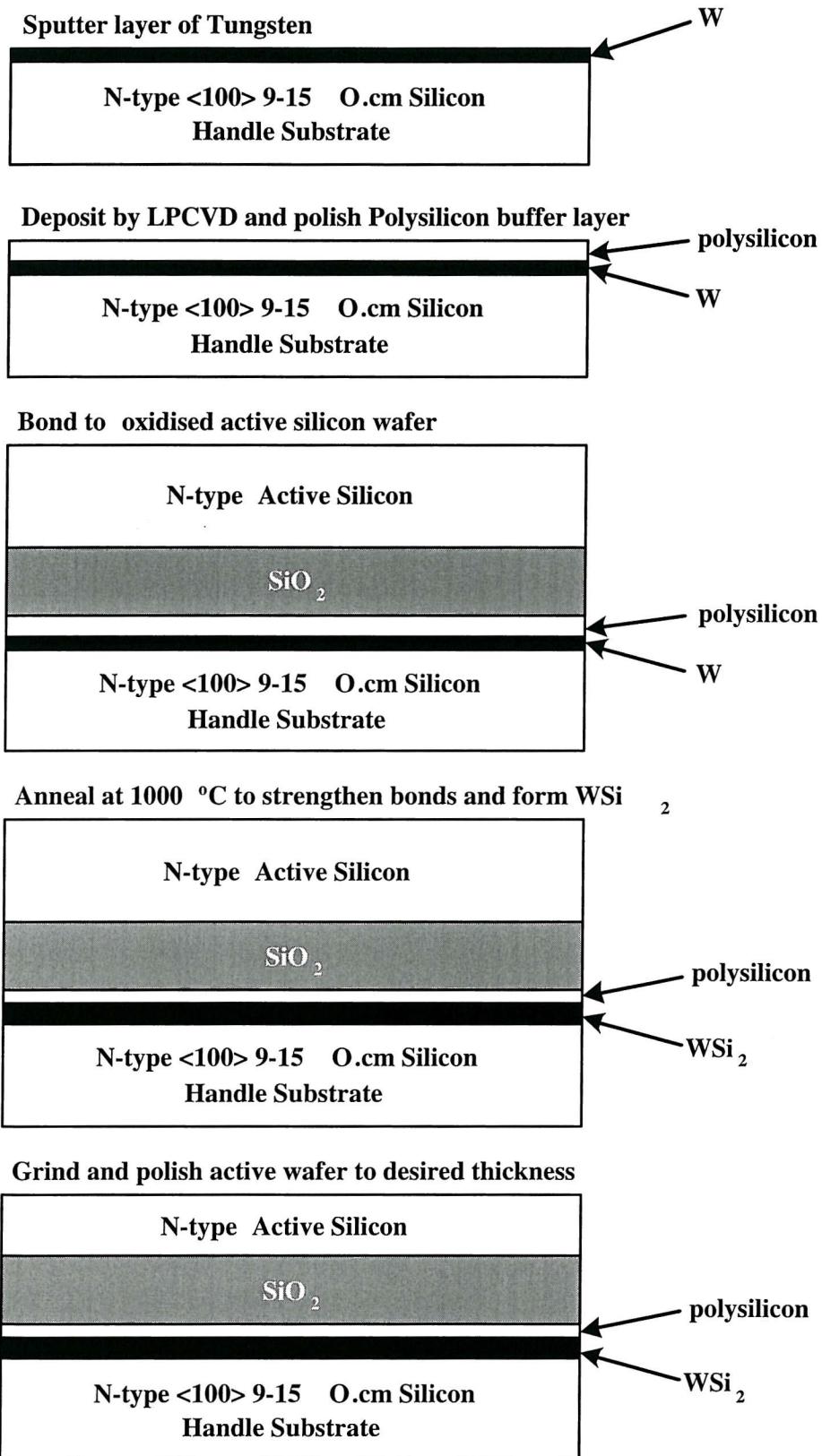

| 3.2  | GPSOI substrate manufacturing process. . . . .                                                                                                                                                                                                    | 15 |

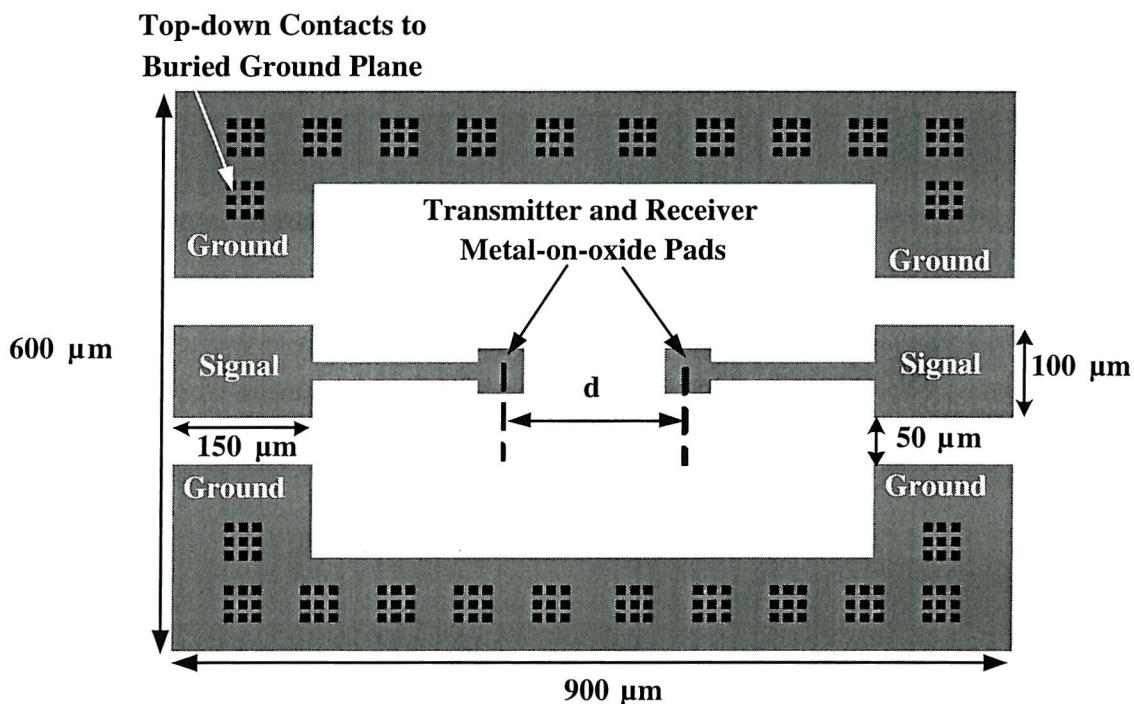

| 3.3  | The two substrate configurations under investigation: GPSOI substrate (left), control SOI (right) . . . . .                                                                                                                                       | 16 |

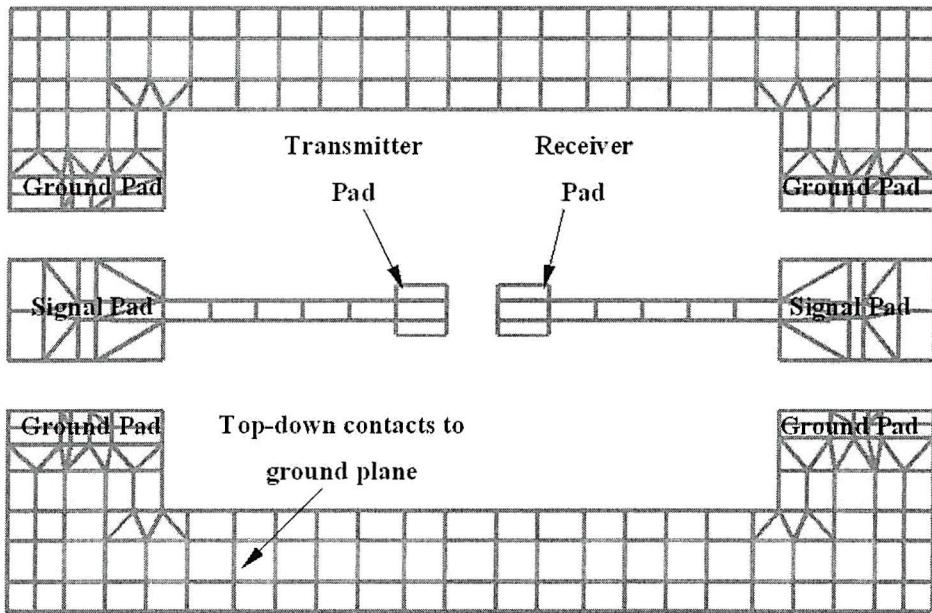

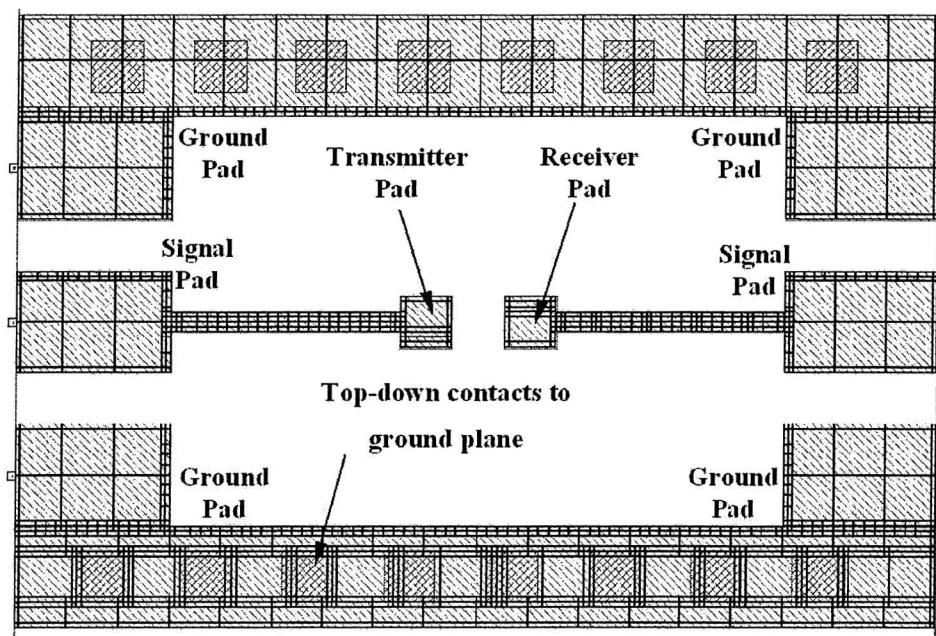

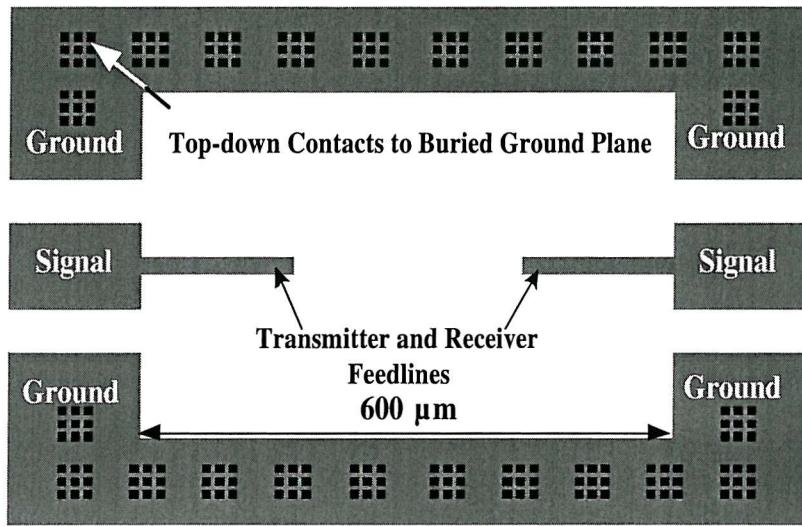

| 3.4  | Plan view of the test structure for substrate crosstalk studies on ground plane substrates. . . . .                                                                                                                                               | 16 |

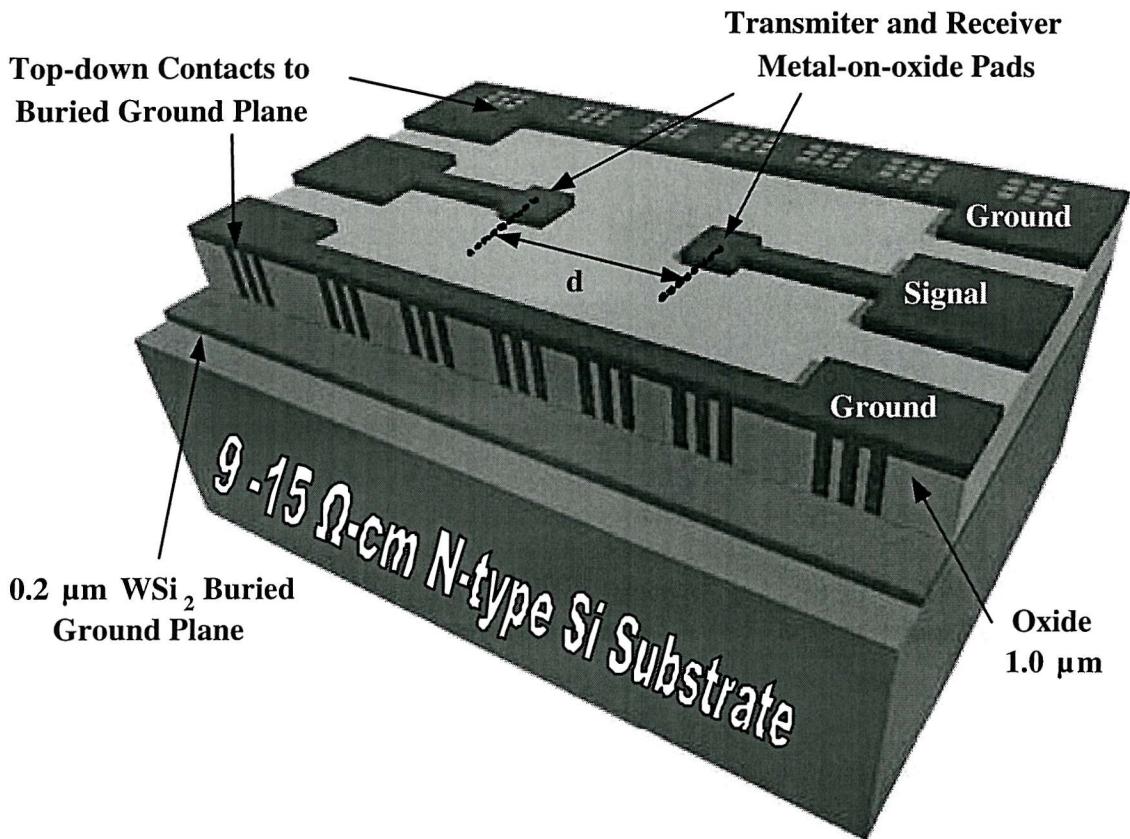

| 3.5  | The CPW crosstalk test structure with a grounded buried WSi <sub>2</sub> plane (Grounded GPSOI). . . . .                                                                                                                                          | 17 |

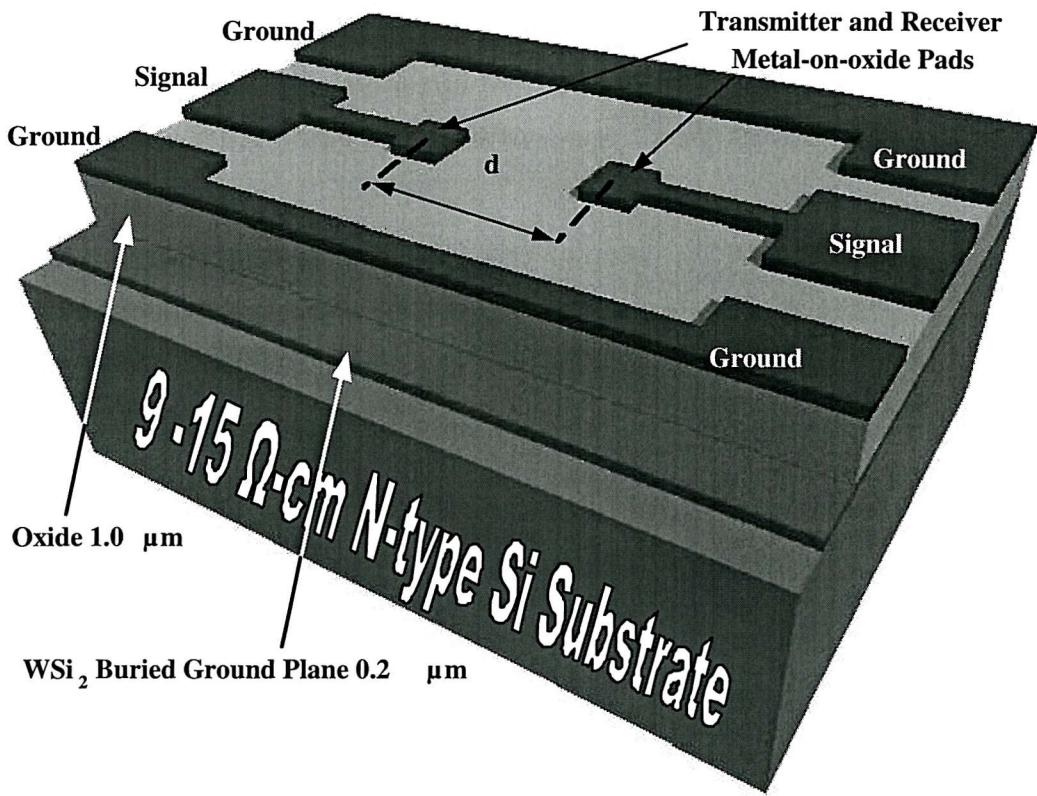

| 3.6  | The CPW crosstalk test structure with a floating buried WSi <sub>2</sub> plane (Floating GPSOI). . . . .                                                                                                                                          | 18 |

| 3.7  | The CPW crosstalk test structure without a buried WSi <sub>2</sub> plane (Control SOI). . . . .                                                                                                                                                   | 19 |

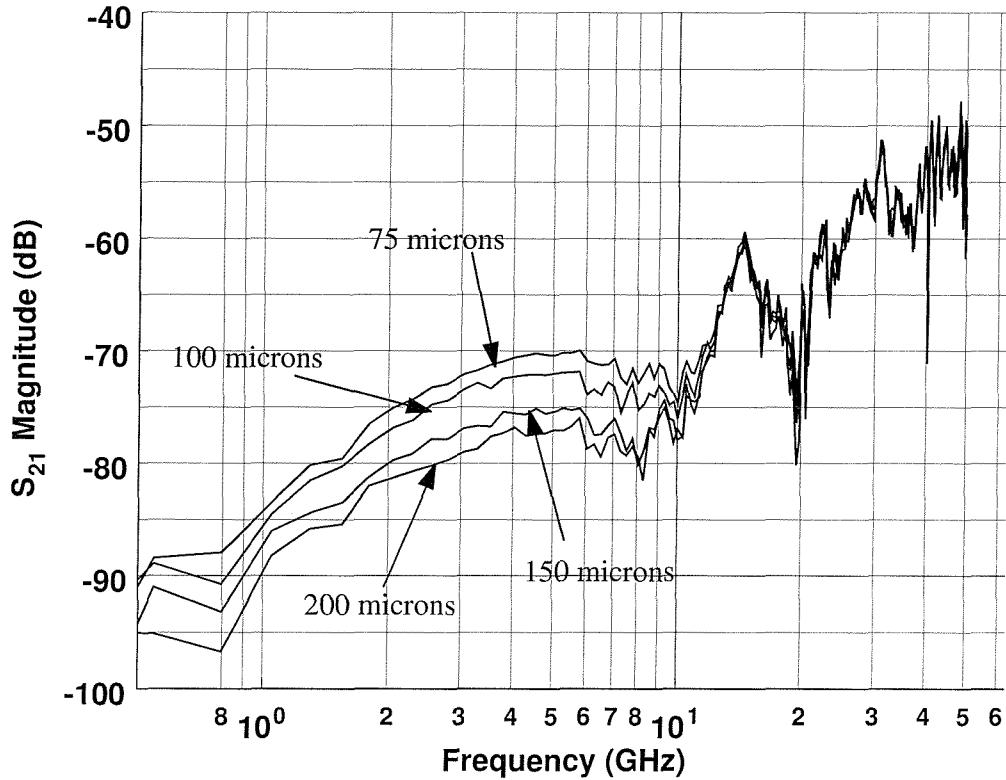

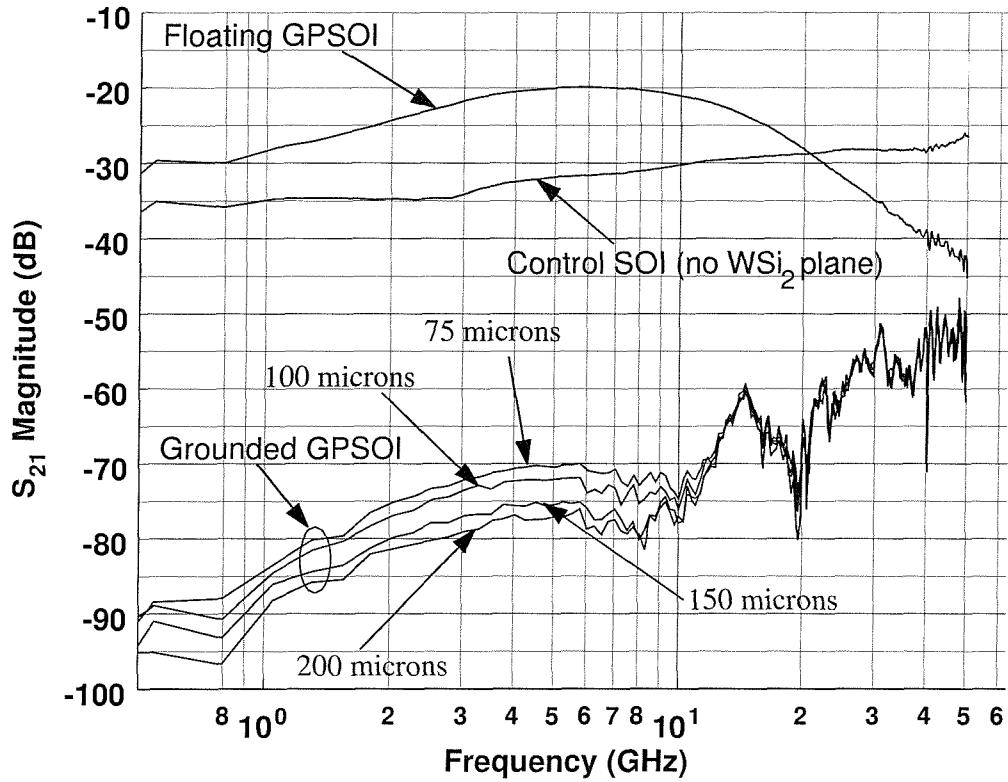

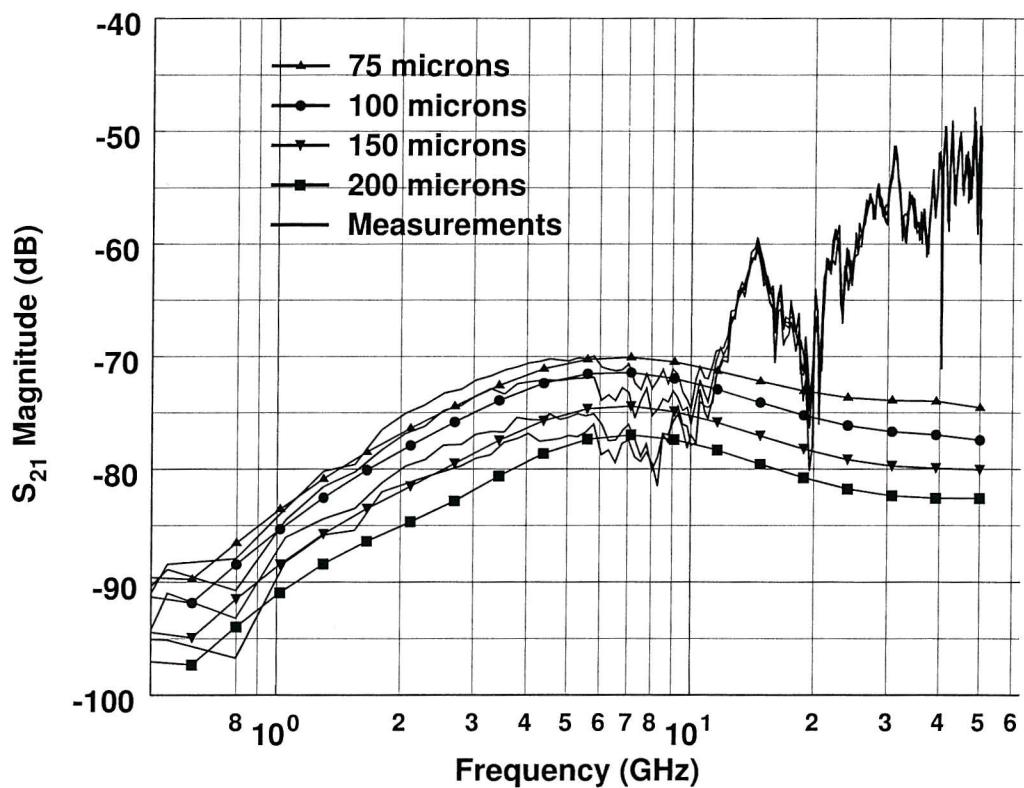

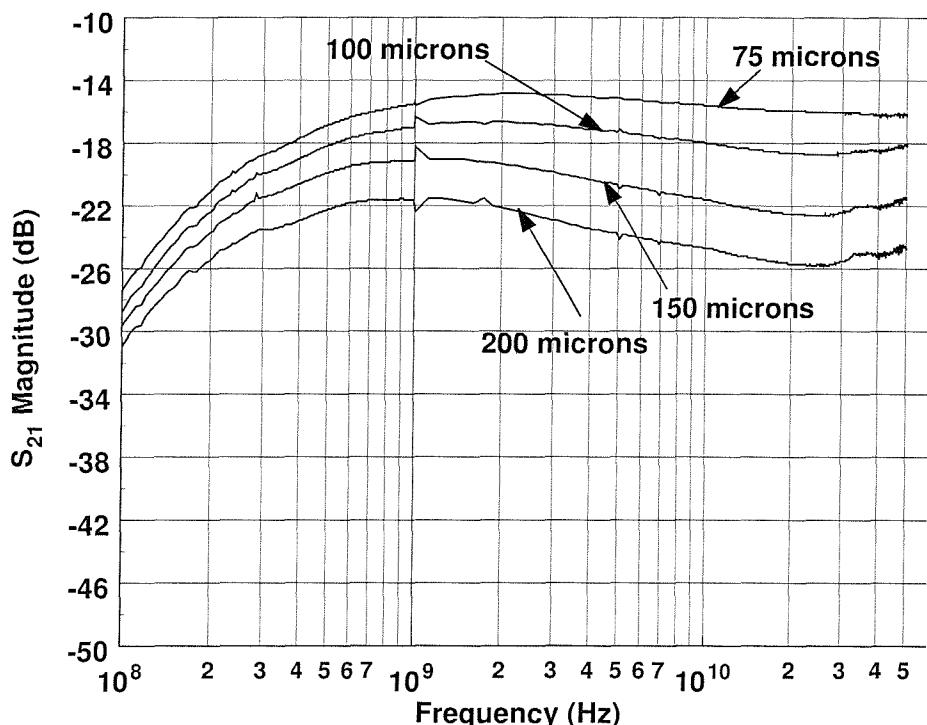

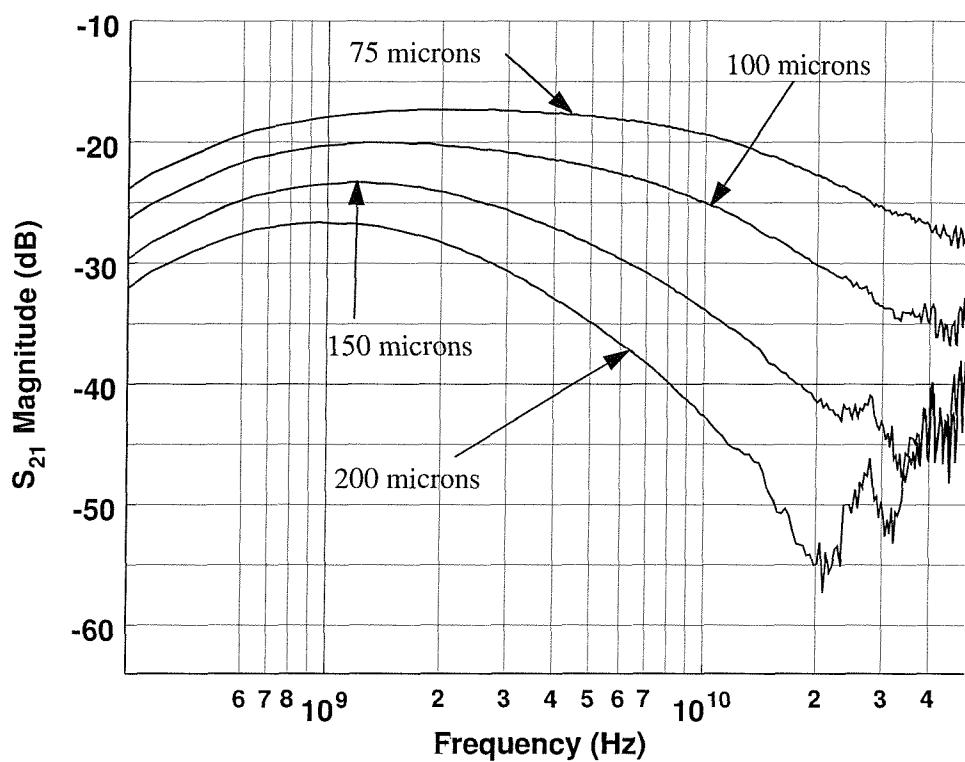

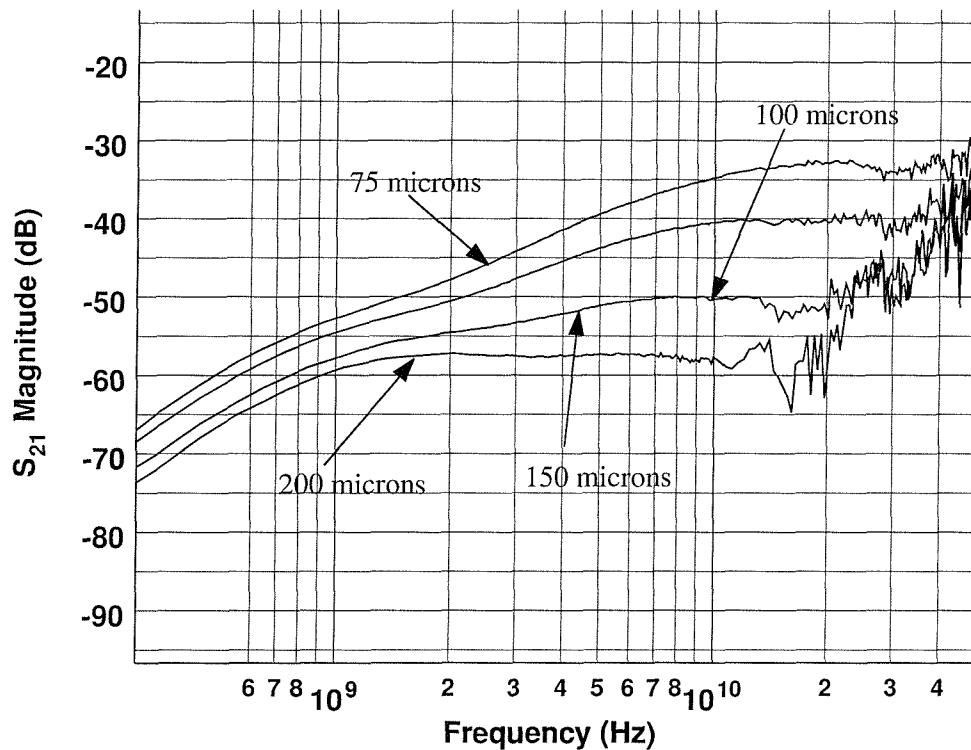

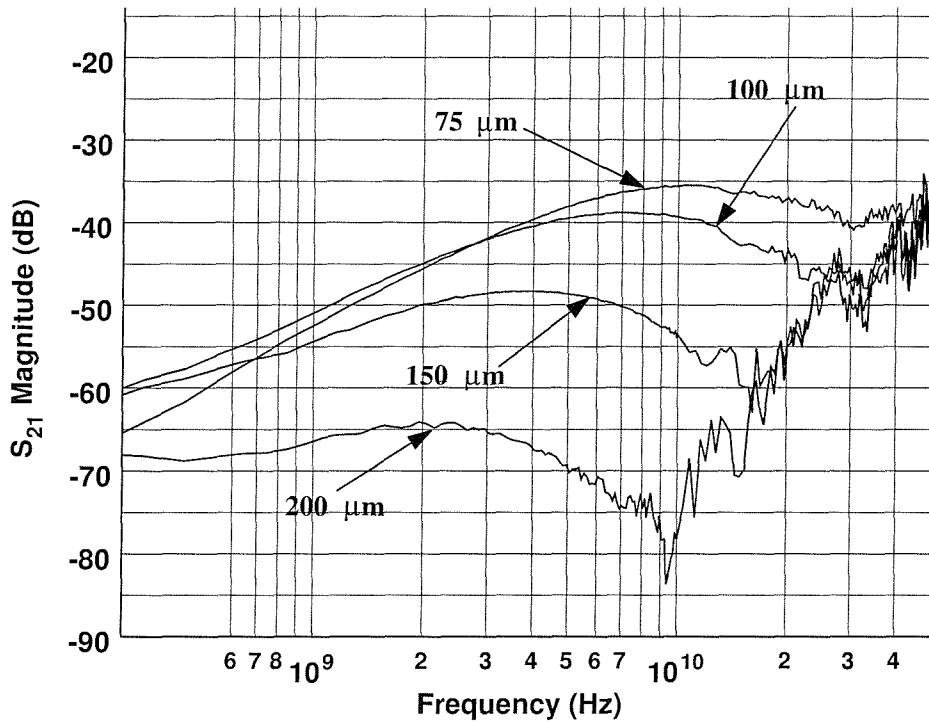

| 3.8  | Measurements of the magnitude of $s_{21}$ from test structures with a grounded buried WSi <sub>2</sub> plane for 75, 100, 150 and 200 $\mu\text{m}$ Tx/Rx pad separations. . . . .                                                                | 20 |

| 3.9  | Measurements of the magnitude of $s_{21}$ from test structures without a buried WSi <sub>2</sub> plane (control SOI) for 75, 100, 150 and 200 $\mu\text{m}$ Tx/Rx pad separations. . . . .                                                        | 21 |

| 3.10 | Measurements of the magnitude of $s_{21}$ from test structures without an electrically floating WSi <sub>2</sub> plane for 75, 100, 150 and 200 $\mu\text{m}$ Tx/Rx pad separations. . . . .                                                      | 22 |

|      |                                                                                                                                                                                                                                                                                               |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

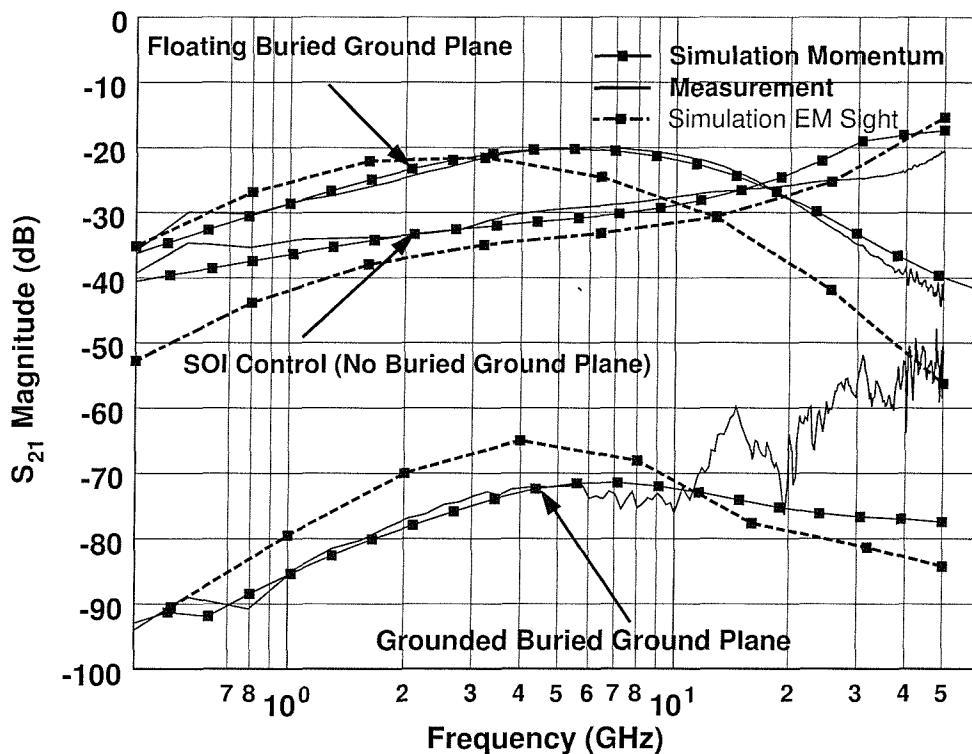

| 3.11 | Comparison of the GPSOI (grounded and floating) with the control SOI measurements. . . . .                                                                                                                                                                                                    | 23 |

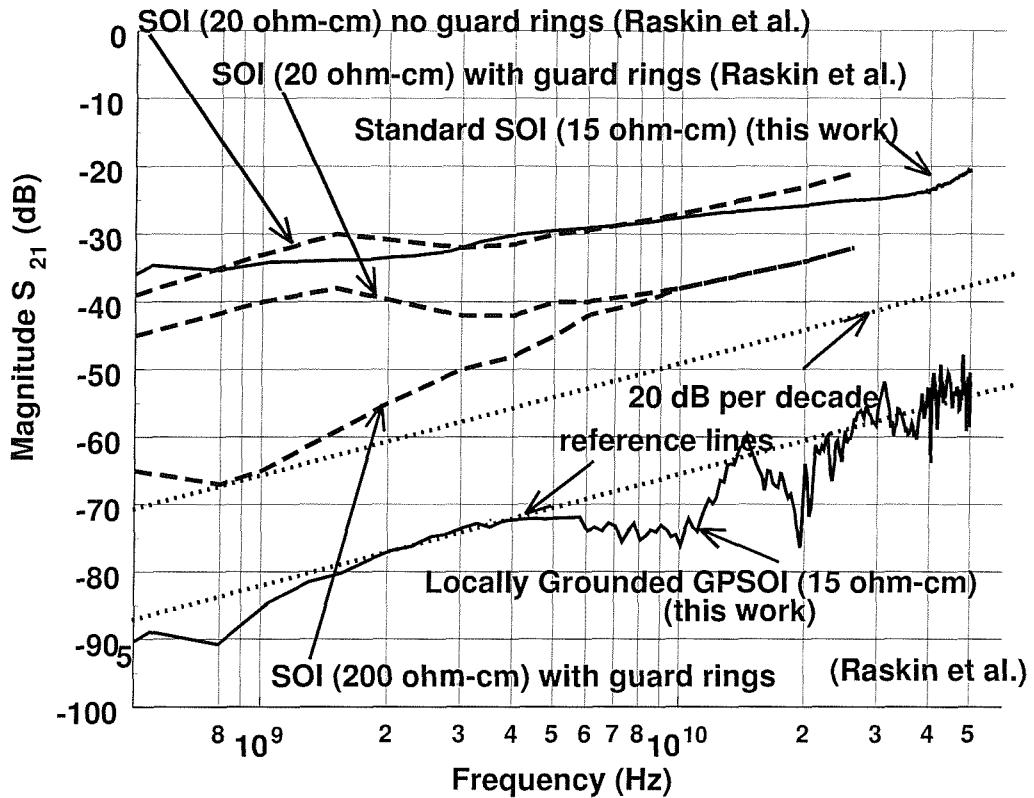

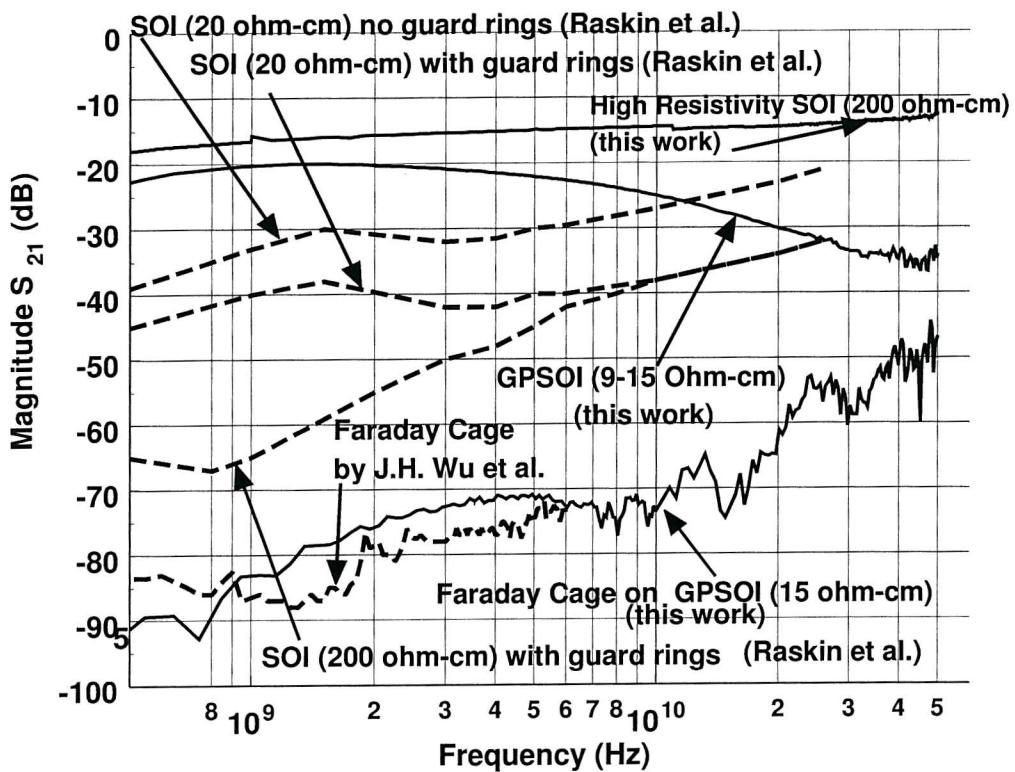

| 3.12 | Measurements of the magnitude of the $s_{21}$ transmission parameter for the locally grounded cross-talk structure on GPSOI and the standard SOI. Results from previous work on low and high resistivity substrate SOI with and without guard rings [1] are shown for comparison [2]. . . . . | 24 |

| 4.1  | Grounded GPSOI test structure after meshing by ADS Momentum. . . . .                                                                                                                                                                                                                          | 26 |

| 4.2  | Grounded GPSOI test structure after meshing by <i>EM-Sight</i> . . . . .                                                                                                                                                                                                                      | 27 |

| 4.3  | Numerical Simulation Data from ADS <i>Momentum</i> of the grounded GPSOI test structures for different separation distances in comparison to measurements. . . . .                                                                                                                            | 27 |

| 4.4  | Numerical simulation data from <i>EM-Sight</i> of the grounded GPSOI test structures for different separation distances in comparison to measurements. . . . .                                                                                                                                | 28 |

| 4.5  | Comparison of measurement and simulation data for the locally grounded, electrically floating GPSOI and control SOI. Tx/Rx pad separation distance is 100 $\mu\text{m}$ . . . . .                                                                                                             | 28 |

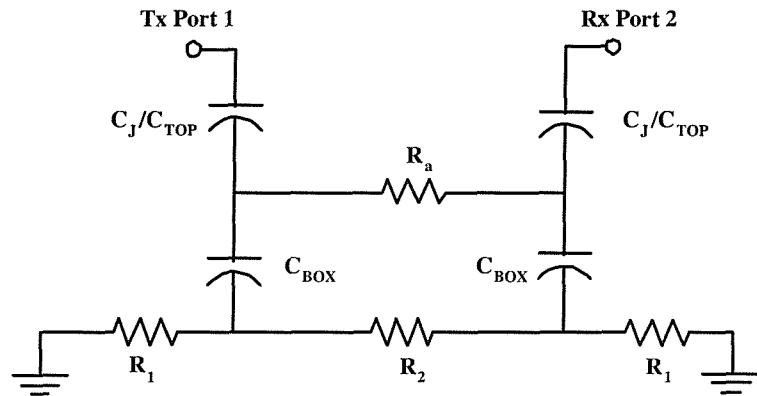

| 4.6  | Lumped element equivalent model describing the crosstalk effects between two devices realized on the control SOI substrate [1]. . . . .                                                                                                                                                       | 29 |

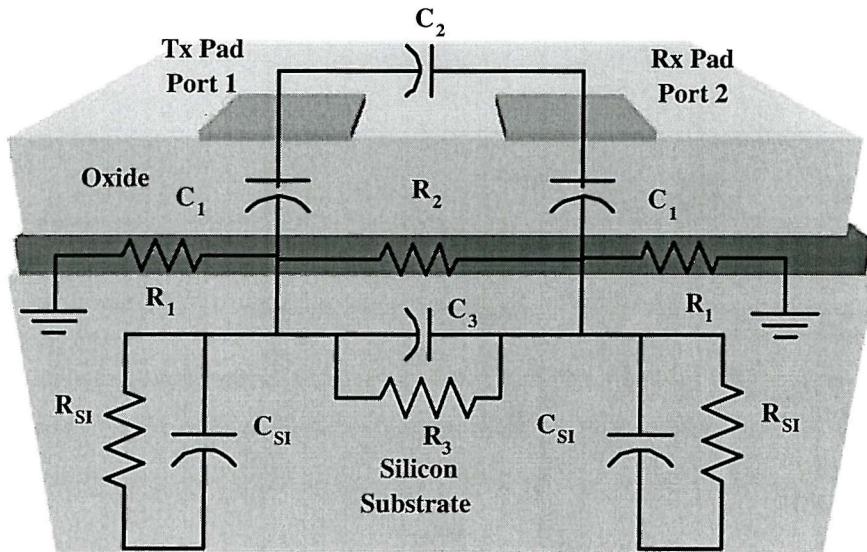

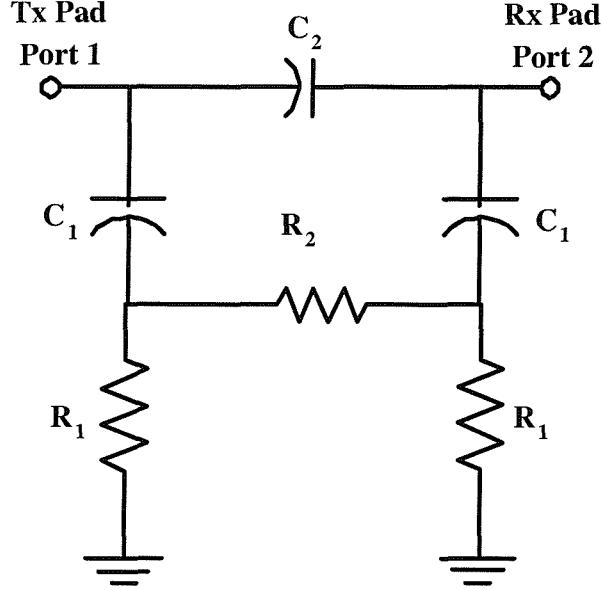

| 4.7  | Lumped element crosstalk model of the grounded GPSOI test structure. . . . .                                                                                                                                                                                                                  | 30 |

| 4.8  | Simplified equivalent crosstalk model of the grounded GPSOI. . . . .                                                                                                                                                                                                                          | 31 |

| 4.9  | Comparison of Grounded GPSOI measurements, numerical simulations and lumped model for a Tx/Rx pad separation of 100 $\mu\text{m}$ . . . . .                                                                                                                                                   | 32 |

| 4.10 | A capacitive $\pi$ -network. . . . .                                                                                                                                                                                                                                                          | 33 |

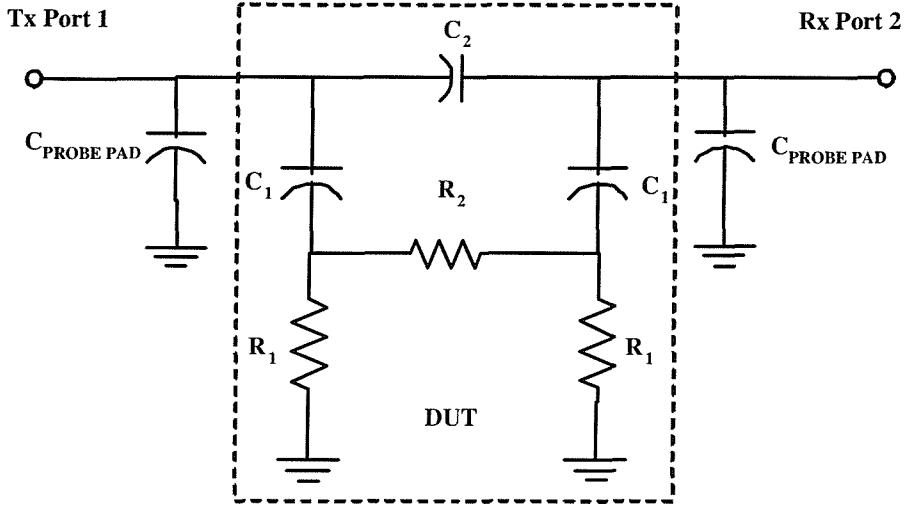

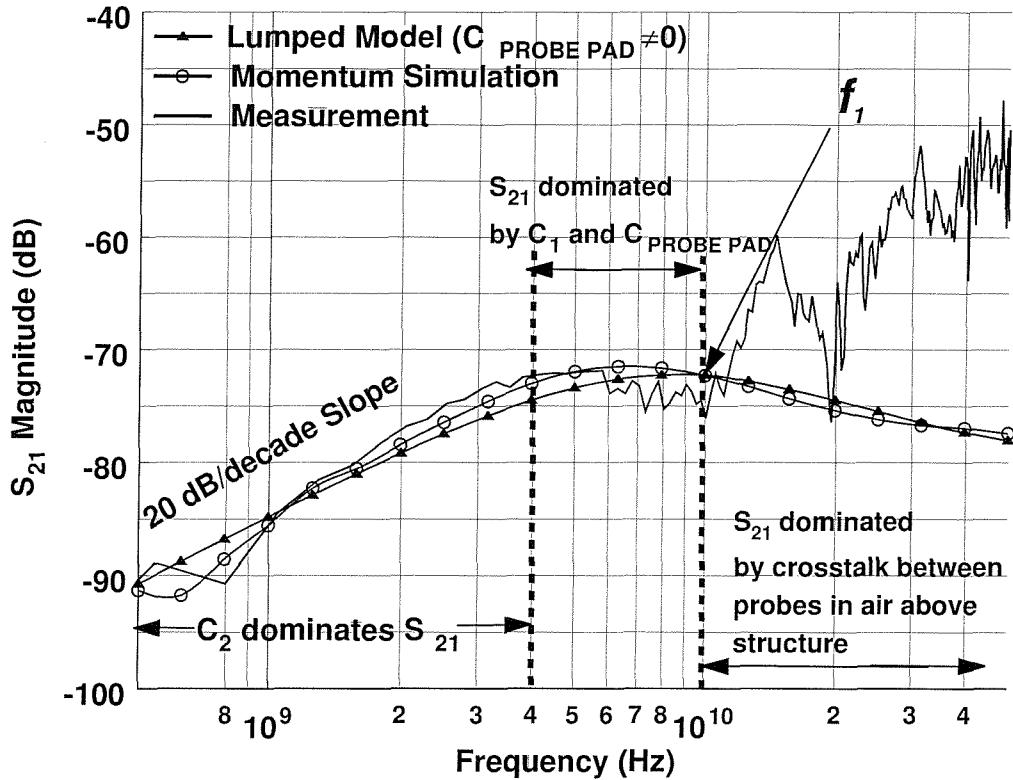

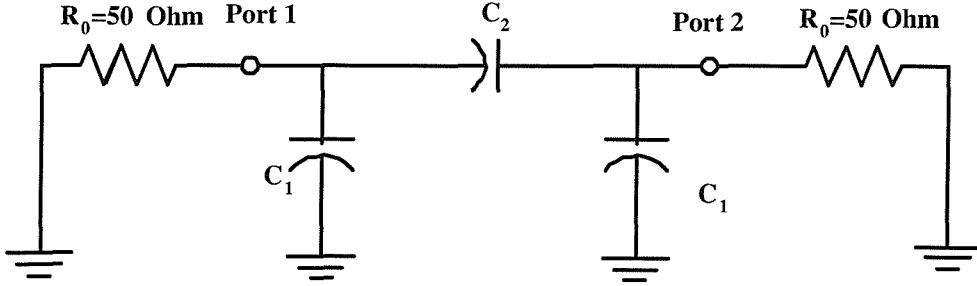

| 4.11 | Substrate crosstalk model without the additional probe pad capacitances. . . . .                                                                                                                                                                                                              | 34 |

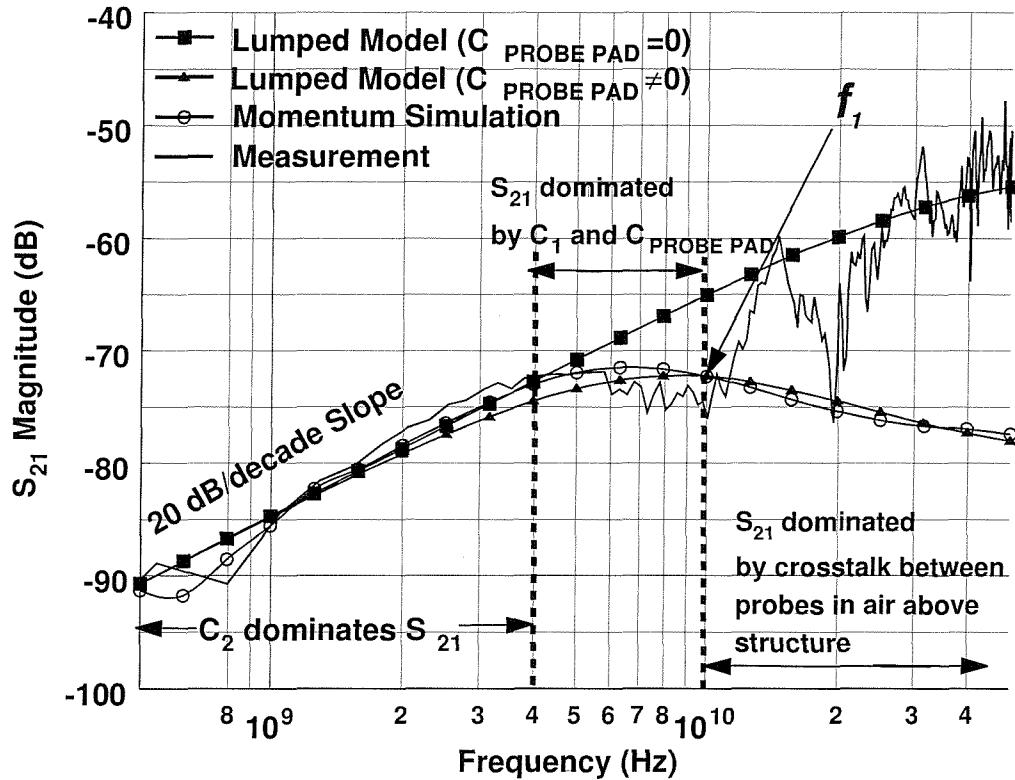

| 4.12 | Effect of the probe pad capacitance ( $C_{PROBEPAD}$ ) on the magnitude of $s_{21}$ . . . . .                                                                                                                                                                                                 | 35 |

| 4.13 | A pair of coupled microstrip lines. . . . .                                                                                                                                                                                                                                                   | 37 |

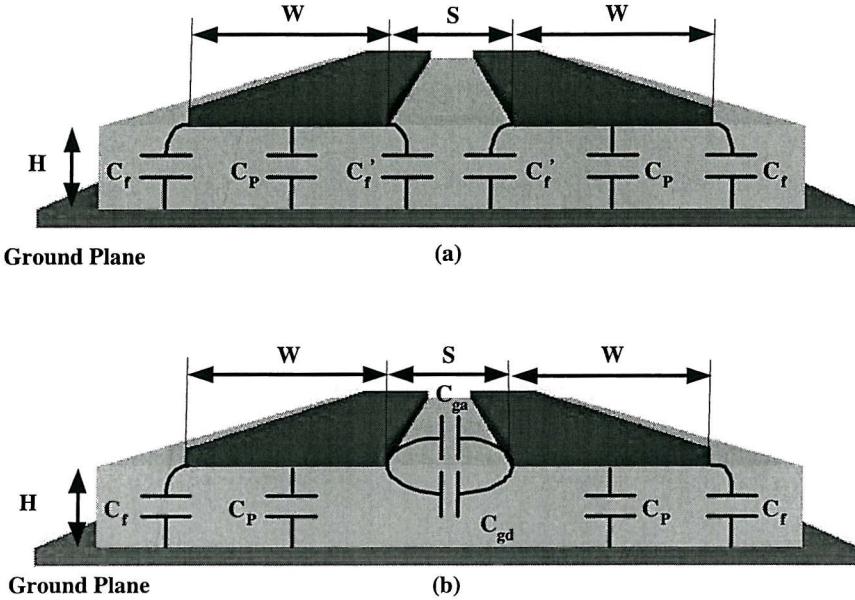

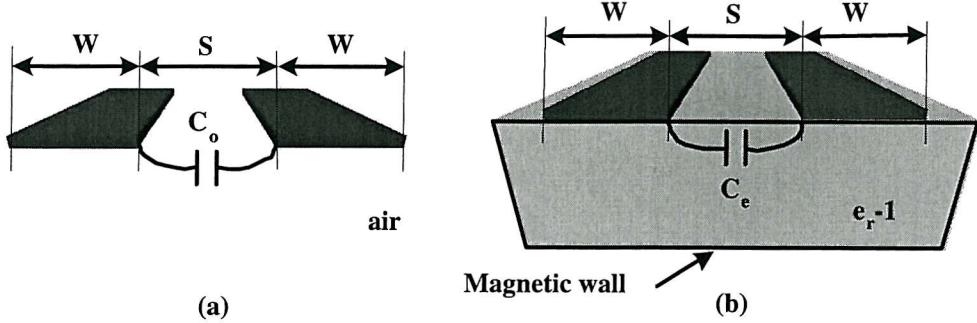

| 4.14 | Decomposition of total capacitance of coupled microstrip lines in terms of various capacitances (a) Even-mode capacitances. (b) Odd-mode capacitances. . . . .                                                                                                                                | 38 |

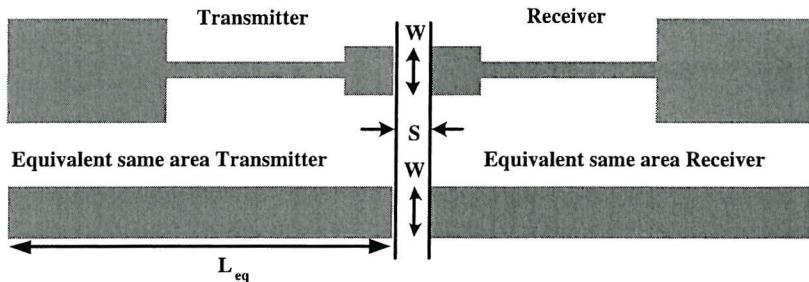

| 4.15 | Equivalent microstrip line geometry used to calculate the crosstalk capacitance according to formulae by [3]. . . . .                                                                                                                                                                         | 40 |

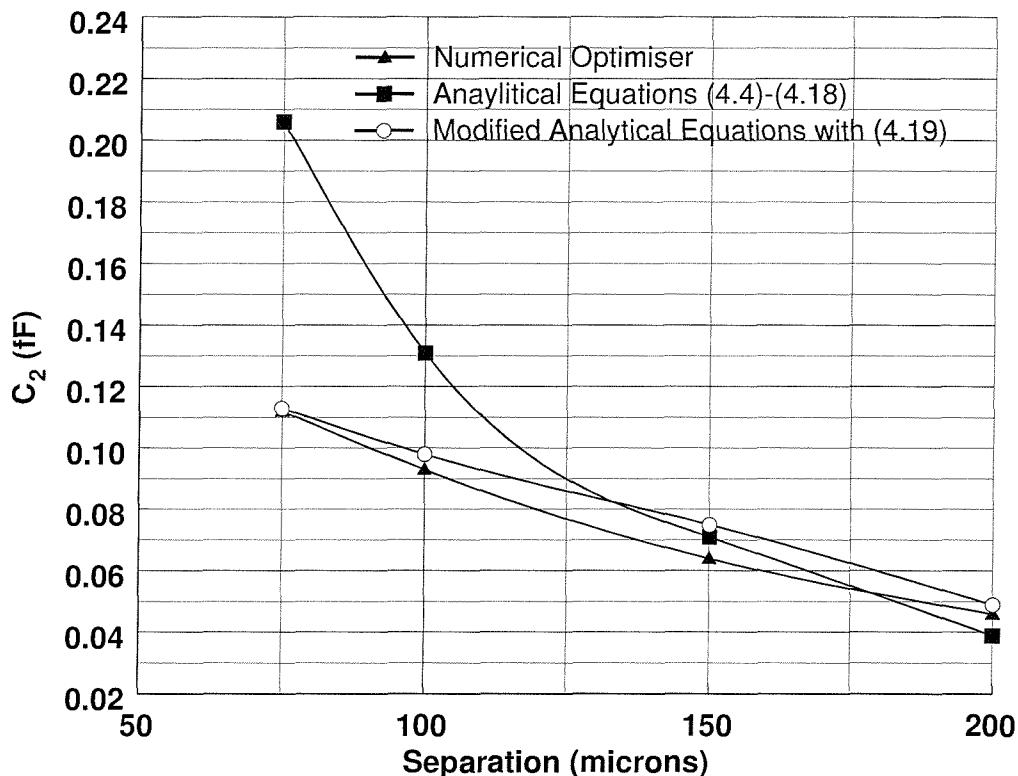

| 4.16 | Comparison of crosstalk capacitance calculations based on the analytical expressions and numerical optimizer values for variable separation distances. . . . .                                                                                                                                | 41 |

|      |                                                                                                                                                                                                                                                                                                                                   |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

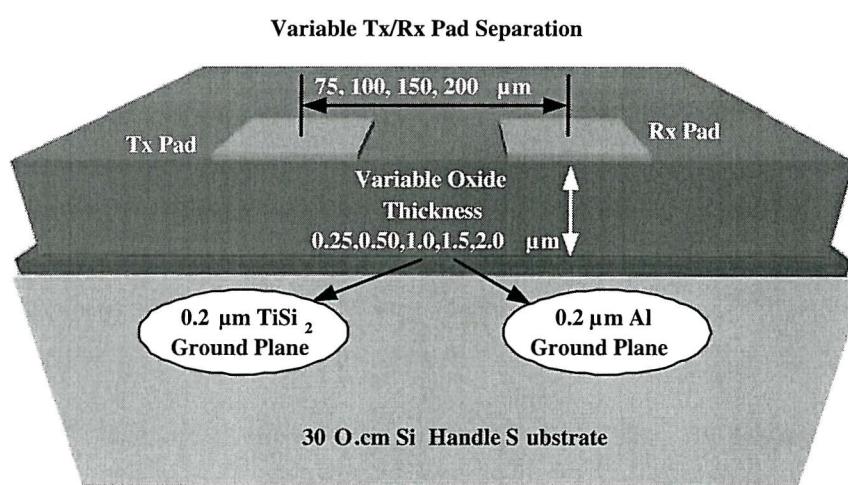

| 5.1  | Process and layout parameter variations for the experiments of this Chapter. The thicknesses of the oxide and the ground plane are the process variables and the Tx/Rx separation distance the layout variable. . . . .                                                                                                           | 44 |

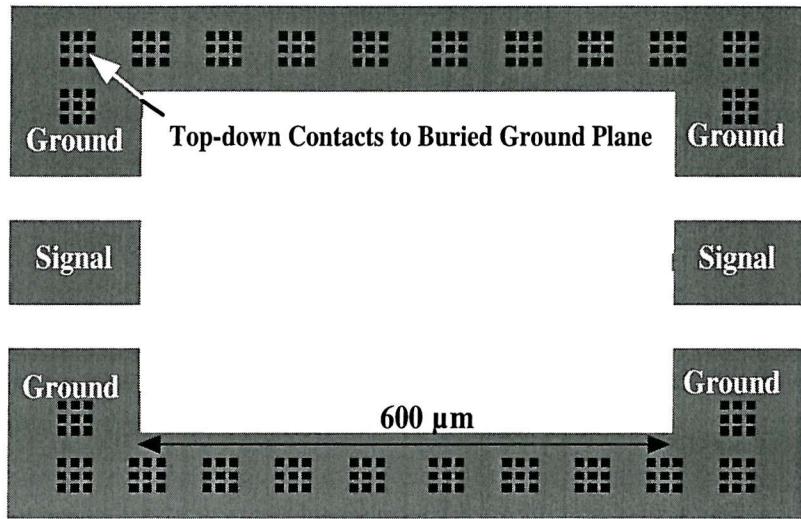

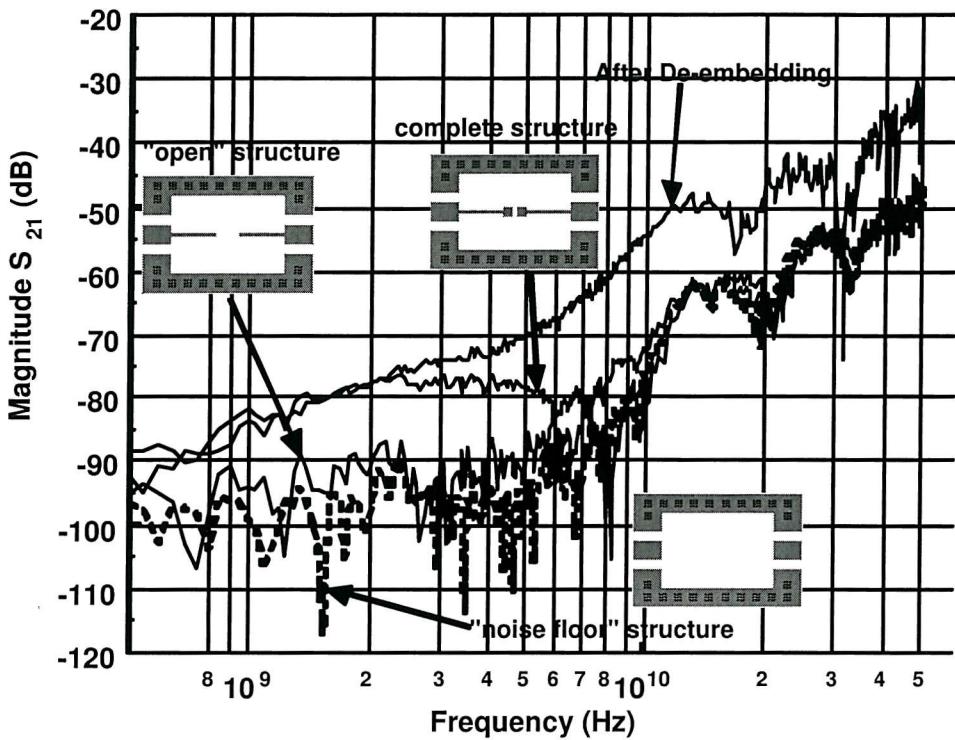

| 5.2  | Plan view of the structure for probe crosstalk and noise-floor measurements. . . . .                                                                                                                                                                                                                                              | 45 |

| 5.3  | Plan view of "open" structure for de-embedding. . . . .                                                                                                                                                                                                                                                                           | 46 |

| 5.4  | Plan view of complete substrate crosstalk structure with two square Tx/Rx pads (50 $\mu\text{m}$ wide) . . . . .                                                                                                                                                                                                                  | 47 |

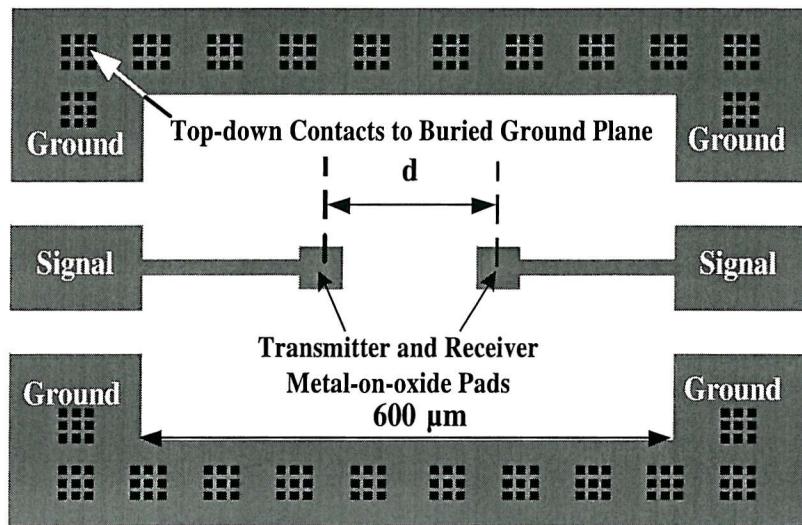

| 5.5  | Measurement data taken from the structure of Figure 5.2 for different oxide thicknesses on both Al and TiSi <sub>2</sub> ground planes. Probe pad separation is 600 $\mu\text{m}$ . . . . .                                                                                                                                       | 47 |

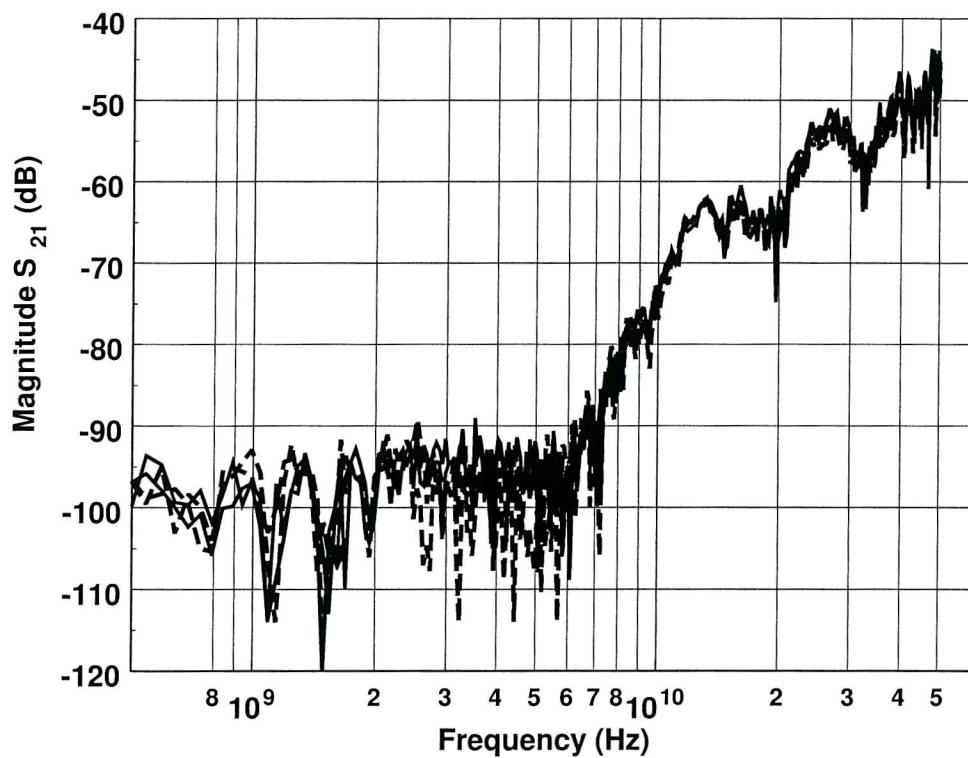

| 5.6  | Measurement data from a "noise-floor", an open and a complete test structure before and after de-embedding for a Tx/Rx pad separation of 75 $\mu\text{m}$ , on 1.0 $\mu\text{m}$ of oxide and a TiSi <sub>2</sub> ground plane. . . . .                                                                                           | 48 |

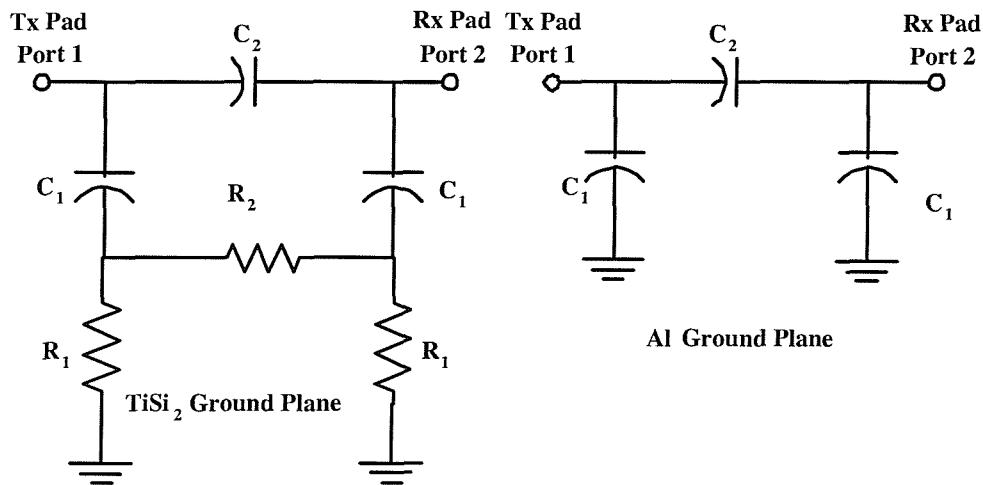

| 5.7  | Lumped model of crosstalk in a buried ground plane test structure and its reduction to a capacitive $\pi$ -network when R <sub>1</sub> and R <sub>2</sub> are assumed negligible. . . . .                                                                                                                                         | 49 |

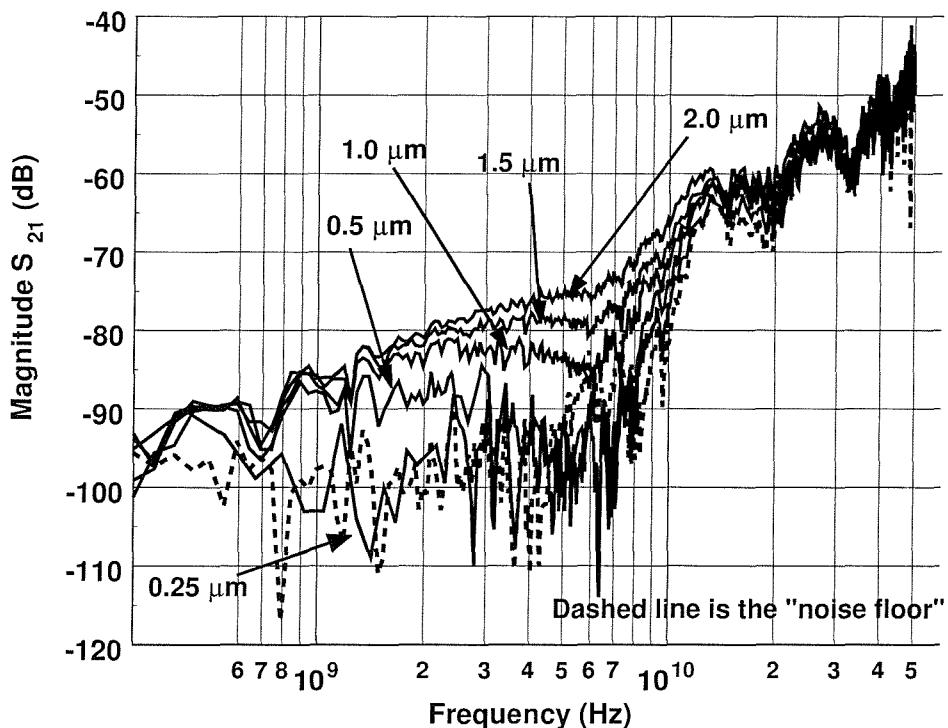

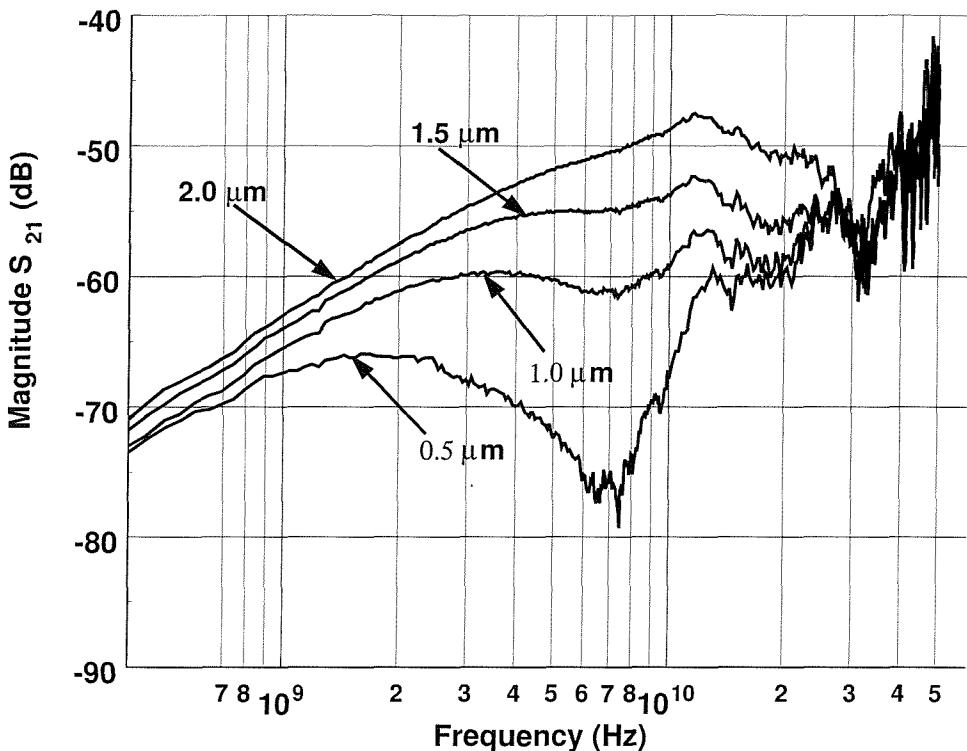

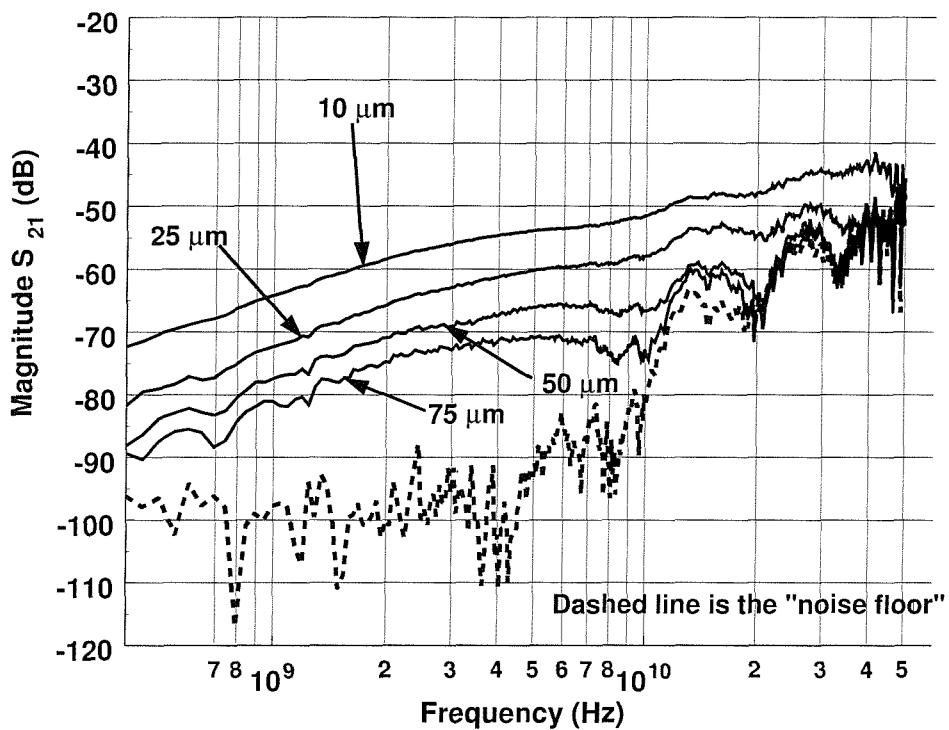

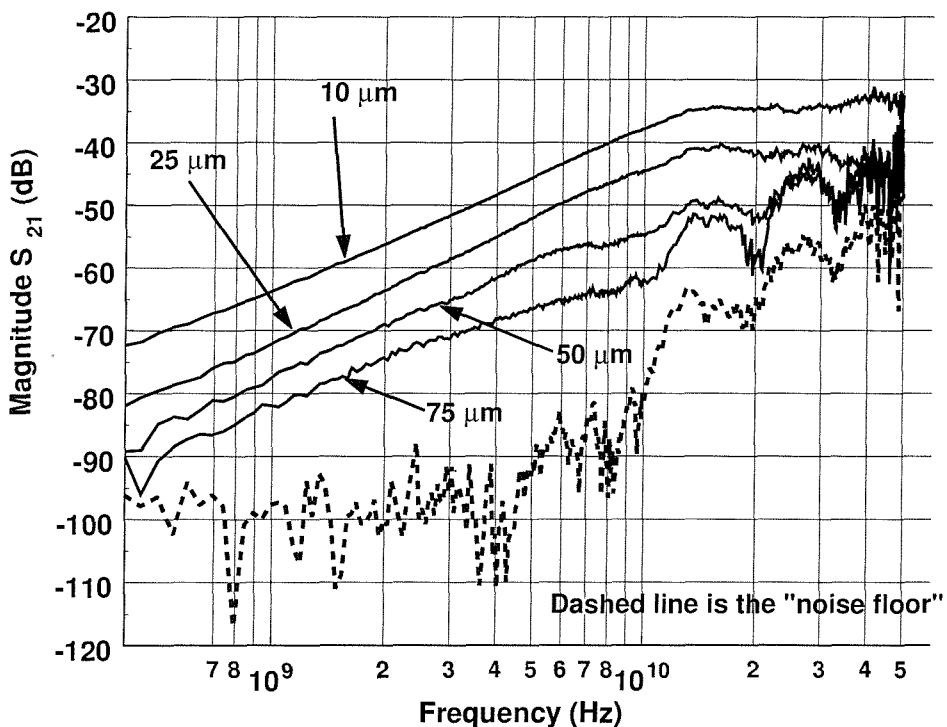

| 5.8  | Crosstalk measurement data for a test structure with 100 $\mu\text{m}$ Tx/Rx pad separation, aluminium ground plane and variable oxide thickness (0.25, 0.5, 1, 1.5, 2.0 $\mu\text{m}$ ). . . . .                                                                                                                                 | 49 |

| 5.9  | Crosstalk measurement data for a test structure with 100 $\mu\text{m}$ Tx/Rx pad separation, a TiSi <sub>2</sub> ground plane and variable oxide thickness (0.25, 0.5, 1, 1.5, 2.0 $\mu\text{m}$ ). . . . .                                                                                                                       | 50 |

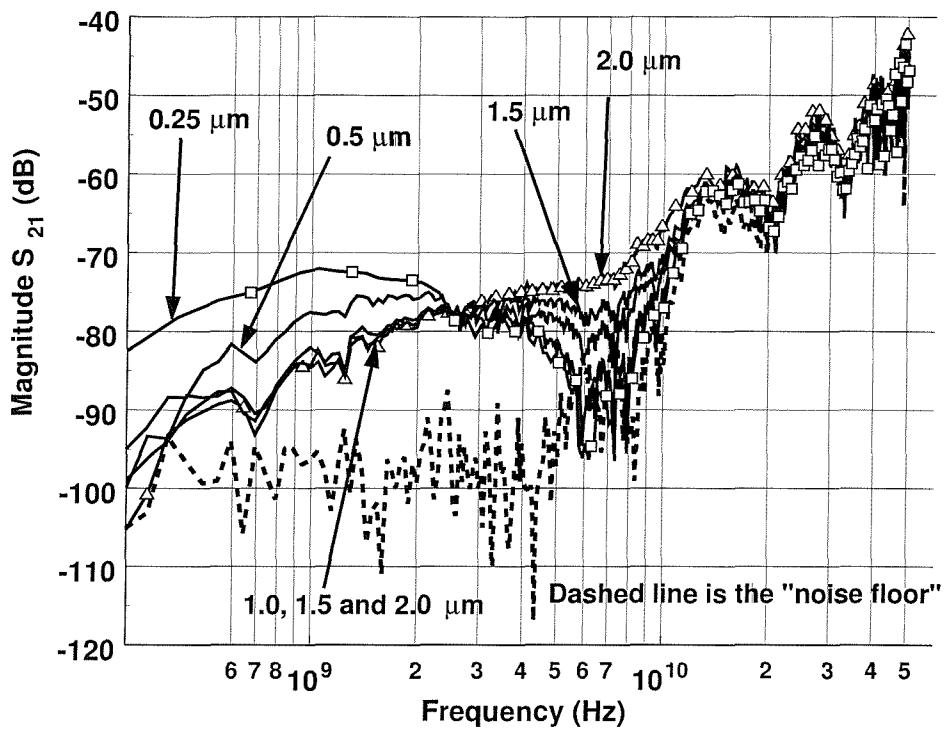

| 5.10 | <i>EM-Sight</i> simulations of variable oxide thickness on TiSi <sub>2</sub> lossy ground plane. . . . .                                                                                                                                                                                                                          | 50 |

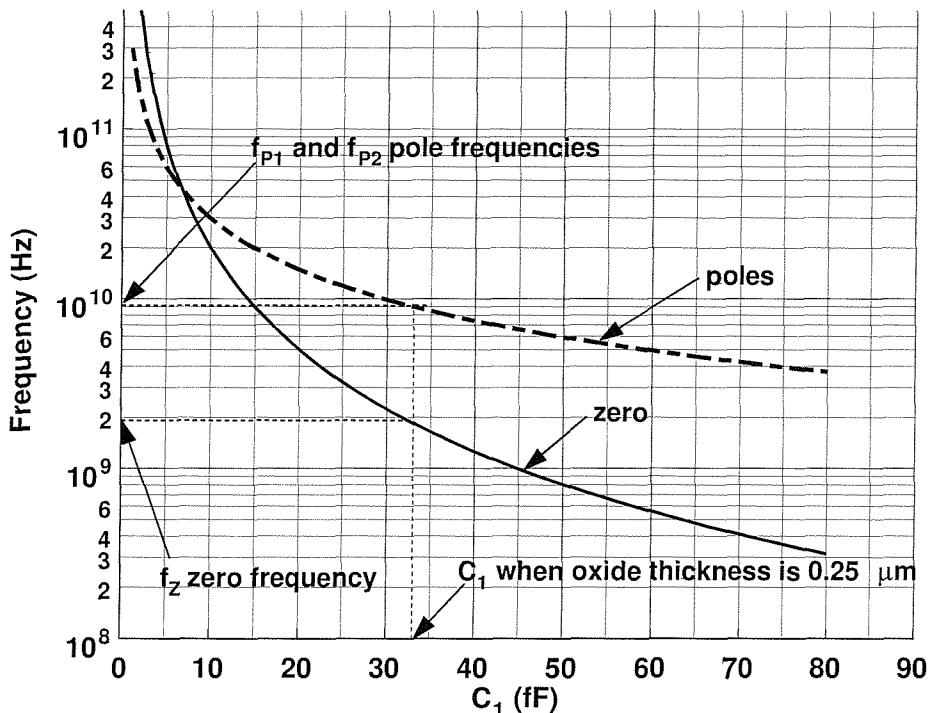

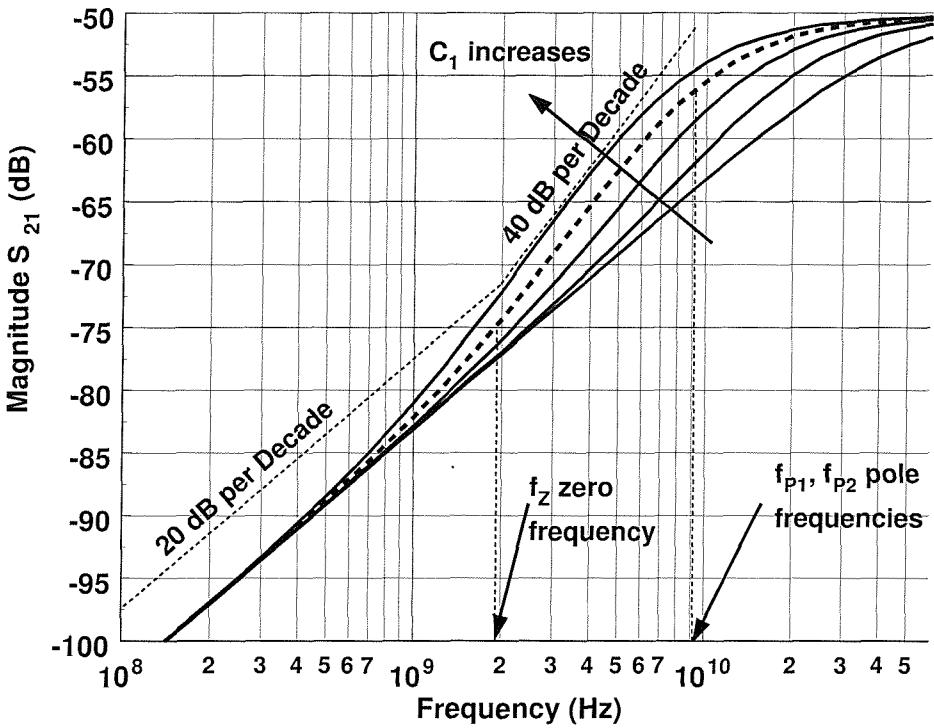

| 5.11 | Location of zeros and poles according to equations ( 4.6) to ( 4.20) as a function of the oxide capacitance C <sub>1</sub> . An example of poles and zero frequency values for an oxide of 0.25 $\mu\text{m}$ is also shown. . . . .                                                                                              | 52 |

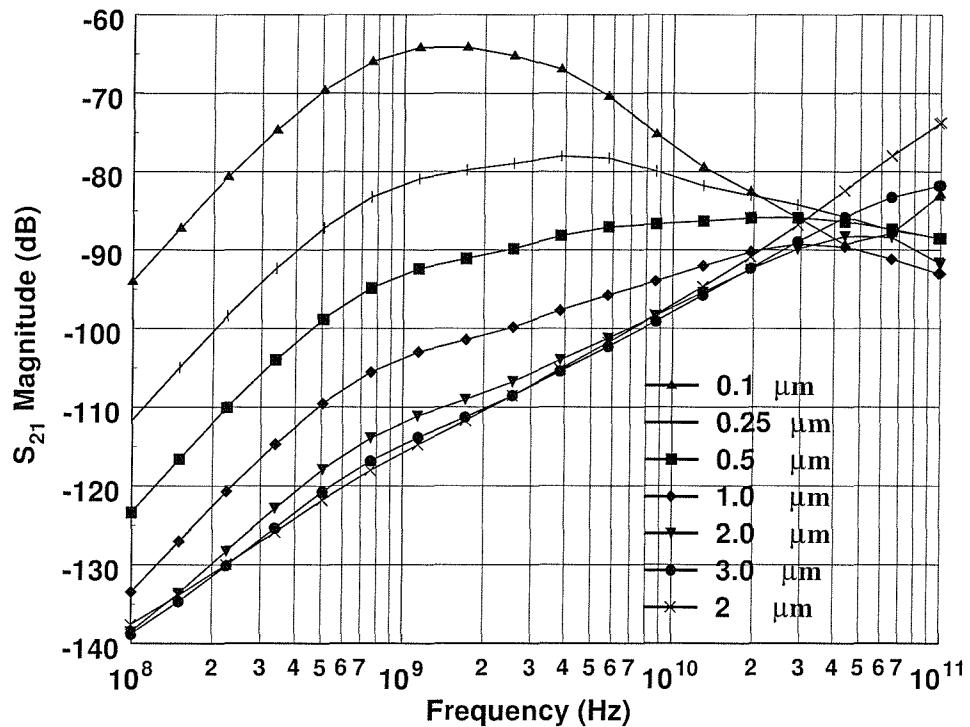

| 5.12 | Magnitude of s <sub>21</sub> frequency response of the lumped model of Figure 5.7 when C <sub>1</sub> is increased and C <sub>2</sub> , R <sub>1</sub> , R <sub>2</sub> are kept constant. The dashed line shows the response, when the value of C <sub>1</sub> corresponds to an oxide thickness of 0.25 $\mu\text{m}$ . . . . . | 53 |

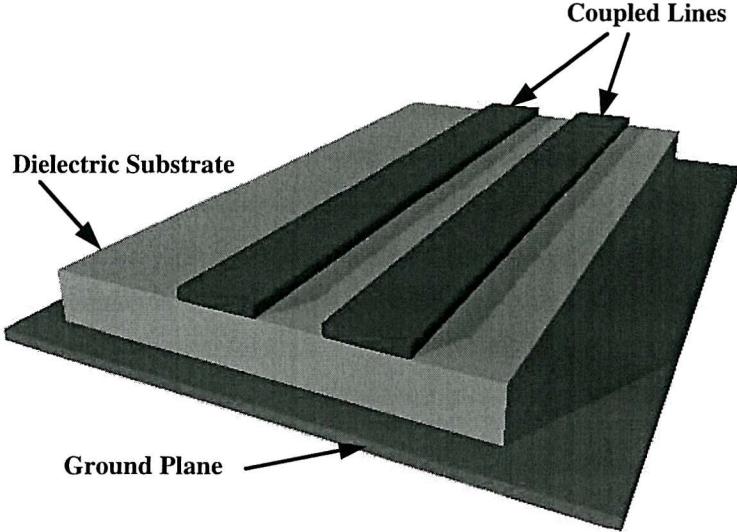

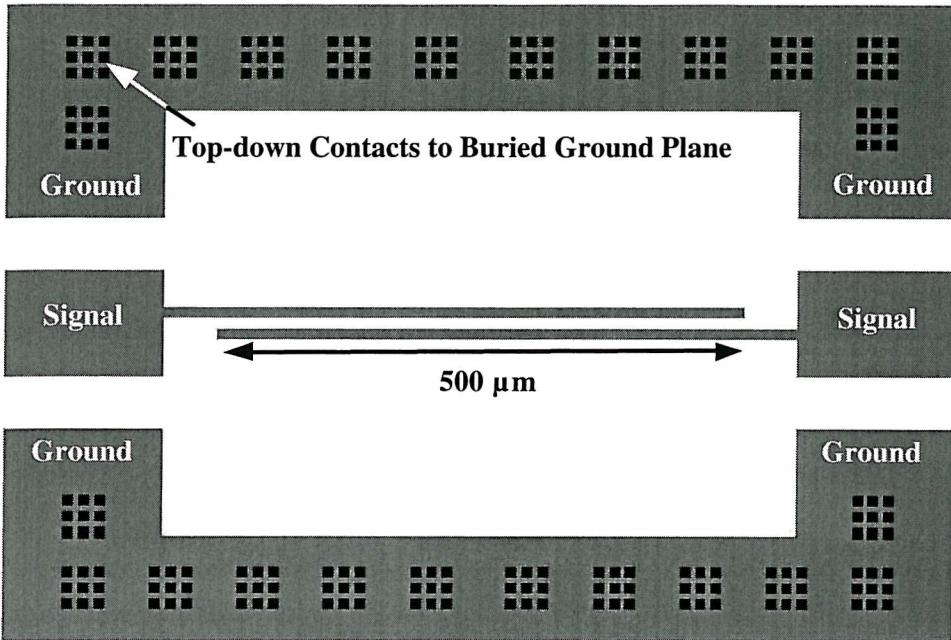

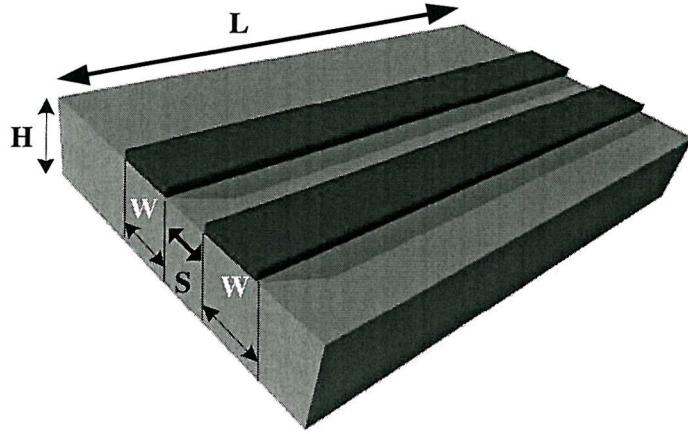

| 5.13 | Coplanar waveguide structure containing two 500 $\mu\text{m}$ long, 10 $\mu\text{m}$ wide coupled microstrip lines, separated by 10 $\mu\text{m}$ . . . . .                                                                                                                                                                       | 54 |

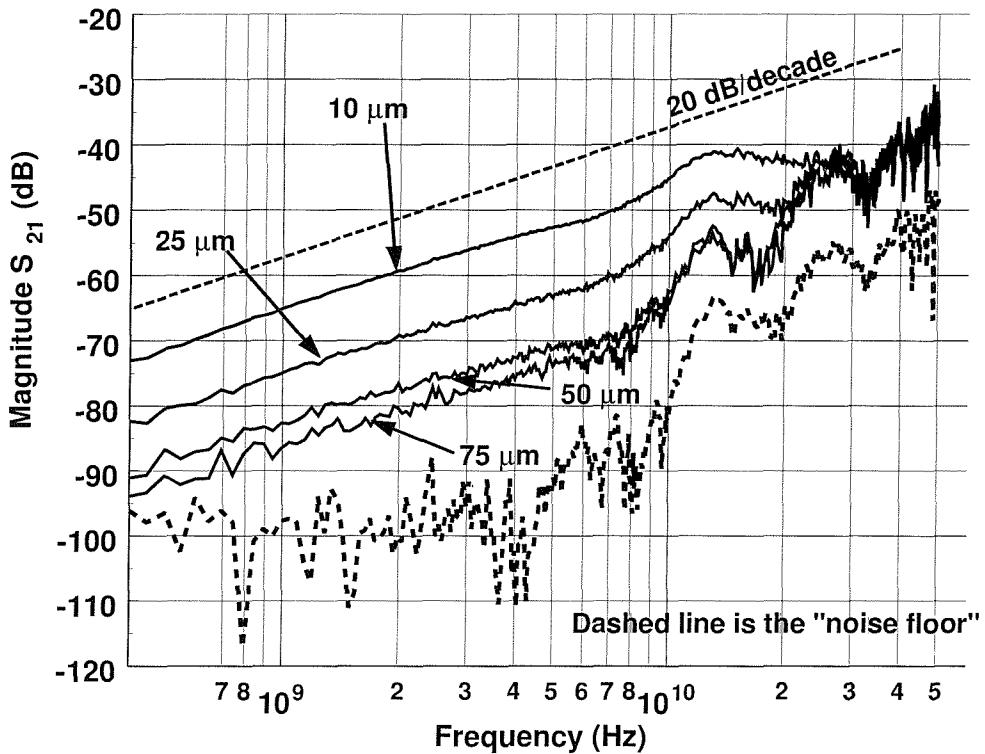

| 5.14 | Measurement data from two coupled microstrip lines of 500 $\mu\text{m}$ length, 10 $\mu\text{m}$ width and variable spacing on an aluminum ground plane. The oxide thickness is 1 $\mu\text{m}$ . . . . .                                                                                                                         | 55 |

|      |                                                                                                                                                                                                                                                                                    |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

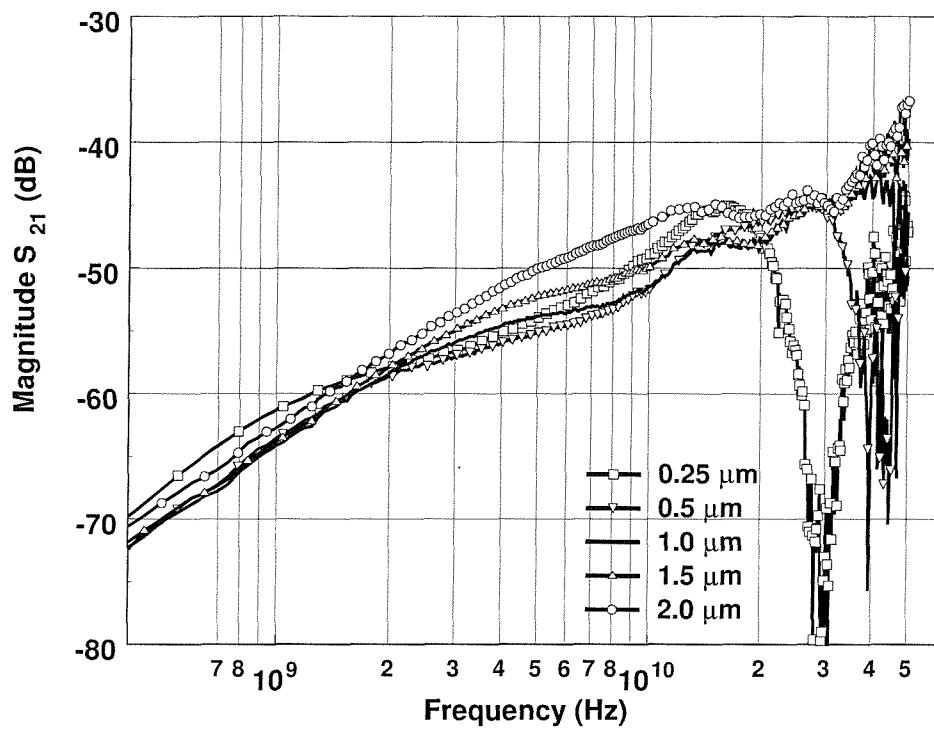

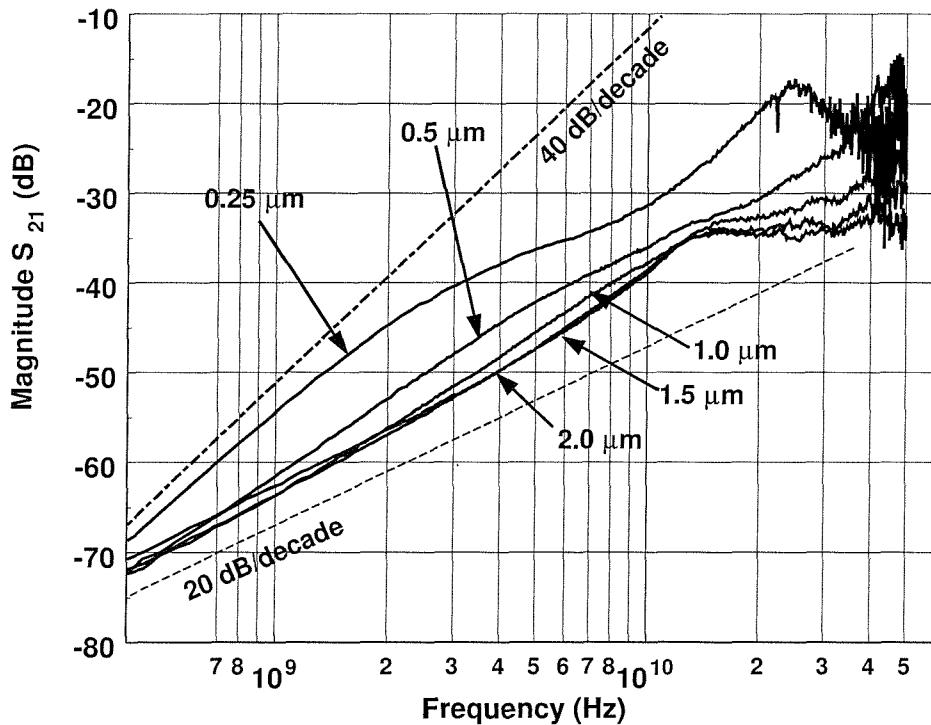

| 5.15 | Measurement data from two coupled microstrip lines of $500 \mu\text{m}$ length, $10 \mu\text{m}$ width and variable oxide thickness on an aluminium ground plane. The separation is $10 \mu\text{m}$ . . . . .                                                                     | 56 |

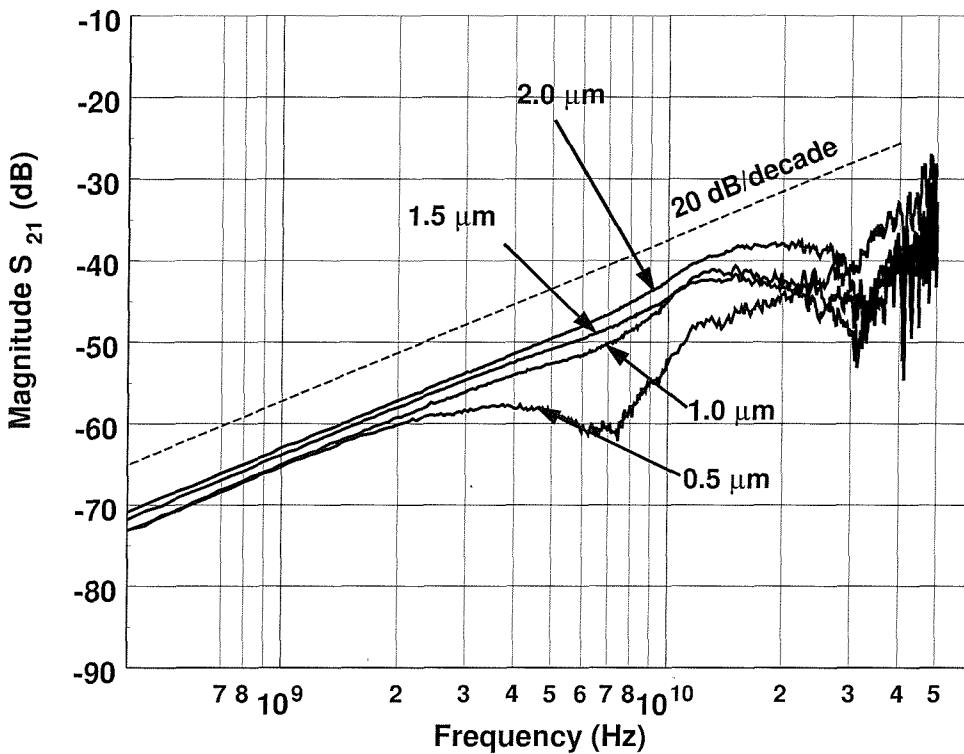

| 5.16 | De-embedded measurement data from two coupled microstrip lines of $500 \mu\text{m}$ length, $10 \mu\text{m}$ width and variable spacing on an aluminum ground plane. The oxide thickness is $1.0 \mu\text{m}$ . . . . .                                                            | 57 |

| 5.17 | De-embedded measurement data from two coupled microstrip lines of $500 \mu\text{m}$ length, $10 \mu\text{m}$ width and variable oxide thickness on an aluminum ground plane. The separation is $10 \mu\text{m}$ . . . . .                                                          | 58 |

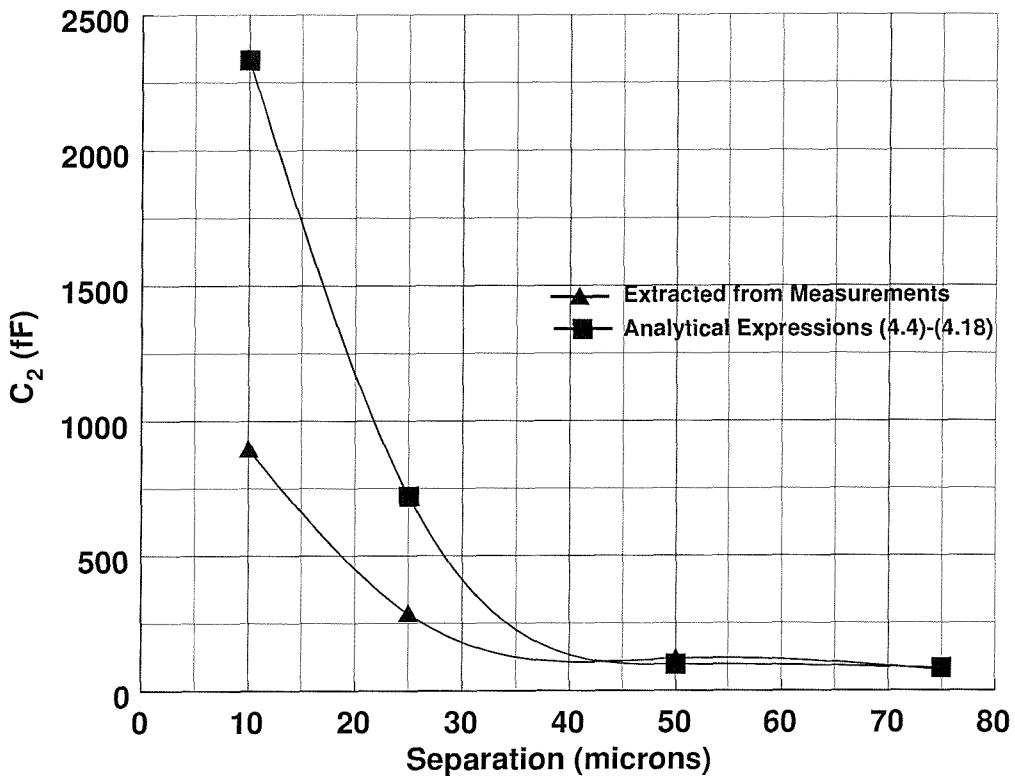

| 5.18 | Comparison of values for $C_2$ extracted from measurements and the analytical expressions ( 4.6) to ( 4.20) for two coupled microstrip lines on $1.0 \mu\text{m}$ of oxide and aluminium ground plane and variable line spacing. . . . .                                           | 59 |

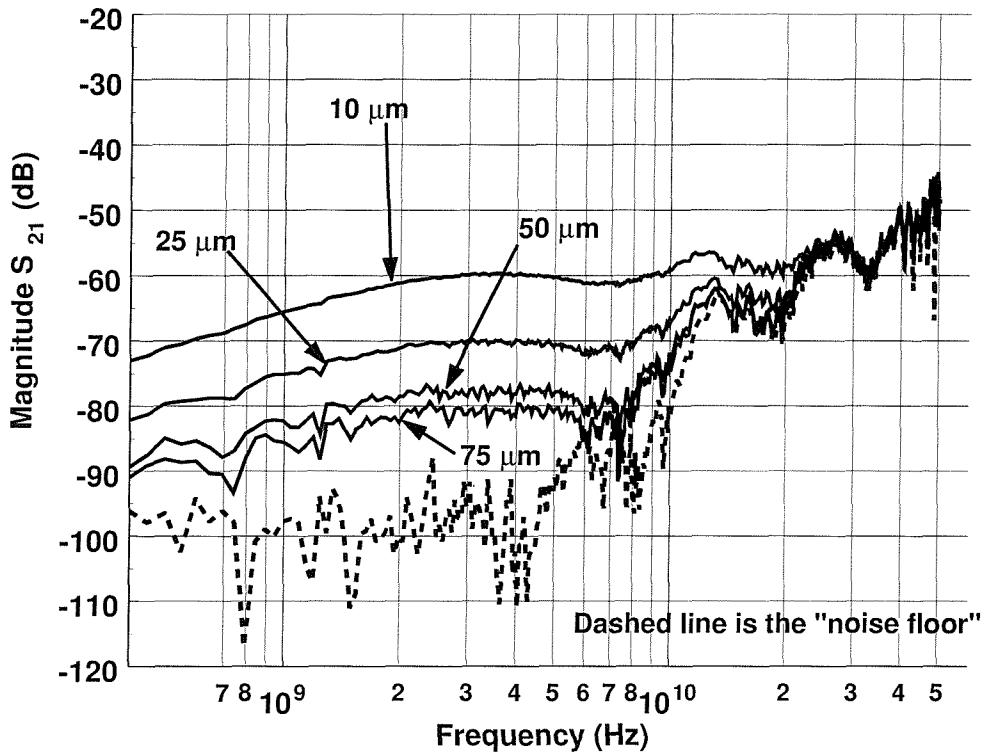

| 5.19 | Measurement data from two coupled microstrip lines of $500 \mu\text{m}$ length, $10 \mu\text{m}$ width and variable spacing on a lossy $\text{TiSi}_2$ plane. The oxide thickness is $1.0 \mu\text{m}$ . . . . .                                                                   | 60 |

| 5.20 | De-embedded measurement data from two coupled microstrip lines of $500 \mu\text{m}$ length, $10 \mu\text{m}$ width and variable spacing on a lossy $\text{TiSi}_2$ plane. The oxide thickness is $1.0 \mu\text{m}$ . . . . .                                                       | 60 |

| 5.21 | Measurement data from two coupled microstrip lines of $500 \mu\text{m}$ length, $10 \mu\text{m}$ width on a lossy $\text{TiSi}_2$ plane. The oxide thickness is varied from $0.5 \mu\text{m}$ to $2.0 \mu\text{m}$ and the line spacing is $10 \mu\text{m}$ . . . . .              | 61 |

| 5.22 | De-embedded measurement data from two coupled microstrip lines of $500 \mu\text{m}$ length, $10 \mu\text{m}$ width on a lossy $\text{TiSi}_2$ plane. The oxide thickness is varied from $0.25 \mu\text{m}$ to $2.0 \mu\text{m}$ and the line spacing is $10 \mu\text{m}$ . . . . . | 61 |

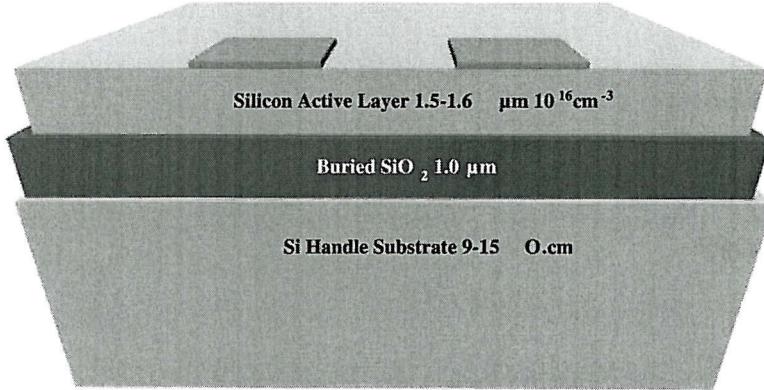

| 6.1  | Cross-sectional view of the SOI substrate. . . . .                                                                                                                                                                                                                                 | 64 |

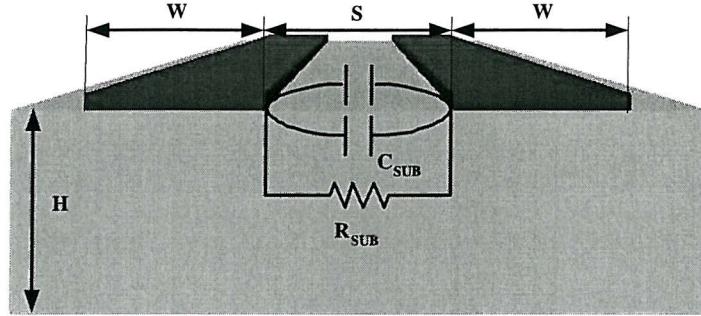

| 6.2  | Substrate coupling lumped model for two zero thickness conductors on a silicon substrate. . . . .                                                                                                                                                                                  | 65 |

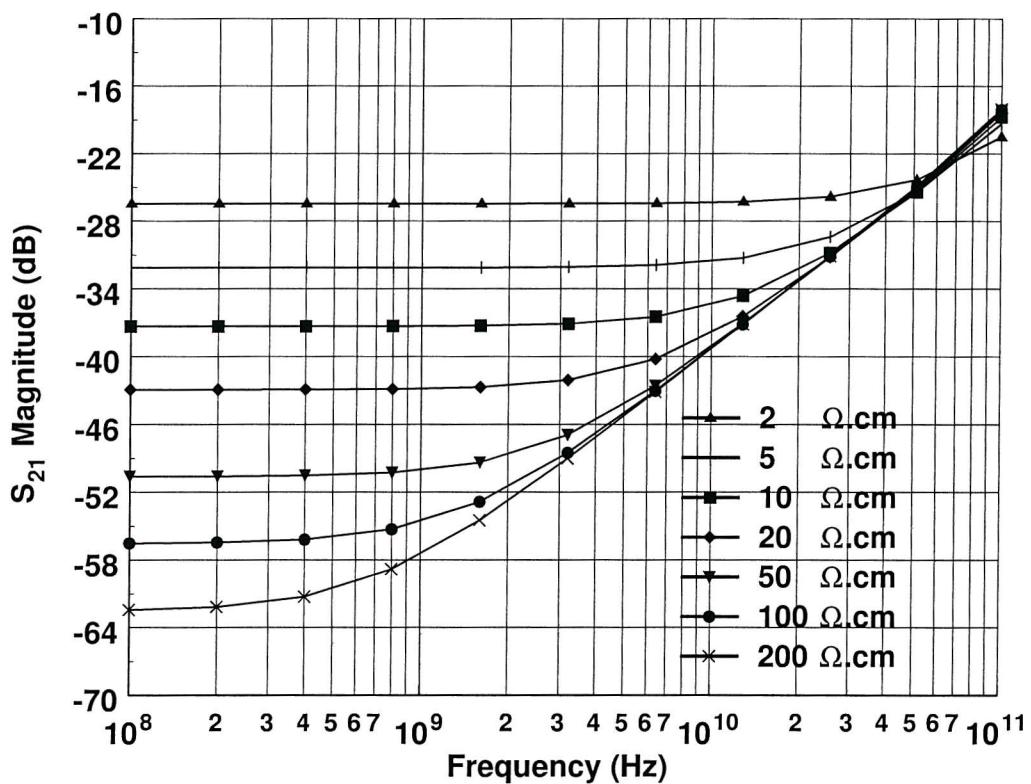

| 6.3  | Magnitude of $s_{21}$ (dB) versus frequency for various substrate resistivity values of two square metal pads ( $50 \times 50 \mu\text{m}^2$ ) of zero thickness on a very high thickness Si substrate. . . . .                                                                    | 65 |

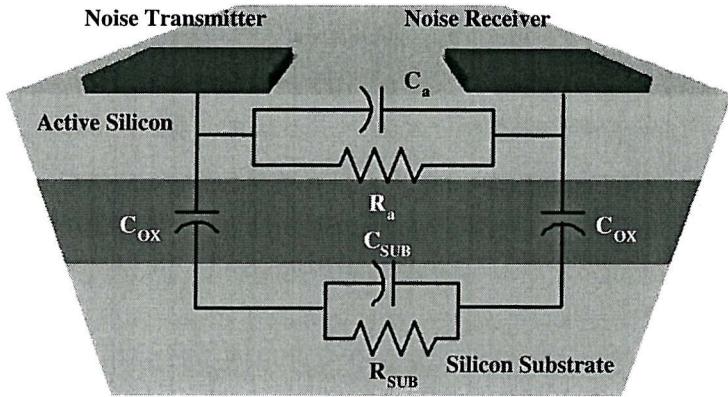

| 6.4  | SOI substrate and substrate crosstalk model of two pads lying on this substrate. . . . .                                                                                                                                                                                           | 67 |

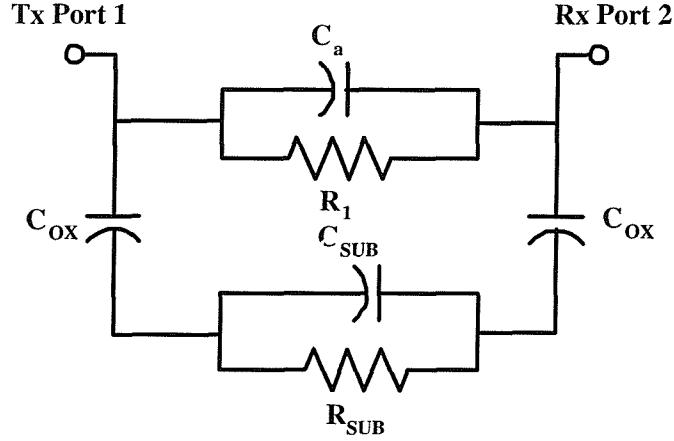

| 6.5  | Equivalent circuit of the SOI substrate crosstalk model. . . . .                                                                                                                                                                                                                   | 68 |

| 6.6  | Equivalent circuit of a crosstalk model for a SOI substrate with a handle substrate of very high resistivity compared to the active layer. . . . .                                                                                                                                 | 68 |

|      |                                                                                                                                                                                                                                                             |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

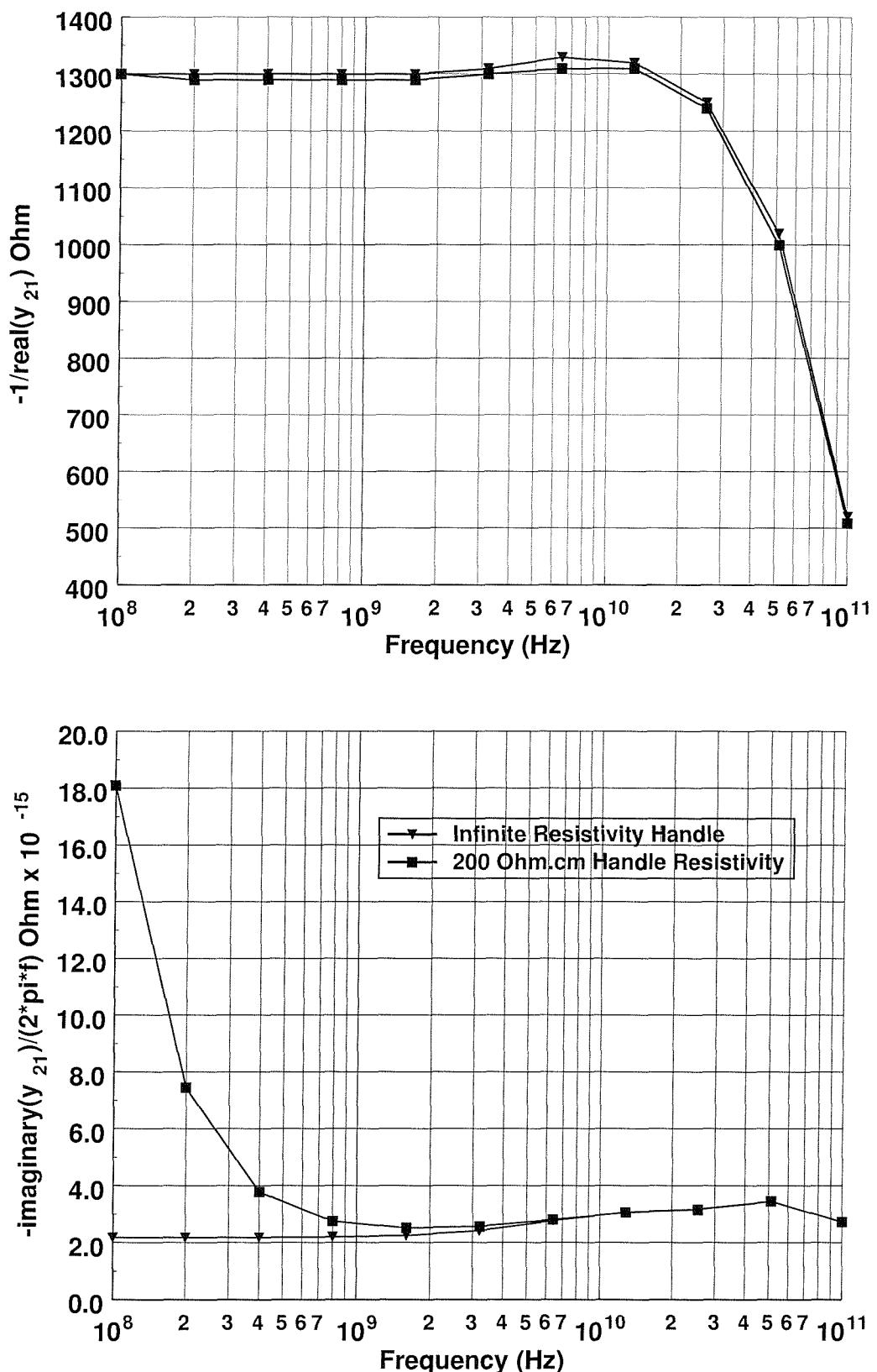

| 6.7  | Real part of $y_{21}$ as a function of frequency for two zero thickness square pads on a SOI substrate with high ( $200 \Omega\text{.cm}$ )(top) and infinite resistivity handle (bottom). Active layer doping is $10^{16} \text{ cm}^{-3}$ . . . . .       | 69 |

| 6.8  | Real and Imaginary parts of $y_{21}$ as extracted from ( 6.5) and ( 6.5). . . . .                                                                                                                                                                           | 71 |

| 6.9  | Symmetrical double-strip coplanar waveguide on a substrate with finite thickness. . . . .                                                                                                                                                                   | 72 |

| 6.10 | Partial capacitances for coupling capacitance calculation in the double-strip coplanar waveguide problem. . . . .                                                                                                                                           | 73 |

| 6.11 | Two configurations for the derivation of the two coupling models through the silicon layers. . . . .                                                                                                                                                        | 74 |

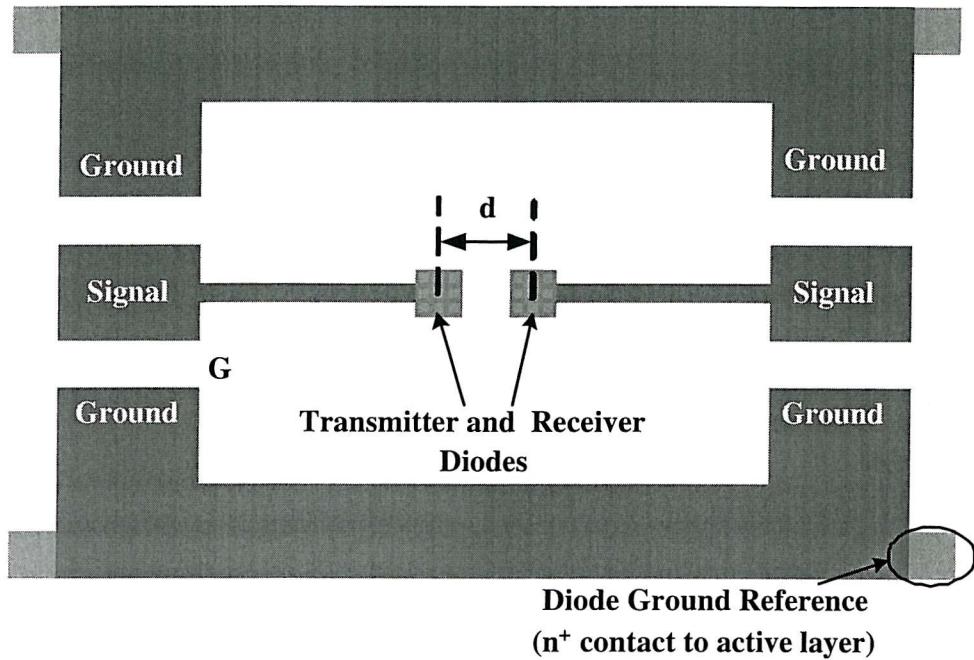

| 6.12 | Plan view of the test structures for the SOI crosstalk experiments. . . . .                                                                                                                                                                                 | 76 |

| 6.13 | Cross-sectional view of the test structure for the SOI experiments, showing in detail the different layers of the substrate and test structure. . . . .                                                                                                     | 77 |

| 6.14 | Measurements of substrate crosstalk on a high resistivity SOI wafer with variable pad separation before de-embedding the coplanar GSG structure. . . . .                                                                                                    | 78 |

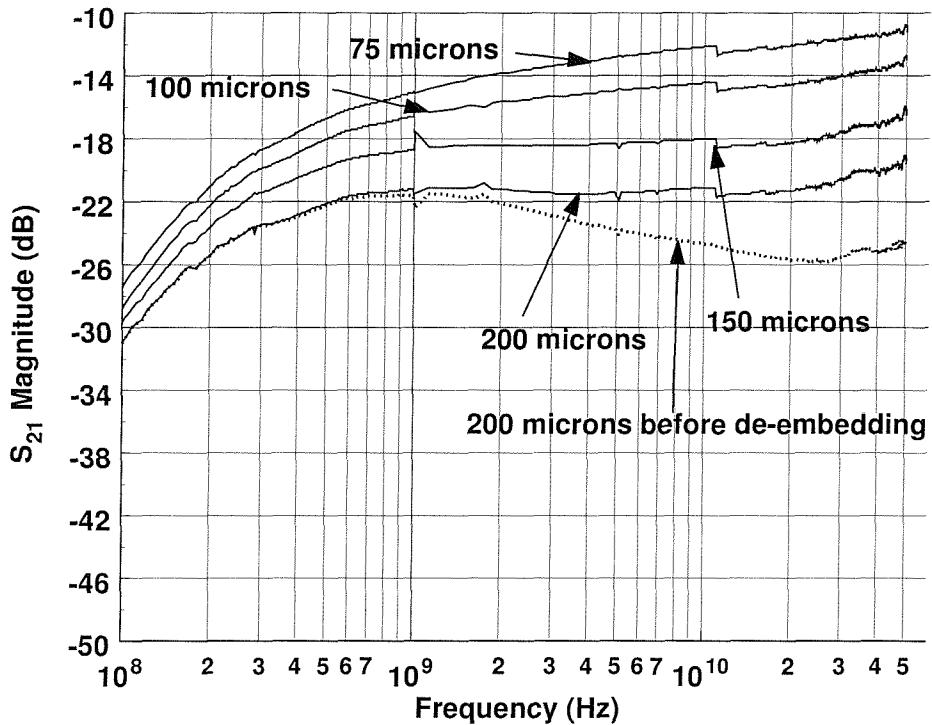

| 6.15 | De-embedded measurements of substrate crosstalk on a high resistivity SOI wafer with variable pad separation. The dashed line indicates the difference between deembedded and non-dembedded measurements for the $200 \mu\text{m}$ separation case. . . . . | 79 |

| 6.16 | Electromagnetic simulation data and comparison with measurements for different Tx/Rx pad separations. . . . .                                                                                                                                               | 81 |

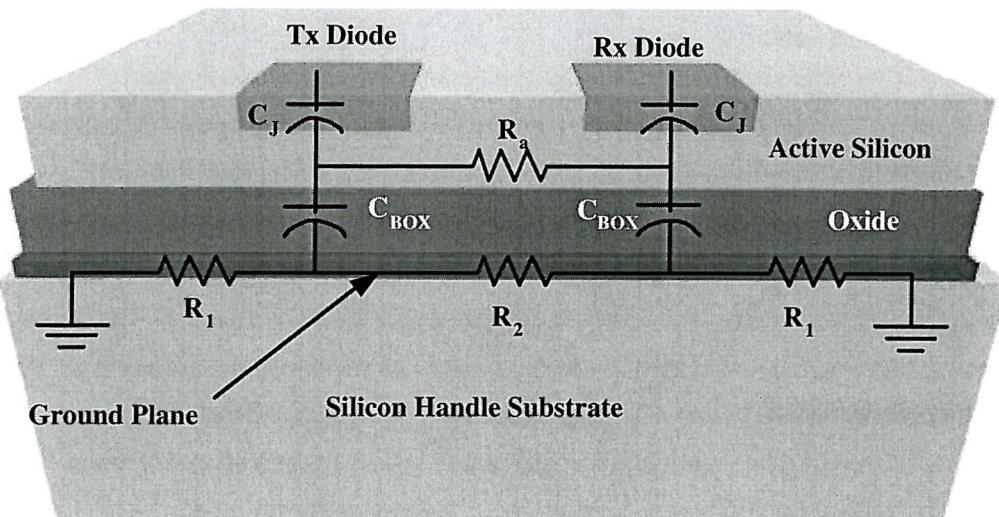

| 6.17 | Equivalent lumped element model of high resistivity SOI crosstalk after the introduction of the depletion capacitance $C_J$ . . . . .                                                                                                                       | 82 |

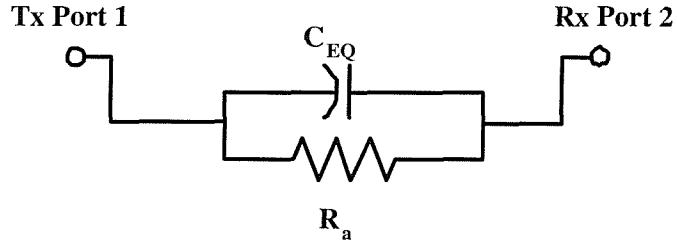

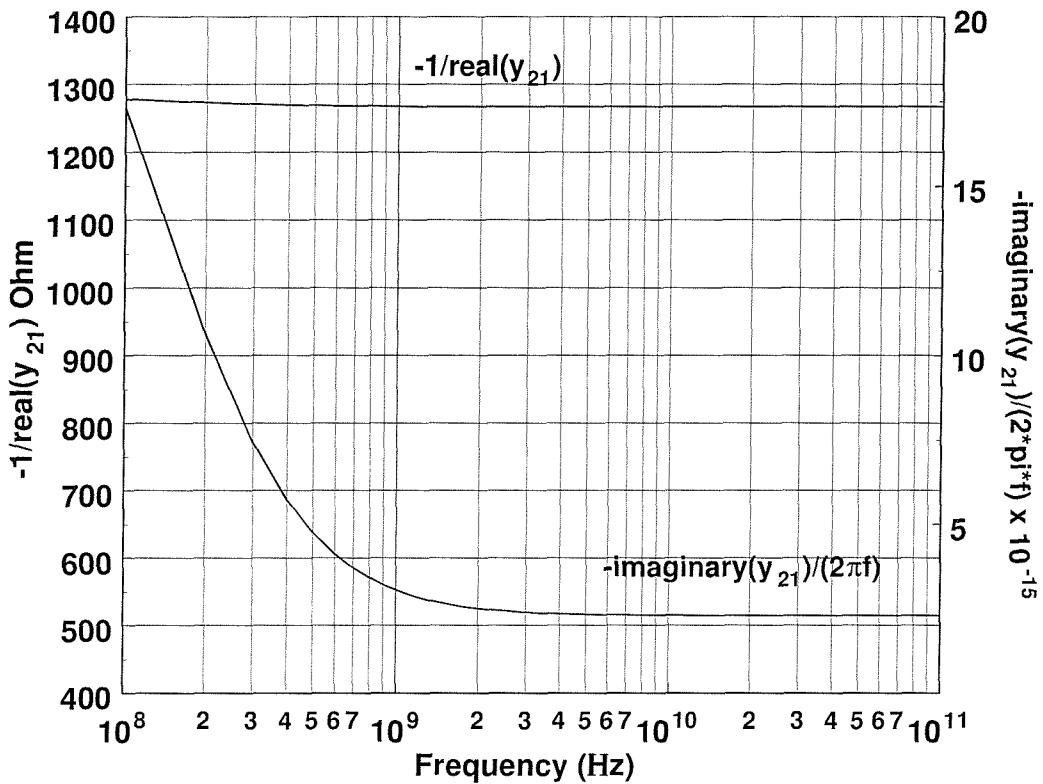

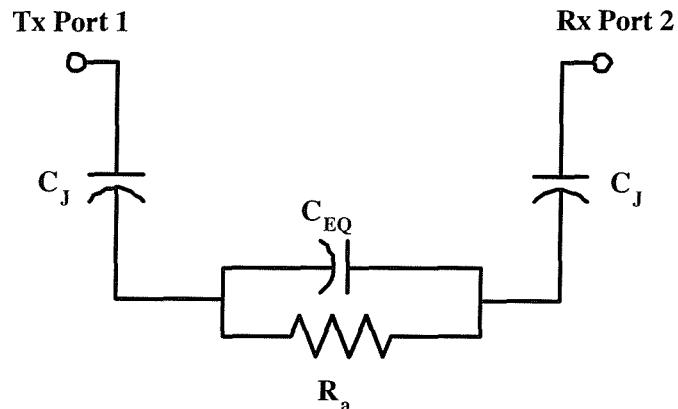

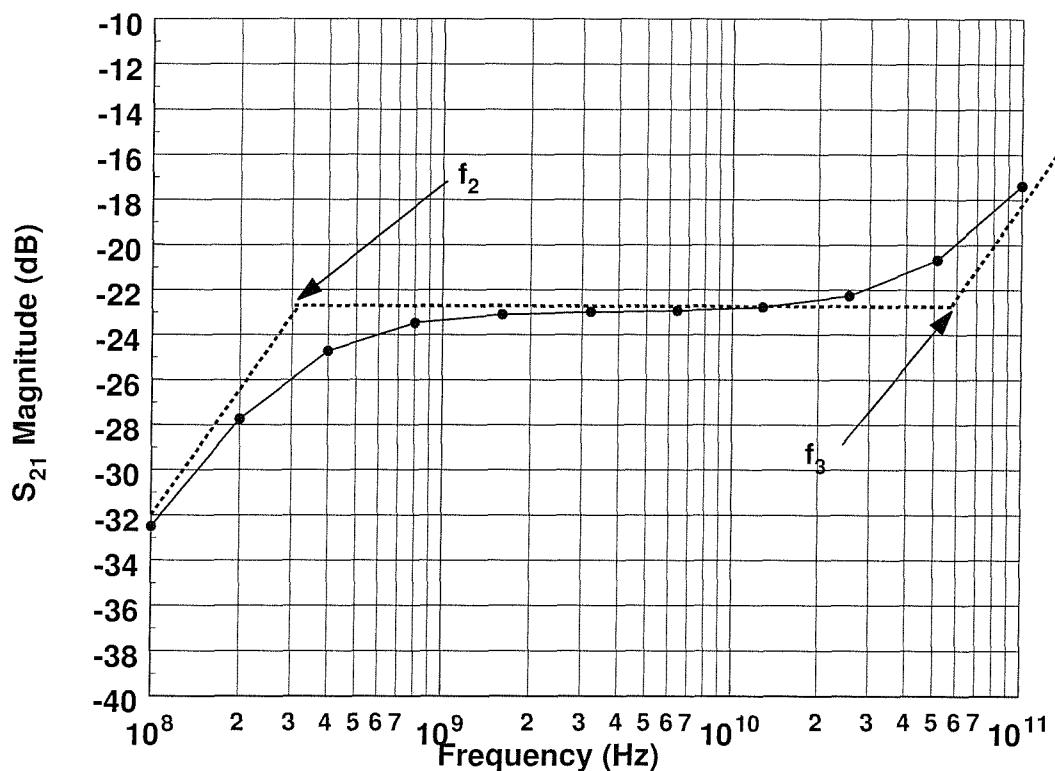

| 6.18 | $S_{21}$ response of the model of Figure 6.17 when $C_J=0.8 \text{ pF}$ $R_a=1300 \Omega$ and $C_{EQ}=2\text{fF}$ . . . . .                                                                                                                                 | 82 |

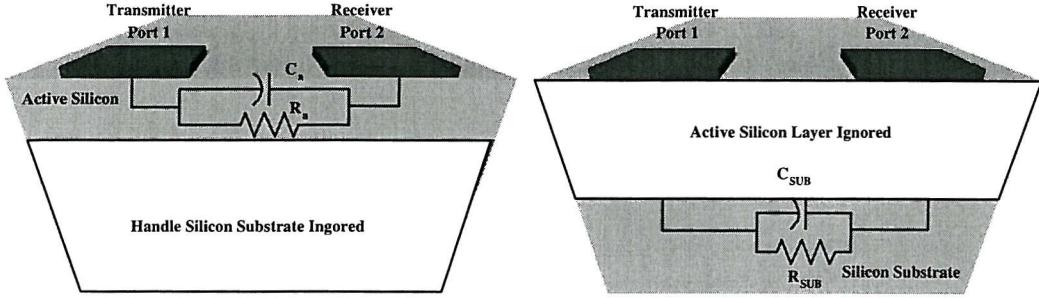

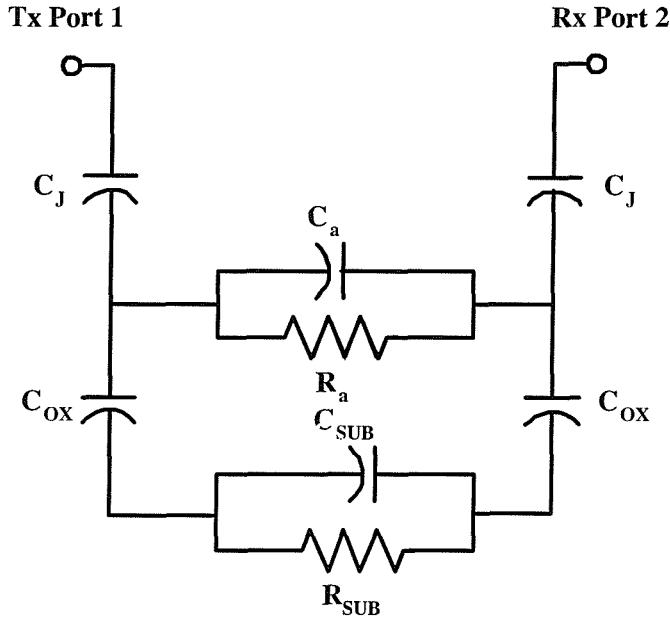

| 6.19 | Lumped element model topology for SOI substrate crosstalk with diode noise transmitters and receivers. . . . .                                                                                                                                              | 83 |

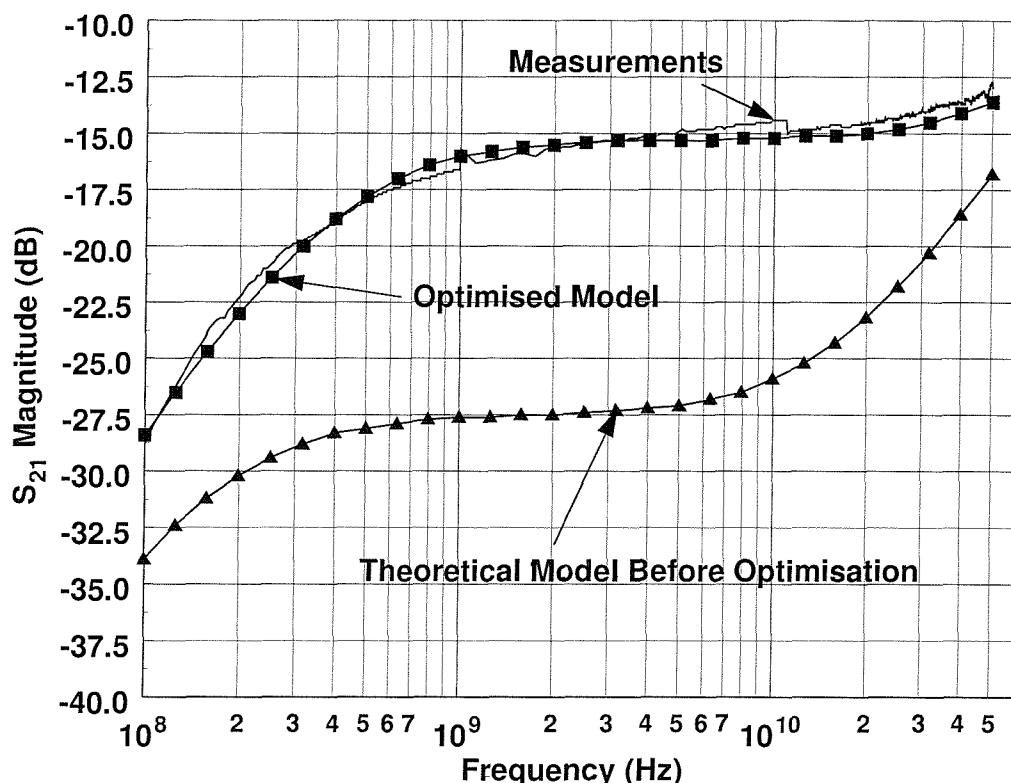

| 6.20 | Theoretical and optimised substrate crosstalk model response of two diode pads on a high resistivity SOI substrate separated by $100 \mu\text{m}$ . . . . .                                                                                                 | 85 |

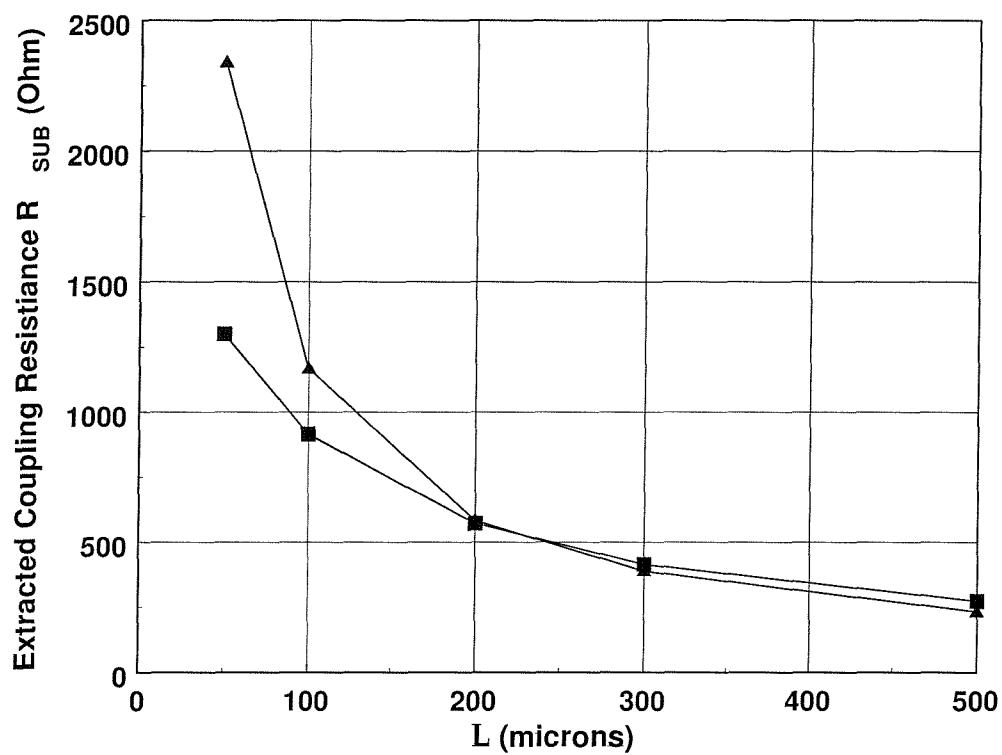

| 6.21 | Theoretical and extracted $R_{SUB}$ versus pad length L for two pads with $50 \mu\text{m}$ width and $50 \mu\text{m}$ spacing on $2.0 \mu\text{m}$ of silicon. . . . .                                                                                      | 87 |

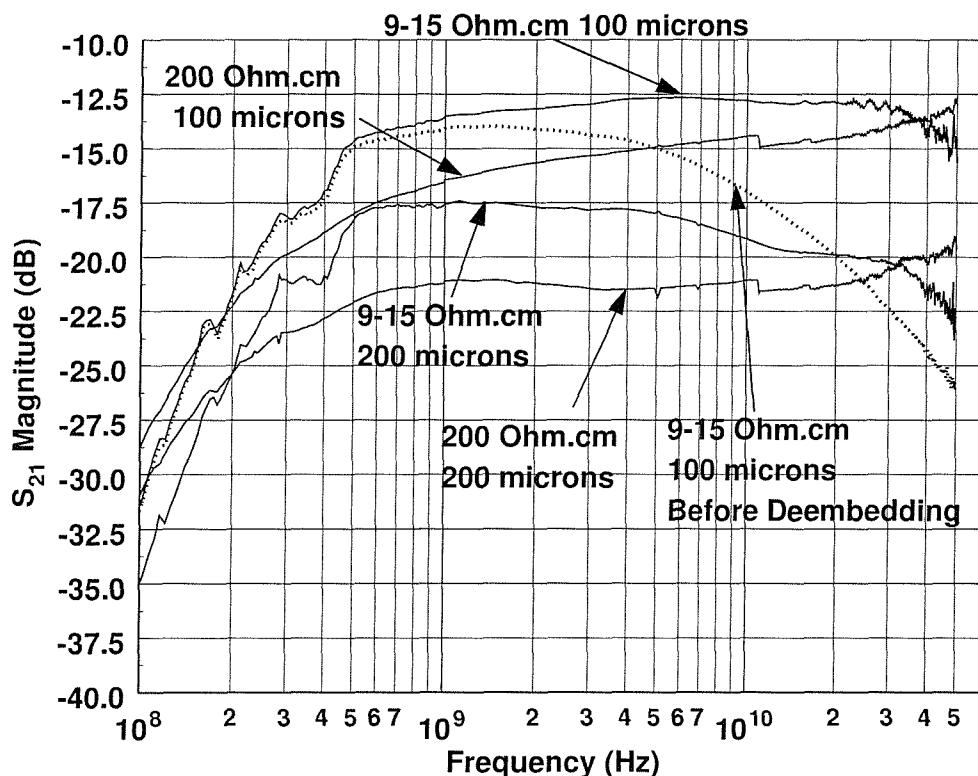

| 6.22 | Measurements of crosstalk in high ( $200 \Omega\text{.cm}$ ) and standard ( $9-15 \Omega\text{.cm}$ ) resistivity SOI substrates for $200 \mu\text{m}$ and $100 \mu\text{m}$ Tx/Rx pad separation. . . . .                                                  | 87 |

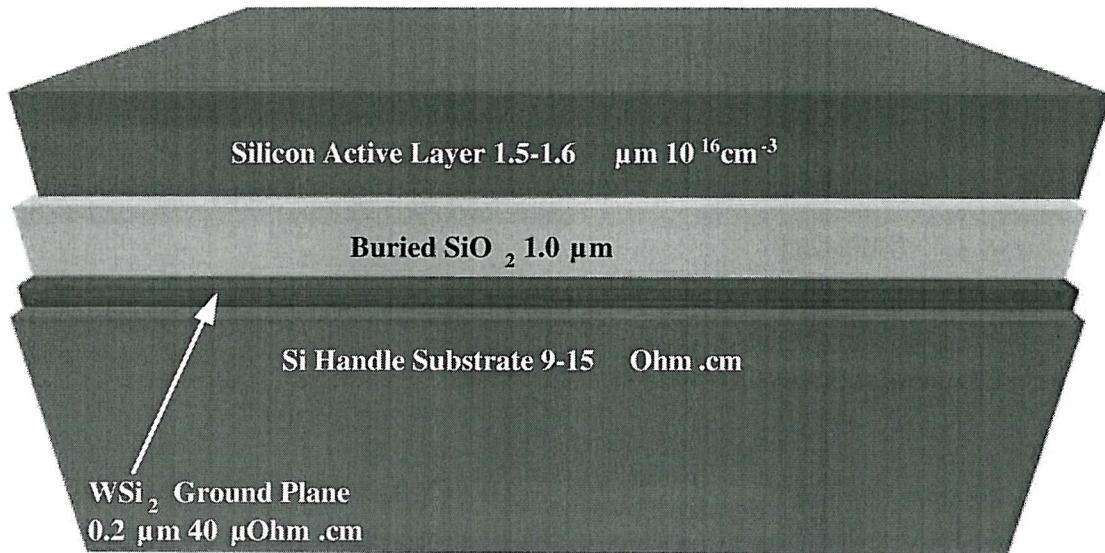

| 7.1  | Cross-sectional illustration of the GPSOI substrate . . . . .                                                                                                                                                                                               | 91 |

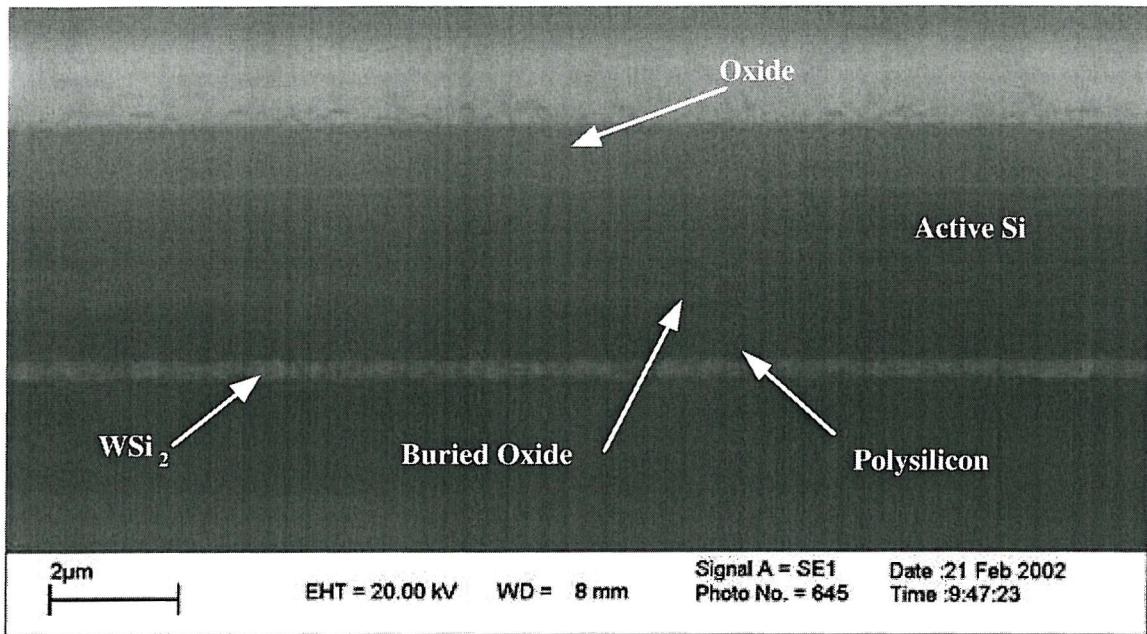

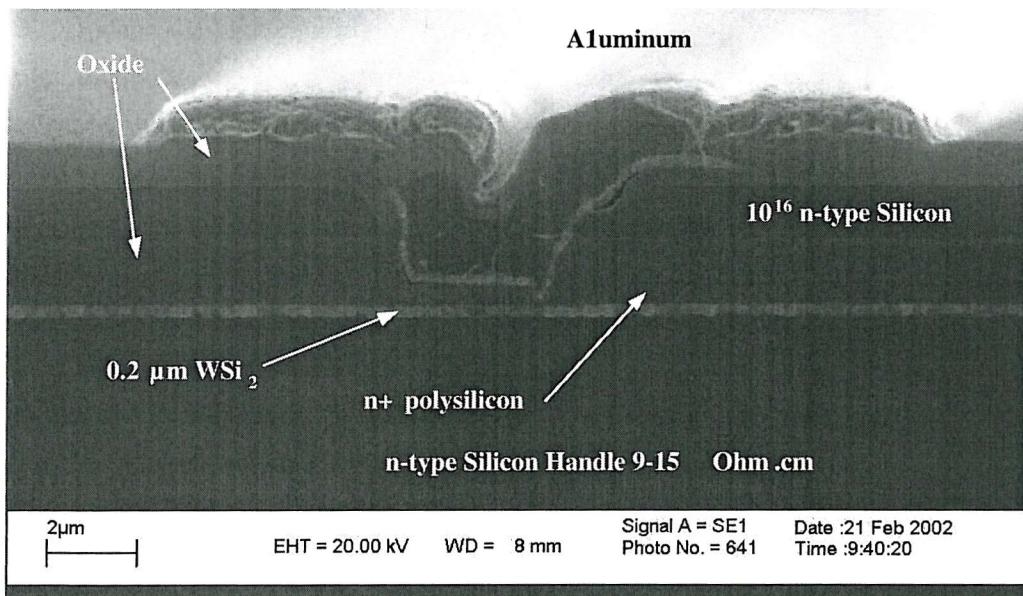

| 7.2  | SEM image of a fabricated GPSOI substrate showing in detail the different layers. The surface of the active layer has been oxidised. . . . .                                                                                                                | 92 |

|      |                                                                                                                                                                                                                                         |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

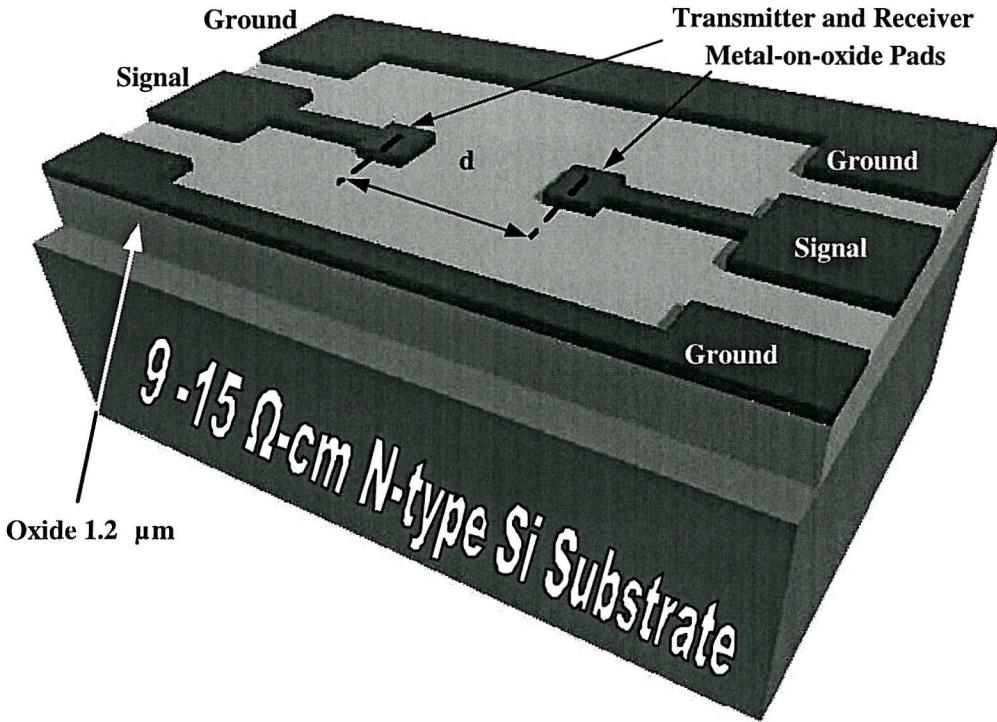

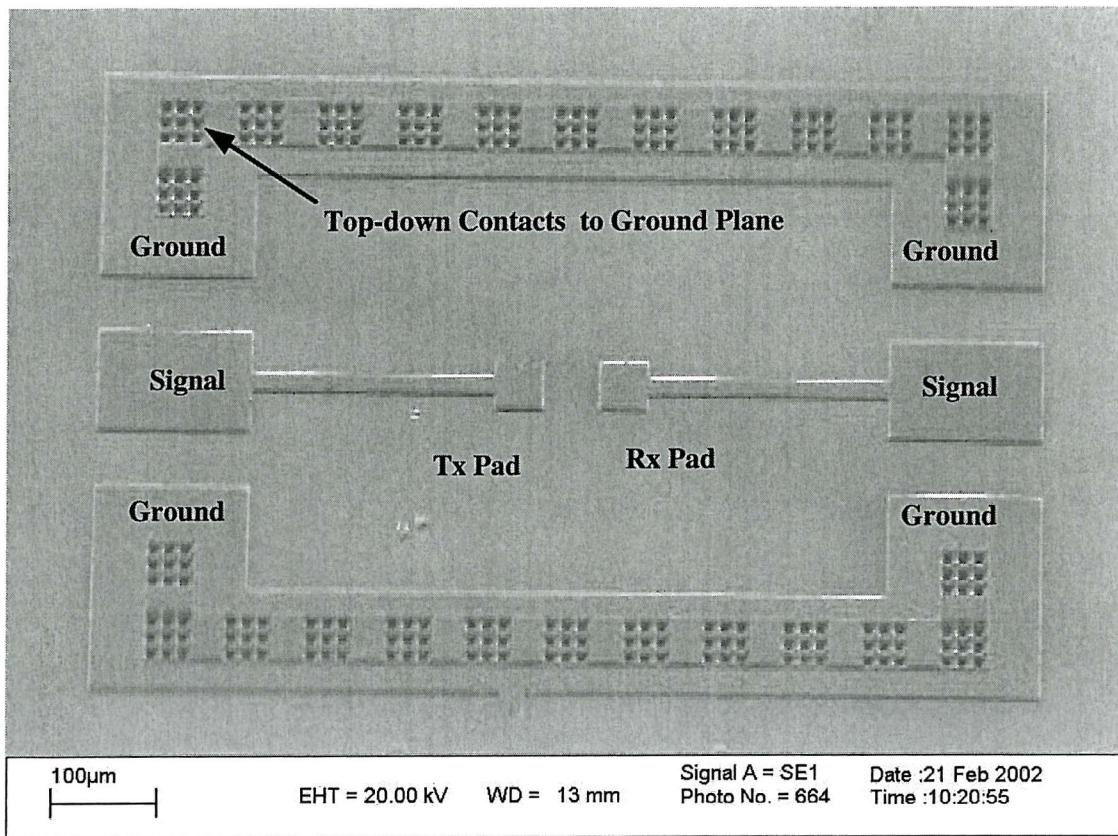

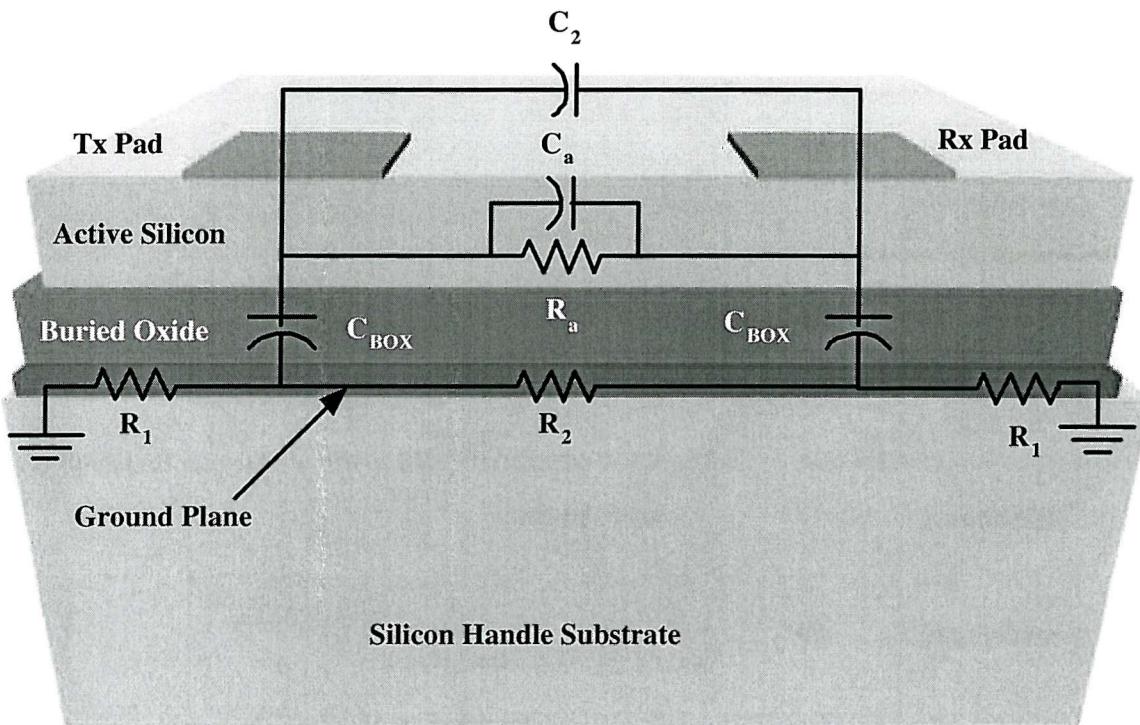

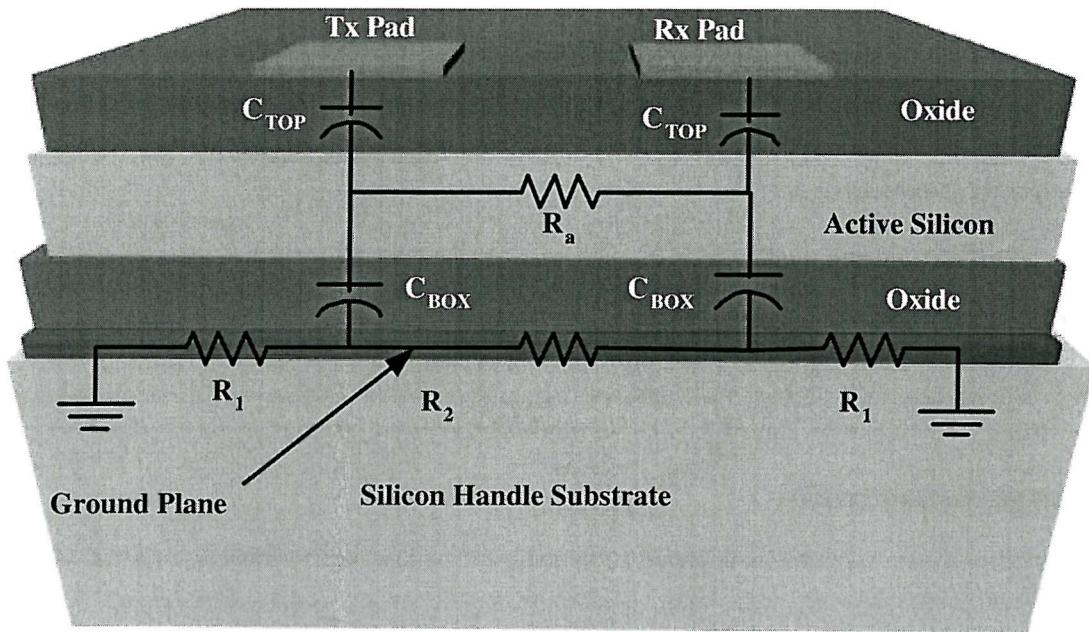

| 7.3  | Cross-sectional illustration of a crosstalk test structure on GPSOI. The Tx/Rx may be diode or metal-on-oxide pads. . . . .                                                                                                             | 93  |

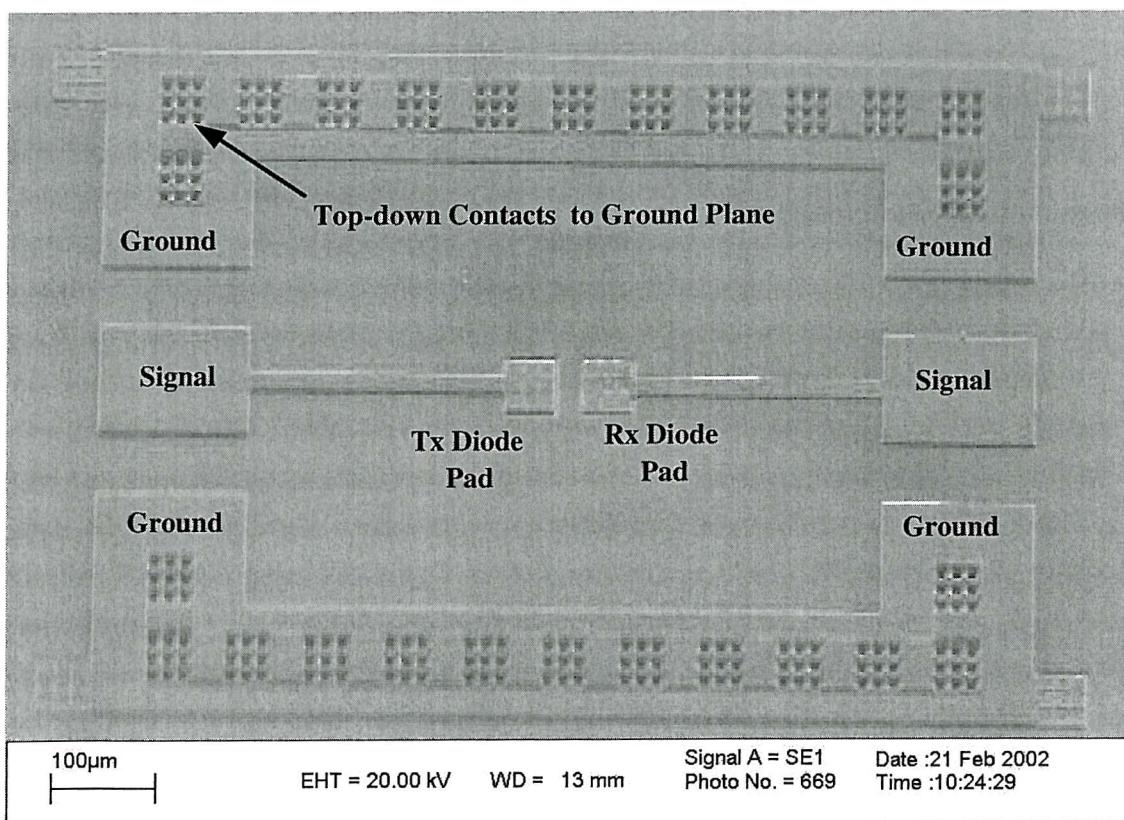

| 7.4  | SEM images of the fabricated test structures with (a) metal-on-oxide and (b) diode Tx/Rx pads. . . . .                                                                                                                                  | 94  |

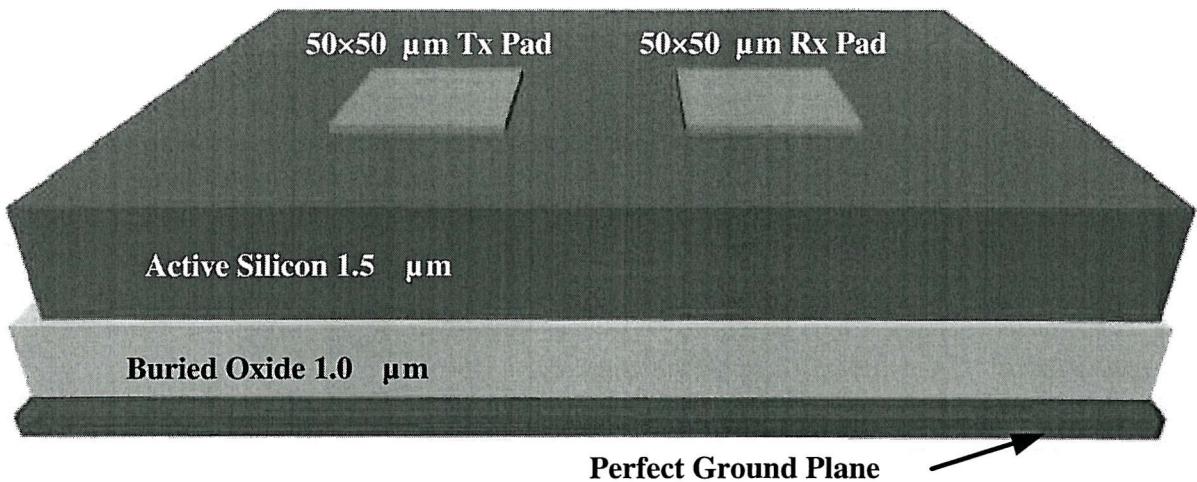

| 7.5  | Simplified GPSOI substrate structure simulated with EM-Sight. . .                                                                                                                                                                       | 95  |

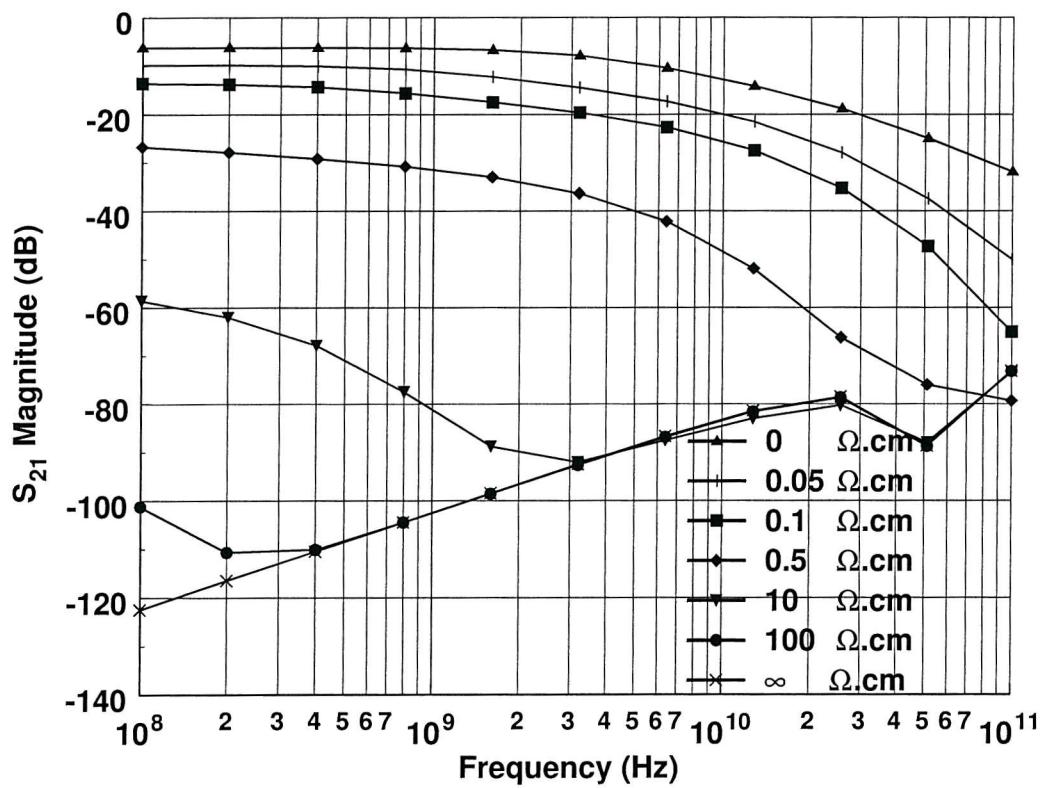

| 7.6  | Magnitude of $s_{21}$ versus frequency simulations of the substrate shown in Figure 7.5 with variable active layer resistivity. . . . .                                                                                                 | 95  |

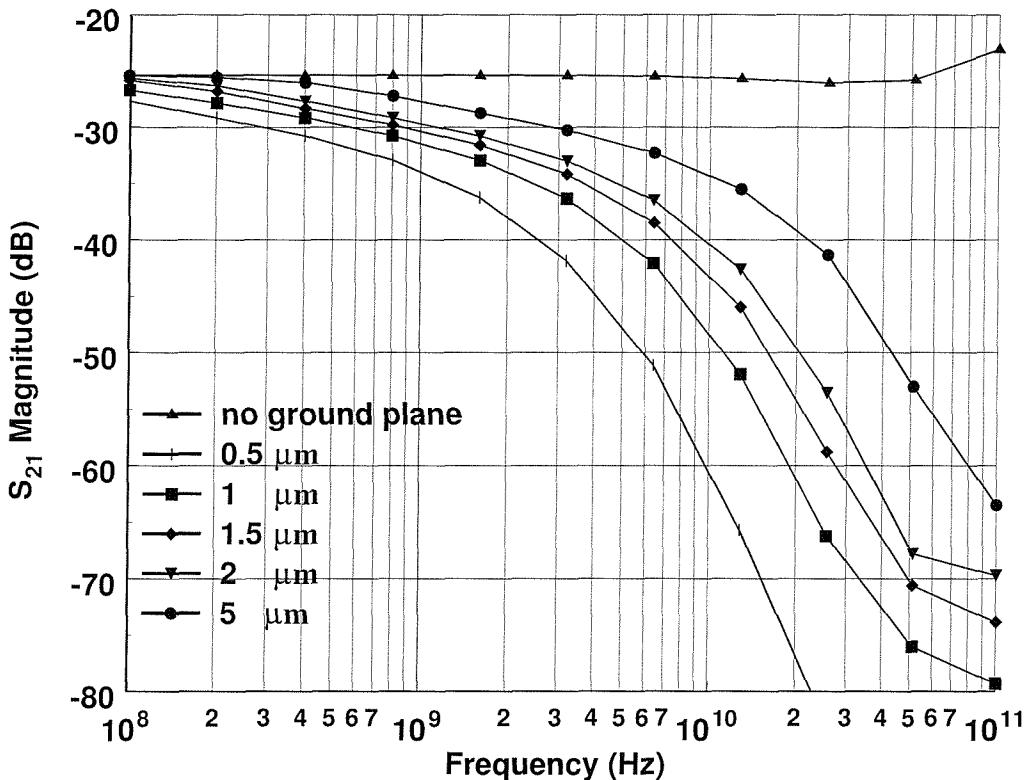

| 7.7  | Magnitude of $s_{21}$ versus frequency simulations of the substrate shown in Figure 7.5 with variable buried oxide layer thickness. . . . .                                                                                             | 96  |

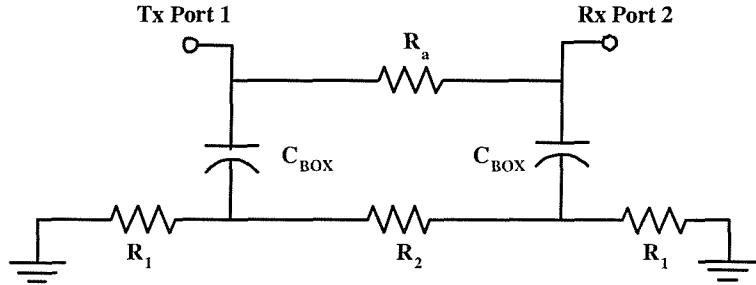

| 7.8  | The GPSOI substrate crosstalk model before its simplification. . . .                                                                                                                                                                    | 97  |

| 7.9  | A simplified compact lumped element GPSOI crosstalk model. . . .                                                                                                                                                                        | 98  |

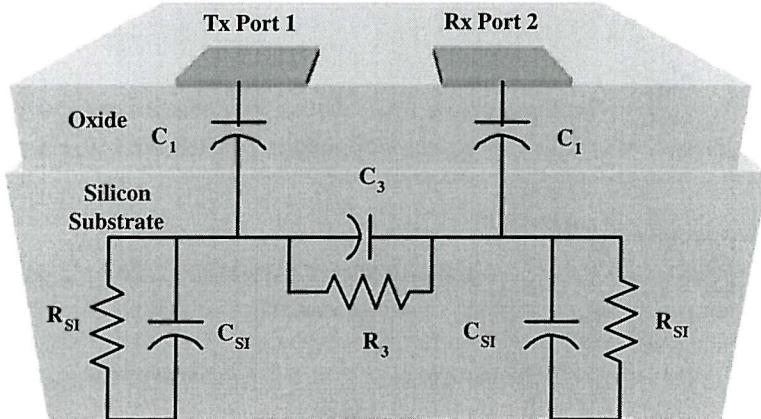

| 7.10 | Lumped element crosstalk model of two metal-on-oxide pads fabricated on the GPSOI substrate. . . . .                                                                                                                                    | 99  |

| 7.11 | Lumped element crosstalk model of two diode Tx/Rx pads fabricated on the GPSOI substrate. . . . .                                                                                                                                       | 99  |

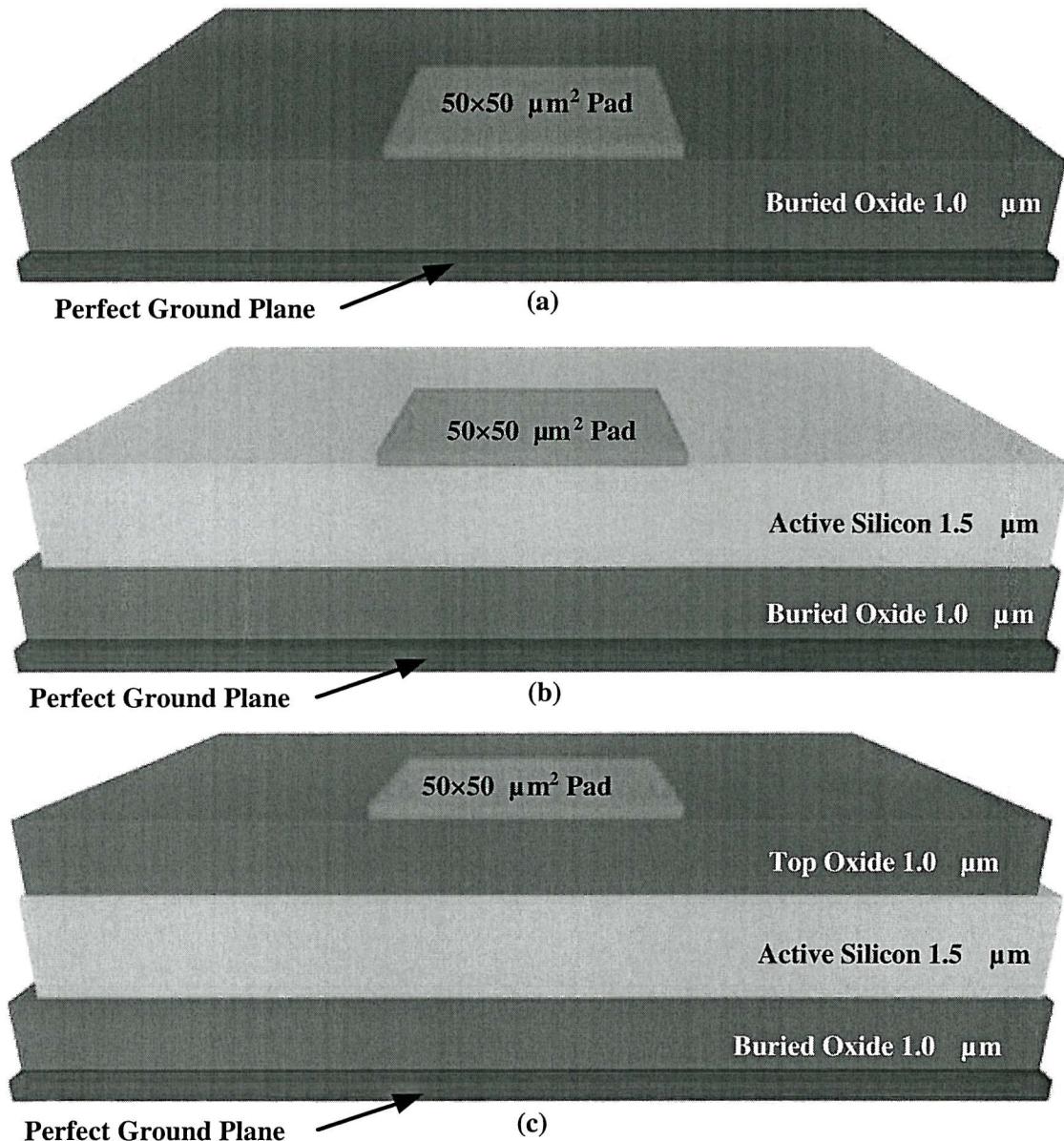

| 7.12 | $50 \times 50 \mu\text{m}^2$ pad on: (a) $1.0 \mu\text{m}$ of oxide (b) $1.5 \mu\text{m}$ silicon on oxide $1.0 \mu\text{m}$ (c) on $1.0 \mu\text{m}$ of oxide on GPSOI. A ground plane exists at the bottom of each structure. . . . . | 100 |

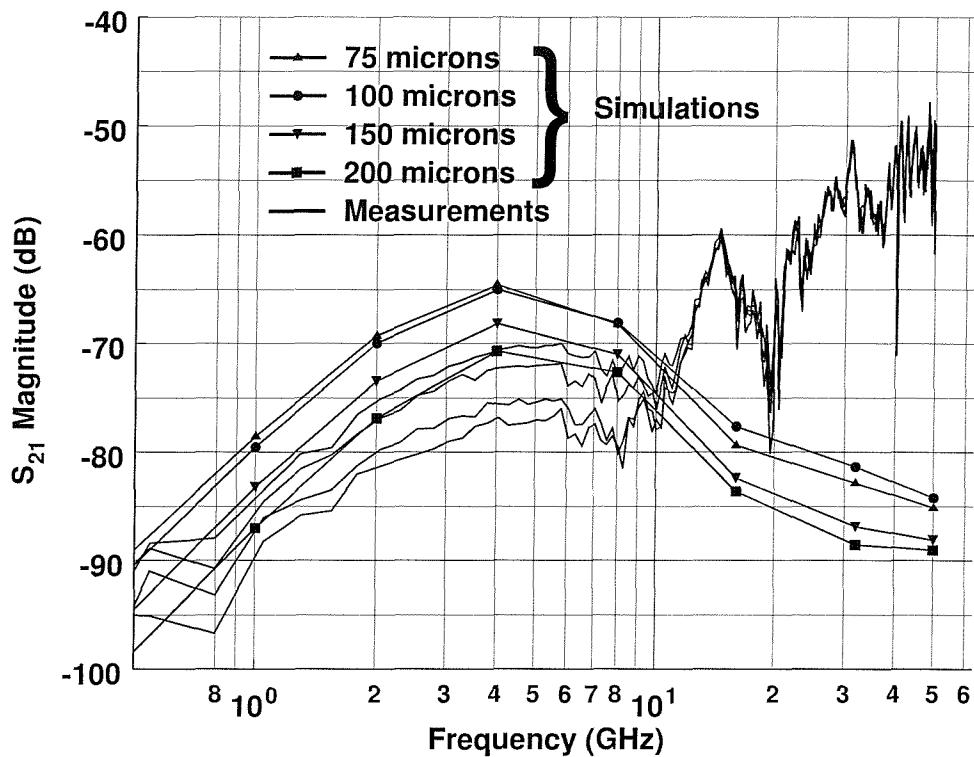

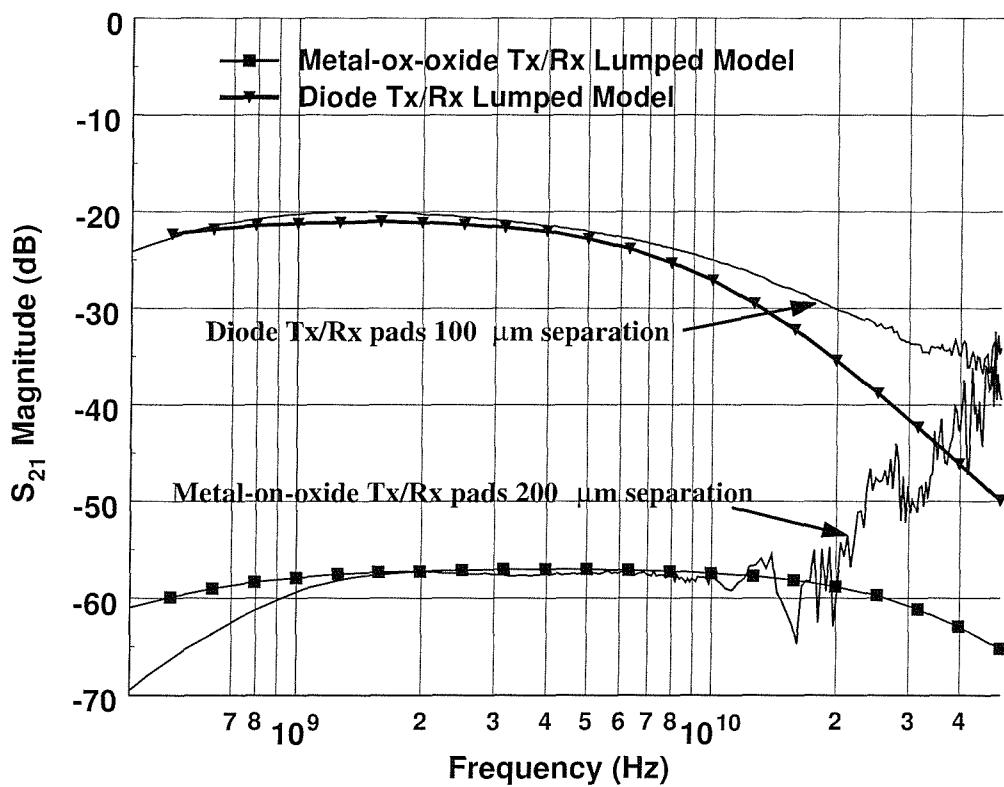

| 7.13 | De-embedded measurements from test structures on GPSOI with diode Tx/Rx pads separated by 75, 100, 150 and 200 $\mu\text{m}$ . . . . .                                                                                                  | 103 |

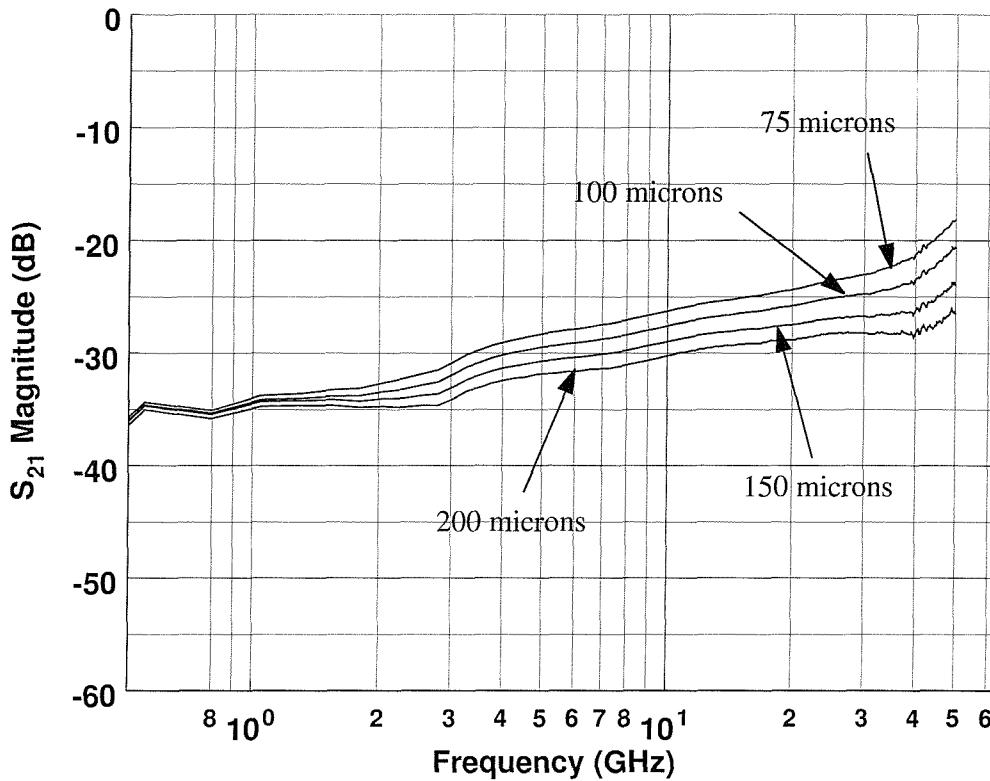

| 7.14 | De-embedded measurements from test structures on GPSOI with metal-on-oxide Tx/Rx pads separated by 75, 100, 150 and 200 $\mu\text{m}$ . . . . .                                                                                         | 103 |

| 7.15 | Equivalent GPSOI substrate crosstalk model, applicable to both diode and metal-on-oxide Tx/Rx pads. . . . .                                                                                                                             | 104 |

| 7.16 | Model validation for two GPSOI test structures with $100 \mu\text{m}$ diode Tx/Rx pad separation and $200 \mu\text{m}$ metal-on-oxide Tx/Rx pad separation. . . . .                                                                     | 104 |

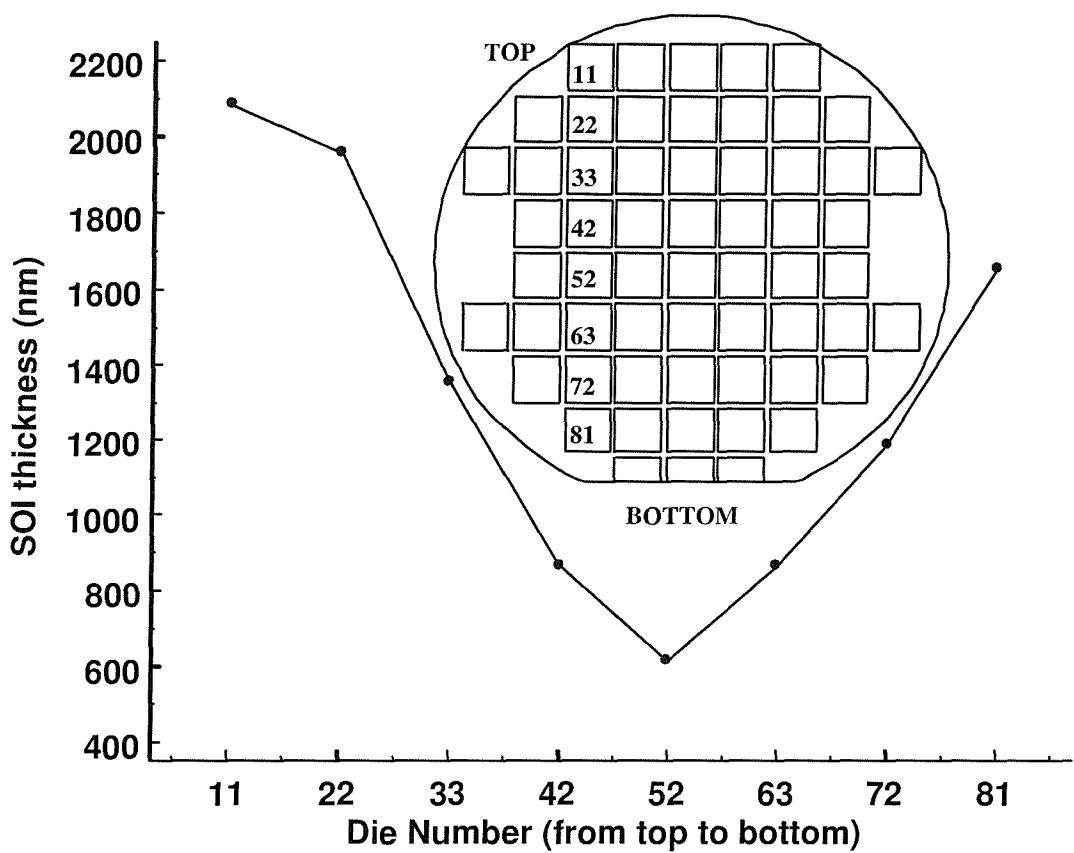

| 7.17 | Active layer thickness variation on a GPSOI wafer. . . . .                                                                                                                                                                              | 106 |

| 7.18 | Measurements of signal isolation between two diode Tx/Rx pads on a GPSOI substrate with $0.62 \mu\text{m}$ of active silicon. The junction depth is $0.5 \mu\text{m}$ . . . . .                                                         | 106 |

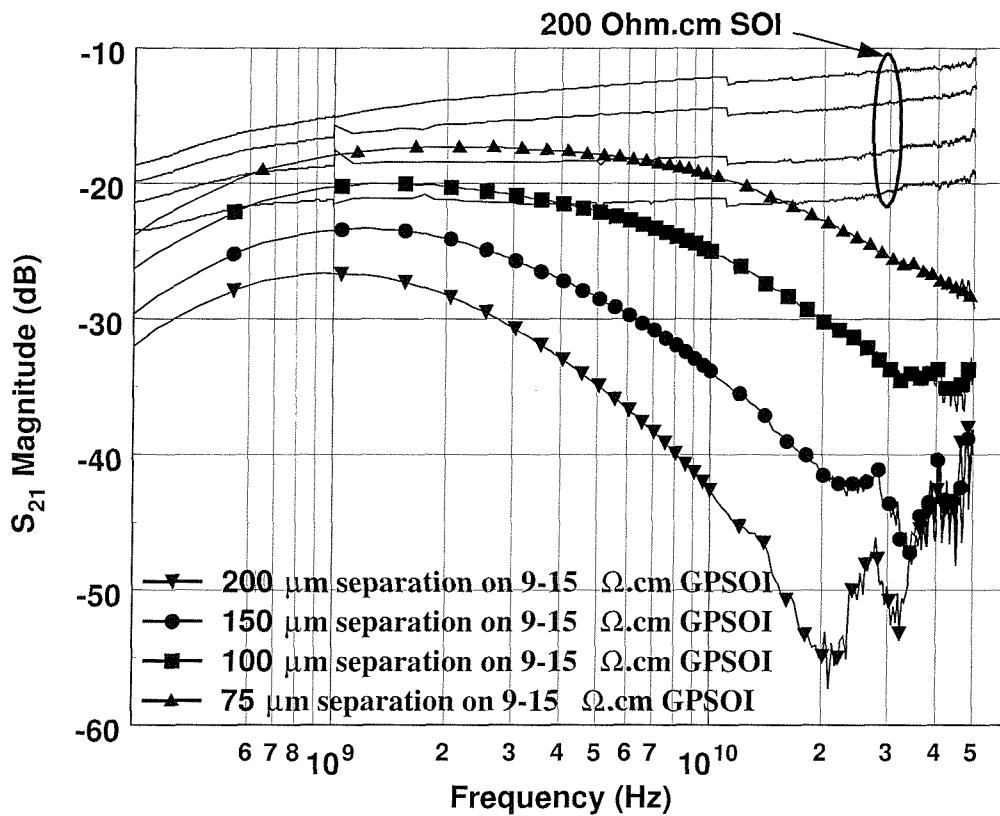

| 7.19 | Comparison of signal isolation between diode Tx/Rx pads in higher resistivity ( $200 \Omega\cdot\text{cm}$ ) SOI and standard ( $9-15 \Omega\cdot\text{cm}$ ) GPSOI substrates for different separations. . . . .                       | 107 |

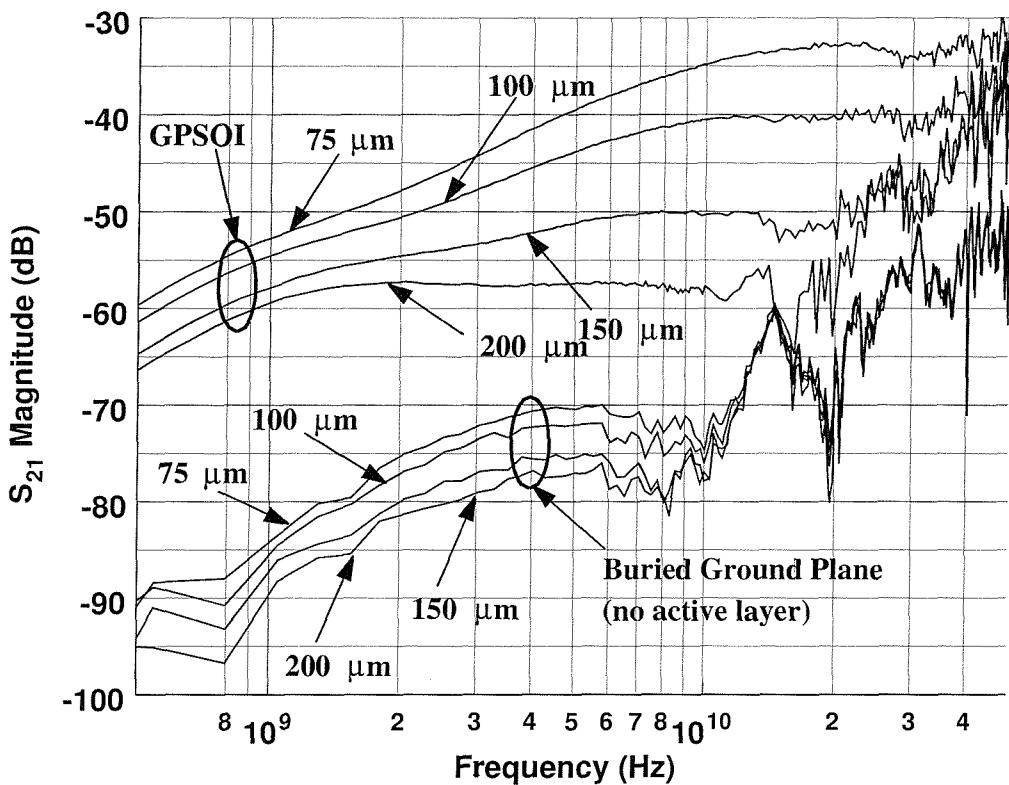

| 7.20 | Comparison of signal isolation between metal-on-oxide Tx/Rx pads standard ( $9-15 \Omega\cdot\text{cm}$ ) GPSOI and buried ground plane substrate (without an active layer) for different separations. . . . .                          | 108 |

|      |                                                                                                                                                                                                                                                                    |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

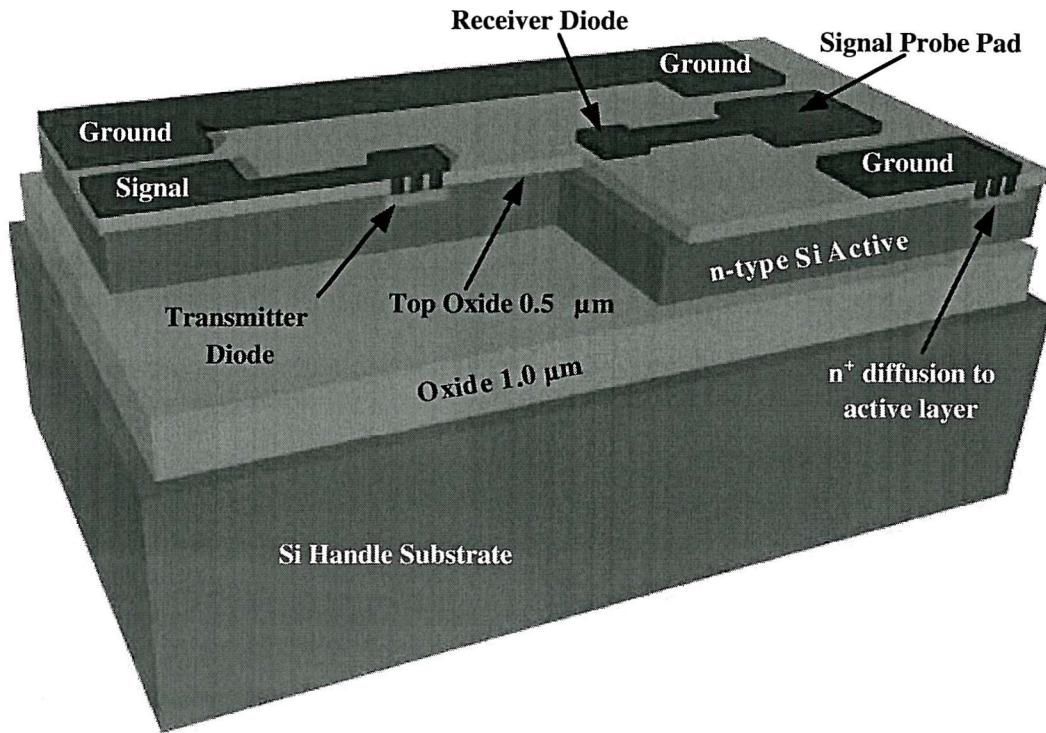

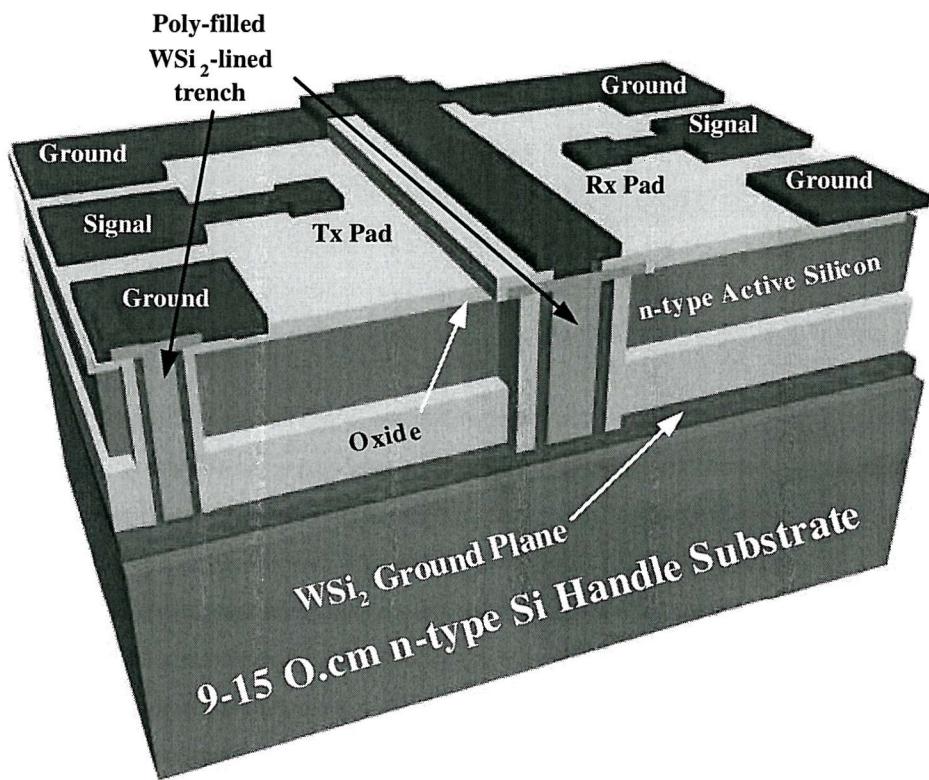

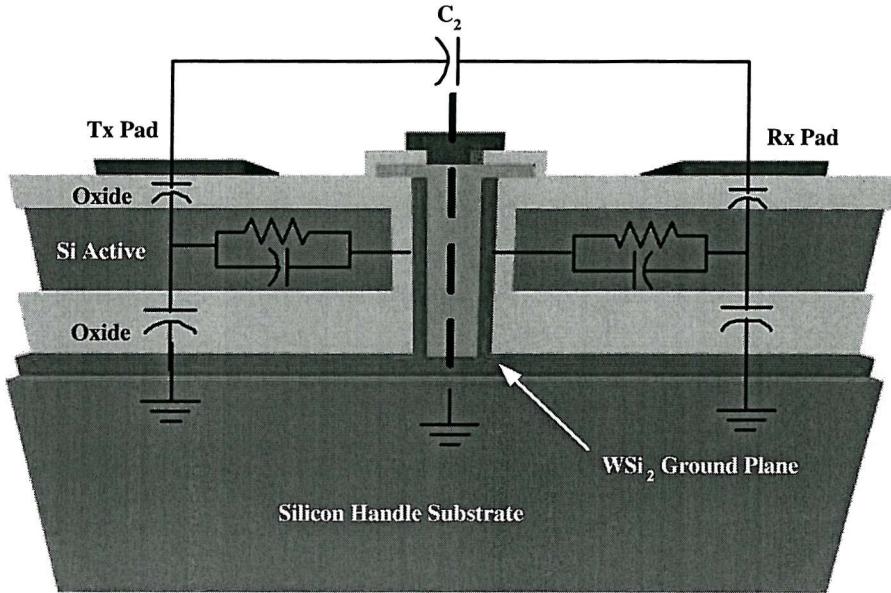

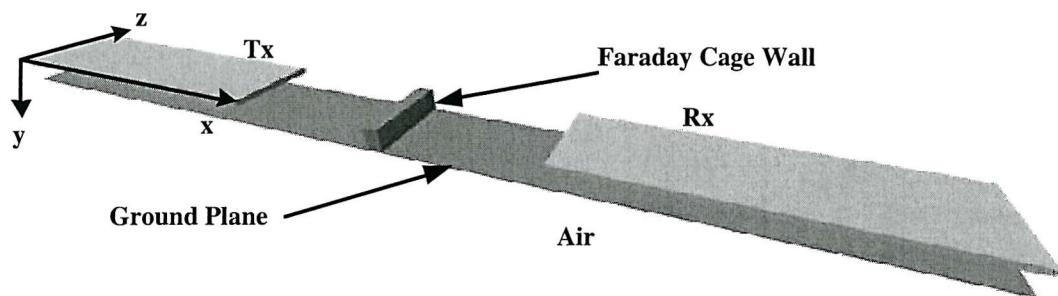

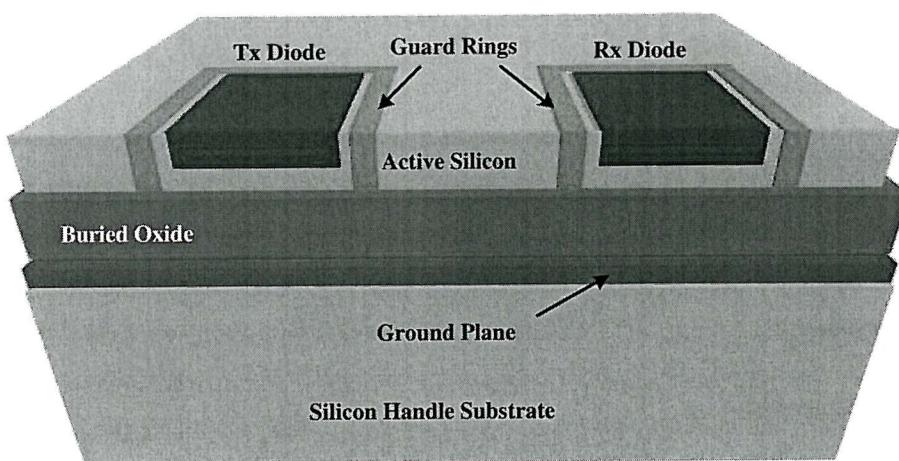

| 8.1  | Three-dimensional illustration of a Faraday cage structure realised on a GPSOI substrate . . . . .                                                                                                                                                                 | 111 |

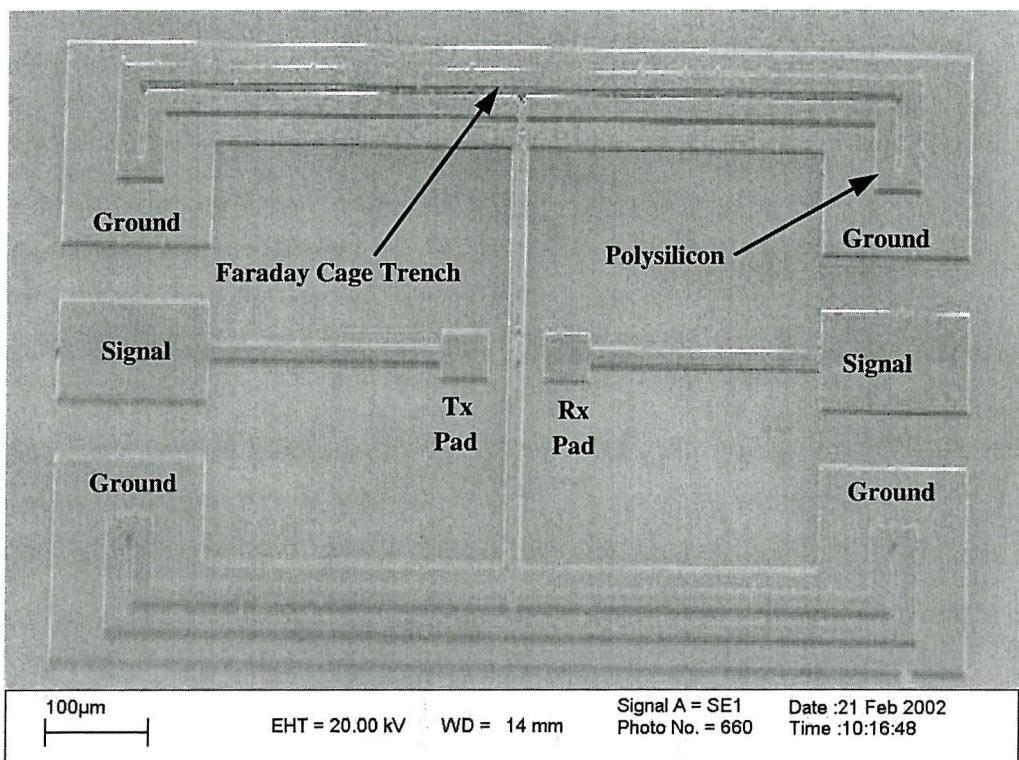

| 8.2  | SEM plan view of a Faraday cage structure with metal-on-oxide Tx/Rx pads. . . . .                                                                                                                                                                                  | 112 |

| 8.3  | Cross-sectional SEM image of a Faraday cage trench. . . . .                                                                                                                                                                                                        | 112 |

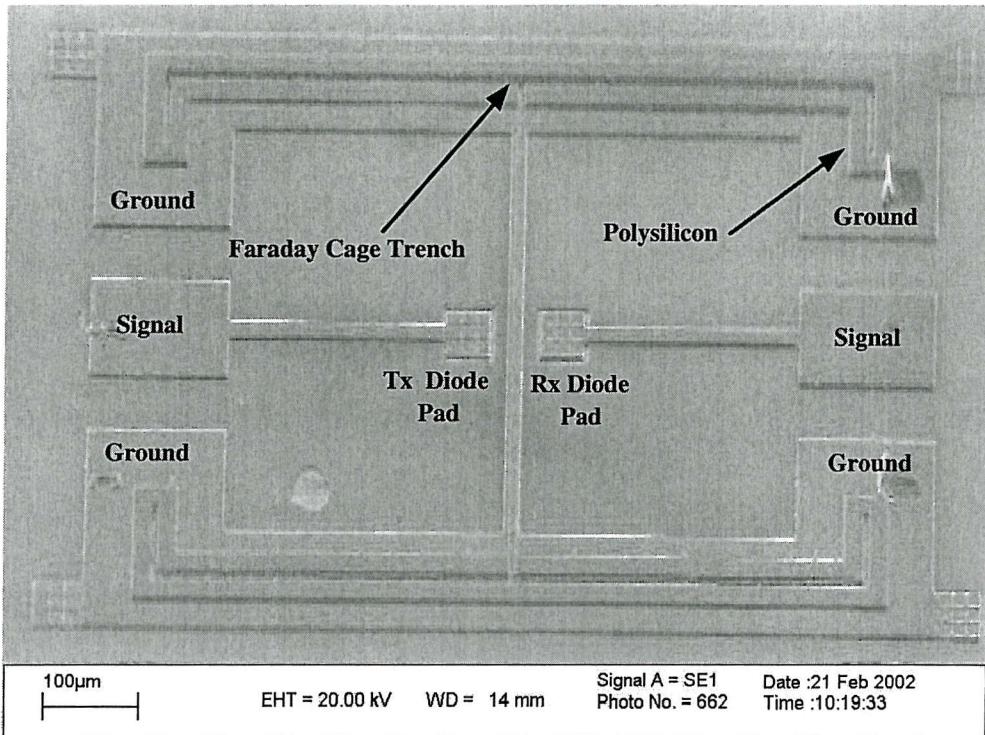

| 8.4  | Plan SEM image of a Faraday cage test structure with diode Tx/Rx pads. . . . .                                                                                                                                                                                     | 113 |

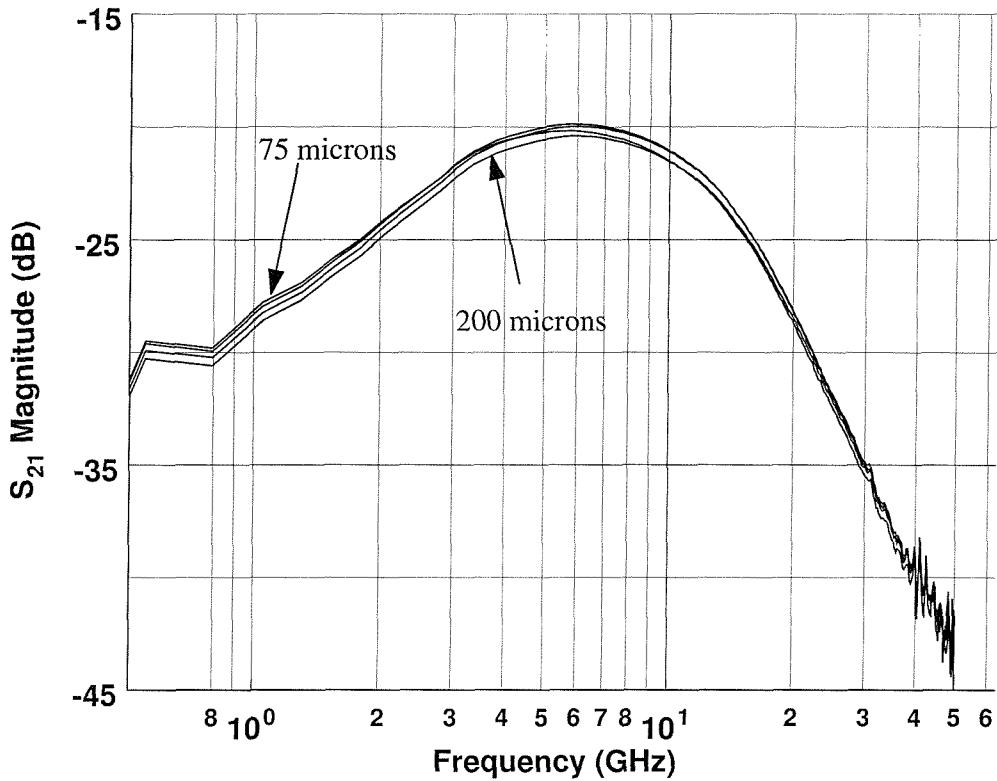

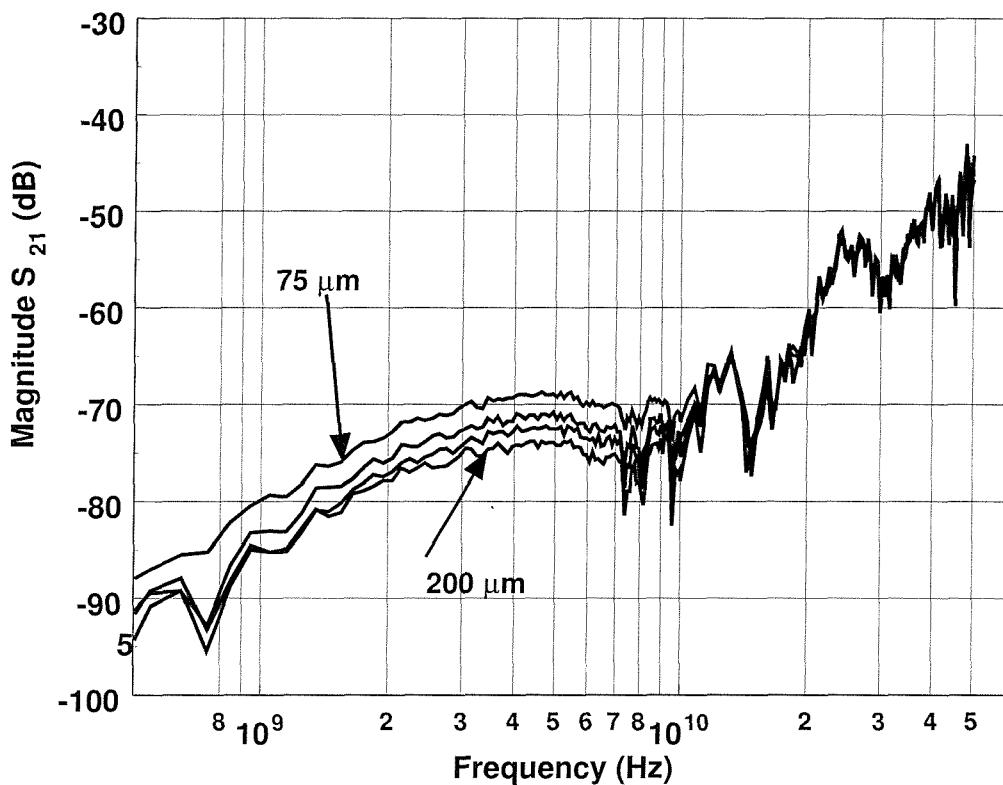

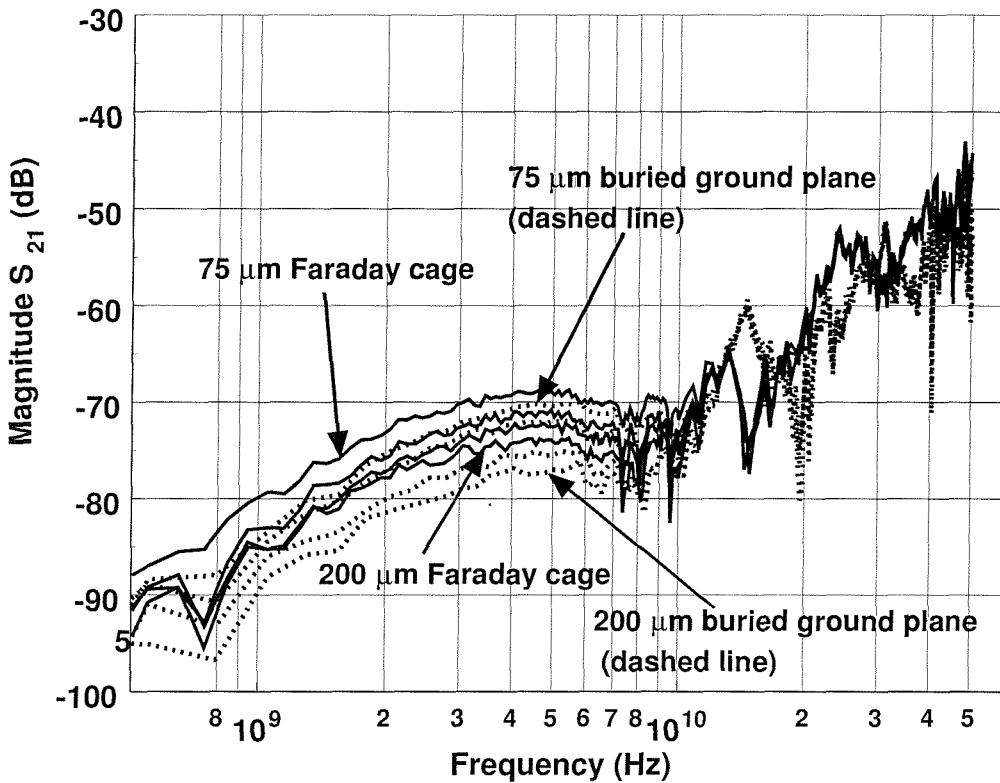

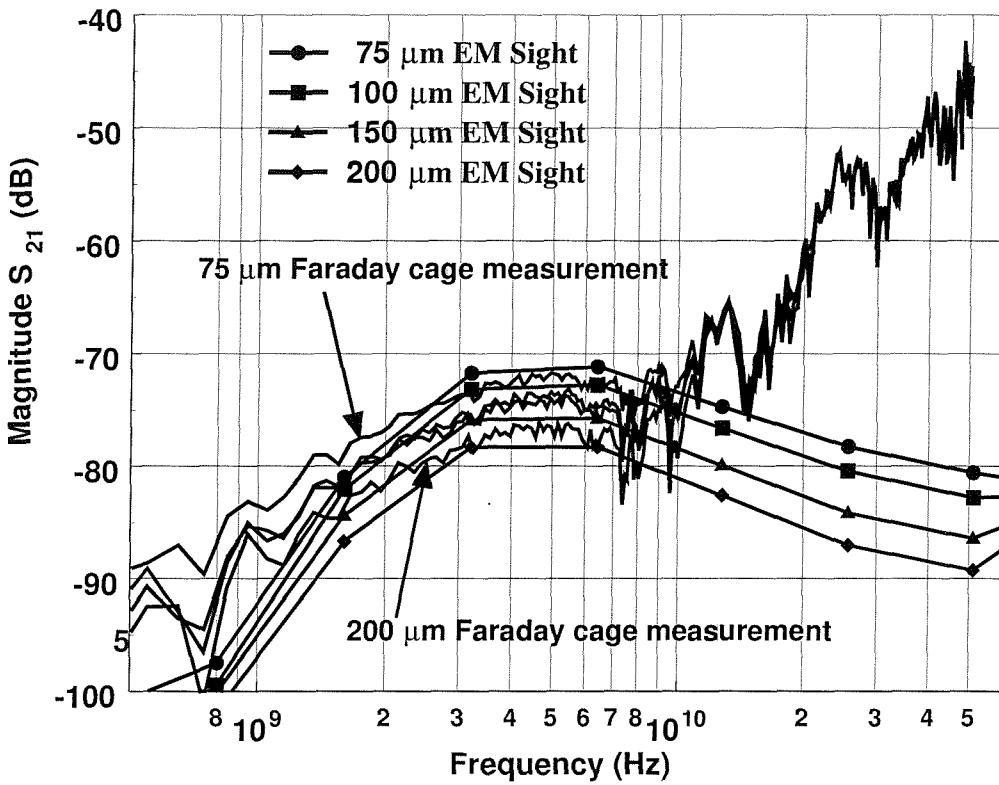

| 8.5  | Magnitude of $s_{21}$ measurements of Faraday cage test structures with diode Tx/Rx pads separated by 75, 100, 150 and 200 $\mu\text{m}$ . . . . .                                                                                                                 | 114 |

| 8.6  | Comparison of $s_{21}$ measurements between the Faraday cage test structures with diode Tx/Rx pads and the buried ground plane measurements of Chapters 3 and 4. . . . .                                                                                           | 115 |

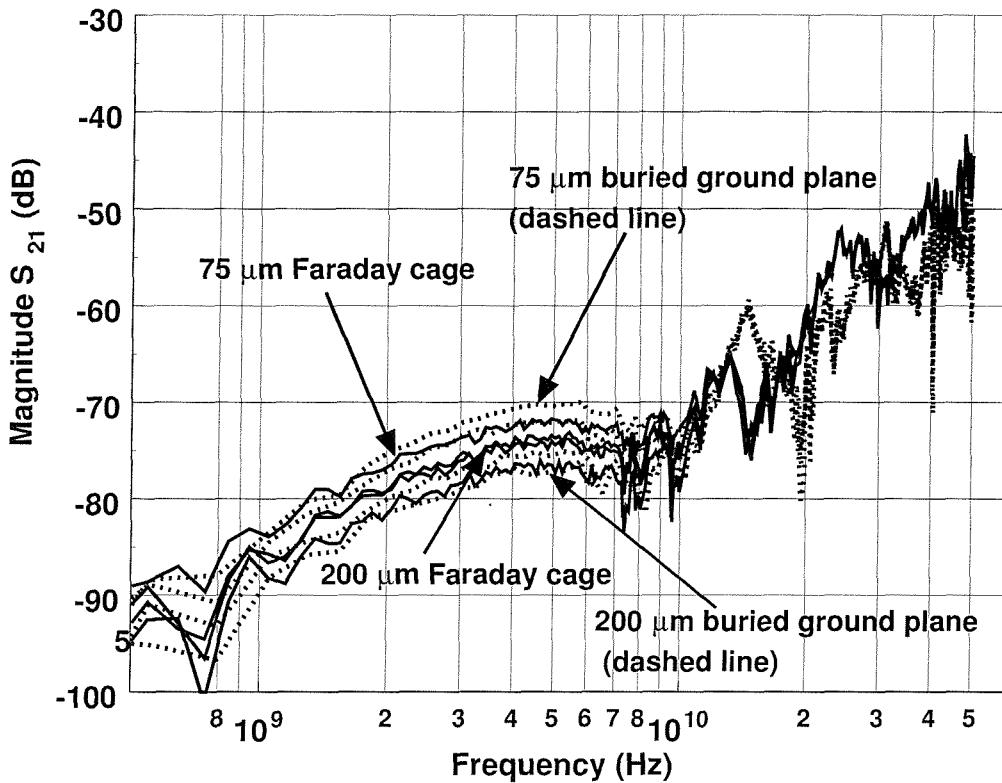

| 8.7  | Comparison of $s_{21}$ measurements between the Faraday cage test structures with metal on oxide Tx/Rx pads and the buried ground plane measurements of Chapters 3 and 4. . . . .                                                                                  | 116 |

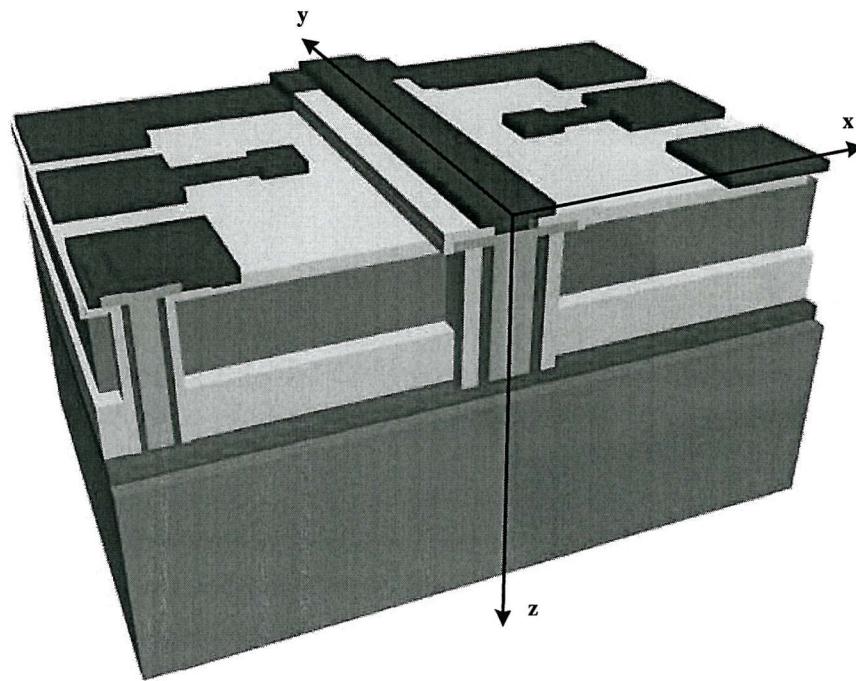

| 8.8  | Three-dimensional illustration of the Faraday cage structure showing the symmetry line, imposed by the trench, that reduces the equivalent lumped element model to a simpler $\pi$ -network. The resistances of the buried ground plane have been omitted. . . . . | 117 |

| 8.9  | Three-dimensional illustration of the Faraday cage structure with the x, y and z-axes as defined for use by the electromagnetic solvers. . .                                                                                                                       | 118 |

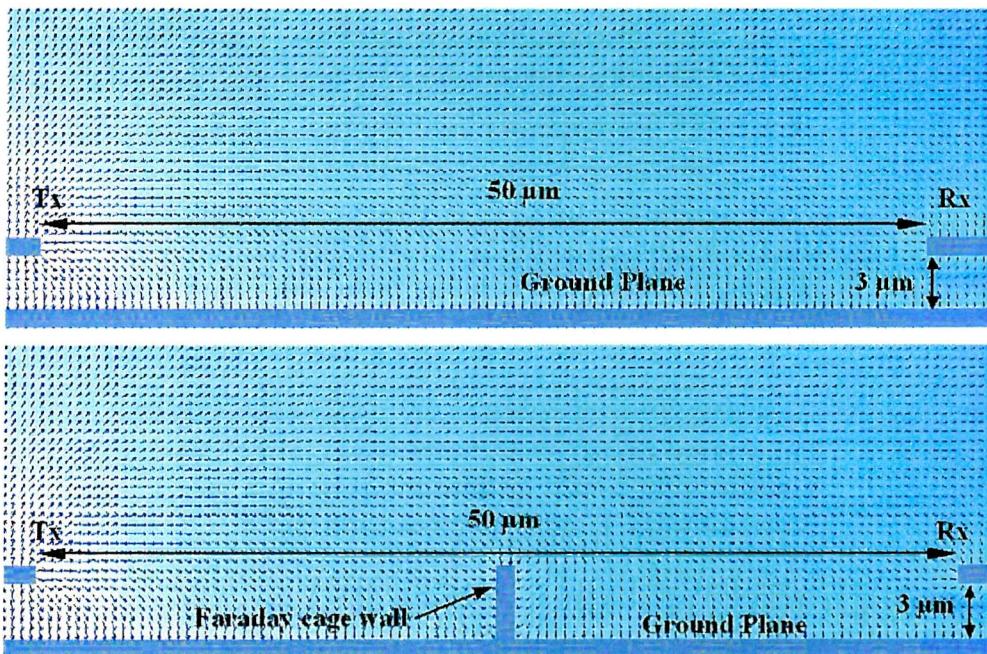

| 8.10 | Graphical illustration of a strip line structure that along the x and y axes emulates the air coupling of the Faraday cage structures. . . .                                                                                                                       | 118 |

| 8.11 | EM simulations of two strip lines in air emulating the electric field lines between Tx and Rx pads based on the structure of Figure 8.10, with and without the Faraday cage strip. . . . .                                                                         | 119 |

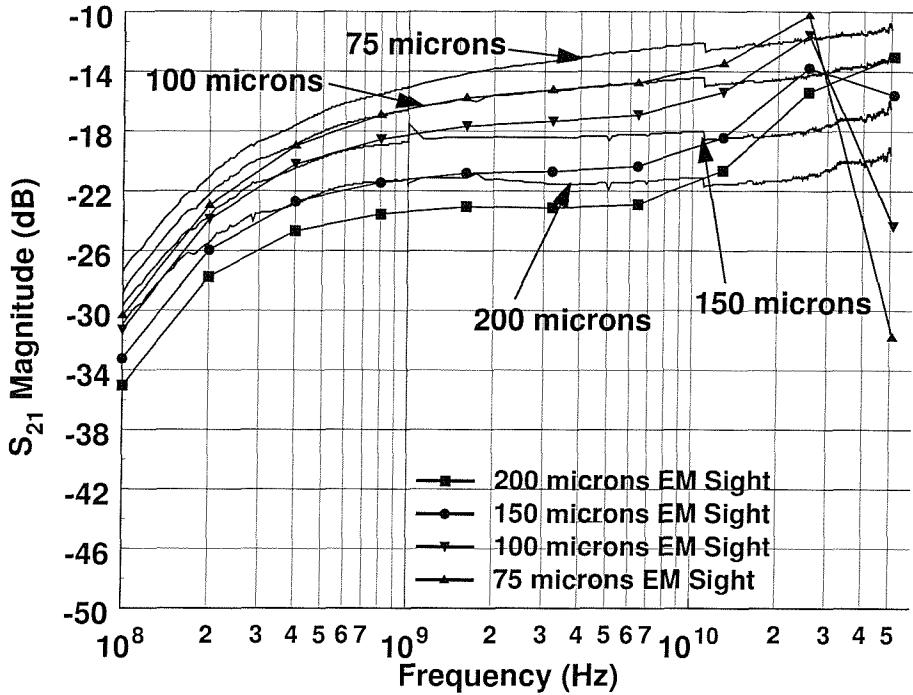

| 8.12 | Electromagnetic simulations of the Faraday cage structures with metal-on-oxide Tx/Rx pads with EM Sight and comparison with measurements for different Tx/Rx separations. . . . .                                                                                  | 120 |

| 8.13 | Comparison of measurements of Faraday cage test structures with the SOI and GPSOI test structures of chapters 6 and 7 for different Tx/Rx separations. . . . .                                                                                                     | 121 |

| 8.14 | Comparison of the Faraday cage with other technologies, including high resistivity thin film SOI [1] and a Faraday cage structure by Wu et. al [4]. The Tx/Rx pad separation is 100 $\mu\text{m}$ . . . . .                                                        | 122 |

| 8.15 | Cross-sectional illustration of a structure with diode Tx/Rx pads surrounded by guard rings, which are deep enough to make contact to the buried oxide of the GPSOI. . . . .                                                                                       | 122 |

# List of Tables

|     |                                                                                                                                                                                                                                       |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Maxwell's Electromagnetic Equations . . . . .                                                                                                                                                                                         | 11  |

| 4.1 | Substrate definition used for the electromagnetic simulations with ADS Momentum and <i>EM-Sight</i> . . . . .                                                                                                                         | 26  |

| 4.2 | Lumped element model parameters of the simplified grounded GP-SOI model as described in Figure 4.8 . . . . .                                                                                                                          | 31  |

| 4.3 | Comparison of analytically derived crosstalk capacitance $C_2$ values with those extracted from the numerical optimiser. . . . .                                                                                                      | 40  |

| 5.1 | Comparison of extracted (from measurements) and analytical (from equations (4.6) to (4.20)) model parameters for coupled microstrip lines of different spacing $S$ , on 1.0 $\mu\text{m}$ of oxide and aluminum ground plane. . . . . | 57  |

| 6.1 | Theoretical parameters of a high resistivity SOI substrate crosstalk model for different Tx/Rx pad separations. . . . .                                                                                                               | 85  |

| 6.2 | Optimised $R_a$ and $C_J$ of a high resistivity SOI substrate crosstalk model for 100 $\mu\text{m}$ Tx/Rx pad separation. . . . .                                                                                                     | 85  |

| 7.1 | Extracted and calculated value of the buried oxide capacitance for a buried ground plane substrate without a silicon active layer. . . . .                                                                                            | 101 |

| 7.2 | Extracted and calculated values of the buried oxide capacitance for a buried ground plane substrate with a silicon active layer and top oxidation. . . . .                                                                            | 102 |

| 7.3 | Crosstalk model parameters of two diodes and metal-on-oxide Tx/Rx pads separated by 100 and 200 $\mu\text{m}$ respectively. . . . .                                                                                                   | 105 |

| 9.1 | Summary of isolation performance of the substrates investigated in this work. . . . .                                                                                                                                                 | 129 |

# Acknowledgements

I would like to thank my supervisor, Professor John S. Hamel for his support and for offering me the opportunity to pursue my research on such an interesting topic. I am also grateful to my co-supervisors, Professor Henri A. Kemhadjian and Dr. Michael Kraft for their support and encouragement during the second half of my PhD studies.

I would also like to thank Professor Harry S. Gamble of the Northern Ireland Semiconductor Research Centre (NIRC) and the Department of Electrical and Electronic Engineering of the Queen's University of Belfast for assisting with the fabrication of the SOI substrates presented in this thesis.

Many thanks to the clean room staff and especially A. Blackburn, J. Humphry and Mike Josey for their guidance on fabrication issues and G. Leach for his advise and help with the HPADS software and the high frequency measurement equipment. Many thanks also to Dr Andrew Waite and Khairil Osman for their help in the clean room with the SEM.

The Department of Electronics and Computer Science must be thanked for providing the necessary financial support and my colleagues within the Microelectronics Group for having to put up with me for three years.

Last, but certainly not least, I would like to thank and dedicate this work to my parents and my brother. Their love and support helped me through the most difficult of times during the past three years.

Stefanos Stefanou

*To my parents,

Niko and Anastasia

Στούς γονείς μου,

Νίκο και Αναστασία*

# List of Symbols

|              |                                             |

|--------------|---------------------------------------------|

| $C$          | capacitance                                 |

| $C_a$        | active layer capacitance                    |

| $C_{BOX}$    | buried oxide capacitance                    |

| $C_e$        | even mode capacitance                       |

| $C_J$        | junction capacitance                        |

| $C_o$        | odd mode capacitance                        |

| $C_{OX}$     | oxide capacitance                           |

| $C_{SUB}$    | handle substrate capacitance                |

| $\epsilon_0$ | permittivity of free space                  |

| $\epsilon_r$ | relative permittivity                       |

| $f$          | frequency                                   |

| $f_c$        | cutoff frequency                            |

| $G$          | conductivity                                |

| $H$          | substrate thickness                         |

| $K(k_1)$     | complete elliptic integral                  |

| $\rho$       | resistivity                                 |

| $R$          | resistance                                  |

| $R_a$        | active layer resistance                     |

| $R_{SUB}$    | handle substrate resistance                 |

| $R_0$        | $50 \Omega$ source and load                 |

| $S$          | spacing                                     |

| $s_{21}$     | forward transmission scattering coefficient |

| $\omega$     | angular frequency ( $2 \cdot \pi \cdot f$ ) |

| $W$          | width                                       |

| $y$          | admittance parameters                       |

# Acronyms

|        |                                                     |

|--------|-----------------------------------------------------|

| ACP    | Air CoPlanar                                        |

| BiCMOS | Bipolar Complementary Metal Oxide Semiconductor     |

| CAD    | Computer Aided Design                               |

| CMOS   | Complementary Metal Oxide Semiconductor             |

| CPW    | CoPlanar Waveguide                                  |

| DUT    | Device Under Test                                   |

| EM     | ElectroMagnetic                                     |

| FET    | Field Effect Transistor                             |

| GP     | Ground Plane                                        |

| GPSOI  | Ground Plane Silicon On Insulator                   |

| GSG    | Ground Signal Ground                                |

| IC     | Integrated Circuit                                  |

| ITRS   | International Technology Roadmap for Semiconductors |

| LPCVD  | Low Pressure Chemical Vapour Deposition             |

| LRRM   | Load-Reflect-Reflect-Match                          |

| MCM    | Multi-Chip Module                                   |

| MOS    | Metal Oxide Semiconductor                           |

| PECVD  | Plasma Enhanced Chemical Vapour Deposition          |

| RF     | Radio Frequency                                     |

| Rx     | Receiver                                            |

| SEM    | Scanning Electron Microscope                        |

| SOA    | Silicon-On-Anything                                 |

| SoC    | System on Chip                                      |

| SOI    | Silicon-On-Insulator                                |

| SOS    | Silicon-On-Sapphire                                 |

| SSOI   | Silicide Silicon-On-Insulator                       |

| TEOS   | TetraEthOxySilane                                   |

| Tx     | Transmitter                                         |

# Chapter 1

## Introduction

The continuous trend towards miniaturisation and the increase of the operating speed of Integrated Circuits (IC's) has nowadays made the influence of on chip parasitics very important. The interaction between several parts of an IC or its packaging, referred as crosstalk or noise coupling, has been the subject of research for many years, since it represents a limiting factor in IC technology especially at very high operating frequencies. Higher levels of integration deteriorate the problem, which appears in its worst form in radio frequency (RF), microwave mixed signal ICs, including switched capacitor filters and A/D and D/A converters.

Noise coupling within an IC occurs through the common substrate and through the capacitances of interconnect lines. The common substrate acts as a collector, integrator and distributor of coupled noise. The analogue part of a mixed signal IC suffers the most from substrate crosstalk. The digital part is characterised by strong and sudden signal switching which has as an immediate effect the injection of significant levels of noise into the substrate. Sensitive analogue circuitry lying on the same substrate is affected significantly by the transmitted noise. The performance degradation can be so severe, it can lead to physical separation of the digital and analogue parts in different chips. Although hybrid multi-chip modules (MCM) may be adequate they are limited by inter-chip interconnect parasitics. Single chip implementations, however, are often the smallest, lower cost and lowest power solutions. Hence, substrate crosstalk is a fundamental limitation of today's mixed signal IC design and fabrication.

It must be noted that apart from the analogue part, high speed sequential circuits sharing a common substrate can be affected by noise coupling transients. Aragones et. al. [5] have demonstrated how noise transients can cause permanent errors on a RAM cell during read and write cycles.

Crosstalk reduction techniques can be categorized as follows: (a) those that minimize the strength of the noise source, and (b) those that reduce the noise coupling. The first approach requires fundamental changes in the design methodologies and incorporation of additional circuitry to compensate for the substrate losses. Liu et. al. [6] have proposed an active technique based on negative feedback. Coupling minimisation has been addressed by introducing new structures such as capacitive guard rings [1], [7], [8], [9], [10], [11], [12] that surround the sensitive devices and break the coupling path of the substrate. More sophisticated substrates, compared to bulk, can also provide increased isolation. Several studies have been performed on SOI substrates and it has been shown that they offer superior isolation performance at least for frequencies up to 1 GHz [1]. Higher frequencies of operation for RF IC's dictate the use of high resistivity substrates as preferred substrate for mixed signal integration. Raskin et. al. [1] have shown the efficiency of the latter in conjunction with the use of guard rings. High resistivity SOI substrates present, however, a more expensive solution compared to substrates used in mainstream CMOS processes. Bulk CMOS substrates usually have a resistivity at least ten times lower than that of high resistivity substrates.

Besides measuring the absolute isolation level of different substrates structures, it is vital that a deeper understanding of the dynamics and physics involved in substrate coupling is acquired. The effect of parameters such as the separation distance of the noise source from the sensor and the effect of different dielectrics has to be known, in order to be able to predict the behaviour of such substrates under operating conditions. Such research can be accomplished with the help of Computer Aided Design (CAD) Tools and particularly numerical simulators.

A great deal of research on numerical methods that attempt to accurately evaluate and model substrate parasitics has been done over the past few years [13], [14], [6]. The disadvantages, however, of these methods are the long simulation times and the large requirements of computer resources. Simpler lumped element models are needed that can accurately capture the behaviour of substrate parasitics and that can simultaneously be used in circuit simulators, such as SPICE. These models ideally have to be scalable and valid over a wide frequency range [1]-[15].

This work investigates the isolation performance of SOI substrates with buried ground planes. The ground plane SOI (GPSOI) substrate is effectively an SOI substrate with a thin buried metallic layer below the insulator. The buried metallic plane is called buried ground plane because it is connected to ground. The material is new and is manufactured as described in [16], [17], [18]. Substrate crosstalk studies for this material are performed for the first time and its noise suppression

performance is compared to different existing isolations schemes. The studies are concentrated on frequencies in the GHz range.

This thesis is organised as follows: Chapter 2 discusses different existing crosstalk reduction schemes studies. A detailed reference to all the schemes and their performance is included along with the advantages and disadvantages of each of them. A methodology of studying substrate coupling along with the figures of merit for isolation performance is explained in detail. Such methodology has been used for most high frequency crosstalk studies. Modelling issues are also discussed along with a description of the capabilities and the efficiency of the CAD tools used to model the specific substrate. Finally, lumped element models introduced so far in the literature are presented as a base for future use with the ground plane substrate.

Chapter 3 presents the test structures fabricated on the GPSOI substrate to evaluate its noise suppression performance. The choice of such structures is justified as part of the methodology mentioned in the previous chapter. Issues regarding the fabrication process are also presented along with a detailed description of the measurement technique. Such a discussion will provide insight into the problems that may appear when measuring low crosstalk structures at very high frequencies. Careful control of the measurement conditions is necessary to ensure high levels of repeatability and consistency over a number of measurements.

Electromagnetic and lumped element modelling of crosstalk in substrates with buried ground planes is presented and discussed in Chapter 4 with emphasis on the specific test structures presented in Chapter 3. Simulation results from two electromagnetic solvers verify the measurement results of the previous chapter. Lumped element equivalent circuits that are based on the theory of coupled microstrip lines and model the behaviour of the test structures are also presented and validated against simulation and measurement data. Chapter 5 presents experimental results of pseudo-ground plane test structures used to emulate the behaviour of the buried ground plane test structures of chapters 3 and 4. These test structures are realised using a two metal layer process, where the first metal acts as a buried ground plane. The effects of the buried oxide thickness and the resistivity of the ground plane are discussed not only for the conventional test structures already shown in previous chapters but also for long ( $500 \mu\text{m}$ ) microstrip lines. Measurement results and analysis of test structures with variable oxide thickness and ground planes of different materials (aluminium and titanium silicide) are included.

An analysis of crosstalk between two diodes realised on standard ( $9\text{-}15 \Omega\text{.cm}$ ) and high ( $200 \Omega\text{.cm}$ ) resistivity substrates is presented in Chapter 6. Electromagnetic simulations and microwave strip line theory are employed and equivalent circuits of

substrate crosstalk in similar test structures are developed. This chapter acts as a "bridge" between the analysis of a buried ground plane in a substrate and the SOI substrates of Chapter 6.

Having analysed separately the impact of a ground plane on crosstalk and the coupling between two devices on a SOI substrate, Chapter 7 presents a model of substrate crosstalk in GPSOI substrates. The development of the model is based on the conclusions drawn from the analyses of previous chapters. Measurement results of test structures on GPSOI are compared with SOI substrates and the model is validated against them.

Chapter 8 of this work introduces a Faraday cage structure having advanced crosstalk suppression capabilities. Vertical metal-filled trenches and the buried ground plane underneath the oxide form a cage and surround the noise transmitter and receiver nodes. The superior performance of this structure is explained with the aid of electromagnetic simulations.

Chapter 9 summarises the results of this work, focusing at the same time at research topics that may be pursued in the future.

# Chapter 2

## Substrate Crosstalk Theory and Literature Review

### 2.1 Introduction

Substrate crosstalk or coupling is defined in this chapter. Metrics of performance are discussed and several isolation schemes that have been researched previously in the literature are presented. Comparison of these isolation schemes provides some insight into the level of the crosstalk suppression that have been achieved to date in SOI substrates. A brief reference to the electromagnetic solvers that will be used to analyse substrate crosstalk concludes this chapter.

### 2.2 Substrate Crosstalk Definition and Metrics

The undesirable interaction between different parts of an integrated circuit is referred to as crosstalk. When this interaction exists through the common silicon substrate, where the different components of an IC are fabricated, it is called substrate crosstalk or substrate coupling. Decreasing the substrate crosstalk can result in higher degrees of isolation between devices, circuits and systems. Crosstalk is measured under small signal operation and the measurement techniques can be divided into two categories: time domain measurements and frequency domain measurements.

Time domain measurements employ transient analysis of the test structure and measurement of a time dependent parameter [19], [5], [20]. This kind of technique has been used to model crosstalk between interconnect lines, where one line acts as a noise transmitter ("aggressor" line) and the other lines are the noise receivers or "victim" lines. A noise transient can also be injected into the substrate through a transistor (usually MOS). As a result fluctuations are caused and propagate through the substrate to a remote sensor, usually a diffused contact. The level of substrate

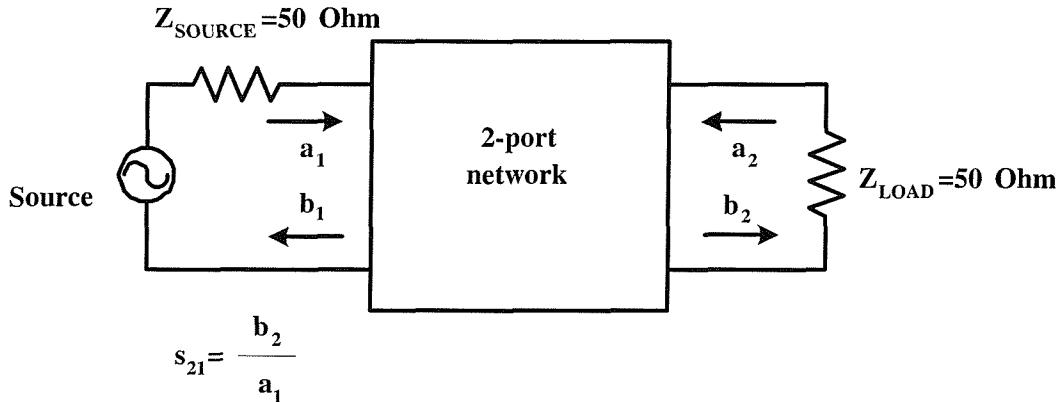

Figure 2.1: Scattering transmission coefficient definition.

crosstalk is then determined by measuring the peak-to-peak level of the fluctuations at the sensor.

When the level of crosstalk is determined in the frequency domain, a particular parameter is measured over a certain frequency range. Scattering parameters (S parameters) are used for RF measurements and have been established as the preferred parameters for system characterisation compared to impedance, admittance, hybrid, and transmission parameters because they overcome the problem of practically unachievable open- or short-circuit conditions for measurement. Scattering parameters describe a network's input-output properties in terms of incident and reflected power waves. An accepted quantitative measure of crosstalk in the frequency domain is the magnitude of the forward scattering coefficient  $s_{21}$  [1]-[10].  $S_{21}$  is the ratio of the transmitted power wave at port 2 over the incident power at port 1 of a two-port network. In the case of crosstalk studies, port one is a noise transmitter and port two is the noise receiver. The lower the magnitude of  $s_{21}$ , the lower the crosstalk and hence the higher the degree of isolation. Crosstalk suppression in this work is accessed only by measuring the magnitude of  $s_{21}$  and not through time domain measurements.

### 2.3 Comparison of Crosstalk in Different Technologies

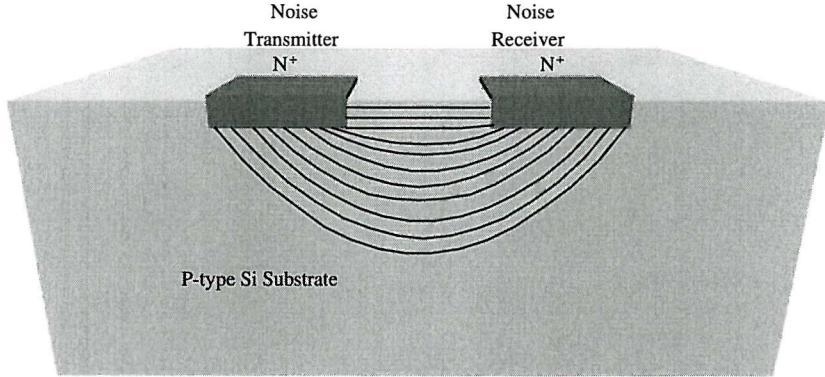

In standard bulk CMOS processes the devices are integrated at the surface of a uniformly doped Si substrate. Figure 2.2 shows the coupling path of the noise injected from an input node and received by an output node. It can be observed that crosstalk is a surface phenomenon since the most important coupling path is located at the surface of the substrate [1]. The coupling decreases with depth. Crosstalk can be decreased by increasing the separation between the crosstalk source (input) and sensor (output).

Figure 2.2: Bulk CMOS coupling path.

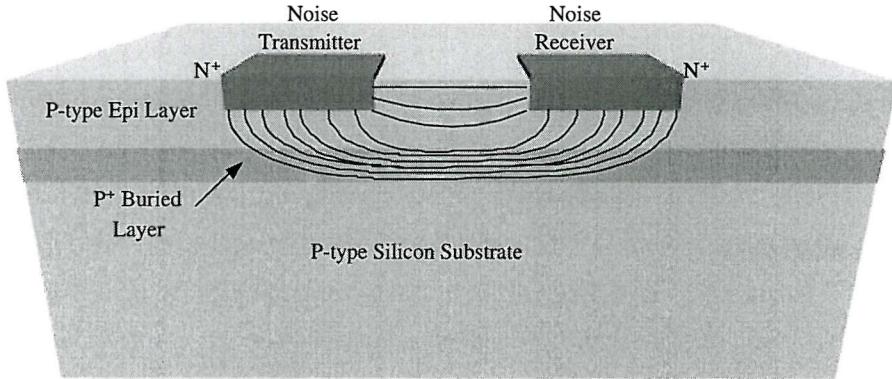

Figure 2.3: Heavily doped  $p^+$  buried layer coupling path.

Recent bipolar and BiCMOS processes integrate transistors on a standard resistivity epitaxial silicon layer grown on the top of a heavily doped substrate [1]. The main reason for this is to reduce latch-up problems. The buried plane, however, acts as a collector and distributor of noise. The higher doping of the buried layer compared to the doping of the epitaxial layer results in a less resistive coupling path located in the buried layer (Figure 2.3). Alternatively, it can be viewed as a single node located under the noise transmitter and receiver. The current injected by the noise source flows almost directly down to the buried layer and is propagated to the entire chip. Physical separation of the noise transmitter and receiver does not affect drastically the isolation properties of such substrates [1], [11], [21].

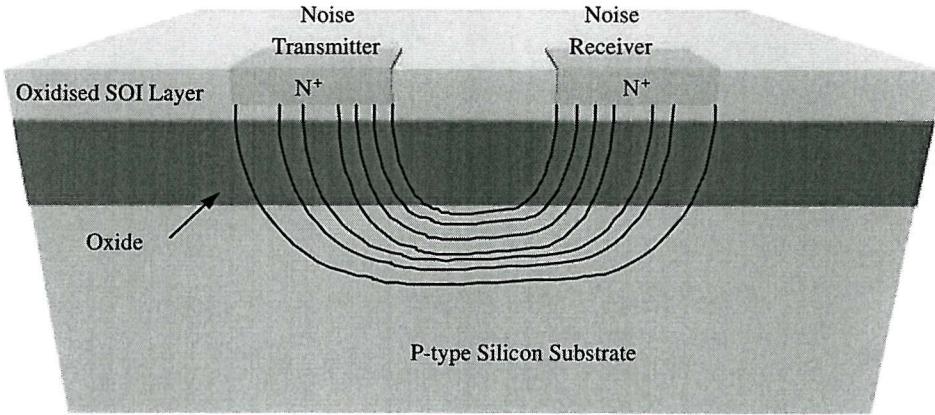

Crosstalk studies have been carried out in thin-film SOI technology [1], [7], [8], [10]. The devices are built in a thin (80 nm) silicon film, which is located on top of a buried oxide that separates it from the silicon substrate. This structure allows easy

Figure 2.4: Thin film SOI coupling path [1].

integration of shallow junctions and complete elimination of the dc coupling between the noise transmitter and receiver. (Figure 2.4). Compared to the heavily doped buried layer technology mentioned previously, the coupling path is now shifted even further below the buried oxide. The coupling is now purely capacitive nature down to the substrate and is found to be proportional to the separation distance [1]. At higher frequencies the buried oxide gradually becomes "transparent", increasing the crosstalk. An advantage of the SOI substrates is the possibility of using a high resistivity handle wafer to improve crosstalk suppression while at the same time not influencing latch-up susceptibility. High resistivity bulk CMOS substrates present technological difficulties in processing that increase cost. It is difficult to retain the high resistivity nature (i.e. reduced doping) of the substrate because of the diffusion of small quantities of dopants.

## 2.4 Isolation Schemes