UNIVERSITY OF SOUTHAMPTON

FABRICATION AND CHARACTERIZATION OF P-MOSFETS

WITH A STRAINED SIGE CHANNEL

Urs Norman Straube

A thesis submitted for the degree of

Doctor of Philosophy

Department of Electronics and Computer Science

Faculty of Engineering and Applied Science

March 2002

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

Faculty of Engineering and Applied Science

Department of Electronics and Computer Science

Doctor of Philosophy

FABRICATION AND CHARACTERIZATION OF P-MOSFETS WITH A

STRAINED SIGE CHANNEL

by Urs Norman Straube

Strained SiGe heterostructures possess transport properties superior to Si. Their integration in the channel of MOSFETs can lead to an enhanced speed performance and is therefore an alternative to the scaling of the channel length.

This thesis reports on the fabrication and characterization of p-MOSFETs with a strained SiGe channel. As both design and material properties determine the performance of MOSFETs, the mobility in the SiGe heterostructure must be seen in context with the MOSFET design. SiGe heterostructures fabricated by molecular beam (MBE) and solid phase (SPE) epitaxial growth have been successfully integrated in the channel of p-MOSFETs.

A manufacturable SiGe CMOS process based on SPE has been demonstrated. A slightly enhanced oxidation rate and an increased interface state density have been observed for Si oxidized after  $Ge^+$  implantation. The low performance of the SiGe p-MOSFETs is explained by the scattering and trapping of carriers at the degraded interface. This suggests that changing the annealing conditions could improve the SiGe p-MOSFETs.

Devices have been fabricated on a locally grown MBE layer. A considerable mobility enhancement over Si references has been shown for devices with a SiGe layer grown by MBE - more than or nearly a factor of two for devices with an LTO or thermal gate oxide, respectively. The devices fabricated on pillars display considerably better transport properties than the devices not fabricated on pillars. Altering the standard cleaning procedures has enabled us to achieve the required process control of one nanometer. Otherwise, the carriers would not be confined in the buried SiGe channel and would not profit from its enhanced transport properties. Low source and drain resistances have been obtained for SiGe p-MOSFETs subject to a maximum processing temperature of  $800^\circ C$ .

# Acknowledgments

I would like to thank my supervisors Prof. A. G. R. Evans and Prof. H. Kemhadjian for their support. The composure, patience and excellent guidance of Prof. A. G. R. Evans was the prerequisite for the enjoyable working environment.

Special thanks goes to the coworkers from other universities. Prof. E. H. C. Parker, Prof. T. E. Whall, Dr. G. Braithwaite, Dr. Tim Grasby, Dr. M. Palmer, Dr. C. Parry, Dr. P. Phillips, and A. Capewell from the University of Warwick were involved in the MBE growth for my SiGe devices and low energy SIMS analysis. Prof. P. L. F. Hemment, Dr. H. Graoui, Dr. C. Jeynes, and Dr. A. Nejim from the University of Surrey did critical implants, TEM or RBS analysis work of my samples. Prof. A. G. Cullis, Dr. G. Hill and Dr. D. J. Norris from the University of Sheffield analyzed my samples by SEM and TEM. Dr. S. Kaya and Dr. J. Watling from the University of Glasgow provided information about the SiGe heterostructure theory. Dr. K. Michelakis from Imperial College did s-parameter measurements on my devices.

Many thanks goes as well to my coworkers Dr. R. Sidek, Dr. Y. Tang and Dr. A. Waite as to helpful fellow students (Dr. I. Anteney, Dr. N. D'Hallewijn, J. Benson, Dr. T. Niblock, Dr. M. Routley, and S. Stefanou) from the University of Southampton.

My sincere appreciation is expressed to all staff of the Microelectronics Group. I especially would like to thank Dr. N. Afshar-Hanaii, Dr. J. Bonar, Dr. N. Lloyd, Dr. P. Routley, B. Ault, R. Baily, T. Blackburn, J. Clarke, S. Croucher, J. Humphrey, M. Josey, C. Kratovila, A. MacManus, I. McNally and A. Purdy.

Besides, I would like to thank Dr. A. Holmes-Siedle for his advice to do a Ph.D. at the University of Southampton and my parents for their continual support.

Urs N. Straube

Southampton

March 2002

# Glossary of Symbols

| Symbol                | Description                                                                               |

|-----------------------|-------------------------------------------------------------------------------------------|

| $a$ :                 | lattice constant                                                                          |

| $A$ :                 | frequency factor                                                                          |

| $A$ :                 | Richardson's constant                                                                     |

| $A_g$ :               | gate area                                                                                 |

| $a_o$ :               | lattice constant of an unstrained $Si_{1-x}Ge_x$ alloy                                    |

| $a_c$ :               | hydrostatic deformation potential of the conduction band                                  |

| $a_c^{dir}$ :         | hydrostatic deformation potential of the direct conduction band                           |

| $a_c^{ind}$ :         | hydrostatic deformation potential of the indirect conduction band                         |

| $a_v$ :               | hydrostatic deformation potential of the valence band                                     |

| $a_{\parallel}$ :     | lattice constant of an strained $Si_{1-x}Ge_x$ epilayer parallel to the growth plane      |

| $a_{\perp}$ :         | lattice constant of an strained $Si_{1-x}Ge_x$ epilayer perpendicular to the growth plane |

| $b$ :                 | amount of the Burgers vector                                                              |

| $b_0$ :               | amount of the Burgers vector of a perfect dislocation ( $a/2 < 101 >$ )                   |

| $b_1$ :               | amount of the Burgers vector of a $a/6 < 211 >$ dislocation                               |

| $b_2$ :               | amount of the Burgers vector of a $a/6 < 1\bar{1}2 >$ dislocation                         |

| $b_e$ :               | edge component of the Burgers vector                                                      |

| $b_s$ :               | screw component of the Burgers vector                                                     |

| $C$ :                 | series capacitance of $C_{ox}$ and $C_{cap}$                                              |

| $C_b$ :               | capacitance due to the bulk charge                                                        |

| $C_d$ :               | depletion region capacitance                                                              |

| $C_g$ :               | gate capacitance                                                                          |

| $C_g$ :               | oxygen concentration in the gas stream                                                    |

| $C_{gc}$ :            | gate-channel capacitance                                                                  |

| $C_i$ :               | capacitance due to the inversion charge                                                   |

| $C_i$ :               | oxygen concentration at the $SiO_2$ interface                                             |

| $C_o$ :               | oxygen concentration in the oxide                                                         |

| $C_{ox}$ :            | gate oxide capacitance                                                                    |

| $C_{cap}$ :           | cap layer capacitance                                                                     |

| $C_s$ :               | space region capacitance                                                                  |

| $C_s$ :               | oxygen concentration in the gas stream at the wafer surface                               |

| $c_{ij,Ge}$ :         | elastic constant of pure Ge                                                               |

| $c_{ij,Si}$ :         | elastic constant of pure Si                                                               |

| $d$ :                 | atomic spacing along the crystallographic direction                                       |

| $d$ :                 | deformation potential                                                                     |

| $\overline{D_{it}}$ : | mean surface state density                                                                |

| $D_n$ :               | diffusion constant for electrons                                                          |

| $D_{O_2}$ :           | diffusion coefficient of oxygen in $SiO_2$                                                |

| Symbol         | Description                                                 |

|----------------|-------------------------------------------------------------|

| $D_s$ :        | surface diffusivity                                         |

| $E$ :          | electrical field                                            |

| $E$ :          | incident energy                                             |

| $E_d$ :        | energy barrier for the desorption                           |

| $E_a$ :        | activation energy                                           |

| $E_b$ :        | binding energy                                              |

| $E_b$ :        | potential barrier                                           |

| $E_B$ :        | kinetic energy associated with boron                        |

| $E_{BF_2}$ :   | kinetic energy associated with $BF_2$                       |

| $E_c$ :        | conduction band energy                                      |

| $E_o$ :        | vacuum energy                                               |

| $E_f$ :        | Fermi energy                                                |

| $E_{eff}$ :    | effective vertical field                                    |

| $E_{fm}$ :     | Fermi energy of metal                                       |

| $E_g$ :        | energy gap                                                  |

| $E_i$ :        | intrinsic Fermi energy                                      |

| $E_{ox}$ :     | Fermi energy of silicon dioxide                             |

| $E_{si}$ :     | electric field at the oxide interface in $Si$               |

| $E_{ox}$ :     | electric field at the oxide interface in $SiO_2$            |

| $E_T$ :        | total energy                                                |

| $E_v$ :        | valence band energy                                         |

| $E_{v,1}$ :    | light hole valence band                                     |

| $E_{v,2}$ :    | heavy hole valence band                                     |

| $E_{v,3}$ :    | split-off band                                              |

| $E_\delta$ :   | energy accommodated by the dislocations                     |

| $E_\epsilon$ : | energy associated with the elastic strain                   |

| $f$ :          | frequency                                                   |

| $f$ :          | lattice mismatch                                            |

| $f_c$ :        | cutoff frequency                                            |

| $f'$ :         | pre-exponential factor                                      |

| $F_o$ :        | desorbing flux                                              |

| $F_\delta$ :   | force due to the selfenergy of the interfacial dislocations |

| $F_\epsilon$ : | elastic force                                               |

| $g$ :          | shear strain potential                                      |

| $g_d$ :        | conductance                                                 |

| $g_m$ :        | transconductance                                            |

| $G$ :          | epilayer shear modulus                                      |

| $Ge_{max}$ :   | critical Ge dose                                            |

| $h$ :          | epilayer thickness                                          |

| $h$ :          | Planck's constant                                           |

| $H$ :          | Henry's gas constant                                        |

| $h_g$ :        | mass transport coefficient                                  |

| $H_{21}$ :     | current gain                                                |

| $I_{cp}$       | charge pumping current                                      |

| $I_{ds}$ :     | current between source and drain                            |

| $I_{dsat}$ :   | saturation current                                          |

| $I_1$ :        | source and drain current                                    |

| $I_1$ :        | current at port 1                                           |

| Symbol       | Description                                |

|--------------|--------------------------------------------|

| $I_2$ :      | substrate current                          |

| $I_2$ :      | current at port 2                          |

| $j_{inc}$ :  | incident flux of adatoms                   |

| $J_n$ :      | electron current density                   |

| $j_s$ :      | surface current density of adatoms         |

| $j_v$ :      | net flux of adatoms                        |

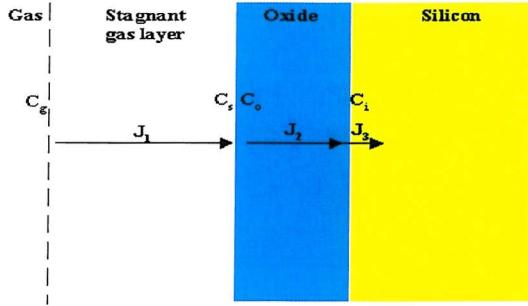

| $J_1$ :      | oxygen flow through the stagnant gas layer |

| $J_2$ :      | oxygen flow through $SiO_2$ layer          |

| $J_3$ :      | oxygen flow reacting with Si               |

| $J_S$ :      | saturation current density                 |

| $k_s$ :      | chemical rate constant                     |

| $K_p$ :      | Preston coefficient                        |

| $l_d$ :      | length of the pinch-off region             |

| $L$ :        | effective channel length                   |

| $L_o$ :      | drawn channel length                       |

| $L_D$ :      | Debye length for holes                     |

| $L_m$ :      | drawn channel length                       |

| $M_B$ :      | mass of boron                              |

| $M_{BF_2}$ : | mass of $BF_2$                             |

| $m_{hh}$ :   | heavy hole mass                            |

| $m_{lh}$ :   | light hole mass                            |

| $m^*$ :      | effective mass                             |

| $n$ :        | free electron density                      |

| $n_o$ :      | electron density at thermal equilibrium    |

| $n_i$ :      | intrinsic carrier concentration            |

| $n_s$ :      | density of adsorbed atoms                  |

| $n_s$ :      | electron surface concentration             |

| $N_s$ :      | density of surface positions               |

| $n_{seq}$ :  | equilibrium density of adsorbed atoms      |

| $N_a$ :      | acceptor density                           |

| $N$ :        | impurity concentration                     |

| $N_{asd}$ :  | acceptor density in source and drain       |

| $N_b$ :      | net bulk doping                            |

| $N_d$ :      | donator density                            |

| $p$ :        | free hole density                          |

| $p$ :        | pressure                                   |

| $P_g$ :      | partial pressure of oxygen in the gas flow |

| $p_o$ :      | hole density at thermal equilibrium        |

| $q$ :        | elementary charge                          |

| $Q_o$ :      | effective interface charge                 |

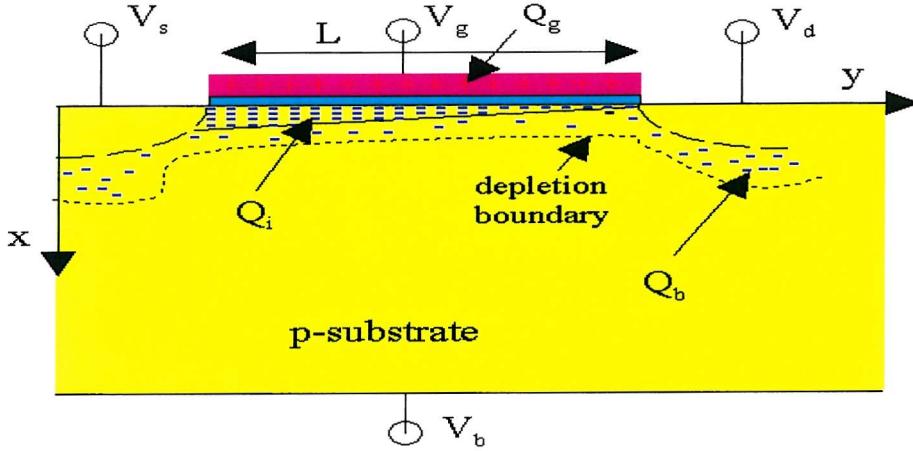

| $Q_b$ :      | bulk charge                                |

| $Q_g$ :      | gate charge                                |

| $Q_i$ :      | inversion charge                           |

| $Q_{id}$ :   | inversion charge at the drain end          |

| $Q_{is}$ :   | inversion charge at the source end         |

| $Q_s$ :      | space charge                               |

| $r_o$ :      | dislocation core parameter                 |

| $R$ :        | deposition rate                            |

| Symbol                             | Description                                              |

|------------------------------------|----------------------------------------------------------|

| $R$ :                              | removal rate                                             |

| $R_c$ :                            | contact resistance                                       |

| $r_{ch}$ :                         | channel sheet resistance                                 |

| $R_{ch}$ :                         | channel resistance                                       |

| $R_d$ :                            | drain resistance                                         |

| $\bar{R}_p$ :                      | projected range                                          |

| $R_s$ :                            | source resistance                                        |

| $R_{sd}$ :                         | combined source and drain resistance                     |

| $s_{11}, s_{12}, s_{21}, s_{22}$ : | s-parameters                                             |

| $T$ :                              | absolute temperature                                     |

| $t_{ch}$ :                         | thickness of the channel                                 |

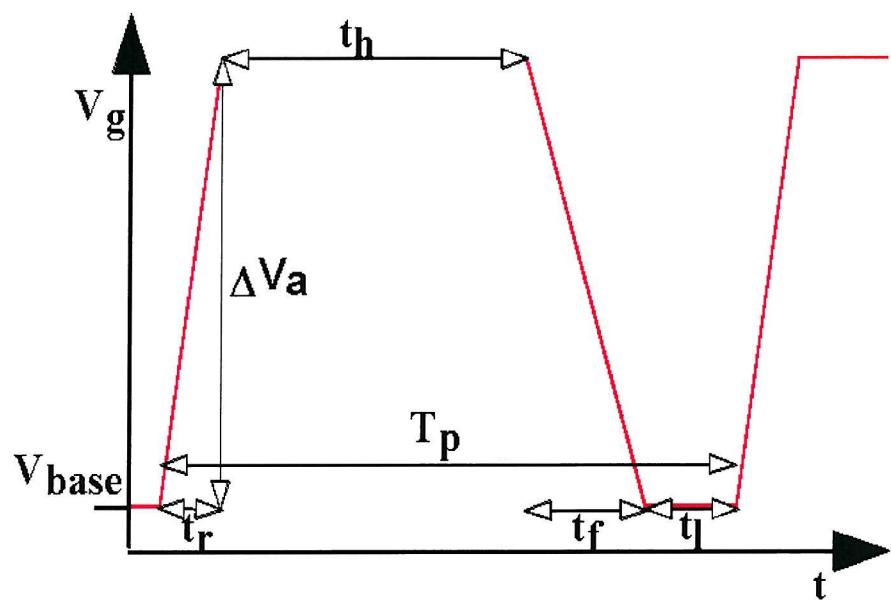

| $t_f$ :                            | fall time                                                |

| $t_h$ :                            | time at high voltage                                     |

| $t_l$ :                            | time at low voltage                                      |

| $t_{ox}$ :                         | gate oxide thickness                                     |

| $t_r$ :                            | rise time                                                |

| $T$ :                              | absolute temperature                                     |

| $T_p$ :                            | period                                                   |

| $U_s$ :                            | energy barrier                                           |

| $v$ :                              | relative velocity                                        |

| $V$ :                              | voltage                                                  |

| $v_o$ :                            | superimposed signal                                      |

| $V_b$ :                            | potential between bulk and source                        |

| $V_{base}$ :                       | base voltage                                             |

| $V_{cb}$ :                         | potential between channel surface and source             |

| $V_{ds}$ :                         | potential between source and drain                       |

| $V_{dsat}$ :                       | drain saturation voltage                                 |

| $V_{fb}$ :                         | flat band voltage                                        |

| $V_g$ :                            | potential between gate and substrate                     |

| $V_{gd}$ :                         | potential between gate and drain                         |

| $V_{ox}$ :                         | potential dropped across the oxide                       |

| $V_{pt}$ :                         | punch-through voltage                                    |

| $V_{rev}$ :                        | reverse bias                                             |

| $V_t$ :                            | thermal voltage                                          |

| $V_{th}$ :                         | threshold voltage                                        |

| $V_{thd}$ :                        | threshold voltage for a short channel device             |

| $W$ :                              | effective channel width                                  |

| $W$ :                              | width of depletion region                                |

| $W_{disl}$ :                       | selfenergy of misfit dislocations                        |

| $W_{fault}$ :                      | selfenergy of stacking faults                            |

| $W_{layer}$ :                      | strain energy of the epilayer                            |

| $W_s$ :                            | activation energy                                        |

| $y_{11}, y_{12}, y_{21}, y_{22}$ : | y-parameters                                             |

| $x$ :                              | distance from the $Si/SiO_2$ -interface into the silicon |

| $x$ :                              | Ge content                                               |

| $x_d$ :                            | end of the space charge region                           |

| $X_{Ge}^{peak}$ :                  | peak Ge concentration                                    |

| $y$ :                              | distance from the edge of the source along the channel   |

| Symbol                   | Description                                                                                                                 |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| $y_c$ :                  | position of the amorphous/crystalline interface                                                                             |

| $Z_i$ :                  | proton number of ion                                                                                                        |

| $Z_t$ :                  | proton number of target                                                                                                     |

| $\alpha$ :               | factor describing the energy of the dislocation core                                                                        |

| $\beta$ :                | gain factor                                                                                                                 |

| $\beta$ :                | kurtosis                                                                                                                    |

| $\gamma$ :               | body factor                                                                                                                 |

| $\gamma$ :               | skewness                                                                                                                    |

| $\gamma$ :               | stacking fault energy                                                                                                       |

| $\delta$ :               | lattice strain mismatch relieved through the formation of misfit dislocations                                               |

| $\Delta_o$ :             | spin orbit splitting parameter                                                                                              |

| $\Delta E_c$ :           | conduction band offset                                                                                                      |

| $\Delta E_v$ :           | valence band offset                                                                                                         |

| $\Delta E_c^i$ :         | shift of the conduction band valley i                                                                                       |

| $\Delta E_{c,av}$ :      | shift of the position of the average conduction band                                                                        |

| $\Delta E_{v,av}$ :      | shift of the position of the average valence band                                                                           |

| $\Delta E_{v,1}$ :       | shift of the light hole valence band                                                                                        |

| $\Delta E_{v,2}$ :       | shift of the heavy hole valence band                                                                                        |

| $\Delta E_{v,3}$ :       | shift of the split-off band                                                                                                 |

| $\Delta G$ :             | free energy change                                                                                                          |

| $\Delta G_n$ :           | free energy per unit volume                                                                                                 |

| $\Delta L$ :             | difference between drawn and electrical channel length                                                                      |

| $\Delta \bar{R}_p$ :     | standard deviation of the projected range                                                                                   |

| $\Delta V_a$ :           | amplitude of superimposed signal                                                                                            |

| $\Delta \Delta L$ :      | error of $\Delta L$                                                                                                         |

| $\epsilon$ :             | dielectric constant                                                                                                         |

| $\epsilon$ :             | lattice mismatch strain between epitaxial layer and substrate                                                               |

| $\epsilon^*$ :           | equilibrium strain                                                                                                          |

| $\epsilon_{ch}$ :        | permittivity of the SiGe channel                                                                                            |

| $\epsilon_o$ :           | initial lattice mismatch strain                                                                                             |

| $\epsilon_o$ :           | vacuum permittivity                                                                                                         |

| $\epsilon_{ox}$ :        | dielectric constant of $SiO_2$                                                                                              |

| $\epsilon_s$ :           | initial density of dislocations                                                                                             |

| $\epsilon_{si}$ :        | dielectric constant of silicon                                                                                              |

| $\epsilon_{\parallel}$ : | lattice mismatch strain between epitaxial layer and substrate parallel to the plane of the interface                        |

| $\epsilon_{\perp}$ :     | lattice mismatch strain between epitaxial layer and substrate perpendicular to the plane of the interface                   |

| $\Theta$ :               | angle between the dislocation line and its Burgers vector                                                                   |

| $\Theta$ :               | sum of $\Theta_o$ and $R_{sd}$                                                                                              |

| $\Theta_b$ :             | mobility degradation factor due to the substrate voltage                                                                    |

| $\Theta_c$ :             | mobility degradation due to the voltage between source and drain                                                            |

| $\Theta_o$ :             | mobility degradation factor                                                                                                 |

| $\lambda$ :              | angle between the misfit dislocation Burgers vector and a line in the interface drawn perpendicular to the dislocation line |

| $\lambda$ :              | channel length modulation factor                                                                                            |

| $\lambda$ :              | propagation constant                                                                                                        |

| $\lambda_s$ :            | mean migration length                                                                                                       |

| Symbol                | Description                                                      |

|-----------------------|------------------------------------------------------------------|

| $\mu$ :               | mobility                                                         |

| $\mu_{eff}$ :         | effective mobility                                               |

| $\mu_{effv}$ :        | effective mobility taking into account the variation of $C_{gc}$ |

| $\mu_{FE}$ :          | field-effect mobility                                            |

| $\mu_{Ge}$ :          | mobility in Ge                                                   |

| $\mu_l$ :             | mobility due to the longitudinal field                           |

| $\mu_n$ :             | electron mobility                                                |

| $\mu_o$ :             | low-field mobility                                               |

| $\mu_s$ :             | surface mobility                                                 |

| $\mu_{Si}$ :          | mobility in Si                                                   |

| $\mu_t$ :             | mobility due to the transversal field                            |

| $\nu$ :               | epilayer Poisson ratio                                           |

| $\rho$ :              | charge density                                                   |

| $\sigma$ :            | DIBL parameter                                                   |

| $\sigma$ :            | supersaturation parameter                                        |

| $\sigma$ :            | surface energy                                                   |

| $\sigma_n$ :          | capture cross section of electrons                               |

| $\sigma_p$ :          | capture cross section of holes                                   |

| $\sigma_{R_{sd}}$ :   | standard deviation of $R_{sd}$                                   |

| $\sigma_{r_{ch}}$ :   | standard deviation of $r_{ch}$                                   |

| $\sigma_{\Delta L}$ : | standard deviation of $\Delta L$                                 |

| $\sigma_{\mu_o}$ :    | standard deviation of $\mu_o$                                    |

| $\sigma_{\Theta_o}$ : | standard deviation of $\Theta_o$                                 |

| $\tau_t$ :            | transport scattering time                                        |

| $v$ :                 | carrier velocity                                                 |

| $\phi$ :              | electrical potential                                             |

| $\phi$ :              | implantation dose                                                |

| $\phi_b$ :            | barrier height                                                   |

| $\phi_{bi}$ :         | built-in potential of a pn-junction                              |

| $\phi_f$ :            | Fermi potential                                                  |

| $\phi_{fi}$ :         | intrinsic Fermi potential                                        |

| $\phi_{fn}$ :         | quasi-Fermi potential for n-type silicon                         |

| $\phi_{fp}$ :         | quasi-Fermi potential for p-type silicon                         |

| $\phi_s$ :            | surface potential                                                |

| $\phi_{ss}$ :         | constant value for the surface potential                         |

| :                     | in the subthreshold region model                                 |

| $\Phi_m$ :            | metal work function                                              |

| $\Phi_{max}$ :        | critical implant dose                                            |

| $\Phi_{ms}$ :         | gate to substrate work function difference                       |

| $\Phi_s$ :            | semiconductor work function                                      |

| $\chi_s$ :            | electron affinity of silicon                                     |

| $\chi_{ox}$ :         | electron affinity of silicon dioxide                             |

| $\Psi$ :              | critical angel for channelling                                   |

| $\omega_c$ :          | cutoff frequency                                                 |

# Contents

|          |                                                                   |           |

|----------|-------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                               | <b>1</b>  |

|          | From the Dawn of the IC Era to SiGe CMOS . . . . .                | 1         |

|          | Objective of this Project . . . . .                               | 2         |

|          | Organization of the Thesis . . . . .                              | 3         |

| <b>2</b> | <b>SiGe Heterostructures</b>                                      | <b>7</b>  |

| 2.1      | Crystal Structure . . . . .                                       | 7         |

| 2.2      | Strain Relaxation of $Si_{1-x}Ge_x/Si$ Heterostructures . . . . . | 9         |

| 2.3      | Band Structure of SiGe . . . . .                                  | 15        |

| 2.3.1    | Effect of Strain on the Valence Band . . . . .                    | 17        |

| 2.3.2    | Effect of Strain on the Conduction Band . . . . .                 | 18        |

| 2.4      | Effective Masses of SiGe . . . . .                                | 20        |

| 2.5      | Dielectric Constant . . . . .                                     | 22        |

| 2.6      | Mobility . . . . .                                                | 22        |

| 2.7      | Ternary $Si_{1-x-y}Ge_xC_y$ Alloys . . . . .                      | 24        |

| 2.8      | Conclusion . . . . .                                              | 24        |

| <b>3</b> | <b>MOSFET Theory</b>                                              | <b>32</b> |

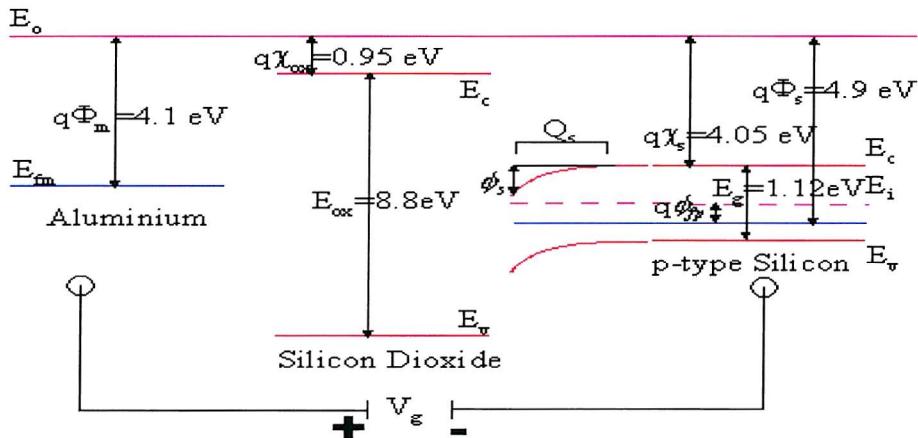

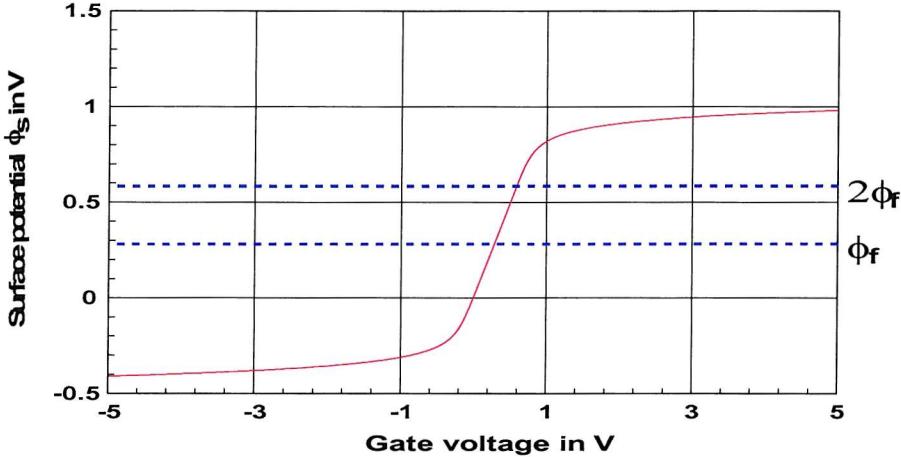

| 3.1      | Gate Voltage . . . . .                                            | 33        |

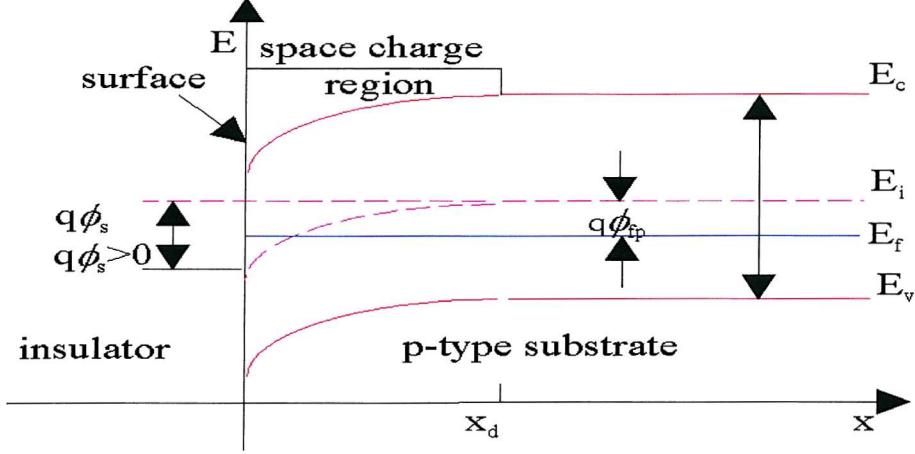

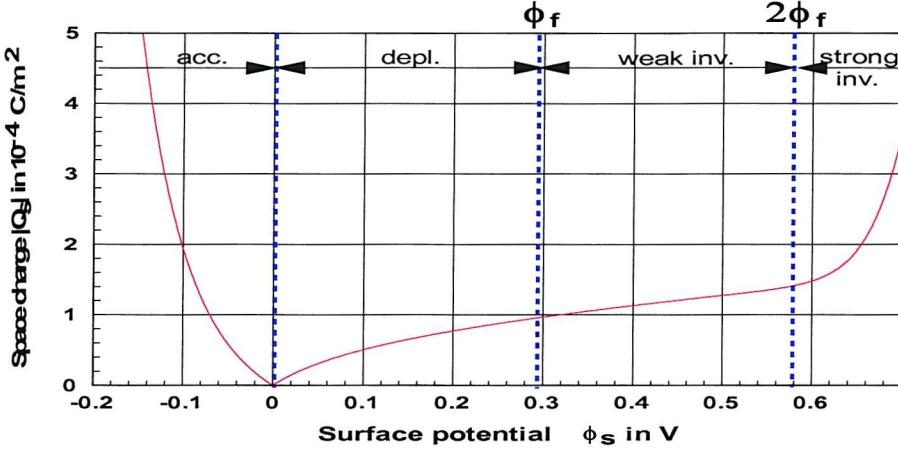

| 3.1.1    | Space Charge in the MOS Structure . . . . .                       | 35        |

| 3.1.2    | Gate Capacitance . . . . .                                        | 37        |

| 3.2      | MOSFET DC Model . . . . .                                         | 39        |

| 3.2.1    | Linear Region of MOSFET Operation . . . . .                       | 39        |

| 3.2.2    | Saturation Region . . . . .                                       | 42        |

| 3.2.3    | Subthreshold Region Model . . . . .                               | 42        |

| 3.2.4    | Device Speed . . . . .                                            | 44        |

| 3.3      | Modern MOSFETs . . . . .                                          | 44        |

| 3.3.1    | Change in Device Behavior . . . . .                               | 44        |

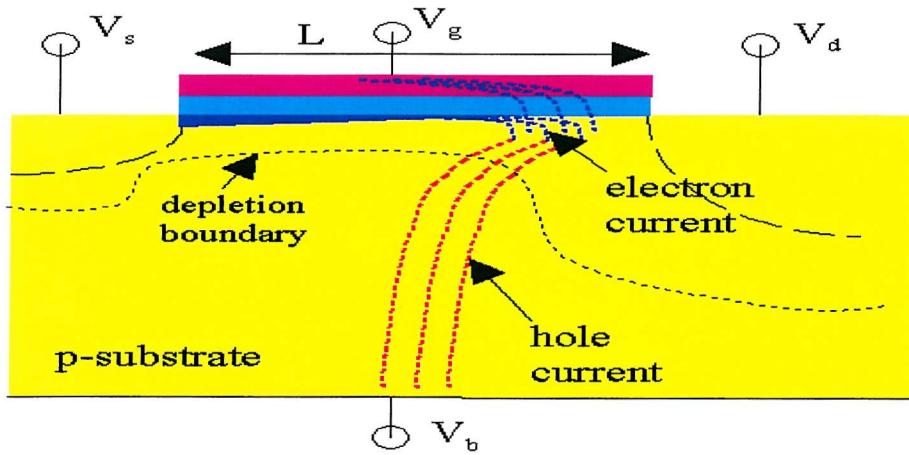

| 3.3.2    | Hot Carrier Effects . . . . .                                     | 45        |

|          |                                                                |           |

|----------|----------------------------------------------------------------|-----------|

| 3.4      | SiGe for MOSFET applications . . . . .                         | 47        |

| 3.5      | Conclusion . . . . .                                           | 48        |

| <b>4</b> | <b>Electrical Characterization of MOSFETs</b>                  | <b>51</b> |

| 4.1      | Split-CV Measurements . . . . .                                | 51        |

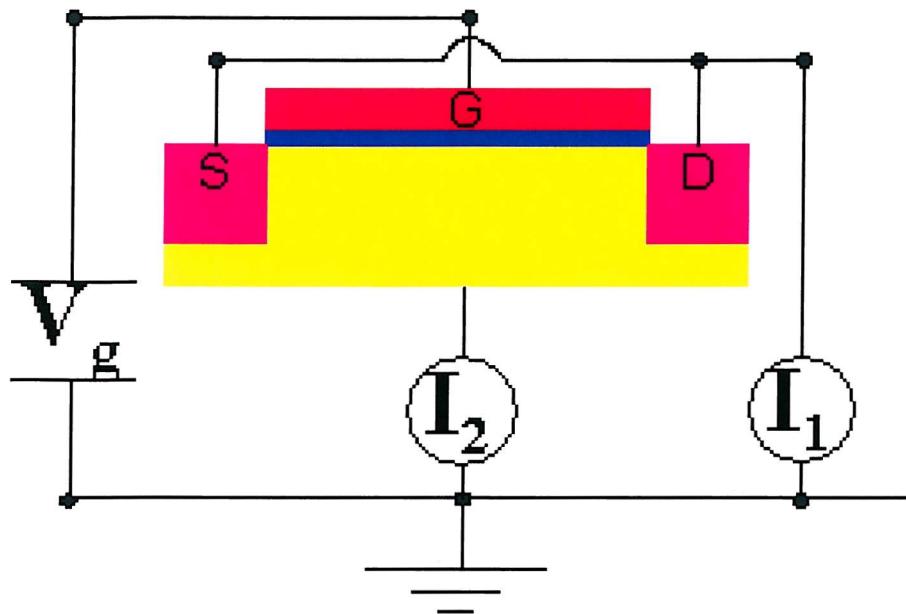

| 4.2      | S-Parameter Measurements . . . . .                             | 53        |

| 4.2.1    | Measurement of a Two-Port System at High Frequencies . . . . . | 53        |

| 4.2.2    | Calibration and Deembedding . . . . .                          | 54        |

| 4.2.3    | Mobility Extraction . . . . .                                  | 56        |

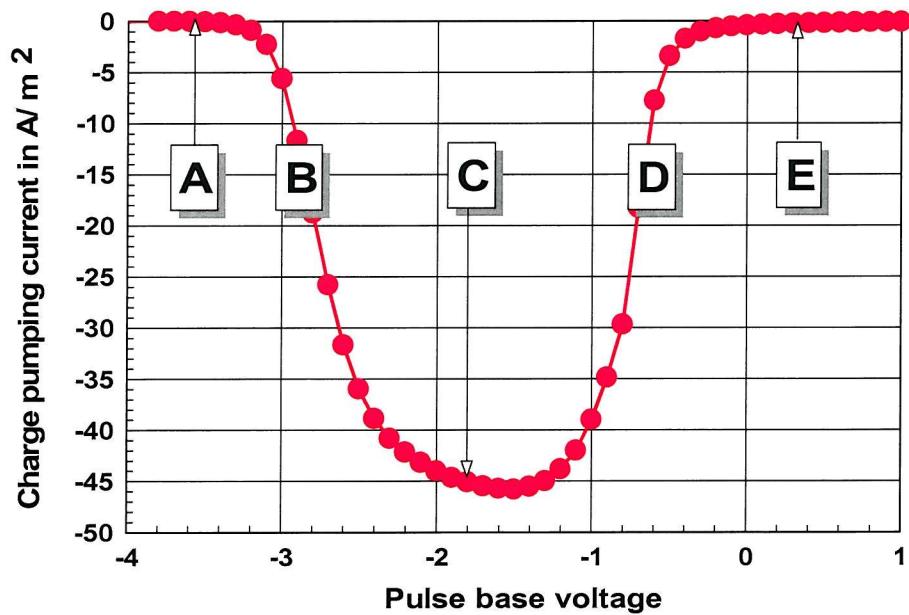

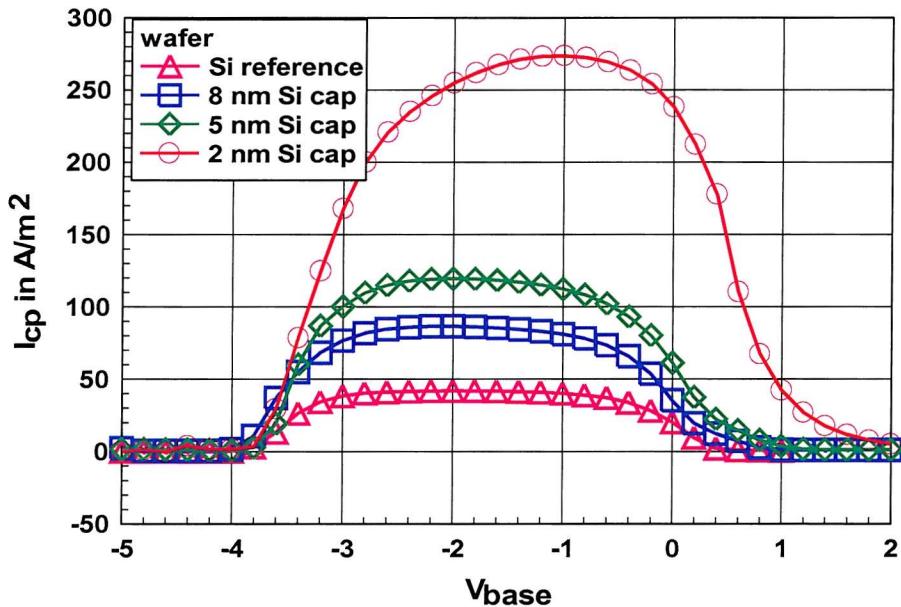

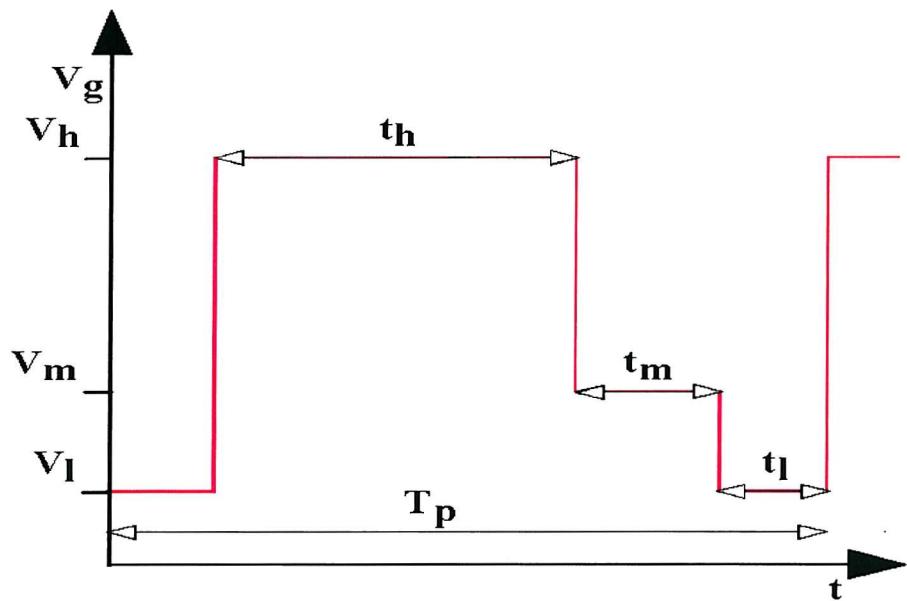

| 4.3      | Charge Pumping Measurements . . . . .                          | 57        |

| 4.4      | Parameter Extraction for Conventional MOSFETs . . . . .        | 62        |

| 4.5      | Parameter Extraction Routine for HMOSFETs . . . . .            | 66        |

| 4.6      | Validity of the Constant Capacitance Approximation . . . . .   | 69        |

| 4.7      | Conclusion . . . . .                                           | 71        |

| <b>5</b> | <b>Vapor-Phase Deposition</b>                                  | <b>75</b> |

| 5.1      | Chemical Vapor Deposition . . . . .                            | 75        |

| 5.1.1    | CVD Growth and Reactor . . . . .                               | 75        |

| 5.1.2    | Different CVD Methods . . . . .                                | 77        |

| 5.1.3    | Deposition of Thin Films by CVD . . . . .                      | 79        |

| 5.2      | Physical Vapor Phase Deposition . . . . .                      | 84        |

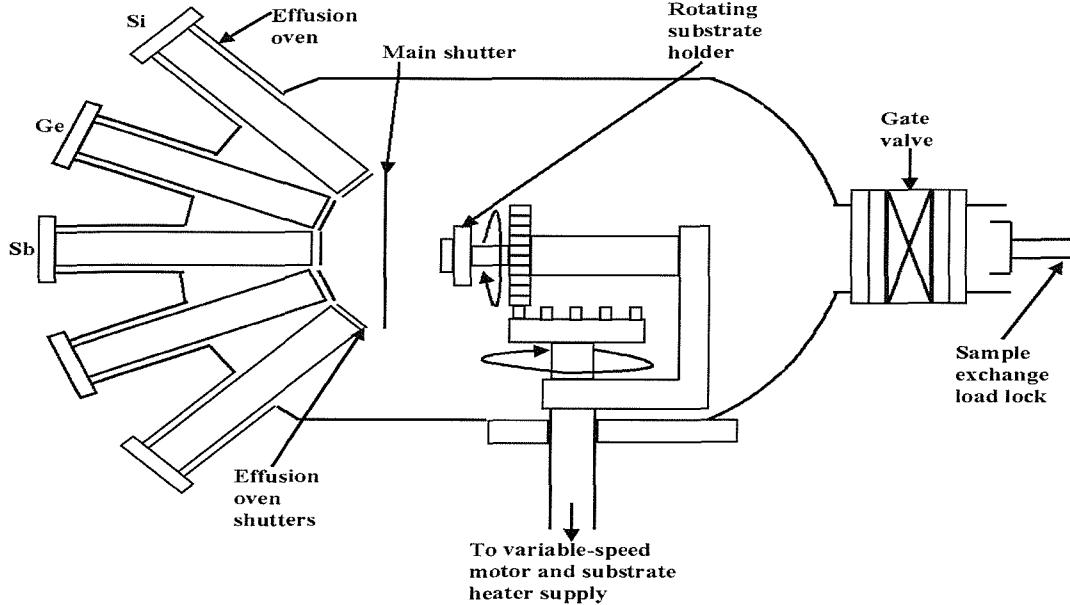

| 5.2.1    | Molecular Beam Epitaxy . . . . .                               | 84        |

| 5.2.2    | Sputtering . . . . .                                           | 88        |

| 5.3      | Conclusion . . . . .                                           | 89        |

| <b>6</b> | <b>Processing</b>                                              | <b>93</b> |

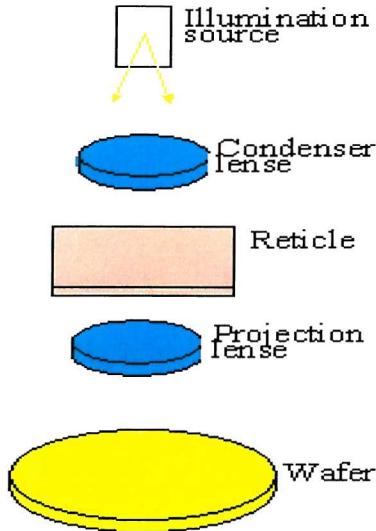

| 6.1      | Lithography . . . . .                                          | 93        |

| 6.1.1    | Lithography Techniques . . . . .                               | 93        |

| 6.1.2    | Photoresist . . . . .                                          | 95        |

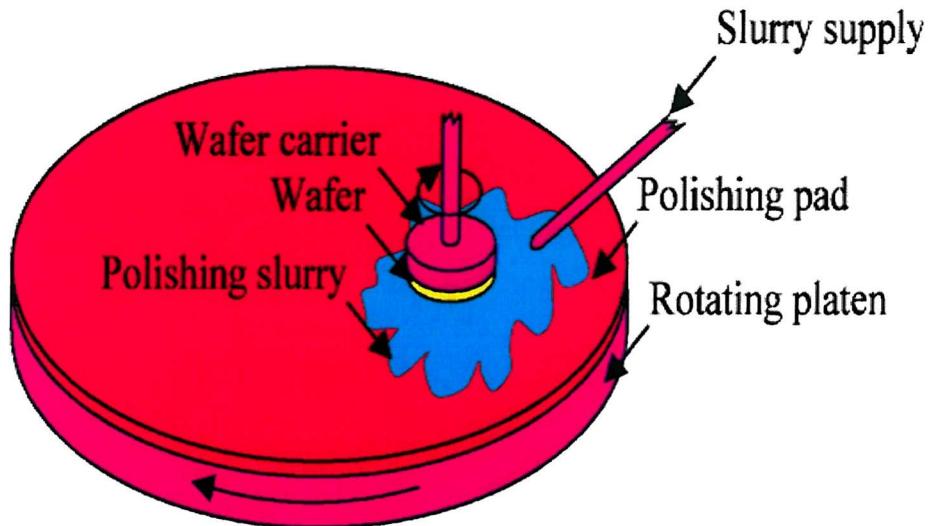

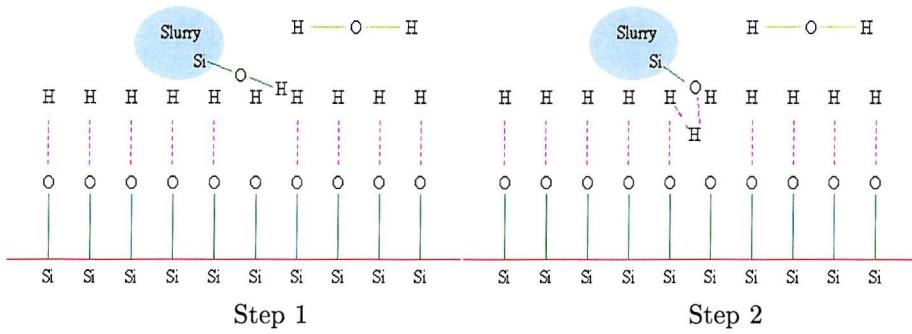

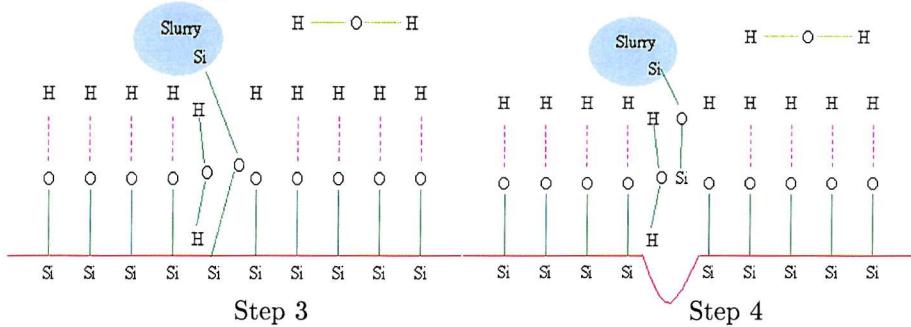

| 6.2      | Chemical/Mechanical Polishing . . . . .                        | 96        |

| 6.3      | Thermal Oxidation of Si and SiGe . . . . .                     | 98        |

| 6.4      | Rapid Thermal Processes . . . . .                              | 102       |

| 6.5      | Etching . . . . .                                              | 103       |

| 6.5.1    | Wet Etching . . . . .                                          | 103       |

| 6.5.2    | Dry Etching . . . . .                                          | 103       |

| 6.6      | Wafer Cleaning Technology . . . . .                            | 104       |

| 6.7      | Ion Implantation . . . . .                                     | 106       |

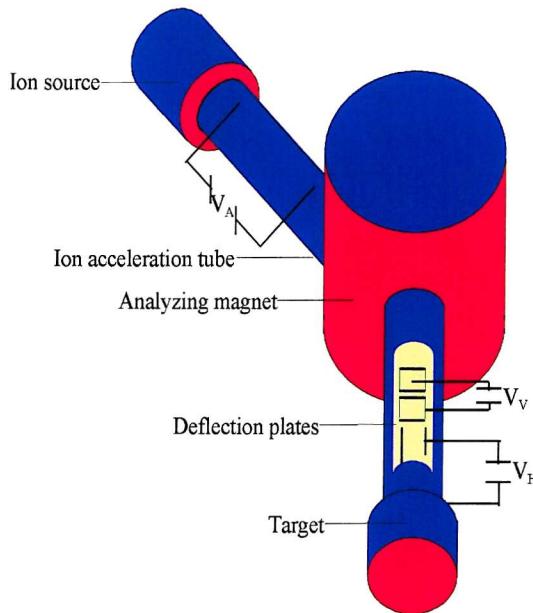

| 6.7.1    | Ion Implanter . . . . .                                        | 107       |

| 6.8      | Implantation Profile . . . . .                                 | 108       |

|           |                                                                     |            |

|-----------|---------------------------------------------------------------------|------------|

| 6.8.1     | Implantation Damage and Solid Phase Epitaxial Growth . . . . .      | 110        |

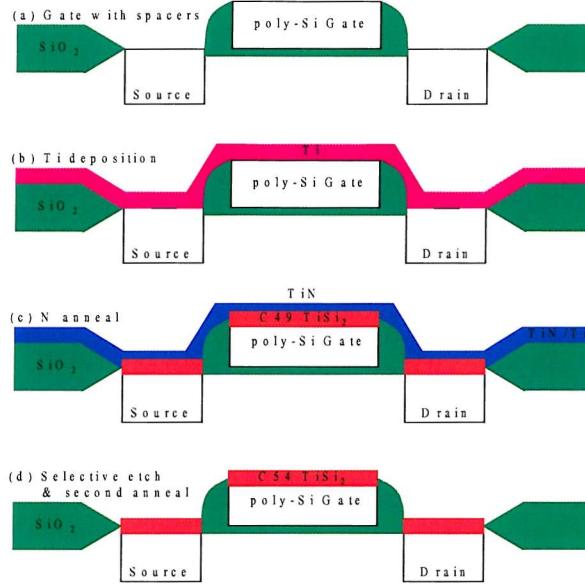

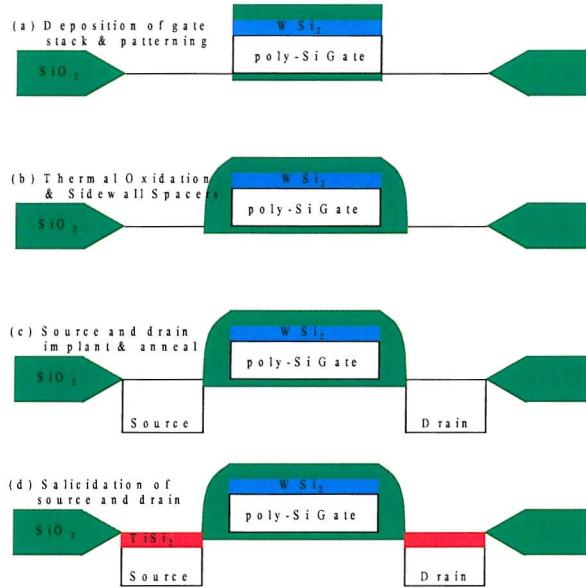

| 6.9       | Silicidation . . . . .                                              | 111        |

| 6.9.1     | Metal-Semiconductor Contact . . . . .                               | 111        |

| 6.9.2     | Silicidation Process . . . . .                                      | 113        |

| 6.10      | Conclusion . . . . .                                                | 115        |

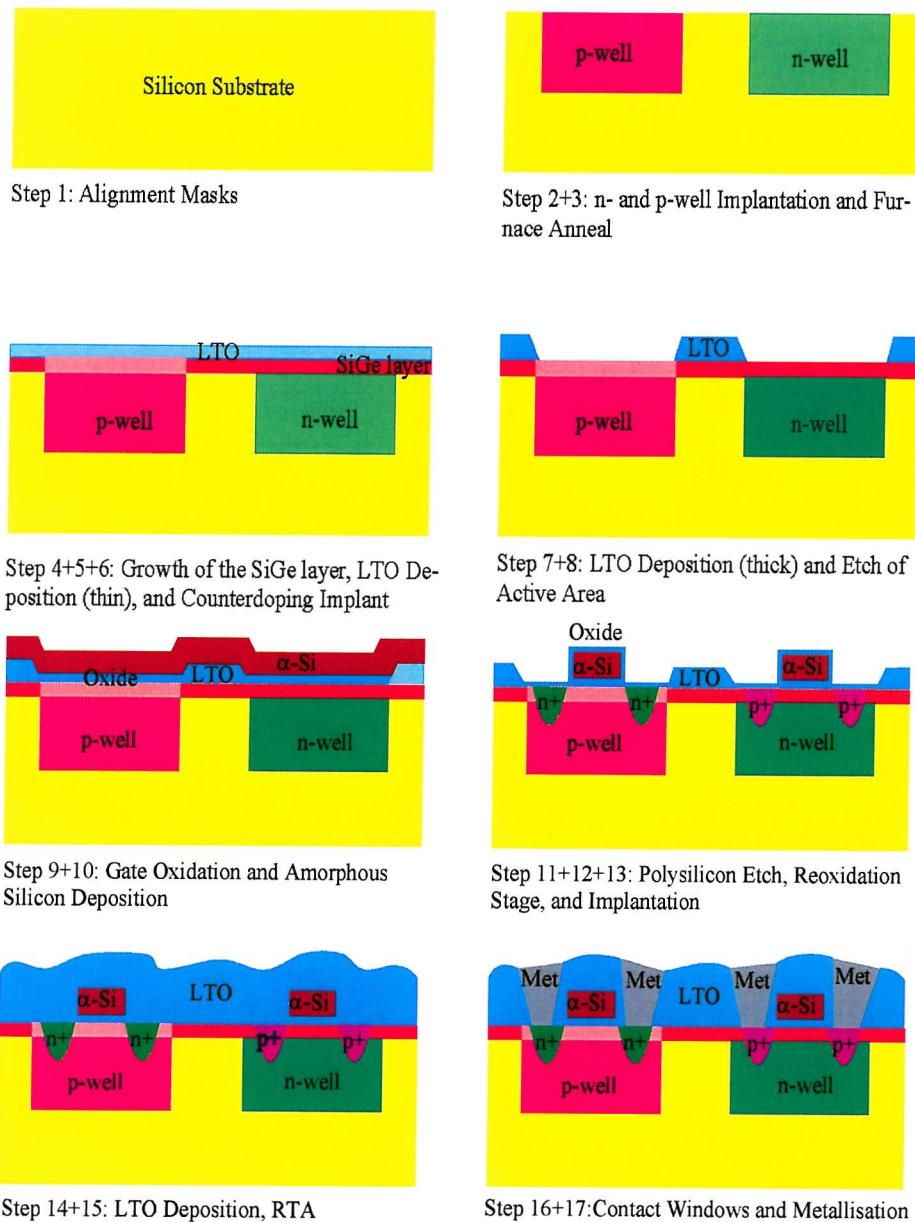

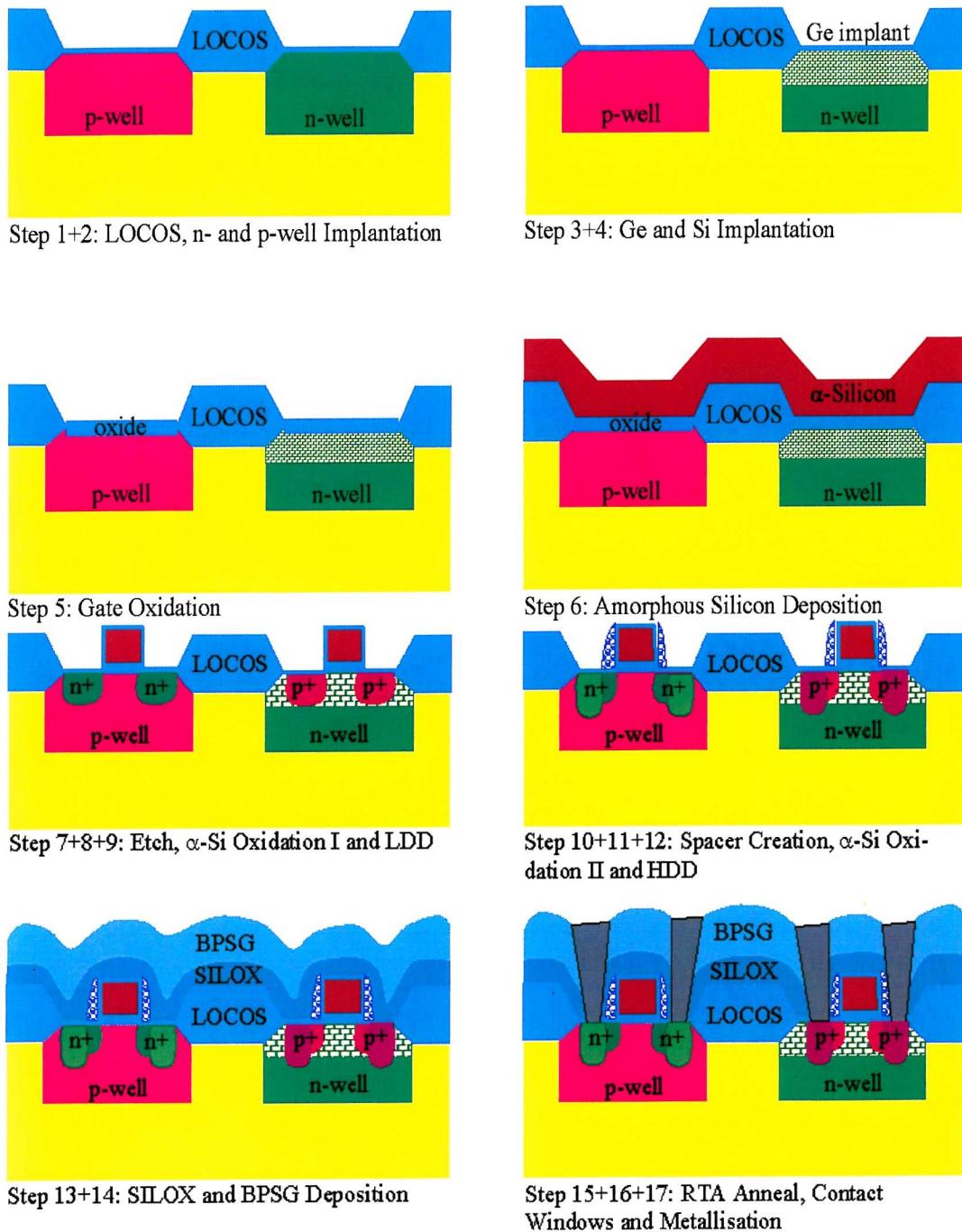

| <b>7</b>  | <b>Pseudomorphic SiGe CMOS Process</b>                              | <b>122</b> |

| 7.1       | Fabrication Process . . . . .                                       | 123        |

| 7.2       | Electrical Results . . . . .                                        | 128        |

| 7.3       | Analysis of the Layer Structure . . . . .                           | 130        |

| 7.4       | Conclusion . . . . .                                                | 134        |

| <b>8</b>  | <b>SiGe CMOS/<math>Ge^+</math> Implantation Process</b>             | <b>136</b> |

| 8.1       | Fabrication Process . . . . .                                       | 136        |

| 8.2       | Results . . . . .                                                   | 140        |

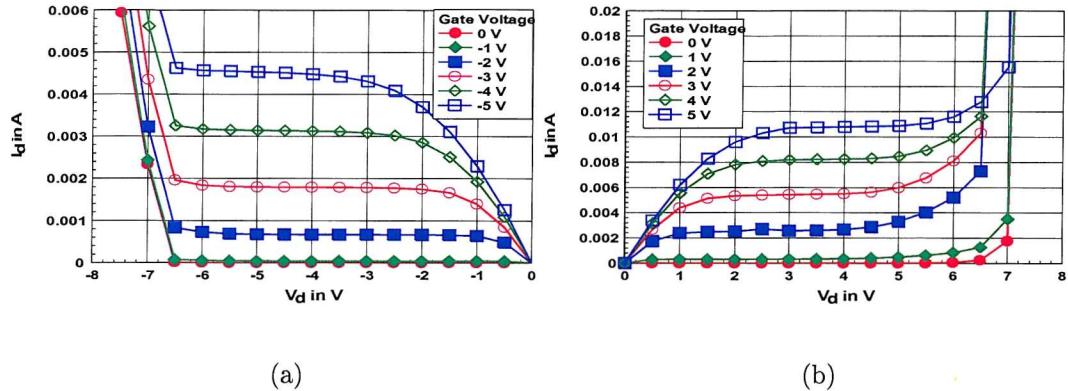

| 8.2.1     | P-MOSFETs . . . . .                                                 | 141        |

| 8.2.2     | N-MOSFETs . . . . .                                                 | 151        |

| 8.2.3     | Ring Oscillators . . . . .                                          | 153        |

| 8.3       | Conclusion . . . . .                                                | 154        |

| <b>9</b>  | <b>SiGe Virtual Substrate/Limited Area PMOS Process</b>             | <b>157</b> |

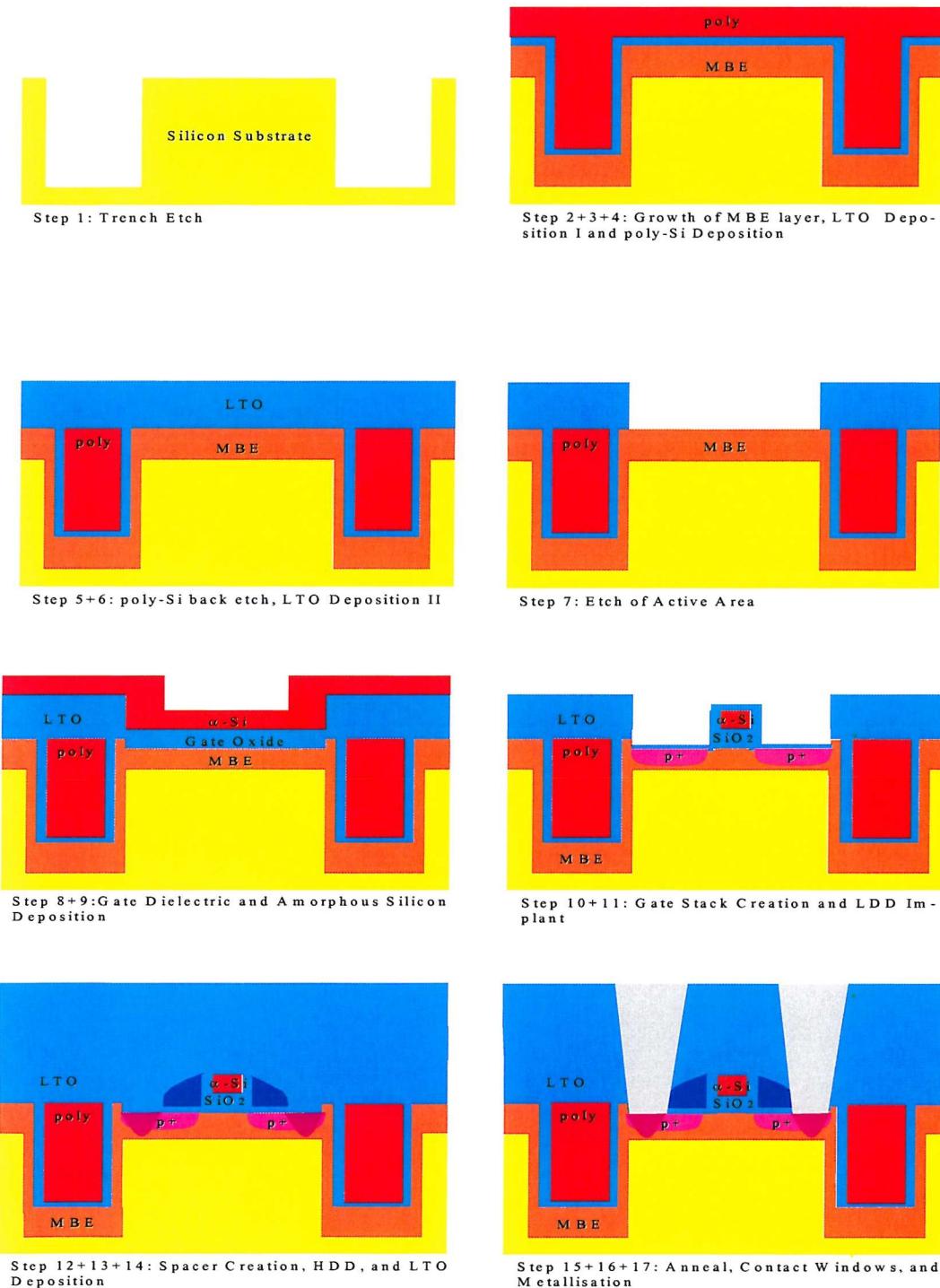

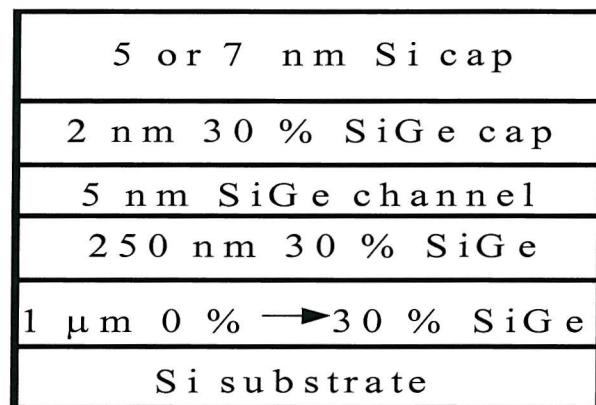

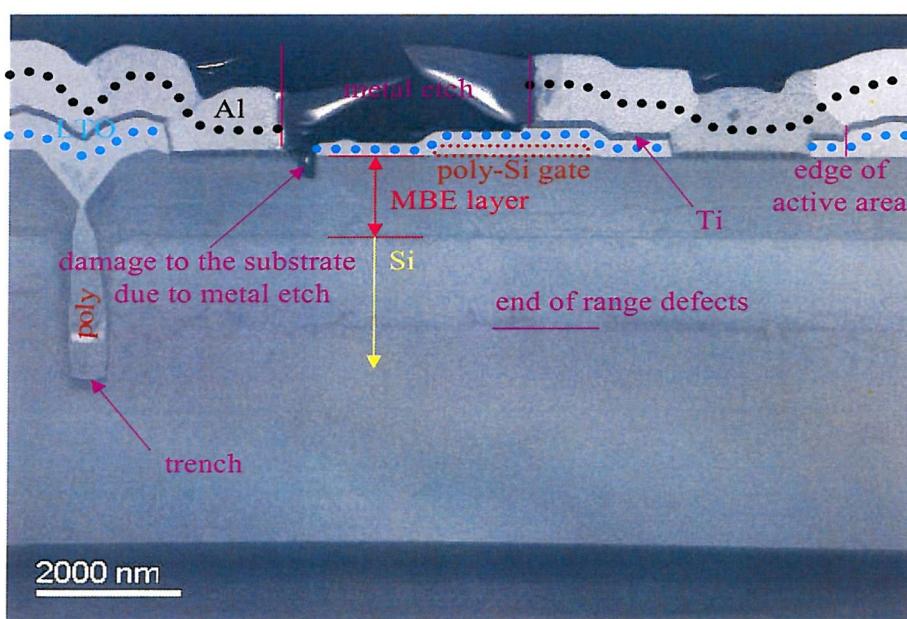

| 9.1       | Fabrication Process . . . . .                                       | 157        |

| 9.2       | Measurements and Parameter Extraction . . . . .                     | 163        |

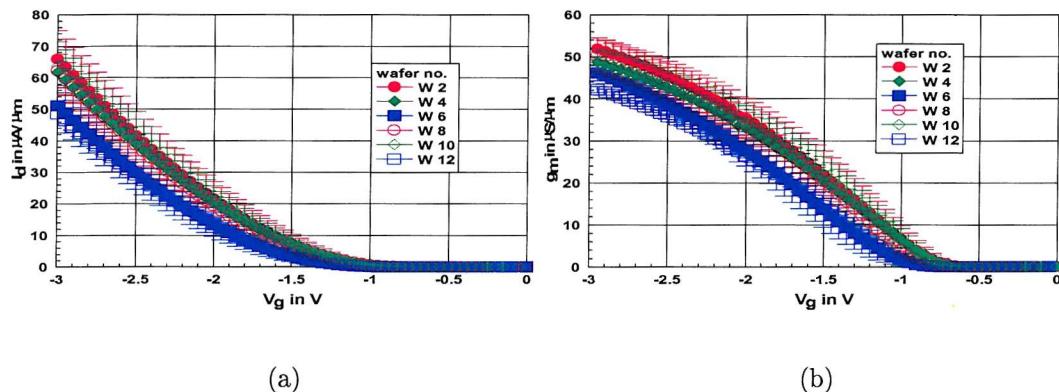

| 9.3       | Results . . . . .                                                   | 163        |

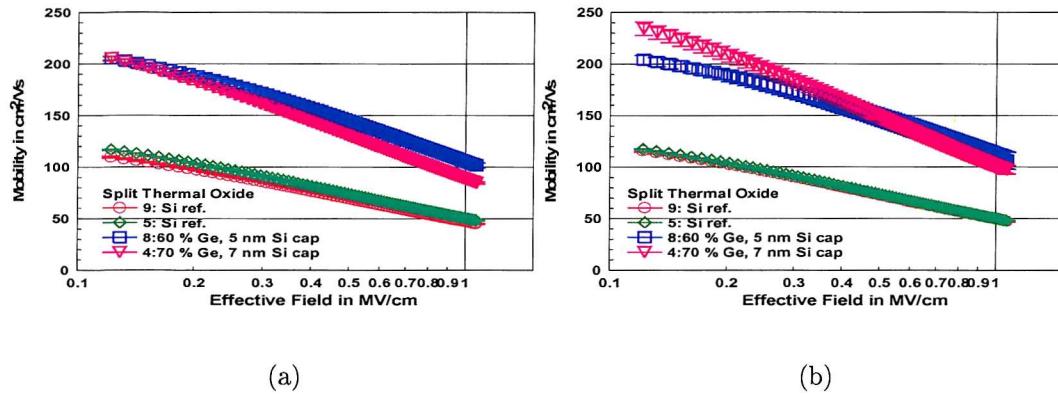

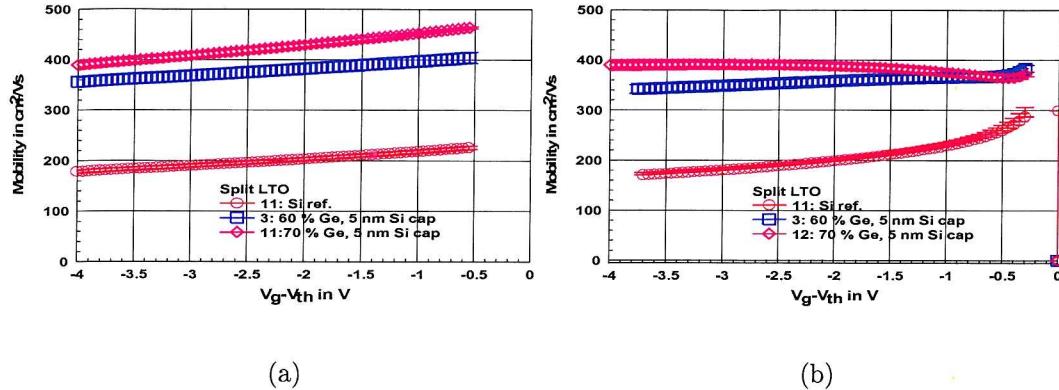

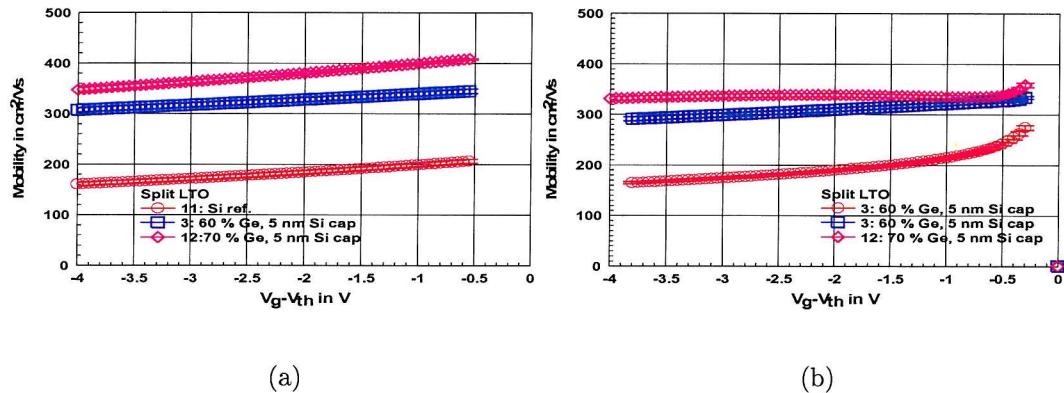

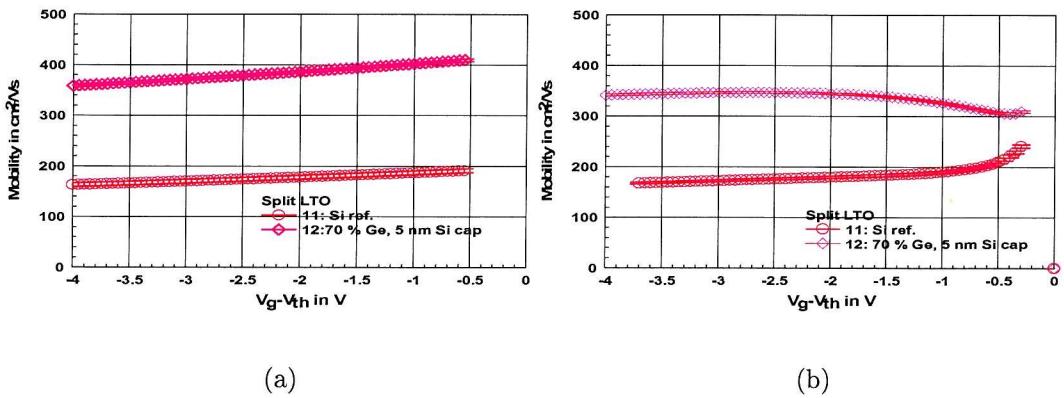

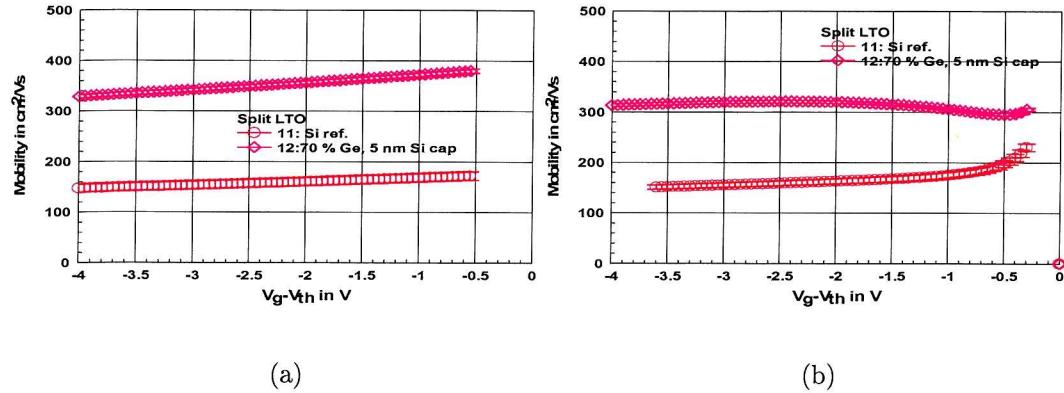

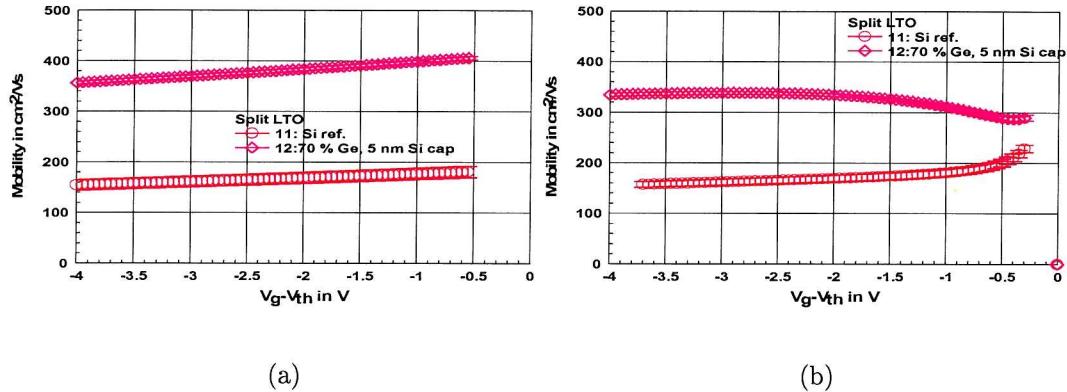

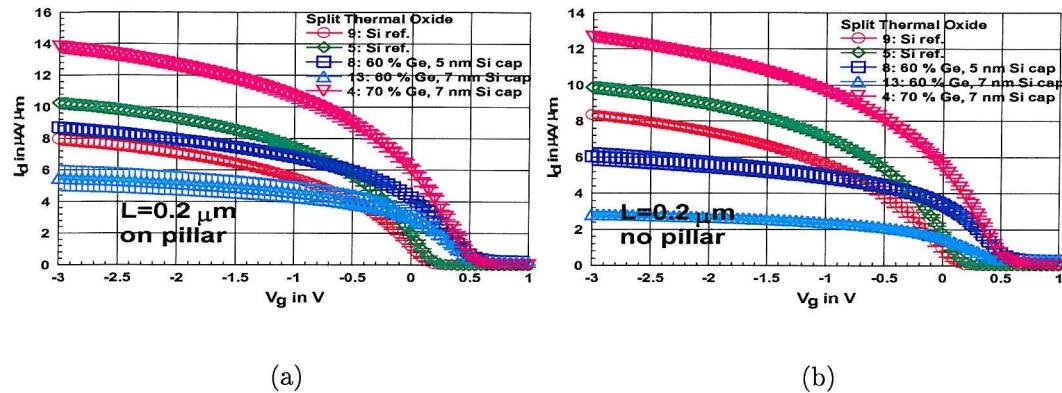

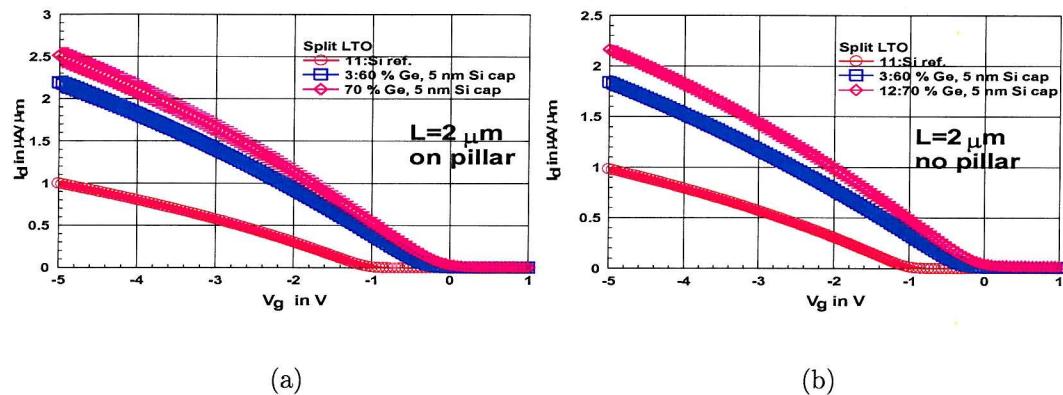

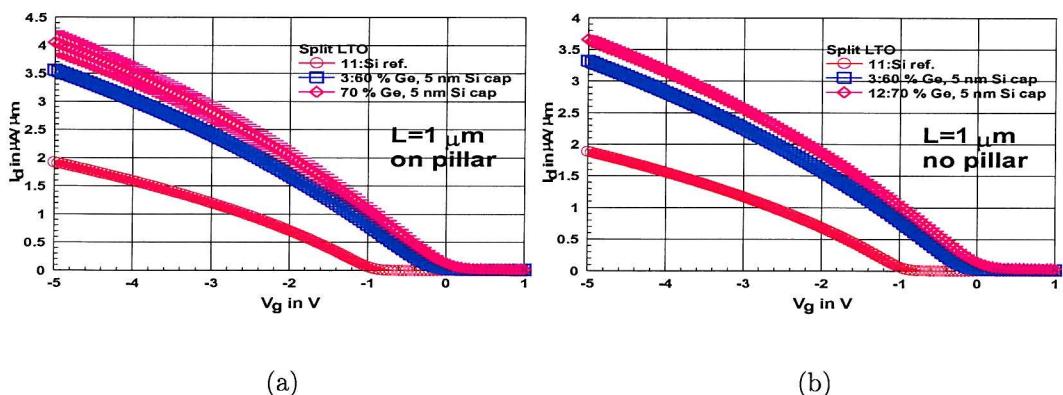

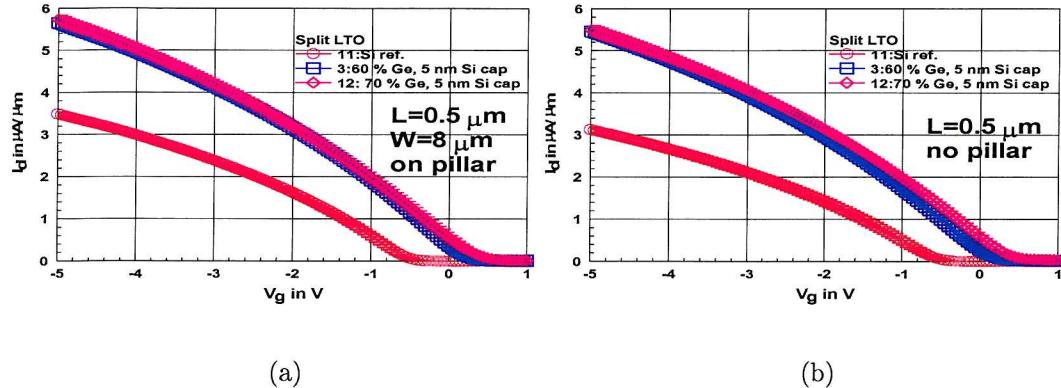

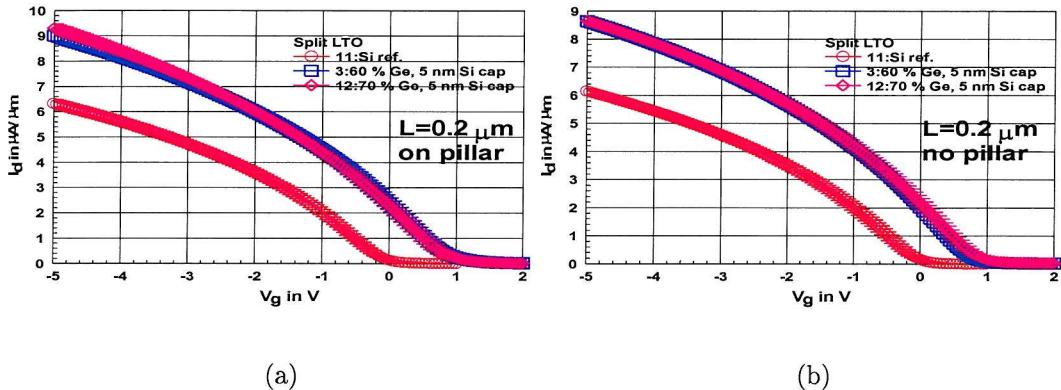

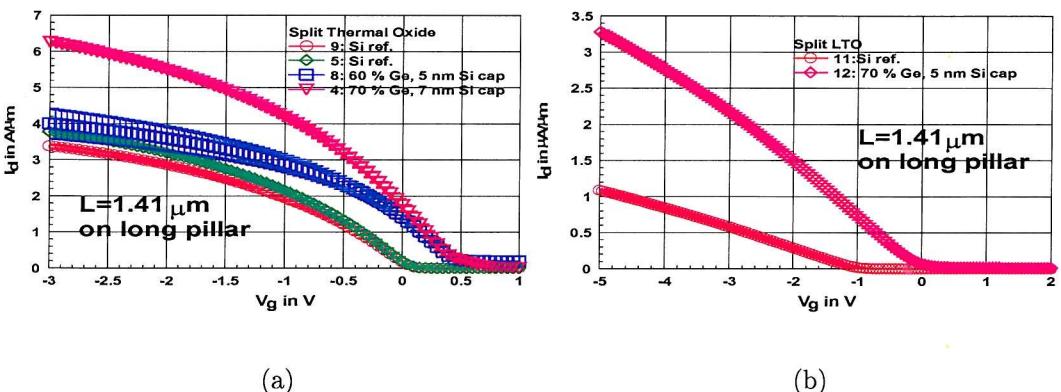

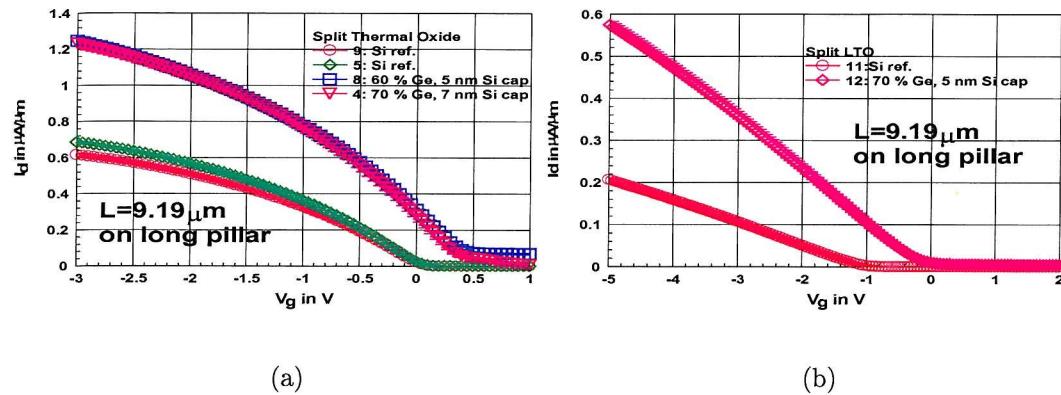

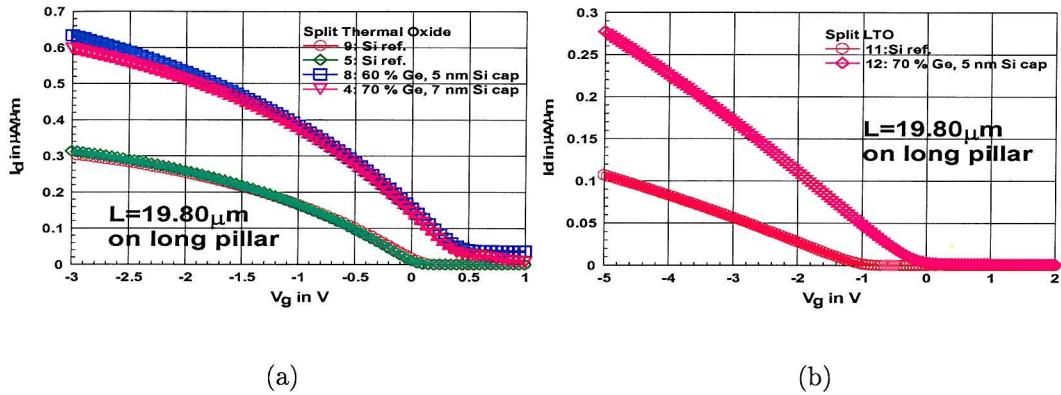

| 9.3.1     | MOSFETs with an LTO Gate Oxide . . . . .                            | 163        |

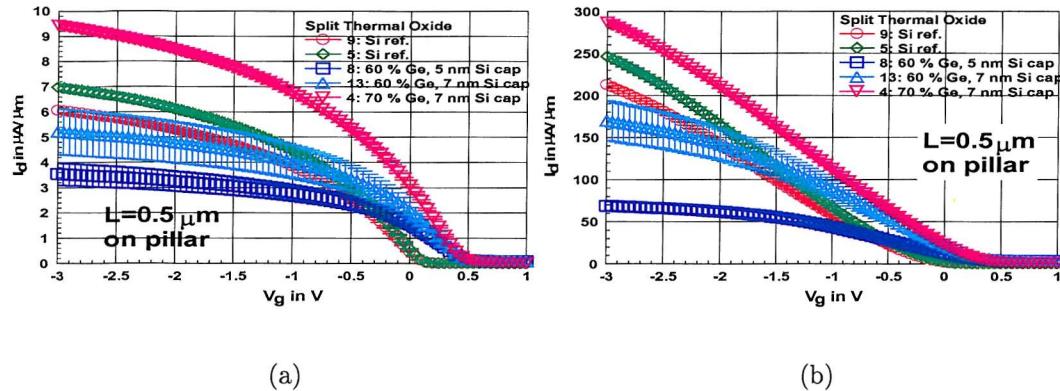

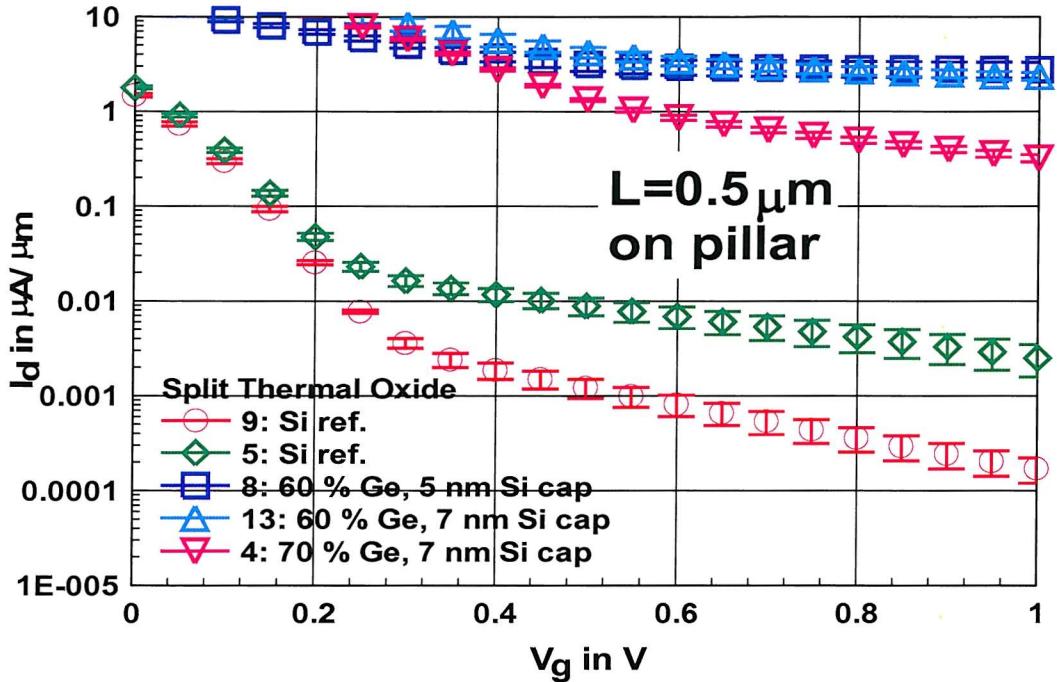

| 9.3.2     | MOSFETs with a Thermal Gate Oxide . . . . .                         | 168        |

| 9.4       | Conclusion . . . . .                                                | 171        |

| <b>10</b> | <b>Conclusions and Suggestions for Further Work</b>                 | <b>175</b> |

| 10.1      | Integration of Heterostructures in the Channel of MOSFETs . . . . . | 175        |

| 10.1.1    | Substrate Doping . . . . .                                          | 175        |

| 10.1.2    | Thermal Budget . . . . .                                            | 176        |

| 10.1.3    | Layer Architecture and Process Flow . . . . .                       | 176        |

| 10.1.4    | Wafer Cleaning . . . . .                                            | 176        |

| 10.2      | Fabricated Batches . . . . .                                        | 177        |

| 10.2.1    | Pseudomorphic SiGe CMOS Process . . . . .                           | 177        |

| 10.2.2    | SiGe CMOS/ $Ge^+$ Implantation Process . . . . .                    | 178        |

| 10.2.3    | SiGe Virtual Substrate/Limited Area Process . . . . .               | 179        |

| 10.3      | Further Work . . . . .                                              | 179        |

|                                                                         |            |

|-------------------------------------------------------------------------|------------|

| <b>A Calculation of the Error for Linear Curve Fitting</b>              | <b>184</b> |

| <b>B Process Listings</b>                                               | <b>187</b> |

| B.1 Pseudomorphic SiGe CMOS Process . . . . .                           | 187        |

| B.2 SiGe CMOS/ $Ge^+$ Implantation Process . . . . .                    | 190        |

| B.3 SiGe virtual substrate/limited area PMOS Process . . . . .          | 194        |

| <b>C Comparison between two parameter extraction routines</b>           | <b>198</b> |

| C.1 Measurements . . . . .                                              | 198        |

| C.2 Comparison of Results . . . . .                                     | 198        |

| C.3 Conclusion . . . . .                                                | 200        |

| <b>D Virtual Substrate/Limited Area PMOS Process - Complete Results</b> | <b>202</b> |

| D.1 Measurements . . . . .                                              | 202        |

| D.2 Extracted Parameters . . . . .                                      | 202        |

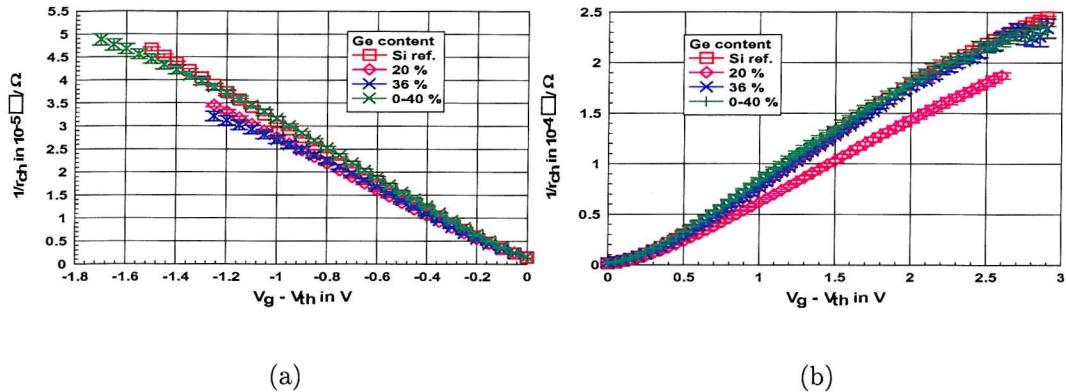

| D.3 Extracted Mobilities as a Function of the Gate Drive . . . . .      | 207        |

| D.4 Drain Current Measurements for $V_d = -50\text{ mV}$ . . . . .      | 212        |

| <b>E List of Publications</b>                                           | <b>218</b> |

# Chapter 1

## Introduction

### From the Dawn of the IC Era to SiGe MOS

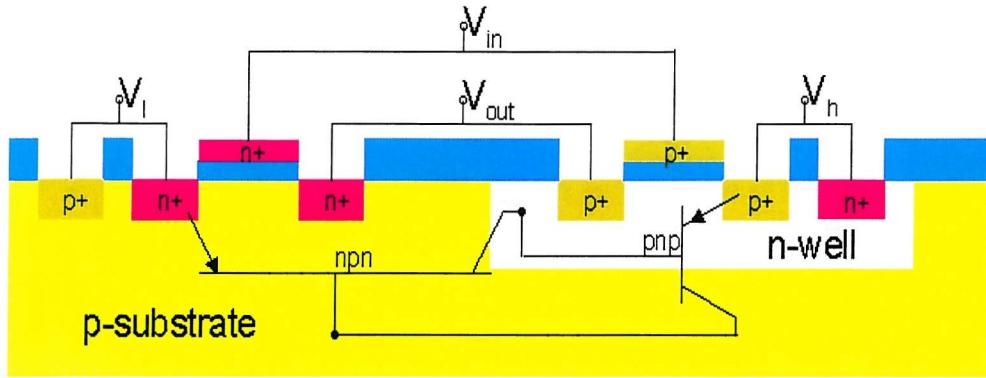

The MOSFET (Metal-Oxide-Semiconductor-Field-Effect-Transistor) [1-4] was proposed in the early 1930s by Lilienfeld and Heil. After Pearson and Shockley had studied the MOSFET in the late 1940s, Kahng and Atalla fabricated the first MOSFET using a thermally oxidized silicon structure in 1960. At the beginning of the IC era in 1959, ICs based on bipolar transistors occupied the broadest market share. Because of the advantages in device miniaturization, low power consumption, and high yield, the sales volume of CMOS (complementary MOS) based ICs that employs the pairing of n- and p-channel MOSFETs has steadily soared. In 1993, the MOSFET market share amounted to 75 % of the total IC market and is predicted to capture 88% by the year 2000. Apart from Si based MOSFETs and bipolar transistors, III-IV compound semiconductors for high speed devices form the third major IC group.

The speed performance of the MOSFET has steadily been improved by shrinking the channel length and gate oxide thickness. Today, scaling is close to reaching its performance and physical limits. Thin gate oxides result in the tunneling of carriers through the gate oxide degrading continuously the oxide quality. The negative effect of scaling the gate length on the subthreshold characteristics has to be compensated by increasing the bulk doping concentration. However, the increase of the bulk doping concentration leads to the reduction of the mobility and an increase of the electrical field at the source and drain junctions favoring hot carrier generation.

Semiconductor heterostructures were suggested by Shockley in a patent for the first time in 1951. Since the beginning, Ge has been an obvious candidate for the fabrication of silicon based heterostructures because it is chemically compatible with Si. However, the large lattice mismatch between Si and Ge makes it difficult to grow Ge epilayers on a Si substrate. In the late 1960s and early 1970s, the first unsuccessful attempts to grow Ge epilayers on a Si substrate were performed.

The first strained SiGe heterostructure devices were realized by Erich Kasper based on the

concept of Frank and Van der Merwe. The first SiGe FET was reported in 1985 [5]. SiGe can be used in gate, source and drain or substrate. In the gate, SiGe can reduce the gate resistance and adjust the threshold voltage. In source and drain, SiGe can improve the short channel characteristics and prevent parasitic bipolar transistor action. The interest in strained SiGe layers for the application in the channel arose from the discovery that strained SiGe layers possess a higher mobility than silicon and was soon adopted as an alternative approach to enhance the speed performance of MOSFETs.

## Objective of this Project

This work focuses on the use of strained SiGe layers in the channel of p-MOSFETs. A considerable performance improvement of SiGe MOSFETs in comparison to Si reference MOSFETs was found [6]. However, the SiGe MOSFETs presented in ref. [6], do not have a performance comparable to state-of-the-art MOSFETs because the process was tailored for the requirements imposed by the incorporation of strained SiGe layers.

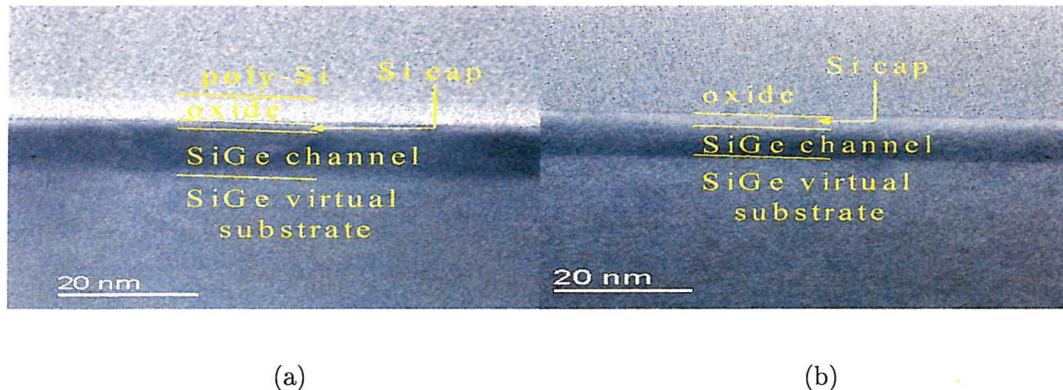

The integration of an MBE grown SiGe layer into a competitive CMOS process is one of the three major objectives of this project. Fundamental problems are the thermal budget and the control of the Si cap layer. A high thermal budget can lead to the relaxation of the SiGe layer and, in consequence, a deteriorated performance. A thin Si cap layer is essential for the confinement of the carriers in the SiGe channel.

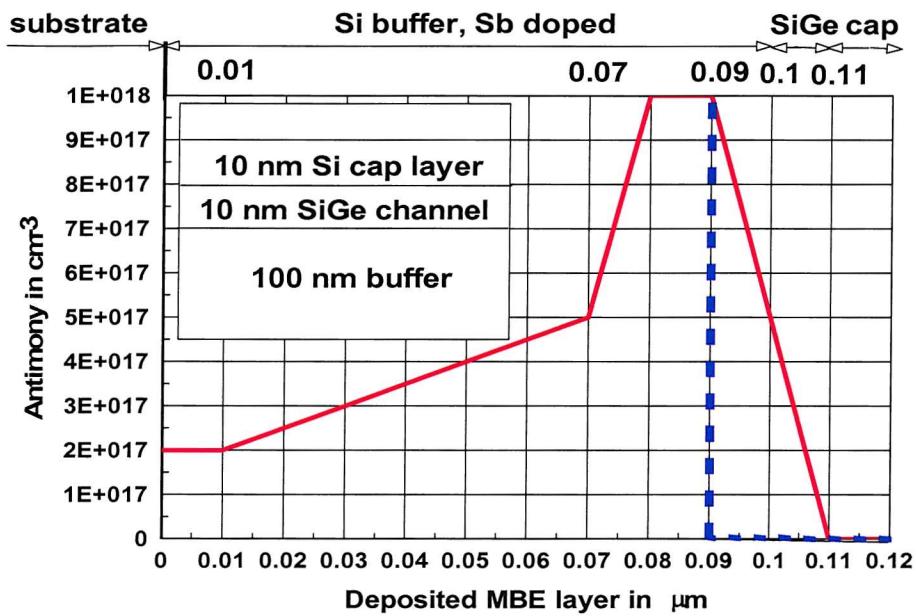

A thick Si buffer layer is supposed to be the prerequisite for a high hole mobility in the SiGe channel. However, small geometry devices require a sufficient dopant concentration in the bulk in order to prevent short channel effects. Implantation may damage the integrity of the heterostructure and little is known about the incorporation of dopants during MBE. The incorporation of an insitu doped MBE layers poses further problems in CMOS as MBE does not allow selective growth. A thick, insitu doped MBE layer must either be etched off or counterdoped for the n-MOSFETs.

The fabrication of MOSFETs with a  $Ge^+$  implanted channel [7-10] is a further objective of this work. MBE is the ideal technique for the fabrication of high quality heterostructures. But, its major drawback is that heterostructures grown by MBE cannot be easily integrated into CMOS. Besides, MBE does not have a high throughput and is expensive. Although strained heterostructures with only low Ge concentration can be achieved by ion implantation compared to MBE, the low cost for implantation and the capability to implant  $Ge^+$  into a selected area may render ion implantation an attractive alternative to MBE. In solid phase epitaxial growth (SPEG), strained SiGe layers can be grown in a recrystallization step after the implantation of  $Ge^+$ .  $Ge^+$  implantation does not allow the fabrication of a Si cap layer on top of the SiGe channel which reduces carrier scattering at the  $Si/SiO_2$ -interface. As proposed in ref. [7], the performance of  $Ge^+$  implanted p-MOSFETs might be enhanced due to Ge segregation during

gate oxide growth resulting in a higher Ge peak concentration. The EPIFAB process (epitaxial regrowth across phase boundaries) developed at the University of Surrey enables the fabrication of SiGe/Si heterojunctions without extended defects [11-15].

The third and last objective of this project is the investigation of p-HMOSFETs displaying a considerable mobility enhancement. A high Ge content in the strained SiGe channel resulting in a considerable mobility enhancement can be achieved only if grown on top of a virtual substrate [16-20]. As the virtual substrate has to be relaxed, a thick MBE layer is in general required.

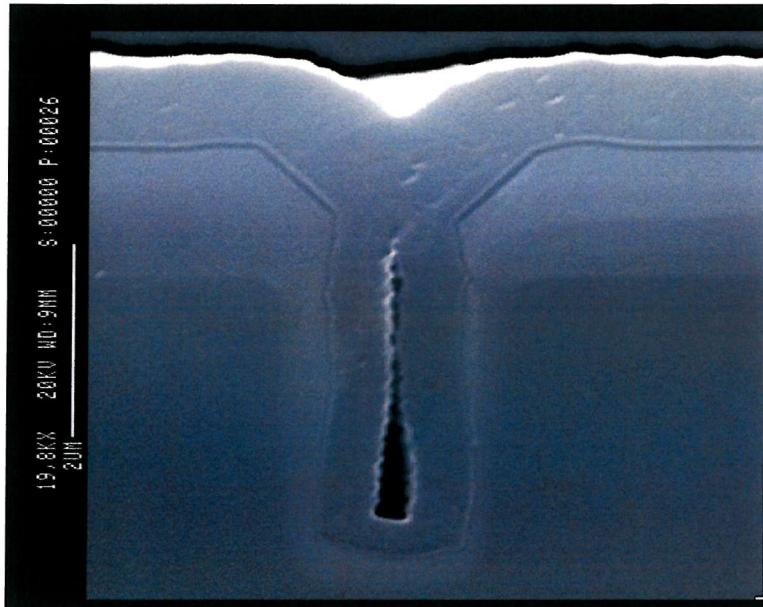

The local MBE growth on microscopic pillars can reduce the required thickness of the virtual substrate layer, crosshatch, and threading dislocations [21, 22]. Trenches etched into the Si substrate interrupt the MBE layer and are suitable sites for the nucleation of dislocations. SiGe MOSFETs fabricated on pillars should have a better performance than those on a flat surface.

## Organization of the Thesis

The thesis contains 10 chapters and 4 appendices. All symbols are explained in the table at the beginning of the thesis.

The first chapter introduces the reader into the topic of the thesis. Chapters 2-6 give an overview over issues related to this work. Chapter 2 addresses the physical properties of SiGe heterojunctions. Strain is inherent in SiGe heterojunctions due to the lattice mismatch between Si and Ge and improves the electrical characteristics of SiGe alloys.

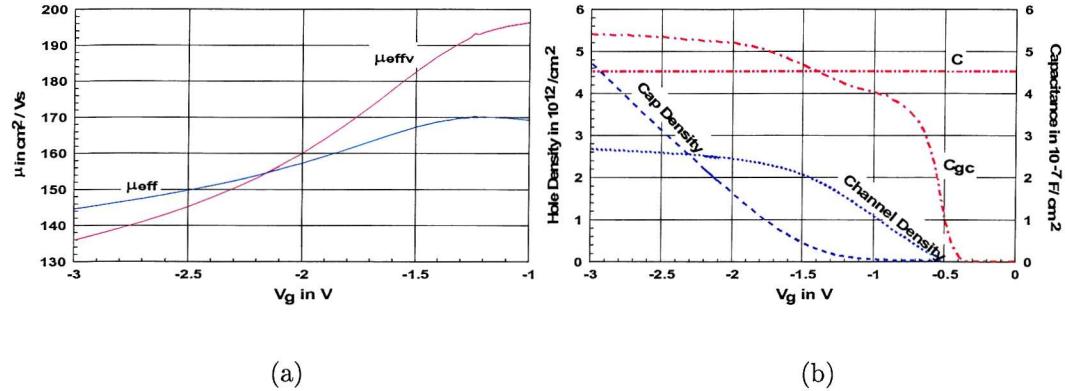

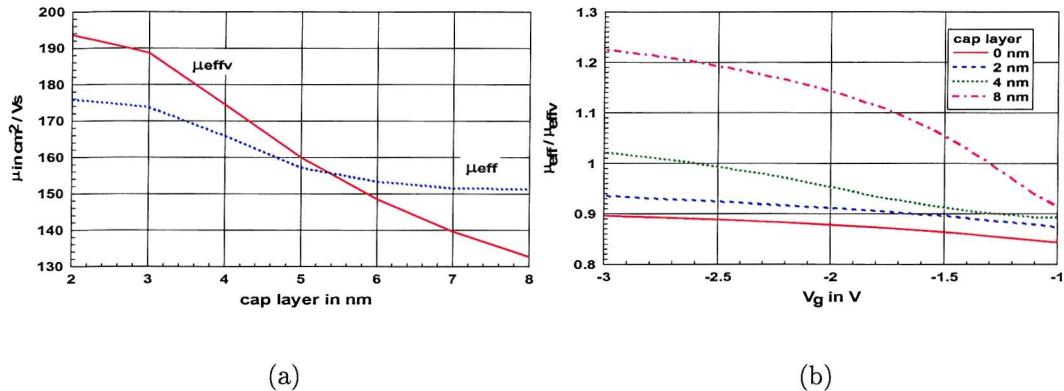

The third chapter describes the theory of conventional MOSFETs. The drain current characteristics of HMOSFETs with a strained SiGe layer differ slightly from those of conventional MOSFETs. The gate capacitance and the mobility can be a strong function of the gate bias. The constant capacitance approximation and a simple mobility degradation model are usually not justified. No analytical expression for the HMOSFET is given, but the different device behavior can be explained qualitatively.

In the fourth chapter, parameter extraction routines for conventional and HMOSFETs are discussed. The mobility extraction for HMOSFETs is investigated. It is shown that split-CV measurements developed for conventional MOSFETs with an ultrathin oxide are the appropriate methods for mobility extraction.

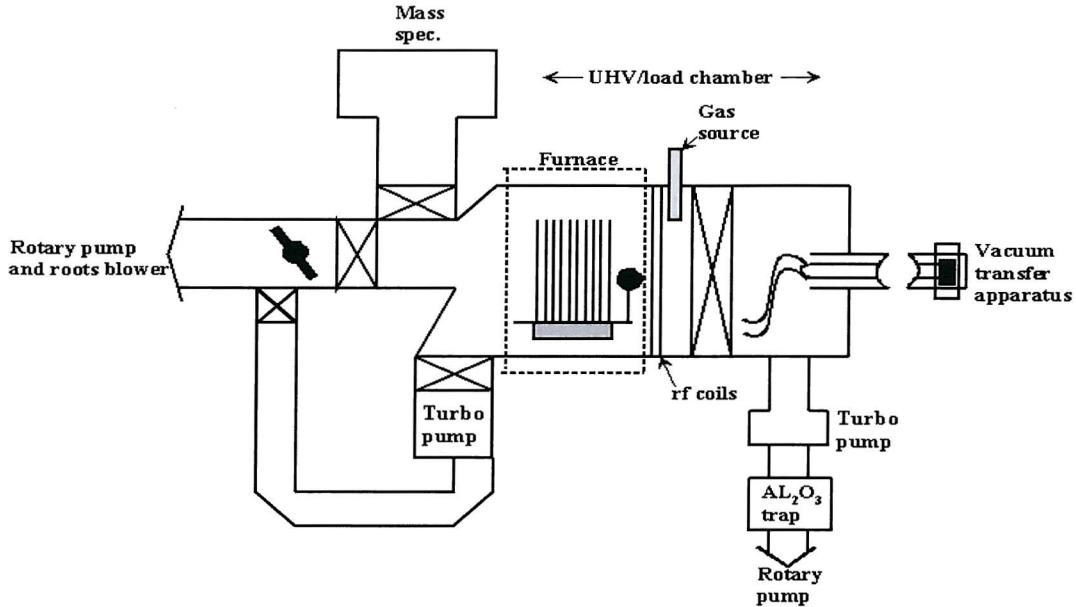

Chapter 5 deals with vapor phase deposition. Vapor-phase methods are predominant in the deposition of thin films. UHVCVD and MBE - both vapor phase deposition methods - are the most common methods for the fabrication of strained SiGe heterostructures. Chapter 6 reviews further standard processing steps that are also used in SiGe technology. The adaptations which may be imposed by the presence of strained SiGe layers (layer control, thermal budget, integrity of the heterojunction) and the potential benefits arising from the use of Ge are discussed.

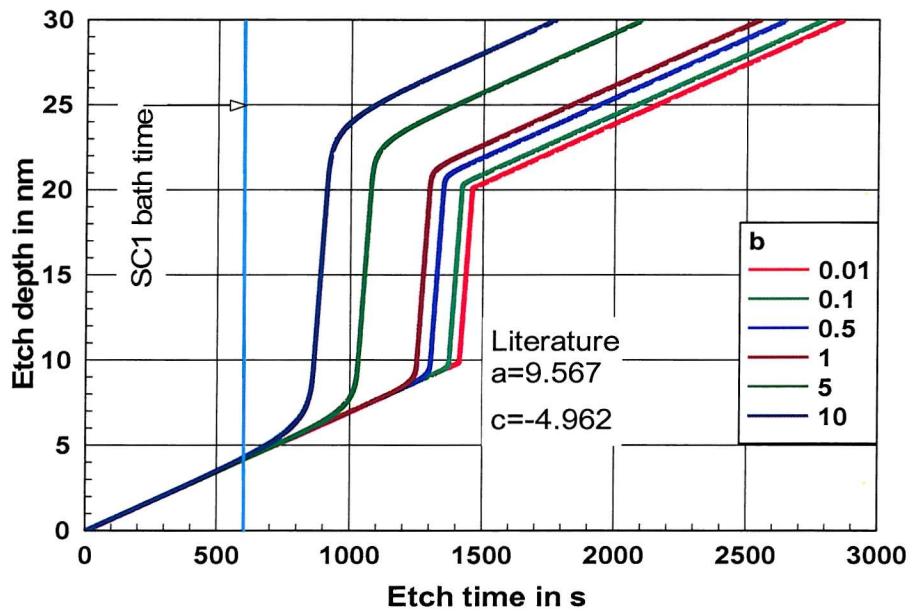

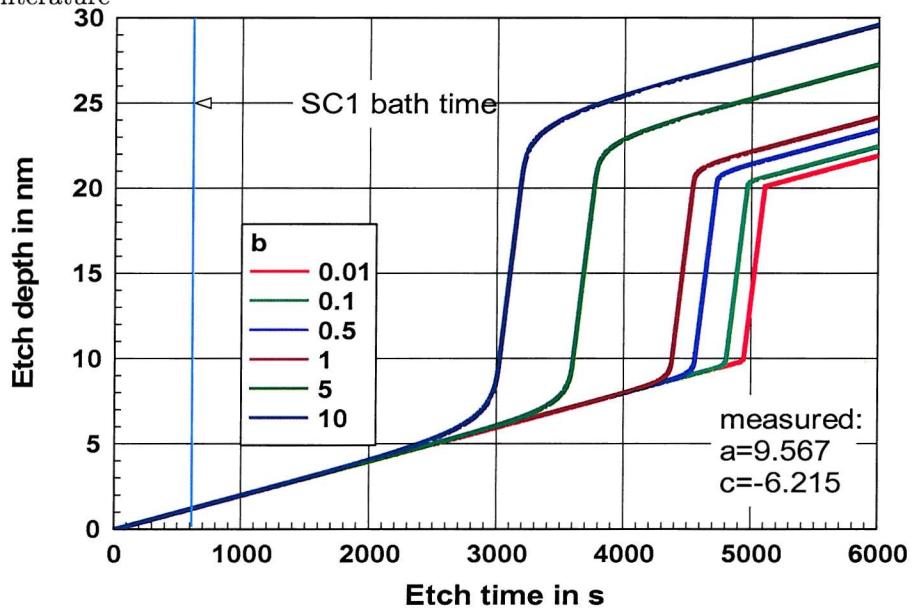

Chapters 7-9 present SiGe batches processed in the course of this work. A SiGe CMOS process with a thin thermal gate oxide, an elevated thermal budget, a thin Si cap, and an insitu

doped MBE layer is investigated in chapter 7. The MBE layer is counterdoped for the fabrication of n-MOSFETs. The initial cap layer is thinned by several cleans and the growth of the thermal gate oxide. The calculation of the final cap layer thickness is based on an internal experiment on the etch rate of standard cleans. The control of the Si cap layer is even more critical than previously thought.

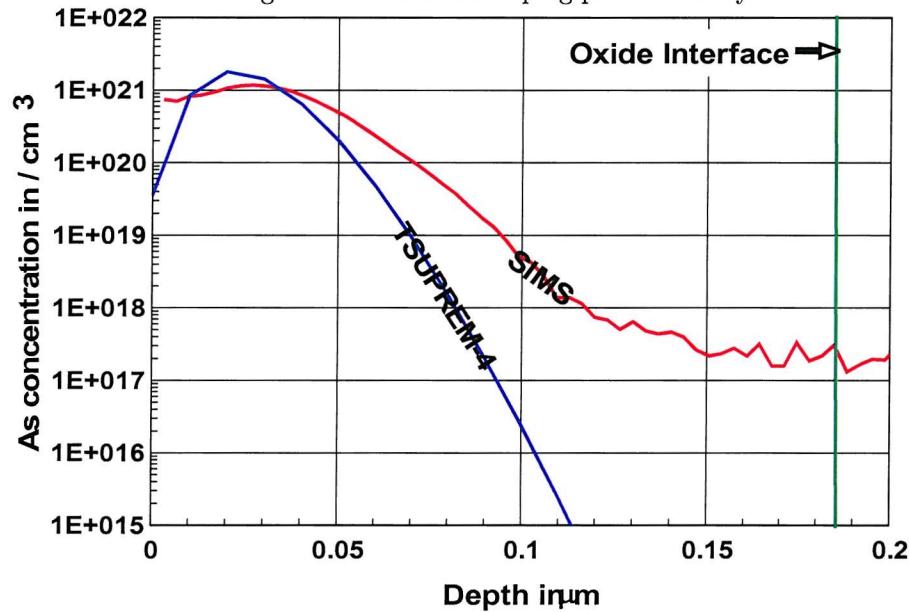

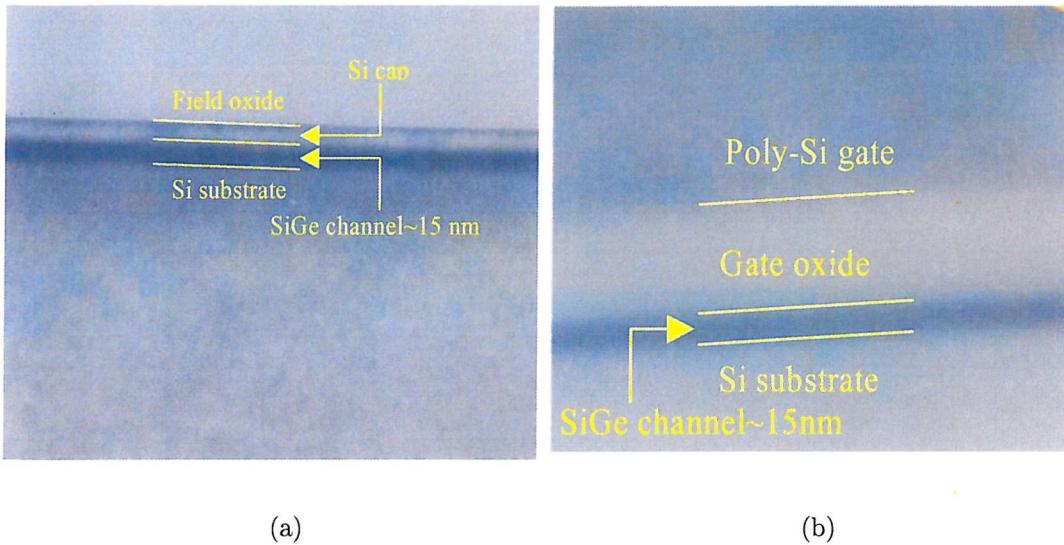

Chapter 8 presents a SiGe CMOS/ $Ge^+$  implantation batch. This batch is based on a conventional CMOS batch and the EPIFAB process developed at the University of Surrey and is subject to the thermal budget of a conventional CMOS batch. The amorphous layer is recrystallized during gate oxide growth. Emphasis is put on the characterization of the  $Si/SiO_2$ -interface which may be modified due to the segregation of Ge during gate oxidation.

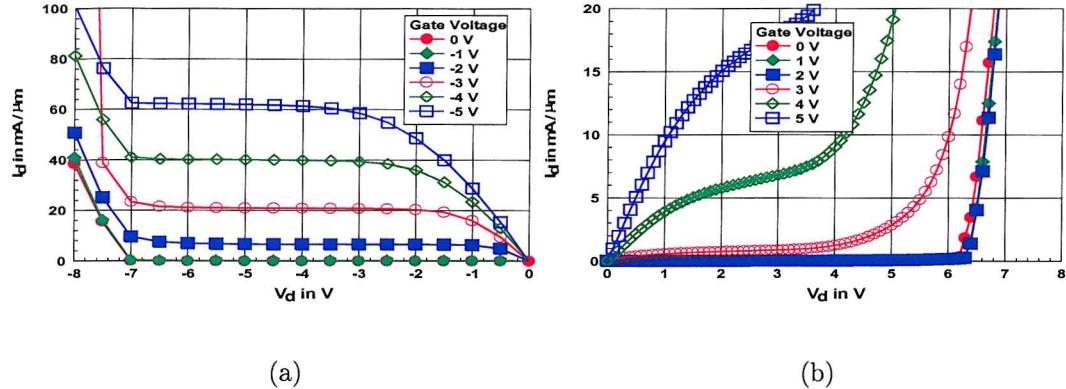

A SiGe virtual substrate/limited area PMOS batch is described in chapter 9. A virtual substrate layer is grown in order to achieve a high Ge content in the SiGe channel. The devices are fabricated on tiny pillars surrounded by trenches reducing the thickness of the virtual substrate and improving its quality. Such devices are compared to Si reference p-MOSFETs and p-HMOSFETs which are not fabricated on pillars.

In chapter 10, a conclusion of this project and a proposal for further work are given. In appendix A, a formula used in error calculation is derived. The detailed process listings of all three fabrication processes are given in appendix B. Appendix C presents electrical results for the SiGe CMOS/  $Ge^+$  implantation batch extracted with an alternative parameter extraction routine. Appendix D lists the complete results for the limited area/virtual substrate batch.

# Bibliography

- [1] C. Y. Chang and S. M. Sze, "ULSI Technology", McGraw-Hill, 1996

- [2] S. M. Sze, "Physics of Semiconductor Devices", John Wiley & Sons, 1981

- [3] N. Afshar-Hanaii, "Some Aspects of Submicron CMOS Technology", Ph.D. thesis, University of Southampton, 1993

- [4] S. C. Jain, "Germanium-Silicon Strained Layers and Heterostructures", Academic Press, 1994

- [5] T. P. Pearsall, J. C. Bean, R. People, and A. T. Fiory, " $Ge_xSi_{1-x}$  modulation-doped p-channel field-effect transistors", in Proc. 1st Int. Symp. Silicon Molecular Beam Epitaxy, J. C. Bean Ed., Pennington, NJ, Electrochemical Society, pp. 400-405, 1985

- [6] R. M. Sidek, U. N. Straube, A. M. Waite, A. G. R. Evans, C. Parry, P. Phillips, T. E. Whall, and E. H. C. Parker, "SiGe CMOS fabrication using SiGe MBE and anodic/LTO gate oxide", Semicond. Sci. Technol., Vol. 15, pp. 135-138, 2000

- [7] H. Jiang and R. G. Elliman, "Electrical Properties of GeSi Surface- and Buried-Channel p-MOSFET's Fabricated by Ge Implantation", IEEE Transactions on Electron Devices, Vol. 43, No. 1, pp. 97-103, 1996

- [8] K. C. Liu, S. K. Ray, S. K. Oswal, and S. K. Banerjee, "A deep submicron  $Si_{1-x}Ge_x/Si$  Vertical PMOSFET Fabricated by Ge Ion Implantation", IEEE Electron Dev. Lett., Vol. 19, No. 1, pp. 13-15, 1998

- [9] S. Kal, N and B. Chakrabarti, "Strained Silicon-SiGe Devices using Germanium Implantation", IETE J. Res., Vol. 43, No. 2 & 3, pp. 185-192, 1997

- [10] Z. Xia, E. O. Ristolainen and P. H. Holloway, " $SiGe/Si$  heterostructures produced by double-energy  $Si^+$  and  $Ge^+$ , and  $Ge^+$  and  $Ge^{2+}$  ion implantations", J. Vac. Sci. Technol. B, Vol. 16, No. 5, pp. 2629-2632, 1998

- [11] Y. Suprun-Belevich, F. Christiano, A. Nejim, P. L. F. Hemment, and B. J. Sealy, "Evolution of mechanical strain and extended defects in annealed (1 0 0) silicon samples implanted with  $Ge^+$  ions", Nucl. Instr. and Meth. in Phys. Res. B 140, pp. 91-98, 1998

- [12] A. Nejim, N. P. Barradas, C. Jeynes, F. Cristiano, E. Wendler, K. Gaertner, and B. J. Sealy, "Residual post anneal damage of Ge and C co-implantation of Si determined by quantitative RBS-channeling", Nucl. Instr. and Meth. in Phys. Res. B 139, pp. 244-248, 1998

- [13] F. Christiano, A. Nejim, B. de Maudit, A. Claverie, and P. L. F. Hemment, "Characterization of extended defects in SiGe alloys formed by high dose  $Ge^+$  implantation into Si", Nucl. Instr. and Meth. in Phys. Res. B 120, pp. 156-160, 1996

- [14] F. Christiano, A. Nejim, Y. Suprun-Belevich, A. Claverie, and P. L. F. Hemment, "Formation of extended defects and strain relaxation in ion beam synthesised SiGe alloys", Nucl. Instr. and Meth. in Phys. Res. B 147, pp. 35-42, 1999

- [15] F. Christiano, C. Bonafo, A. Nejim, S. Lombardo, M. Omri, D. Alquier, A. Martinez, S. U. Campisano, P. L. F. Hemment, and A. Claverie, "Interstitial trapping efficiency of  $C^+$  implanted into preamorphised silicon - control of EOR defects", Nucl. Instr. and Meth. in Phys. Res. B 127 / 128, pp. 22-26, 1997

- [16] A. J. Pidduck, D. J. Robbinson, D. Wallis, G. M. Williams, A. C. Churchill, J. P. Newey, C. Crumpton, and P. W. Smith, "On the growth of high quality relaxed  $Si_{1-x}Ge_x$  layers on Si by vapour phase epitaxy", Inst. Phys. Conf. Ser., No. 157, pp. 135-144, 1997

- [17] M. Kummer, B. Voegli, and H. Von Kaenel, "STM study of step graded  $Si_{1-x}Ge_x/Si(100)$  buffers", Thin Solid Films, Vol. 336, pp. 100-103, 1998

- [18] E. Muller, R. Hartmann, C. David, and D. Grutzmacher, "Structural characterization of SiGe step graded buffer layers grown on prestructured Si [100] substrates by molecular beam epitaxy", Thin Solid Films, Vol. 336, pp. 92-95, 1998

- [19] K. Lyutovich, E. Kasper, F. Ernst, M. Bauer, and M. Oehme, "Relaxed SiGe buffer layer growth with point defect injection", Materials Science and Engineering, Vol. B71, pp. 14-19, 2000

- [20] E. Kasper, K. Lyutovich, M. Bauer, and Michael Oehme, "New virtual substrate concept for the vertical MOS transistor", Thin Solid Films, pp. 319-322, 1998

- [21] T. Rupp, J. Messarosch, and I. Eisele, "Silicon-germanium molecular beam epitaxy system for high-quality nanostructures and devices", Journal of Crystal Growth, Vol. 183, pp. 99-108, 1998

- [22] T. Rupp, F. Kaesen, W. Hansch, E. Hemmerl, D. J. Gravesteijn, R. Schorer, E. Silveira, G. Abstreiter, and I. Eisele, "Defect-free strain relaxation in locally MBE-grown SiGe heterostructures", Thin Solid Films, Vol. 294, pp. 27-32, 1997

## Chapter 2

# SiGe Heterostructures

The performance of CMOS circuits has steadily been improved by aggressively scaling the device dimensions to the submicron regime. The scaling becomes more and more difficult due to technological and physical limitations. But, the performance of CMOS devices could be improved by applying new materials. Today, silicon dominates microelectronics, whereas other semiconductor materials such as GaAs only occupy niche markets. In the near future, it is unlikely that other materials will substitute silicon whose  $Si - SiO_2$  structure offers unique physical and chemical properties.

However, the development of new compound materials based on silicon could further enhance the performance of integrated circuits. The Si/SiGe system is a strong candidate for a new technology that would be compatible with the existing Si technology and might considerably enhance the speed of microelectronics devices because of higher carrier velocities.

The purpose of this chapter is to review the fundamental physical properties of SiGe heterostructures. SiGe heterojunctions without defects are necessarily strained due to the lattice mismatch between Si and Ge. Strain plays an integral role in the concept of the SiGe heterojunction. Strained SiGe heterostructures have better electrical properties than Si such as a higher carrier mobility. But, the same properties can be degraded by strain relief. Defects are formed if a certain energy barrier which is lowered with increasing temperature is surpassed.

### 2.1 Crystal Structure

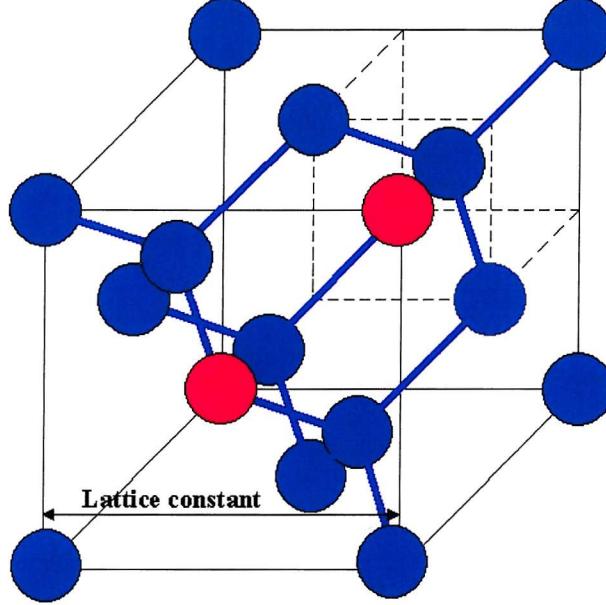

Binary alloys of silicon and germanium are continuously miscible and crystallize in a diamond lattice. The diamond lattice consists of two face-centered cubic lattices displaced a quarter of the space diagonal. Its unit cell contains eight atoms (see fig. 2.1; note: in the  $45^\circ$ -perspective, the two atoms at the front shown in red obscure two atoms at the back).

SiGe [1-13] bulk alloys are never ordered. However, order [1,14] exists at the interfaces of SiGe layers deposited by MBE on Si substrates of (100) orientation at growth temperatures between

Figure 2.1: Diamond structure

| Parameter | Si    | Ge    |

|-----------|-------|-------|

| $c_{11}$  | 165.8 | 128.5 |

| $c_{12}$  | 63.9  | 48.3  |

| $c_{44}$  | 79.6  | 66.8  |

Table 2.1: Elastic constants for *Si* and *Ge*

300° C and 800° C. An energetically more favorable configuration is certainly responsible for the order of thin SiGe layers and not yet fully explained.

The lattice parameter of Si and Ge differ by 4.2% at room temperature. The misfit increases slightly with temperature. The lattice parameter  $a_0(x)$  of  $Si_{1-x}Ge_x$  alloys deviates slightly from Vegard's rule and depends parabolically on the Ge composition [1, chap. 2]:

$$a_0(x) = 0.002733x^2 + 0.01992x + 0.5431(nm) \quad (2.1)$$

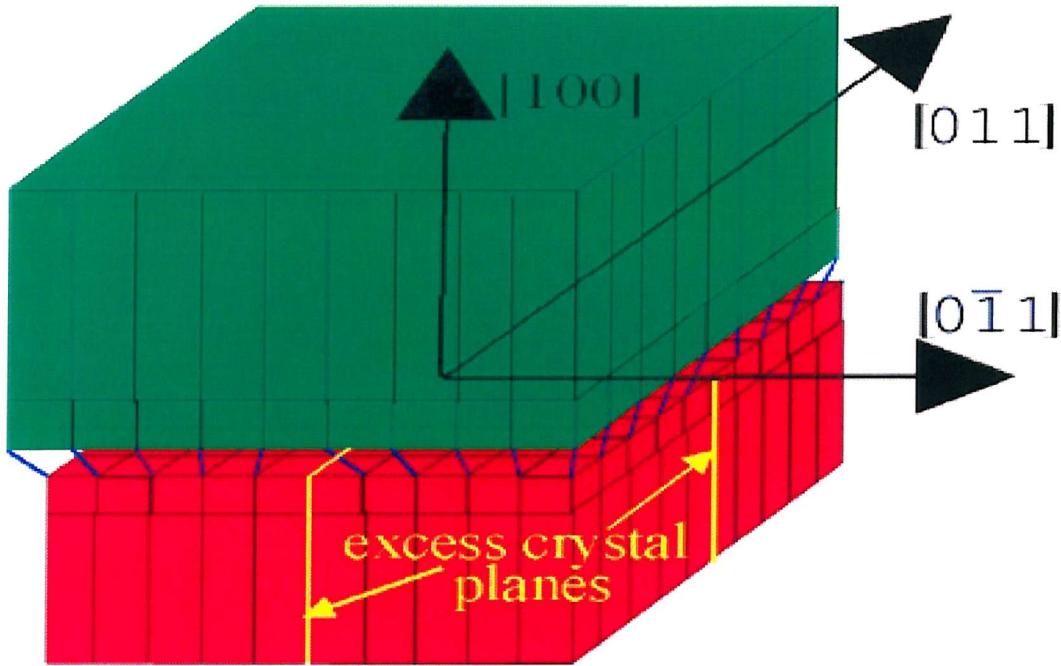

In an epitaxial layer with lattice constant  $a_1$  grown on a substrate with different lattice constant  $a_0$ , the mismatch  $f$  can be accommodated by the tetragonal distortion and the formation of misfit dislocations. In heterojunctions, misfit is exclusively accommodated by misfit strain within the critical thickness. Then, its lattice parameter in the growth plane  $a_{\parallel}$  is completely determined by the underlying substrate. In the strained epilayer, the lattice parameter perpendicular to the growth plane  $a_{\perp}$  is 5.82 Å for strained Ge on relaxed Si and 5.26 Å for strained Si on relaxed Ge.

The elastic constants of SiGe alloys  $c_{ij}$  can be determined from linear interpolation [1, chap. 3.1; 16; 17]:

$$c_{ij} = c_{ij,Ge}x + c_{ij,Si}(1 - x) \quad (2.2)$$

Where  $c_{ij,Ge}$  and  $c_{ij,Si}$  are the elastic constants of pure Si and Ge given in tab. 2.1.

Figure 2.2: Threading dislocation acting as a misfit dislocation source in a capped SiGe layer

The strain parallel to the plane of the interface  $\epsilon_{\parallel}$  is given by [17]:

$$\epsilon_{\parallel} = \frac{a_{\parallel}}{a_0} - 1 \quad (2.3)$$

Where  $a_{\parallel}$  and  $a_0$  are respectively the lattice constant of the substrate and the lattice constant of the relaxed alloy given by equation 2.1. The strain perpendicular to the plane of the interface  $\epsilon_{\perp}$  is given by [17]:

$$\epsilon_{\perp} = \frac{a_{\perp}}{a_0} - 1 \quad (2.4)$$

Where  $a_{\perp}$  is given by [17]:

$$a_{\perp} = a_0 \left[ 1 - D \left( \frac{a_{\parallel}}{a_0} - 1 \right) \right] \quad (2.5)$$

D depends on the interface orientation defined by Miller indices [17]:

$$D^{001} = 2 \frac{c_{12}}{c_{11}} \quad (2.6)$$

$$D^{110} = \frac{c_{11} + 3c_{12} - 2c_{44}}{c_{11} + c_{12} + 2c_{44}} \quad (2.7)$$

$$D^{111} = 2 \frac{c_{11} + 2c_{12} - 2c_{44}}{c_{11} + 2c_{12} + 4c_{44}} \quad (2.8)$$

## 2.2 Strain Relaxation of $Si_{1-x}Ge_x/Si$ Heterostructures

The critical thickness [18-23] is the minimum layer thickness at which the generation of misfit dislocations at the interface is energetically favored and can be found from equilibrium theory. It depends on the growth conditions (temperature, pressure...), the design of the final transistor (ie capped layer or not), the nucleation mechanism, the substrate and the germanium fraction. Capped SiGe layers [1, chap. 1.2] are slightly more stable than uncapped SiGe layers. Misfit strain relief may lag behind equilibrium predictions despite the presence of dislocations as it is often retarded by barriers to nucleation and motion of dislocations (Peierls-Nabarro barrier,

Figure 2.3: Plane (red hollow circles) slips over another plane (yellow solid circles)

[18, p. 215]). The discrepancy between theoretical predictions and experimental results becomes obvious for low growth temperatures. The regime between experimental measurement and theoretical values is often referred to as metastable regime.

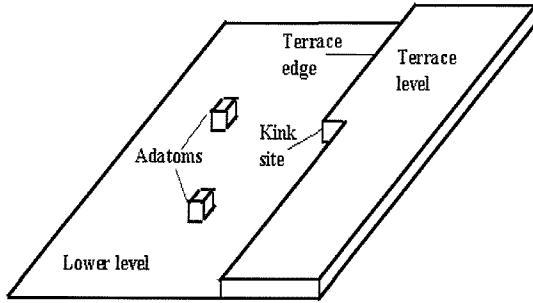

In general, dislocations cannot terminate within the bulk of a crystal, but must either form a closed loop or at a node with another defect, eg other dislocation or surface (image forces, [18, p. 88]). A dislocation segment within a stressed region of a crystal experiences a force that has both climb and glide components. Gliding is opposed by the so-called Peierls barrier that is due to the discrete nature of the crystal, but is usually much faster than climbing that requires material transport. When the stress is too small to overcome the Peierls barrier, dislocations can still migrate by thermal creation, migration of kinks and diffusion.

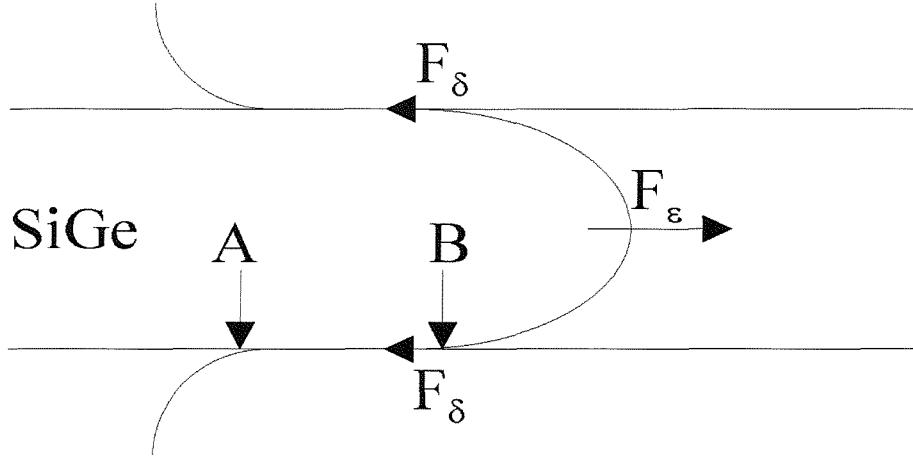

Threading dislocations are the most favorable sources of misfit dislocations. As displayed in fig. 2.2, an existing threading dislocation is bowed under the elastic force  $F_\epsilon$  of the strained  $Si_{1-x}Ge_x$  layer and elongated to form a misfit dislocation line between A and B.

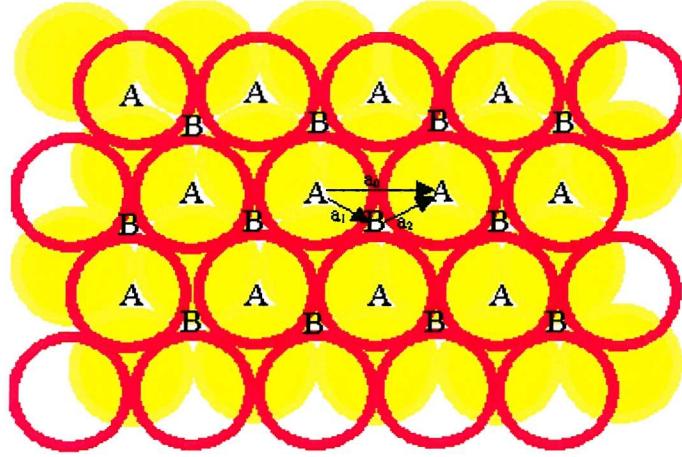

In crystals with diamond lattice, lattice constant  $a$  and covalent bonds like Si and Ge, perfect dislocations whose Burgers vector is a lattice translation vector have Burgers vector  $a/2 < 101 >$  and slip on  $\{111\}$  glide planes. Fig. 2.3 illustrates how the perfect dislocations dissociate into Shockley partial dislocations [1, chap. 1.2; 18, p. 93]:

$$\begin{aligned} a_o &= a_1 + a_2 \\ a/2 < 101 > &= a/6 < 211 > + a/6 < 1\bar{1}2 > \end{aligned} \quad (2.9)$$

Instead of moving directly from a lattice site A to another, it can be energetically favorable to move first to a B site and then to an A site because the energy of a dislocation is proportional to the square of its Burgers vector. The perfect dislocation with Burgers vector  $a/2 < 101 >$  is stable for low Ge concentration and thick epilayers. It splits up otherwise into two dislocations with Burgers vectors  $a/6 < 211 >$  and  $a/6 < 1\bar{1}2 >$ . The angle between the Burgers vector and the misfit dislocation line is  $60^\circ$  for the parent  $a/2 < 101 >$ ,  $30^\circ$  and  $90^\circ$  respectively for

the  $a/6 < 211 >$  and  $a/6 < 1\bar{1}2 >$  dislocations. These two Shockley partial dislocations [18, p. 91] are mutually repelled and glide apart. It results a ribbon of stacking fault between them on the [111] glide planes. The balance of their repulsive interactions and the intervening stacking fault energy determine the equilibrium partial separation which is typically in the order of a few nm for unstrained layers. The lattice mismatch stress is resolved differently onto the two partials (much higher on the  $90^\circ$  than on the  $30^\circ$  partial). Compressive stress reduces the partial separation whereas tensile stress increases the partial separation.

Results of general validity for strain relaxation can be obtained by the application of the common harmonic models [19] although they are quite crude. Harmonic models assign isotropic harmonic interactions to the atoms within the crystal and on both sides of an interface where the atoms are not out of step and unharmonic interactions to the atoms which are out of step. Essentially, harmonic models treat the crystal as an elastic continuum. The two main harmonic approaches differ essentially in the representation of the crystal around the dislocations.

The Frenkel-Kontorowa model supposes that the interfacial force is limited to the atoms at the interface and varies periodically with disregistry (relative tangential displacement). Subsequently, the model was extended for two seminfinite crystals (Nabarro and van der Merwe) and for a monolayer with anisotropic interfacial misfit (Frank and van der Merwe). Unfortunately, the governing equations are mathematically complex and are not solvable for intermediate and thick epilayers.

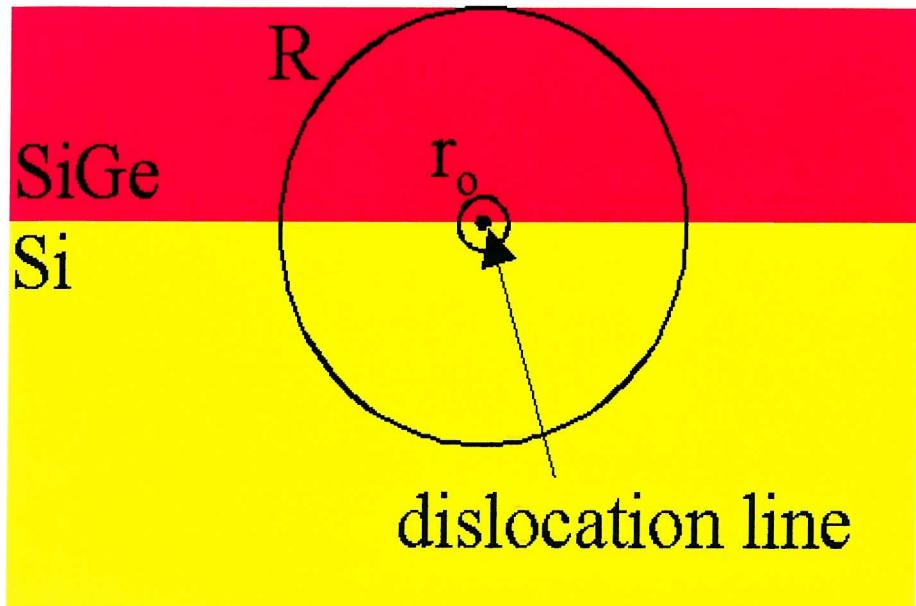

The Volterra model assumes that two crystal halves that can be treated as elastic continua and are "glued" together all over the interface except for a hole of radius  $r_o$  along the dislocation line (see fig. 2.4).  $r_o$  eliminates a singularity in the mathematical description. It is of atomic dimension and provides a "core" energy for the dislocation. An outer radius  $R$  cancels stress fields by other dislocations and by the presence of surfaces.  $R$  is limited by the thickness of the epilayer. The Volterra model is therefore not suitable for very thin epilayers. Besides, it does not account for interactions between individual dislocations. The Volterra model is the basis of the Matthews-Blakeslee theory [20], the most frequently quoted model for the calculation of the critical layer thickness.

In the Matthews-Blakeslee theory, the critical thickness of a uniform and uncapped  $Si_{1-x}Ge_x$ -layer grown on a Si substrate is found by equating the elastic force of the strained  $Si_{1-x}Ge_x$  layer  $F_\epsilon$  and the force due to the selfenergy of the interfacial dislocations  $F_\delta$  (see fig. 2.2, [1, chap. 1.2]):

$$F_\epsilon = F_\delta \quad (2.10)$$

According to the isotropic linear elasticity theory, the elastic force of the strained SiGe layer is given by [1, chap. 1.2]:

$$F_\epsilon = 2Gb\hbar\epsilon \cos\lambda \frac{1+\nu}{1-\nu} \quad (2.11)$$

The dislocation theory gives the following expression for the force due to the selfenergy of

Figure 2.4: Cross section through a dislocation line in the Volterra model

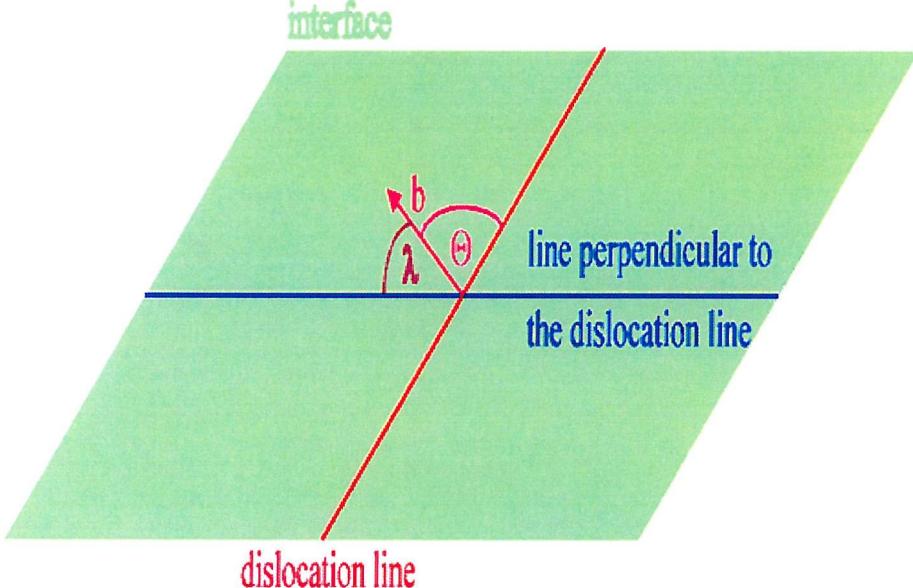

Figure 2.5: Position of  $\lambda$  and  $\Theta$

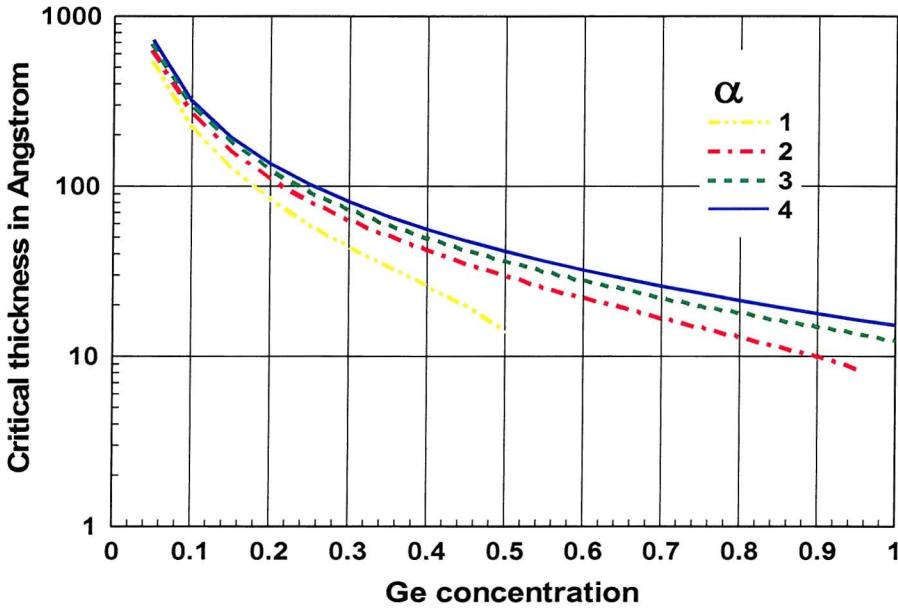

Figure 2.6: Theoretical critical thicknesses for different  $\alpha$

the interfacial dislocations [1, chap. 1.2]:

$$F_\delta = Gb^2 \frac{1 - \nu \cos^2 \Theta}{4\pi(1 - \nu)} \ln \frac{\alpha h}{b} \quad (2.12)$$

Where  $h$  is the epilayer thickness,  $G$  is the shear modulus of the epilayer,  $\nu$  is the Poisson ratio,  $b$  is the magnitude of the Burgers vector,  $\lambda$  is the angle between the misfit dislocation Burgers vector and a line in the interface drawn perpendicular to the dislocation line direction,  $\Theta$  is the angle between the dislocation line and its Burgers vector and  $\alpha$  is a factor describing the energy of the dislocation core (see fig. 2.5). Figure 2.6 shows the results for  $G = 64 \text{ GPa}$ ,  $\nu = 0.28$ ,  $\cos \lambda = 0.5$ ,  $\cos \Theta = 0.5$ ,  $b = 3.9 \text{ \AA}$ ,  $\epsilon = 0.041 x$ . As the core energy of Si and Ge is not definitively known, different values of  $\alpha$  are shown. Critical thicknesses can be calculated for any Ge content in the relaxed substrate and in the strained channel if the appropriate material parameters are chosen.

The Matthews-Blakeslee theory agrees well with experimental findings for  $Si_{1-x}Ge_x$  structures grown at high temperatures. For low growth temperatures the critical layer thickness can exceed the predicted values considerably. In the metastable regime, strain relaxation is prevented by the presence of activation energy barriers to the nucleation and propagation of misfit dislocations. In the metastable regime and at a given temperature, The Dodson-Tsao model describes the time-dependent relaxation [15, p. 51]:

$$\frac{d\epsilon(t)}{dt} = CG^2(\epsilon_o - \epsilon(t) - \epsilon^*)^2(\epsilon(t) + \epsilon_s) \quad (2.13)$$

Where  $\epsilon^*$ ,  $\epsilon_o$ ,  $\epsilon_s$  and  $C$  are respectively the equilibrium strain, the initial lattice mismatch strain, strain due to dislocations present at the beginning and a constant. As these values are most often not known, the Dodson-Tsao model seldom allows predictions concerning the strain relaxation.

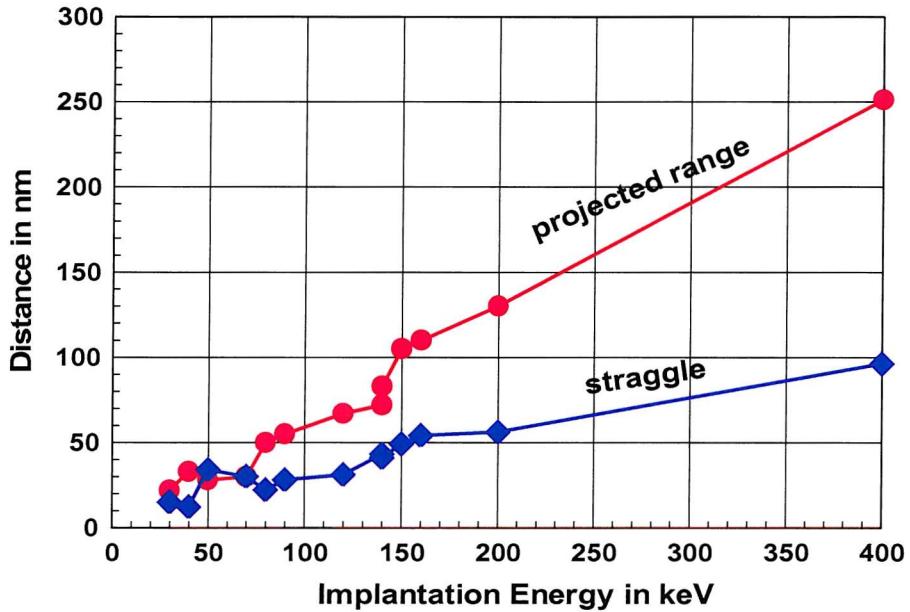

Figure 2.7: Projected range  $R_p$  and straggle  $\Delta R_p$  for Ge [15, p. 160]

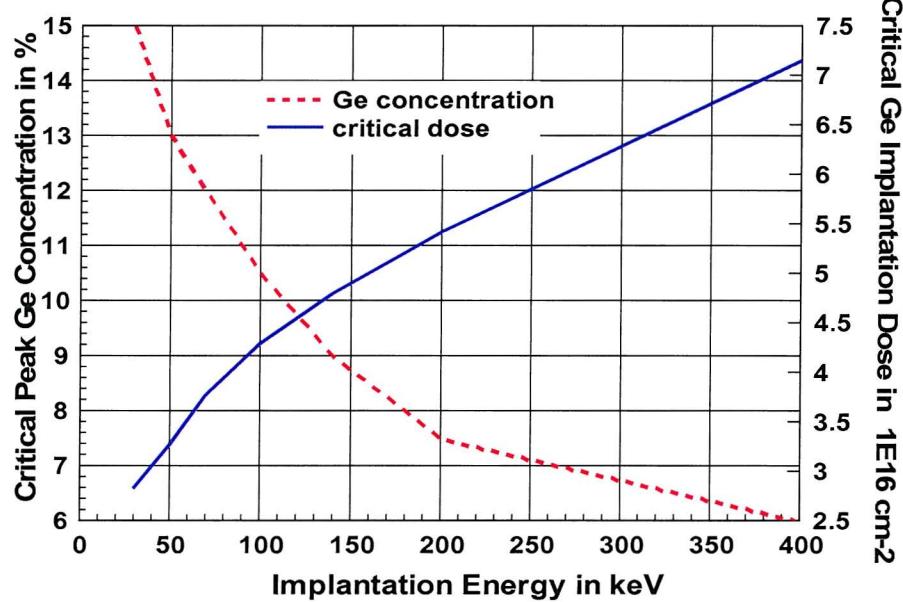

Figure 2.8: Critical peak Ge concentration and dose

Figure 2.9: Band structure [25] of (a) Si (b) Ge

A linearly graded SiGe layer has the same critical thickness as a uniform SiGe layer that has the average Ge concentration of the linearly graded SiGe layer [2]. F. Christiano derived the critical Ge implantation dose [15, 23] from the minimization of the total energy  $E_T = E_\epsilon + E_\delta$ .

The energy  $E_\epsilon$  associated with the elastic strain  $\epsilon$  is given by [15, p. 152]:

$$E_\epsilon = 2G\left(\frac{1+\nu}{1-\nu}\right) \int_0^h \epsilon^2(y) dy \quad (2.14)$$

The energy  $E_\delta$  associated with the misfit  $\delta$  accommodated by dislocations is given by:

$$E_\delta = (f - \epsilon) \frac{Gb}{2\pi(1-\nu)} \left[ \ln\left(\frac{h}{b}\right) + 1 \right] \quad (2.15)$$

The model predicts a critical elastic strain energy of  $310 \text{ mJ/m}^2$  that is independent of the implantation dose. Although the model does not account for stacking faults and is based on an energy balance approach instead of a force balance approach, it agrees with experimental findings [15, p. 160]. Assuming a Gaussian Ge profile, the following formula for the critical implant dose  $\Phi_{max}$  can be derived [24] (see fig. 2.8):

$$\Phi_{max} = \sqrt{2\pi} \Delta R_p \cdot Ge_{max} \cdot \frac{5 \cdot 10^{20}}{\% \cdot \text{cm}^3} \quad (2.16)$$

The projected range  $R_p$  and straggle  $\Delta R_p$  are given in fig. 2.7 [15, p. 155].  $\Phi_{max}$  and the critical Ge implantation dose are shown in fig. 2.8 as a function of the implantation energy.

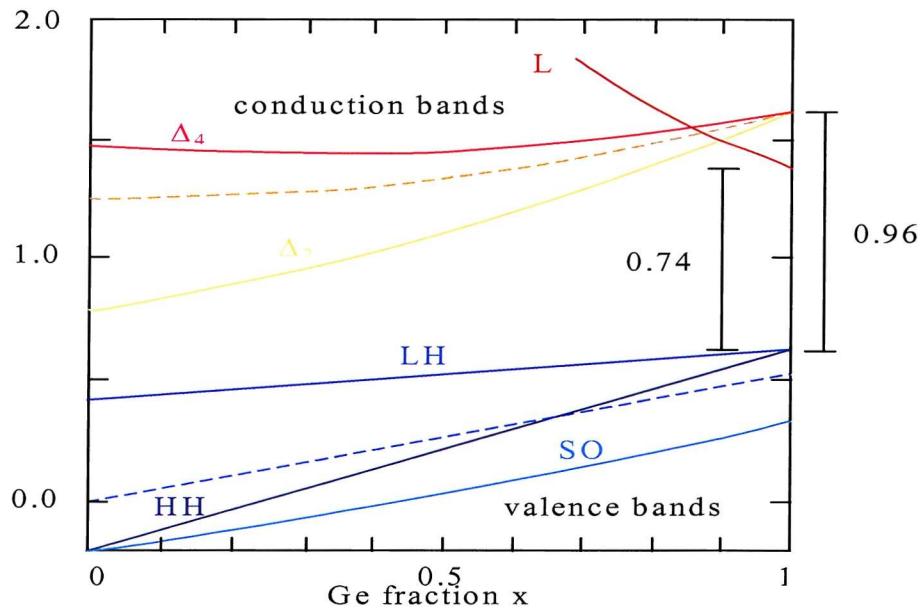

### 2.3 Band Structure of SiGe

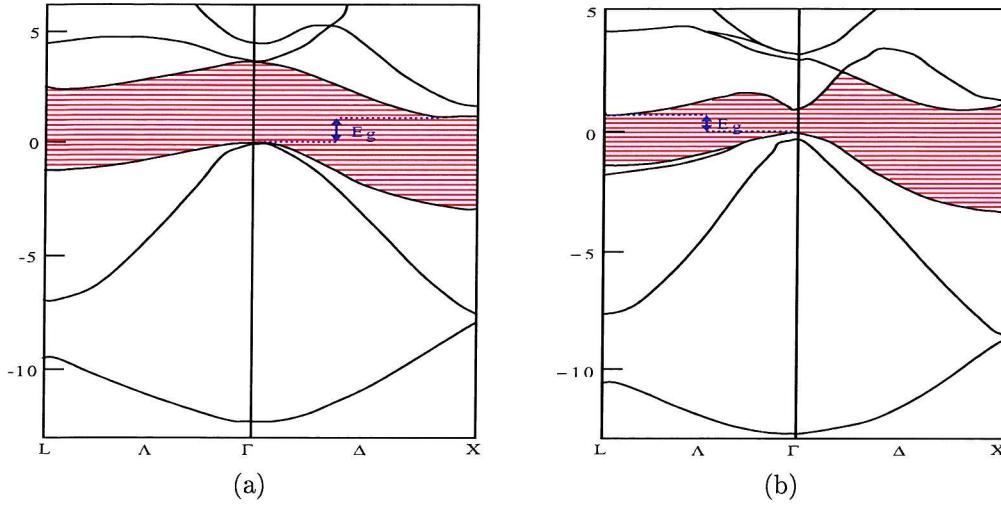

Both Si and Ge possess an indirect fundamental band gap [25, 26]. Like for all semiconductors with a diamond structure, the maximum of the valence band of Si and Ge is situated in the

center of the Brillouin zone ( $\Gamma$  maximum) and consists of two converging subbands that are degenerated in the maximum.

In Si (see fig. 2.9 (a)), the minimum of the conduction band is situated in the (001) direction ( $\Delta$  minimum). Due to the diamond structure of silicon, (100), ( $\bar{1}00$ ), (010), (0 $\bar{1}0$ ), (001) and (00 $\bar{1}$ ) are equivalent directions and the conduction band is sixfold degenerated. At 300 K, the indirect band gap of Si is 1.12 eV.

In Ge (see fig. 2.9 (b)), the minimum of the conduction band is situated in the (111) direction at the edge of the Brillouin zone ( $L$  minimum). Although there are 8 equivalent directions ( $\frac{++\pm}{\pm\pm\pm}$ ), the conduction band is fourfold degenerate because the eight semiellipses can be represented by 4 ellipses centered at the points (111), ( $\bar{1}11$ ), (1 $\bar{1}1$ ) and (11 $\bar{1}$ ). At 300 K, the indirect band gap of Ge is 0.66 eV.

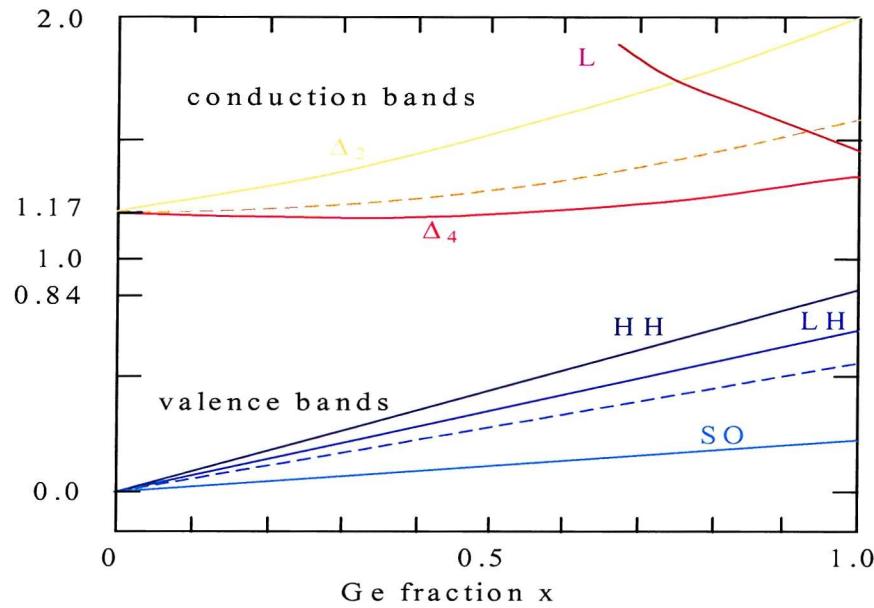

The latest band structure calculations of unstrained SiGe alloys [1, chap. 4; 16; 17] use the molecular coherent potential approximation (MCPA) and nonlocal empirical pseudopotential calculations. The agreement between theory and experiment is excellent if the effect of alloy disorder is accounted for. In bulk alloys [1, chap. 4], the band gap decreases as a function of the Ge concentration. The conduction band structure is silicon-like for Ge concentrations up to 85 % and germanium-like for Ge concentrations over 85 % when the band gap decreases rapidly. The indirect energy gap of a  $Si_{1-x}Ge_x$  alloy for  $x < 0.85$  is given by [1, chap. 4.1]<sup>1</sup>:

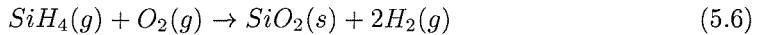

$$E_g = 1.155 - 0.43x + 0.0206x^2 \text{ (eV)} \quad (2.17)$$

And for  $x > 0.85$ :

$$E_g = 2.010 - 1.27x \text{ (eV)} \quad (2.18)$$

The band gap of strained *Si* grown on a relaxed  $Si_{1-x}Ge_x$  substrate is given by [29]:

$$E_g = 1.11 - 0.74x \text{ (eV)} \quad (2.19)$$

The band gap of strained  $Si_{1-x}Ge_x$  grown on a relaxed *Si* substrate for  $x < 0.25$  can be described by [1, chap. 4.1]:

$$E_g = 1.17 - 0.896x + 0.396x^2 \text{ (eV)} \quad (2.20)$$

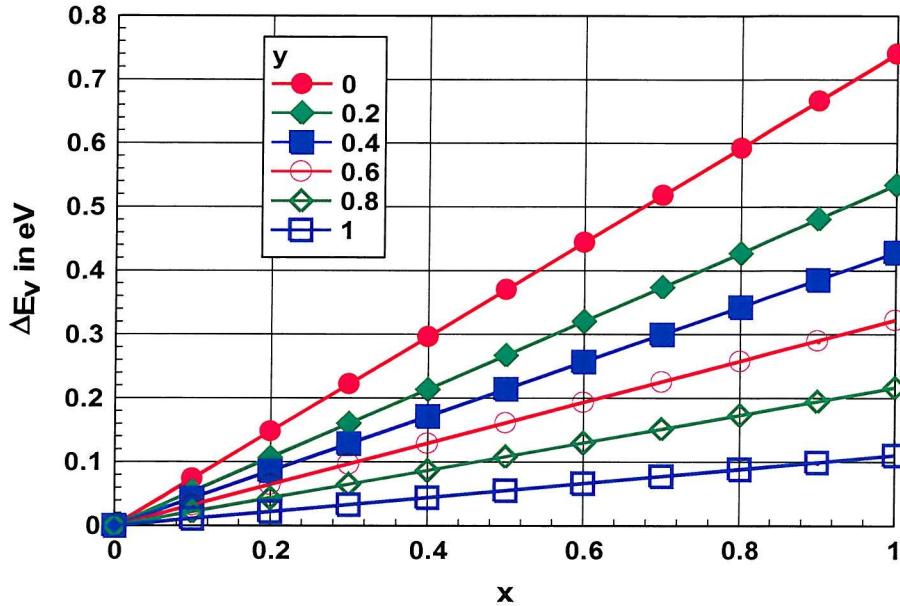

The impact of strain on the band structure was first calculated by C. G. van de Walle and R. M. Martin [16, 17]. Their model-solid theory requires exclusively the knowledge of macroscopic parameters, such as strain. It is based on the local-density-functional theory, the artificial introduction of a supercell that introduces translation invariance into the problem and nonlocal norm-conserving pseudopotentials. The local-density-functional method underestimates the band gaps of semiconductors severely, but is able to determine precisely the shift of the bands

<sup>1</sup>All values for the energy gaps, band offsets, and effective masses have been proposed by the Glasgow device modeling group. Estimated values for  $Si_{1-y}Ge_y$  substrates can often be obtained by replacing  $x$  with  $(x - y)$ , e.g.  $E_g = 1.17 - 0.896x - 0.396x^2$  becomes  $E_g = 1.17 - 0.896(x - y) - 0.396(x - y)^2$ .

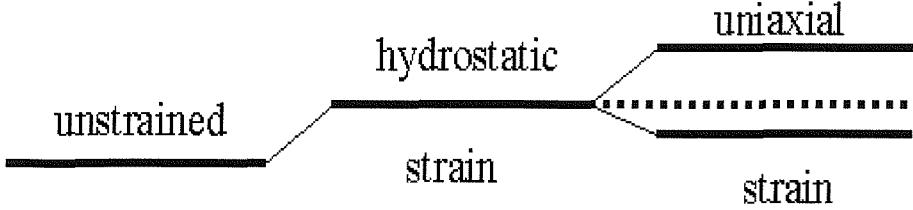

Figure 2.10: Schematic representation of the splitting of a triply degenerate band due to strain

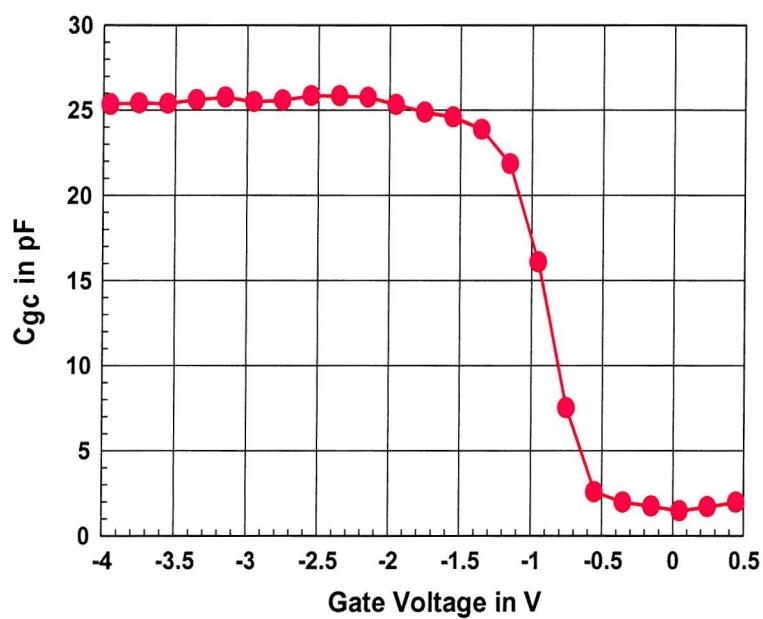

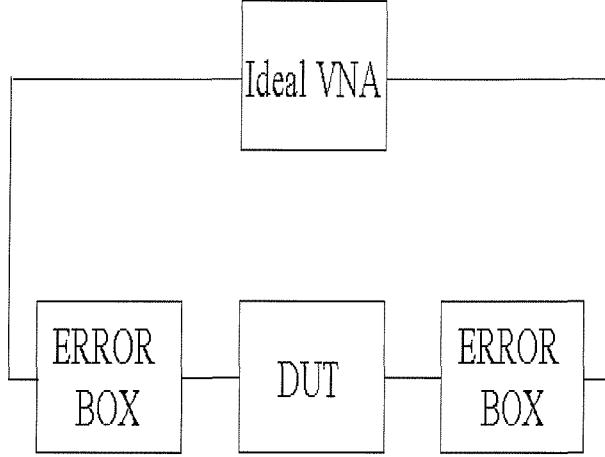

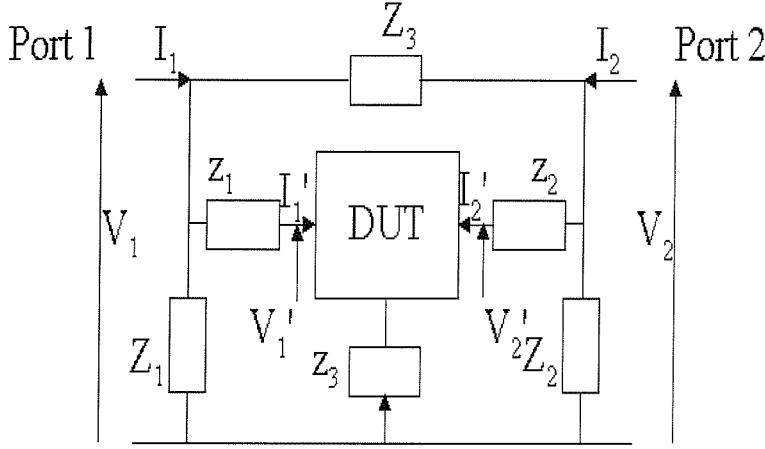

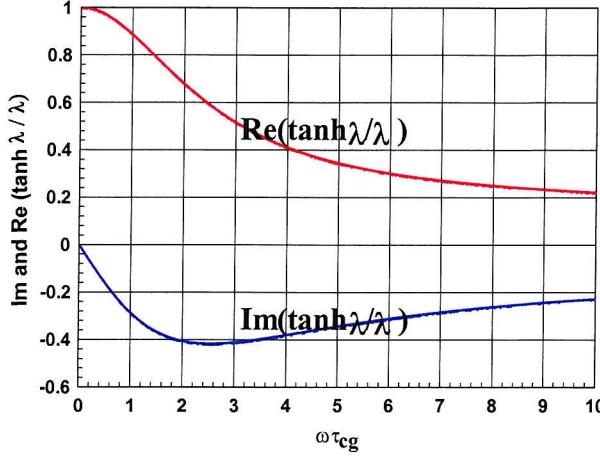

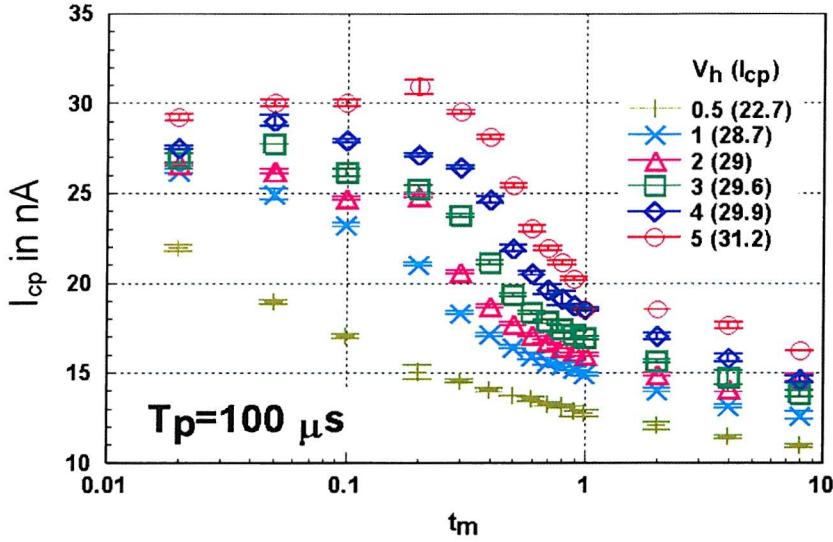

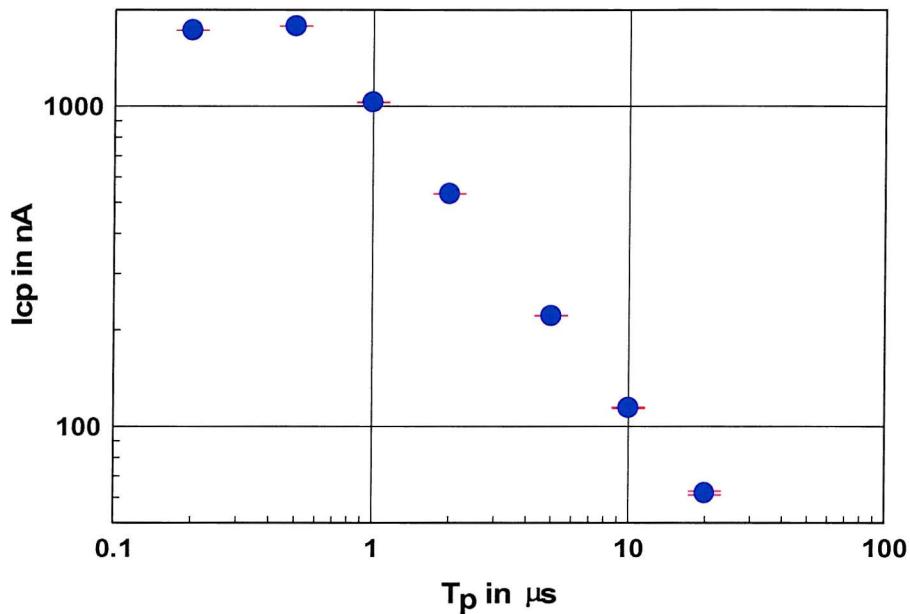

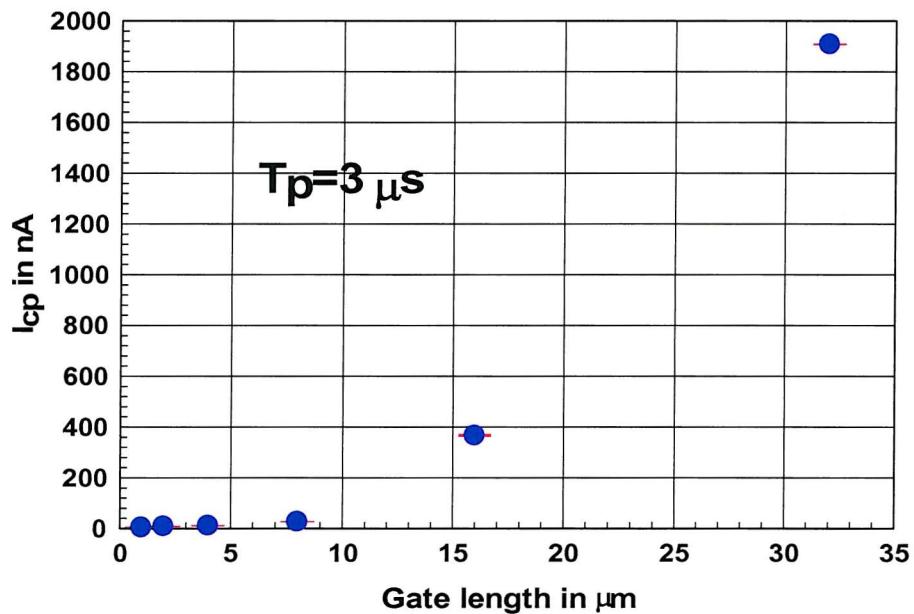

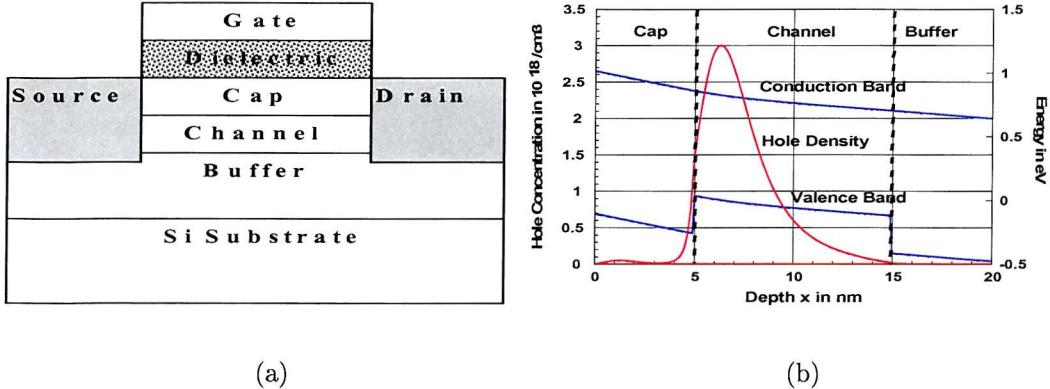

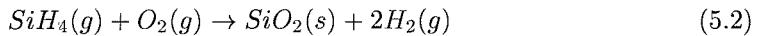

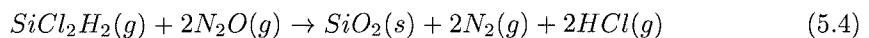

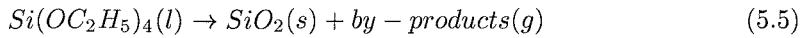

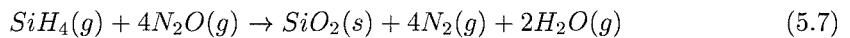

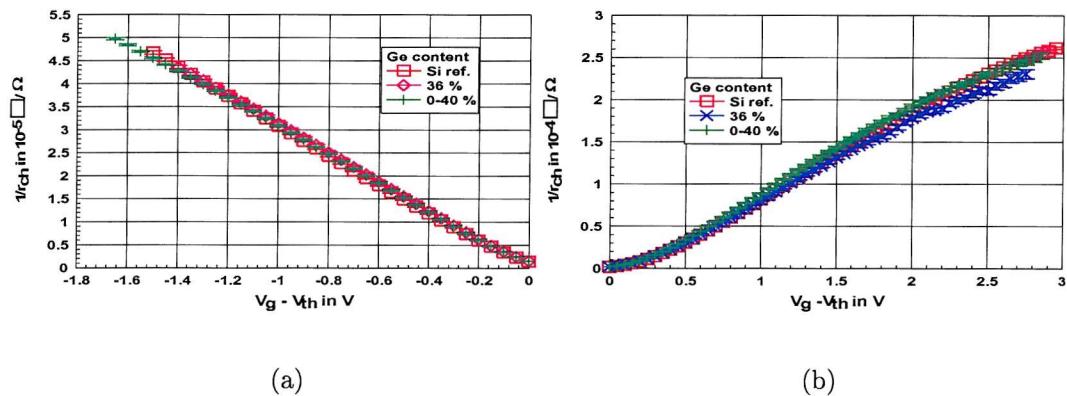

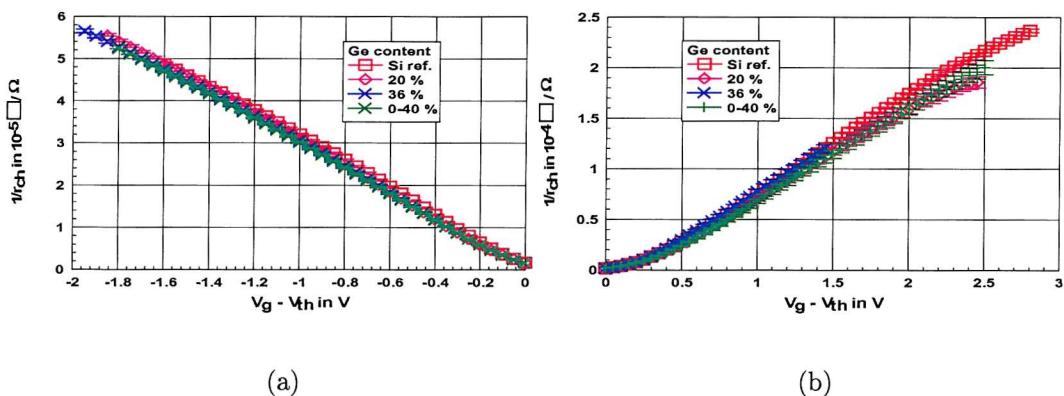

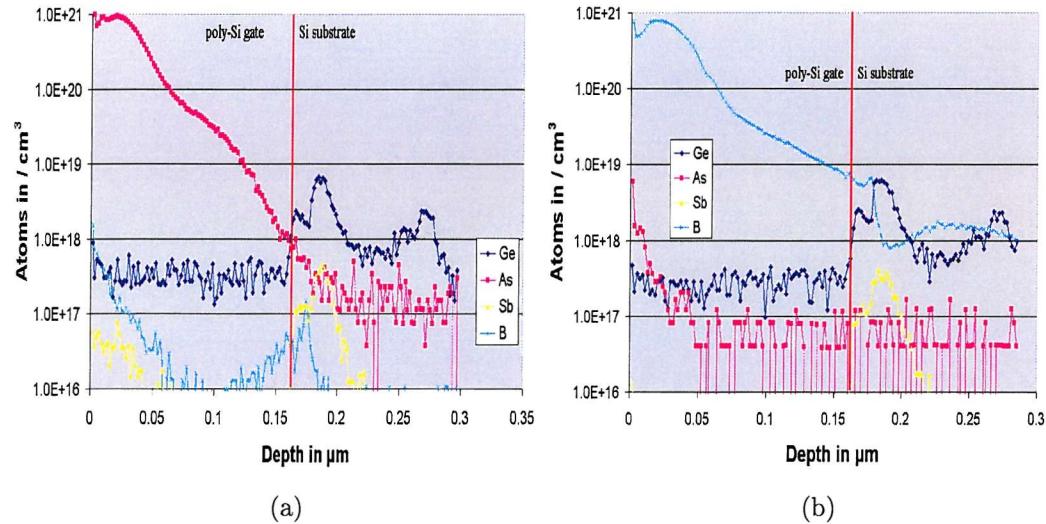

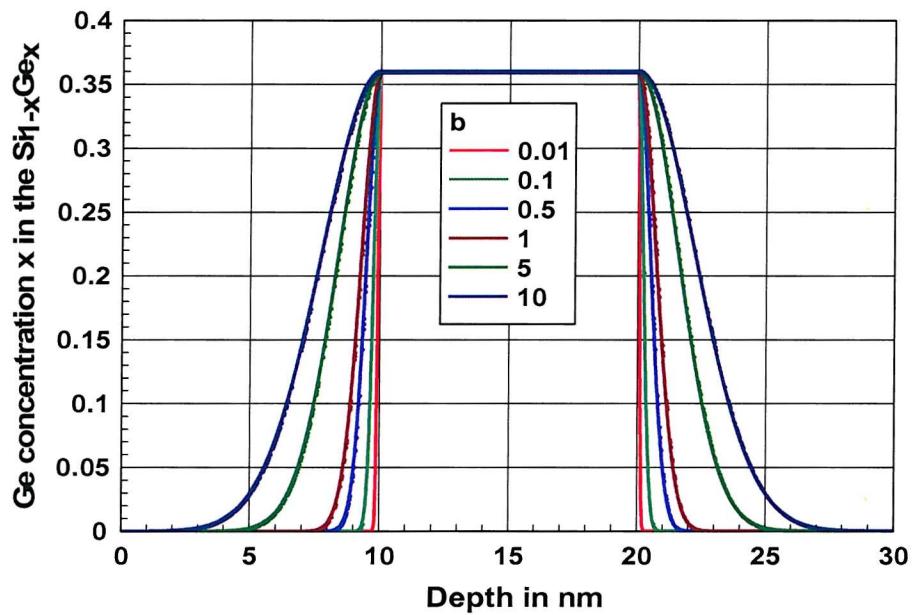

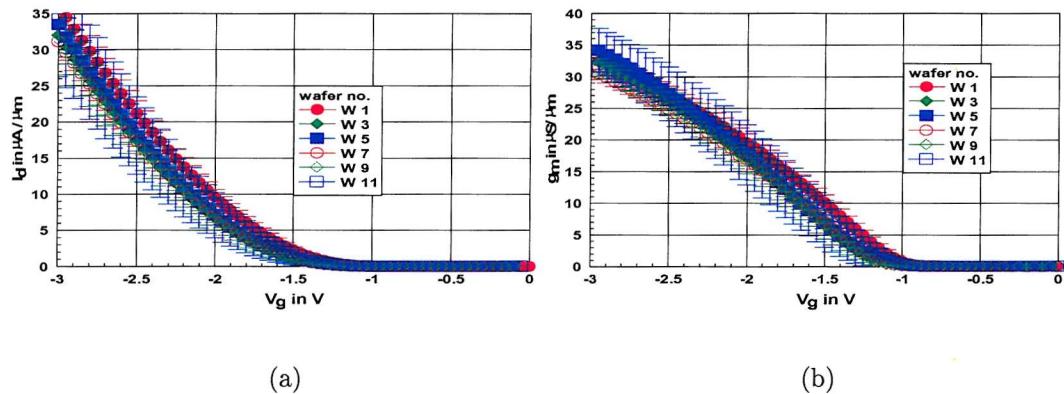

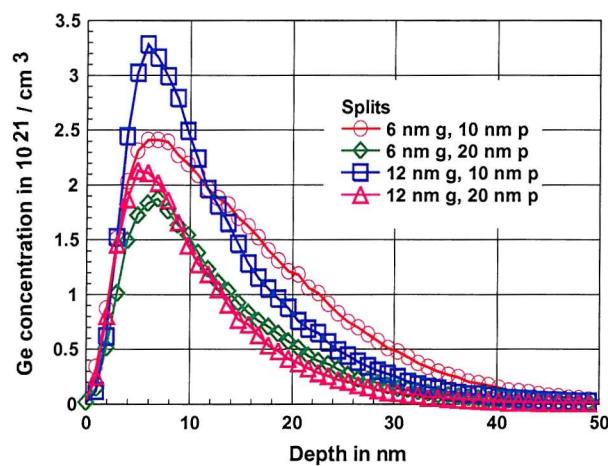

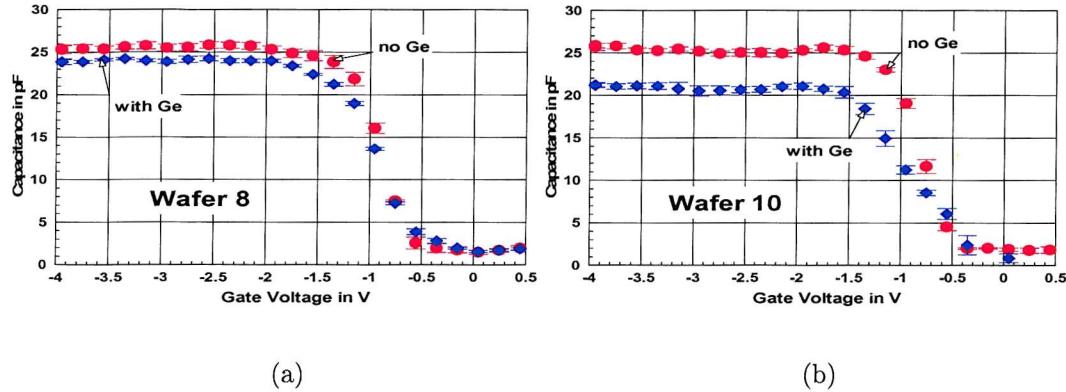

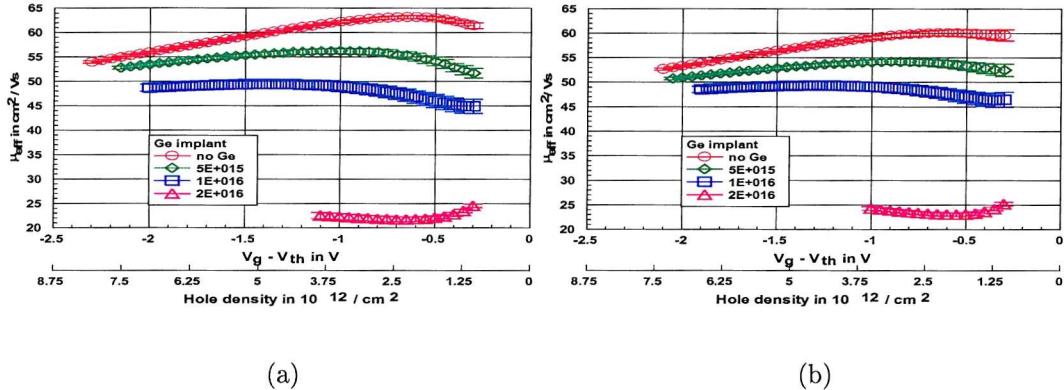

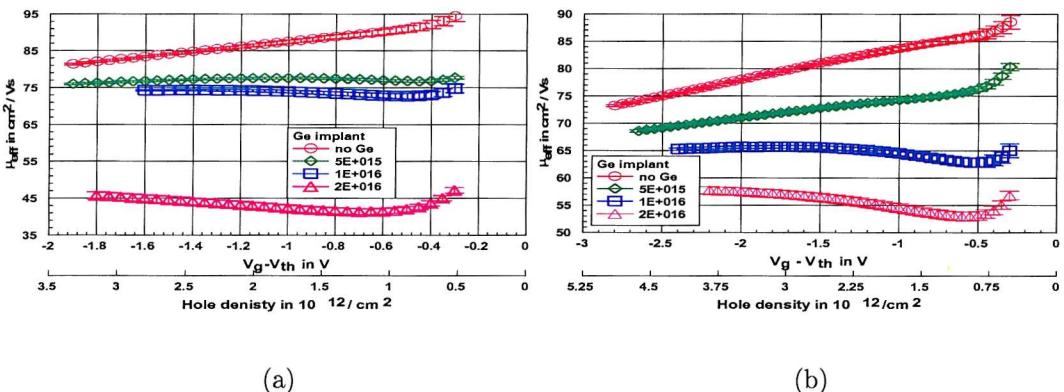

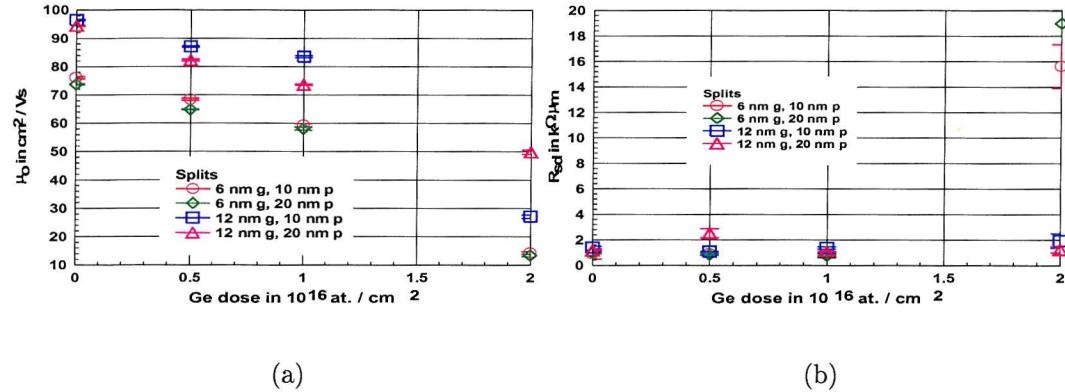

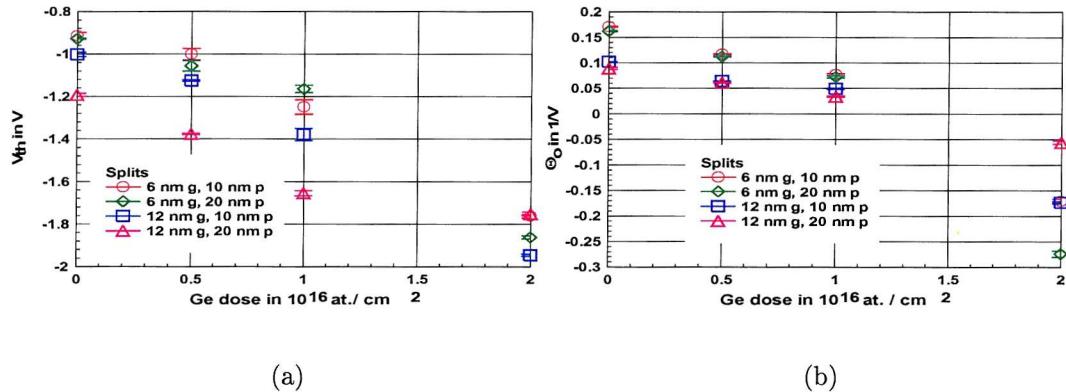

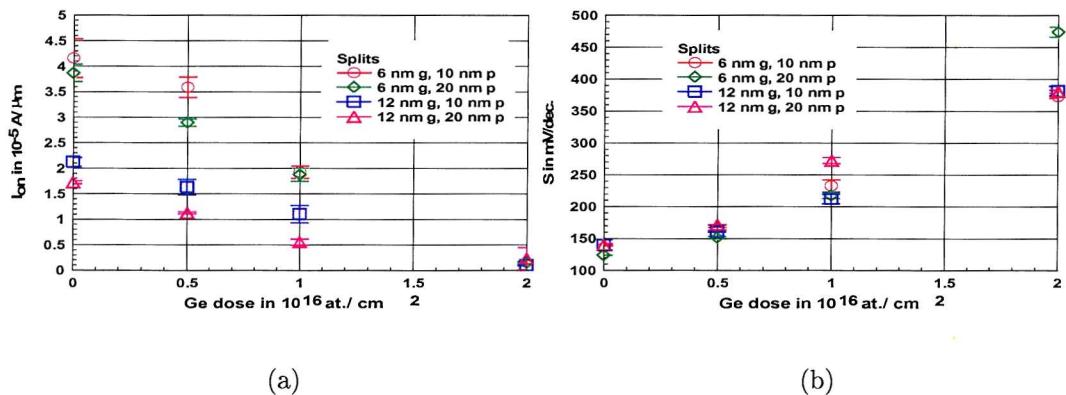

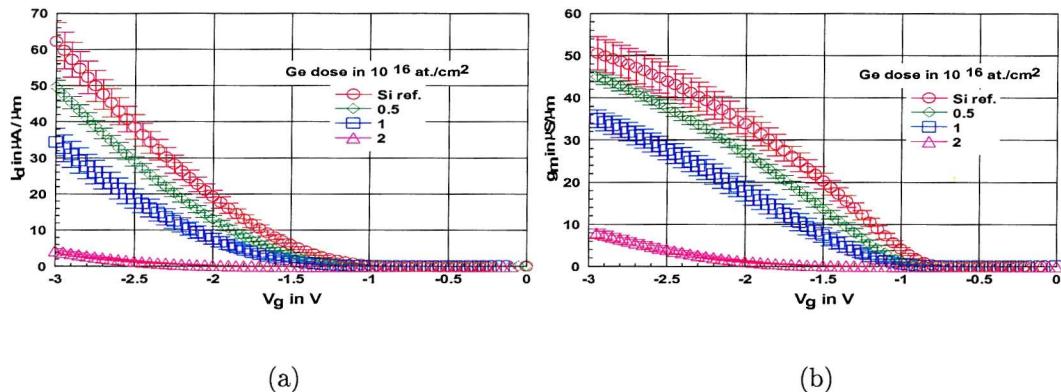

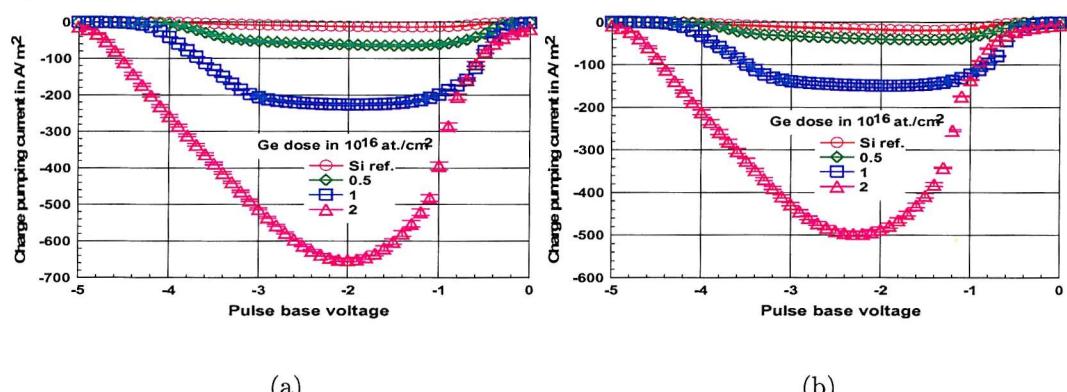

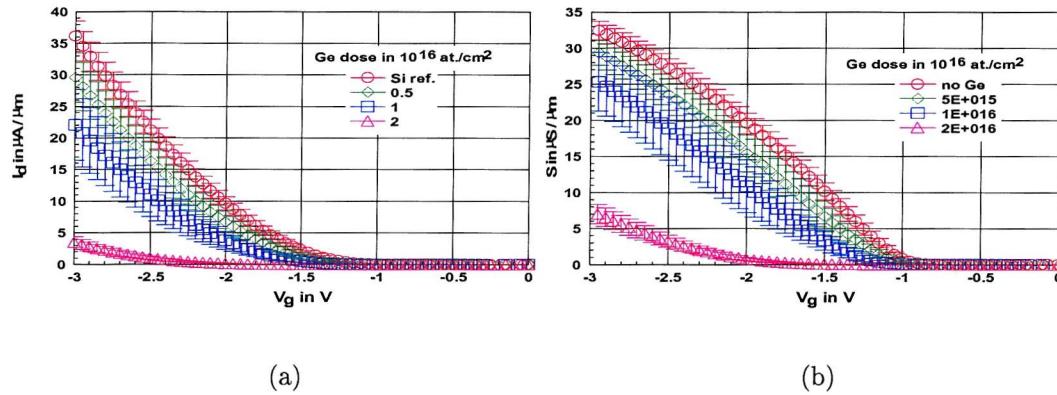

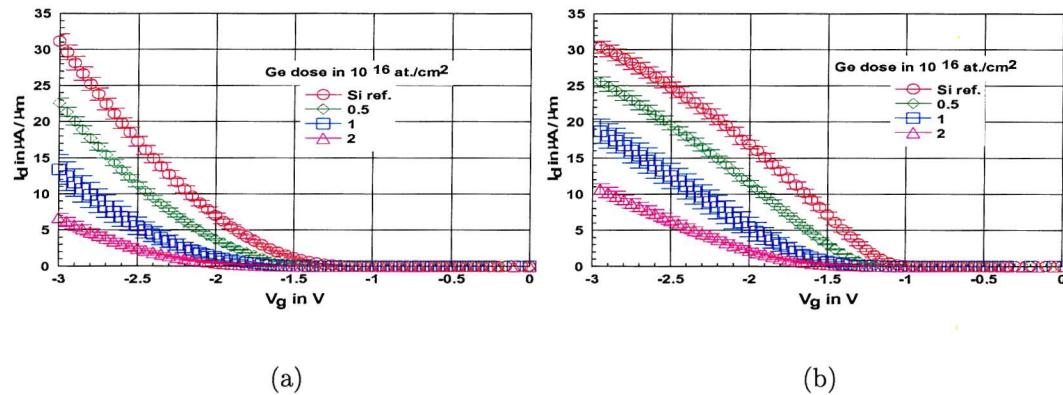

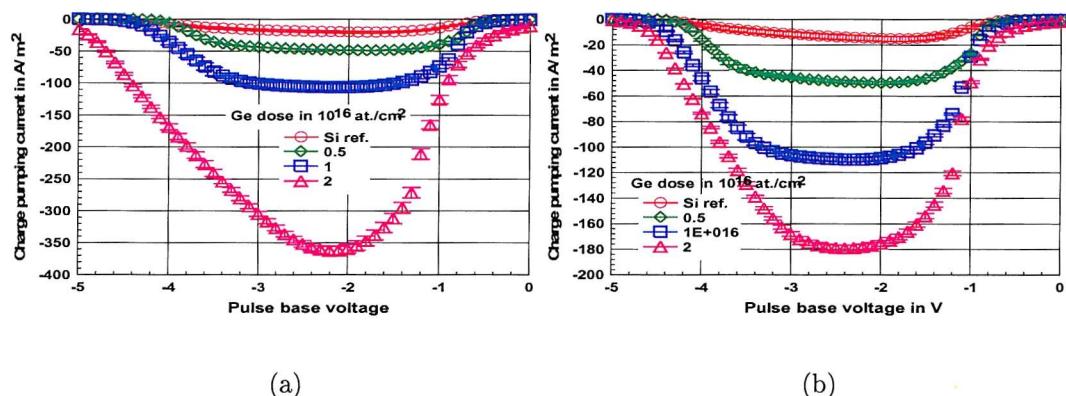

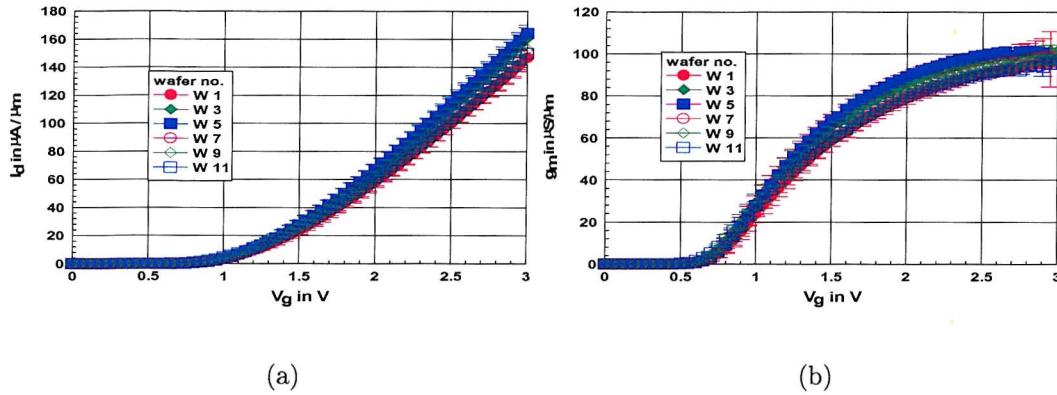

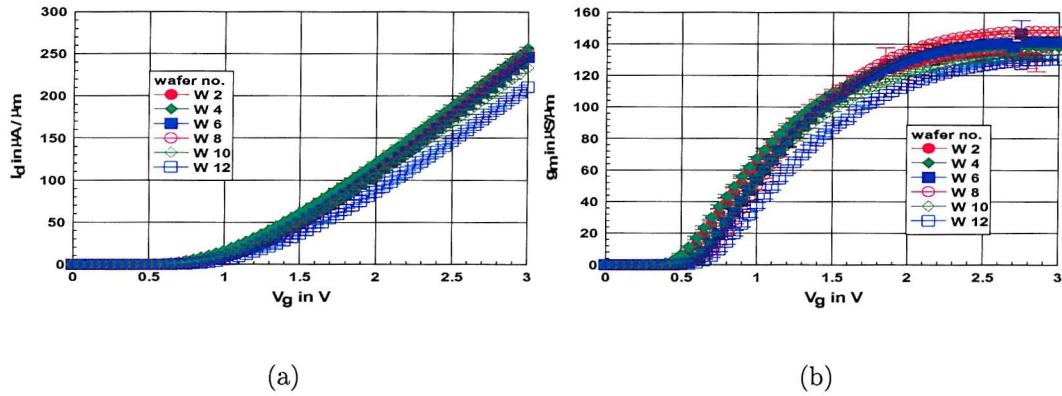

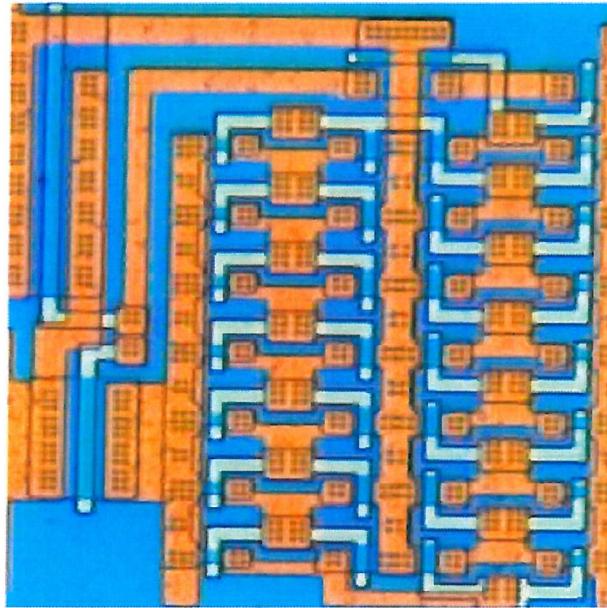

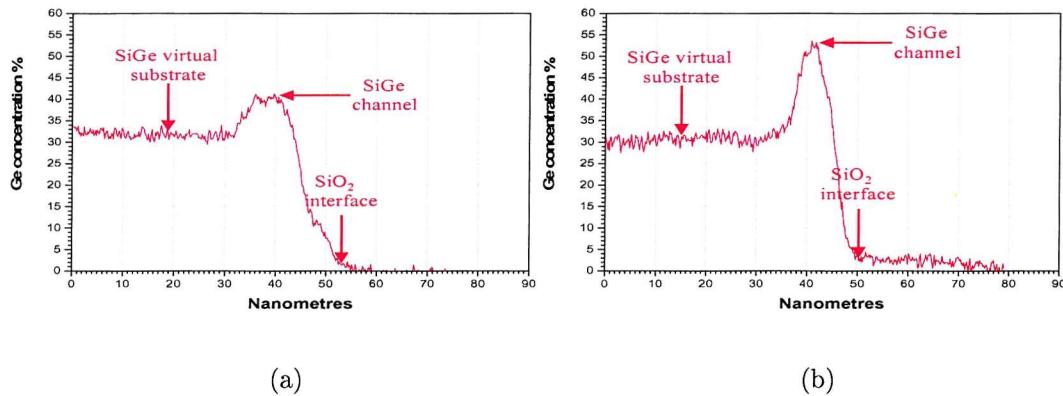

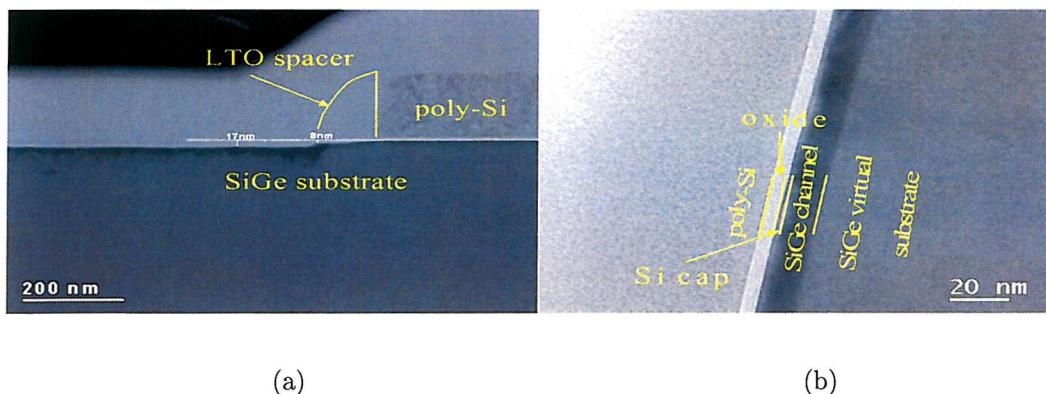

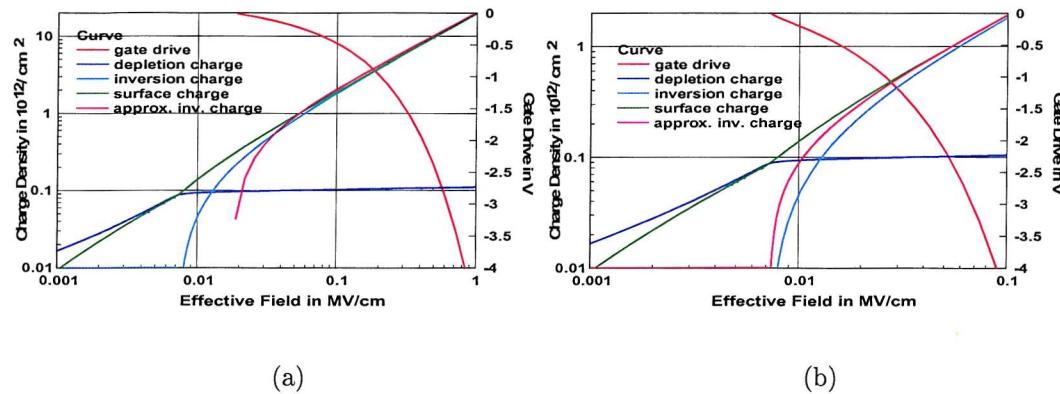

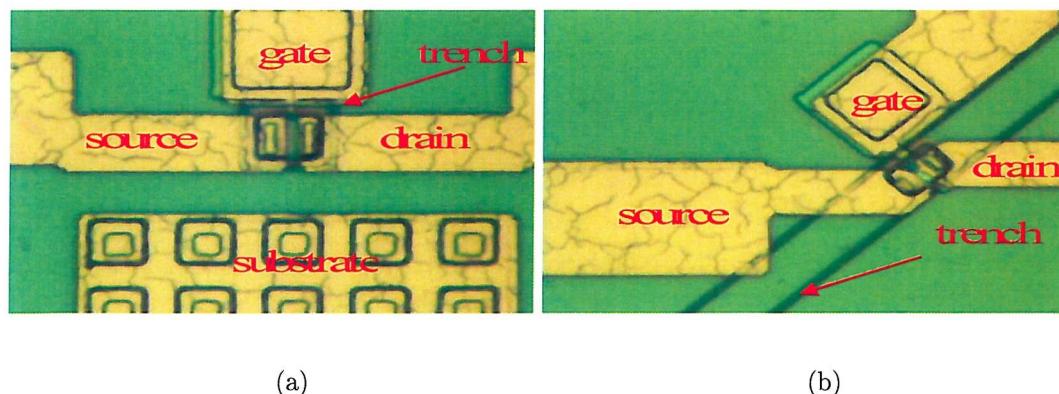

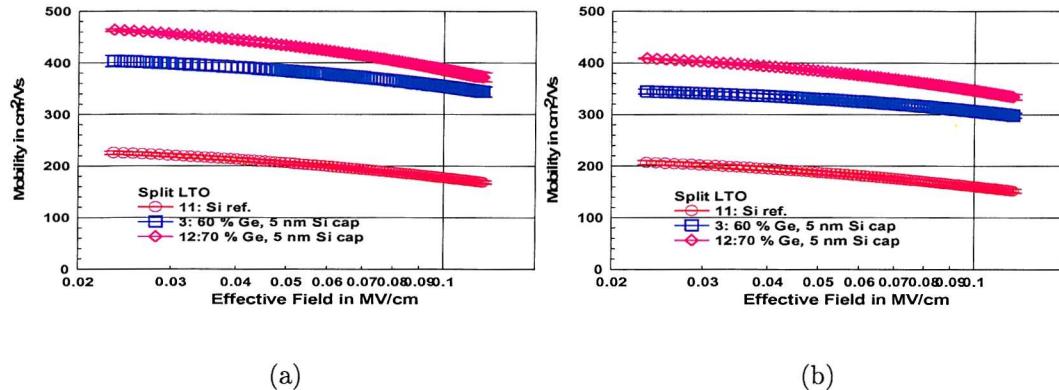

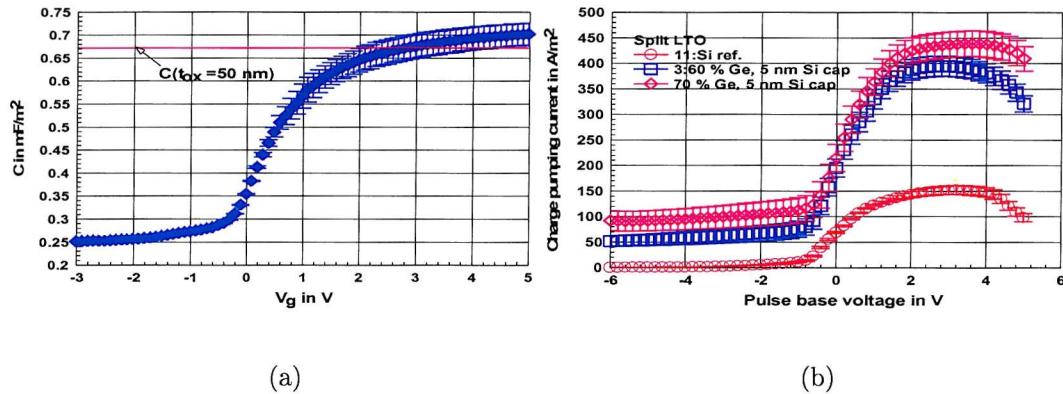

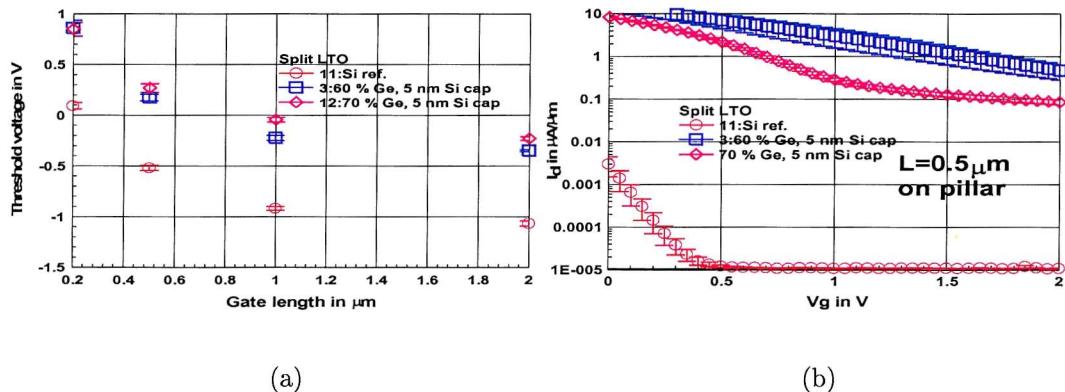

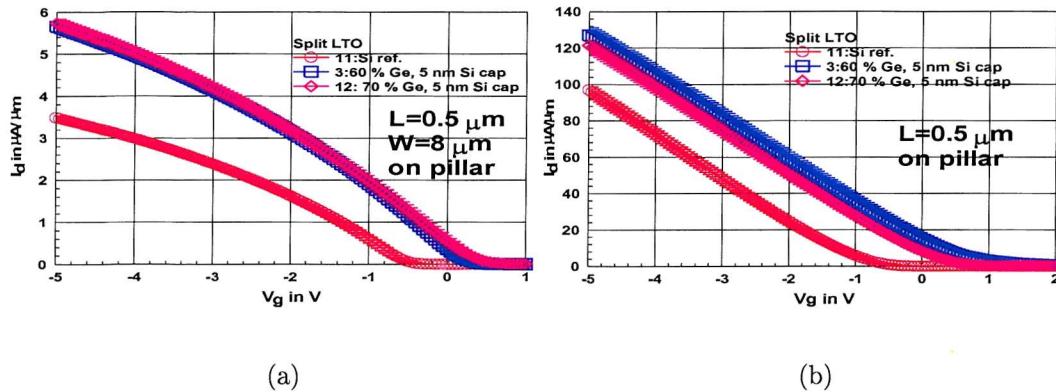

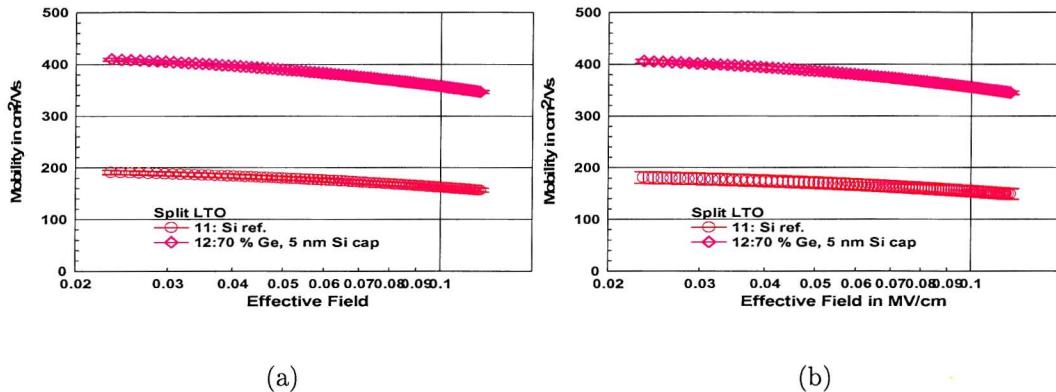

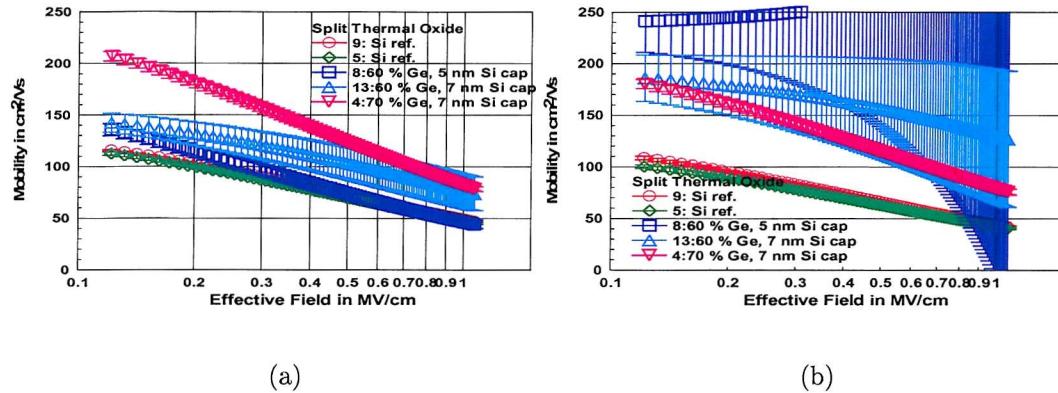

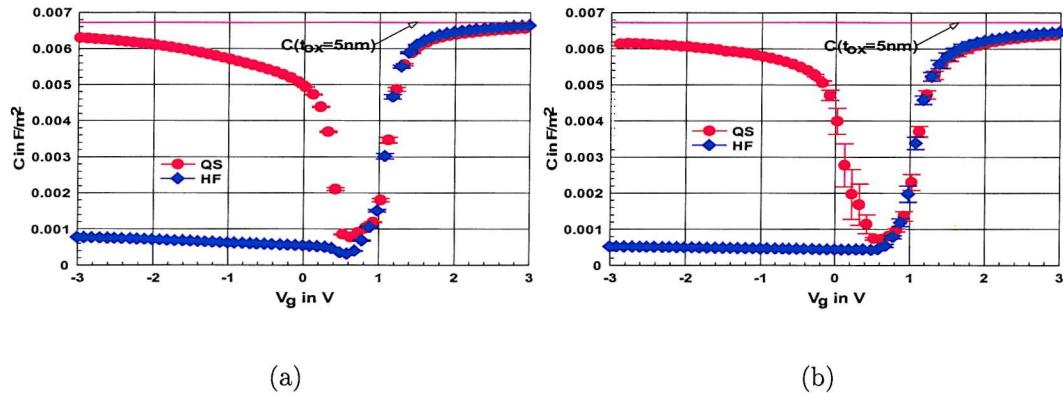

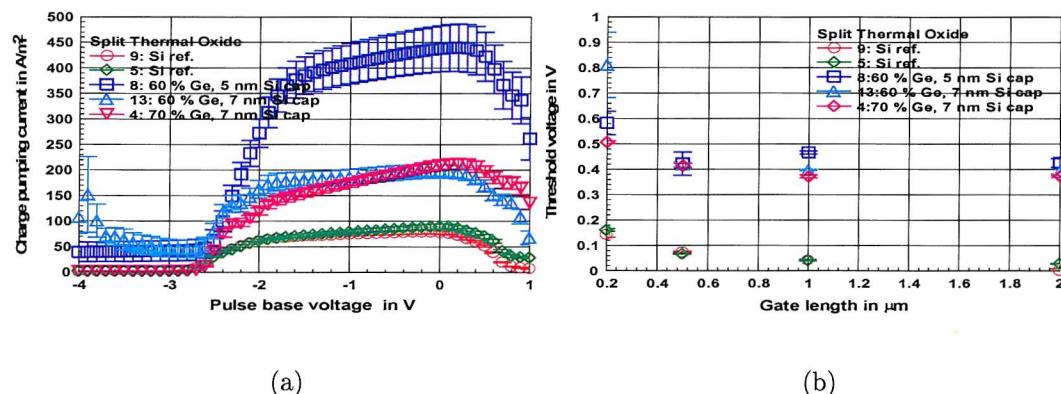

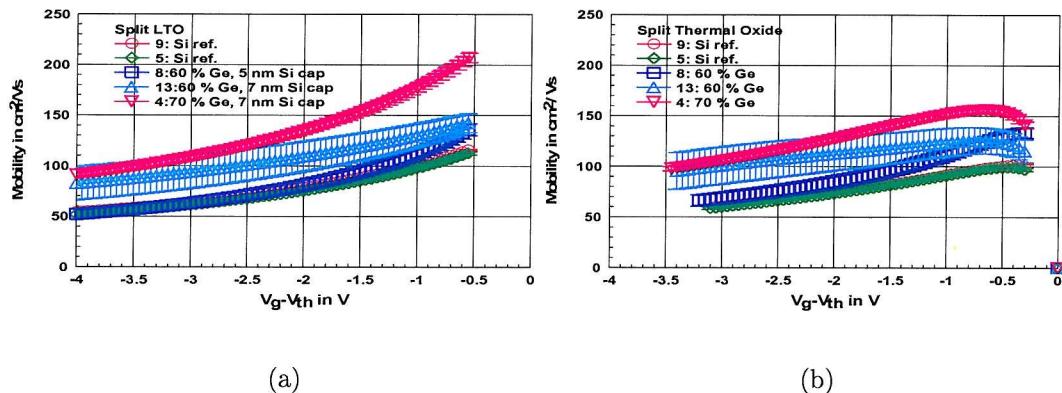

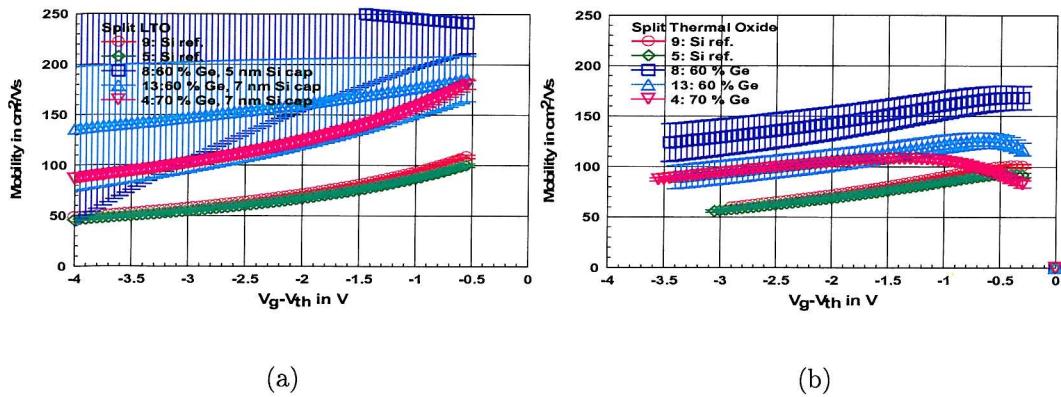

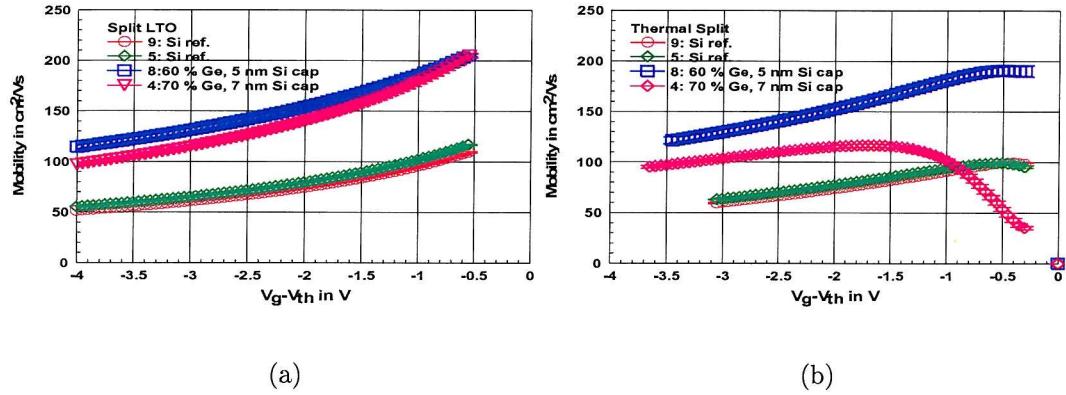

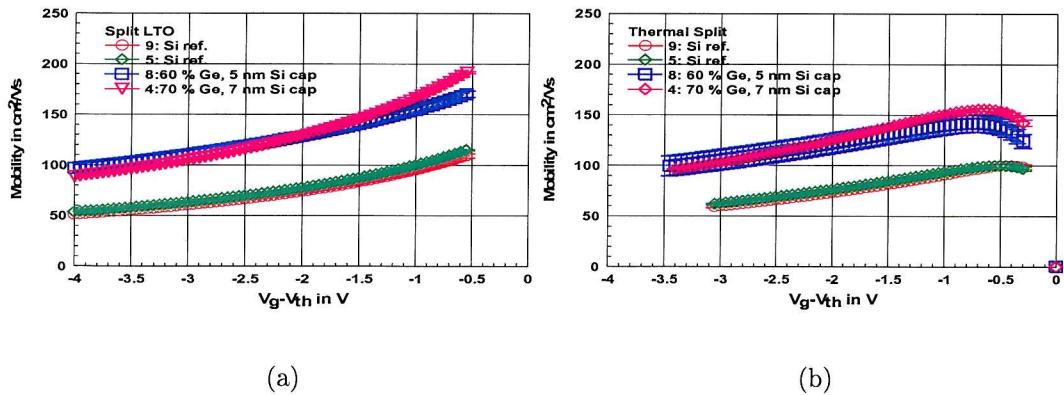

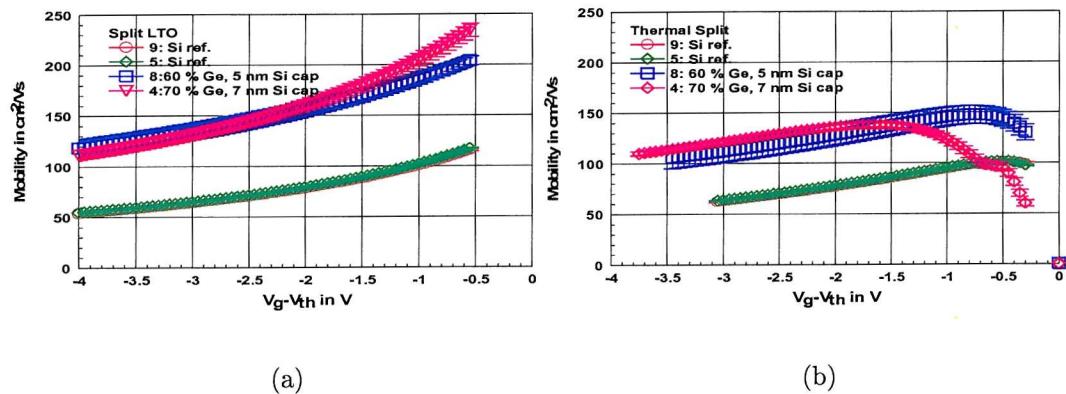

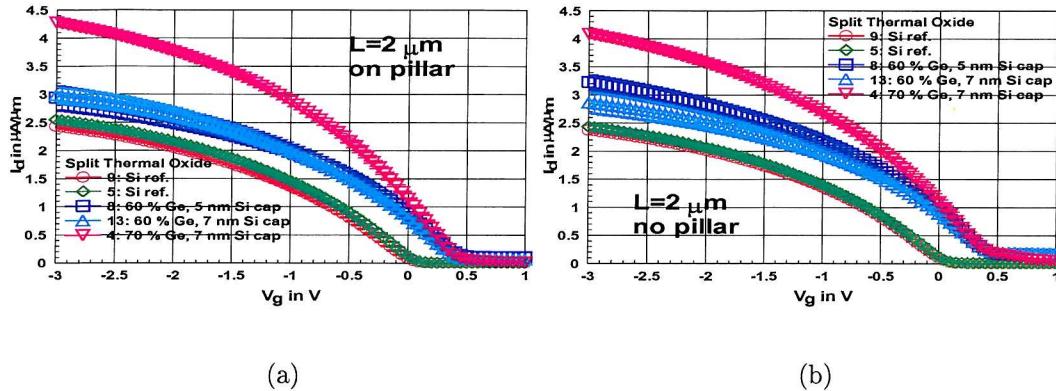

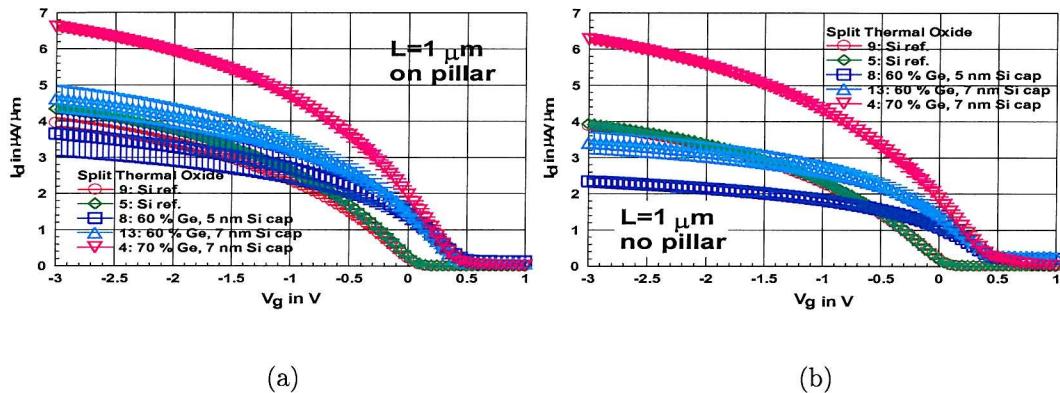

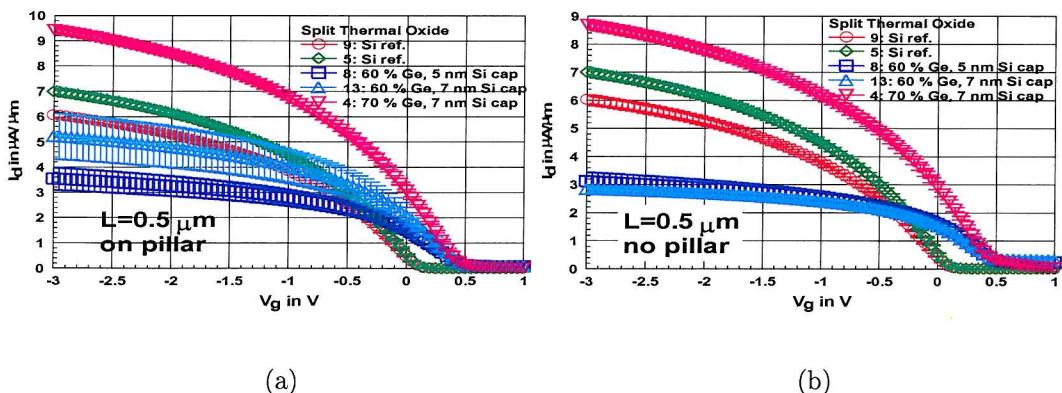

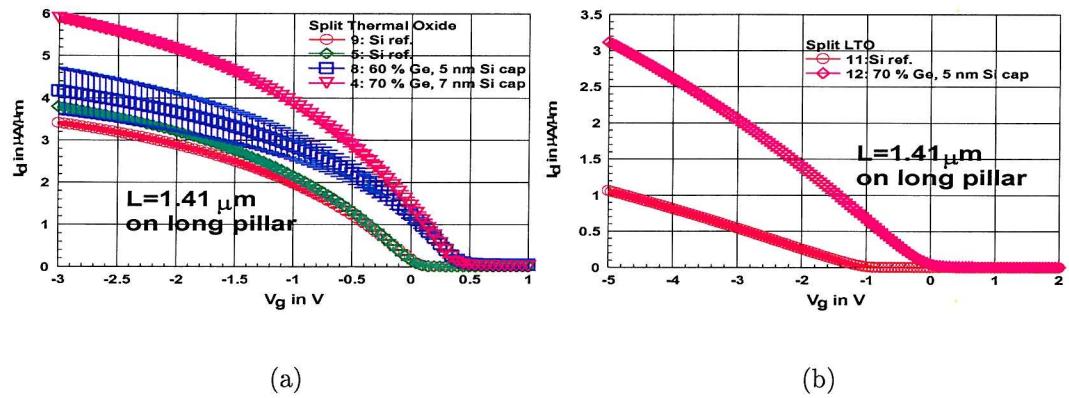

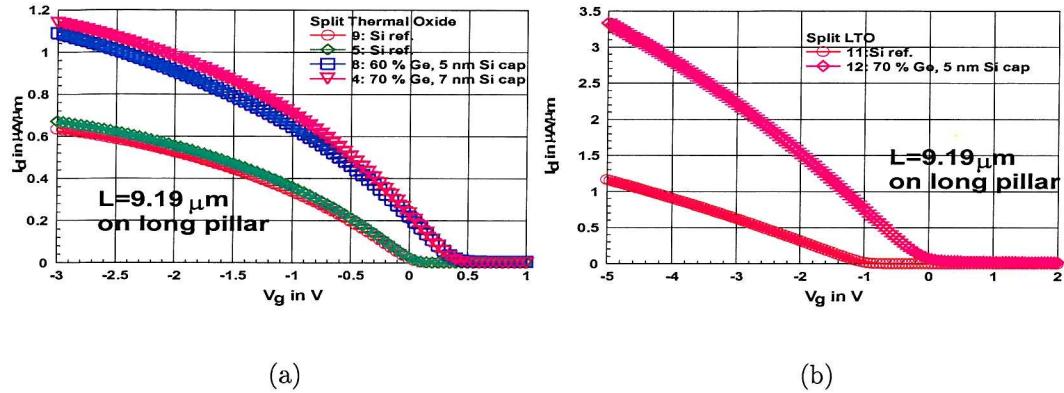

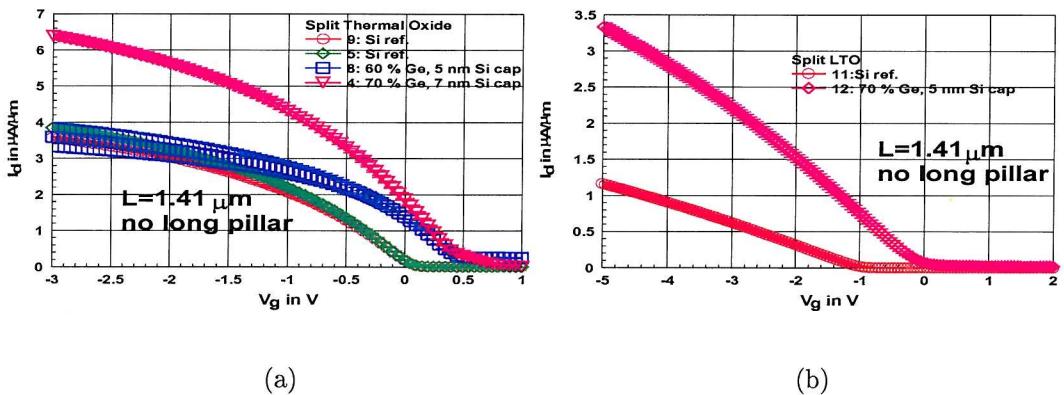

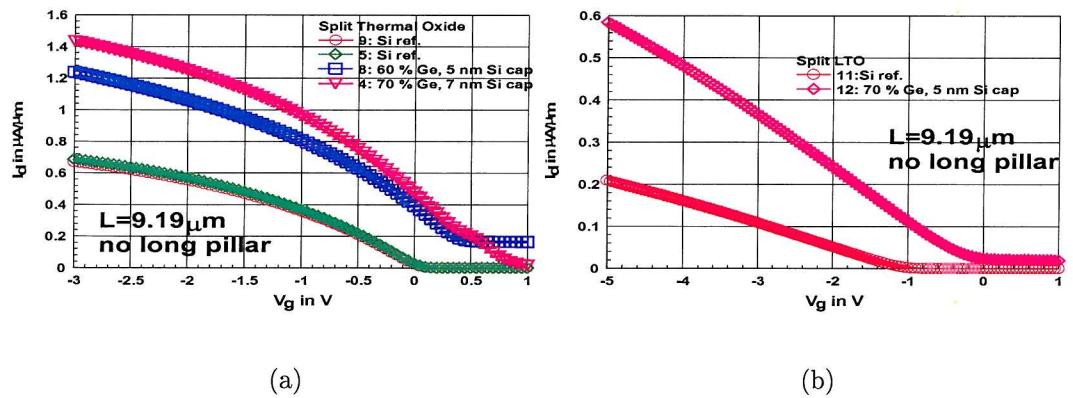

due to strain. In combination with bulk band structure calculations, the calculations provide us with information about the valence and conduction band discontinuities without making any assumptions.